Patents

Literature

742 results about "Single process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Single Process. A single process refers to any color service that is done in one step. It can also be reffered to as a base color or a "root touch up", but it is not restricted to coloring just on the "roots". This is generally a permanent color that is applied either jus to the roots or all over from roots to ends.

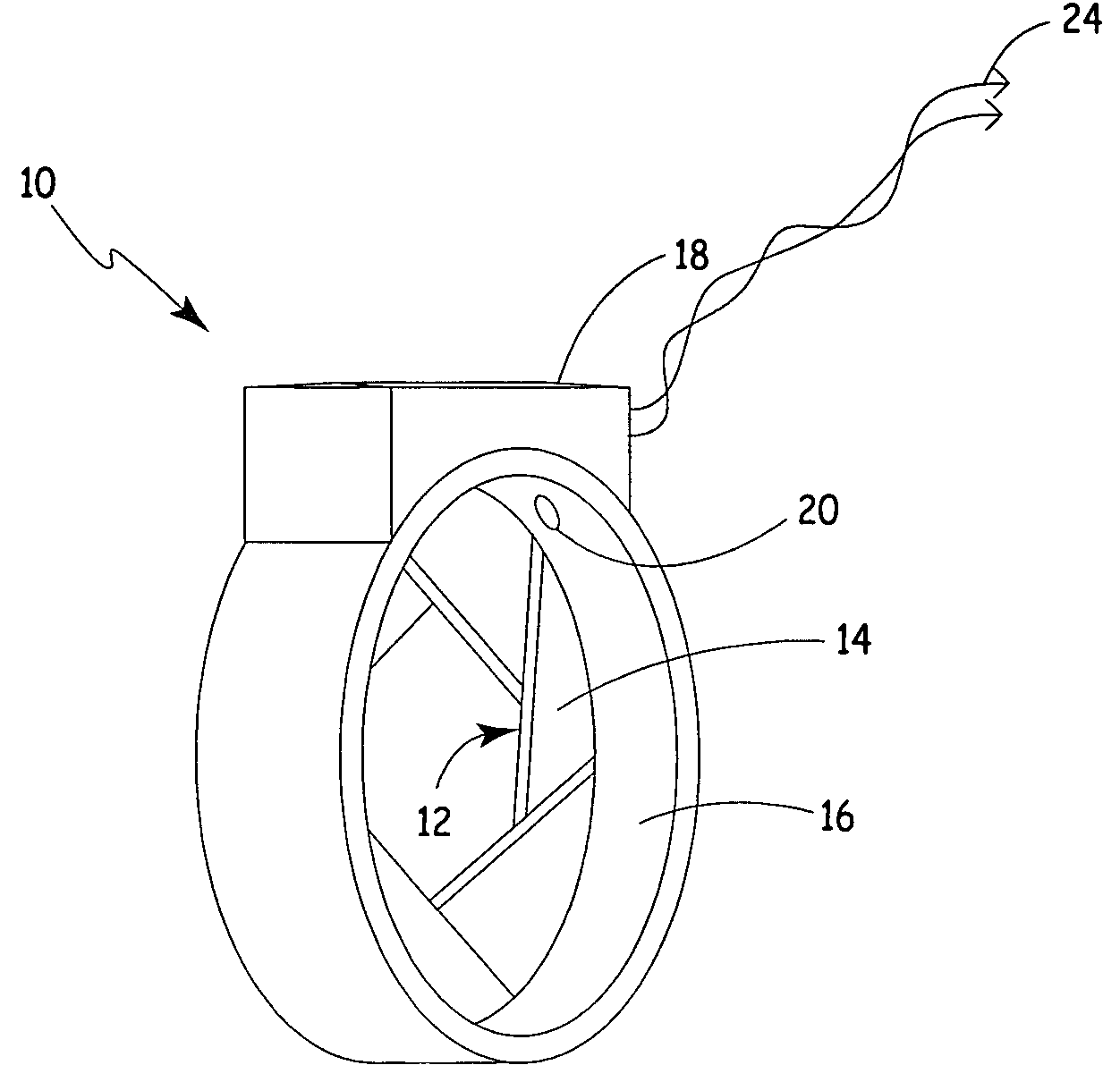

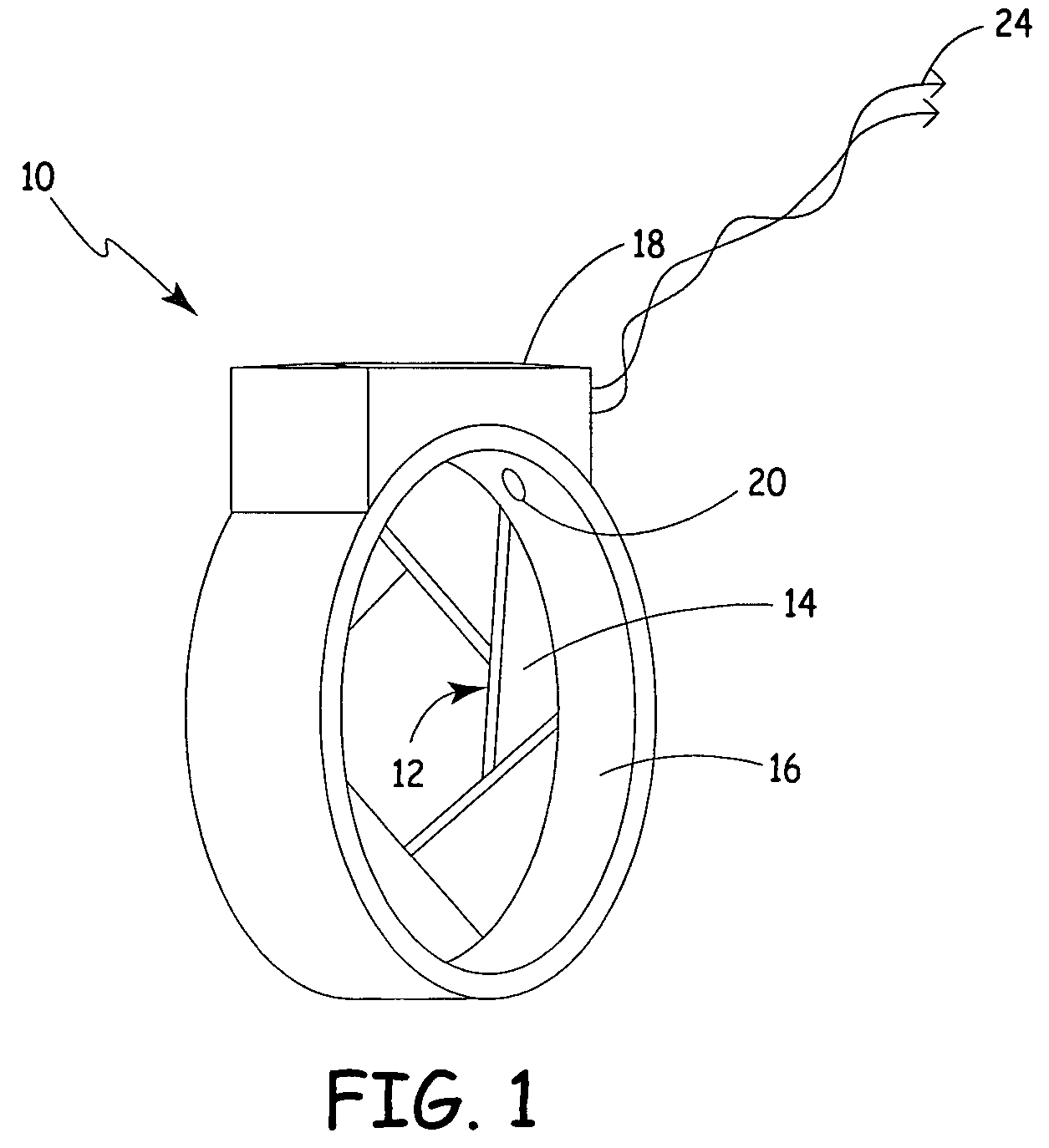

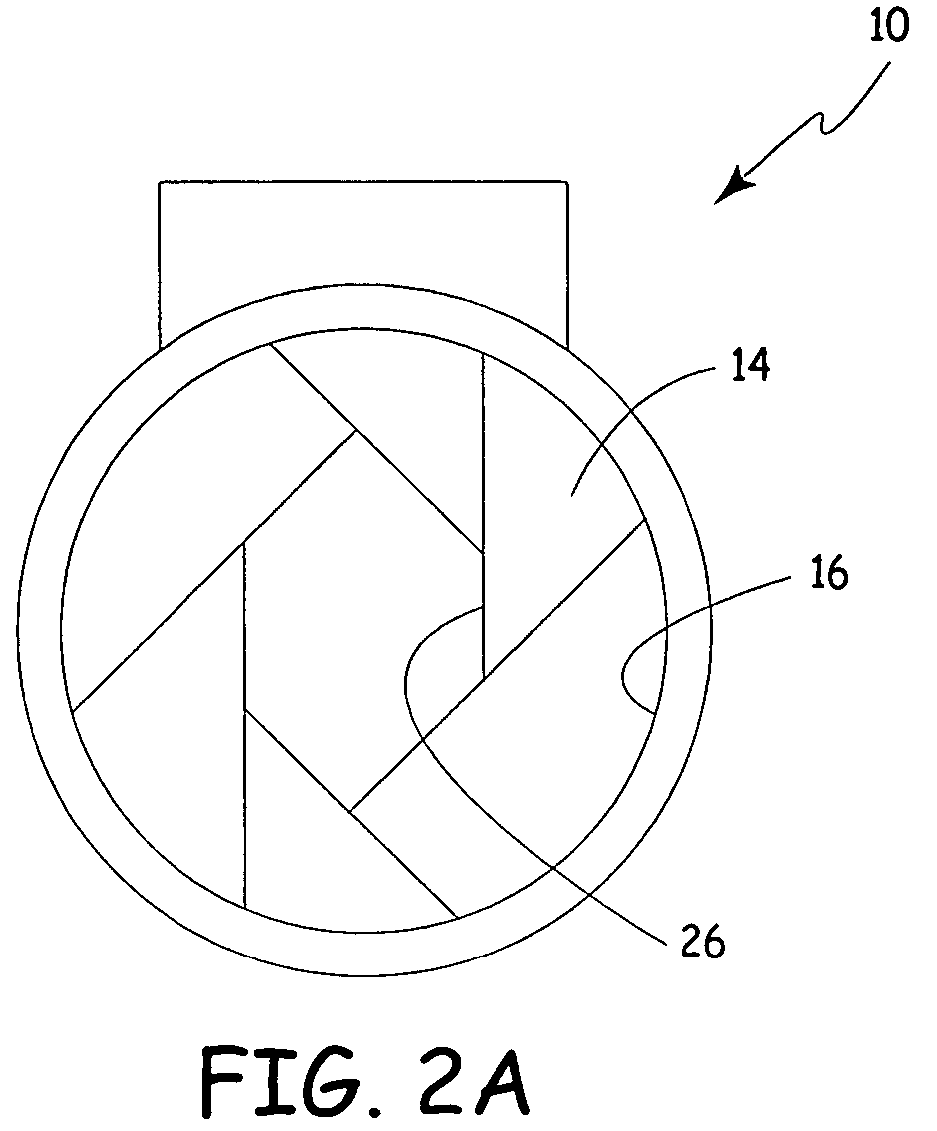

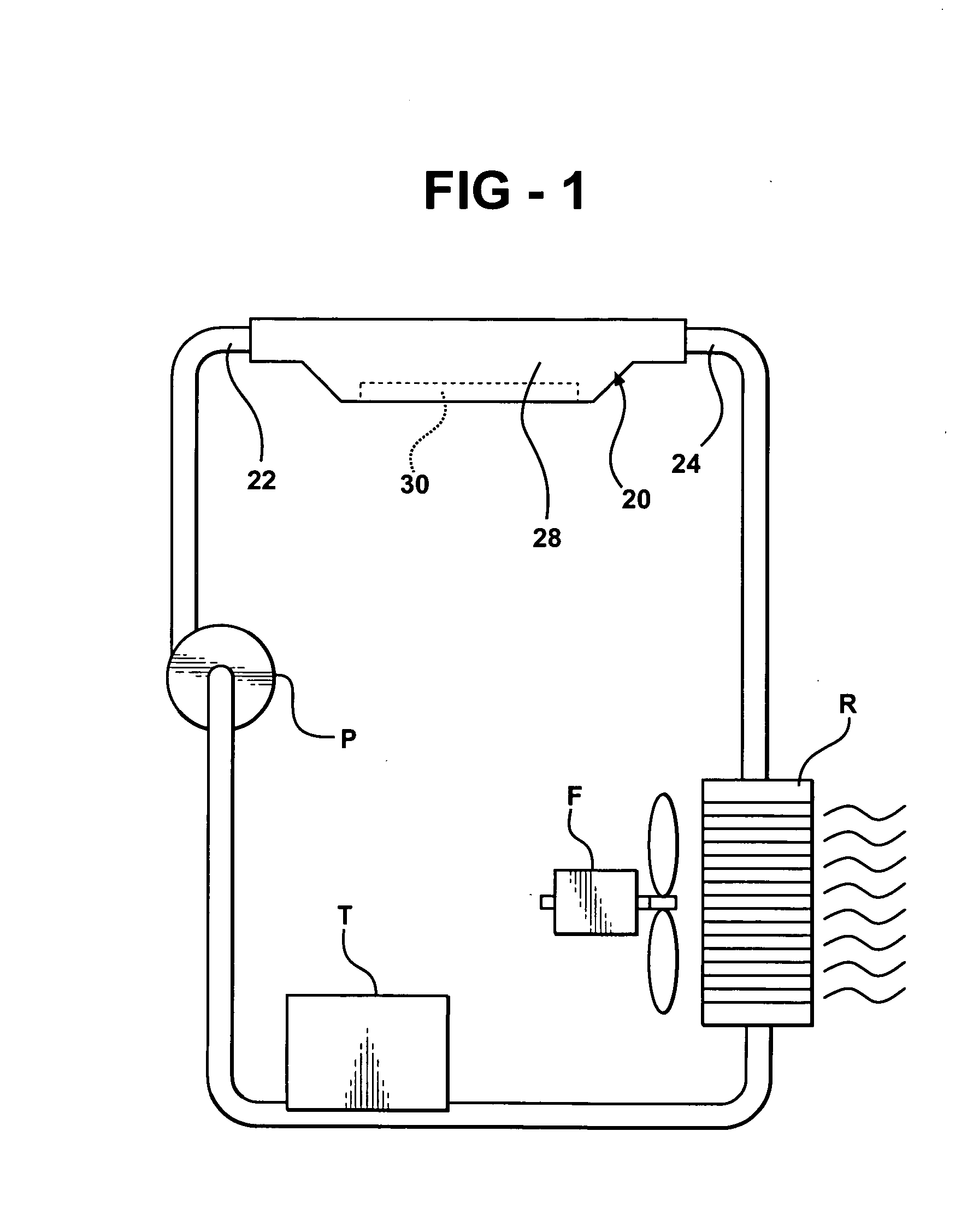

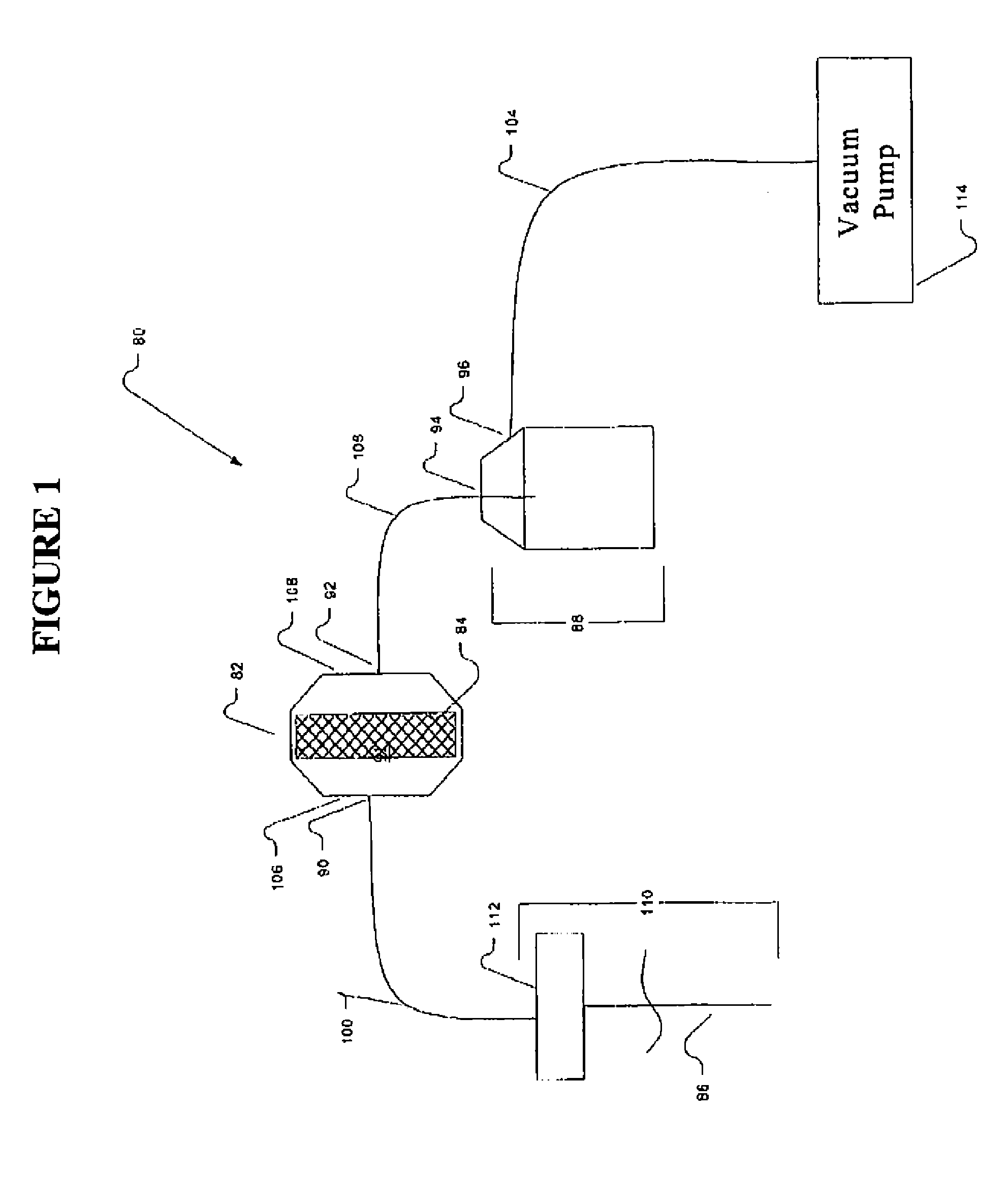

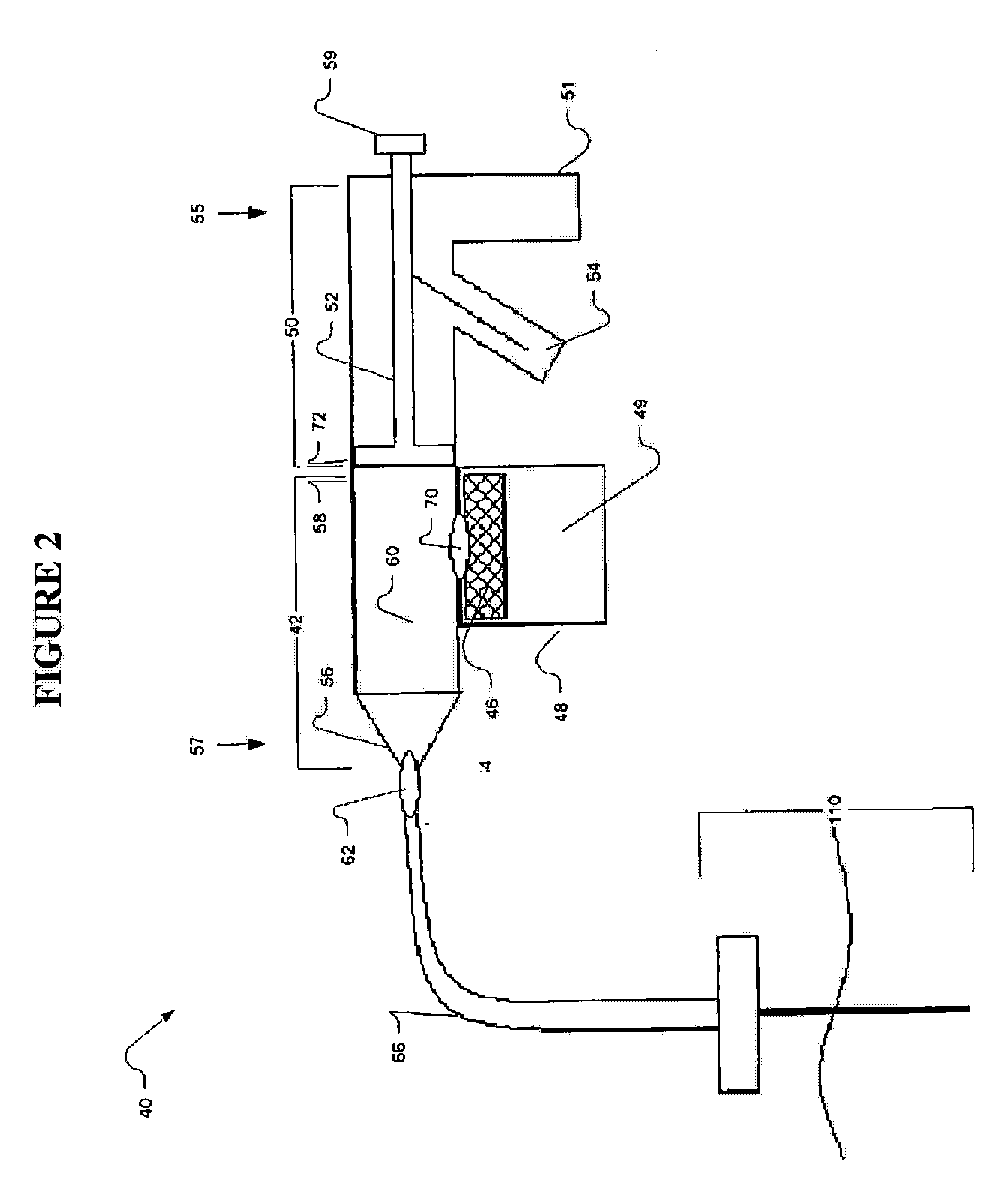

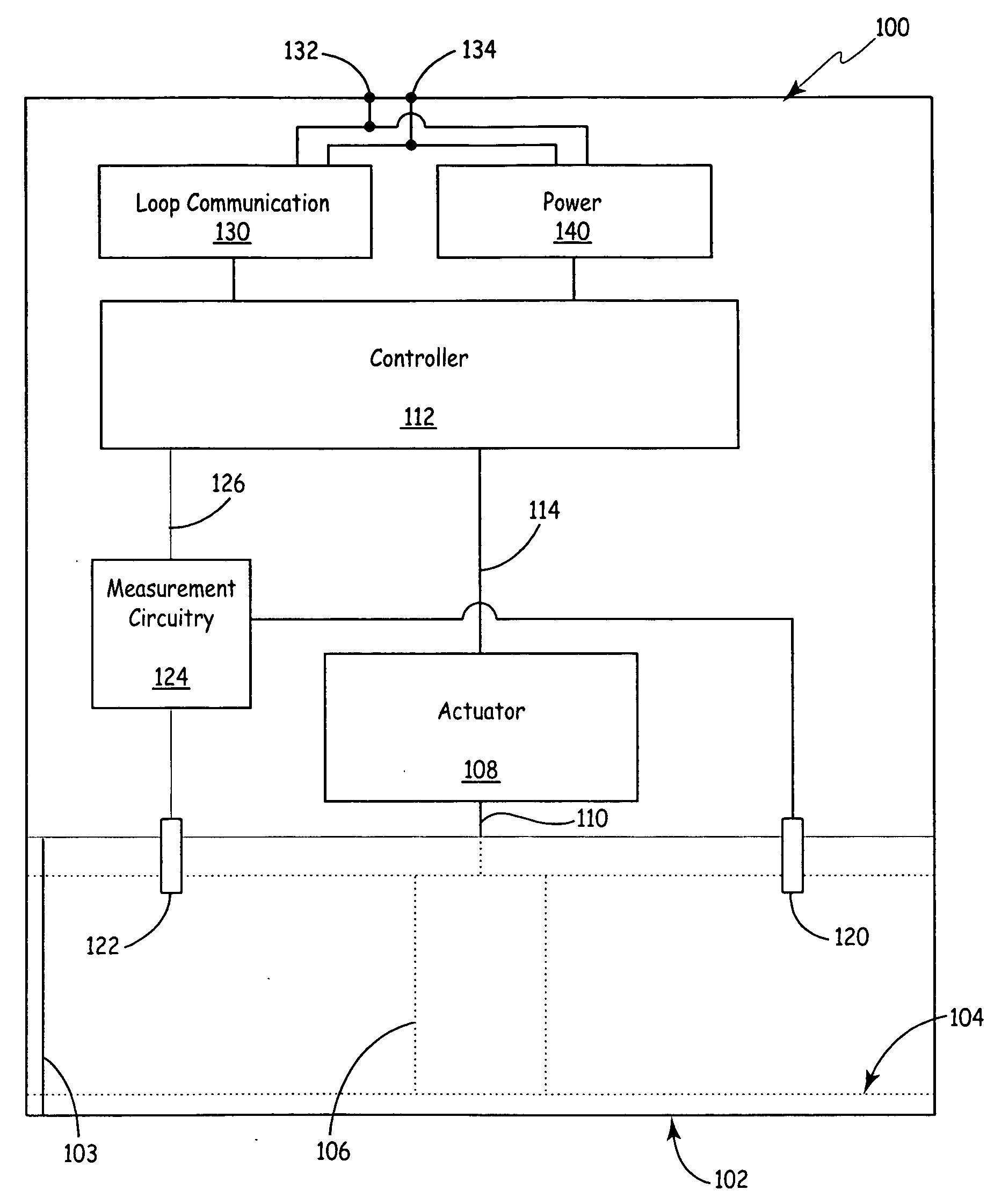

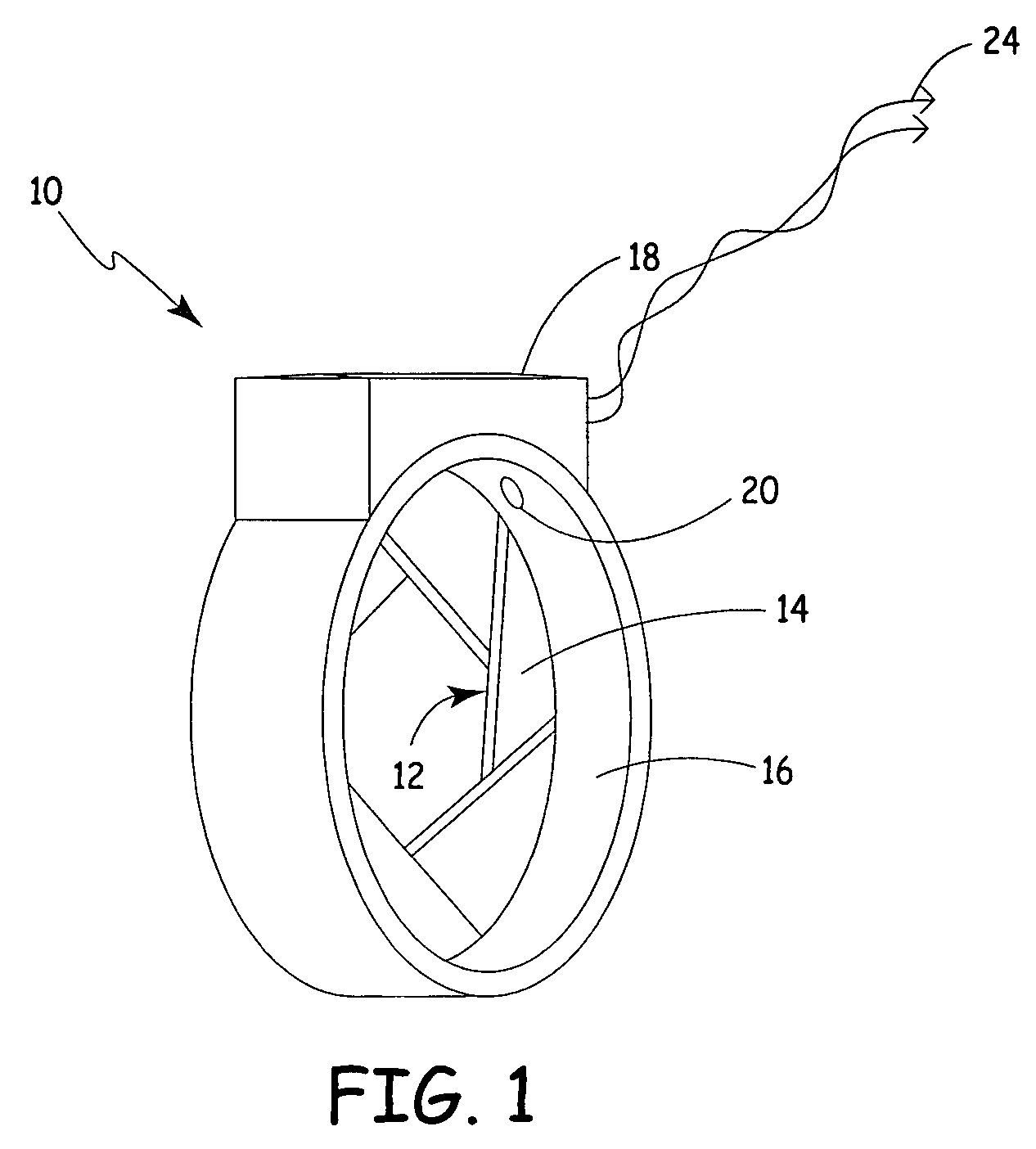

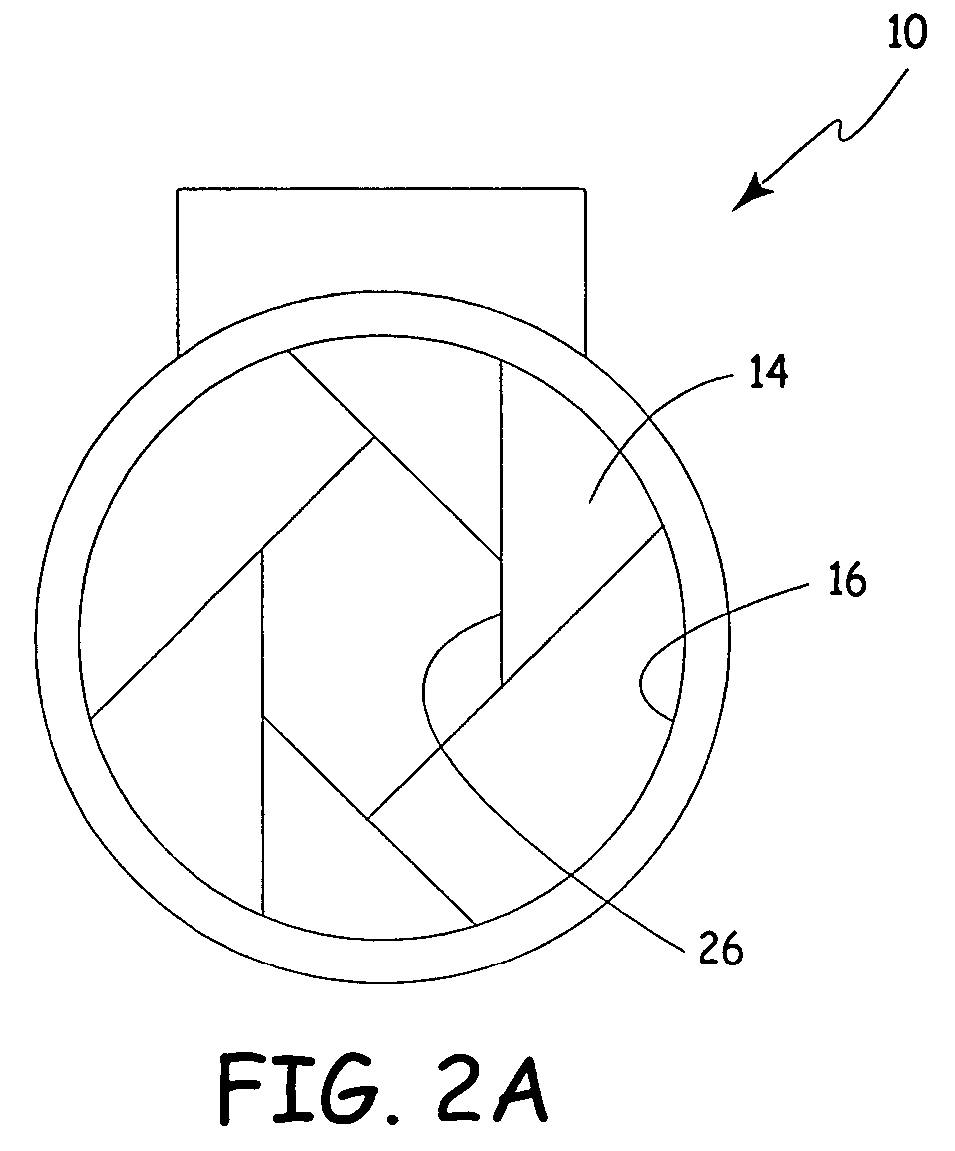

Process fluid flow device with variable orifice

A process device providing total fluid flow control is provided. The device includes a closure mechanism disposed in a flow conduit. The closure mechanism, which is preferably an iris-type diaphragm, provides a variable internal diameter. The device includes a differential pressure sensor for sensing the differential pressure on opposite sides of the diaphragm. A controller receives an indication of differential pressure and generates a control signal to an actuator that actuates the closure mechanism. The closure mechanism, differential pressure sensor and controller create a closed-loop flow controller in a single process device.

Owner:ROSEMOUNT INC

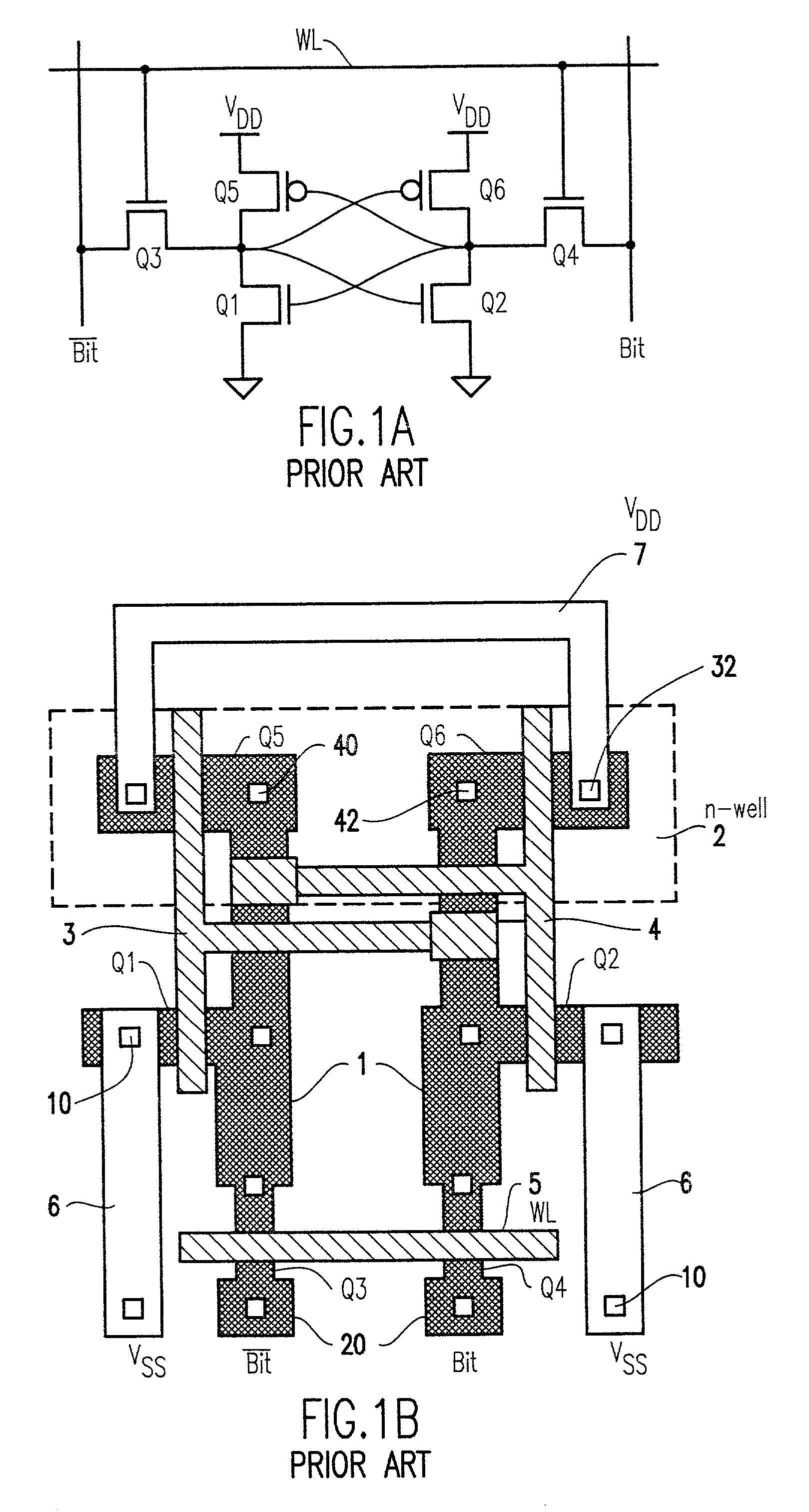

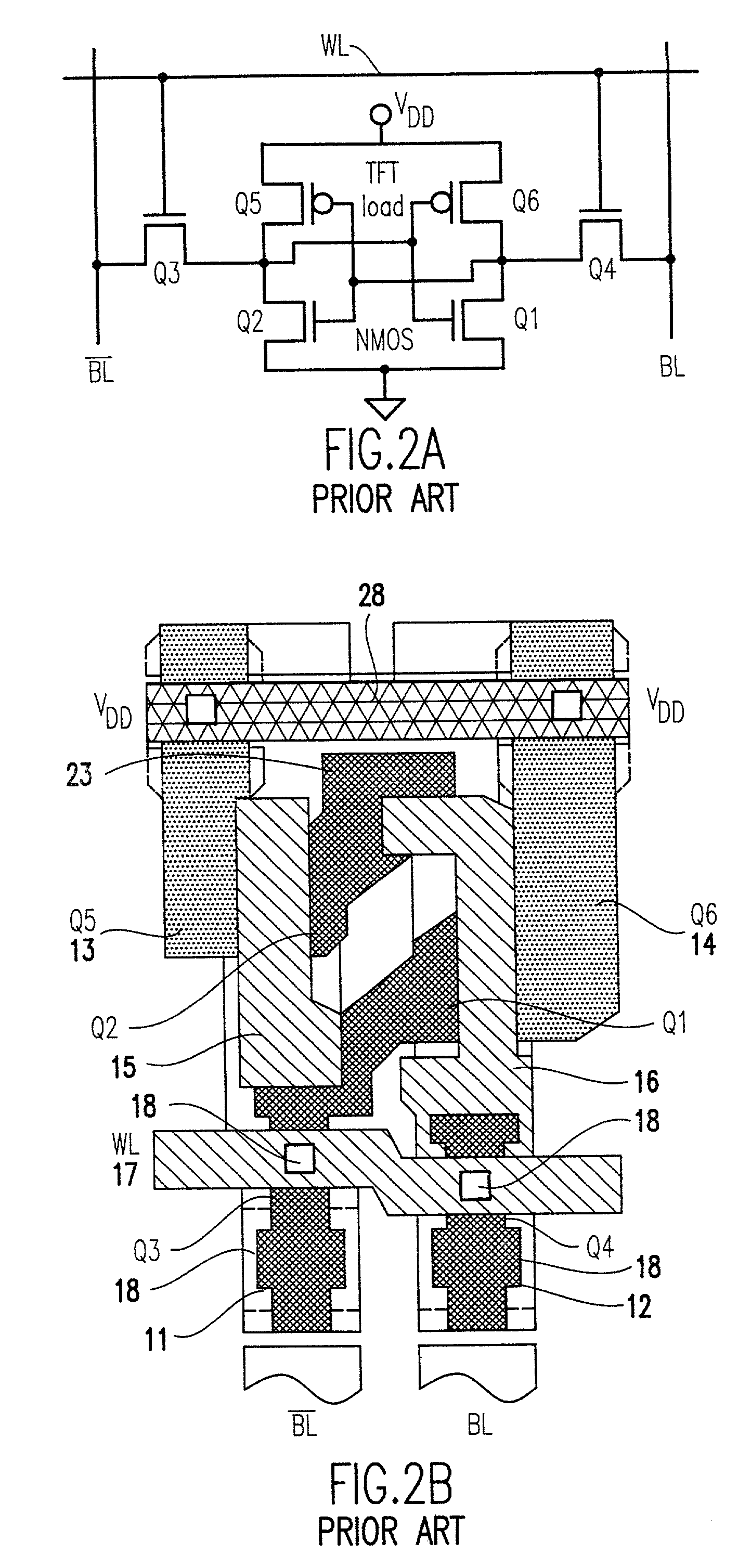

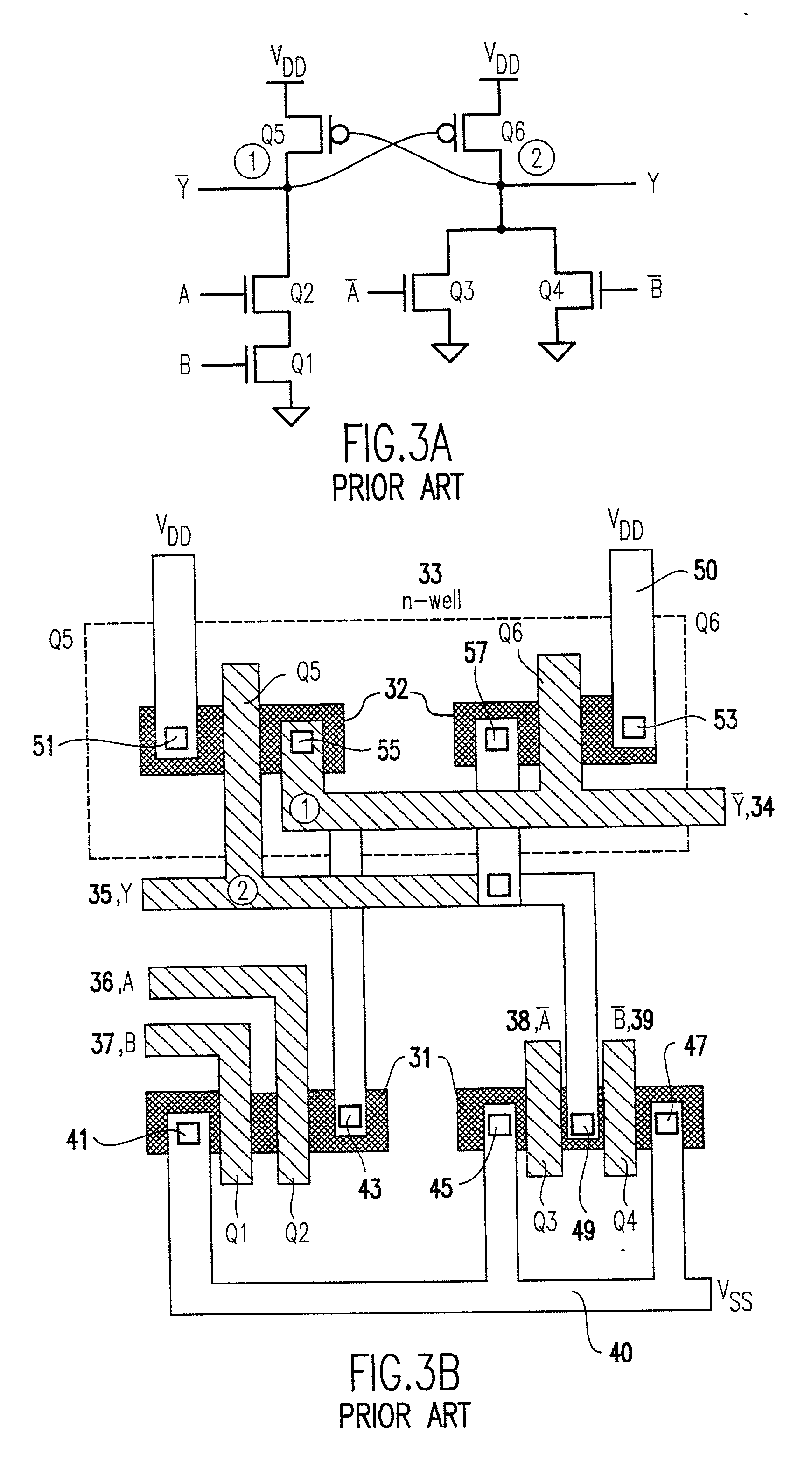

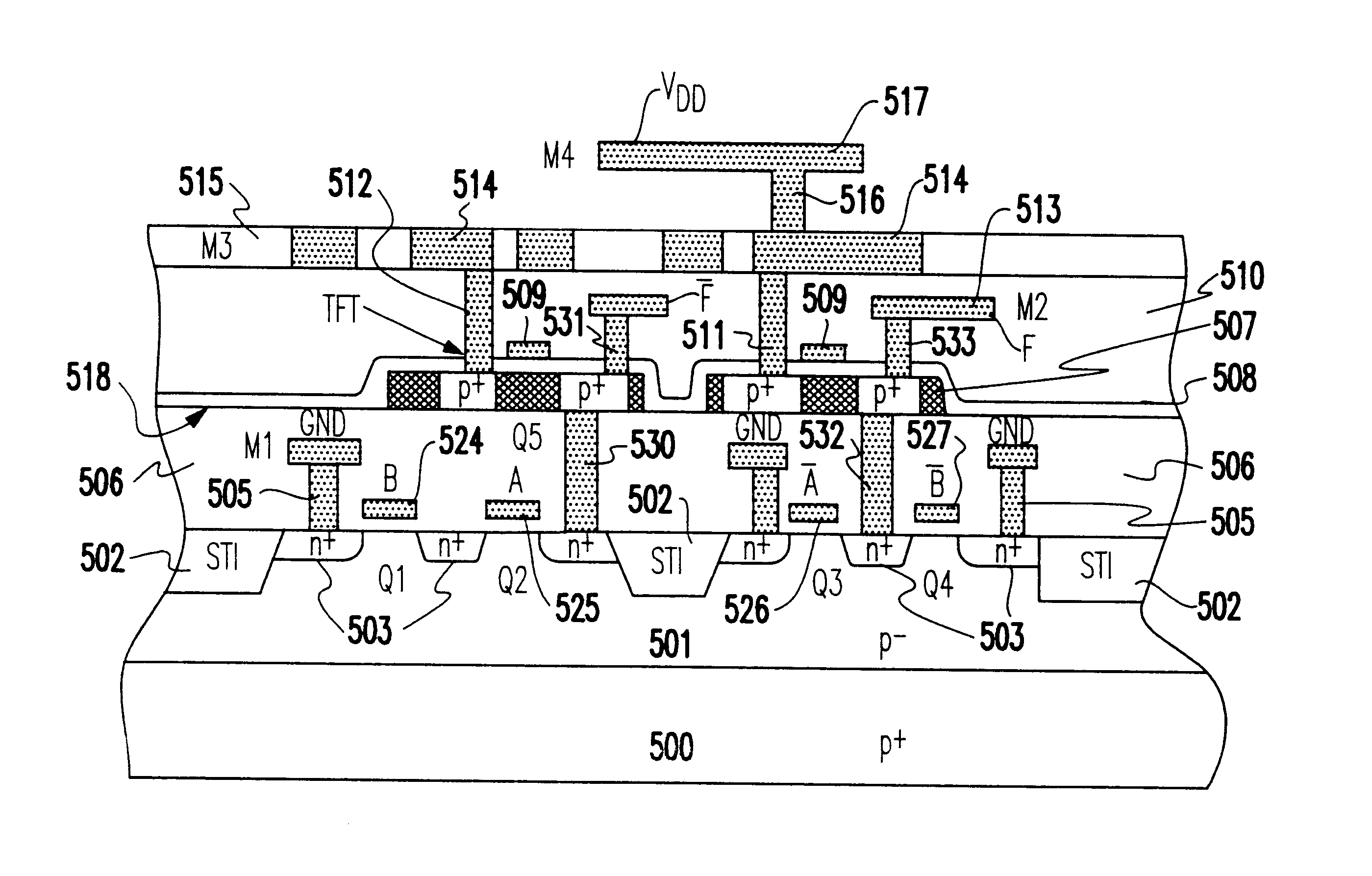

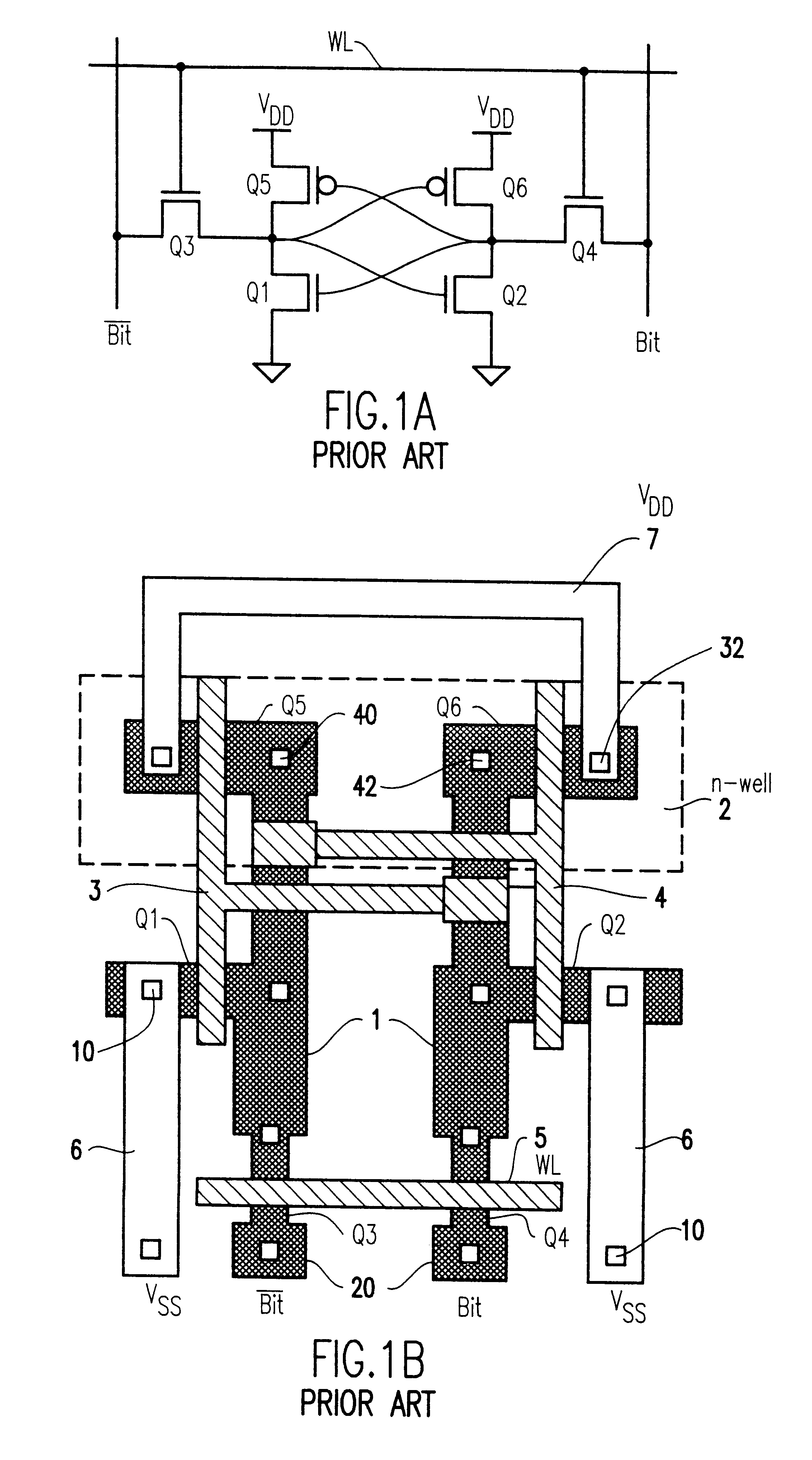

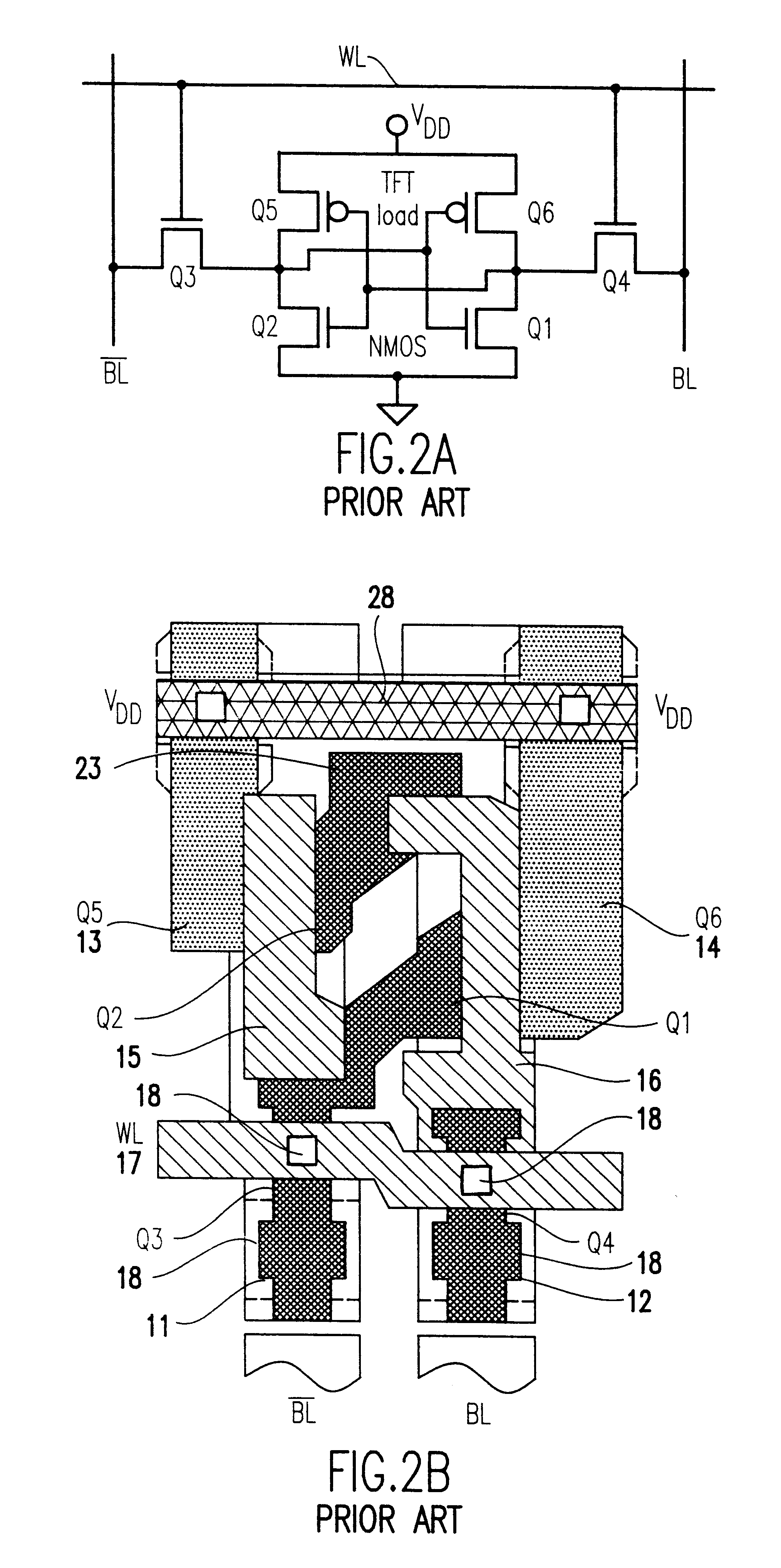

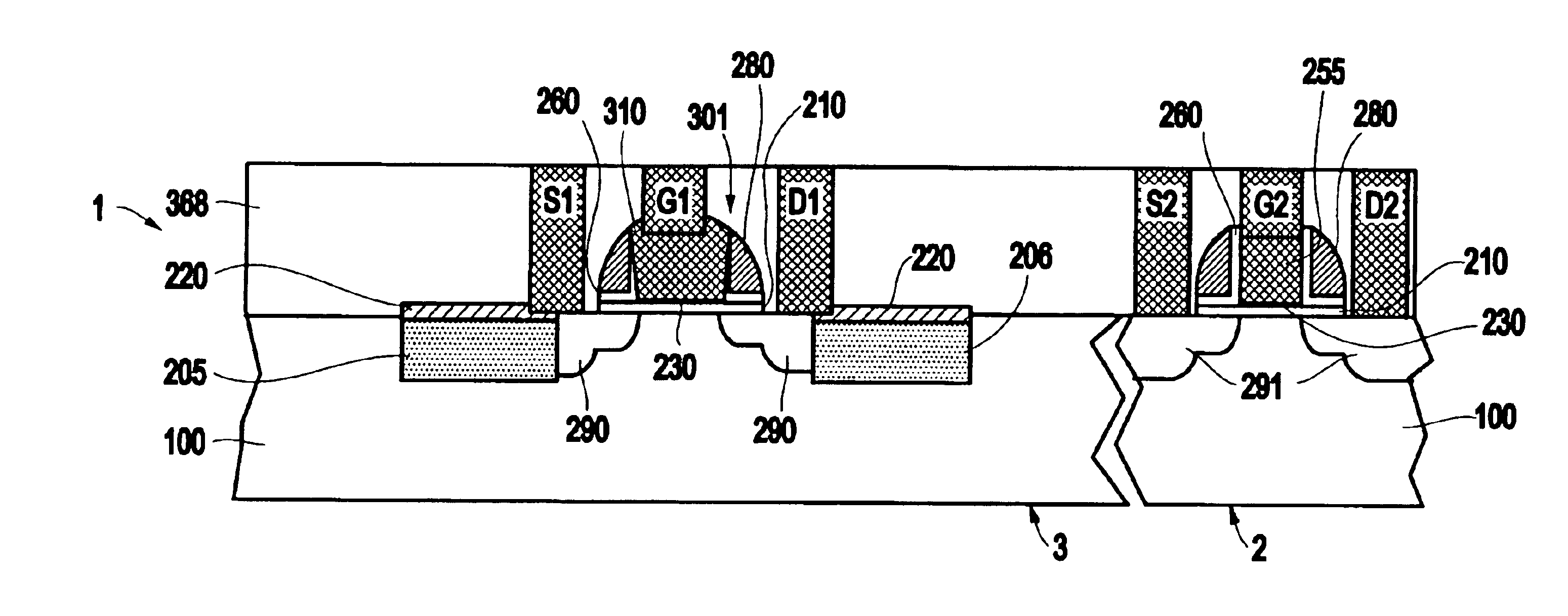

Merged logic and memory combining thin film and bulk Si transistors

InactiveUS20010028059A1Compact and economicalTransistorSolid-state devicesHigh densitySingle process

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

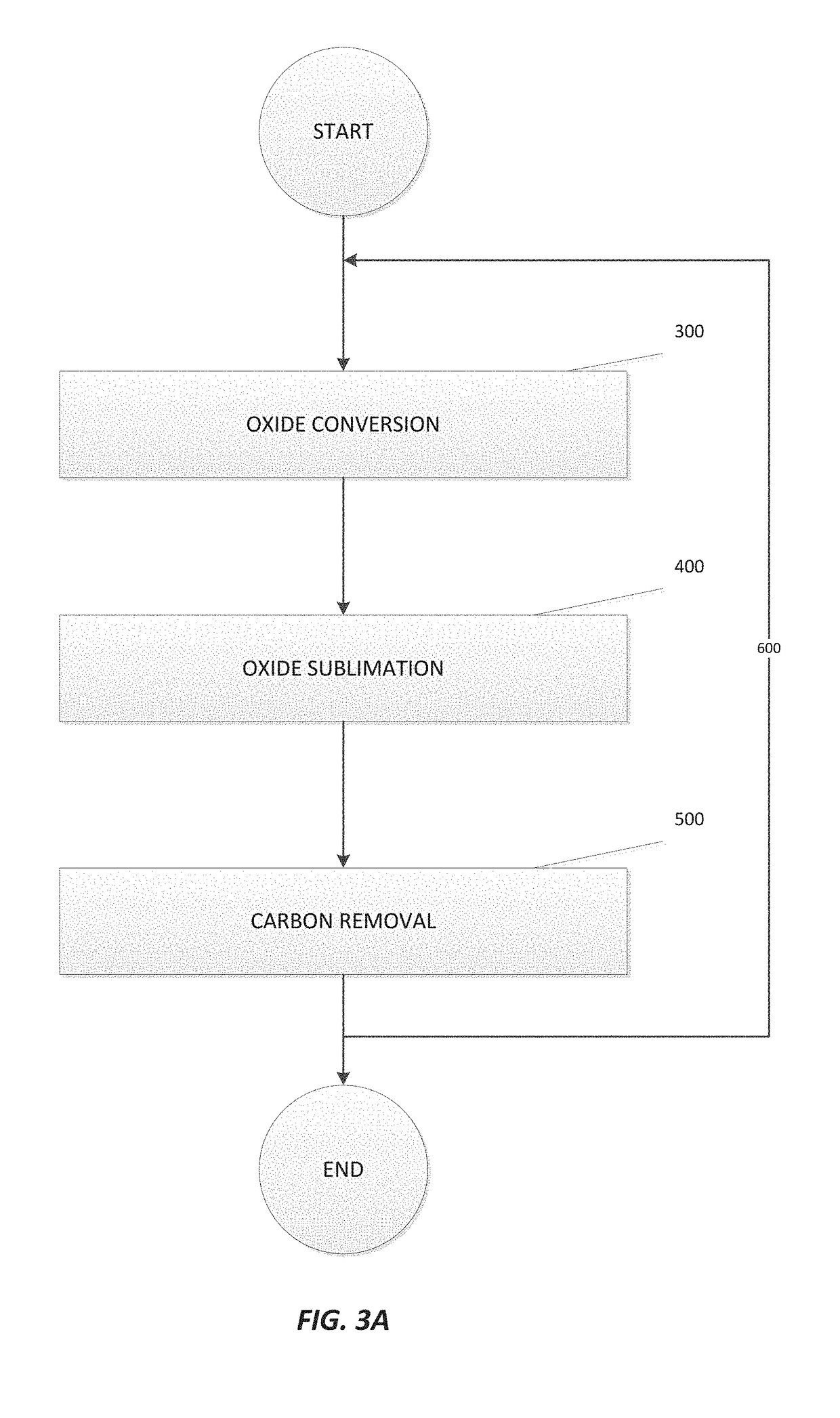

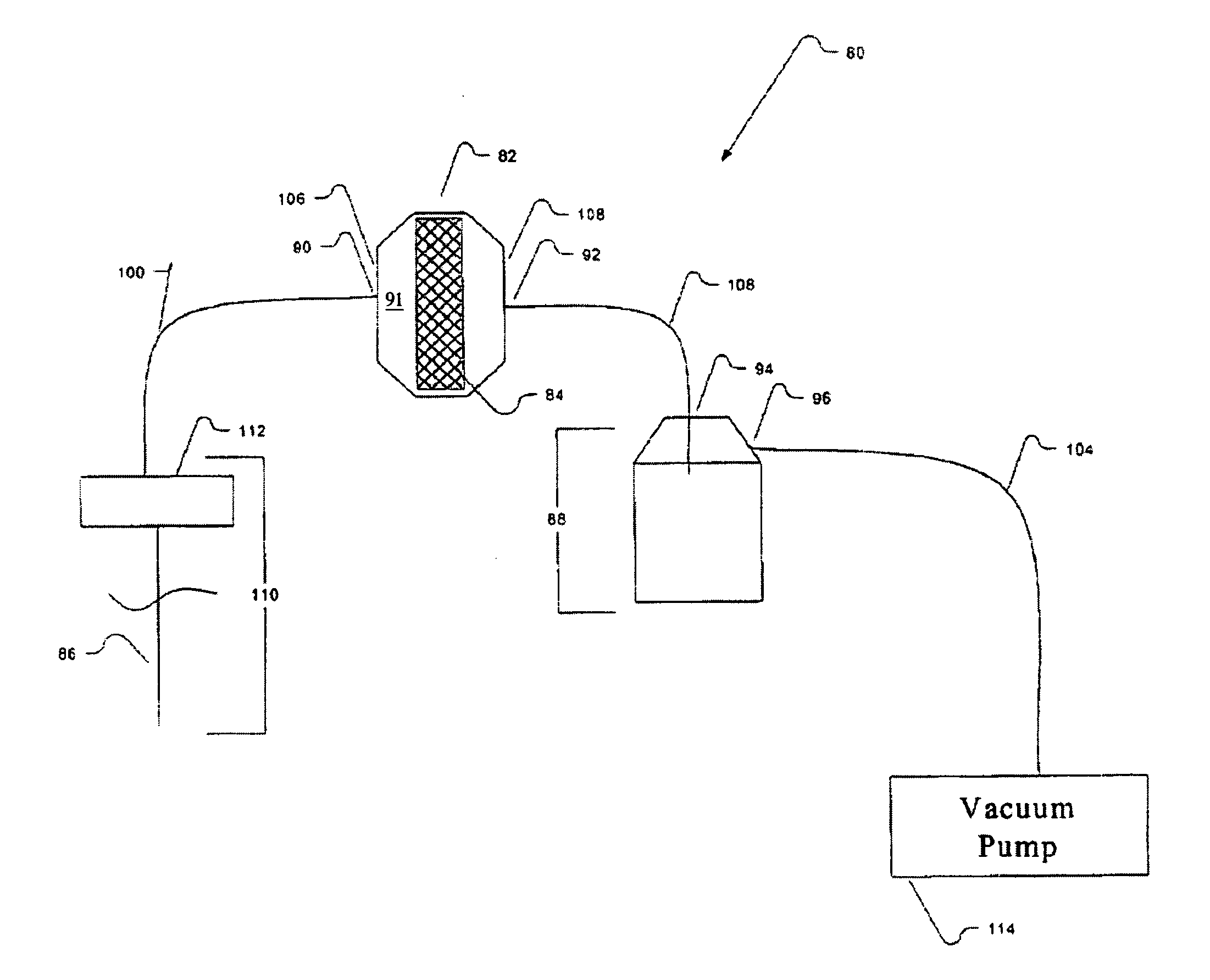

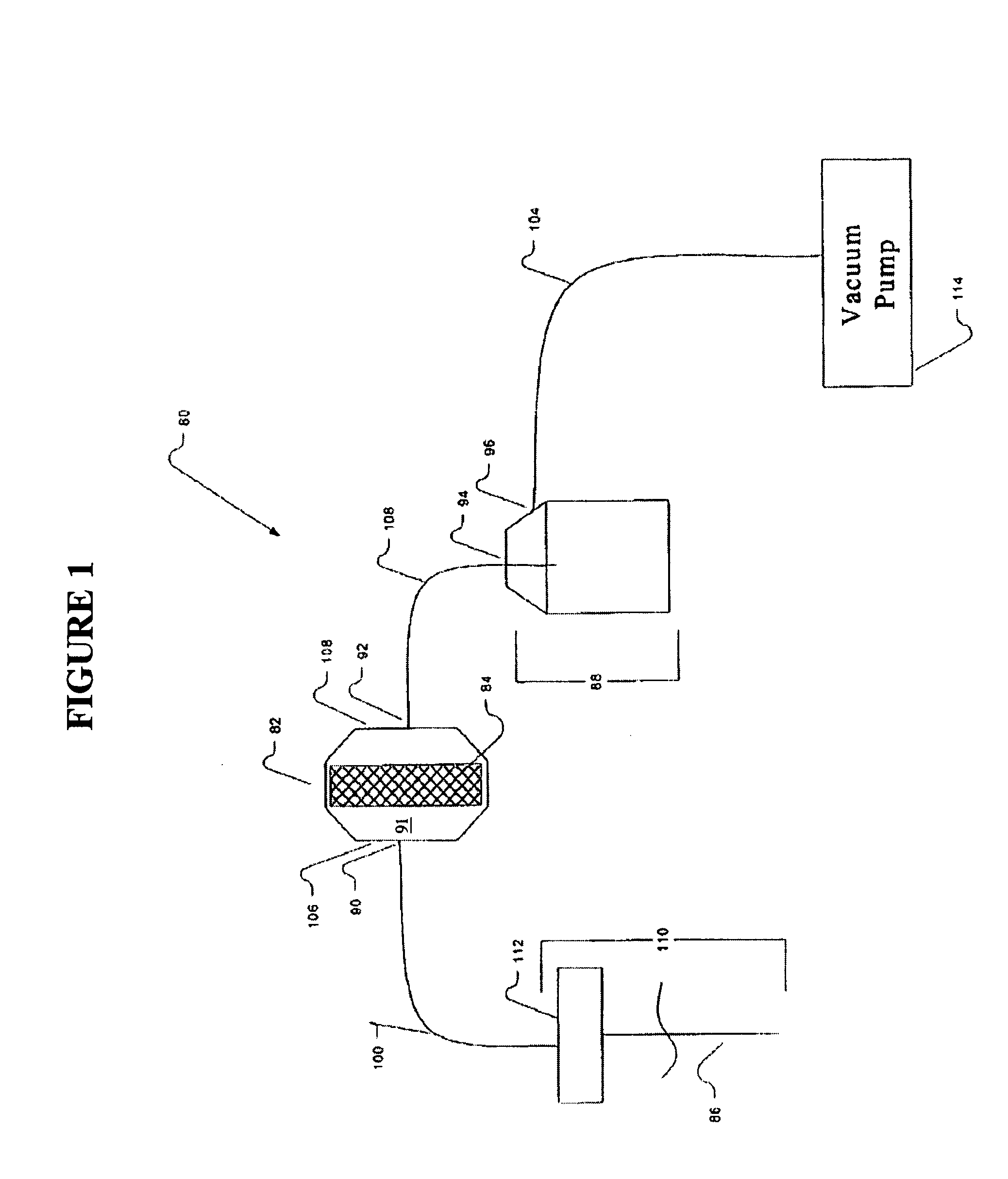

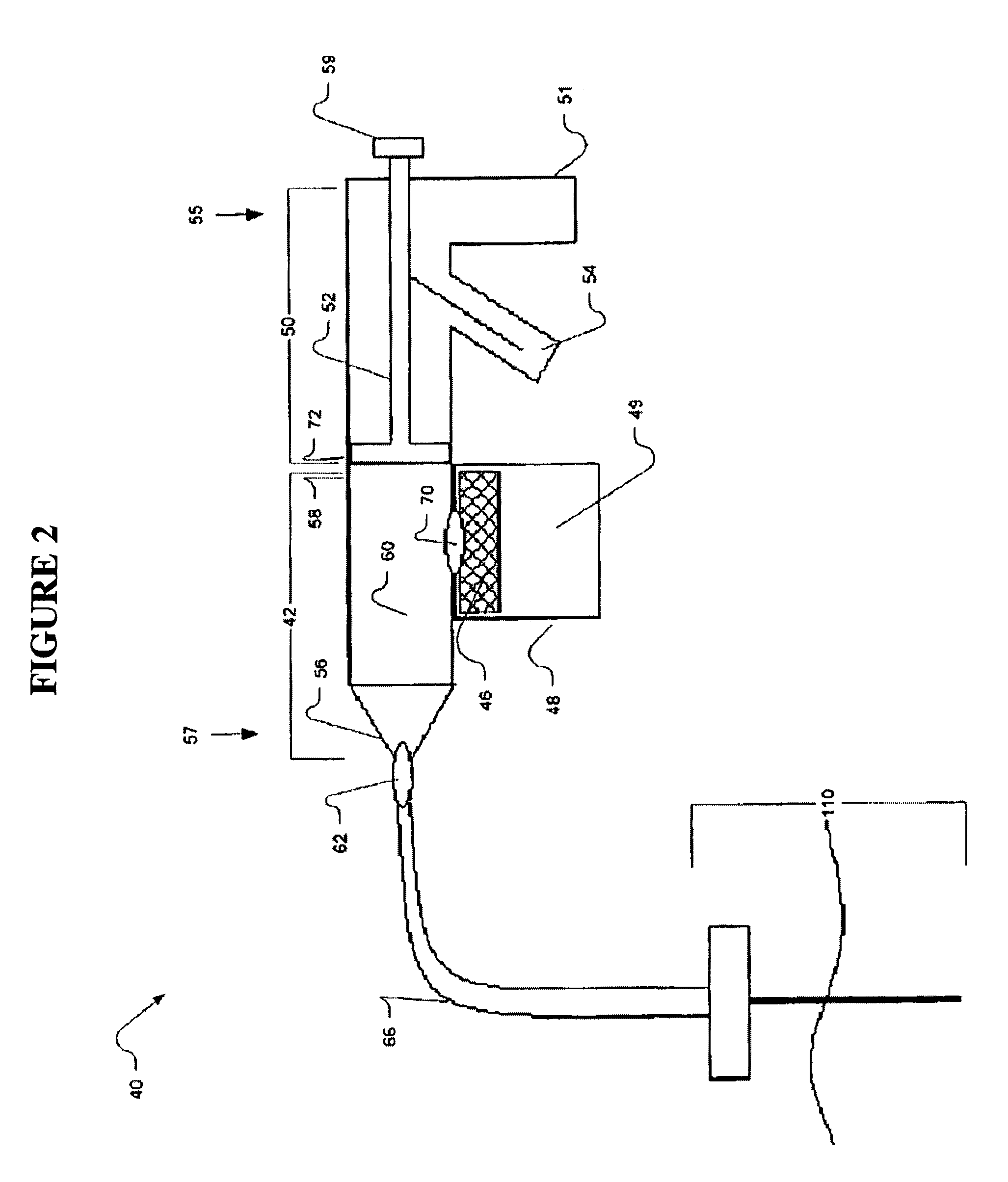

Apparatus and method for removal of oxide and carbon from semiconductor films in a single processing chamber

InactiveUS20190019670A1Electric discharge tubesSemiconductor/solid-state device manufacturingRemote plasmaSingle process

A system and method for removing both carbon-based contaminants and oxygen-based contaminants from a semiconductor substrate within a single process chamber is disclosed. The invention may comprise utilization of remote plasma units and multiple gas sources to perform the process within the single process chamber.

Owner:ASM IP HLDG BV

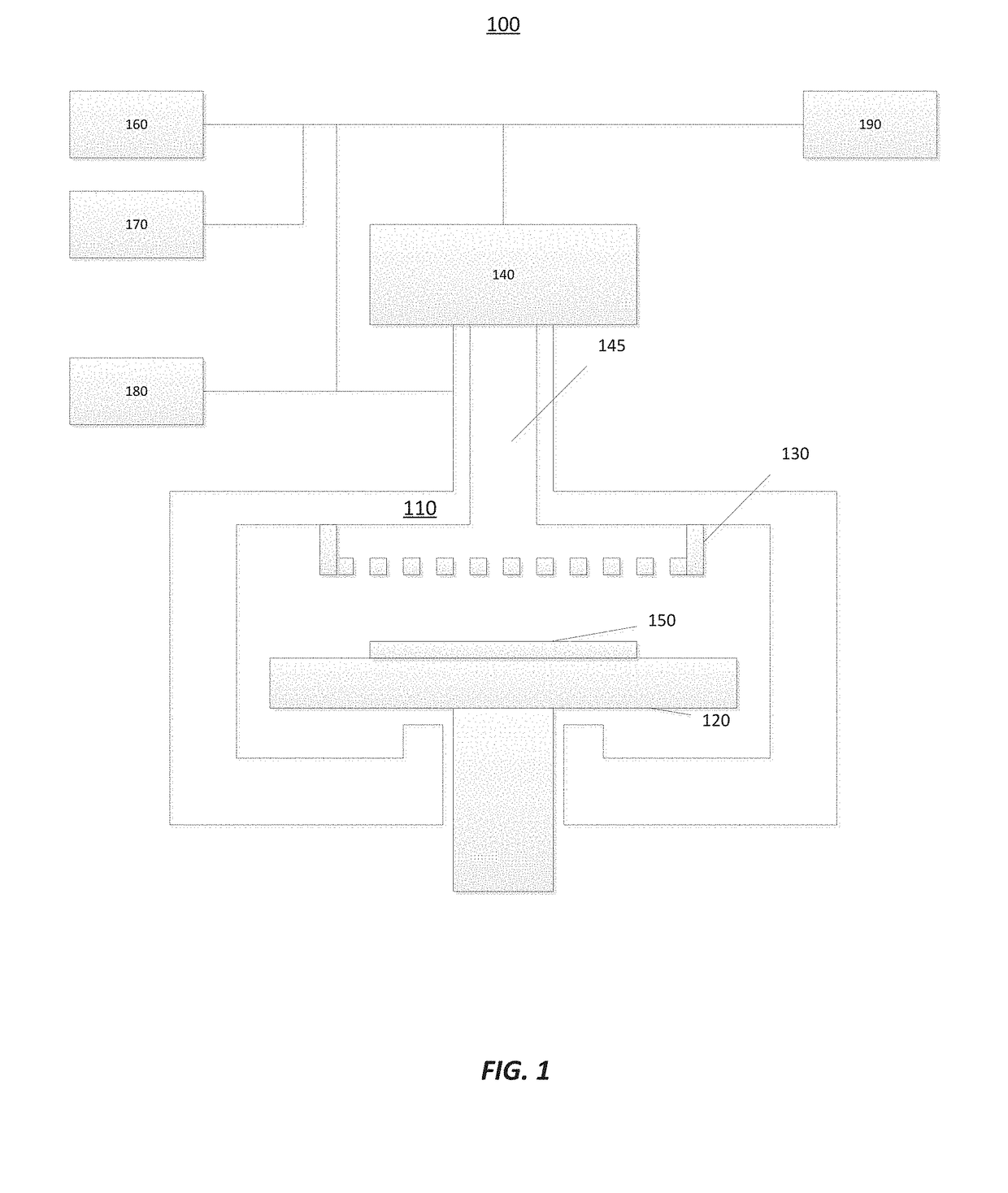

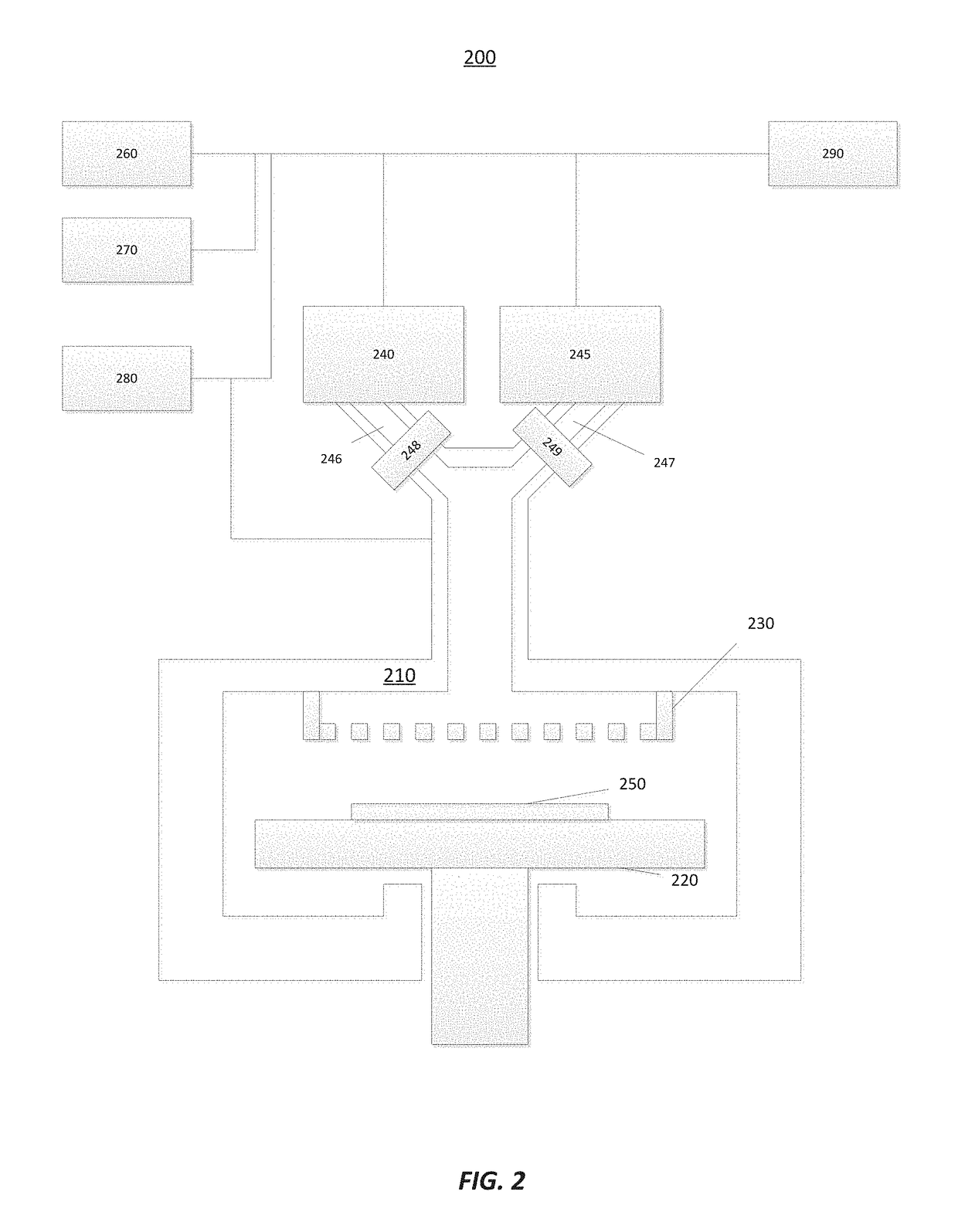

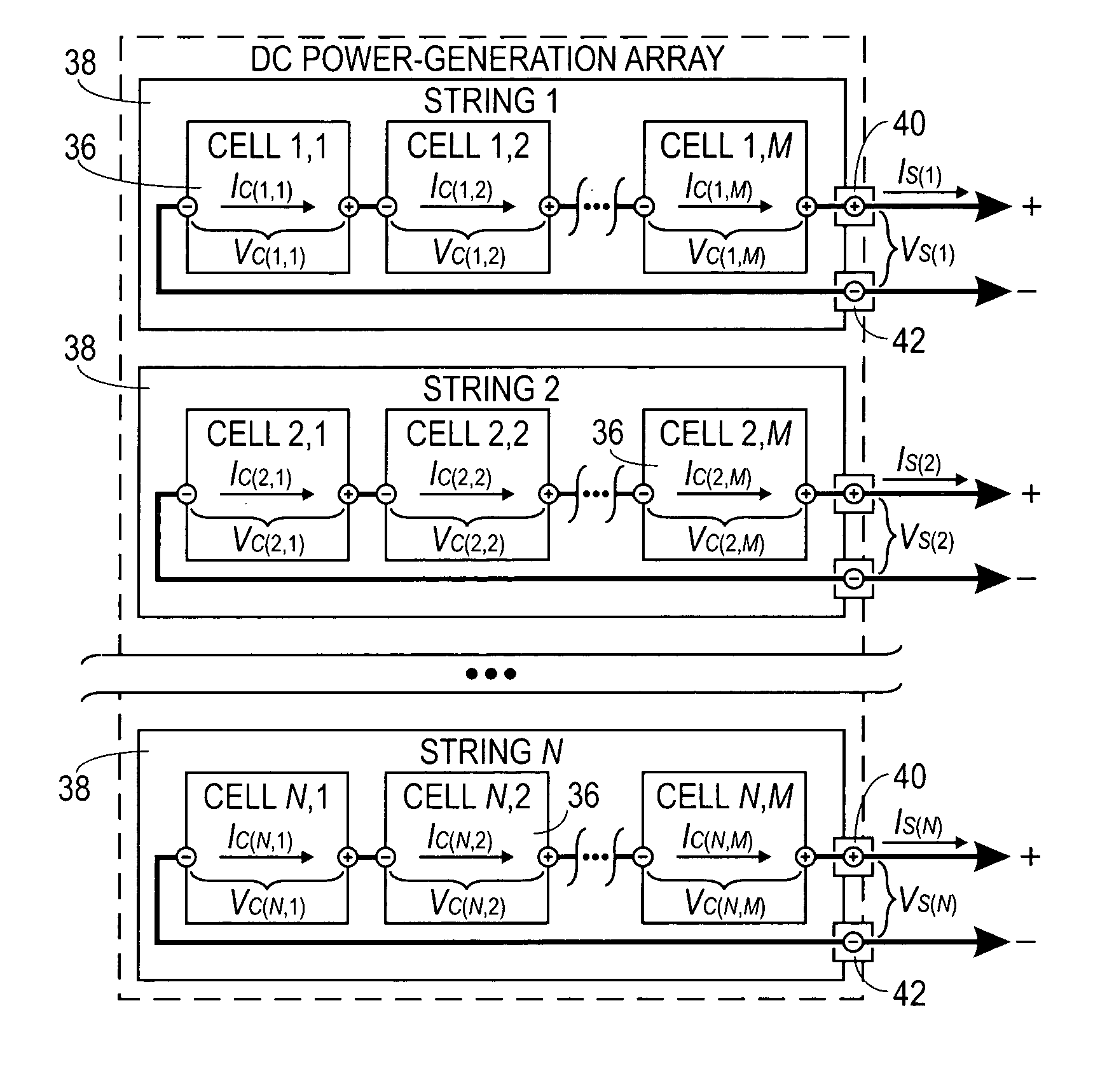

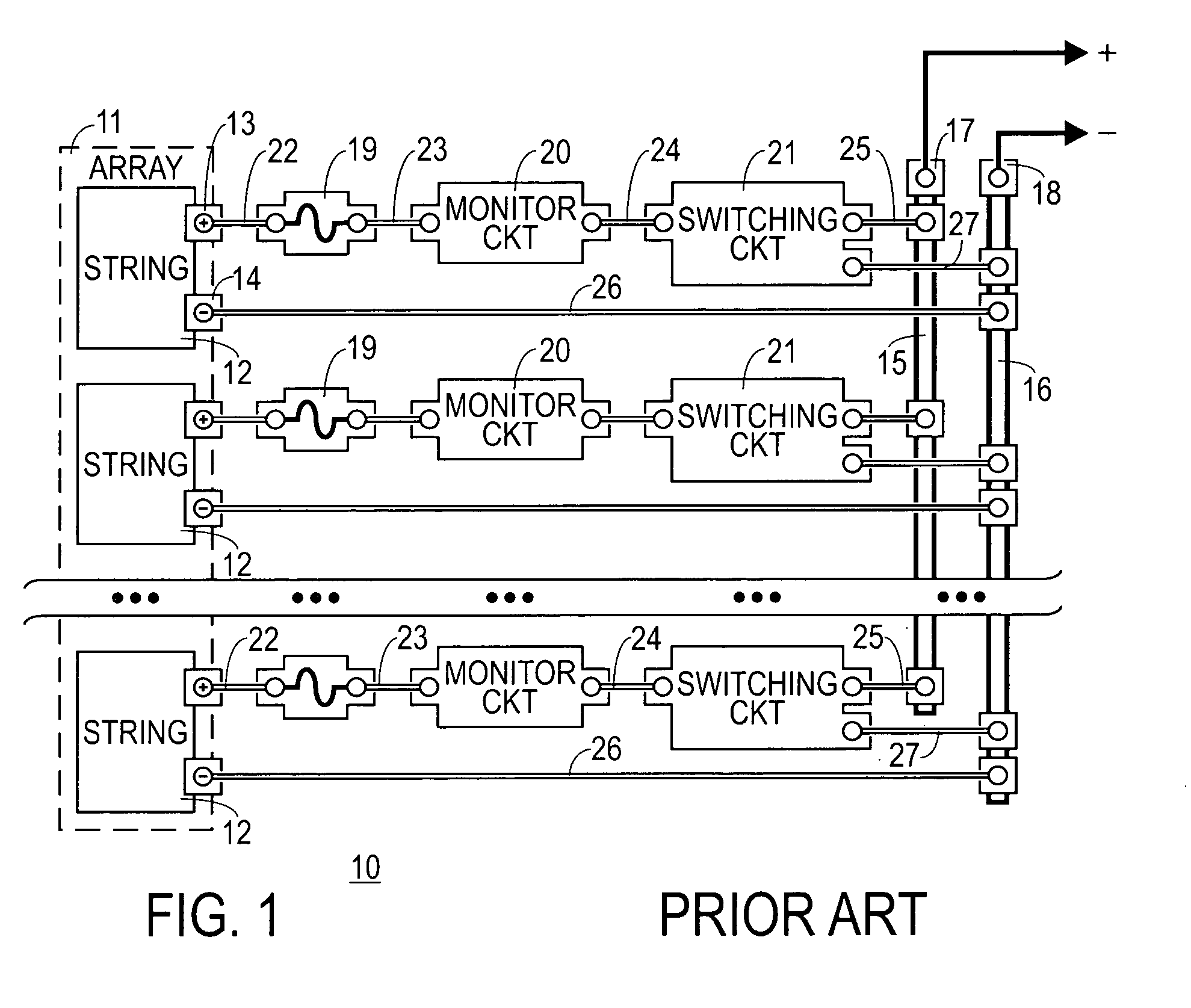

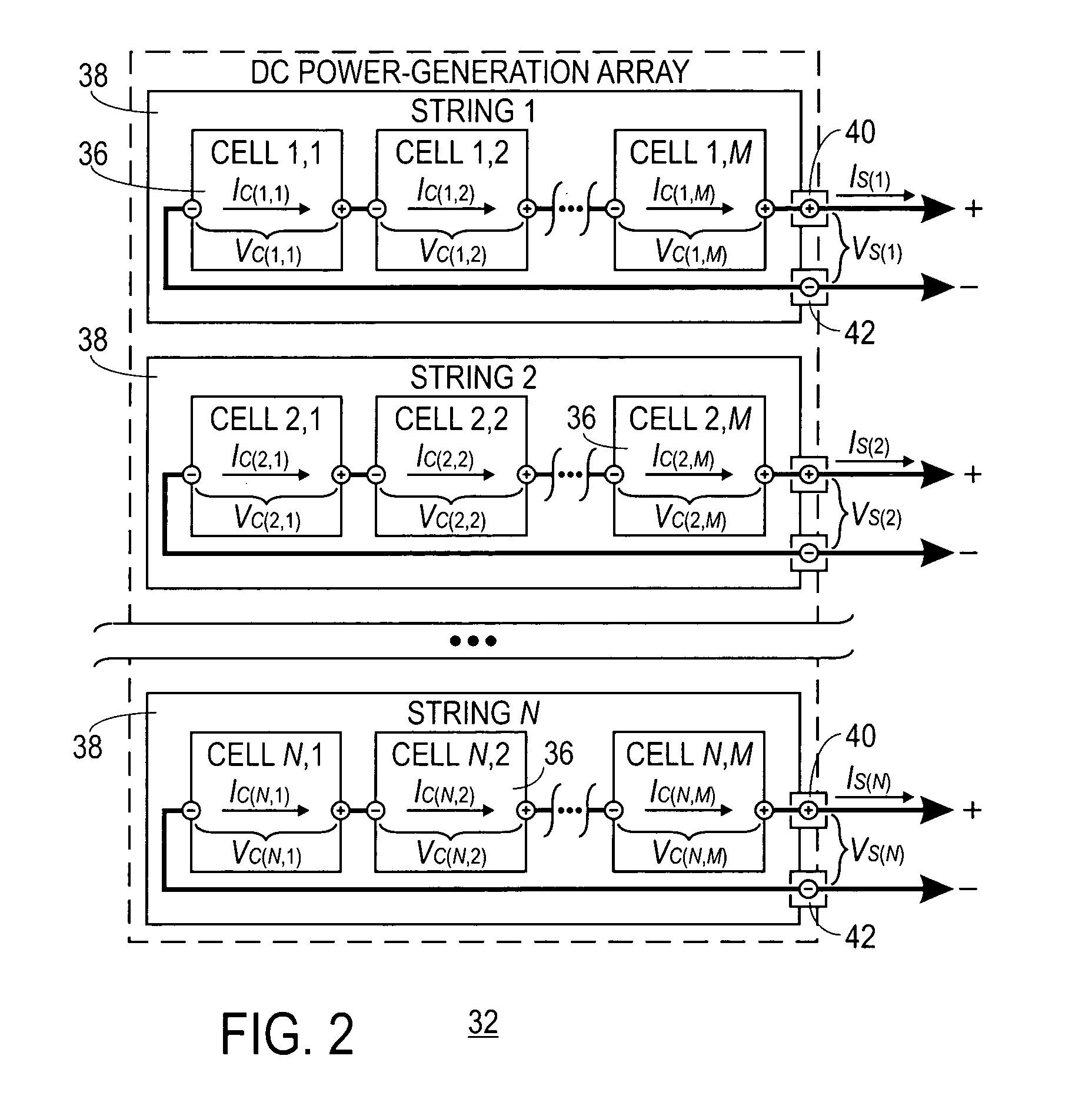

DC power-generation system and integral control apparatus therefor

InactiveUS20070107767A1Shorten assembly timeMinimal numberPhotovoltaic monitoringPV power plantsSingle processComputer module

A DC power-generation array system (30) is made up of an array (32) of power-generation cells (36) arranged as N strings (38) of M cells (36) each. The system (30) incorporates an integral control apparatus (34) having N string units (52) and a single process unit (54). Each string unit (52) is coupled to one of the strings (38), and is made up of monitor module (72) to measure a string current (IS(X)) through that string (38), and a switching module (74) to switch that string (38) into and out of the array (32). The process unit (54) is made up of a processor (90) to evaluate the string currents (IS(X), and a data I / O module (98) to provide a remote monitoring and control of the system (30). The system (30) also has an interface unit (92) to provide local monitoring and control of the system (30). The processor (90) causes the switching modules (74) to couple or decouple strings (38) from array (32) under automatic, remote, and / or local control.

Owner:ARIZONA PUBLIC SERVICE

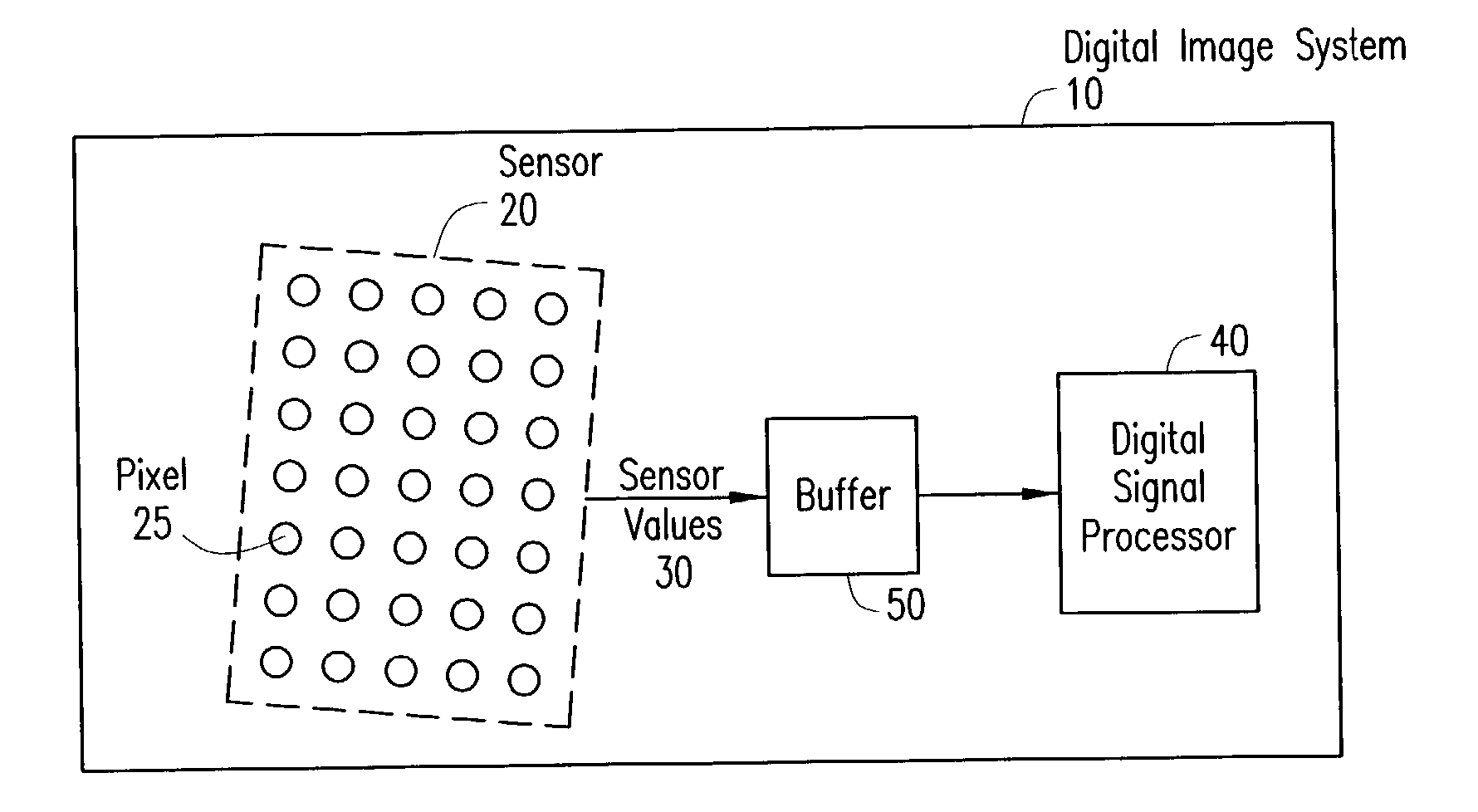

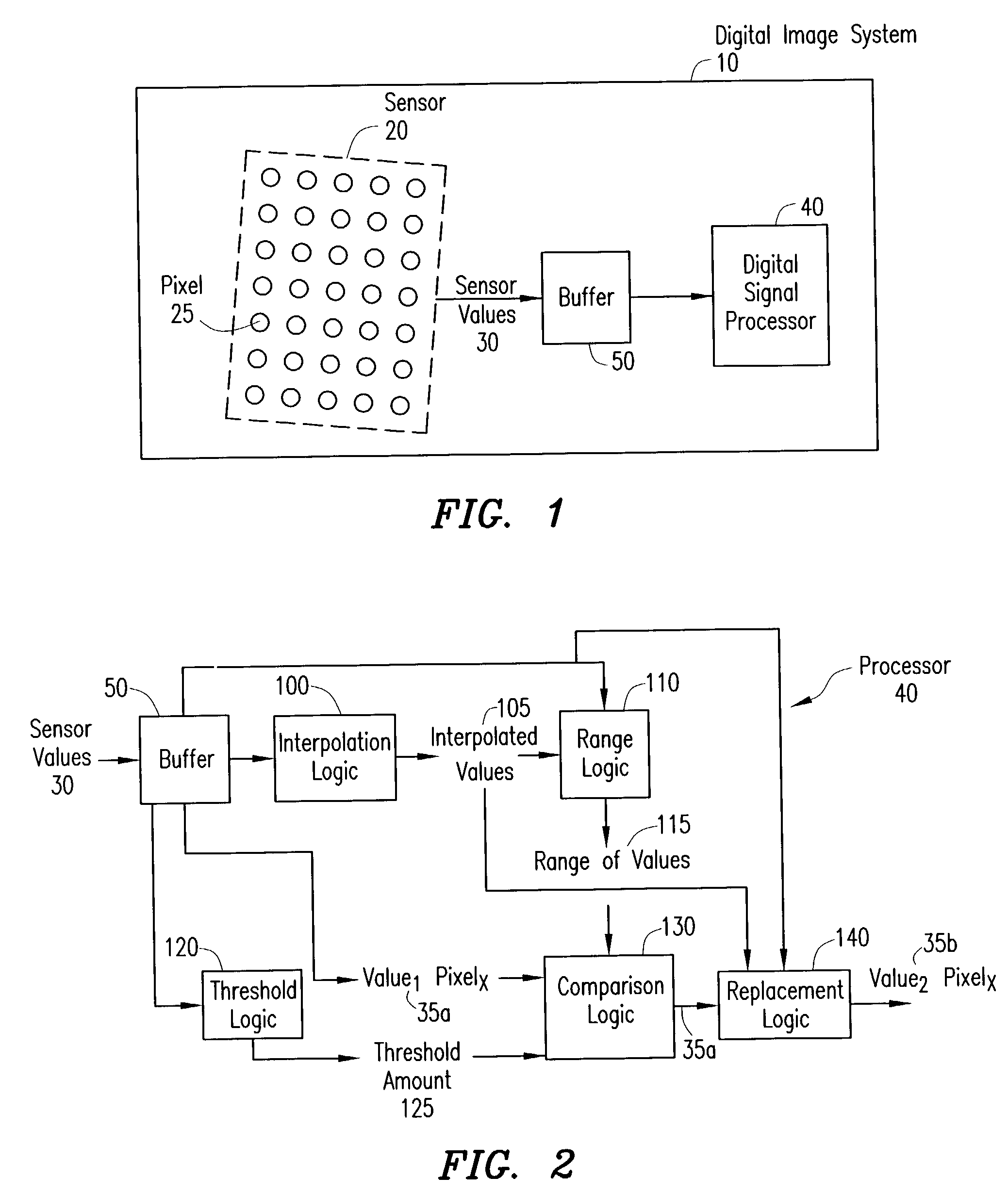

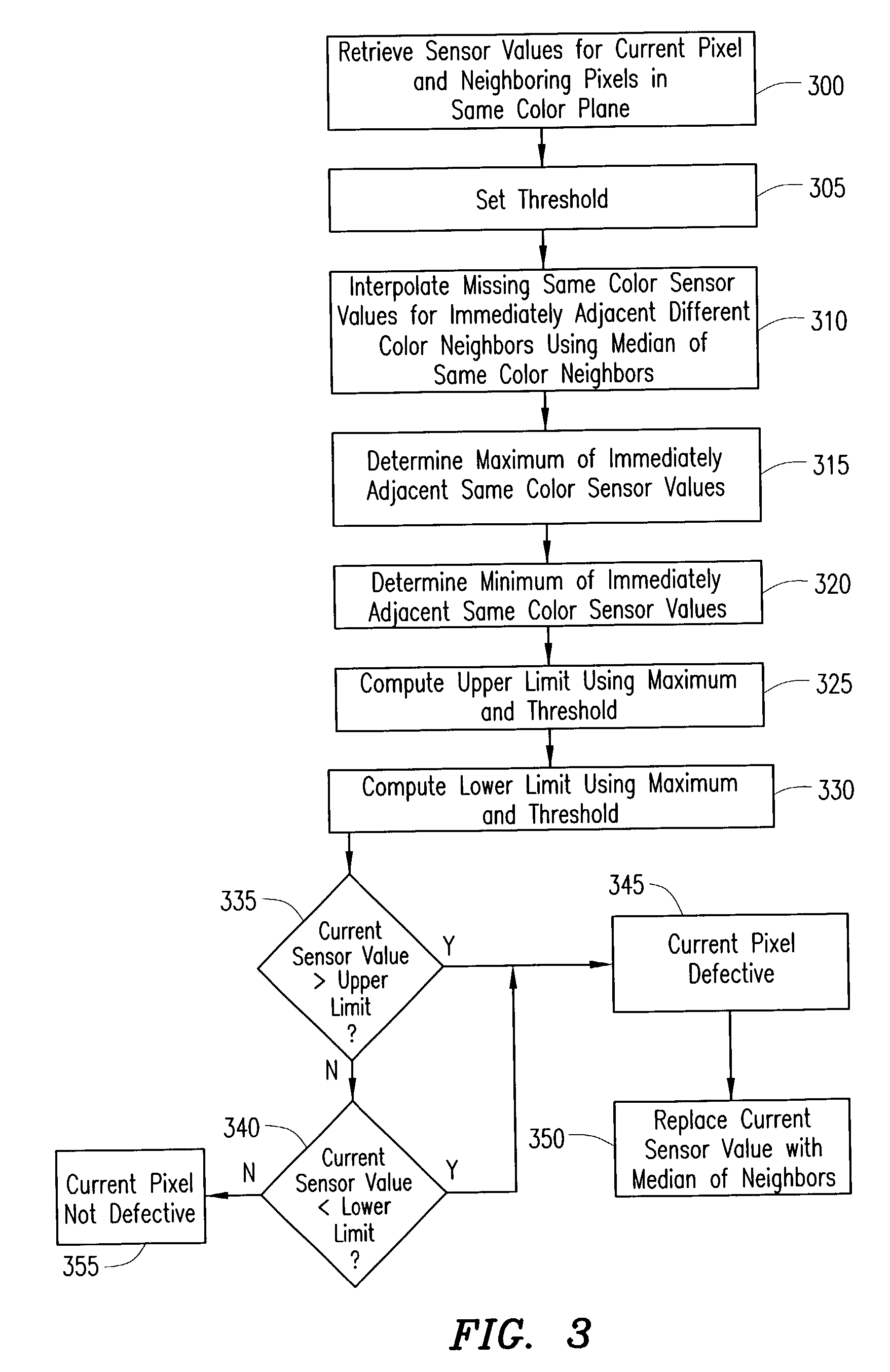

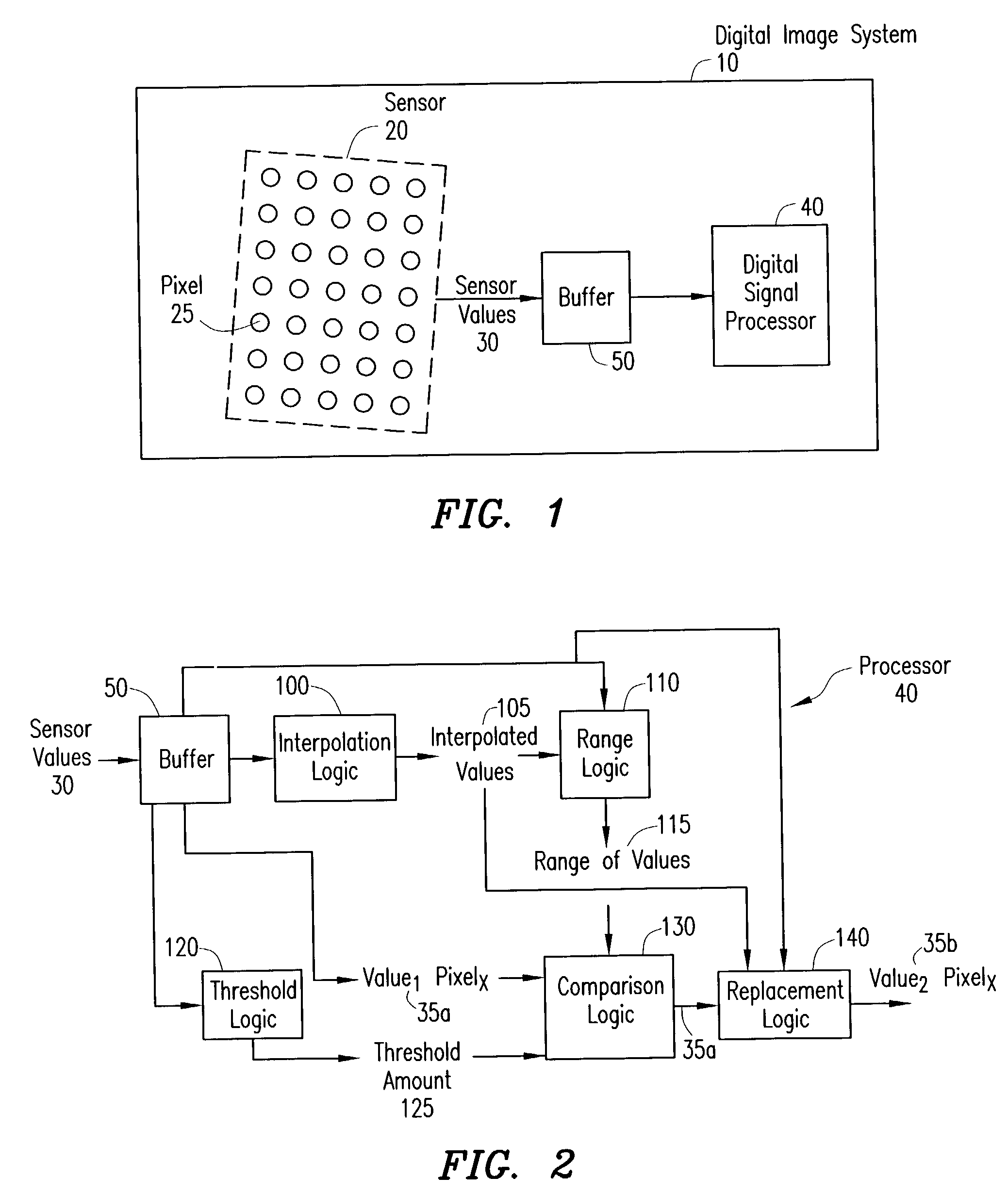

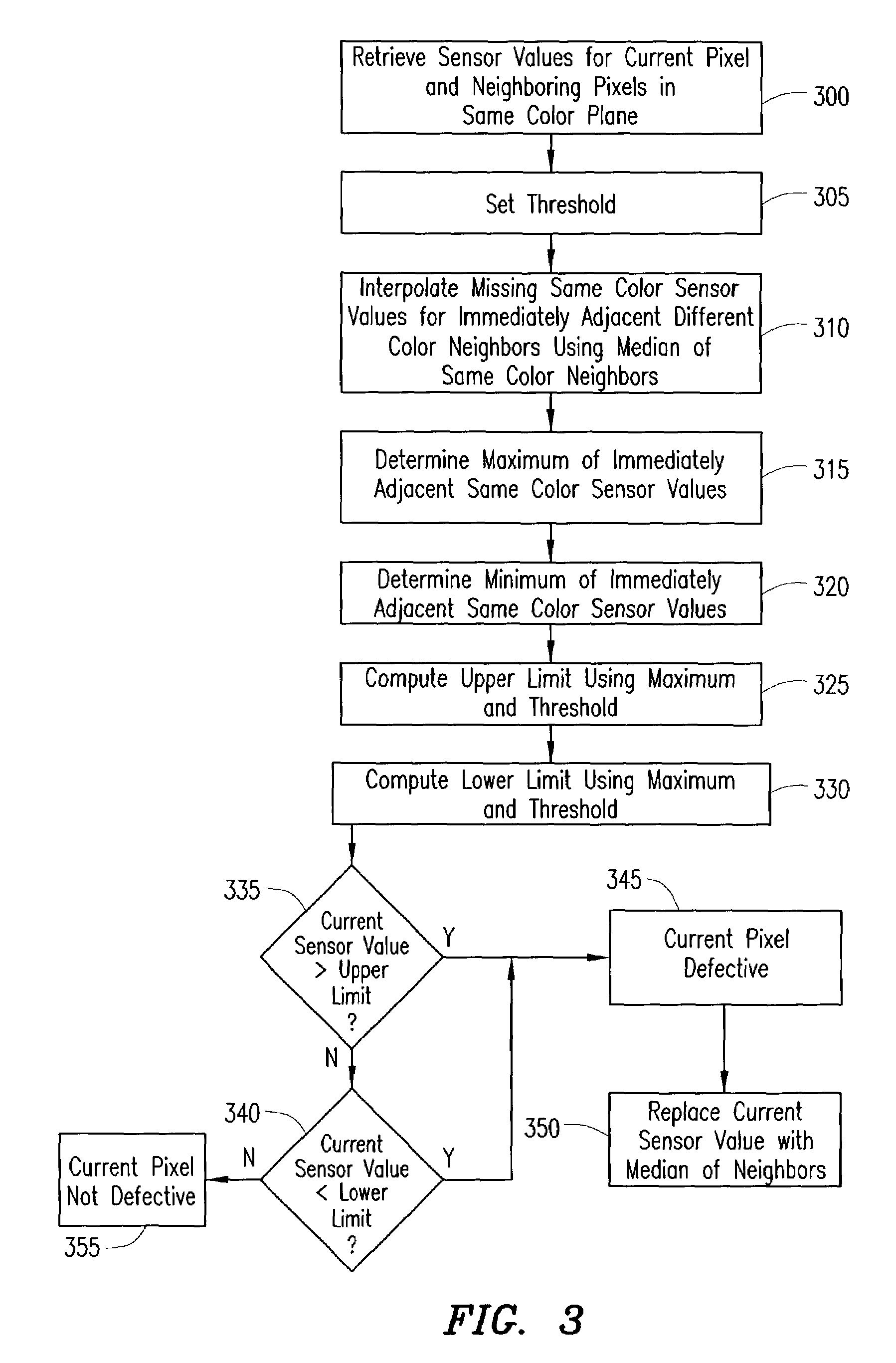

Digital image system and method for combining demosaicing and bad pixel correction

A digital image system and method for combining bad pixel correction and demosaicing in a single process is provided by interpolating sensor values for pixels immediately spatially adjacent to the current pixel being examined to detect defective pixels, and using the interpolated values for demosaicing. If the sensor value of the current pixel being examined is outside of a range of sensor values determined from the interpolated values by more than a configurable threshold amount, the current pixel is considered defective, and replaced using an estimated value from the neighboring pixels. The interpolated values calculated for use in detecting bad pixels can further be used as the interpolated values for demosaicing purposes

Owner:APTINA IMAGING CORP

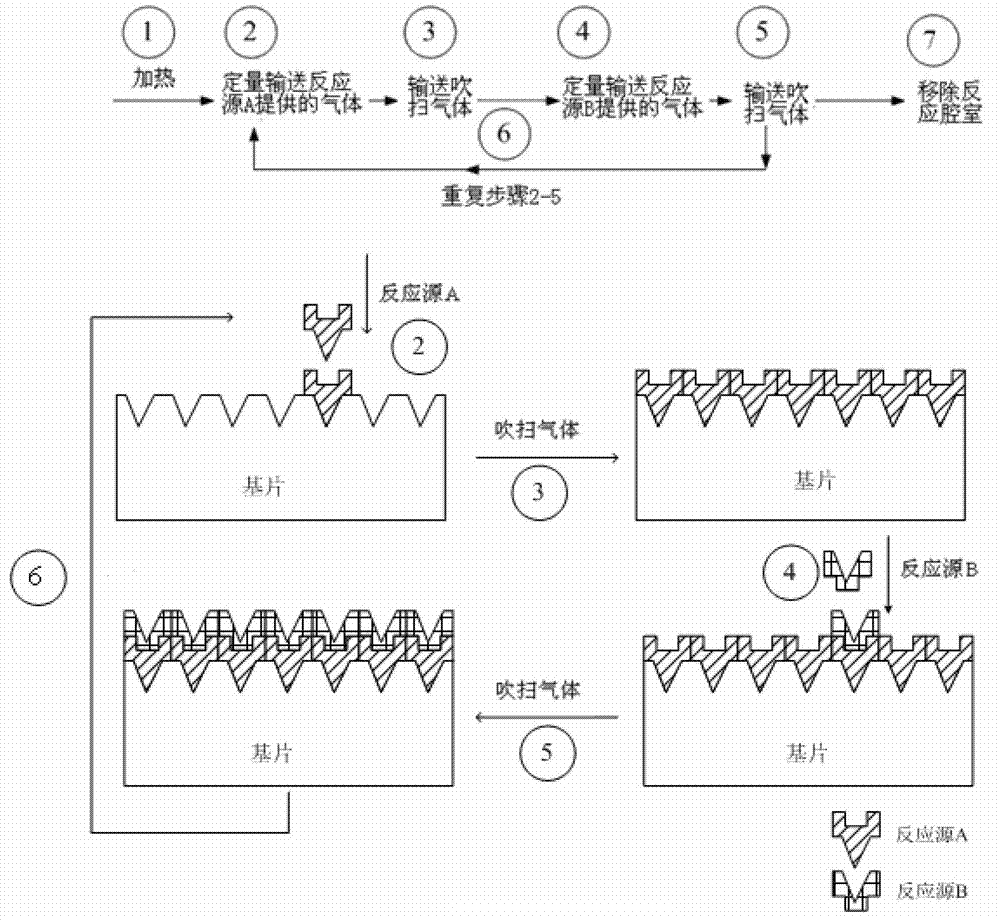

Atomic layer deposition equipment

ActiveCN104233226AImprove processing efficiencyIncrease production capacityChemical vapor deposition coatingSingle processProcess efficiency

The invention provides atomic layer deposition equipment. The atomic layer deposition equipment comprises a reaction chamber which comprises a plurality of sub chambers and a drive unit, wherein a plurality of process positions are arranged on the same horizontal plane in the reaction chamber, the plurality of process positions are arranged at intervals along the peripheral direction of the reaction chamber, and are uniformly arranged in sequence according to the sequence of processes, the quantity and positions of the sub chambers are in one-to-one correspondence with those of the process positions, and each sub chamber is used for completing one process of single processes for a substrate in each sub chamber; the drive unit is used for enabling each substrate to complete the corresponding process in the sub chamber placed on the position of each process according to the sequence of the process. The automatic layer deposition equipment provided by the invention can be used for processing a plurality of substrates at the same time by a single process, so that the process efficiency is improved, and thus, the yield is increased.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

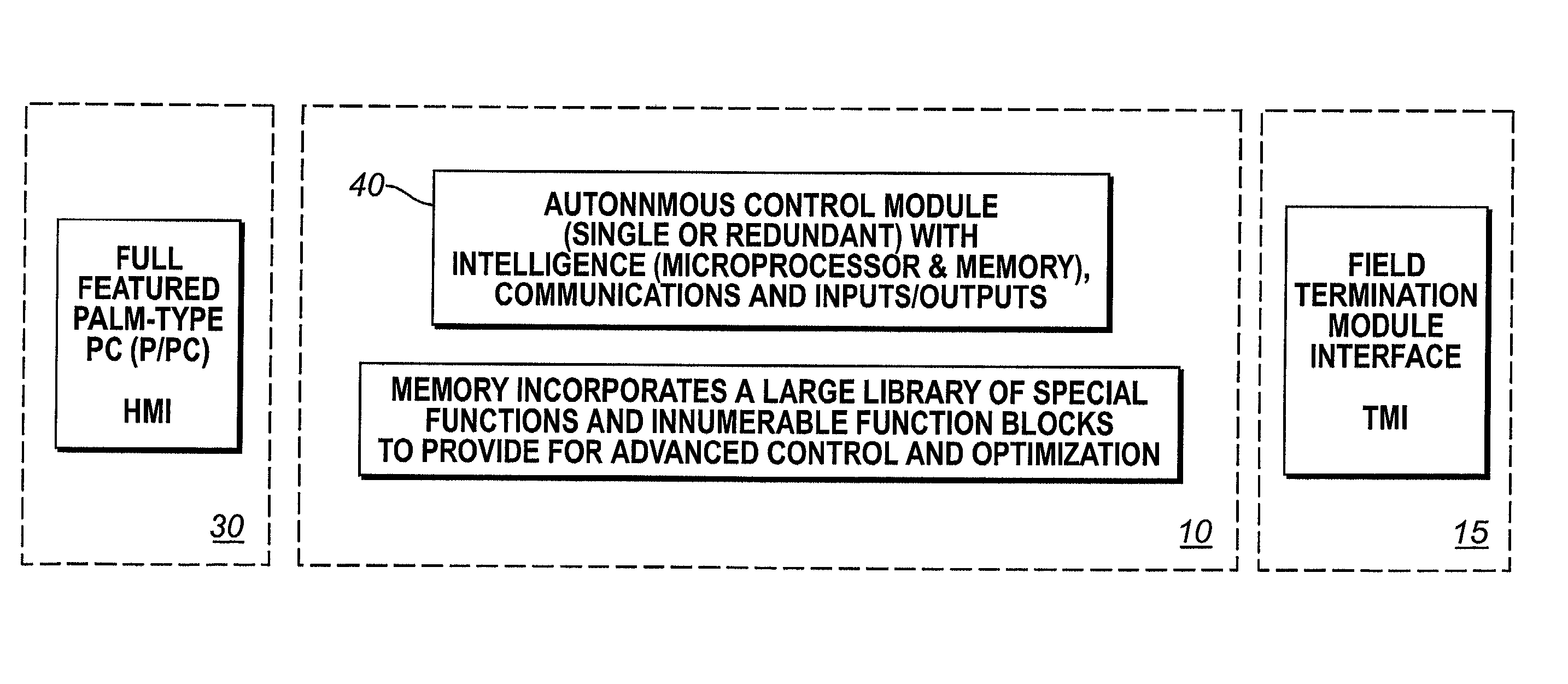

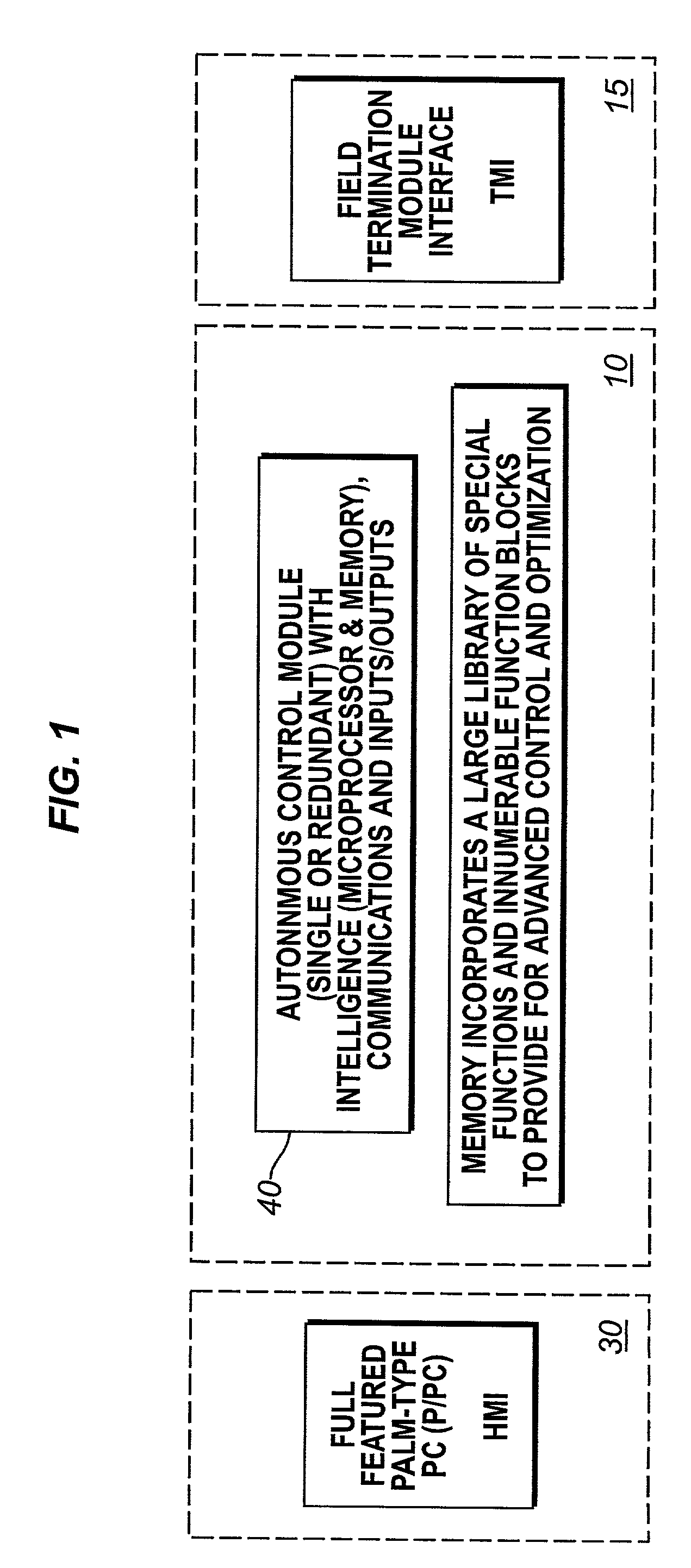

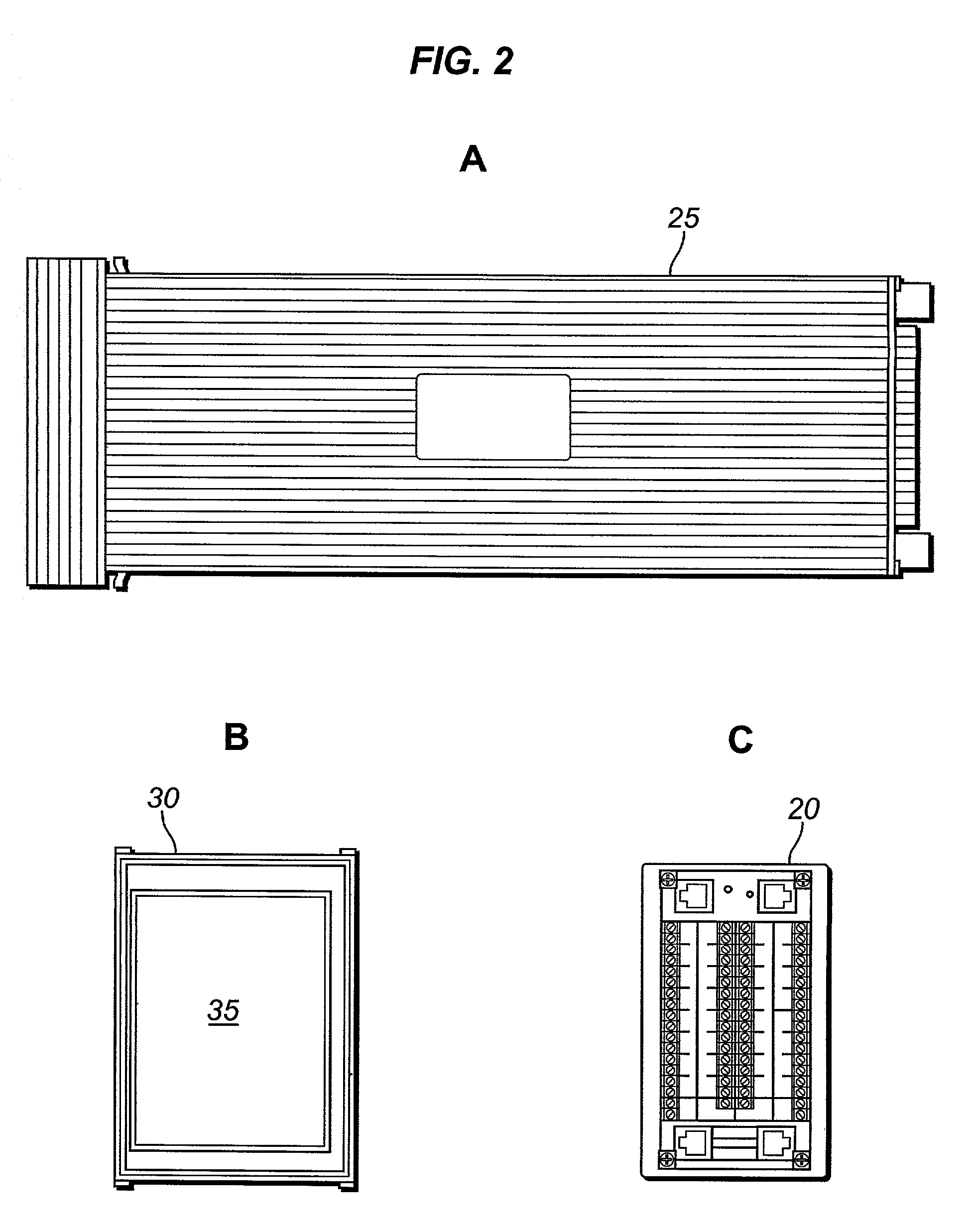

Unit controller with integral full-featured human-machine interface

An integrated unit controller / human-machine interface is disclosed which incorporates high-speed redundant control, sequence of events, supervisory control and data acquisition, alarm handling, trending & historian, process graphics and "open" communications in a compact form factor enclosure (the front panel less than 5x6 inches). The unit controller is composed of two primary hardware elements: the controller module (single or redundant) and the palm type computers (P / PC)-based human-machine interface (HMI) with touch screen. The controller covers a wide span of applications, from single process unit control to networked multi-unit management.

Owner:ICS TRIPLEX TECH

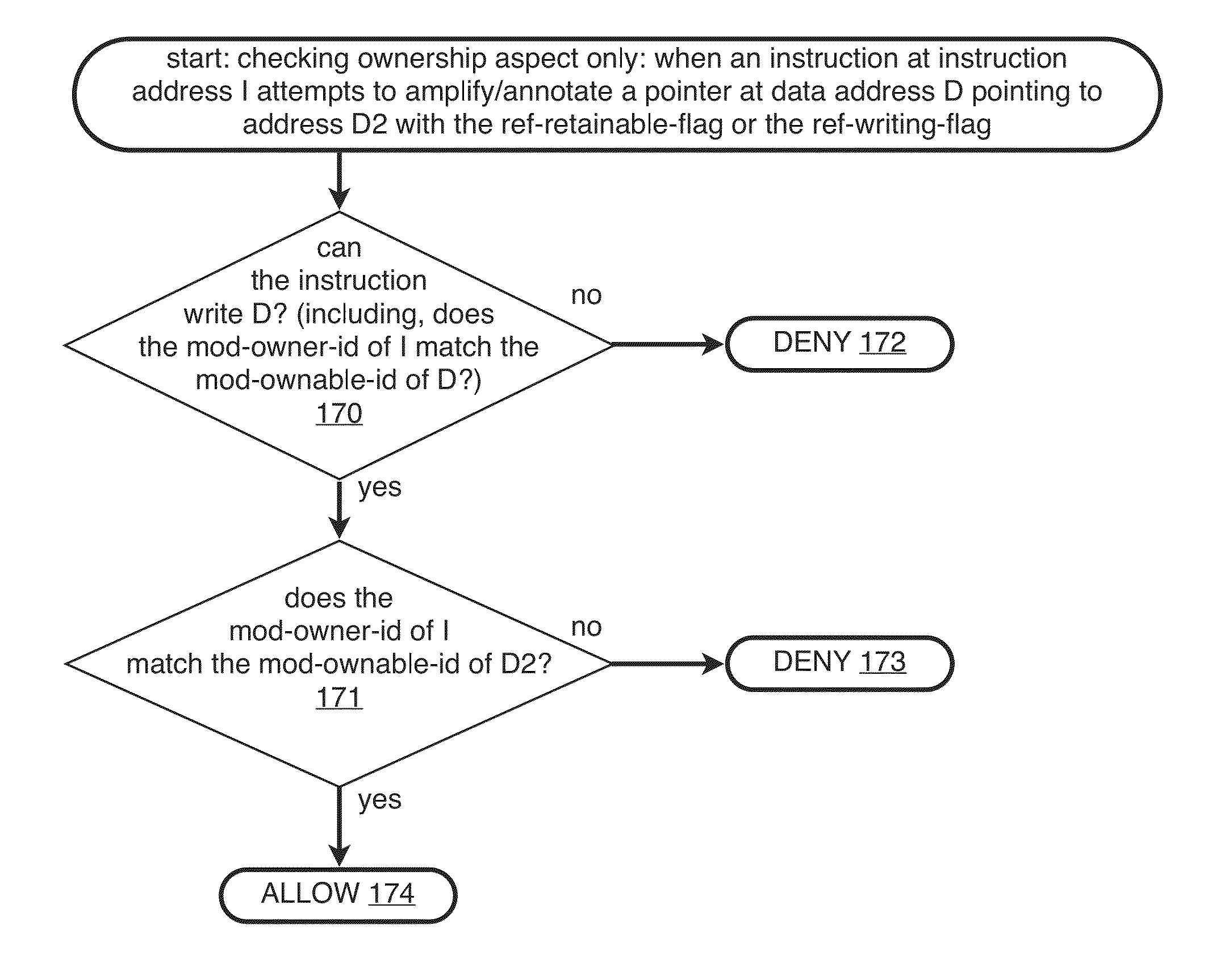

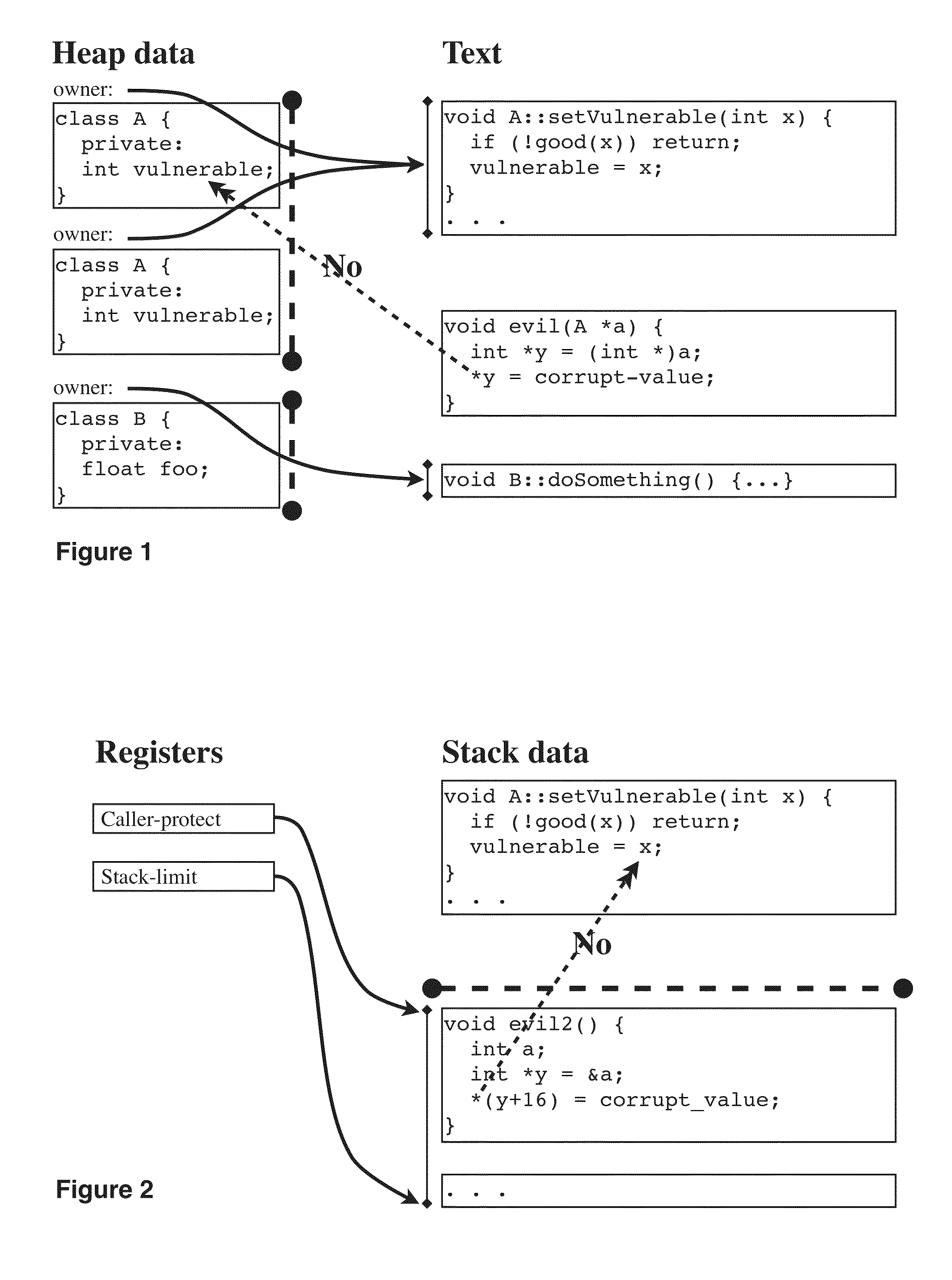

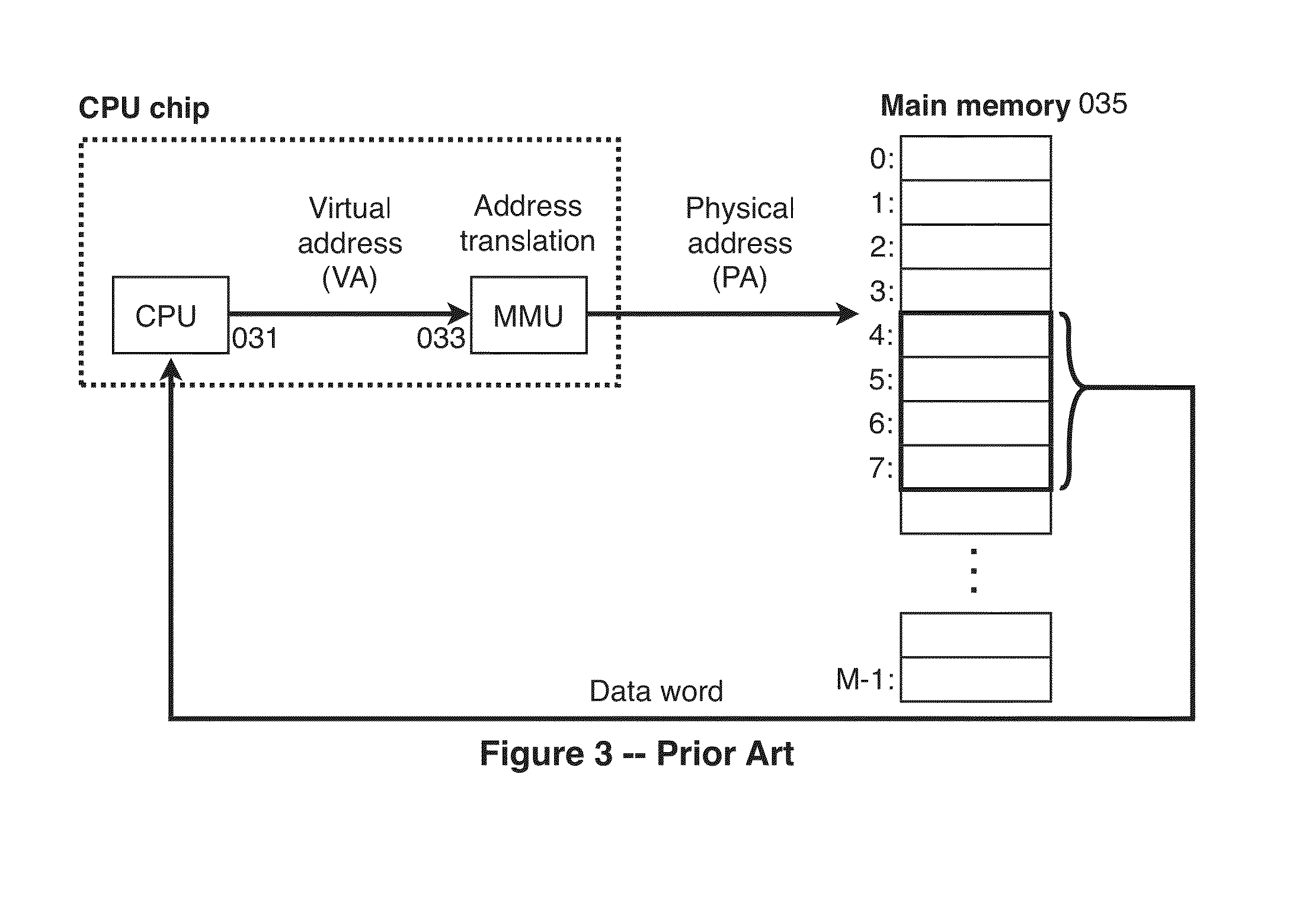

Hard Object: Lightweight Hardware Enforcement of Encapsulation, Unforgeability, and Transactionality

ActiveUS20140283040A1Memory architecture accessing/allocationMemory loss protectionSingle processSoftware correctness

A hardware-implemented method to support three desirable software properties: encapsulation, referential integrity / capabilities, and transactions. These properties in turn may be used to support software correctness, specifically the enforcement of invariants, and computer security, specifically protecting parts of programs from each other within a single process.

Owner:WILKERSON DANIEL SHAWCROSS +1

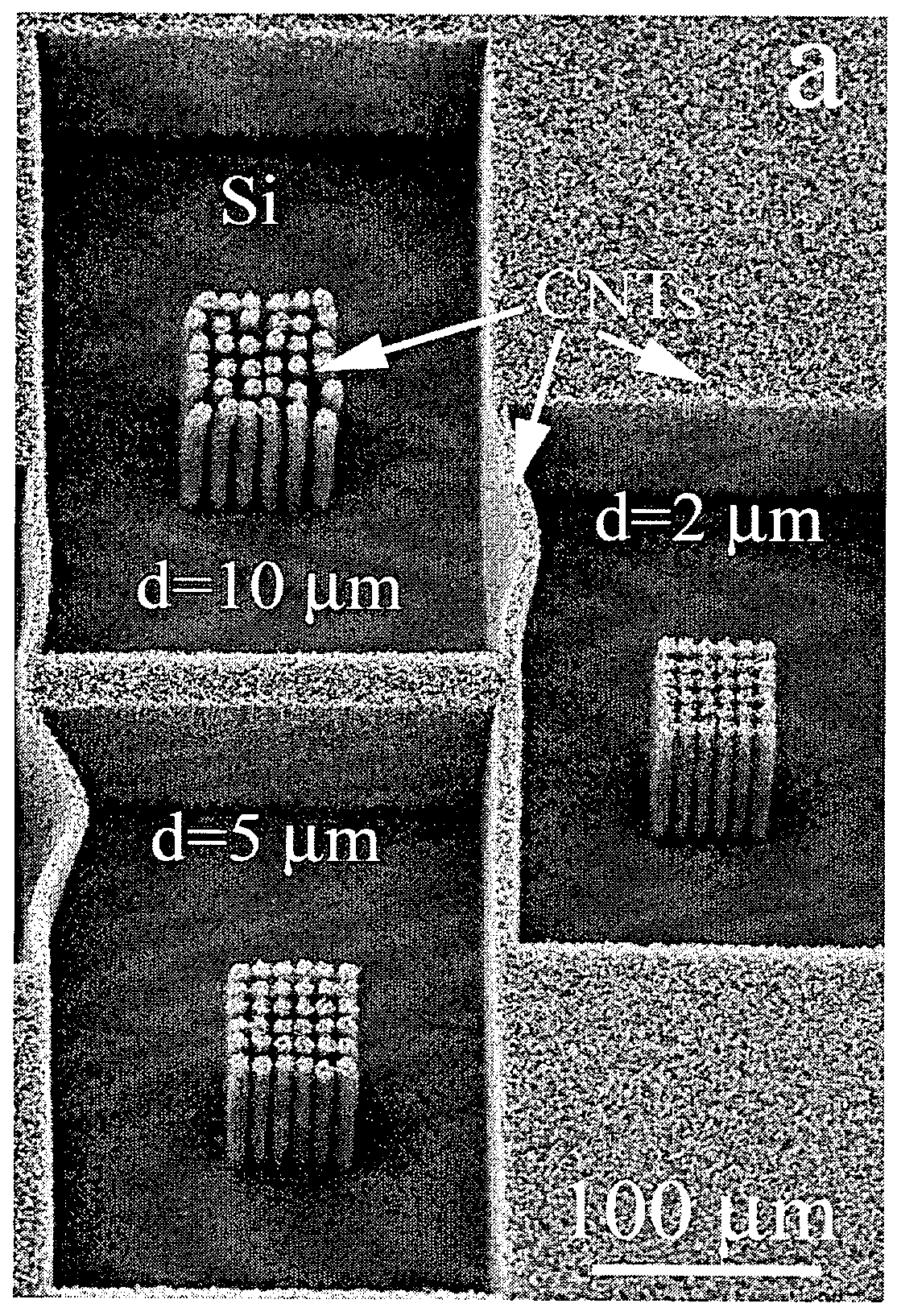

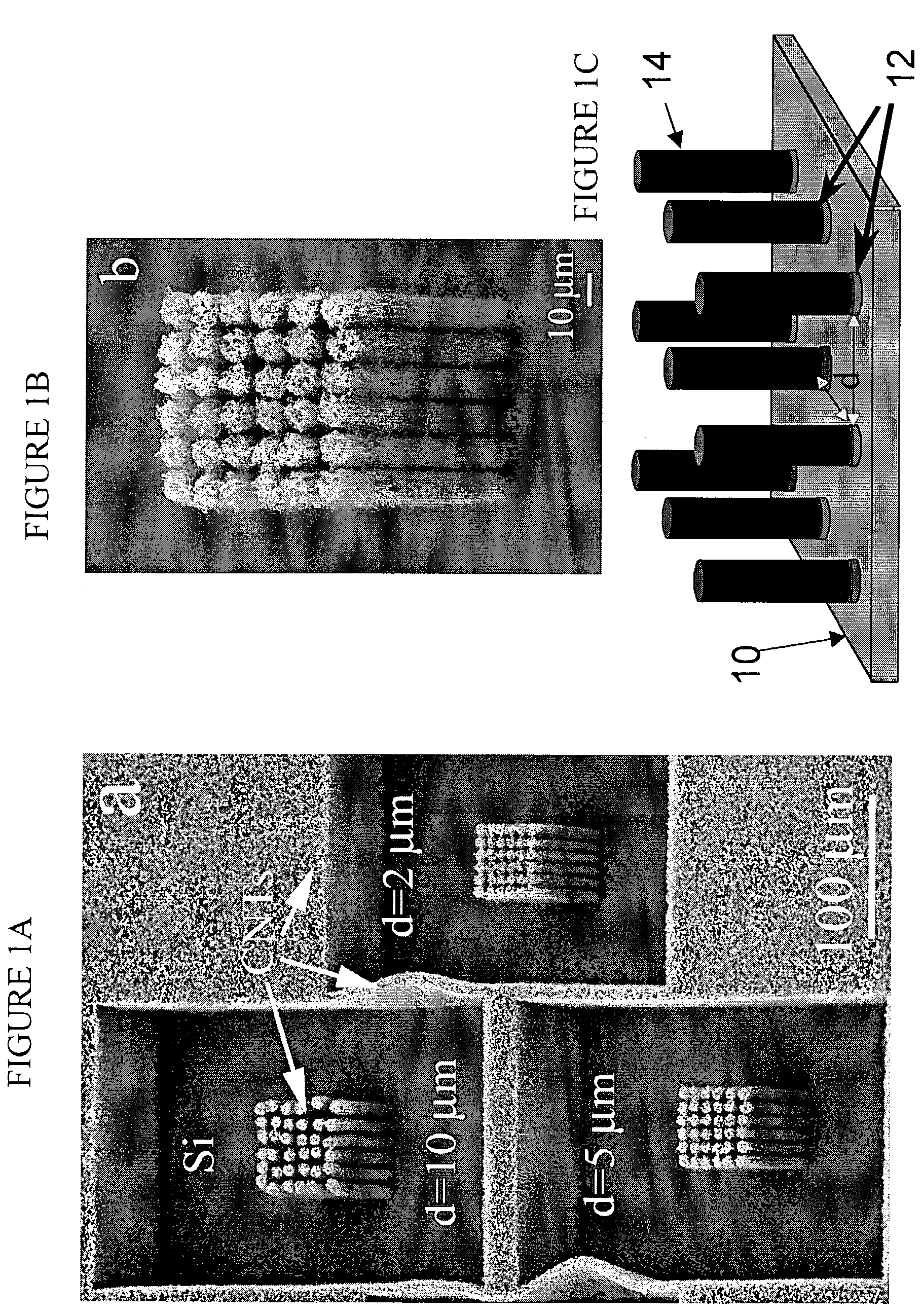

Directed assembly of highly-organized carbon nanotube architectures

A method of controllably aligning carbon nanotubes to a template structure to fabricate a variety of carbon nanotube containing structures and devices having desired characteristics is provided. The method allows simultaneous, selective growth of both vertically and horizontally controllably aligned nanotubes on the template structure but not on a substrate in a single process step.

Owner:RENESSELAER POLYTECHNIC INST

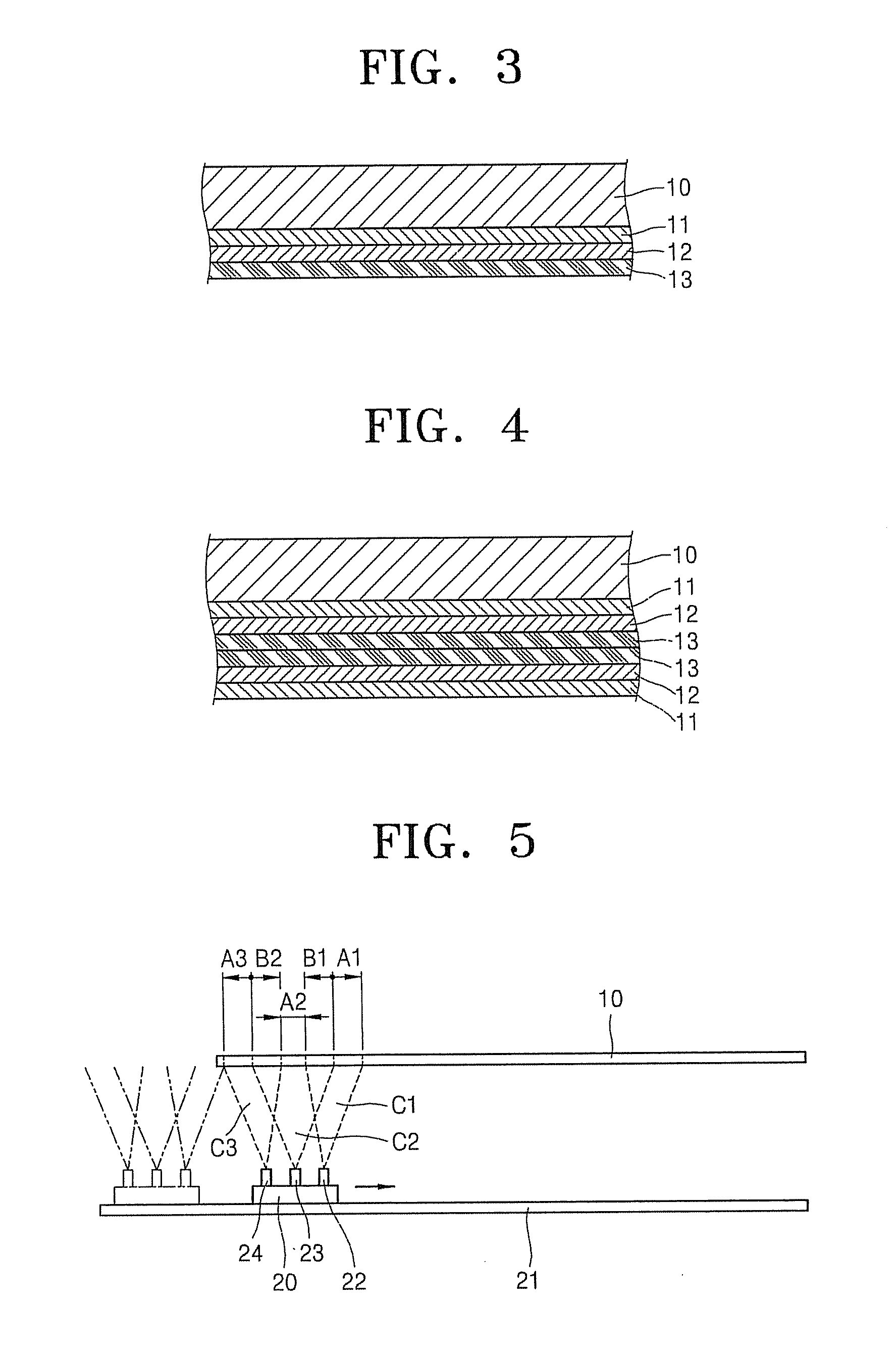

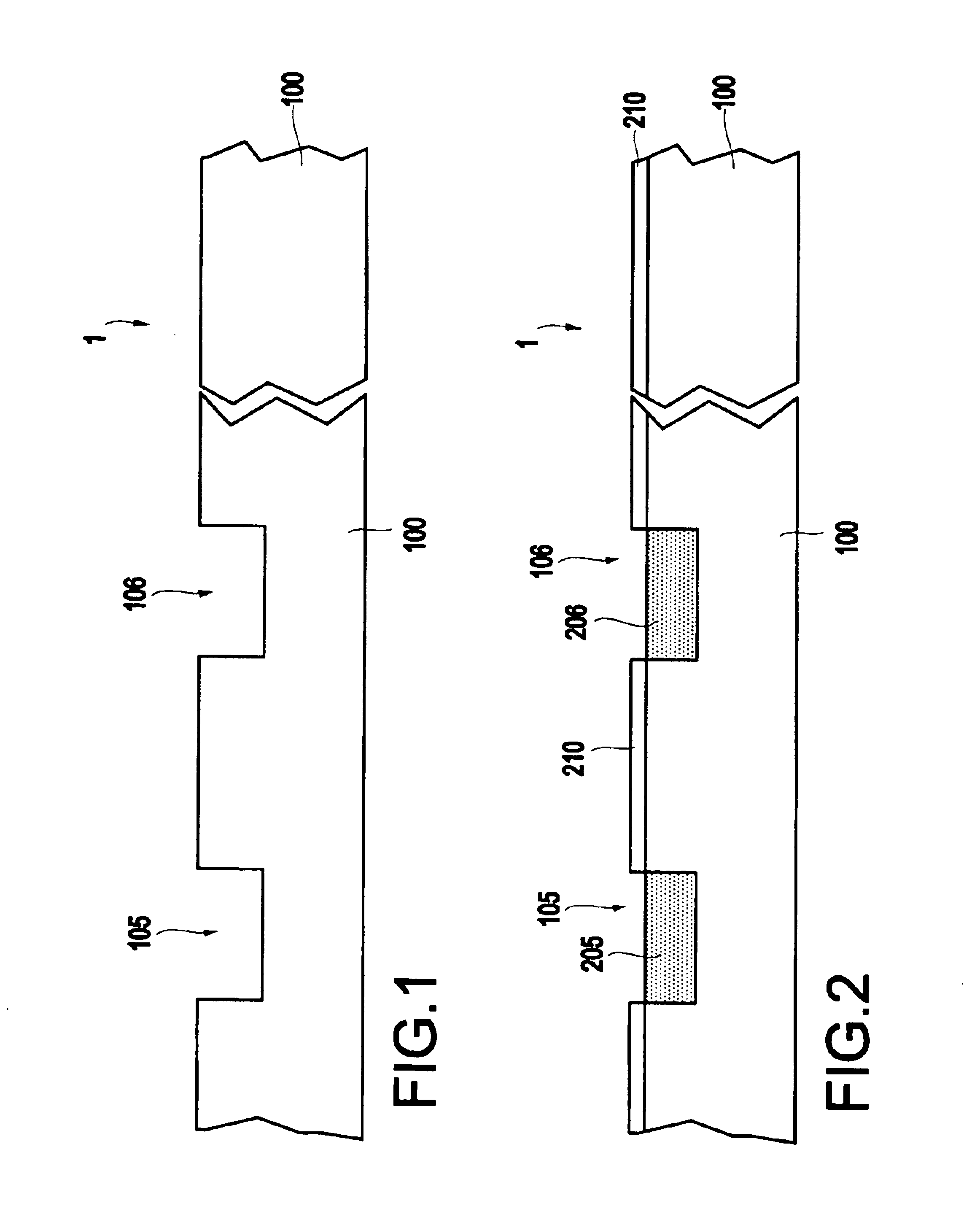

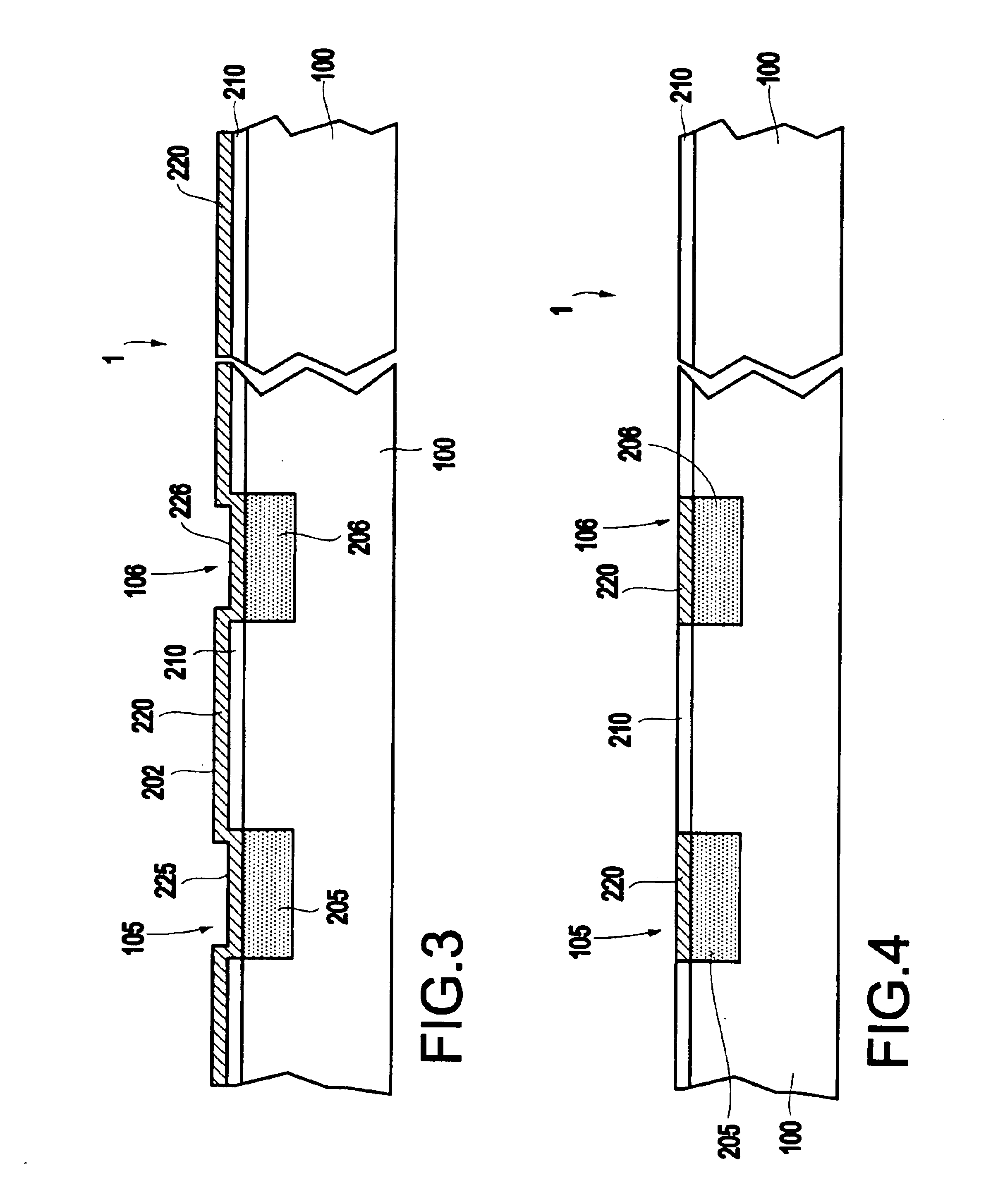

Evaporating method for forming thin film

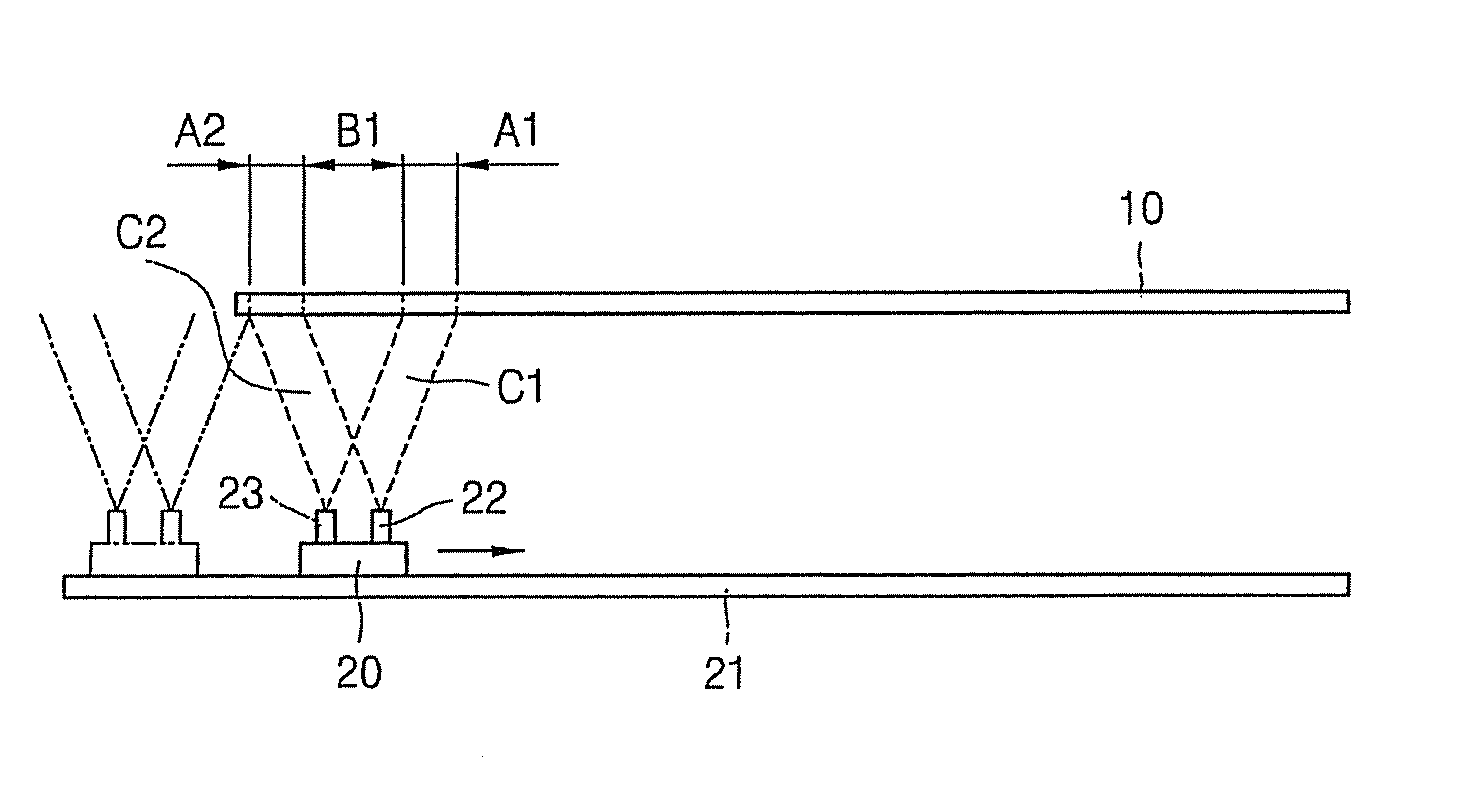

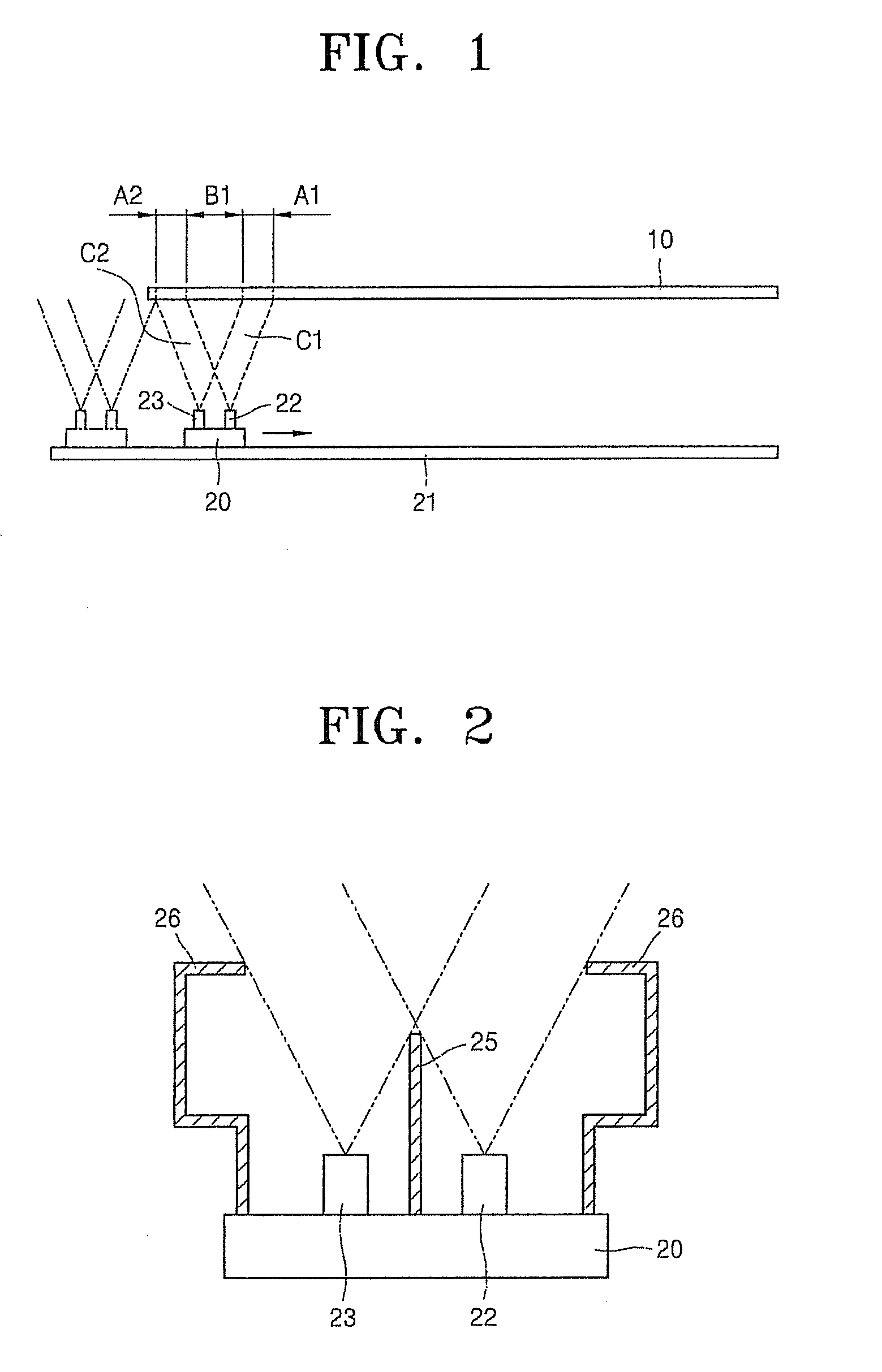

ActiveUS20090232976A1Efficient stackingQuality improvementElectrical apparatusElectroluminescent light sourcesOrganic filmSingle process

A method of forming a plurality of multi-layer organic films in a single process includes preparing a first evaporating source that evaporates a first evaporating source material onto a first deposition region and a second evaporating source that evaporates a second evaporating source material onto a second deposition region, wherein the first evaporating source material and the second evaporating source material are different from each other, adjusting the first evaporating source and the second evaporating source in order to obtain a first overlapping region in which the first deposition region and the second deposition region overlap each other, driving the first evaporating source and the second evaporating source to deposit the first evaporating source material and the second evaporating source material onto a portion of an object to be processed, and moving the first evaporating source and the second evaporating source from a first end of the object to a second end of the object to form a multilayer film comprising a first layer that is a deposition of only the first evaporating source material, a second layer that is a deposition of a mixture of the first evaporating source material and the second evaporating source material and a third layer that is a deposition of only the second source material.

Owner:SAMSUNG DISPLAY CO LTD

Merged logic and memory combining thin film and bulk Si transistors

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

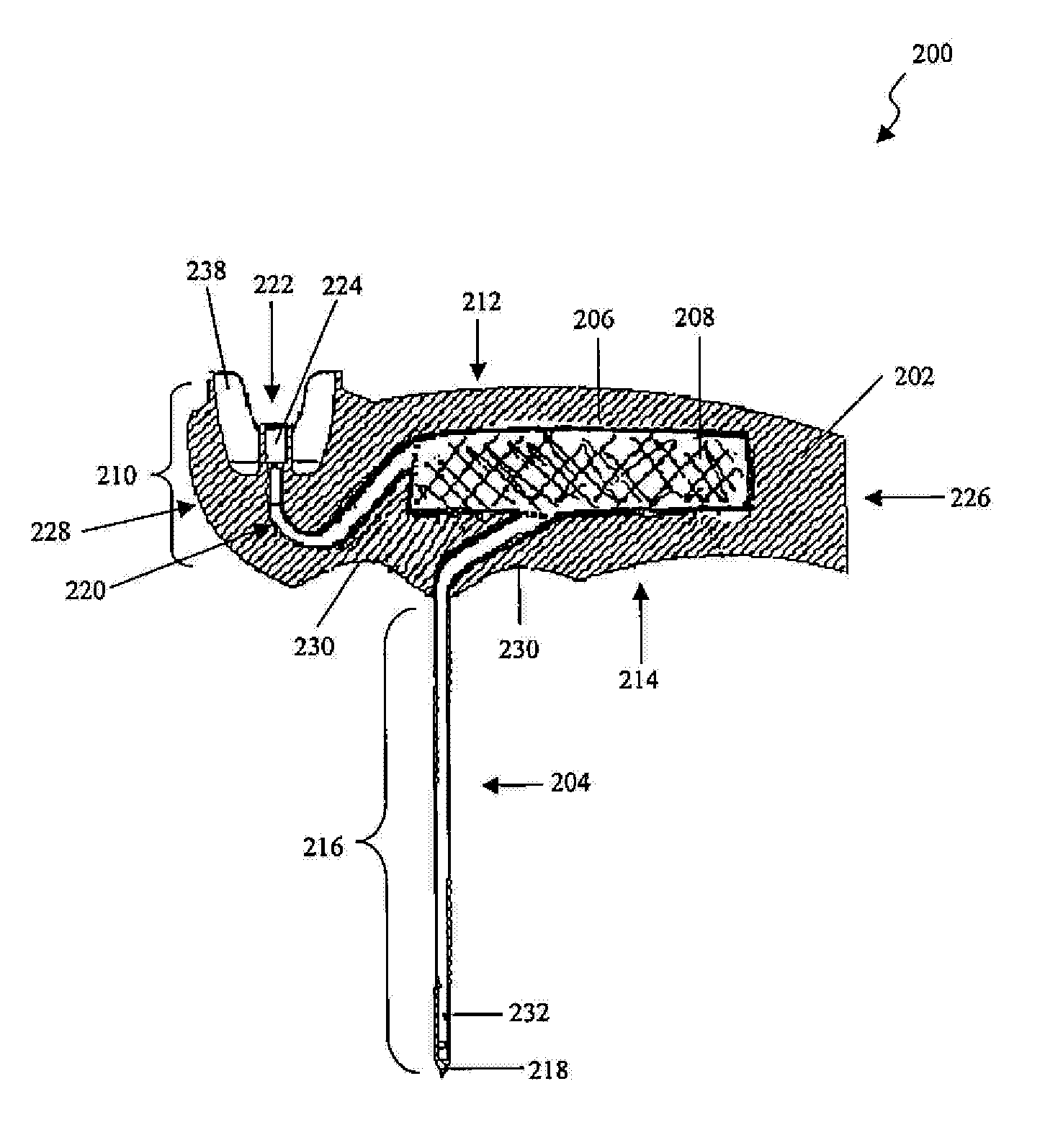

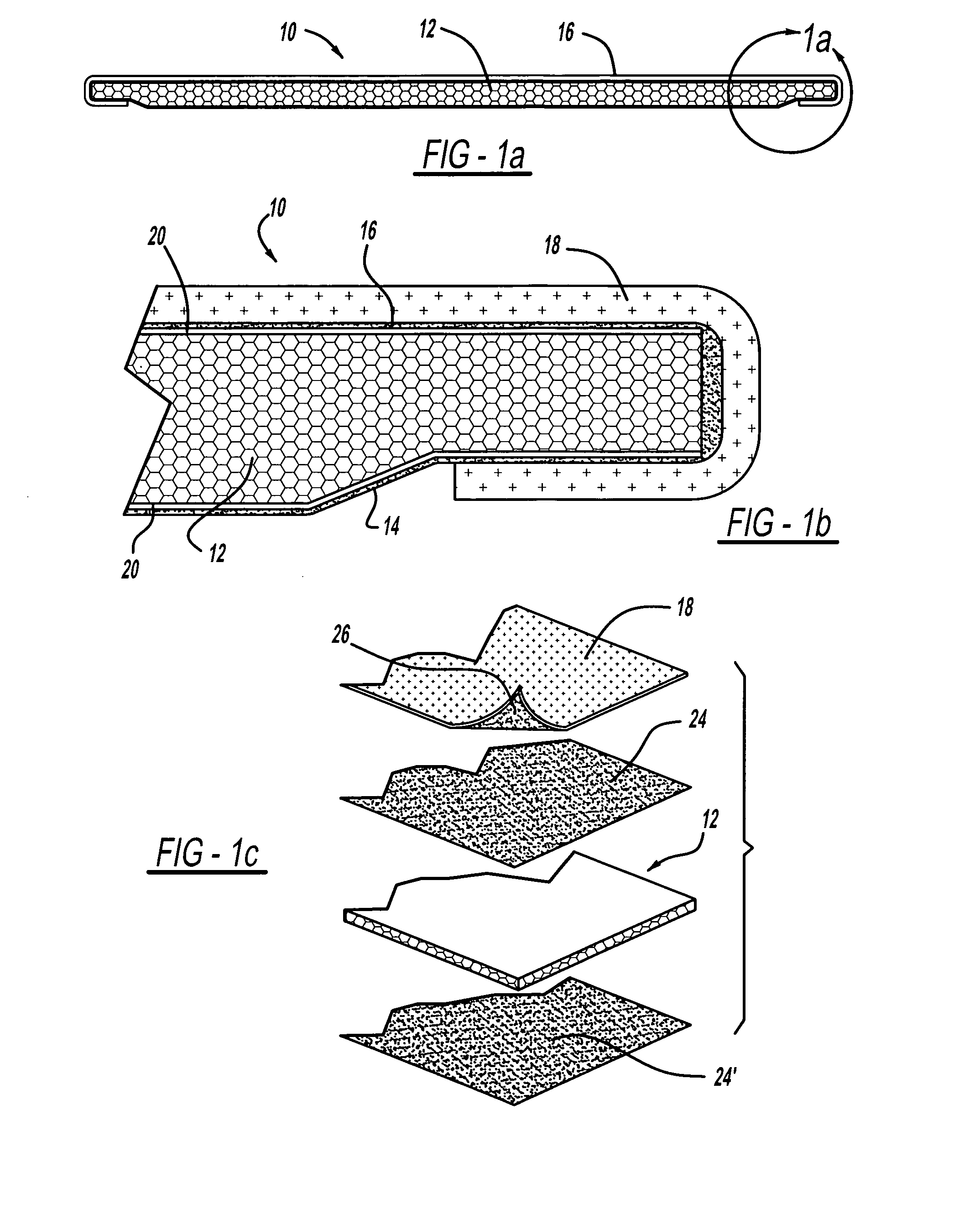

Bone marrow aspiration system

InactiveUS6981948B2Effective controlBone implantSurgical needlesSingle processBiomedical engineering

Bone marrow aspiration devices and methods are disclosed for use in preparing a substrate. In general, the device includes an elongate penetrating element, a chamber adapted to retain a substrate, and a fluid extraction mechanism that is effective to pull fluid through the elongate penetrating element, into the chamber, and through the substrate. The device is particularly advantageous in that it will allow for the removal of fluids from a patient's body and the preparation of a substrate in a single process, thereby providing a more efficient method and device for preparing a substrate.

Owner:DEPUY ACROMED INC

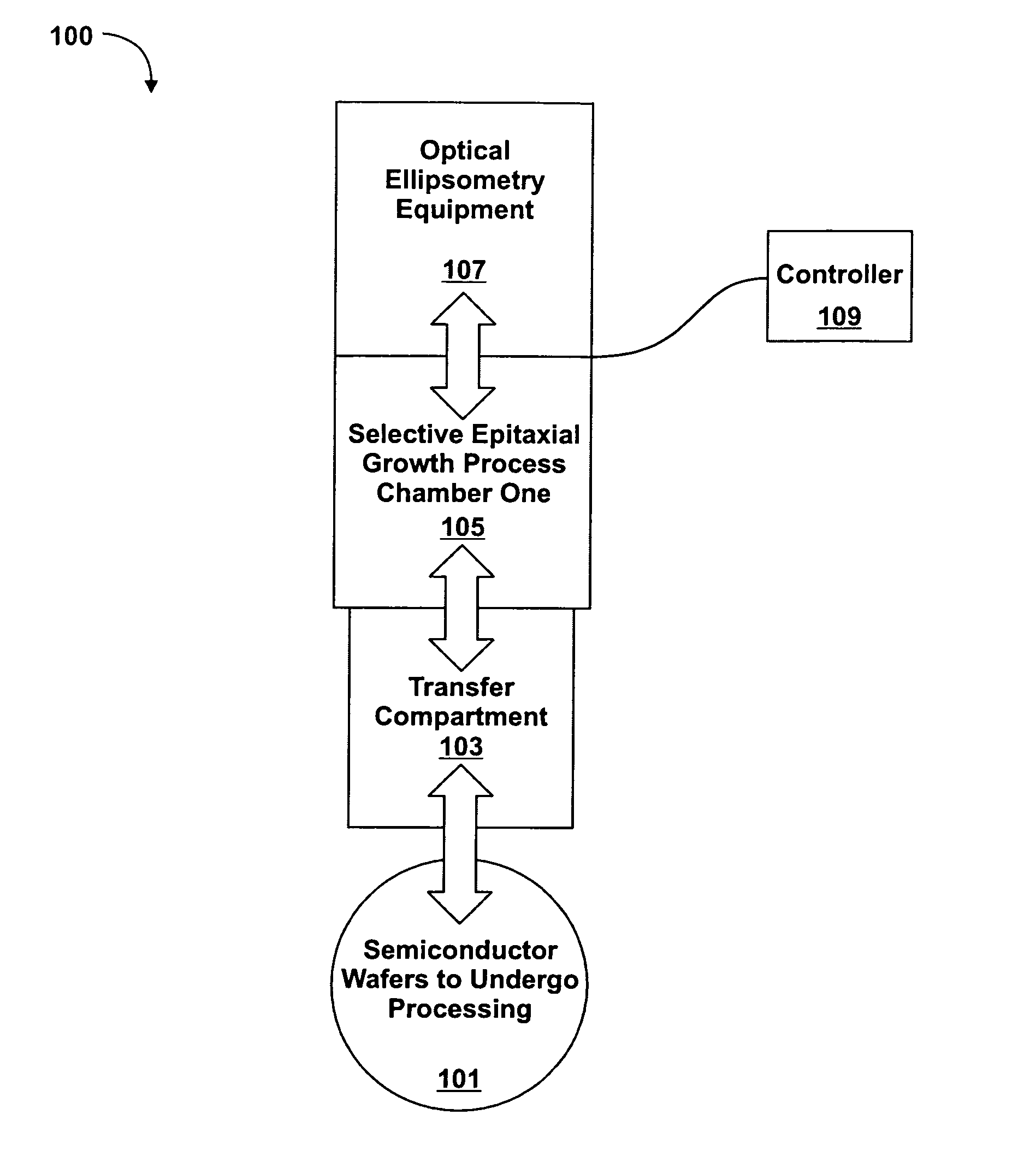

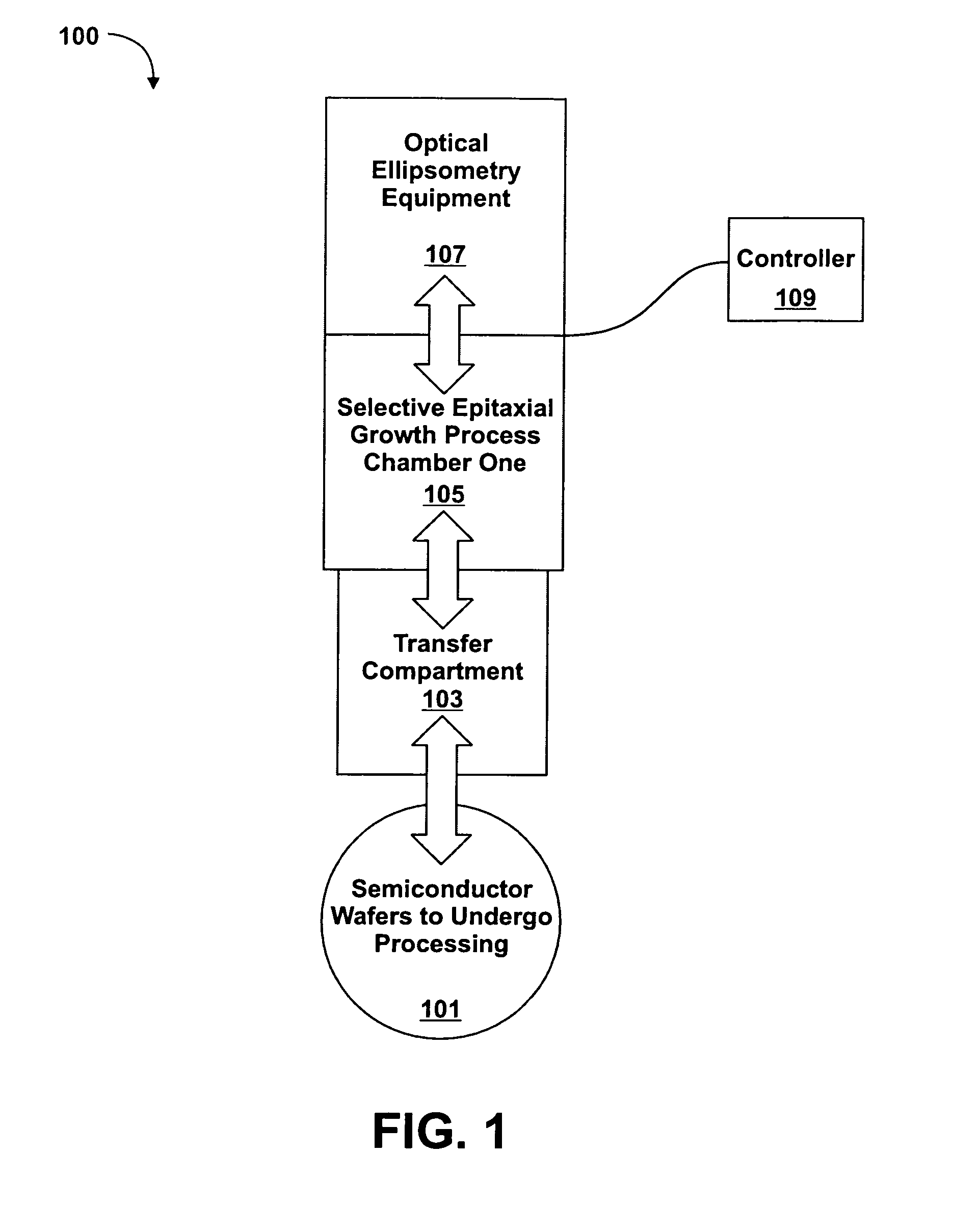

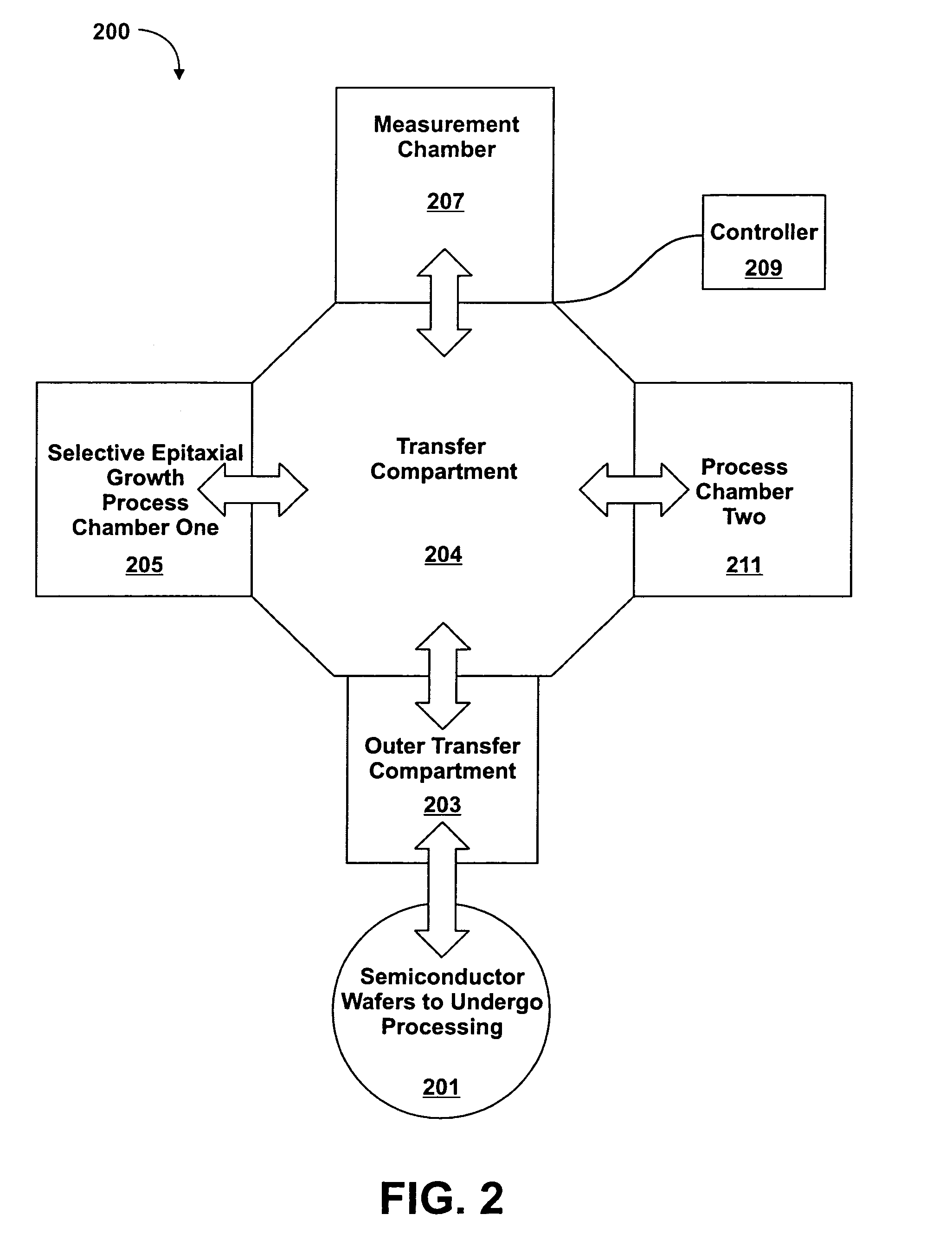

Method and apparatus for controlling the thickness of a selective epitaxial growth layer

Methods and systems for permitting thickness control of the selective epitaxial growth (SEG) layer in a semiconductor manufacturing process, for example raised source / drain applications in CMOS technologies, are presented. These methods and systems provide the capability to measure the thickness of an SEG film in-situ utilizing optical ellipsometry equipment during or after SEG layer growth, prior to removing the wafer from the SEG growth tool. Optical ellipsometry equipment can be integrated into the SEG platform and control software, thus providing automated process control (APC) capability for SEG thickness. The integration of the ellipsometry equipment may be varied, dependent upon the needs of the fabrication facility, e.g., integration to provide ellipsometer monitoring of a single process tool, or multiple tool monitoring, among other configurations.

Owner:ADVANCED MICRO DEVICES INC

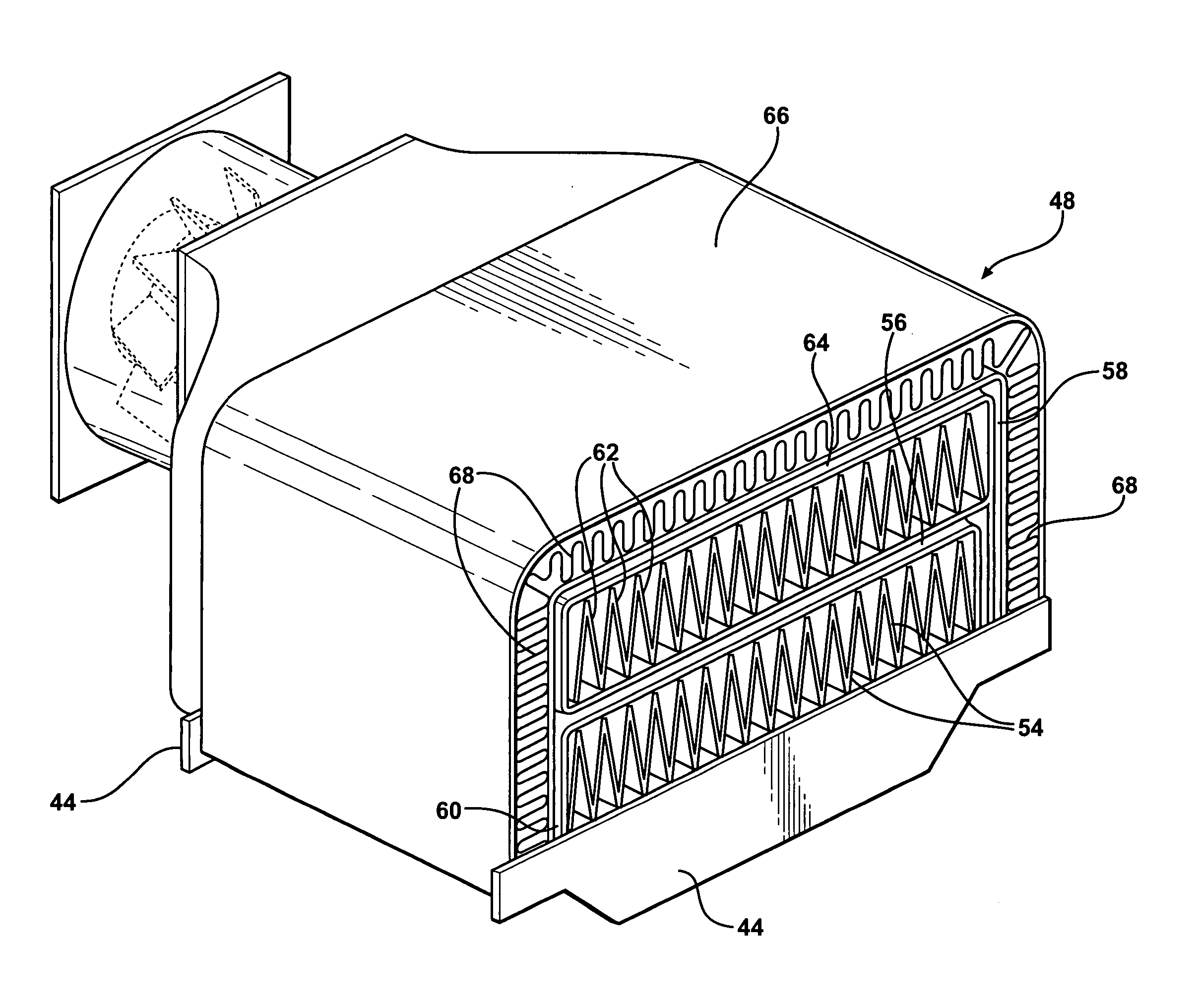

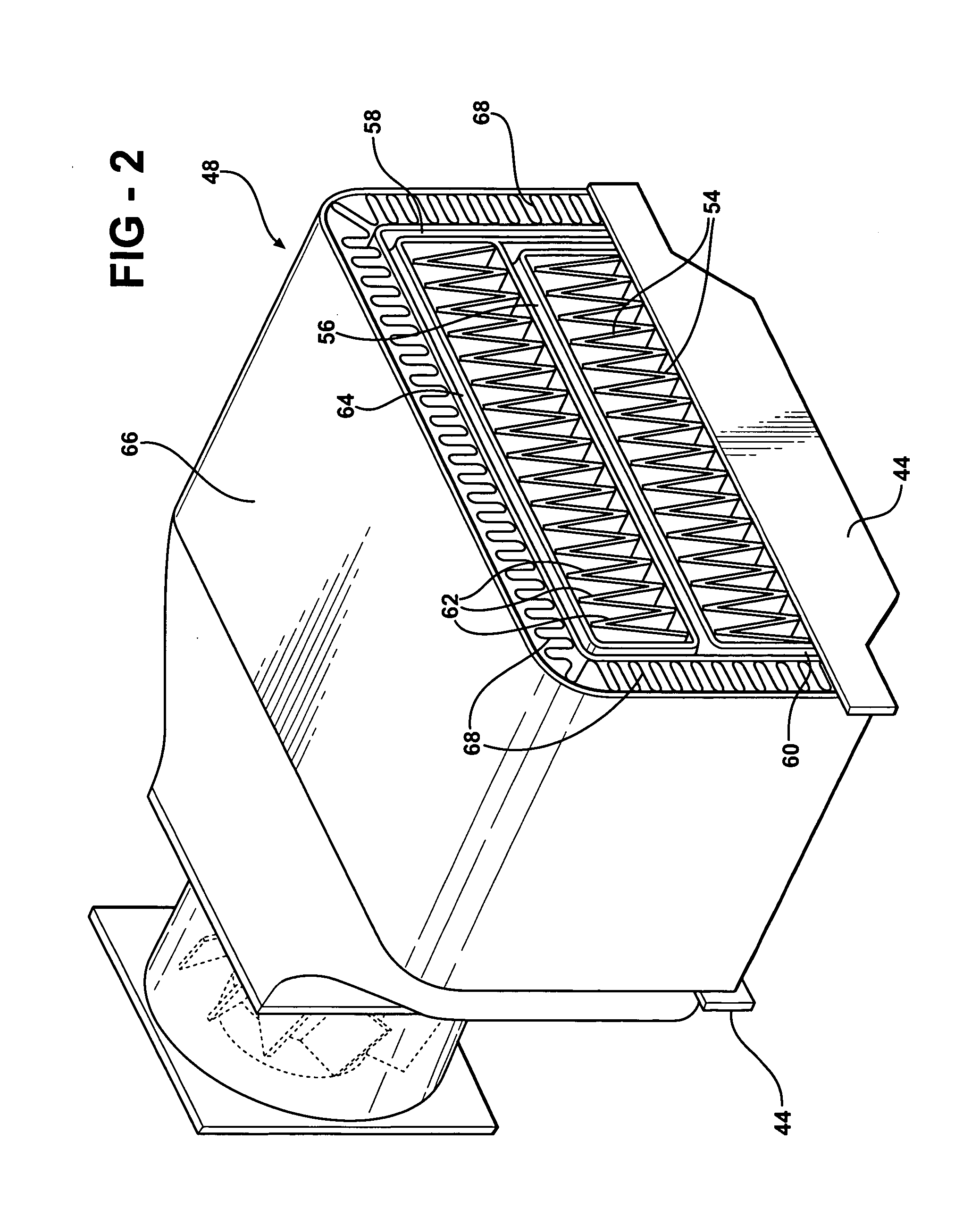

Integrated liquid cooled heat sink for electronic components

InactiveUS20060283579A1Reduce shippingReduce handlingSemiconductor/solid-state device detailsSolid-state devicesSingle processEngineering

A fluid heat exchanger unit cools an electronic device with a cooling fluid supplied to an upper portion of a cooling housing. A refrigerant is disposed in a lower portion of the cooling housing for liquid-to-vapor transformation. A partition divides the upper portion of the cooling housing from the lower portion. A heat rejecter is disposed on and above the upper wall of the cooling housing with a first header extending from and in fluid communication with the liquid coolant outlet. A second header extends upwardly from a rejecter outlet. A plurality of first tubes extend between and in fluid communication with the first header and the second header with a plurality of first air fins disposed between the upper wall and the first tubes. A single unit defines both the cooling housing and the air cooled heat rejecter to thereby allow the manufacture of the unit in a single process with the attendant reduction in shipping, handling and installation.

Owner:COOLIT SYSTEMS INC

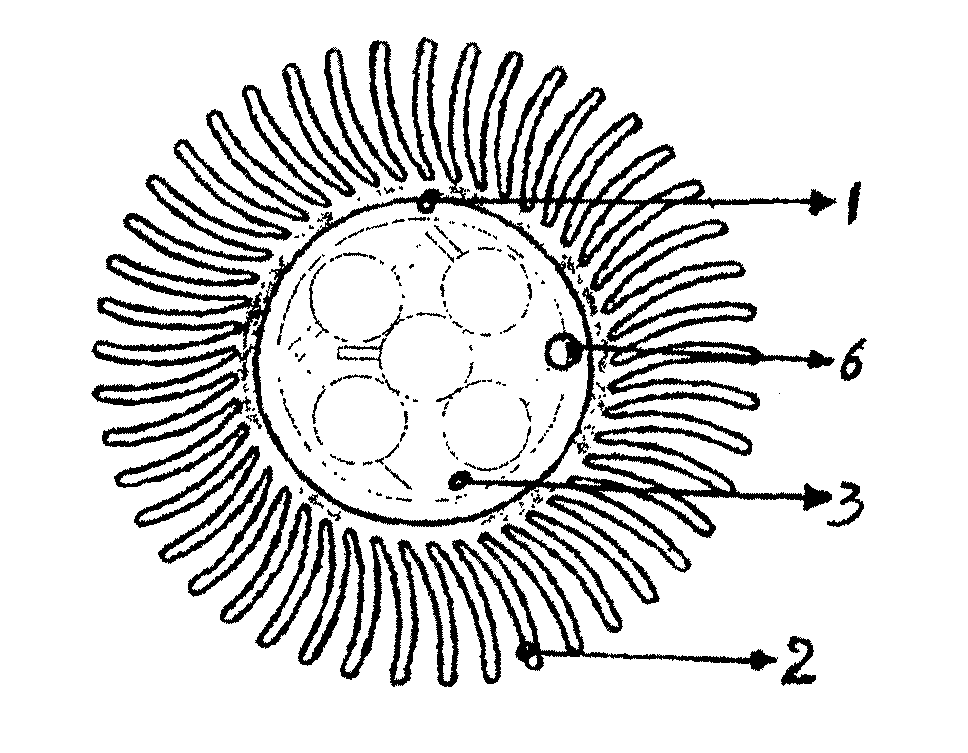

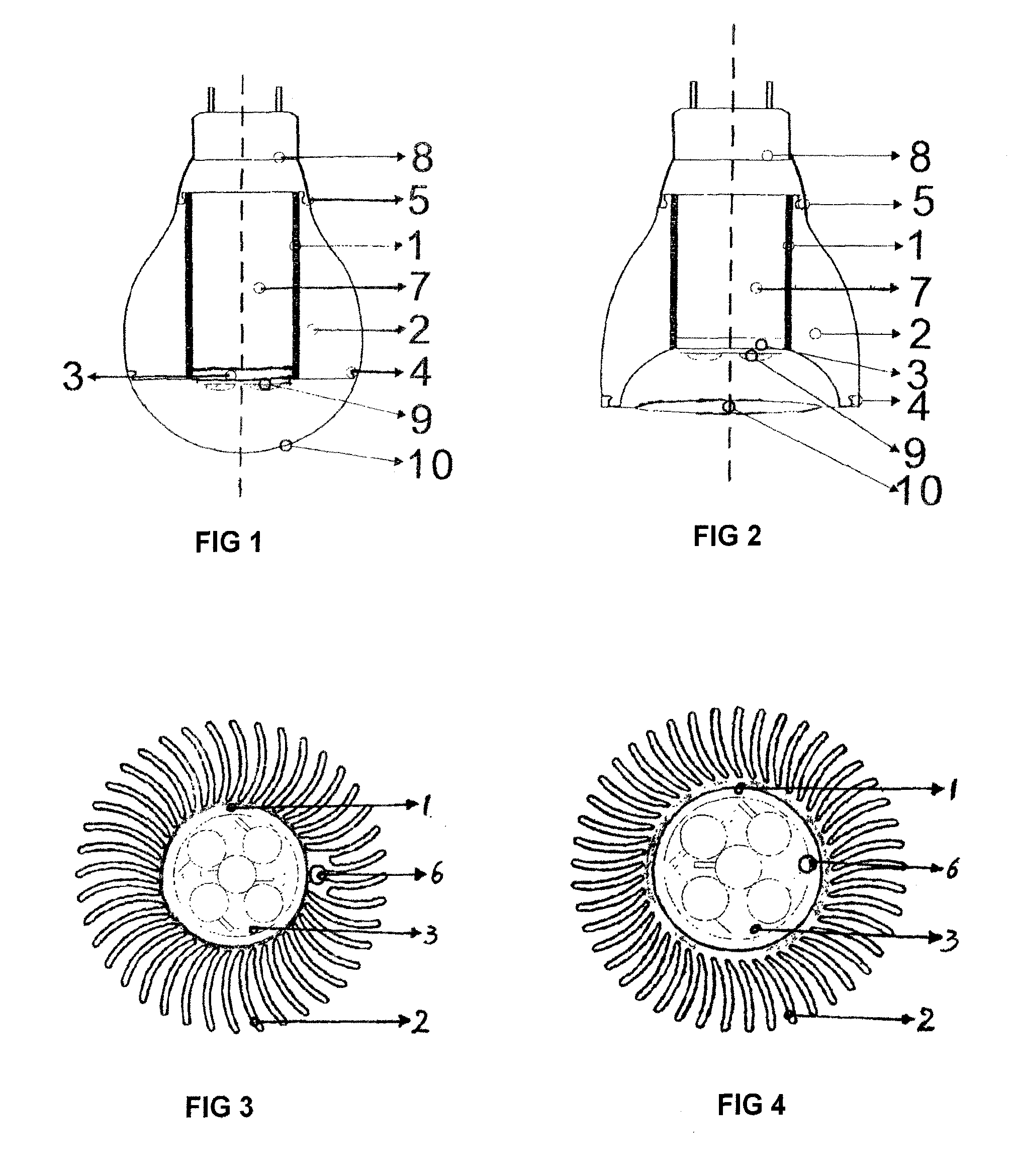

Built-in Heat Diffusion Lamp Body for LED Lamp

InactiveUS20090016063A1Simple materialSimple structurePoint-like light sourceElectric circuit arrangementsDiffusionInterference fit

A built in beat diffusion lamp body for LED lamp was invented. The purpose of the invention is to solve the difficulties of poor heat conduction and diffusion caused by the small heat diffusion surface of the material of a conventional LED lamp. The lamp body is made of a set of heat diffusion vanes encircling the heat diffusion complex. The vanes and heat diffusion complex are made from Aluminum alloy in a single process of extrusion moulding. The transverse section of the heat diffusion body is volute shaped. The bottom of the heat diffusion complex is fixed to an aluminum board or an aluminum circuit: board by interference fit. The heat generated by the LED elements can be absorbed and diffused by the board, the heat diffusion complex and the surrounding diffusion element. The outward appearance of the heat diffusion lamp body may be shaped into cup, ladder, or cylinder likeness to satisfy the application requirement. The advantages of current invention are: efficient heat absorption, conduction, and diffusion, low cost for manufacturing, and aesthetic appearance.

Owner:HU KAI

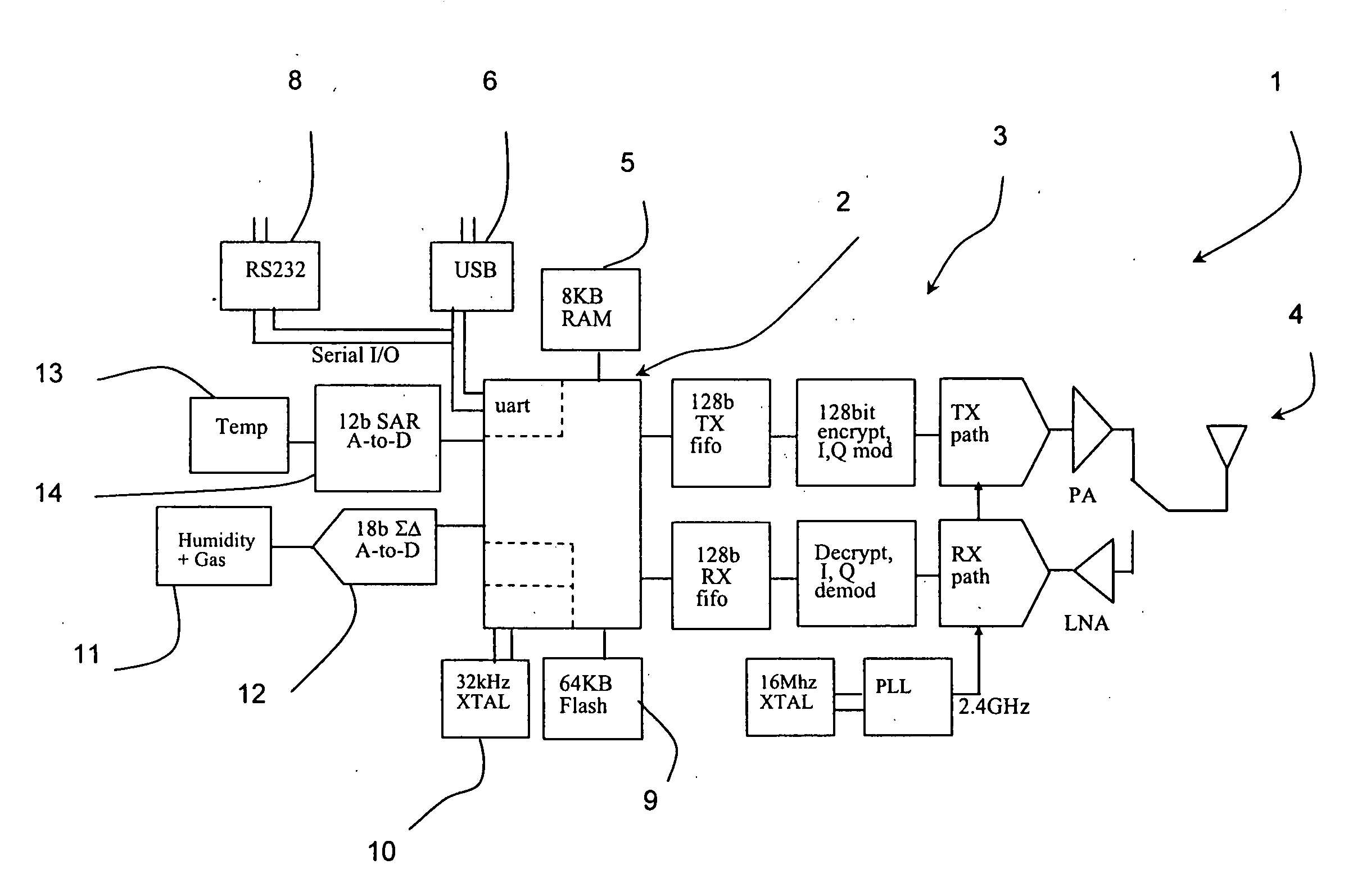

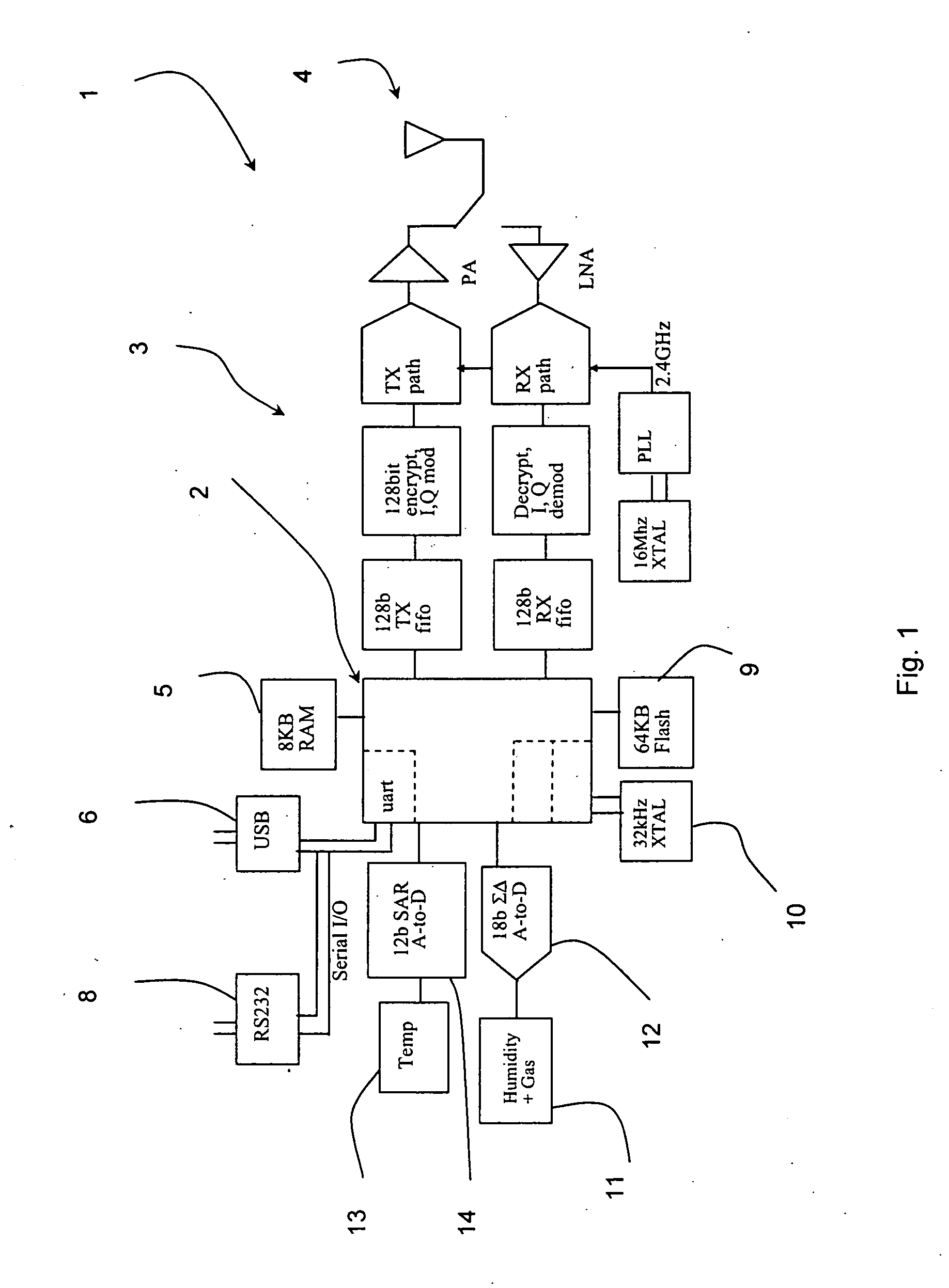

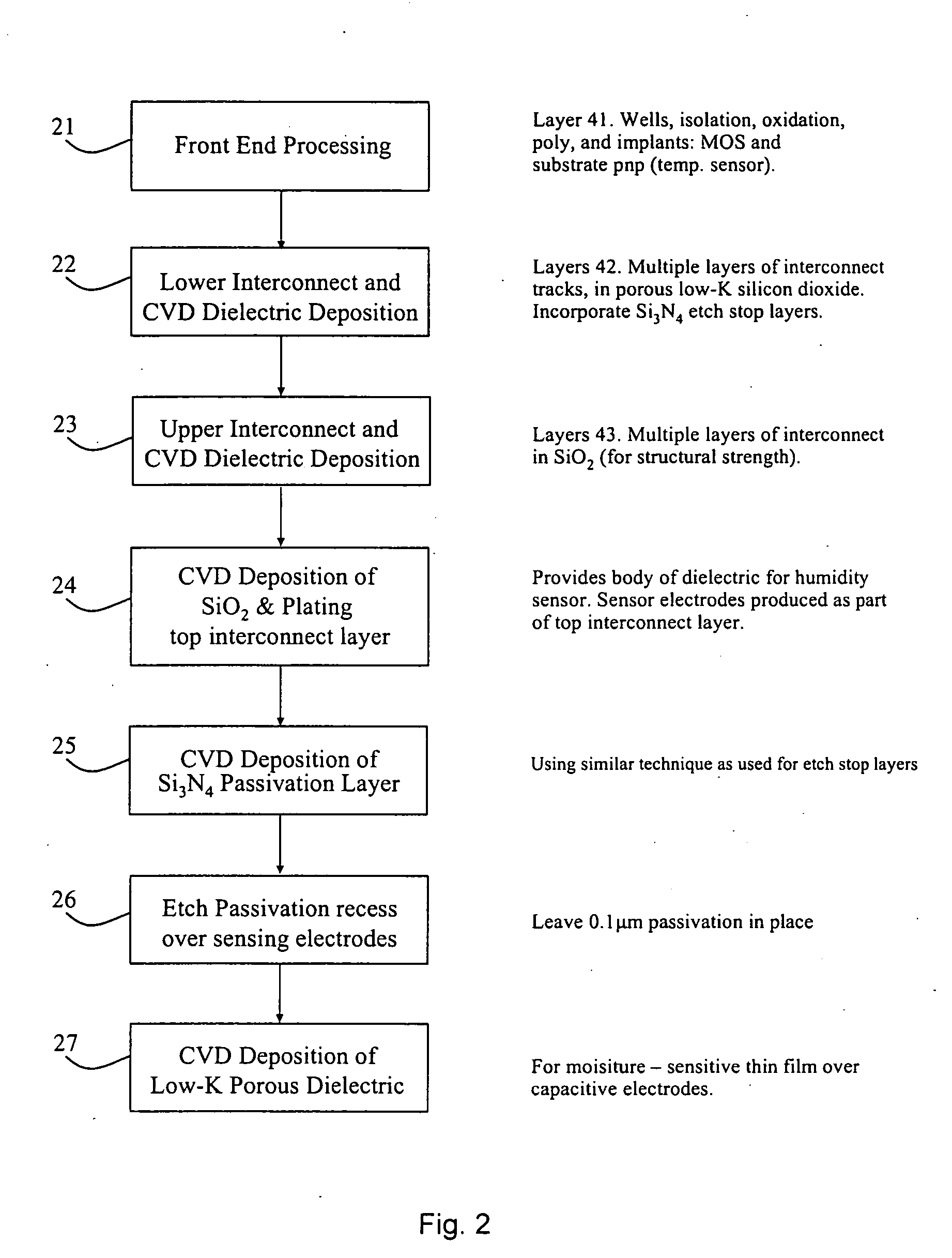

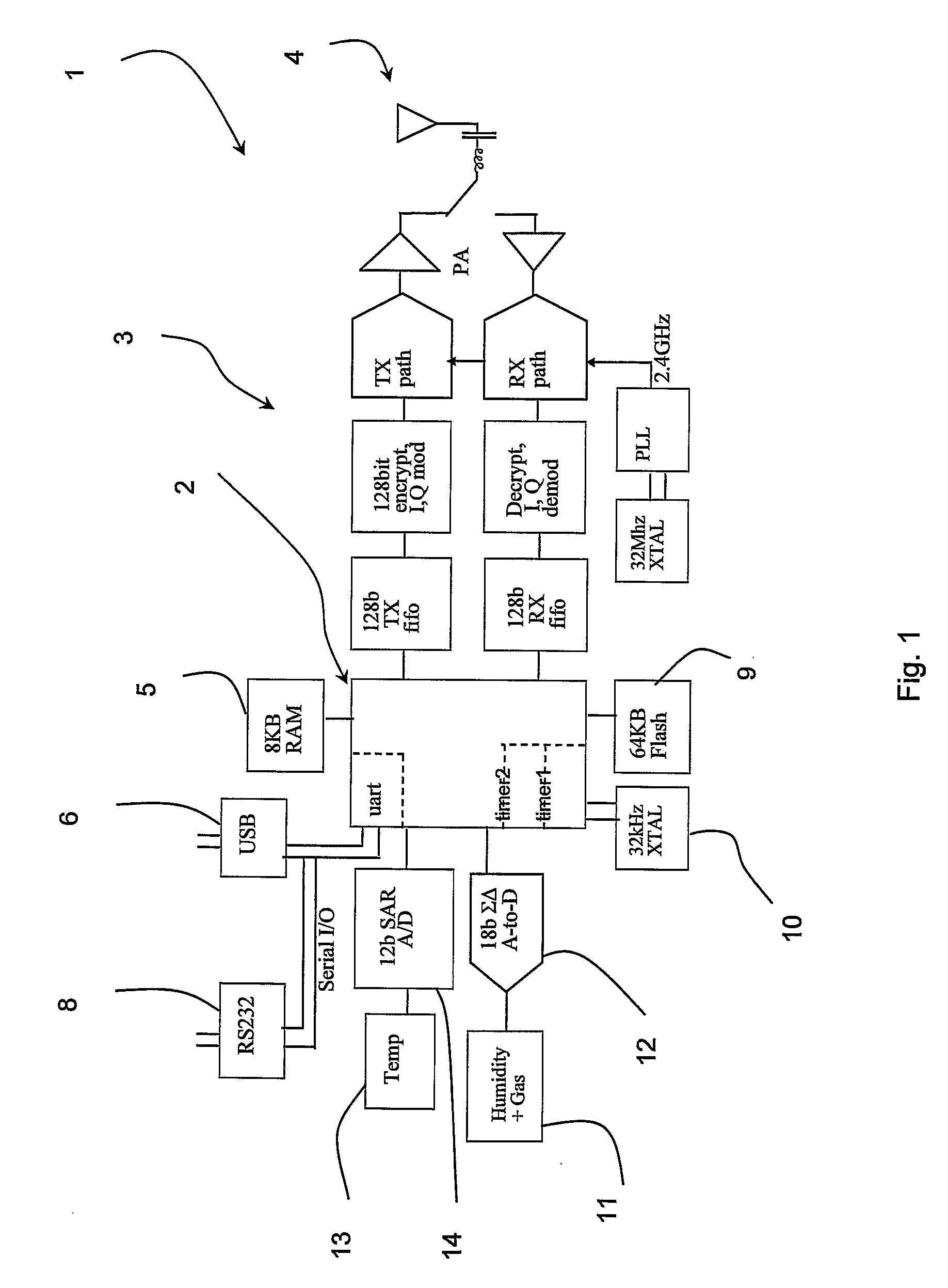

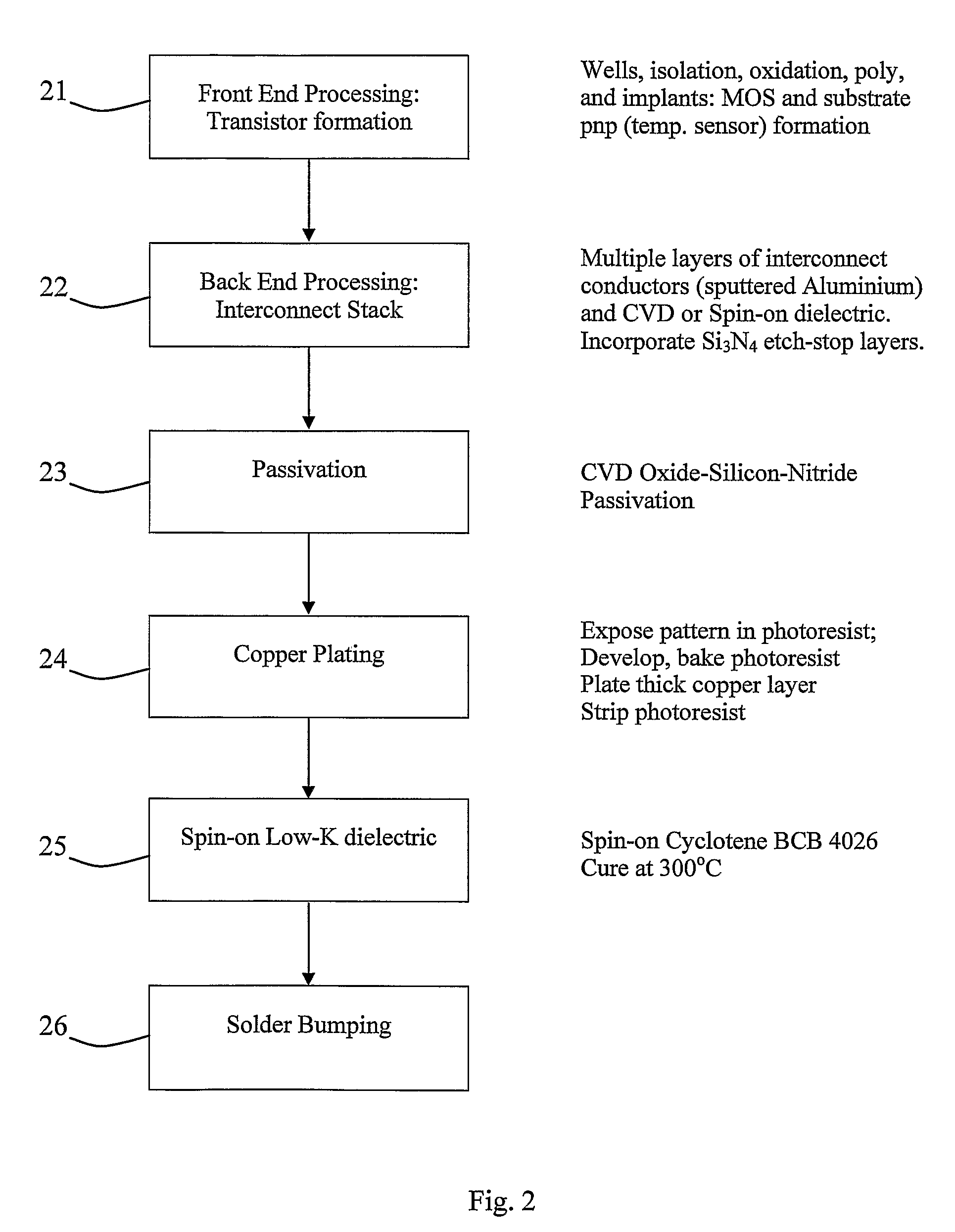

Integrated electronic sensor

ActiveUS20050218465A1Increase productionTransistorSemiconductor/solid-state device detailsMicrocontrollerLine sensor

A single chip wireless sensor (1) comprises a microcontroller (2) connected by a transmit / receive interface (3) to a wireless antenna (4). The microcontroller (2) is also connected to an 8 kB RAM (5), a USB interface (6), an RS232 interface (8), 64kB flash memory (9), and a 32 kHz crystal (10). The device (1) senses humidity and temperature, and a humidity sensor (11) is connected by an 18 bit ΣΔ A-to-D converter (12) to the microcontroller (2) and a temperature sensor (13) is connected by a 12 bit SAR A-to-D converter (14) to the microcontroller (2). The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process.

Owner:SILICON LAB INC

Bone marrow aspiration system

InactiveUS20050288605A1Effective controlBone implantSurgical needlesSingle processBiomedical engineering

Bone marrow aspiration devices and methods are disclosed for use in preparing a substrate. In general, the device includes an elongate penetrating element, a chamber adapted to retain a substrate, and a fluid extraction mechanism that is effective to pull fluid through the elongate penetrating element, into the chamber, and through the substrate. The device is particularly advantageous in that it will allow for the removal of fluids from a patient's body and the preparation of a substrate in a single process, thereby providing a more efficient method and device for preparing a substrate.

Owner:PELLEGRINO RICHARD C +1

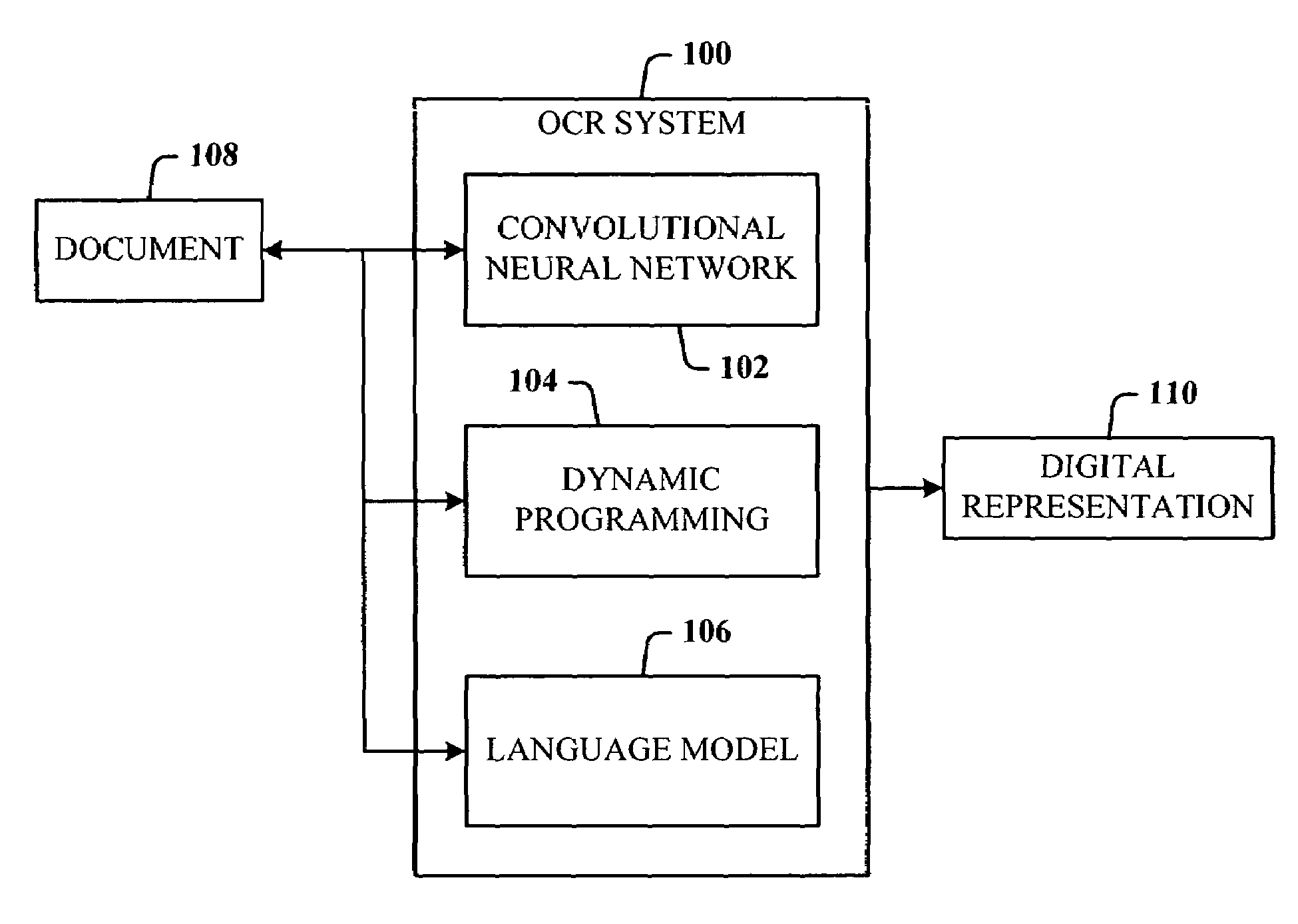

Low resolution OCR for camera acquired documents

ActiveUS7499588B2Low resolution OCRMaximum robustnessBiological modelsCharacter recognitionSingle processGrey level

Owner:MICROSOFT TECH LICENSING LLC

Semiconductor chip using both polysilicon and metal gate devices

InactiveUS6777761B2Improve reliabilityReduce leakage currentTransistorSolid-state devicesSingle processGate dielectric

A semiconductor structure (and method for forming) having transistors having both metal gates and polysilicon gates on a single substrate in a single process is disclosed. The method forms a gate dielectric layer on the substrate and forms the metal seed layer on the gate oxide layer. The method patterns the metal seed layer to leave metal seed material in metal gate seed areas above the substrate. Next, the method patterns a polysilicon layer into polysilicon structures above the substrate. Some of the polysilicon structures comprise sacrificial polysilicon structures on the metal gate seed areas and the remaining ones of the polysilicon structures comprise the polysilicon gates. The patterning of the polysilicon gates forms the sacrificial gates above all the metal gate seed areas. Following that, the invention forms sidewall spacers, and source and drain regions adjacent the polysilicon structures. Then, the invention protects the polysilicon gates, removes the sacrificial polysilicon structures, and plates the metal gate seed areas to form the metal gates. The sidewall spacers self-align the metal gates. The plating process forms the metal gates of pure metal. All thermal processing that raises the temperature above a damage threshold for the metal is performed before the plating process.

Owner:ELPIS TECH INC

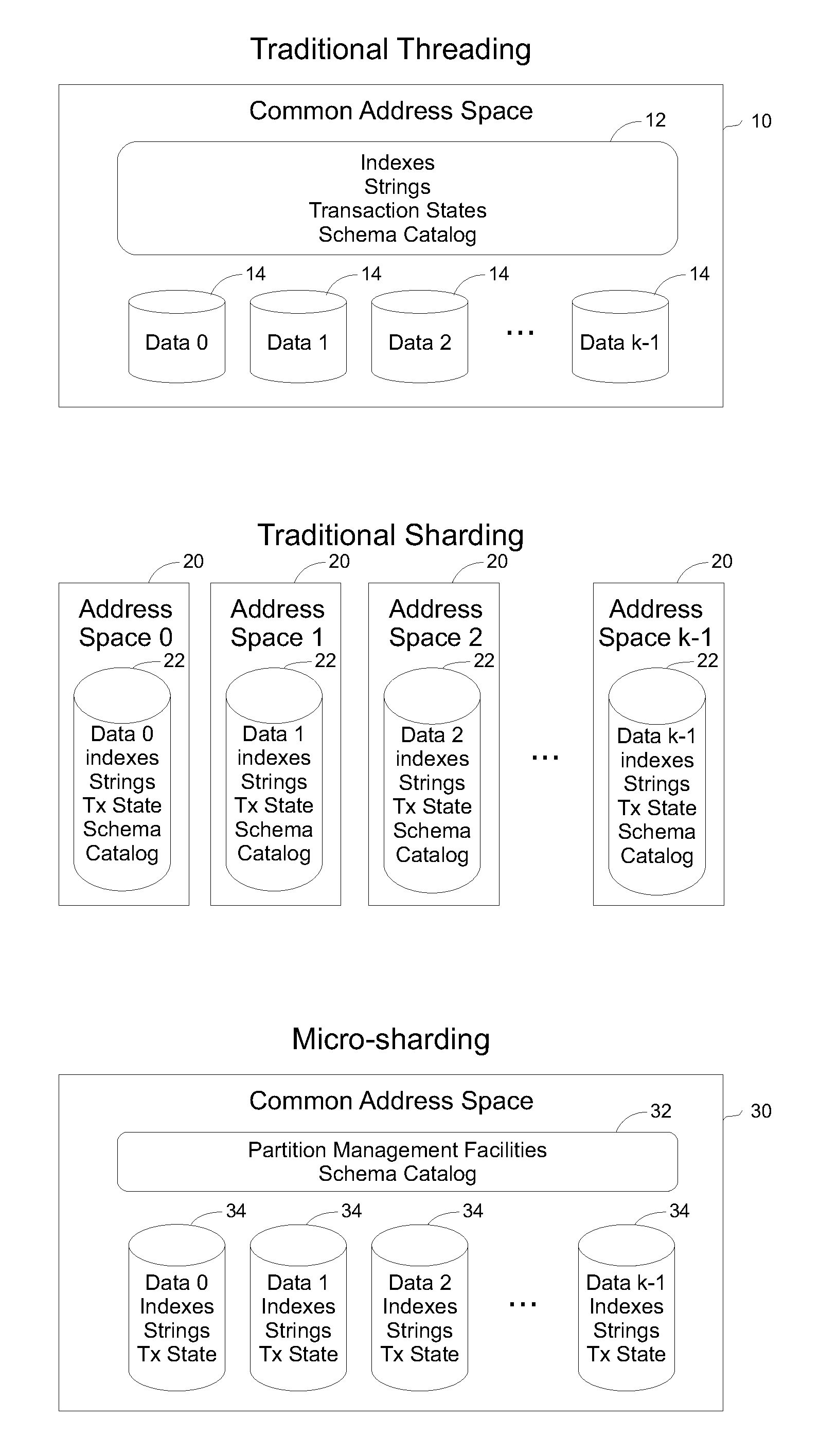

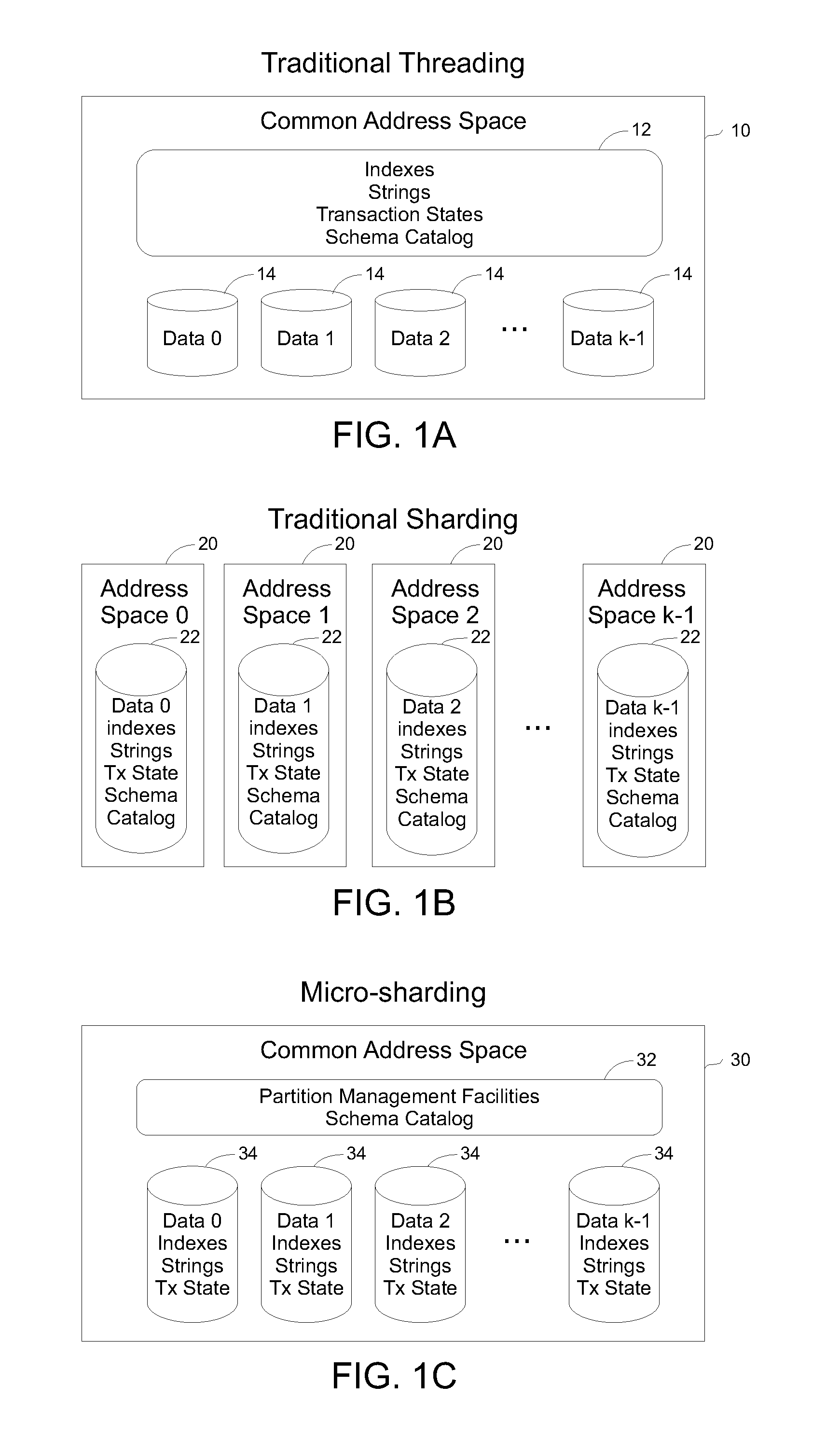

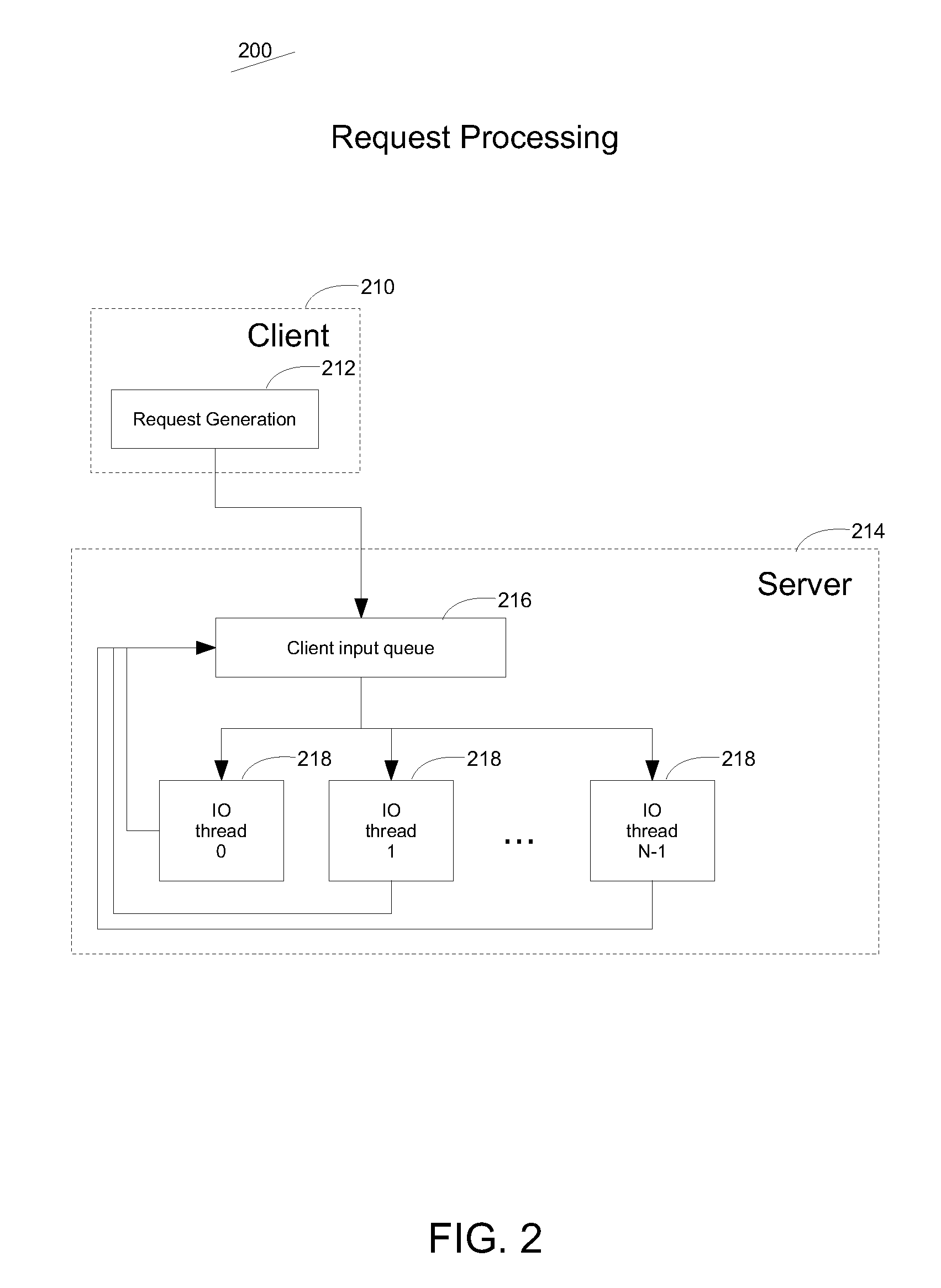

Method and system for parallelizing database requests

ActiveUS20110202929A1Reduce communication overheadReduced response timeDigital data information retrievalMultiprogramming arrangementsClient-sideSingle process

Methods and systems are described for applying the use of shards within a single memory address space. A database request is processed by providing the request from a client to a processor, the processor then distributing the request to multiple threads within a single process but executing in a shared memory address environment, wherein each thread performs the request on a distinct shard, and aggregating the results of the multiple threads being aggregated and returning a final result to the client. By parallelizing operations in this way, the request response time can be reduced and the total amount of communication overhead can be reduced.

Owner:ORACLE INT CORP

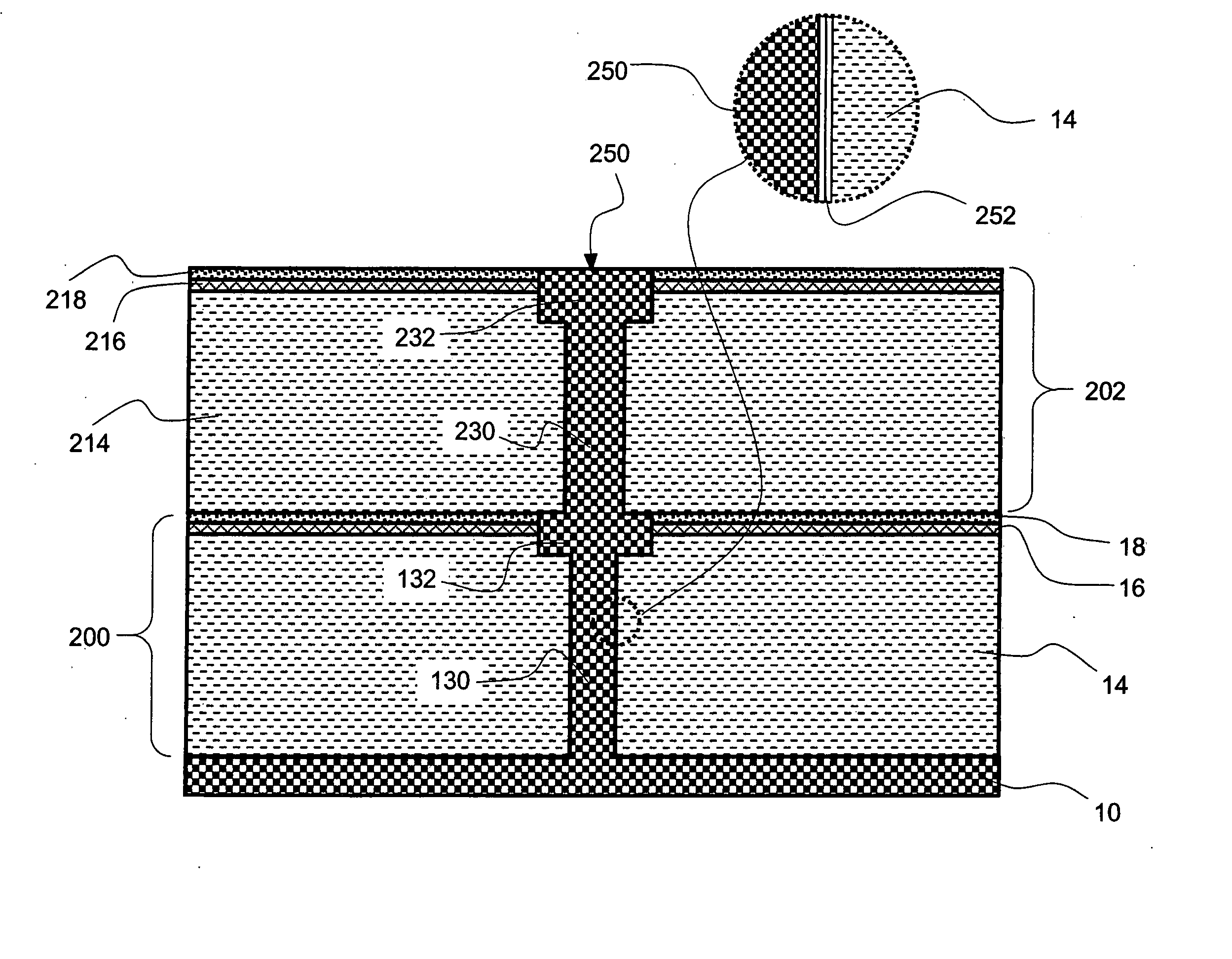

Multilayer metallization

ActiveUS20050110145A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSingle process

Multiple metallization layers in a partially fabricated integrated circuit are formed in a single process step. As a place-holder for the later-deposited metallization layers, sacrificial material is deposited in the integrated circuit at desired locations at various fabrication levels over a substrate. The sacrificial material is then removed to form a contiguous open volume spanning multiple fabrication levels. A conductor is then deposited in the open volume to form multiple metallization layers in a single step.

Owner:ASM INTERNATIONAL

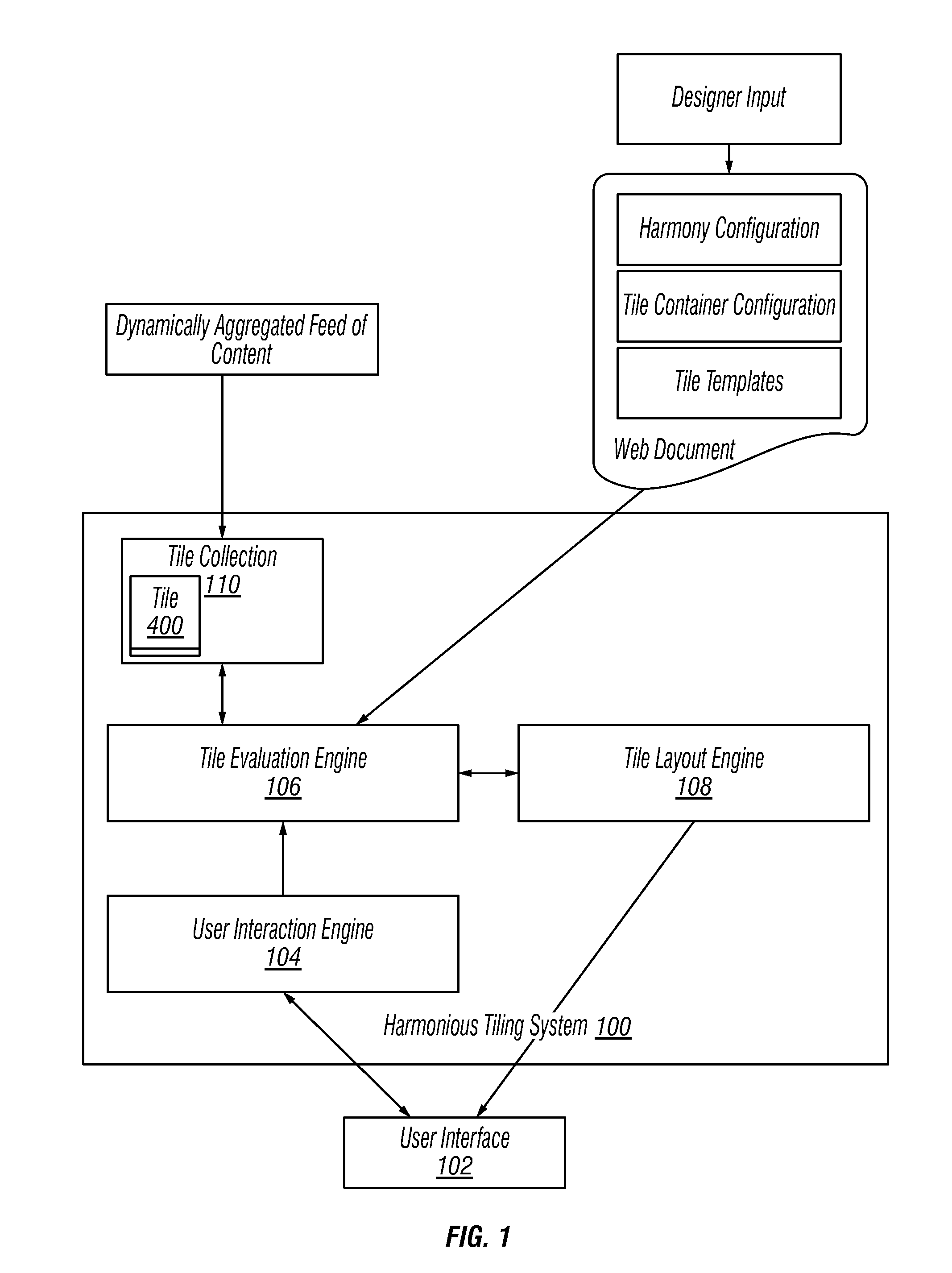

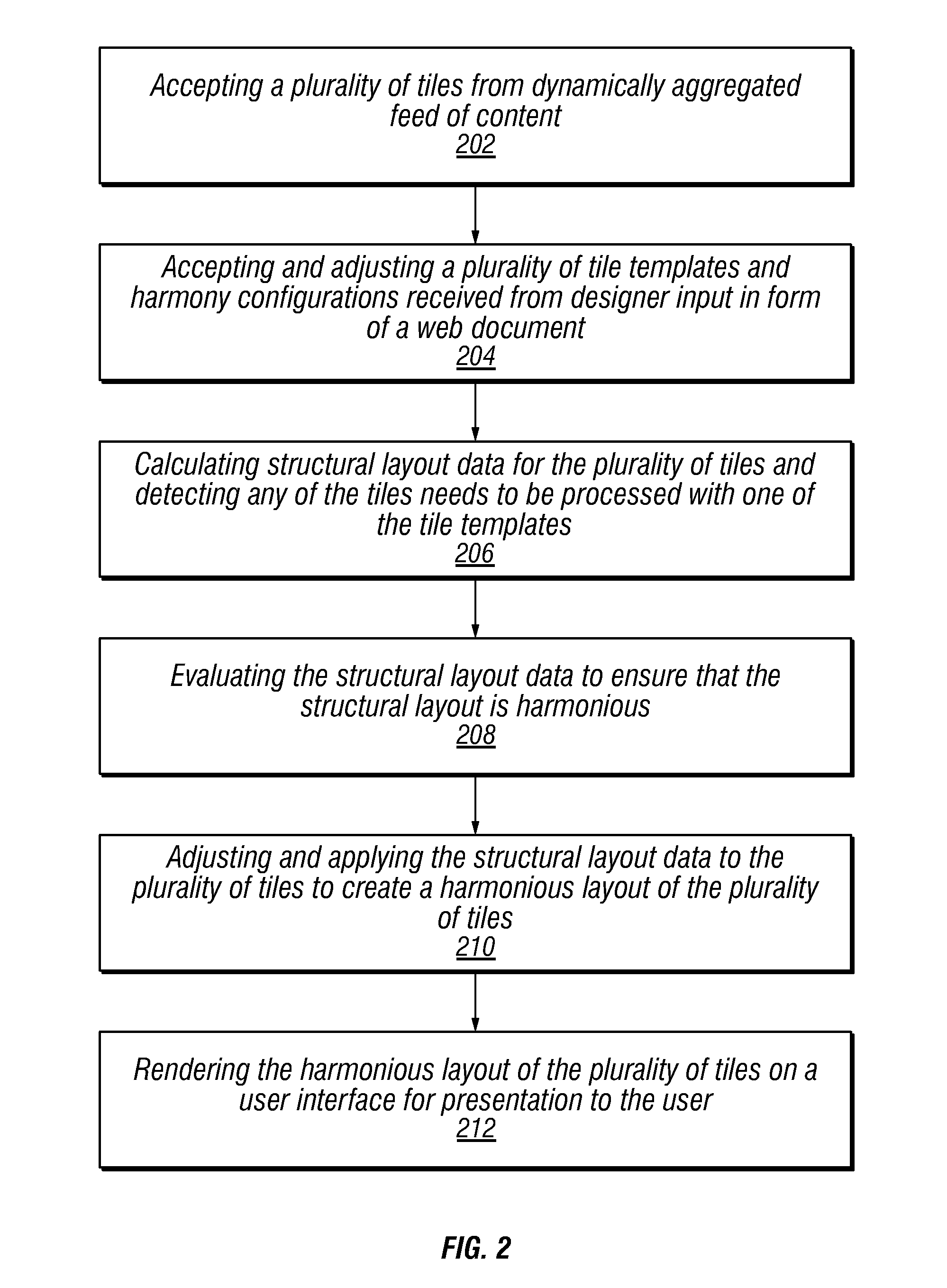

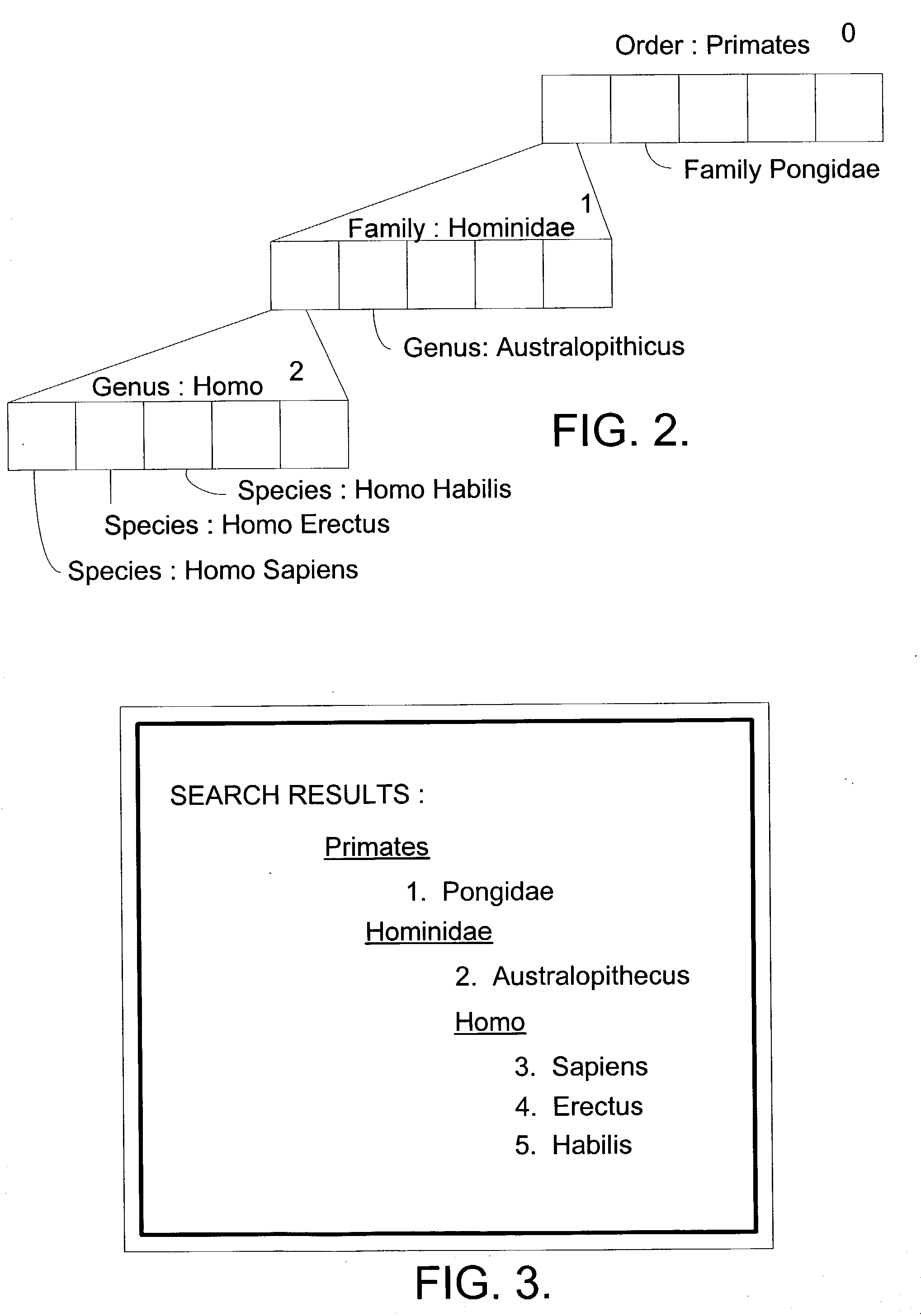

System and method for harmonious tiling search and publishing

InactiveUS20120226971A1Shorten the timeCooperate effectivelyDigital data information retrievalSpecial data processing applicationsData feedVisual presentation

A new approach is proposed that contemplates systems and methods to provide harmonious tiling layout for a single heterogeneous data feed with a unique and brief syntax. The approach provides solutions to fit shapes into a container without having any holes by automatically providing the most optimum harmonious layout and tile presentation “win-out” over time, and a survival of the fittest of visual presentation based on configurable metrics. A single user interface combines the action of searching and publishing as a single process whereby search results are formatted with the intention to facilitate publishing the chosen items.

Owner:RITUWALL

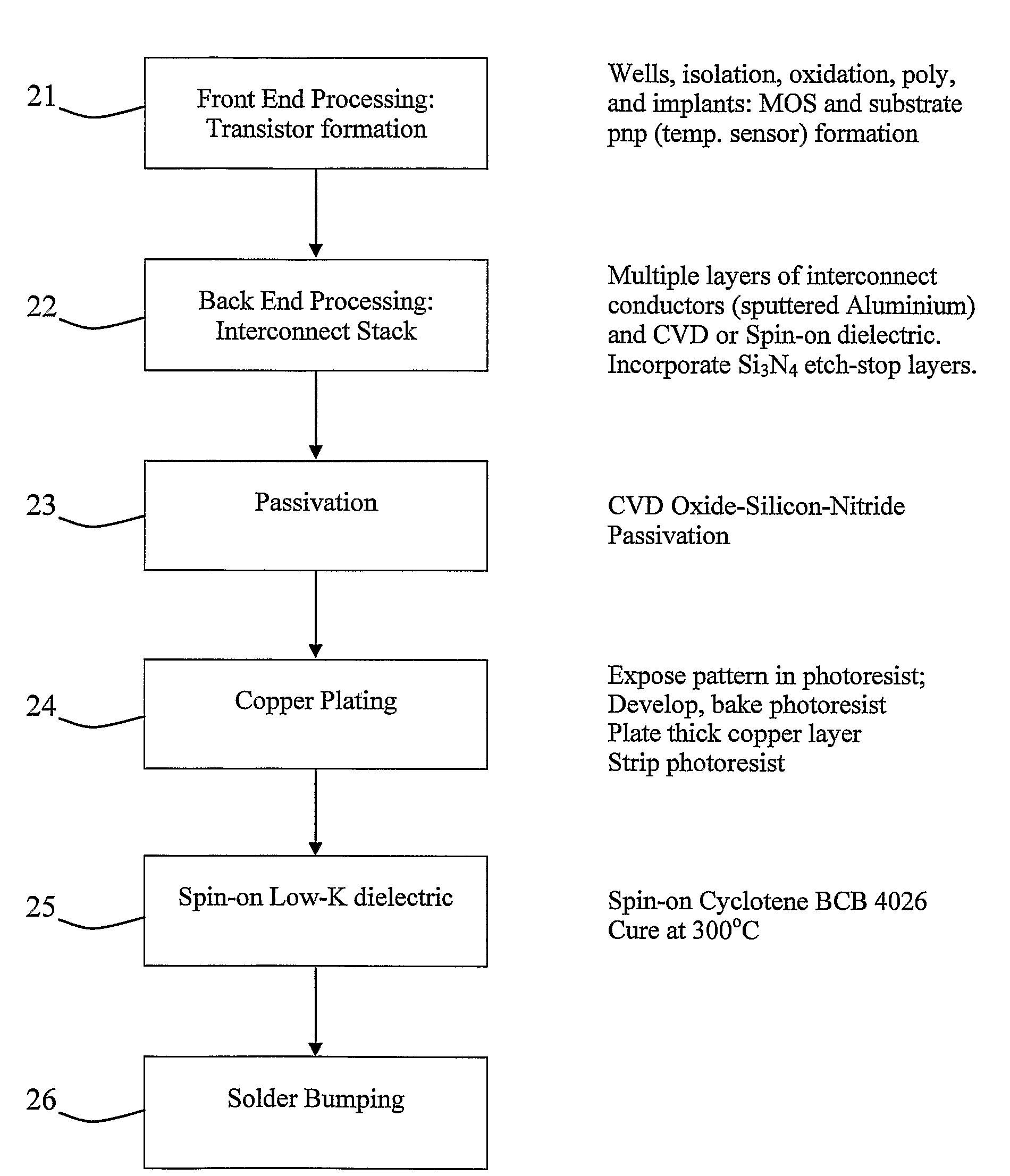

Integrated Electronic Sensor

ActiveUS20090141767A1Improve response characteristicsSufficient free space volumeThermometer detailsAnalysing fluids using sonic/ultrasonic/infrasonic wavesMicrocontrollerLine sensor

A single chip wireless sensor (1) comprises a microcontroller (2) connected to a transmit / receive interface (3), which is coupled to a wireless antenna (4) by an L-C matching circuit. The sensor (1) senses gas or humidity and temperature. The device (1) is an integrated chip manufactured in a single process in which both the electronics and sensor components are manufactured using standard CMOS processing techniques, applied to achieve both electronic and sensing components in an integrated process. A Low-K material (57) with an organic polymer component is spun onto the wafer to form a top layer incorporating also sensing electrodes (60). This material is cured at 300° C., which is much lower than CVD temperatures. The polyimide when cured becomes thermoset, and the lower mass-to-volume ratio resulting in K, its dielectric constant, reducing to 2.9. The thermoset dielectric, while not regarded as porous in the conventional sense, has sufficient free space volume to admit enough gas or humidity for sensing.

Owner:SILICON LAB INC

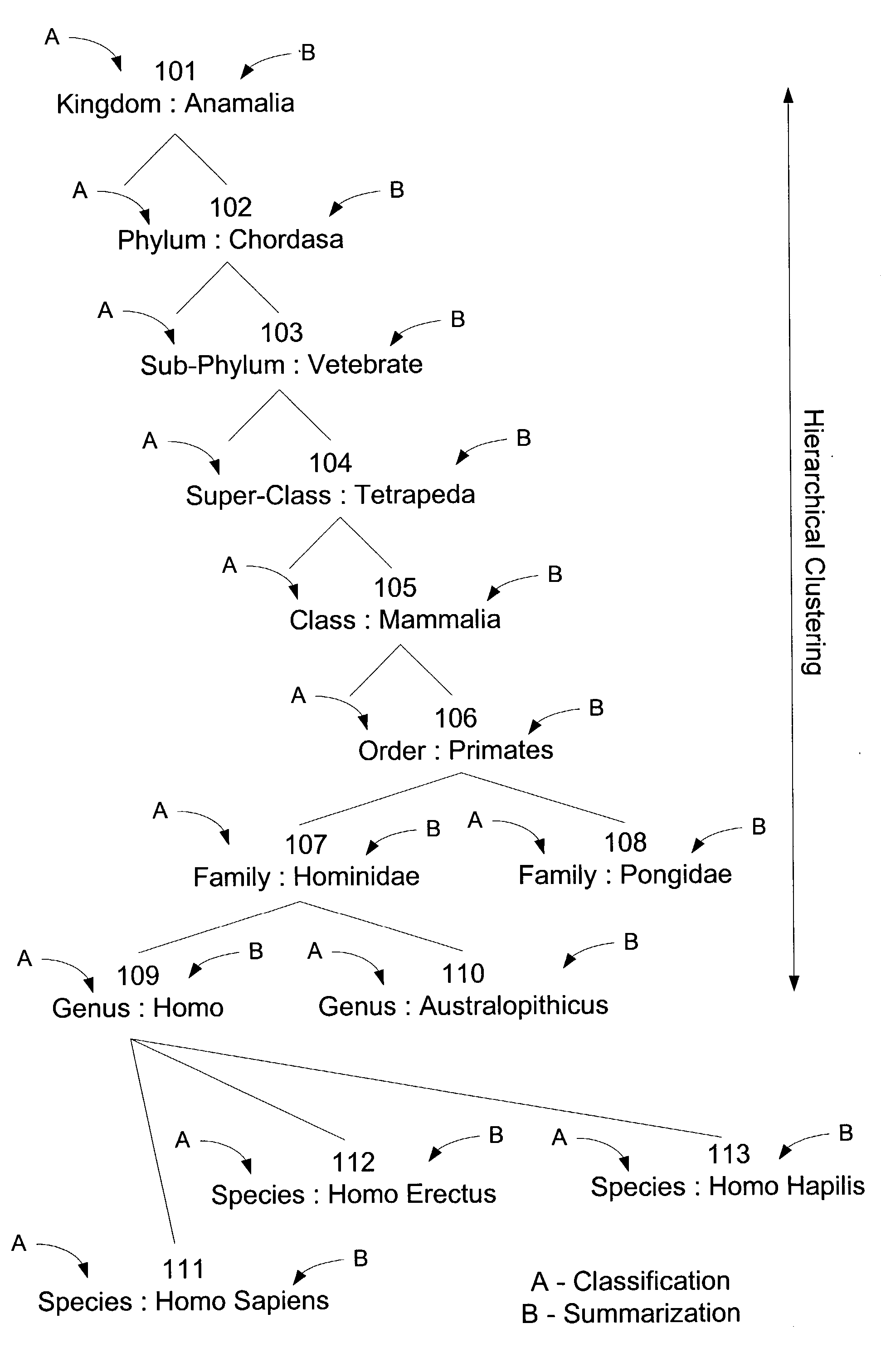

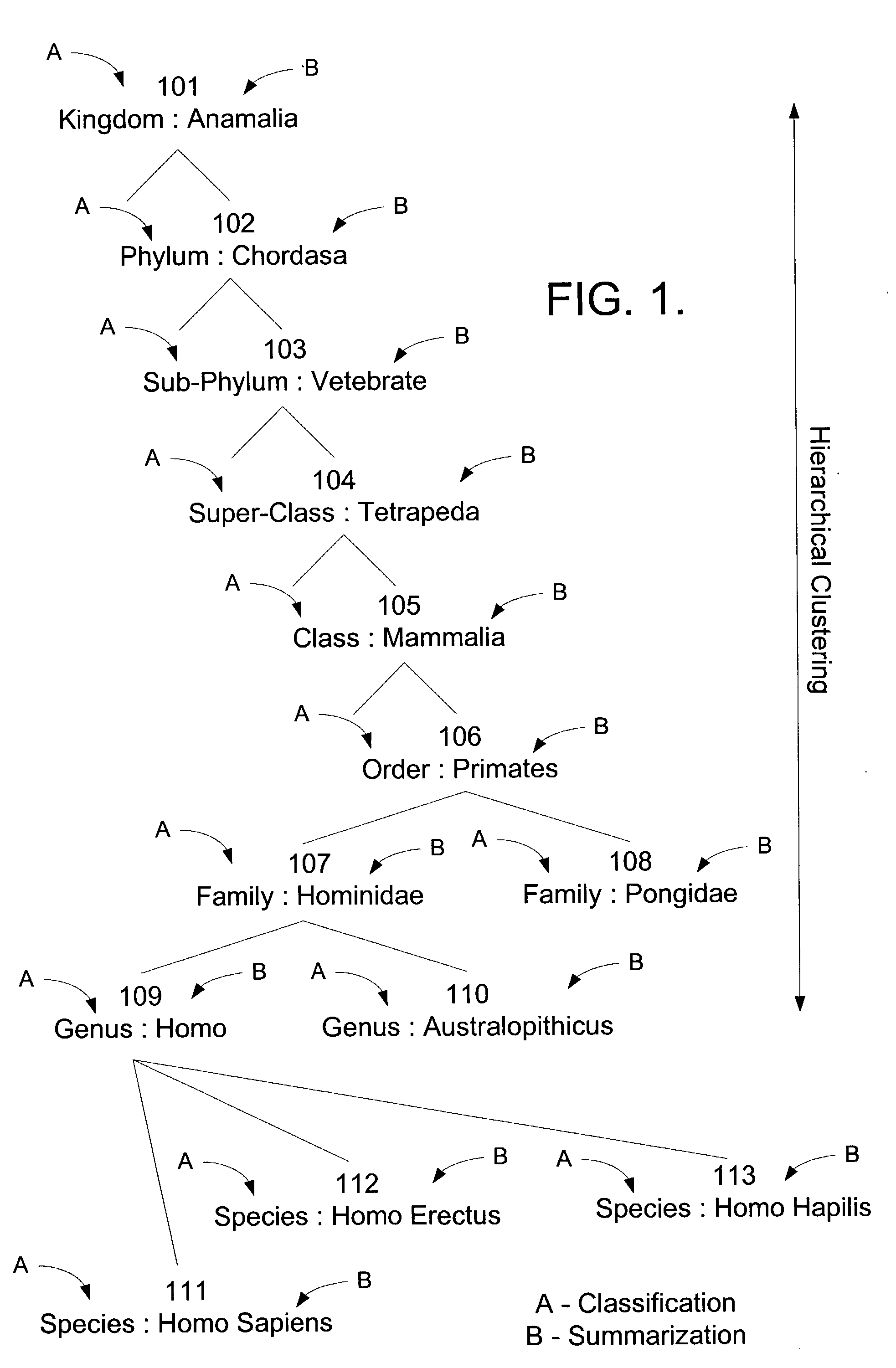

Method for clustering automation and classification techniques

InactiveUS20030061242A1Enhancing process of automated classificationData processing applicationsDigital data information retrievalSingle processRelevant information

Owner:ORACLE OTC SUBSIDIARY

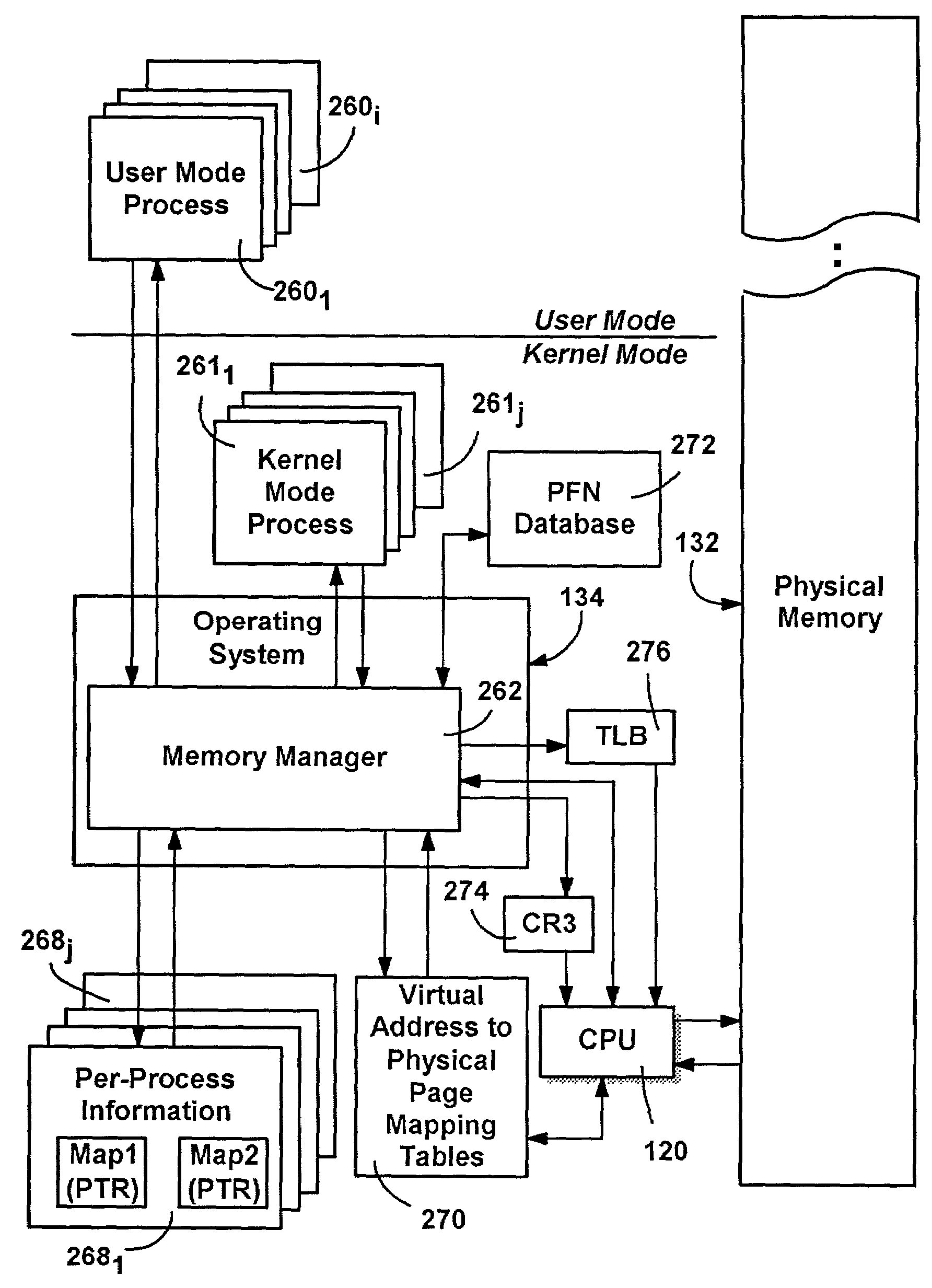

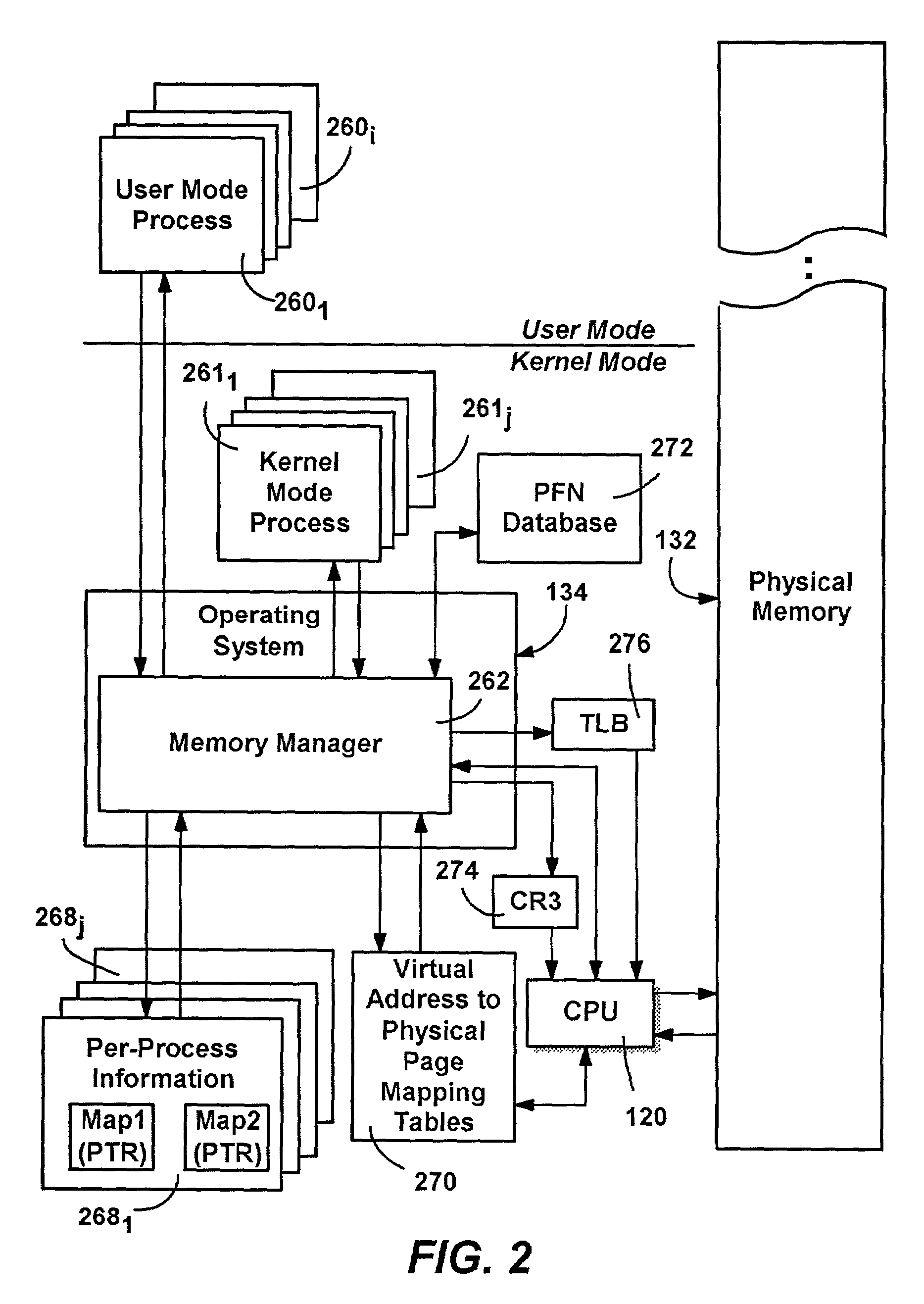

Code and thread differential addressing via multiplex page maps

InactiveUS7073173B1Provide securityOvercome problemsSpecific access rightsMemory adressing/allocation/relocationSingle processParallel computing

Described is a system and method whereby processes may have multiple memory maps associated therewith to provide curtained memory and overcome other memory-related problems. Multiple maps are used to restrict memory access of existing code such as drivers, without changing that code, and without changing existing microprocessors. A thread of a process is associated with one memory map at a time, which by mapping to different memory locations, provides memory isolation without requiring a process switch. Memory isolation may be combined with controlled, closed memory map switching performed only by trusted code, to ensure that some protected memory is inaccessible to all but the trusted code (curtained memory). Map switching among multiple maps eliminates the need to change a process in order to access different memory, thereby allowing expanded memory addressing in a single process and isolating untrusted code run in process from certain memory of that process.

Owner:MICROSOFT TECH LICENSING LLC

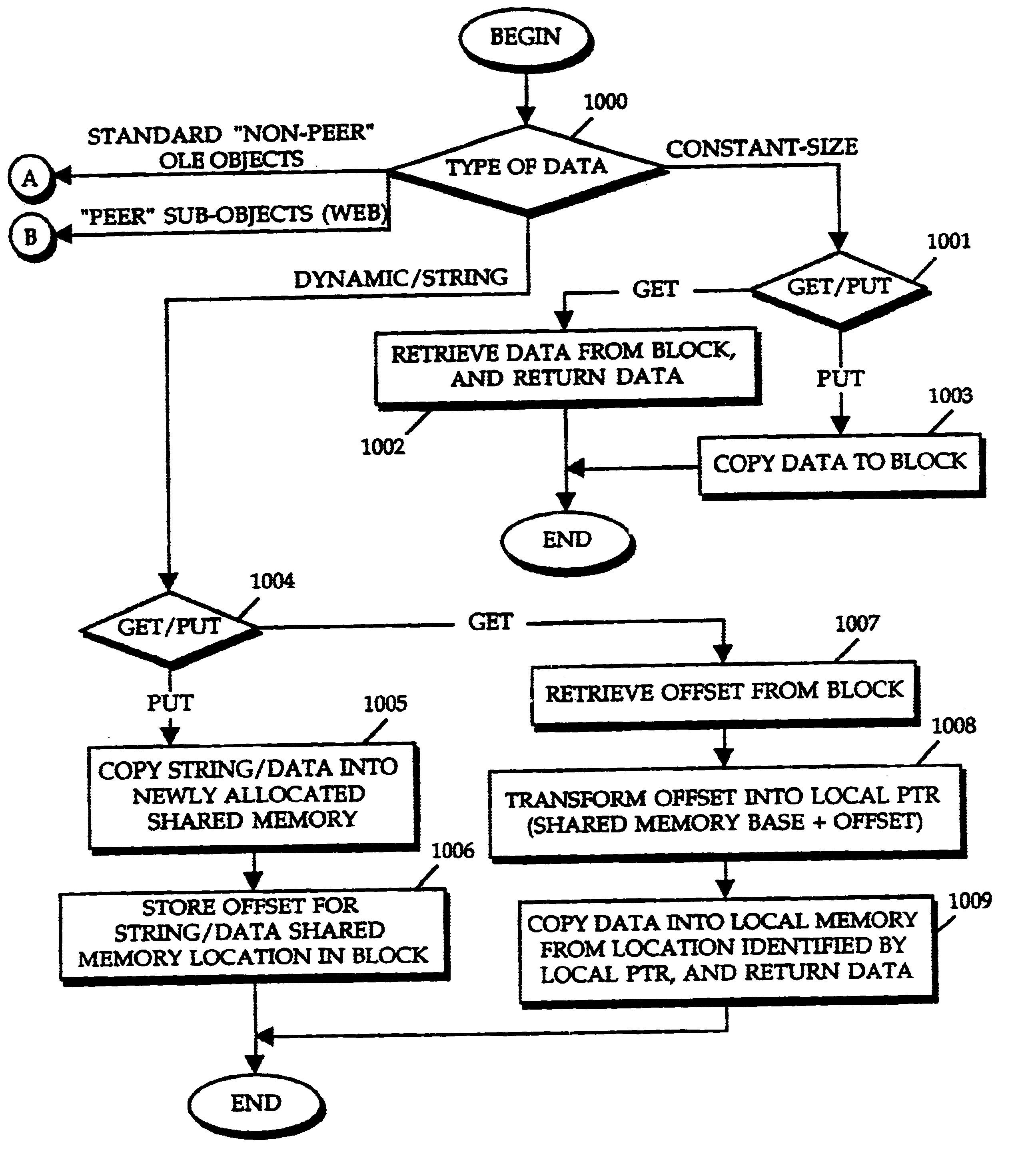

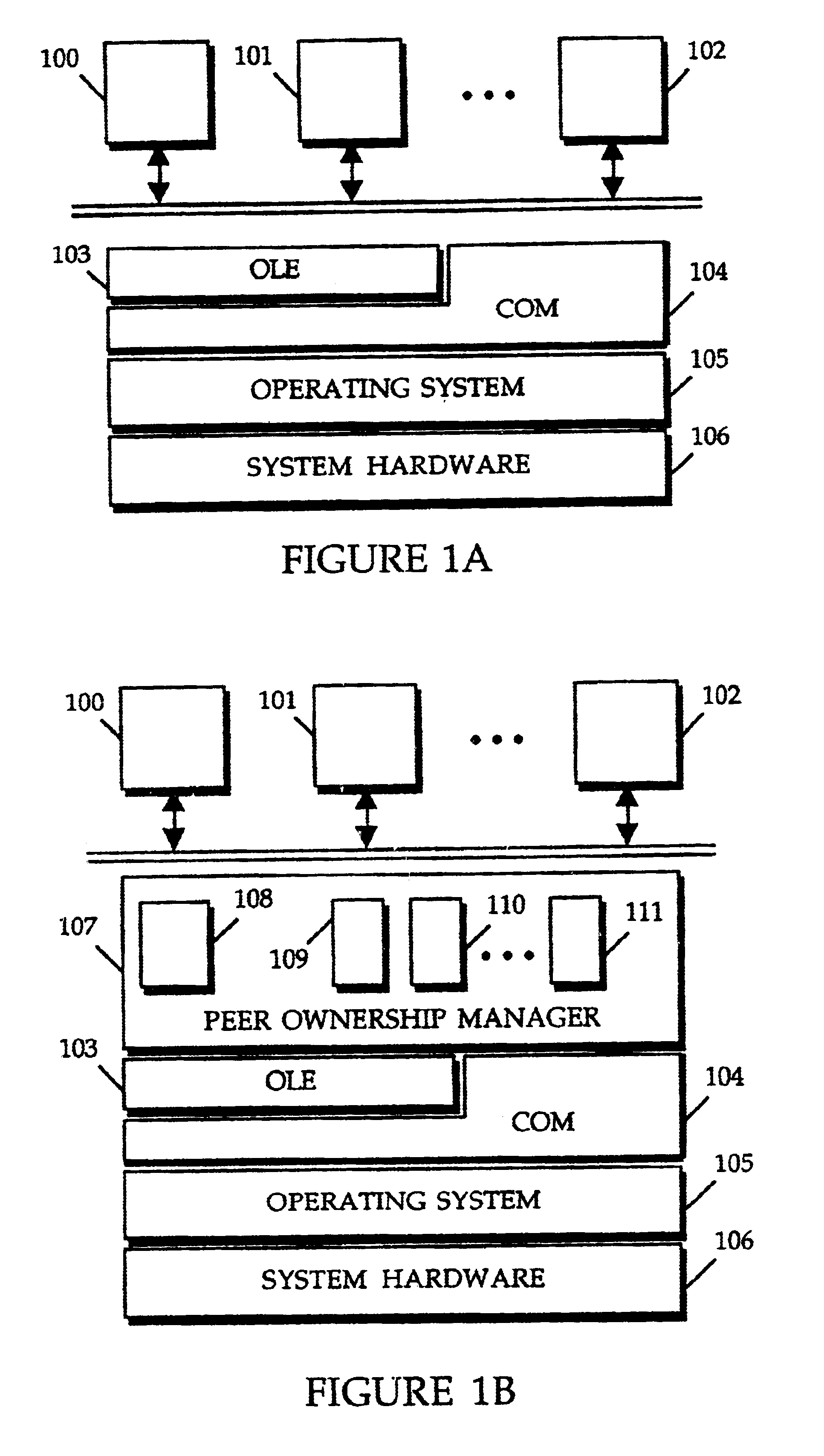

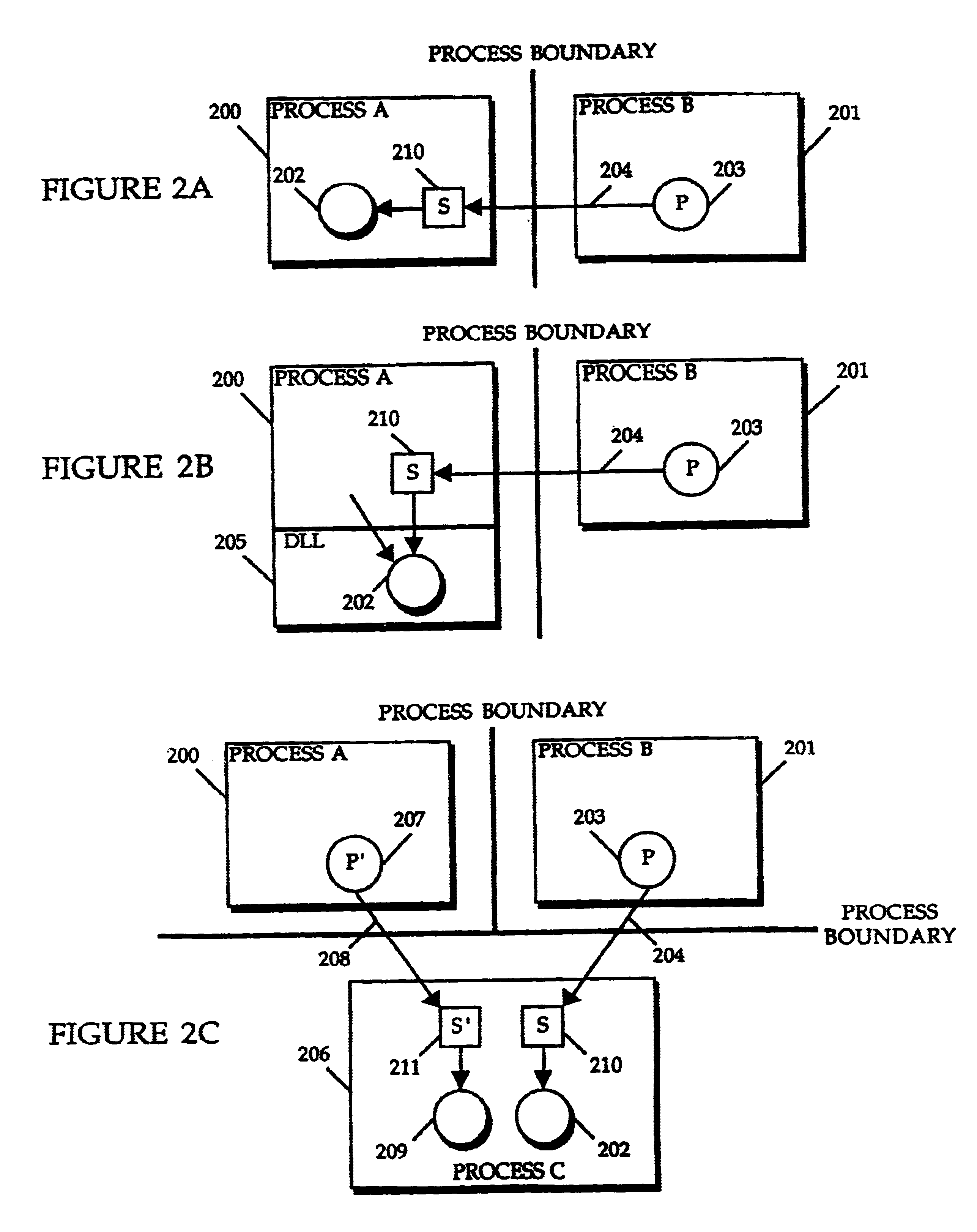

Method and apparatus for providing peer ownership of shared objects

A method and apparatus for providing peer ownership of shared objects. In the invention, shared objects are implemented as a shell object with shared object state stored in shared memory. Each process that shares the object is granted a shell object within their process space which points to the object state in shared memory. All processes share equal access to the shared object, with no single process determining the lifetime of the shared object. The shutdown of any single process results in the termination of that process's respective shell object, without the necessary termination of the shared object state in shared memory. There is therefore no shutdown problem. Further, performance is enhanced because all processes access the shared object state in shared memory in what is essentially an in-process call. In an embodiment of the invention, a peer ownership manager acts as the object server for all shared objects whose object state resides in shared memory. A global table is maintained within the peer ownership manager which contains the shared memory offset location of each object's state referenced by the GID (global identifier number) of the object. Also, for each process, a shell table is maintained in which existing shell objects for a given process are referenced by the offset value for the object's state in shared memory. Methods are provided for supporting object webs in shared memory, and for putting dynamically sized data and standard non-peer objects into shared objects in shared memory.

Owner:VERSATA DEV GROUP

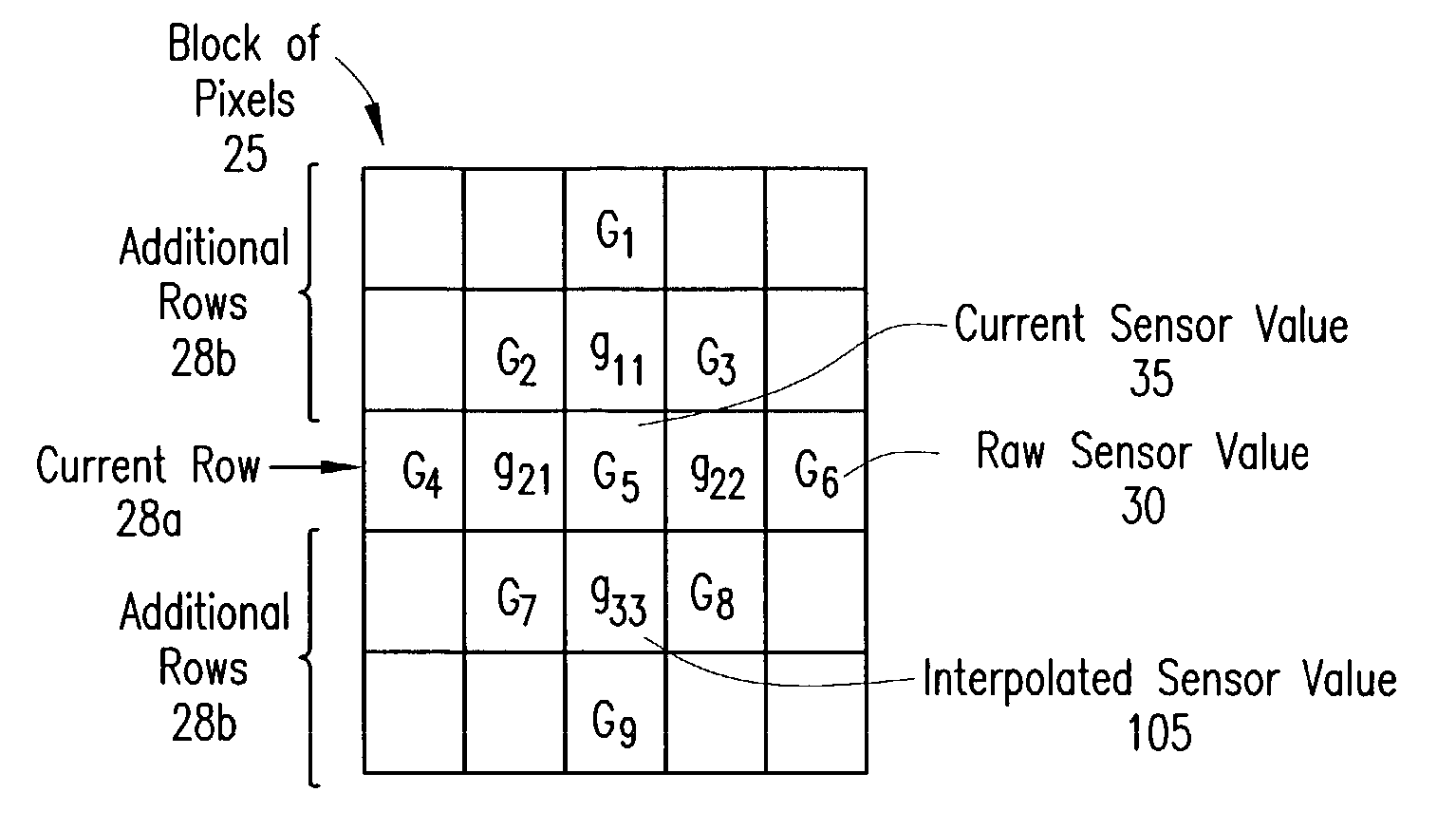

Digital image system and method for combining demosaicing and bad pixel correction

A digital image system and method for combining bad pixel correction and demosaicing in a single process is provided by interpolating sensor values for pixels immediately spatially adjacent to the current pixel being examined to detect defective pixels, and using the interpolated values for demosaicing. If the sensor value of the current pixel being examined is outside of a range of sensor values determined from the interpolated values by more than a configurable threshold amount, the current pixel is considered defective, and replaced using an estimated value from the neighboring pixels. The interpolated values calculated for use in detecting bad pixels can further be used as the interpolated values for demosaicing purposes

Owner:APTINA IMAGING CORP

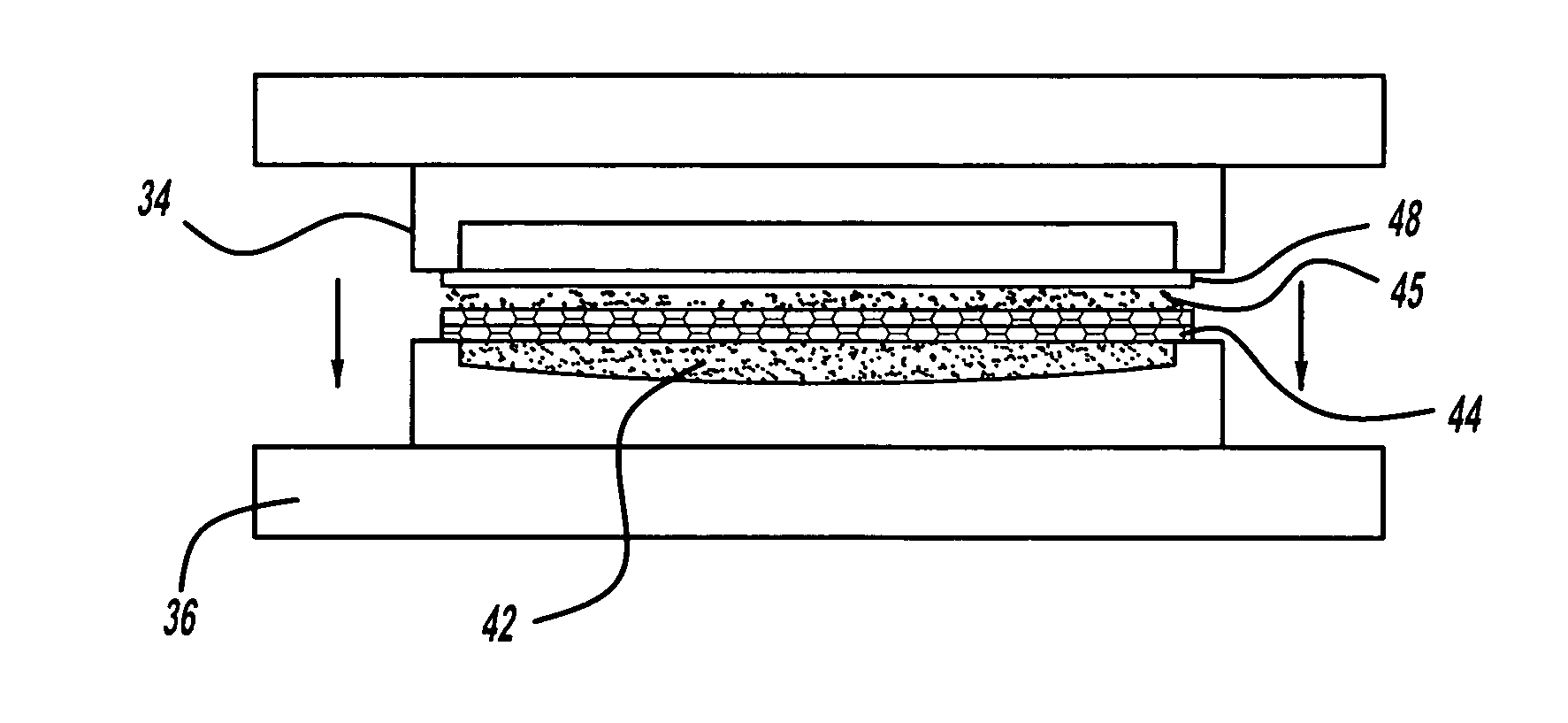

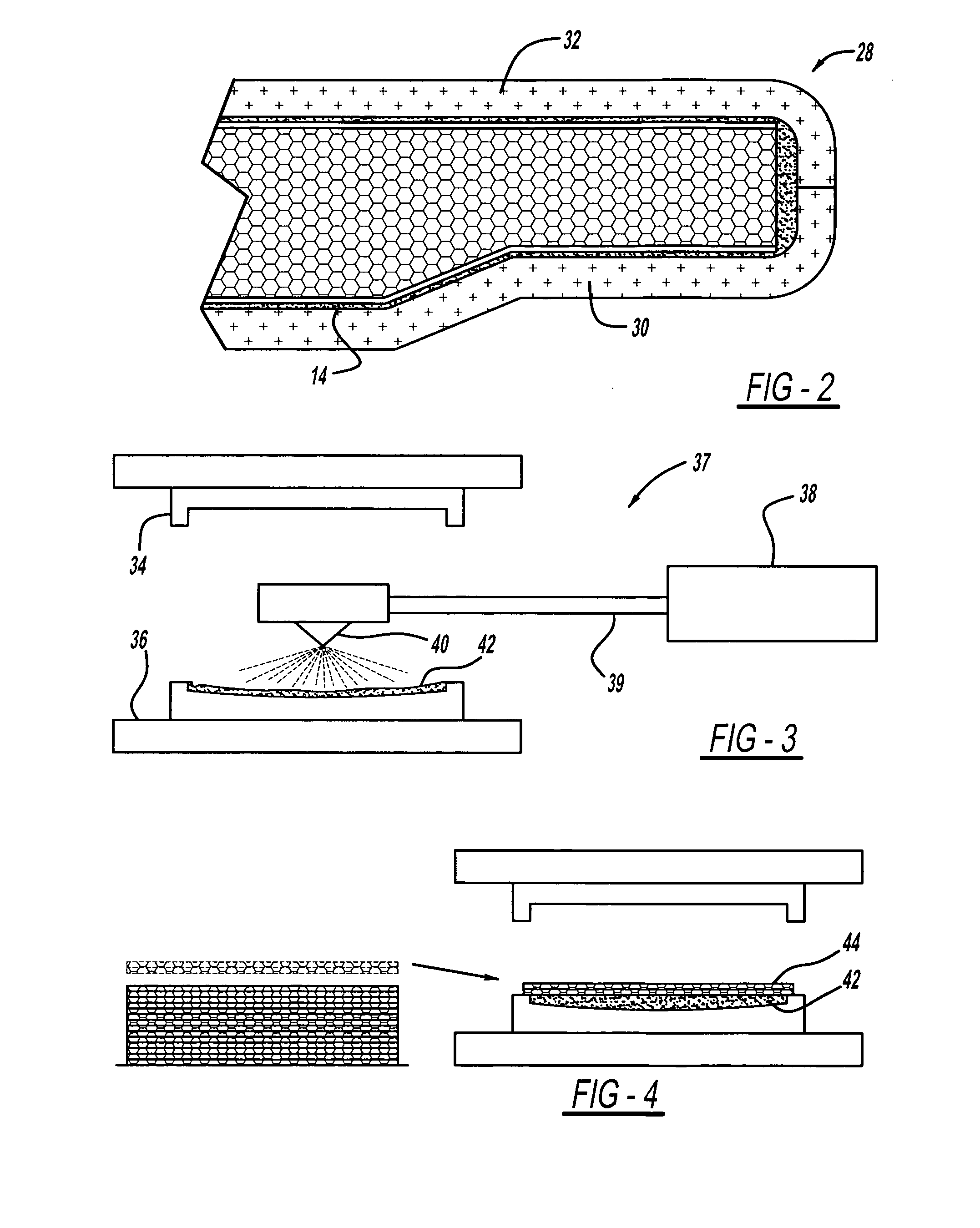

Single press mold process for forming a finished light weight structural component

A single process for forming a finished component is described herewith. The process includes providing a core having two outer layers on each side of the core. A water activated resin system is provided that includes a resin and applicator for applying resin to the outer layers at the core. A film layer used for creating a final finished product is placed over the core and resin layers. The layers are pressed to form the finished product.

Owner:MAGNA INTERNATIONAL INC

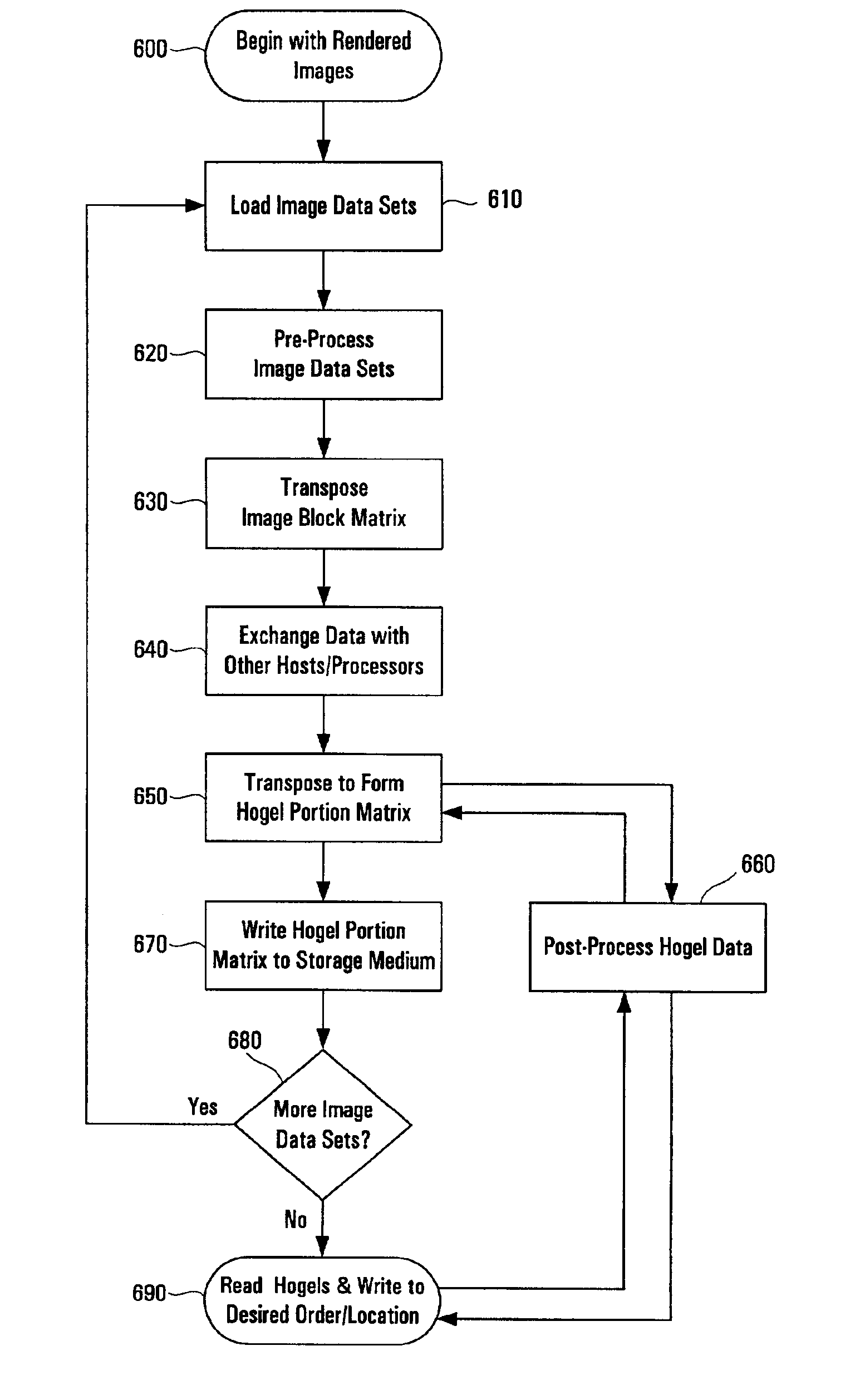

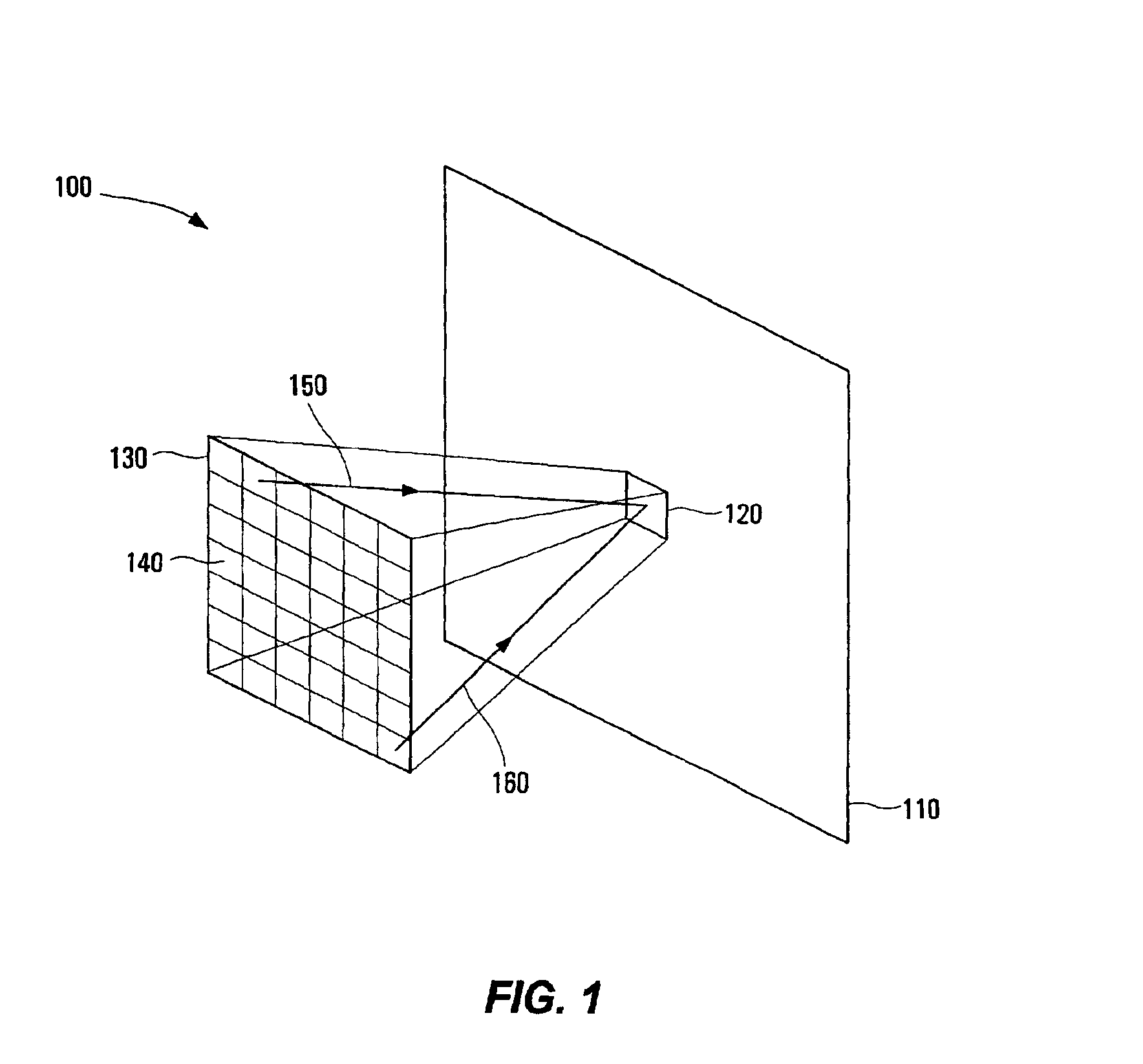

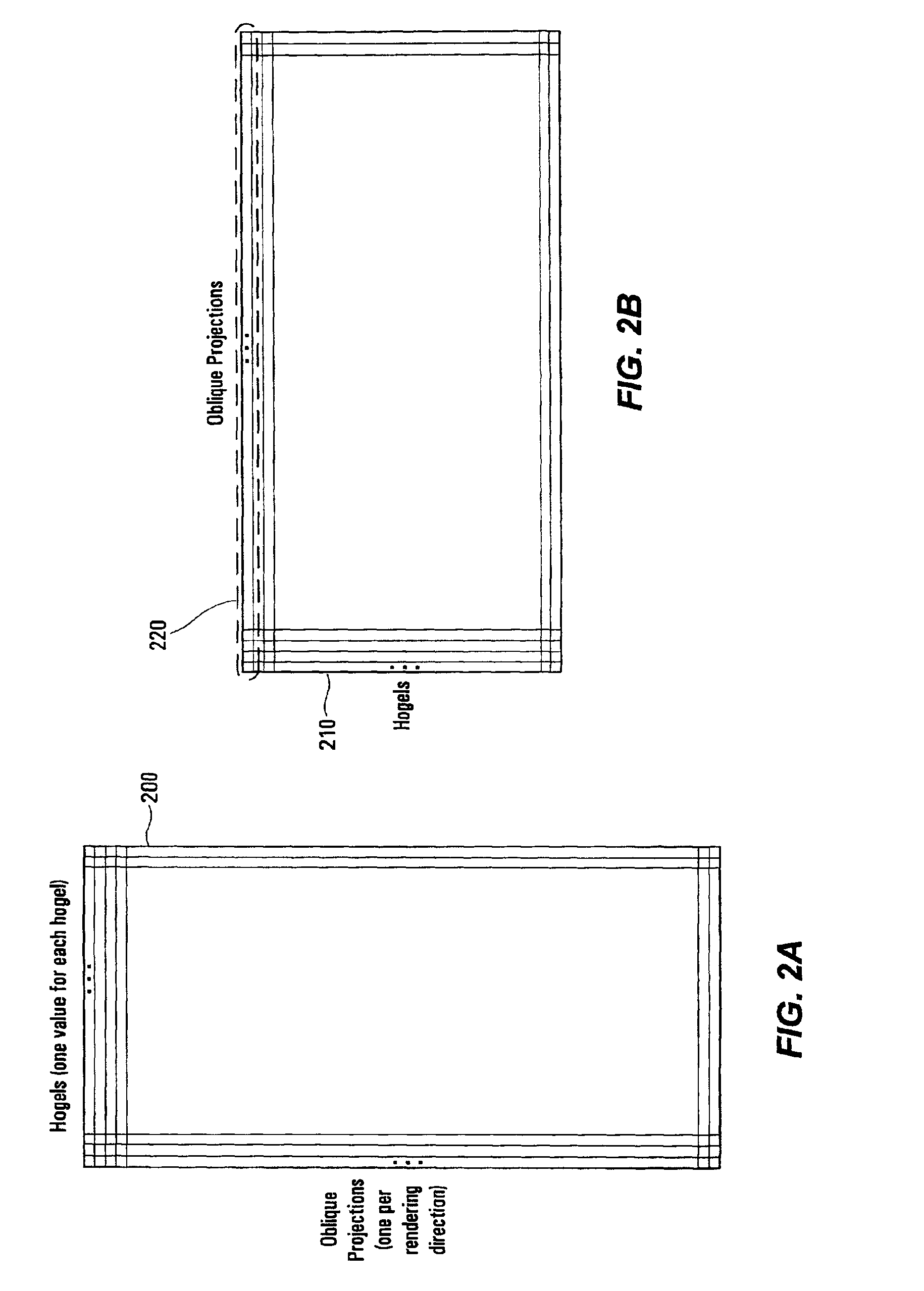

Efficient block transform including pre-processing and post processing for autostereoscopic displays

InactiveUS6868177B1Television system detailsMemory adressing/allocation/relocationSingle processData set

Image data processing techniques utilizing multiple processes operating on one or more processors of one or more computer systems can be used to efficiently rearrange or reparameterizing image data to form hologram element (hogel) images which can then be used to produce holographic stereograms. These techniques utilize matrix manipulation of portions of image data both within a single process, and across multiple processes typically executing on different processors, and each utilizing a subset of the overall set of image data.

Owner:3D PATENTS LLC

Process fluid flow device with variable orifice

A process device providing total fluid flow control is provided. The device includes a closure mechanism disposed in a flow conduit. The closure mechanism, which is preferably an iris-type diaphragm, provides a variable internal diameter. The device includes a differential pressure sensor for sensing the differential pressure on opposite sides of the diaphragm. A controller receives an indication of differential pressure and generates a control signal to an actuator that actuates the closure mechanism. The closure mechanism, differential pressure sensor and controller create a closed-loop flow controller in a single process device.

Owner:ROSEMOUNT INC