Patents

Literature

112 results about "Matrix manipulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Manipulation Matrix. As Eyal describes, the Manipulation Matrix is a simple tool for entrepreneurs, employees, and investors to assess the value of their product to the consumer.

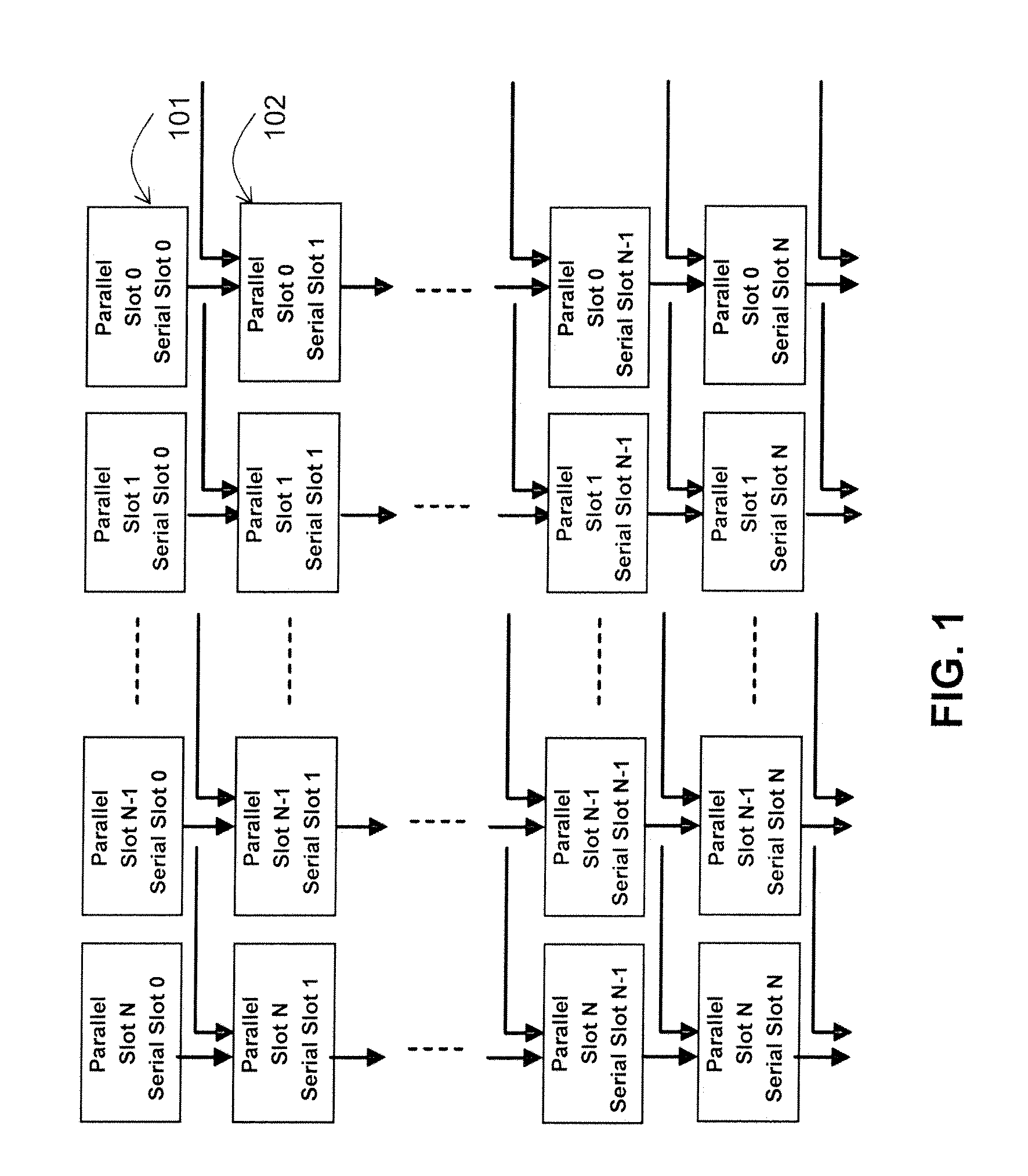

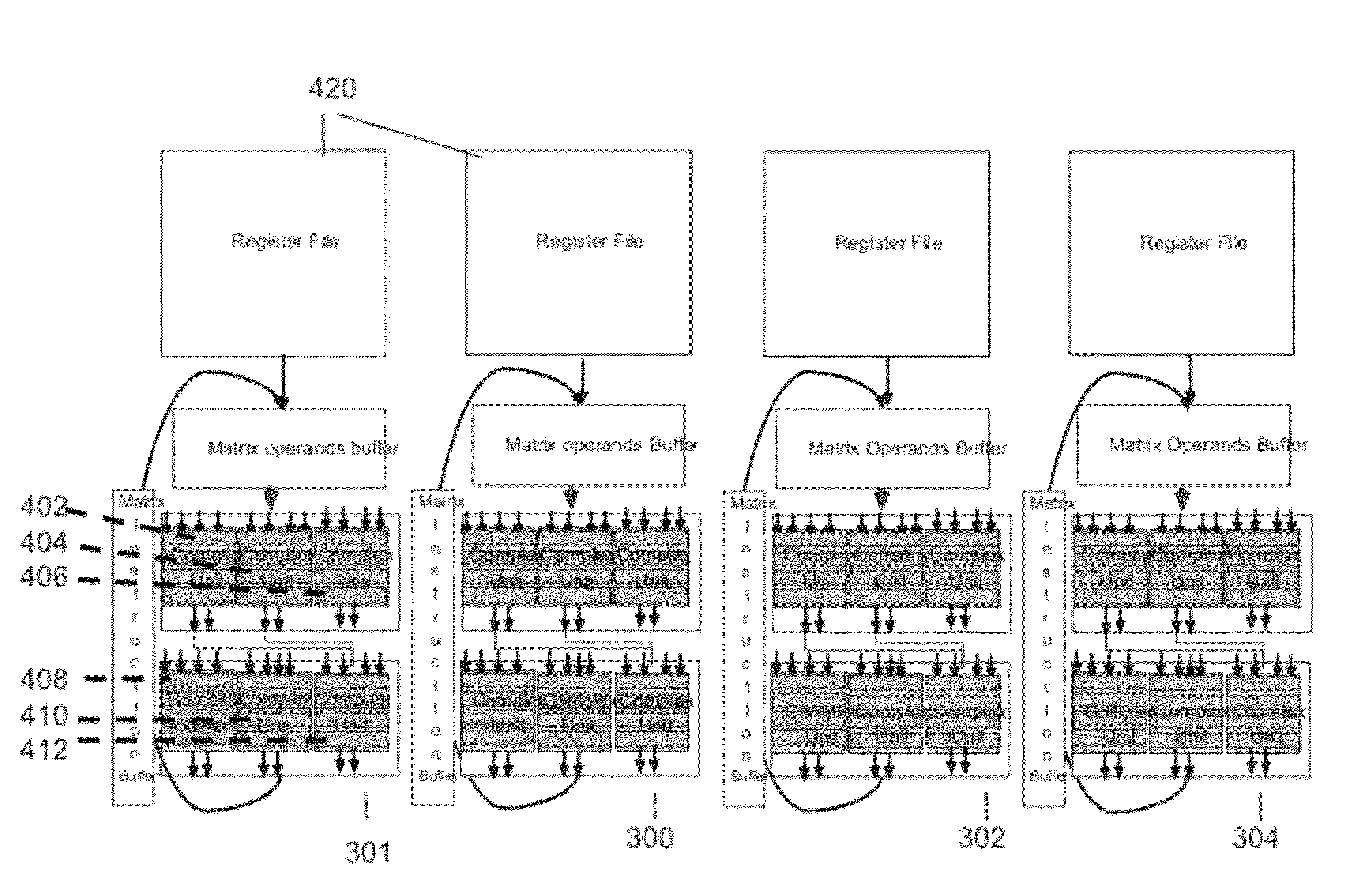

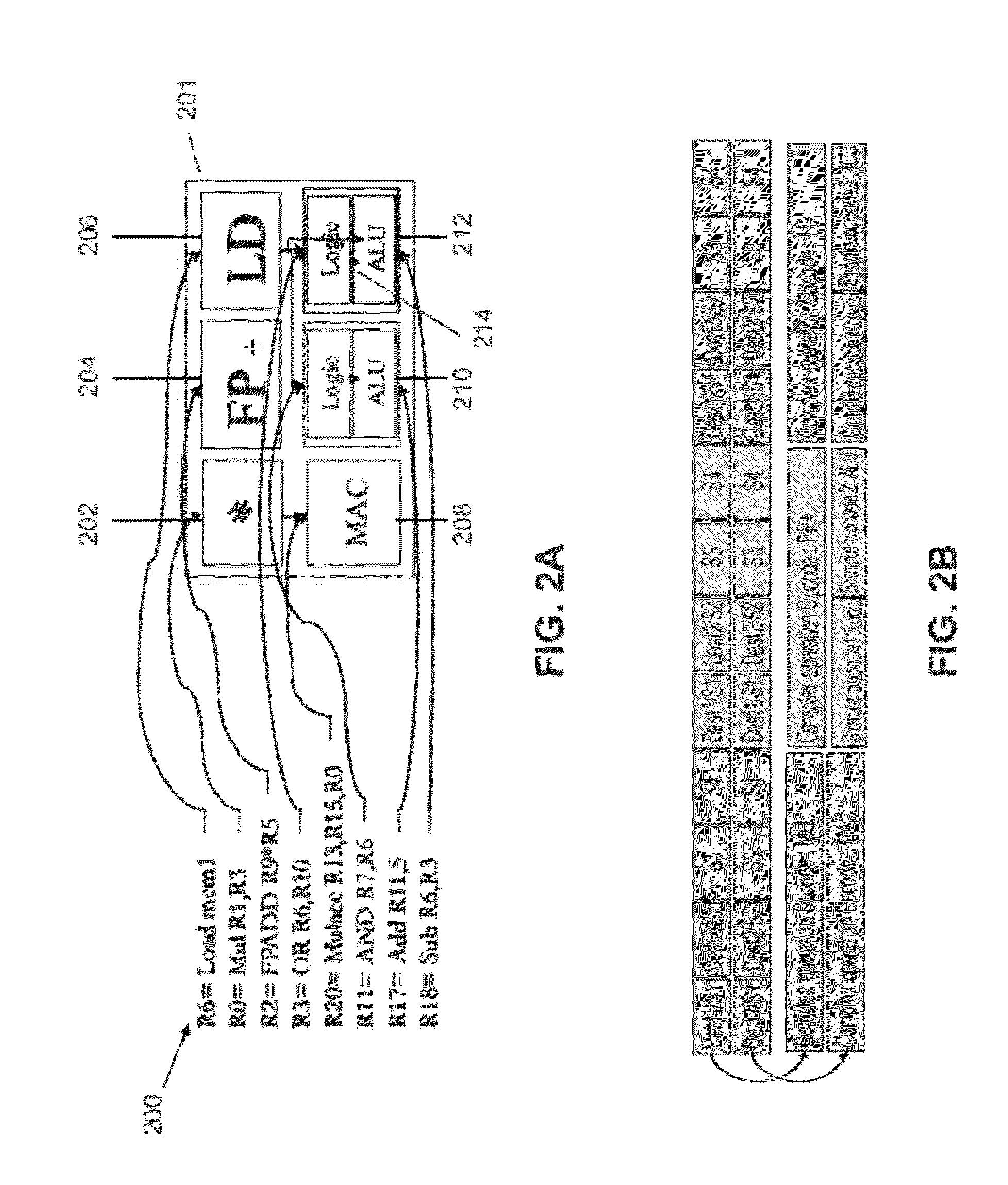

Apparatus and Method for Processing an Instruction Matrix Specifying Parallel and Dependent Operations

ActiveUS20090113170A1Single instruction multiple data multiprocessorsRegister arrangementsParallel computingMatrix manipulation

Owner:INTEL CORP

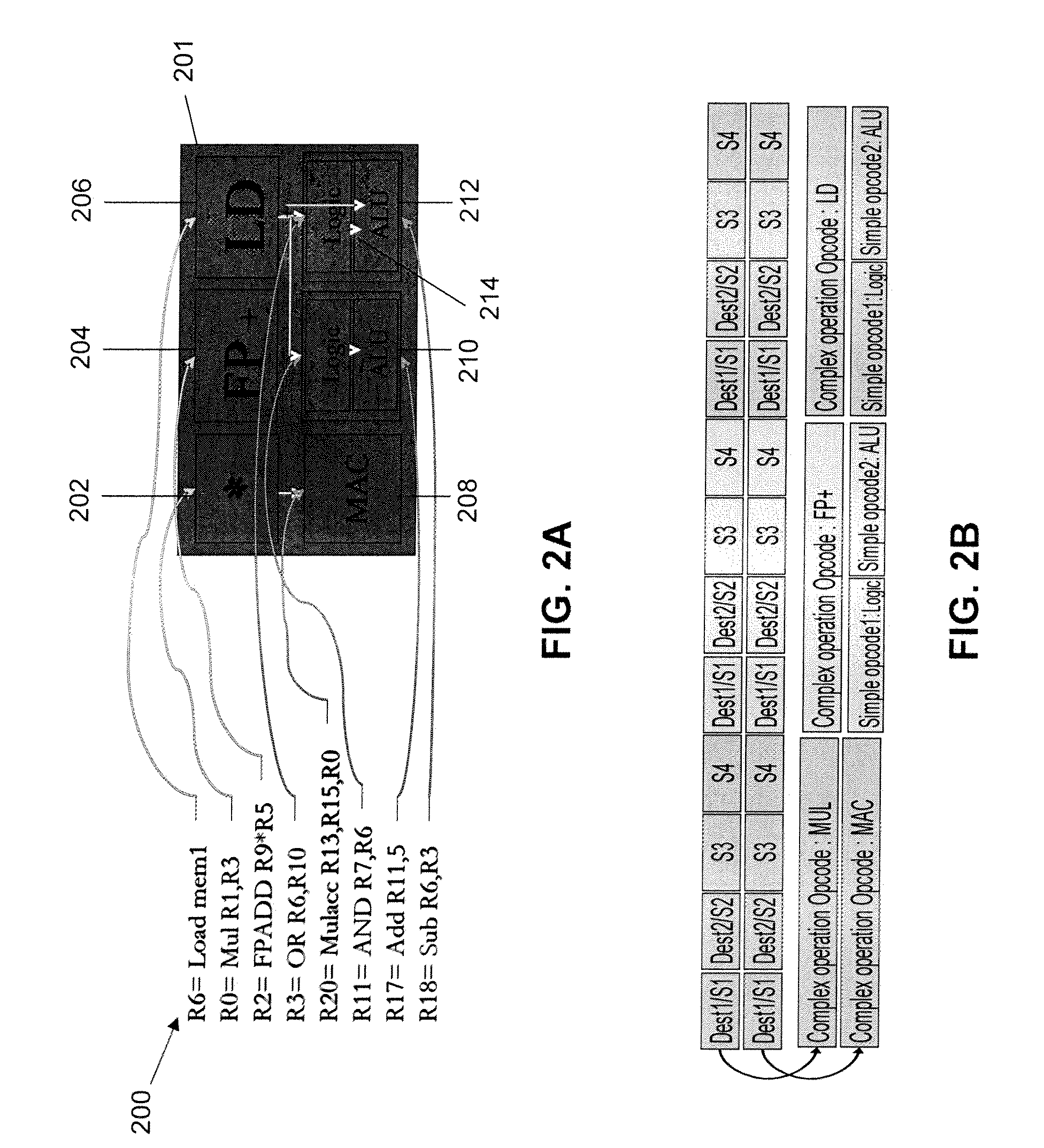

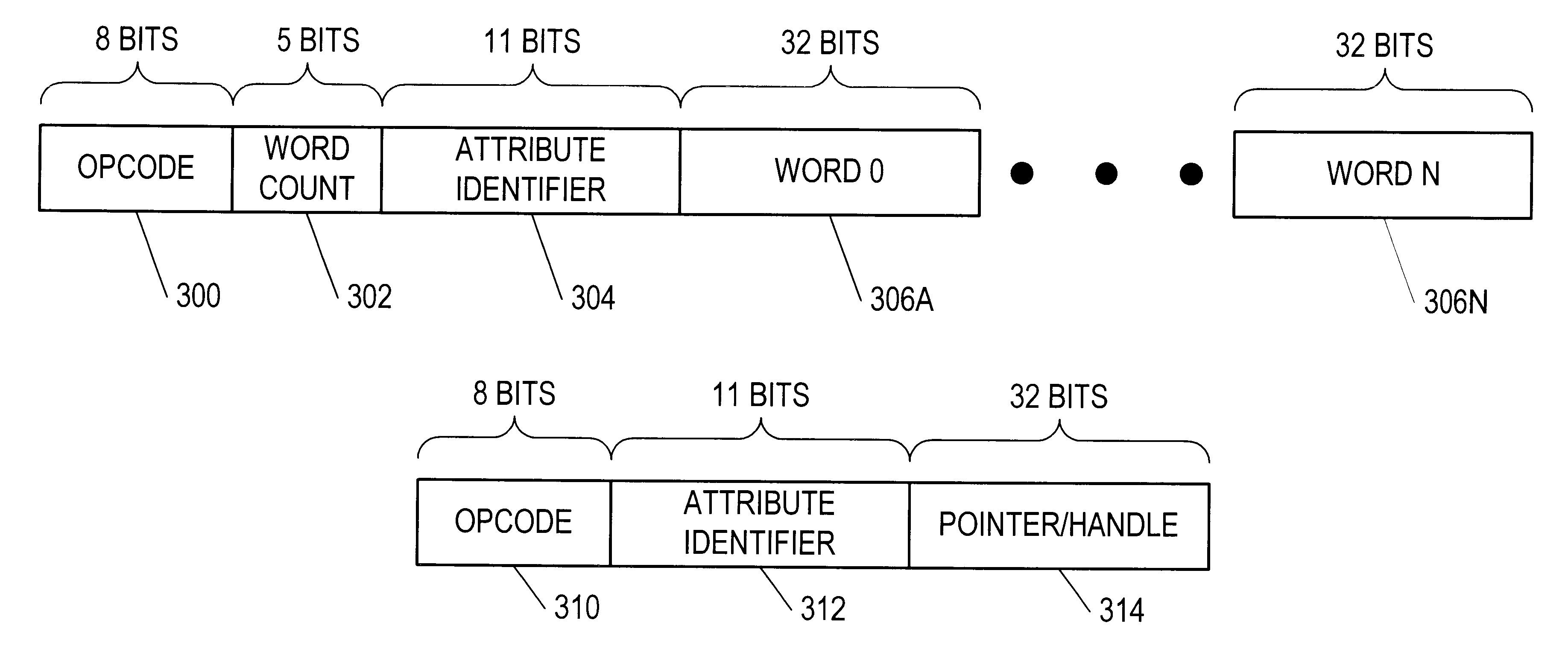

Compressing and decompressing graphics data using gosub-type instructions and direct and indirect attribute settings

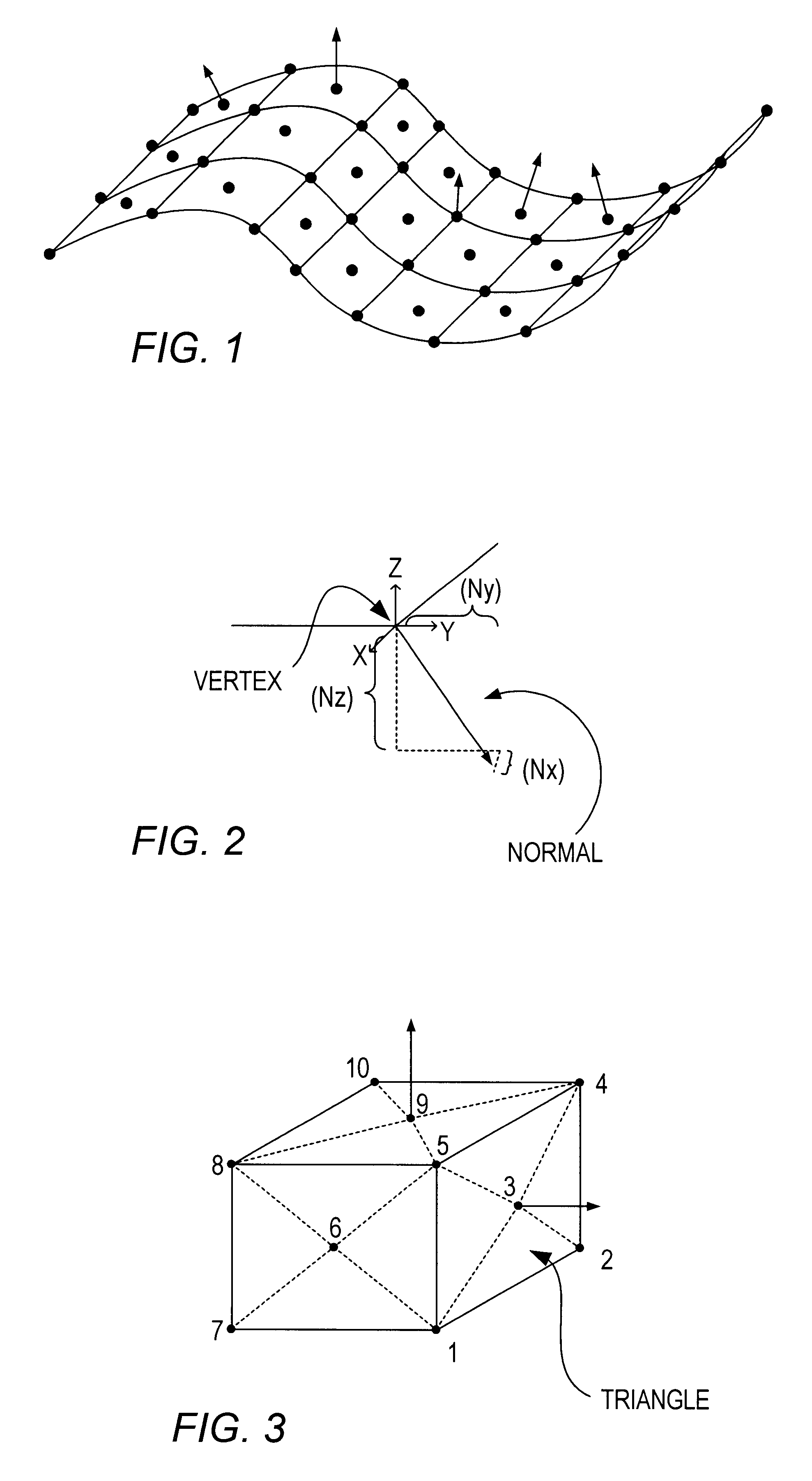

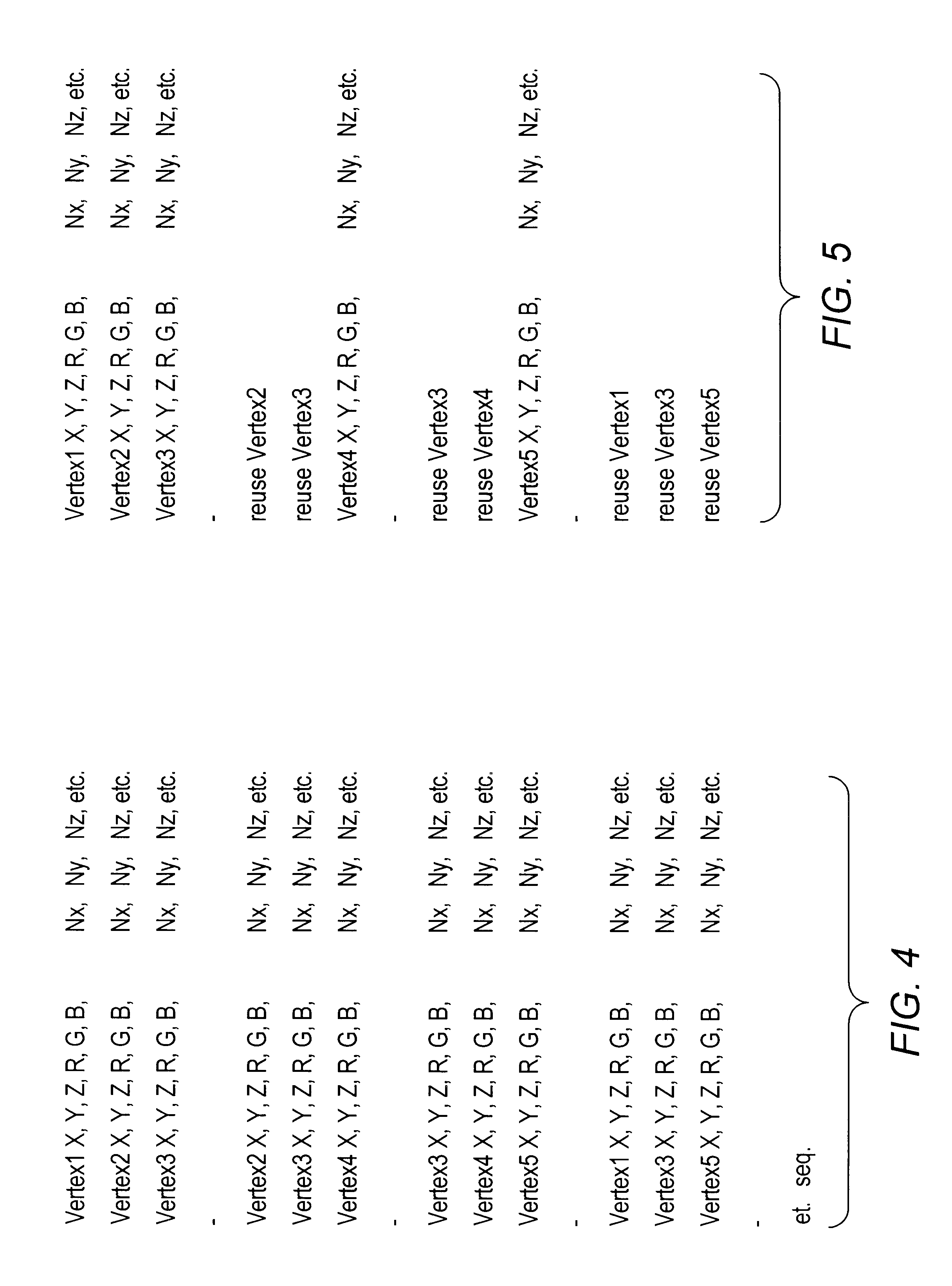

A method and instruction set for geometry compression and decompression is disclosed. The method and instruction set includes one or more of the following attributes and instructions: a gosub-type instruction, a goto-type instruction, direct and indirect attribute-setting instructions, and matrix manipulation instructions. The instructions may be embedded within individual vertex descriptions, or they may be specified independent of any individual vertex in order to set global state information that applies to all vertices that follow the instruction. Individual vertex instructions may temporarily override the global settings. A graphics system configured to execute the instruction set is also disclosed.

Owner:ORACLE INT CORP

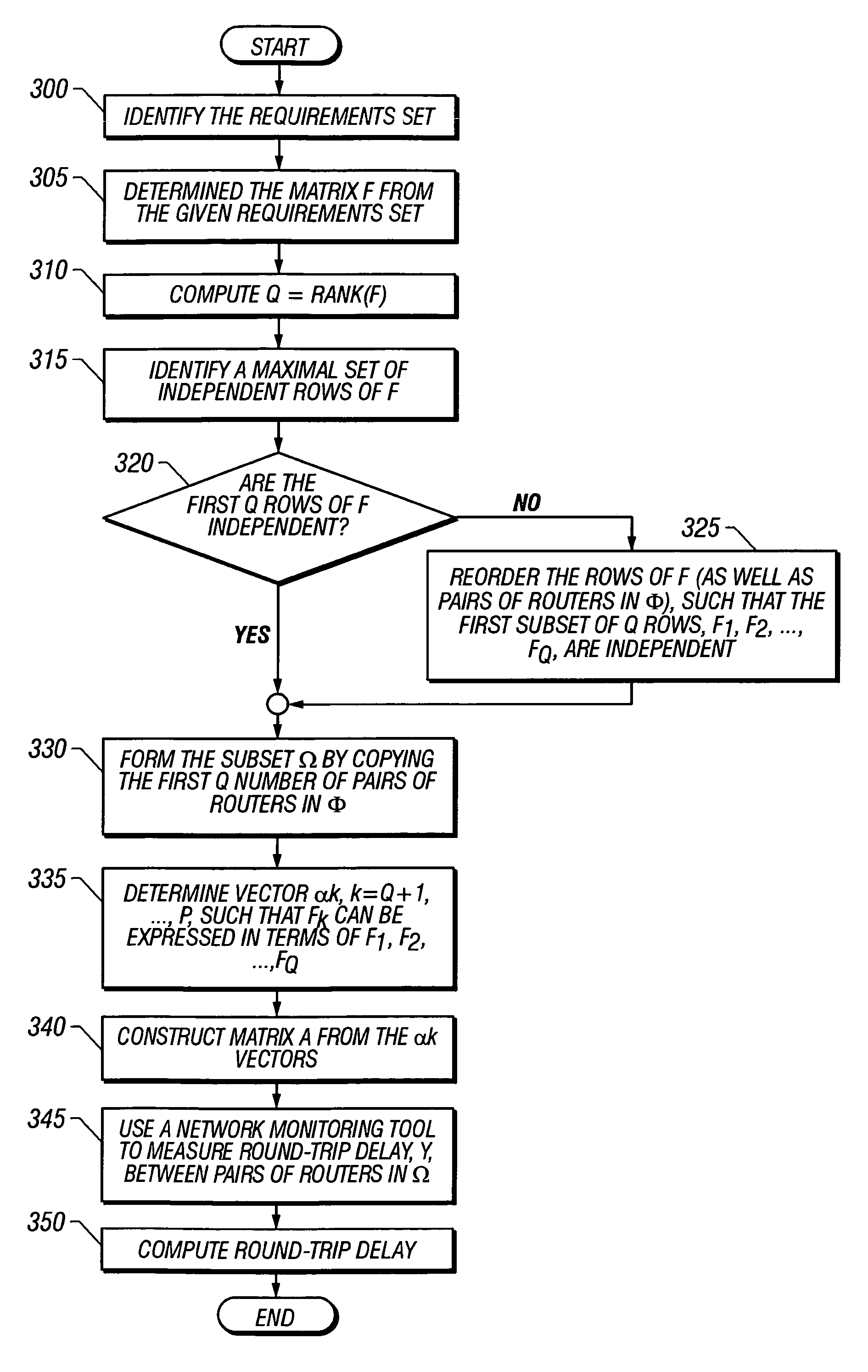

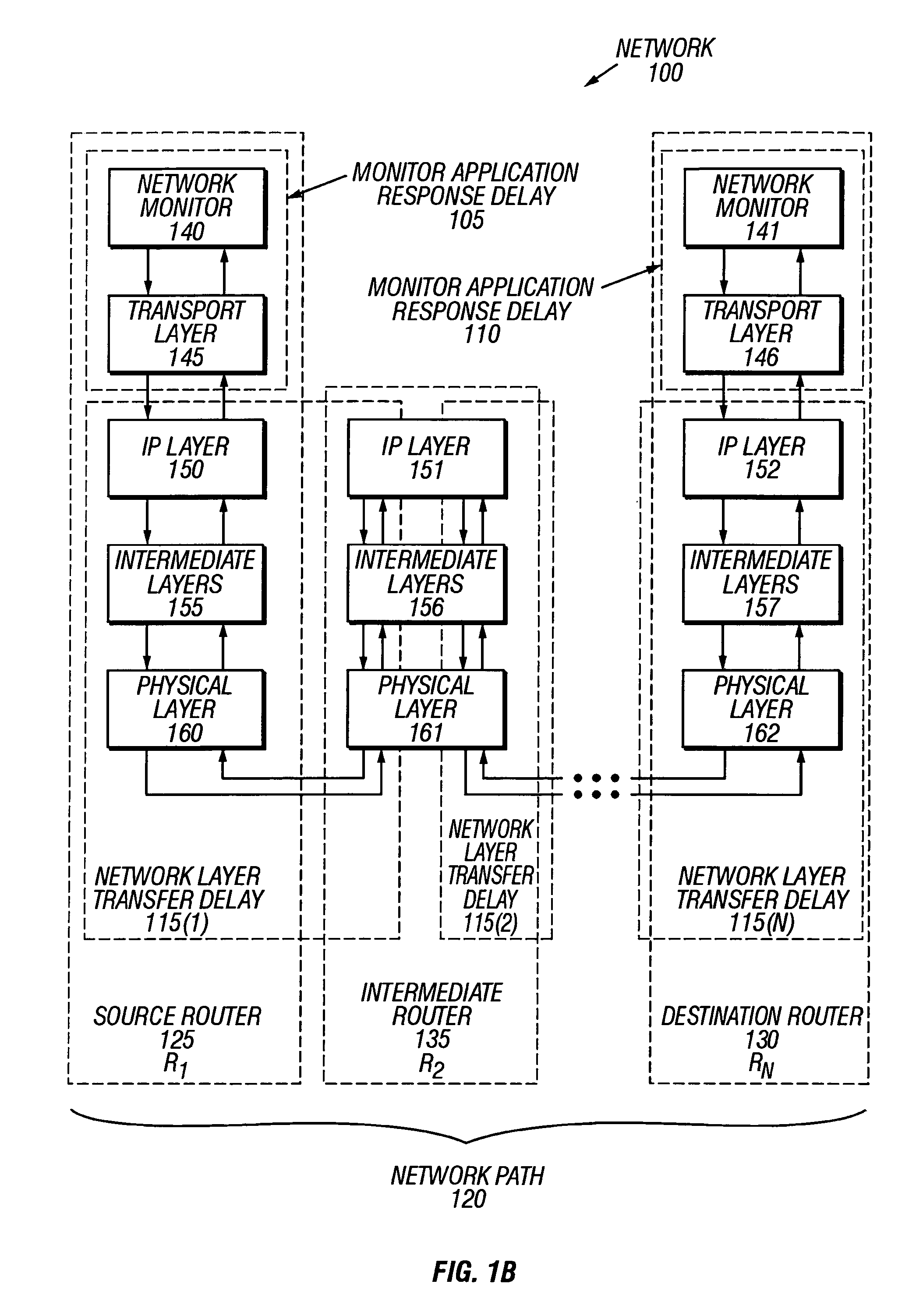

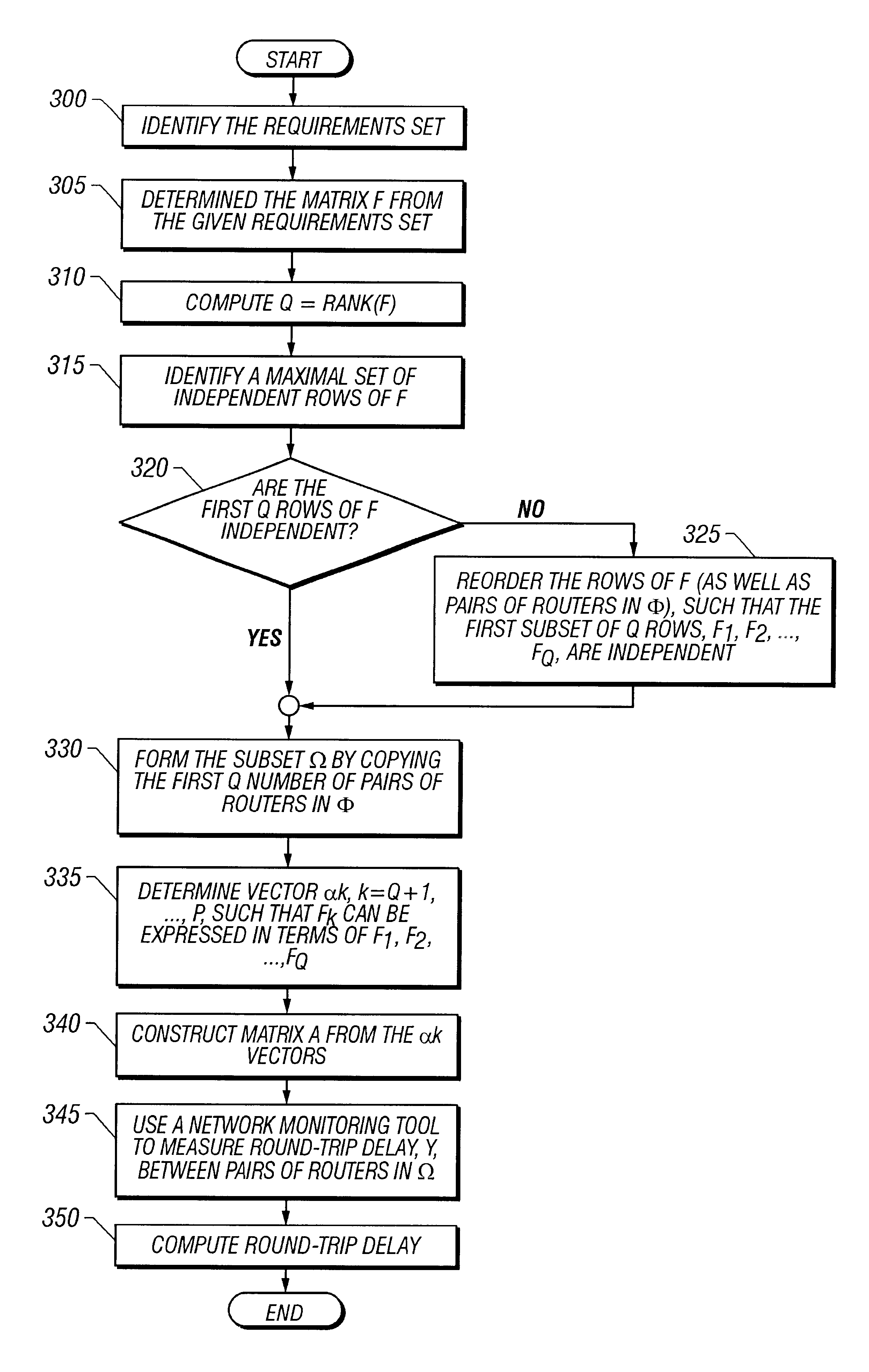

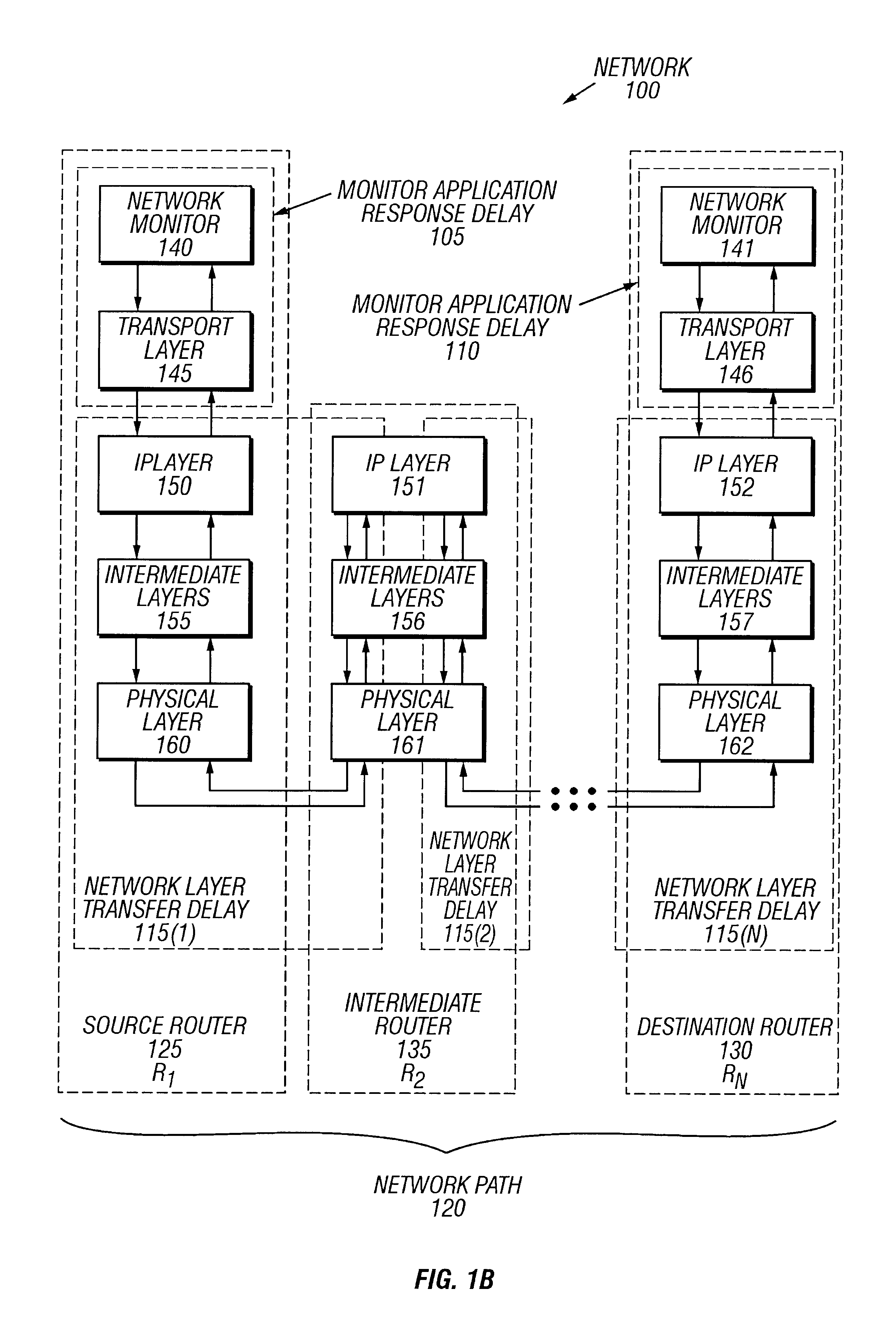

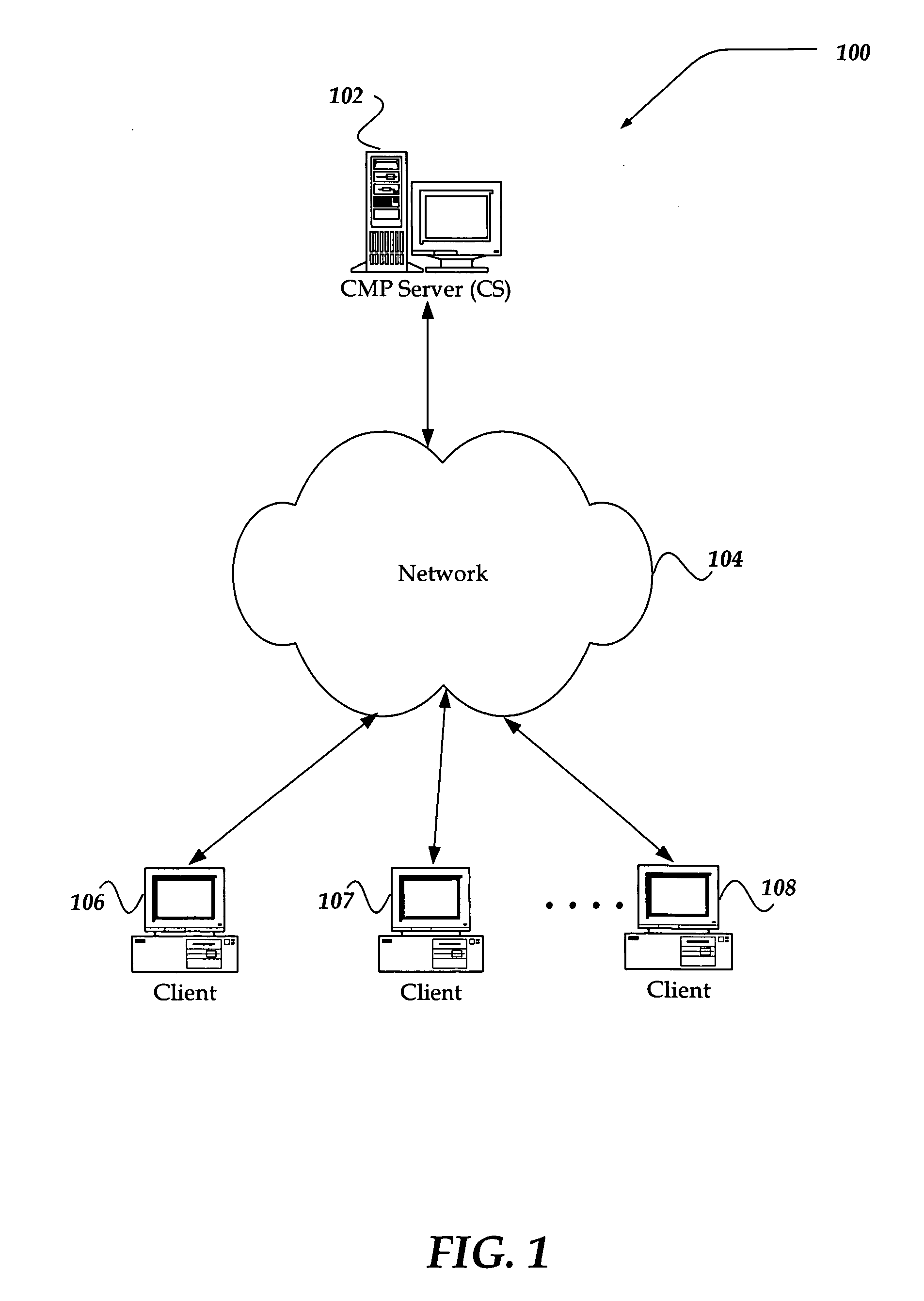

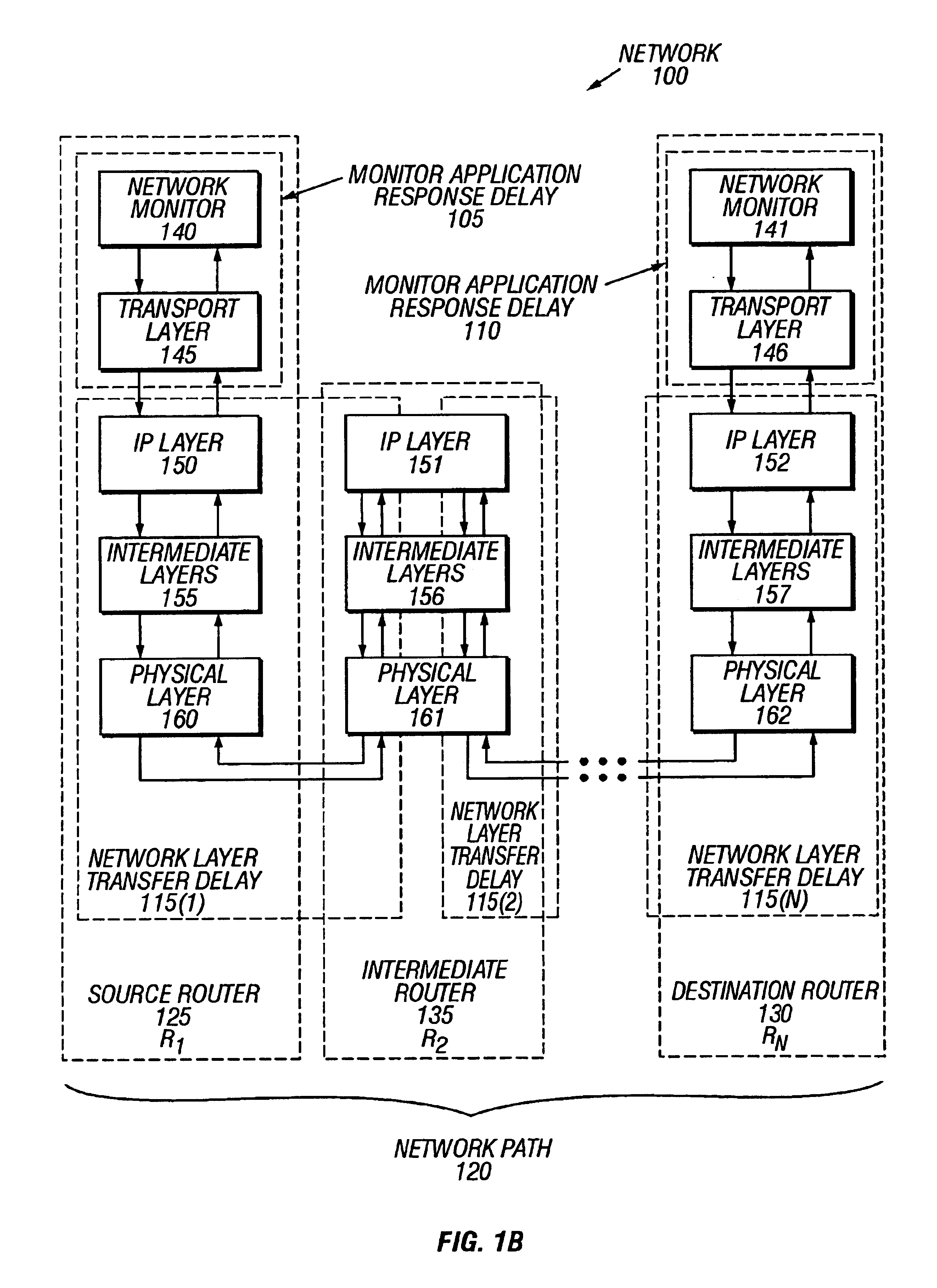

Apparatus for estimating delay and jitter between network routers

InactiveUS7111073B1Reduce traffic overheadEnsure effective implementationError preventionFrequency-division multiplex detailsDistributed computingNetwork router

A delay measurement technique according to an embodiment according to the present invention is based on the precept, ascertained by the inventors, that a link between network nodes will often contribute to the delay encountered between several different pairs of network nodes. Such a technique identifies the path between each pair of nodes by a list of links that form the path. Paths that are orthogonal are treated as being necessary for describing the delays encountered between nodes, and, once the requisite set of orthogonal paths has been derived, all other paths can be described in terms of one or more of these orthogonal paths. Such a technique also lends itself to matrix representation of the paths, and the use of matrix manipulation techniques in deriving delay and jitter.

Owner:CISCO TECH INC

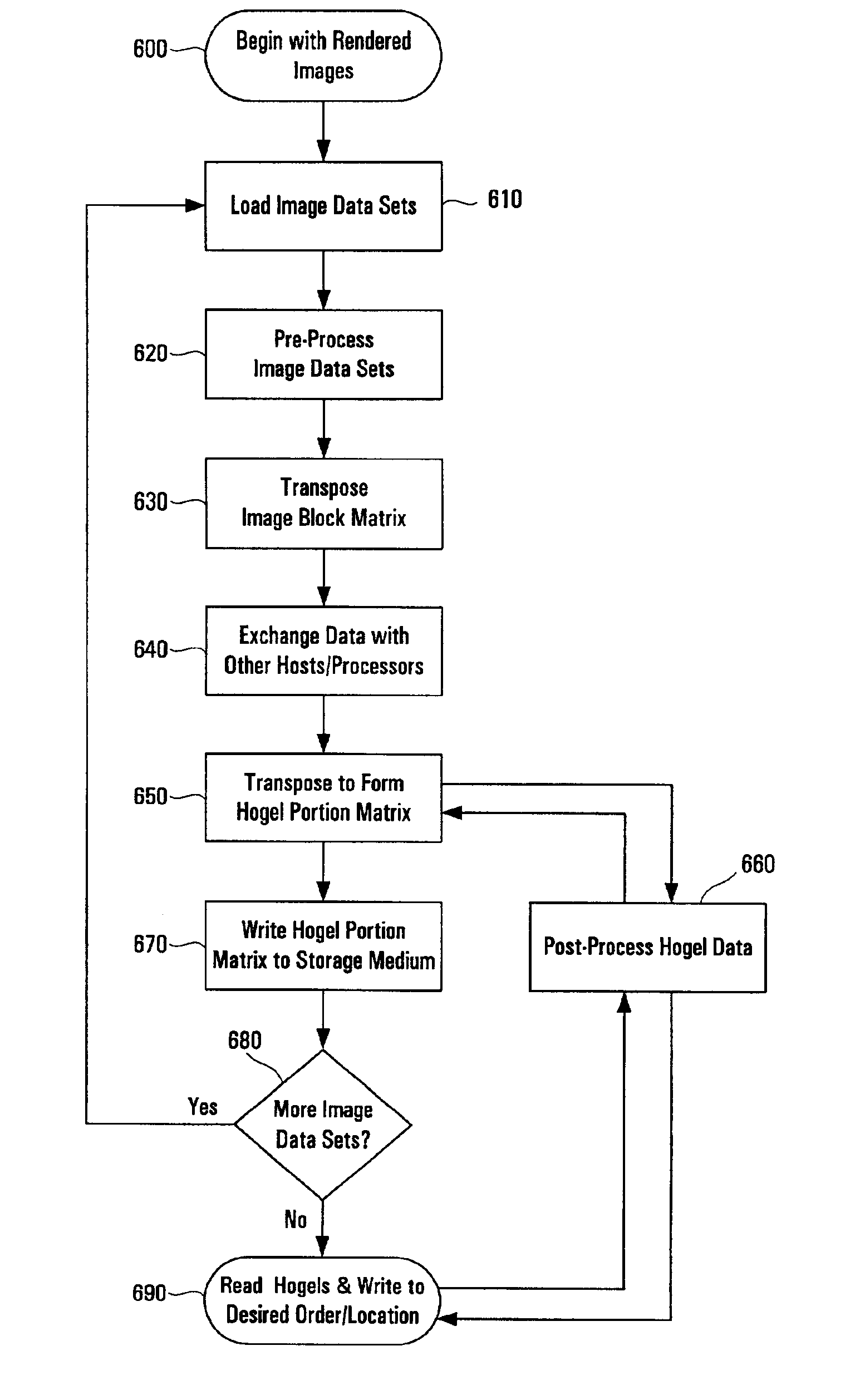

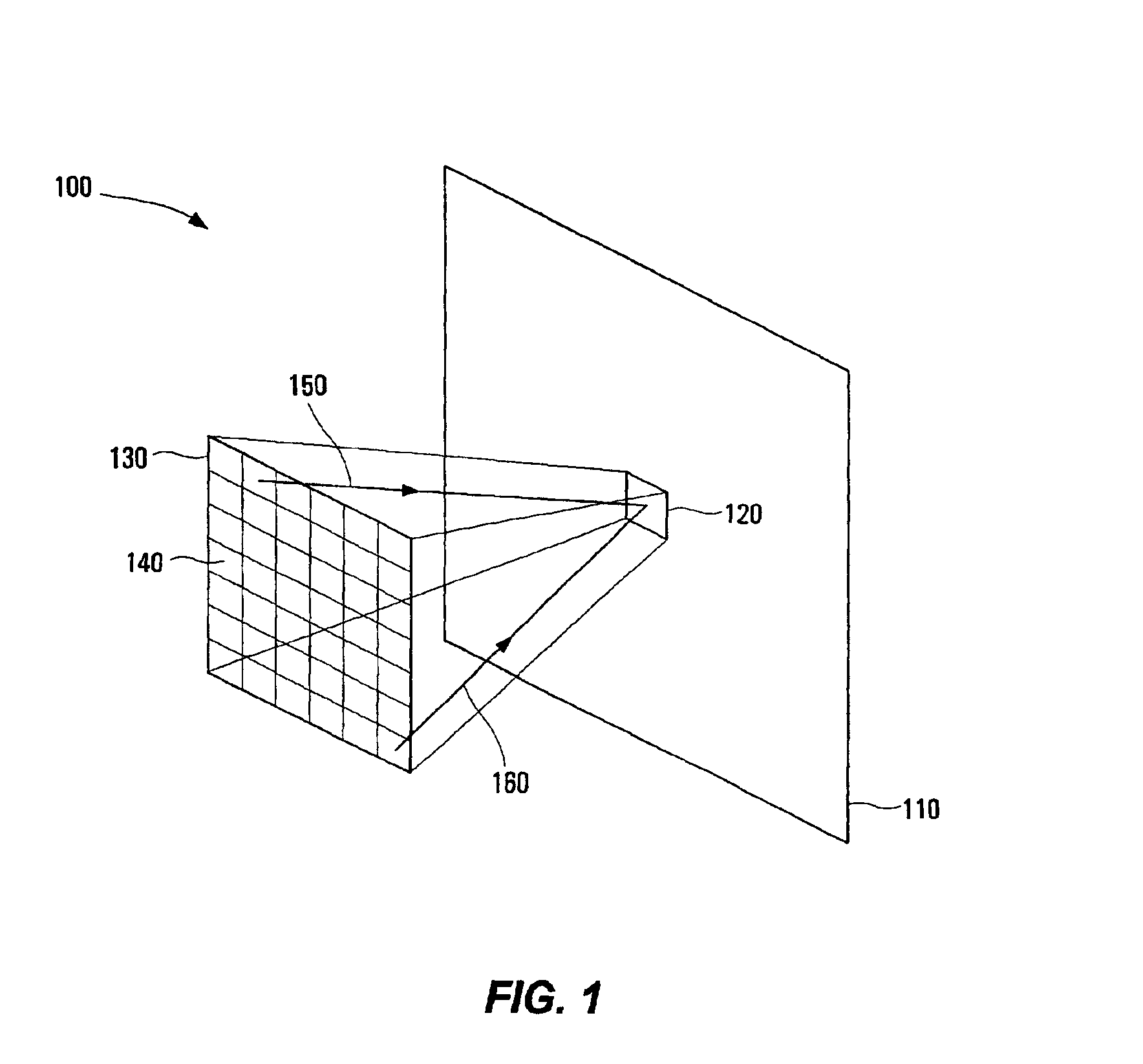

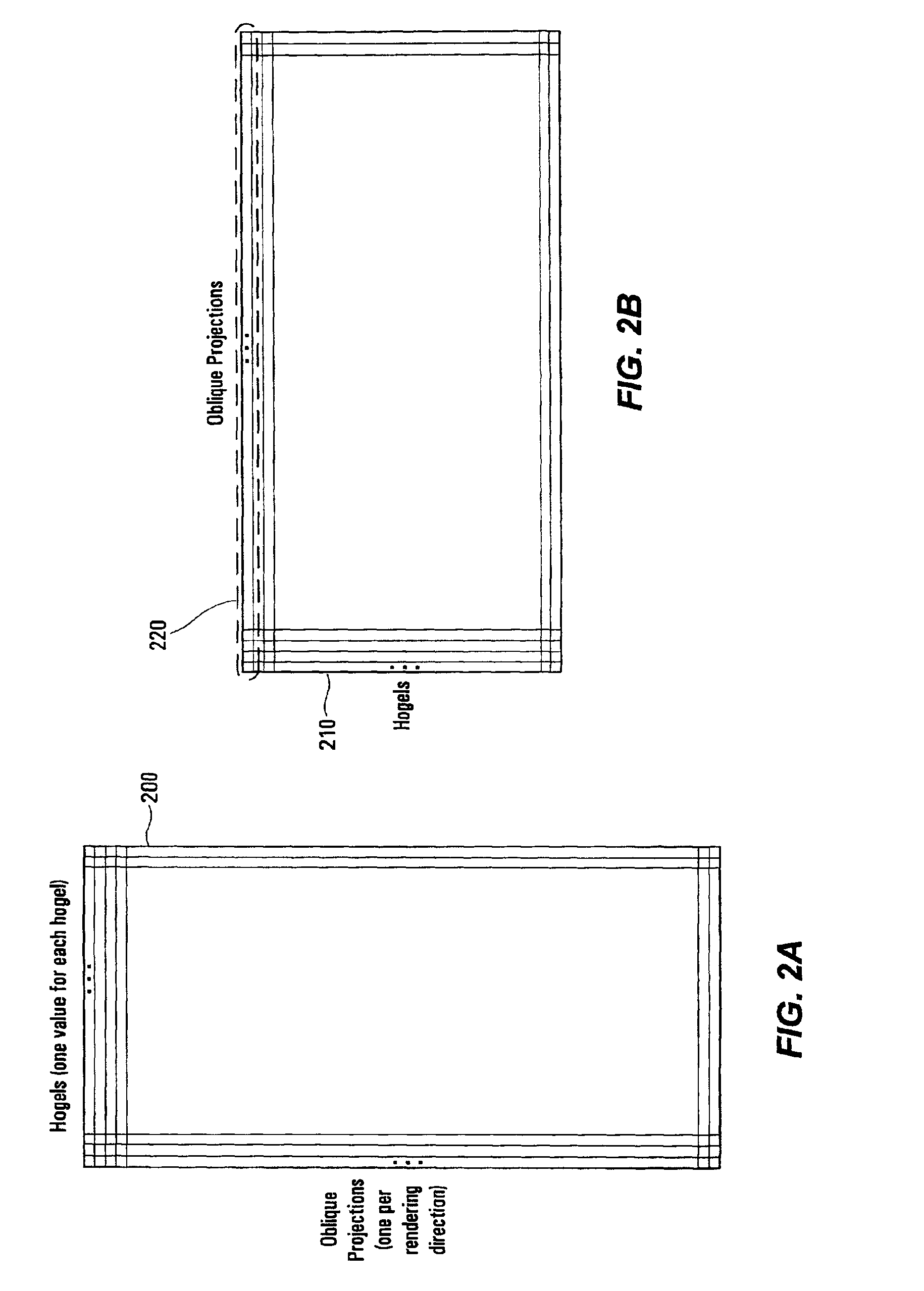

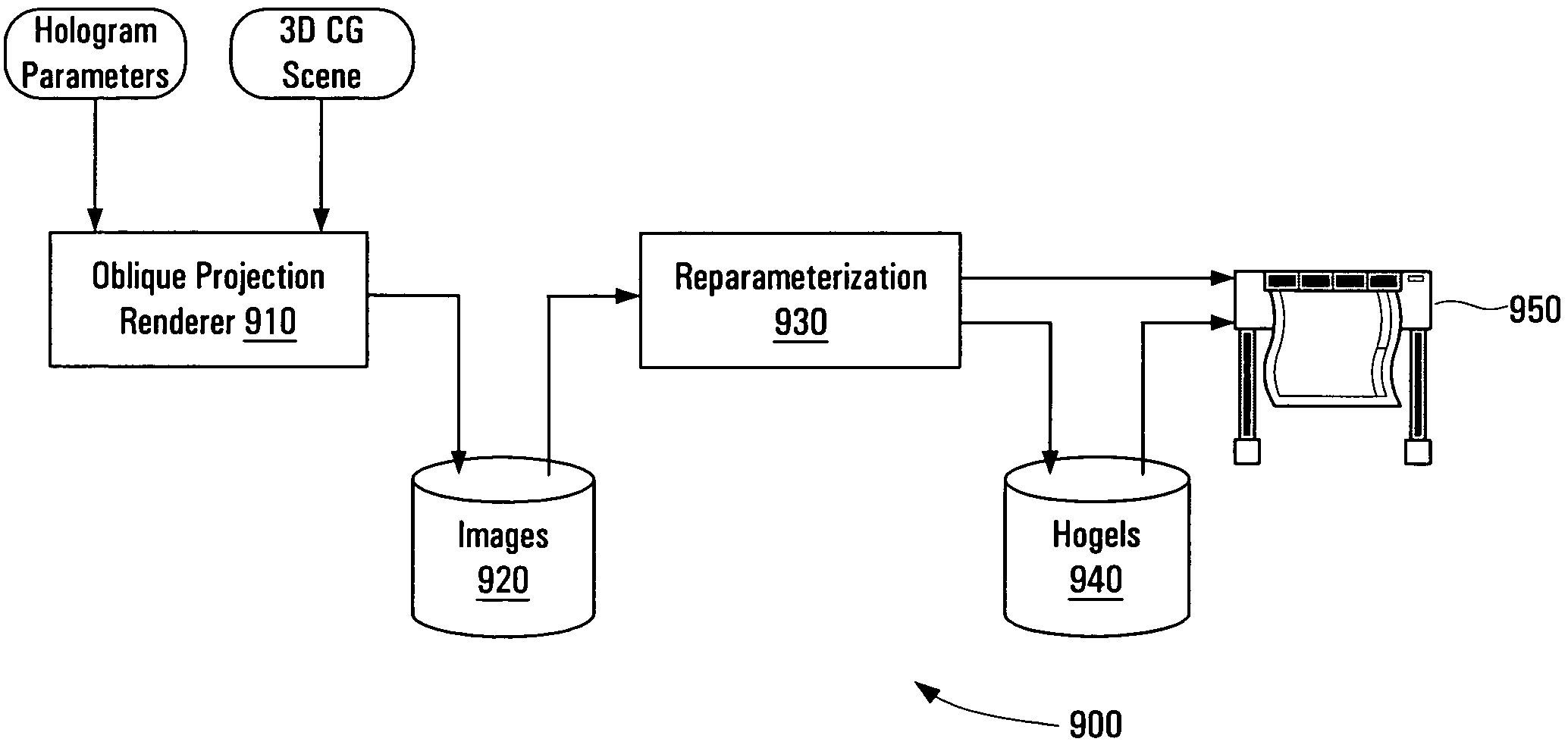

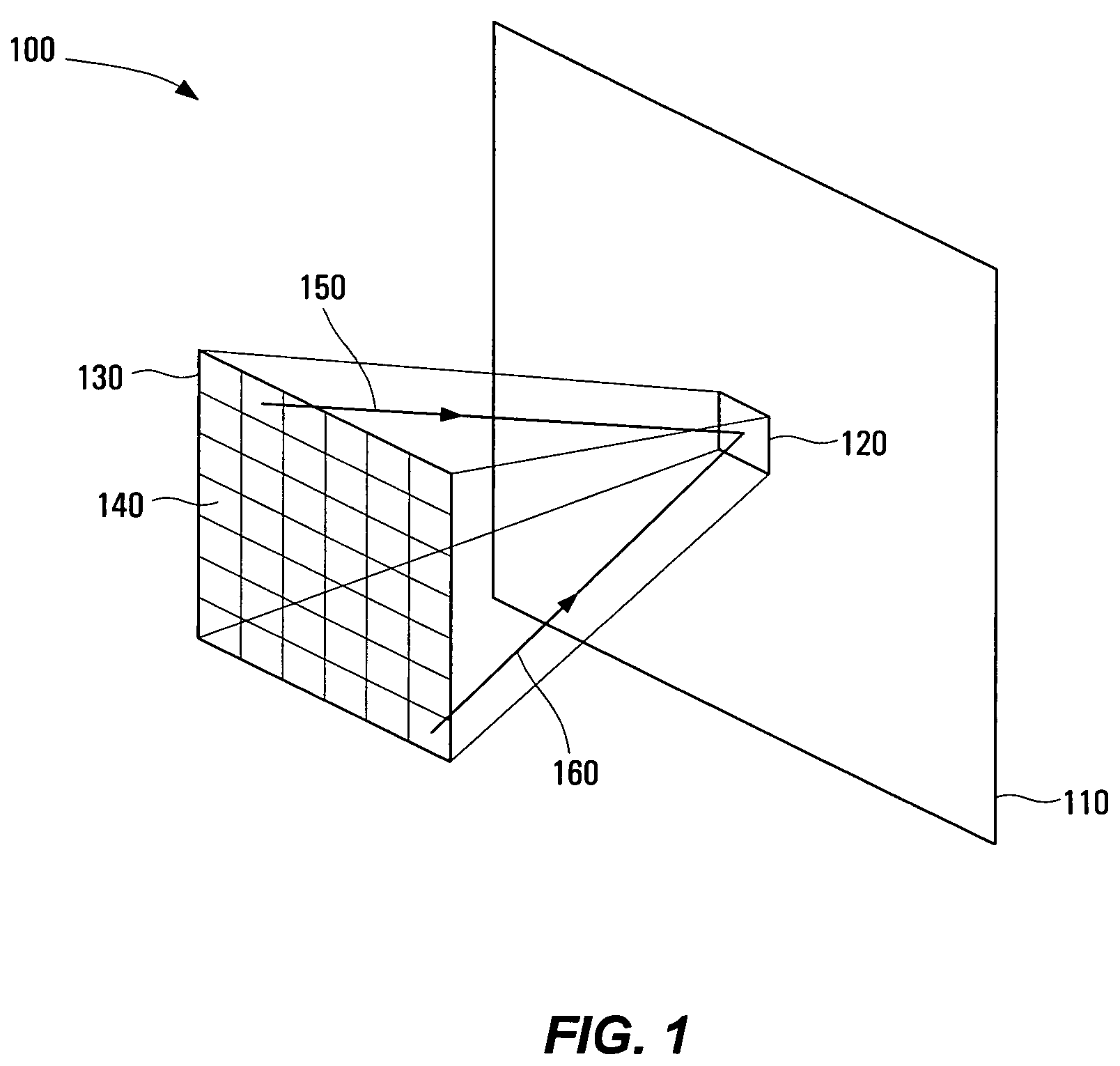

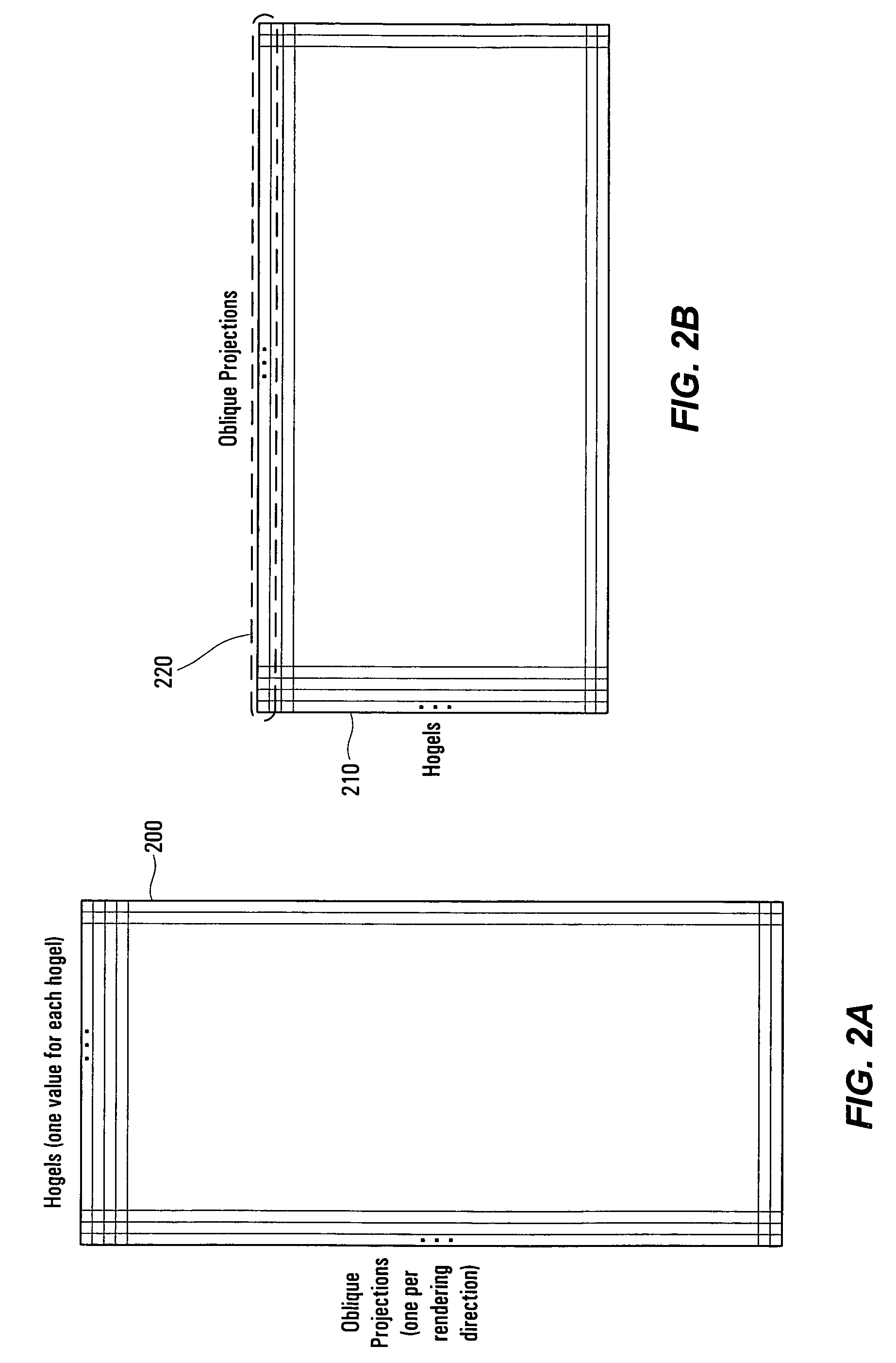

Efficient block transform including pre-processing and post processing for autostereoscopic displays

InactiveUS6868177B1Television system detailsMemory adressing/allocation/relocationSingle processData set

Image data processing techniques utilizing multiple processes operating on one or more processors of one or more computer systems can be used to efficiently rearrange or reparameterizing image data to form hologram element (hogel) images which can then be used to produce holographic stereograms. These techniques utilize matrix manipulation of portions of image data both within a single process, and across multiple processes typically executing on different processors, and each utilizing a subset of the overall set of image data.

Owner:3D PATENTS LLC

Contamination level estimation method for high voltage insulators

ActiveUS20160117845A1Affects colorReadily apparentImage enhancementImage analysisPattern recognitionData set

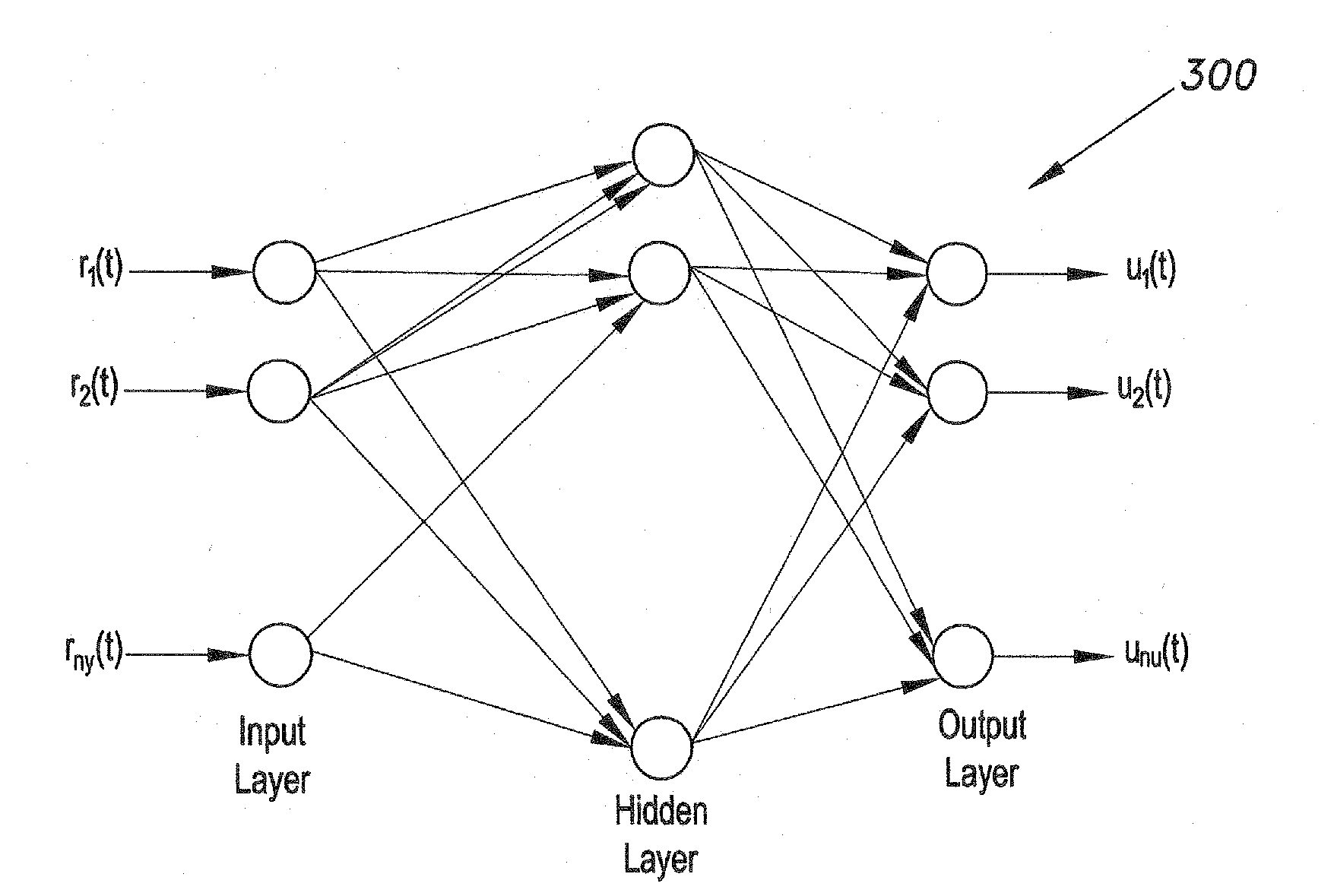

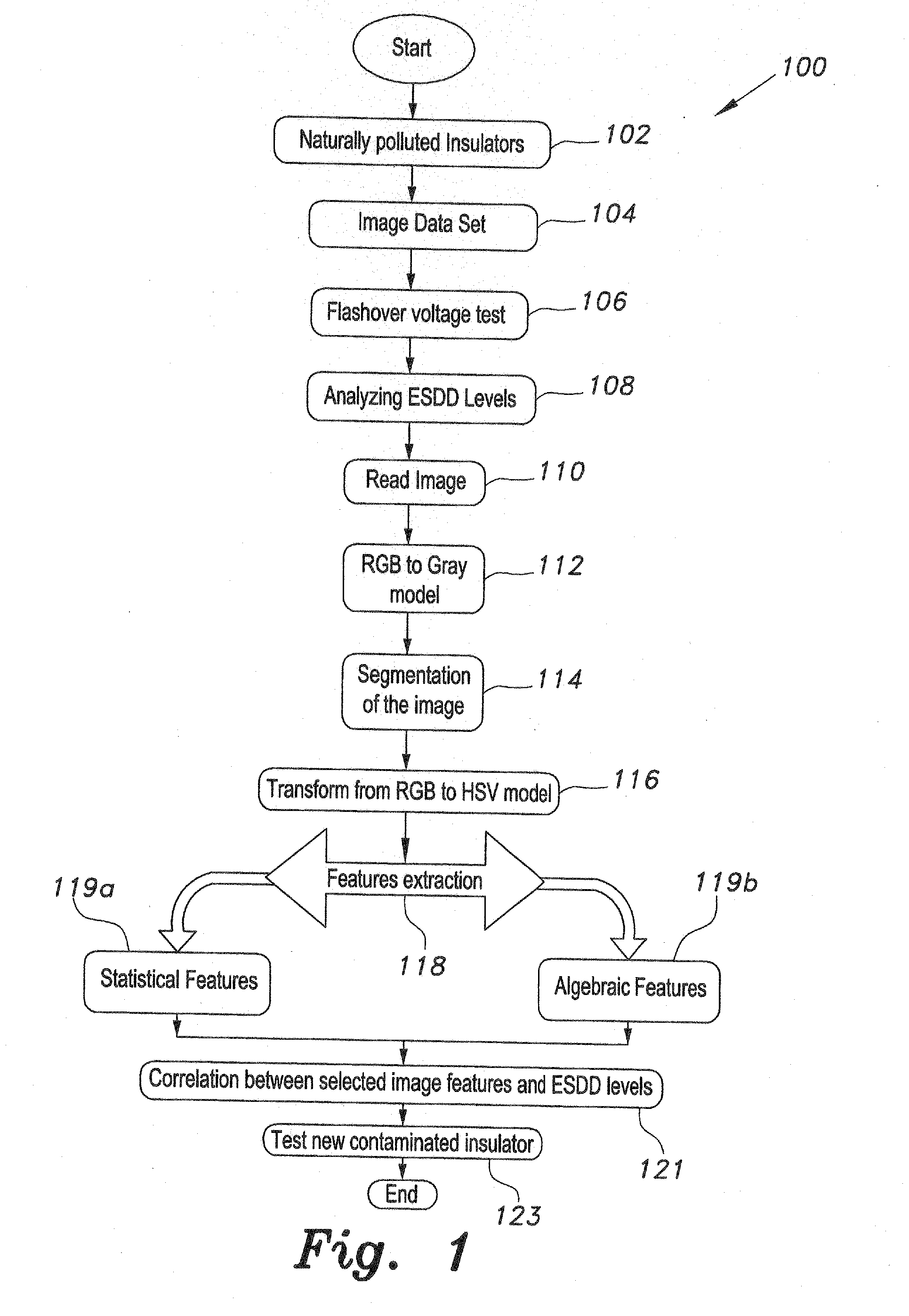

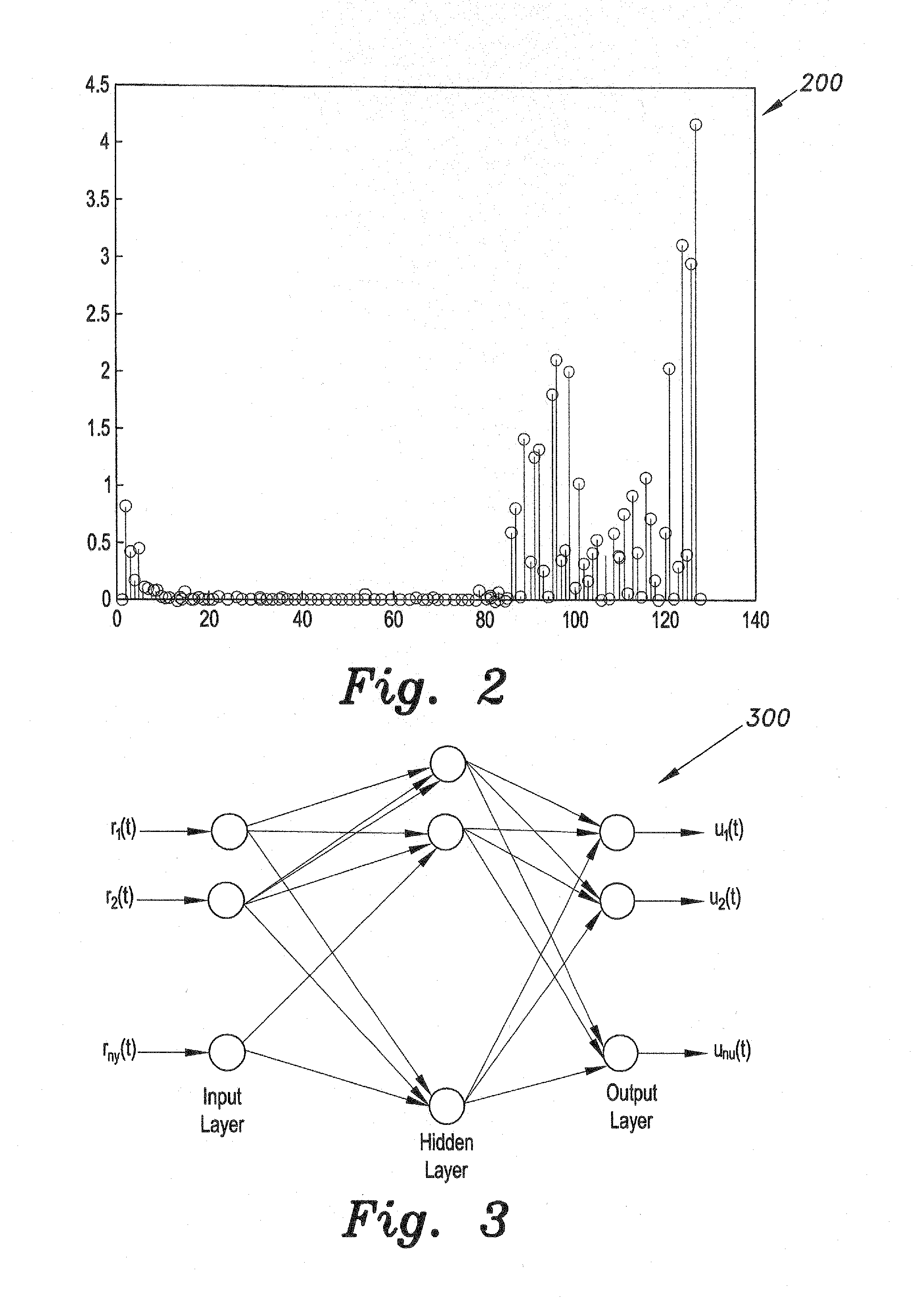

The contamination level estimation method for high voltage insulators collects samples of naturally contaminated insulators and builds an image data set for the collected insulators. Flashover voltages of several insulators samples are measured. ESDD levels of the collected insulators are estimated. Images are input to image processing algorithms to extract representative features. The images are segmented. Transforming the image from RGB color space into grayscale model excludes the background from the image. Subsequently, the segmented images are transferred back to RGB color space model using matrix manipulation. Since contaminants on the insulator surface affect the color of the insulator, the segmented image is transformed from RGB to HSV color space which is used for extracting statistical and linear algebraic features from the hue image. A trained artificial neural network correlates the extracted features to the contamination levels enabling testing of other contaminated insulators.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

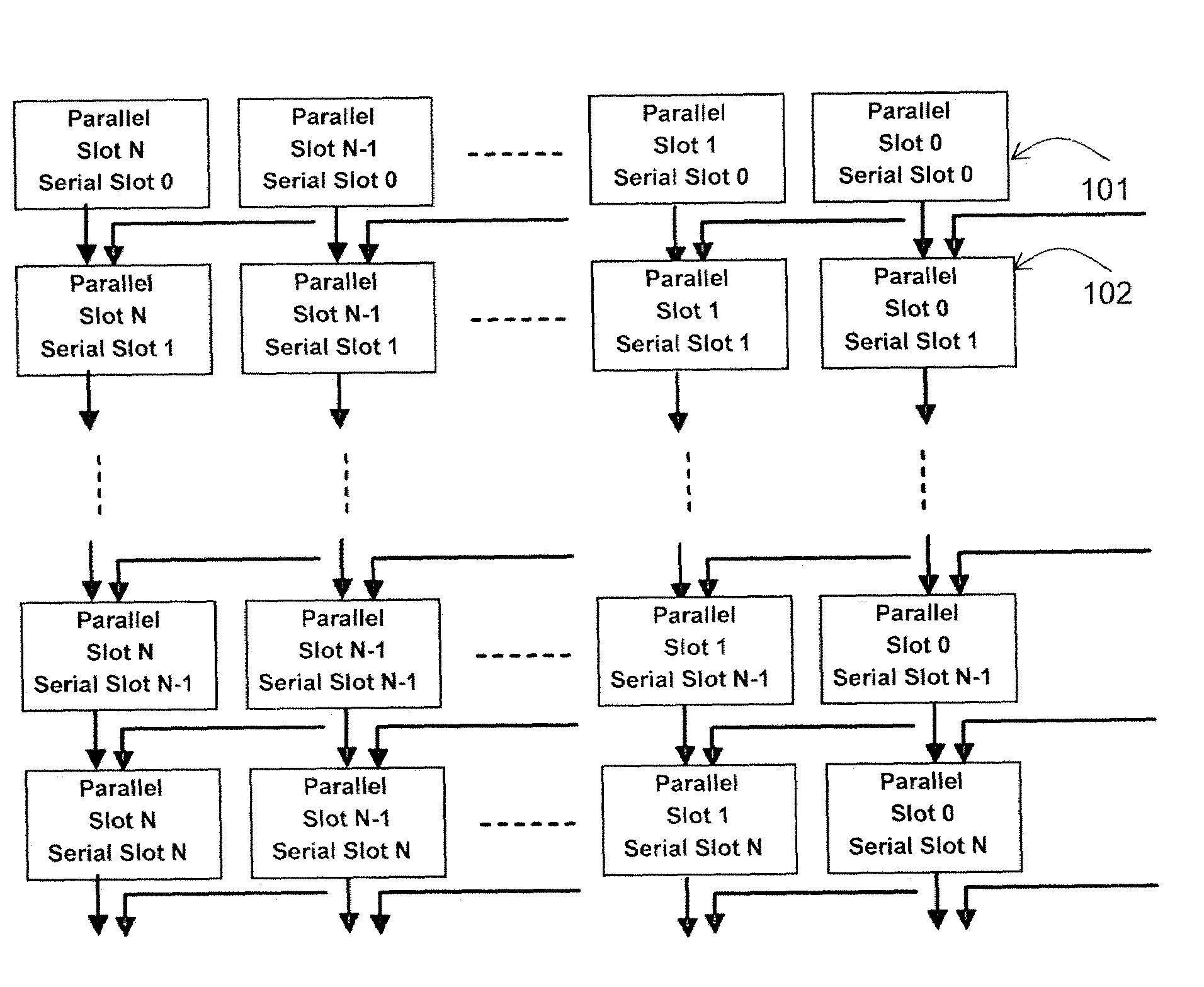

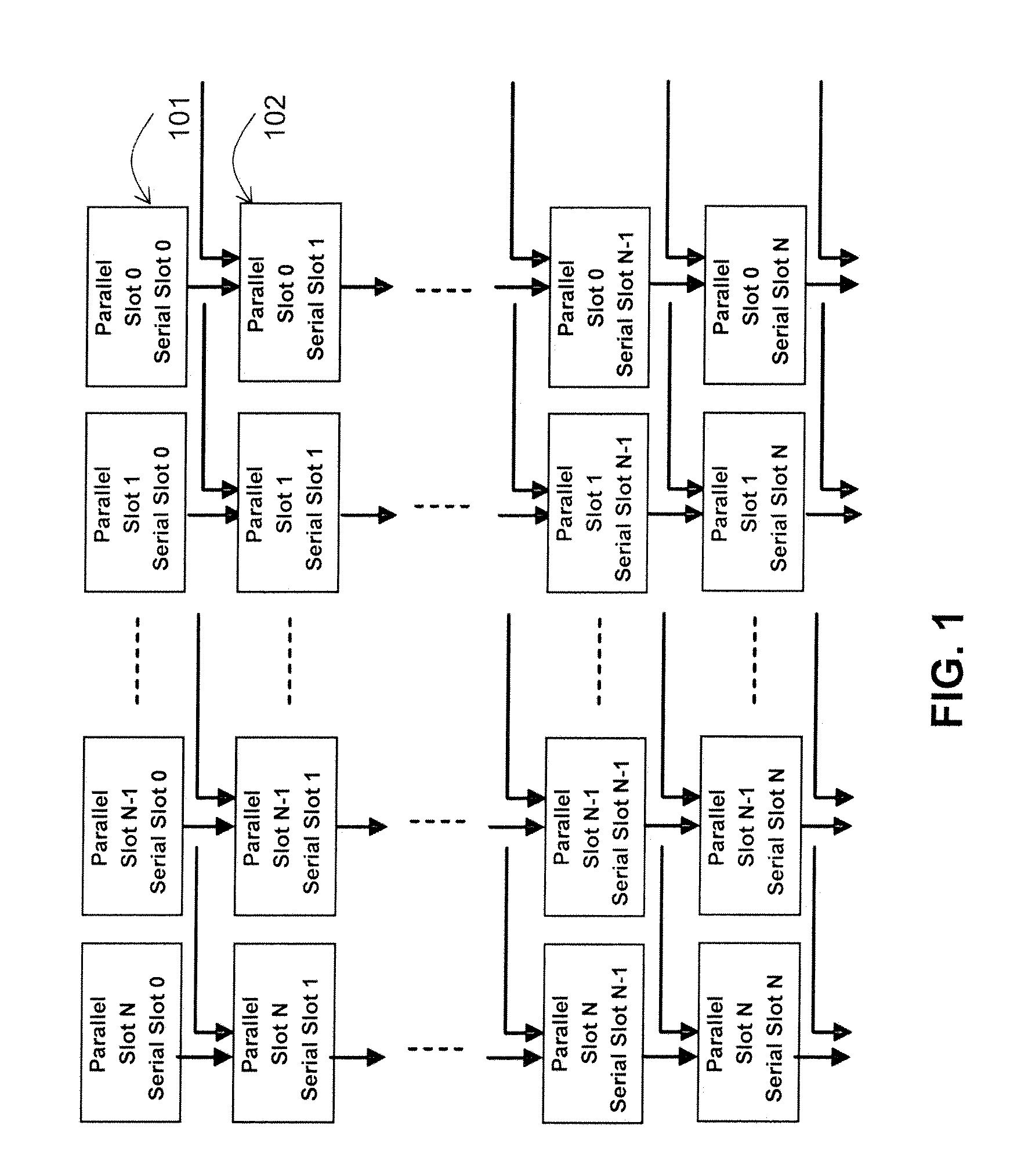

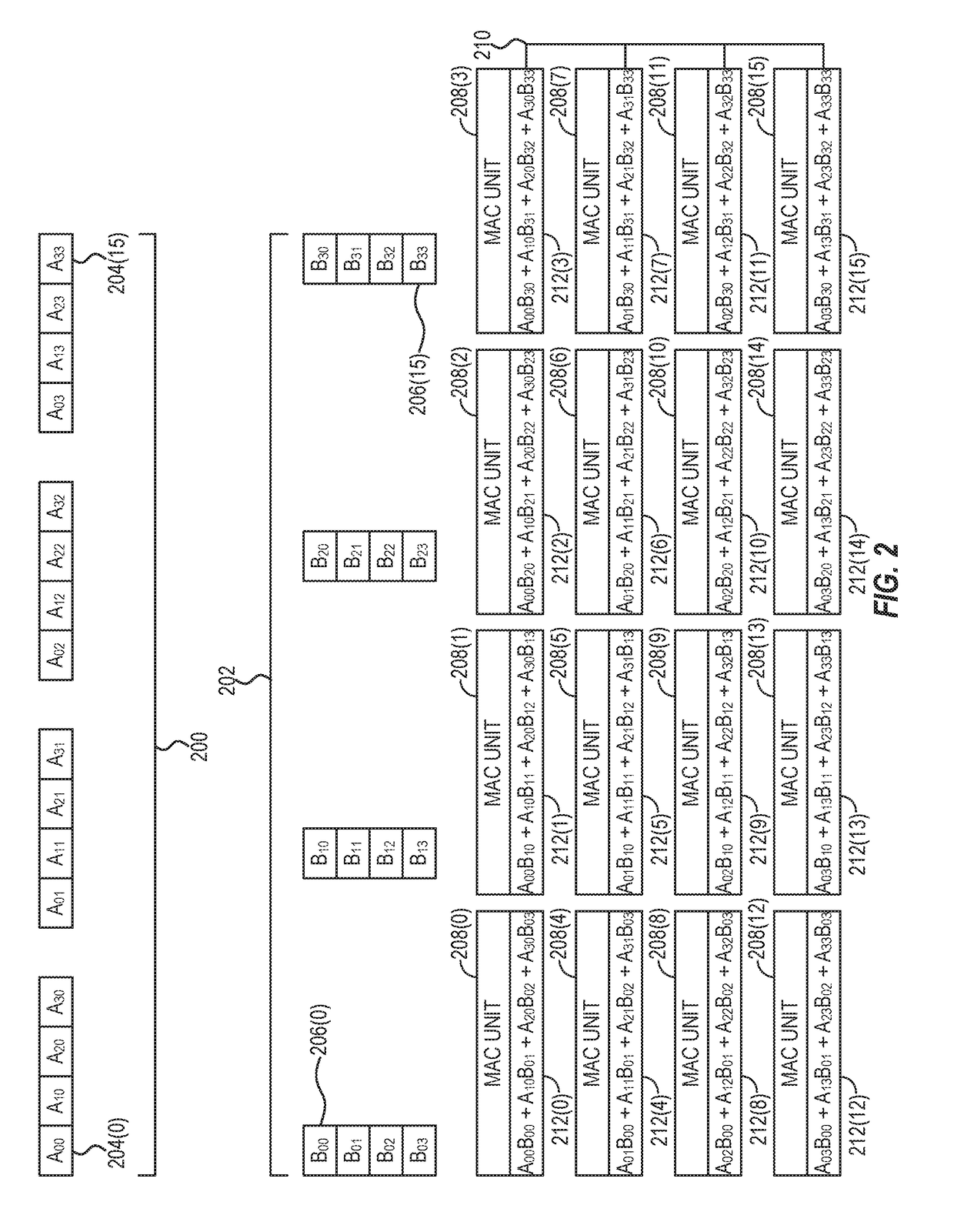

Plural matrices of execution units for processing matrices of row dependent instructions in single clock cycle in super or separate mode

ActiveUS8327115B2Single instruction multiple data multiprocessorsRegister arrangementsParallel computingExecution unit

Owner:INTEL CORP

Method and apparatus for estimating delay and jitter between network routers

InactiveUS6868068B1Lower requirementReduce traffic overheadError preventionFrequency-division multiplex detailsDistributed computingNetwork router

A delay measurement technique according to an embodiment according to the present invention is based on the precept, ascertained by the inventors, that a link between network nodes will often contribute to the delay encountered between several different pairs of network nodes. Such a technique identifies the path between each pair of nodes by a list of links that form the path. Paths that are orthogonal are treated as being necessary for describing the delays encountered between nodes, and, once the requisite set of orthogonal paths has been derived, all other paths can be described in terms of one or more of these orthogonal paths. Such a technique also lends itself to matrix representation of the paths, and the use of matrix manipulation techniques in deriving delay and jitter.

Owner:CISCO TECH INC

Rearranging data between vector and matrix forms in a SIMD matrix processor

ActiveUS6898691B2Register arrangementsHandling data according to predetermined rulesAlgorithmProcessor register

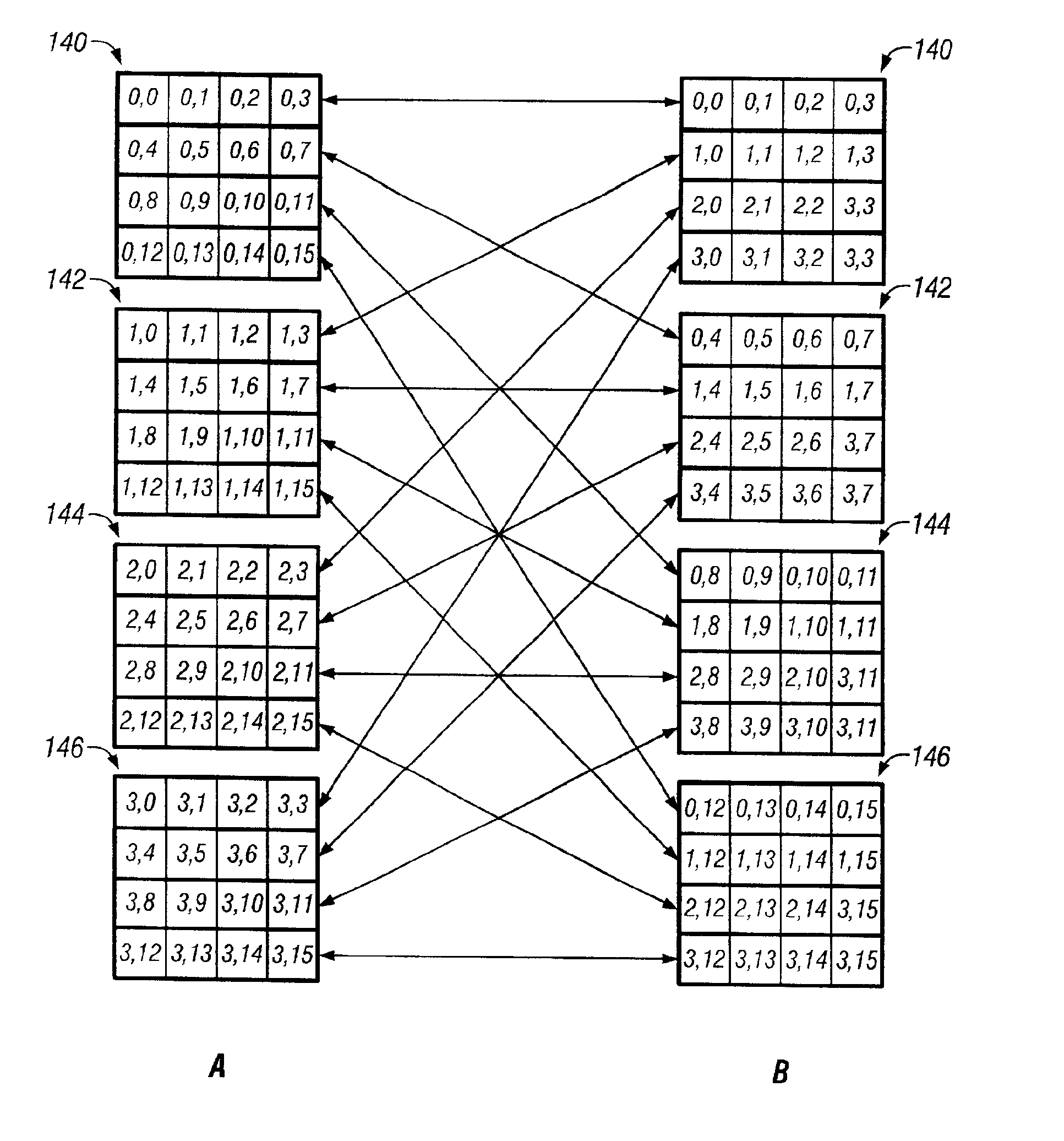

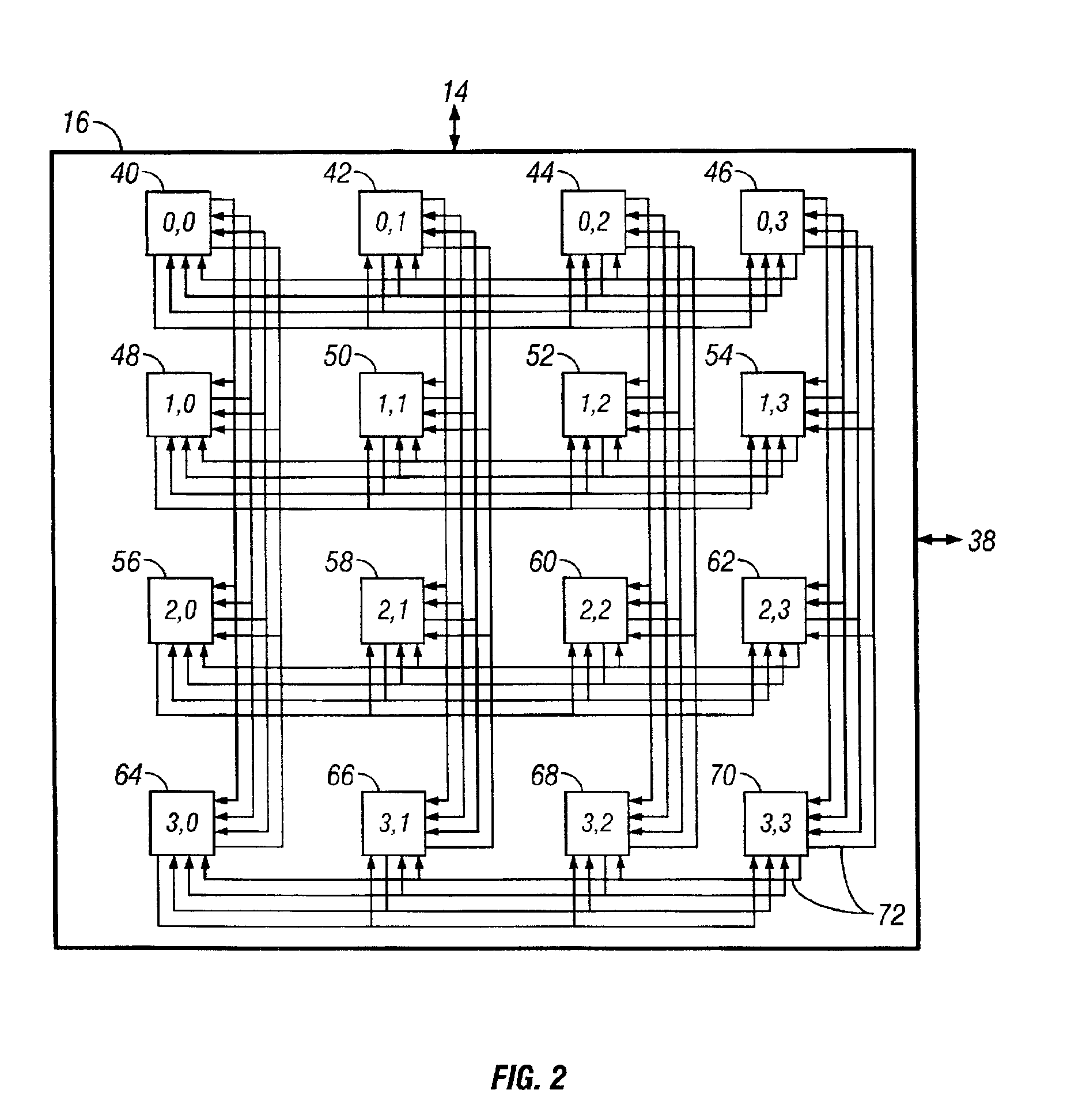

This invention discloses a group of instructions, block4 and block4v, in a matrix processor 16 that rearranges data between vector and matrix forms of an A×B matrix of data 120 where the data matrix includes one or more 4×4 sub-matrices of data 160-166. The instructions of this invention simultaneously swaps row or columns between the first 140, second 142, third 144, and fourth 146 matrix registers according to the instructions that perform predefined matrix tensor operations on the data matrix that includes one of the following group of operations: swapping rows between the different individual matrix registers, or swapping columns between the different individual matrix registers. Additionally, successive iterations or combinations of the block4 and or block4v instructions perform standard tensor matrix operations from the following group of matrix operations: transpose, shuffle, and deal.

Owner:APPLE INC

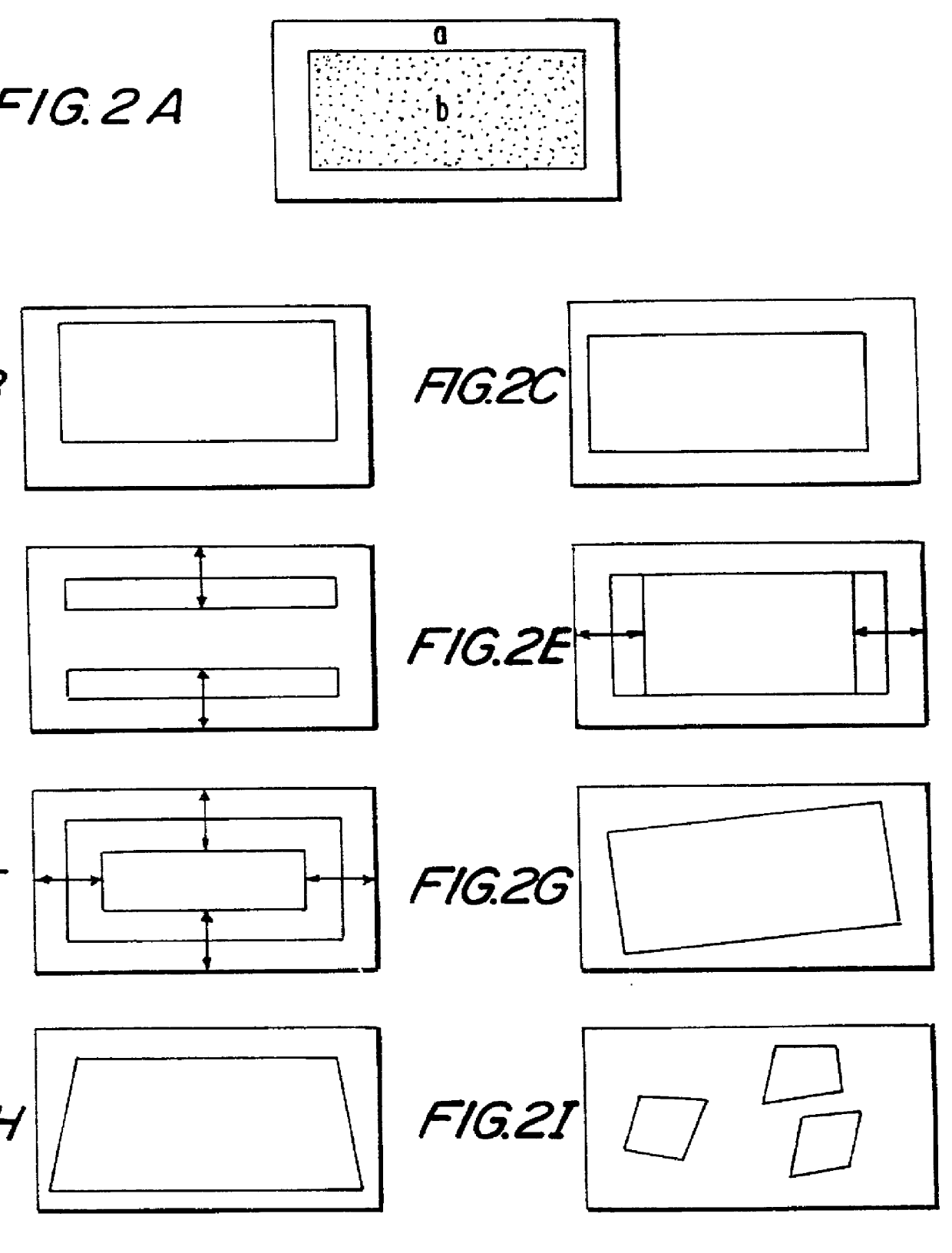

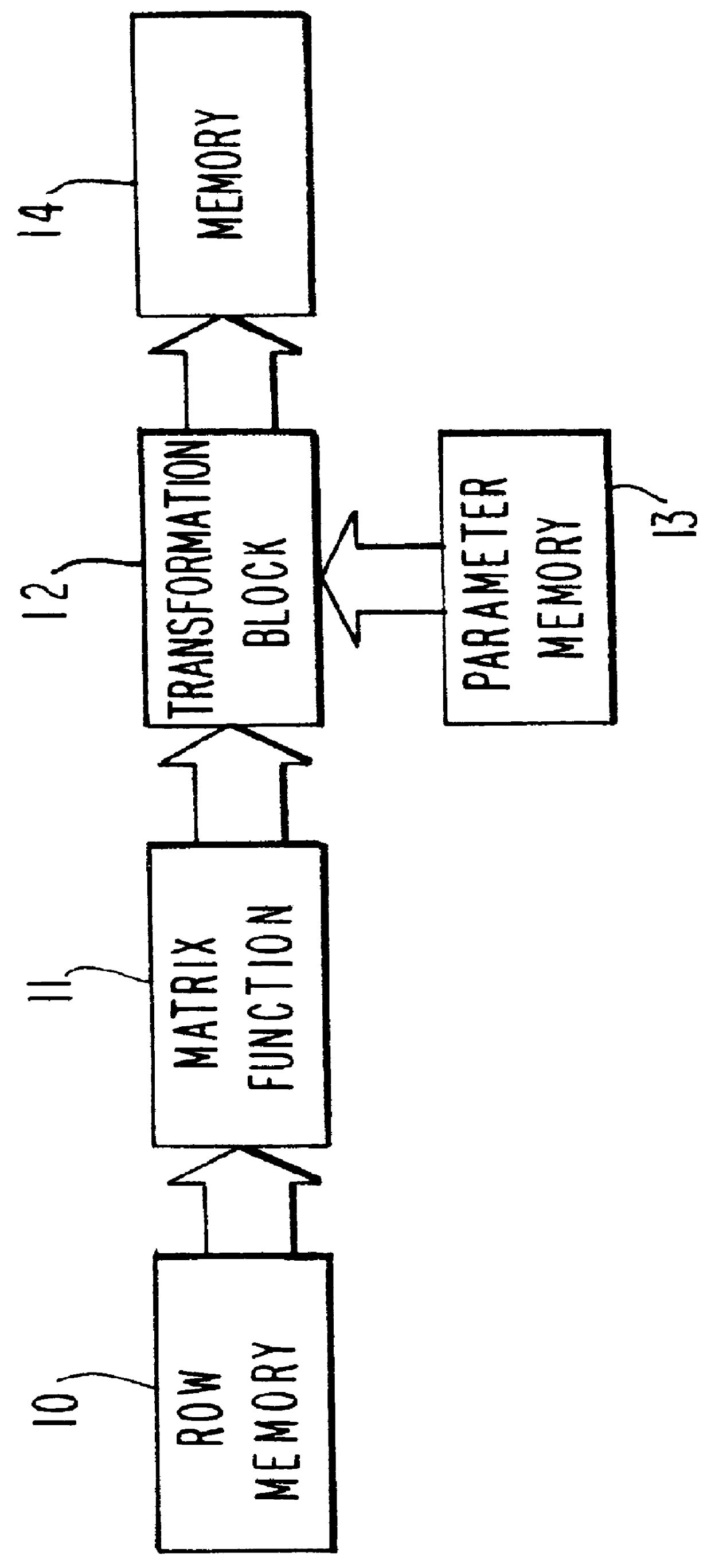

Process for correcting geometric errors in the transfer of information to a printing stock

InactiveUS6024504ACharacter printing data arrangement from carrierError detection/correctionGeometric errorDigital imaging

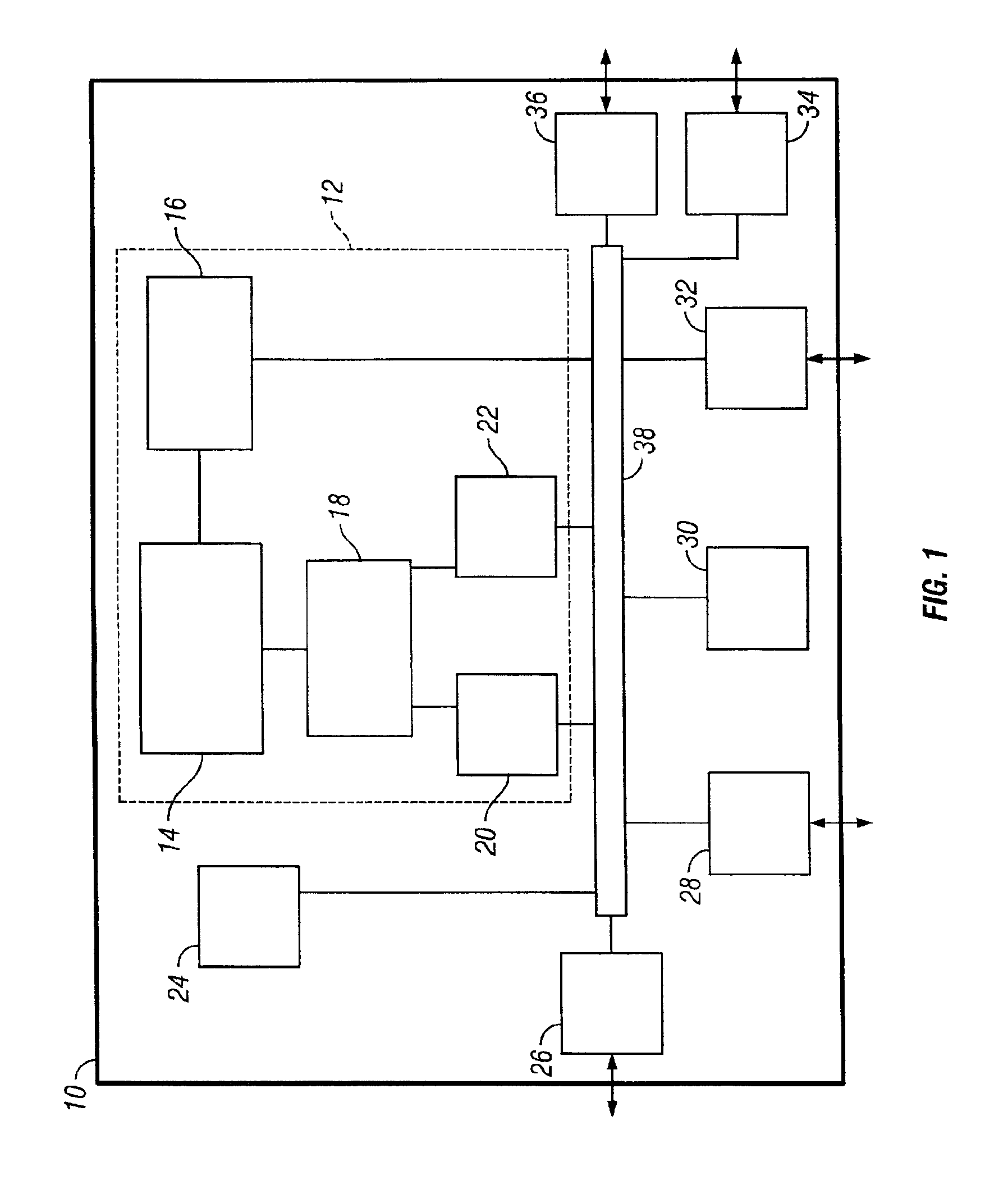

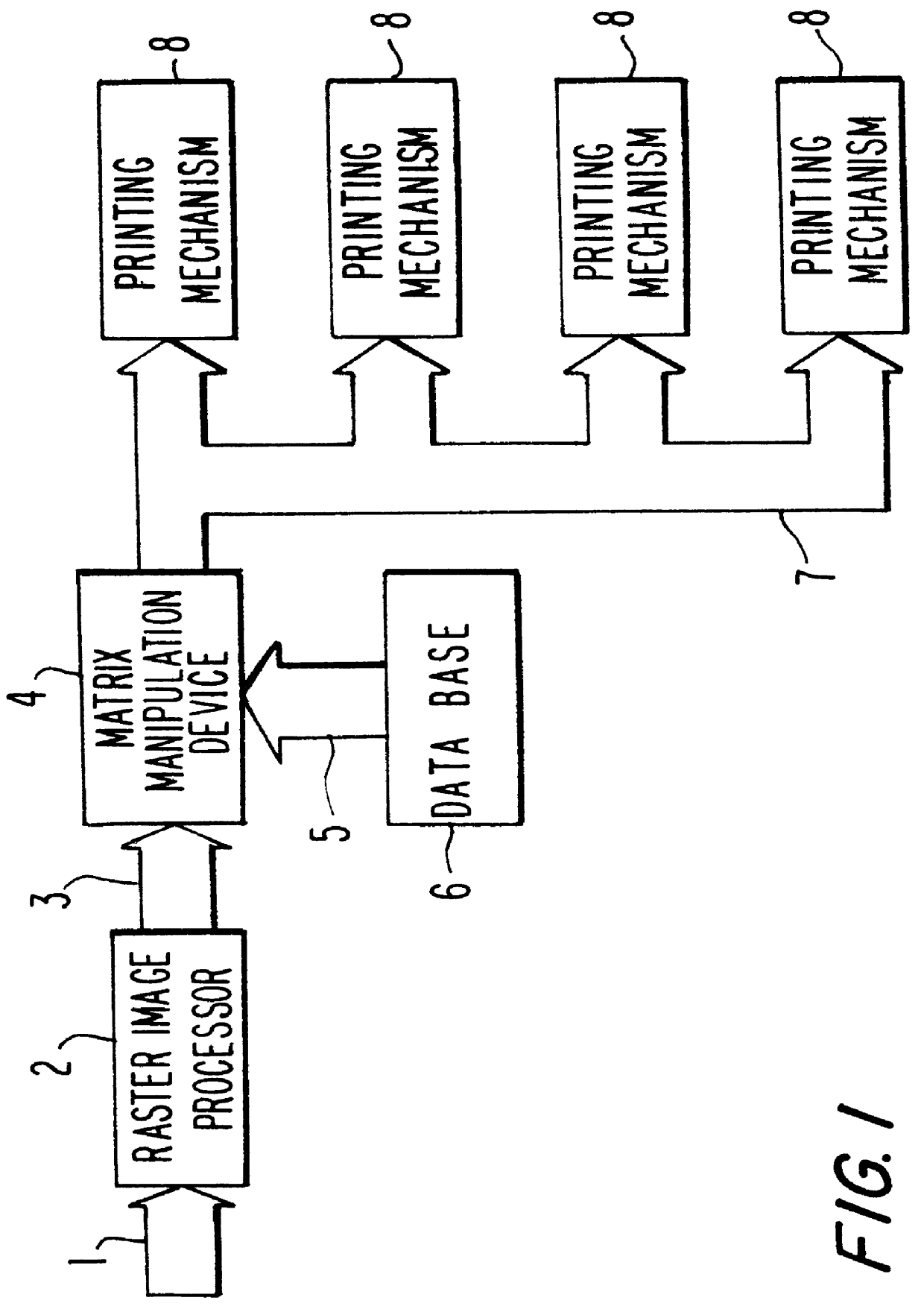

A process corrects geometric errors in the transfer of information without mechanical intervention on the printing form, to compensate for the errors that occur and thus attain optimized print quality prior to imaging. The corrections are visually indiscernible, so that the artifacts created in the printed result by the corrections do not stand out in the image. A device-independent description of the page information to be printed is converted by a Raster Imaging Process into at least one device-dependent digital matrix. Each matrix with m rows and n columns contains the information for a certain color to be printed. After the individual matrices are produced, they are supplied to a matrix manipulation device, which subjects each matrix to a correction transformation using specific parameters. After the matrices are adjusted, they are supplied by a matrix transfer device to the digital imaging devices in the printing mechanisms.

Owner:MANROLANAD AG

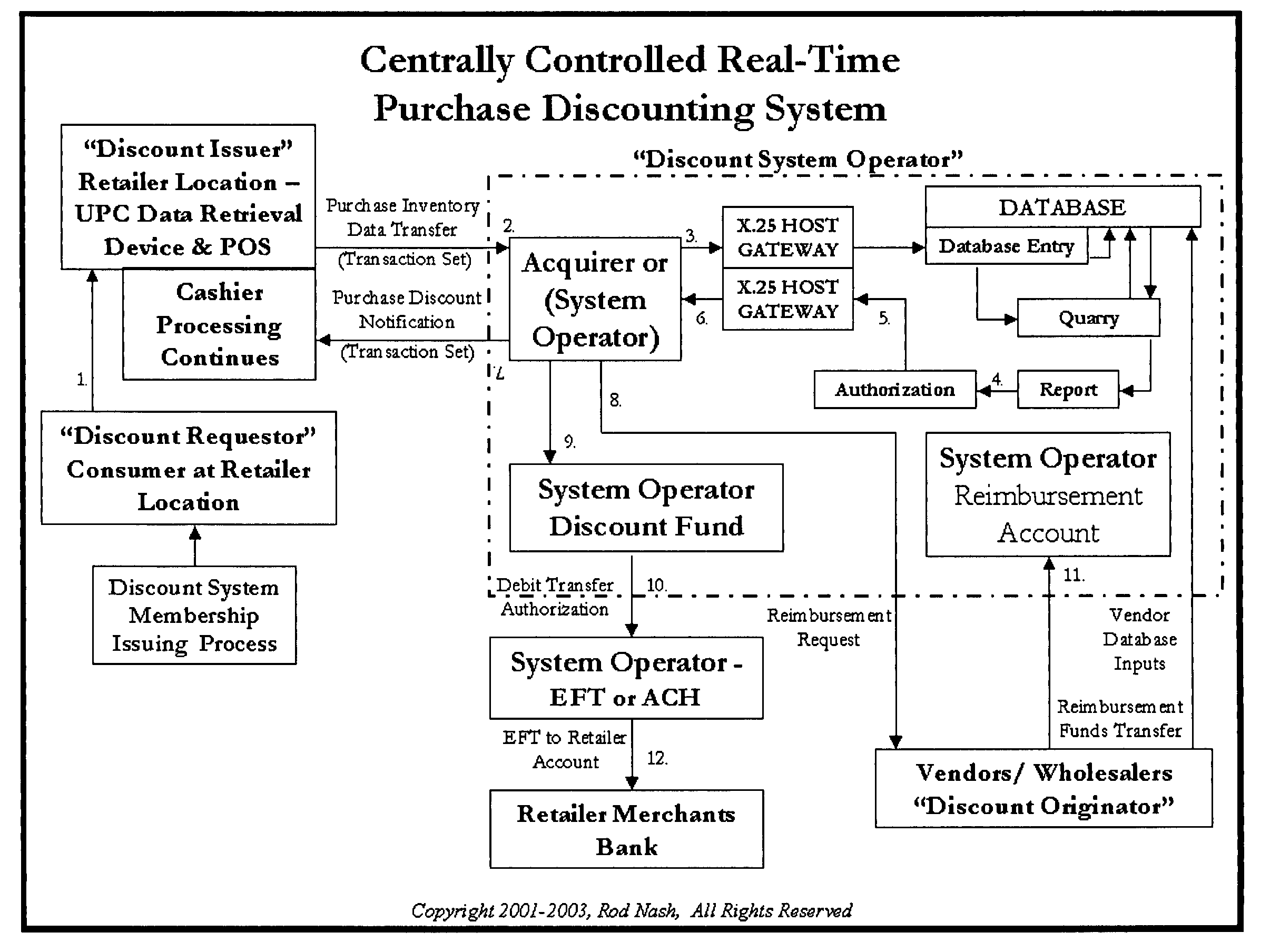

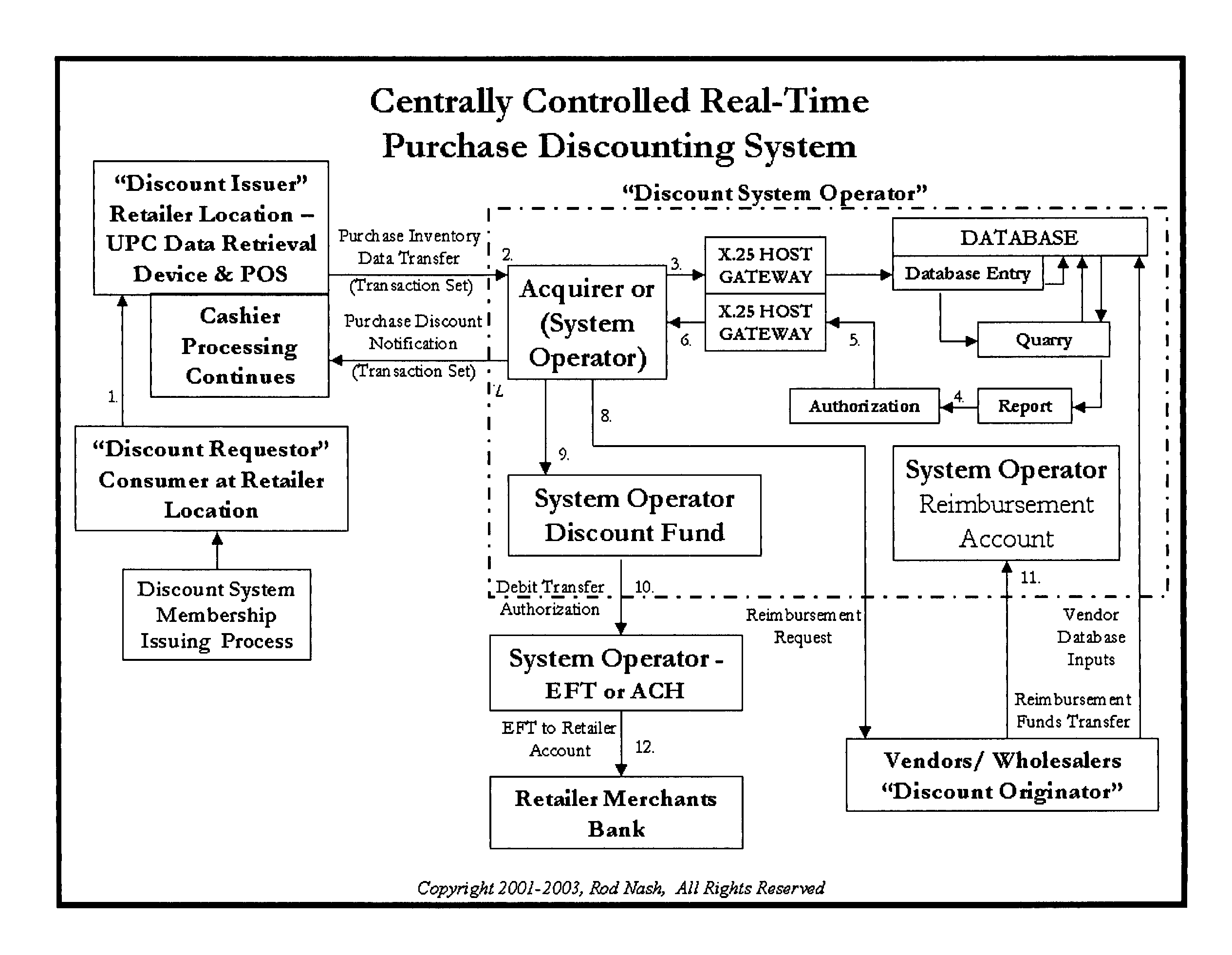

Centrally controlled real-time purchase discounting system

InactiveUS20050075927A1Buying/selling/leasing transactionsPoint-of-sale network systemsData managementData system

This invention is an innovative solution to antiquated paper coupons. It overcomes deficiencies of couponing systems by using electronic data systems to process a plurality of discount transactions in parallel with the consumers purchase via real-time discounting matrix. This consumer focused system comprises a business related process possessing the means of: transceiving consumer purchase data; managing databases related to discount available items, consumer purchase performance, history, preferences, transaction history, etc.; accessing discount matrix. Individual consumers use a variety of technologies to initiate the discounting transaction during the purchase process, to perform the real-time connection, to quarry, and to reporting on matrix transactions for discount authorizations simultaneously for a plurality of retail and Internet based point of sale locations. This discount process provides a means of better determining the consumer's intent to receive discounts on desired retail goods and services through a plurality of measured definitions in the purchase process.

Owner:NASH RODNEY

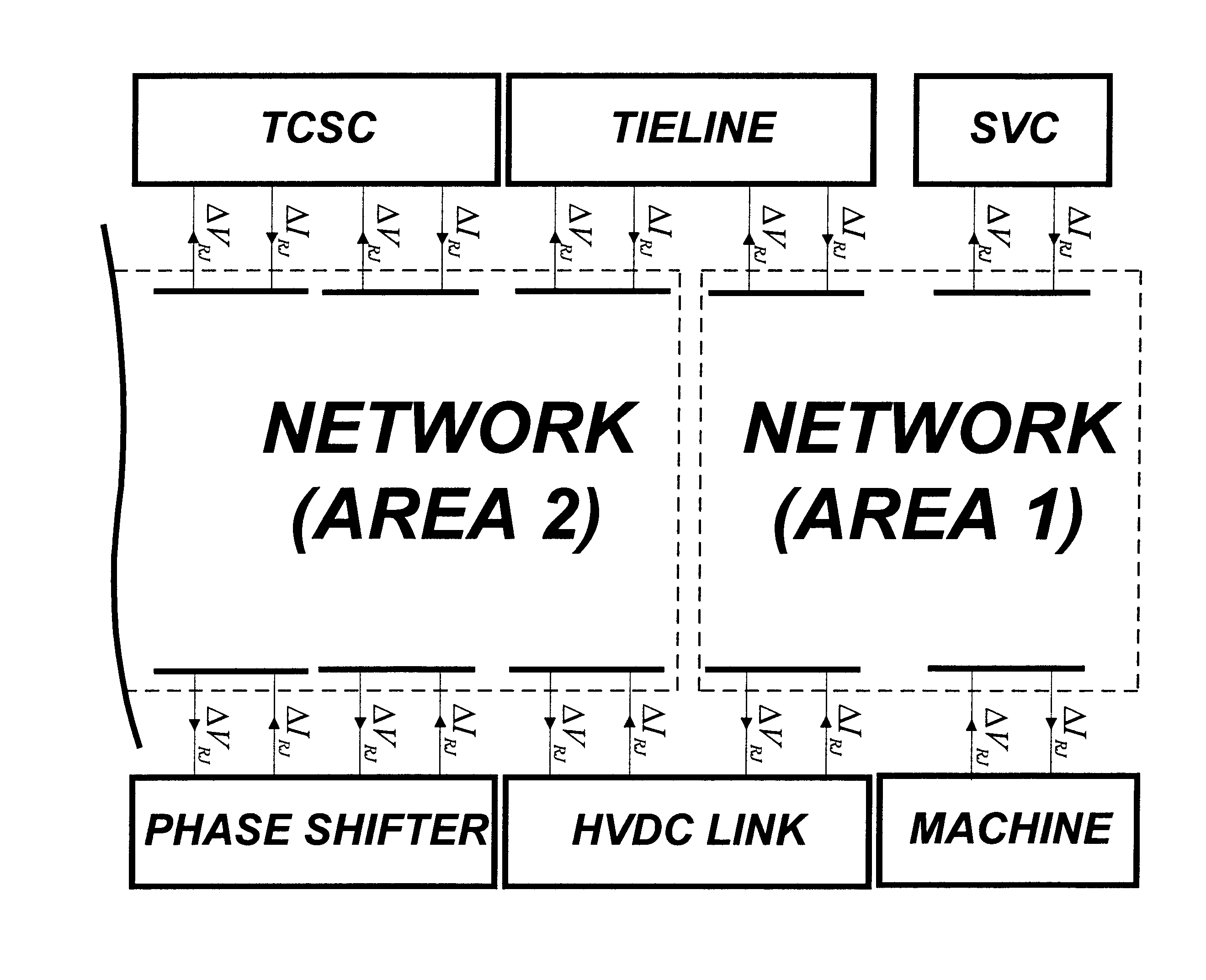

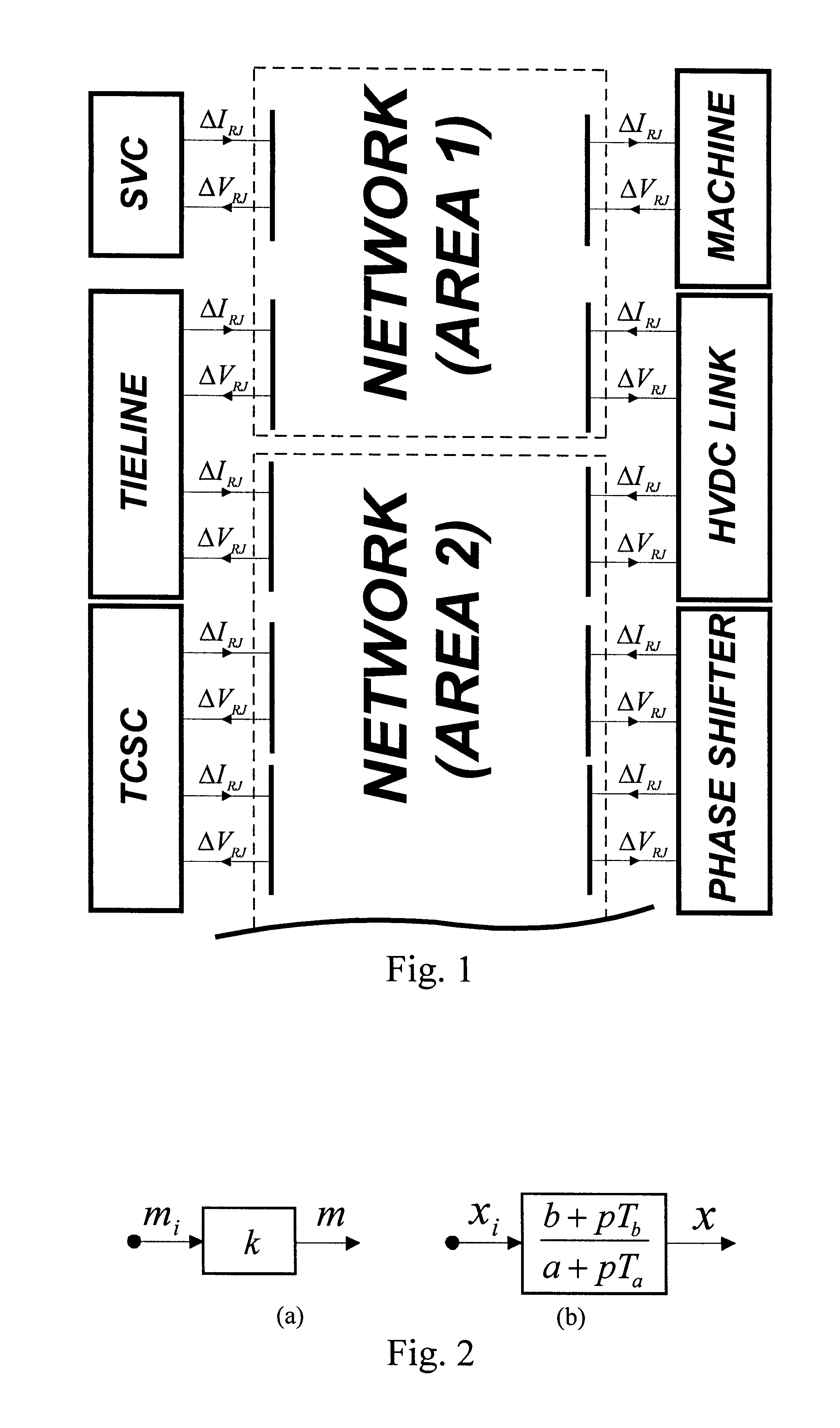

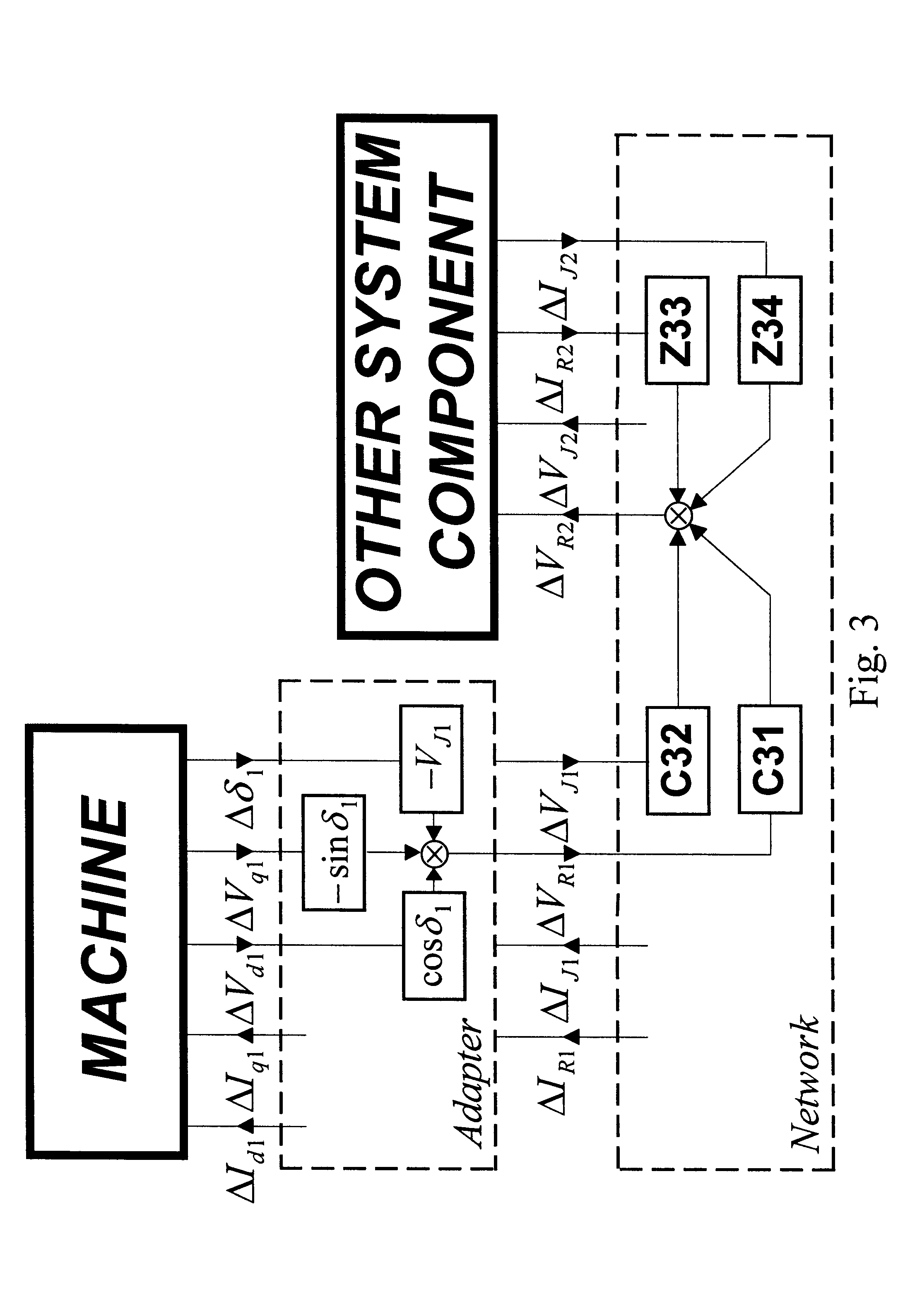

Electrical power network modelling method

InactiveUS6202041B1Analogue computers for electric apparatusElectrical testingElectric power systemPower grid

A versatile modelling for any standard power system component is disclosed, by which the component modules can be easily plugged into the network module to form a small perturbation state space model of the entire system irrespective of the complexity of the system. The state equation is available as explicitly a function of every parameter and the input and output can be any variable, thus providing insight into the physical nature by simple matrix manipulation.

Owner:THE HONG KONG POLYTECHNIC UNIV

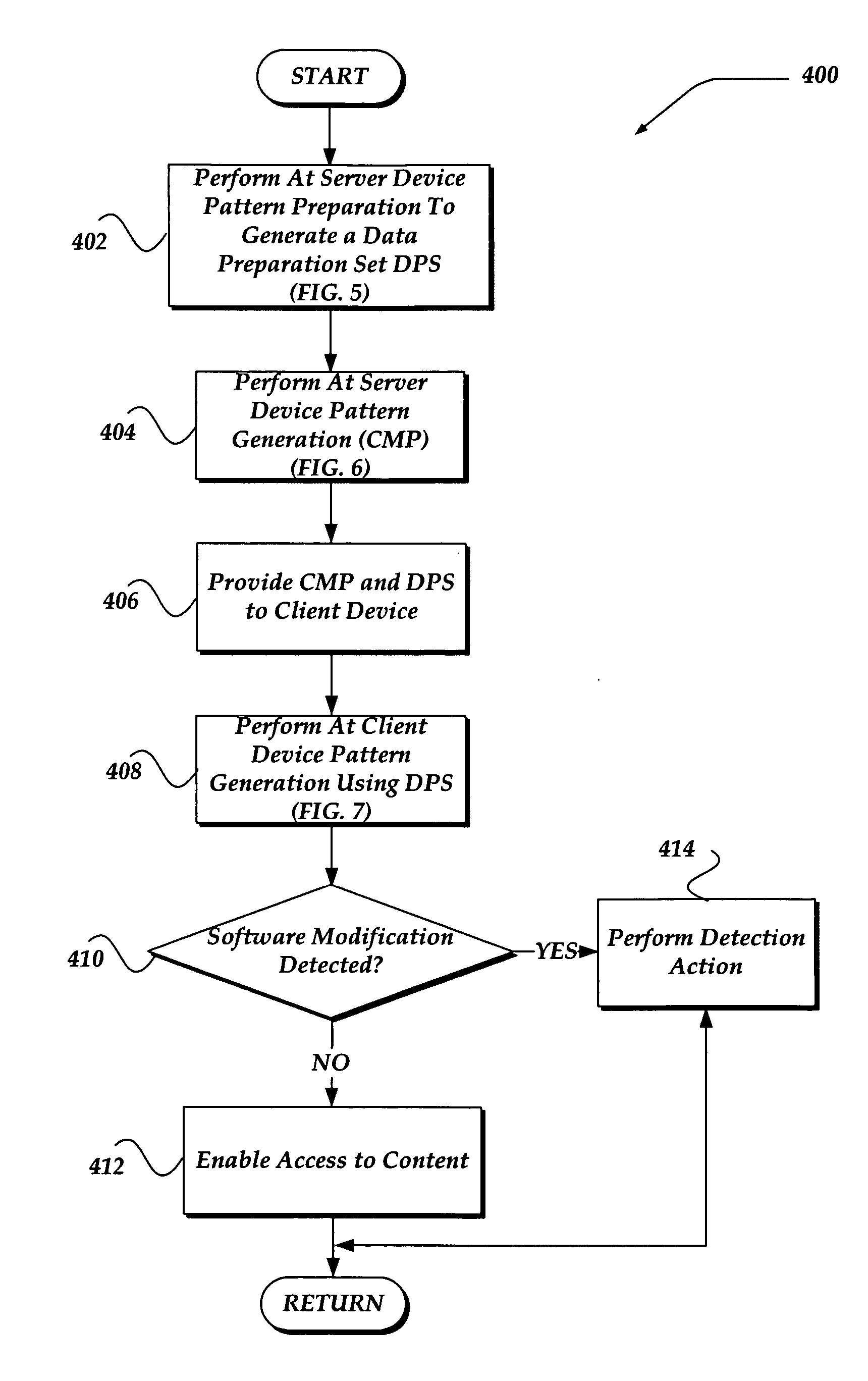

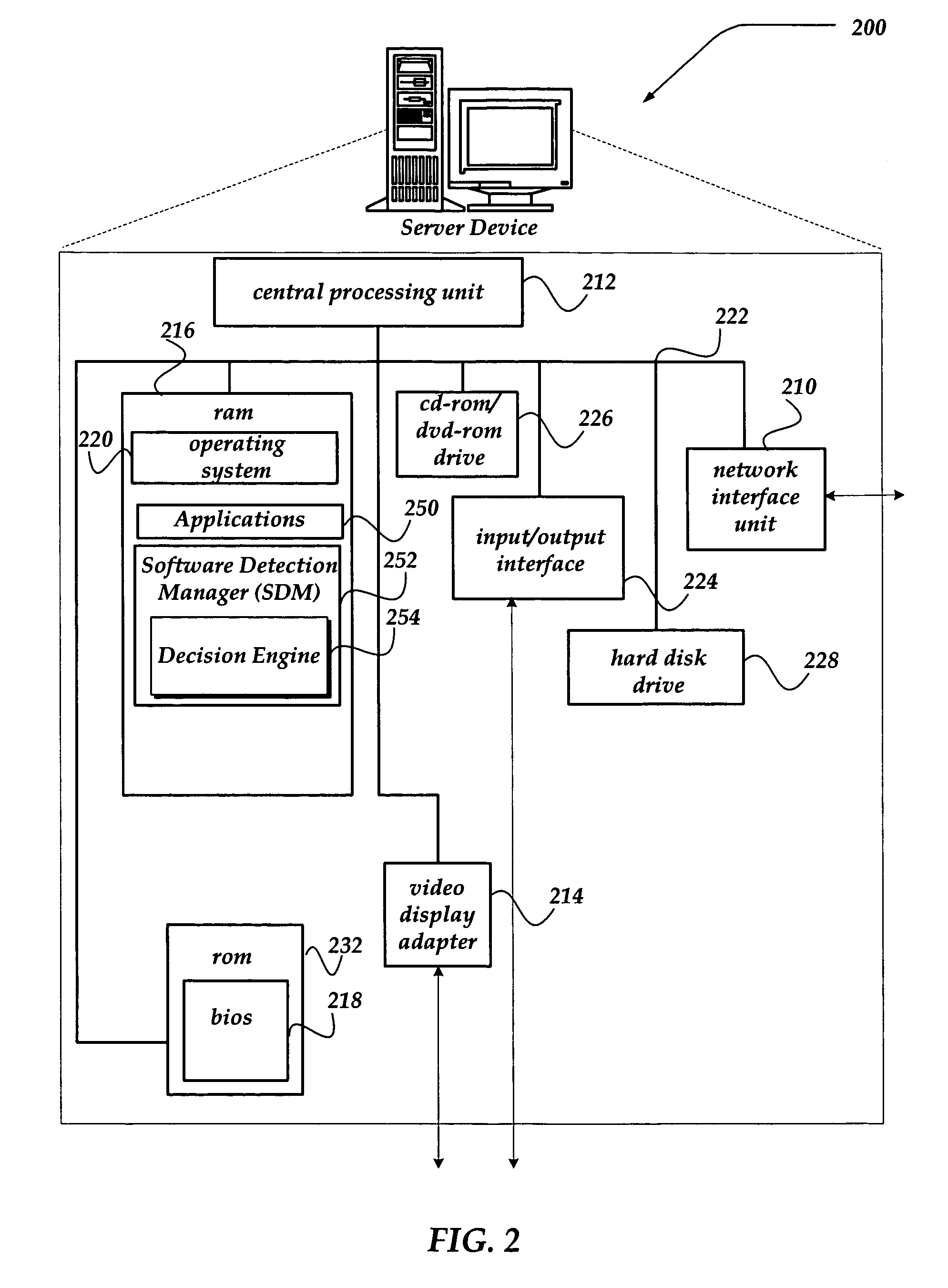

System and method for software tamper detection

A method, system, and apparatus are directed towards detecting unauthorized modification of software, such as virtual smart card software. An analysis is performed on the software to generate a unique pattern that is based on the integrity of the software. The pattern is generated using various portions of the software code. In one embodiment, matrix manipulations that involve a sequence of randomly selected matrix operations are performed on extracted portions of the software code. Sample sizes of the software code, sizes of the matrices, and other initialization parameters may be selected based on a desired security level. The resulting pattern may then be compared to a known normal pattern for the software to detect unauthorized modification. In one embodiment, however, the resulting pattern may be algorithmically combined with another value. The resulting combination may be used to decrypt content, if the software has not been modified.

Owner:GOOGLE LLC

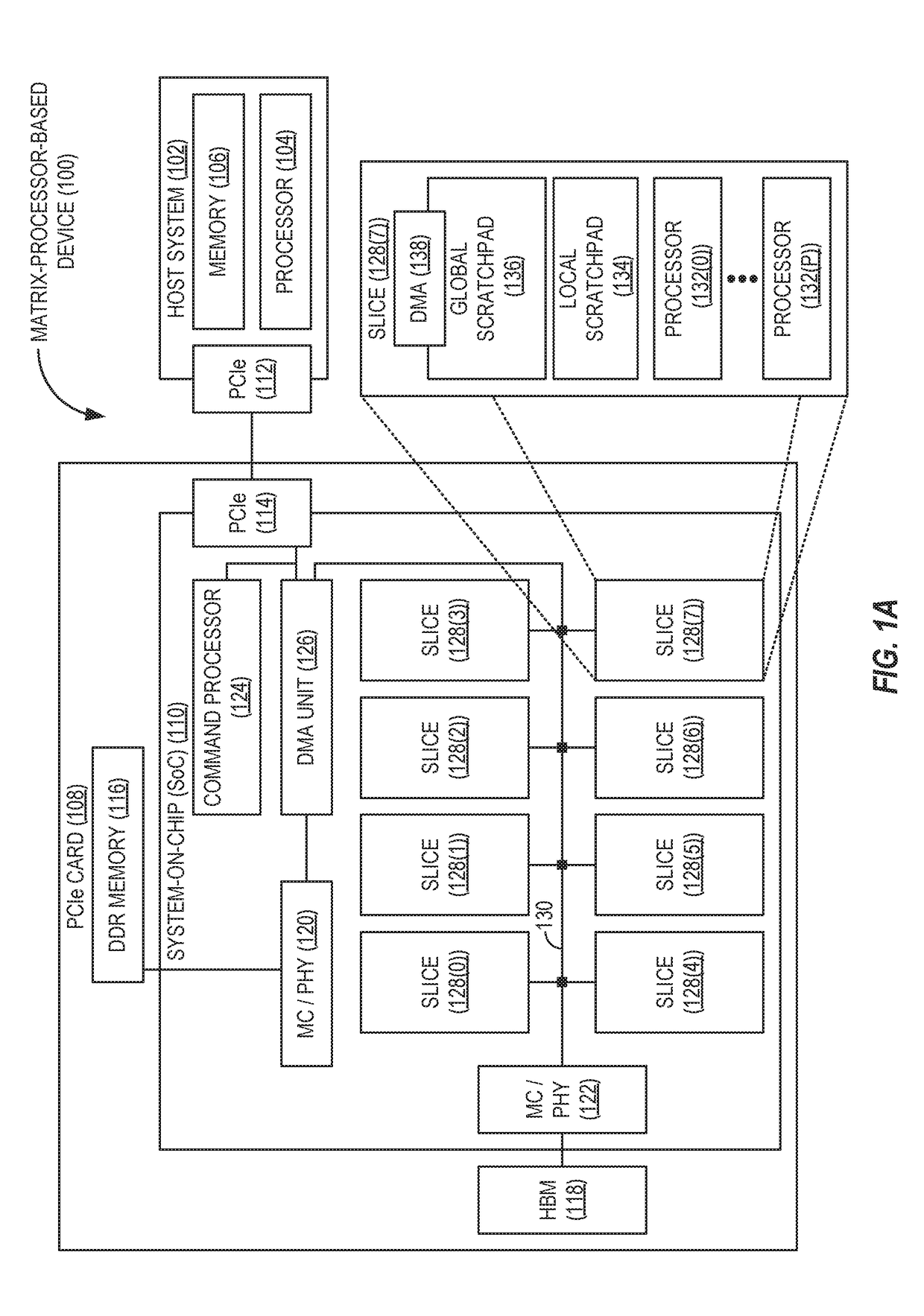

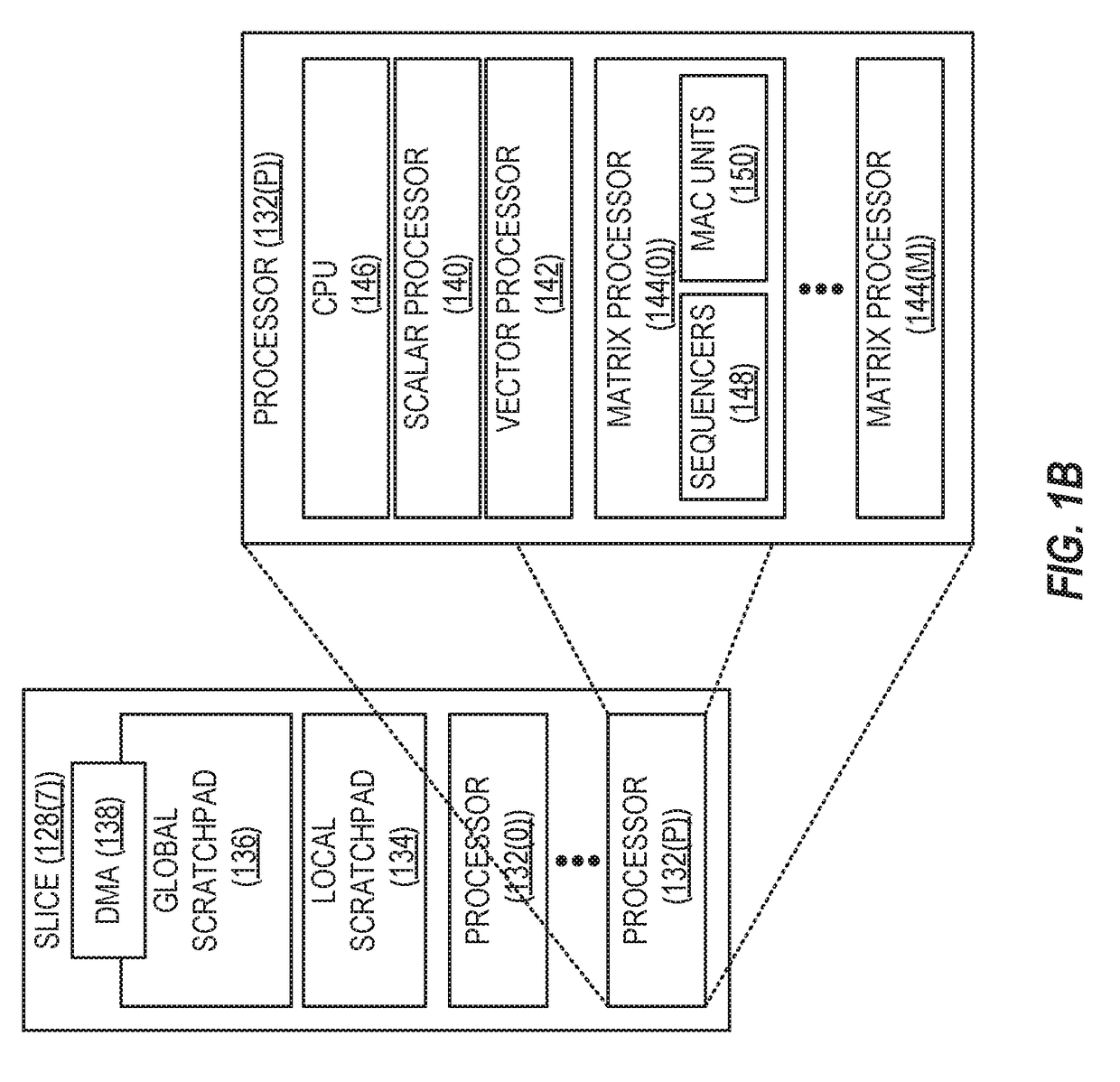

Providing efficient multiplication of sparse matrices in matrix-processor-based devices

ActiveUS20190065150A1Efficient multiplicationSingle instruction multiple data multiprocessorsDigital data processing detailsParallel computingSparse matrix

Owner:QUALCOMM INC

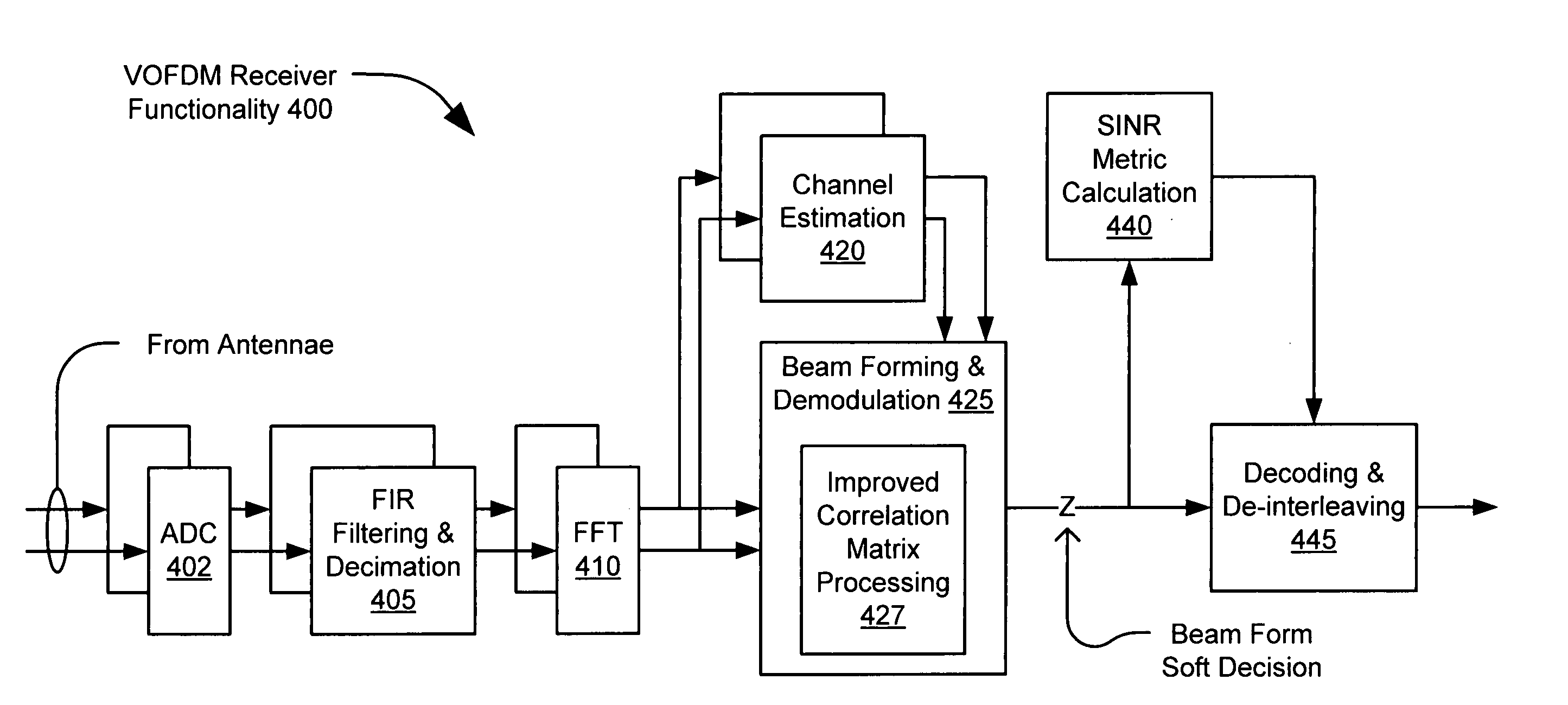

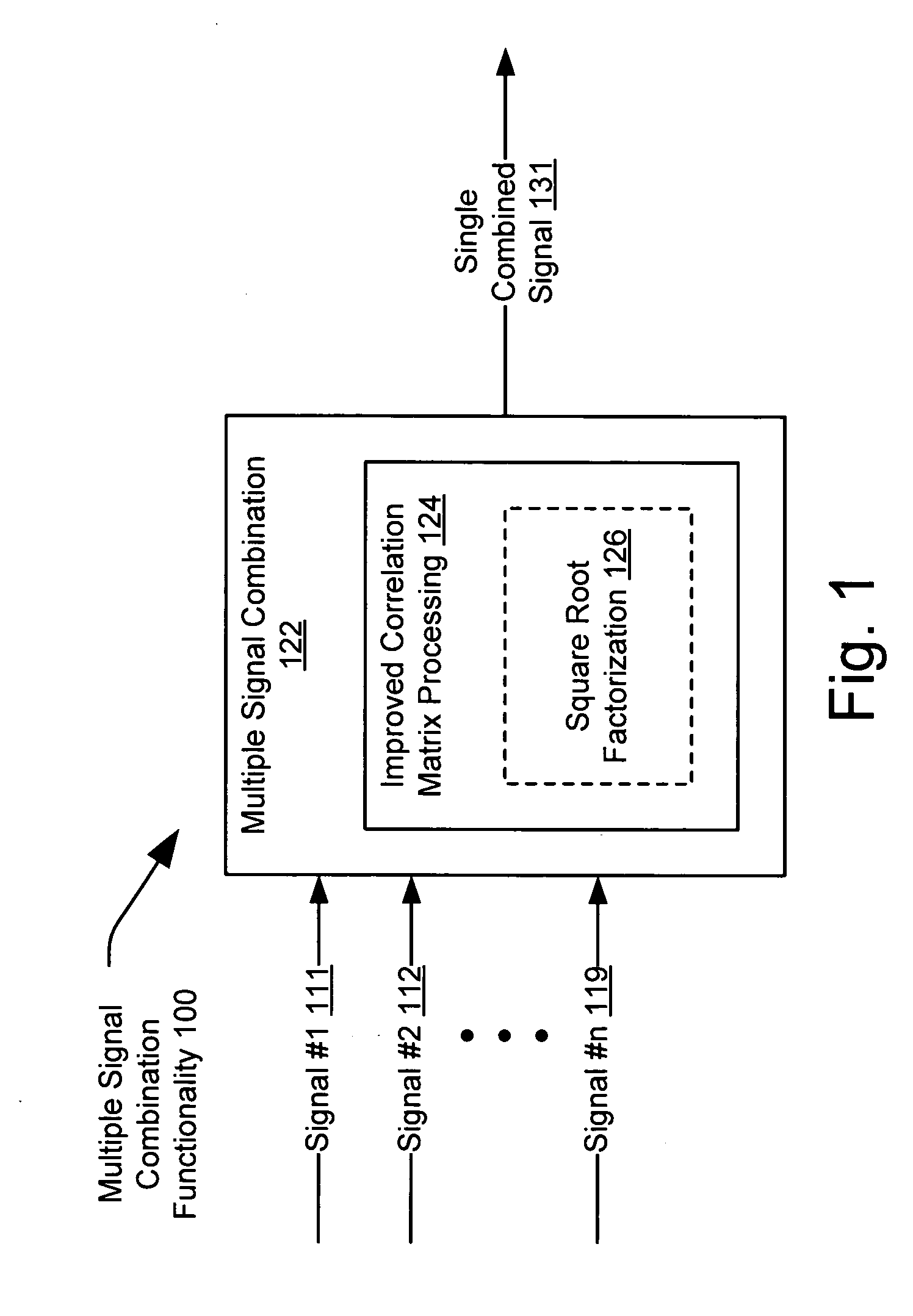

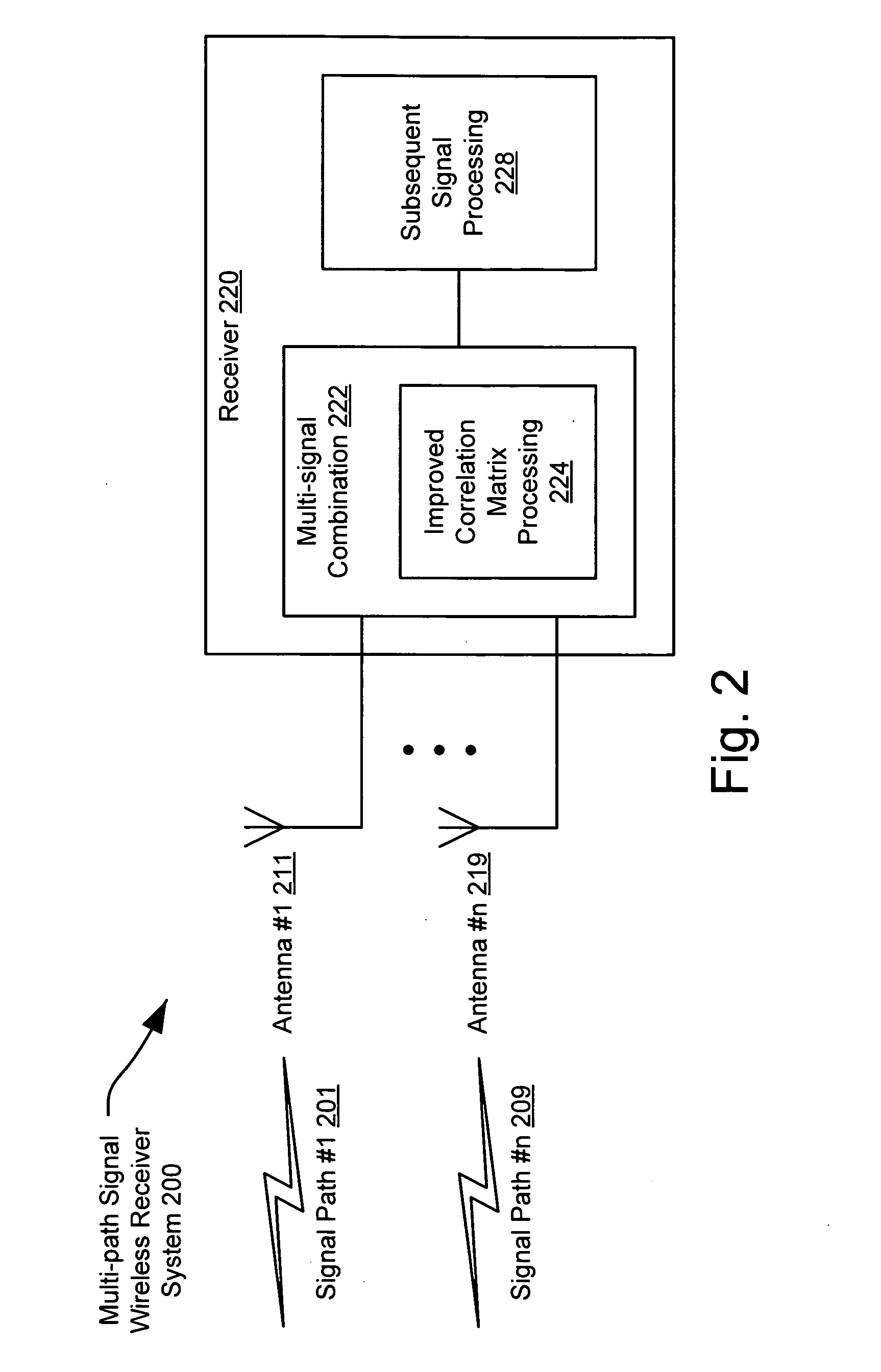

VOFDM receiver correlation matrix processing using factorization

InactiveUS20060008018A1Spatial transmit diversityPolarisation/directional diversityAlgorithmIntermediate variable

Owner:AVAGO TECH INT SALES PTE LTD

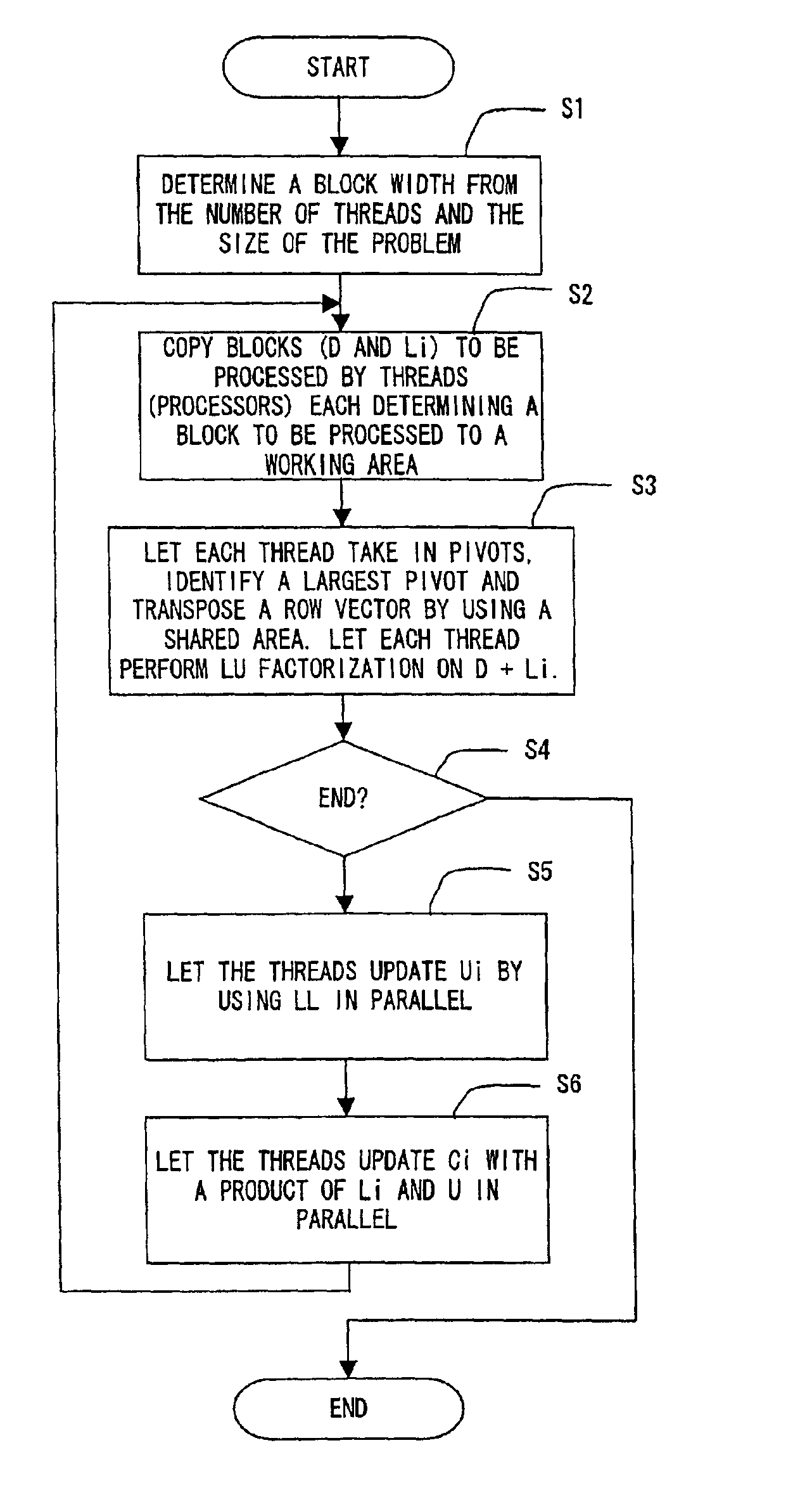

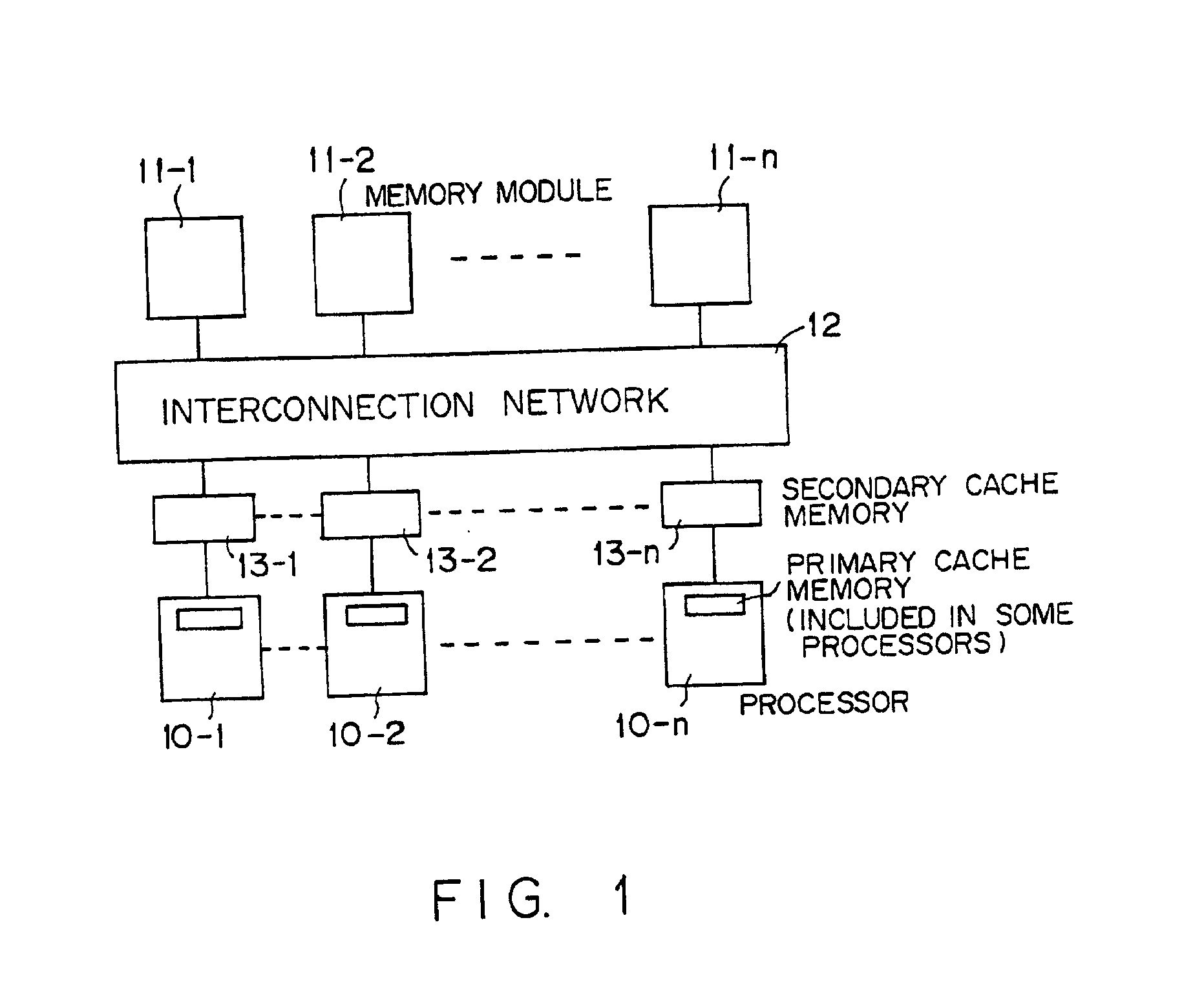

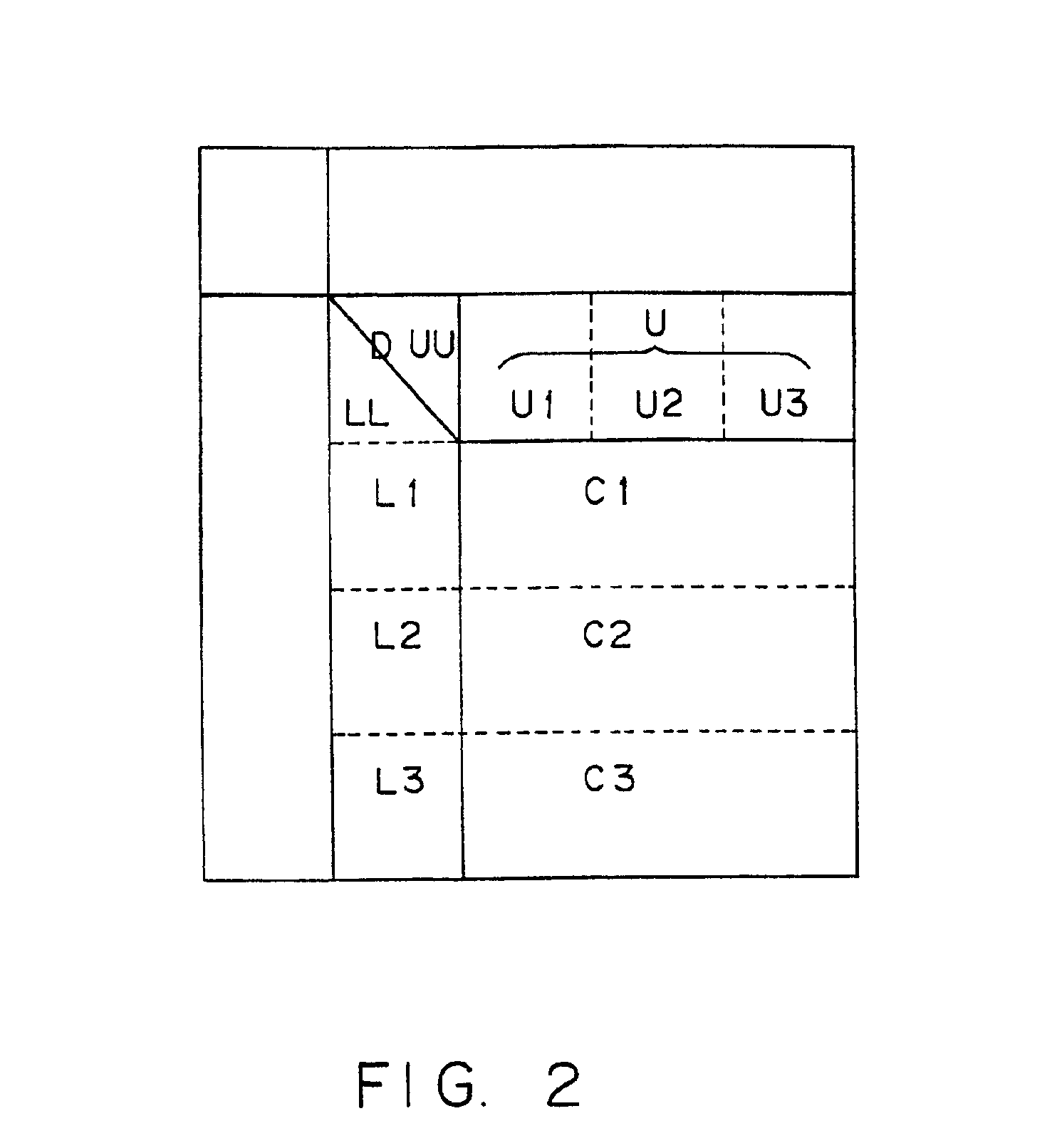

Matrix processing method of shared-memory scalar parallel-processing computer and recording medium

InactiveUS6907513B2Improve efficiencyUtilization areaGeneral purpose stored program computerConcurrent instruction executionLU decompositionDiagonal

In accordance with a parallel matrix processing method adopted in a shared-memory scalar computer, a matrix to be subjected to LU factorization is divided into a block D of the diagonal portion and blocks beneath the D diagonal block such as L1, L2 and L3. Then, D+L1, D+L2 and D+L3 are assigned to 3 processors respectively for processing them in parallel. Next, a block U is updated by adopting an LU-factorization method and C1 to C3 are updated with L1 to L3 and U. By carrying out this processing on the inner side gradually decreasing in size as blocks, finally, a portion corresponding to the D diagonal block remains to be processed. By applying the LU factorization to this D portion, the LU factorization for the entire matrix can be completed.

Owner:FUJITSU LTD

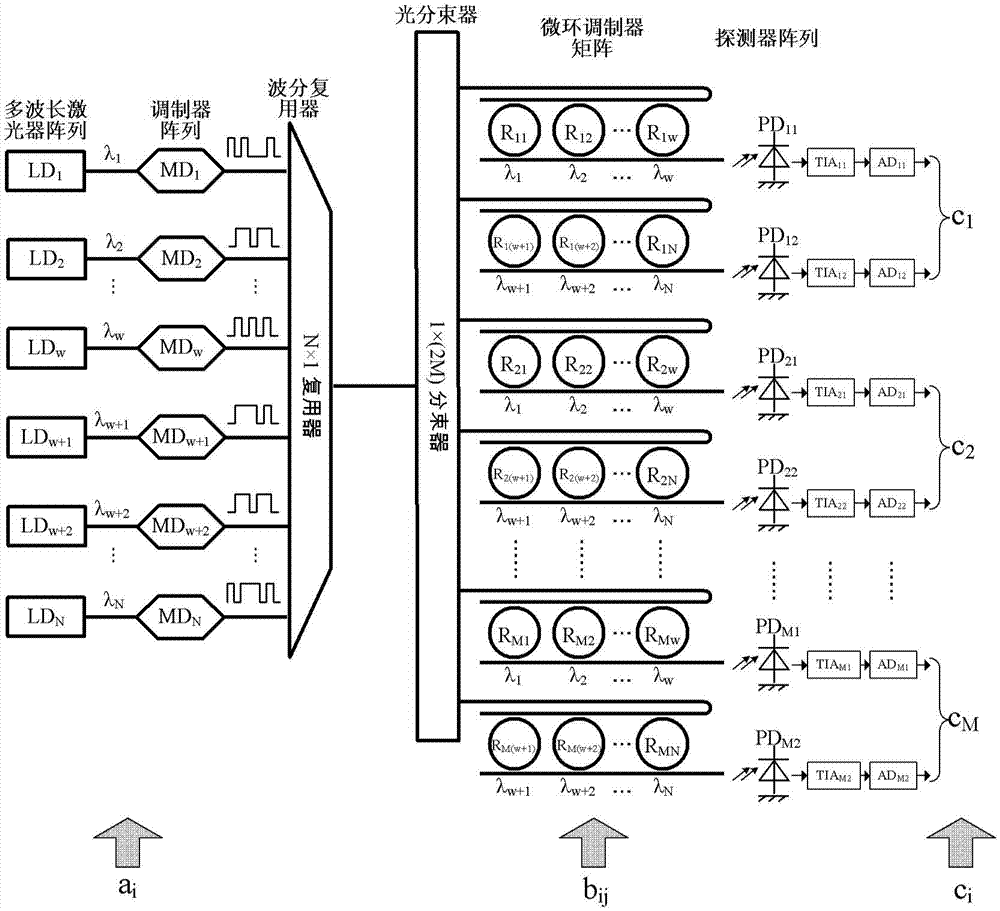

Method for improving data resolution ratio of silica-based optical matrix processor and processor

InactiveCN103678258AReduce resolutionLower requirementComplex mathematical operationsLaser arrayImage resolution

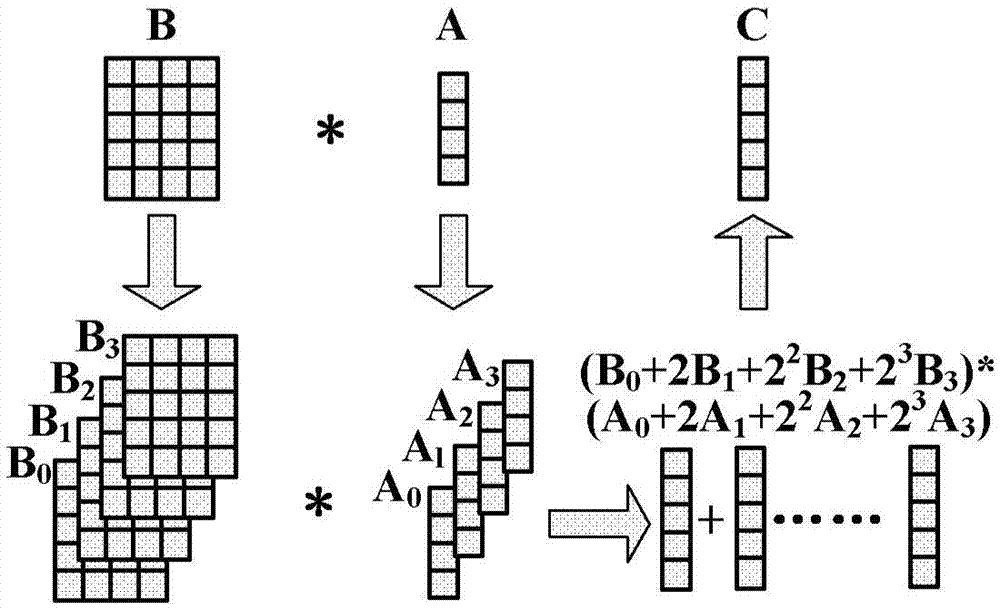

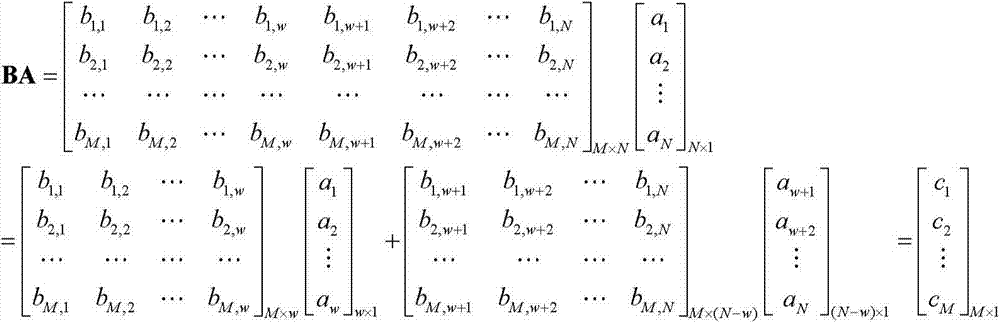

The invention discloses a method for improving the data resolution ratio of a silica-based optical matrix processor and the processor. The method includes the steps that laser signals are output by a laser array and received and modulated by an optical modulator array to an N*1 vector A; a modulator matrix is formed by a micro-ring optical modulator matrix, wherein modulation depths form an M*N matrix B; optical modulation is carried out respectively by dividing the vector A into k subvectors and dividing the matrix B into k submatrixes so as to obtain the product of the k subvectors and the k submatrixes; the obtained product of the subvectors and the k submatrixes is detected by a detector linear array formed by k detectors, and then the product of the vector A and the matrix B is obtained; the element bit wide of each subvector and each submatrix is m, m bit vectors and m bit matrixes are formed after bitwise separation, and the product of the subvectors and the submatrixes is obtained by multiplying the bit vectors by the bit matrixes respectively.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

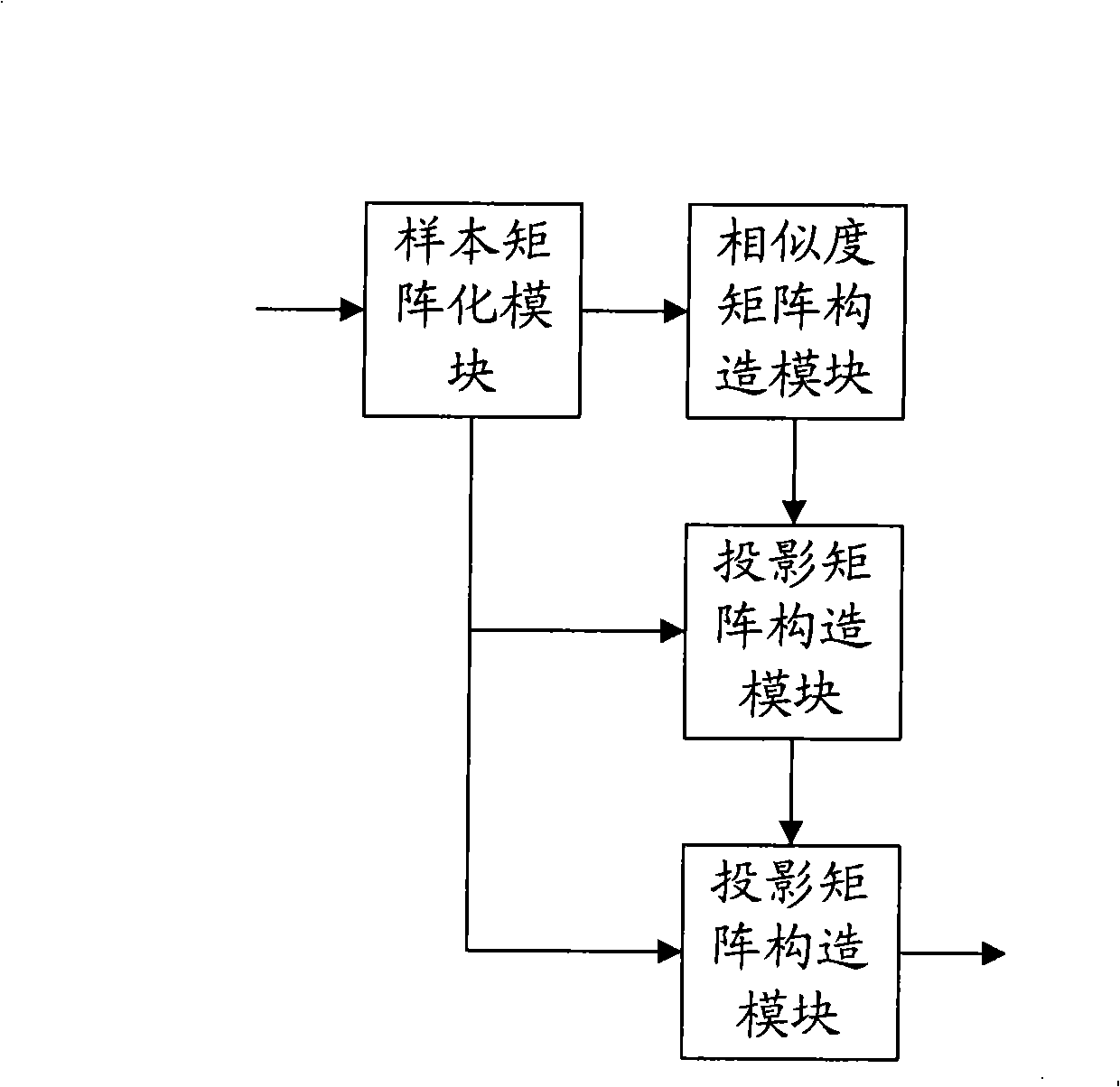

Method and apparatus for extracting human face recognition characteristic

ActiveCN101324923AImprove extraction efficiencyReduce dimensionalityCharacter and pattern recognitionHat matrixFeature extraction

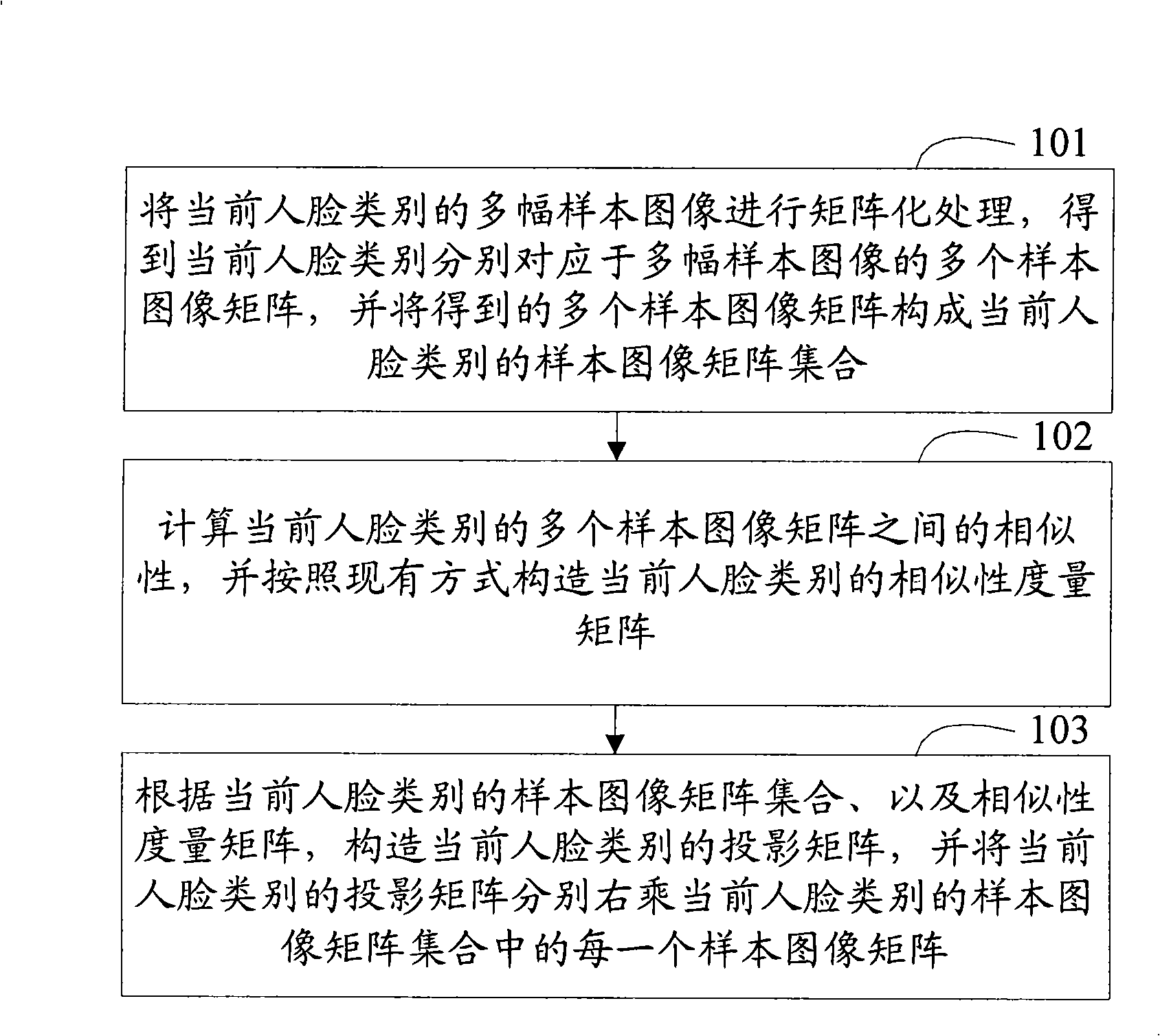

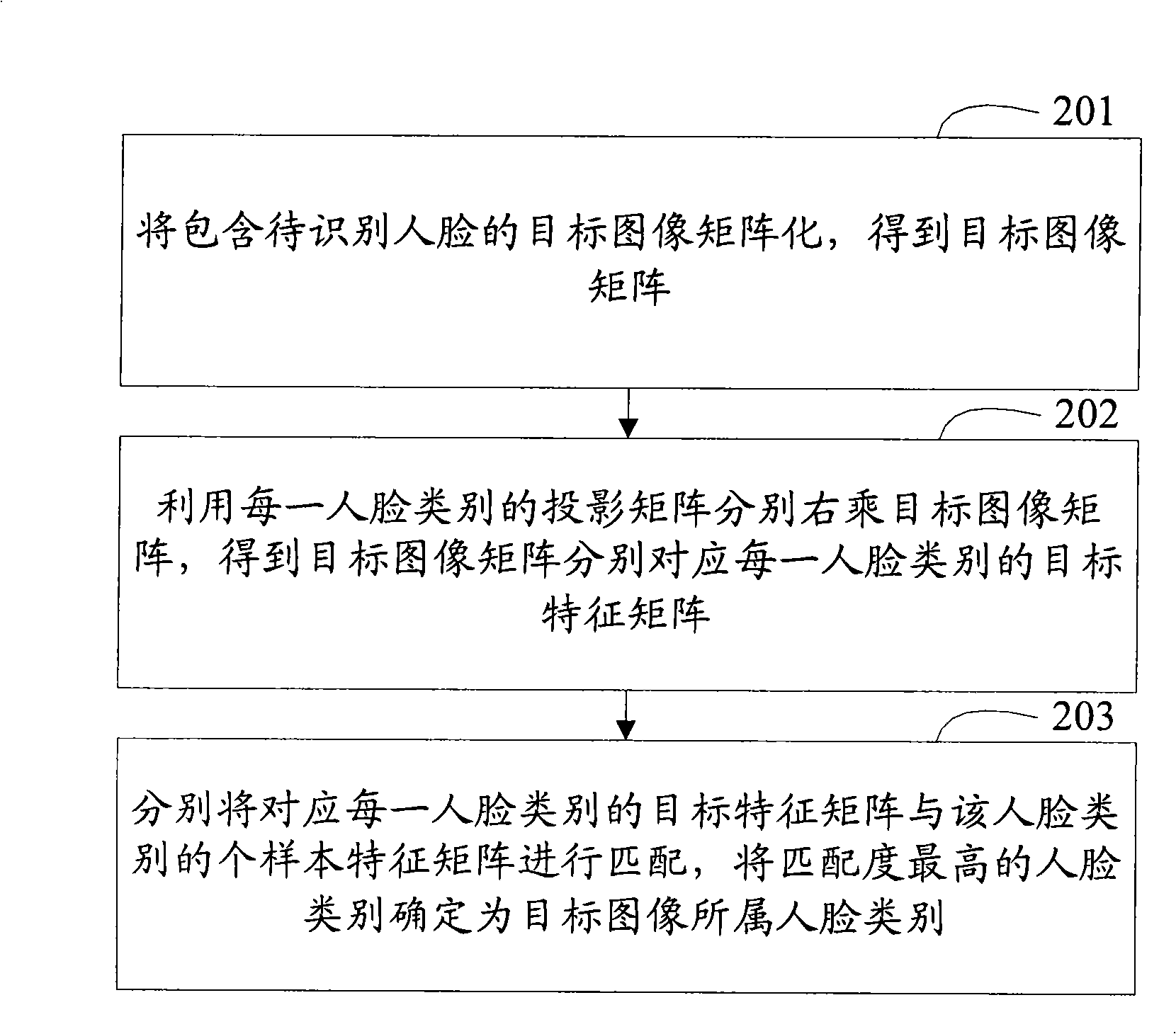

The invention discloses a method and a device of extracting features for identifying a human face. When the identification features of a human face are extracted, a plurality of sample images undergo the matrixing processing instead of the vectorization processing. Furthermore, when the projection matrix is constructed, the dimension of matrix manipulation is reduced, therefore, the average required time for extracting the feature assembly from a plurality of sample images of each human facial type is reduced so as to improve the efficiency for extracting features.

Owner:GUANGDONG VIMICRO

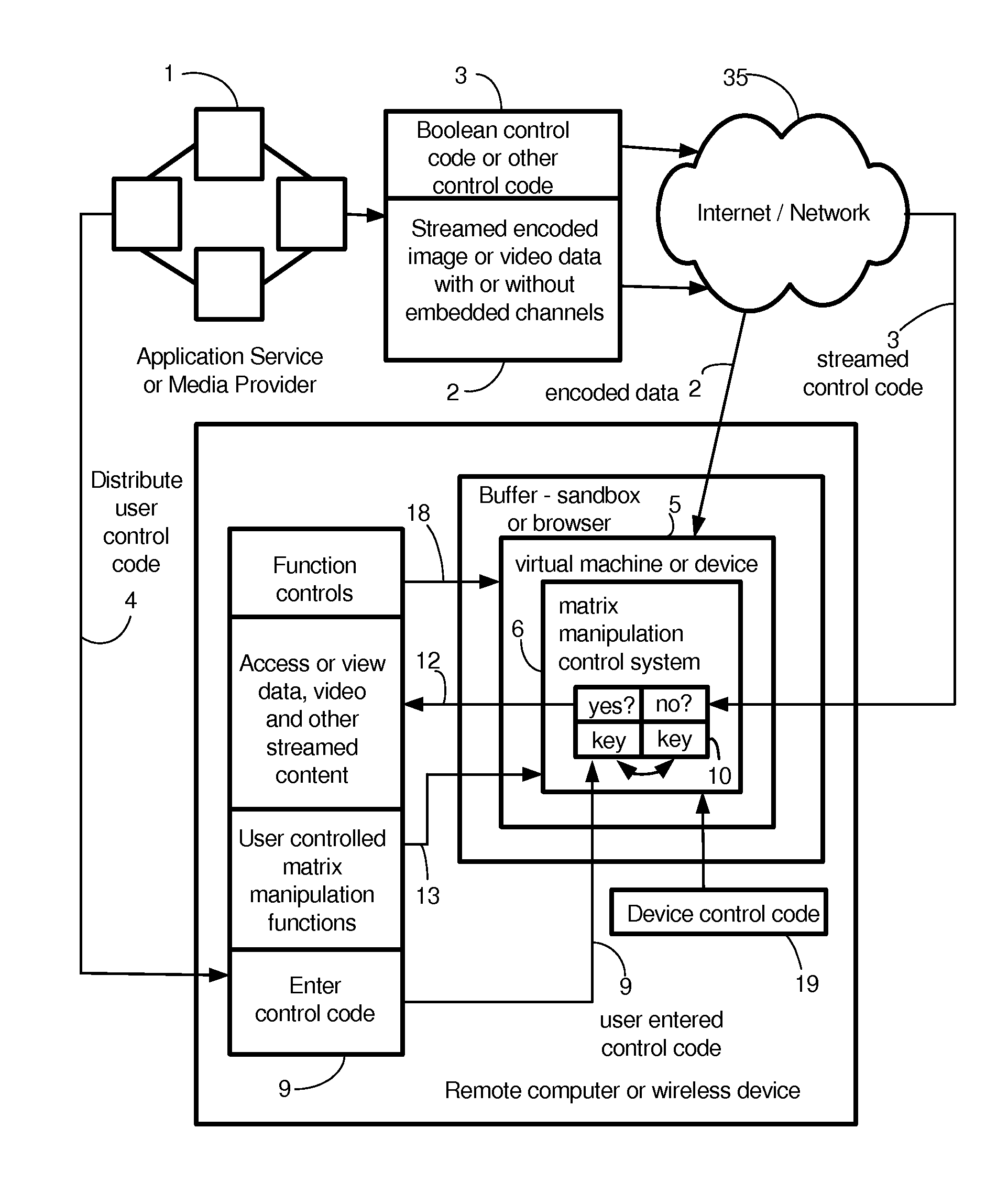

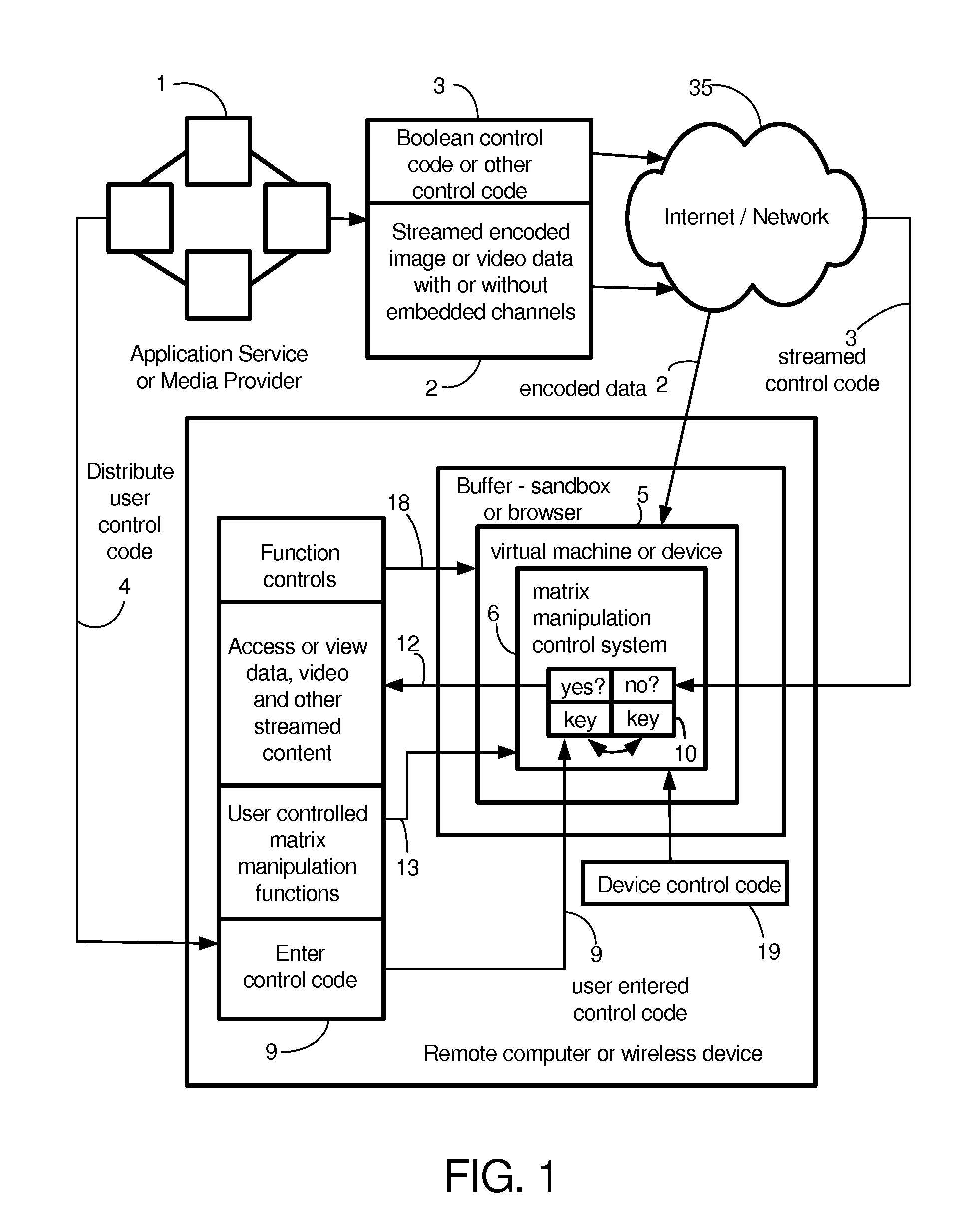

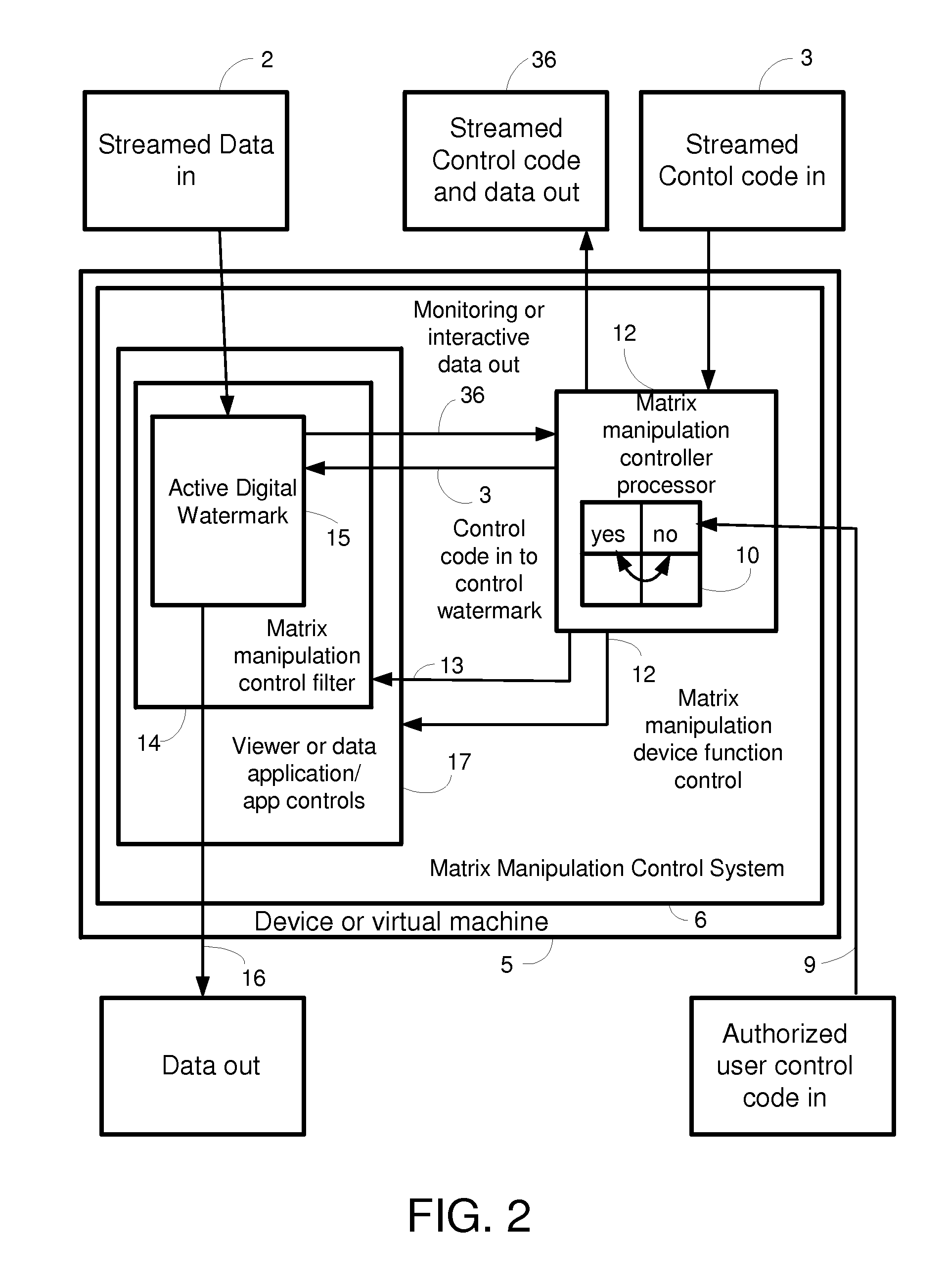

System for interactive matrix manipulation control of streamed data and media

ActiveUS20130238901A1Prevent unauthorized copyingUser identity/authority verificationDigital data protectionStreaming dataComputer hardware

An interactive streaming media and application service provider system can securely stream high resolution, multiple formats of video and data. Different data sets can be included in a single stream. A rights management system controls matrix manipulation and other aspects of user control of the data, including one or more of rendering in various different 2D, 3D, or other media formats, reconstruction and modeling, zooming, frame grab, print frame, parental controls, picture in picture, preventing unauthorized copying, adapting to different data transmission formats, adapting to different resolutions and screen sizes, and actively control functionality contained in embedded data, encryption / decryption. Control can be exerted by an external entity through a user-side virtual machine. Control codes can optionally be embedded in the media, embedded in the user's device, and / or sent separately to the device.

Owner:TAILSTREAM TECH

Method and apparatus for estimating delay and jitter between network routers coupled to background network

InactiveUS6885642B1Reduce traffic overheadEnsure effective implementationError preventionFrequency-division multiplex detailsDistributed computingNetwork router

A delay measurement technique according to an embodiment according to the present invention is based on the precept, ascertained by the inventors, that a link between network nodes will often contribute to the delay encountered between several different pairs of network nodes. Such a technique identifies the path between each pair of nodes by a list of links that form the path. Paths that are orthogonal are treated as being necessary for describing the delays encountered between nodes, and, once the requisite set of orthogonal paths has been derived, all other paths can be described in terms of one or more of these orthogonal paths. Such a technique also lends itself to matrix representation of the paths, and the use of matrix manipulation techniques in deriving delay and jitter.

Owner:CISCO TECH INC

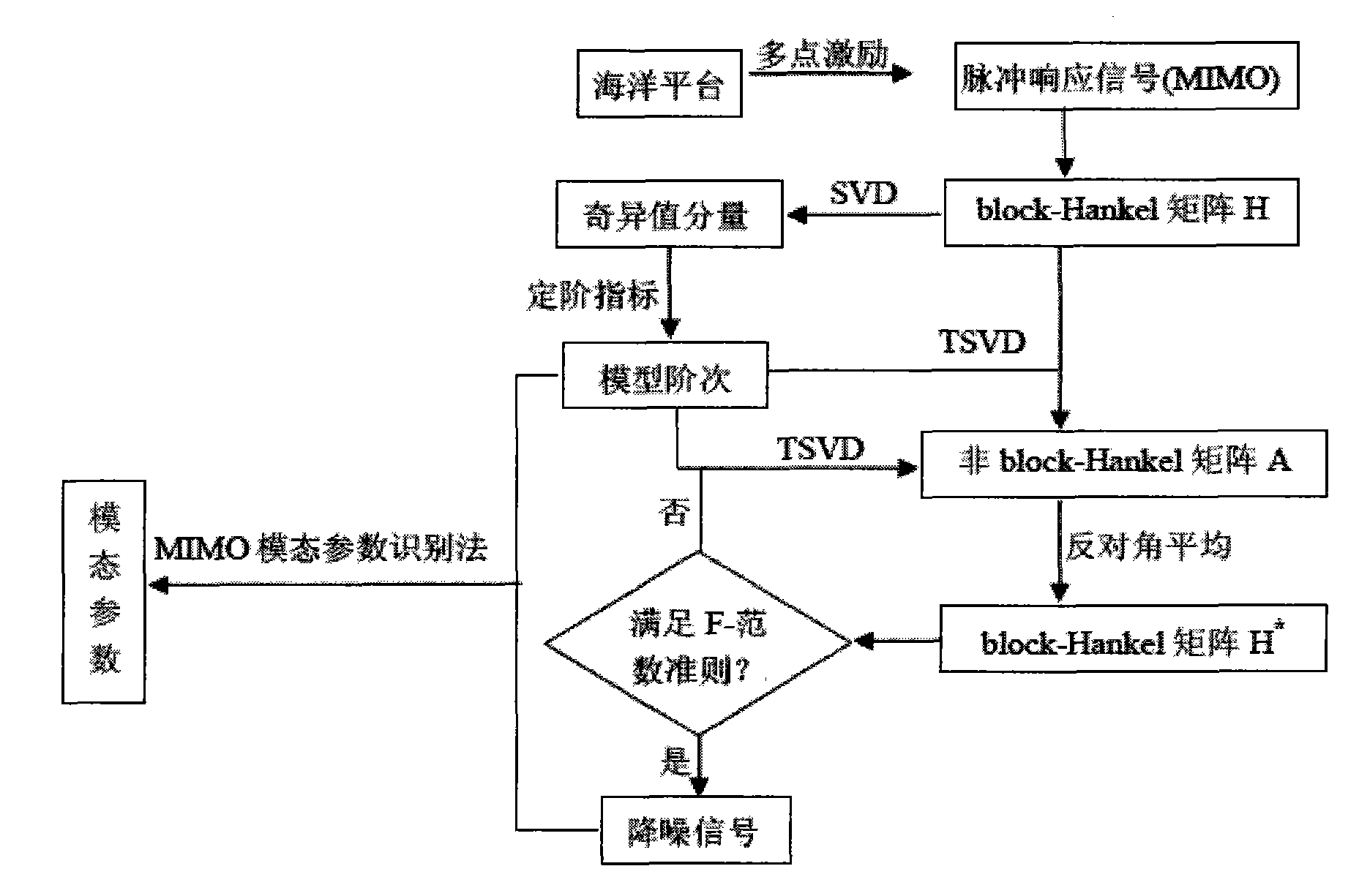

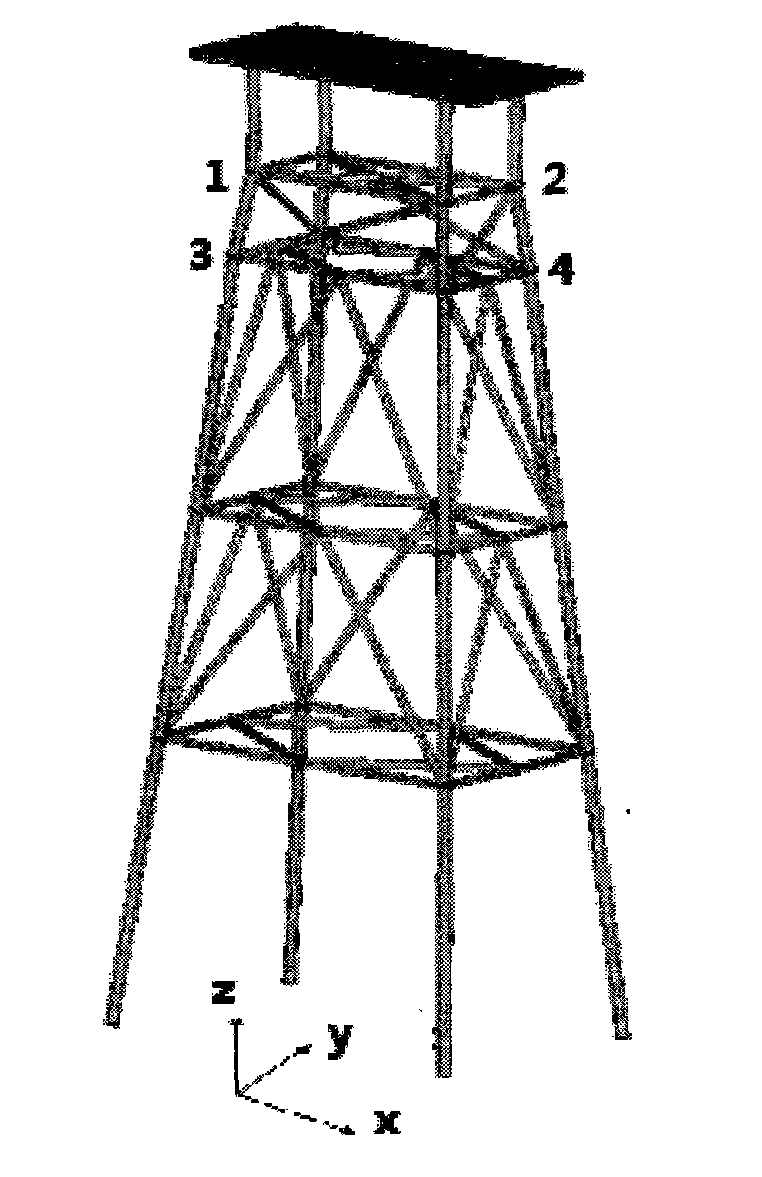

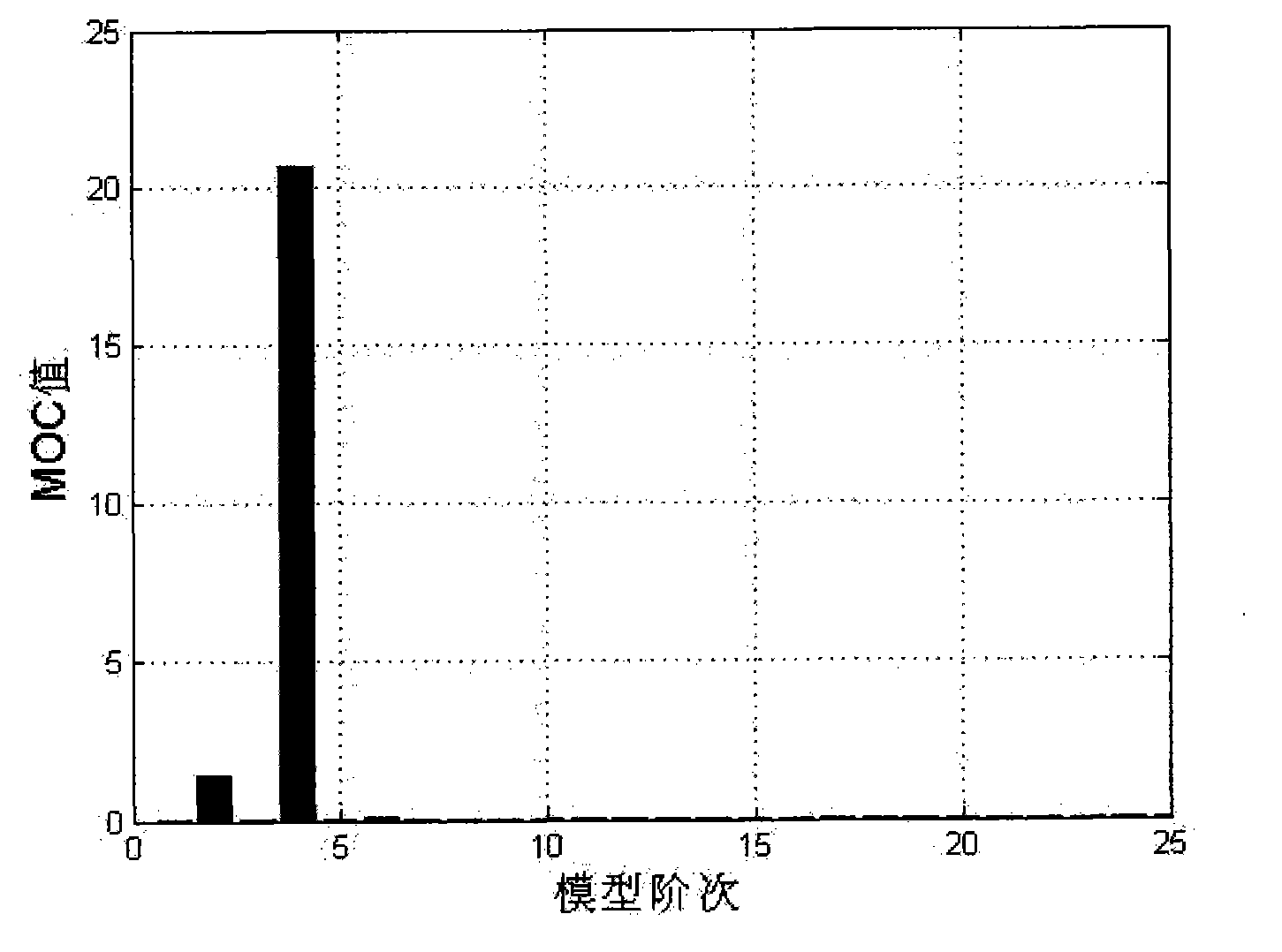

Modal parameter recognizing method based on multi-input multi-output signal noise reduction

InactiveCN103246890ASave machine timeImprove recognition accuracyCharacter and pattern recognitionMulti inputAlgorithm

The invention relates to a modal parameter recognizing method based on multi-input multi-output signal noise reduction. The method is characterized by comprising the steps of step 1, performing block-Hankel matrix conversion on noise-containing multi-point pulse responding signals to obtain a first block-Hankel matrix; step 2, processing the first matrix by utilizing structural low rank approximating according to the rank of the first matrix to obtain a first non-block-Hankel matrix after the low rank approximating; step 3, replacing the elements of each block in a second matrix with math average values of the block elements on a back-diagonal to obtain a second block-Hankel matrix; step 4, repeating the steps 2 and 3 until convergence, thus obtaining the noise-reduced multi-point pulse responding signal; and step 5, performing modal parameter recognizing. The modal parameter recognizing method based on multi-input multi-output signal noise reduction can save machine time and improve recognizing accuracy.

Owner:CHINA UNIV OF PETROLEUM (EAST CHINA)

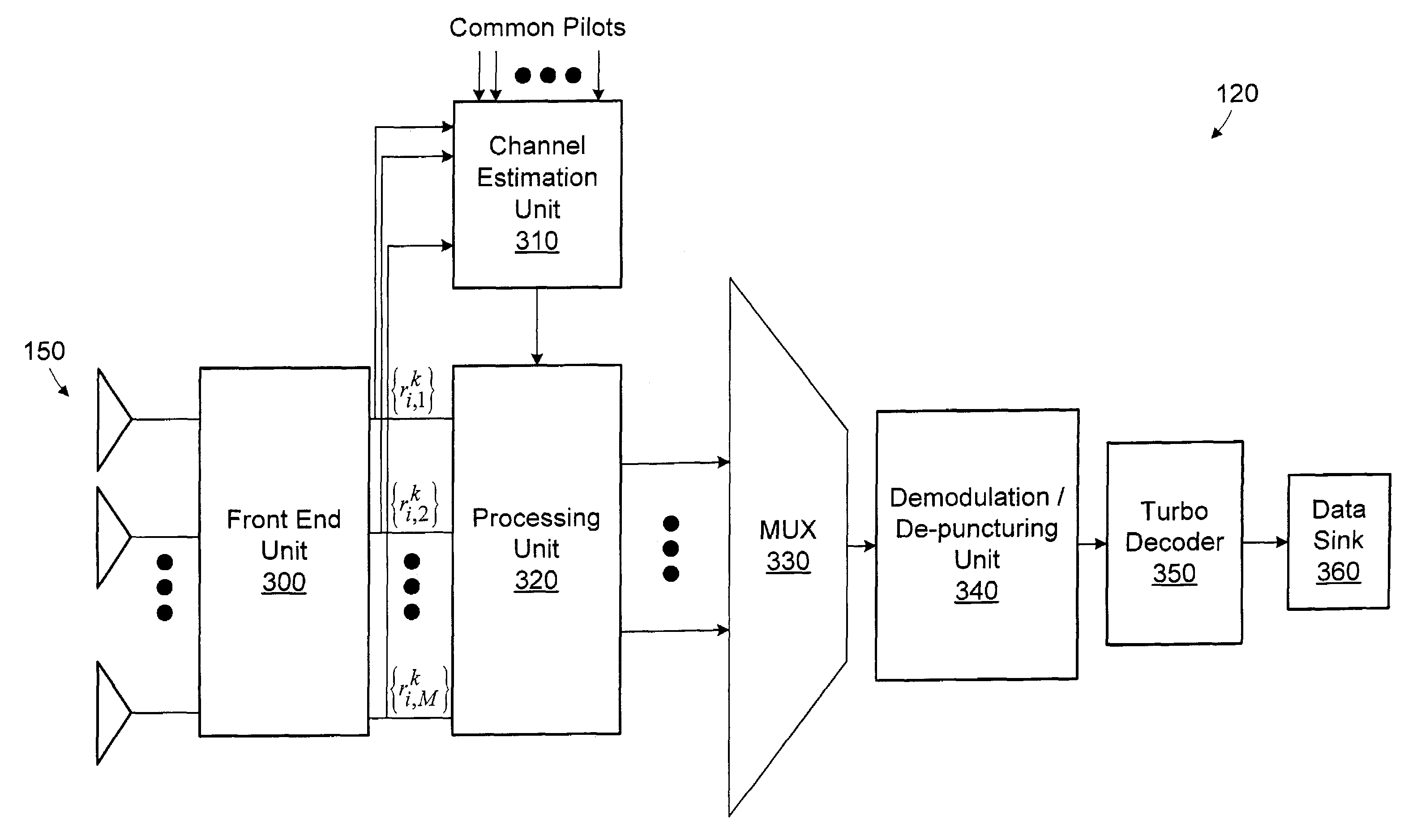

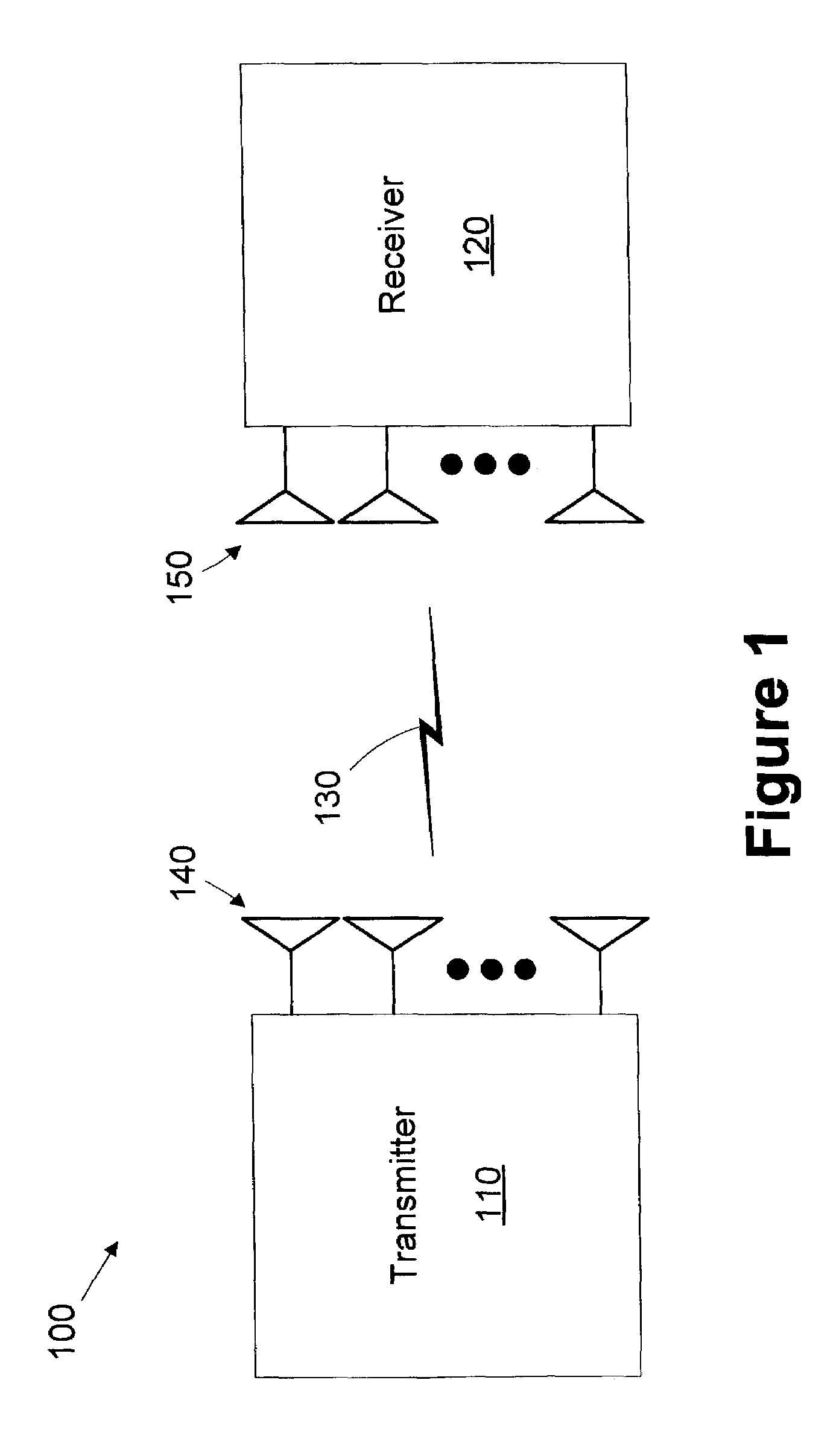

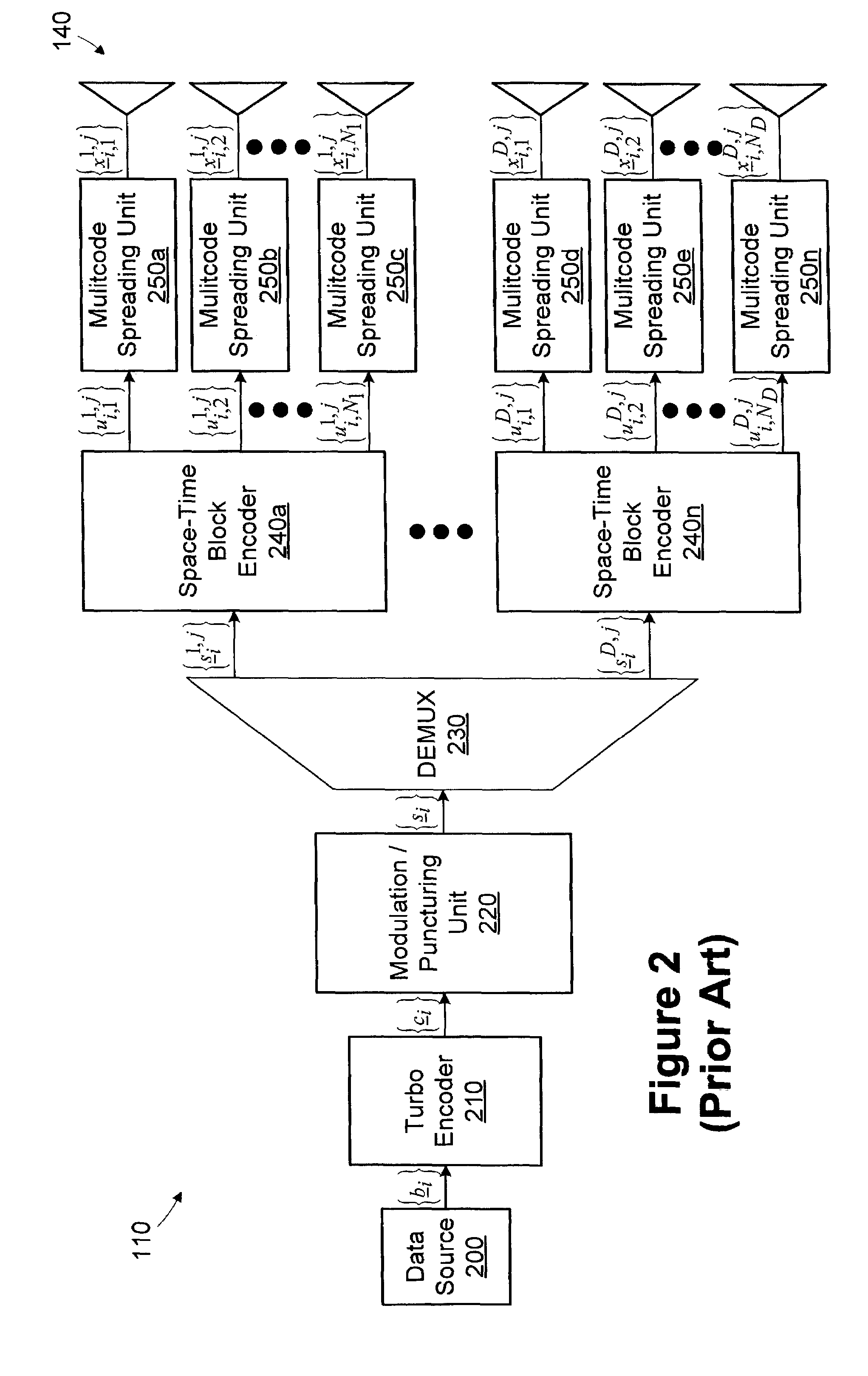

Array processing using an aggregate channel matrix generated using a block code structure

ActiveUS7342970B2Polarisation/directional diversityLine-faulsts/interference reductionArray data structureBlock code

A method includes generating a received signal vector from a signal received over a channel. The received signal vector includes a plurality of symbols encoded in accordance with a block code having a structure. A channel matrix estimated for the channel is transformed based on the structure of the block code to generate an aggregate channel matrix. The symbols are processed using the aggregate channel matrix. A system includes a front end unit configured to generate the received signal vector, a channel estimation unit configured to estimate the channel matrix, and a processing unit configured to generate the aggregate channel matrix and process the symbols using the aggregate channel matrix.

Owner:LUCENT TECH INC

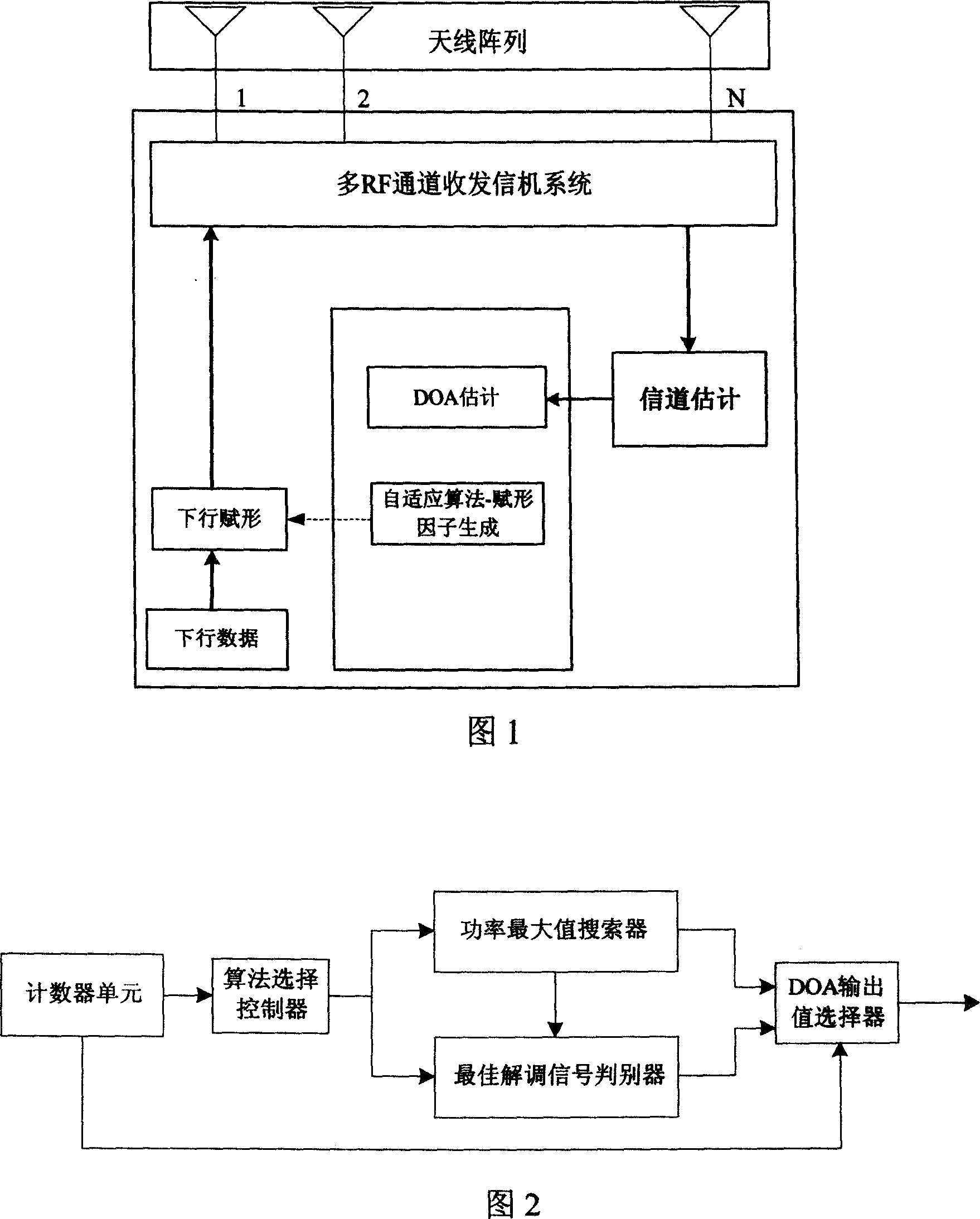

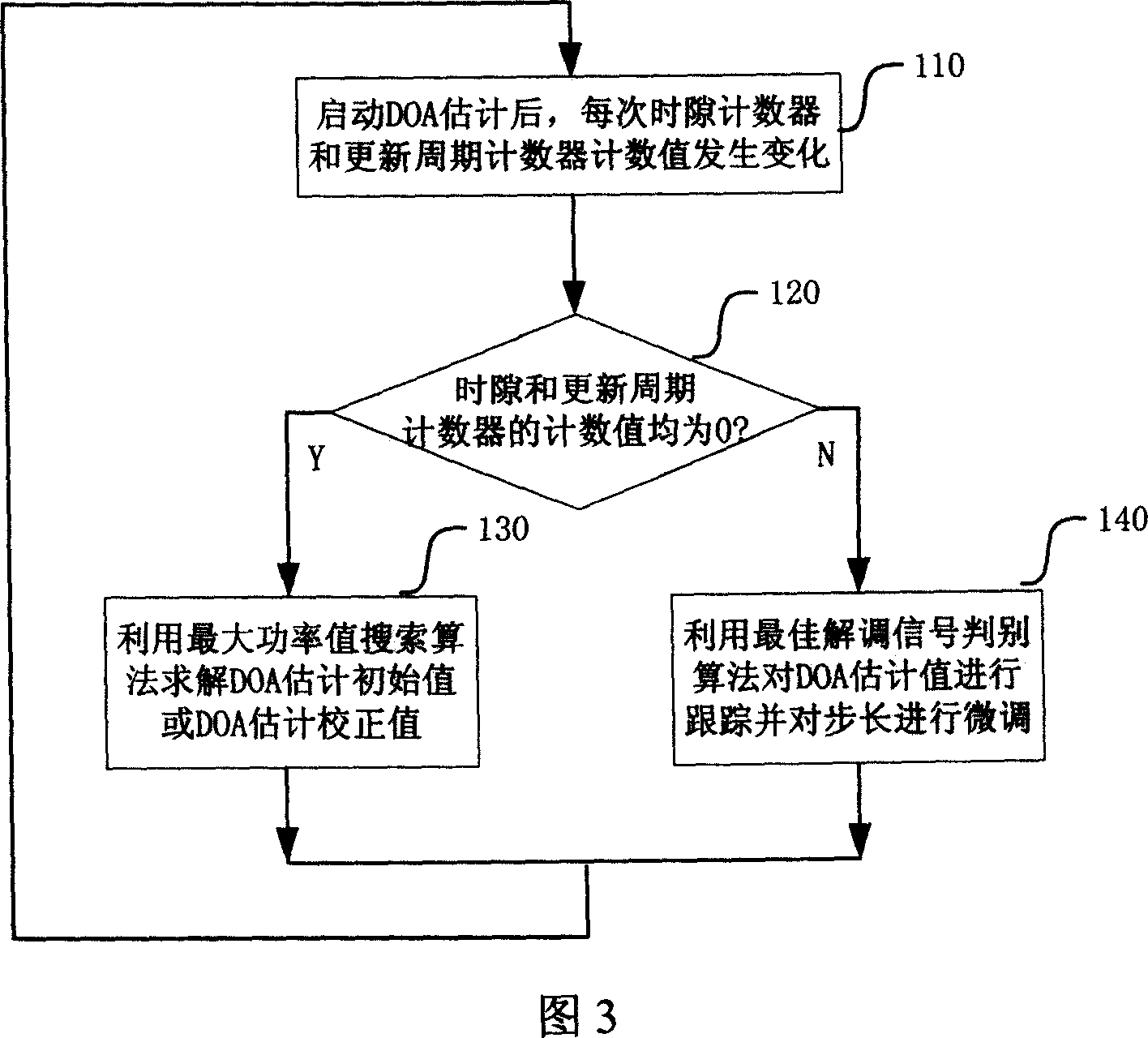

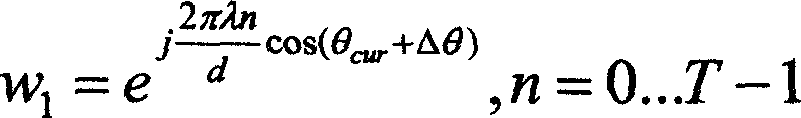

Method and device of estimating space arrival direction

ActiveCN101119147AHigh precisionImprove estimation performanceSpatial transmit diversityCommunications systemEstimation methods

The present invention discloses an estimation method and device of space arrival direction used in wireless communication system which applies the technique of intelligent antenna; an up-link time slot M and a renewal cycle T included in the calibration cycle are set; a time slot comprises one or more than one renewal cycle T; when the DOA estimation of space arrival direction is started, the counting unit calculates the up-link time slot in the calibration cycle and the renewal cycle in every up-link time slot; the calculation is carried out by a controller, based on the above calculating value, in the first renewal cycle of the first time slot of every calibration cycle, activating the searching machine of maximum power value to work out the DOA calibration value which is considered as the primary value or calibration value of DOA calibration; in other time of the calibration cycle, activating the arbiter of optimal demodulation signal to work out the DOA calibration value, realizing the follow of the DOA calibration value; the selector of DOA output value chooses the final DOA calibration value. The invention can lessen the complicated matrix manipulation, providing a much precise DOA calibration value.

Owner:SANECHIPS TECH CO LTD

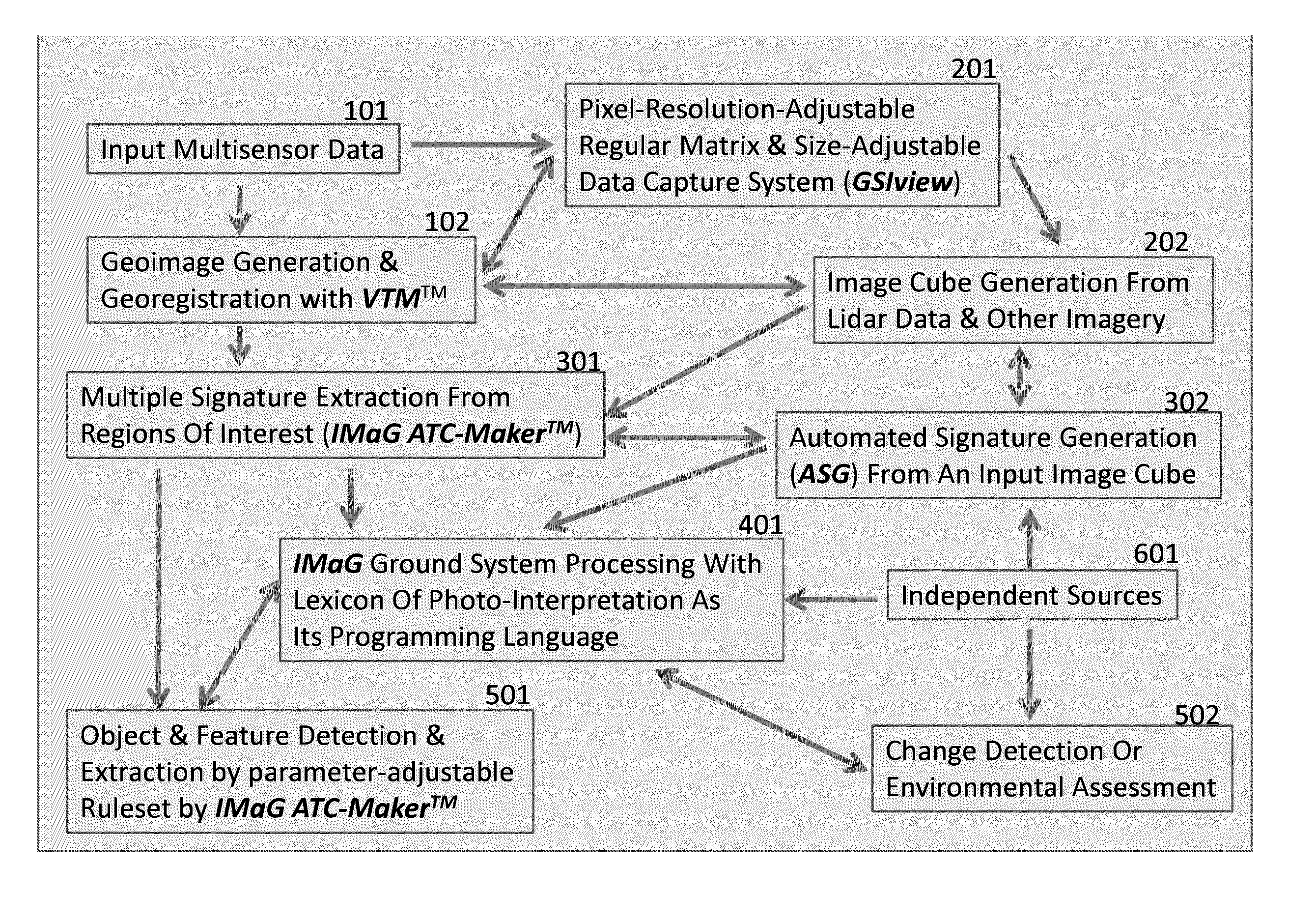

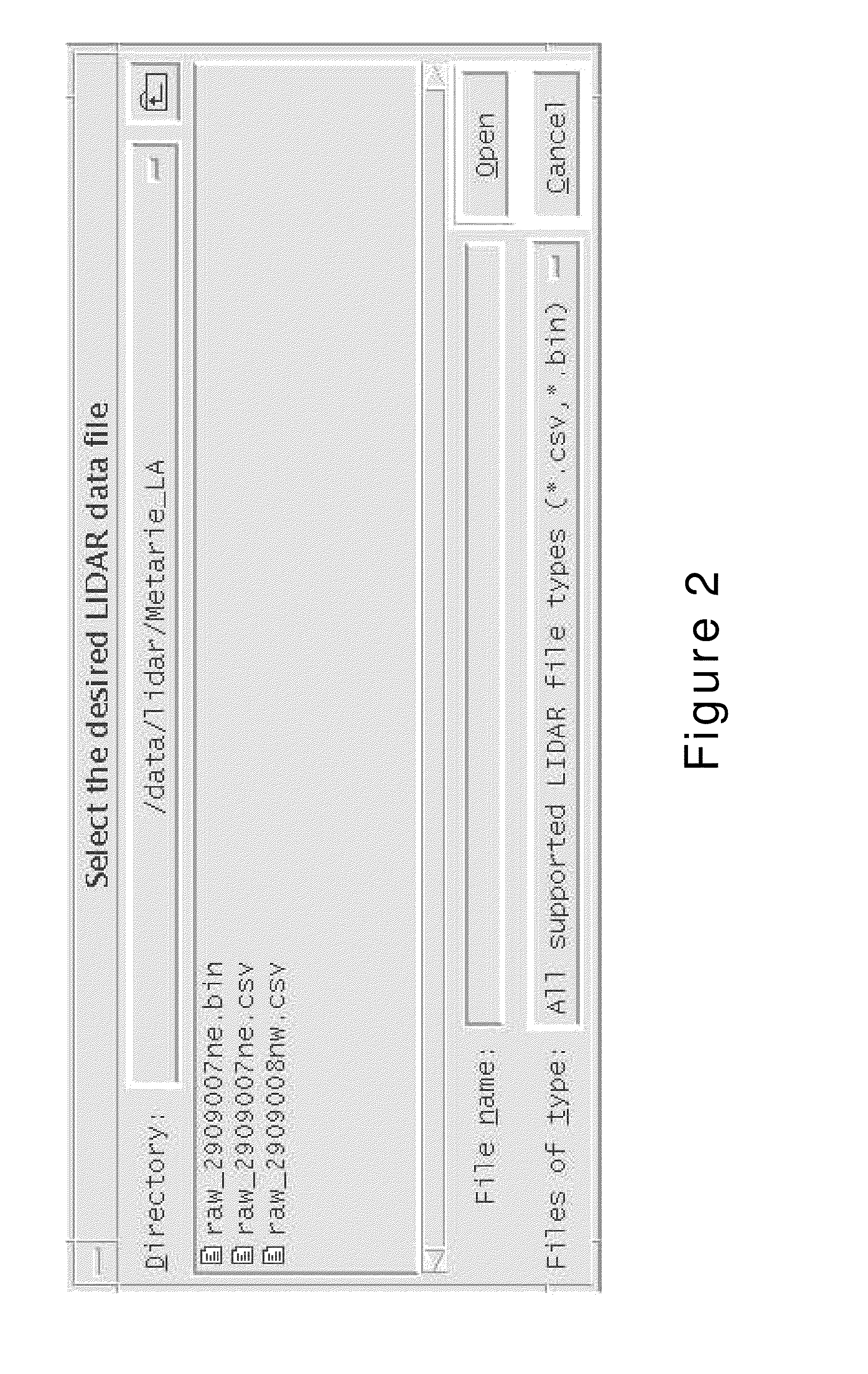

System for capturing, characterizing and visualizing lidar and generic image data

ActiveUS8139863B1Character and pattern recognitionElectromagnetic wave reradiationFeature extractionAlgorithm

A system that offers a method of capturing, analyzing, and visualizing a matrix of data for object and feature extraction. This is accomplished by reading a matrix of data represented by a plurality of data types into a processor via a data capture system. The matrix of data is overlaid by a control grid to form a regular matrix having a plurality of cells. A data search spatial radius is created from a point in each cell. Data is then processed from the matrix and certain characteristics are captured and represent each variable in each cell of the matrix, and then output, respectively.

Owner:HSU SHIN YI

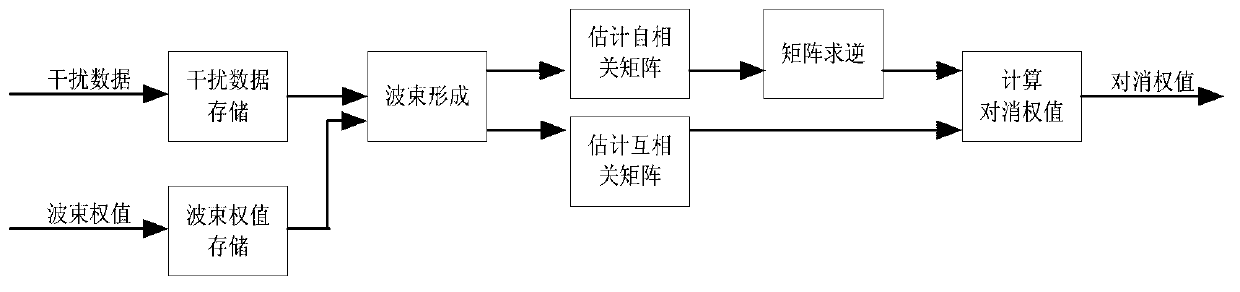

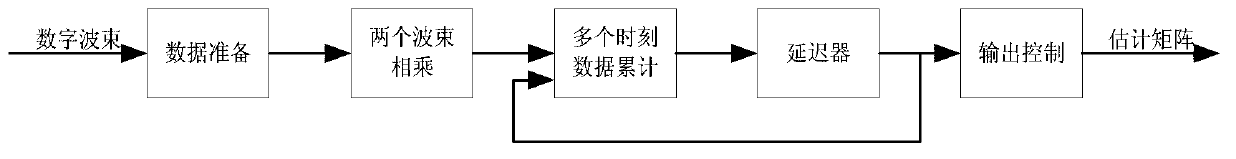

Adaptive side-lobe cancellation weight value method based on FPGA (field programmable gate array)

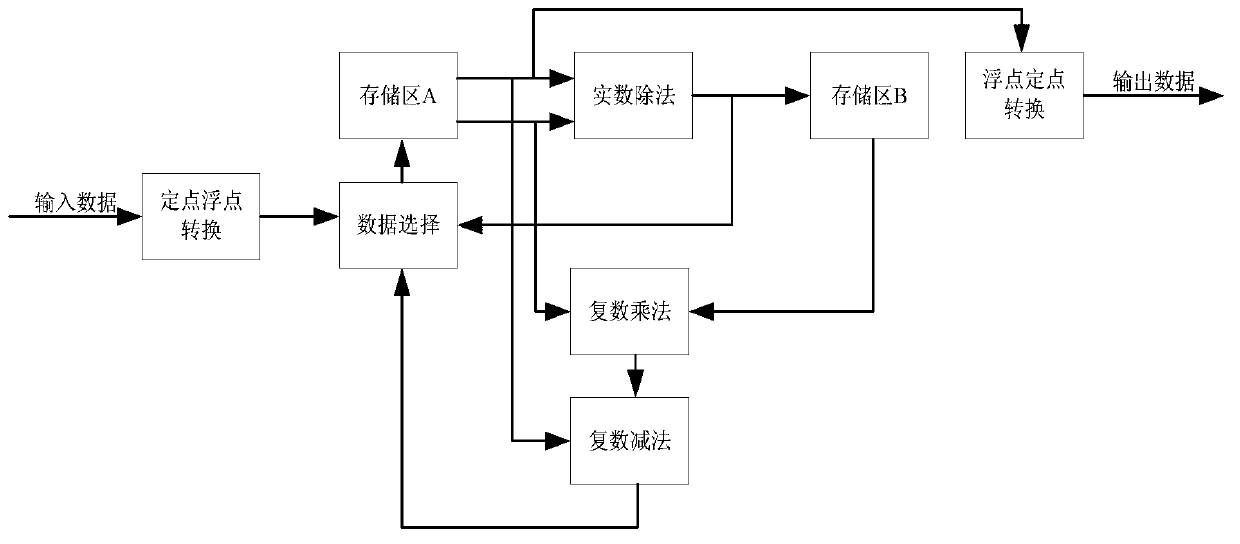

ActiveCN103136165AImprove general performanceImprove efficiencyComplex mathematical operationsCross correlation matrixMatrix multiplication

The invention relates to an adaptive side-lobe cancellation weight value method based on FPGA. The adaptive side-lobe cancellation weight value method based on FPGA utilizes an FPGA hardware platform to accelerate processing and shorten processing delay. In the algorithm, an autocorrelation matrix of auxiliary beams and a cross-correlation matrix of the auxiliary beams and target beams are estimated according to disturbance data, auxiliary beam weight values and target beam weight values, and operations such as a matrix inversion, matrix multiplication are performed in an FPGA device to obtain the adaptive side-lobe cancellation weight value. The delay of the whole processing is determined by matrix estimation and matrix manipulation. The calculation amount of the matrix estimation is relatively small, the processing delay is less, and the operating time is affected by the number of sampling points. The calculation amount of the matrix manipulation is relatively large and is mainly affected by the number of the auxiliary beams; for n auxiliary beams (n<60), the processing delay of the portion is about 60N+N (N-1) clock periods.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

Efficient block transform including pre-processing and post processing for autostereoscopic displays

InactiveUS7151849B1Television system detailsMemory adressing/allocation/relocationSingle processData set

Image data processing techniques utilizing multiple processes operating on one or more processors of one or more computer systems can be used to efficiently rearrange or reparameterizing image data to form hologram element (hogel) images which can then be used to produce holographic stereograms. These techniques utilize matrix manipulation of portions of image data both within a single process, and across multiple processes typically executing on different processors, and each utilizing a subset of the overall set of image data.

Owner:ZEBRA IMAGING

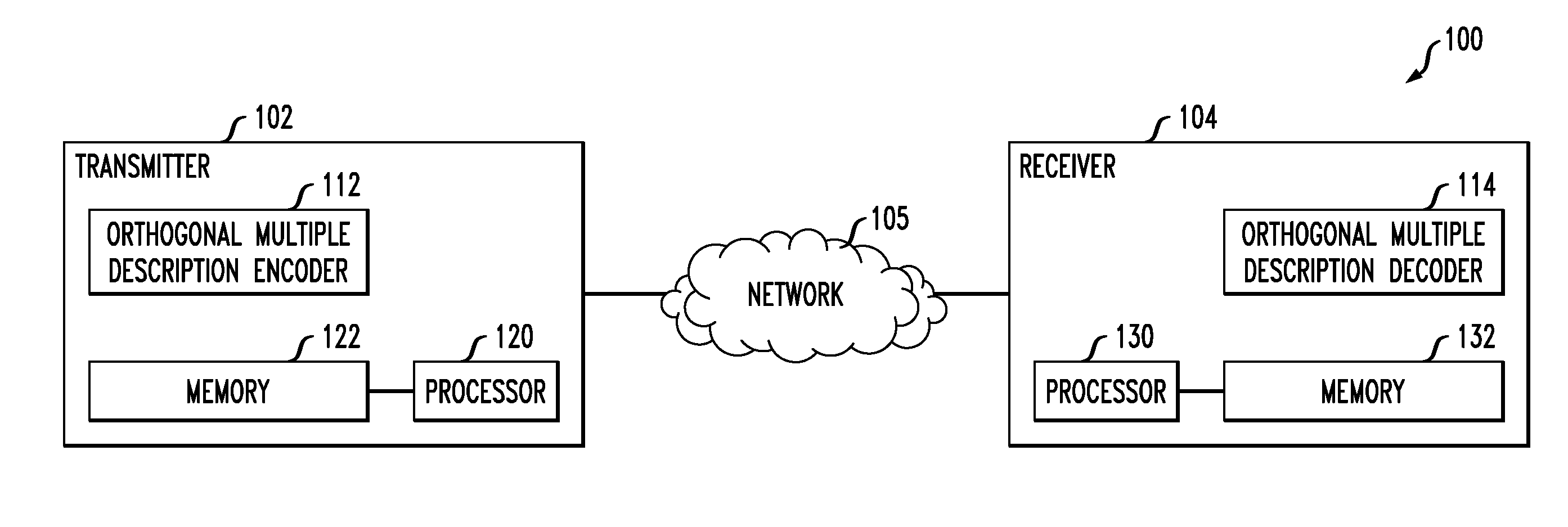

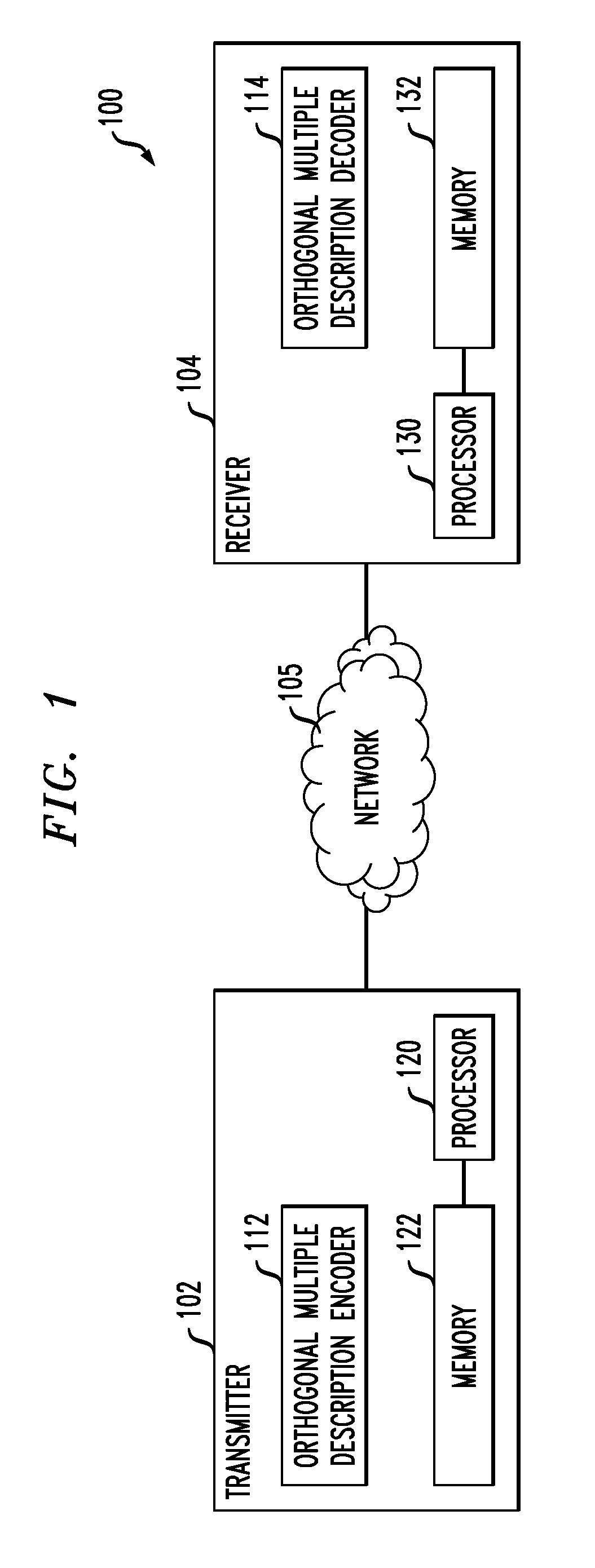

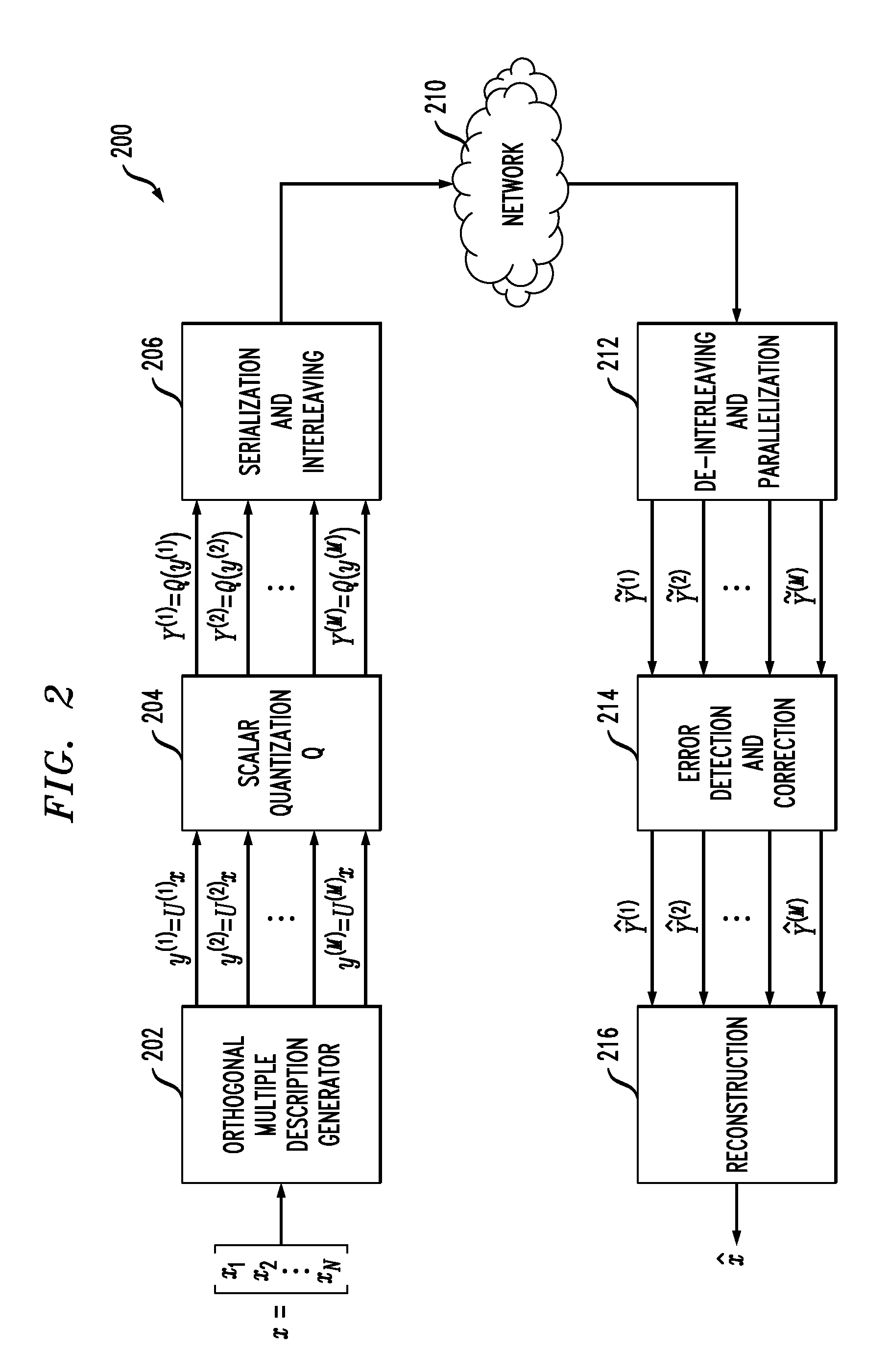

Orthogonal Multiple Description Coding

InactiveUS20110164672A1No wasteImprove reconstruction qualityError preventionCode conversionMultiple descriptionComputer program

In one aspect, an orthogonal multiple description encoder comprises orthogonal multiple description generation circuitry configured to produce multiple descriptions of a given signal by processing the signal using respective ones of a plurality of orthogonal matrices. Each of the multiple descriptions is generated as a function of the signal and a corresponding one of the plurality of orthogonal matrices. Other aspects include an orthogonal multiple description decoder, orthogonal multiple description encoding and decoding methods, and associated computer program products.

Owner:ALCATEL LUCENT SAS

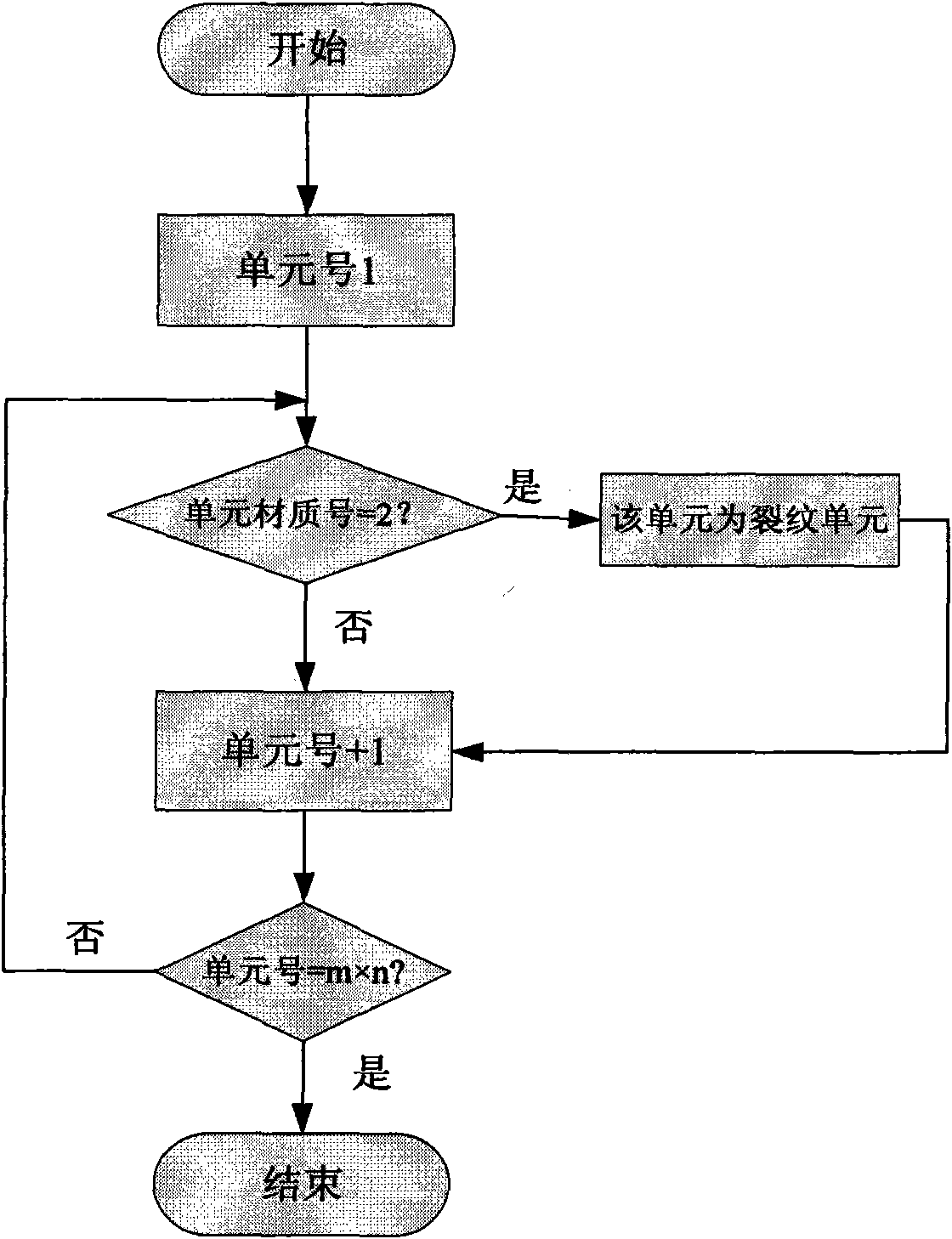

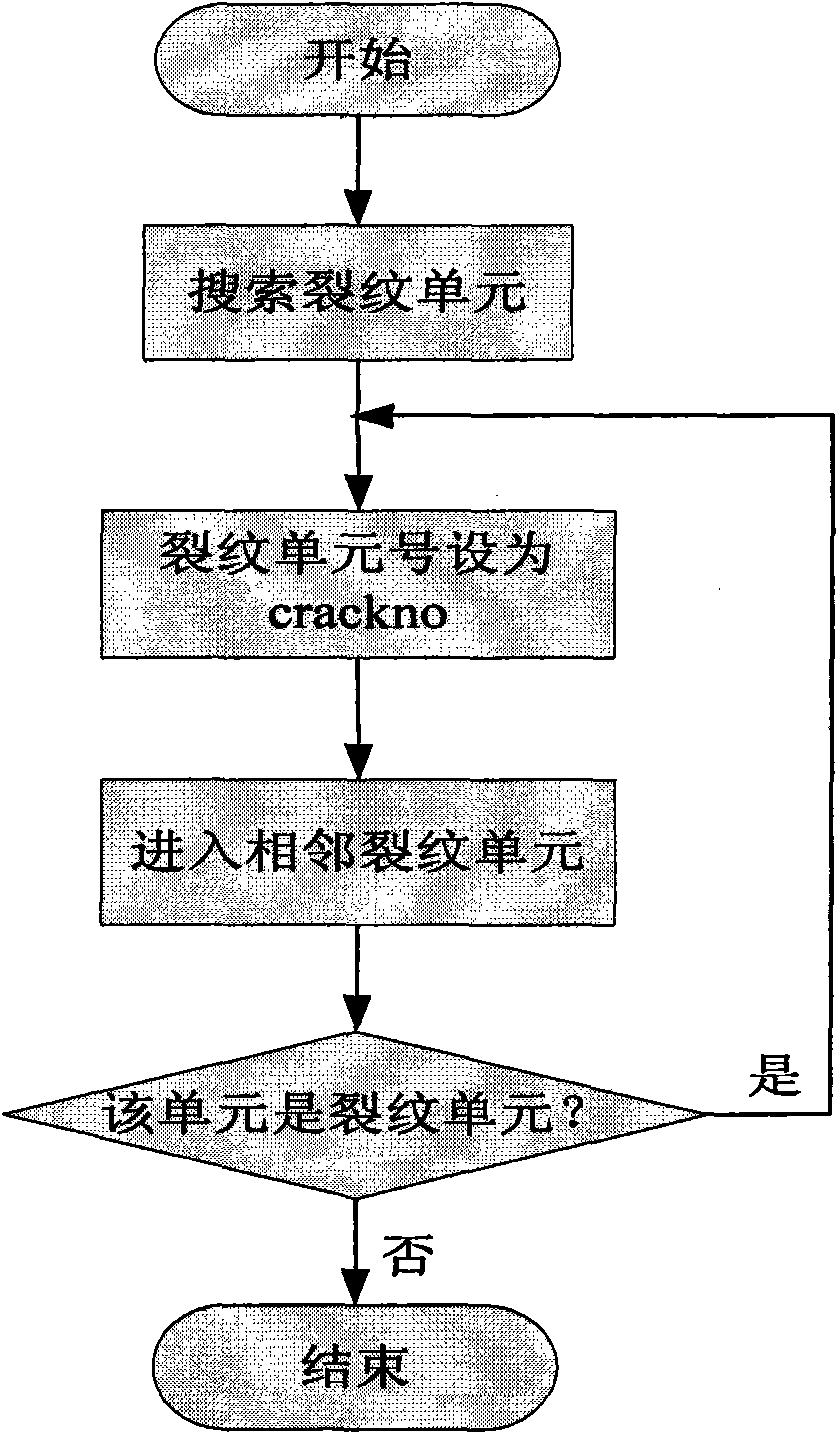

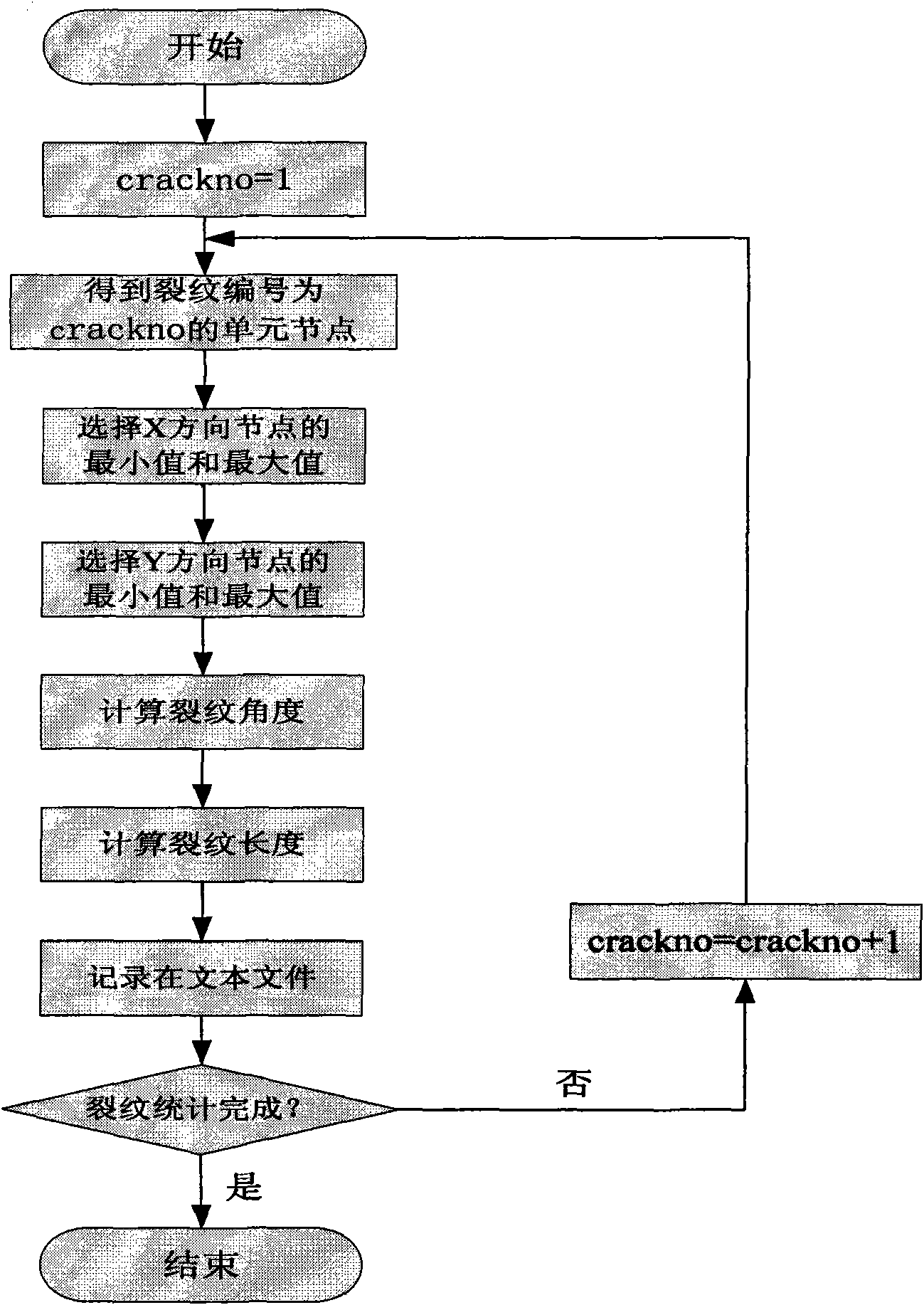

Material microstructure image-based method for automatic mesoscale crack statistics

InactiveCN101604357ASimple and accurate quantitative statisticsMaterial analysis using wave/particle radiationCharacter and pattern recognitionGray levelData information

The invention discloses a material microstructure image-based method for automatic mesoscale crack statistics, which belongs to the field of mesoscale materials science and can simply and accurately perform quantitative crack statistics. The method comprises the following steps: firstly, subjecting a material microstructure image to gray-level matrix treatment, establishing a finite element grid unit corresponding to the pixel points of the material microstructure image and searching all crack units according to the generated finite element grid unit; secondly, recognizing all crack strips in the finite element grid unit according to the result of the research and coding cracks; and finally, performing the length and angle statistics of each crack and outputting data information on crack strips to a result file. The method of the invention can acquire shape and distribution information including crack number, crack length and crack angle on the cracks in an actual material microstructure image and can be directly used in mesoscale material performance finite-element simulation for further study of the relationship between the crack length, crack orientation and the like and basic physical and mechanical properties.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

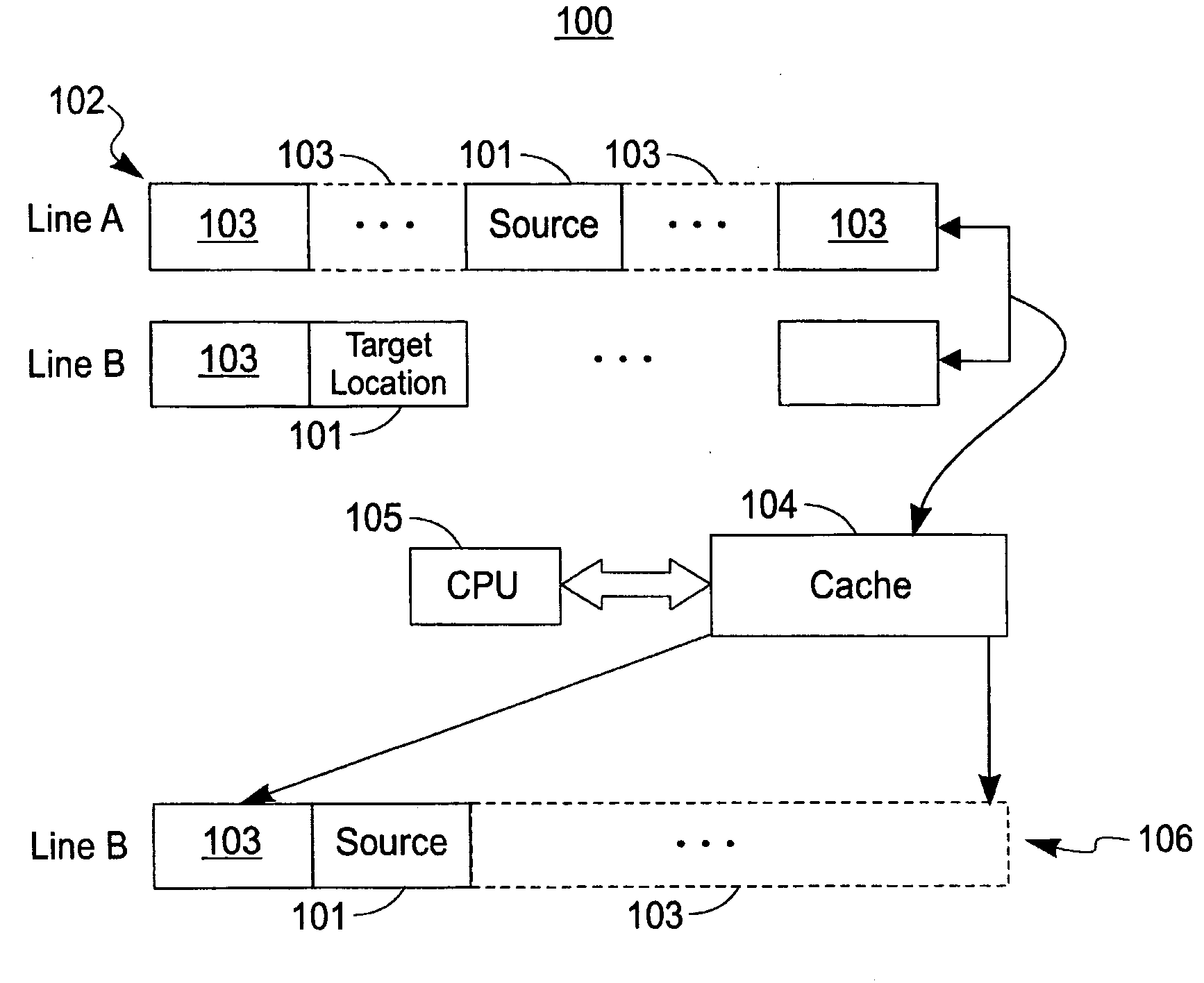

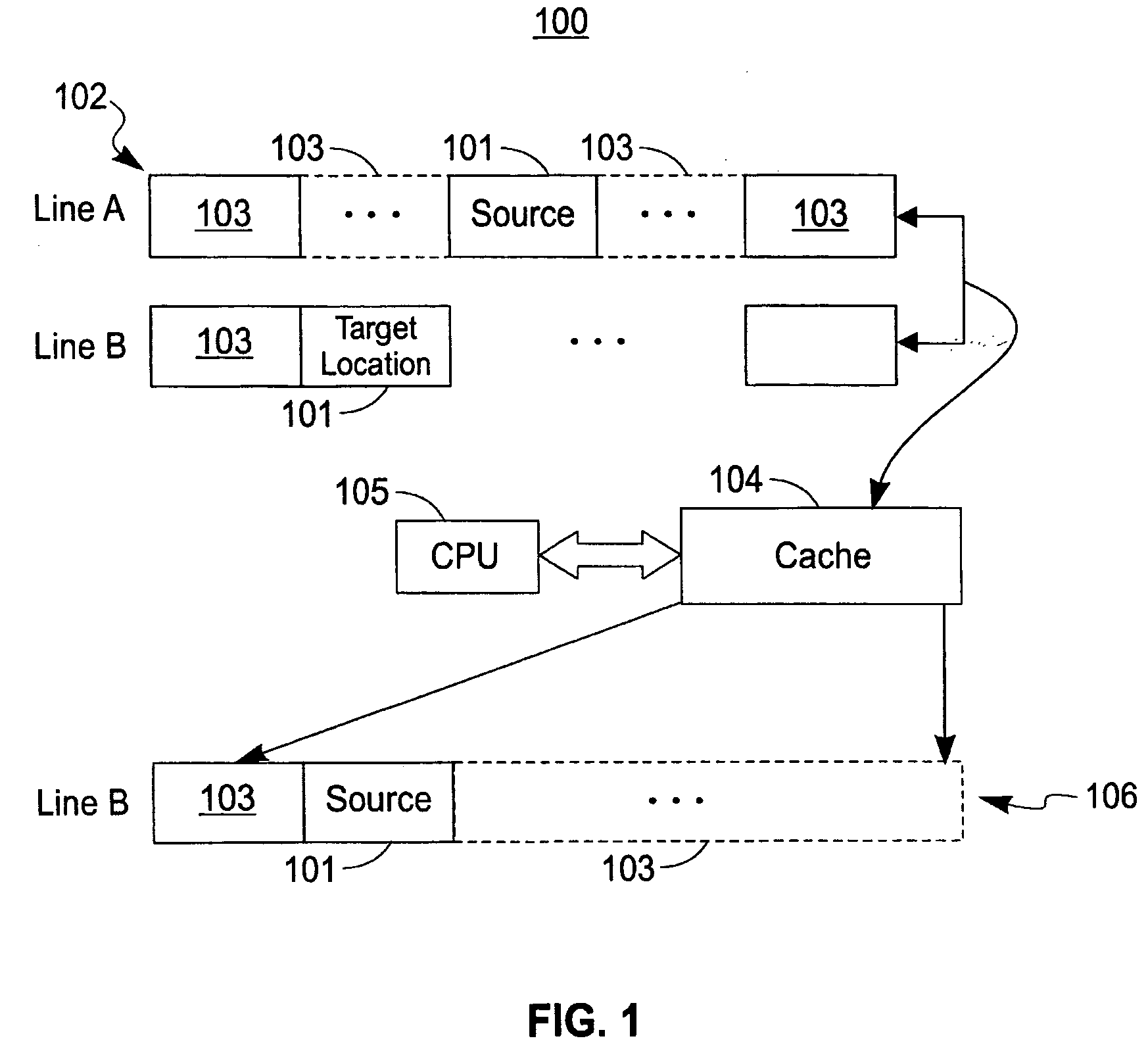

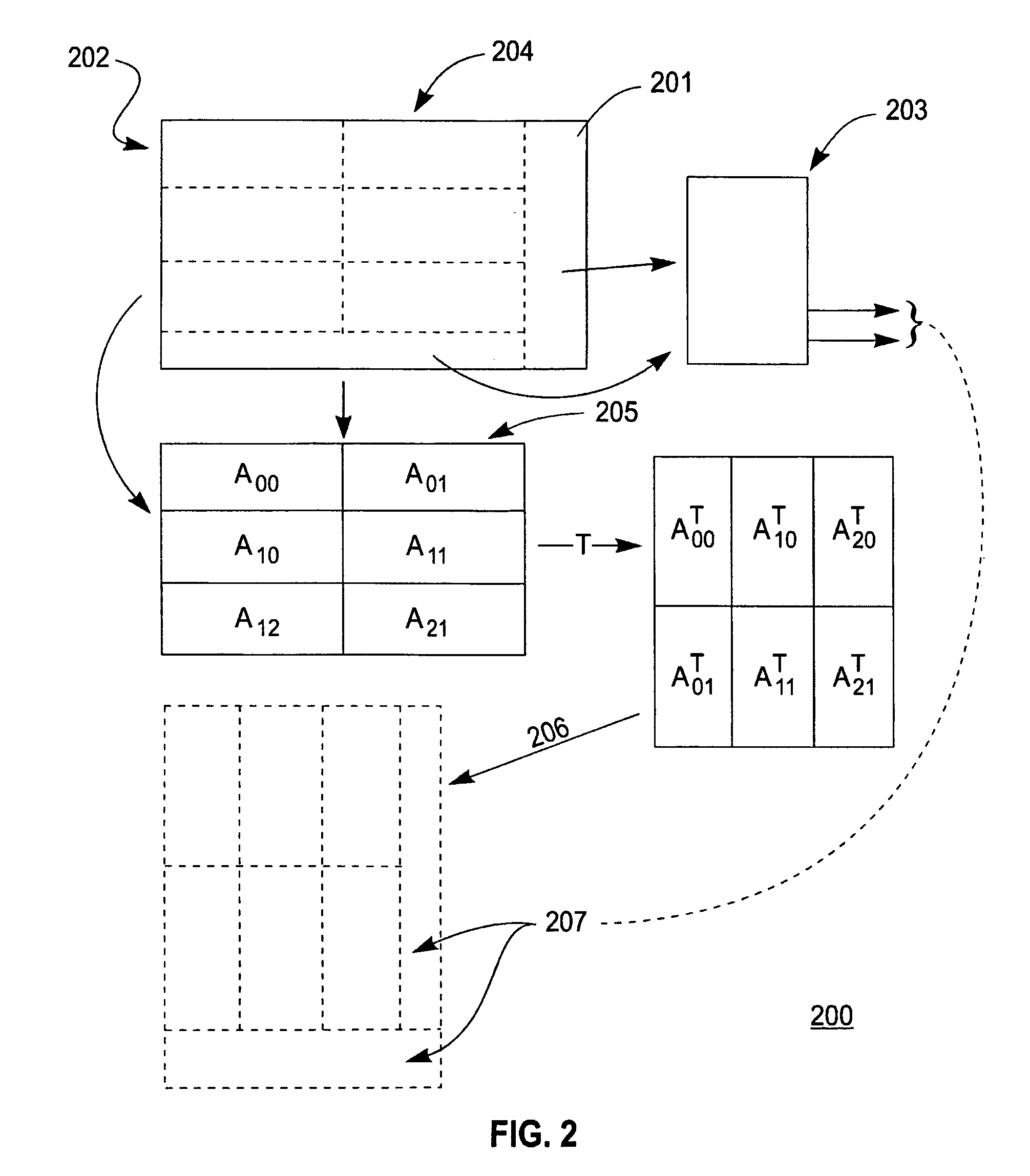

Method and structure for fast in-place transformation of standard full and packed matrix data formats

InactiveUS20090063529A1Efficient executionHandling data according to predetermined rulesMemory systemsComputer scienceData format

A computerized method provides for an in-place transformation of matrix A data including a New Data Structure (NDS) format and a transformation T having a compact representation. The NDS represents data of the matrix A in a format other than a row major format or a column major format, such that the data for the matrix A is stored as contiguous sub matrices of size MB by NB in an order predetermined to provide the data for a matrix processing. The transformation T is applied to the MB by NB blocks, using an in-place transformation processing, thereby replacing data of the block A1 with the contents of T(A1).

Owner:IBM CORP

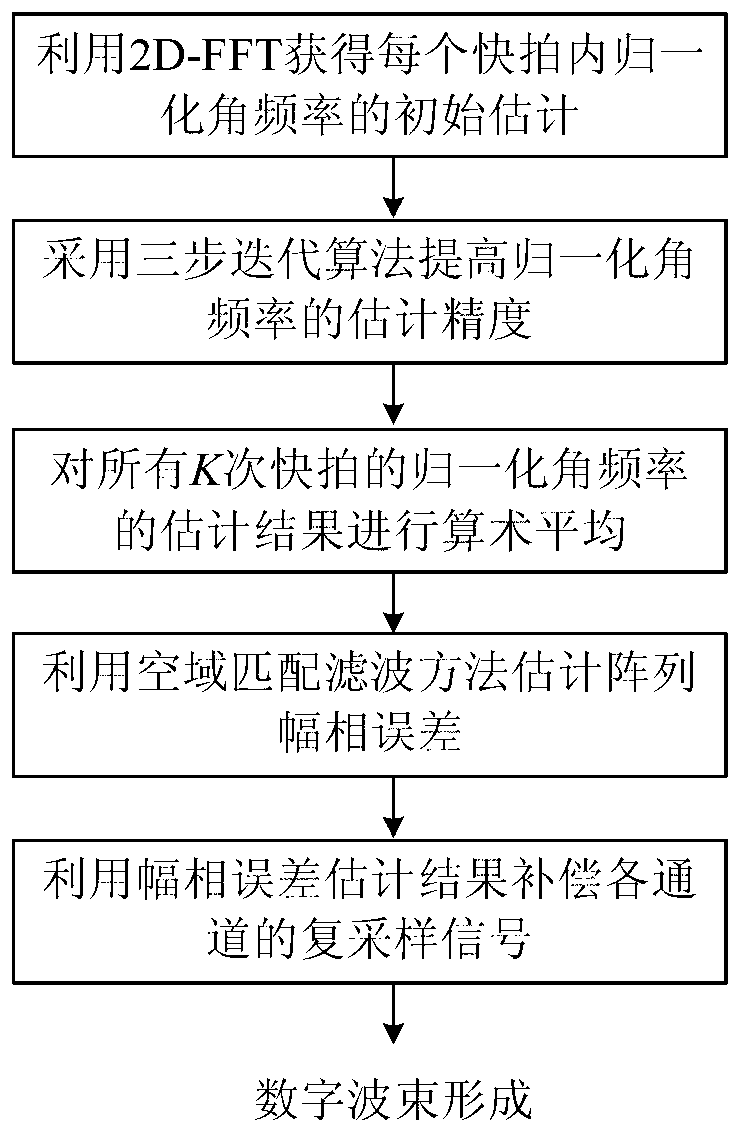

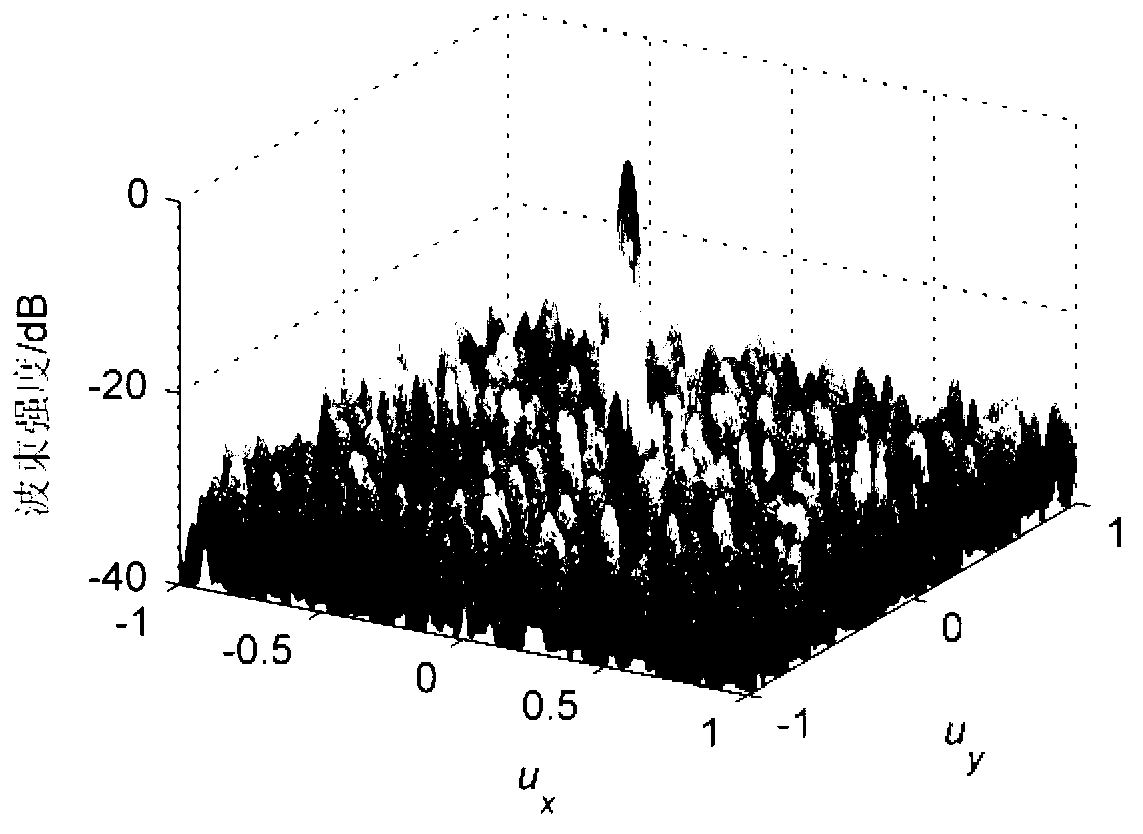

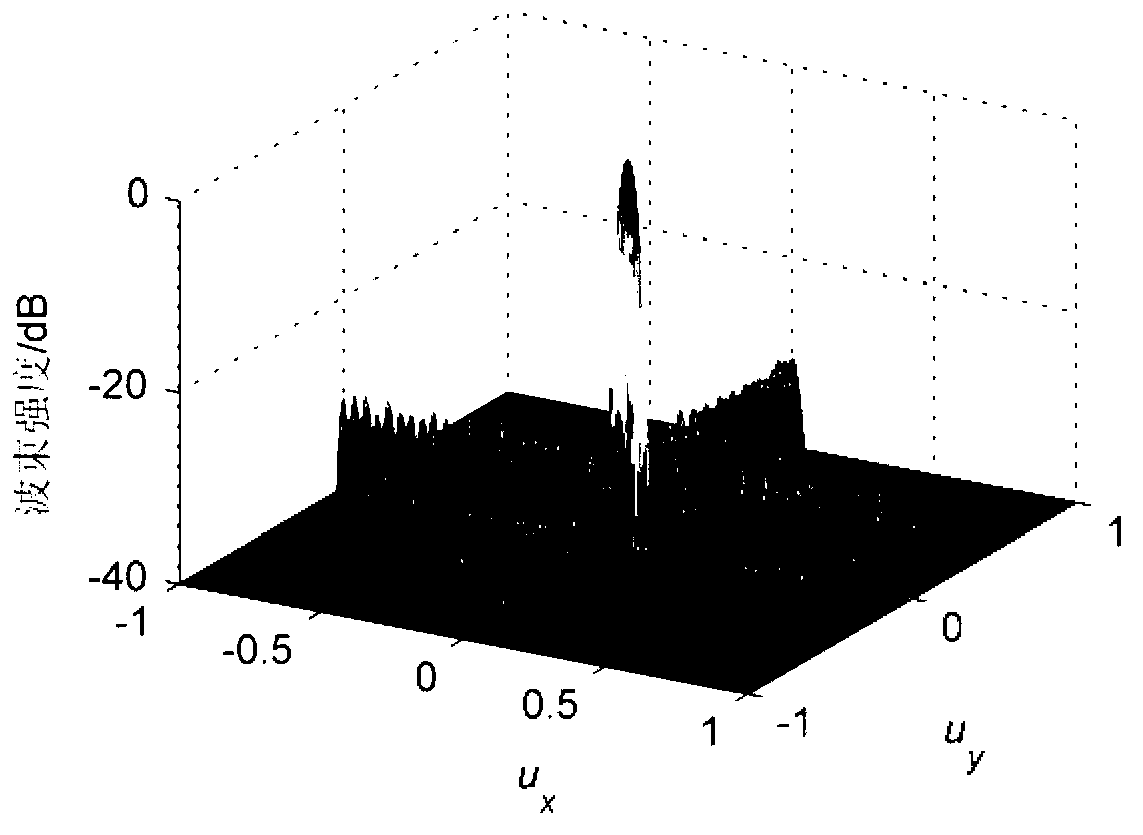

Amplitude-phase error correction method for phased array three-dimensional camera shooting sonar system energy converter array

ActiveCN103323832AHigh amplitude and phase error correction accuracyAvoid cumbersome iterationAcoustic wave reradiationArray data structureFilter algorithm

The invention discloses an amplitude-phase error correction method for a phased array three-dimensional camera shooting sonar system energy converter array. The method comprises the following steps: utilizing two-dimensional fast Fourier transform to acquire original estimation of normalization angular frequency for two-dimensional compound sampling array of a kth sampling snapshot; based on the original estimation, acquiring the estimation value of the normalization angular frequency with higher precision in various sampling snapshots; conducting arithmetic mean on the estimation value of the normalization angular frequency of K times sampling snapshots so as to acquire the robust estimation of the orientation of a corrected source; utilizing the robust estimation and the spatial matched filtering algorithm to estimate amplitude-phase error factors of various energy converter passages in an energy converter array; utilizing the amplitude-phase error factors to compensate compound sampling signals in various energy converter passages, and finally utilizing the number wave beam forming algorithm to acquire three-dimensional camera shooting sonar wave beams going through amplitude-phase error correction. The amplitude-phase error correction method avoids heavy and complicated iteration and matrix manipulation and is small in calculated amount and suitable for on-site correction of large energy converter array in a three-dimensional sonar system.

Owner:ZHEJIANG UNIV

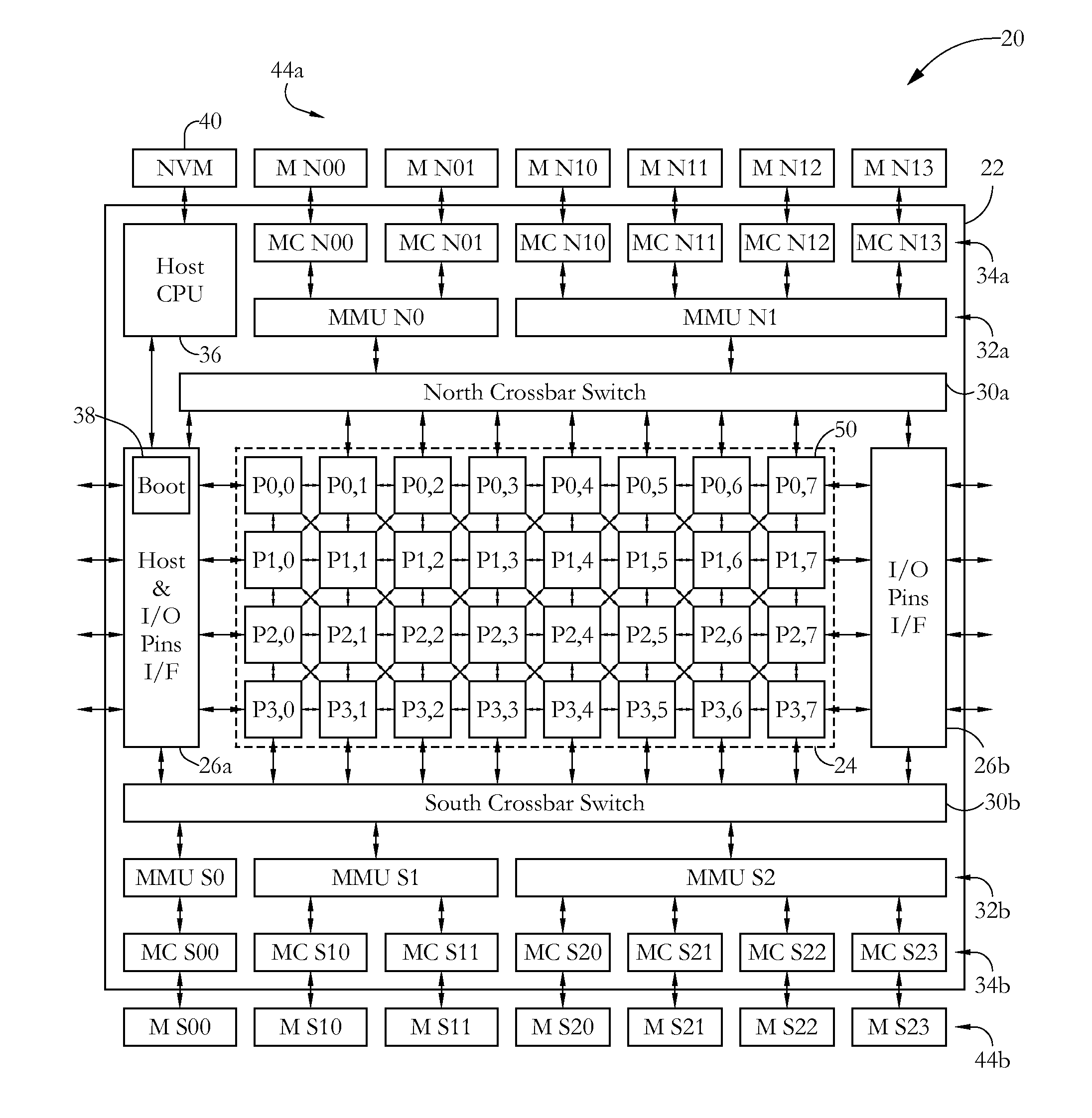

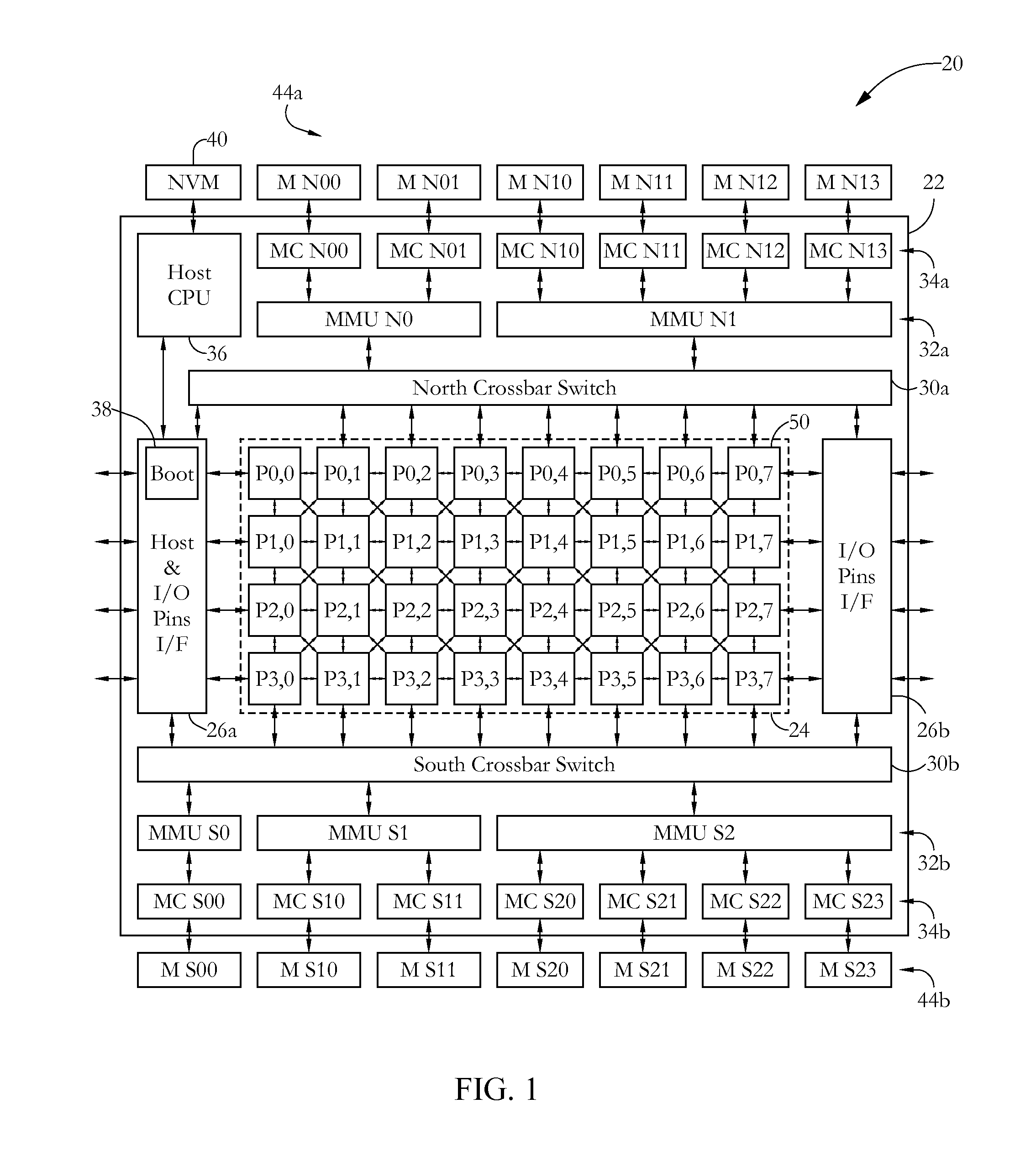

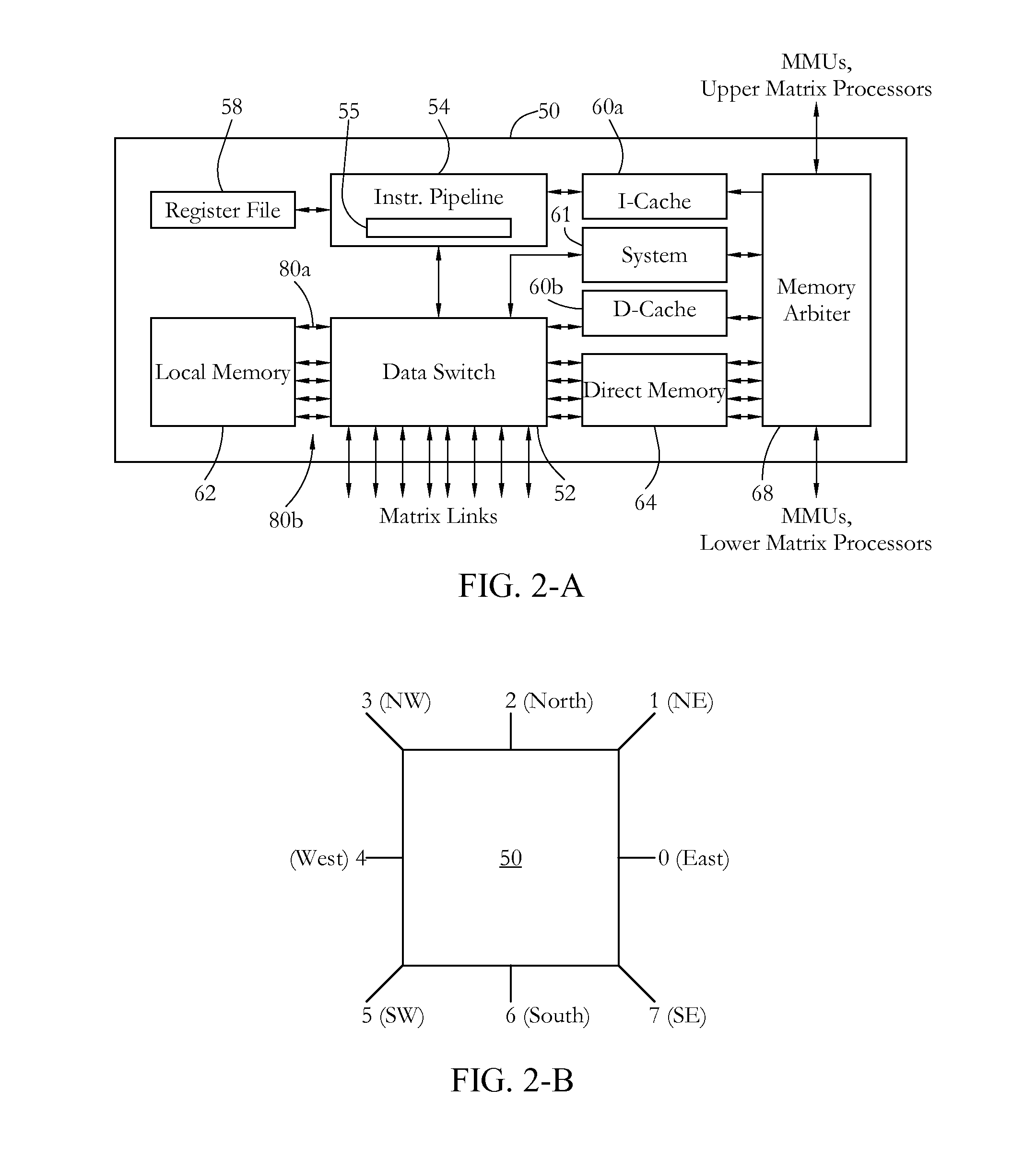

Matrix processor proxy systems and methods

InactiveUS8327114B1Error detection/correctionArchitecture with multiple processing unitsBroadcast domainBroadcasting

In some embodiments, processor-to-processor and / or broadcast proxies are designated in a microprocessor matrix comprising a plurality of mesh-interconnected matrix processors when default processor-to-processor or broadcast routing algorithms used by data switches within the matrix to route messages would not deliver the messages to all intended recipients. The broadcast proxies broadcast messages within individual non-overlapping broadcast domains of the matrix. P-to-P and broadcast proxies may be designated as part of a boot-time testing / initialization sequence. Improving system fault tolerance allows improving semiconductor processing yields, which may be of particular significance in relatively large integrated circuits including large numbers of relatively-complex matrix processors.

Owner:OVICS