Patents

Literature

57 results about "Link time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

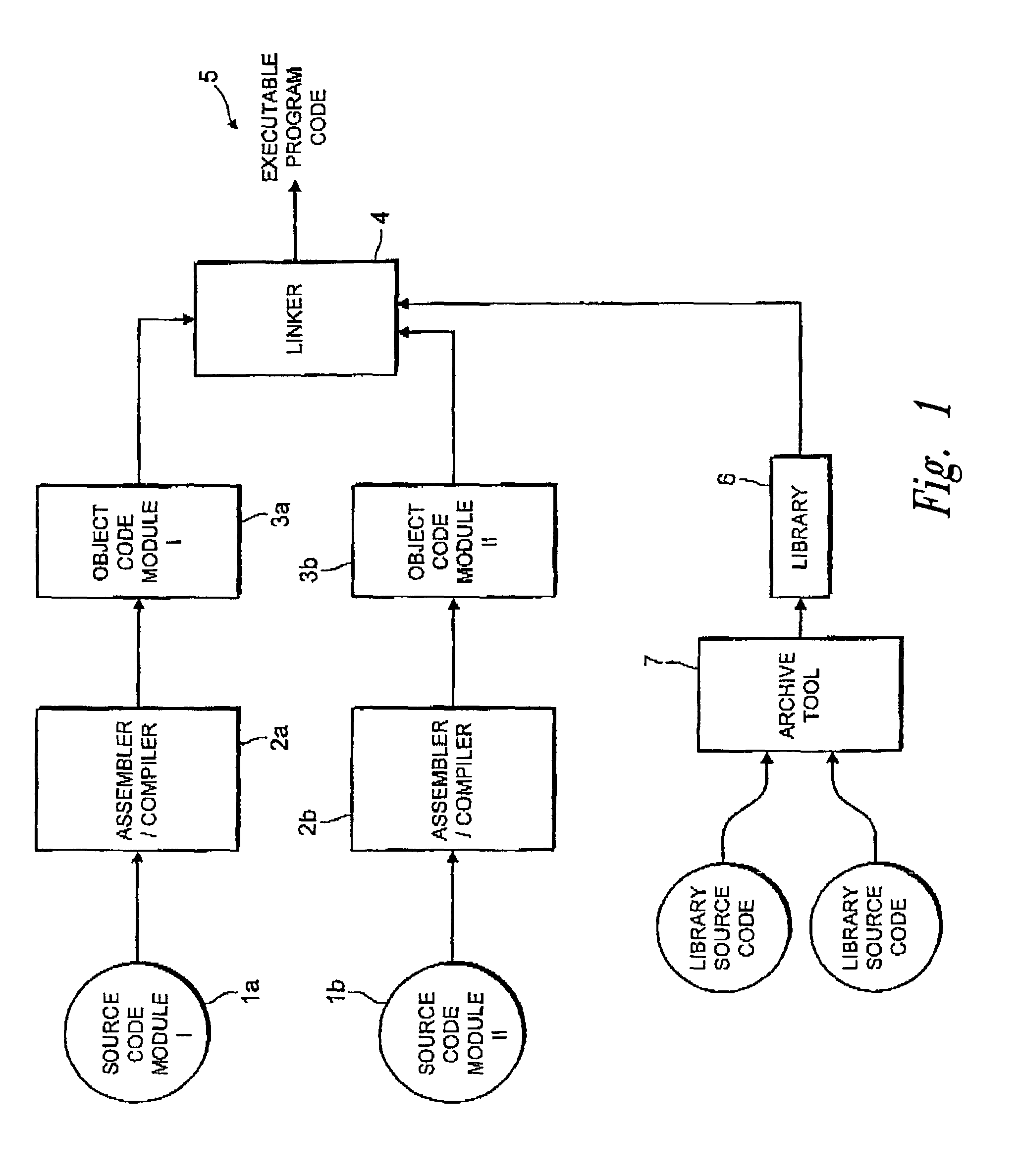

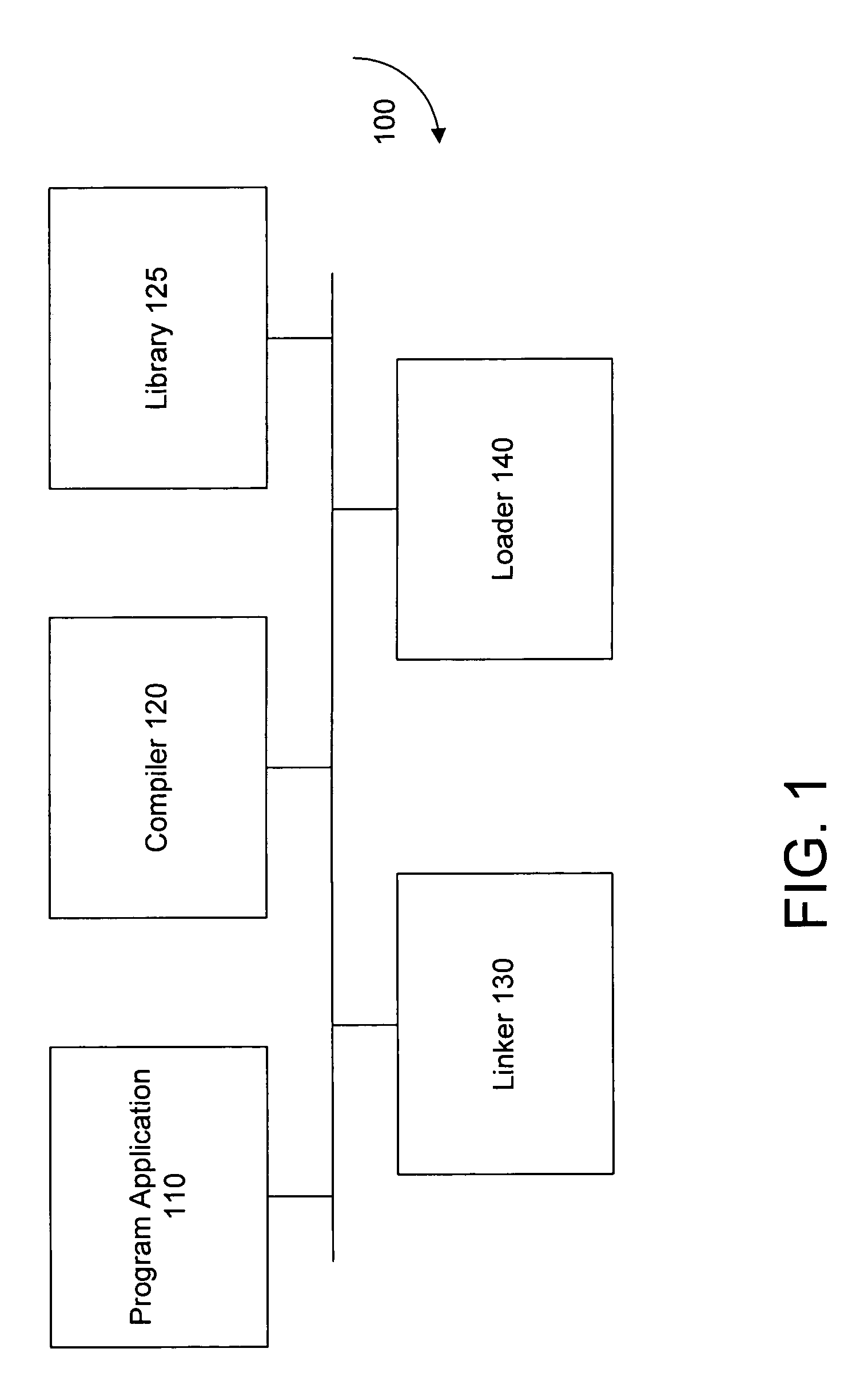

In computer science, link time refers to the period of time, during the creation of a computer program, in which a linker is being applied to that program. Link time occurs after compile time and before runtime (when a program is executed).

System for optimizing data type definition in program language processing, method and computer readable recording medium therefor

InactiveUS6983458B1Simple definitionEasy to detectSoftware engineeringSpecific program execution arrangementsData typeCompile time

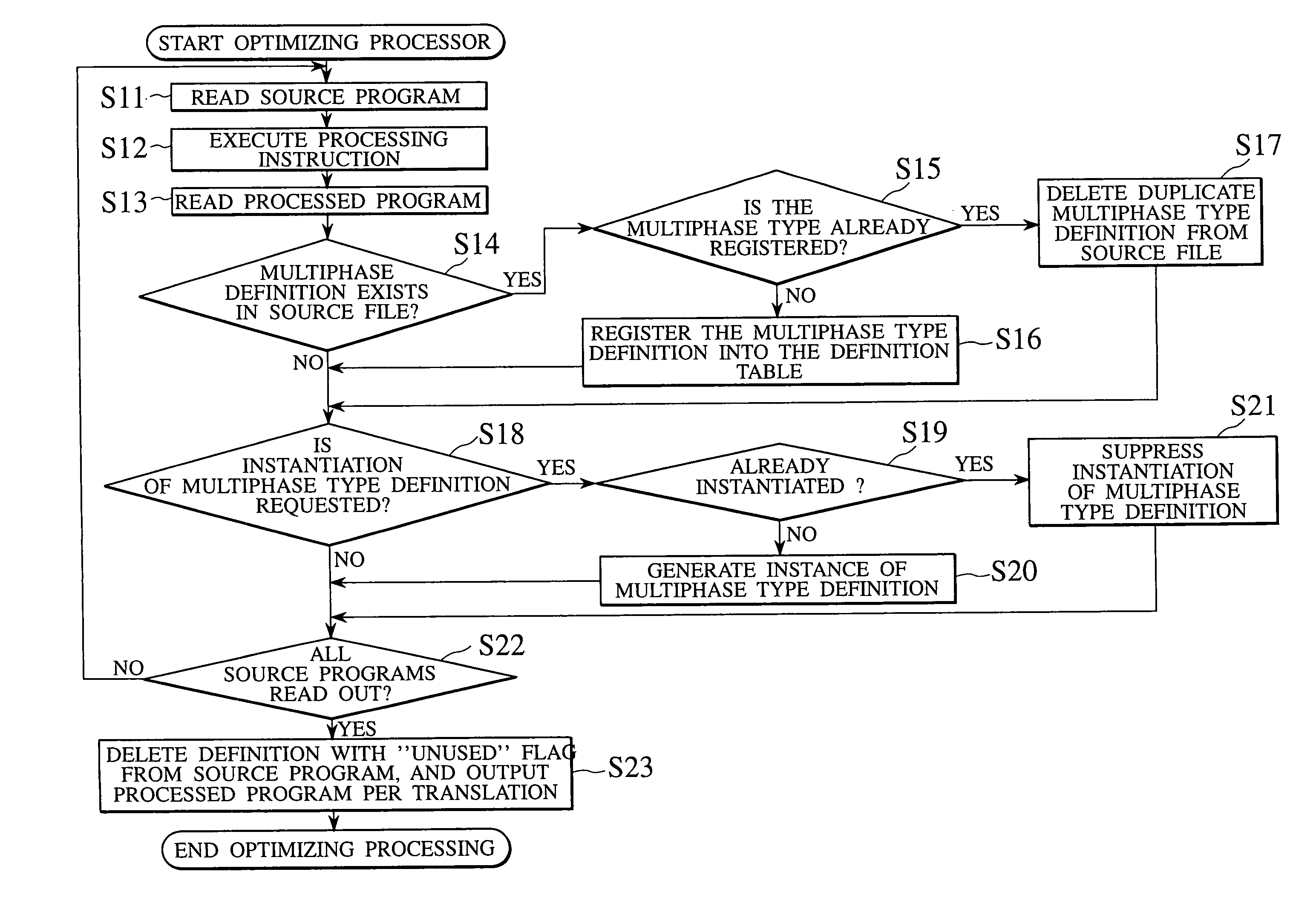

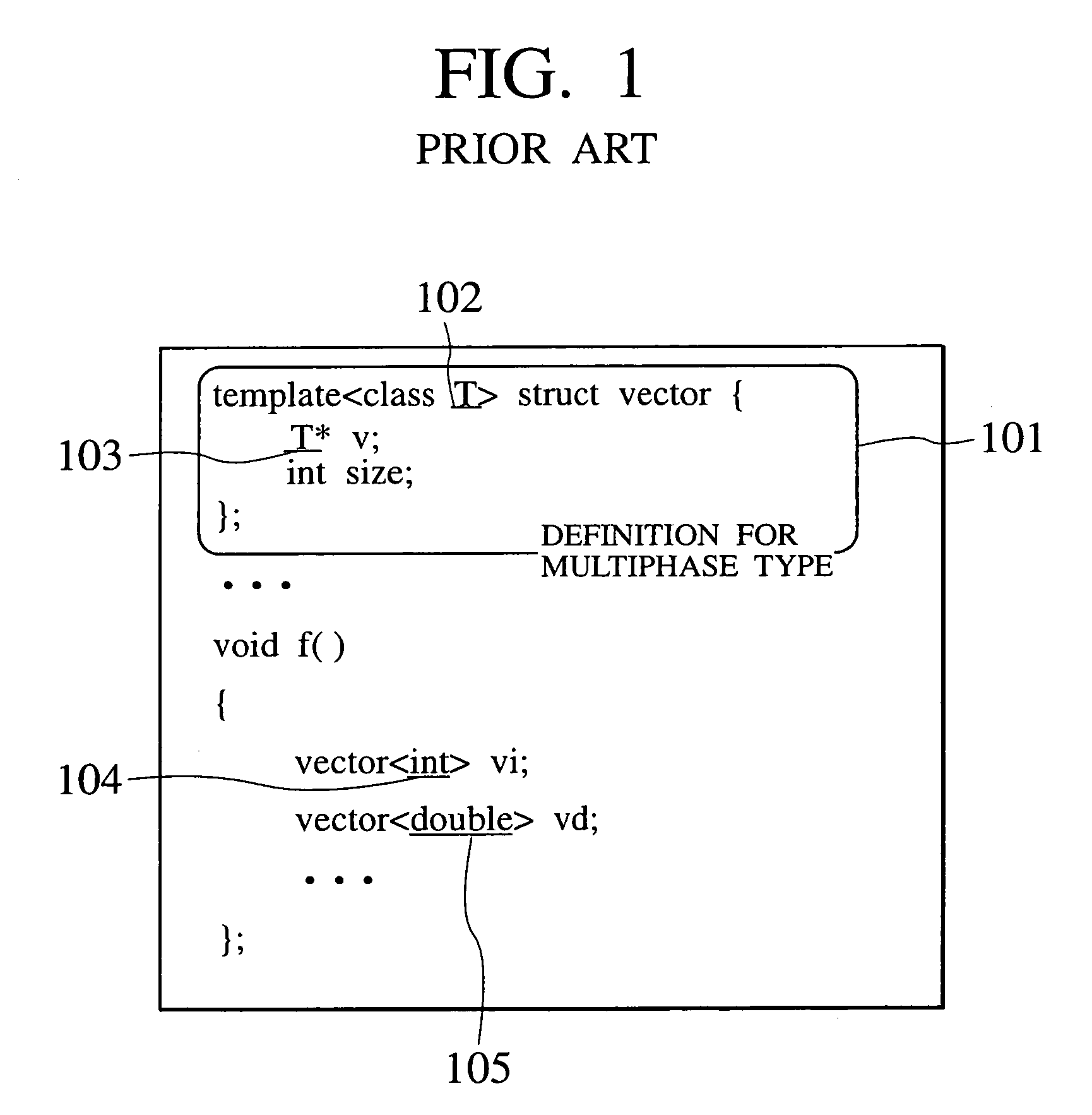

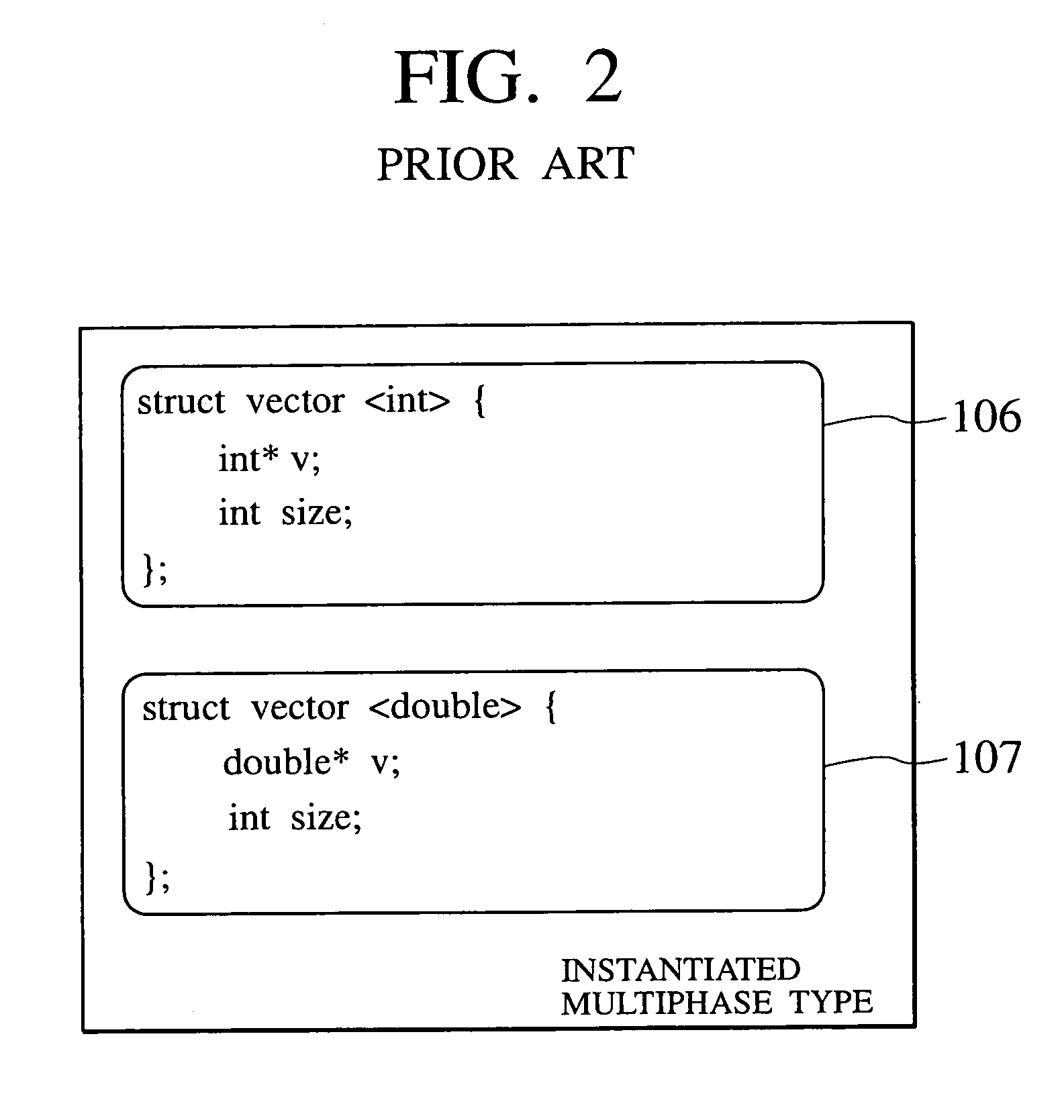

The present invention provides a code optimizing method for a program language processing system which can delete an unnecessary duplicate multiphase type definition and can avoid an unnecessary multiphase type from being instantiated. In this language processing system, all preprocessed source programs to be used as a source for generating an object program are scanned, a duplicate data type definition is deleted from the source programs with reference to a data type definition table, arranged for one object program, for registering a data type definition for data or a function in the source programs, instantiation of a data type definition which has been instantiated as needed is suppressed to optimize the source programs, and the optimized source programs are output in units of translation. Since a code size is reduced by the optimization, a code execution speed increases, and a compile time and a link time can be shortened.

Owner:KK TOSHIBA

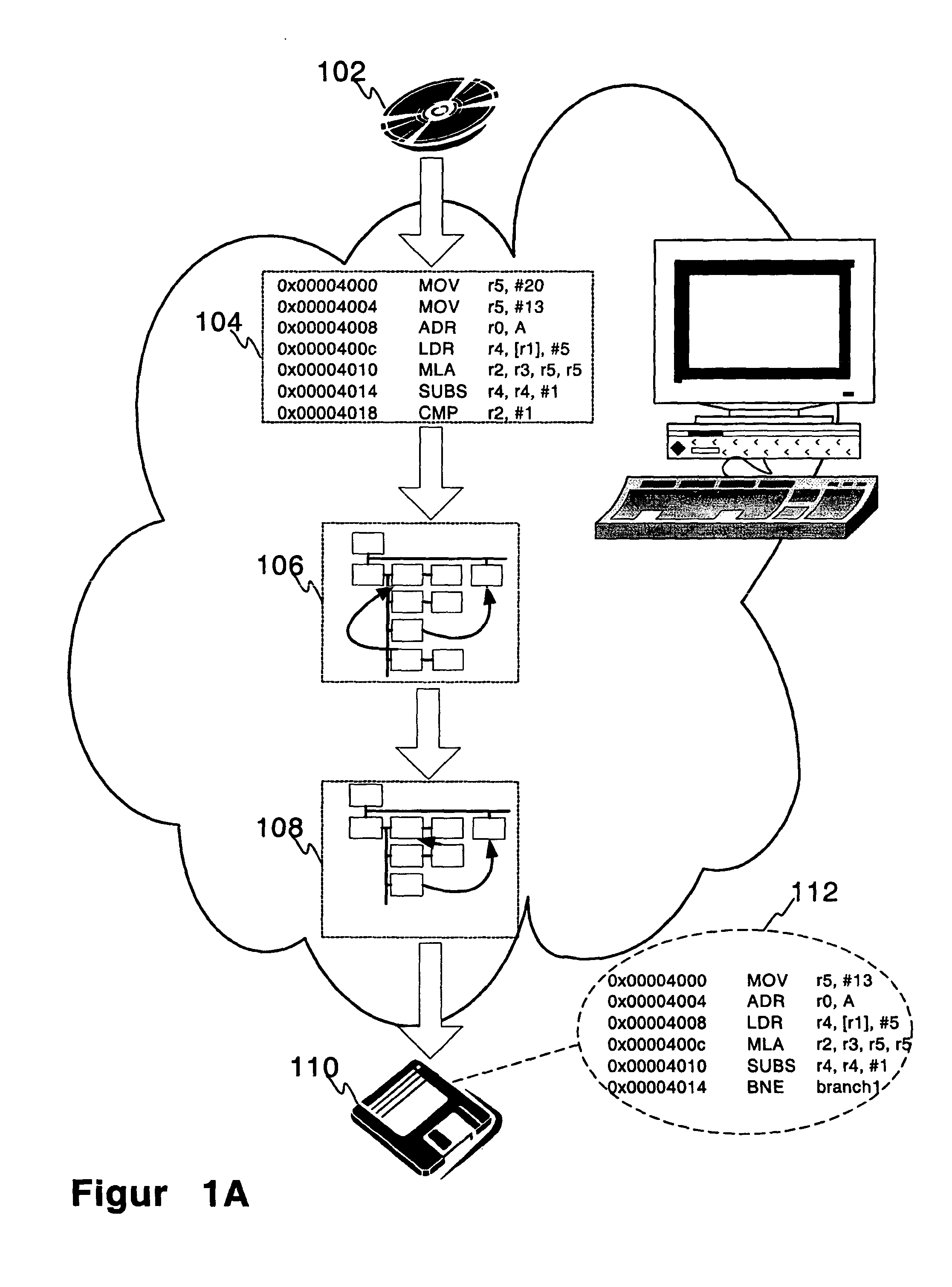

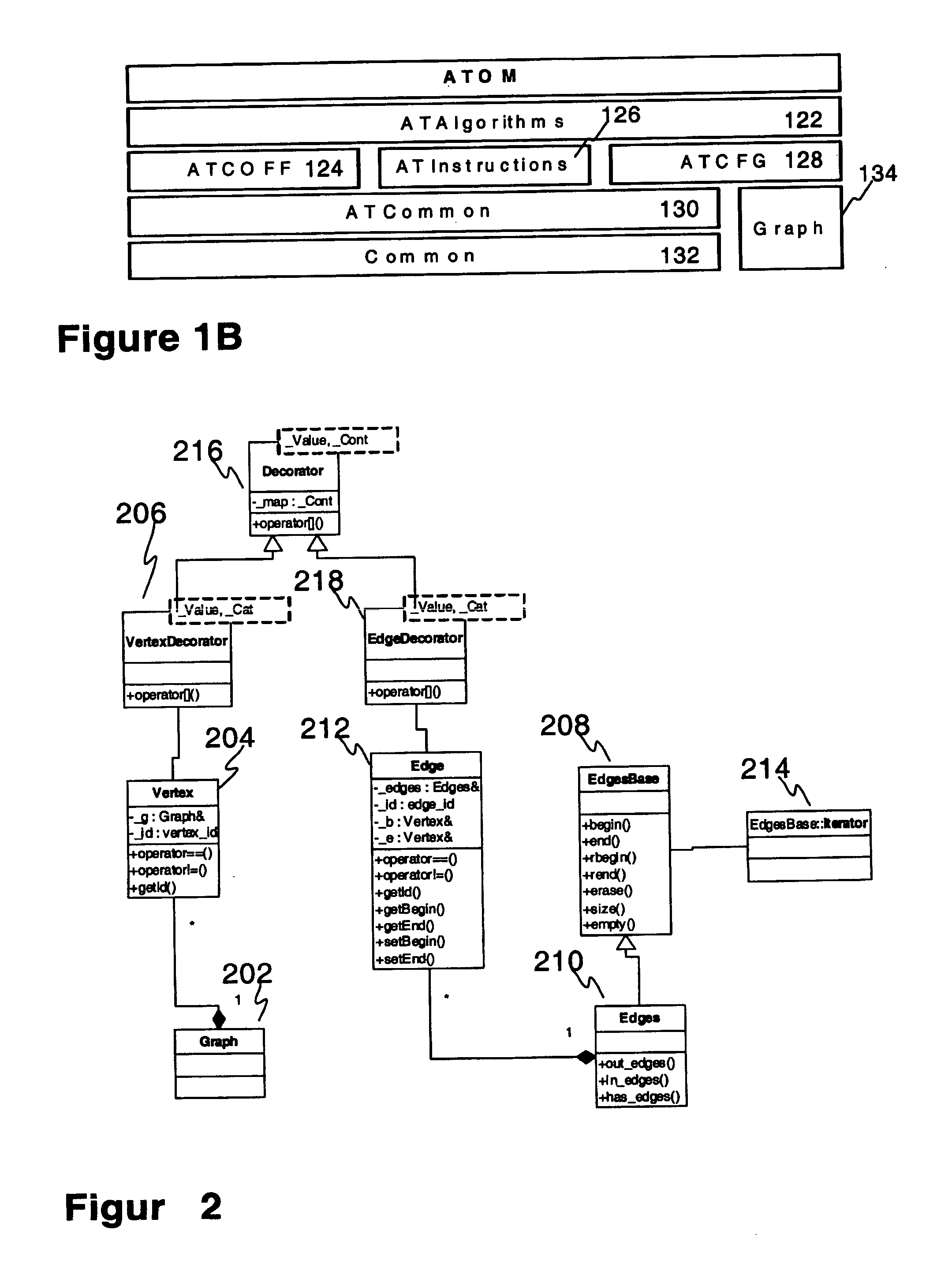

Method and a system for constructing control flows graphs of binary executable programs at post-link time

InactiveUS20050060696A1Clarifies overall structureReduce memory usageSoftware engineeringSoftware simulation/interpretation/emulationControl flowBasic block

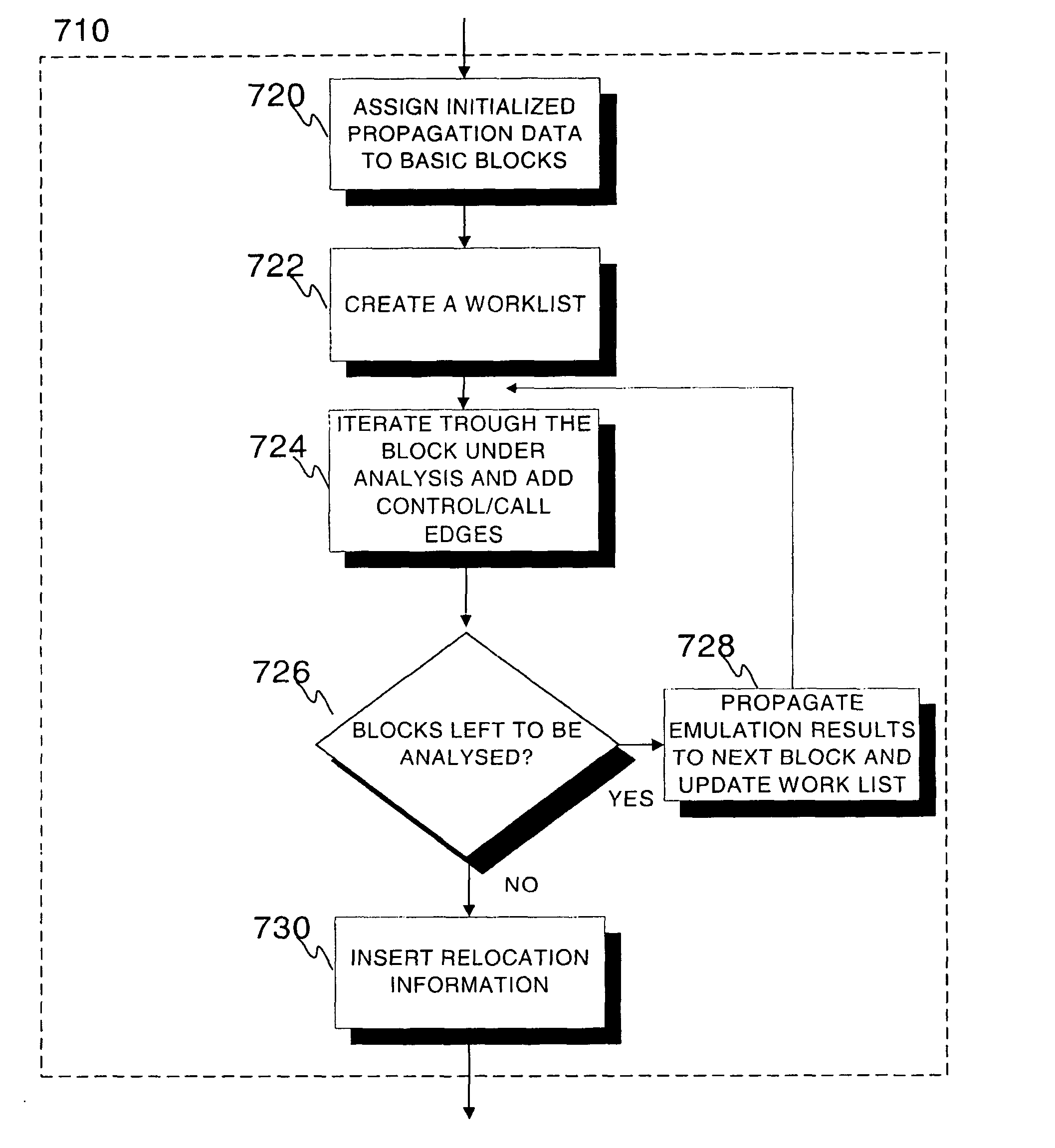

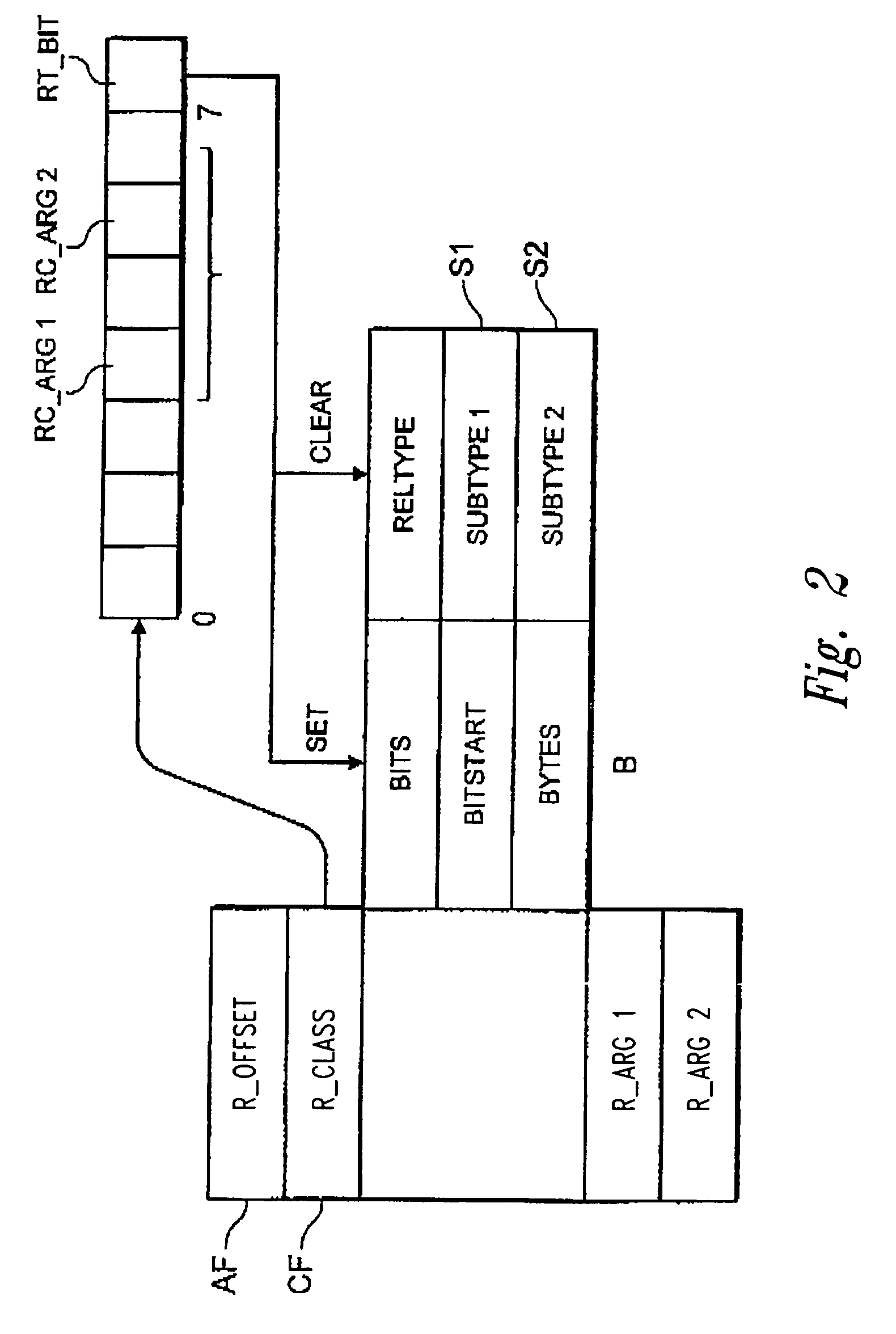

A method and a system for constructing a control flow graph (CFG, 106) from an executable computer program (104). The solution detects data intermixed with instructions and instruction set changes. The method includes the steps of defining block leader types specifying basic block boundaries in the program (104), building a CFG structure (106) according to the basic blocks found in the program, and adding control flow and addressing information to the CFG (106) by propagating through the basic blocks and internals thereof. The CFG (106) may be then optimised (108) and a compacted executable (112) created as a result.

Owner:NOKIA CORP

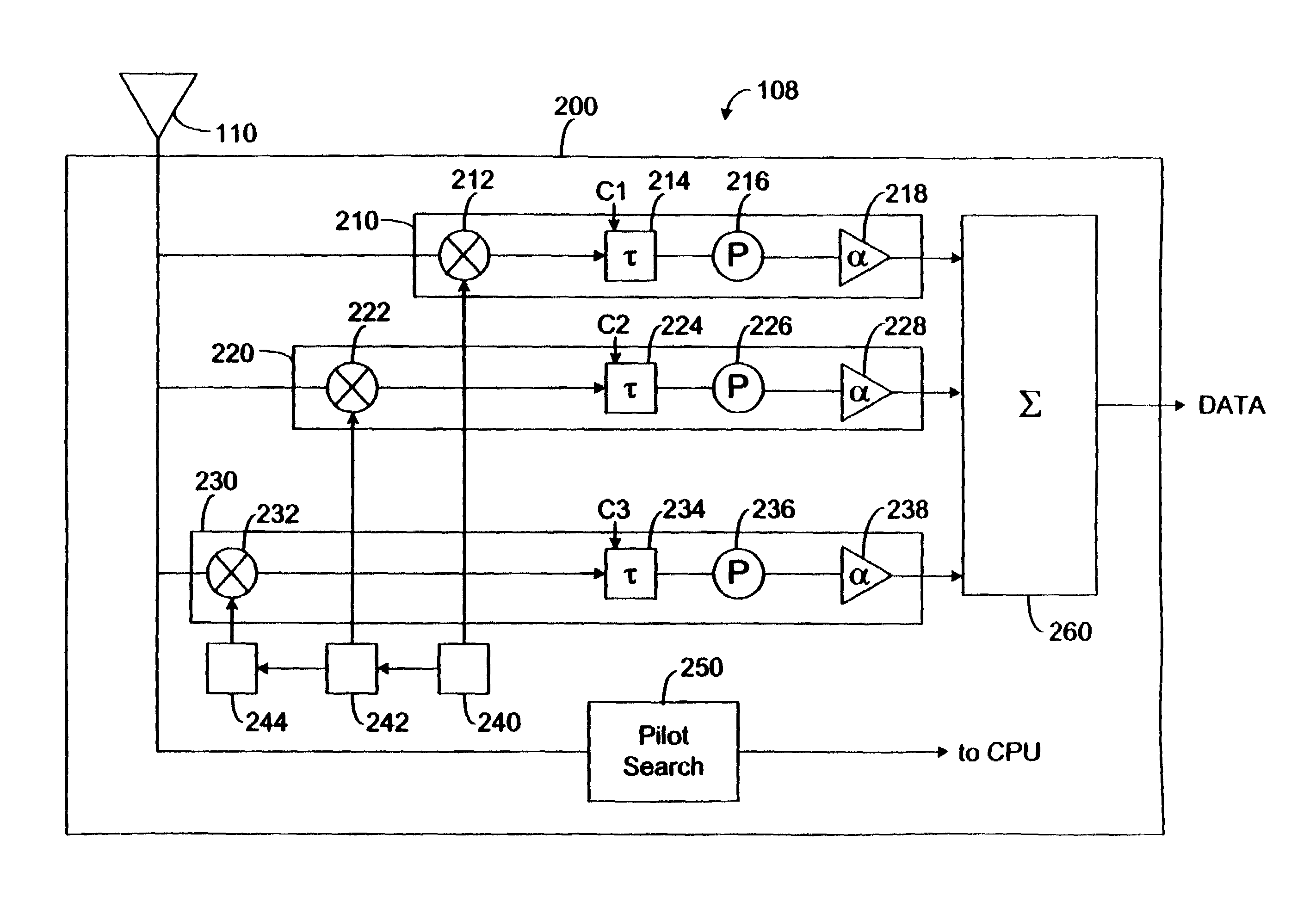

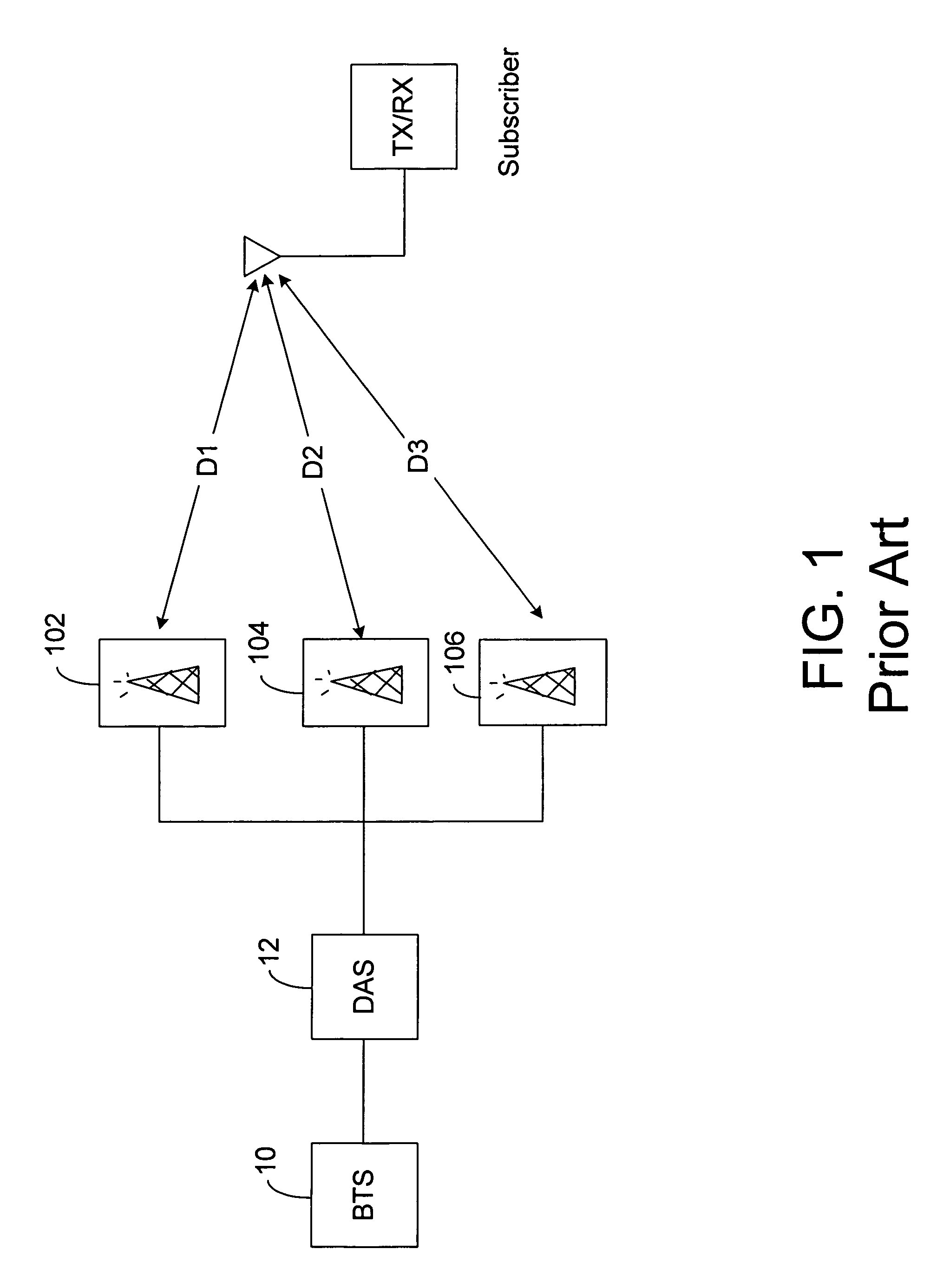

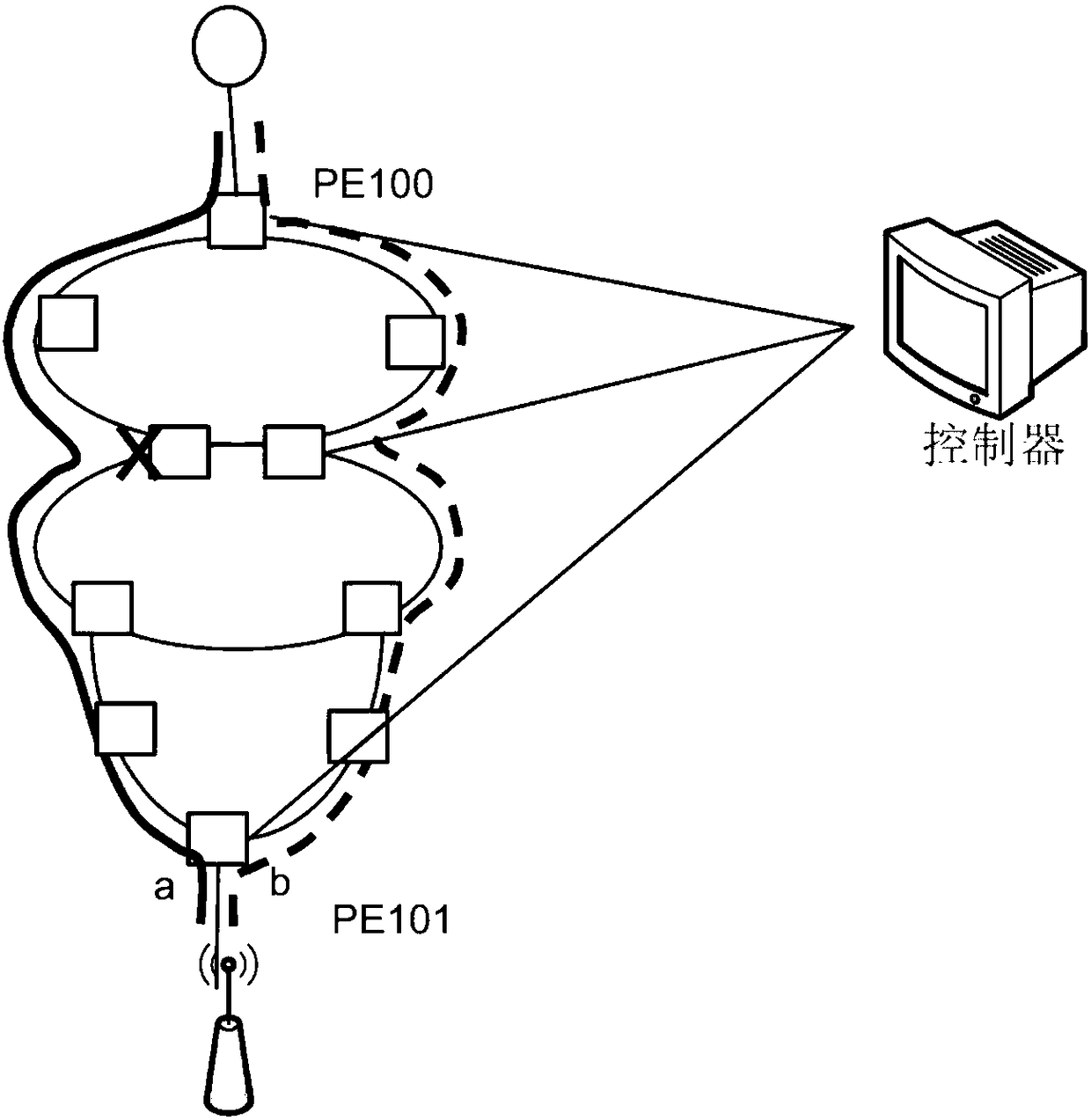

Forward link time delay for distributed antenna system

InactiveUS7236515B1Easy to set upSufficient amountPolarisation/directional diversityError prevention/detection by diversity receptionDistributed antenna systemMeasuring output

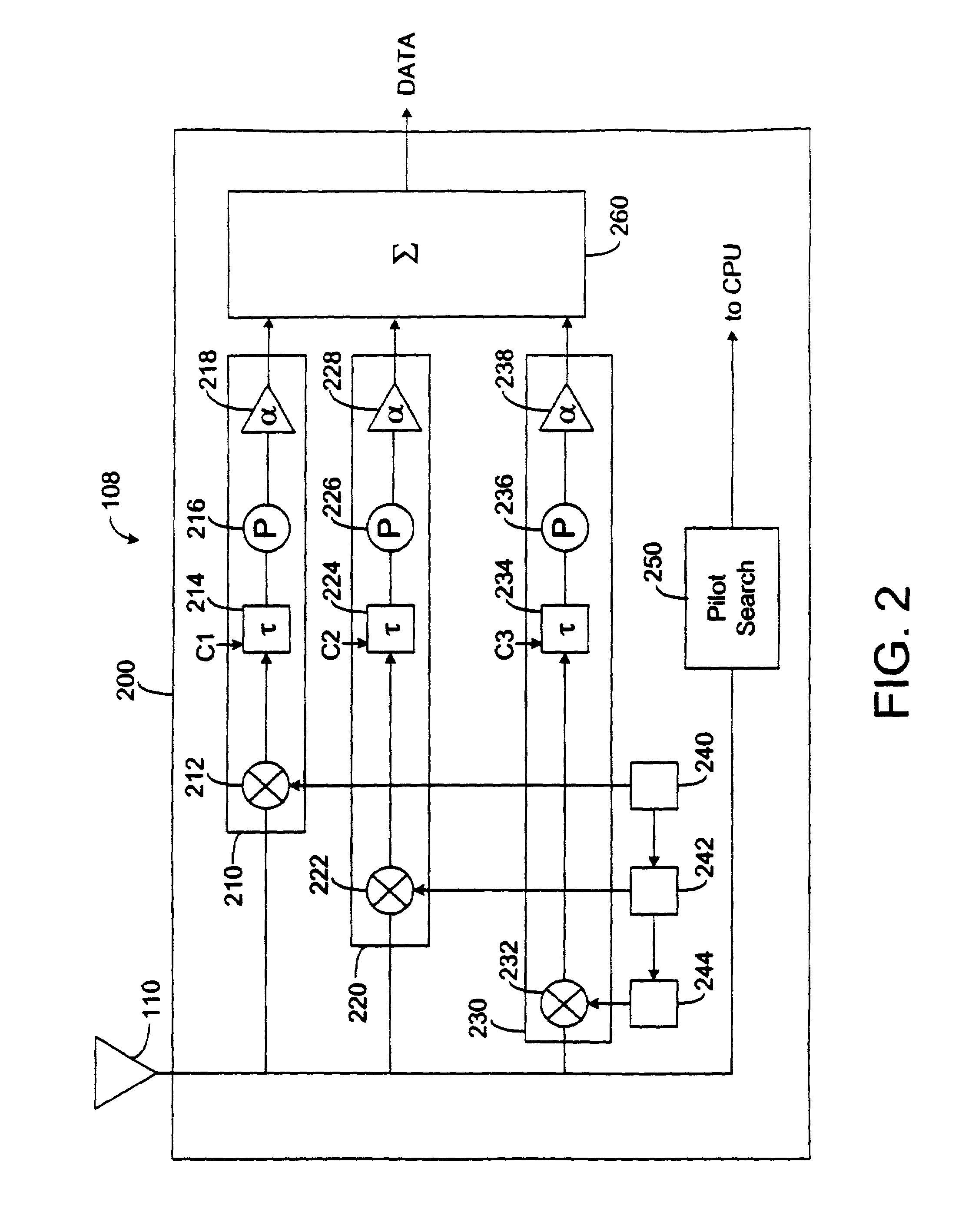

An apparatus and method are shown for receiving multi-path signals. A rake receiver is used to receive multi-path signals. The rake receiver contains multiple fingers that act as correlators, where each finger is synchronized to one of the multi-path signals. Each finger of the rake receiver includes a variable delay element. The delay of the variable delay element in each finger may be determined by calculating the amount of time for a signal to travel from an antenna to the receiver, due to the path traveled, and setting the delay based on the measured travel time. The delay of the variable delay element in each finger may also be determined by scanning through a range of delays of the variable delay element and measuring an output signal level of the finger, the variable delay element then being set to the delay corresponding to the highest measured output signal level.

Owner:SPRING SPECTRUM LP

Link-time profile-based method for reducing run-time image of executables

InactiveUS20060048106A1Image is often very smallImprove performanceProgram loading/initiatingMemory systemsNew ExecutableRunning time

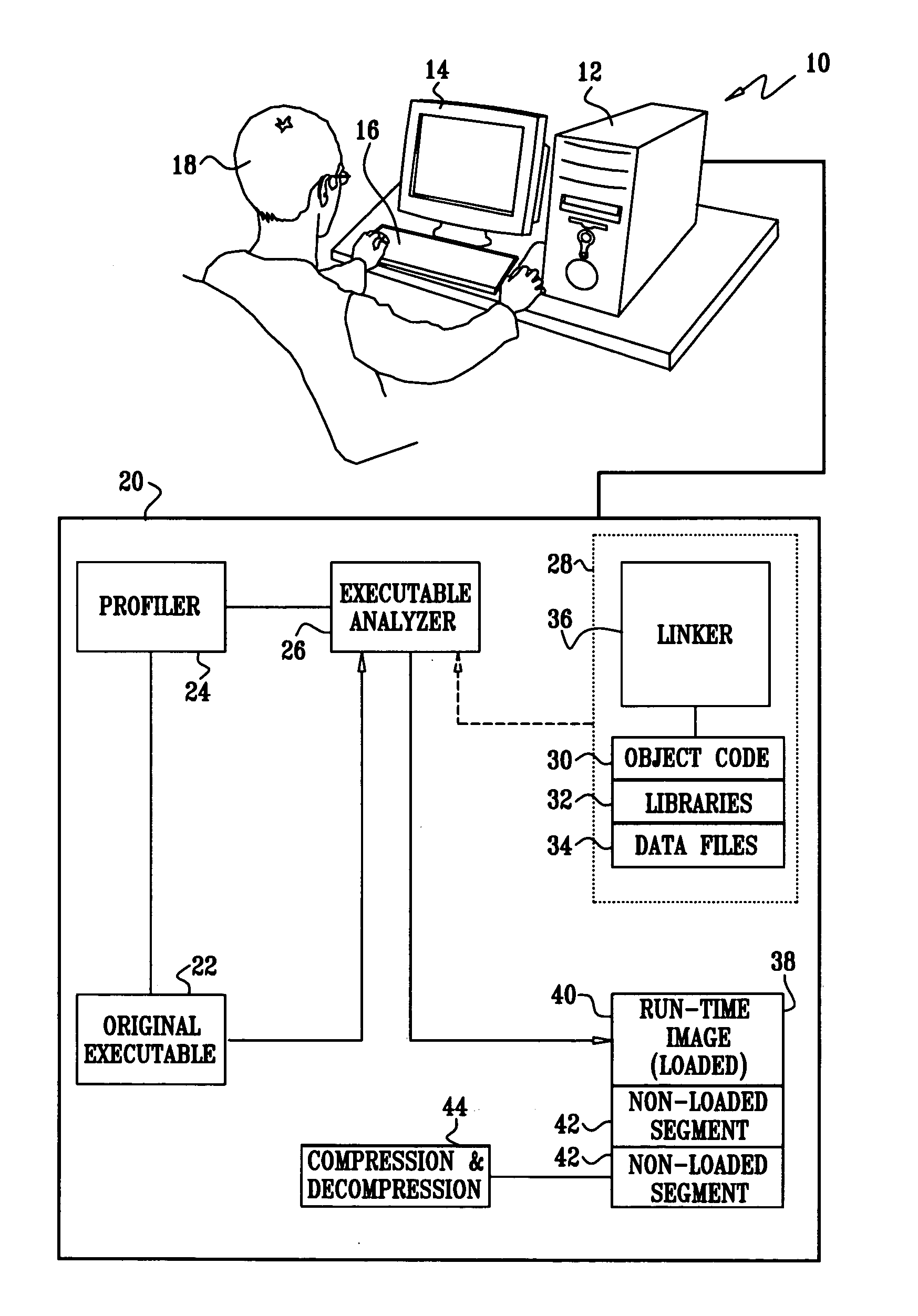

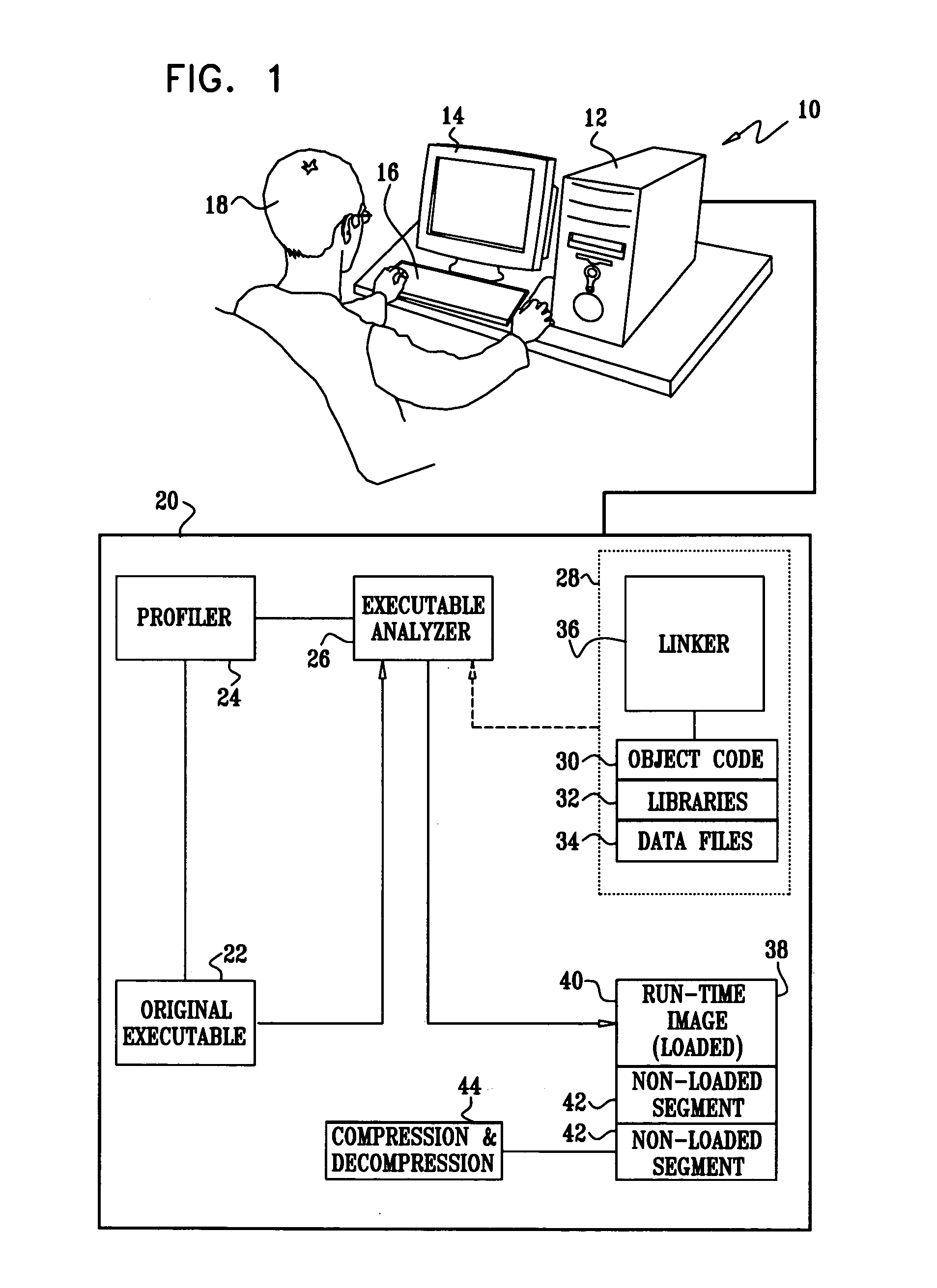

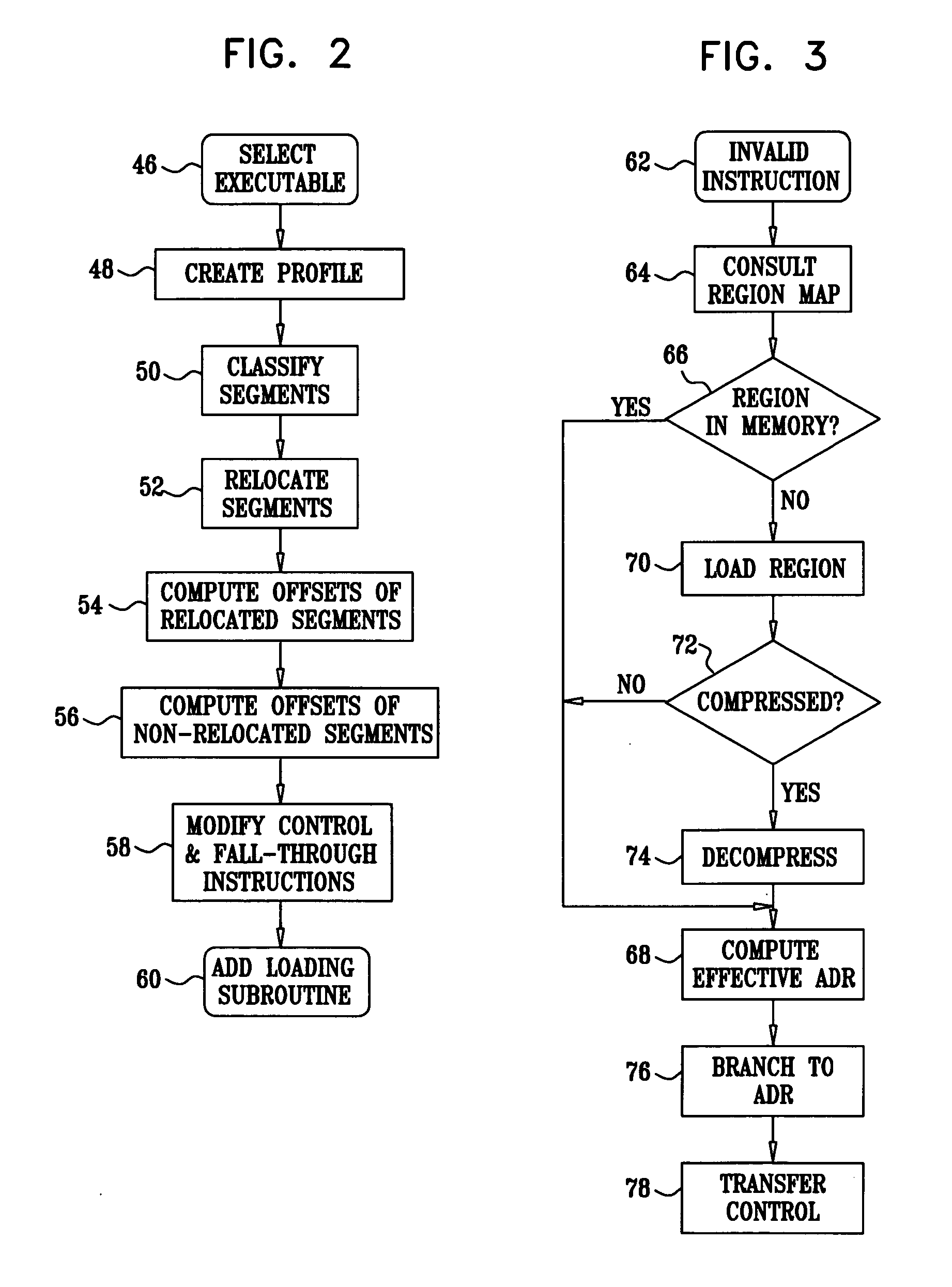

An executable program file is produced, which has a reduced run-time image size and improved performance. Profiling information is obtained from an original executable program. Both the original executable code and the profiling information are used to generate the new executable program file. All frozen basic blocks are grouped together and relocated in a separate non-loading module. Each control transfer to and from the relocated code is replaced by an appropriate interrupt. An interrupt mechanism invokes an appropriate handler for loading the relevant code segments from the non-loading module containing the targeted basic blocks. Since the relocated basic blocks are frozen, the time-consuming interrupt mechanism is rarely if ever invoked during run-time, and therefore, has no significant effect on performance.

Owner:IBM CORP

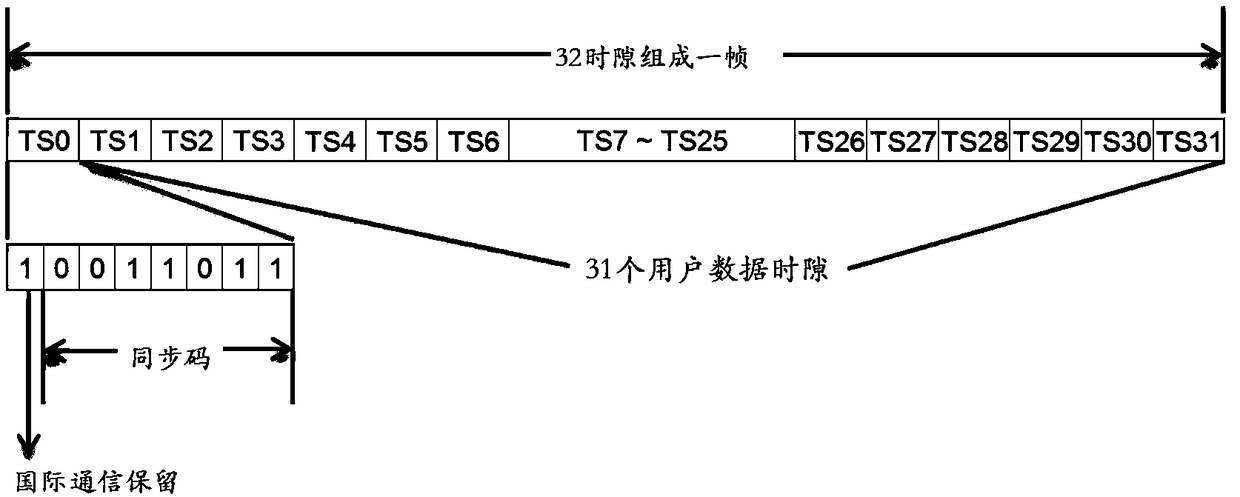

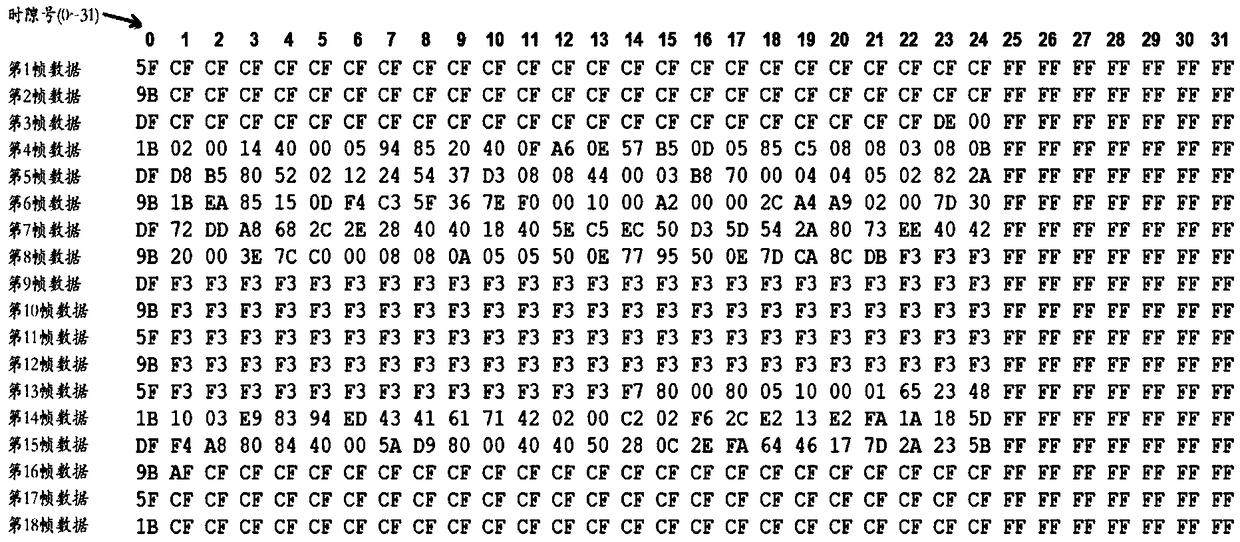

TDMA based long propagation delay wireless link time slot distribution method

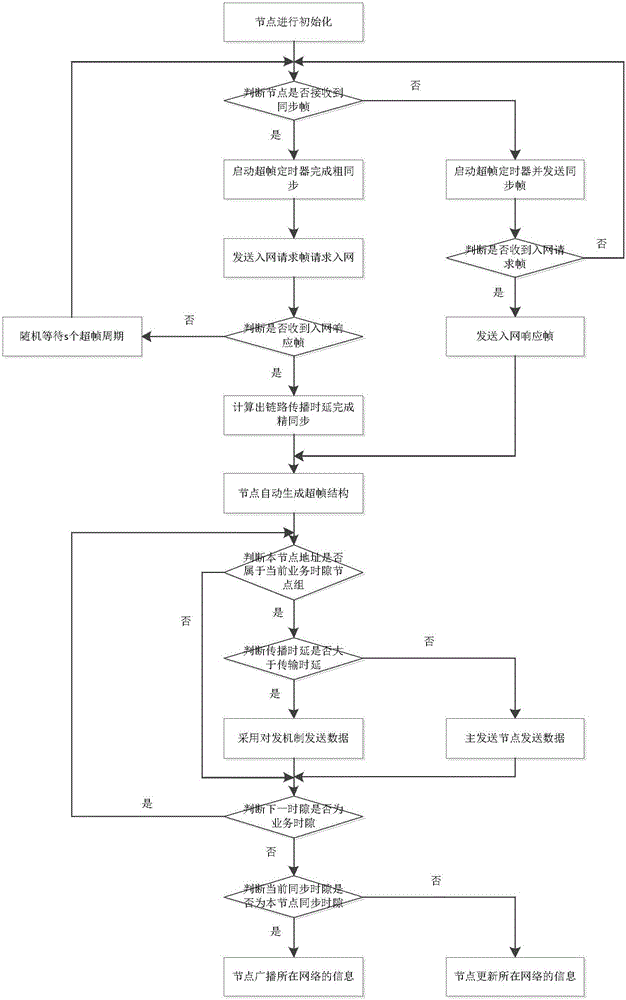

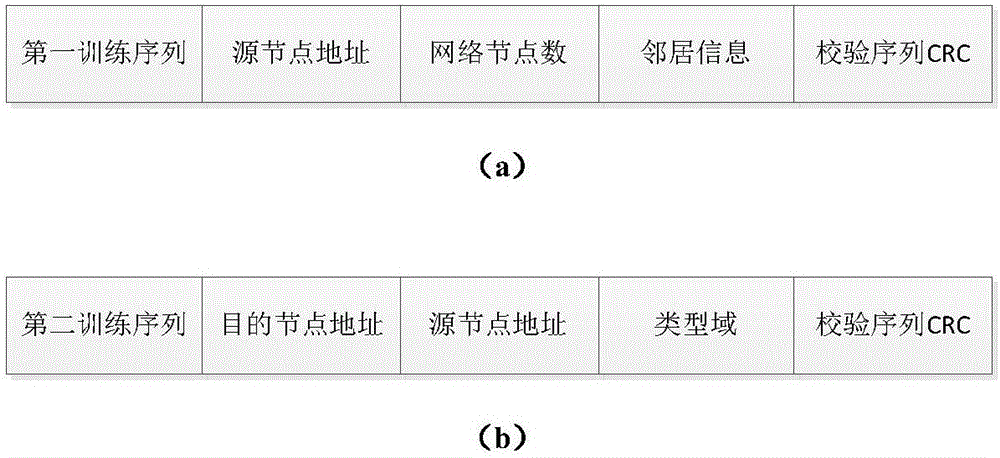

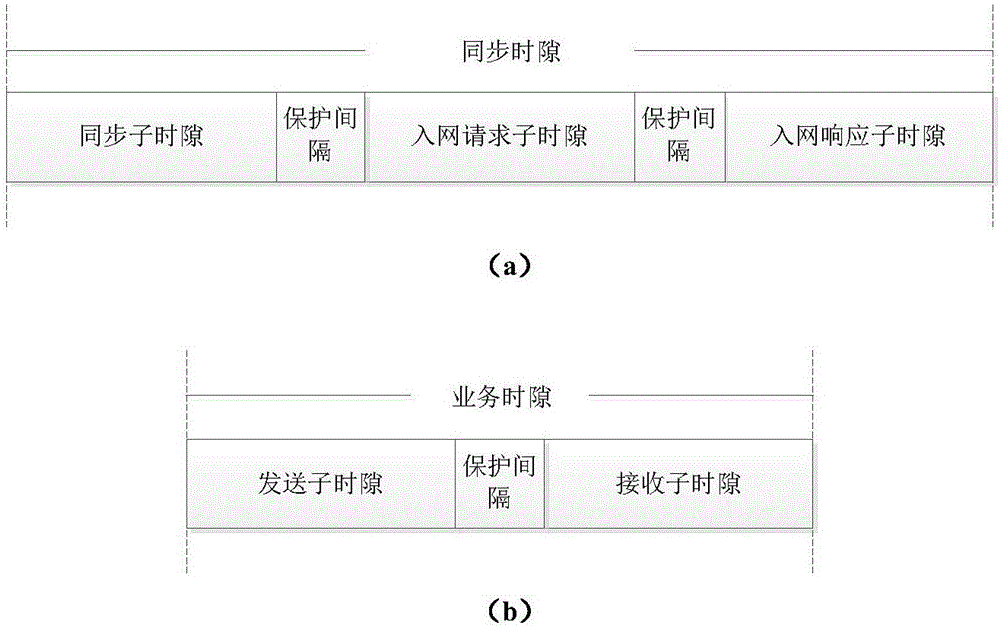

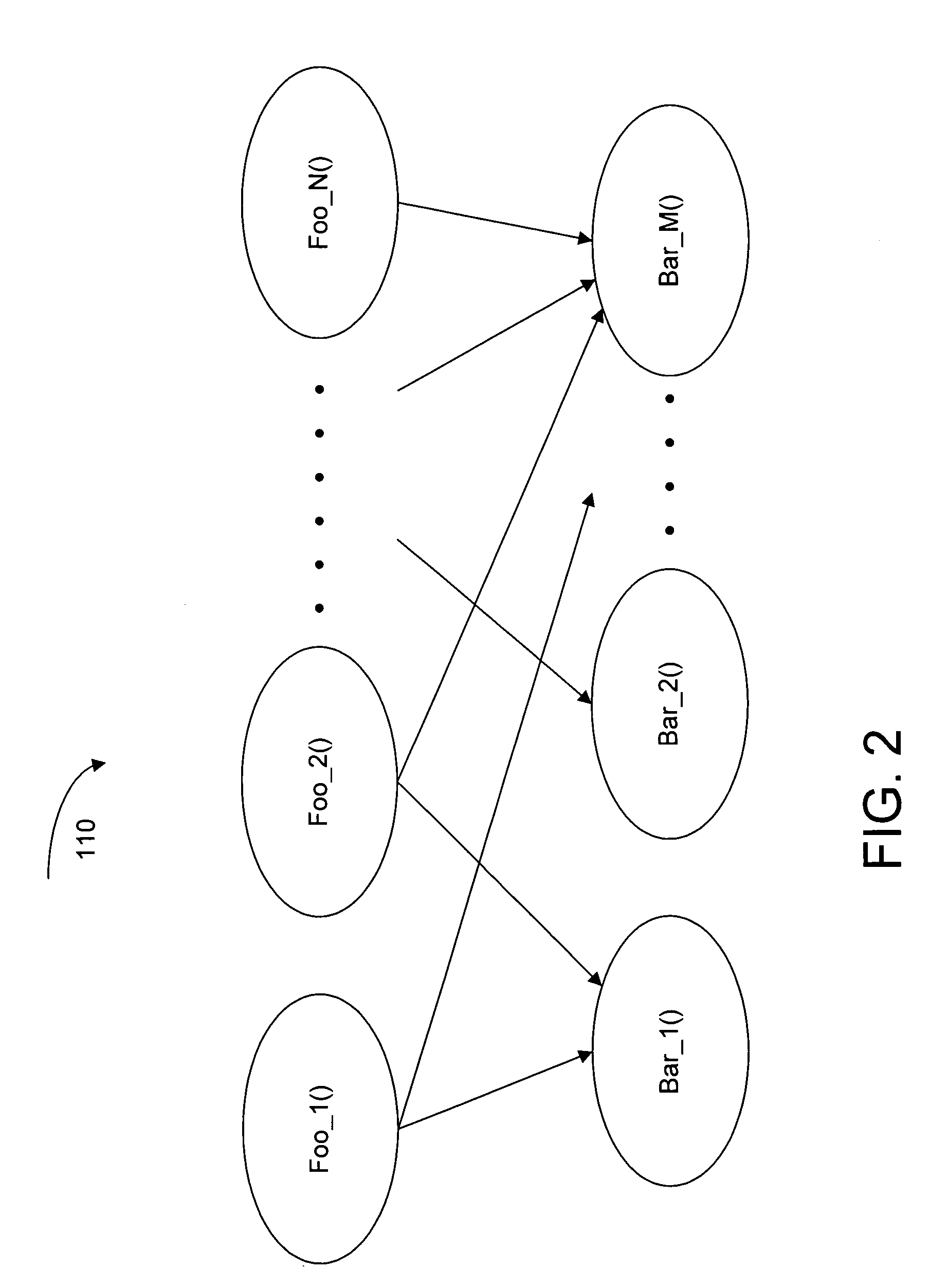

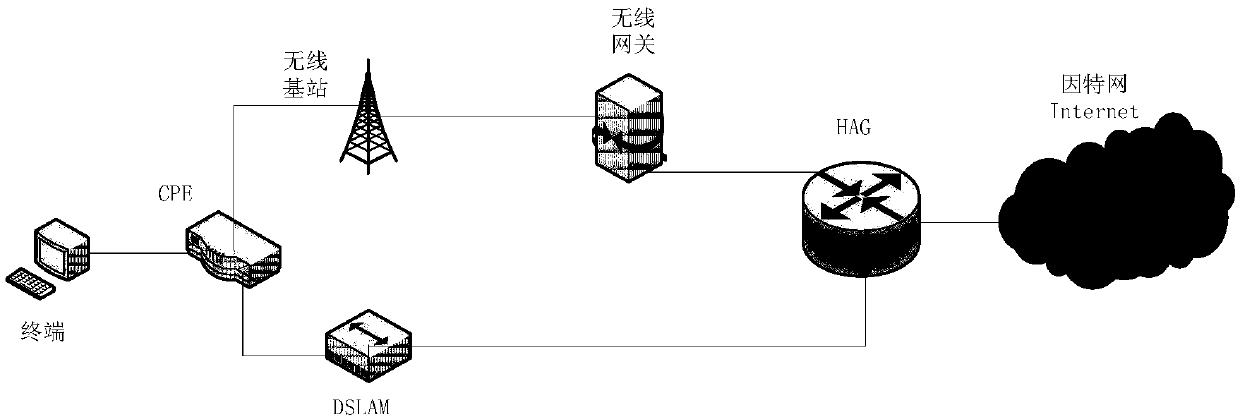

ActiveCN106658735AHigh speedImprove efficiencyTime-division multiplexWireless communicationWireless ad hoc networkSynchronous frame

The invention discloses a TDMA based long propagation delay wireless link time slot distribution method which is mainly used for solving the problem of low throughput rate and low channel utilization rate of an existing long propagation delay wireless ad hoc network. The implementation scheme comprises the steps of 1, initializing a node; 2, judging whether the node receives a synchronous frame, if so, carrying out network access synchronization by the node, and otherwise, building a network by regarding the local clock as a reference by the node; 3, after synchronization is finished, generating a super-frame structure automatically by the node, and dividing the local time into multiple time slots with different functions; and 4, judging whether the current time slot is a service time slot by the node, if so, sending and receiving data, and otherwise, updating network information. as the TDMA is adopted as a channel access mode, the node can access the channel without any conflict; and through an interactive sending mechanism and a data frame queue scheduling mechanism, the network throughput rate and the channel utilization rate are increased, the queuing delay of the data frames is reduced; and the TDMA based long propagation delay wireless link time slot distribution method can be used for a time division multiple access ad hoc network.

Owner:XIDIAN UNIV

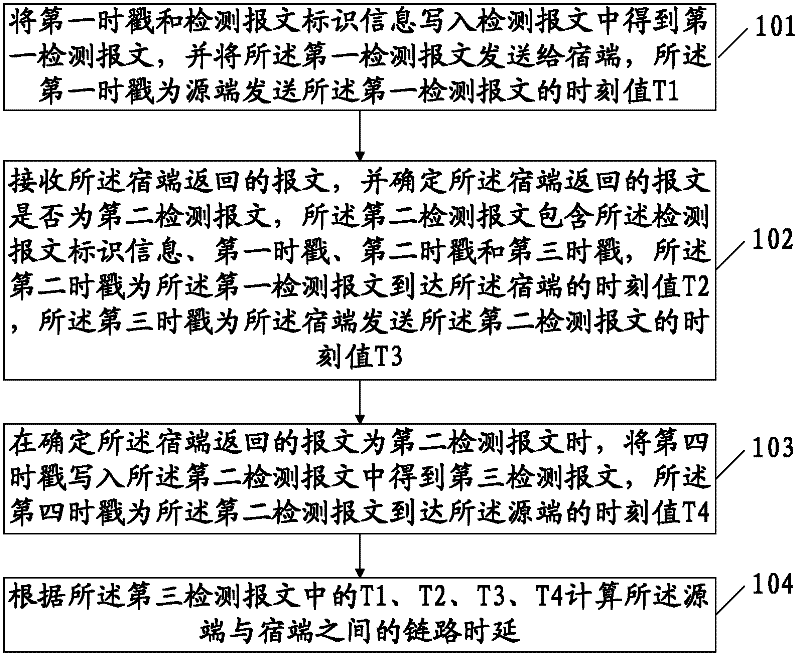

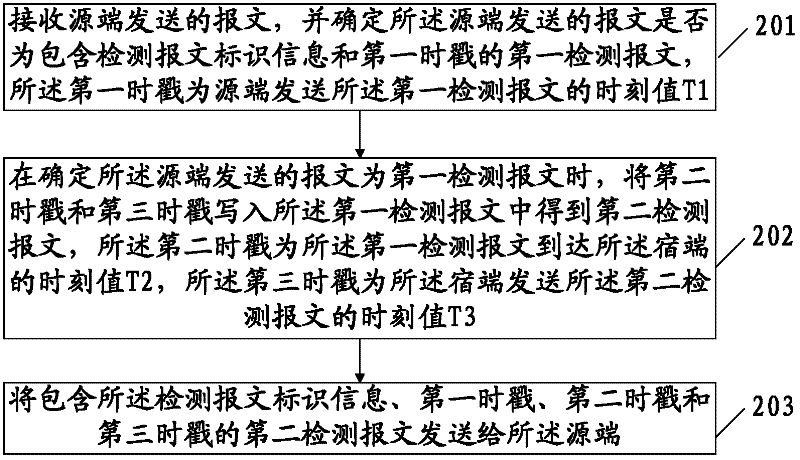

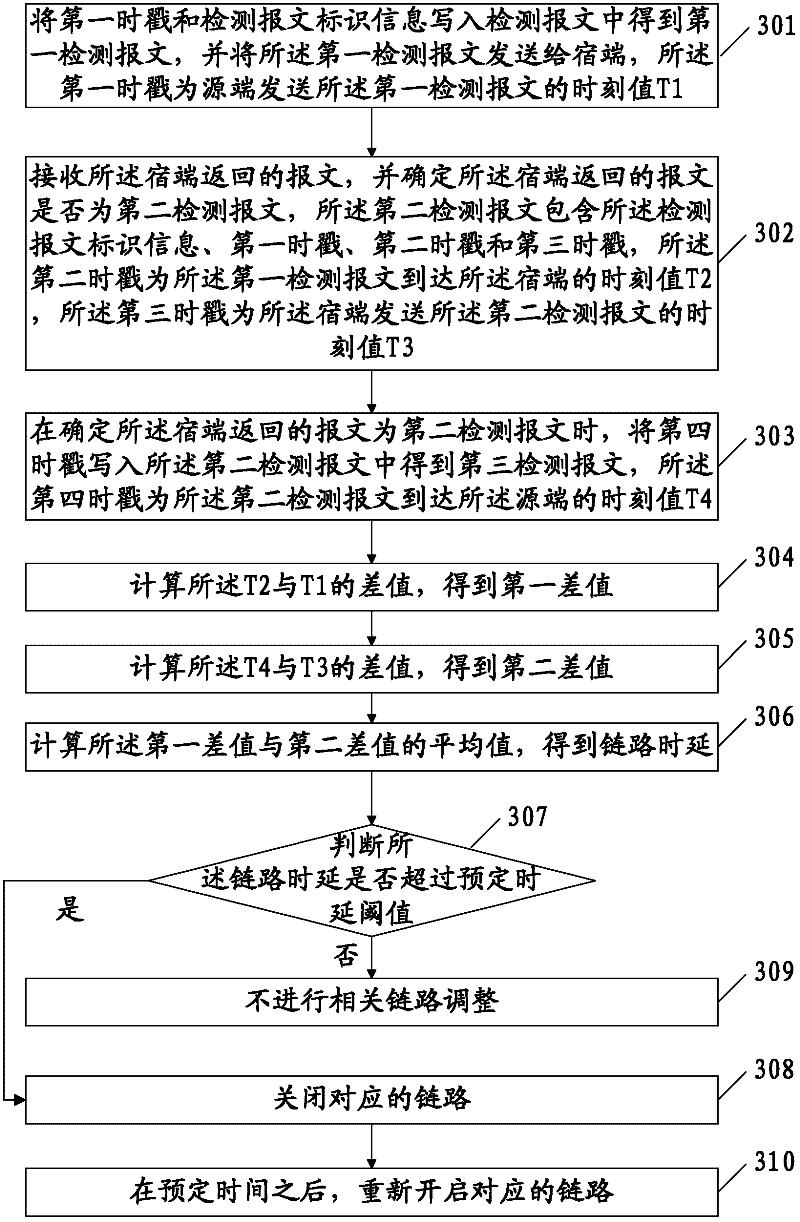

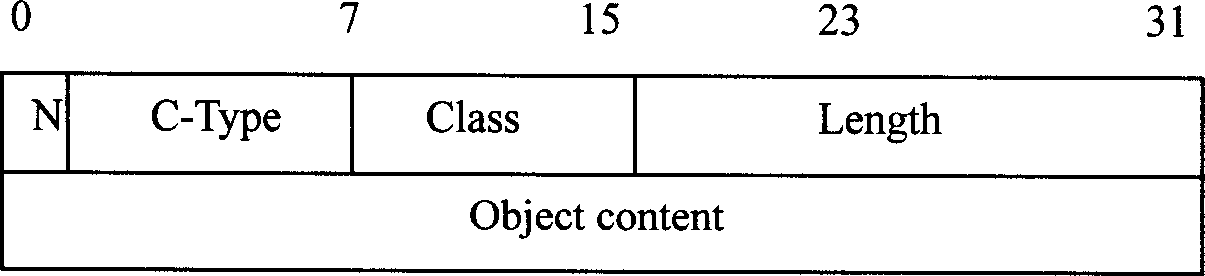

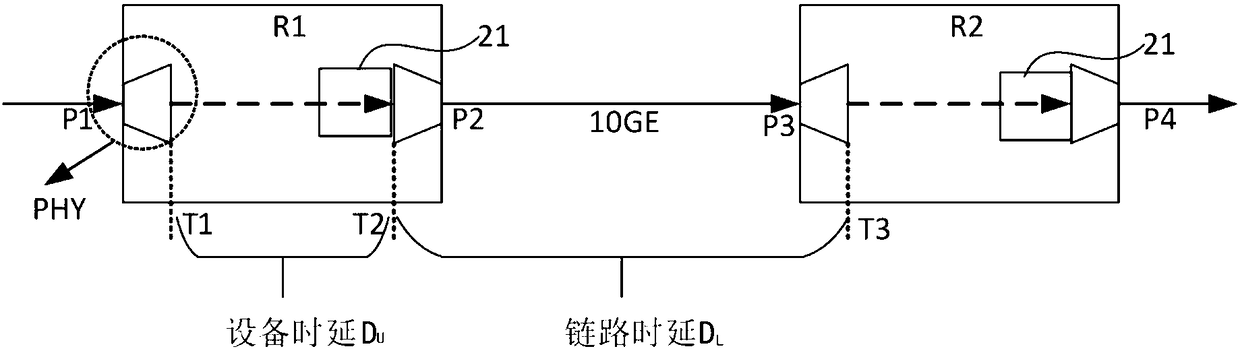

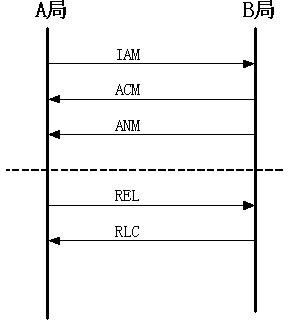

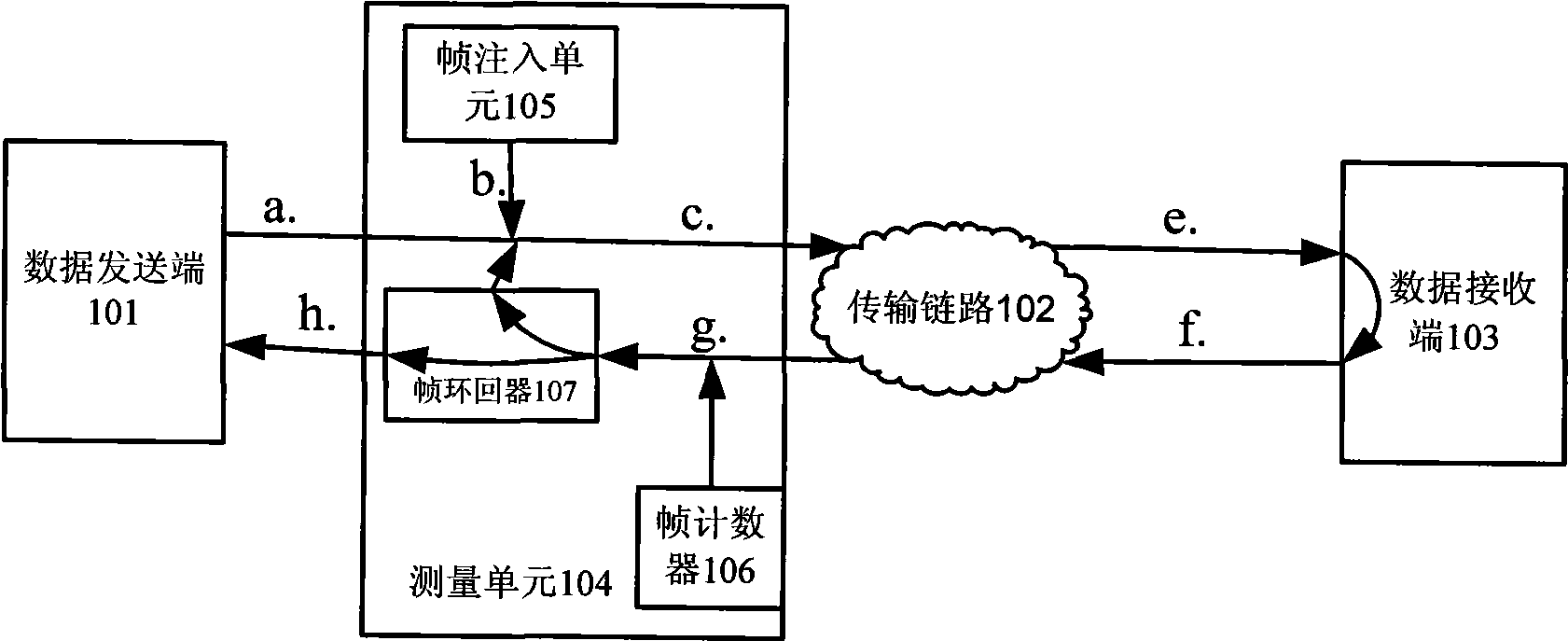

Link time delay detection method, source terminal, destination terminal and system

The embodiment of the invention provides link time delay detection method, source terminal, destination terminal and system, which can prevent time delay detection from influencing the current network service, and relates to the field of communication technology. The method comprises the following steps: a first time stamp and detection message identification information are written into a first detection message and sent to a destination terminal, and the first time stamp is the time T1 at which the source terminal sends the first detection message; a message returned by the destination terminal is received, whether the received message is a second detection message is confirmed, the second detection message comprises detection message identification information, the first time stamp, a second time stamp and a third time stamp, the second time stamp is the time T2 at which the first detection message reaches the destination terminal, and the third time stamp is the time T3 at which the destination terminal sends the second detection message; a fourth time stamp, the time T4 at which the second detection message reaches the source terminal, is written into the second detection message; and the link time delay between the source terminal and the destination terminal is calculated according to the T1, T2, T3 and T4.

Owner:HUAWEI TECH CO LTD

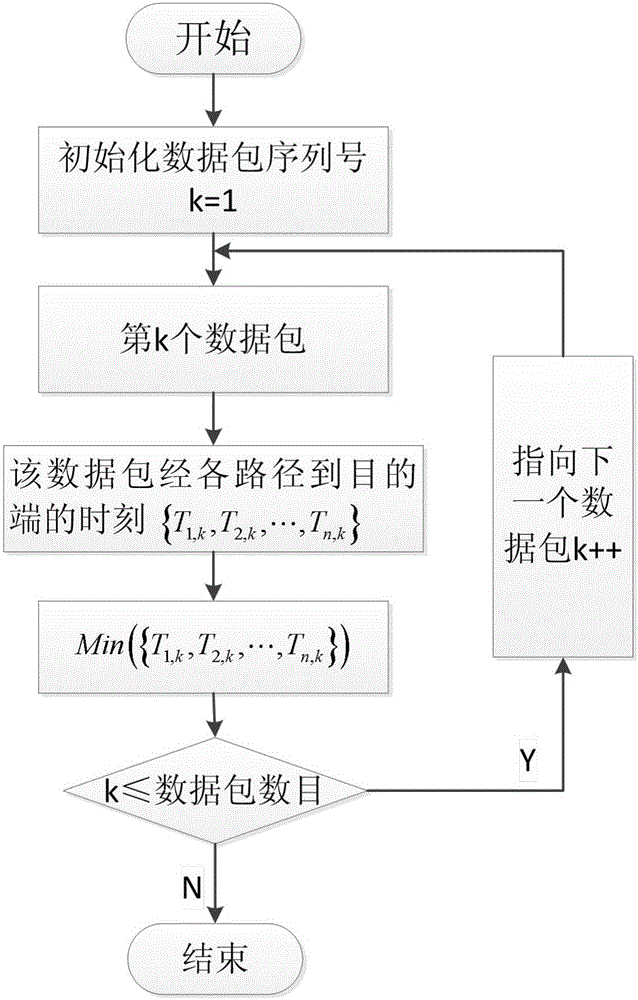

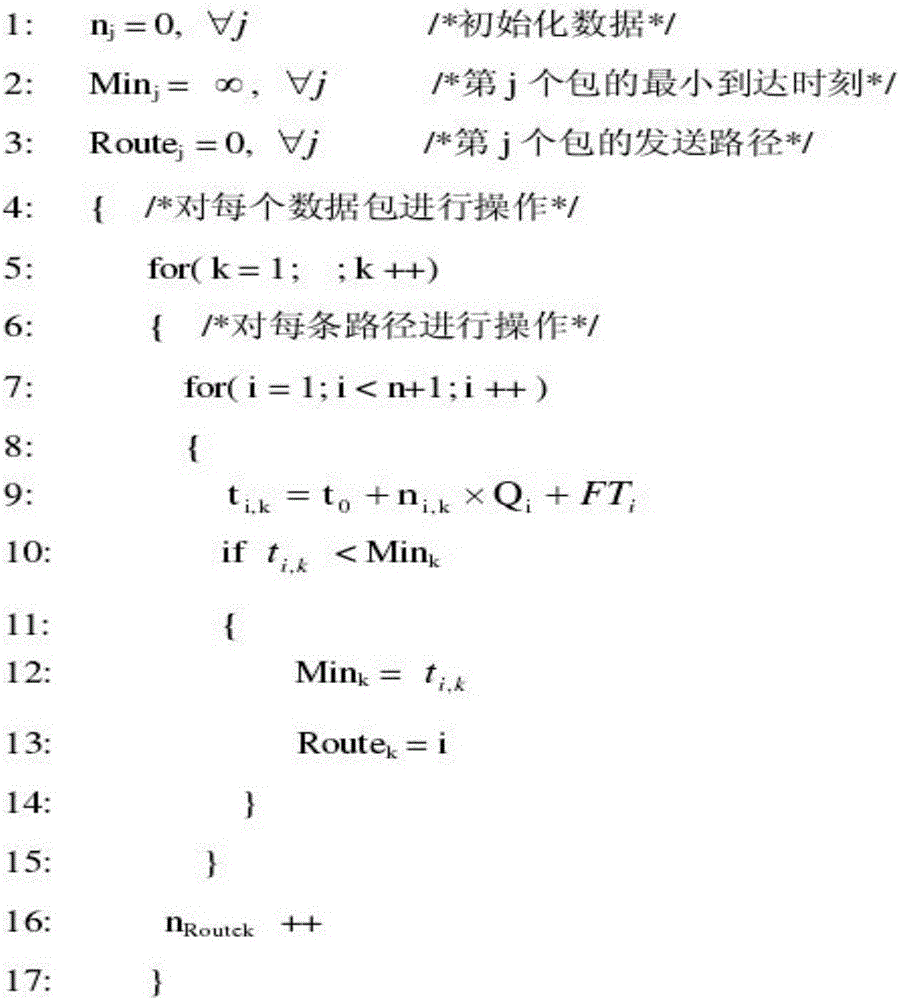

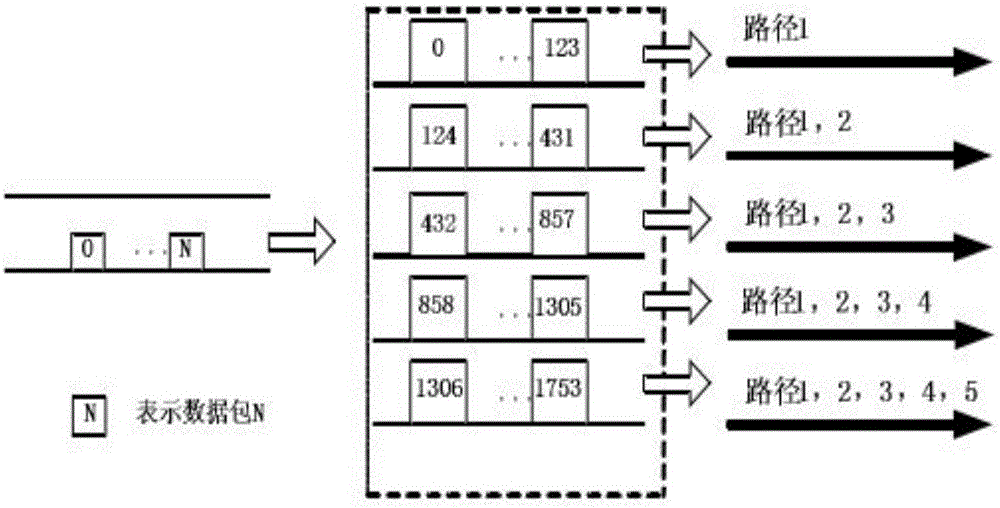

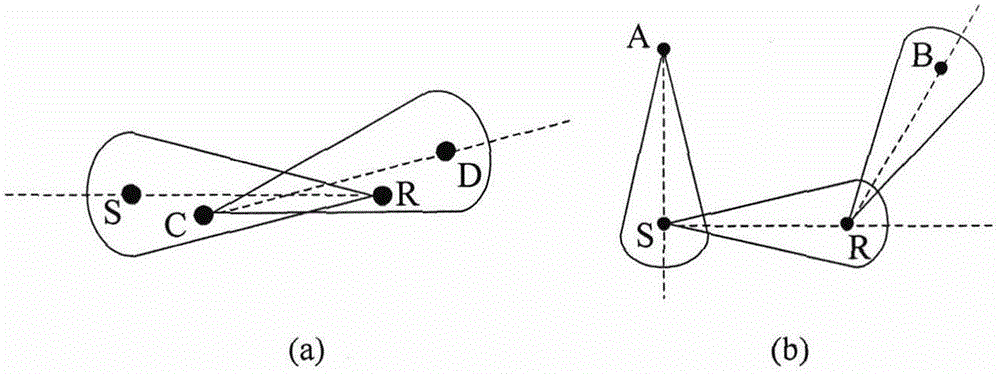

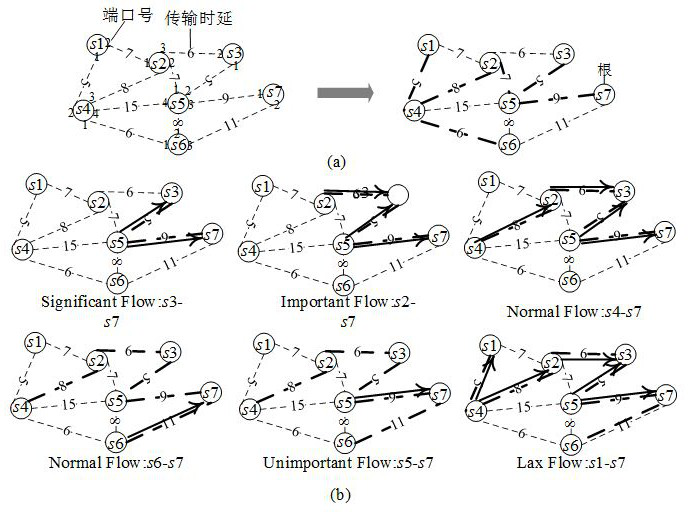

Multipath data packet distributing and scheduling method in wireless Ad Hoc network

PendingCN106102093AReduce disorderReduce the number of sortingNetwork traffic/resource managementNetwork topologiesStart timeData transmission time

The invention relates to a multipath data packet distributing and scheduling method in a wireless Ad Hoc network, and belongs to the field of wireless Ad Hoc networks. The method comprises the following steps: step 1, a source node selects preferable multiple paths with the minimum data transmission time to simultaneously transmit data packets according to round trip time delay of each path and available bandwidth; step 2, the source node dynamically regulates data packet transmission speed of each path according to link time delay situation fed back by a destination node; and step 3, after receiving the data packets transmitted by the source node, the destination node sequentially puts the received data packets into a cache area to waiting for reading, and timely feeds back the time delay situation of each link to the source node. The invention does not utilize the traditional continuous manner, but utilizes an interlacing method to respectively transmit the data packet to the destination node along the multiple paths, so that the data packets can sequentially arrive at the destination node, and the size of the cache area and starting time delay are reduced.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

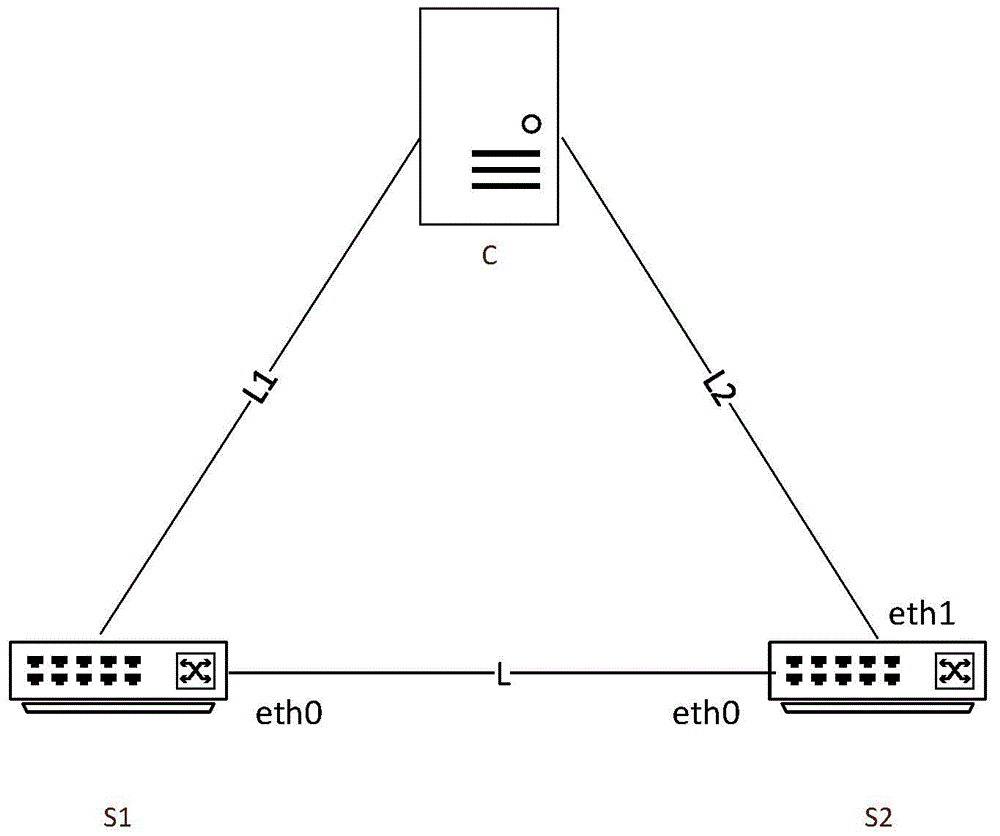

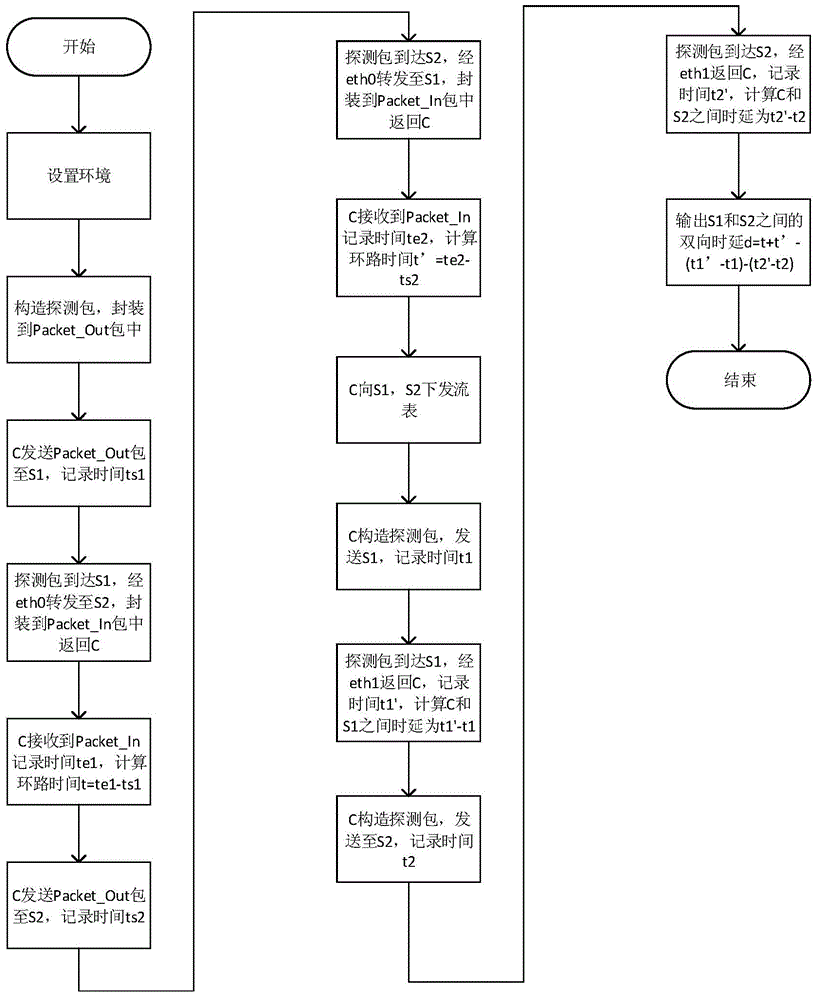

Inter-switch link time delay measuring method based on software defined network

InactiveCN104486159AReal-time measurement of round-trip delayLow costData switching networksTime delaysOpenFlow

The invention discloses an inter-switch link time delay measuring method based on a software defined network. The inter-switch link time delay measuring method comprises the following steps: installing an SDN controller C, an Openflow switch S1, and an Openflow switch S2; enabling the controller C to send a constructed Packet_Out packet to S1; when the Packet_Out packet arrives at S1, enabling S1 to analyze data from the Packet_Out packet, and forward the data from an eth0 interface of S1 to S2; enabling S2 to encapsulate the data packet into a Packet_In packet, and transmit back to the controller C; calculating first loop time by the controller C; in a similar way, sending the constructed Packet_Out packet to S2, and calculating second loop time by the controller C; creating a detecting packet by the controller C, sending the detecting packet to S1, forwarding the packet from an eth1 interface of S1, and returning the packet to the controller C, and sending the constructed detecting packet to S1 by the controller, so as to calculate the bidirectional time delay between the controller C and S2, and calculating the bidirectional time delay between S1 and S2.

Owner:SOUTHEAST UNIV

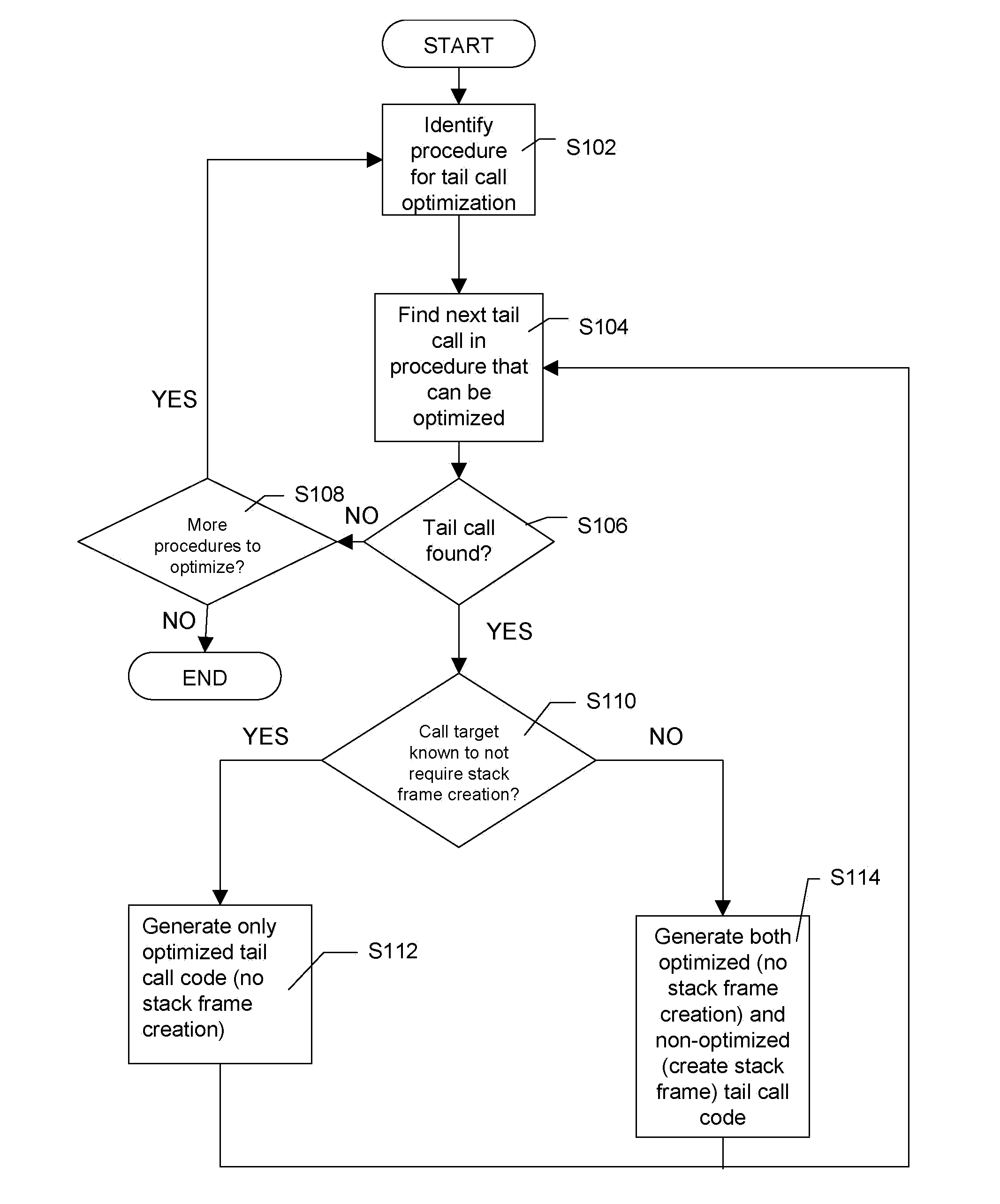

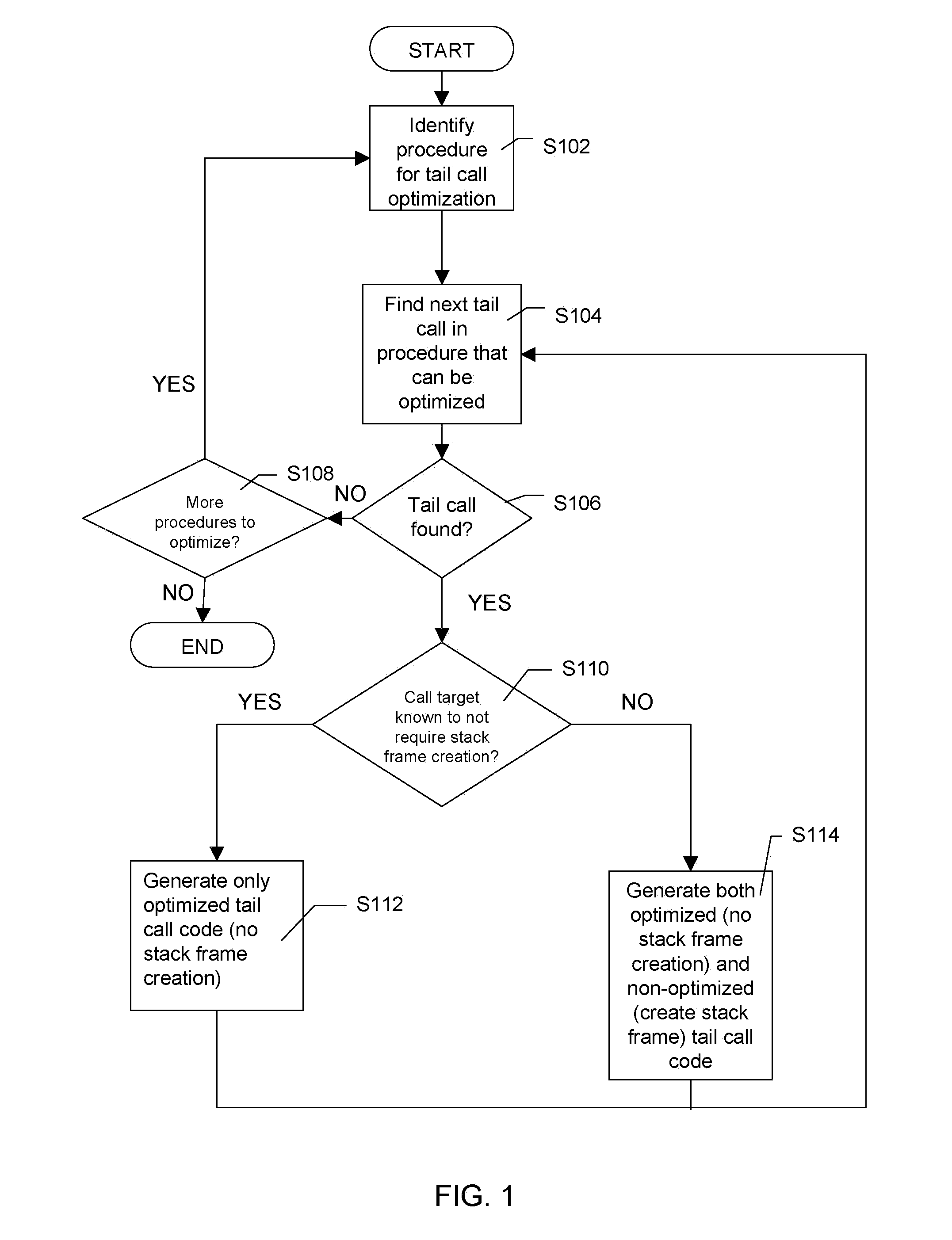

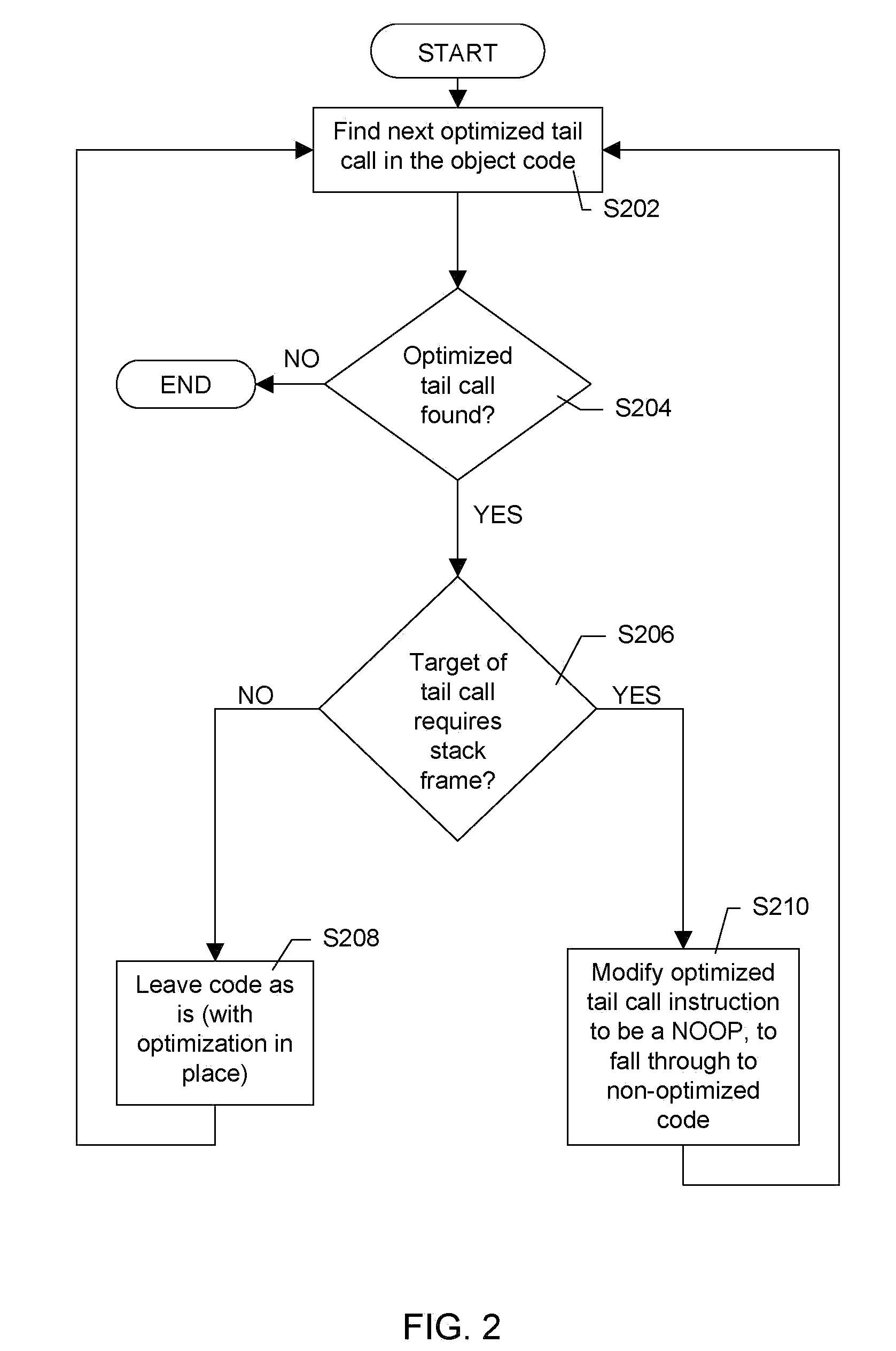

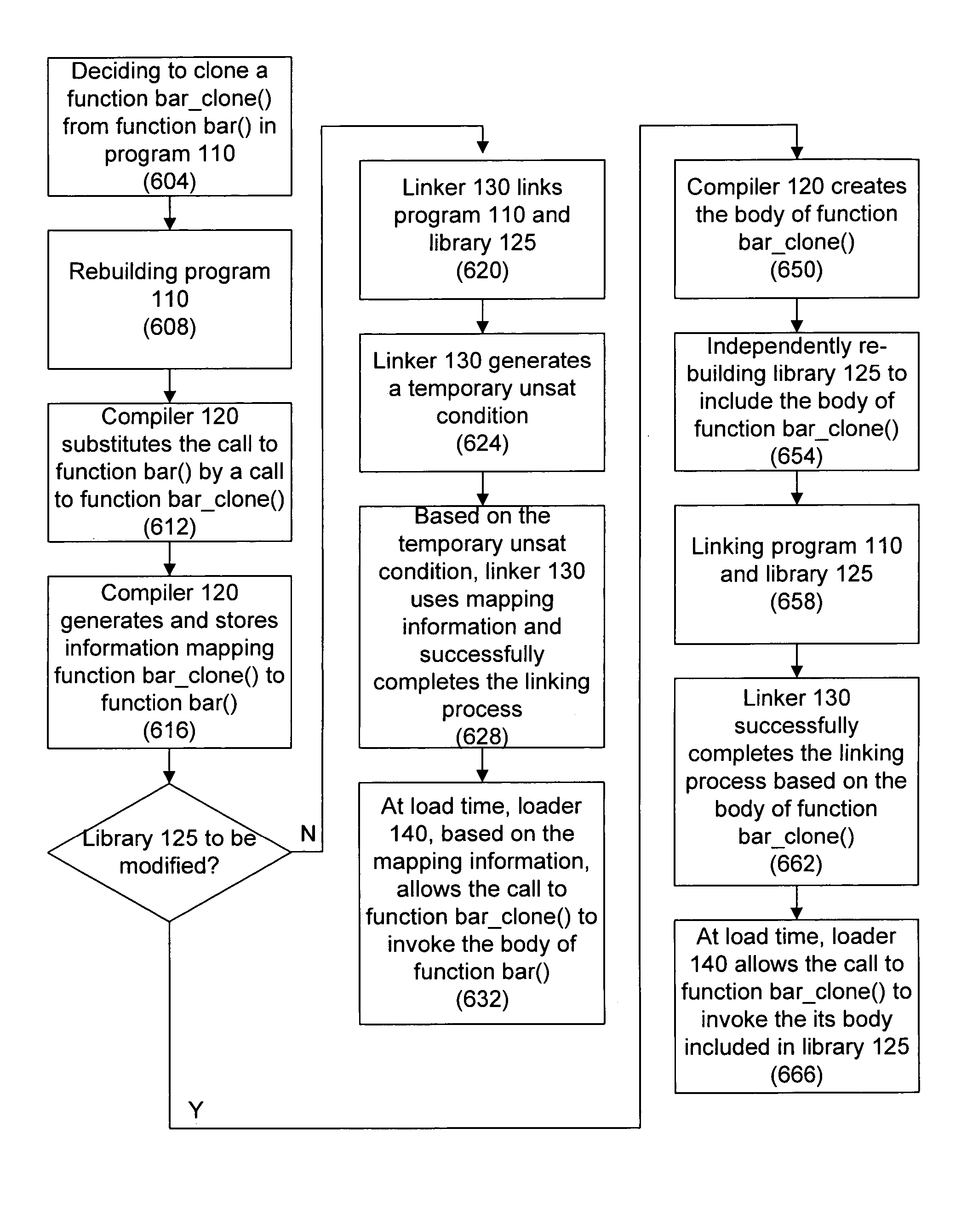

Refining tail call optimizations at link-time

InactiveUS20090187884A1Link editingSpecific program execution arrangementsParallel computingLink time

A method and apparatuses for allowing additional tail call optimizations. The compiler generates both optimized and non-optimized code for tail call candidates. At a later time when there is more information (e.g. regarding program bounds), a decision and a modification to the executable code is made, implementing one of the two earlier codes.

Owner:IBM CORP

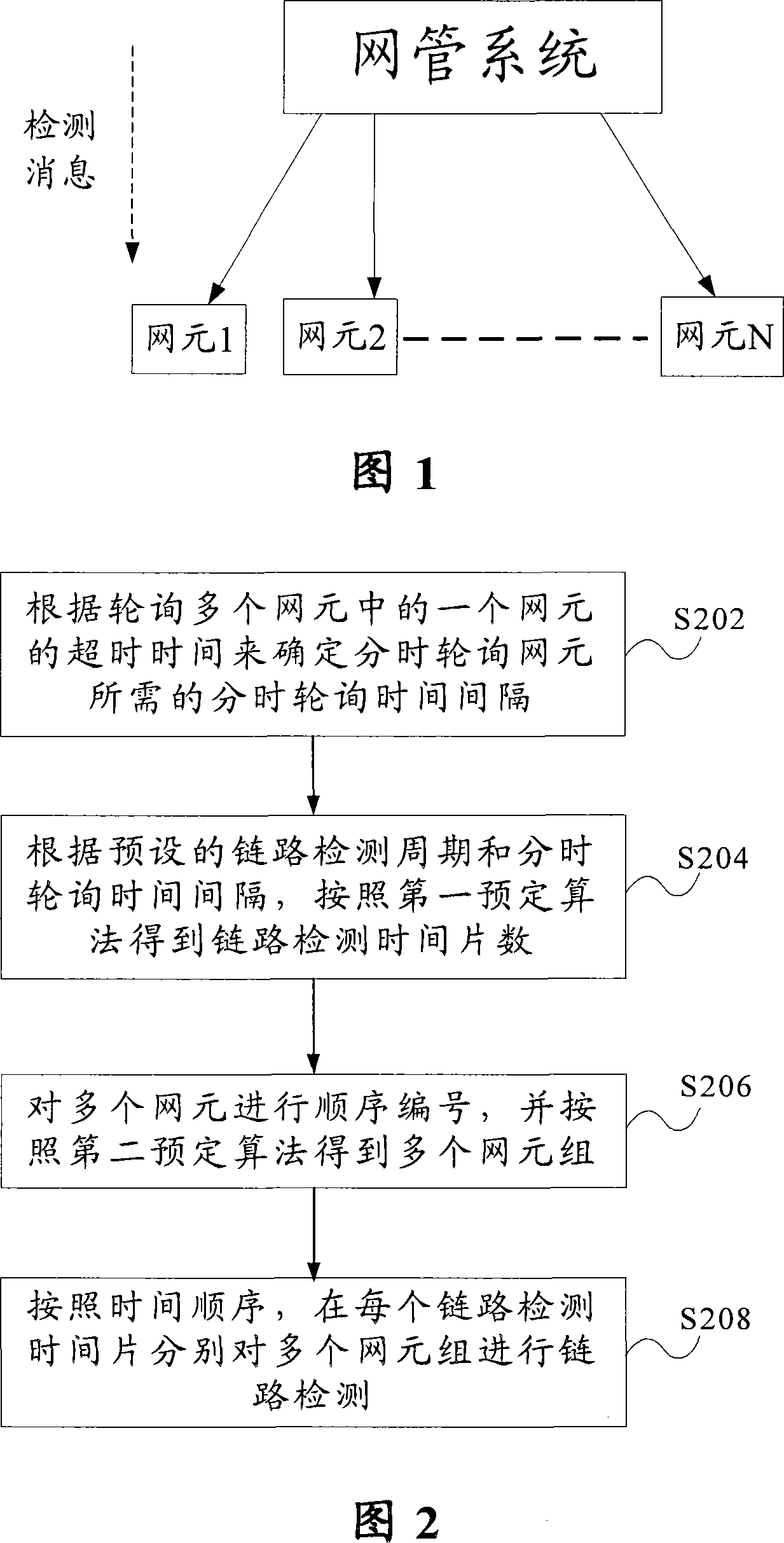

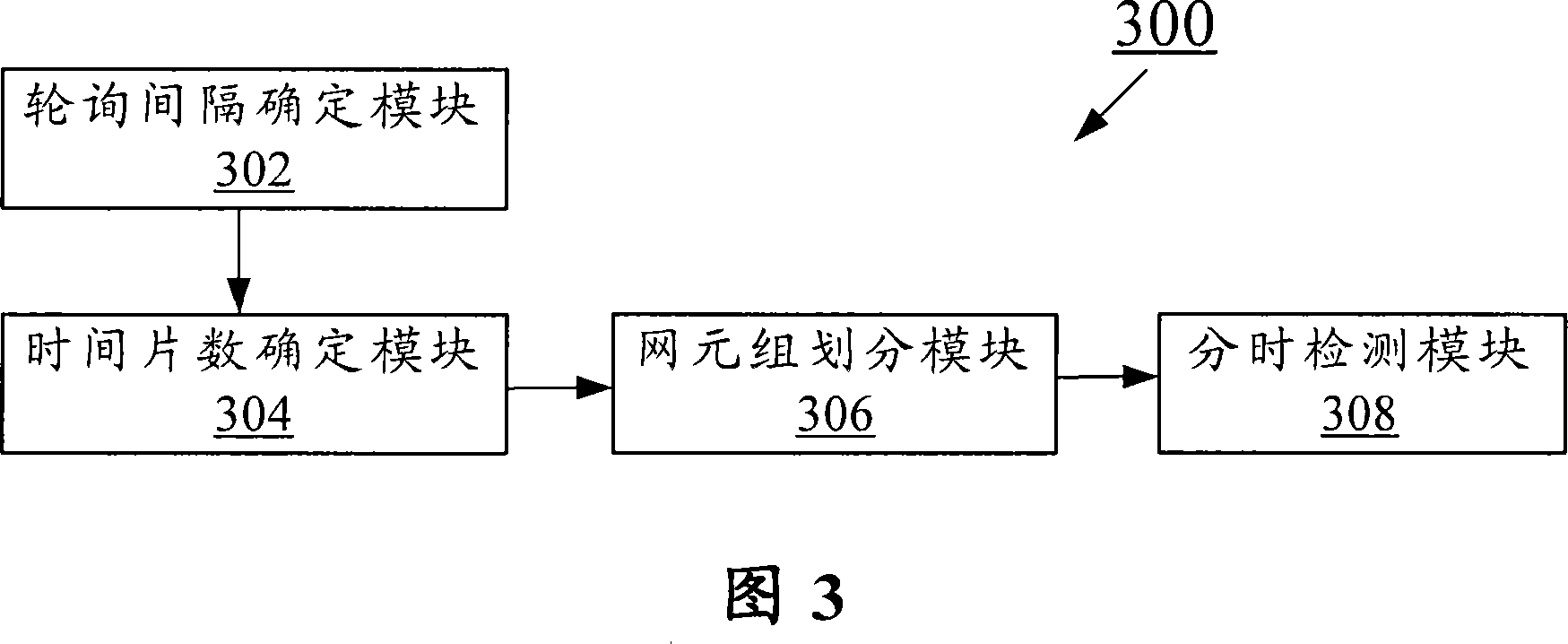

Network element link time-sharing detecting method and device

The invention provides a method and a device for net element link time-sharing detection, wherein, the method includes the following steps: step one, an interval of a time-sharing polling period required by a time-sharing polling net element is determined based on the time out period of one net element in a plurality of polled net elements; step two, a number of link detection time slices can be received according to a first predetermined algorithm, based on predetermined link detection period and time-sharing polling period interval; step three, a plurality of net elements are numbered in sequence, and a plurality of net element groups are obtained based on a second predetermined algorithm; and step four, a plurality of net element groups are respectively processed with a link detection in each link detection time slice according to a time sequence. Therefore, the net element link detection can be executed with balanced load in the whole network management running process by adopting the invention, thereby not only guaranteeing detections of all links can be completed within a specified period, but also detecting that resources required by the net element link are basically balanced in the whole period of network management running period.

Owner:ZTE CORP

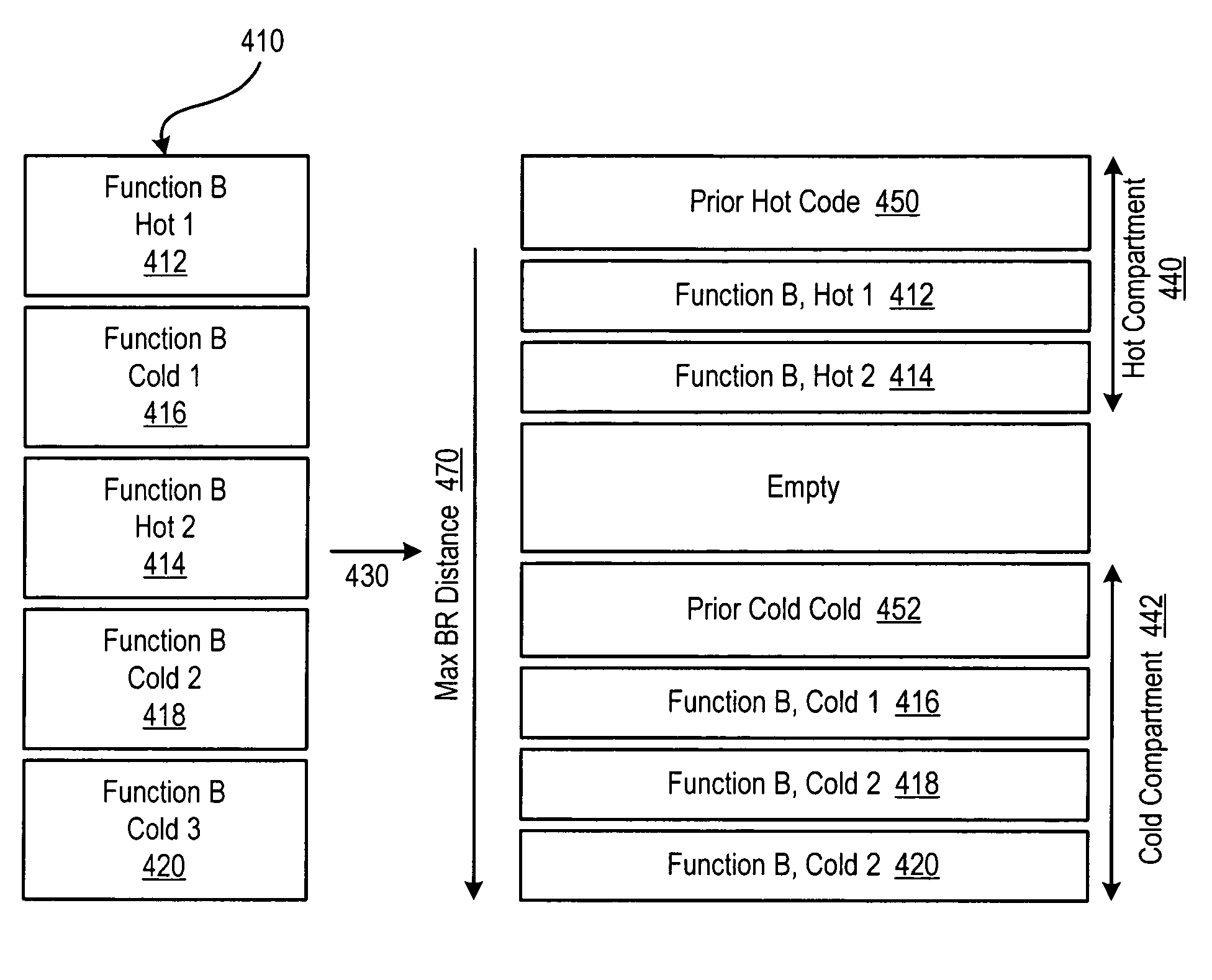

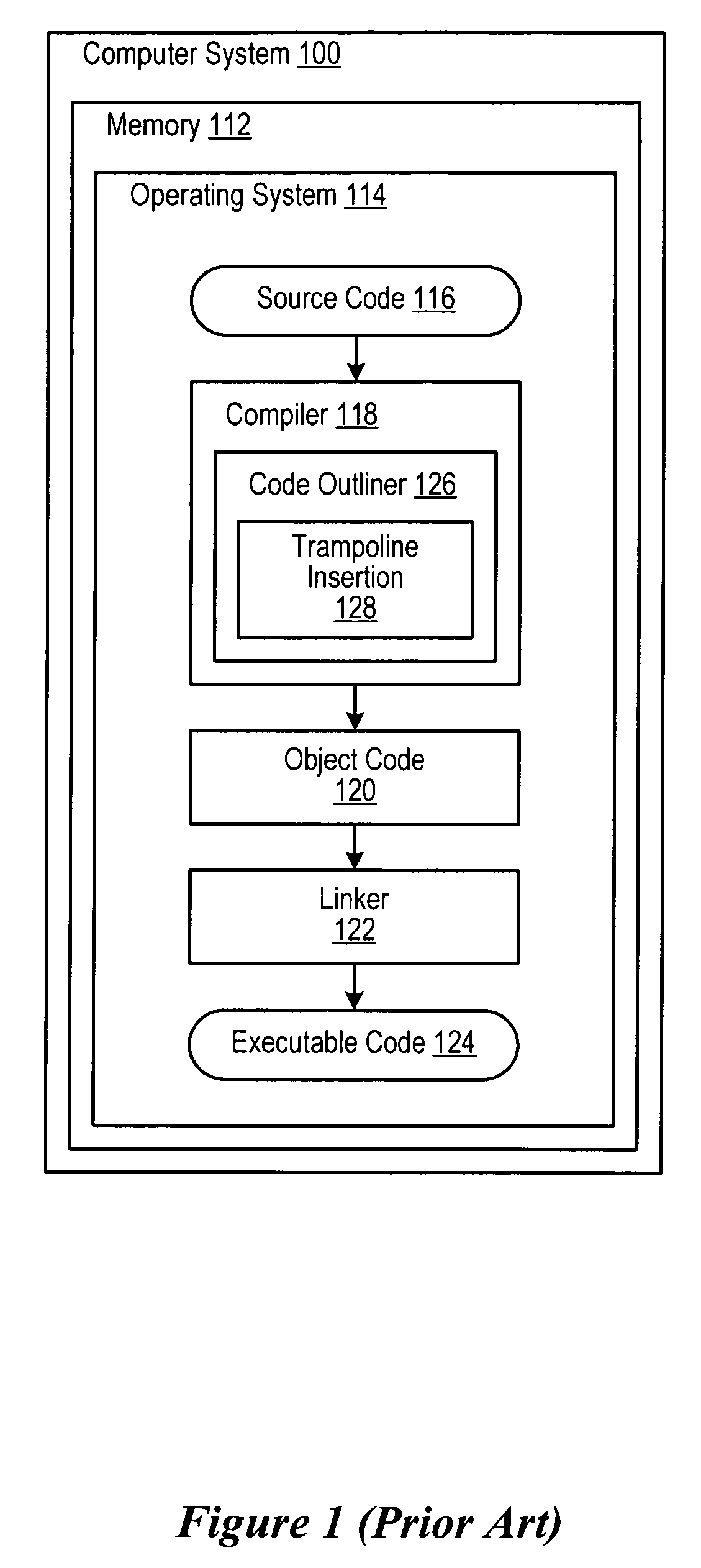

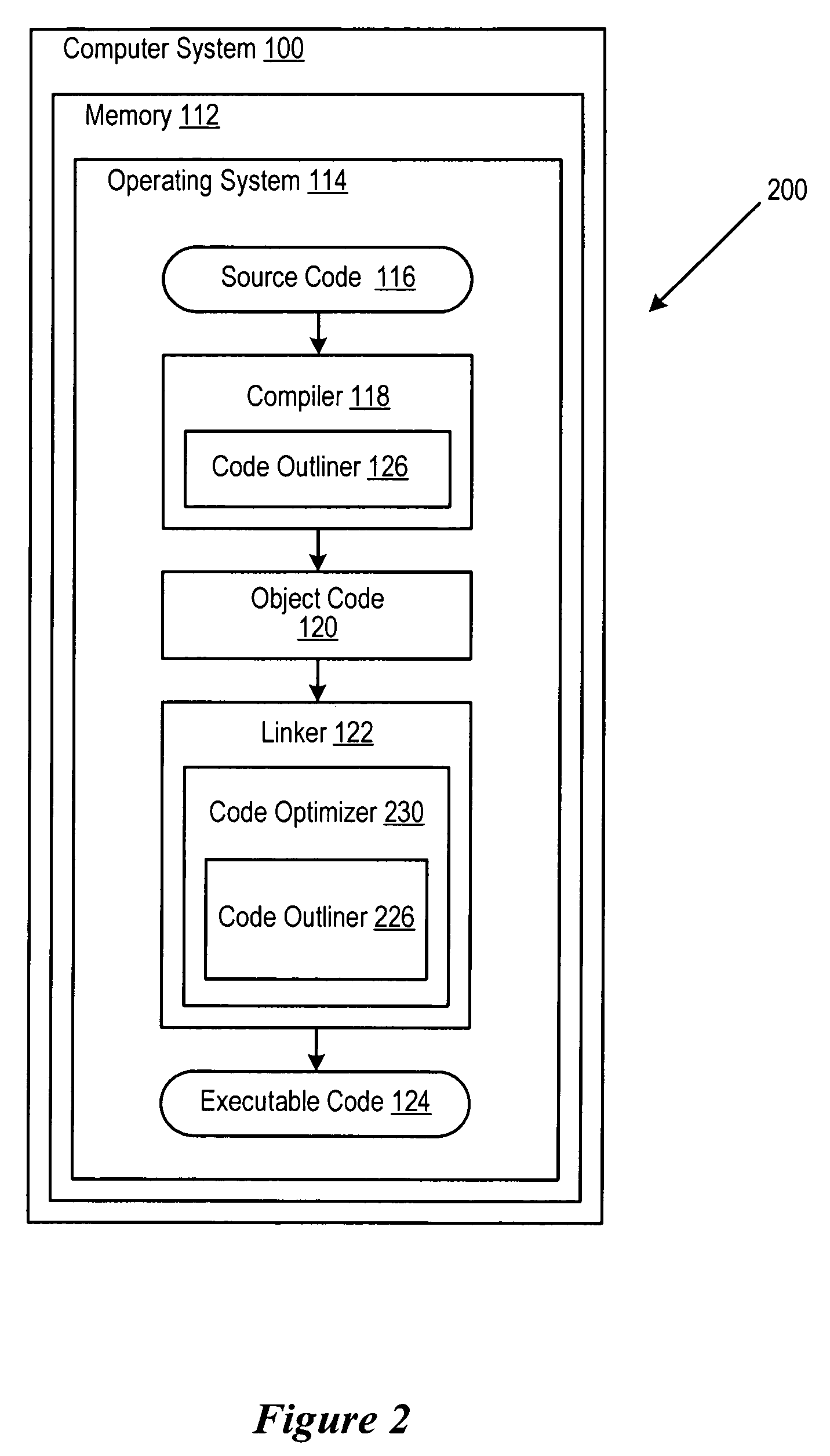

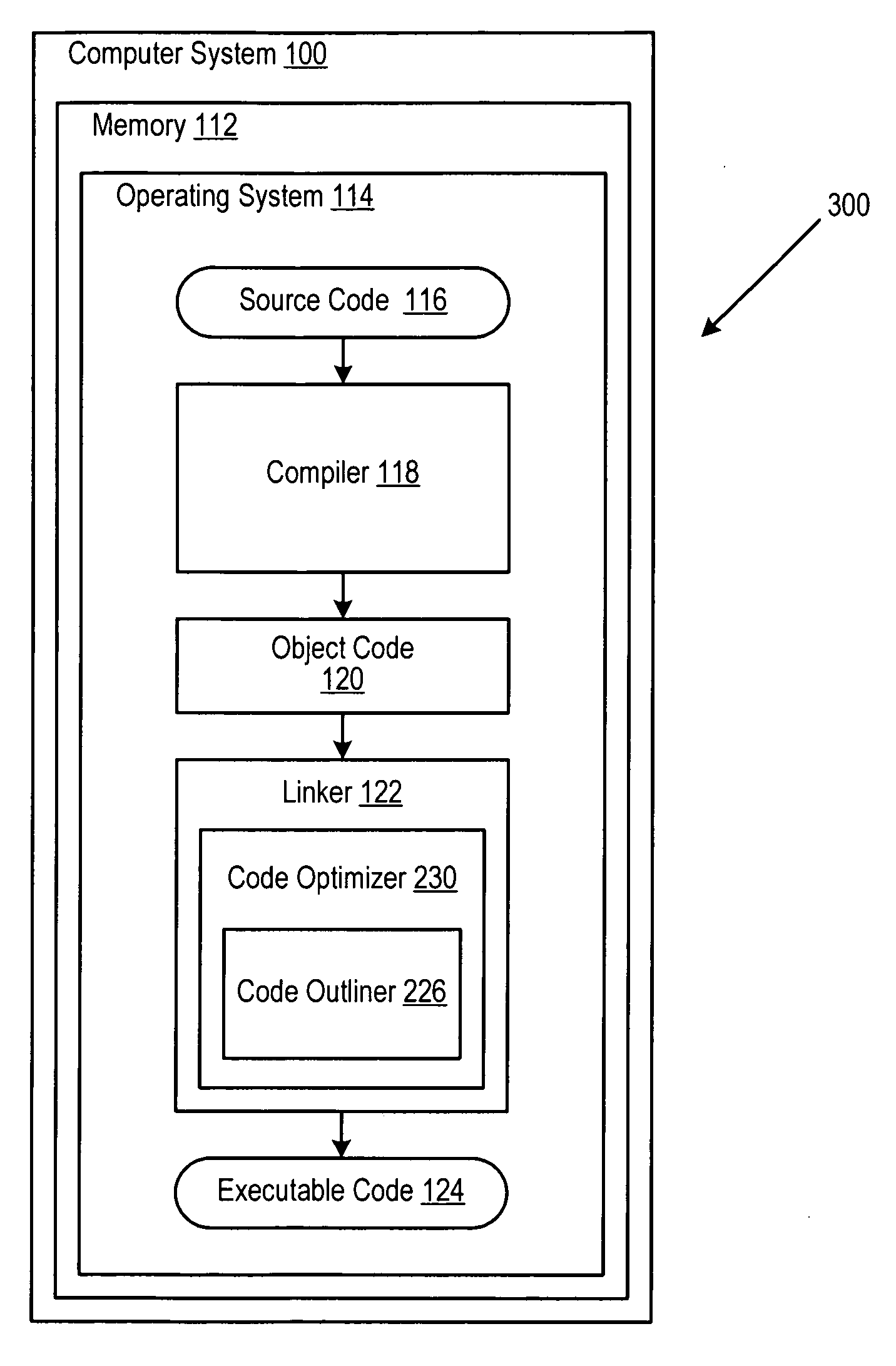

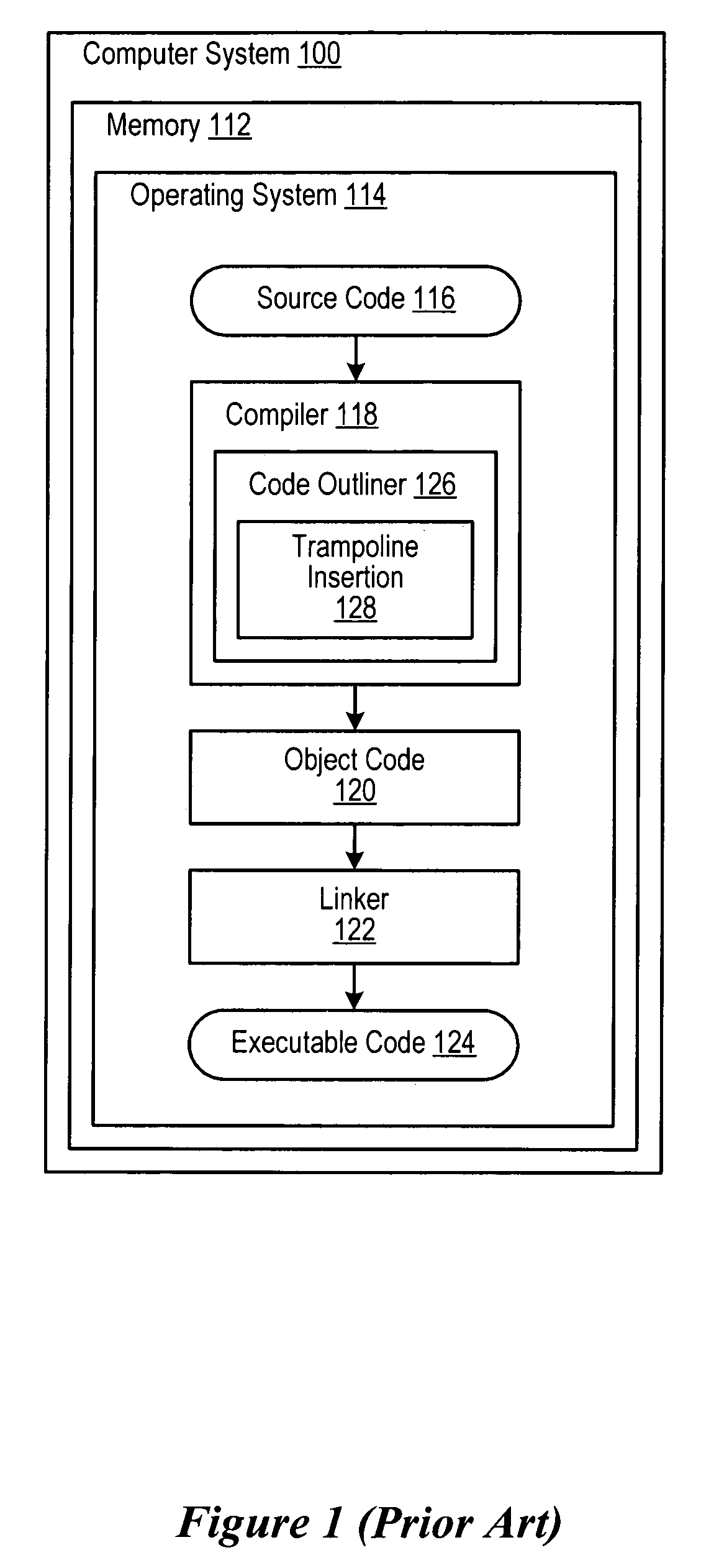

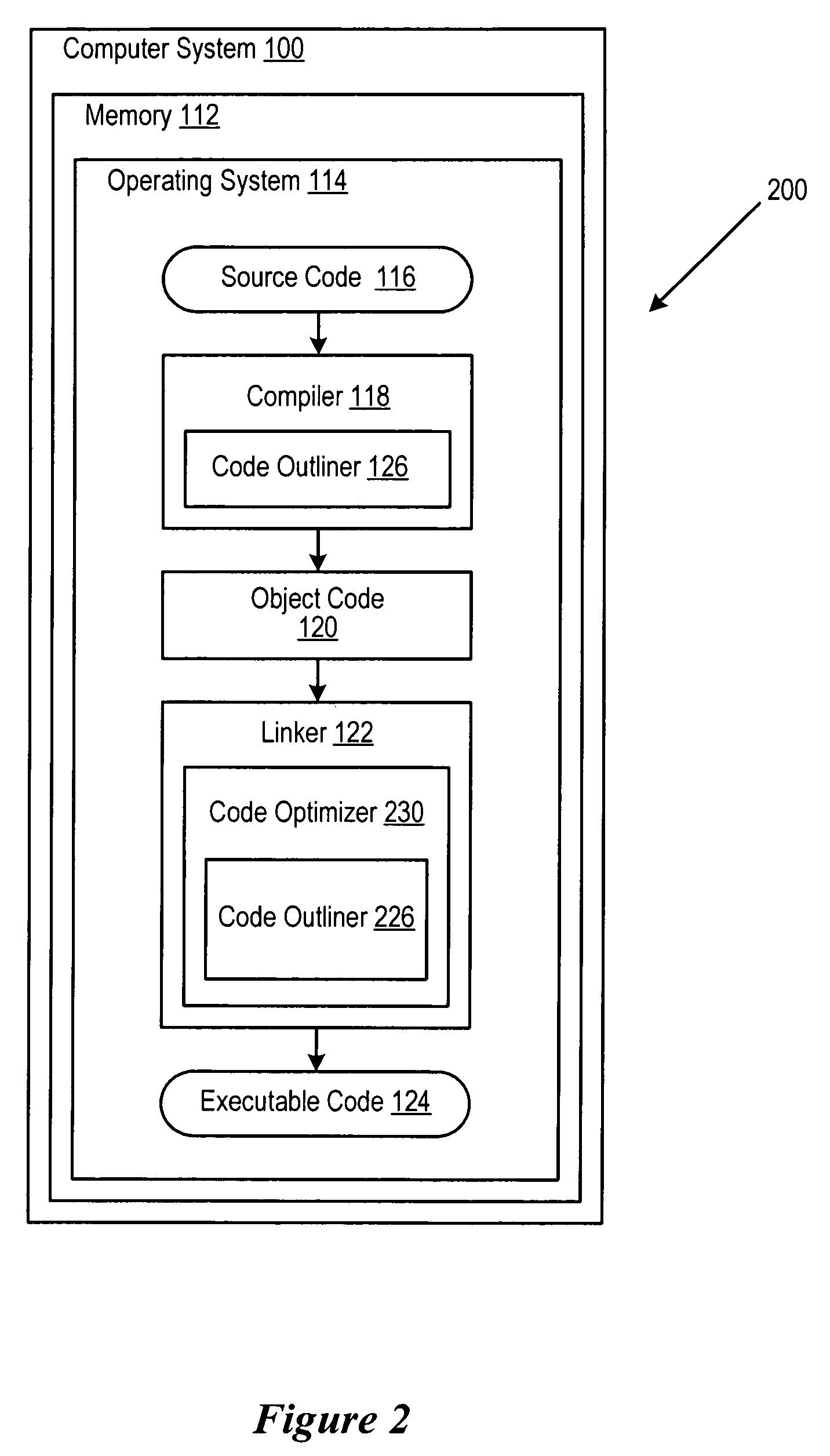

Code outlining without trampolines

ActiveUS7735074B2Optimal code layoutImprove localitySoftware engineeringSpecific program execution arrangementsCoding blockParallel computing

A system and method for optimizing compiler performance including outlining cold code at link time, rather than compile time, such that trampolines are not required. Branch instructions connecting a hot block to a cold block can be converted from a short branch distance limit to a longer branch distance limit, further optimizing code performance. Editors, implementing a plurality of windows that can be maintained for each function, can display the maximum distance that code blocks can be safely outlined. Other implementations allow the optimal placement of code that is significantly greater in size than the maximum possible branch distance.

Owner:ORACLE INT CORP

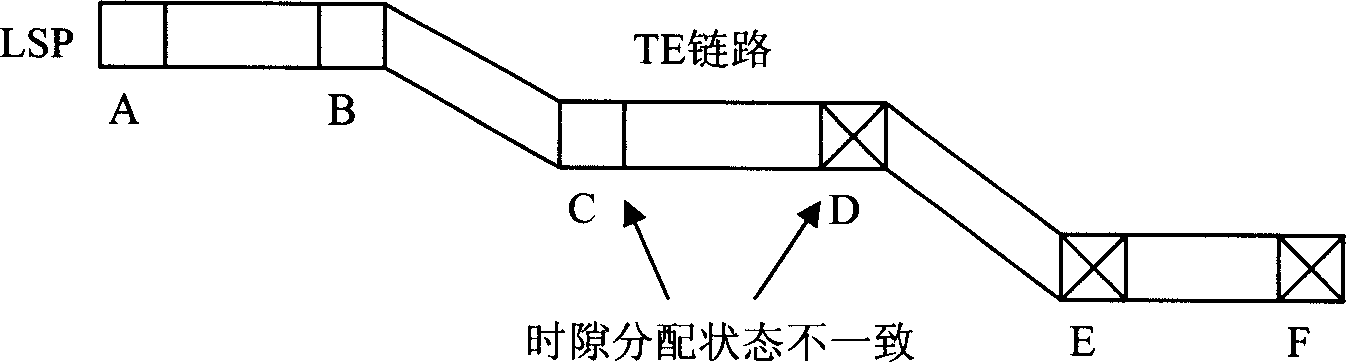

Method for checking flow engineering link time slot state consistency

ActiveCN1859371AEnhanced connection survivabilityTime-division multiplexTransmissionNetwork connectionSoftware engineering

Present invention relates to a flow rate engineering link time slot state consistency check method. It contains A, transmitting end transmitting time slot state check request message contain relevant flow rate engineering link local side time slot state object to receiving end; B, receiving end receiving said message, comparing and checking relevant flow rate engineering link transmitting end time slot state object with local side time slot state object, notifying check result and opposite terminal time slot state object to local side link explorer to make process. The present invention can make regular detection to flow rate engineering link time slot state consistency, in time finding inconsistency abnormal situation, enhancing automatic exchange optical network connection viability.

Owner:HUAWEI TECH CO LTD

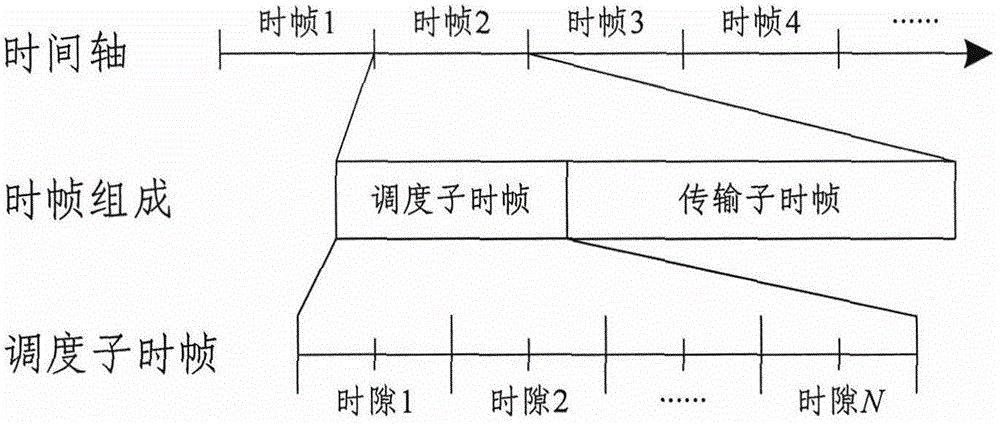

Directional time-division link scheduling method applicable to wireless mesh network

InactiveCN105744641AGood throughput performanceTime-division multiplexWireless communicationWireless mesh networkDirectional antenna

The invention discloses a directional time-division link scheduling method applicable to a wireless mesh network. First, conflict sets of links in a network are defined under the condition of a directional antenna. Then, the time axes of the nodes in the entire network are synchronously divided into a series of continuous time frames of fixed length, each time frame is further divided into a scheduling sub time frame and a transmission sub time frame, and the scheduling sub time frame is composed of a plurality of scheduling time slots. On the basis, all the transmission links in the network are allocated to specific scheduling time slots through a link time slot allocation method according to the conflict set of each link in the network. The nodes complete link transmission scheduling through channel listening in the scheduling sub time frames, and the links after transmission scheduling transmit data in parallel in the transmission sub time frames. Meanwhile, on the basis of the link time slot allocation result, the scheduling time slots are rotated periodically to provide fairness guarantee for the transmission links in the network. The simulation result in an EXata simulation environment proves the effectiveness of the method.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

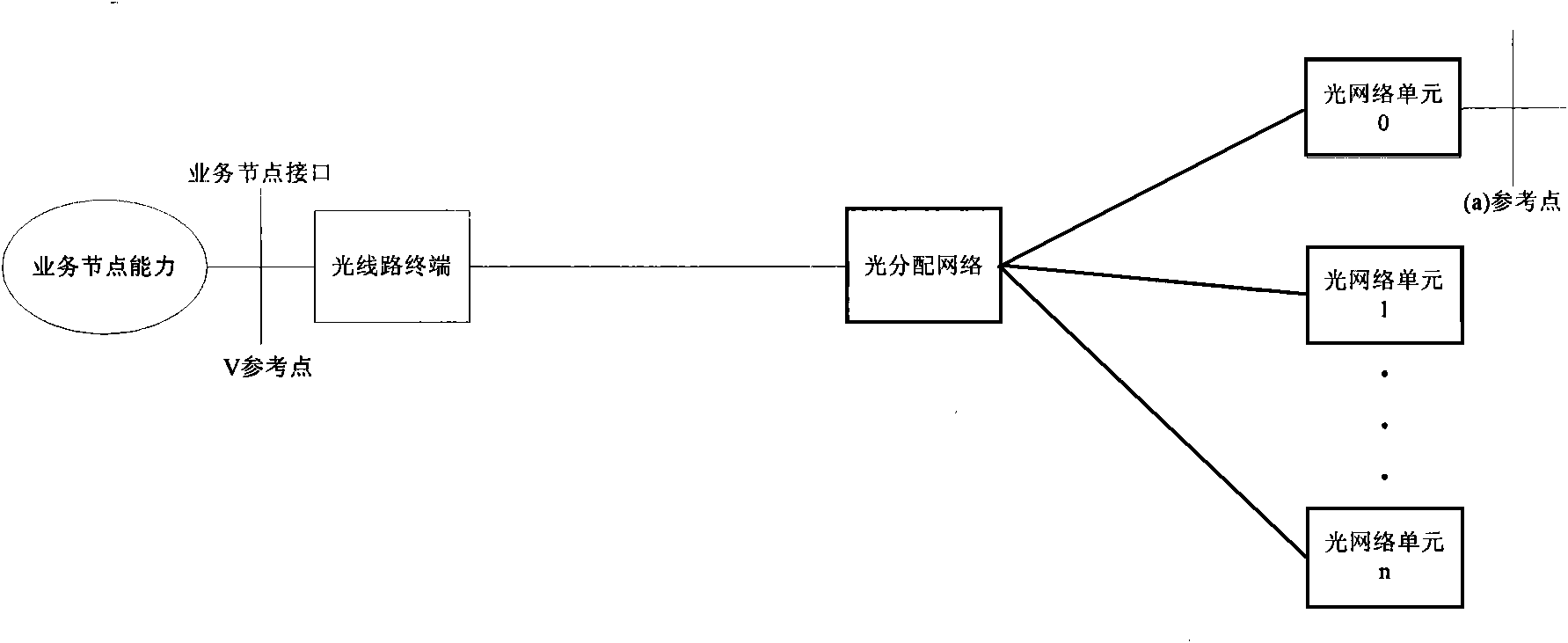

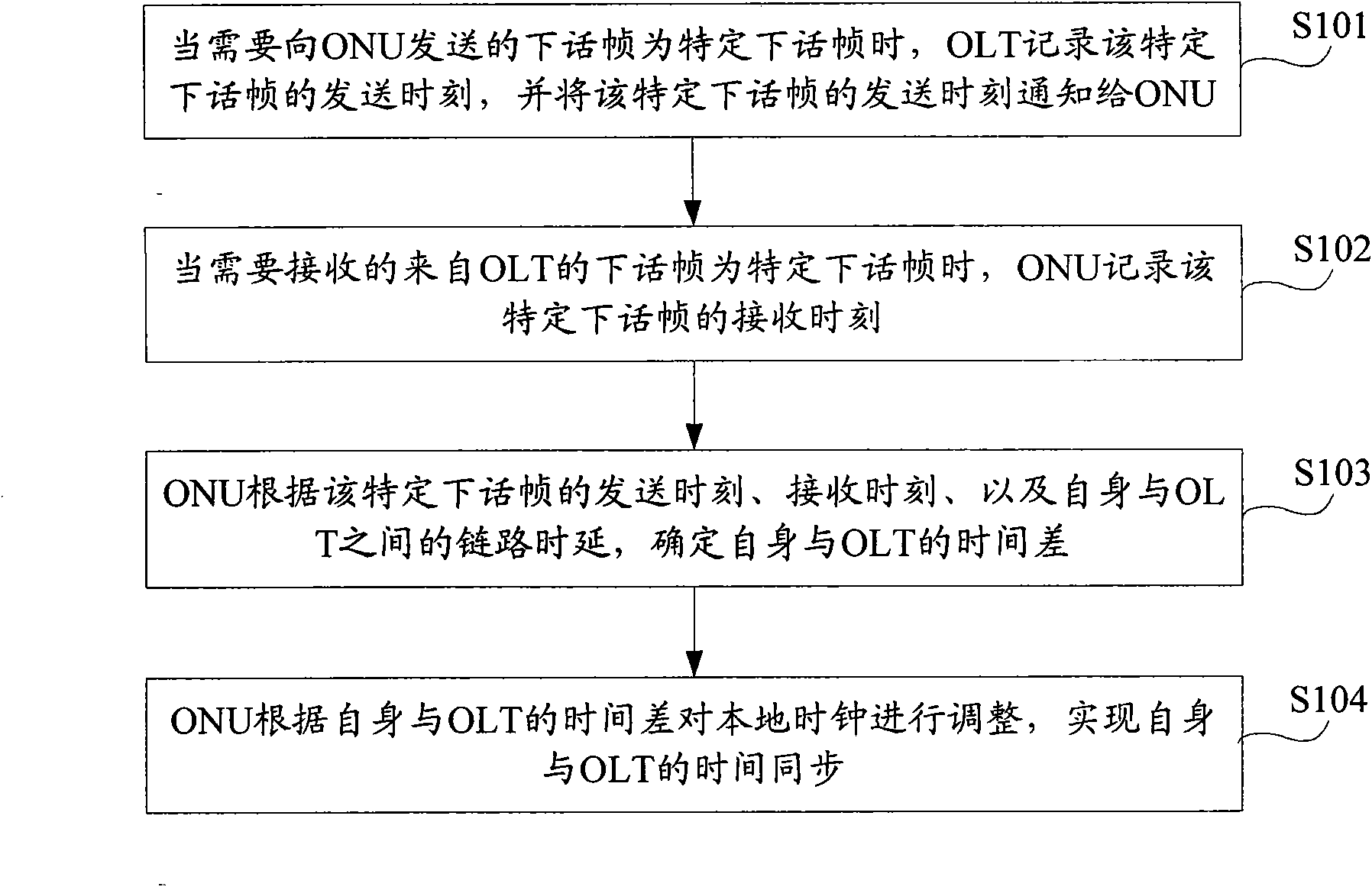

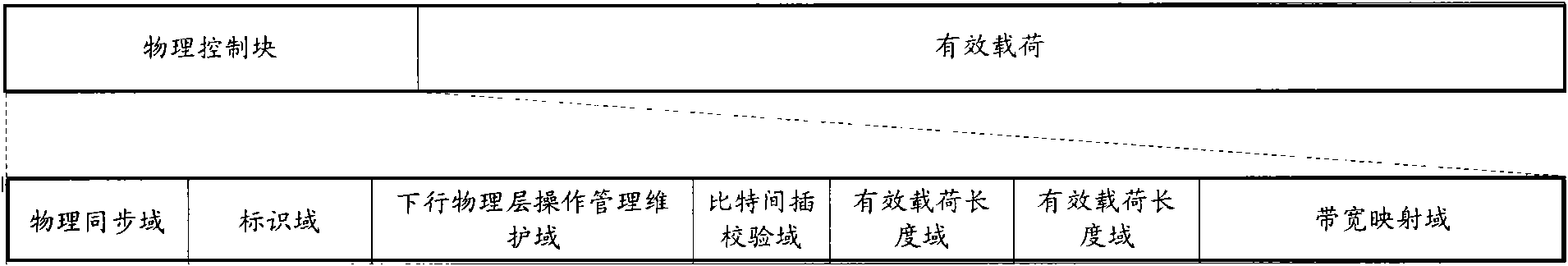

Method and system for realizing time synchronization

InactiveCN101945305ATime synchronizationMultiplex system selection arrangementsTime-division multiplexOptical network unitTime difference

The invention discloses a method and a system for realizing time synchronization, which are used for realizing the time synchronization of an optical network unit ONU and an optical line terminal OLT in a GPON system. The method for realizing the time synchronization comprises the following steps that: when a lower voice frame which is needed to be sent to the ONU is a specific lower voice frame, the OLT records the sending moment of the specific lower voice frame and informs the ONU of the sending moment of the specific lower voice frame; when a lower voice frame which is needed to be received and is from the OLT is a specific lower voice frame, the ONU records the receiving moment of the specific lower voice frame; and the ONU determines the time difference of the ONU and the OLT according to the sending moment and the receiving moment of the specific lower voice frame and the link time delay of the ONU and the OLT, and adjusts a local clock according to the time difference to realize the time synchronization of the ONU and the OLT.

Owner:DATANG MOBILE COMM EQUIP CO LTD

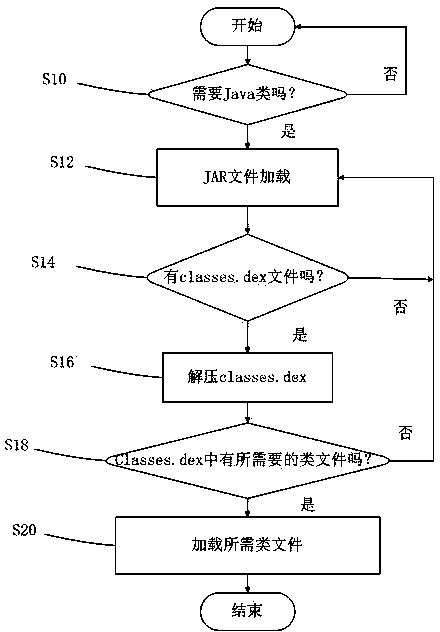

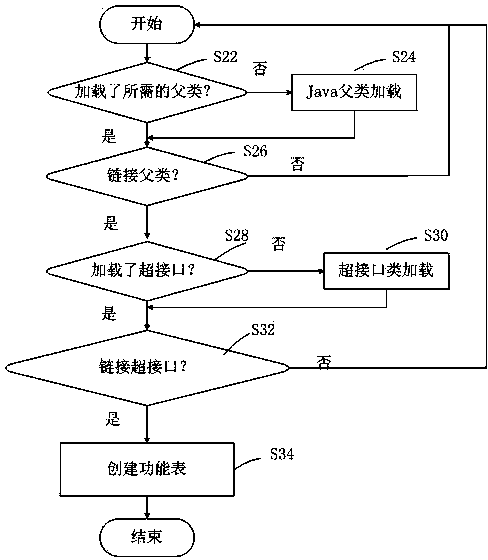

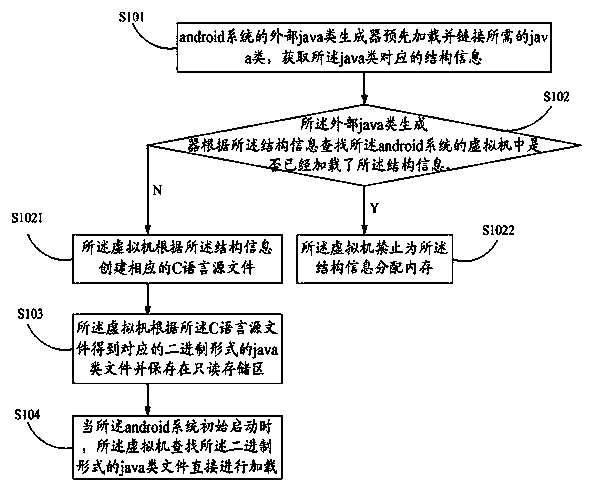

Method and system for loading java class on virtual machine of android system

InactiveCN103473096AReduce initial startup timeImprove execution efficiencyProgram loading/initiatingJava class fileStructure of Management Information

The invention discloses a method and a system for loading java class on a virtual machine of an android system. The method comprises the following steps that an external java class generator of the android system pre-loads and links required java class, and structural information corresponding to the java class is obtained; the external java class generator looks up the loading situation of the structural information in the virtual machine of the android system according to the structural information, if the structural information is loaded in the virtual machine, the virtual machine forbids memory allocation for the structural information, and if the structural information is not loaded in the virtual machine, the virtual machine establishes a corresponding C-language source file according to the structural information; the virtual machine obtains a corresponding binary-form java class file according to the C-language source file and saving the binary-form java class file in a read-only memory area; when the android system is started initially, the virtual machine looks up the binary-form java class file and performs direct loading. The java class in the virtual machine is pre-generated and memorized in a read-only memory (ROM) for usage, the loading and linking time of the java class in the virtual machine is shortened, and the execution efficiency of android programs can be improved.

Owner:ZHEJIANG UNIV CITY COLLEGE

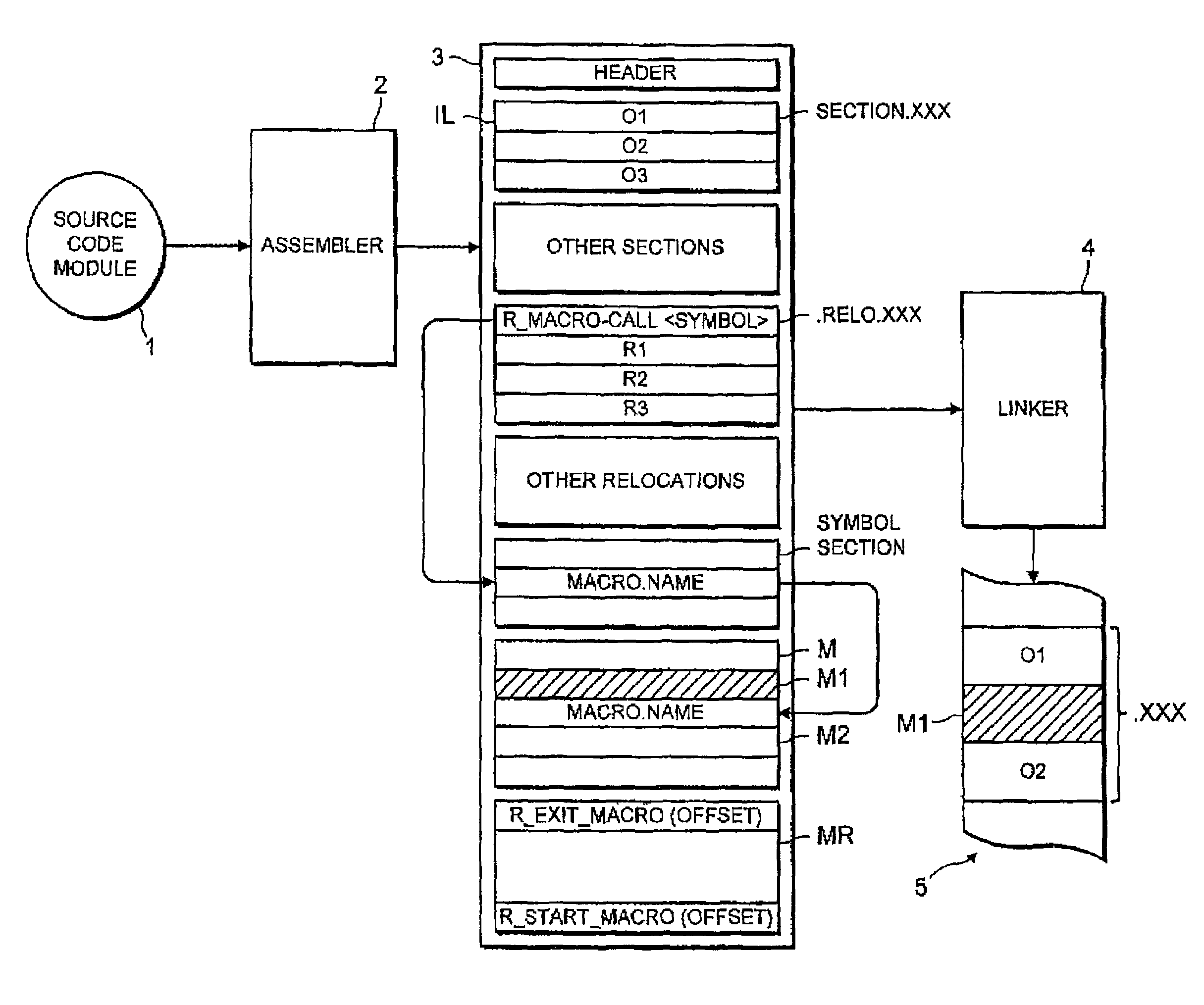

Method, apparatus and article for generation of debugging information

InactiveUS7353508B2Easy to codeEconomical in spaceLink editingProgram loading/initiatingParallel computingLink time

Call frame information is used by debugging software. It records how to restore the parent stack frame at any point during execution of a program. It is normally generated during compilation and stored in the executable in a compressed format, consisting of sequences of instructions that describe how the current call frame changes during execution of each function. Described herein is a means of generating call frame information at link time, using linker macro calls generated by a small set of assembler macros.

Owner:STMICROELECTRONICS LTD

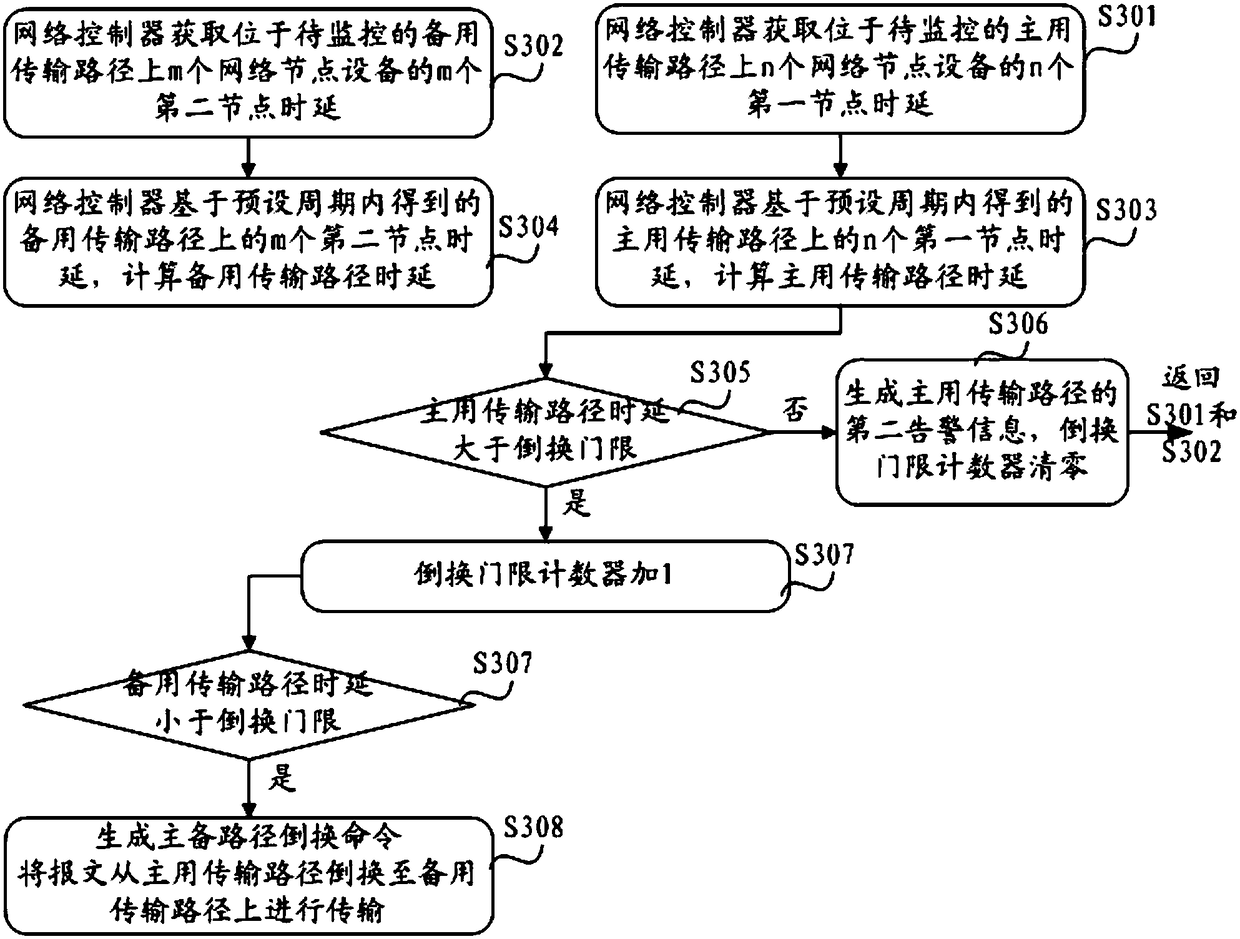

Transmission path control method based on time delay, network controller and system

The invention discloses a transmission path control method based on time delay, a network controller and a system. The application provides a transmission path control method, device and system basedon time delay. The method includes the following steps: acquiring the equipment time delay of each network node equipment on a primary transmission path and a standby transmission path, acquiring thelink time delay between each network node equipment, and calculating the time delay of the primary transmission path and the time delay of the standby transmission path based on the respective equipment time delay and link time delay; and then, based on a switching mechanism of time delay decisions, when the time delay of the primary transmission path is greater than a switching threshold and thetime delay of the standby transmission path is less than the switching threshold, generating a primary and standby path switching command, and switching a message from the primary transmission path tothe standby transmission path for transmission based on the primary and standby path switching command. Thereby, the scheme of the invention can provide protection for the transmission path of time delay sensitive services and ensure the service requirements of the service transmission path for the time delay.

Owner:HUAWEI TECH CO LTD

Code outlining without trampolines

ActiveUS20070089106A1Optimal code layoutBetter cache localitySoftware engineeringSpecific program execution arrangementsCoding blockParallel computing

A system and method for optimizing compiler performance including outlining cold code at link time, rather than compile time, such that trampolines are not required. Branch instructions connecting a hot block to a cold block can be converted from a short branch distance limit to a longer branch distance limit, further optimizing code performance. Editors, implementing a plurality of windows that can be maintained for each function, can display the maximum distance that code blocks can be safely outlined. Other implementations allow the optimal placement of code that is significantly greater in size than the maximum possible branch distance.

Owner:ORACLE INT CORP

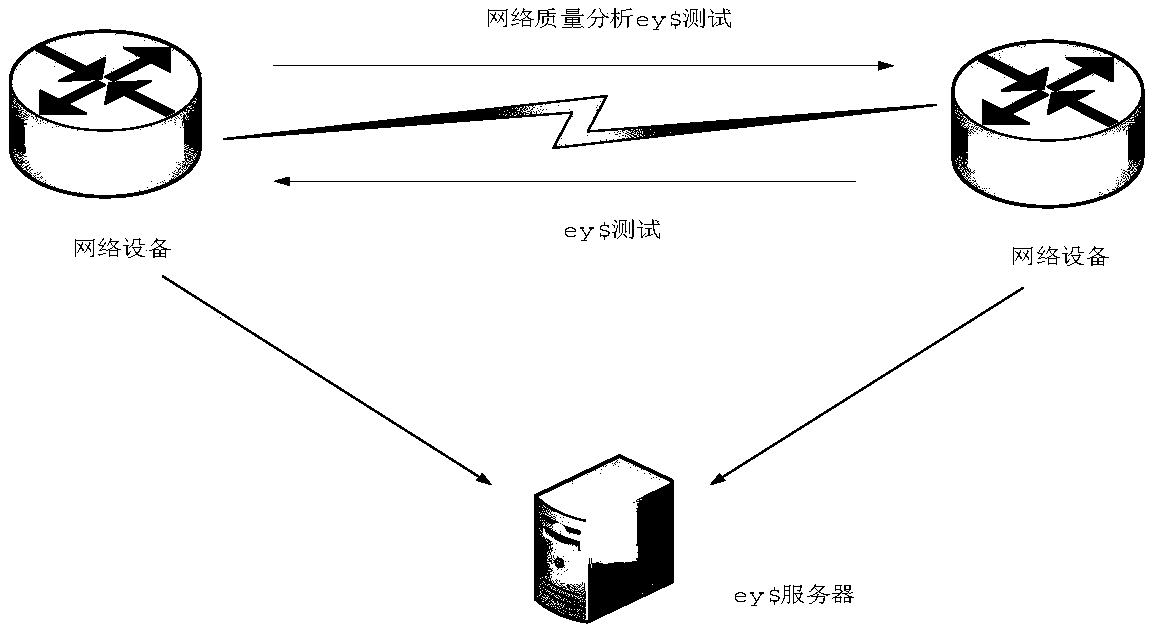

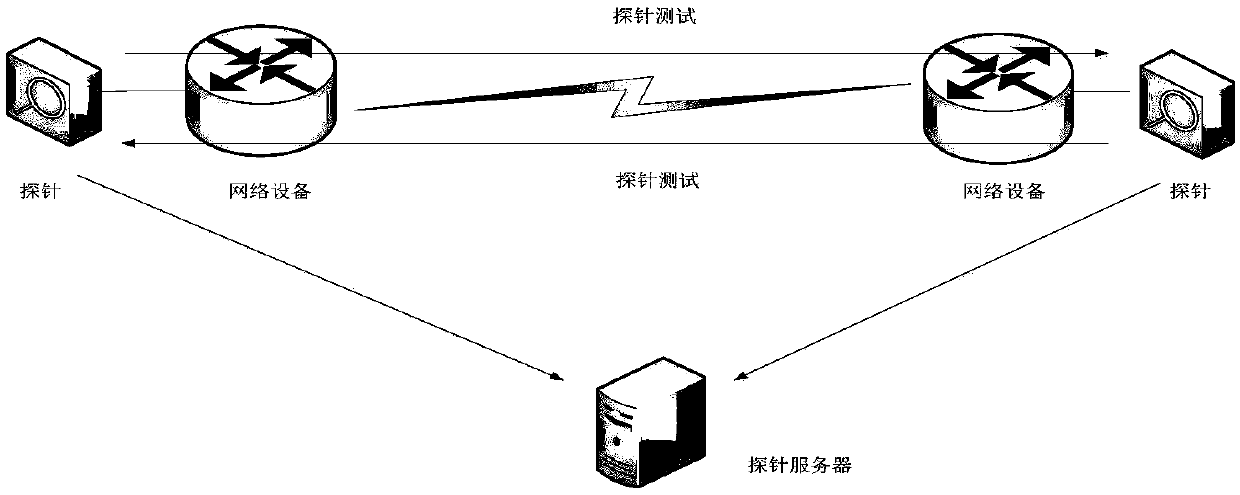

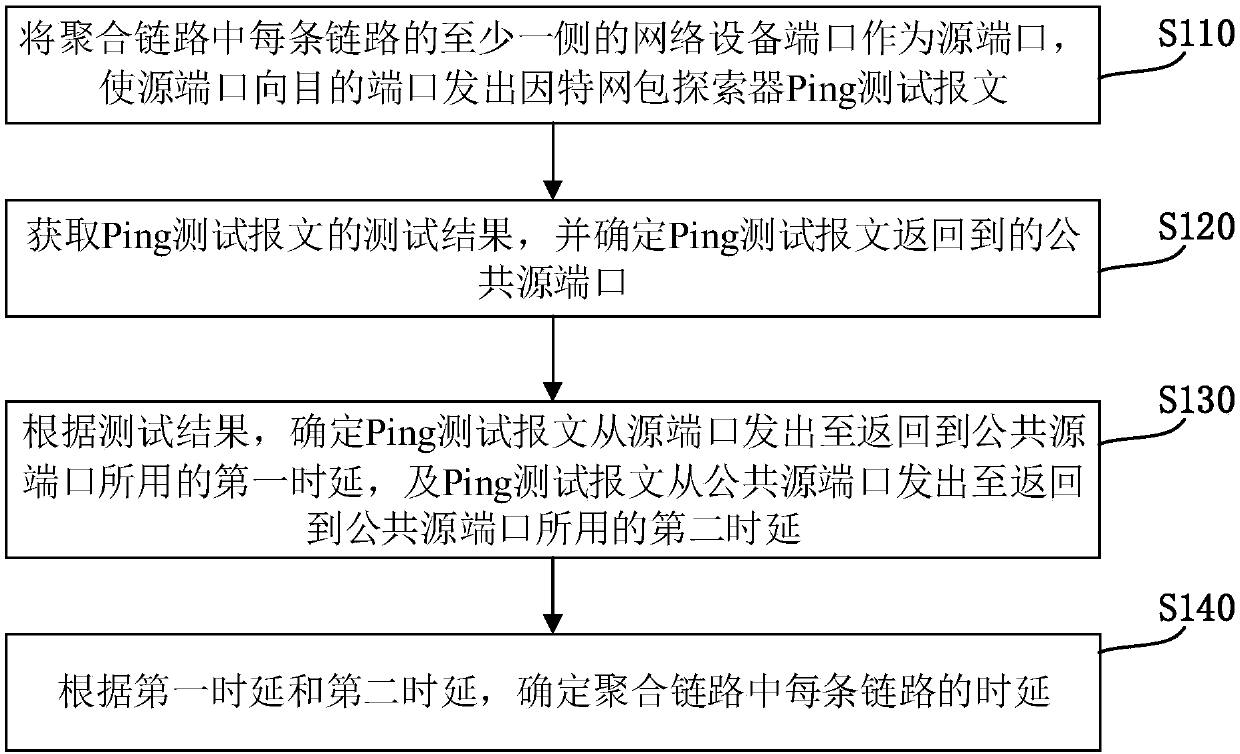

Link time delay detection method and device, equipment and medium

The invention discloses a link time delay detection method and device, equipment and a medium. The method comprises the following steps: taking a network equipment port on at least one side of each link in an aggregation link as a source port, and enabling the source port to send an Internet packet explorer Ping test message to a destination port; obtaining a test result of the Ping test message,and determining a common source port to which the Ping test message returns; according to the test result, determining a first time delay from sending of the Ping test message from the source port toreturning to the public source port and a second time delay from sending of the Ping test message from the public source port to returning to the public source port; and determining the time delay ofeach link in the aggregated link according to the first time delay and the second time delay. According to the embodiment of the invention, the time delay of each link in the aggregated link can be detected.

Owner:LIAONING MOBILE COMM +1

Signaling data acquisition single link time delay correction method

ActiveCN102307109AImprove accuracyImprove reliabilityData switching networksWireless communicationTime delaysAcquisition time

In order to solve problems that in the prior art reliability of a signaling data acquisition time delay processing method is poor, the method depends on experience and intuition, efficiency and quality are hard to guarantee and the like in a signaling data acquisition system, the invention provides a signaling data acquisition single link time delay correction method. According to the method in the invention, through determining whether signaling data acquisition point arrival order of request and response messages has an error or not, whether signaling data acquisition generates time delay or not is determined, link average time delay correction is employed to adjust an acquisition time adjusting module of an acquisition machine, each side data acquisition point of a single link signaling data acquisition point is subjected to time delay correction to realize bidirectional time delay correction of a single link signaling data acquisition point pair, accuracy and reliability of signaling data acquisition time delay correction are effectively raised, correctness of subsequent signaling analysis and processing are ensured, and obtainment of a correct signaling flow is ensured.

Owner:重庆华沐网络科技有限公司

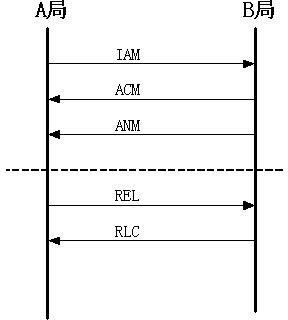

Cloning programming code

Techniques for cloning programming code are disclosed. In an embodiment, the cloned code is in the form of functions in the C language. Further, in a method embodiment, a clone of a function is invoked, and information mapping the clone to the function is generated. At link time, if no function body of the clone is accessible by a linker, then the linker uses information mapping the clone to the function to satisfy a linker's requirement. At load time, if no function body of the clone is accessible by a loader, then the loader, based on the mapping information, allows selection of a body of the function. However, if the body function of the clone is accessible by the loader, then the loader allows selection of the body of the clone.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

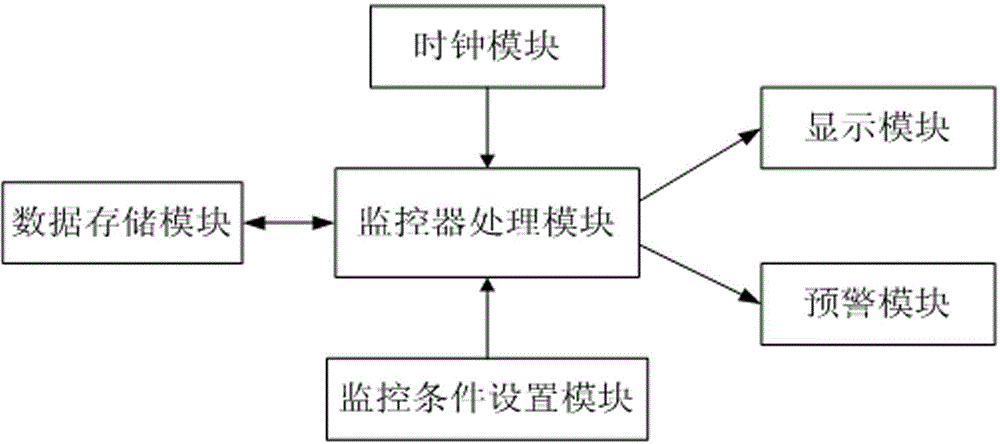

Business expansion controllable link time limit monitor and processing method

InactiveCN104881799AAvoid situations such as overdueTimely processingMarketingTime conditionComputer science

The invention relates to a business expansion controllable link time limit monitor and a processing method in an electric power marketing business application system. The business expansion controllable link time limit monitor comprises a monitor processing module, a data storage module, a clock module, a monitoring condition setting module, a display module and an early warning module, wherein the monitor processing module is connected with the data storage module, the clock module, the monitoring condition setting module, the display module and the early warning module. According to the invention, analysis is carried out on the whole business expansion process, and acquired relevant unit conditions are more visual and fairer. Time conditions and expiration warning of each business expansion process are absolutely clear, timeliness of data monitoring is achieved, and the inspection period is shortened. The business expansion controllable link time limit monitor is simple to operate, can monitor each controllable node of the business expansion process directly, and avoids stagnation in promotion of the work caused by personnel variations or business trips.

Owner:PANJIN POWER SUPPLY COMPANY OF STATE GRID LIAONING ELECTRIC POWER SUPPLY +1

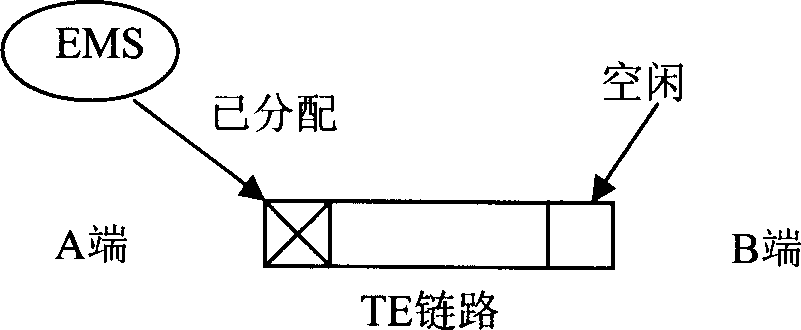

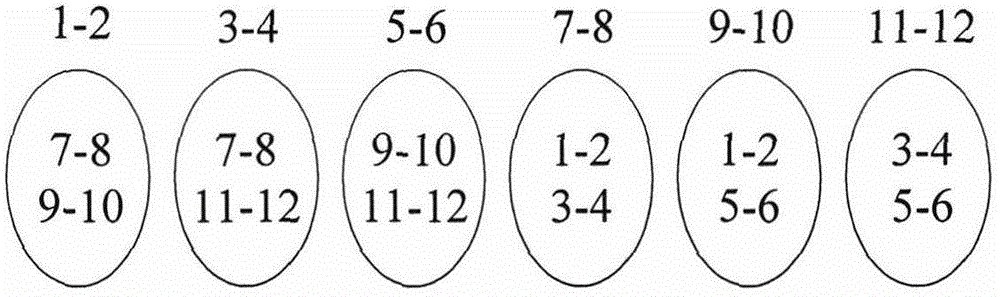

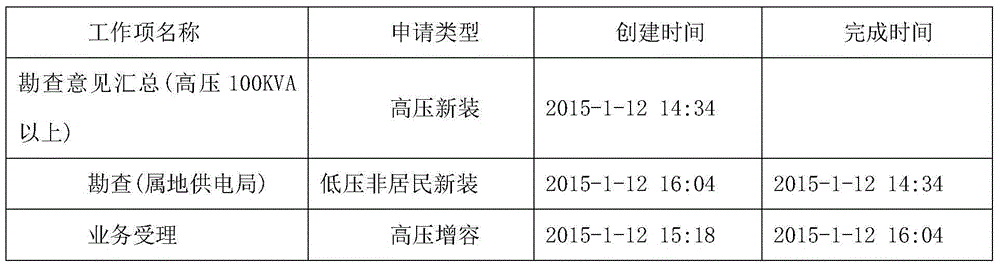

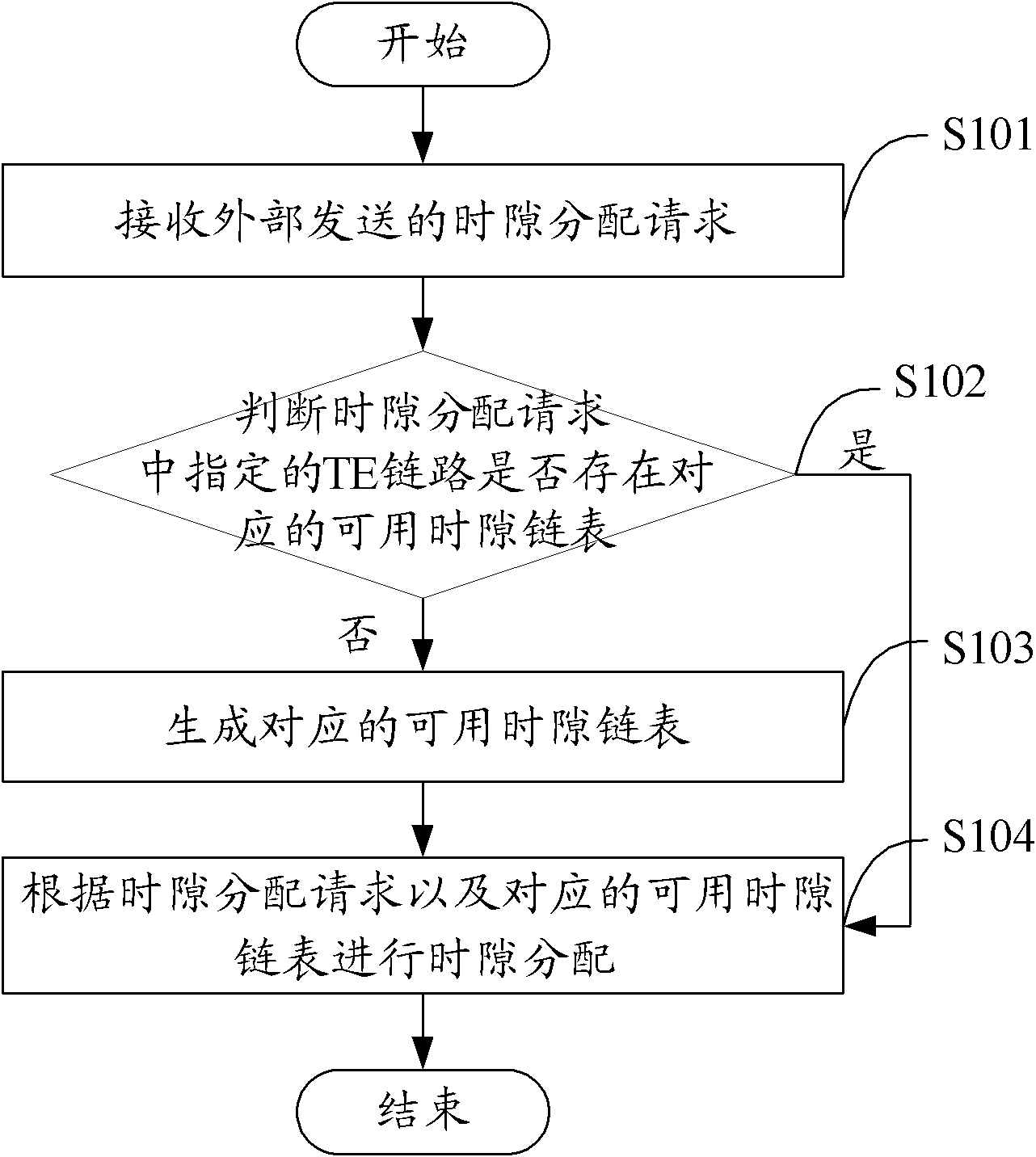

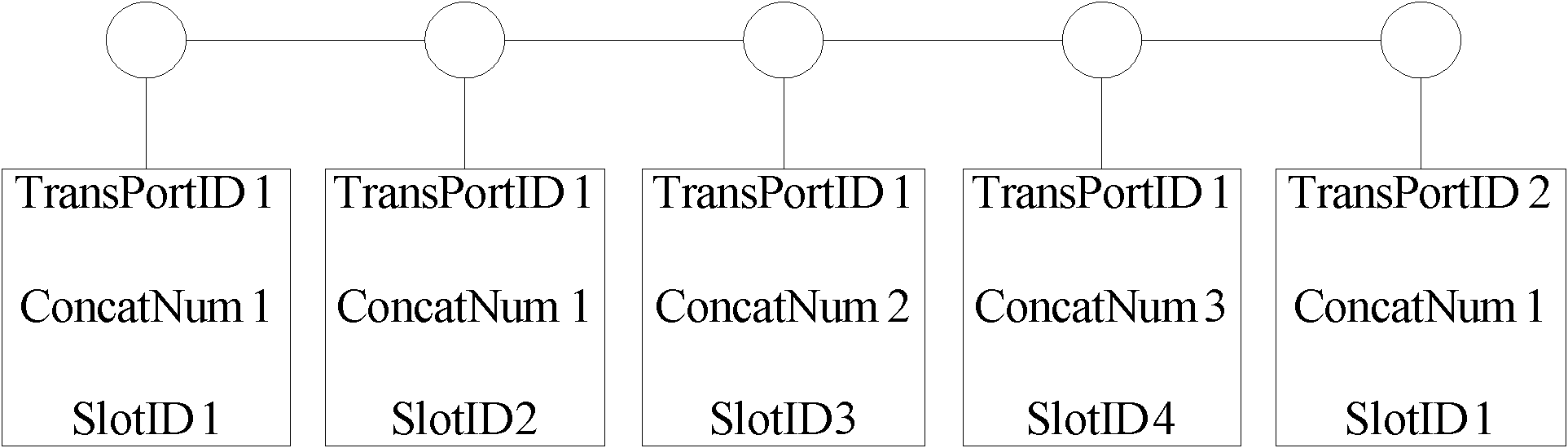

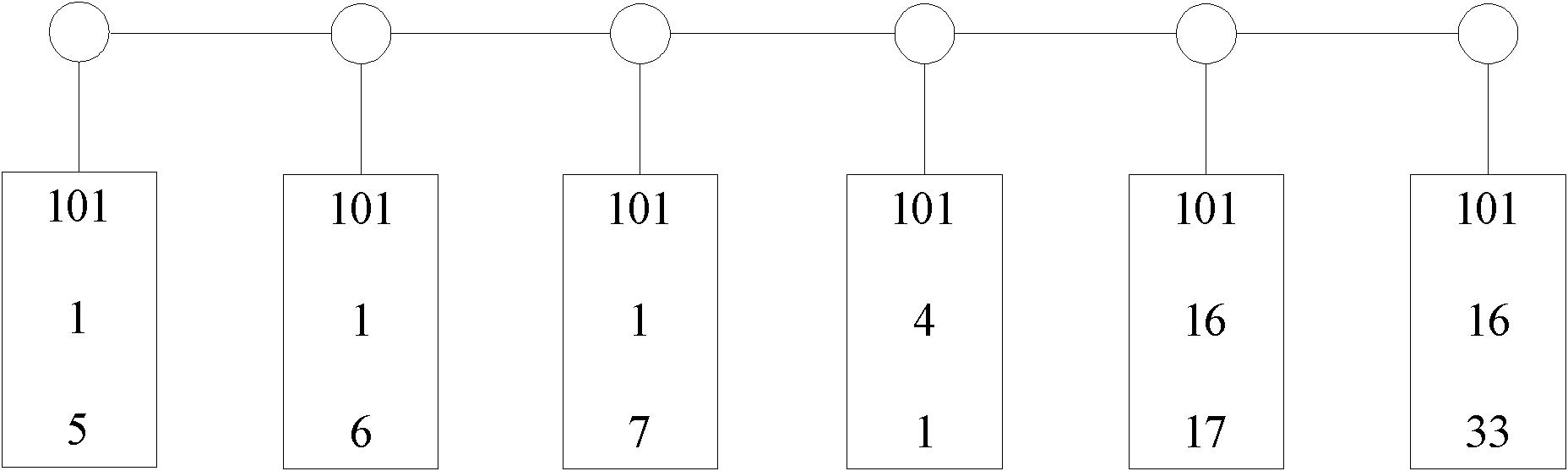

Time slot distribution management method and apparatus thereof

ActiveCN102487303AGuaranteed carrying capacitySolve the problem of time slot allocationTime-division multiplexData switching networksLarge particleLinked list

The invention relates to a time slot distribution management method and an apparatus thereof. The method comprises the following steps: receiving an externally transmitted time slot distribution request; determining whether an appointed TE link has an available time slot list in the time slot distribution request; if the appointed TE link does not have the available time slot list, generating the corresponding available time slot list; carrying out time slot distribution according to the time slot distribution request and the corresponding available time slot list. In the invention, when the TE link is generated or the time slot distribution request is arrived, the corresponding available time slot list is generated. During a subsequent time slot application and release process, an operation is only needed to be performed to the available time slot list. Working efficiency can be substantially increased. The time slot application uses a query list mode but not a polling mode, which can greatly reduce time slot fragments brought during a time slot distribution process and maximumly guarantee a bearing capability of a link to a large particle service. The list aims at one TE link but not a transmission interface. A bundled link time slot distribution problem can be effectively solved.

Owner:HUAWEI TEHCHNOLOGIES CO LTD

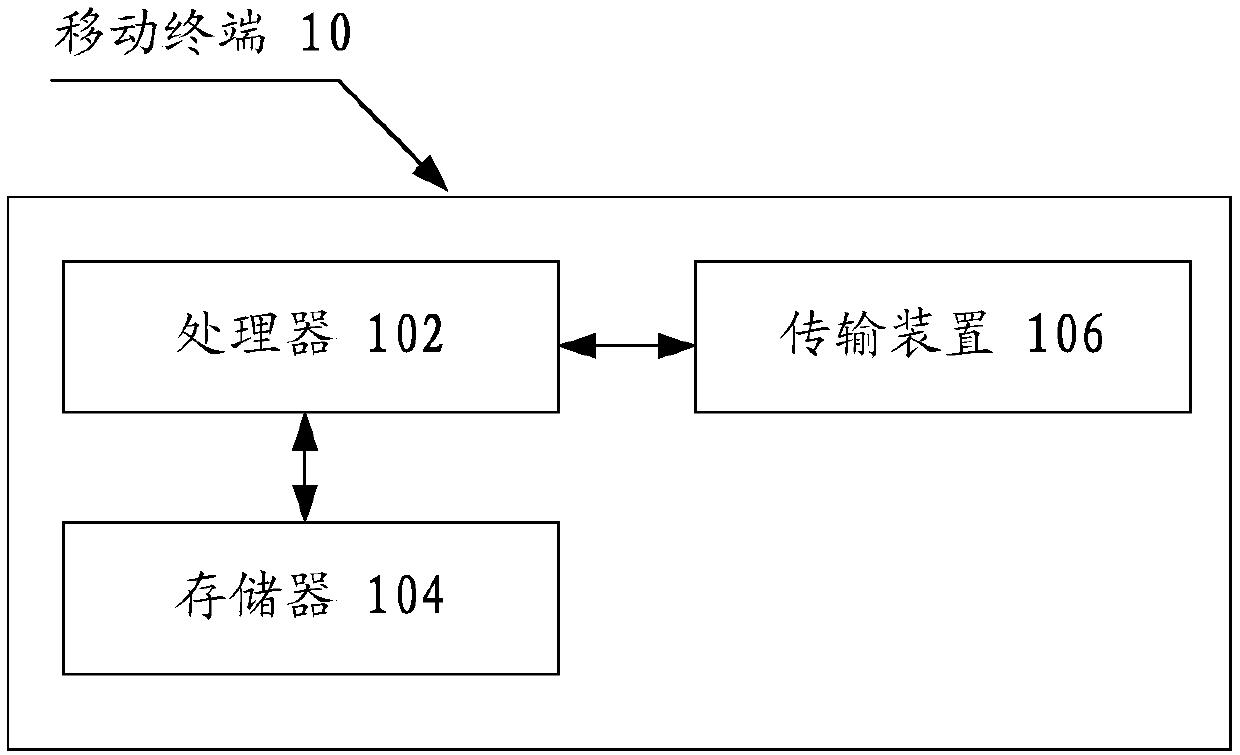

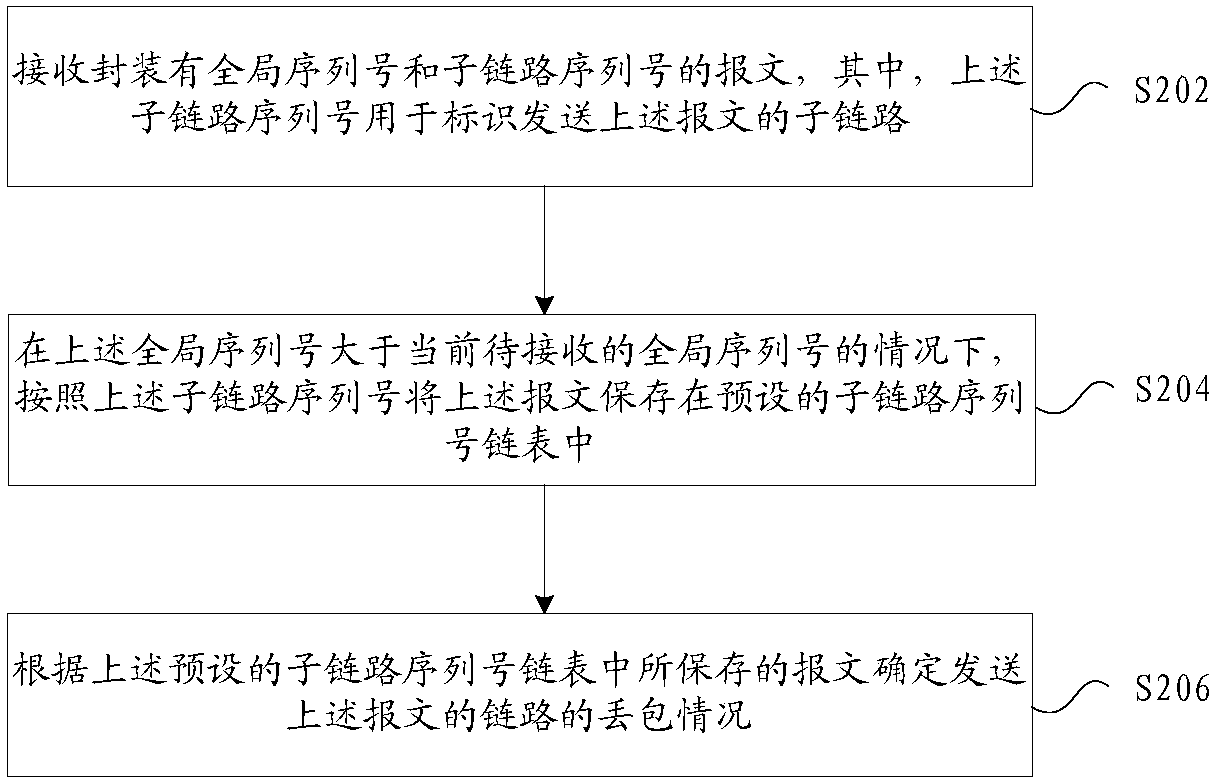

Link packet loss detection method and device, storage medium and processor

The invention provides a link packet loss detection method and device, a storage medium and a processor, and the method comprises the steps: receiving a message packaged with a global serial number and a sub-link serial number, the sub-link serial number being used for identifying a sub-link for sending the message; when the global serial number is greater than the current global serial number tobe received, storing the message into a preset sub-link serial number linked list according to the sub-link serial number; and determining the packet loss condition of the link for sending the messageaccording to the message stored in the preset sublink serial number linked list. Through the link packet loss detection method and the link packet loss detection device, the problems of single link packet loss detection method and increased link time delay in the prior art are solved, and the effect of rapidly detecting the link packet loss condition is achieved.

Owner:ZTE CORP

Apparatus, system, and method for link maintenance

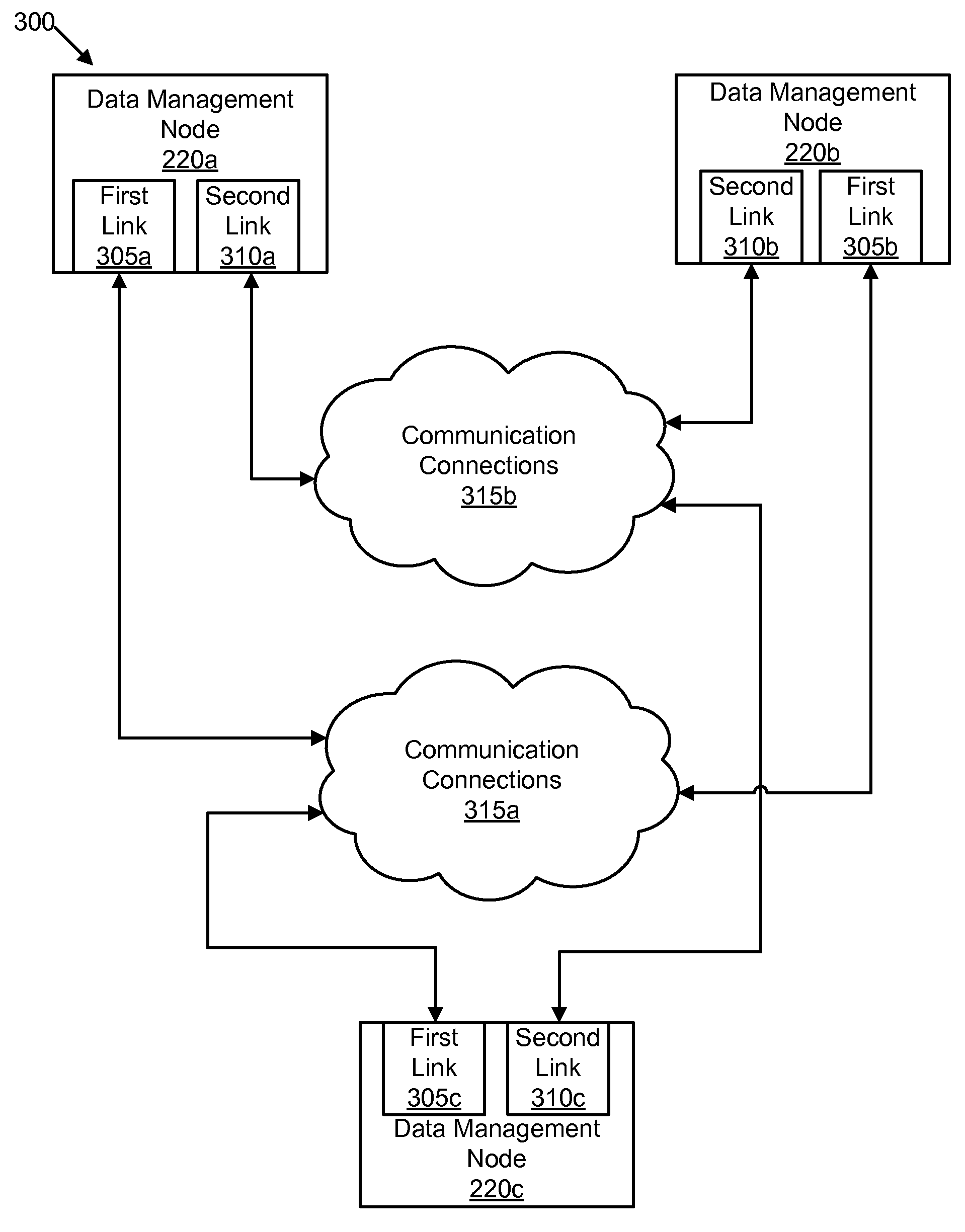

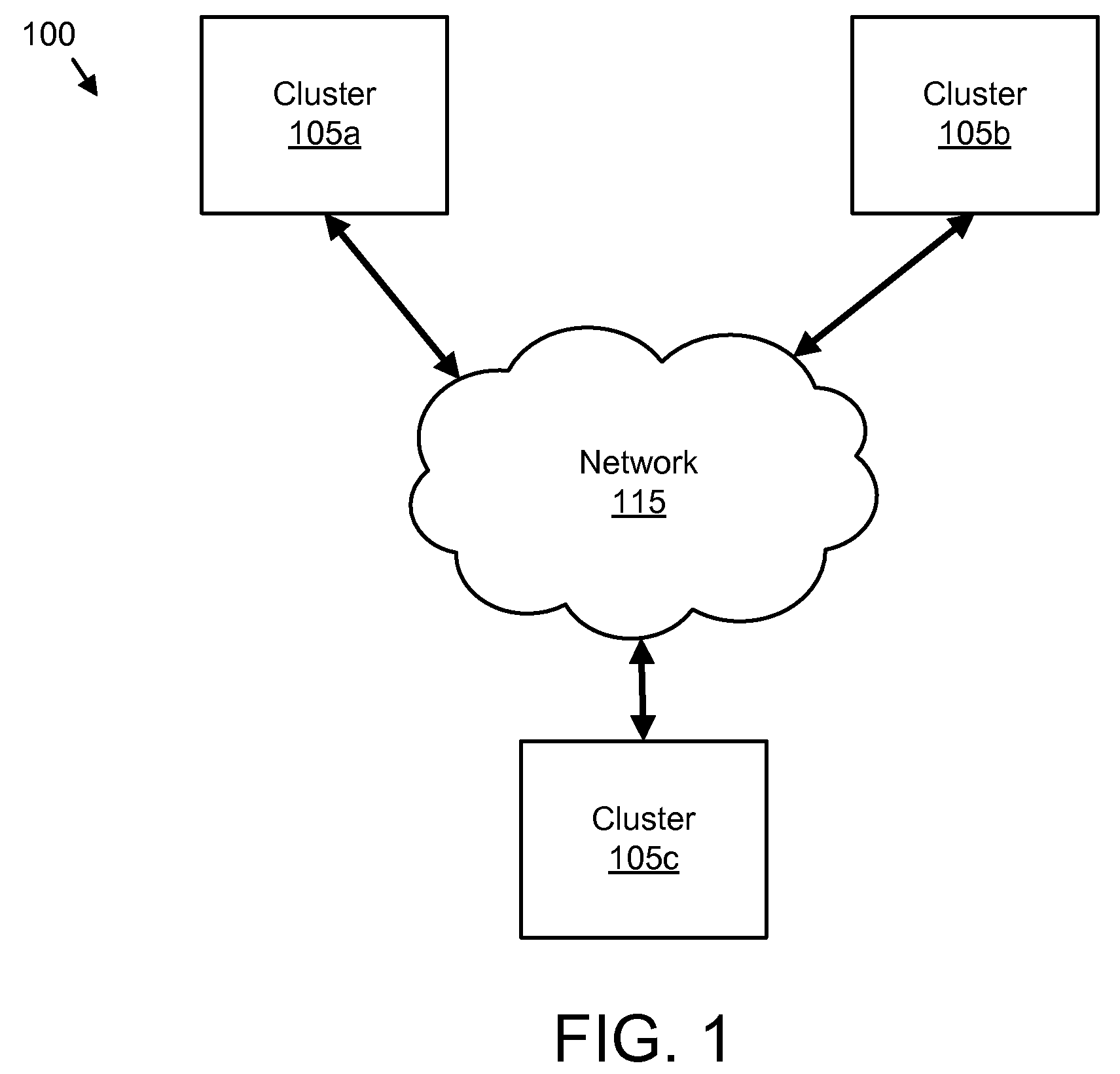

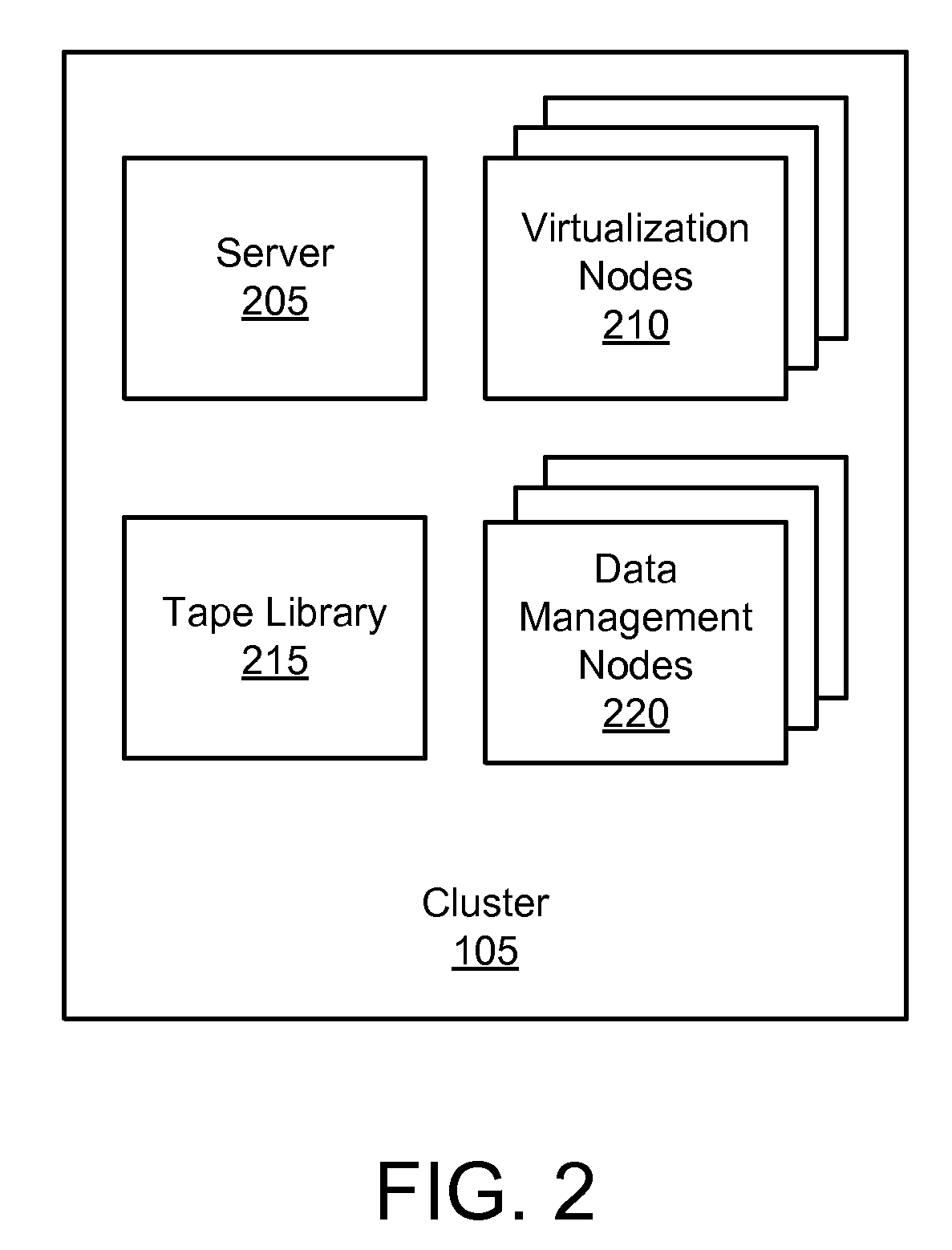

InactiveUS20100180147A1Error preventionFrequency-division multiplex detailsData managementState switching

An apparatus, system, and method are disclosed for link maintenance. A plurality of state machines operate a plurality of first links between data management nodes with each first link in an online state. A transition module transitions the plurality of first links from the online state to a degraded state and from the online state to an offline pending state in response to an offline request. The transition module further transitions the plurality of first links from the degraded state to an online pending state when a degraded link time interval expires and from the offline pending state to an offline state if all pending tasks on the plurality of first links are completed. The transition module further transitions the plurality of first links from the online pending state to the online state if each first link is validated.

Owner:IBM CORP

Network real-time video transmission method and device of adaptive learning

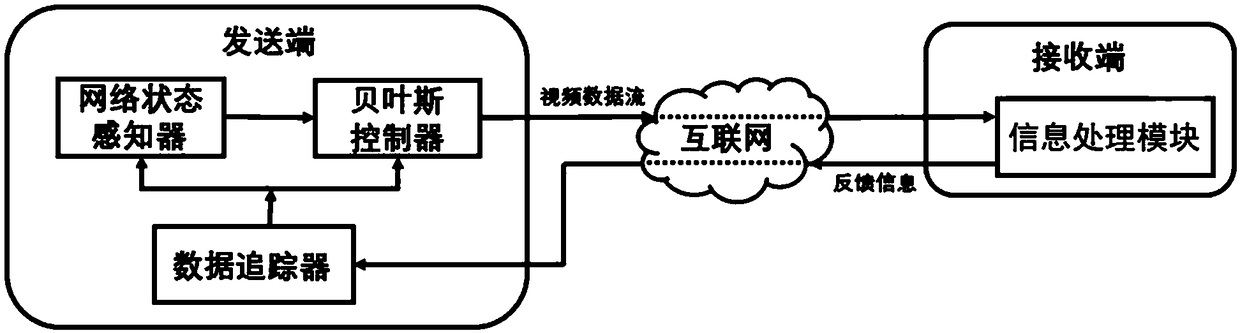

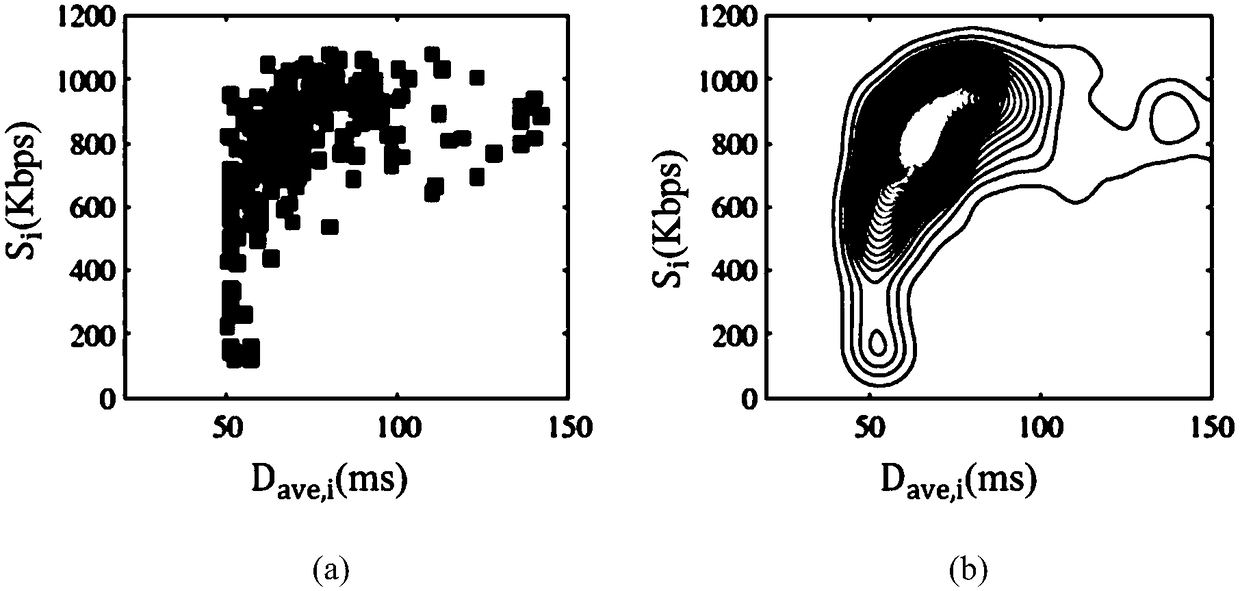

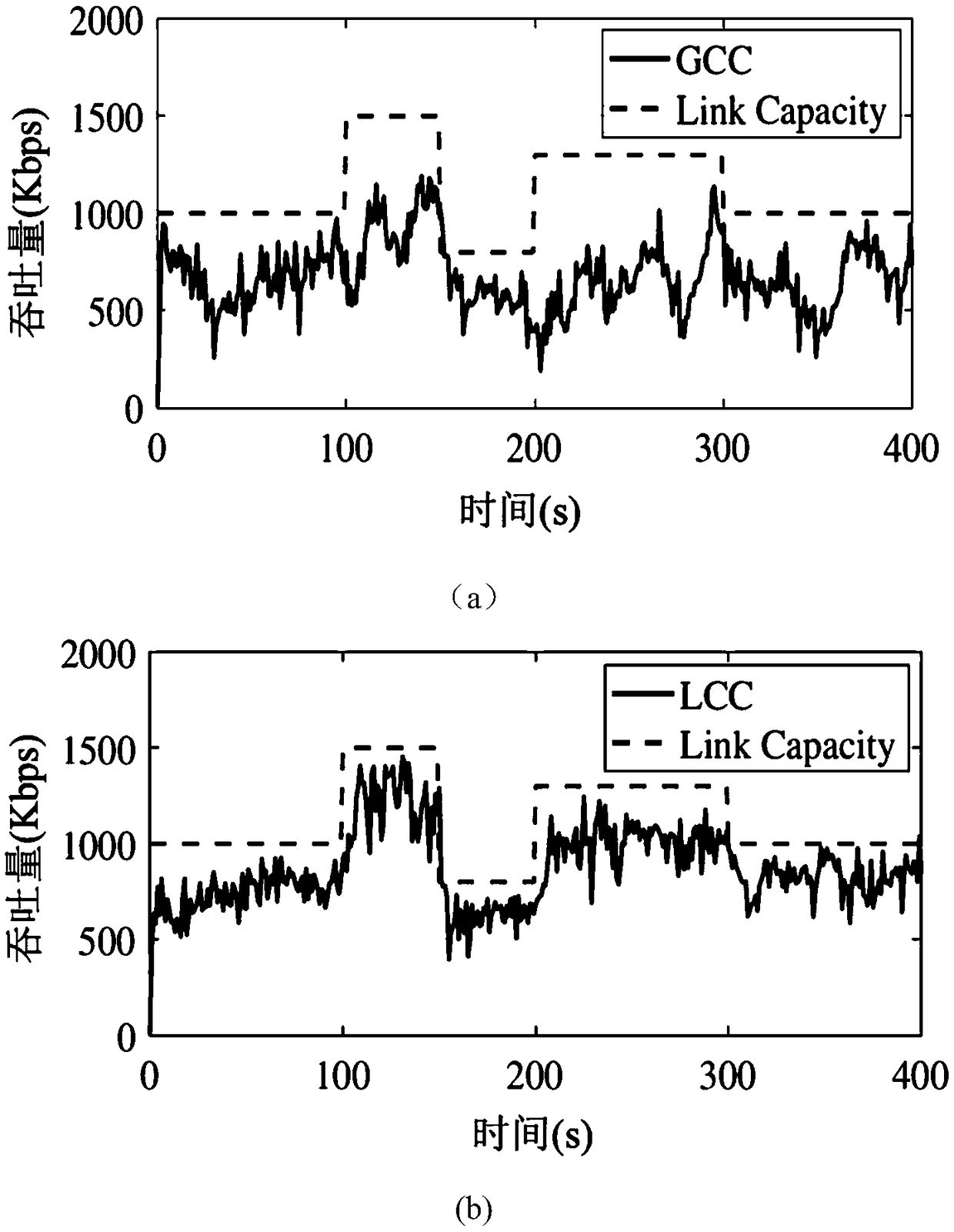

ActiveCN108848415ATake advantage ofImprove experienceSelective content distributionData switching networksAdaptive learningVideo transmission

The invention relates to a network real-time video transmission method and device of adaptive learning. The method is mainly aimed at an end-to-end video transmission application scene in the wirelessnetwork. According to the method, the sending rate is controlled under cooperation among a data tracking module, a network state sensing module and a Bayesian controller in the sending end, and congestion is avoided. The receiving end is mainly responsible for information feedback, and helps data collection in the sending end. Via the method, the network state can be sensed timely, and an optimalsending rate is decided via a rate decision mechanism based on historical data and the Bayes theorem. In the whole decision process, the characteristic that the wireless network is highly variable istaken into full consideration, long-term change of the network environment is sensed via the historical data, the sending rate is adjusted by means of link time delay, instant fluctuation of the network is adapted to, and thus, the bandwidth utilization rate is improved, the link time delay is reduced, and the user experience of the real-time video application is improved.

Owner:PEKING UNIV

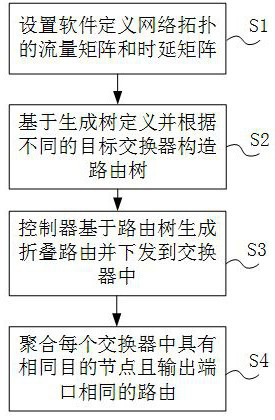

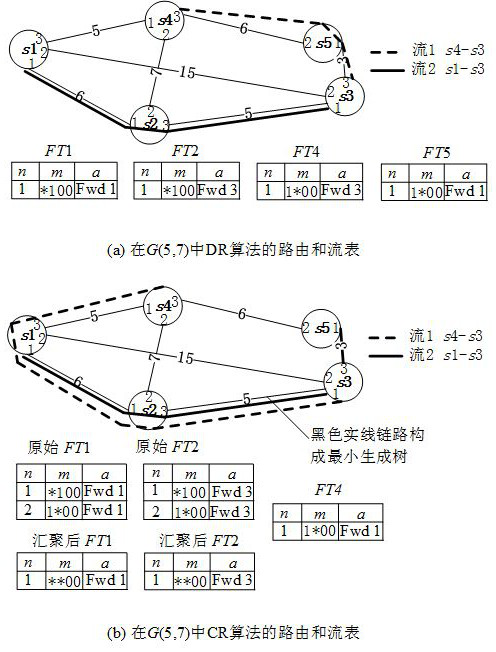

Flow table compression method based on spanning tree folding routing in software defined network

The invention discloses a spanning tree folding routing-based flow table compression method in a software defined network, and the method comprises the following steps: collecting data packet requests of each node in a certain time period according to a given network topology to obtain a flow matrix, and obtaining a time delay matrix according to link time delay among the nodes; by taking minimization of path cost and time delay cost and maximization of a link coincidence rate as targets, achieving an optimal target by constraining constraint conditions such as the maximum capacity of each section of link and the maximum time delay of each path and exhaustion of all feasible paths. Compared with the prior art, the method has the following advantages that the folded routing is explored through the integer linear programming ILP (Integer Linear Program), so all solution spaces can be flexibly solved, meanwhile, effective compromise is made between the transmission time delay and the cost that only chip hardware can be stored in the flow table, and optimal configuration of flow table compression is achieved while the data packet transmission efficiency is guaranteed.

Owner:HENAN UNIVERSITY OF TECHNOLOGY

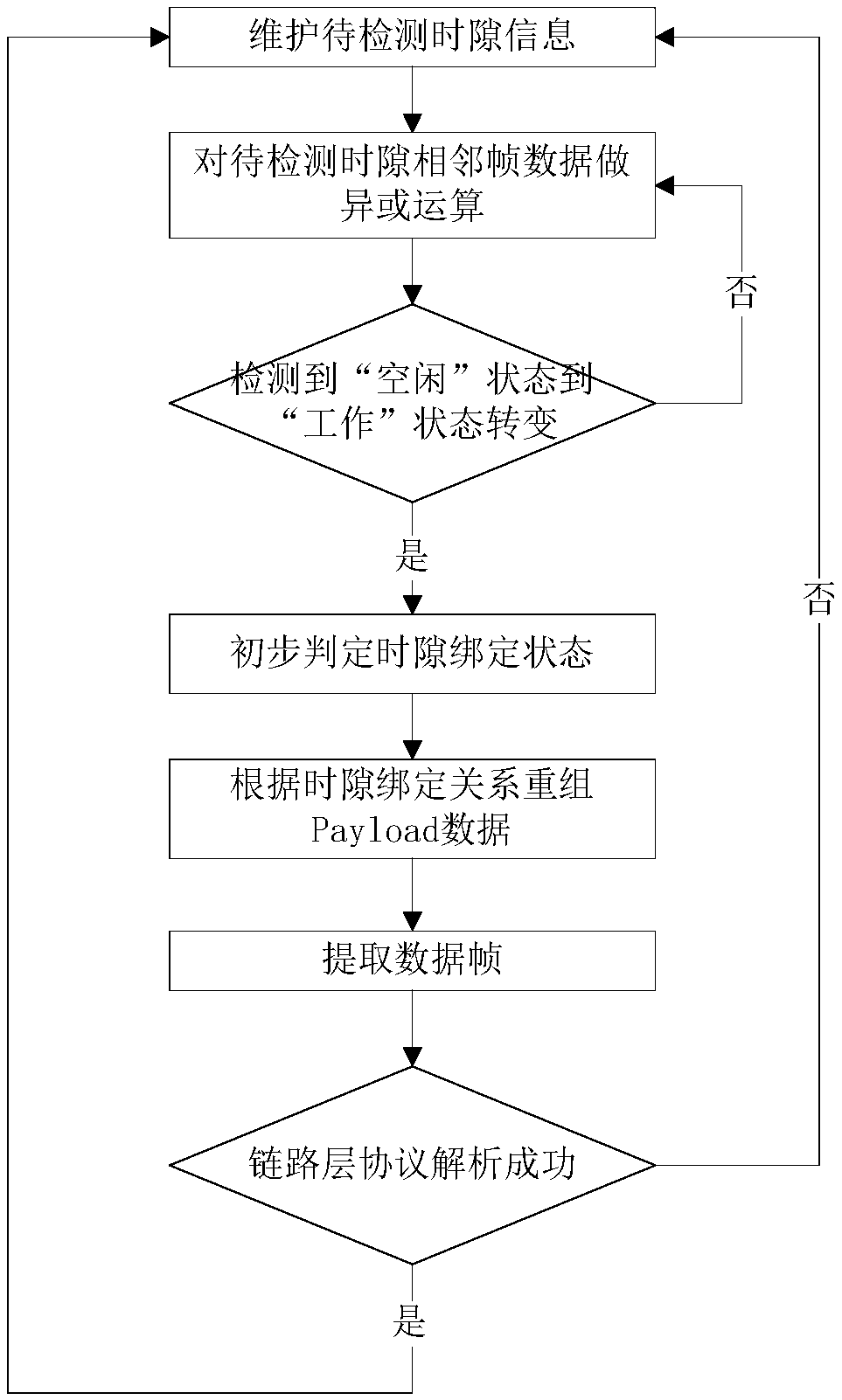

Method and device for detecting E1/T1 link time slot binding mode

ActiveCN109412895AReduce lossHigh speedData switching networksWireless communicationSerializationBinding time

The invention discloses a method and a device for detecting an E1 / T1 link time slot binding mode. The method comprises the following steps: from to-be-detected time slots, preliminarily judging the time slot which changes from an 'idle' state into a 'work' state in continuous M frames as a bound time slot, wherein M is greater than or equal to 2, and M is an integer; for the time slot primarily judged as being bound, recombining the data of the time slot to be Payload data according to bound time slot serialization; removing idle filling in the Payload data, and extracting data frames; and parsing the data frames through a supported link layer protocol. The method and the device provided by the invention have the advantages of fast speed and high efficiency. Under a condition where usage of cache data is not considered, just by one frame of the Payload data, the E1 / T1 link time slot binding mode can be judged, and loss of the Payload data can be reduced. Moreover, the method and the device provided by the invention are not confined to HDLC analogous data, can be applied to a wider range, and also can be automatically adaptive to dynamically changing scenes of the E1 / T1 link time slot binding mode.

Owner:电信科学技术第五研究所有限公司

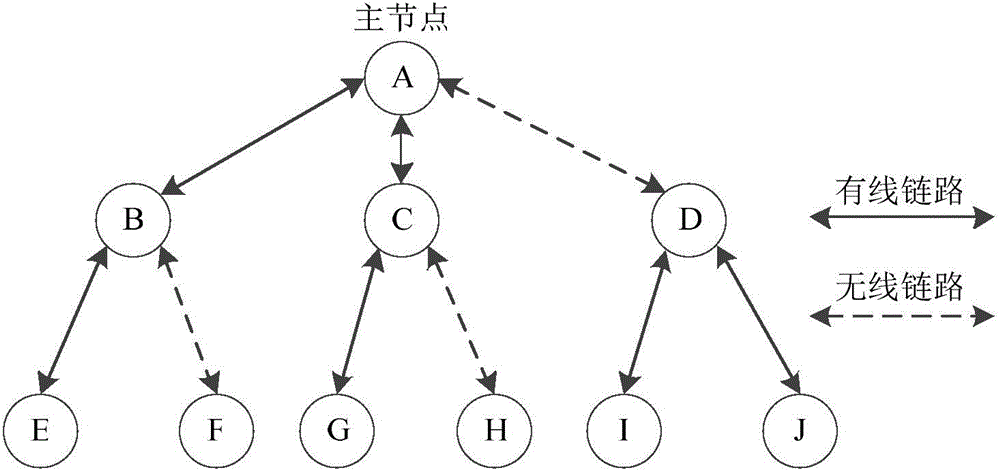

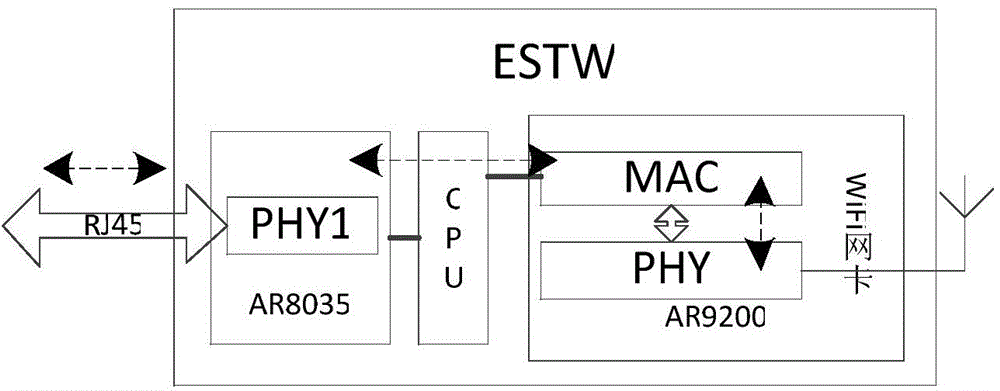

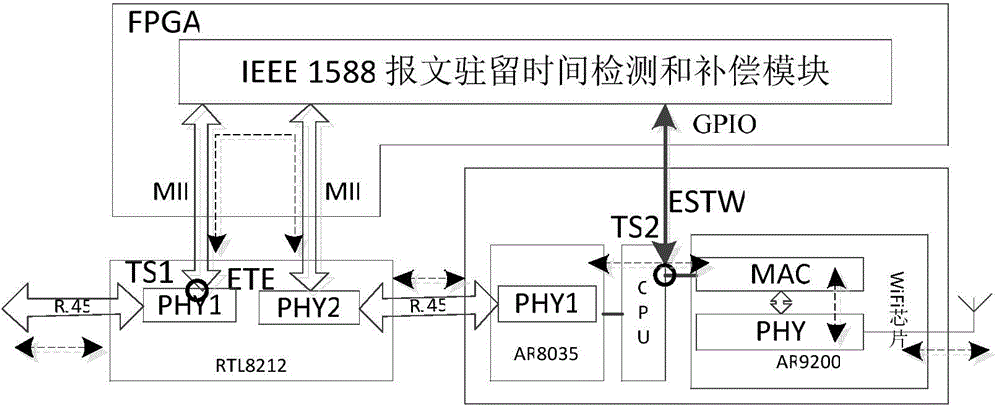

Wireless link time delay compensation device and method facing industrial heterogeneous network

ActiveCN105812117ARealize delay compensationImprove scalabilitySynchronising arrangementProtocol overheadComputer module

The invention discloses a wireless link time delay compensation device and method facing industrial heterogeneous, and particularly relates to the wireless link time delay compensation device and method based on an IEEE 1588 time synchronization protocol under the industrial heterogeneous network. The wireless link time delay compensation device comprises an ESTW module, an ETE module and an IEEE 1588 message residence time detection and compensation module. The method comprises steps of adopting an ESTW module to realize the wireless communication between the specific Ethernet nodes, utilizing the FPGA to realize the specific IEEE 1588 message residence time detection of the ESTW module, adding the message residence time into a corresponding IEEE 1588 message correction domain to finish the wireless link time delay compensation. The wireless link time delay compensation device and method reduce the protocol overhead without correcting the current IEEE 1588 protocol, improves the network throughput, satisfies the link time delay compensation real time performance requirement, improves the time synchronization accuracy, reduces the extra hardware development requirement without affecting the current Ethernet device and enhances the practicability.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

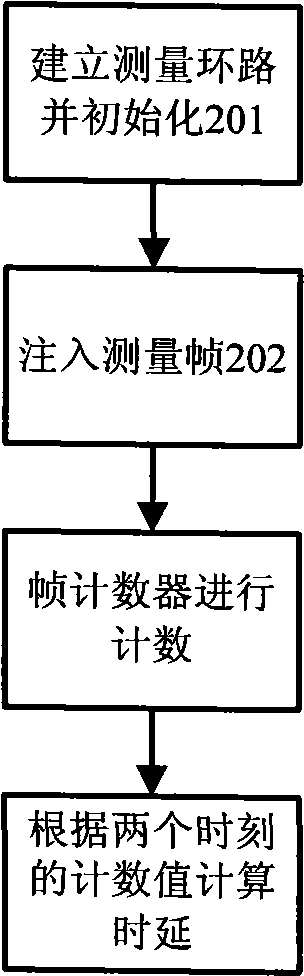

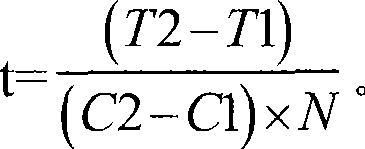

Packet data transmission link time-delay measuring unit, system and method

InactiveCN101534220AExtend the intervalLower clock requirementsData switching networksTime delaysPacket data transmission

The invention discloses packet data transmission link time-delay measuring unit, a system and a method; and the average loop time delay of a transmission link is calculated by making a loop for measuring frame vibration on the transmission link and measuring the flow of a measuring frame. As the invention converts measurement on time-delay quantity into measurement on the flow, and the measurement on the flow only needs a clock which is relatively stable for a long time, the requirement of the measurement on the clock is greatly reduced. In order to improve measurement precision, measurement error can be greatly reduced by only simply improving time interval for measuring the flow.

Owner:彭方方