Quad flat no-lead package and manufacturing method thereof

A leadless packaging, square flat technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as chip electrode prolapse, thermal stress residue, etc., to reduce thermal stress, save costs, The effect of saving joint reinforcement structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

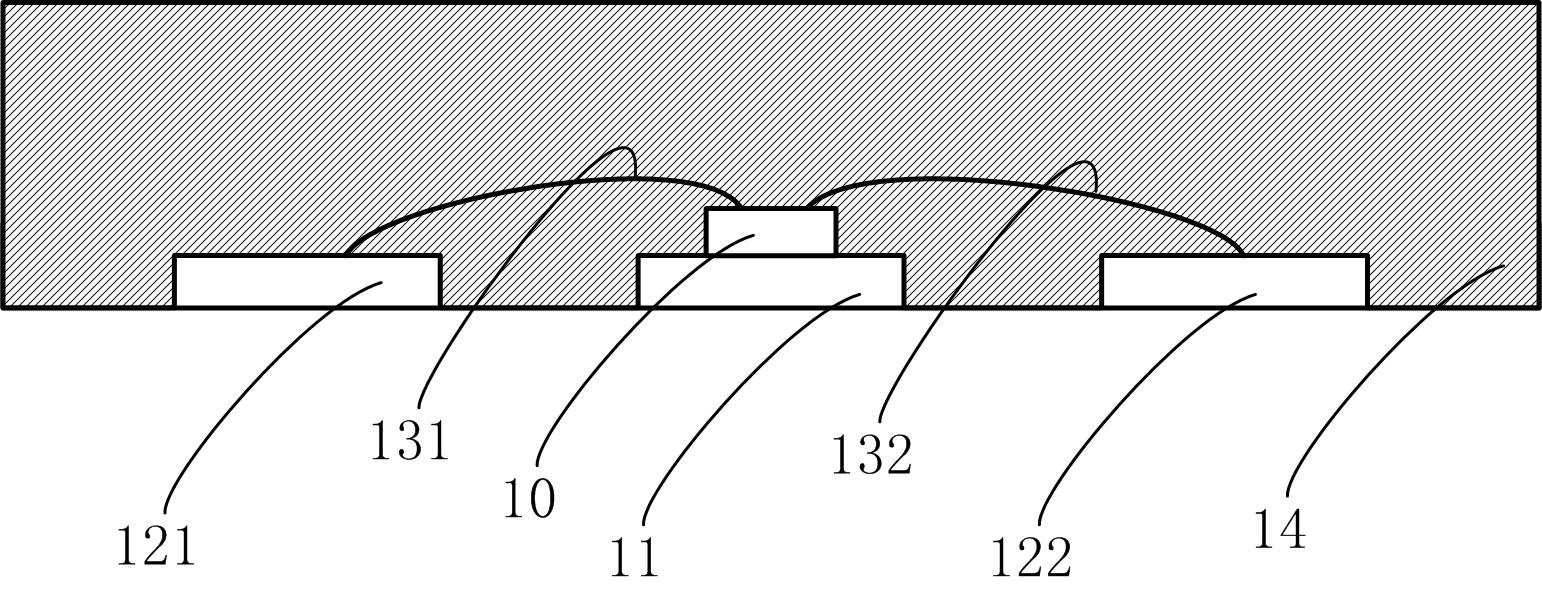

[0014] A specific implementation of a quad flat no-lead package and its manufacturing method provided by the present invention will be described in detail below with reference to the accompanying drawings.

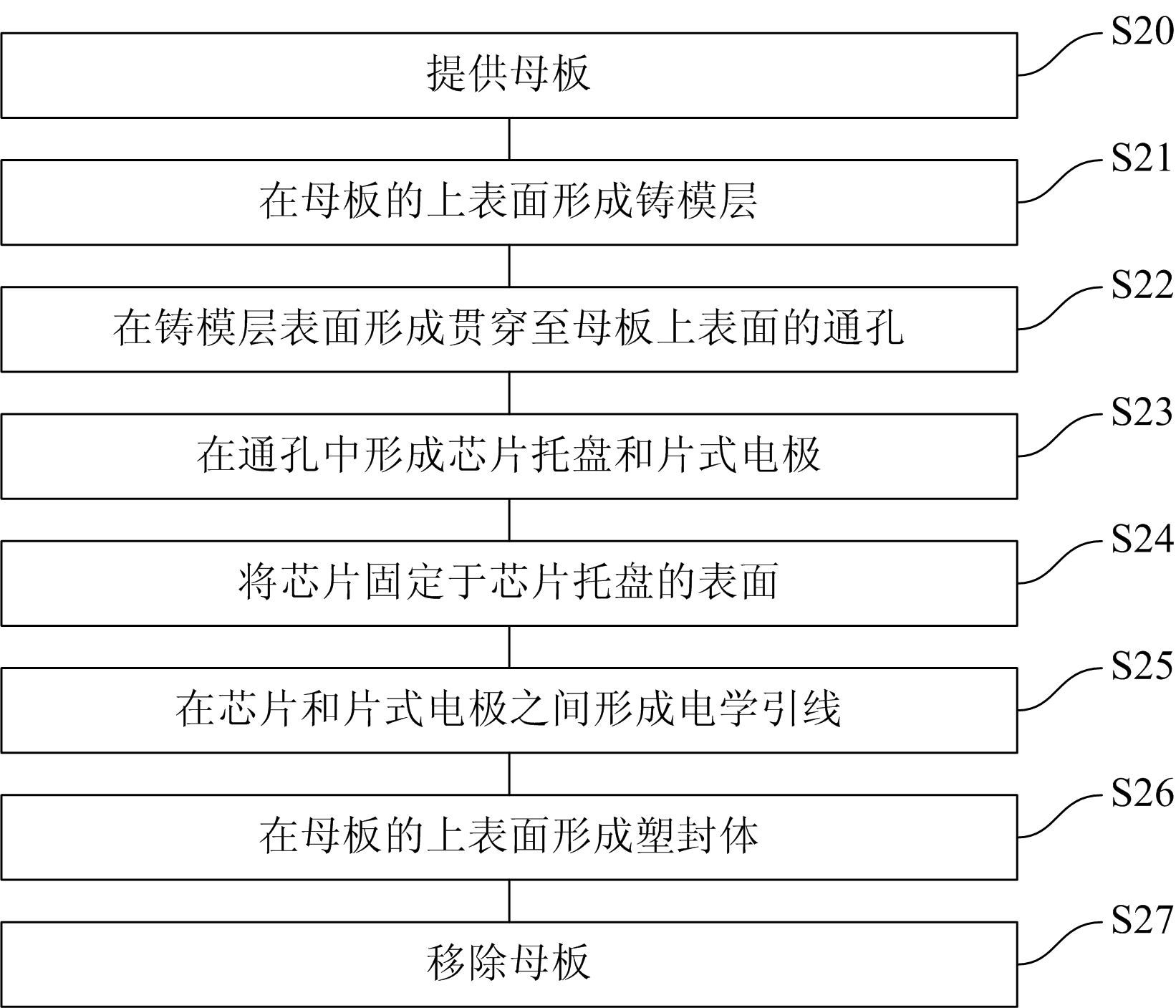

[0015] attached figure 2 Shown is a schematic diagram of the implementation steps of the specific embodiment of the method of the present invention, including the following steps: step S20, providing a motherboard; step S21, forming a mold layer on the upper surface of the motherboard; step S22, forming a through-to A through hole on the upper surface of the motherboard; step S23, forming a chip tray and a chip electrode in the through hole; step S24, fixing the chip on the surface of the chip tray; step S25, forming an electrical lead between the chip and the chip electrode; Step S26, forming a plastic package on the upper surface of the motherboard; step S27, removing the motherboard to expose the chip tray and chip electrodes embedded in the plastic package.

[0016] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More