Patents

Literature

3349results about "Contactless circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

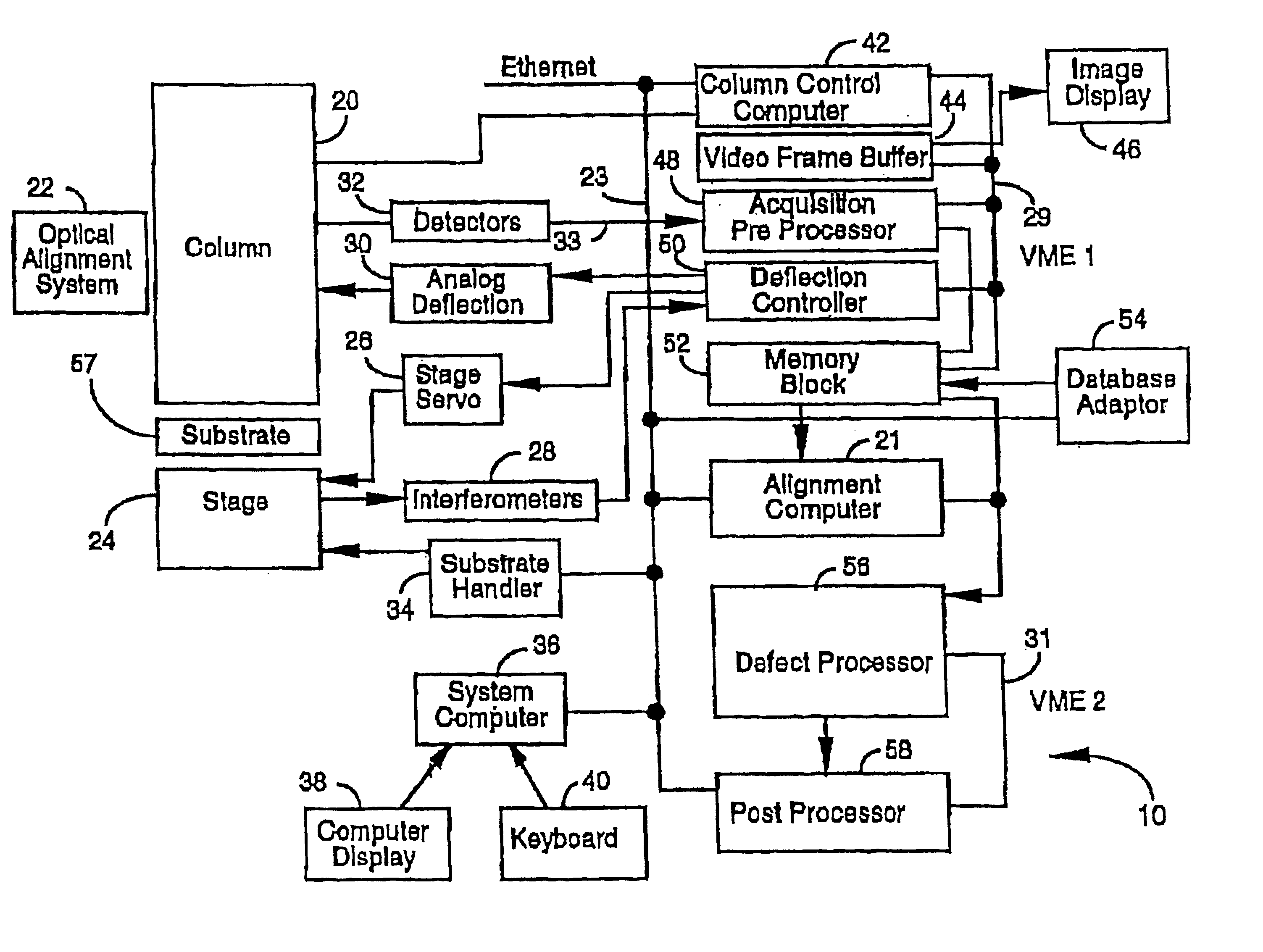

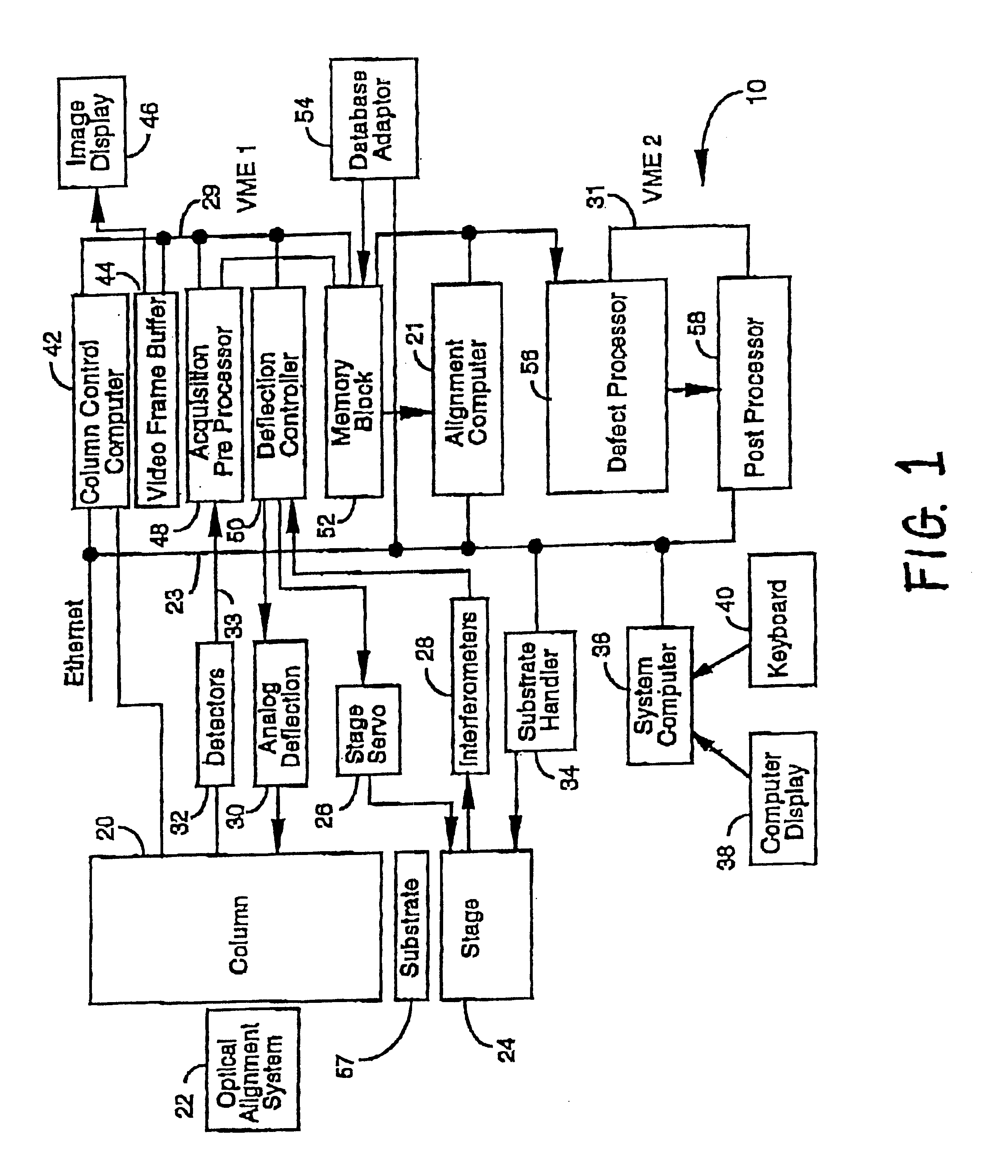

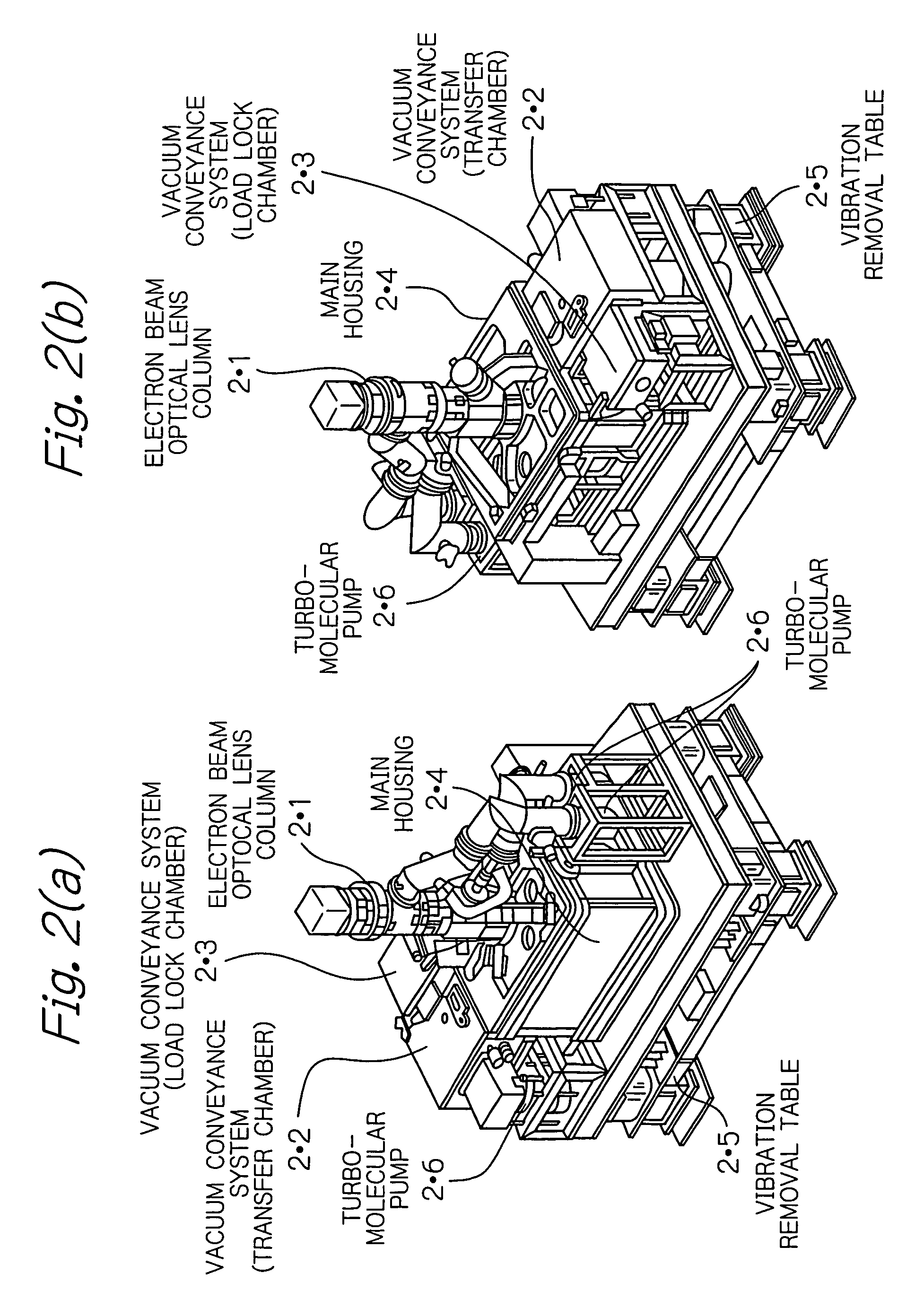

Testing apparatus using charged particles and device manufacturing method using the testing apparatus

ActiveUS20050045821A1Material analysis using wave/particle radiationElectric discharge tubesAtomic physicsPhysics

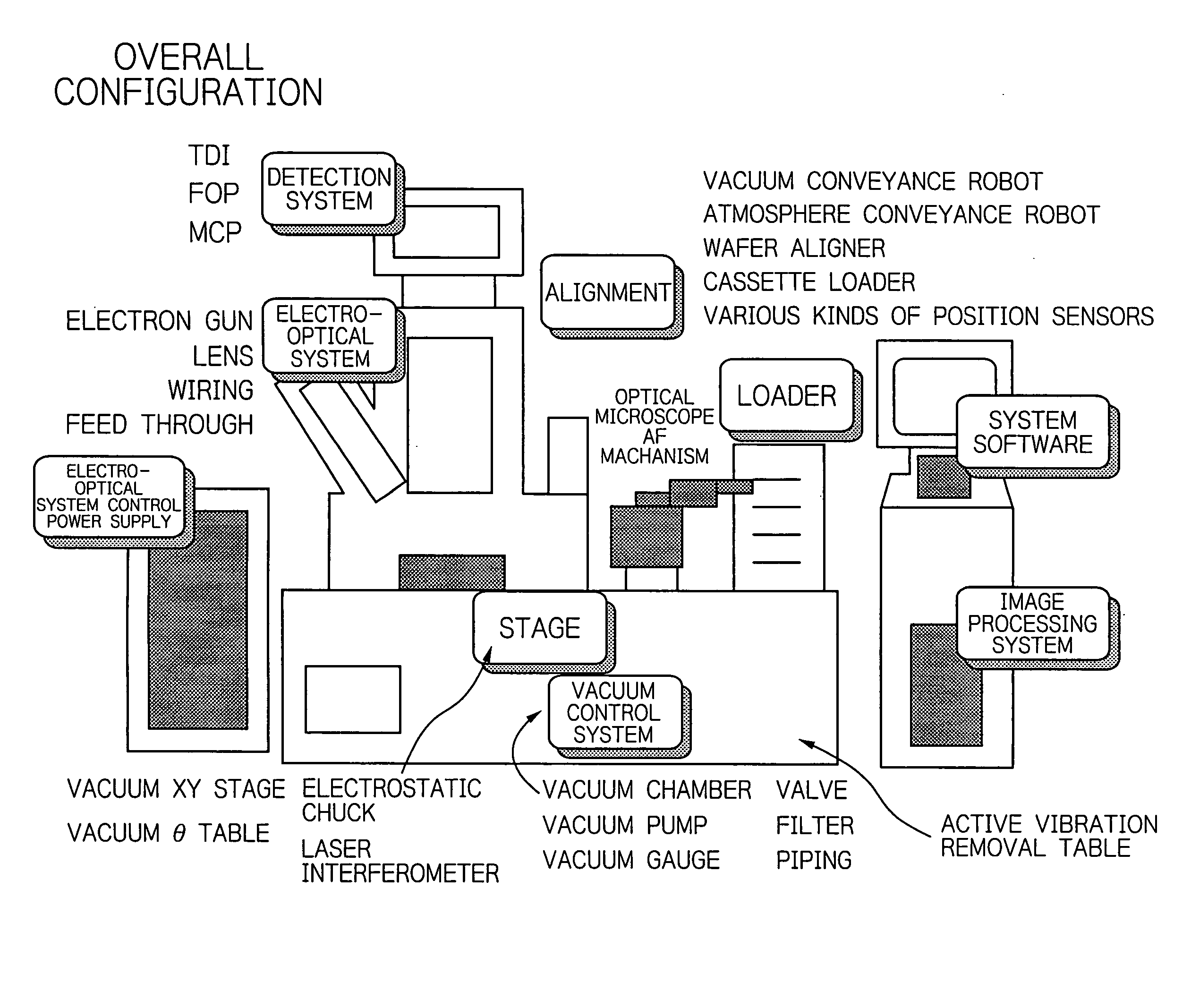

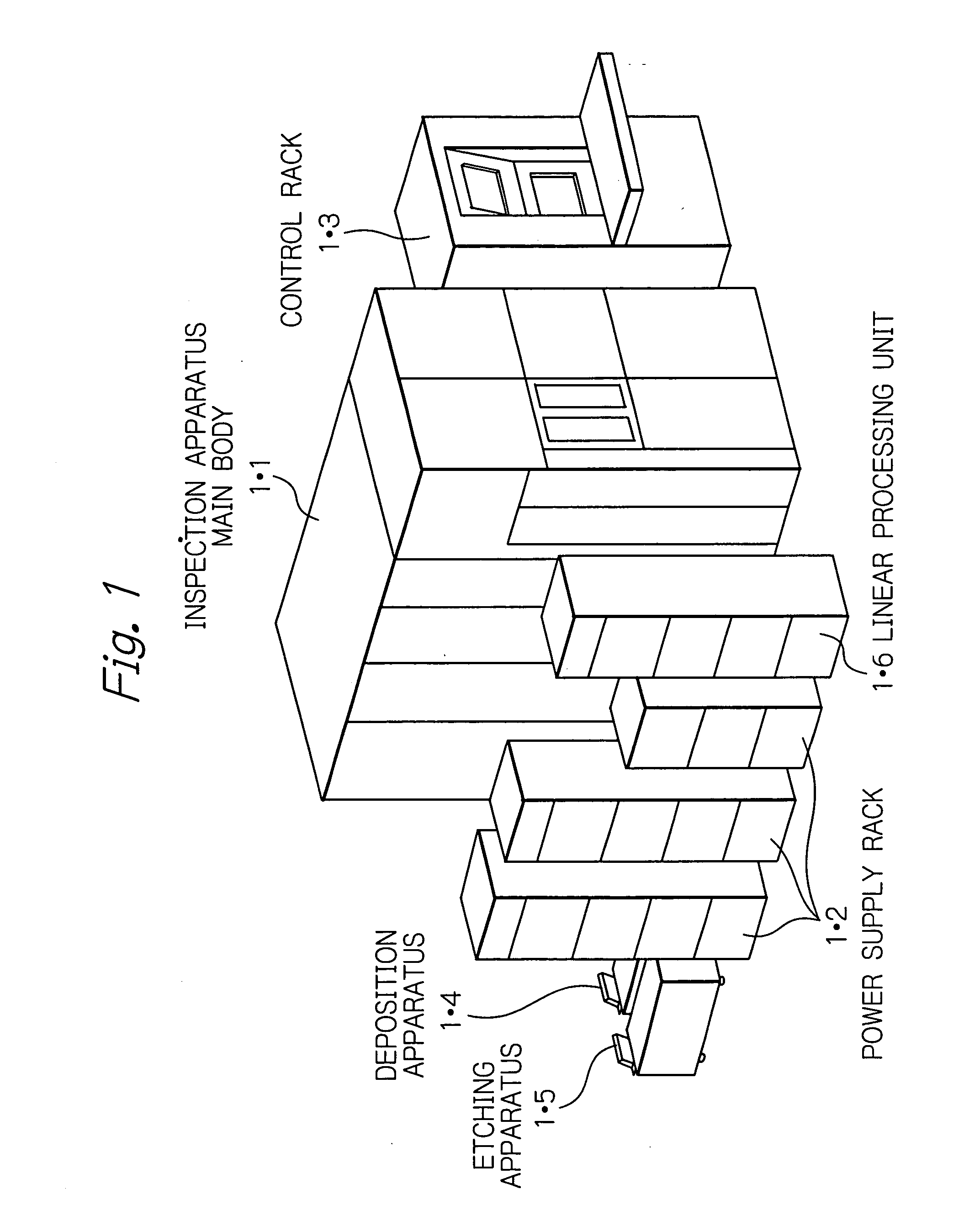

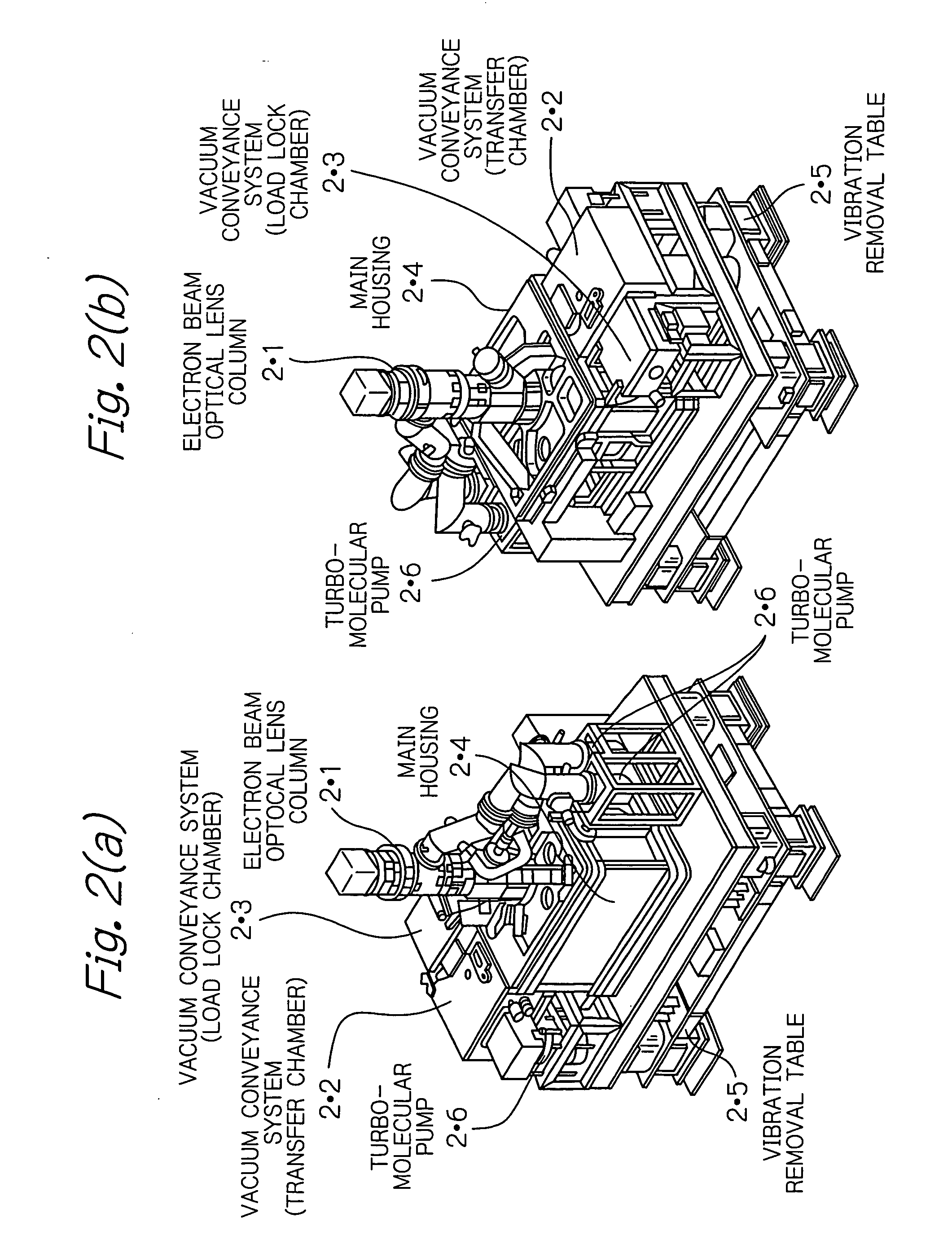

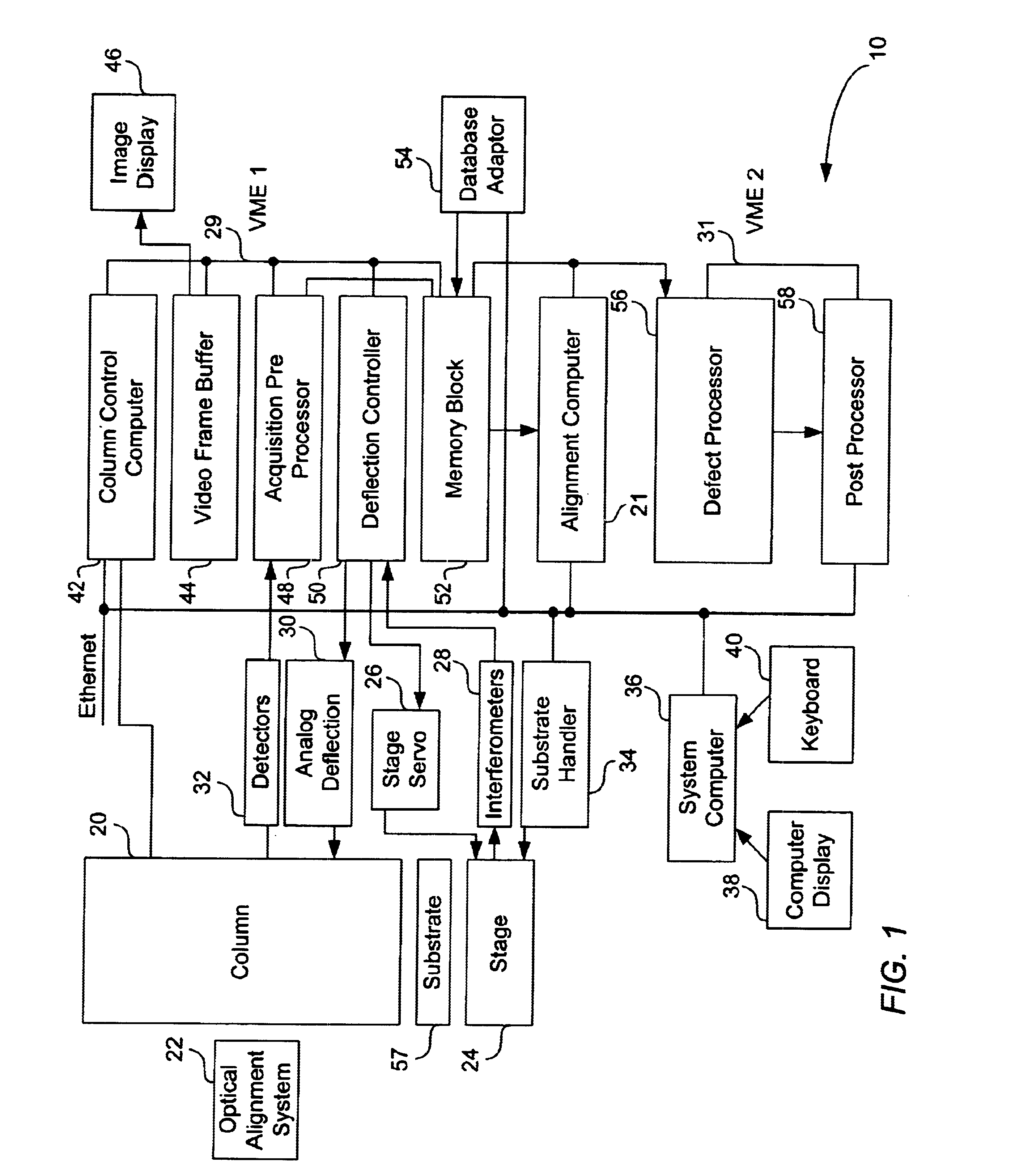

A system for further enhancing speed, i.e. improving throughput in a SEM-type inspection apparatus is provided. An inspection apparatus for inspecting a surface of a substrate produces a crossover from electrons emitted from an electron beam source 25••1, then forms an image under a desired magnification in the direction of a sample W to produce a crossover. When the crossover is passed, electrons as noises are removed from the crossover with an aperture, an adjustment is made so that the crossover becomes a parallel electron beam to irradiate the substrate in a desired sectional form. The electron beam is produced such that the unevenness of illuminance is 10% or less. Electrons emitted from the sample W are detected by a detector 25•11.

Owner:EBARA CORP

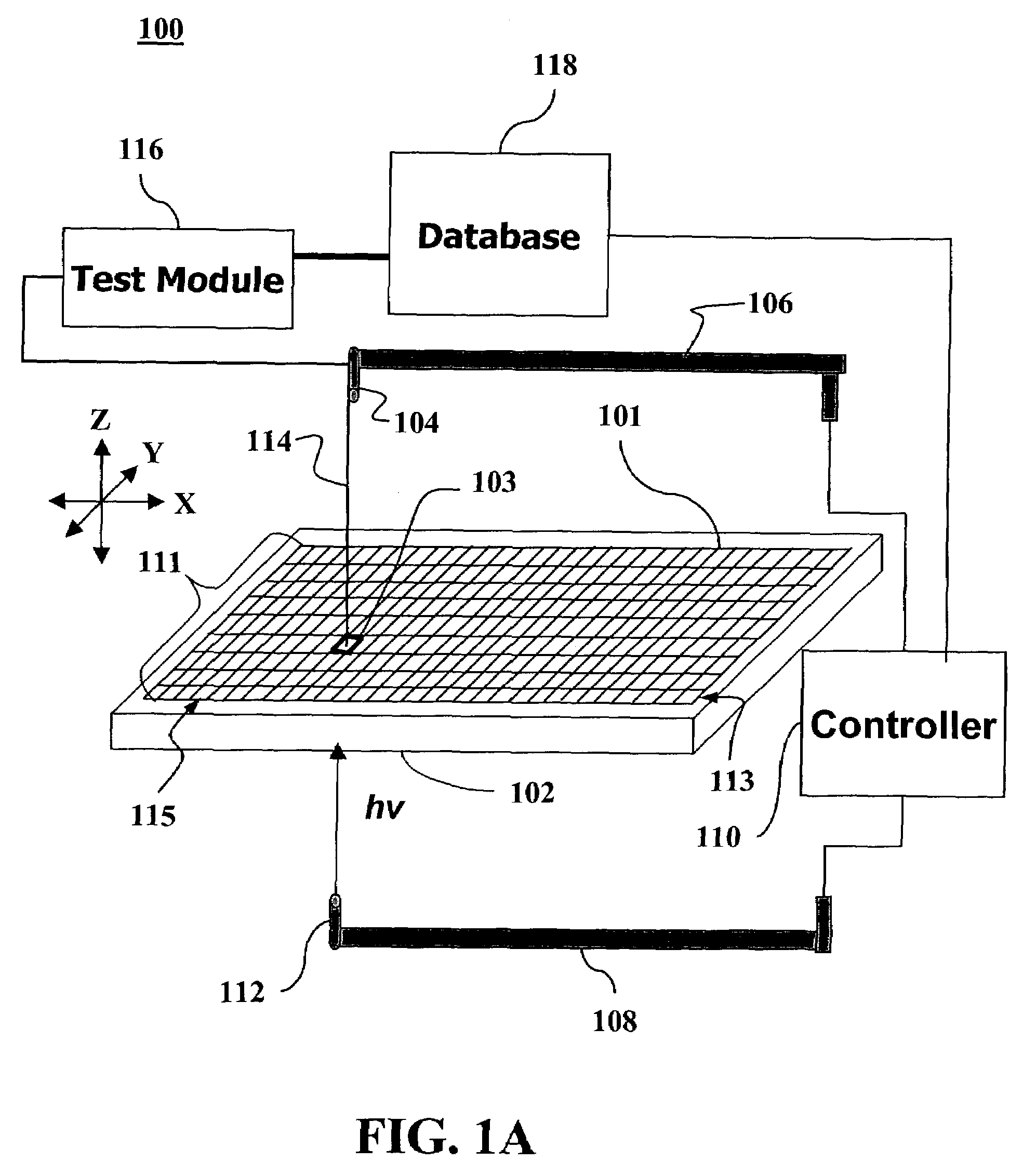

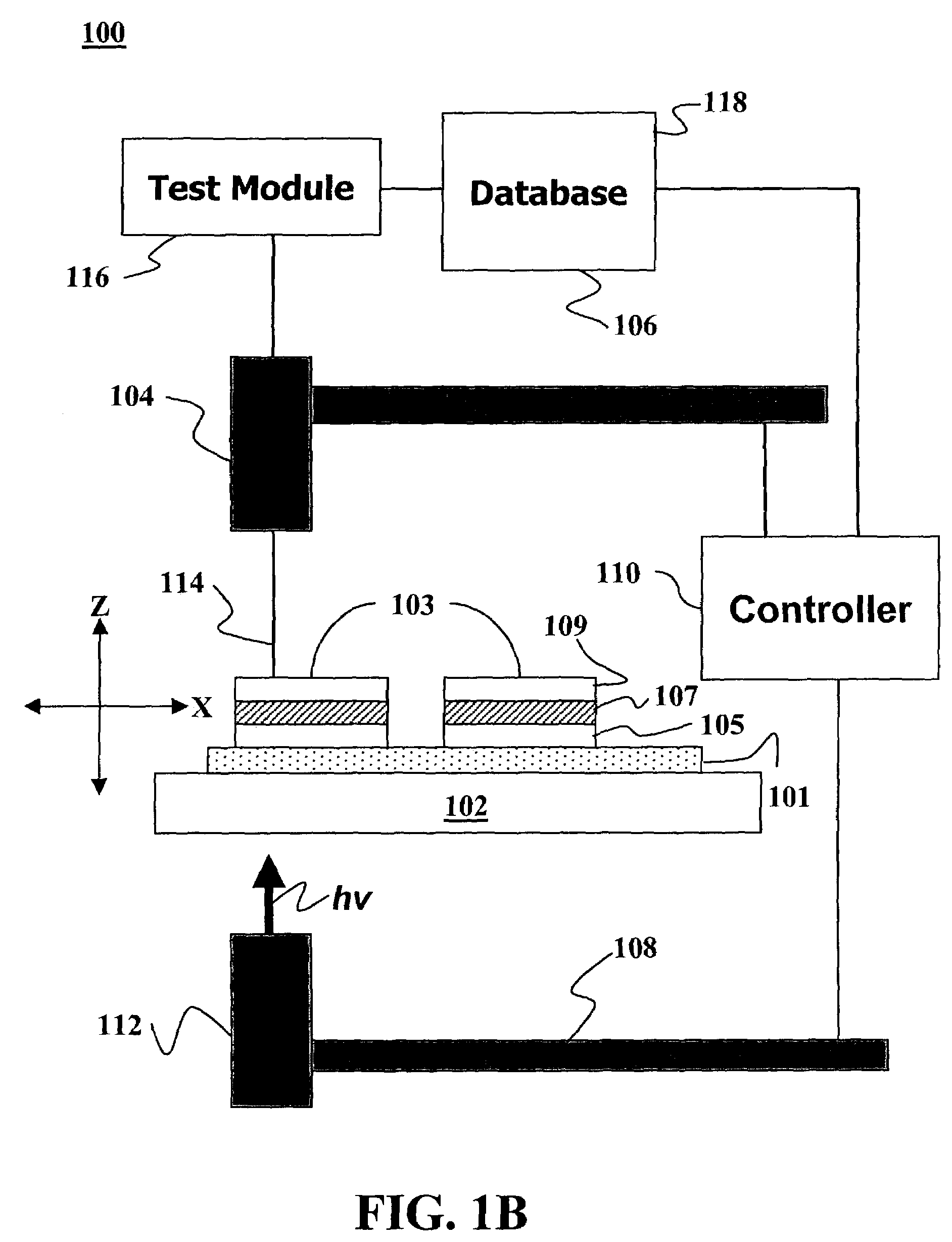

Combinatorial fabrication and high-throughput screening of optoelectronic devices

InactiveUS7247346B1Solid-state devicesSpecial surfacesHigh-Throughput Screening MethodsComputer science

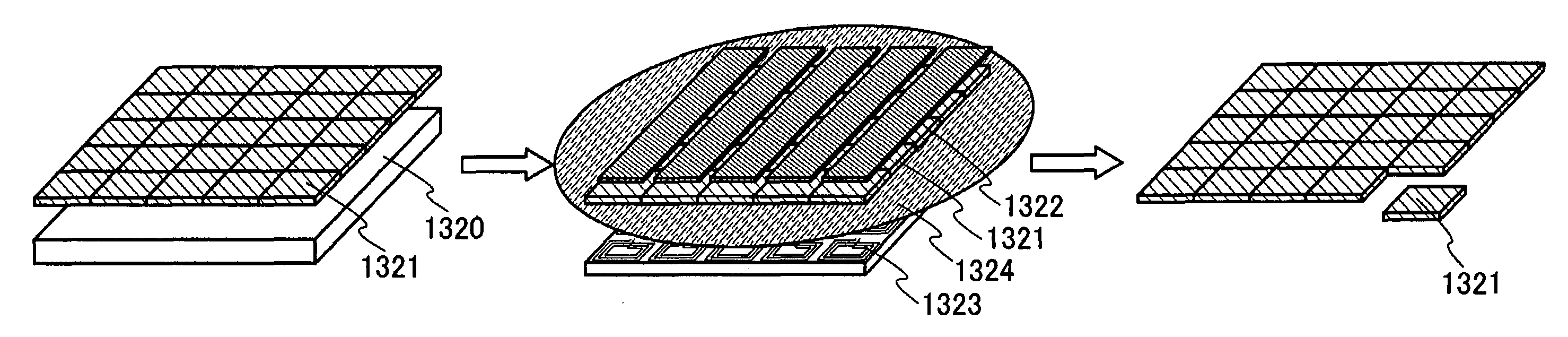

Methods and apparatus for the rapid and parallel synthesis of optoelectronic cell devices and for the high-throughput screening of such devices for useful properties are disclosed. The methods comprise the parallel synthesis of arrays of optoelectronic devices fabricated within an addressable sample-holding matrix. Each optoelectronic device is created and tested within an addressable sample-holder in the fabrication device.

Owner:AERIS CAPITAL SUSTAINABLE IP

Method for forming conductive bumps for the purpose of contrructing a fine pitch test device

InactiveUS20020011859A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A system is described for using with fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The system is also usable for transfer of data, energy, for collecting data measurements or measurement-related data between two pieces, and for effecting at least part of an identification process. The disclosed embodiment includes a substrate having a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be connected. A conductive elastomeric probe is permanently formed on the circuit pads of the substrate such that the probe is malleable and allows repetitive electrical contact. The system may also contain an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the substrate.

Owner:EPITECH +1

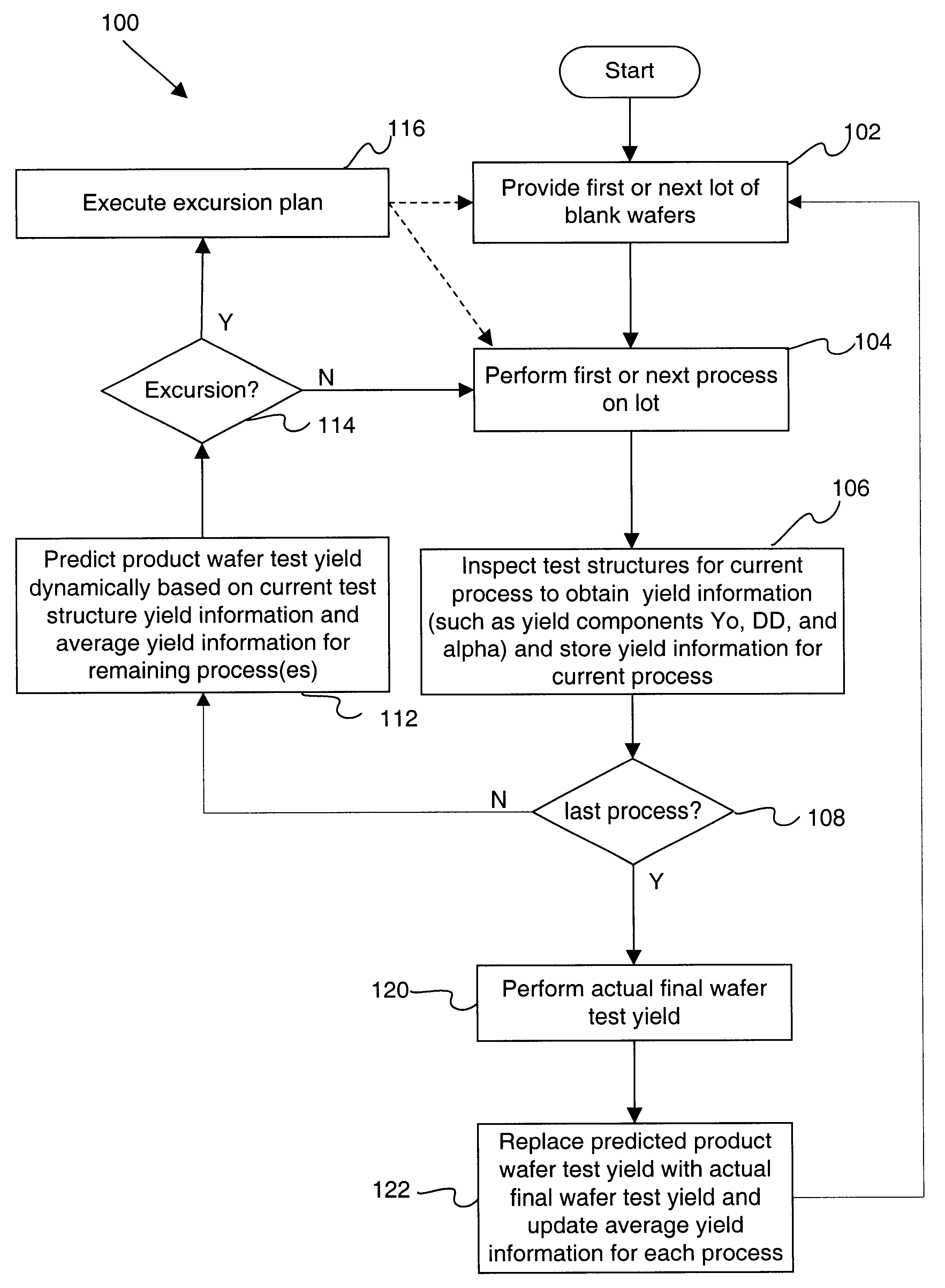

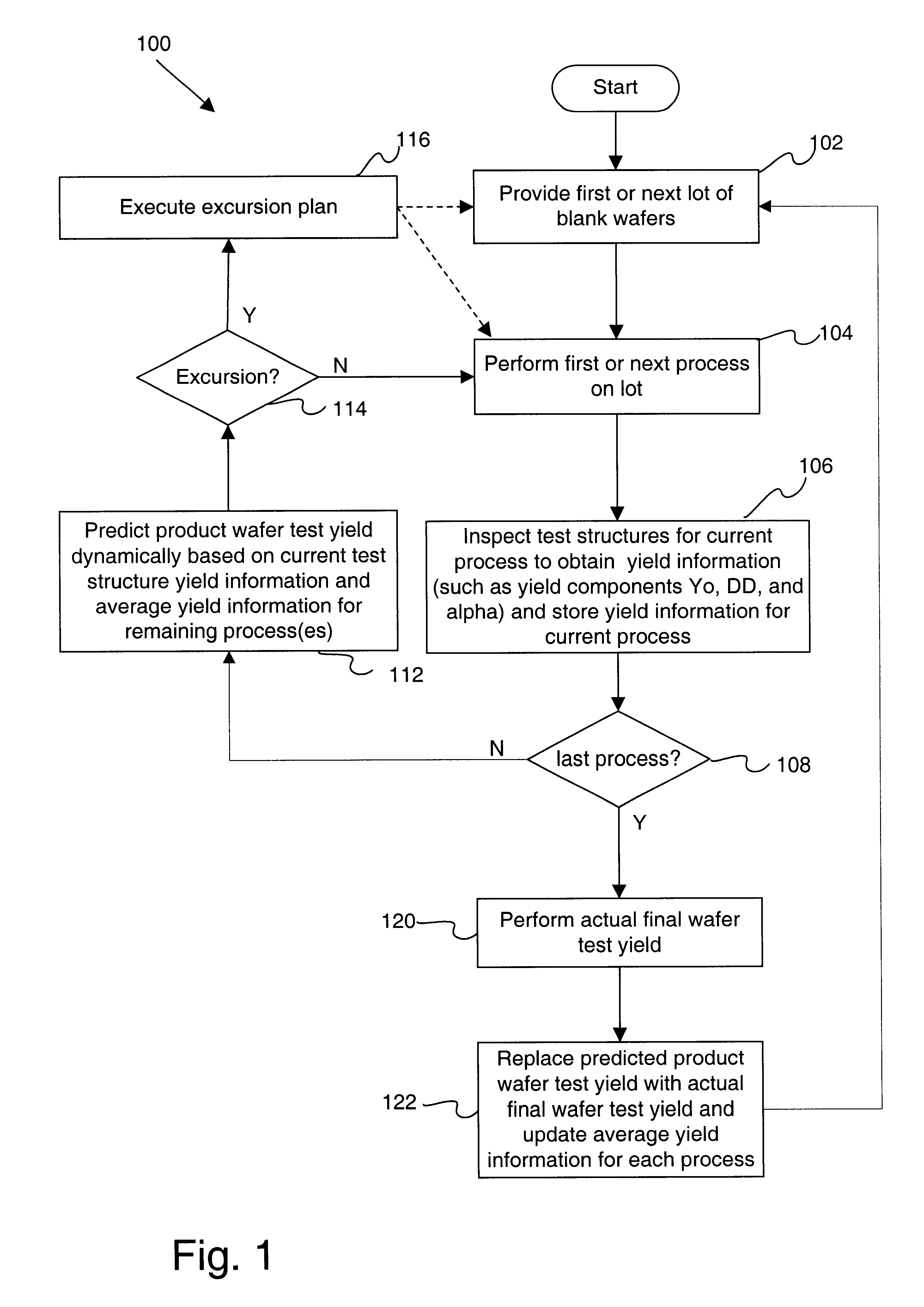

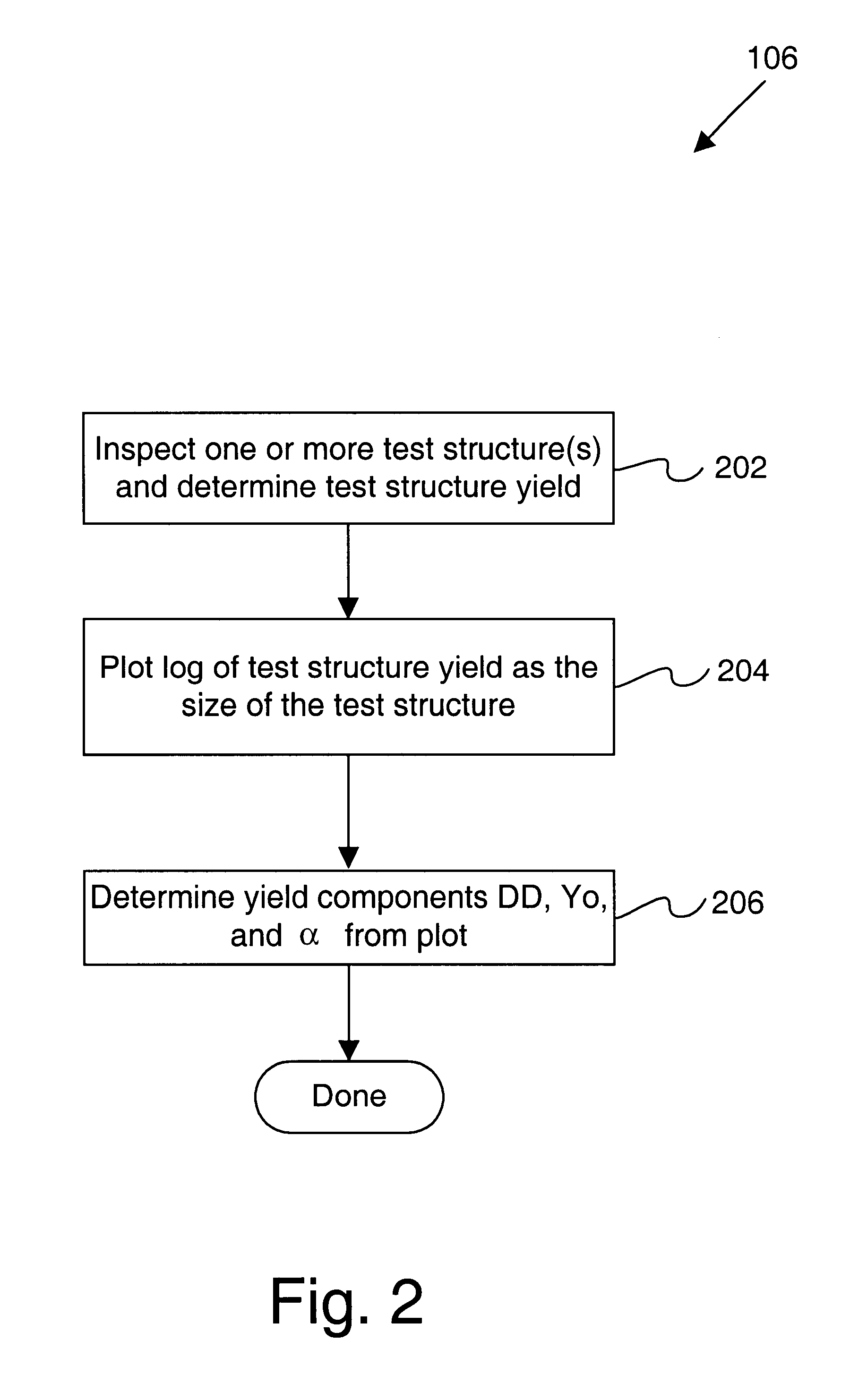

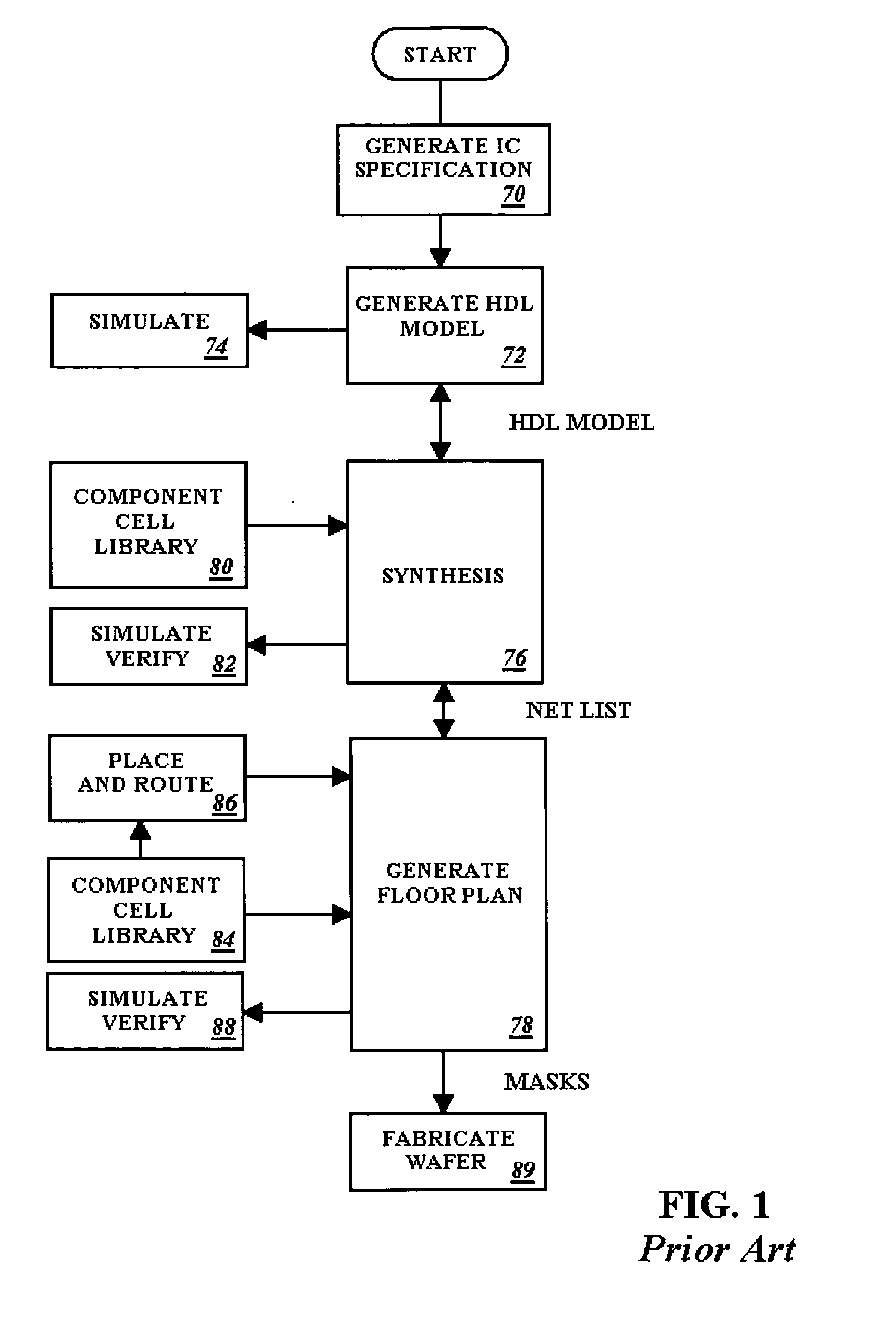

Methods and systems for predicting IC chip yield

InactiveUS6751519B1Semiconductor/solid-state device testing/measurementNuclear monitoringProcess engineeringReliability engineering

Disclosed are methods and apparatus for efficiently managing IC chip yield learning. In general terms, as each wafer lot moves through fabrication, yield information is obtained from each set of test structures for a particular process or defect mechanism. The nature of the yield information is such that it may be used directly or indirectly to predict product wafer test yield. In one implementation, the yield information includes a systematic yield (Y.sub.0), a defect density (DD), and a defect clustering factor (.alpha.) determined based on the inspected test structure's yield. A running average of the yield information for each process or defect mechanism is maintained as each wafer lot is processed. As a particular wafer lot moves through the various processes, a product wafer-sort test yield may be predicted at any stage in the fabrication process based on the running-average yield information maintained for previously fabricated wafer lots.

Owner:KLA TENCOR TECH CORP

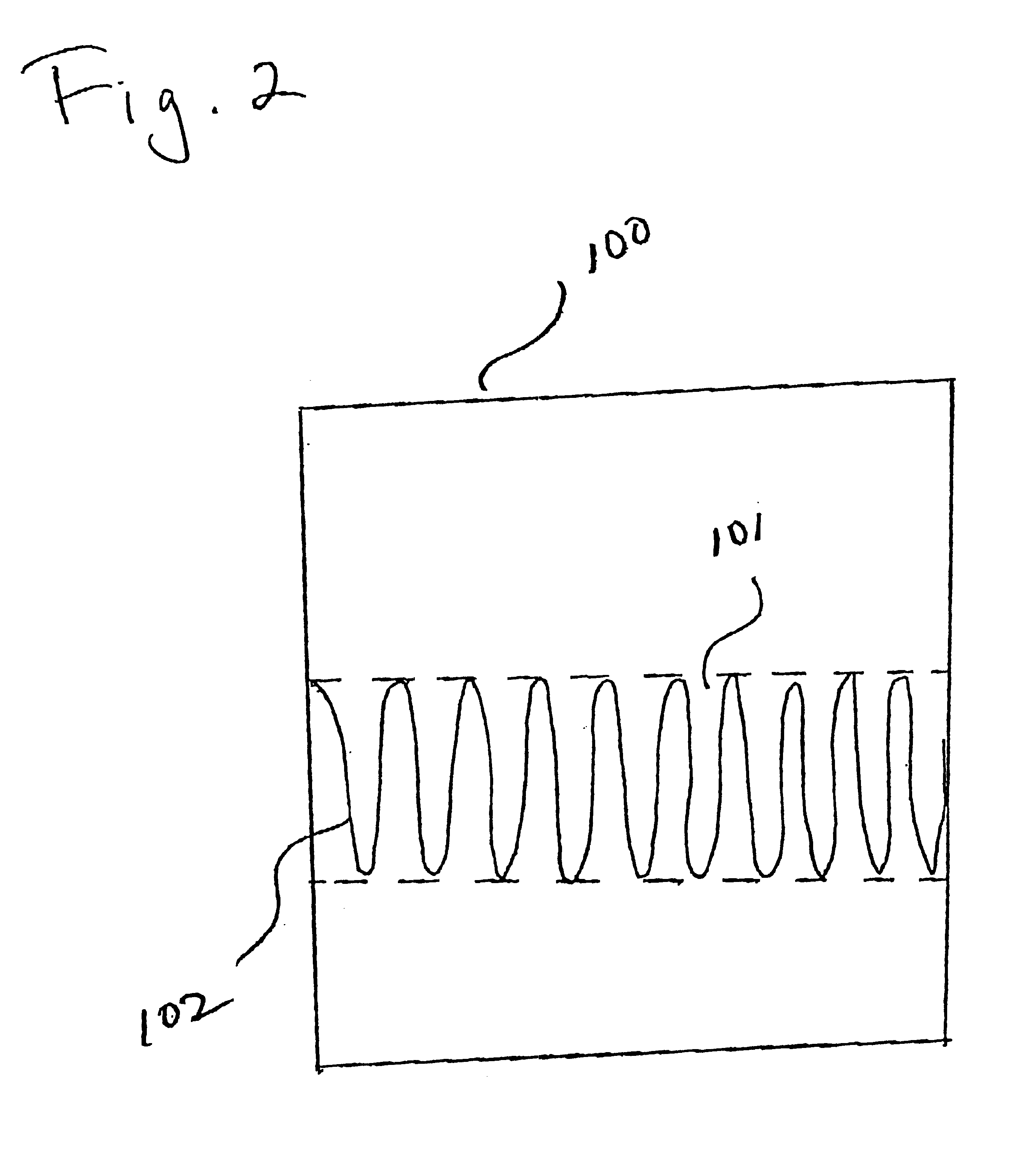

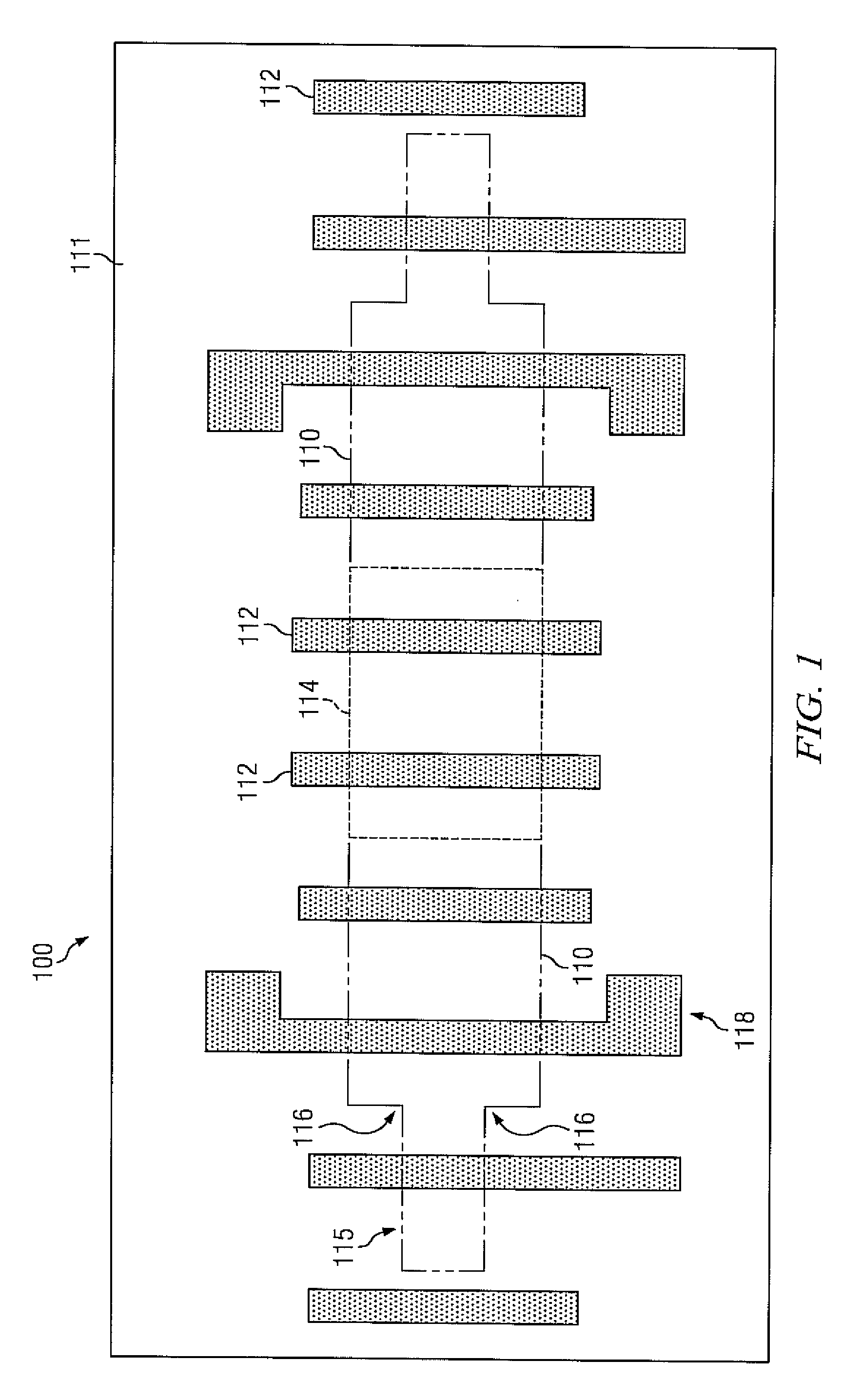

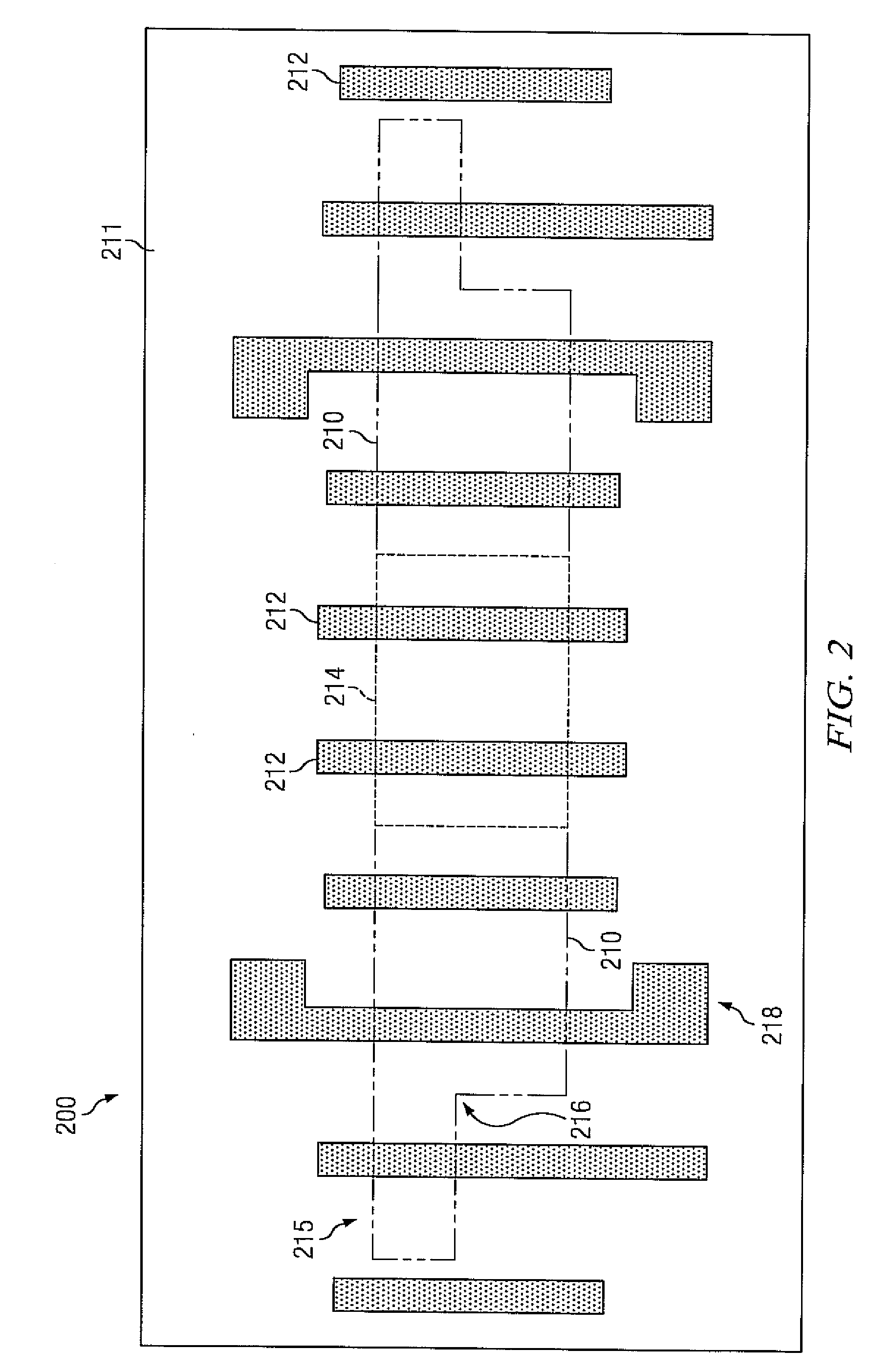

Stepper type test structures and methods for inspection of semiconductor integrated circuits

InactiveUS6633174B1Reduce pressureNanotechSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

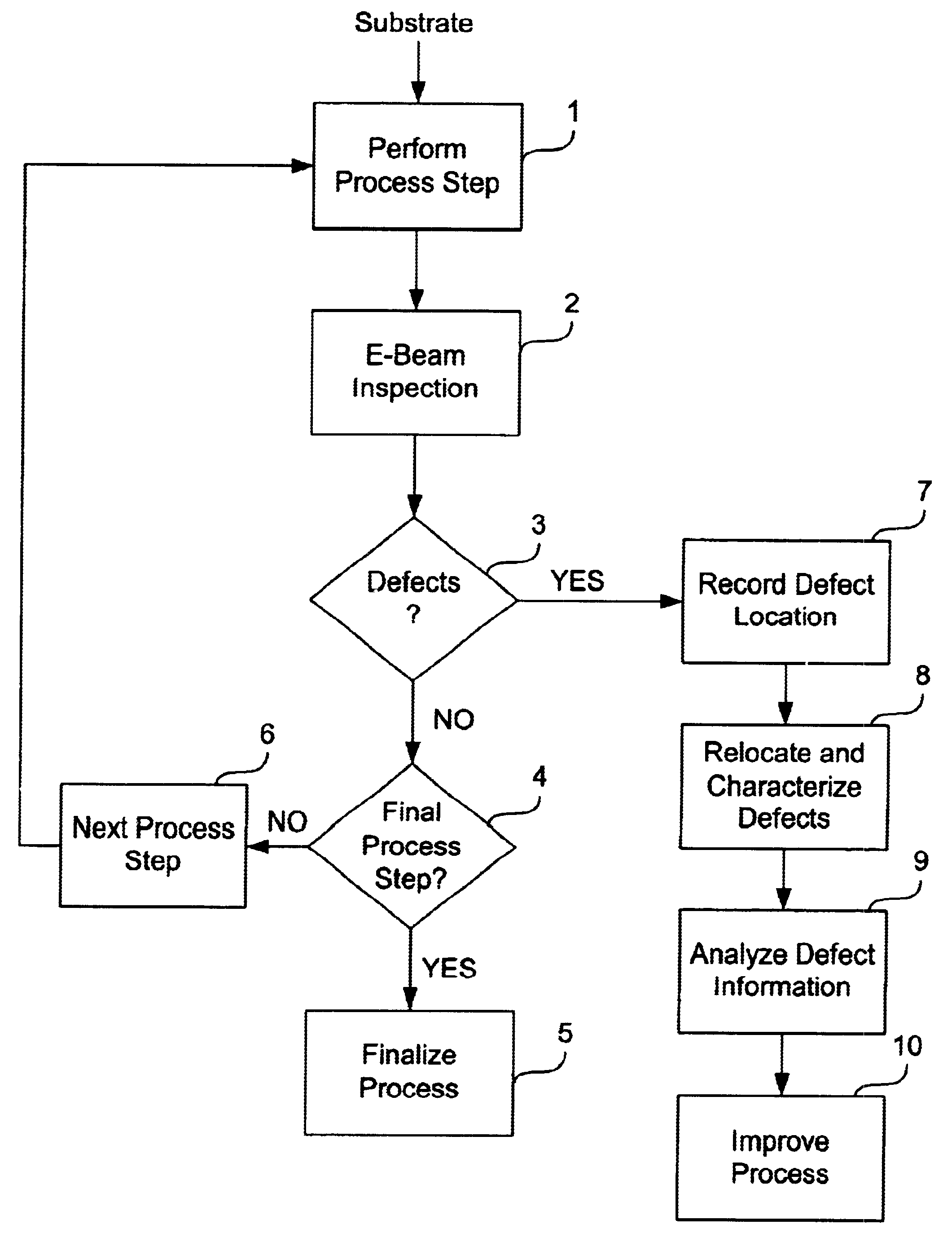

Disclosed is a method of inspecting a sample. The method includes moving to a first field associated with a first group of test structures. The first group of test structures are partially within the first field. The method further includes scanning the first field to determine whether there are any defects present within the first group of test structures. When it is determined that there are defects within the first group of test structures, the method further includes repeatedly stepping to areas and scanning such areas so as to determine a specific defect location within the first group of test structures. A suitable test structure for performing this method is also disclosed.< / PTEXT>

Owner:KLA TENCOR TECH CORP

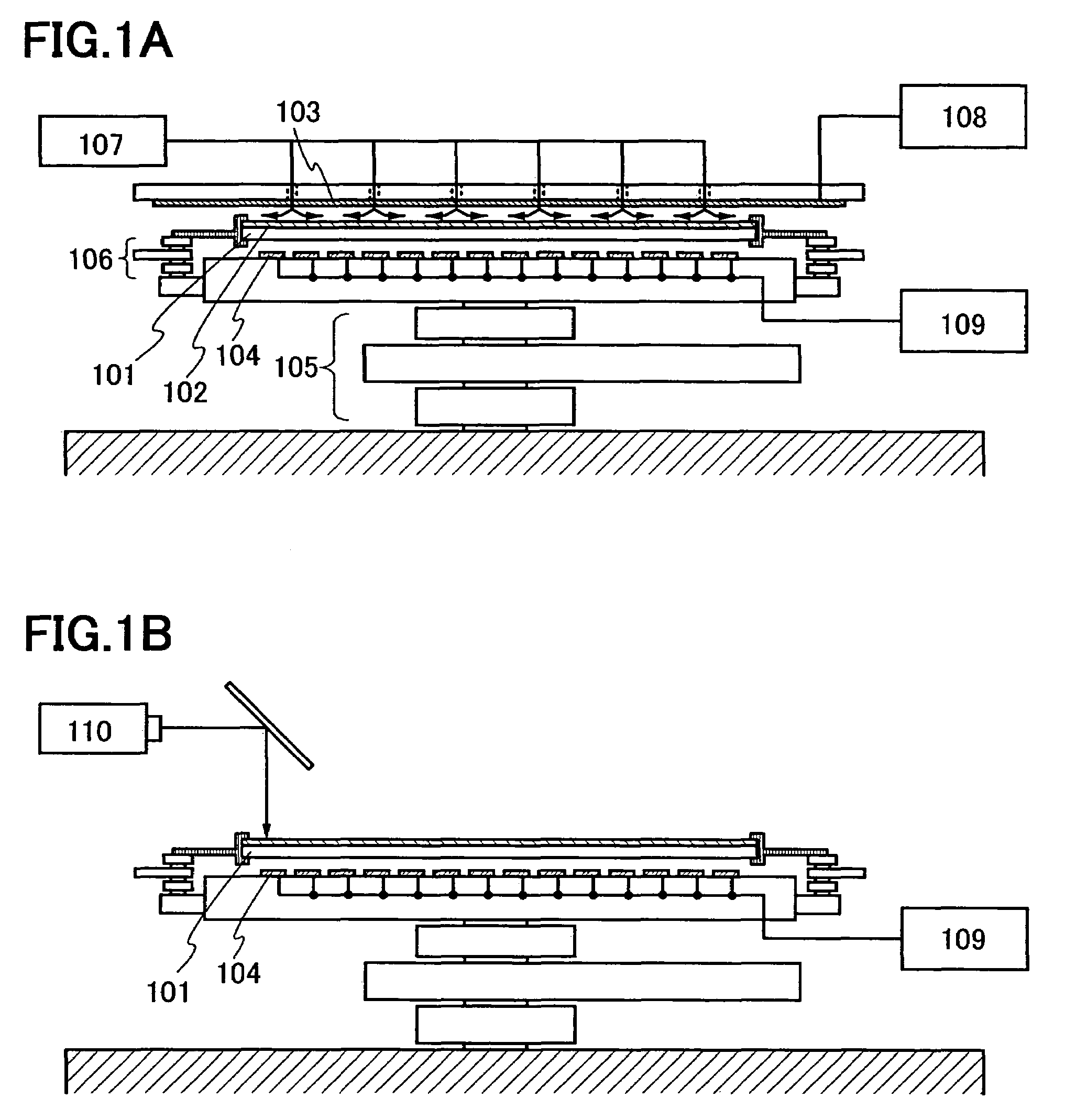

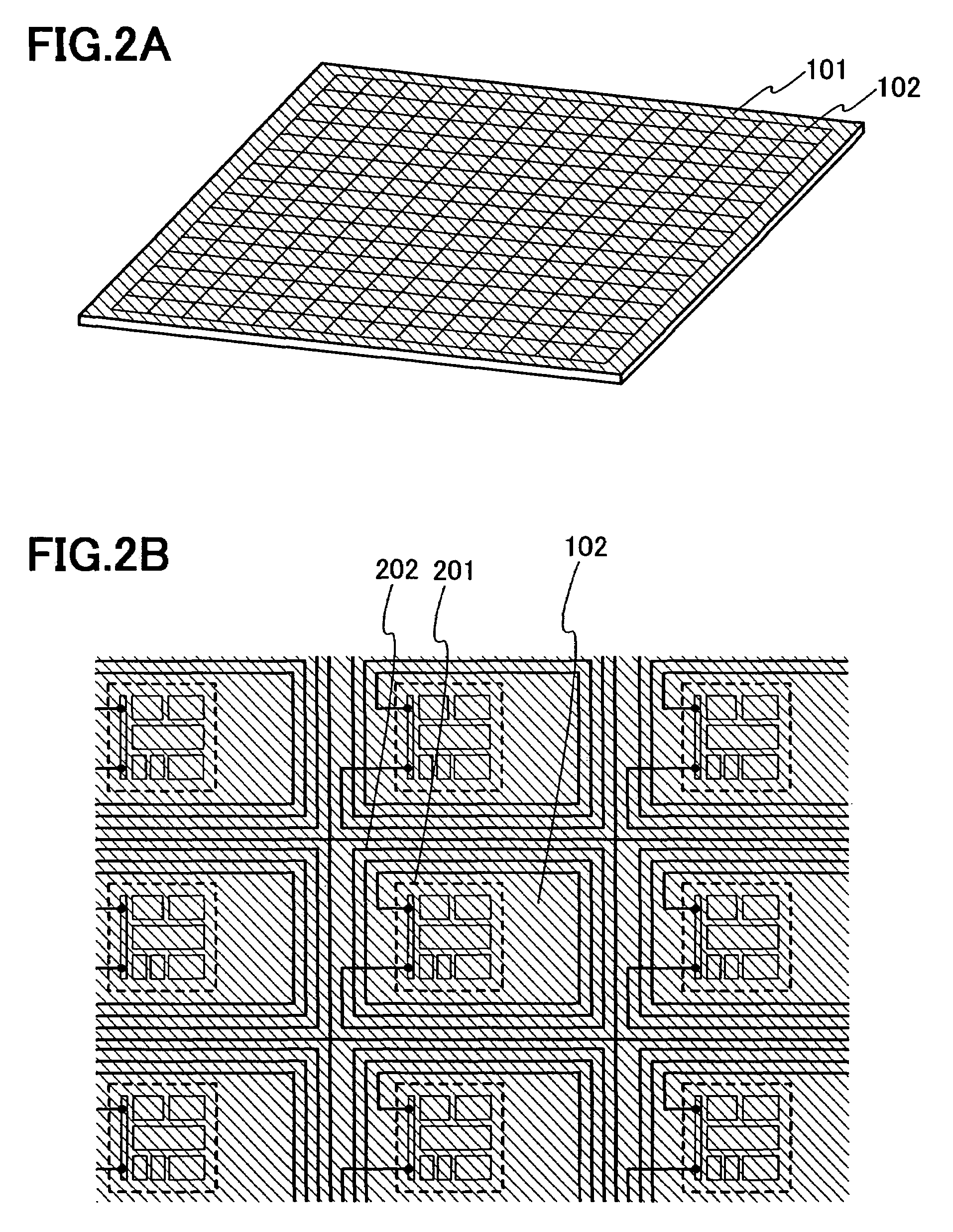

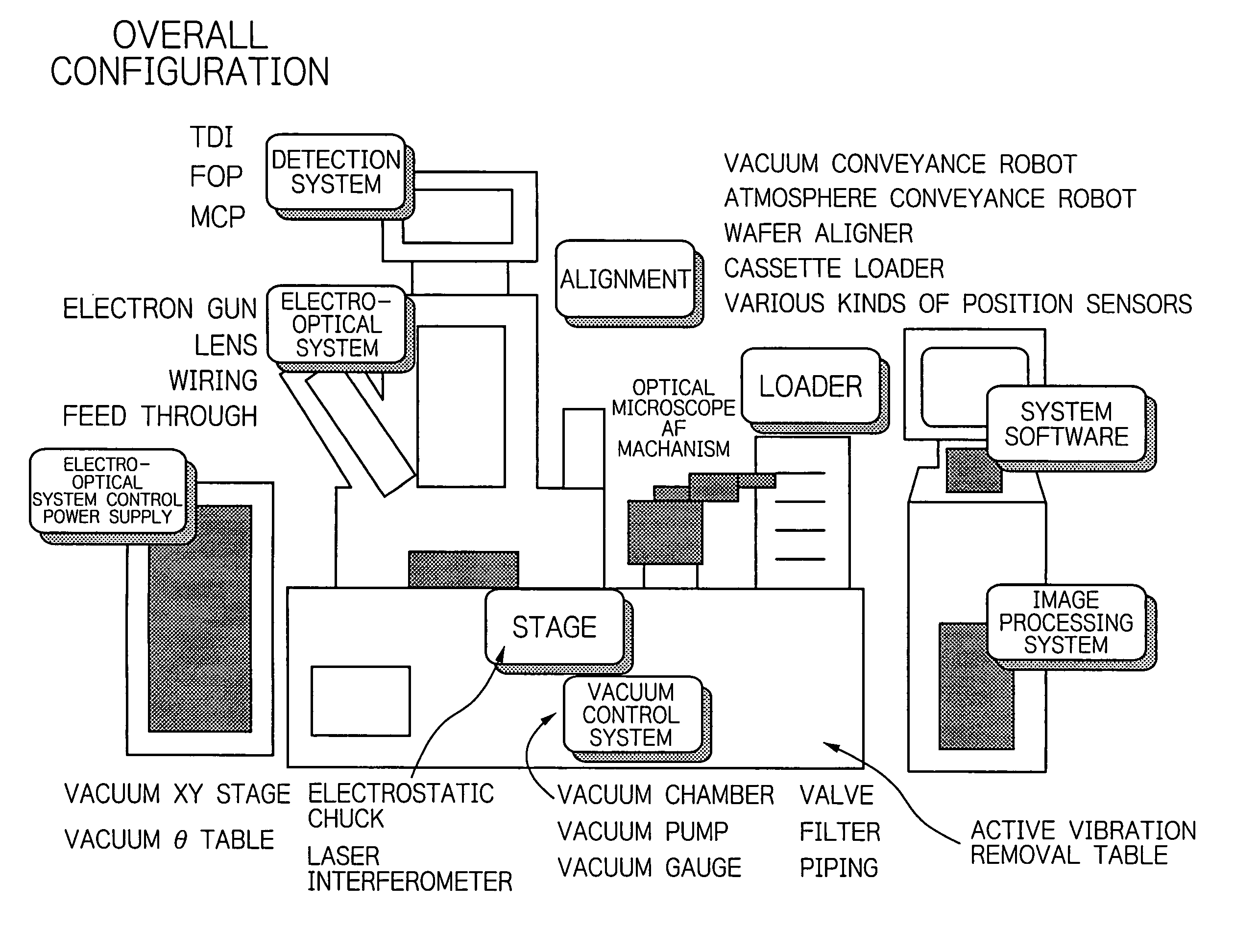

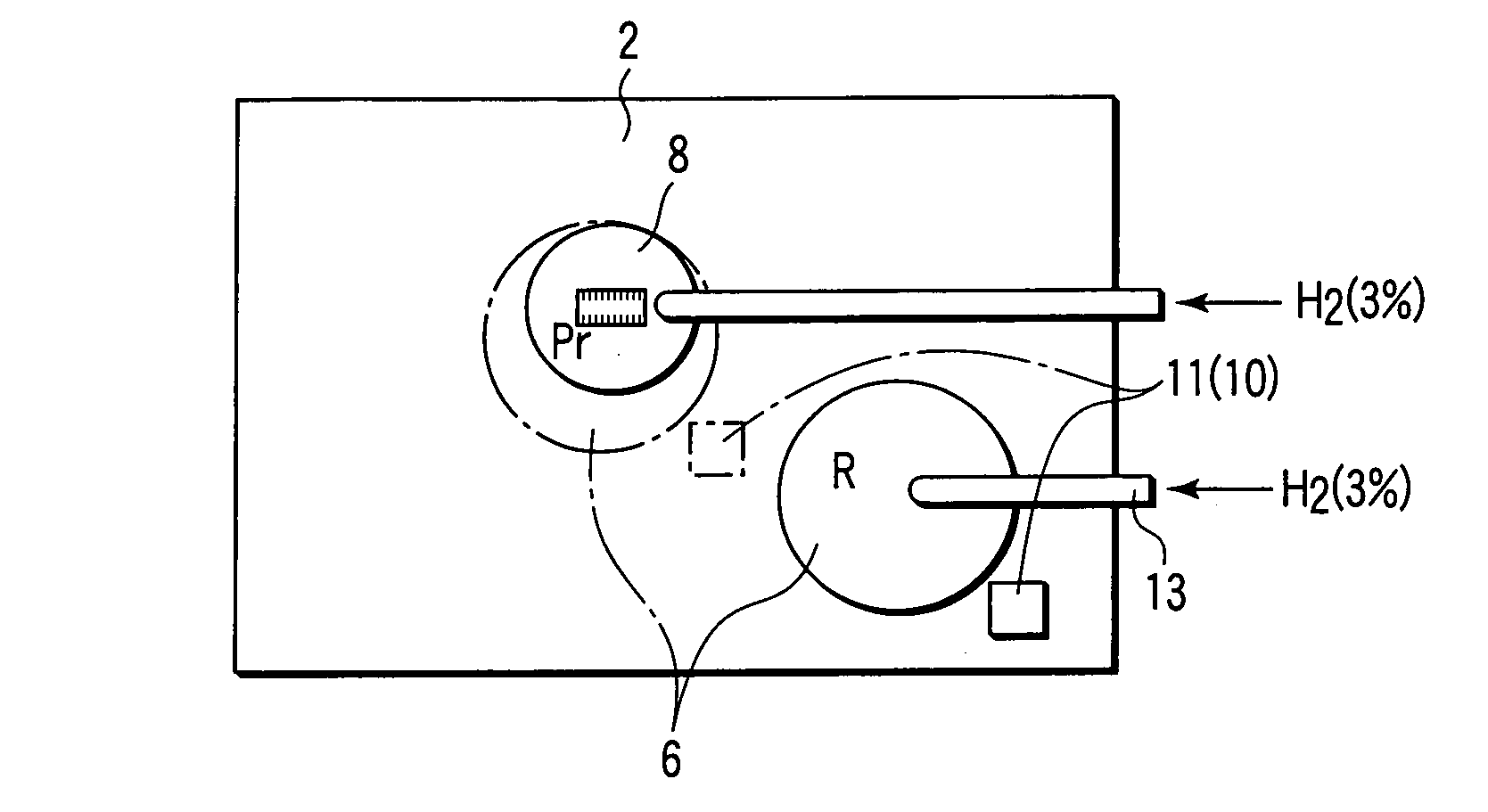

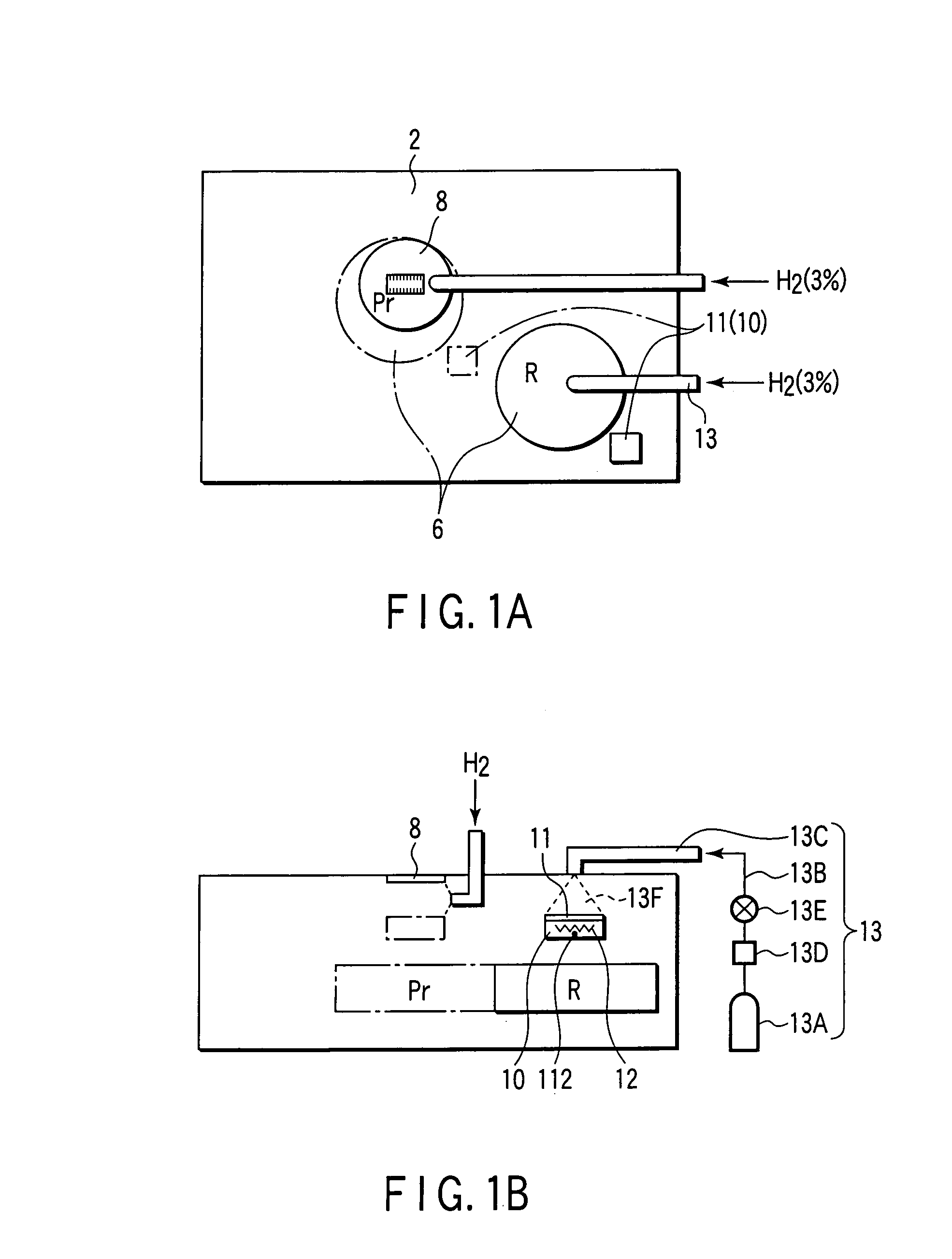

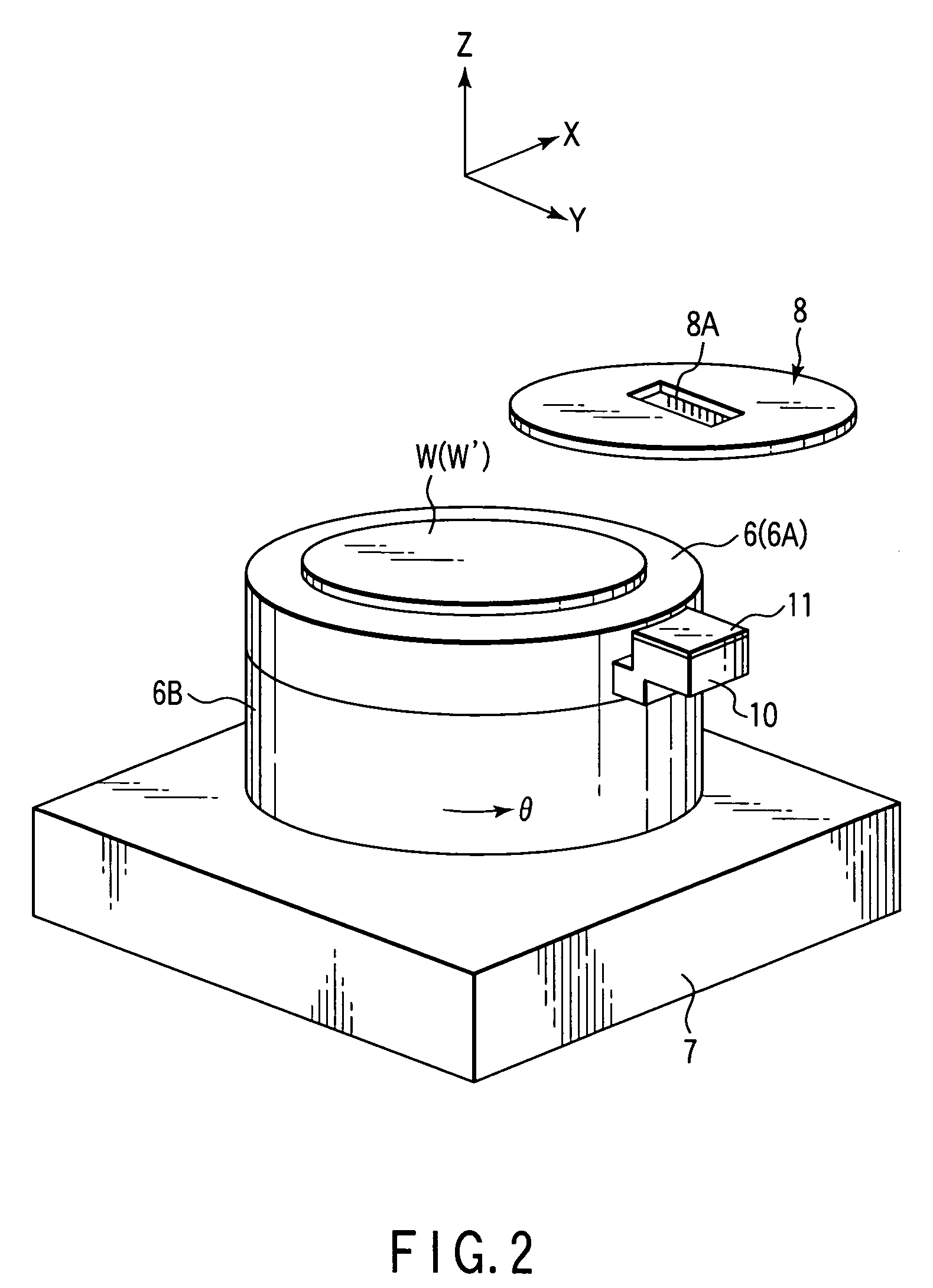

Inspection system, inspection method, and method for manufacturing semiconductor device

InactiveUS7112952B2Reduce in quantityImprove throughputTesting sensing arrangementsSemiconductor/solid-state device testing/measurementPosition controlSemiconductor

Owner:SEMICON ENERGY LAB CO LTD

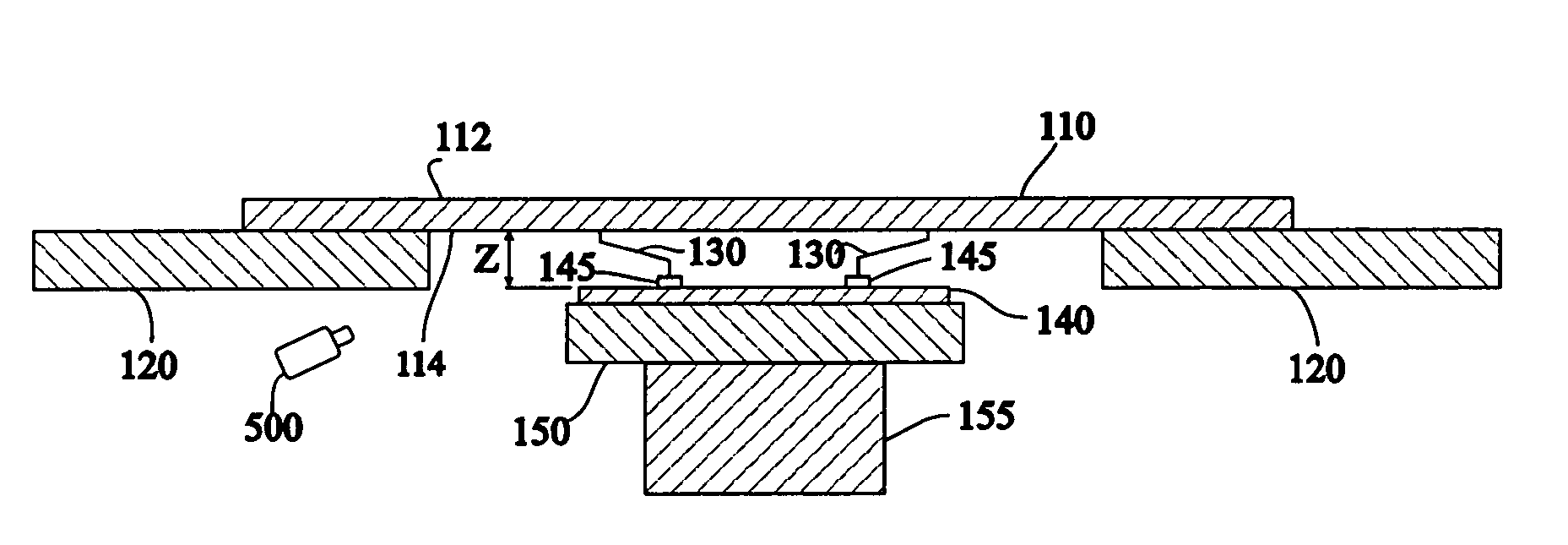

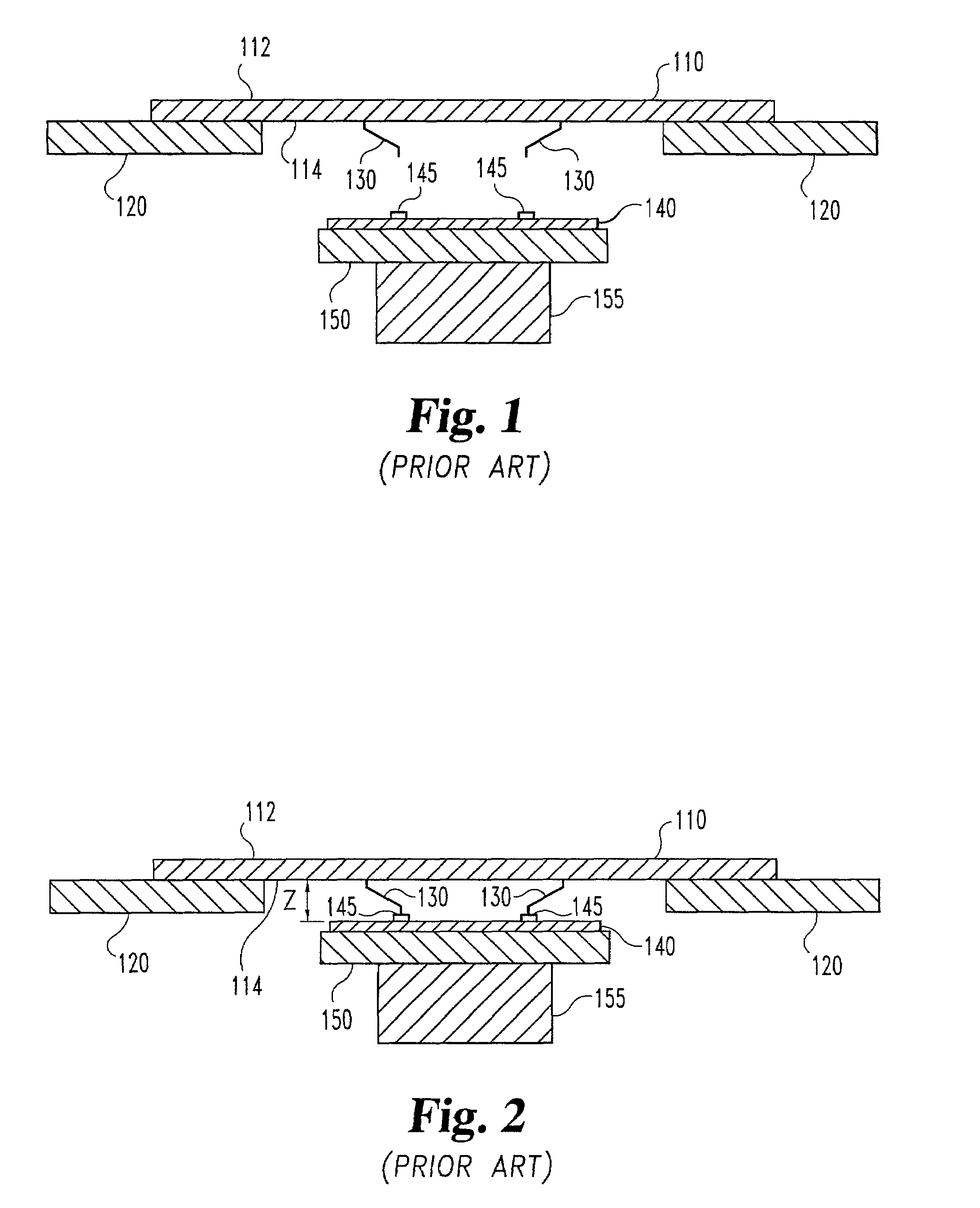

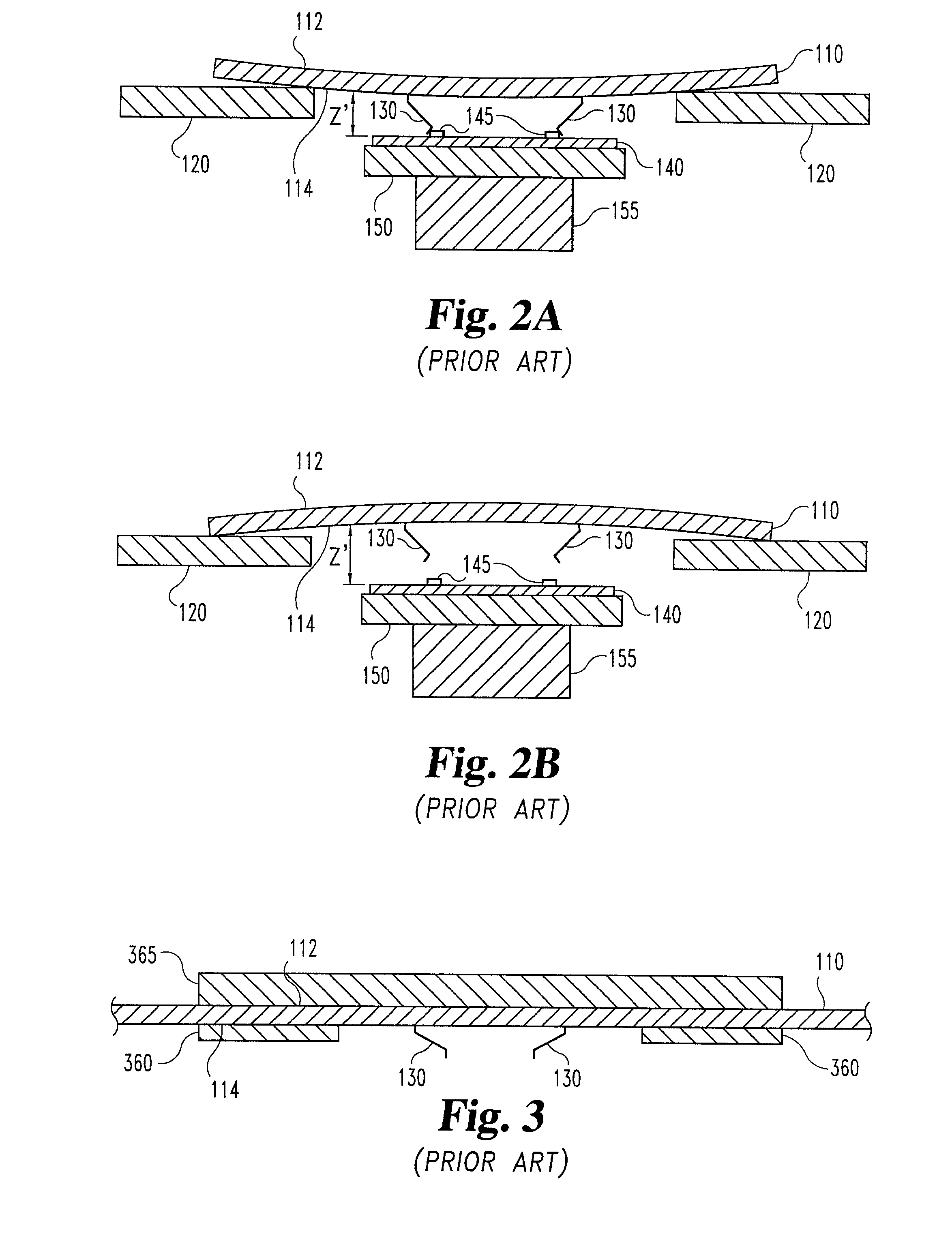

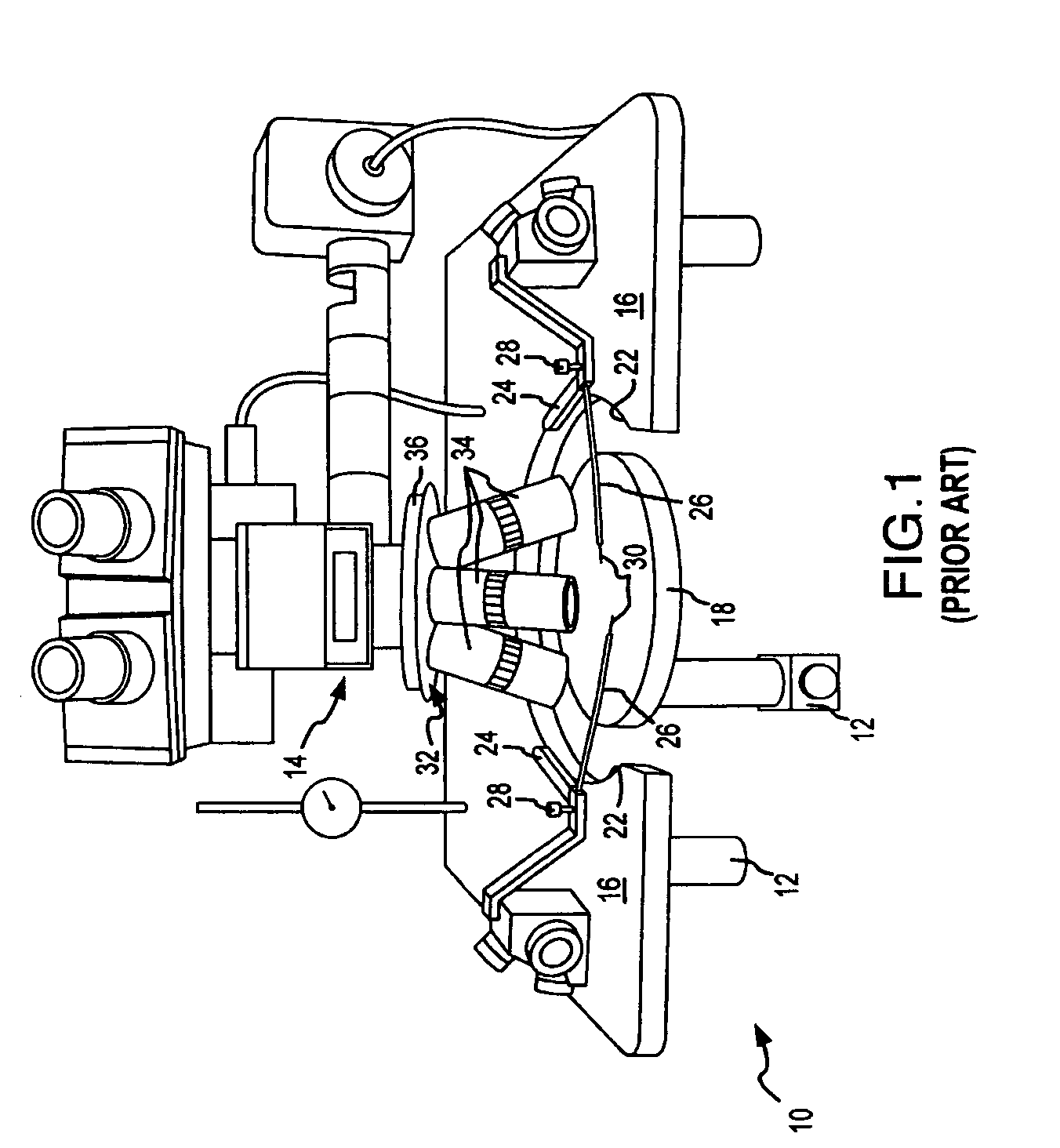

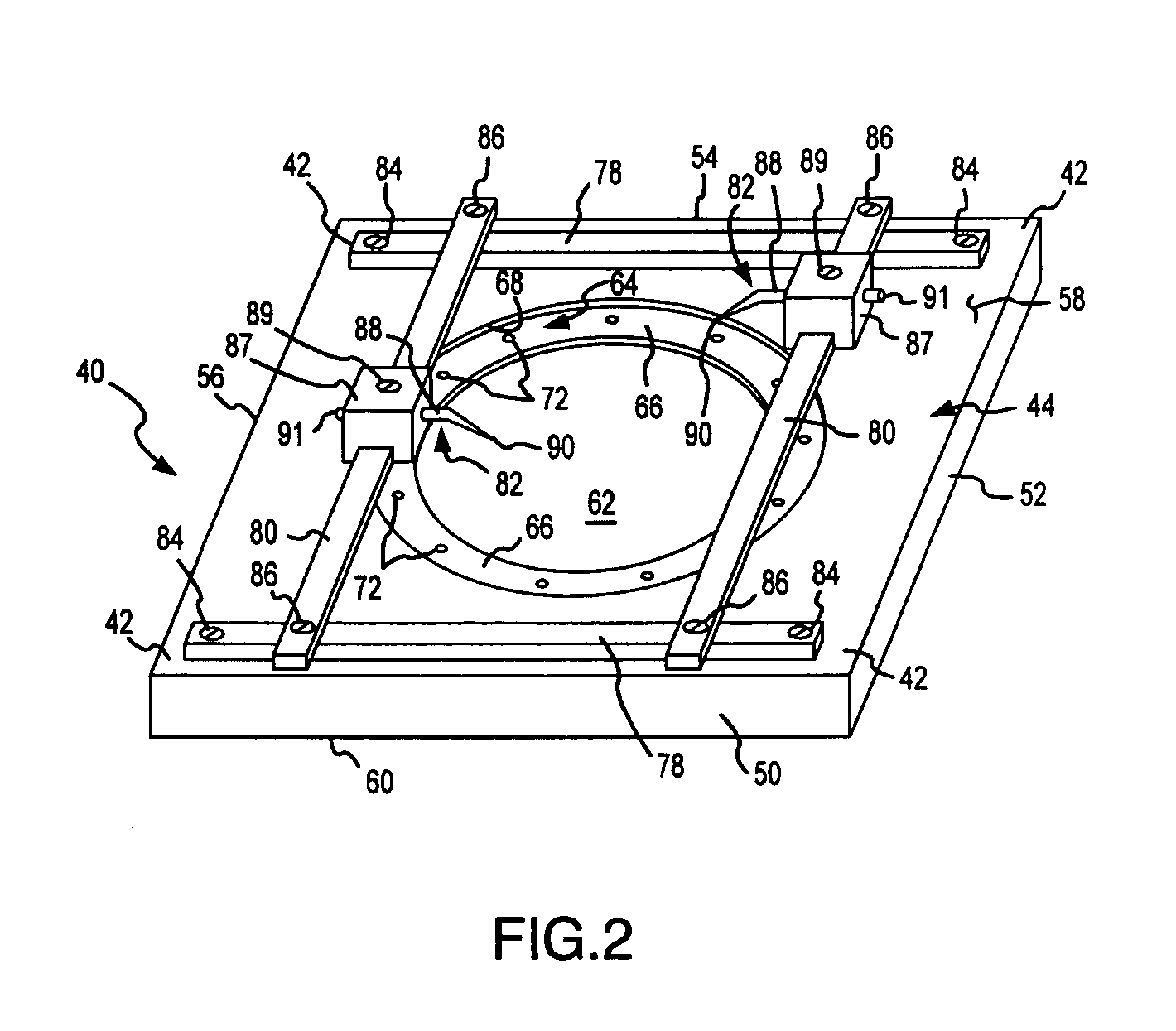

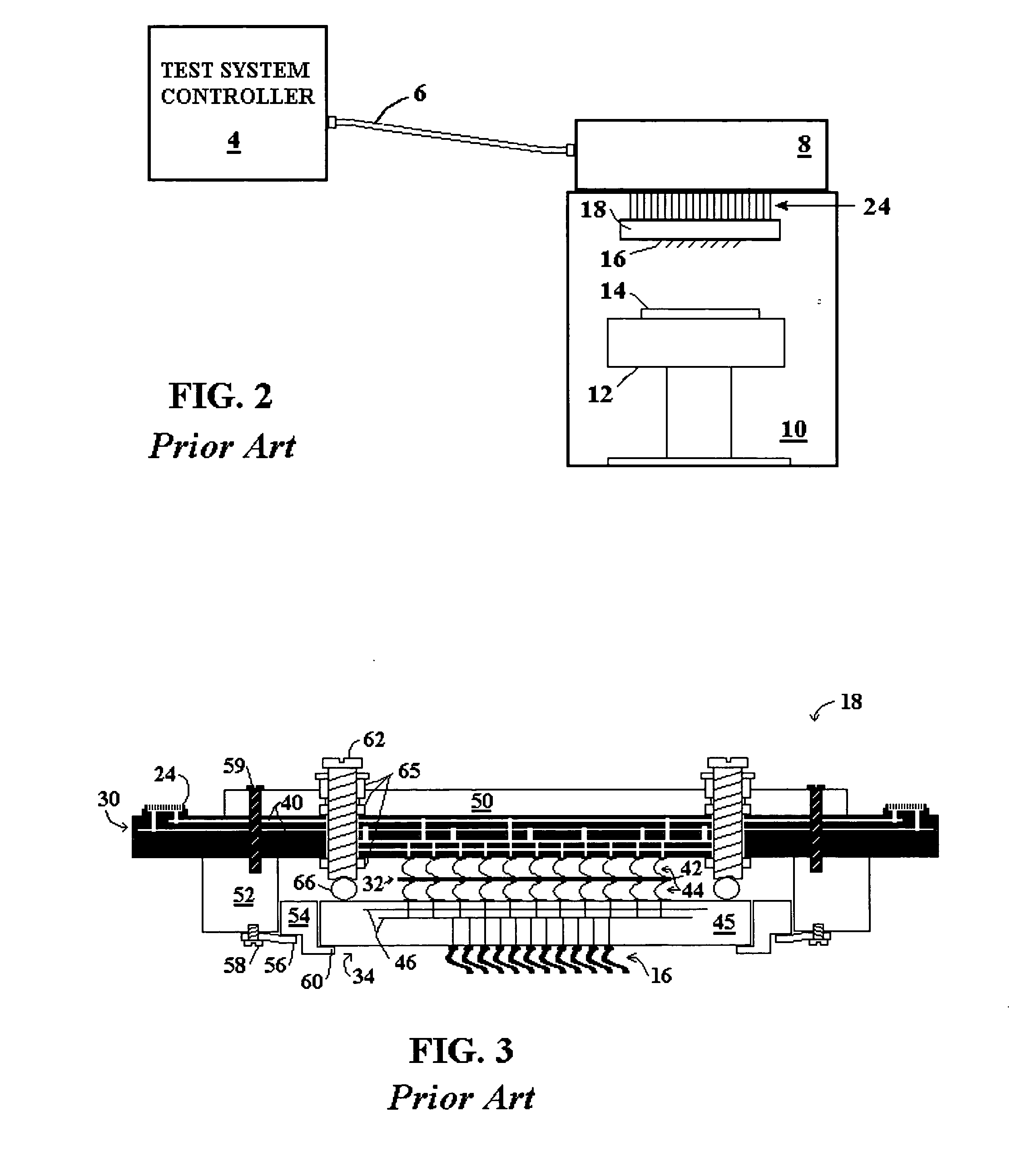

Method and system for compensating thermally induced motion of probe cards

InactiveUS7002363B2Electric/magnetic detection for well-loggingSemiconductor/solid-state device testing/measurementTemperature controlProbe card

The present invention discloses a method and system compensating for thermally induced motion of probe cards used in testing die on a wafer. A probe card incorporating temperature control devices to maintain a uniform temperature throughout the thickness of the probe card is disclosed. A probe card incorporating bi-material stiffening elements which respond to changes in temperature in such a way as to counteract thermally induced motion of the probe card is disclosed including rolling elements, slots and lubrication. Various means for allowing radial expansion of a probe card to prevent thermally induced motion of the probe card are also disclosed. A method for detecting thermally induced movement of the probe card and moving the wafer to compensate is also disclosed.

Owner:FORMFACTOR INC

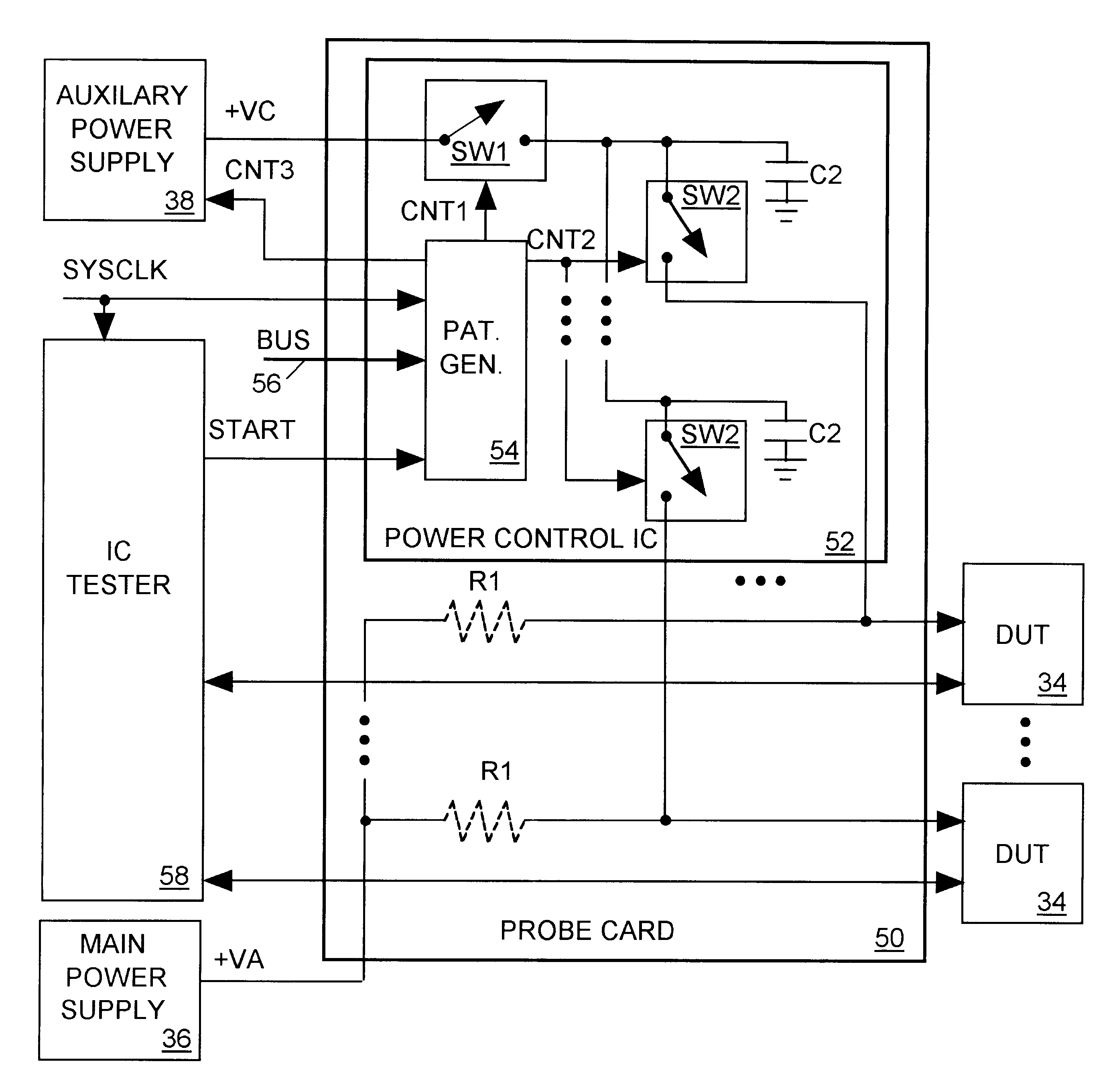

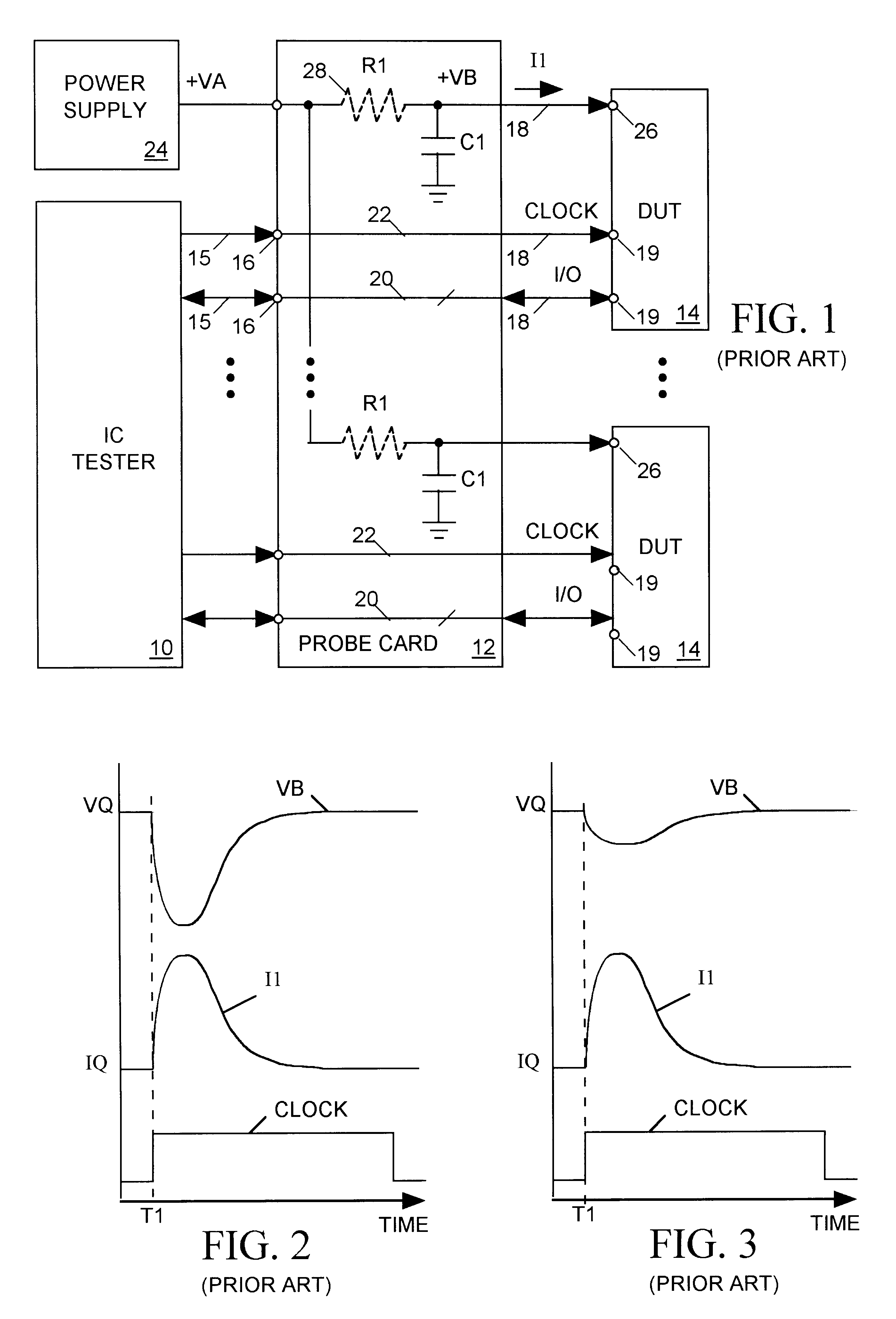

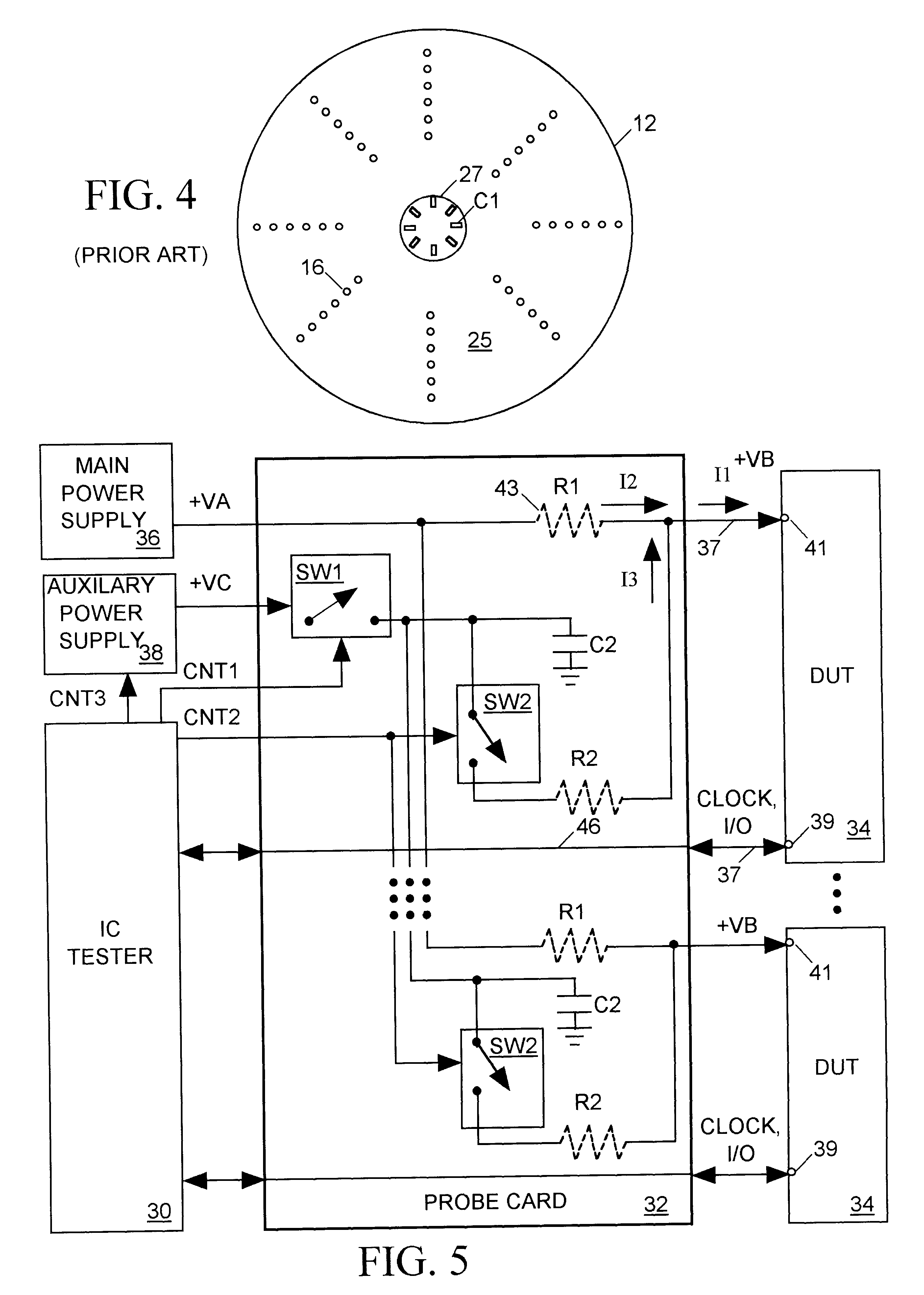

Apparatus for reducing power supply noise in an integrated circuit

InactiveUS6339338B1Reduce power supply noiseSuppress mutationDigital circuit testingVolume/mass flow measurementCapacitanceState variation

A main power supply continuously provides a current to a power input terminal of an integrated circuit device under test (DUT). The DUT's demand for current at the power input terminal temporarily increases during state changes in synchronous logic circuits implemented within the DUT. To limit variation (noise) in voltage at the power input terminal arising from these temporary increases in current demand, a charged capacitor is connected to the power input terminal during each DUT state change. The capacitor discharges into the power input terminal to supply additional current to meet the DUT's increased demand. Following each DUT state change the capacitor is disconnected from the power input terminal and charged to a level sufficient to meet a predicted increase in current demand during a next DUT state change.

Owner:FORMFACTOR INC

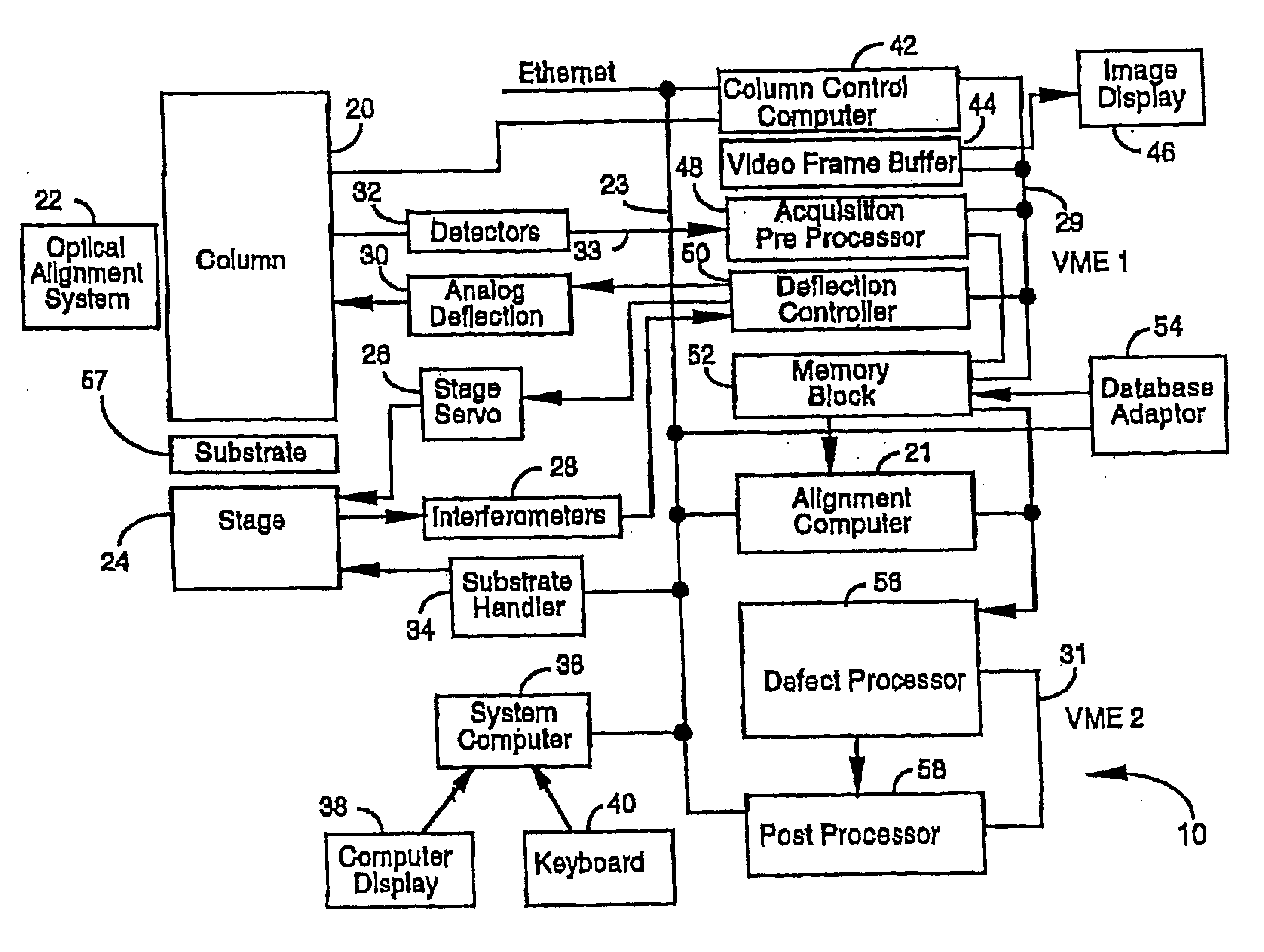

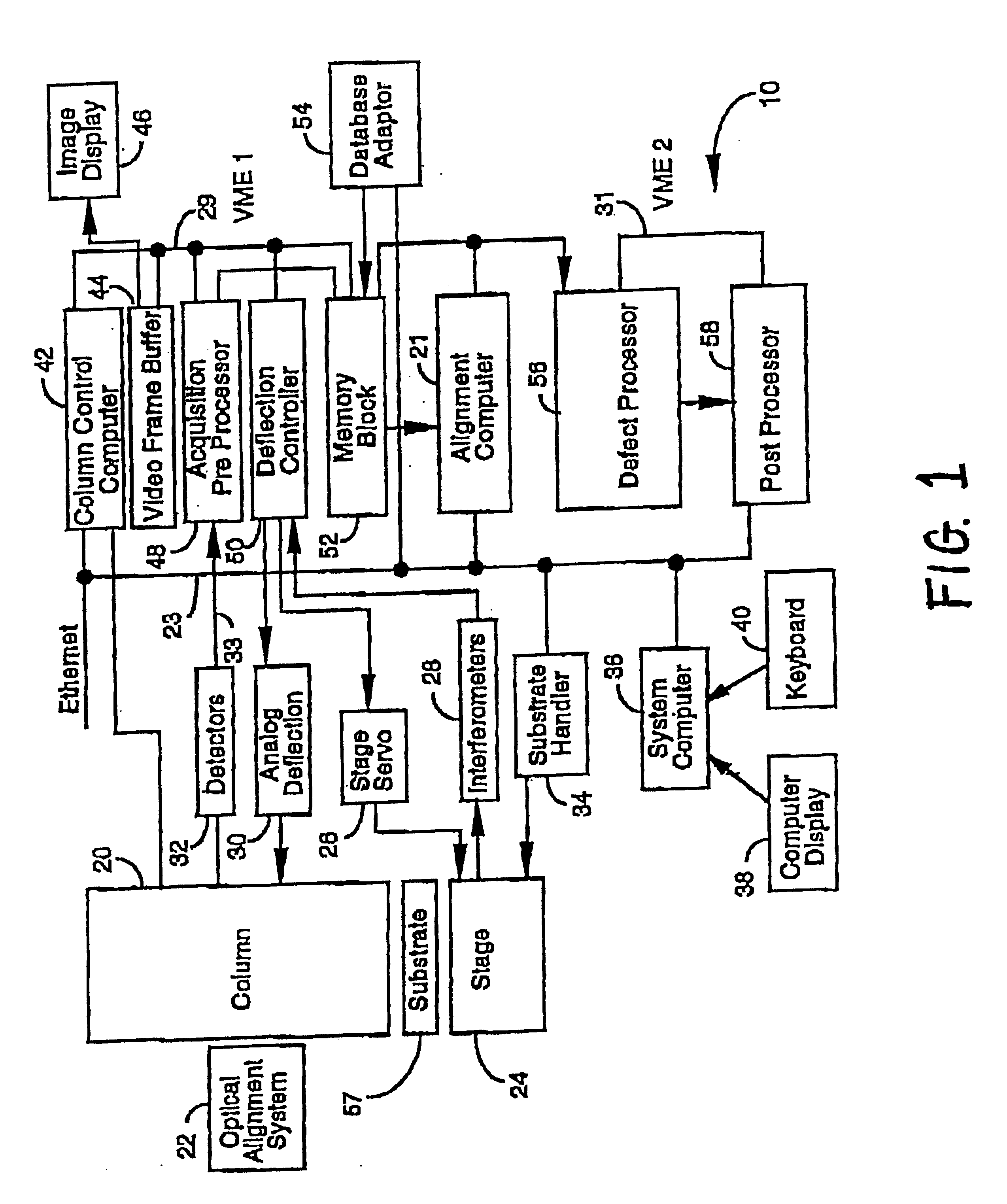

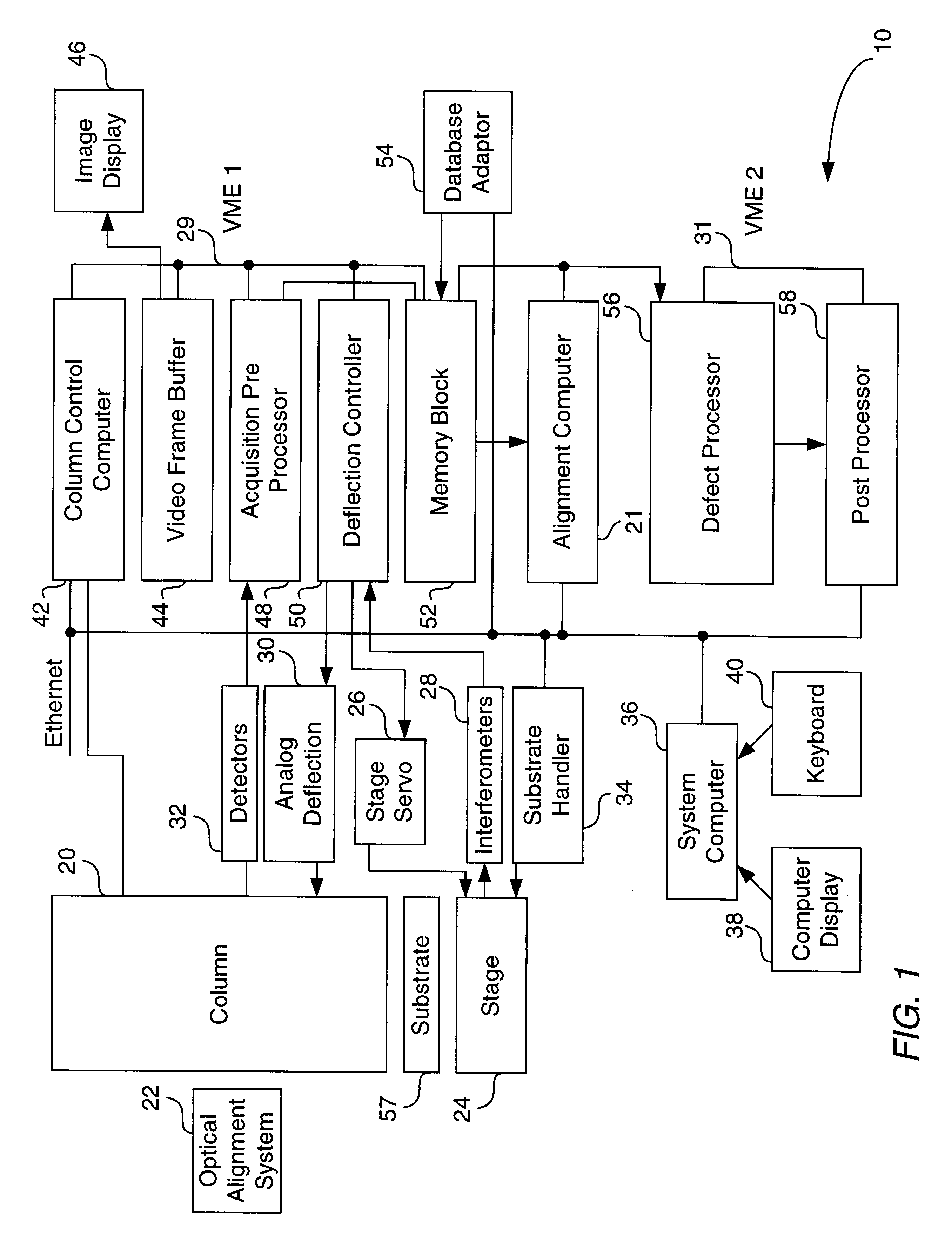

Methods and apparatus for optimizing semiconductor inspection tools

InactiveUS6433561B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

Disclosed is a method of inspecting a sample. At least a portion of the sample is illuminated. Signals received from the illuminated portion are detected, and the detected signals are processed to find defects present on the sample. The processing of the detected signals is optimized, at least in part, based upon results obtained from voltage contrast testing. In one implementation, the illumination is an optical illumination. In another embodiment, the processing comprises automated defect classification, and setup of the automated classification is optimized using the results obtained from voltage contrast testing. In another implementation, the results relate to a probability that a feature present on the sample represents an electrical defect.

Owner:KLA TENCOR TECH CORP

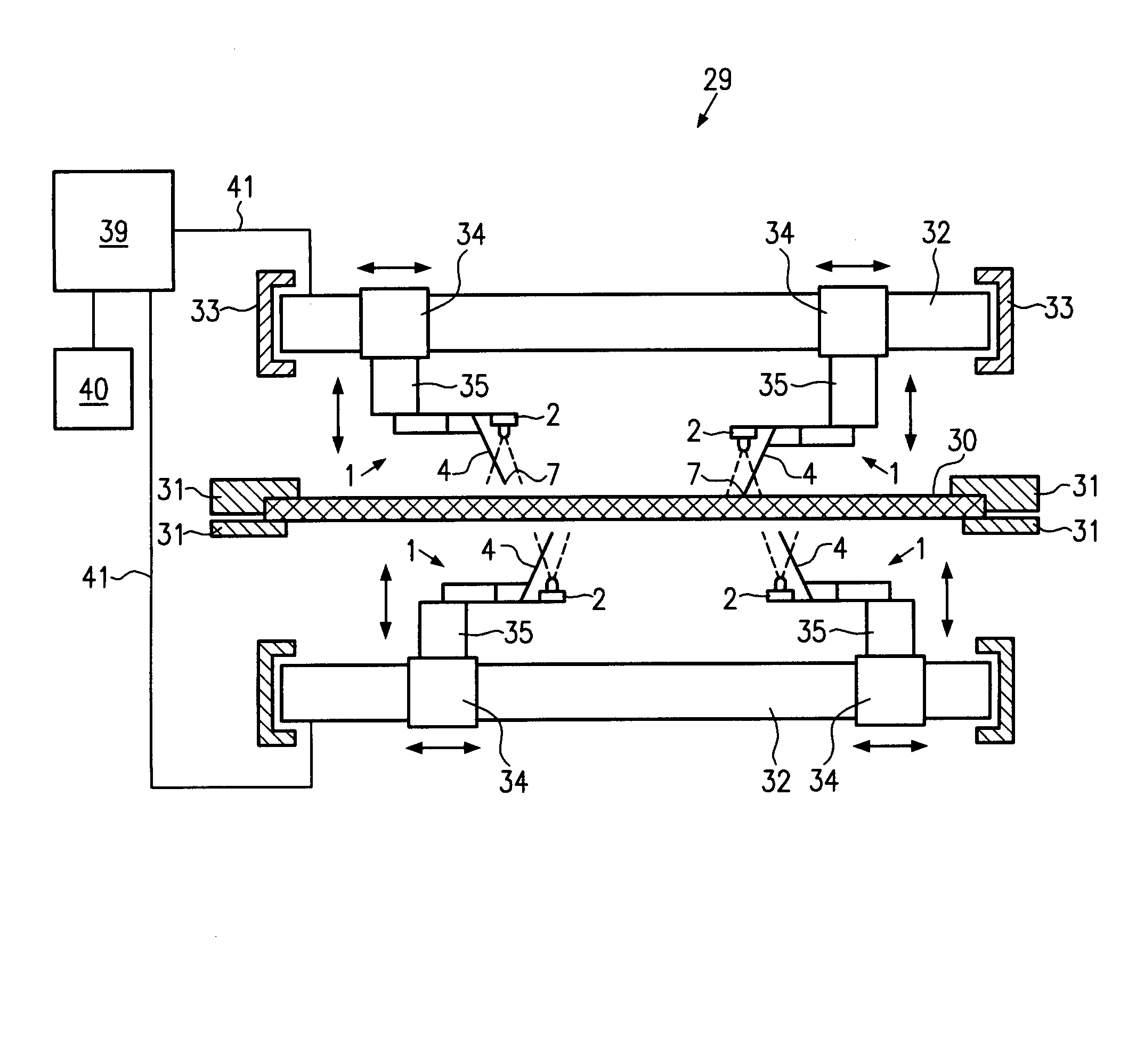

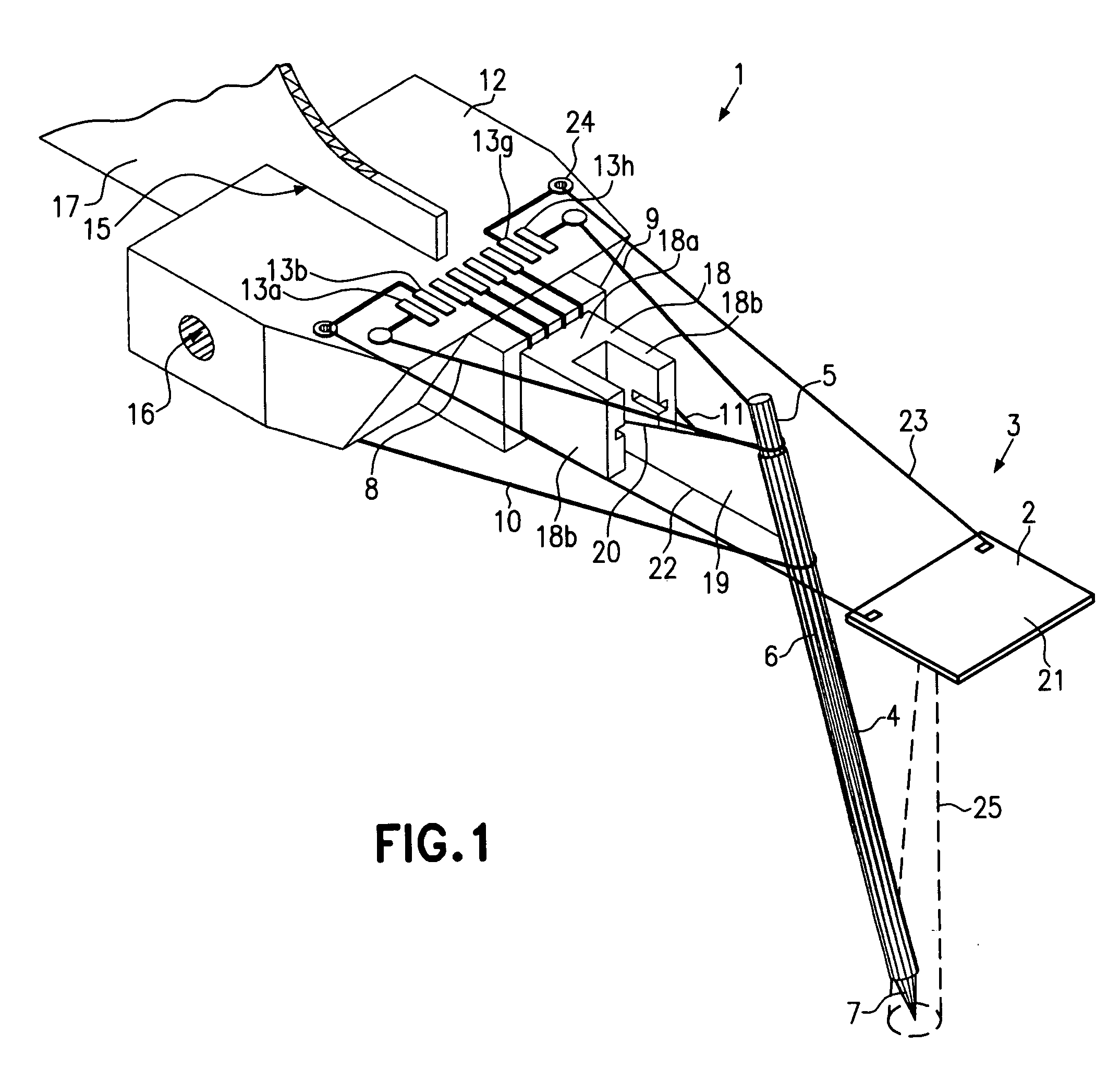

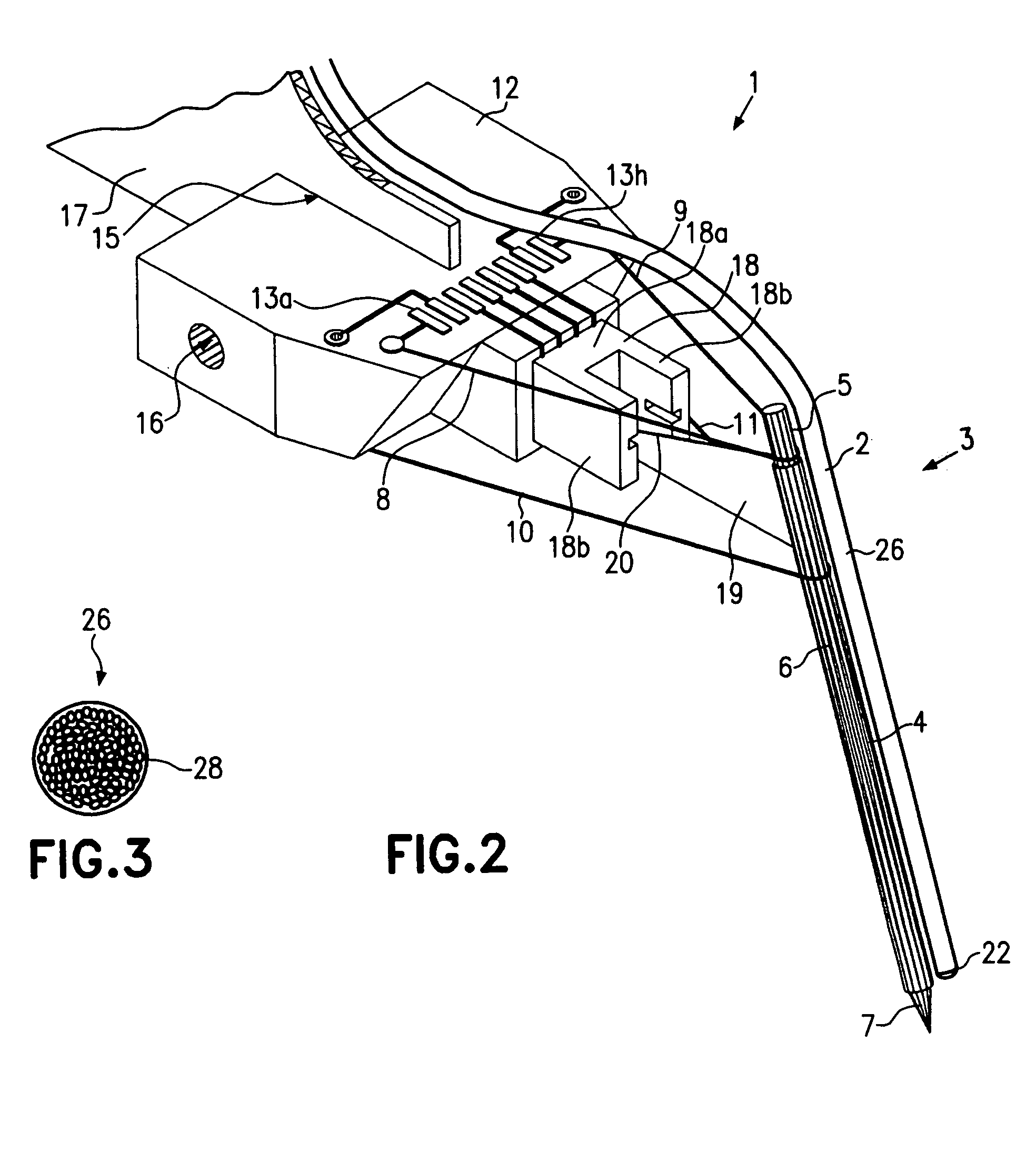

Apparatus and method for the testing of circuit boards, and test probe for this apparatus and this method

InactiveUS7015711B2Improve reliabilityLess calibration timeMeasurement leads/probesPrinted circuit testingTest probeTest point

An apparatus and a method for the testing of circuit boards, together with a test probe for this apparatus and this method, in which the contact tips of a test finger of a finger tester are monitored during the testing process by an optical detection device and their movement, at least when approaching a part of the circuit board test points of a circuit board to be tested, is corrected on the basis of the result determined by the optical detection device in such a way that the contact tip makes reliable contact with the circuit board test point concerned. The correction data hereby obtained may be used in the calculation of calibration data.

Owner:ATG TEST SYST

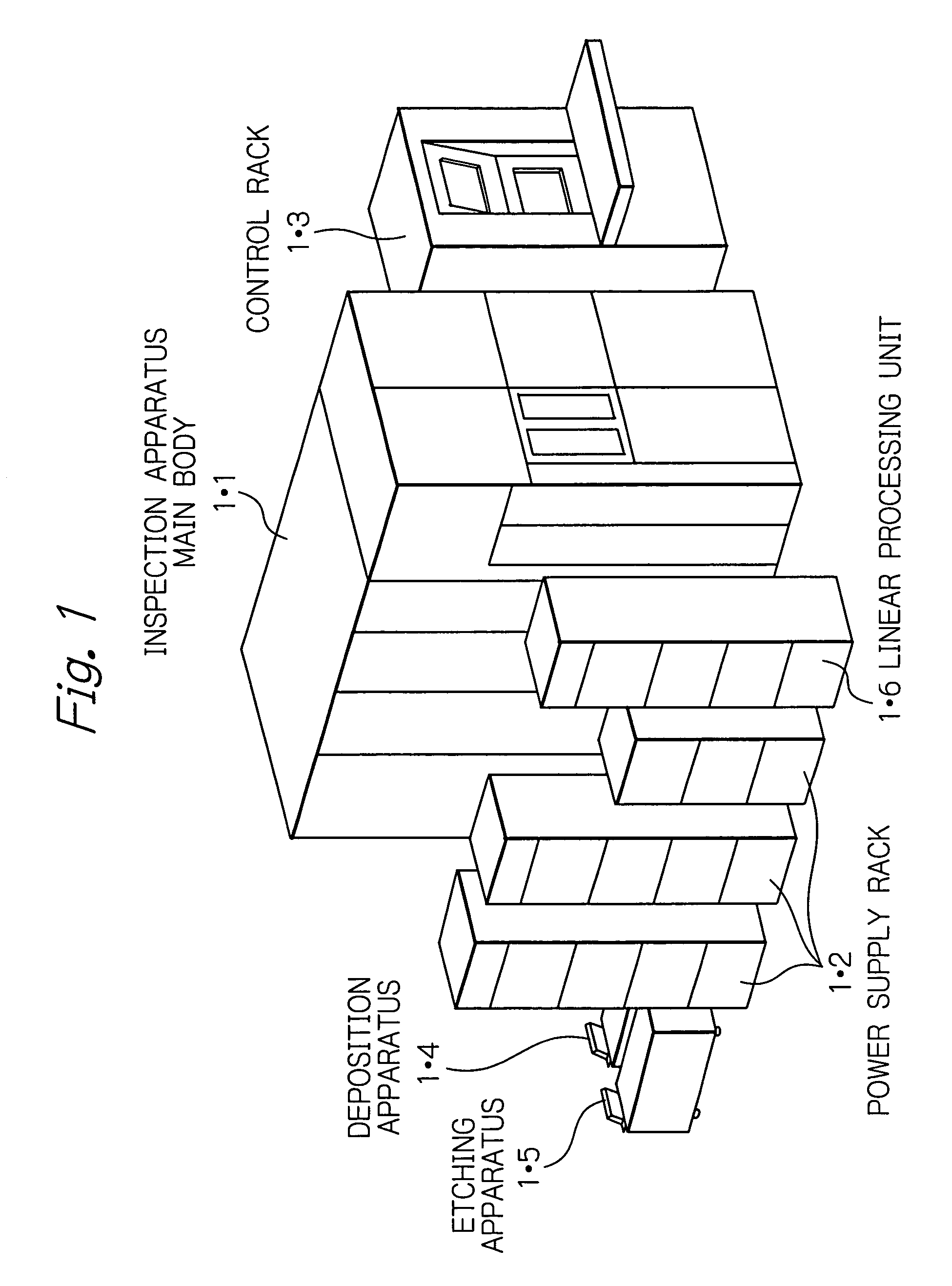

Testing apparatus using charged particles and device manufacturing method using the testing apparatus

ActiveUS7138629B2Material analysis using wave/particle radiationElectric discharge tubesIlluminanceBeam source

Owner:EBARA CORP

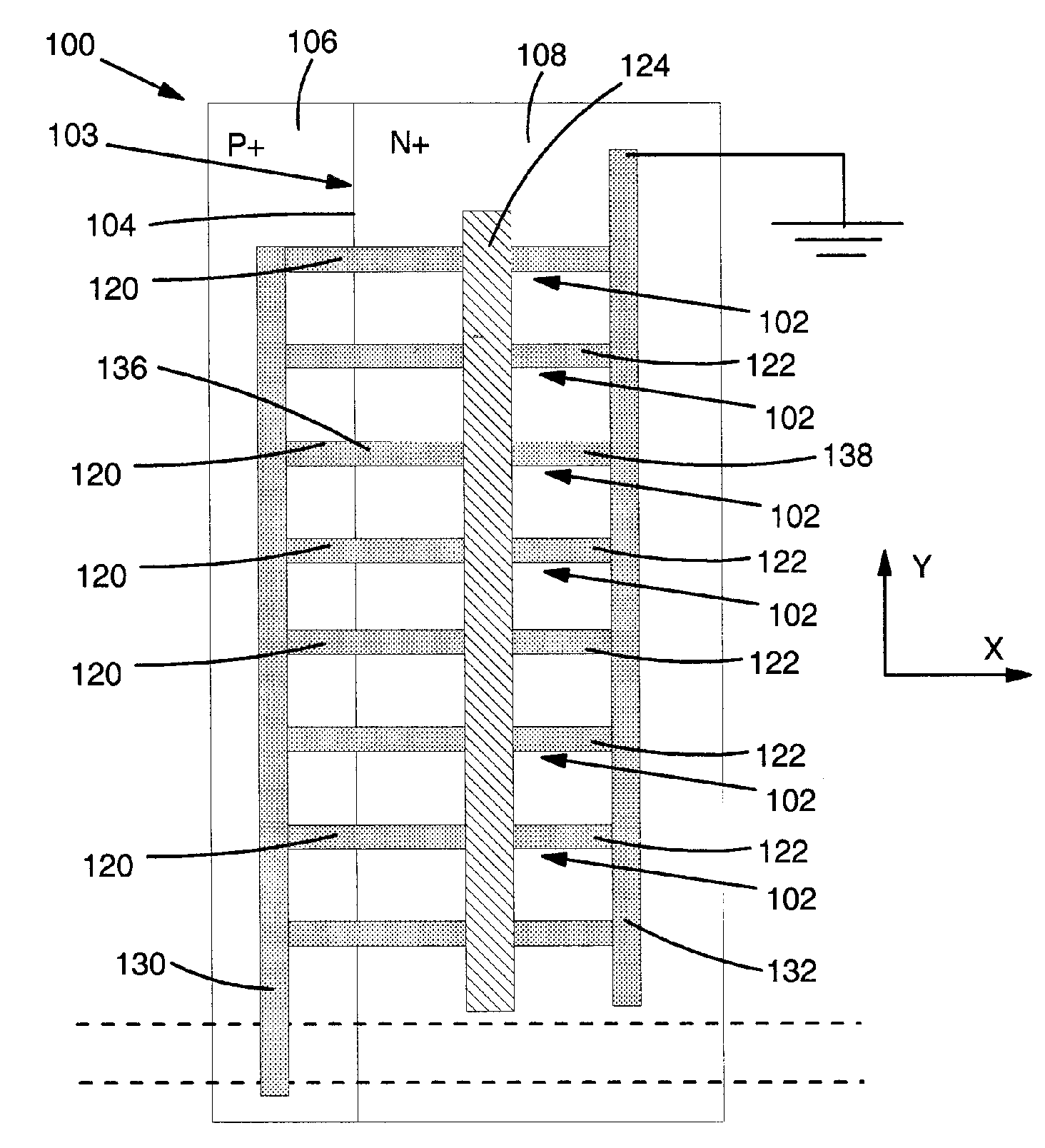

Inspectable buried test structures and methods for inspecting the same

InactiveUS6509197B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesVoltage contrastSemiconductor

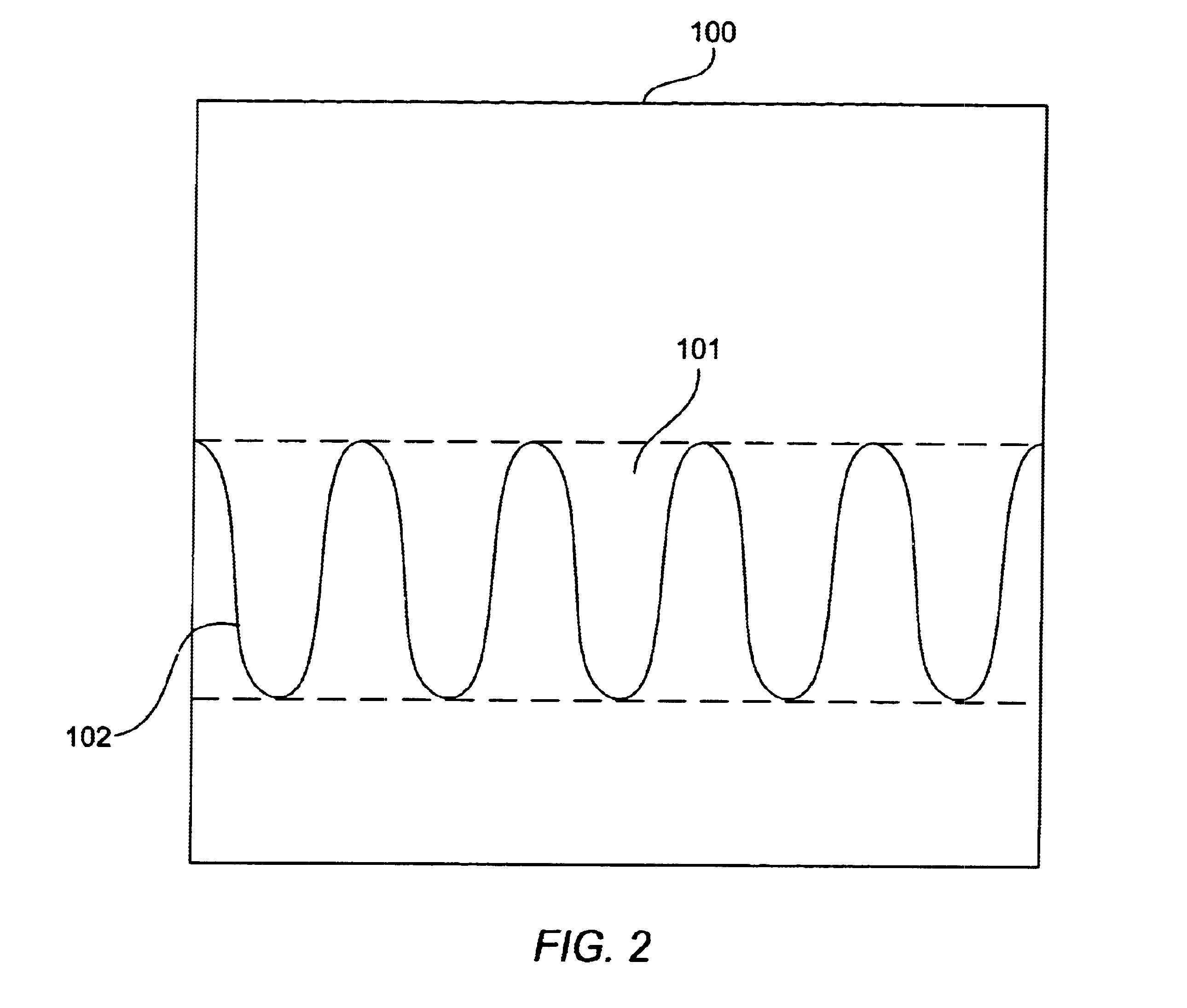

Disclosed is a semiconductor die having a lower test structure formed in a lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end. The first end is coupled to a predetermined voltage level. The semiconductor die also includes an insulating layer formed over the lower metal layer. The die further includes an upper test structure formed in an upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure. The upper metal layer is formed over the insulating layer. In a specific implementation, the first end of the lower test structure is coupled to ground. In another embodiment, the semiconductor die also includes a substrate and a first via coupled between the first end of the lower test structure and the substrate. In yet another aspect, the lower test structure is an extended metal line, and the upper test structure is a voltage contrast element. Methods for inspecting and fabricating such semiconductor die are also disclosed.

Owner:KLA TENCOR CORP

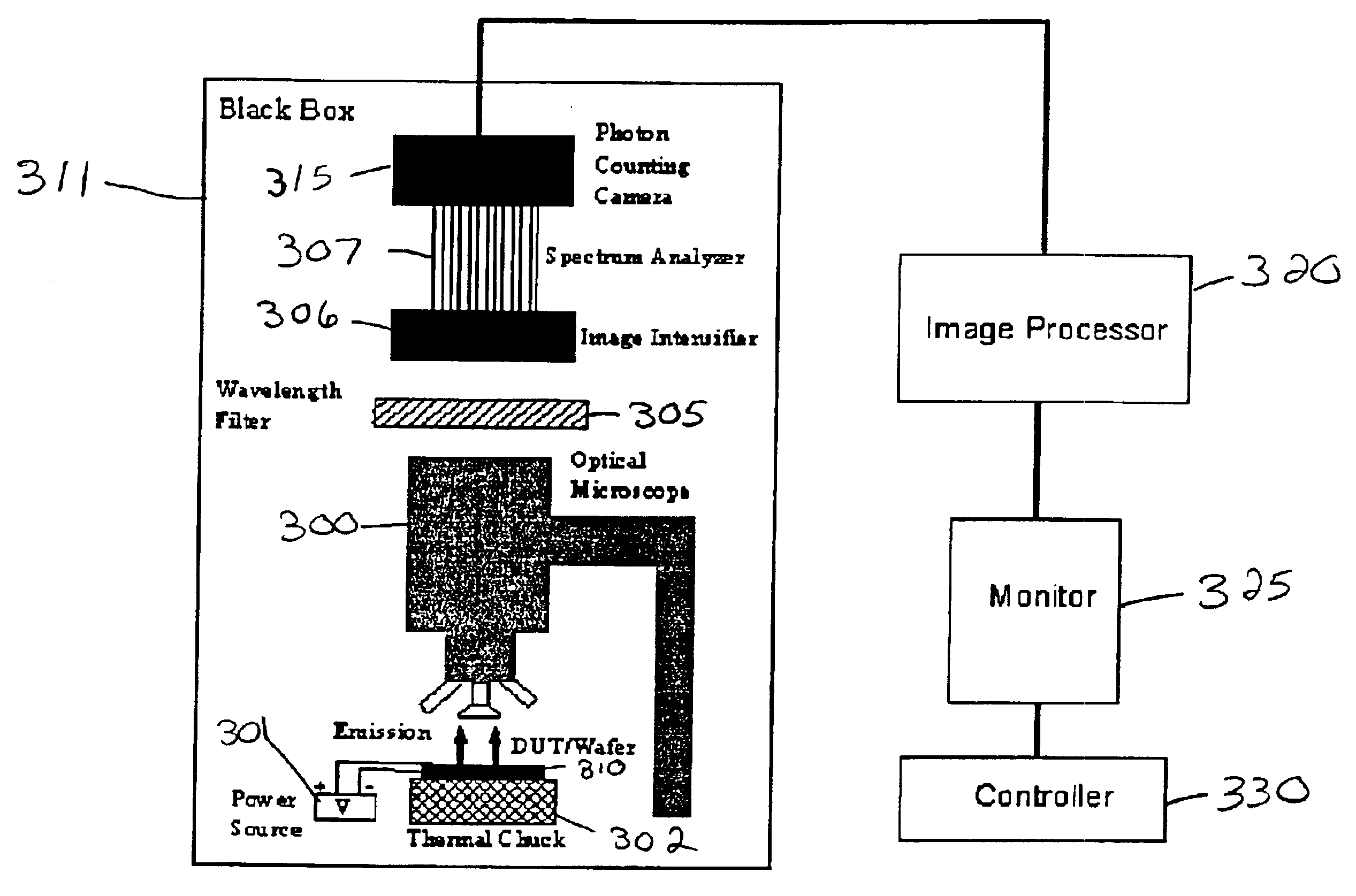

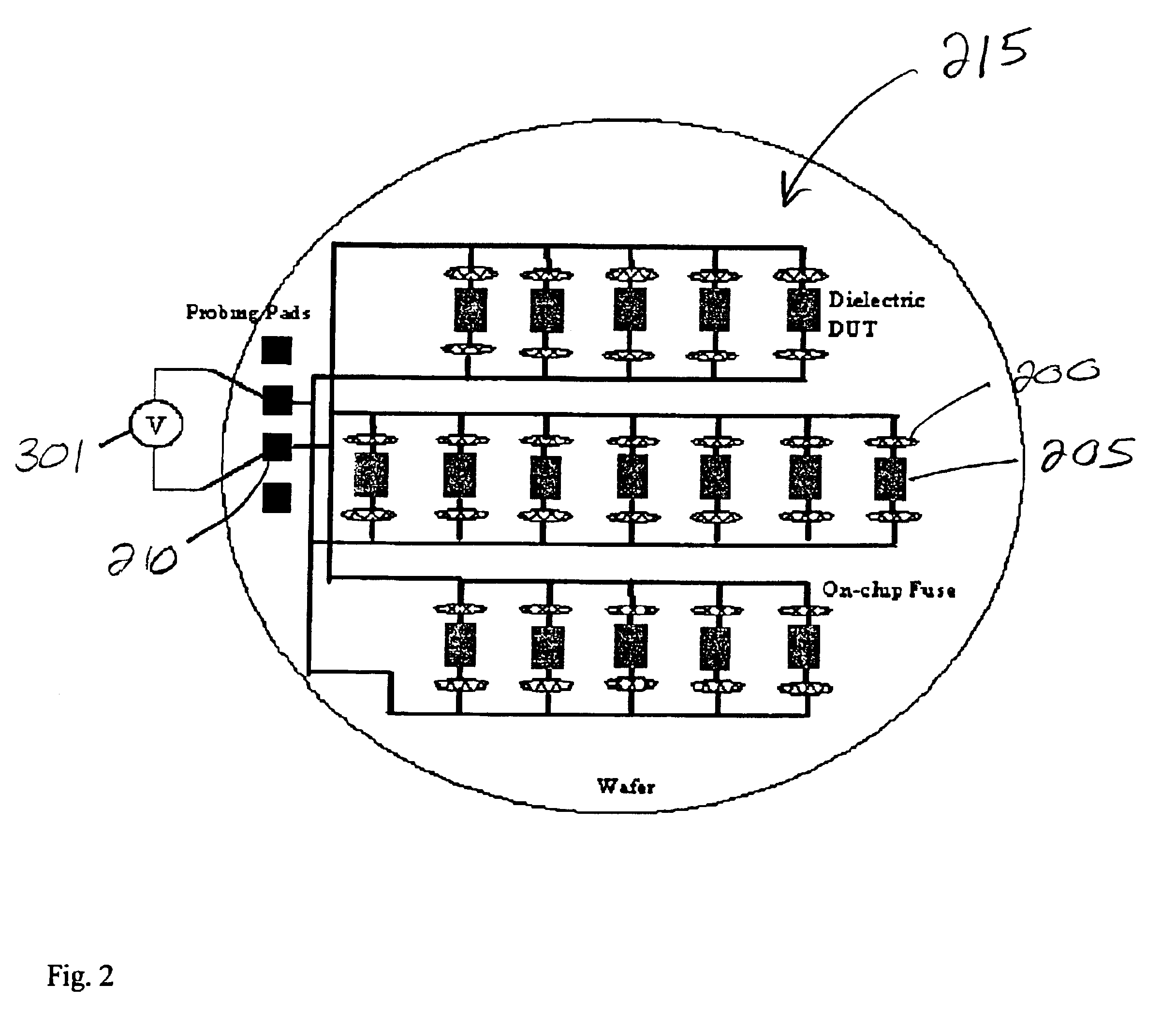

Methodology and apparatus using real-time optical signal for wafer-level device dielectrical reliability studies

InactiveUS6788093B2Easy to detectImprove accuracyTesting dielectric strengthIndividual semiconductor device testingElectricityDielectric reliability

Owner:GLOBALFOUNDRIES U S INC

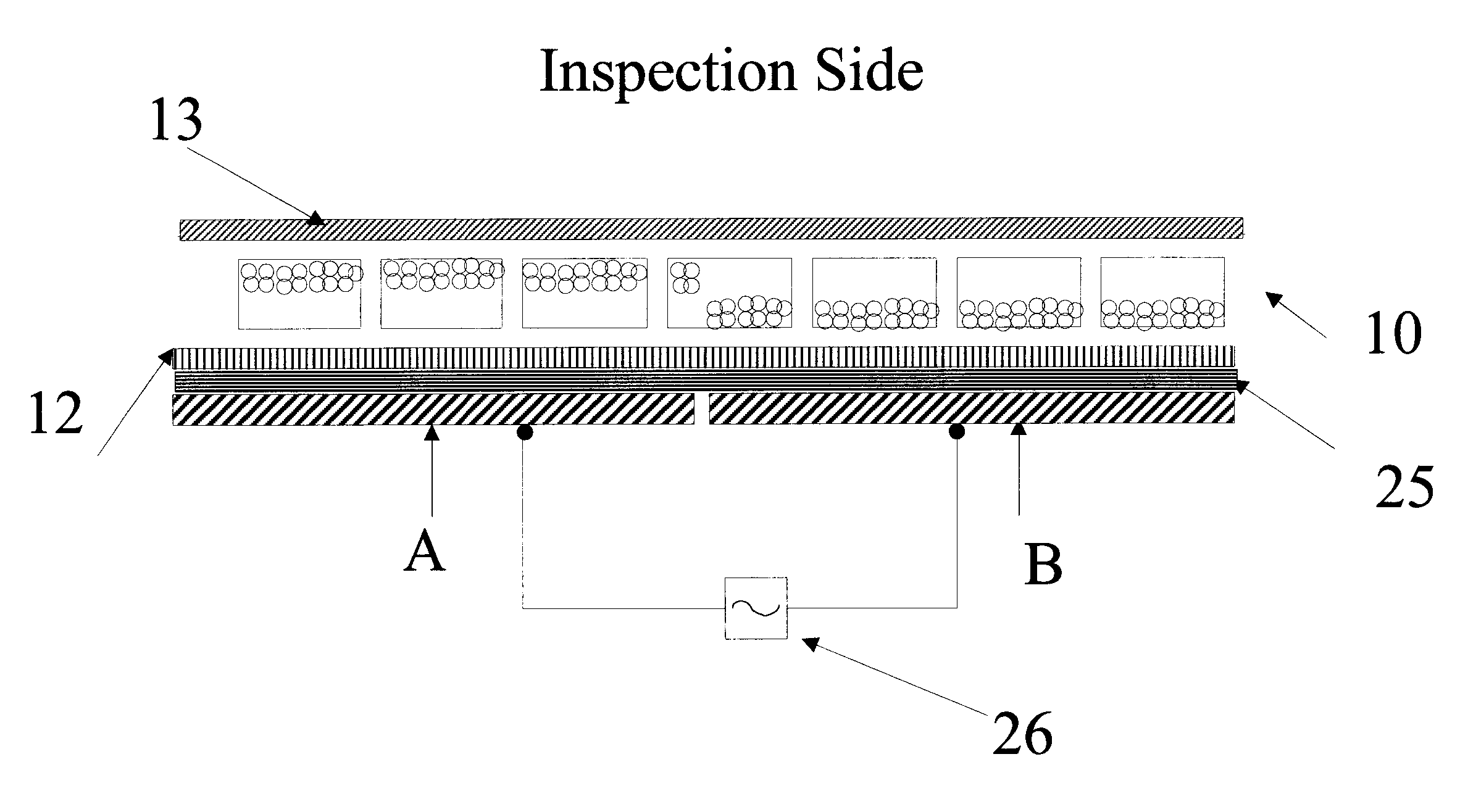

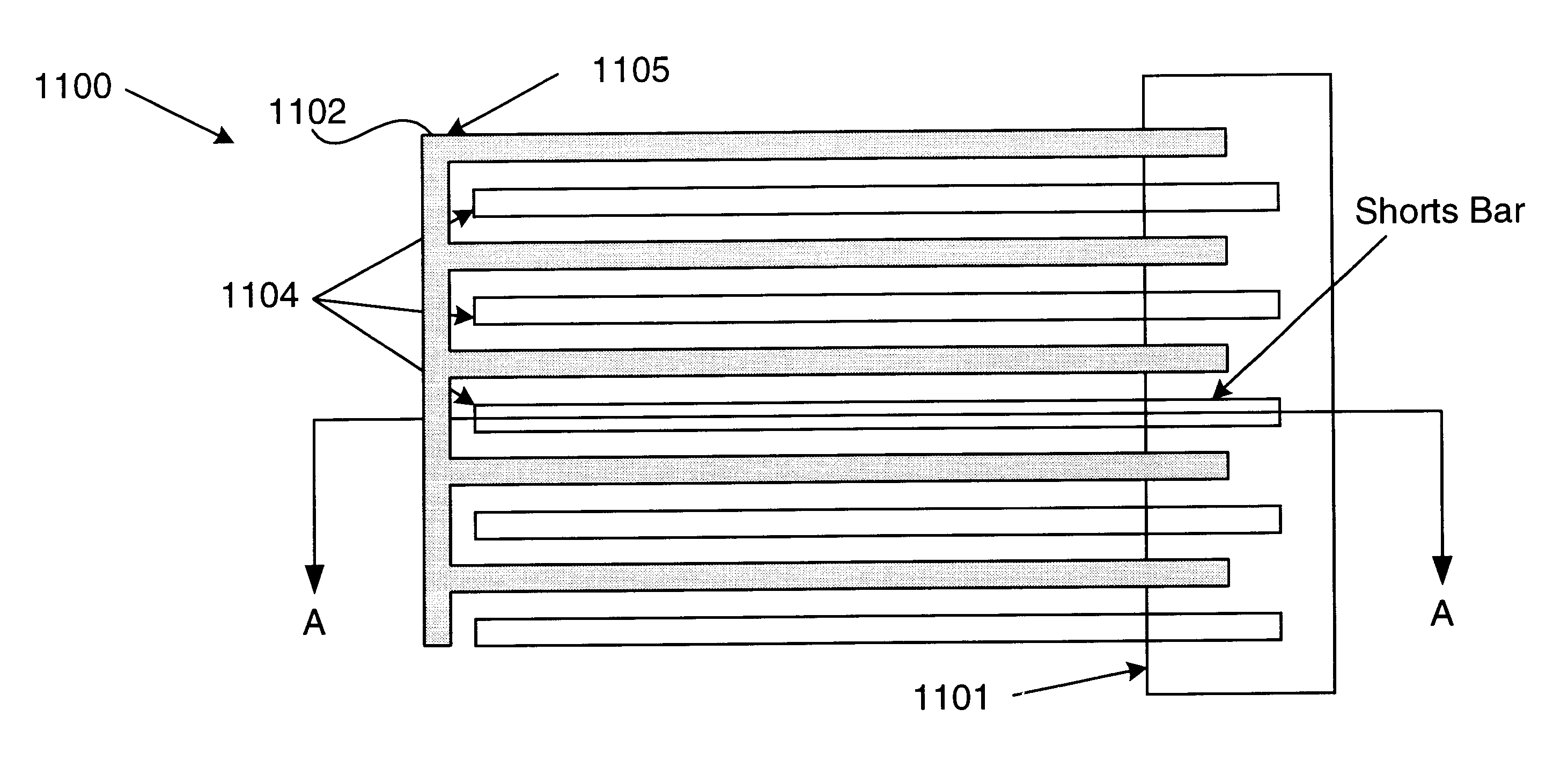

Inspection methods for defects in electrophoretic display and related devices

InactiveUS7982479B2Cathode-ray tube indicatorsInput/output processes for data processingElectrophoresisDisplay device

The present invention relates to methods for inspection of defects in an electrophoretic display and related devices. The method may be carried out with one or more testing electrodes. The method comprises applying a voltage difference to two testing electrodes which are in contact with the display panel, or applying a voltage difference to a testing electrode and a electrode layer. The methods may be applied in in-line or off-line inspection of a display panel.

Owner:E INK CALIFORNIA

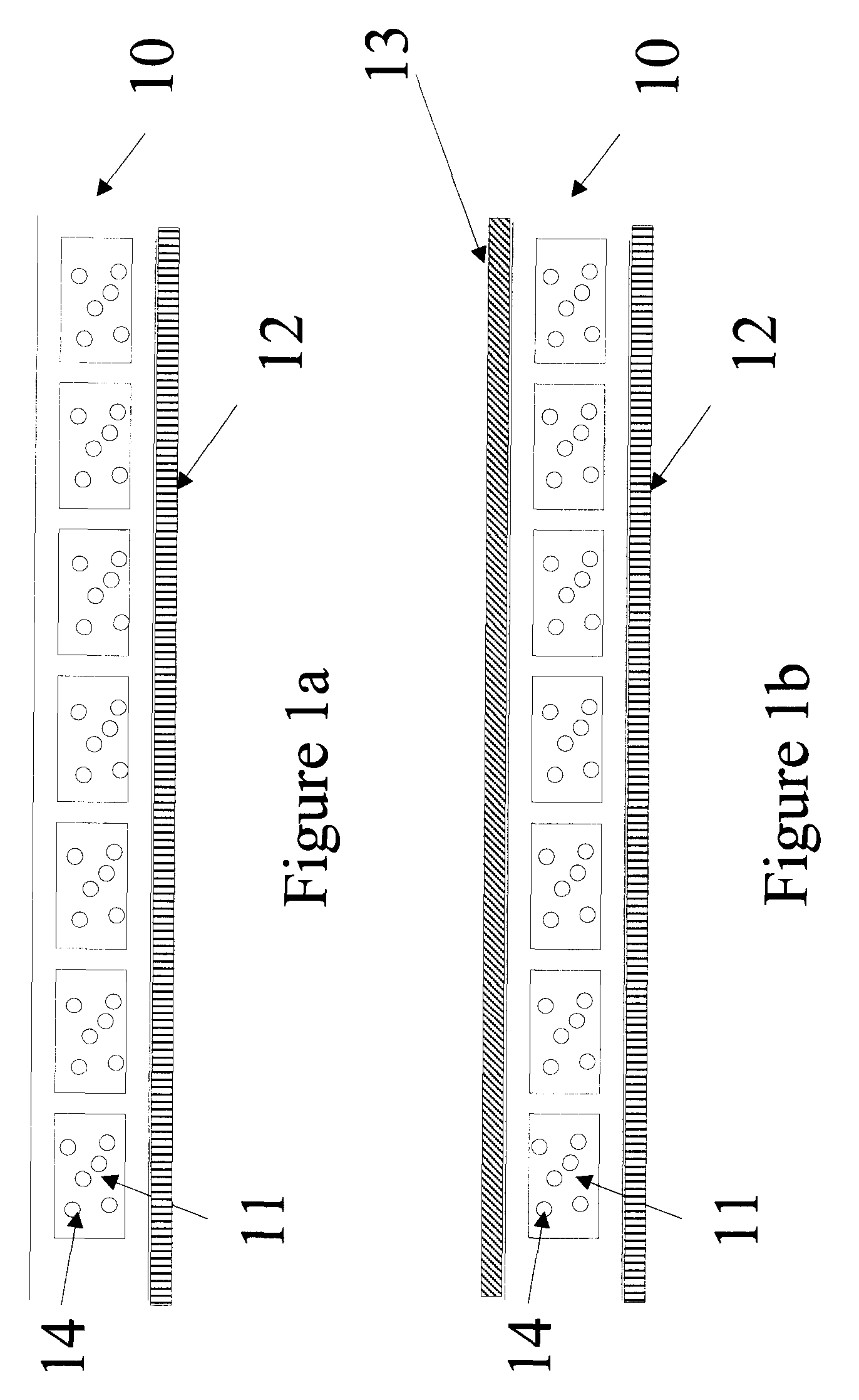

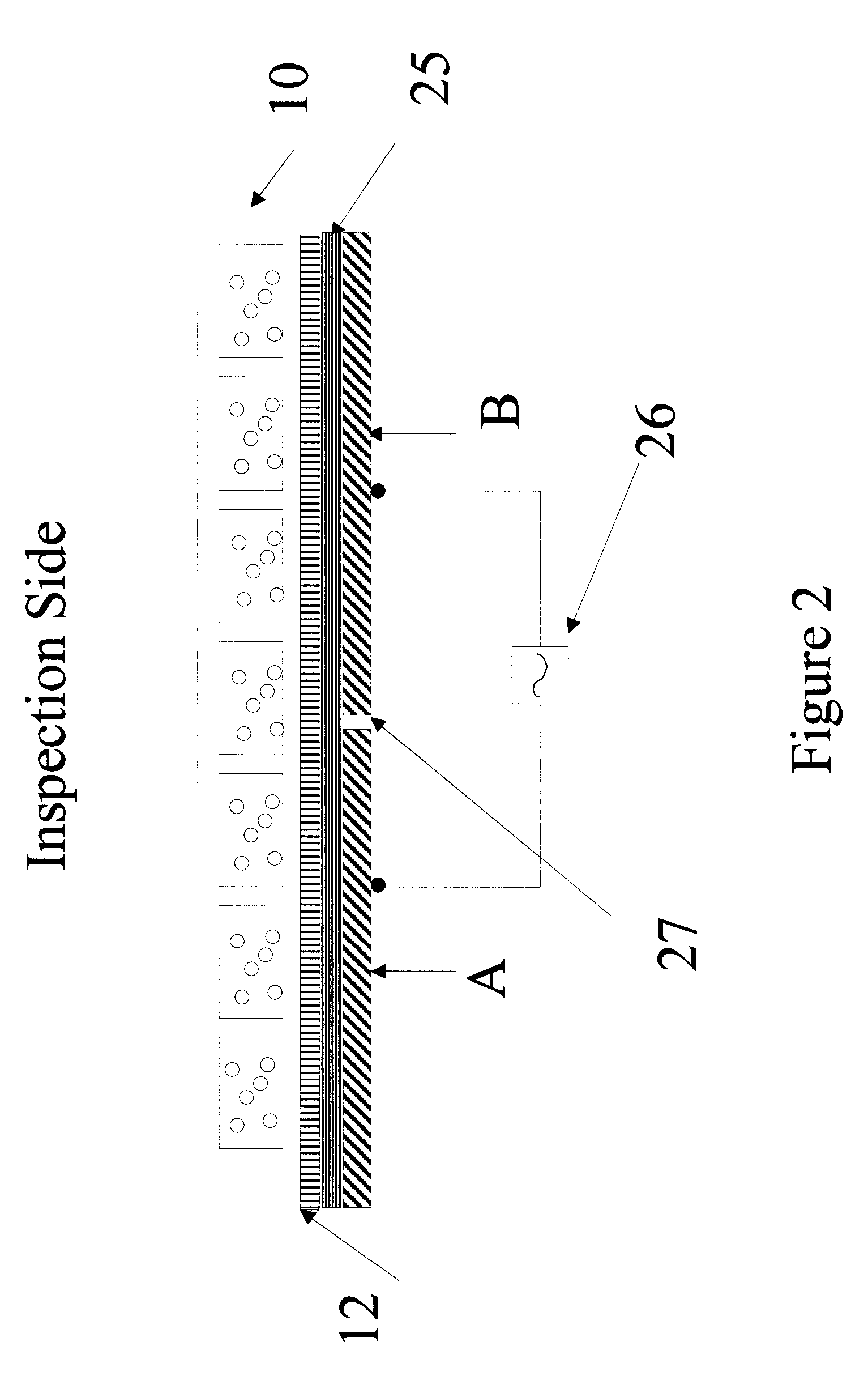

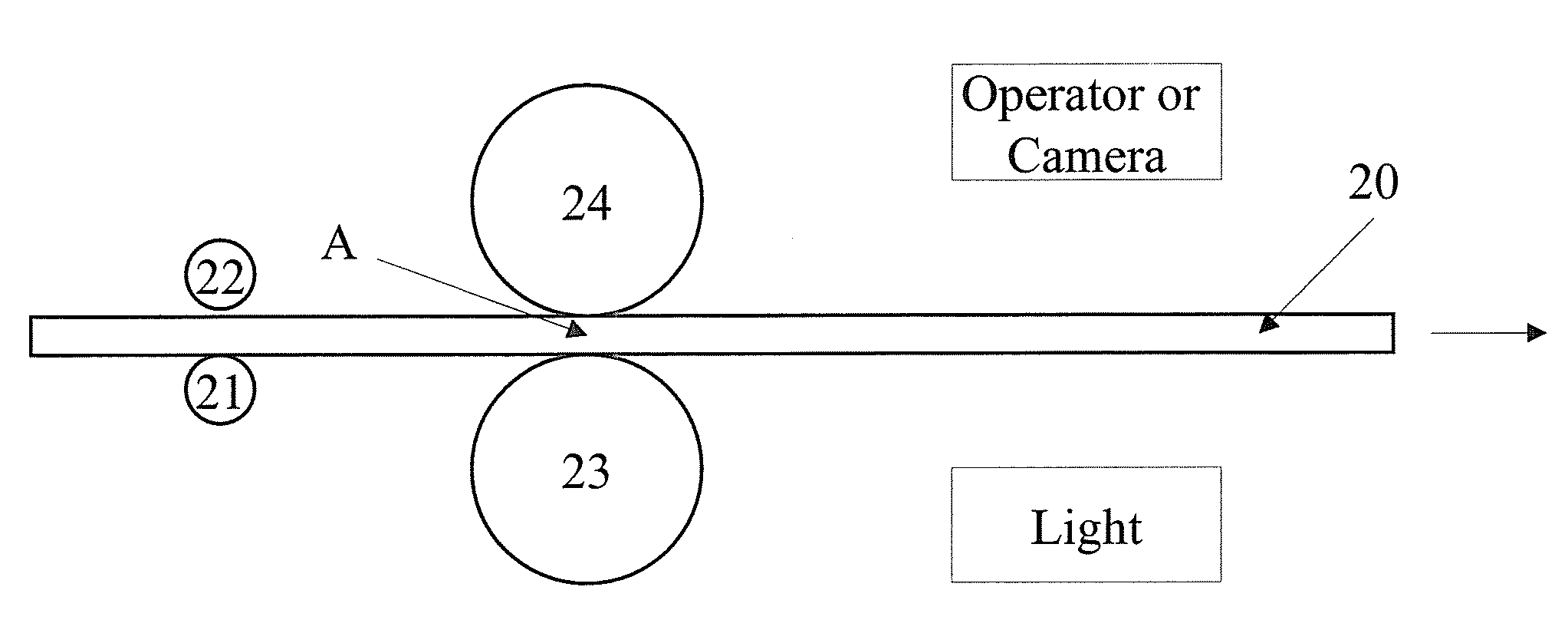

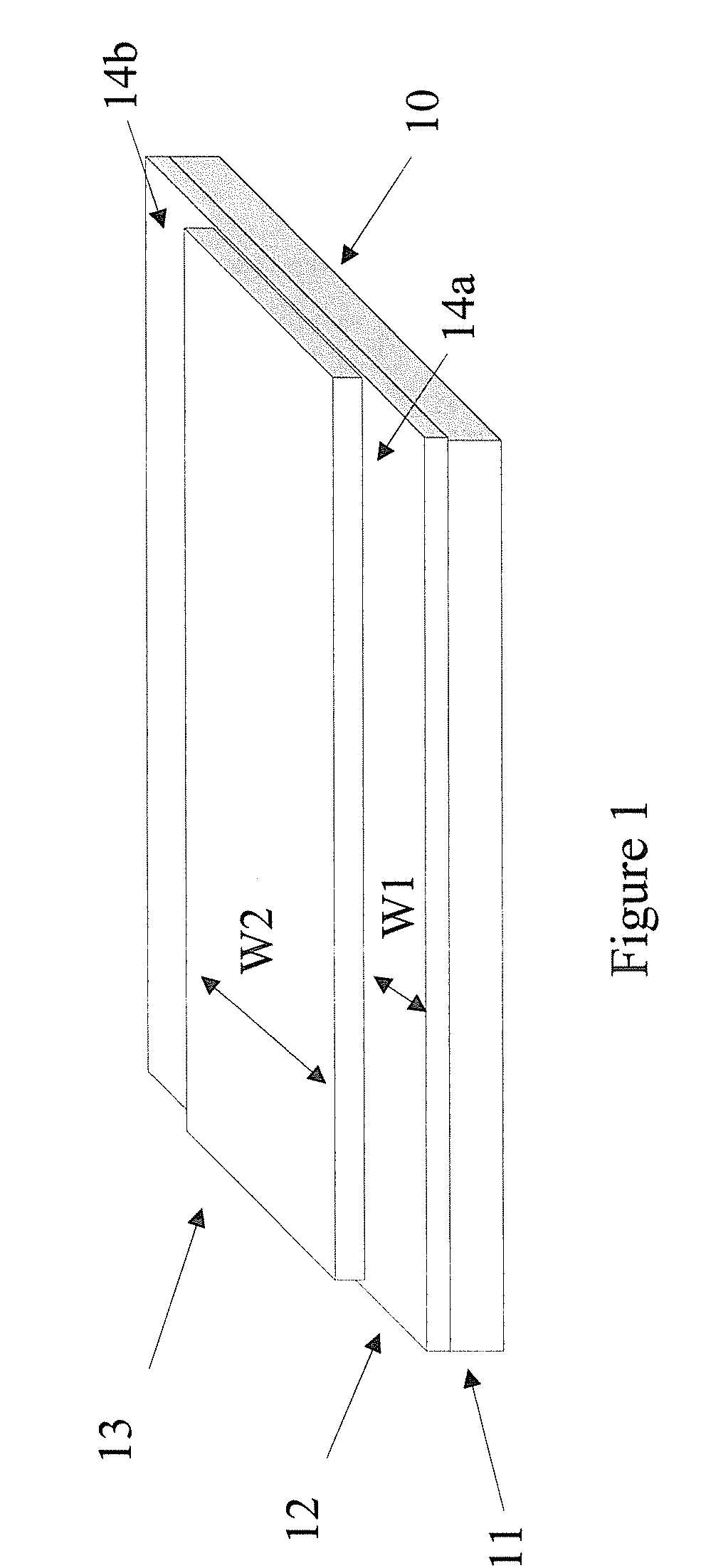

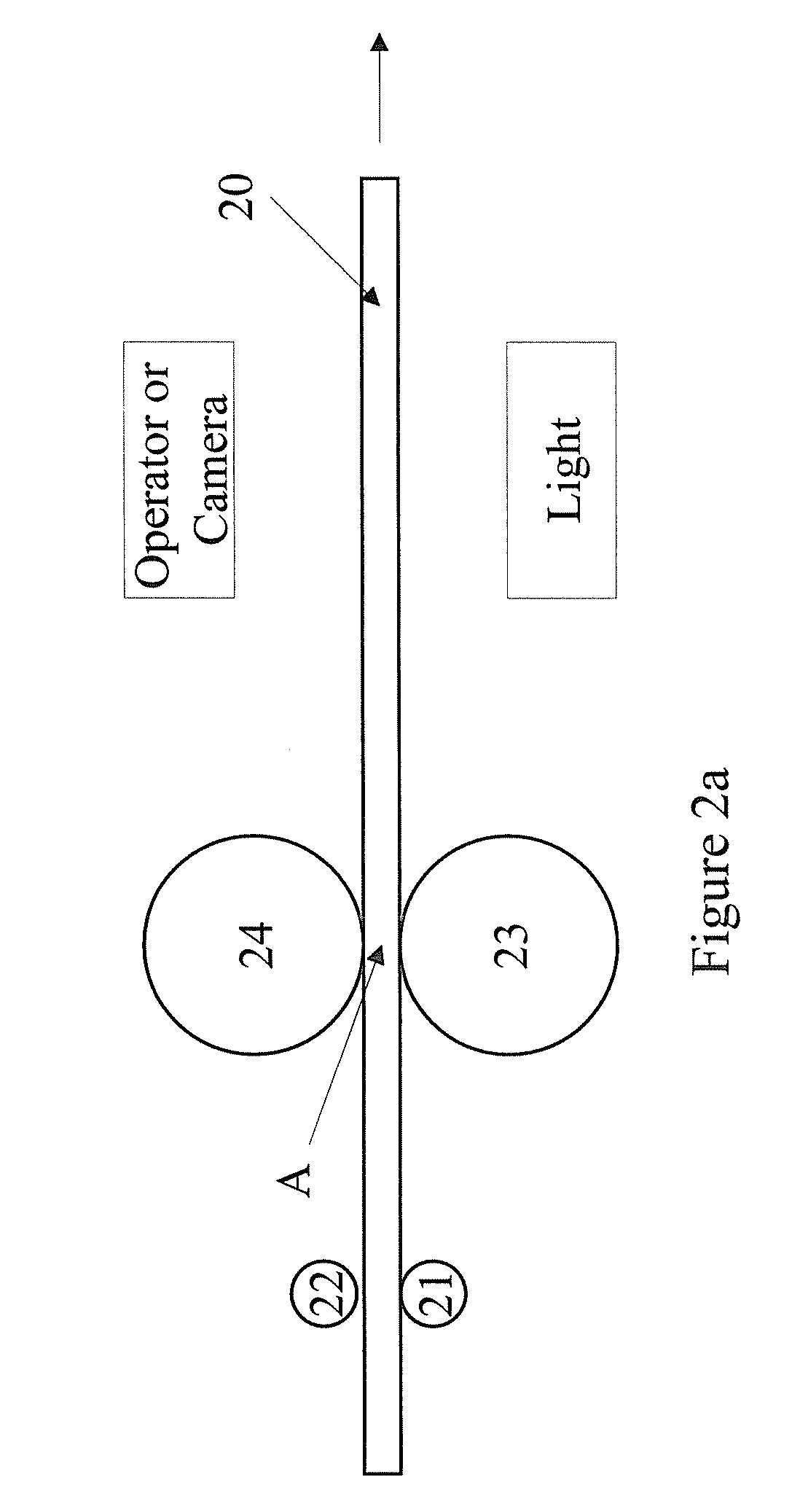

Flexible display testing and inspection

The present invention provides methods and systems for testing and inspection of a display panel. The methods involve the application of voltages to rollers or testing conductive films. By applying a potential difference to the appropriate rollers or testing conductive films, different optical states of a display panel can be displayed for inspection.

Owner:E INK CALIFORNIA

Dual probe test structures for semiconductor integrated circuits

InactiveUS6636064B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

Disclosed is a semiconductor die having an upper layer and a lower layer. The die includes a lower test structure formed in the lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end, wherein the first end is coupled to a predetermined voltage level. The die also has an insulating layer formed over the lower metal layer and an upper test structure formed in the upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure, and the upper metal layer being formed over the insulating layer. The die further includes at least one probe pad coupled with the upper test structure. Preferably, the first end of the lower test structure is coupled to a nominal ground potential. In another implementation, the upper test structure is a voltage contrast element. In another embodiment, a semiconductor die having a scanning area is disclosed. The semiconductor die includes a first plurality of test structures wherein each of the test structures in the first plurality of test structures is located entirely within the scanning area. The die includes a second plurality of test structures wherein each of the test structures in the first plurality of test structures is located only partially within the scanning area. The first plurality of test structures or the second plurality of test structures has a probe pad coupled to at least one test structure.

Owner:KLA TENCOR TECH CORP

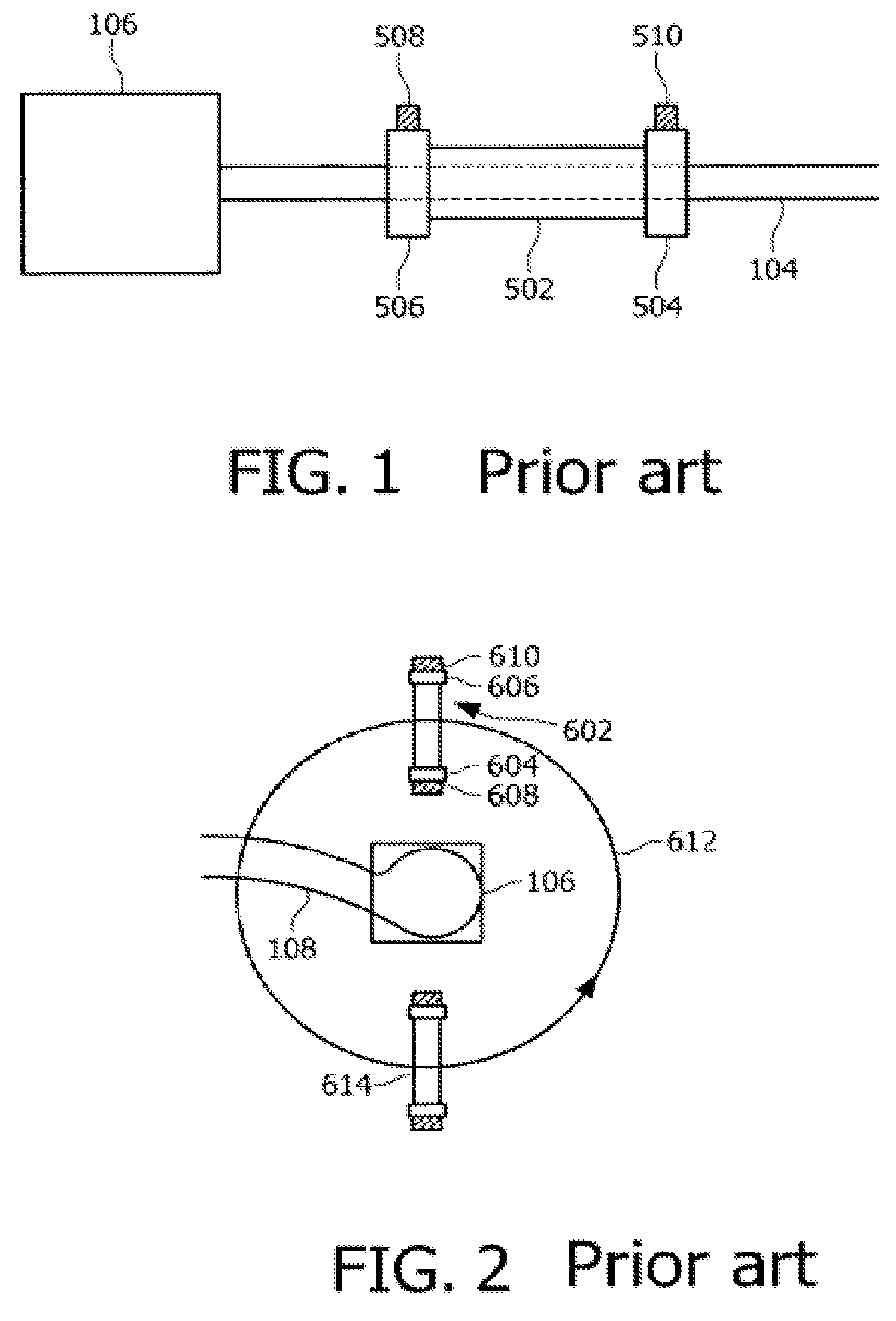

AC coupled parameteric test probe

InactiveUS20070296435A1Increase signal couplingSemiconductor/solid-state device testing/measurementMeasurement leads/probesElectricityCoupling parameter

A probe for contacting and testing ICs on a semiconductor device includes a dielectric insulating material tip. The dielectric tip does not contaminate the surface being probed unlike metal probe tips. A contact scrub is further not required with signals being capacitively or inductively coupled from the probe tip to the IC. Testing can be performed during early fabrication steps of the wafer without the need for applying a metalization layer to the wafer to form bond pads. Testing can be performed by inductively coupling an AC signal to the probe tip, with coupling enhanced by including a magnetic material in the dielectric probe tip. Using an AC test signal enables testing of ICs without requiring separate power and ground connections.

Owner:FORMFACTOR INC

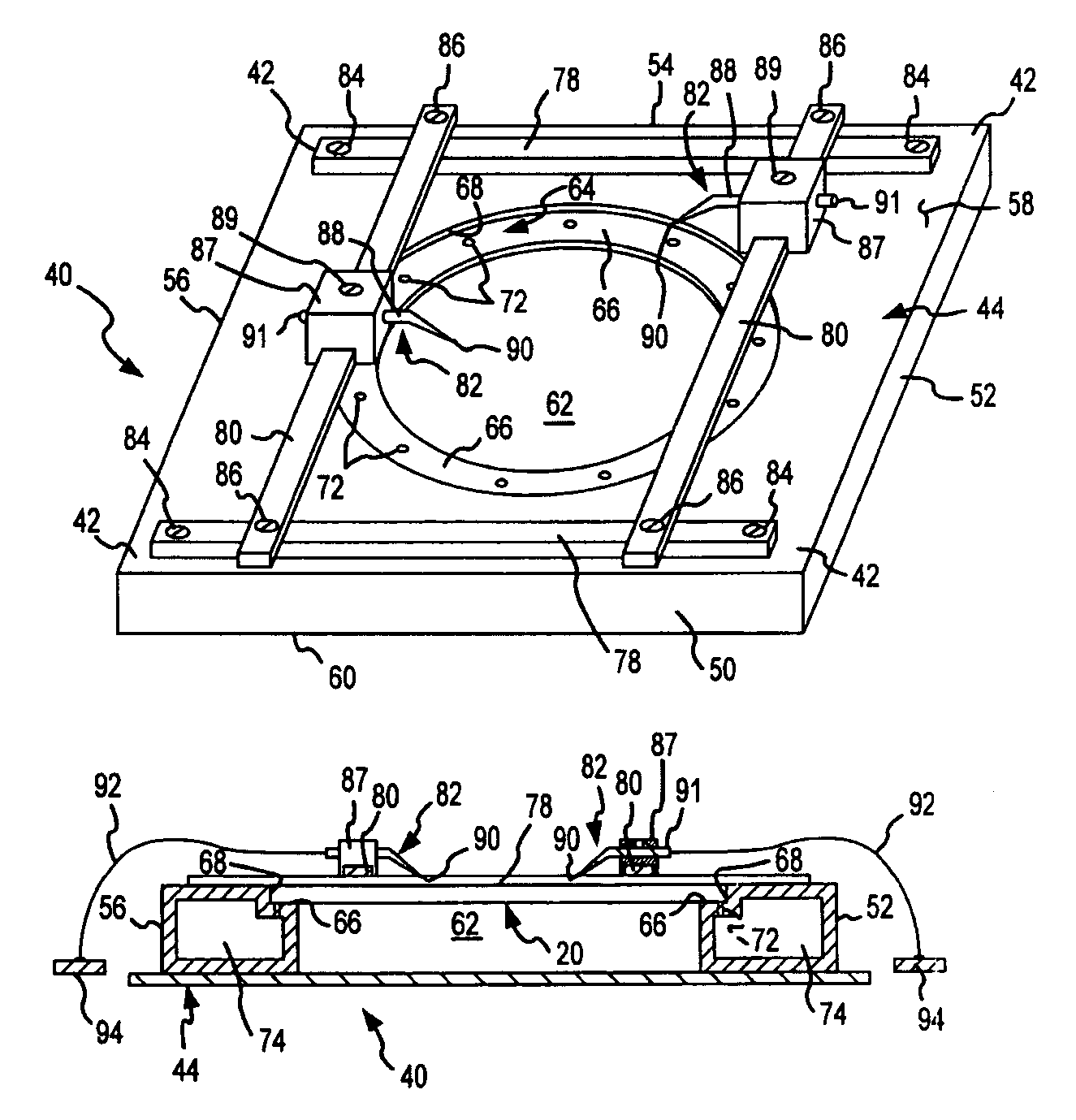

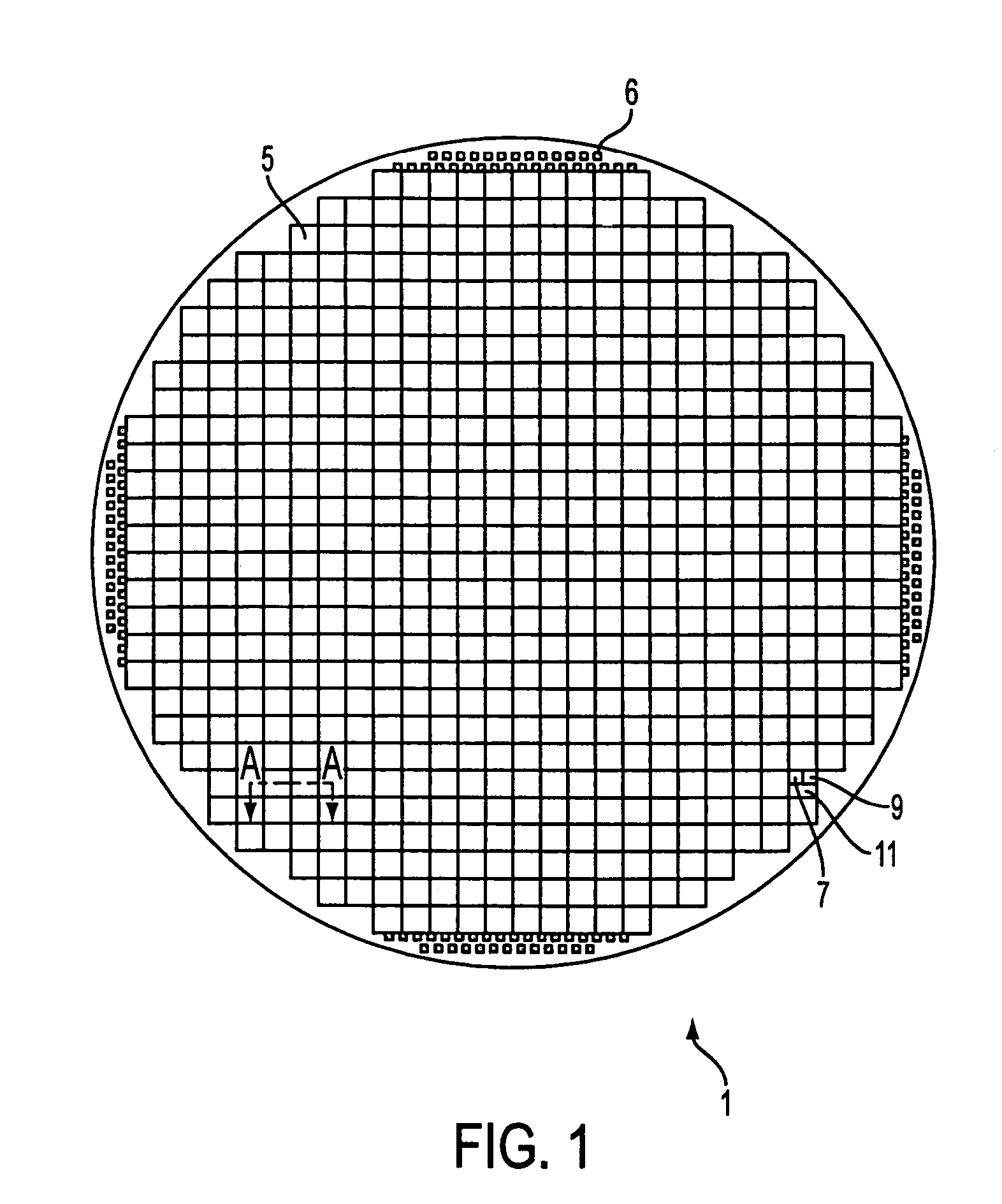

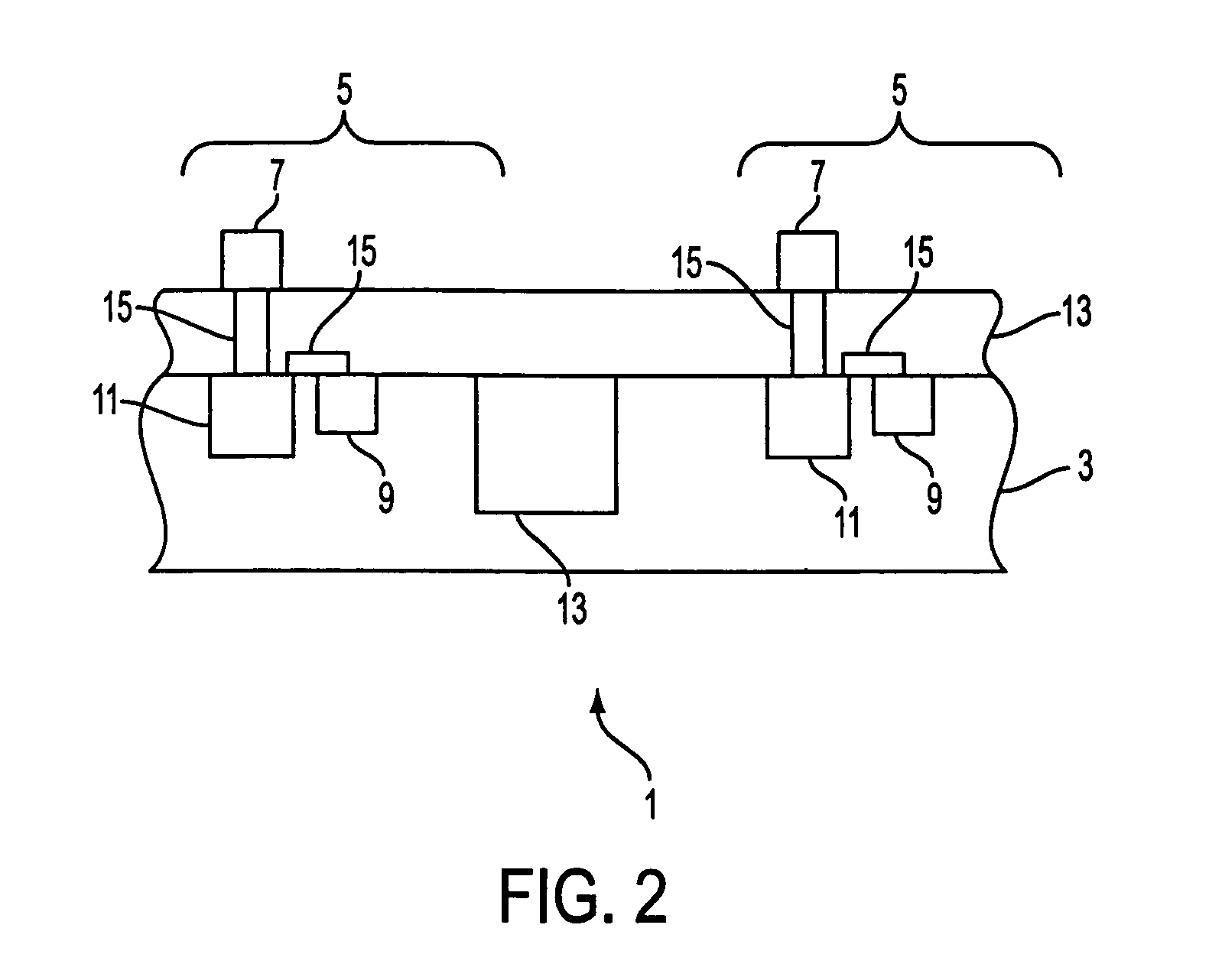

Method for probing a semiconductor wafer

InactiveUS6927079B1Avoid difficultyShorten the timeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingWaferingEngineering

A semiconductor wafer is placed into a probe fixture with a front side of the wafer facing up. Power and signal probes are then placed on an integrated circuit (IC) formed on the front side of the wafer. The probe fixture is retained at a test station either in a upright or an inverted position for testing and optical failure analysis. The probe fixture includes a position adjustment mechanism to locate the entire probe above the wafer and to more precisely position a tip of the probe on the IC. Optical failure analysis techniques are performed on the front side or the back side of the wafer while the wafer is retained in the test fixture and the probes are connected to the IC.

Owner:BELL SEMICON LLC

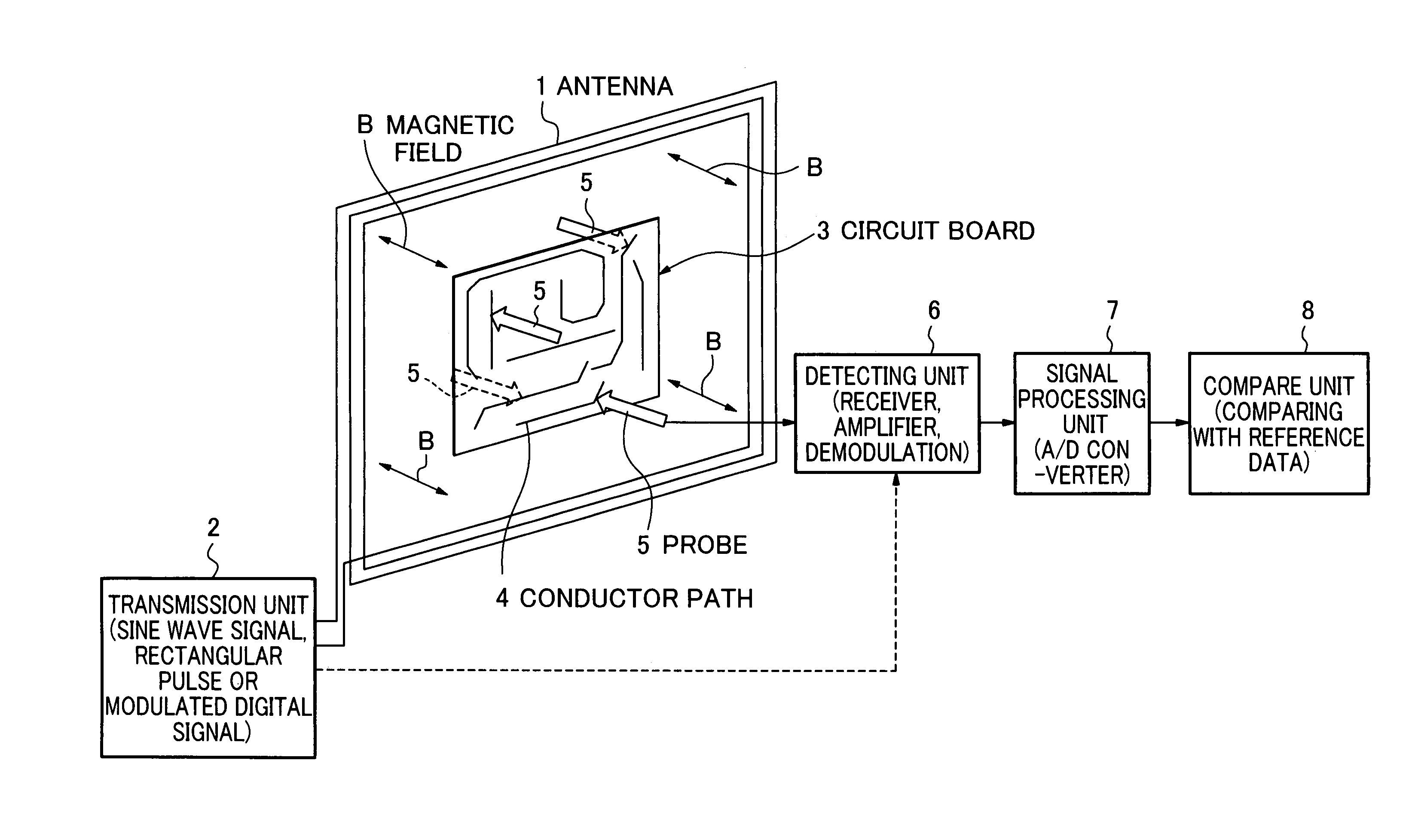

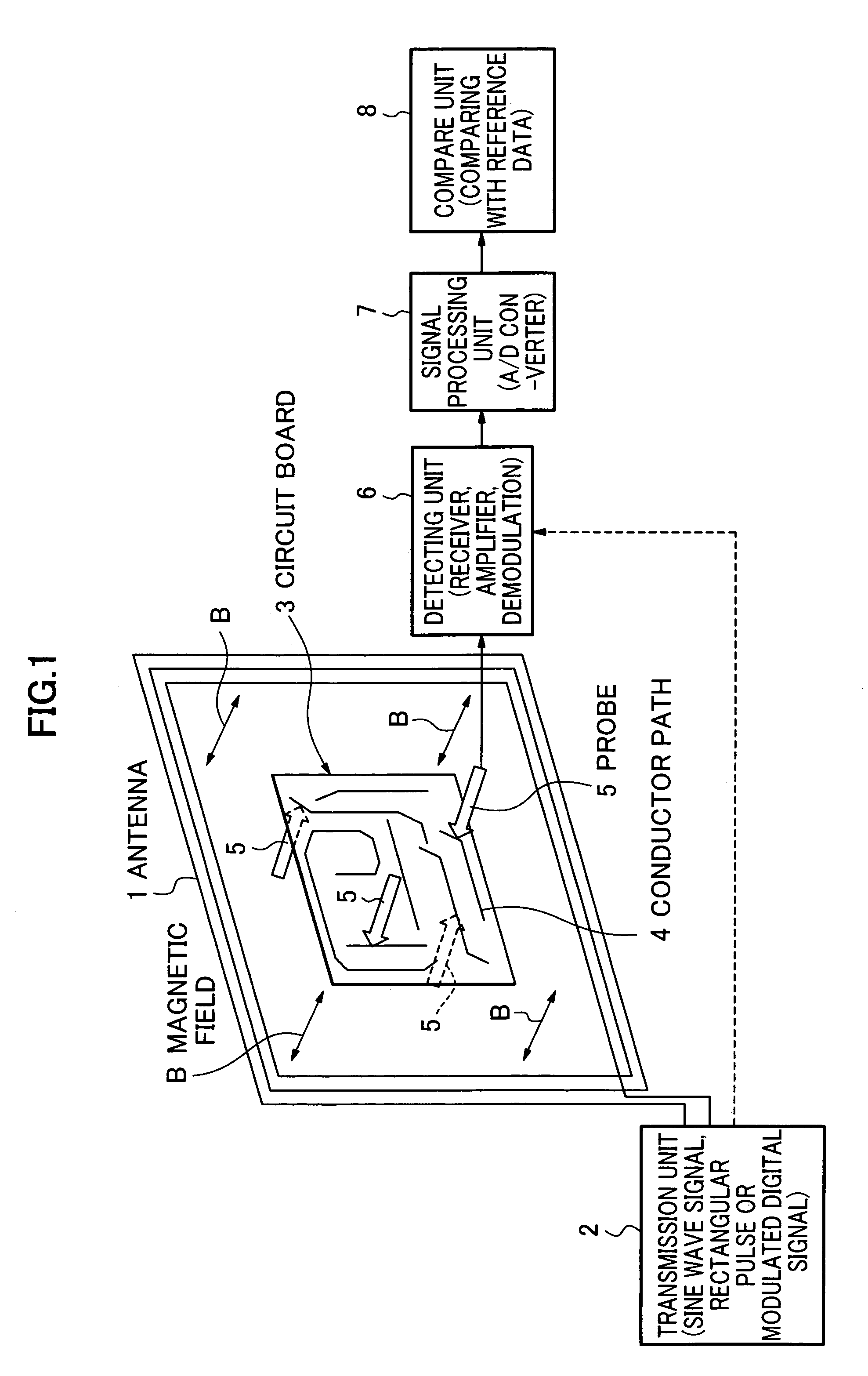

Method and apparatus for testing circuit boards

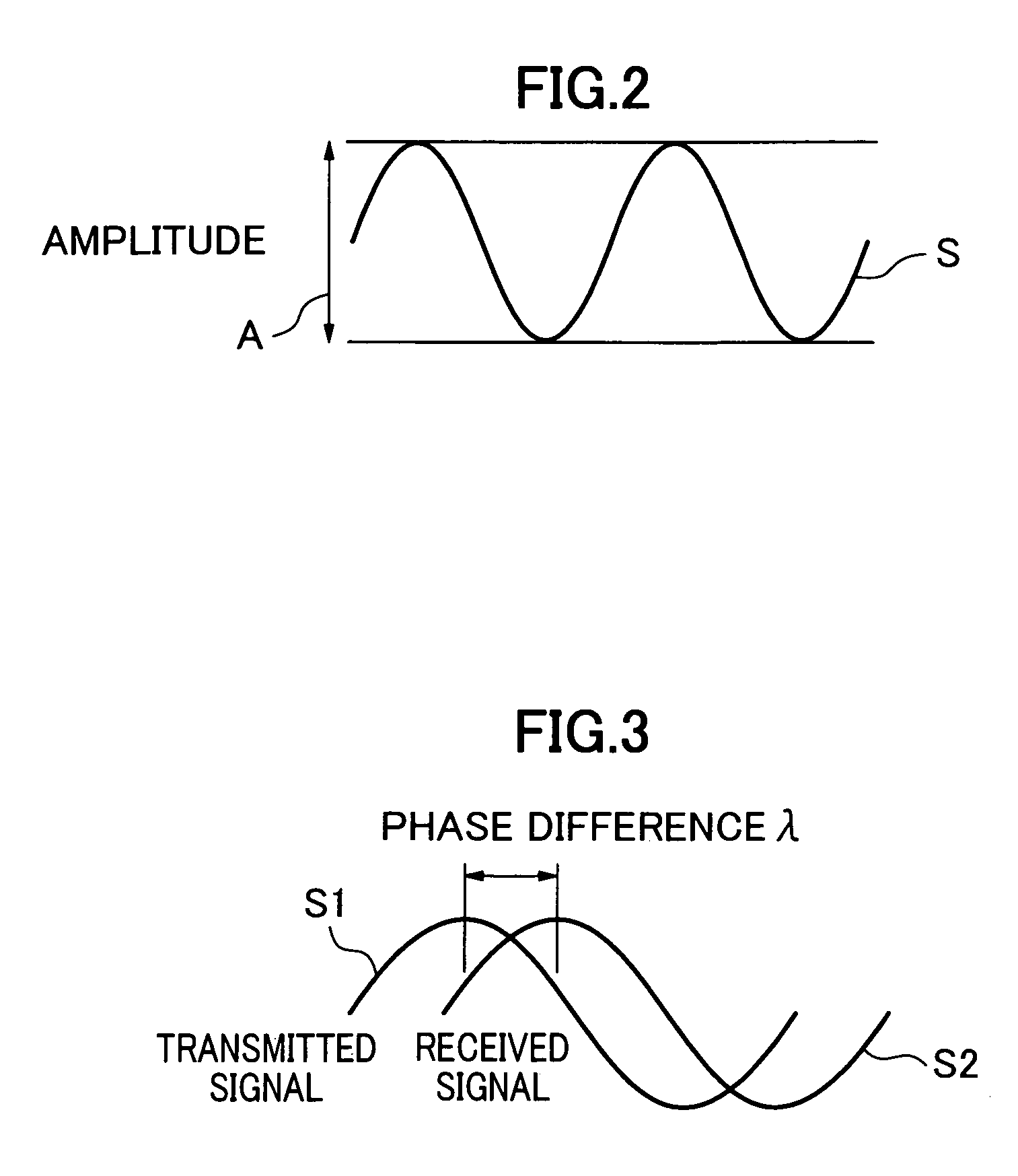

ActiveUS7188037B2Shorten the timeHigh-precision detectionResistance/reactance/impedenceError detection/correctionElectrical conductorPath network

The invention provides a method of apparatus for testing circuit boards which does not require any inner wide power plane so as to detect an open circuit defect and / or a short circuit defect in a conductor path network formed in the circuit board quickly and accurately. An apparatus for testing a circuit board according to the present invention includes a transmission unit (2) for transmitting electromagnetic (radio) wave signal by way of an antenna (1) to a circuit board (3) to be tested, a detecting unit (3) for detecting signal received by a conductor path (4) of the circuit board (3) by using the conductor path (4) as a receiving antenna, and compare unit (8) for determining whether or not there is an open circuit defect or a short circuit defect in the conductor path (4) by comparing the detected signal with reference data of corresponding to a conductor path not including any defect.

Owner:MICROCRAFT

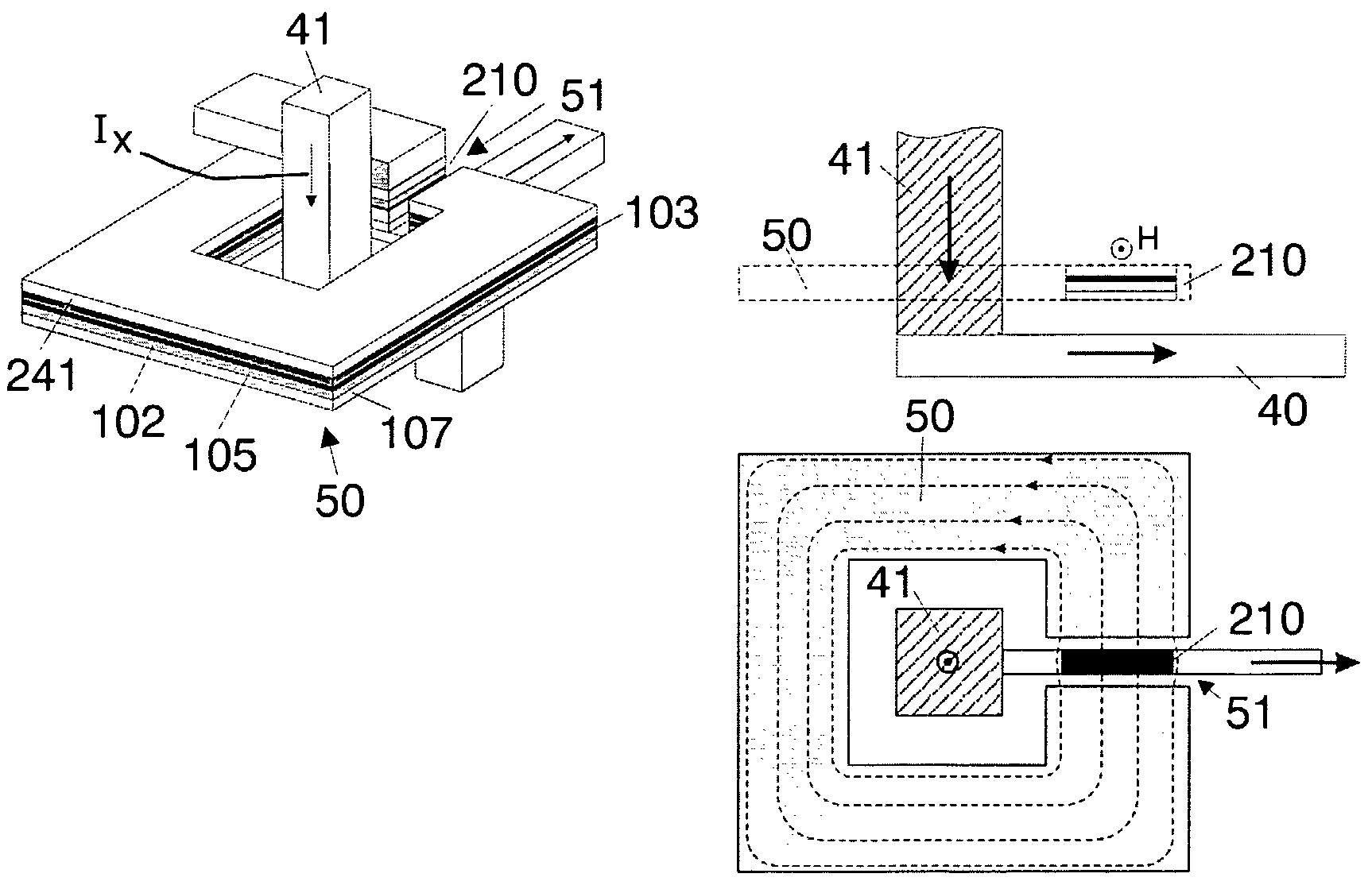

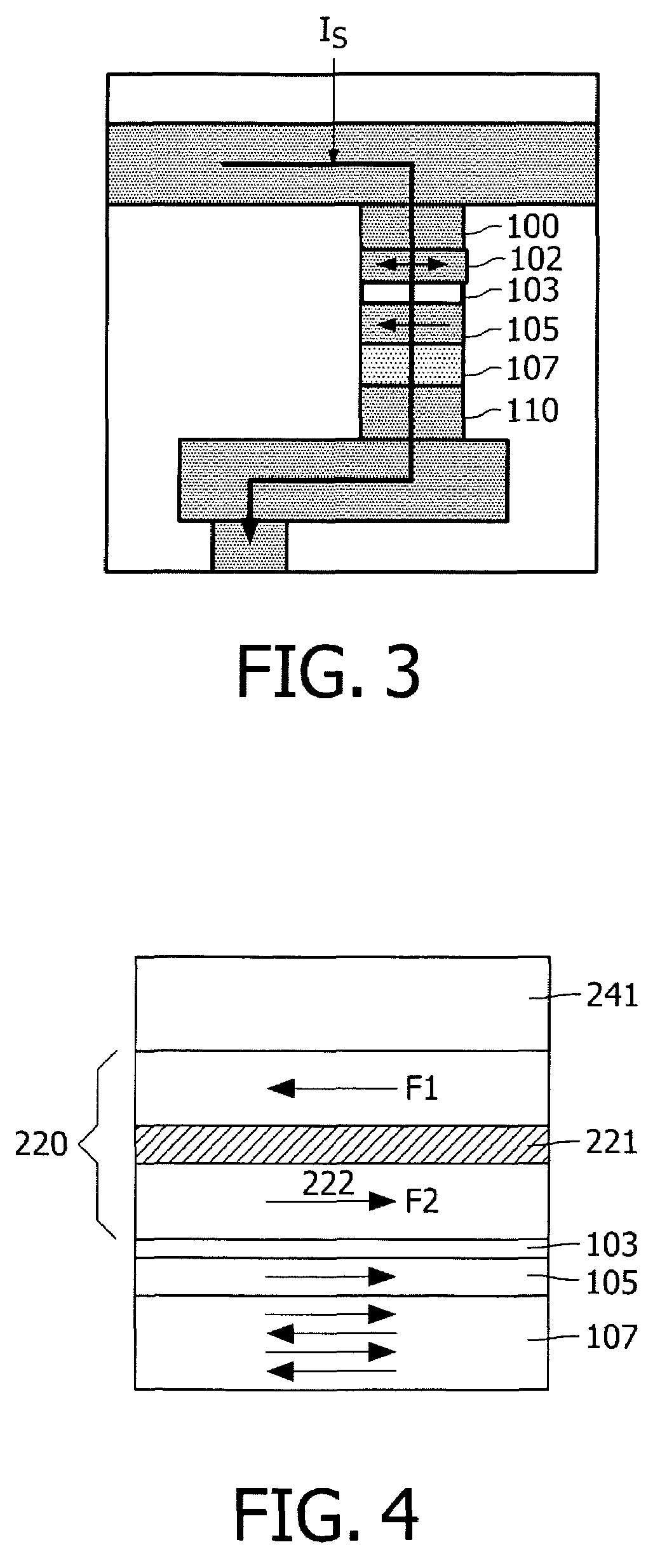

High sensitivity magnetic built-in current sensor

InactiveUS7619431B2Improve sensor sensitivityHigh sensitivityMagnetic measurementsDigital storageElectrical conductorEngineering

A sensor for contactlessly detecting currents, has a sensor element having a magnetic tunnel junction (MTJ), and detection circuitry, the sensor element having a resistance which varies with the magnetic field, and the detection circuitry is arranged to detect a tunnel current flowing through the tunnel junction. The sensor element may share an MTJ stack with memory elements. Also it can provide easy integration with next generation CMOS processes, including MRAM technology, be more compact, and use less power. Solutions for increasing sensitivity of the sensor, such as providing a flux concentrator, and for generating higher magnetic fields with a same current, such as forming L-shaped conductor elements, are given. The greater sensitivity enables less post processing to be used, to save power for applications such as mobile devices. Applications include current sensors, built-in current sensors, and IDDQ and IDDT testing, even for next generation CMOS processes.

Owner:ELIPOSKI REMOTE

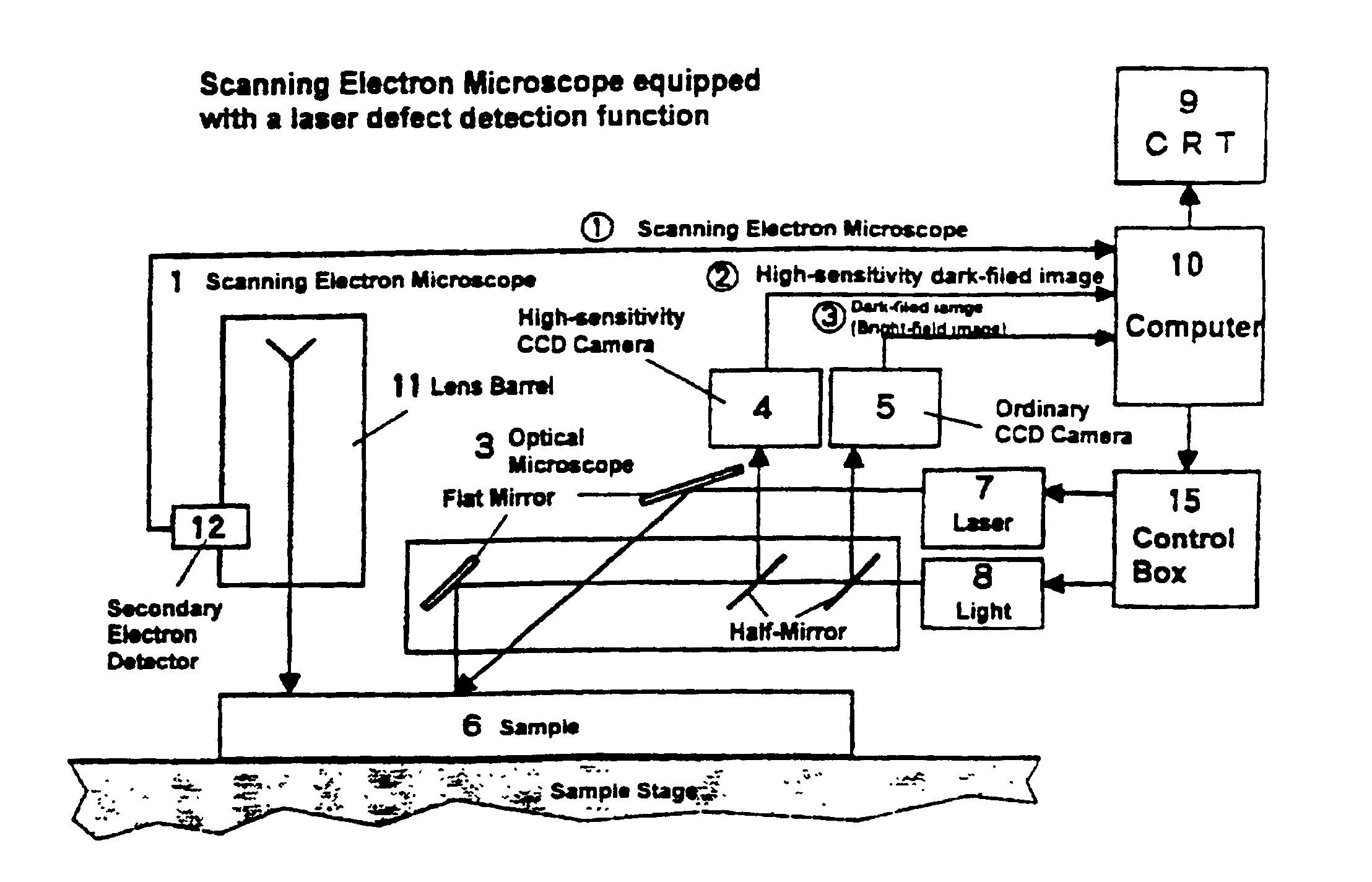

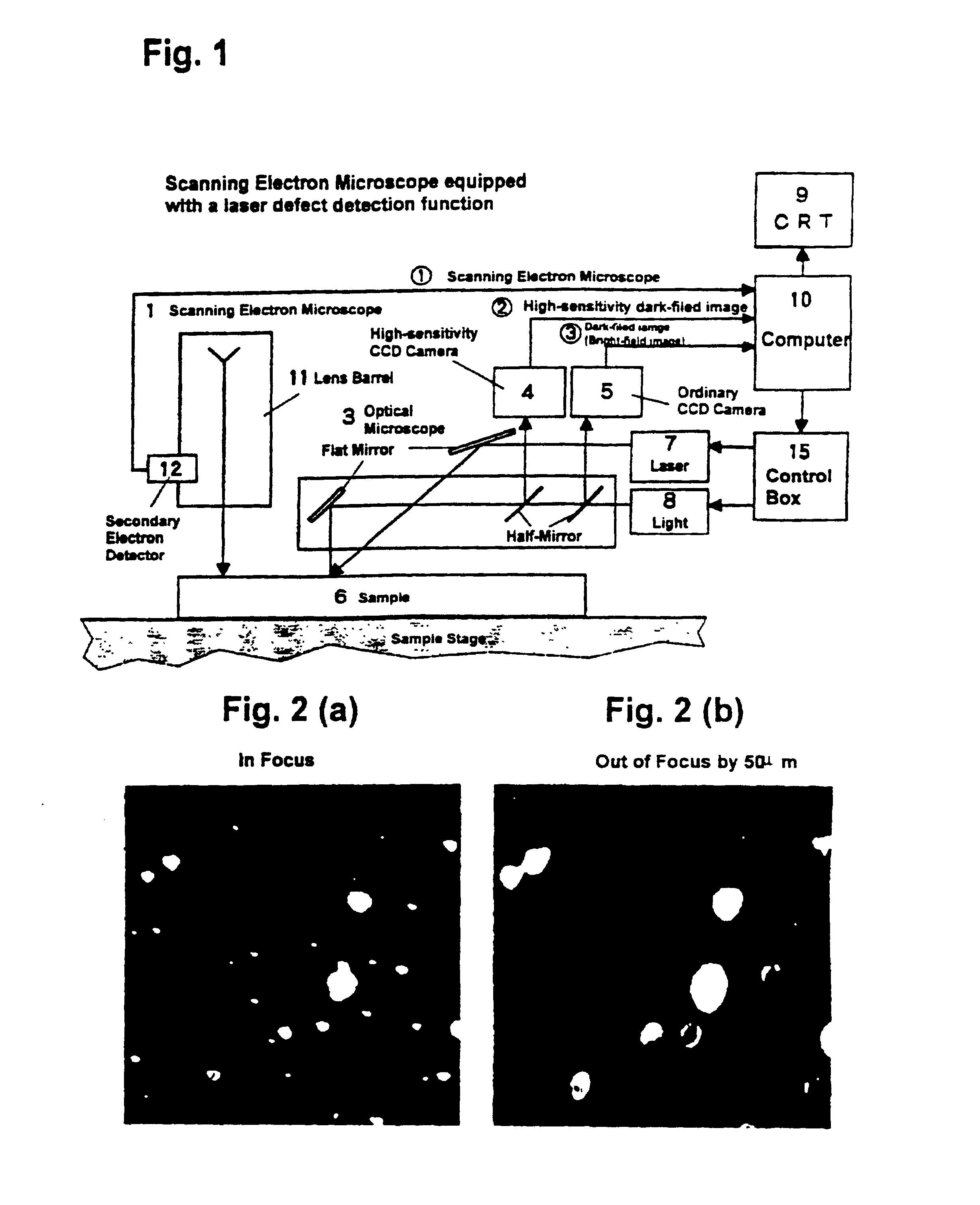

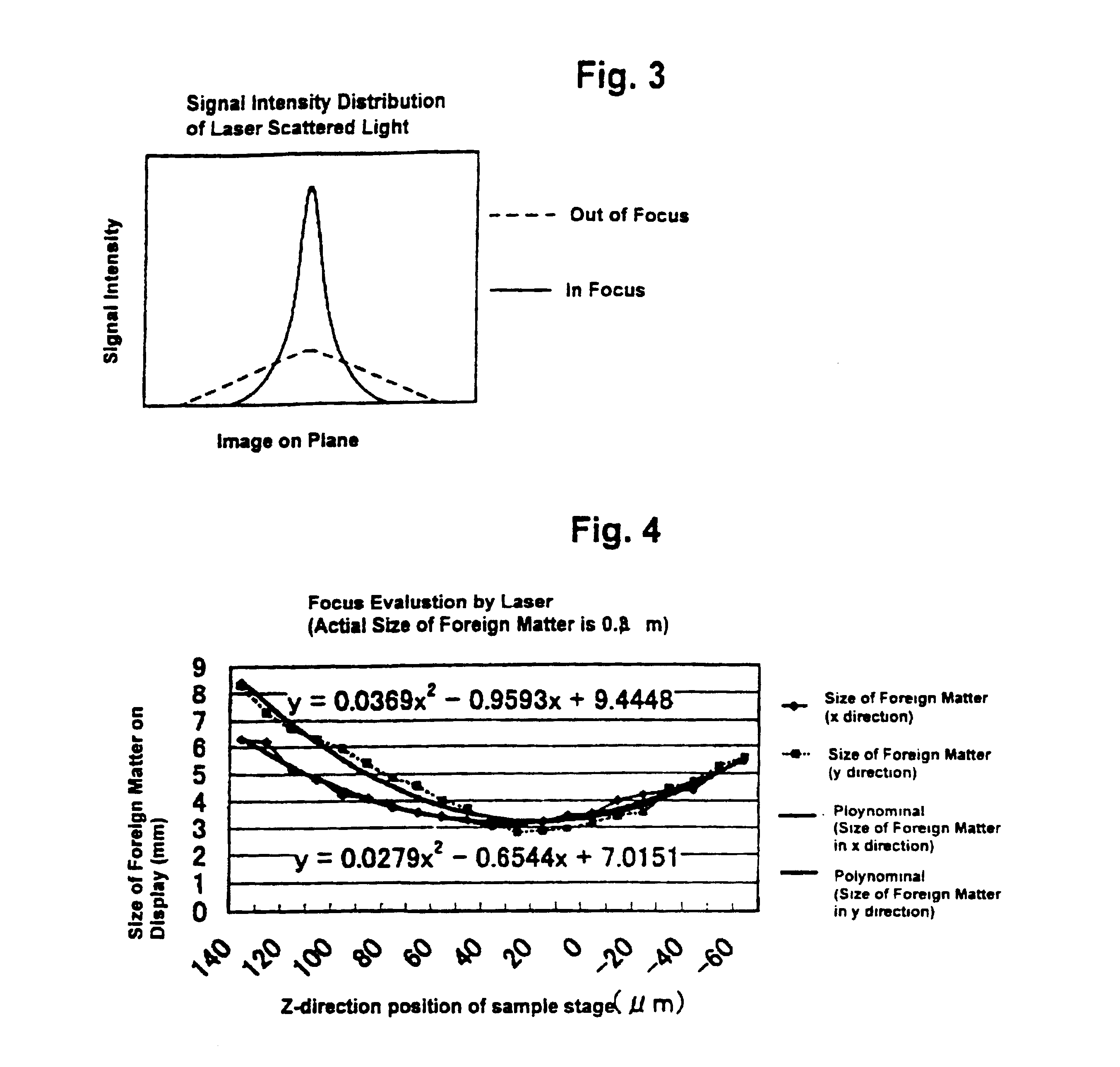

Automatic focusing system for scanning electron microscope equipped with laser defect detection function

InactiveUS6621082B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementImage detectionElectron microscope

A scanning electron microscope equipped with a laser defect detection function has an automatic focusing function that performs the steps of: obtaining a deviation (offset) amount between focal positions of an optical microscope and a scanning electron microscope; detecting a defect by a laser dark-field image of the optical microscope; analyzing the dark-field image to readjust a focus of the optical microscope to adjust a height of the optical microscope; and automatically adjusting a focus of the scanning electron microscope by adding a readjusted amount of the focus of the optical microscope to the offset amount before an observation is conducted by the scanning electron microscope.

Owner:HITACHI HIGH TECH SCI CORP

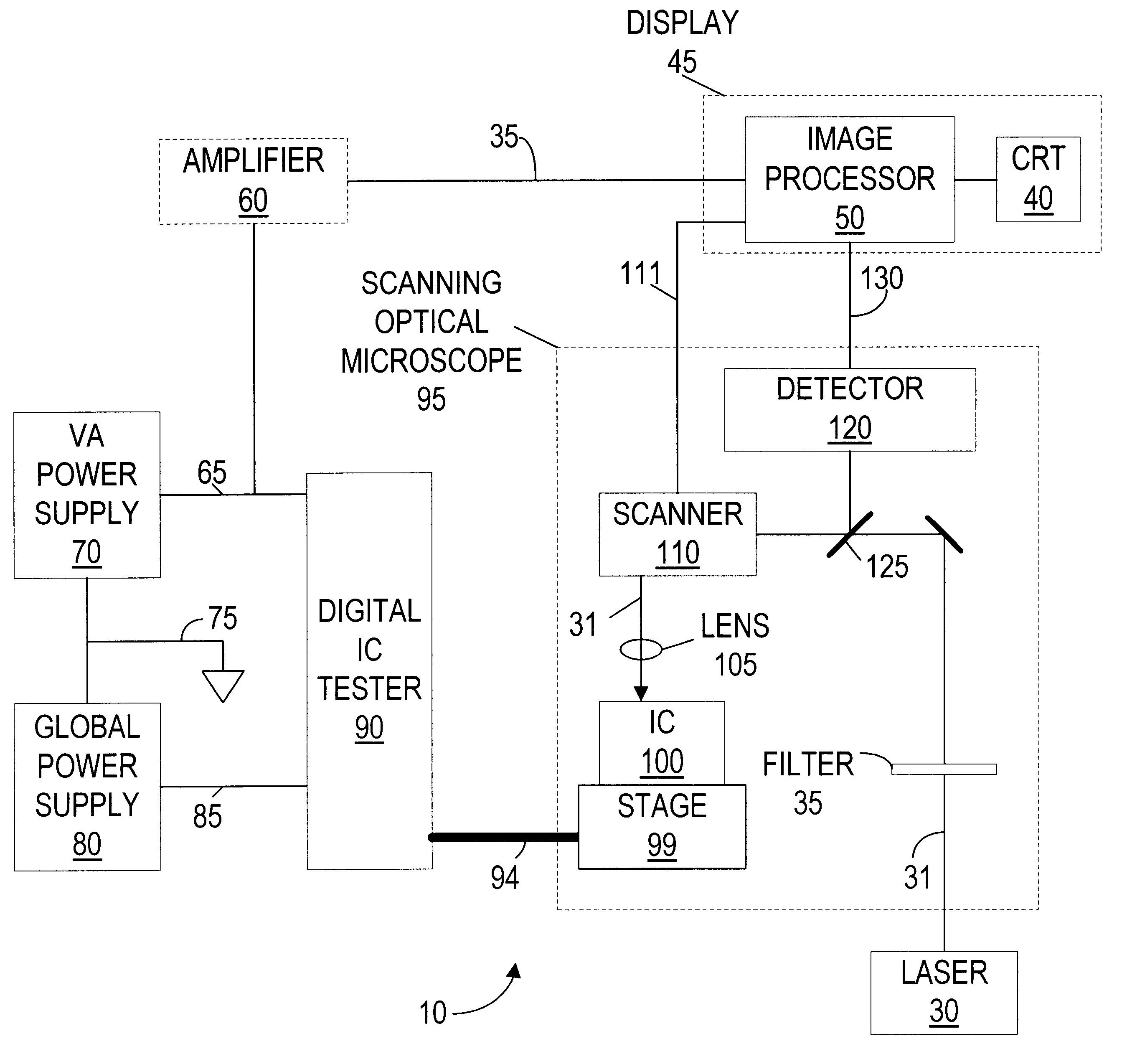

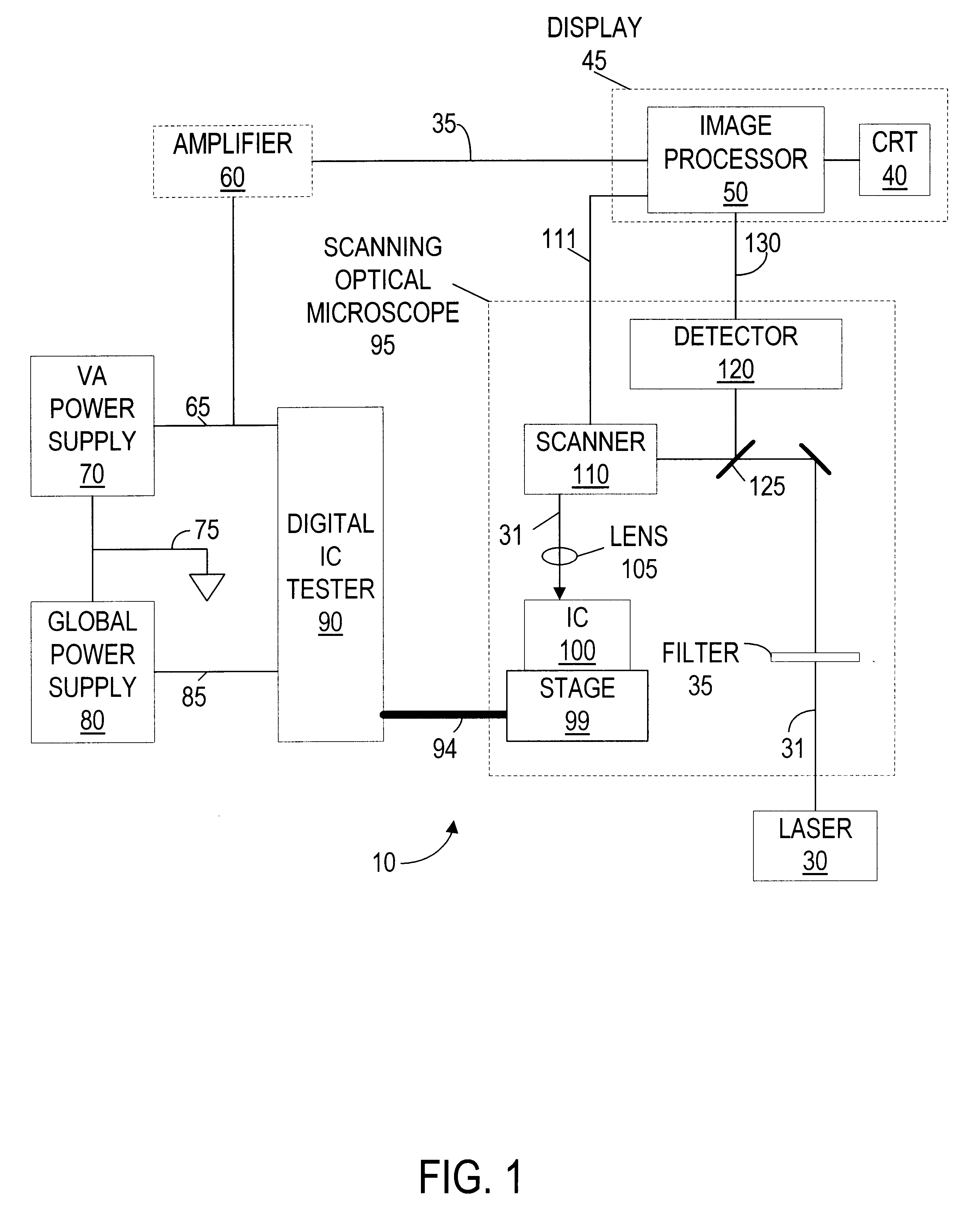

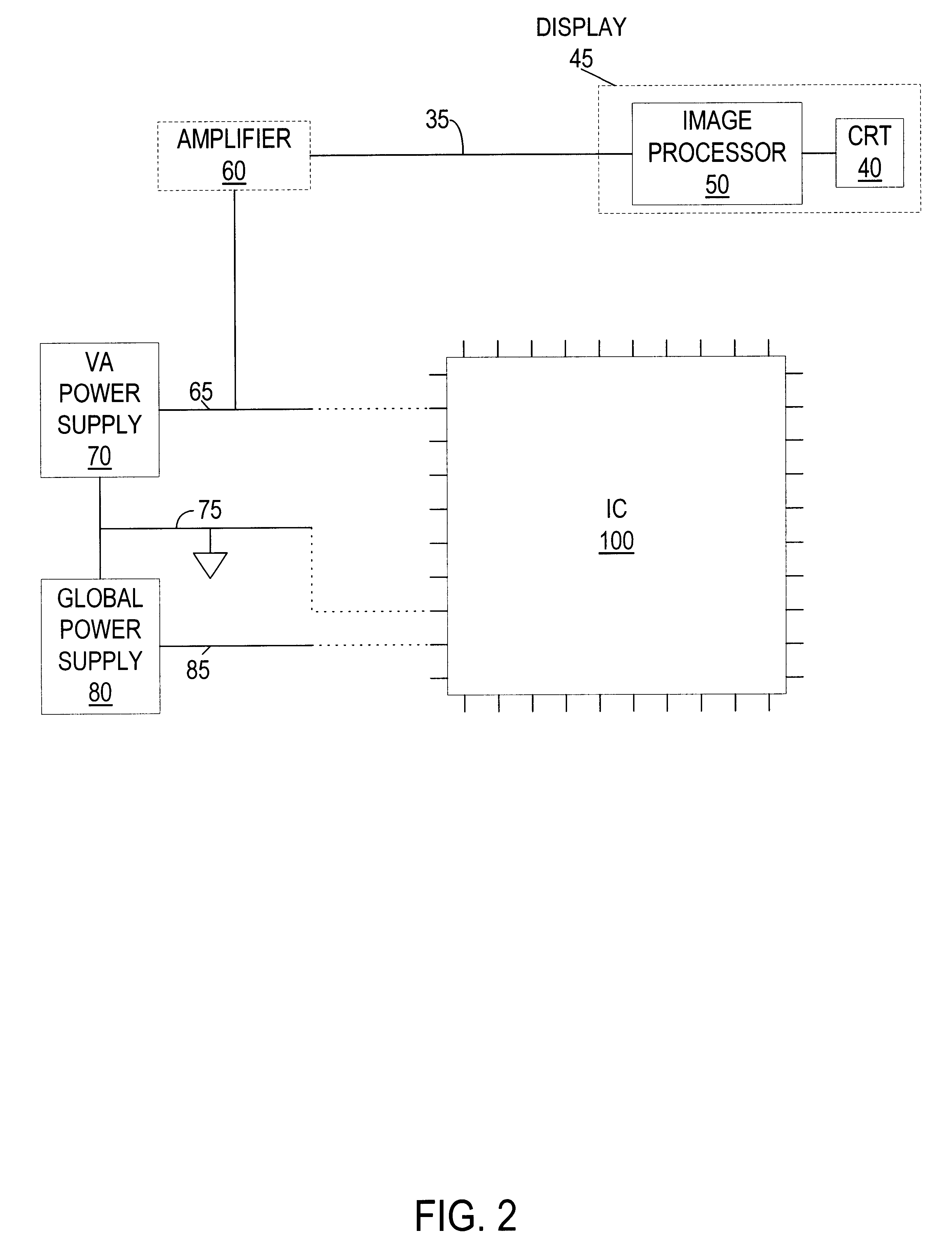

Laser intrusive technique for locating specific integrated circuit current paths

InactiveUS6617862B1Reduce the noise floorHigh sensitivityDigital circuit testingIndividual semiconductor device testingVoltage variationLaser beams

A method and apparatus for locating integrated circuit defects associated with different aspects of the integrated circuit industry. The integrated circuit is configured in a known failing mode, with a first power supply providing a constant voltage and variable current. Next, one or more additional dedicated power supplies are connected to various points of interest throughout the integrated circuit, wherein these dedicated power supplies have a preset current and the voltage is allowed to vary. The integrated circuit is then scanned with a laser beam, which induces current changes on in the integrated circuit especially in defective areas. These current changes then cause voltage changes on the dedicated power supplies. When such a voltage change occurs on the dedicated power supplies, its position is noted.

Owner:GLOBALFOUNDRIES INC

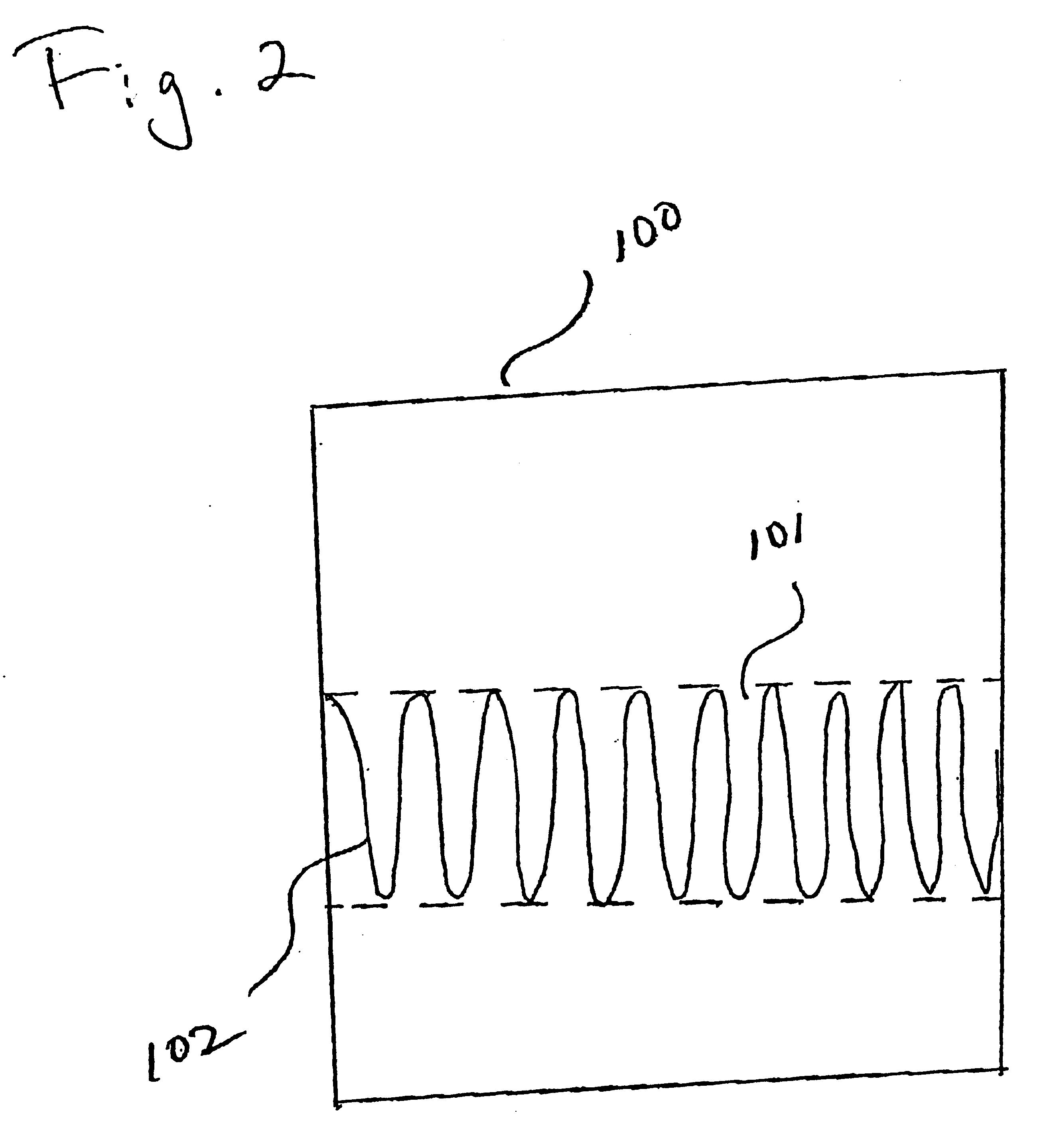

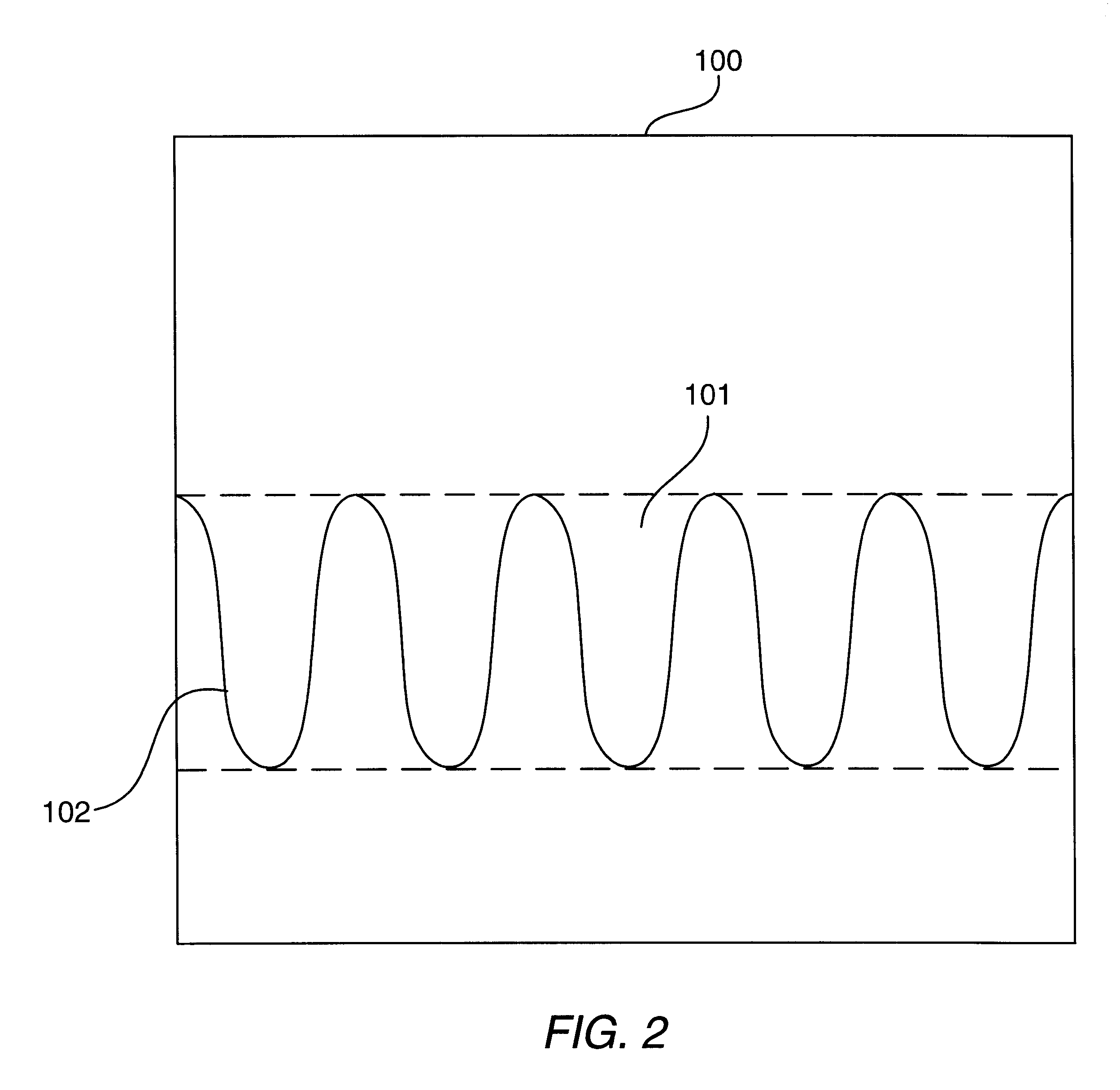

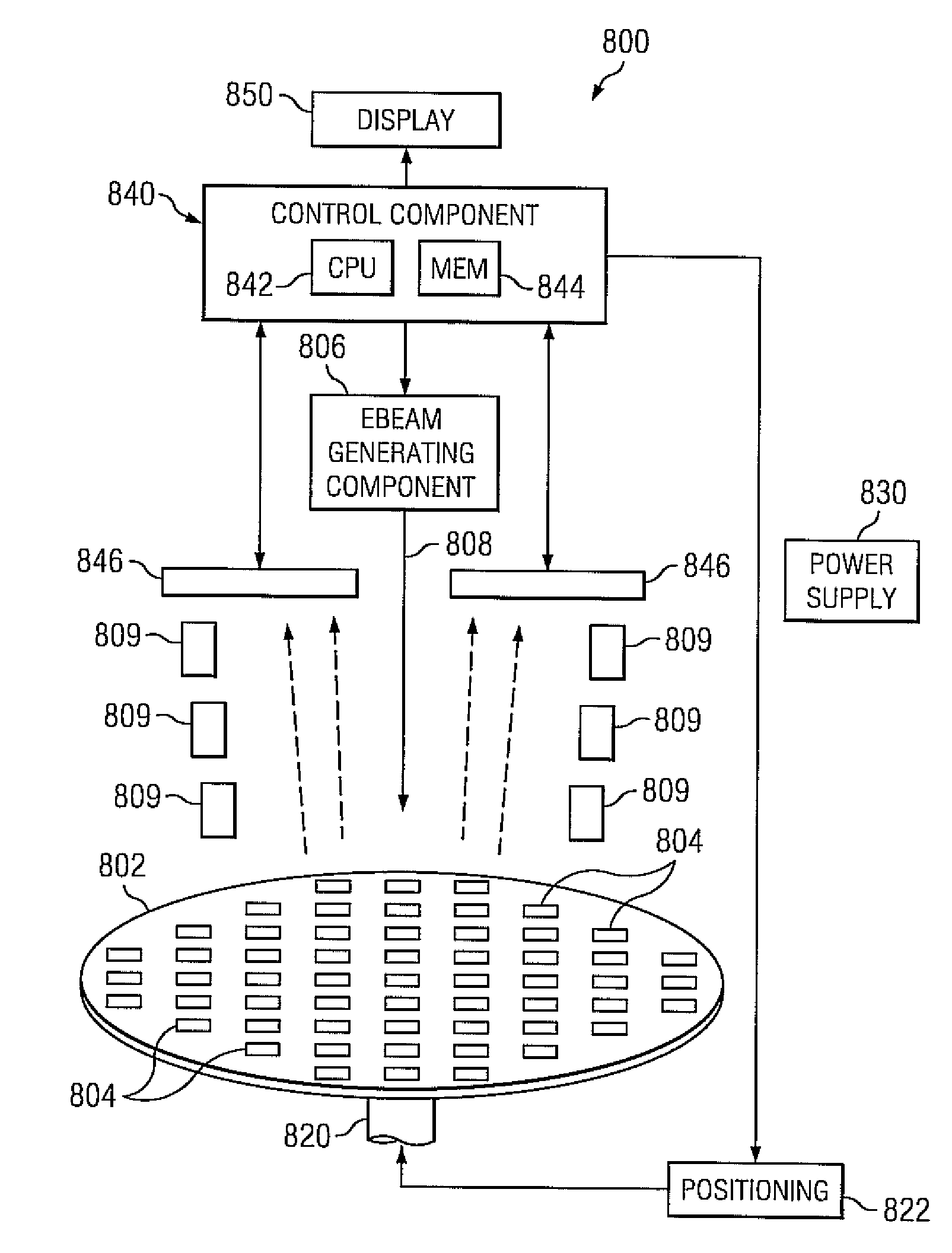

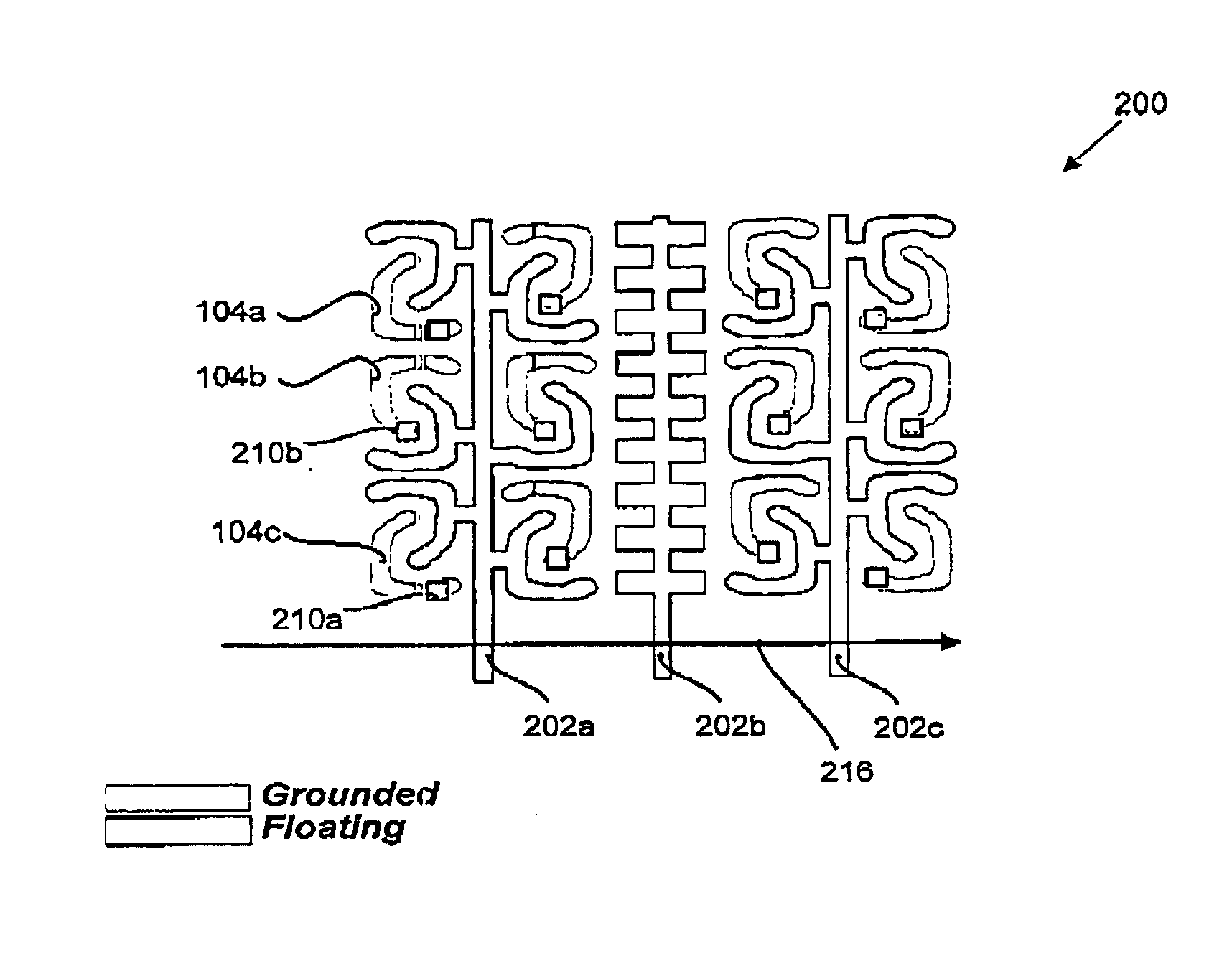

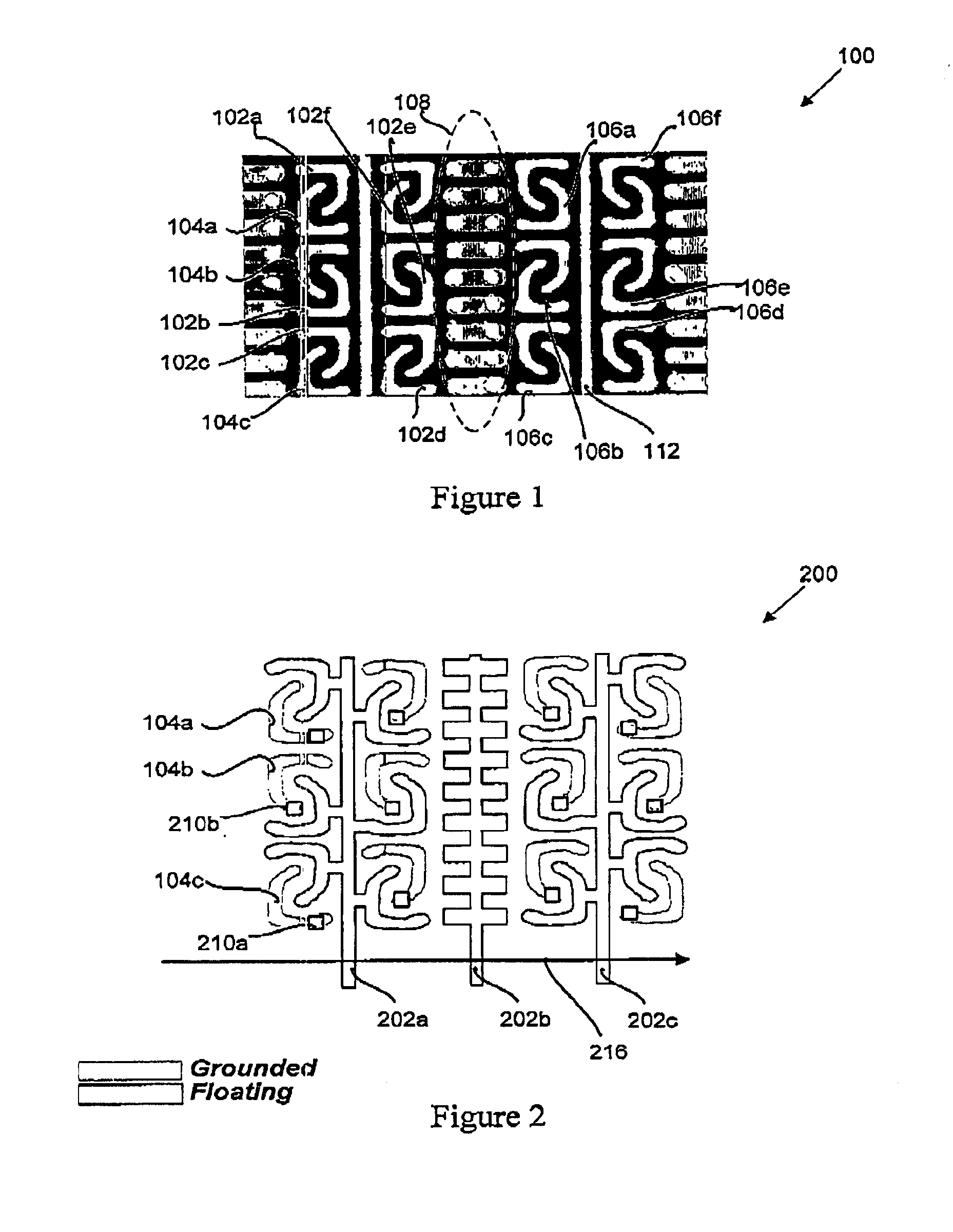

Test structures for e-beam testing of systematic and random defects in integrated circuits

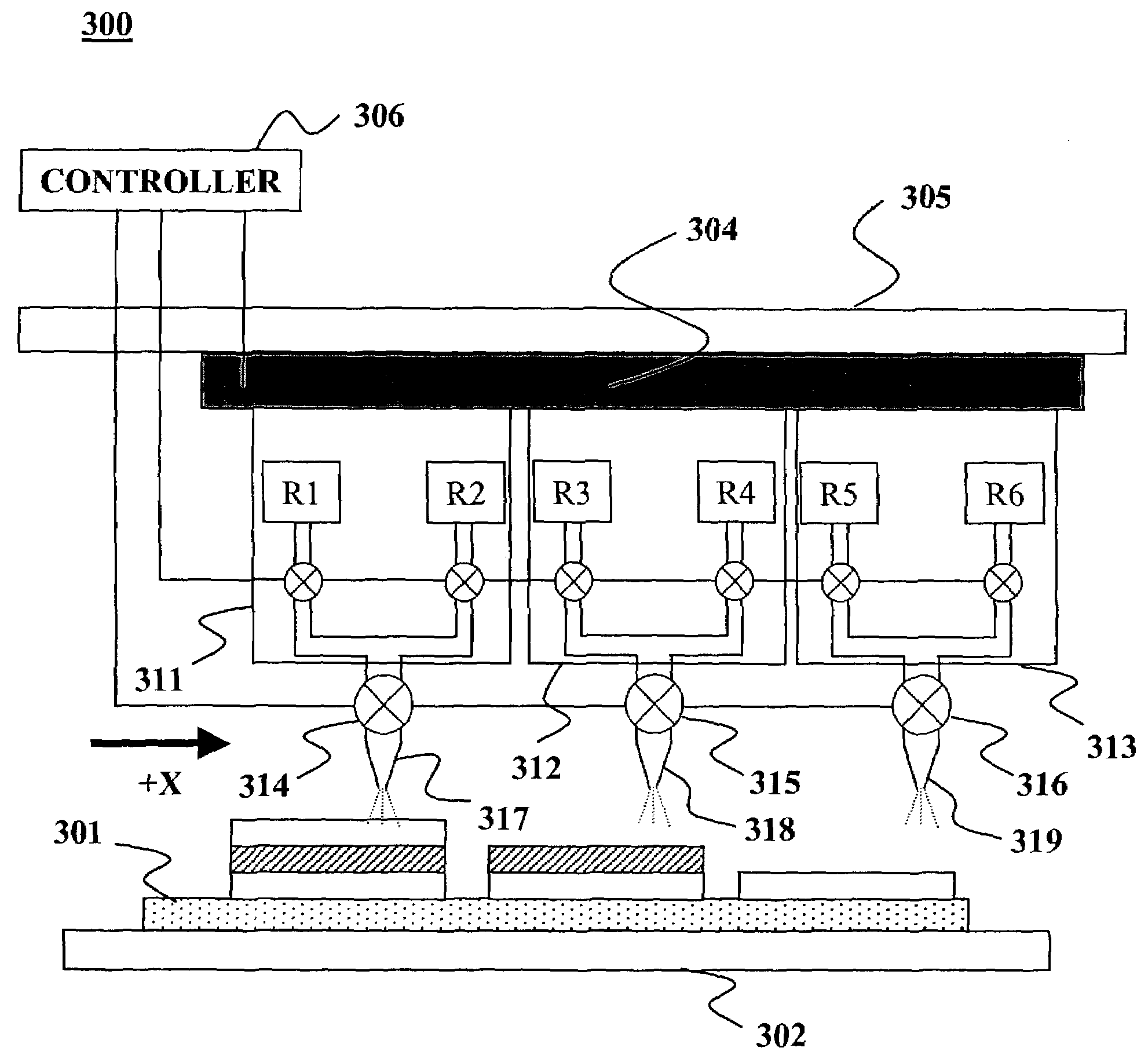

InactiveUS20090102501A1Non-uniform stressMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectron beam testingDislocation

In accordance with the invention, there are electron beam inspection systems, electron beam testable semiconductor test structures, and methods for detecting systematic defects, such as, for example contact-to-gate shorts, worm hole leakage paths, holes printing issues, and anomalies in sparse holes and random defects, such as, current leakage paths due to dislocations and pipes during semiconductor processing.

Owner:TEXAS INSTR INC

Methods and apparatus for generating spatially resolved voltage contrast maps of semiconductor test structures

InactiveUS6445199B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesSpatially resolvedEngineering

Disclosed is a method of inspecting a sample. The sample is illuminated with an incident beam, thereby causing voltage contrast within structures present on the sample. Voltage contrast is detected within the structures. Information from the detected voltage contrast is stored, and position data concerning the location of features corresponding to at least a portion of the stored voltage contrast information is also stored. In a specific embodiment, the features represent electrical defects present on the sample. In another embodiment, the stored position data is in the form of a two dimensional map. In another aspect, the sample is re-inspected and the stored position data is used in analyzing data resulting from the re-inspection.

Owner:KLA CORP

Probe pins zero-point detecting method, and prober

InactiveUS7023226B2Avoid damageImprove accuracySemiconductor/solid-state device testing/measurementFault location by increasing destruction at faultProbe cardConductive materials

A zero-point detecting method of this invention is performed prior to testing the electrical characteristics of a wafer by bringing an object to be tested on a stage and probes of a probe card into contact with each other. The surface of a zero-point detection plate is made of a conductive material (e.g., copper). The zero-point detection plate is used to detect a zero point as a position where the surface of the object to be tested comes into contact with the probe pins.

Owner:OCTEC INC +1

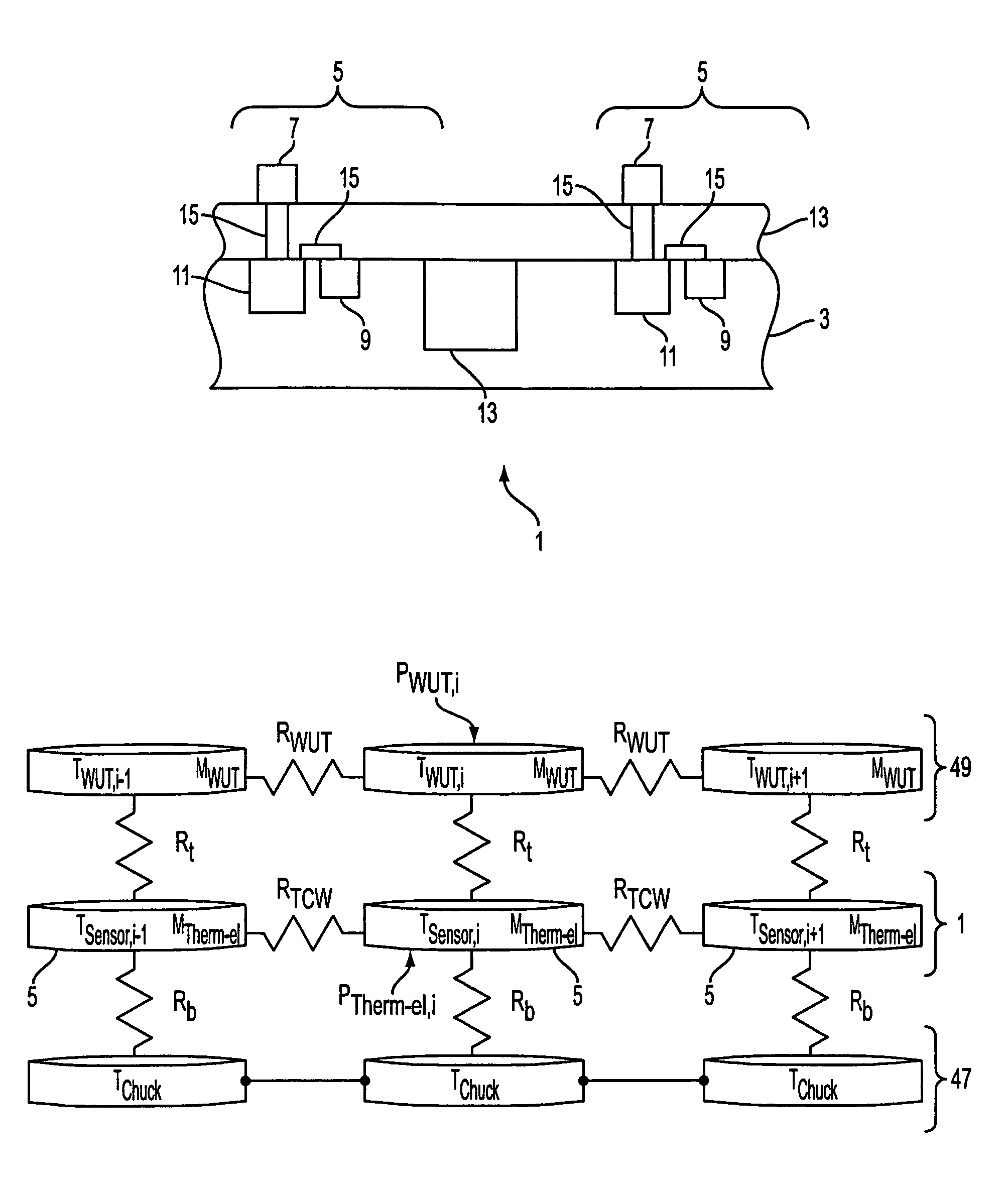

Thermal control of a DUT using a thermal control substrate

A solid state thermal control device contains a substrate and a plurality of solid state thermal elements on the substrate. The thermal elements are adapted to provide thermal control to a device under test (DUT). Each solid state thermal element contains at least one solid state heater and an active control circuit adapted to control a thermal output of the heater. Optionally, the each thermal element may also include a solid state temperature sensor.

Owner:DELTA DESIGN

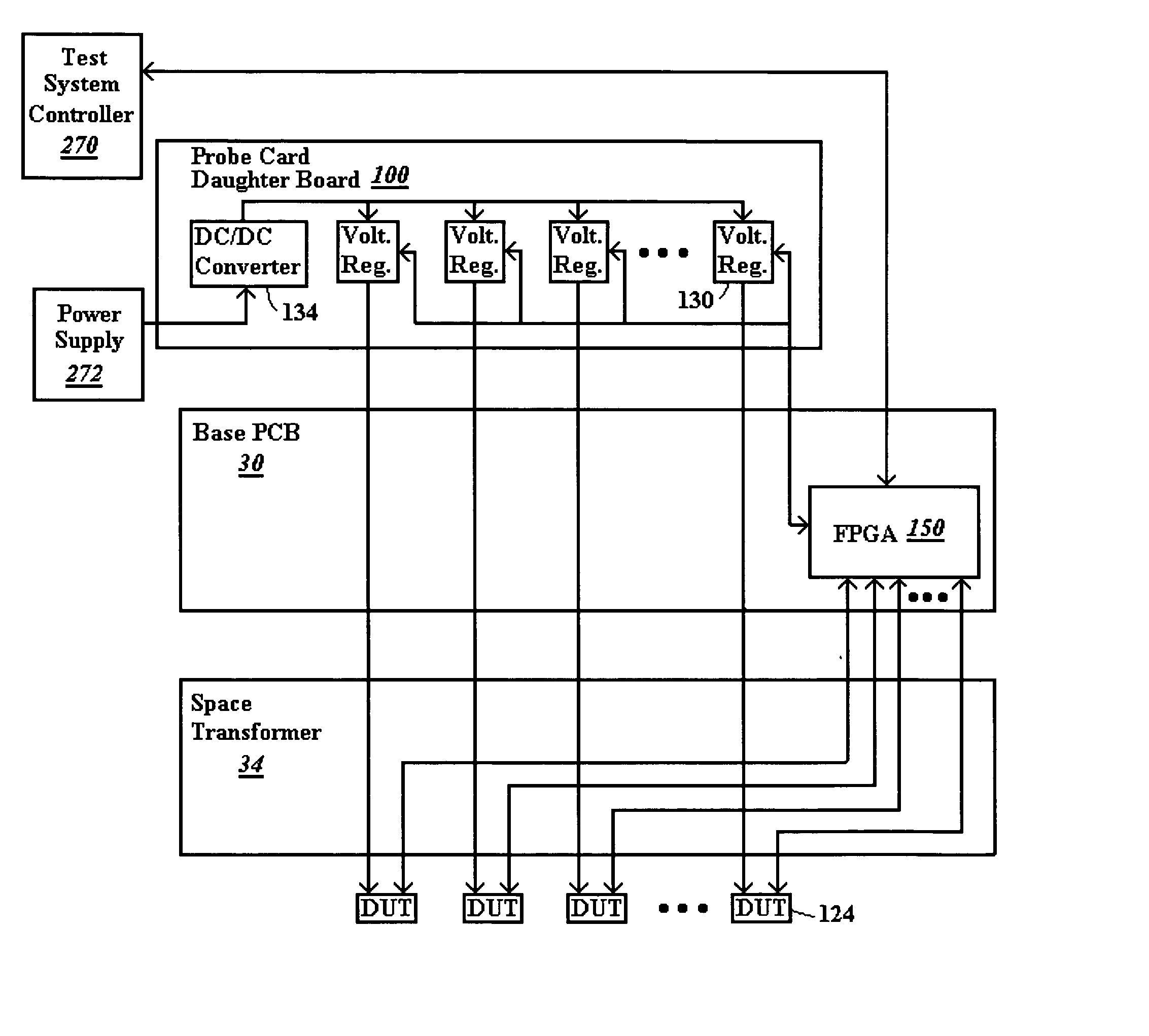

Method of designing an application specific probe card test system

InactiveUS20060273809A1Eliminate needDigital circuit testingOverload protection arrangementsProbe cardOn board

A method is provided for design and programming of a probe card with an on-board programmable controller in a wafer test system. Consideration of introduction of the programmable controller is included in a CAD wafer layout and probe card design process. The CAD design is further loaded into the programmable controller, such as an FPGA to program it: (1) to control direction of signals to particular ICs, even during the test process (2) to generate test vector signals to provide to the ICs, and (3) to receive test signals and process test results from the received signals. In some embodiments, burn-in only testing is provided to limit test system circuitry needed so that with a programmable controller on the probe card, text equipment external to the probe card can be eliminated or significantly reduced from conventional test equipment.

Owner:FORMFACTOR INC

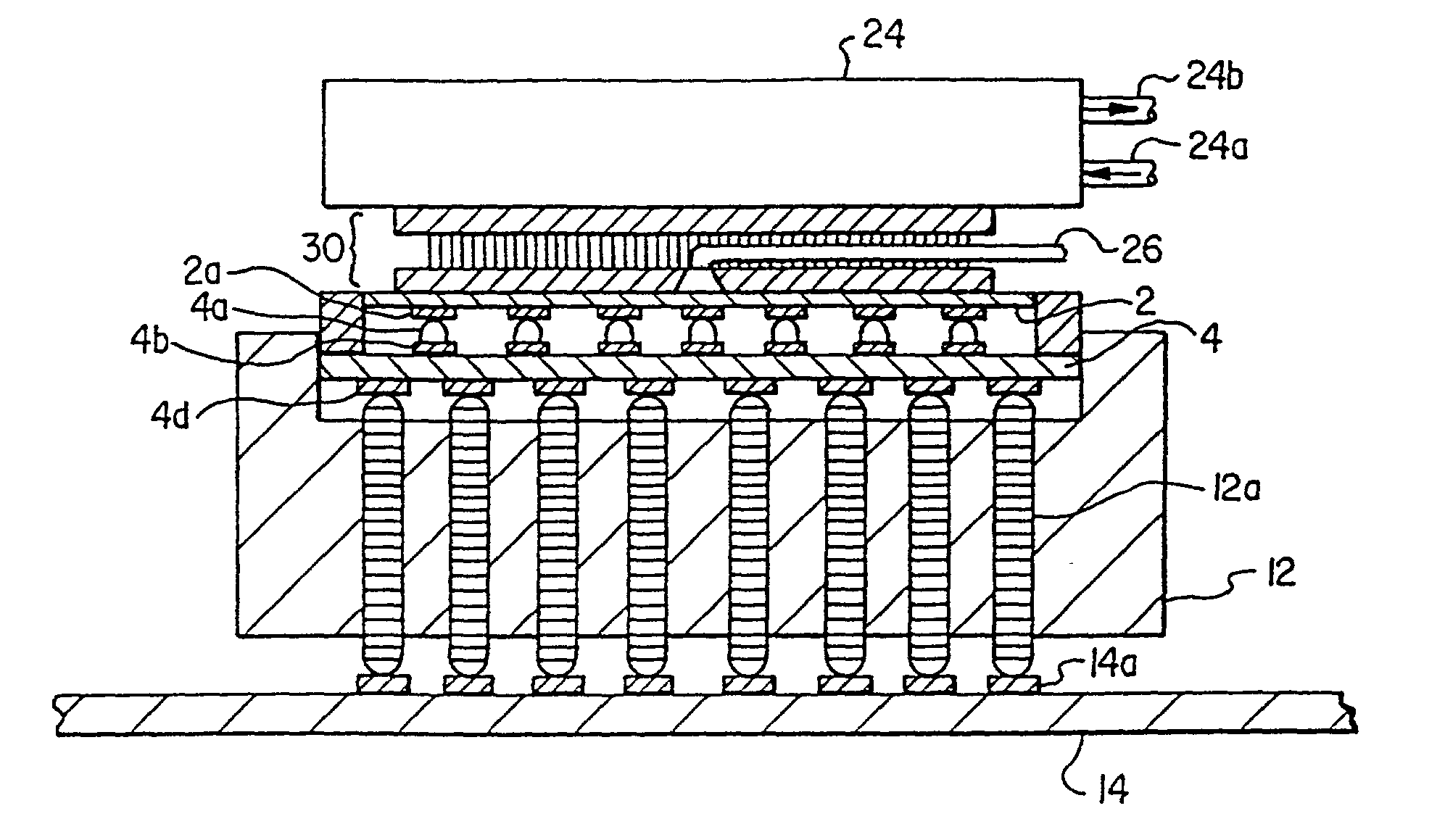

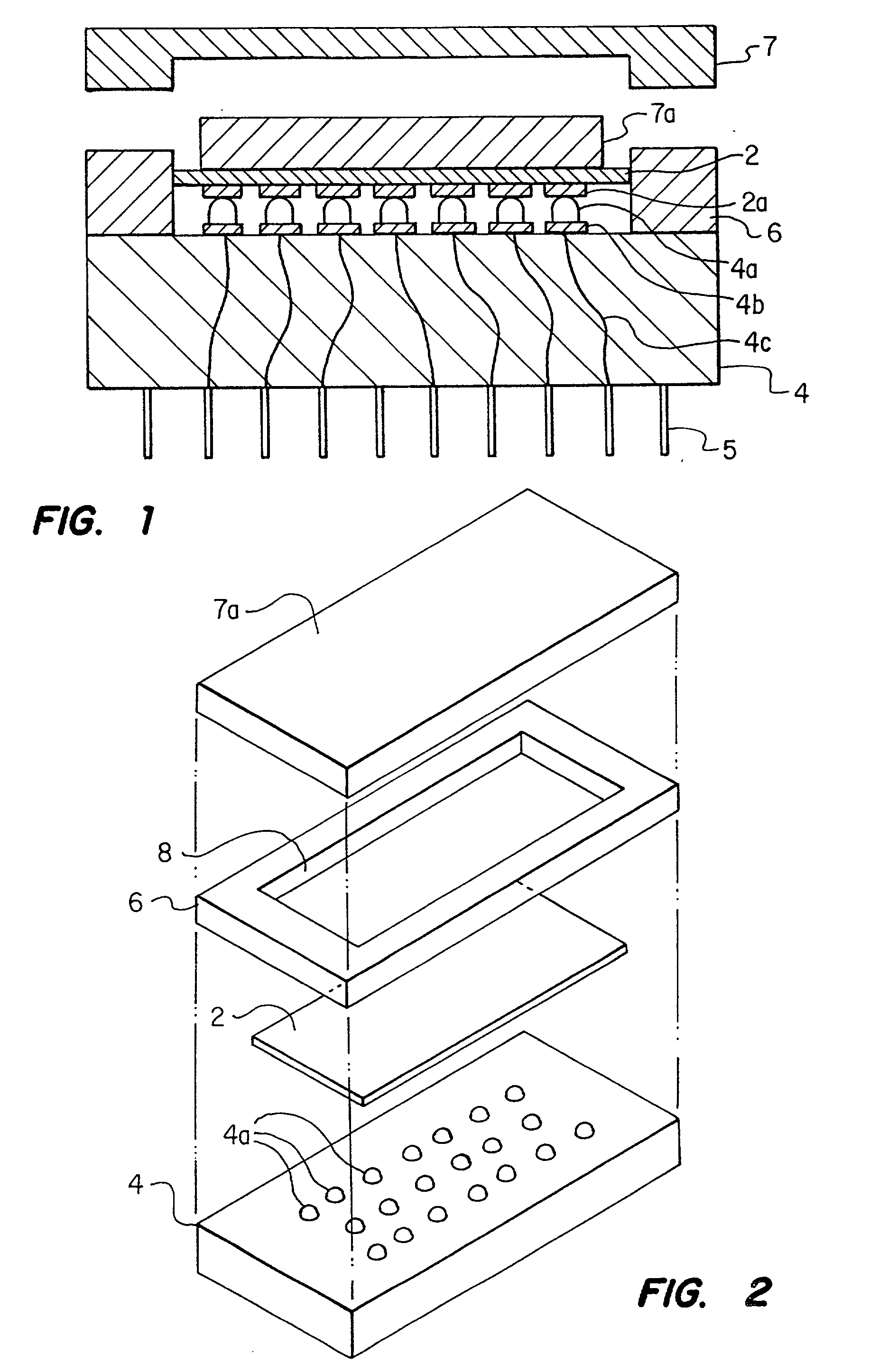

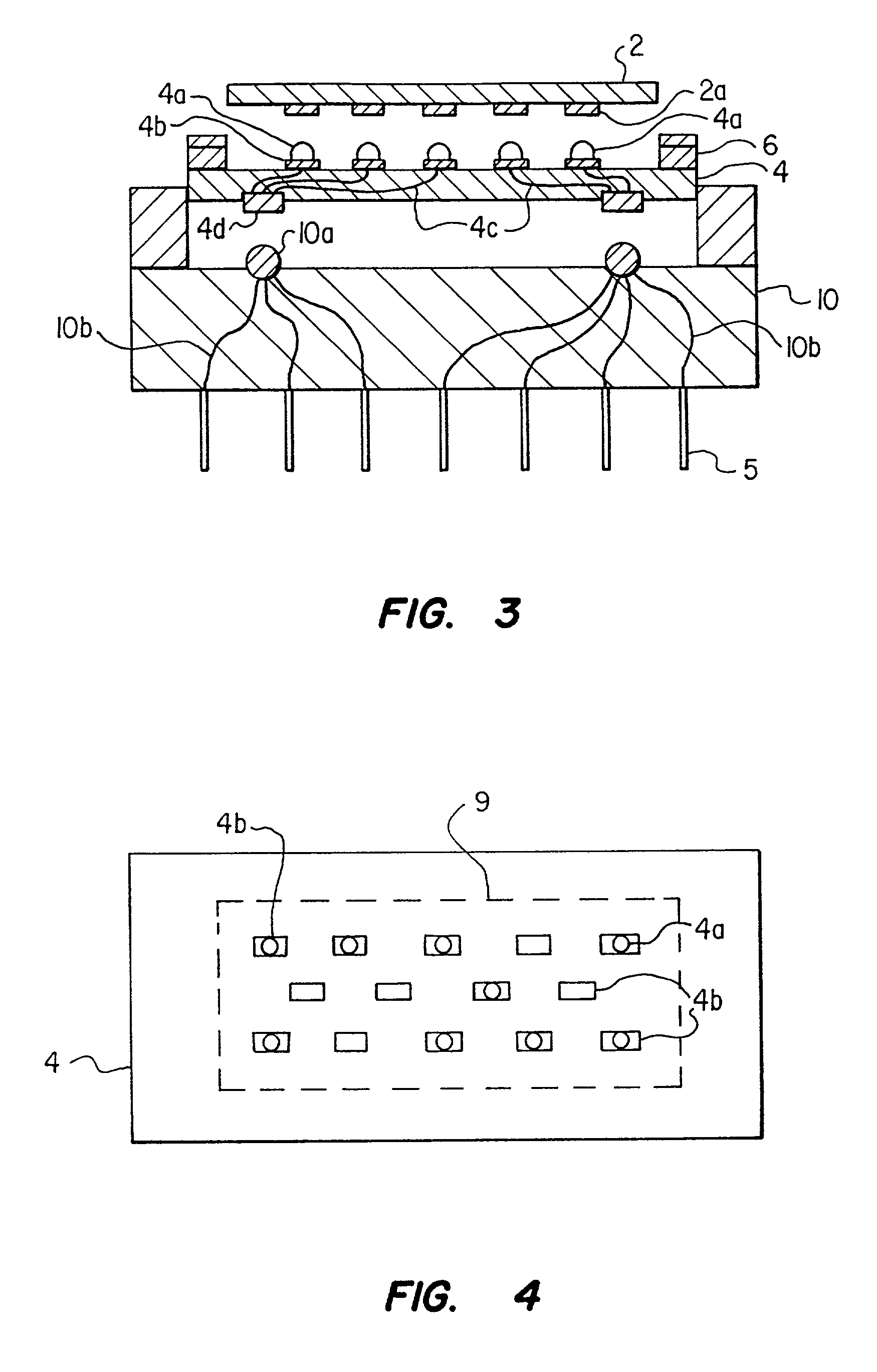

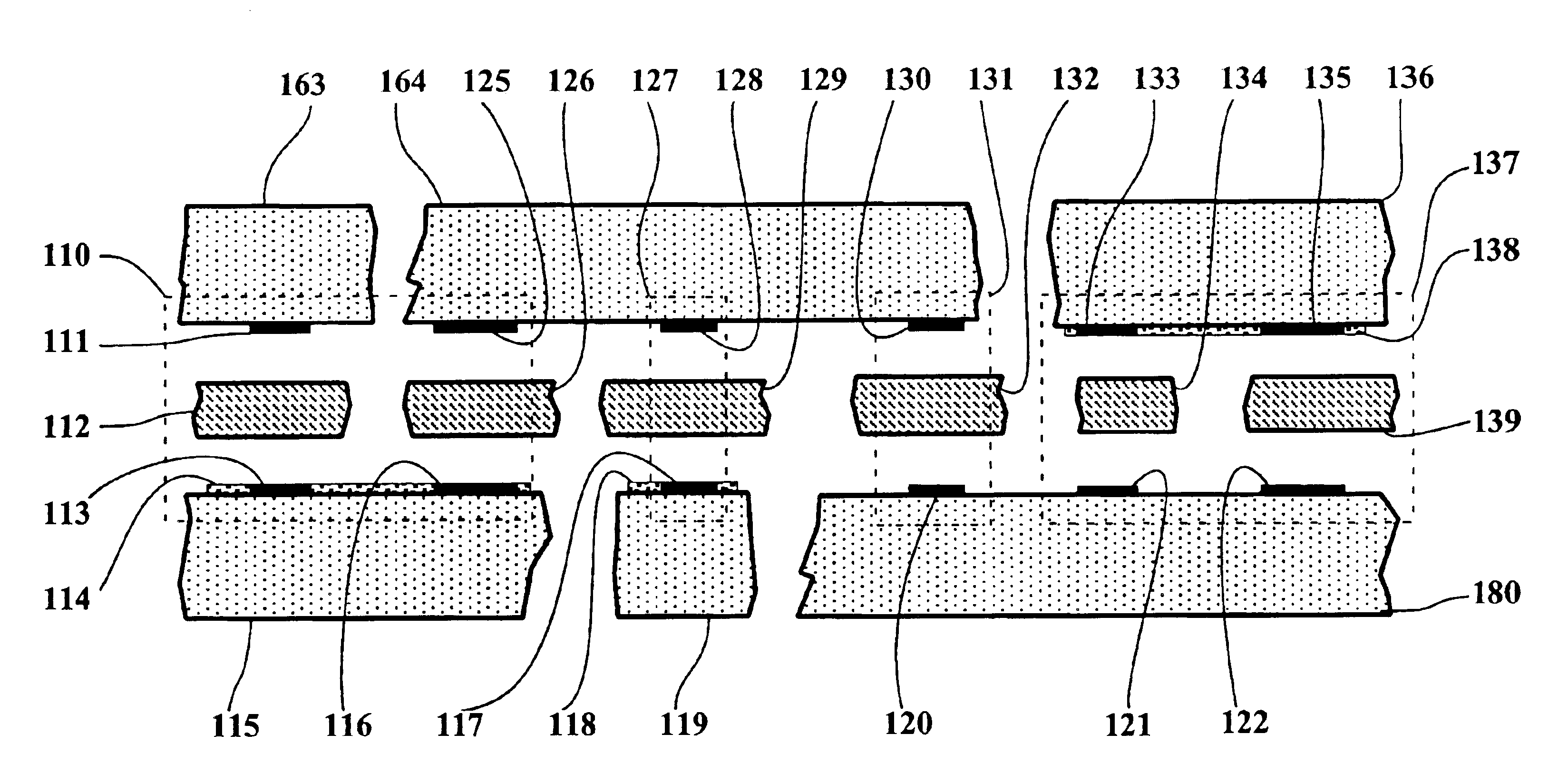

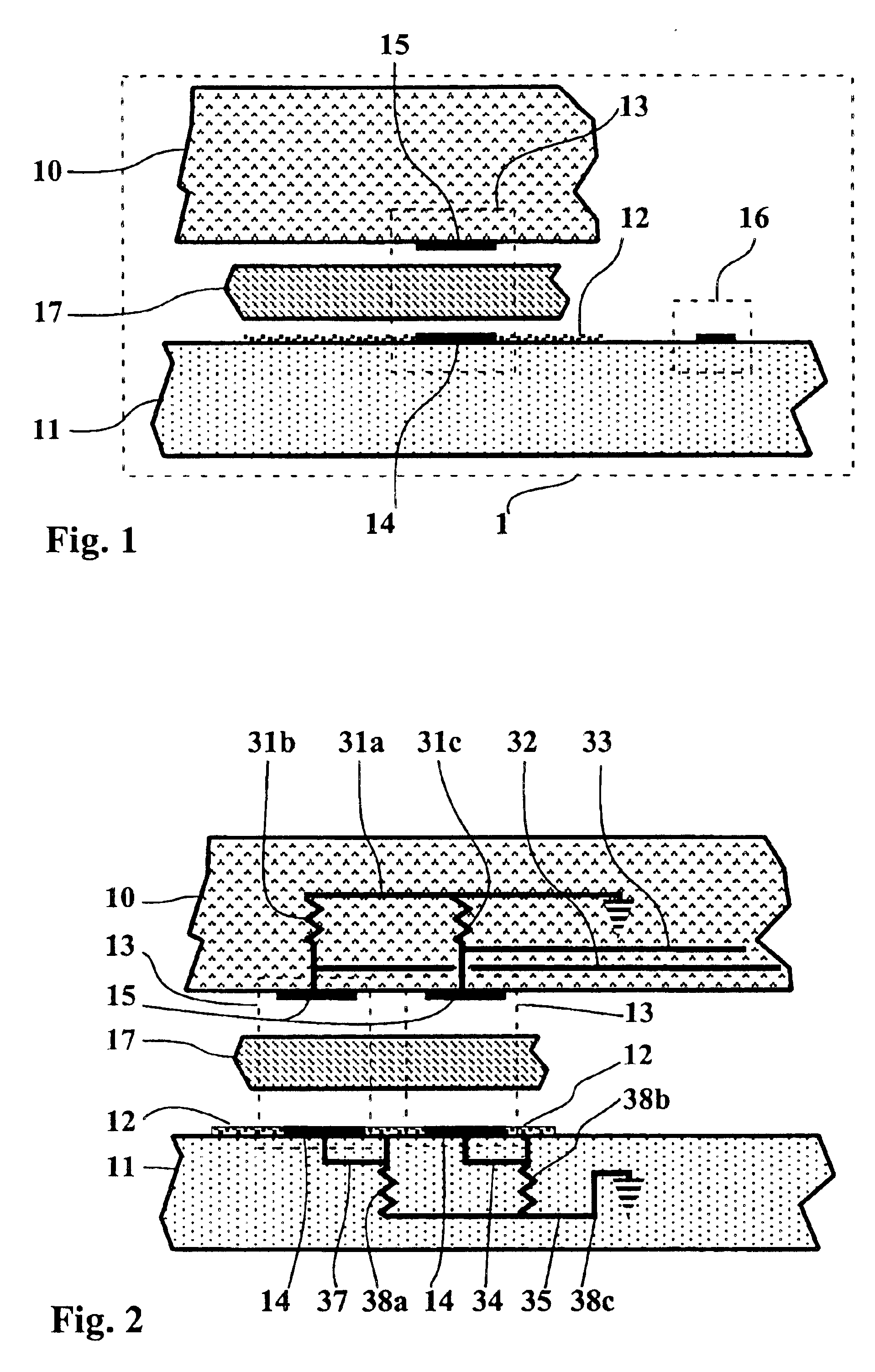

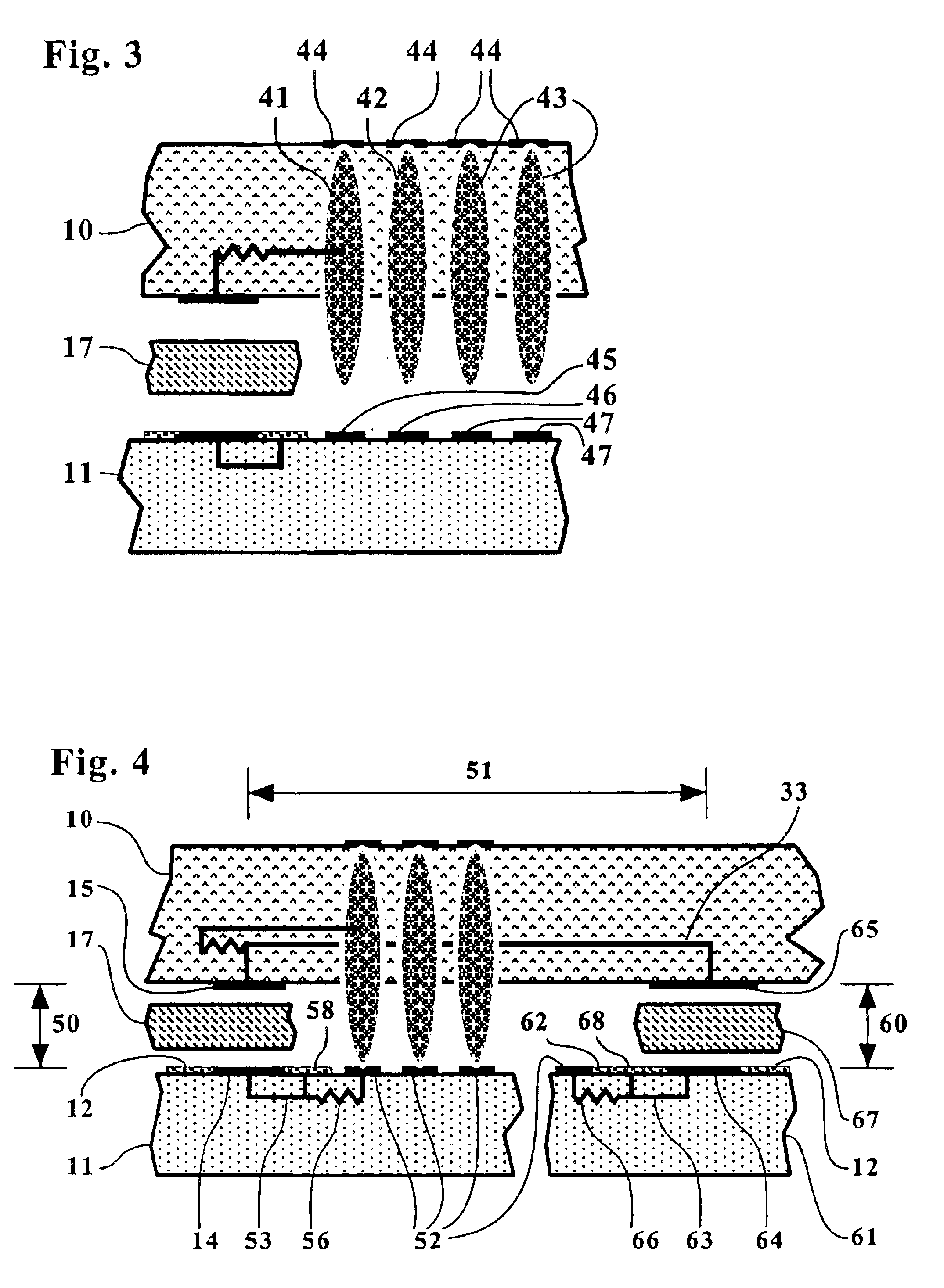

Method and apparatus for non-conductively interconnecting integrated circuits

InactiveUS6916719B1Increased signal noiseIncrease speedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsLead bondingComputer module

Methods and apparatus are described for capacitively signaling between different semiconductor chips and modules without the use of connectors, solder bumps, wire-bond interconnections or the like. Preferably, pairs of half-capacitor plates, one half located on each chip, module or substrate are used to capacitively couple signals from one chip, module or substrate to another. The use of plates relaxes the need for high precision alignment as well as reduces the area needed to effect signaling, and reduces or eliminates the requirements for exotic metallurgy.

Owner:SUN MICROSYSTEMS INC

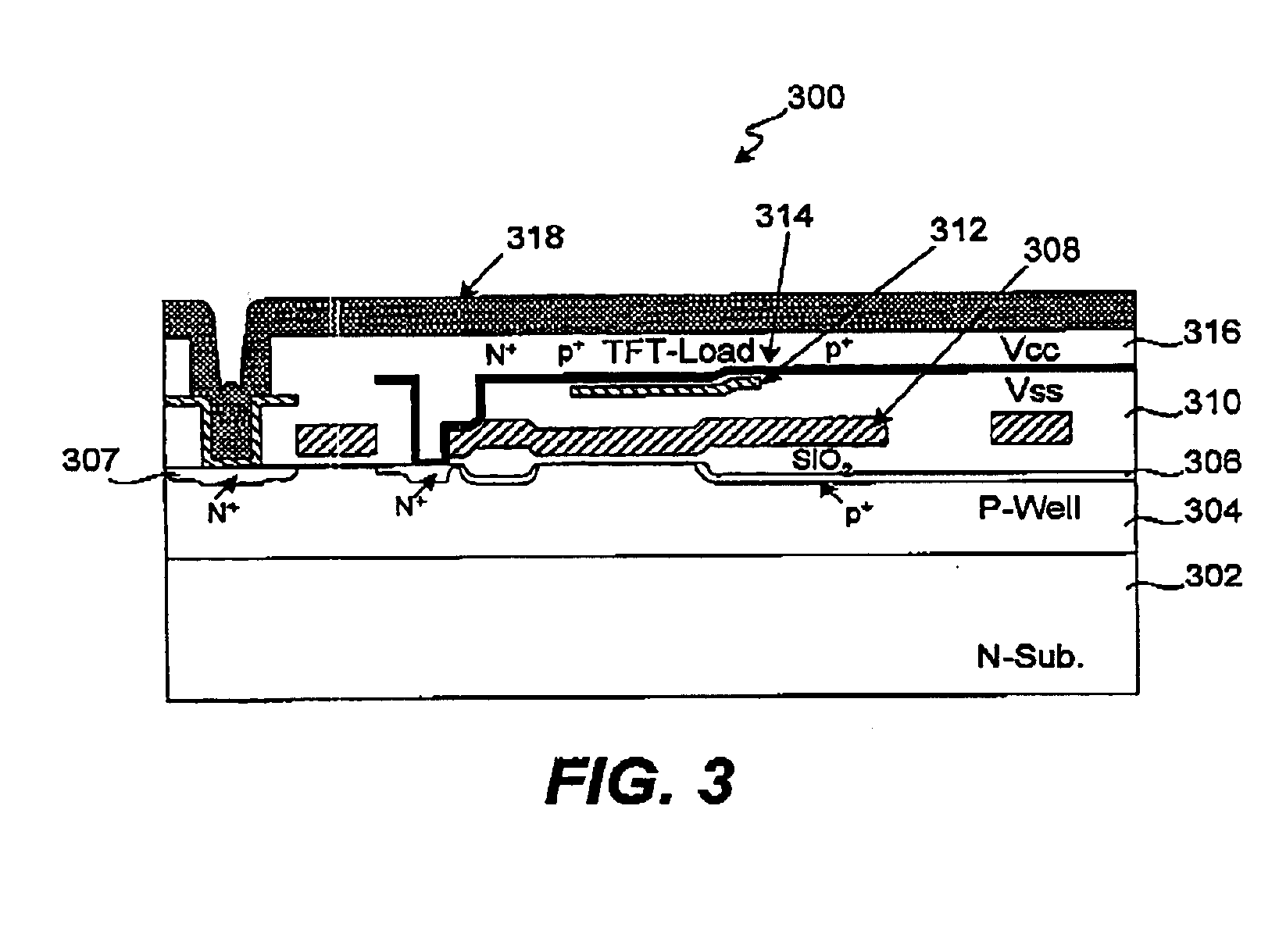

Apparatus and methods for determining and localization of failures in test structures using voltage contrast

InactiveUS6861666B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVoltage contrastProduct layer

Disclosed is test structure that can be fabricated with minimal photolithography masking steps and in which defects may be localized to specific layers. Mechanisms for fabricating such test structures are also provided. In one embodiment, a semiconductor test structure suitable for a voltage contrast inspection is provided. The test structure includes one or more test layers corresponding to one or more product layers selected from a plurality of product layers of an integrated circuit (IC) product structure. The number of the selected one or more test layers is less than a total number of the plurality of product layers of the product structure, and the test layers include at least a first portion that is designed to have a first potential during the voltage contrast inspection and a second portion that is designed to have a second potential during the voltage contrast inspection. The first potential differs from the second potential. The selected one or more test layers which correspond to product layers are selected from the plurality of product layers such that defects found in the test layers of the test structure during the voltage contrast inspection represent a prediction of defects in the corresponding product structure.

Owner:KLA TENCOR TECH CORP

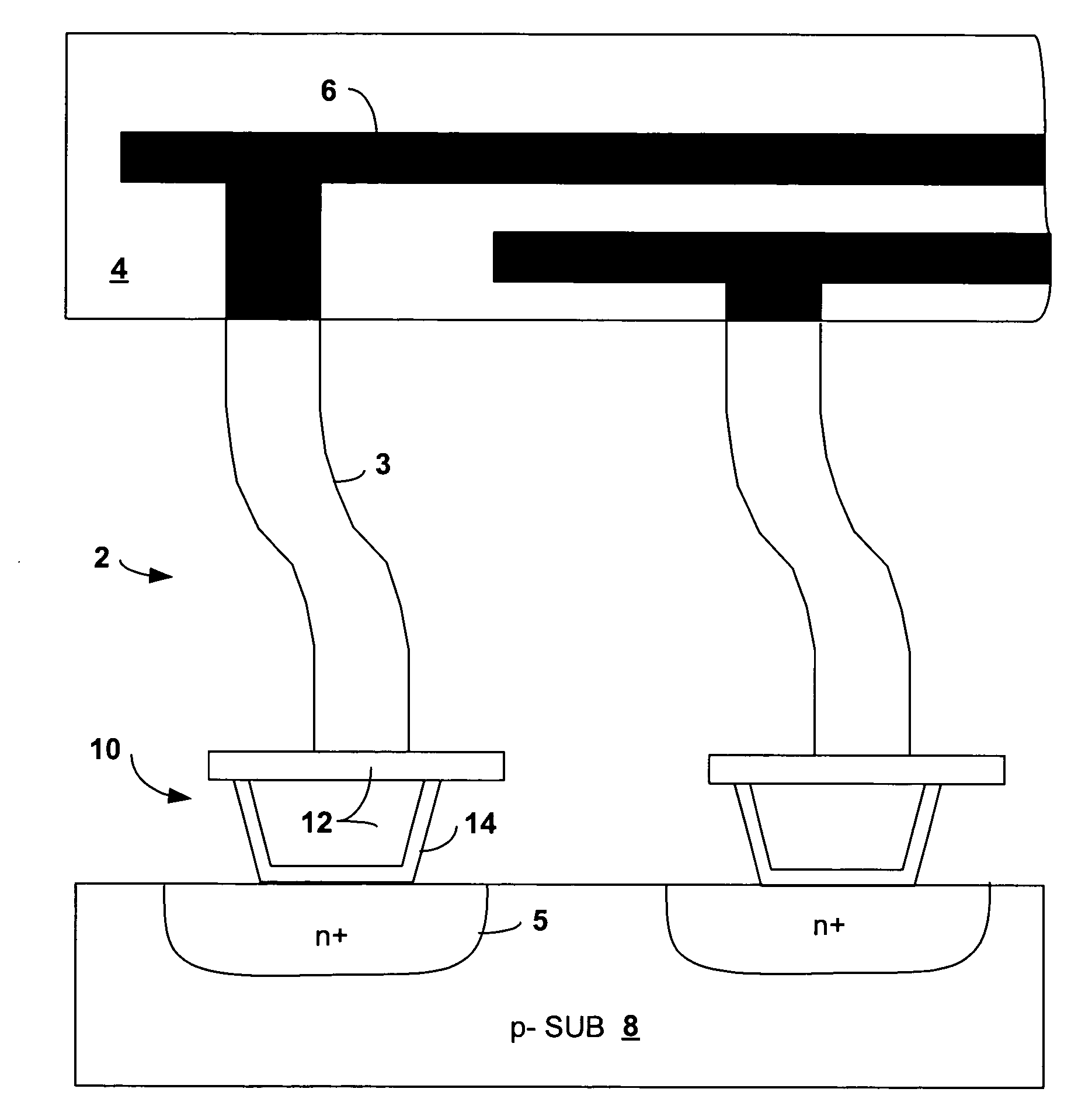

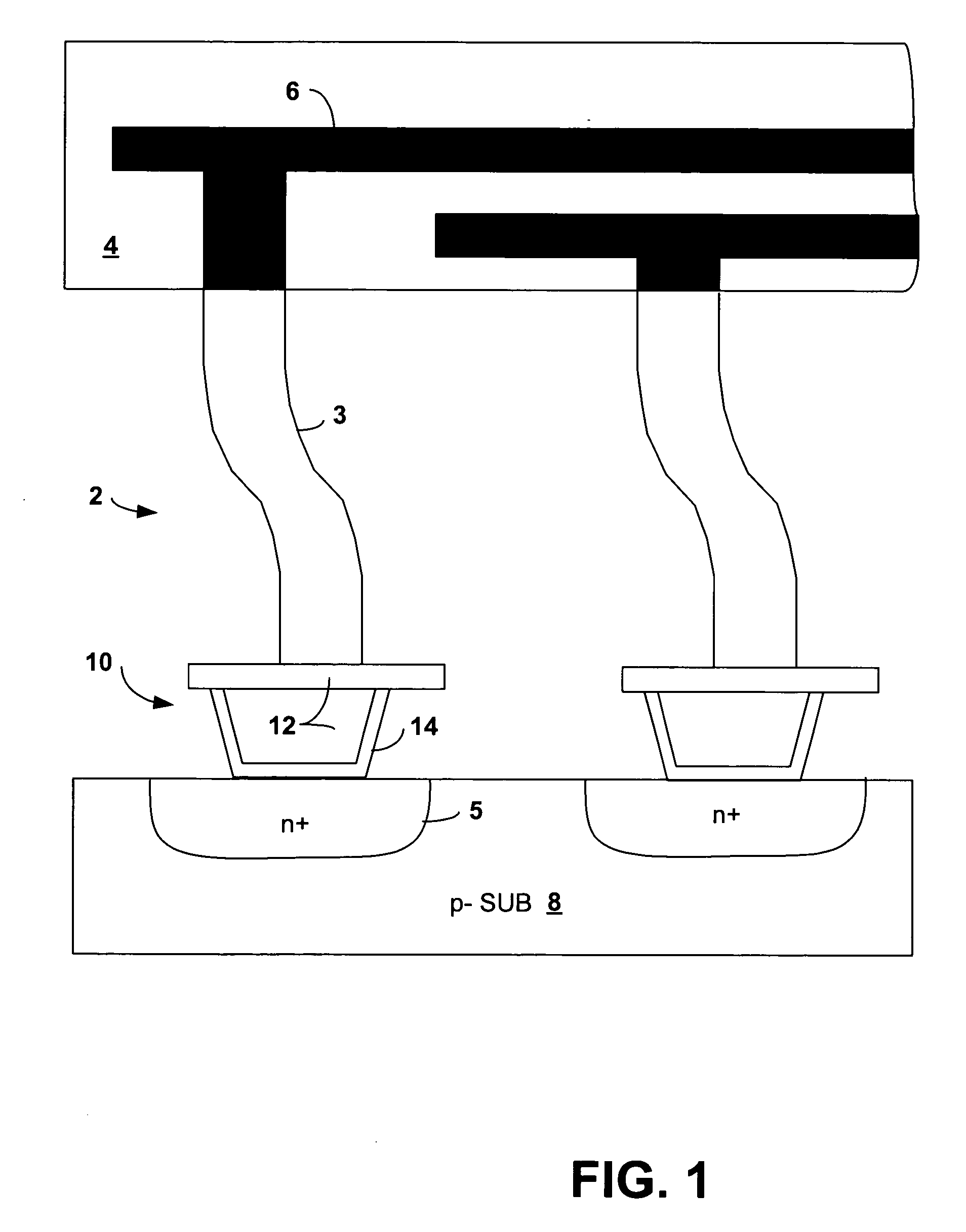

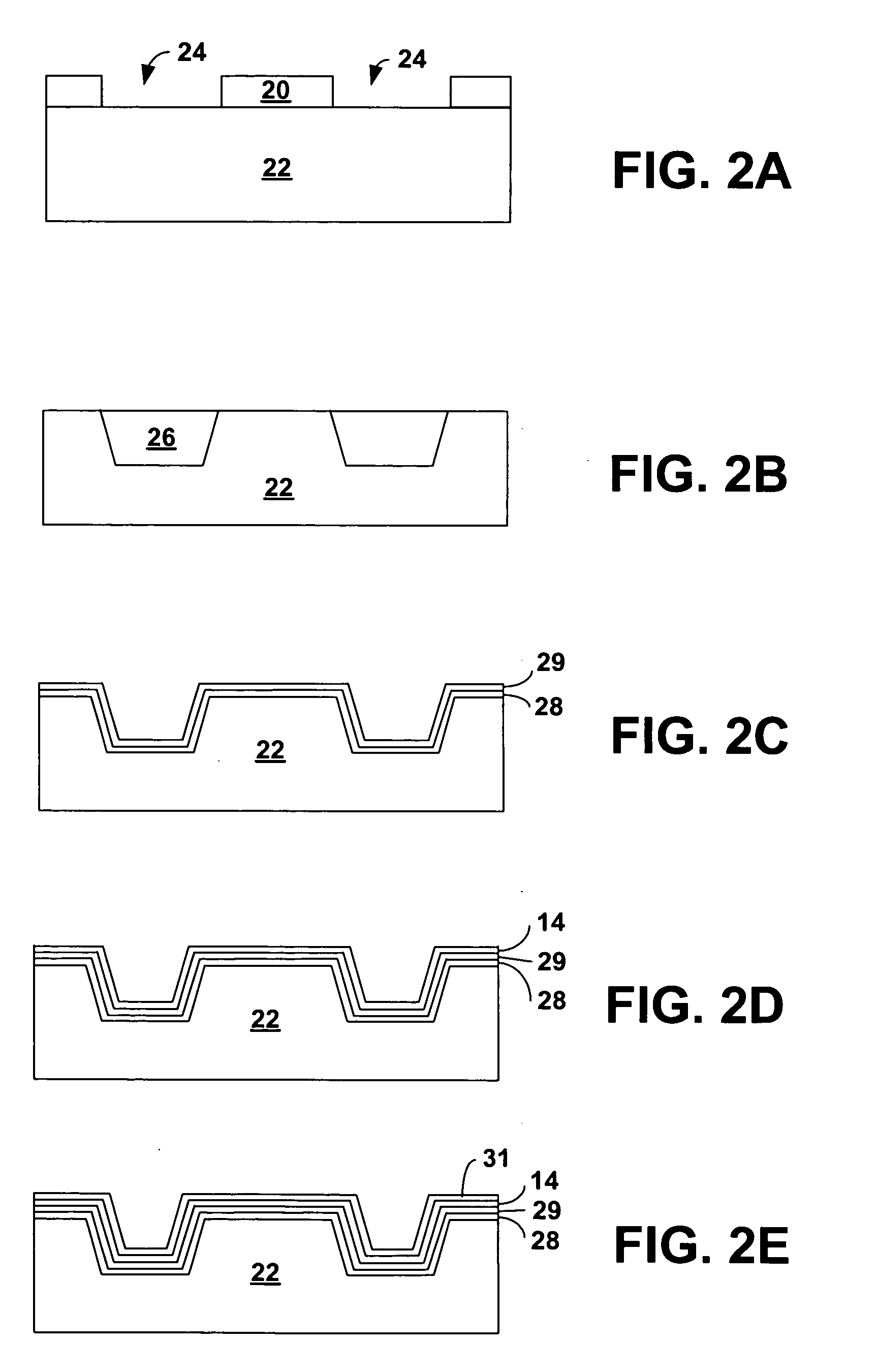

Buried short location determination using voltage contrast inspection

Structure and methods of determining the complete location of a buried short using voltage contrast inspection are disclosed. In one embodiment, a method includes providing a test structure having a PN junction thereunder; and using the PN junction to determine the location of the buried short using voltage contrast (VC) inspection. A test structure may include a plurality of test elements each having a PN junction thereunder, wherein a location of the buried short within the test structure can be determined using the PN junction and the VC inspection. The PN junction forces a change in illumination brightness of a test element including the buried short, thus allowing determination of the complete location of a buried short.

Owner:GLOBALFOUNDRIES INC