Patents

Literature

194 results about "Voltage contrast" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

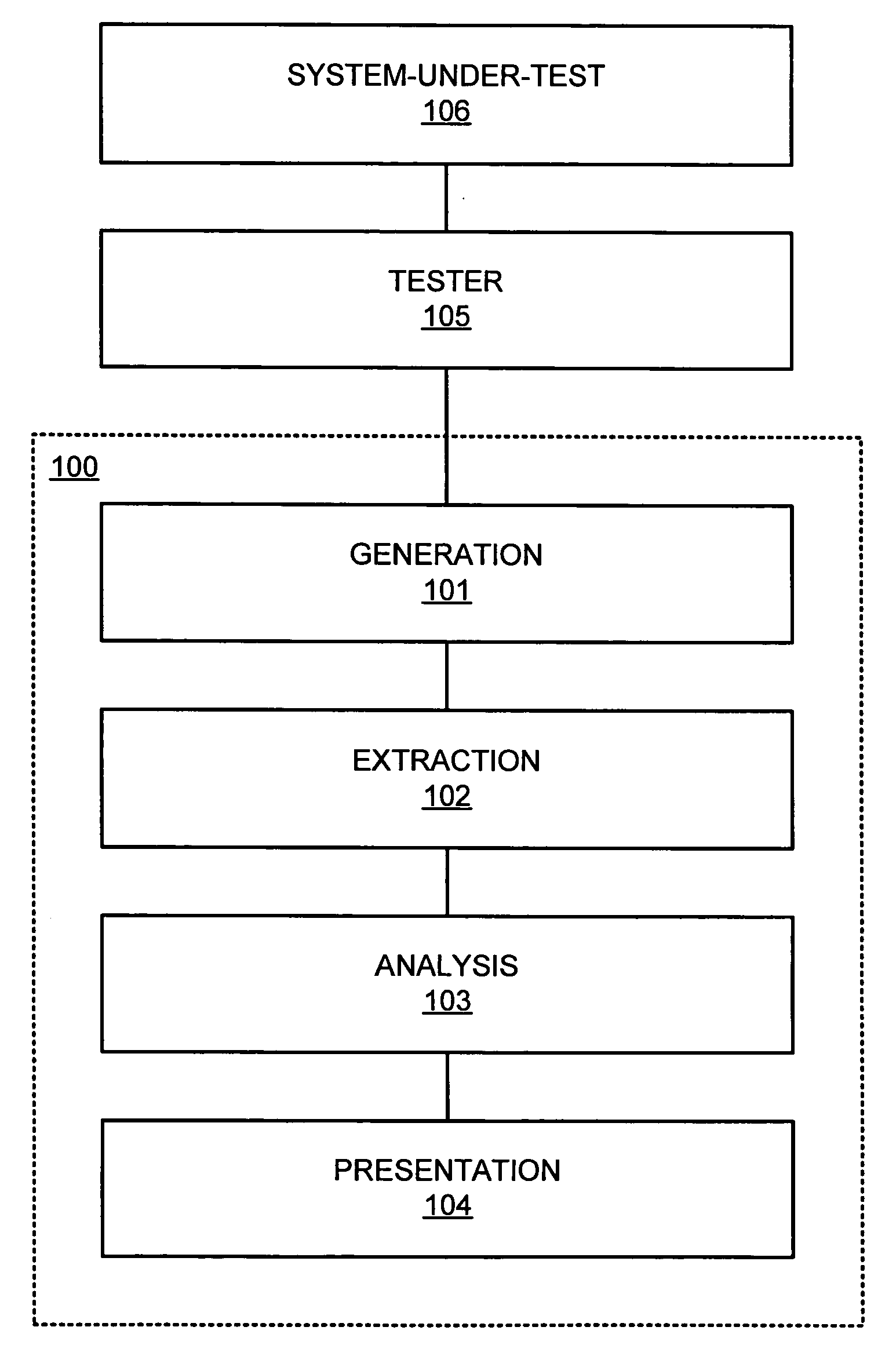

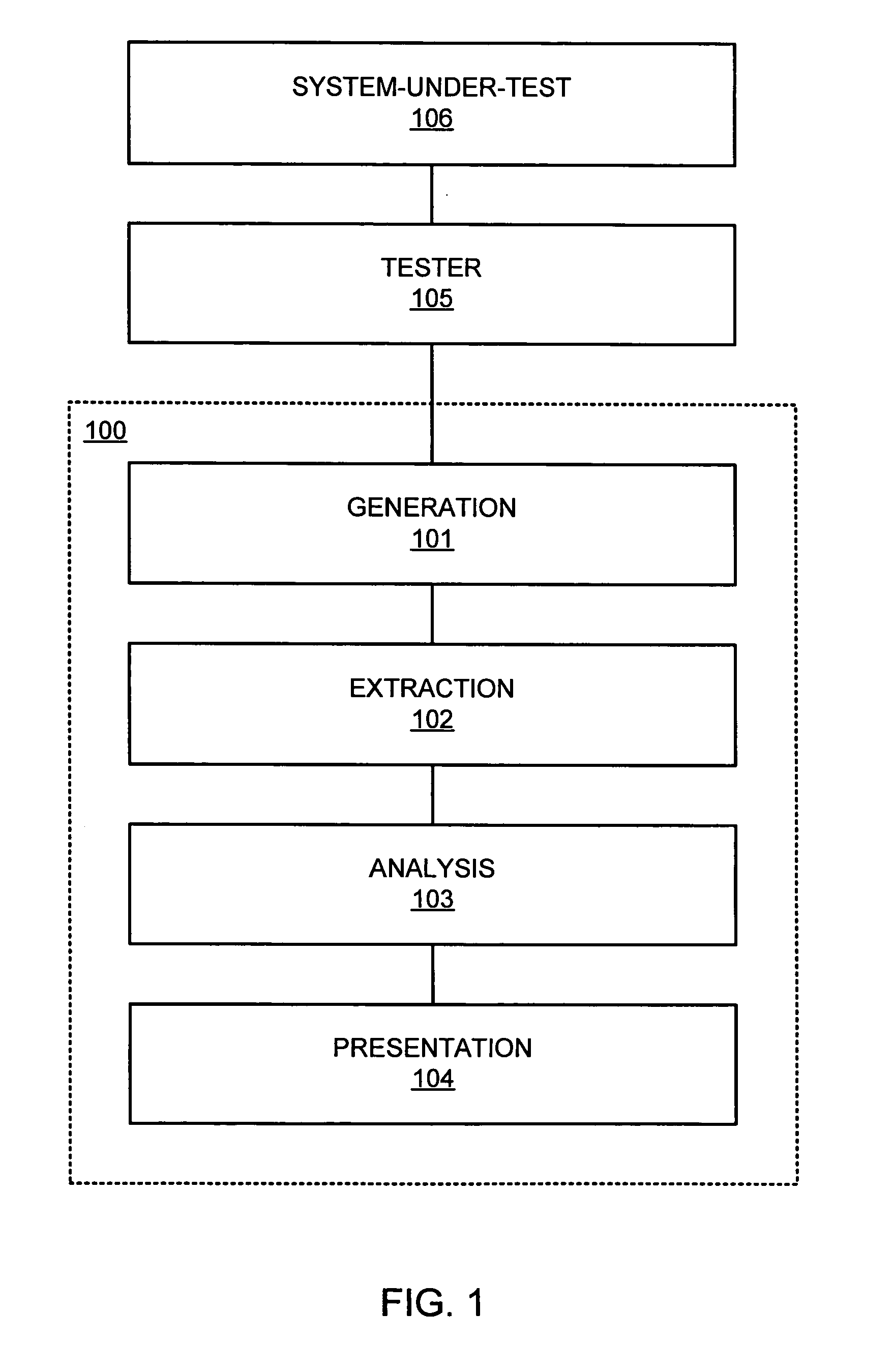

VOLTAGE CONTRAST: A REVIEW. Abstract. Voltage contrast enables potentials and potential distributions to be observed in the SEM. Its origin is due to the low energy secondary electrons gaining or losing energy as the emission point potential is lowered below or raised above earth.

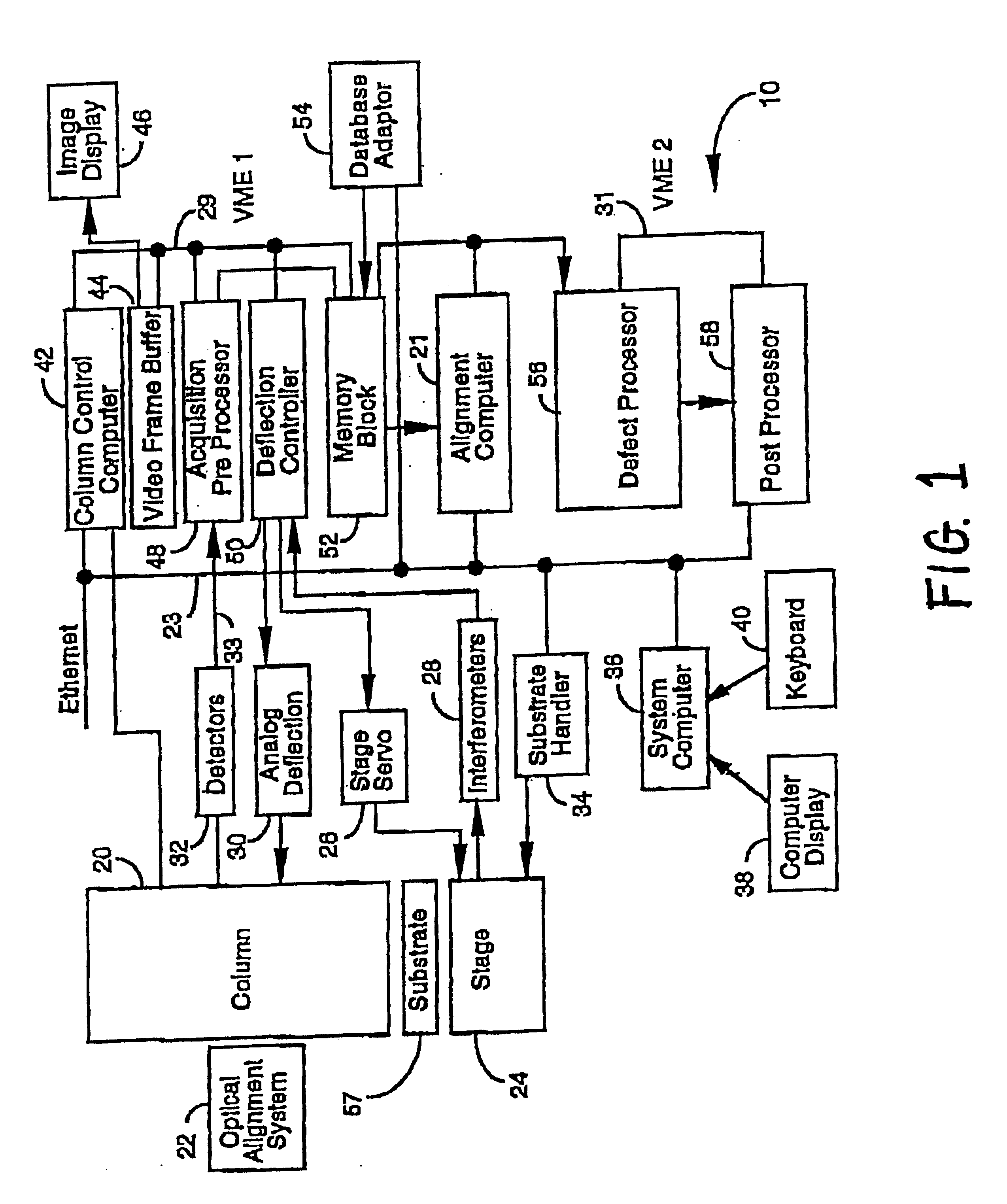

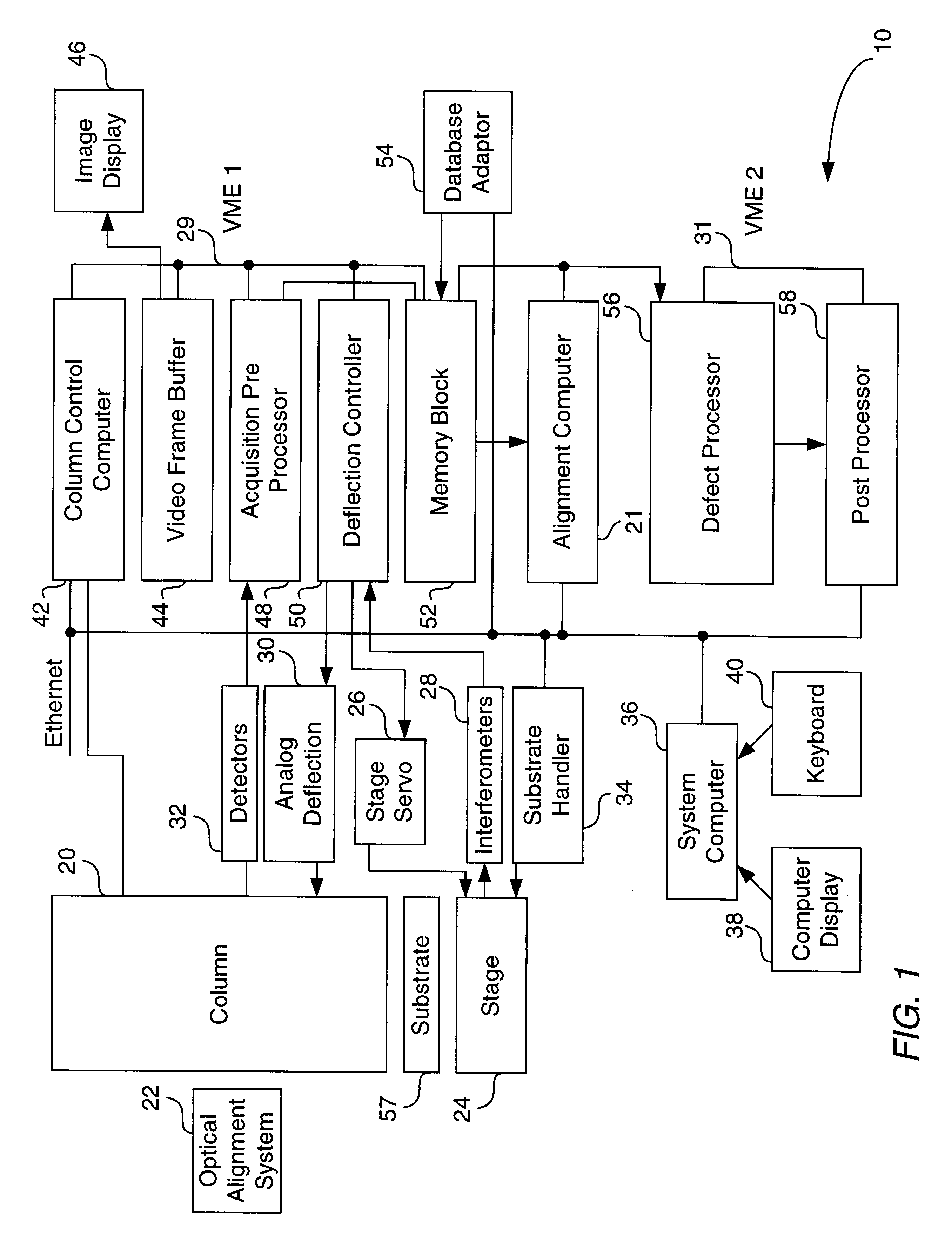

Methods and apparatus for optimizing semiconductor inspection tools

InactiveUS6433561B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

Disclosed is a method of inspecting a sample. At least a portion of the sample is illuminated. Signals received from the illuminated portion are detected, and the detected signals are processed to find defects present on the sample. The processing of the detected signals is optimized, at least in part, based upon results obtained from voltage contrast testing. In one implementation, the illumination is an optical illumination. In another embodiment, the processing comprises automated defect classification, and setup of the automated classification is optimized using the results obtained from voltage contrast testing. In another implementation, the results relate to a probability that a feature present on the sample represents an electrical defect.

Owner:KLA TENCOR TECH CORP

Inspectable buried test structures and methods for inspecting the same

InactiveUS6509197B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesVoltage contrastSemiconductor

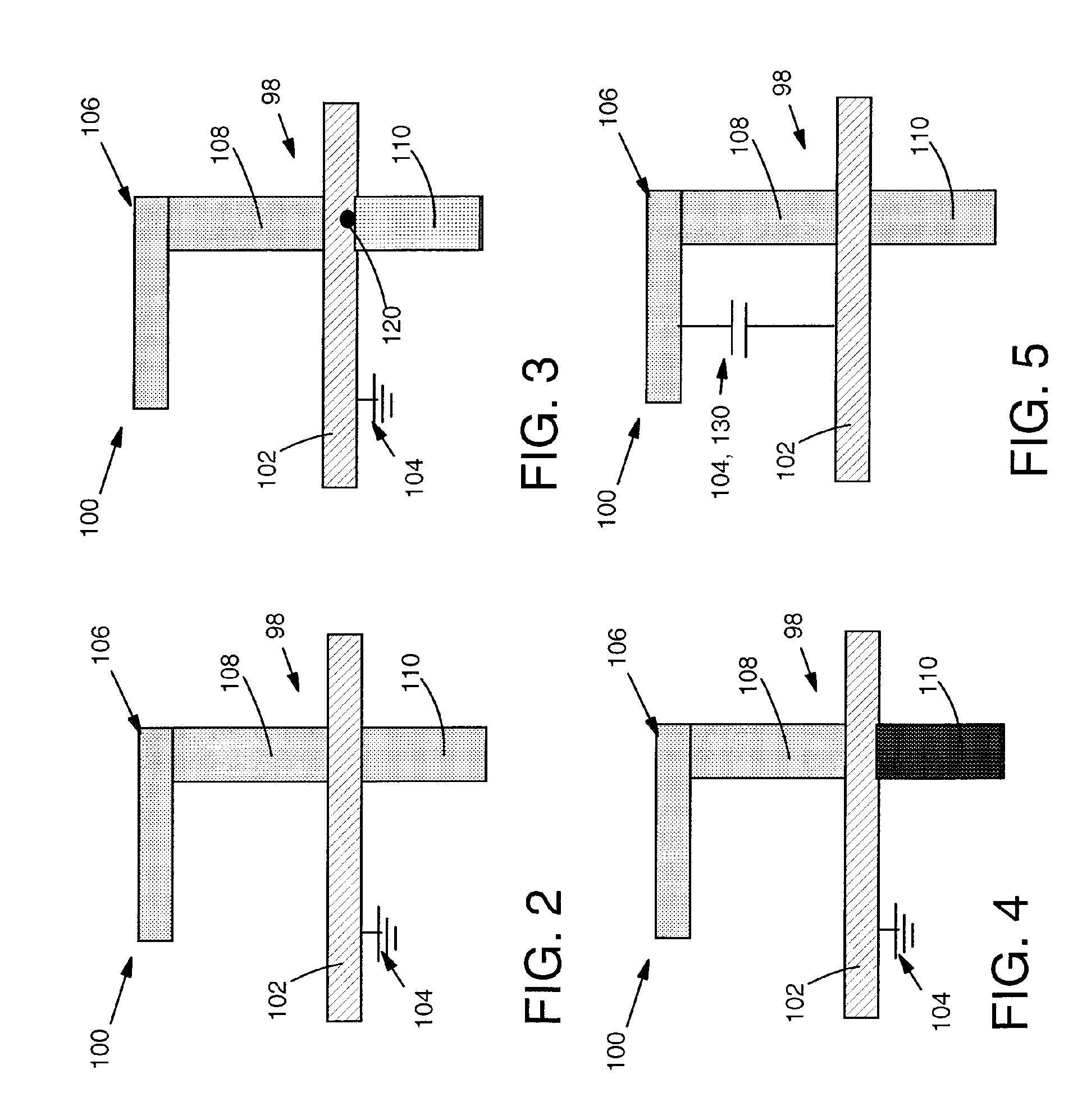

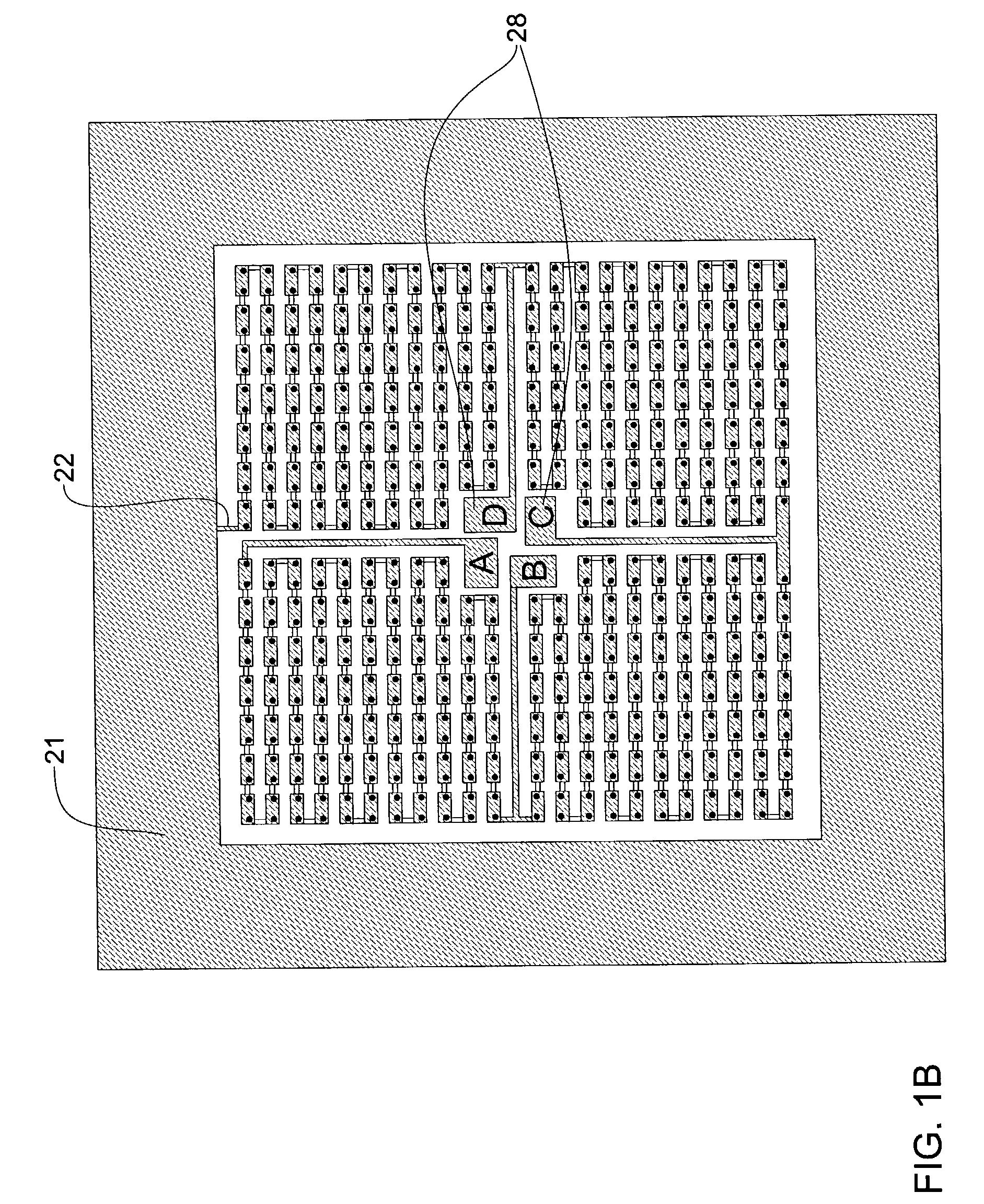

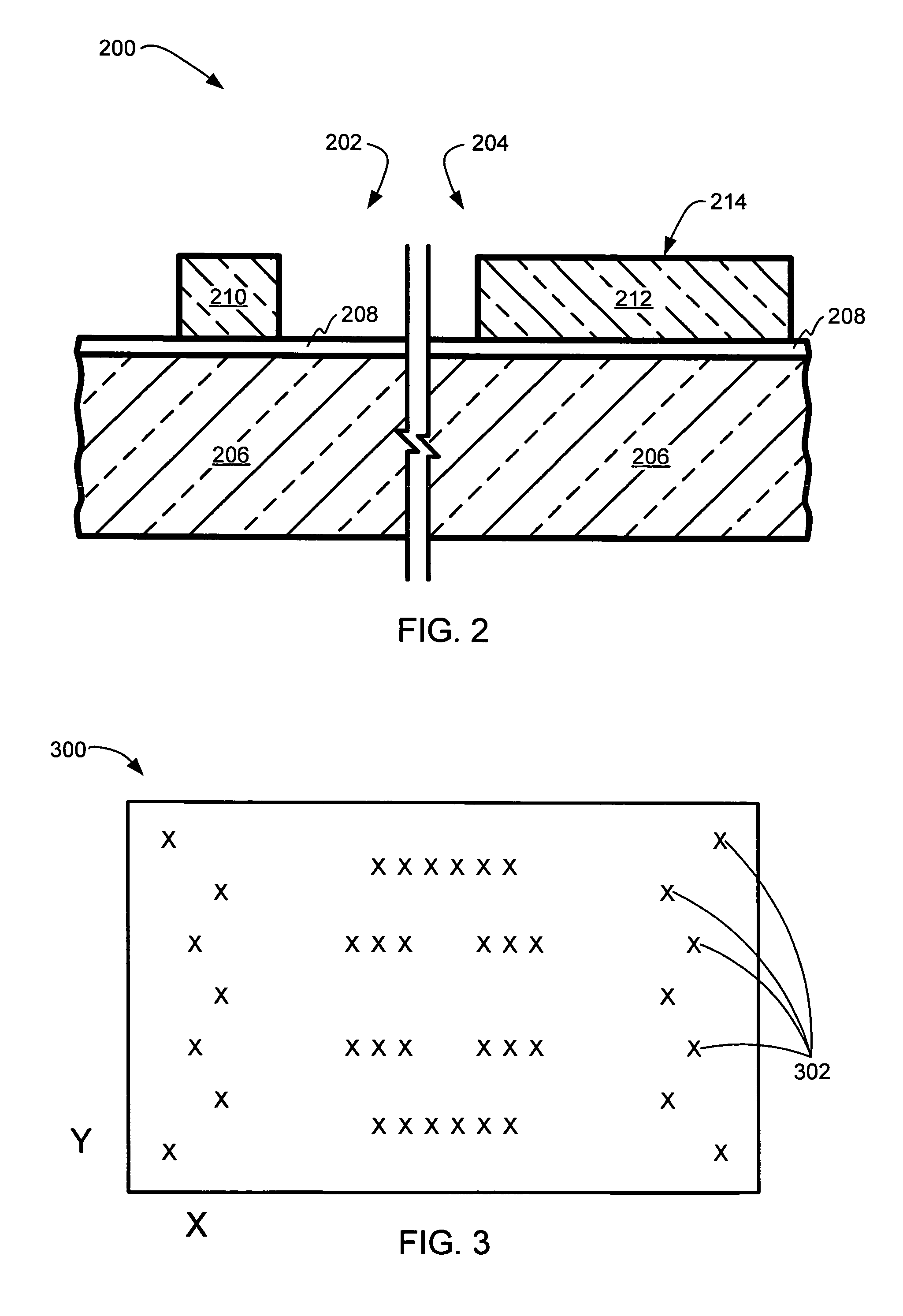

Disclosed is a semiconductor die having a lower test structure formed in a lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end. The first end is coupled to a predetermined voltage level. The semiconductor die also includes an insulating layer formed over the lower metal layer. The die further includes an upper test structure formed in an upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure. The upper metal layer is formed over the insulating layer. In a specific implementation, the first end of the lower test structure is coupled to ground. In another embodiment, the semiconductor die also includes a substrate and a first via coupled between the first end of the lower test structure and the substrate. In yet another aspect, the lower test structure is an extended metal line, and the upper test structure is a voltage contrast element. Methods for inspecting and fabricating such semiconductor die are also disclosed.

Owner:KLA TENCOR CORP

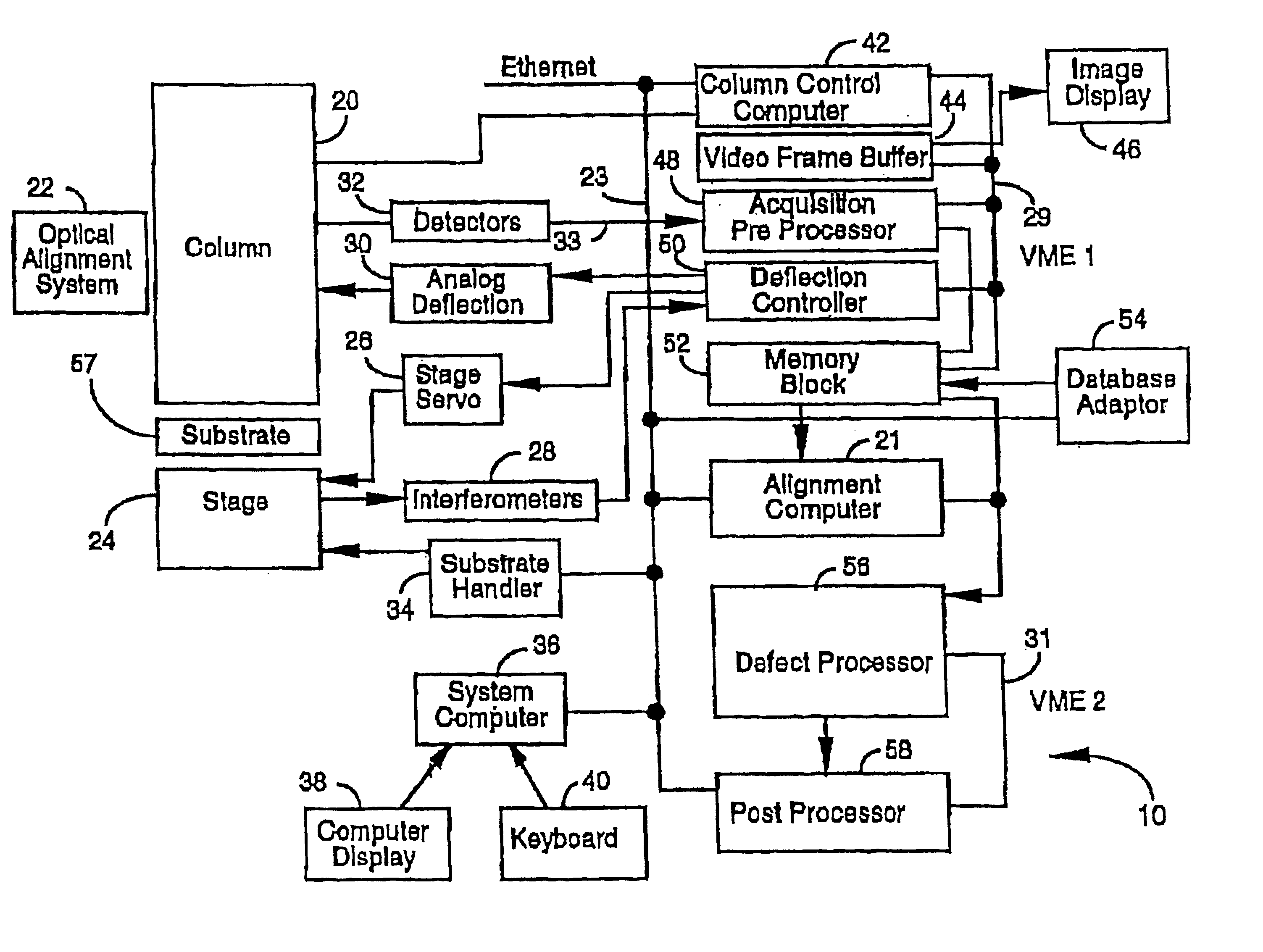

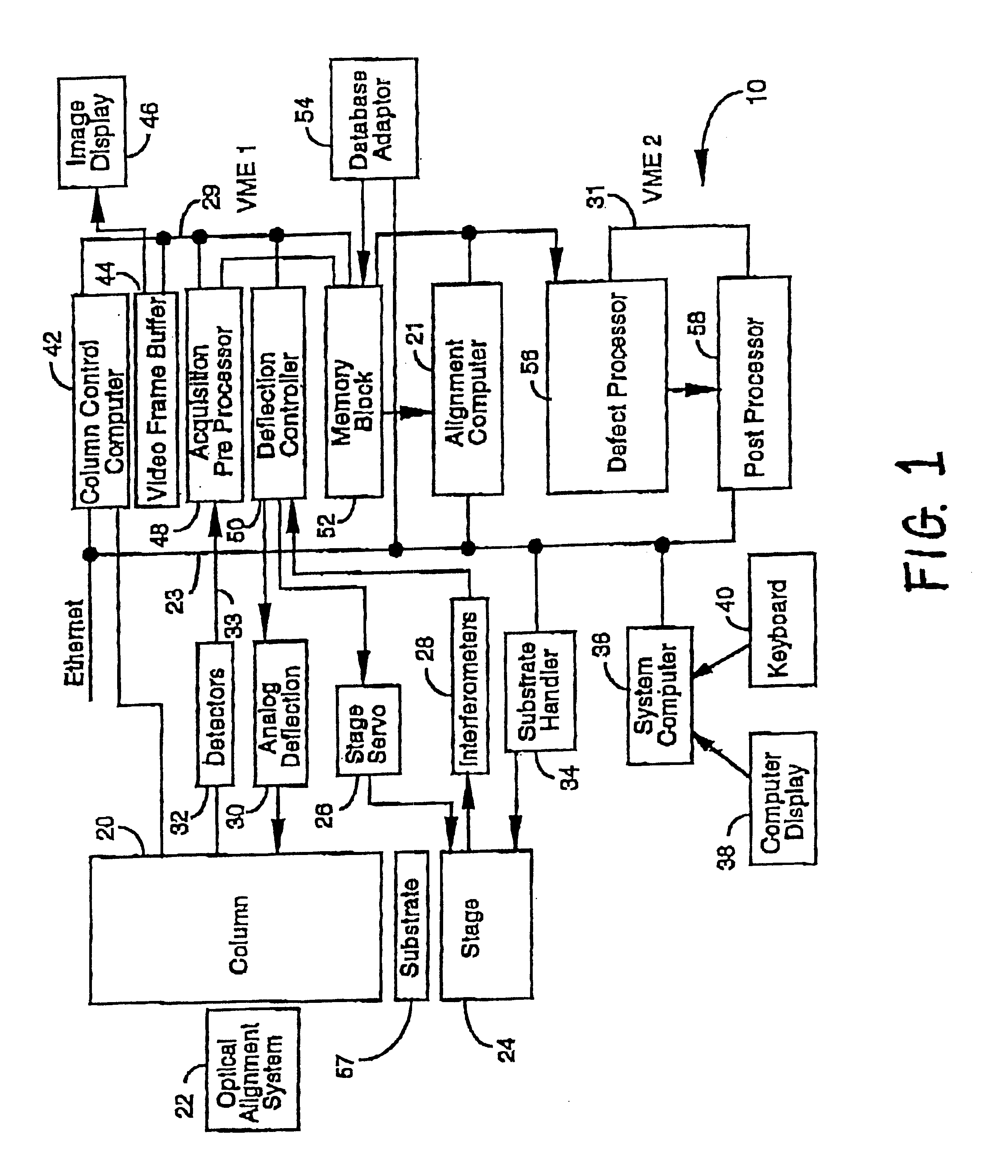

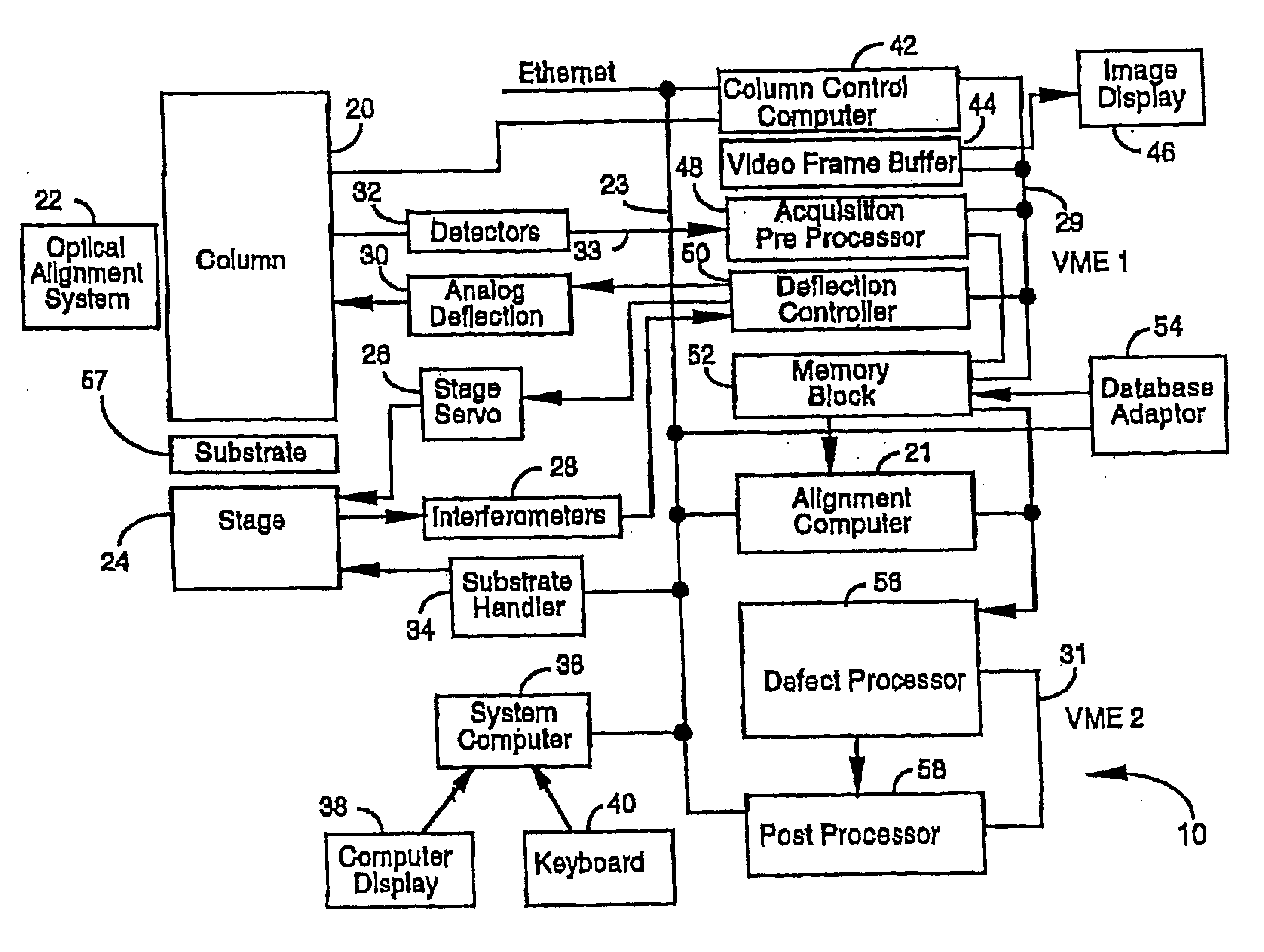

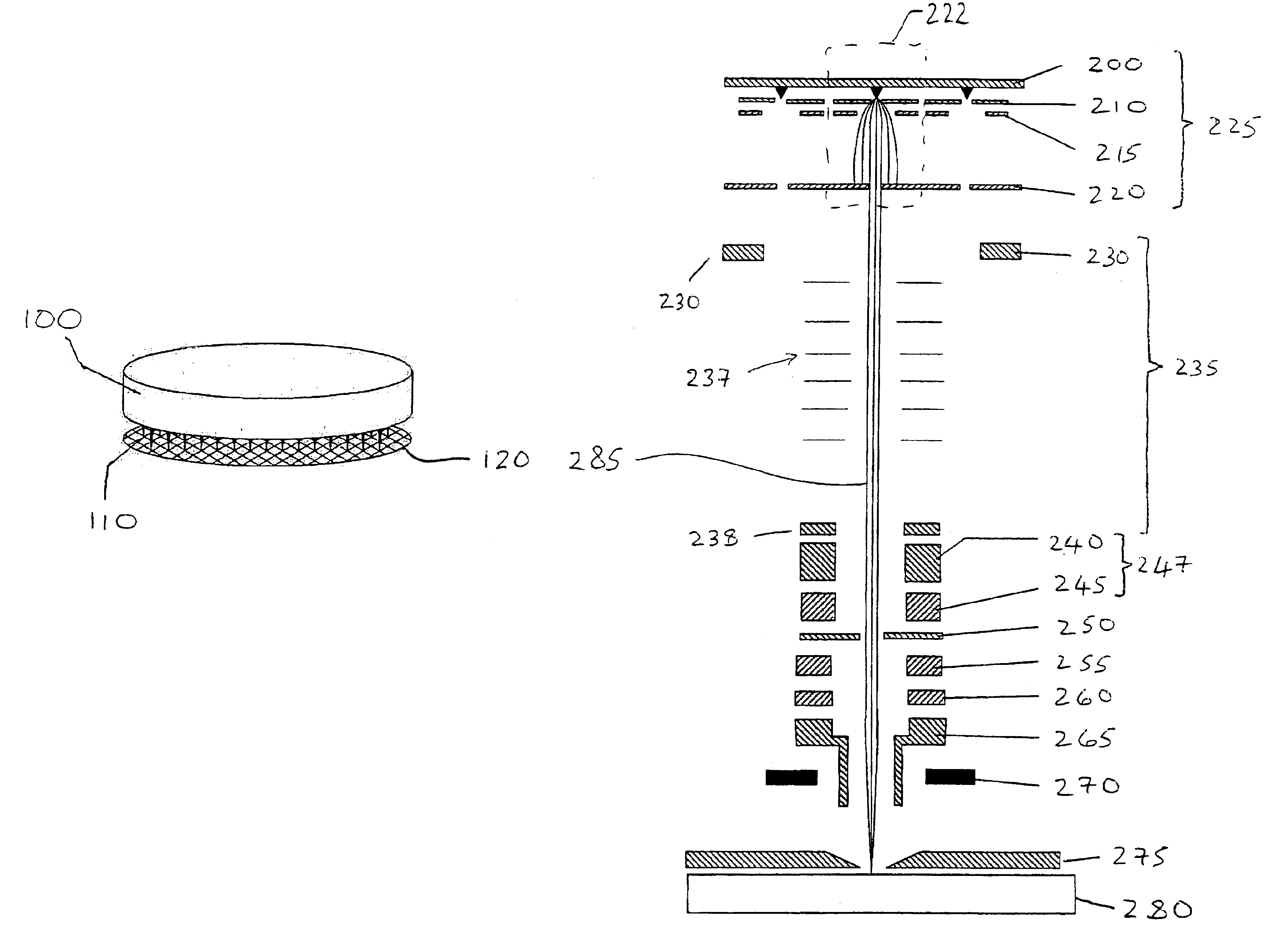

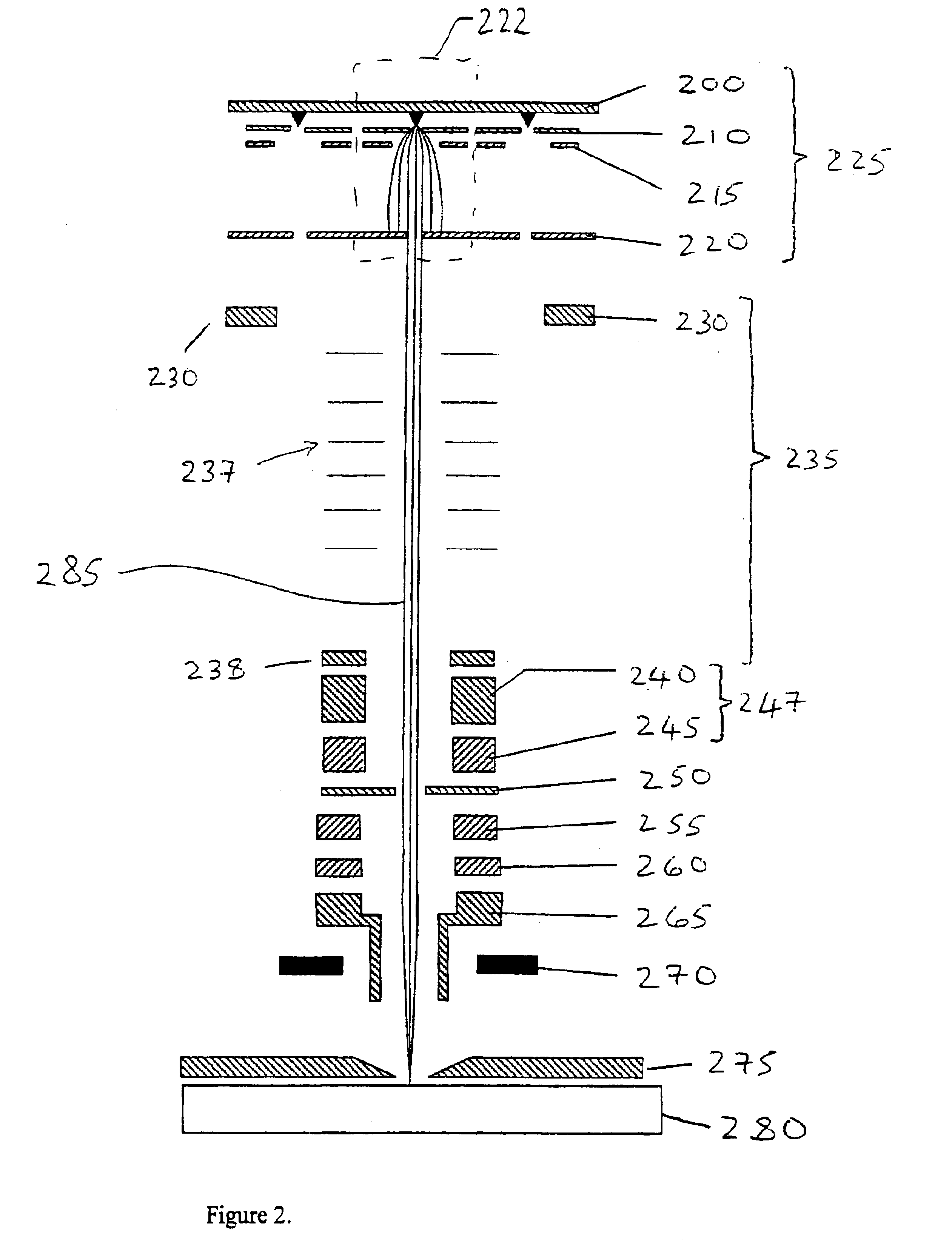

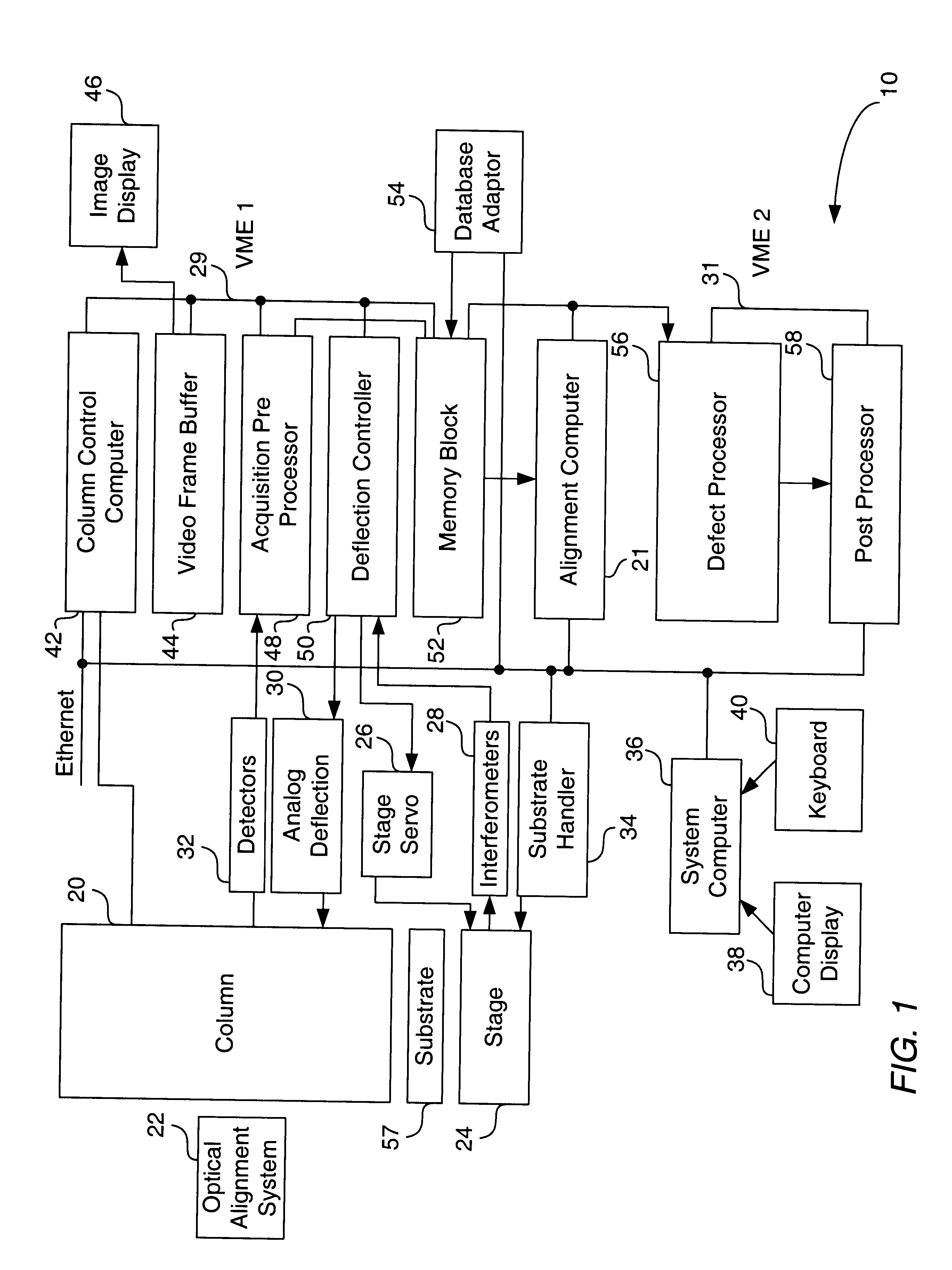

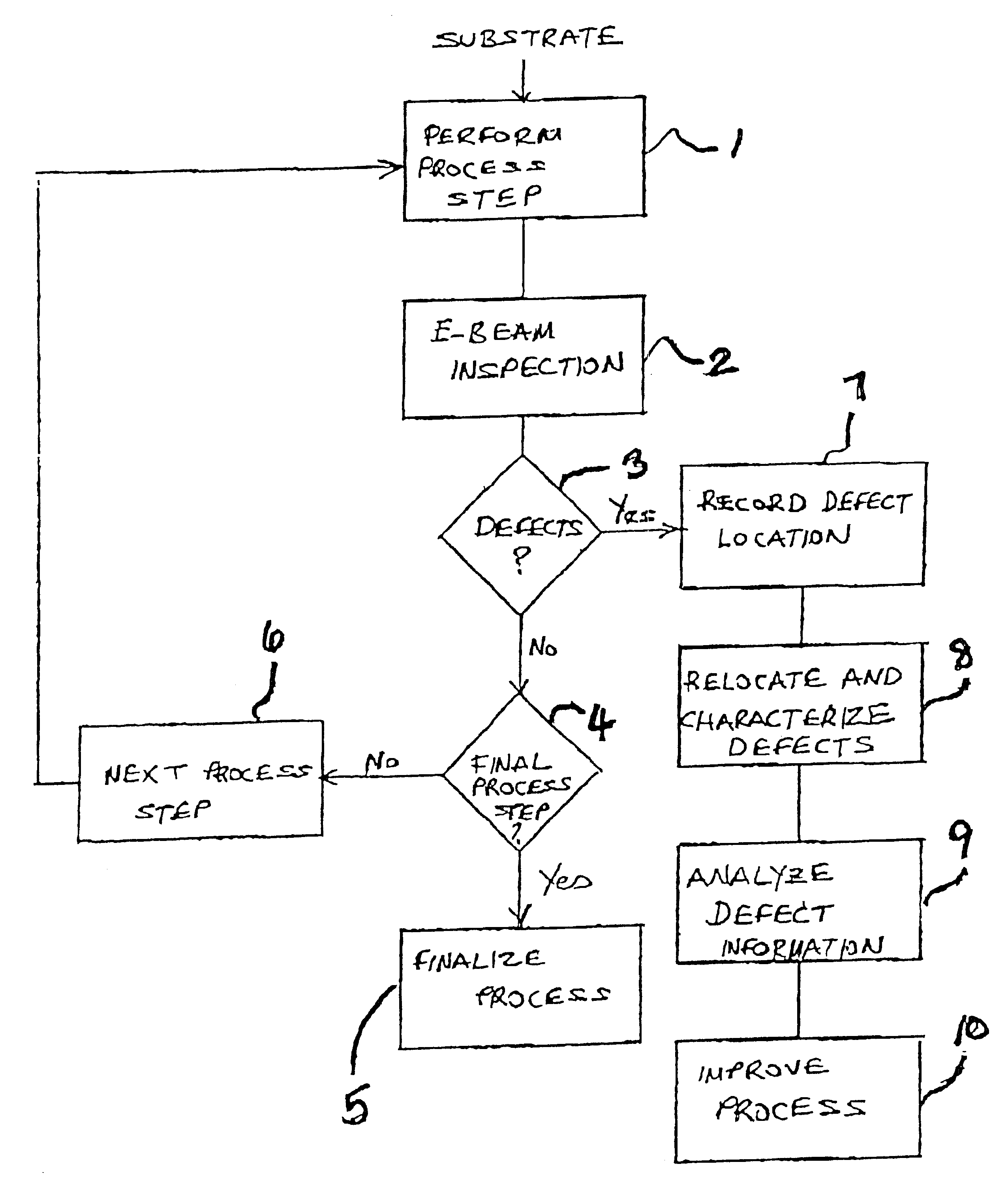

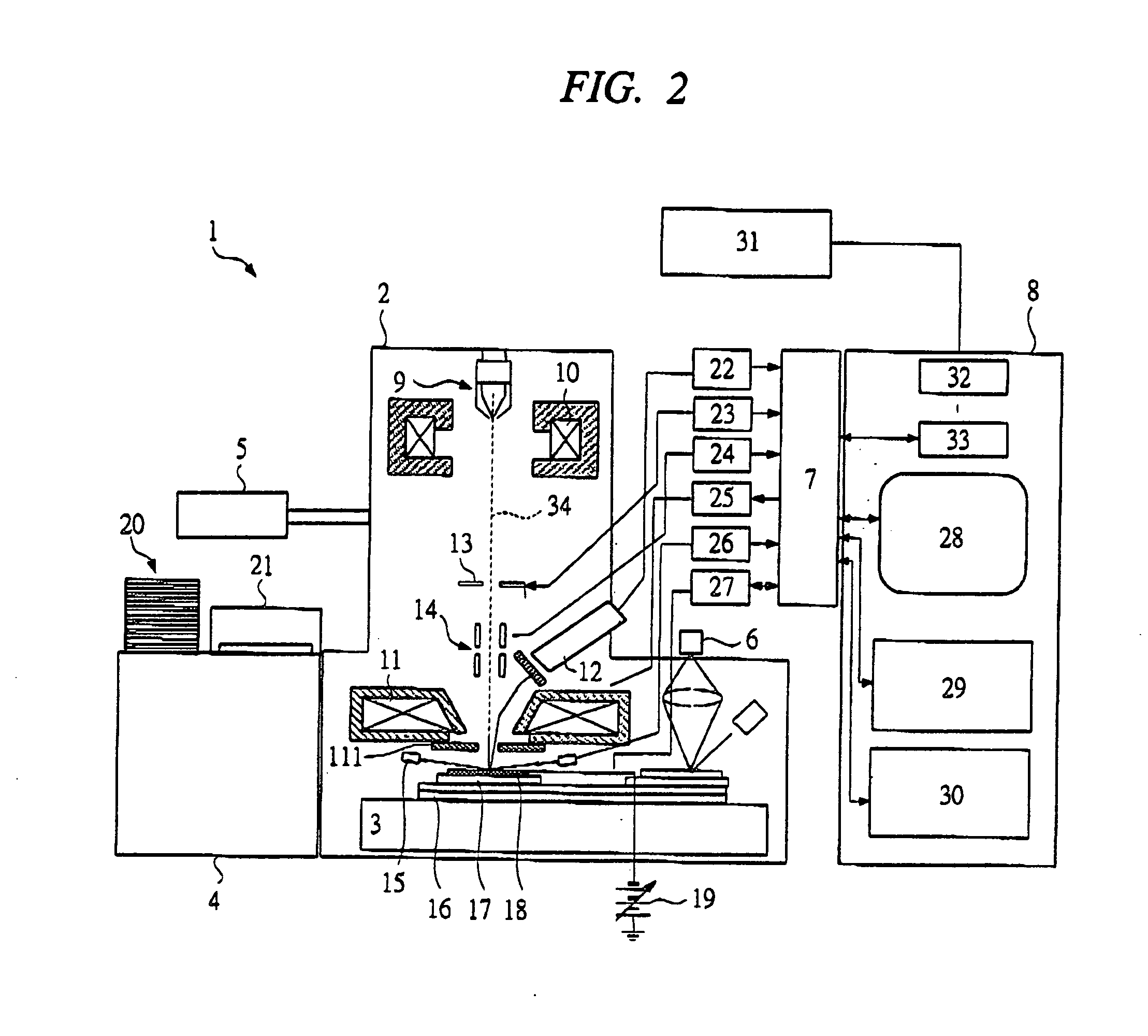

Multi-beam multi-column electron beam inspection system

InactiveUS6844550B1Material analysis using wave/particle radiationRadiation/particle handlingSystems designData stream

A multi-column electron beam inspection system is disclosed herein. The system is designed for electron beam inspection of semiconductor wafers with throughput high enough for in-line use. The system includes field emission electron sources, electrostatic electron optical columns, a wafer stage with six degrees of freedom of movement, and image storage and processing systems capable of handling multiple simultaneous image data streams. Each electron optical column is enhanced with an electron gun with redundant field emission sources, a voltage contrast plate to allow voltage contrast imaging of wafers, and an electron optical design for high efficiency secondary electron collection.

Owner:MULTIBEAM CORP

Dual probe test structures for semiconductor integrated circuits

InactiveUS6636064B1Easily dry-etchedEasy to processSemiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

Disclosed is a semiconductor die having an upper layer and a lower layer. The die includes a lower test structure formed in the lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end, wherein the first end is coupled to a predetermined voltage level. The die also has an insulating layer formed over the lower metal layer and an upper test structure formed in the upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure, and the upper metal layer being formed over the insulating layer. The die further includes at least one probe pad coupled with the upper test structure. Preferably, the first end of the lower test structure is coupled to a nominal ground potential. In another implementation, the upper test structure is a voltage contrast element. In another embodiment, a semiconductor die having a scanning area is disclosed. The semiconductor die includes a first plurality of test structures wherein each of the test structures in the first plurality of test structures is located entirely within the scanning area. The die includes a second plurality of test structures wherein each of the test structures in the first plurality of test structures is located only partially within the scanning area. The first plurality of test structures or the second plurality of test structures has a probe pad coupled to at least one test structure.

Owner:KLA TENCOR TECH CORP

Inspectable buried test structures and methods for inspecting the same

InactiveUS6576923B2Reduce pressureNanotechSemiconductor/solid-state device testing/measurementEngineeringVoltage contrast

Disclosed is a semiconductor die having a lower test structure formed in a lower metal layer of the semiconductor die. The lower conductive test structure has a first end and a second end. The first end is coupled to a predetermined voltage level. The semiconductor die also includes an insulating layer formed over the lower metal layer. The die further includes an upper test structure formed in an upper metal layer of the semiconductor die. The upper conductive test structure is coupled with the second end of the lower conductive test structure. The upper metal layer is formed over the insulating layer. In a specific implementation, the first end of the lower test structure is coupled to ground. In another embodiment, the semiconductor die also includes a substrate and a first via coupled between the first end of the lower test structure and the substrate. In yet another aspect, the lower test structure is an extended metal line, and the upper test structure is a voltage contrast element. Methods for inspecting and fabricating such semiconductor die are also disclosed.

Owner:KLA CORP

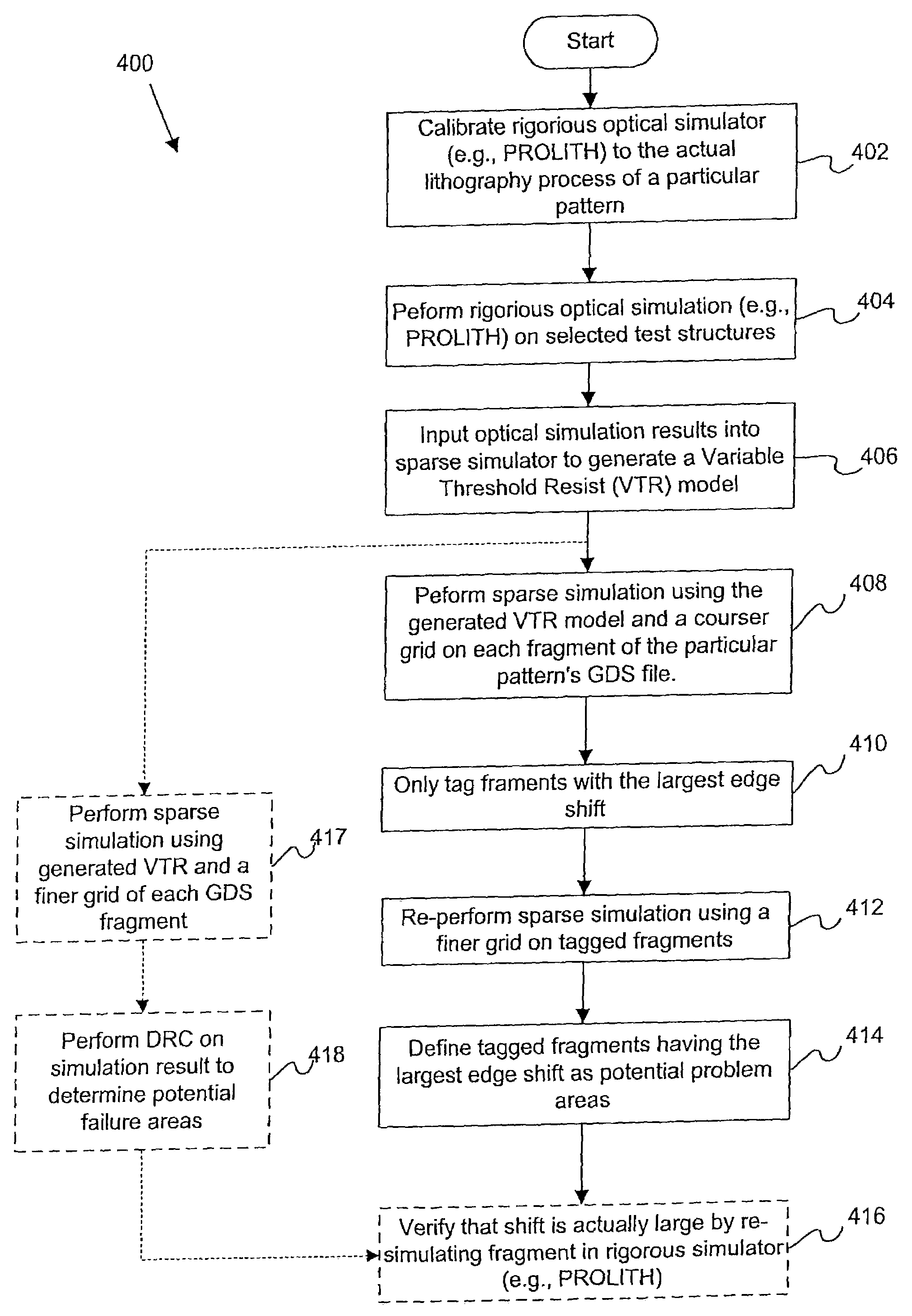

Apparatus and methods for detection of systematic defects

ActiveUS7280945B1Electrical testingComputation using non-denominational number representationResistSystem failure

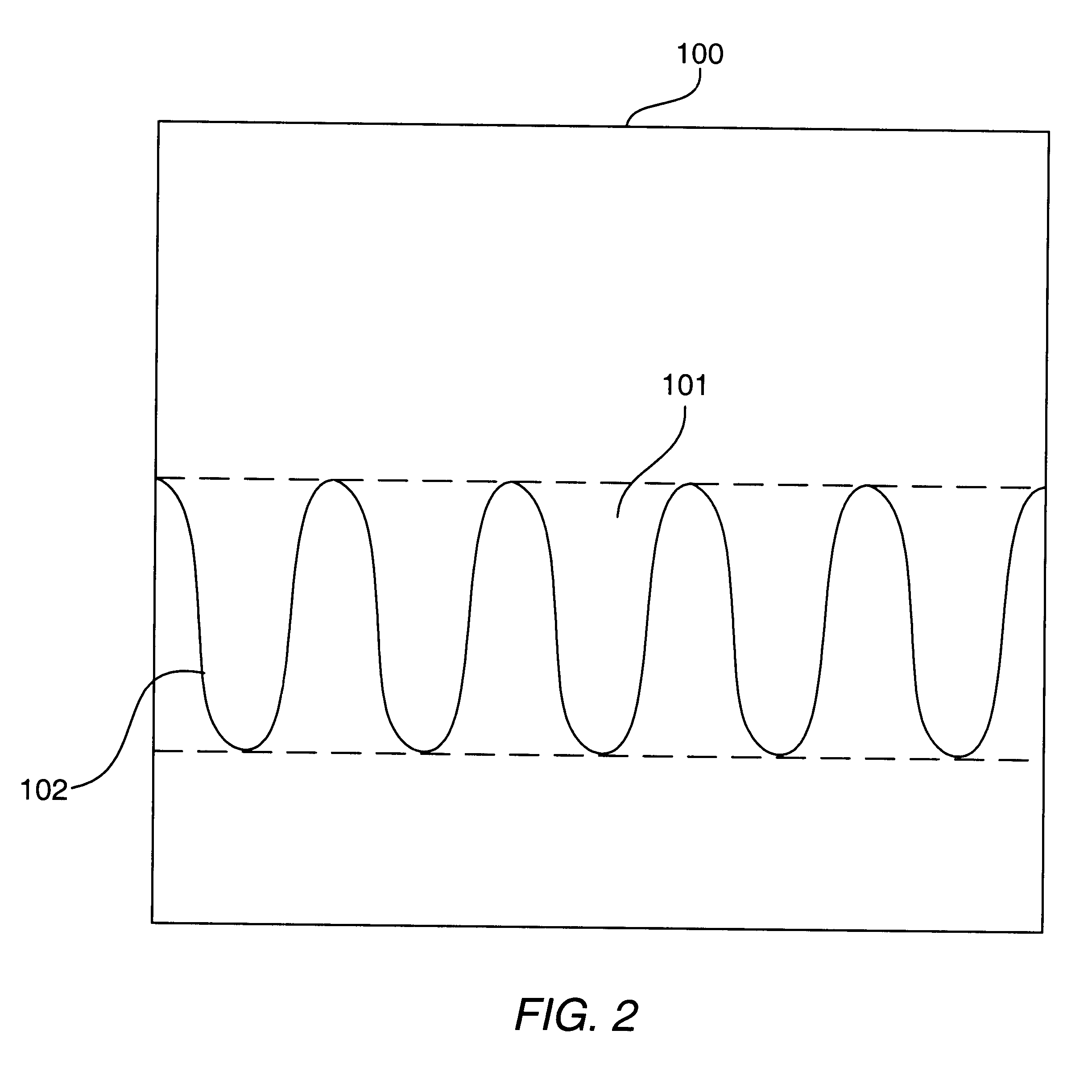

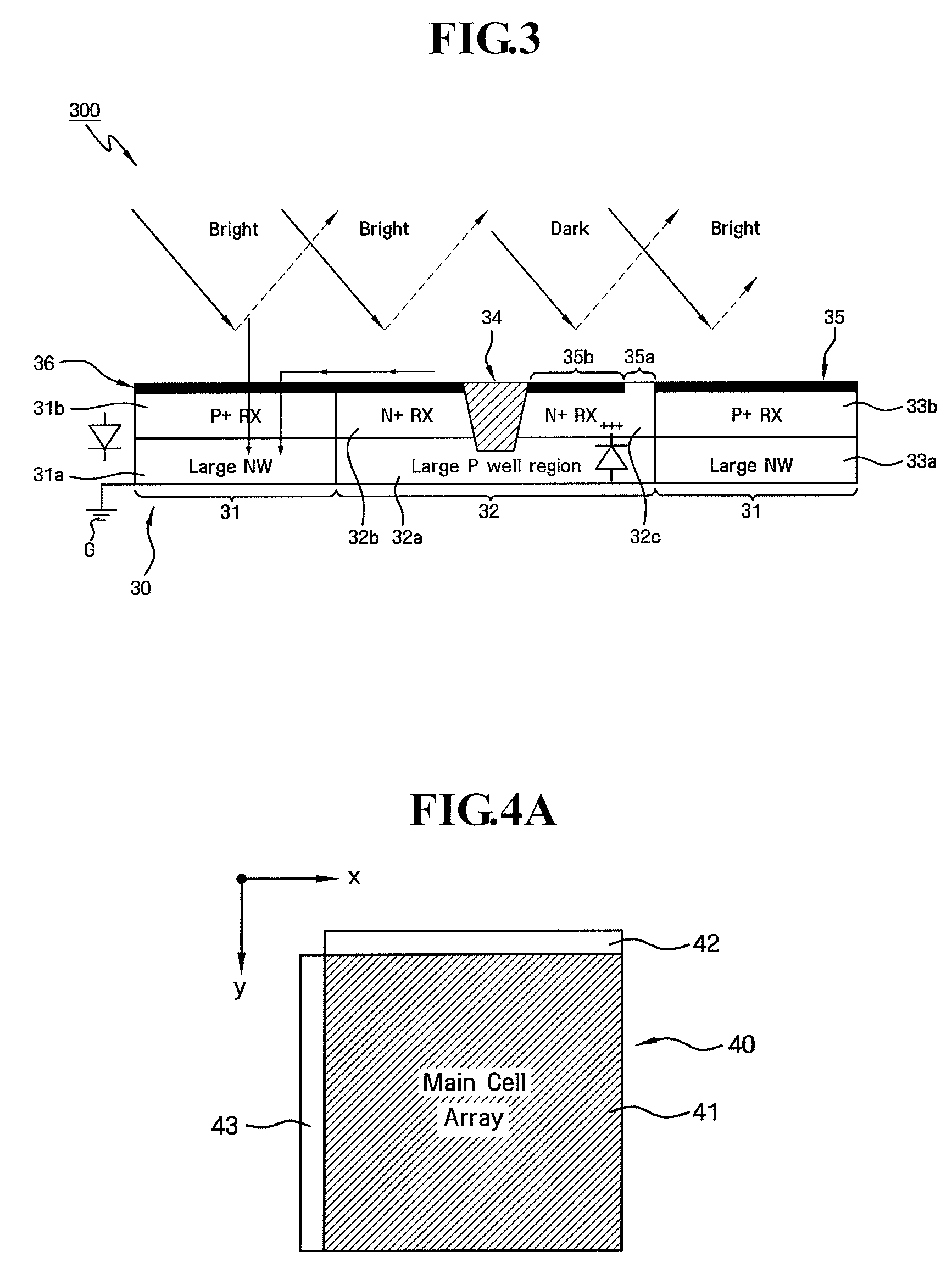

Disclosed are mechanisms are provided for determining whether a particular integrated circuit (IC) pattern is susceptible to systematic failure, e.g., due to process fluctuations. In one embodiment, final resist patterns for such IC pattern are simulated using a sparse type simulator under various process settings. The sparse type simulator uses a model (e.g., a variable threshold resist model) for a particular photolithography process in which the IC pattern is to be fabricated. The model is generated from measurements taken from a plurality of simulated structures output from a rigorous type simulator. The simulated final resist patterns may then be analyzed to determine whether the corresponding IC pattern is susceptible to systematic failure. After an IC pattern which is susceptible to systematic failure has been found, a test structure may be fabricated from a plurality of IC patterns or cells. The cells of the test structure are arranged to have a particular pattern of voltage potential or brightness levels during a voltage contrast inspection. Mechanisms for quickly inspecting such test structures to thereby predict systematic yield of a product device containing patterns similar to the test structure cells are also disclosed.

Owner:KLA TENCOR TECH CORP

Methods and apparatus for generating spatially resolved voltage contrast maps of semiconductor test structures

InactiveUS6445199B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesSpatially resolvedEngineering

Disclosed is a method of inspecting a sample. The sample is illuminated with an incident beam, thereby causing voltage contrast within structures present on the sample. Voltage contrast is detected within the structures. Information from the detected voltage contrast is stored, and position data concerning the location of features corresponding to at least a portion of the stored voltage contrast information is also stored. In a specific embodiment, the features represent electrical defects present on the sample. In another embodiment, the stored position data is in the form of a two dimensional map. In another aspect, the sample is re-inspected and the stored position data is used in analyzing data resulting from the re-inspection.

Owner:KLA CORP

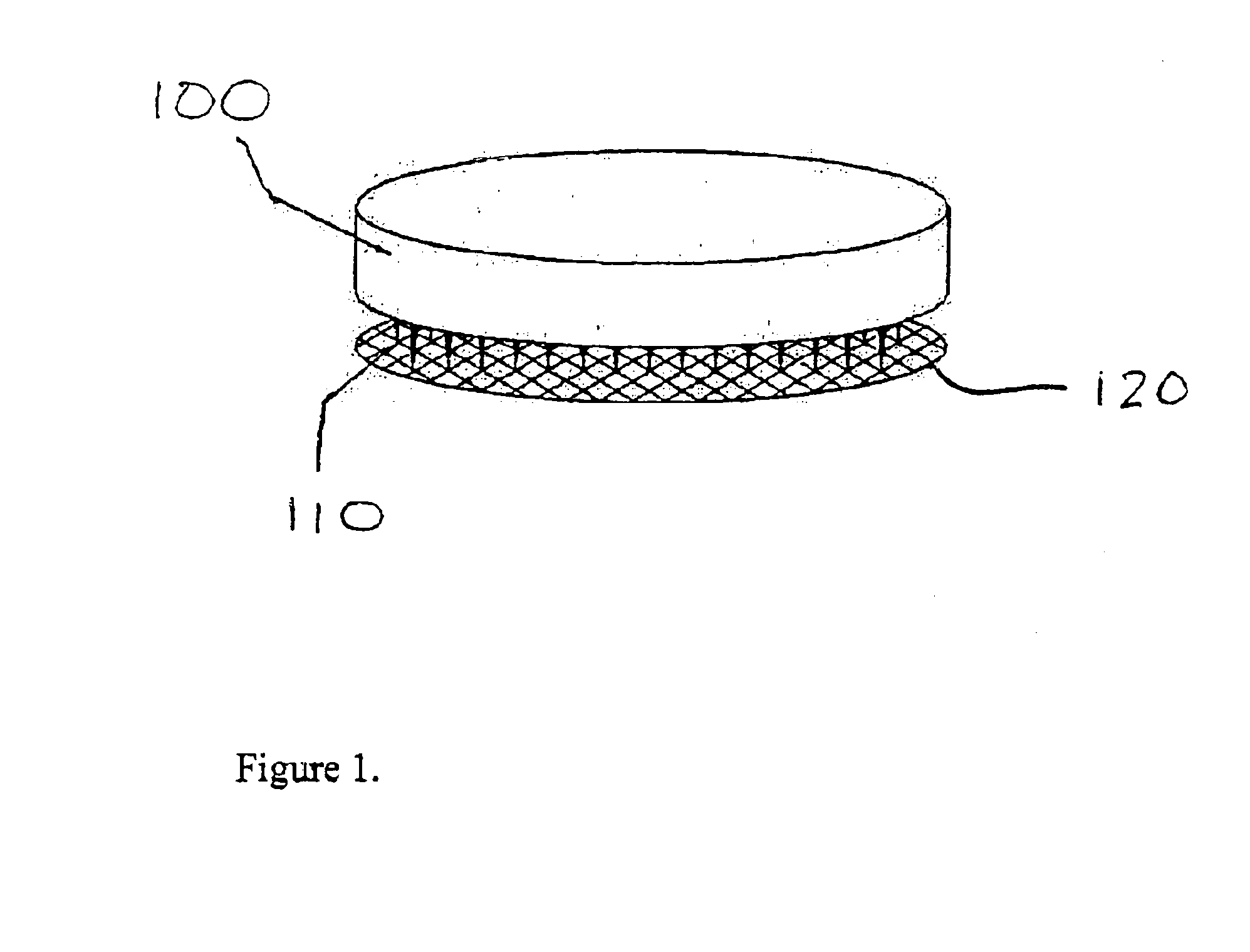

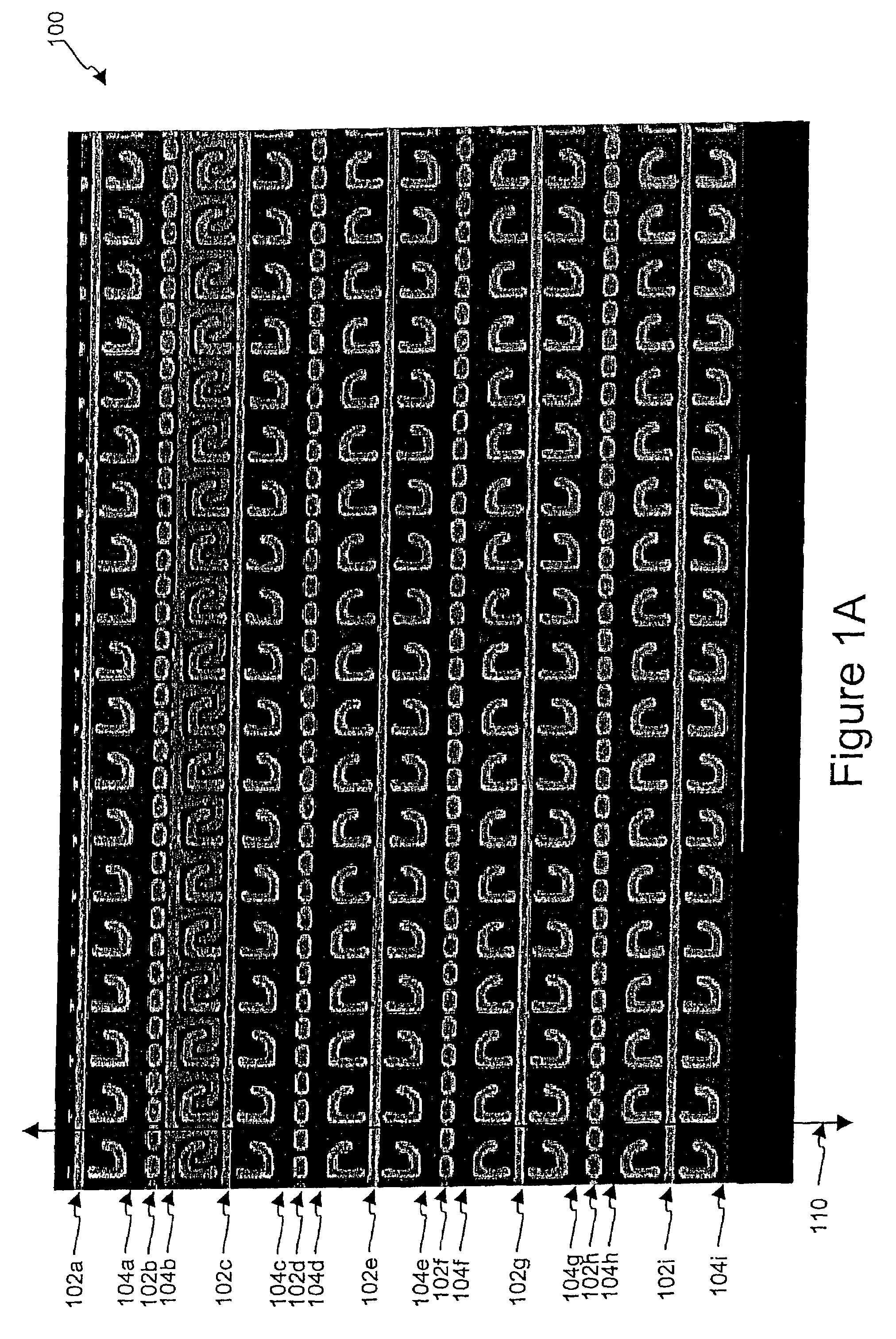

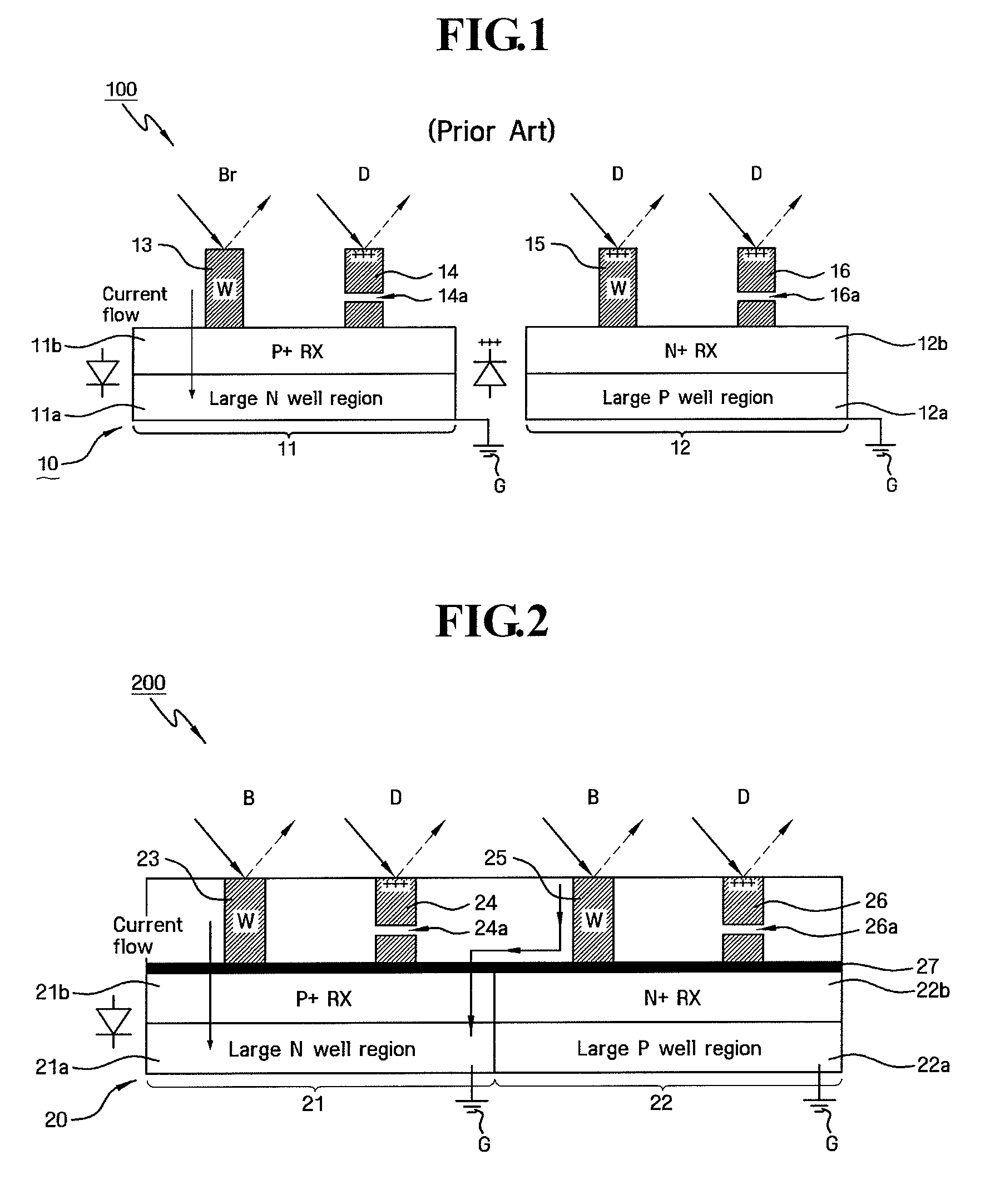

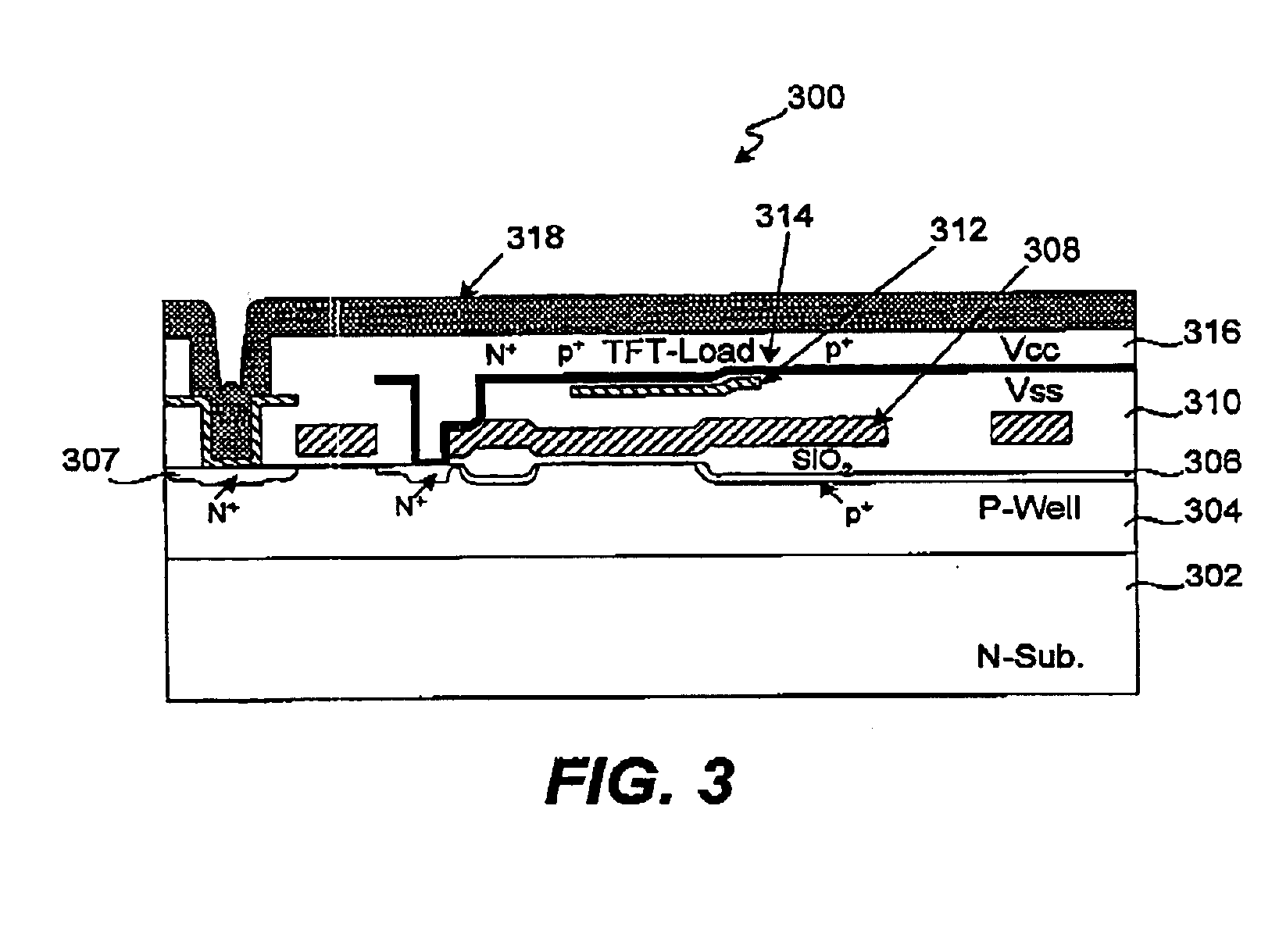

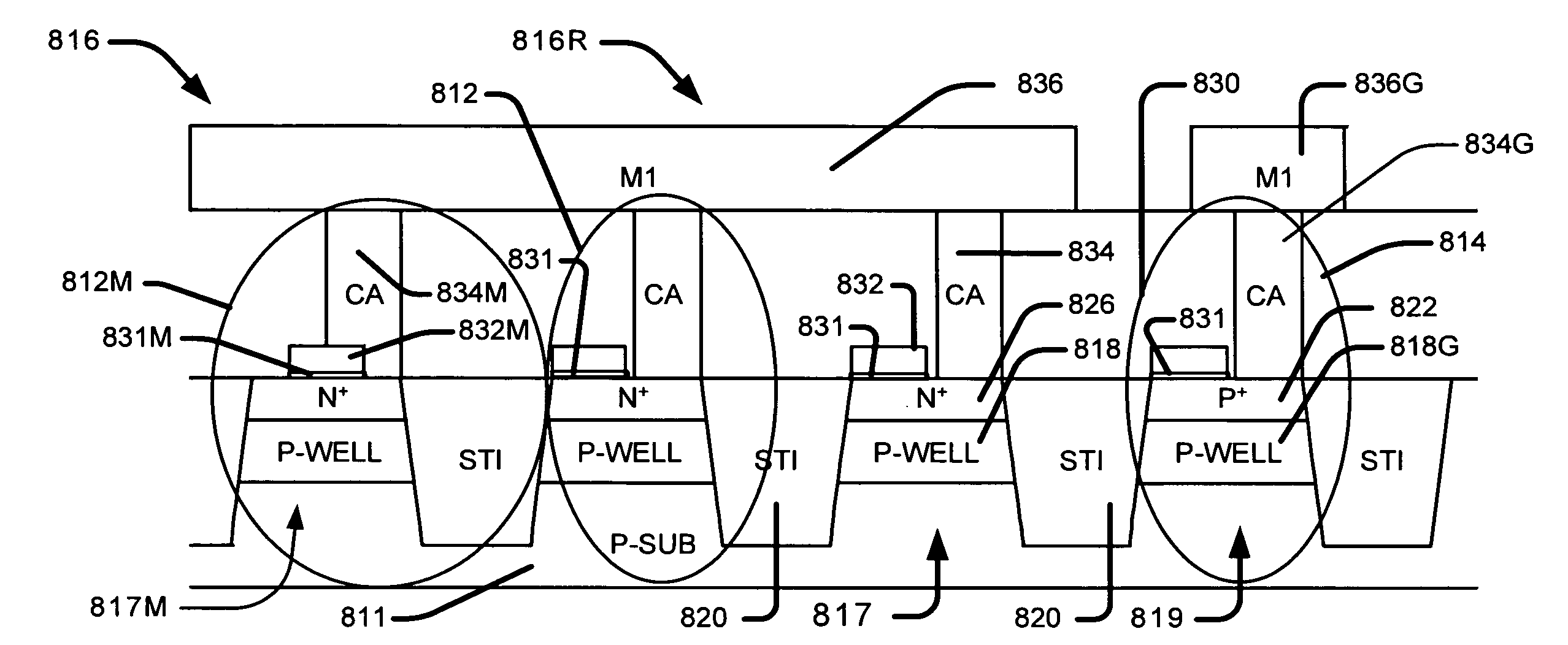

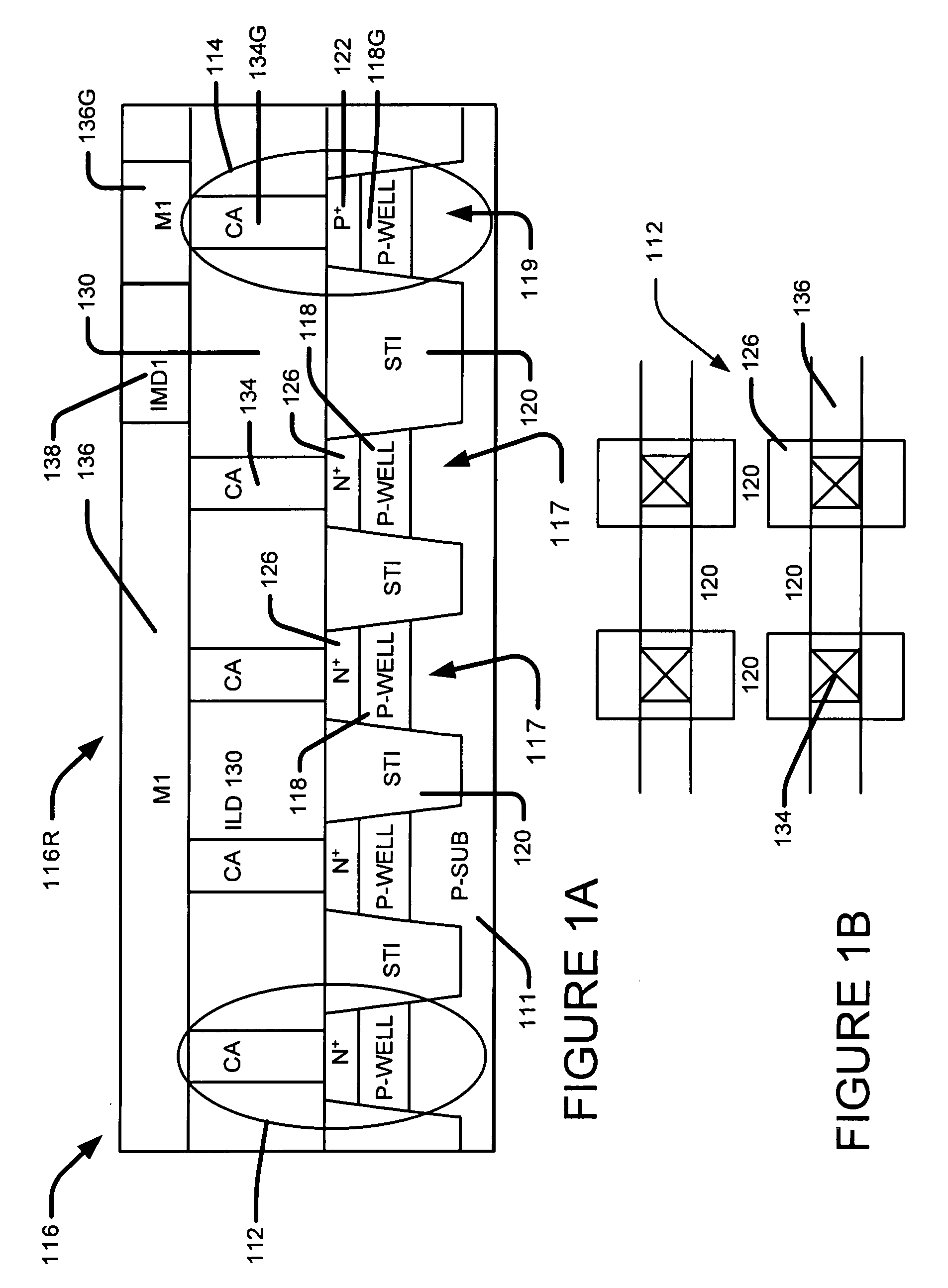

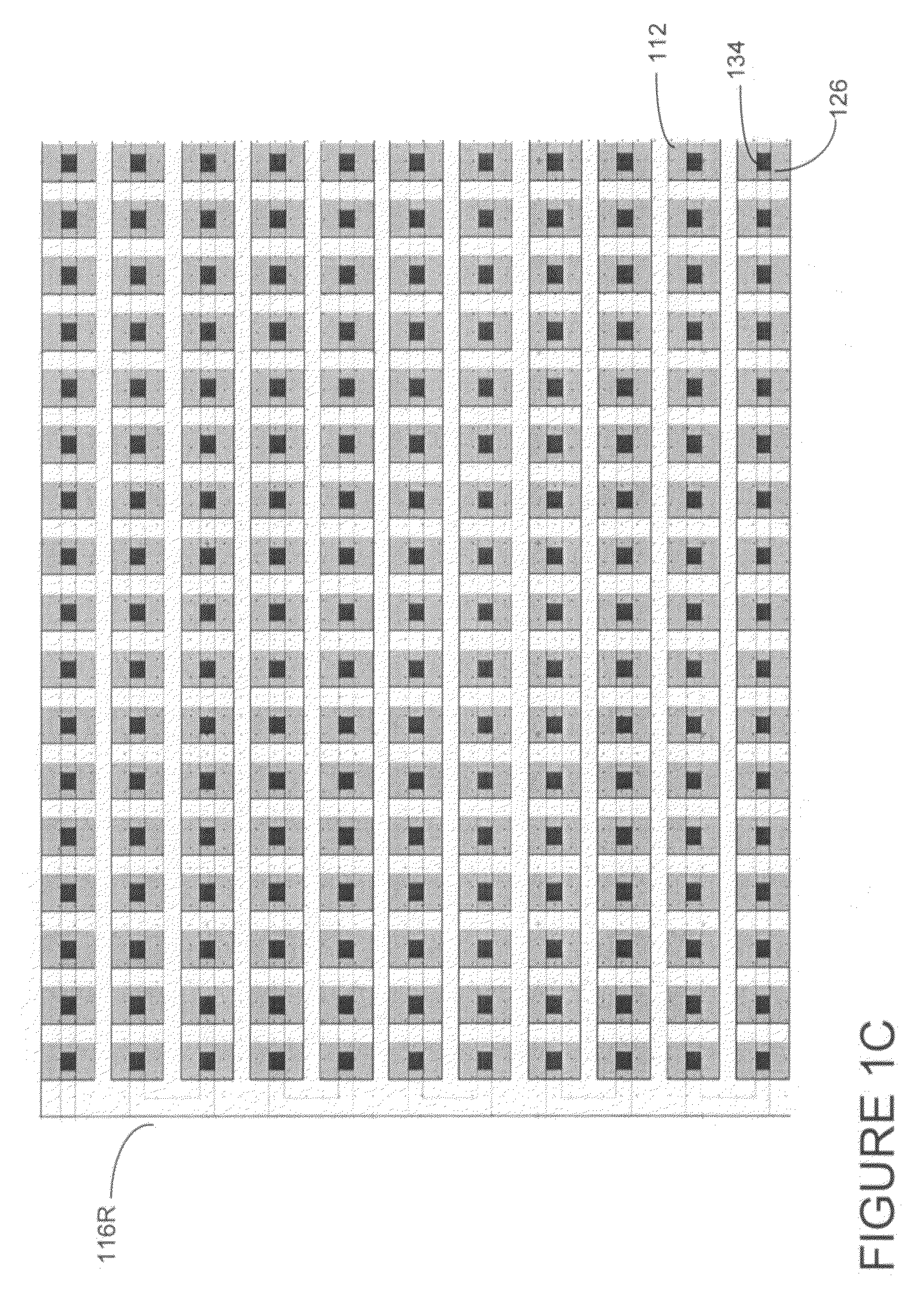

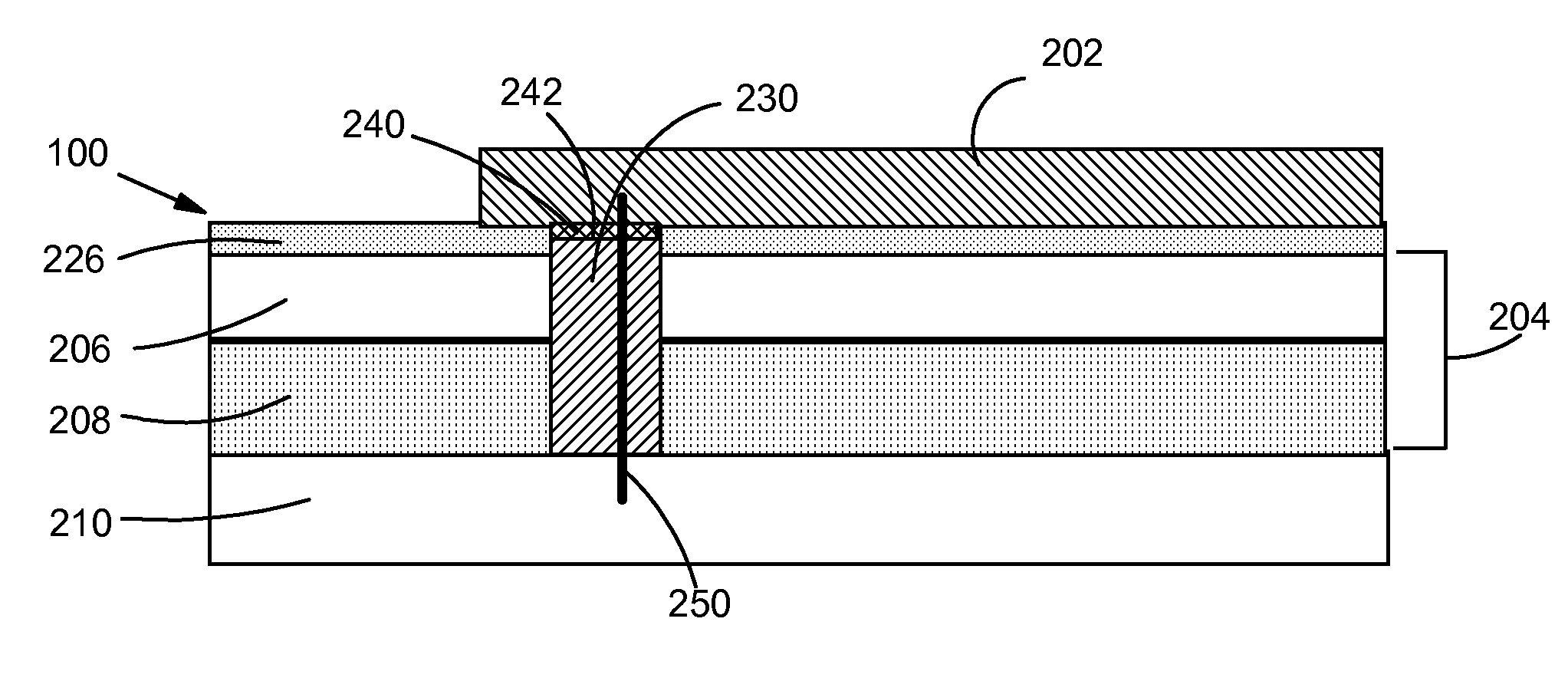

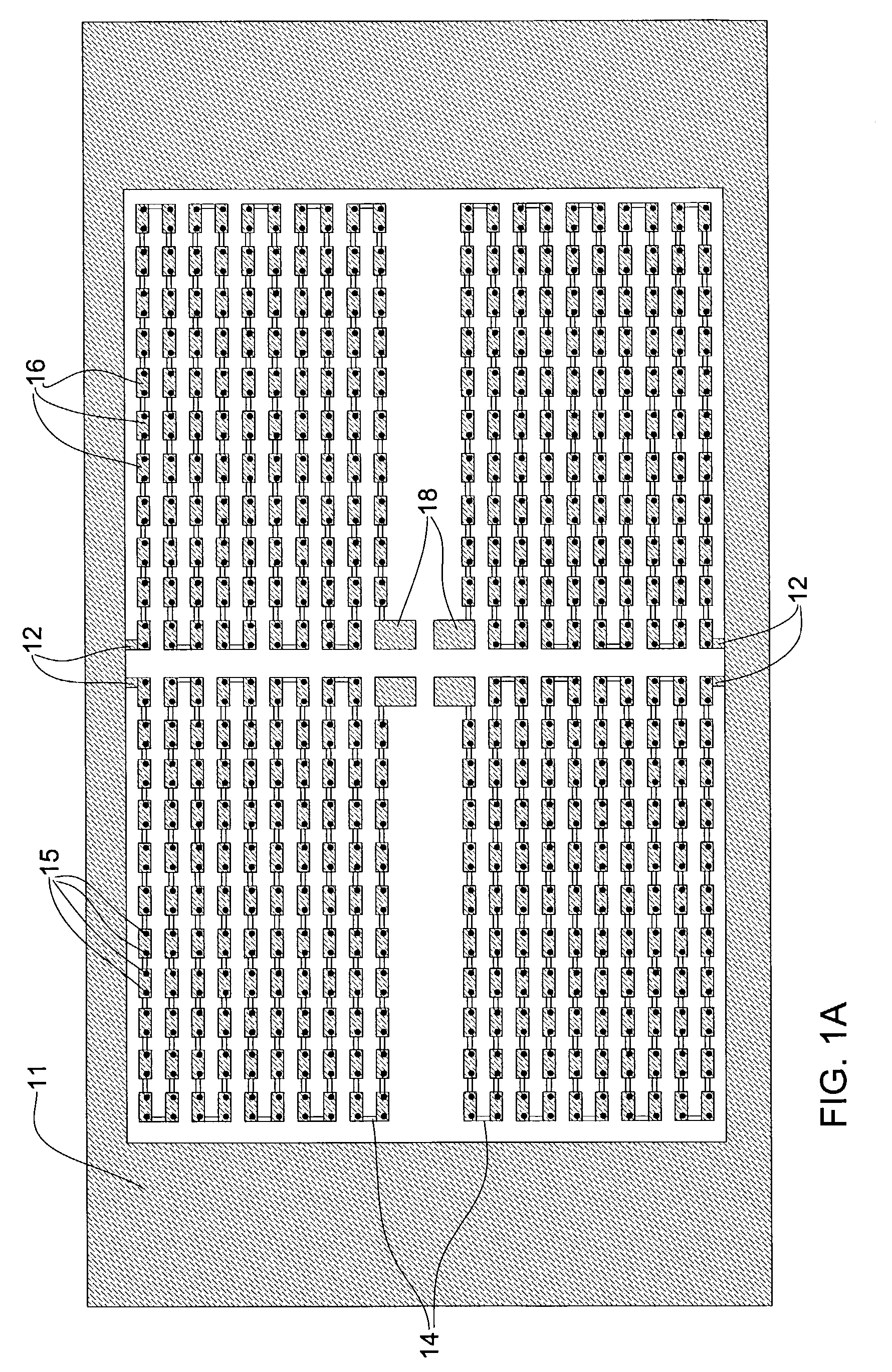

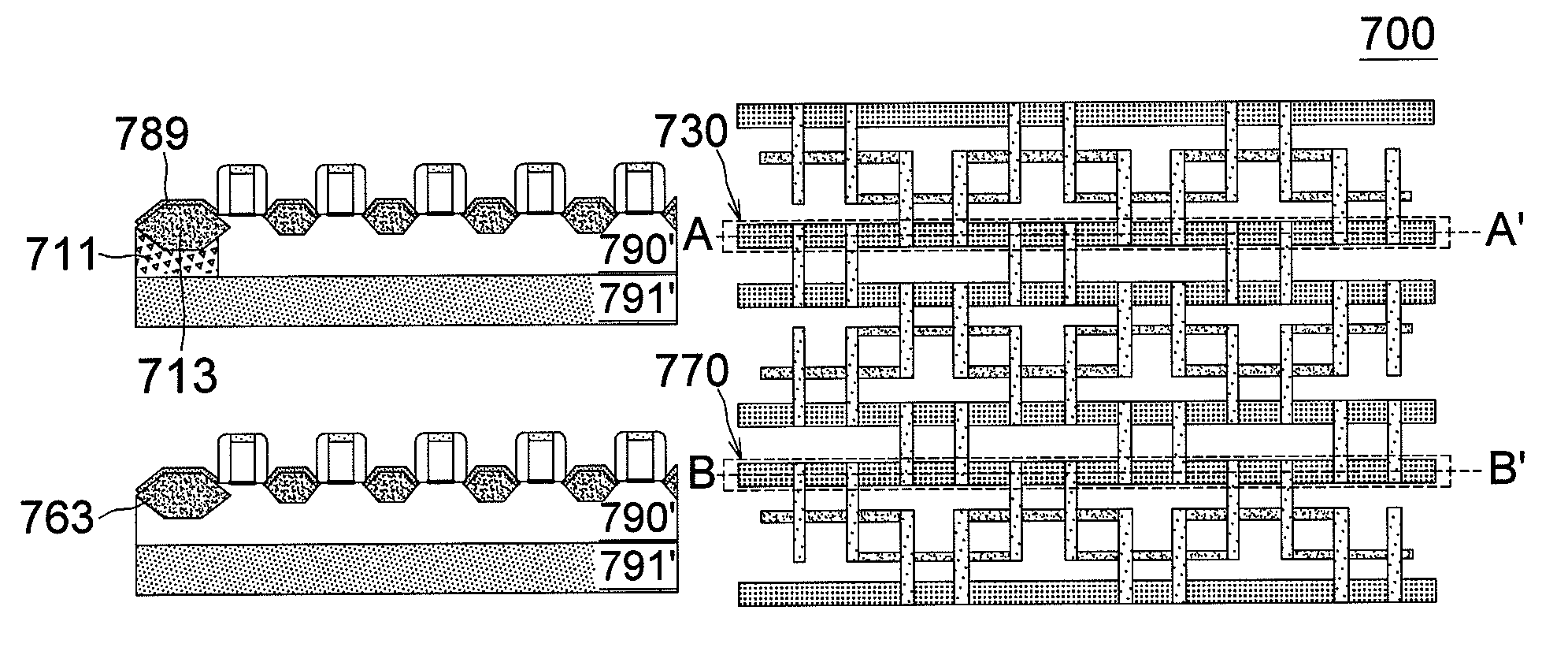

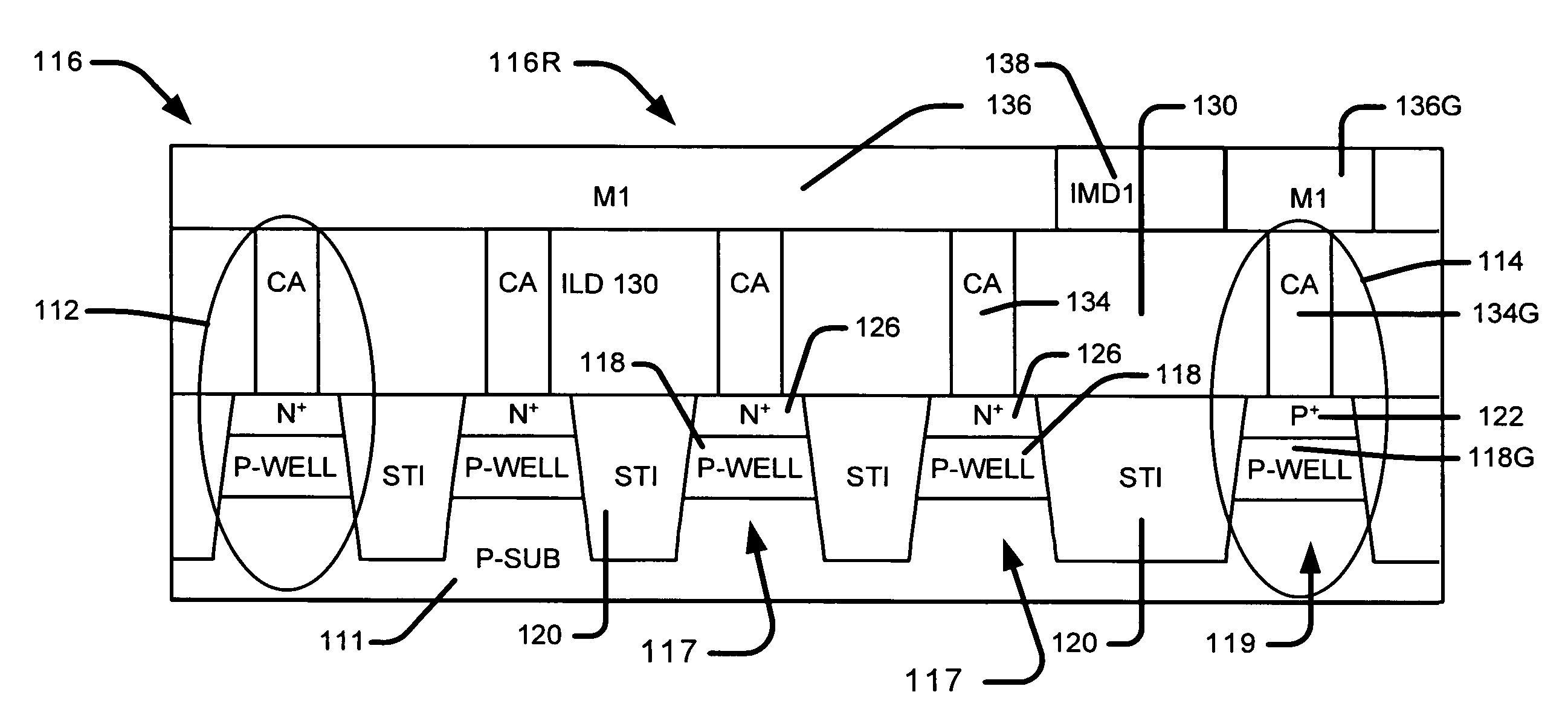

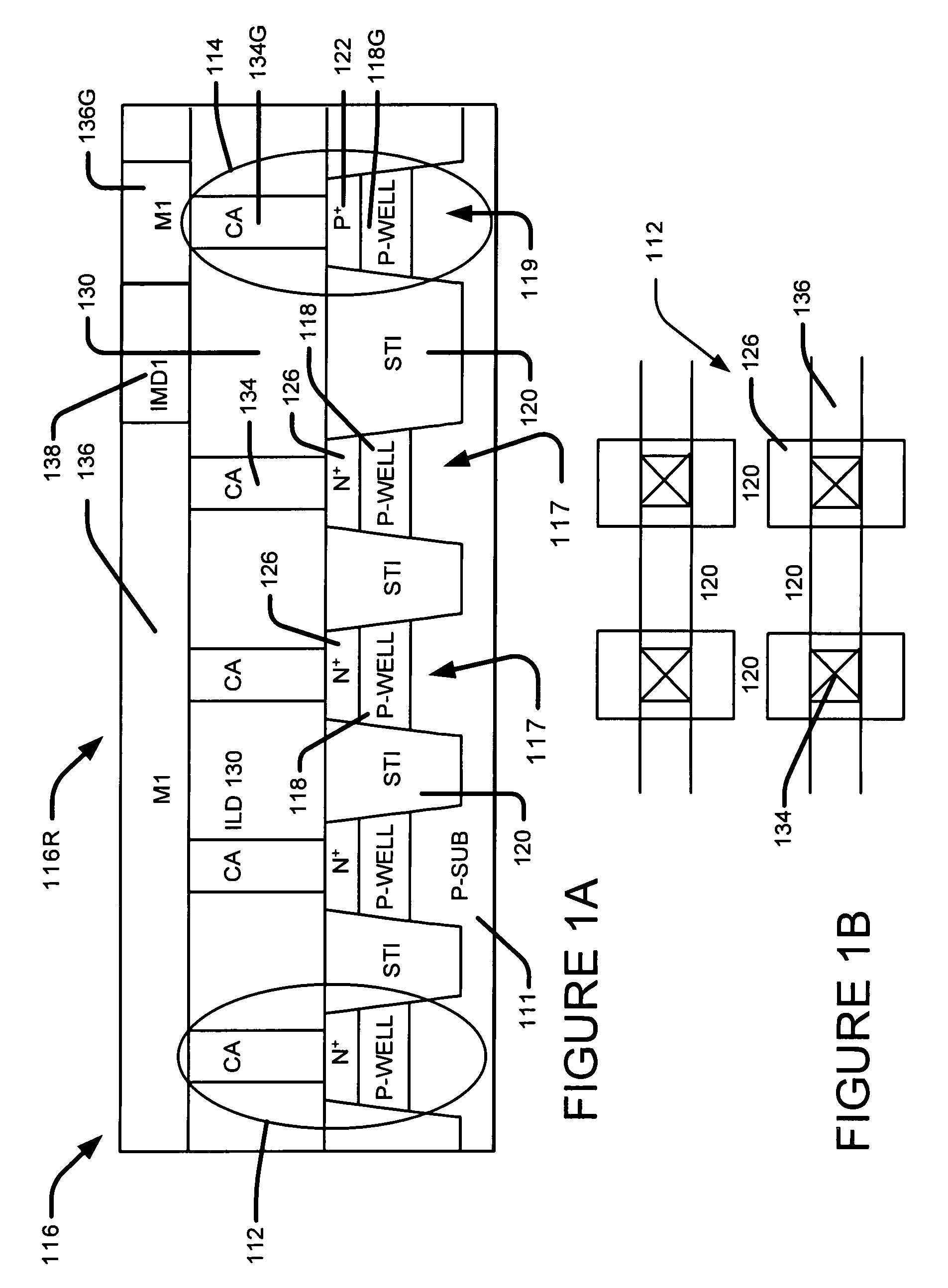

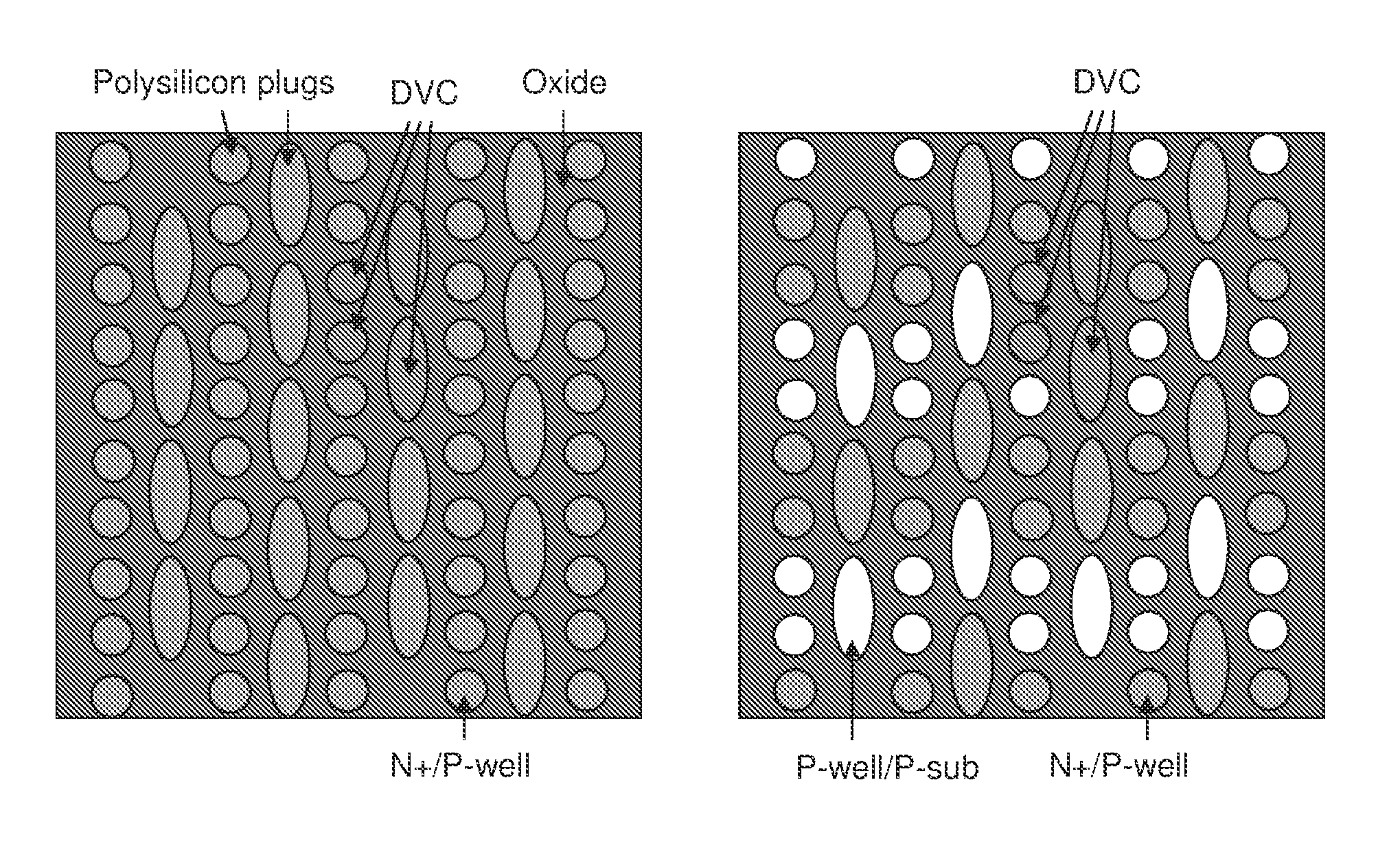

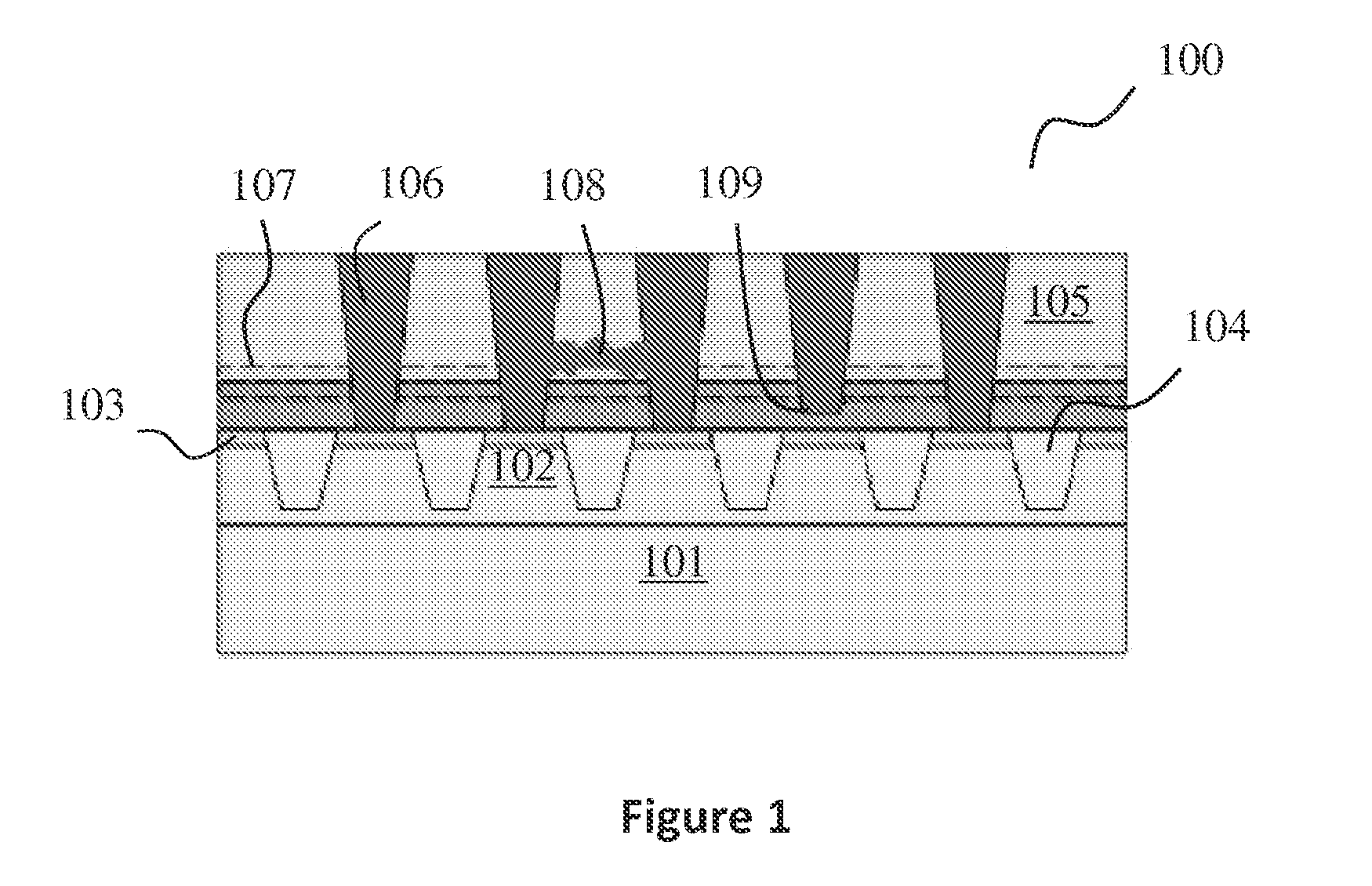

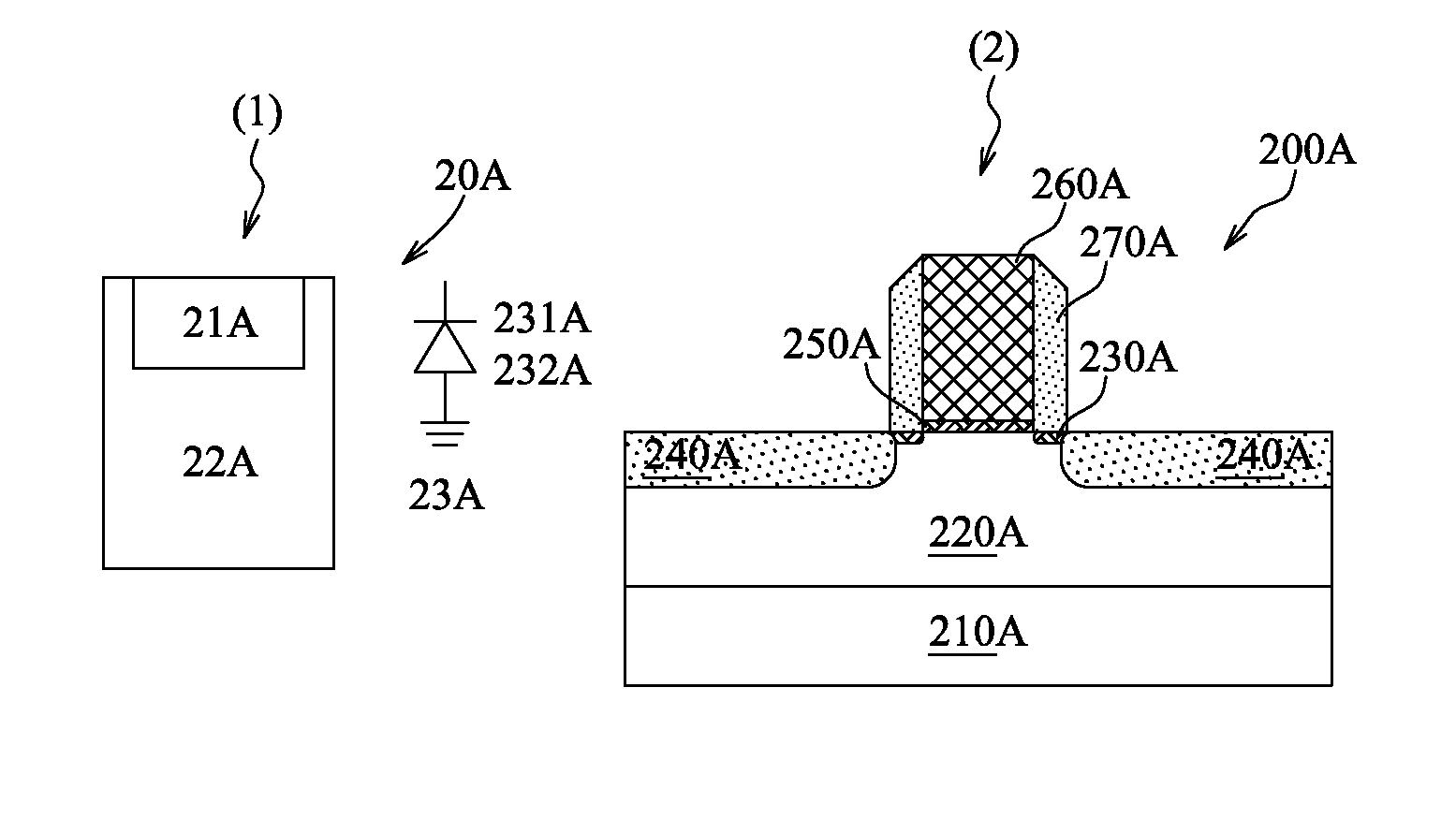

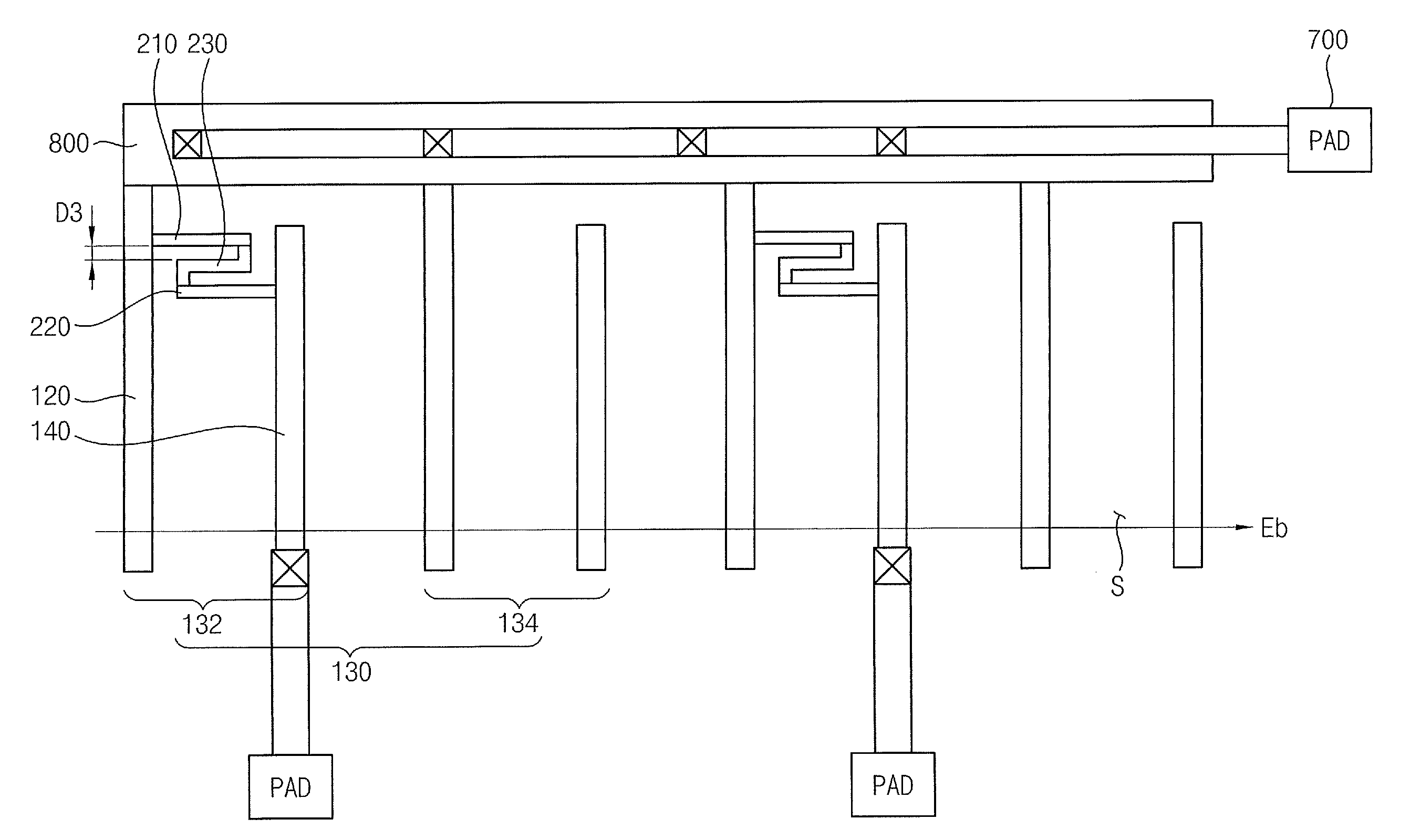

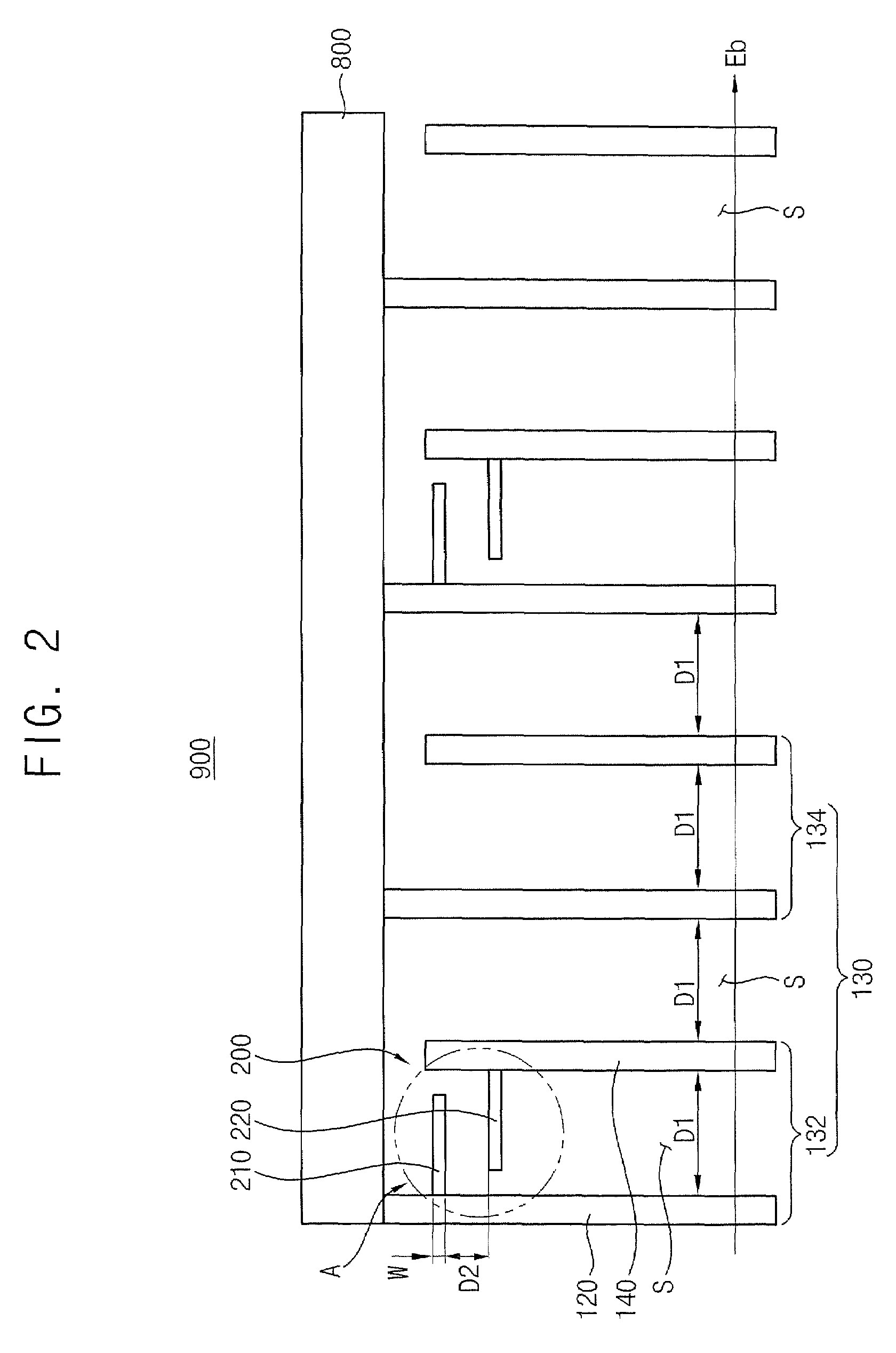

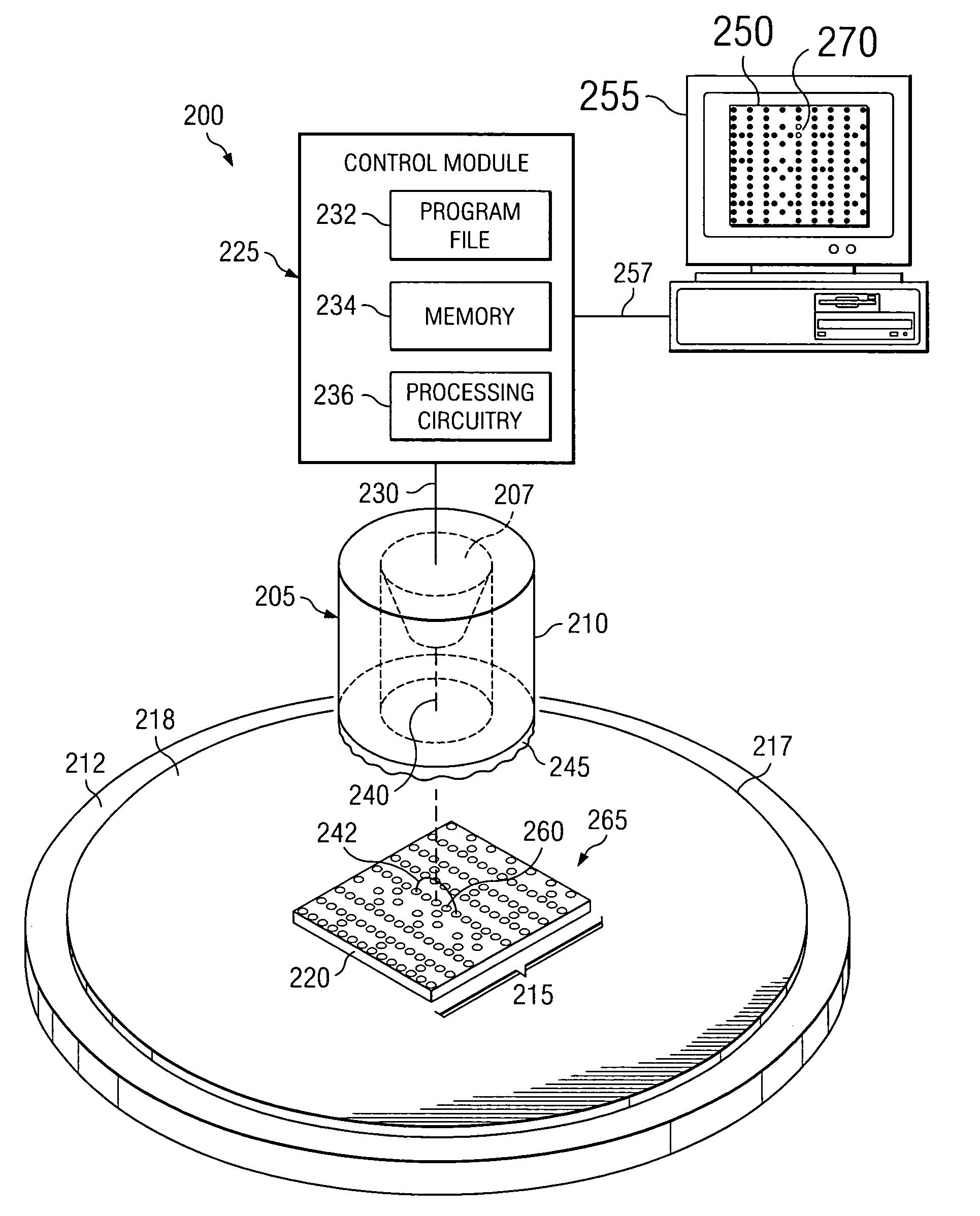

Semiconductor integrated test structures for electron beam inspection of semiconductor wafers

ActiveUS7679083B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCMOSEngineering

Semiconductor integrated test structures are designed for electron beam inspection of semiconductor wafers. The test structures include pattern features that are formed in designated test regions of the wafer concurrently with pattern features of integrated circuits formed on the wafer. The test structures include conductive structures that are designed to enable differential charging between defective and non-defective features (or defective and non-defection portions of a given feature) to facilitate voltage contrast defect detection of CMOS devices, for example, using a single, low energy electron beam scan, notwithstanding the existence of p / n junctions in the wafer substrate or other elements / features.

Owner:SAMSUNG ELECTRONICS CO LTD +2

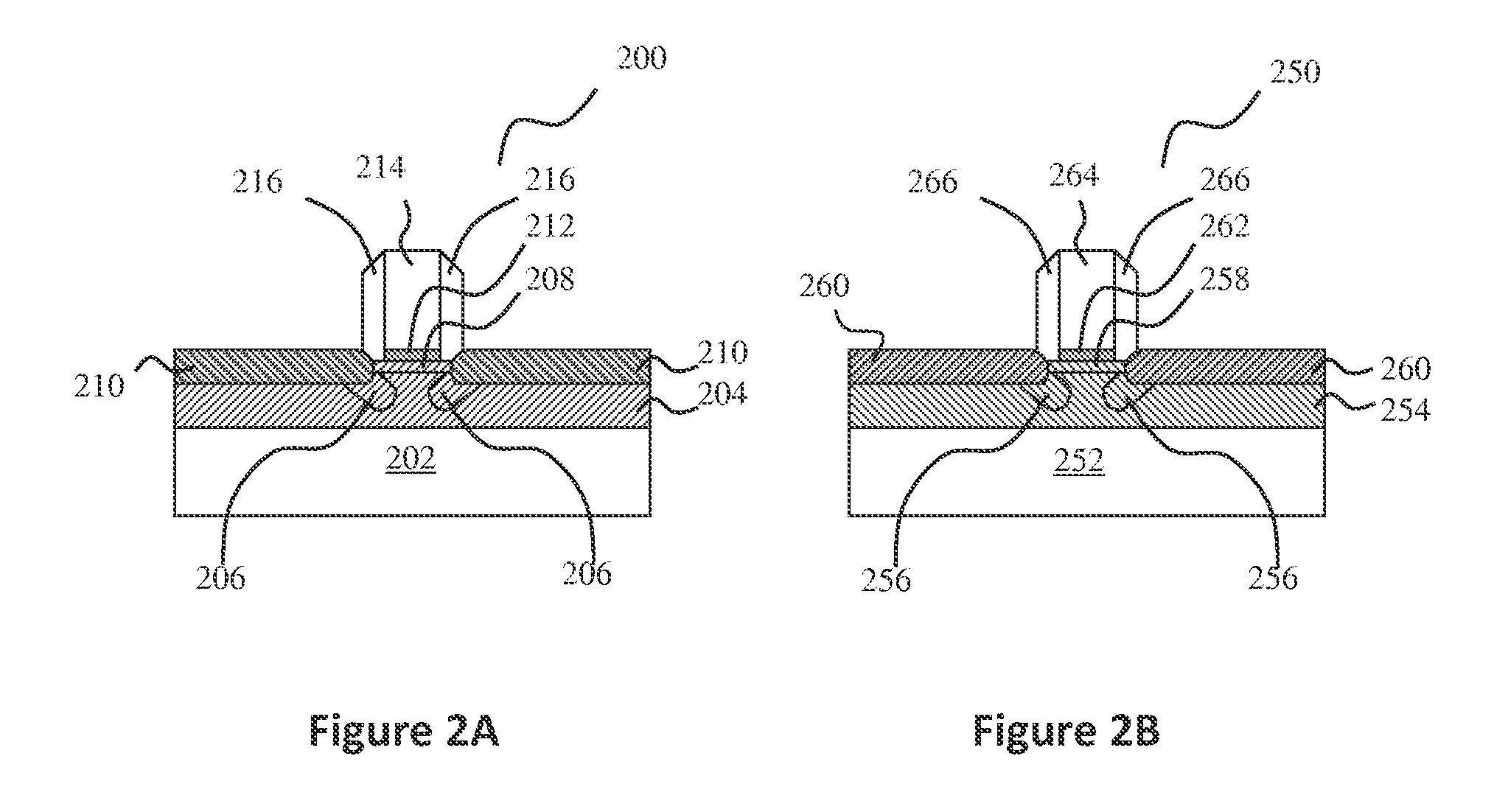

Apparatus and methods for determining and localization of failures in test structures using voltage contrast

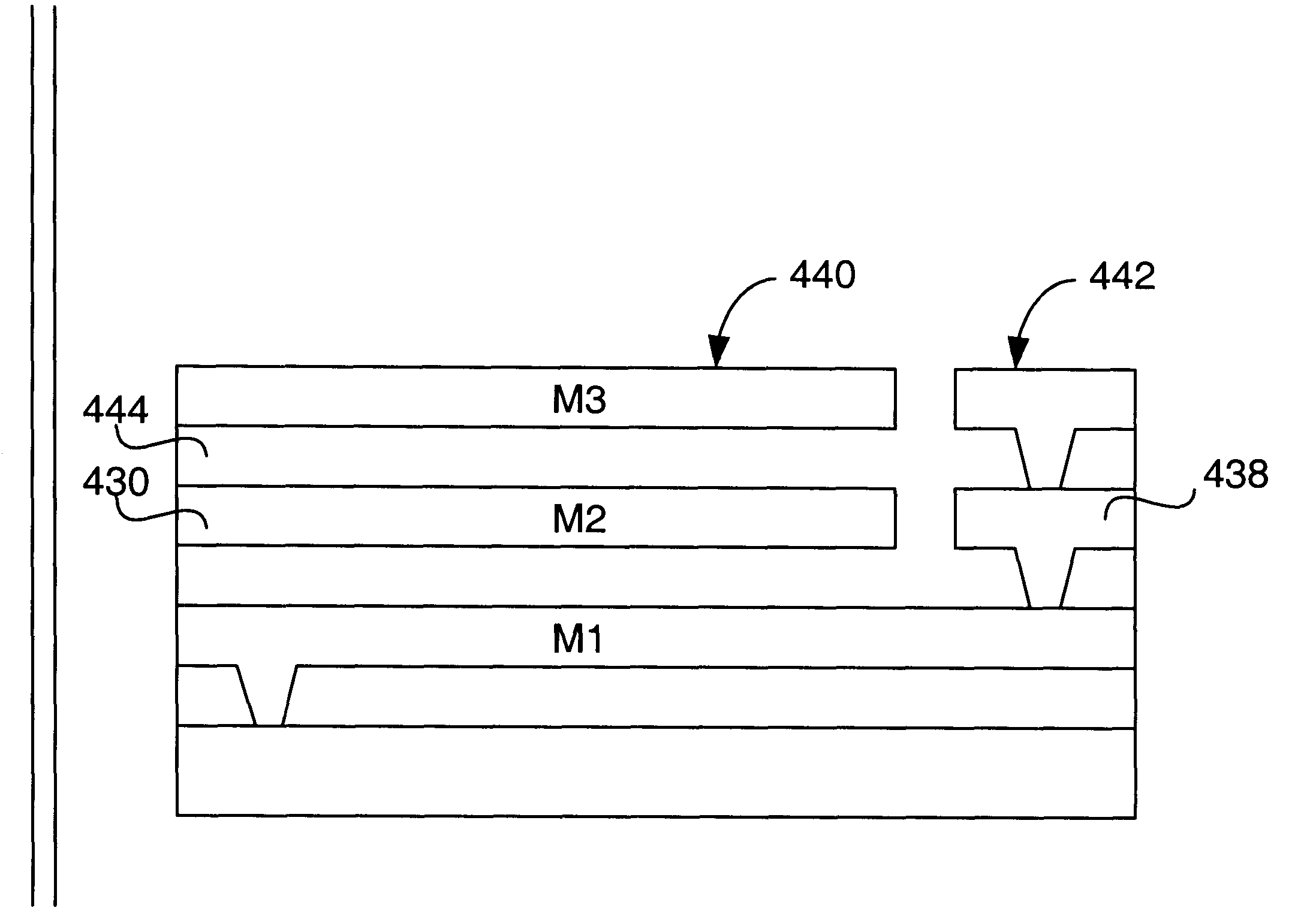

InactiveUS6861666B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsVoltage contrastProduct layer

Disclosed is test structure that can be fabricated with minimal photolithography masking steps and in which defects may be localized to specific layers. Mechanisms for fabricating such test structures are also provided. In one embodiment, a semiconductor test structure suitable for a voltage contrast inspection is provided. The test structure includes one or more test layers corresponding to one or more product layers selected from a plurality of product layers of an integrated circuit (IC) product structure. The number of the selected one or more test layers is less than a total number of the plurality of product layers of the product structure, and the test layers include at least a first portion that is designed to have a first potential during the voltage contrast inspection and a second portion that is designed to have a second potential during the voltage contrast inspection. The first potential differs from the second potential. The selected one or more test layers which correspond to product layers are selected from the plurality of product layers such that defects found in the test layers of the test structure during the voltage contrast inspection represent a prediction of defects in the corresponding product structure.

Owner:KLA TENCOR TECH CORP

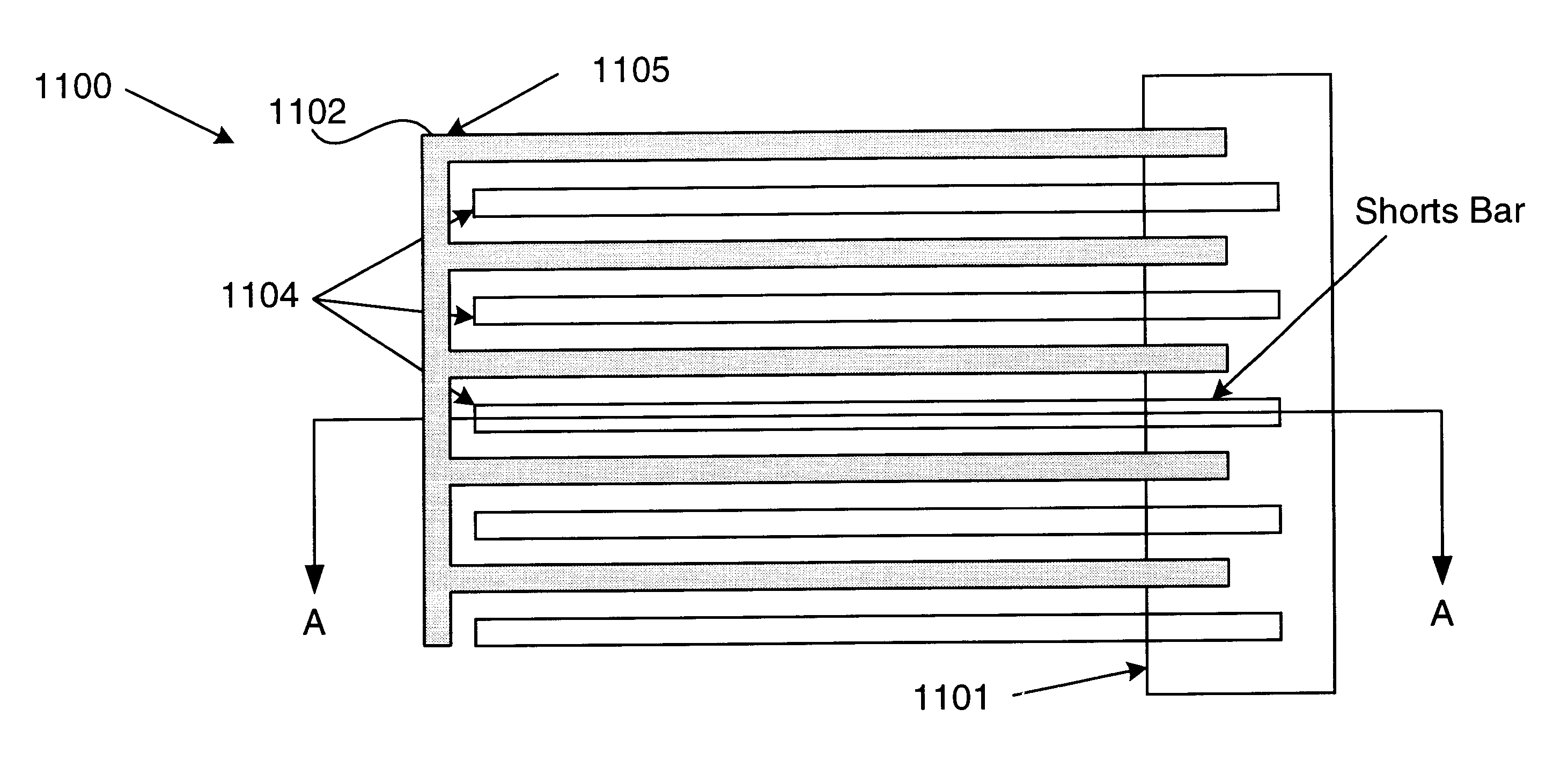

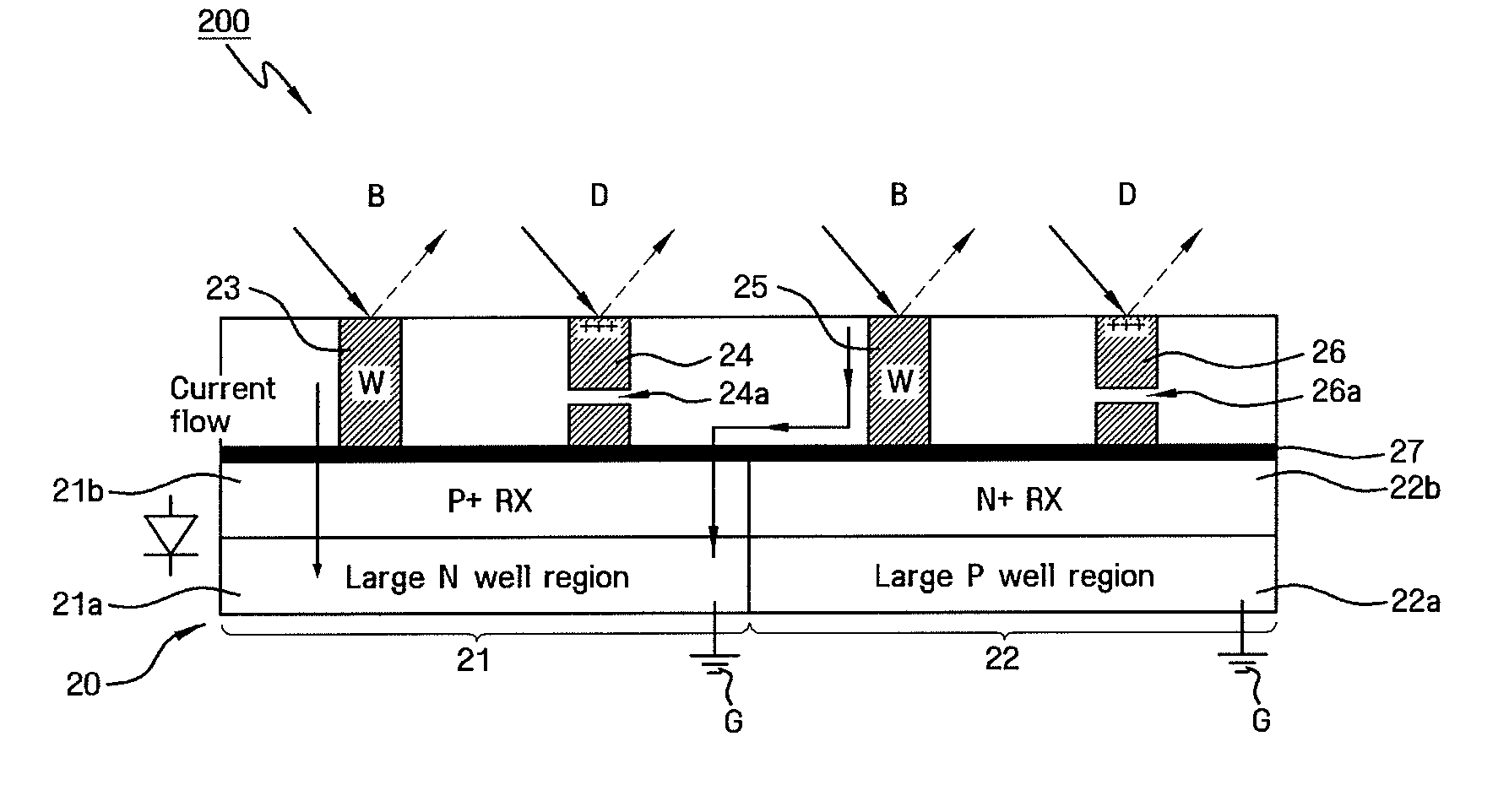

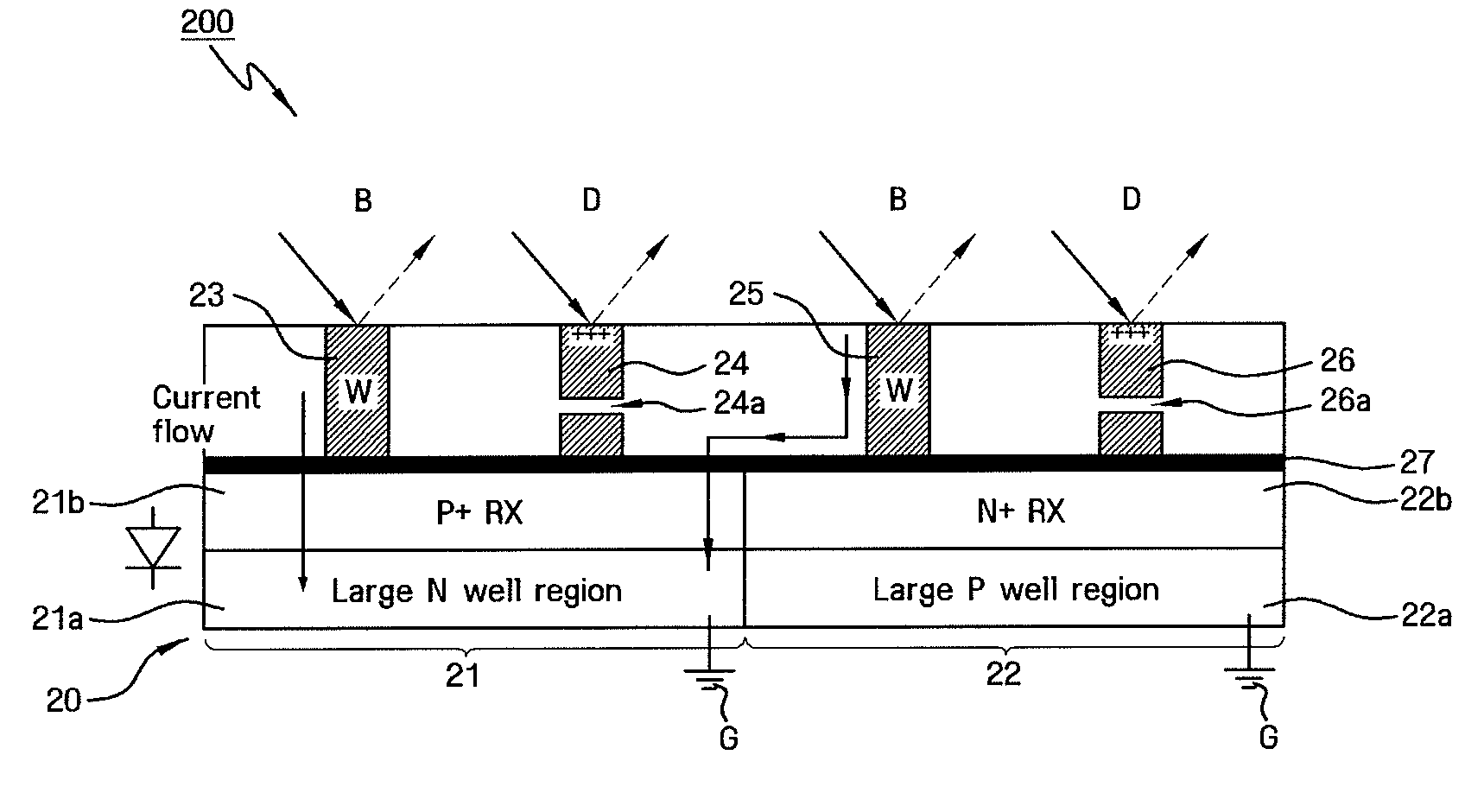

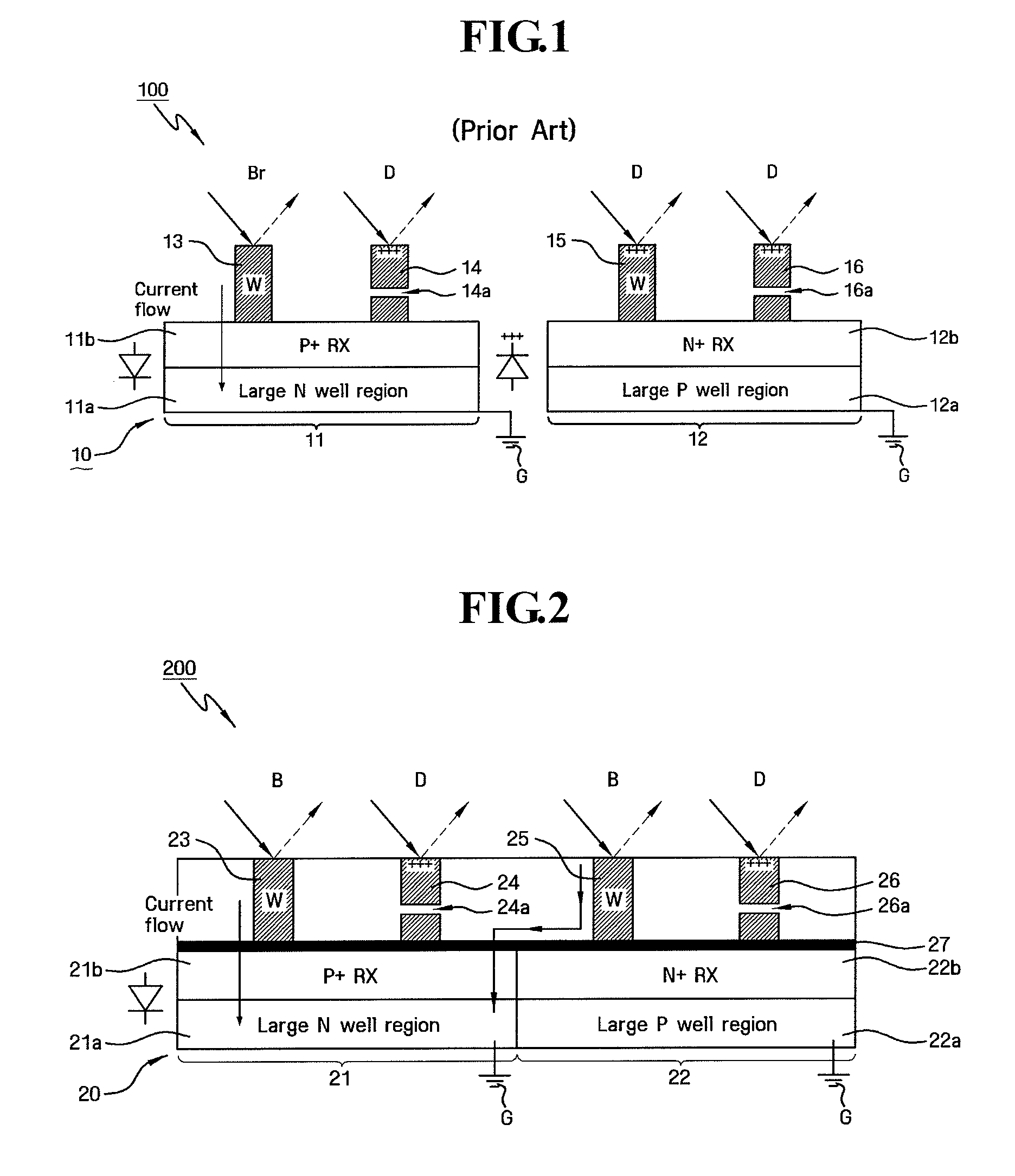

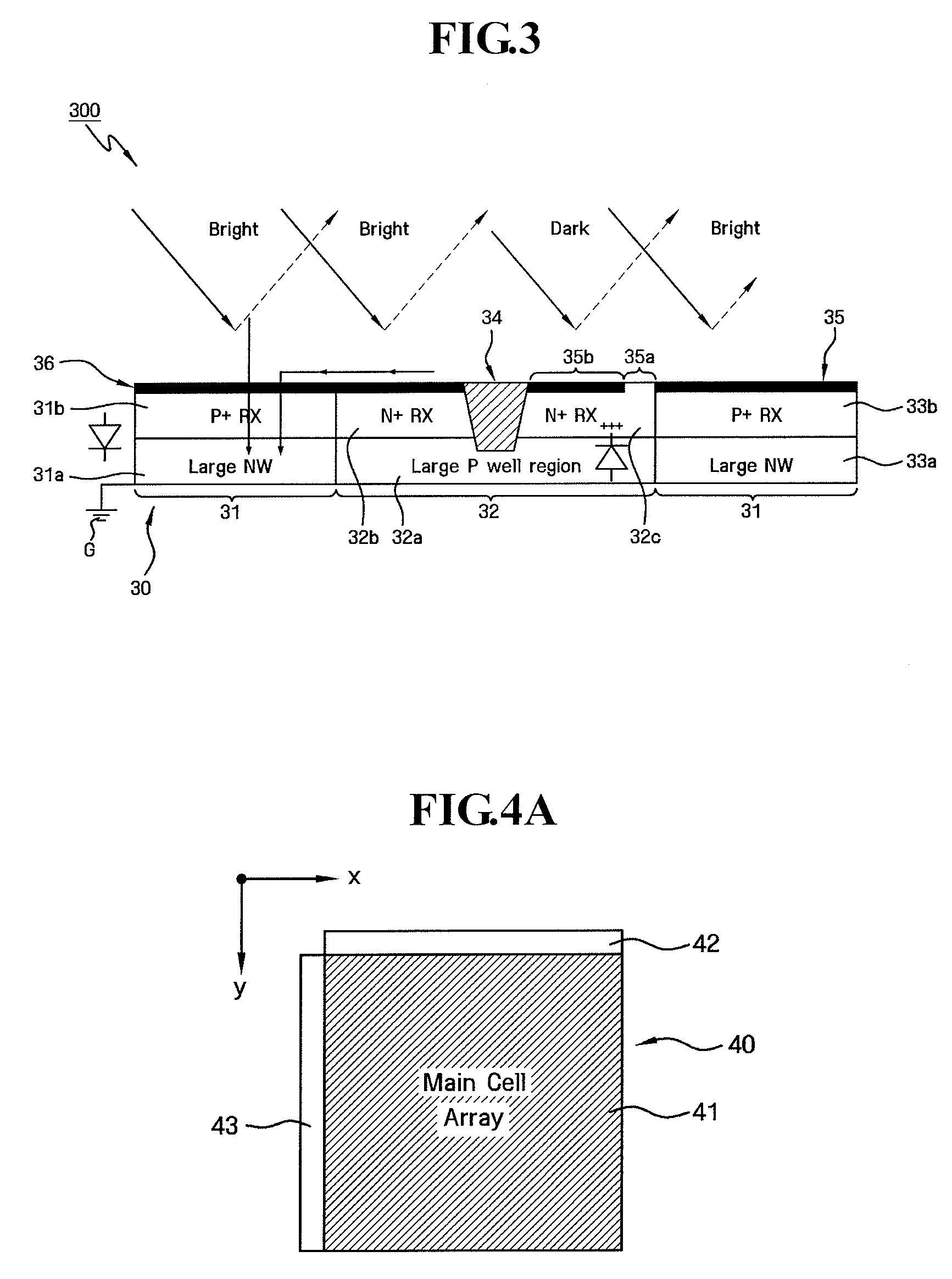

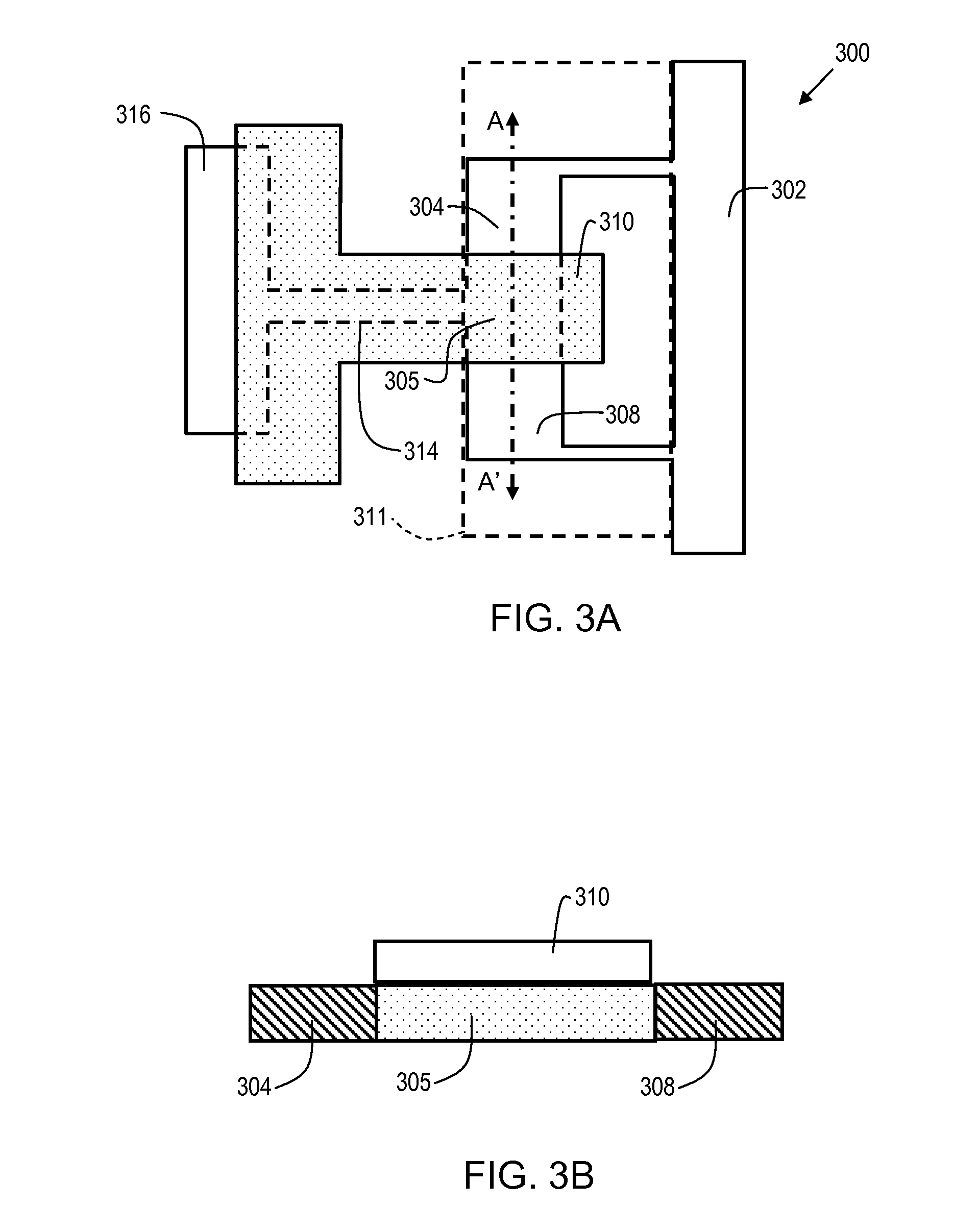

Buried short location determination using voltage contrast inspection

Structure and methods of determining the complete location of a buried short using voltage contrast inspection are disclosed. In one embodiment, a method includes providing a test structure having a PN junction thereunder; and using the PN junction to determine the location of the buried short using voltage contrast (VC) inspection. A test structure may include a plurality of test elements each having a PN junction thereunder, wherein a location of the buried short within the test structure can be determined using the PN junction and the VC inspection. The PN junction forces a change in illumination brightness of a test element including the buried short, thus allowing determination of the complete location of a buried short.

Owner:GLOBALFOUNDRIES INC

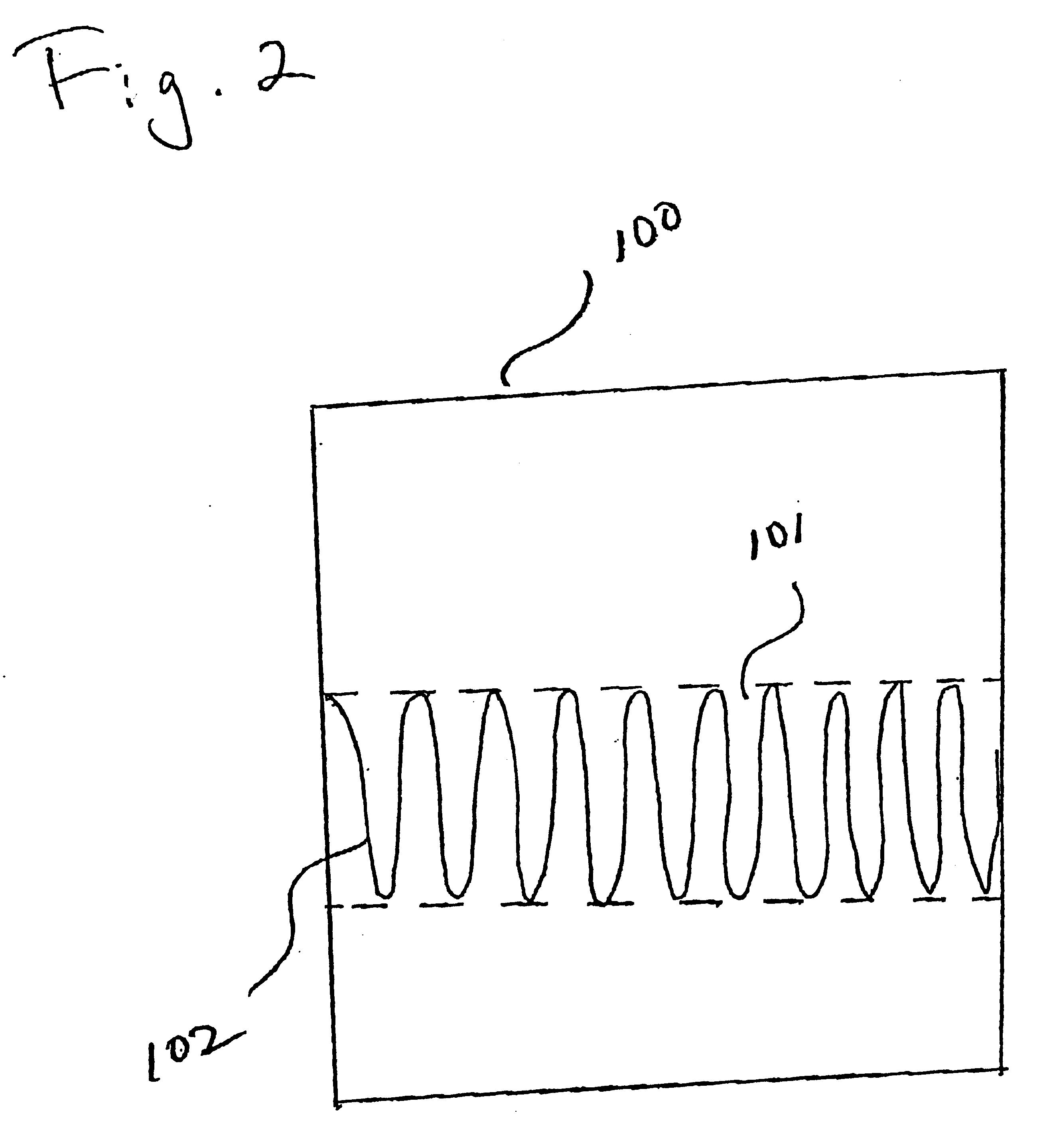

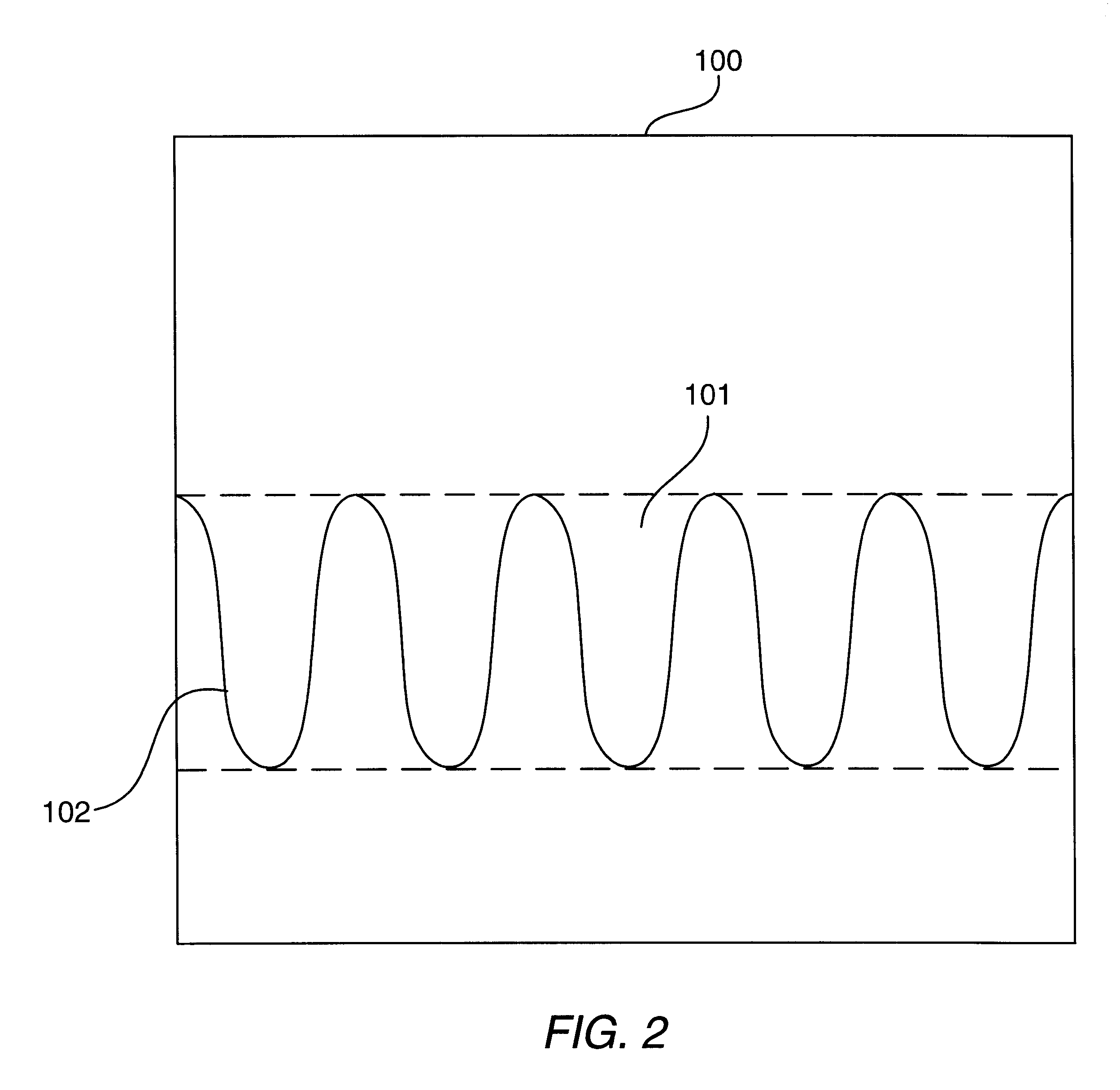

Continuous movement scans of test structures on semiconductor integrated circuits

InactiveUS6524873B1Reduce pressureSemiconductor/solid-state device testing/measurementElectric discharge tubesElectricityEngineering

Disclosed is, a method for detecting electrical defects on test structures of a semiconductor die. The semiconductor die includes a plurality of electrically-isolated test structures and a plurality of non-electrically-isolated test structures. Voltages are established for the plurality of electrically-isolated test structures. These voltages are different than the voltages of the plurality of non-electrically-isolated test structures. A region of the semiconductor die is continuously inspected in a first direction thereby obtaining voltage contrast data indicative of whether there are defective test structures. The voltage contrast data is analyzed to determine whether there are one or more defective test structures.

Owner:KLA CORP

E-beam inspection structure for leakage analysis

InactiveUS20090057664A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityGate dielectric

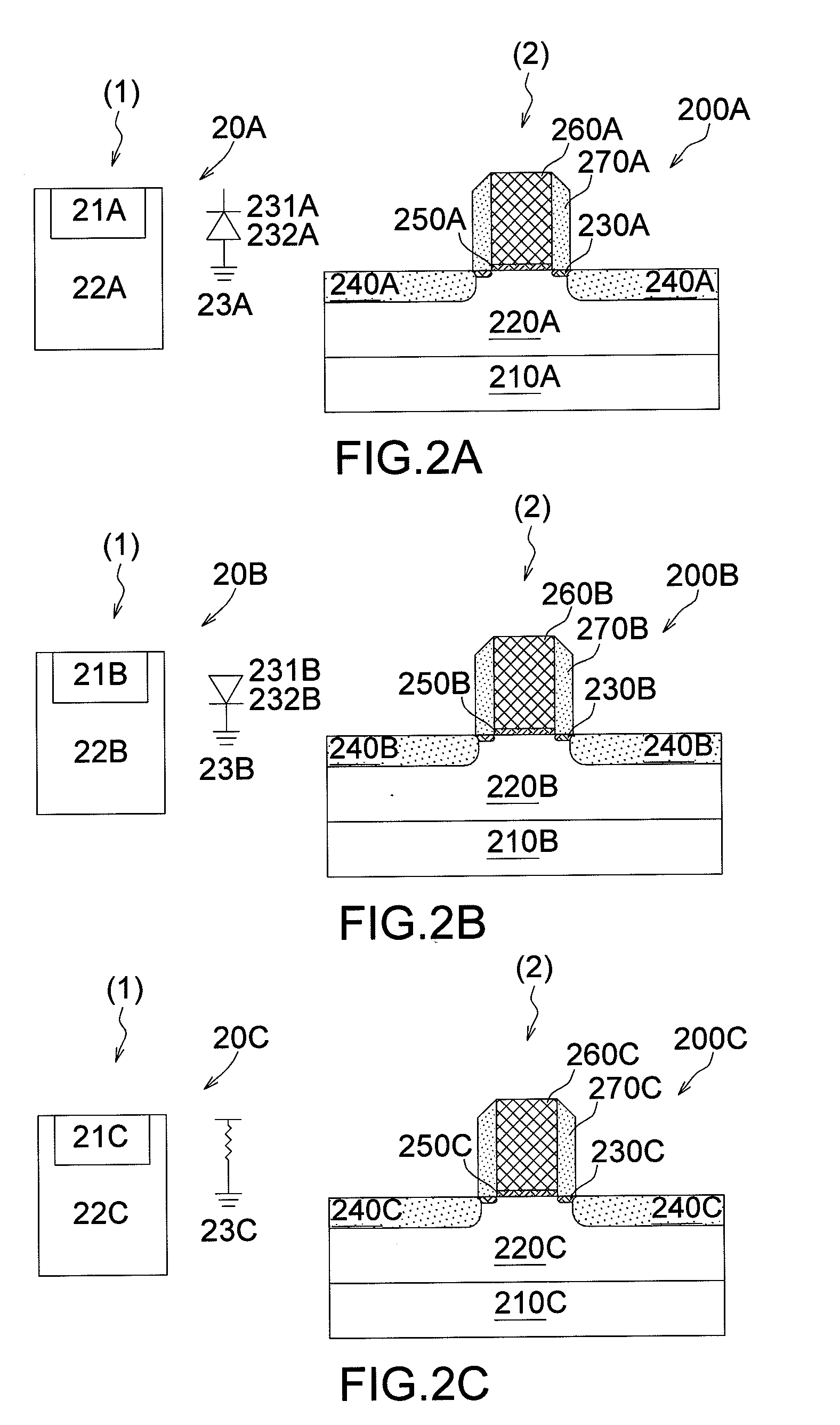

A testing structure, and method of using the testing structure, where the testing structure comprised of at least one of eight test structures that exhibits a discernable defect characteristic upon voltage contrast scanning when it has at least one predetermined structural defect. The eight test structures being: 1) having an Active Area (AA) / P-N junction leakage; 2) having an isolation region to ground; 3) having an AA / P-N junction and isolation region; 4) having a gate dielectric leakage and gate to isolation region to ground; 5) having a gate dielectric leakage through AA / P-N junction to ground leakage; 6) having a gate dielectric to ground and gate / one side isolation region leakage to ground; 7) having an oversized gate dielectric through AA / P-N junction to ground leakage; and 8) having an AA / P-N junction leakage gate dielectric leakage.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Semiconductor Integrated Test Structures For Electron Beam Inspection of Semiconductor Wafers

ActiveUS20080237586A1Easy to detectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCMOSEngineering

Semiconductor integrated test structures are designed for electron beam inspection of semiconductor wafers. The test structures include pattern features that are formed in designated test regions of the wafer concurrently with pattern features of integrated circuits formed on the wafer. The test structures include conductive structures that are designed to enable differential charging between defective and non-defective features (or defective and non-defection portions of a given feature) to facilitate voltage contrast defect detection of CMOS devices, for example, using a single, low energy electron beam scan, notwithstanding the existence of p / n junctions in the wafer substrate or other elements / features.

Owner:SAMSUNG ELECTRONICS CO LTD +2

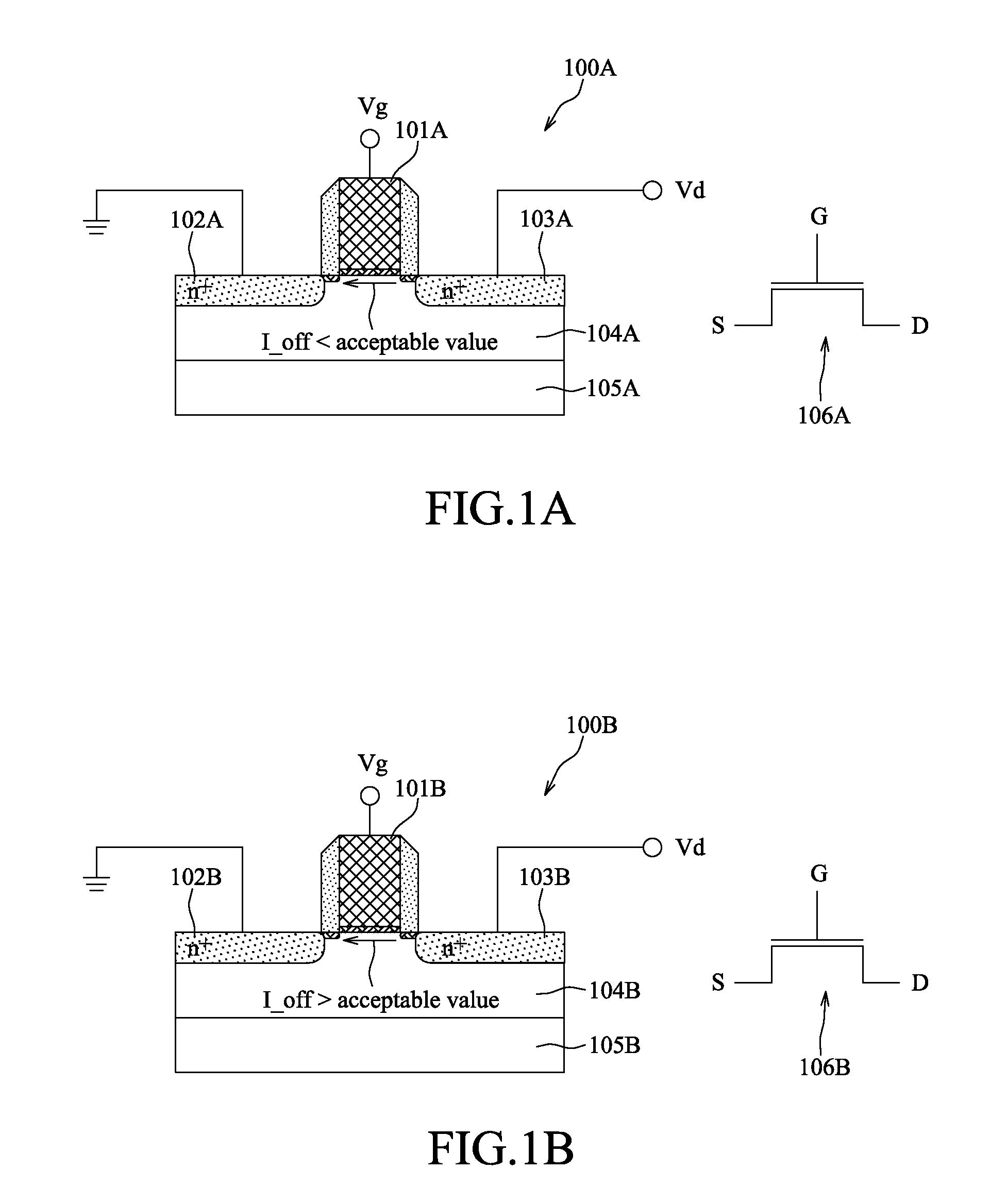

Test structures and method of defect detection using voltage contrast inspection

InactiveUS7456636B2Shorter learning cycleSemiconductor/solid-state device detailsSolid-state devicesDielectricElectricity

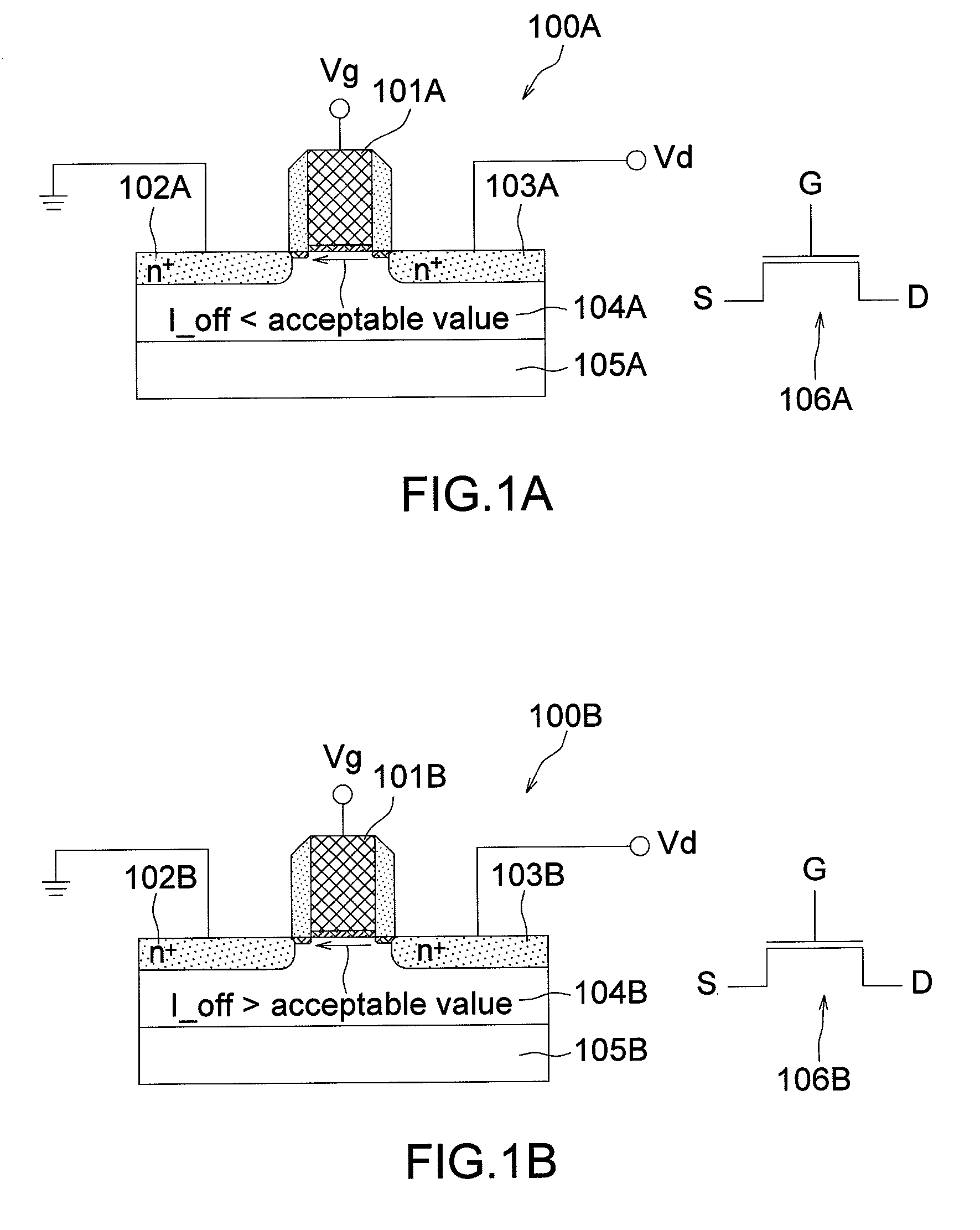

Test structures and a method for voltage contrast (VC) inspection are disclosed. In one embodiment, the test structure includes: a gate stack that is grounded by a ground to maintain the gate stack in an off state during VC inspection, which allows NFET defect detection using VC inspection prior to contact dielectric deposition. The test structure may alternatively include a gate stack that is biased by a bias to maintain the gate stack in an on state during VC inspection. The method may detect source-to-drain shorts in a transistor using VC inspection by providing a gate stack over a source and drain region of the transistor that is grounded by a ground to maintain the gate stack in an off state during VC inspection; and inspecting the transistor using voltage contrast. If the drain of the NFET brightens during VC inspection, this indicates a source to drain short.

Owner:INT BUSINESS MASCH CORP

Voltage contrast test structure

InactiveUS7217579B2Increase speedNo wasteMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityVoltage contrast

A method for electrically testing a semiconductor wafer during integrated-circuit fabrication process, the method including: (i) providing a scanning charged-particle microscope (SCPM), having a defined scanning plane and operative, while in any one mechanical state, to scan a surface in the scanning plane within a two-dimensional scanning window, which has a given maximum size; (ii) providing in association with any layer of the wafer, it being a test layer, one or more test structures, each test structure including normally conductive areas within a normally non-conductive background in one or more layers, which include said test layer, the conductive areas formed as one or more patterns; the patterns in said test layer include one or more clusters of mutually isolated pads; each pad is conductively connected with a corresponding distinct point on the patterns and all the pads in any one cluster are sized and arranged so that at least a significant portion of each pad falls within a common window whose size does not exceed said maximum size of said scanning window; (iii) with said test layer forming the top surface of the wafer, placing the wafer on the SCPM and adjusting the mechanical state of the SCPM so that at least a significant portion of each pad in any one of said clusters is within said scanning window; (iv) causing the SCPM, while in said mechanical state, to scan all of the pads of said one cluster and thereby to provide information about the electrical state of the respective test structure.

Owner:APPL MATERIALS ISRAEL LTD

Test structure for resistive open detection using voltage contrast inspection and related methods

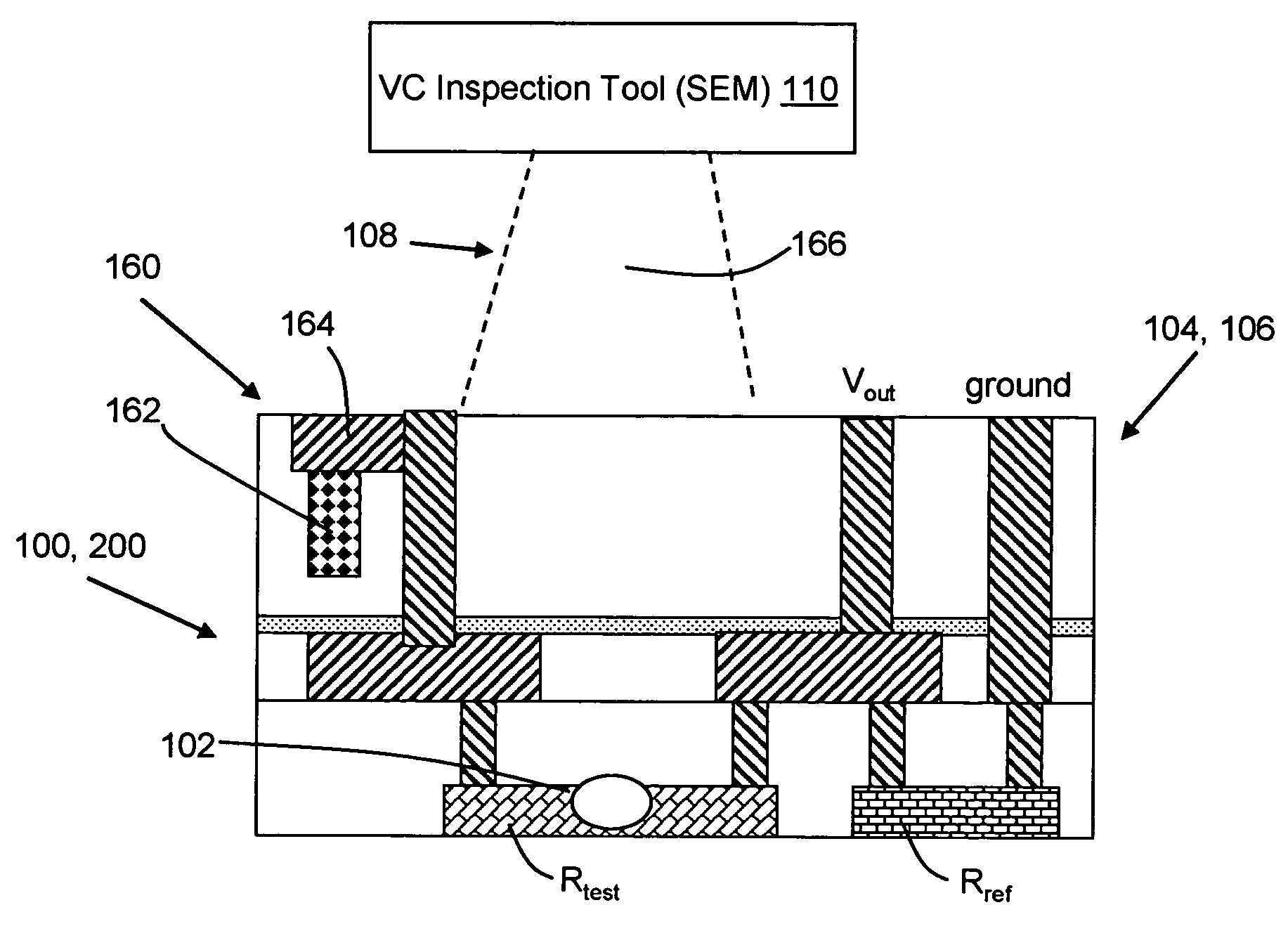

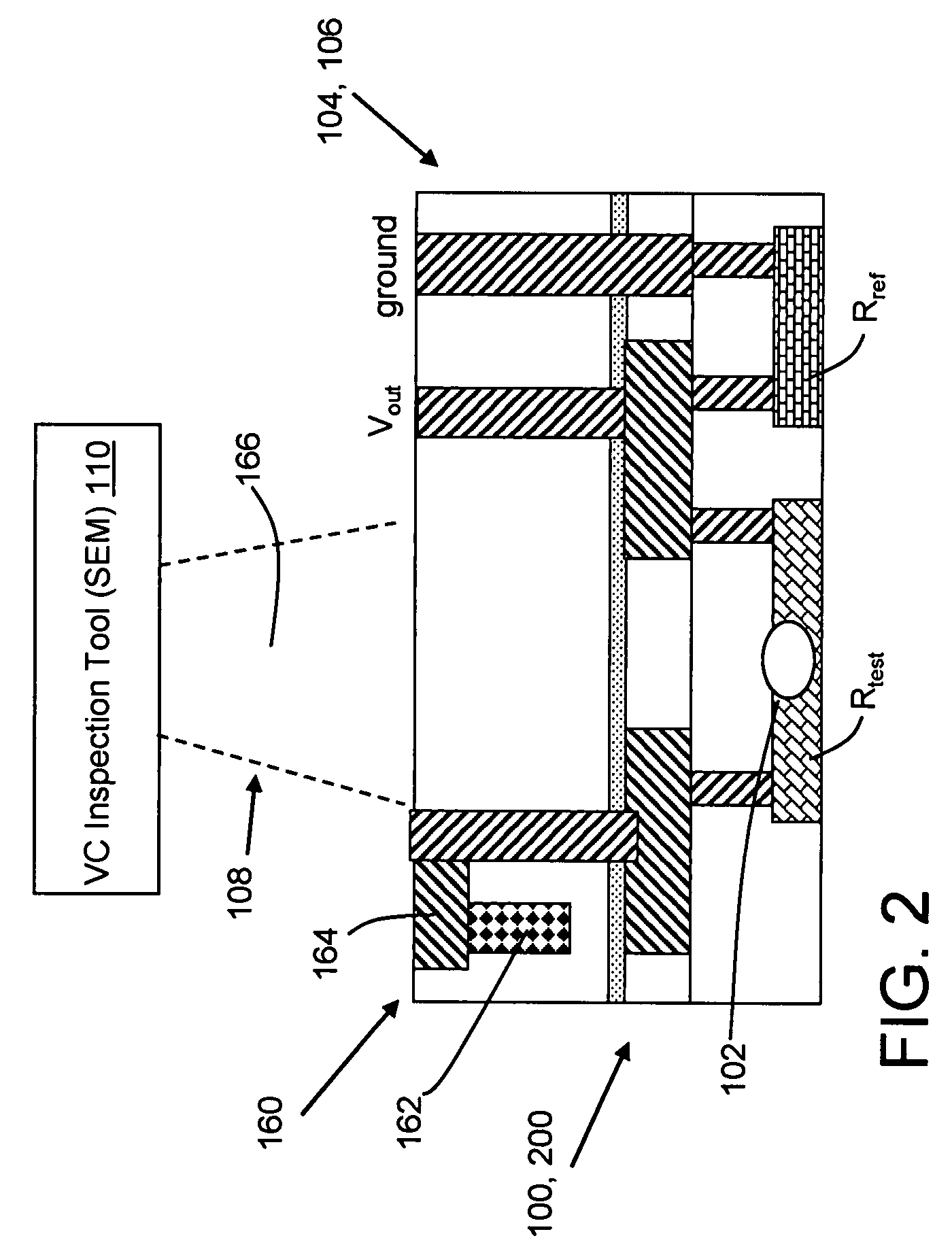

ActiveUS7733109B2Semiconductor/solid-state device testing/measurementElectric discharge tubesElectrical resistance and conductanceOutput compare

A test structure for resistive open detection using voltage contrast (VC) inspection and method for using such structure are disclosed. The test structure may include a comparator within the IC chip for comparing a resistance value of a resistive element under test to a reference resistance and outputting a result of the comparing that indicates whether the resistive open exists in the resistive element under test, wherein the result is detectable by the voltage contrast inspection.

Owner:TWITTER INC

Padless structure design for easy identification of bridging defects in lines by passive voltage contrast

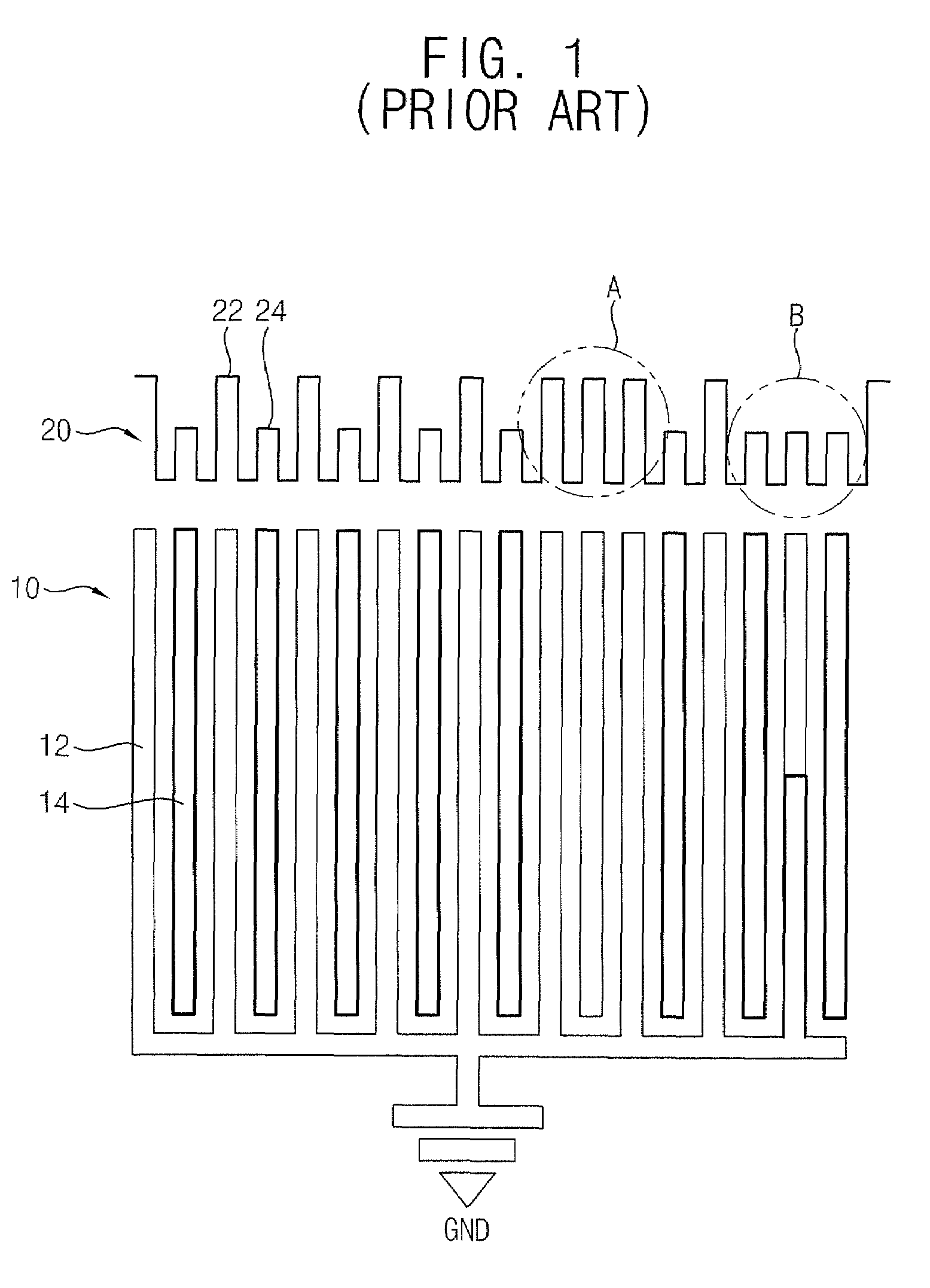

InactiveUS6949765B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementEngineeringElectron microscope

A new test structure to locate bridging defects in a conductive layer of an integrated circuit device is achieved. The test structure comprises a line comprising a conductive layer overlying a substrate. The line is coupled to ground. A plurality of rectangles comprises the conductive layer. The rectangles are not connected to the line or to other rectangles. Near edges of the rectangles and of the line are parallel. The rectangles are floating. The test structure is used with a passive voltage contrast test in a scanning electron microscope. A test structure and method to measure critical dimensions is disclosed.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

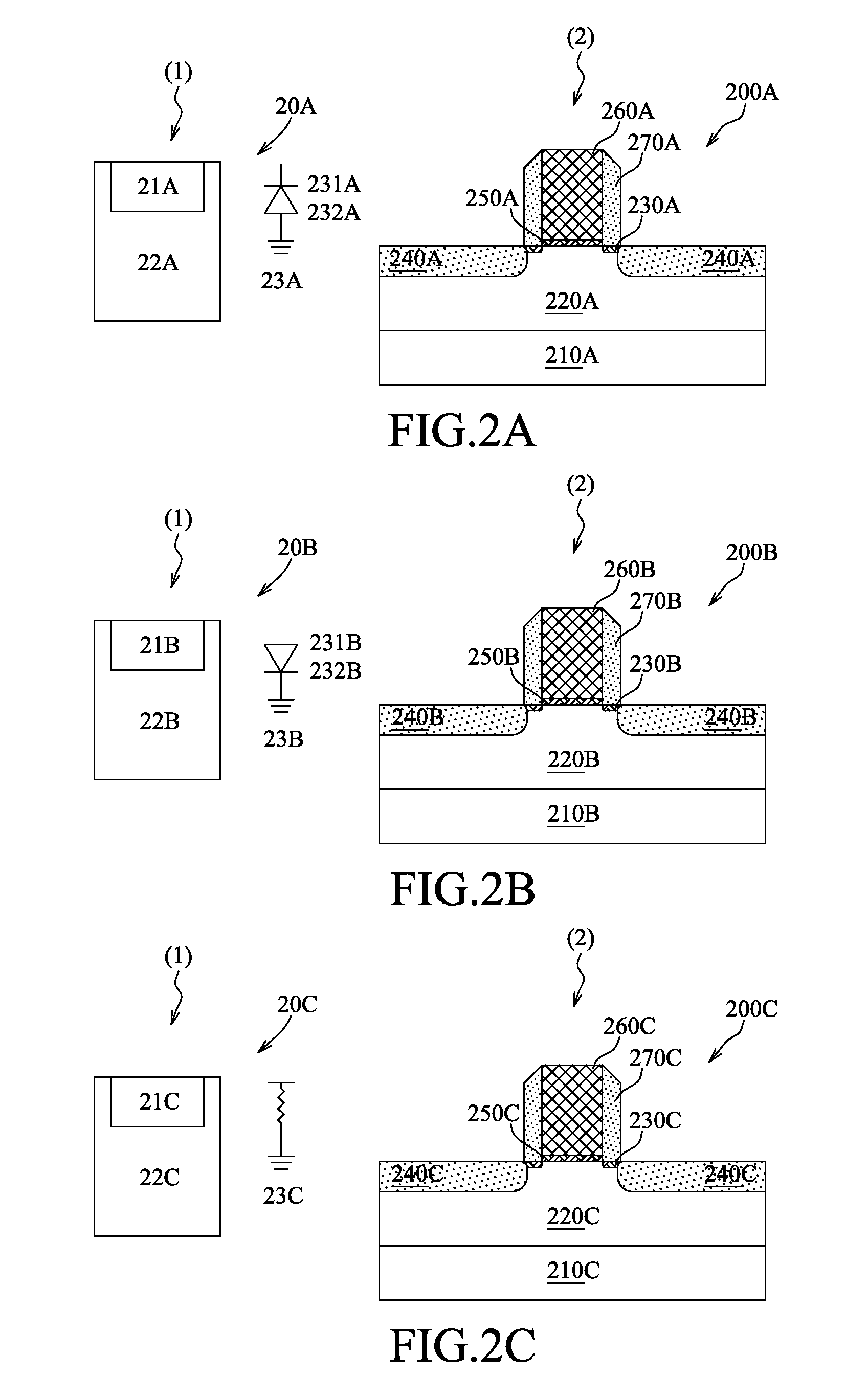

Test structure for charged particle beam inspection and method for defect determination using the same

ActiveUS20110013826A1TransistorSemiconductor/solid-state device detailsVoltage contrastSemiconductor

A test structure and method thereof for determining a defect in a sample of semiconductor device includes at least one transistor rendered grounded. The grounded transistor is preferably located at least one end of a test pattern designed to be included in the sample. When the test structure is inspected by charged particle beam inspection, the voltage contrast (VC) of the transistors in the test pattern including the grounded transistor is observed for determination of the presence of defect in the sample.

Owner:ASML NETHERLANDS BV

E-beam inspection structure for leakage analysis

InactiveUS7939348B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementGate dielectricVoltage contrast

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

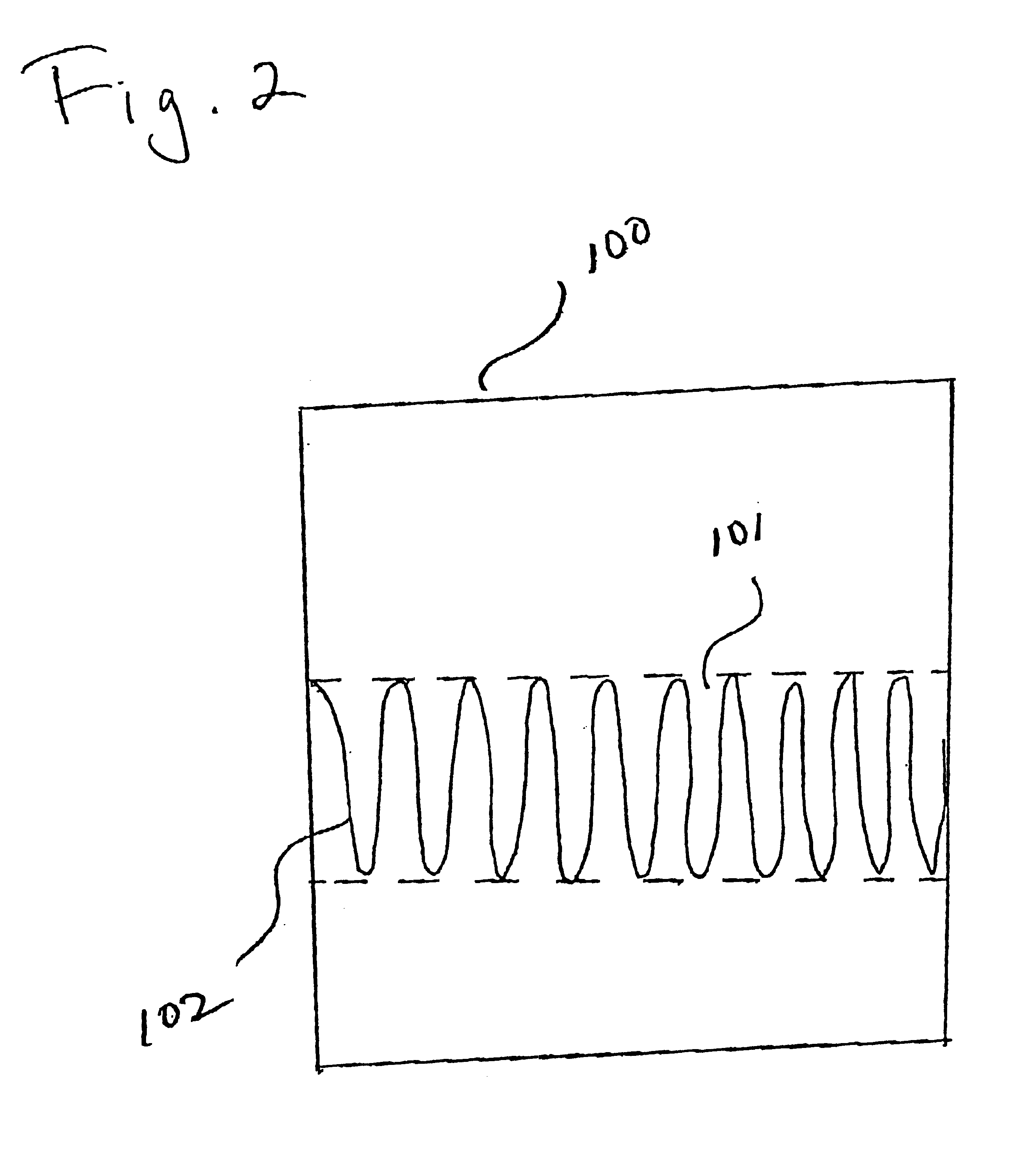

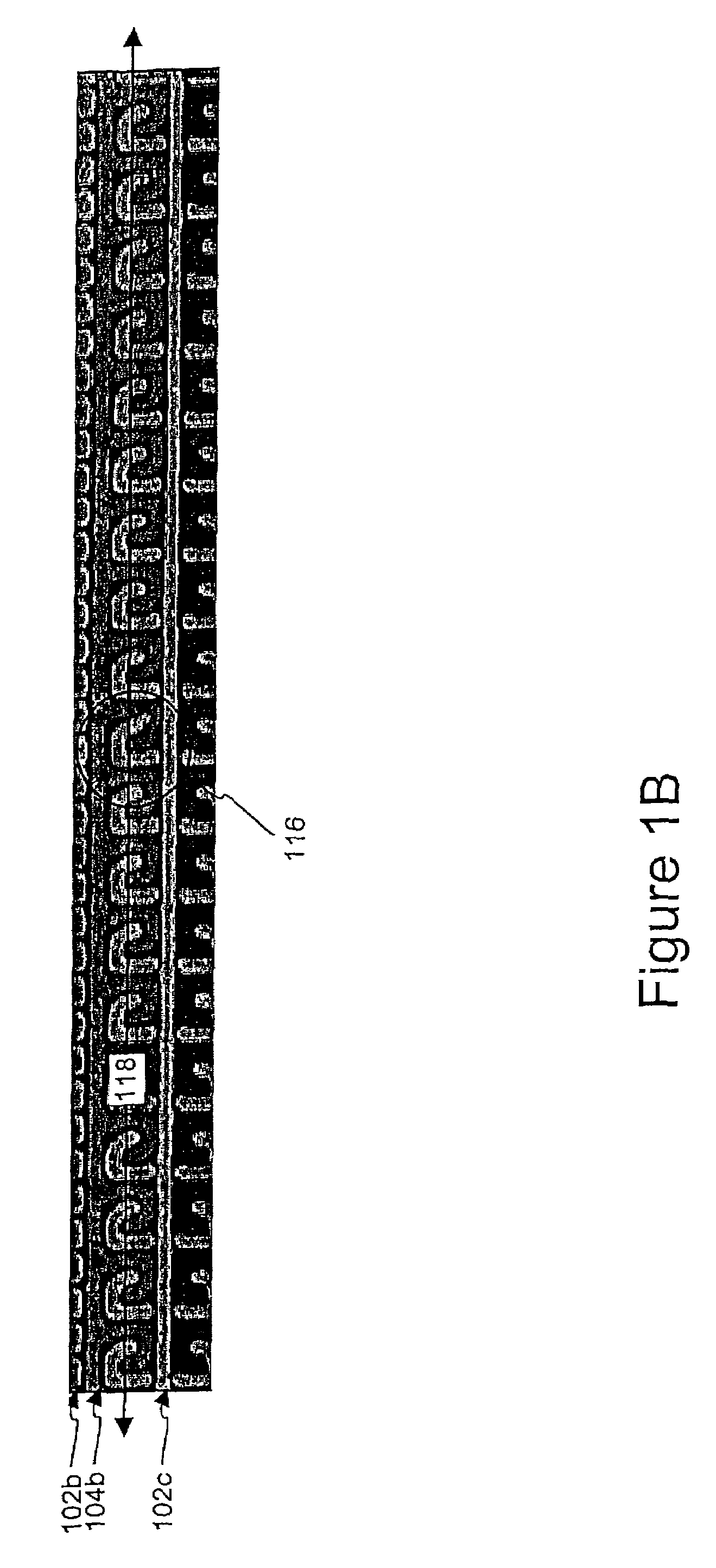

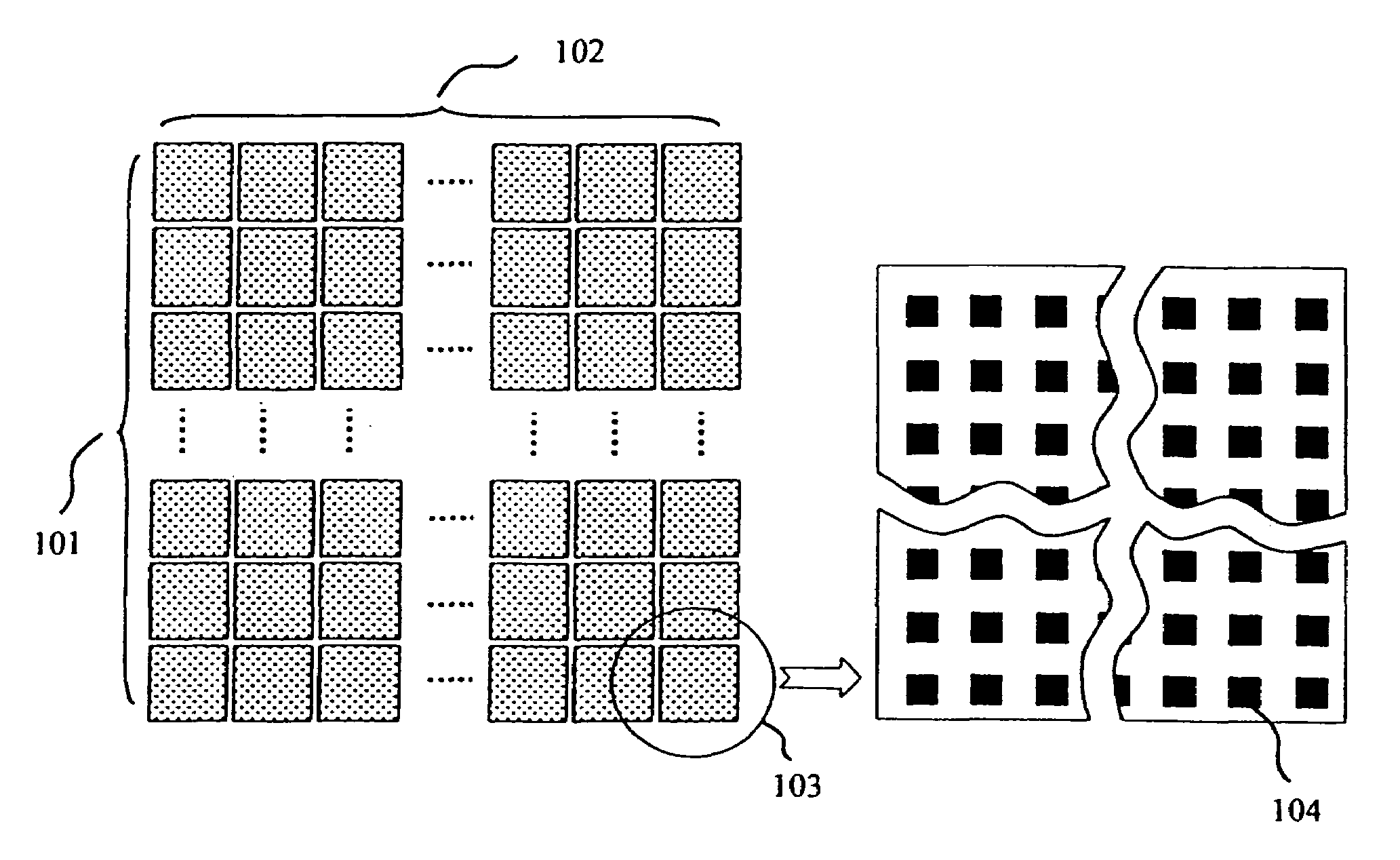

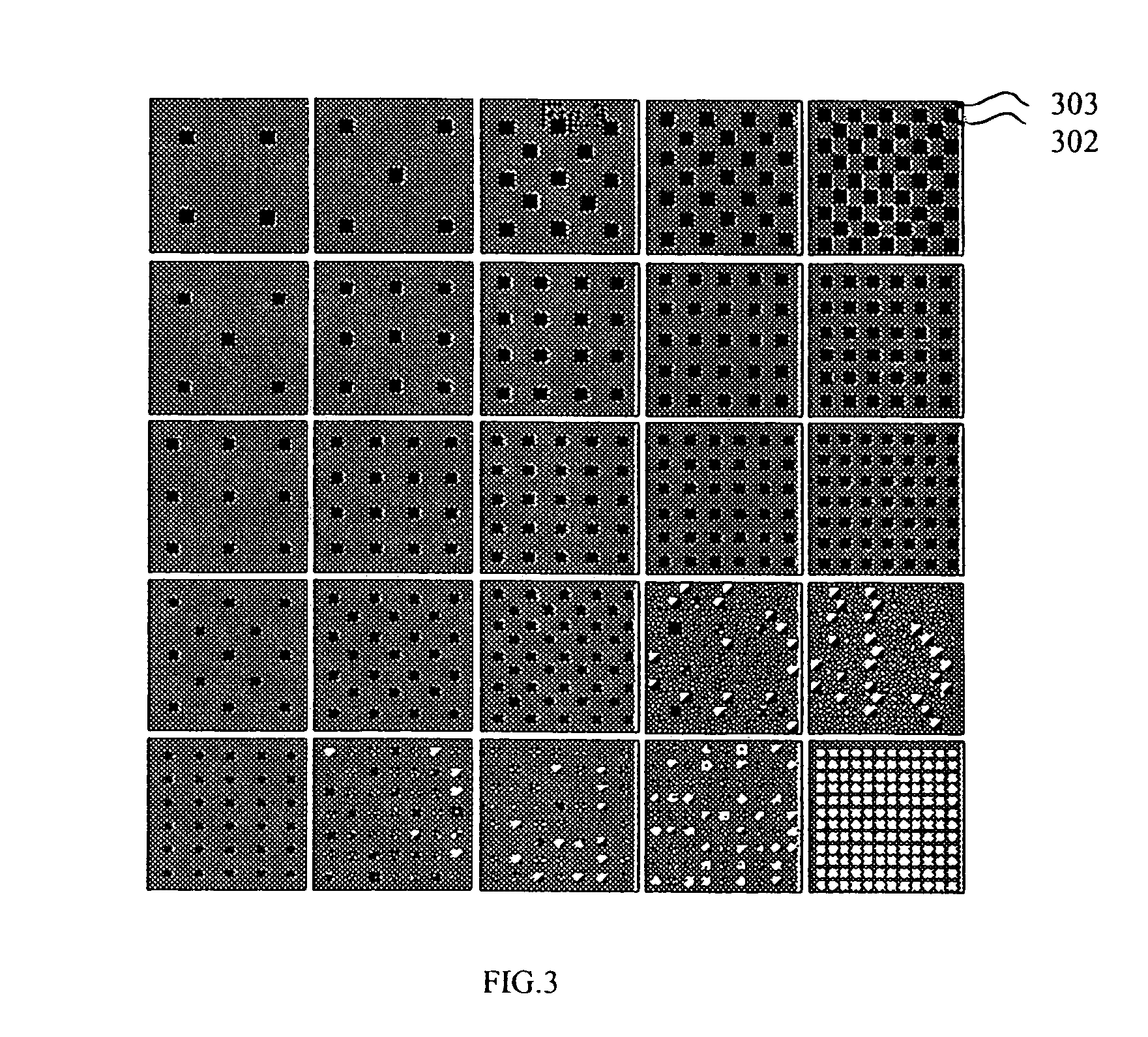

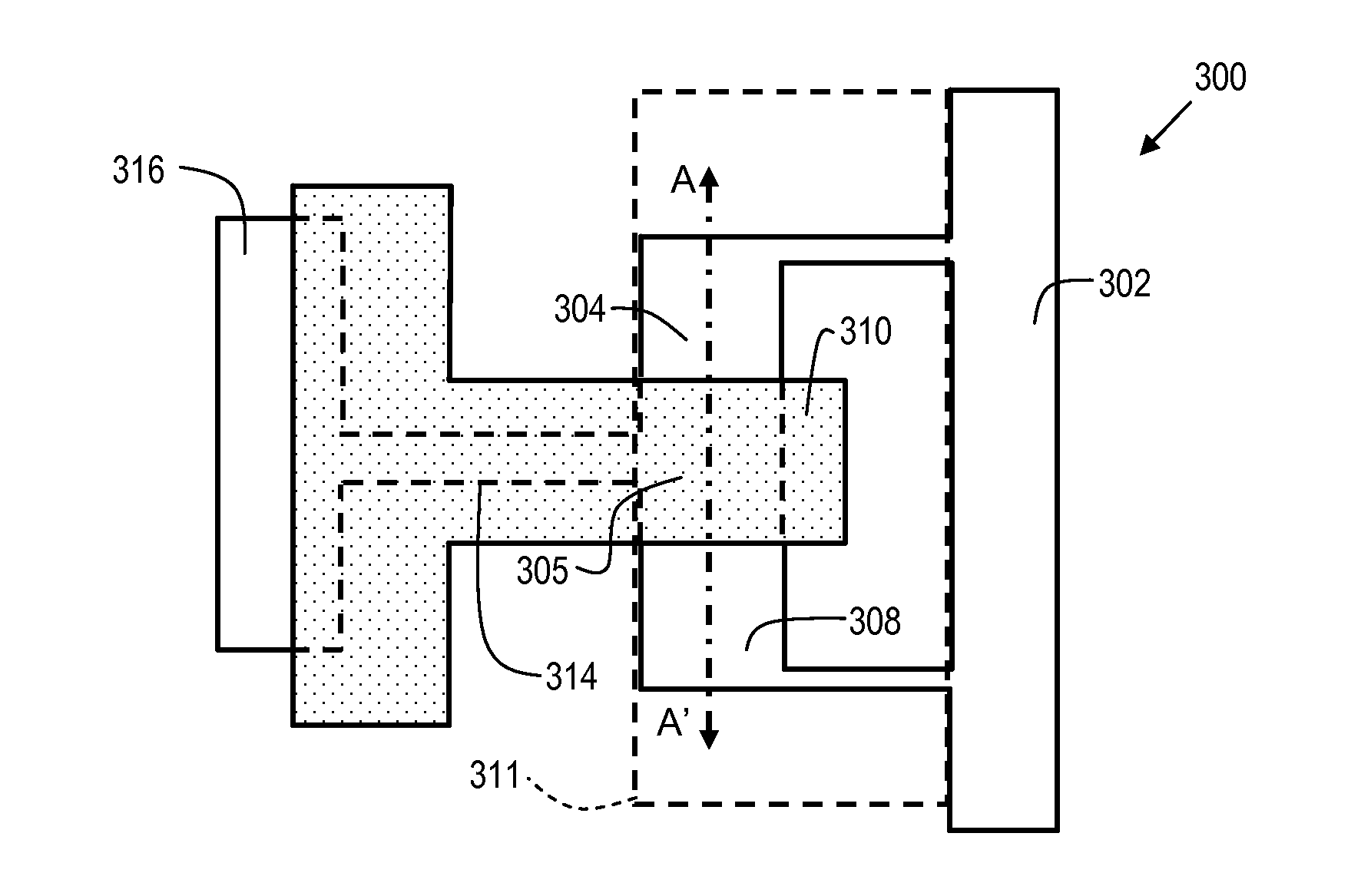

Methodologies for efficient inspection of test structures using electron beam scanning and step and repeat systems

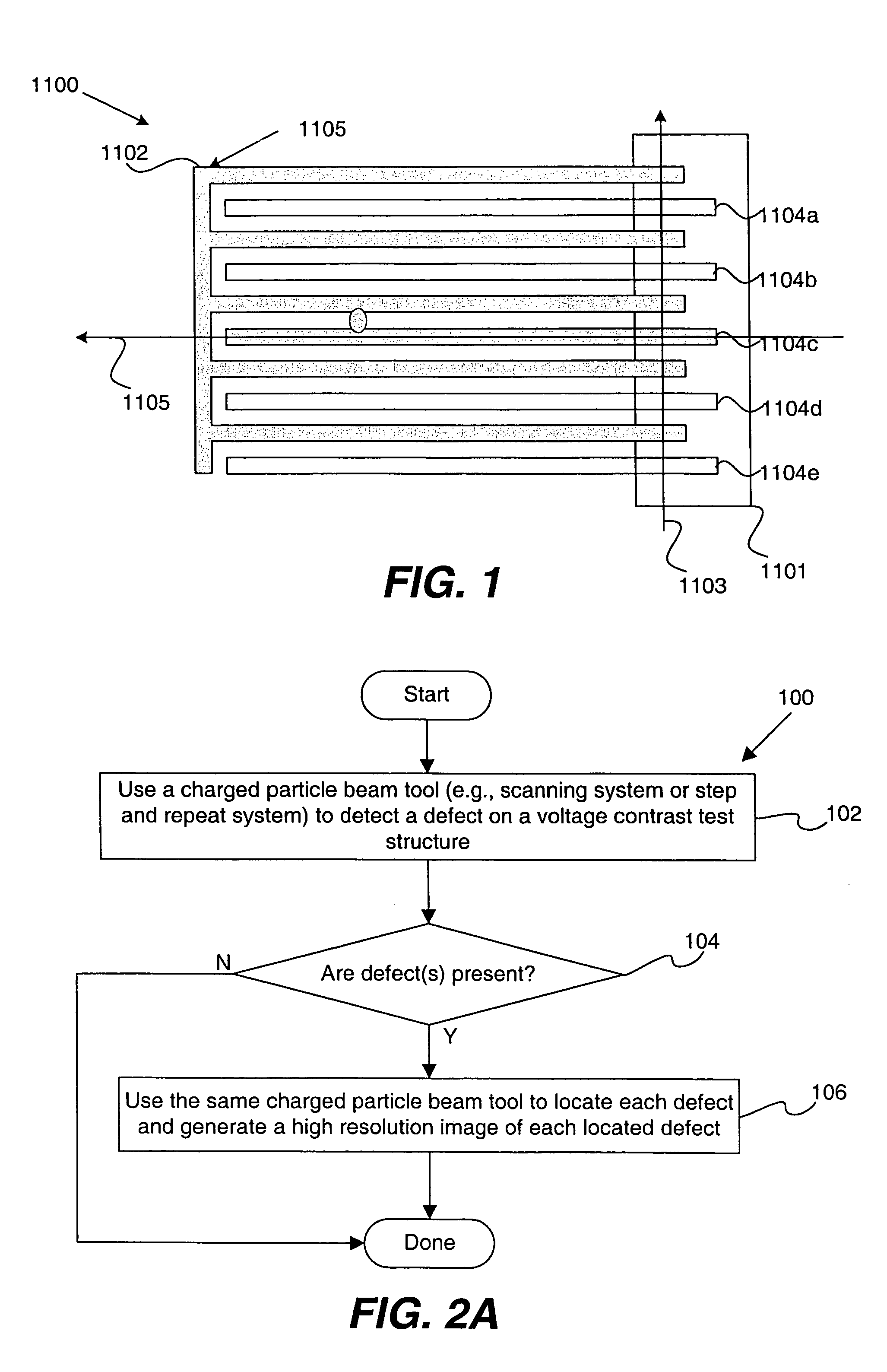

ActiveUS7198963B2Analog circuit testingSemiconductor/solid-state device testing/measurementImage resolutionBeam scanning

Disclosed are techniques for efficiently inspecting defects on voltage contrast test. In one embodiment, methodologies and test structures allow inspection to occur entirely within a charged particle system. In a specific embodiment, a method of localizing and imaging defects in a semiconductor test structure suitable for voltage contrast inspection is disclosed. A charged particle beam based tool is used to determine whether there are any defects present within a voltage contrast test structure. The same charged particle beam based tool is then used to locate defects determined to be present within the voltage contrast test structure. Far each localized defect, the same charged particle beam based tool may then be used to generate a high resolution image of the localized defect whereby the high resolution image can later be used to classify the each defect. In one embodiment, the defect's presence and location are determined without rotating the test structure relative to the charged particle beam.

Owner:KLA TENCOR TECH CORP

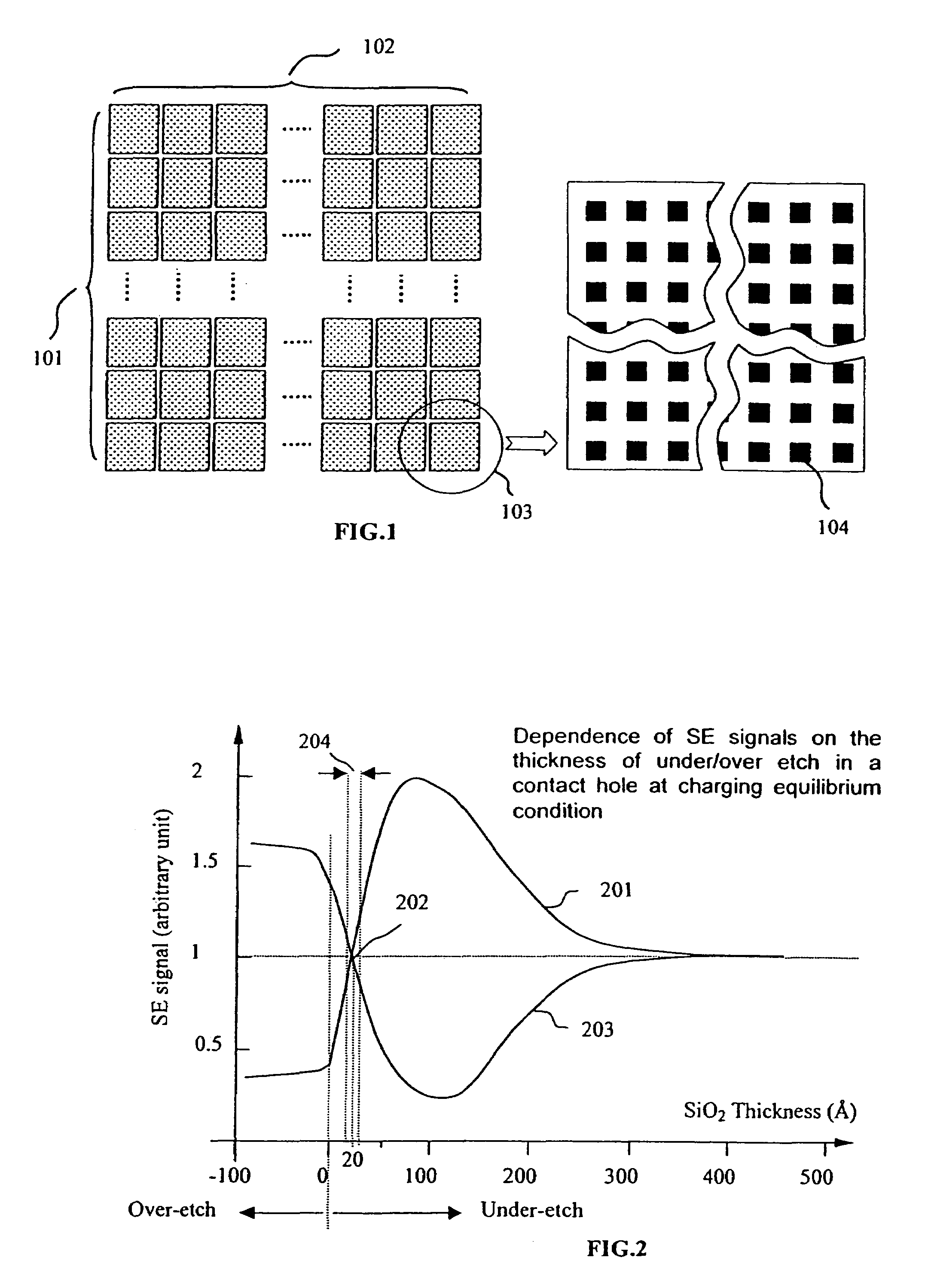

Method for in-line monitoring of via/contact holes etch process based on test structures in semiconductor wafer manufacturing

InactiveUS7105436B2Reduce contactSemiconductor/solid-state device testing/measurementVacuum gauge using ionisation effectsImaging processingEngineering

Owner:HERMES MICROVISION TAIWAN +2

Structure and method for determining a defect in integrated circuit manufacturing process

ActiveUS8089297B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementIntegrated circuit manufacturingEngineering

The present invention discloses a structure and method for determining a defect in integrated circuit manufacturing process, wherein the structure comprises a plurality of normal active areas formed in a plurality of first arrays and a plurality of defective active areas formed in a plurality of second arrays. The first arrays and second arrays are interlaced, and the defect is determined by monitoring a voltage contrast from a charged particle microscope image of the active areas.

Owner:ASML NETHERLANDS BV

In-line voltage contrast detection of PFET silicide encroachment

InactiveUS8039837B2TransistorSemiconductor/solid-state device testing/measurementBody contactEngineering

Owner:INT BUSINESS MASCH CORP

Test structure for charged particle beam inspection and method for defect determination using the same

ActiveUS8421009B2Material analysis using wave/particle radiationContactless circuit testingVoltage contrastSemiconductor

A test structure and method thereof for determining a defect in a sample of semiconductor device includes at least one transistor rendered grounded. The grounded transistor is preferably located at at least one end of a test pattern designed to be included in the sample. When the test structure is inspected by charged particle beam inspection, the voltage contrast (VC) of the transistors in the test pattern including the grounded transistor is observed for determination of the presence of defect in the sample.

Owner:ASML NETHERLANDS BV

In-line voltage contrast determination of tunnel oxide weakness in integrated circuit technology development

InactiveUS7101722B1Semiconductor/solid-state device testing/measurementRead-only memoriesTechnology developmentCell region

A method for determination of tunnel oxide weakness is provided. A tunnel oxide layer is formed on a semiconductor wafer. At least one poly gate is formed on the tunnel oxide layer in a flash memory region of the semiconductor wafer. At least one poly island, which is substantially larger than the poly gate, is formed on the tunnel oxide layer in a voltage contrast cell region of the semiconductor wafer. The poly island and the tunnel oxide layer therebeneath form a voltage contrast tunnel oxide cell. A voltage contrast measurement is performed on the voltage contrast tunnel oxide cell. The voltage contrast measurement is then compared with prior such voltage contrast measurements on other such voltage contrast tunnel oxide cells. The tunnel oxide weakness of the tunnel oxide layer is then determined from the voltage contrast measurement comparisons.

Owner:ADVANCED MICRO DEVICES INC

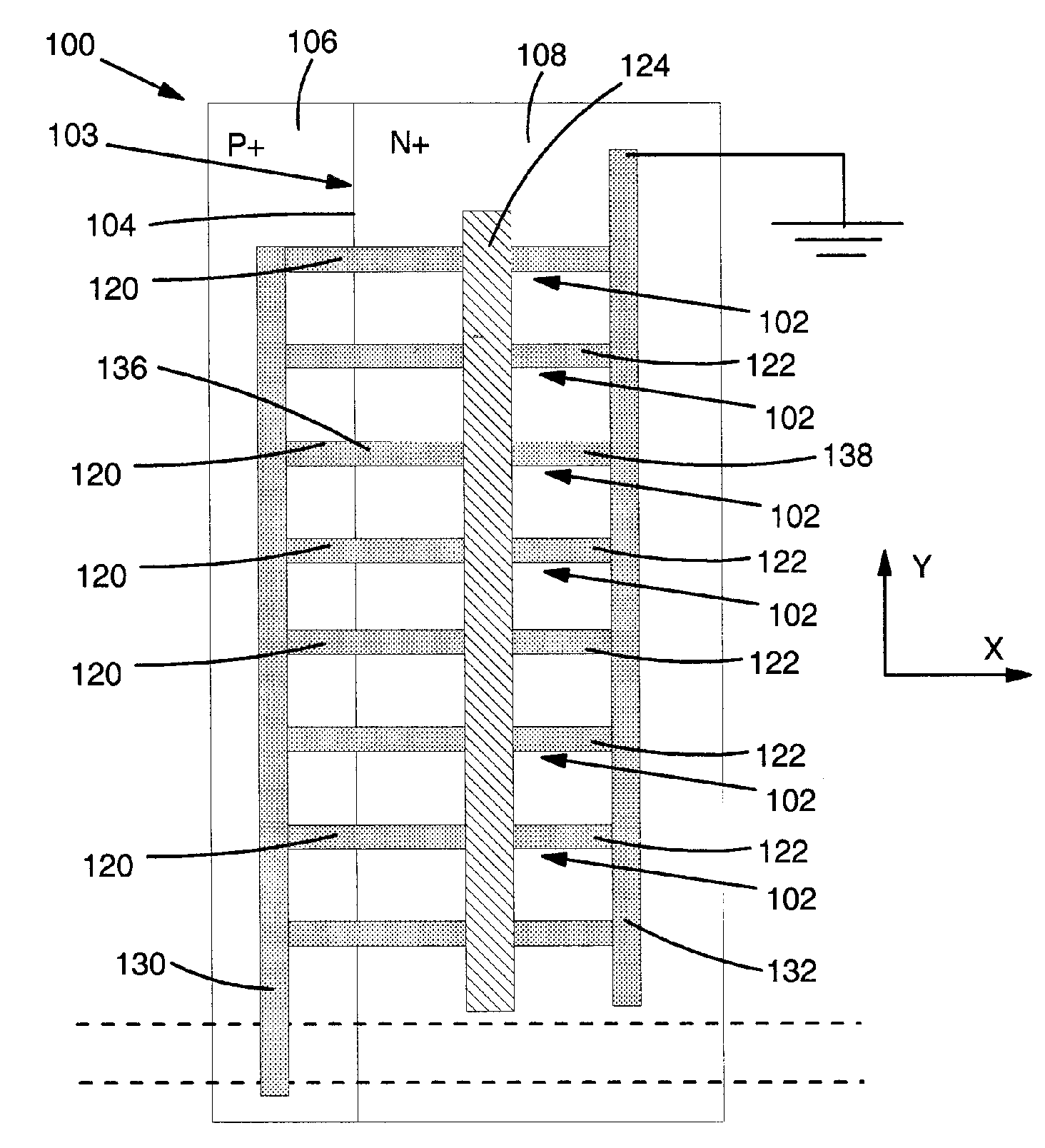

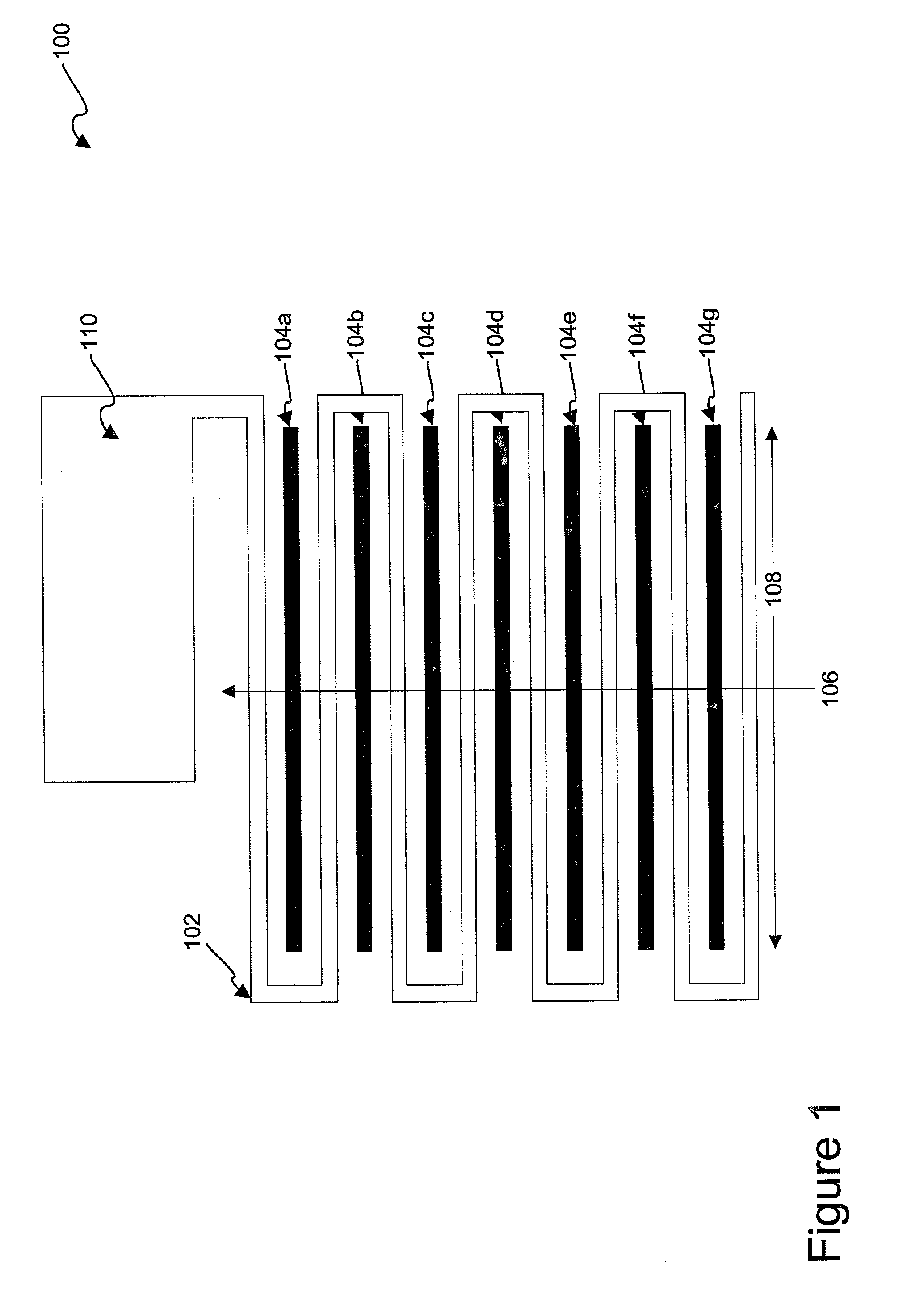

Methods for identifying an allowable process margin for integrated circuits

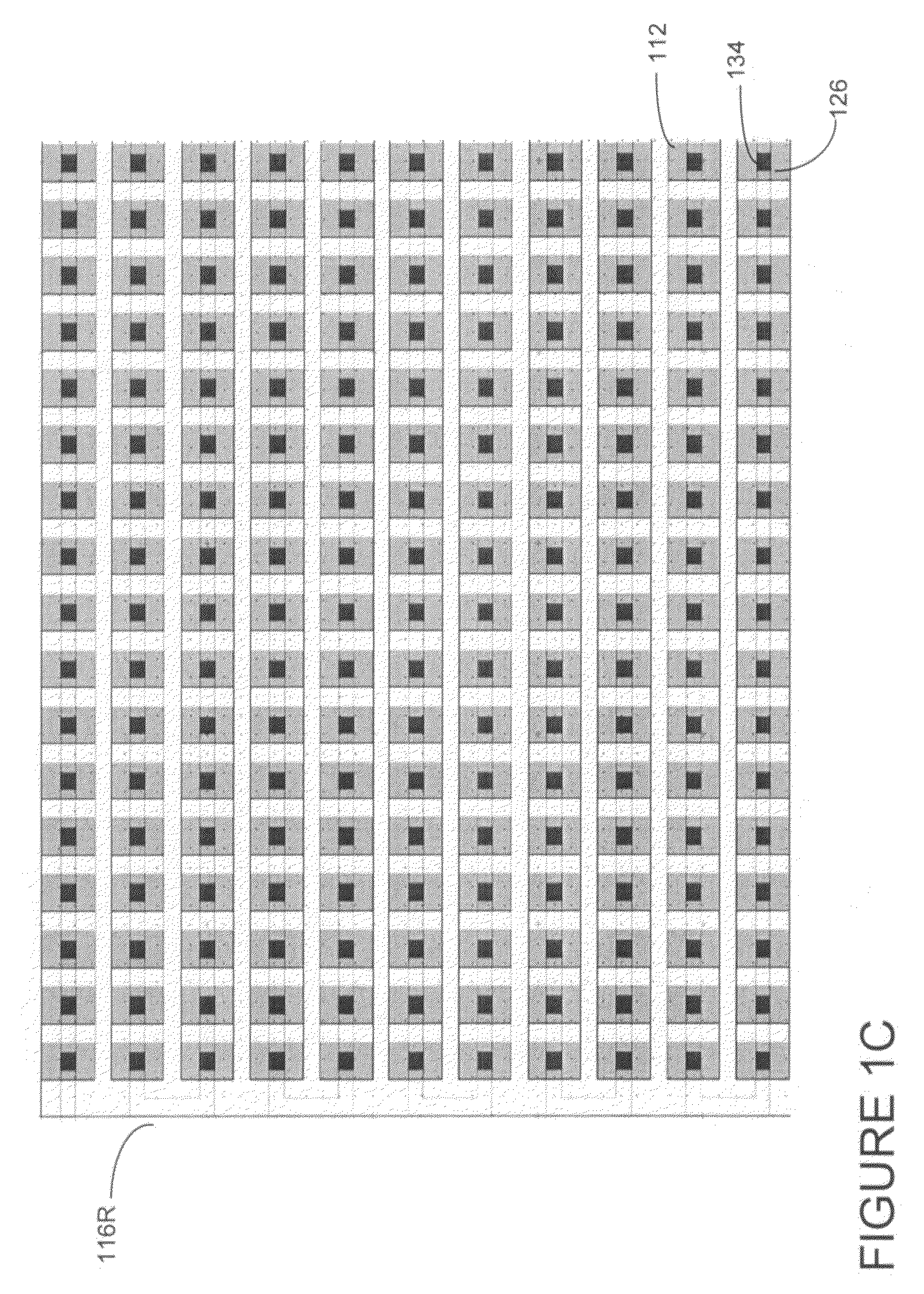

ActiveUS7642106B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsManufacturing technologyDevice material

A test structure for inspecting an allowable process margin in a manufacturing process for a semiconductor device is provided. The test structure includes a plurality of grounded conductive lines on a substrate and electrically grounded to the substrate. A plurality of floating conductive lines are provided, each of the plurality of conductive lines being spaced apart from the grounded conductive lines and electrically separated from the grounded conductive lines on the substrate. A plurality of supplementary patterns are provided for measuring the allowable process margin by a voltage contrast between the grounded conductive lines and the floating conductive lines. Related methods of testing are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

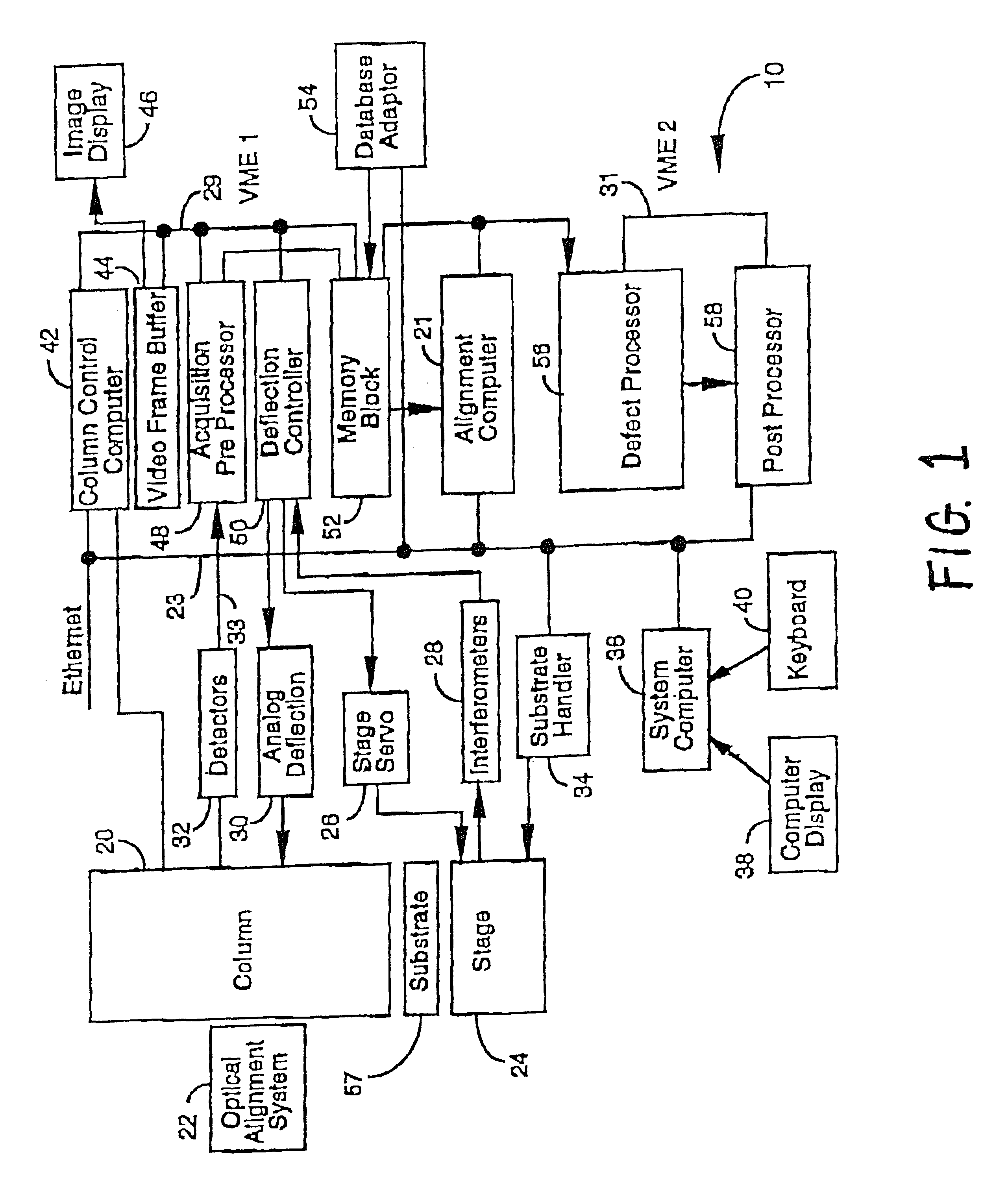

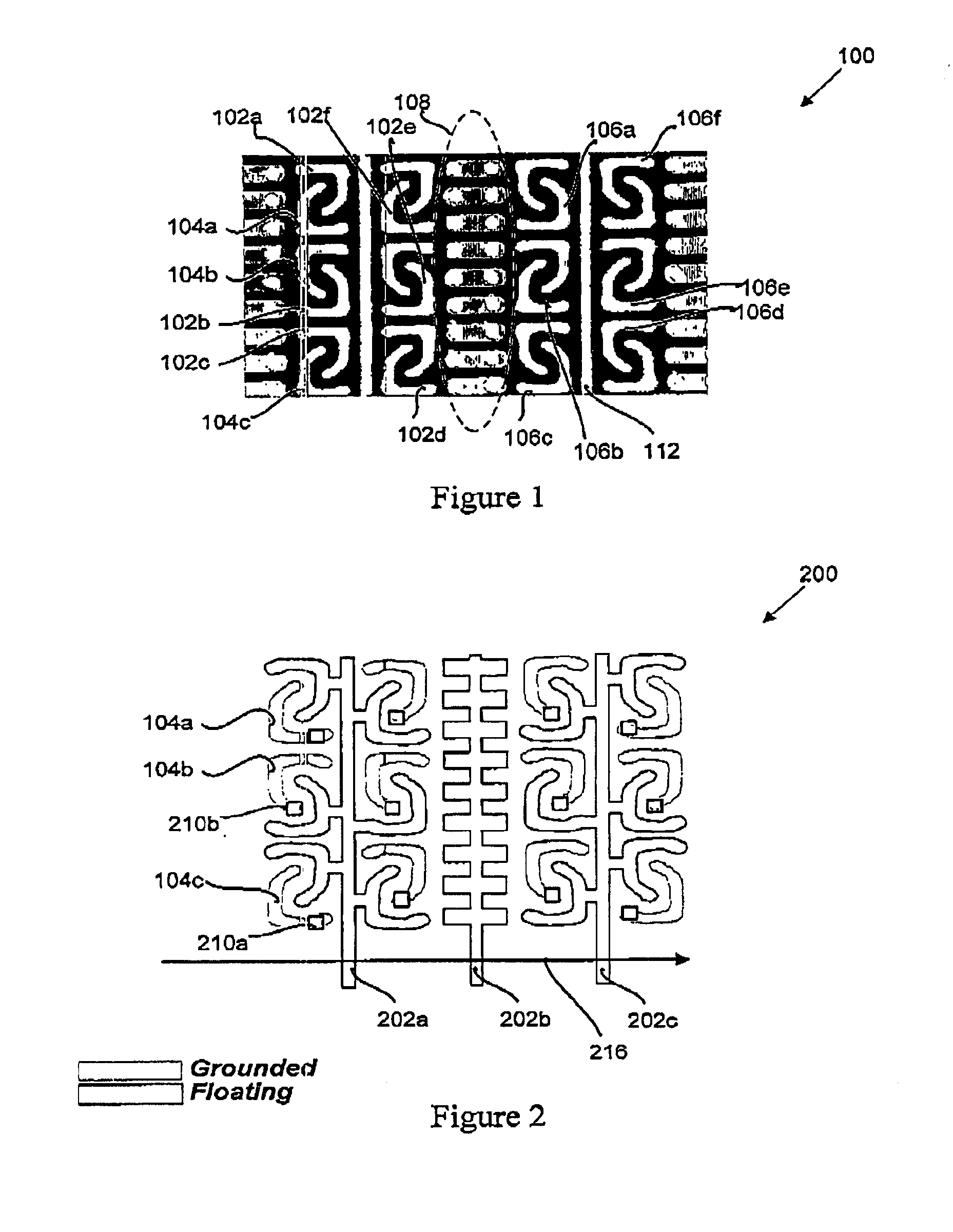

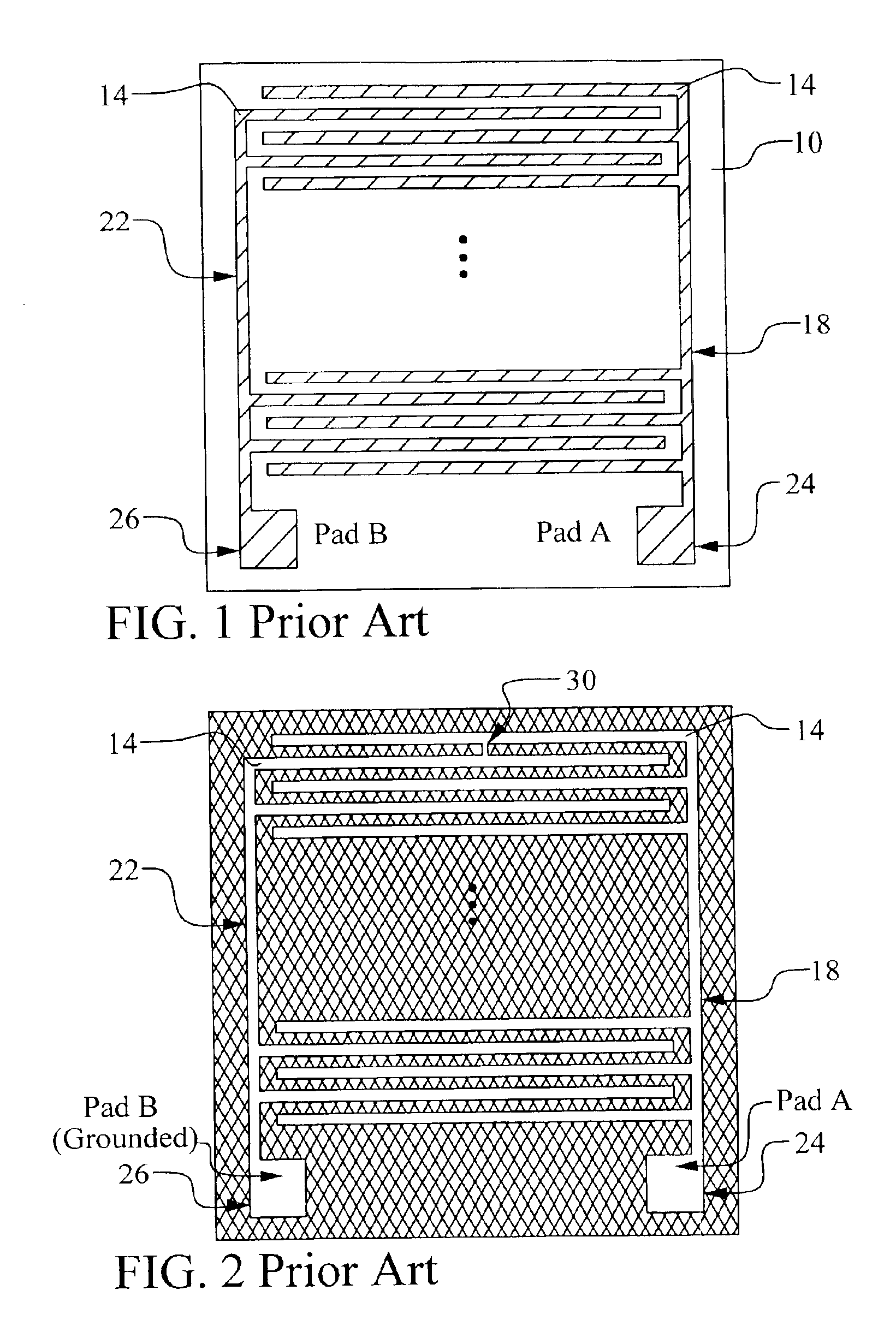

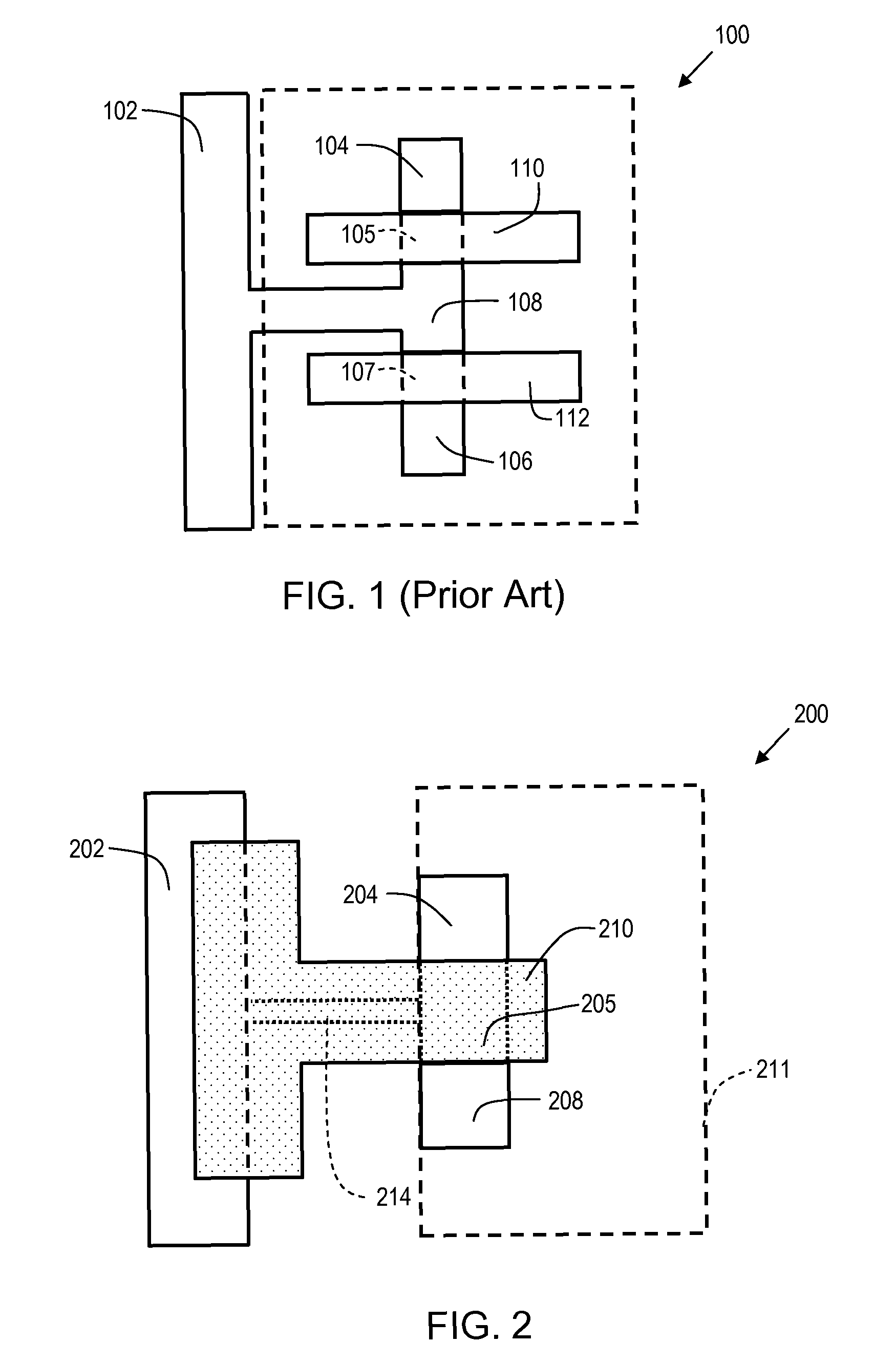

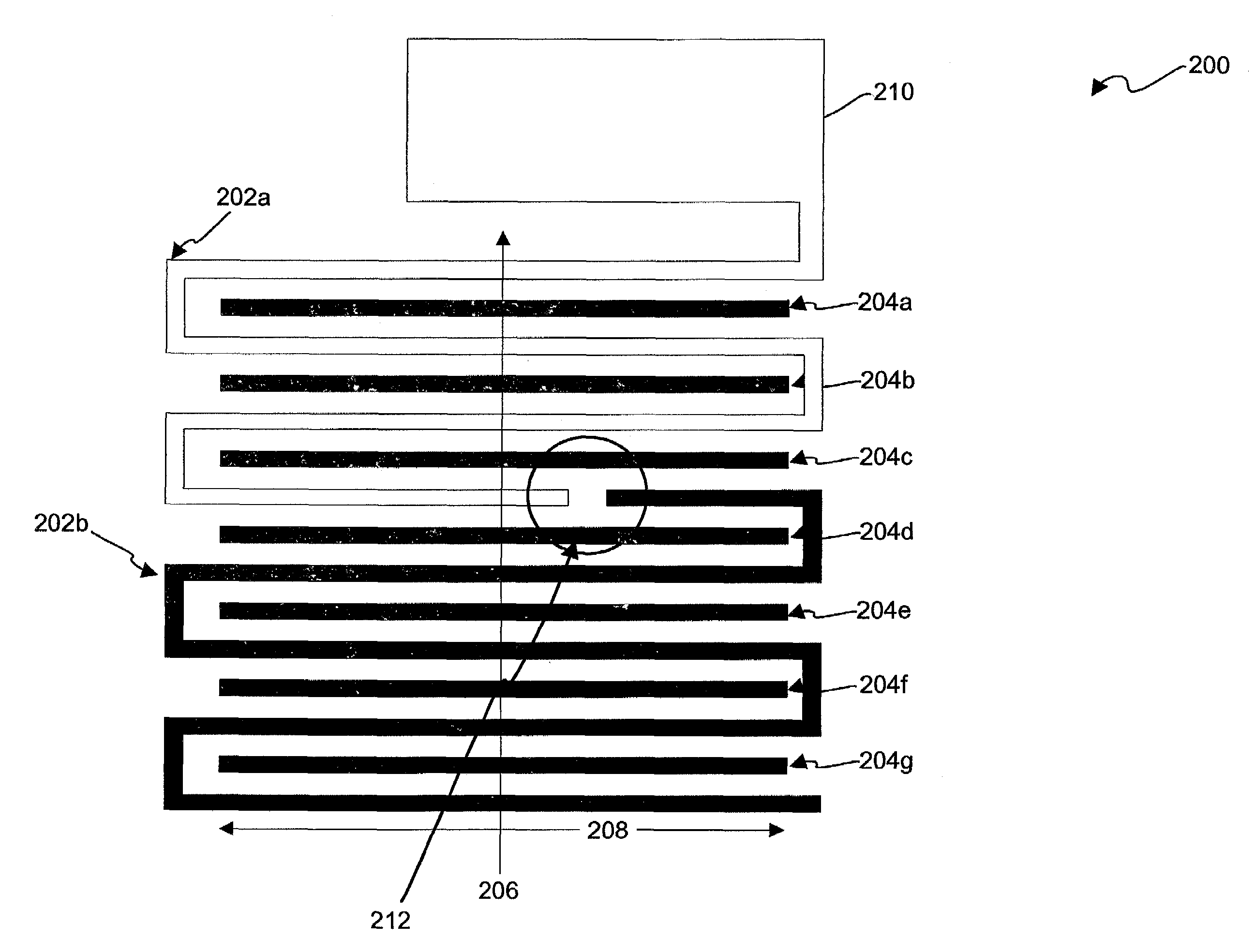

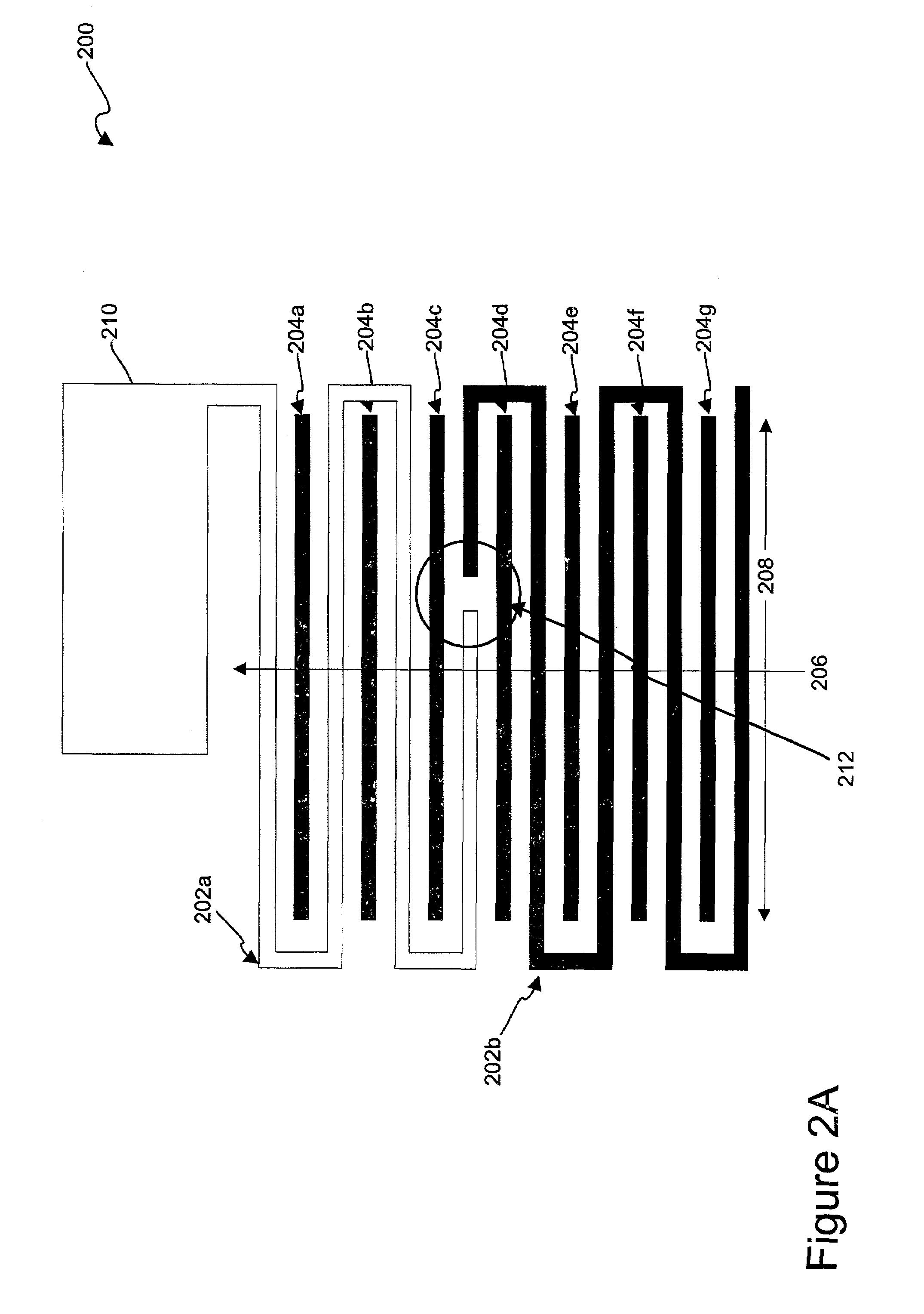

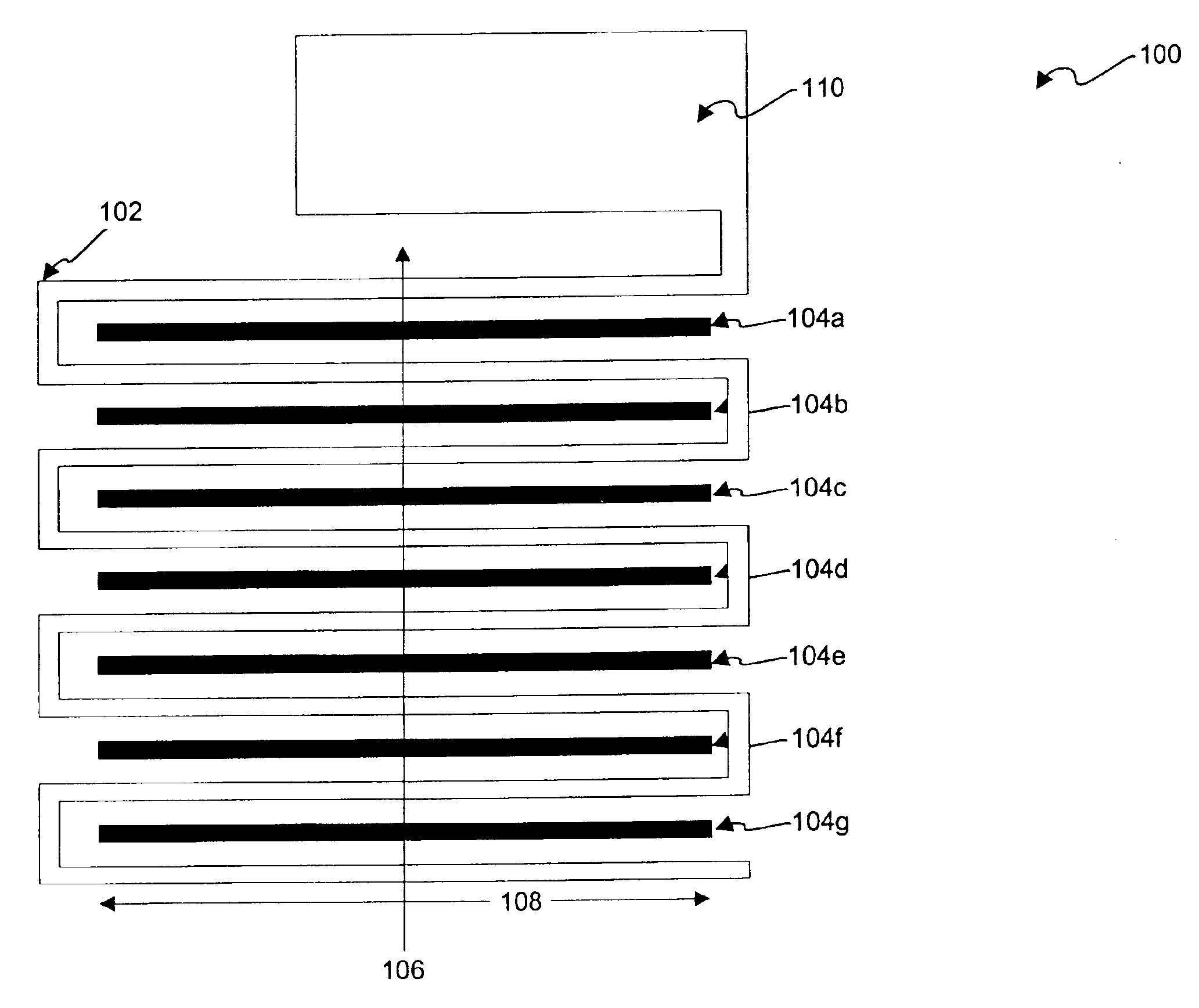

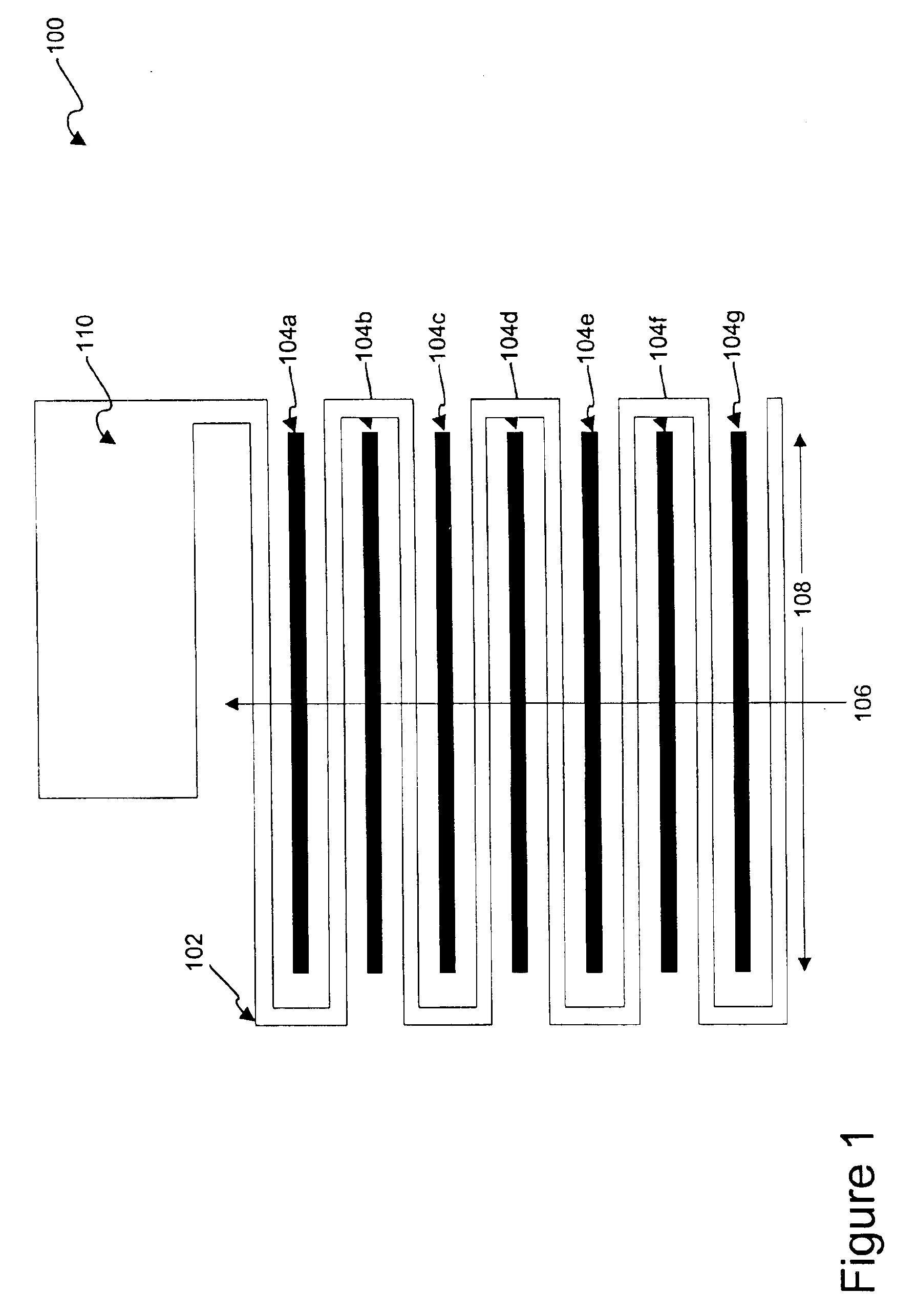

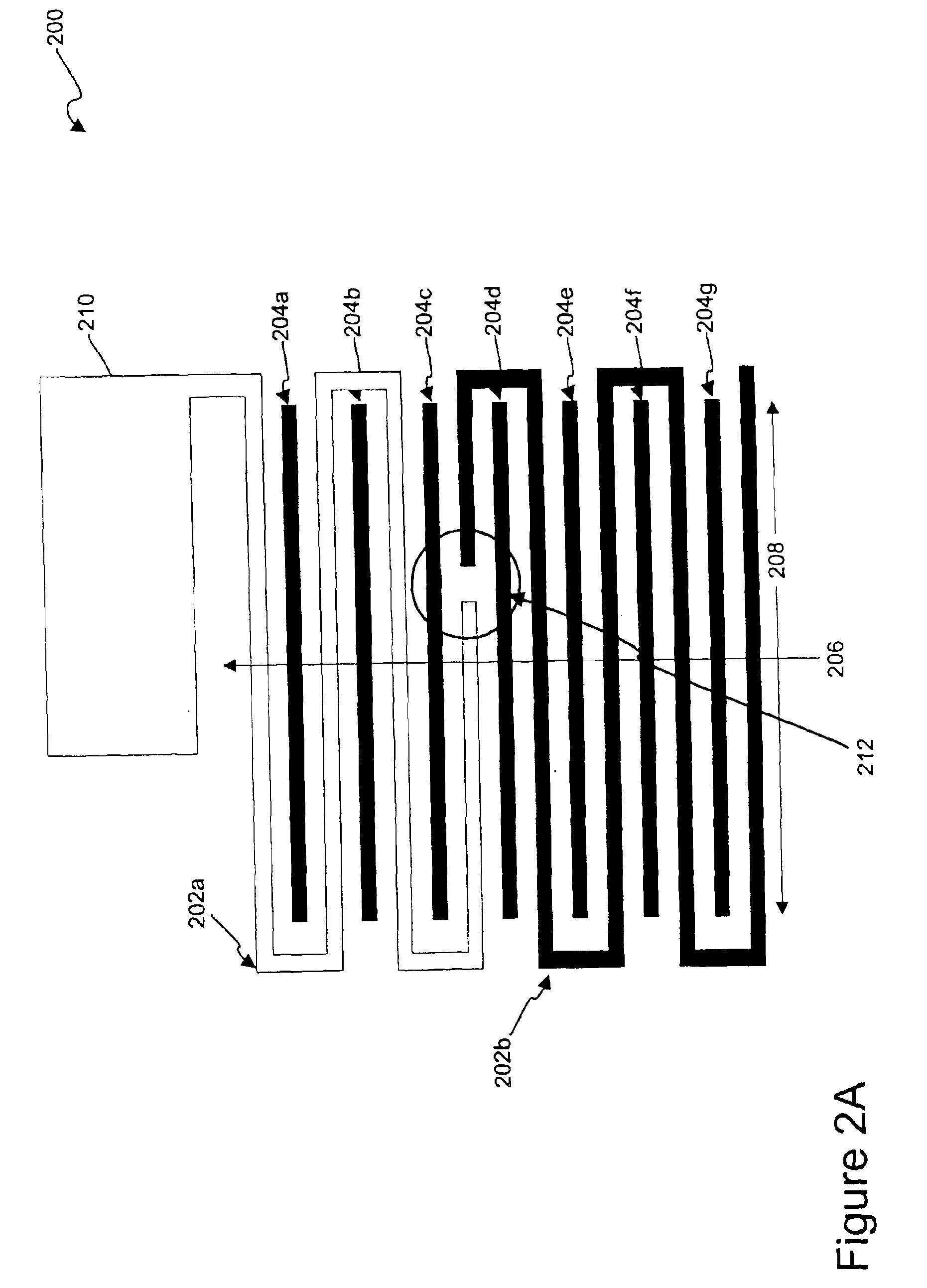

Apparatus and methods for semiconductor IC failure detection

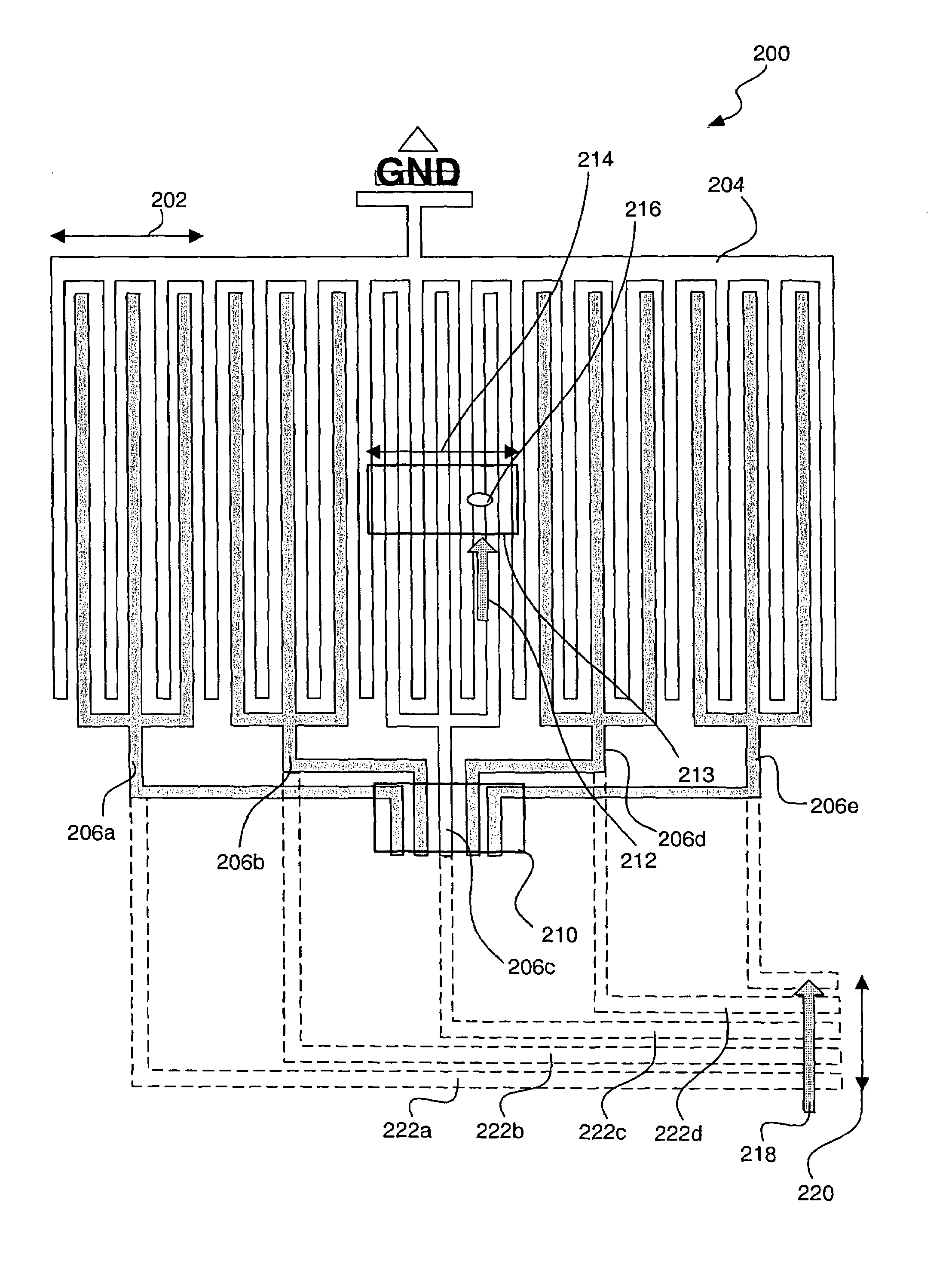

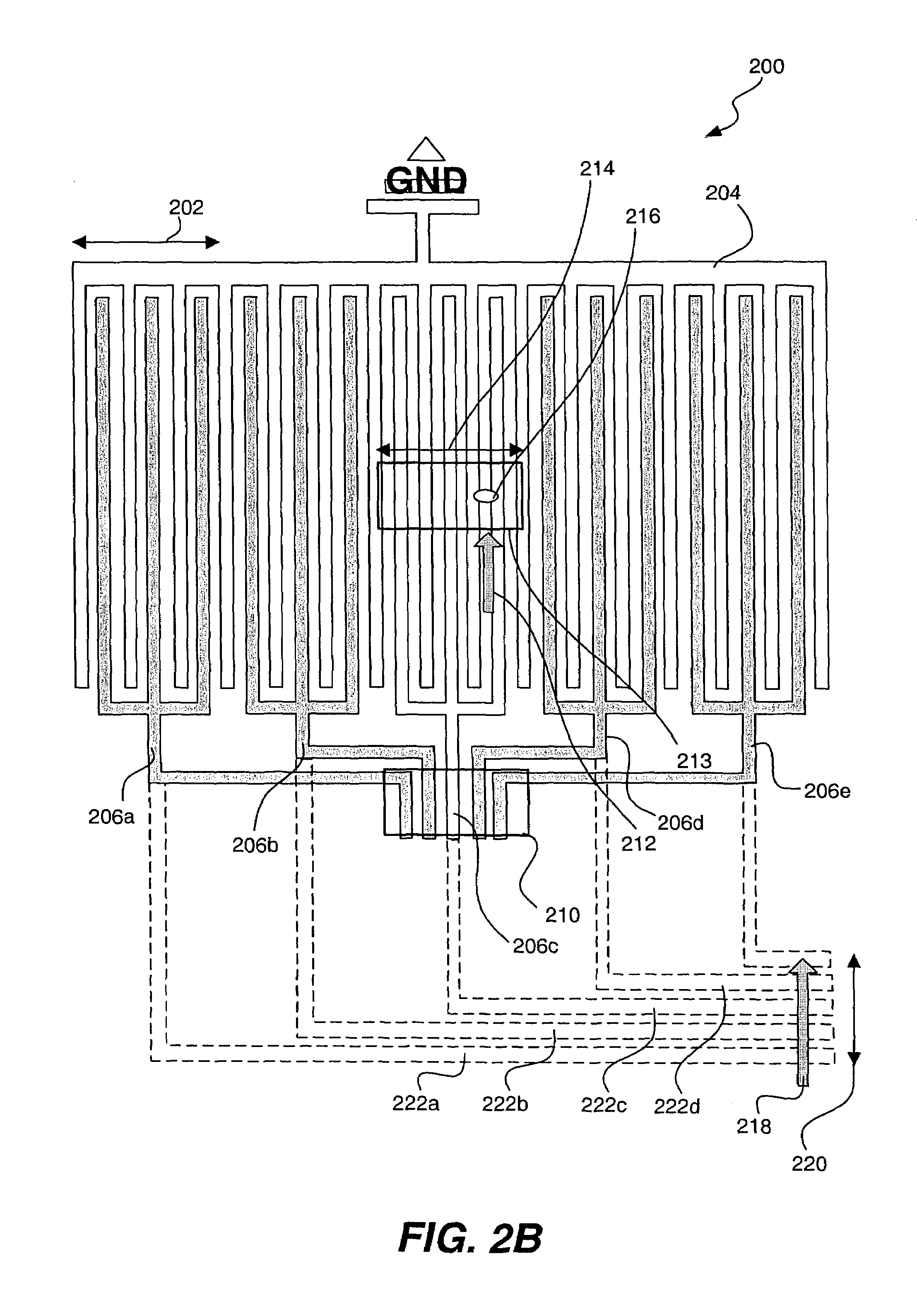

InactiveUS7067335B2Semiconductor/solid-state device testing/measurementElectric discharge tubesEngineeringVoltage contrast

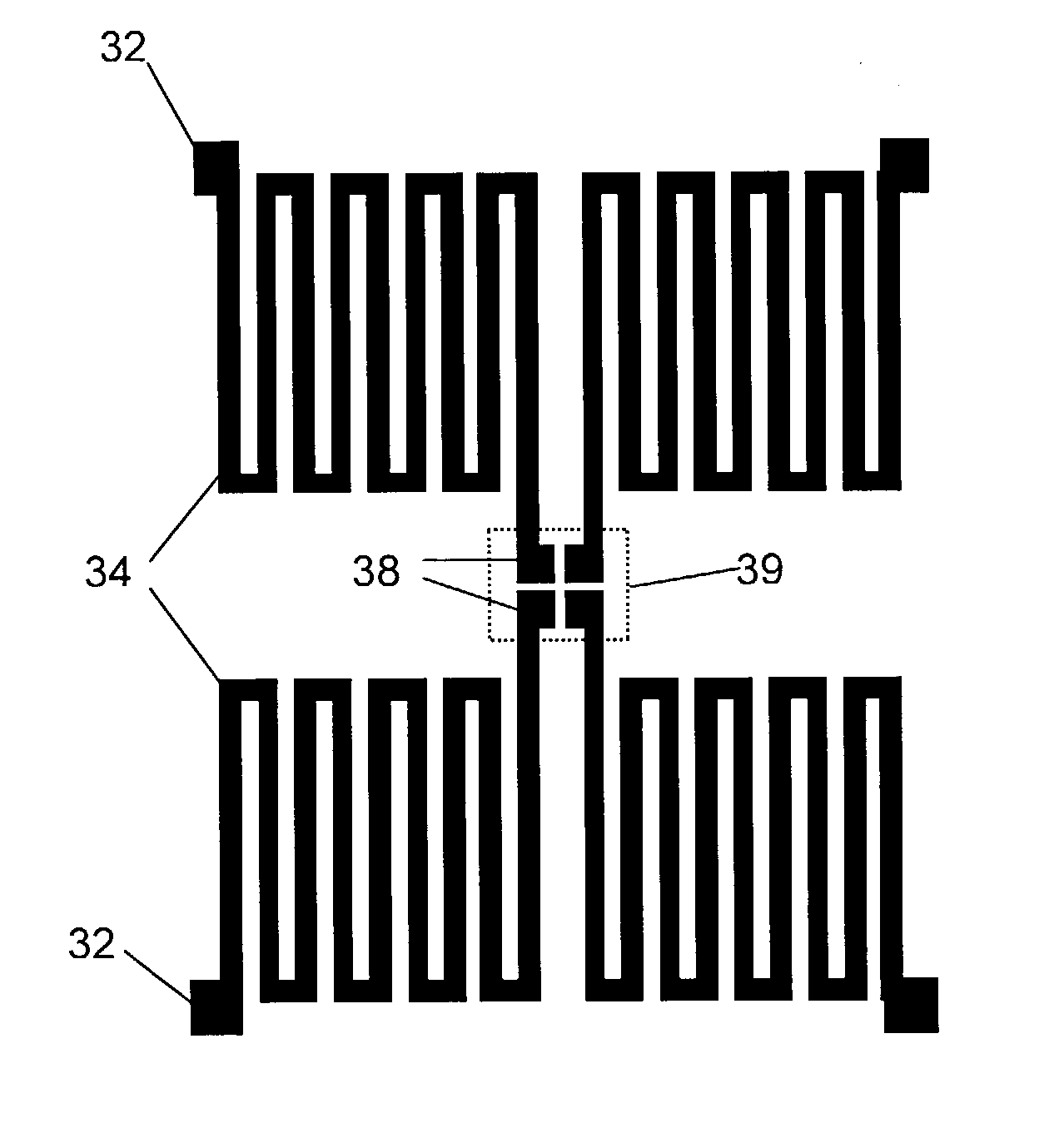

An improved voltage contrast test structure is disclosed. In general terms, the test structure can be fabricated in a single photolithography step or with a single reticle or mask. The test structure includes substructures which are designed to have a particular voltage potential pattern during a voltage contrast inspection. For example, when an electron beam is scanned across the test structure, an expected pattern of intensities are produced and imaged as a result of the expected voltage potentials of the test structure. However, when there is an unexpected pattern of voltage potentials present during the voltage contrast inspection, this indicates that a defect is present within the test structure. To produce different voltage potentials, a first set of substructures are coupled to a relatively large conductive structure, such as a large conductive pad, so that the first set of substructures charges more slowly than a second set of substructures that are not coupled to the relatively large conductive structure. Mechanisms for fabricating such a test structure are also disclosed. Additionally, searching mechanisms for quickly locating defects within such a test structure, as well as other types of voltage contrast structures, during a voltage contrast inspection are also provided.

Owner:KLA TENCOR TECH CORP

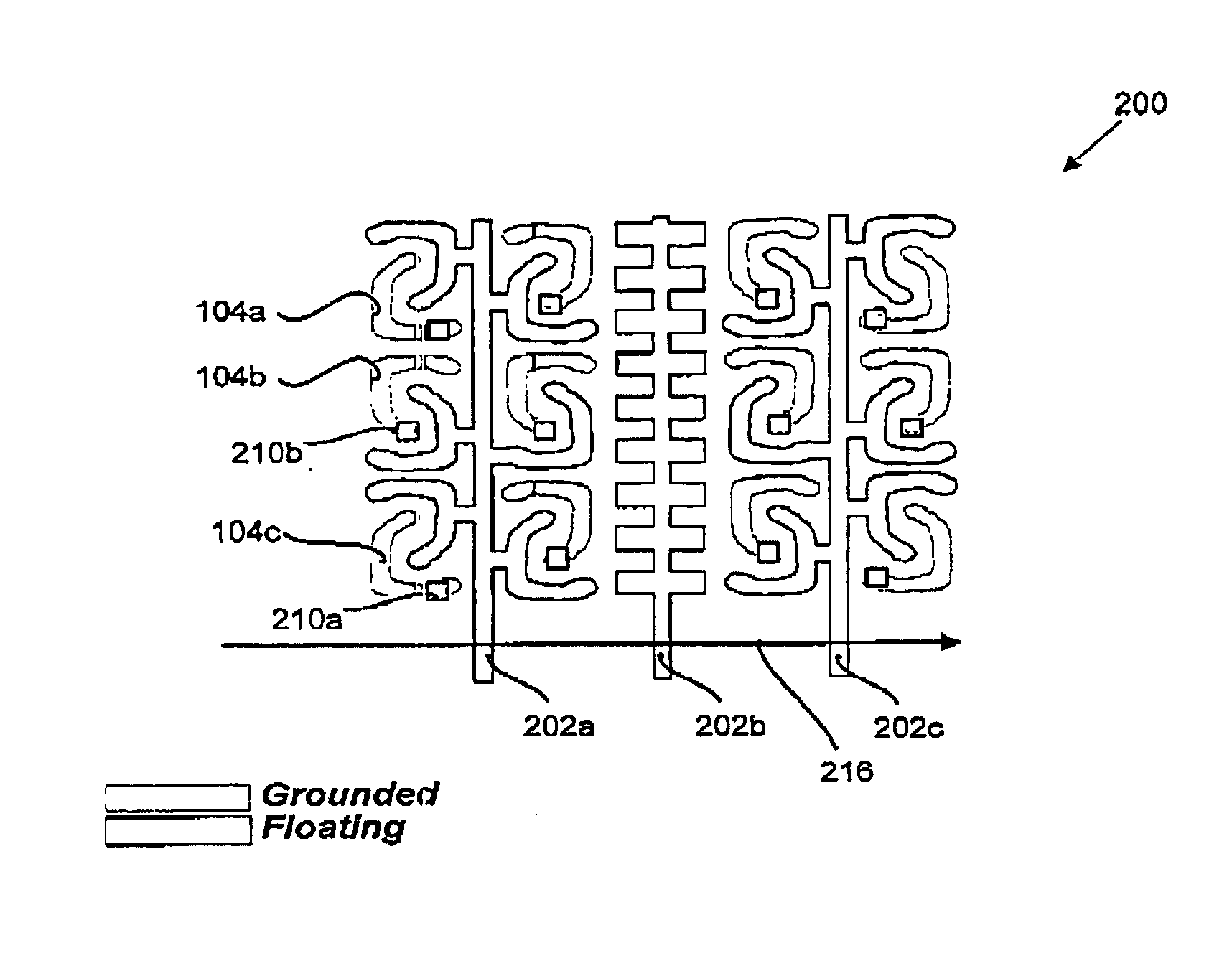

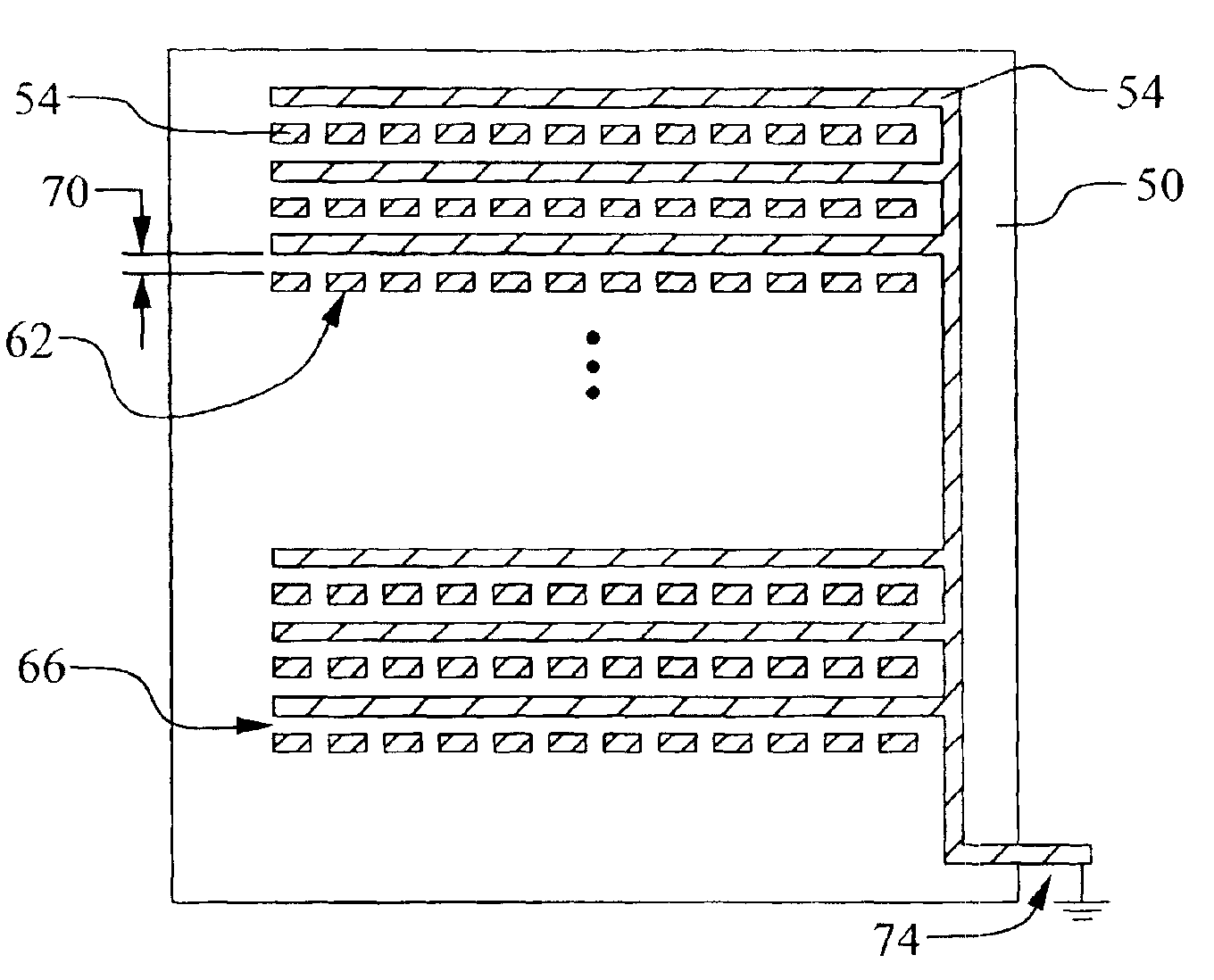

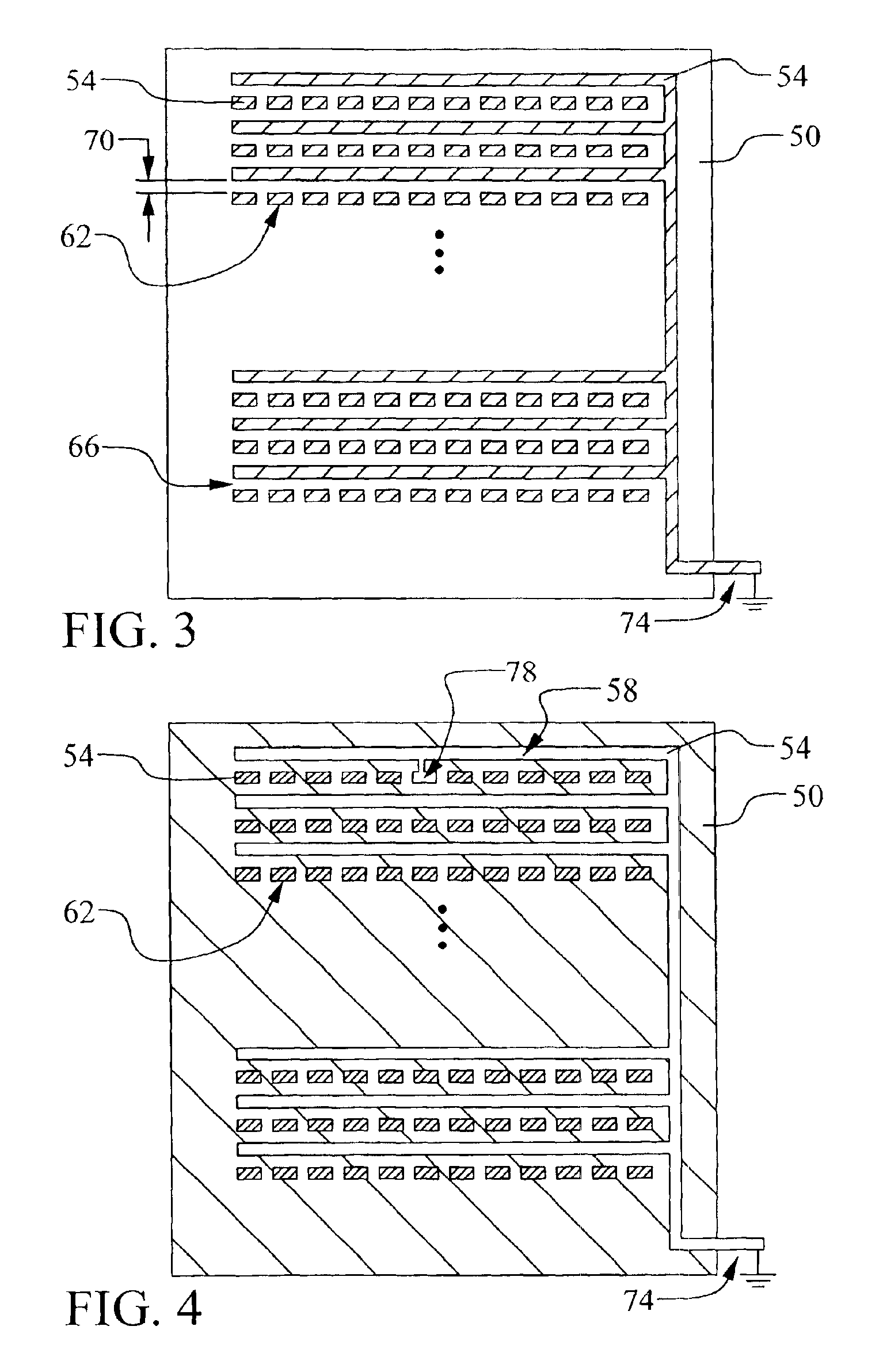

Apparatus and methods for semiconductor IC failure detection

InactiveUS6995393B2Semiconductor/solid-state device testing/measurementElectric discharge tubesVoltage contrastUltimate tensile strength

An improved voltage contrast test structure is disclosed. In general terms, the test structure can be fabricated in a single photolithography step or with a single reticle or mask. The test structure includes substructures which are designed to have a particular voltage potential pattern during a voltage contrast inspection. For example, when an electron beam is scanned across the test structure, an expected pattern of intensities are produced and imaged as a result of the expected voltage potentials of the test structure. However, when there is an unexpected pattern of voltage potentials present during the voltage contrast inspection, this indicates that a defect is present within the test structure. To produce different voltage potentials, a first set of substructures are coupled to a relatively large conductive structure, such as a large conductive pad, so that the first set of substructures charges more slowly than a second set of substructures that are not coupled to the relatively large conductive structure. Mechanisms for fabricating such a test structure are also disclosed. Additionally, searching mechanisms for quickly locating defects within such a test structure, as well as other types of voltage contrast structures, during a voltage contrast inspection are also provided.

Owner:KLA TENCOR TECH CORP

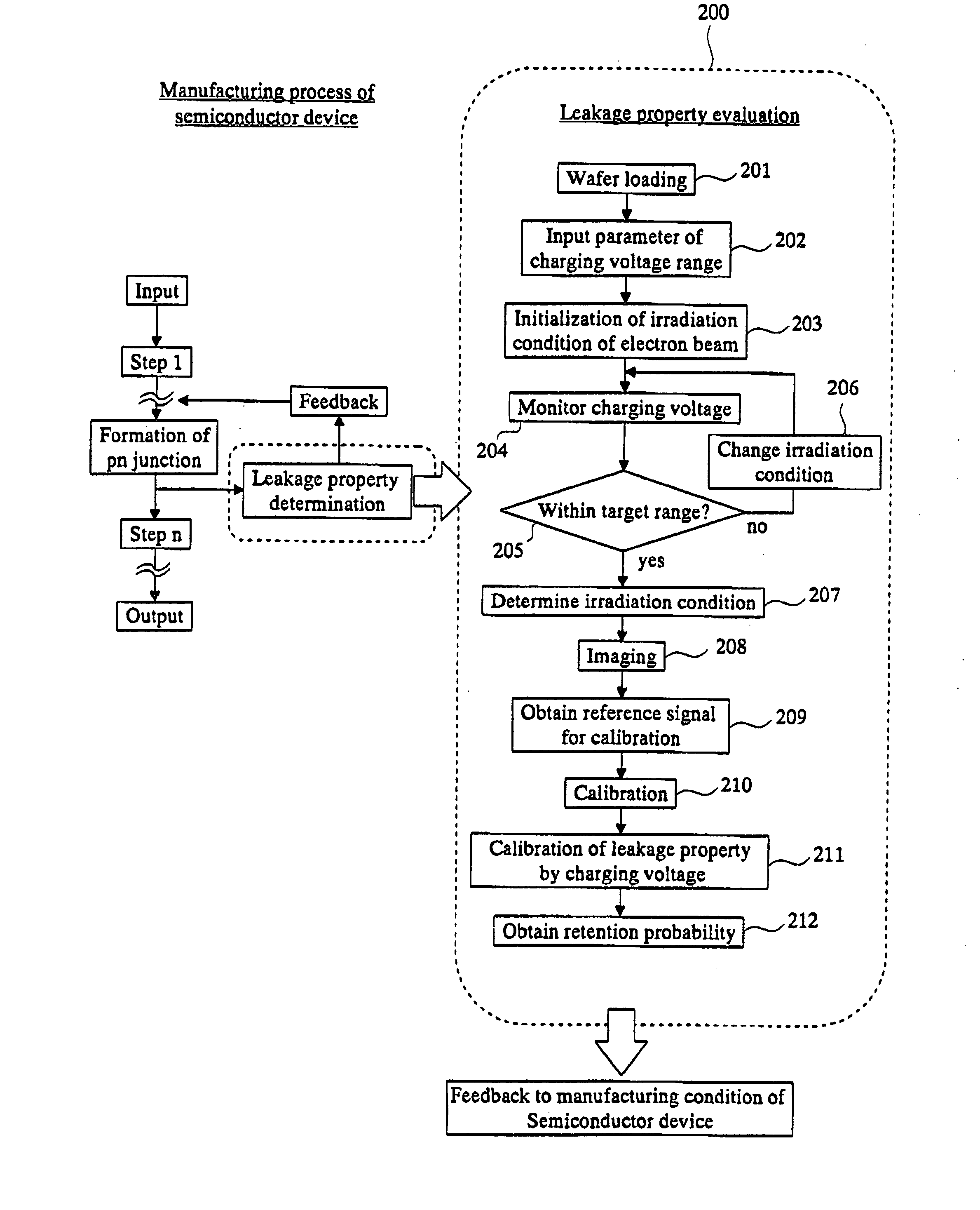

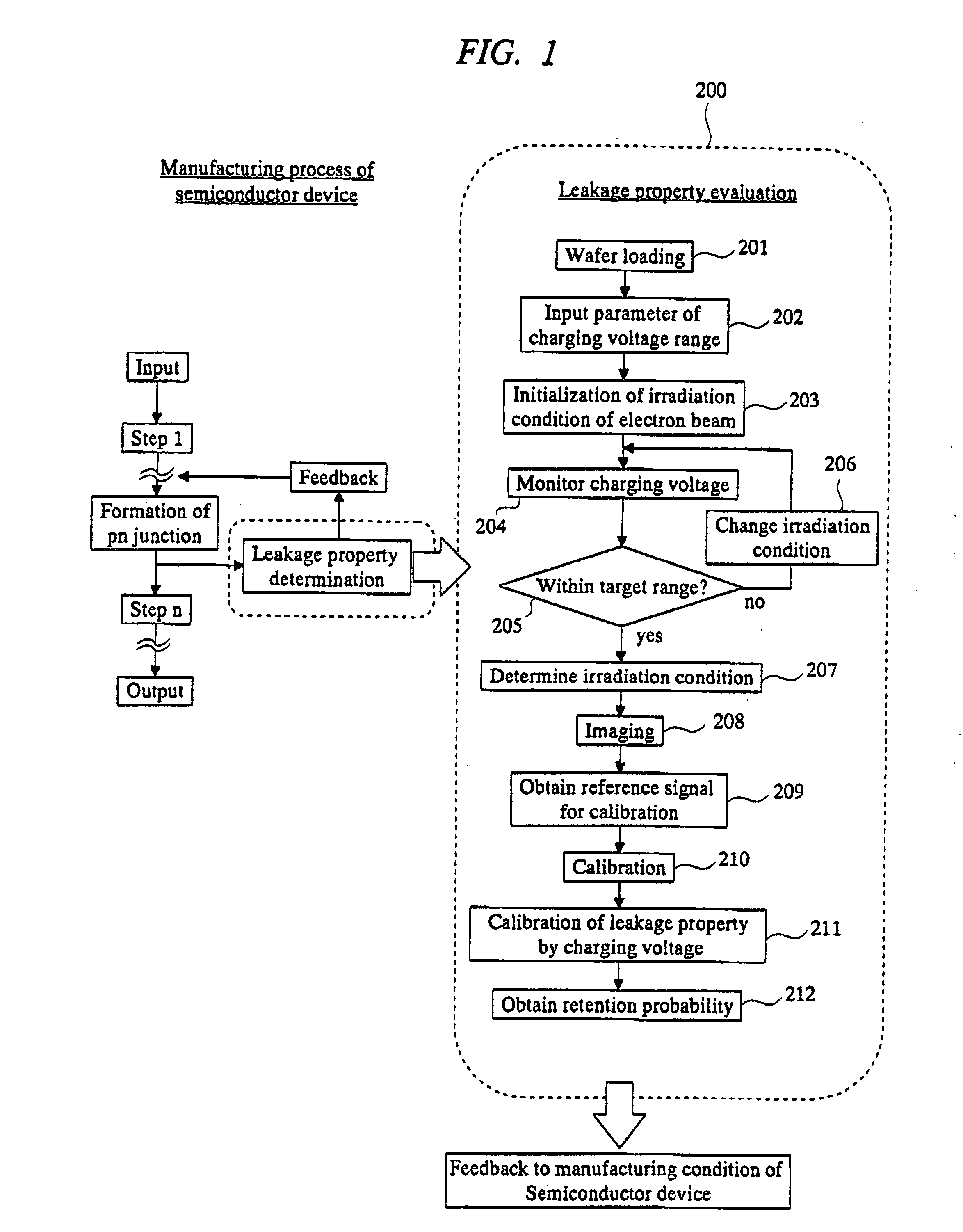

Evaluation method and manufacturing method of semiconductor device

InactiveUS20060022295A1Accurate measurementQuick measurementSemiconductor/solid-state device testing/measurementElectric discharge tubesDevice materialSecondary electrons

The electron beam is irradiated several times at predetermined intervals to the wafer surface on which the plugs are exposed in the course of the manufacturing process so that the pn junction is in the reverse bias state. Then, the irradiation conditions of the electron beam are changed while monitoring the charging voltage on the plug surface, and the secondary electron signals of the circuit pattern are obtained under the irradiation conditions that the charging is within a desired range, thereby evaluating the leakage property. Since the charging voltage of the pn junction is relaxed depending on the magnitude of the leakage current during the interval, the leakage property is evaluated based on the luminance signals of the voltage contrast image. By measuring the charging voltage and setting it within a desired range, the evaluation result reflects the state in the actual operation. Therefore, the accuracy is enhanced.

Owner:HITACHI LTD +1

Method to detect and predict metal silicide defects in a microelectronic device during the manufacture of an integrated circuit

ActiveUS7443189B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingSalicideMetal silicide

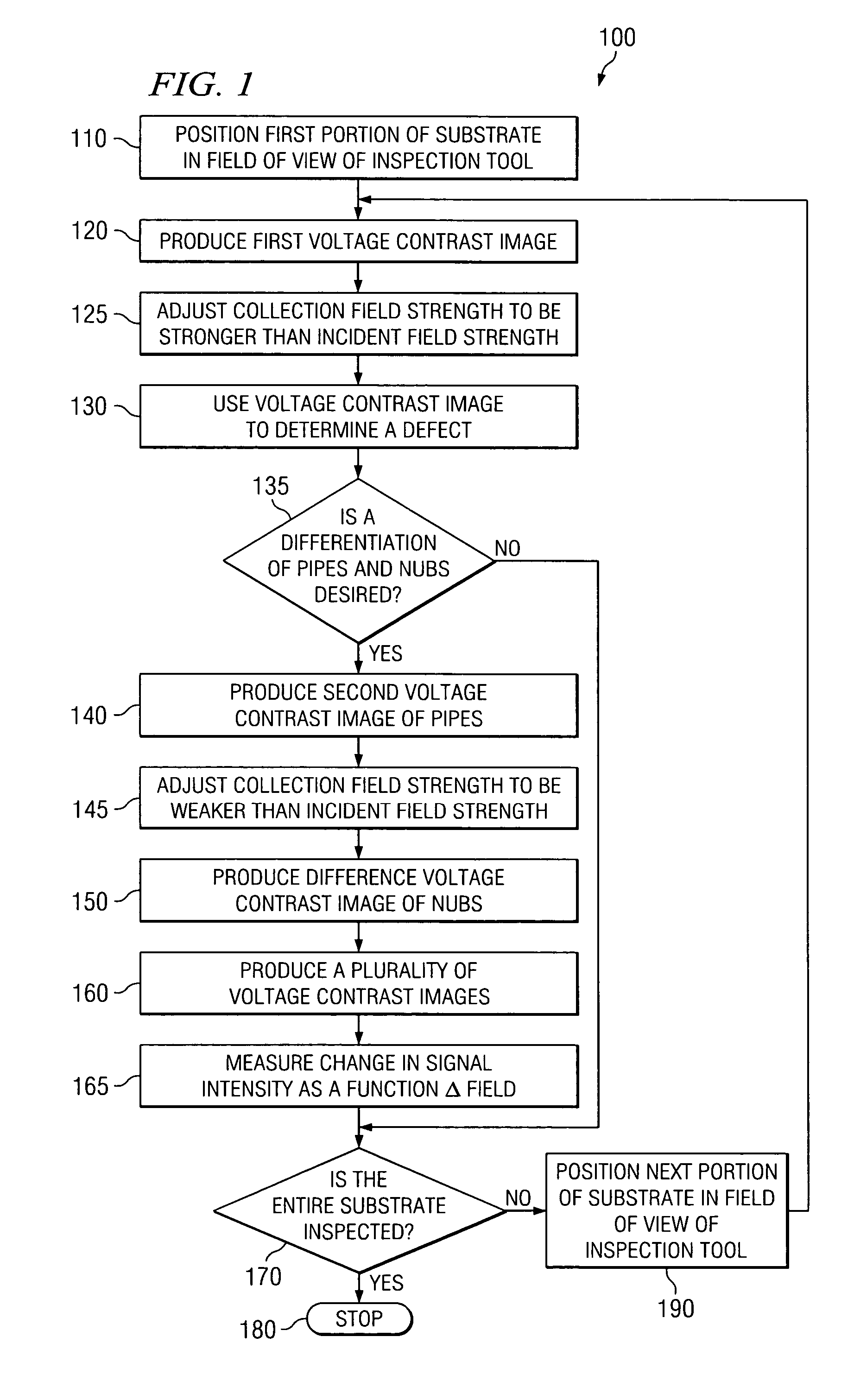

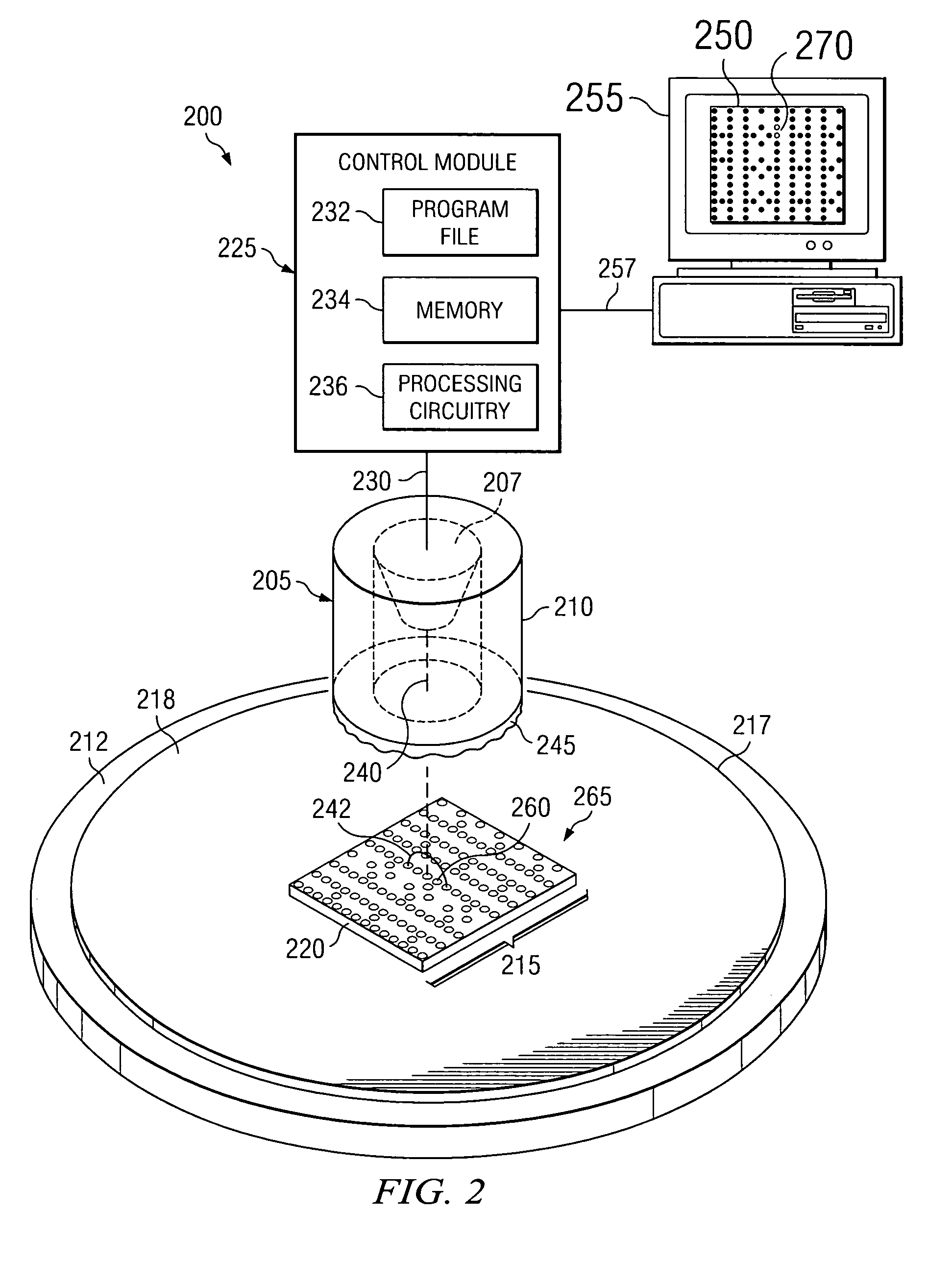

The present teachings provide methods for detection of metal silicide defects in a microelectronic device. In an exemplary embodiment, a portion of a semiconductor substrate may be positioned in a field of view of an inspection tool. The method also includes producing (120) a voltage contrast image of the portion, wherein the image is obtained using a collection field that is stronger than an incident field. The method also includes using (130) the voltage contrast image to determine a metal silicide defect in a microelectronic device. Other embodiments include an inspection system (200) for detecting metal silicide defects and a method of manufacturing an integrated circuit (300).

Owner:TEXAS INSTR INC