Test structures and method of defect detection using voltage contrast inspection

a voltage contrast inspection and test structure technology, applied in the field of semiconductor fabrication, can solve the problems of nfet and pfet structures not being similar devices of n-type field effect transistors (nfets) not working, and nfet and pfet structures cannot be inspected in the same scan, so as to achieve short learning cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

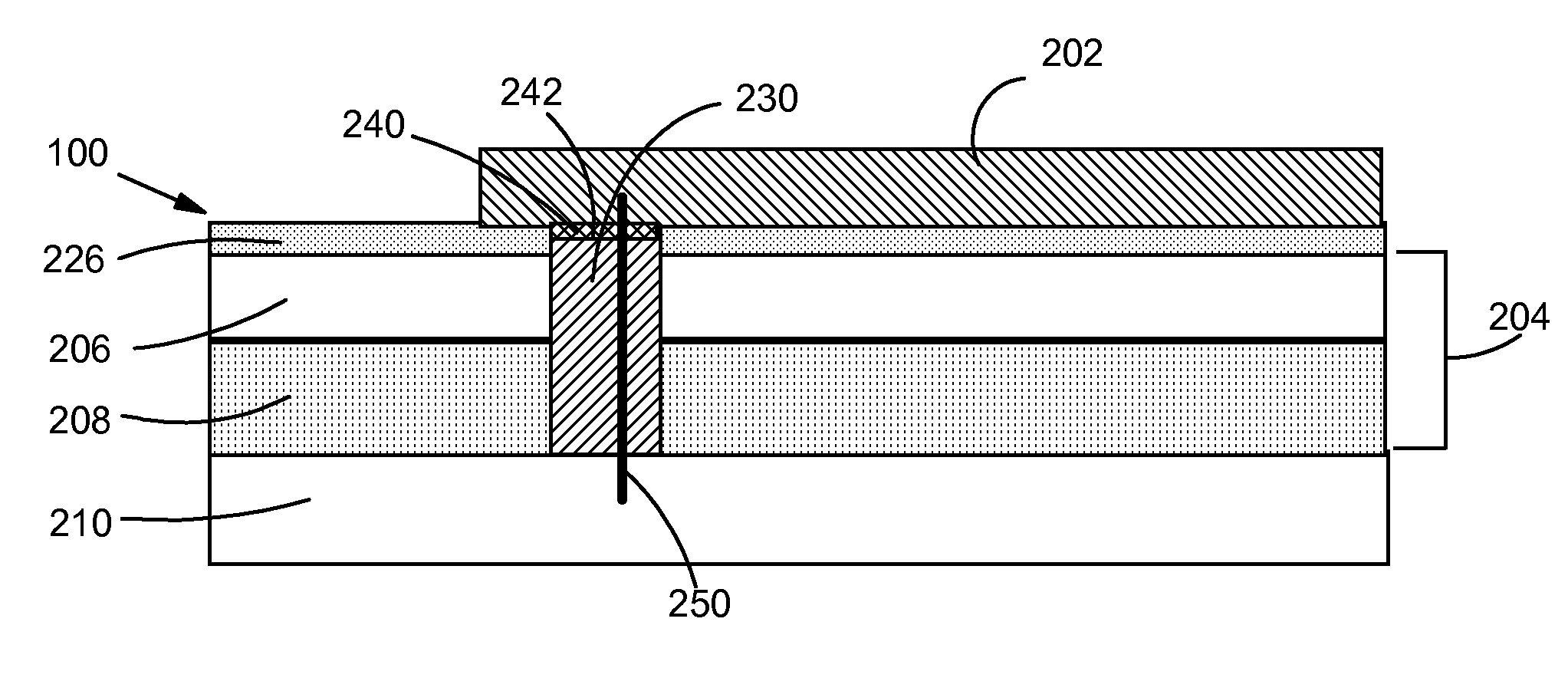

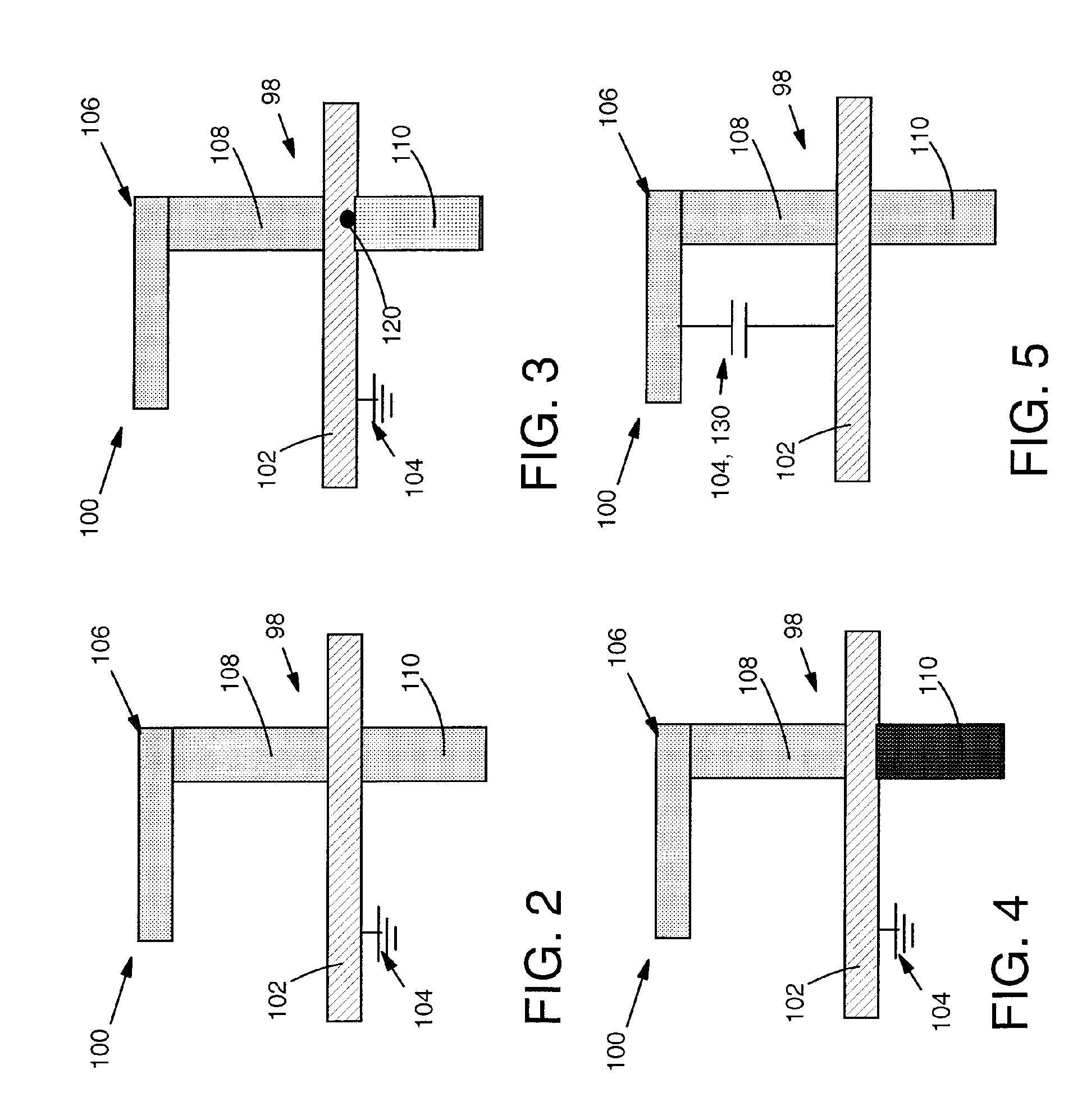

[0026]Turning to FIG. 2, as indicated above, embodiments of the invention provide test structures and a method for voltage contrast (VC) inspection of a transistor 98 (FIG. 2). In one embodiment, a test structure 100 includes: a gate stack 102, e.g., of polysilicon, that is grounded by a ground 104 to maintain a channel (not shown) under gate stack 102 in an off state during VC inspection. Test structure 100 may further include an active region 106 including a source region 108 and a drain region 110. Where ground 104 is part of an n-type field effect transistor (NFET) 98, it prevents a channel (not visible, where gate stack 102 and active region 106 intersect) of the NFET from conducting during VC inspection using electron extraction conditions if no defect exists in a gate dielectric and the channel of the NFET. In contrast, where gate stack 102 is part of a p-type field effect transistor (PFET) 98, it prevents a channel (not visible, where gate stack 102 and active region 106 int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More