Patents

Literature

919results about "Fault location by increasing destruction at fault" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

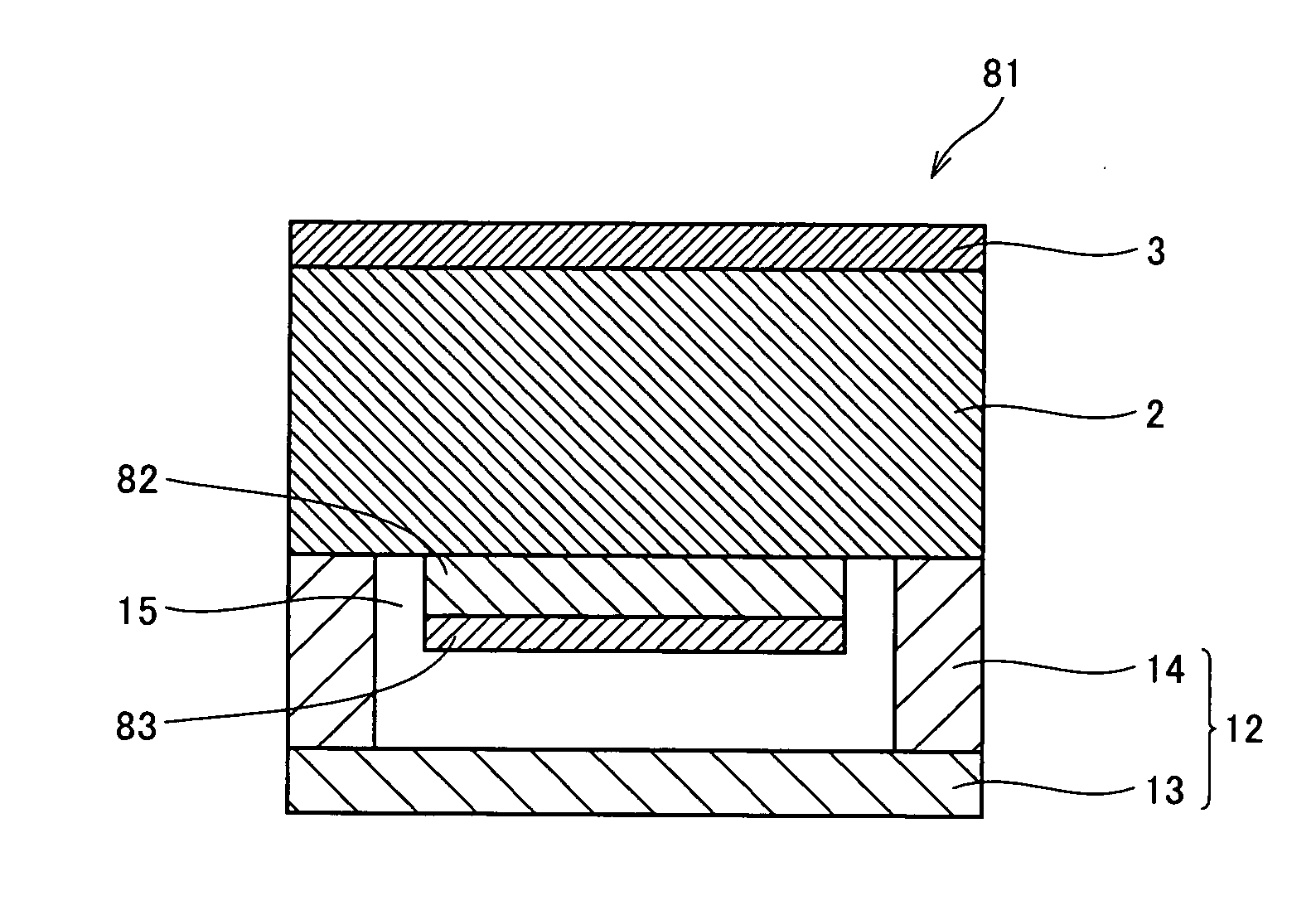

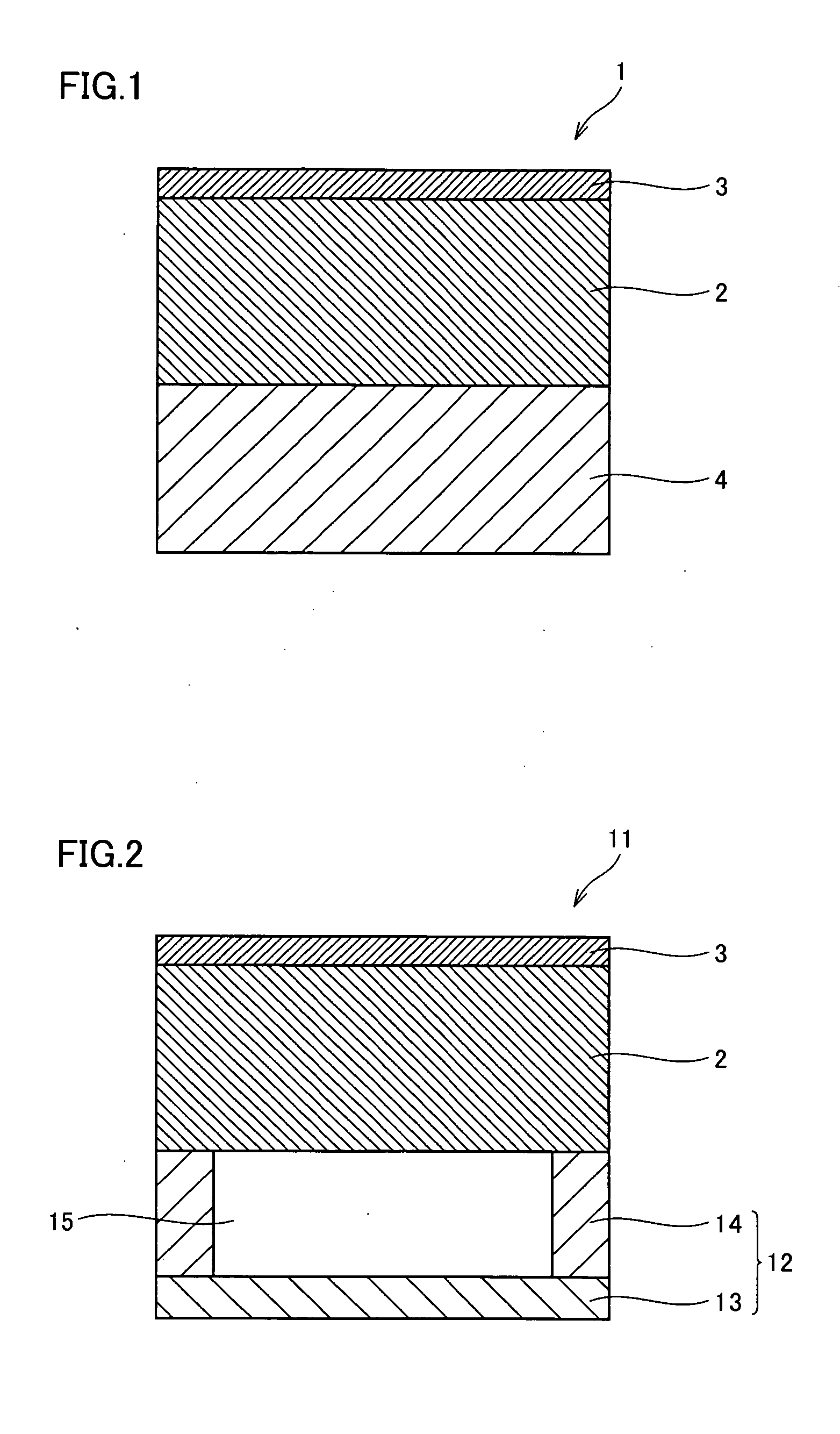

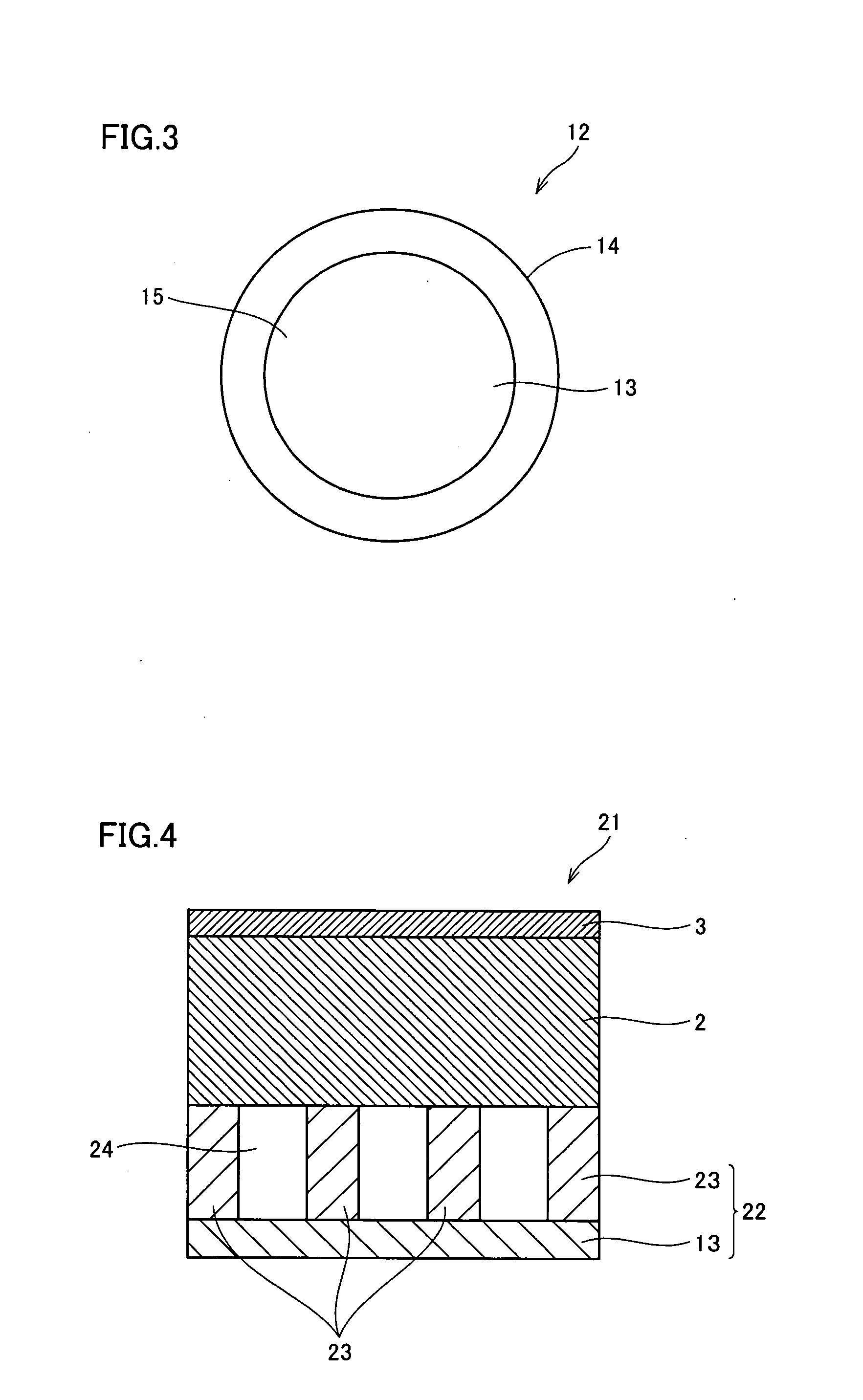

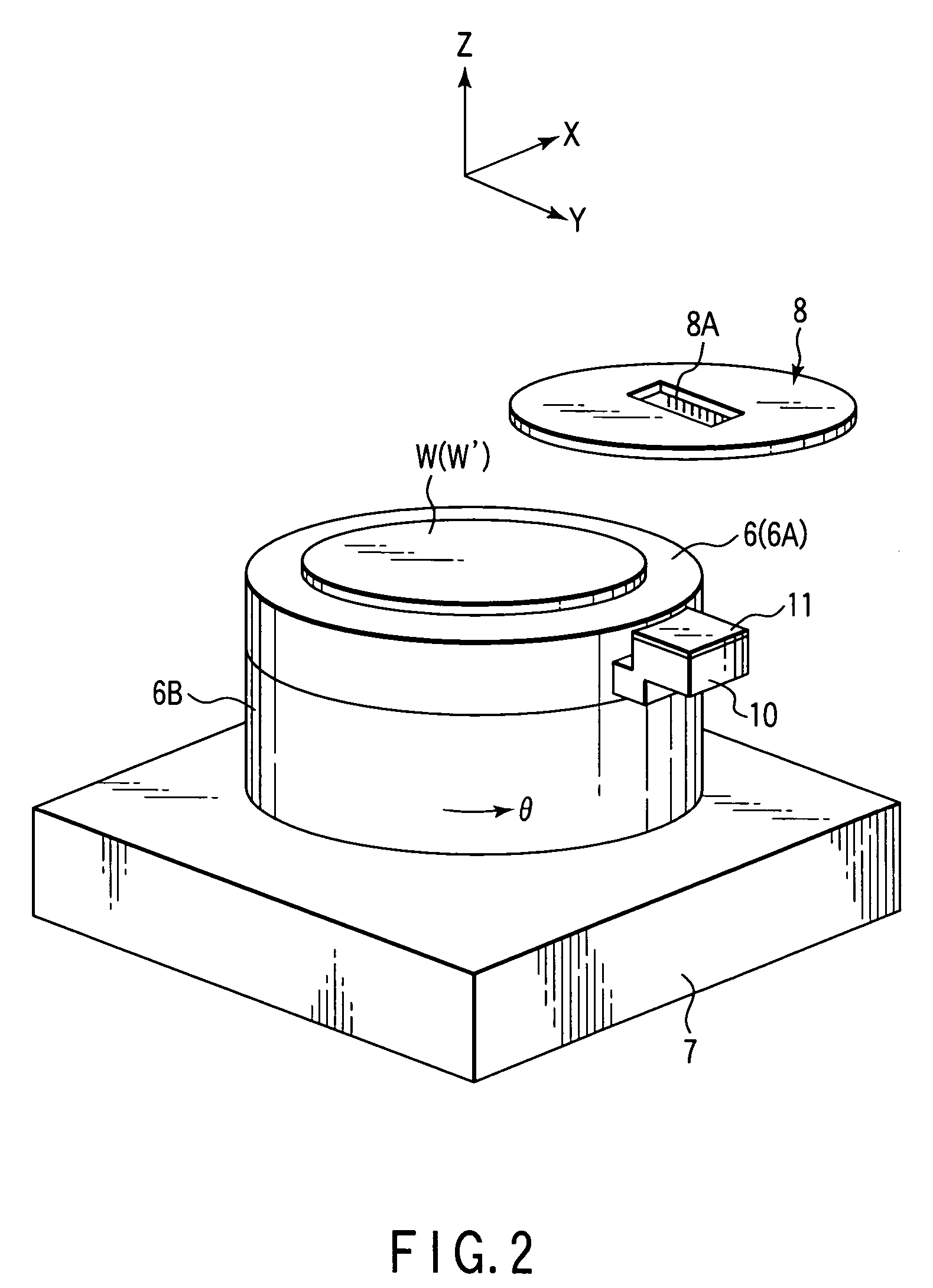

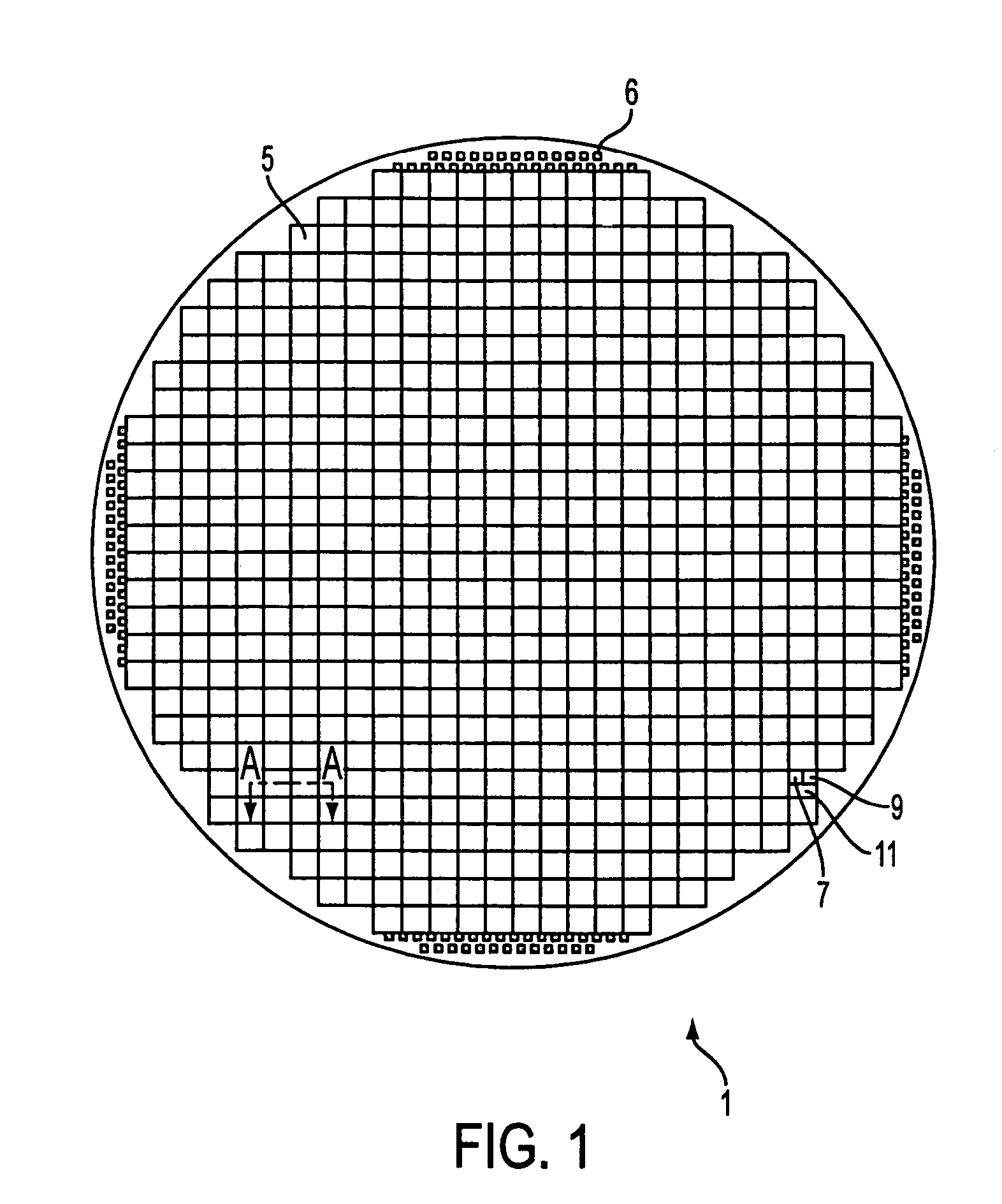

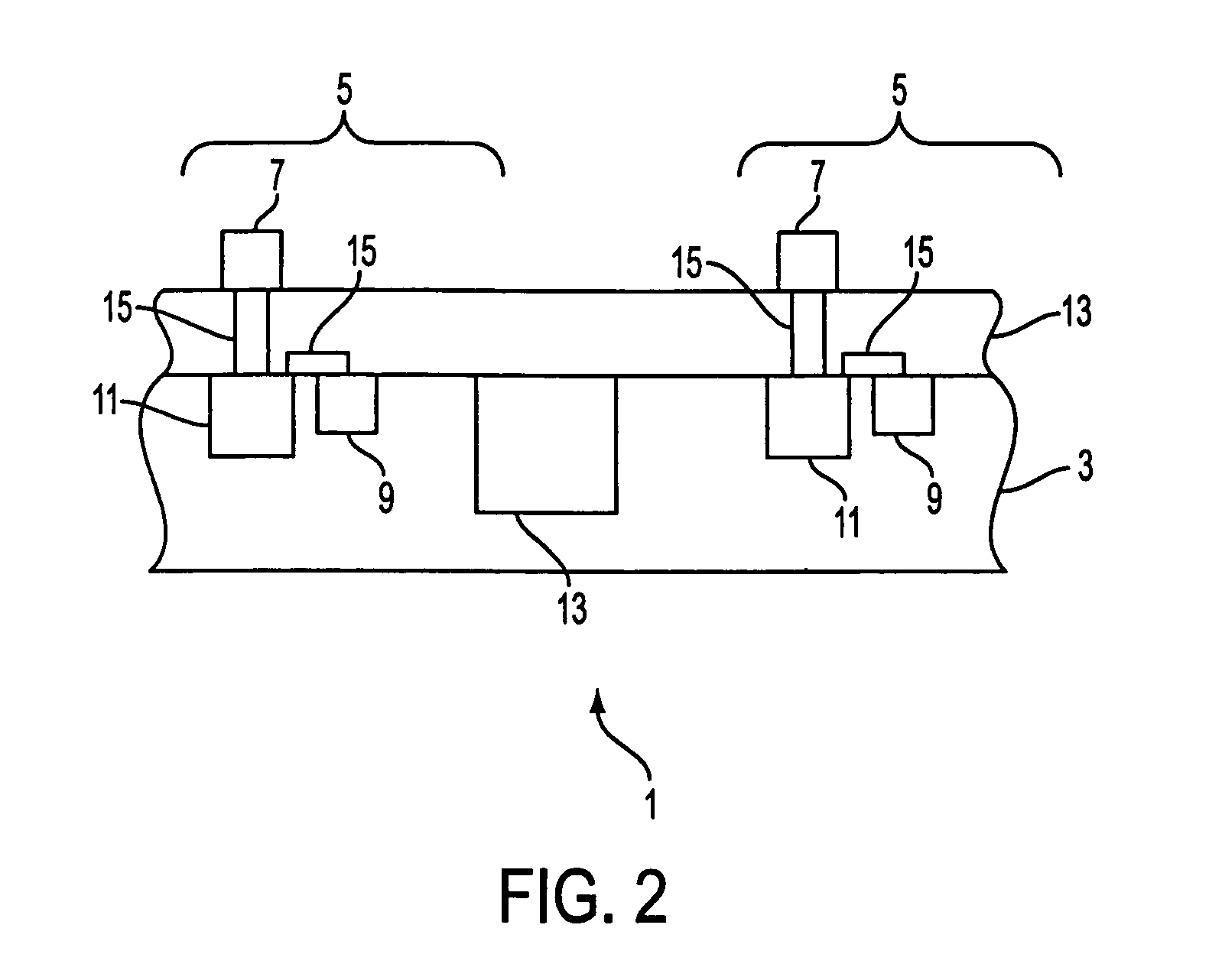

Wafer holder, heater unit used for wafer prober and having wafer holder, and wafer prober

InactiveUS20080211526A1Avoid contact failureAvoid temperature riseSleeve/socket jointsTurning machine accessoriesContact failureSemiconductor chip

By wafer holder including a chuck top for mounting a wafer and a supporter supporting the chuck top and having flatness of at most 0.1 mm, a heater unit for a wafer prober and the wafer prober using the wafer holder, a wafer holder and a wafer prober apparatus hardly deformable even under high load and capable of effectively preventing contact failure, and capable of preventing temperature increase in a driving system when a semiconductor wafer having semiconductor chips with minute circuitry that requires high accuracy is heated can be provided. In the wafer holder of the present invention, the flatness of the supporter is preferably at most 0.05 mm, and more preferably at most 0.01 mm.

Owner:SUMITOMO ELECTRIC IND LTD

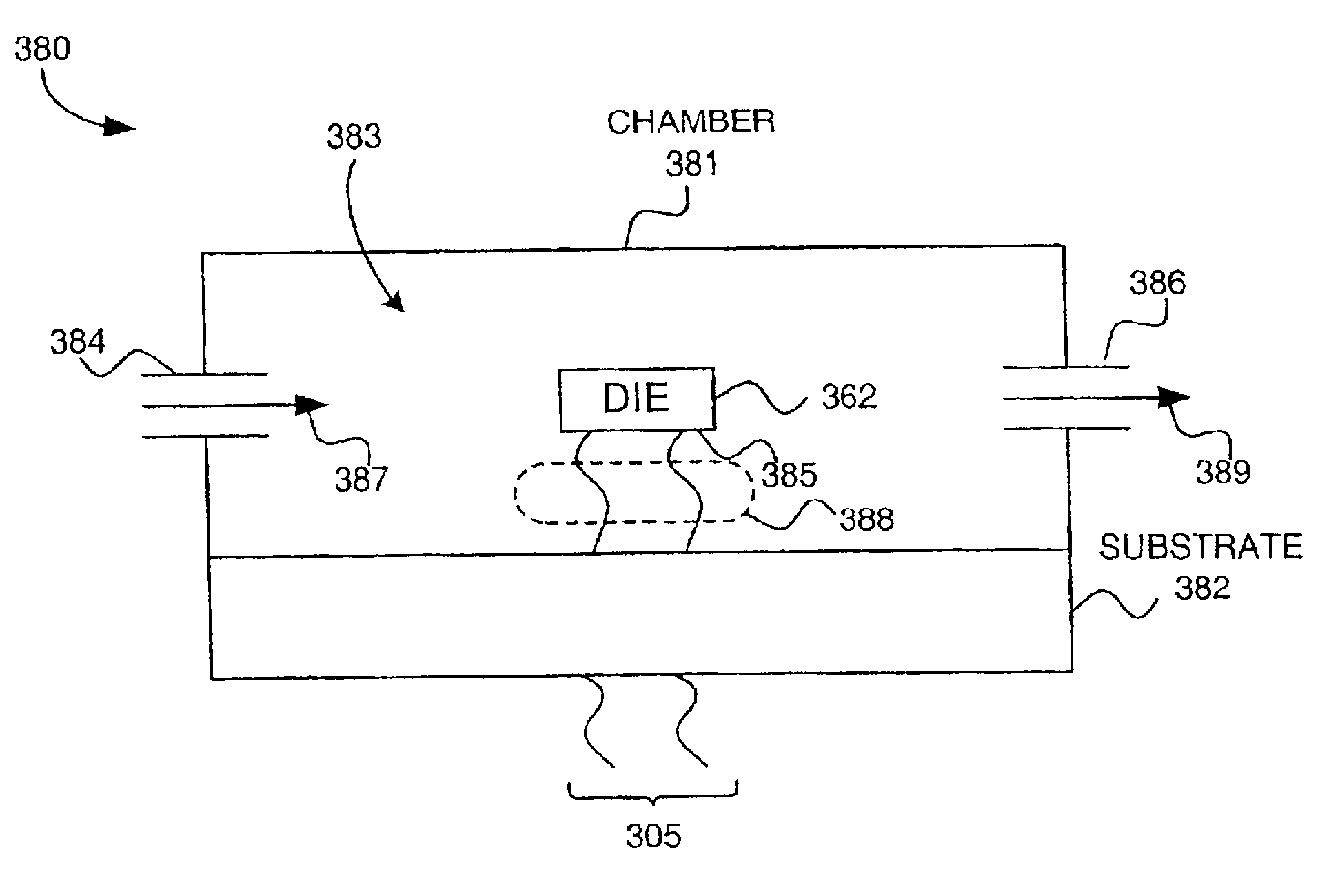

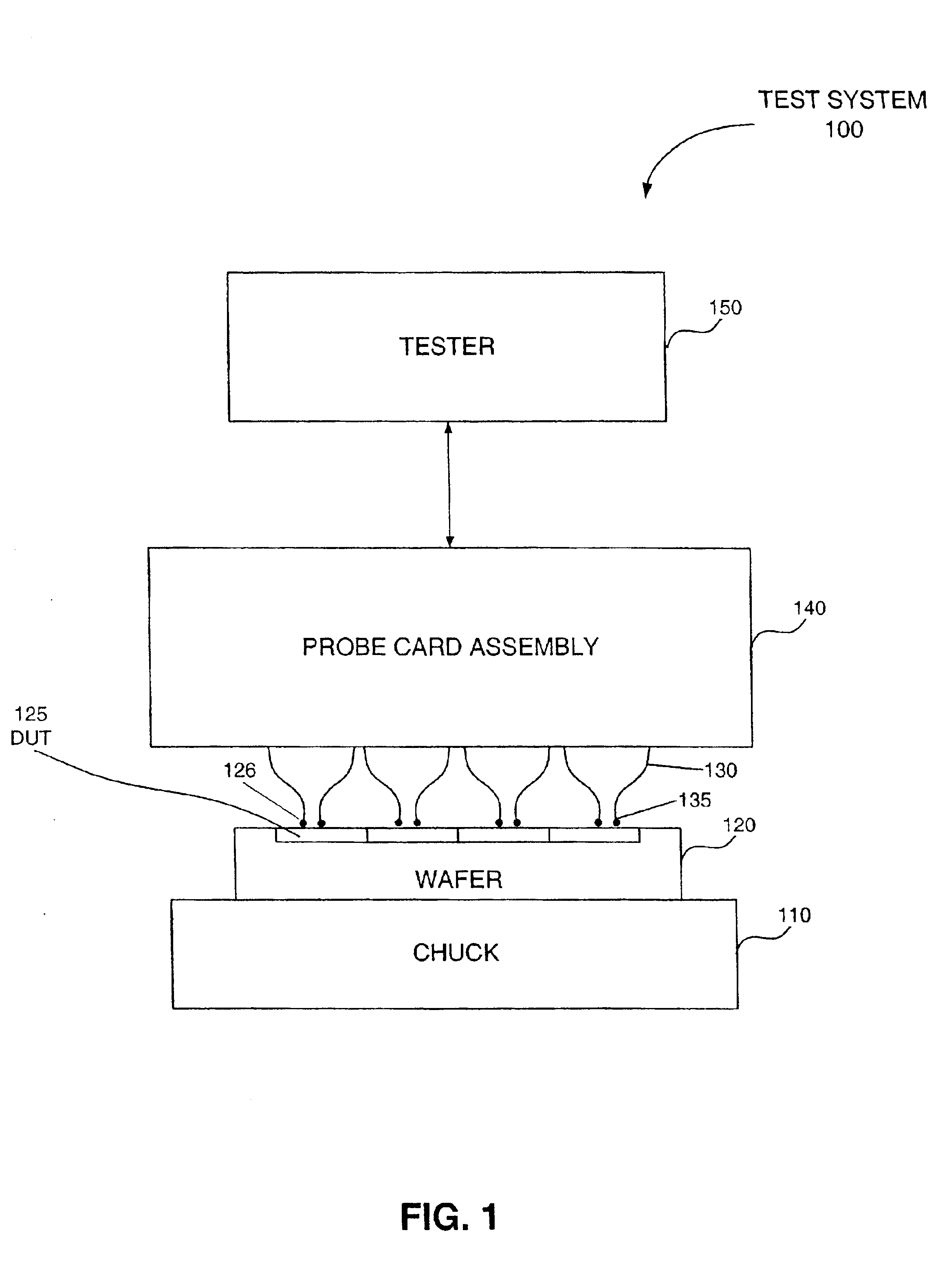

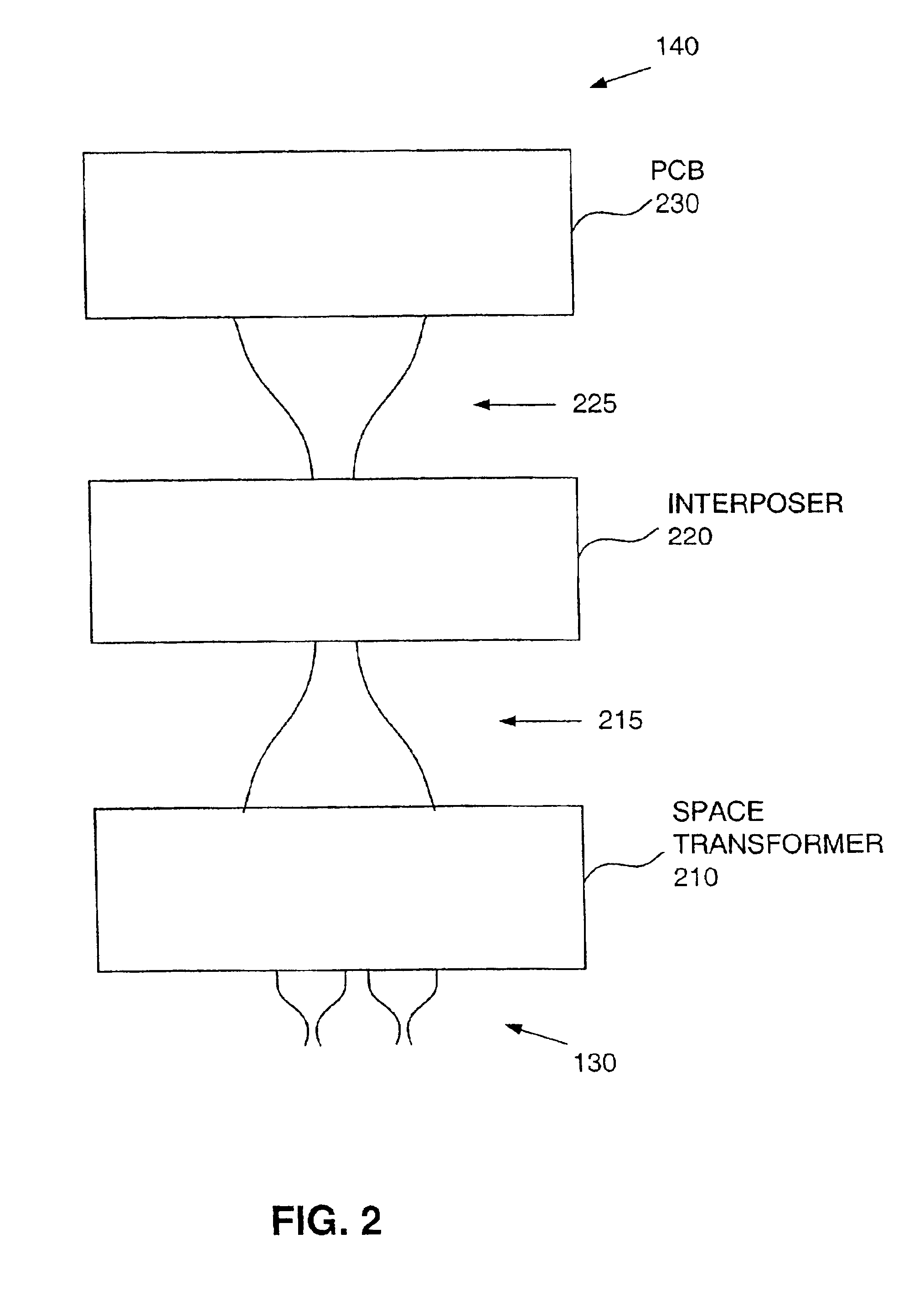

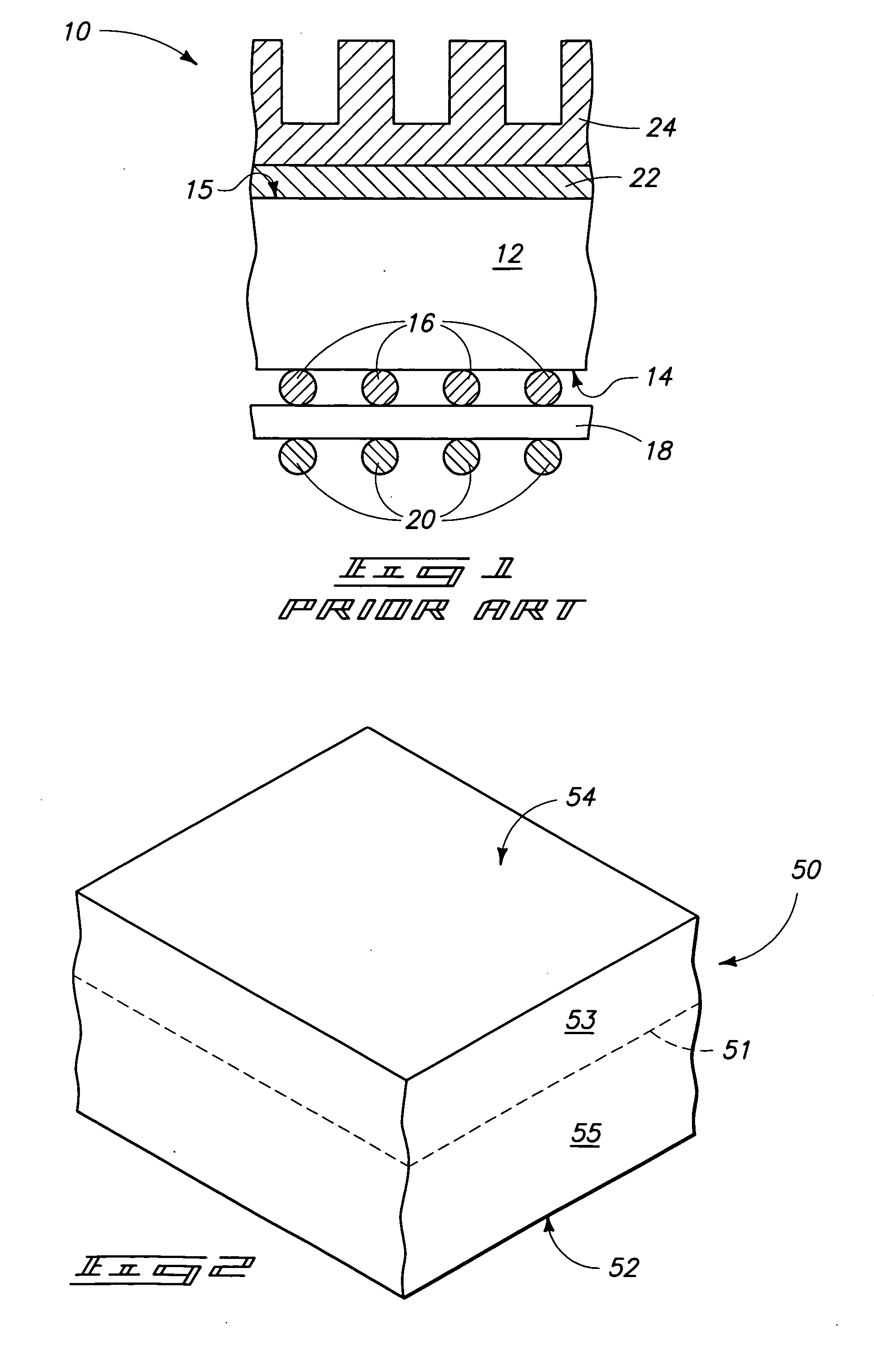

Probe card cooling assembly with direct cooling of active electronic components

InactiveUS6891385B2Shorten the conduction pathImprove performanceElectronic circuit testingElectrical measurement instrument detailsProbe cardHigh density

A probe card cooling assembly for use in a test system includes a package with one or more dies cooled by direct cooling. The cooled package includes one or more dies with active electronic components and at least one coolant port that allows a coolant to enter the high-density package and directly cool the active electronic components of the dies during a testing operation.

Owner:FORMFACTOR INC

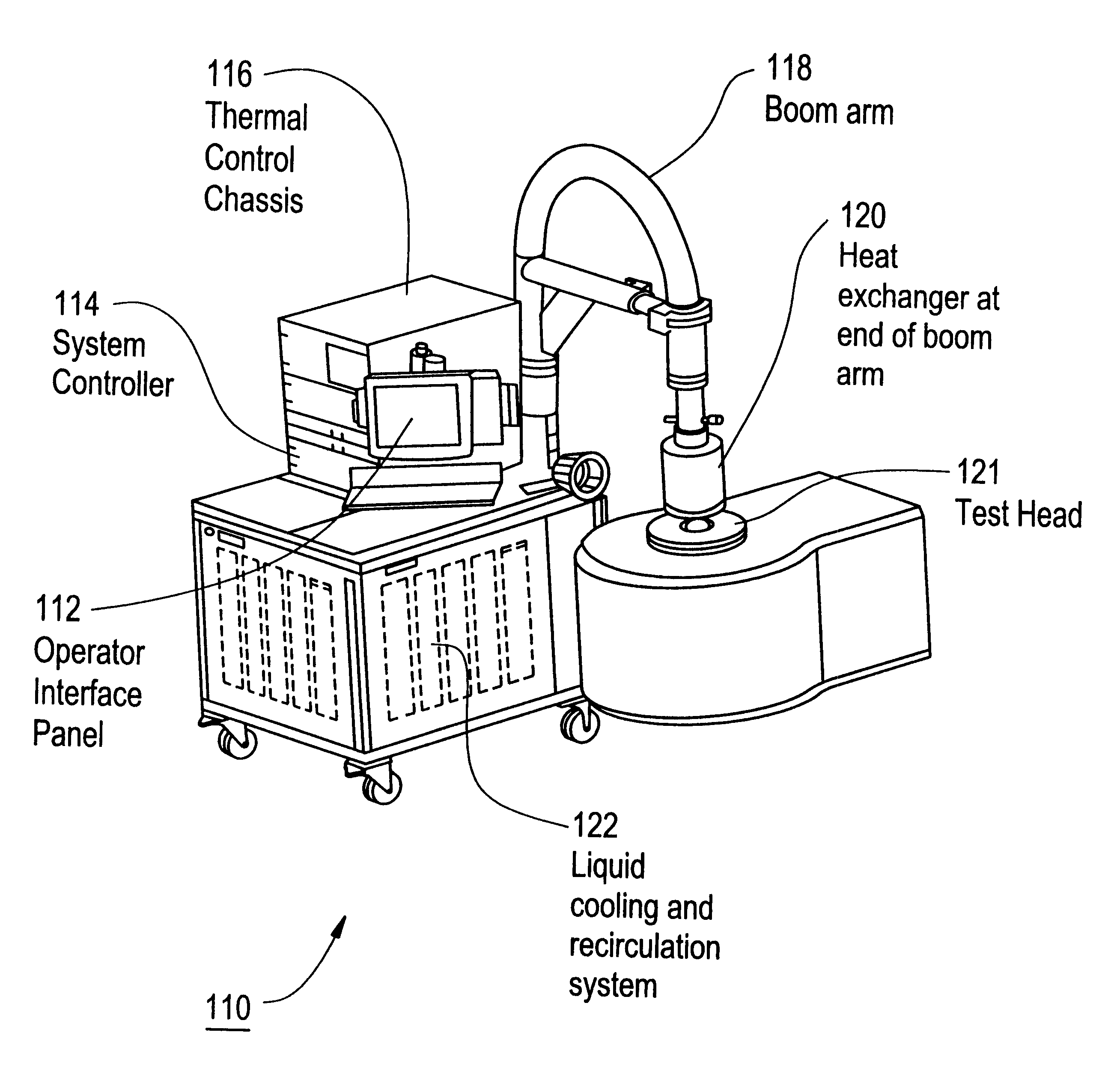

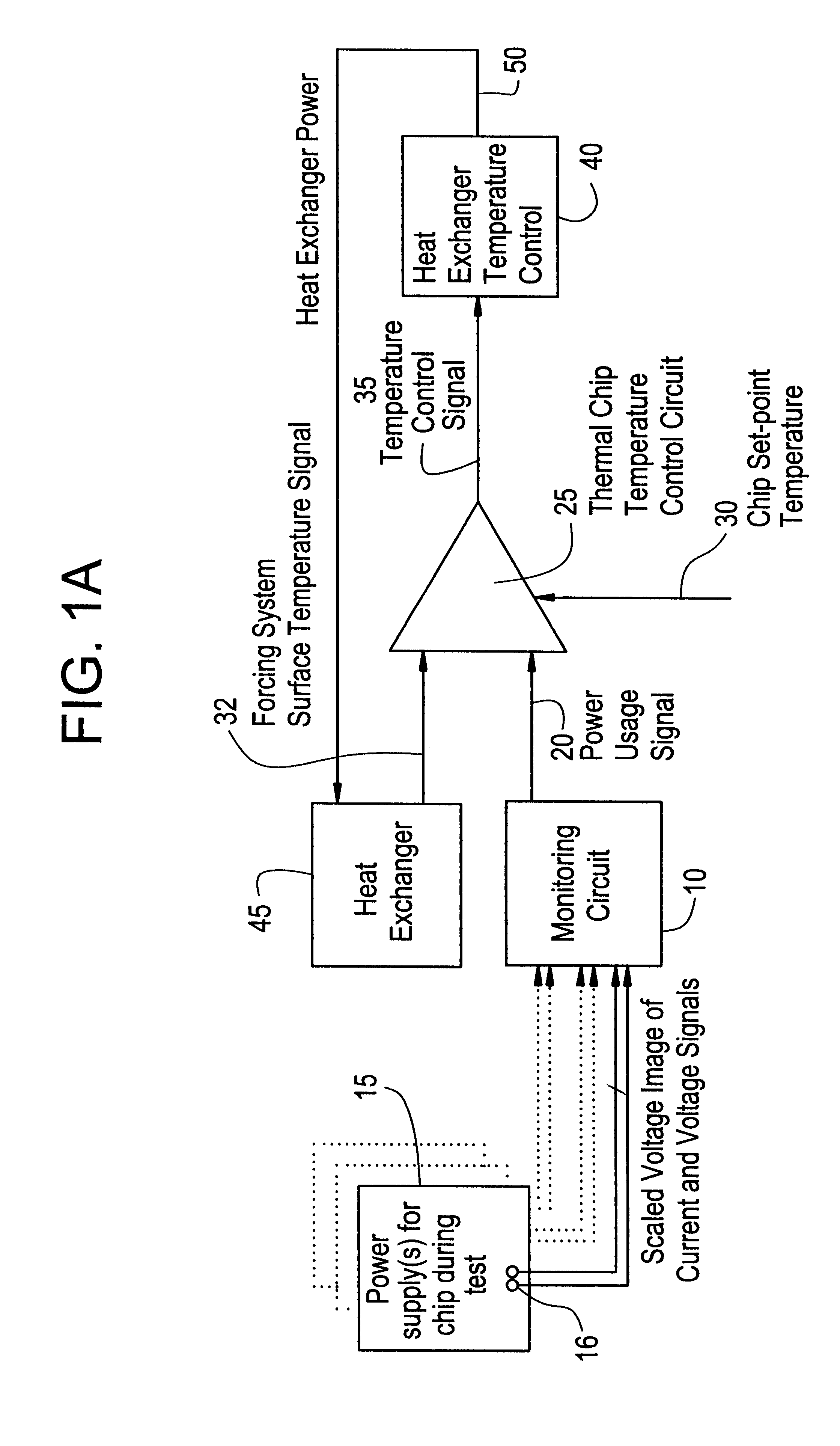

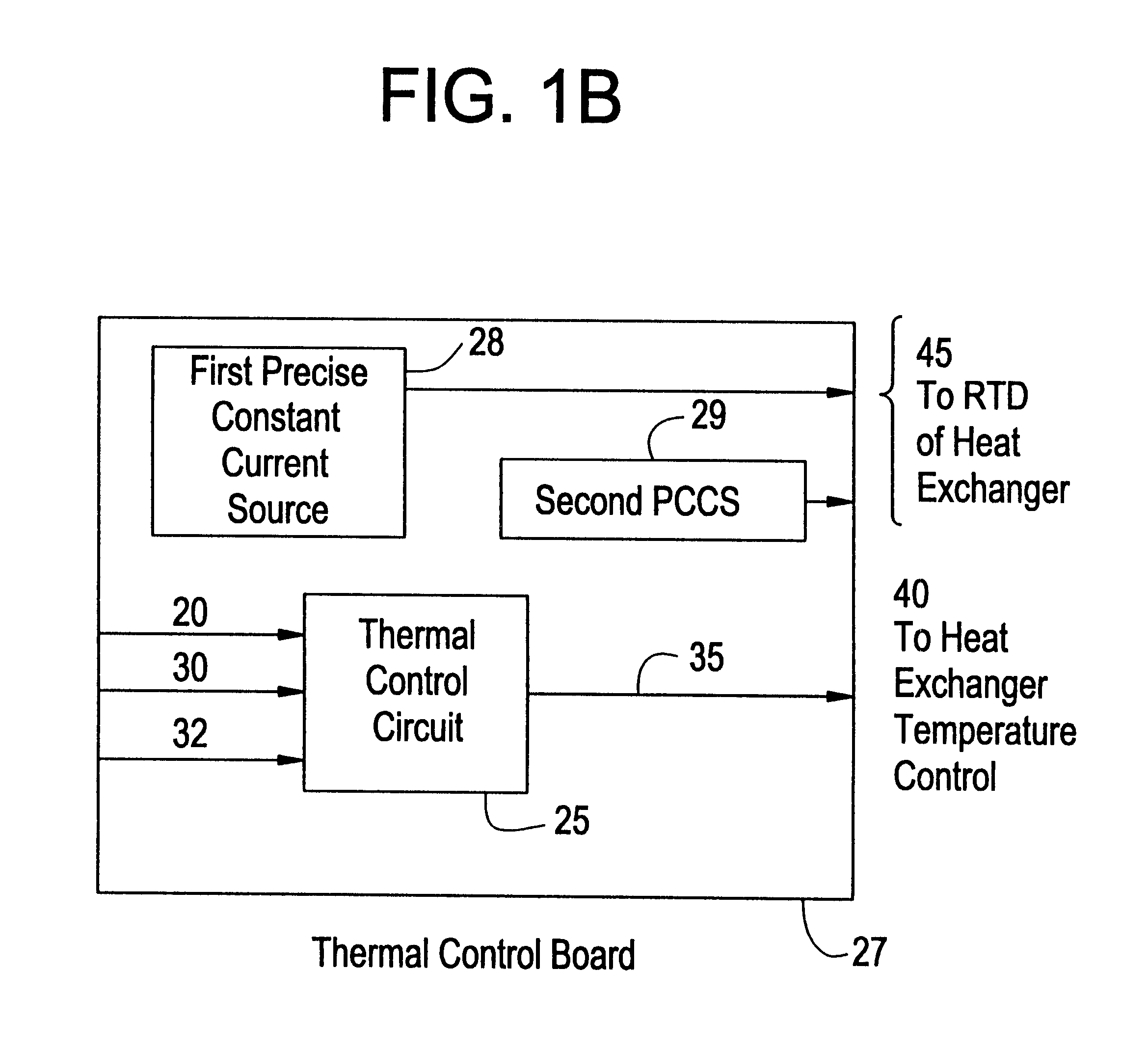

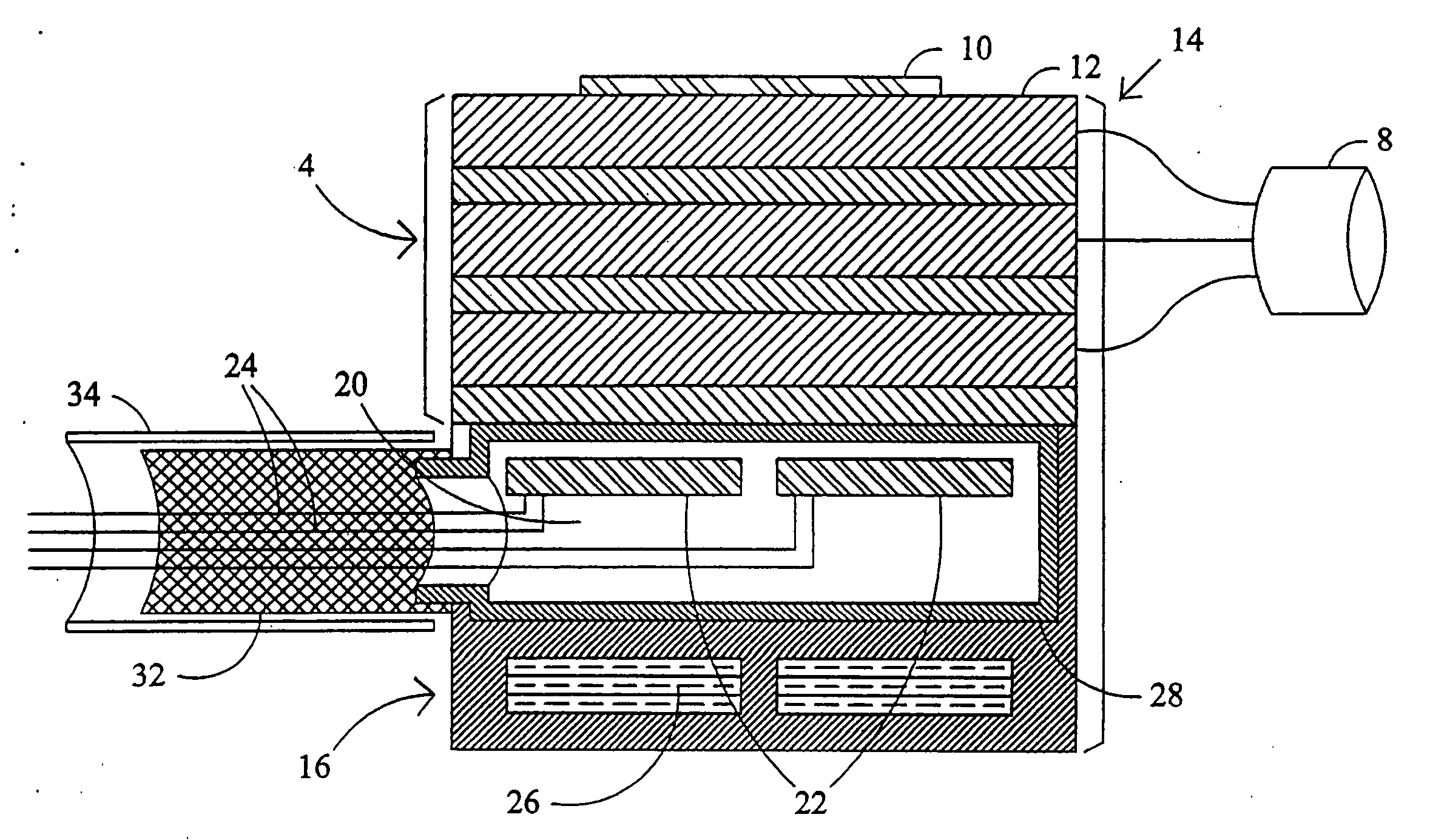

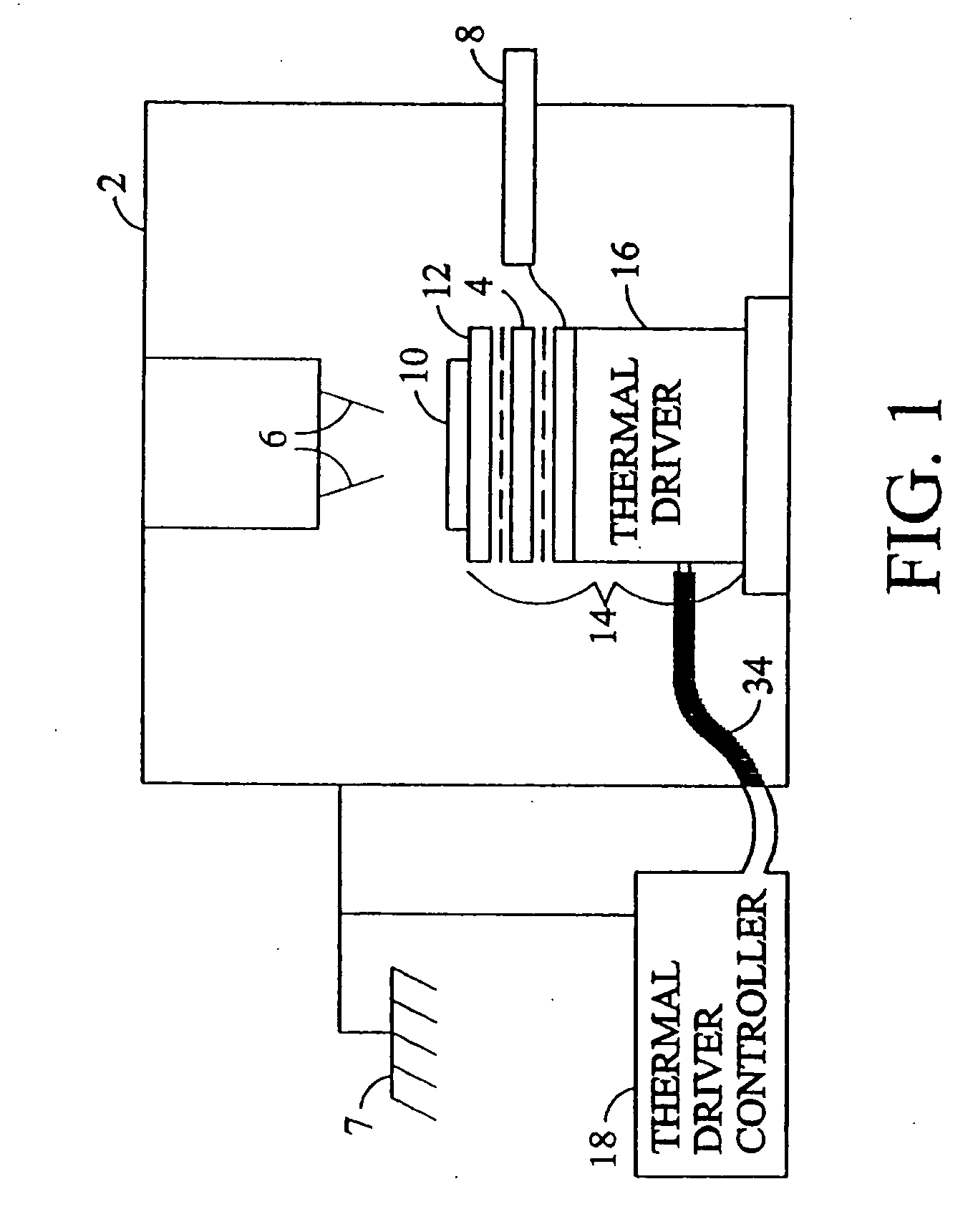

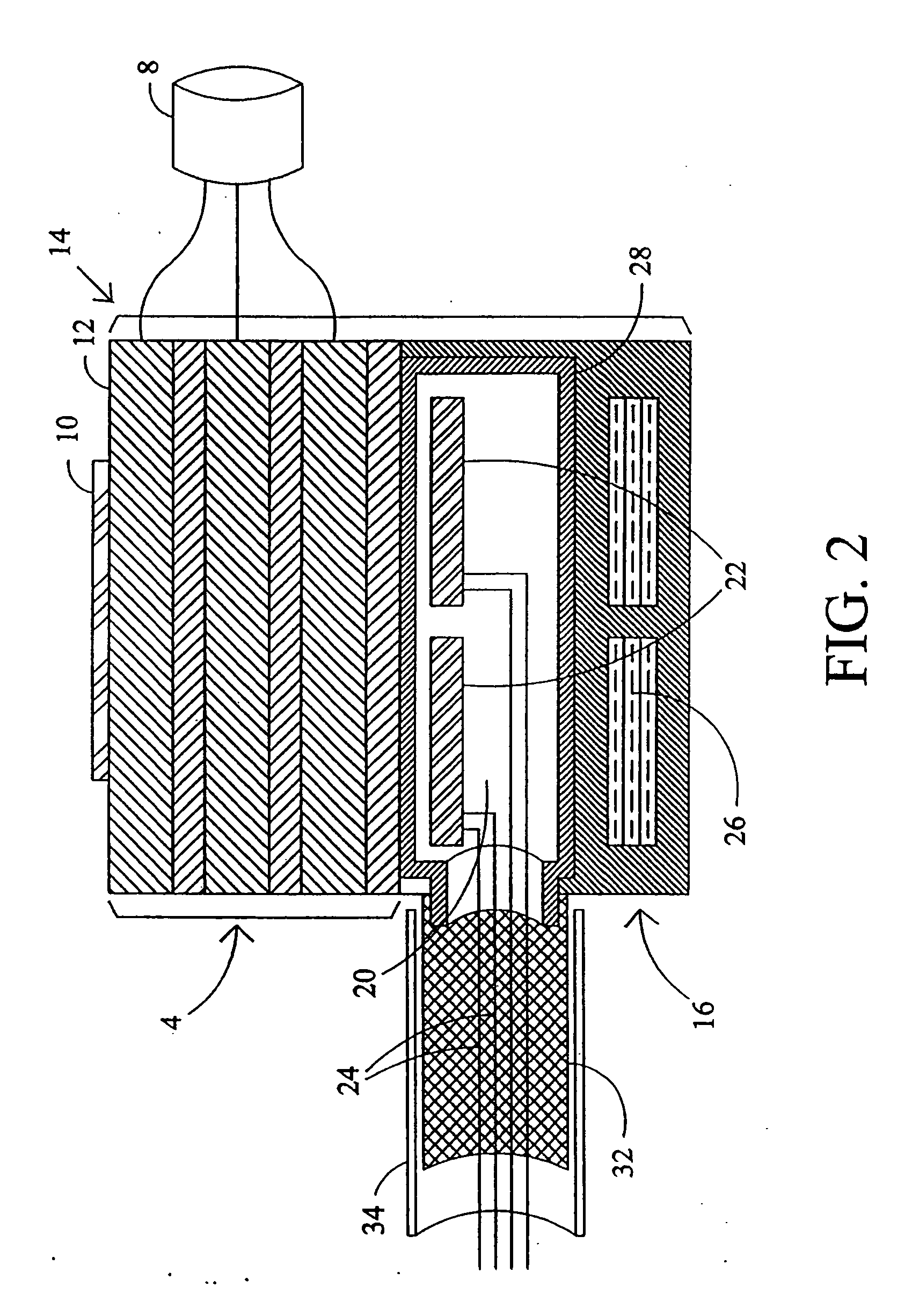

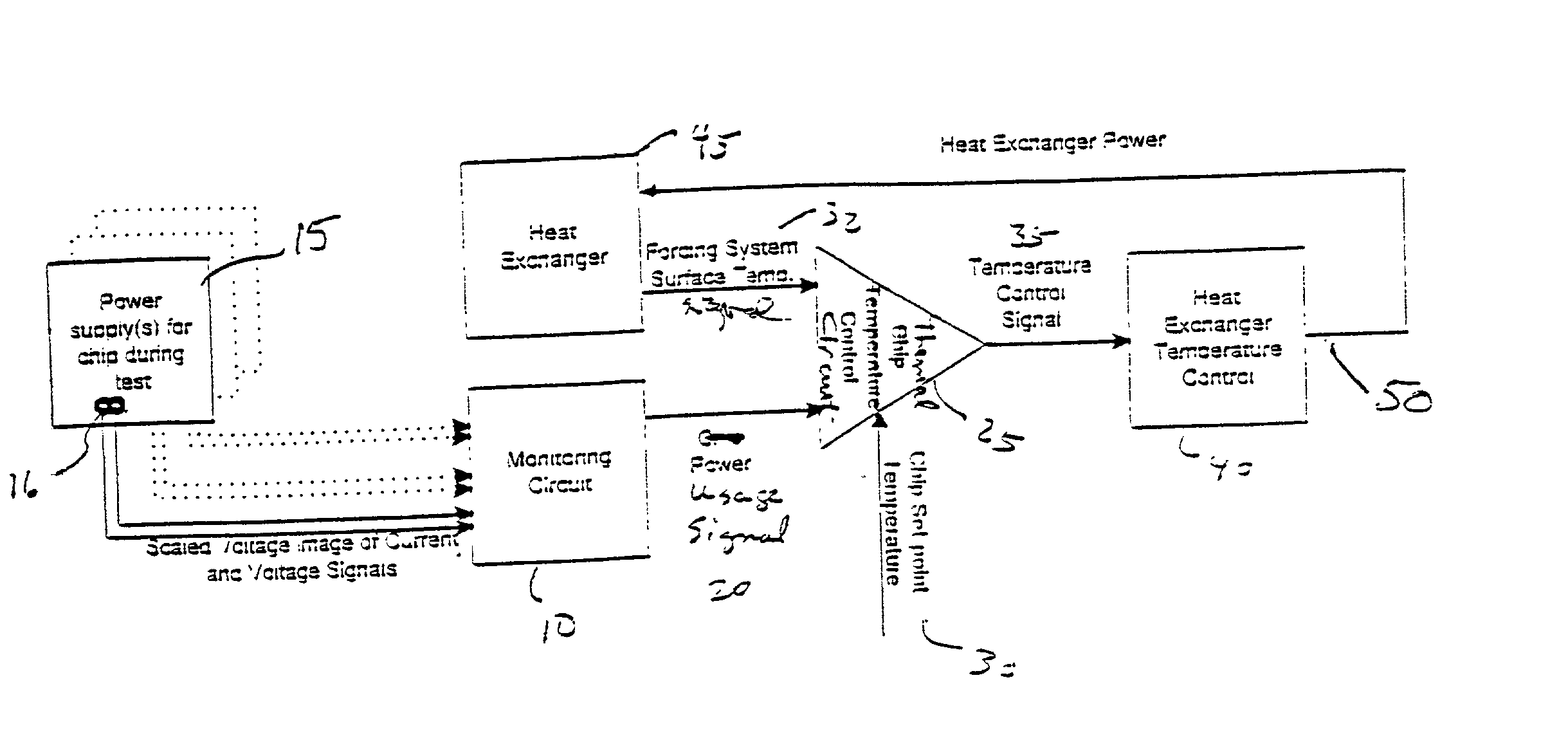

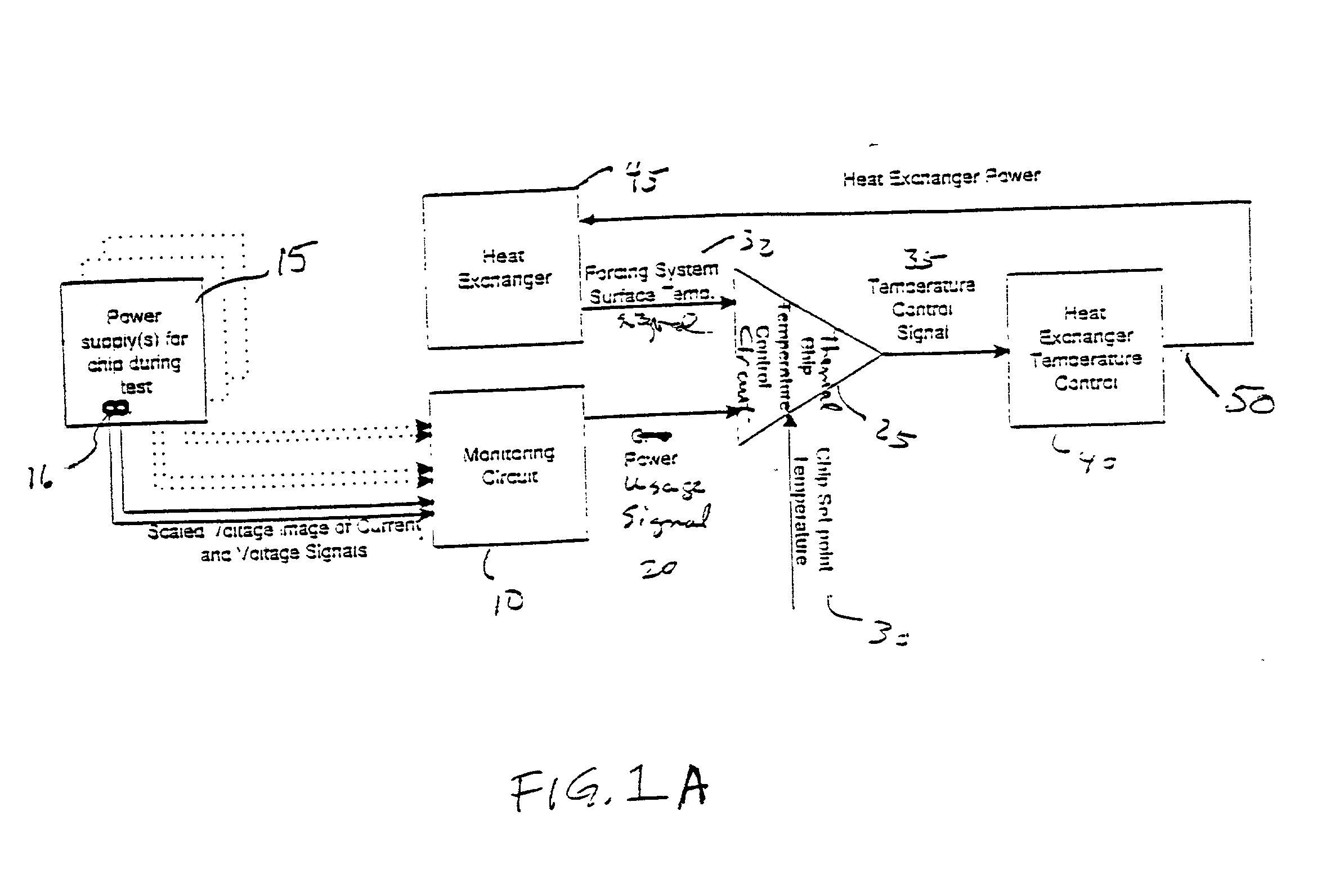

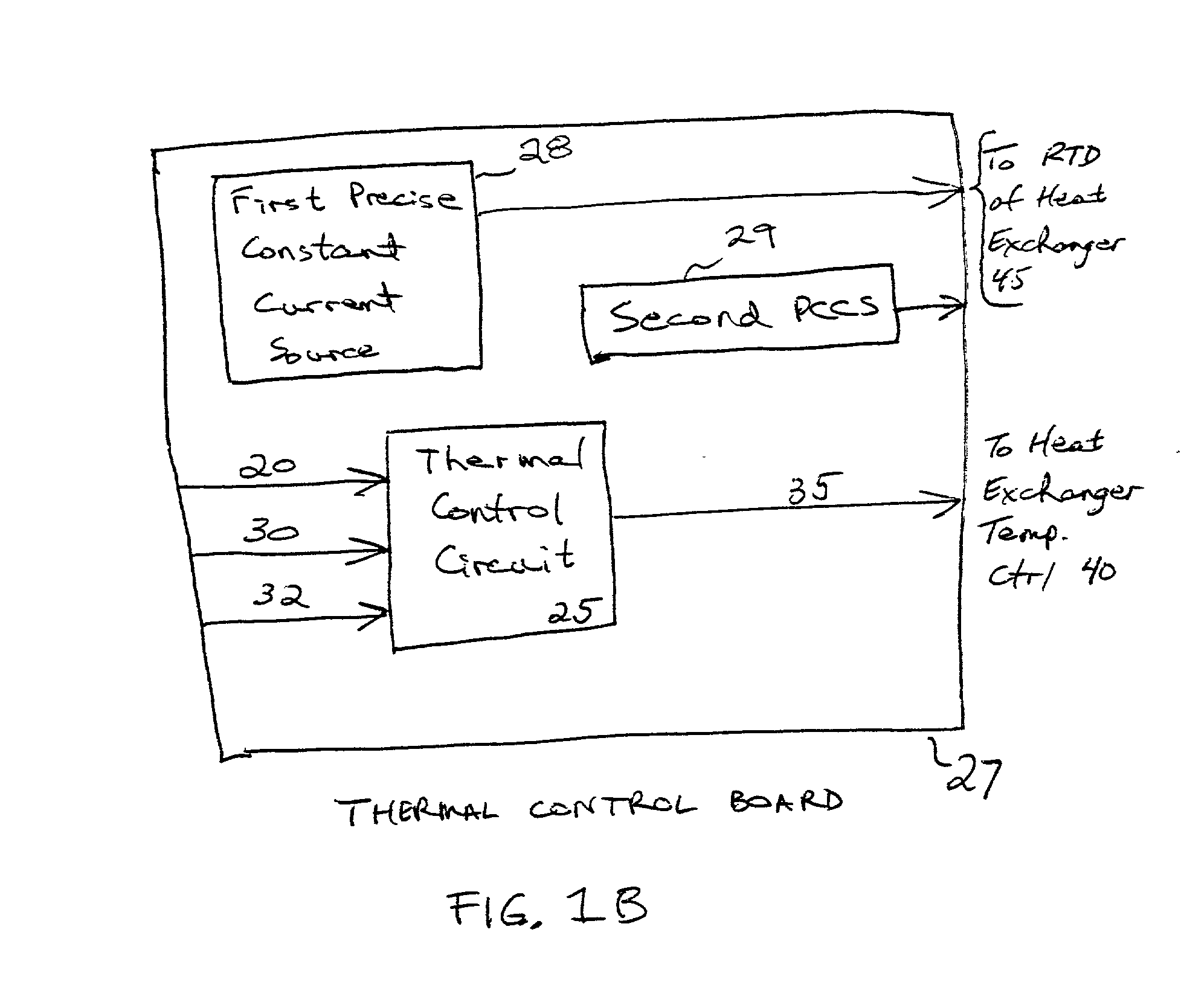

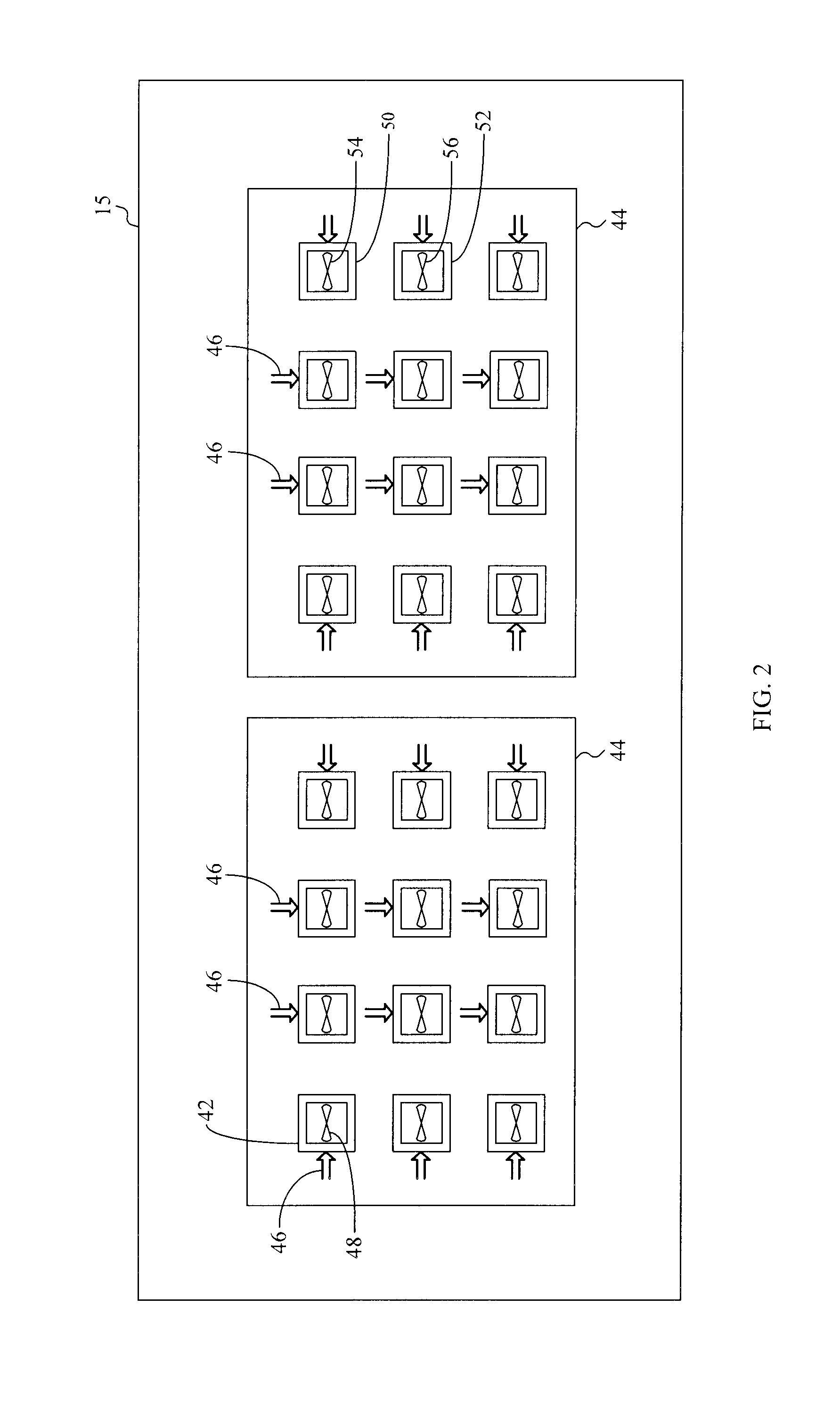

Temperature control of electronic devices using power following feedback

InactiveUS6489793B2Easy to useEliminate needTemperatue controlSemiconductor/solid-state device detailsTemperature controlEngineering

A method for controlling a device temperature measures a parameter related to device power consumption and utilizes the parameter to control the device temperature. This can be achieved with a system including a heat exchanger, a power monitor, and a circuit which controls the temperature setting of the heat exchanger. The circuit uses as inputs the power level, heat exchanger temperature, and set point. The system thus eliminates the need for temperature sensing devices in or connected to a chip, responds to the temperature of the device and not the package, can be used for high volume chip manufacturing, does not require significant surface area of a device for temperature sensing, and eliminates the need for chip power profiles. Significantly, the system allows a set point to be maintained with minimal overshoot or undershoot.

Owner:SCHLUMBERGER AUTOMATED TEST EQUIP +1

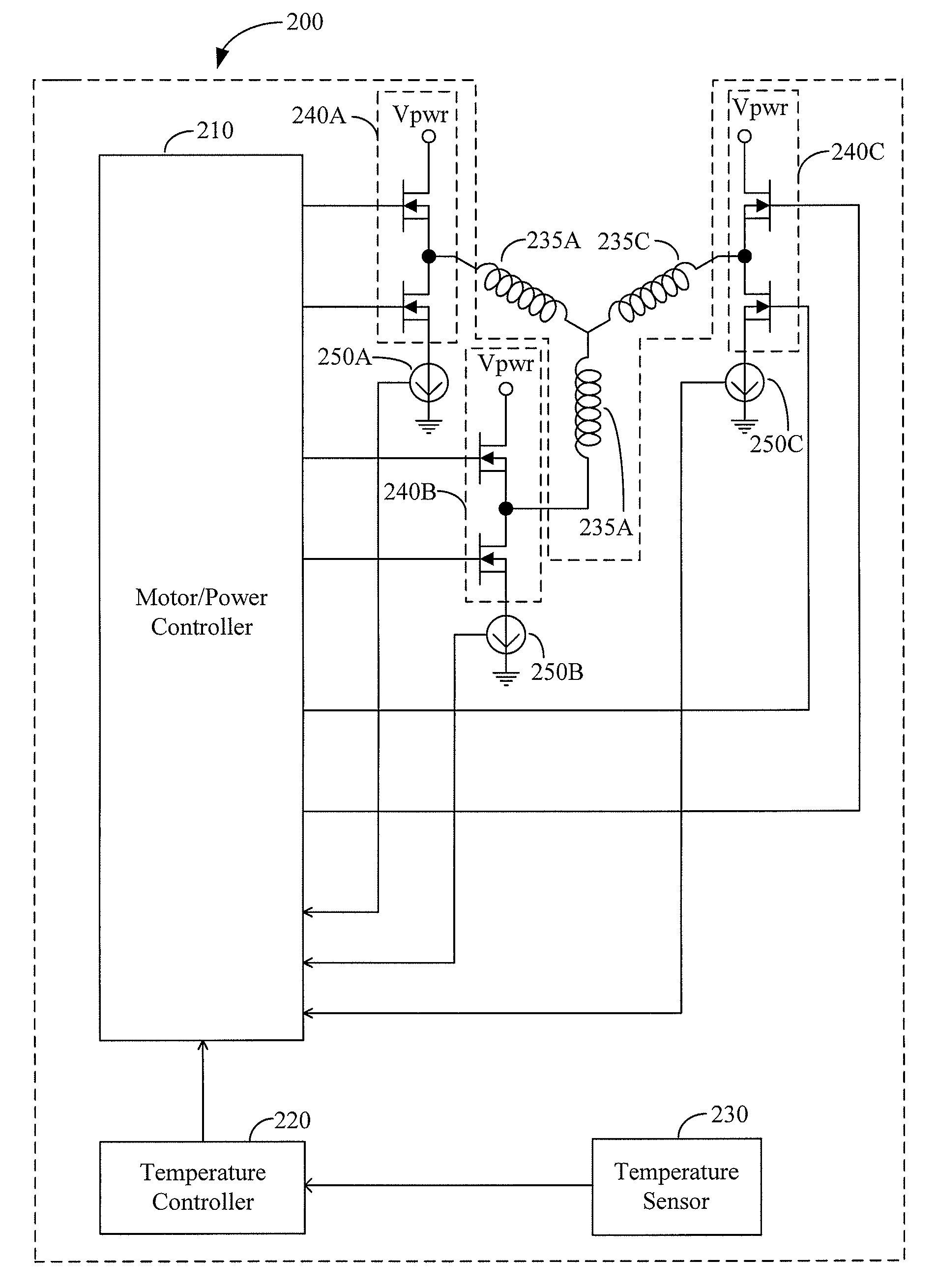

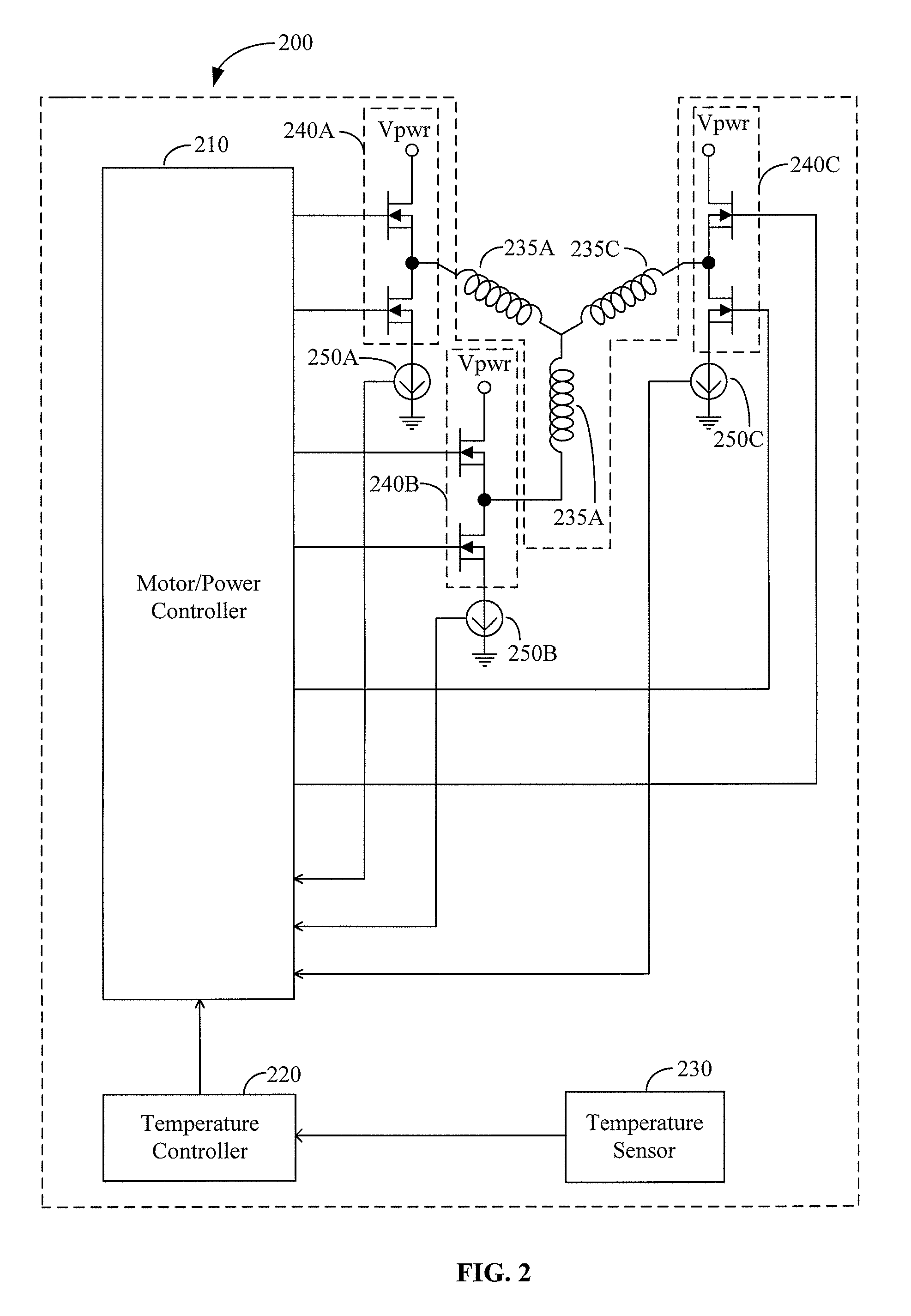

Self-heating integrated circuit

ActiveUS8358145B1Driving/moving recording headsSemiconductor/solid-state device detailsDriver circuitEngineering

Self-heating integrated circuits are provided. In one embodiment, a self-heating integrated circuit comprises a drive circuit configured to drive a device and a controller configured to selectively operate the drive circuit in a first mode or a second mode. In the first mode, the controller is configured to operate the drive circuit to drive the device and, in the second mode, the controller is configured to operate the drive circuit to heat the integrated circuit to a target temperature.

Owner:WESTERN DIGITAL TECH INC

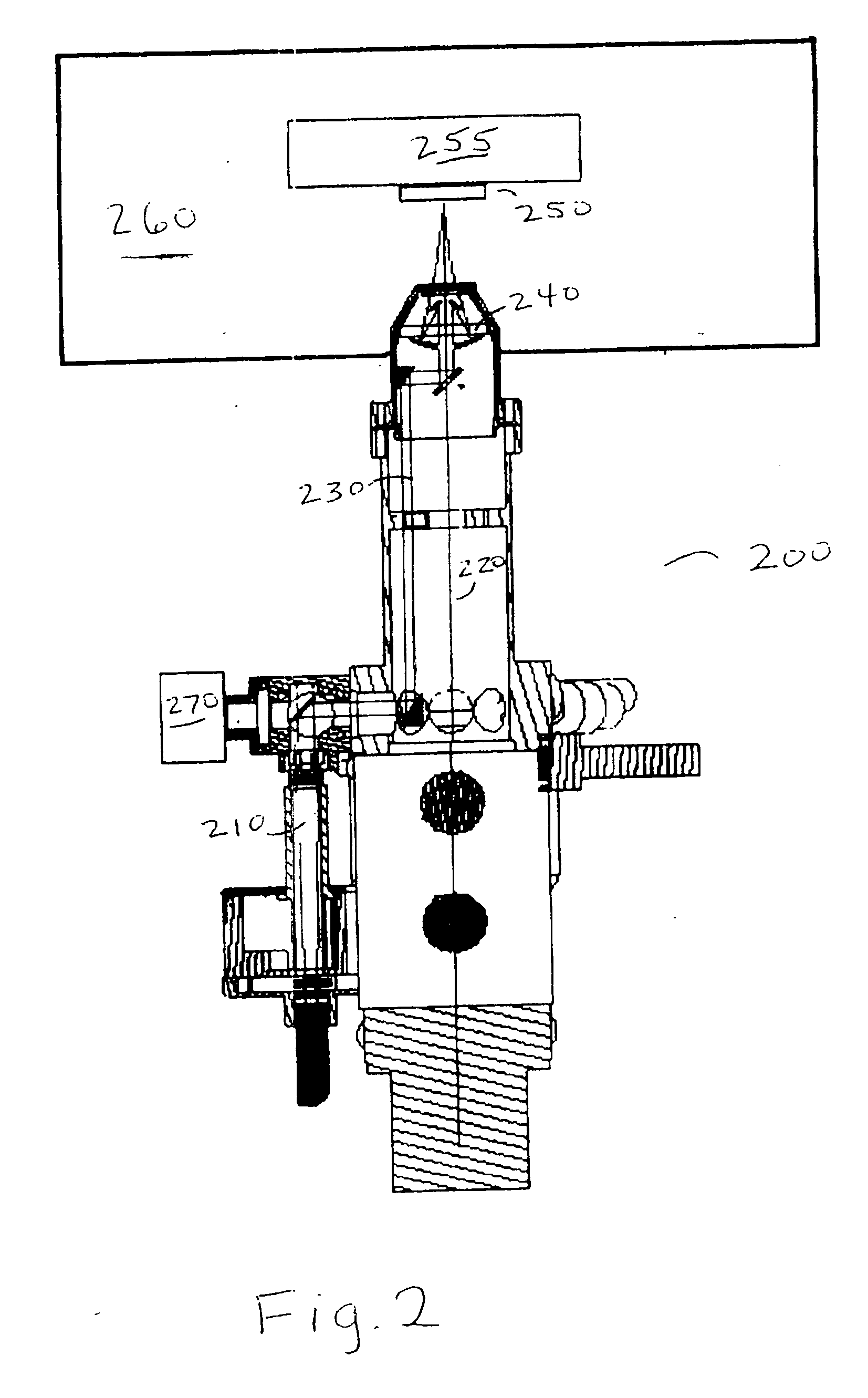

Probe pins zero-point detecting method, and prober

InactiveUS7023226B2Avoid damageImprove accuracySemiconductor/solid-state device testing/measurementFault location by increasing destruction at faultProbe cardConductive materials

A zero-point detecting method of this invention is performed prior to testing the electrical characteristics of a wafer by bringing an object to be tested on a stage and probes of a probe card into contact with each other. The surface of a zero-point detection plate is made of a conductive material (e.g., copper). The zero-point detection plate is used to detect a zero point as a position where the surface of the object to be tested comes into contact with the probe pins.

Owner:OCTEC INC +1

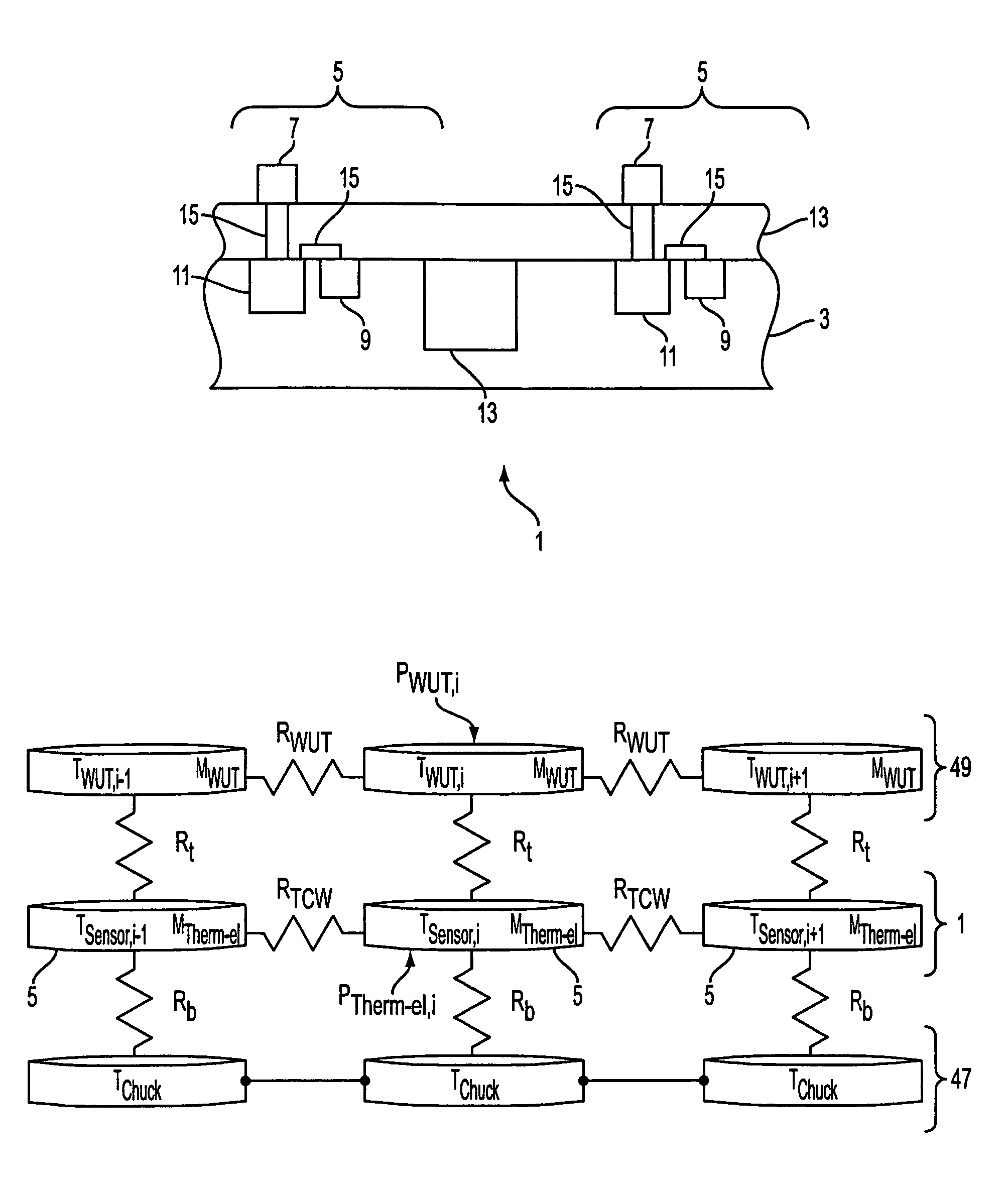

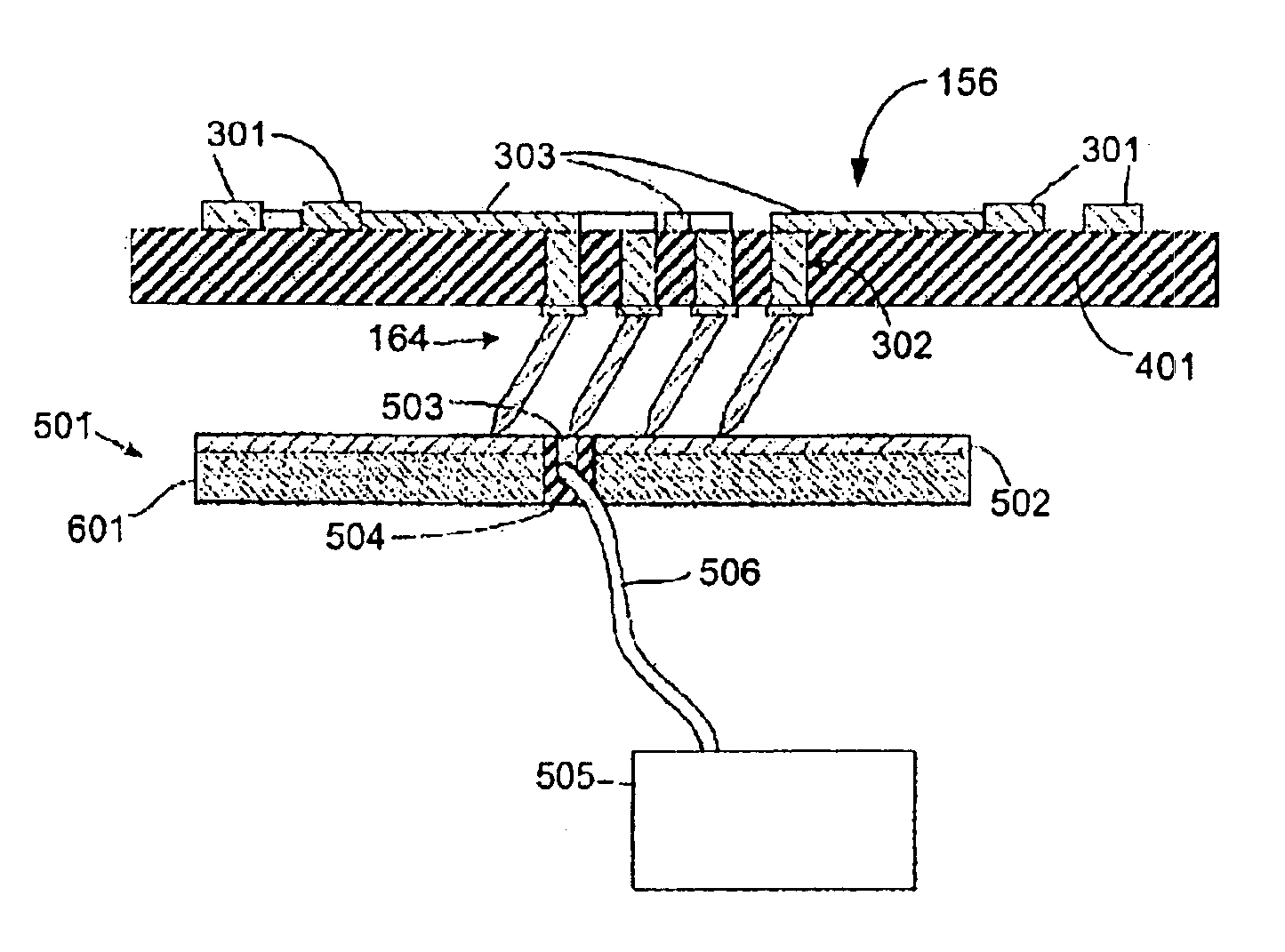

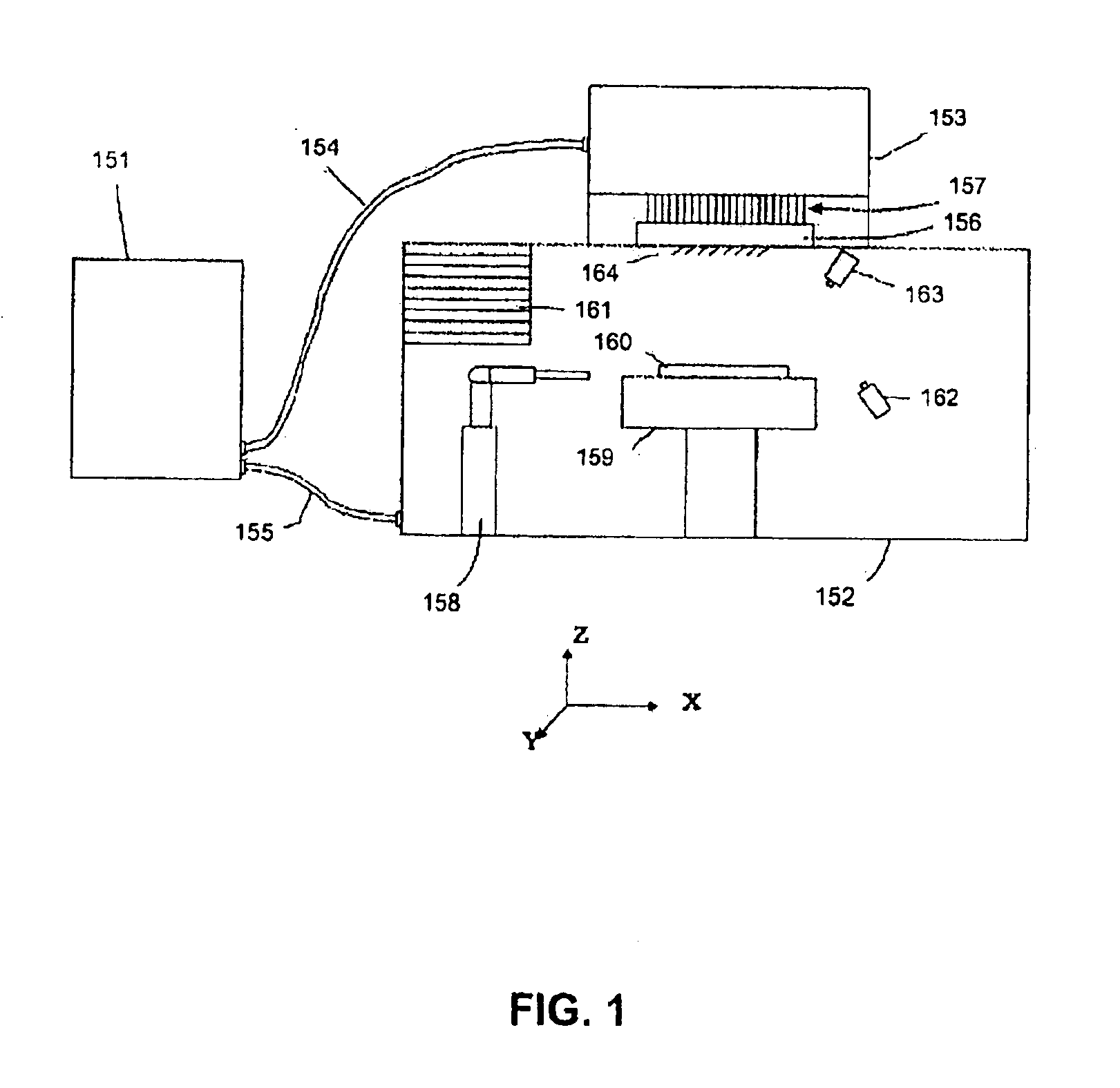

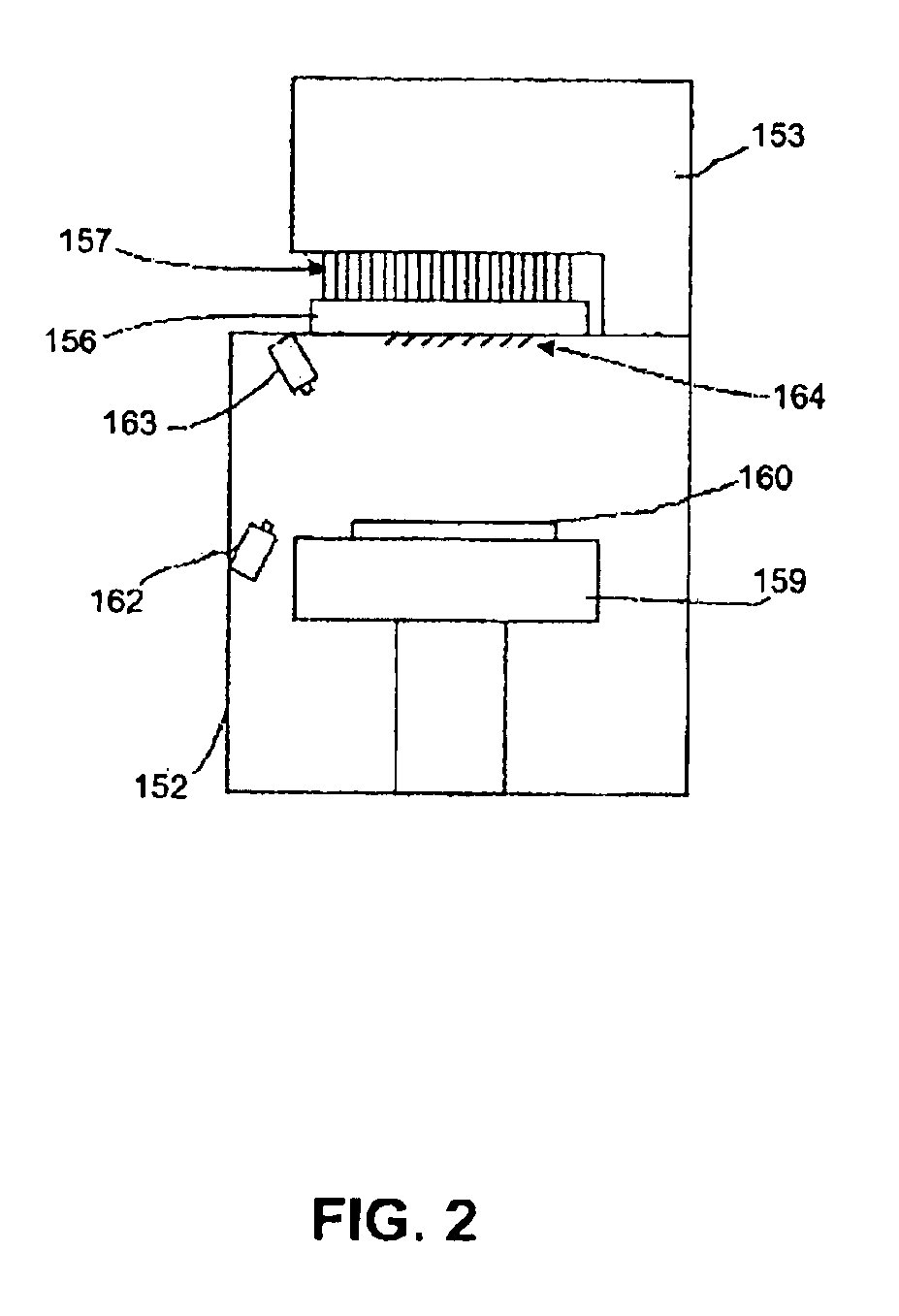

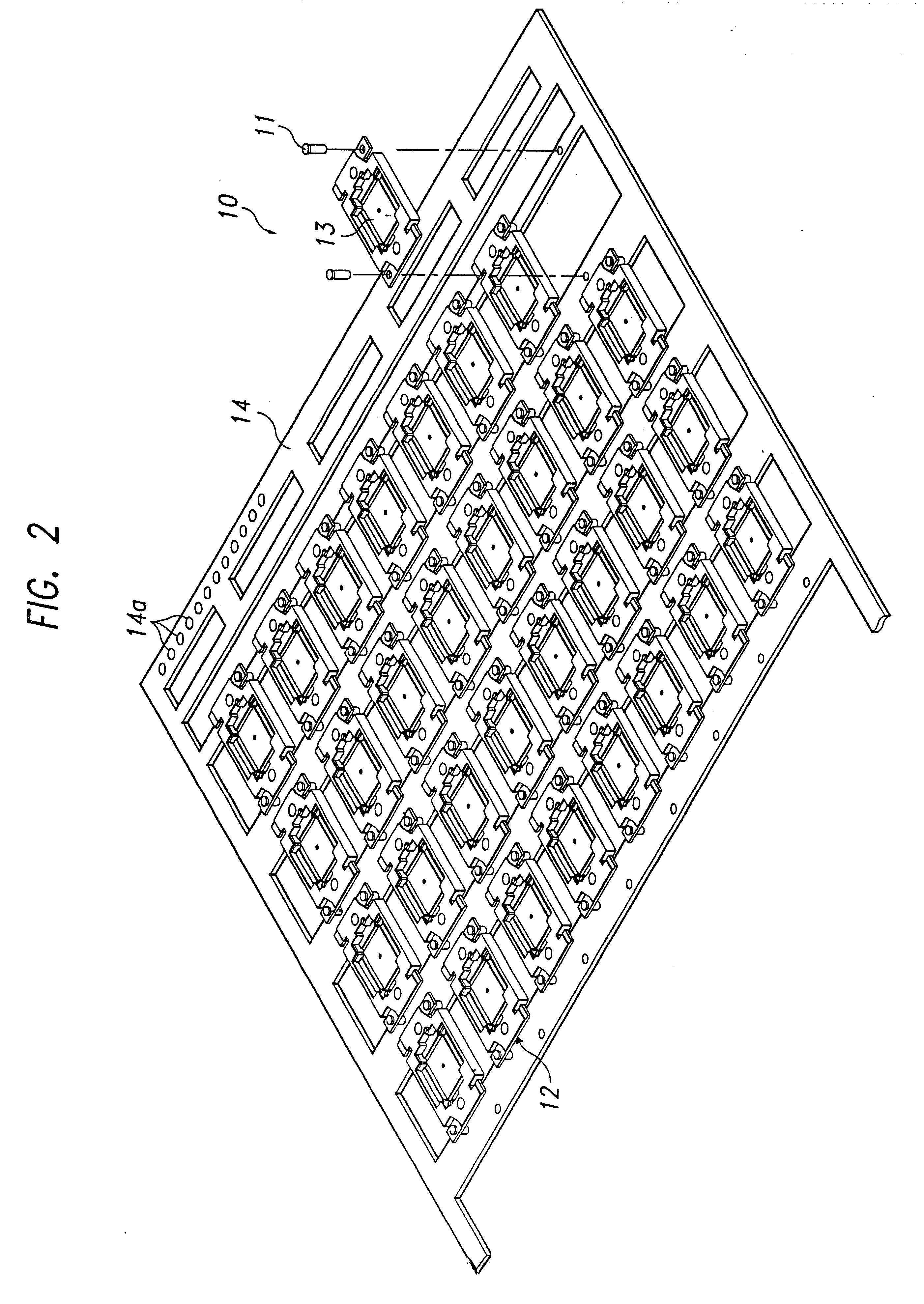

Thermal control of a DUT using a thermal control substrate

A solid state thermal control device contains a substrate and a plurality of solid state thermal elements on the substrate. The thermal elements are adapted to provide thermal control to a device under test (DUT). Each solid state thermal element contains at least one solid state heater and an active control circuit adapted to control a thermal output of the heater. Optionally, the each thermal element may also include a solid state temperature sensor.

Owner:DELTA DESIGN

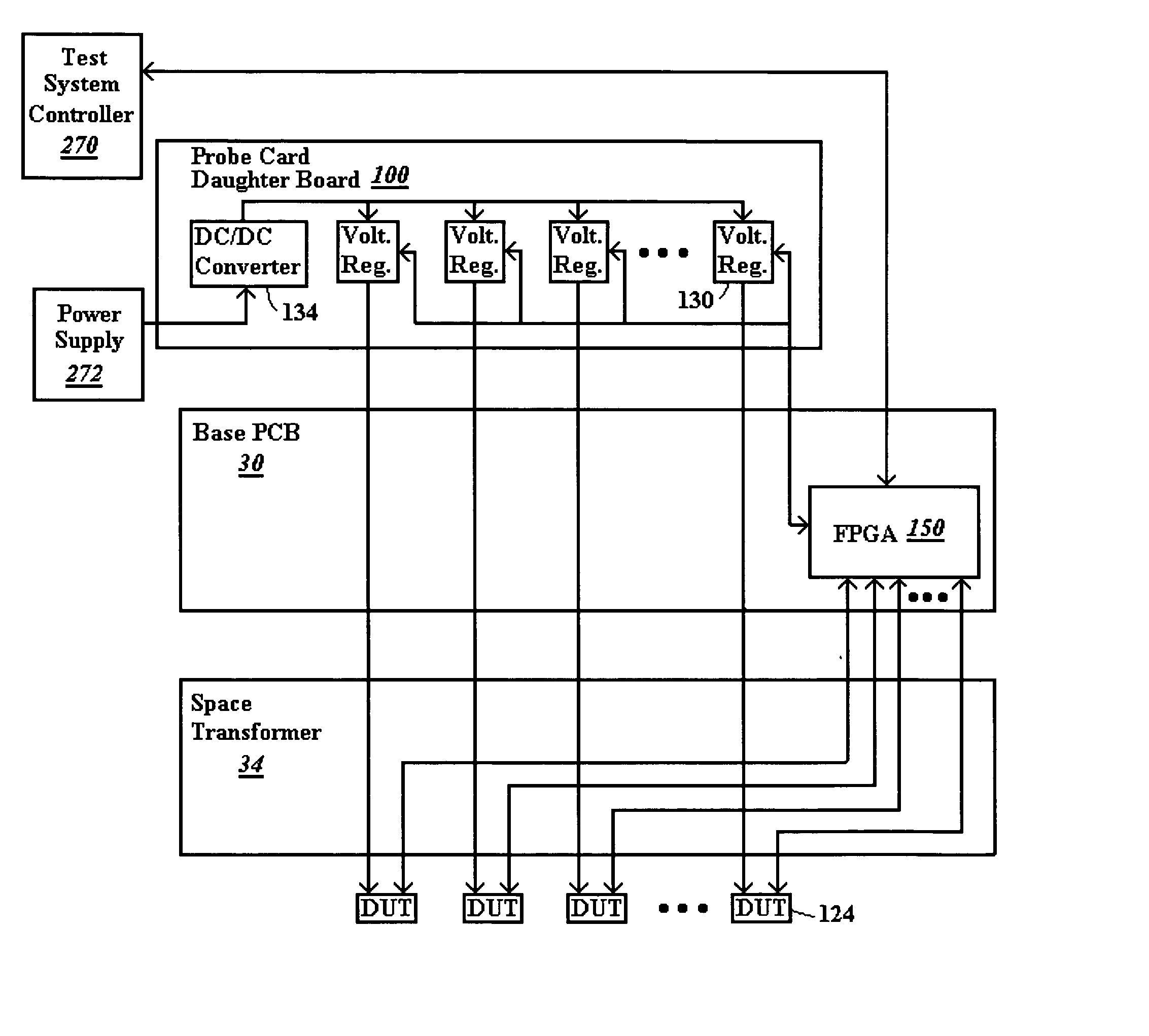

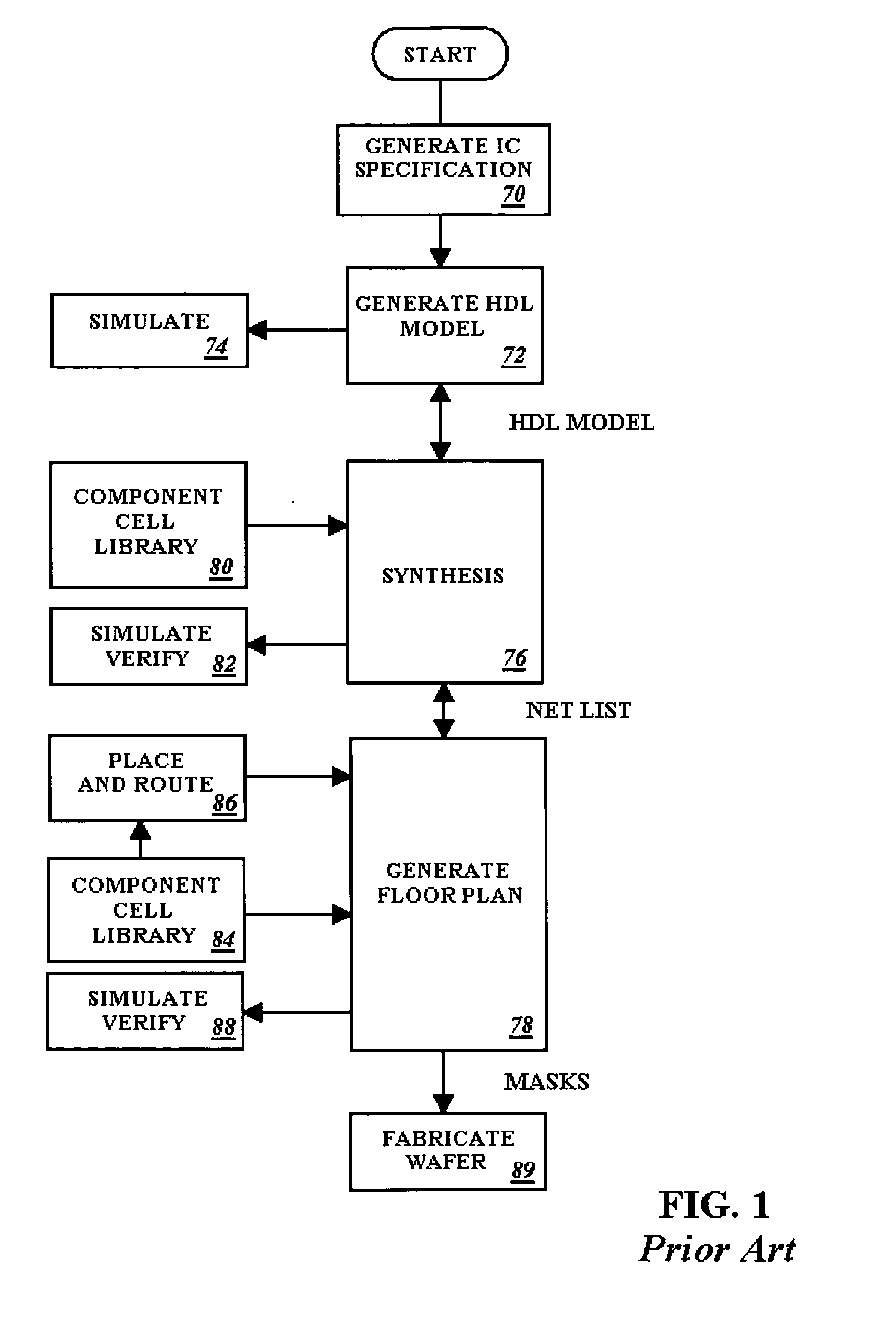

Method of designing an application specific probe card test system

InactiveUS20060273809A1Eliminate needDigital circuit testingOverload protection arrangementsProbe cardOn board

A method is provided for design and programming of a probe card with an on-board programmable controller in a wafer test system. Consideration of introduction of the programmable controller is included in a CAD wafer layout and probe card design process. The CAD design is further loaded into the programmable controller, such as an FPGA to program it: (1) to control direction of signals to particular ICs, even during the test process (2) to generate test vector signals to provide to the ICs, and (3) to receive test signals and process test results from the received signals. In some embodiments, burn-in only testing is provided to limit test system circuitry needed so that with a programmable controller on the probe card, text equipment external to the probe card can be eliminated or significantly reduced from conventional test equipment.

Owner:FORMFACTOR INC

Apparatus and method for electromechanical testing and validation of probe cards

InactiveUS6911814B2Electrical measurement instrument detailsFault location by increasing destruction at faultProbe cardEngineering

A method of testing a probe card includes the step of positioning the probe card in a prober over a verification wafer that is placed on a stage. The probe card is brought in contact with a contact region on the verification wafer. The verification wafer includes a shorting plane surrounding the contact region. A test signal is sent through the verification wafer to the probe card. A response signal from the probe card is received and analyzed.

Owner:FORMFACTOR INC

Method and apparatus for remotely changing signal characteristics of a signal generator

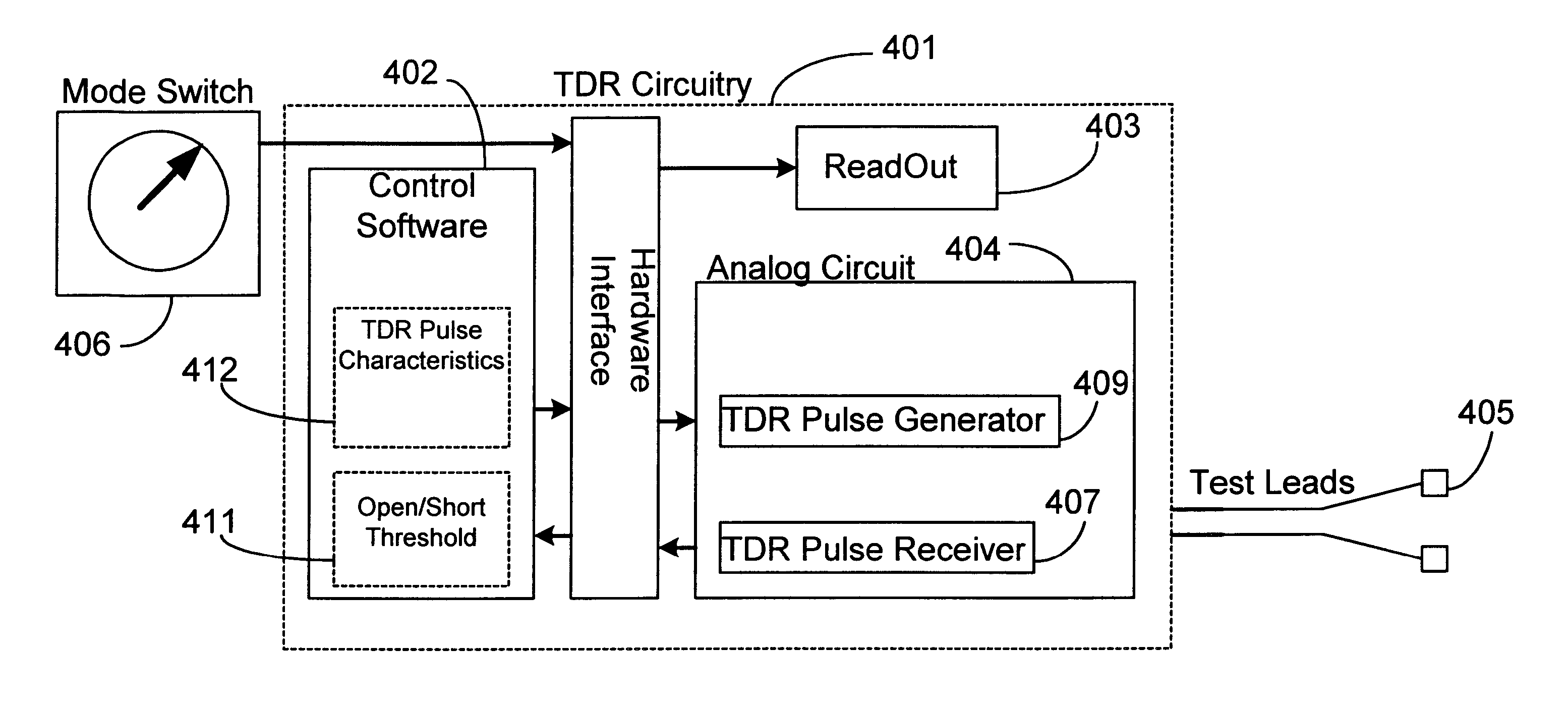

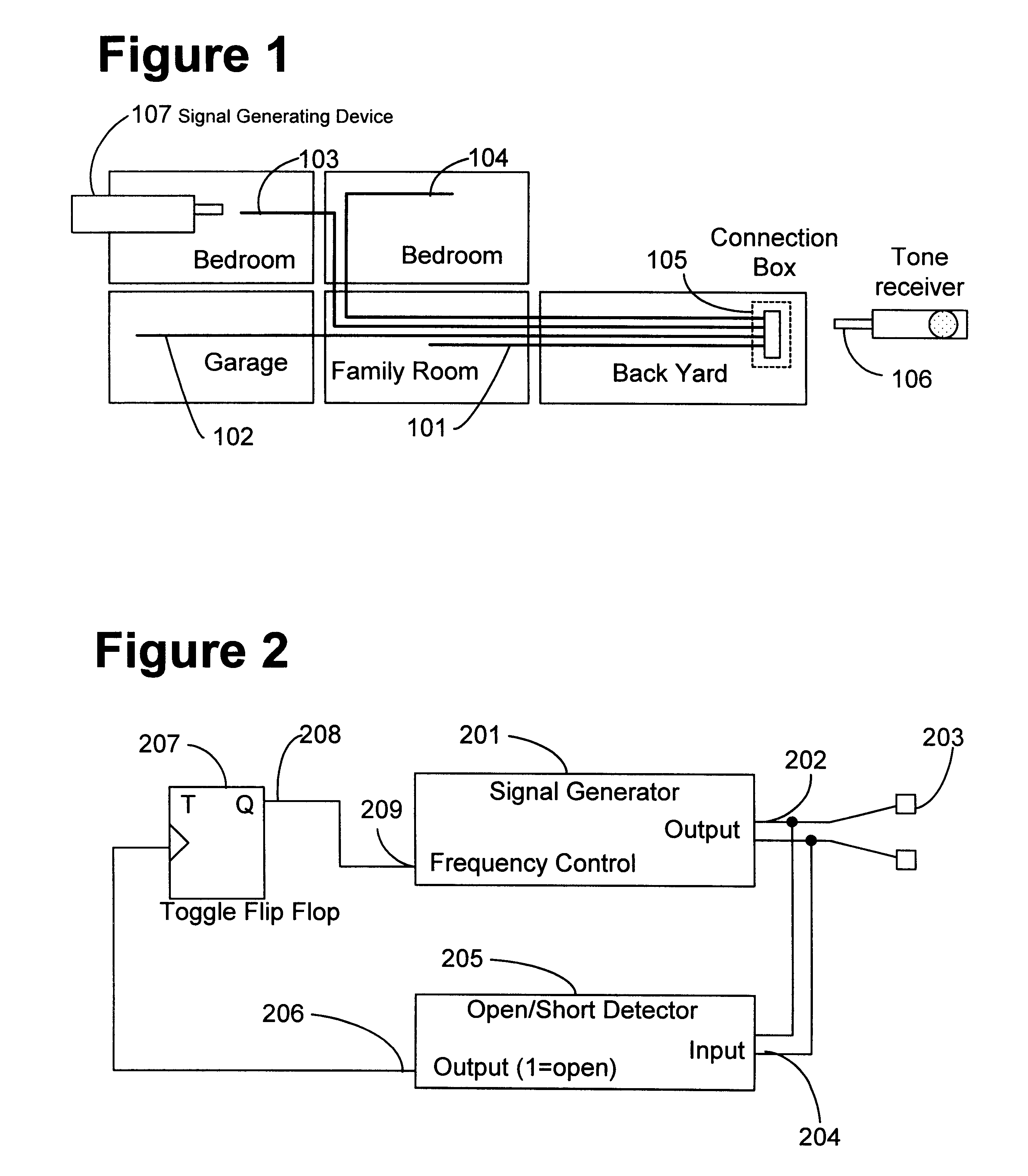

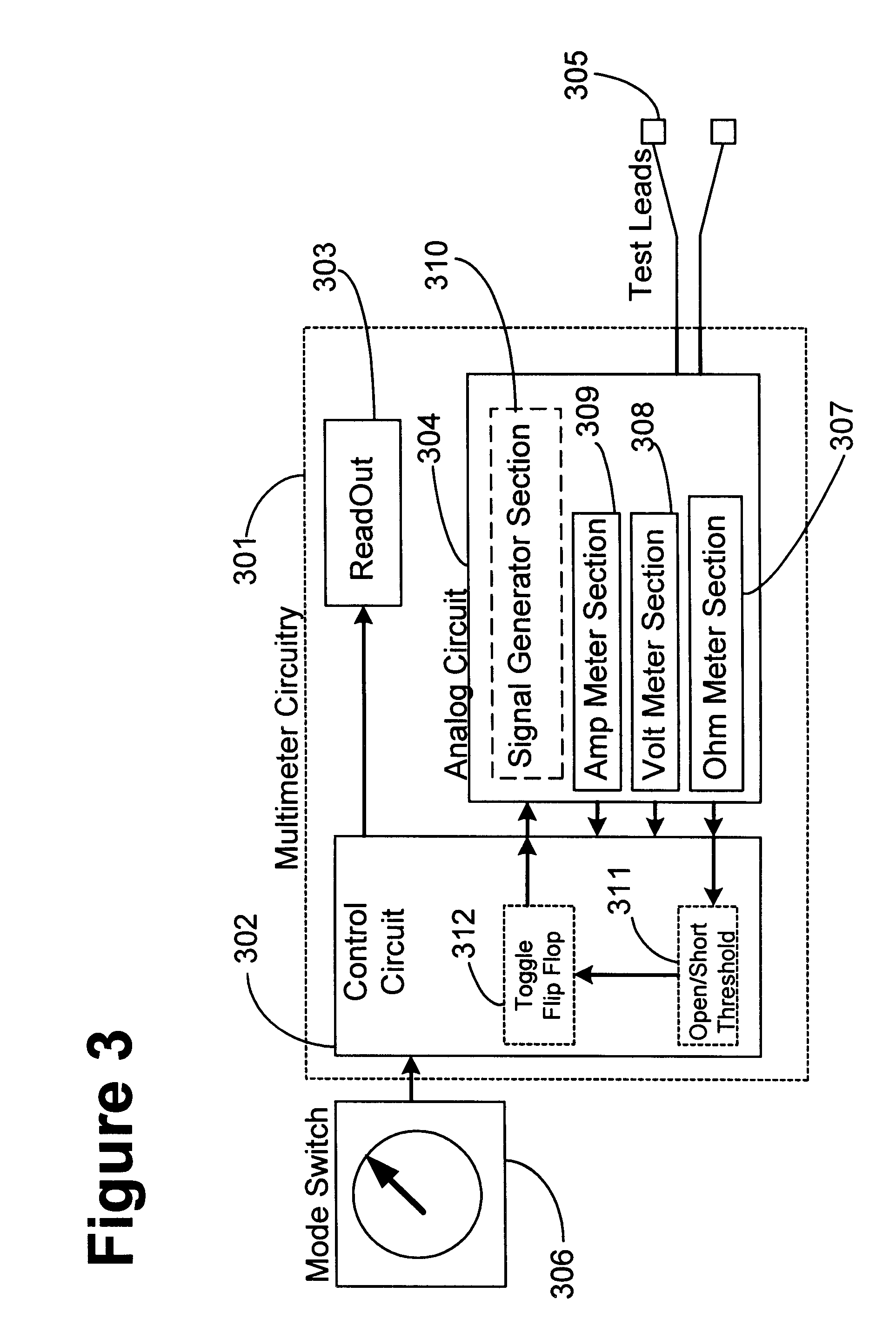

InactiveUS6323654B1Minimal and even additional costFault location by increasing destruction at faultFault location by pulse reflection methodsTime-domain reflectometerTime domain

A detector and a variable signal generator are coupled so that one or more specific changes in the output of the detector will cause a change in the characteristics of the generated signal. This change in signal characteristics is non-transient, the change remaining in effect until such time that another change in the detector output causes another change in the signal characteristic. The system can provide remote-end positive wire identification with no additional instrumentation at the remote end. When this invention is embodied in an already existing piece of test equipment, such as a multimeter or time domain reflectometer, there need be no additional hardware instrumentation at either end.

Owner:JOHN FLUKE MFG CO INC

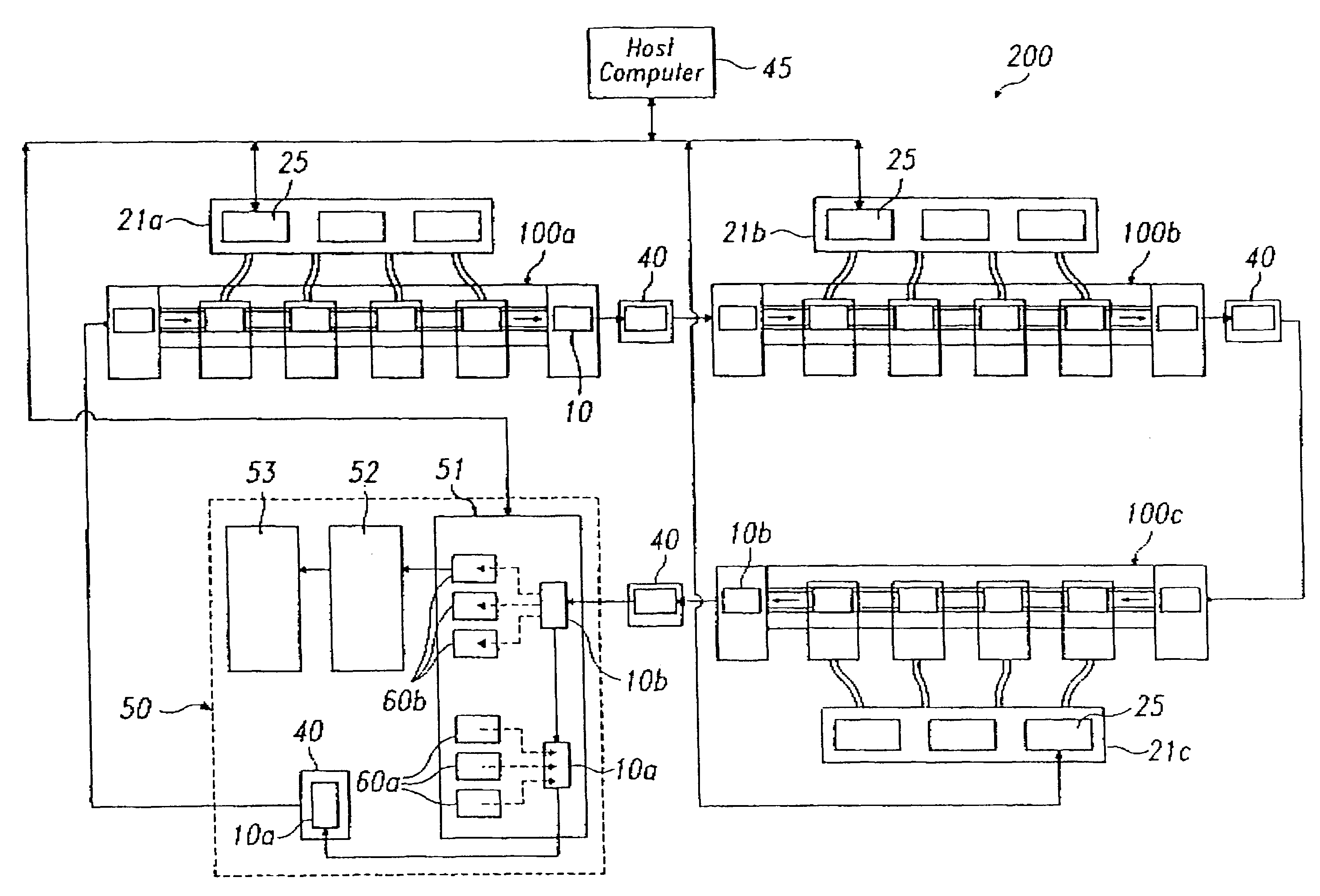

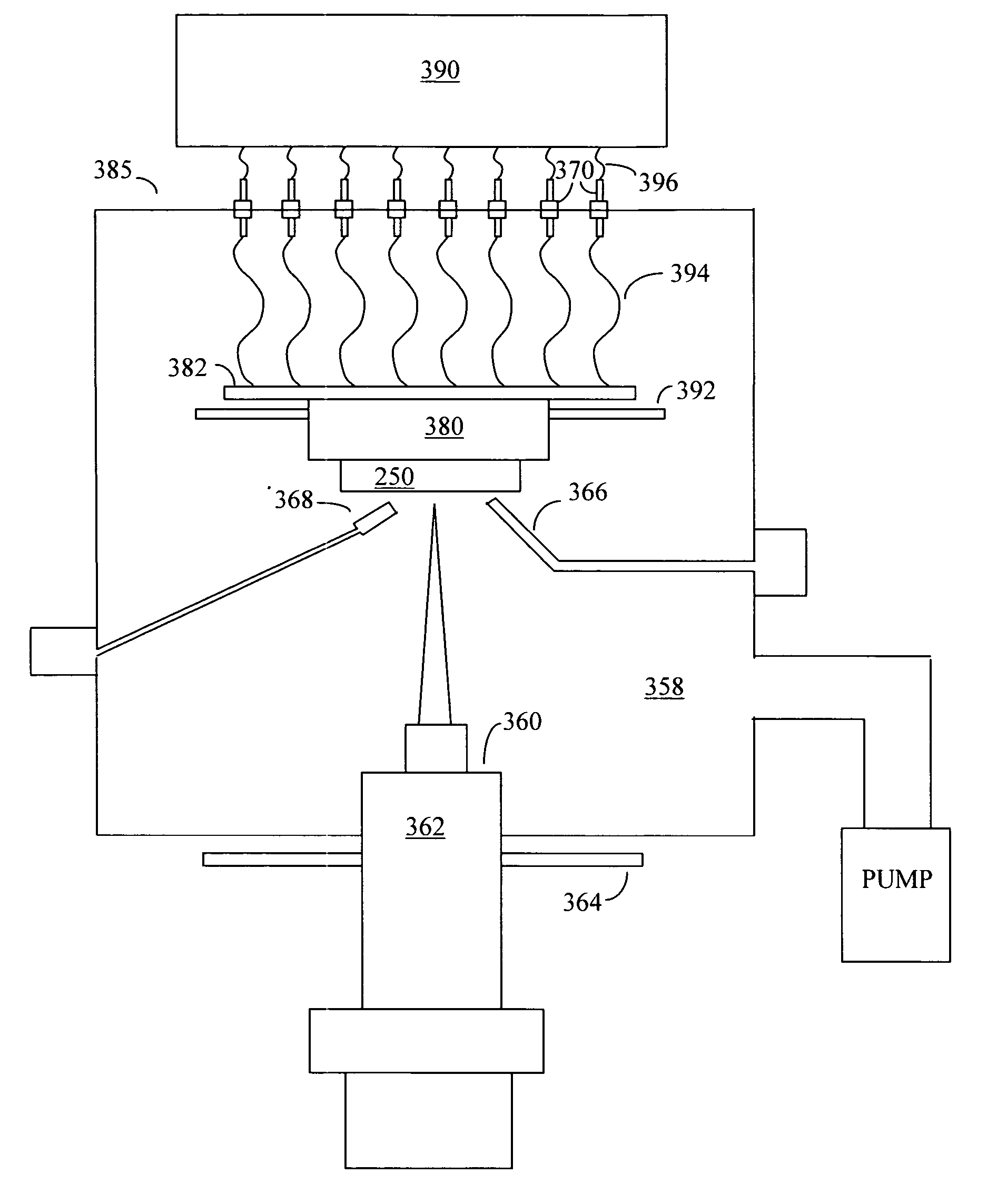

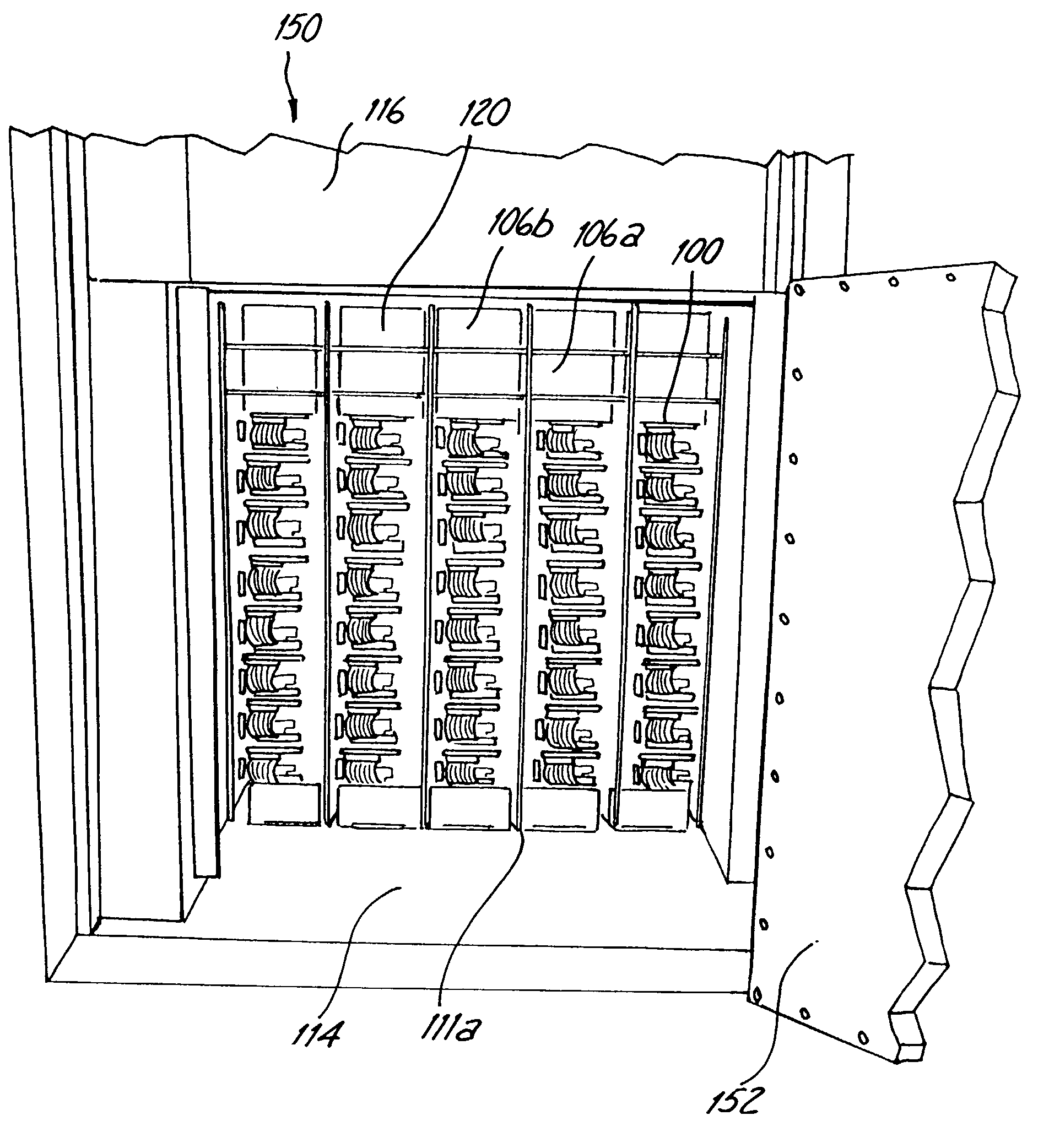

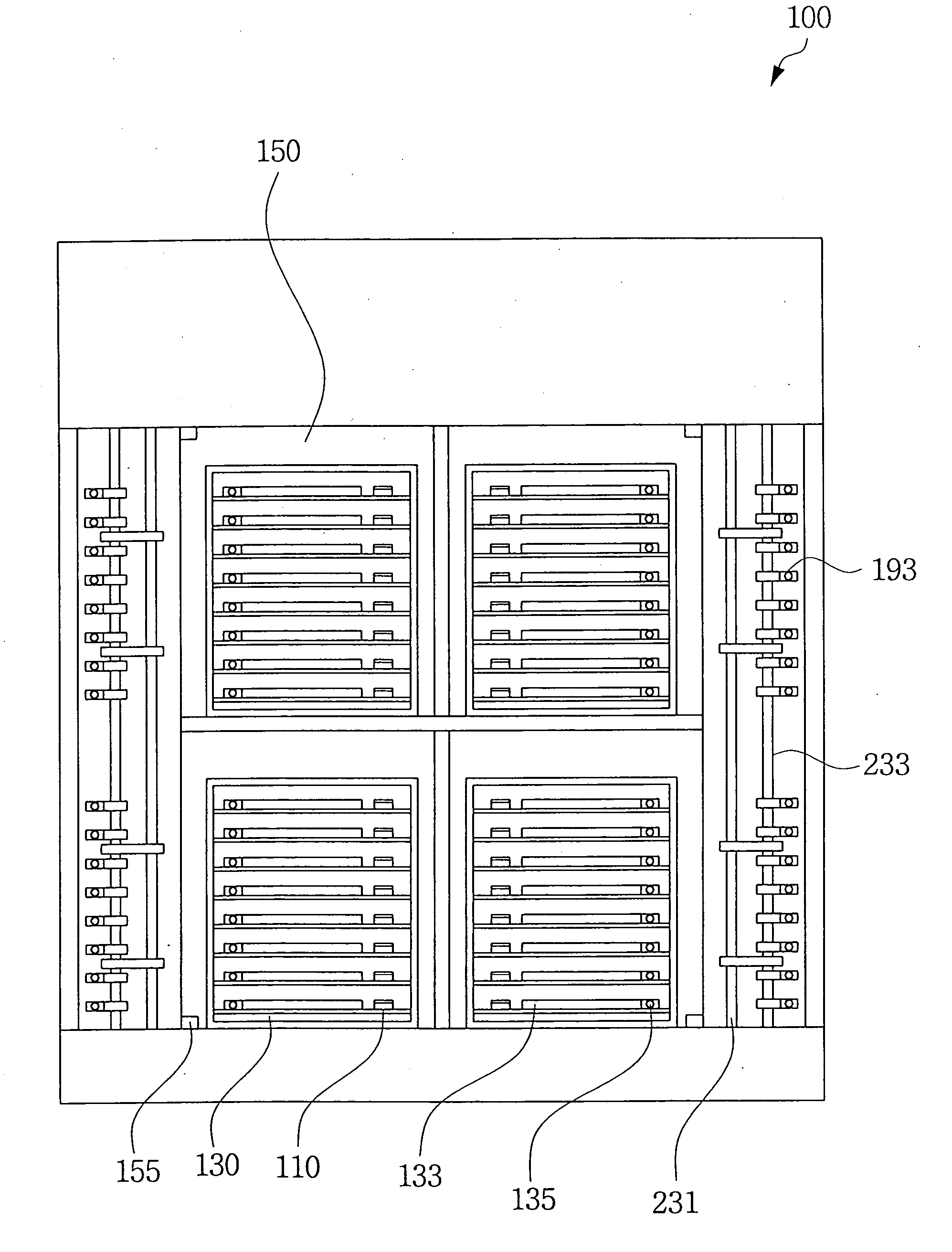

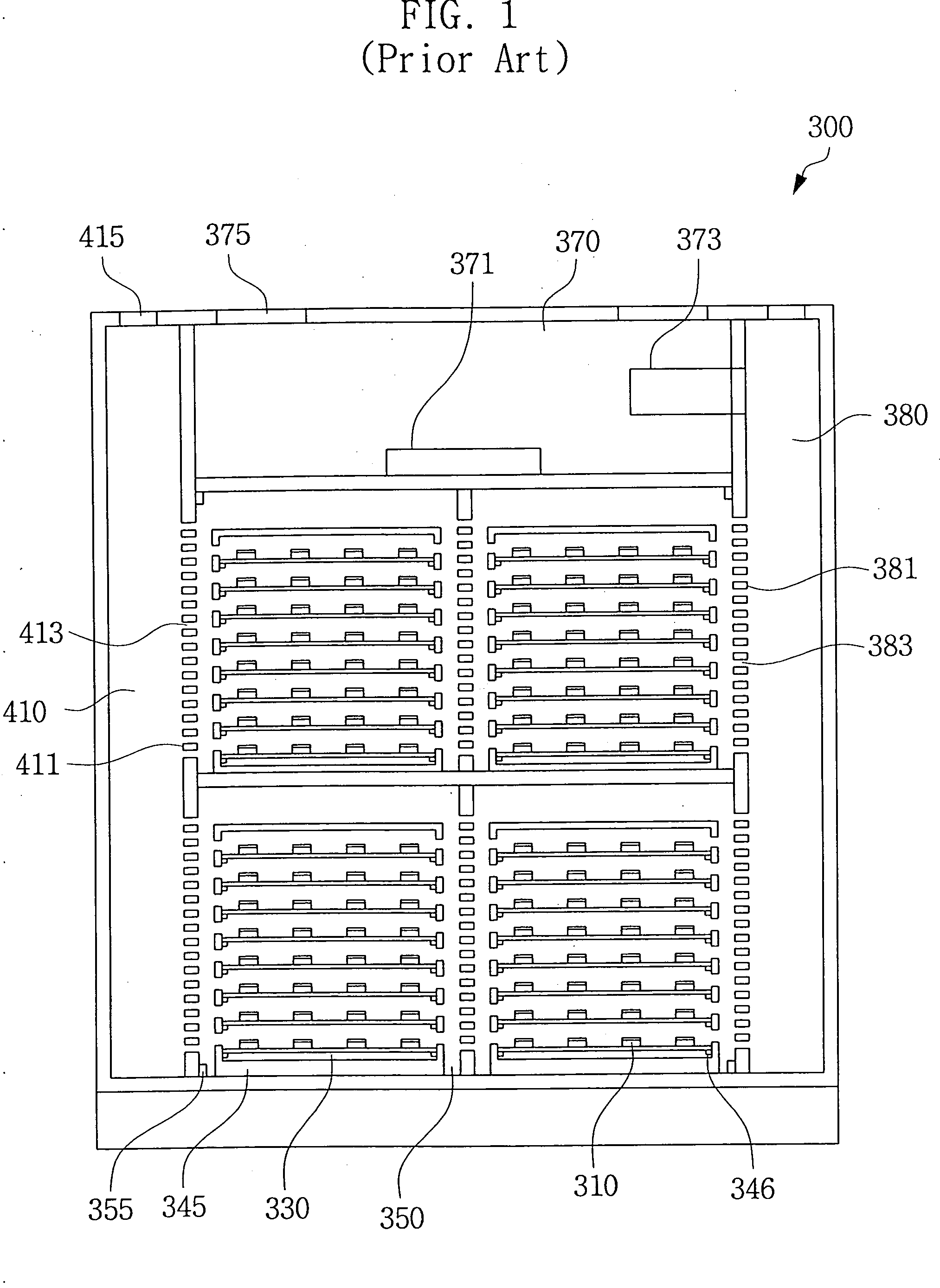

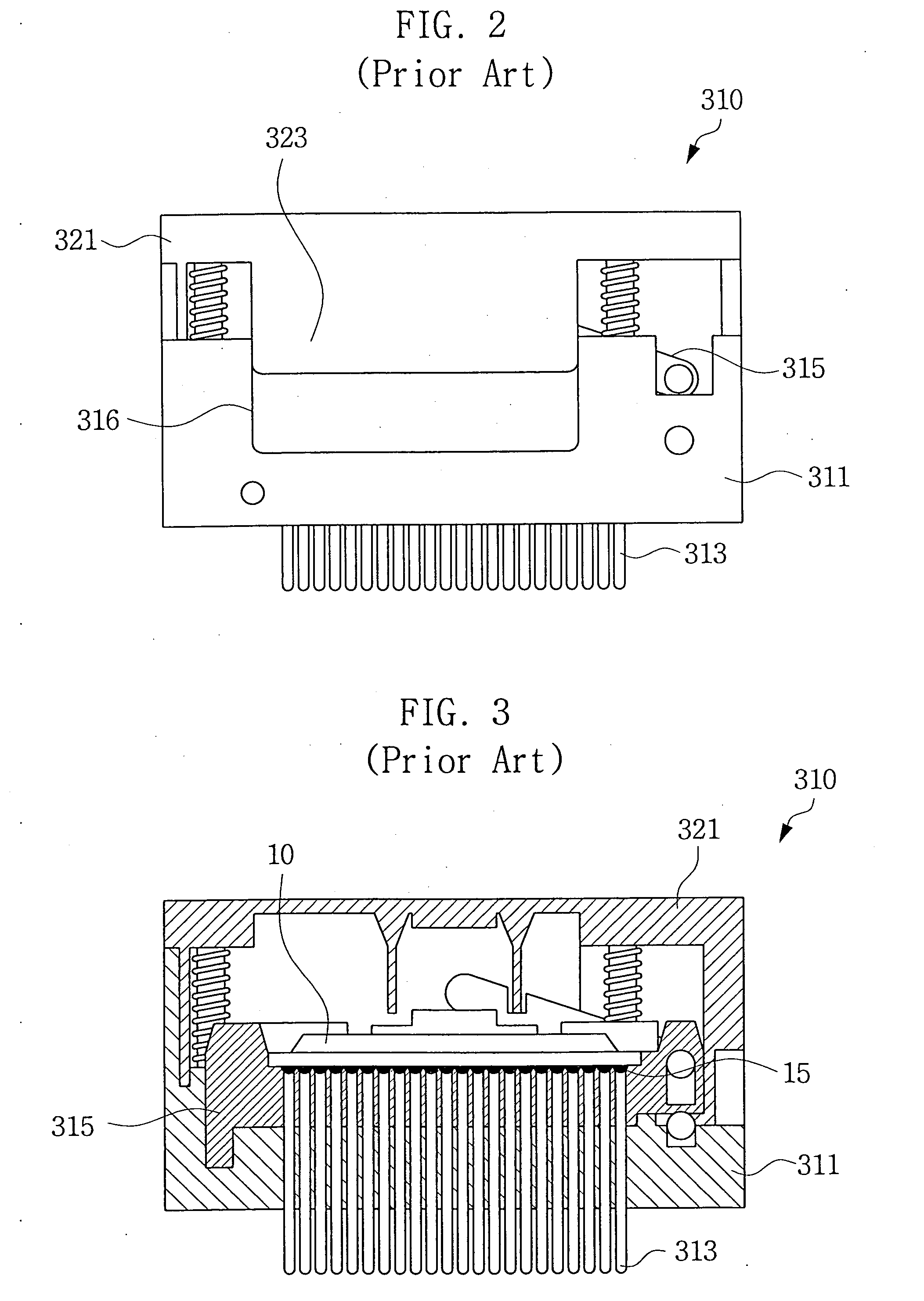

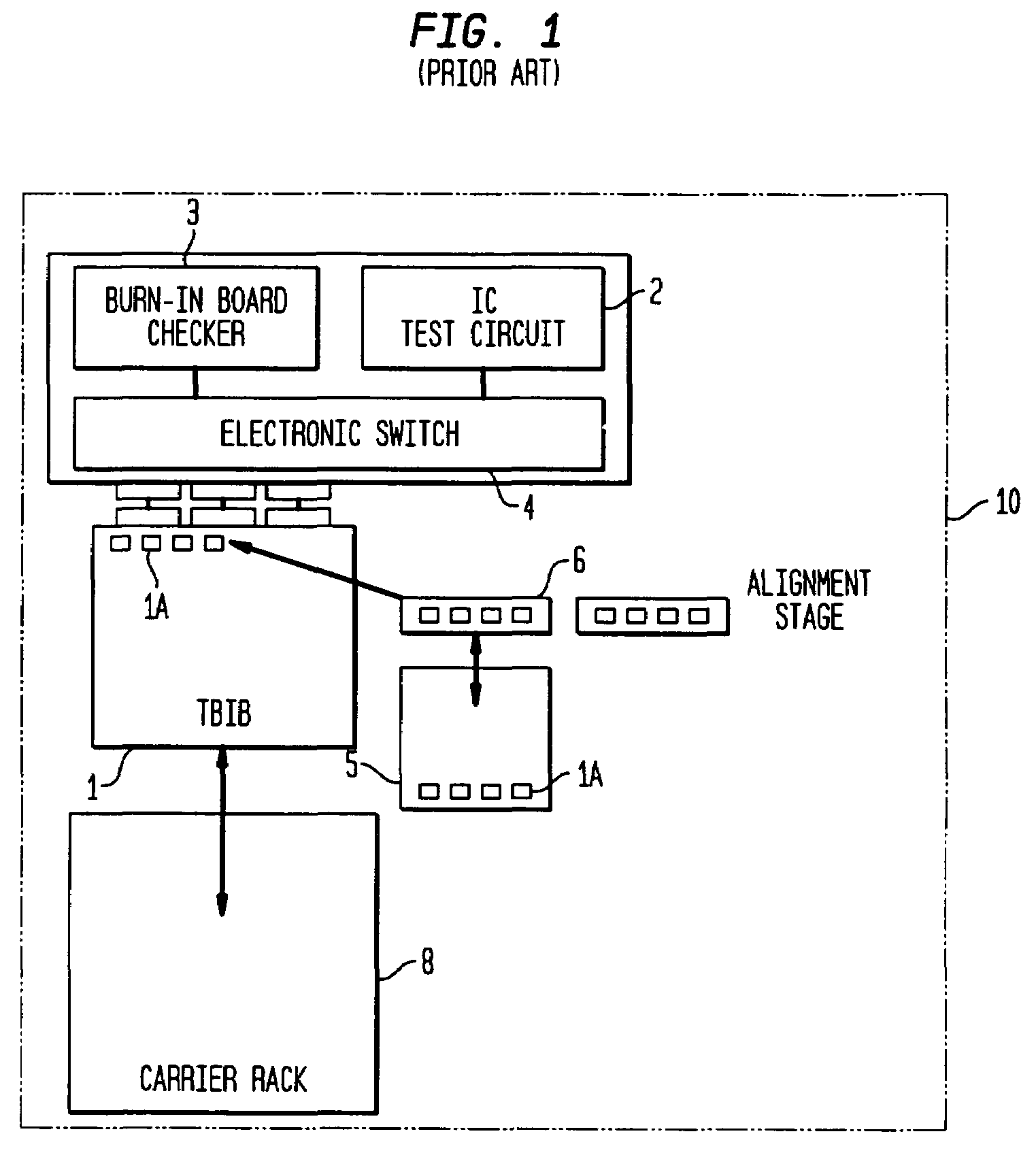

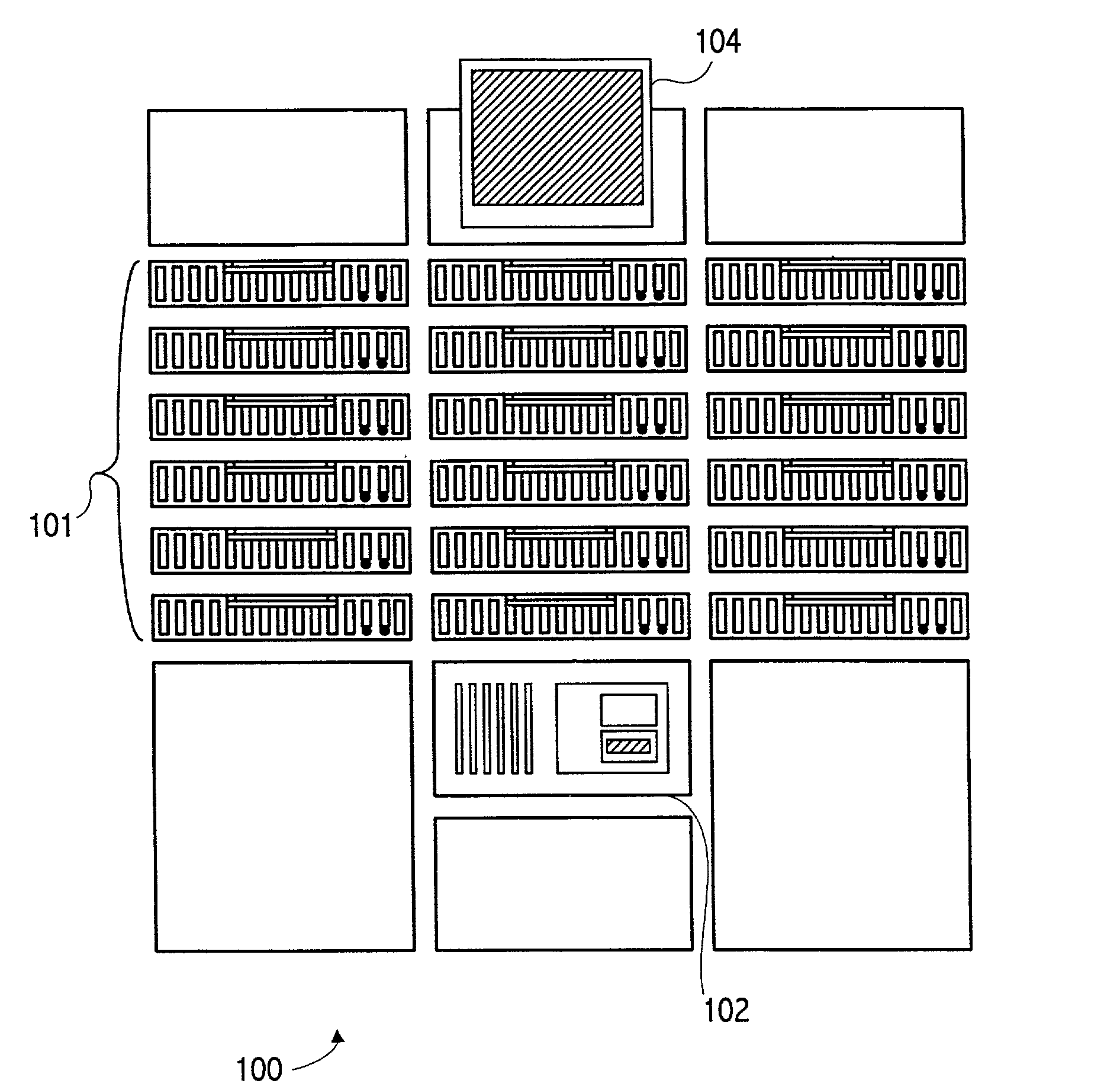

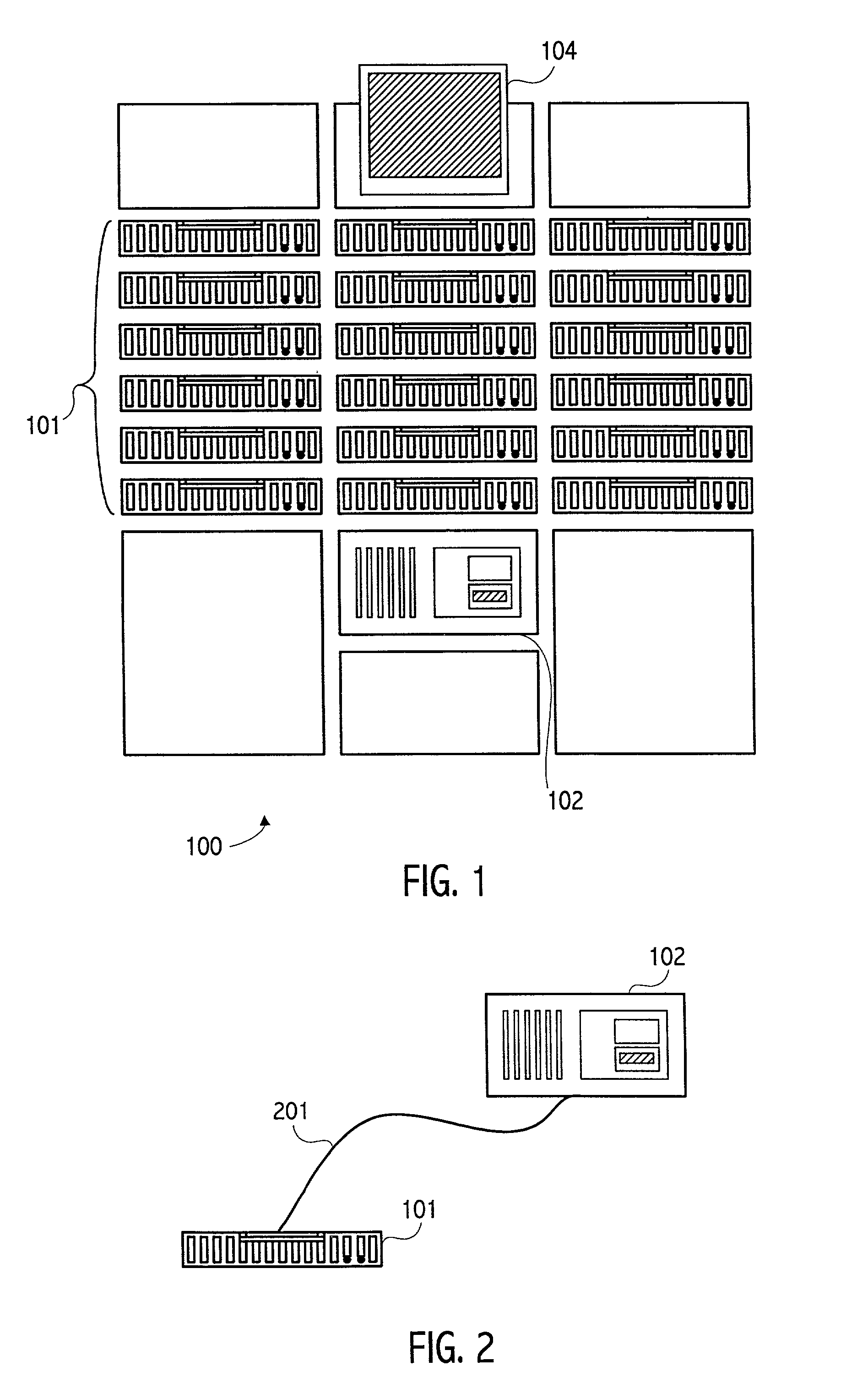

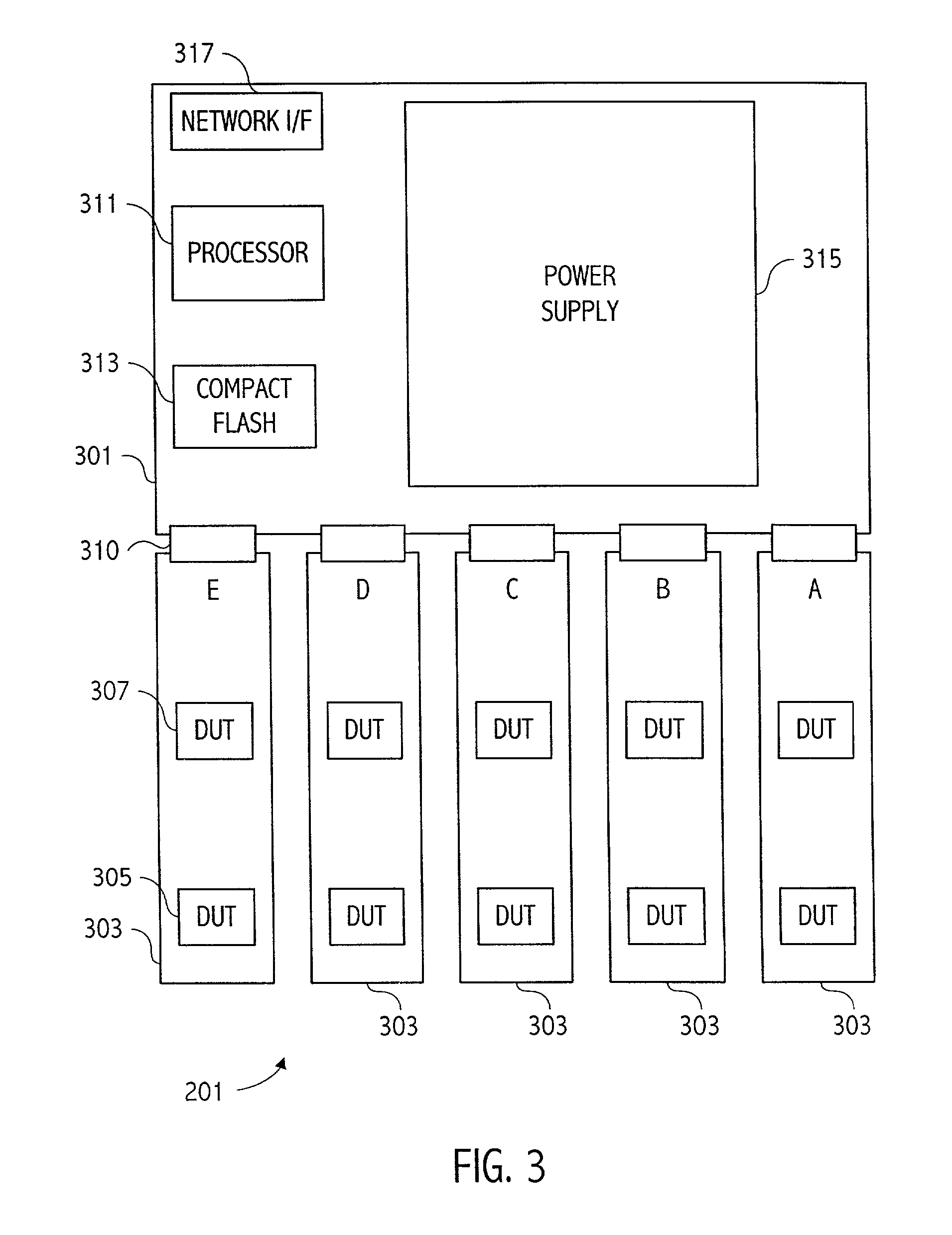

Test and burn-in apparatus, in-line system using the test and burn-in apparatus, and test method using the in-line system

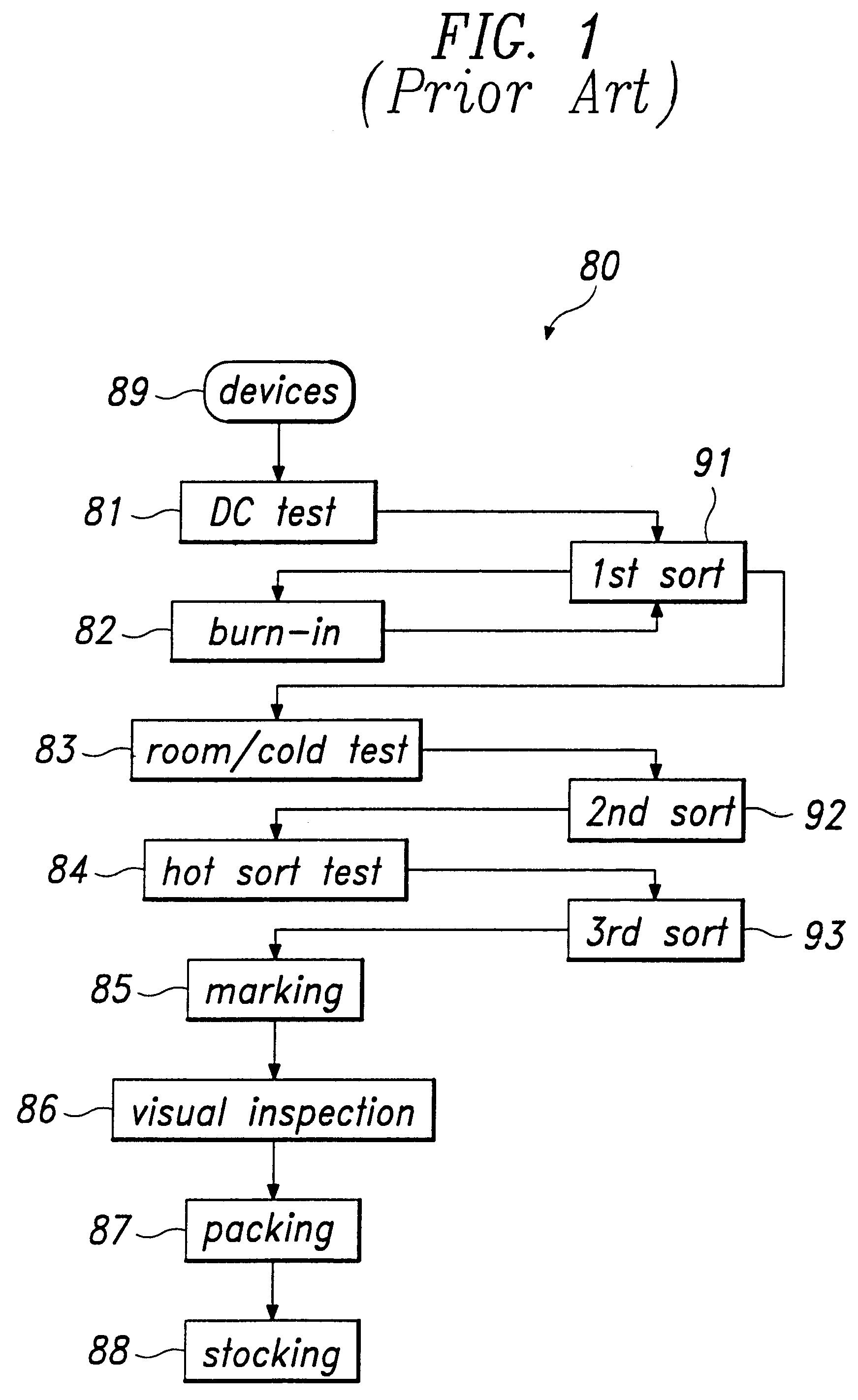

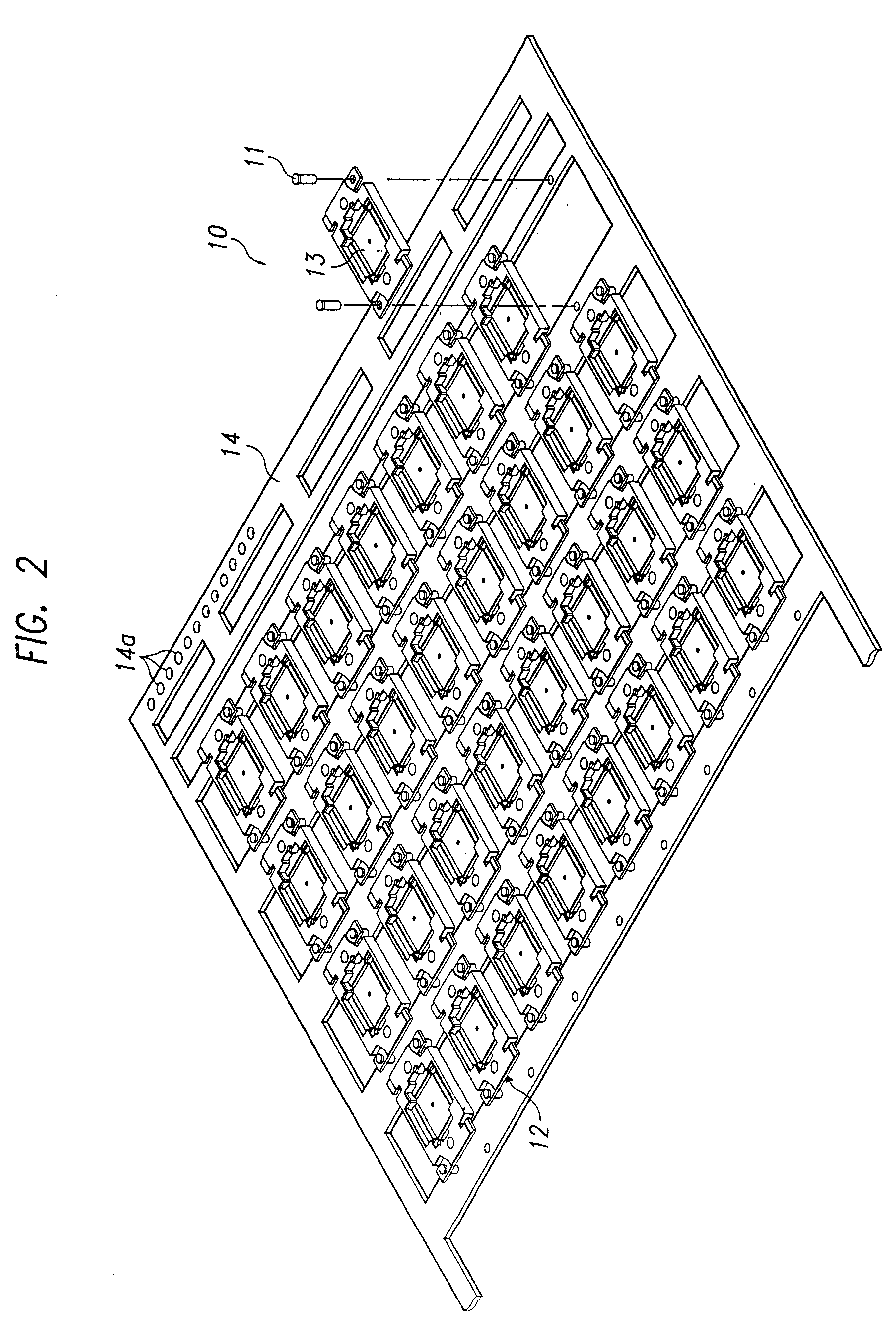

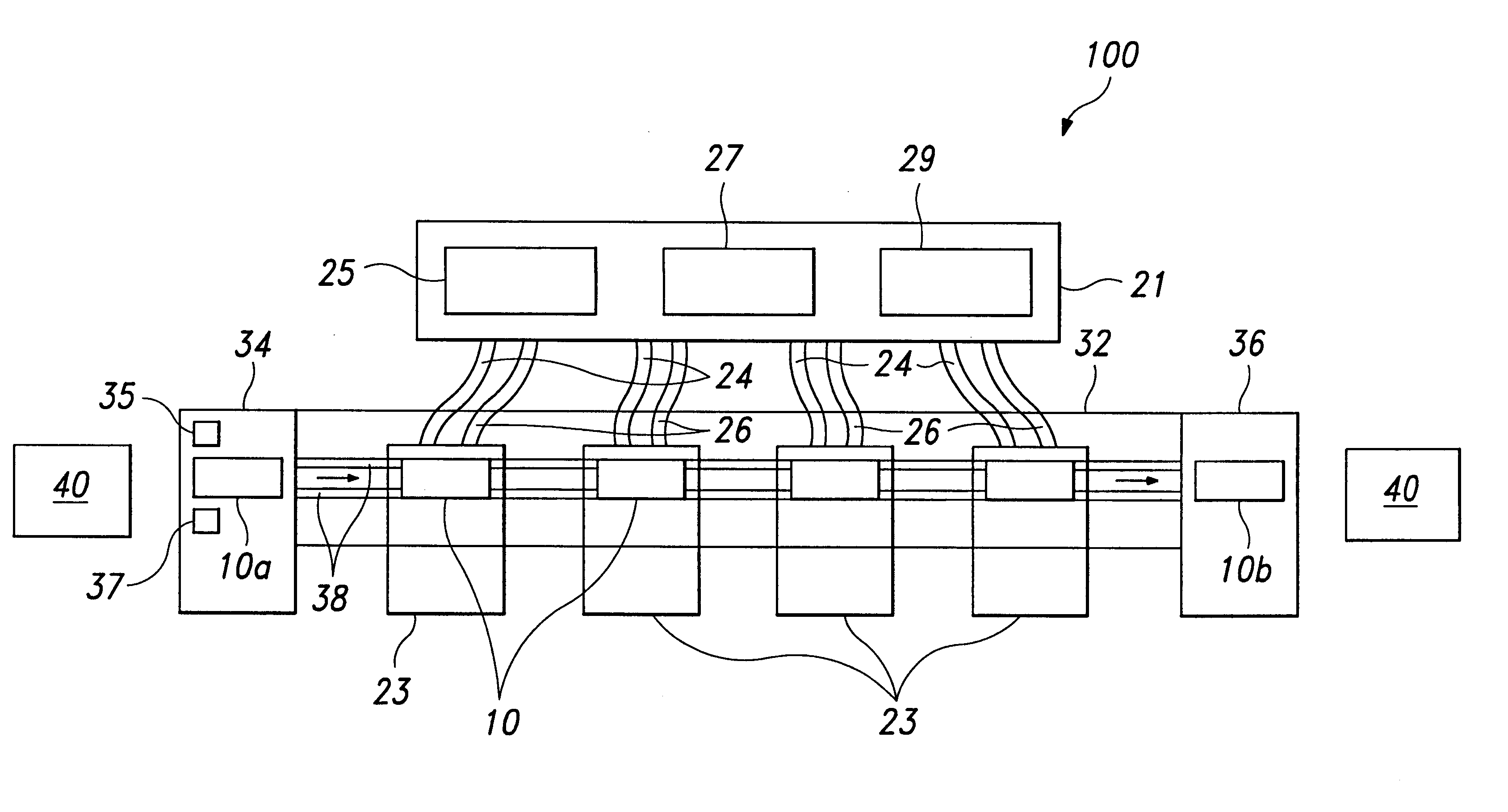

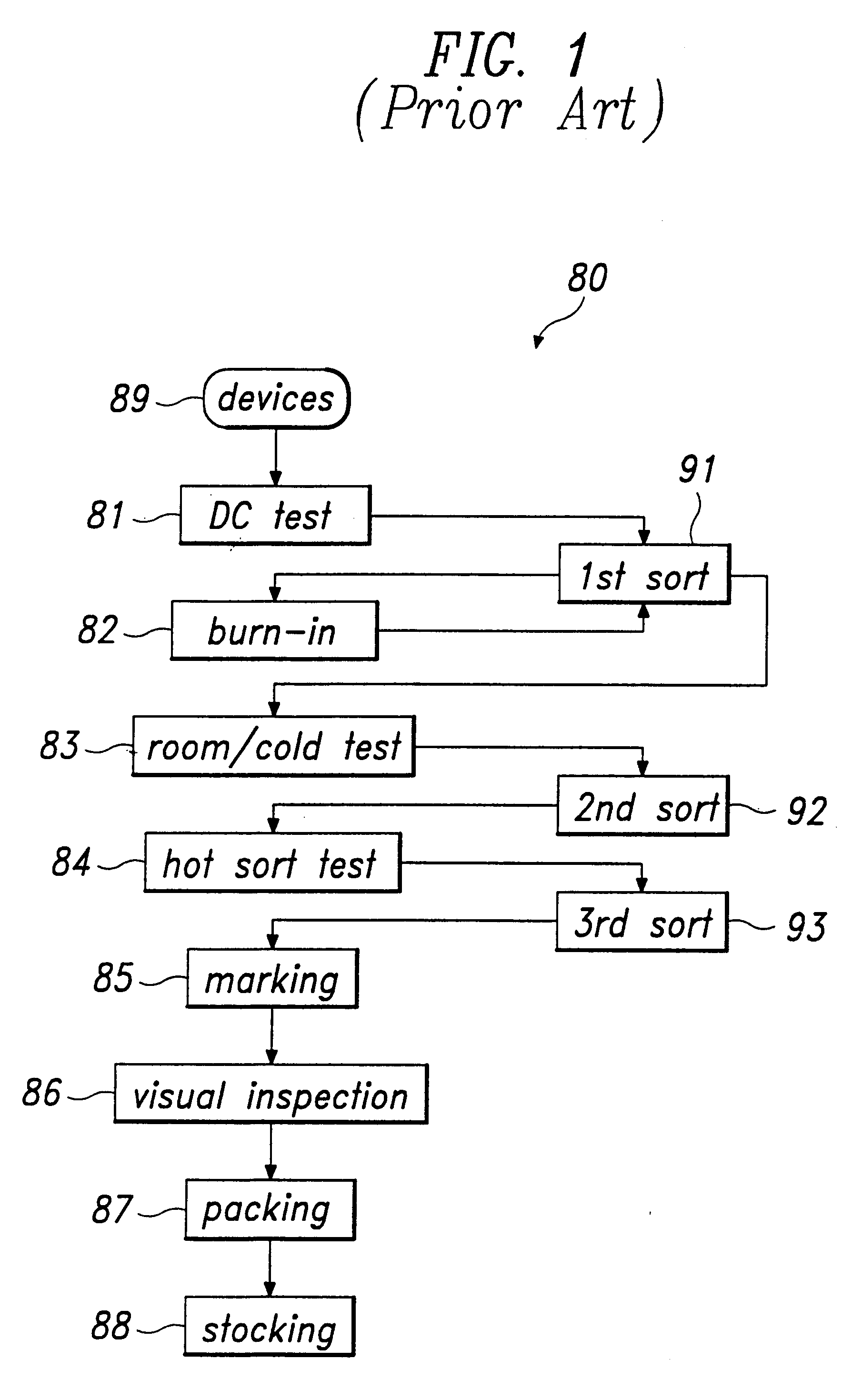

InactiveUS6563331B1Reduced number of stepAvoid excess performanceSemiconductor/solid-state device testing/measurementElectronic circuit testingDevice materialTest phase

An apparatus for testing semiconductor devices allows various testing processes, including a burn-in process, to be performed at the same testing stage. Test trays which contain the semiconductor devices are used throughout an in-line system so that an entire back-end process can be performed without loading / unloading the semiconductor devices between the various tests. The in-line system includes multiple test and burn-in apparatuses as well as a single sorting unit which performs a composite sorting operation after all the testing processes. A method for testing semiconductor devices in the in-line system includes testing the semiconductor devices in the test trays using the test and burn-in apparatus, transferring the test trays to a different testing apparatus for a second testing, and finally sorting the semiconductor devices after all testing processes have been performed based on a final sorting map created by combining test tray maps generated during each of the tests.

Owner:SAMSUNG ELECTRONICS CO LTD

Test and burn-in apparatus, in-line system using the test and burn-in apparatus, and test method using the in-line system

InactiveUS6313652B1Reduced number of stepAvoid excess performanceSemiconductor/solid-state device testing/measurementElectronic circuit testingGeneration processDevice material

A test and burn-in apparatus for semiconductor chip package devices, an in-line system which includes the test and burn-in apparatus, and a test method which employs the in-line system are provided. A test and burn-in apparatus for testing semiconductor devices allows various testing processes, including a burn-in process, to be performed at the same testing stage. The apparatus employs test trays which contain the semiconductor devices. These test trays are used throughout the in-line system so that an entire back-end process can be performed without the need for loading / unloading the semiconductor devices into and from device trays between the various tests. The test and burn-in apparatus according to this invention can therefore occupy less space than the prior art testing apparatuses. The in-line system includes multiple test and burn-in apparatuses as well as a single sorting unit which performs a composite sorting operation after all the testing processes have been performed. Furthermore, the method for testing the semiconductor devices in the in-line system includes testing the semiconductor devices in the test trays using the test and burn-in apparatus, generating a test tray map corresponding to results of the test, transferring the test trays to a different testing apparatus for a second testing and test tray map generation process, and finally sorting the semiconductor devices in the sorting unit after all testing processes have been performed based on a final sorting map created by combining the test tray maps of each of the tests. The benefits of this invention are reduced time and space requirements because neither transferring the devices to device trays between tests nor performing multiple sorting steps are required.

Owner:SAMSUNG ELECTRONICS CO LTD

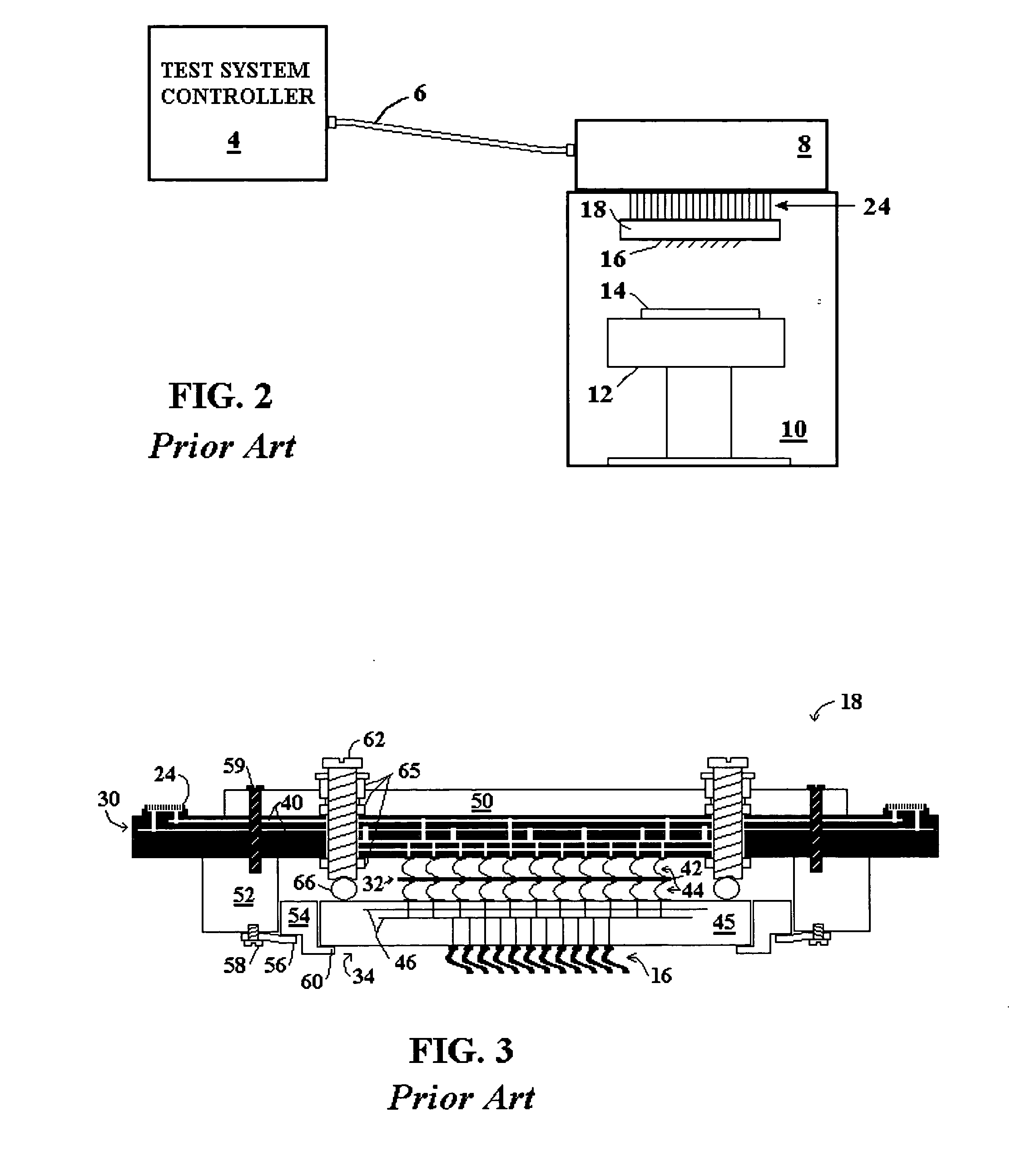

Probe station thermal chuck with shielding for capacitive current

InactiveUS20070030021A1Semiconductor/solid-state device testing/measurementThermoelectric device with peltier/seeback effectCapacitanceElectricity

To reduce noise in measurements obtained by probing a device supported on surface of a thermal chuck in a probe station, a conductive member is arranged to intercept current coupling the thermal unit of the chuck to the surface supporting the device. The conductive member is capacitively coupled to the thermal unit but free of direct electrical connection thereto.

Owner:FORMFACTOR BEAVERTON INC

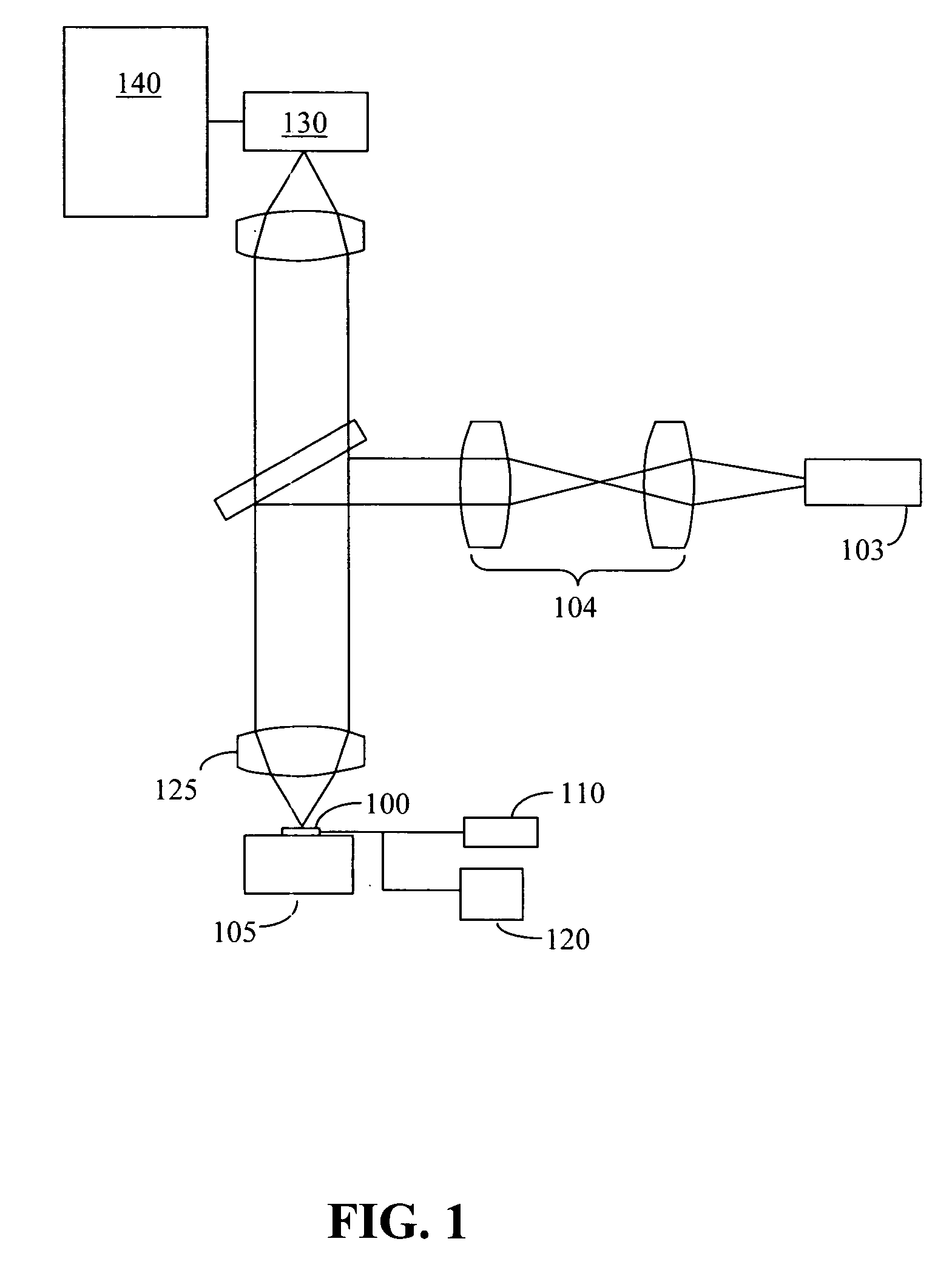

Integration of photon emission microscope and focused ion beam

InactiveUS20060012385A1Vacuum gauge using ionisation effectsFault location by increasing destruction at faultPhoton emissionIon beam

An integrated FIB / PEM apparatus and method for performing failure analysis on integrated circuits. In-situ failure analysis is enabled by integrating Photon Emission Microscopy into a Focused Ion Beam system, thereby improving throughput and efficiency of Failure Analysis. An iterative method is described for identifying and localizing fault sites on the circuit.

Owner:DCG SYST

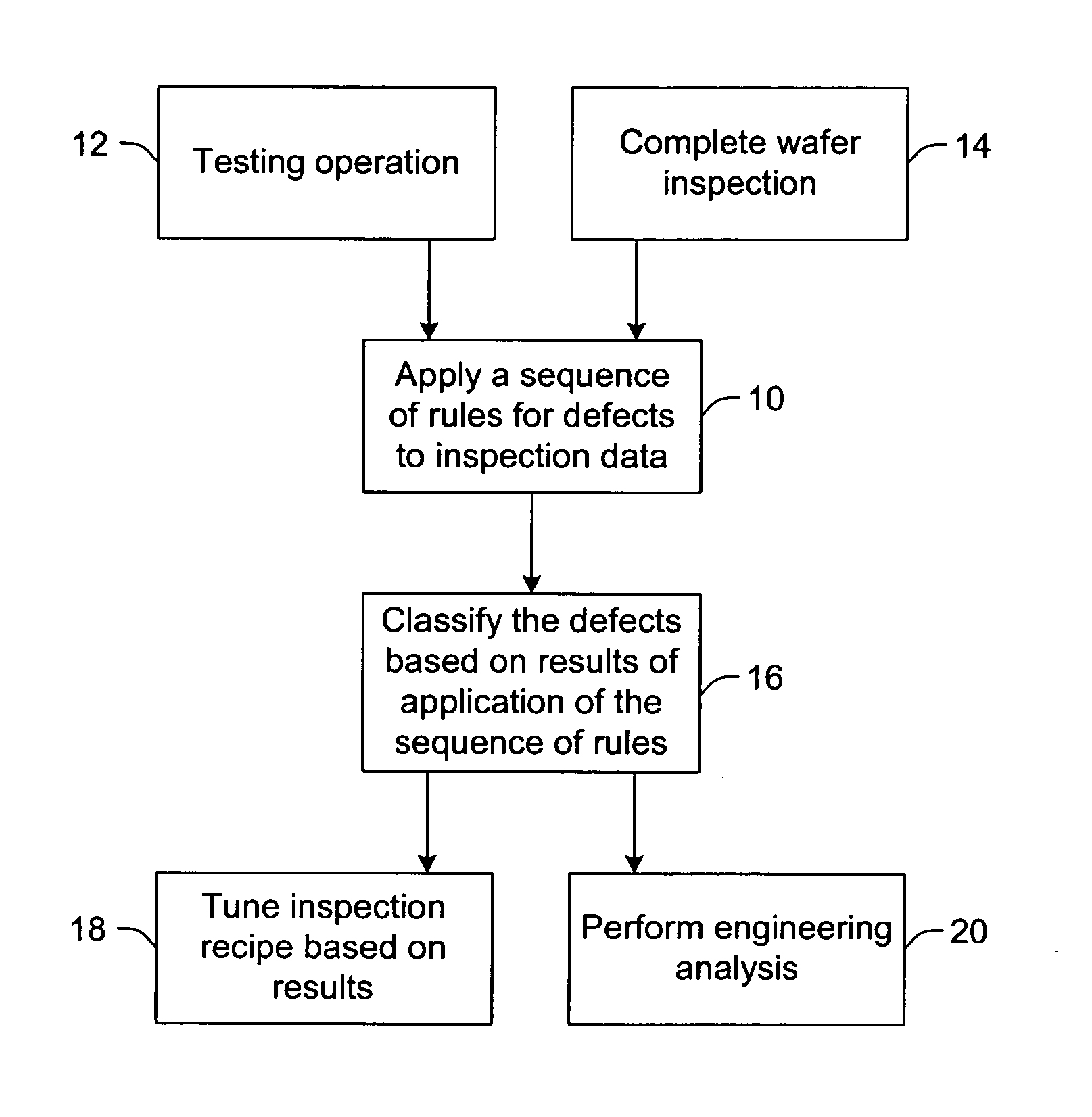

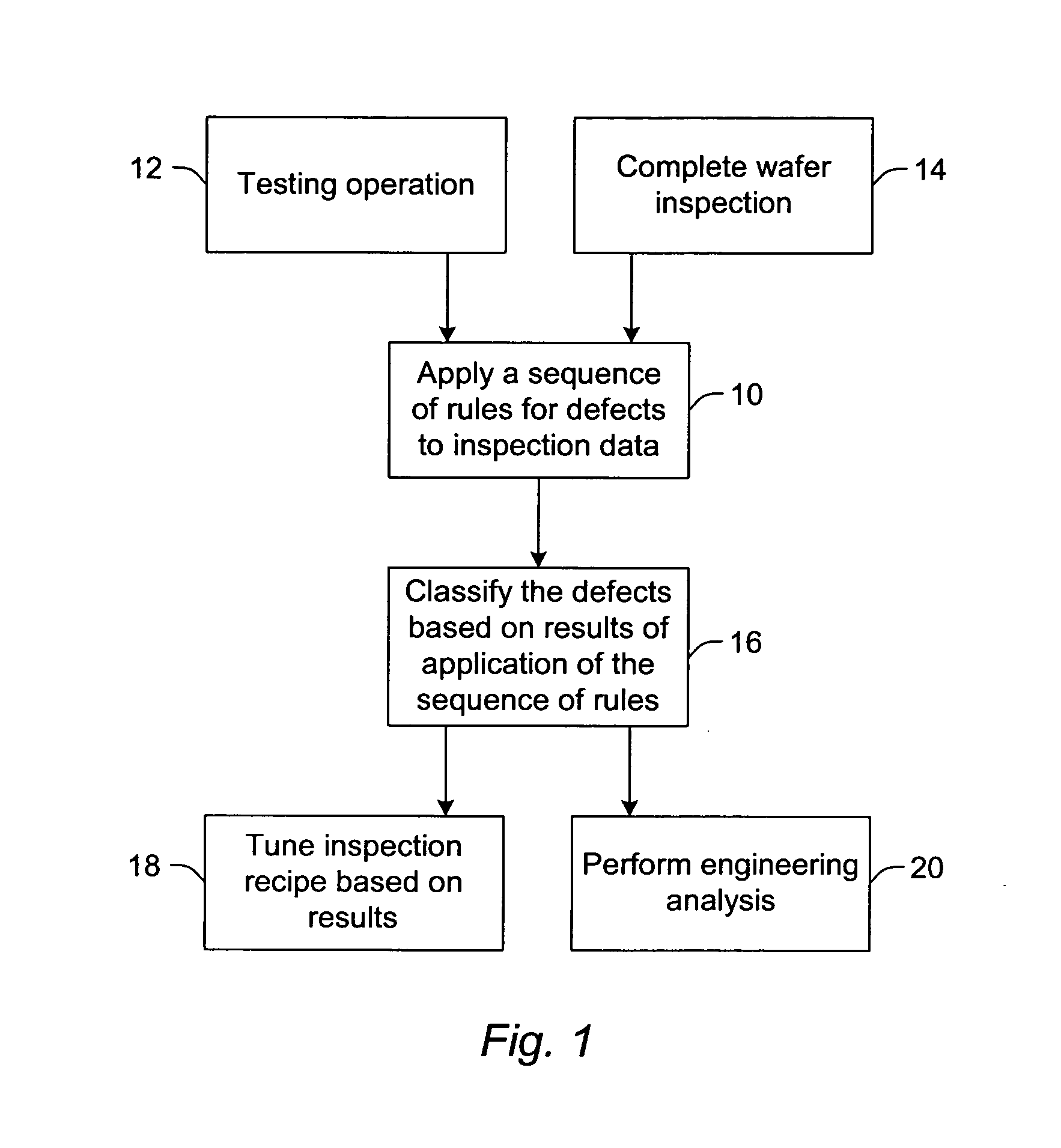

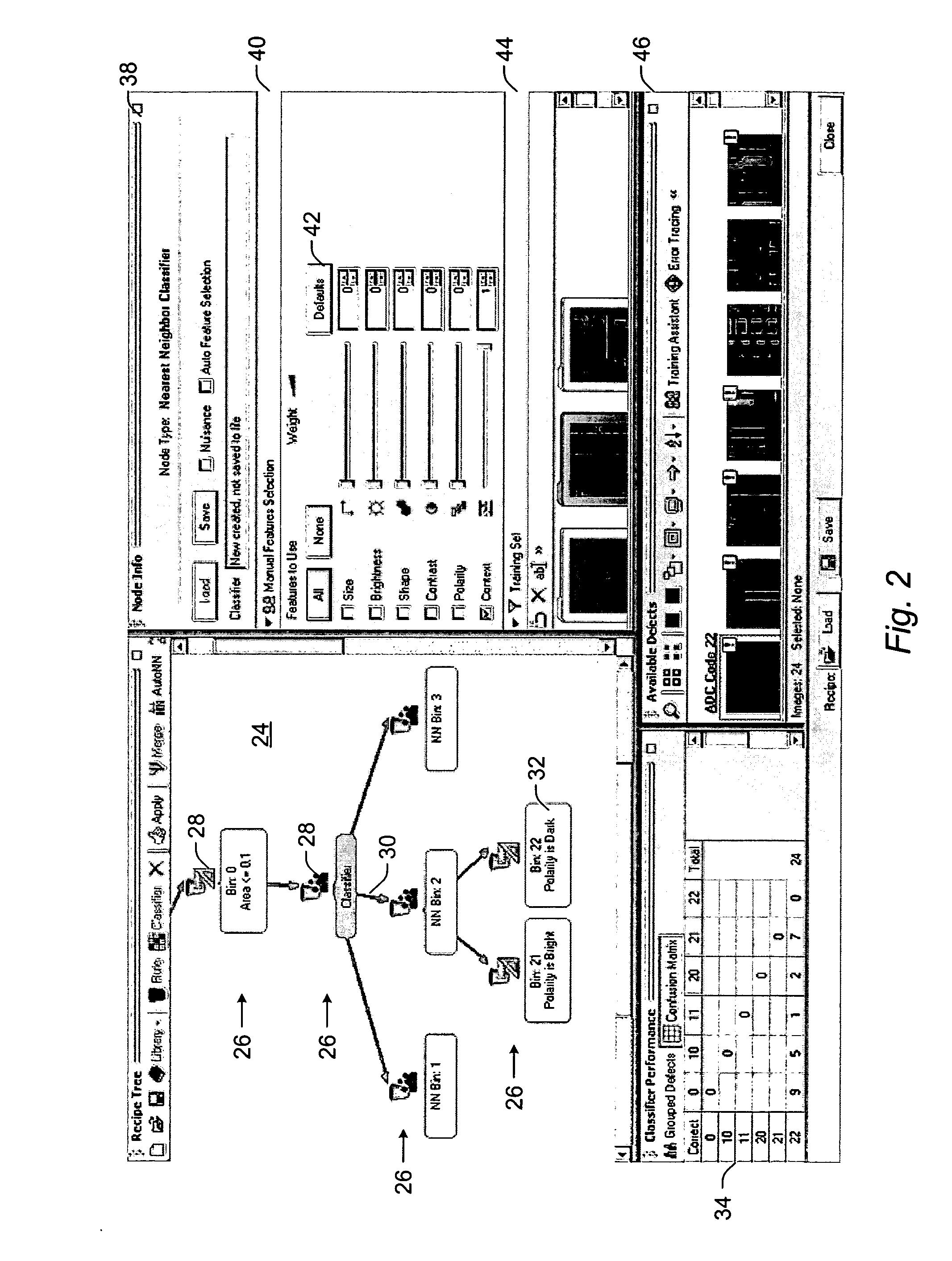

Flexible hybrid defect classification for semiconductor manufacturing

ActiveUS20060265145A1Fast executionSetup of such a classifier is relatively simpleImage enhancementImage analysisHybrid approachAlgorithm

Hybrid methods for classifying defects in semiconductor manufacturing are provided. The methods include applying a flexible sequence of rules for defects to inspection data. The sequence of rules includes deterministic rules, statistical rules, hybrid rules, or some combination thereof. The rules included in the sequence may be selected by a user using a graphical interface The method also includes classifying the defects based on results of applying the sequence of rules to the inspection data.

Owner:KLA TENCOR TECH CORP

Environmental test chamber and a carrier for use therein

InactiveUS7070323B2Easy to adaptReduce the total massWeather/light/corrosion resistanceElectronic circuit testingBrickEngineering

One aspect of the present invention is a system of fabricating a barrier wall between the testing and tester volumes of an environmental test chamber. This aspect may use a plurality of pallets adapted to receive a device under test and a testing apparatus, a framework adapted to receive a plurality of pallets, and a plurality of insulation bricks associated with the plurality of pallets. The insulation bricks may be adapted such that they can cooperate to form an insulating barrier between the device under test and the testing apparatus.

Owner:BENCHMARK ELECTRONICS SUZHOU

Wafer probe card

InactiveUS6265888B1Electrical measurement instrument detailsFault location by increasing destruction at faultProbe cardSpeed test

An apparatus to heat and test a semiconductor wafer includes a probe card and tests a plurality of die simultaneously at the wafer level. In the present invention, the apparatus heats the wafer to sufficient temperatures to perform burn-in and a speed test. A method of testing the semiconductor allows certain die to be repaired that would otherwise be scrapped in a conventional process where bun-in and other tests are performed on packaged die. The method also eliminates steps associated with handling individually packaged parts, reduces burn-in space and consolidates certain test steps.

Owner:SCS HIGHTECH +1

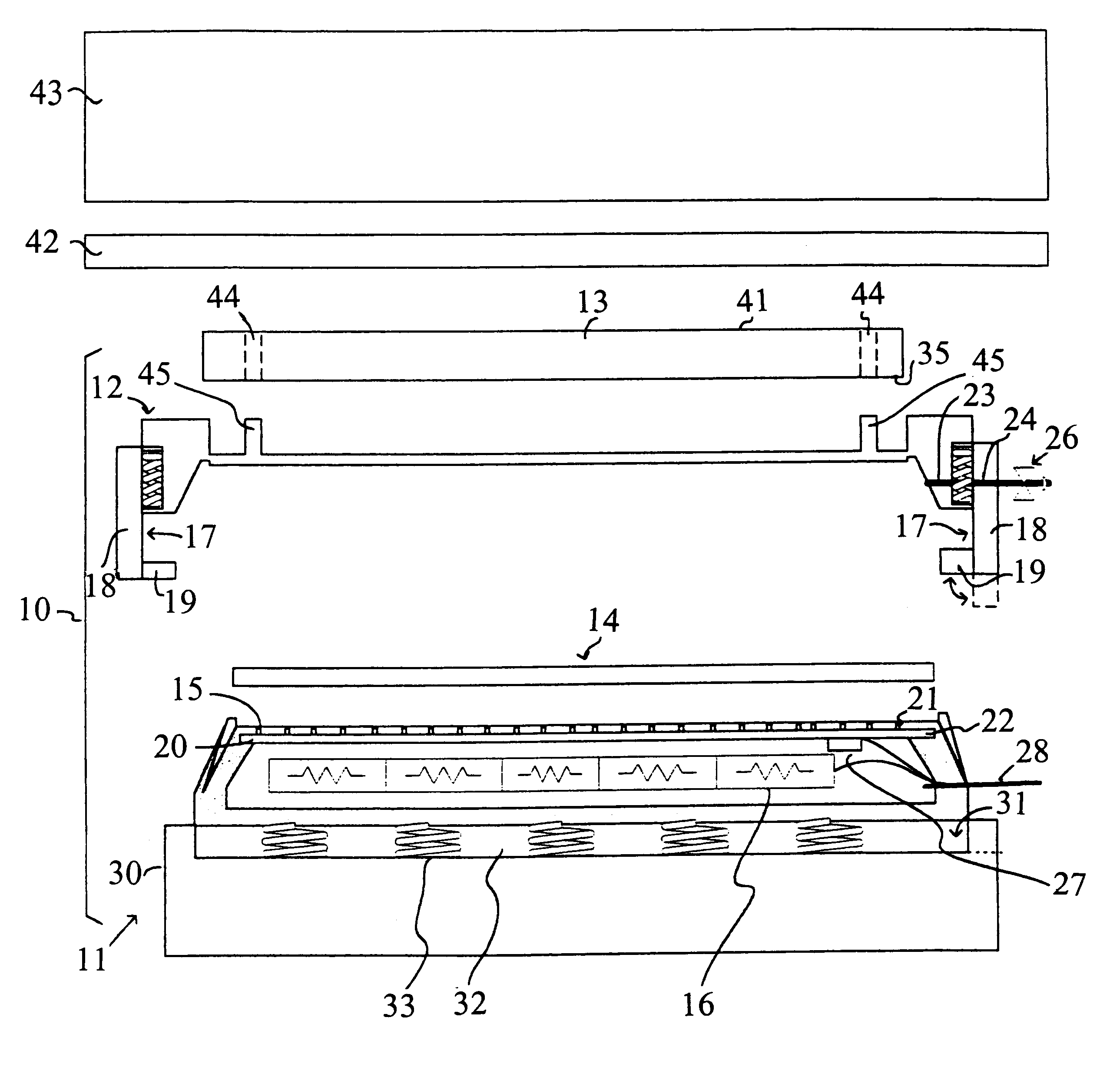

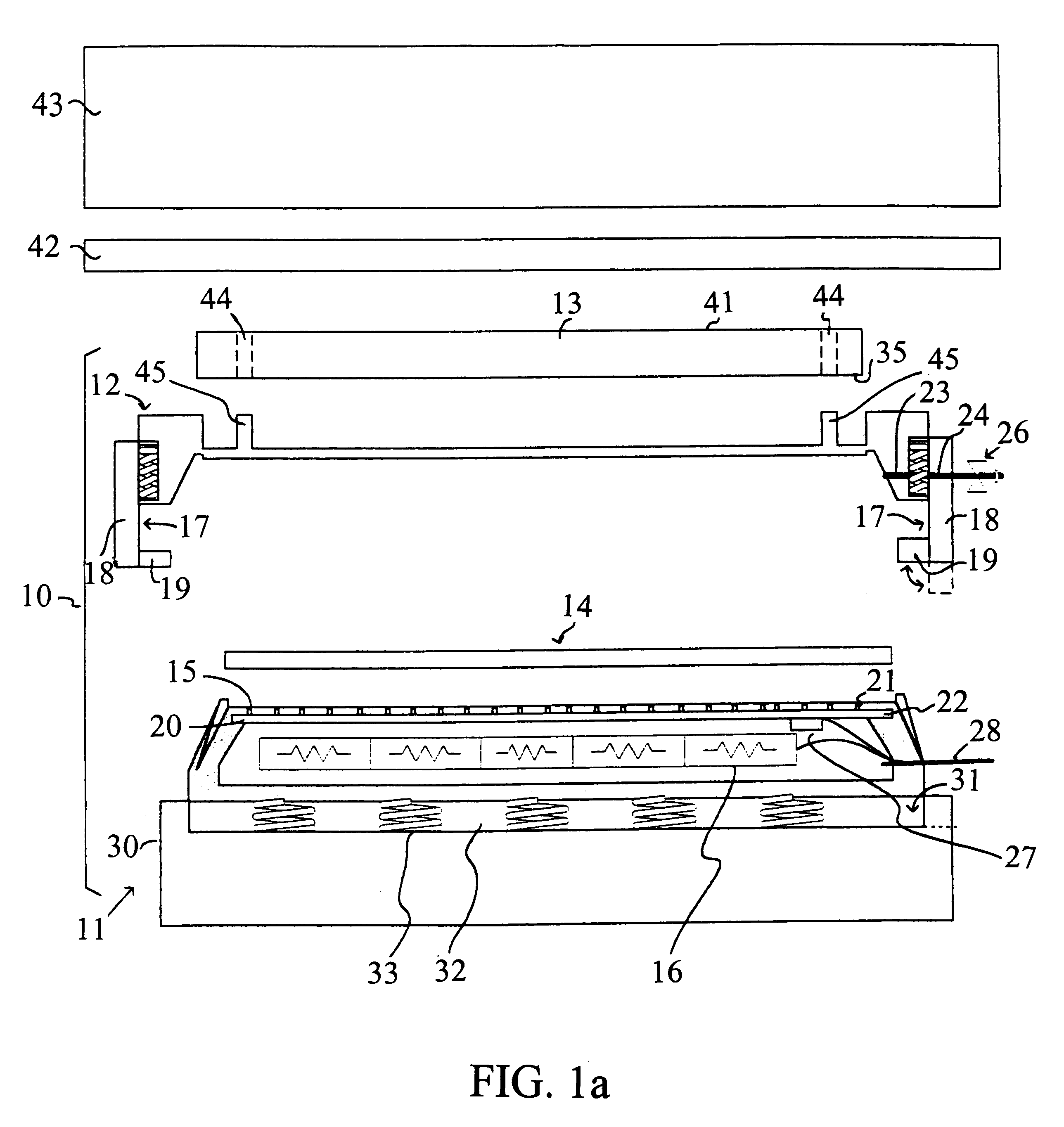

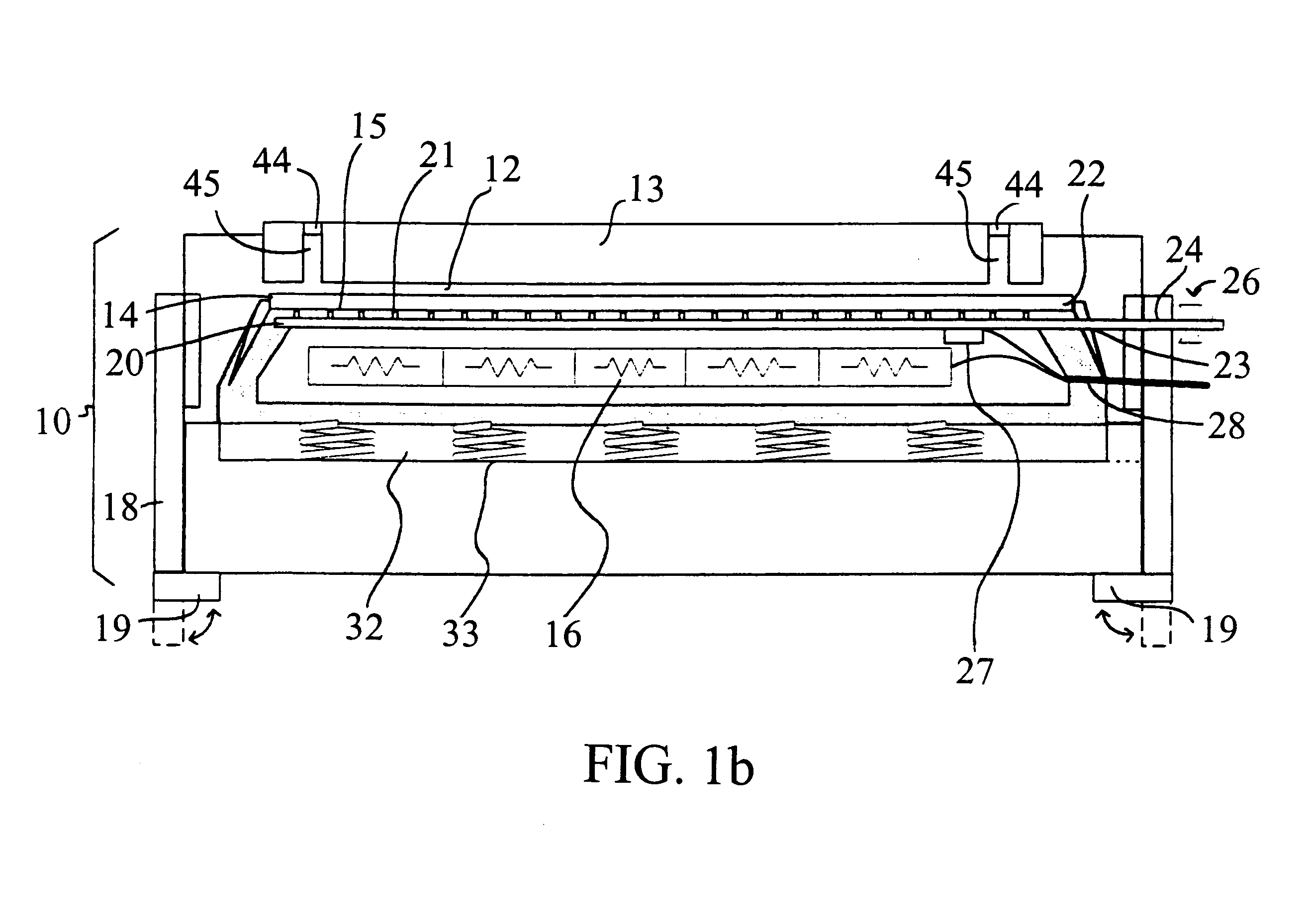

Test apparatus for electronic components

InactiveUS6104203AImprove mechanical stabilityMinimise and eliminateAir-treating devicesElectronic circuit testingTemperature controlMechanical stability

A test apparatus (1) has a temperature controlled chuck (8) which provides good mechanical stability across a wide temperature range. This significantly reduces the number of times the probes (9) must be re-positioned, and in some cases eliminates such re-positioning. The chuck (8) has a support plate (20) which is connected to a base plate (35) by pillars (40) which have a low thermal expansion coefficient. This limits thermal expansion between the support plate (20) and the base plate (35). In addition, the heat transfer means is mounted so that thermal expansion is accommodated internally.

Owner:TRIO TECH INT

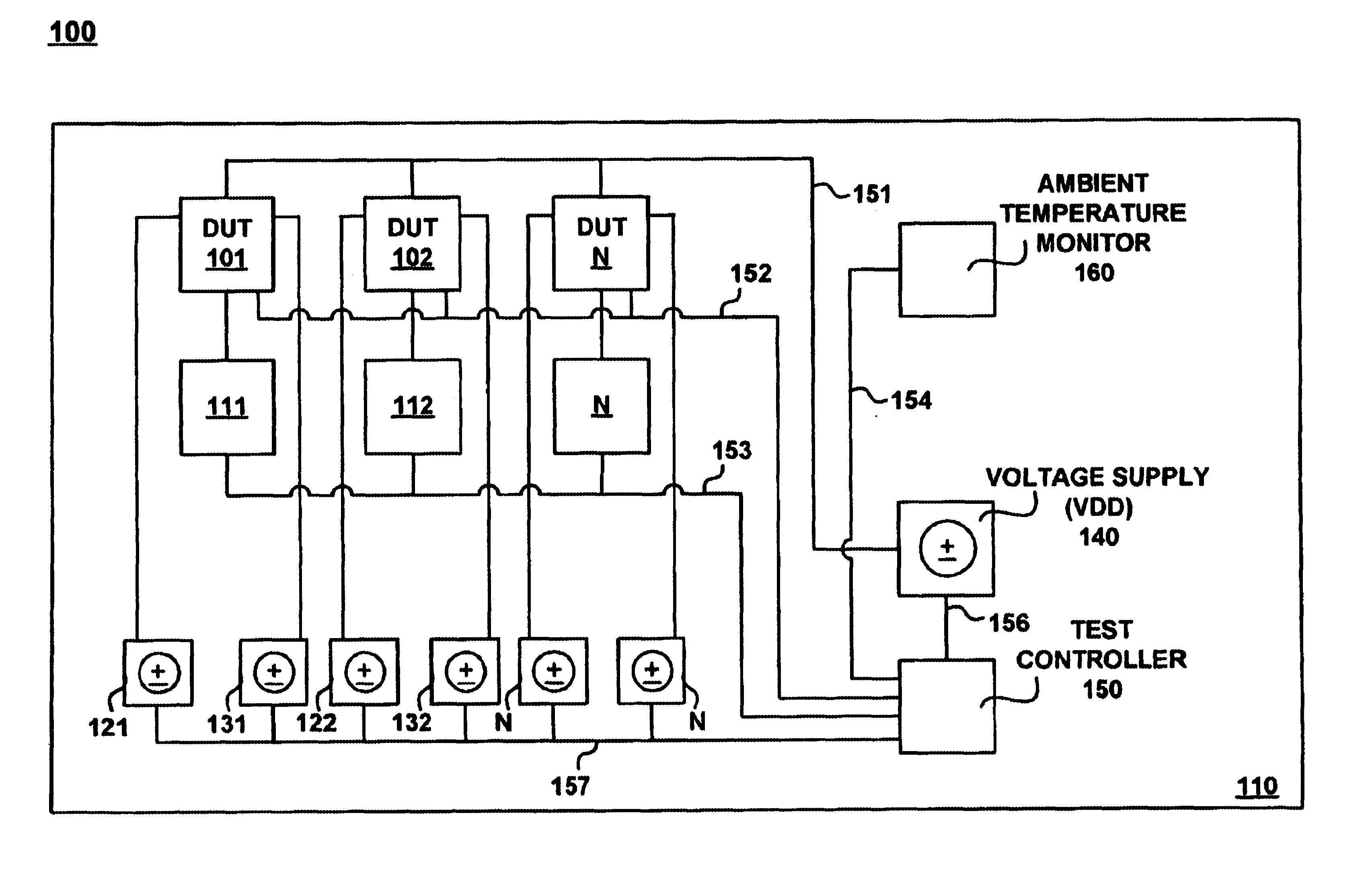

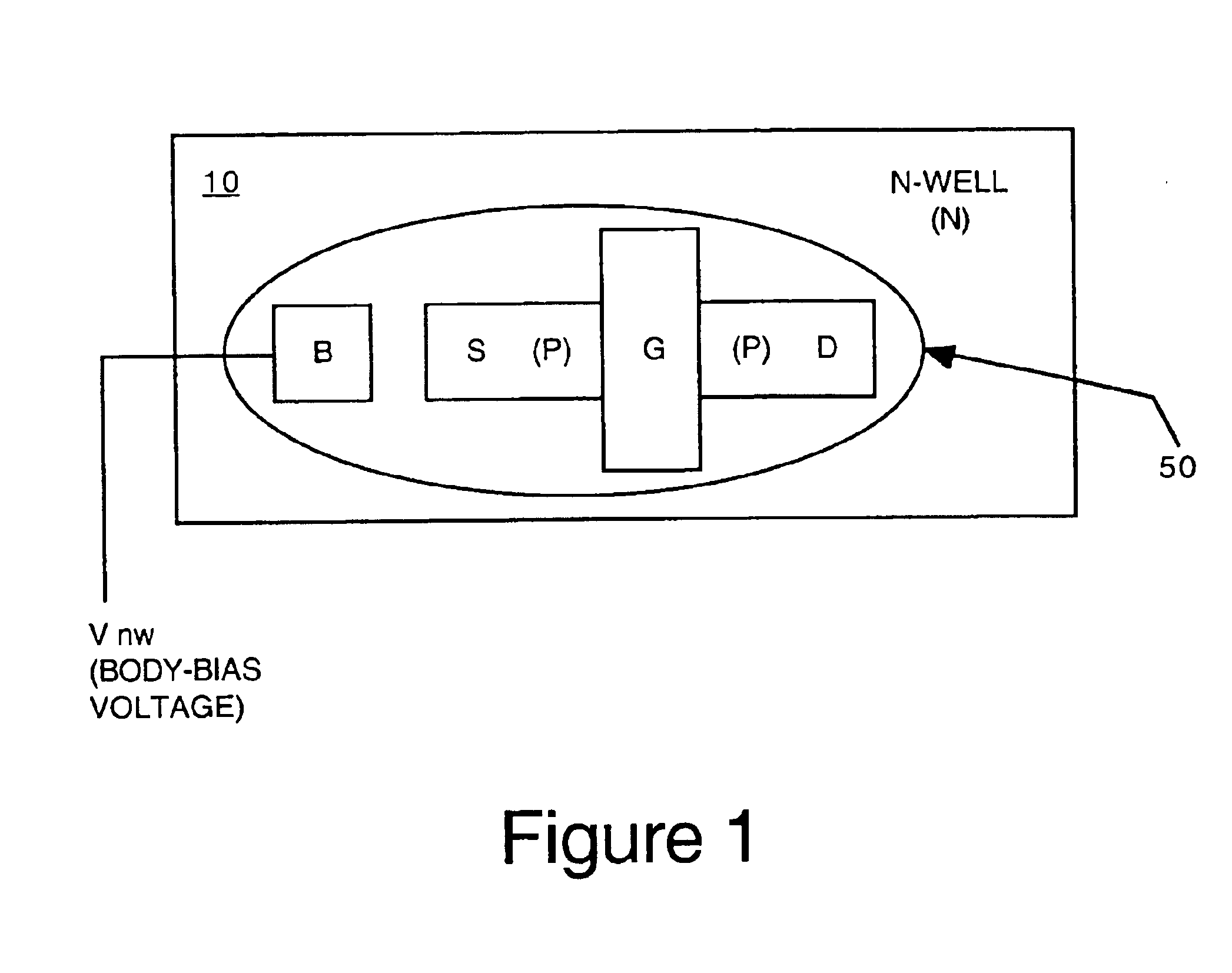

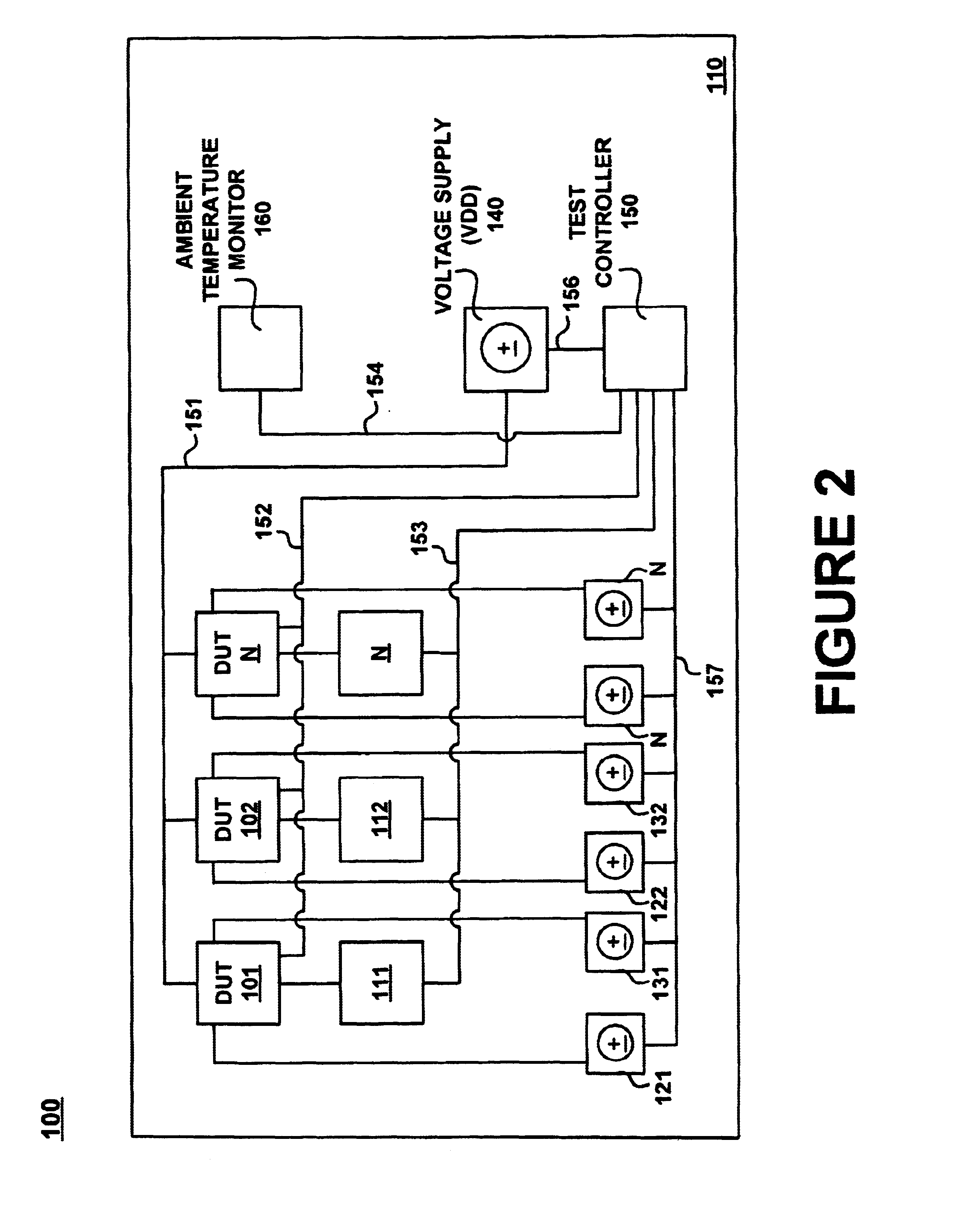

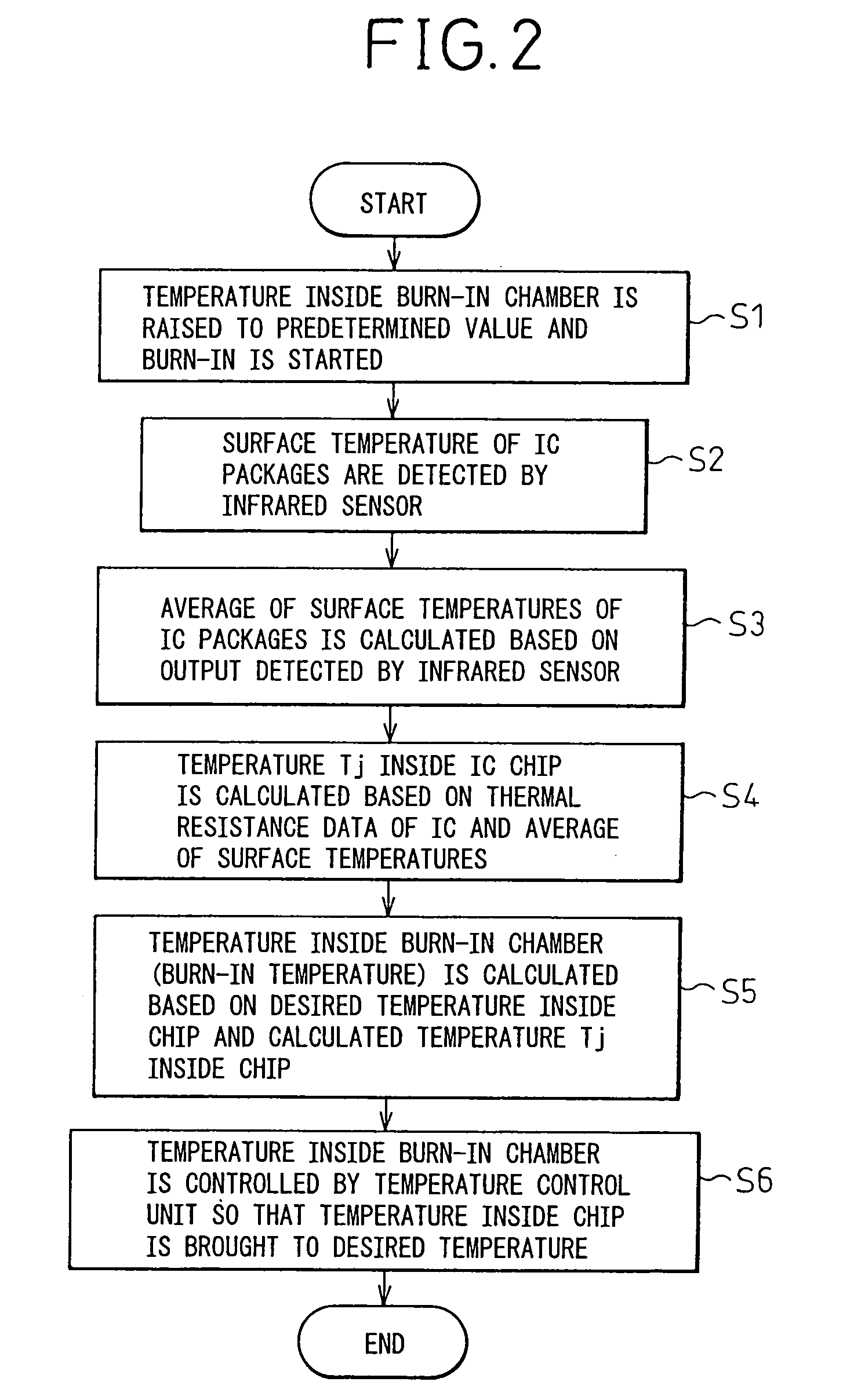

System and method for controlling temperature during burn-in

ActiveUS6900650B1Electronic circuit testingFault location by increasing destruction at faultJunction temperatureVoltage

Systems and methods for reducing temperature dissipation during burn-in testing are described. Devices under test are each subject to a body bias voltage. The body bias voltage can be used to control junction temperature (e.g., temperature measured at the device under test). The body bias voltage applied to each device under test can be adjusted device-by-device to achieve essentially the same junction temperature at each device.

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

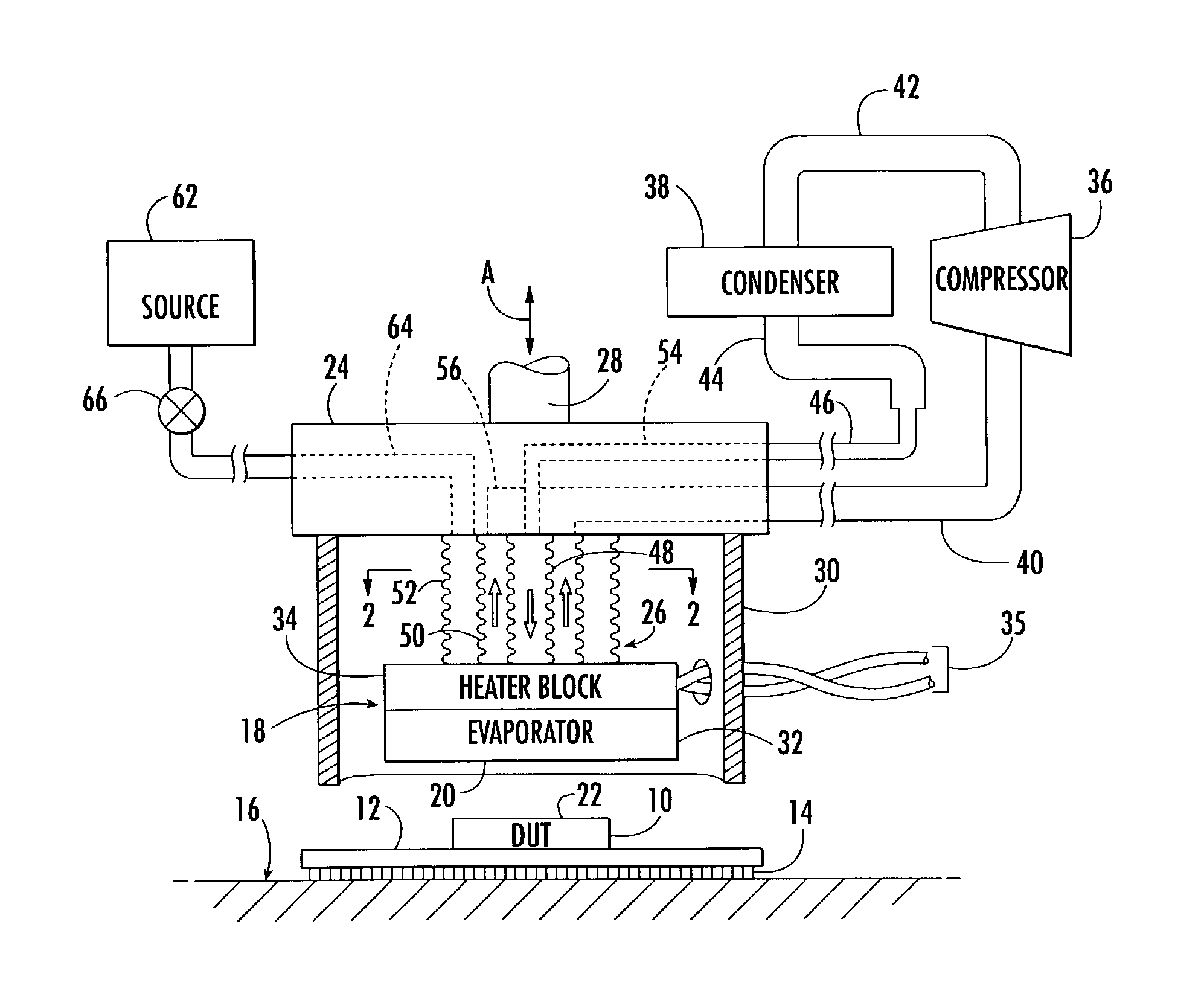

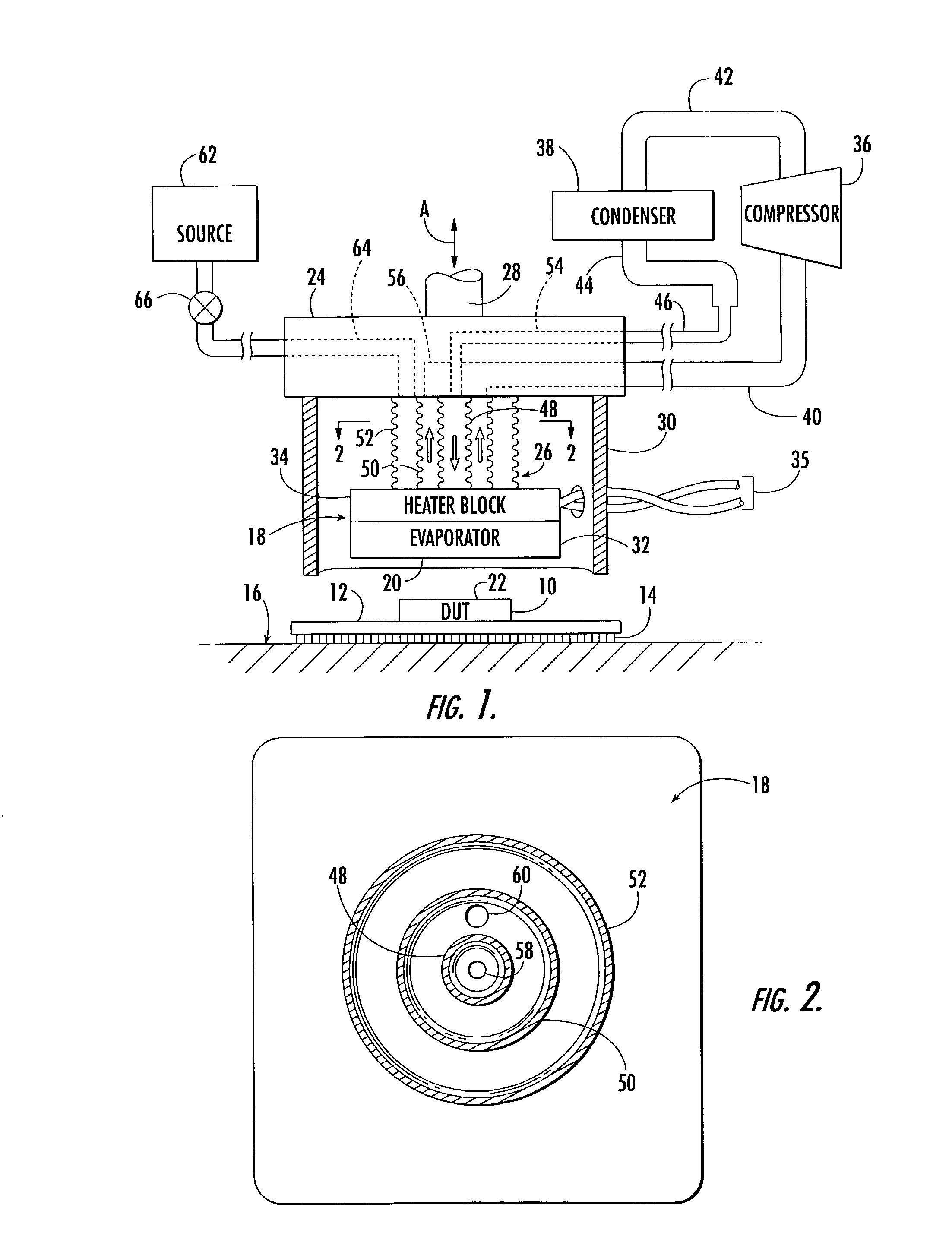

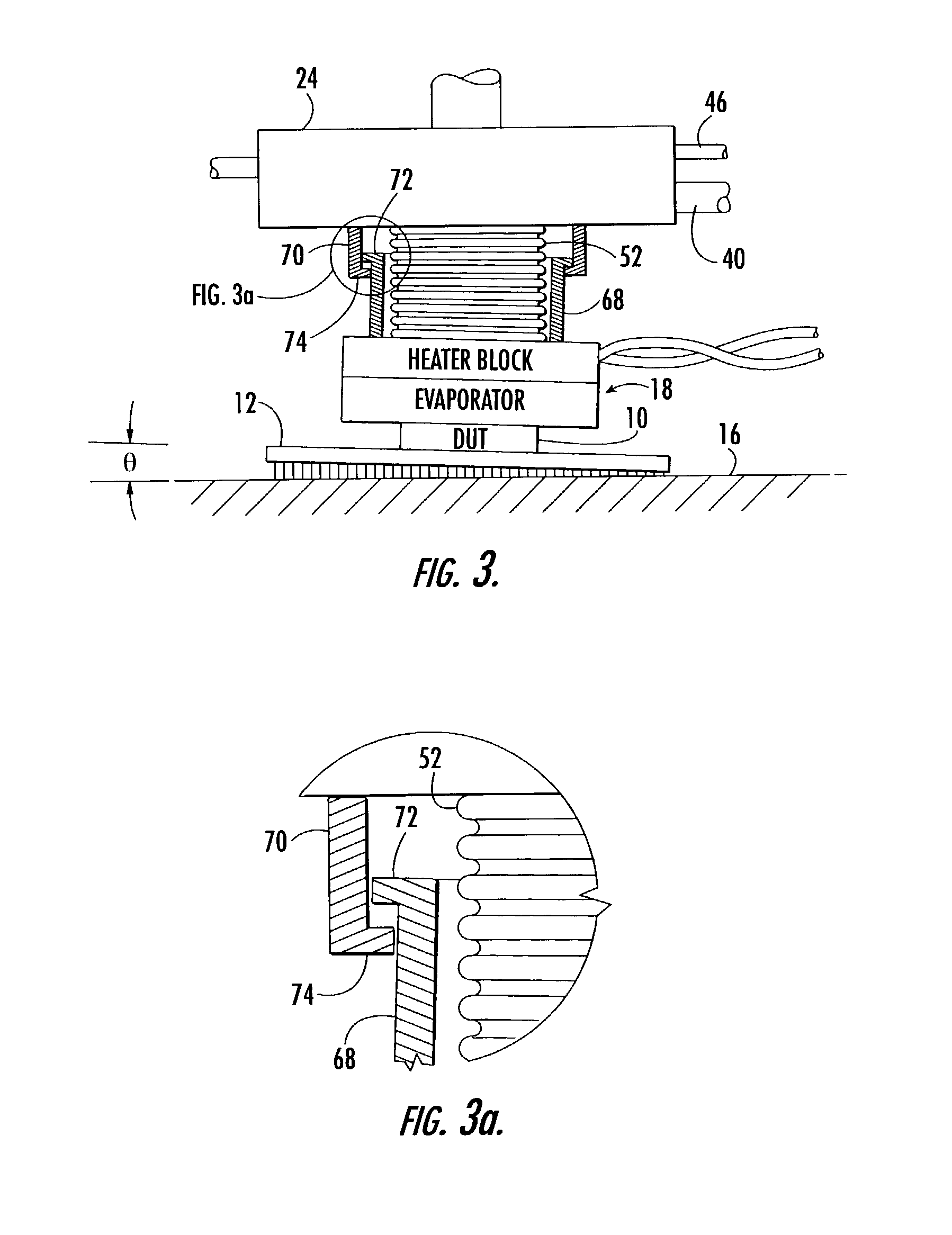

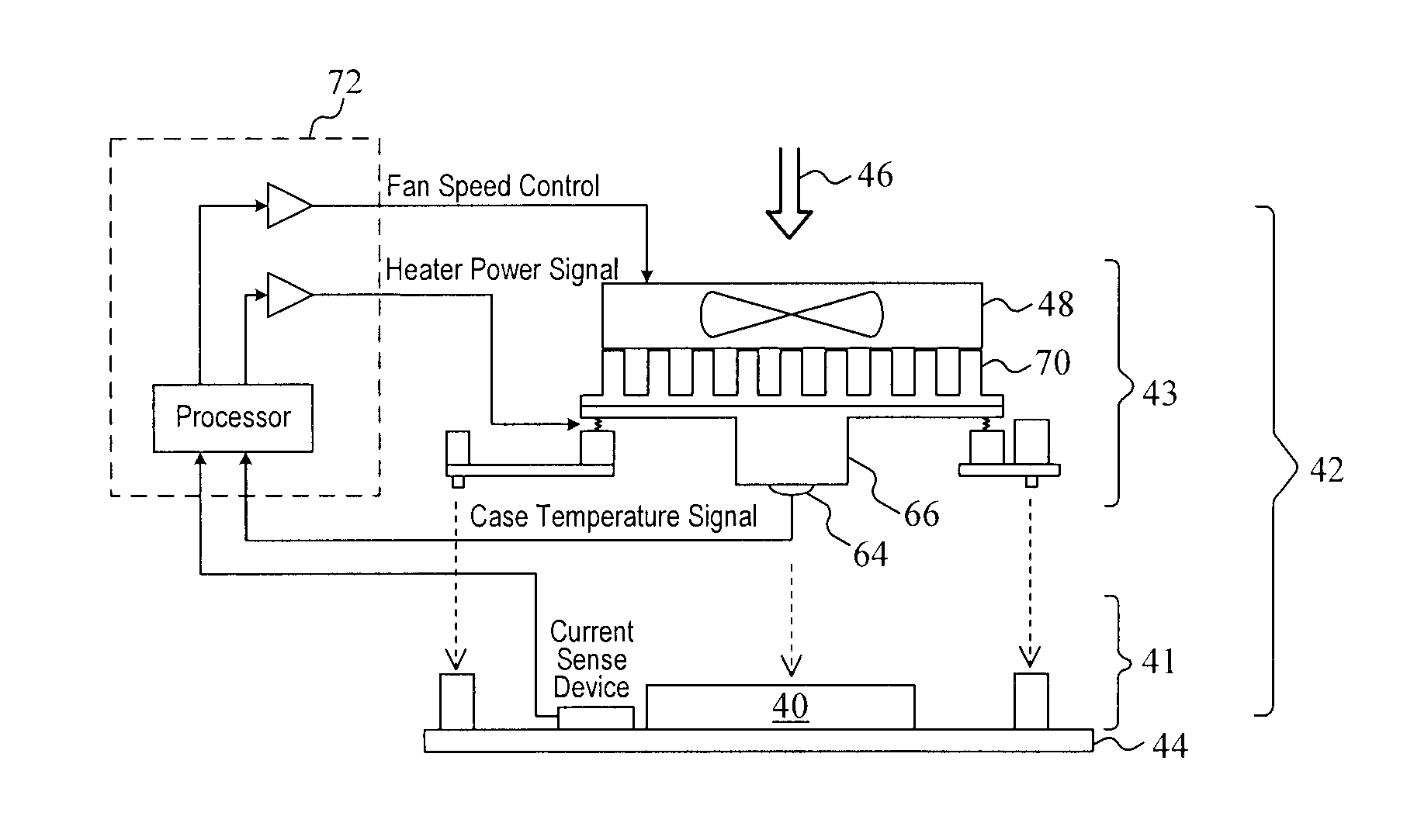

Apparatus and method having mechanical isolation arrangement for controlling the temperature of an electronic device under test

InactiveUS7100389B1Good electrical contactMechanical apparatusElectronic circuit testingEngineeringRefrigeration

An apparatus and method for controlling the temperature of an electronic device under test utilizes a thermal head spaced apart from a movable support structure by a mechanical isolation assembly. The support structure has a manifold configured to route refrigerant fluid between the evaporator head and components of a refrigeration system. The mechanical isolation assembly is configured to compensate for variations in the planar orientation of the device under test. Moreover, the mechanical isolation assembly preferably includes bellows through which the refrigerant fluid is conducted.

Owner:ADVANTEST CORP +1

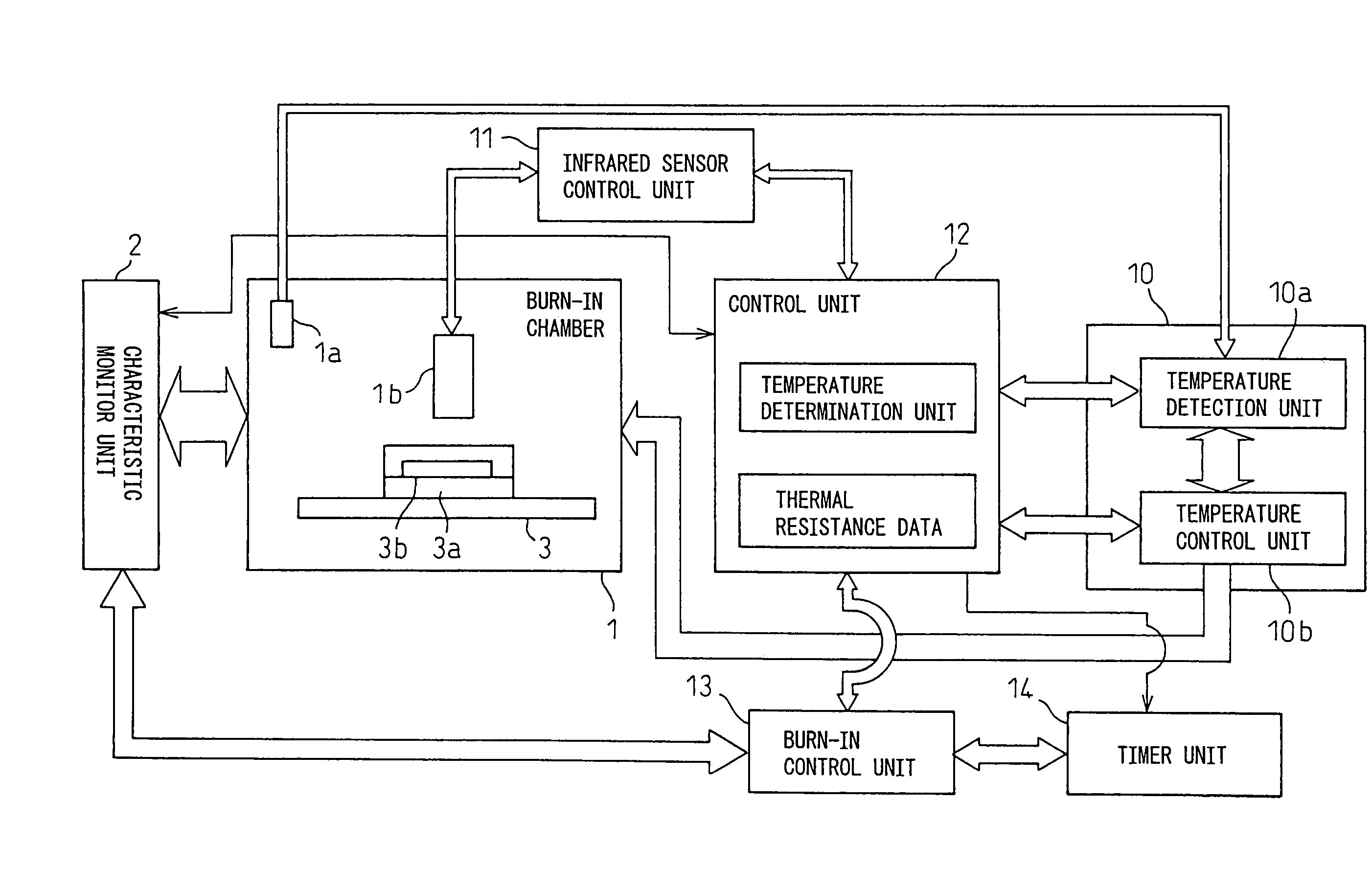

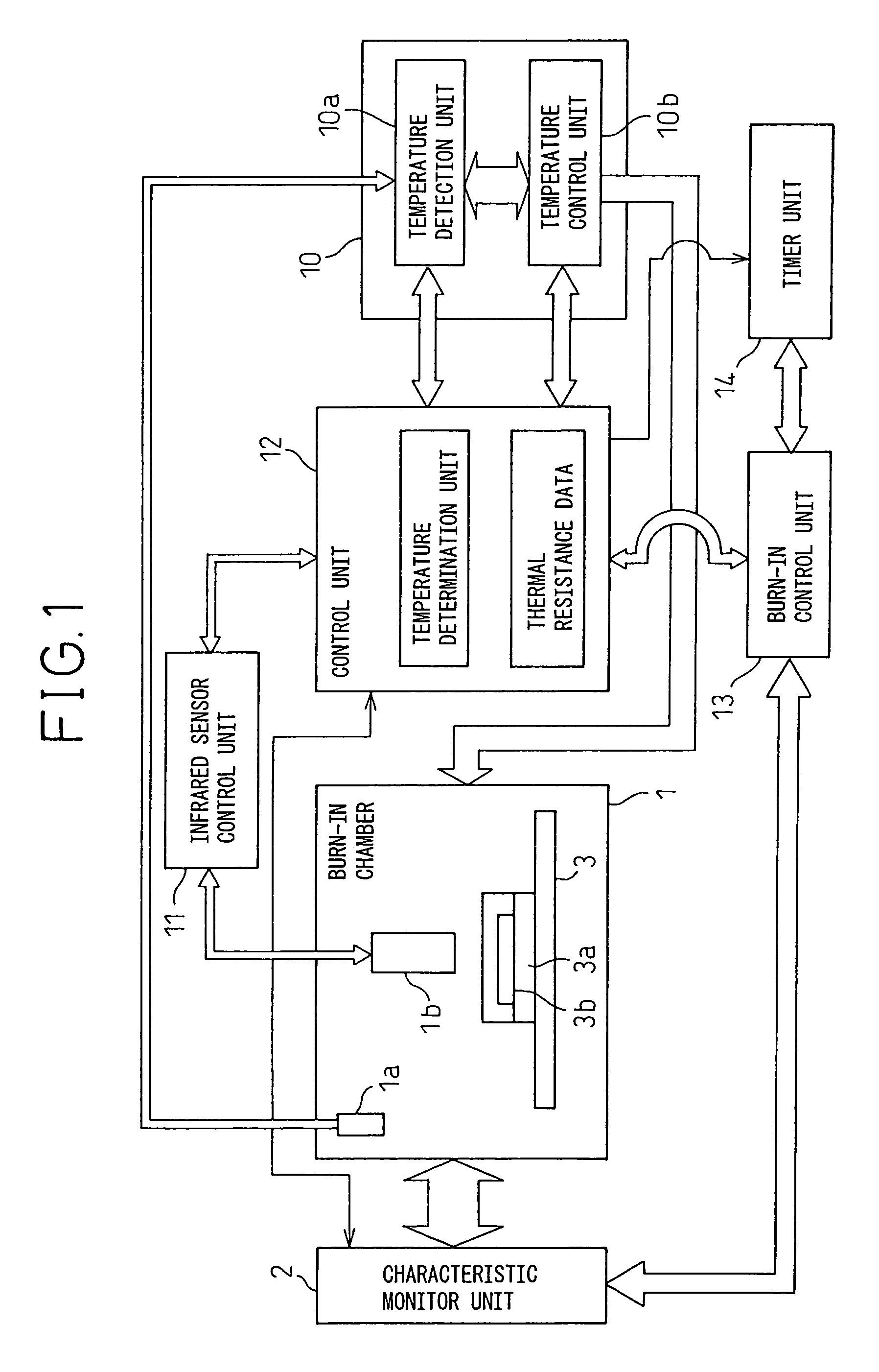

Dynamic burn-in equipment

InactiveUS7023229B2Easy to controlFault location by increasing destruction at faultIndividual semiconductor device testingEngineeringInternal temperature

An infrared sensor is provided in a burn-in chamber. The surface temperatures of two or more semiconductor devices are measured by the sensor. A control unit calculates the internal temperatures of the semiconductor devices based on the thermal resistance values of the semiconductor device packages and controls the temperature inside the burn-in chamber so that the average of the internal temperatures is brought to a desired temperature by using a temperature controller. Further, an acceleration coefficient is obtained based on the internal temperatures, a burn-in time is determined based on the acceleration coefficient and a preliminarily given accelerated period, and a burn-in acceleration test is conducted. Moreover, when a defective semiconductor is found, the defective portion of the defective semiconductor device is specified based on the surface temperature distribution of the semiconductor device measured by the infrared sensor.

Owner:FUJITSU LTD

Burn-in test apparatus for BGA packages using forced heat exhaust

InactiveUS20050179457A1Semiconductor/solid-state device testing/measurementOhmic-resistance electrodesEngineeringForced-air

A forced air heat exhaust type of burn-in test apparatus for packages: A first air supply duct provides air to the burn-in chamber and a second air supply duct provides air to supply tubes that direst air into the test sockets that hold the packages. The test sockets have a structure that allows air ventilation of the conductive balls. Accordingly, the apparatus can control the temperature around the packages as well as the temperature in the burn-in chamber, thus preventing conductive ball-melting.

Owner:SAMSUNG ELECTRONICS CO LTD

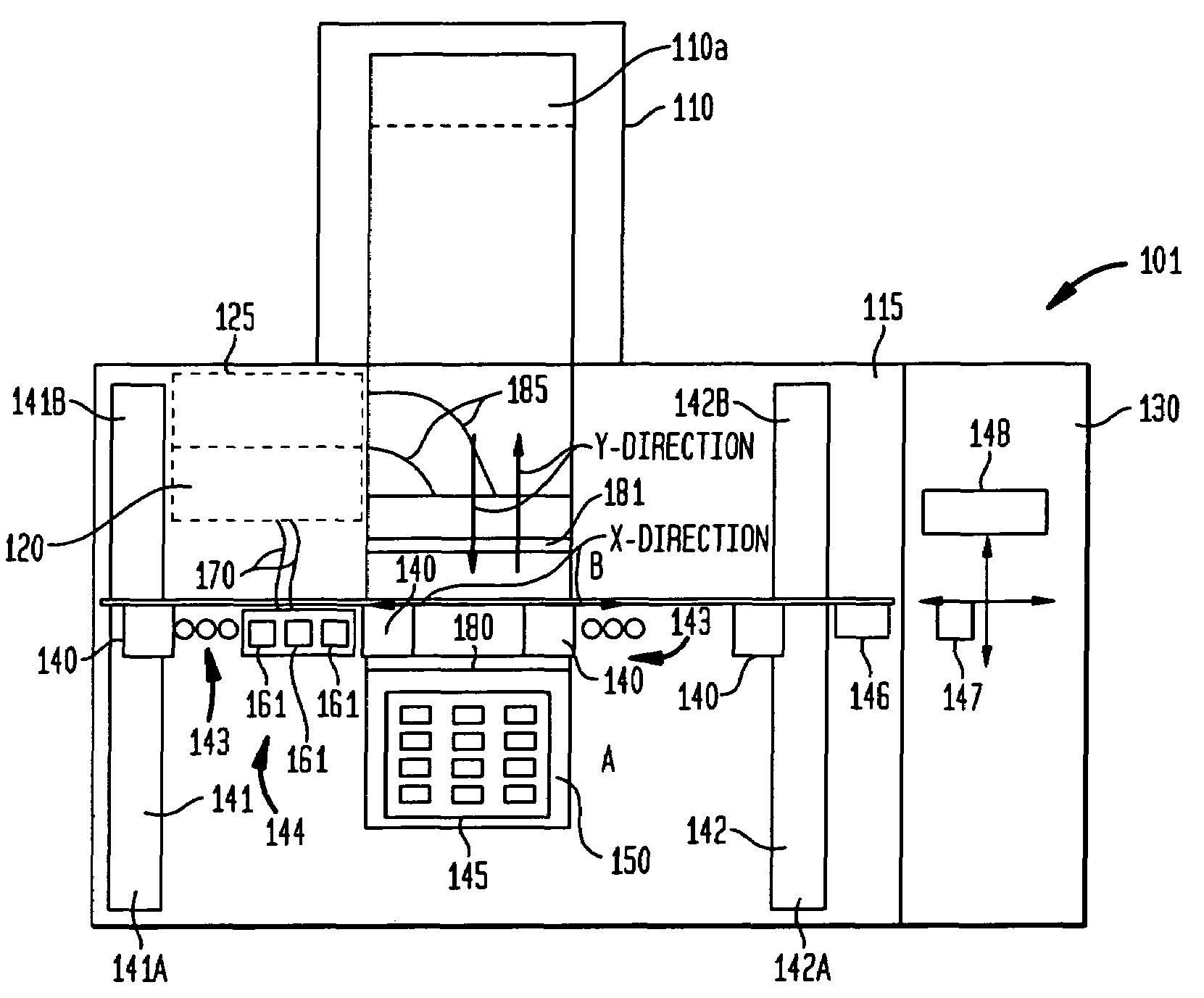

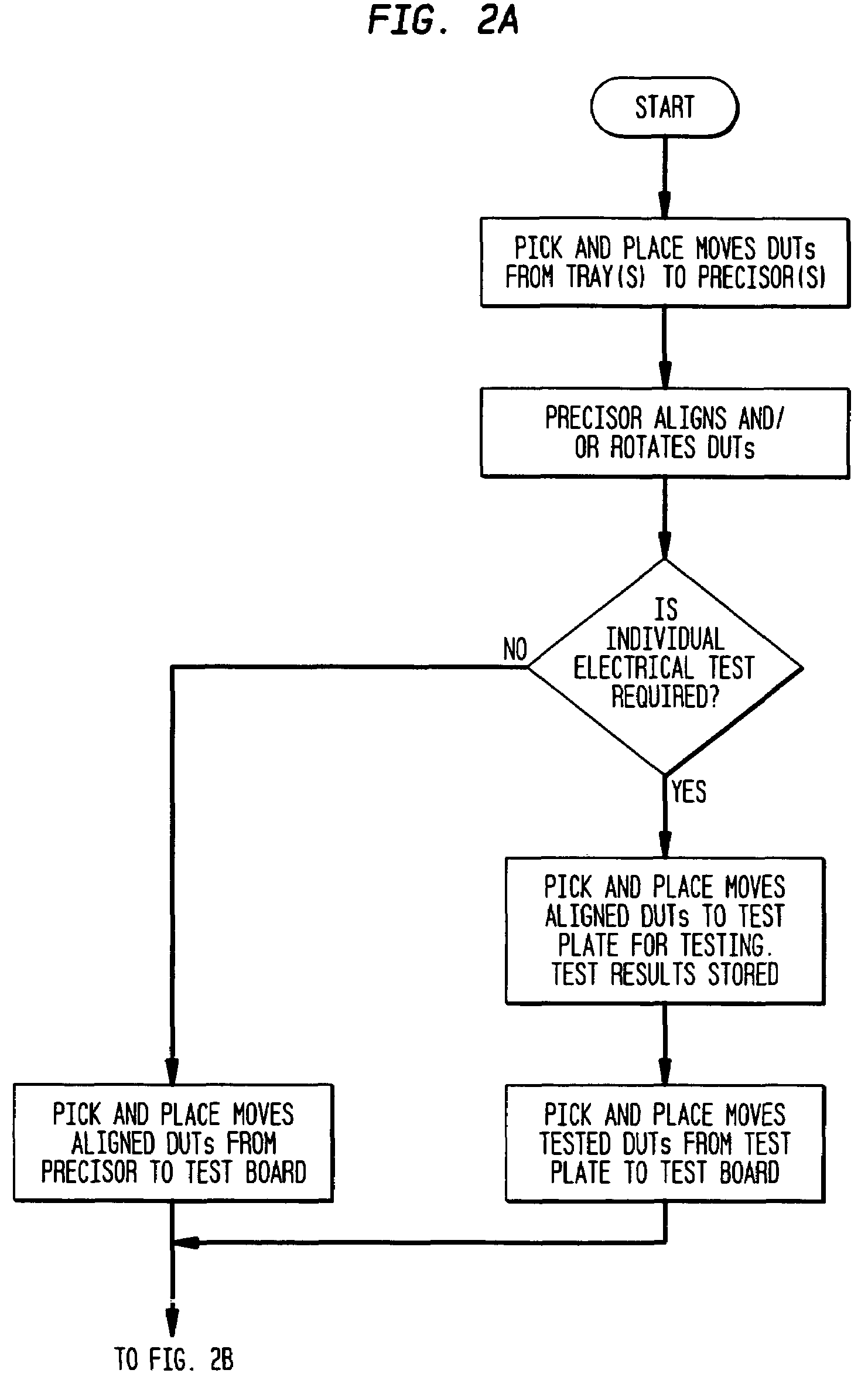

Method for testing semiconductor devices and an apparatus therefor

InactiveUS7151388B2Good flexibilityEfficient loadingSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A method for testing integrated circuit devices and loading such devices into a test board for further testing and an apparatus therefor is disclosed. The method allows for selection between two modes of operation. In a first mode, the integrated circuit devices are subjected to an electrical test before being placed into the test board for further testing. In a second mode, the integrated circuit devices are tested after being placed in the test board. The apparatus allows for the selection between the first mode and the second mode. In either mode, information about the tested devices and the sockets in the test board is used to load the test boards intelligently. Intelligent loading means that devices under test (DUTs) are not placed in bad sockets and devices that do test bad are removed from the test board, with an option of replacing the failed DUT with another DUT before subsequent environmental testing of the DUTs in the test board is carried out.

Owner:KES SYST

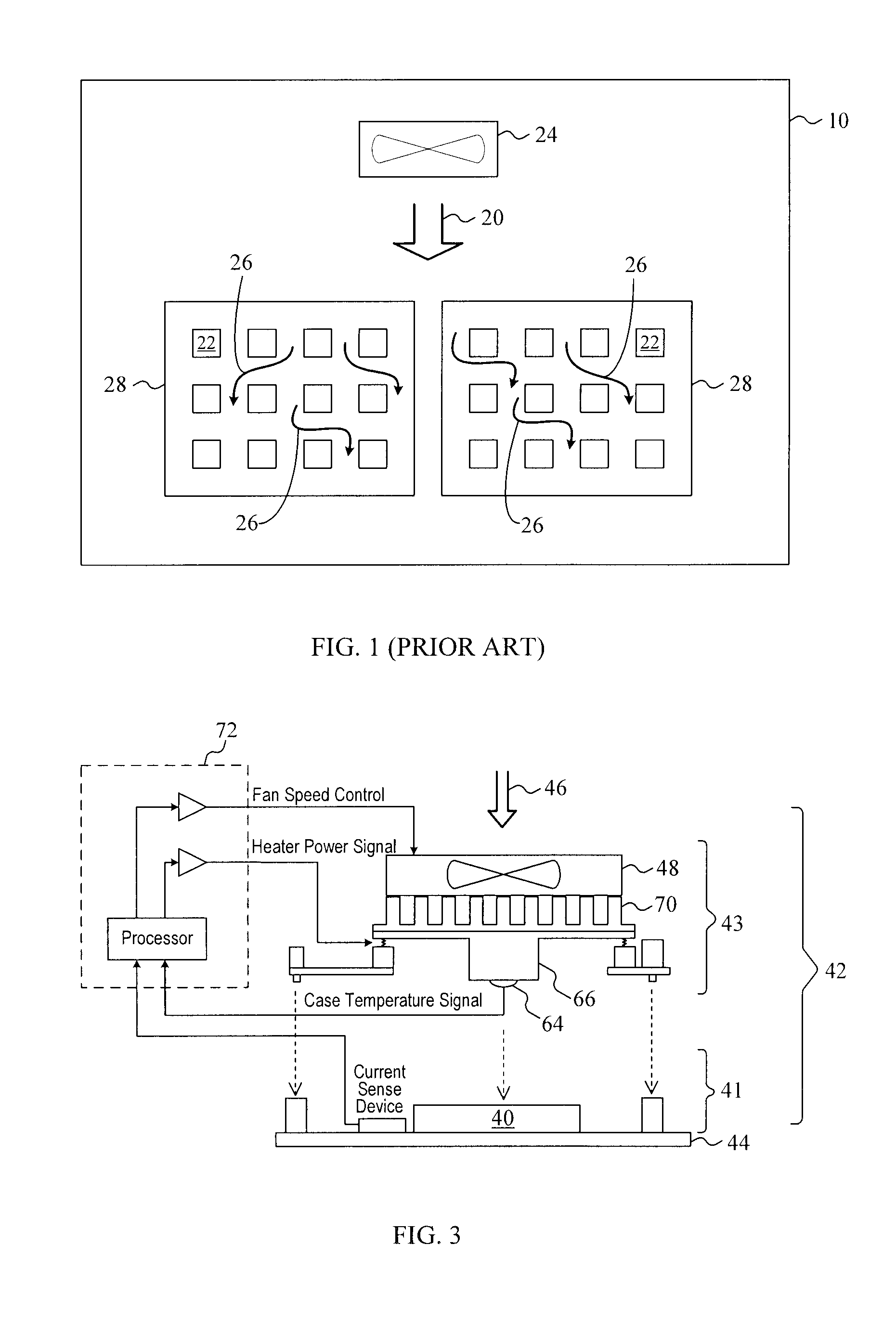

Tester with independent control of devices under test

InactiveUS20020121913A1Electronic circuit testingFault location by increasing destruction at faultTester deviceEngineering

A burn-in tester that provides independent control of the devices under test. The various operating parameters such as temperature, voltage, frequency of operation or test pattern being applied can be independently changed on one device without affecting the operating parameters of the other devices. Thus, e.g., the amount of cooling applied to one device is independent of the amount of cooling applied to another device. In addition, the testing being done on each device may be independently controlled. Thus, a test can be changed on one of the devices under test without affecting the tests being run on any of the other devices. Similarly, the voltage and frequency of operation can be controlled independently to allow for changes to the voltage and / or frequency of one device without affecting those parameters on other devices being tested.

Owner:ADVANCED MICRO DEVICES INC

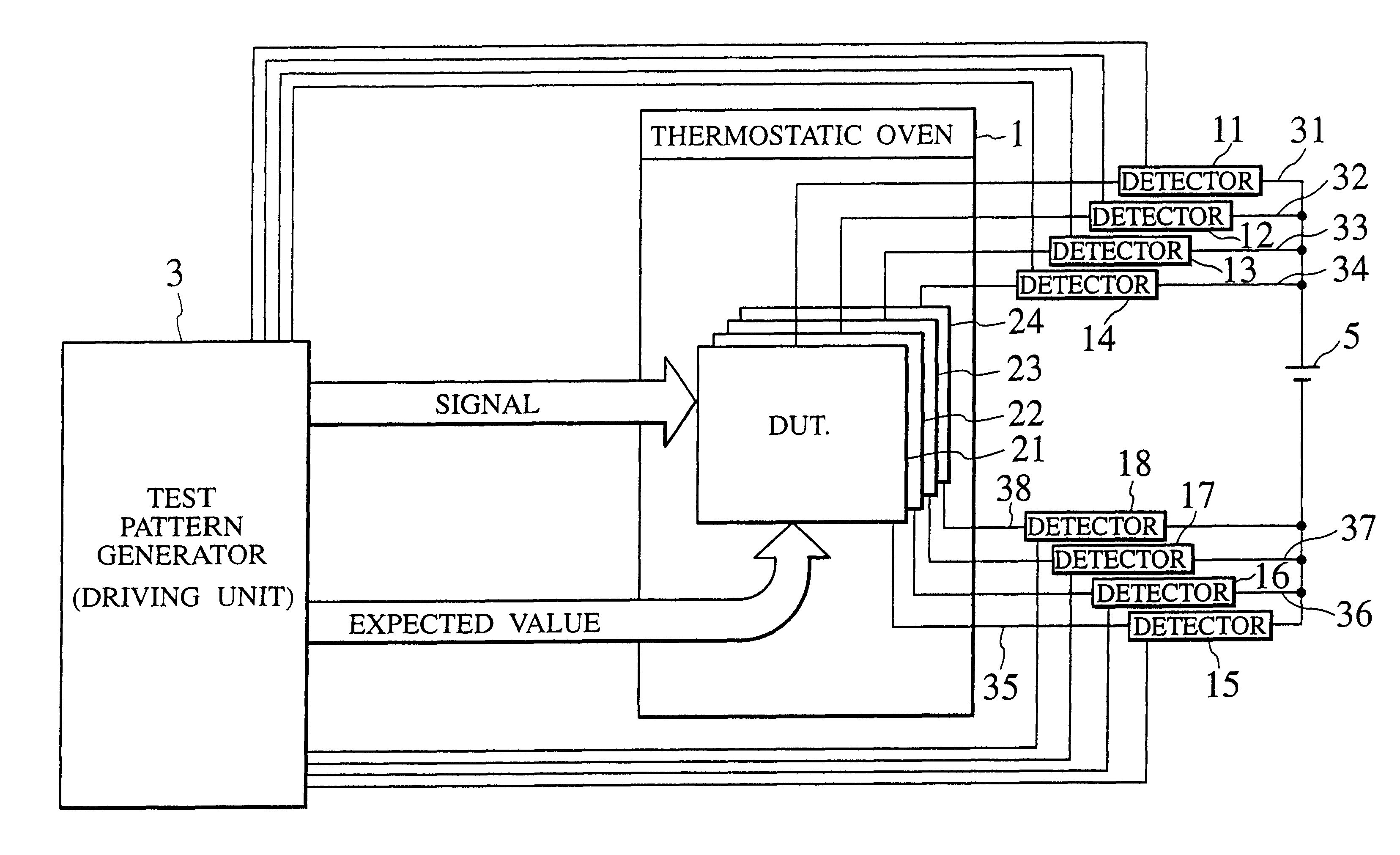

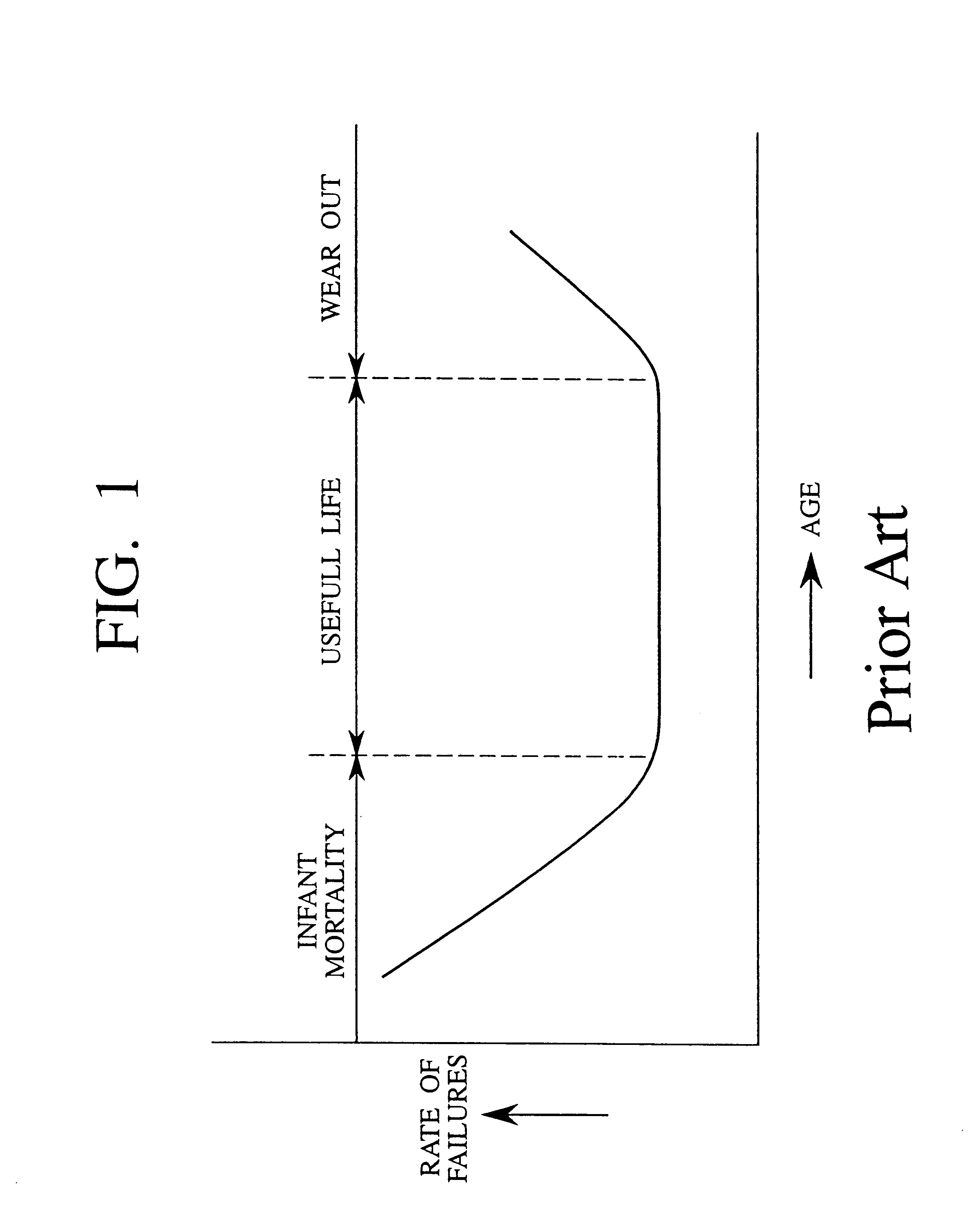

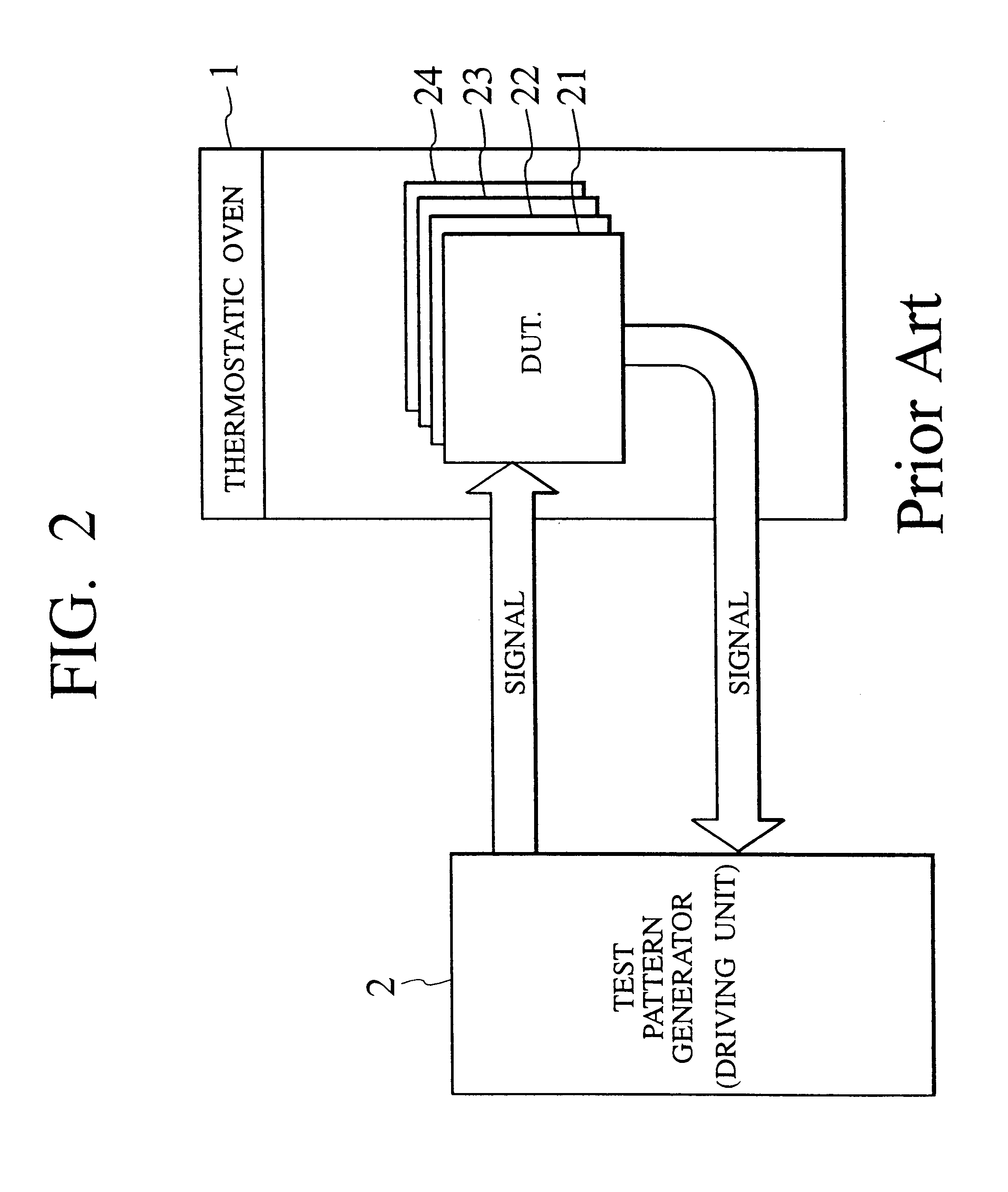

Dynamic burn-in test equipment

InactiveUS6215324B1Semiconductor/solid-state device testing/measurementElectronic circuit testingTested timeGround line

There is provided a dynamic burn-in test equipment being capable of testing a large number of multi-pin LSI chips in a short test time and at a low cost. The dynamic burn-in test equipment includes at least a thermostatic oven for storing DUTs, a driving unit for applying the input signal to the input terminal of each DUT to apply a predetermined expected value to the output terminal of each DUT, a power supply for applying a predetermined power supply voltage to each DUT through a higher level power supply line and a lower level power supply line (ground line), and a current detector arranged on at least one of the higher level power supply line and the lower level power supply line (ground line). The dynamic burn-in test equipment monitors a power supply current to detect a failure.

Owner:NIPPON SCI

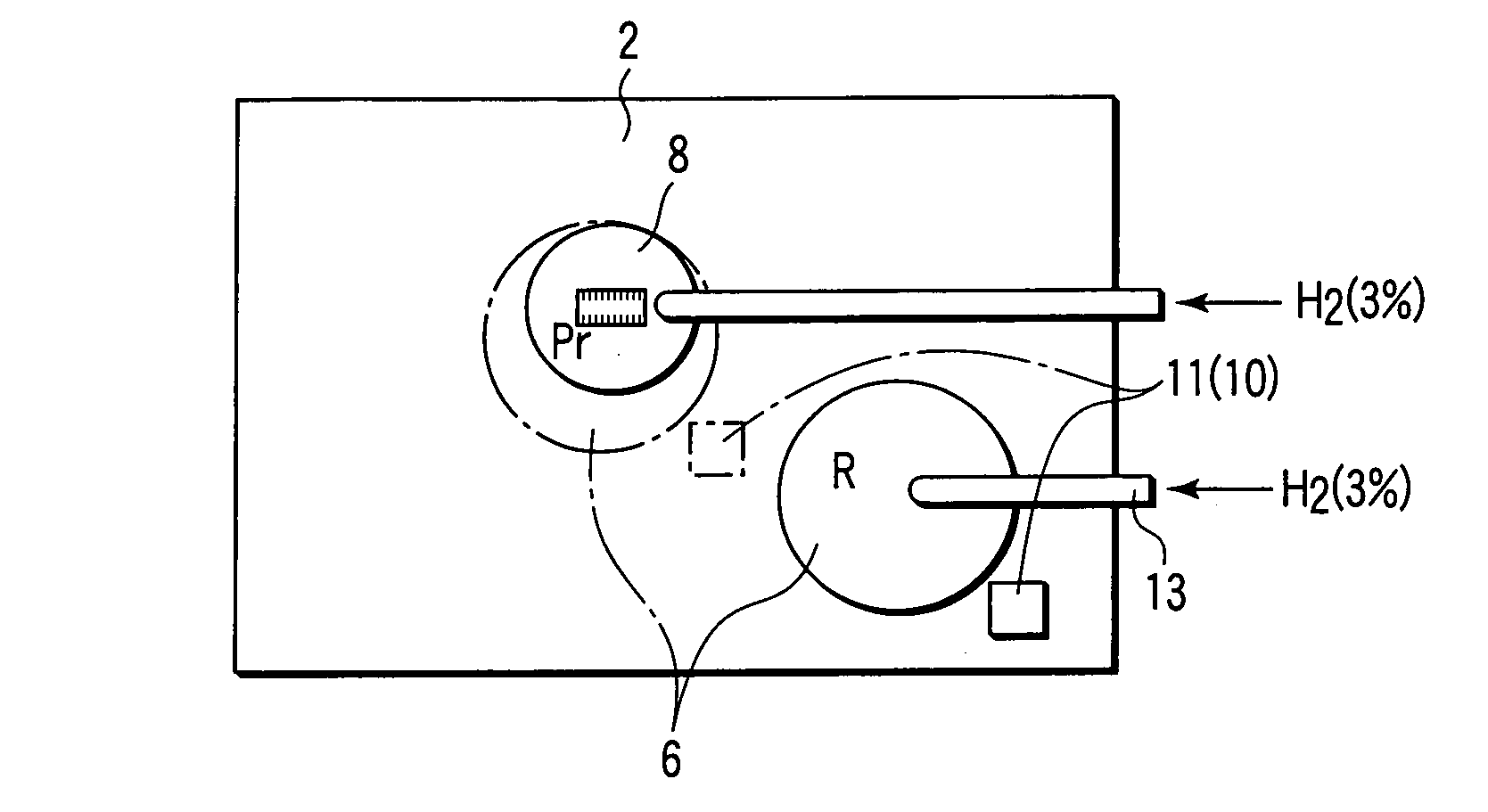

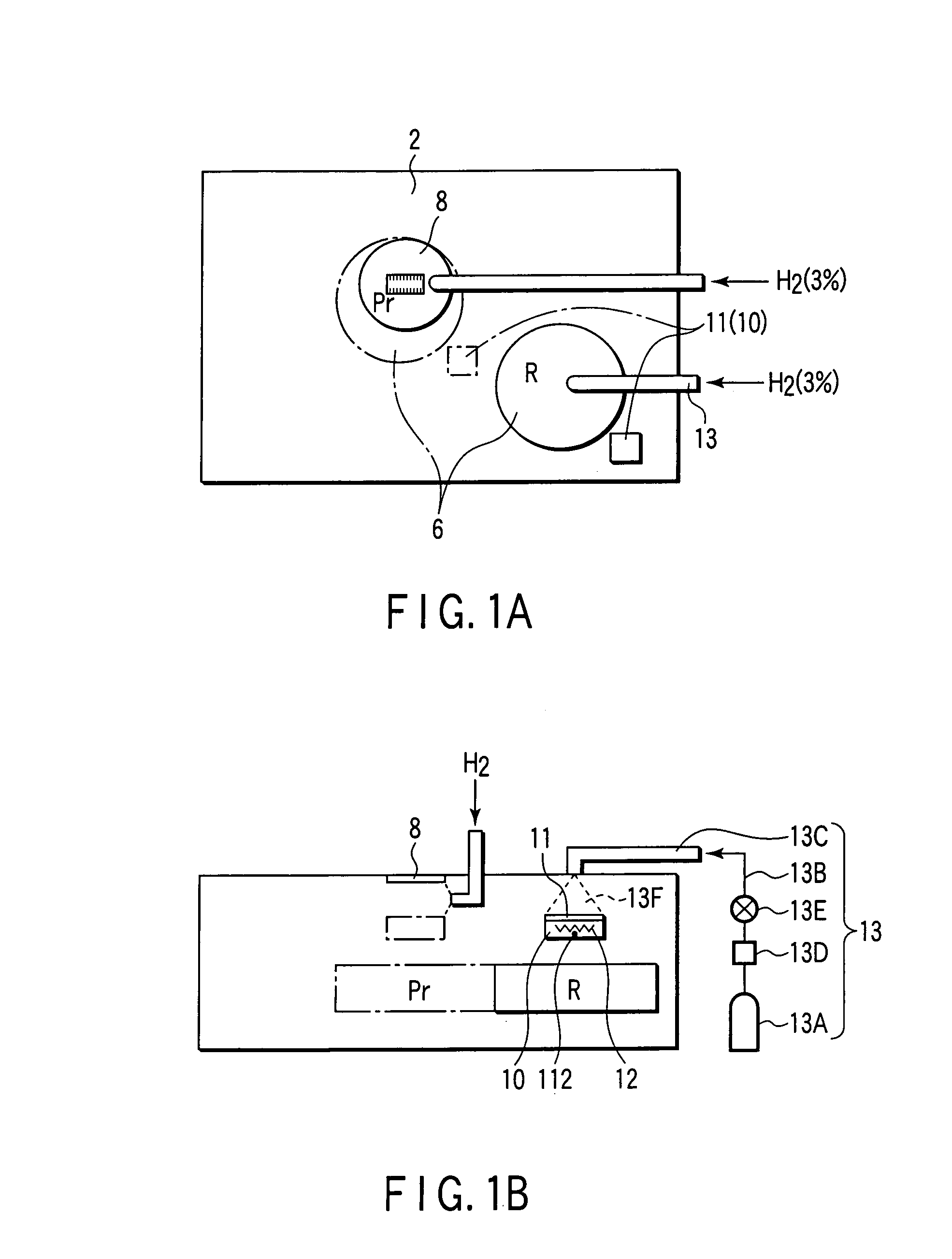

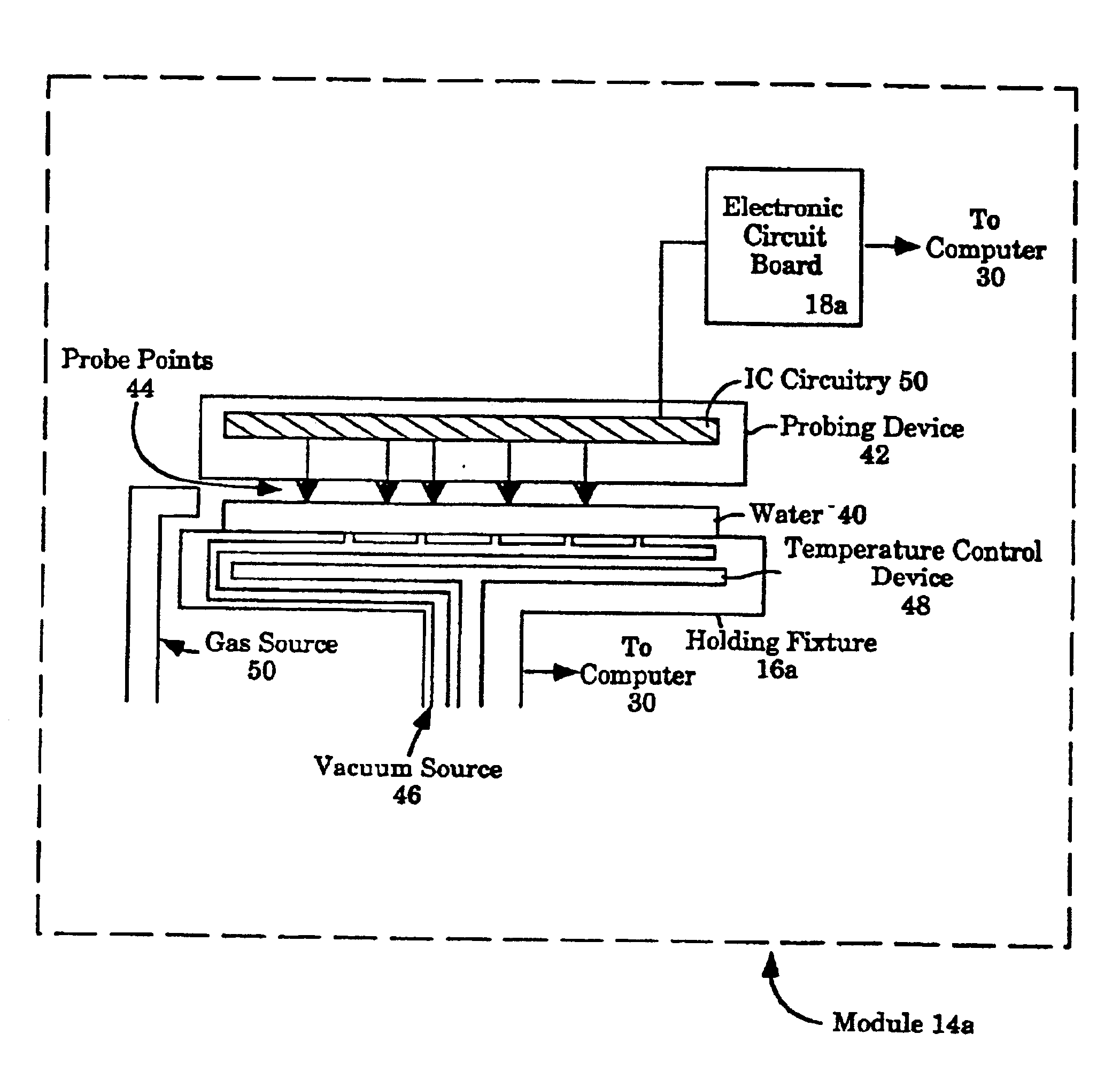

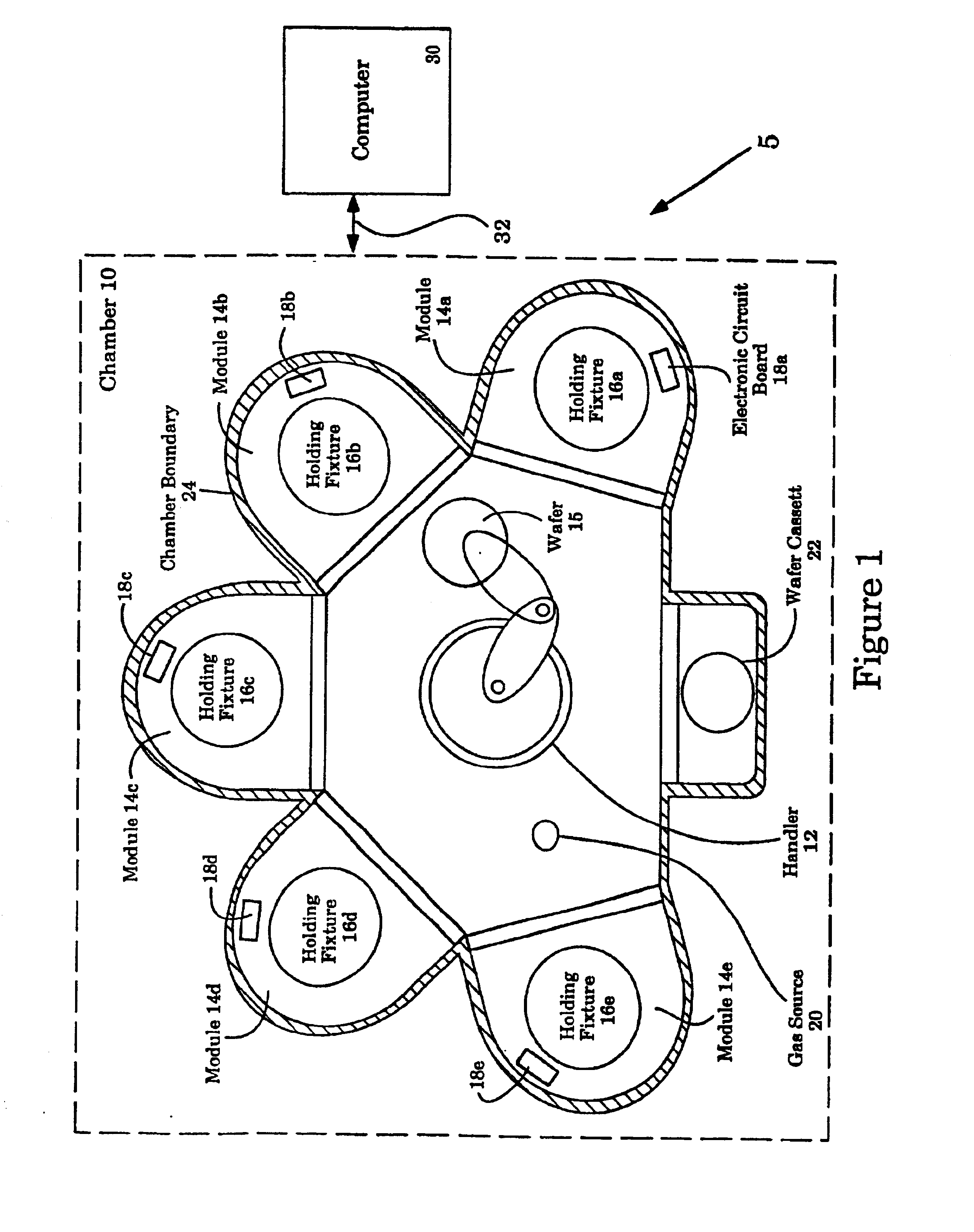

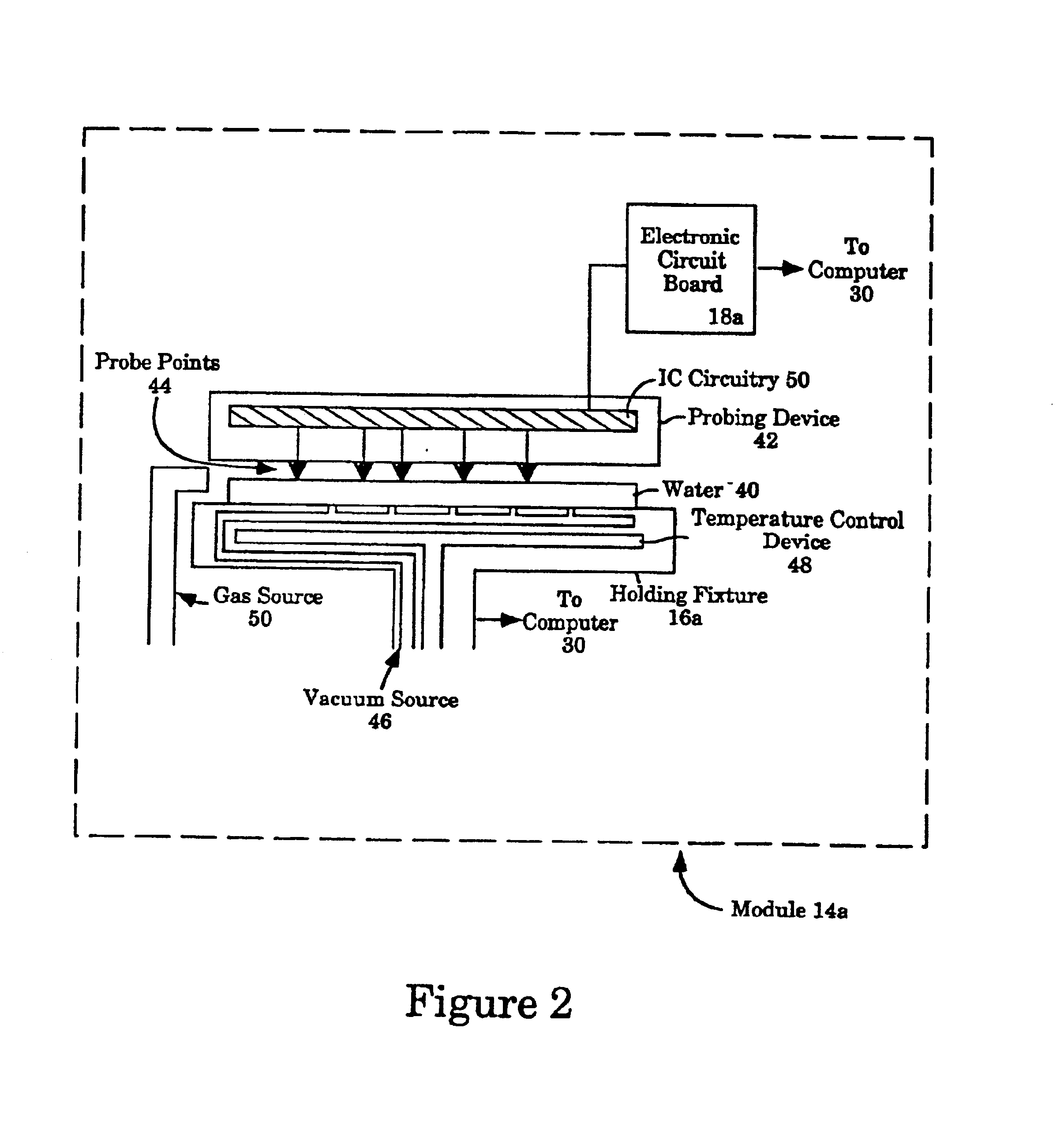

Method and system for probing, testing, burn-in, repairing and programming of integrated circuits in a closed environment using a single apparatus

InactiveUS6838896B2Reduce thicknessAnalog circuit testingDigital circuit testingTemperature controlContact pad

A single gas tight system may perform multi-functions including reducing the thickness of oxides on contact pads and probing, testing, burn-in, repairing, programming and binning of integrated circuits. A holding fixture holds a wafer having integrated circuits and aligns the wafer to a full-substrate probing device. A temperature control device is used to heat the wafer during an oxide reduction process or during burn-in of the wafer. During the oxide reduction process, hydrogen is introduced into the chamber, and the wafer is heated so that the oxides on the contact pads can combine with hydrogen to form water vapor, thus reducing the thickness of the oxides. A computer analyzes the test and / or burn-in data and provides control signals for repairing or programming the integrated circuits.

Owner:ELM TECH

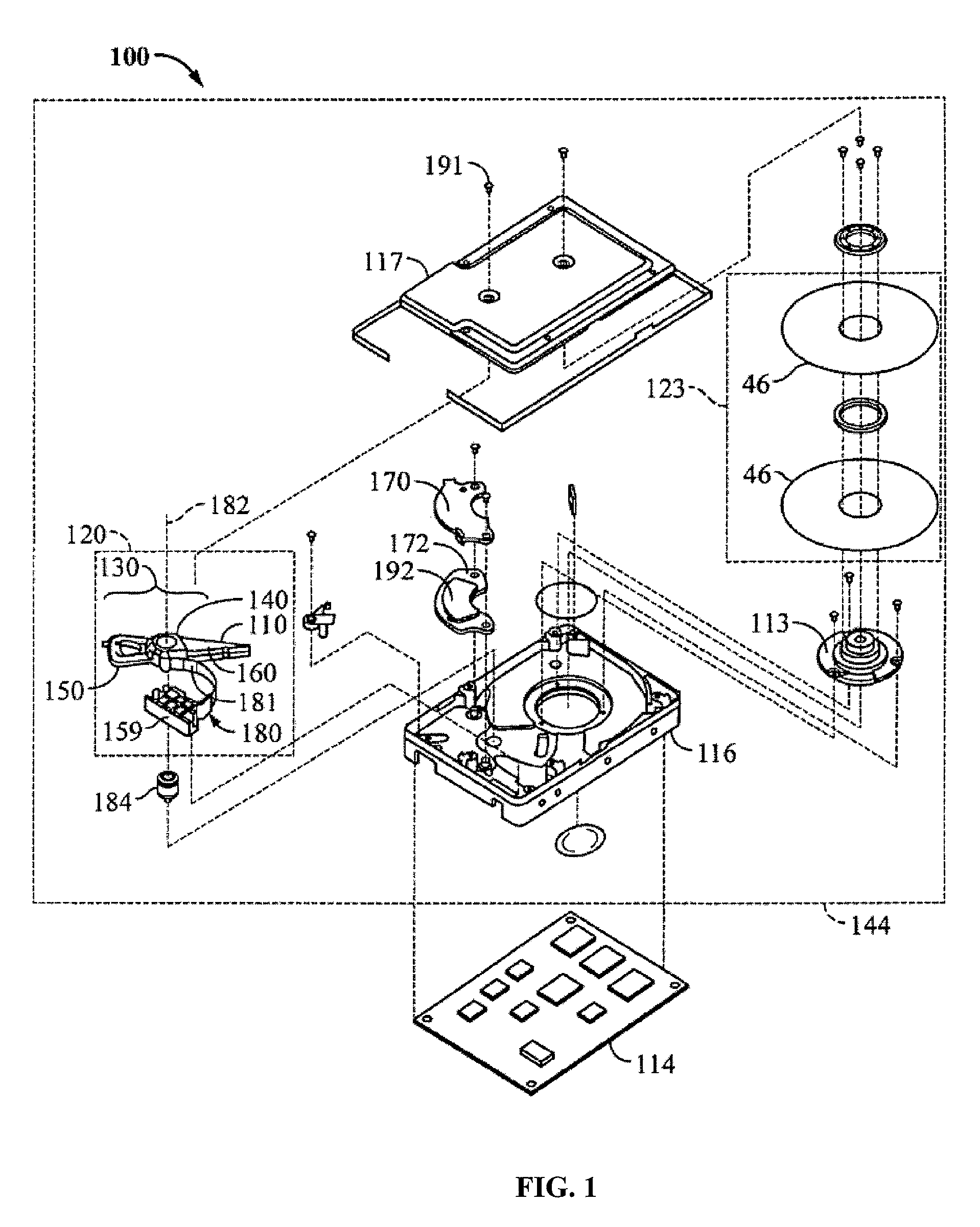

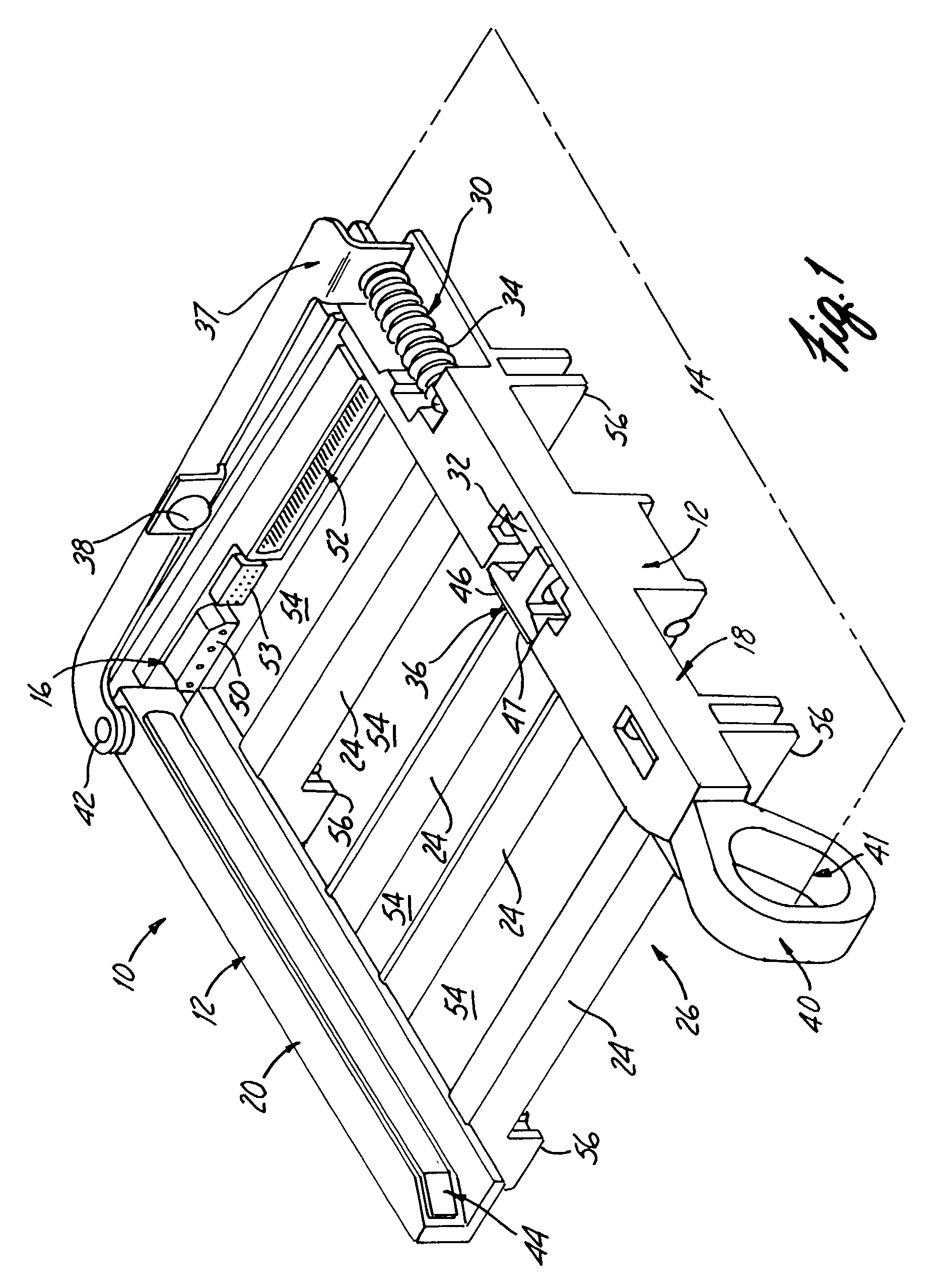

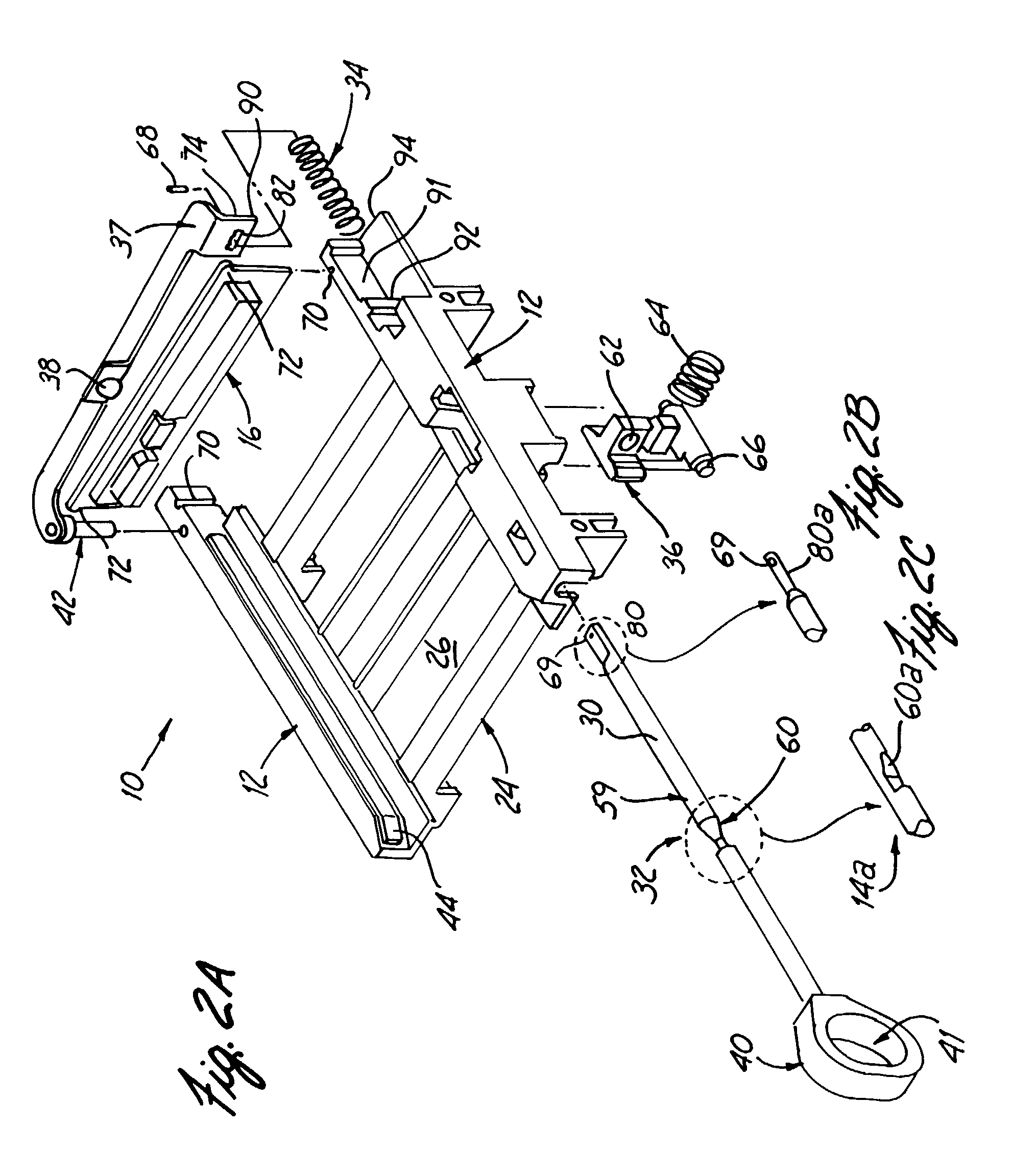

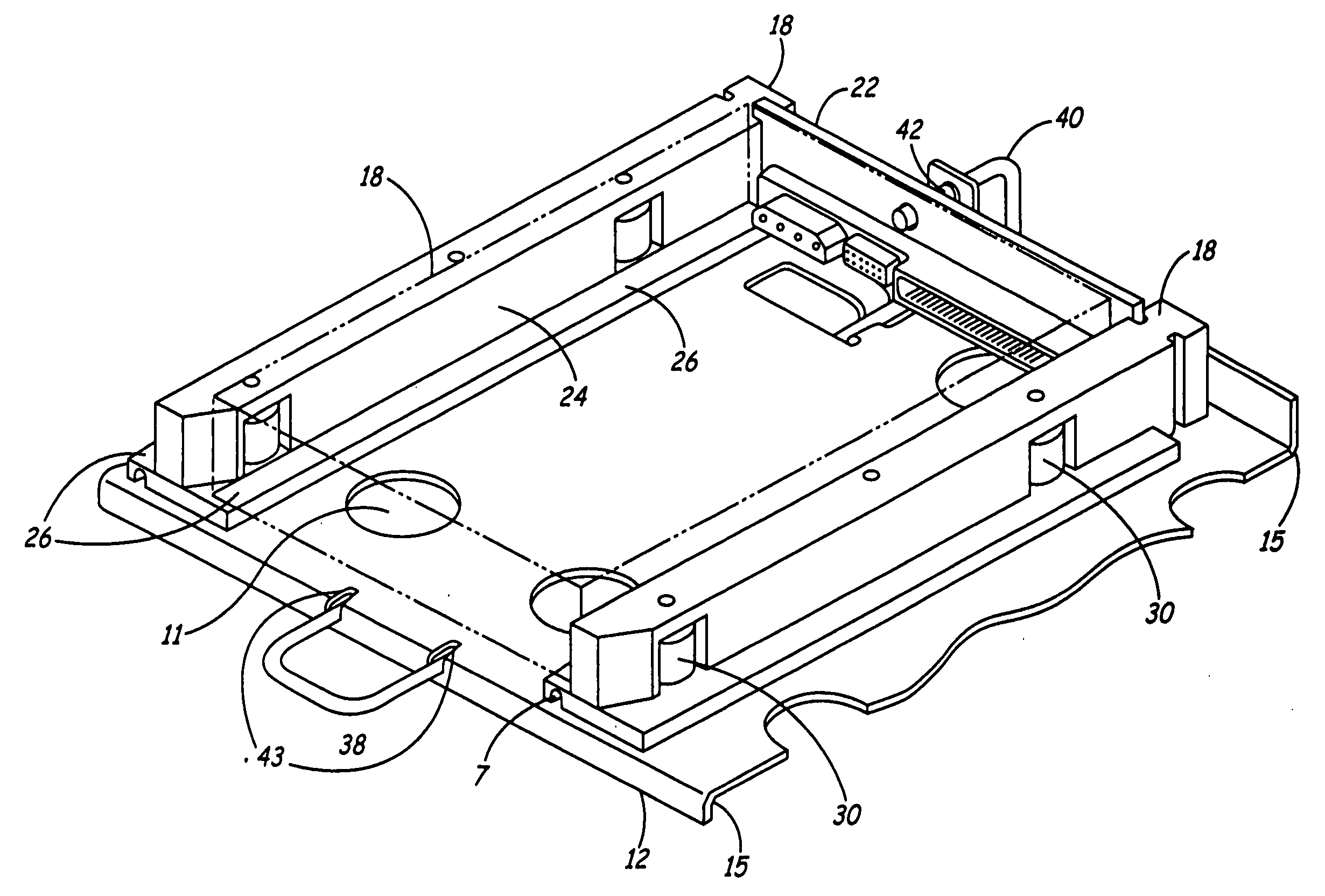

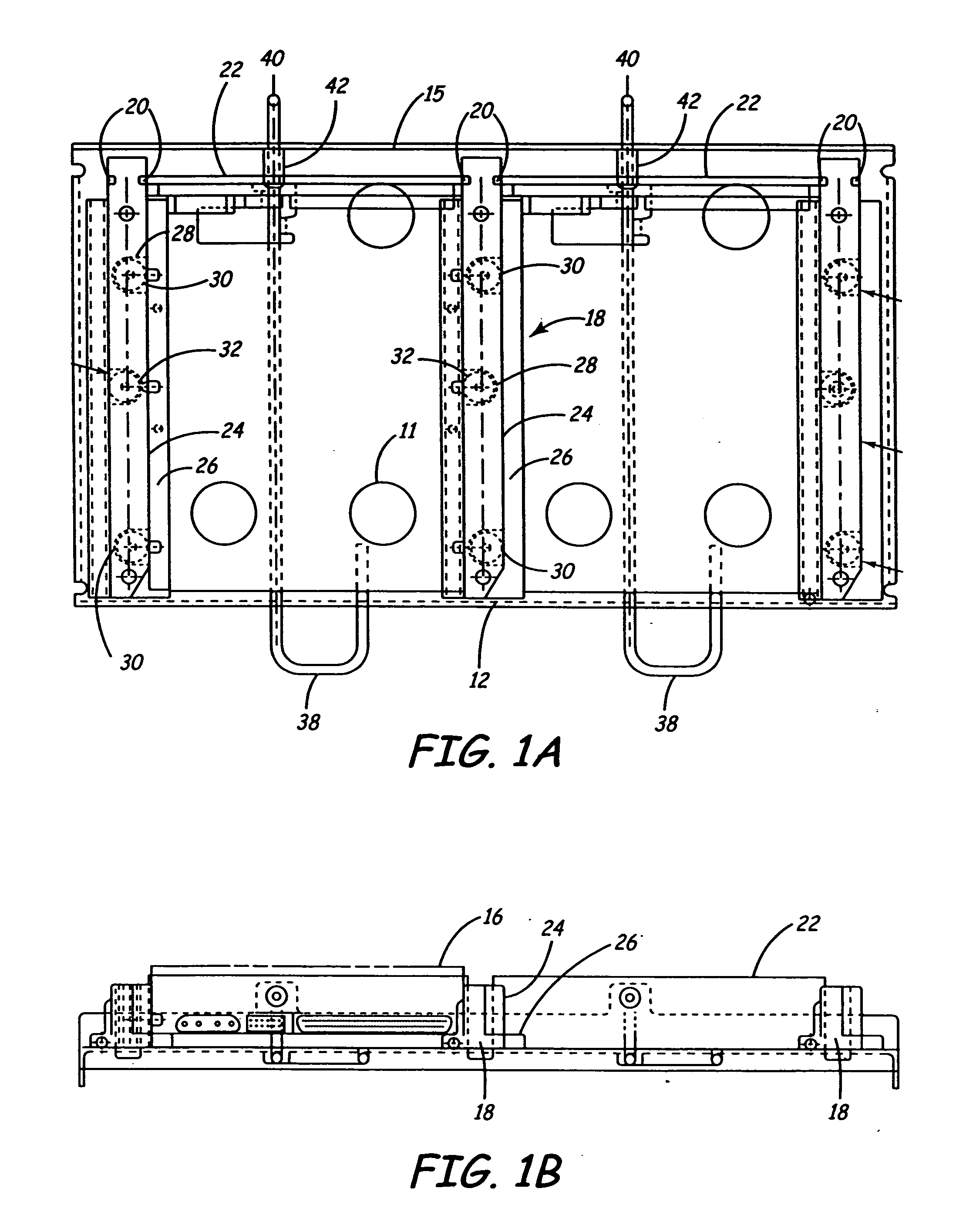

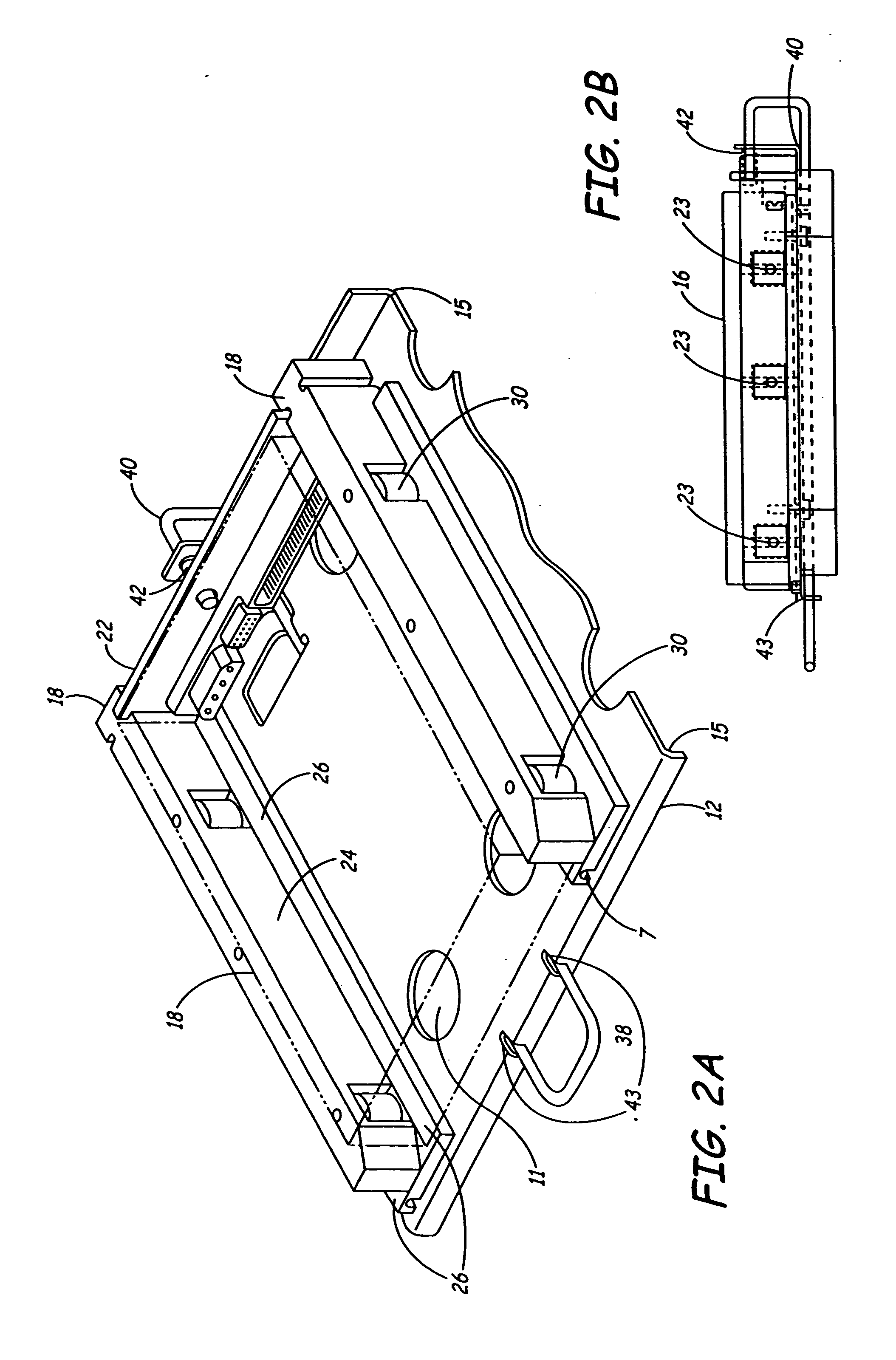

Hard drive test fixture

InactiveUS20050116702A1Easy to disassembleEasy to adaptCarrier constructional parts dispositionElectrical measurement instrument detailsHard disc driveQuality control

The present invention is a hard drive test fixture for supporting a hard drive during quality control testing. The test fixture includes a pan having a base. Rails are attached to the base of the pan for providing structural support to the pan and for positioning of the hard drive. A connection card is removably attached to the rails and is adapted for connection to the hard drive. The test fixture includes an ejection rod for facilitating removal of the hard drive from the test fixture.

Owner:PEMSTAR

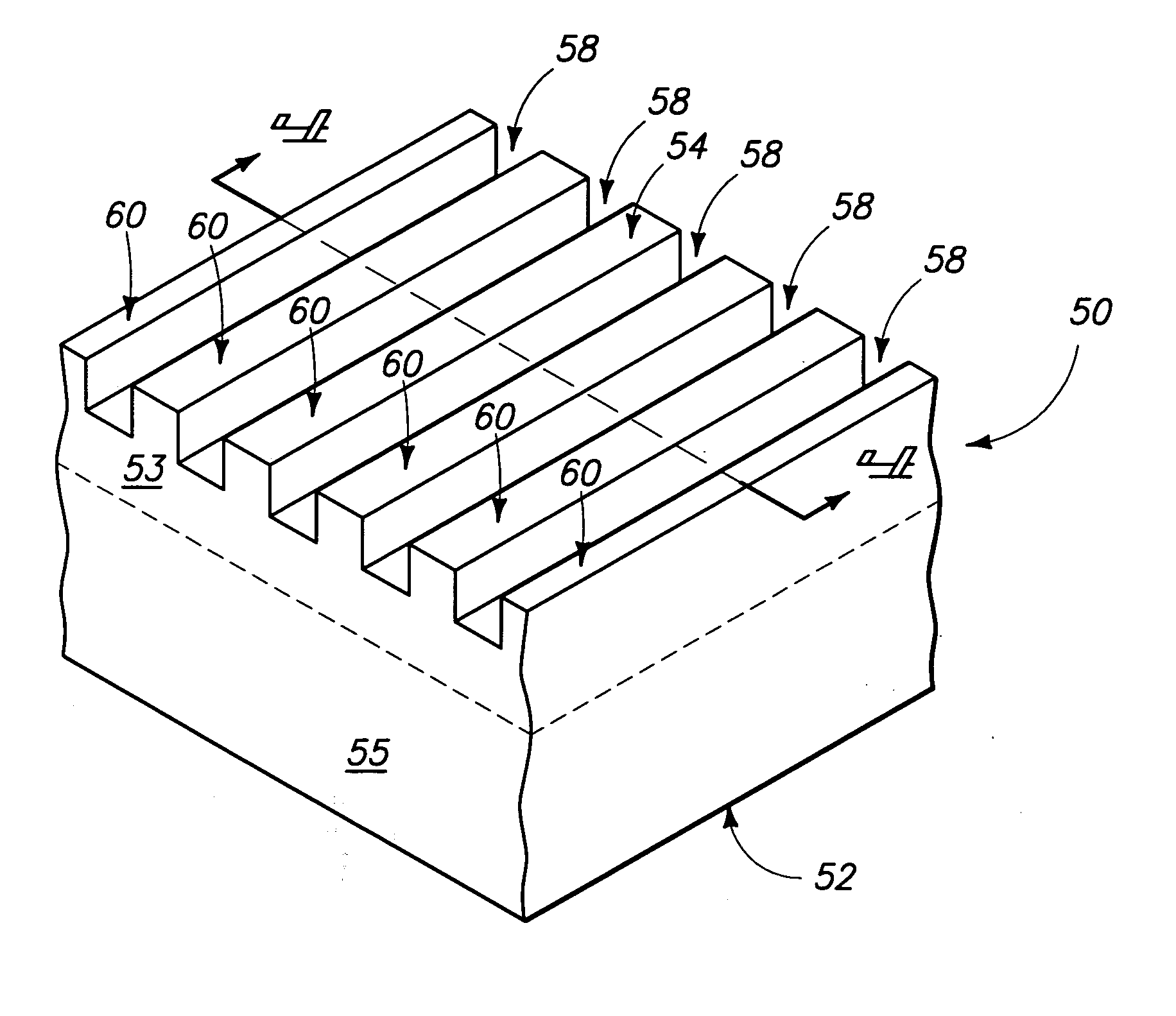

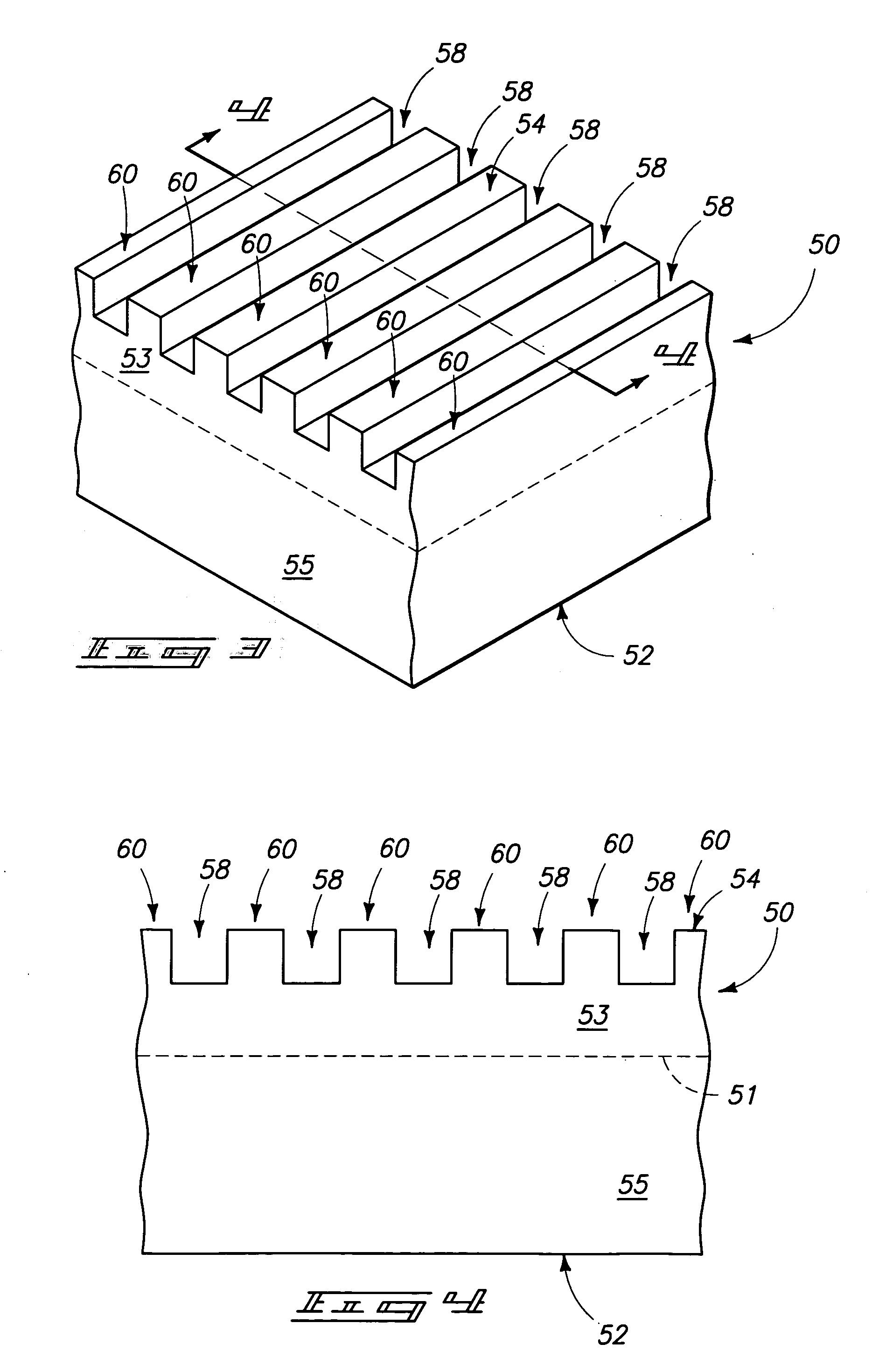

Semiconductor packages, methods of forming semiconductor packages, and methods of cooling semiconductor dies

The invention includes semiconductor packages having grooves within a semiconductor die backside; and includes semiconductor packages utilizing carbon nanostructures (such as, for example, carbon nanotubes) as thermally conductive interface materials. The invention also includes methods of cooling a semiconductor die in which coolant is forced through grooves in a backside of the die, and includes methods of making semiconductor packages.

Owner:MICRON TECH INC

Temperature control of electronic devices using power following feedback

InactiveUS20020050833A1Easy to useEliminate needTemperatue controlSemiconductor/solid-state device detailsTemperature controlEngineering

A method for controlling a device temperature measures a parameter related to device power consumption and utilizes the parameter to control the device temperature. This can be achieved with a system including a heat exchanger, a power monitor, and a circuit which controls the temperature setting of the heat exchanger. The circuit uses as inputs the power level, heat exchanger temperature, and set point. The system thus eliminates the need for temperature sensing devices in or connected to a chip, responds to the temperature of the device and not the package, can be used for high volume chip manufacturing, does not require significant surface area of a device for temperature sensing, and eliminates the need for chip power profiles. Significantly, the system allows a set point to be maintained with minimal overshoot or undershoot.

Owner:SCHLUMBERGER AUTOMATED TEST EQUIP +1

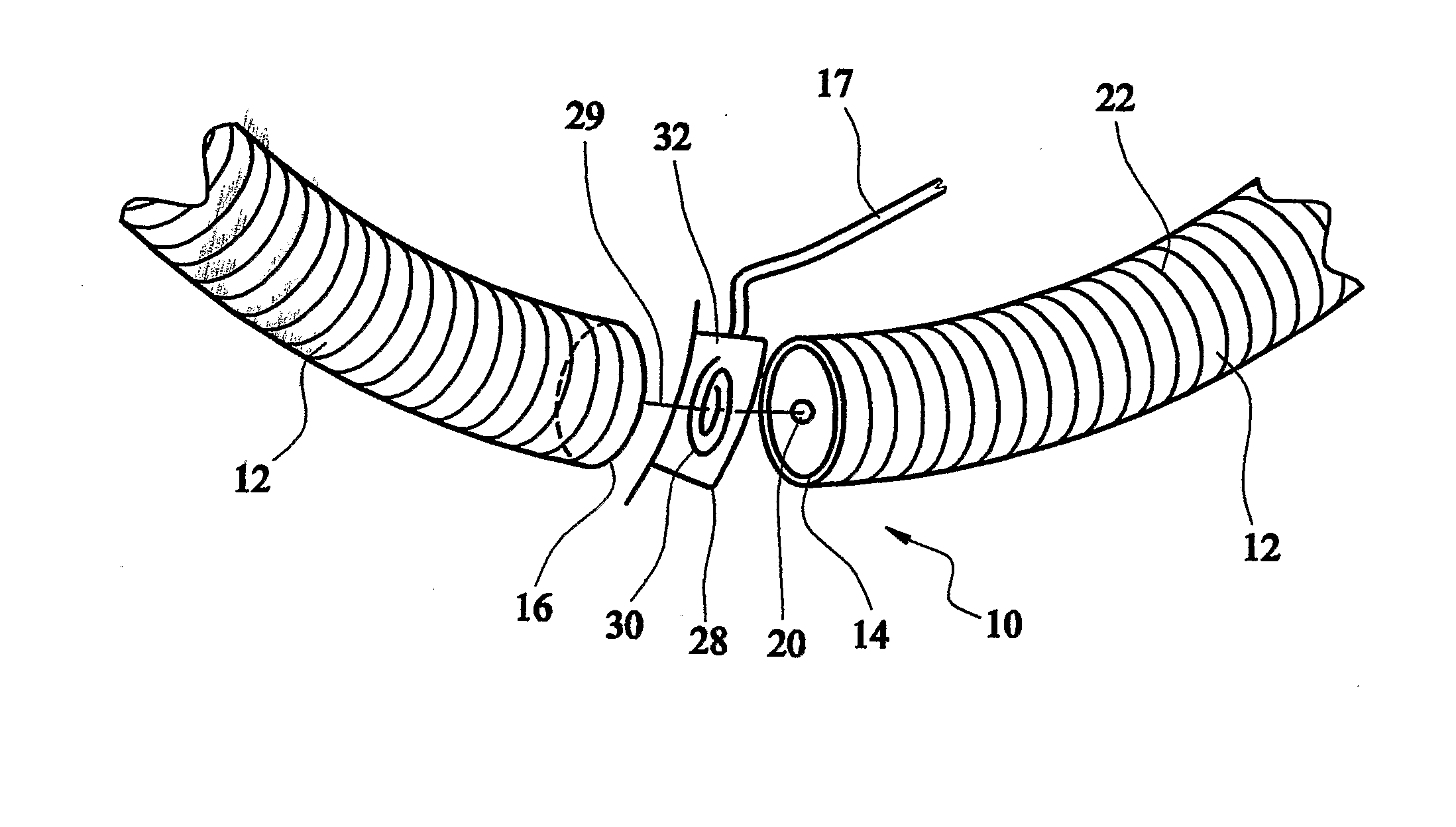

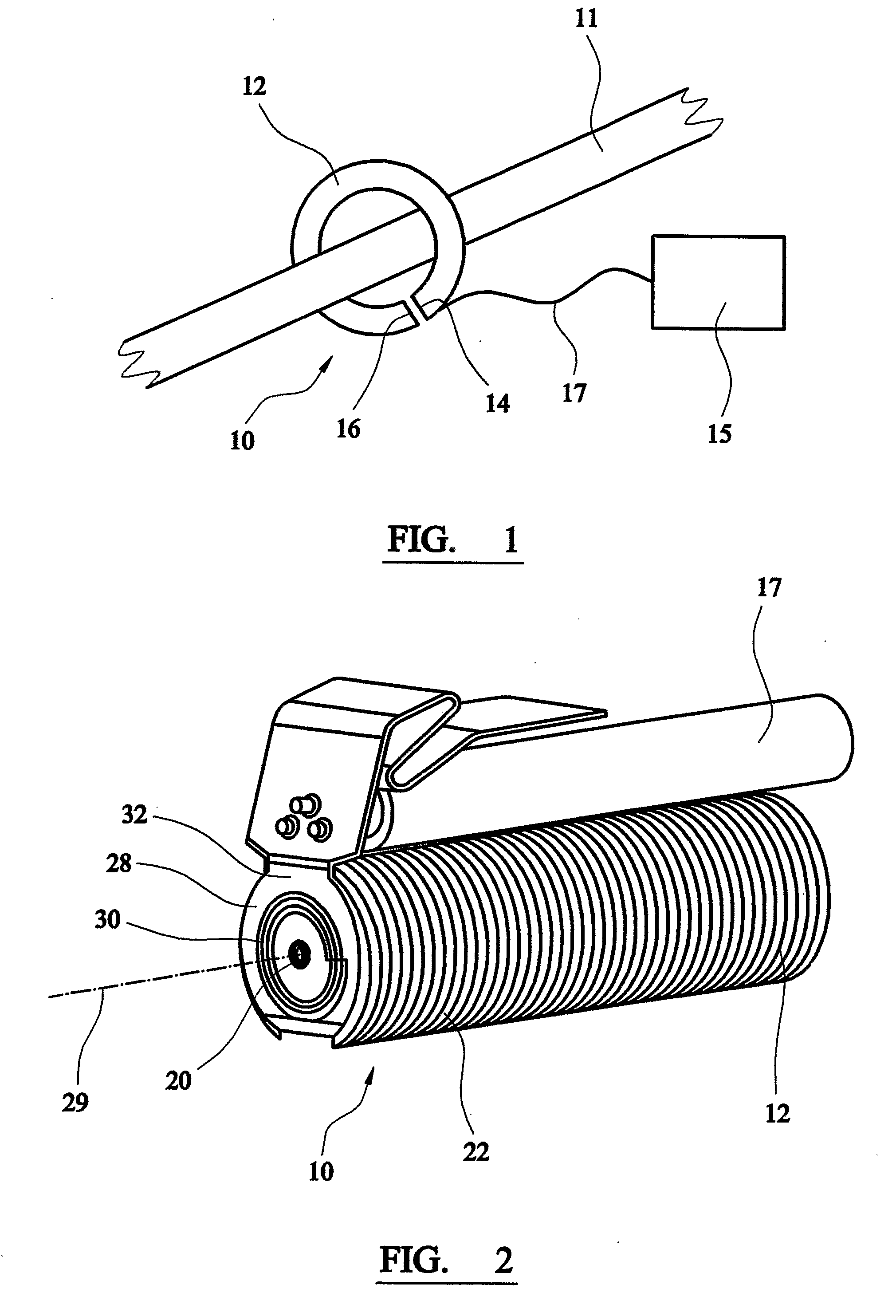

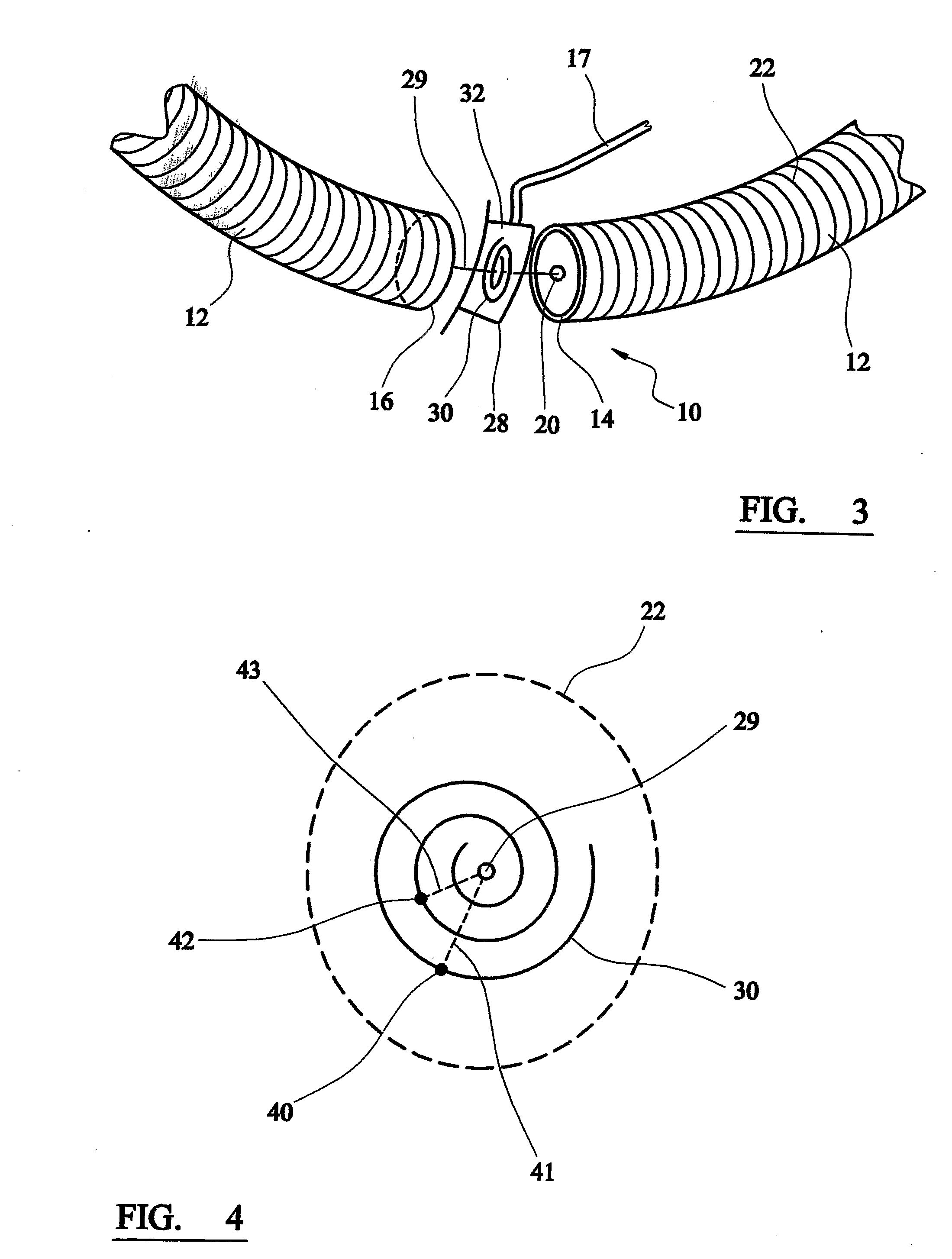

Method and Apparatus for Measuring Current

ActiveUS20070290695A1Magnetic measurementsCurrent/voltage measurementMeasurement deviceElectrical conductor

Current testing / measuring apparatus 10 comprises a flexible member 12 having a first end 14 and a second end 16. In use, the flexible member 12 is arranged to locate around a conductor 11 carrying a current to be measured. In particular, the current measuring apparatus 10 comprises a Rogowski coil. The ends of the flexible member 12 are coupled together in use but a gap is created between the ends. This distance can generate errors in the current measurement and the present invention provides compensation means 28 in the form of a compensation windings. The compensation windings comprise a planar spiral conductor provided on a printed circuit board to compensate for the separation distance between the first end and the second end.

Owner:LEM HEME

Temperature control in IC sockets

InactiveUS20060290370A1Maintain surface temperatureMaintain temperatureElectrical measurement instrument detailsFault location by increasing destruction at faultTemperature controlElectronic controller

A system and method are provided which provides more accurate temperature control of integrated circuits. A system for testing integrated circuit (IC) packages comprises a plurality of IC testing socket bases arranged on a testing board and configured to receive a plurality of IC packages. A plurality of IC testing socket lids are arranged to attach to the testing board. Each IC testing socket lid comprises a temperature sensor to thermally contact the IC package and measure a surface temperature of the IC package, a heater or cooler to directly contact the IC package, and an electronic controller to receive signals from the temperature sensor. The electronic controller is programmed to change the temperature of the heater or cooler responsive to the measured surface temperature of the IC package. A plurality of cooling devices individually removes heat generated by the plurality of IC packages. The electronic controller in each IC testing socket lid is further programmed to control a corresponding cooling device to maintain the surface temperature of the plurality of IC packages within a desired temperature range.

Owner:WELLS CTI LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com