Patents

Literature

241results about "Integrated circuit testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

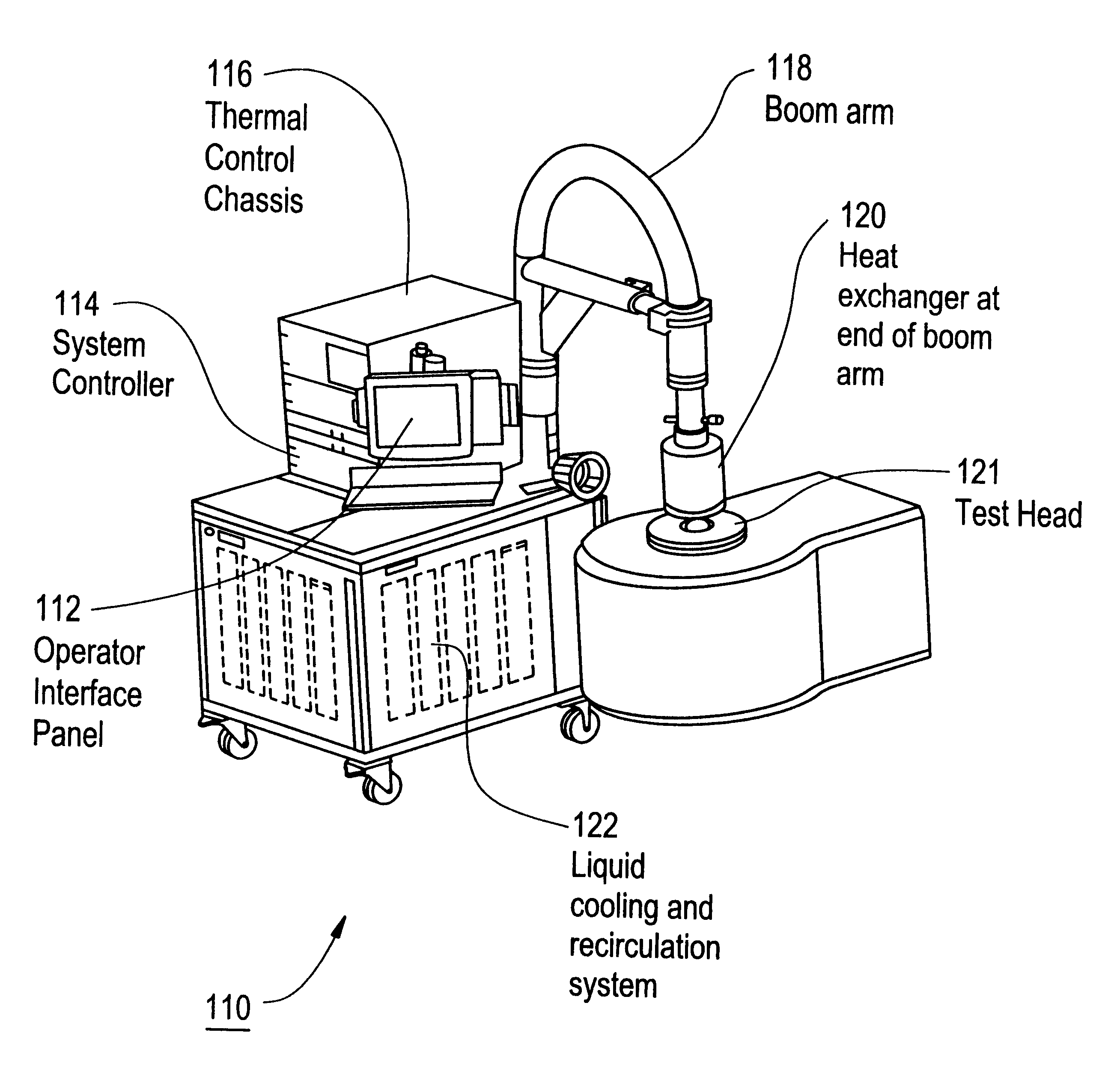

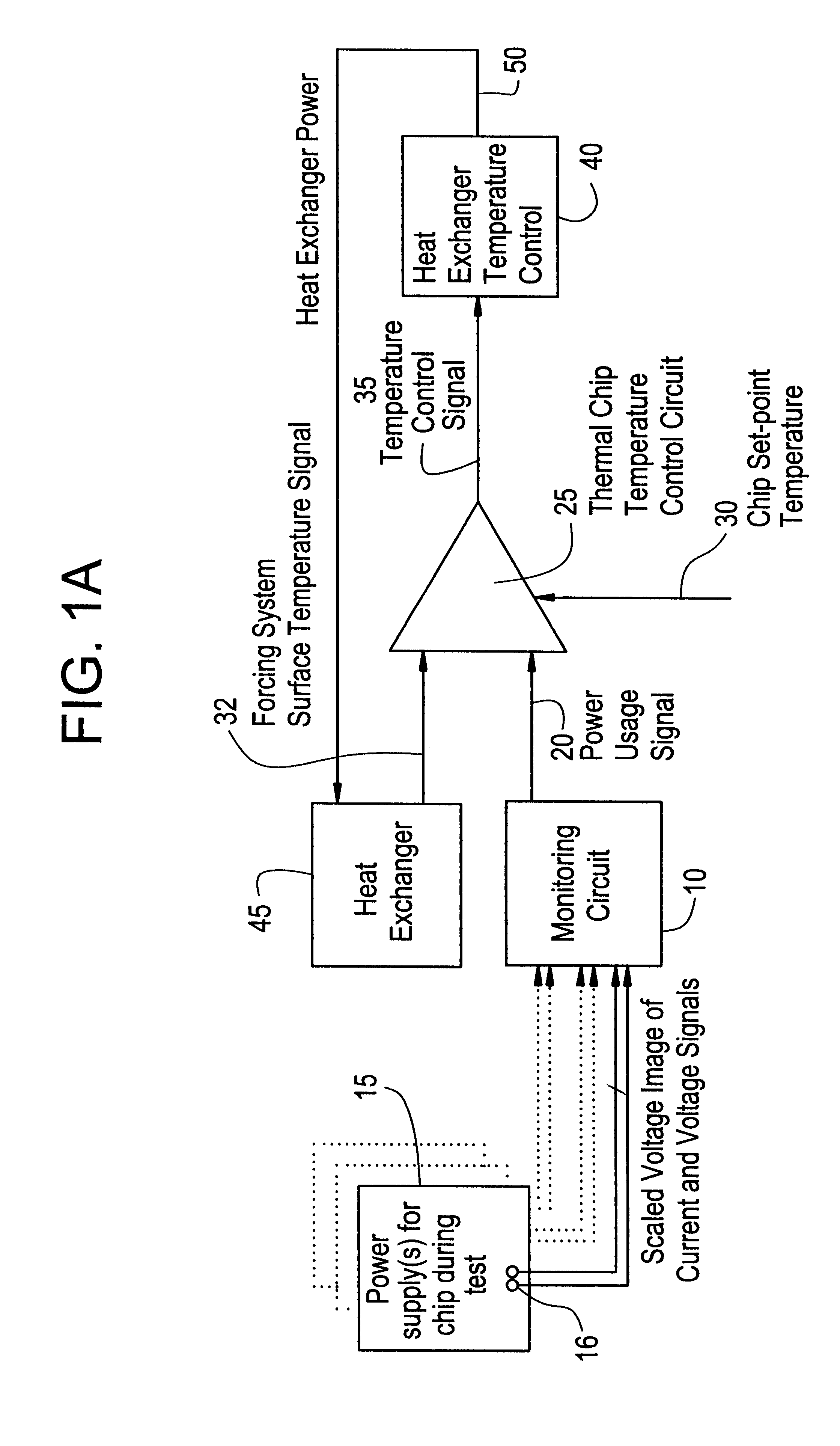

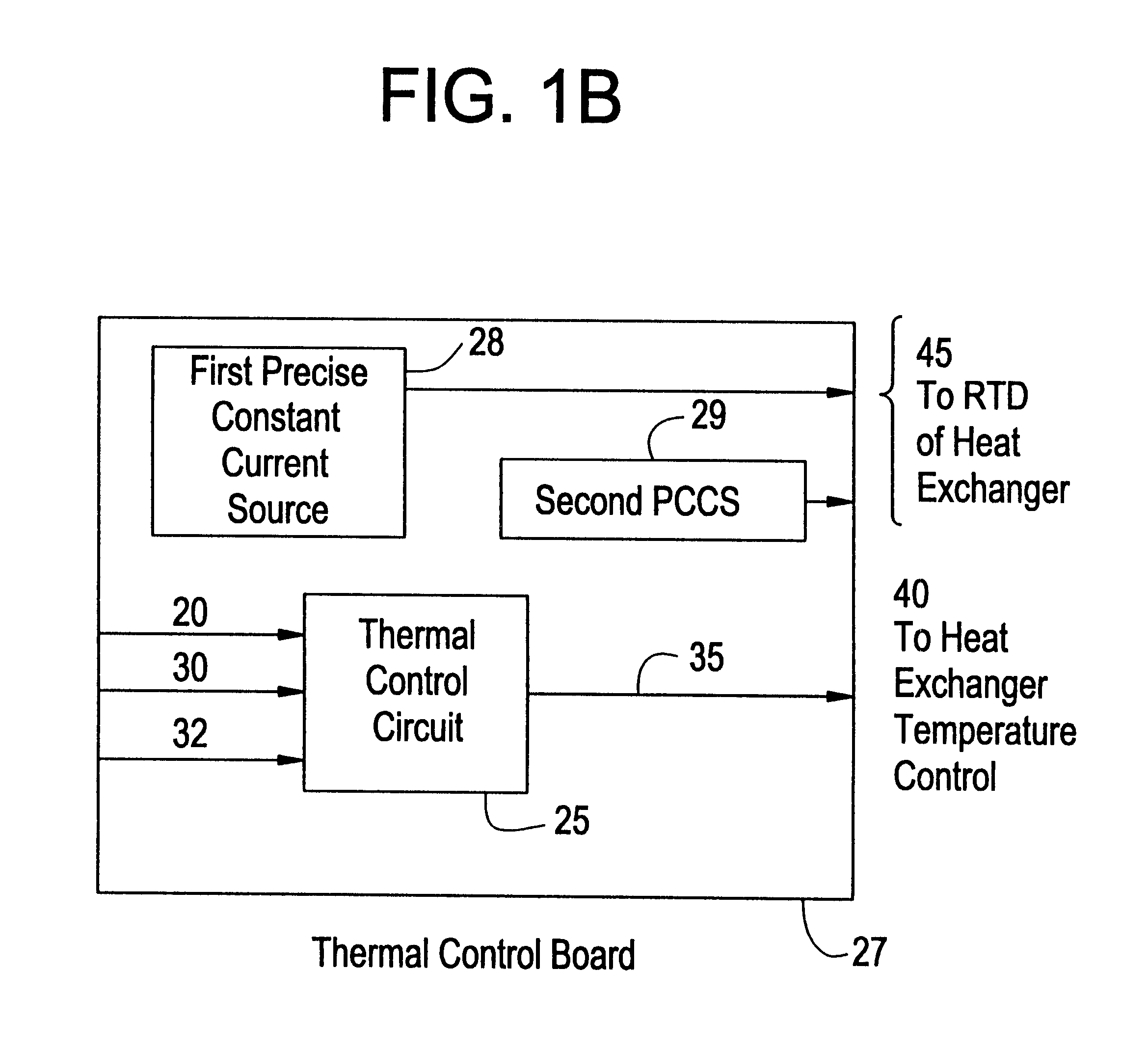

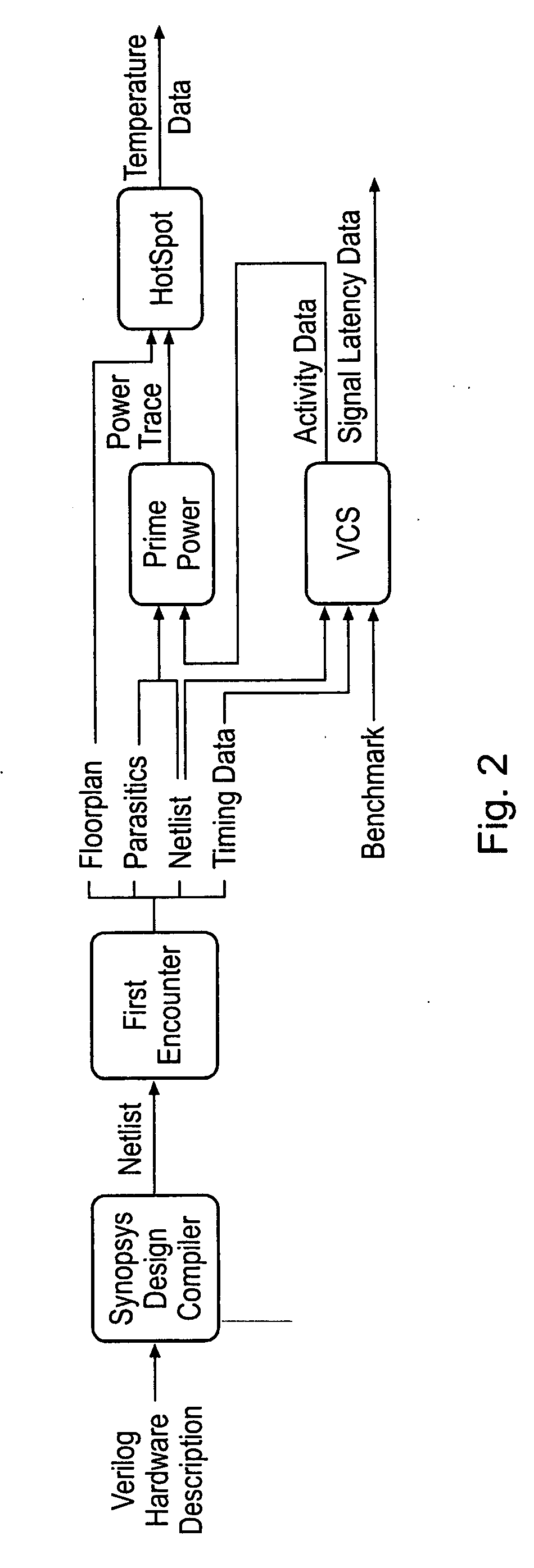

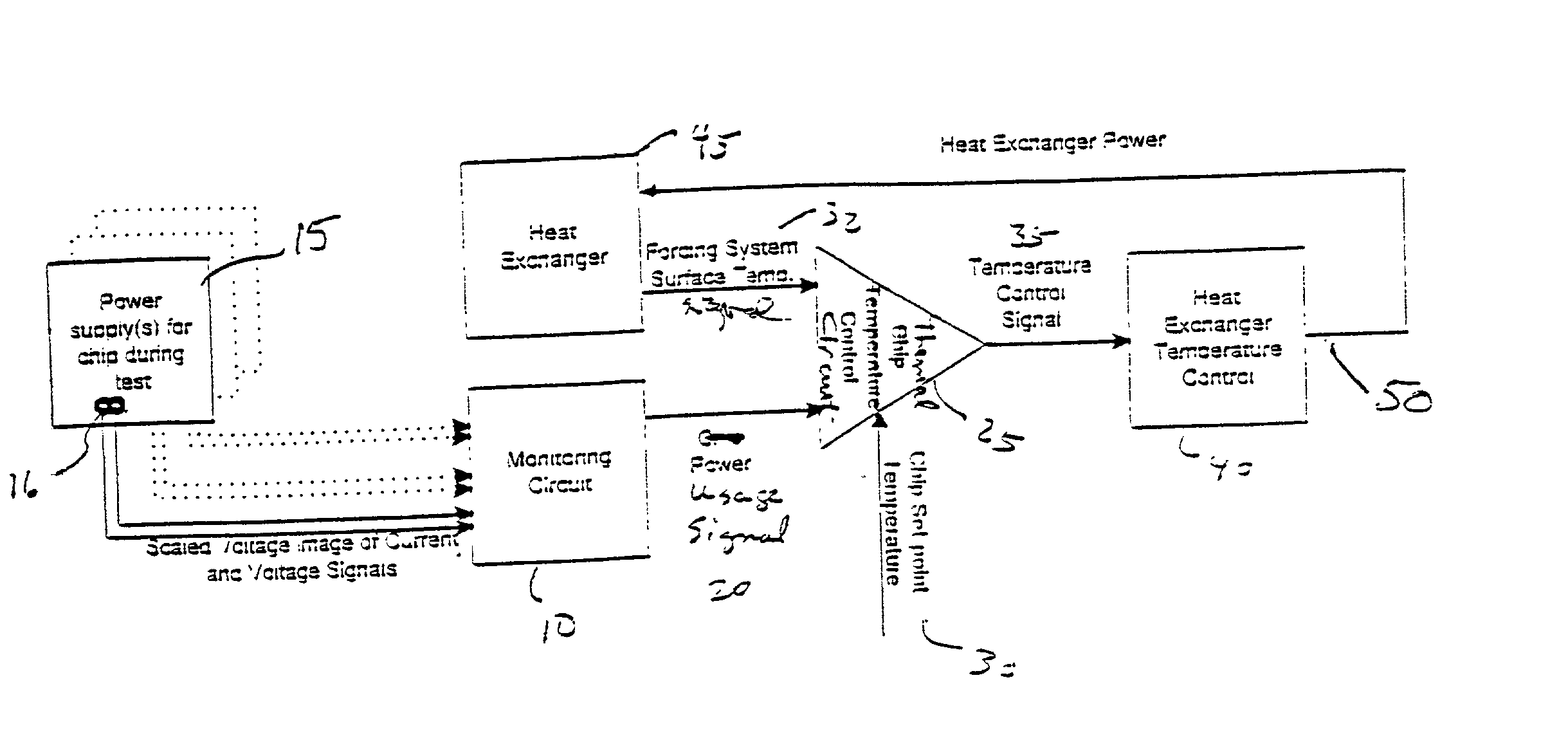

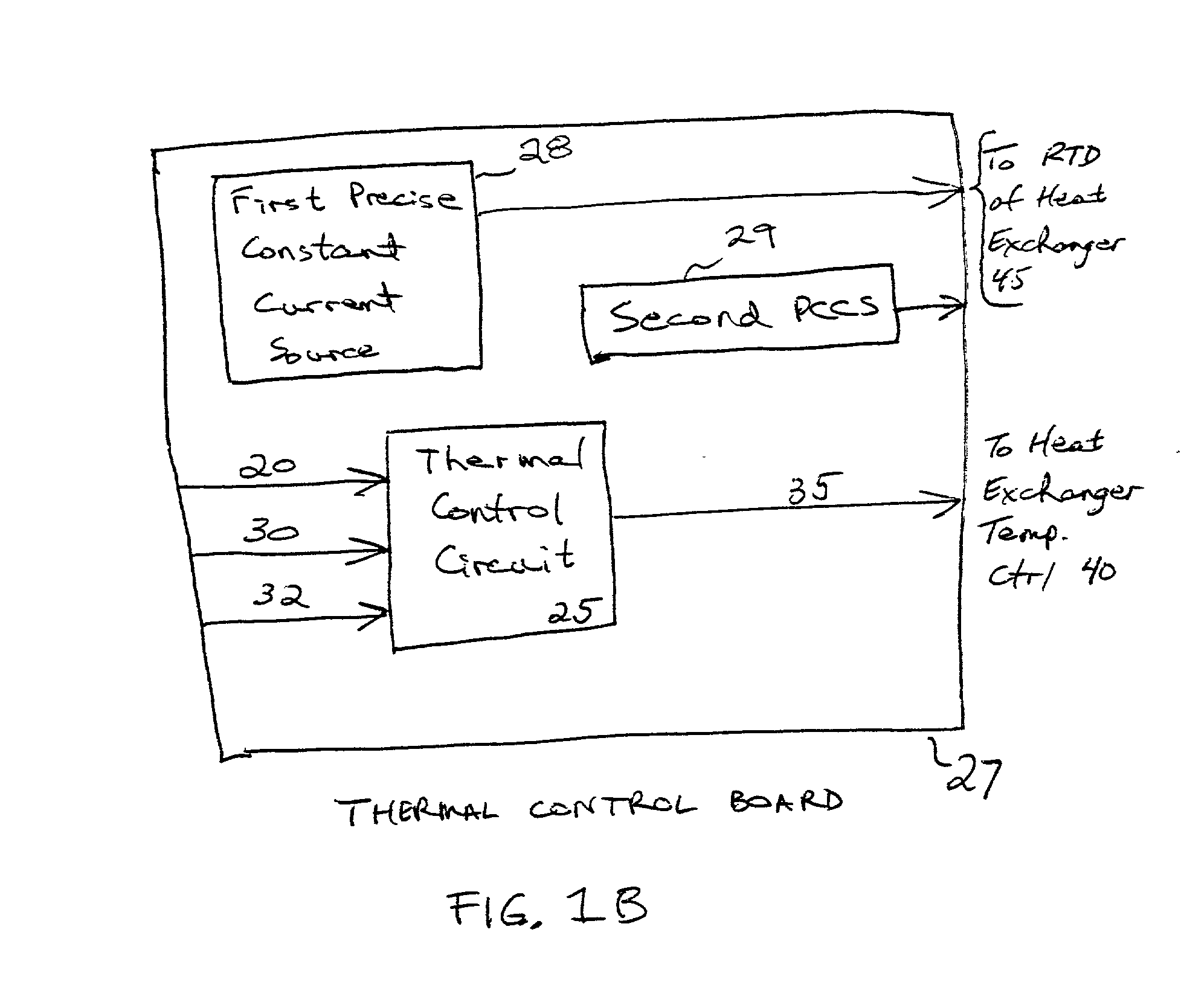

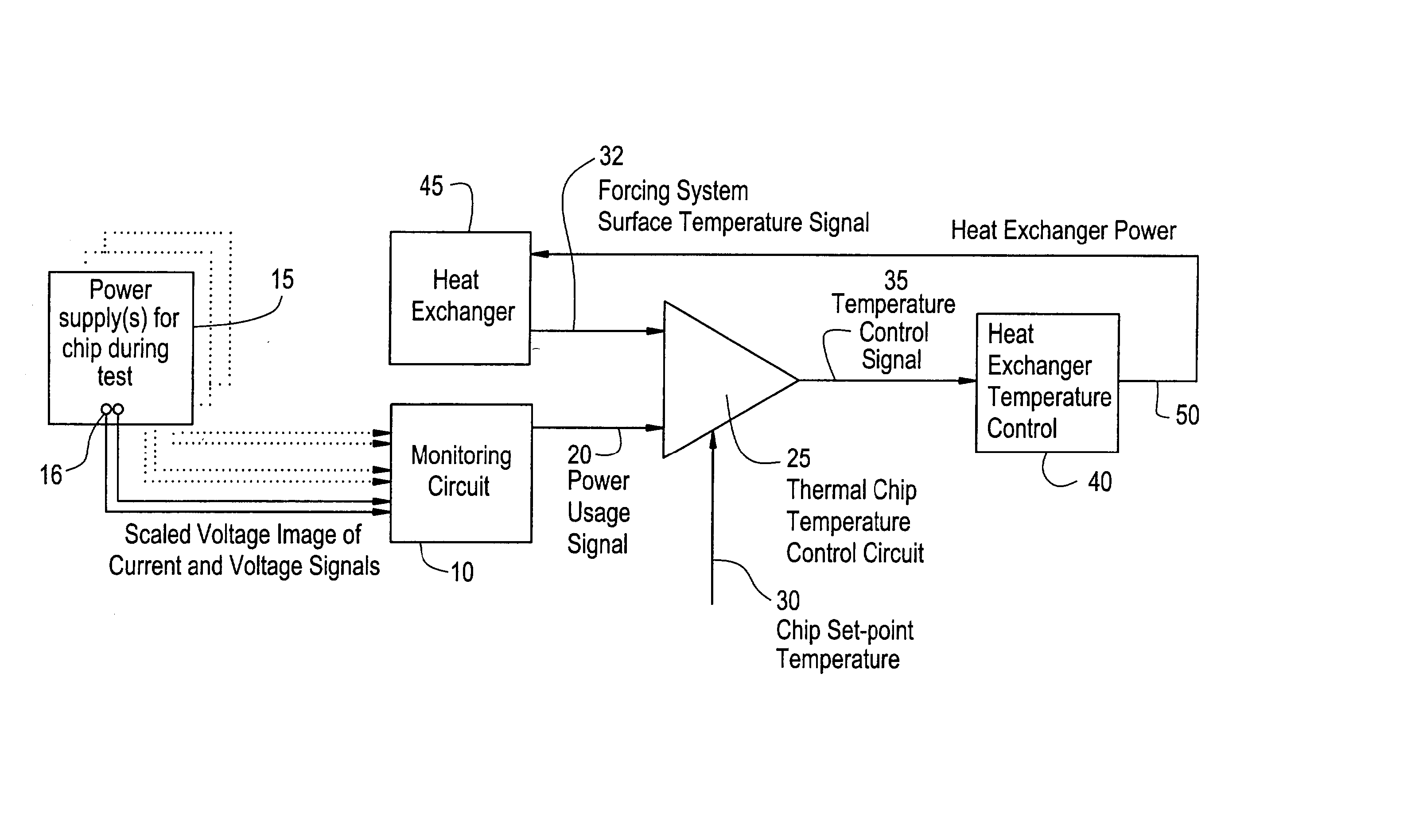

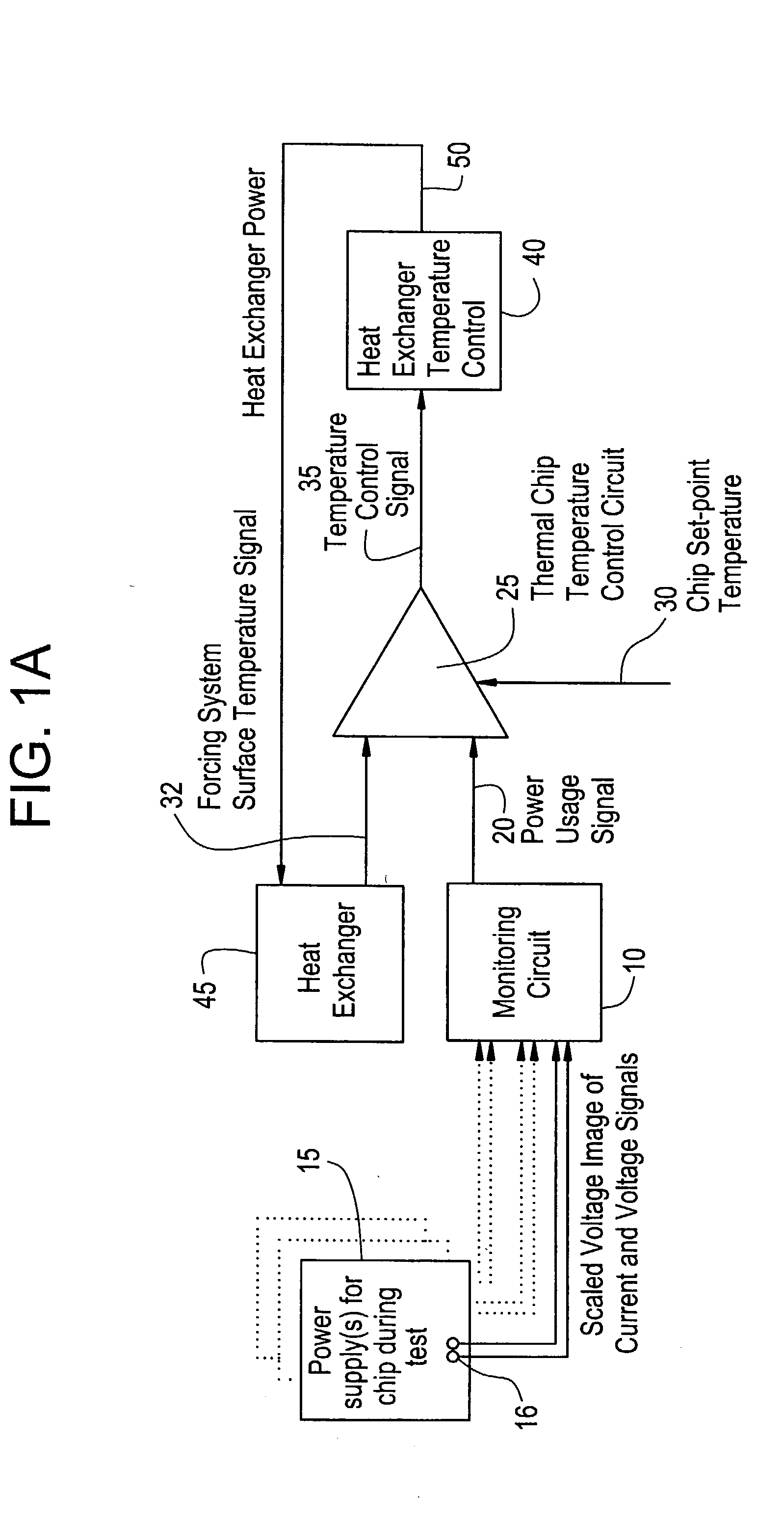

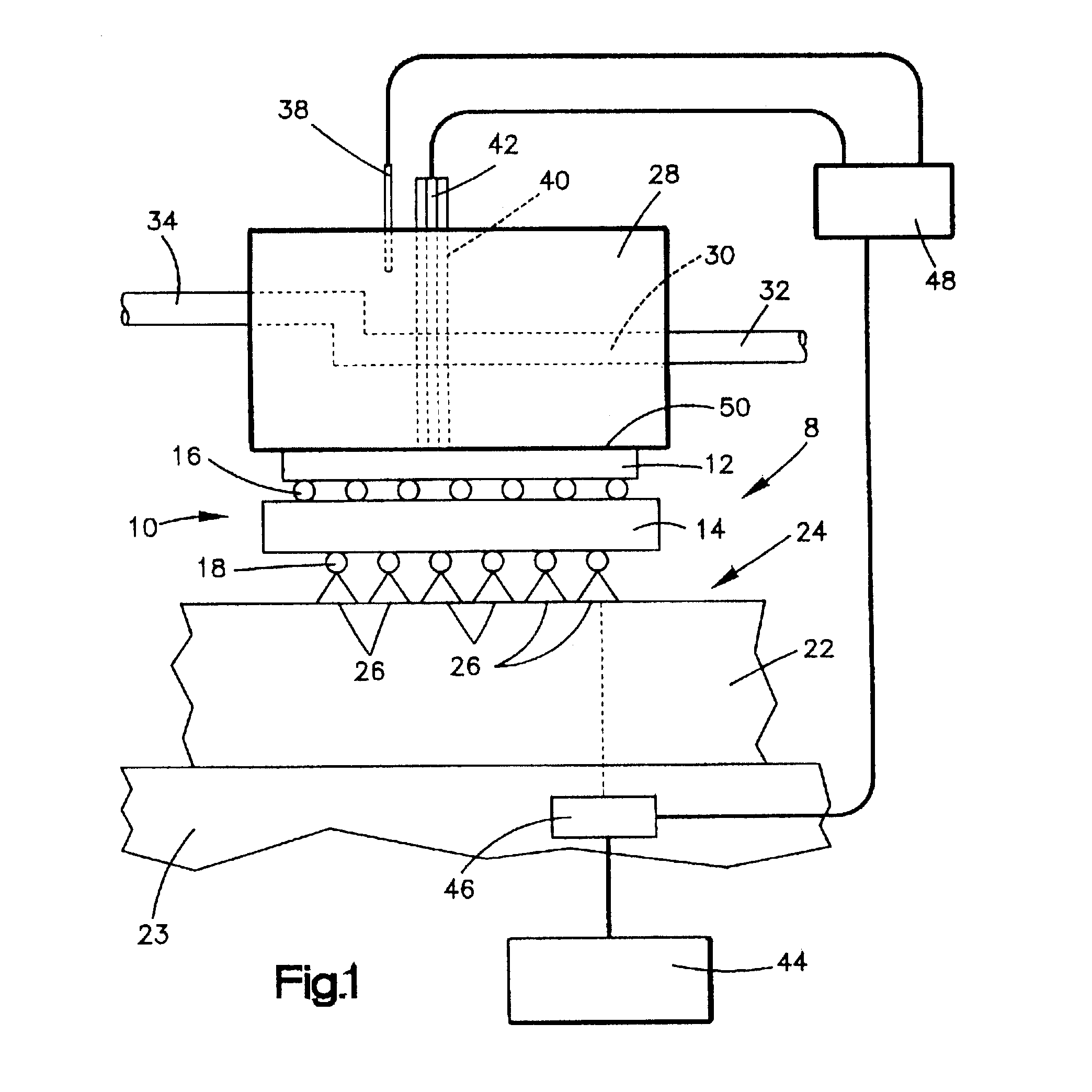

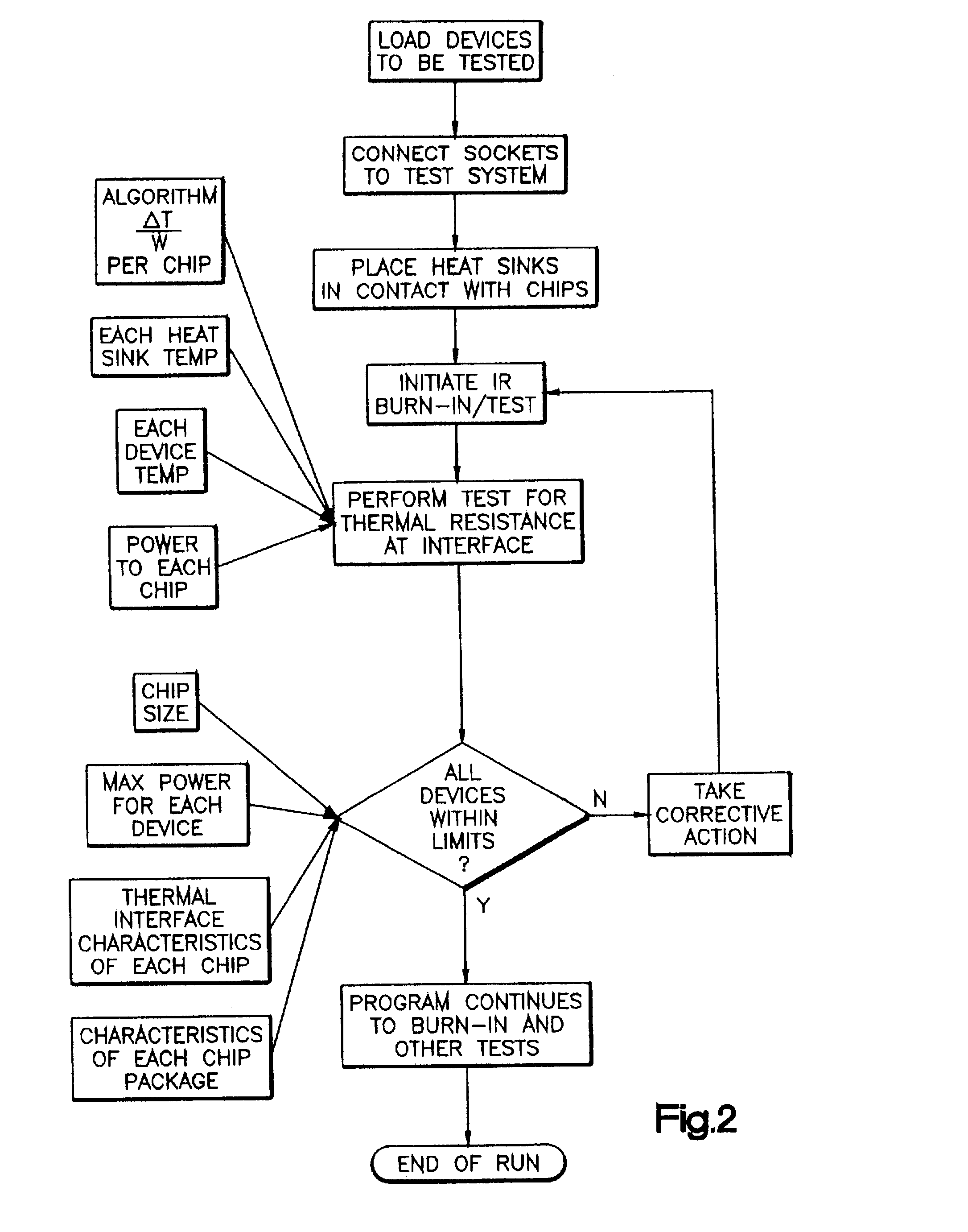

Temperature control of electronic devices using power following feedback

InactiveUS6489793B2Easy to useEliminate needTemperatue controlSemiconductor/solid-state device detailsTemperature controlEngineering

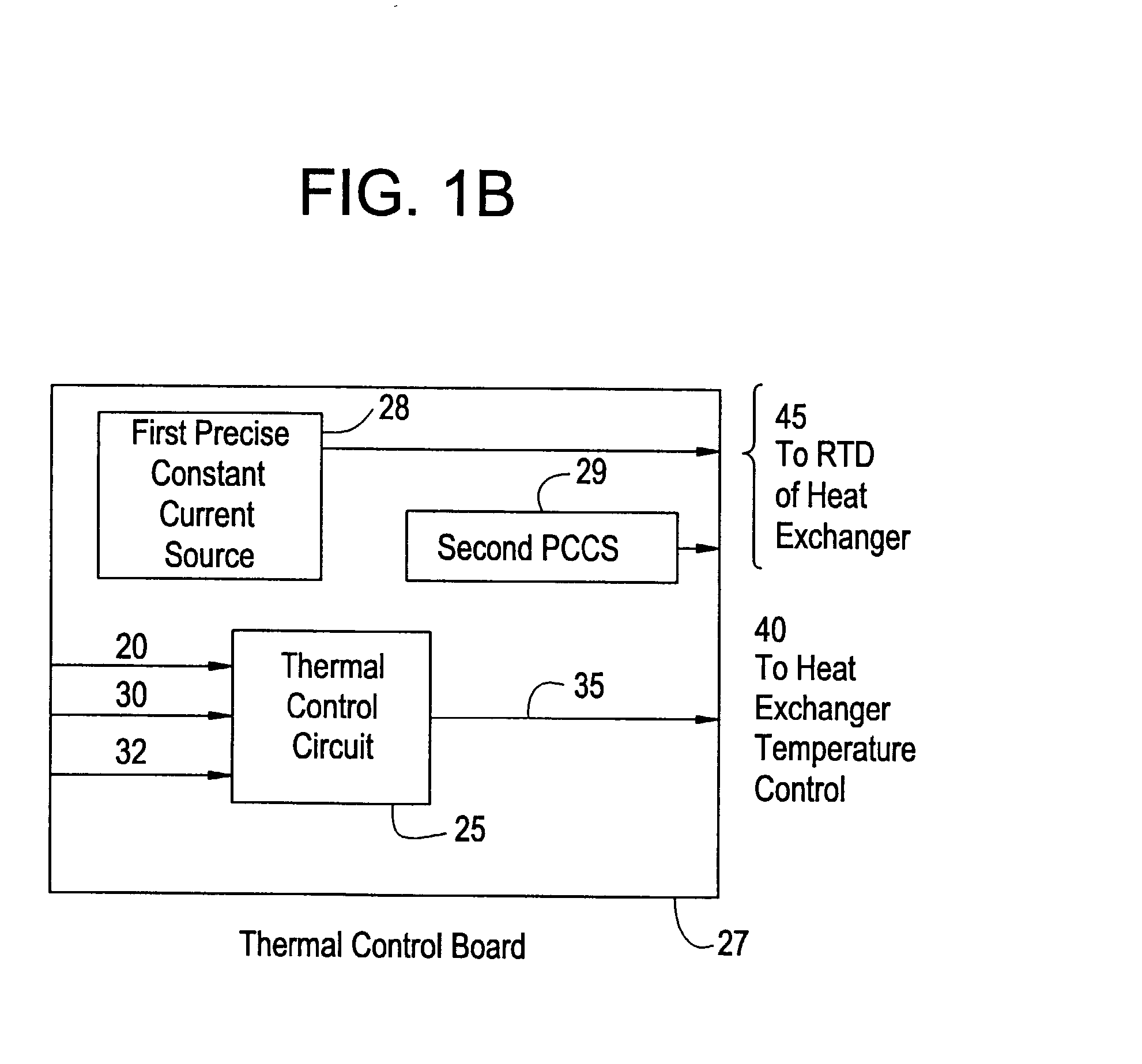

A method for controlling a device temperature measures a parameter related to device power consumption and utilizes the parameter to control the device temperature. This can be achieved with a system including a heat exchanger, a power monitor, and a circuit which controls the temperature setting of the heat exchanger. The circuit uses as inputs the power level, heat exchanger temperature, and set point. The system thus eliminates the need for temperature sensing devices in or connected to a chip, responds to the temperature of the device and not the package, can be used for high volume chip manufacturing, does not require significant surface area of a device for temperature sensing, and eliminates the need for chip power profiles. Significantly, the system allows a set point to be maintained with minimal overshoot or undershoot.

Owner:SCHLUMBERGER AUTOMATED TEST EQUIP +1

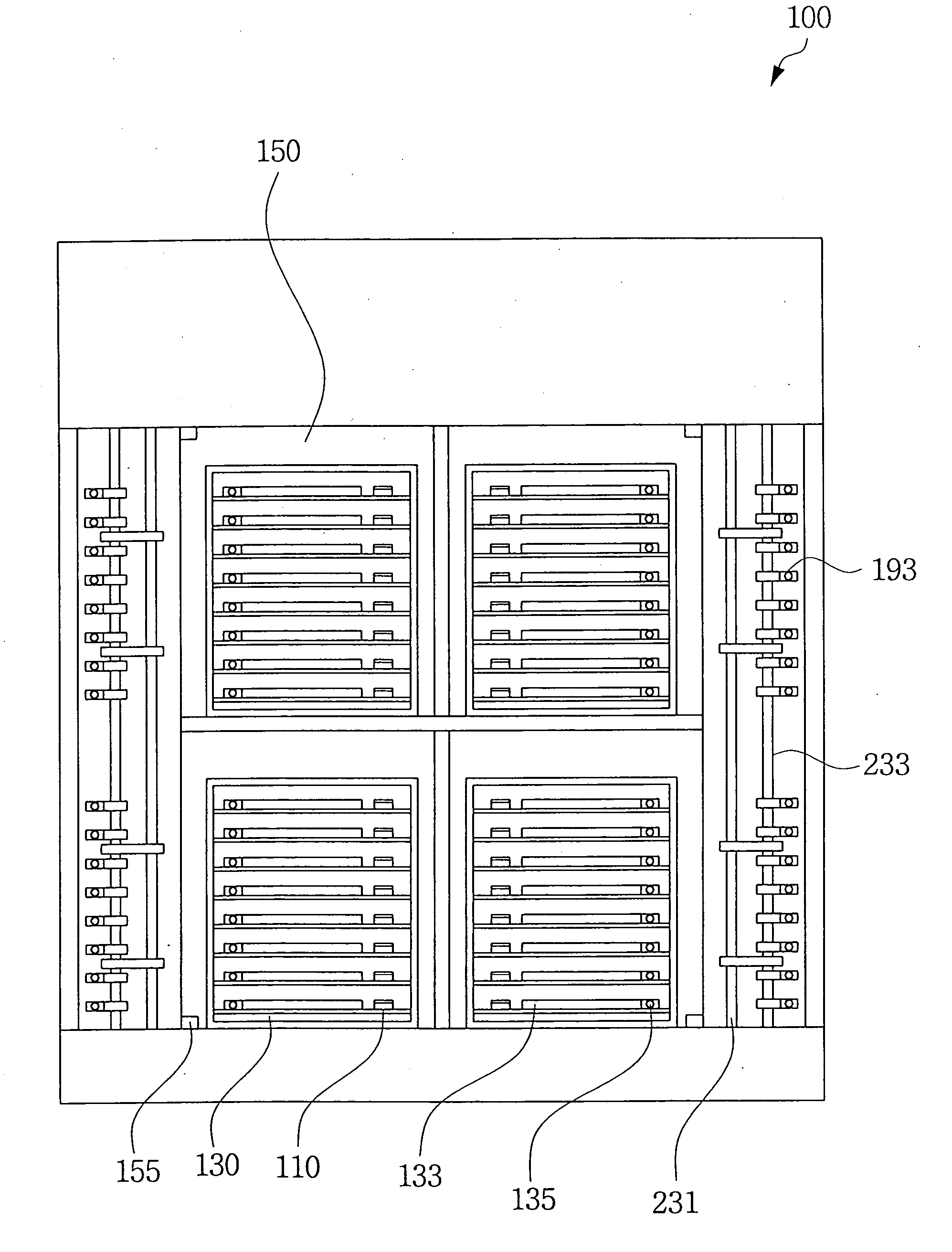

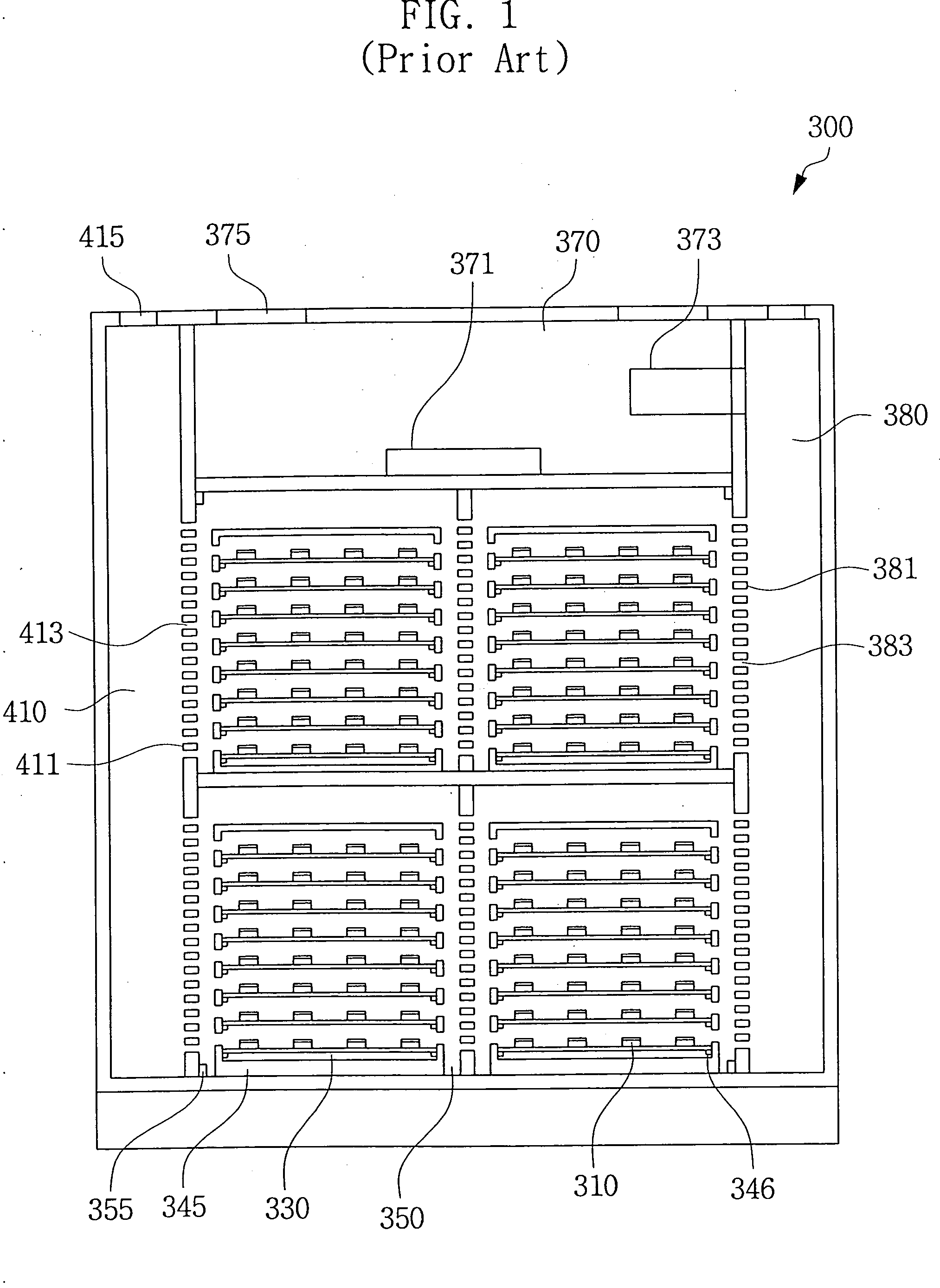

Burn-in test apparatus for BGA packages using forced heat exhaust

InactiveUS20050179457A1Semiconductor/solid-state device testing/measurementOhmic-resistance electrodesEngineeringForced-air

A forced air heat exhaust type of burn-in test apparatus for packages: A first air supply duct provides air to the burn-in chamber and a second air supply duct provides air to supply tubes that direst air into the test sockets that hold the packages. The test sockets have a structure that allows air ventilation of the conductive balls. Accordingly, the apparatus can control the temperature around the packages as well as the temperature in the burn-in chamber, thus preventing conductive ball-melting.

Owner:SAMSUNG ELECTRONICS CO LTD

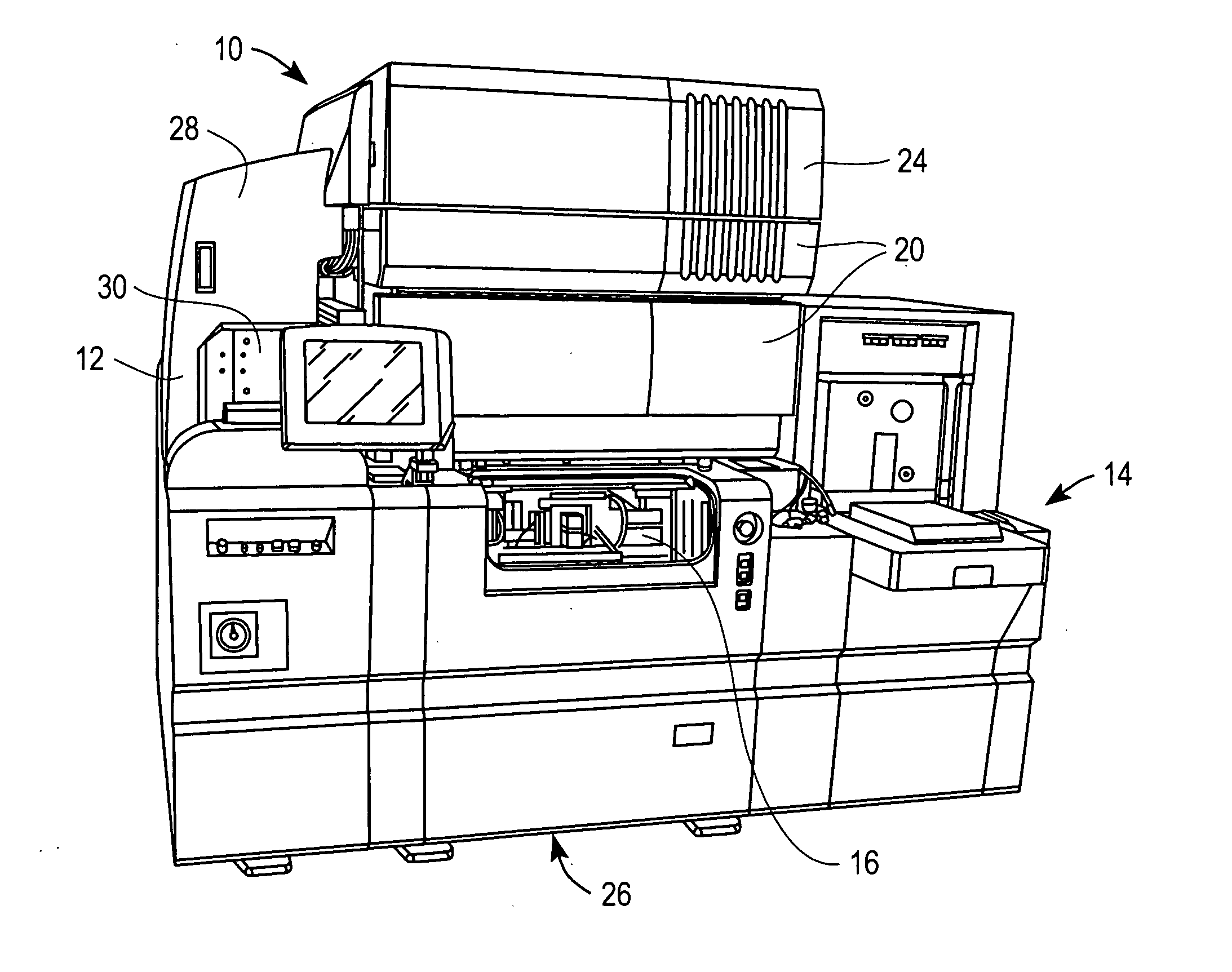

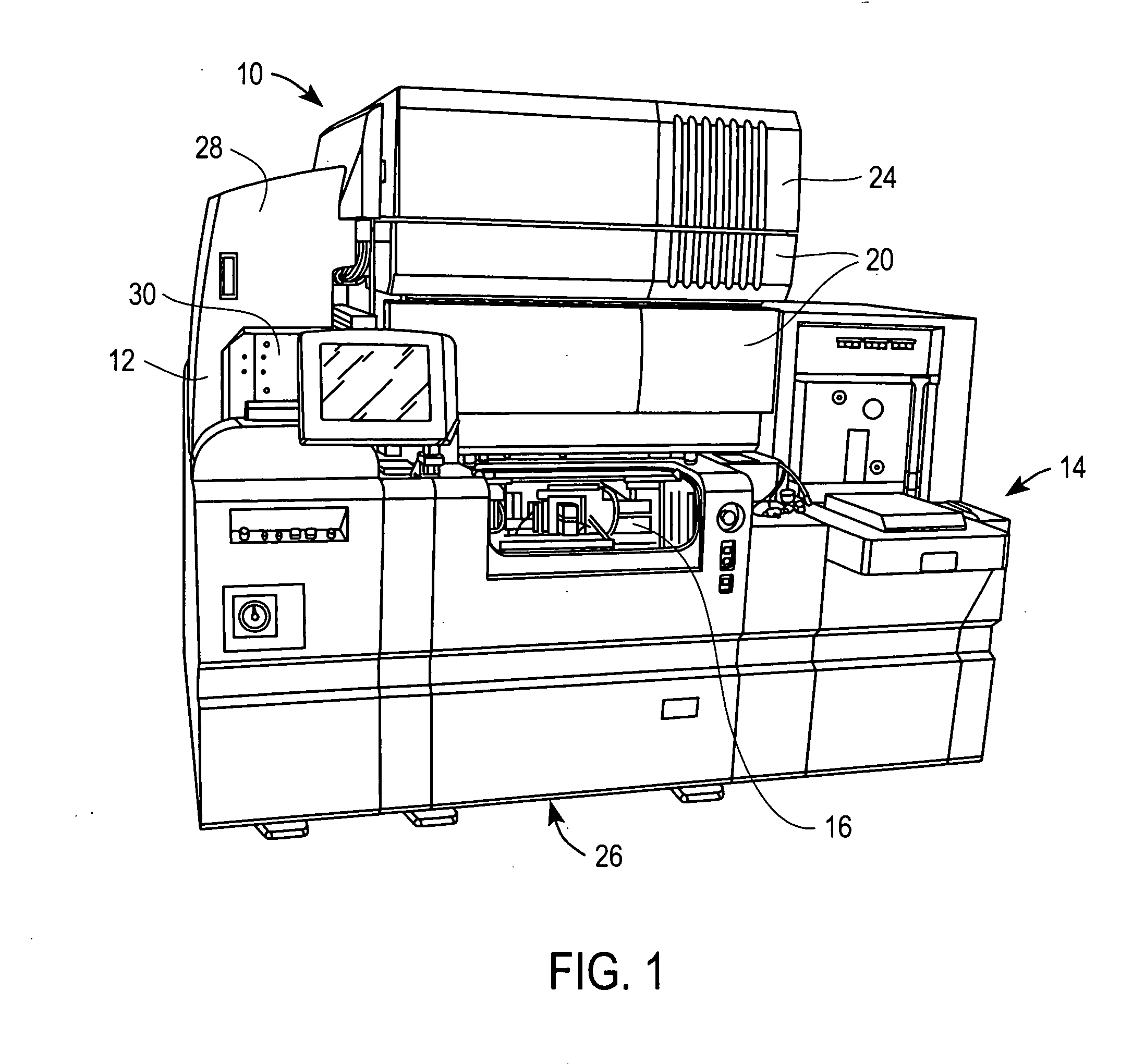

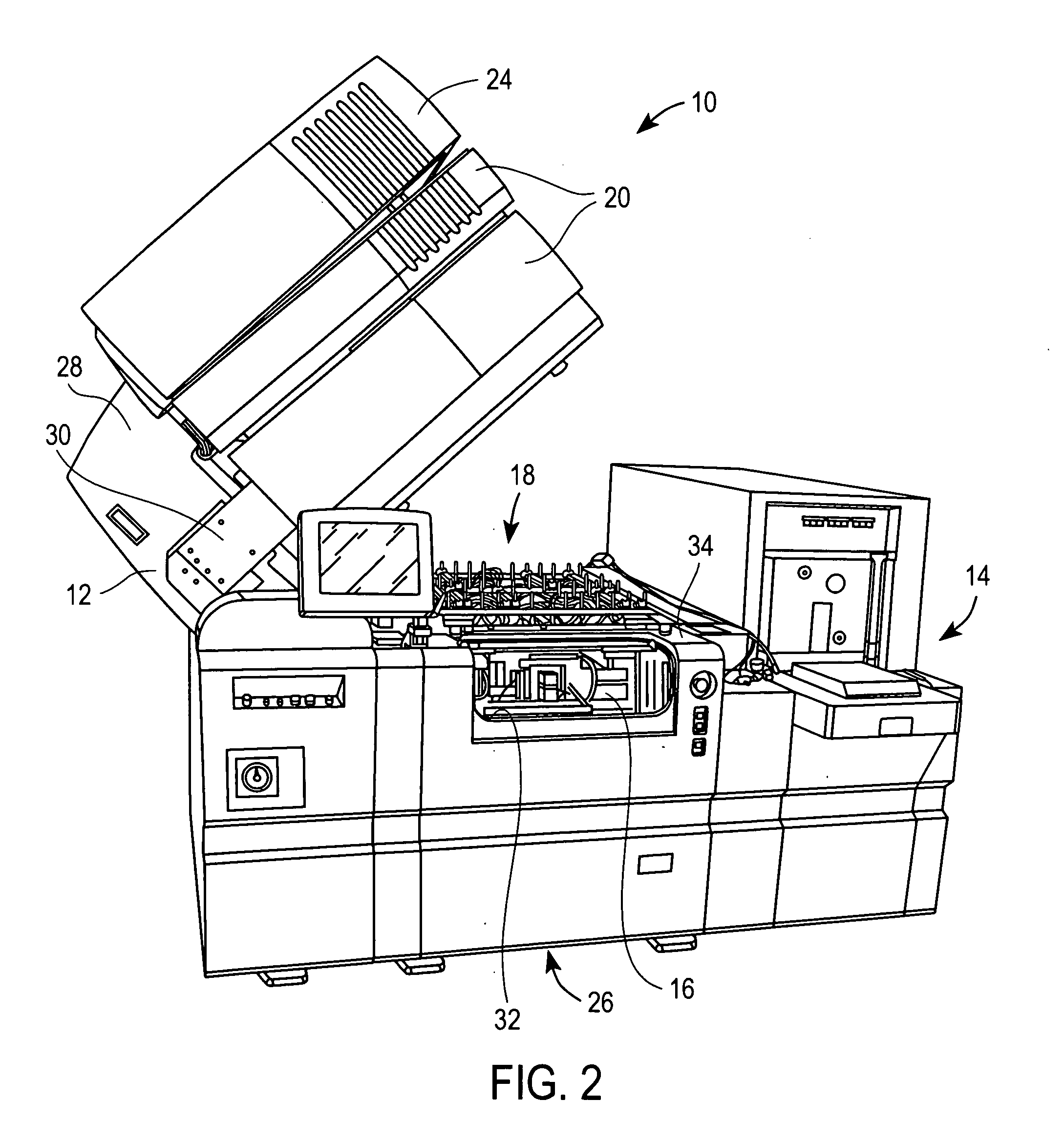

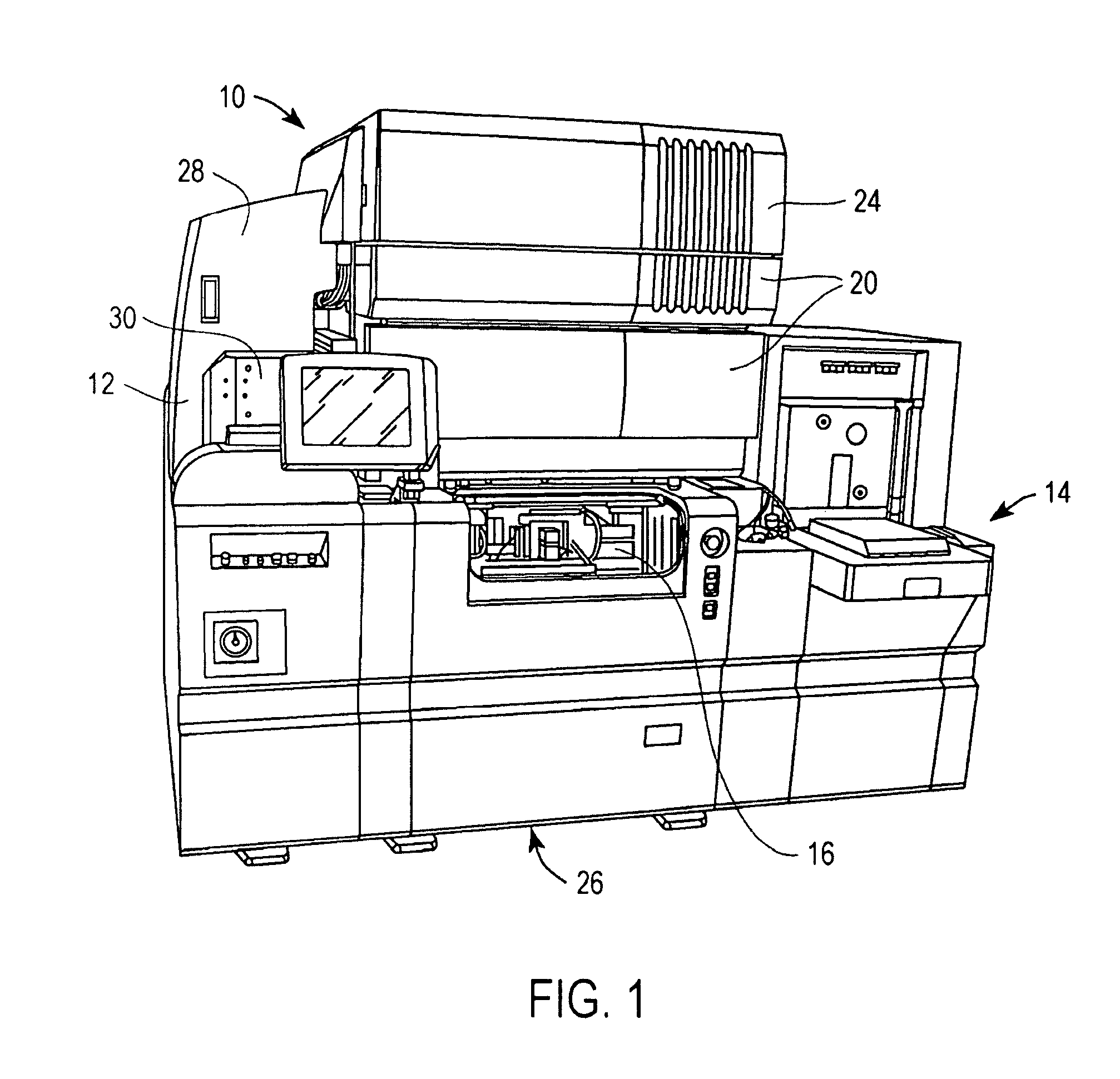

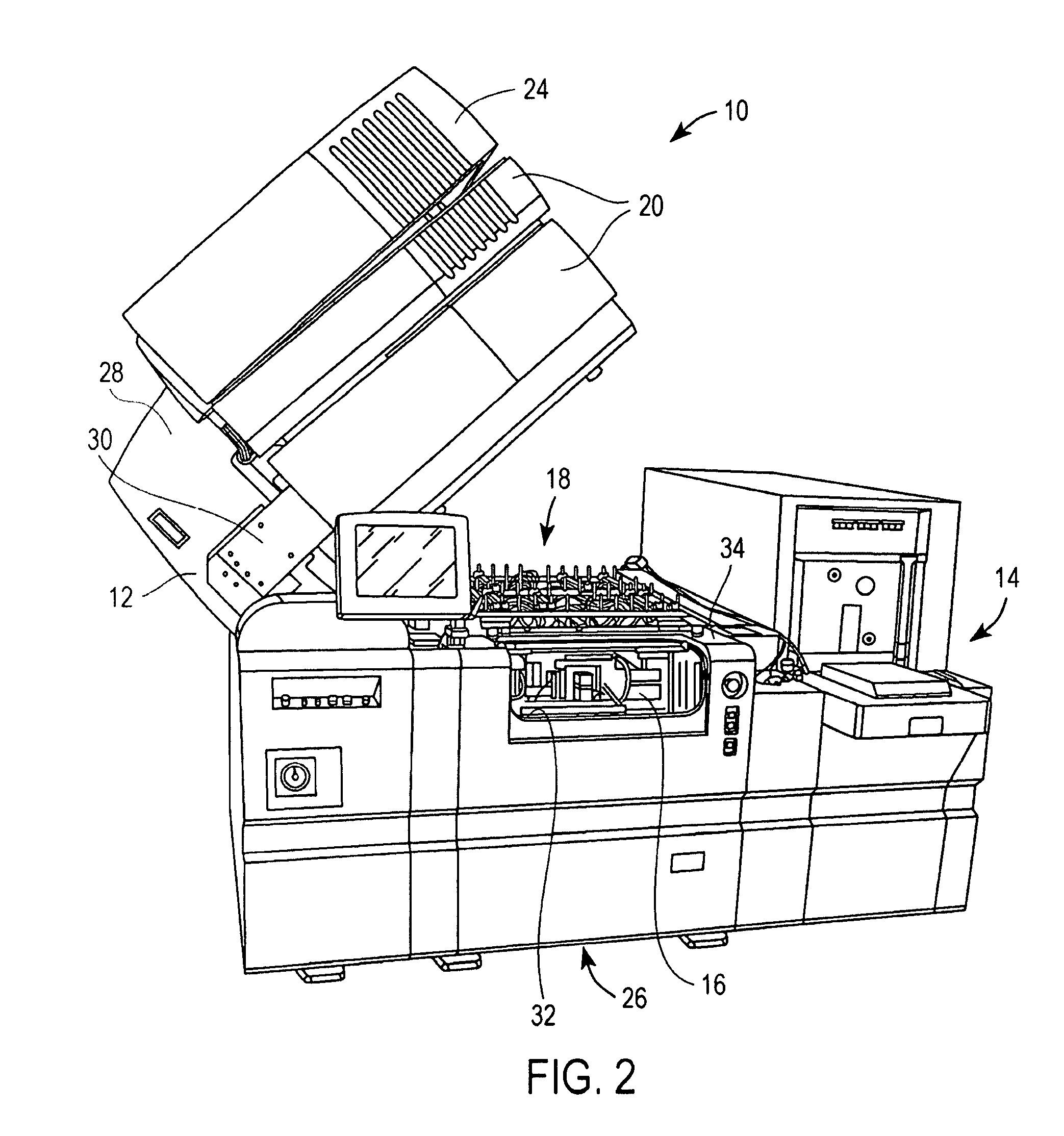

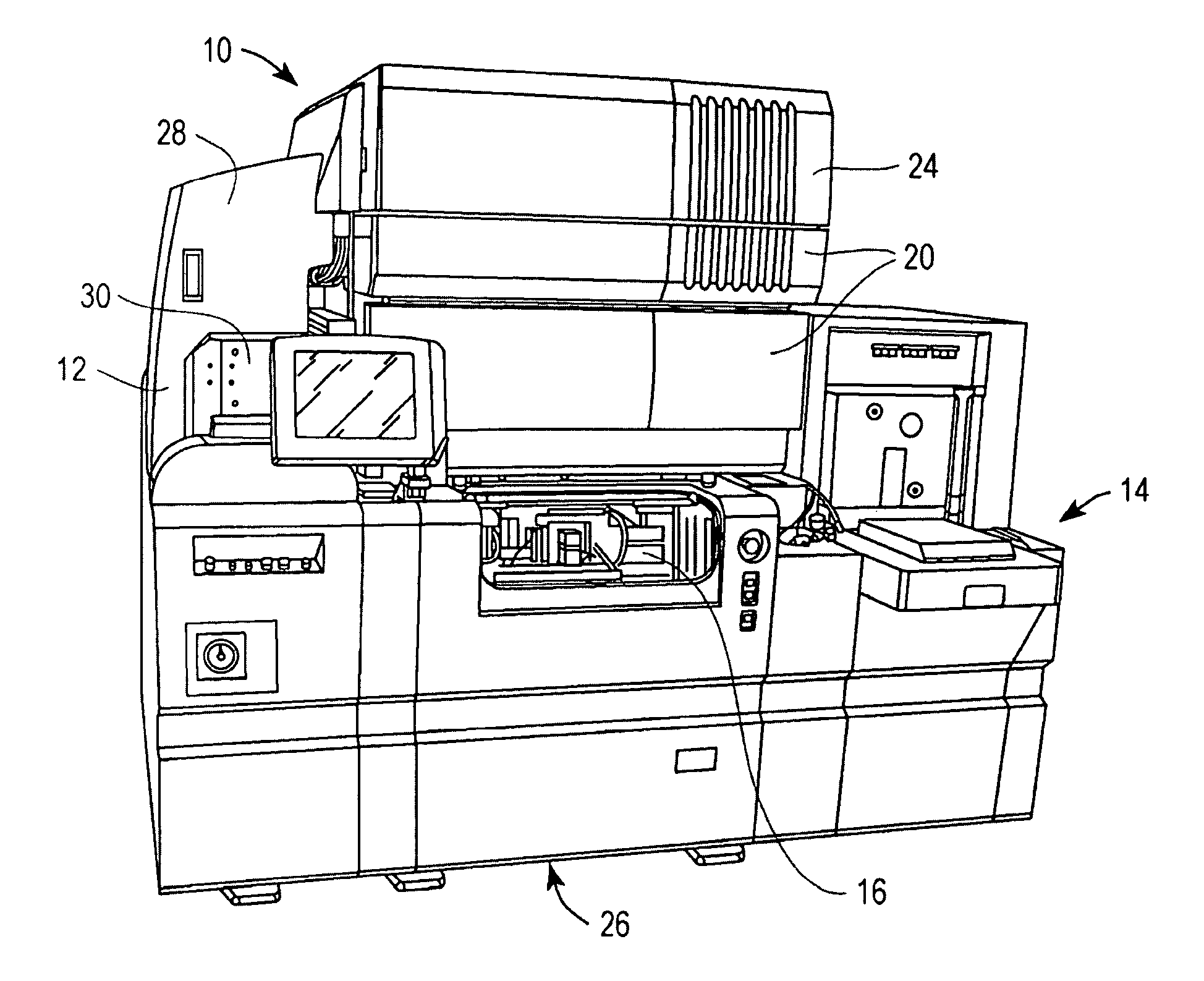

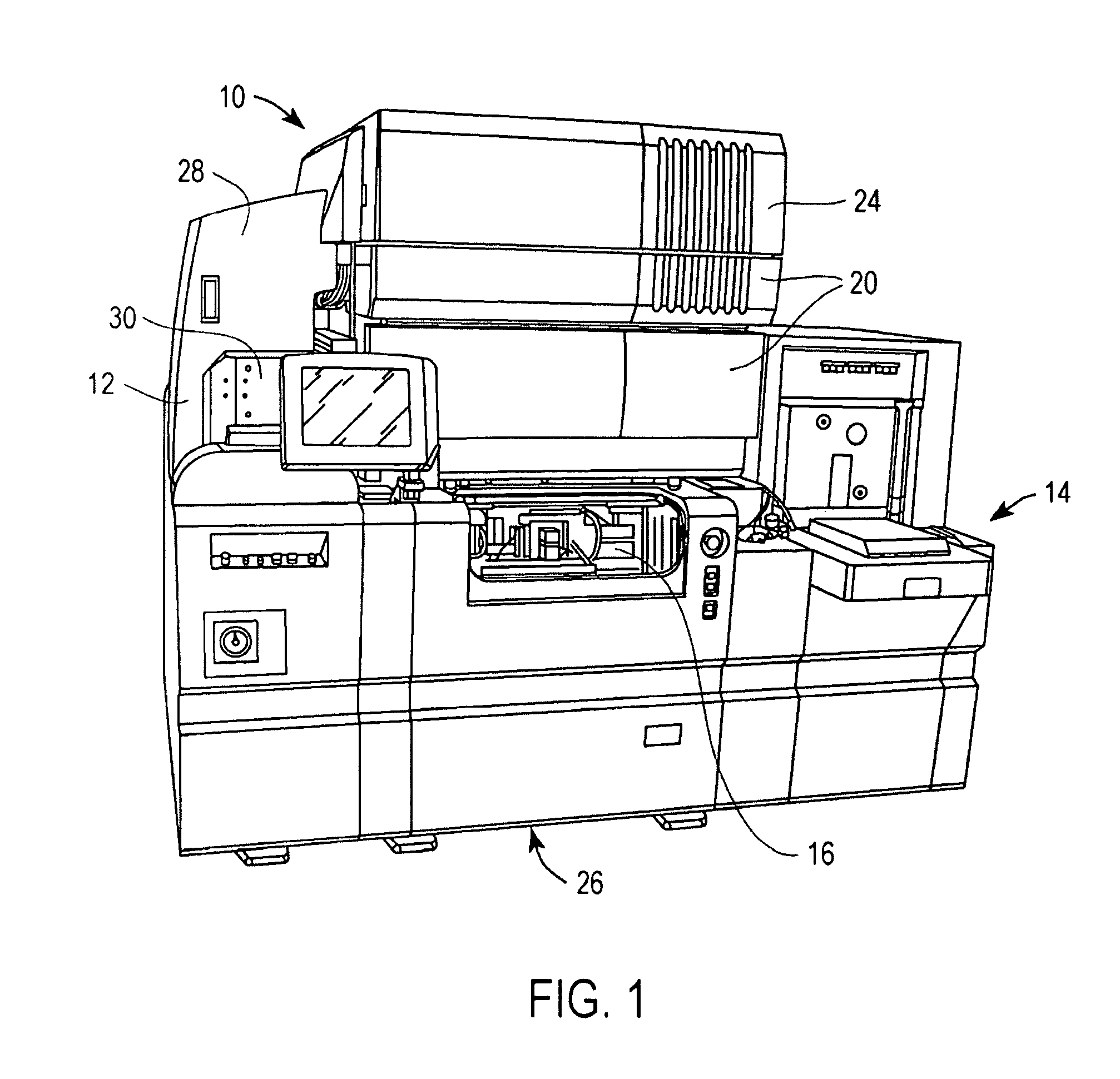

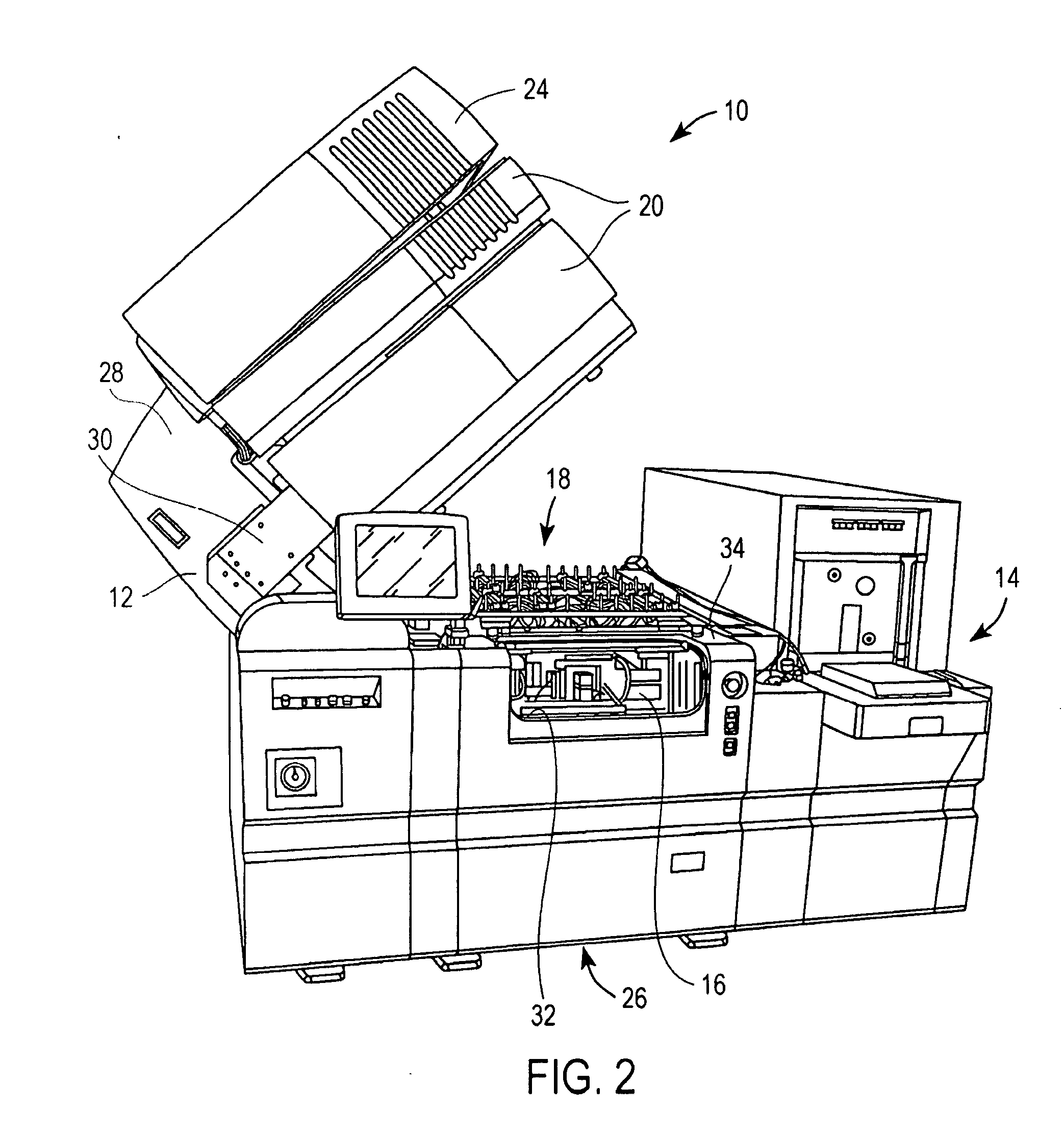

Apparatus for testing electronic devices

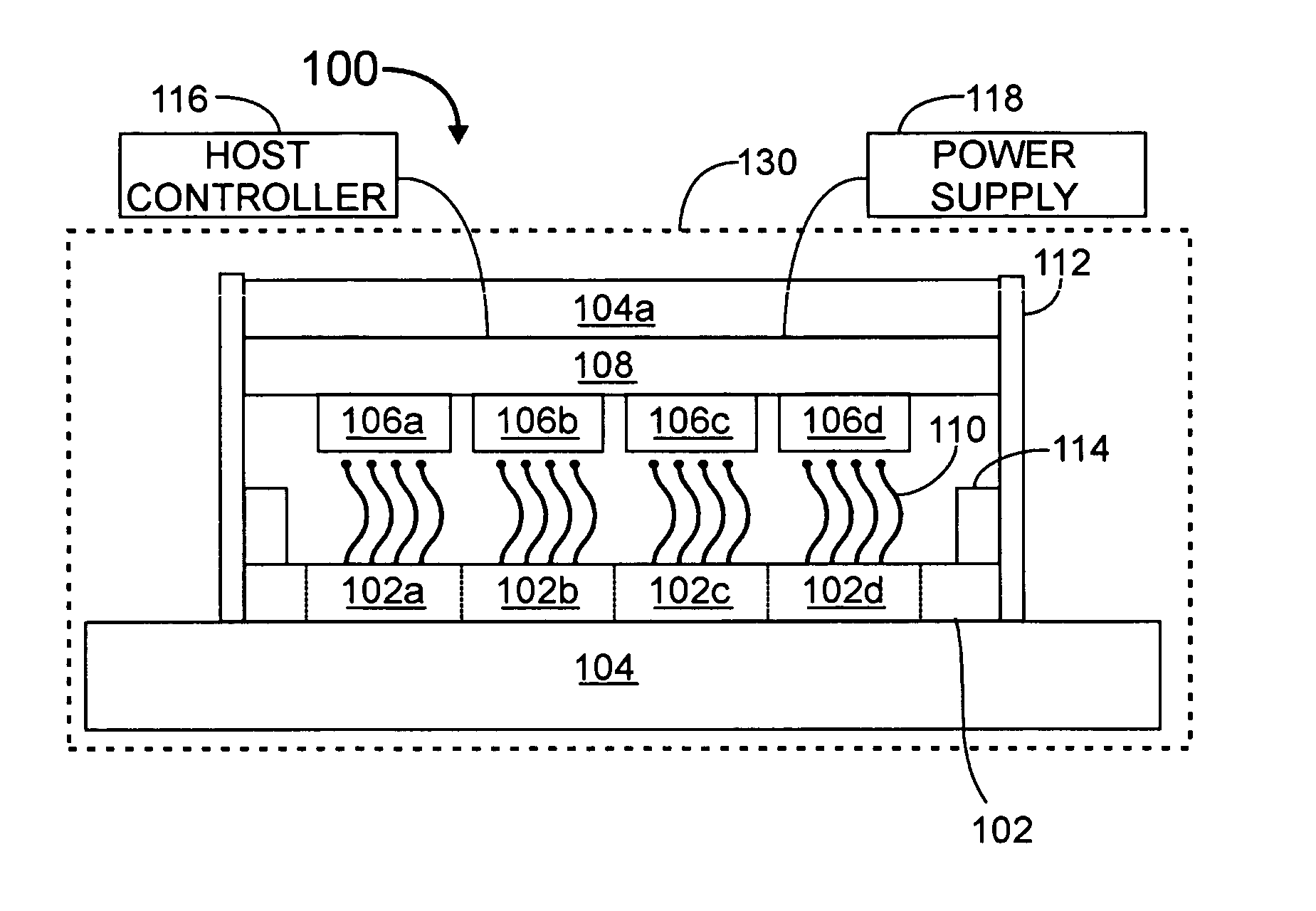

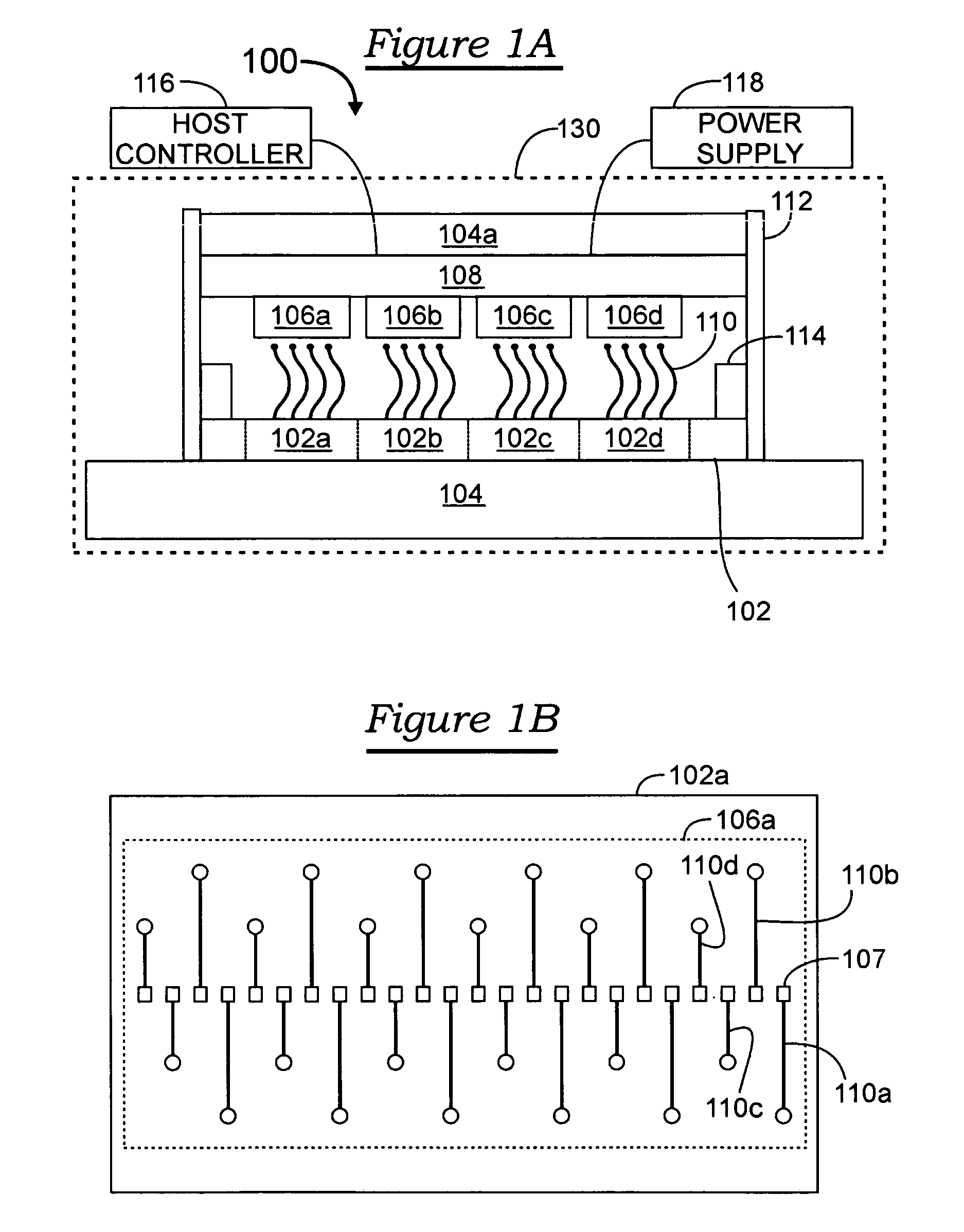

ActiveUS20070001790A1Semiconductor/solid-state device testing/measurementSemiconductor operation lifetime testingFunctional testingMicroelectronic circuits

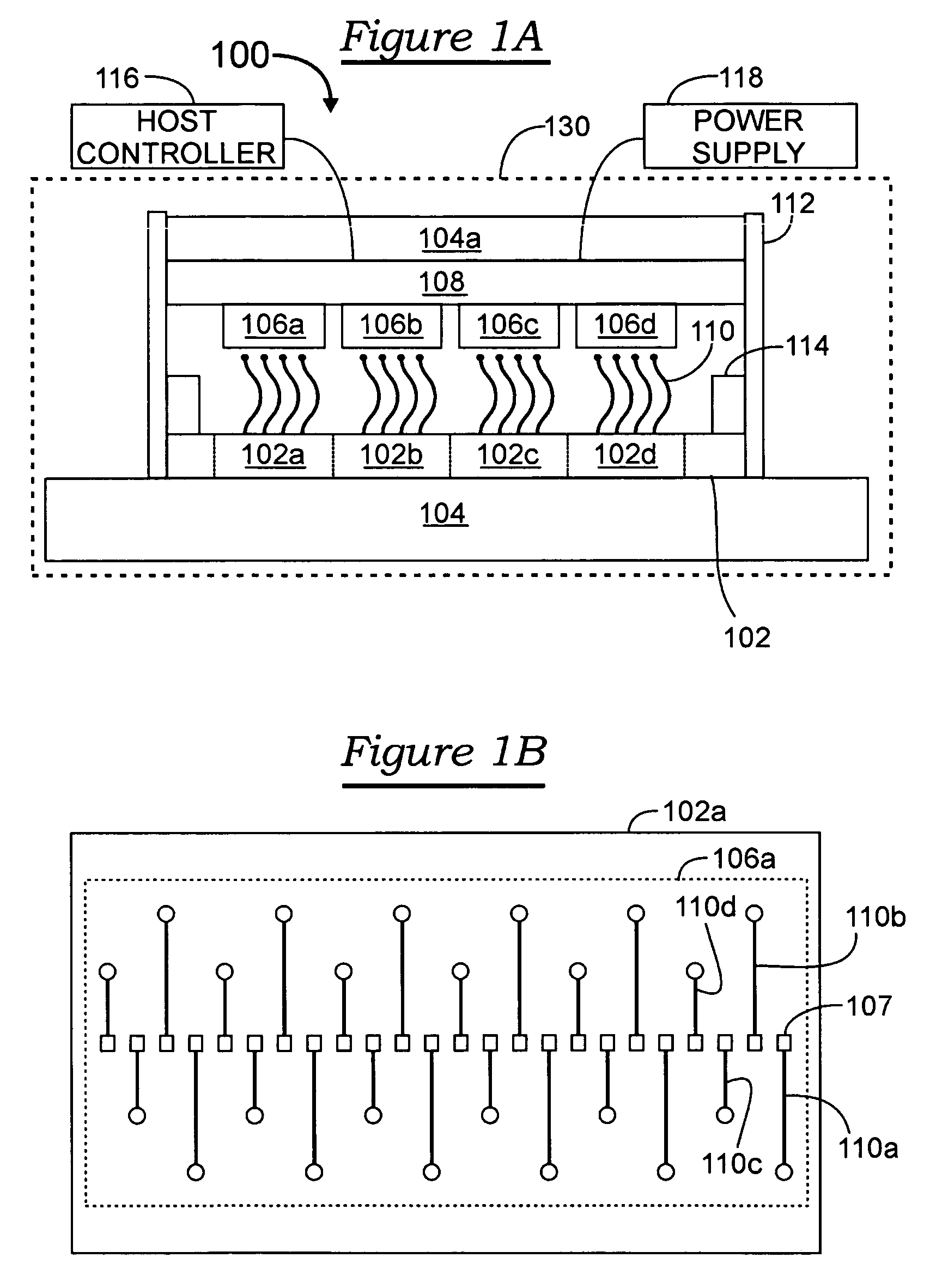

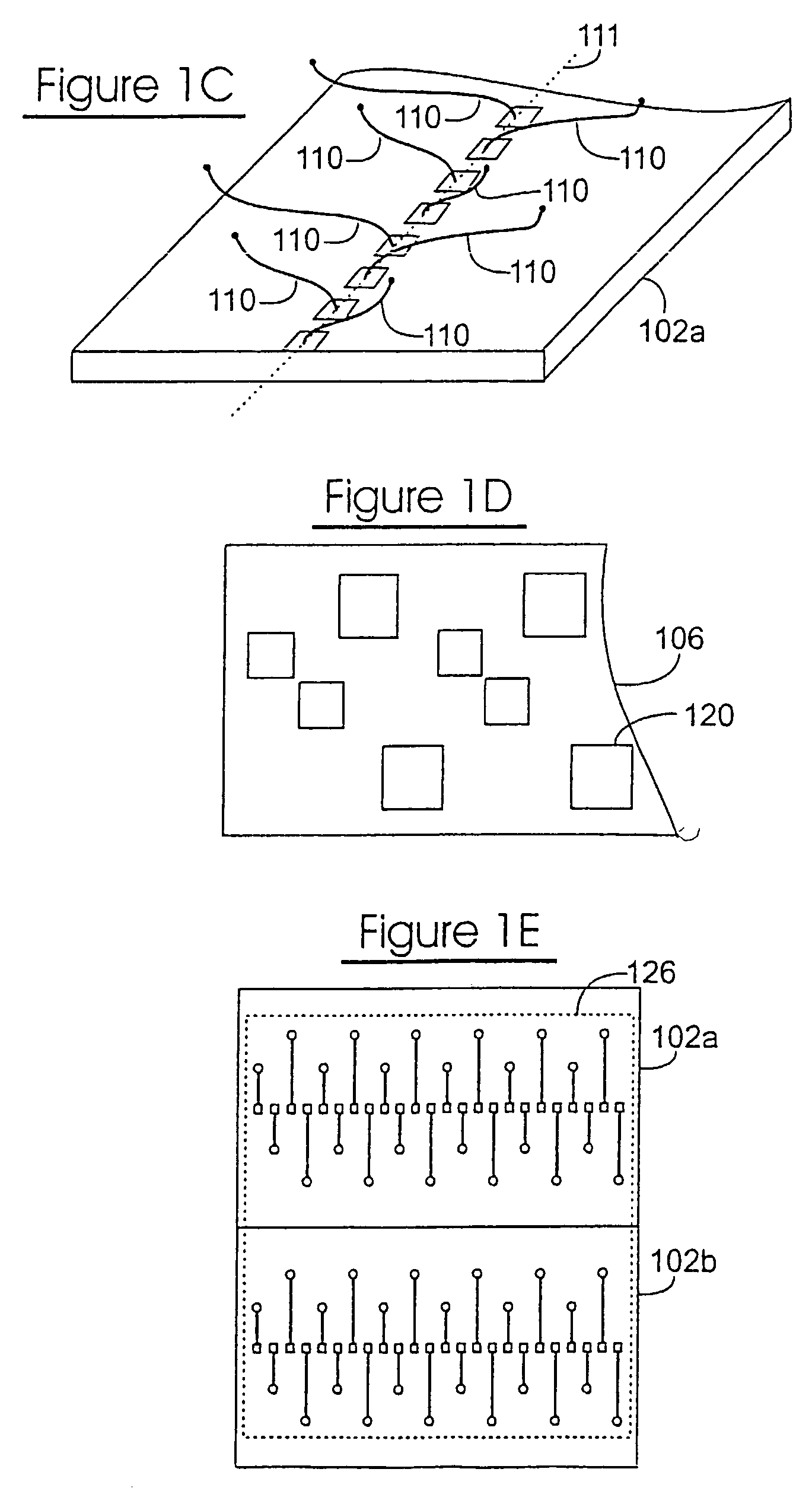

An apparatus is described for burn-in and / or functional testing of microelectronic circuits of unsingulated wafers. A large number of power, ground, and signal connections can be made to a large number of contacts on a wafer. The apparatus has a cartridge that allows for fanning-in of electric paths. A distribution board has a plurality of interfaces that are strategically positioned to provide a dense configuration. The interfaces are connected through flexible attachments to an array of first connector modules. Each one of the first connector modules can be independently connected to a respective one of a plurality of second connector modules, thereby reducing stresses on a frame of the apparatus. Further features include for example a piston that allows for tight control of forces exerted by terminals onto contacts of a wafer.

Owner:AEHR TEST SYST

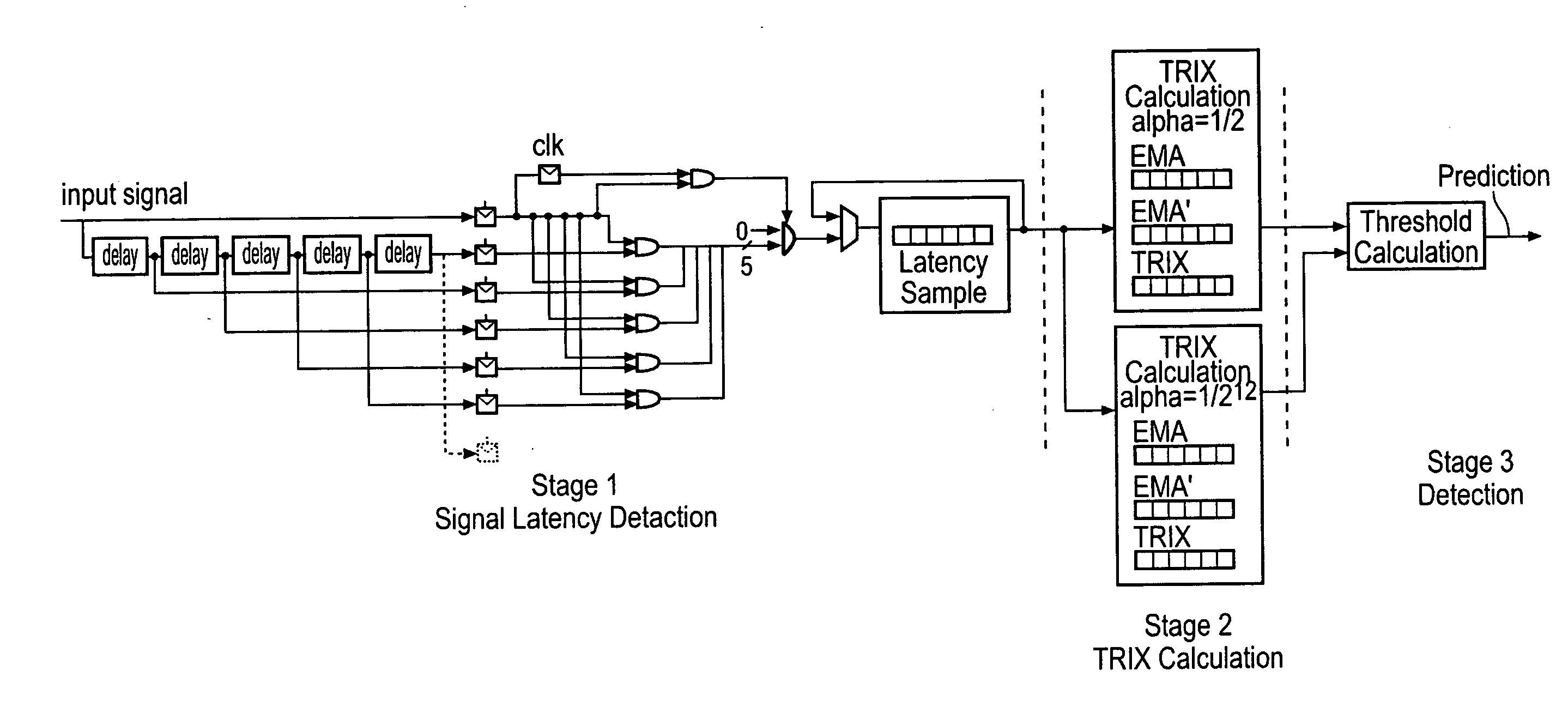

Integrated circuit wearout detection

InactiveUS20080036487A1Reduce operating frequencyIncrease operating voltageIntegrated circuit testingIndividual semiconductor device testingComputer scienceEmbedded system

An integrated circuit is provided with latency detecting circuitry for detecting signal generation latency within one or more functional circuits and in response thereto to generate a wearout response. The wearout response can take a variety of different forms such as reducing the operating frequency, increasing the operating voltage, operating task allocation within a multiprocessor system, manufacturing test binning and other wearout responses.

Owner:ARM LTD +1

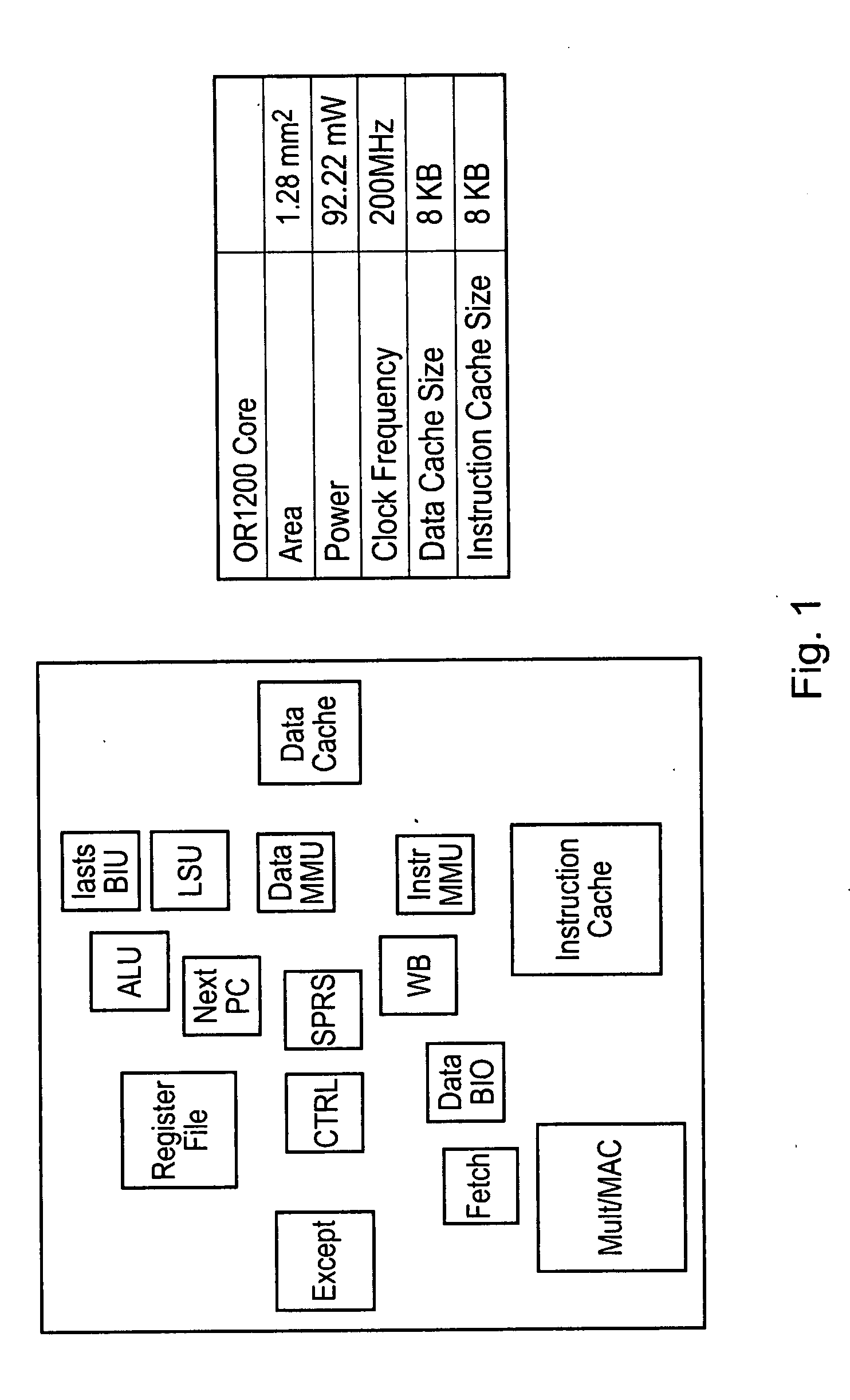

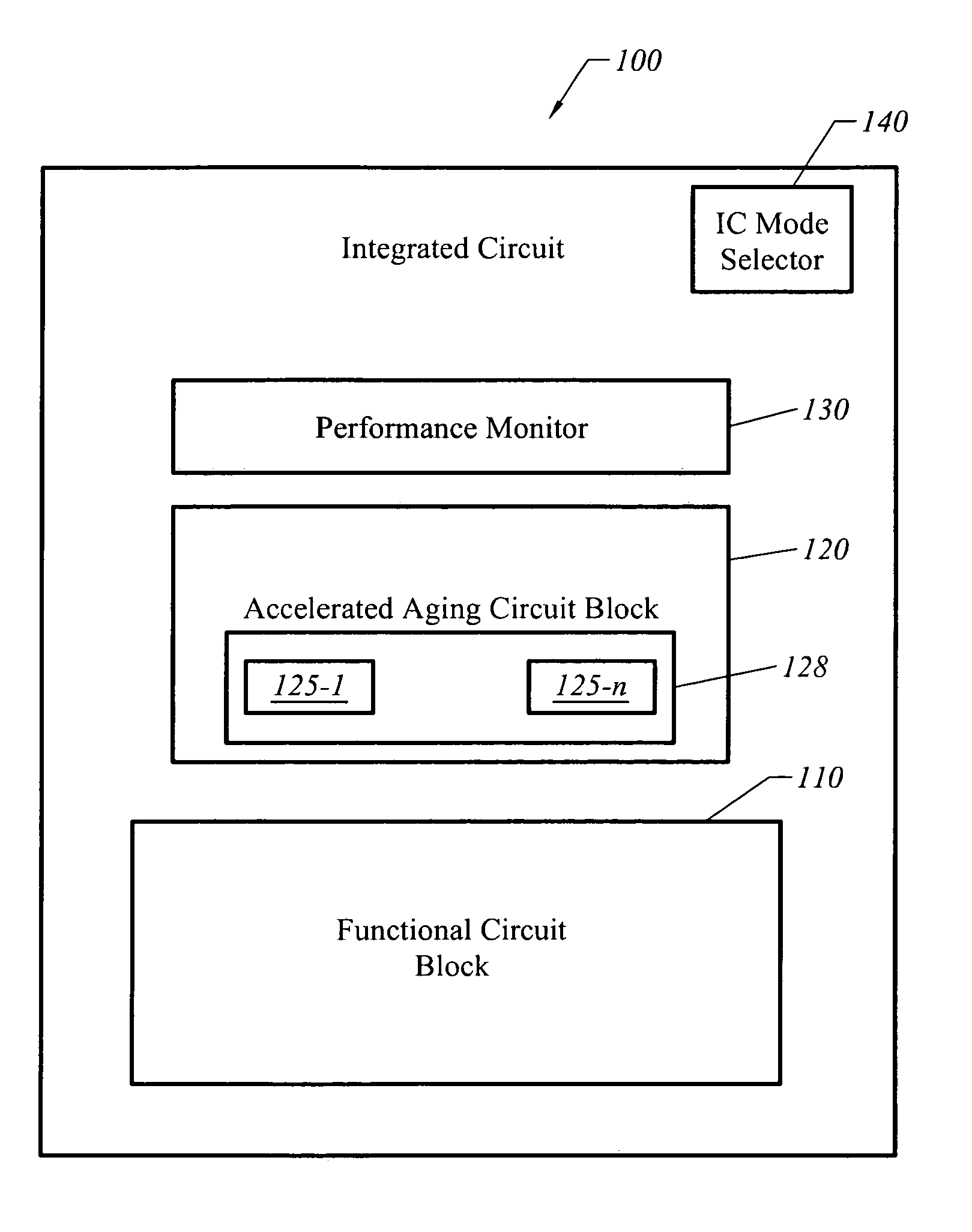

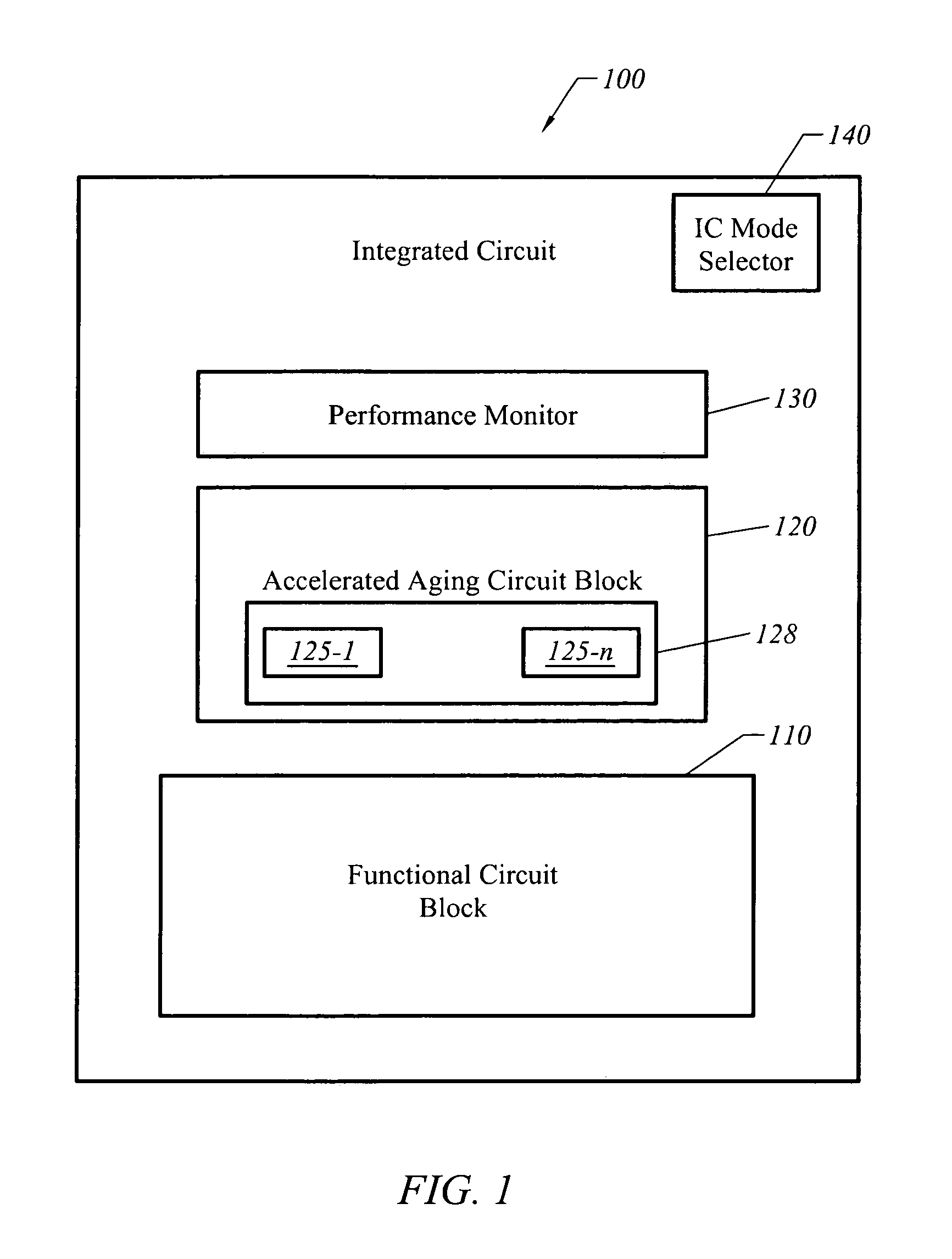

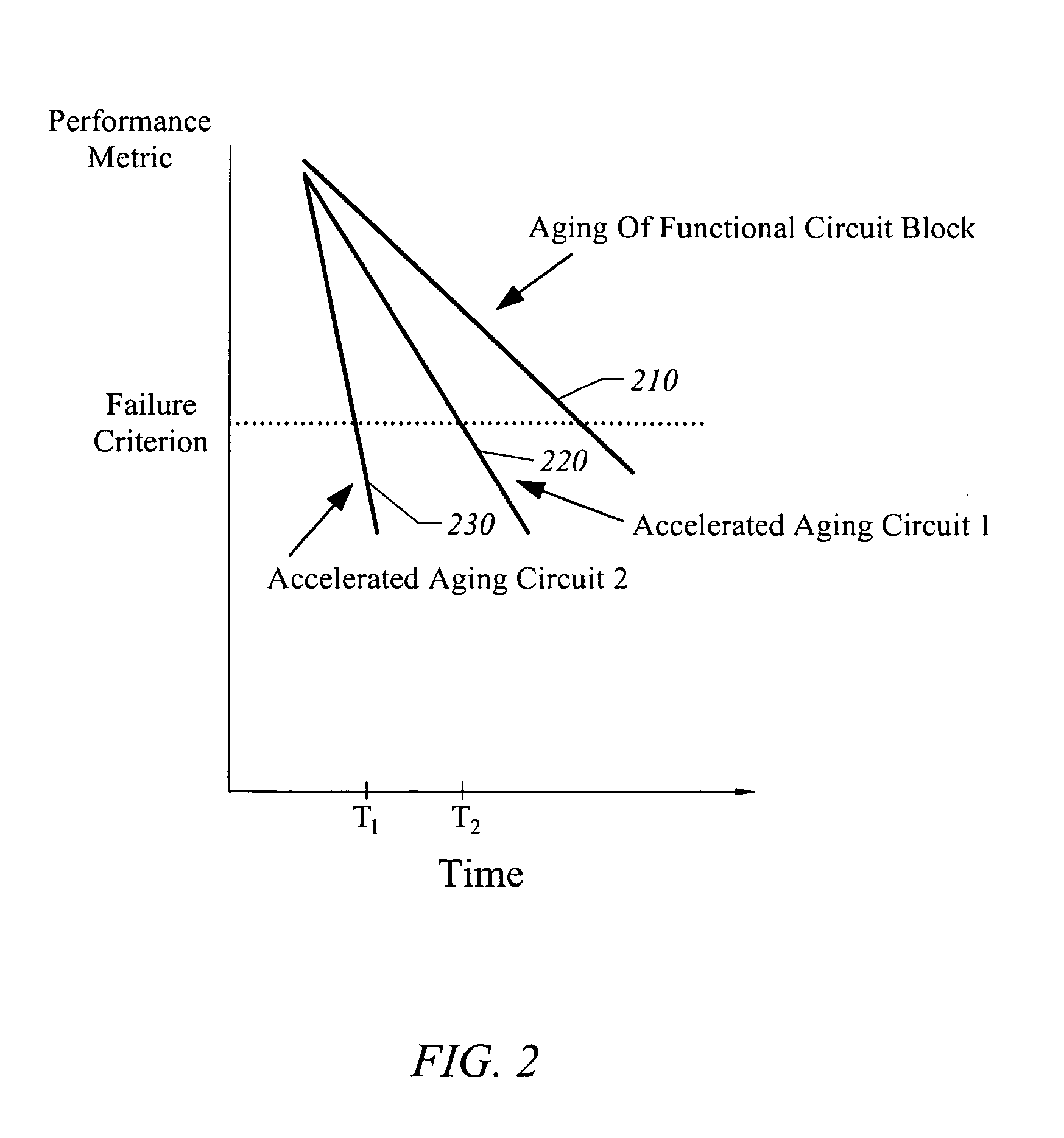

Apparatus, system, and method for managing aging of an integrated circuit

ActiveUS7005871B1Reduce aging rateElectric digital data processingIntegrated circuit testingElectricityAccelerated aging

An integrated circuit includes an accelerated aging circuit block that has at least one circuit that ages at a faster rate than a functional circuit block. The accelerated aging circuit block is monitored during normal operation of the integrated circuit. Changes in the accelerated aging circuit block are used to generate data indicative of an aging trend for the functional circuit block.

Owner:NVIDIA CORP

Temperature control of electronic devices using power following feedback

InactiveUS20020050833A1Easy to useEliminate needTemperatue controlSemiconductor/solid-state device detailsTemperature controlEngineering

A method for controlling a device temperature measures a parameter related to device power consumption and utilizes the parameter to control the device temperature. This can be achieved with a system including a heat exchanger, a power monitor, and a circuit which controls the temperature setting of the heat exchanger. The circuit uses as inputs the power level, heat exchanger temperature, and set point. The system thus eliminates the need for temperature sensing devices in or connected to a chip, responds to the temperature of the device and not the package, can be used for high volume chip manufacturing, does not require significant surface area of a device for temperature sensing, and eliminates the need for chip power profiles. Significantly, the system allows a set point to be maintained with minimal overshoot or undershoot.

Owner:SCHLUMBERGER AUTOMATED TEST EQUIP +1

Temperature control of electronic devices using power following feedback

InactiveUS20030001605A1Temperatue controlSemiconductor/solid-state device detailsTemperature controlEquipment temperature

A system and method for controlling a temperature of a device during testing with a thermal controller and a heat exchanger includes measuring an instantaneous power consumption of the device during testing. The heat exchanger is controlled with the thermal controller using the measured instantaneous power consumption by the device to regulate the temperature of the device during testing, wherein the heat exchanger is in conductive contact with the device.

Owner:DELTA DESIGN

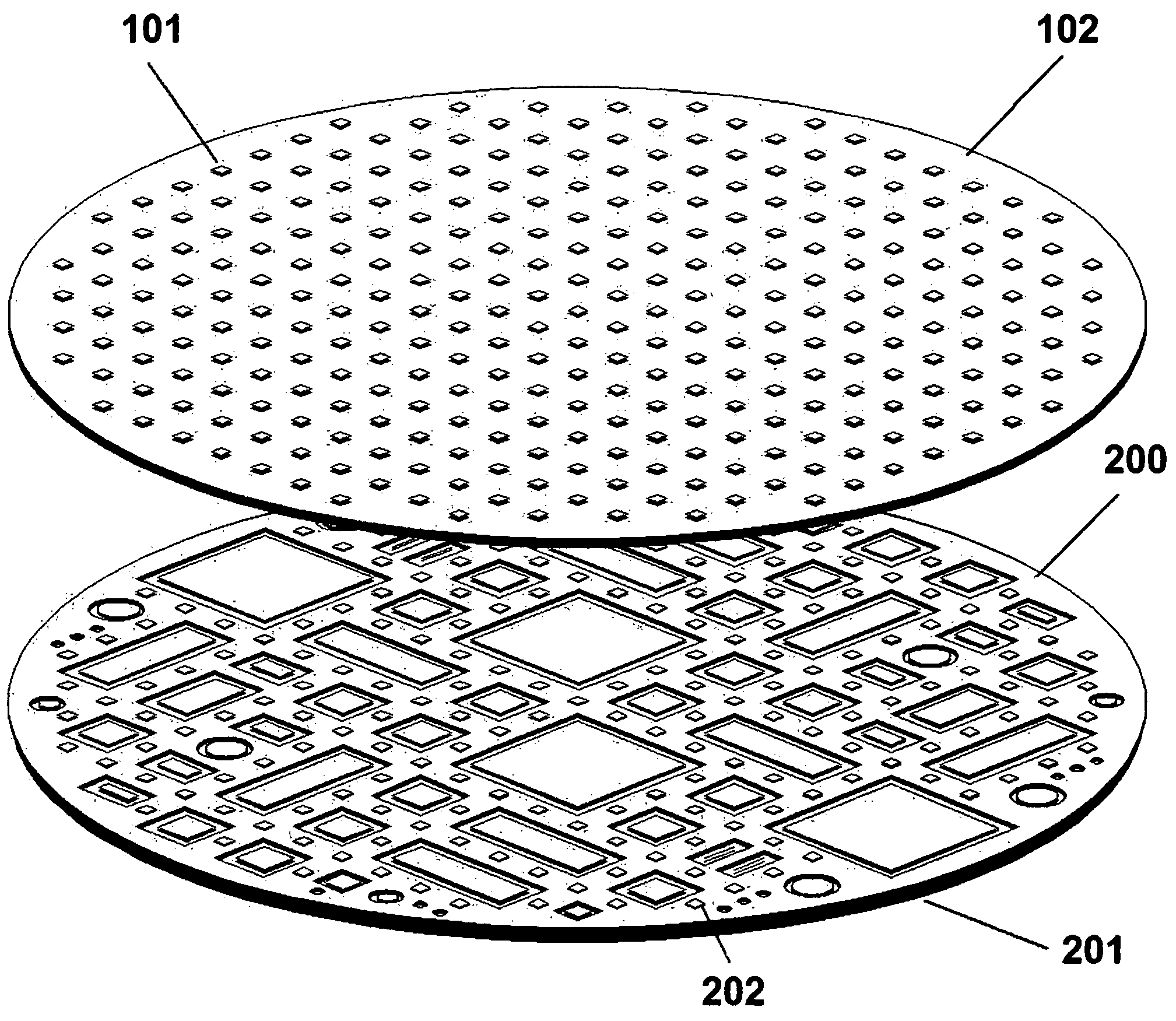

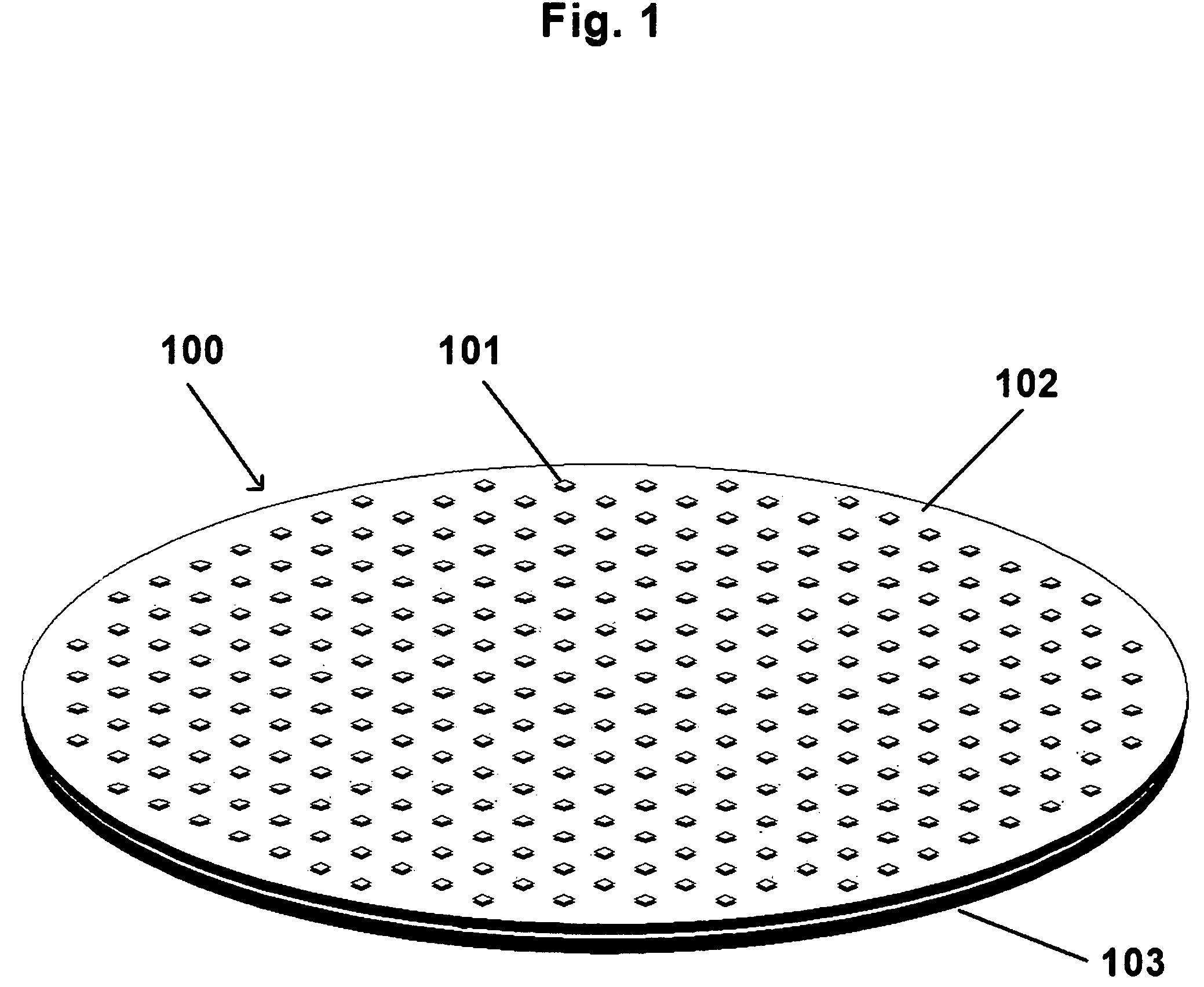

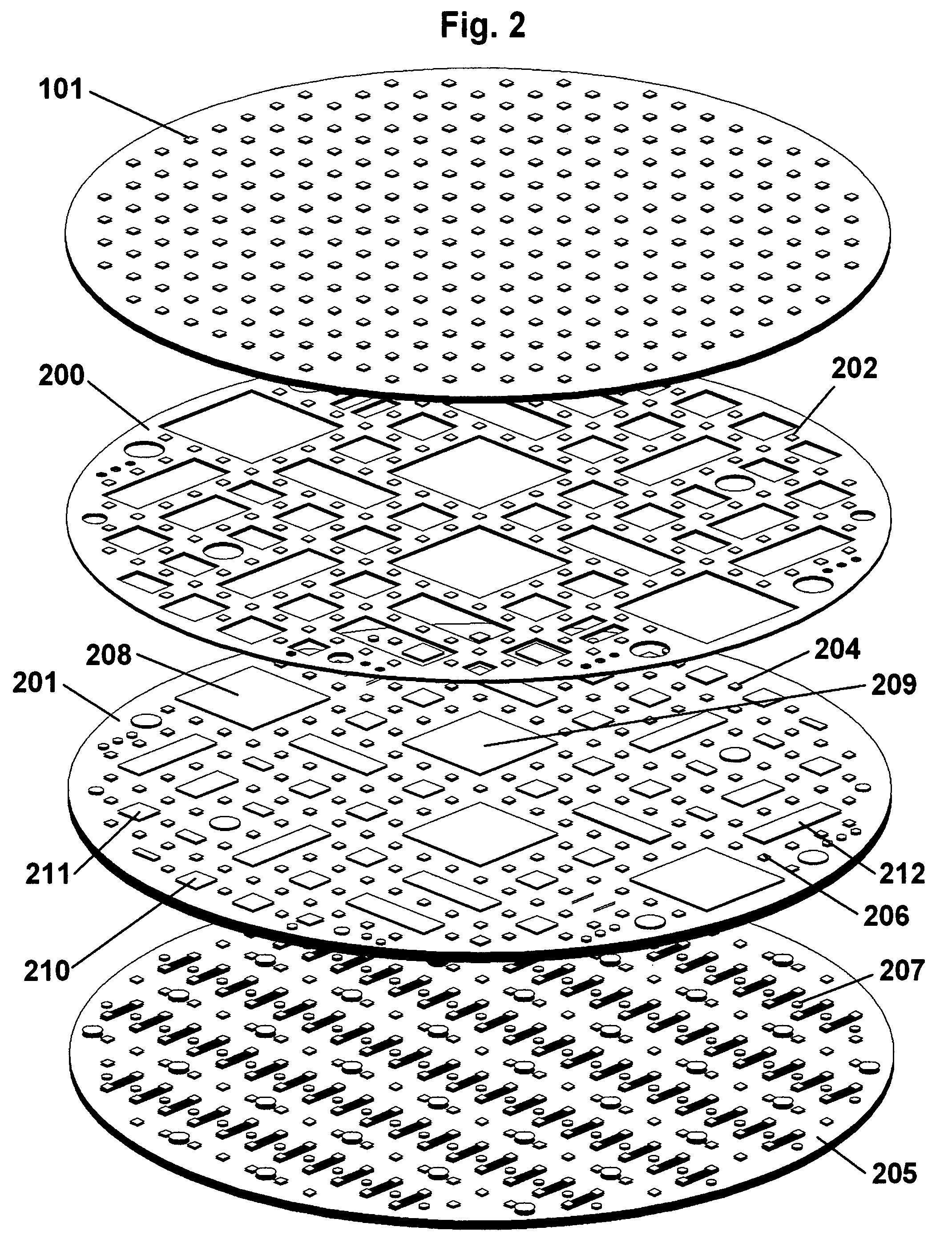

Wafer-level burn-in and test

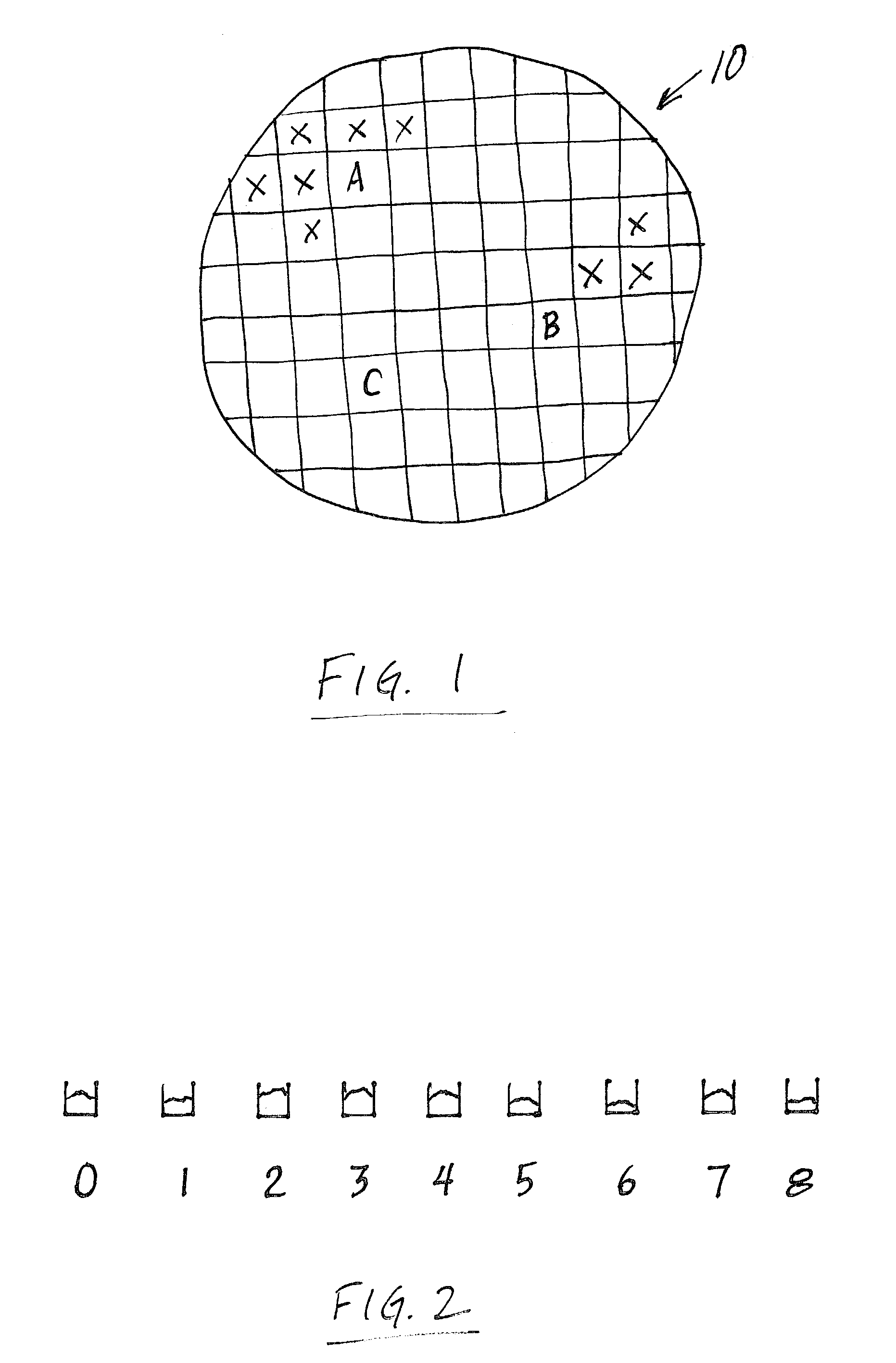

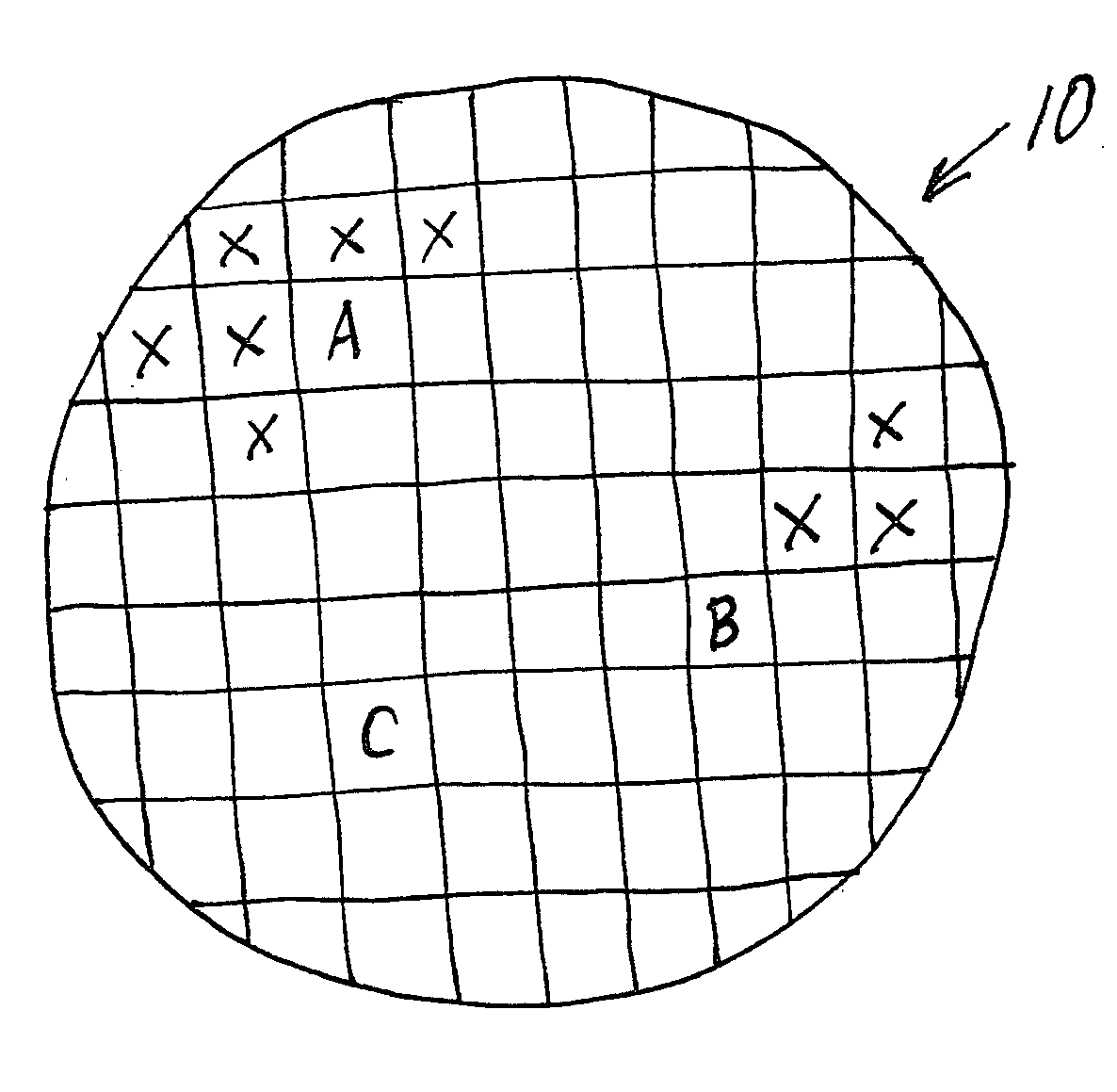

InactiveUS7078926B2Solid-state devicesFault location by increasing destruction at faultEngineeringInterconnection

Owner:FORMFACTOR INC

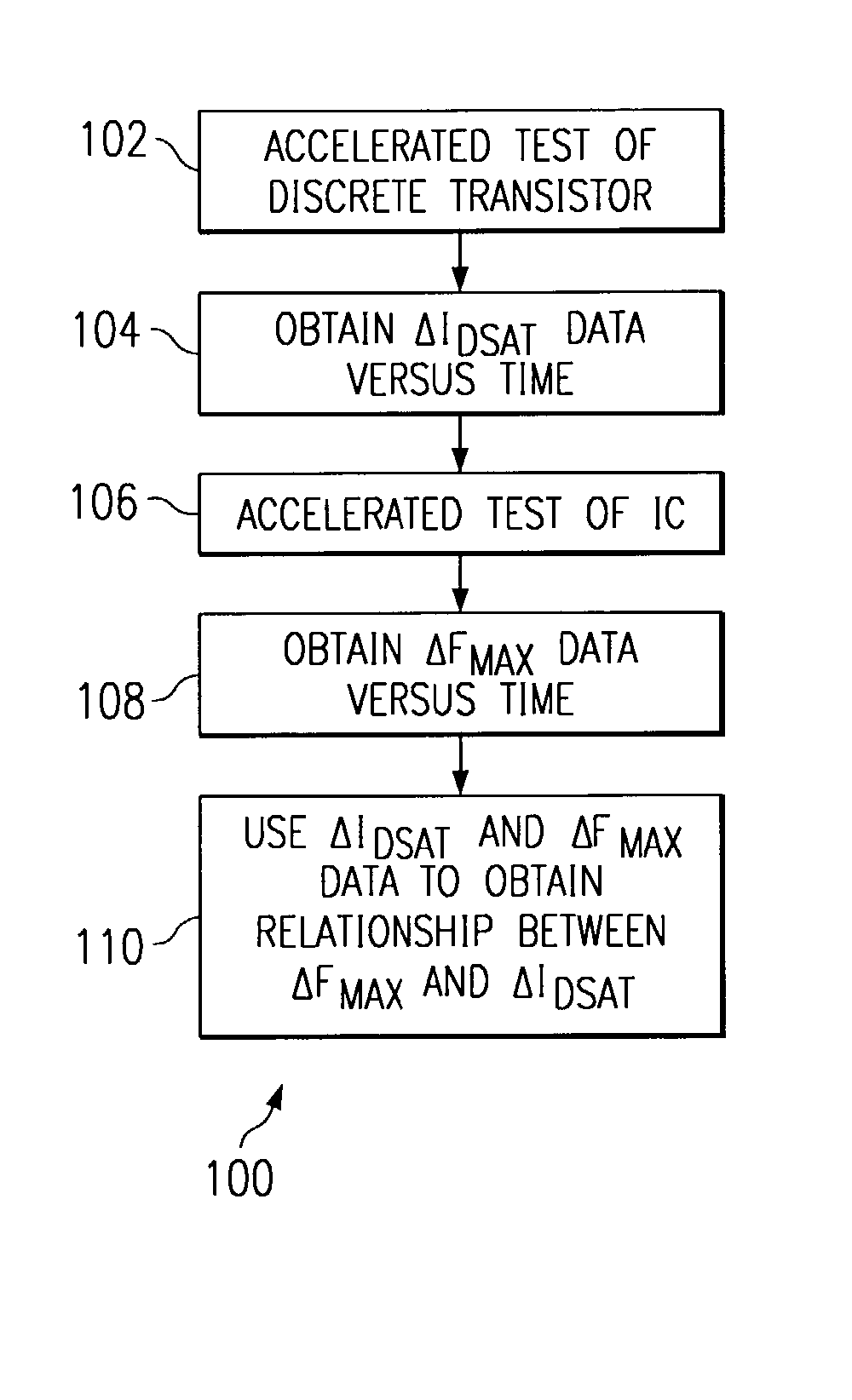

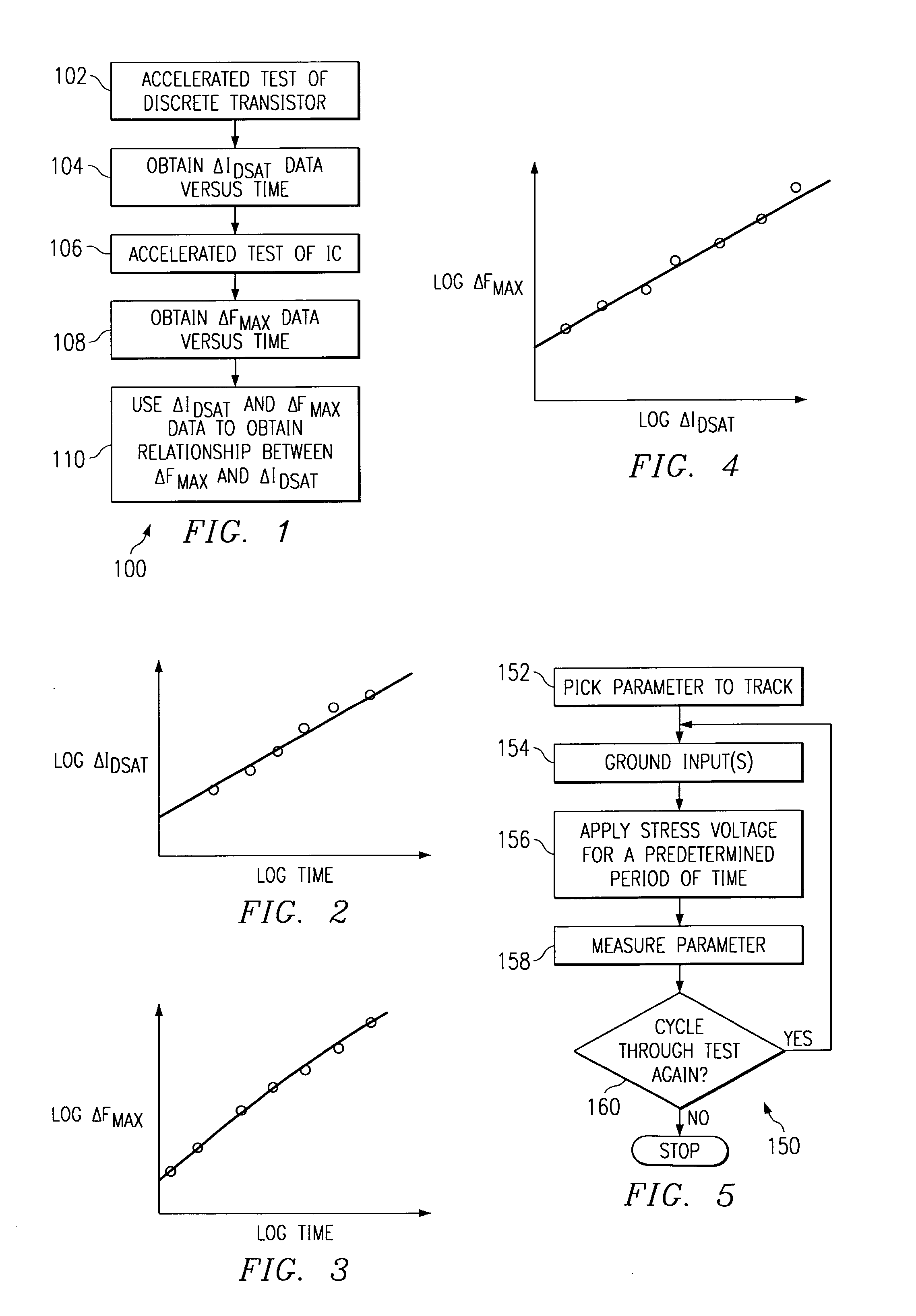

Method for predicting the degradation of an integrated circuit performance due to negative bias temperature instability

InactiveUS20030233624A1Easy and cheap to testEasy and faster and cheap to estimateDigital circuit testingDetecting faulty computer hardwareNegative-bias temperature instabilityIntegrated circuit

A method is provided of correlating integrated circuit NBTI-induced performance degradation to discrete transistor NBTI-induced performance degradation and using that correlation to estimate integrated circuit degradation over time using test results based on a discrete transistor. Because discrete transistors are easier and cheaper to test, the technique described herein makes it easier, faster and cheaper to estimate the degradation of an integrated circuit over time than testing the integrated circuit itself.

Owner:TEXAS INSTR INC

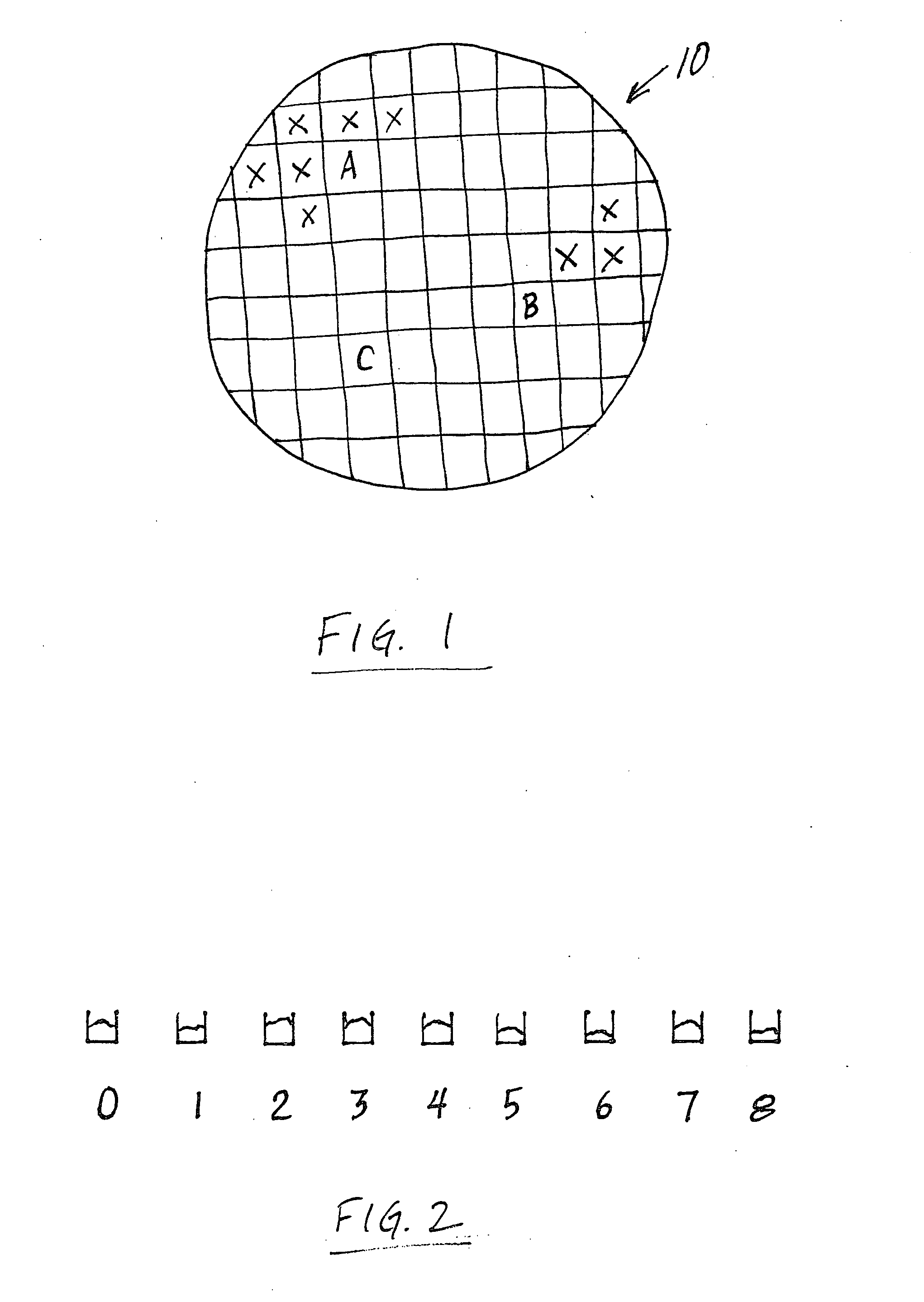

Burn-in stress test mode

InactiveUS6037792ADigital storageFault location by increasing destruction at faultIntegrated circuitBurn-in

An integrated circuit structure and method provides a burn-in stress test mode that facilitates stress testing of an integrated circuit device in a burn-in oven. The integrated circuit structure and method is capable of disabling a time-out feature of an IC memory device during a stress test mode of the device in order to facilitate stress testing of the device in a burn-in oven. The integrated circuit structure provides for entry into the burn-in stress test mode when a supply voltage supplied to the integrated circuit device exceeds a predetermined voltage level and / or the temperature of the integrated circuit device exceeds a predetermined temperature level.

Owner:MICRON TECH INC

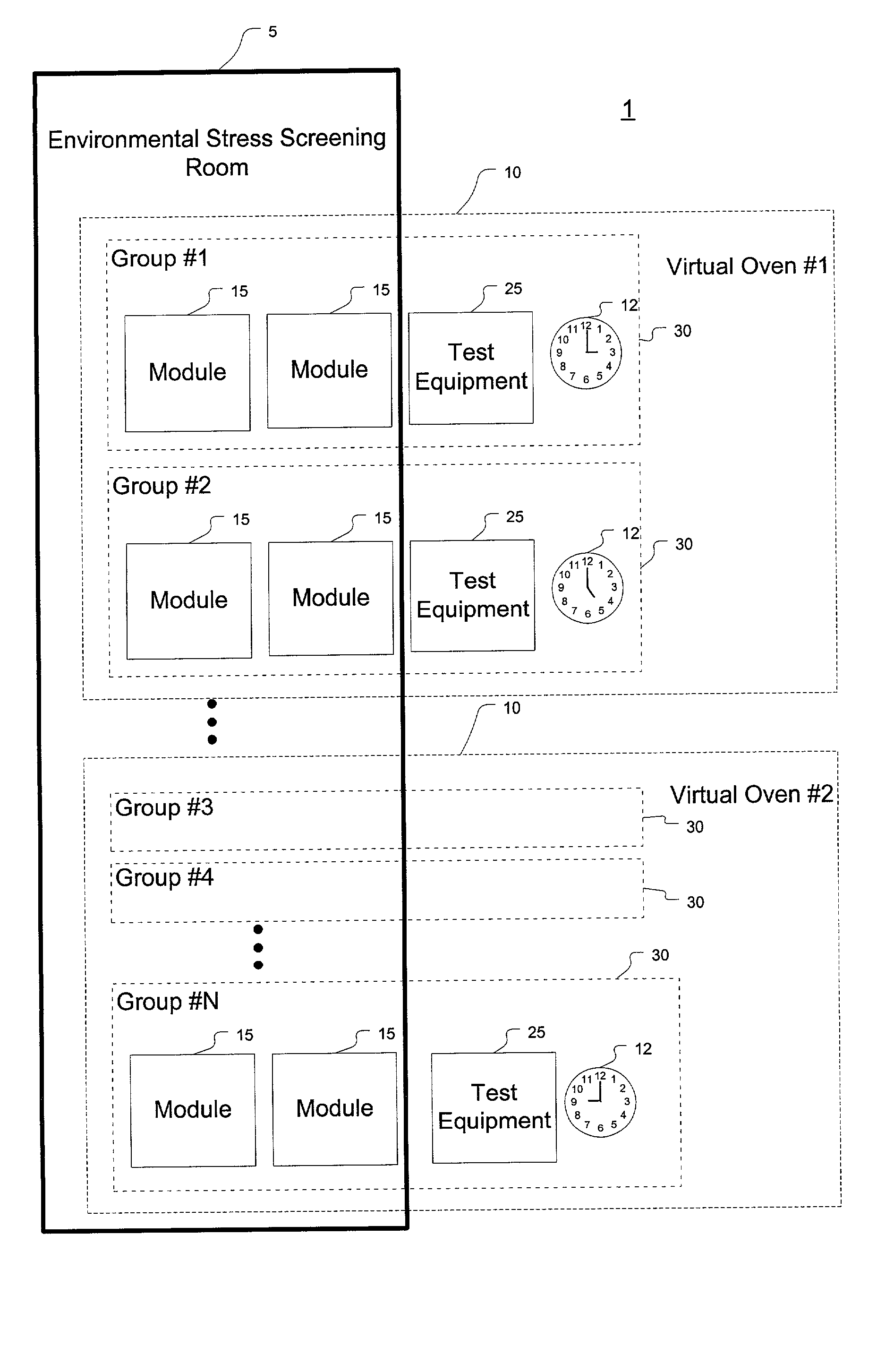

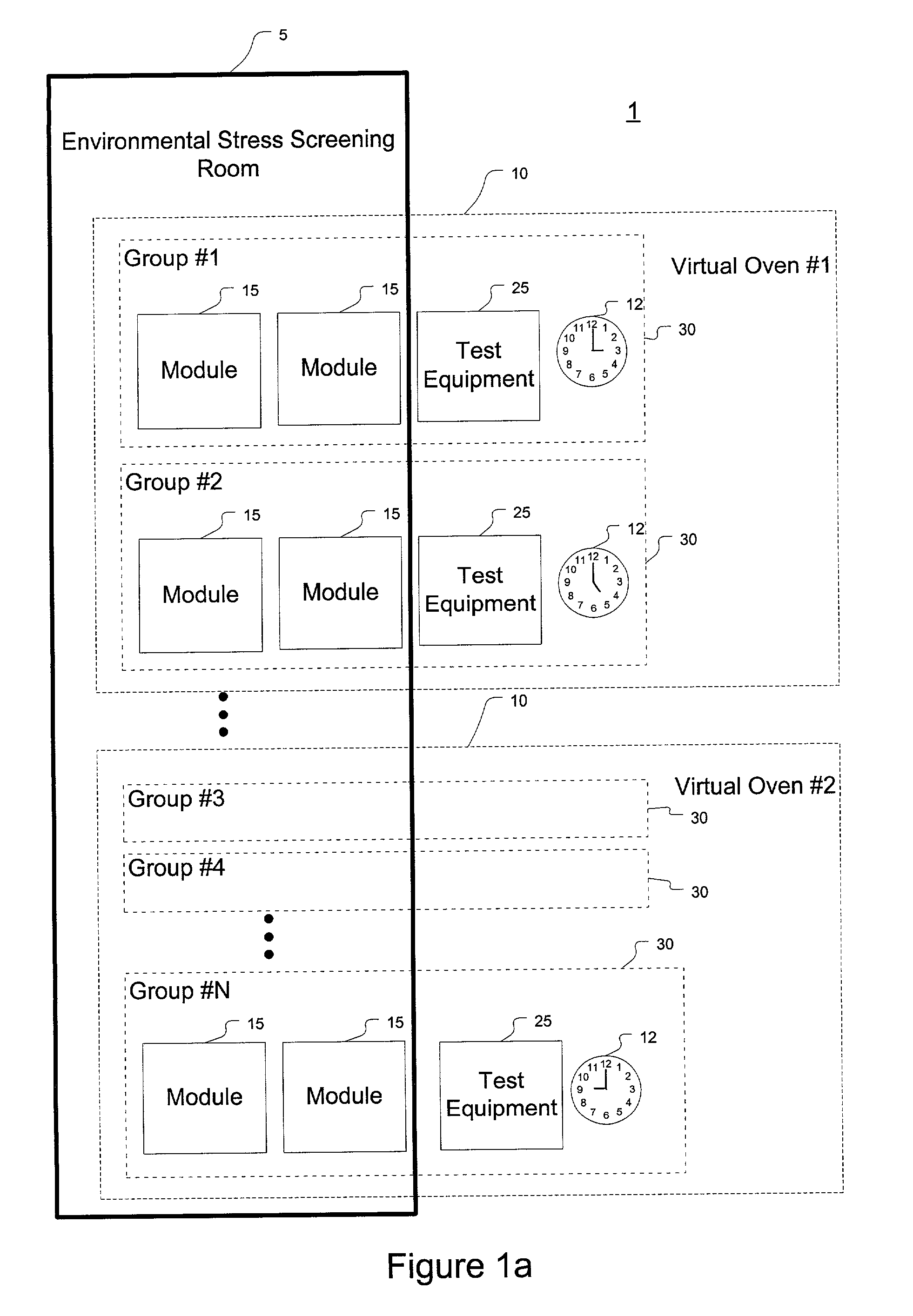

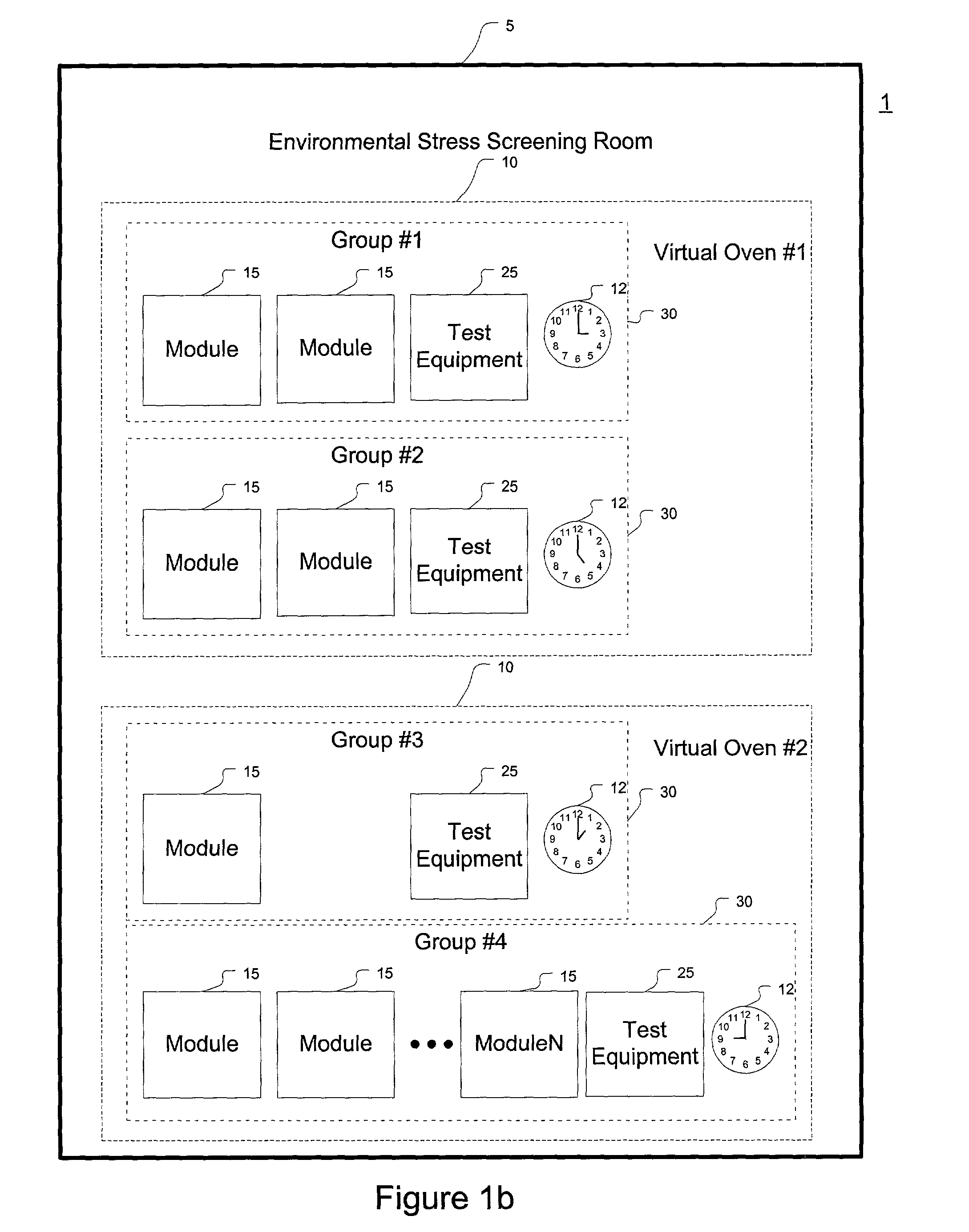

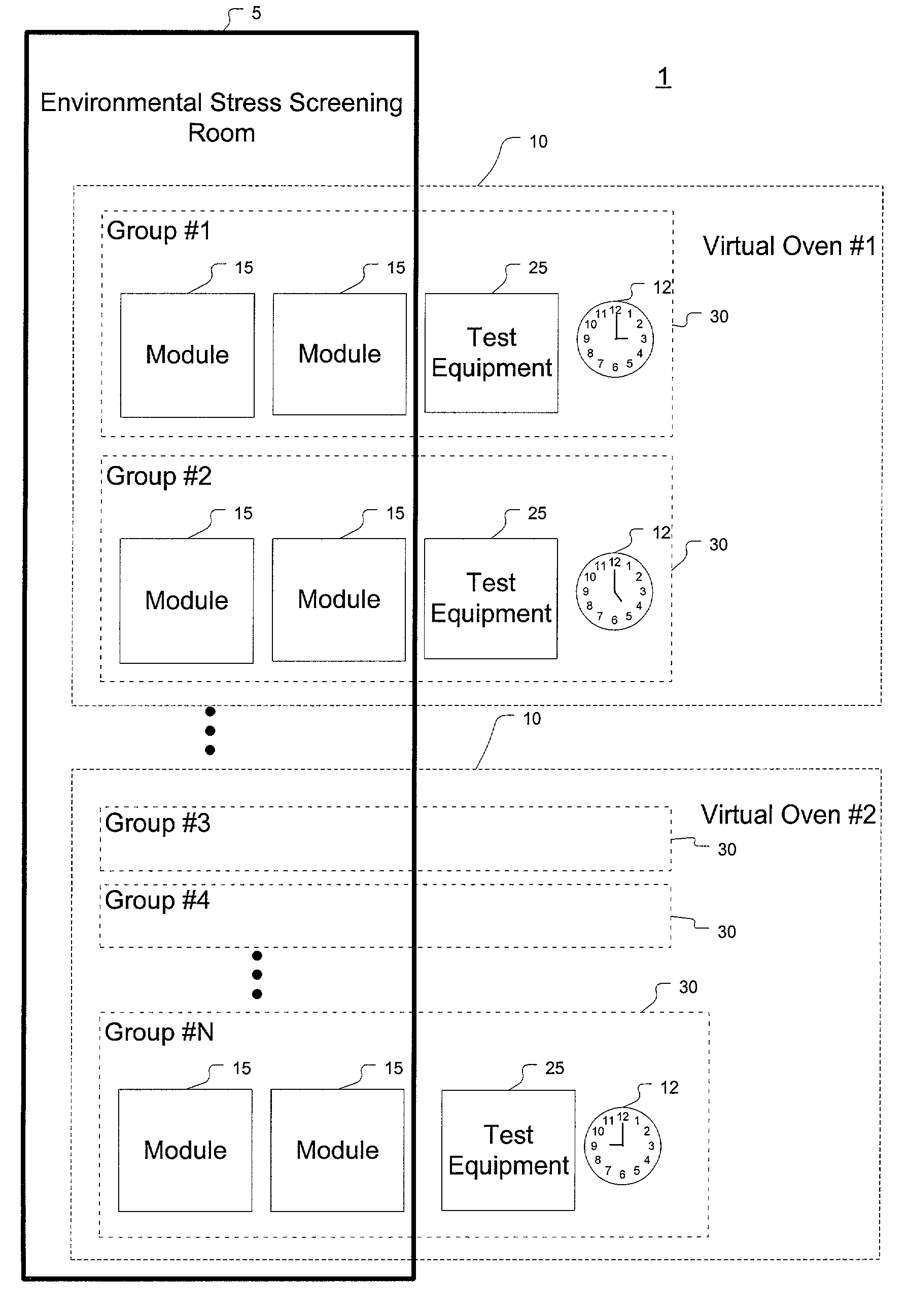

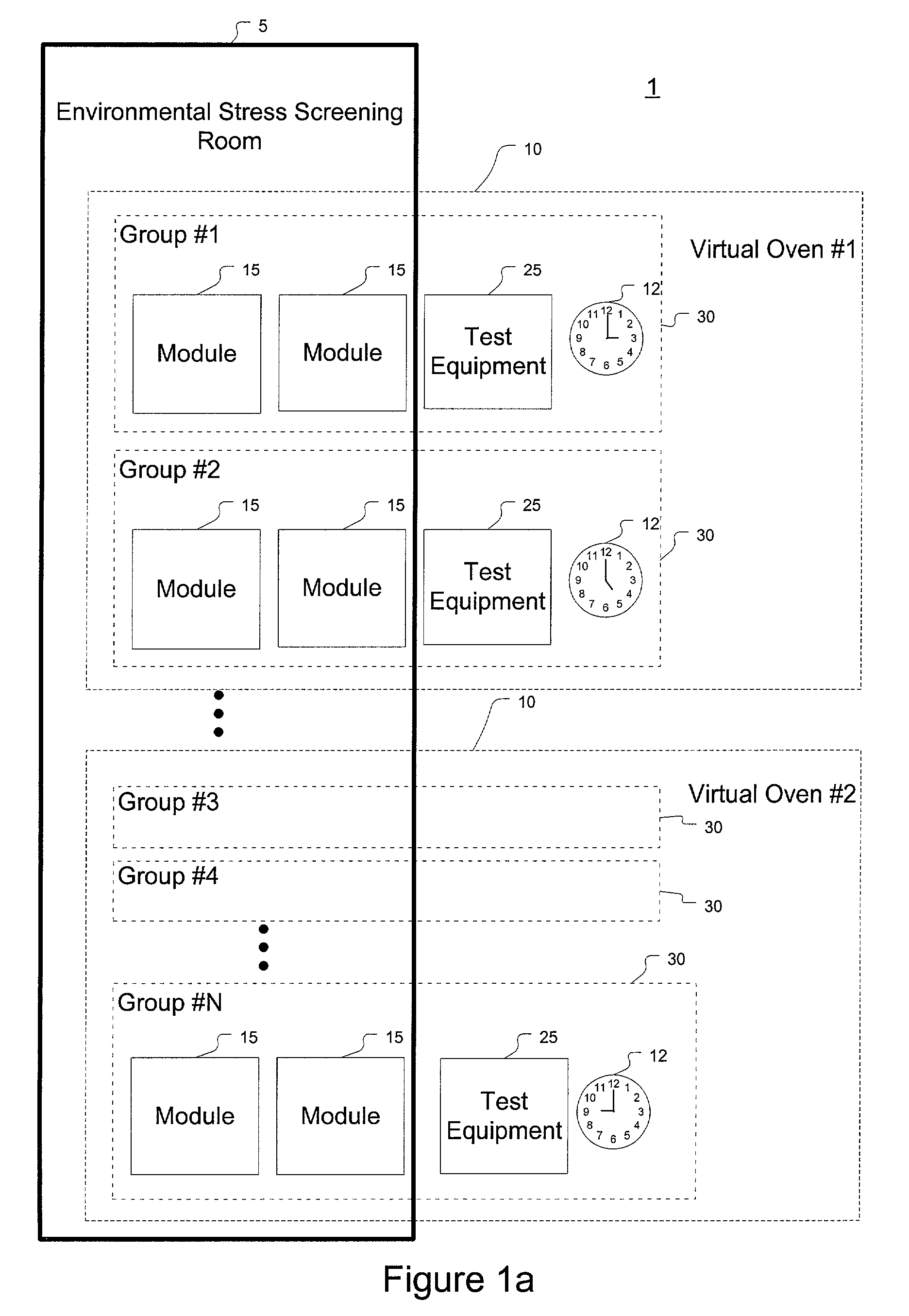

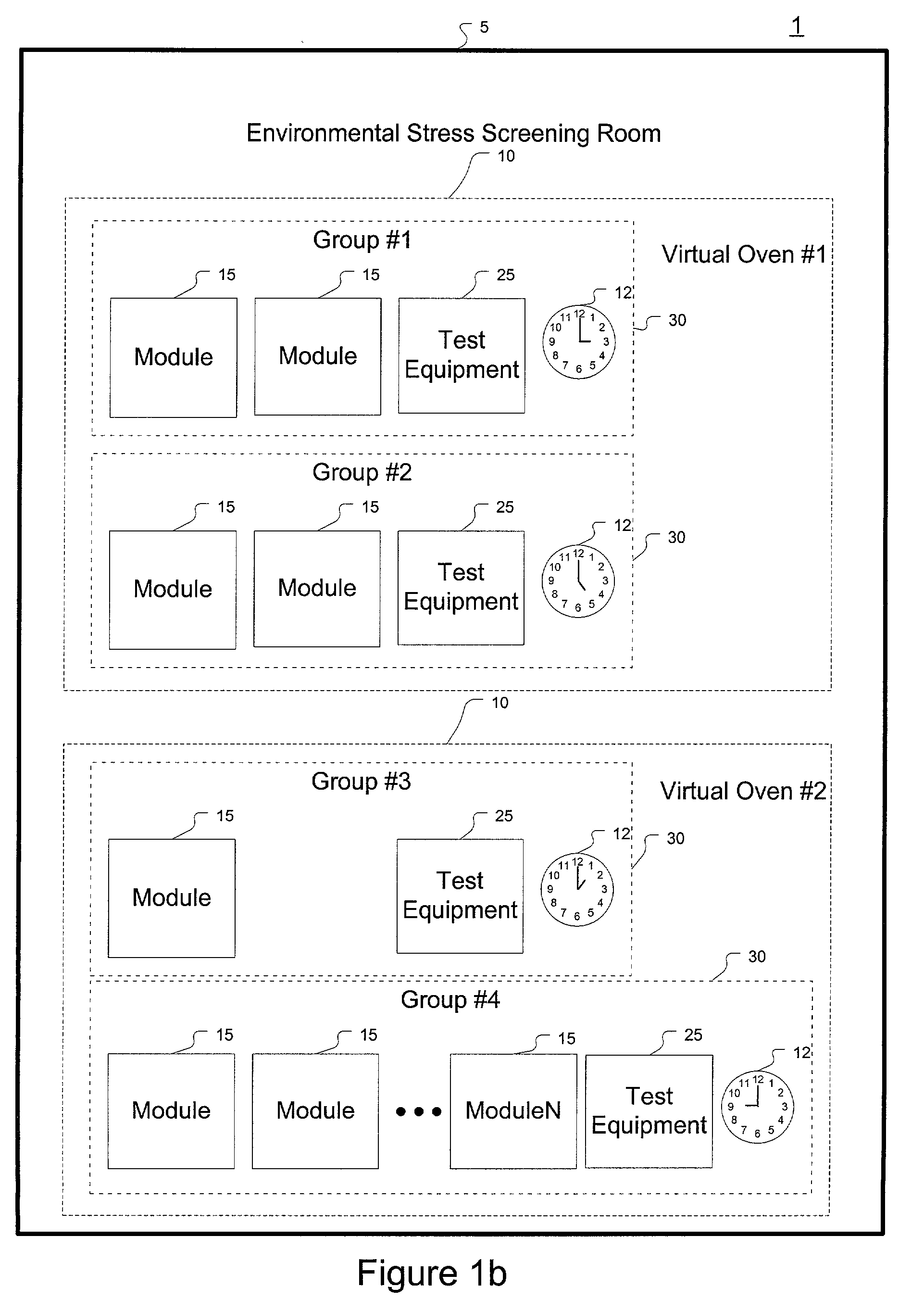

Automated monitoring system, virtual oven and method for stress testing logically grouped modules

InactiveUS20020105355A1Data processing applicationsResistance/reactance/impedenceComputer hardwareNetwork connection

A virtual oven efficiently conducts stress testing of large numbers of modules. The virtual oven includes a logical grouping of modules, a controller, test instruments and a database which are all connected via a network. The logical groupings of modules of several virtual ovens may be physically accommodated within a single environmental stress screening room. Switching between modules in a logical group permits a single test piece of test equipment to be time-shared among the modules in the logical group. The method of bum-in testing a logical group of modules rotates a test sequence, including passive and active test cycles, between the modules. A test signal is split and supplied to multiple modules. Passive testing may be performed by monitoring parameters of the module while the test signal is supplied to the module. Active testing may be a functional test of the module in which the test signal is supplied to, processed by, and output from the module. Such test signals output from the modules are switched to the test equipment on a time-share basis. In this way, the number or expensive test equipment set-ups may reduced. The controller for each virtual oven also generates displays so that a user can track the test progress of all modules within the virtual oven. The controller also builds a database of the active and passive tests for each module. A graphical user interface may be used to interact with the virtual oven, control the testing, and view the database.

Owner:CIENA

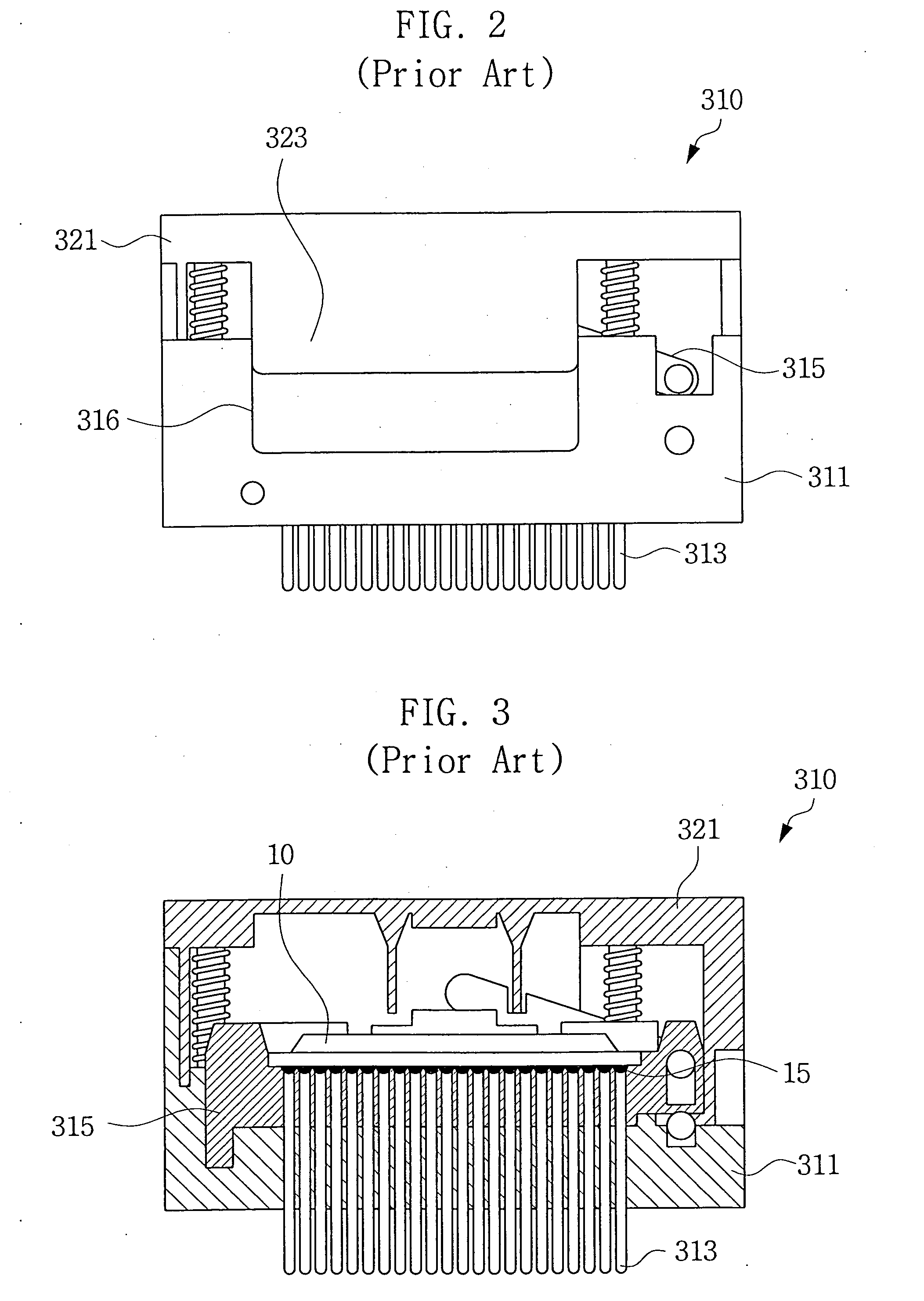

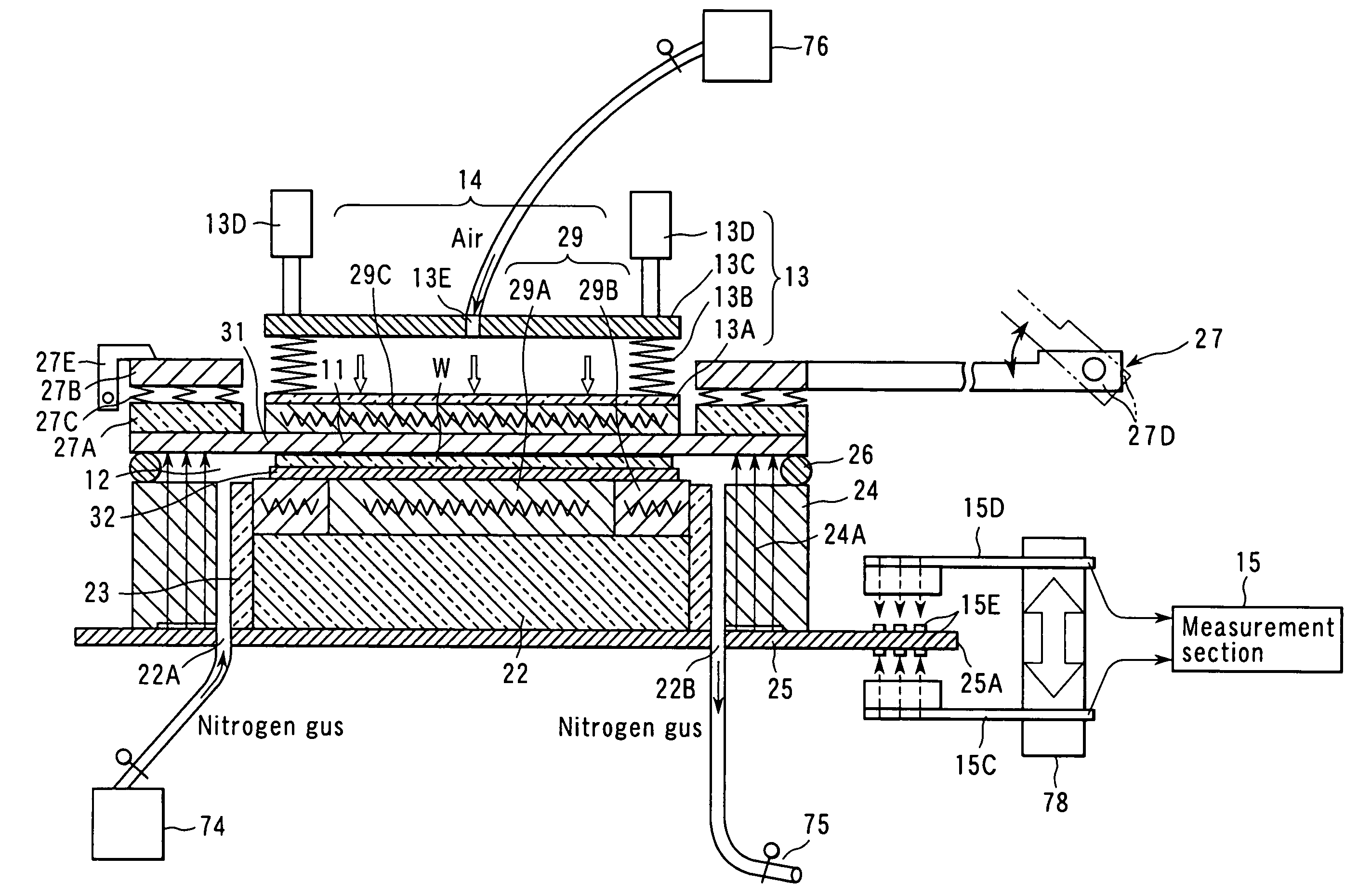

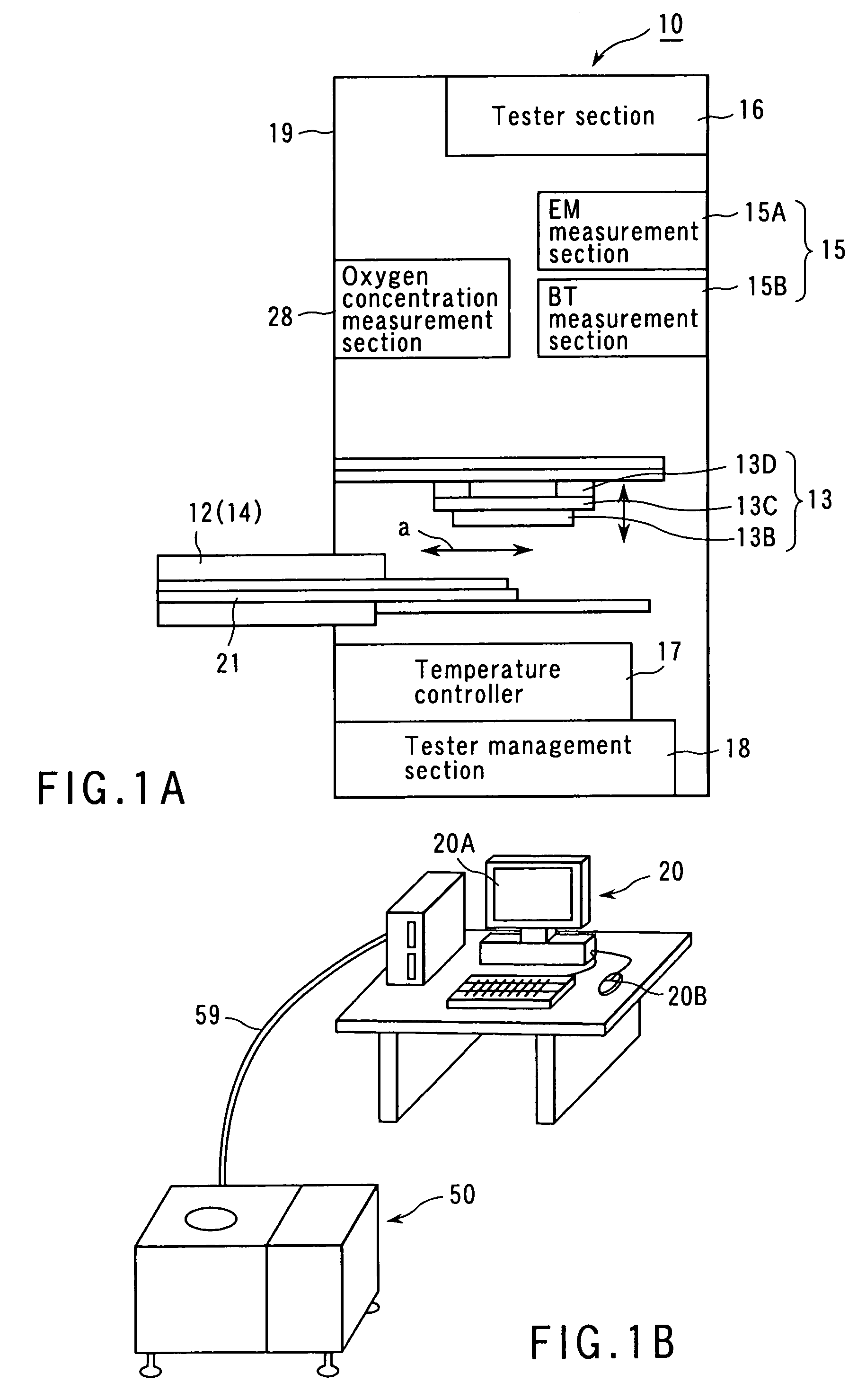

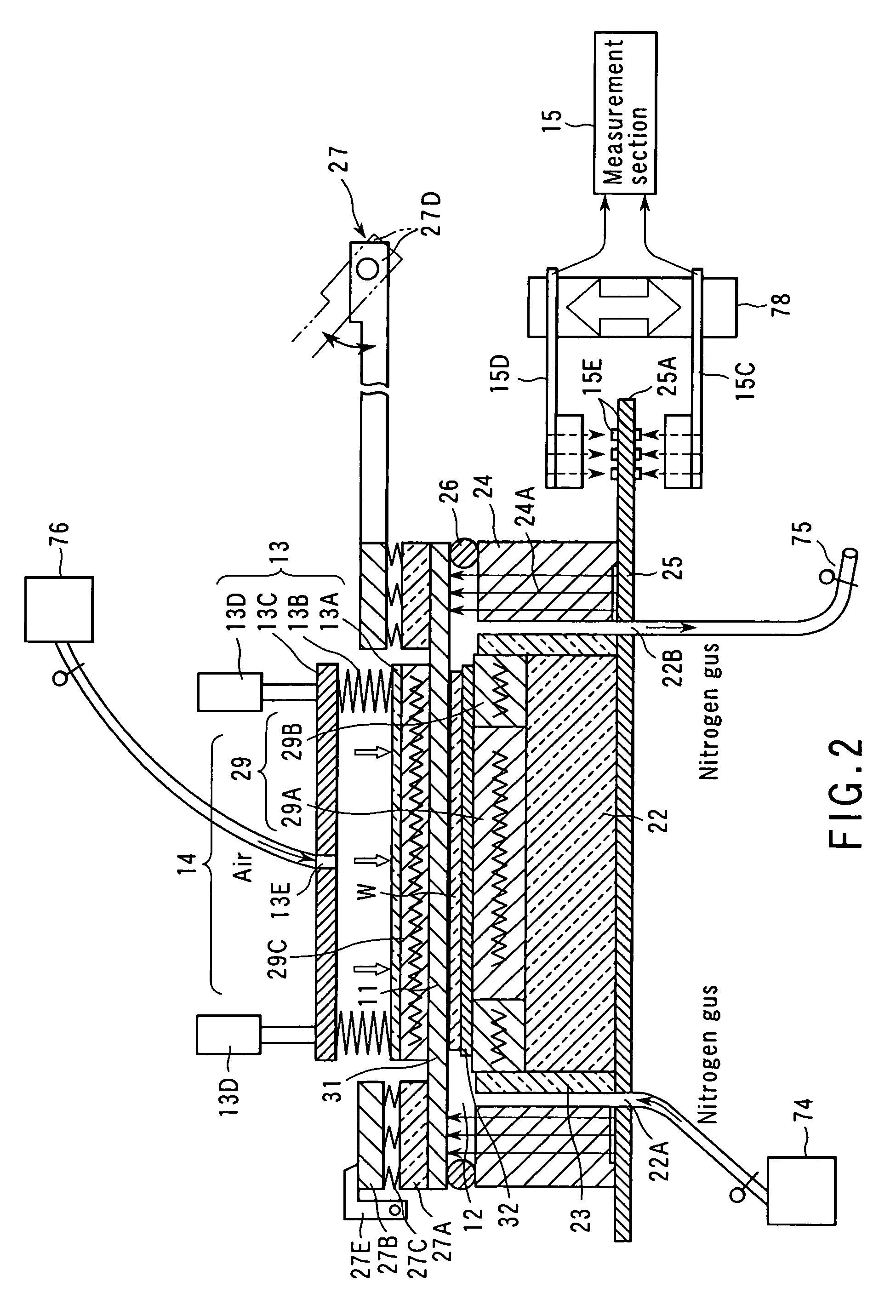

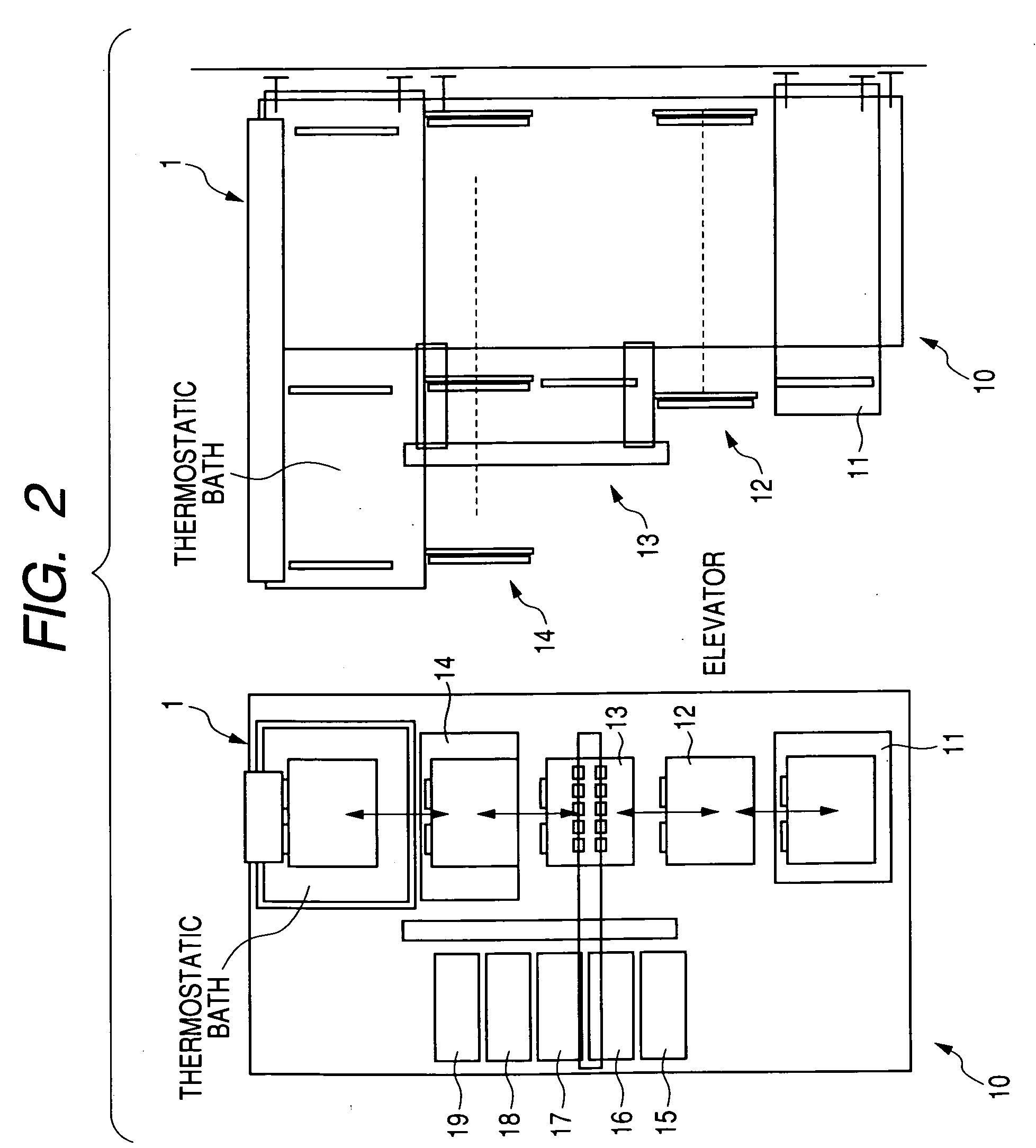

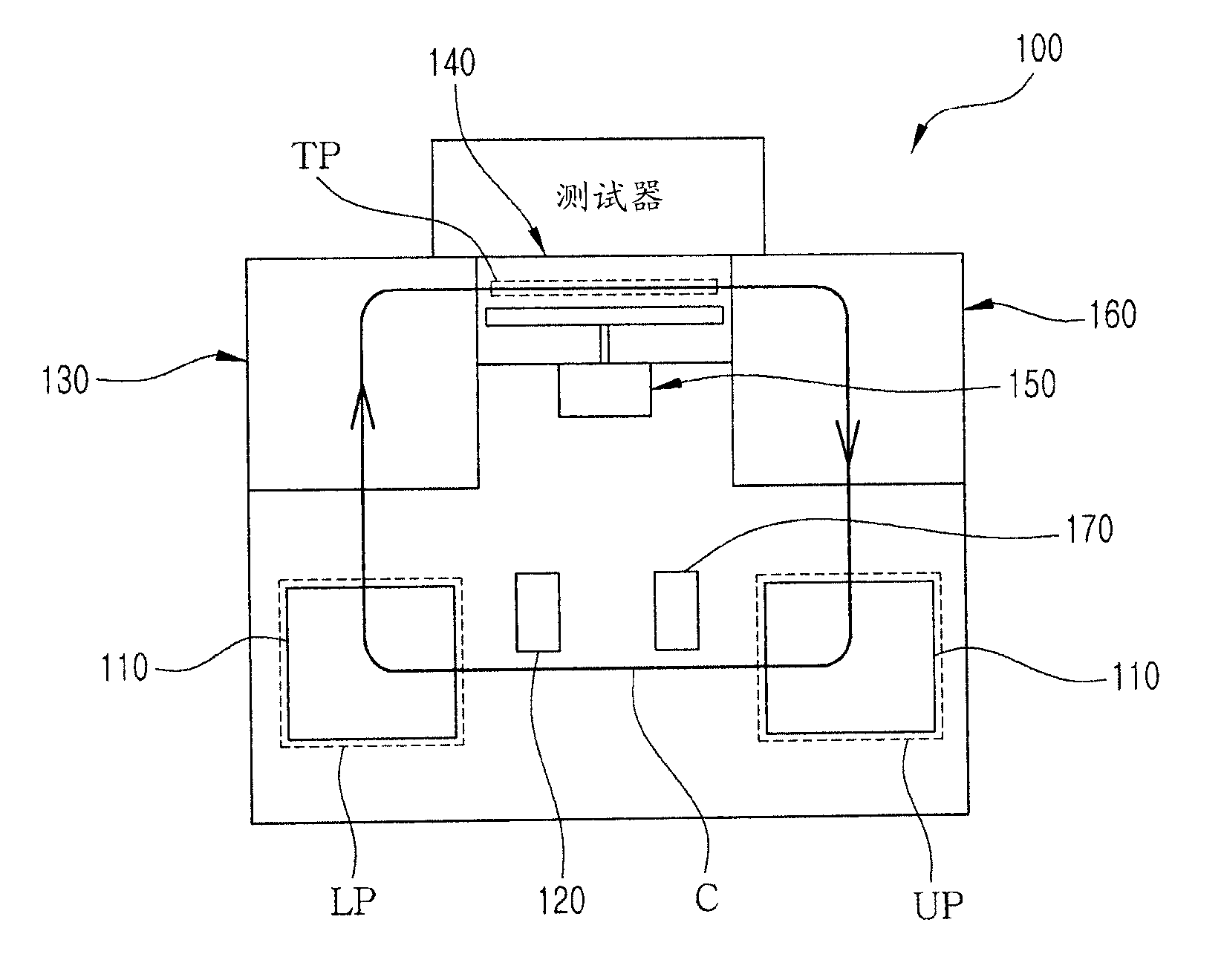

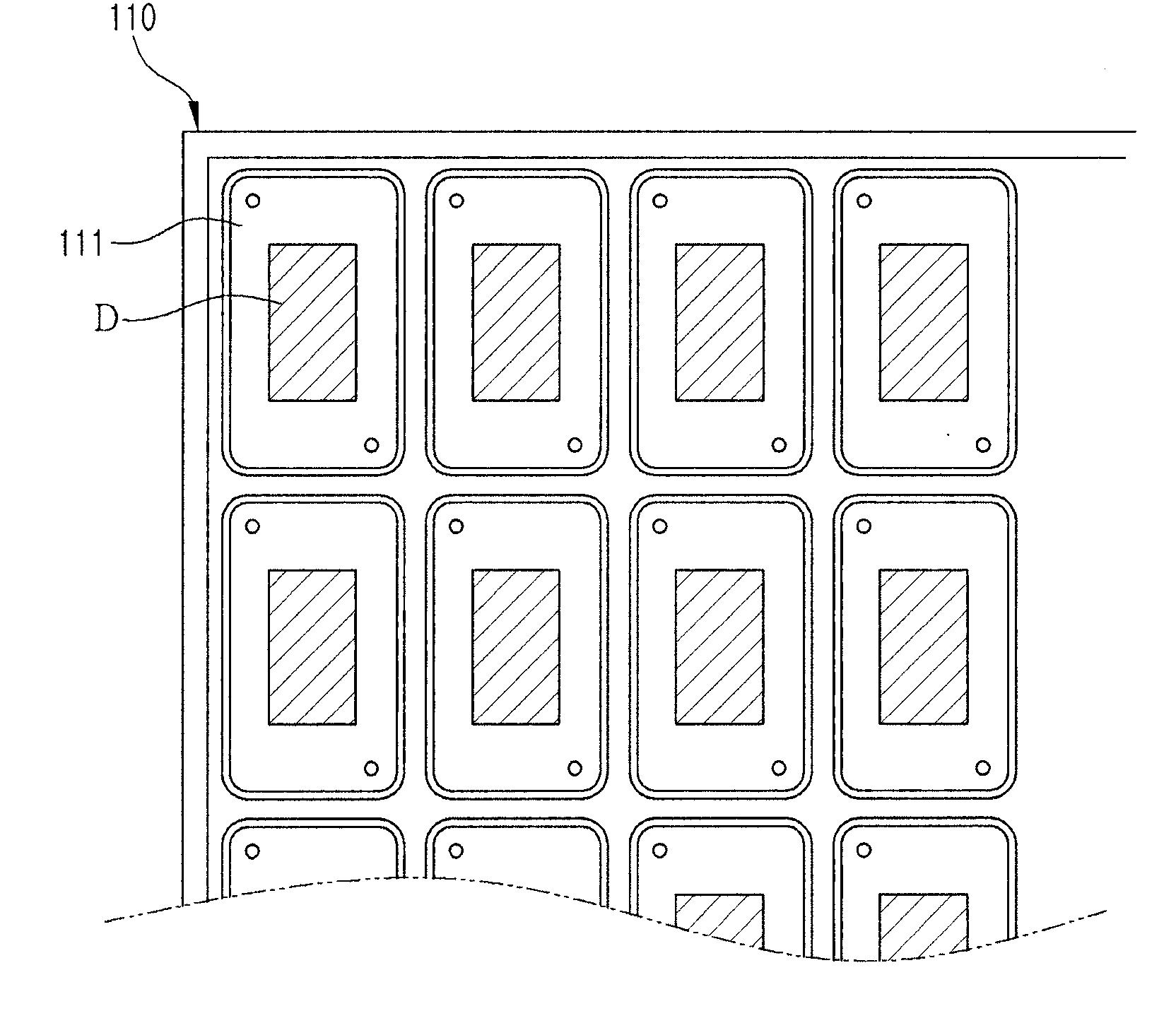

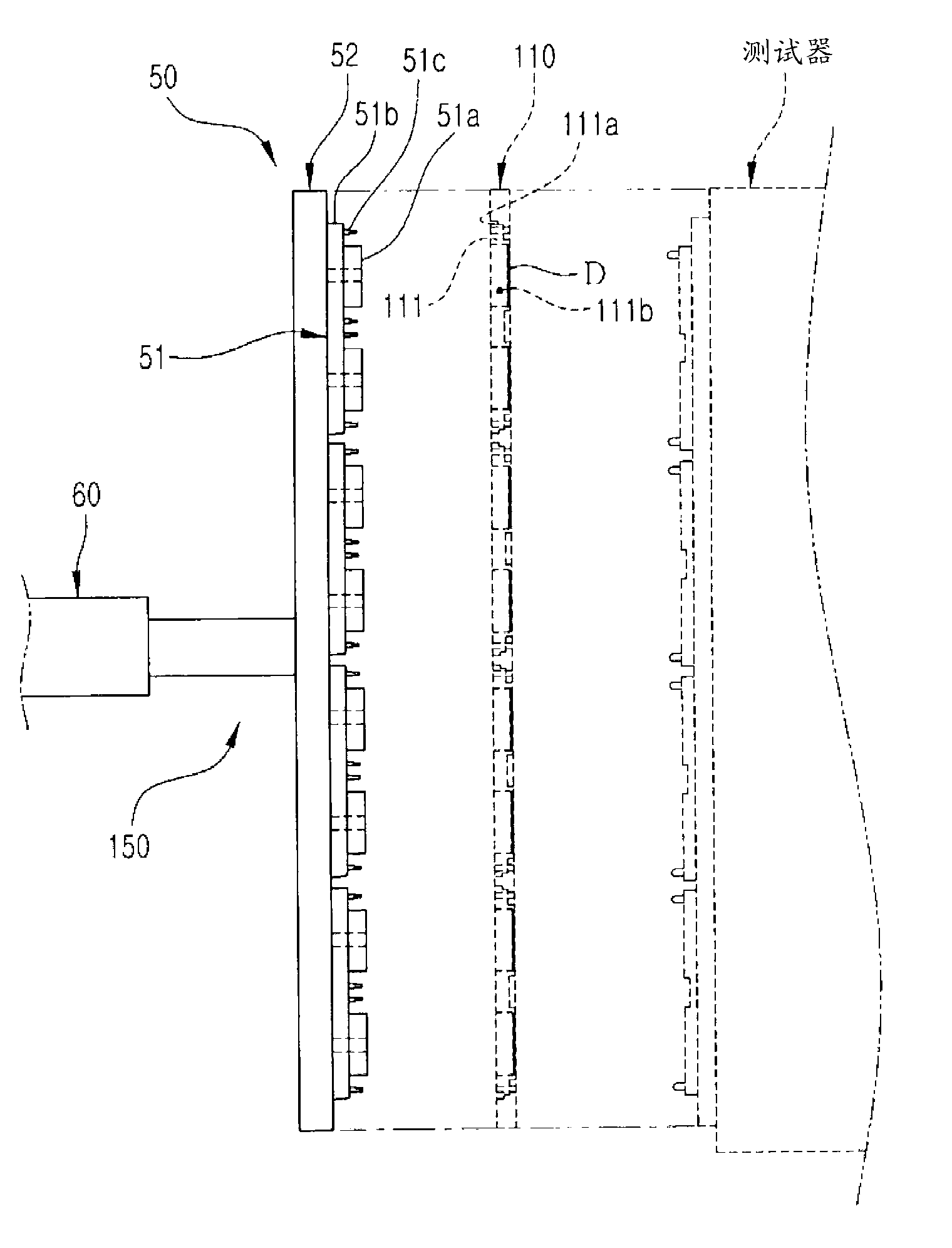

Reliability evaluation test apparatus, reliability evaluation test system, contactor, and reliability evaluation test method

InactiveUS7091733B2Quick and efficientReliable executionSemiconductor/solid-state device testing/measurementFault location by increasing destruction at faultElectricityDevice form

A reliability evaluation test apparatus of this invention includes a wafer storage section which stores a wafer in a state wherein the electrode pads of a number of devices formed on the wafer and the bumps of a contactor are totally in electrical contact with each other. The wafer storage section transmits / receives a test signal to / from a measurement section and has a hermetic and heat insulating structure. The wafer storage section has a pressure mechanism which presses the contactor and a heating mechanism which directly heats the wafer totally in contact with the contactor to a predetermined high temperature. The reliability of an interconnection film and insulating film formed on the semiconductor wafer are evaluated under an accelerated condition.

Owner:IBIDEN CO LTD +1

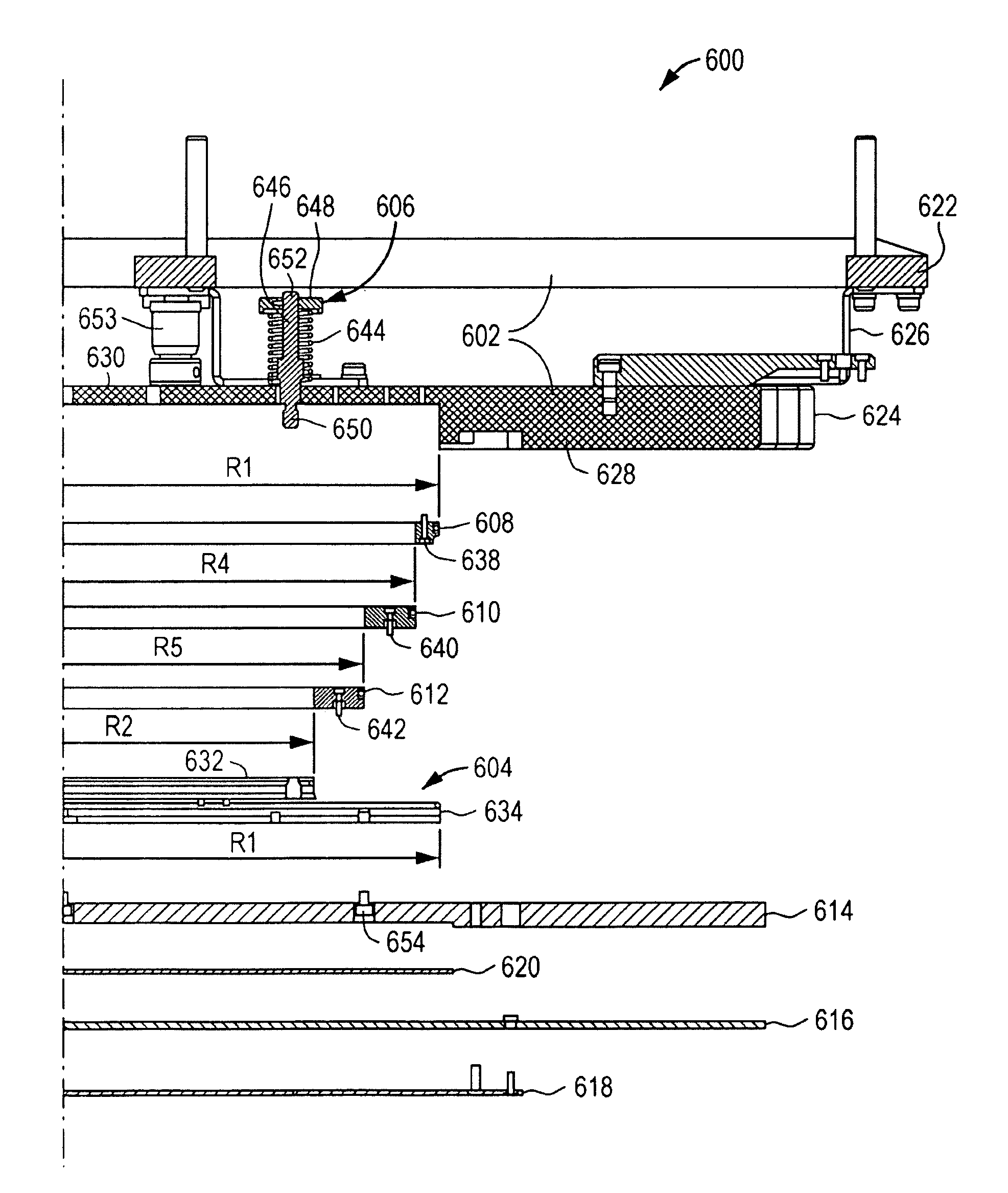

System for testing an integrated circuit of a device and its method of use

A cartridge, including a cartridge frame, formations on the cartridge frame for mounting the cartridge frame in a fixed position to an apparatus frame, a contactor support structure, a contactor interface on the contactor support structure, a plurality of terminals, held by the contactor support structure, for contacting contacts on a device, and a plurality of conductors, held by the contactor support structure, connecting the interface to the terminals.

Owner:AEHR TEST SYST

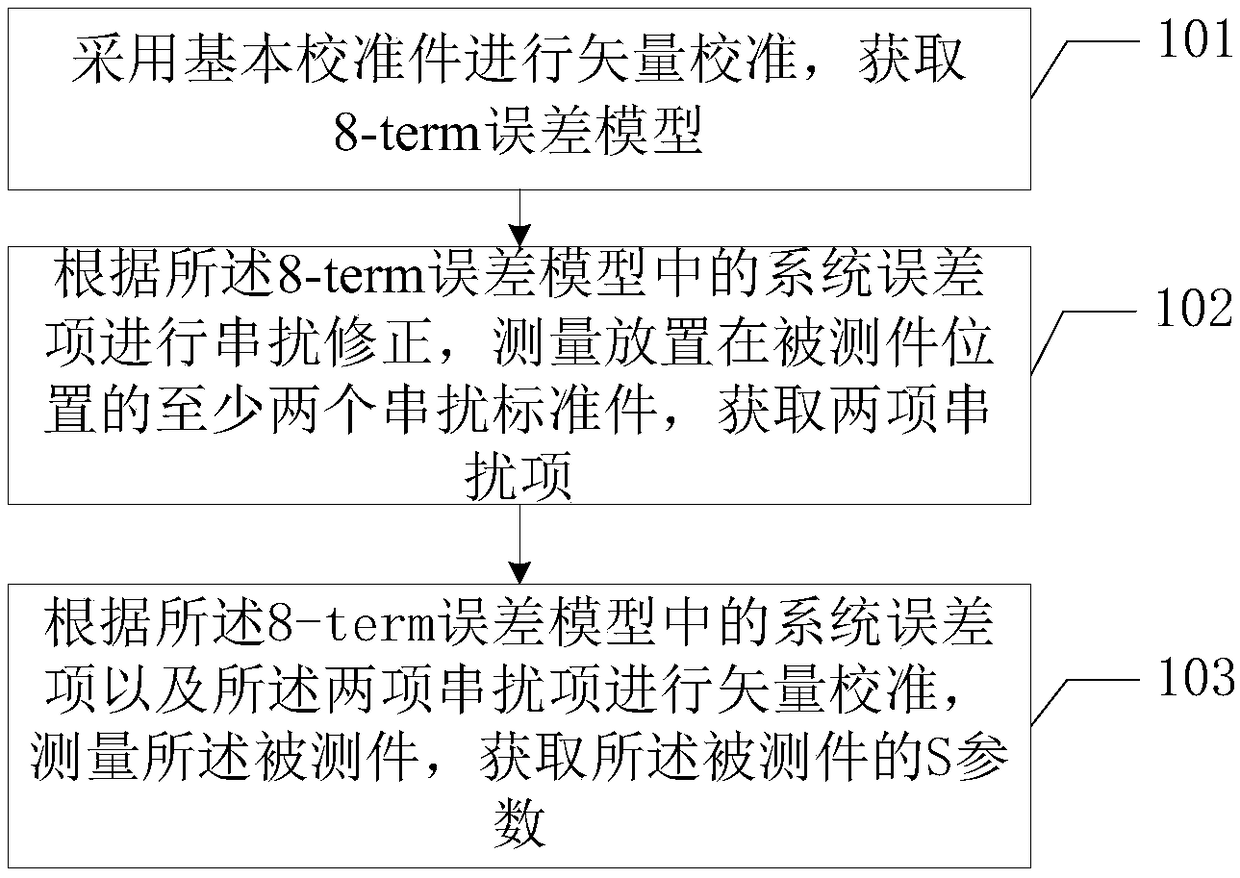

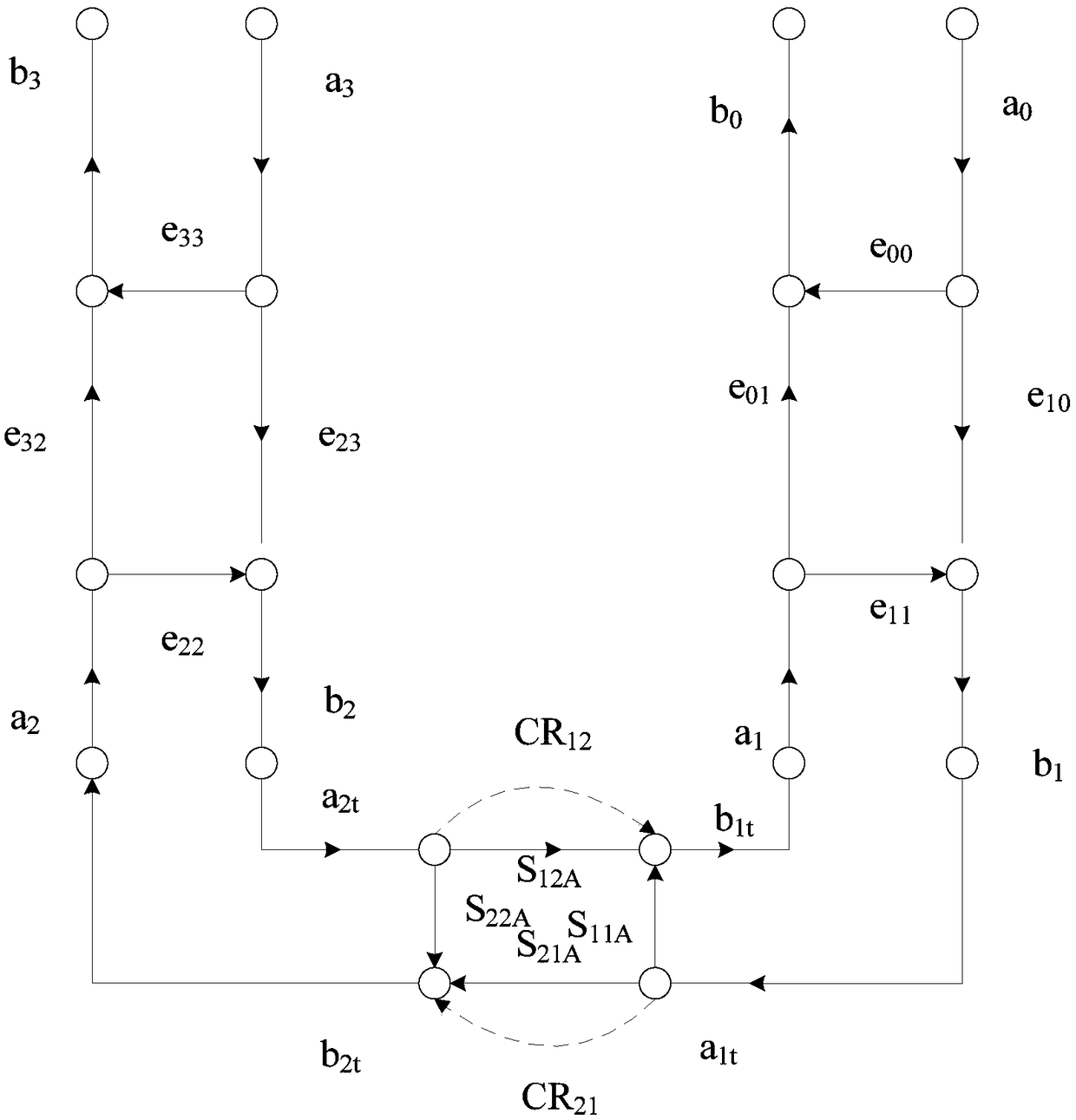

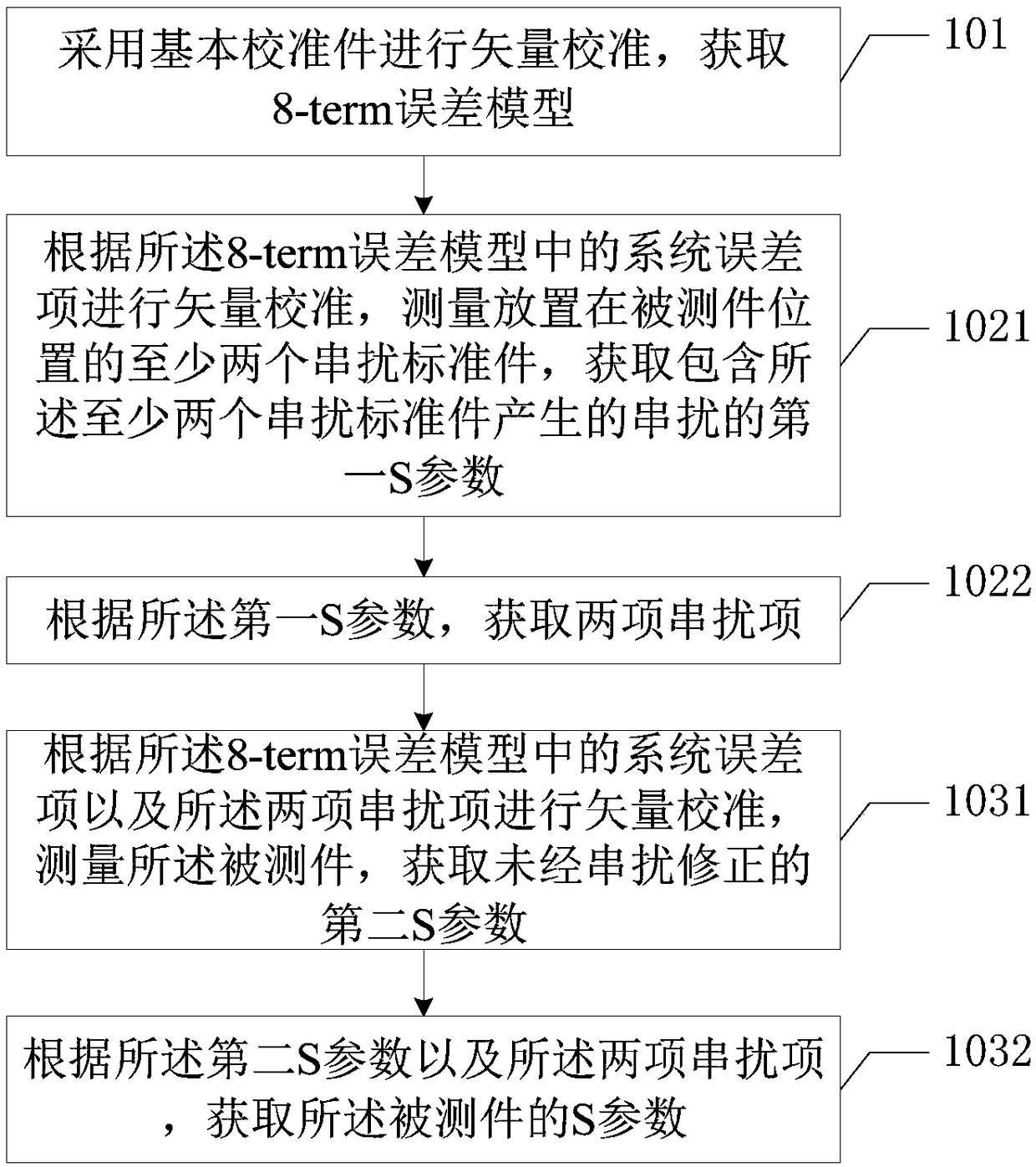

Method for measuring S parameter and terminal equipment

ActiveCN109444721AAddressing the effects of crosstalk error termsImprove measurement accuracyRadiofrequency circuit testingIntegrated circuit testingMicrowaveTerminal equipment

The invention is applicable to the technical field of measurement of microwave characteristics of wafer-level semiconductor devices, and provides a method for measuring an S parameter and terminal equipment. The method comprises the steps that vector calibration is conducted by using a basic calibration kit, and an 8-term error model is obtained; according to a system error item in the 8-term error model, crosstalk correction is conducted, at least two standard crosstalk pieces at the position of a to-be-measured piece are measured, and two crosstalk items are obtained; according to the systemerror item in the 8-term error model and the two crosstalk items, vector calibration is conducted, the to-be-measured piece is measured, and the S parameter of the to-be-measured piece is obtained. By means of the method, the problem about the influence of the crosstalk error items between probes in the high-frequency on-chip measurement process and the problem about a large random error caused by a single crosstalk standard in the crosstalk correction process can be solved, and the measurement accuracy of the high-frequency on-chip S parameter is further improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

System for testing an integrated circuit of a device and its method of use

ActiveUS20090160468A1Reduce pressureAir-break switch detailsIntegrated circuit testingElectrical conductorEngineering

A cartridge, including a cartridge frame, formations on the cartridge frame for mounting the cartridge frame in a fixed position to an apparatus frame, a contactor support structure, a contactor interface on the contactor support structure, a plurality of terminals, held by the contactor support structure, for contacting contacts on a device, and a plurality of conductors, held by the contactor support structure, connecting the interface to the terminals.

Owner:AEHR TEST SYST

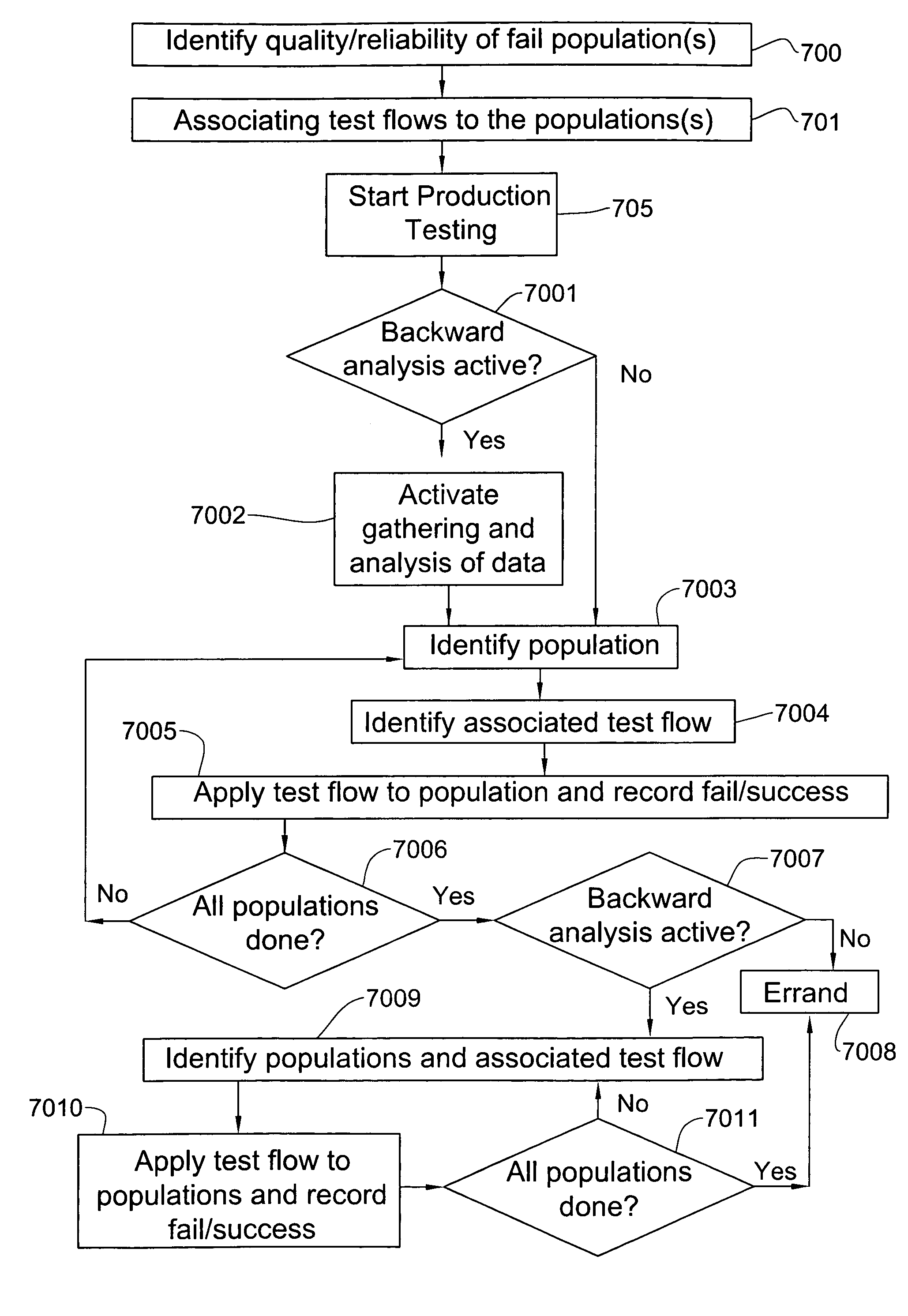

Augmenting semiconductor's devices quality and reliability

ActiveUS7340359B2Improve reliabilityImprove quality and reliabilityResistance/reactance/impedenceStatic storageTest flowCrowds

A method for augmenting quality or reliability of semiconductor units, including providing few populations of semiconductor units that are subject to quality or reliability testing. The populations include few quality or reliability fail candidate populations and other population(s). The method includes the step of associating test flows to the populations. Each test flow includes stress testing sequence. The stress testing sequence for the quality or reliability fail candidate population includes a stress test of increased duration compared to duration of a stress test in the test flow of the other population. The stress test sequence for the other population includes a stress test of increased voltage compared to corresponding operating voltage specification for a semiconductor unit. The method further includes the step of applying, within a sort testing stage, the corresponding test flow to the populations and identifying any unit which failed the stress sequence.

Owner:OPTIMAL PLUS

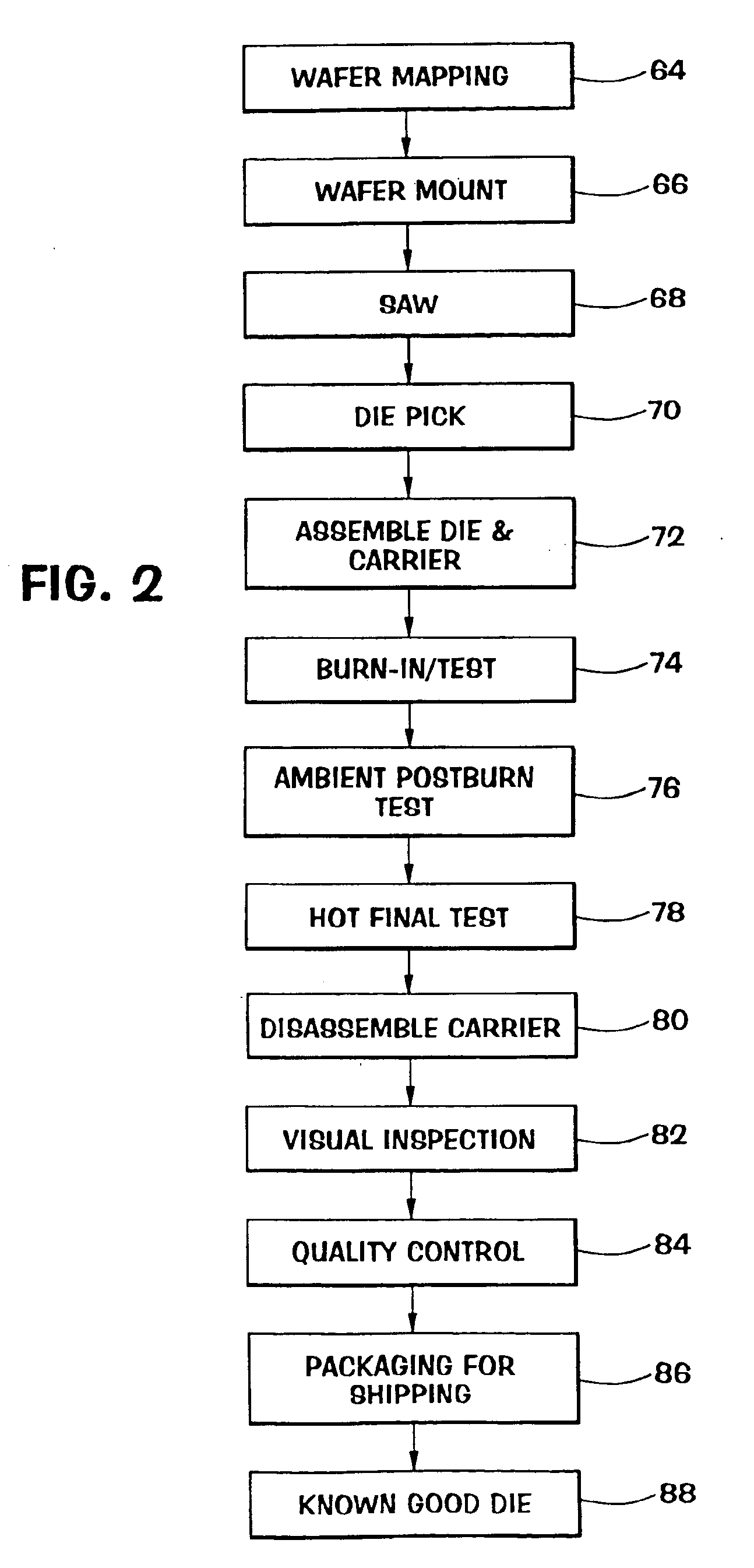

Method and apparatus for manufacturing known good semiconductor die

InactiveUS6983536B2Simple methodEasy to assembleSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSelf limitingSemiconductor chip

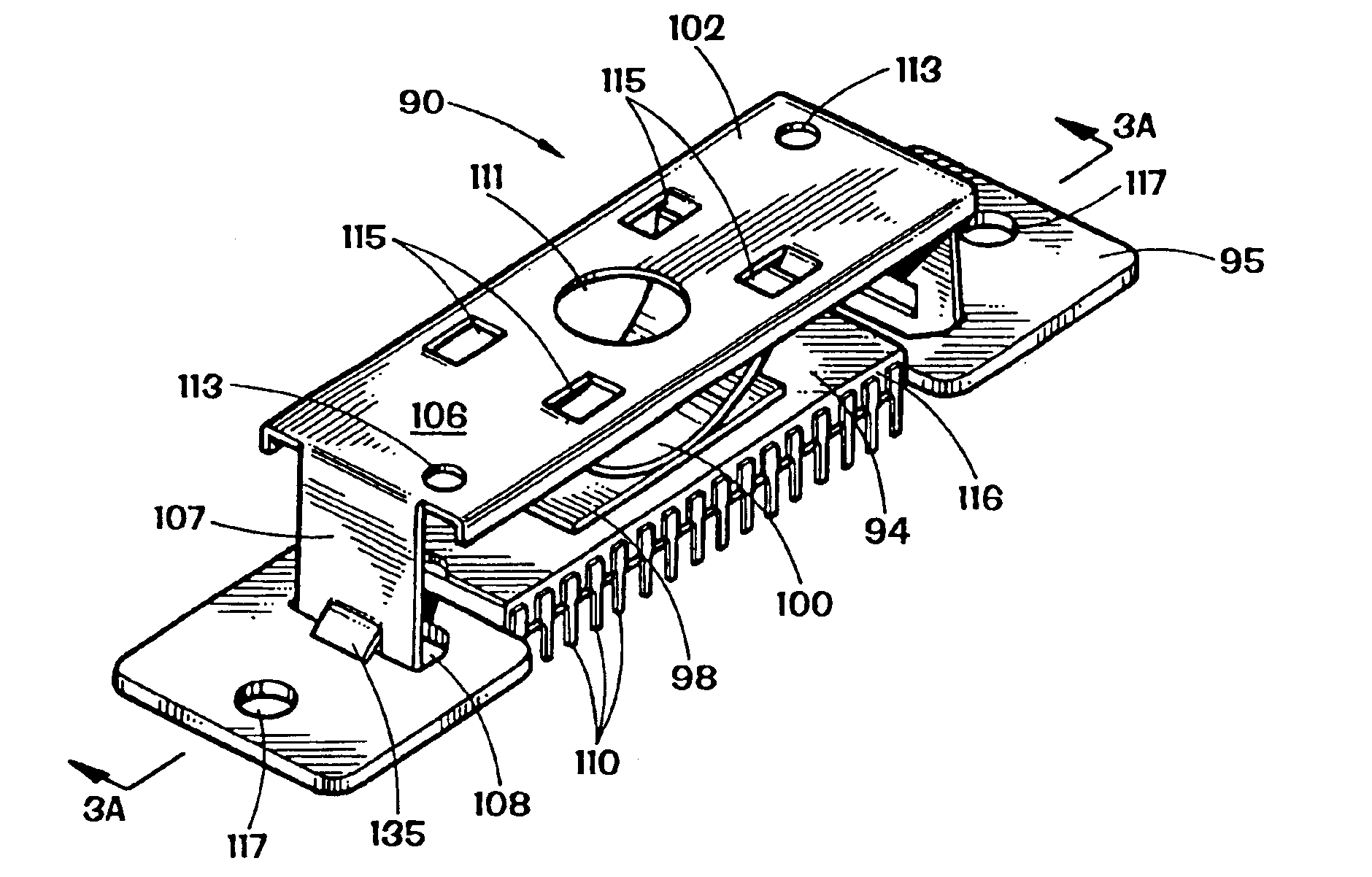

A method and apparatus for fabricating known good semiconductor dice are provided. The method includes the steps of: testing the gross functionality of dice contained on a semiconductor wafer; sawing the wafer to singulate a die; and then testing the die by assembly in a carrier having an interconnect adapted to establish electrical communication between the bond pads on the die and external test circuitry. The interconnect for the carrier can be formed using different contact technologies including: thick film contact members on a rigid substrate; self-limiting contact members on a silicon substrate; or microbump contact members with a textured surface. During assembly of the carrier, the die and interconnect are optically aligned and placed into contact with a predetermined contact force. This establishes an electrical connection between the contact members on the interconnect and the bond pads of the die. In the assembled carrier the die and interconnect are biased together by a force distribution mechanism that includes a bridge clamp, a pressure plate and a spring clip. Following testing of the die, the carrier is disassembled and the tested die is removed.

Owner:MICRON TECH INC

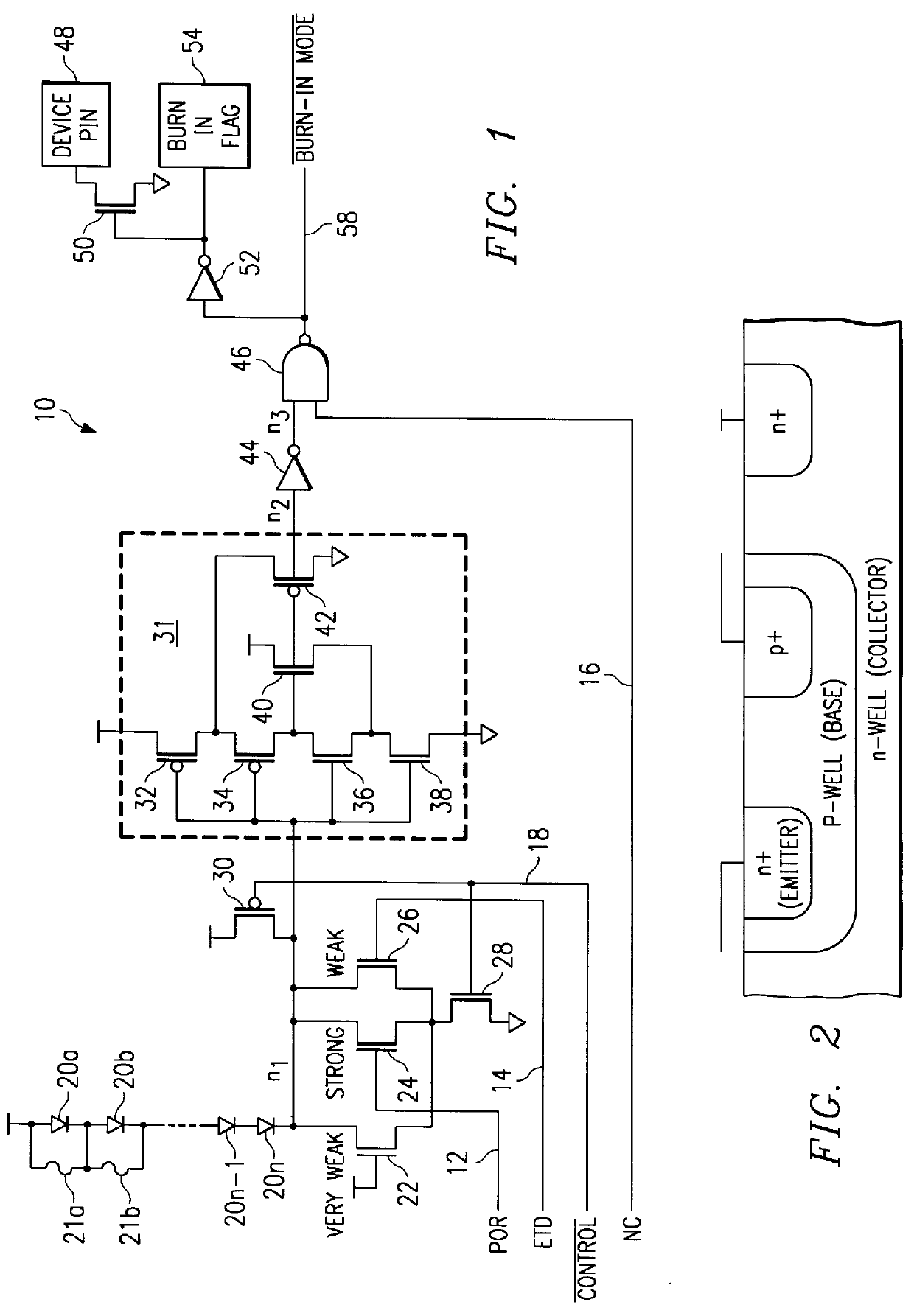

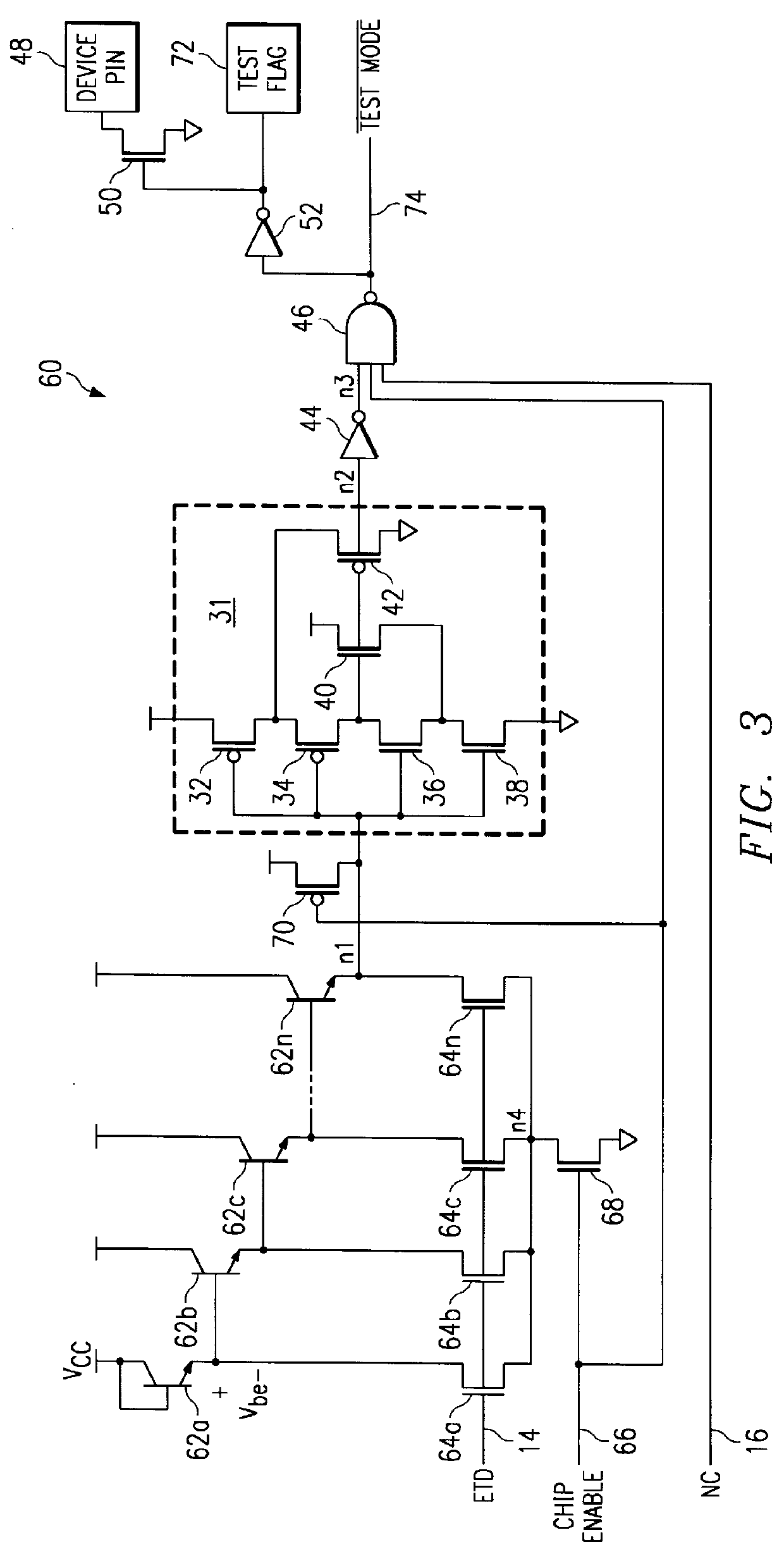

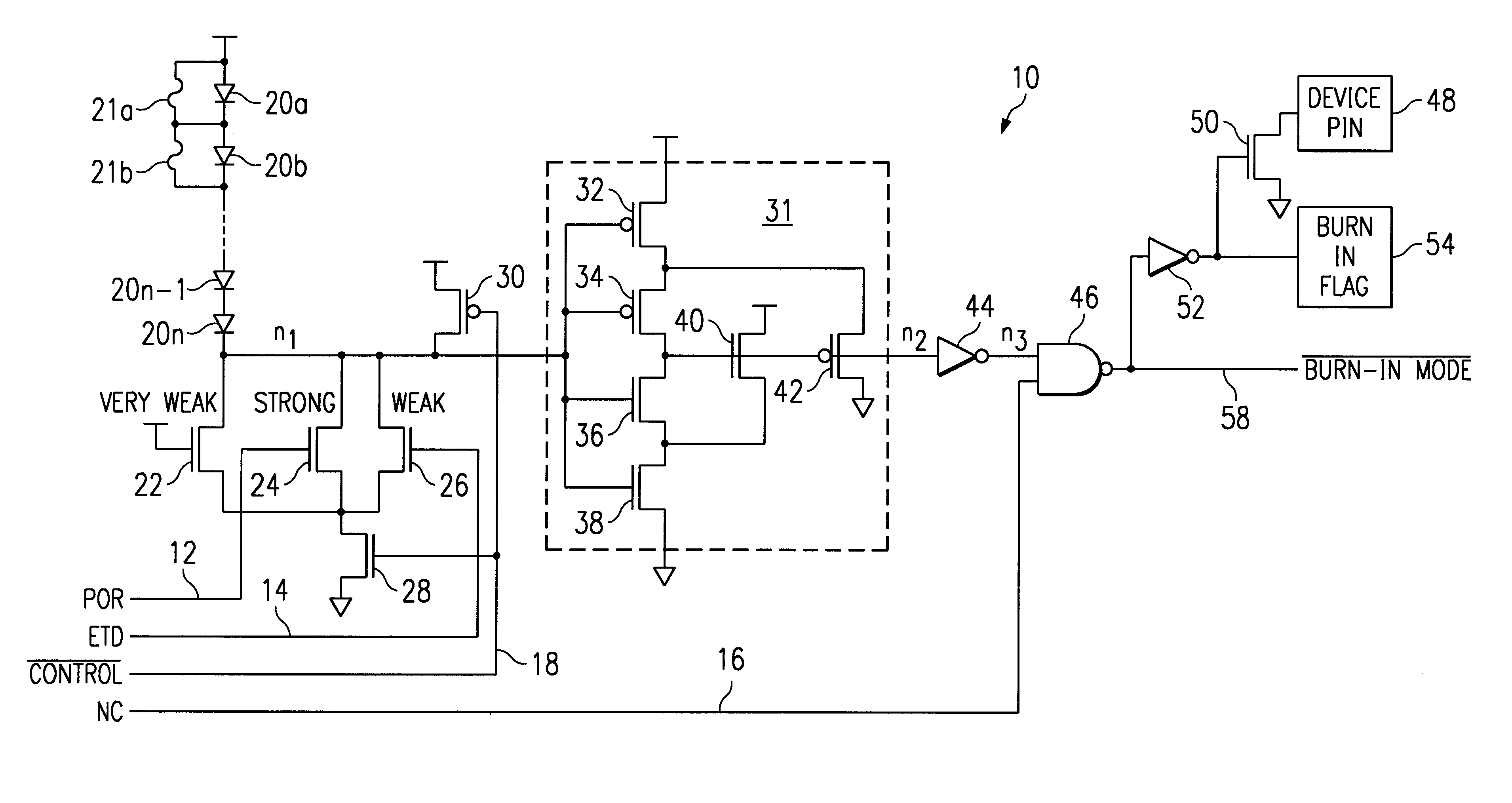

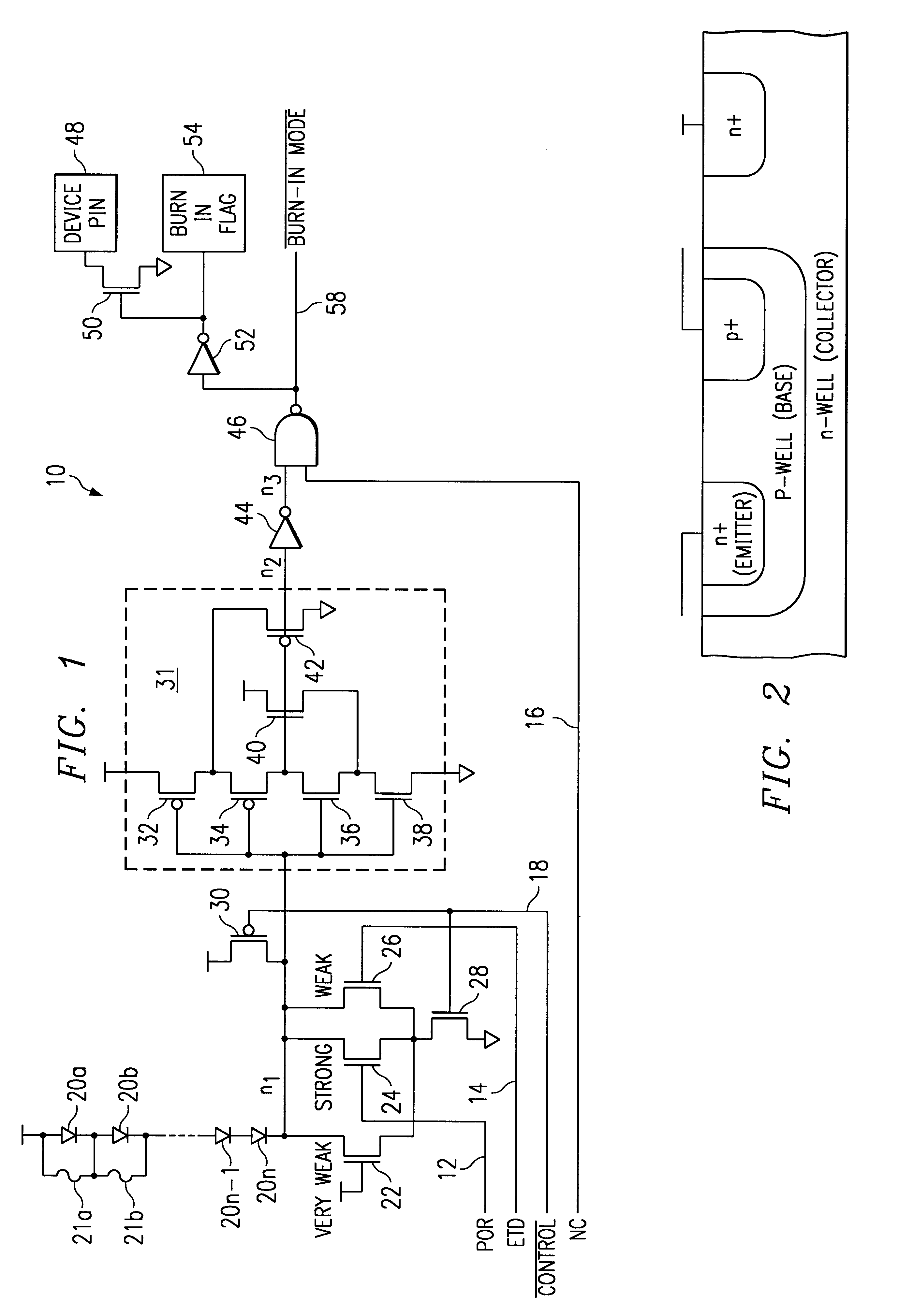

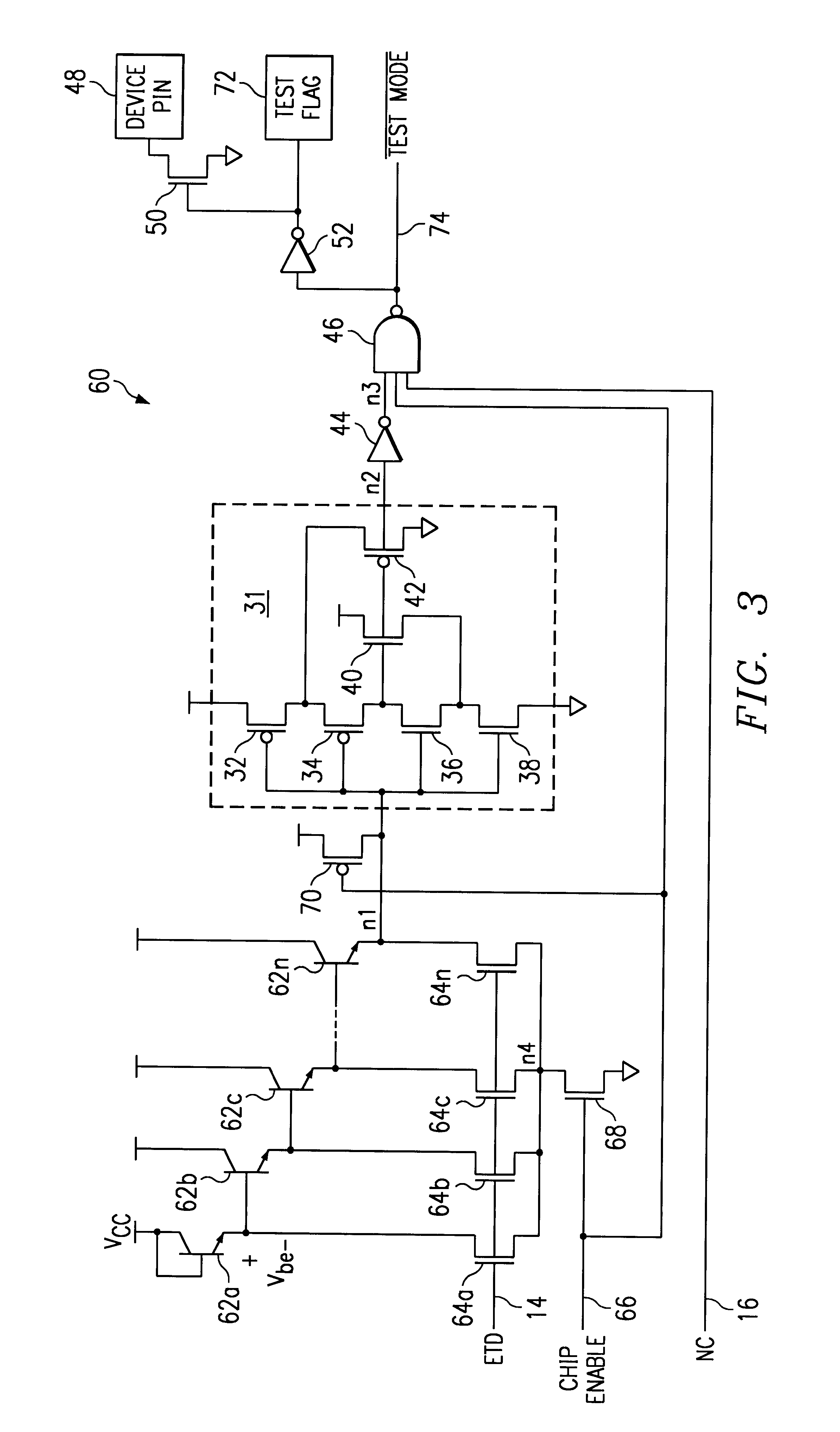

Integrated circuit device having a burn-in mode for which entry into and exit from can be controlled

InactiveUS6310485B1Digital storageFault location by increasing destruction at faultElectricityEngineering

An integrated circuit structure and method provides a burn-in stress test mode that facilitates stress testing of an integrated circuit device in a burn-in oven. The integrated circuit structure and method is capable of disabling a time-out feature of an IC memory device during a stress test mode of the device in order to facilitate stress testing of the device in a burn-in oven. The integrated circuit structure provides for entry into the burn-in stress test mode when a supply voltage supplied to the integrated circuit device exceeds a predetermined voltage level and / or the temperature of the integrated circuit device exceeds a predetermined temperature level.

Owner:STMICROELECTRONICS SRL

Augmenting semiconductor's devices quality and reliability

ActiveUS20060267577A1Improve reliabilityStatic storageIntegrated circuit testingTest flowTest sequence

A method for augmenting quality / reliability of semiconductor units, including providing few populations of semiconductor units that are subject to quality / reliability testing. The populations include few quality / reliability fail candidate populations and other population(s). The method includes the step of associating test flows to the populations. Each test flow includes stress testing sequence. The stress testing sequence for the quality / reliability fail candidate population includes a stress test of increased duration compared to duration of a stress test in the test flow of the other population. The stress test sequence for the other population includes a stress test of increased voltage compared to corresponding operating voltage specification for a semiconductor unit. The method further includes the step of applying, within a sort testing stage, the corresponding test flow to the populations and identifying any unit which failed the stress sequence.

Owner:OPTIMAL PLUS

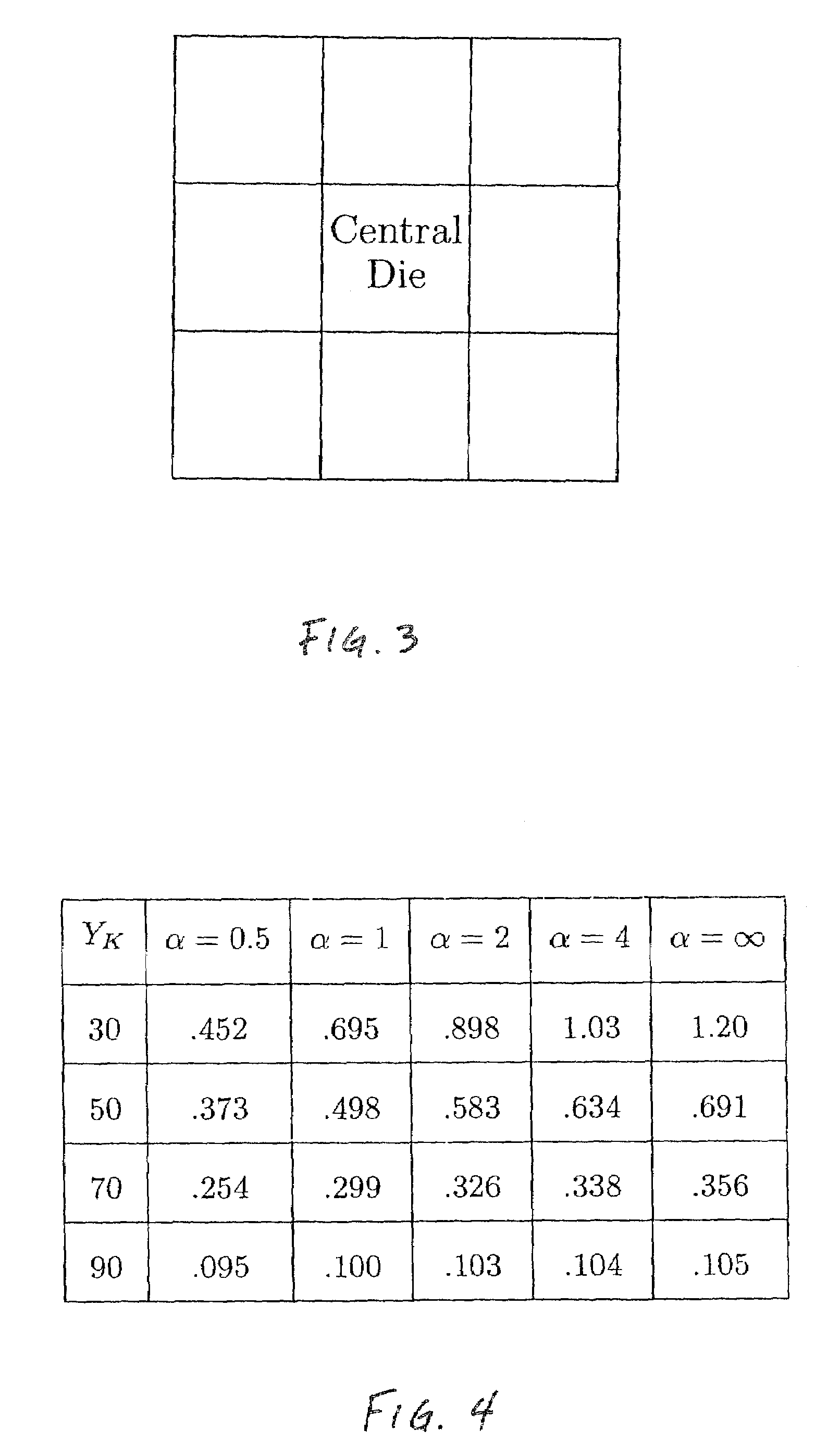

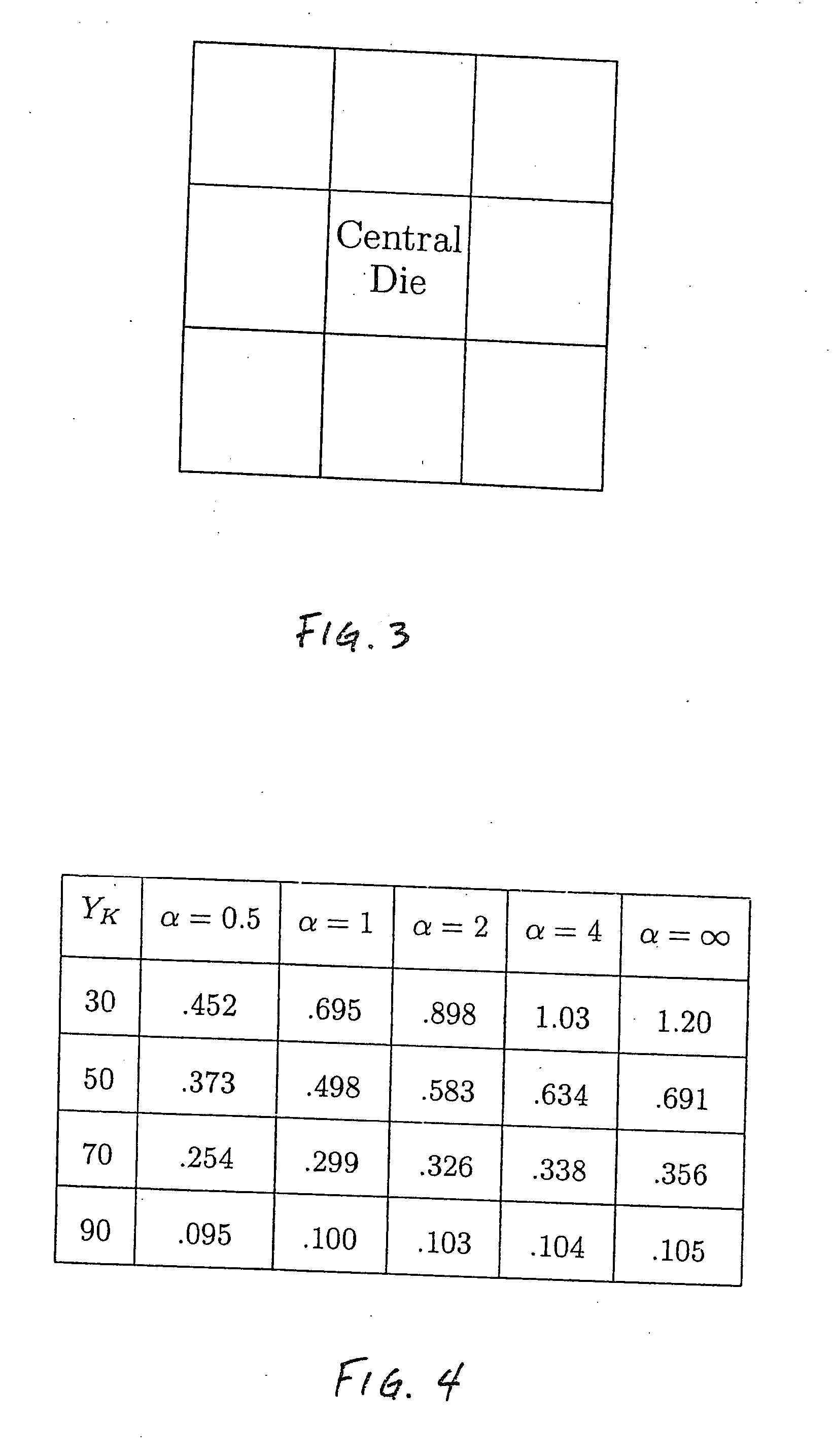

System and method for estimating reliability of components for testing and quality optimization

InactiveUS7194366B2Short aging timeEasy to optimizeSemiconductor/solid-state device testing/measurementDigital computer detailsQuality optimizationElectronic component

A system and method for determining the early life reliability of an electronic component, including classifying the electronic component based on an initial determination of a number of fatal defects, and estimating a probability of latent defects present in the electronic component based on that classification with the aim of optimizing test costs and product quality.

Owner:AUBURN UNIV

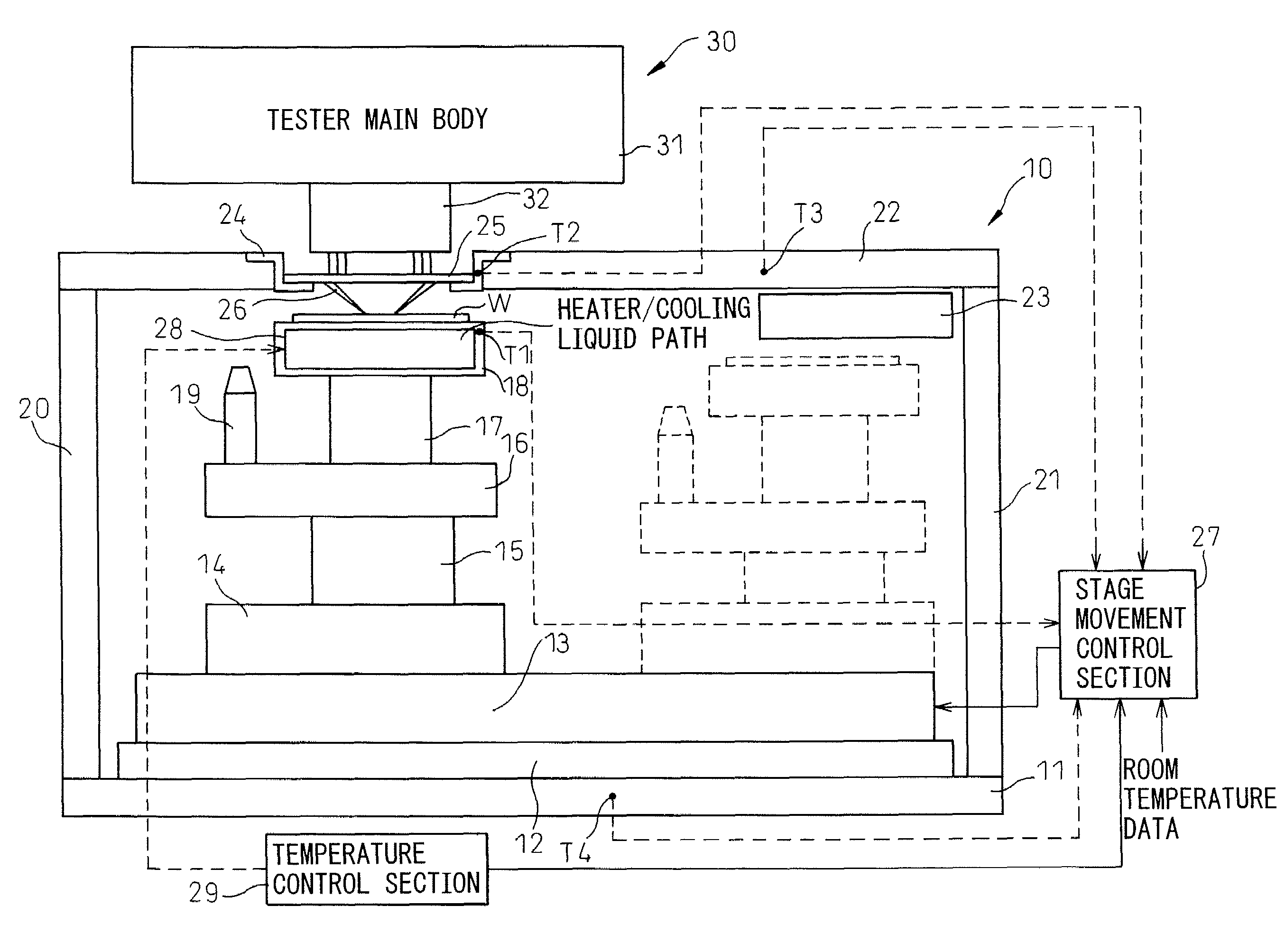

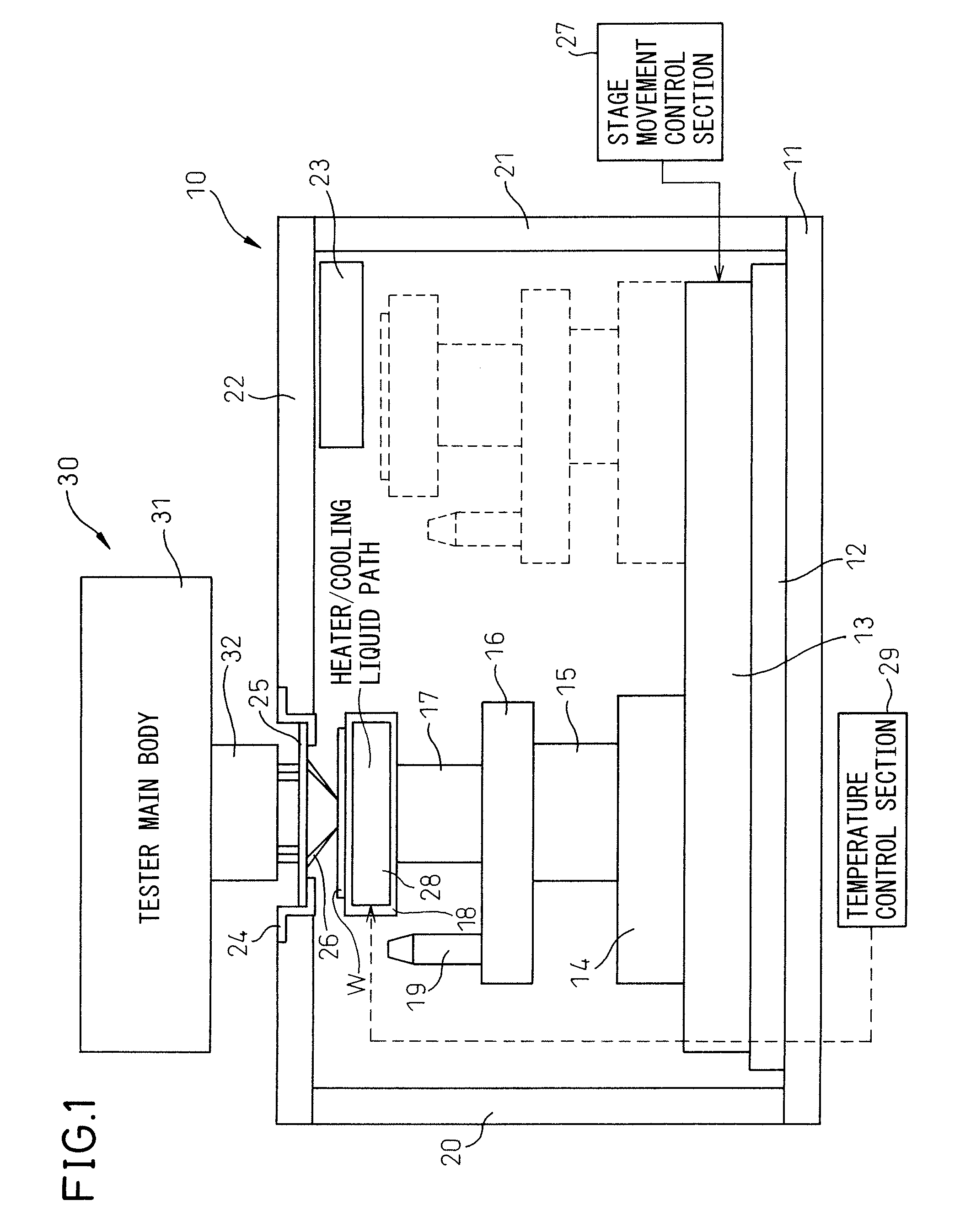

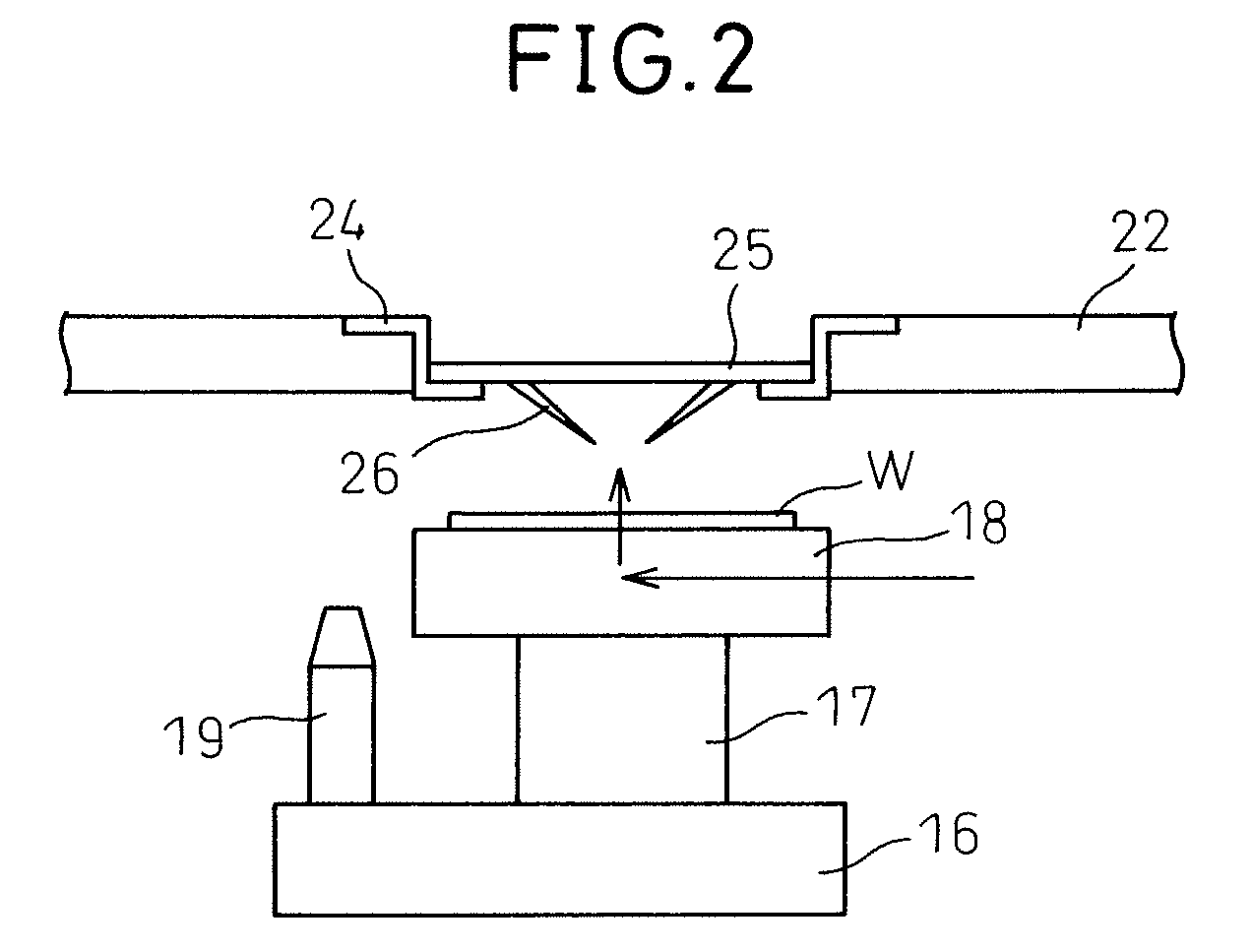

Prober and probe contact method

InactiveUS7405584B2Reduce throughputPrecise positioningSemiconductor/solid-state device testing/measurementFault location by increasing destruction at faultProbe cardContact method

A prober that has improved positional precision of probing without reducing throughput is disclosed. The prober comprises a probe card having a probe, a wafer stage, a stage temperature adjustment mechanism, a wafer stage movement mechanism, a movement control section, and an alignment mechanism that detects the relative position between an electrode and the probe, wherein the movement control section controls the movement mechanism so as to cause the electrode to come into contact with the probe based on the detected relative position, and the prober further comprises a plurality of temperature sensors that detect the temperatures of a plurality of portions of the prober including the wafer stage and a predicted change amount calculation section that calculates the amount of change in relative position between the electrode and the probe based on a prediction model that uses at least part of the temperatures of the plurality of portions and the temperature difference between the wafer stage and the other sections as a variable.

Owner:TOKYO SEIMITSU

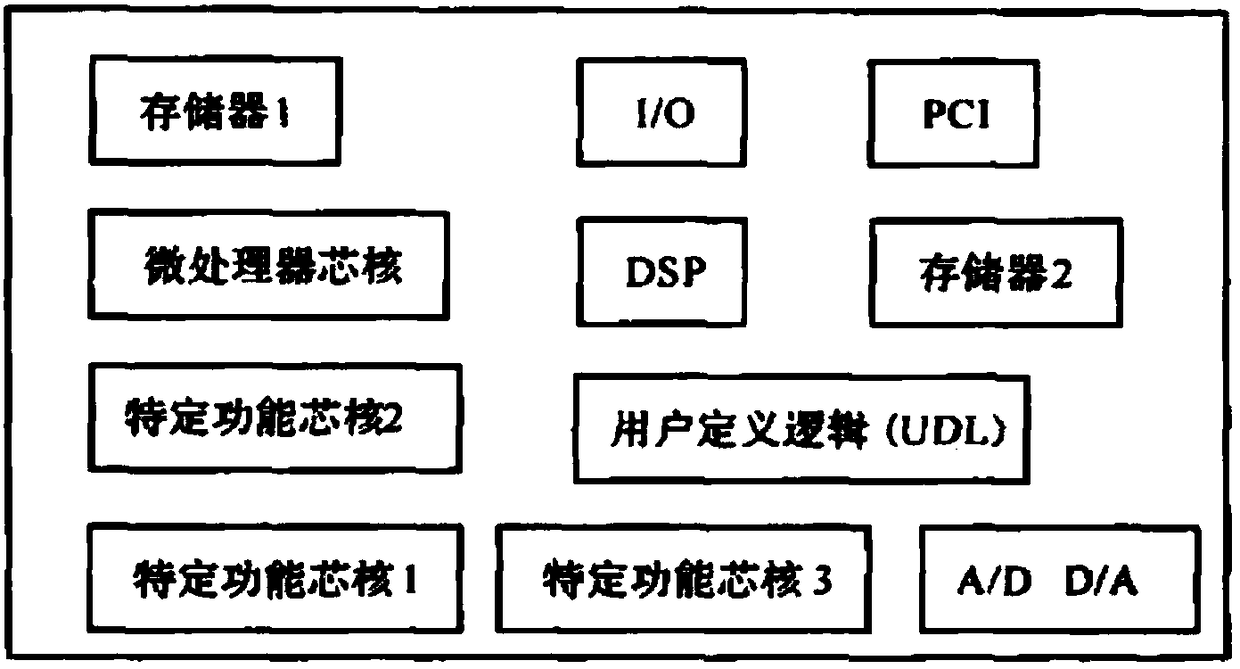

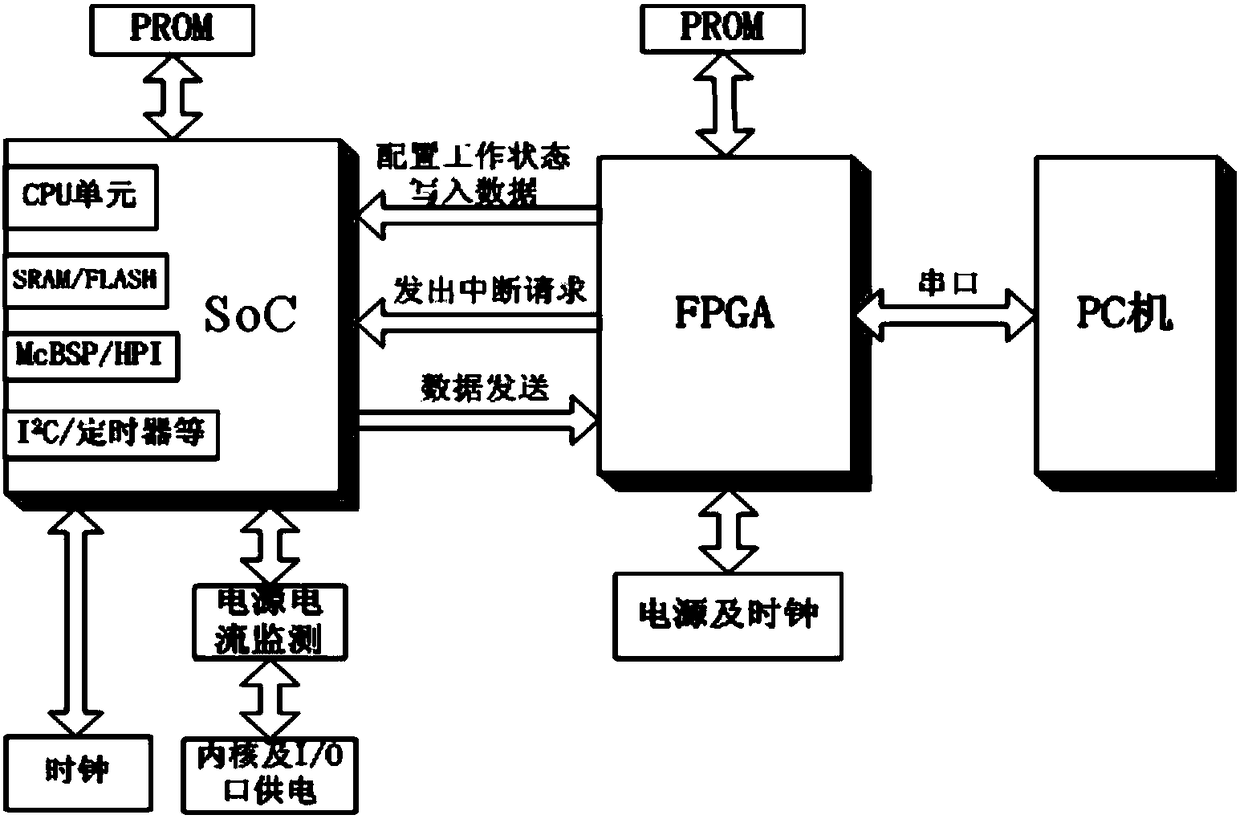

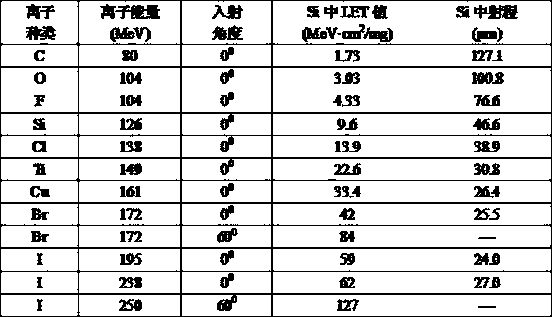

Single-event effect test method for SoC

ActiveCN108226748AImprove test coverageSimple test vectorTesting electric installations on transportMeasuring interference from external sourcesLogic cellComputer science

The invention provides a single-event effect test method for an SoC (System on Chip). The single-event effect test method provided by the invention comprises steps of testing single-event effects of aCPU, a memory unit and a user-defined logical unit inside an SoC processor as well as AD, DA, a serial interface circuit and other peripheral units, can effectively test the single-event effects of different structural units inside the SoC processor, and realizes comprehensive and reasonable evaluation on the single-event effect of the SoC processor.

Owner:SHANGHAI PRECISION METROLOGY & TEST RES INST +1

Wafer-level burn-in and test

InactiveUS20050017750A1Solid-state devicesFault location by increasing destruction at faultDevice materialEngineering

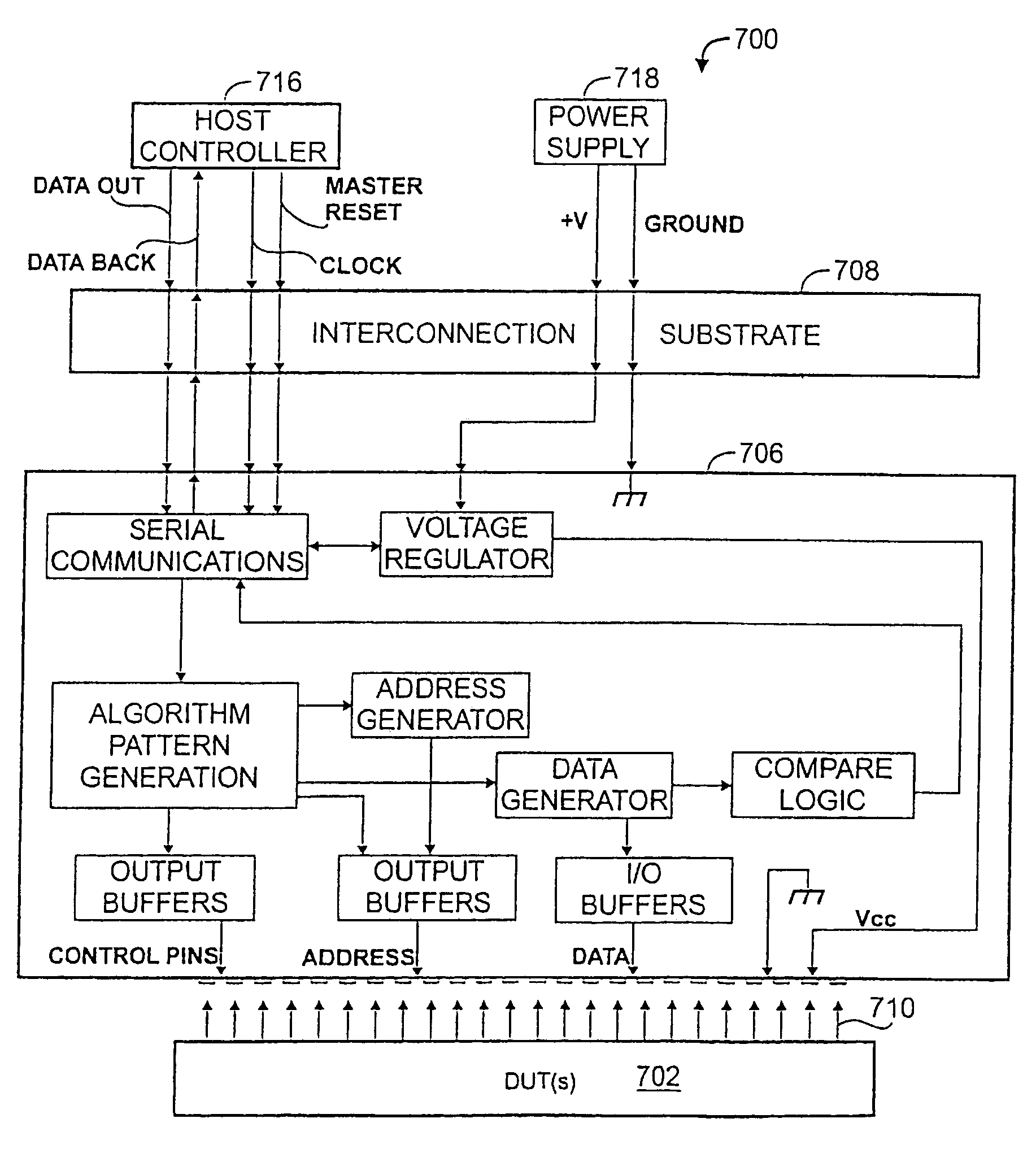

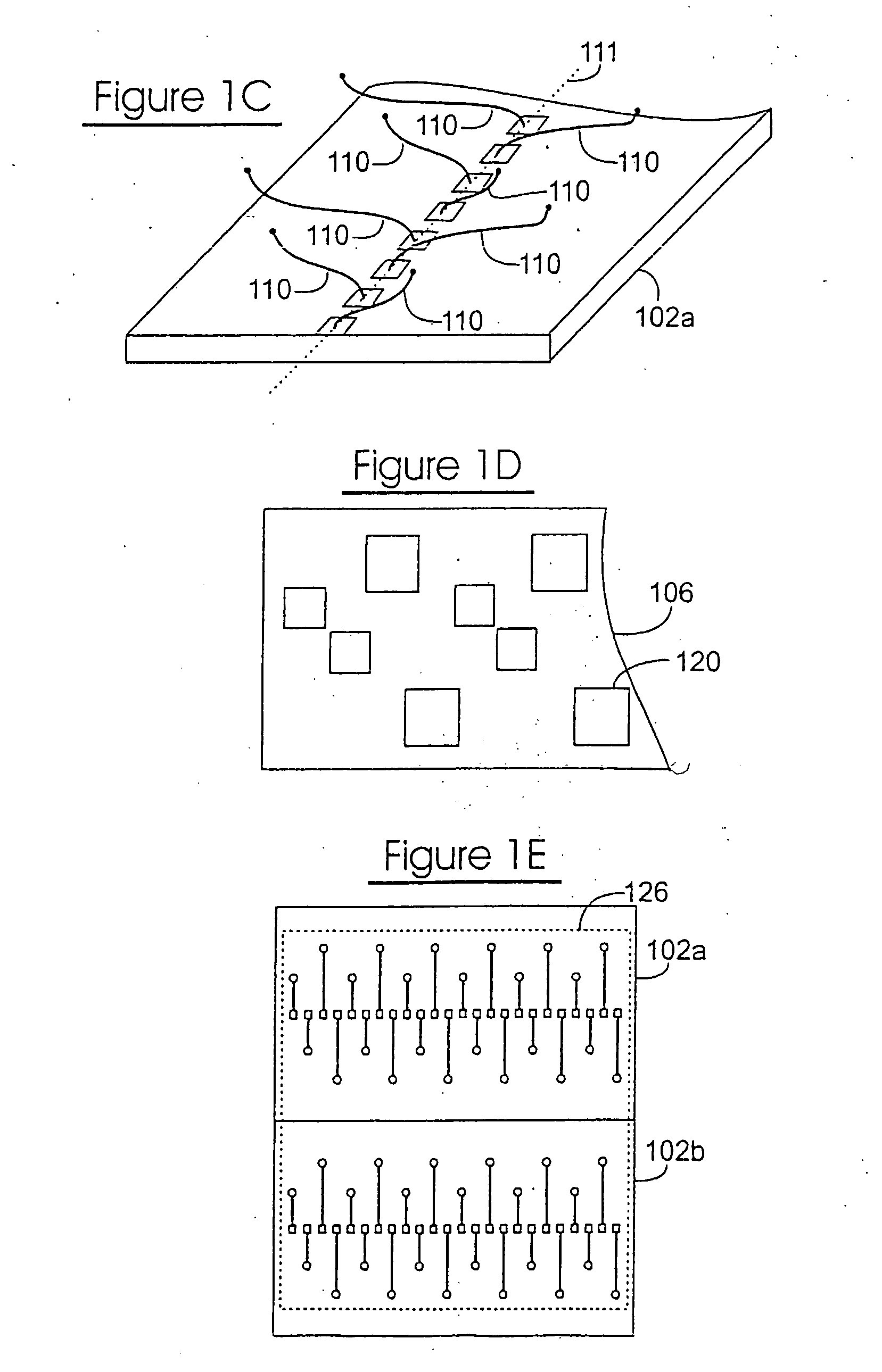

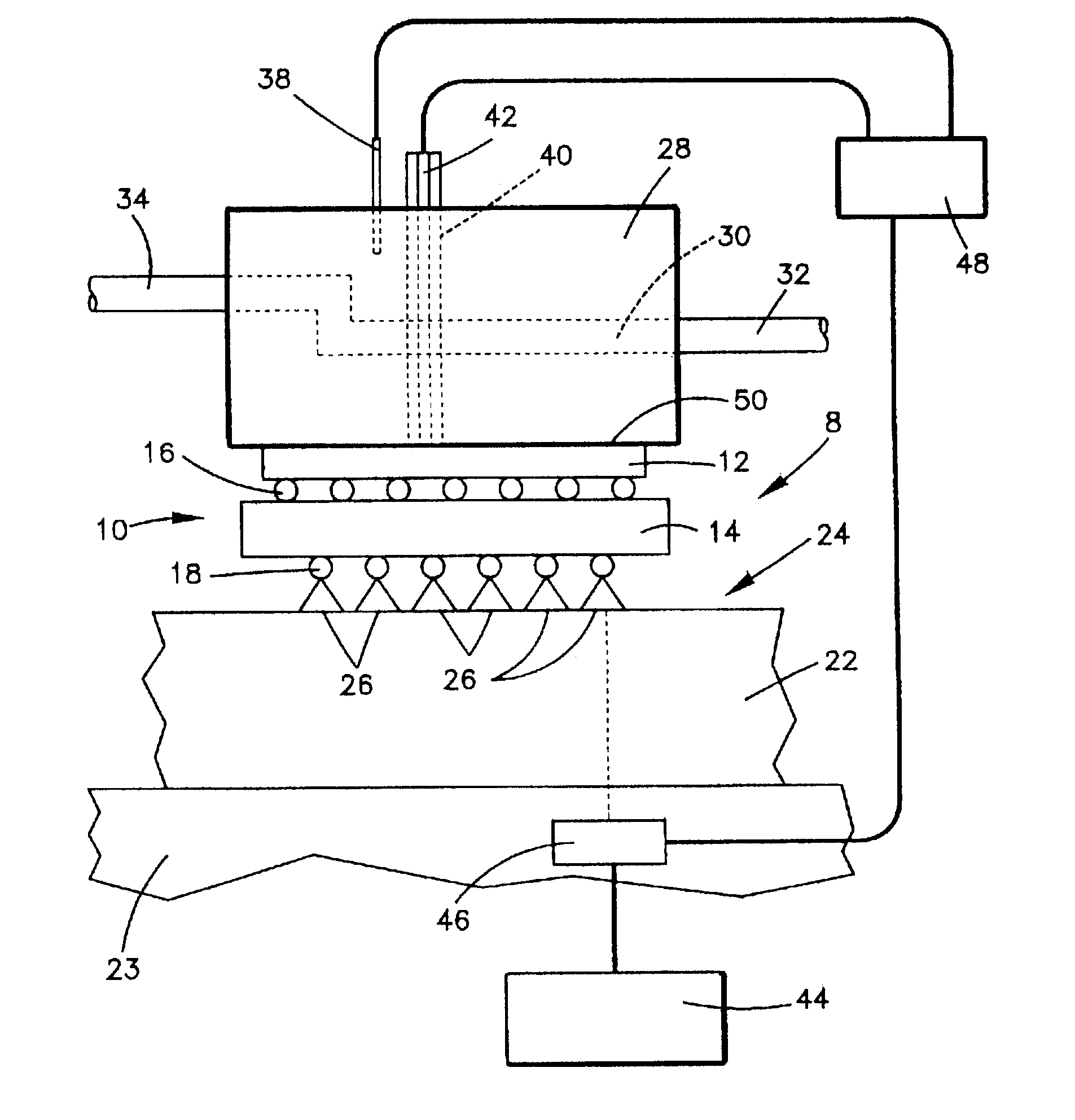

Techniques for performing wafer-level burn-in and test of semiconductor devices include a test substrate having active electronic components such as ASICs mounted to an interconnection substrate or incorporated therein, metallic spring contact elements effecting interconnections between the ASICs and a plurality of devices-under-test (DUTs) on a wafer-under-test (WUT), all disposed in a vacuum vessel so that the ASICs can be operated at temperatures independent from and significantly lower than the burn-in temperature of the DUTs. The spring contact elements may be mounted to either the DUTs or to the ASICs, and may fan out to relax tolerance constraints on aligning and interconnecting the ASICs and the DUTs. Physical alignment techniques are also described.

Owner:FORMFACTOR INC

Method of burning in an integrated circuit chip package

InactiveUS6577146B2Fault location by increasing destruction at faultIntegrated circuit testingImproved methodChip-scale package

Owner:GOOGLE LLC

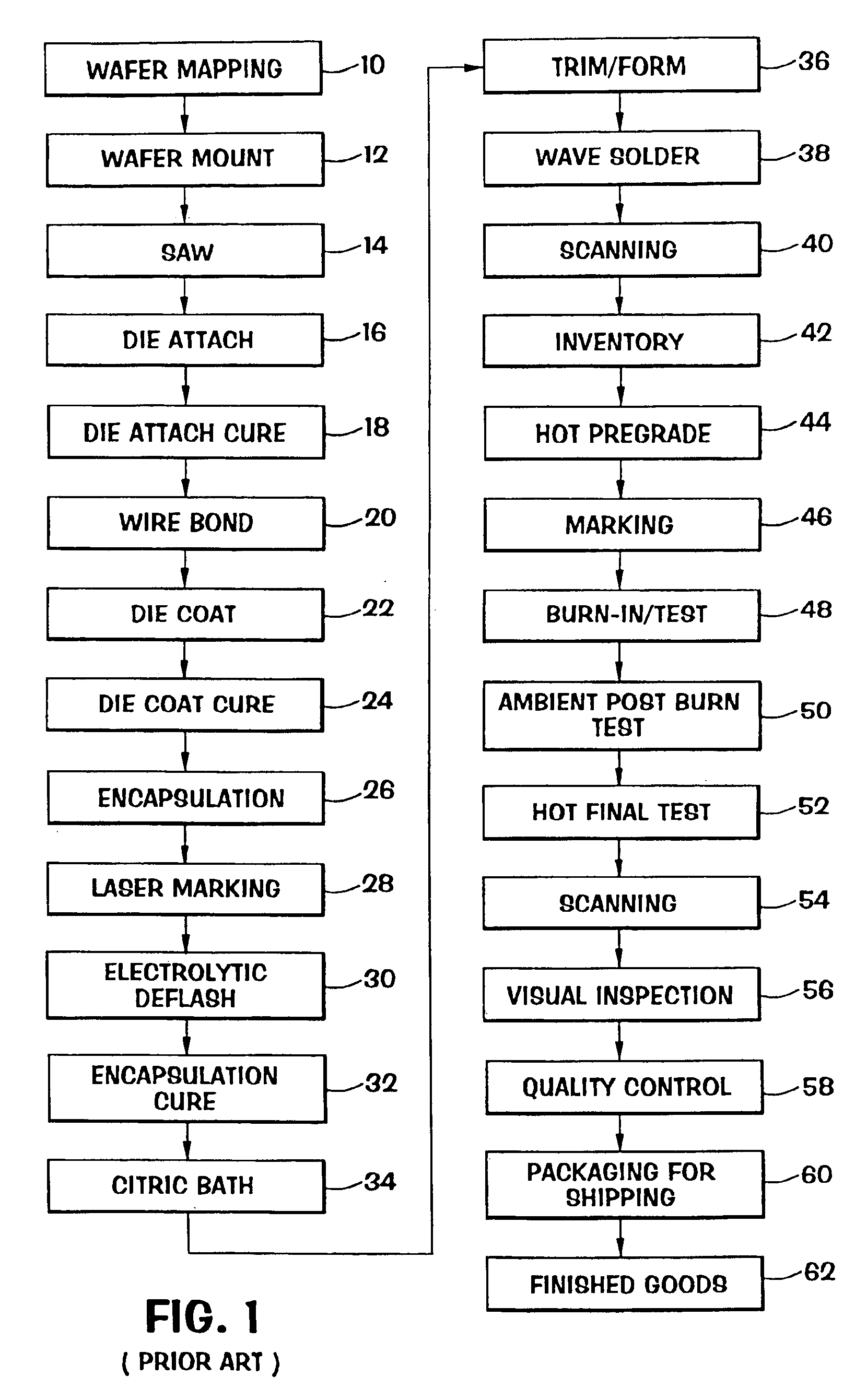

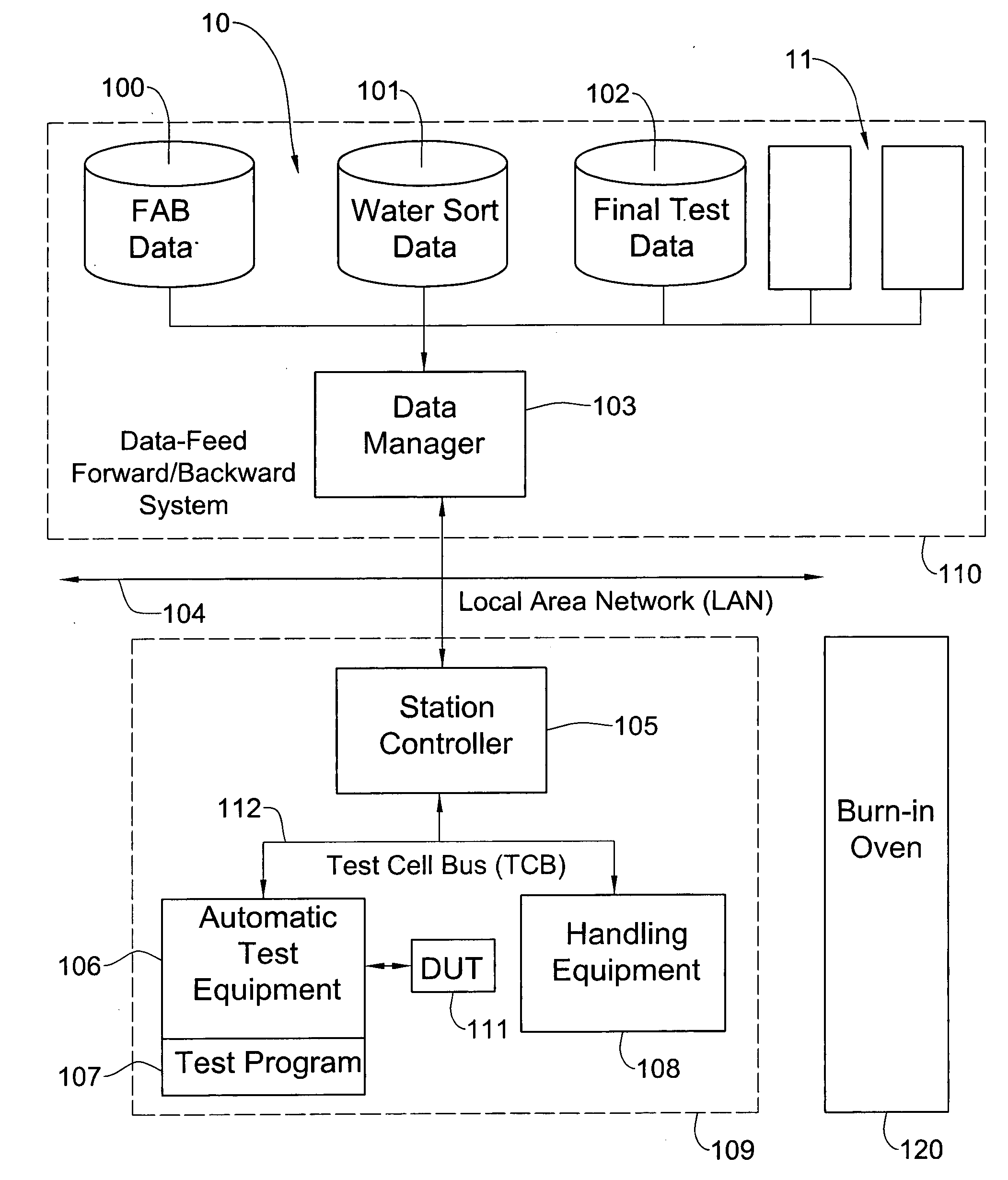

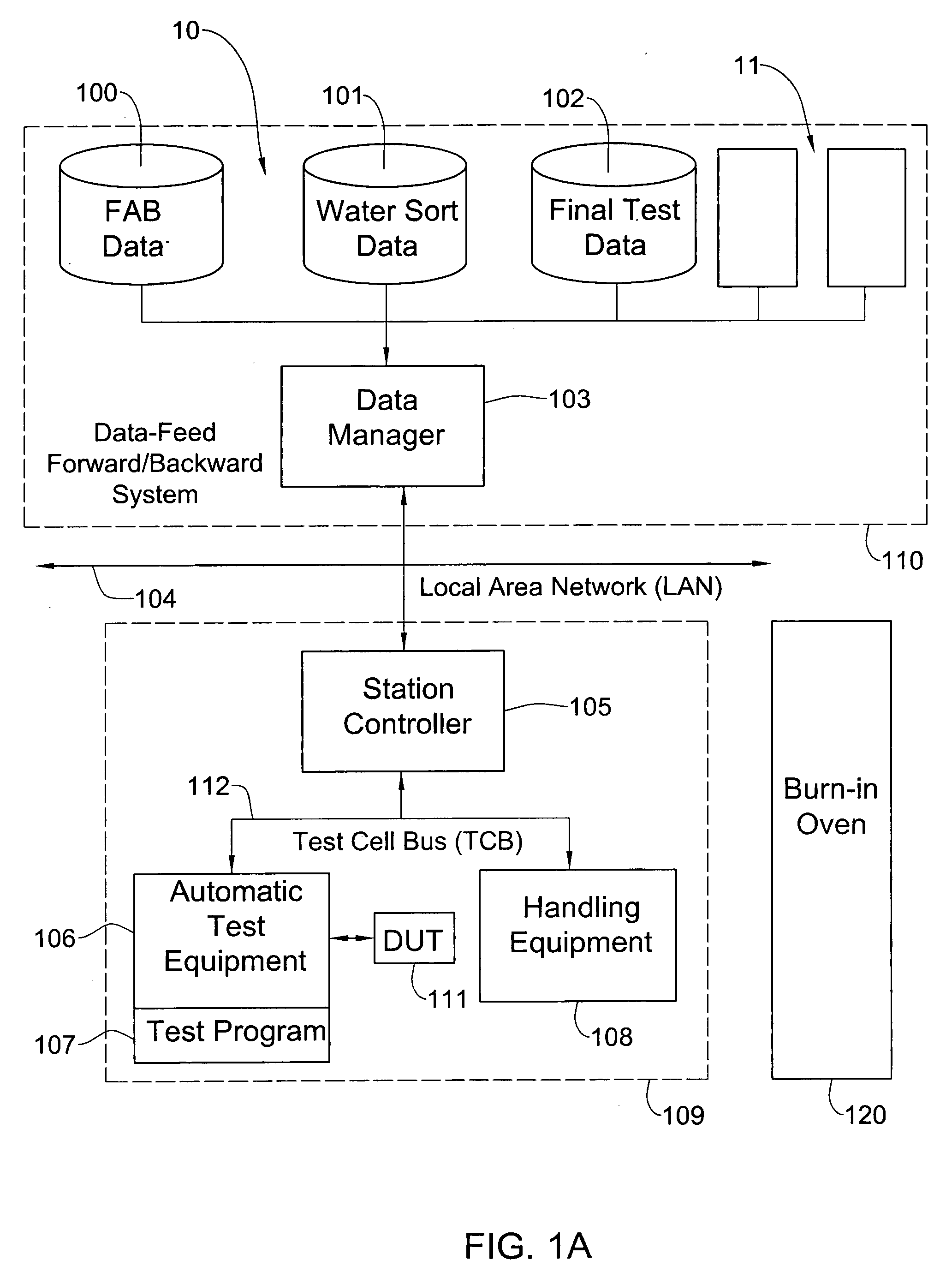

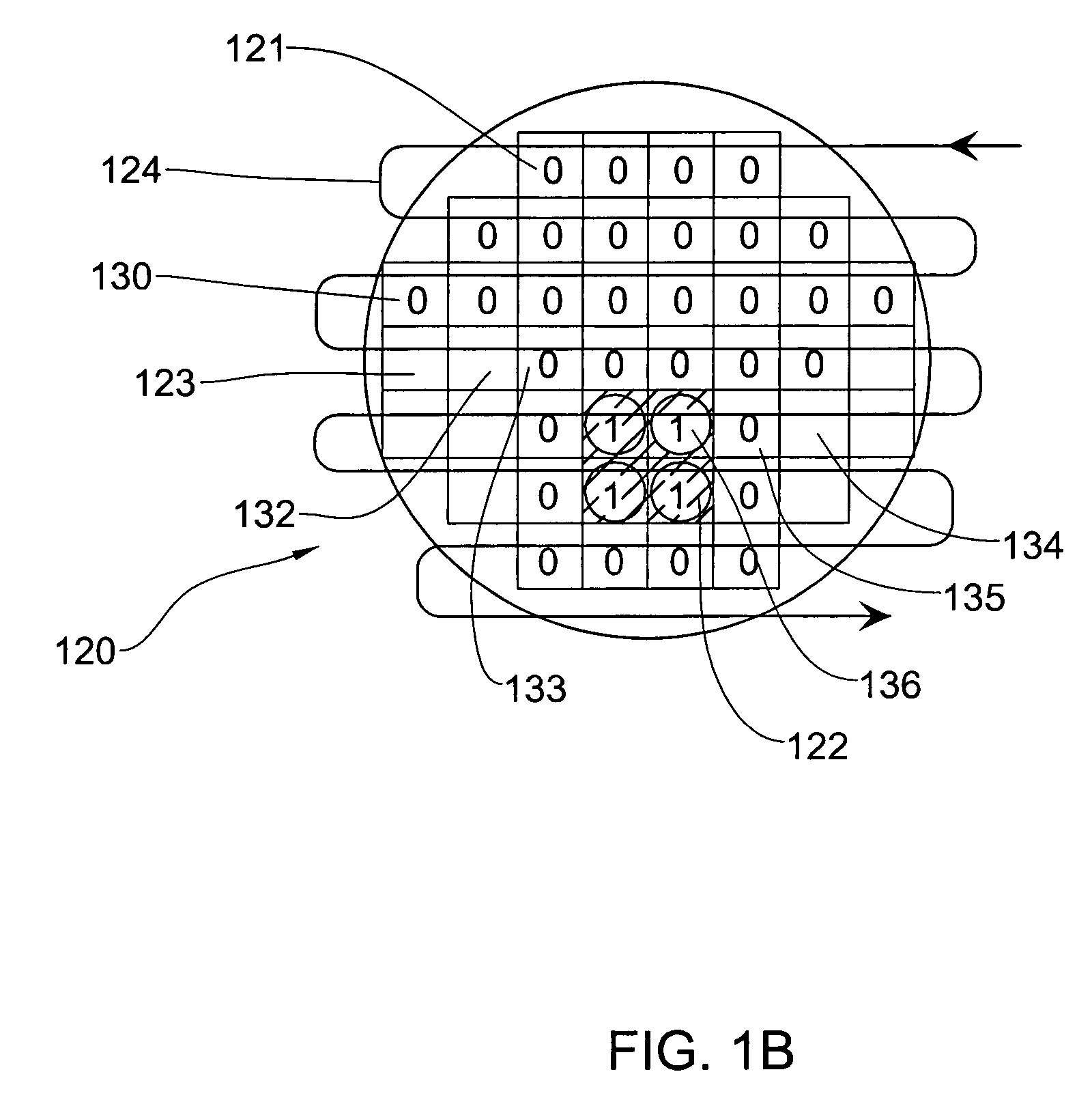

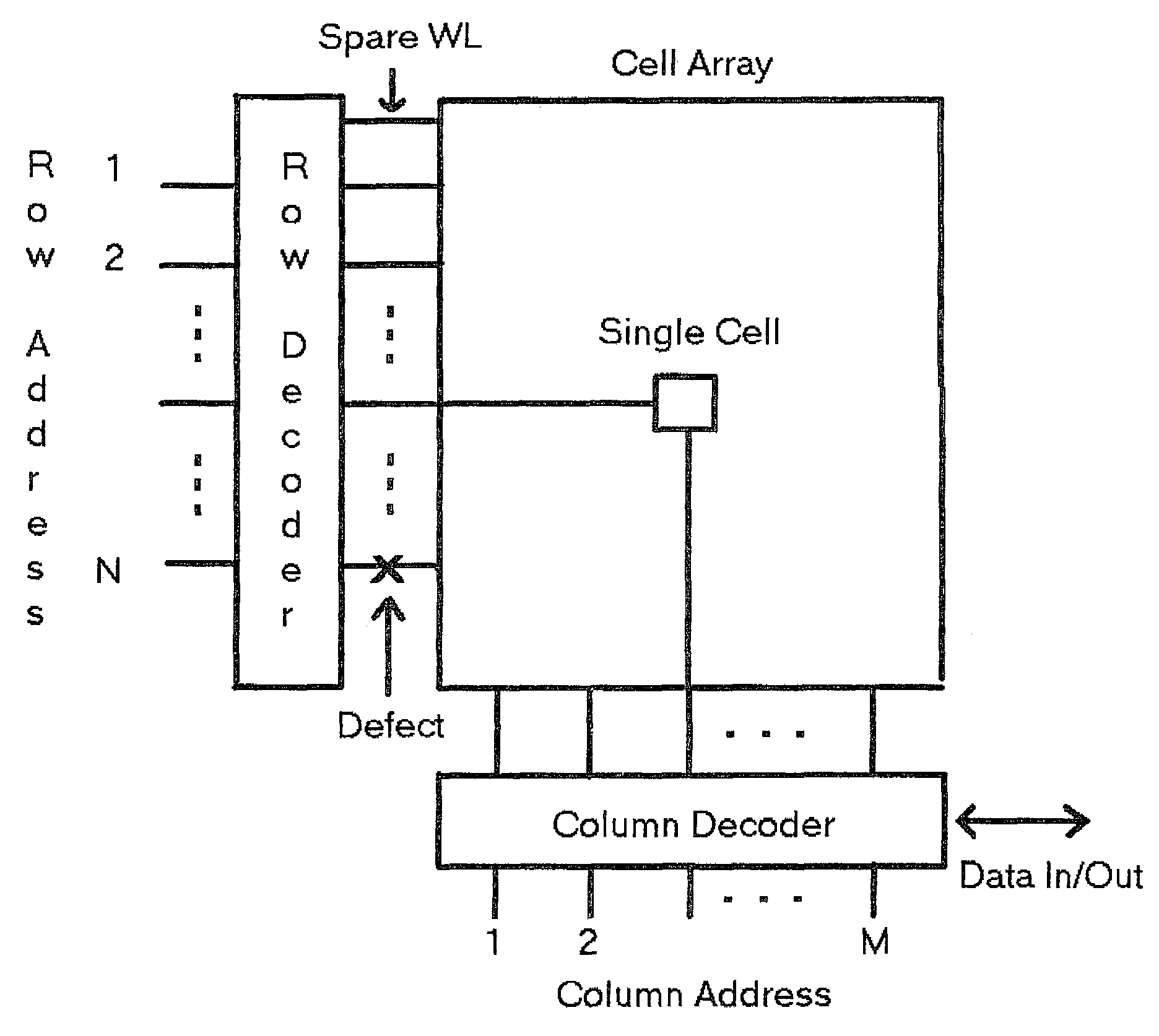

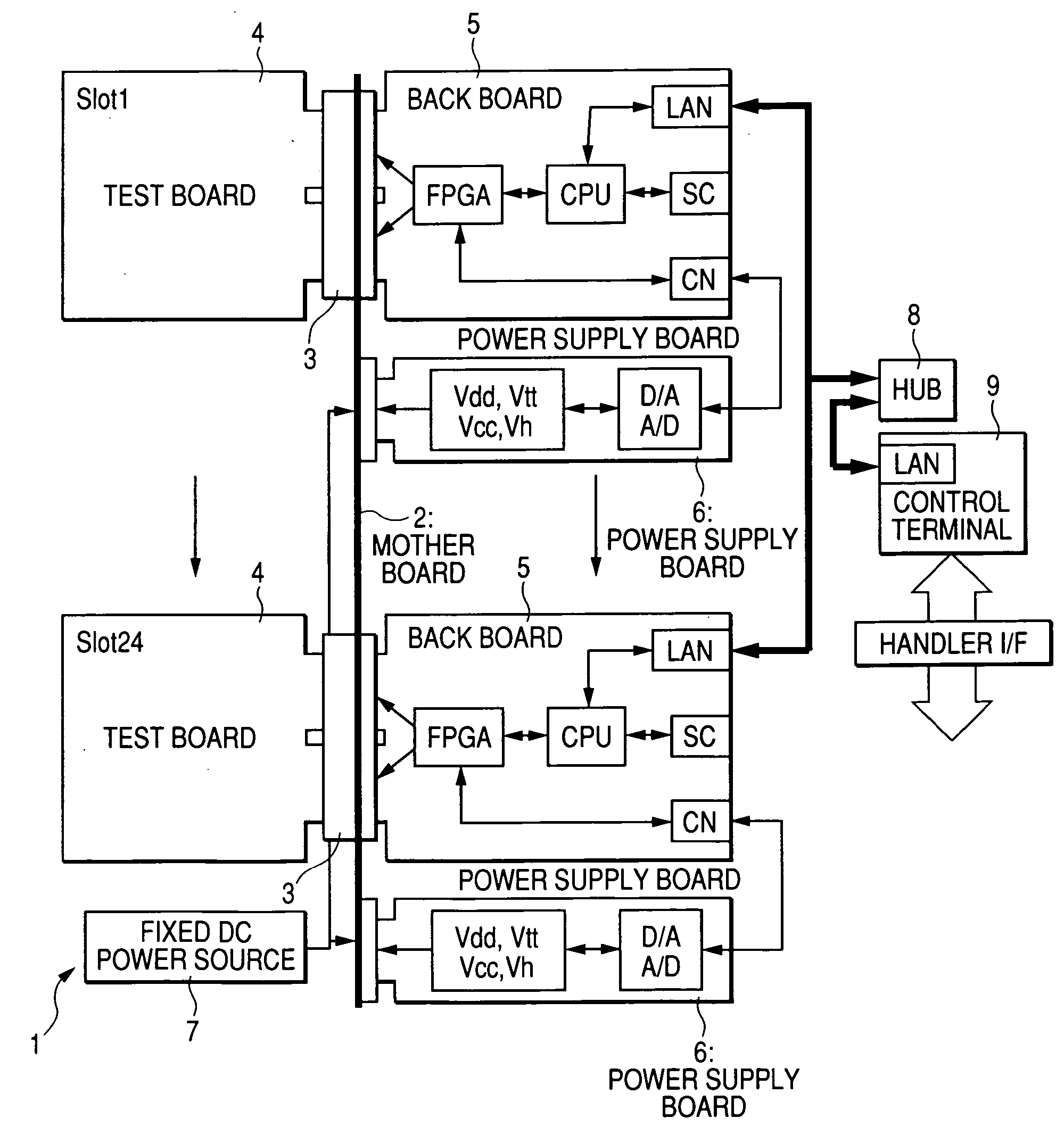

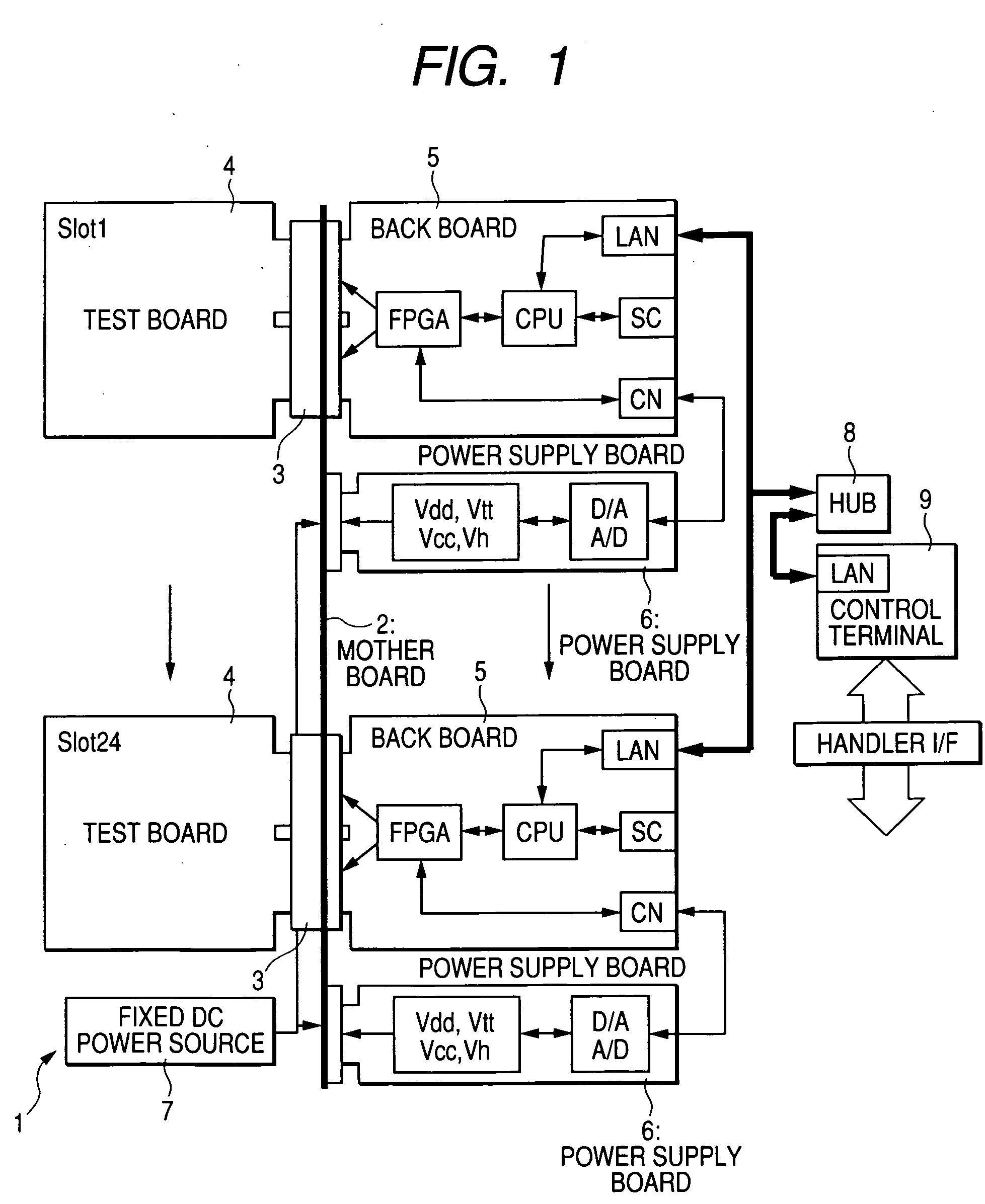

Fabrication method of semiconductor integrated circuit device

InactiveUS20050153465A1Shorten the timeLow costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringMonoboard

A memory test is carried out on semiconductor integrated circuit devices including a semiconductor memory at low cost with efficiency. In a test burn-in system, twenty-four test boards are processed in sequence with time differences, and the test boards are circulated one by one. In this case, the memory test is conducted with the sequence of single board processing: the test is started with a test board in which semiconductor integrated circuit devices have been embedded, and semiconductor integrated circuit devices are discharged, beginning with a test board that has undergone the test.

Owner:RENESAS ELECTRONICS CORP

Apparatus for translated wafer stand-in tester

A translated wafer stand-in tester (TWST), being a hybrid apparatus capable of emulating the form factor and some or all behaviors of a translated wafer under test, which is operable to store, quantify, encode and convey, either directly or remotely, data from a testing system, including but not limited to pad pressure, electrical contact and temperature. The TWST may include several stacked and attached layers, at least one internal layer including electronic components operable to interact with a test system.

Owner:TRANSLARITY INC

System and method for estimating reliability of components for testing and quality optimization

InactiveUS20070162242A1Improve efficiencyImprove modeling accuracySemiconductor/solid-state device testing/measurementSpecial data processing applicationsQuality optimizationElectronic component

Owner:AUBURN UNIV

Test sorting machine

The invention discloses a test sorting machine. In the test sorting machine, a matching plate of a pushing unit is provided with a position correction pin which has a position correction function. The position correction pin can move test trays which deviate from correct positions, so that the test trays get back to the correct positions, thereby improving reliability of the test sorting machine.

Owner:TECHWING CO LTD

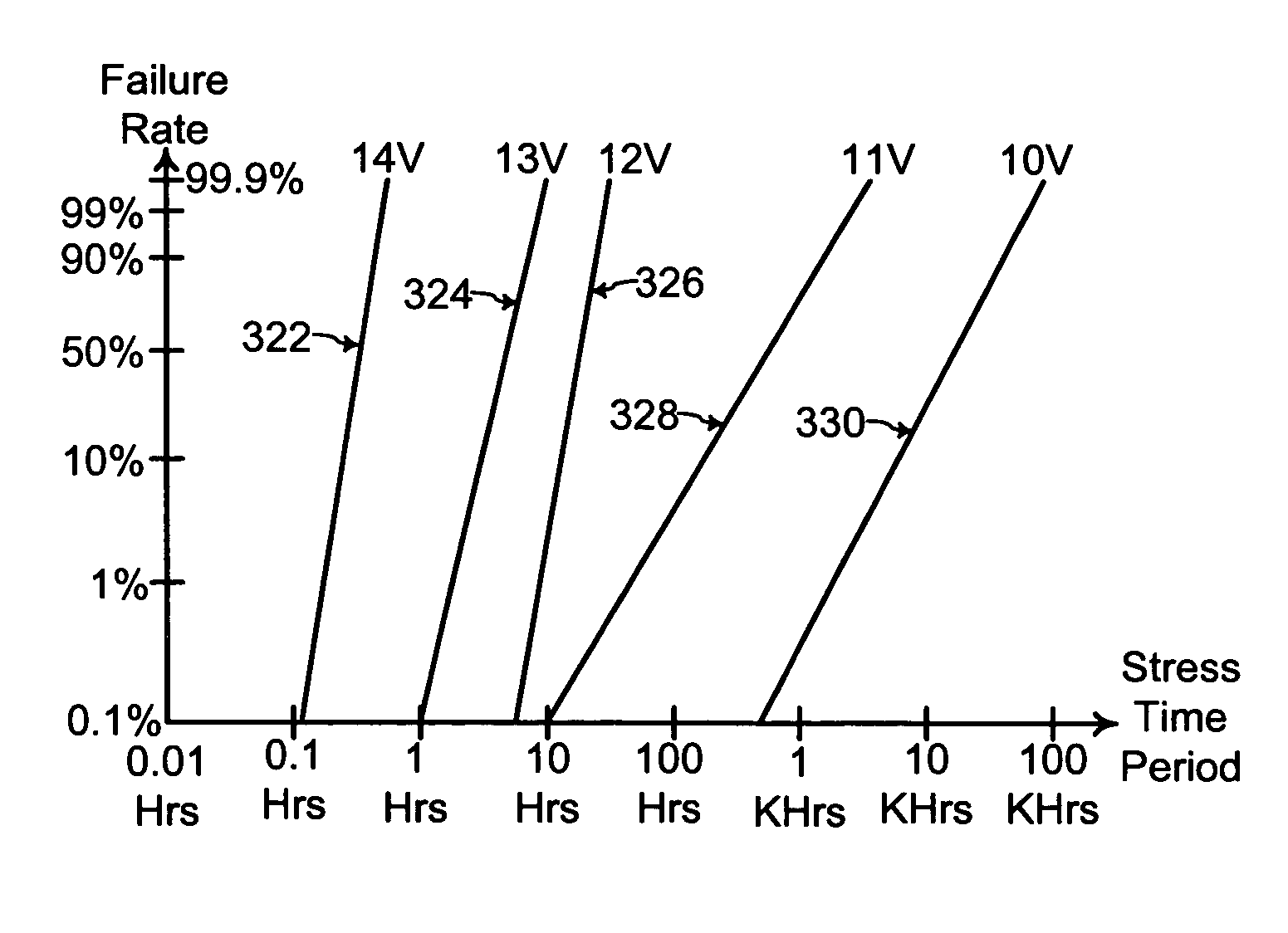

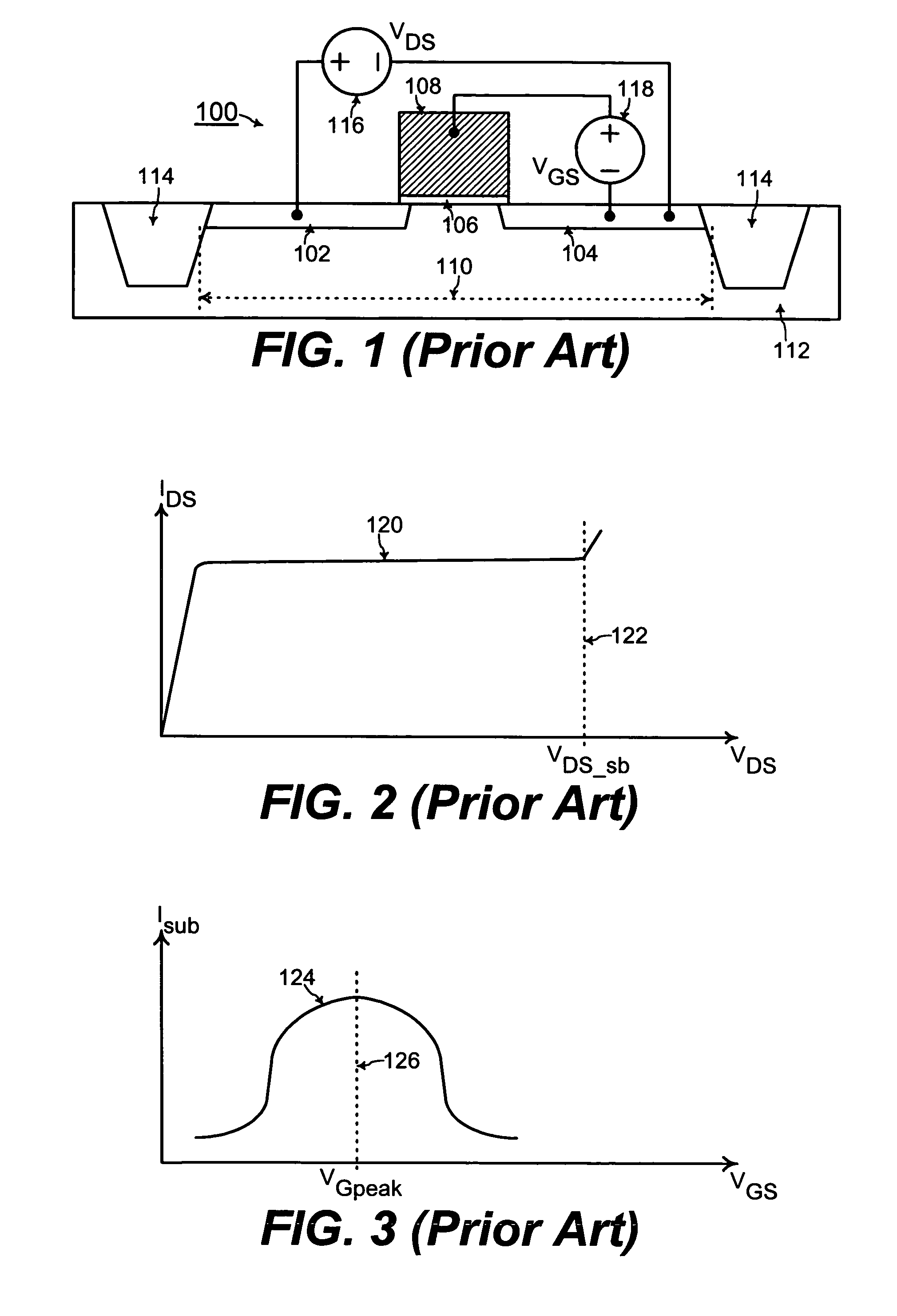

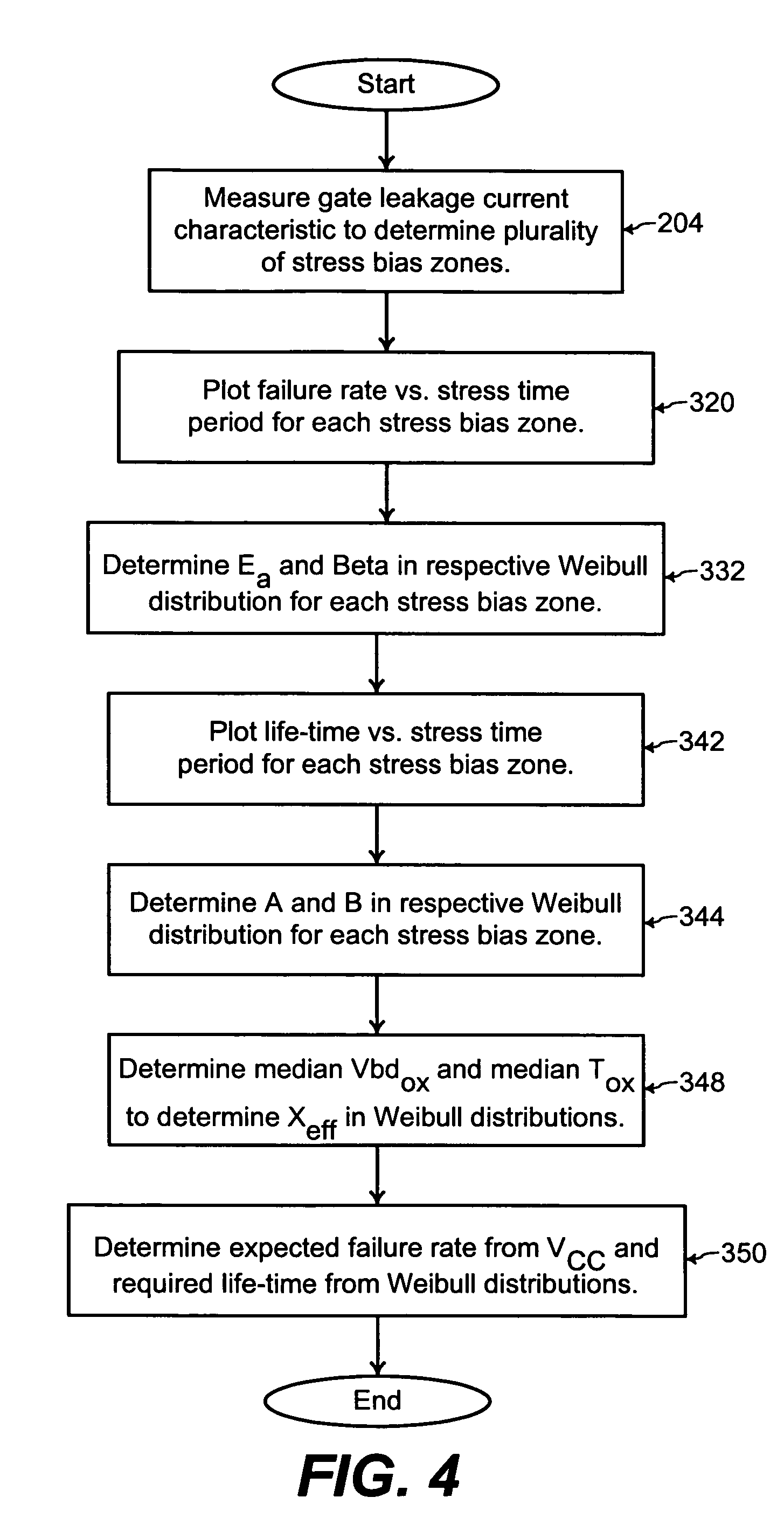

Determination of device failure characteristic

InactiveUS7155359B1Resistance/reactance/impedenceSemiconductor operation lifetime testingDrain currentDevice failure

For determining a failure characteristic of a semiconductor device, a leakage current characteristic is measured for the semiconductor device to determine a plurality of stress bias zones. A respective set of parameters that define a respective failure characteristic of the semiconductor device is determined for each of the stress bias zones such that the failure characteristic is accurately determined for a wide range of operating voltages.

Owner:ADVANCED MICRO DEVICES INC

Stress-test information database structure and method of use

A database architecture and method of using a database is disclosed. The database is intended for use with a product stress testing system in which a large number of different modules may be subjected to a variety of stressors including environmental stressors and functional load testing. The database also enables a wide variety of test and communication equipment to be used in an efficient manner to test and communicate with the module being tested. Generic commands may be translated to test and communication equipment specific command strings as well as module specific command strings. Data collected from these various devices by the stress testing system may also be parsed and stored in fields associated with the corresponding module being tested. The product table, result table, process table, and equipment command & communication tables are interrelated through defined data associations. These data entities and their mutual data relationships revolve around the module being subjected to the stress test. In this way the stress test results may be associated with the various products, the results may be mapped against product-specific test criteria, and generic commands may be translated to product-specific commands. A virtual oven may be used as the stress-testing system and includes a logical grouping of modules, a controller, test instruments which are all connected via a network to the database for collection of the data, control of the system, and generating displays and reports.

Owner:CIENA