Single-event effect test method for SoC

A single event effect and test method technology, which is applied in the direction of electronic circuit test, integrated circuit test, and electrical device test in transportation, etc., can solve the problem of no single event effect test method description, etc., and achieve comprehensive and reasonable test results and test coverage The effect of high performance and simple test vector

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

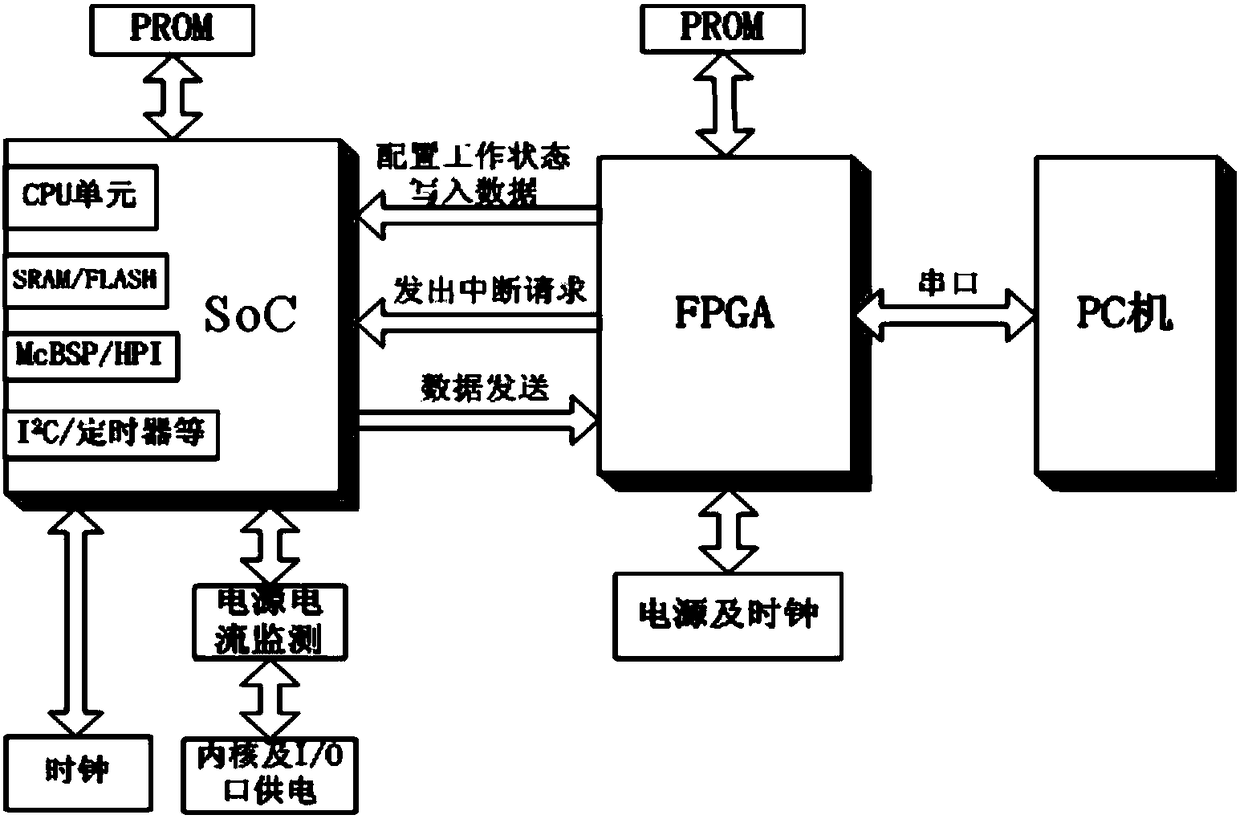

[0032] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

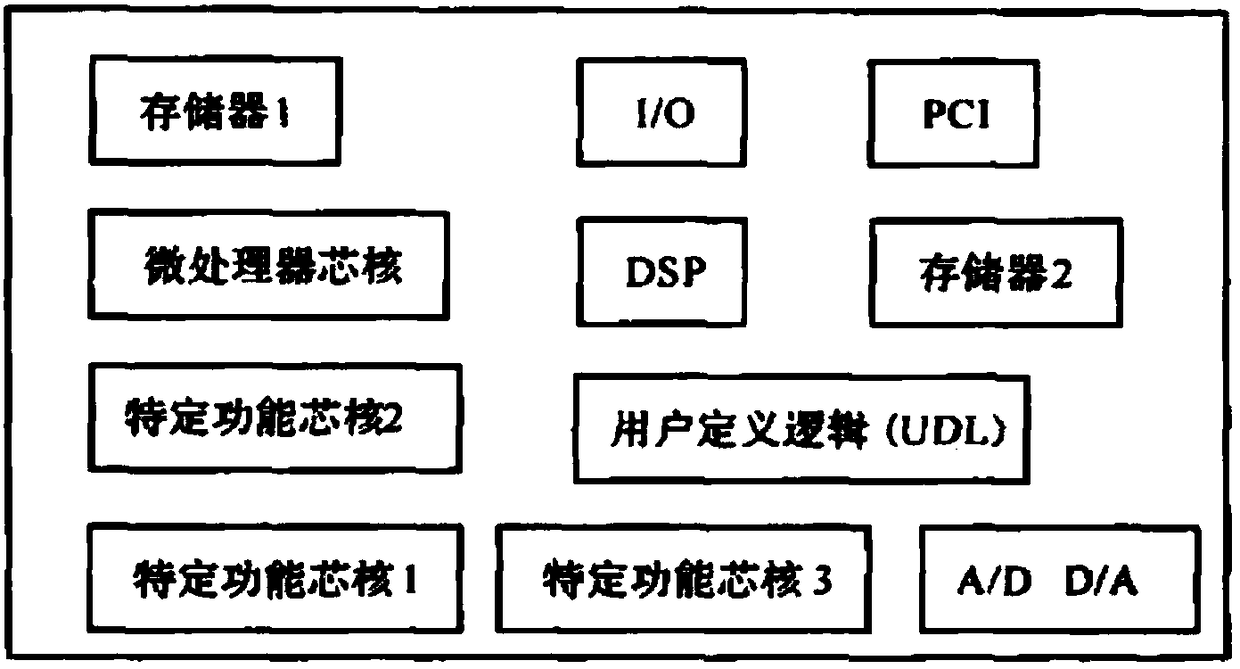

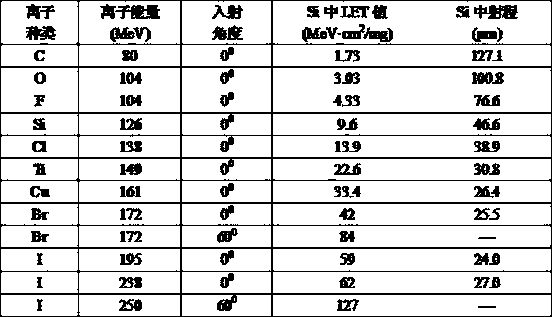

[0033] Single-event effects sensitive to SoC processors mainly include single-event upset, single-event function interruption, and single-event latch-up. Among them, single event reversal means that a single high-energy particle is incident and generates a large amount of charge inside the device. If the collected charge is greater than the critical charge required for circuit state reversal, a transient current will be formed, triggering the logic circuit, and causing the stored information of the logic bit inside the device. From "1" to "0" or from "0" to "1", the logic state of the circuit will be reversed, changing the logic information stored in the memory unit. Single event latch-up refers to the phenomenon that the power su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More