Patents

Literature

699results about "Semiconductor operation lifetime testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electric-heat-aging junction temperature calculation model establishing method of IGBT module

ActiveCN106443400AImplement junction temperature prediction functionImproved thermal managementSemiconductor operation lifetime testingElectricityCoupling

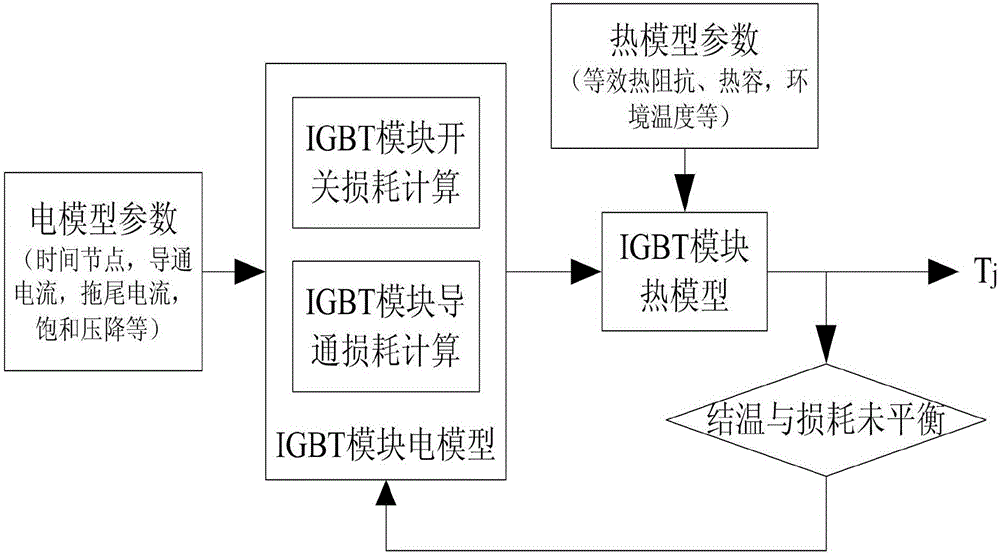

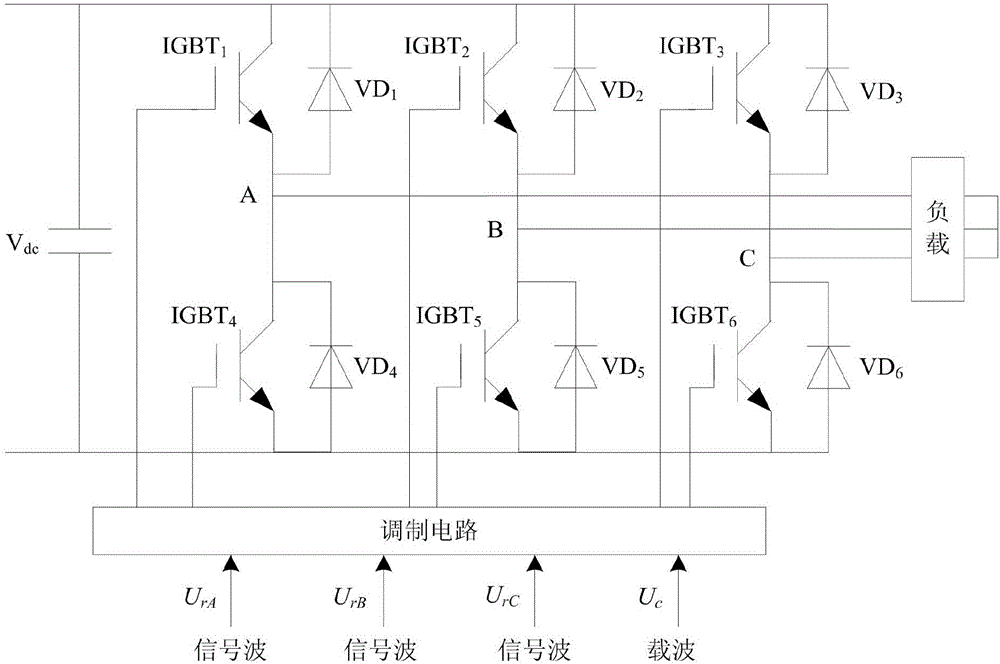

The invention relates to an electric-heat-aging junction temperature calculation model establishing method of an IGBT module. The method is technologically characterized by comprising the following steps of testing electric heating parameters of the IGBT module in different aging degrees, acquiring a three-dimensional relation curved surface and establishing an electric heating data sheet in different aging degrees; establishing an electric model of the IGBT module and a thermal network model of the IGBT module, inputting a power loss which is calculated through the electric model of the IGBT module into the thermal network model of the IGBT module in a current source manner, performing real-time feedback of the junction temperature which is calculated by the thermal network model to the electric model, and finishing establishment of an electric-heat coupling model of the IGBT module; performing aging state evaluation on the IGBT module; and performing junction temperature calculation on the IGBT module. According to the electric-heat-aging junction temperature calculation model establishing method, the corresponding electric heating parameters for different aging processes are acquired and furthermore the electric heating parameters are input into the electric-heat coupling model for performing junction temperature calculation, namely the parameter of the electric-heat coupling model is dynamically changed in real time according to the aging degree of the model, thereby realizing a junction temperature prediction function for the module aging degree.

Owner:HEBEI UNIV OF TECH

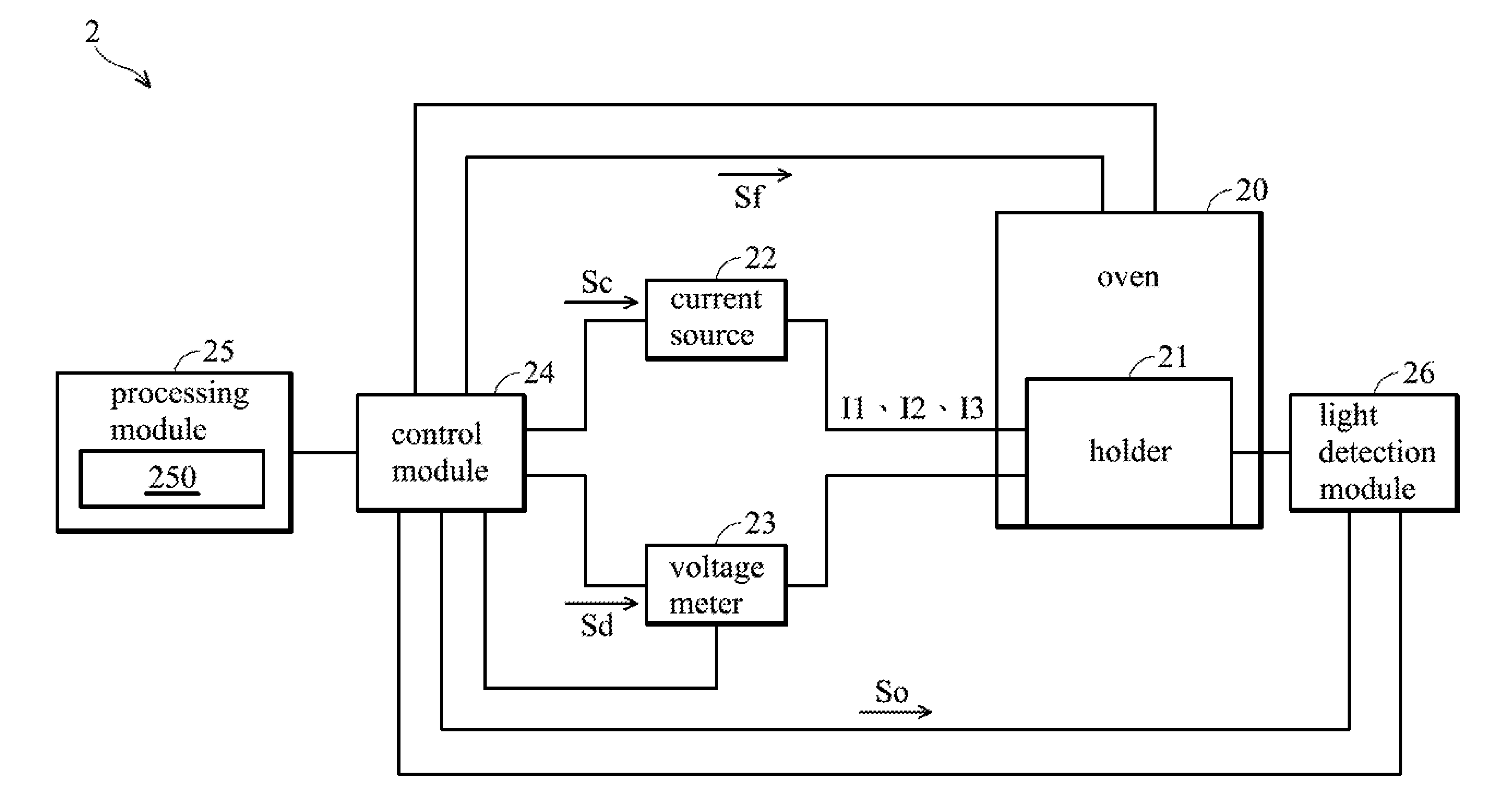

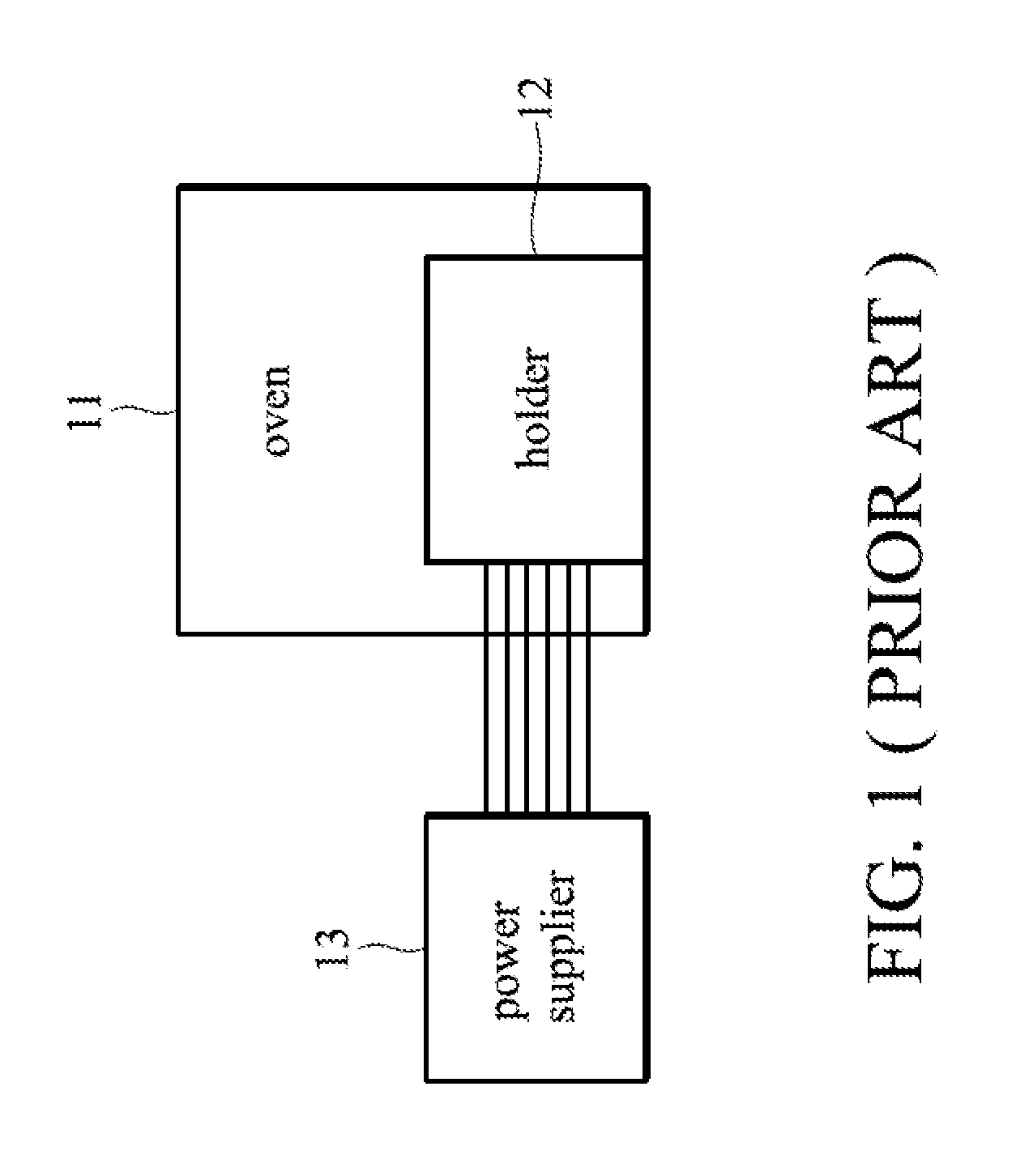

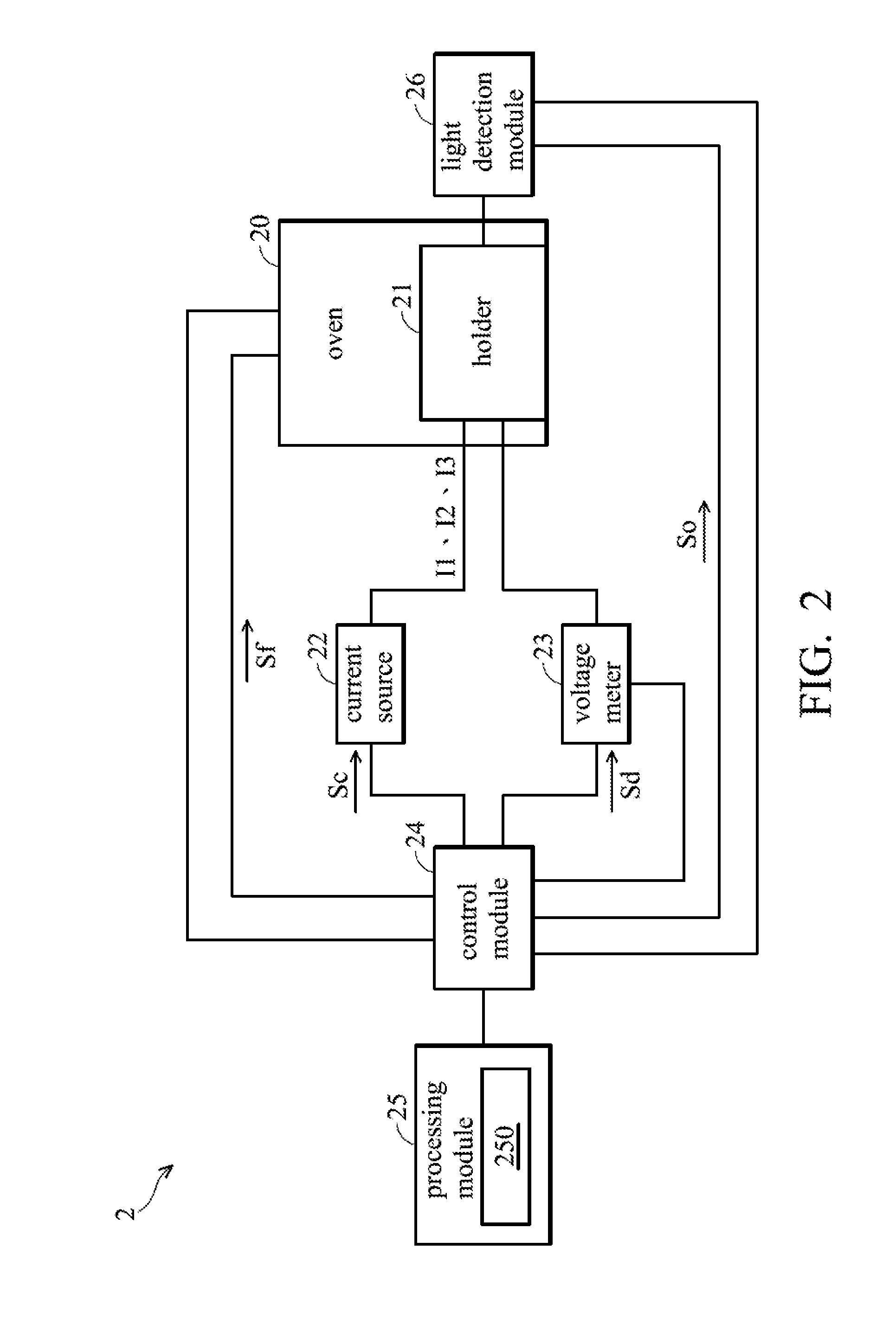

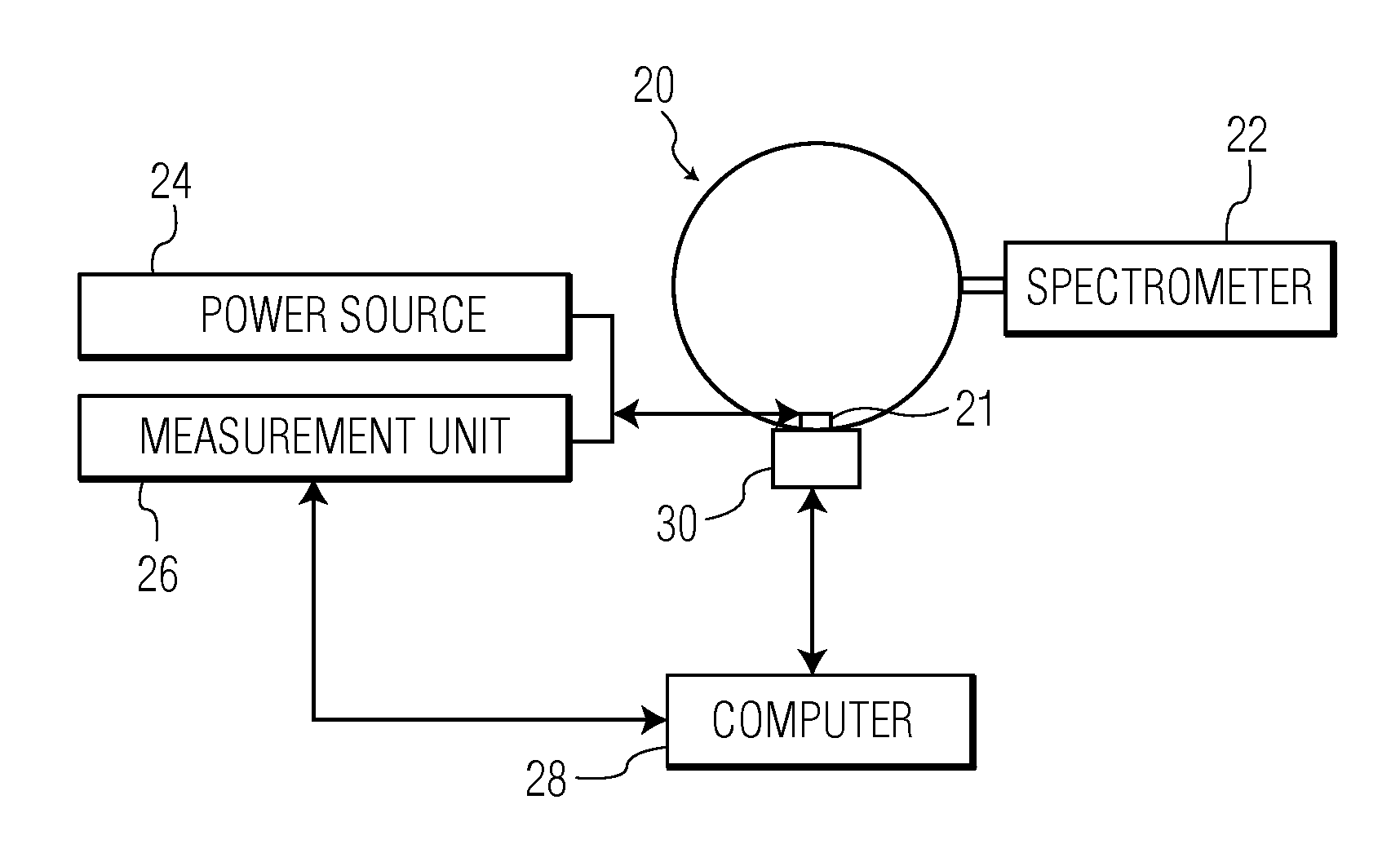

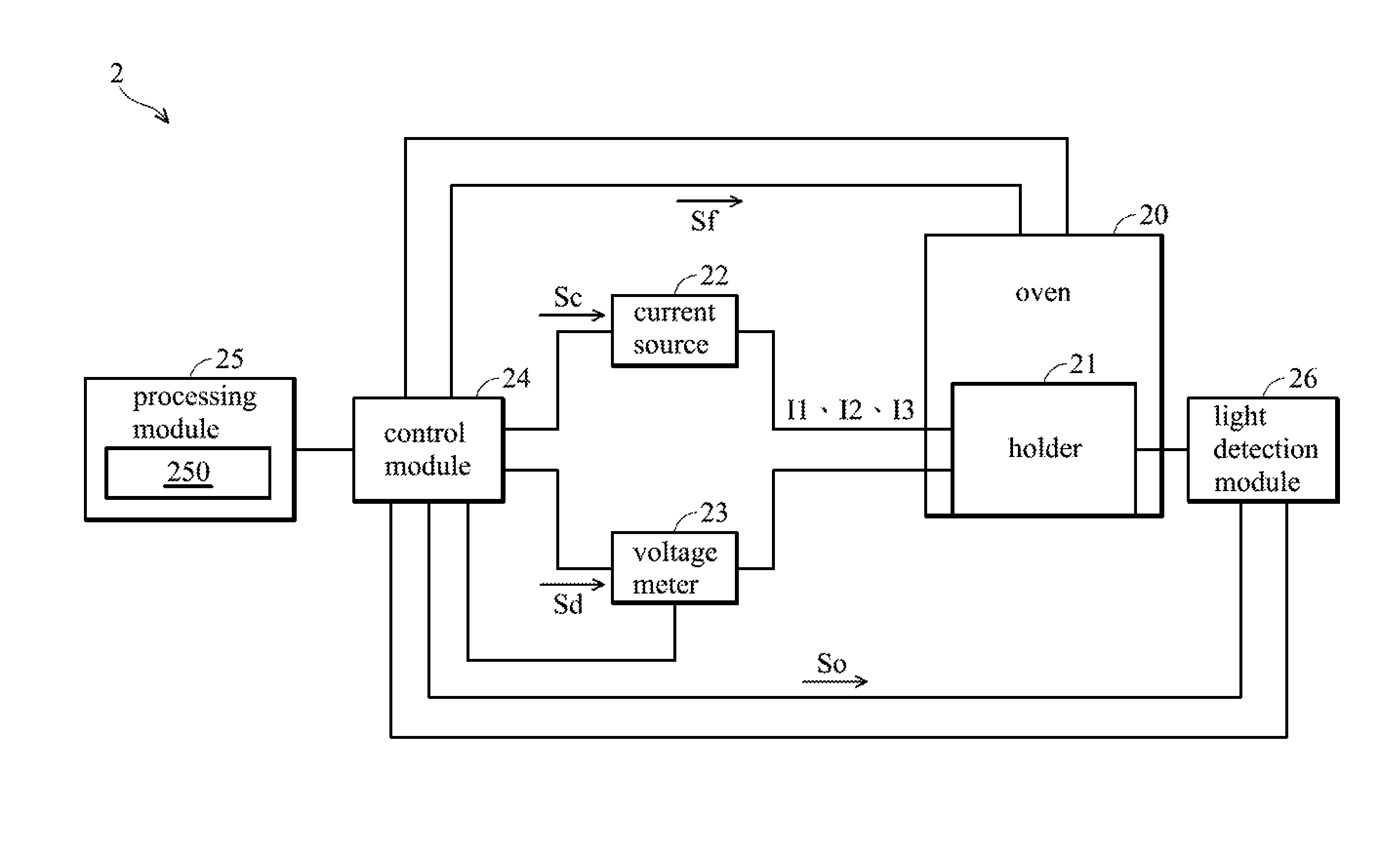

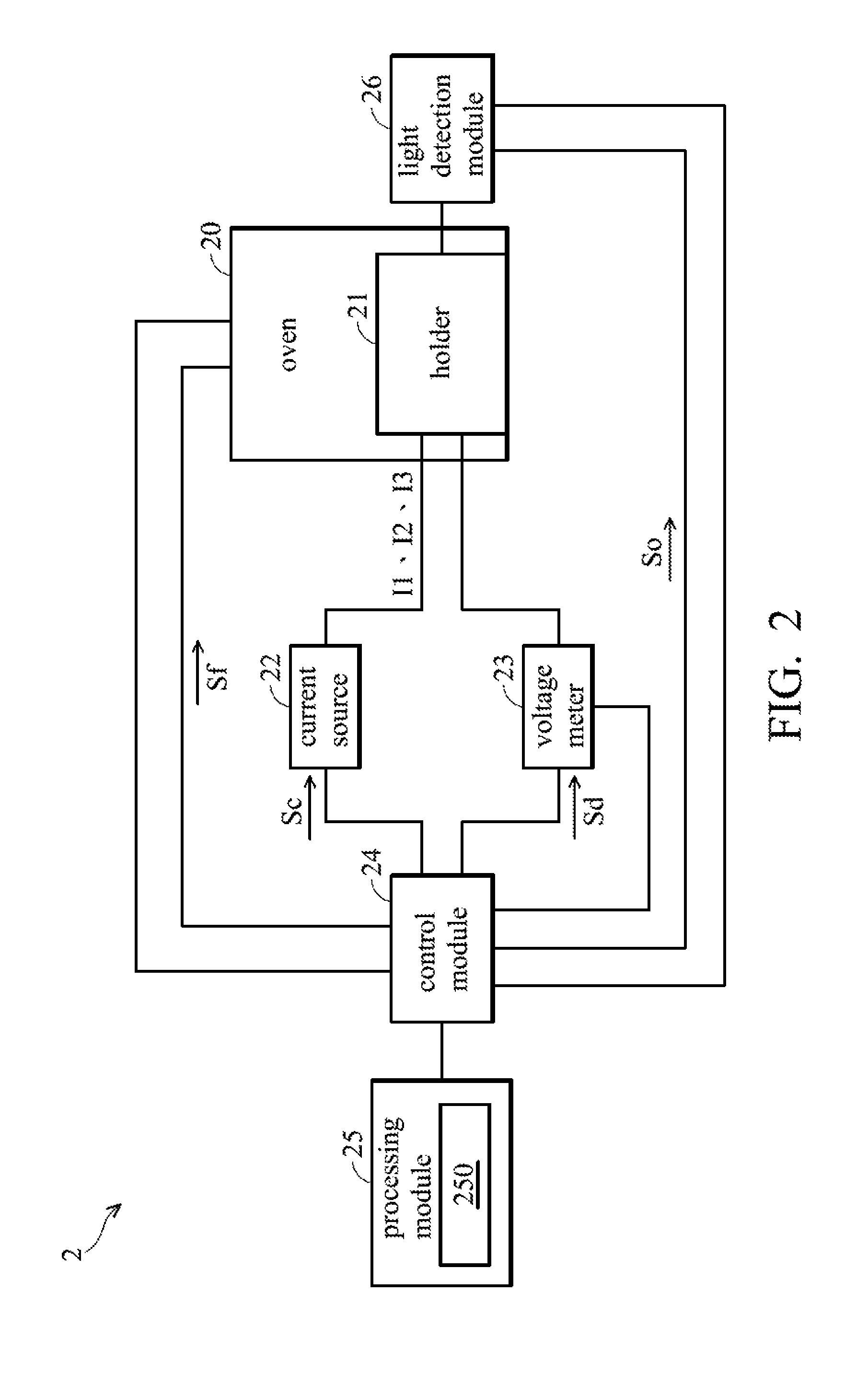

Devices And Methods For LED Life Test

A life test device comprises an oven, a current source, a voltage meter, a control module, and a process module. A light-emitting diode (LED) is disposed in the oven. The temperature of the oven is gradually changed in a first period and remains at a set temperature in a second period. The current source provides a first current and a second current to the LED. The voltage meter measures forward voltages of the LED. The control module controls the current source to output the first or second current to the LED and controls the voltage meter to measure the forward voltages of the LED. The process module calculates a junction temperature of the LED according to the forward voltages and a variation relationship formula between the forward voltages and the temperature of the oven.

Owner:IND TECH RES INST

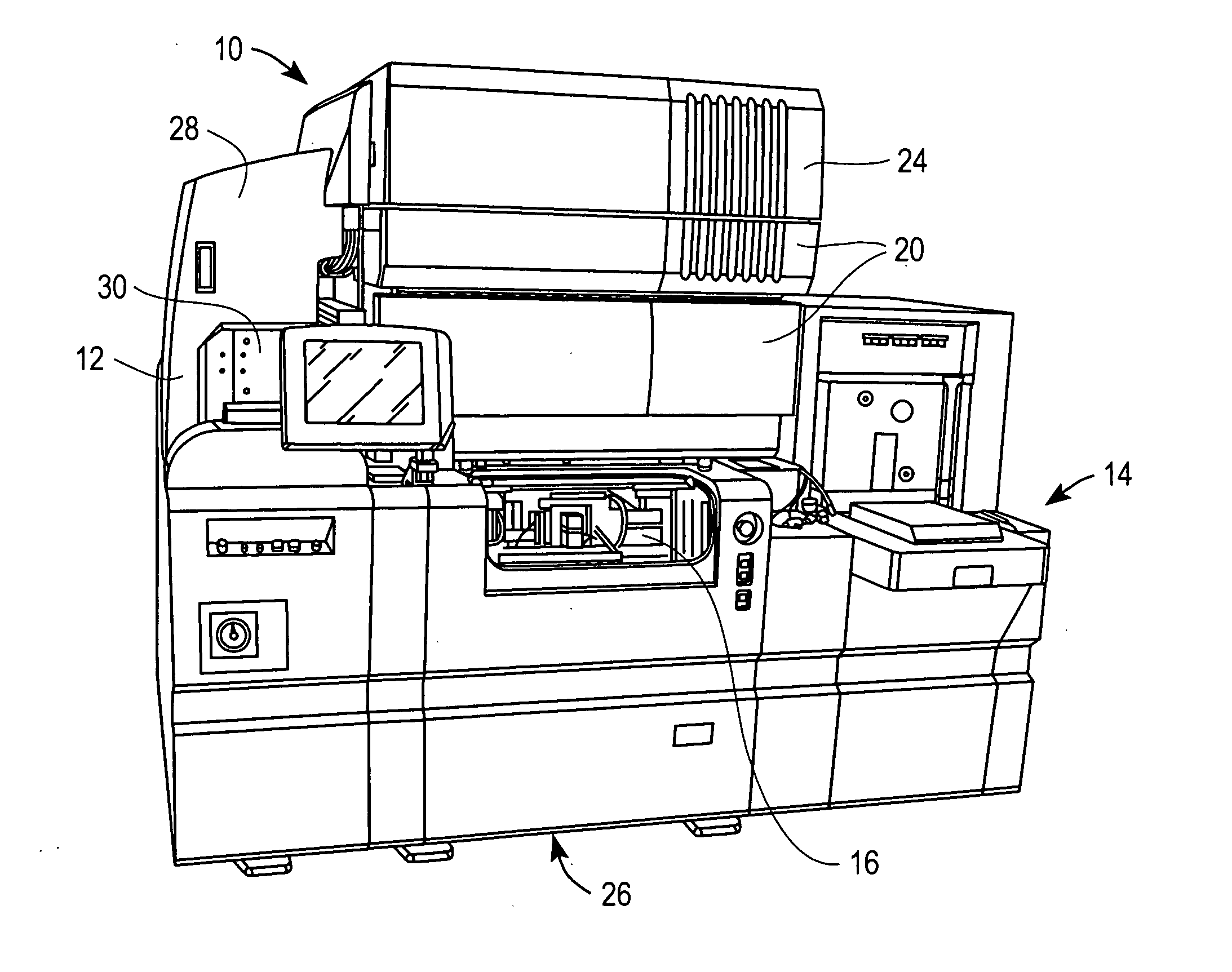

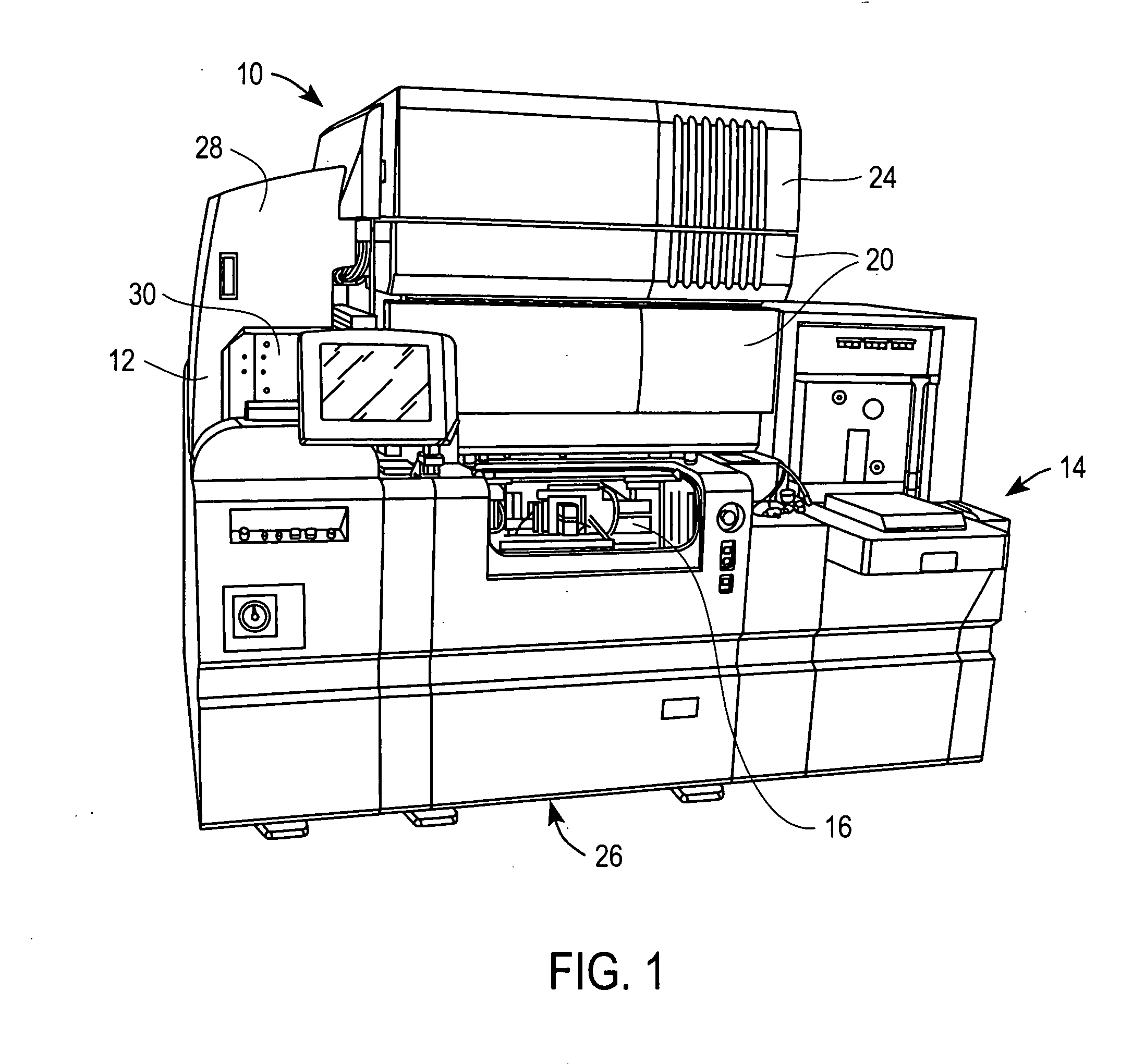

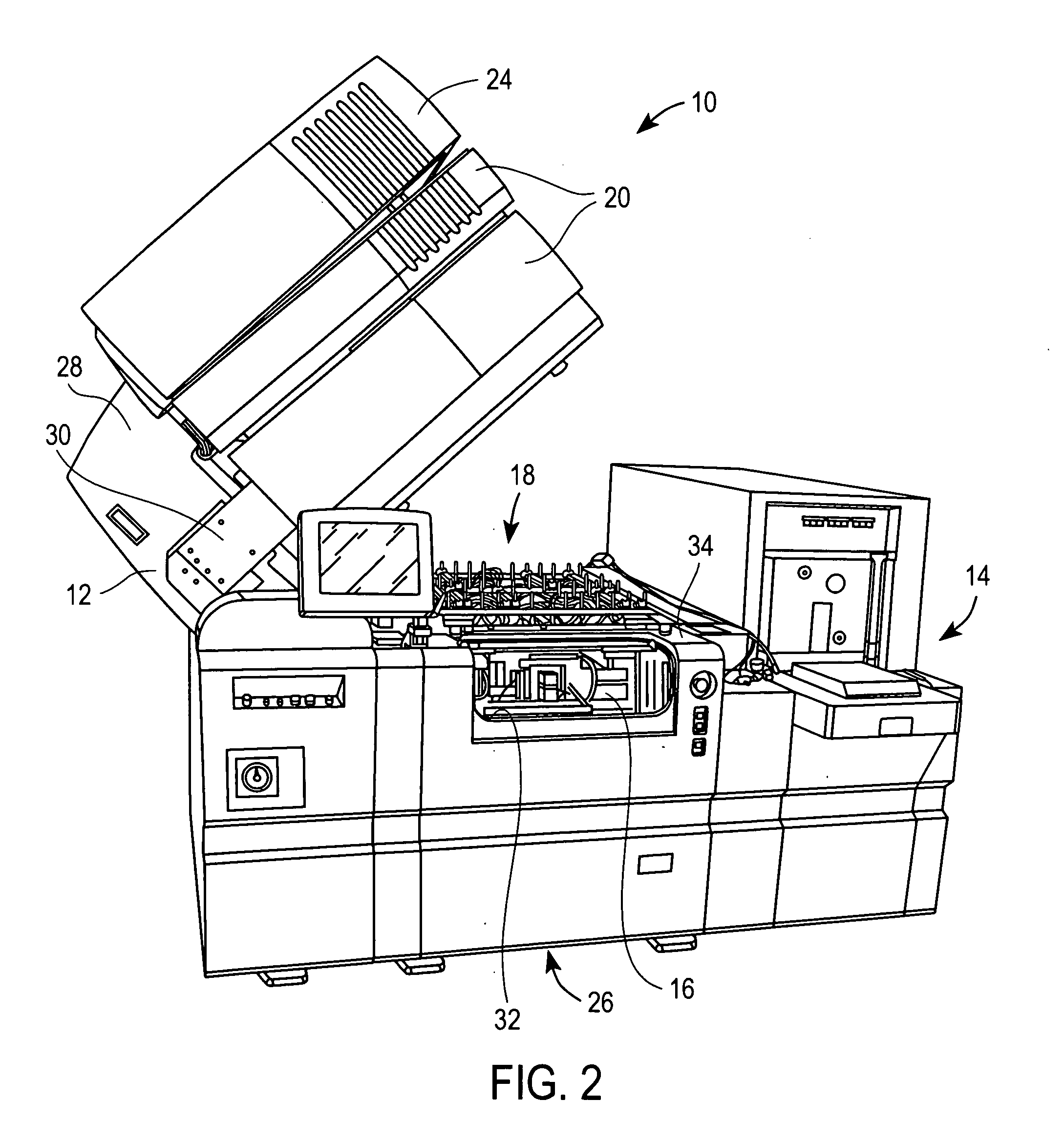

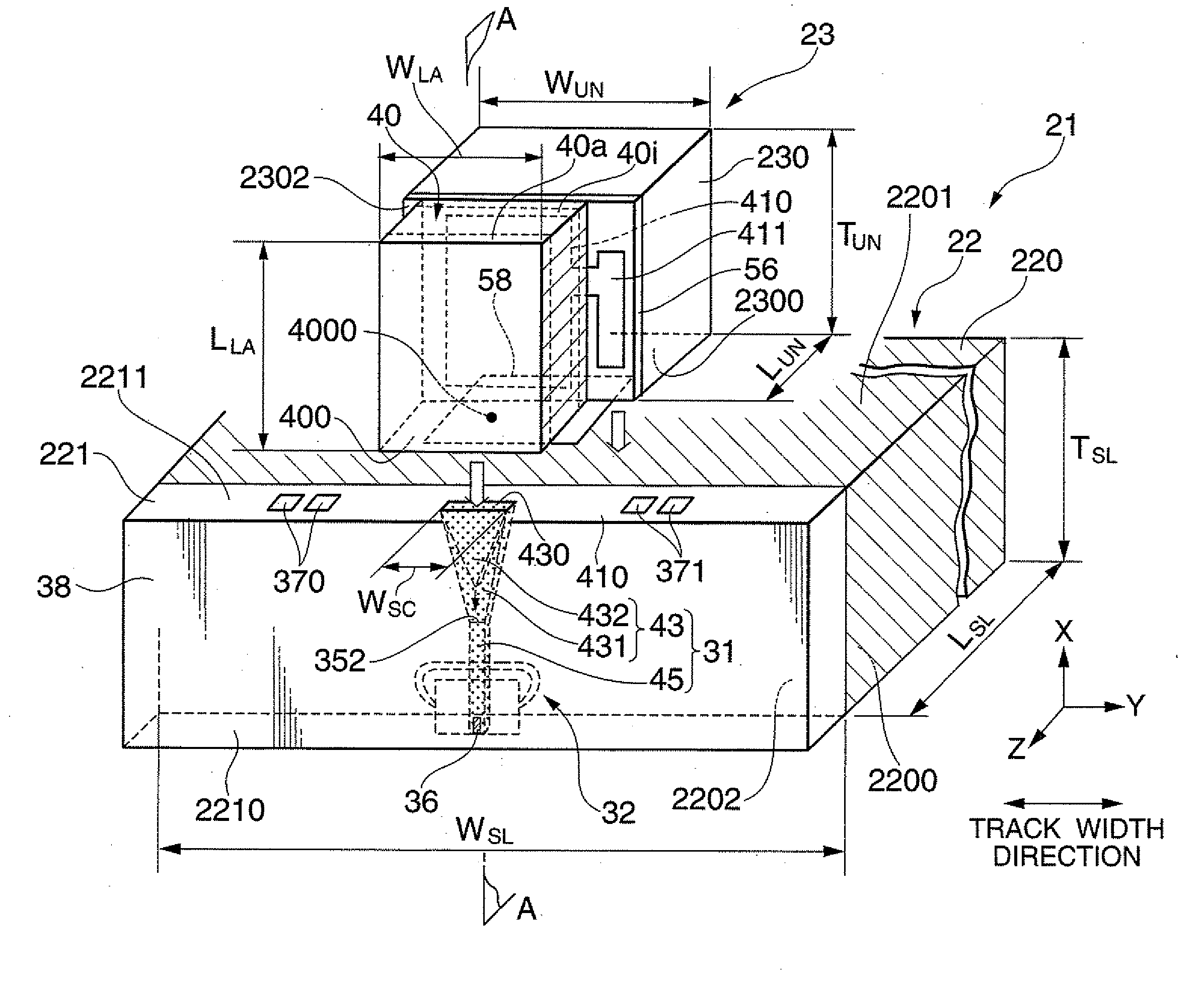

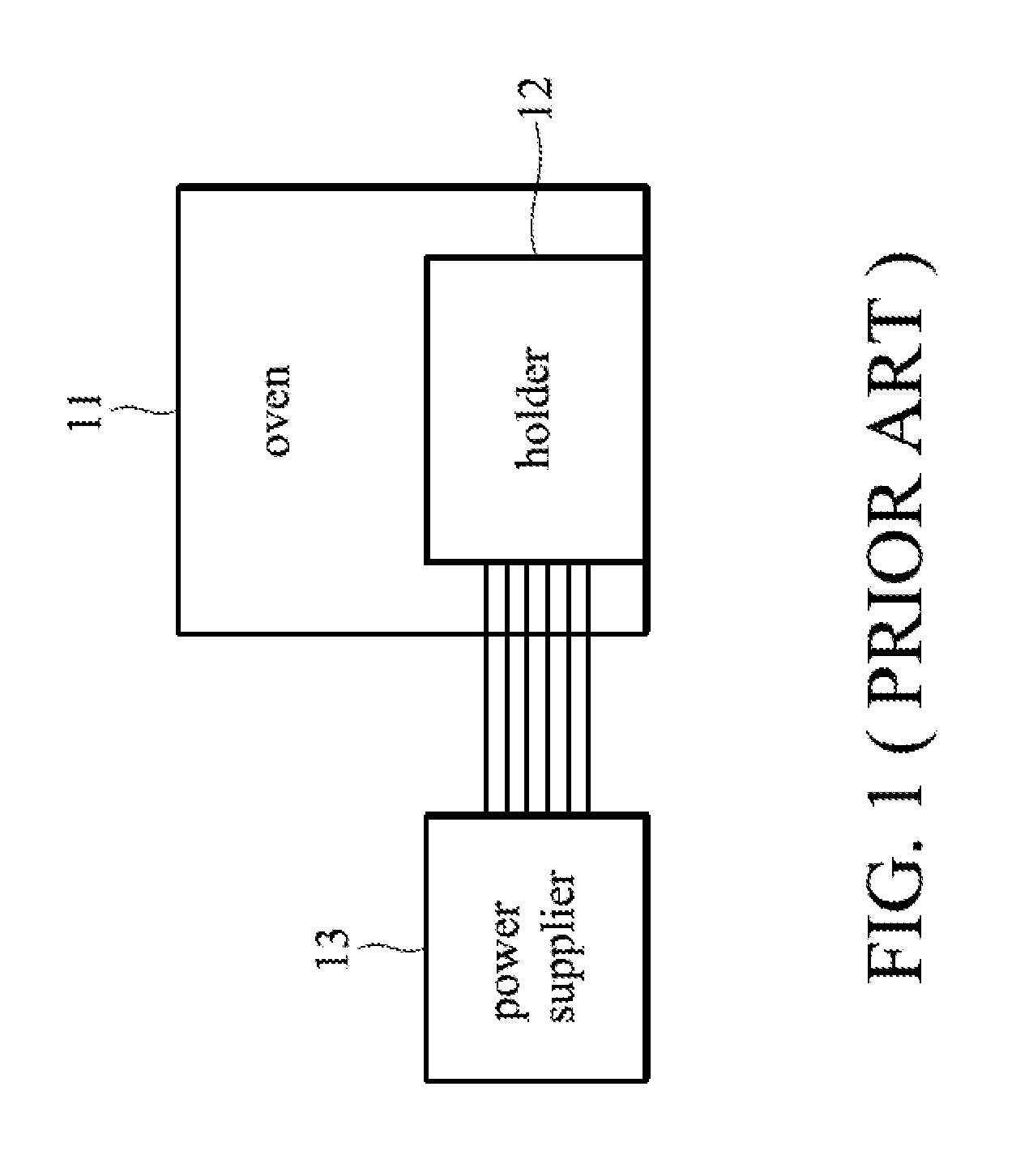

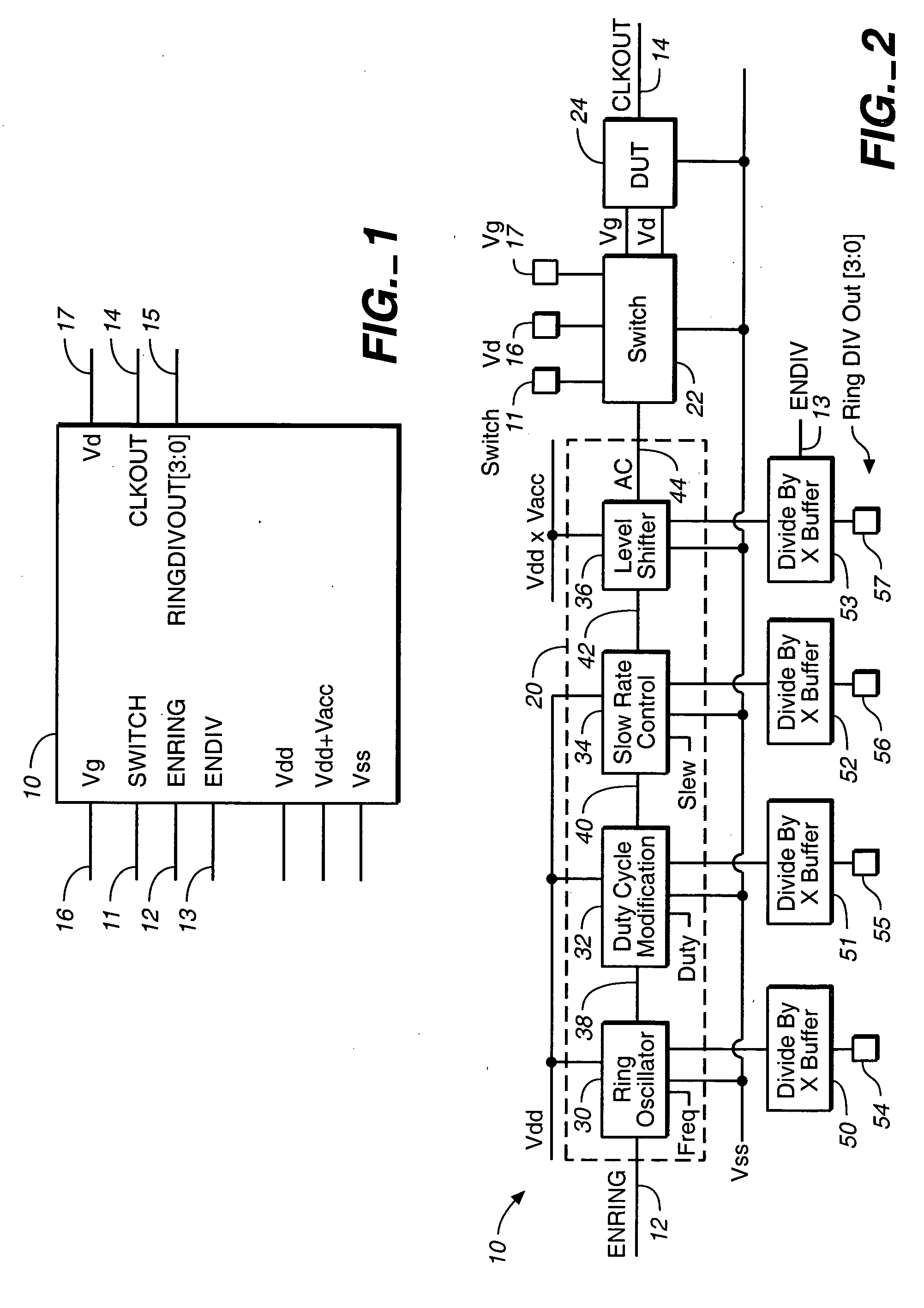

Apparatus for testing electronic devices

ActiveUS20070001790A1Semiconductor/solid-state device testing/measurementSemiconductor operation lifetime testingFunctional testingMicroelectronic circuits

An apparatus is described for burn-in and / or functional testing of microelectronic circuits of unsingulated wafers. A large number of power, ground, and signal connections can be made to a large number of contacts on a wafer. The apparatus has a cartridge that allows for fanning-in of electric paths. A distribution board has a plurality of interfaces that are strategically positioned to provide a dense configuration. The interfaces are connected through flexible attachments to an array of first connector modules. Each one of the first connector modules can be independently connected to a respective one of a plurality of second connector modules, thereby reducing stresses on a frame of the apparatus. Further features include for example a piston that allows for tight control of forces exerted by terminals onto contacts of a wafer.

Owner:AEHR TEST SYST

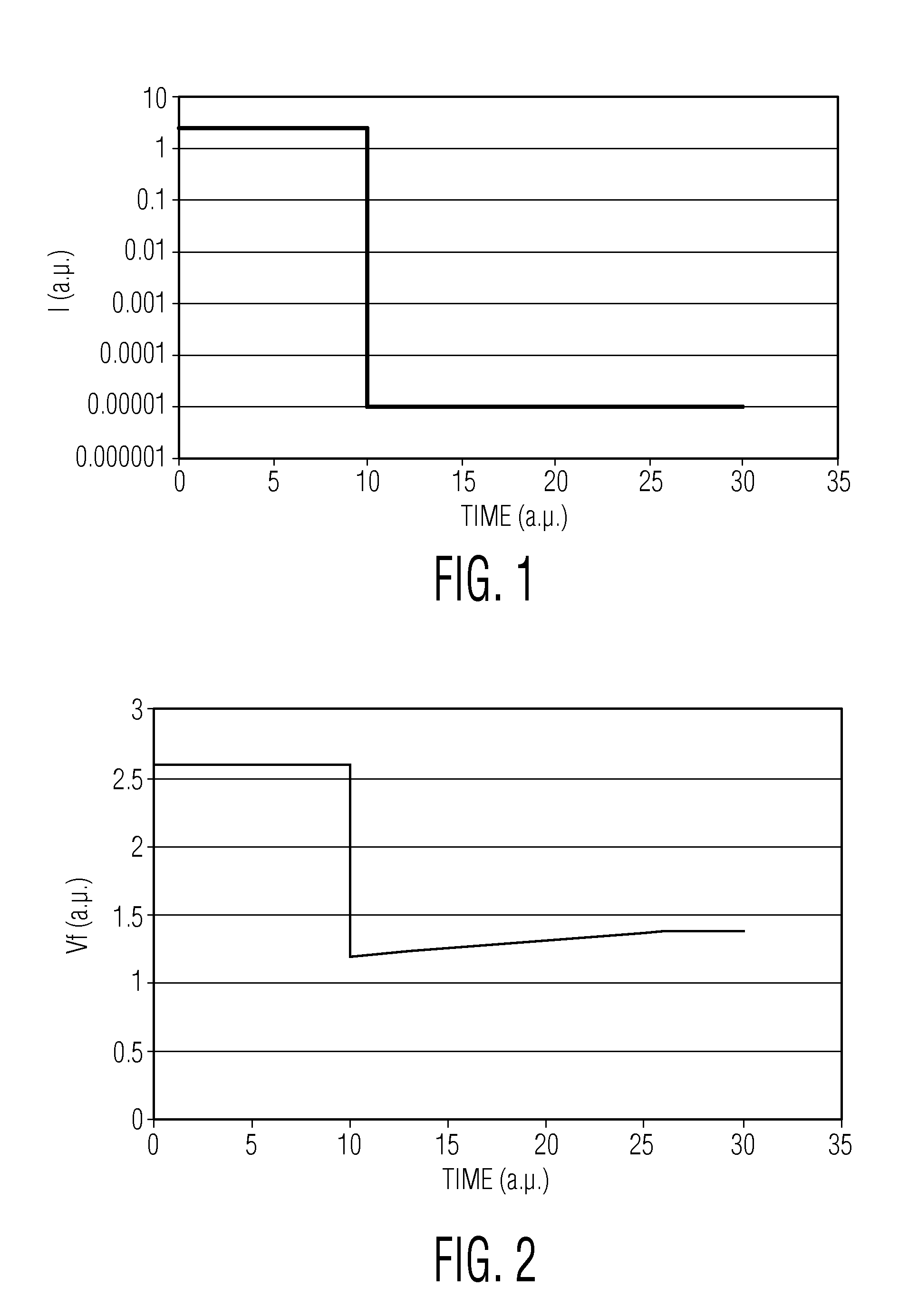

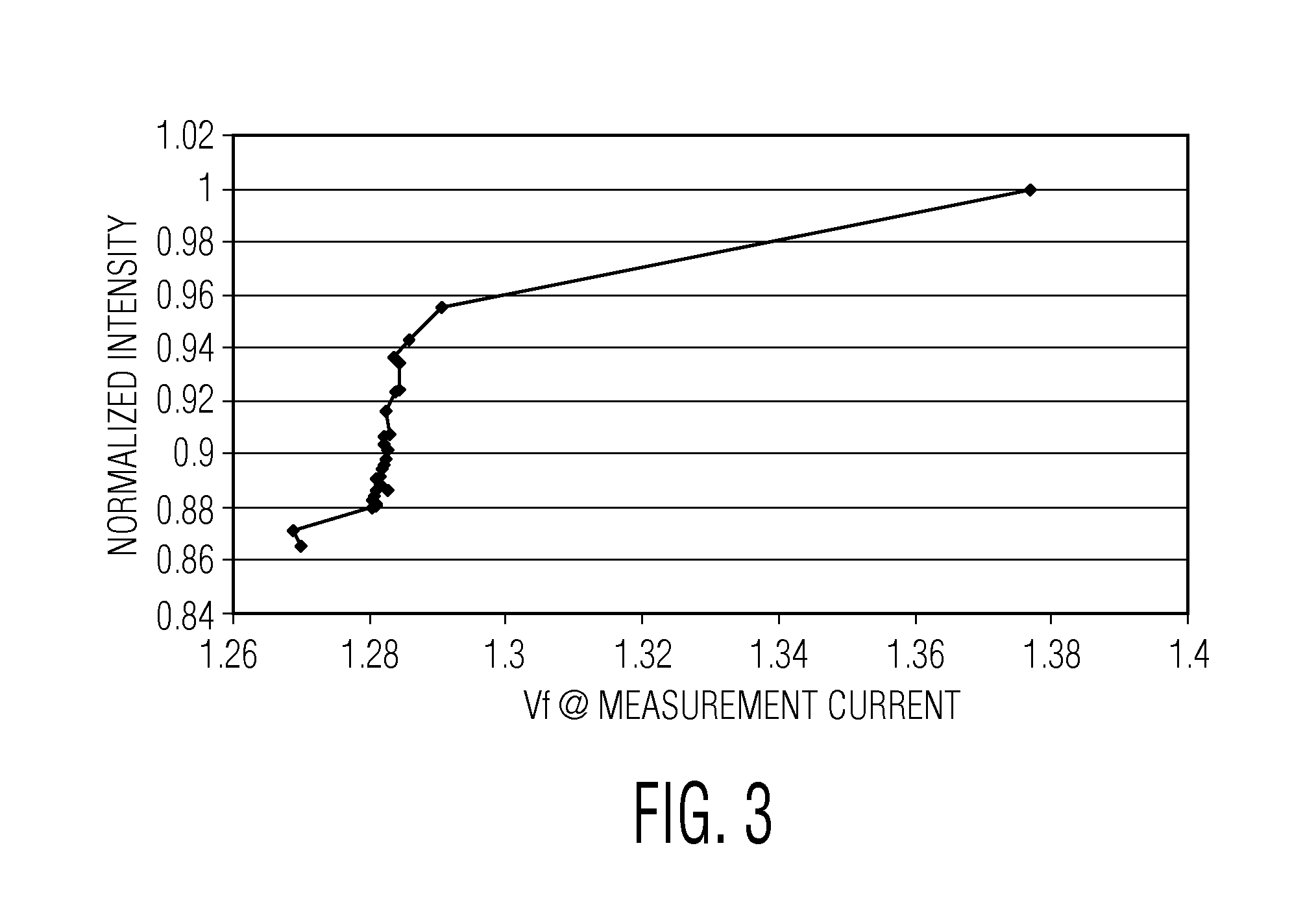

Testing of leds

InactiveUS20110084701A1Improve aging performanceShorten the timeElectrical apparatusDiode testingAccelerated agingElectrical and Electronics engineering

A method of determining the ageing characteristics of an LED comprises applying a current stress pulse to the LED. The LED is monitored to determine when the thermal heating induced by the current stress pulse has been dissipated to a desired level. The operational characteristics of the LED are then measured before applying the next stressing pulse.This method accelerates the effect of aging in a reproducible way and therefore is able to greatly reduce the time needed for a reliability test.

Owner:NXP BV

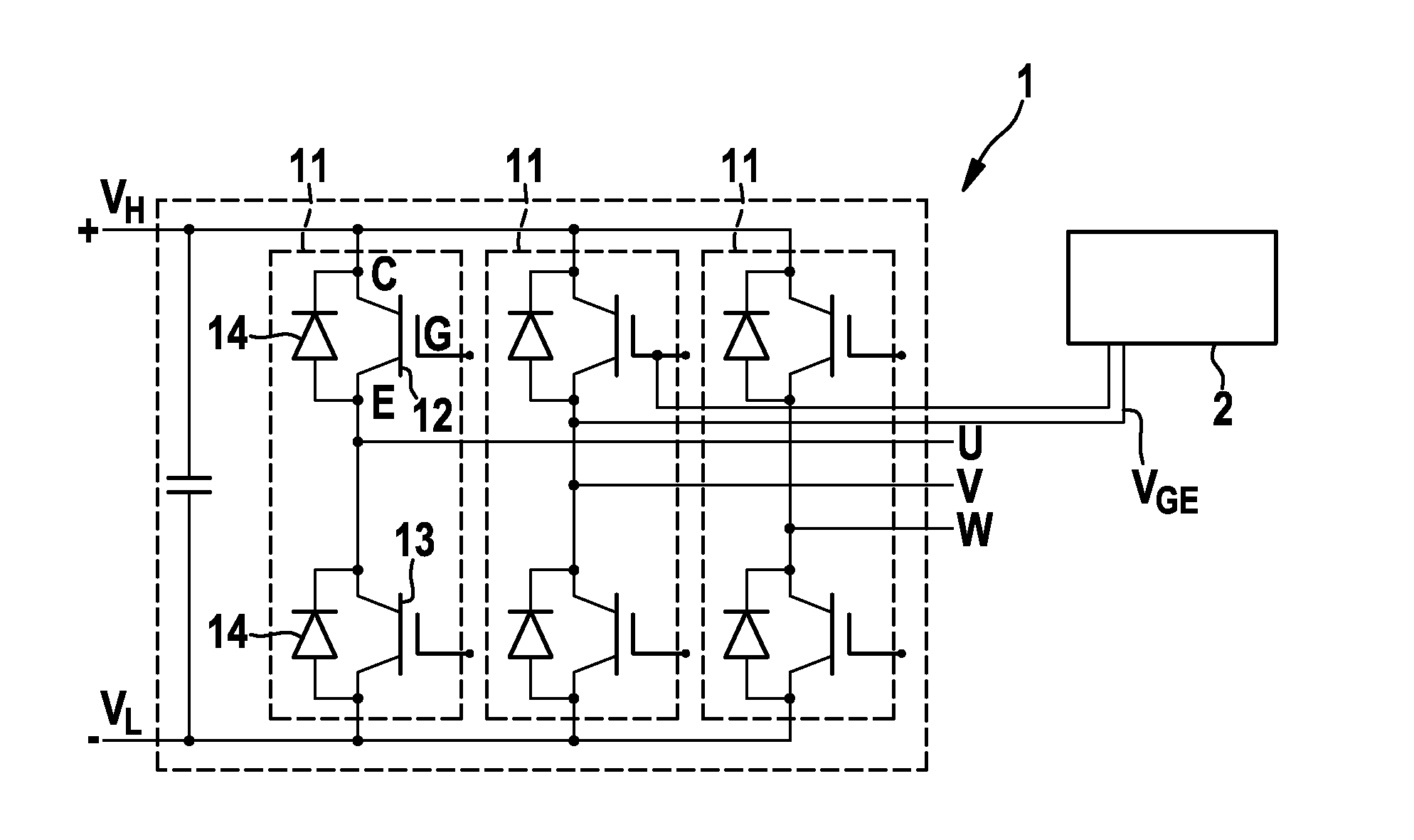

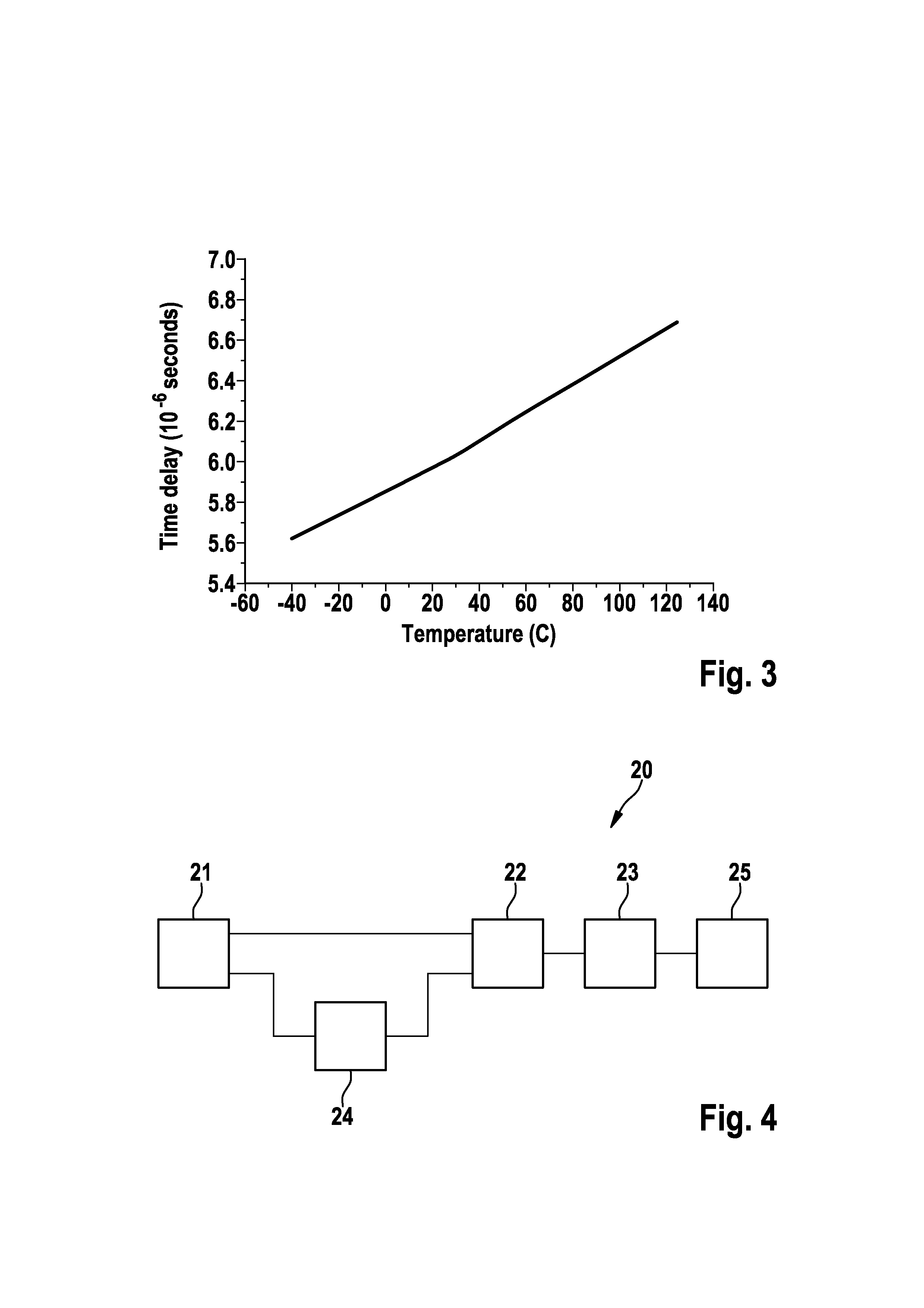

System and method for monitoring in real time the operating state of an IGBT device

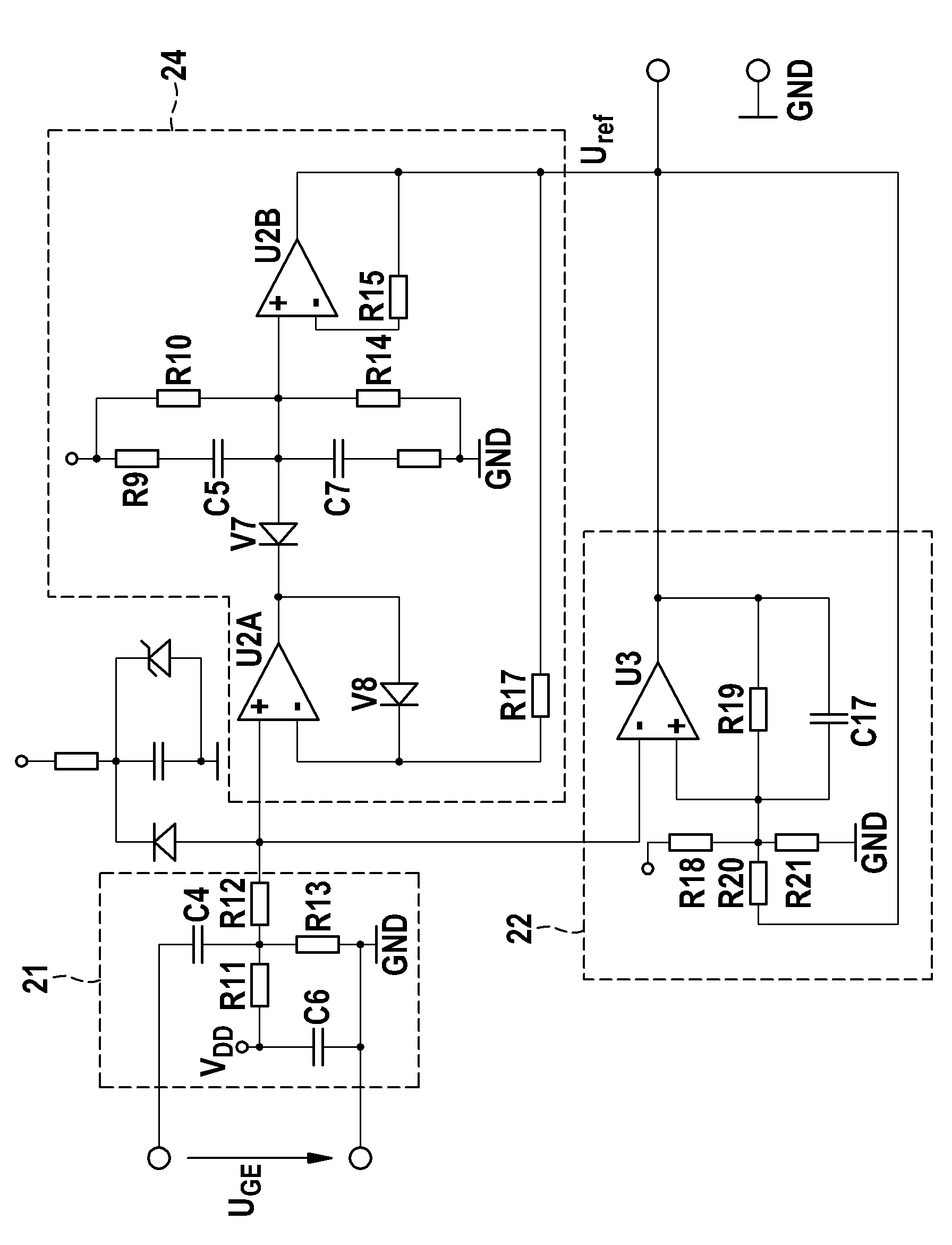

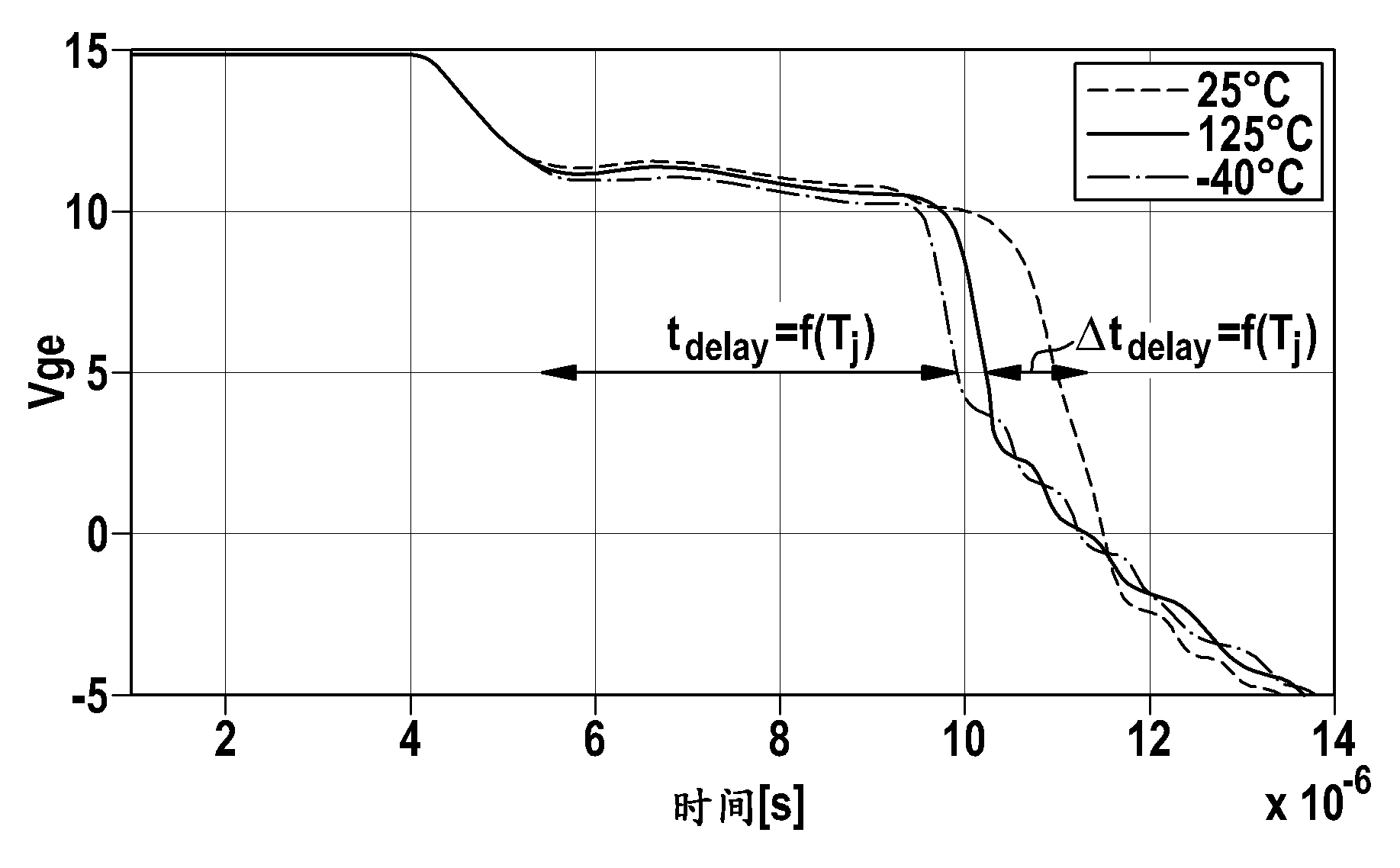

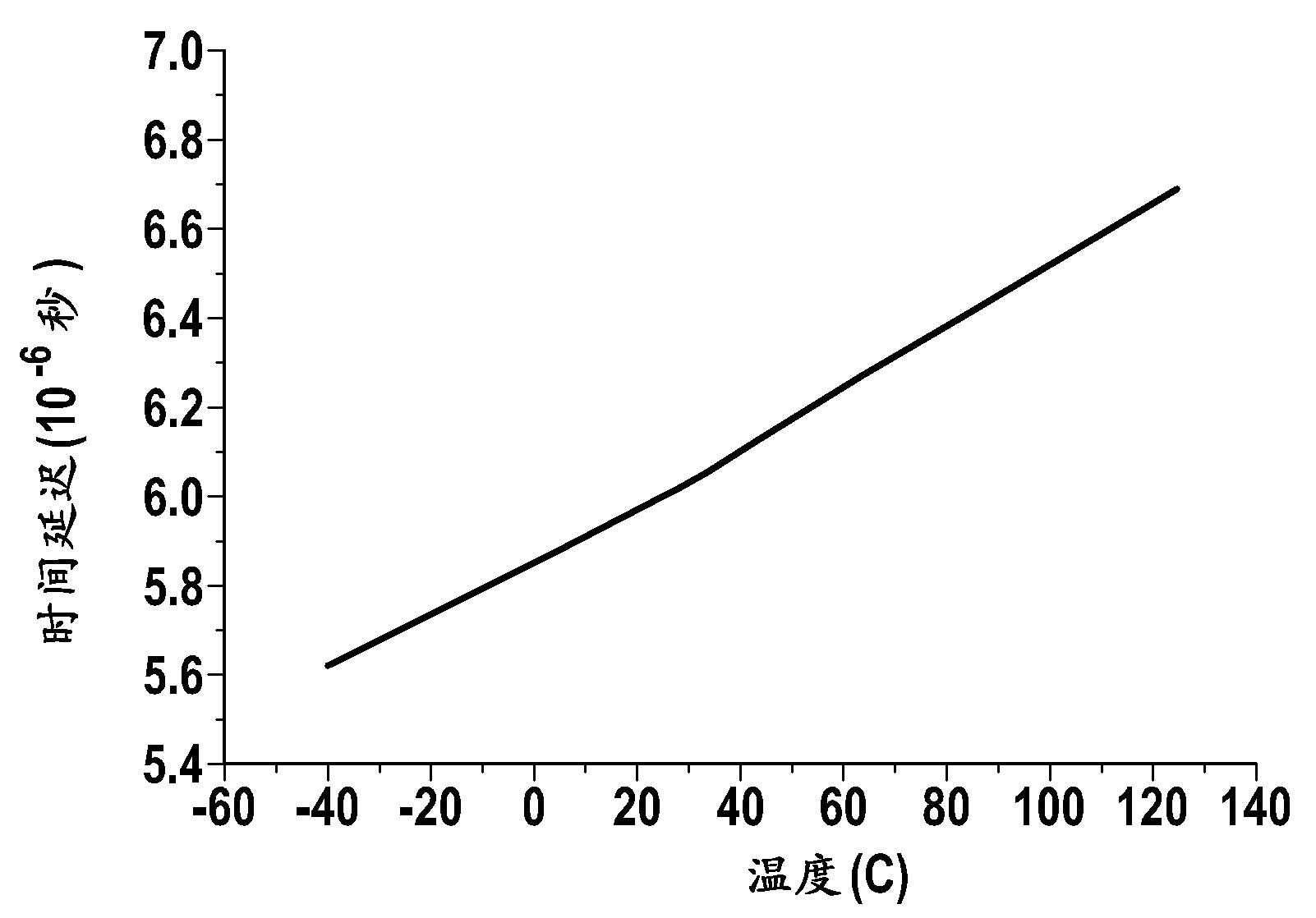

ActiveCN103207362ASemiconductor/solid-state device testing/measurementThermometers using electric/magnetic elementsTime delaysJunction temperature

The present invention relates to a system for monitoring in real time the operating state of an IGBT device, in particular for determining a junction temperature and / or a remaining lifetime of an IGBT device, comprising: -a differential unit for receiving a gate-emitter voltage characteristic of the IGBT device to be measured and for differentiating the gate-emitter voltage characteristic to obtain pulses correlating with edges formed by a Miller plateau phase during a switch-off phase of the IGBT device; -a timer unit for measuring the time delay between the obtained pulses indicating the start and end of the Miller plateau phase during the switch-off phase of the IGBT device; -a junction temperature calculation unit for determining the junction temperature and / or the remaining lifetime of the IGBT device based on the measured time delay.

Owner:ABB (SCHWEIZ) AG

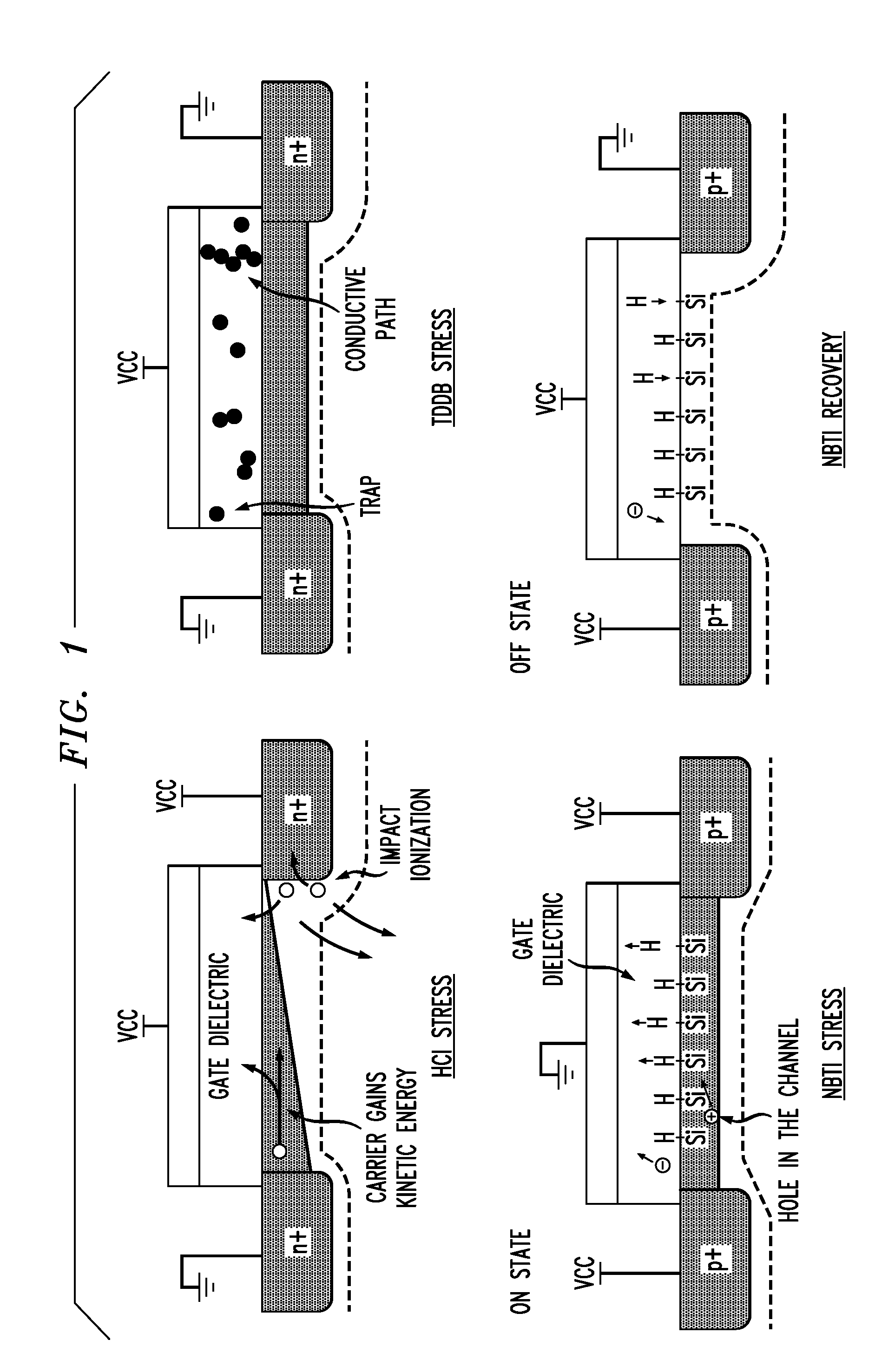

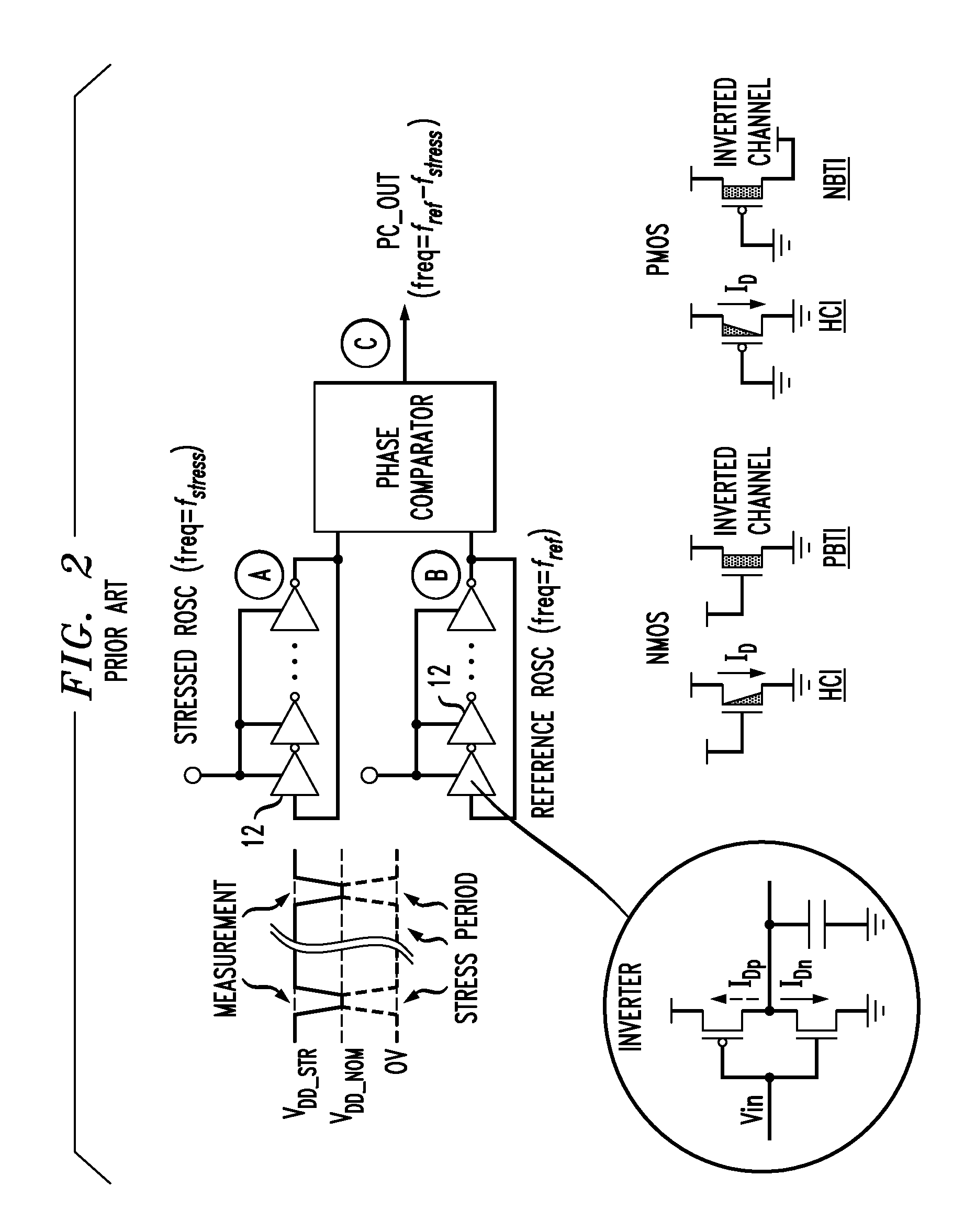

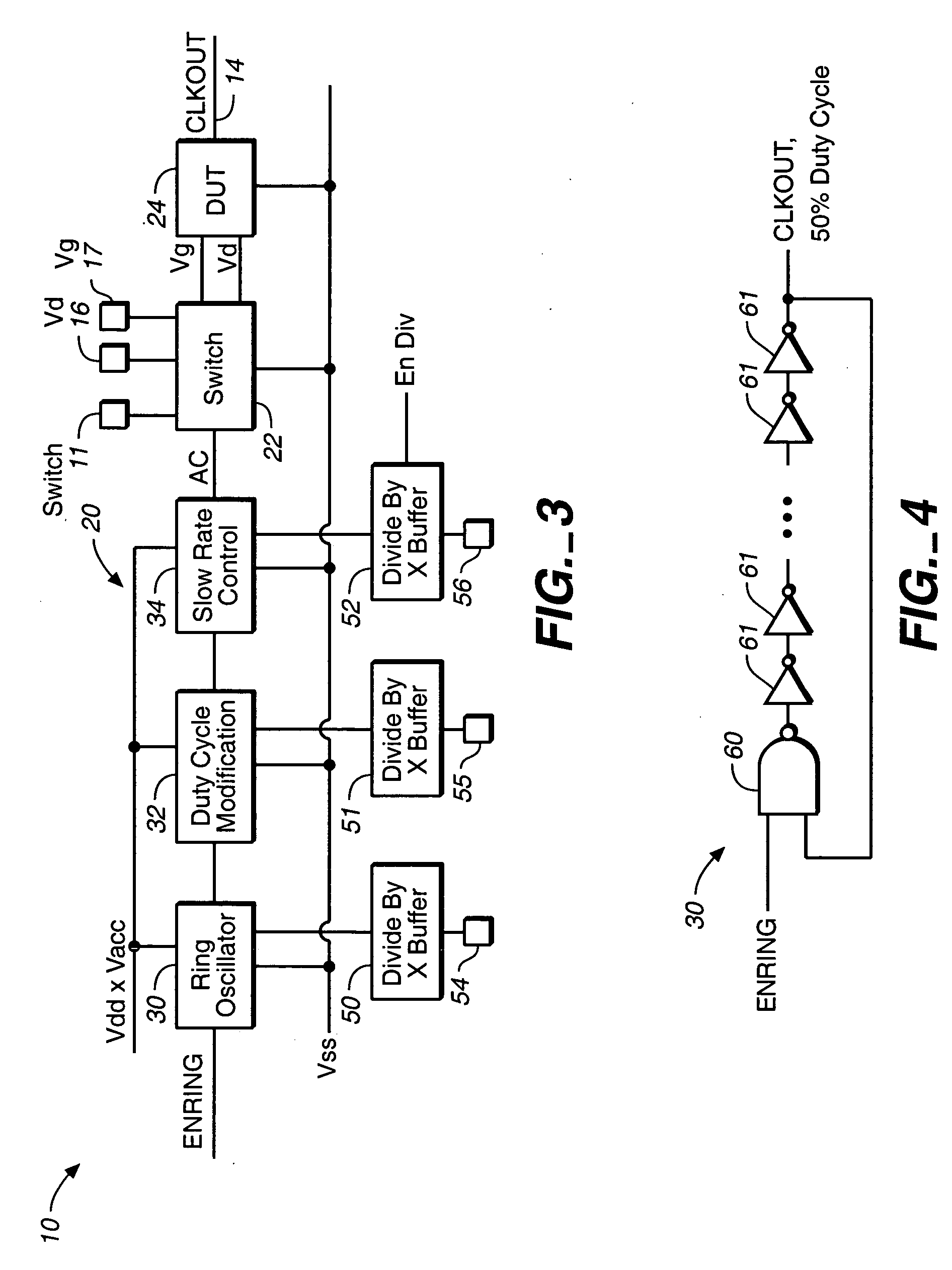

Apparatus and method for measuring degradation of CMOS VLSI elements

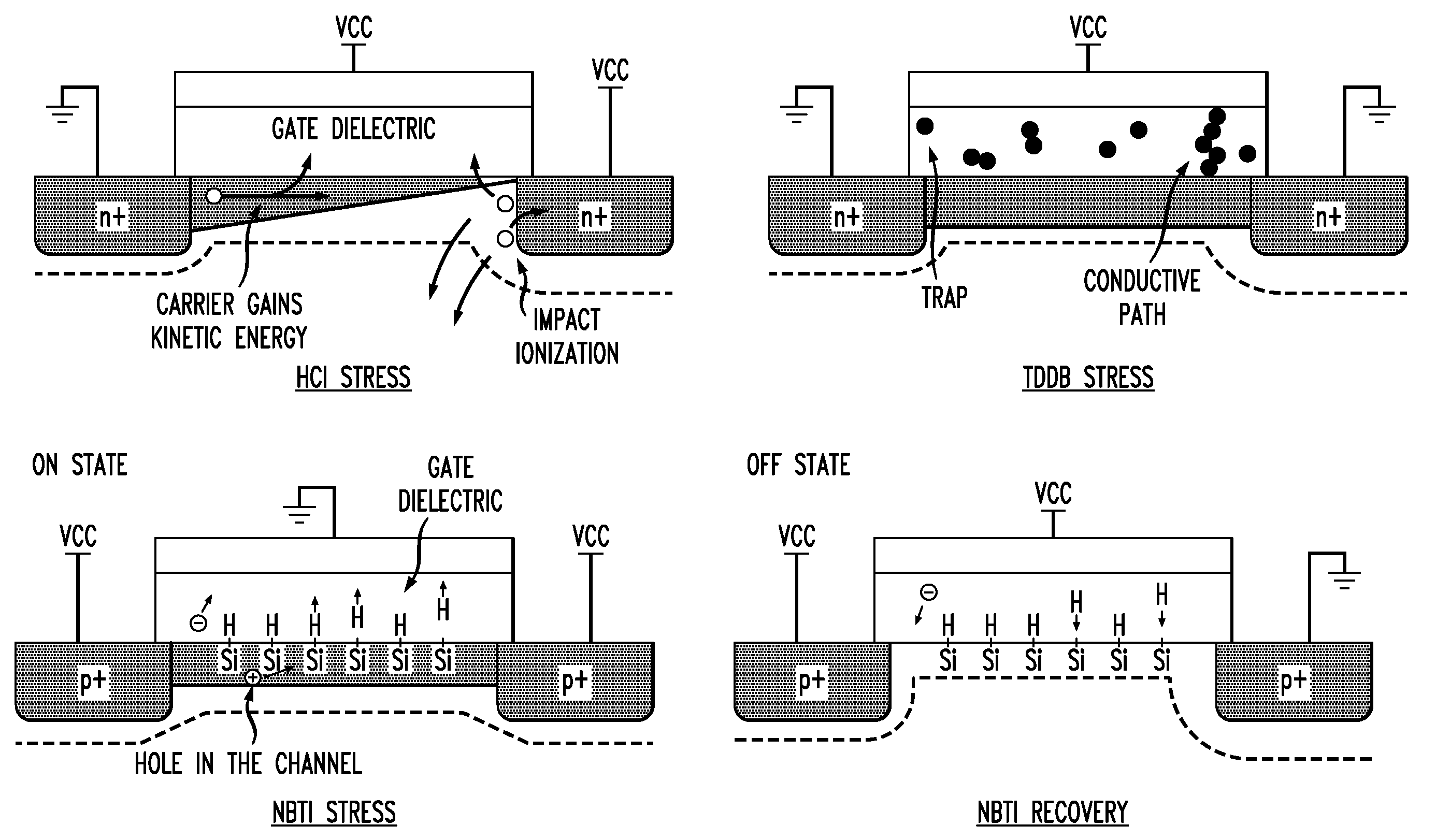

ActiveUS20130015876A1Minimization requirementsEliminate the effects ofSemiconductor operation lifetime testingDielectricAND gate

The reliability of an integrated circuit is inferred from the operational characteristics of sample metal oxide semiconductor (MOS) devices switchably coupled to drain / source bias and gate input voltages that are nominal, versus voltage and current conditions that elevate stress and cause temporary or permanent degradation, e.g., hot carrier injection (HCI), bias temperature instability (BTI, NBTI, PBTI), time dependent dielectric breakdown (TDDB). The MOS devices under test (preferably both PMOS and NMOS devices tested concurrently or in turn) are configured as current sources in the supply of power to a ring oscillator having cascaded inverter stages, thereby varying the oscillator frequency as a measure of the effects of stress on the devices under test, but without elevating the stress applied to the inverter stages.

Owner:TAIWAN SEMICON MFG CO LTD

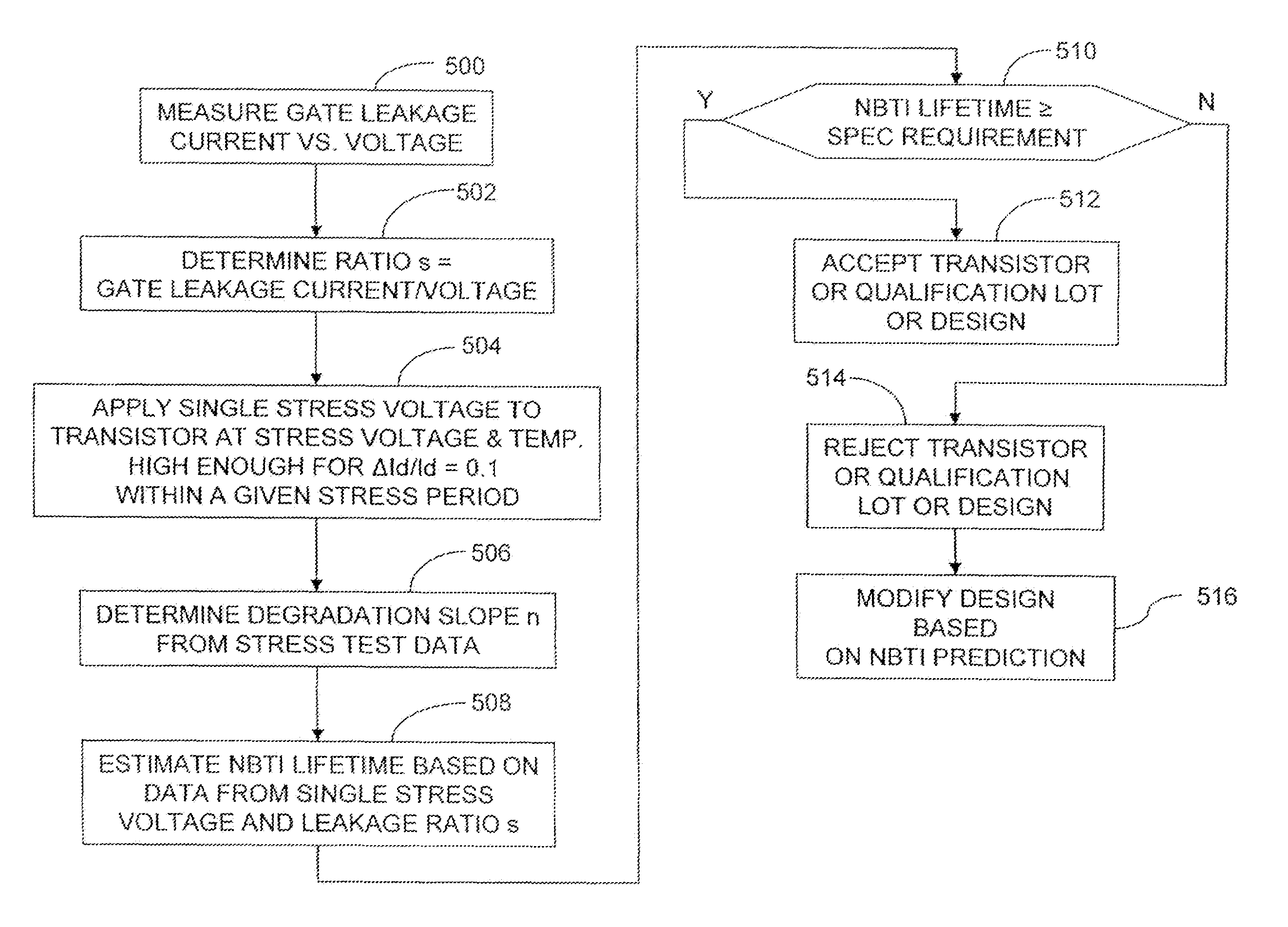

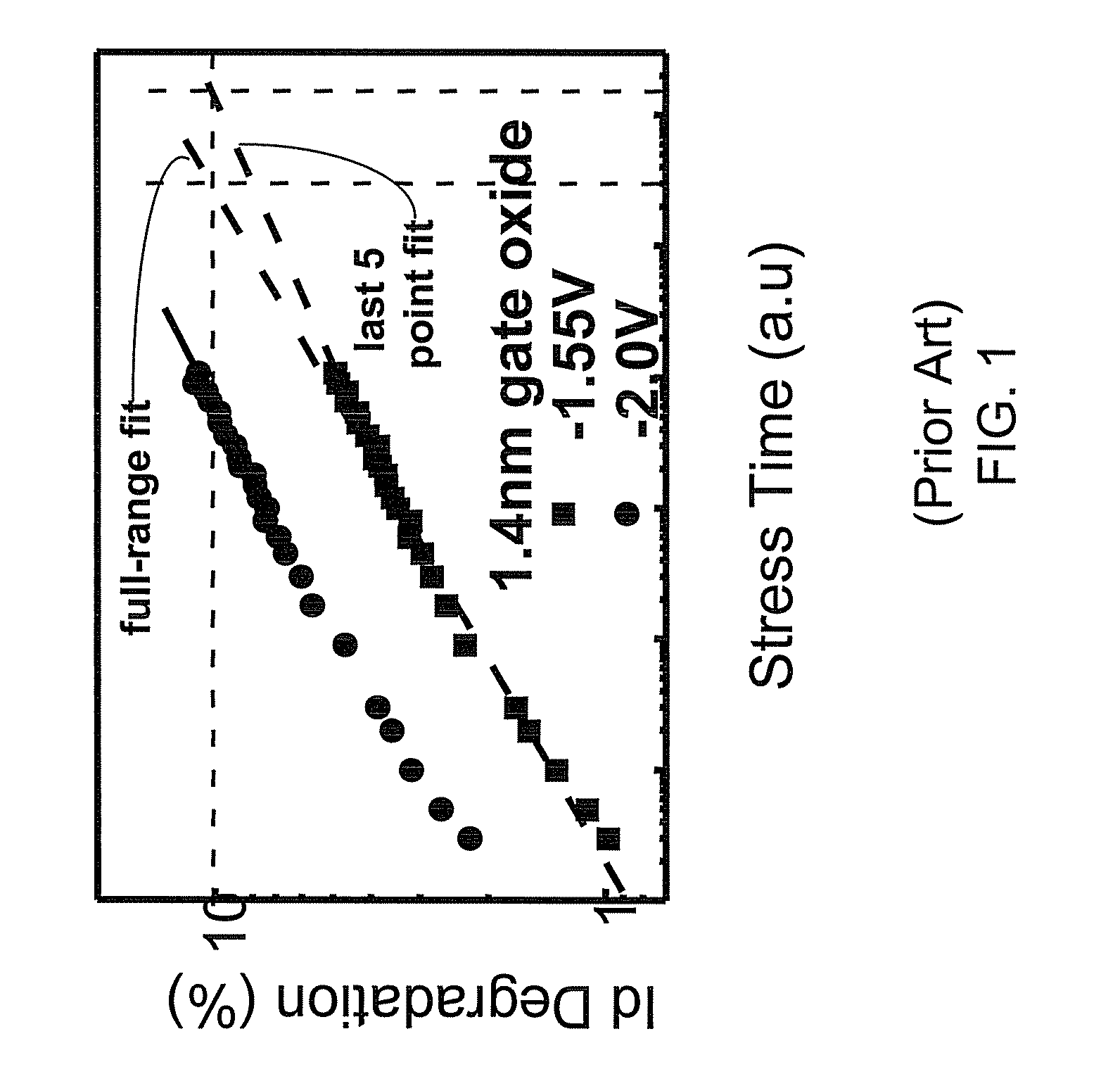

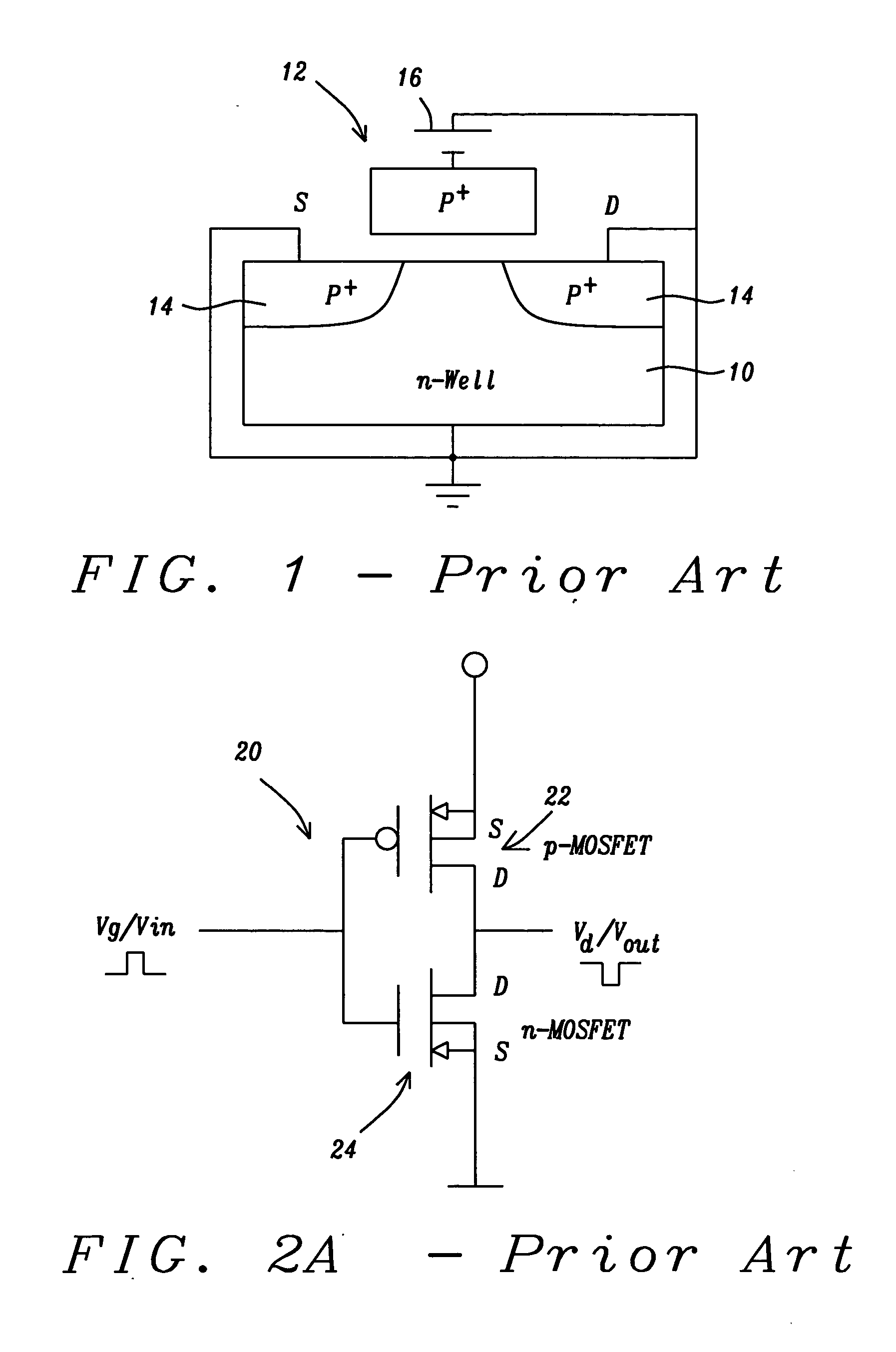

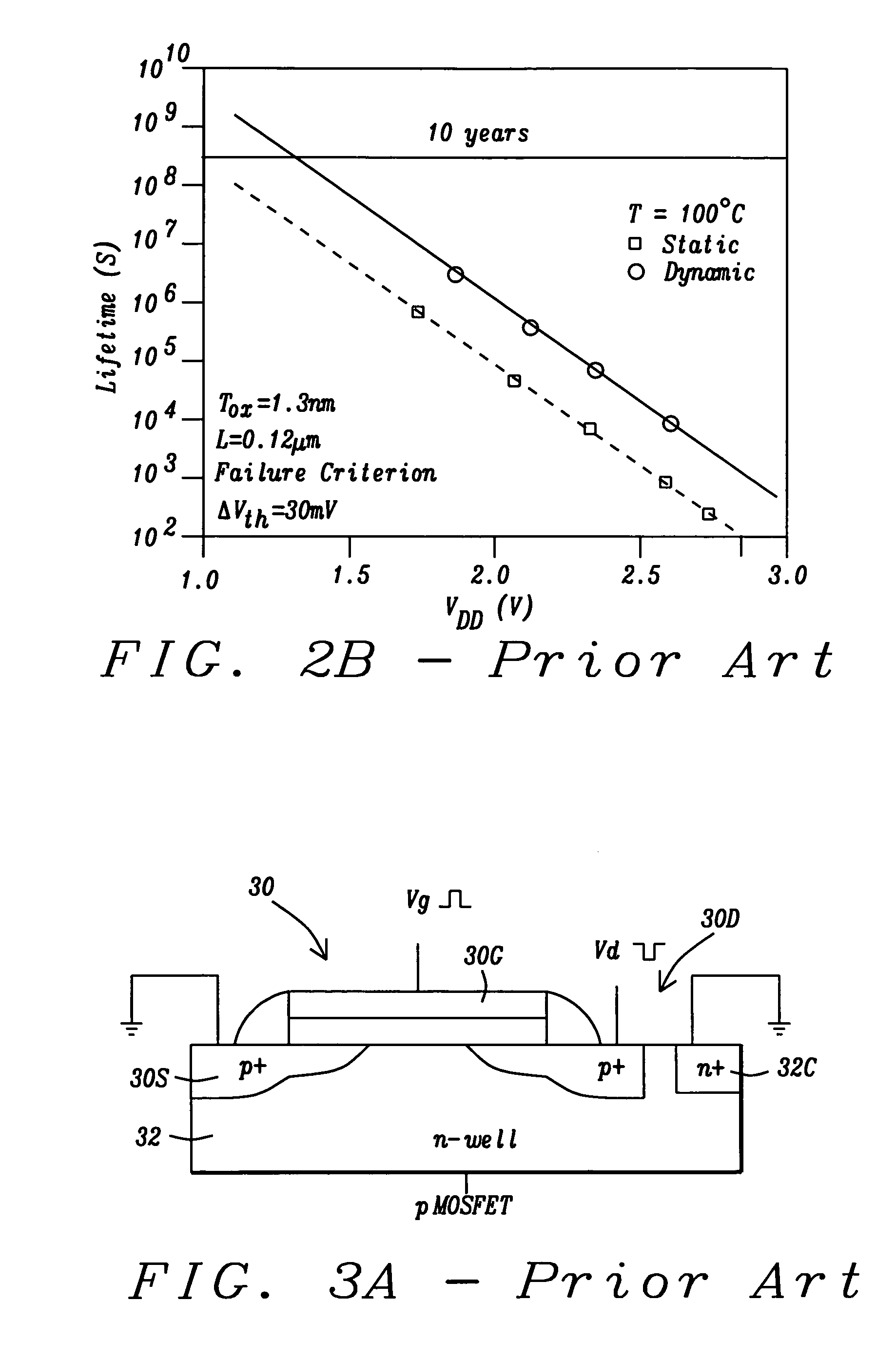

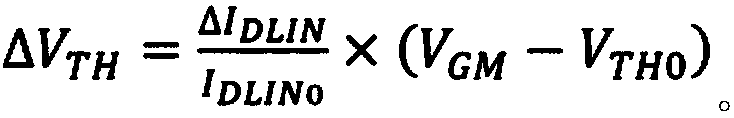

Method of NBTI prediction

InactiveUS7268575B1Semiconductor operation lifetime testingMarginal circuit testingGate leakage currentDriving current

A method includes measuring a gate leakage current of at least one transistor. A single stress bias voltage is applied to the at least one transistor at a given temperature for a stress period t. The stress bias voltage causes a 10% degradation in a drive current of the transistor at the given temperature within the stress period t. A negative bias temperature instability (NBTI) lifetime τ of the transistor is estimated based on the measured gate leakage current and a relationship between drive current degradation and time observed during the applying step.

Owner:TAIWAN SEMICON MFG CO LTD

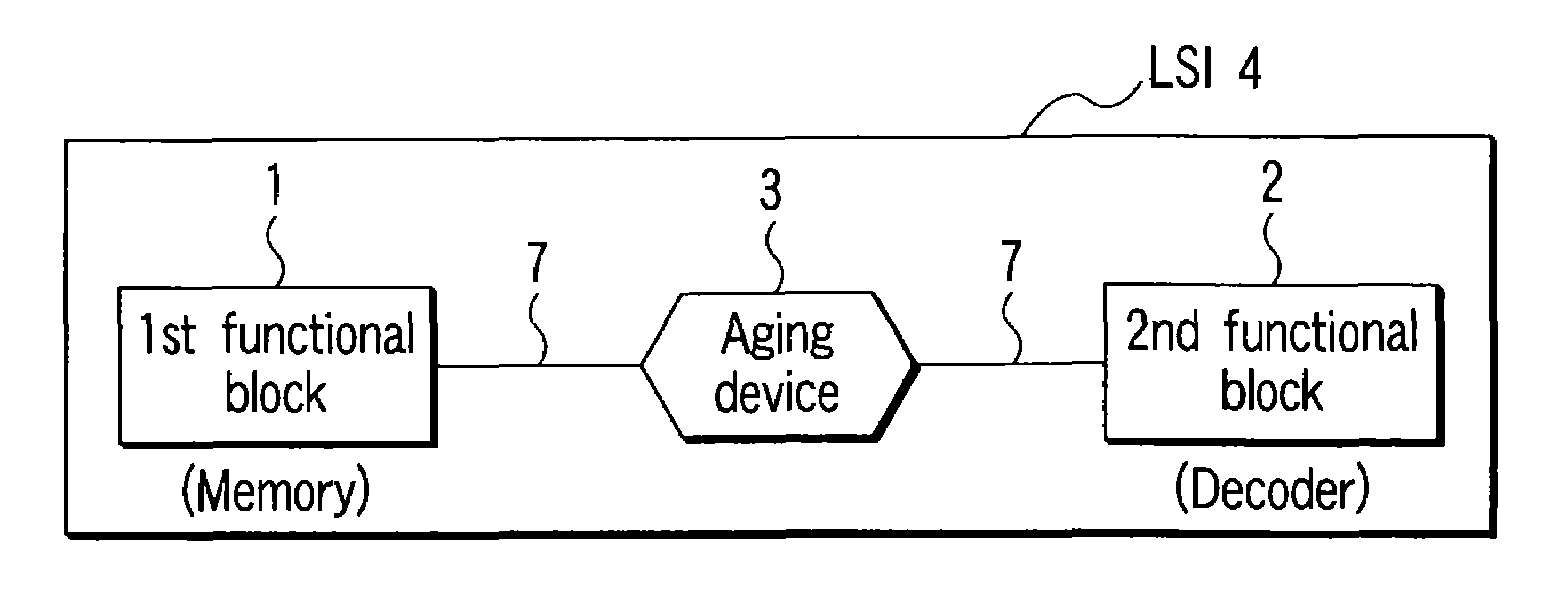

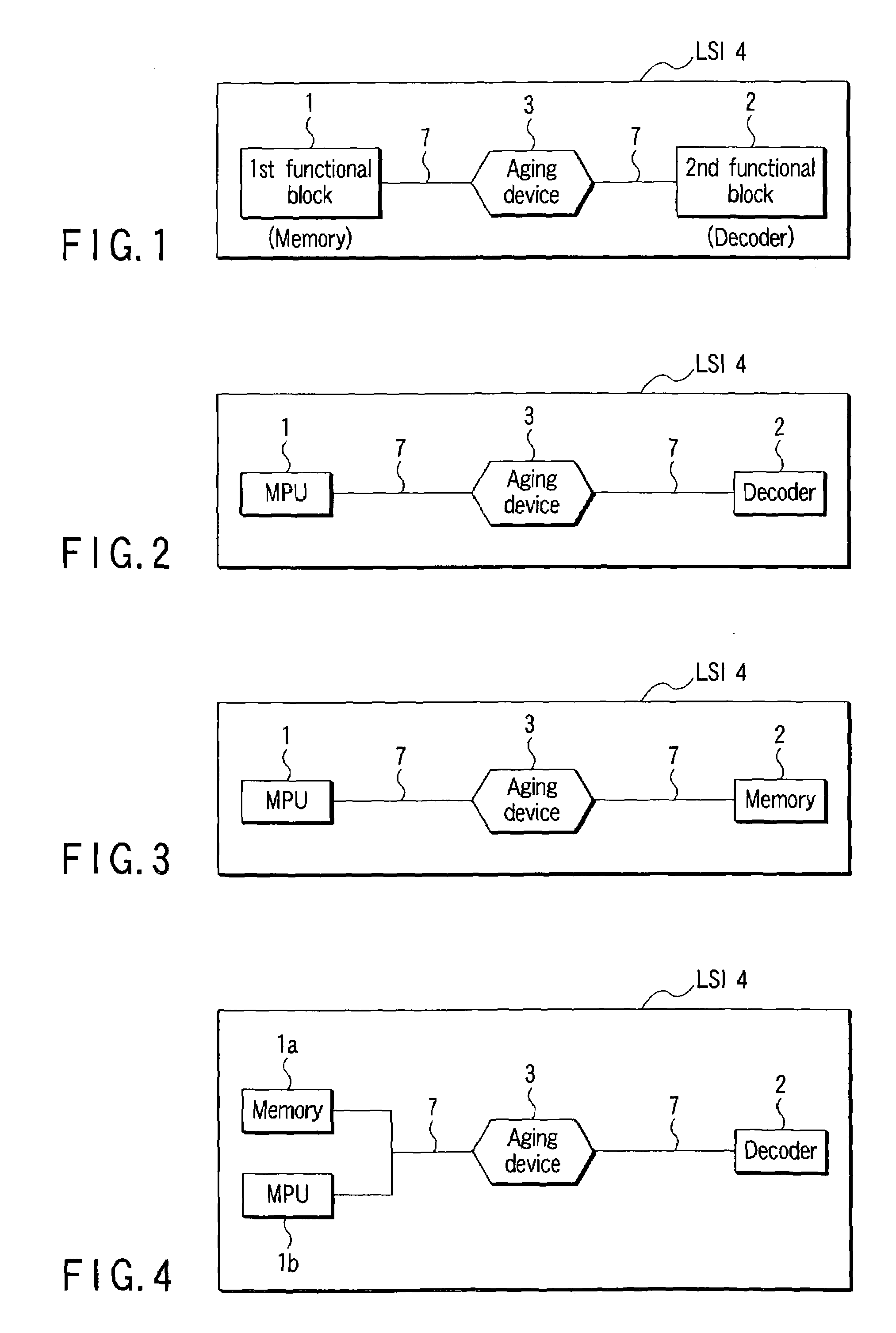

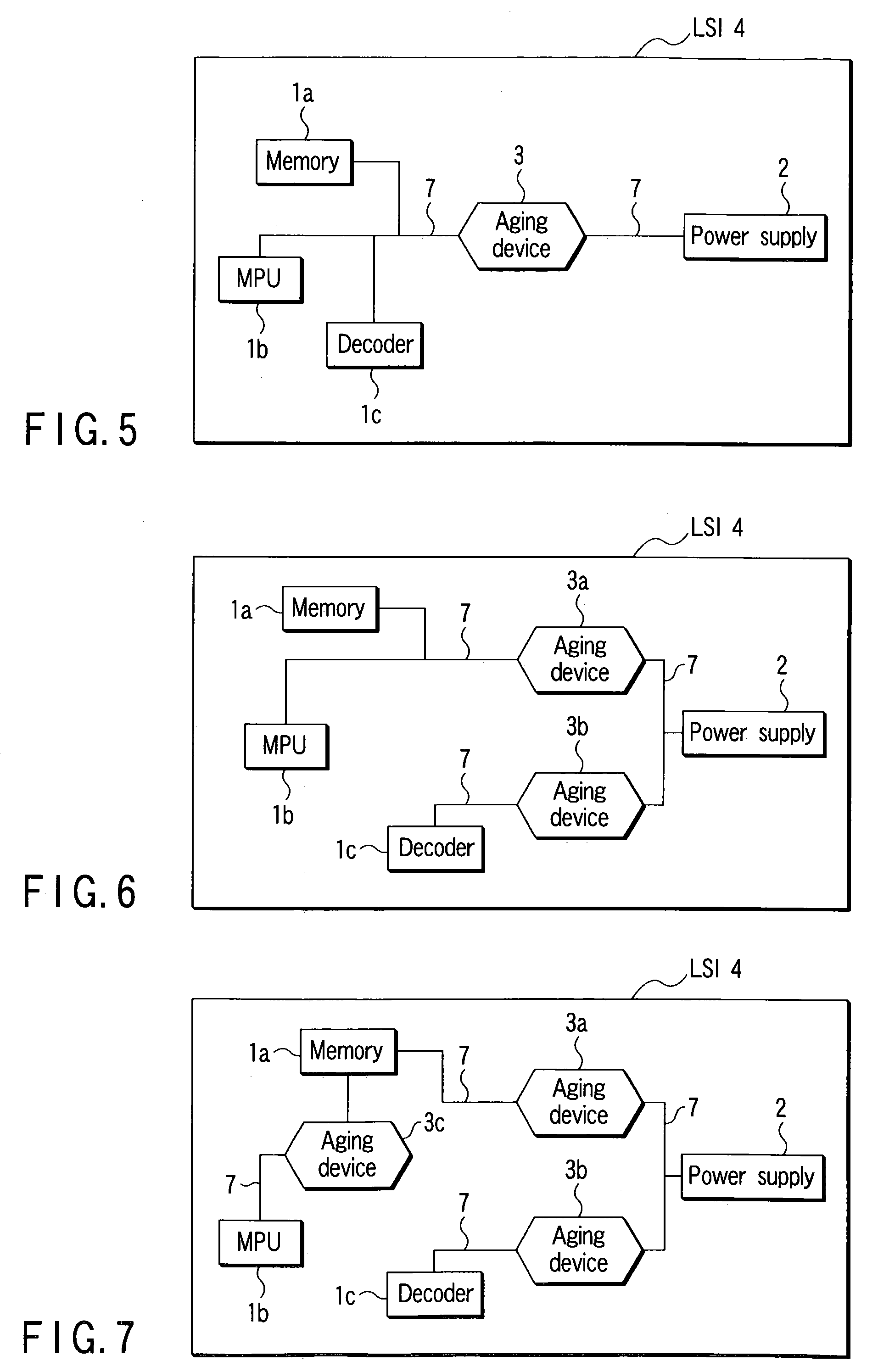

Time limit function utilization

A time limit function utilization apparatus includes a first function block, a second function block, a signal line which connects the first and second function blocks and allows using a desired function that is generated by accessing the first and second function blocks with each other, and a semiconductor time switch interposed in or connected to the signal line, and disables or enables mutual access between the first and second function blocks upon the lapse of a predetermined time.

Owner:KK TOSHIBA

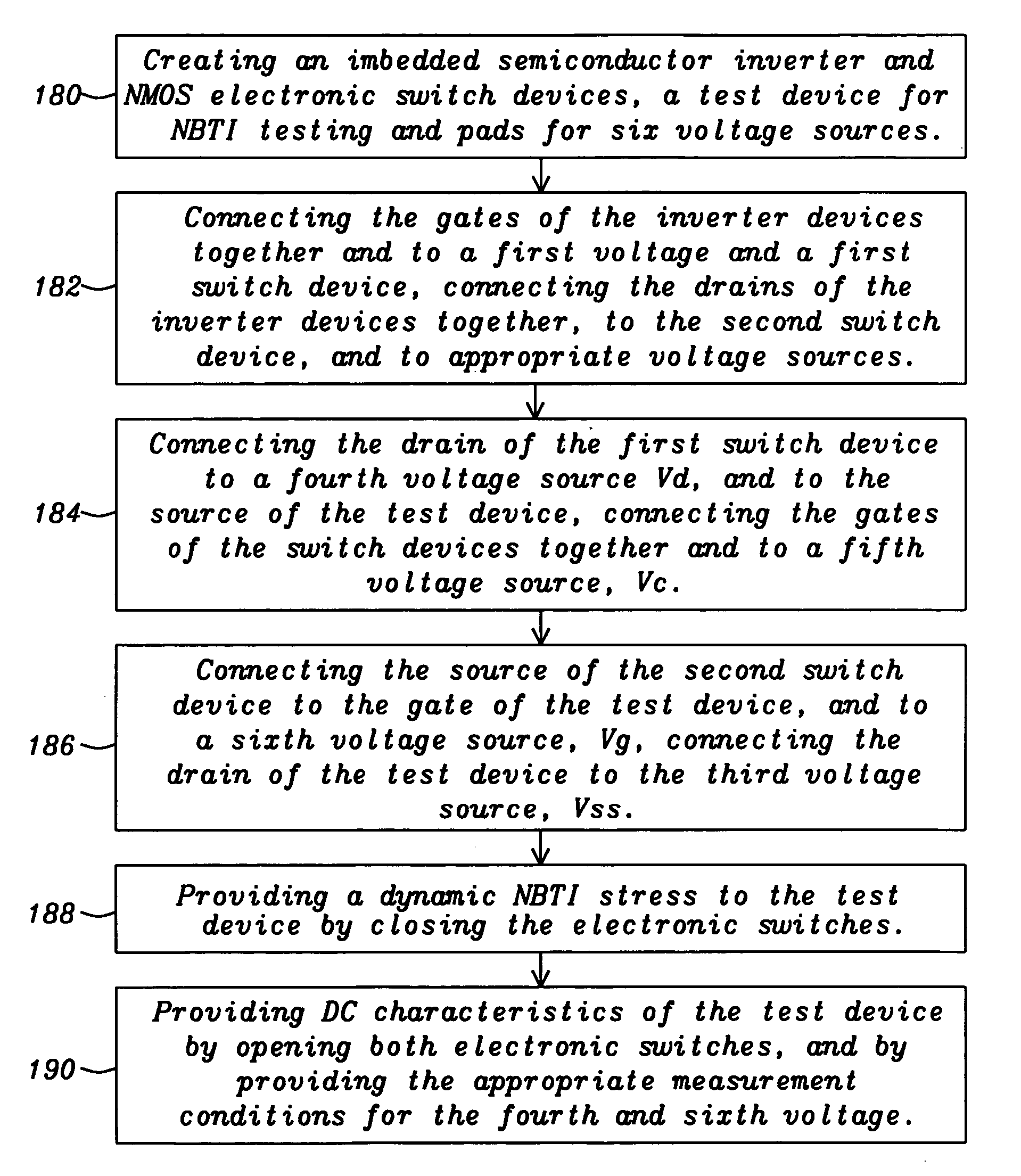

System and method for monitoring in real time the operating state of an IGBT device

ActiveUS20130177041A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsTime delaysJunction temperature

A system and method are provided for monitoring in real time the operating state of an IGBT device, to determine a junction temperature and / or the remaining lifetime of an IGBT device. The system includes a differential unit configured to receive a gate-emitter voltage characteristic of the IGBT device to be measured and to differentiate the gate-emitter voltage characteristic to obtain pulses correlating with edges formed by a Miller plateau phase during a switch-off phase of the IGBT device. The system also includes a timer unit configured to measure the time delay between the obtained pulses indicating the start and end of the Miller plateau phase during the switch-off phase of the IGBT device, and a junction temperature calculation unit configured to determine at least one of the junction temperature of the IGBT device and / or the remaining lifetime of the IGBT device based on the measured time delay.

Owner:ABB (SCHWEIZ) AG

Novel test structure for automatic dynamic negative-bias temperature instability testing

InactiveUS20050278677A1Minimize parasitic capacitanceMinimizes parasitic capacitanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectronic switchEngineering

The invention describes a novel test structure and process to create the structure for performing automatic dynamic stress testing of PMOS devices for Negative Bias Temperature Instability (NBTI). The invention consists of an integrated inverter, two integrated electronic switches for switching from stress mode to device DC characterization measurement mode, and a PMOS FET device under test (DUT). The inverter assures the proper 180 degree phase relationship between the test device source and gate voltage while the imbedded electronic switches provide isolation of the test device during DC characterization testing. Another embodiment of the invention enables the testing of multiple devices under test (DUT's).

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

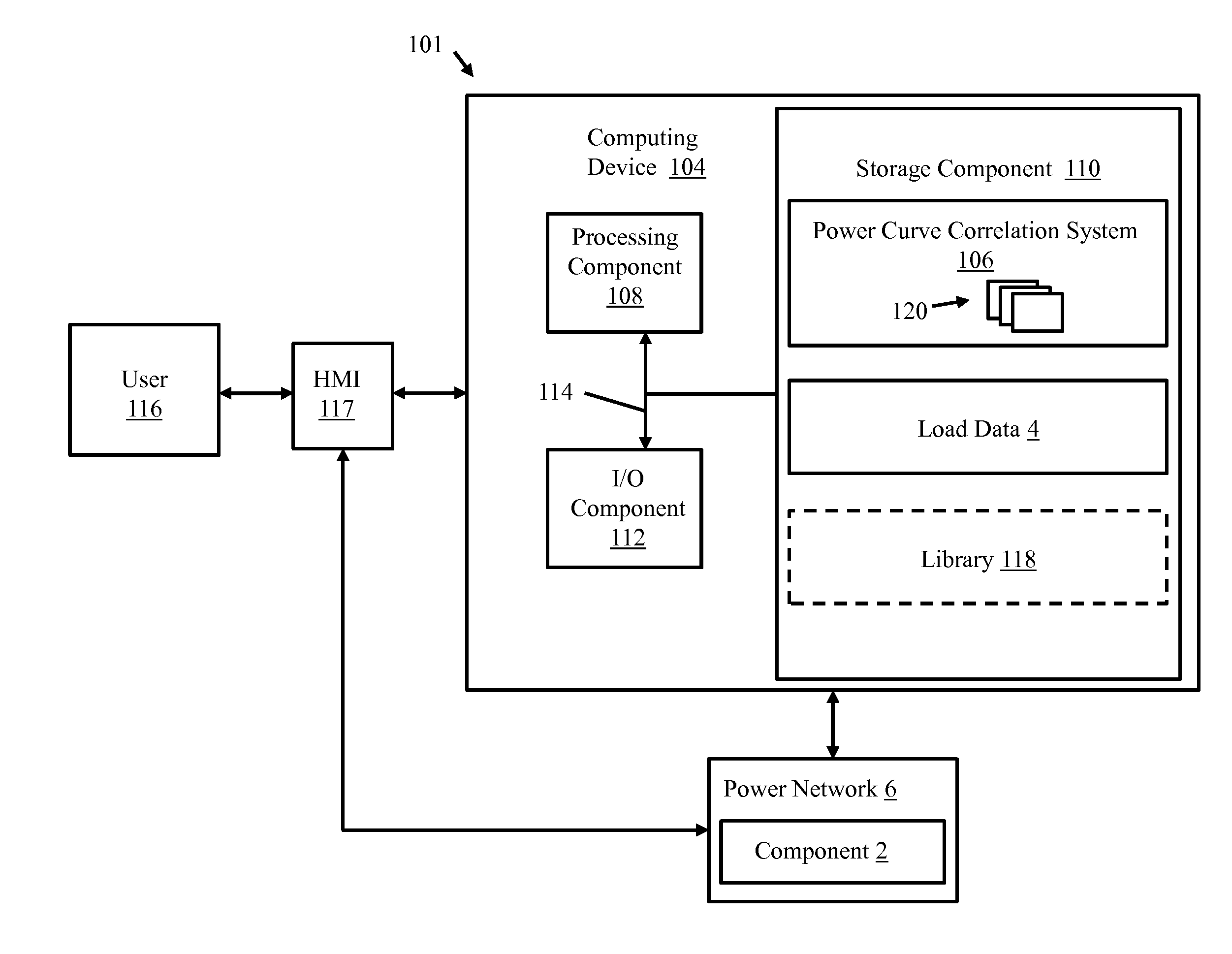

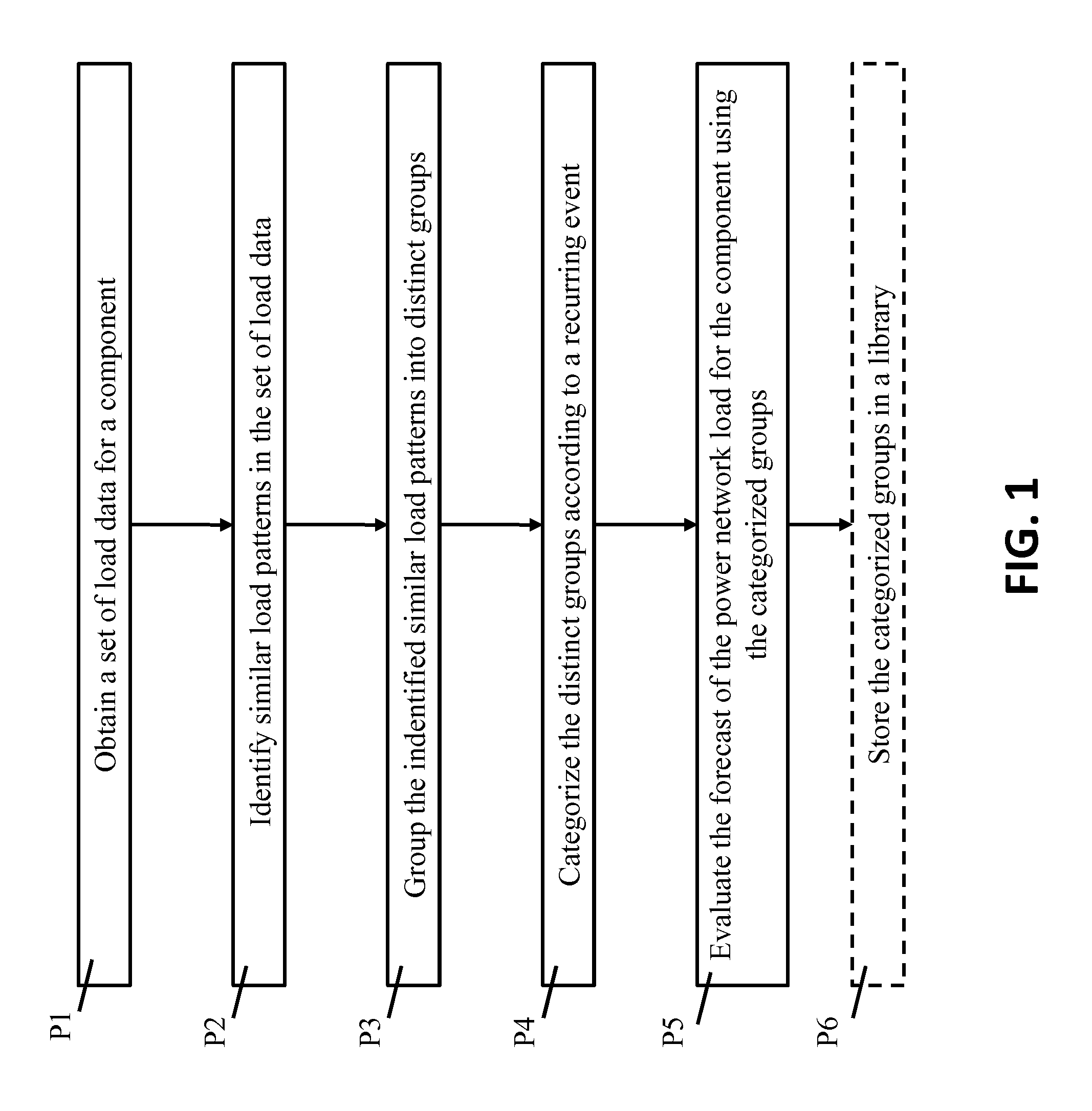

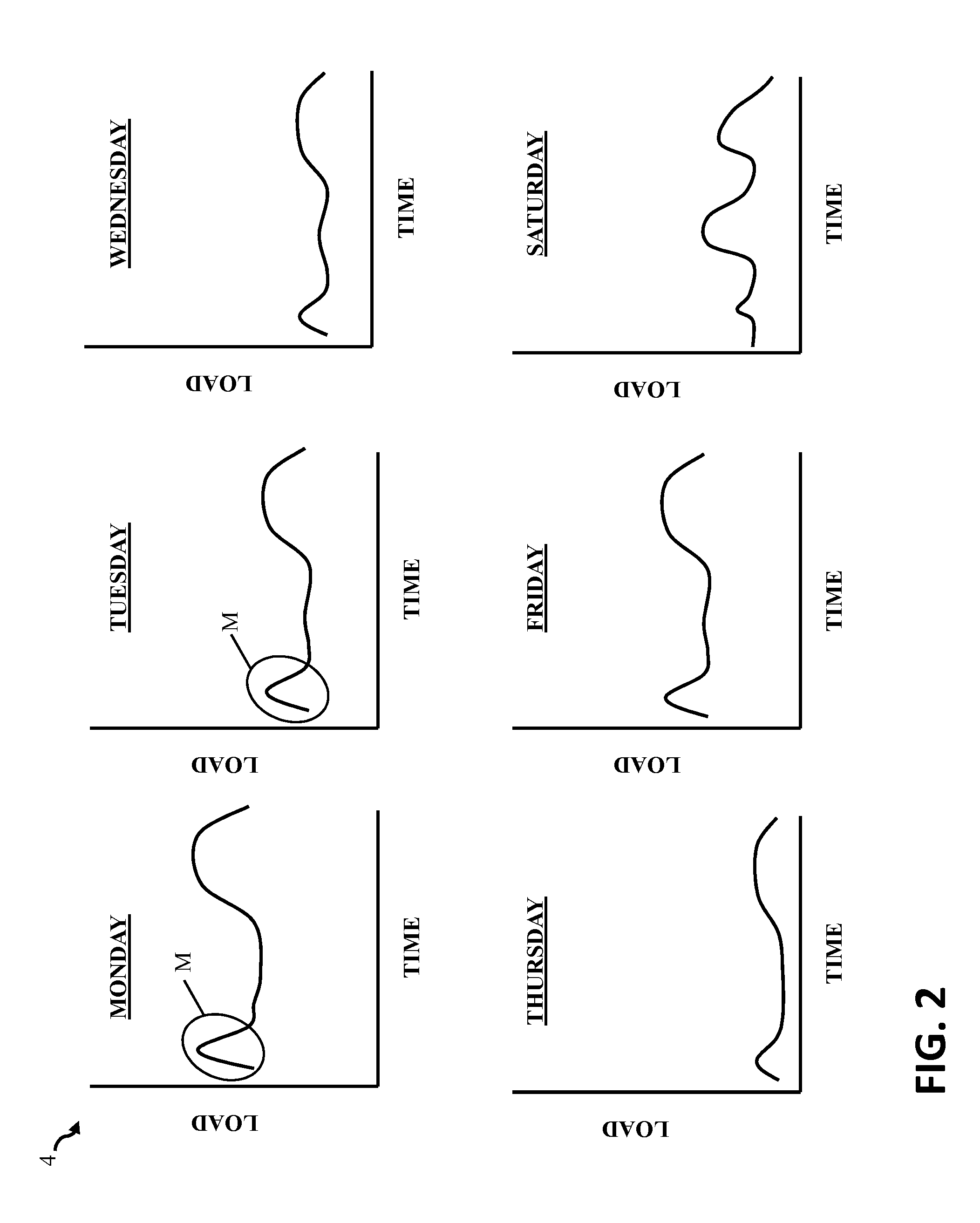

Power curve correlation system

ActiveUS20130173191A1Electric devicesElectrical measurement instrument detailsComponent LoadParallel computing

A power curve correlation system is disclosed. The power curve correlation system includes a system including: at least one computing device configured to verify a forecast of a power network load for a component by performing actions including: obtaining a set of load data for the component in the power network over a period; identifying similar load patterns in the set of load data using a pattern recognition technique, independent of at least one of: a scale for a component load, a minimum component load value or a maximum component load value; grouping the identified similar load patterns into distinct groups; categorizing at least one of the distinct groups according to a recurring event associated with a load pattern in the at least one distinct group; and providing the categorized group for verifying the forecast of the power network load for the component using the at least one categorized group.

Owner:GENERAL ELECTRIC CO

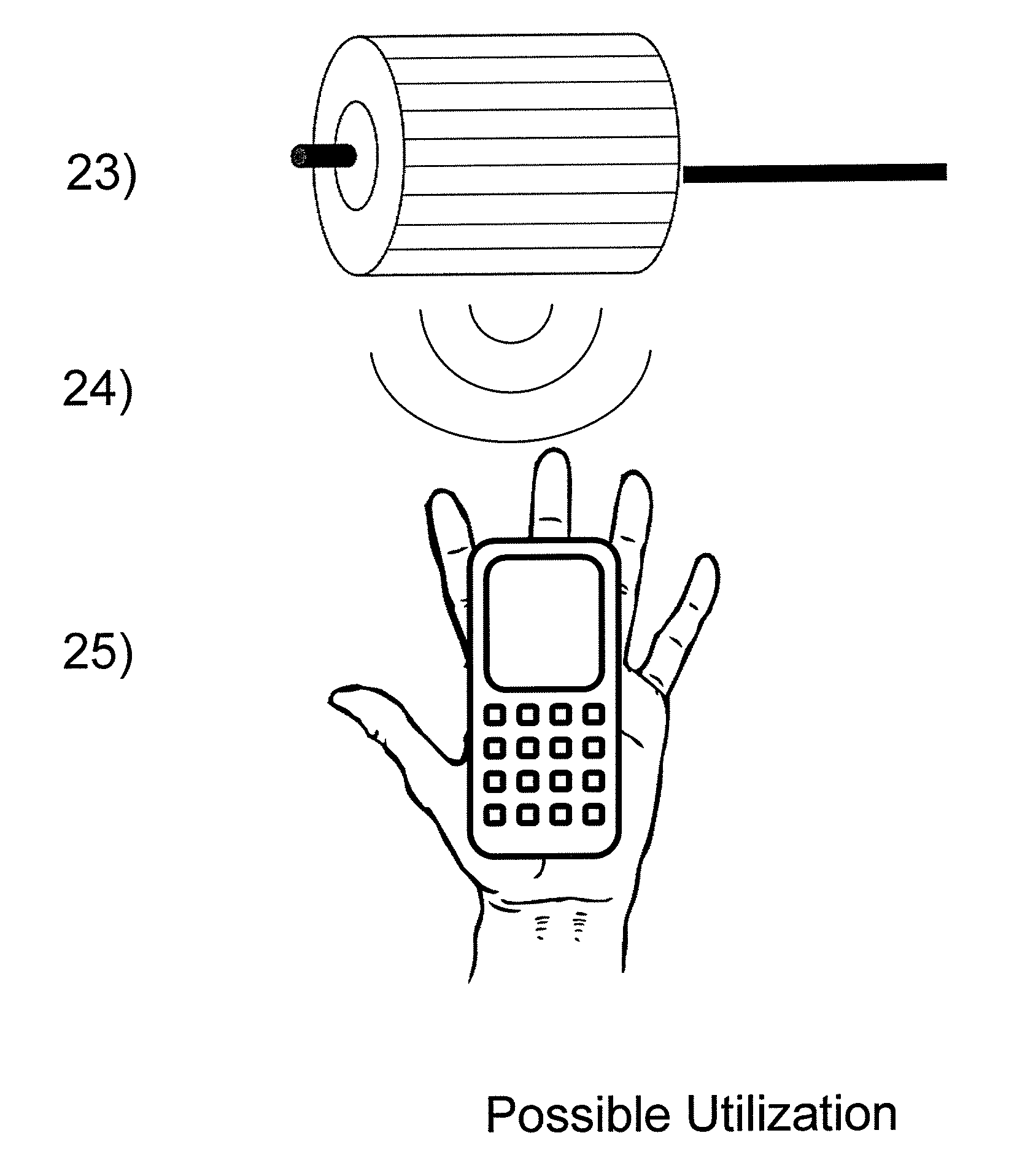

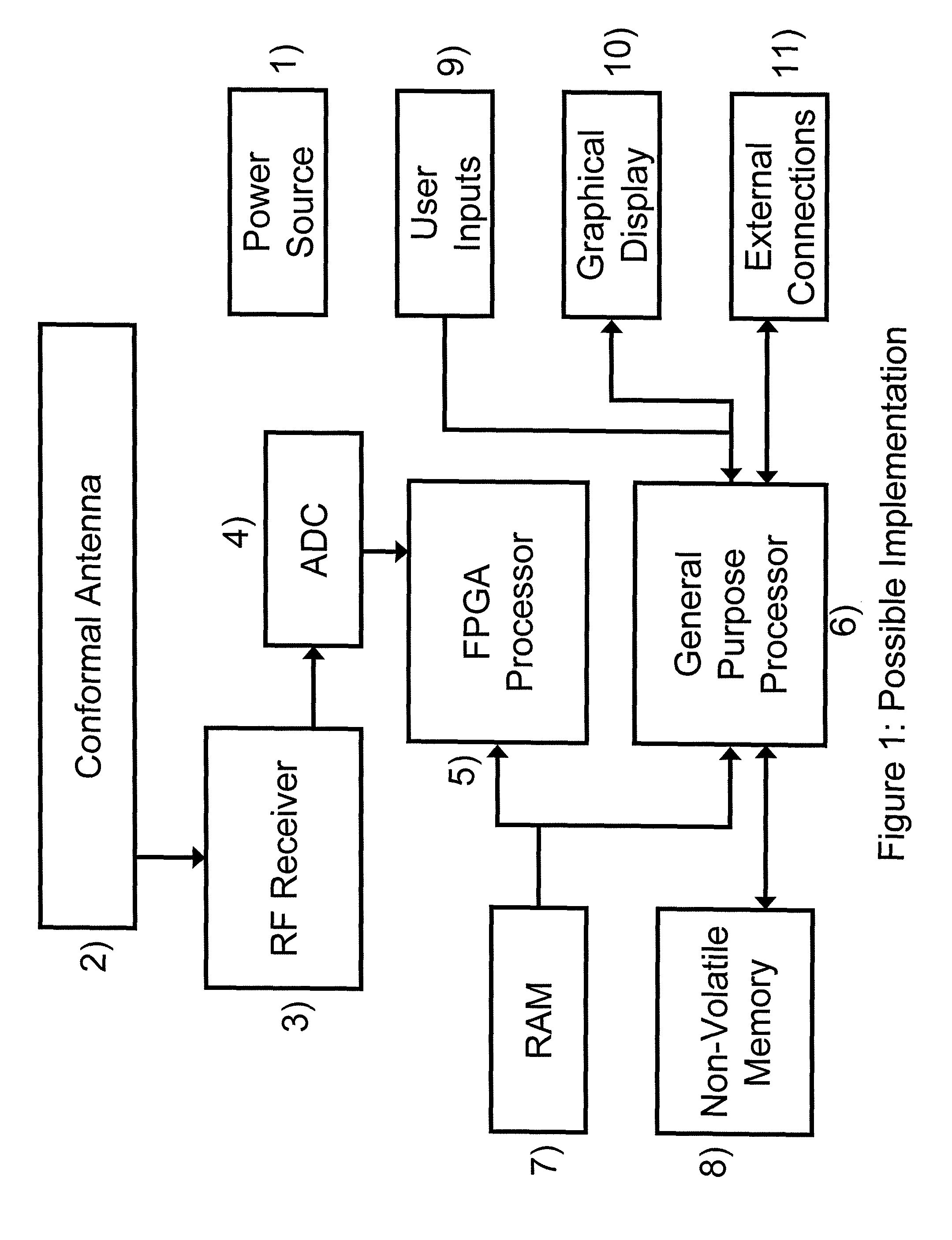

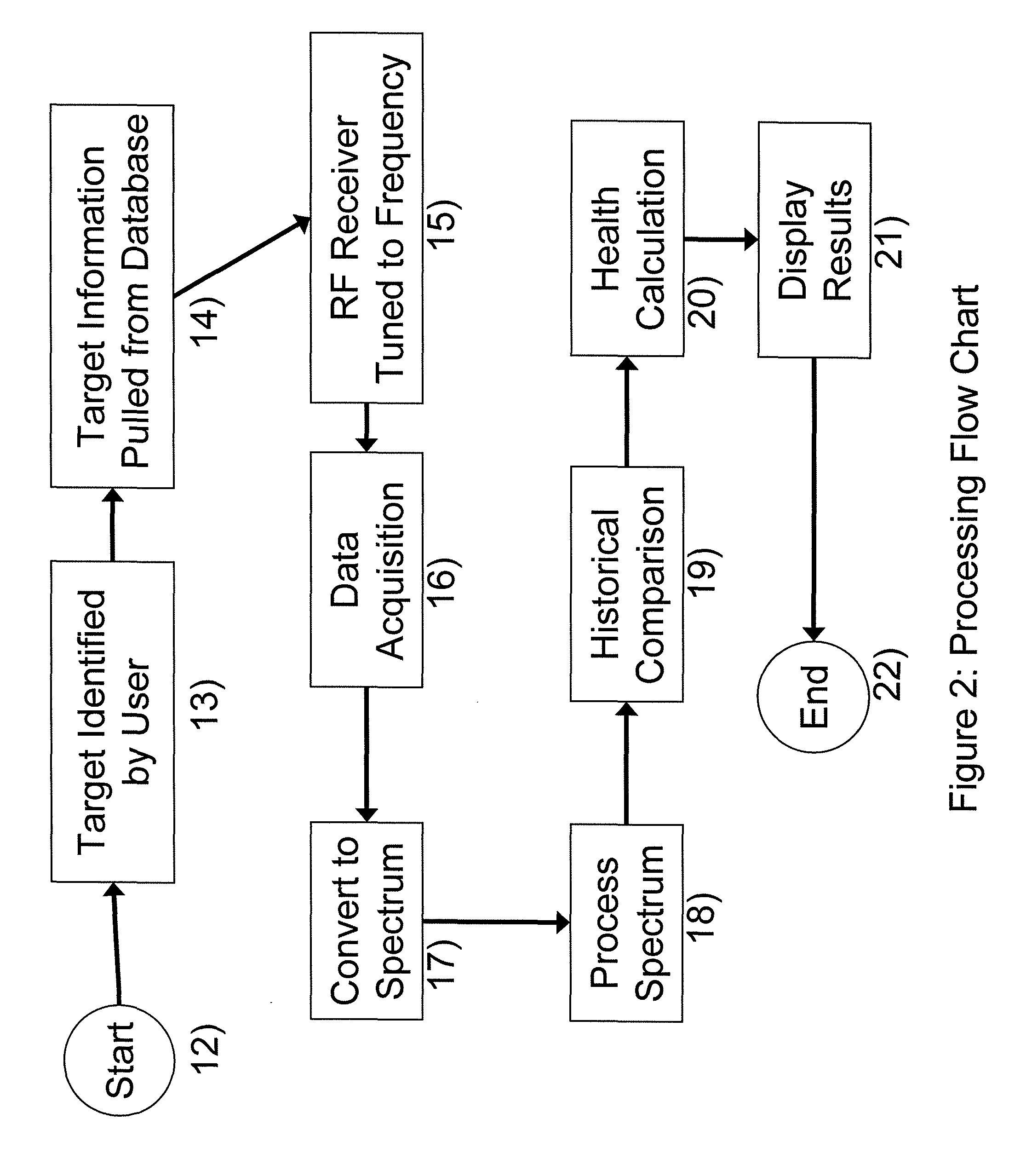

Advance manufacturing monitoring and diagnostic tool

ActiveUS8643539B2Easily employedEasy accessElectric winding testingTransformers testingElectricityElectrical devices

The current invention relates to a monitoring and analysis device and a method for monitoring and analysis that utilizes the unintended electromagnetic emissions of electrically powered systems. The present invention monitors electrical devices by taking detailed measurements of the electromagnetic fields emitted by any component or system utilizing electricity. The measurements will be analyzed to both record a baseline score for future measurements and to be used in detailed analysis to determine the status of the analyzed system or component.

Owner:NOKOMIS

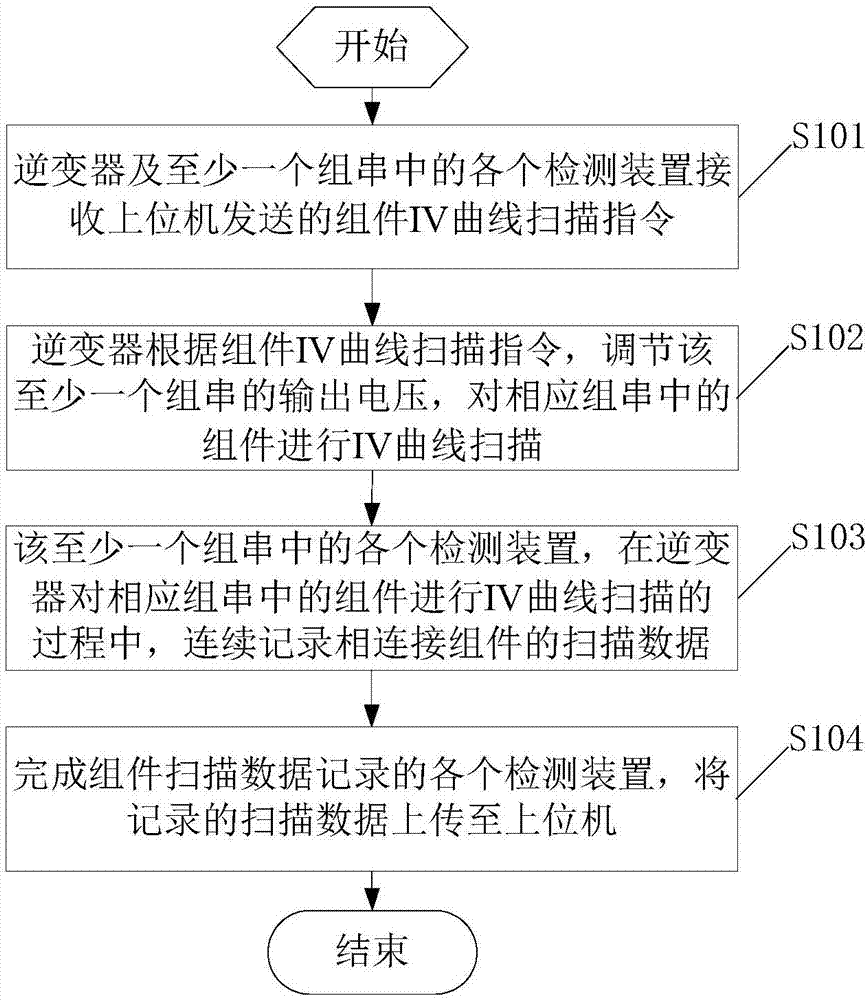

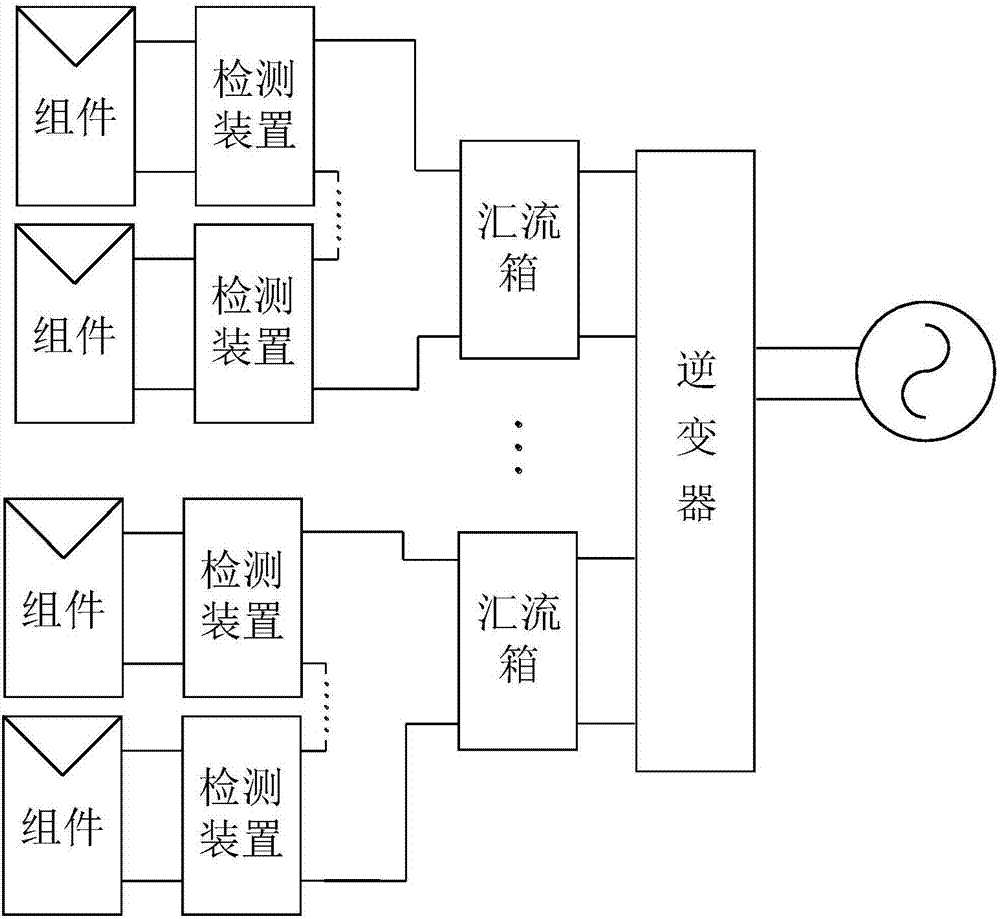

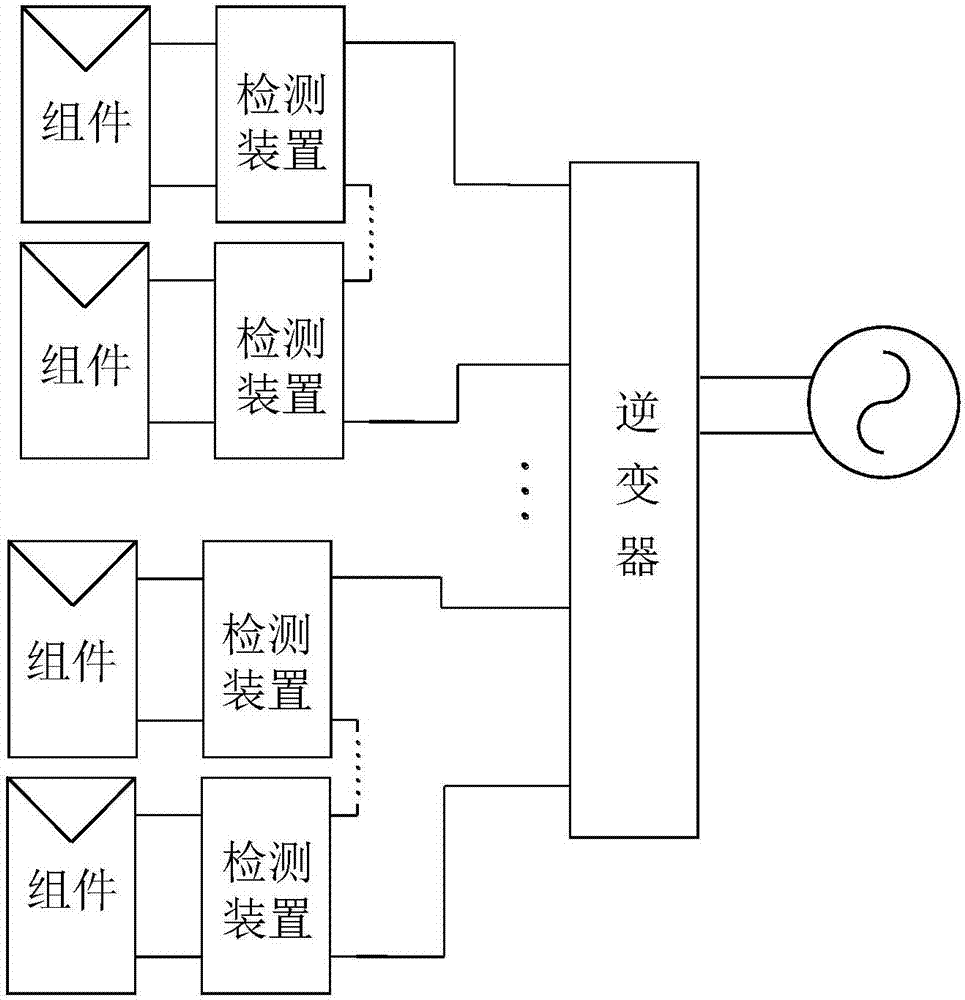

Photovoltaic power generation system and assembly IV curve scanning method thereof

ActiveCN107017836APhotovoltaic monitoringSemiconductor operation lifetime testingVoltagePhotovoltaic power generation

The present invention provides a photovoltaic power generation system and an assembly IV curve scanning method thereof. According to the photovoltaic power generation system and the assembly IV curve scanning method thereof of the invention, assembly-level detection devices are additionally adopted; when an inverter adjusts the output voltage of at least one detection device string and performs IV curve scanning on the corresponding detection device strings, corresponding detection devices continuously record the scanning data of assemblies connected with the detection devices; after completing recording the scanning data, the detection devices upload the recorded scanning data to a host computer; and therefore, the scanning data of individual assemblies can be obtained.

Owner:SUNGROW POWER SUPPLY CO LTD

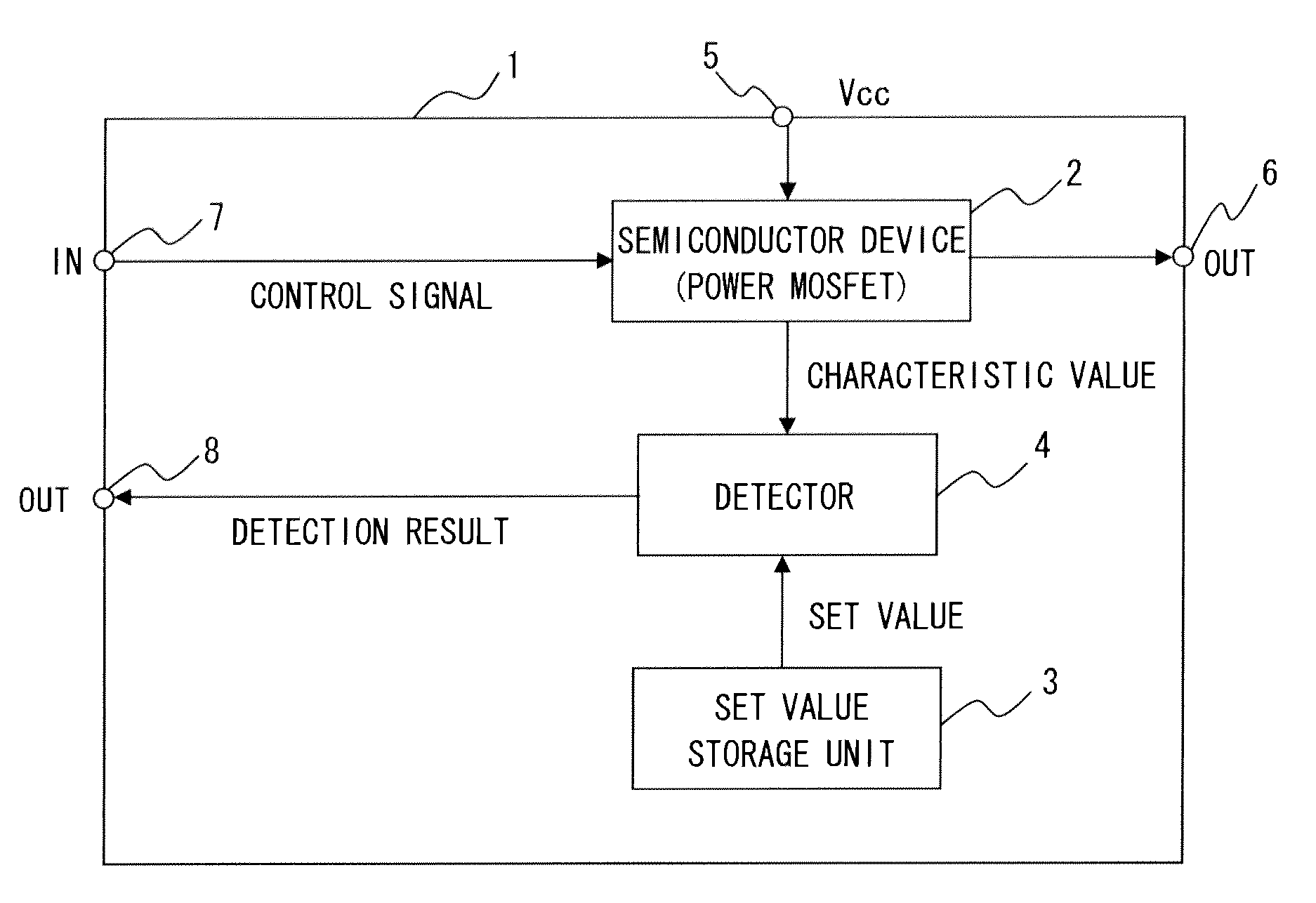

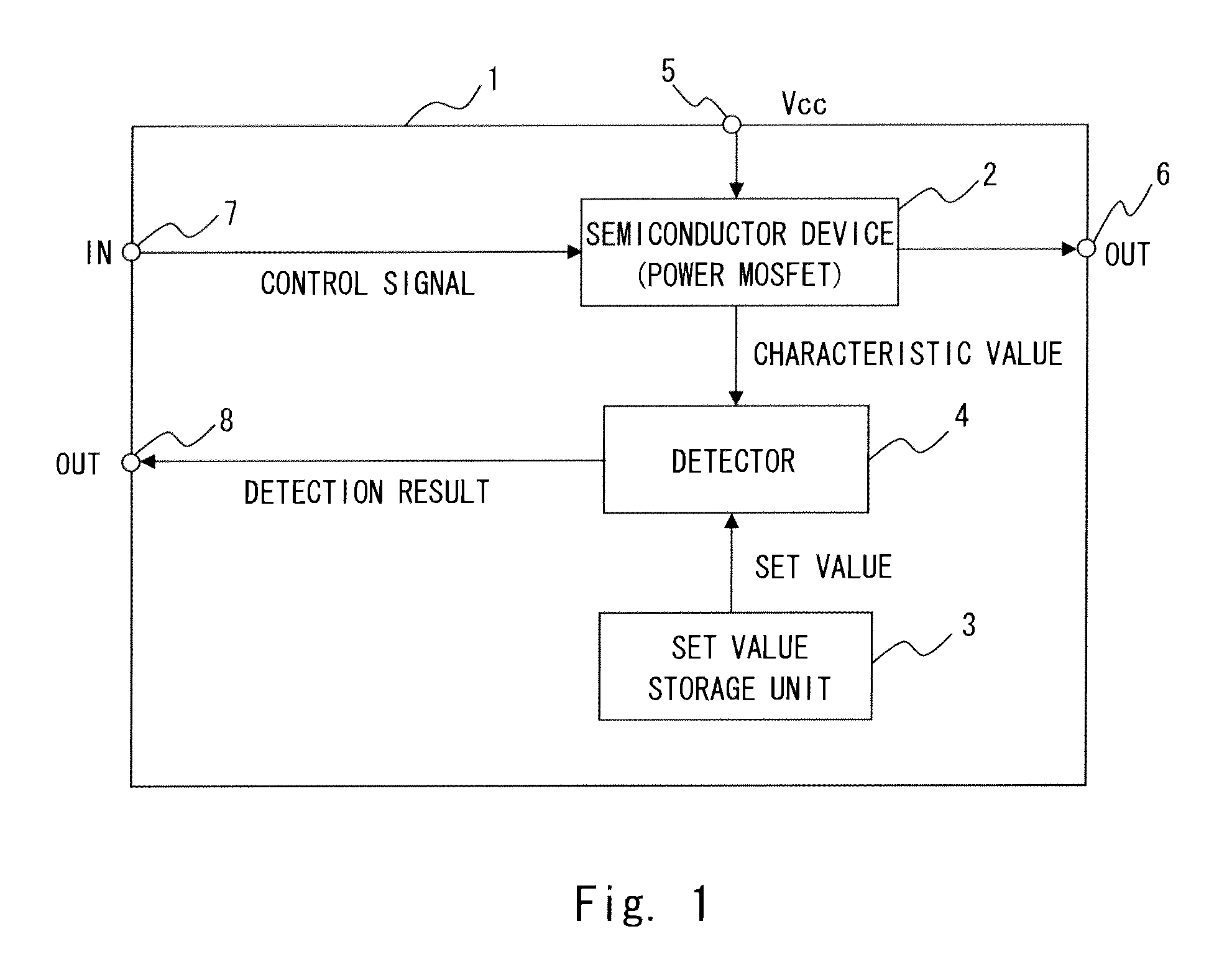

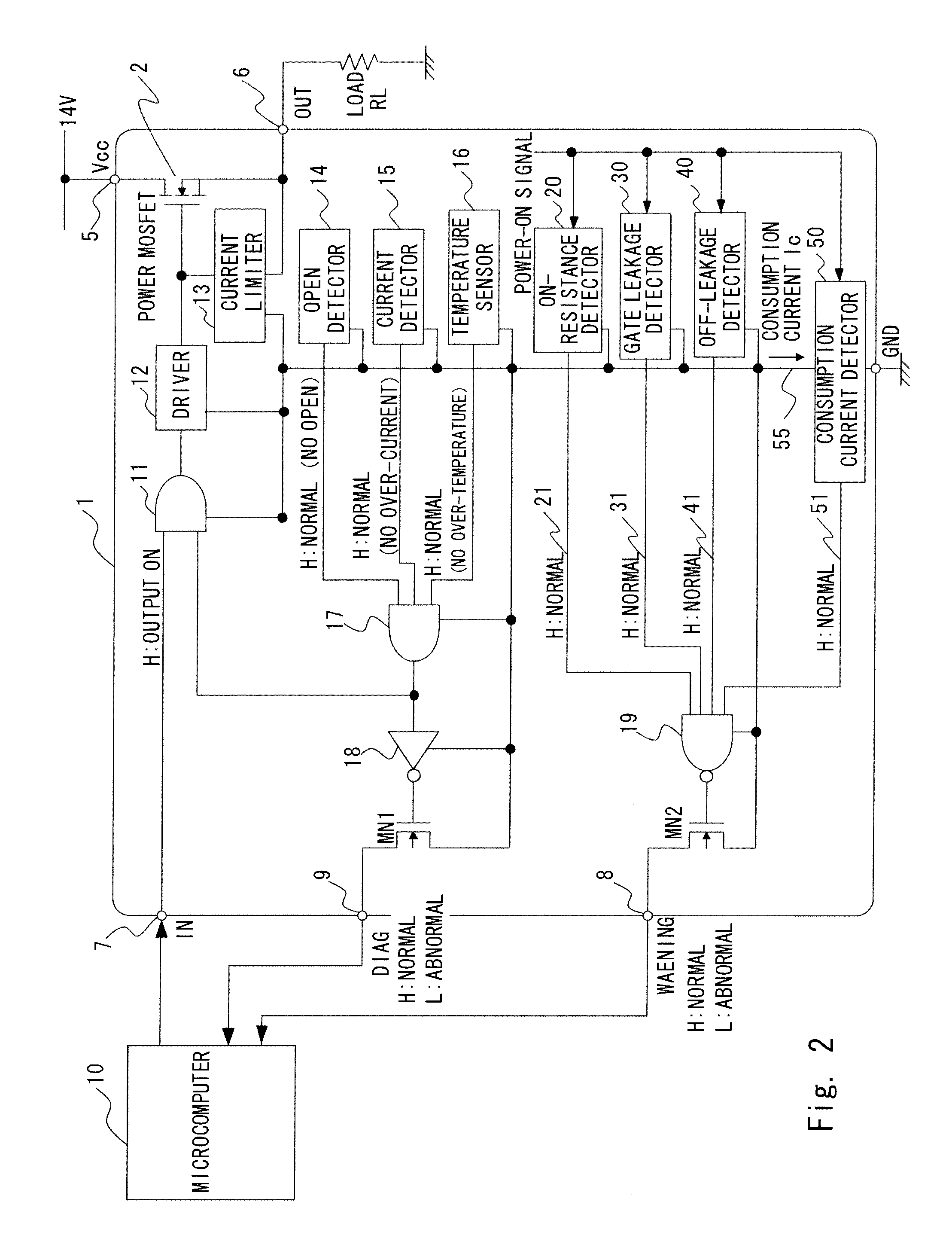

Semiconductor apparatus and method of detecting characteristic degradation of semiconductor apparatus

ActiveUS20110068818A1Avoid failureDetect degradationSemiconductor operation lifetime testingPhysical chemistryEngineering

A semiconductor apparatus (IPD) includes a set value storage unit that stores a set value determined based on an initial characteristic value of the IPD, and a detector that detects characteristic degradation of the IPD based on a characteristic value of the IPD at given timing and the set value stored in the set value storage unit. Further, a method of detecting characteristic degradation of a semiconductor apparatus (IPD) includes storing a set value determined based on an initial characteristic value of the IPD, and detecting characteristic degradation of the IPD based on a characteristic value of the IPD at given timing and the stored set value.

Owner:RENESAS ELECTRONICS CORP

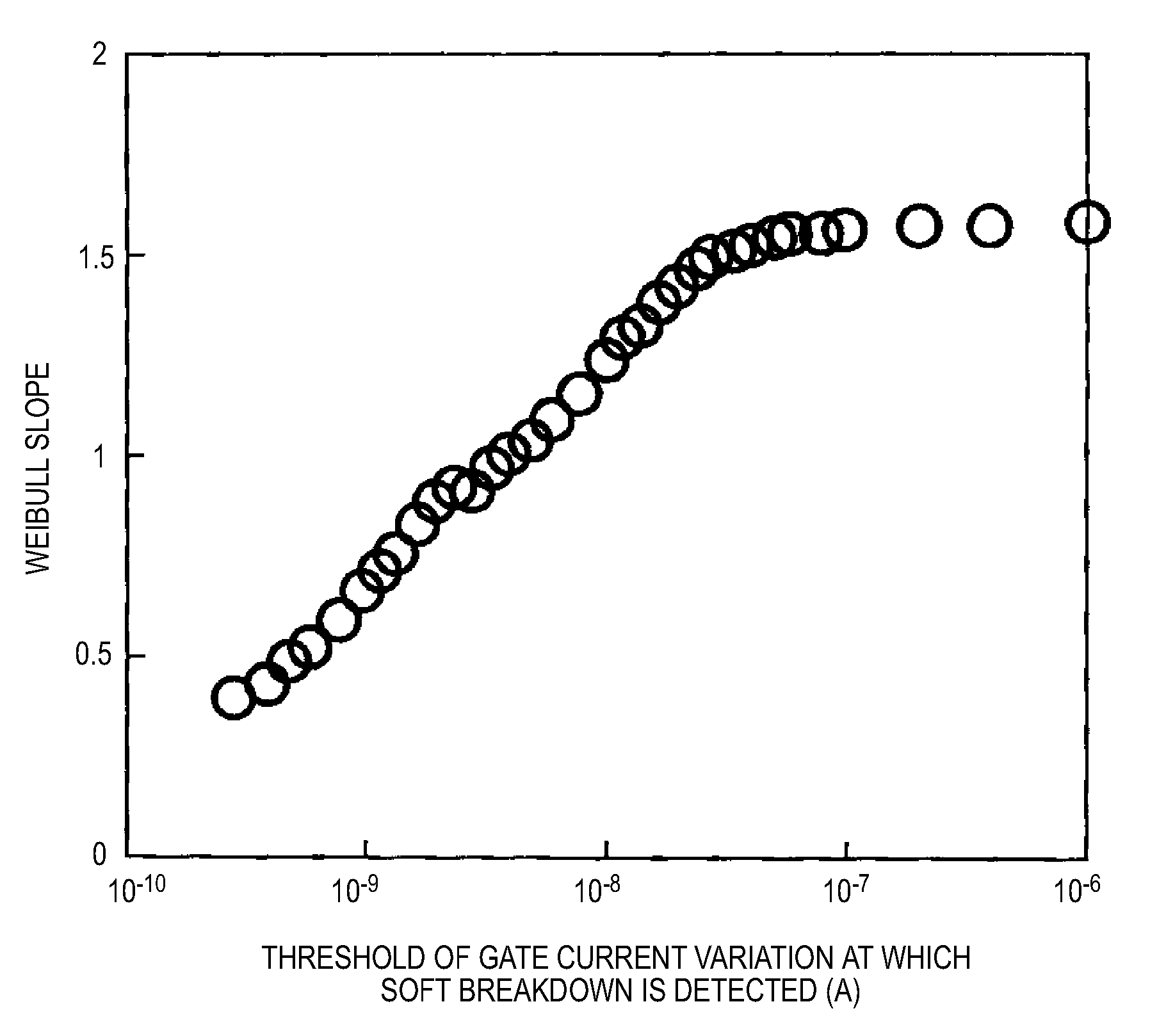

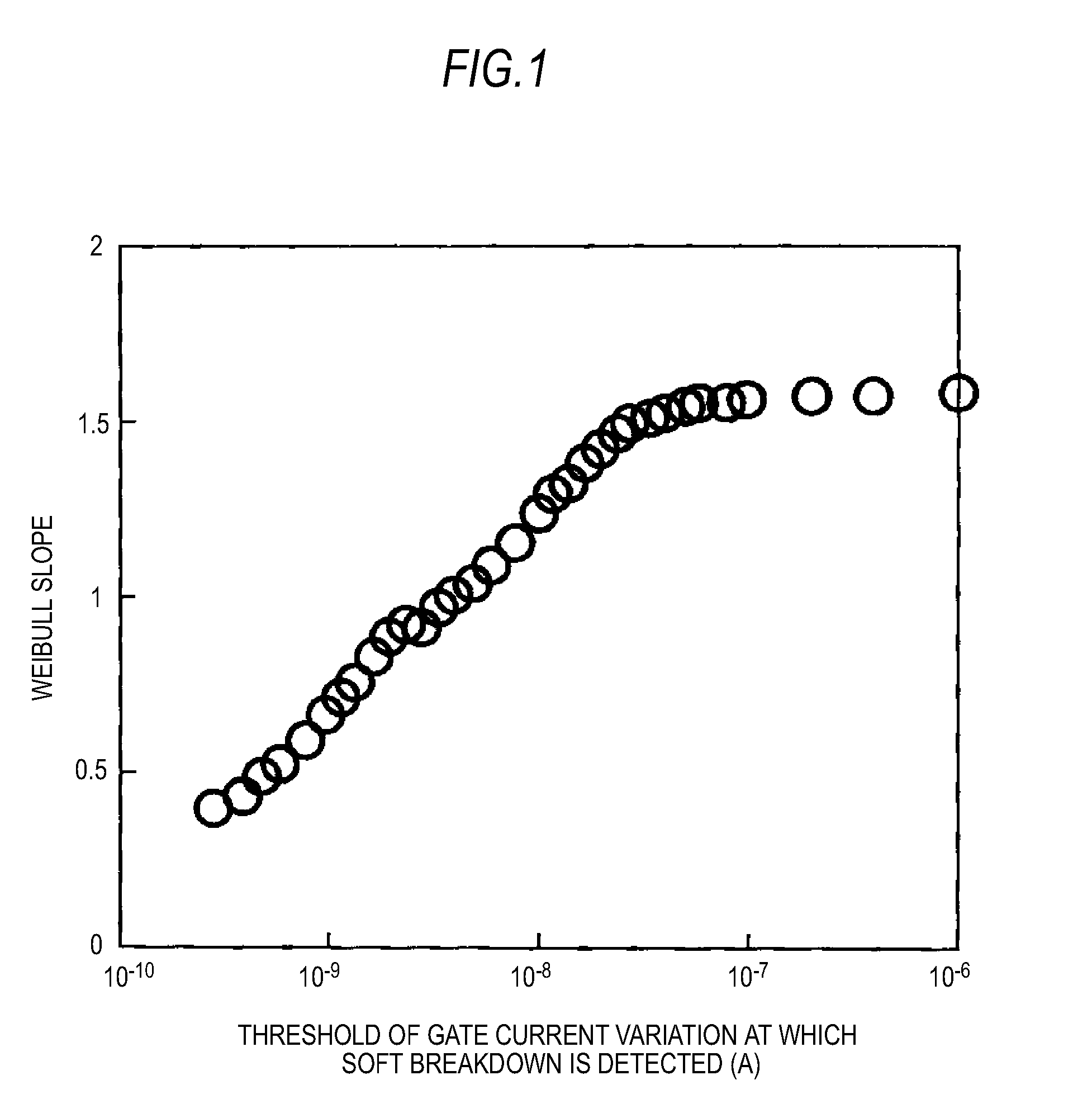

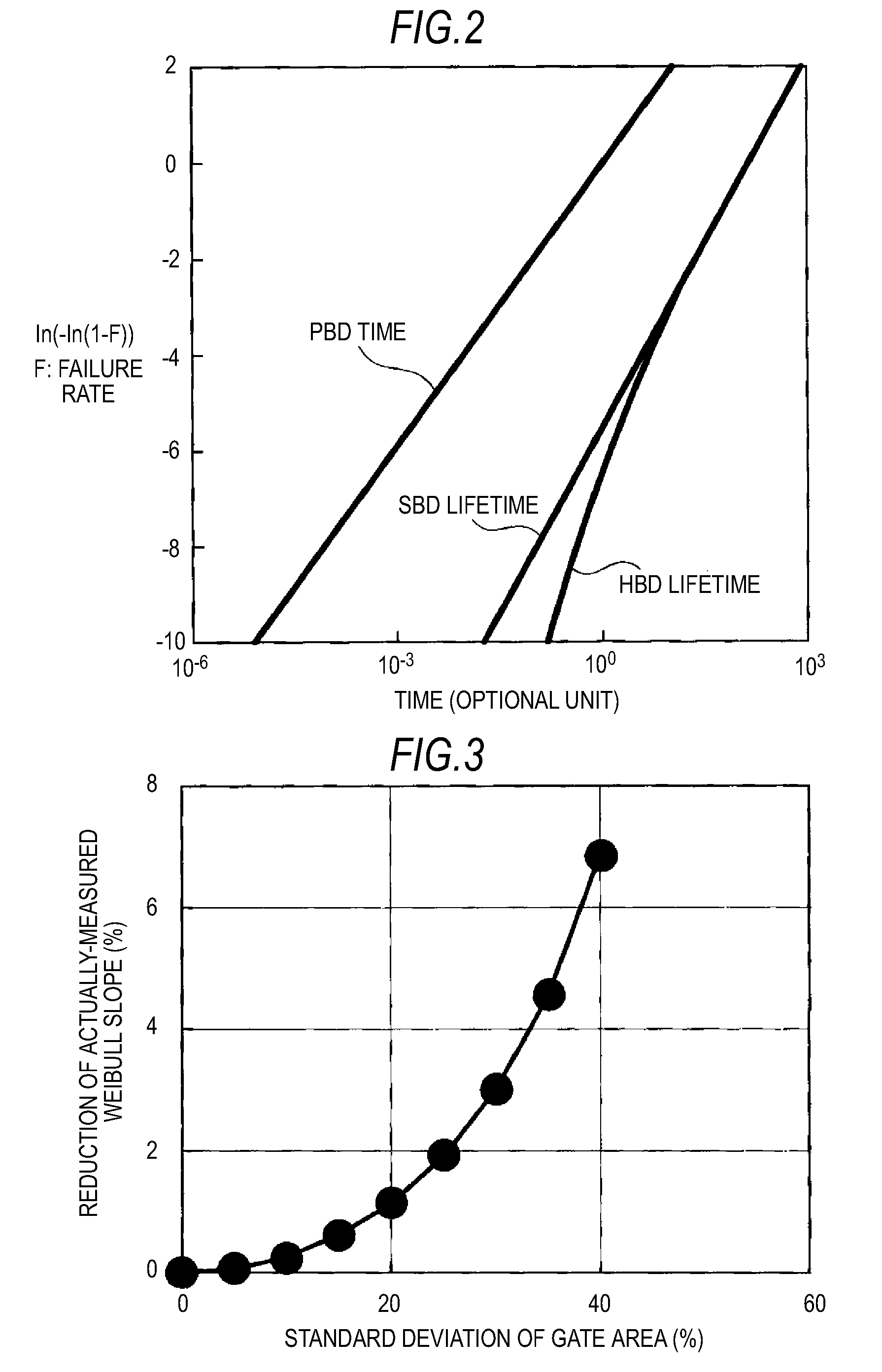

Valuation method of dielectric breakdown lifetime of gate insulating film, valuation device of dielectric breakdown lifetime of gate insulating film and program for evaluating dielectric breakdown lifetime of gate insulating film

InactiveUS20110031981A1Allocation is accurateAccurate assessmentTesting dielectric strengthSemiconductor operation lifetime testingEngineeringWeibull slope

A valuation method of a dielectric breakdown lifetime of a gate insulating film for evaluating the dielectric breakdown lifetime of the gate insulating film of a MOS type element includes the steps of: deciding a Weibull slope of lifetime distribution until reaching a soft breakdown of the gate insulating film of the MOS type element; deciding a detection condition of the soft breakdown from the decided Weibull slope after the above step; and executing a dielectric breakdown test by using the decided detection condition.

Owner:SONY CORP

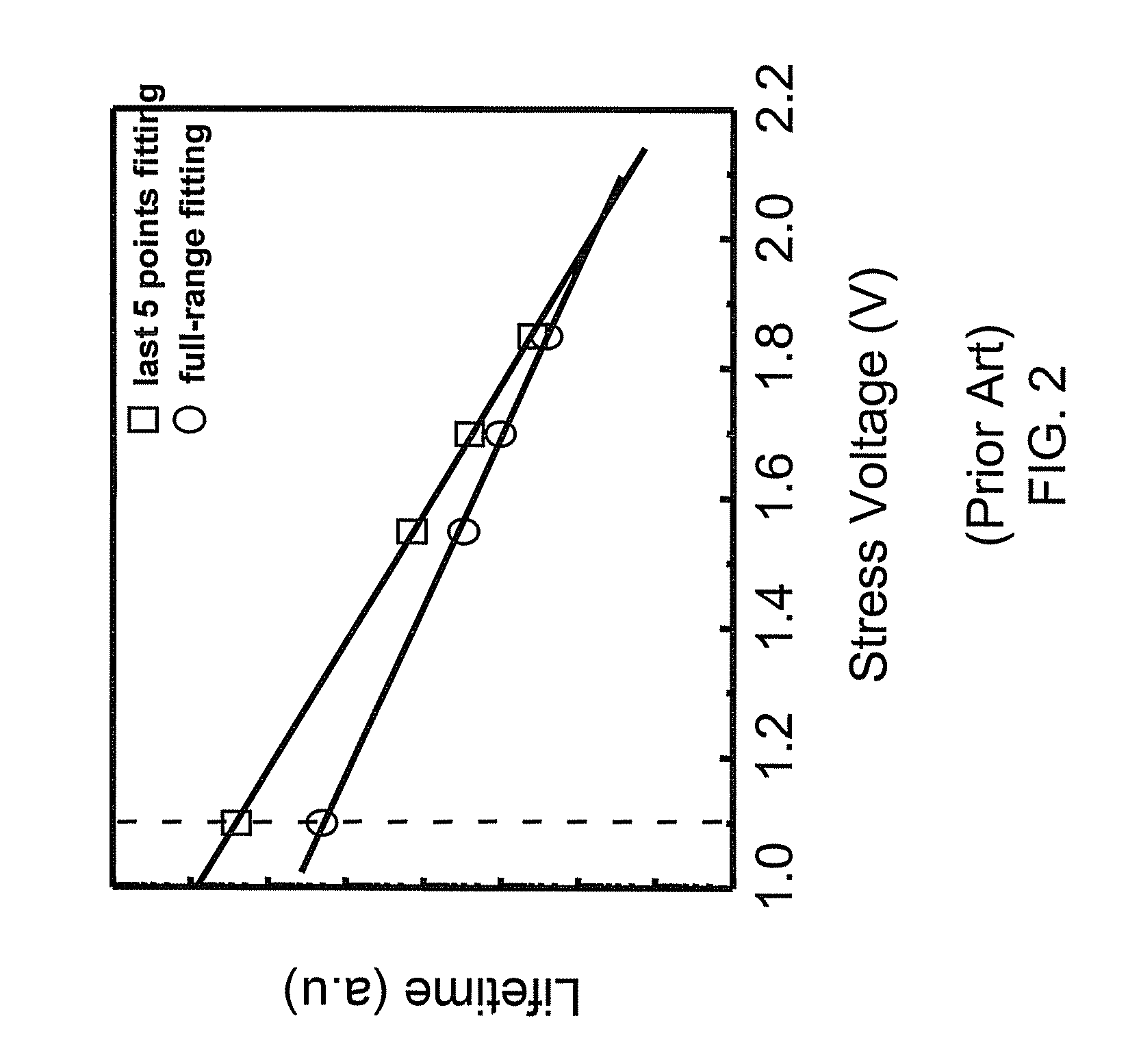

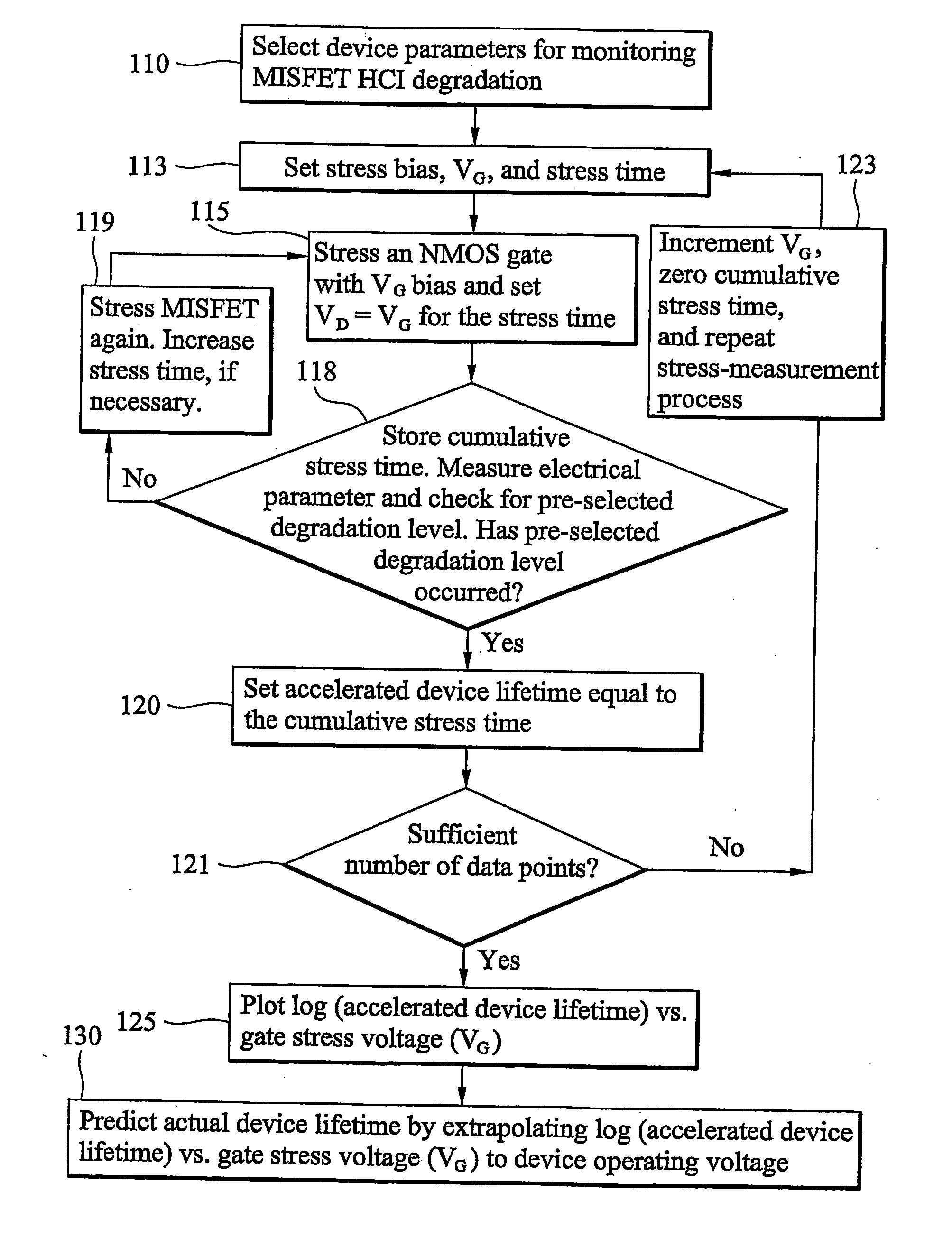

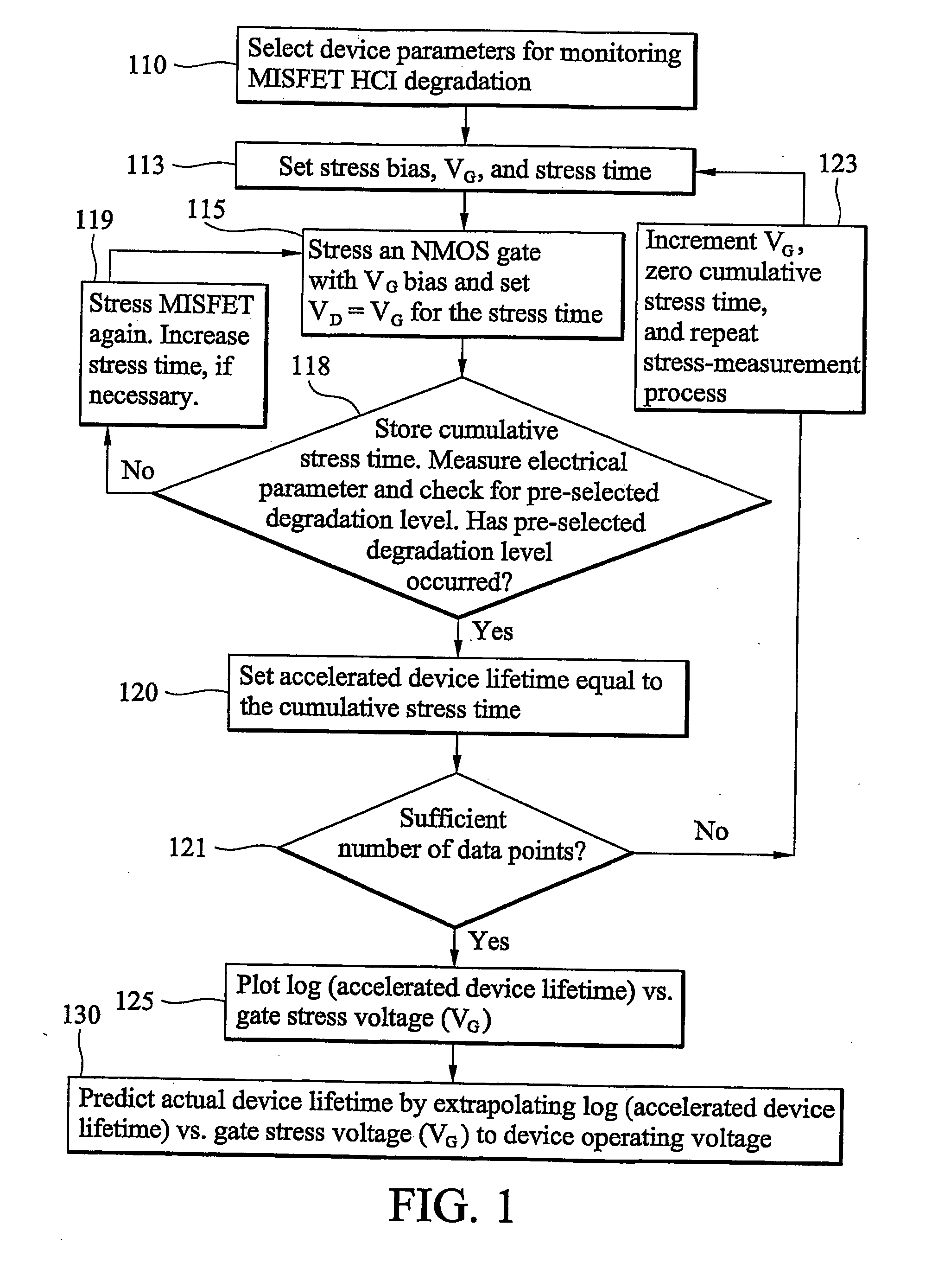

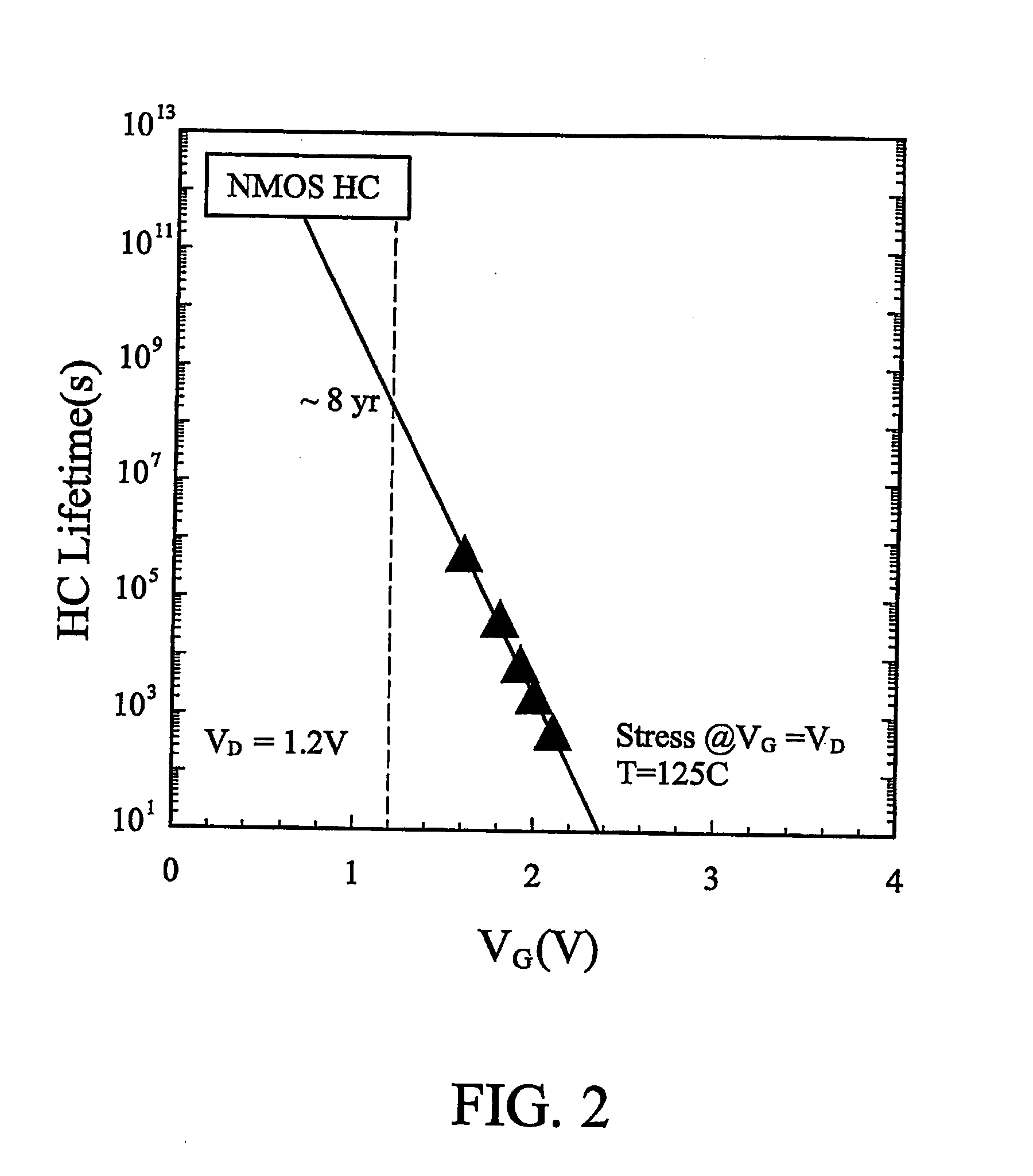

Method of predicting high-k semiconductor device lifetime

InactiveUS20060158210A1Semiconductor/solid-state device manufacturingSemiconductor operation lifetime testingDielectricElectricity

A preferred embodiment of the invention provides a method for testing a MISFET to determine the effect of hot carrier injection (HCI) on integrated circuit lifetime. The method comprises applying a positive stress voltage to a gate having a high-k dielectric, while simultaneously holding a drain voltage equal to the stress voltage. Using a stress voltage that is greater than a normal operating voltage accelerates the degradation and failure of the integrated circuit. Embodiments include monitoring electrical parameters such as threshold voltage, transconductance, linear drain current, or saturation drain current. A pre-selected shift in a monitored electrical parameter indicates device failure. Embodiments include analyzing the data by plotting the logarithm of an accelerated device lifetime versus the gate stress voltage. The device lifetime under operating conditions is predicted by extrapolating the plot for a given device operating voltage.

Owner:TAIWAN SEMICON MFG CO LTD

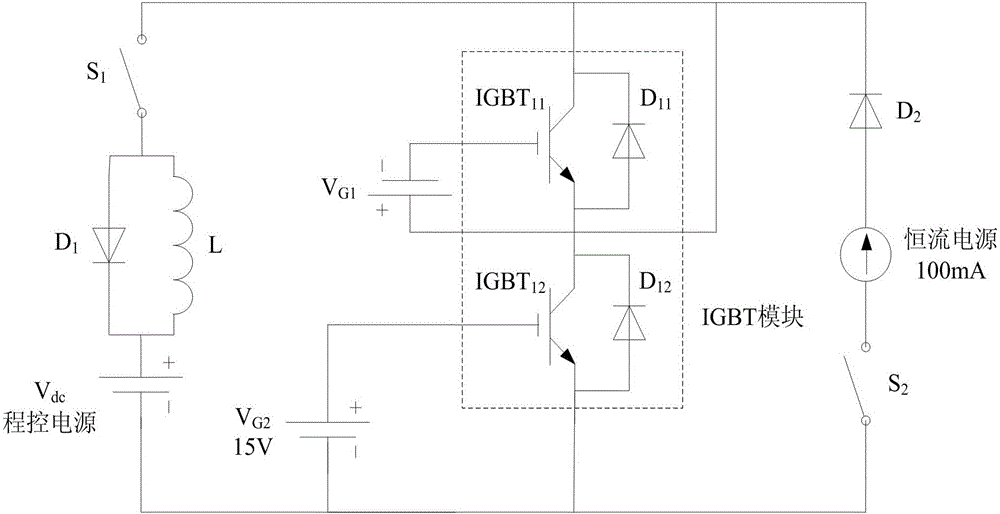

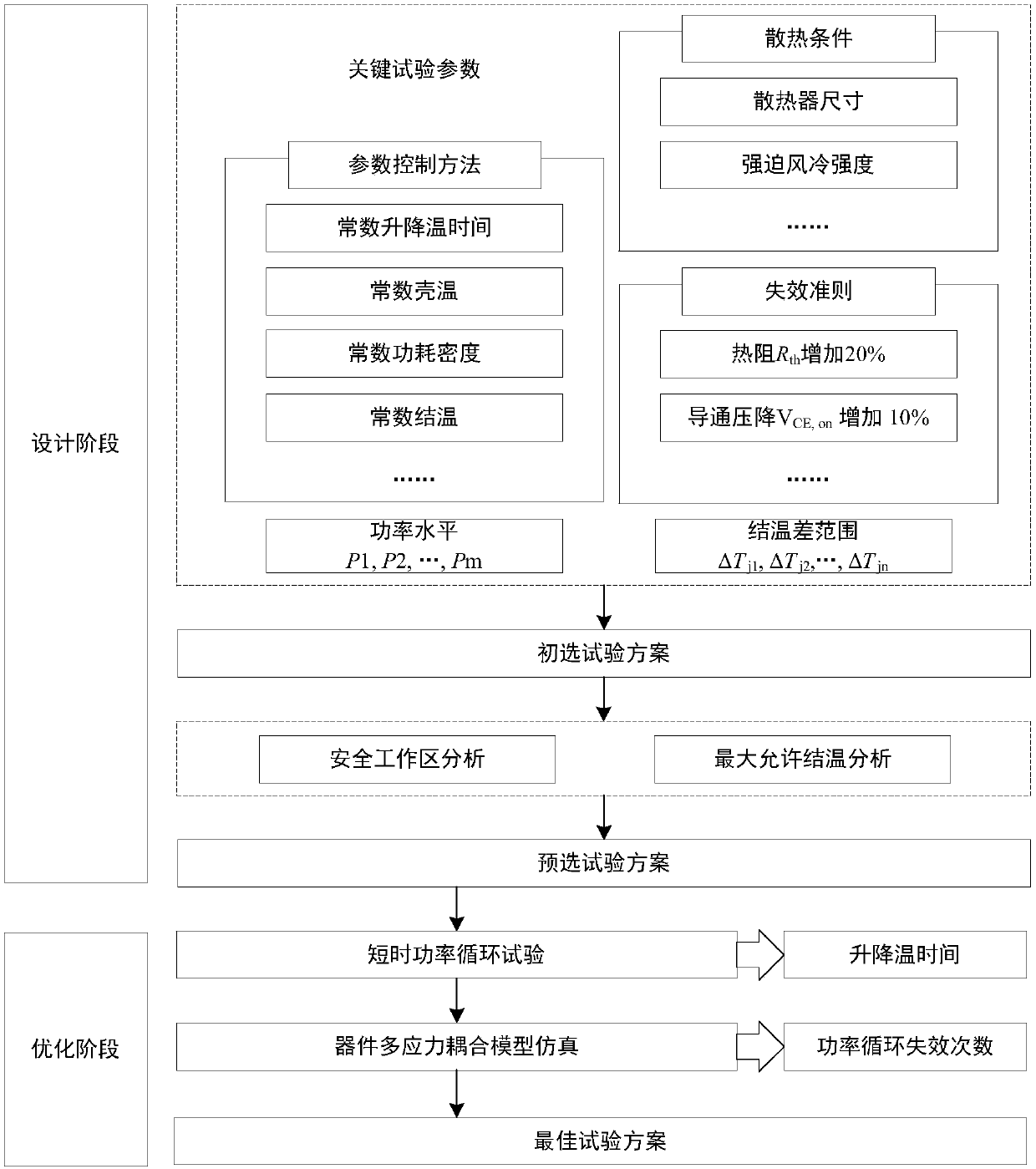

IGBT intermittent life test method based on simulation modeling and short-time test

InactiveCN107861040ABipolar transistor testingSemiconductor operation lifetime testingJunction temperatureSimulation

The invention relates to an IGBT intermittent life test method based on simulation modeling and a short-time test. The method comprises the following steps of step1, determining a heat dissipation condition; step2, determining a parameter control method; step3, determining a failure criterion; step4, determining a device power size and a junction temperature control range; step5, carrying out safeoperation area and maximum allowable junction temperature analysis; step6, implementing the short-time test; step7, carrying out simulation modeling analysis; and step8, optimizing an intermittent life test scheme. In the method, the heat dissipation condition, the parameter control method, the power size, a temperature range, the safe operation area, a failure mechanism and other factors are comprehensively considered; several sets of intermittent life test schemes are preselected; through carrying out a short-time power circulation test, temperature increasing and decreasing time of a device in single circulation is acquired; a simulation method is used to acquire a power circulation frequency before device failure; and actual power circulation test time of each preselection scheme is pre-estimated so that an optimal intermittent life test scheme is acquired through optimization. The method belongs to the power device reliability evaluation technology field.

Owner:BEIHANG UNIV

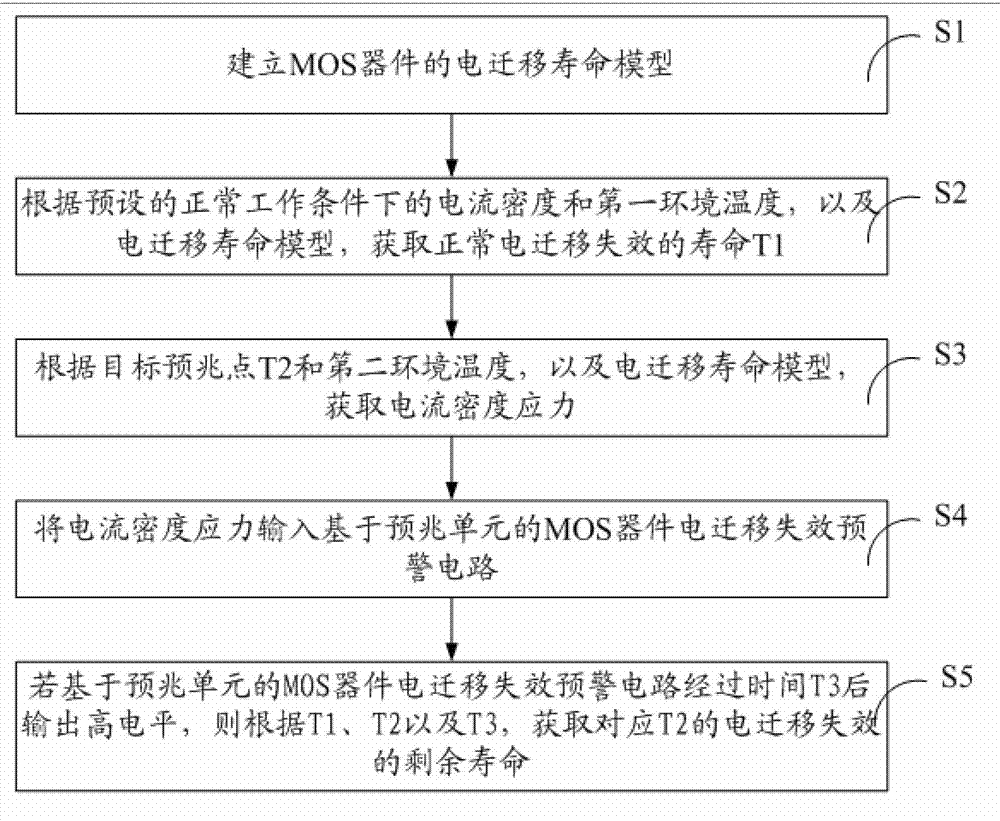

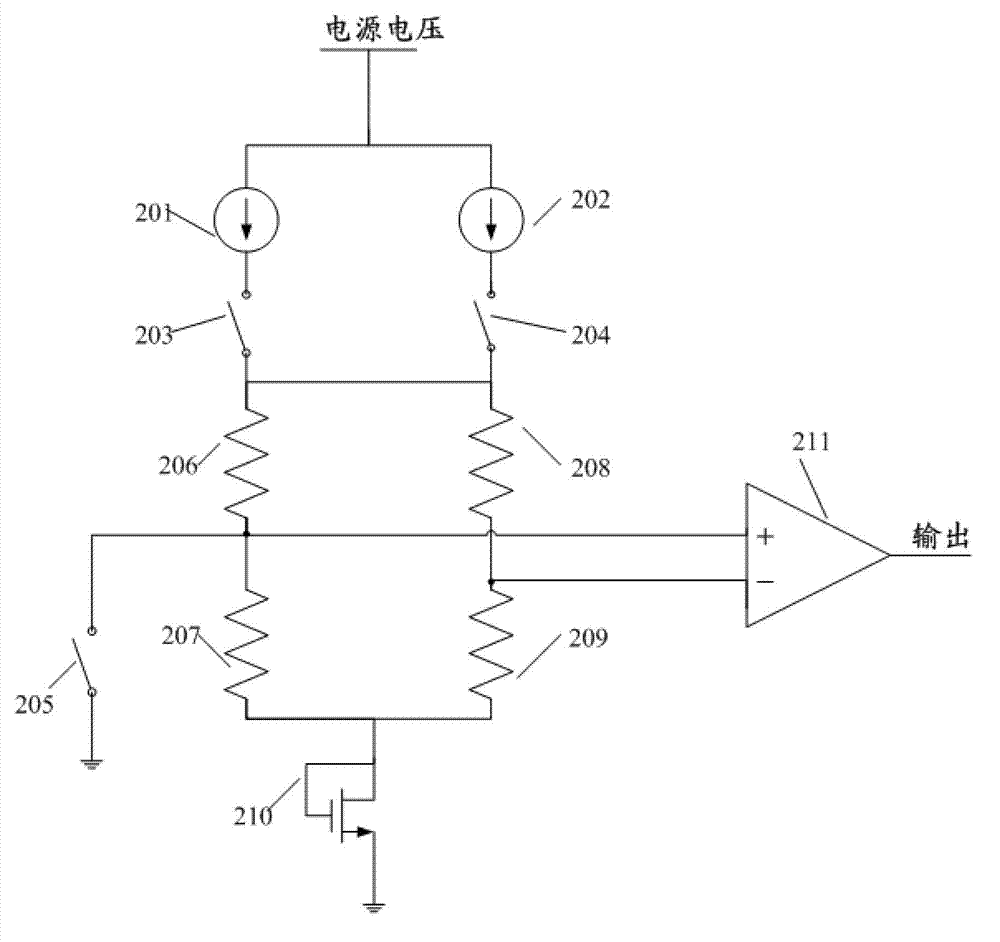

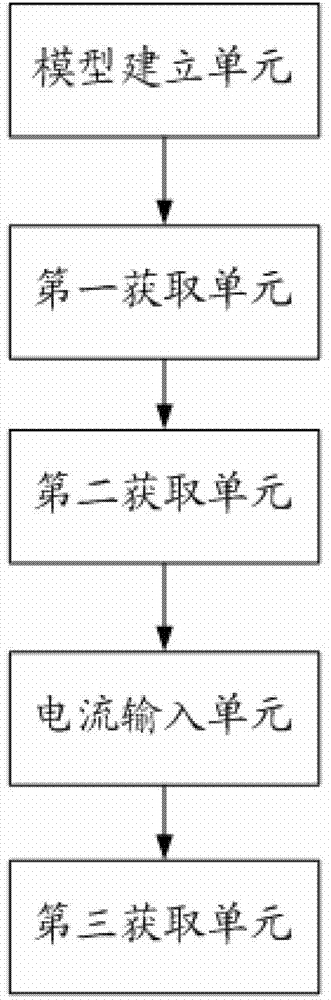

Residual life predication method and device for electromigration failure

ActiveCN102955121ATimely replacementGuaranteed reliabilitySemiconductor operation lifetime testingElectrical currentElectromigration

The invention provides a residual life predication method and device for the electromigration failure. The residual life predication method comprises the following steps of: building an electromigration life model of an MOS (metal oxide semiconductor) device; according to the current density and the first environment temperature as well as the electromigration life model under the preset normal working condition, obtaining the life T1 of normal electromigration failure; according to a target prognostic point T2, a second environment temperature and the electromigration life model, obtaining current density stress; inputting the current density stress into an MOS device electromigration failure early warning circuit based on a prognostic cell; if the MOS device electromigration failure early warning circuit based on the prognostic cell processes the current density stress for time T3, outputting a high electrical level; and according to T1, T2 and T3, obtaining the residual life of the electromigration failure corresponding to T2. The invention also provides a residual life predication device for the electromigration failure, which has the characteristics that the reliability on predicting the residual life of the electromigration failure of the MOS device can be improved, the prediction efficiency is improved, and the cost is lowered.

Owner:FIFTH ELECTRONICS RES INST OF MINIST OF IND & INFORMATION TECH

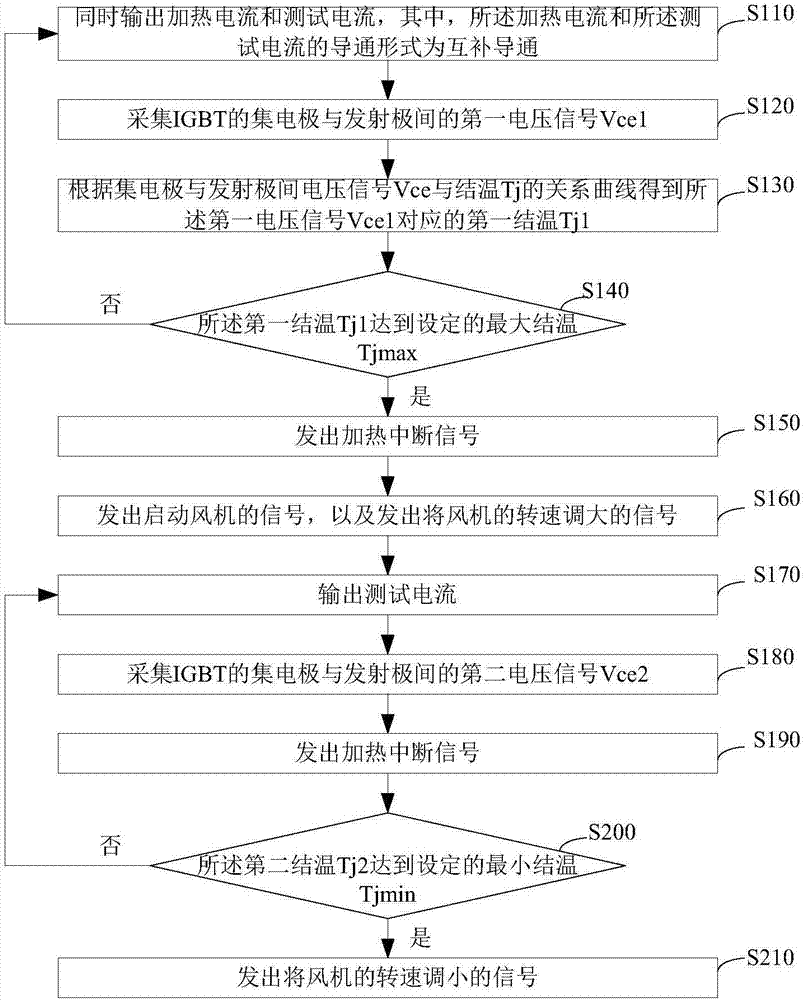

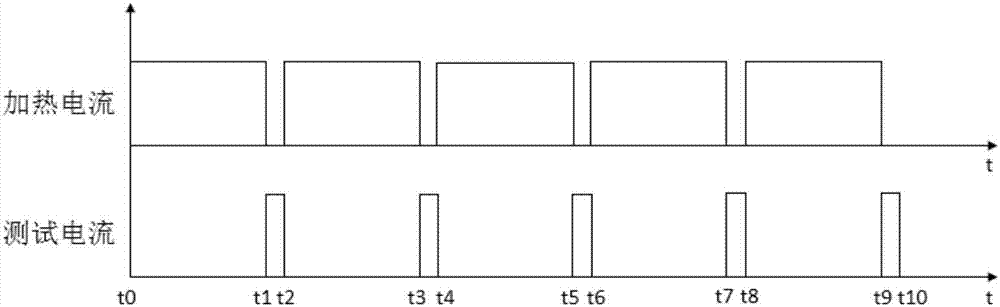

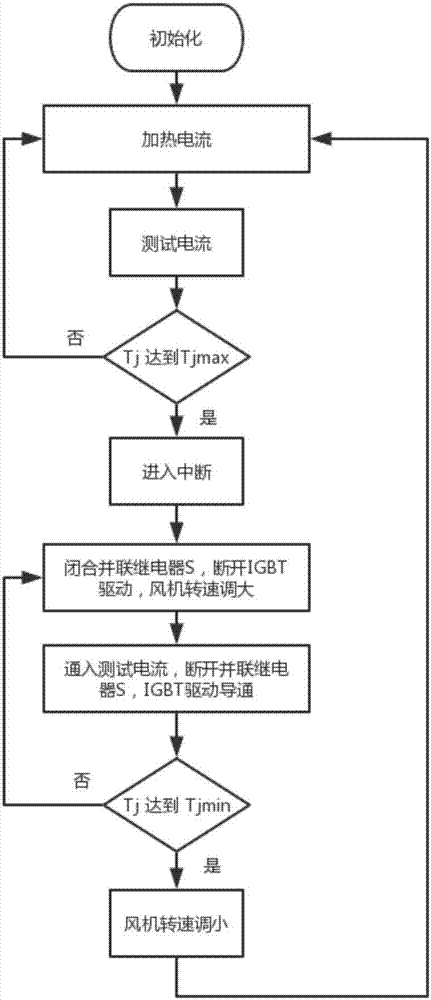

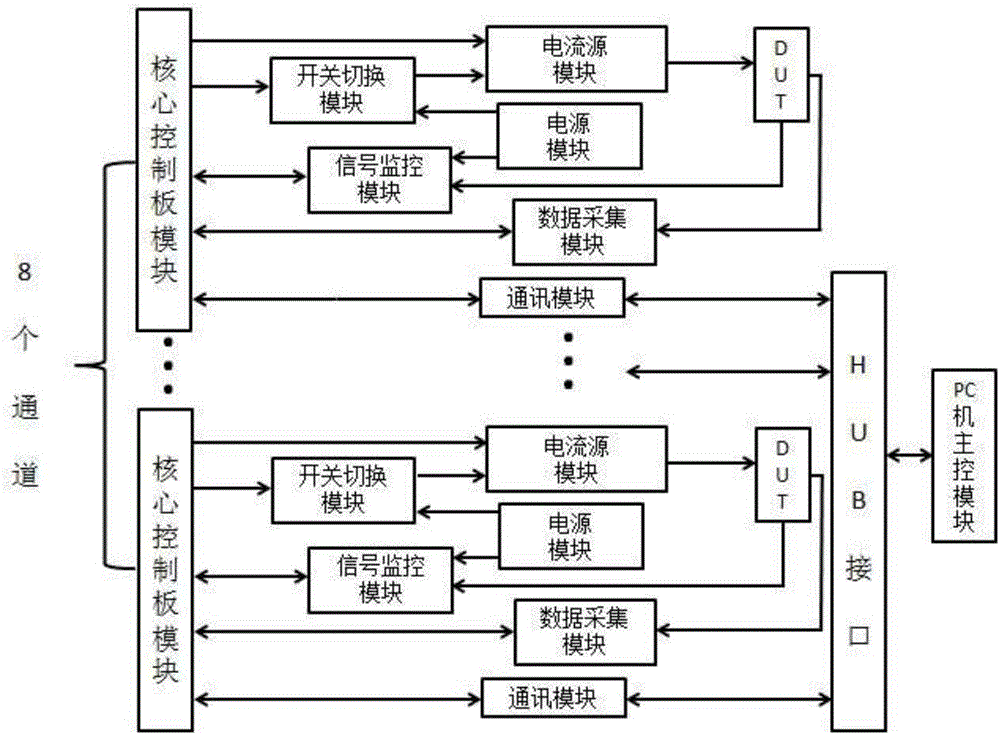

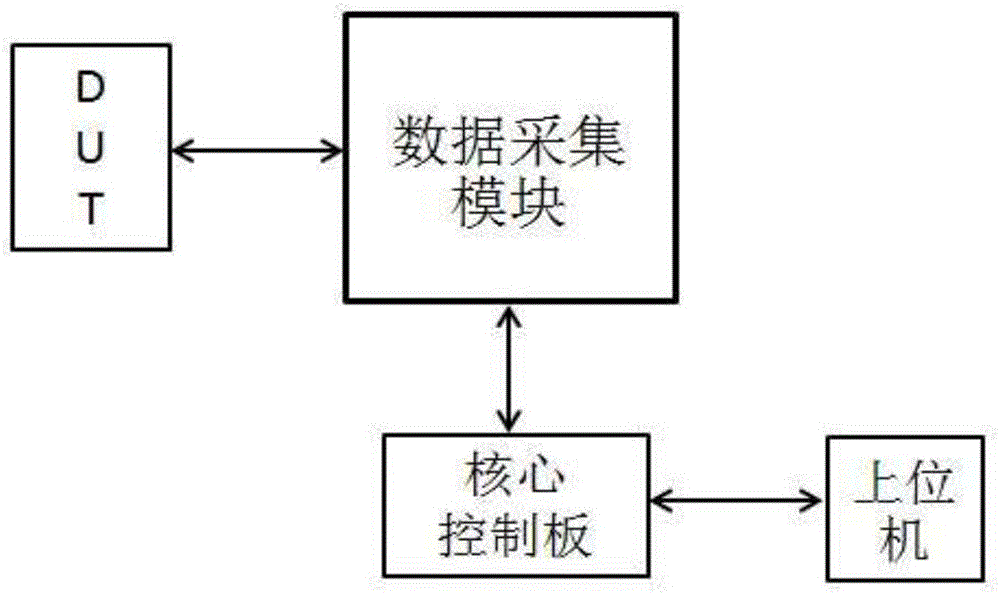

Control method, device and system of IGBT (insulated gate bipolar translator) reliability test

InactiveCN107991597AHigh precisionProcessing speedProgramme controlComputer controlJunction temperatureEngineering

The invention relates to the technical field of semiconductor power devices, and particularly discloses a control method of an IGBT (insulated gate bipolar translator) reliability test. The method comprises the steps as follows: outputting a heating current and a test current; acquiring a first voltage signal Vce1 between a collector and an emitter of an IGBT; obtaining a first junction temperature Tj1 corresponding to the first voltage signal Vce1; judging whether the first junction temperature Tj1 reaches a set maximum junction temperature Tjmax, and emitting a heating interruption signal ifthe maximum junction temperature is reached; sending a fan starting signal and sending a fan rotation speed increase signal; outputting the test current; acquiring a second voltage signal Vce2 between the collector and the emitter of the IGBT; obtaining a second junction temperature Tj2 corresponding to the second voltage signal Vce2; judging whether the second junction temperature Tj2 reaches the set minimum junction temperature Tjmin, and sending a fan rotation speed reduction signal if the minimum junction temperature is reached. The invention further discloses a control device and systemof the IGBT reliability test. The provided control method of the IGBT reliability test has the advantages of high control accuracy and high efficiency.

Owner:JIANGSU CAS IGBT TECHNOLOGY CO LTD

Method for performing burn-in test

ActiveUS20120139566A1Improve surface roughnessStable and reliable burn-in testDiode testingSemiconductor operation lifetime testingSurface roughnessHigh surface

Provided is a method for performing a burn-in test on an object under test in which a plurality of electrodes are provided in positions at different heights. The method comprising steps of: preparing an object under test in which an electrode in a higher position have a higher surface roughness among the plurality of electrodes; bringing a plurality of sheet-type probes into contact with the plurality of electrodes, respectively; and supplying an electric current with the plurality of electrodes through the plurality of sheet-type probes. By implementing the method, the sheet-type probes can be kept in stable contact with the electrodes because electrodes in a higher position have a higher surface roughness Ra than electrodes in a lower position. Consequently, stable and reliable burn-in test can be performed.

Owner:TDK CORPARATION +1

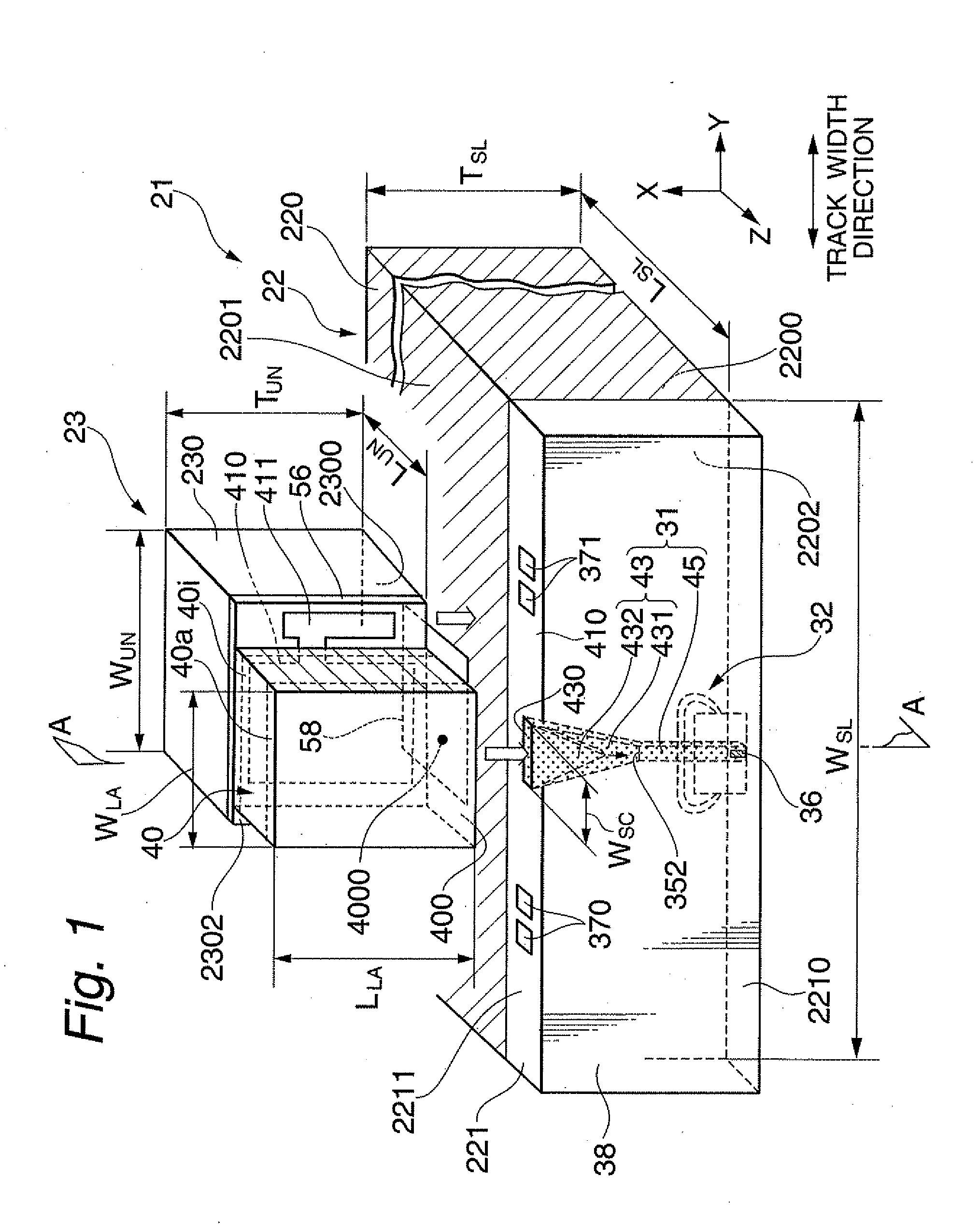

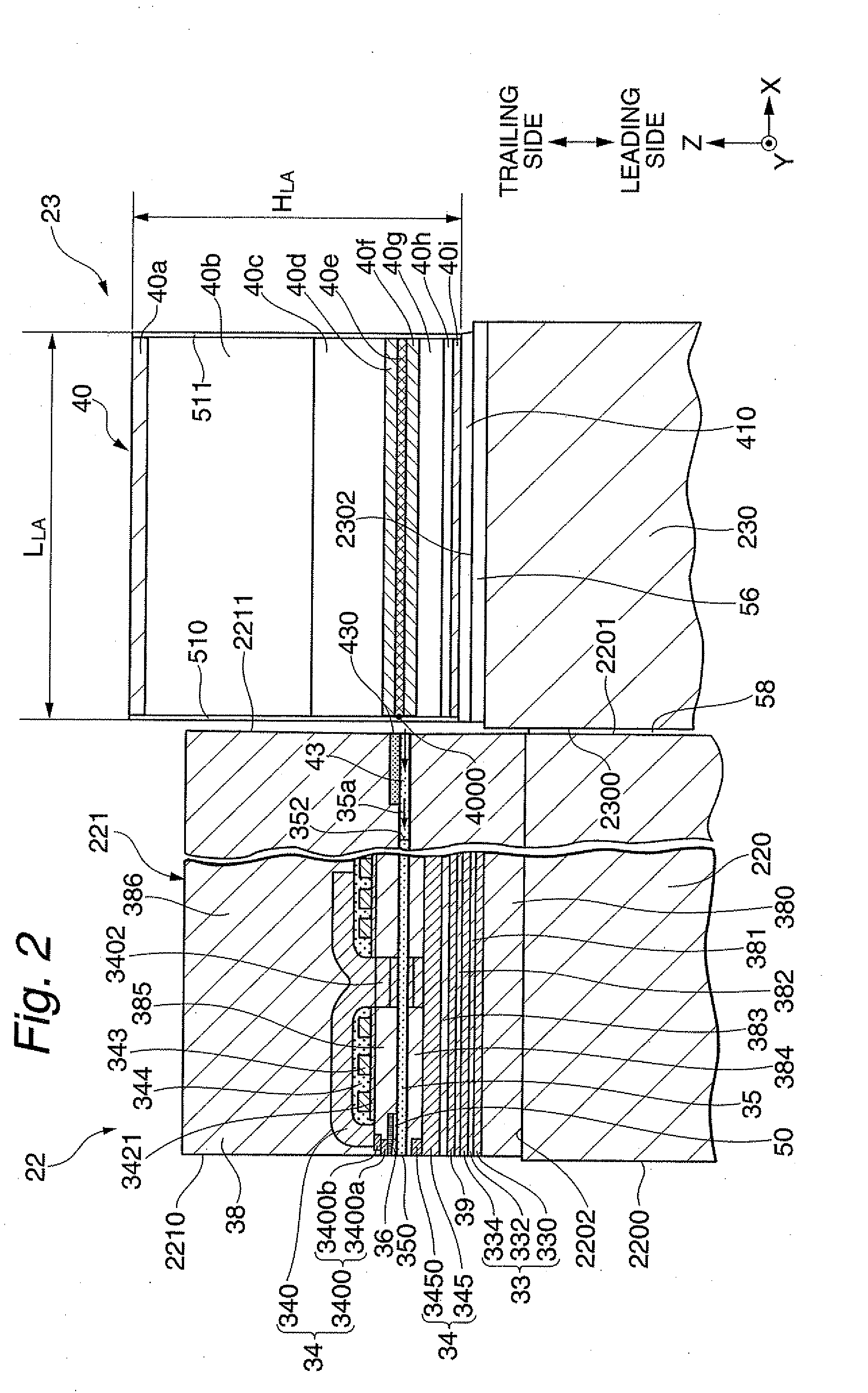

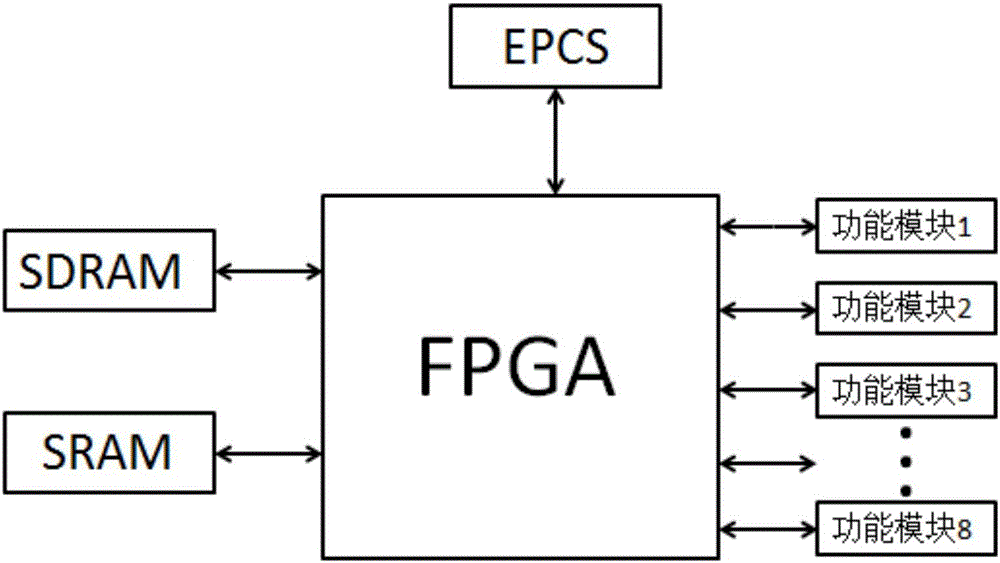

Multi-path IGBT junction temperature and thermal fatigue real-time monitoring system

InactiveCN105929316AReal-time protectionSemiconductor operation lifetime testingFpga implementationsJunction temperature

The invention discloses a multi-path IGBT junction temperature and thermal fatigue real-time monitoring system. The system is a reliability testing system which is realized based on FPGA and is suitable for the real-time monitoring of the junction temperature of IGBT. The system selects the voltage VGE during the short circuit of the grid and collector as the temperature sensitive parameter of the IGBT, During the cooling process, the temperature sensitive parameter is measured, and by means of linear fitting and a least square method, the relation of the junction temperature and time t is deduced, and then the junction temperature is deduced reversely. The system not only can monitor the junction temperature of a device to be monitored in real time, and can accelerate the failure process of a product by means of a PID self-calibration algorithm, thereby effectively shortening the experiment time and completing the IGBT thermal fatigue experiment at the end. On the basis, over-current, over-voltage, and over-temperature protection tasks are additionally provided, and by means of alarming and automatic shutdown, the IGBT device can be protected in real time, and the thermal fatigue monitoring task can be completed. The system can be expanded and improved in functions based on the actual needs, and the function of the IGBT junction temperature and thermal fatigue real-time monitoring system can be further enriched.

Owner:BEIJING UNIV OF TECH

Devices and methods for LED life test

Owner:IND TECH RES INST

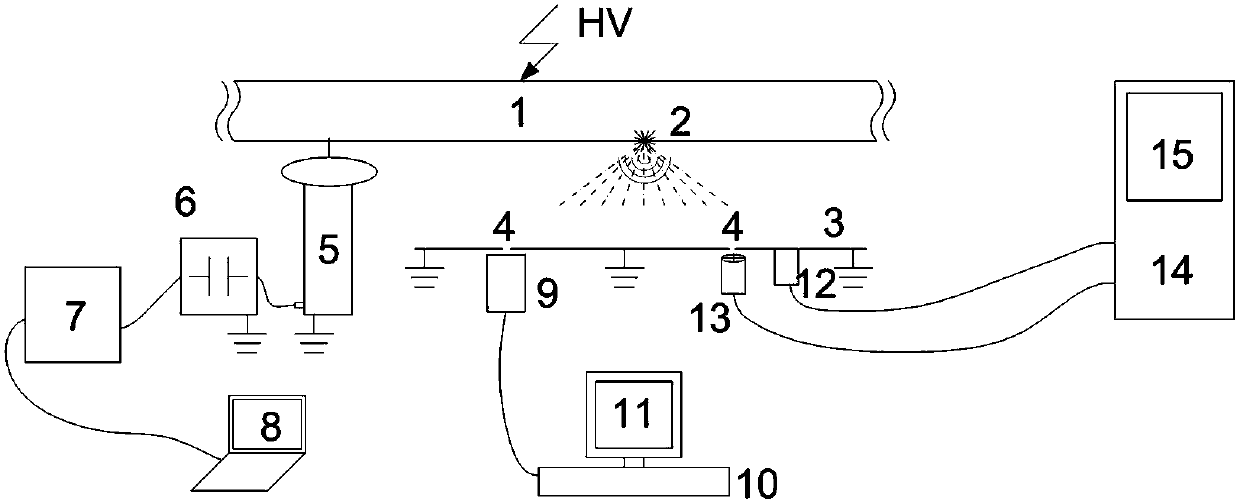

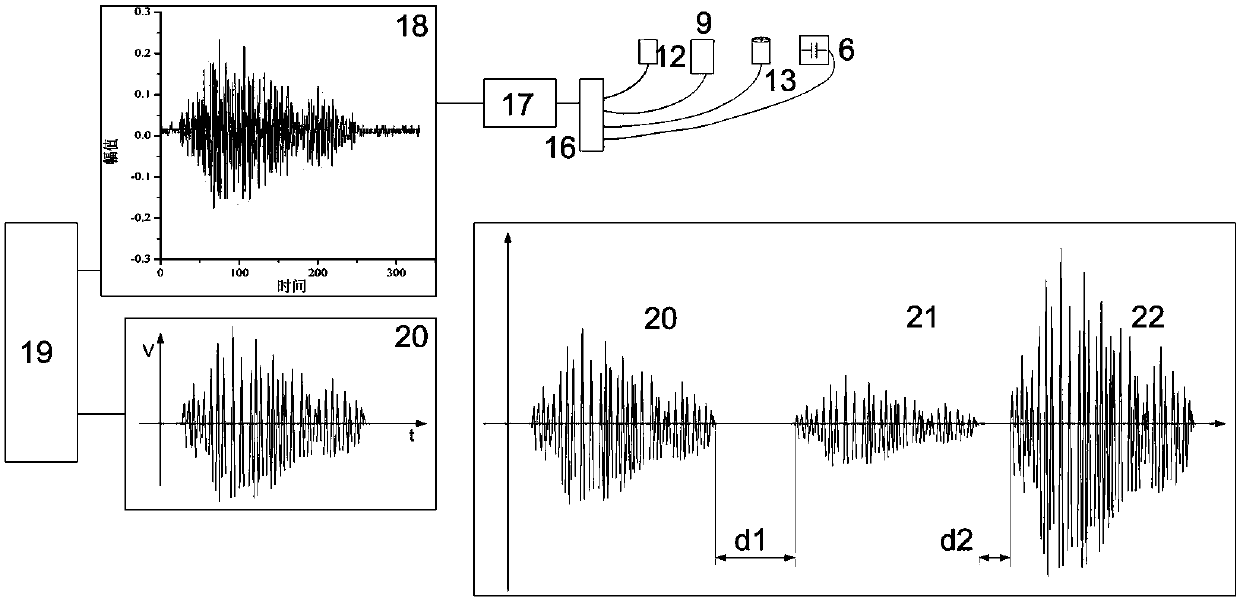

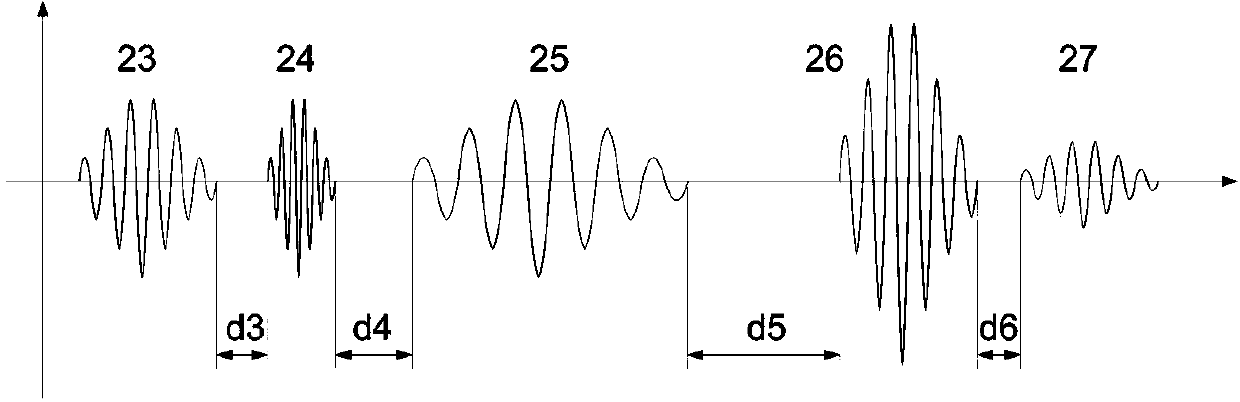

Method for testing performance of different types of partial discharge detector mainframes based on analog voltage signal injection

ActiveCN103472424AReproducibleQuantifiableCurrent/voltage measurementSemiconductor operation lifetime testingTest performanceSimulation based

The invention discloses a method for testing performance of different types of partial discharge detector mainframes based on analog voltage signal injection. A function generator with adjustable output frequency of 0-3.5 GHz and an adjustable output amplitude of 0-10 V is adopted in the method disclosed by the invention, and equivalent analog voltage signals generated by the function generator and based on partial discharge waveforms actually tested by a pulse current partial discharge detection sensor, an ultrasonic partial discharge detection sensor and an ultrahigh frequency partial discharge detection sensor are correspondingly and directly injected into the mainframes of a pulse current partial discharge detector, an ultrasonic partial discharge detector and an ultrahigh frequency partial discharge detector or through DC blocking elements with frequency bands of 10 kHz to 10 MHz. The method disclosed by the invention has the excellent advantages that the testing method is universal and standard, the testing result is reproducible and quantifiable, the range of application of testing objects is wide, the testing contents are comprehensive, and the like.

Owner:YUN NAN ELECTRIC TEST & RES INST GRP CO LTD ELECTRIC INST +1

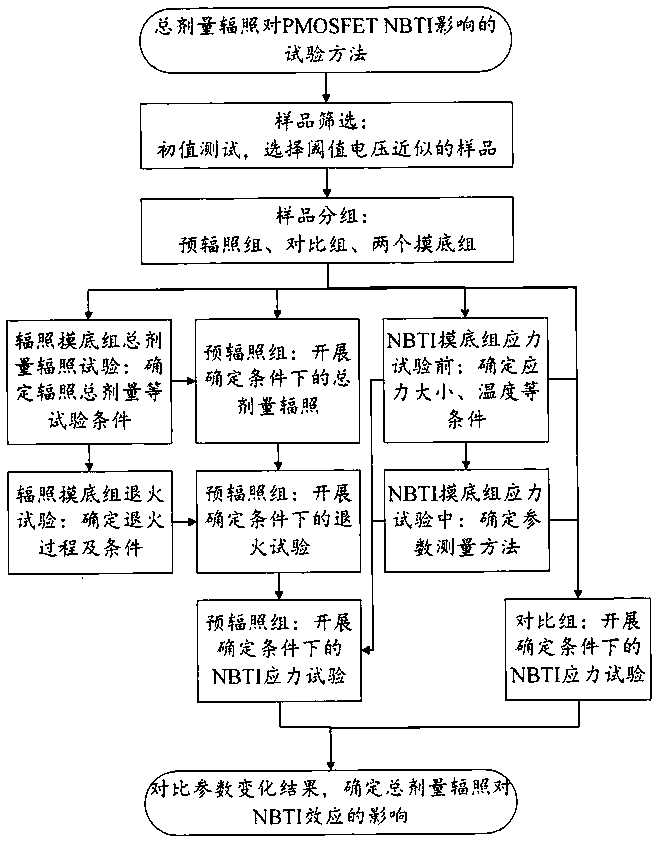

Test method for influence of total dose irradiation on PMOSFET negative bias temperature instability

ActiveCN108037438AEnsure consistencySemiconductor operation lifetime testingPre irradiationTest sample

The invention relates to a method for testing the influence of total dose irradiation on the PMOSFET negative bias temperature instability. The method includes test sample grouping and test parameterselection; the total dose irradiation and annealing tests of the test sample; and the negative bias temperature instability measurement of the test sample. In order to ensure the consistency and accuracy of the test result, the sample is divided into a pre-irradiation group, a comparison group and two pre-test groups, and on the basis of the pre-test, the total dose irradiation and annealing testsare carried out on the pre-irradiation group under the determination condition, the comparison group and the pre-irradiation group are subjected to a negative bias temperature instability test underthe same condition, and the test result is compared, the influence of the total dose irradiation on the negative bias temperature instability of the sample is obtained. The method provided by the invention can represent the influence of the total dose irradiation on the negative bias temperature instability of a P-channel metal oxide semiconductor field effect transistor.

Owner:XINJIANG TECHN INST OF PHYSICS & CHEM CHINESE ACAD OF SCI

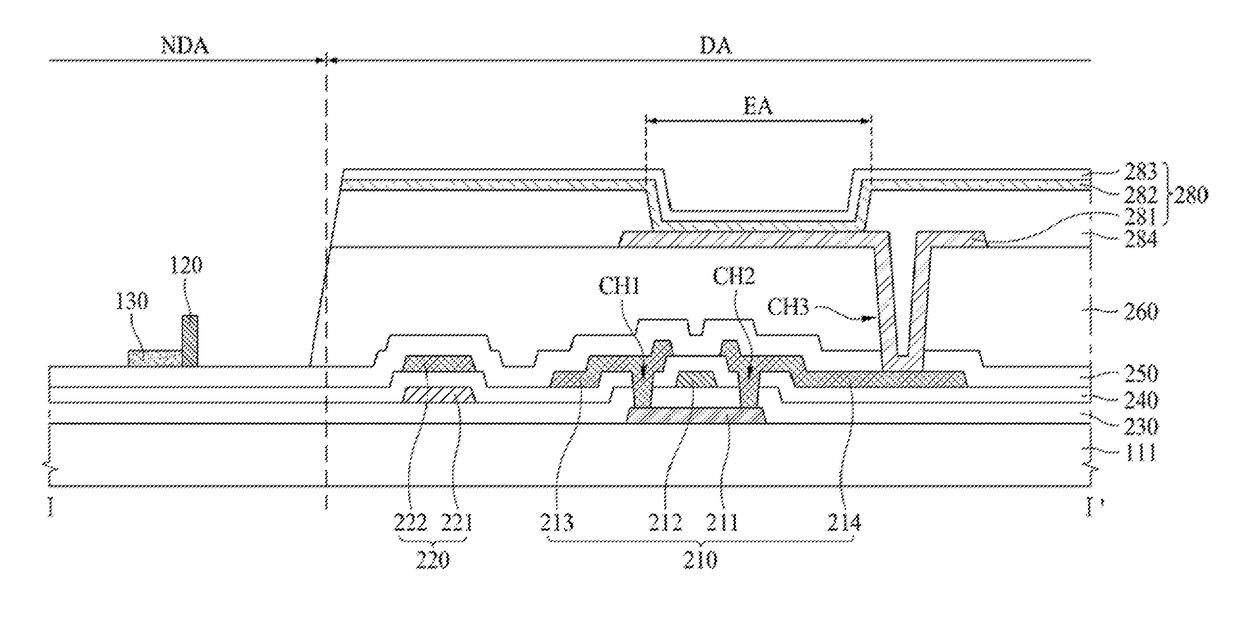

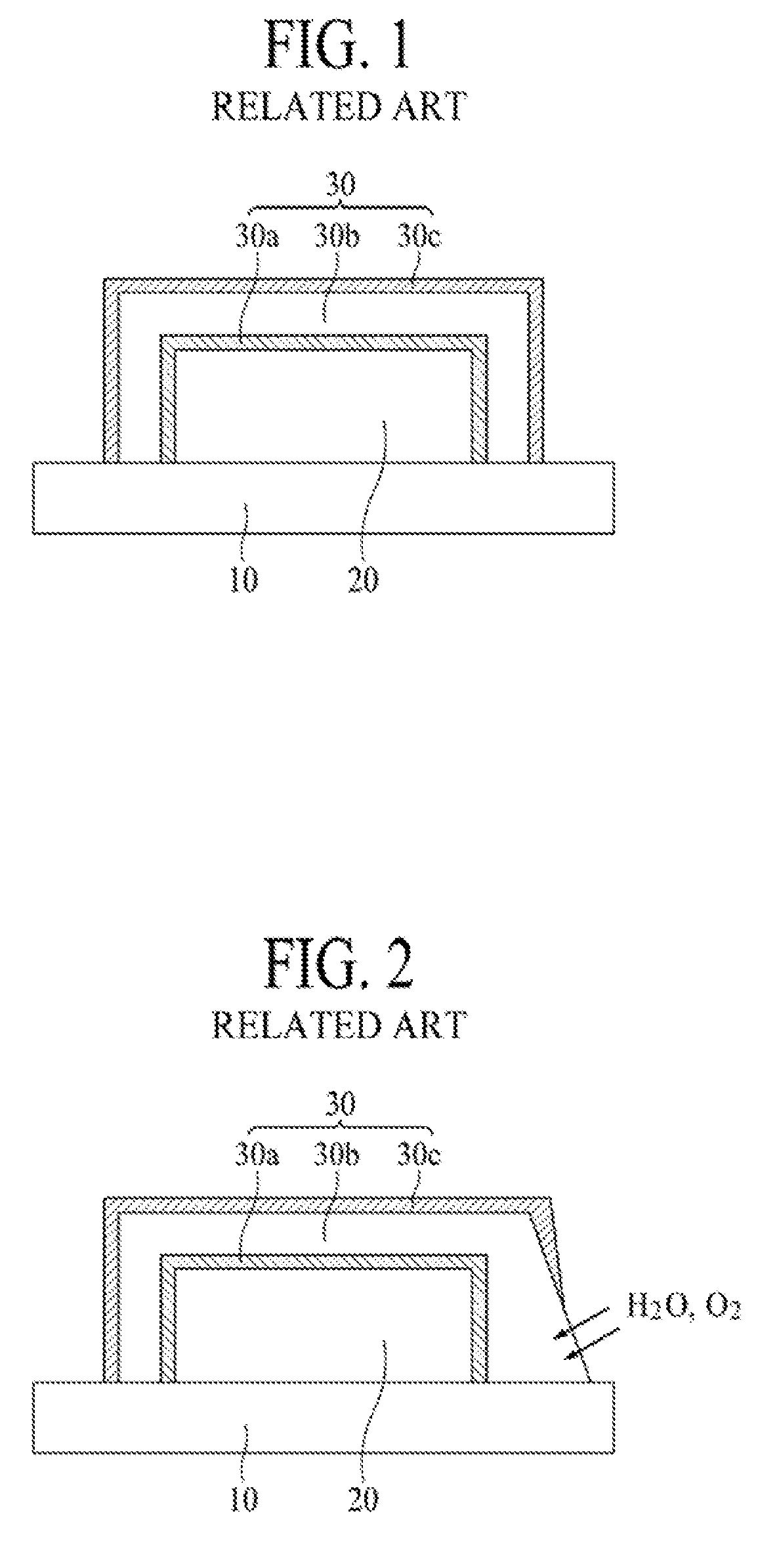

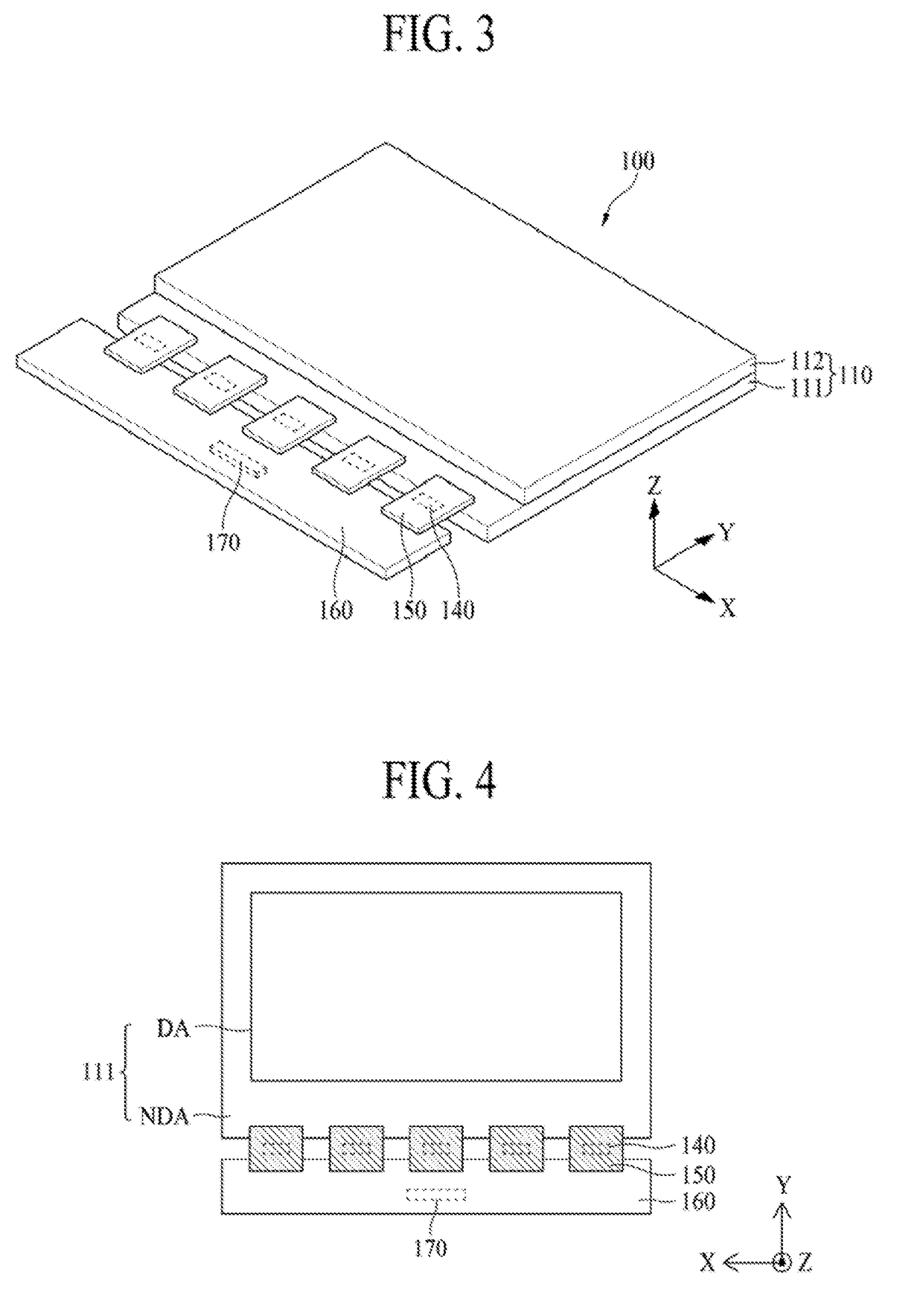

Display device and testing method thereof

ActiveUS20180061722A1Many problemSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceOrganic filmDisplay device

A display device and a testing method thereof are disclosed, in which a defect caused by an overflow of an organic film constituting an encapsulation film can be detected. The display device comprises a substrate including a display area where pixels are arranged, and a pad area including a plurality of pads formed outside the display area; an encapsulation film covering the display area, including at least one inorganic film and at least one organic film; a dam arranged between the display area and the pad area; and a conductive testing line arranged between the dam and the pad area and not electrically connected with another conductive line or electrode arranged on the substrate.

Owner:LG DISPLAY CO LTD

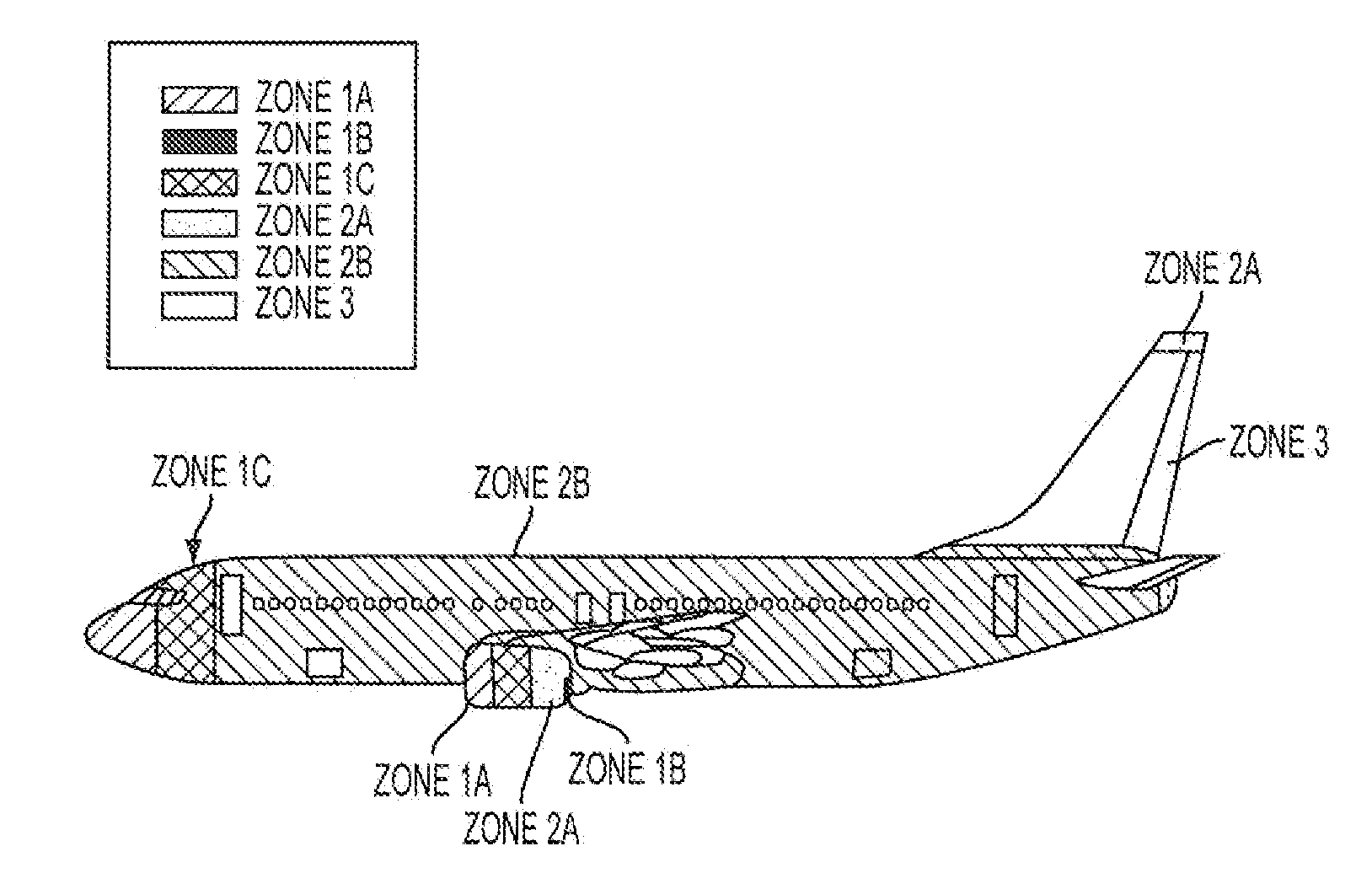

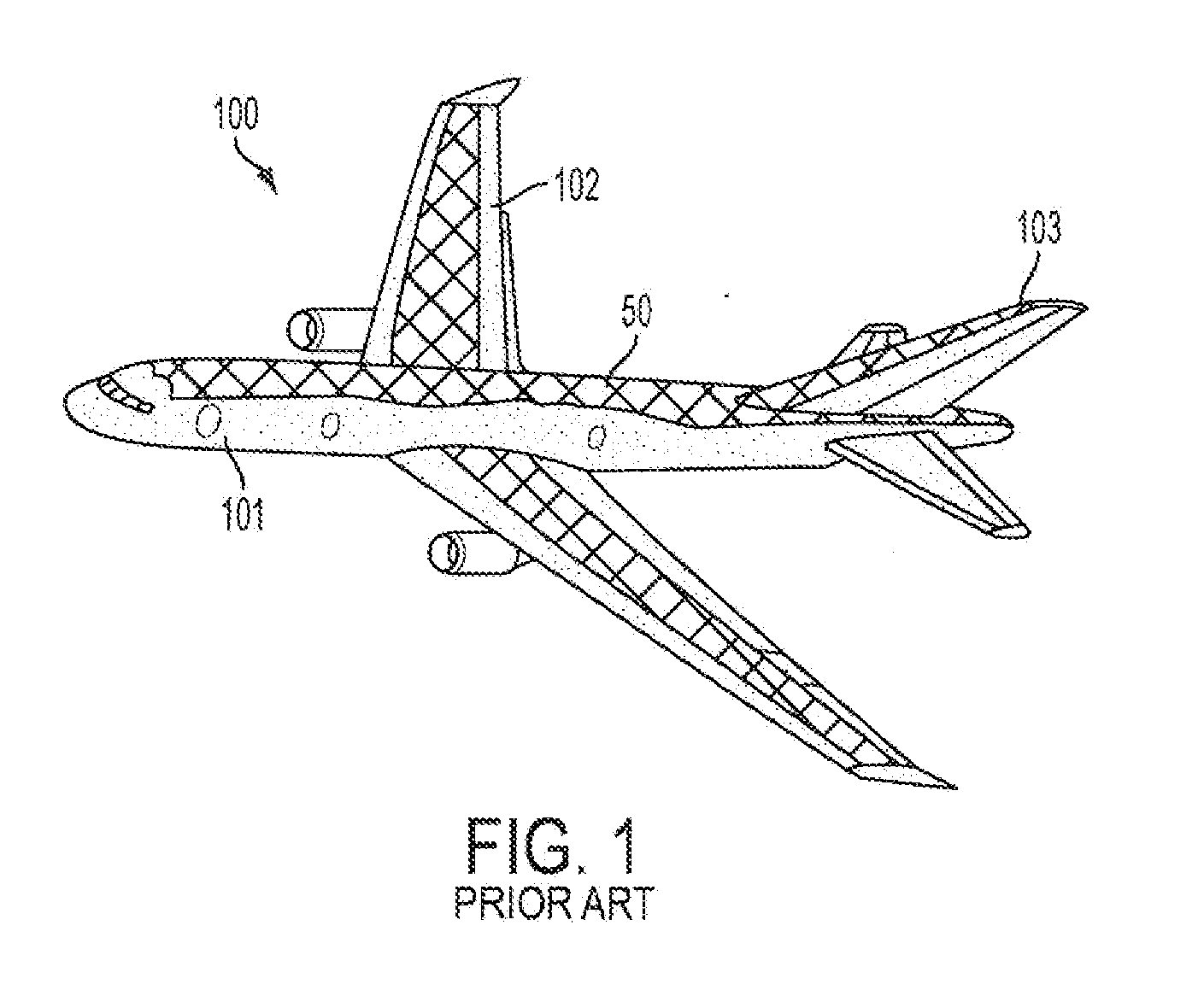

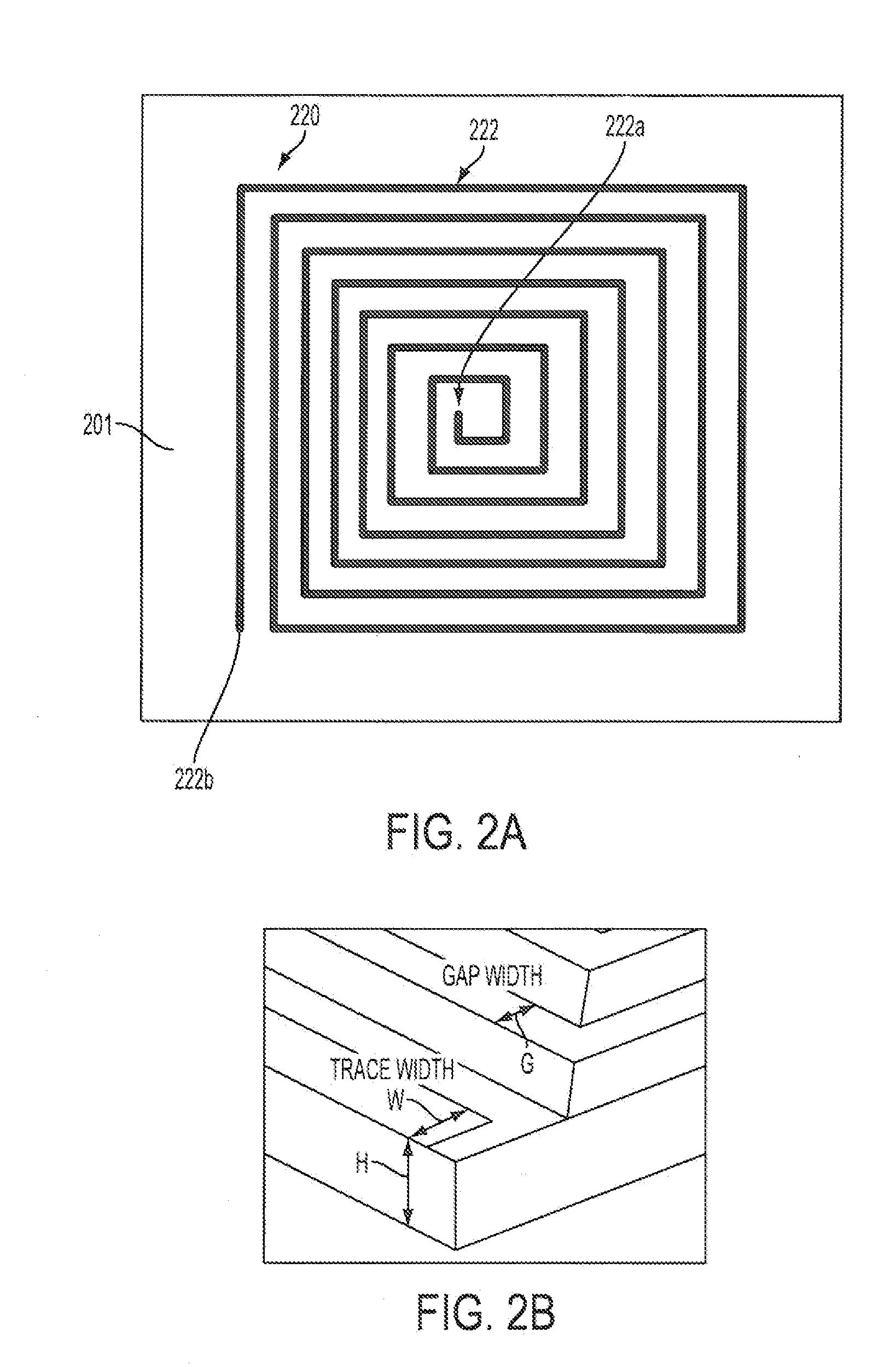

Lightning Protection and Detection System

A lightning protection and detection system includes a non-conductive substrate material of an apparatus; a sensor formed of a conductive material and deposited on the non-conductive substrate material of the apparatus. The sensor includes a conductive trace formed in a continuous spiral winding starting at a first end at a center region of the sensor and ending at a second end at an outer corner region of the sensor, the first and second ends being open and unconnected. An electrical measurement system is in communication with the sensor and receives a resonant response from the sensor, to perform detection, in real-time, of lightning strike occurrences and damage therefrom to the sensor and the non-conductive substrate material.

Owner:NASA

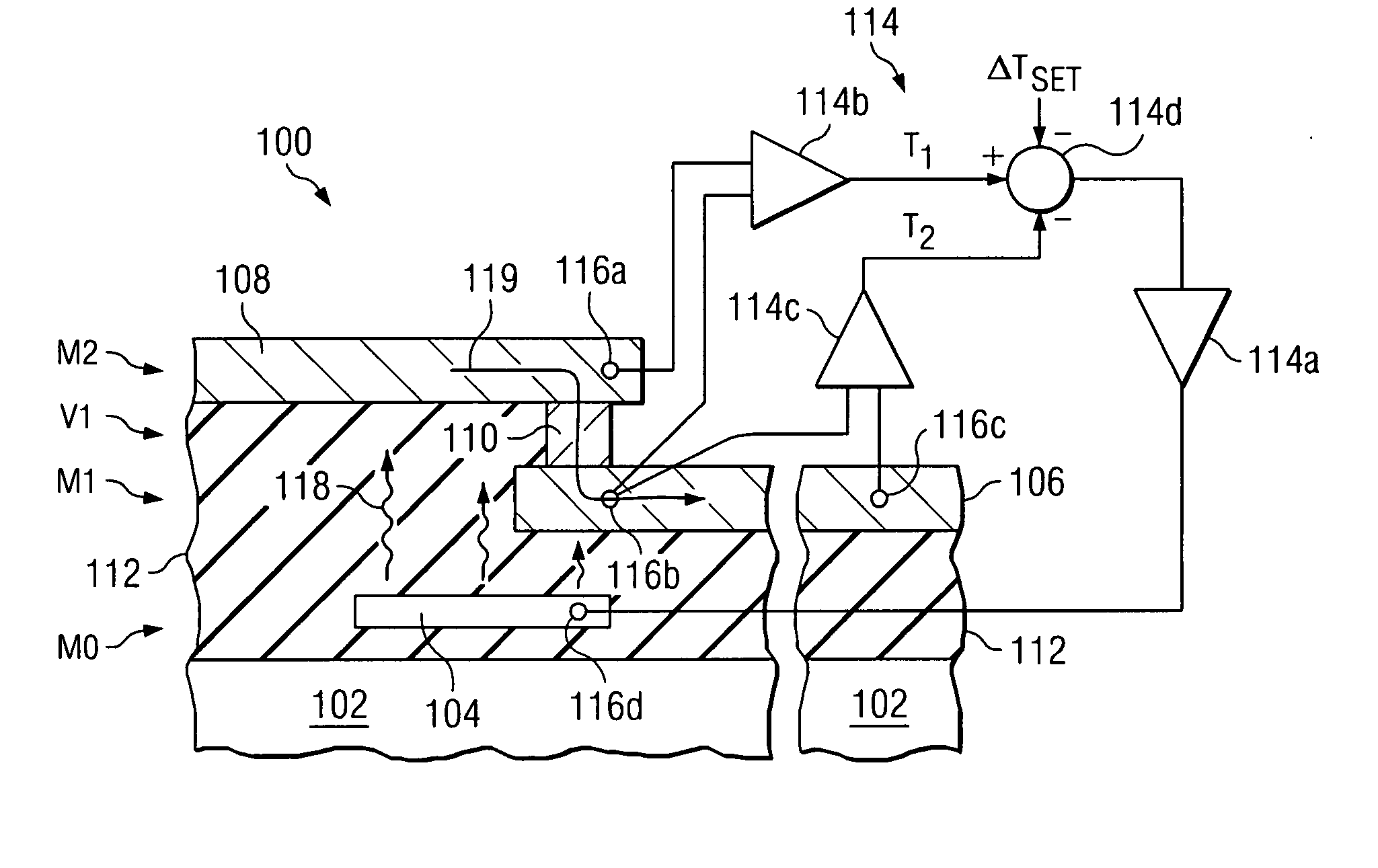

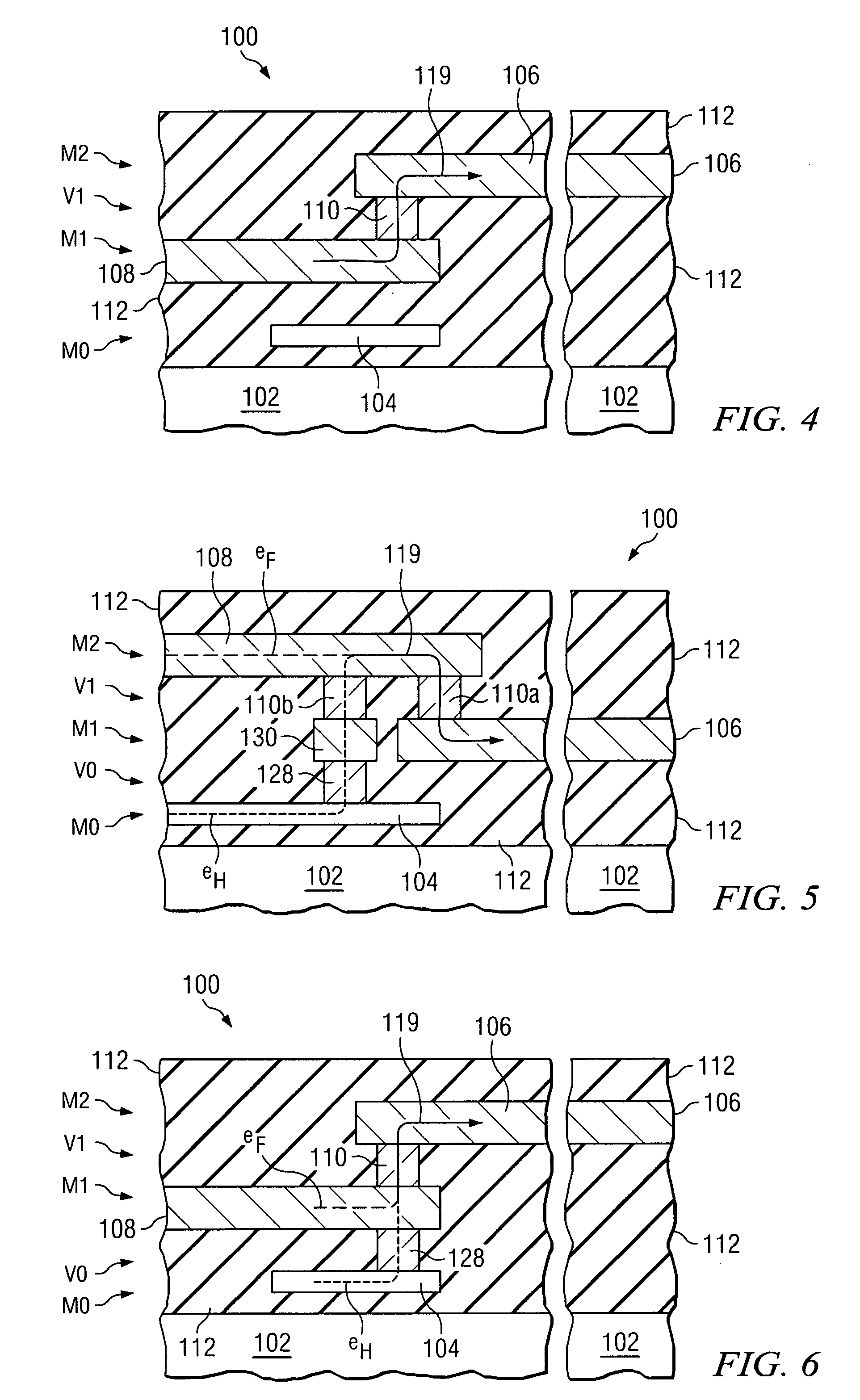

Semiconductor device test structures and methods

ActiveUS20080206908A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringSemiconductor

Semiconductor device test structures and methods are disclosed. In a preferred embodiment, a test structure includes a feed line, a stress line disposed proximate the feed line, and a conductive feature disposed between the stress line and the feed line. The test structure includes a temperature adjuster proximate at least the conductive feature, and at least one feedback device coupled to the temperature adjuster and at least the conductive feature.

Owner:INFINEON TECH AG

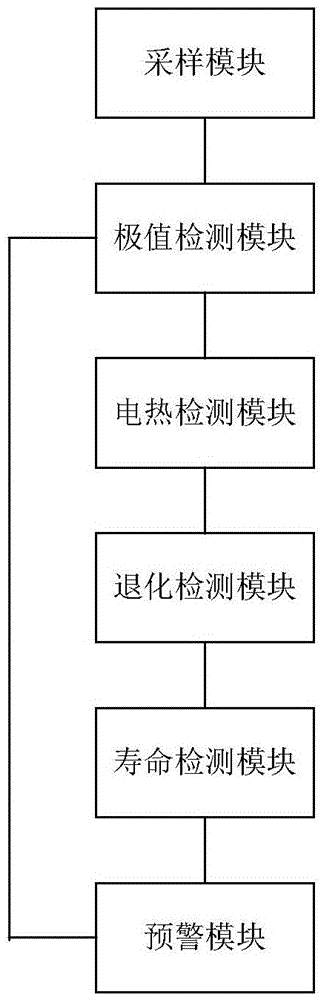

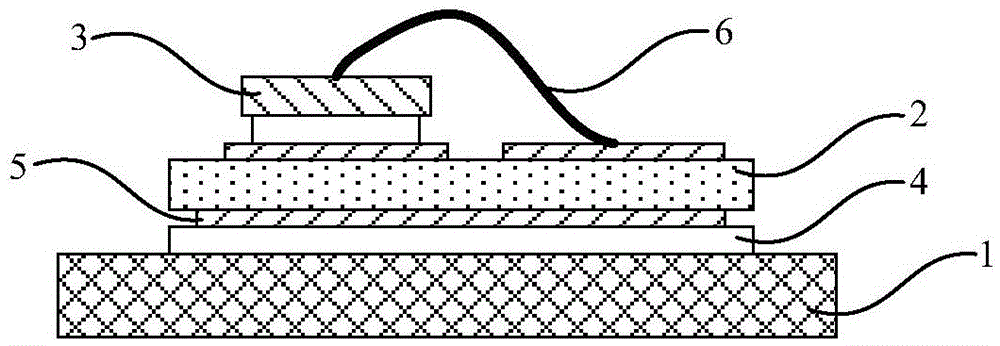

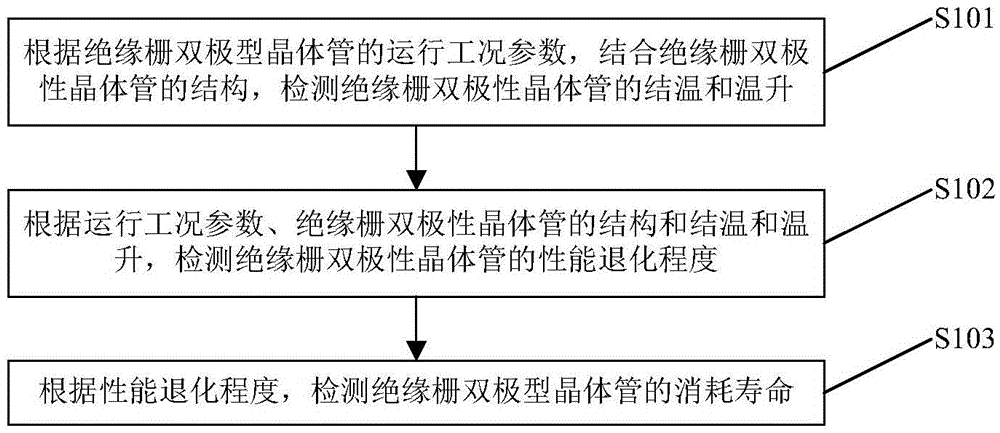

Device and method for on-line health management of insulated gate bipolar transistor

ActiveCN105486992ATimely maintenanceTimely maintenance and replacementThermometers using electric/magnetic elementsSemiconductor operation lifetime testingJunction temperatureComputer module

The invention discloses a device for on-line health management of an insulated gate bipolar transistor, and belongs to the technical field of electronic circuits, so as to solve technical problems in the prior art that life of an IGBT cannot be detected in an operating process of the IGBT. The device for on-line health management comprises an electric heating detection module, a degradation detection module, and a life detection module. The electric heating detection module is used to detect junction temperature and temperature rise of the insulated gate bipolar transistor according to operating condition parameters of the insulated gate bipolar transistor, combined with the structure of the insulated gate bipolar transistor. The degradation detection module is used to detect performance degradation degree of the insulated gate bipolar transistor according to the operating condition parameters, the structure of the insulated gate bipolar transistor, and the junction temperature and temperature rise. The life detection module is used to detect consumption life of the insulated gate bipolar transistor according to the performance degradation degree.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

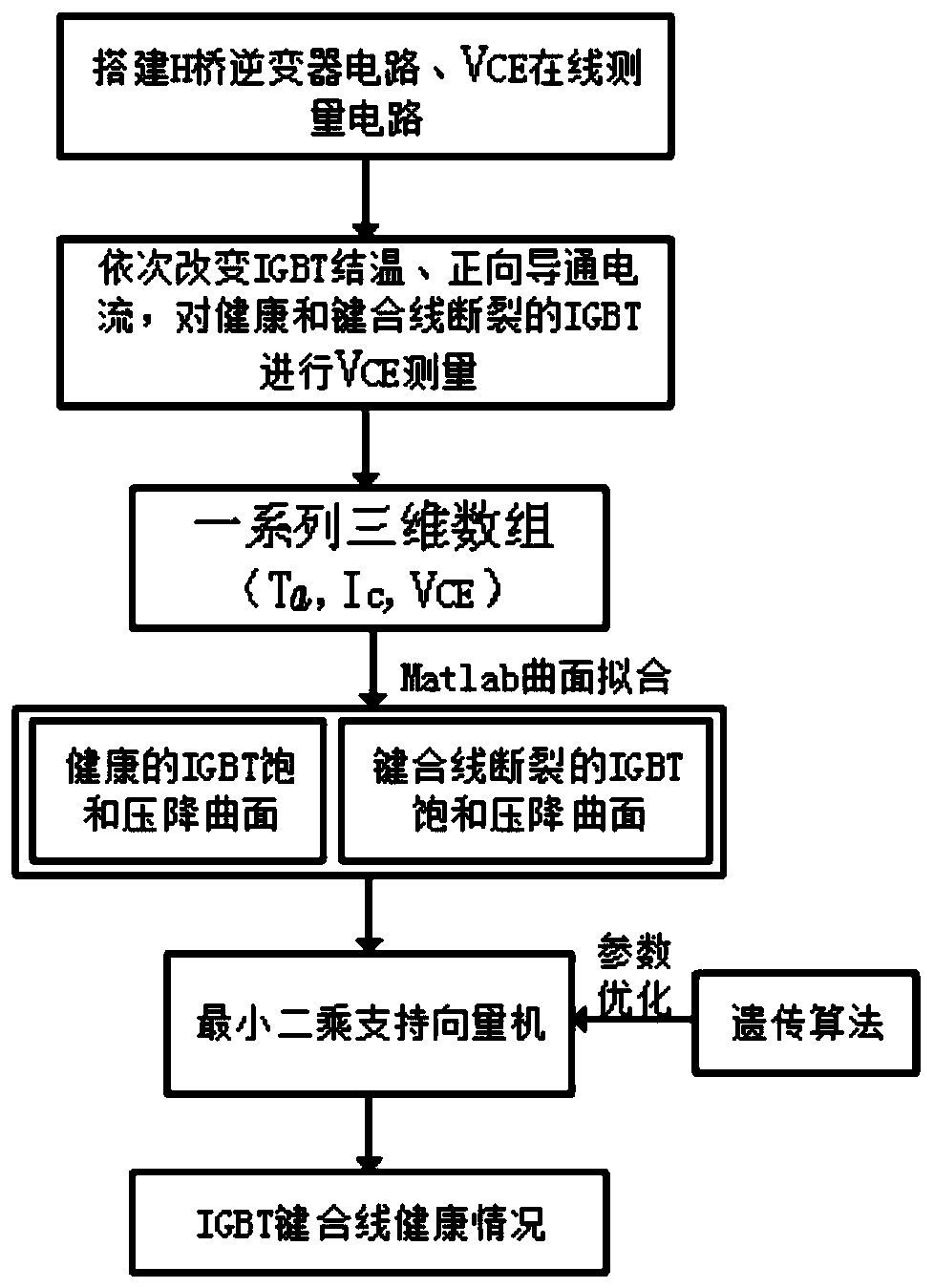

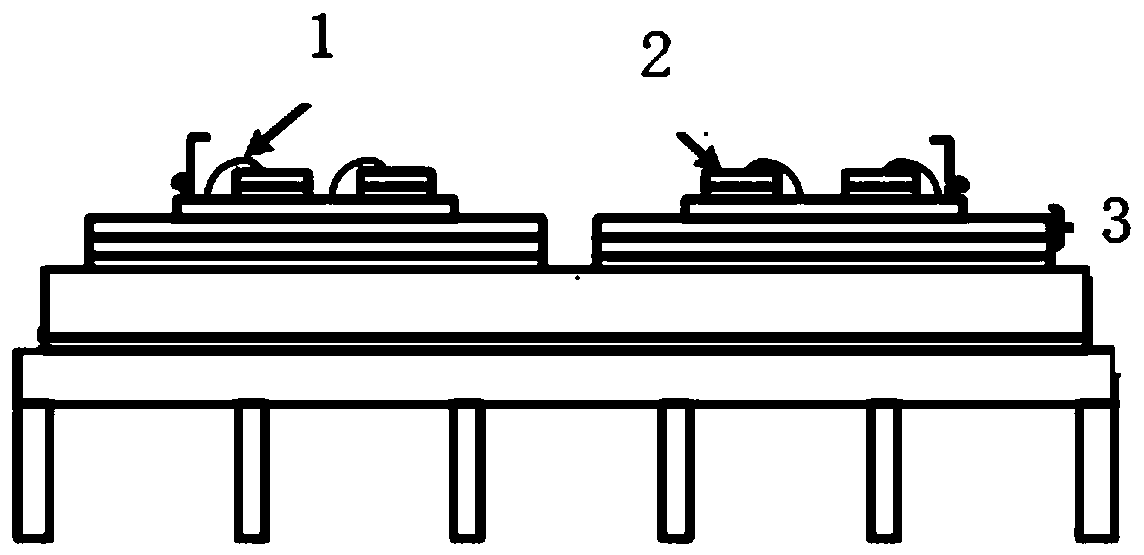

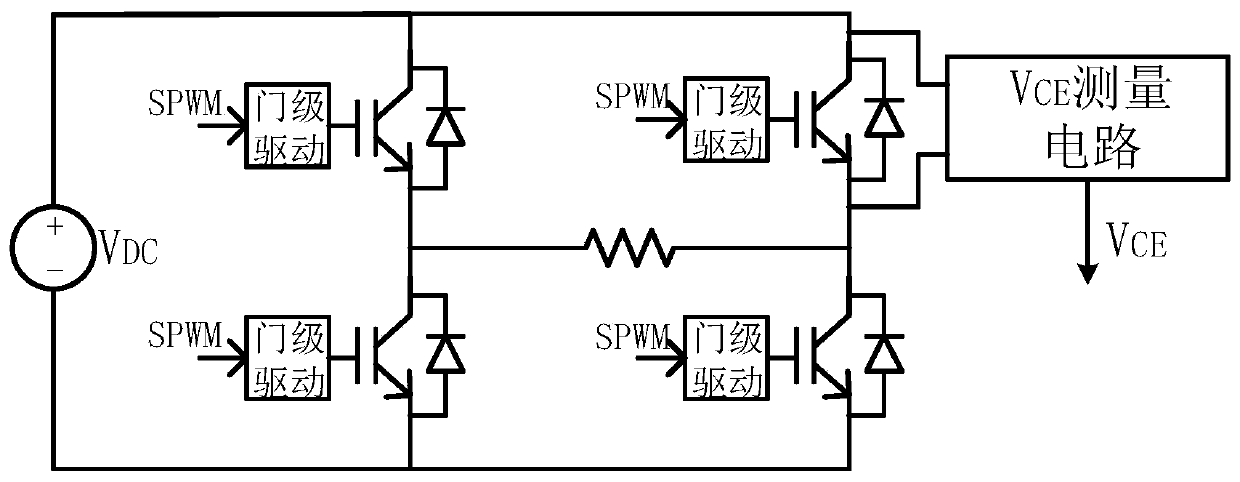

Method for monitoring online condition of IGBT module bonding wire

ActiveCN110221189AAccurate saturation pressure dropImprove anti-interference abilityBipolar transistor testingCurrent/voltage measurementComputer moduleLeast squares support vector machine

A method for monitoring online condition of an IGBT module bonding wire comprises the following steps of step 1, building a full-bridge inverter circuit and a VCE online measurement circuit, and connecting both input terminals of the VCE online measurement circuit to the collector and emitter of the IGBT power module of the full-bridge inverter circuit to realize the connection between the full-bridge inverter circuit and the VCE online measurement circuit; step 2, establishing a three-dimensional data model of the healthy IGBT; step 3, establishing an IGBT three-dimensional data model of thebond wire break; step 4, optimizing the least squares support vector machine by a genetic algorithm; and step 5, using the optimized least squares support vector machine to evaluate the state of the 3D data model obtained in the steps 2 and 3. The method provided by the invention closely links the online monitoring and state evaluation, and helps to improve the health management mechanism of the IGBT module bonding wire.

Owner:HEFEI UNIV OF TECH

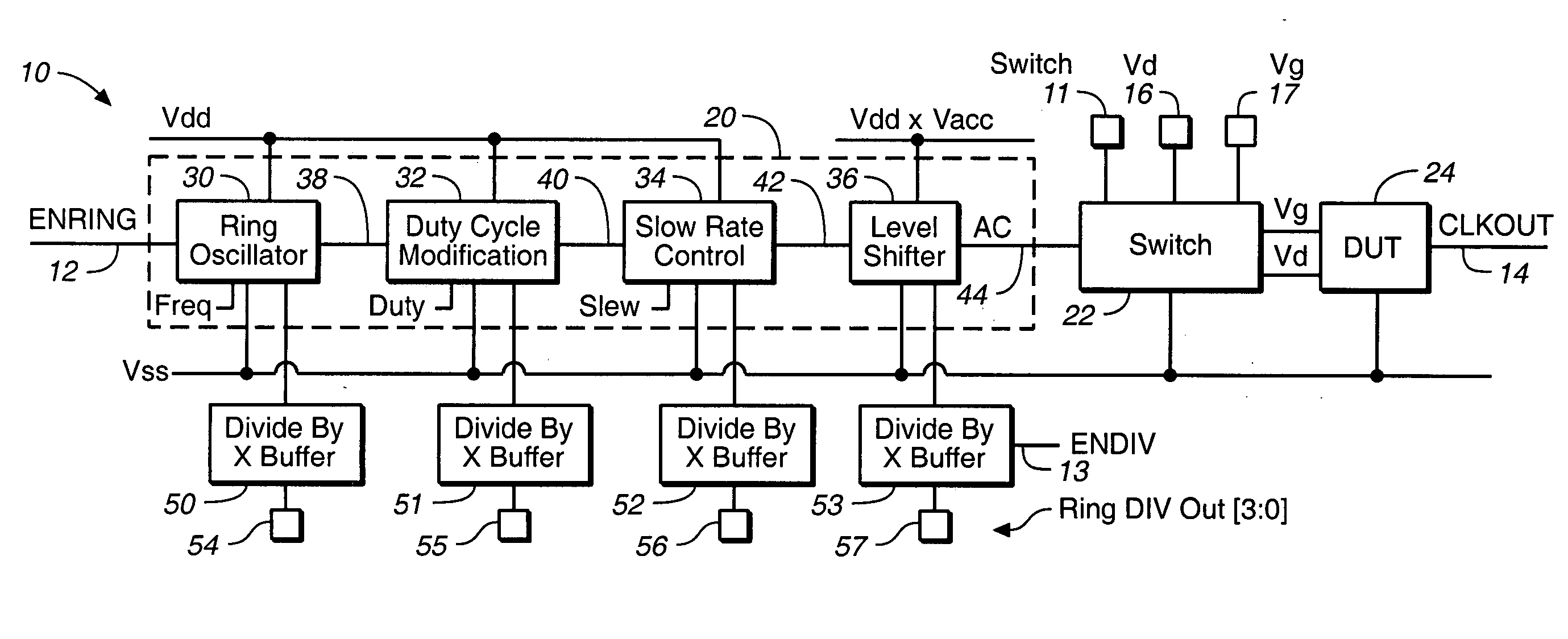

Reliability circuit for applying an AC stress signal or DC measurement to a transistor device

InactiveUS20060076972A1Semiconductor/solid-state device testing/measurementSolid-state devicesDriver circuitEngineering

An integrated circuit is provided, which includes a transistor device under test, an AC drive circuit, an AC bias circuit and a DC bias circuit. The AC drive circuit generates an AC drive signal. The AC bias circuit biases the transistor device under AC bias conditions in response to the AC drive signal. The DC bias circuit biases the transistor device under DC bias conditions. A switch circuit selectively couples the transistor device to the AC bias circuit in an AC stress mode and to the DC bias circuit in a DC measurement mode.

Owner:AVAGO TECH INT SALES PTE LTD