Patents

Literature

37 results about "Soft breakdown" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reprogrammable non-volatile memory using a breakdown phenomena in an ultra-thin dielectric

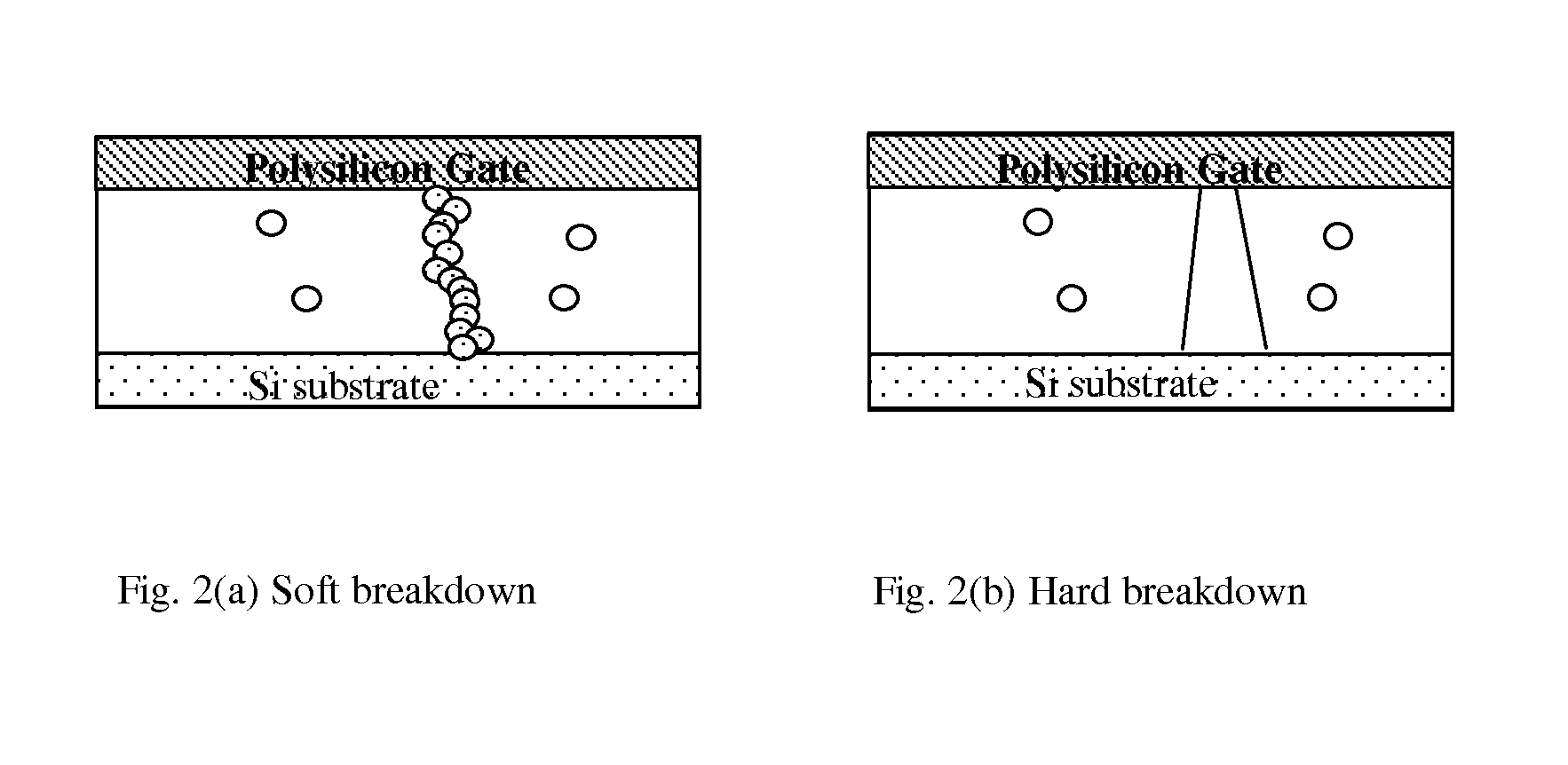

A reprogrammable non-volatile memory array and constituent memory cells is disclosed. The semiconductor memory cells each have a data storage element constructed around an ultra-thin dielectric, such as a gate oxide. The gate oxide is used to store information by stressing the ultra-thin dielectric into breakdown (soft or hard breakdown) to set the leakage current level of the memory cell. The memory cell is read by sensing the current drawn by the cell. A suitable ultra-thin dielectric is high quality gate oxide of about 50 Å thickness or less, as commonly available from presently available advanced CMOS logic processes. The memory cells are first programmed by stressing the gate oxide until soft breakdown occurs. The memory cells are then subsequently reprogrammed by increasing the breakdown of the gate oxide.

Owner:SYNOPSYS INC

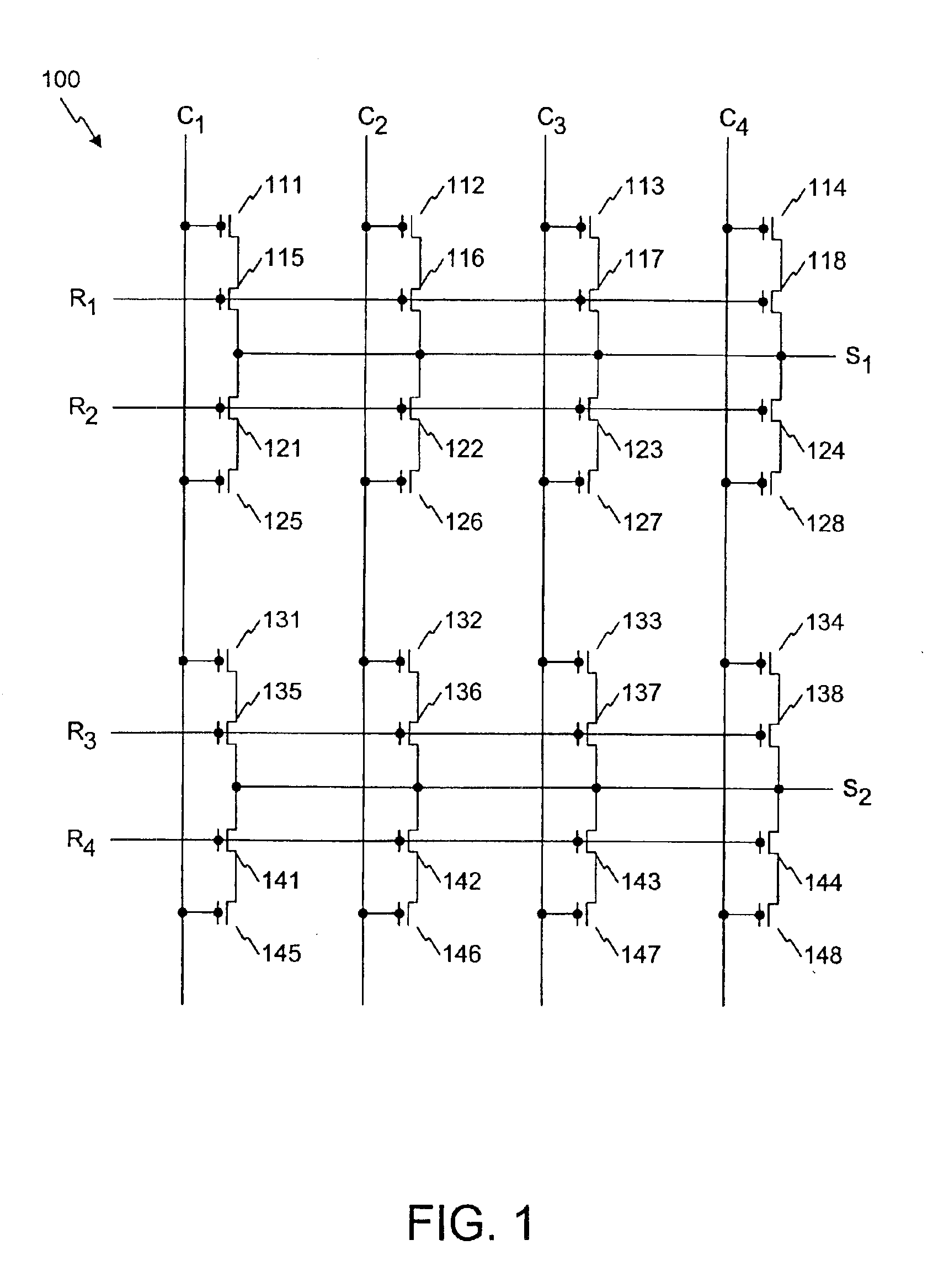

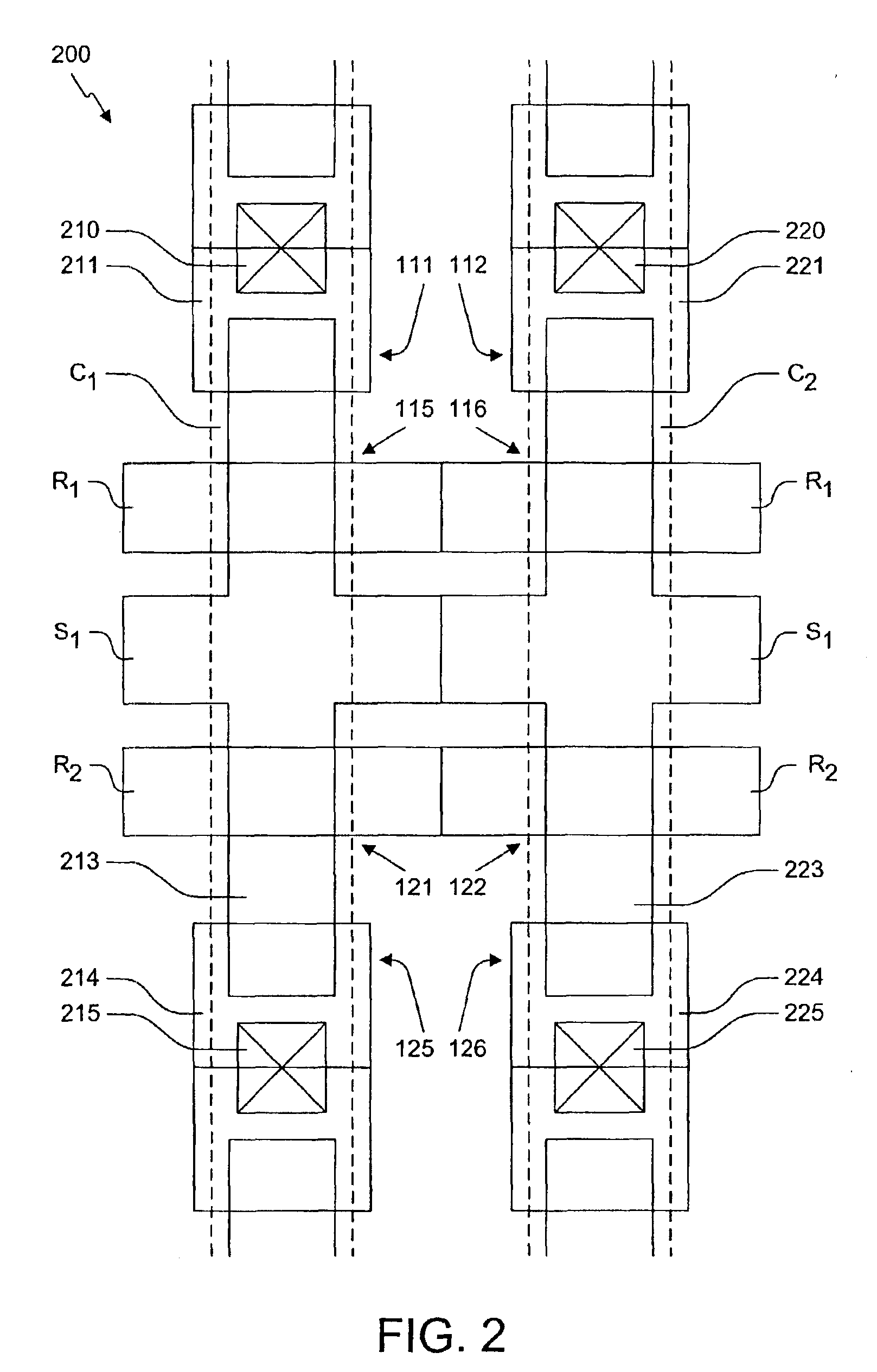

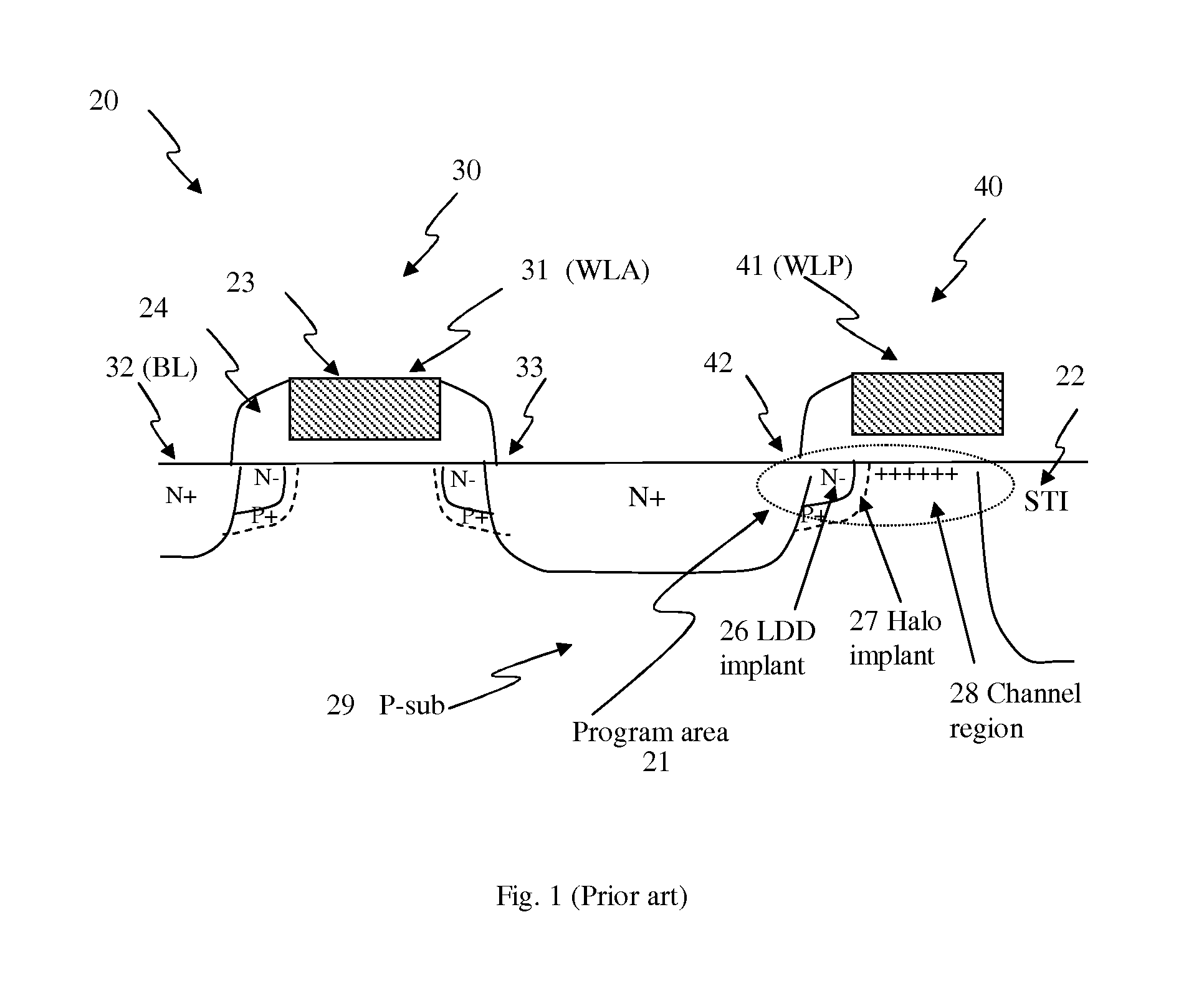

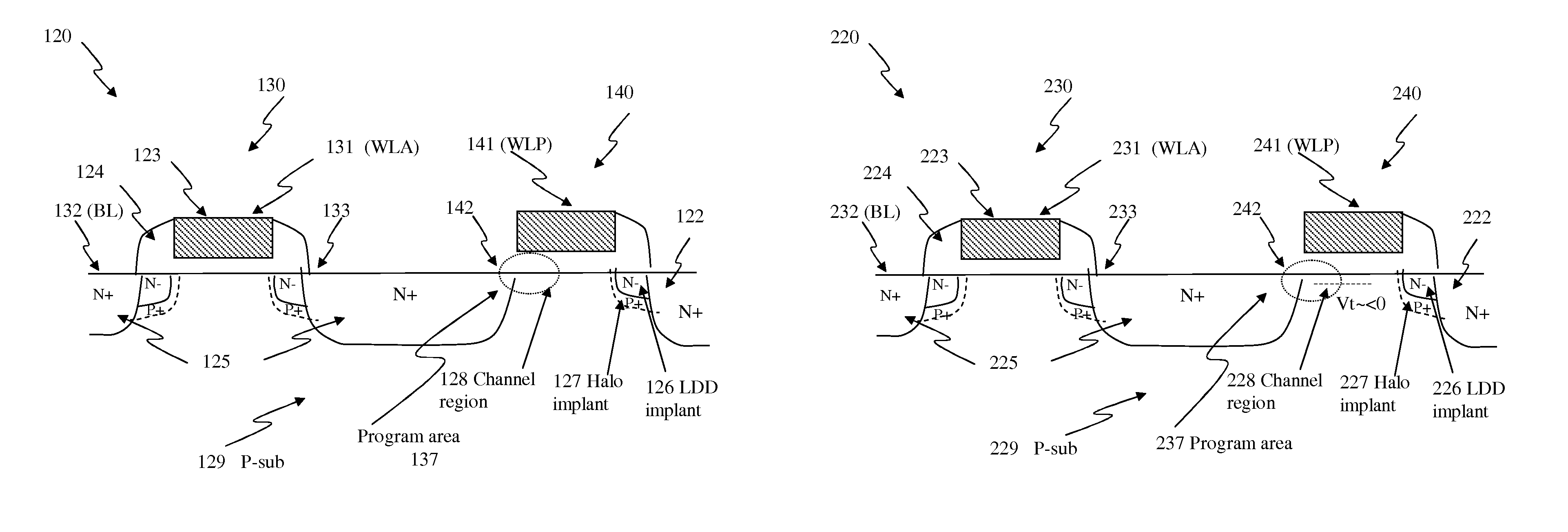

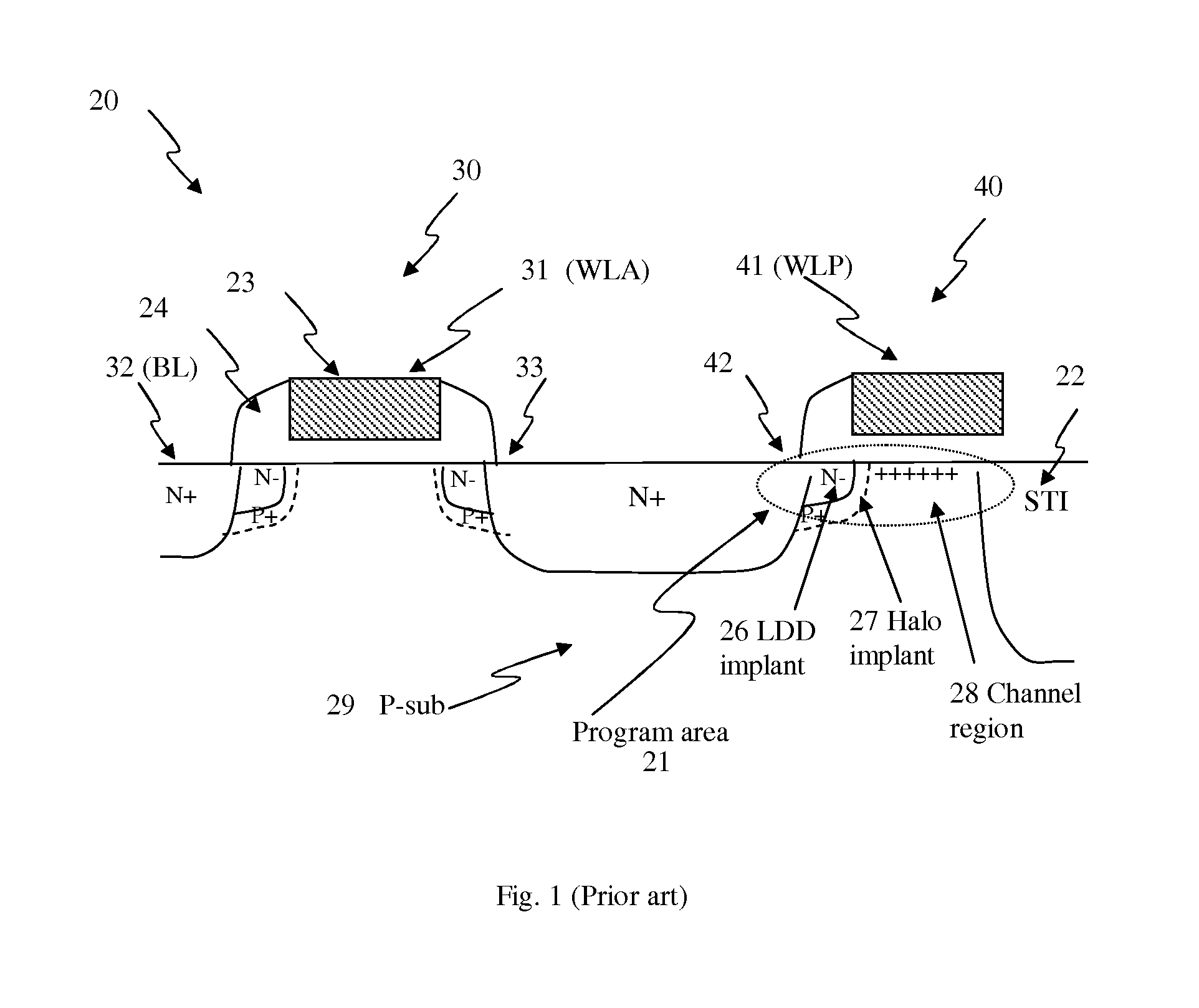

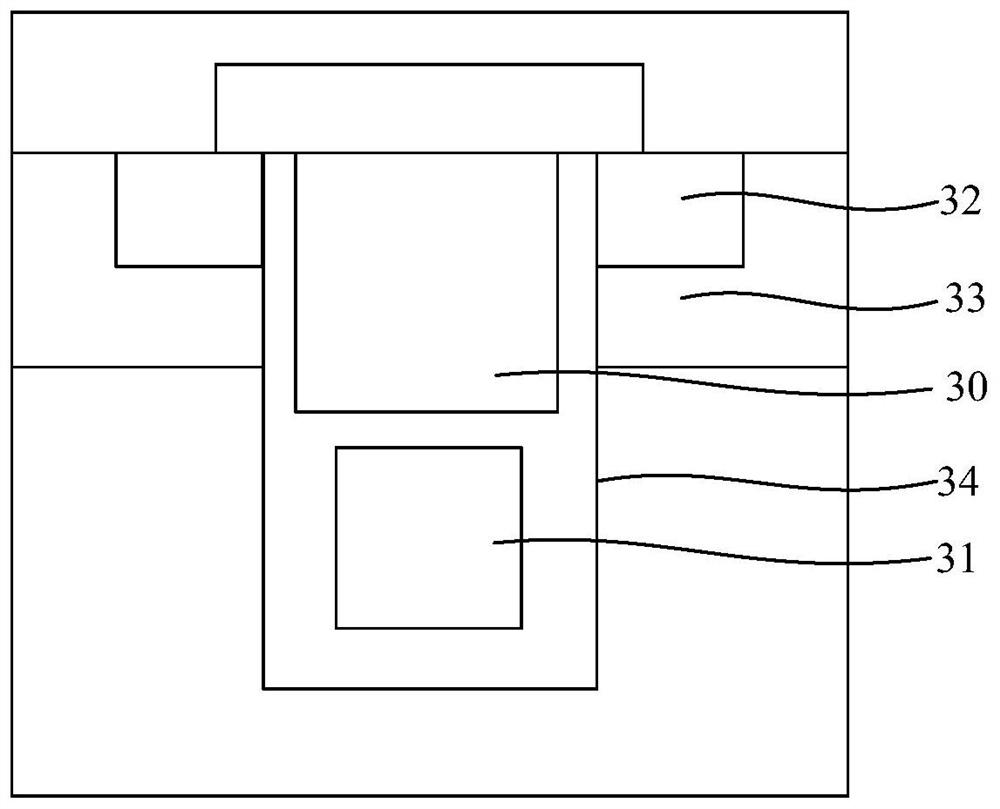

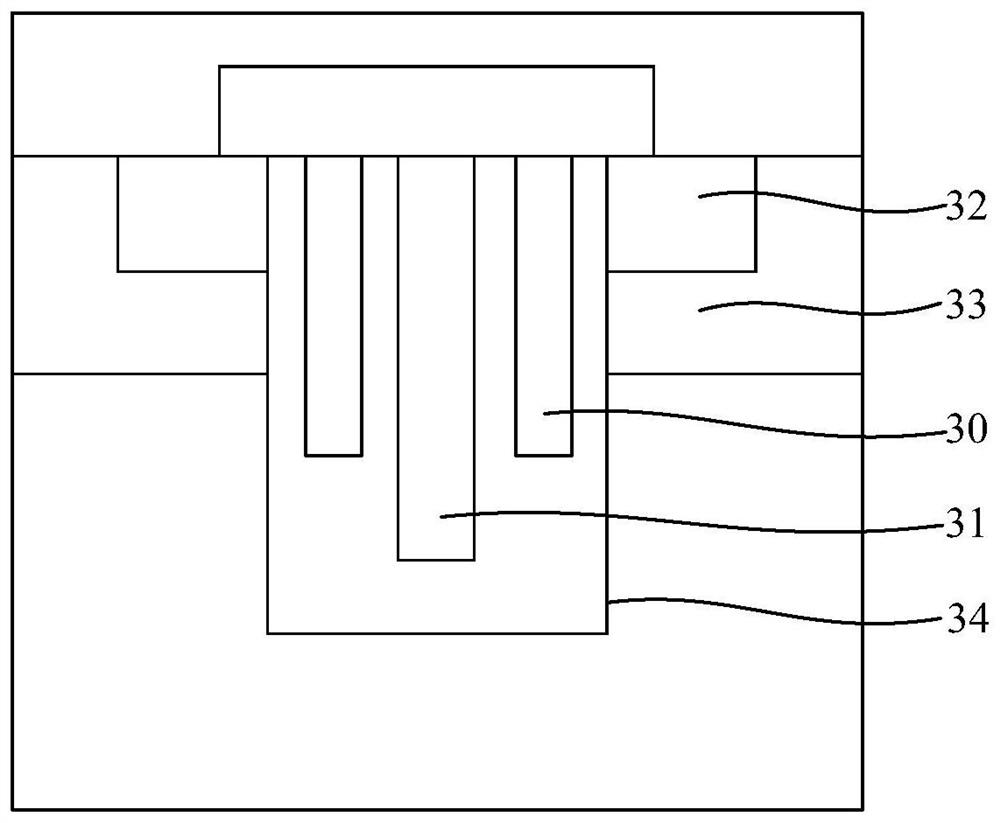

Circuit and System of Aggregated Area Anti-Fuse in CMOS Processes

ActiveUS20120039107A1Enhance program yieldImprove reliabilityTransistorSemiconductor/solid-state device detailsAntifuseElectric field

Gate oxide breakdown anti-fuse suffers notorious soft breakdown that reduces yield and reliability. This invention discloses circuit and system to enhance electrical field by blocking LDD so that the electrical field is higher and more focused near the drain junction, to make electrical field in the channel more uniform by creating slight conductive or conductive in part or all of the channel, or to neutralize excess carriers piled up in the oxide by applying alternative polarity pulses. The embodiments can be applied in part, all, or any combinations, depending on needs. This invention can be embodied as a 2 T anti-fuse cell having an access and a program MOS with drain area in the program MOS, or 1.5 T anti-fuse cell without any drain in the program MOS. Similarly this invention can also be embodied as a 1 T anti-fuse cell having a portion of the channel made conductive or slightly conductive to merge the access and program MOS into one device with drain area, or 0.5 T anti-fuse cell without any drain.

Owner:ATTOPSEMI TECH CO LTD

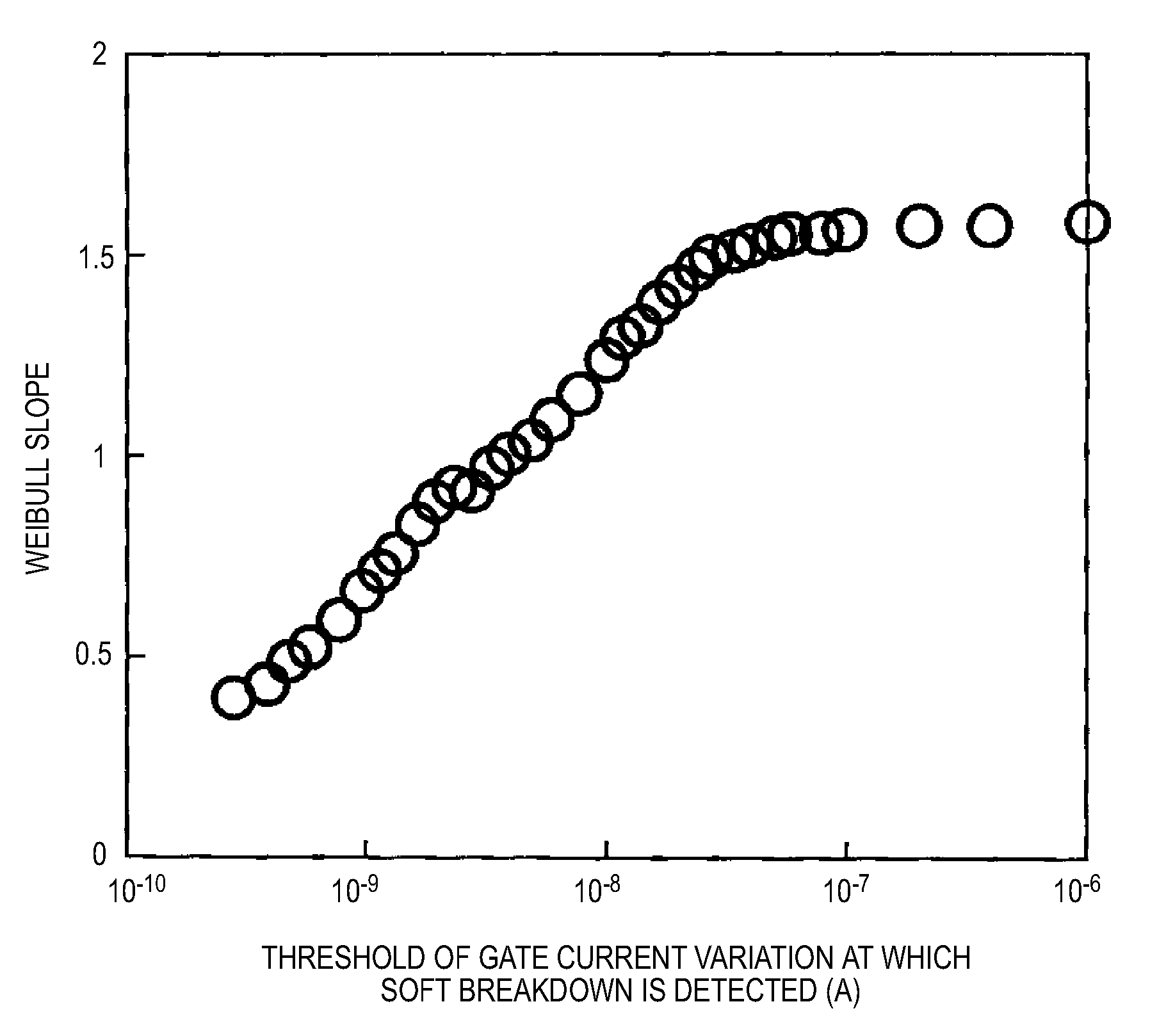

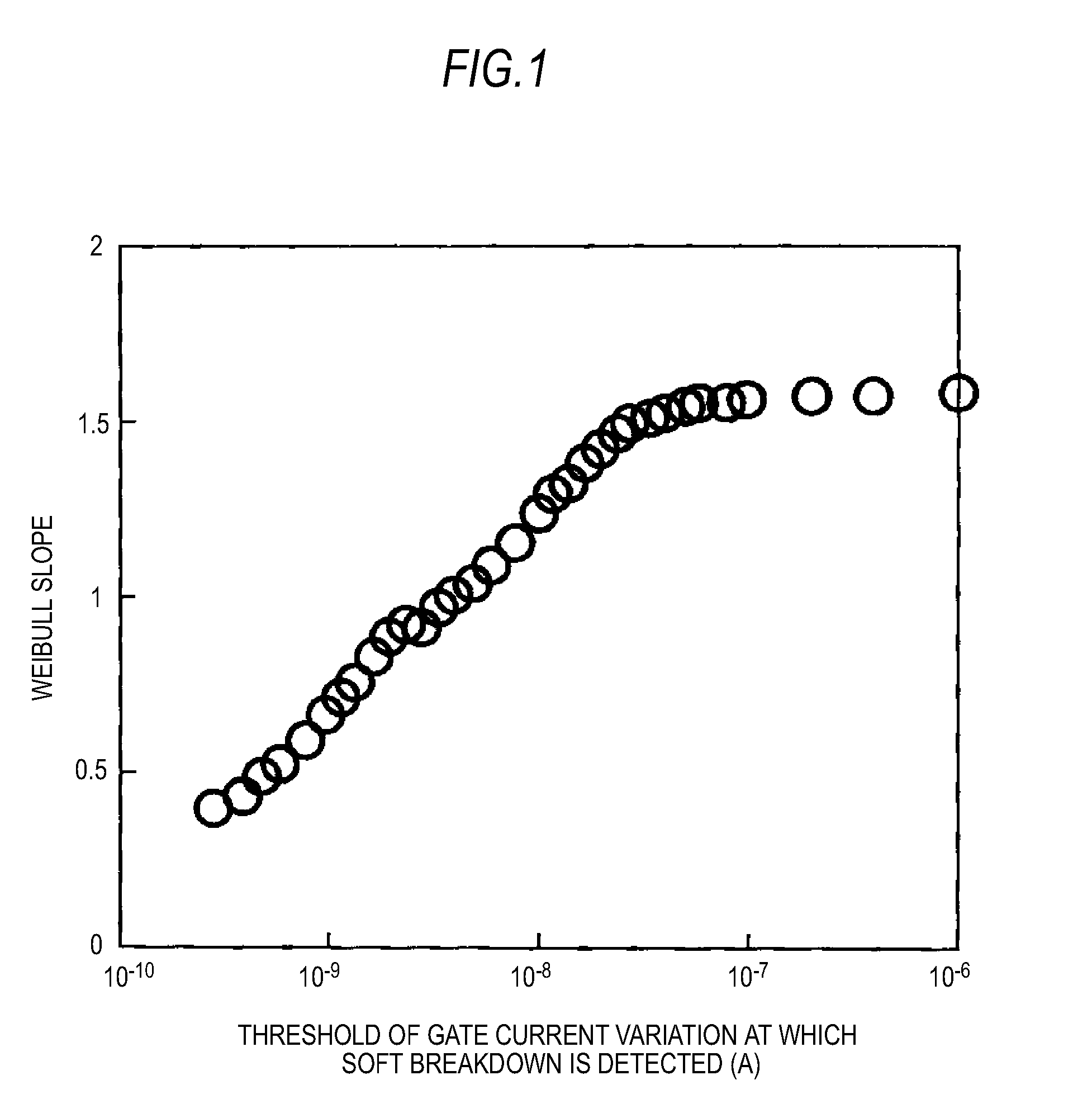

Valuation method of dielectric breakdown lifetime of gate insulating film, valuation device of dielectric breakdown lifetime of gate insulating film and program for evaluating dielectric breakdown lifetime of gate insulating film

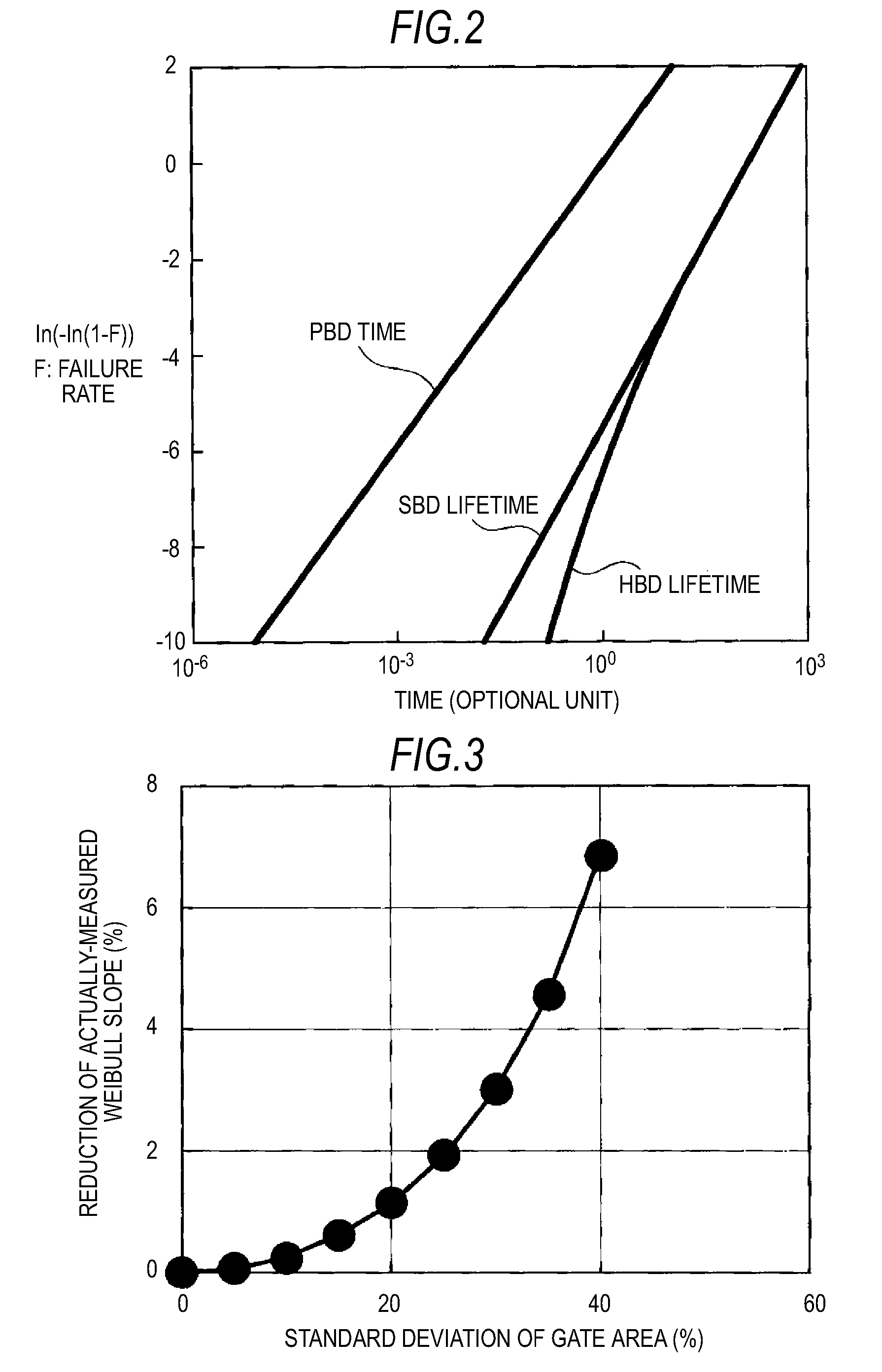

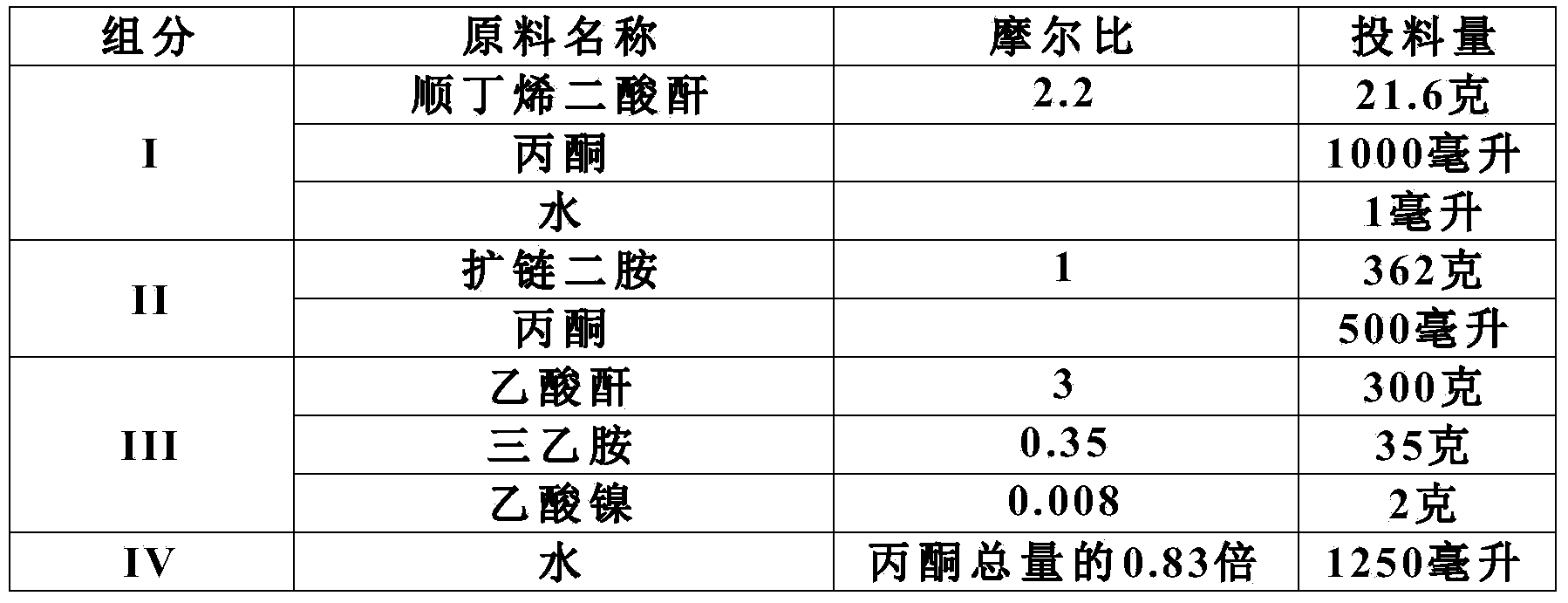

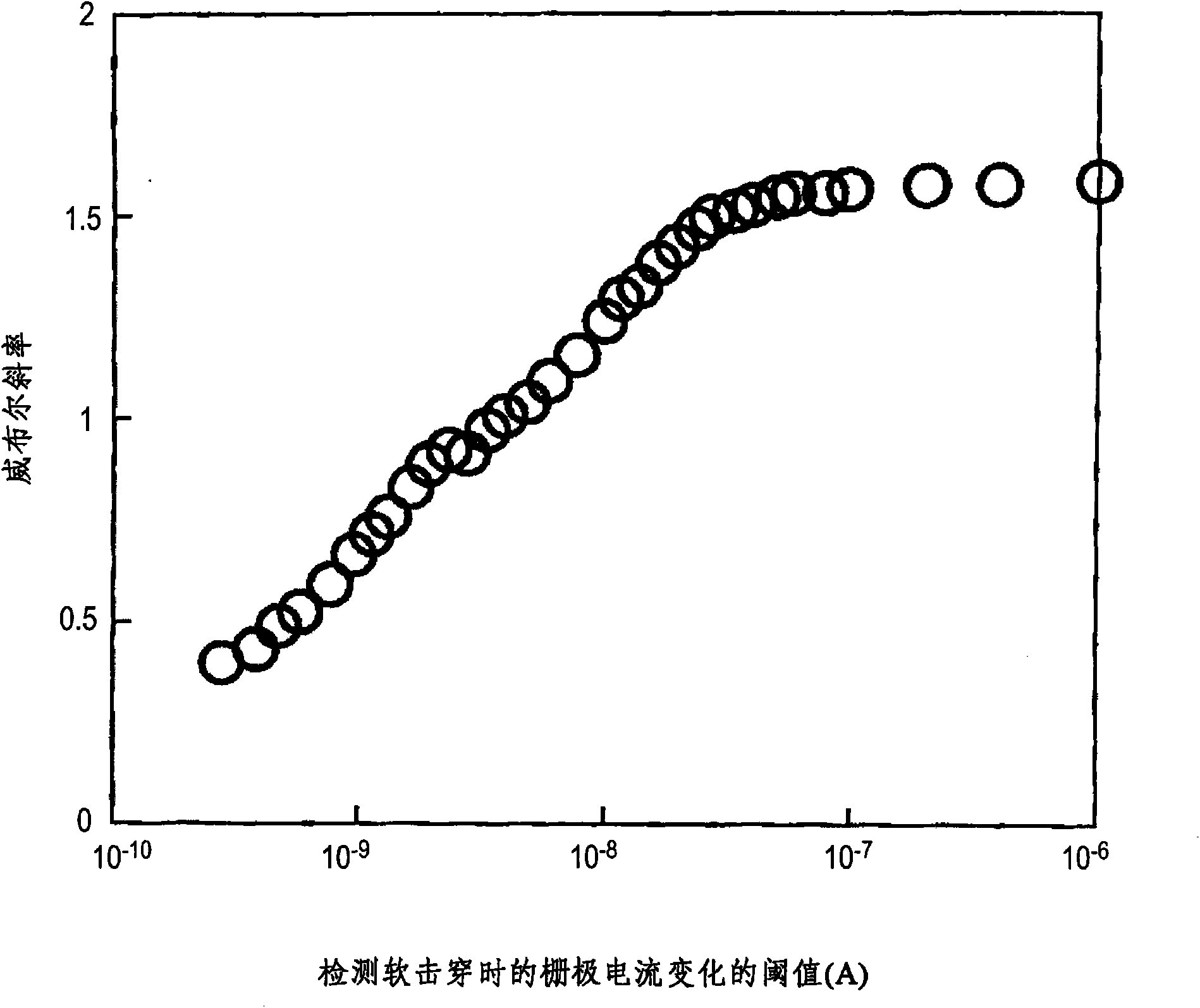

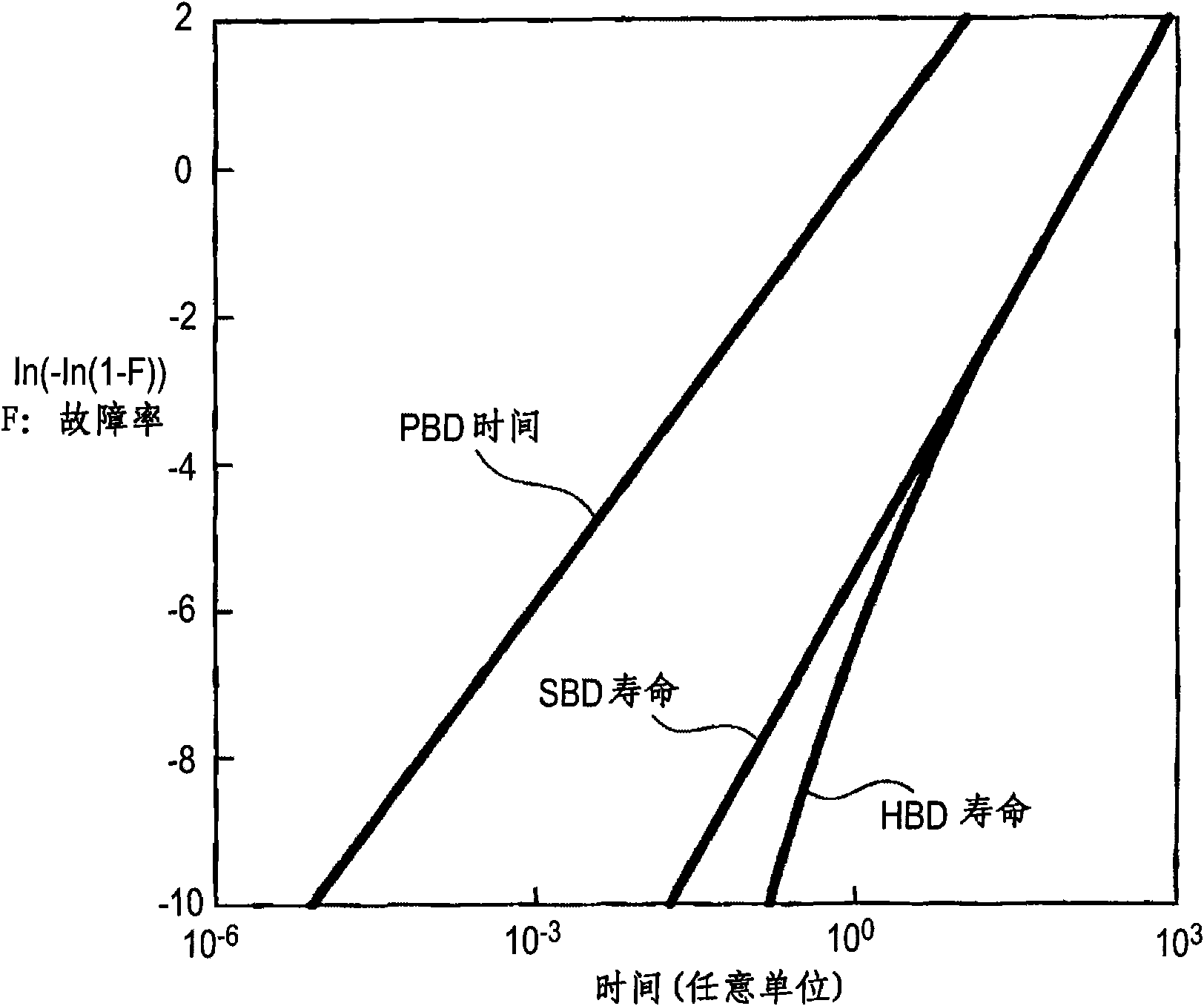

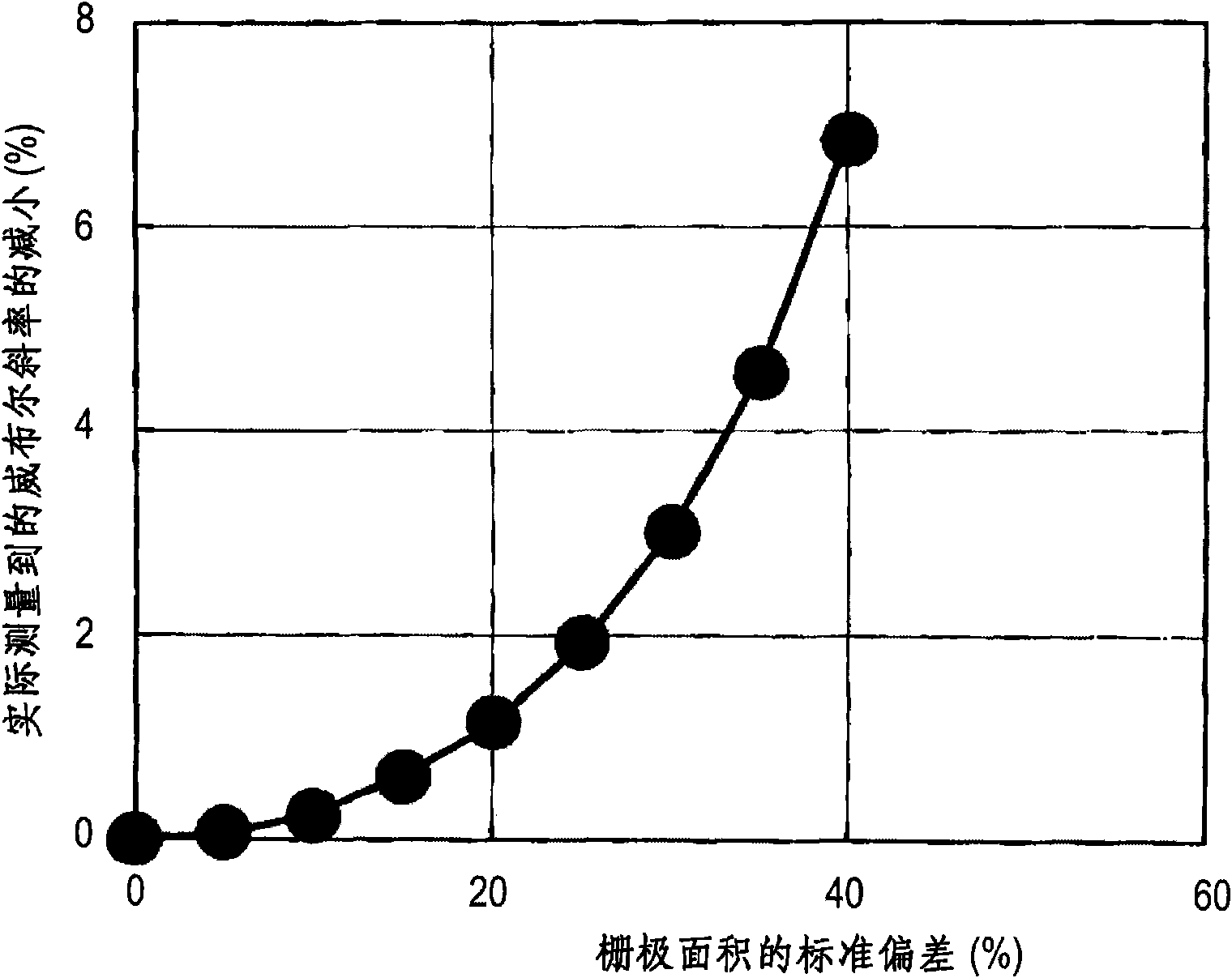

InactiveUS20110031981A1Allocation is accurateAccurate assessmentTesting dielectric strengthSemiconductor operation lifetime testingEngineeringWeibull slope

A valuation method of a dielectric breakdown lifetime of a gate insulating film for evaluating the dielectric breakdown lifetime of the gate insulating film of a MOS type element includes the steps of: deciding a Weibull slope of lifetime distribution until reaching a soft breakdown of the gate insulating film of the MOS type element; deciding a detection condition of the soft breakdown from the decided Weibull slope after the above step; and executing a dielectric breakdown test by using the decided detection condition.

Owner:SONY CORP

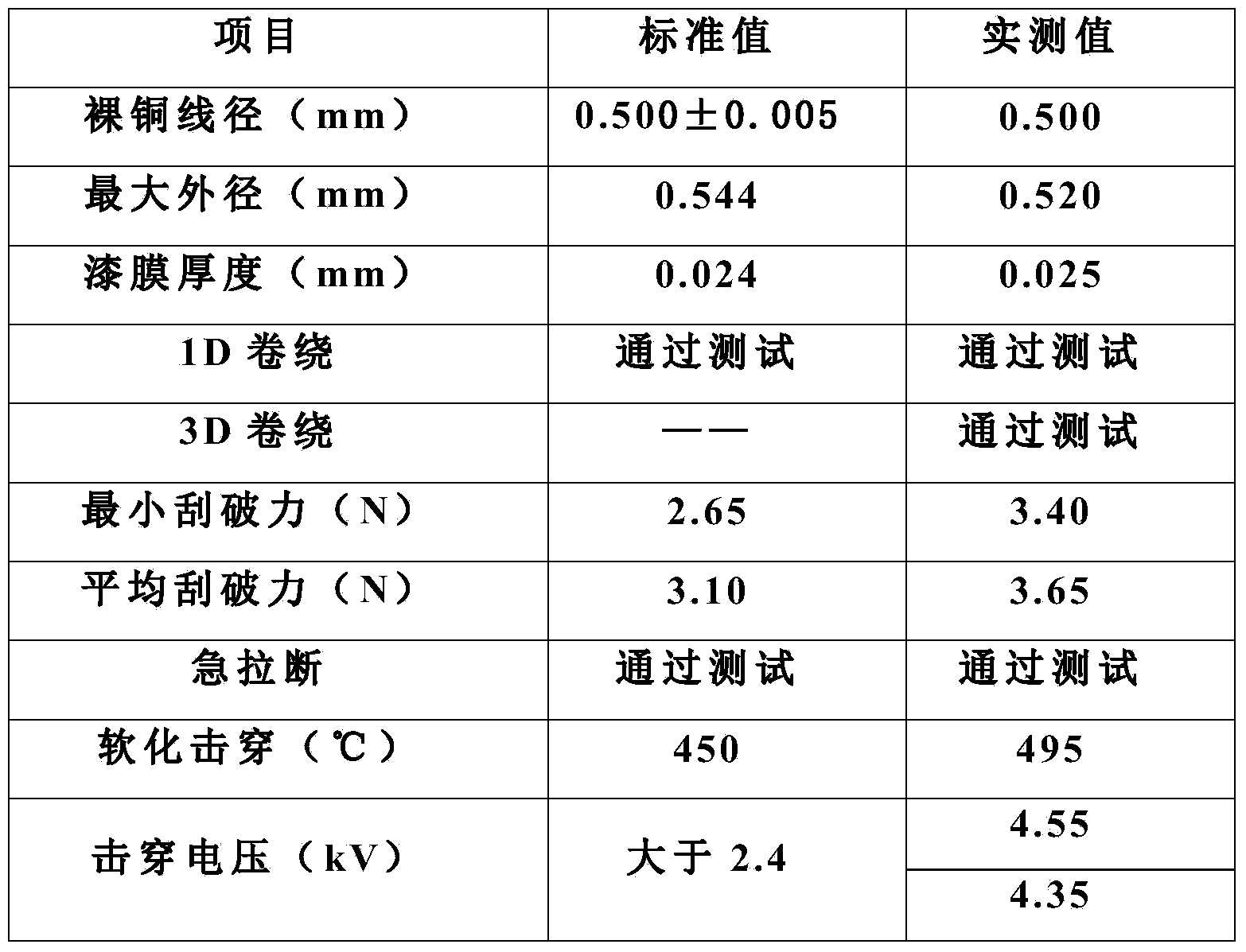

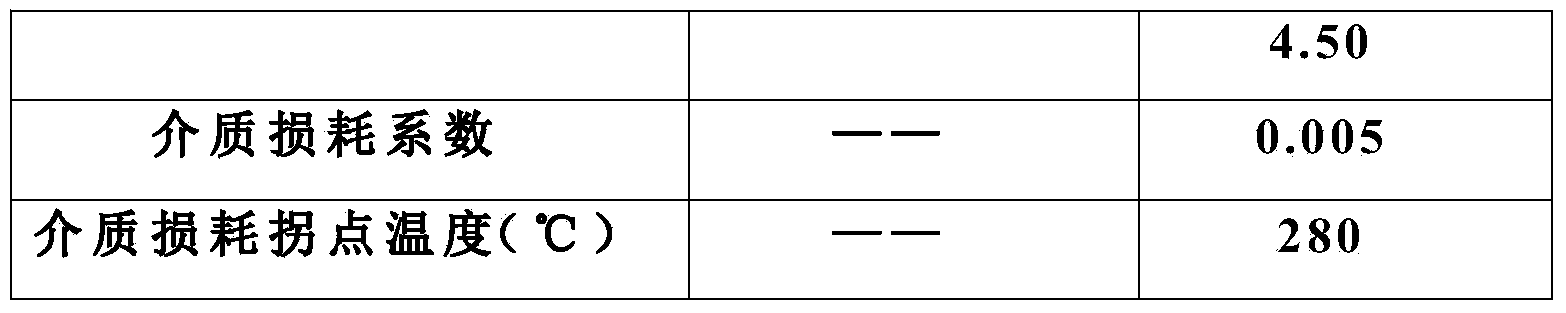

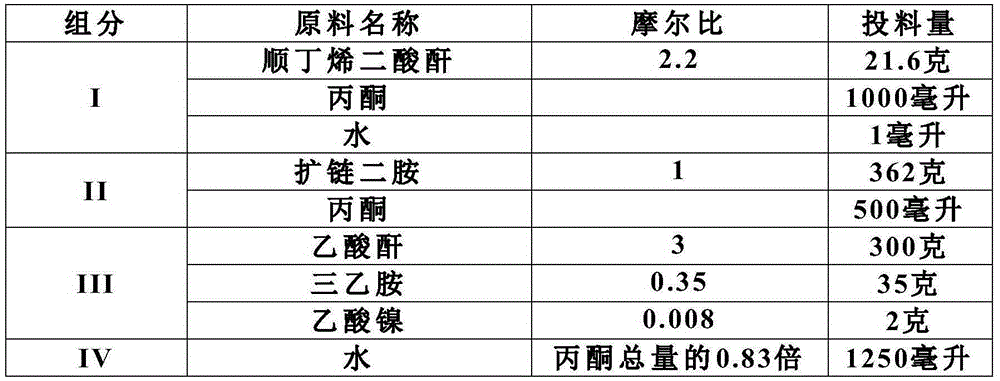

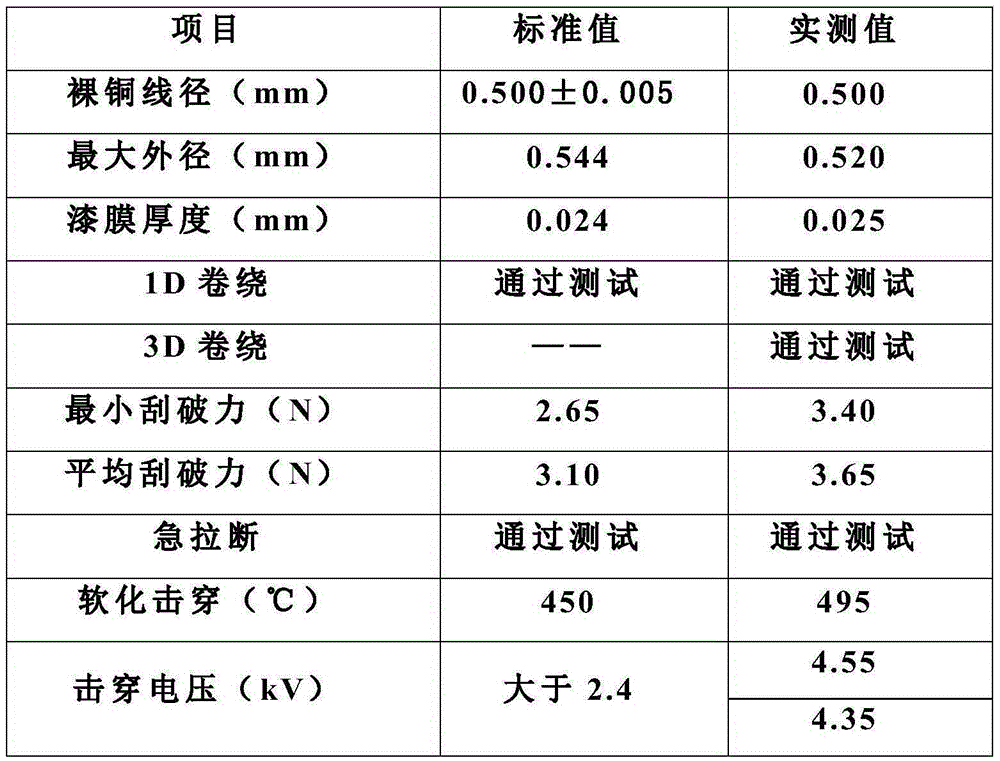

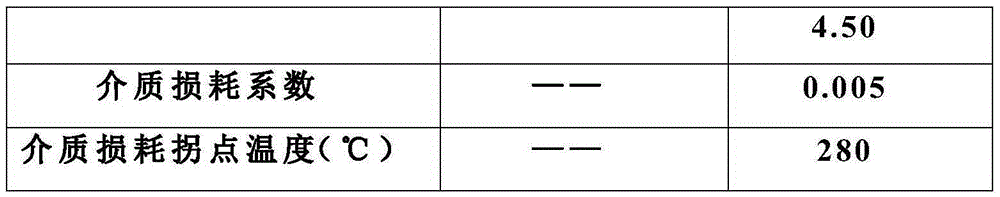

High-temperature resistant polyimide wire enamel and preparation method thereof

The invention discloses high-temperature resistant polyimide wire enamel and a preparation method thereof. The wire enamel comprises the following components in percent by weight based on total mass of enamel liquor: 50-80 percent of polyimide acid solution with solid content of 30 percent and 0-40 percent of chain-extended bismaleimide prepolymer solution with solid content of 30 percent. The preparation method of the high-temperature resistant polyimide wire enamel comprises the steps of mixing the polyimide acid solution and the chain-extended bismaleimide prepolymer solution according to proportions, adding an organic solvent to adjust the solid content and viscosity of the enamel liquor, and stirring to uniformly mix, thus obtaining claret-red transparent viscose polyimide wire enamel. The wire enamel disclosed by the invention is good in storage stability, resistant to high temperature, uniform in enamel film, good in flexibility, simple and easy to operate in an enamel and wire preparation process, high in raw material utilization rate, little in three-waste pollution and easy to realize industrialization; the soft breakdown voltage and the breakdown voltage of the wire enamel are remarkably higher than 240-level polyimide enamelled round copper wire standard in China respectively. The high-temperature resistant polyimide wire enamel can be used for insulation of a high-load, high-power and refrigerant-resistant motor and has broad market prospects.

Owner:HUAWEI TEHCHNOLOGIES CO LTD

Valuation method of dielectric breakdown lifetime of gate insulating film, valuation device of dielectric breakdown lifetime of gate insulating film and program for evaluating dielectric breakdown lifetime of gate insulating film

InactiveCN101995536AAccurate assessmentNo loss of detectionTesting dielectric strengthSemiconductor/solid-state device testing/measurementRoom temperatureElectric stress

The present invention discloses a valuation method, a valuation device and a valuation program of dielectric breakdown lifetime of a gate insulating film, used for evaluating dielectric breakdown lifetime of the gate insulating film of a MOS type element. The valuation method includes the following steps of: deciding a Weibull slope of lifetime distribution until reaching a soft breakdown of the gate insulating film of the MOS type element; deciding a detection condition of the soft breakdown from the decided Weibull slope after the above step; and executing a dielectric breakdown test by using the decided detection condition. The valuation device includes: a voltage supply unit to supply a voltage for the MOS type element so as to apply an electric stress to the MOS type element; a current measuring unit to measure a leakage current across the gate insulating film; and a temperature holding unit to hold temperature of a testing element containing the MOS type element to below a room temperature. According to the valuation method, the valuation device and the valuation program, the dielectric breakdown lifetime can be determined suitably.

Owner:SONY CORP

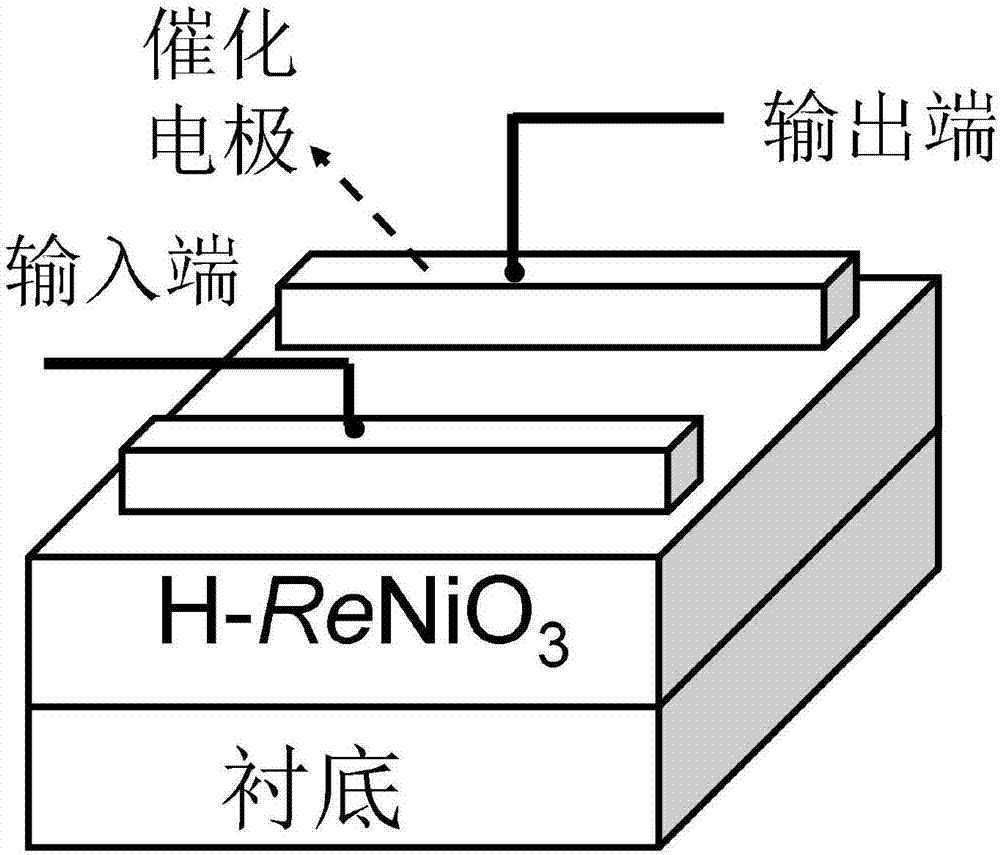

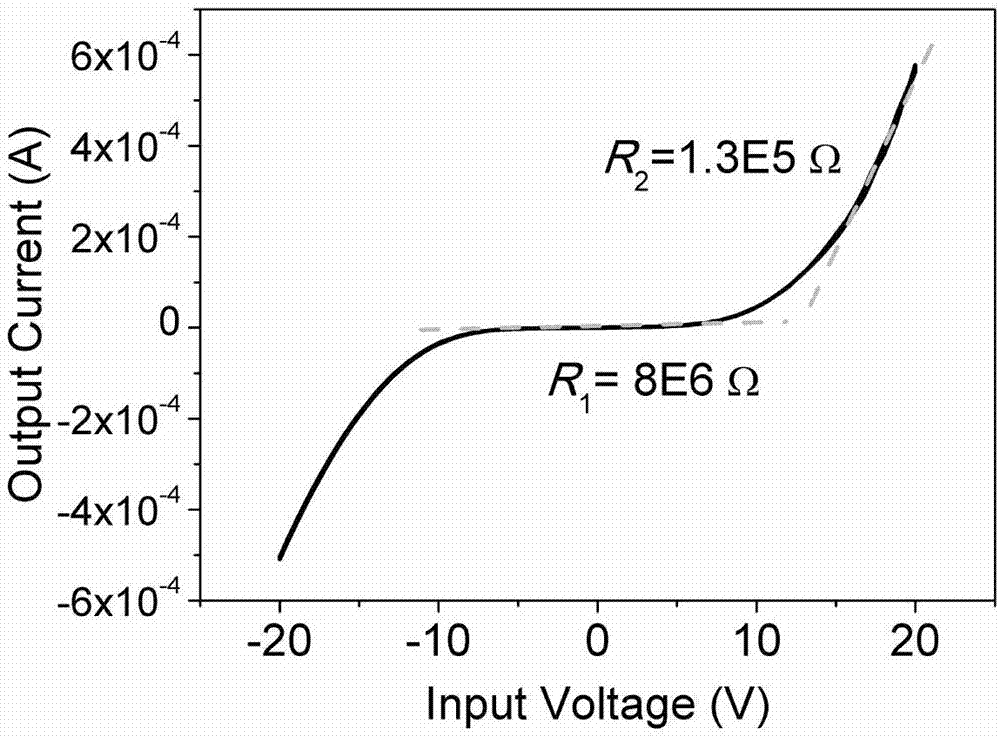

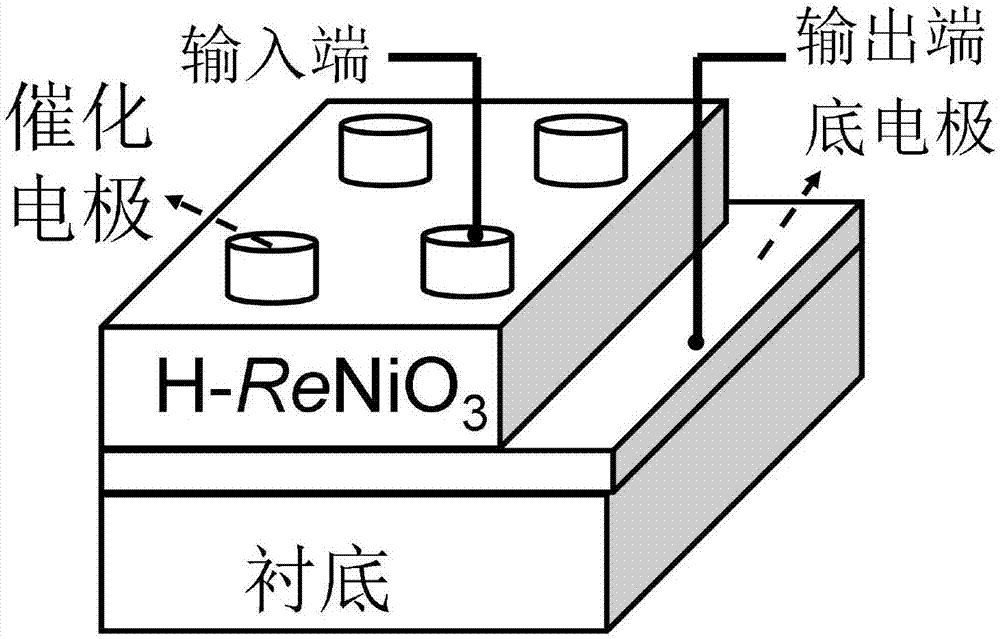

Method for preparing nonlinear resistor based on hydrogenated rare earth nickel-based perovskite oxide

ActiveCN107240641ASuitable for reducing atmosphereLower momentaryElectrical apparatusTitanium oxideElectron

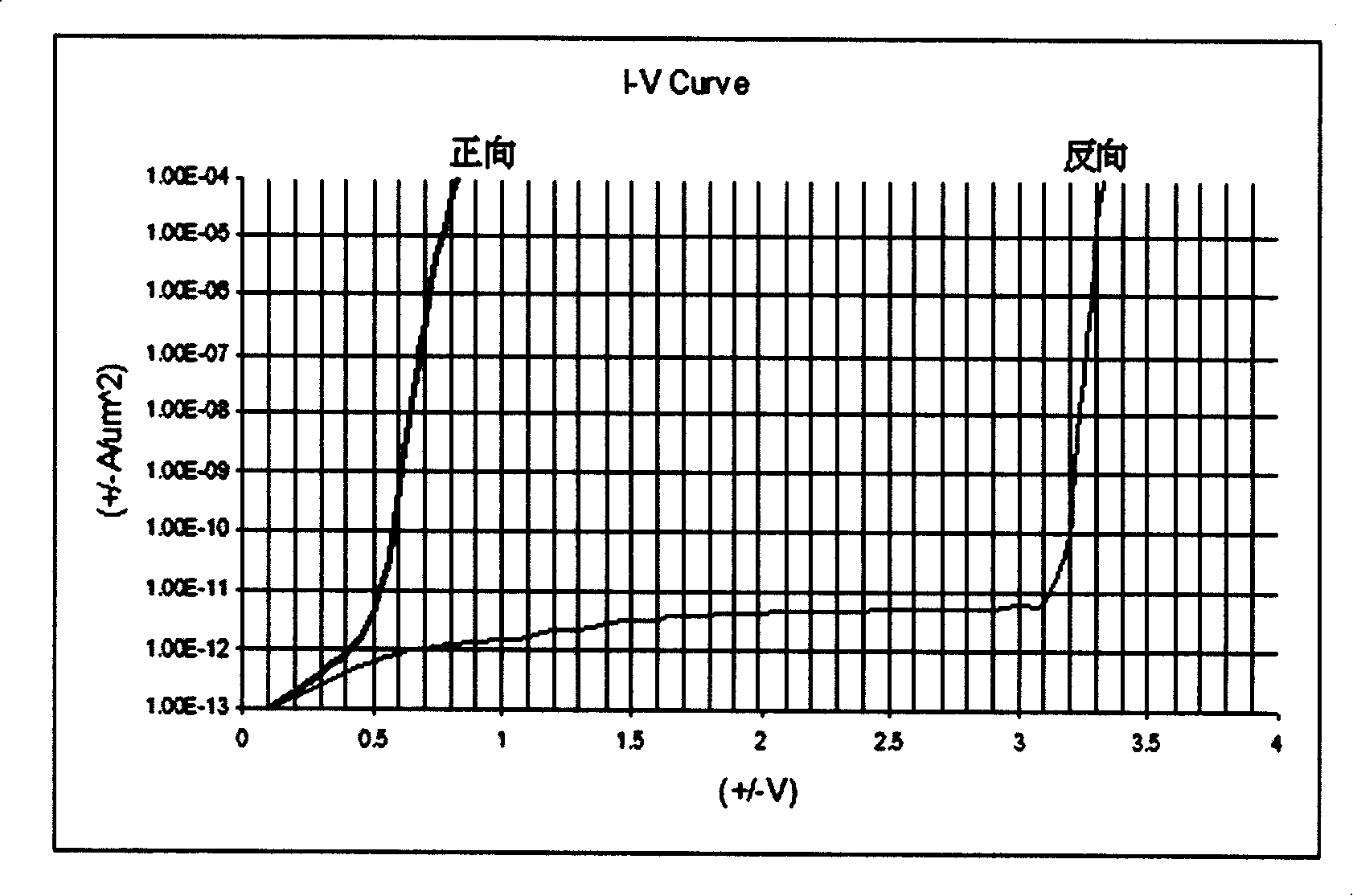

The invention relates to a method for preparing and using a nonlinear resistor based on hydrogenated rare earth nickel-based perovskite oxide, and belongs to the field of electronic strong correlation materials and electronic devices. As doped protons in a material increase with electric field intensity and gradually migrate to trigger transformation of a nickel element in the material from a strong correlation electron localized state insulator phase to a weak electron non-localized state metal or semiconductor phase, thereby realizing variation of material resistance with impressed voltage, i.e., realizing a current-voltage nonlinear variation relation. Through control of conditions of the rare earth element type, crystal structure, crystal particle crystal boundary state and stress state of the material, migration activation energy and a soft breakdown characteristic of protons in hydrogenated rare earth nickel-based perovskite oxide are controlled, thereby realizing control of a dynamic change process of material nonlinear resistance. The preparation method provide by the invention can be applied to aspects of piezoresistors, smoothing and rectification, electrical signal sensing, overvoltage protection and the like. Compared with traditional pressure-sensitive nonlinear resistance materials of zinc oxide, titanium oxide and the like, a device prepared by the method is more suitable for a reducing atmosphere.

Owner:UNIV OF SCI & TECH BEIJING

Circuit and system of aggregated area anti-fuse in CMOS processes

ActiveUS9224496B2Improve reliabilityHigh yieldTransistorSemiconductor/solid-state device detailsElectrical polarityEngineering

Gate oxide breakdown anti-fuse suffers notorious soft breakdown that reduces yield and reliability. This invention discloses circuit and system to enhance electrical field by blocking LDD so that the electrical field is higher and more focused near the drain junction, to make electrical field in the channel more uniform by creating slight conductive or conductive in part or all of the channel, or to neutralize excess carriers piled up in the oxide by applying alternative polarity pulses. The embodiments can be applied in part, all, or any combinations, depending on needs. This invention can be embodied as a 2 T anti-fuse cell having an access and a program MOS with drain area in the program MOS, or 1.5 T anti-fuse cell without any drain in the program MOS. Similarly this invention can also be embodied as a 1 T anti-fuse cell having a portion of the channel made conductive or slightly conductive to merge the access and program MOS into one device with drain area, or 0.5 T anti-fuse cell without any drain.

Owner:ATTOPSEMI TECH CO LTD

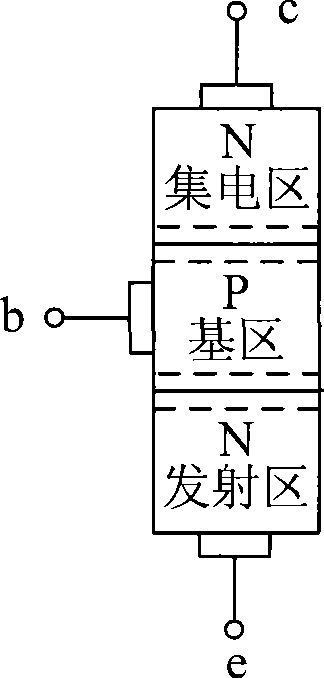

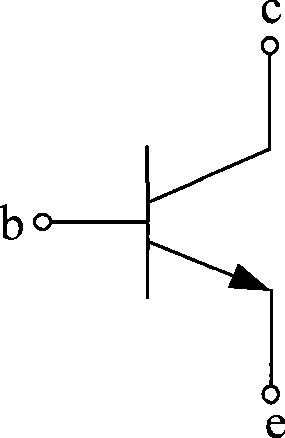

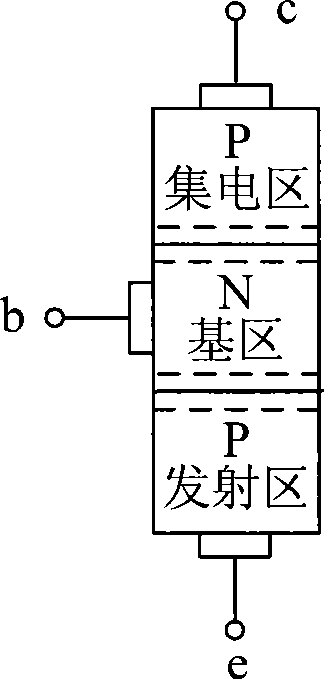

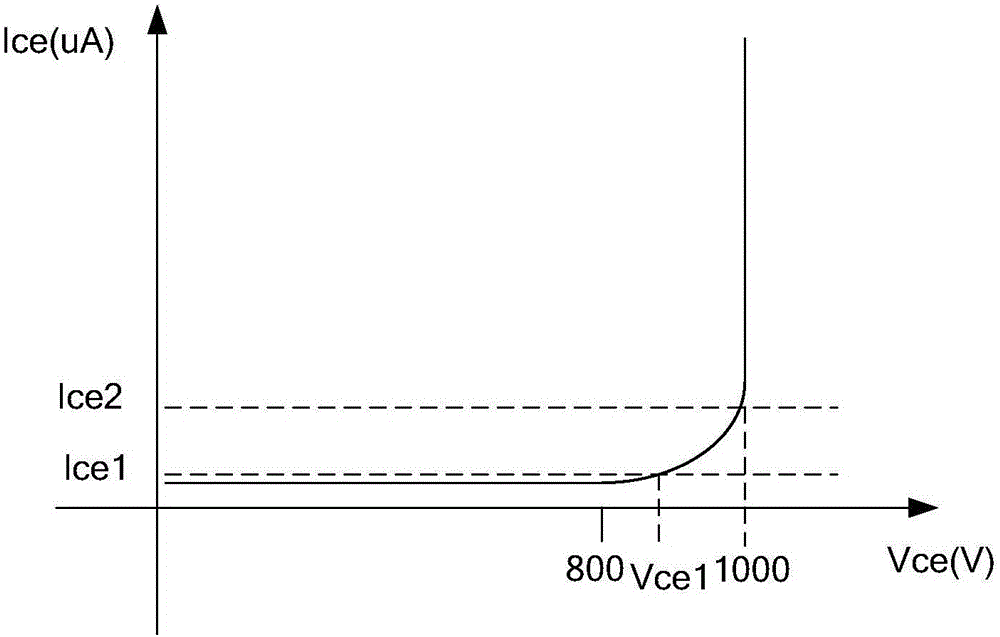

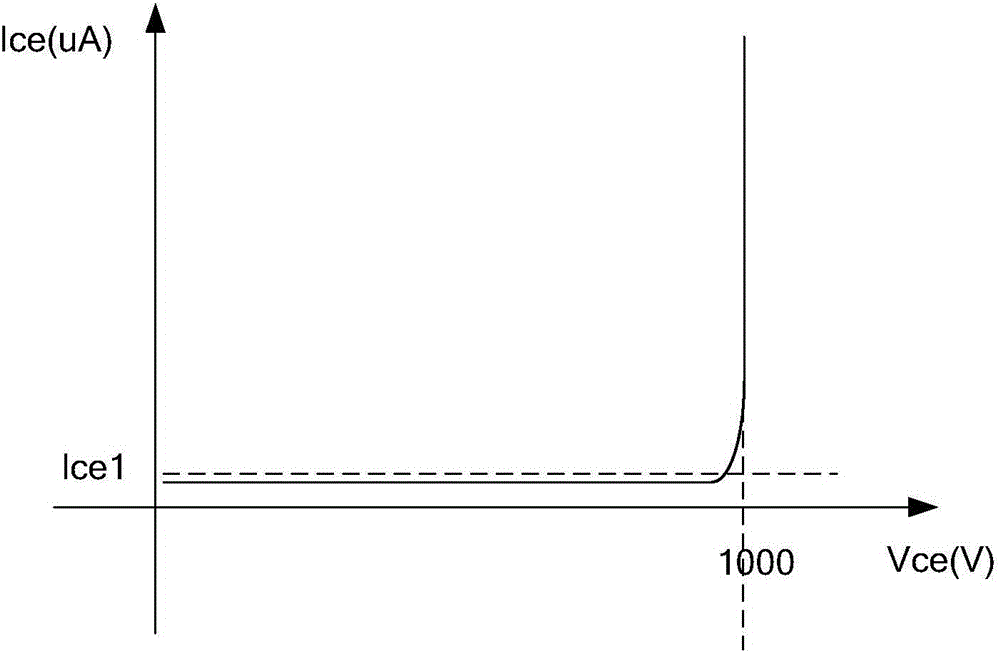

Method for testing BVceo soft breakdown of semiconductor triode

ActiveCN101419270AImprove detection efficiencyImprove detection accuracyIndividual semiconductor device testingDelta-vHigh volume manufacturing

The invention discloses a test method for judging whether a semiconductor dynatron suffers BVCEO soft breakdown. A current nominal value ICEO1 of test condition IC of BVCEO is regarded as an initial condition to measure corresponding voltage VCEO 1; current value ICEO 2 is used as newly added initial condition to measure corresponding voltage VCEO 2; or VCE which has a voltage difference delta V with the voltage value VCEO 1, is used as newly added initial condition, to measure corresponding current value ICEO2'; and the ratio of the VCEO1 to the VCEO2 is compared with a first set standard value, or the measured ICEO2' is compared with a second set standard value. The method has high screening success rate, is favorable for quality control, can improve detecting efficiency, meet the requirements of mass production, reduce production cost and enhance competitiveness of an enterprise.

Owner:FOSHAN BLUE ROCKET ELECTRONICS

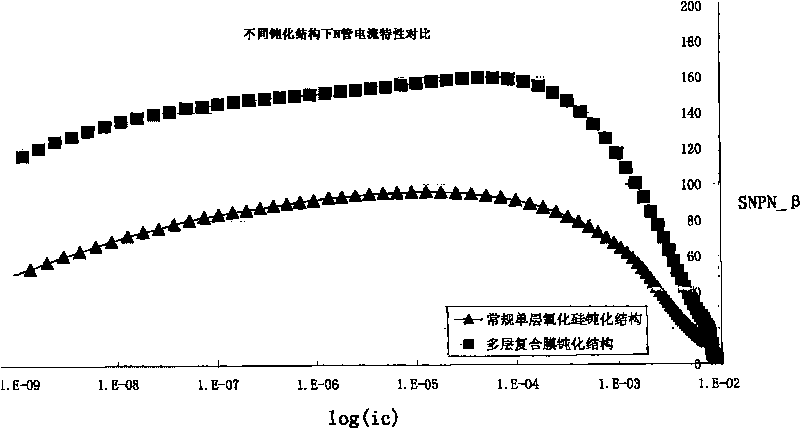

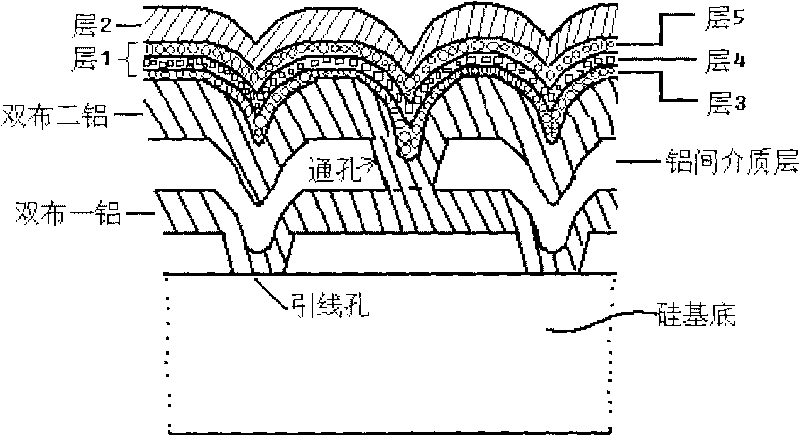

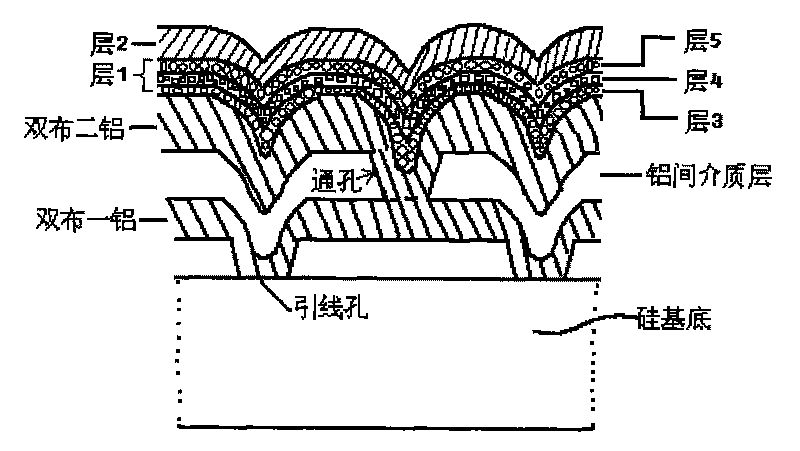

Multi-layer compound passivation layer structure of Bipolar circuit and manufacturing process thereof

InactiveCN101710580AReduce stressImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHigh densitySilicon oxide

The invention provides a multi-layer compound passivation film structure of a Bipolar circuit, which comprises a bottom silicon oxide film layer and a silicon nitride film layer, wherein the silicon oxide film layer is deposited on the surface of a silicon substrate, and the silicon nitride film layer is deposited on the silicon oxide film layer; a certain proportion of phosphine is doped in the silicon oxide film layer; and the silicon oxide film layer sequentially comprises an undoped silicon oxide layer, a doped phosphorosilicate glass layer and an undoped silicon oxide layer. Meanwhile, the invention also provides a manufacturing process of the multi-layer compound passivation film of the Bipolar circuit. The multi-layer compound passivation film structure of the Bipolar circuit has scratch resistance, moisture resistance, high density, low film stress, higher impurity absorbing ability, better step covering ability and excellent photoelectric properties, electrical characteristics and heat stability, reduces the soft breakdown, and solves the problems of poor reliability, and the like.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

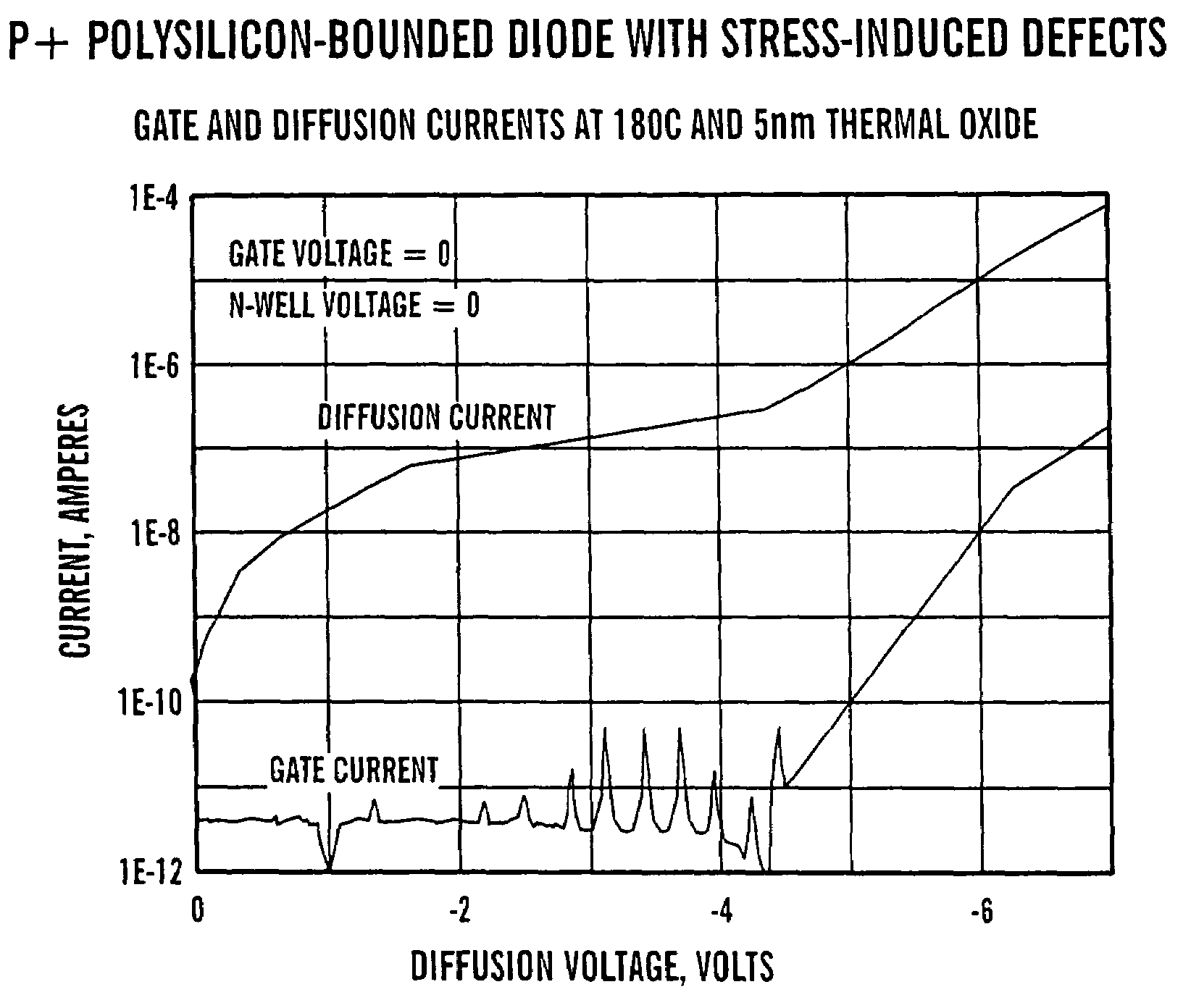

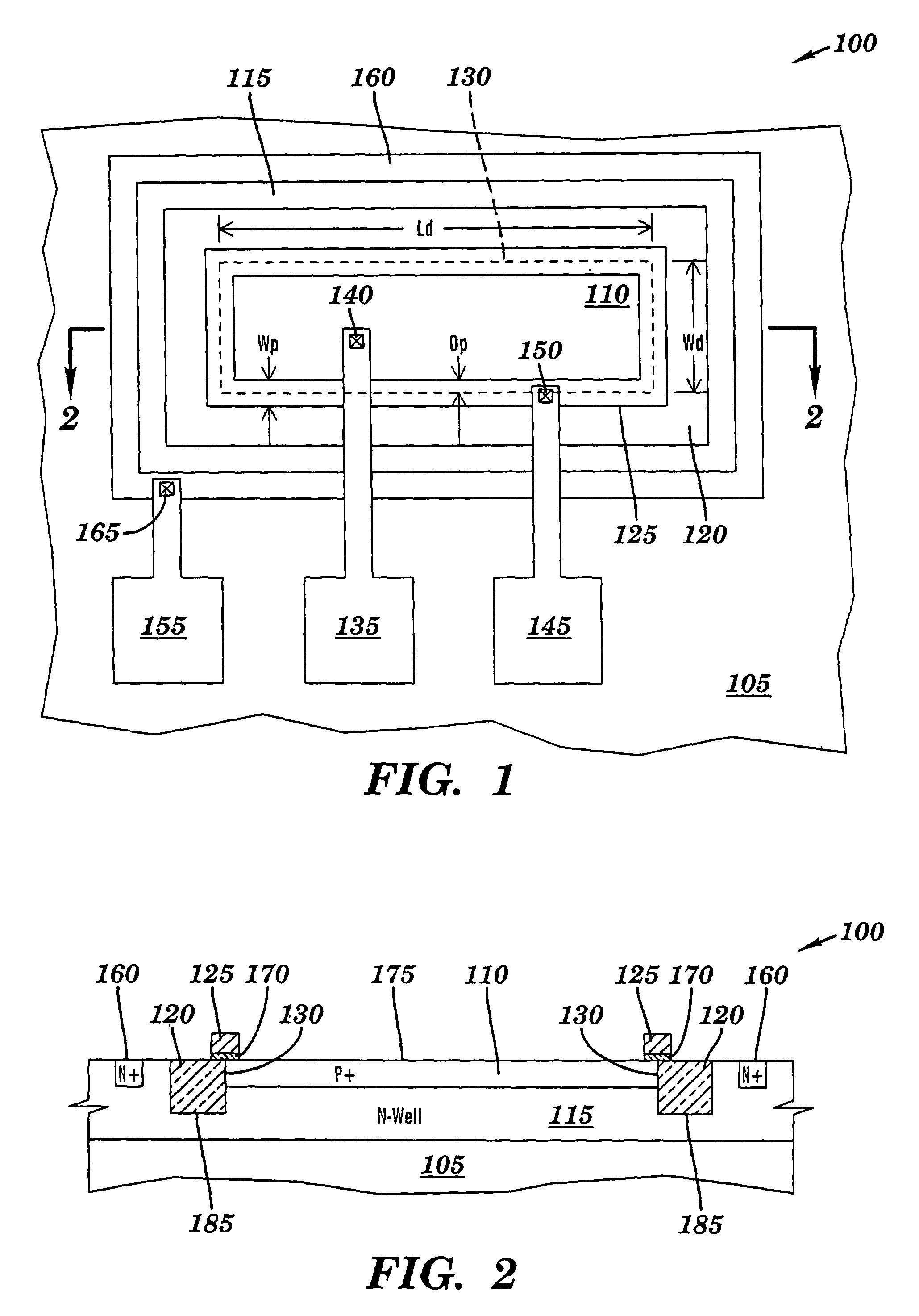

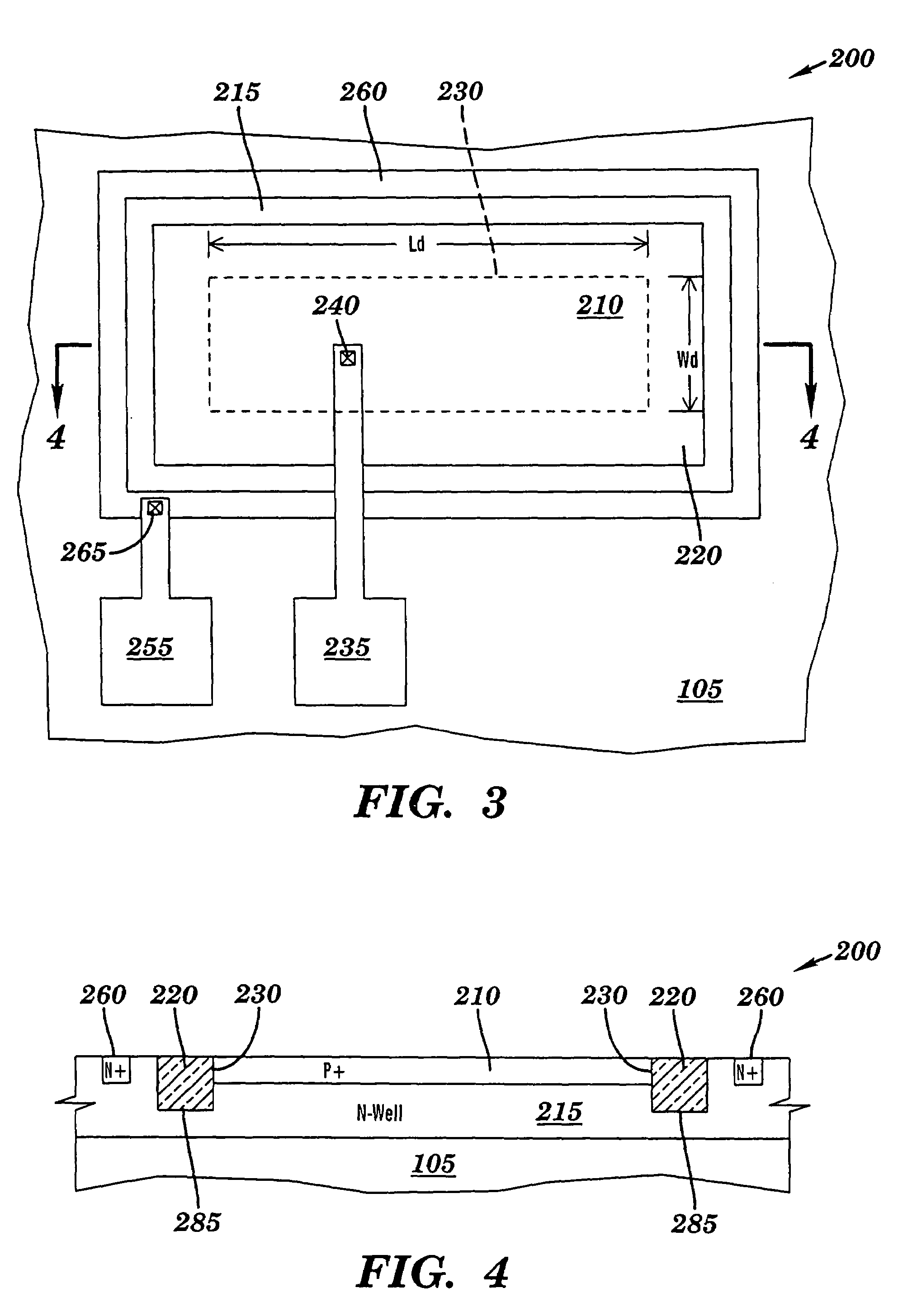

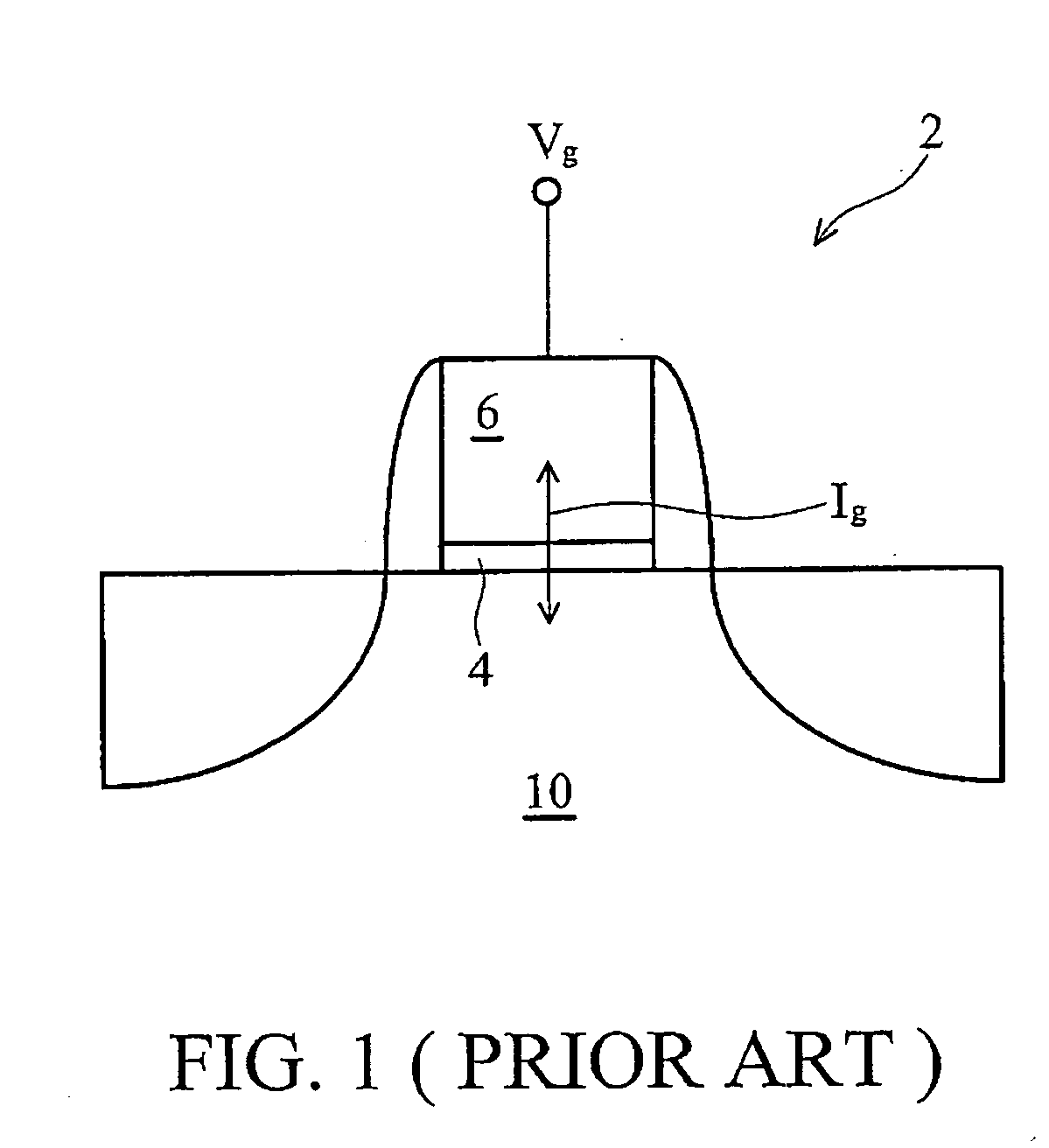

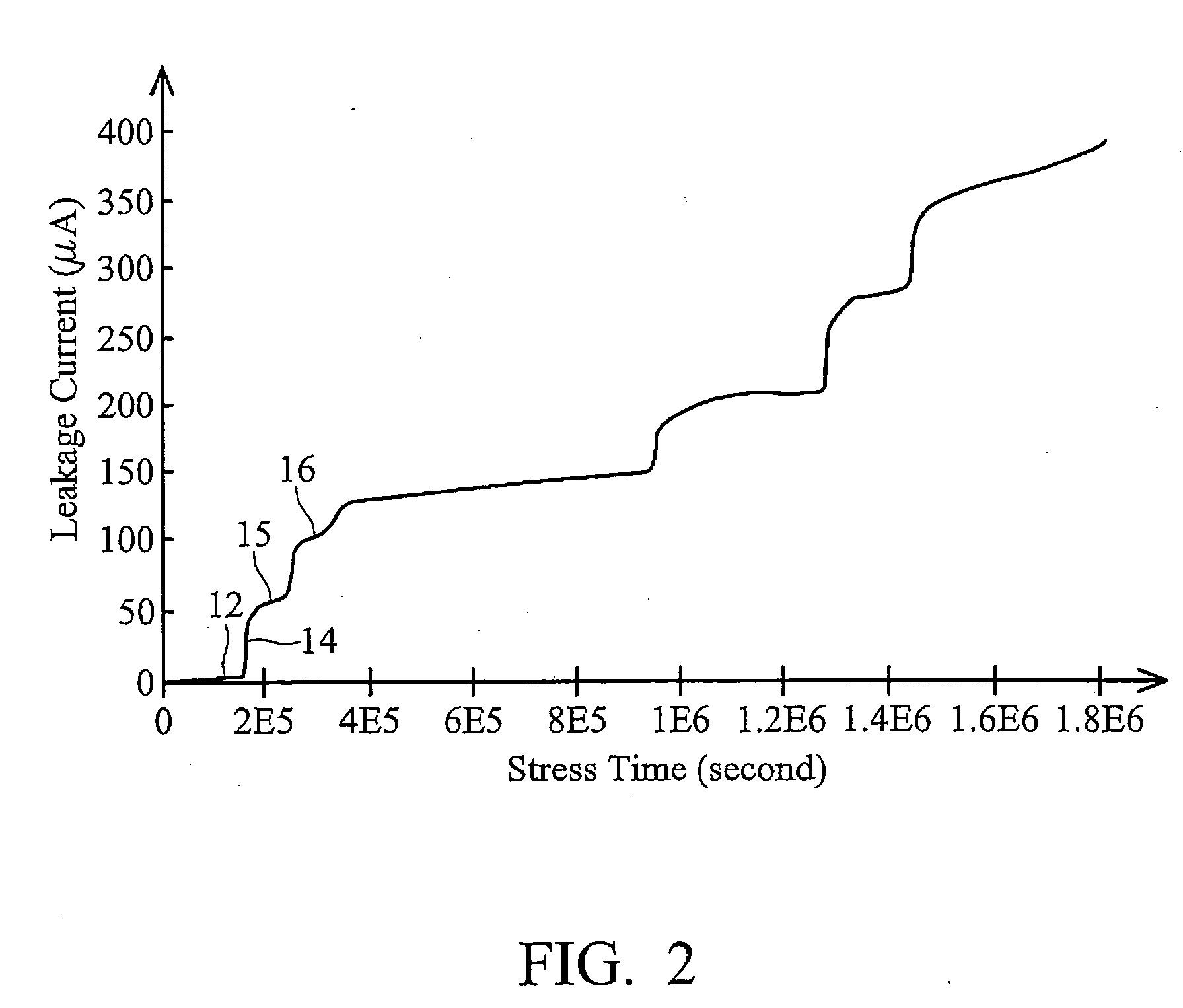

Test structure and methodology for semiconductor stress-induced defects and antifuse based on same test structure

InactiveUS7132325B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsStress inducedAntifuse

A method for detecting semiconductor process stress-induced defects. The method comprising: providing a polysilicon-bounded test diode, the diode comprising a diffused first region within an upper portion of a second region of a silicon substrate, the second region of an opposite dopant type from the first region, the first region surrounded by a peripheral dielectric isolation, a peripheral polysilicon gate comprising a polysilicon layer over a dielectric layer and the gate overlapping a peripheral portion of the first region; stressing the diode; and monitoring the stressed diode for spikes in gate current during the stress, determining the frequency distribution of the slope of the forward bias voltage versus the first region current at the pre-selected forward bias voltage and monitoring, after stress, the diode for soft breakdown. A DRAM cell may be substituted for the diode. The use of the diode as an antifuse is also disclosed.

Owner:IBM CORP

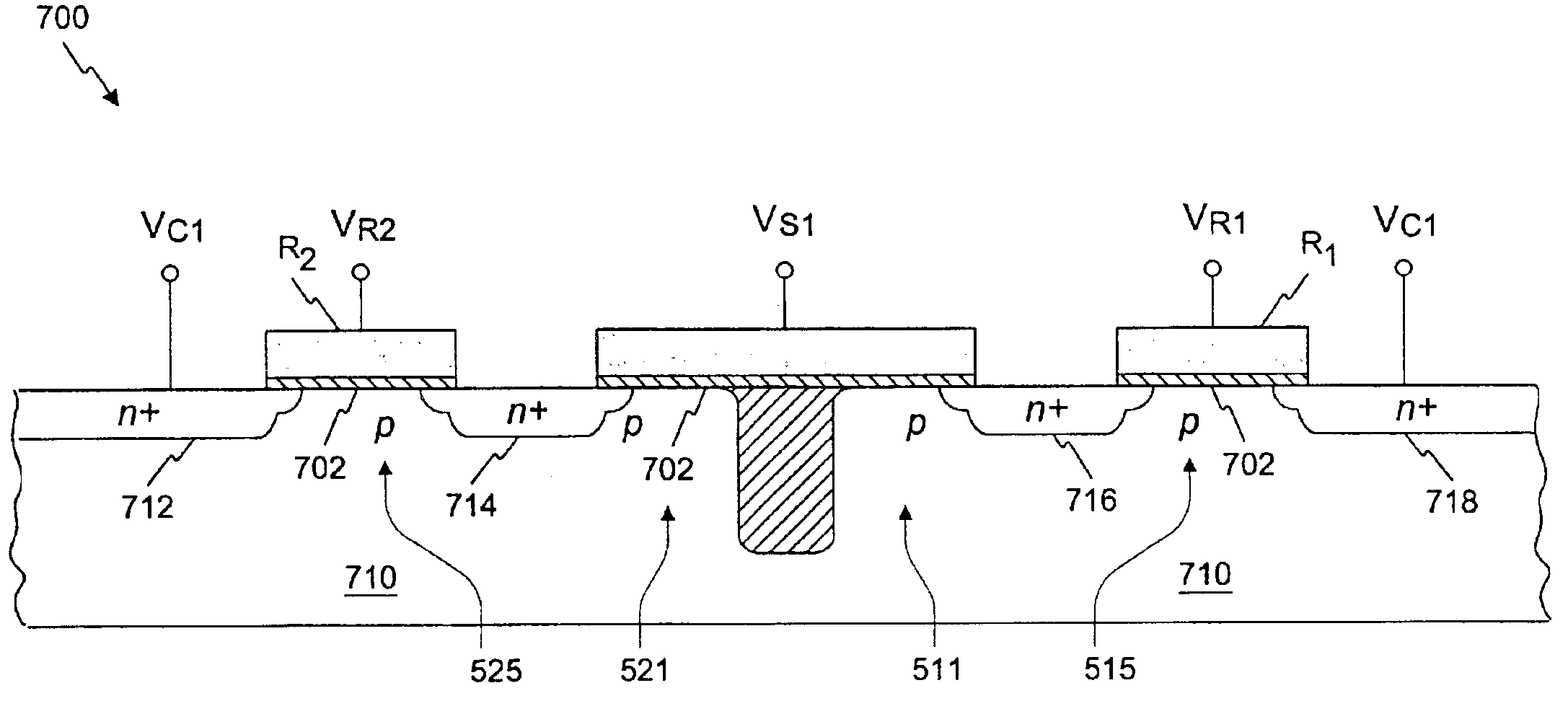

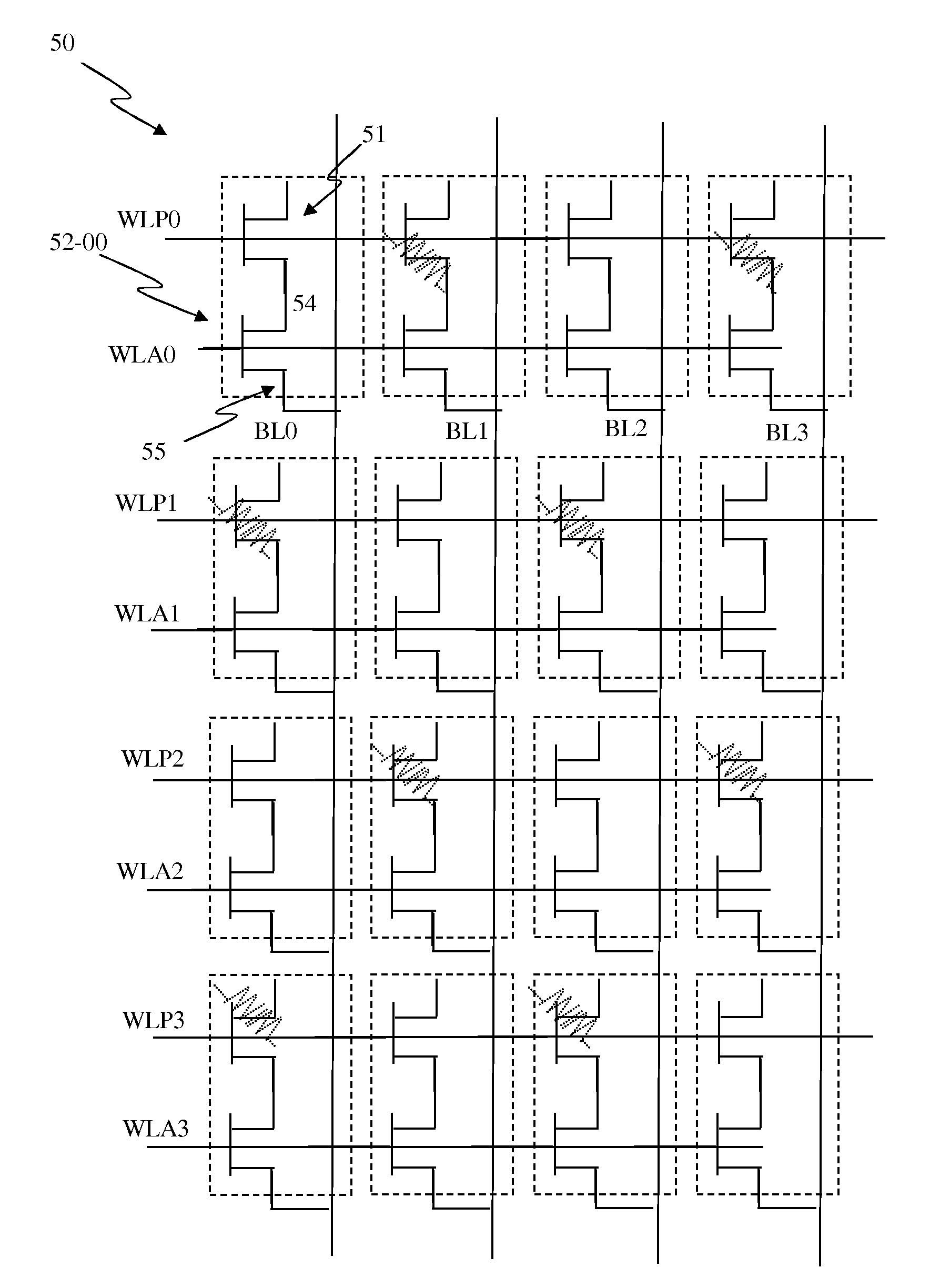

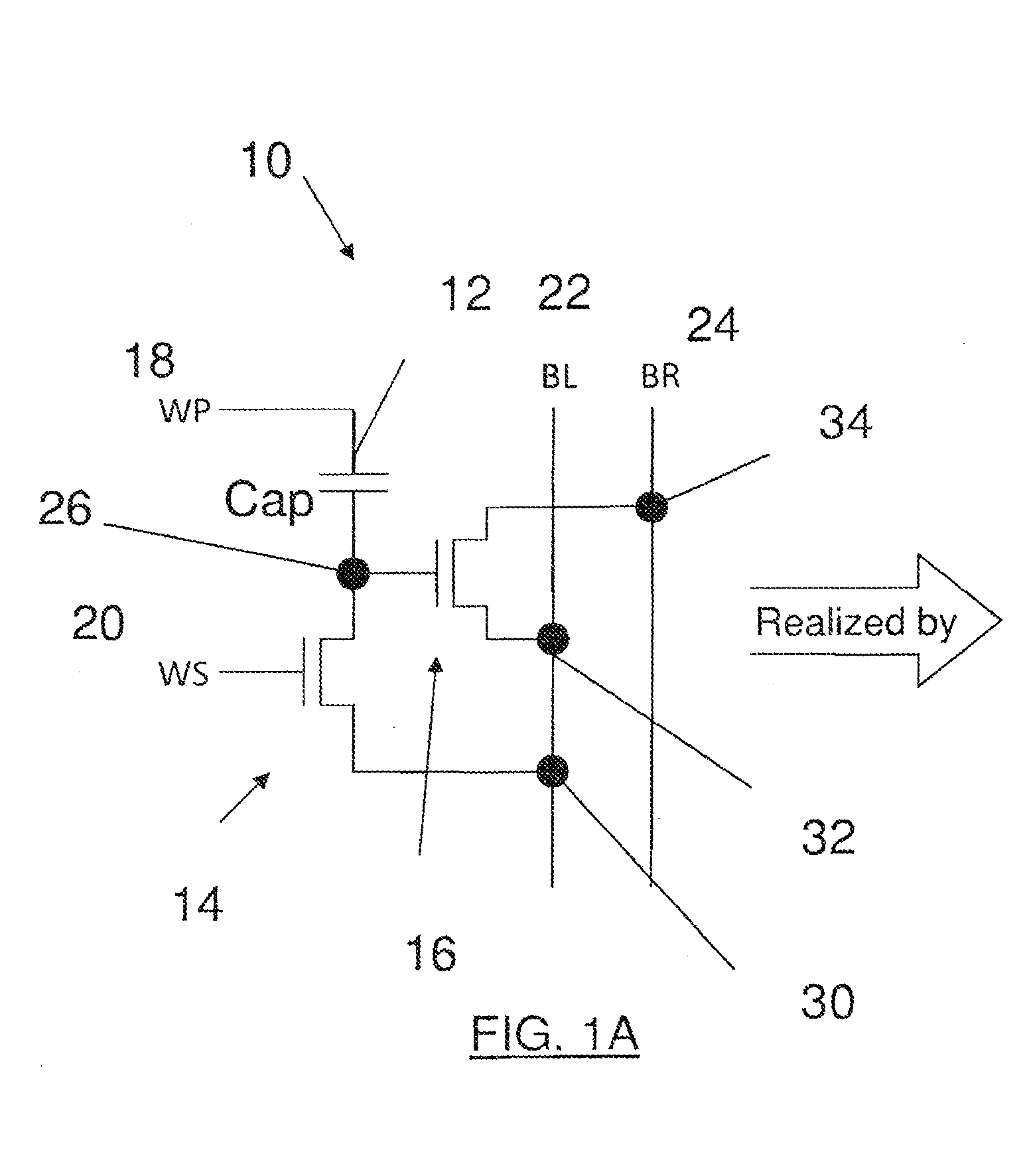

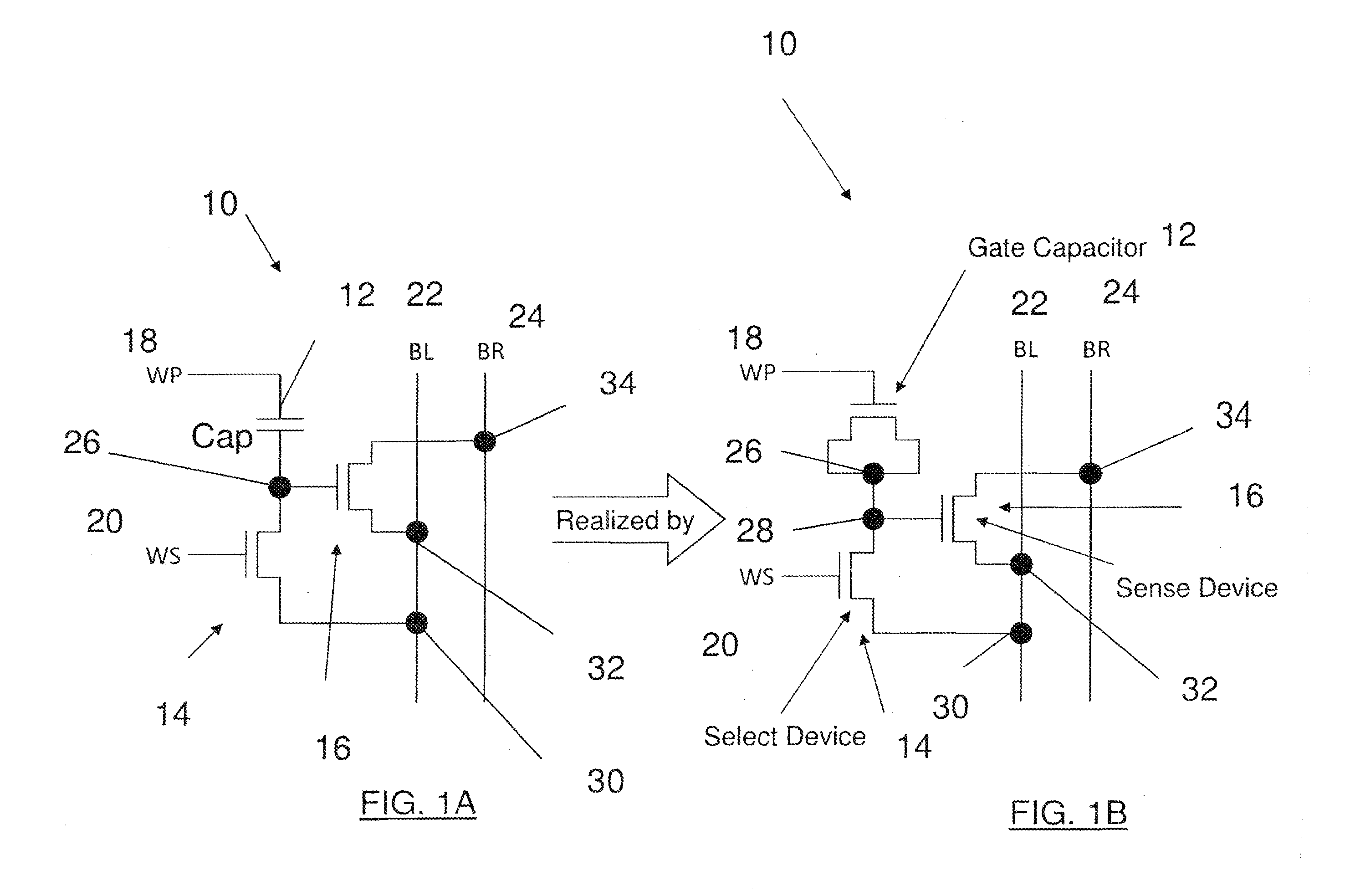

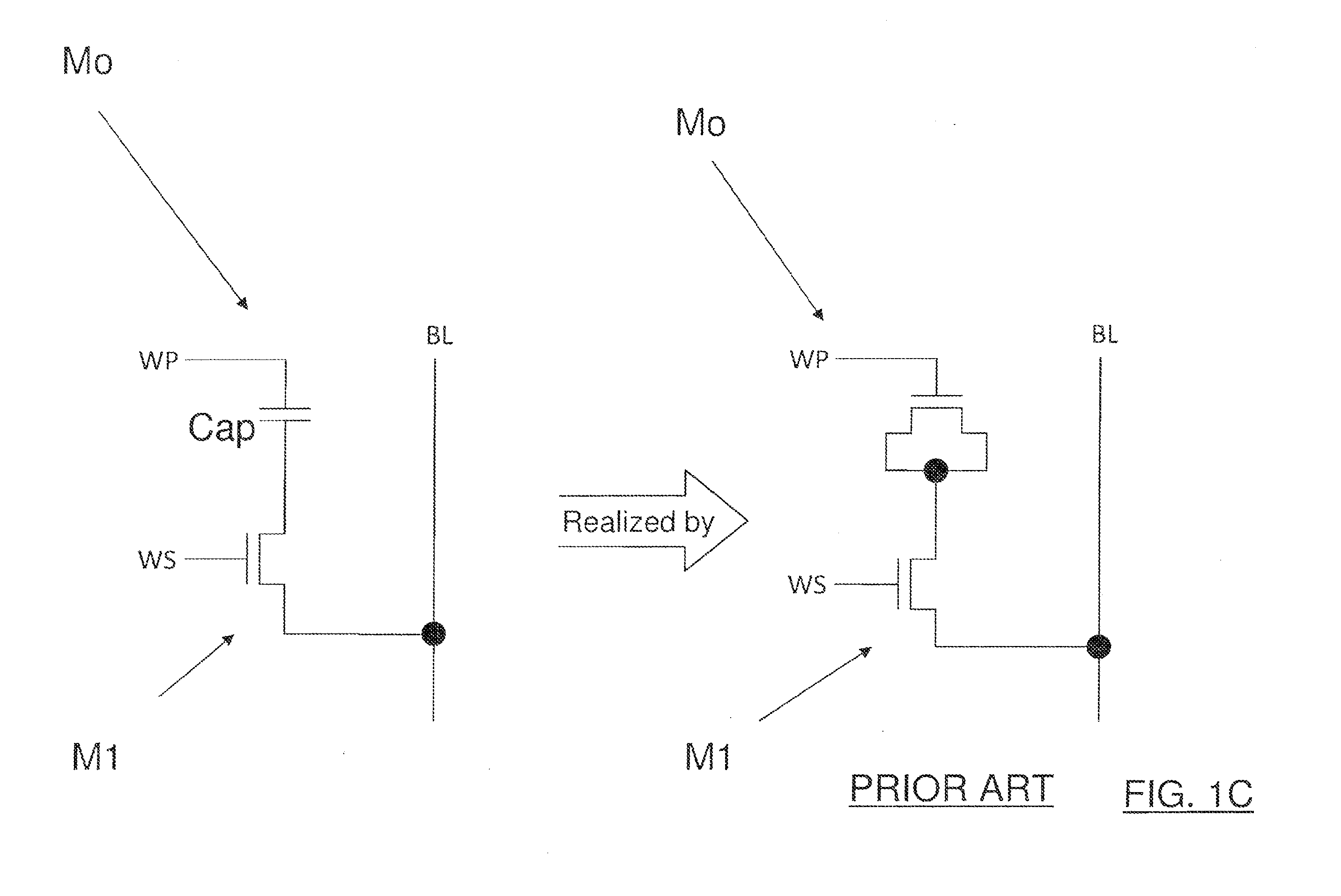

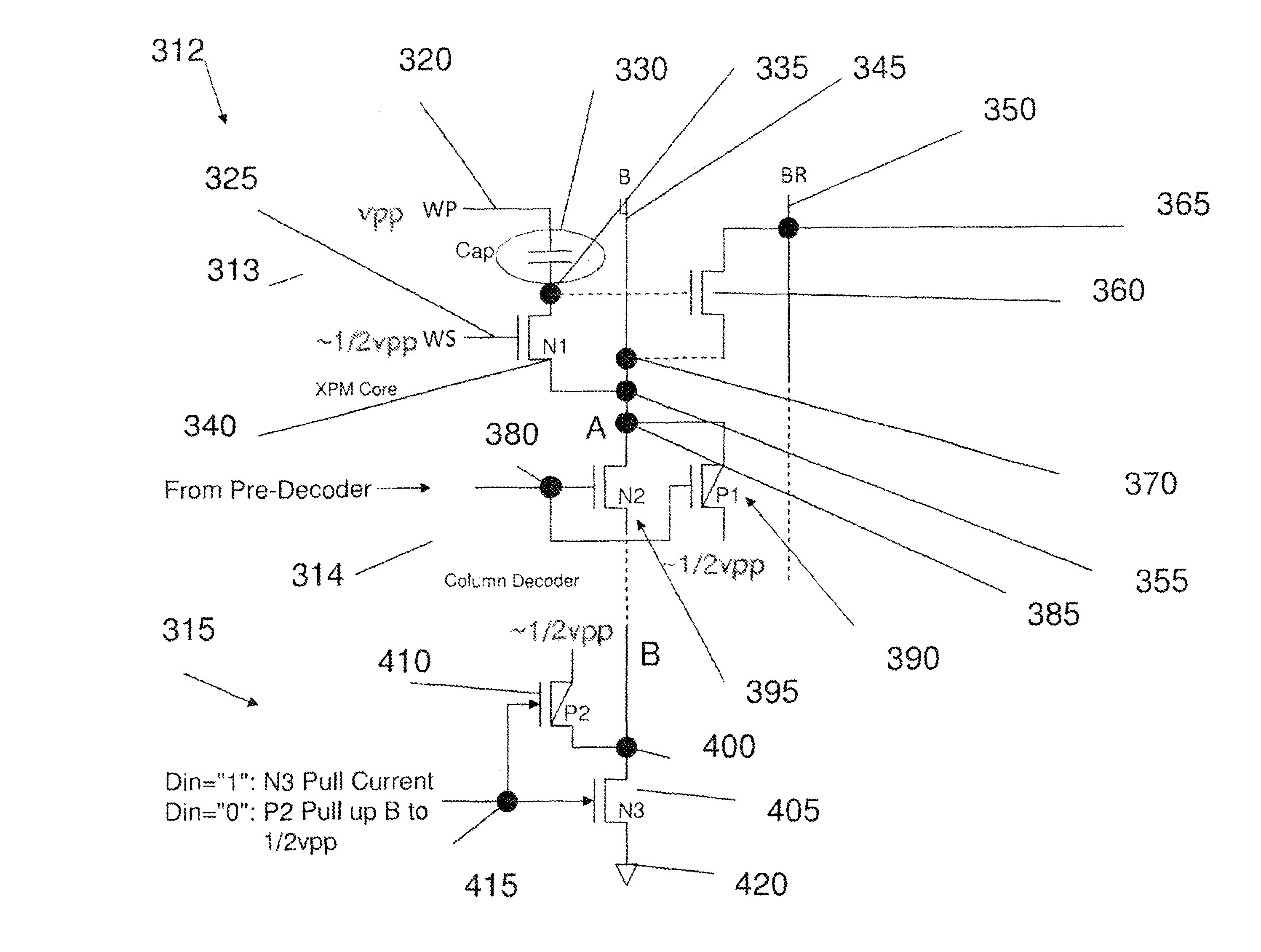

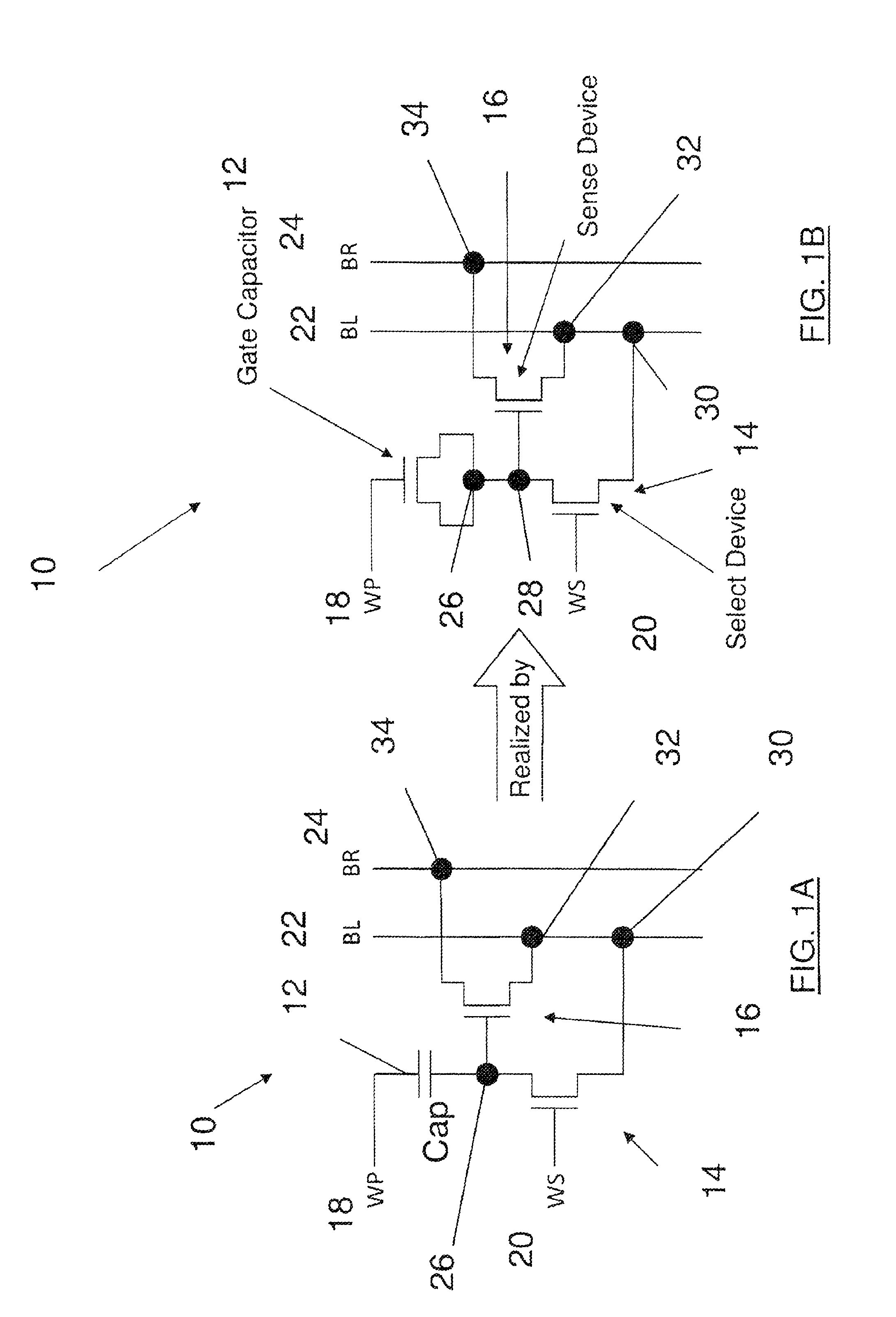

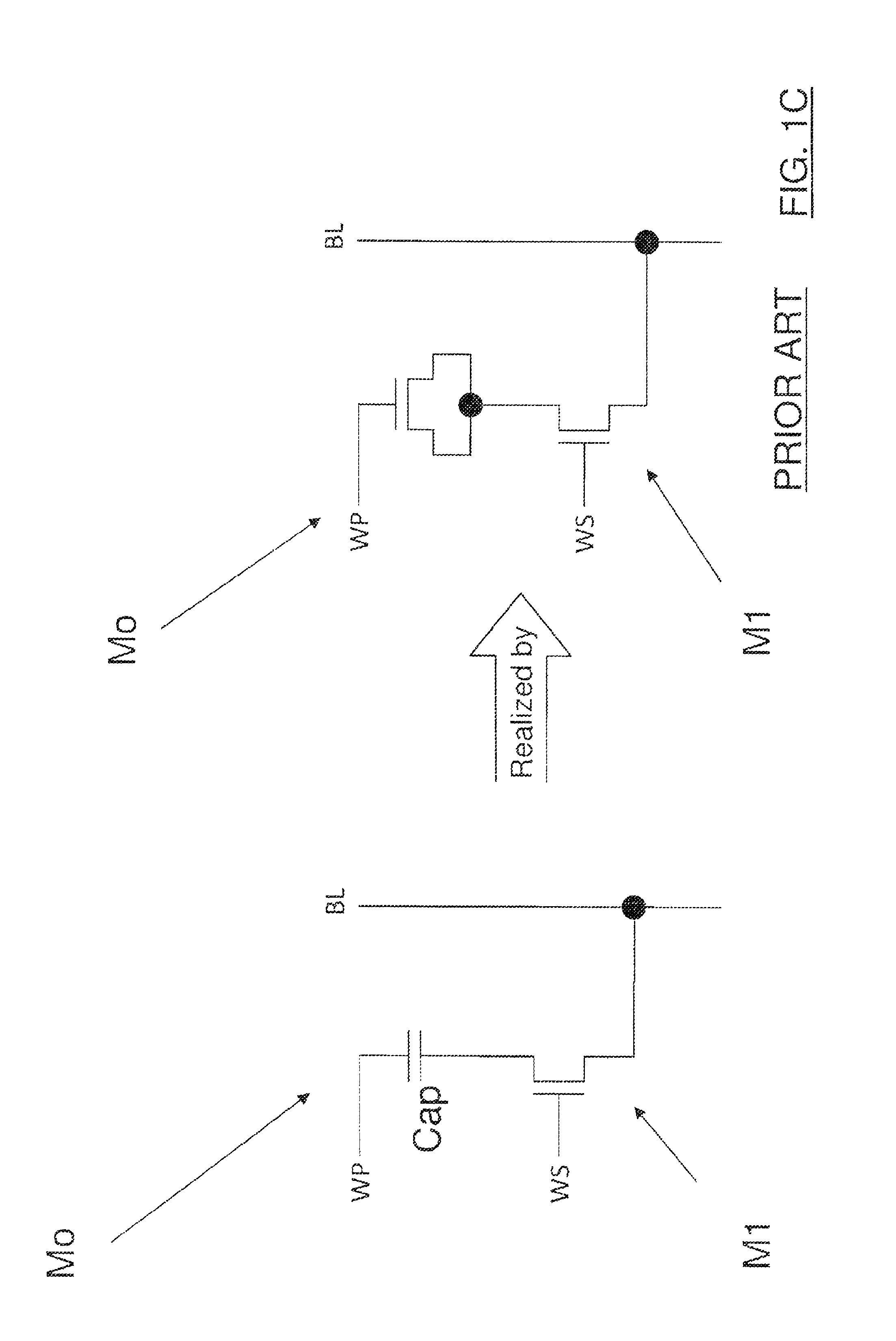

Soft breakdown mode, low voltage, low power antifuse-based non-volatile memory cell

A non-volatile memory cell uses two transistors only, a bit select and a sense device. Each cell further comprises an antifuse device implemented, for example, with a field-effect transistor operated to behave like an antifuse when the cell is selected and a modest programming voltage under 5.5 volts and under 5-μA is applied. Only a soft breakdown is needed in the thin gate oxide because a local sense transistor is used during read operations to detect the programming and amplify it for column sense amplifiers. Reading also only requires low voltages of about one volt.

Owner:CHENGDU KILOWAY ELECTRONICS CO LTD

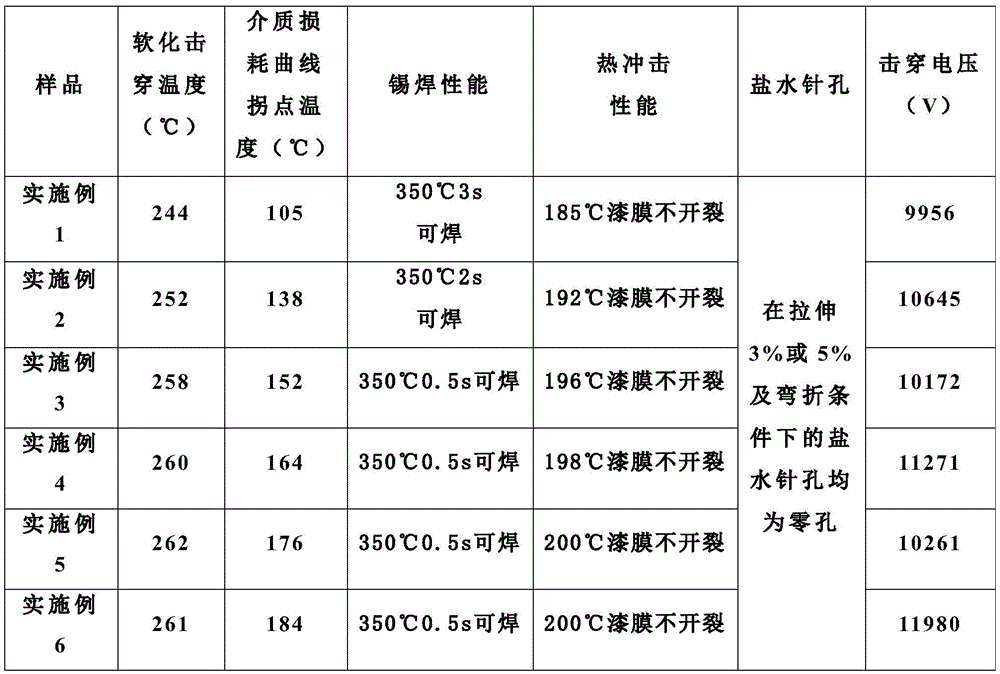

Preparation method of 180 grade polyurethane enamelled wire insulating paint used for ultra-fine wire

InactiveCN102936451AImprove the level ofNo sparklePolyurea/polyurethane coatingsUltra fineZinc Acetate Dihydrate

The invention relates to 180 grade polyurethane enamelled wire insulating paint used for an ultra-fine wire. The insulating paint is prepared by the following components of 14-20 parts of an imide-modified polyester resin, 36-50 parts of a blocked isocyanate resin, 0.02 part of zinc acetate, 0.35-0.75 part of an amino condensation compound, 0.02-0.05 part of silicone oil, 0.2-0.6 part of acrylic ester, 17-27 parts of dimethylbenzene, 7-17 parts of phenol and 5 parts of n-butyl alcohol. High heat grade non-pinhole rapid direct-welding polyurethane enamelled wire insulating paint is produced by mixing paint with the above materials at a temperature of 60-70 DEG C. Compared with a conventional insulating paint, the enamelled wire insulating paint provided by the invention has good leveling property, and can meet the requirements of a production process with specification of 0.02 mm and production speed of 1500 m / min. The prepared enamelled wire has smooth and bright surfaces and has no shining points. The prepared enamelled wire has high a soft breakdown temperature which is higher than 260 DEG C. The prepared enamelled wire has good salt-water pinhole resistant performance and is resistant to knead and stretch salt-water pinholes in salt water. The prepared enamelled wire has good directly welding performance and is capable of being directly welded at a temperature of 375 DEG C. The prepared enamelled wire has wide process redundancy and is convenient for realizing stable process production.

Owner:上海晟然绝缘材料有限公司

Soft breakdown mode, low voltage, low power antifuse-based non-volatile memory cell

Owner:CHENGDU KILOWAY ELECTRONICS CO LTD

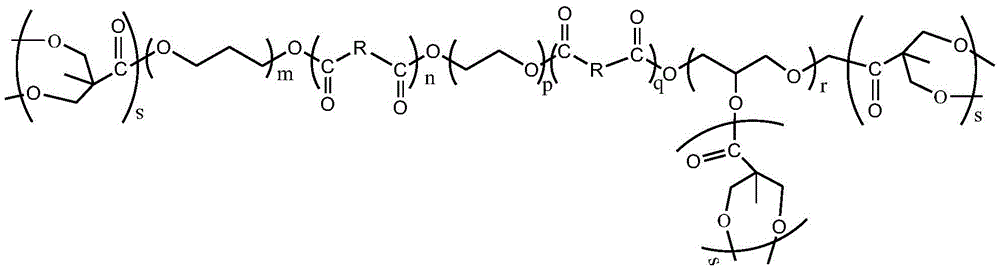

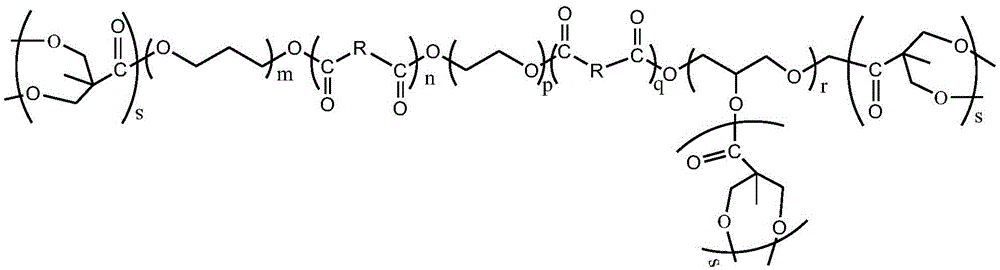

Hyper-branched polyester polyol and preparation method thereof

ActiveCN105622904AMany branchesNot easy to tanglePolyurea/polyurethane coatingsLead bondingConductor Coil

The invention provides hyperbranched polyester polyol for polyurethane wire coating enamel and a preparation method of the hyperbranched polyester polyol. The hyperbranched polyester polyol has the characteristics of high branching, low intermolecular winding possibility, large quantities of branch chains and terminated functional groups, three-dimensional net structure and the like. The preparation method comprises the following steps: taking polyatomic alcohol, polyacidand polybasic anhydride as main raw materials to prepare polyester polyol; then, adding 2,2-dimethylolpropionic acid to prepare the hyperbranched polyester polyol. The preparation method is simple; multistep separation purification is eliminated; the production cost is relatively low; the suitability for large-scale industrial production is high. The wire coating enamel prepared from the hyperbranched polyester polyol is excellent in hot impact resistance and soft breakdown resistance, low in dielectric loss, and high in tin-lead bonding performance.

Owner:CHANGSHU INSTITUTE OF TECHNOLOGY

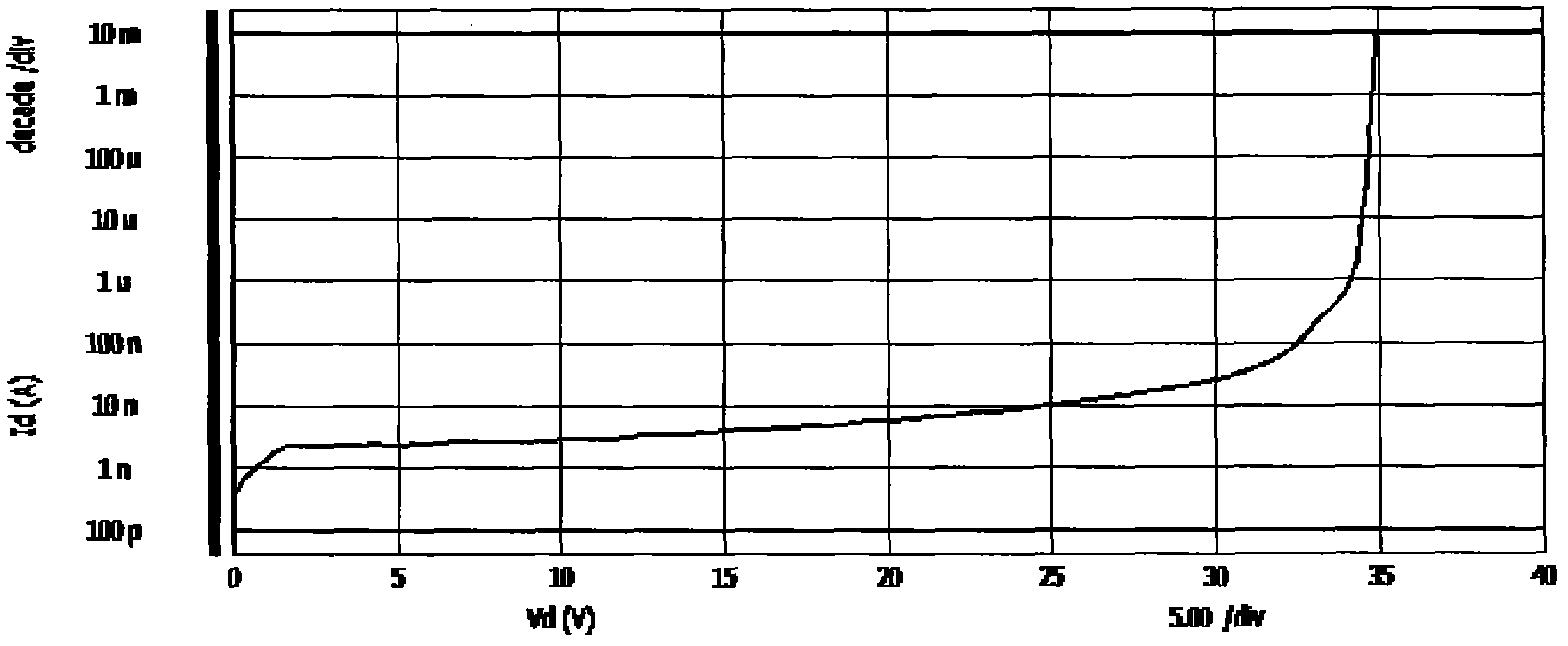

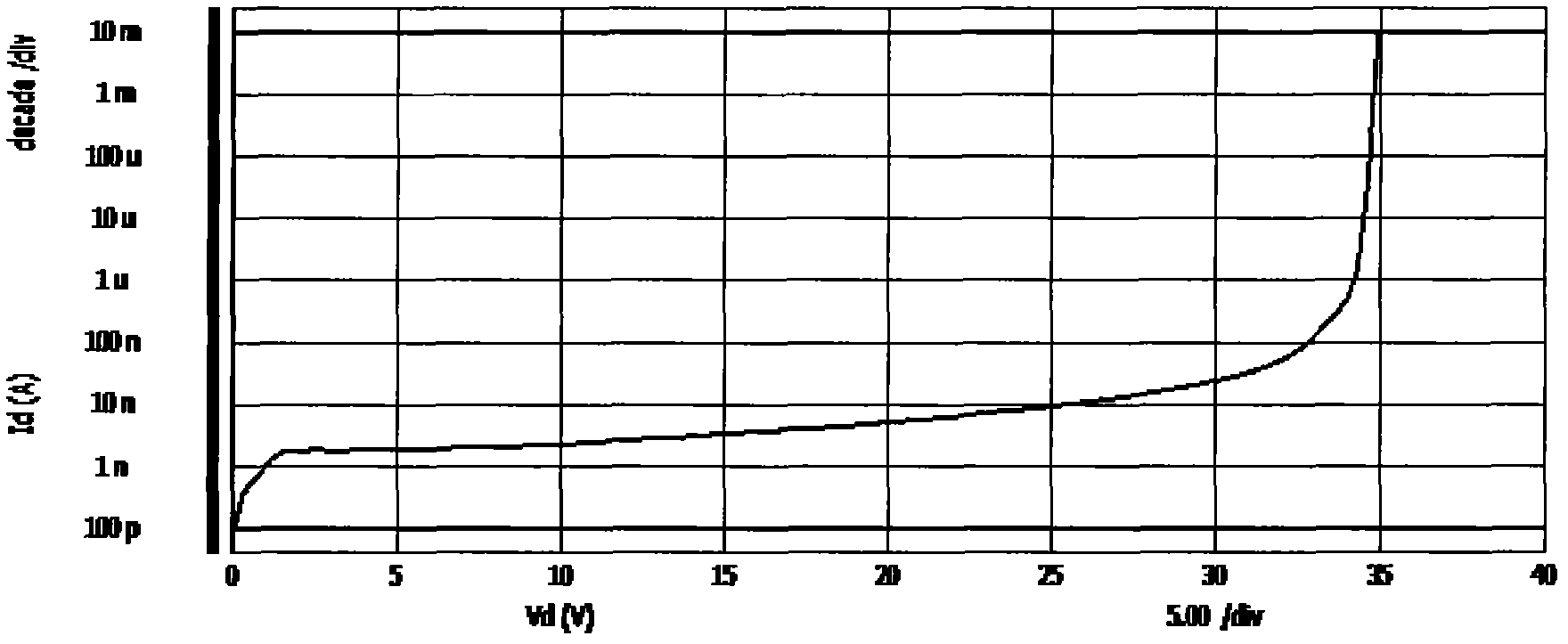

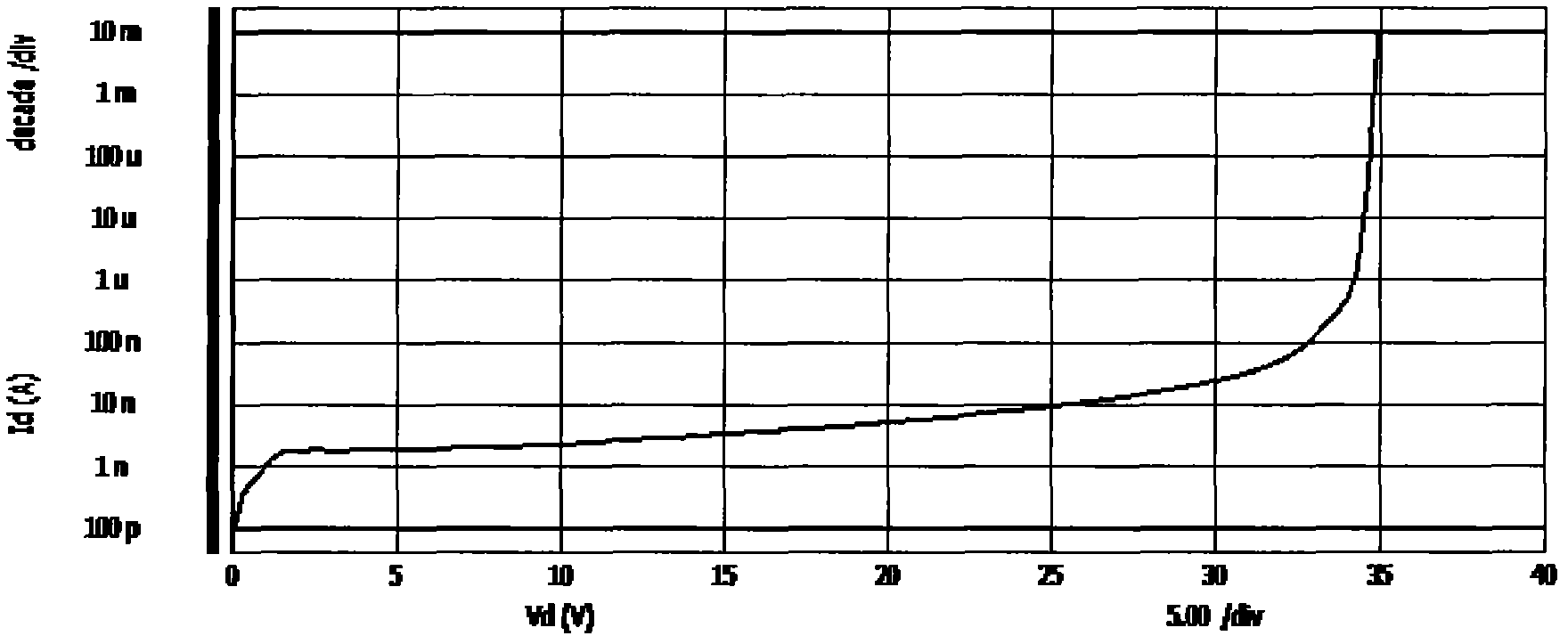

Semiconductor voltage regulation device

InactiveCN101226933AImproved "soft breakdown" characteristicsSolid-state devicesSemiconductor devicesCapacitanceGate leakage current

The invention discloses a low voltage semiconductor voltage stabilizer, which has the characteristics of low leakage current and hard breakdown, simultaneously has low junction capacitance. The technical scheme is that the voltage stabilizer of the invention comprises two portions which are a double junction type diode and an additional PN junction, the double junction type diode is used as the main body of the voltage stabilizer, and the PN junction is used to forward conduct. Two opposite PN junctions are arranged in the double junction type diode, and an external capacitance is reduced because the two PN junctions are connected in series. On the other hand, when an imposed voltage leads a PN junction to reversely offset, the positive barrier of the other PN junction deadens the zener leakage of the reverse offset junction in early period, thereby improving the characteristics of soft breakdown. The invention is used in the field of semiconductor components.

Owner:上海维恩佳得数码科技有限公司

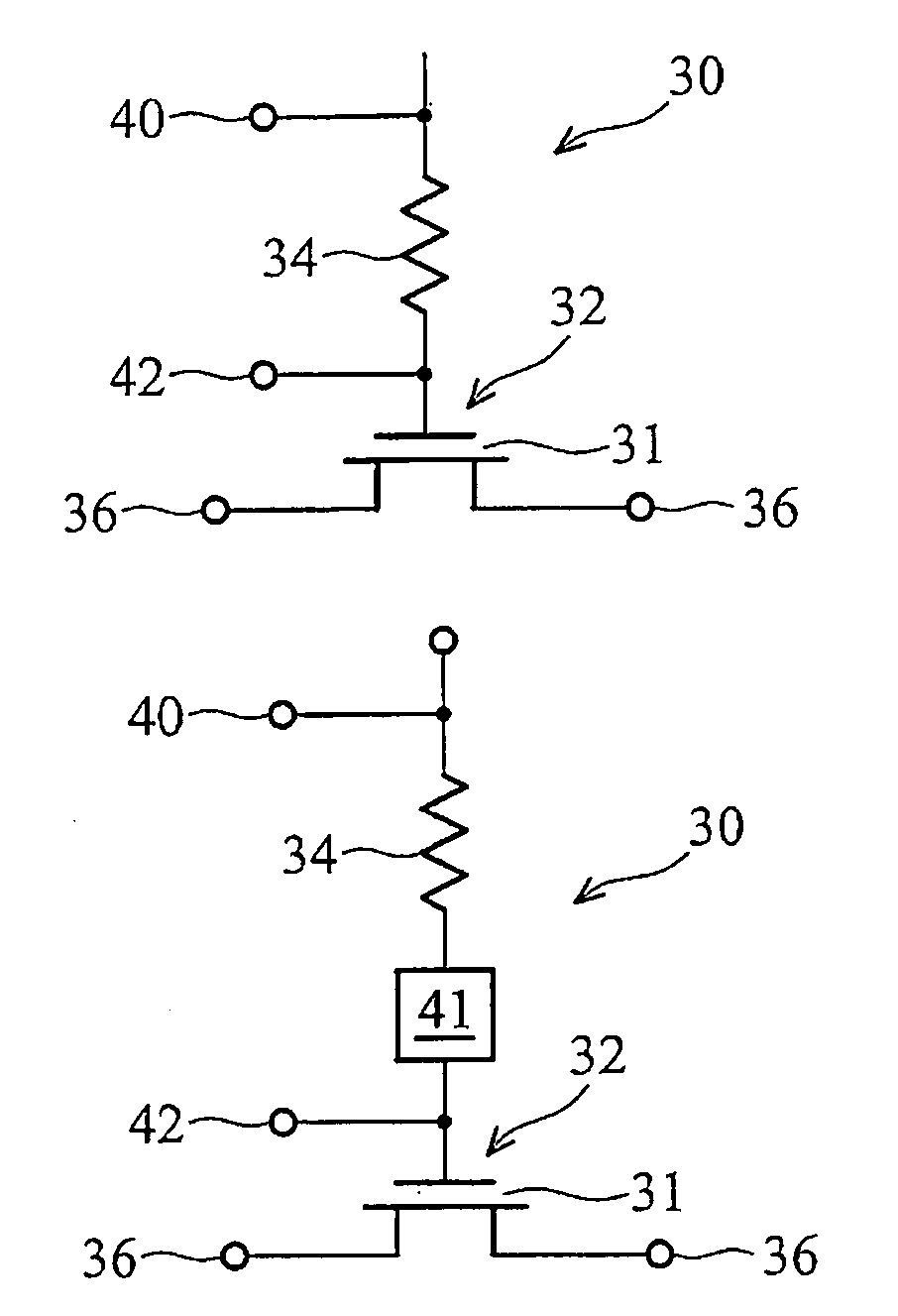

One time programming memory cell using MOS device

A non-volatile memory cell based on a soft breakdown mechanism is provided. The memory cell comprises a resistor coupled serially to a gate or source / drain regions of a MOS device. When a soft breakdown occurs to the MOS device, leakage current flowing through the gate dielectric increases. The change of the leakage current is used to indicate different states.

Owner:TAIWAN SEMICON MFG CO LTD

Organosilicon wire enamel with thermal level up to 155 DEG C or above and preparation method of organosilicon wire enamel

InactiveCN103725154AImprove performanceFlat surfaceEpoxy resin coatingsEpoxyHexamethylphosphoric Triamide

The invention discloses organosilicon wire enamel with a thermal level up to 155 DEG C or above and a preparation method of the organosilicon wire enamel. The organosilicon wire enamel is characterized by being prepared from raw materials in parts by weight as follows: 13-16 parts of E-44 epoxy resin, 5-8 parts of nano aluminum oxide, 2-3 parts of dimethylaminoethyl methacrylate, 10-12 parts of nylon 12, 10-12 parts of novolac epoxy resin, 5-7 parts of organic silicon resin, 4-6 parts of a titanate coupling agent TMC-TTS, 8-15 parts of m-amino methylamine, 8-10 parts of magnesium hydroxide, 4-5 parts of hexamethylphosphoric triamide, 2-3 parts of dysprosium oxide, 7-9 parts of an assistant, 80-90 parts of m, p-cresol and 100-120 parts of xylene. The organosilicon wire enamel has the advantages as follows: the follow-up coating baking process is easy to control, the molecular weight is uniform, and the consistency is good; peculiar smell is reduced at the normal temperature and during baking; products can be stably stored, the coating process is good, and the surface of a finished product is smooth and uniform; the temperature classification of the finished product is up to 155 DEG C (F level) or above, the hot punching is up to 180 DEG C or above, and the soft breakdown is up to 240 DEG C or above; and the medium resistance is excellent, and the organosilicon wire enamel has excellent adhesiveness.

Owner:铜陵天河特种电磁线有限公司

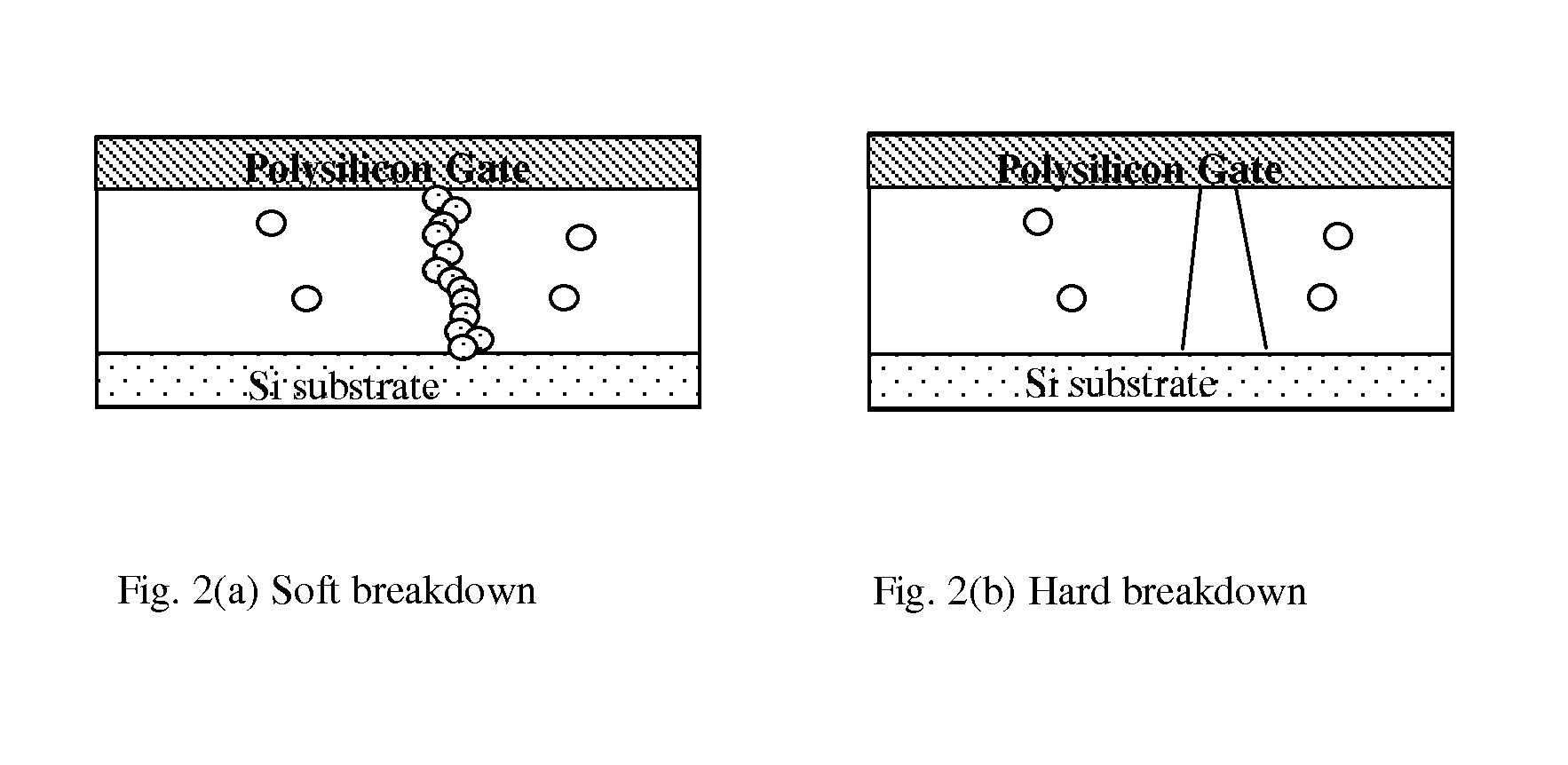

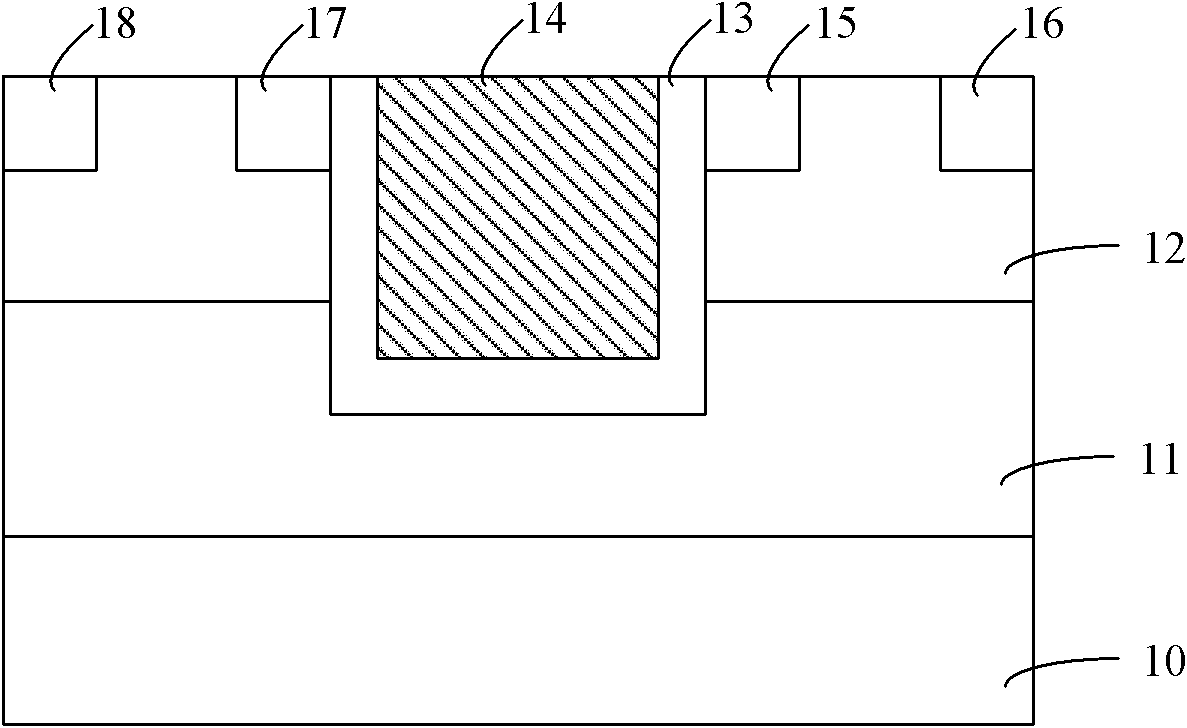

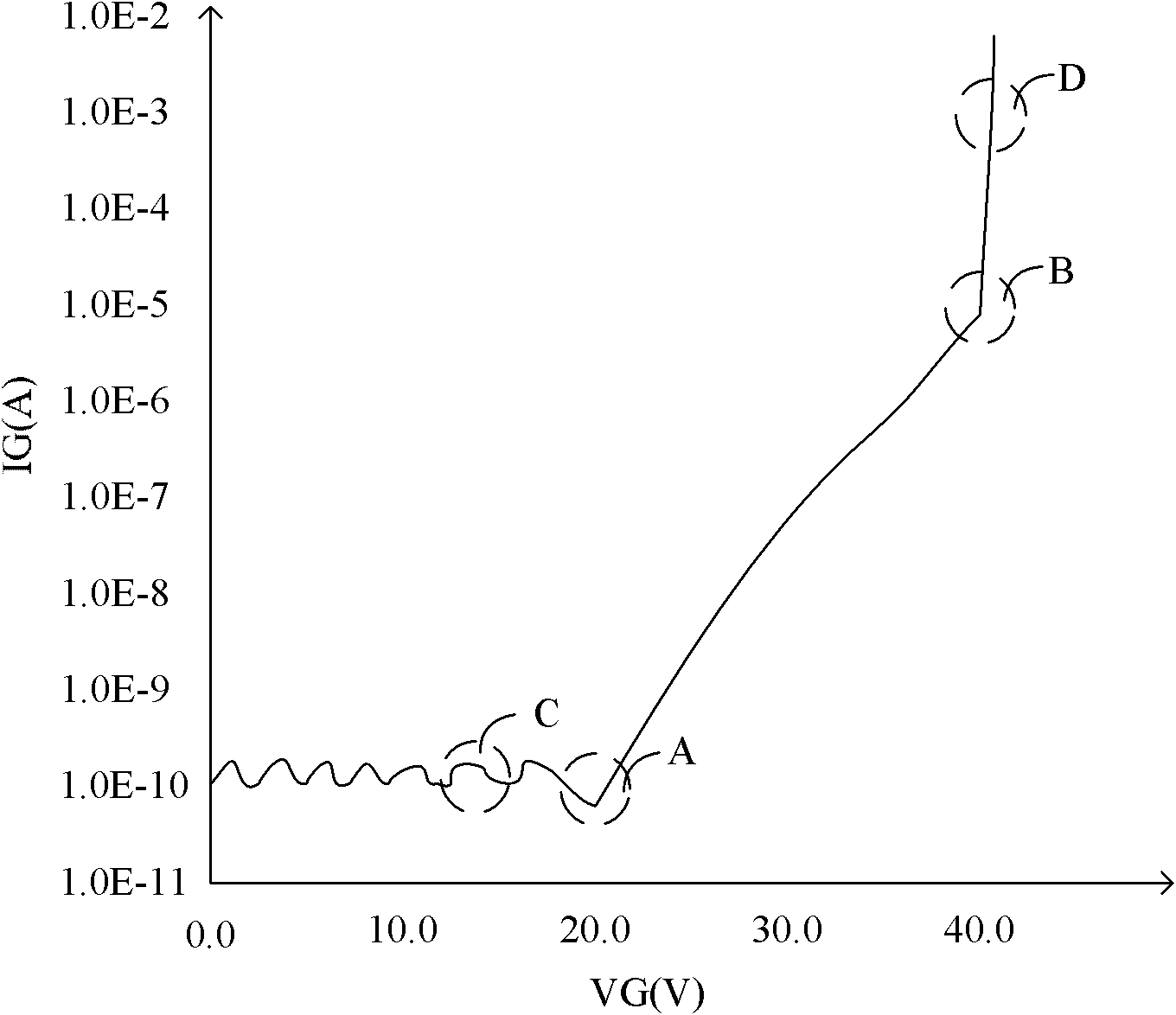

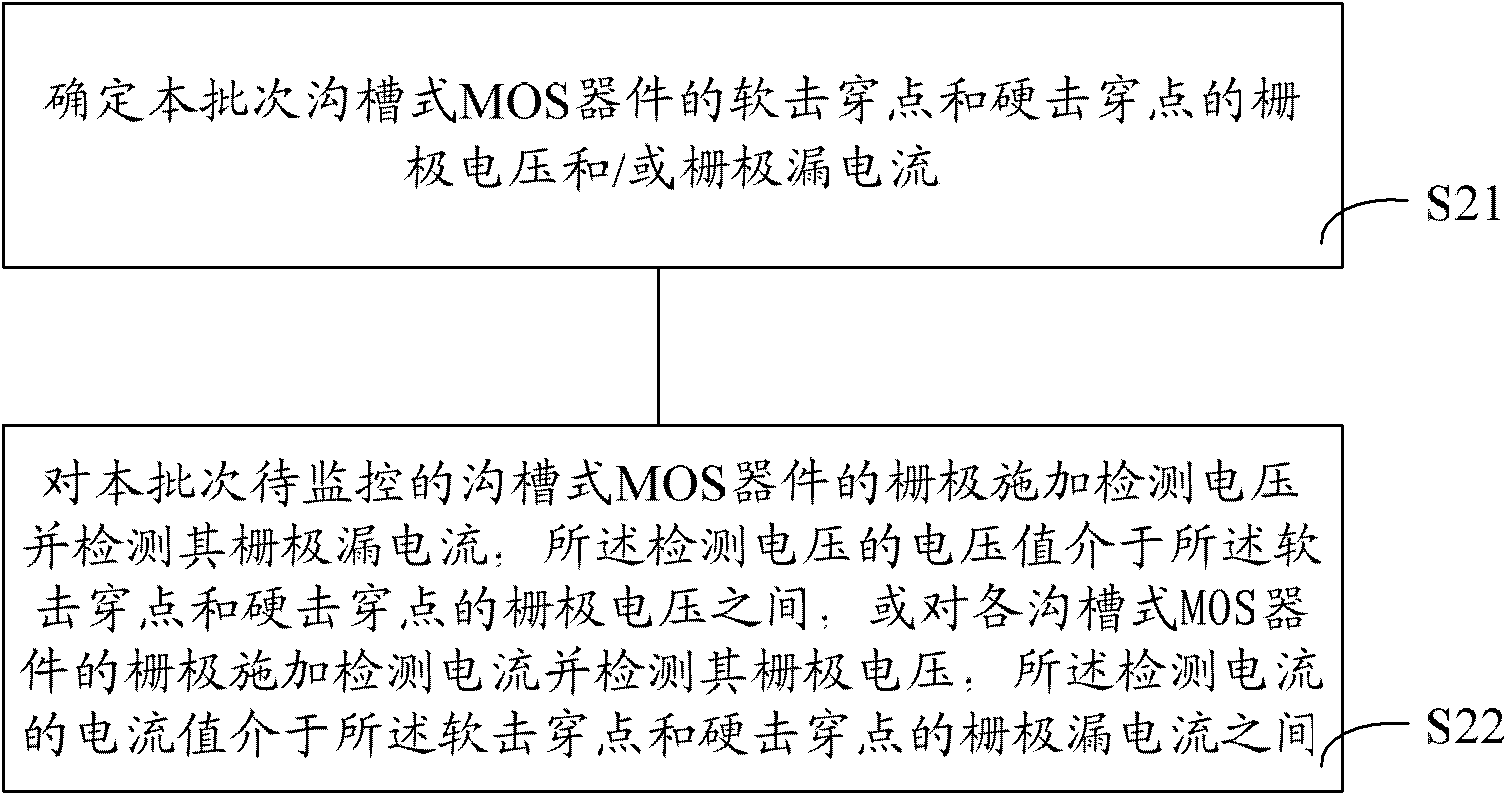

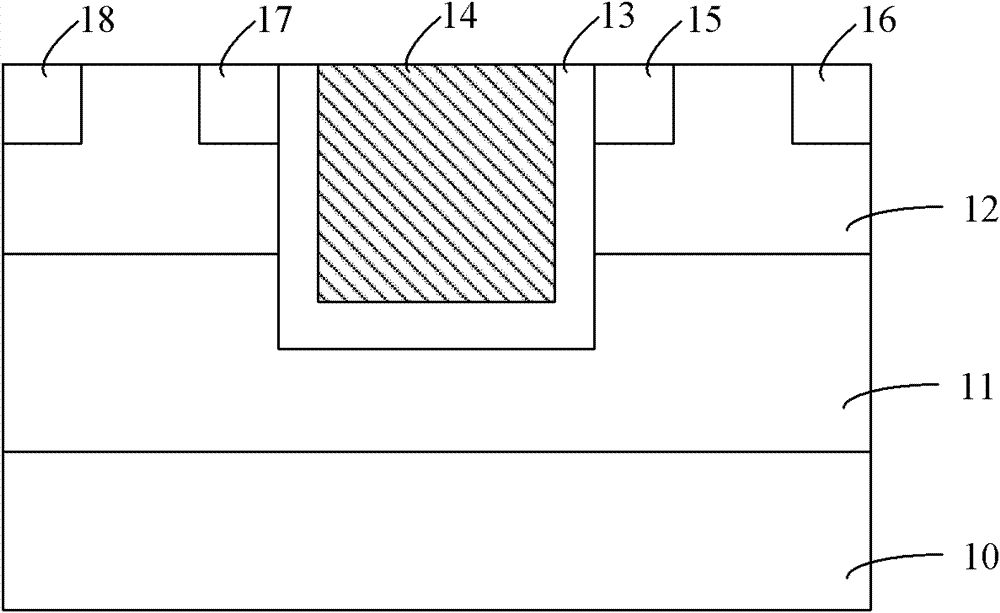

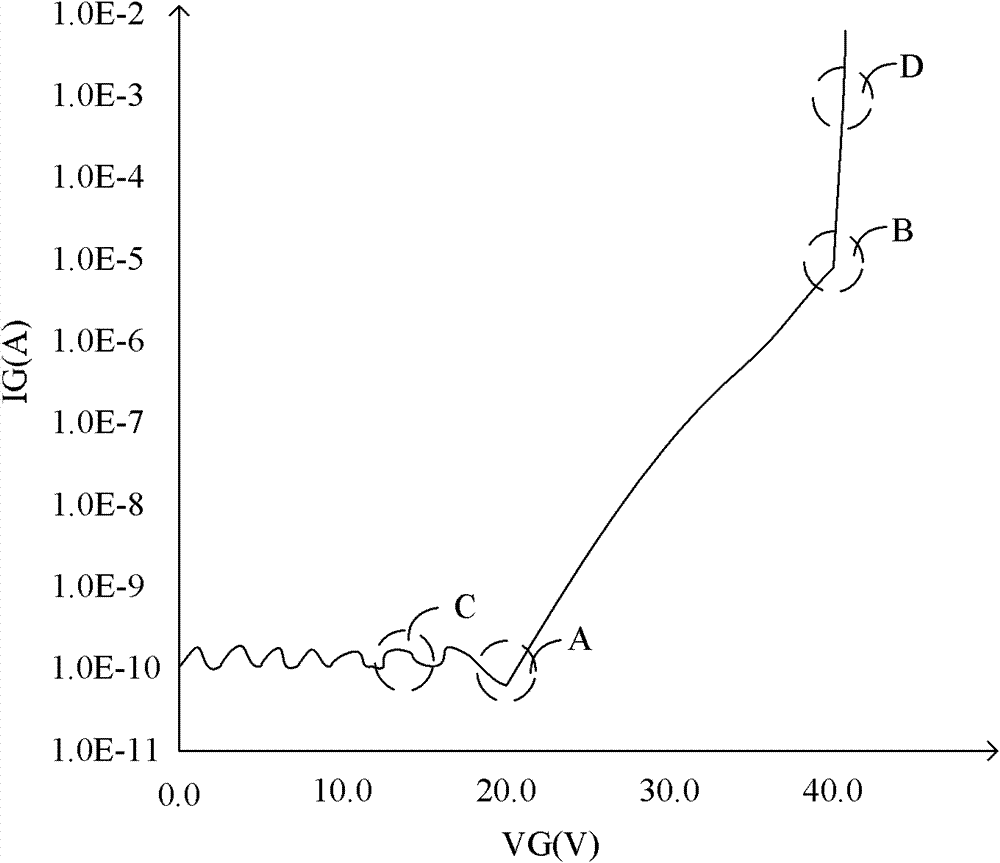

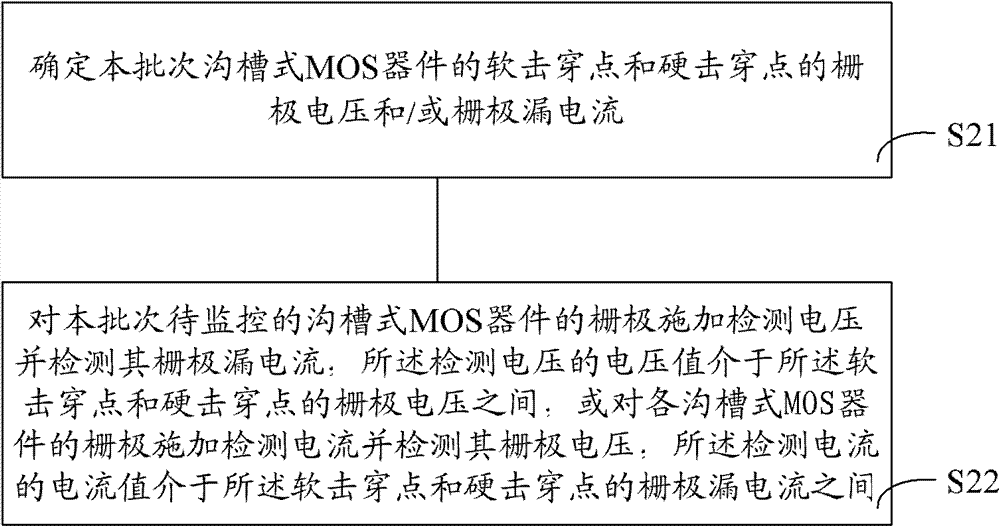

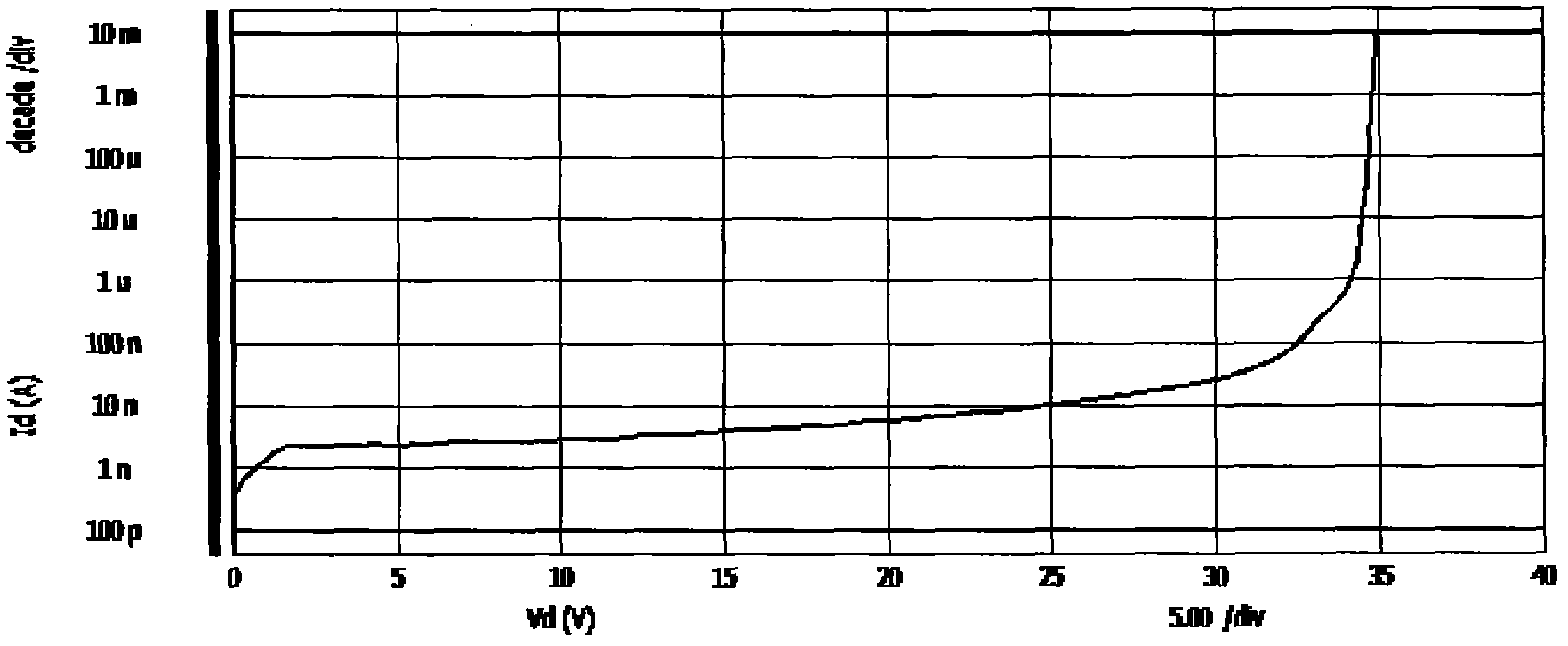

Process monitoring method and device for channel MOS devices

ActiveCN102157414AProcess drift sensitiveImprove monitoring effectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringGrid voltage

The invention relates to a process monitoring method and device for channel MOS devices. The method comprises the following steps of: determining the grid voltage and / or the grid leakage current of the soft breakdown point and the hard breakdown point of the batch of MOS devices; and applying detection voltage to the grid electrodes of the batch of channel MOS devices to be monitored, detecting the grid leakage current of the grid electrodes of the batch of channel MOS devices, and causing the voltage value of the detection voltage to range between the grid voltage of the soft breakdown point and that of the hard breakdown point, or applying detection current to the grid electrode of each channel MOS device, detecting the grid voltage of the grid electrode of each channel MOS device, and causing the value of the detection current to range between the grid leakage current of the soft breakdown point and that of the hard breakdown point. The invention can improve the process monitoring effect, and accurately detect the problem of process drift of the devices.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

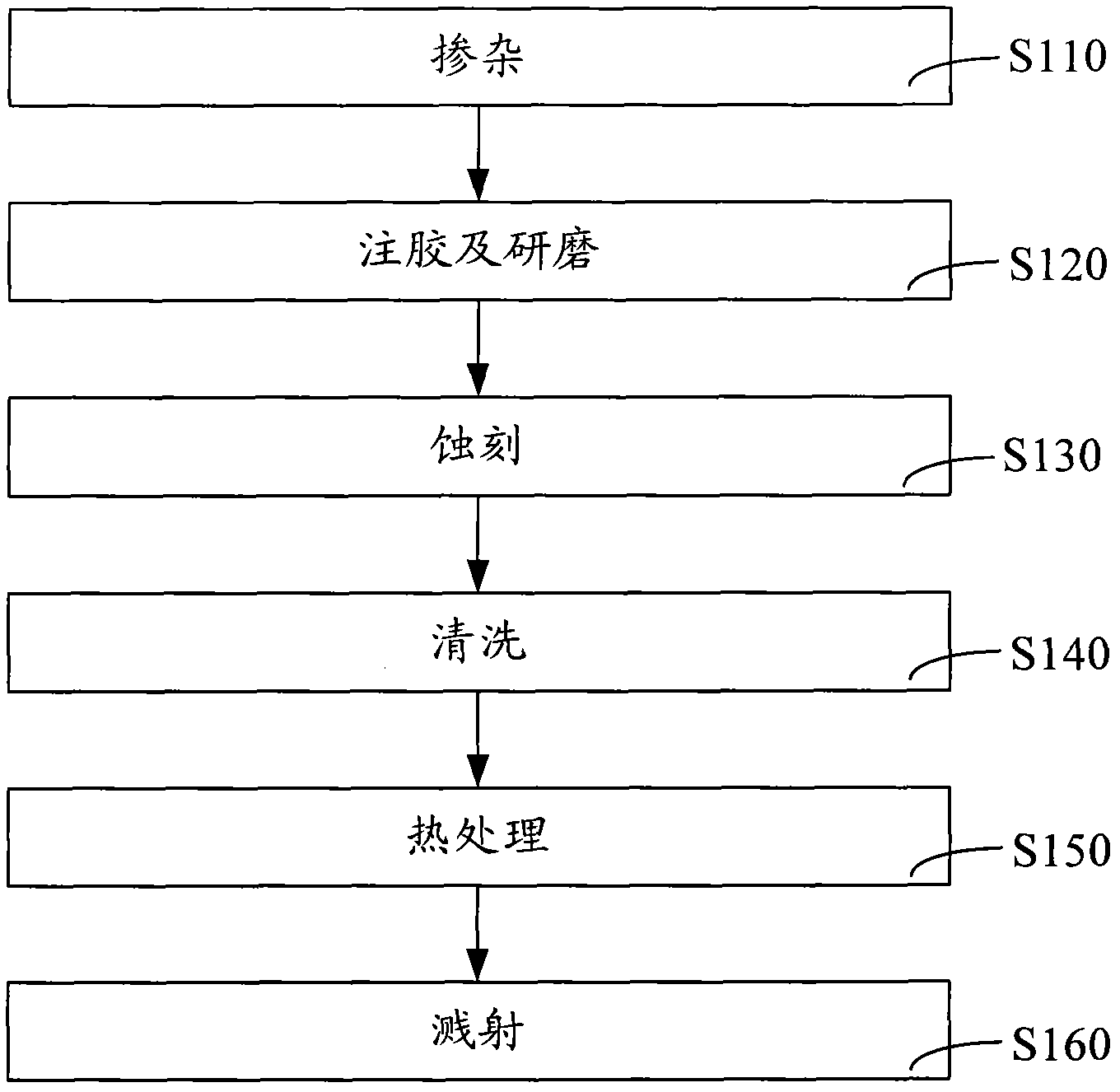

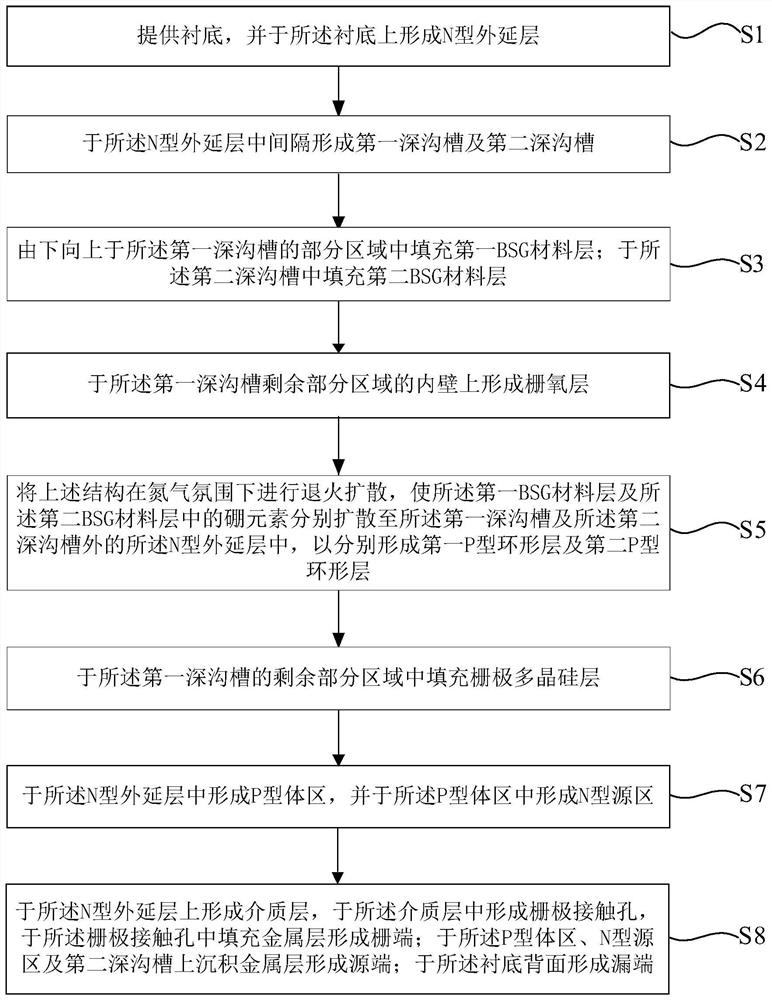

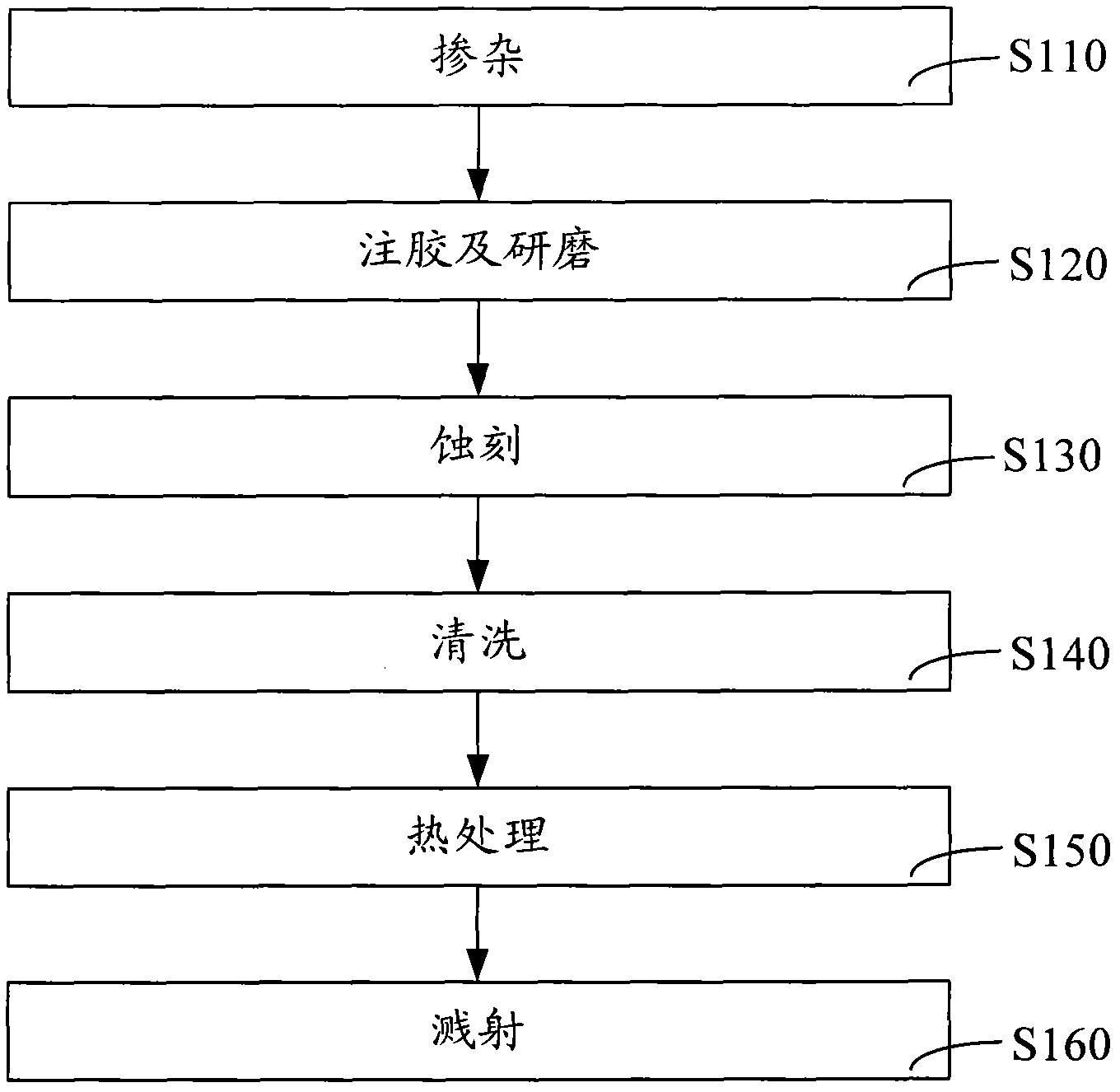

Manufacturing method and device of channel double-diffusion metal oxide semiconductor

ActiveCN102403225AQuality improvementLow costSemiconductor/solid-state device manufacturingEtchingDouble diffusion

The invention relates to a manufacturing method and a device of a channel double-diffusion metal oxide semiconductor. The manufacturing method comprises the following steps of: doping; glue-injecting and grinding; etching; cleaning; heat treatment; and spattering. In a treatment process on the back, after the heat treatment process is adopted, the situation that the source and drain (source electrode and drain electrode) soft breakdown failure does not occur in the channel double-diffusion metal oxide semiconductor is effectively improved by detecting the data of a wafer. Meanwhile, the adopted device can be realized correspondingly by the existing high-temperature furnace without specially purchasing new equipment or special equipment, so that the cost is saved, and the economic benefit is improved.

Owner:CSMC TECH FAB2 CO LTD

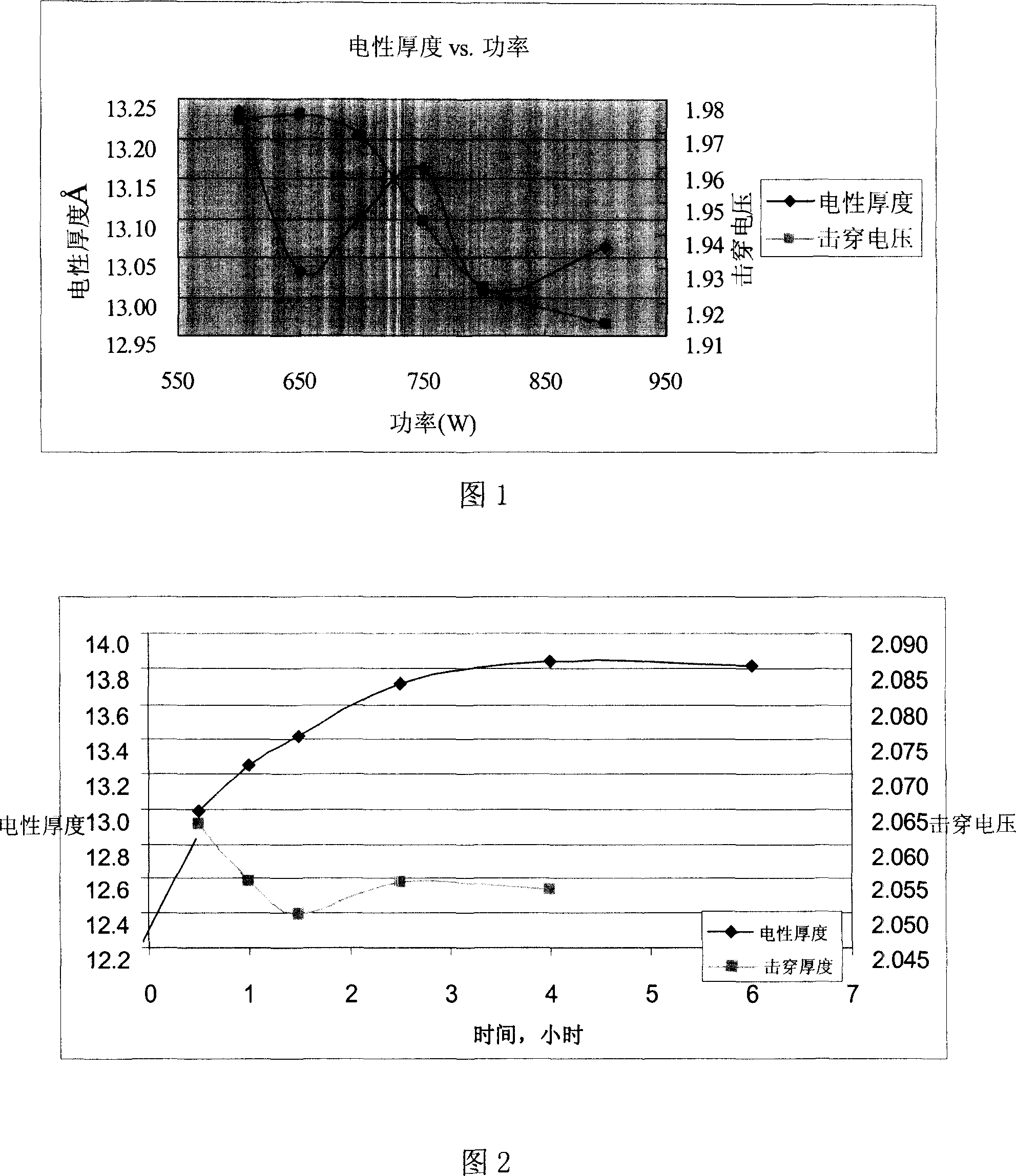

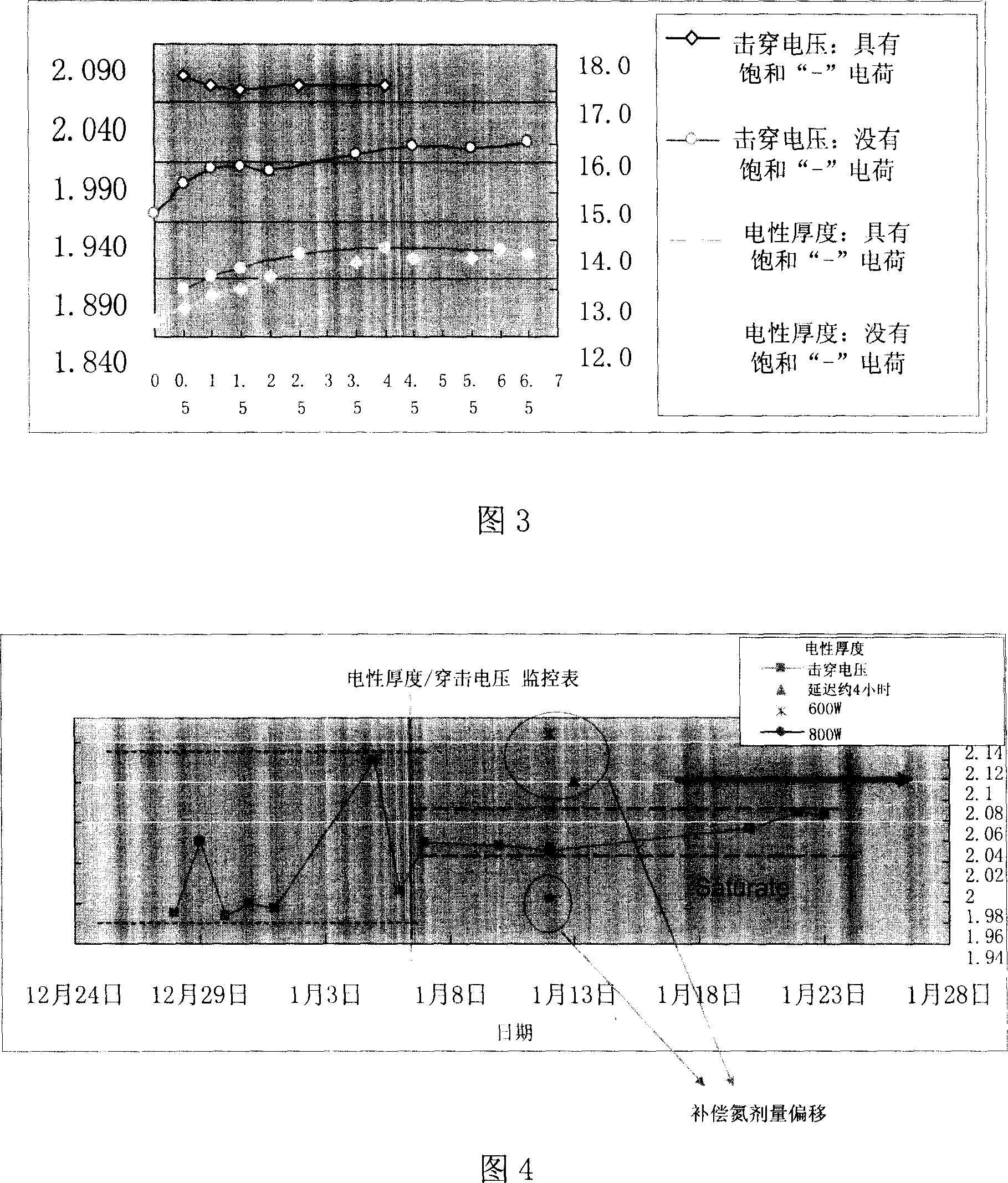

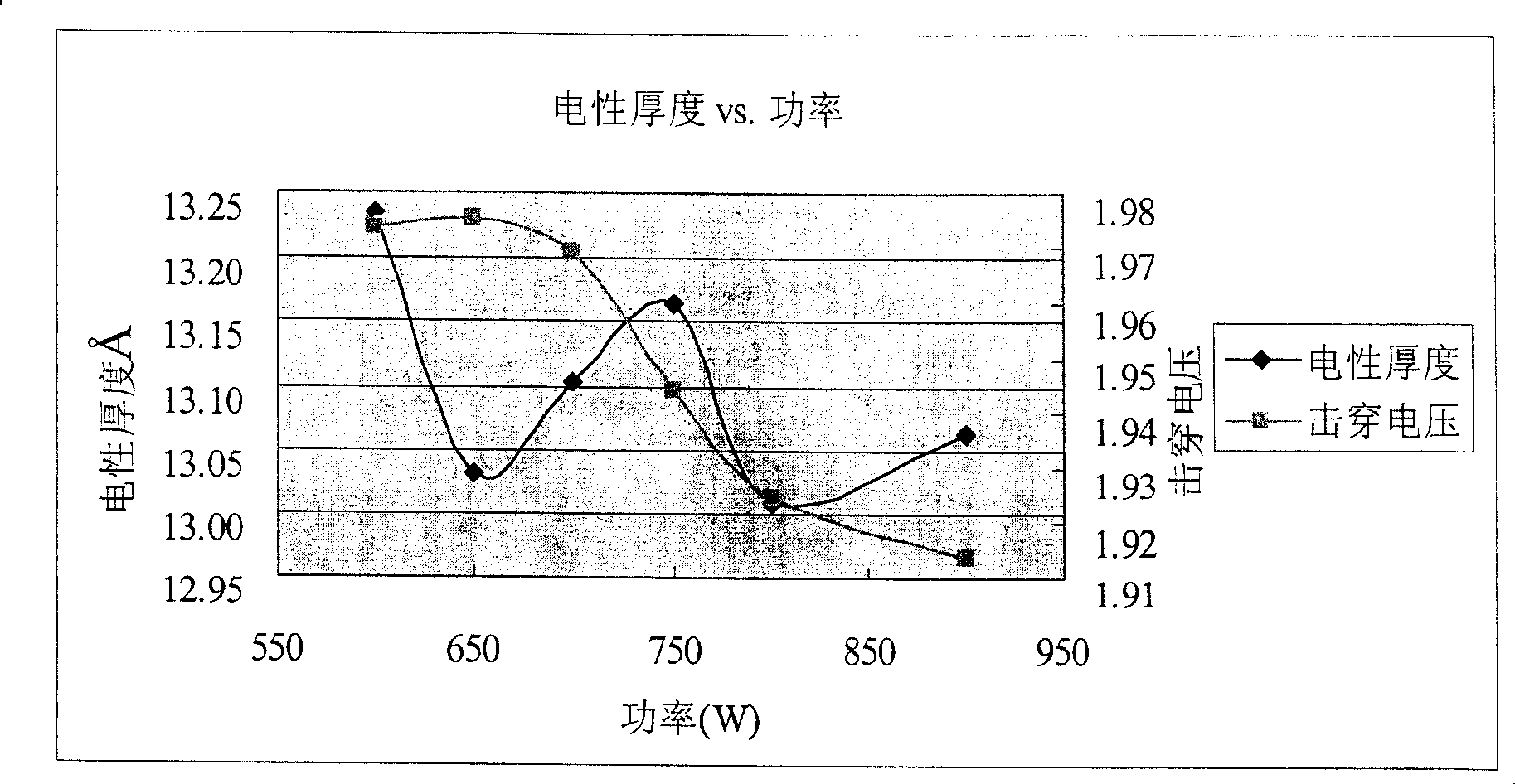

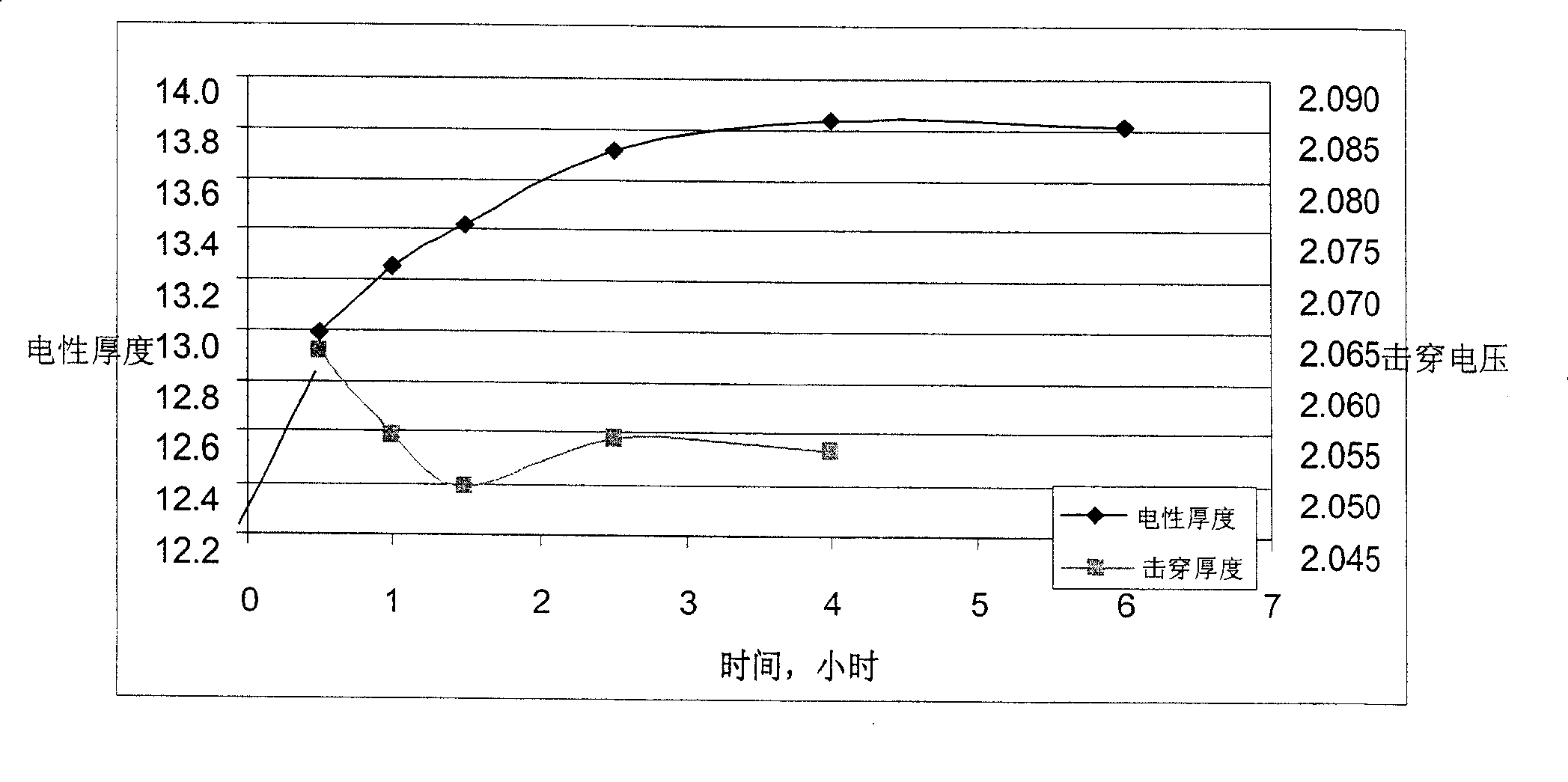

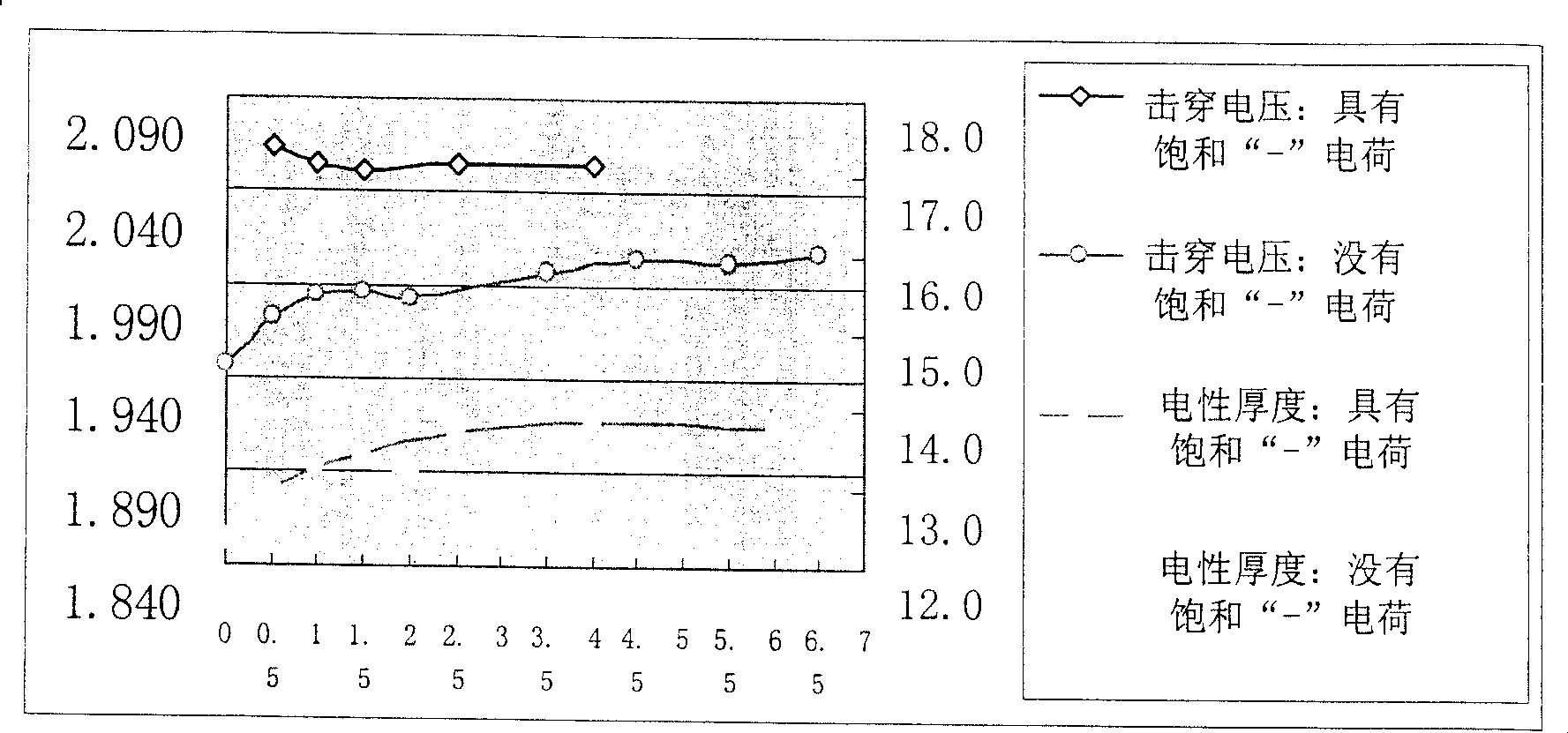

Method for improving ultrathin plasma silicon oxy nitride electrical test accurancy

InactiveCN1937195AShorten the timeImprove efficiencySemiconductor/solid-state device testing/measurementEquivalent oxide thicknessUnstable status

In technique of semiconductor device manufacture, measurement of equivalent oxide thickness (EOT), and voltage of soft breakdown is a very important key for oxide of gate in 90 Nano manufacturing procedure. When conventional quasi C-V method is applied to azotized oxide, there are lots of noises caused by unstable charges in oxide. Especially, it is takes long time for positive charges brought from nitridation of plasma to be discharged and stabilized. Otherwise, unstable state of charges makes measured result contain lots of noises. Usually, it needs to take round the day to make charges stable before formal measurement. The disclosed method makes charges in testing sample stable rapidly, and prevents issue of noise.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

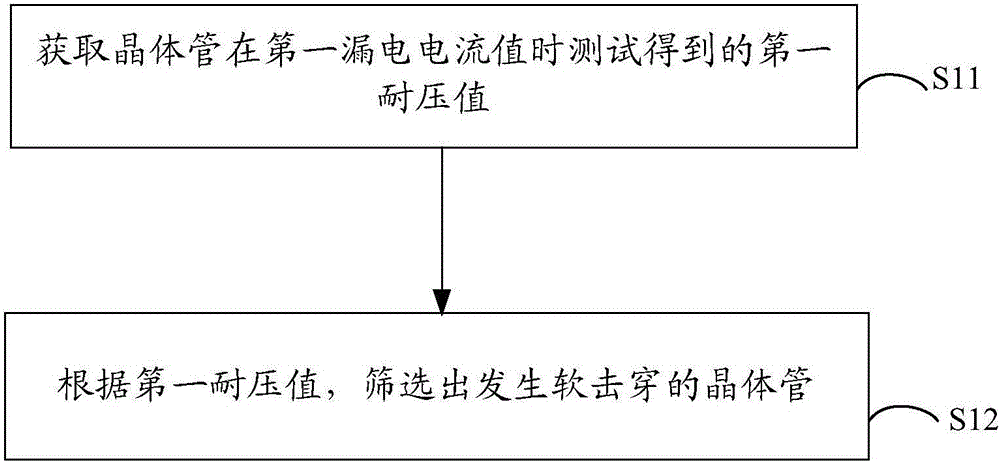

Method and apparatus of screening transistor

InactiveCN106646176ATesting dielectric strengthIndividual semiconductor device testingEngineeringTransistor

The invention discloses a method and apparatus of screening transistors. The method includes the steps of determining a first electric leakage current value that is greater than a rated electric leakage current value of transistors, obtaining a first voltage resistance value through testing when the transistors are at the first electric leakage current value, and screening out transistors that have undergone soft breakdown according to the first voltage resistance value. Through the embodiment of the invention, transistors high in qualified rate can be screened.

Owner:GREE ELECTRIC APPLIANCES INC

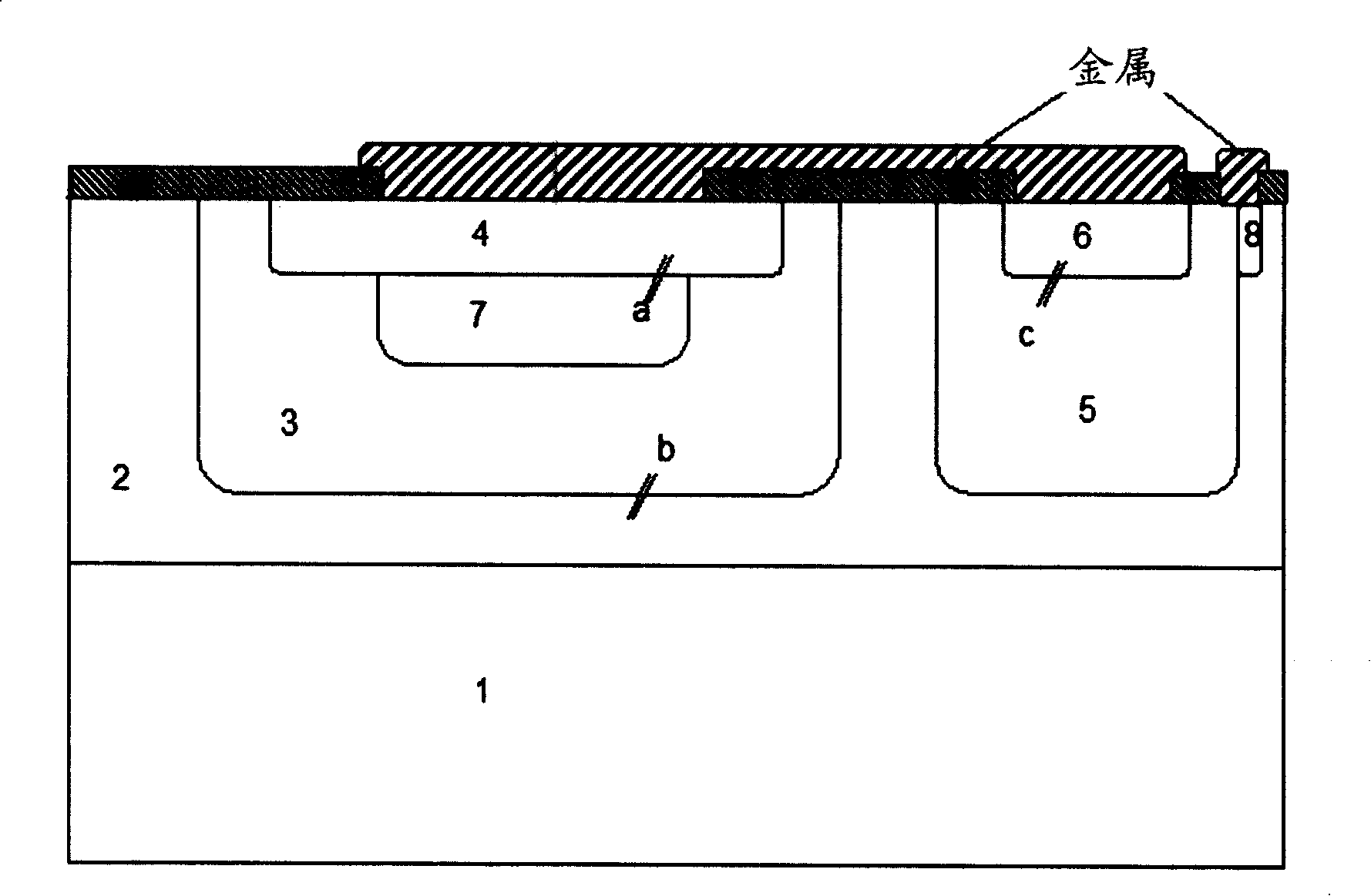

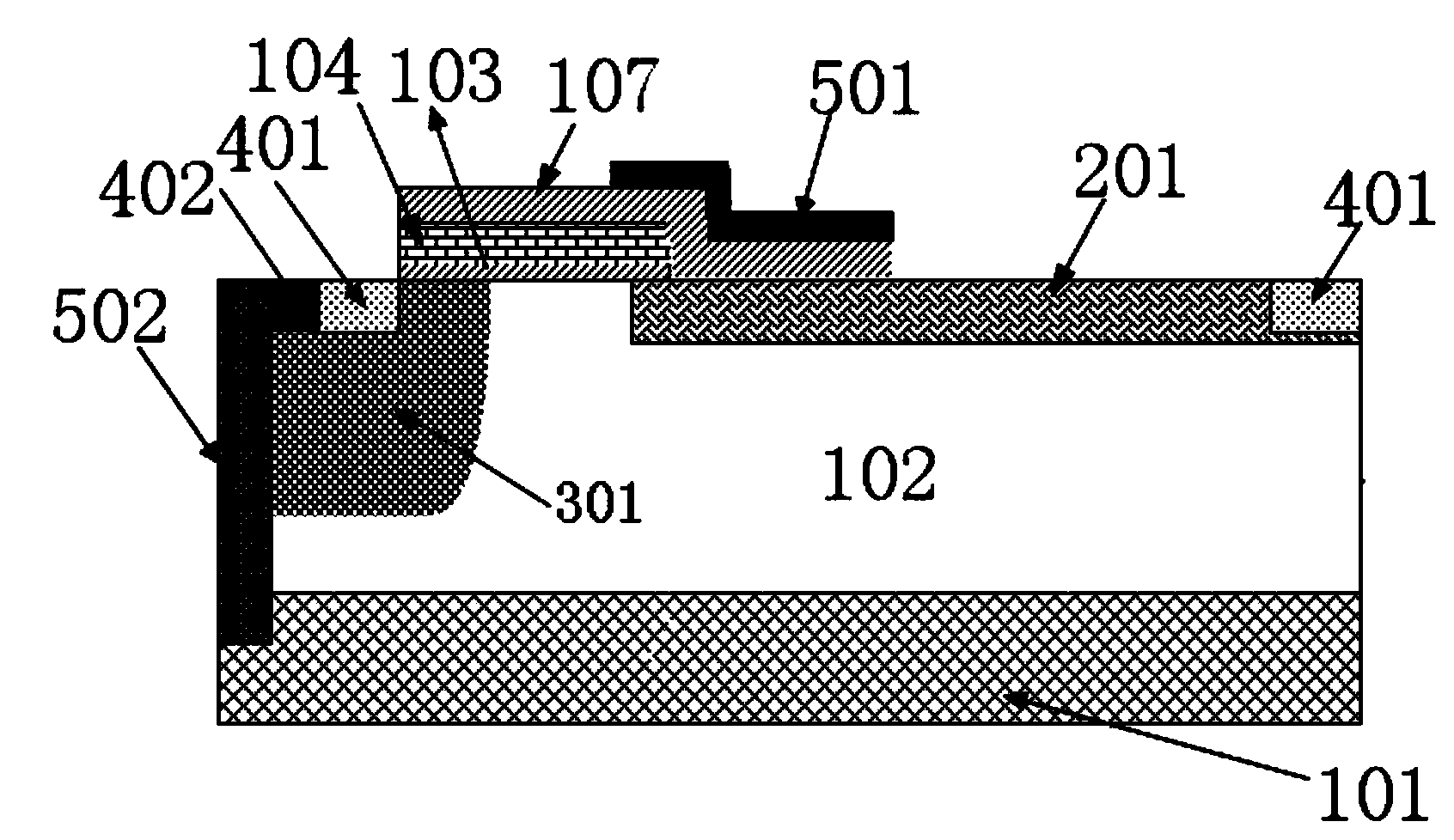

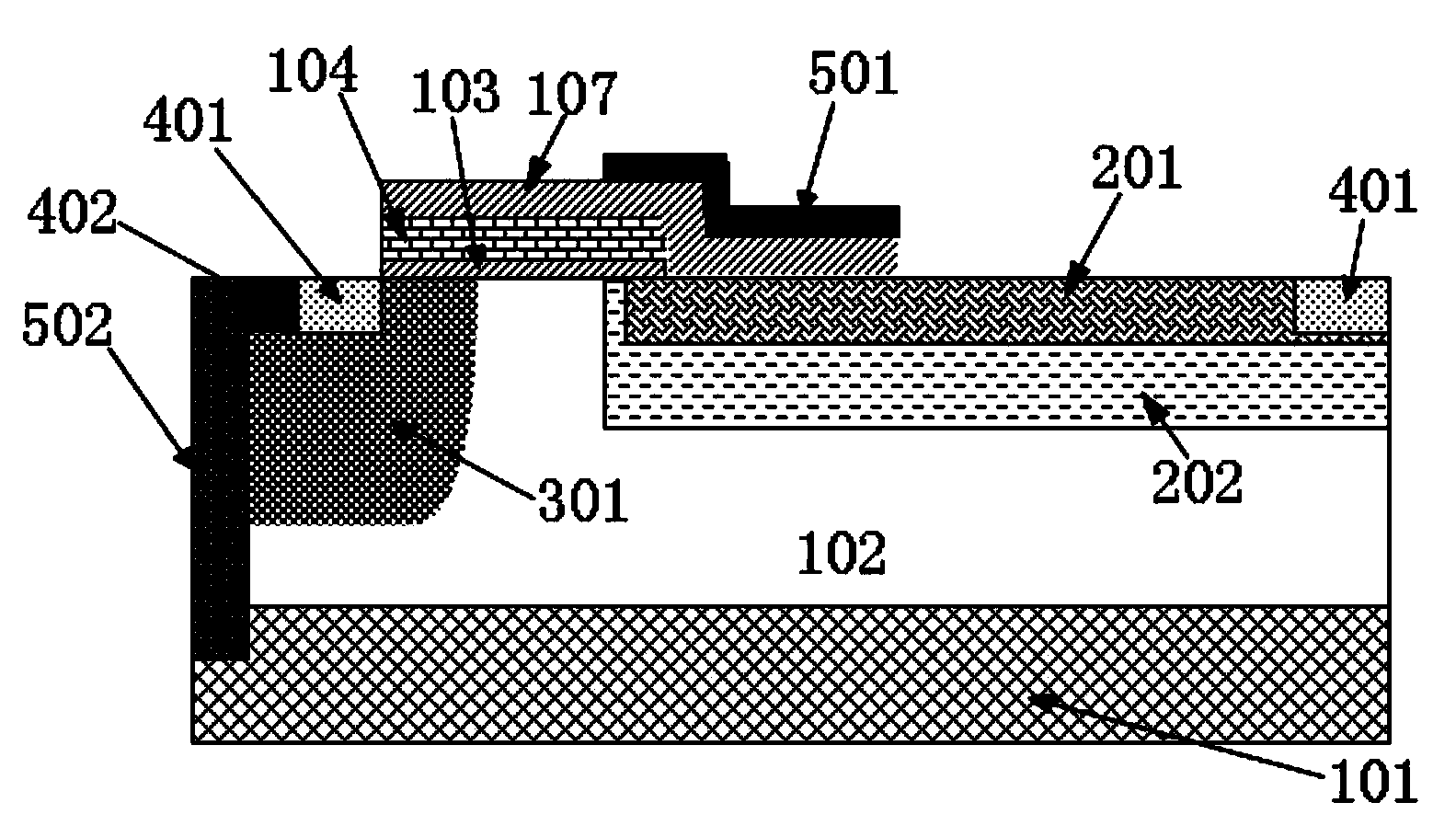

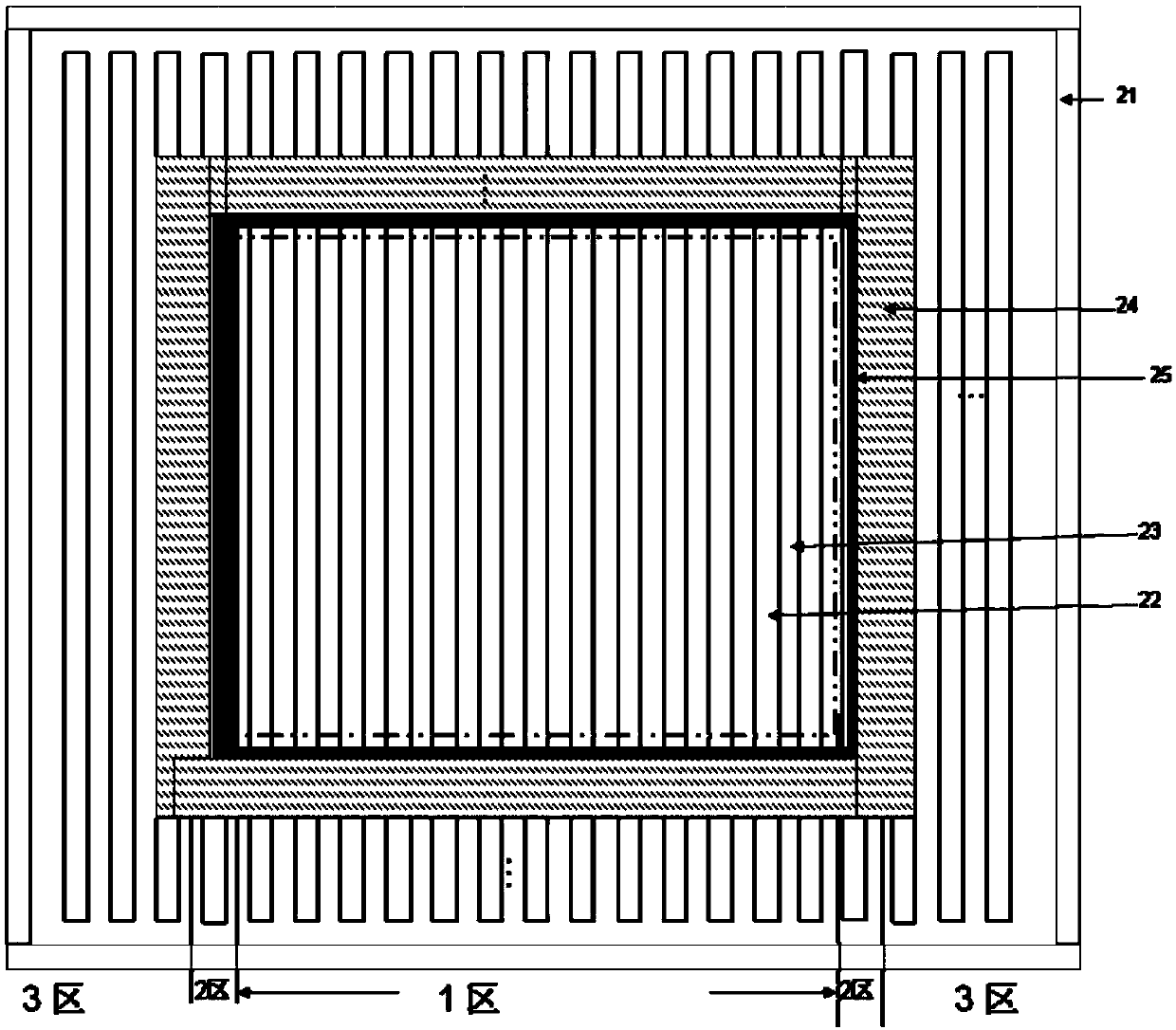

Radio frequency LDMOS device and manufacture method

InactiveCN104347706AReduce leakage currentInject evenlySemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSRadio frequency

The invention discloses a radio frequency LDMOS device. The radio frequency LDMOS device is provided with double lightly-doped drift regions, under the condition that quite high breakdown voltage is maintained, has quite low conduction resistance at the same time, and helps to improve the soft breakdown problem of the device. The invention further discloses a manufacture method of the radio frequency LDMOS device. The uniform lightly-doped drift regions can be formed simply by adding a step of deep ion implantation. The method is simple in technical process and easy to implement.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

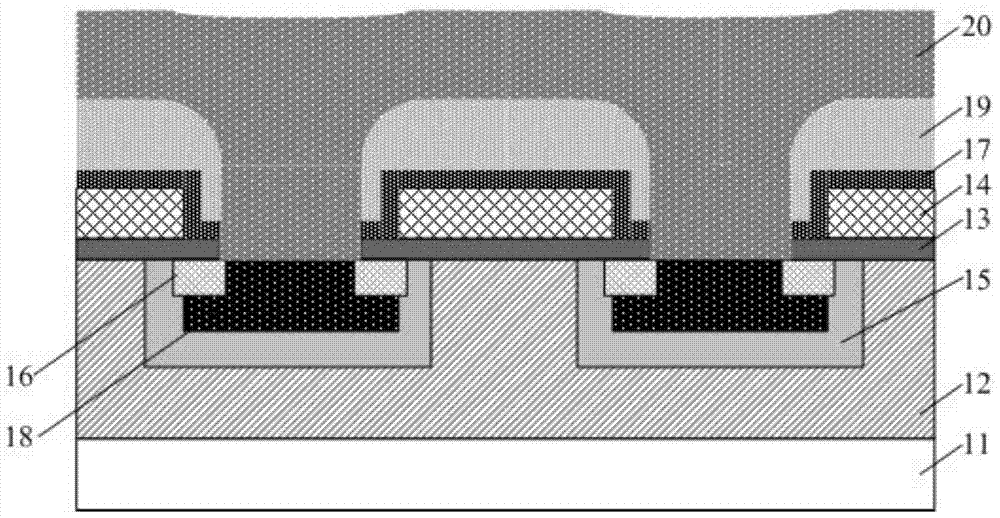

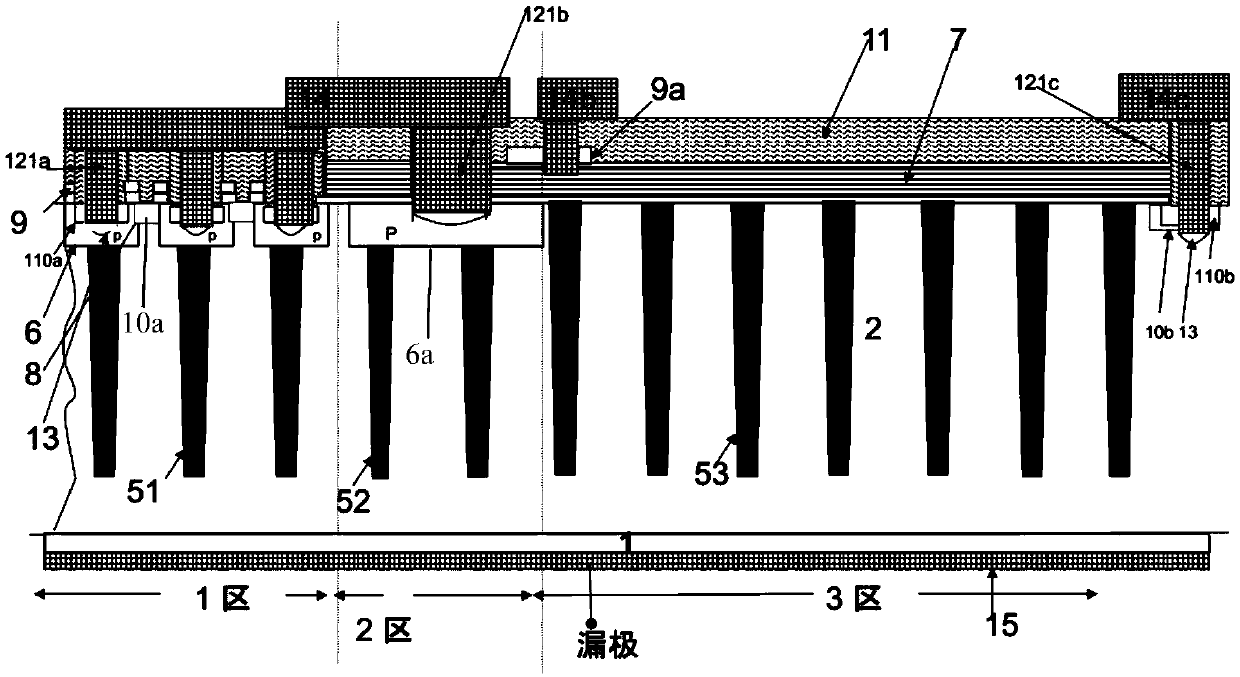

Shield gate trench field effect transistor structure and preparation method thereof

PendingCN113299753AReduce static lossReduce gate-drain overlap areaSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceField effect

The invention provides a shield gate trench field effect transistor structure and a preparation method thereof. The first deep grooves and the second deep grooves are arranged in different deep grooves at intervals, so that the problem that the transistor is not synchronously turned on or turned off is avoided, and a plurality of resistors RDS (on) with the same resistance are connected in parallel; the total resistance is equivalent to RDS (on) / n, and n is the number of cells, so that the on-resistance is greatly reduced, and the static loss of the device is reduced; the bottom region of the first deep groove is filled with a BSG material, so the gate-drain overlapping area of the device is reduced, the gate-drain capacitance is reduced, the switching speed of the device is improved, and the dynamic loss of the device is reduced; the first P-type annular layer and the second P-type annular layer are respectively depleted with the N-type epitaxial layer, and the depletion layers of the adjacent first deep trench and second deep trench are communicated with each other along with the increase of the voltage, so that the drain-source leakage current Idss of the device is further reduced, the static loss of the device is reduced, and the soft breakdown is prevented; and the process steps are simple and the cost is low.

Owner:瑶芯微电子科技(上海)有限公司

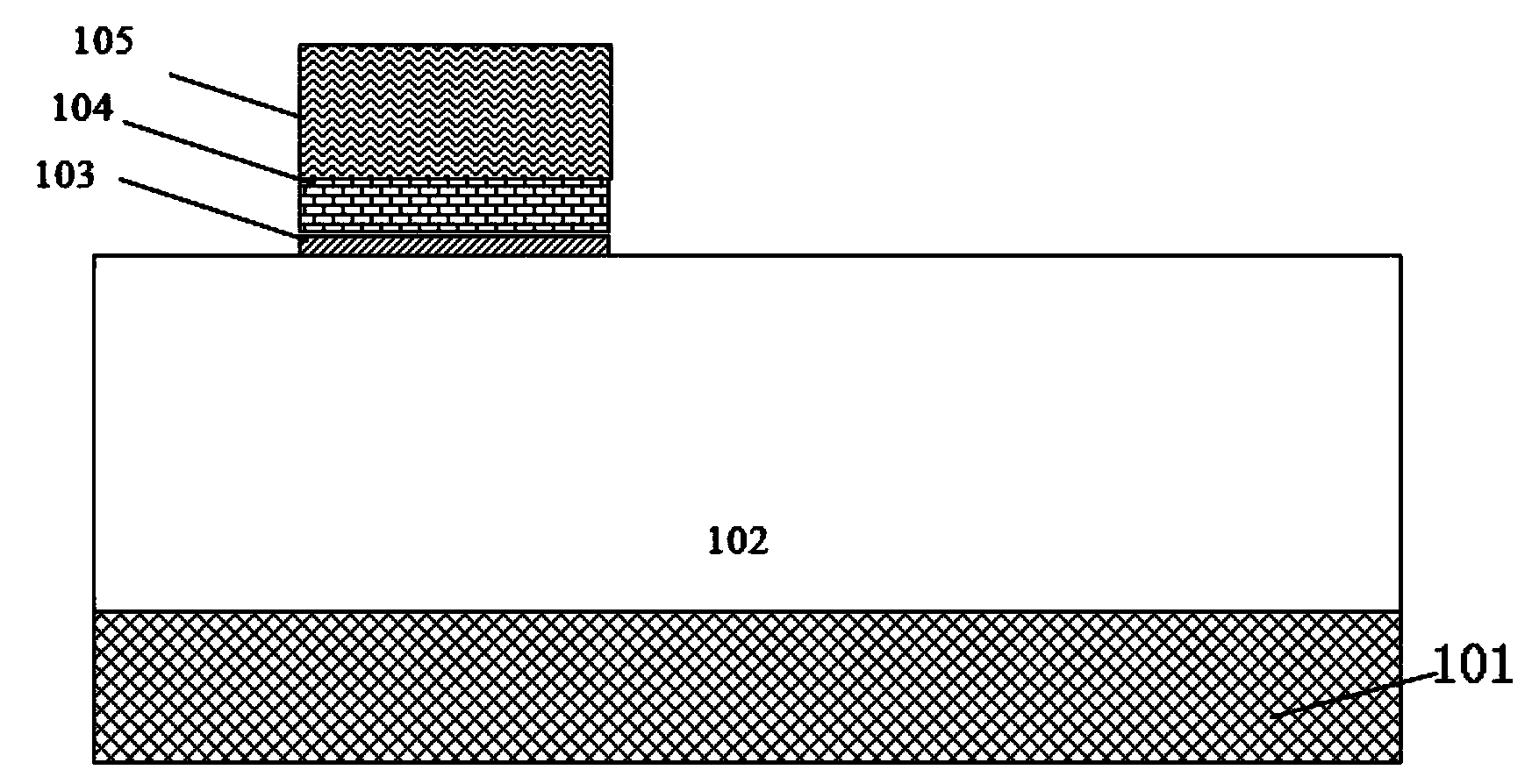

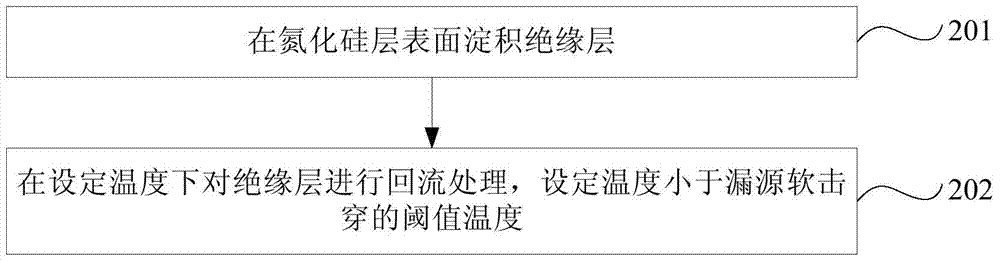

Manufacturing method of vertical double diffused metal oxide semiconductor field effect transistor

ActiveCN104867832BDrain-source soft breakdown solutionElectrical parameters have no effectSemiconductor/solid-state device manufacturingMaterial resourcesField-effect transistor

The invention provides a method for manufacturing a vertical double-diffusion metal oxide semiconductor field effect transistor. The method includes: depositing an insulating layer on the surface of the silicon nitride layer; performing reflow treatment on the insulating layer at a set temperature, and the set temperature is lower than the threshold temperature of drain-source soft breakdown. In the manufacturing method of the vertical double-diffused metal oxide semiconductor field effect transistor provided by the present invention, the insulating layer is reflowed at a set temperature lower than the threshold temperature of the drain-source soft breakdown, and the source is reduced by reducing the temperature during the reflow process. The distance of lateral diffusion in the region becomes shorter, and the effective channel length of the body region becomes longer, which reduces the risk of the body region depletion layer punching through to the source region under the reverse biased state of the device body region / epitaxial layer drift region junction, and achieves the solution of device leakage. source for soft breakdown purposes. Moreover, the method basically has no influence on the remaining electrical parameters of the device, thereby avoiding waste of manpower and material resources.

Owner:FOUNDER MICROELECTRONICS INT

Process monitoring method and device for trench mos devices

ActiveCN102157414BProcess drift sensitiveImprove monitoring effectSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringGrid voltage

The invention relates to a process monitoring method and device for channel MOS devices. The method comprises the following steps of: determining the grid voltage and / or the grid leakage current of the soft breakdown point and the hard breakdown point of the batch of MOS devices; and applying detection voltage to the grid electrodes of the batch of channel MOS devices to be monitored, detecting the grid leakage current of the grid electrodes of the batch of channel MOS devices, and causing the voltage value of the detection voltage to range between the grid voltage of the soft breakdown point and that of the hard breakdown point, or applying detection current to the grid electrode of each channel MOS device, detecting the grid voltage of the grid electrode of each channel MOS device, and causing the value of the detection current to range between the grid leakage current of the soft breakdown point and that of the hard breakdown point. The invention can improve the process monitoring effect, and accurately detect the problem of process drift of the devices.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for improving ultrathin plasma silicon oxy nitride electrical test accurancy

InactiveCN100461362CShorten the timeImprove efficiencySemiconductor/solid-state device testing/measurementEquivalent oxide thicknessEngineering

In technique of semiconductor device manufacture, measurement of equivalent oxide thickness (EOT), and voltage of soft breakdown is a very important key for oxide of gate in 90 Nano manufacturing procedure. When conventional quasi C-V method is applied to azotized oxide, there are lots of noises caused by unstable charges in oxide. Especially, it is takes long time for positive charges brought from nitridation of plasma to be discharged and stabilized. Otherwise, unstable state of charges makes measured result contain lots of noises. Usually, it needs to take round the day to make charges stable before formal measurement. The disclosed method makes charges in testing sample stable rapidly, and prevents issue of noise.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Manufacturing method and device of channel double-diffusion metal oxide semiconductor

ActiveCN102403225BQuality improvementLow costSemiconductor/solid-state device manufacturingEtchingDouble diffusion

The invention relates to a manufacturing method and a device of a channel double-diffusion metal oxide semiconductor. The manufacturing method comprises the following steps of: doping; glue-injecting and grinding; etching; cleaning; heat treatment; and spattering. In a treatment process on the back, after the heat treatment process is adopted, the situation that the source and drain (source electrode and drain electrode) soft breakdown failure does not occur in the channel double-diffusion metal oxide semiconductor is effectively improved by detecting the data of a wafer. Meanwhile, the adopted device can be realized correspondingly by the existing high-temperature furnace without specially purchasing new equipment or special equipment, so that the cost is saved, and the economic benefit is improved.

Owner:CSMC TECH FAB2 CO LTD

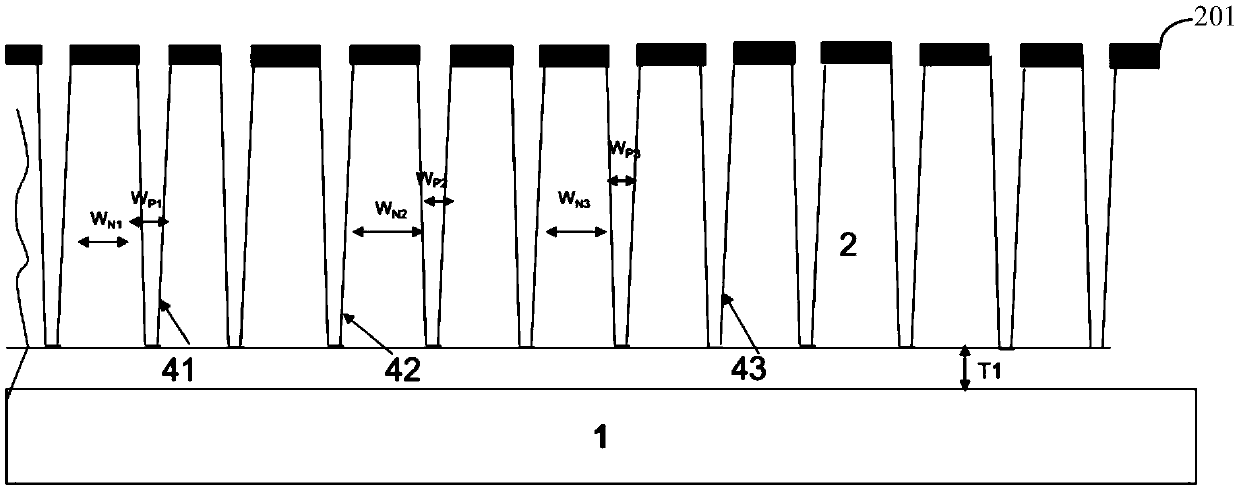

Super-junction device and manufacturing method thereof

PendingCN111200009AReduce gate-to-drain capacitanceReduce switching lossesSemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyJFET

The invention discloses a super-junction device, which is characterized in that cut-off regions of a current flowing region and a terminal region are opened by a protective epoxy film, and P-type wells are formed at the top of P-type columns of a super-junction structure of the current flowing region; JFET ion implantation is self-aligned and defined by the protective epoxy film, and a JFET regionand an electric field barrier layer surrounding the cut-off region are formed at the same time; the gate structure adopts a split-gate planar gate structure, and JFET ion implantation is carried outbefore a forming process of a gate oxide film of the split-gate planar gate, so that JFET ion implantation impurities have a structure for carrying out annealing propulsion through a thermal oxidationprocess of the gate oxide film. The invention further discloses a manufacturing method of the super-junction device. According to the invention, better diffusion of the JFET region and the electric field barrier layer can be realized, so that the on-resistance of the device can be reduced, the reliability of the device can be improved, soft breakdown at the cut-off region can be prevented, and the current impact resistance of the device can be improved. Meanwhile, the process cost cannot be increased, and the switching loss is reduced.

Owner:SHENZHEN SANRISE TECH CO LTD

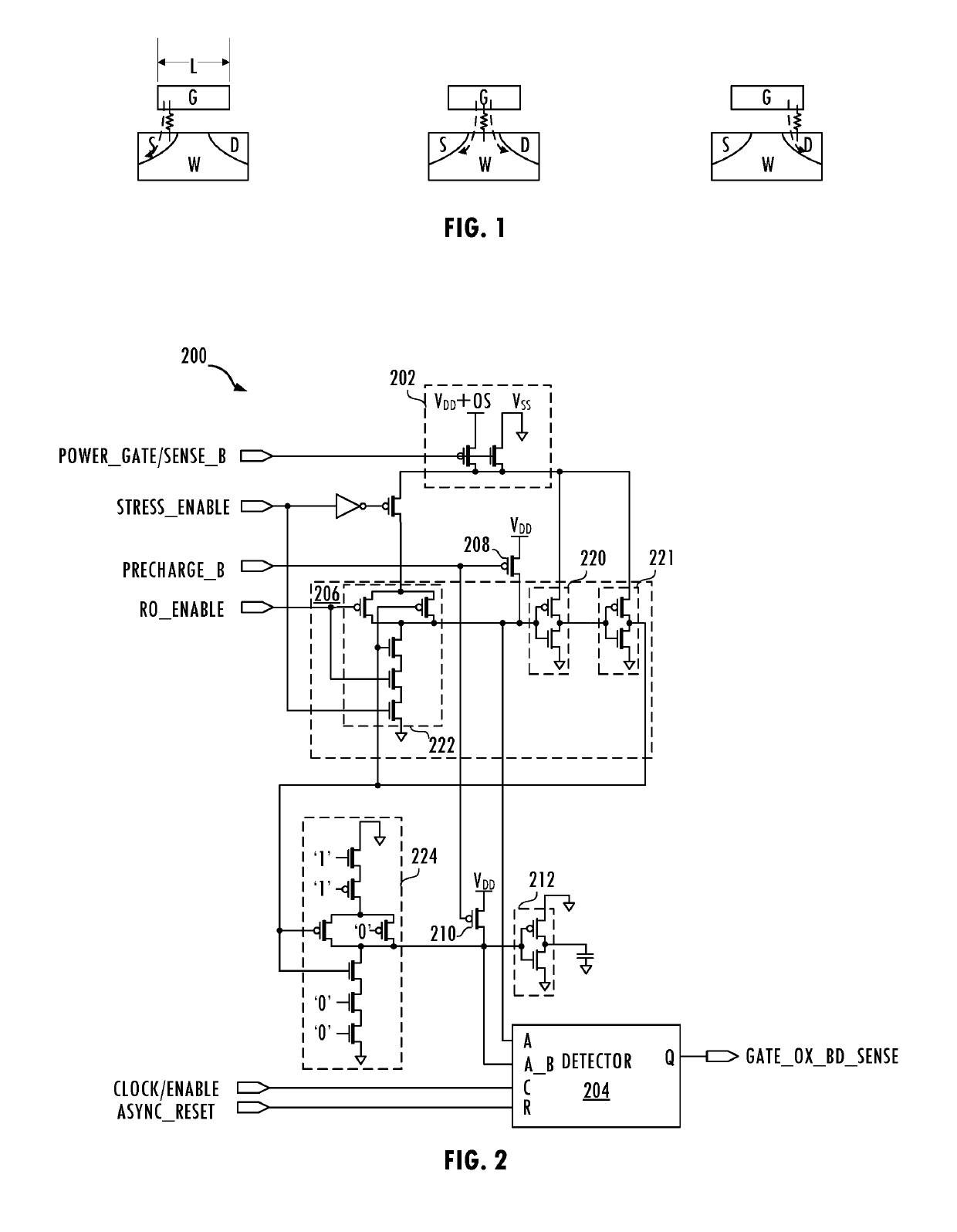

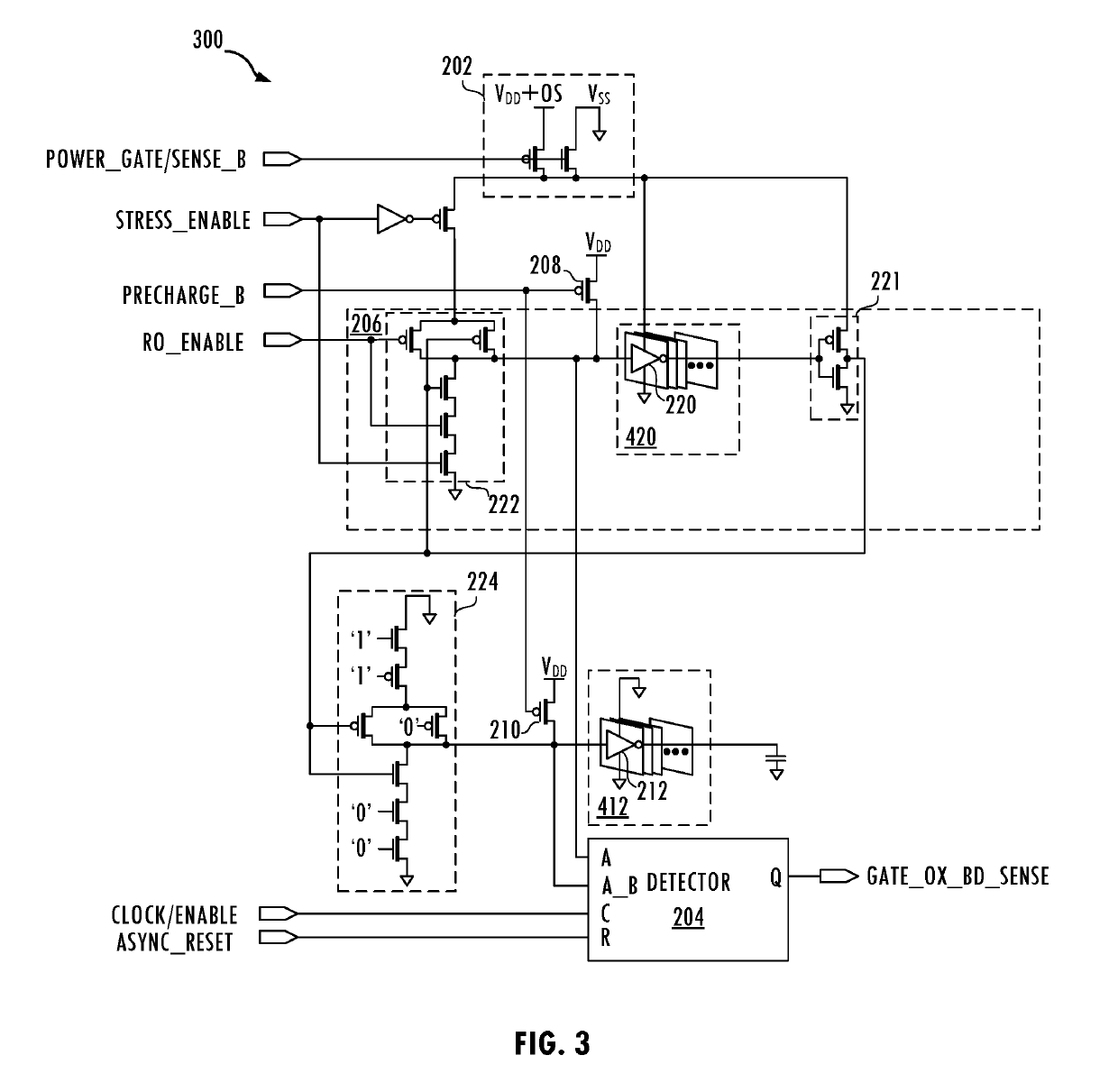

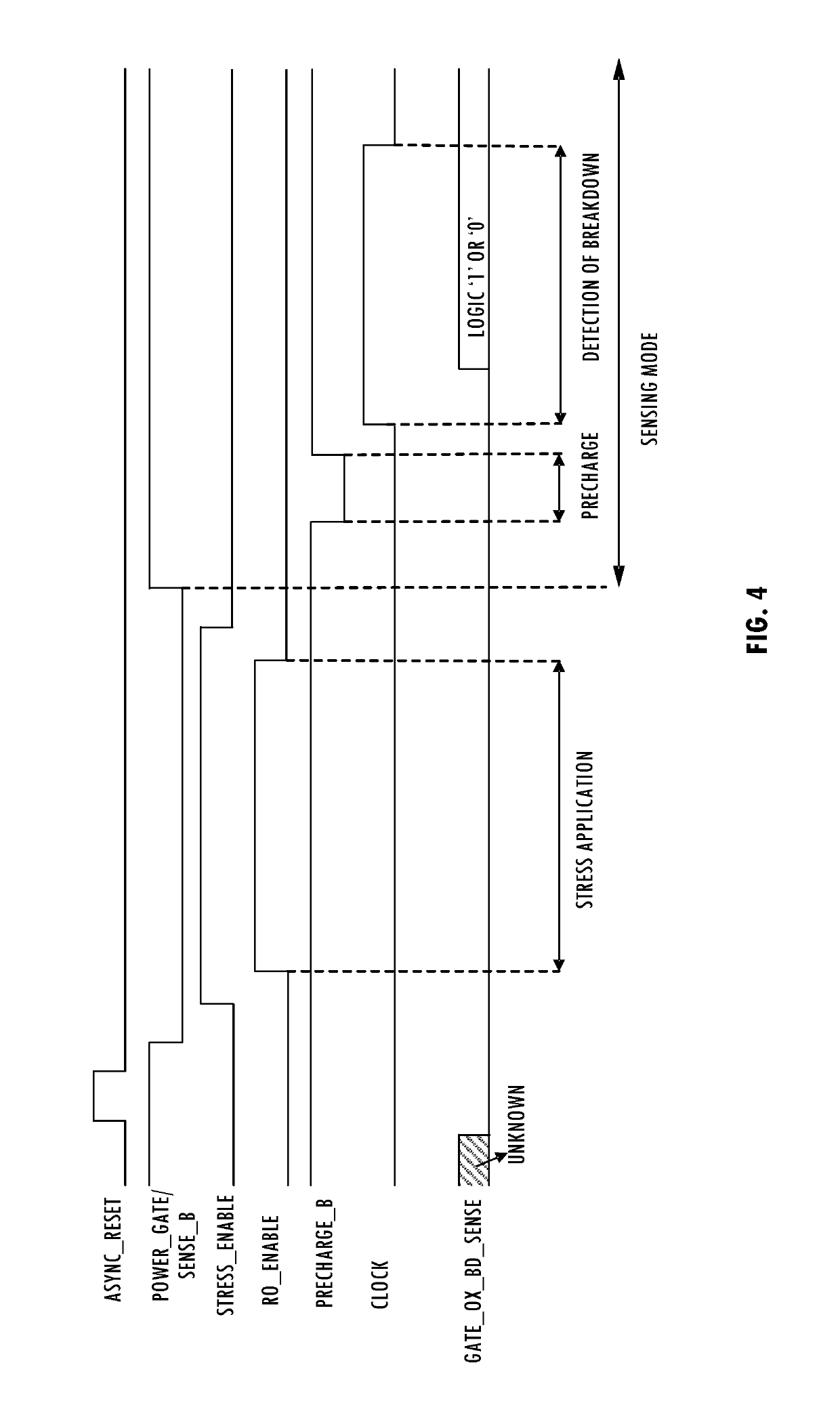

Gate oxide soft breakdown detection circuit

ActiveUS10247770B2Delay line applicationsPulse generation by logic circuitsAudio power amplifierDrain current

Various embodiments of a gate oxide breakdown detection technique detect gate oxide degradation due to stress on a per part basis without destroying functional circuits for an intended application. Stress on the gate oxide may be applied while nominal drain currents flow through a device, thereby stressing the device under conditions similar to actual operating conditions. The technique is relatively fast and does not require analog amplifiers or tuning of substantial amounts of other additional circuitry as compared to conventional gate oxide breakdown detection techniques.

Owner:ADVANCED MICRO DEVICES INC

High temperature resistant polyimide wire enamel and preparation method thereof

The invention discloses high-temperature resistant polyimide wire enamel and a preparation method thereof. The wire enamel comprises the following components in percent by weight based on total mass of enamel liquor: 50-80 percent of polyimide acid solution with solid content of 30 percent and 0-40 percent of chain-extended bismaleimide prepolymer solution with solid content of 30 percent. The preparation method of the high-temperature resistant polyimide wire enamel comprises the steps of mixing the polyimide acid solution and the chain-extended bismaleimide prepolymer solution according to proportions, adding an organic solvent to adjust the solid content and viscosity of the enamel liquor, and stirring to uniformly mix, thus obtaining claret-red transparent viscose polyimide wire enamel. The wire enamel disclosed by the invention is good in storage stability, resistant to high temperature, uniform in enamel film, good in flexibility, simple and easy to operate in an enamel and wire preparation process, high in raw material utilization rate, little in three-waste pollution and easy to realize industrialization; the soft breakdown voltage and the breakdown voltage of the wire enamel are remarkably higher than 240-level polyimide enamelled round copper wire standard in China respectively. The high-temperature resistant polyimide wire enamel can be used for insulation of a high-load, high-power and refrigerant-resistant motor and has broad market prospects.

Owner:HUAWEI TEHCHNOLOGIES CO LTD