Patents

Literature

145results about How to "Reduce gate-to-drain capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

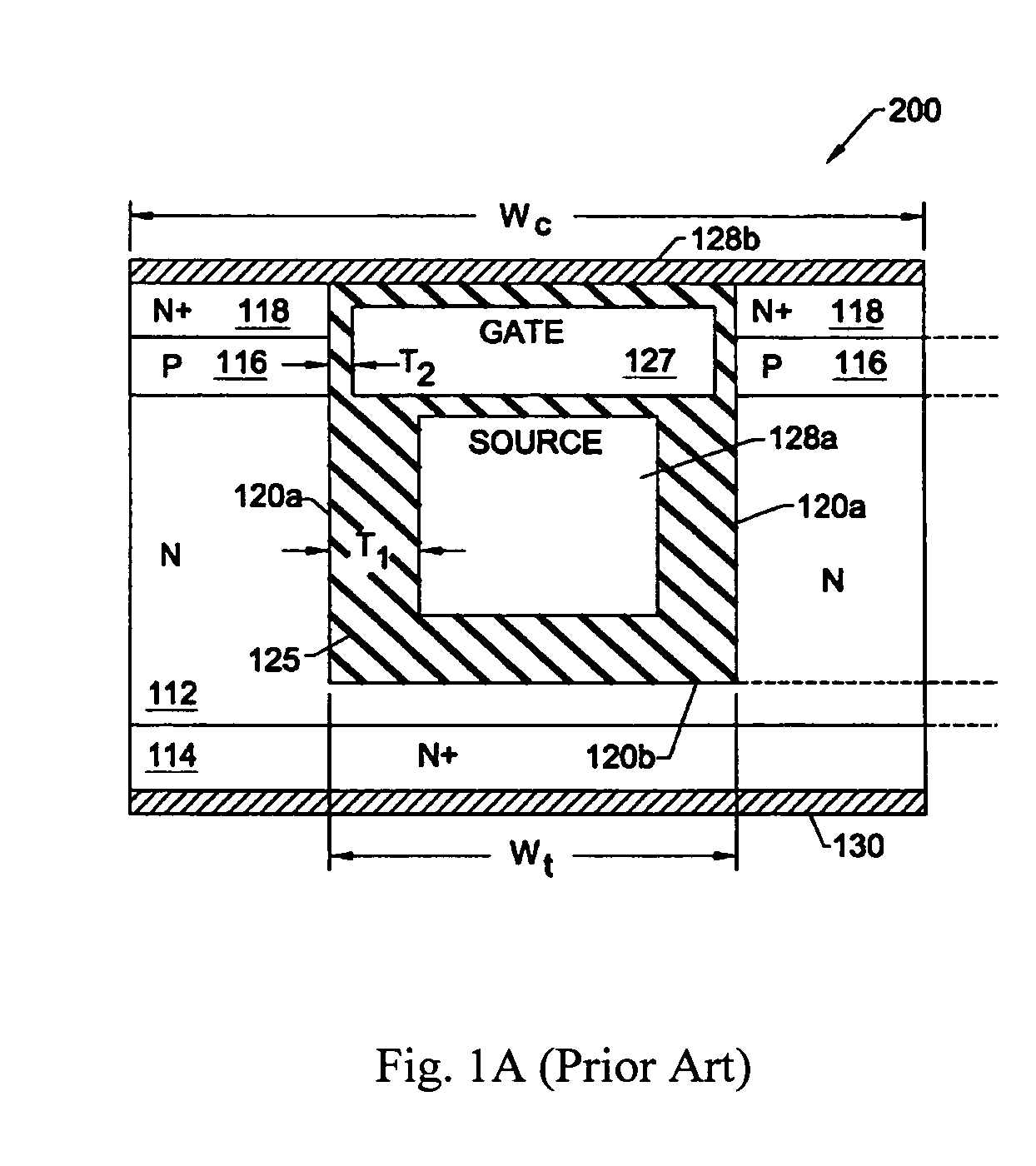

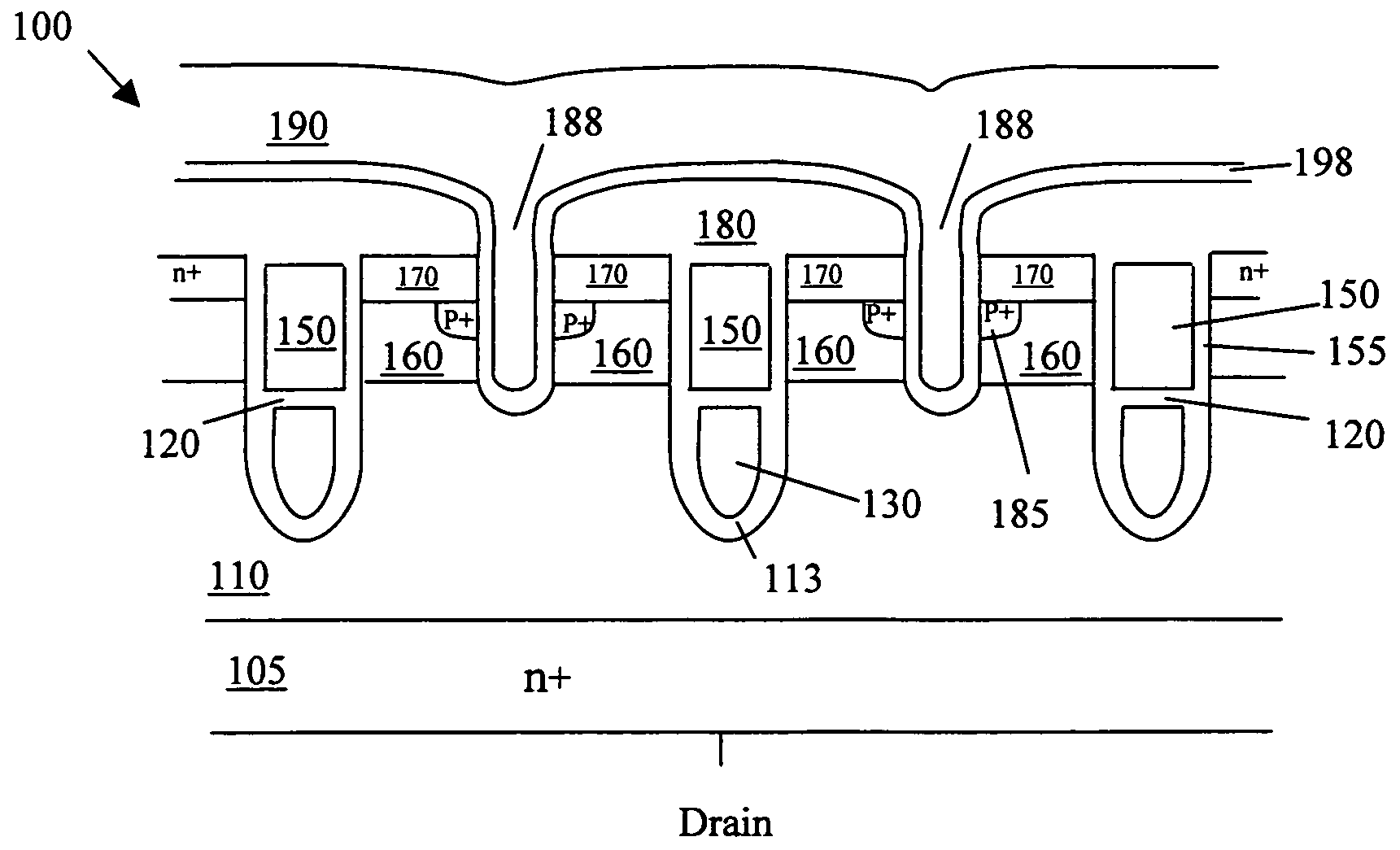

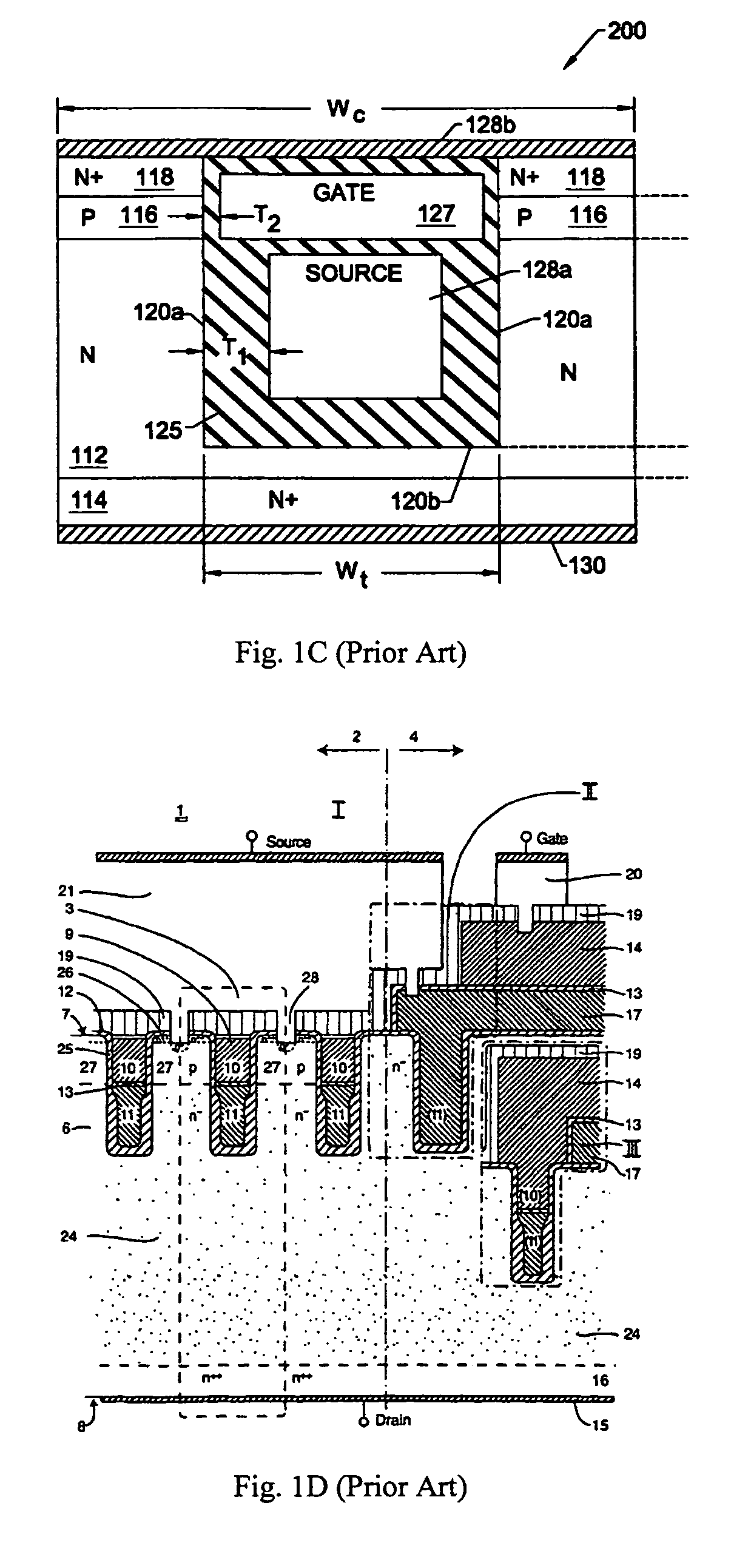

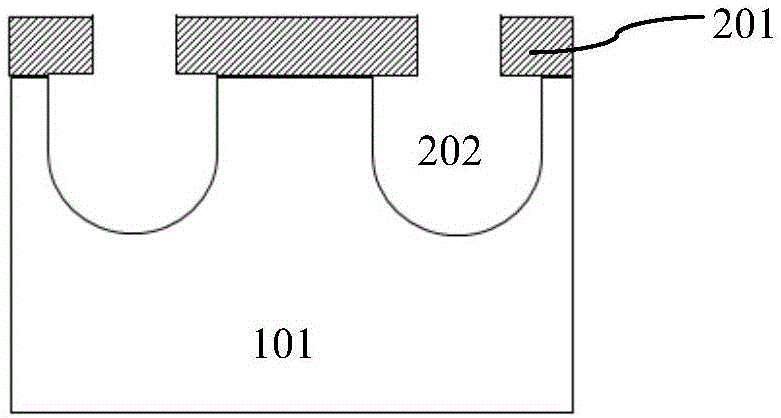

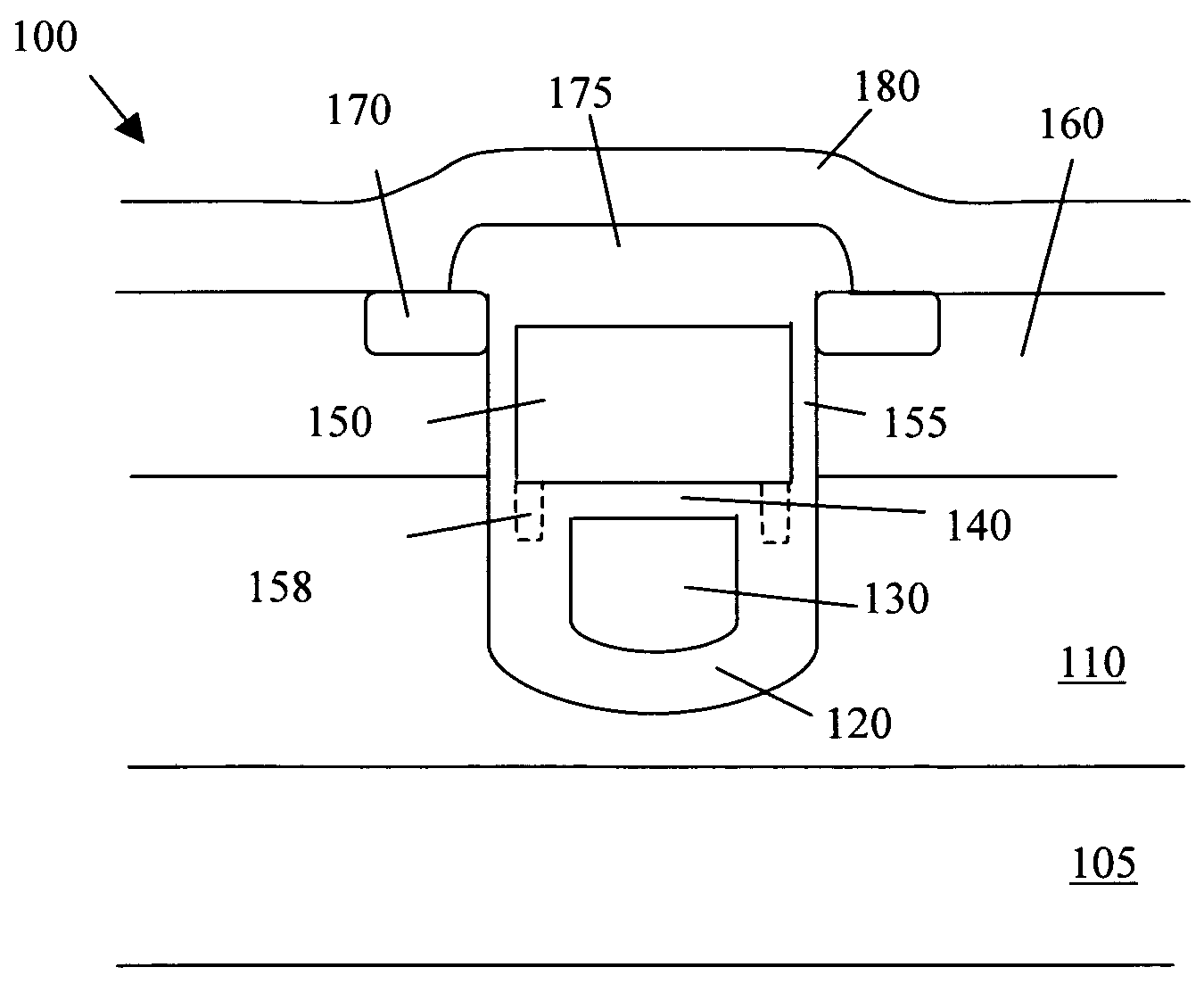

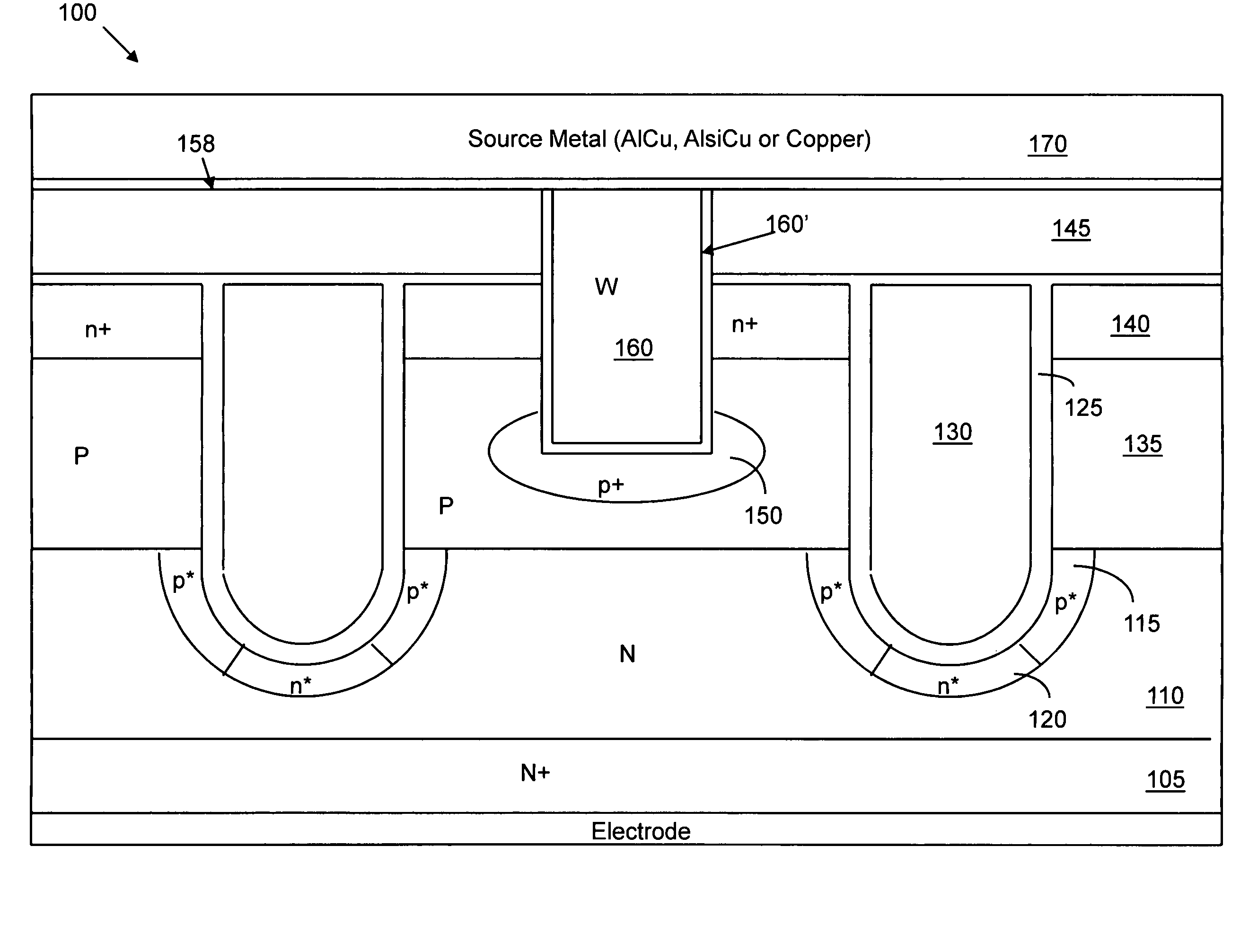

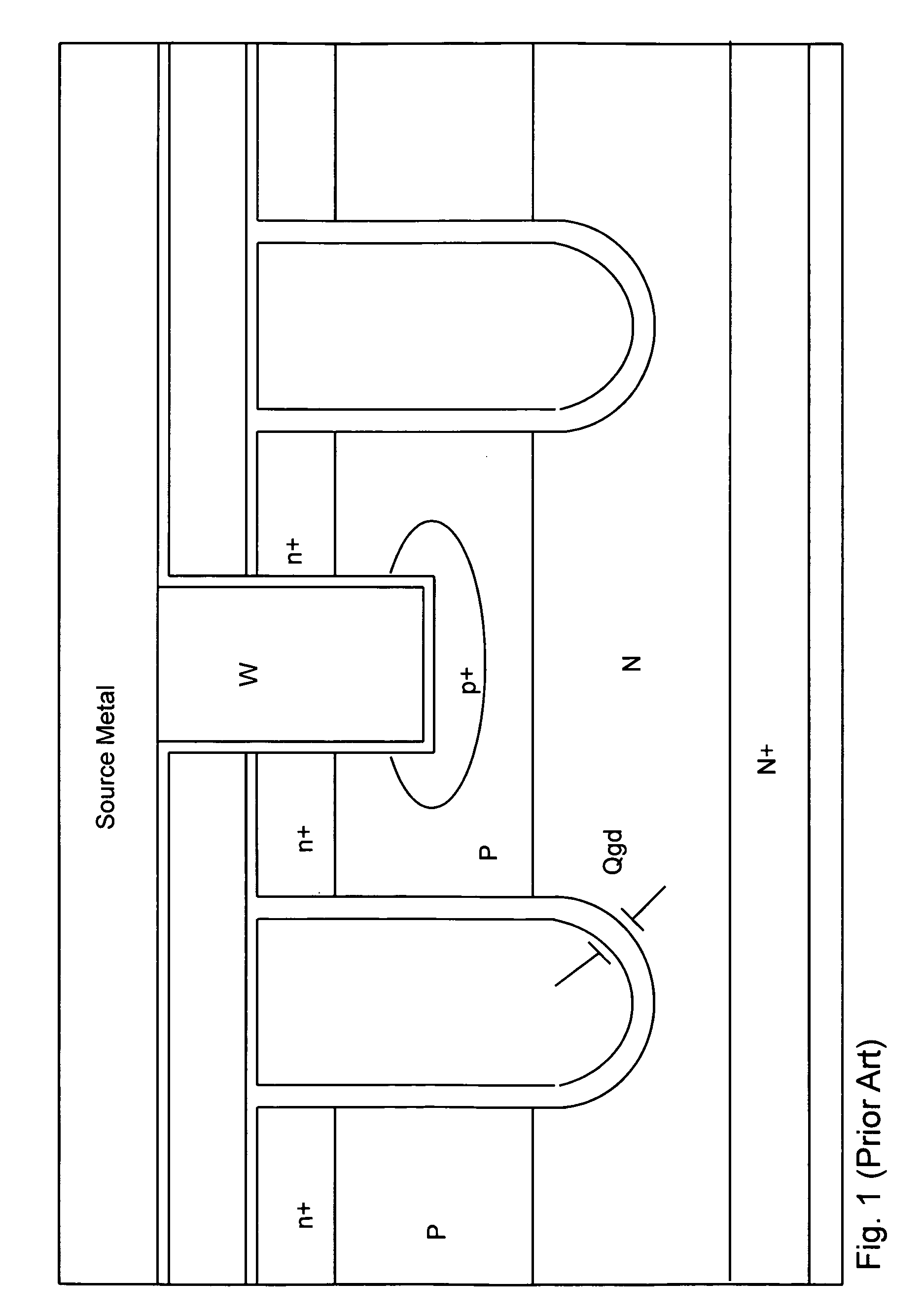

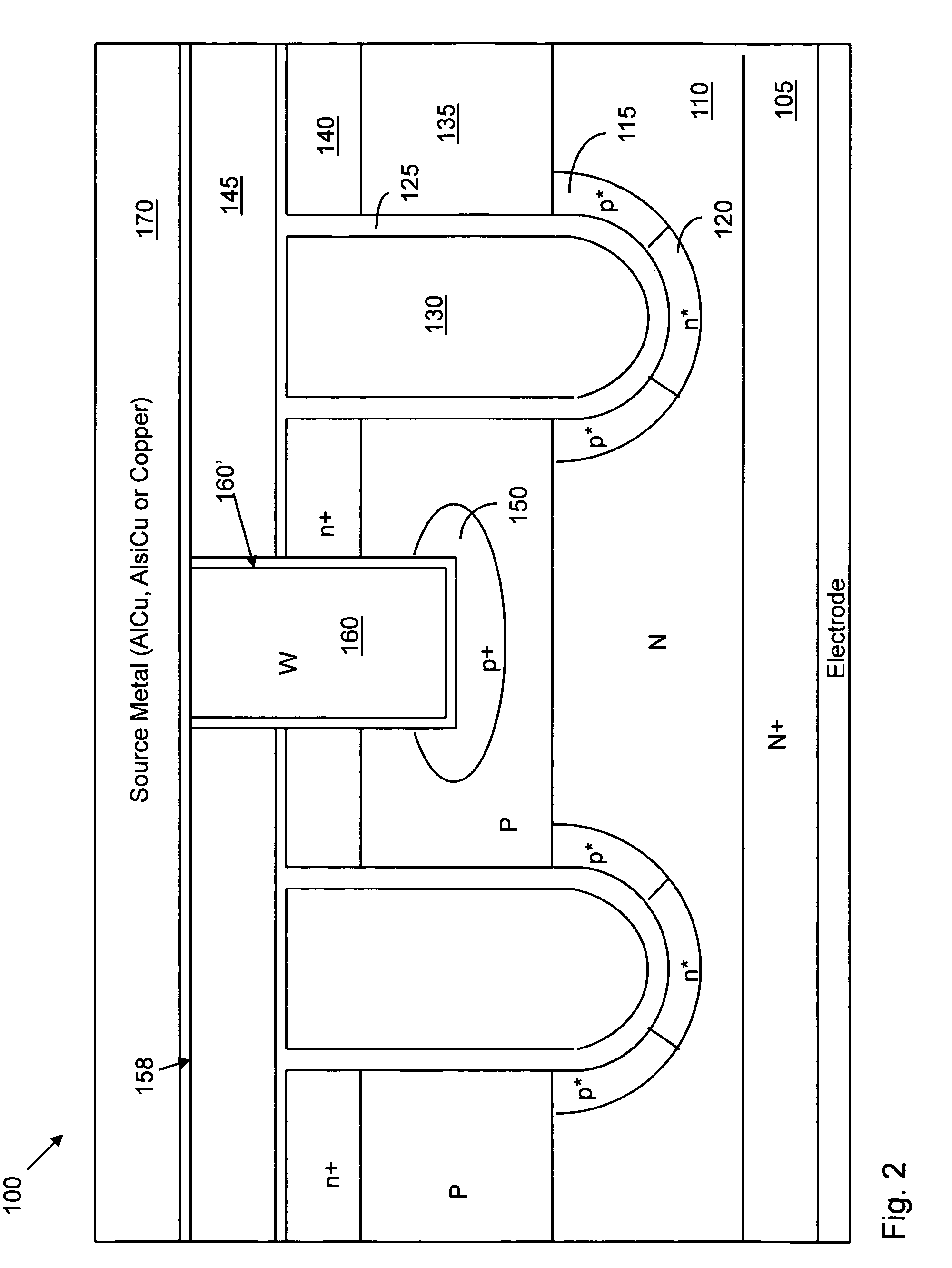

Super trench MOSFET including buried source electrode and method of fabricating the same

InactiveUS7183610B2Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

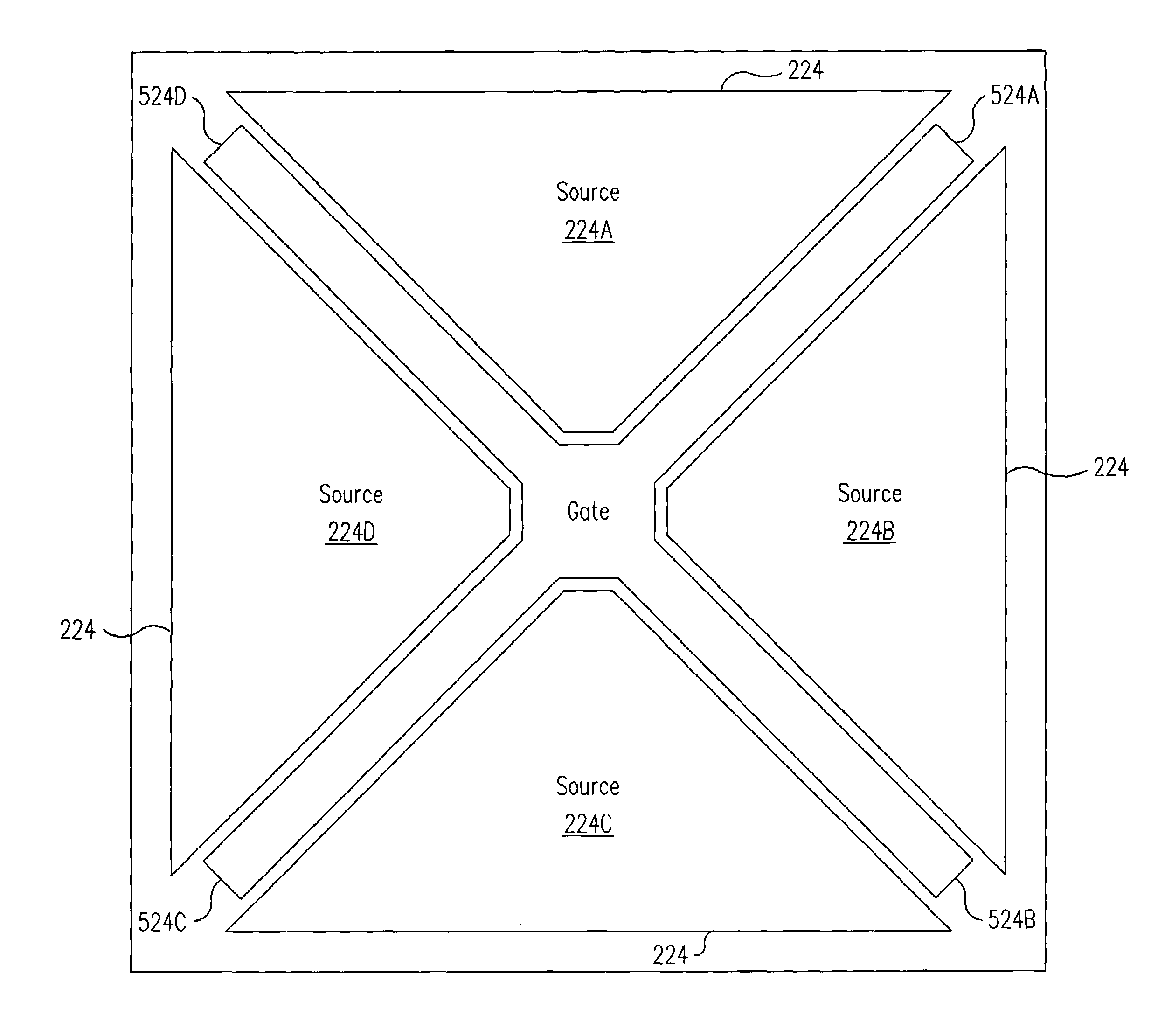

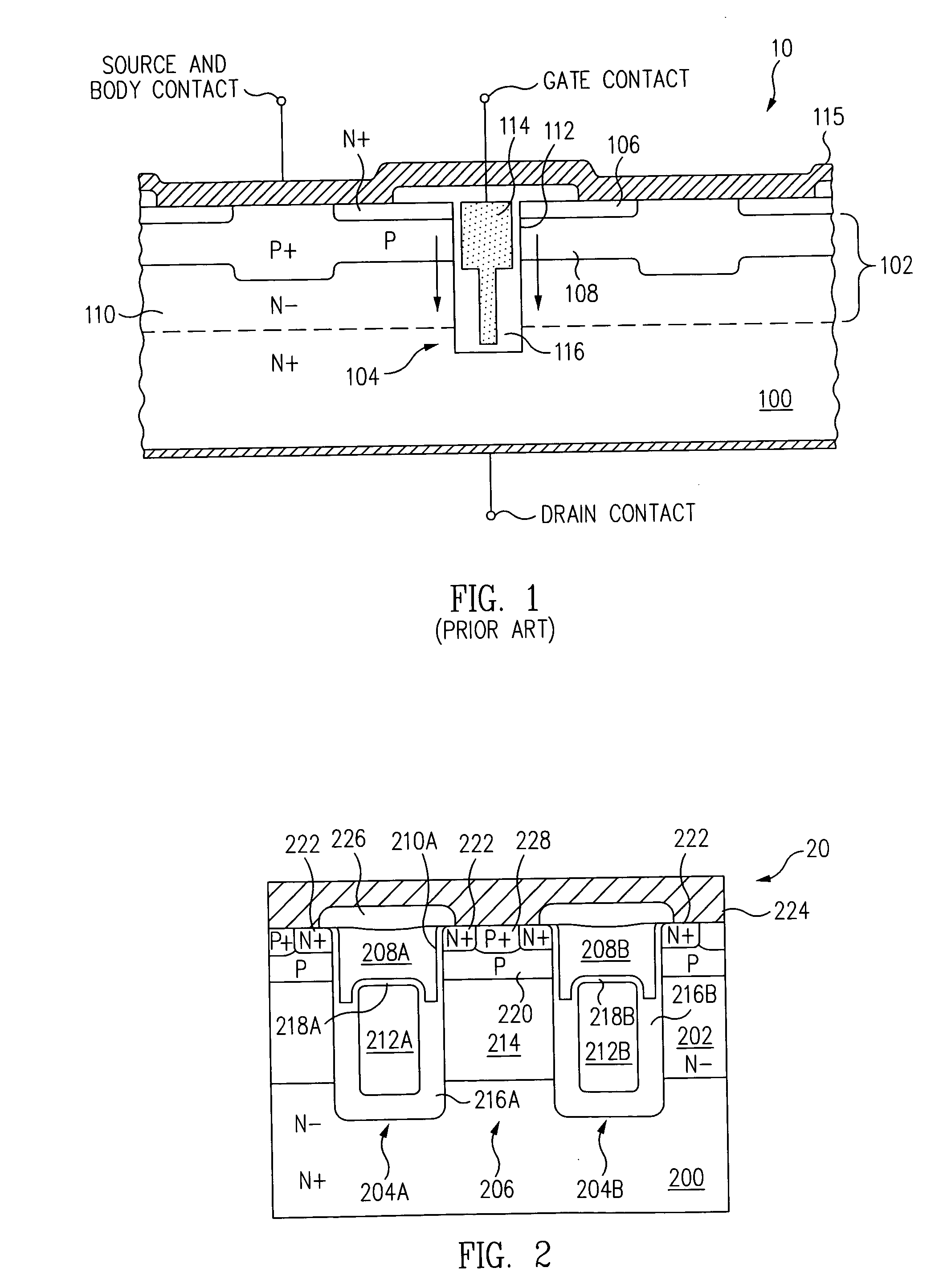

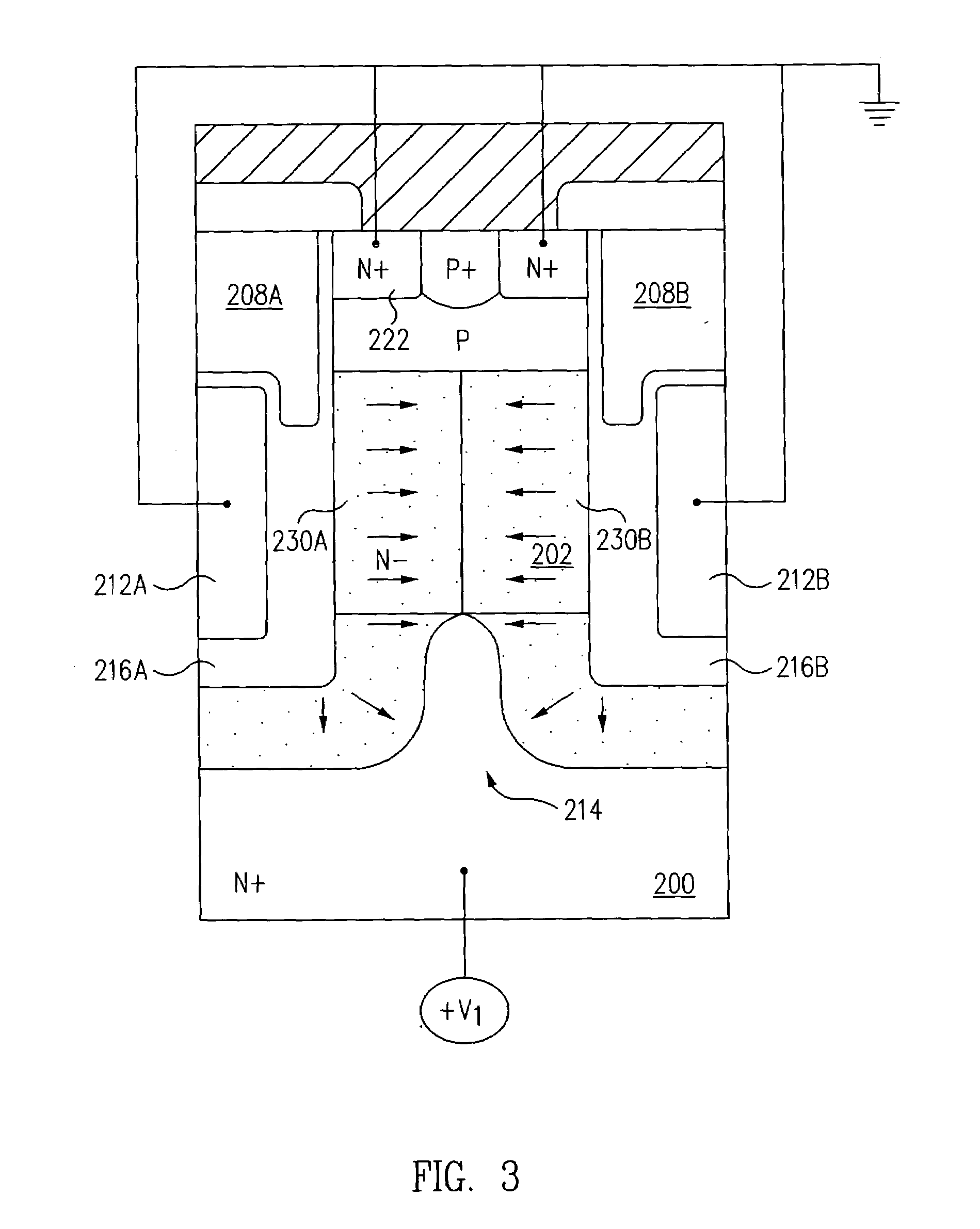

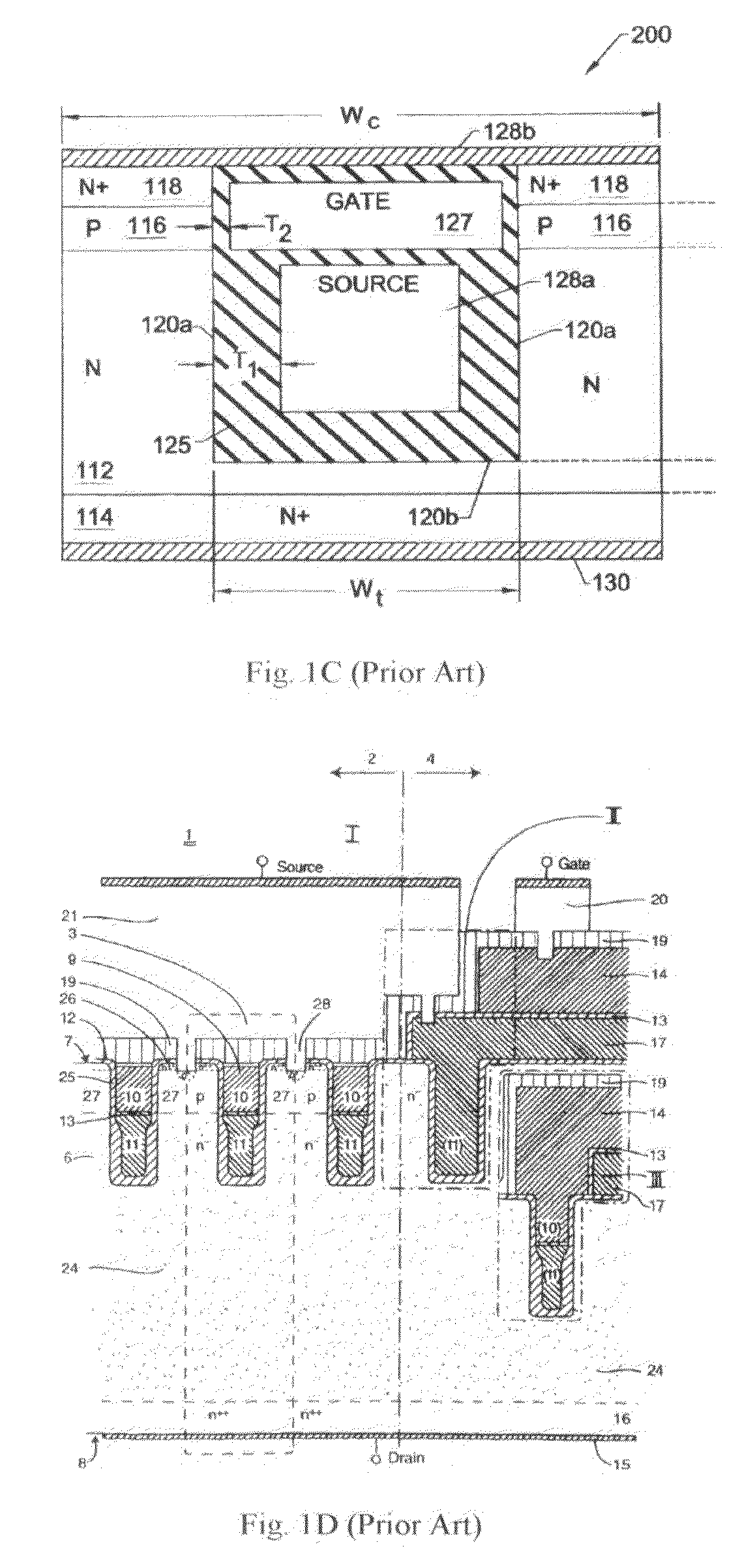

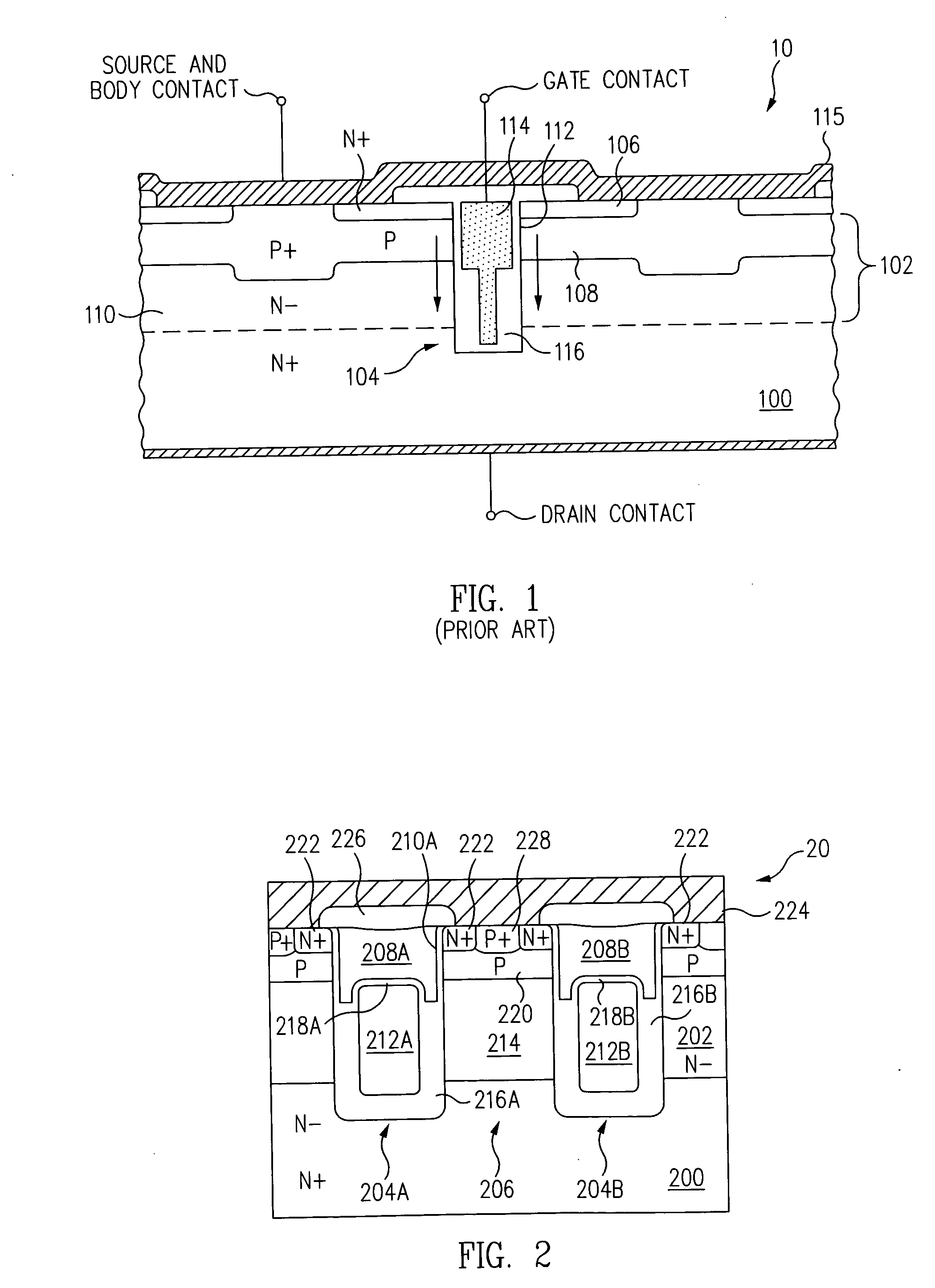

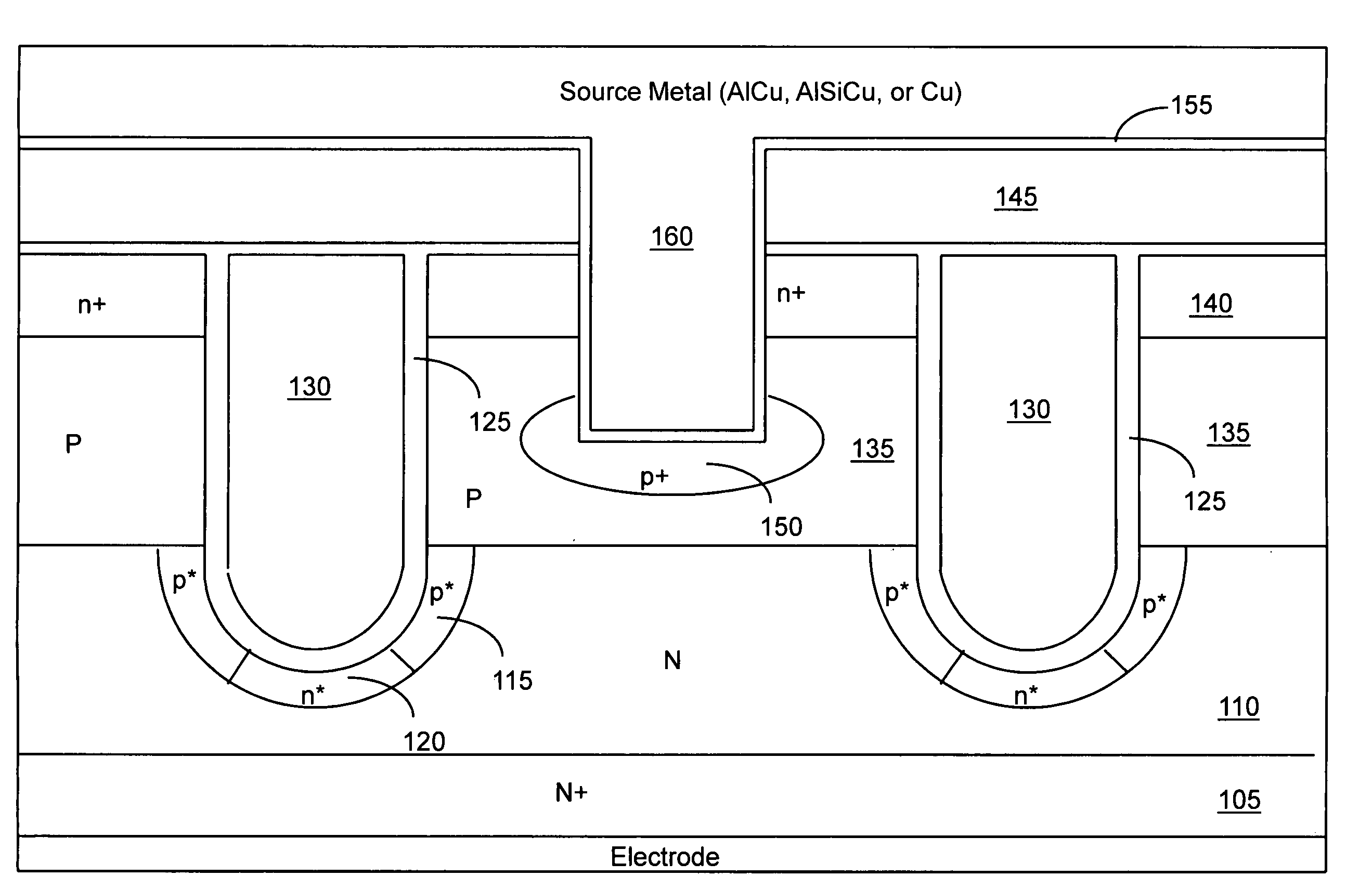

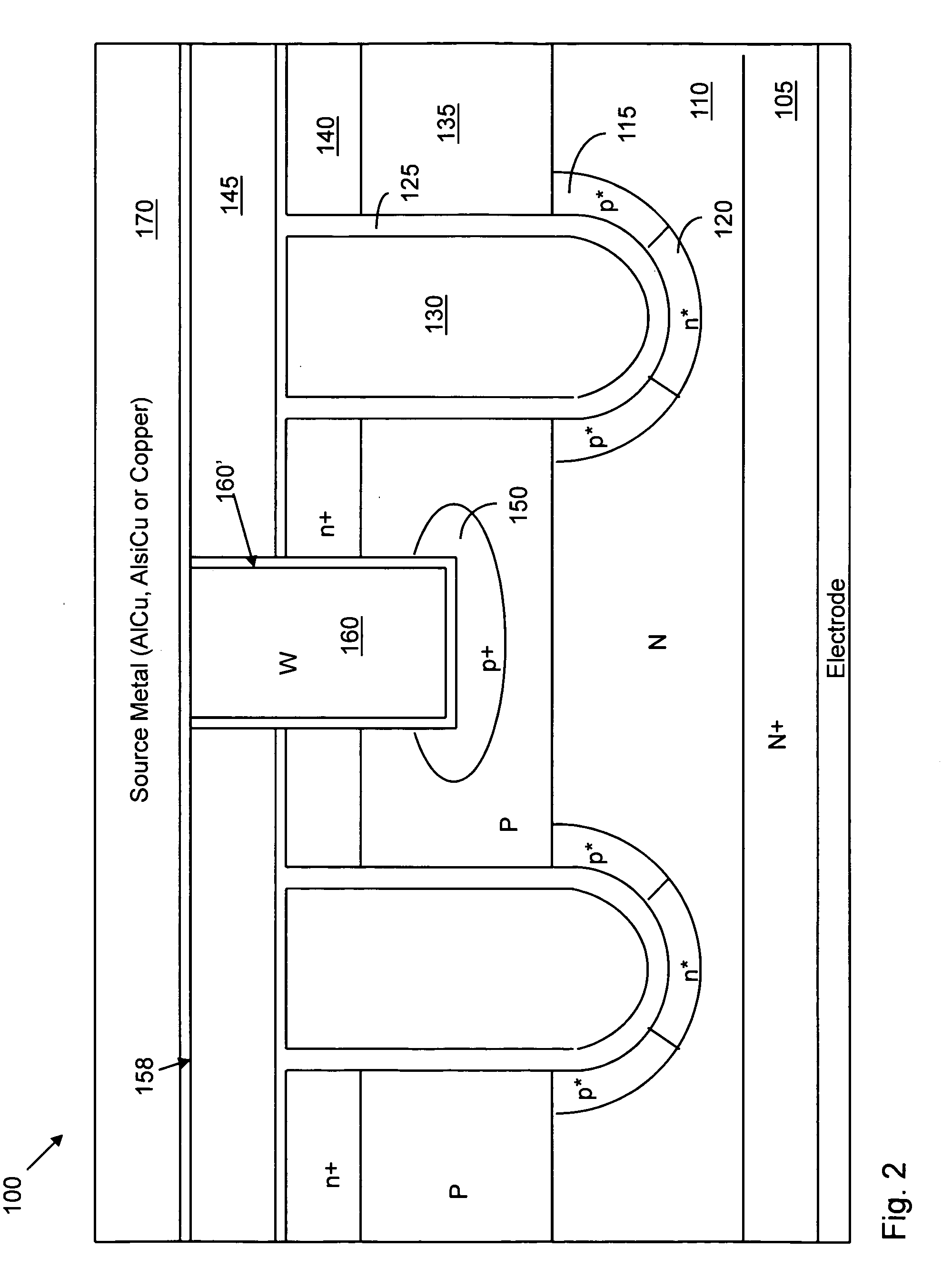

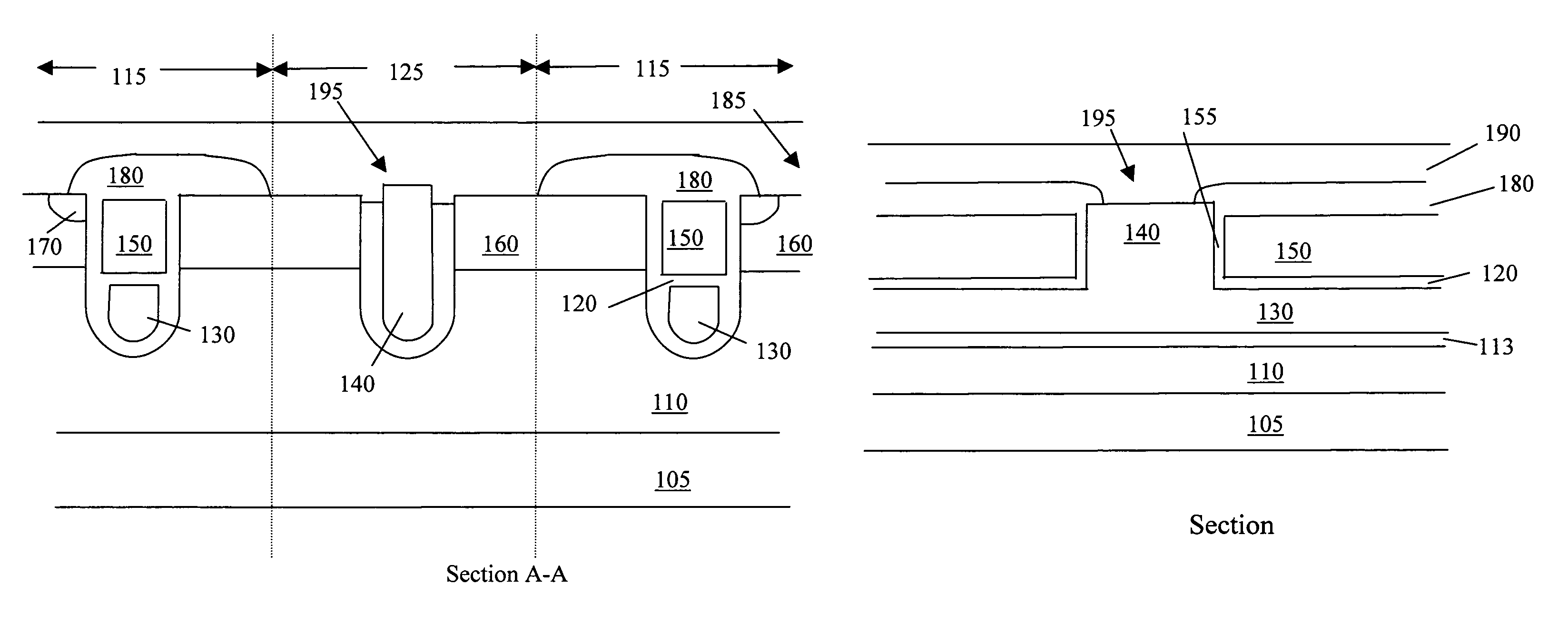

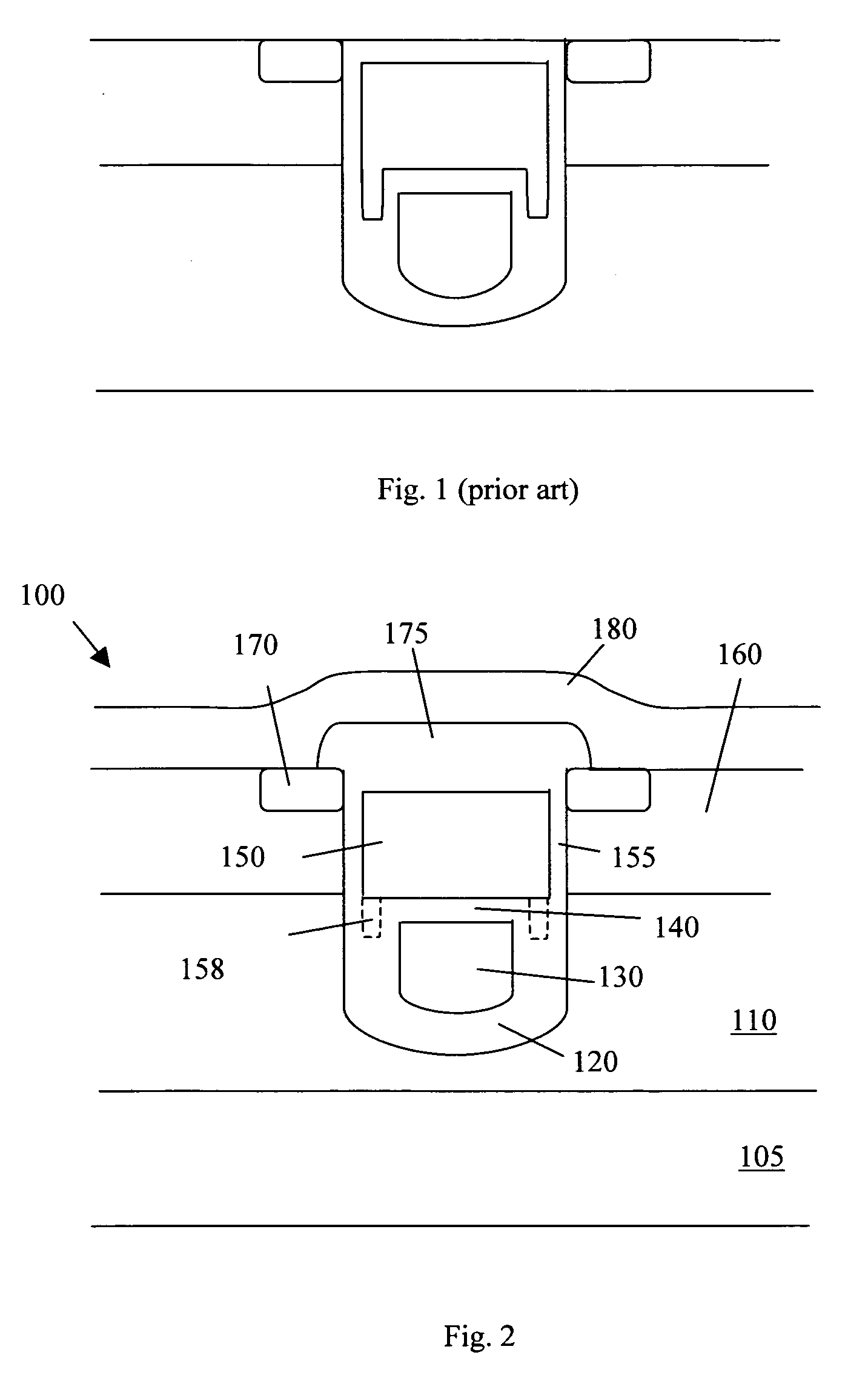

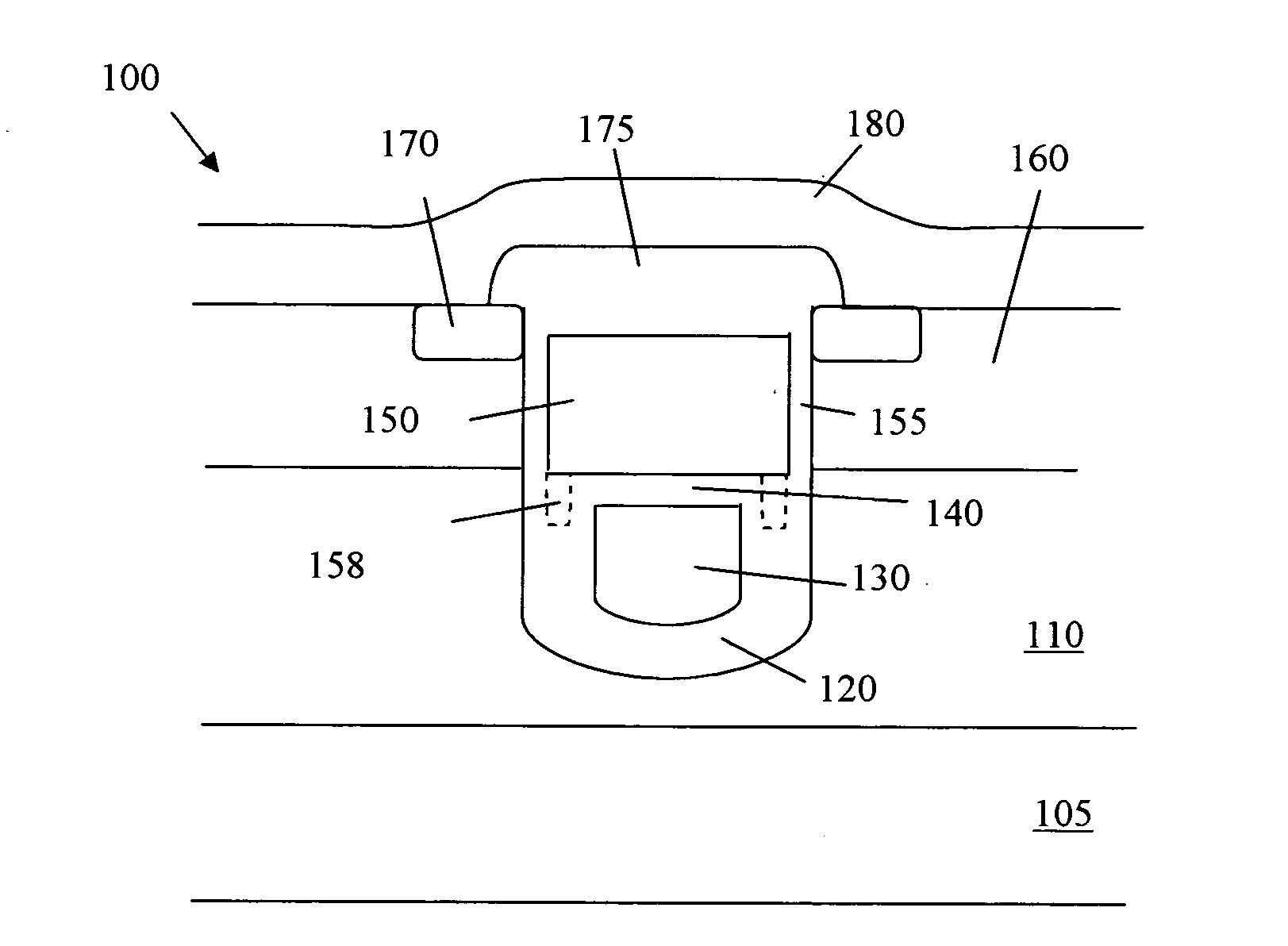

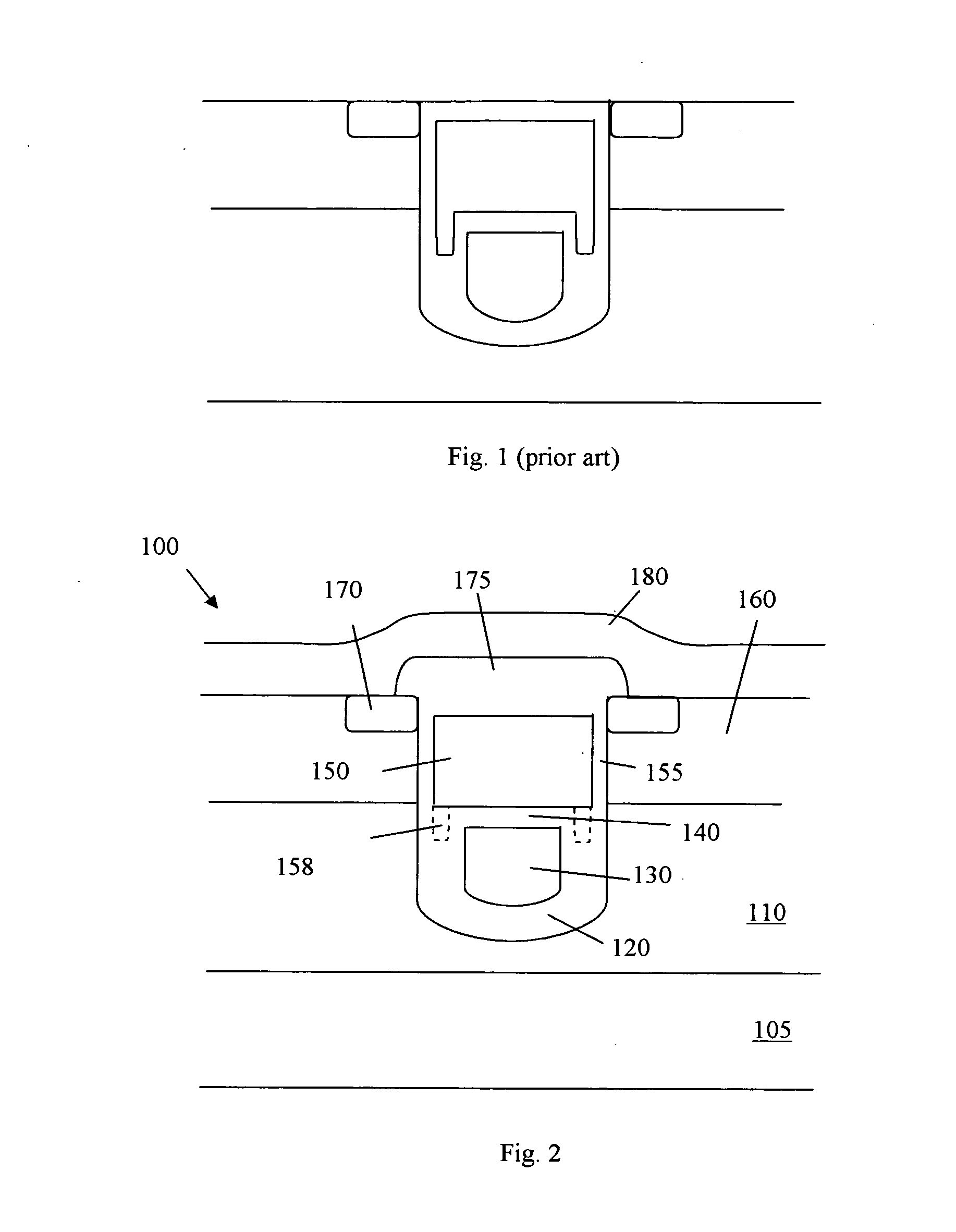

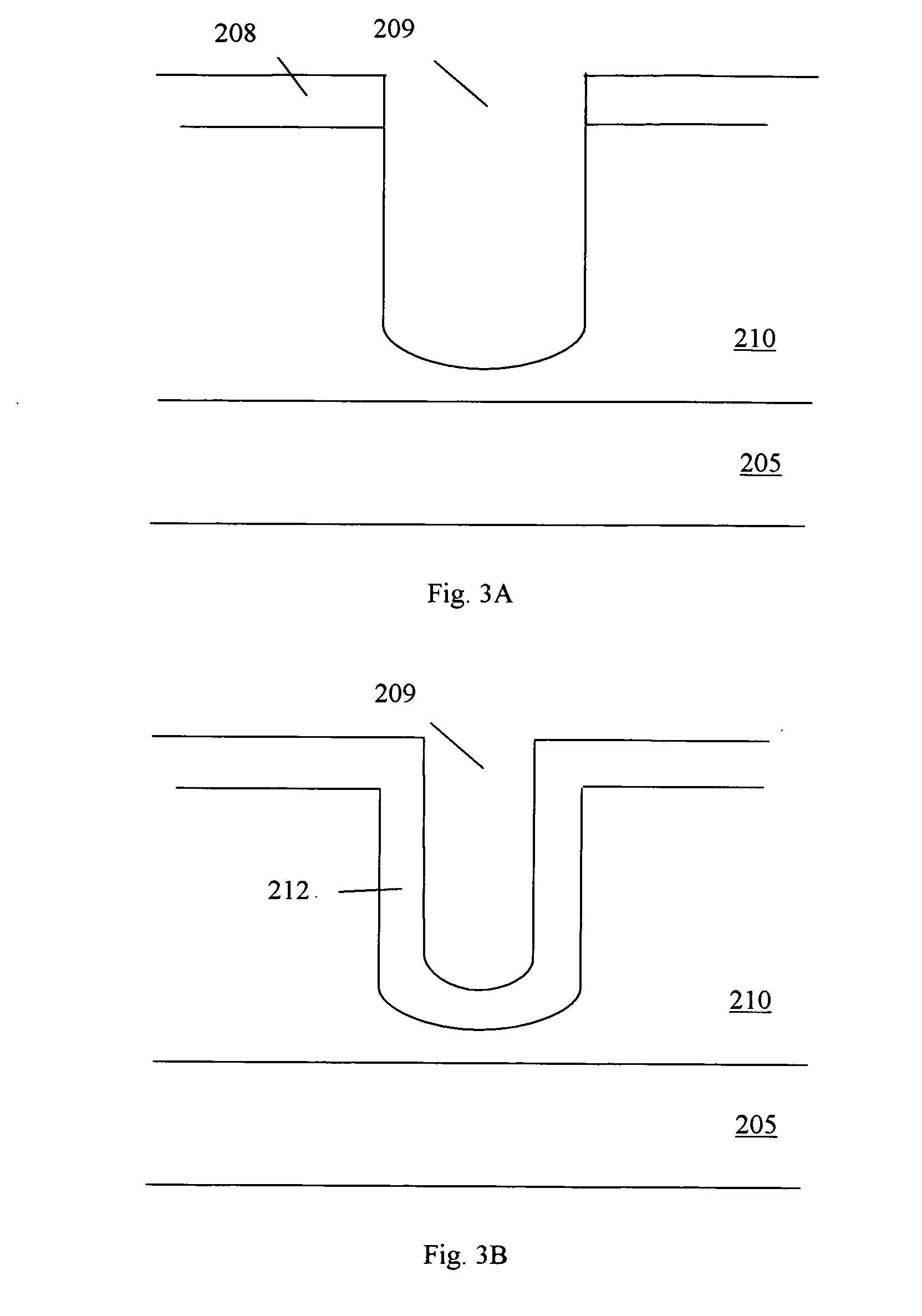

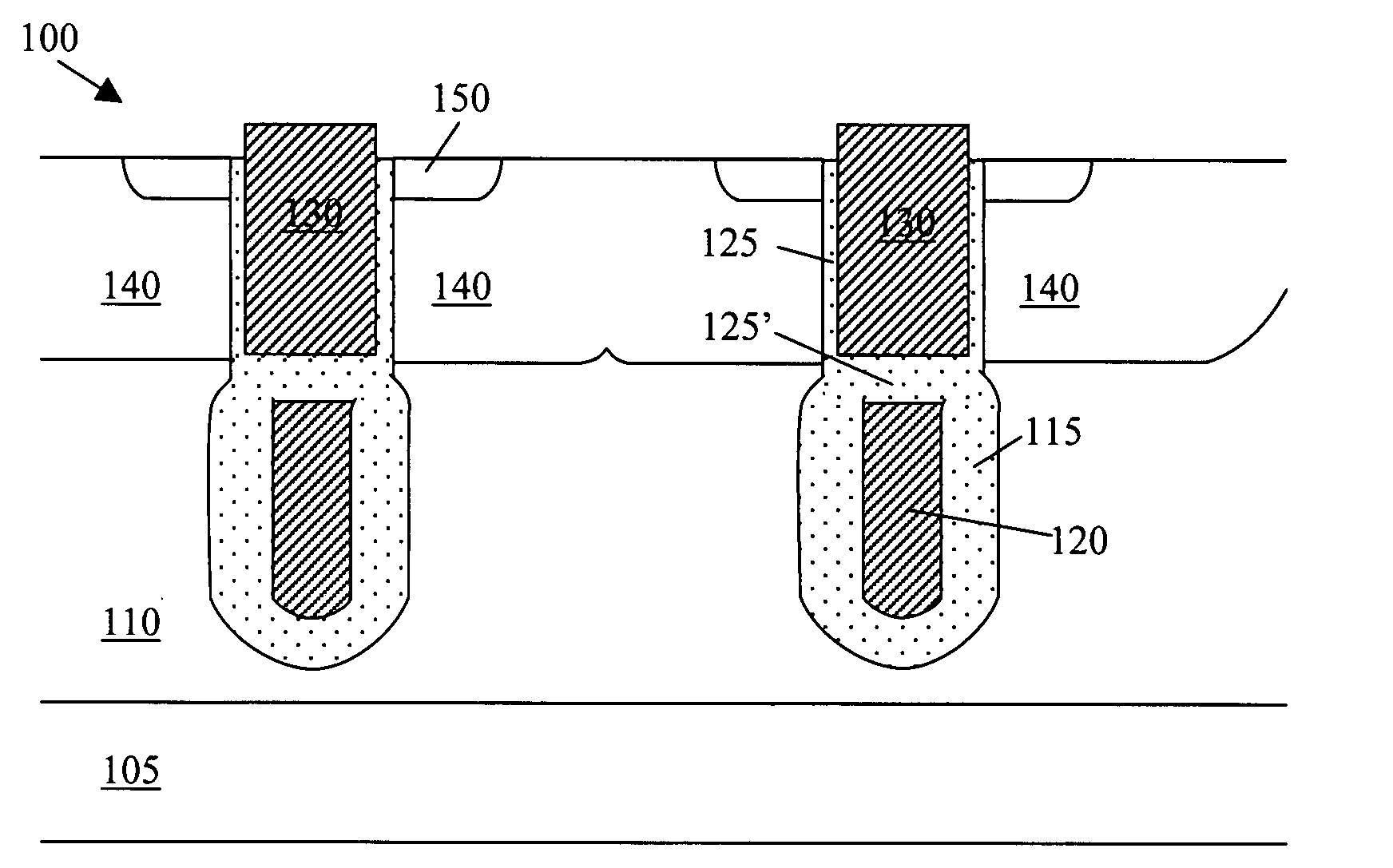

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

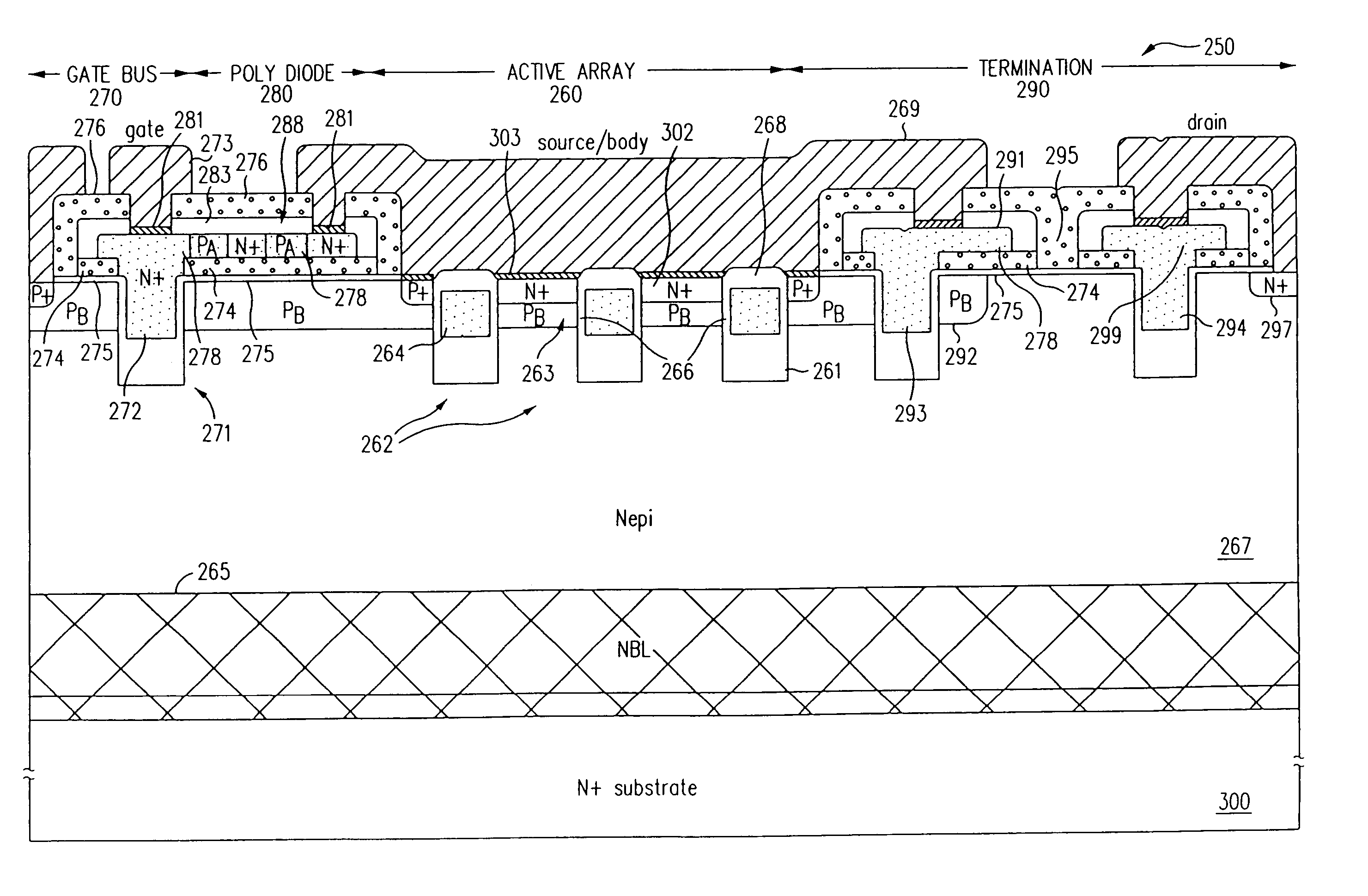

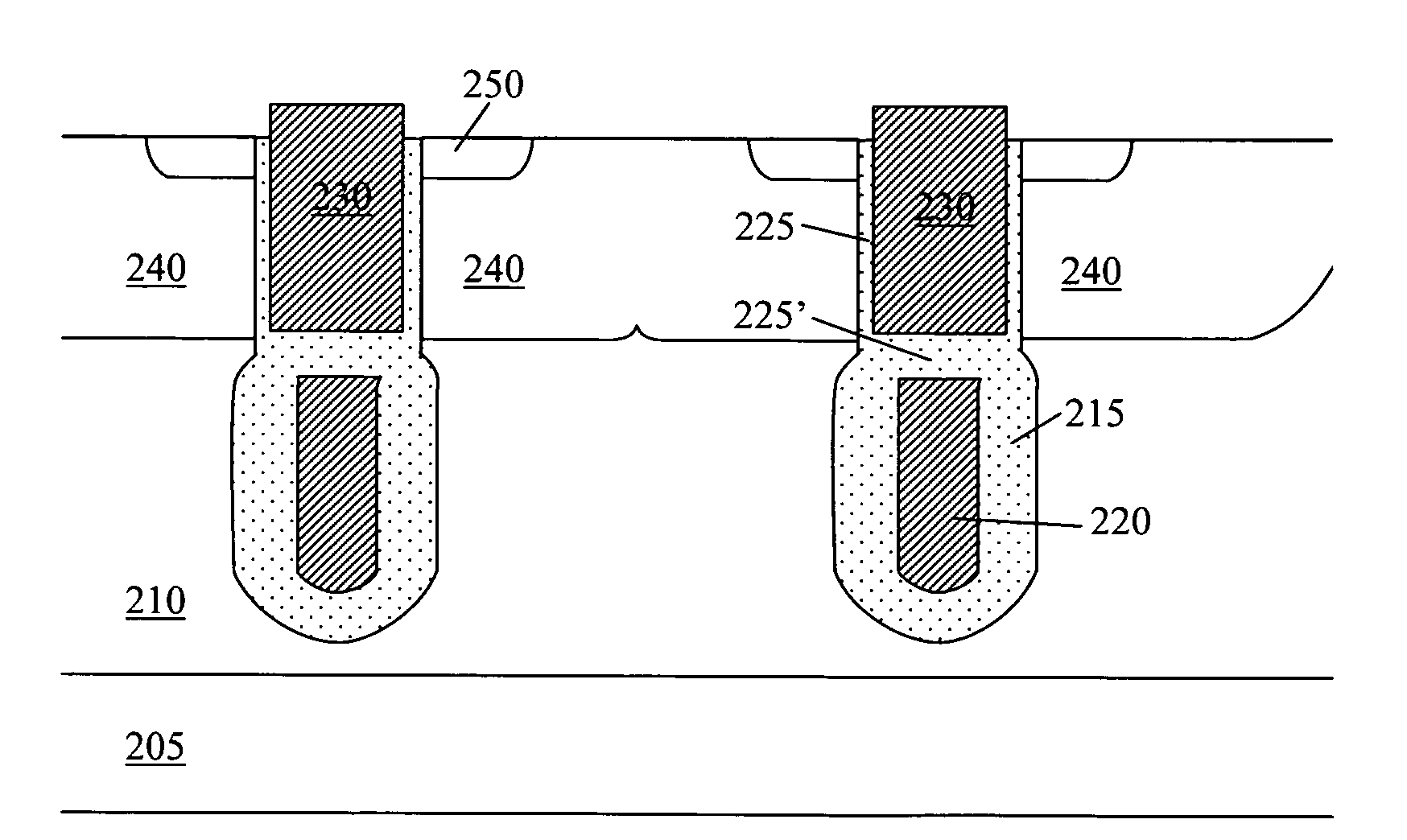

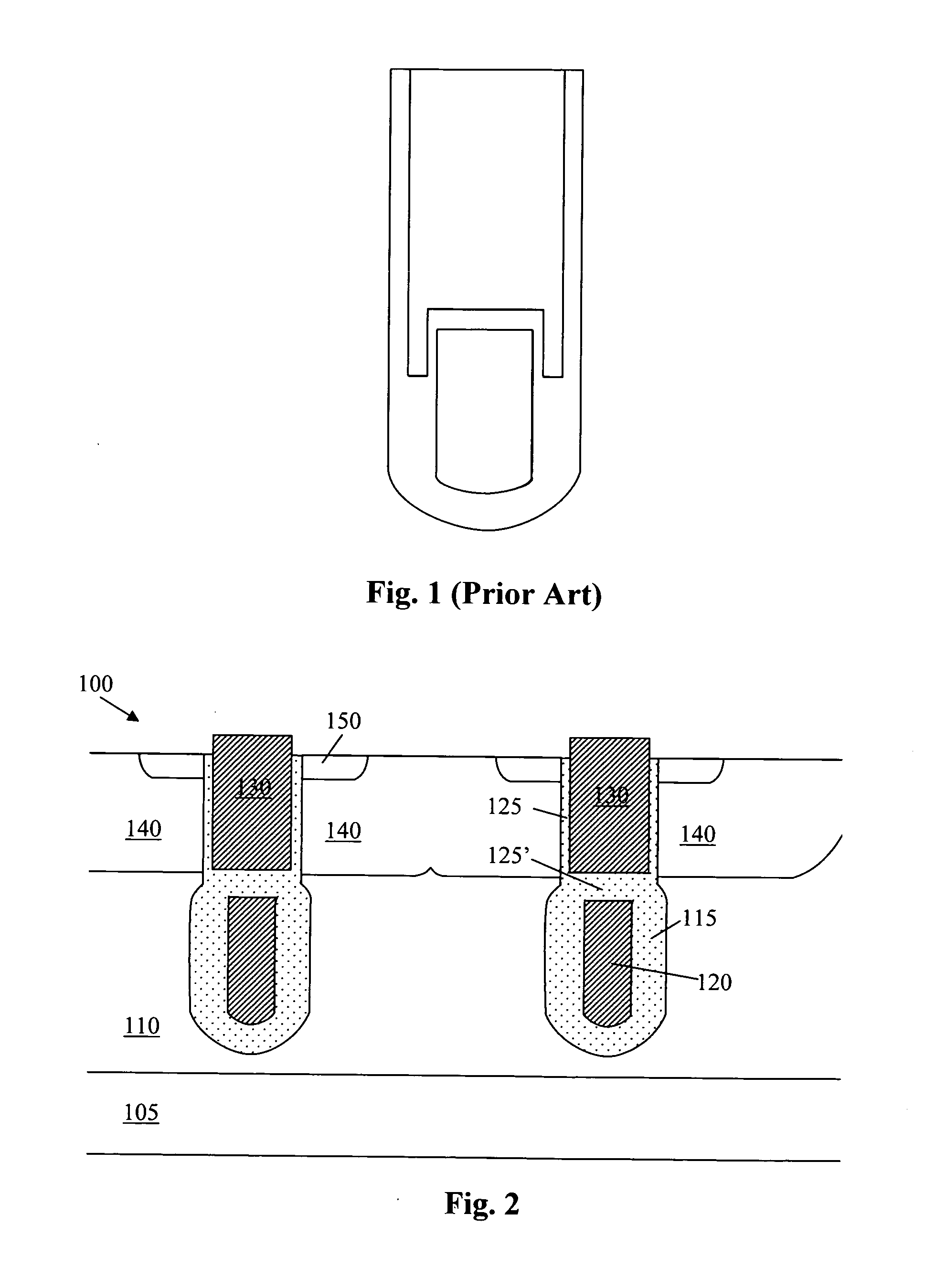

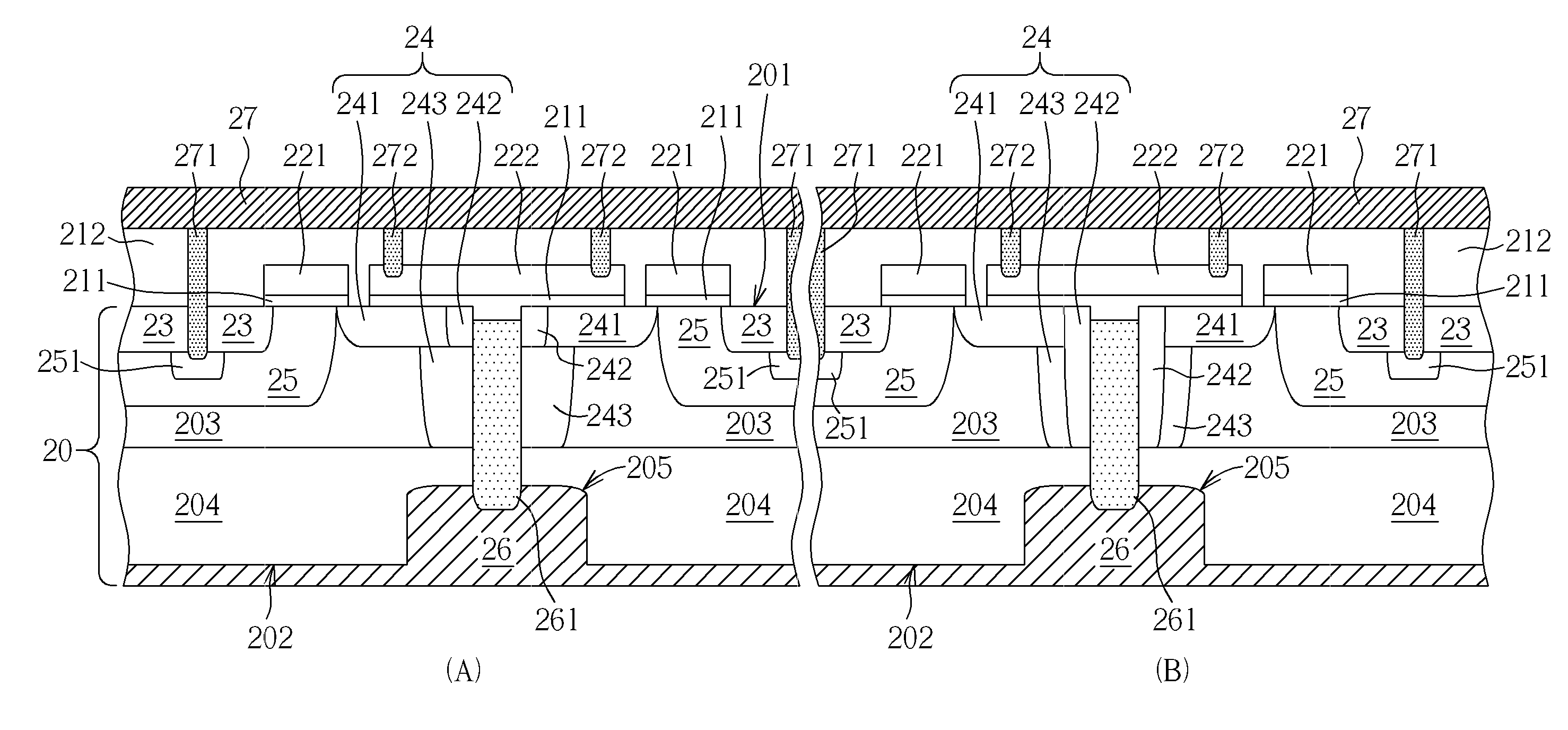

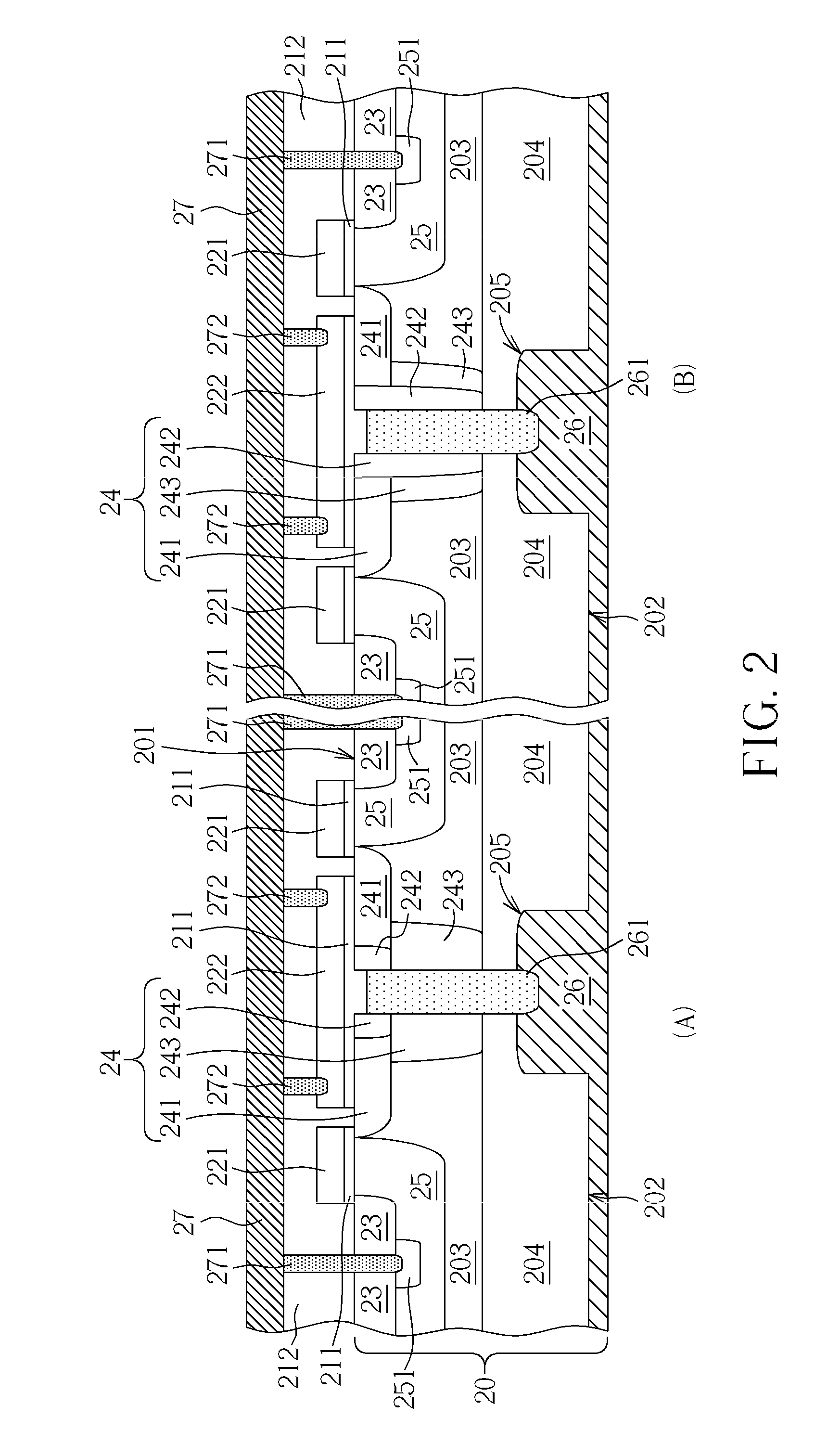

Shielded gate trench (SGT) MOSFET devices and manufacturing processes

ActiveUS20070194374A1Strengthen connectionSmooth connectionSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSemiconductor

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one of the cells constituting an active cell has a source region disposed next to a trenched gate electrically connecting to a gate pad and surrounding the cell. The trenched gate further has a bottom-shielding electrode filled with a gate material disposed below and insulated from the trenched gate. At least one of the cells constituting a source-contacting cell surrounded by the trench with a portion functioning as a source connecting trench is filled with the gate material for electrically connecting between the bottom-shielding electrode and a source metal disposed directly on top of the source connecting trench. The semiconductor power device further includes an insulation protective layer disposed on top of the semiconductor power device having a plurality of source openings on top of the source region and the source connecting trench provided for electrically connecting to the source metal and at least a gate opening provided for electrically connecting the gate pad to the trenched gate.

Owner:ALPHA & OMEGA SEMICON LTD

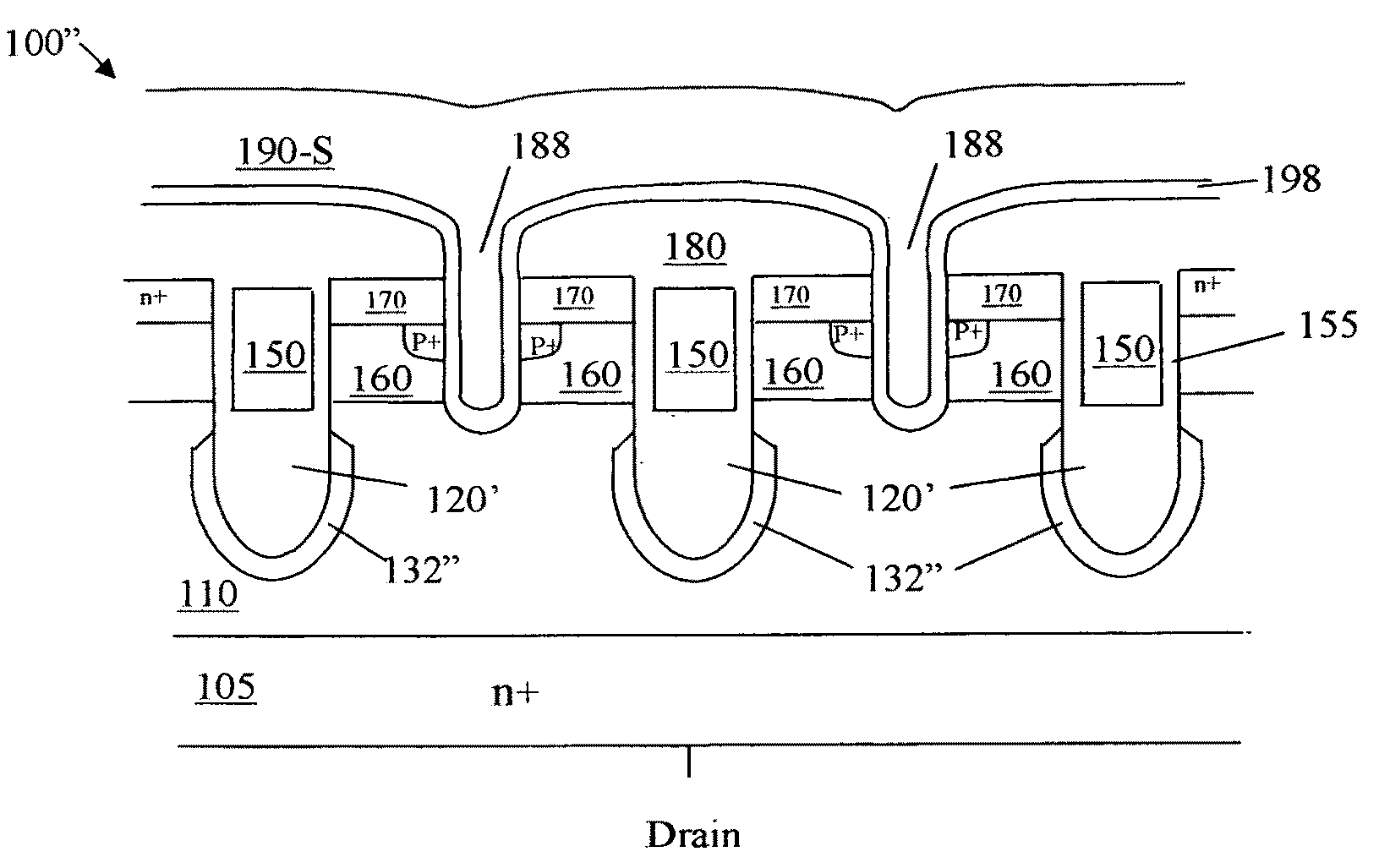

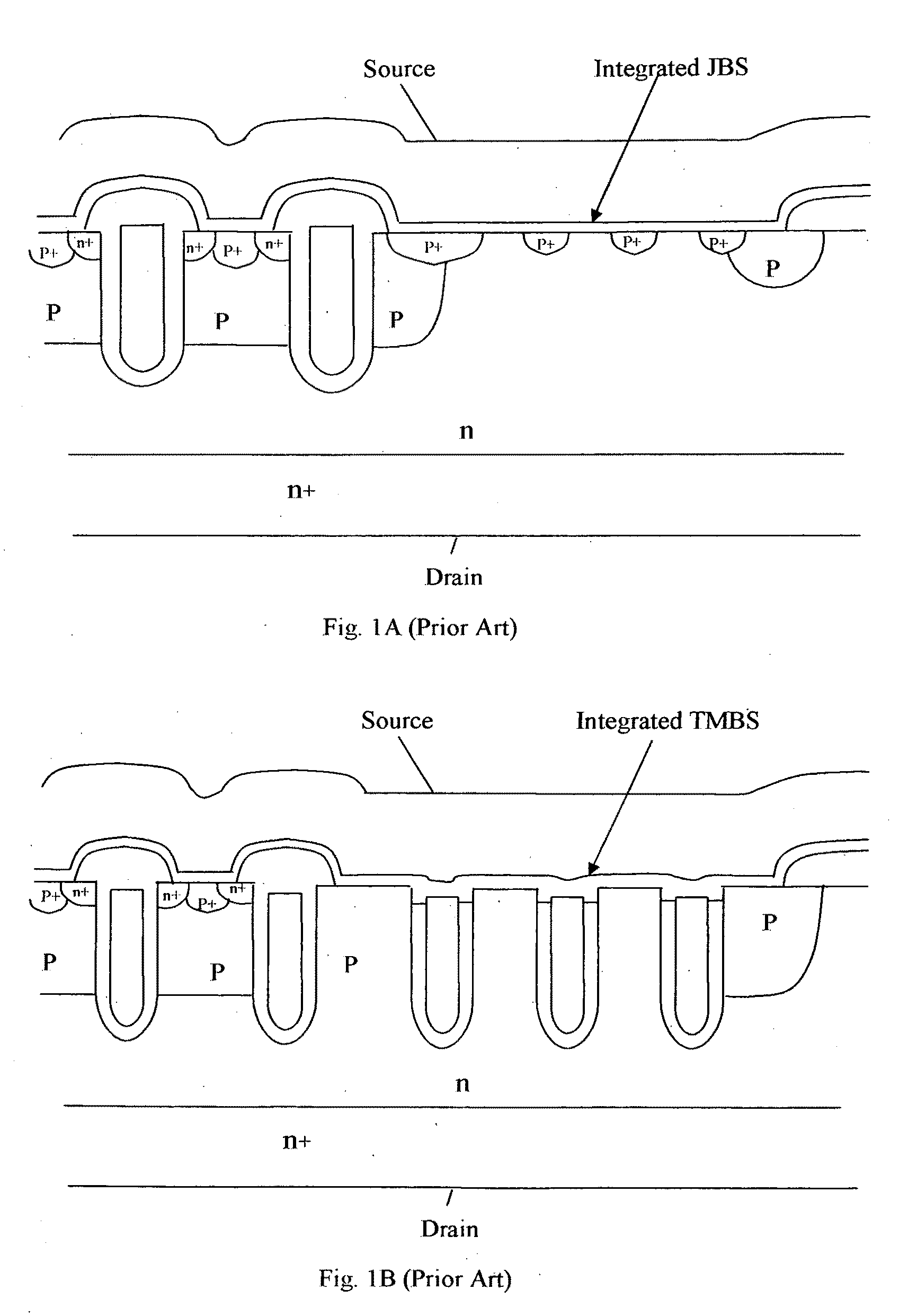

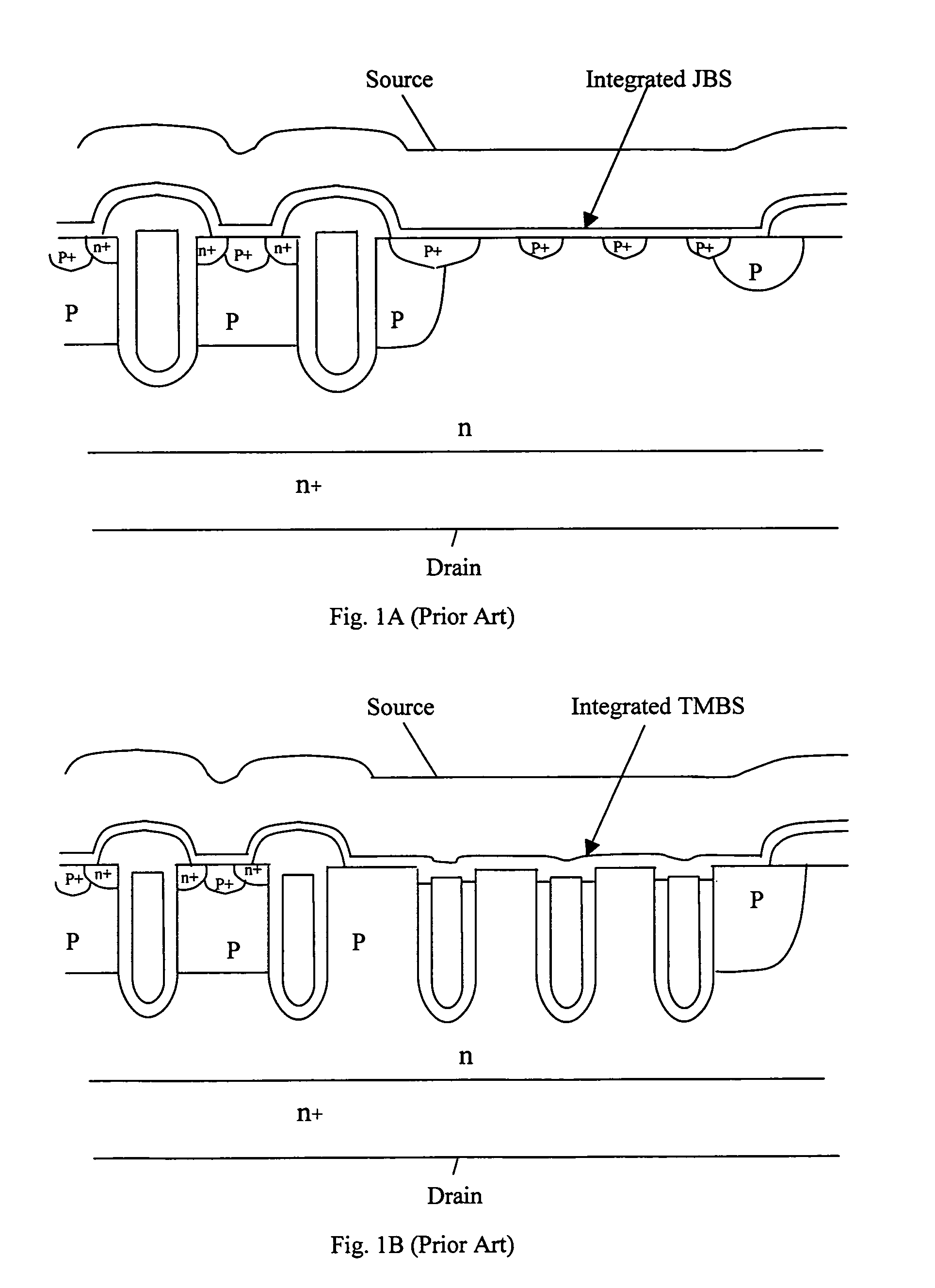

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS20090072301A1Improve switching performanceImprove area efficiencySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETInsulation layer

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one active cell further includes a trenched source contact opened between the trenches wherein the trenched source contact opened through a source region into a body region for electrically connecting the source region to a source metal disposed on top of an insulation layer wherein a trench bottom surface of the trenched source contact further covered with a conductive material to function as an integrated Schottky barrier diode in said active cell. A shielding structure is disposed at the bottom and insulated from the trenched gate to provide shielding effect for both the trenched gate and the Schottky diode.

Owner:ALPHA & OMEGA SEMICON LTD

Super trench MOSFET including buried source electrode and method of fabricating the same

InactiveUS20050242392A1Less resistivityIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

In a trench MOSFET, the lower portion of the trench contains a buried source electrode, which is insulated from the epitaxial layer and semiconductor substrate but in electrical contact with the source region. When the MOSFET is in an “off” condition, the bias of the buried source electrode causes the “drift” region of the mesa to become depleted, enhancing the ability of the MOSFET to block current. The doping concentration of the drift region can therefore be increased, reducing the on-resistance of the MOSFET. The buried source electrode also reduces the gate-to-drain capacitance of the MOSFET, improving the ability of the MOSFET to operate at high frequencies. The substrate may advantageously include a plurality of annular trenches separated by annular mesas and a gate metal layer that extends outward from a central region in a plurality of gate metal legs separated by source metal regions.

Owner:SILICONIX

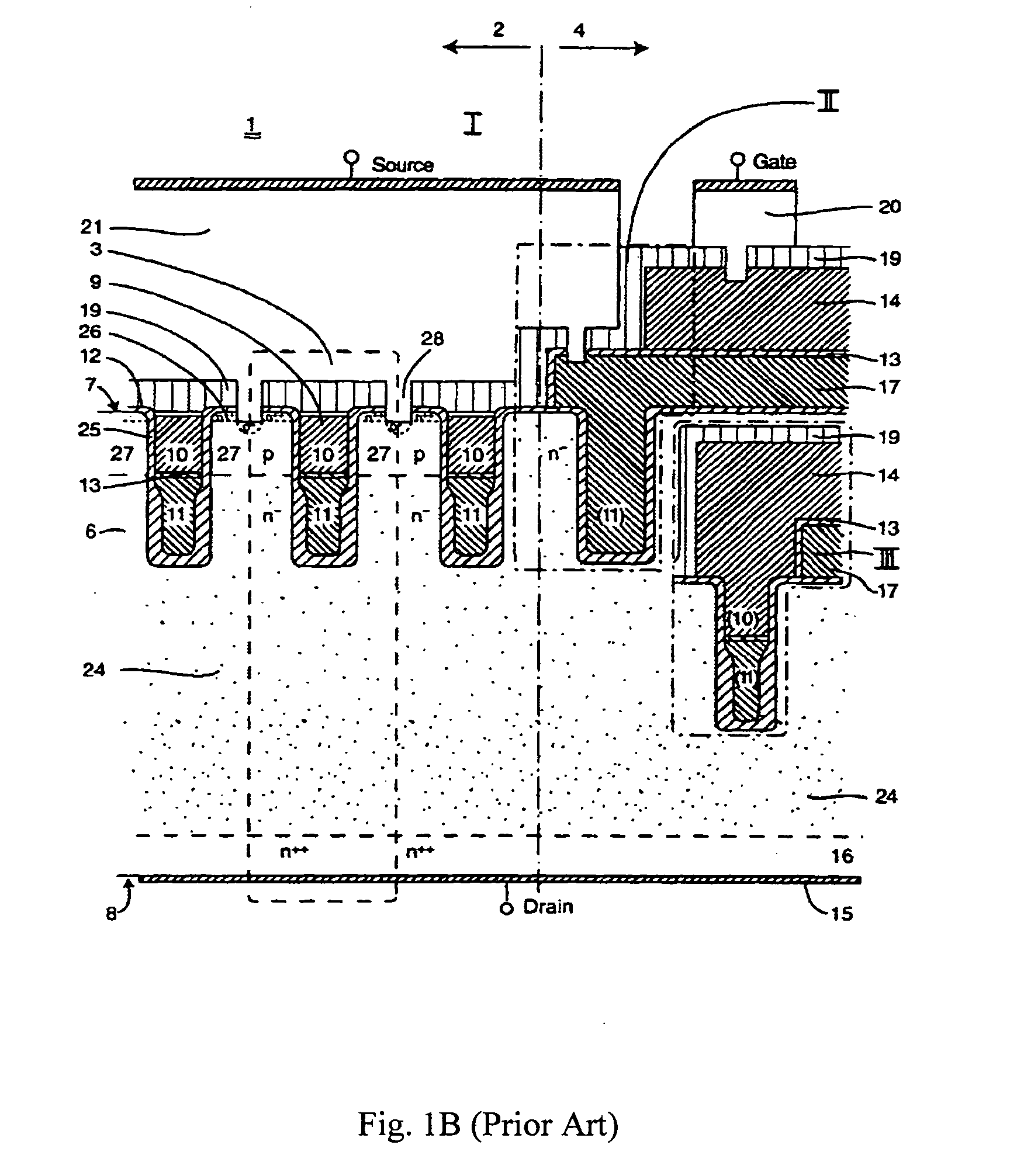

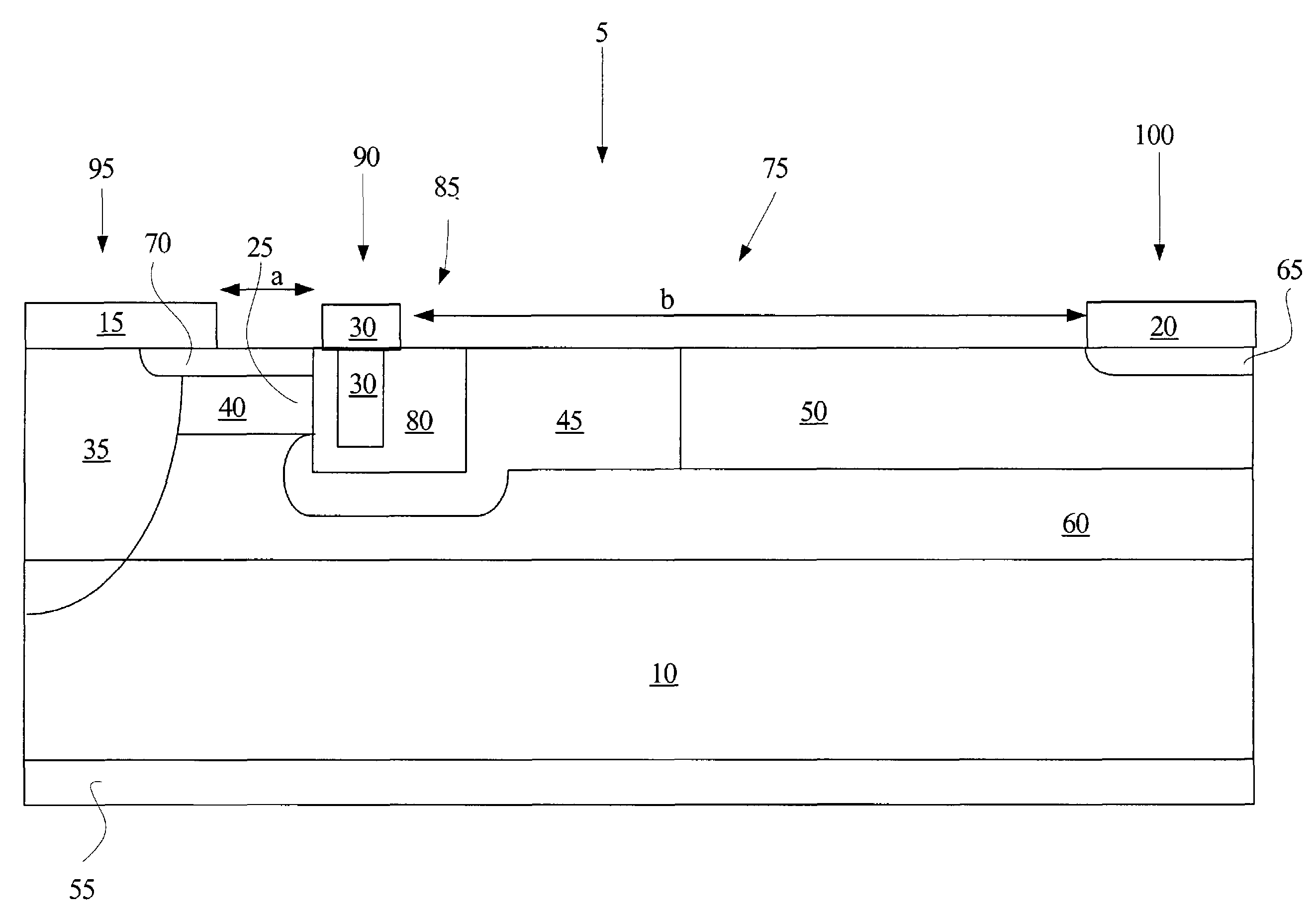

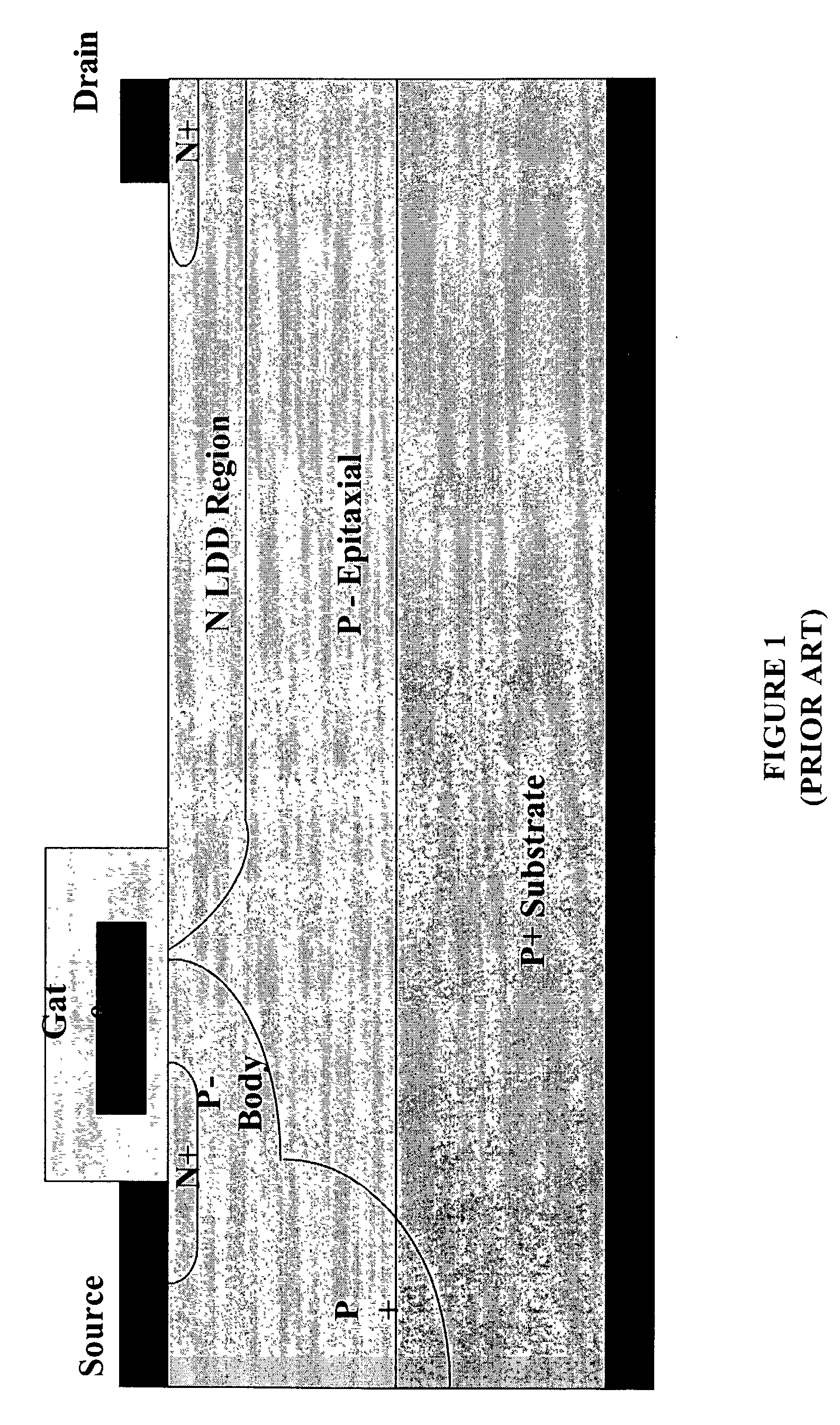

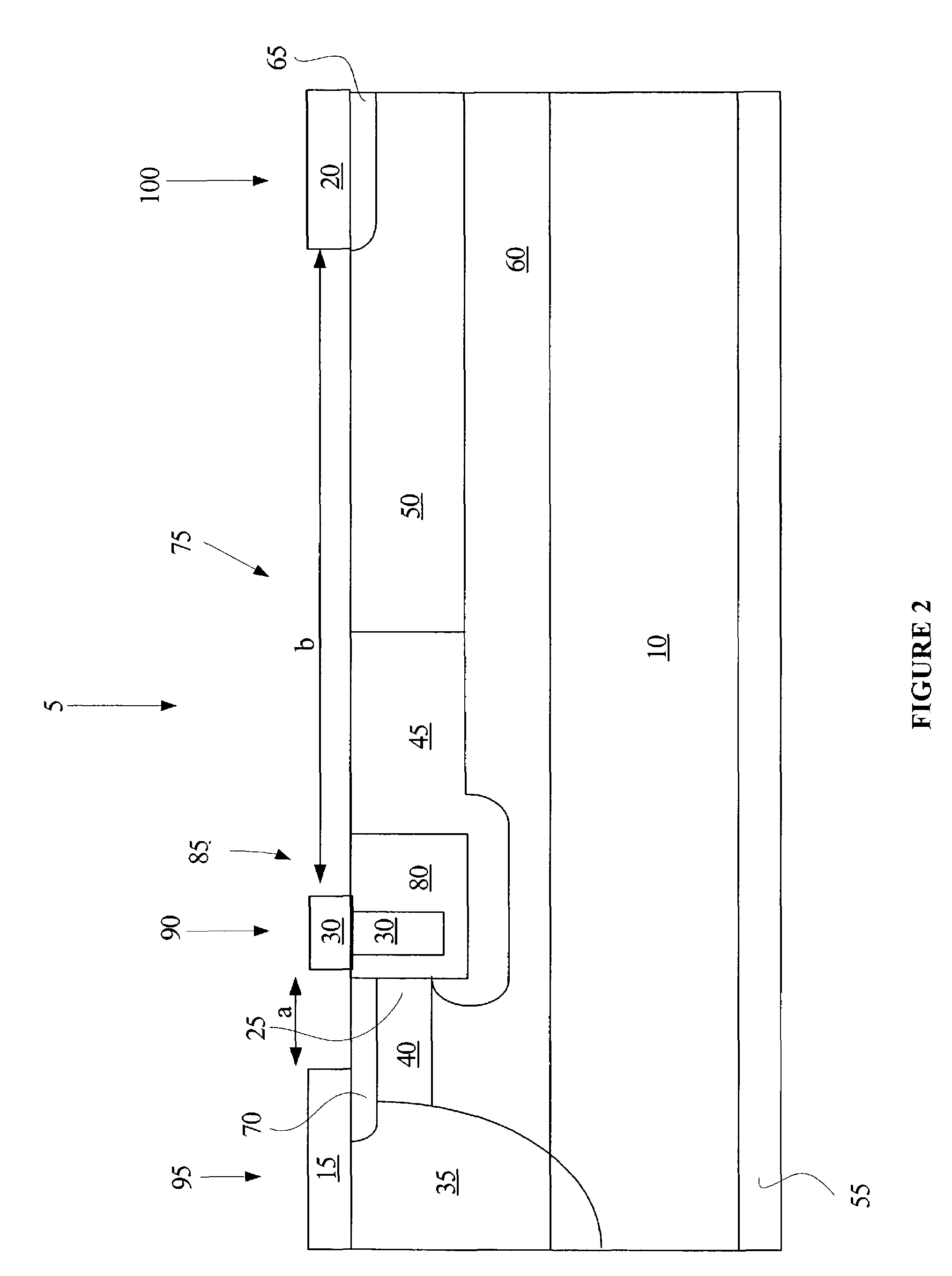

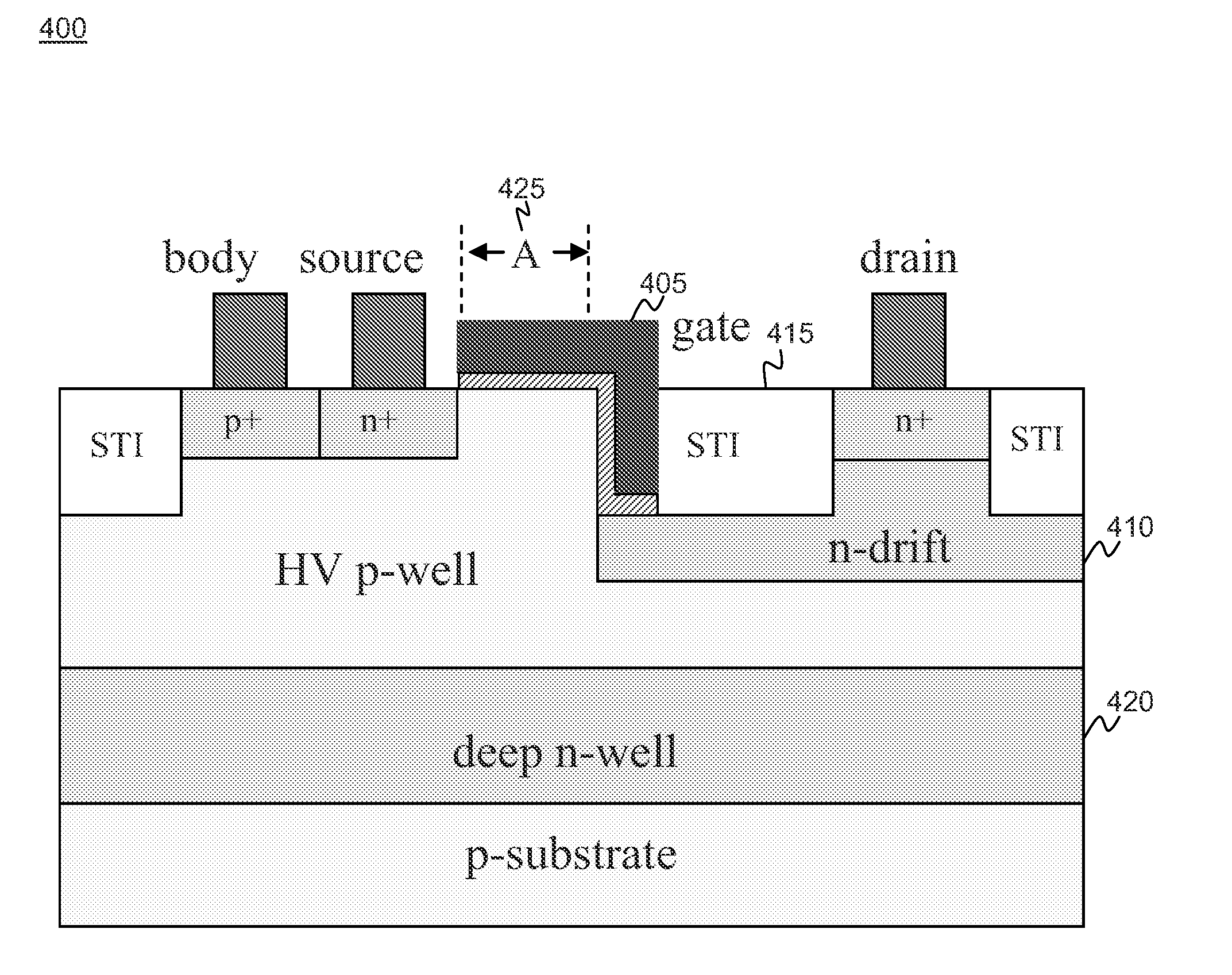

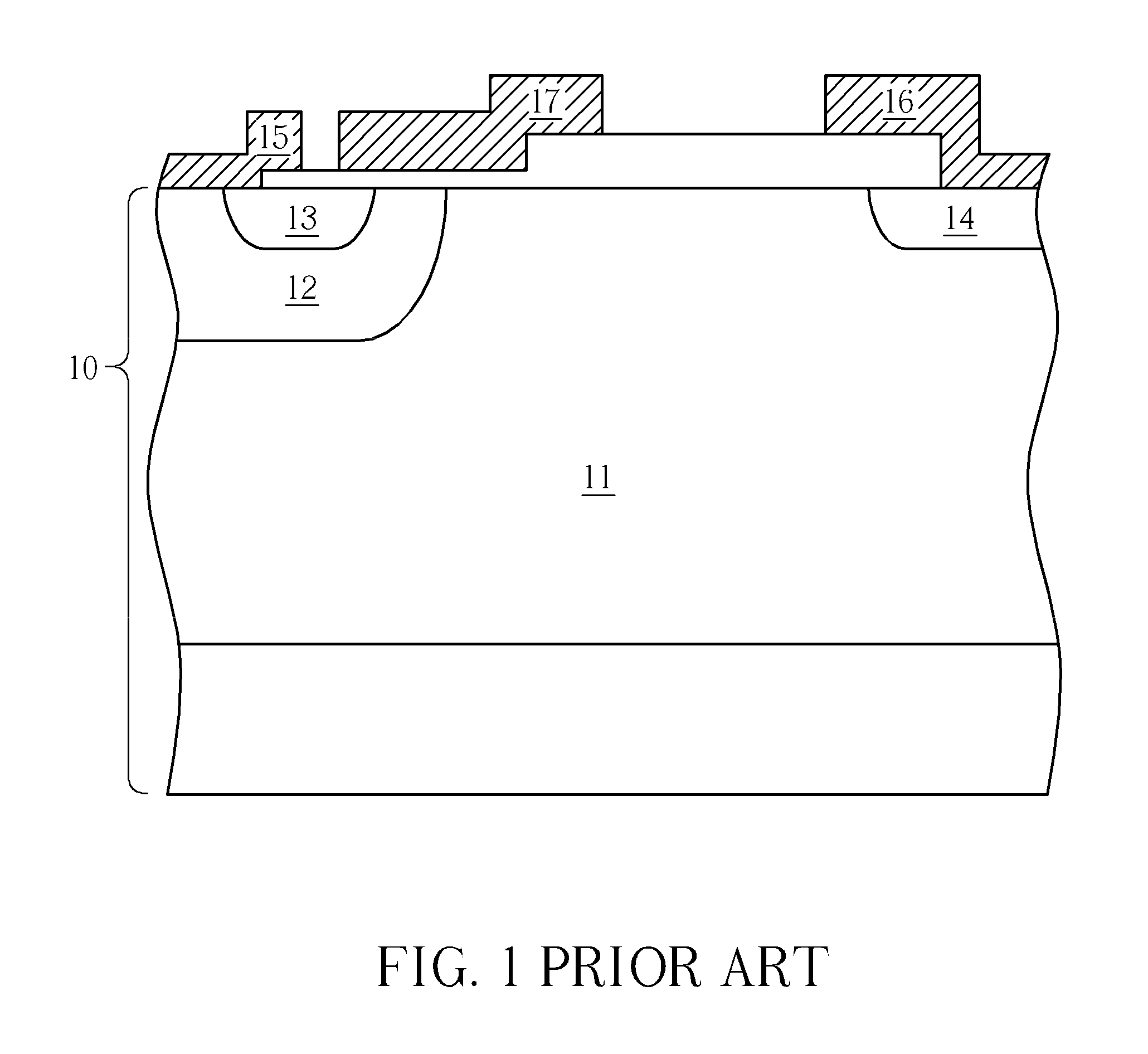

Trench gate laterally diffused MOSFET devices and methods for making such devices

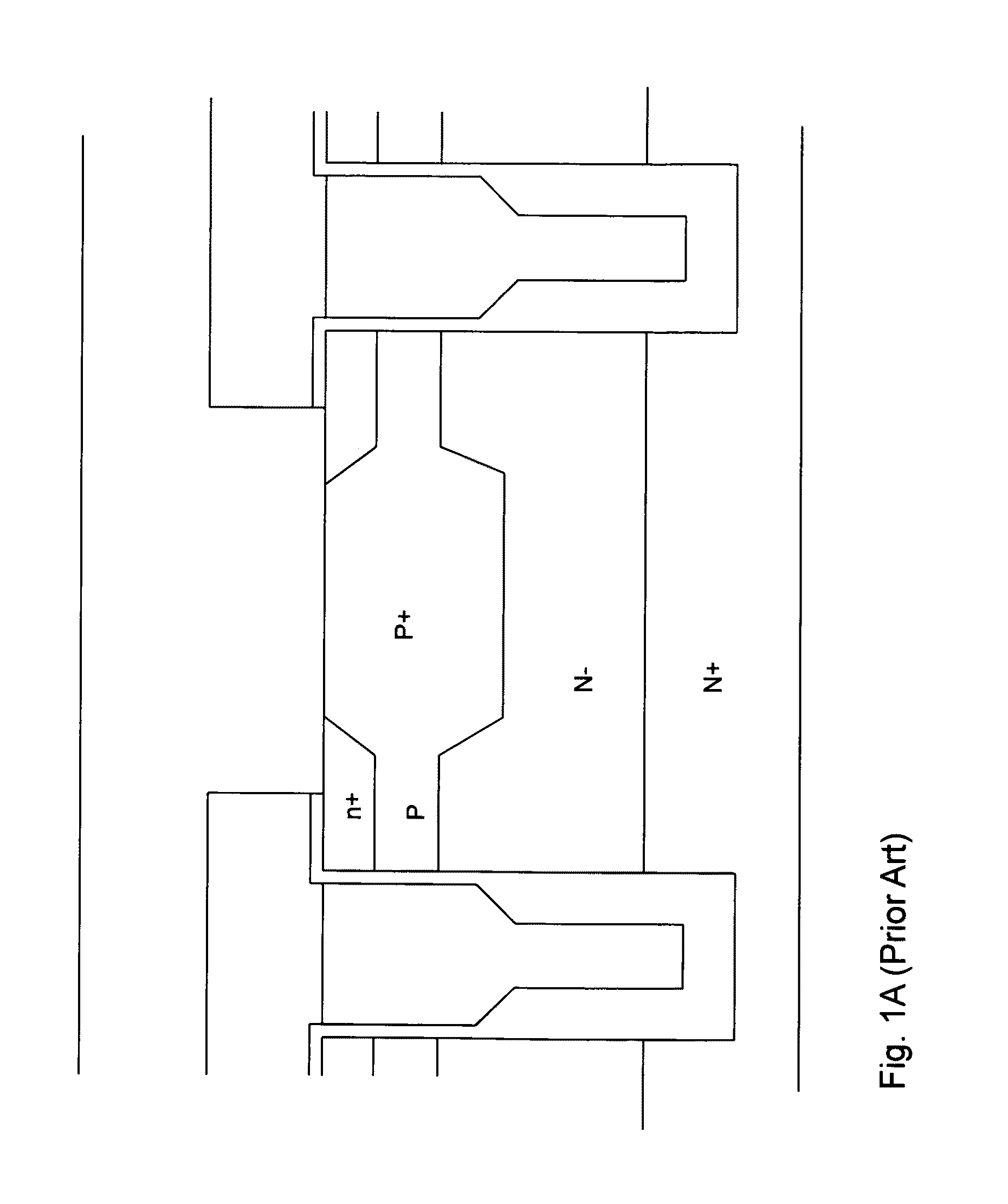

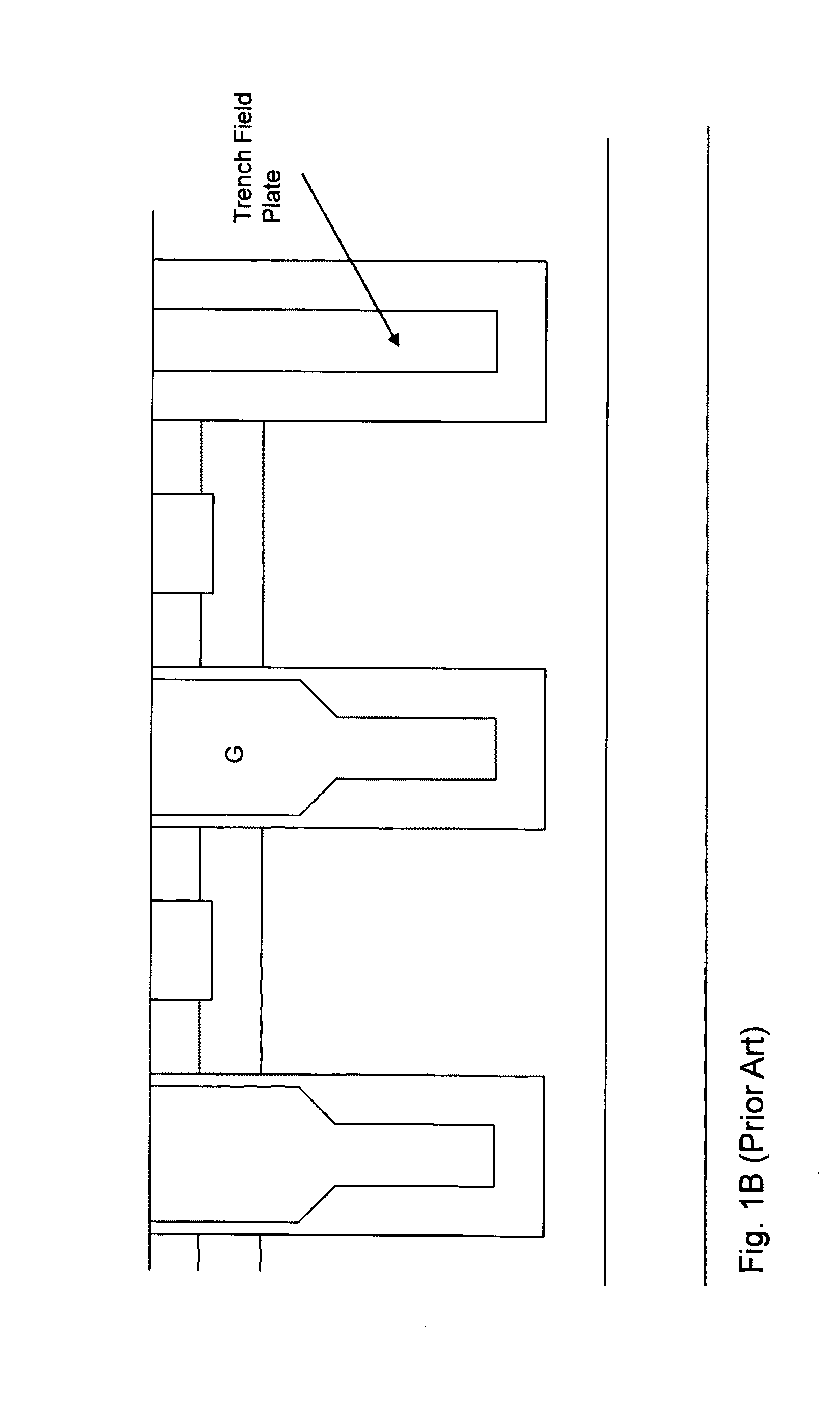

InactiveUS7033891B2Well breakdown capabilityLow gate-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesHot carrier effectElectric field

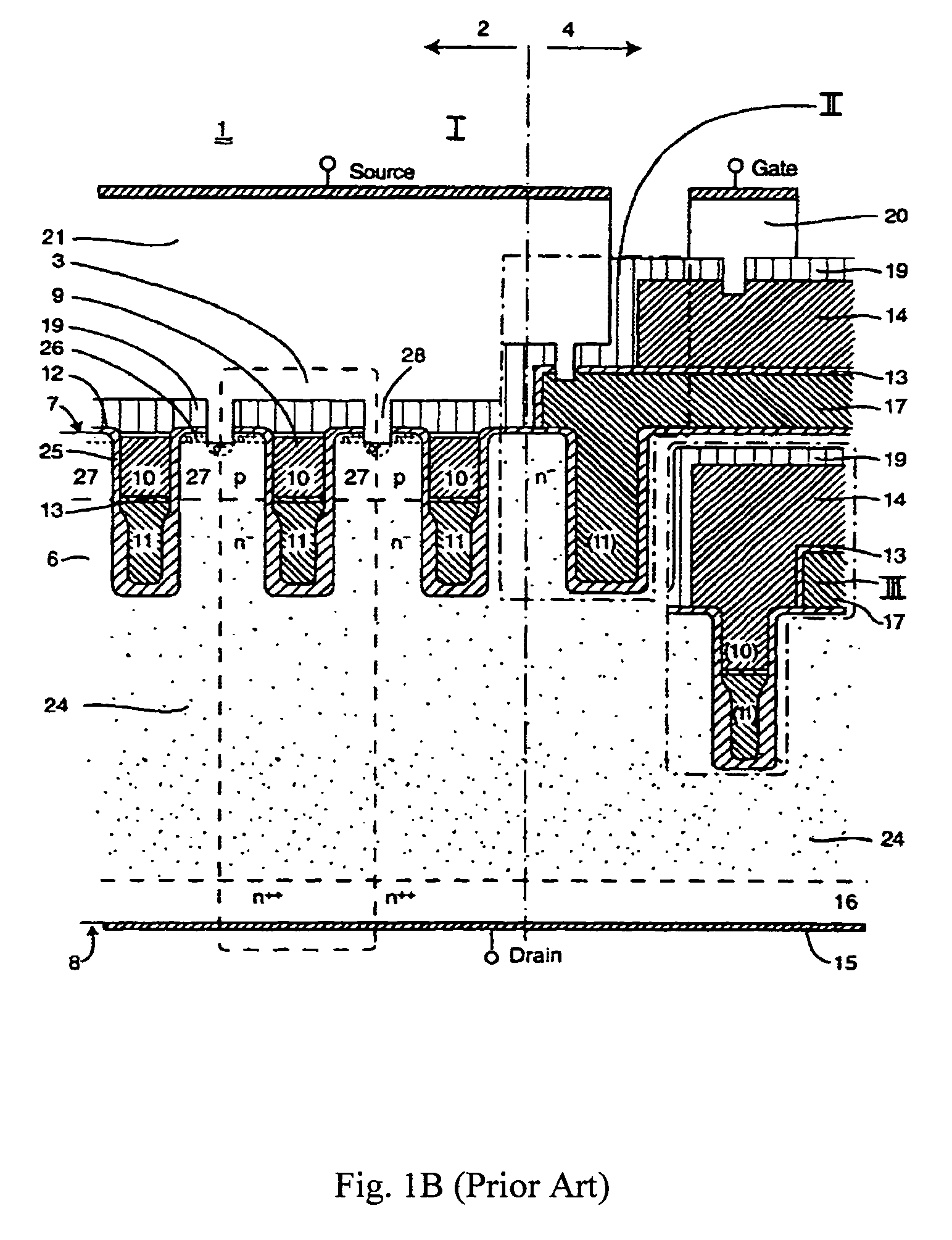

A MOSFET device for RF applications that uses a trench gate in place of the lateral gate used in lateral MOSFET devices is described. The trench gate in the devices of the invention is provided with a single, short channel for high frequency gain. The device of the invention is also provided with an asymmetric oxide in the trench gate, as well as LDD regions that lower the gate-drain capacitance for improved RF performance. Such features allow these devices to maintain the advantages of the LDMOS structure (better linearity), thereby increasing the RF power gain. The trench gate LDMOS of the invention also reduces the hot carrier effects when compared to regular LDMOS devices by reducing the peak electric field and impact ionization. Thus, the devices of the invention will have a better breakdown capability.

Owner:SEMICON COMPONENTS IND LLC

Shielded gate trench (SGT) MOSFET cells implemented with a schottky source contact

ActiveUS7453119B2Improve switching performanceImprove area efficiencyTime-division multiplexDiodeMOSFETInsulation layer

Owner:ALPHA & OMEGA SEMICON LTD

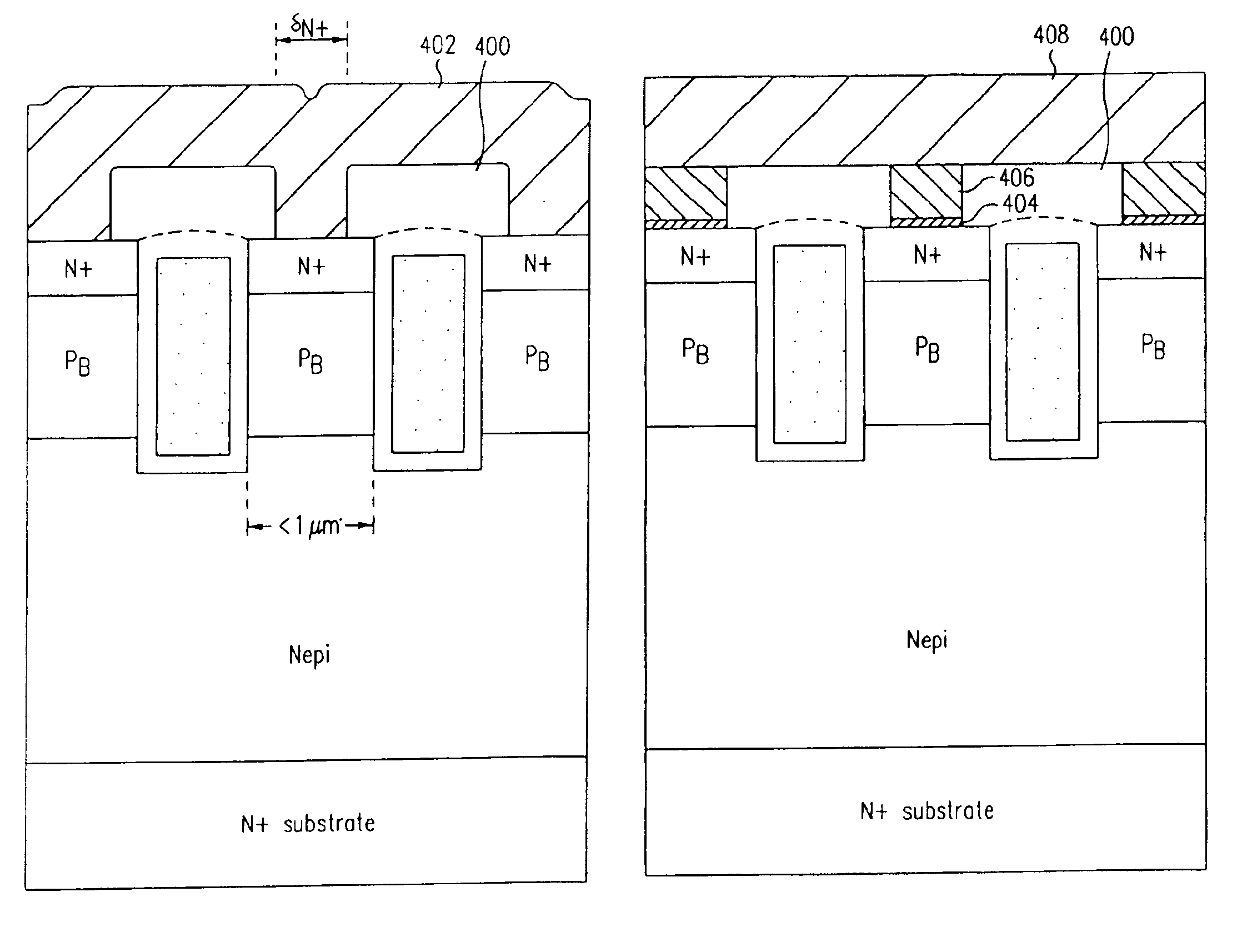

Self-aligned trench transistor using etched contact

InactiveUS6924198B2Avoid problemsAvoid shortingSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceMOSFET

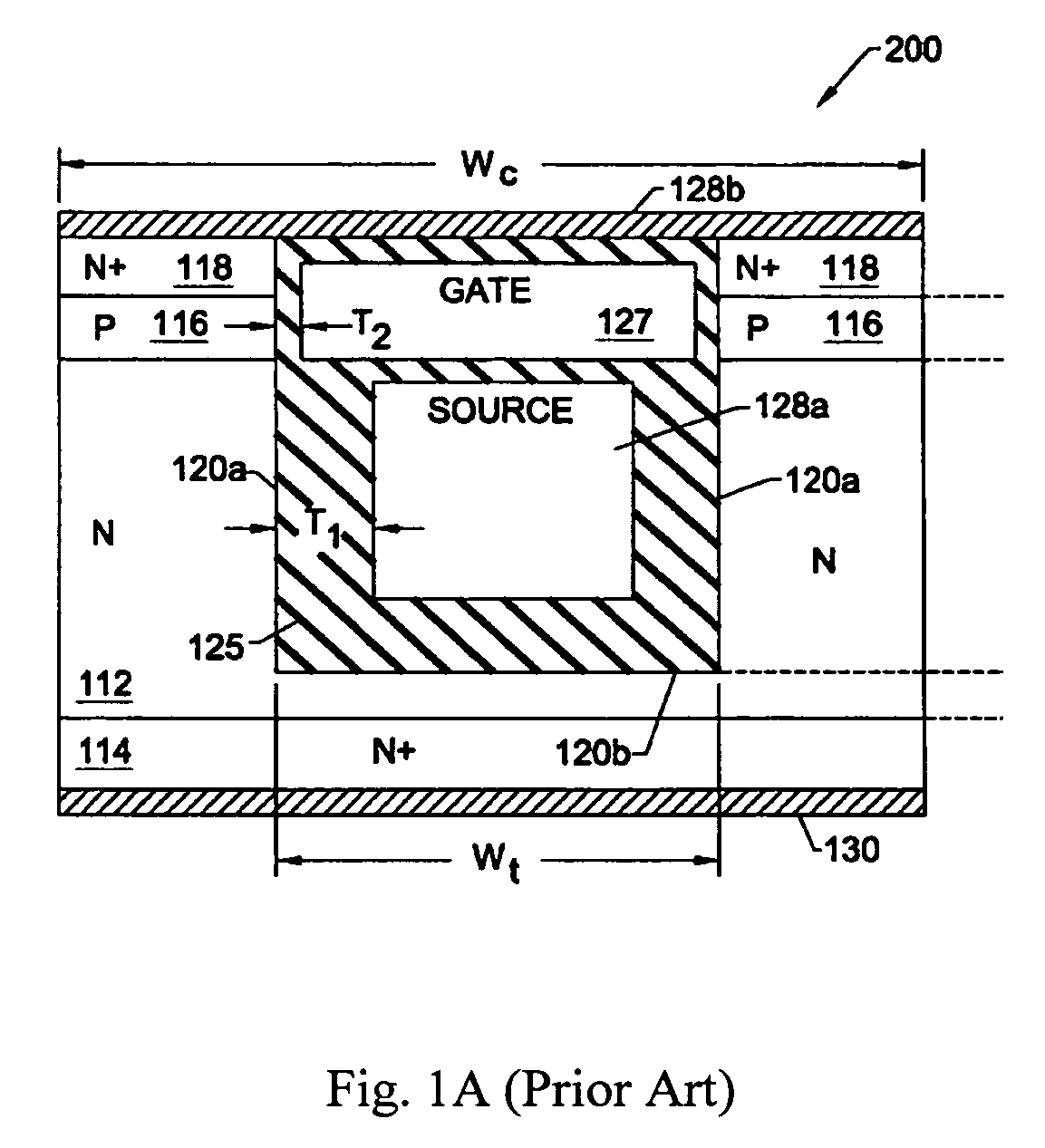

A trench-gated MOSFET formed using a super self aligned (SSA) process employs an insulating layer such as a glass layer and a contact mask to define contact openings for electrical connections to source regions of the MOSFET. Use a contact mask and an intervening glass in otherwise self-aligned process reduces the coupling capacitance between source metal and the top of the embedded trench gate. A metal layer deposited to make electrical contact to source regions can be planarized, for example, ground flat using chemical-mechanical polishing to provide a flat surface to avoid formation of conductive traces that extend over the steps that the glass layer forms.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

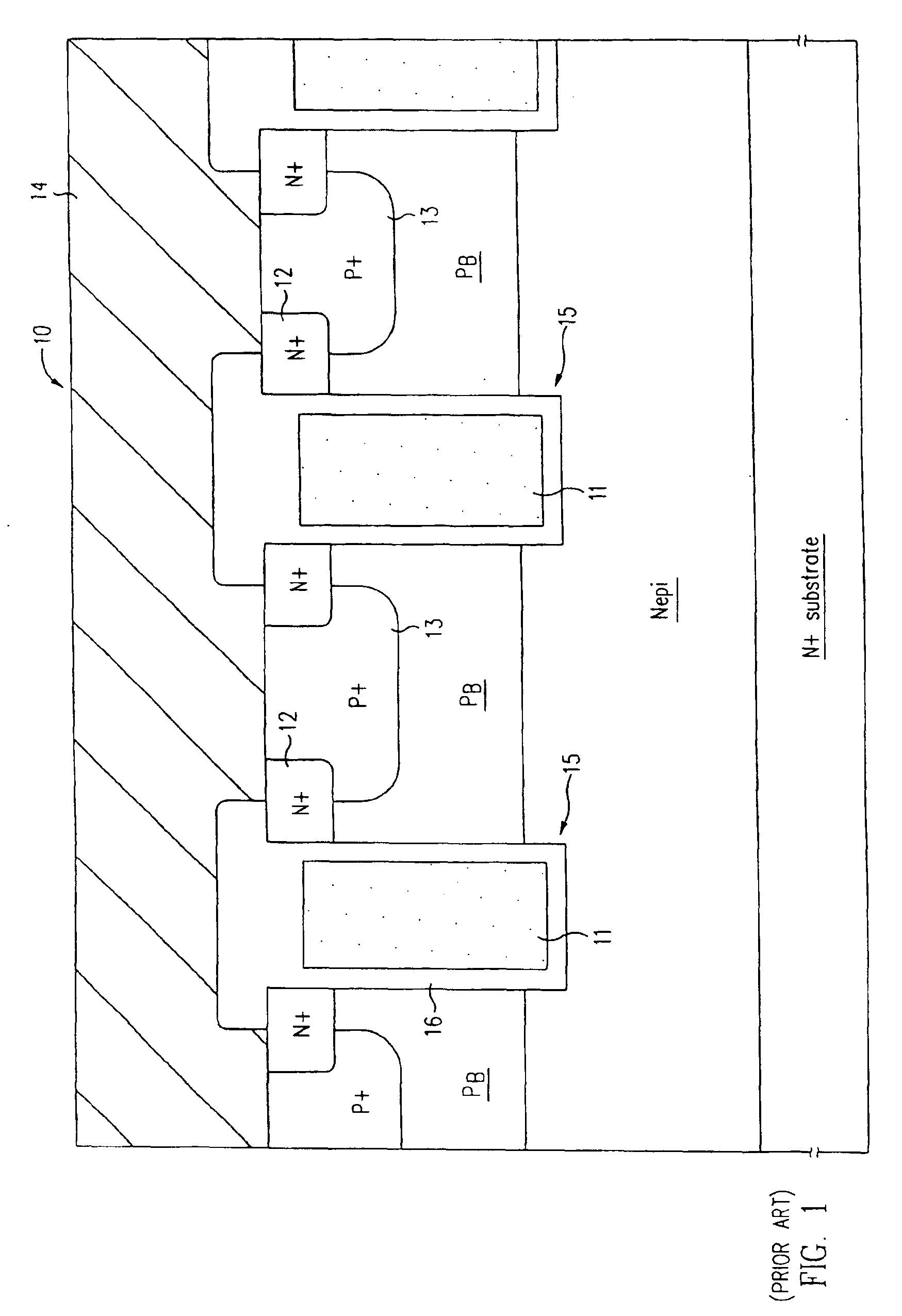

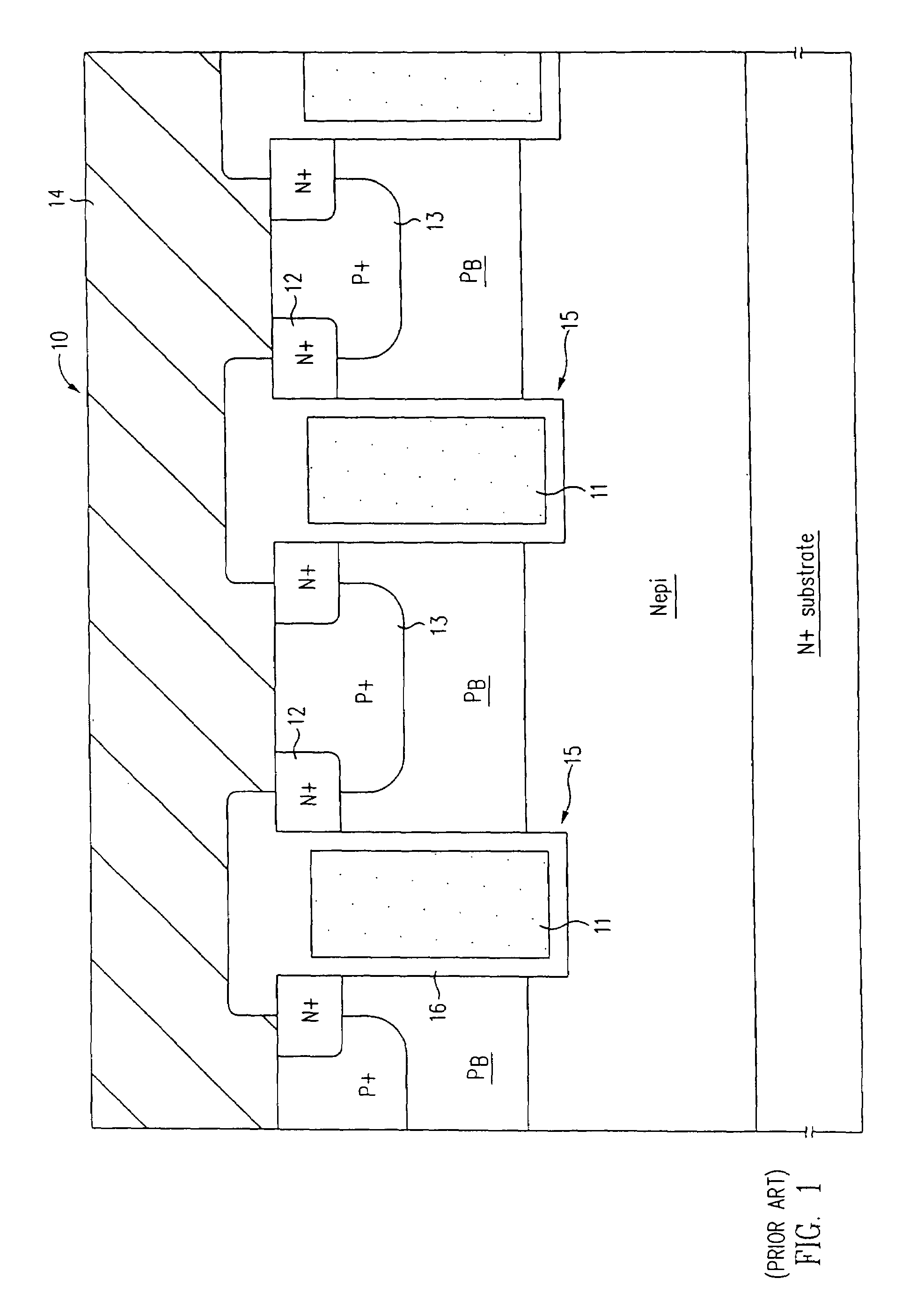

Method of forming trench transistor with chained implanted body including a plurality of implantation with different energies

InactiveUS7052963B2Width of the mesa between segments of the trench can be made smallerIncrease cell densitySolid-state devicesSemiconductor/solid-state device manufacturingMedicineDevice form

A “chained implant” technique forms a body region in a trench gated transistor. In one embodiment, a succession of “chained” implants can be performed at the same dose but different energies. In other embodiments different doses and energies can be used, and particularly, more than one dose can be used in a single device. This process produces a uniform body doping concentration and a steeper concentration gradient (at the body-drain junction), with a higher total body charge for a given threshold voltage, thereby reducing the vulnerability of the device to punchthrough breakdown. Additionally, the source-body junction does not, to a first order, affect the threshold voltage of the device, as it does in DMOS devices formed with conventional diffused body processes.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

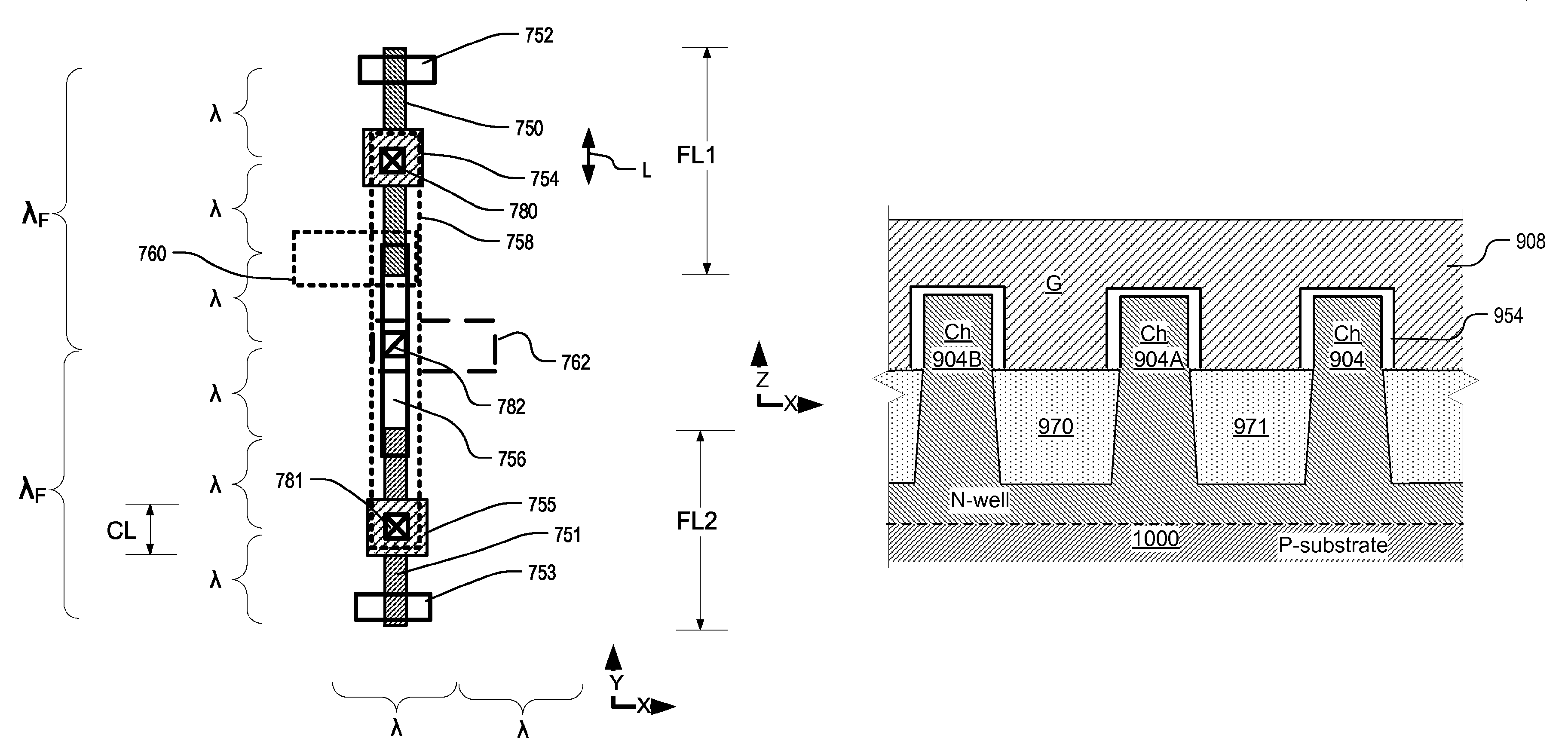

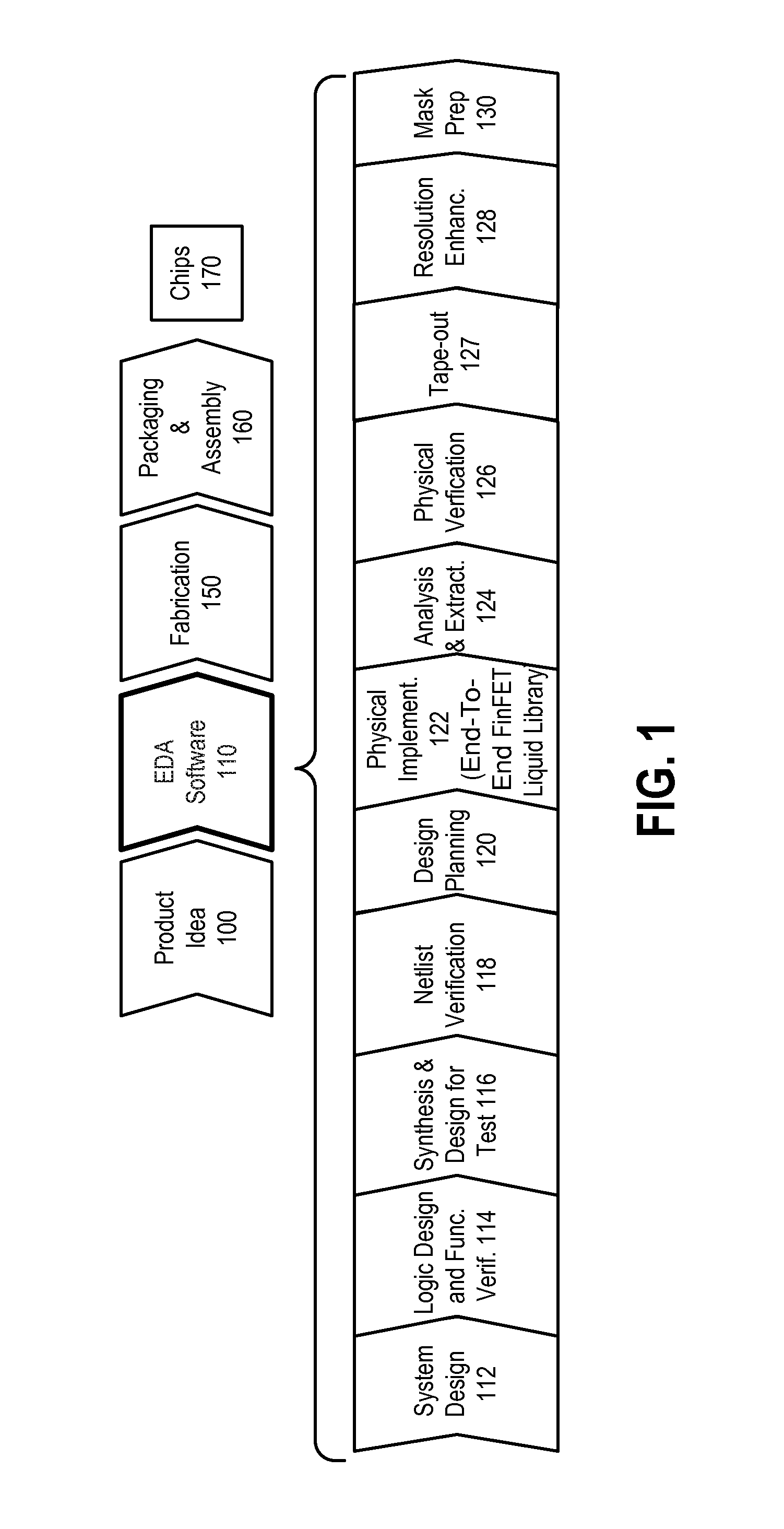

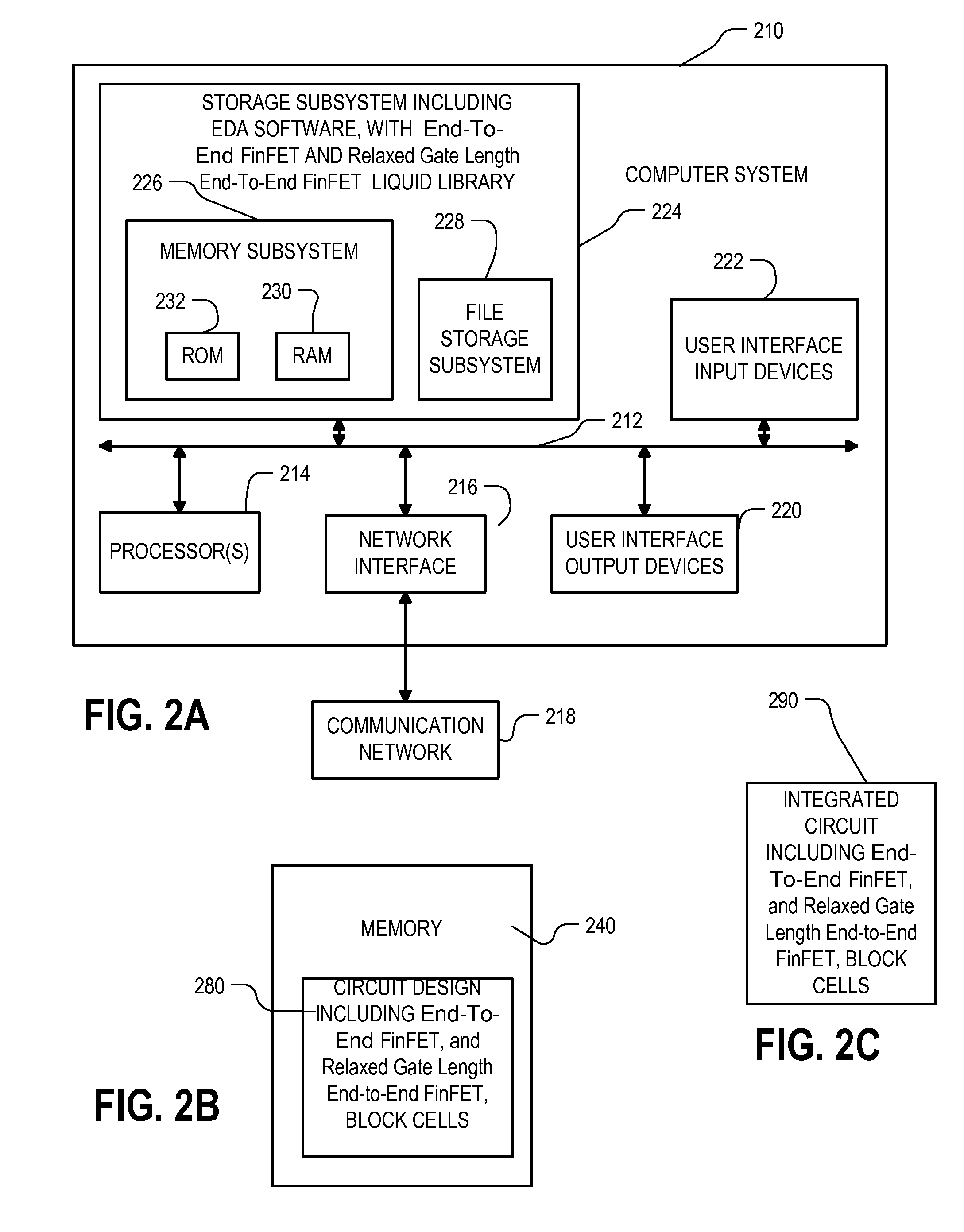

N-channel and P-channel end-to-end finFET cell architecture with relaxed gate pitch

ActiveUS8723268B2Increase channel lengthSuppress leakageSemiconductor/solid-state device detailsSolid-state devicesEngineering physicsSemiconductor

A finFET block architecture uses end-to-end finFET blocks in which the fin lengths are at least twice the contact pitch, whereby there is enough space for interlayer connectors to be placed on the proximal end and the distal end of a given semiconductor fin, and on the gate element on the given semiconductor fin. A first set of semiconductor fins having a first conductivity type and a second set of semiconductor fins having a second conductivity type can be aligned end-to-end. Interlayer connectors can be aligned over corresponding semiconductor fins which connect to gate elements.

Owner:SYNOPSYS INC

High speed orthogonal gate EDMOS device and fabrication

InactiveUS8357986B2Minimizes the gate to drain overlapLow technical requirementsSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

An orthogonal gate extended drain MOSFET (EDMOS) structure provides a low gate-to-drain capacitance (CGD) and exhibits increased reliability. It has a gate electrode that is folded into the shallow trench isolation (STI) oxide region. Horizontal and vertical gate electrode segments provide gate control. It accommodates both high voltage devices and standard CMOS components on the same substrate. Reduced surface field (RESURF) technology is employed to optimize tradeoffs between high breakdown voltage and specific on-resistance. Device fabrication steps are compatible with standard CMOS flow and process modules can be added or removed from baseline CMOS technology.

Owner:ASAHI KASEI ELECTRONICS CO LTD

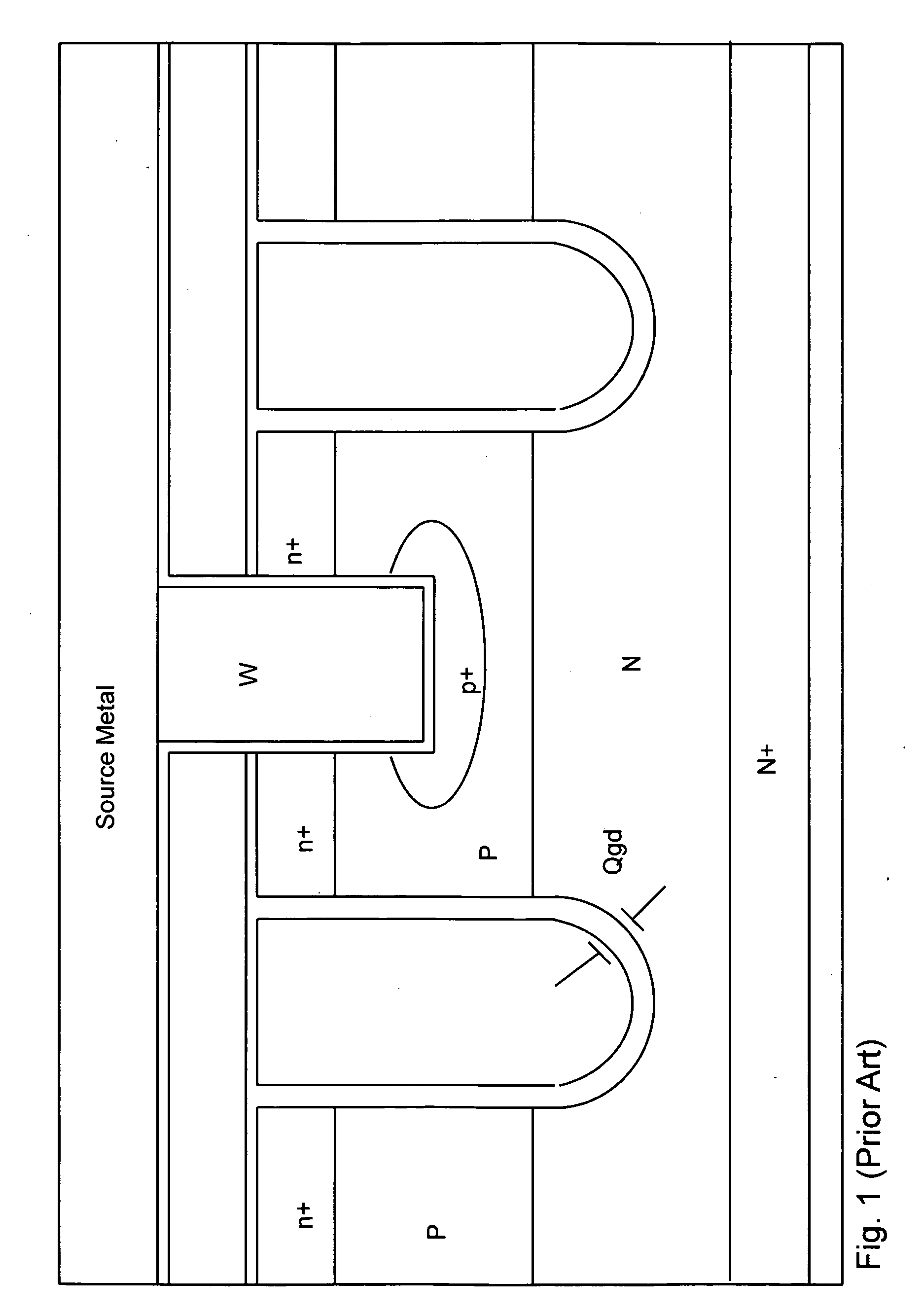

Trench metal oxide semiconductor field effect transistor (MOSFET) with low gate to drain coupled charges (Qgd) structures

ActiveUS20100163975A1Coupling chargeReduce chargeSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDopant

A trenched semiconductor power device includes a plurality of trenched gates surrounded by source regions near a top surface of a semiconductor substrate encompassed in body regions. The trenched semiconductor power device further comprises tilt-angle implanted body dopant regions surrounding a lower portion of trench sidewalls for reducing a gate-to-drain coupling charges Qgd between the trenched gates and a drain disposed at a bottom of the semiconductor substrate. The trenched semiconductor power device further includes a source dopant region disposed below a bottom surface of the trenched gates for functioning as a current path between the drain to the source for preventing a resistance increase caused by the body dopant regions surrounding the lower portions of the trench sidewalls.

Owner:FORCE MOS TECH CO LTD

Shielded gate trench (SGT) MOSFET devices and manufacturing processes

This invention discloses a semiconductor power device that includes a plurality of power transistor cells surrounded by a trench opened in a semiconductor substrate. At least one of the cells constituting an active cell has a source region disposed next to a trenched gate electrically connecting to a gate pad and surrounding the cell. The trenched gate further has a bottom-shielding electrode filled with a gate material disposed below and insulated from the trenched gate. At least one of the cells constituting a source-contacting cell surrounded by the trench with a portion functioning as a source connecting trench is filled with the gate material for electrically connecting between the bottom-shielding electrode and a source metal disposed directly on top of the source connecting trench. The semiconductor power device further includes an insulation protective layer disposed on top of the semiconductor power device having a plurality of source openings on top of the source region and the source connecting trench provided for electrically connecting to the source metal and at least a gate opening provided for electrically connecting the gate pad to the trenched gate.

Owner:ALPHA & OMEGA SEMICON LTD

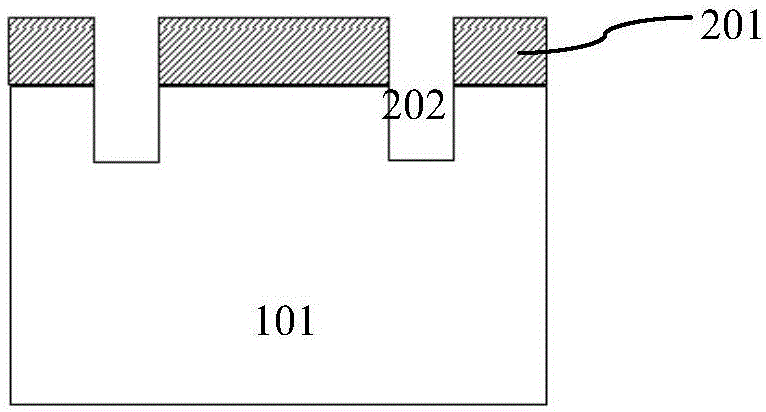

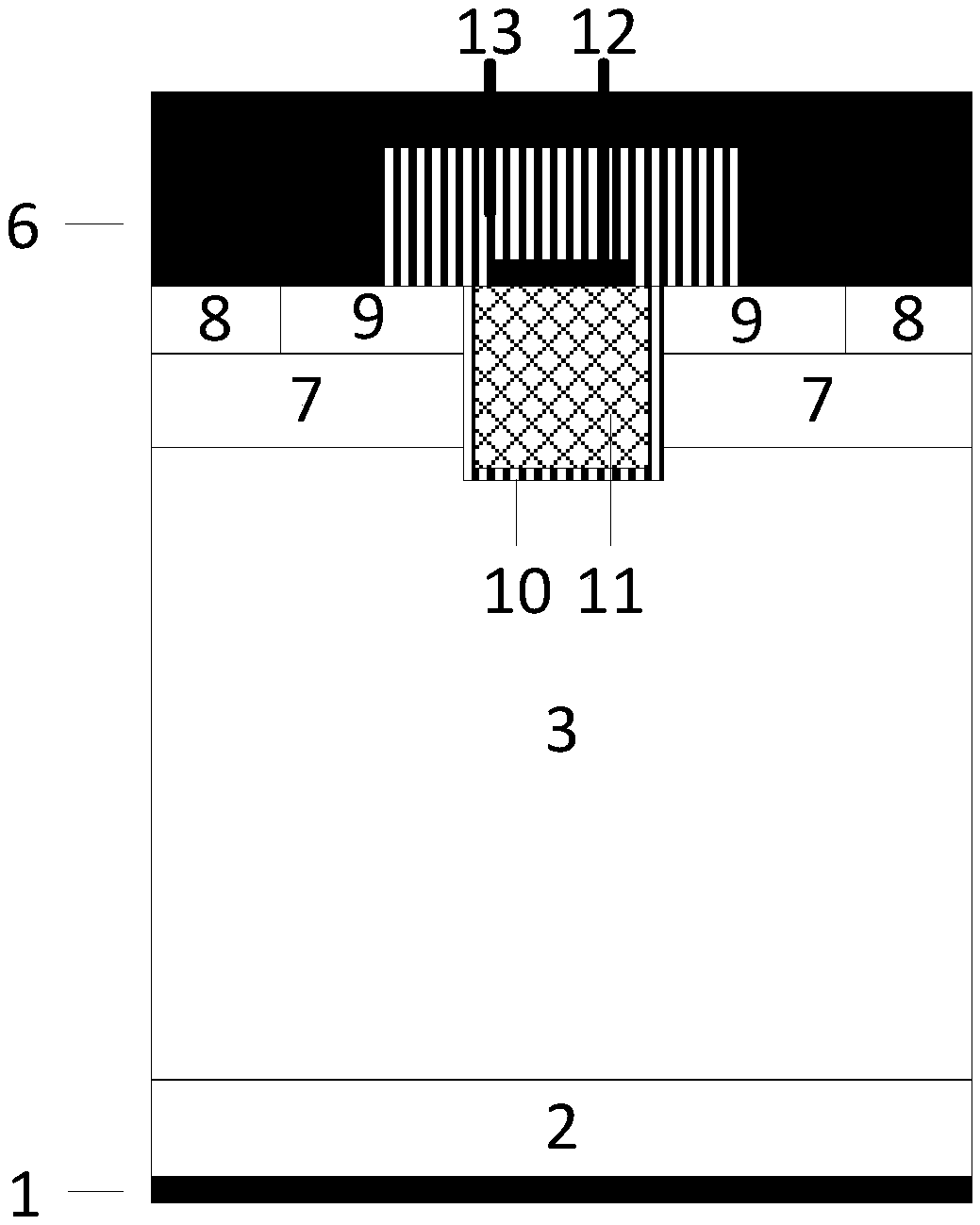

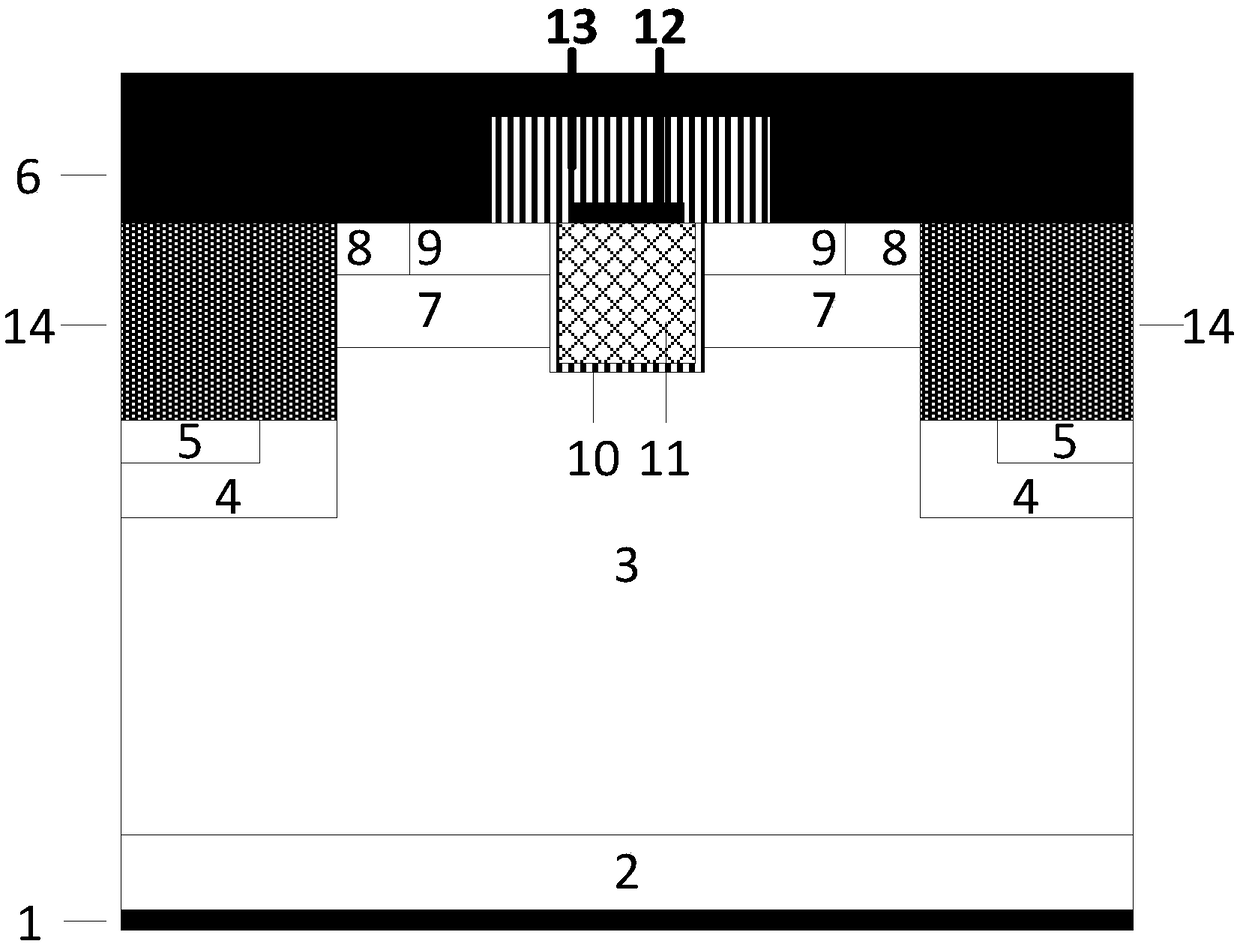

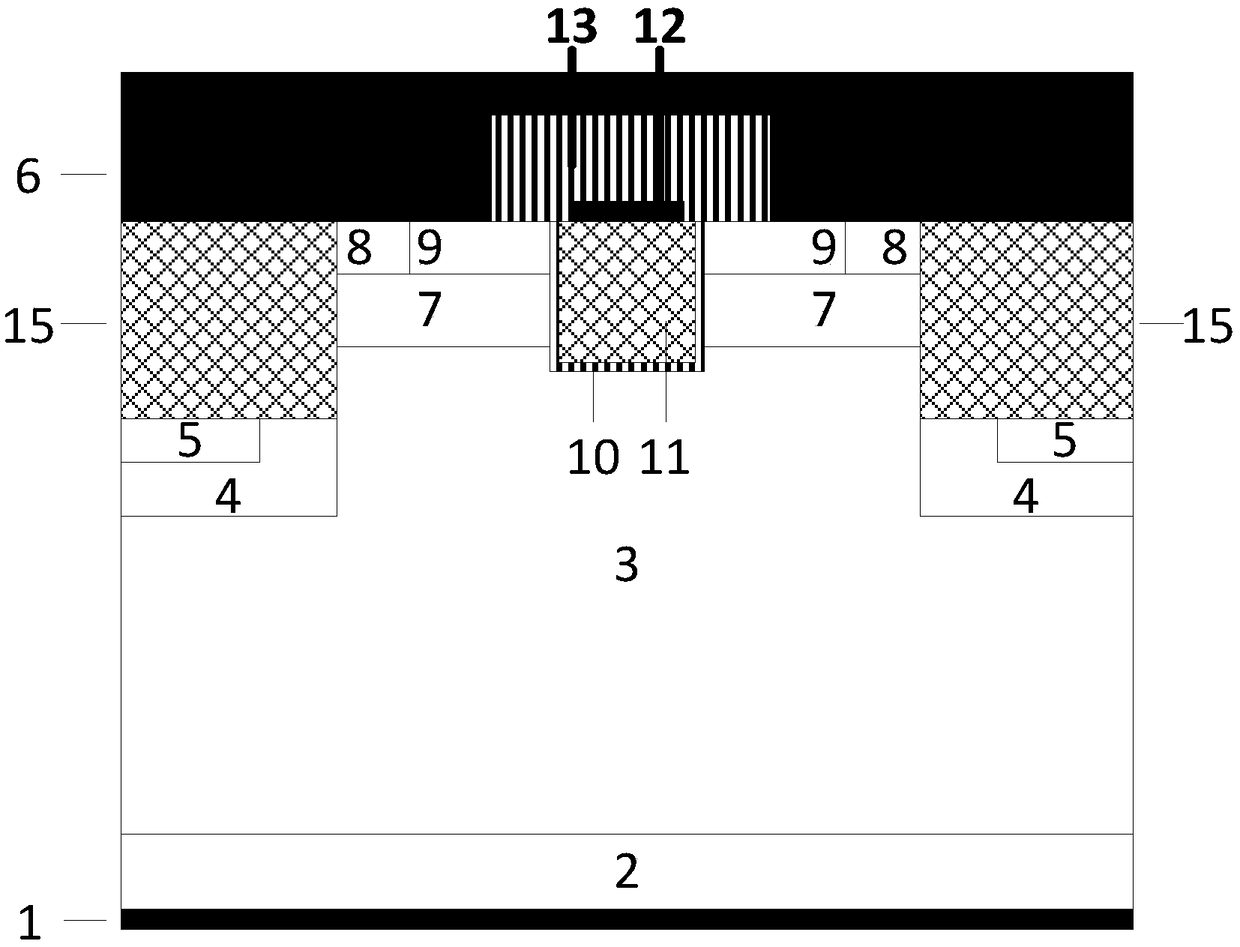

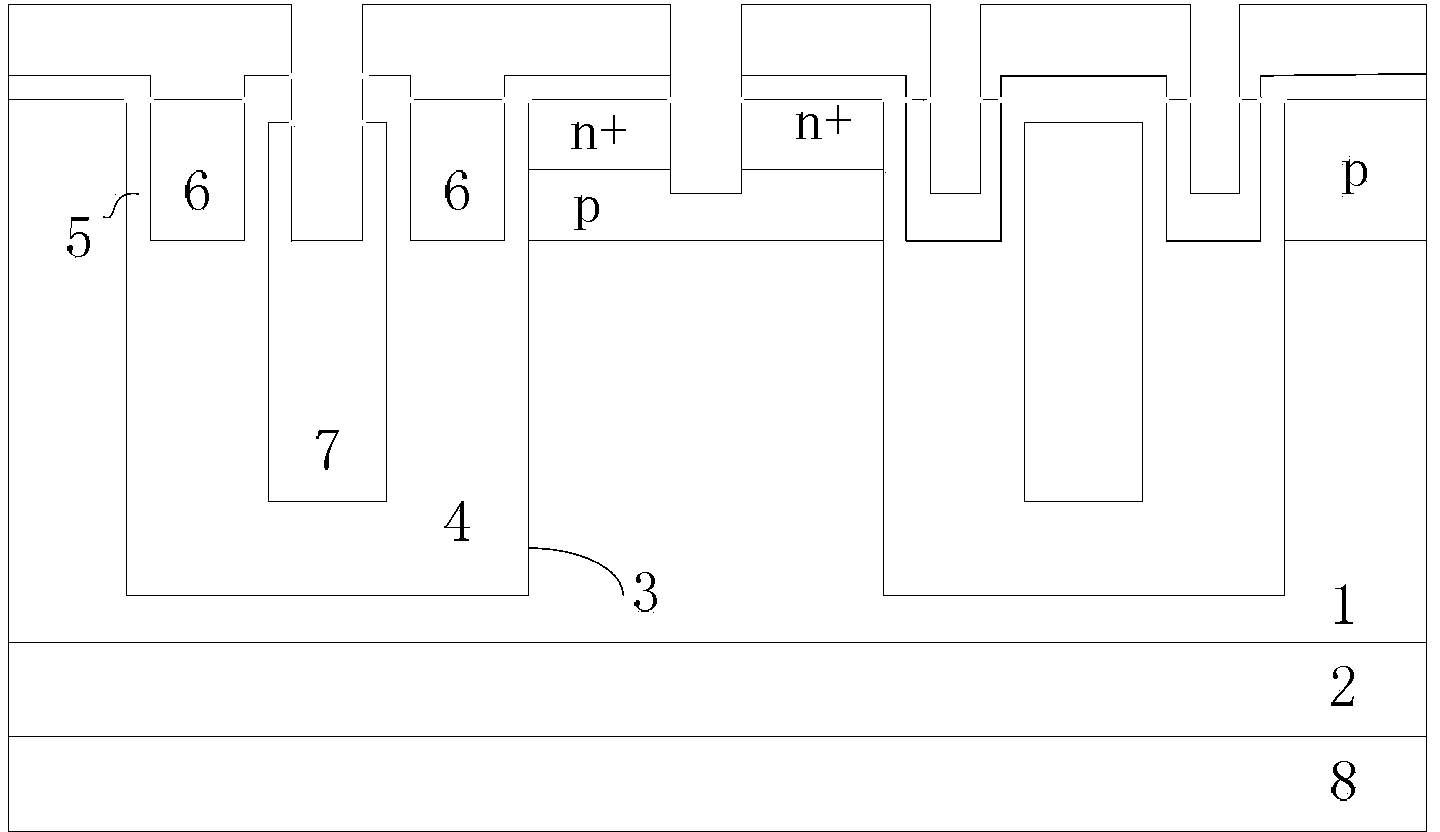

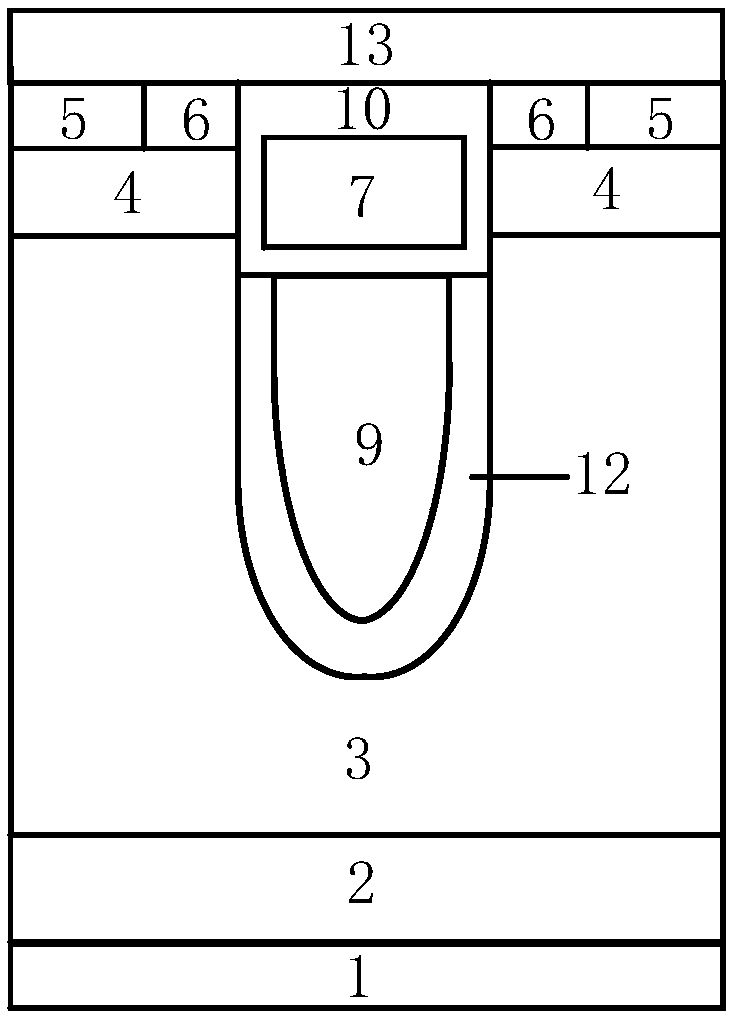

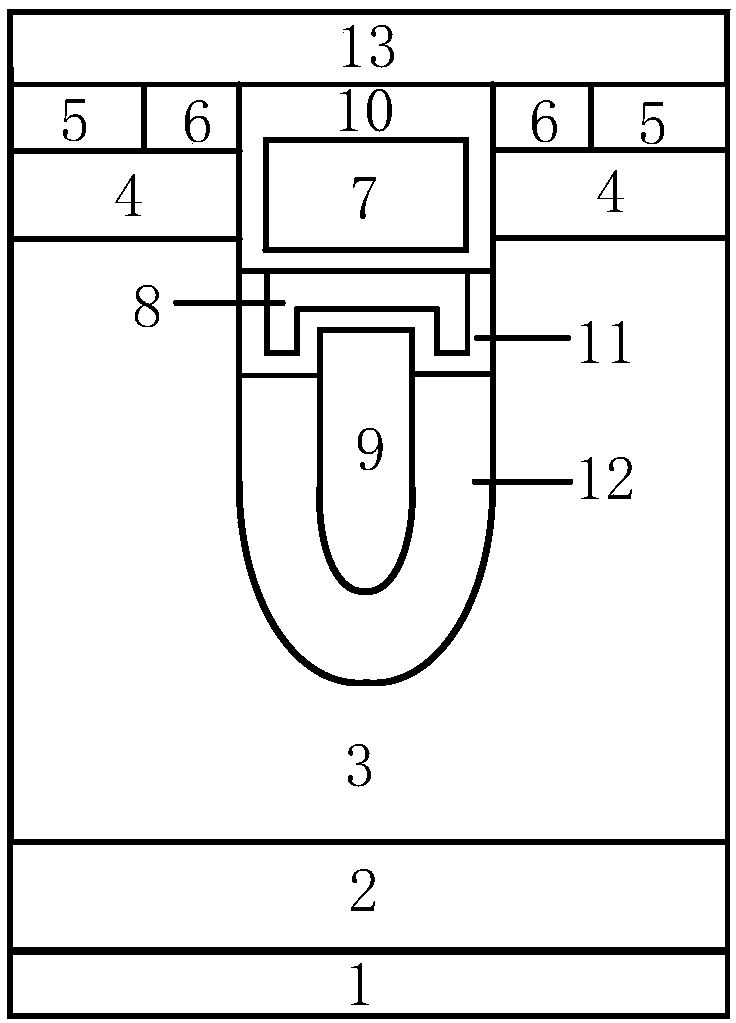

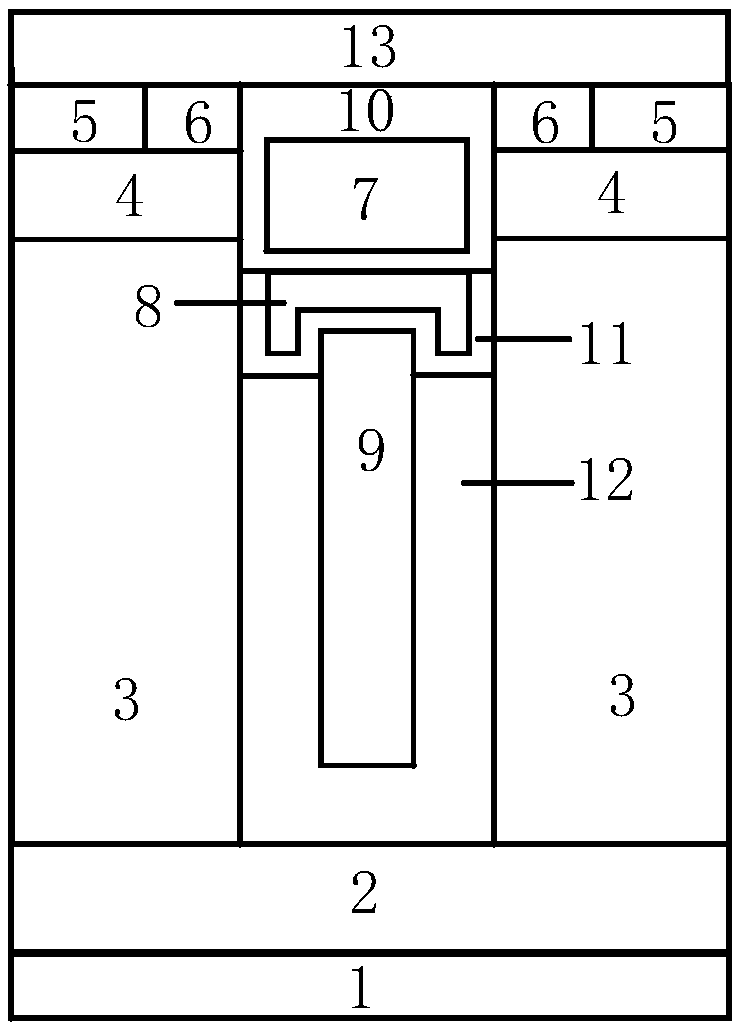

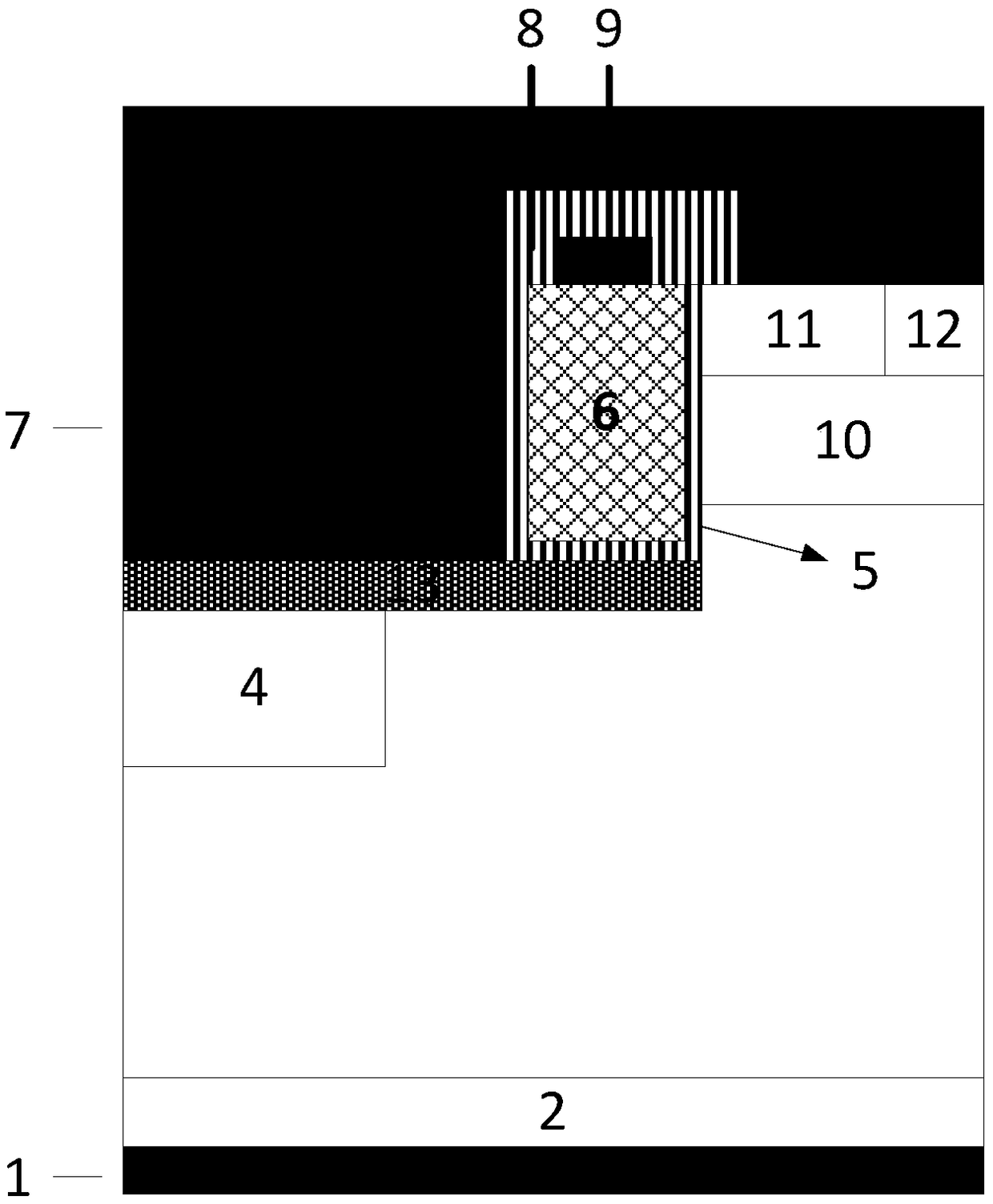

Shield gate trench MOSFET and manufacture method

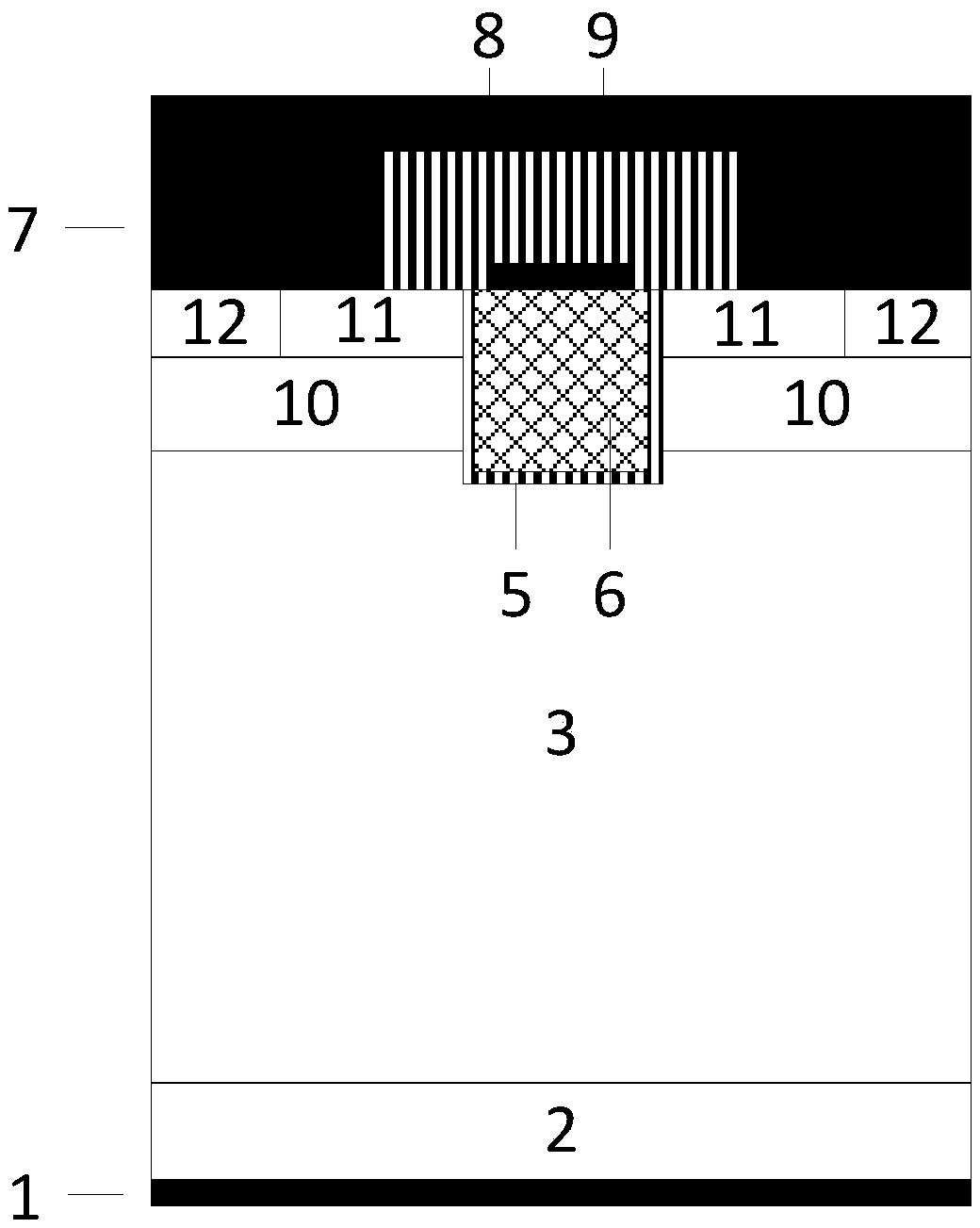

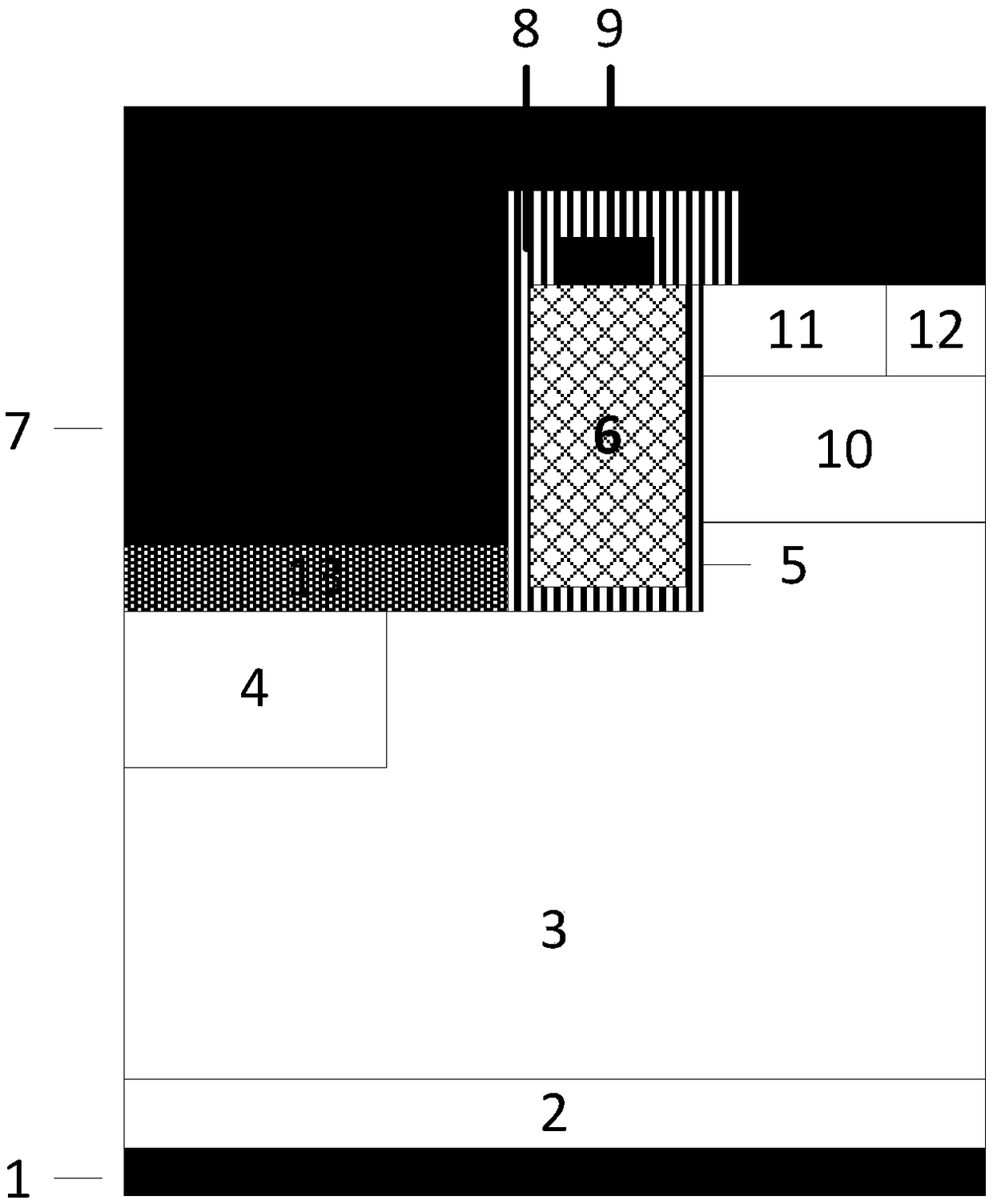

ActiveCN107527948AReduce gate-to-drain capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceTrench mosfet

The invention discloses a shield gate trench MOSFET. The gate trench includes a top trench and a bottom trench. A polysilicon gate is formed on both sides of the top trench. Source polysilicon is located in the middle of the gate trench and extends longitudinally through the entire gate trench. Channel regions are formed on semiconductor substrate surfaces between gate structures and source regions are formed on the surfaces of the channel regions. A polysilicon gate on one side of the top trench is connected to a gate formed by a front metal layer. A polysilicon gate on the other side of the top trench and the source regions are connected to a source through a second contact hole to form a structure for reducing the gate-drain capacitance of a device. The second contact hole reduces the distance between the gate trenches and reduces the on-resistance of the device and form an on-resistance compensation structure. The invention also discloses a method for manufacturing the shield gate trench MOSFET. The shield gate trench MOSFET can reduce the gate-drain capacitance, can increase the switching speed of the device, and can reduce the size of a unit device and improve an integration level.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

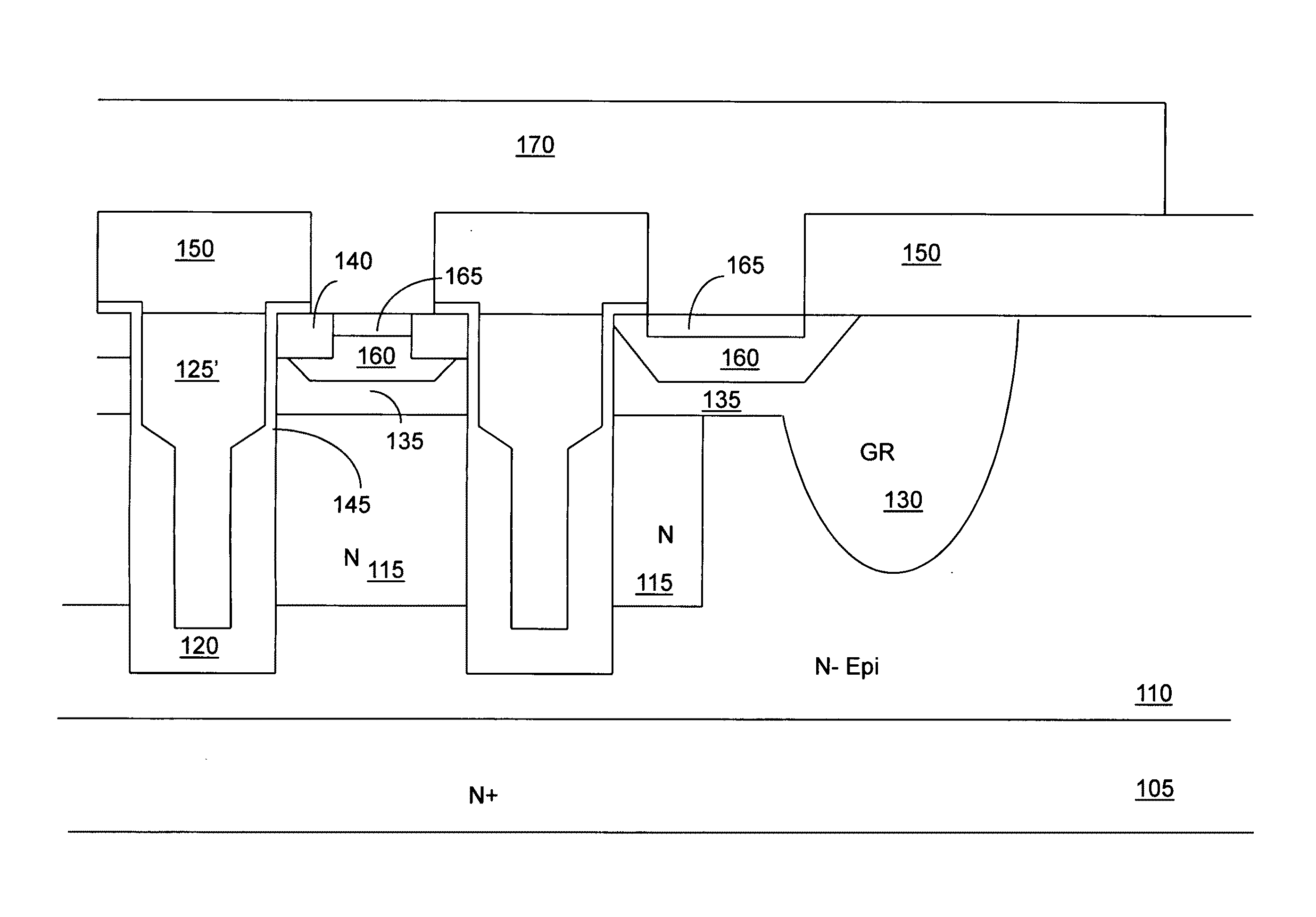

Power mosfet device structure for high frequency applications

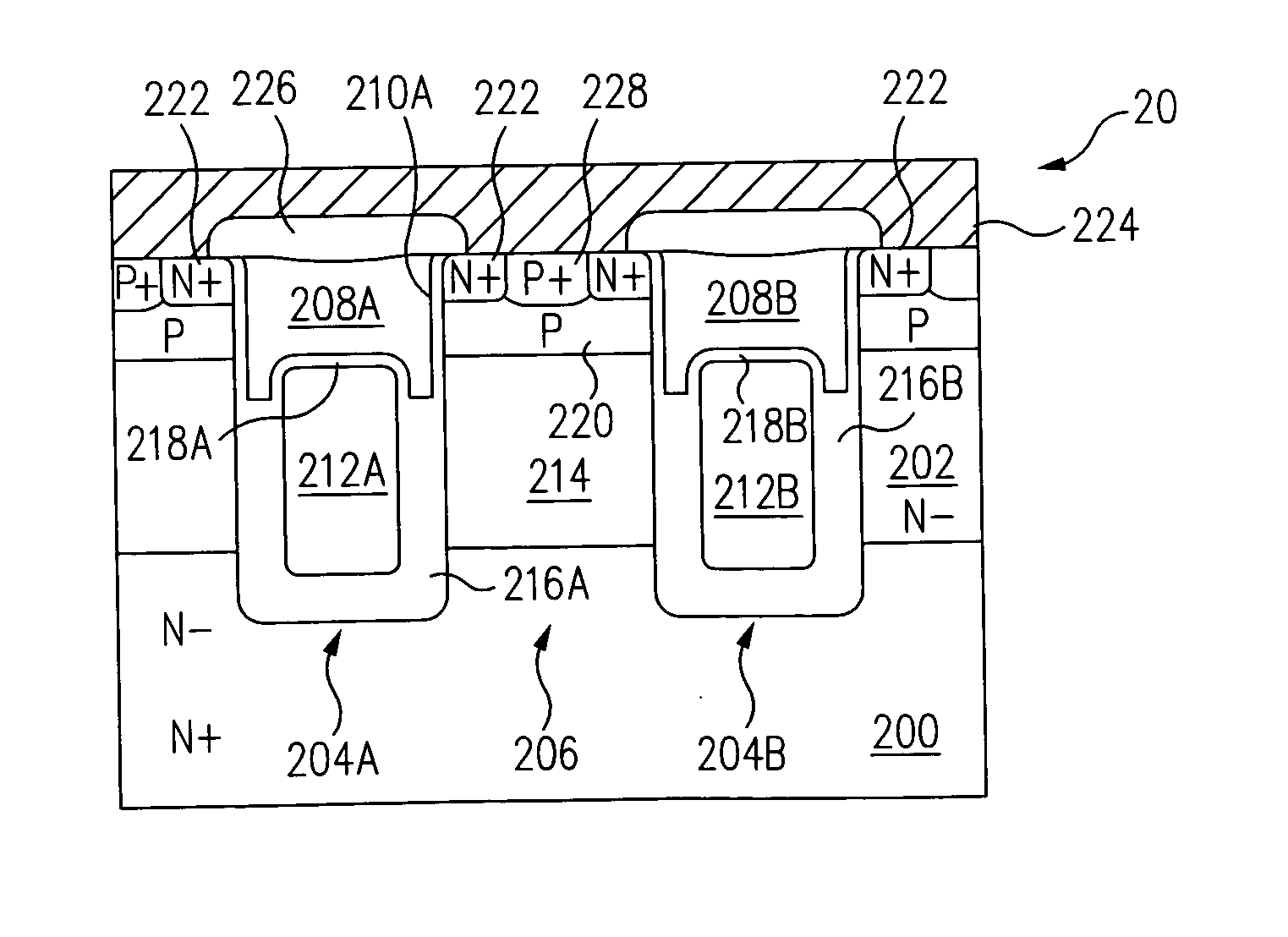

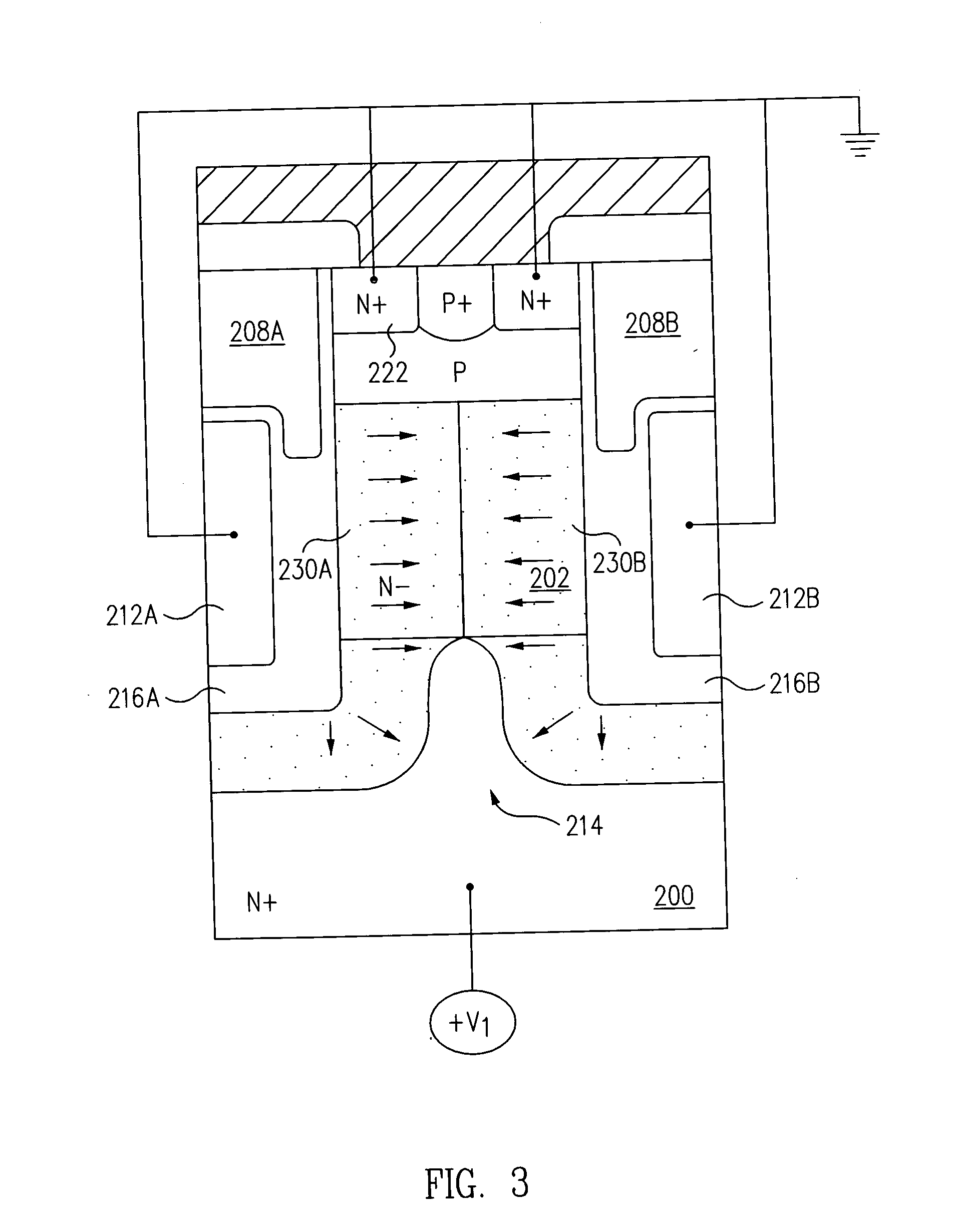

InactiveUS20100148246A1Reduce gate-to-drain capacitanceReduce areaSemiconductor/solid-state device manufacturingSemiconductor devicesDopantInsulation layer

This invention discloses a new switching device supported on a semiconductor that includes a drain disposed on a first surface and a source region disposed near a second surface of said semiconductor opposite the first surface. The switching device further includes an insulated gate electrode disposed on top of the second surface for controlling a source to drain current. The switching device further includes a source electrode interposed into the insulated gate electrode for substantially preventing a coupling of an electrical field between the gate electrode and an epitaxial region underneath the insulated gate electrode. The source electrode further covers and extends over the insulated gate for covering an area on the second surface of the semiconductor to contact the source region. The semiconductor substrate further includes an epitaxial layer disposed above and having a different dopant concentration than the drain region. The insulated gate electrode further includes an insulation layer for insulating the gate electrode from the source electrode wherein the insulation layer having a thickness depending on a Vgsmax rating of the vertical power device.

Owner:ALPHA & OMEGA SEMICONDUCTOR INC

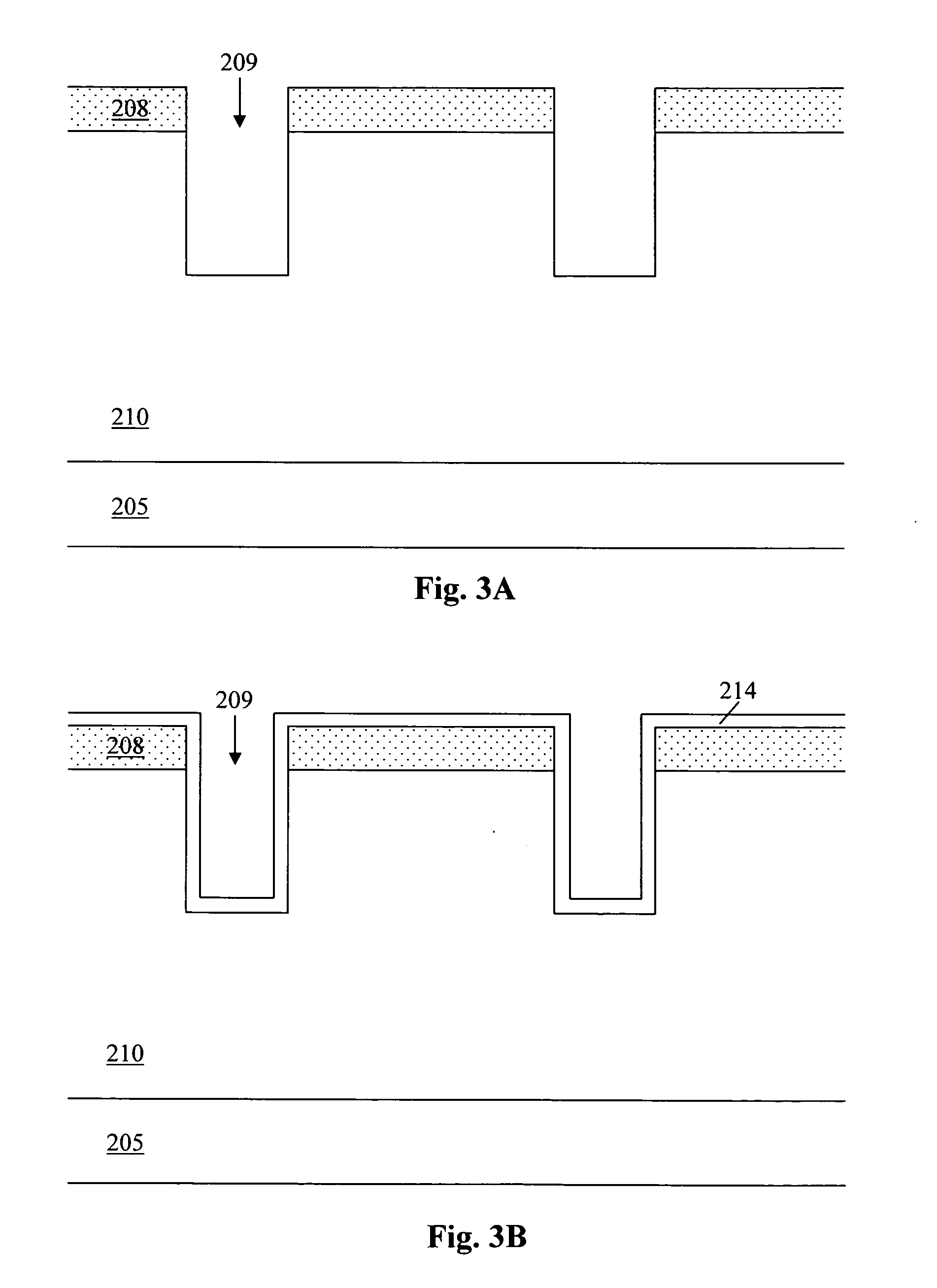

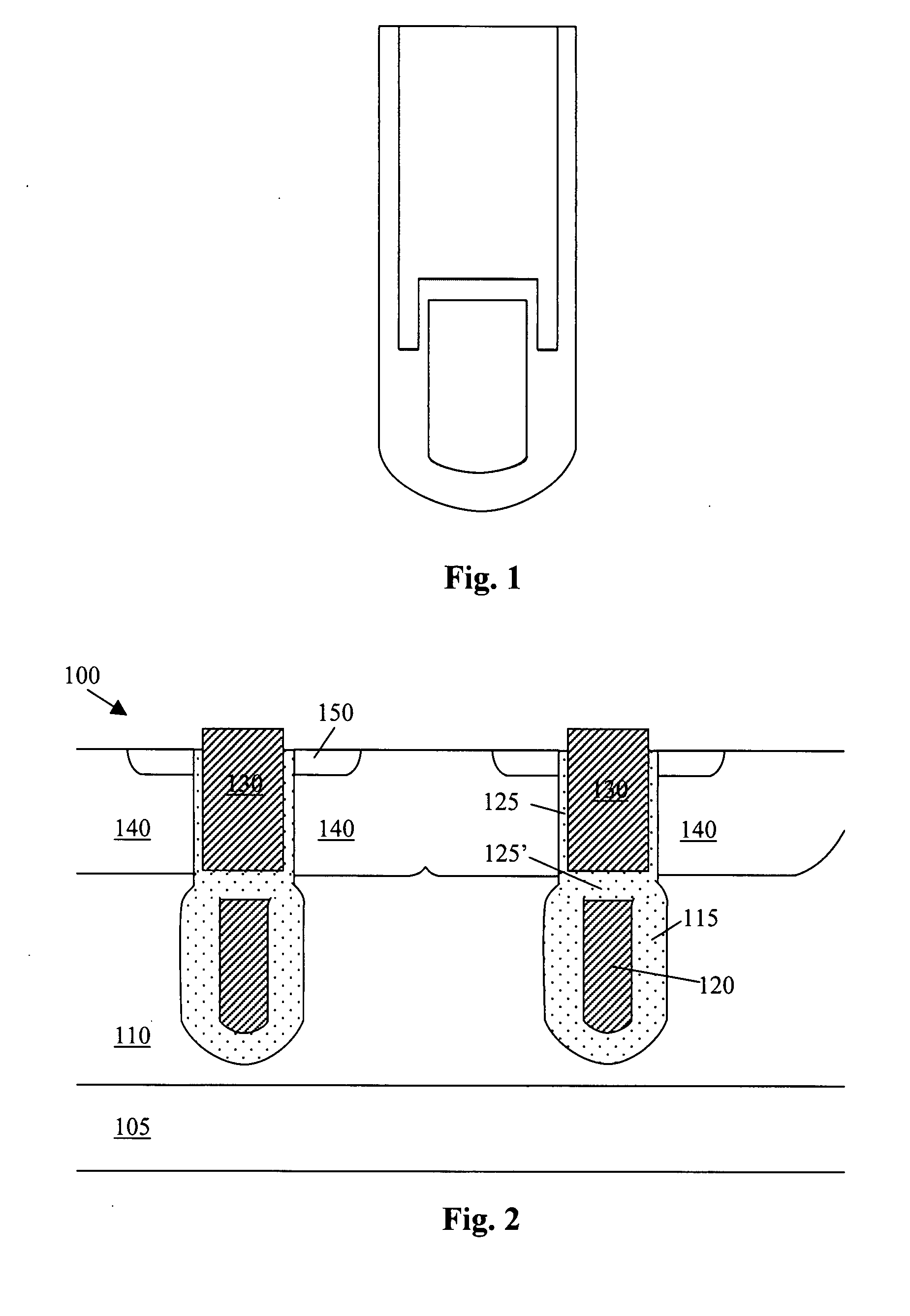

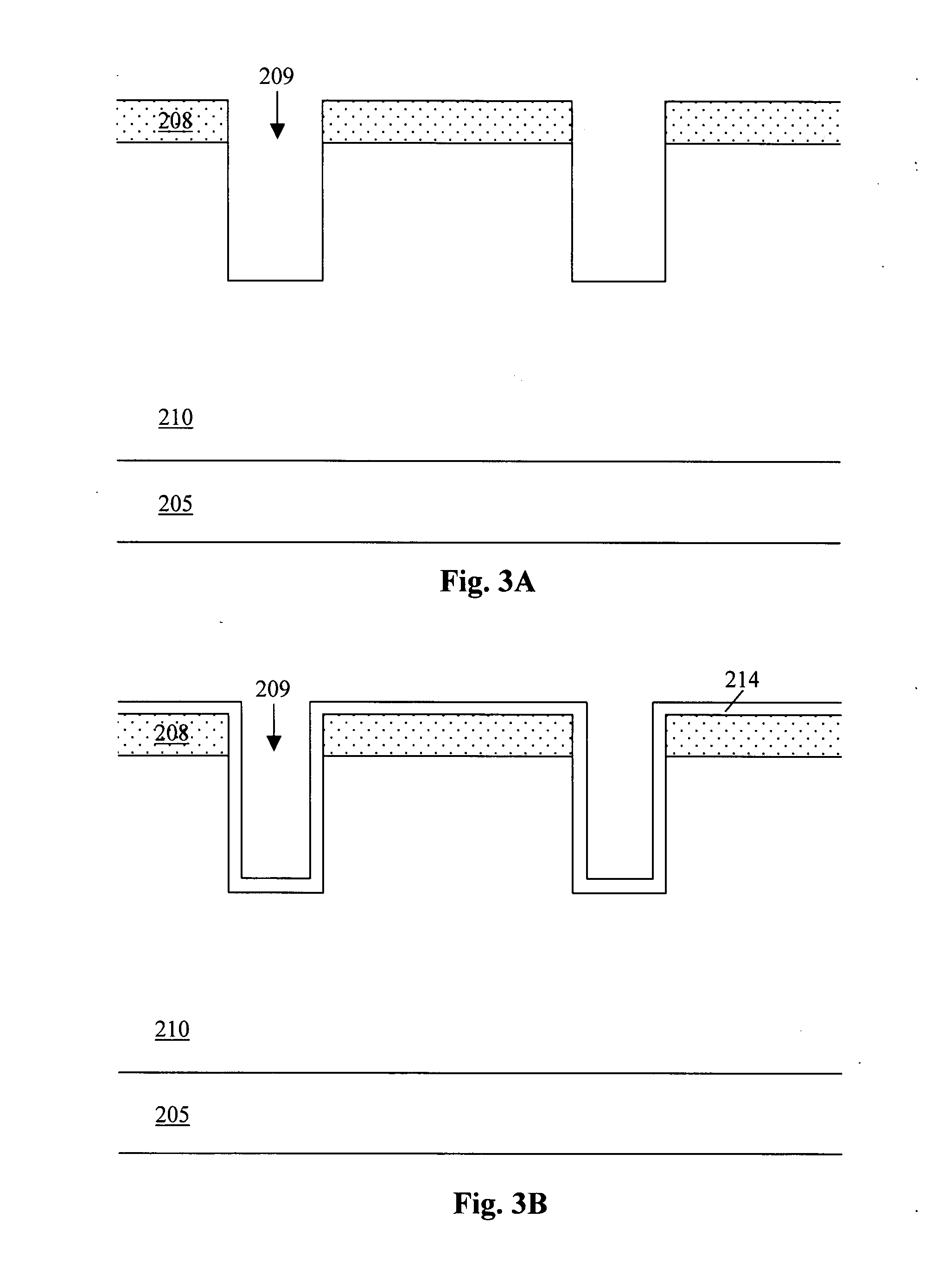

Method of fabricating trench MIS device with graduated gate oxide layer

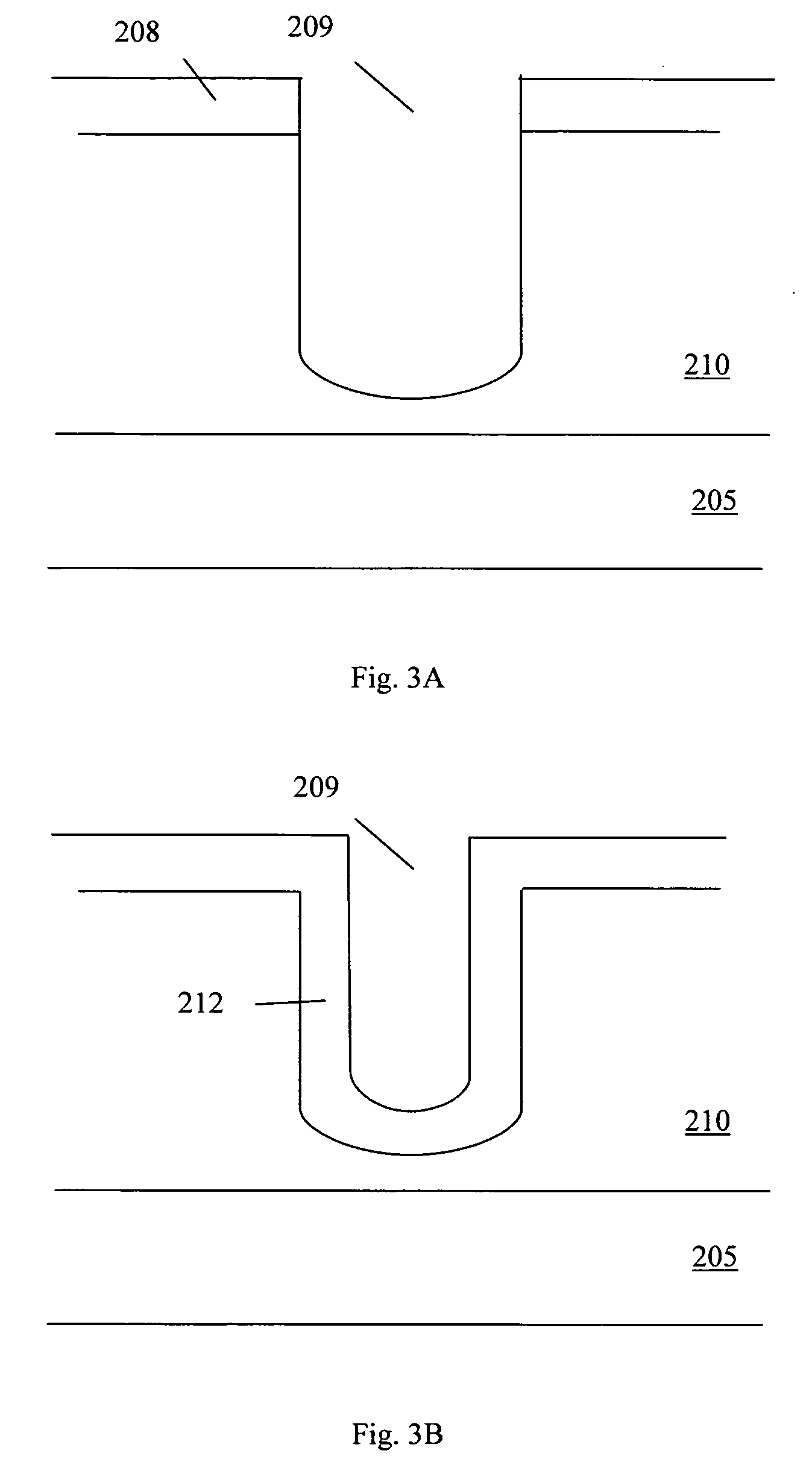

InactiveUS6875657B2Reduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantP–n junction

A process for manufacturing a trench MIS device includes depositing a conformal nitride layer in the trench; etching the nitride layer to create an exposed area at the bottom of the trench; and heating the substrate and thereby growing an oxide layer in the exposed area. This process causes the mask layer to “lift off”, creating a “bird's beak” structure. This becomes a “transition region”, where the thickness of the oxide layer decreases gradually in a direction away from the exposed area. The method further includes diffusing a dopant into the substrate, the dopant forming a PN junction with a remaining portion of said substrate, and controlling the diffusion such that the PN junction intersects the trench in the transition region. Because the thickness of the oxide layer decreases gradually, the PN junction does not need to be located at a particular point, i.e., there is a margin of error. This improves the manufacturability of the device and enhances its breakdown characteristics.

Owner:SILICONIX

Double gate manufactured with locos techniques

InactiveUS20100015770A1Avoid overetchingEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesLOCOSInterface point

Owner:ALPHA & OMEGA SEMICON LTD

Silicon carbide MOSFET device and manufacturing method thereof

ActiveCN108807504AImprove leakageReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Silicon carbide deep P injection is performed in a specified region, groove etching and deposition of metal or polysilicon are performed above a silicon carbide deep P doped region, and the deposited metal or polysilicon is in direct contact with the silicon carbide N-epitaxy to form a Schottky contact or aSi / SiC heterojunction contact having rectifying characteristics. Therefore, the integration of multiple sub-rectifiers is achieve while optimizing the basic performance of the conventional silicon carbide UMOSFET, the working performance of the third quadrant of the device is greatly optimized, the gate-drain capacitance of the device is reduced and the switching speed of the device is improved.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

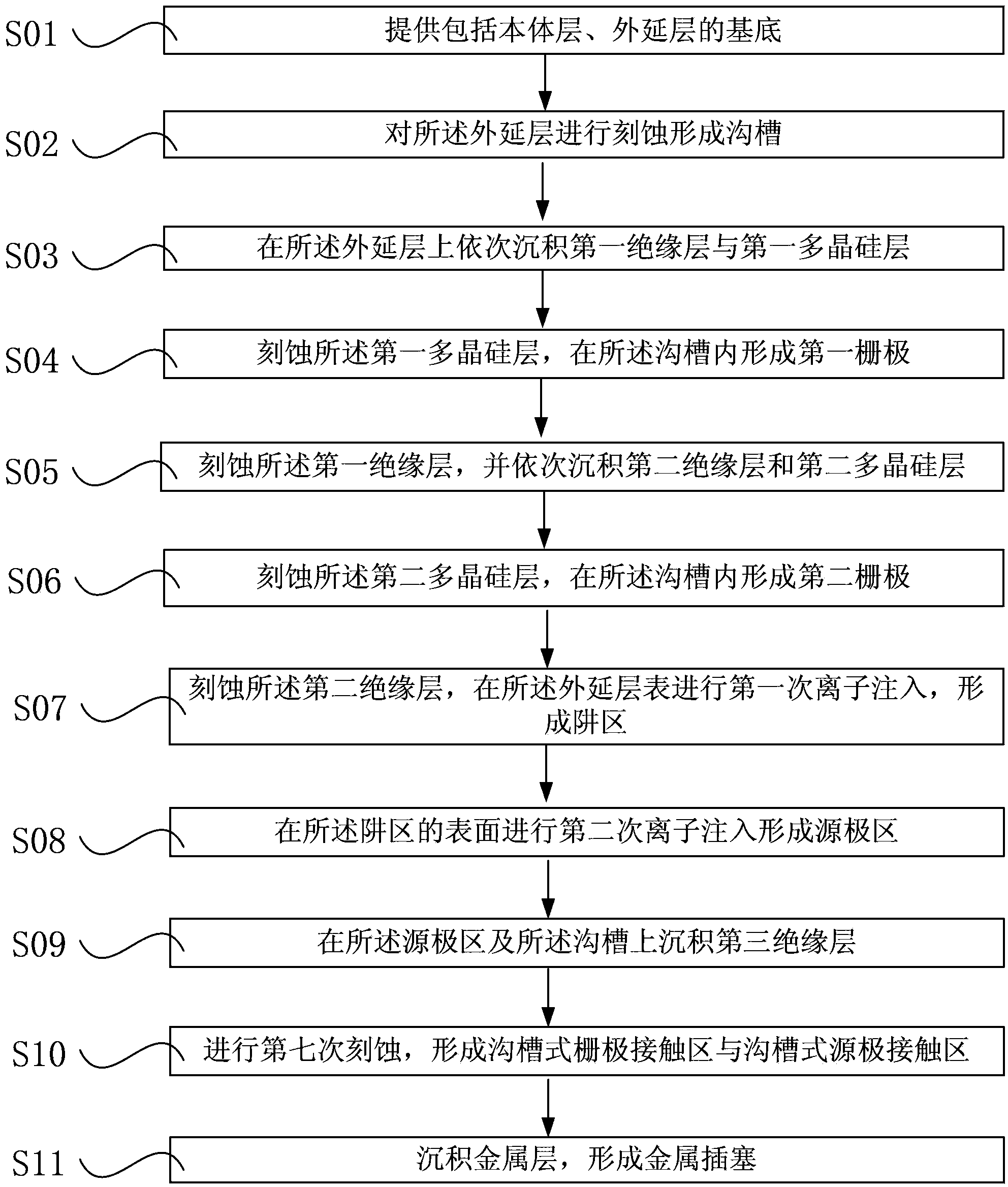

Groove MOSFET device and manufacturing method thereof

ActiveCN103413765ALower threshold voltageLow switching currentSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetIon implantation

The invention provides a groove MOSFET device and a manufacturing method thereof. The manufacturing method includes the steps that a substrate with an epitaxy layer is provided; a groove is formed in the epitaxy layer; a first insulating layer, a first gate electrode, a second insulating layer and a second gate electrode are sequentially formed in the groove through deposition and etching; ions are ejected into the two sides of the groove to form a well region and a source electrode region; groove type contact regions and a metal connector are formed. By means of the manufacturing method, the first gate electrode and the second gate electrode are separated, the thickness of the first insulating layer between the lower portion of the first gate electrode and the epitaxy layer is large, the thickness of the second insulating layer between the second gate electrode and the well region and between the second gate electrode and the source electrode region is small, and the two separated gate electrodes are connected through the metal connector, so that the device is good in high voltage resistance while the threshold voltage of the device is low. The device is stable in performance, simple in preparing method and low in preparing cost.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

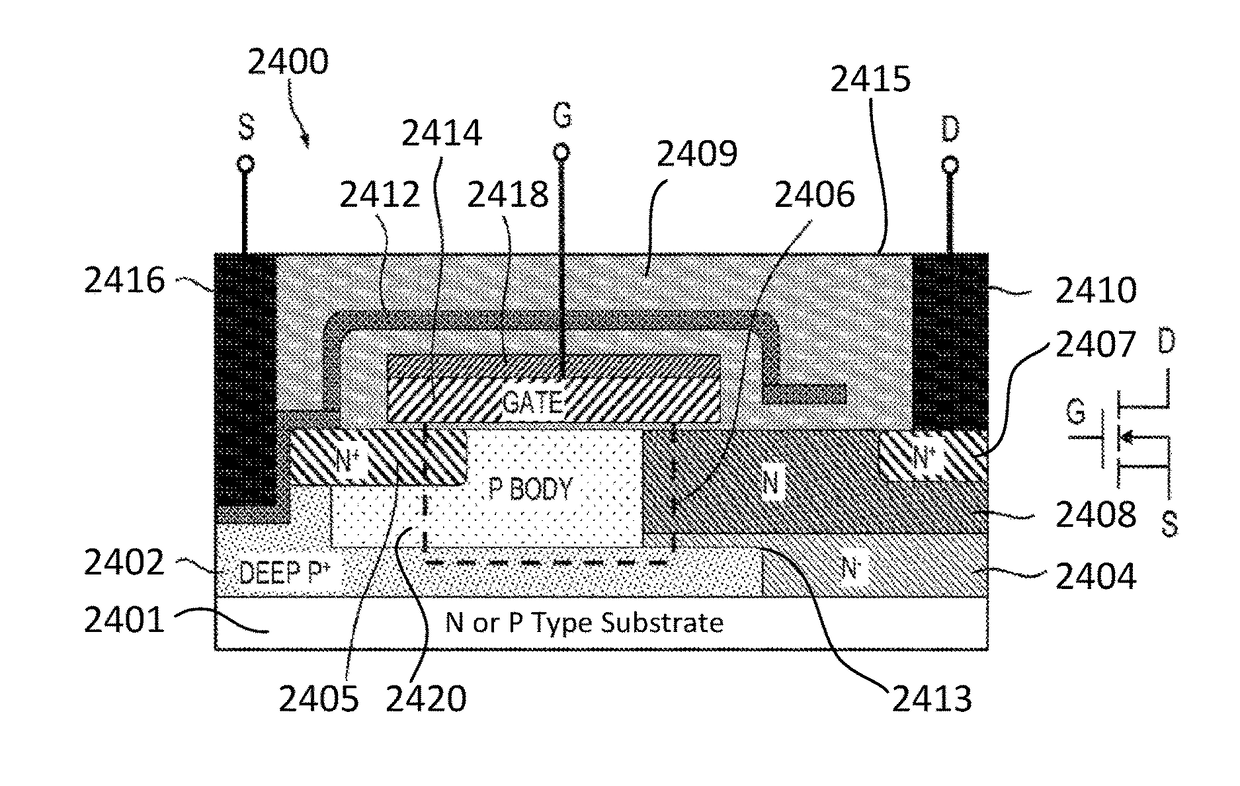

Power device on bulk substrate

ActiveUS20170229536A1Reduce decreaseImprove long-term reliabilityTransistorThyristorMOSFETField-effect transistor

A metal-oxide-semiconductor field-effect transistor (MOSFET) power device includes an active region formed on a bulk semiconductor substrate, the active region having a first conductivity type formed on at least a portion of the bulk semiconductor substrate. A first terminal is formed on an upper surface of the structure and electrically connects with at least one other region having the first conductivity type formed in the active region. A buried well having a second conductivity type is formed in the active region and is coupled with a second terminal formed on the upper surface of the structure. The buried well and the active region form a clamping diode which positions a breakdown avalanche region between the buried well and the first terminal. A breakdown voltage of at least one of the power devices is a function of characteristics of the buried well.

Owner:SILANNA ASIA

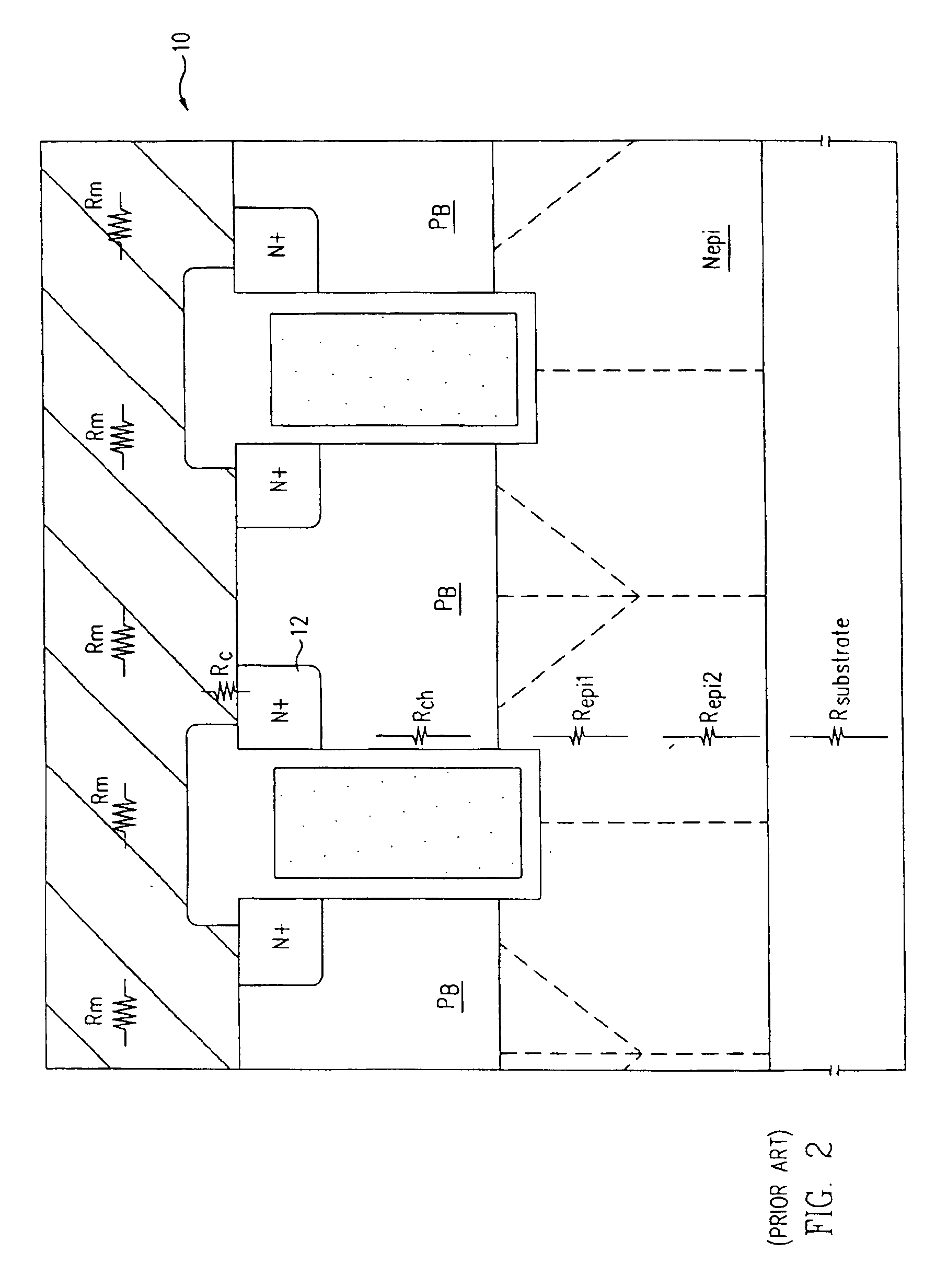

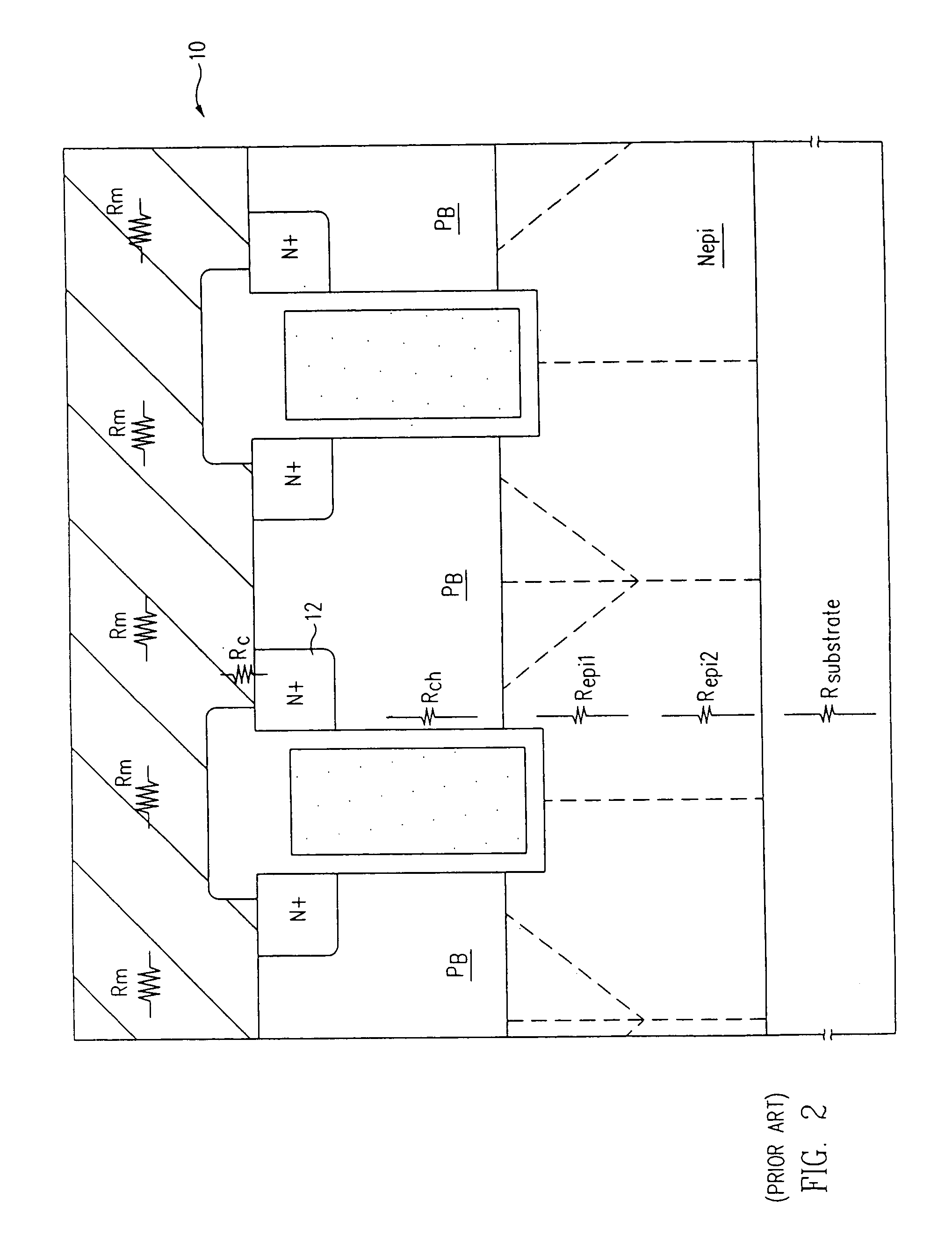

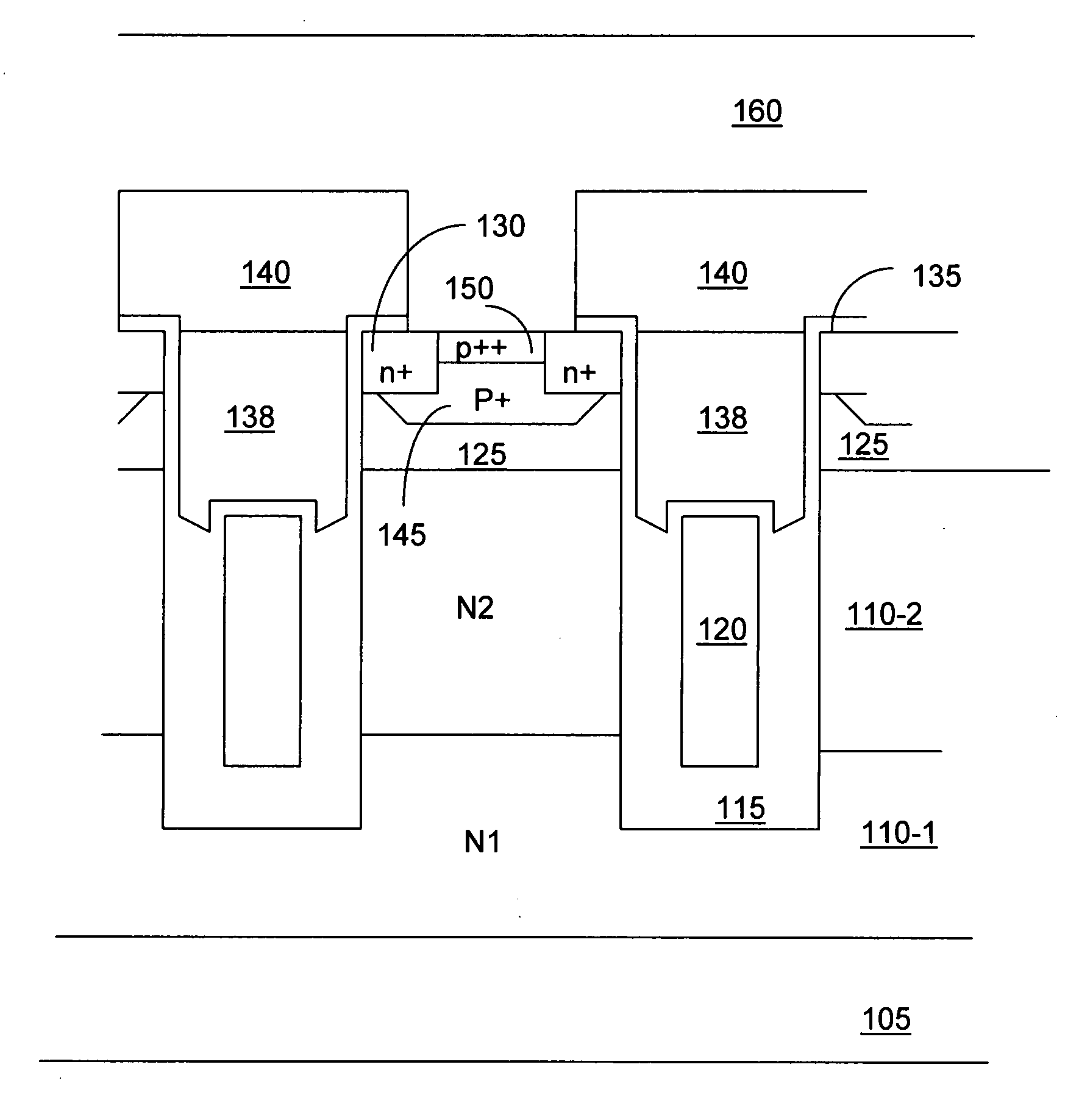

Trench mosfet with double epitaxial structure

ActiveUS20090206395A1Low epitaxial resistivityReduced device resistanceTransistorSemiconductor/solid-state device manufacturingTrench mosfetInsulation layer

A trenched semiconductor power device includes a plurality of trenched gates surrounded by source regions near a top surface of a semiconductor substrate encompassed in body regions. The trenched semiconductor power device further includes a first epitaxial layer above heavily doped substrate and beyond the trench bottom and a second epitaxial layer above said first epitaxial layer wherein a resistivity N1 of said first epitaxial layer is greater than a resistivity N2 of said second epitaxial layer represented by a functional relationship of N1>N2. In an exemplary embodiment, each of the trenched gates include an upper gate portion and lower gate portion formed with single polysilicon deposition processes wherein the lower gate portion is surrounded with a lower gate insulation layer having a greater thickness than an upper gate insulation layer surrounding the upper gate portion.

Owner:FORCE MOS TECH CO LTD

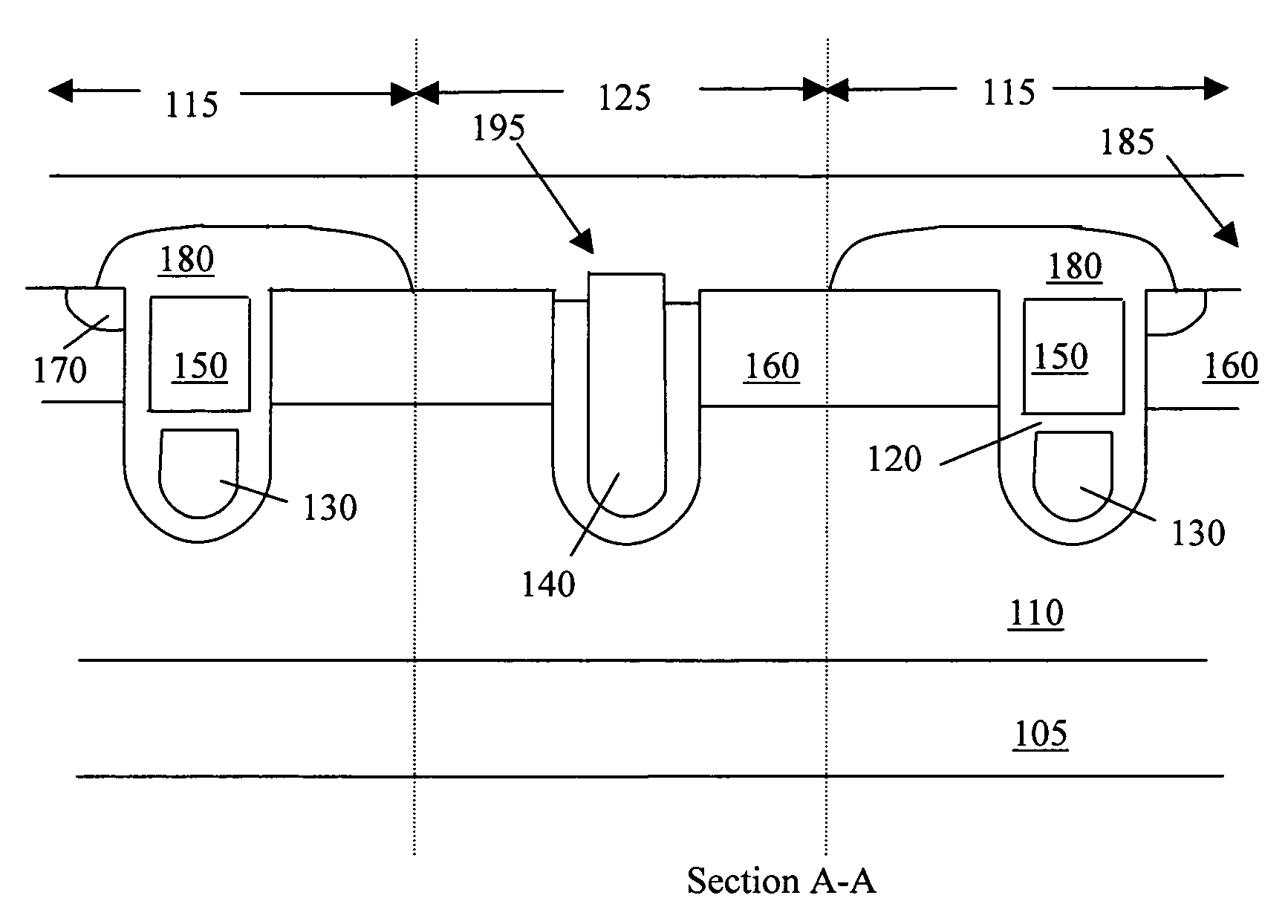

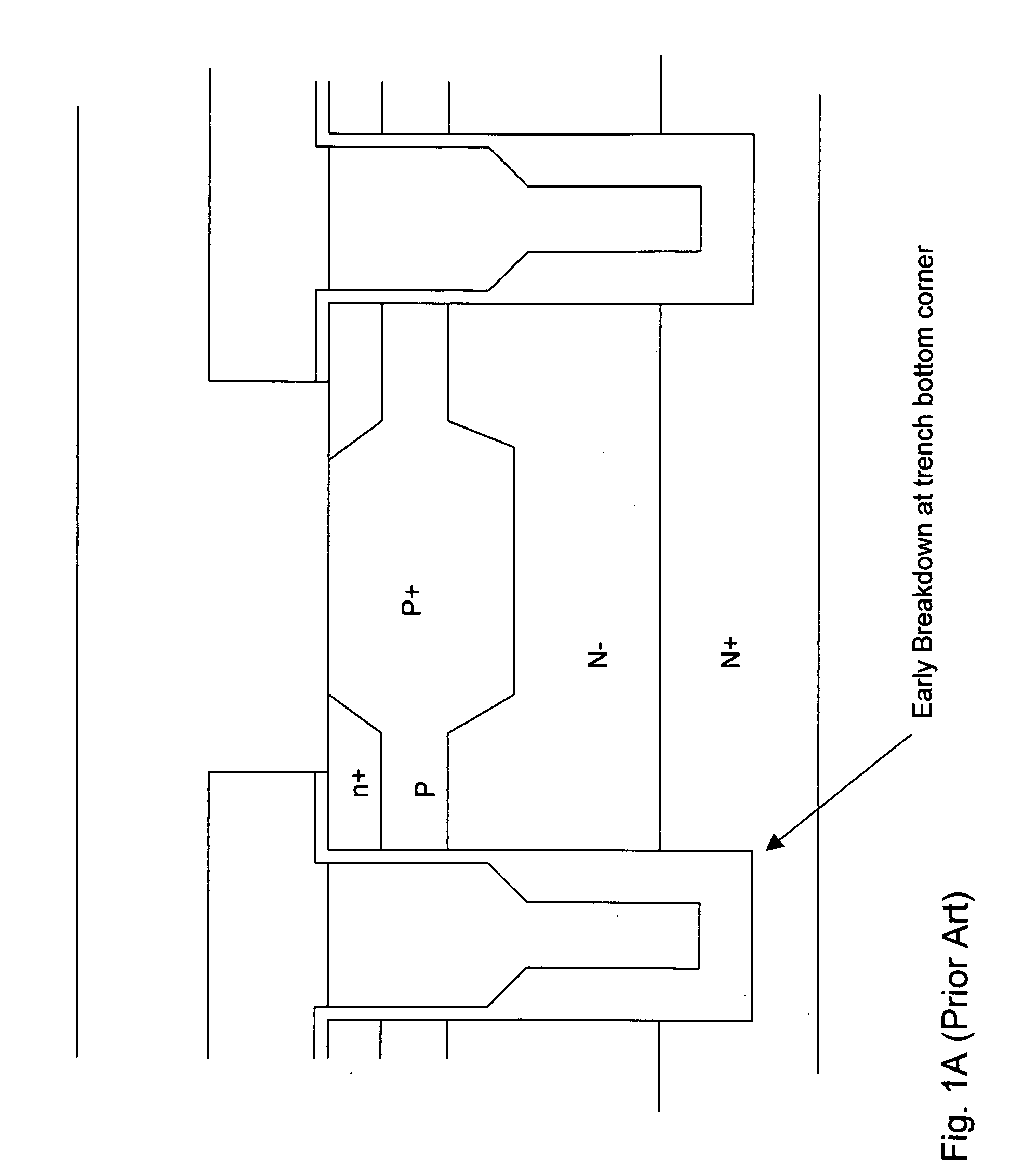

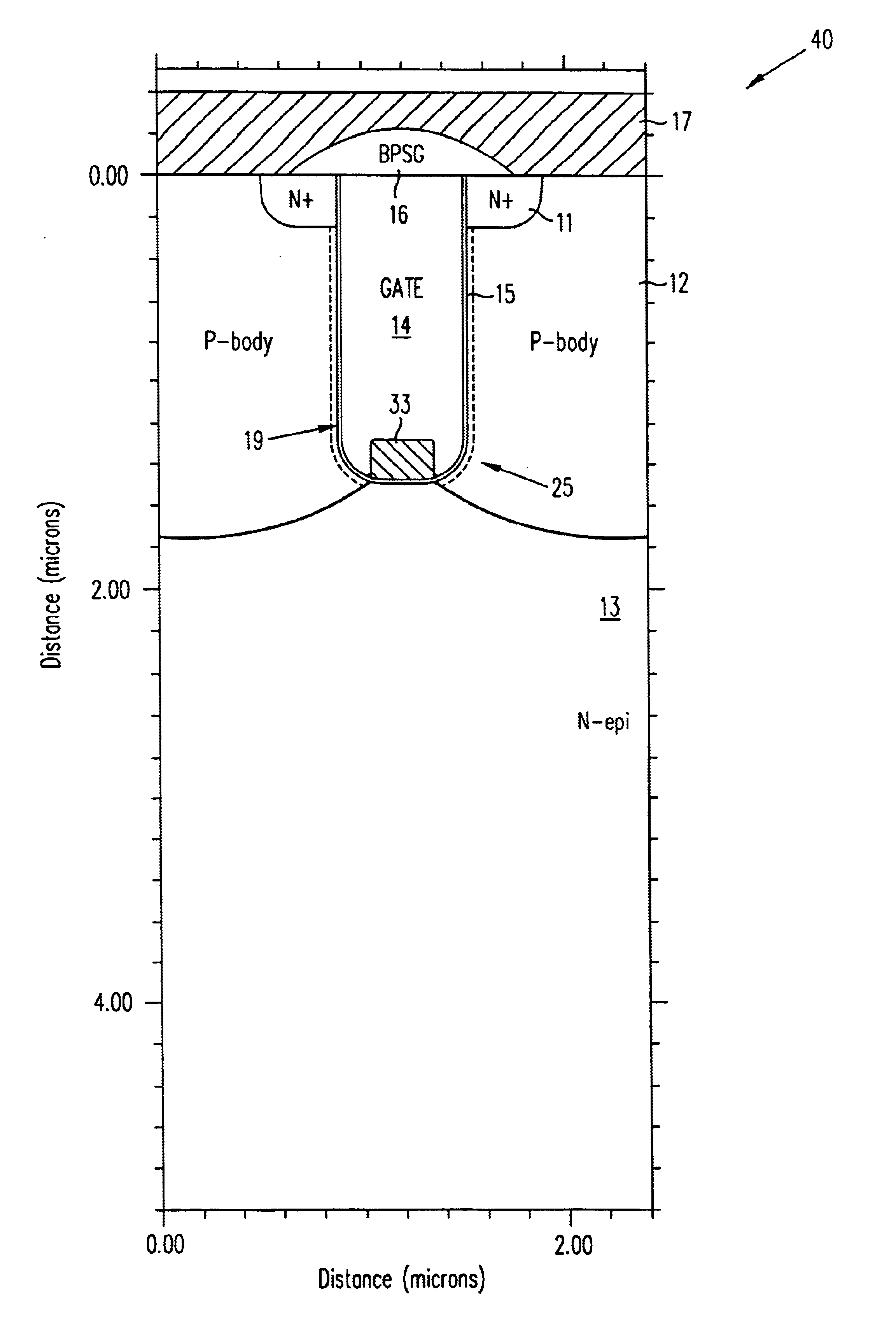

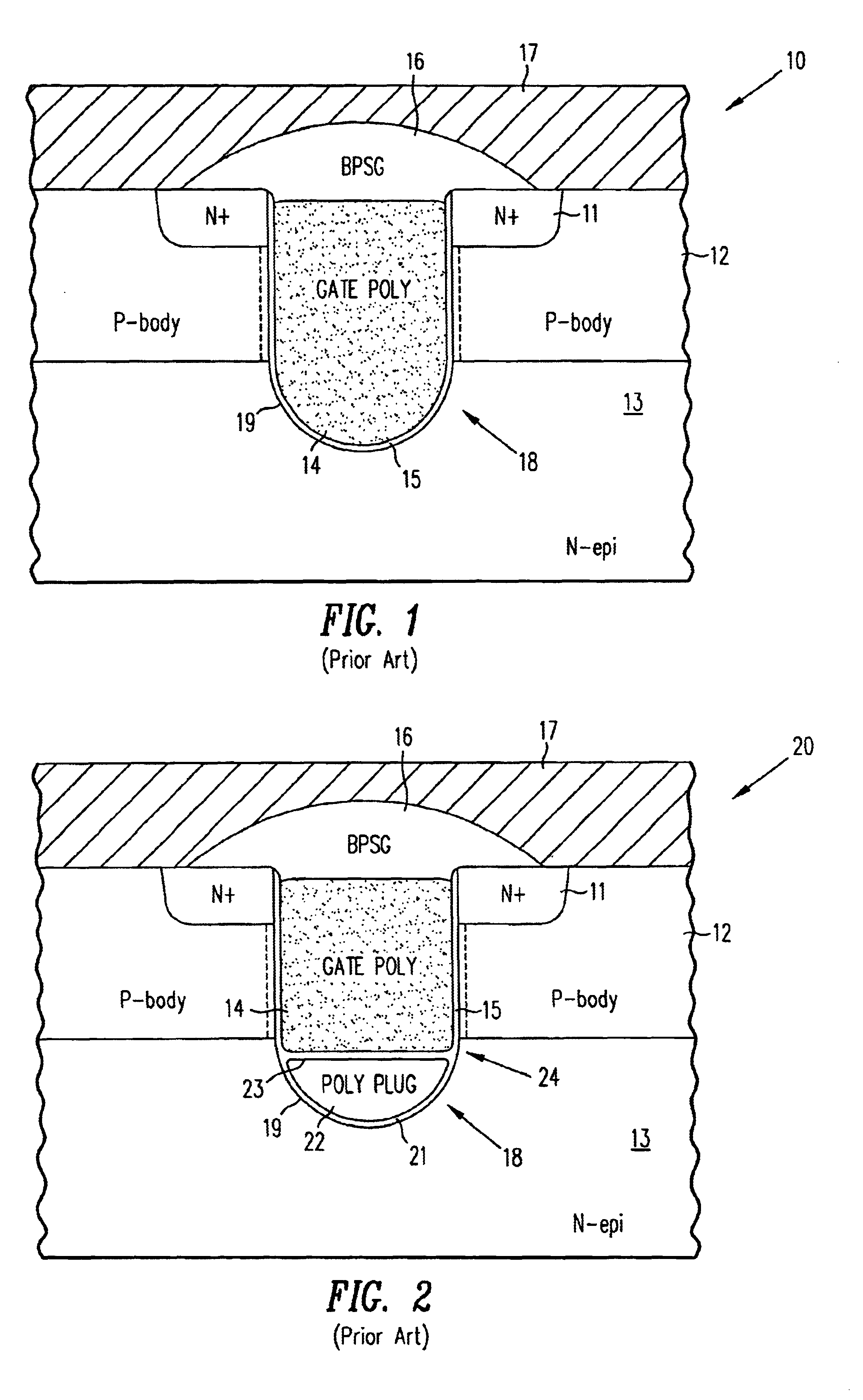

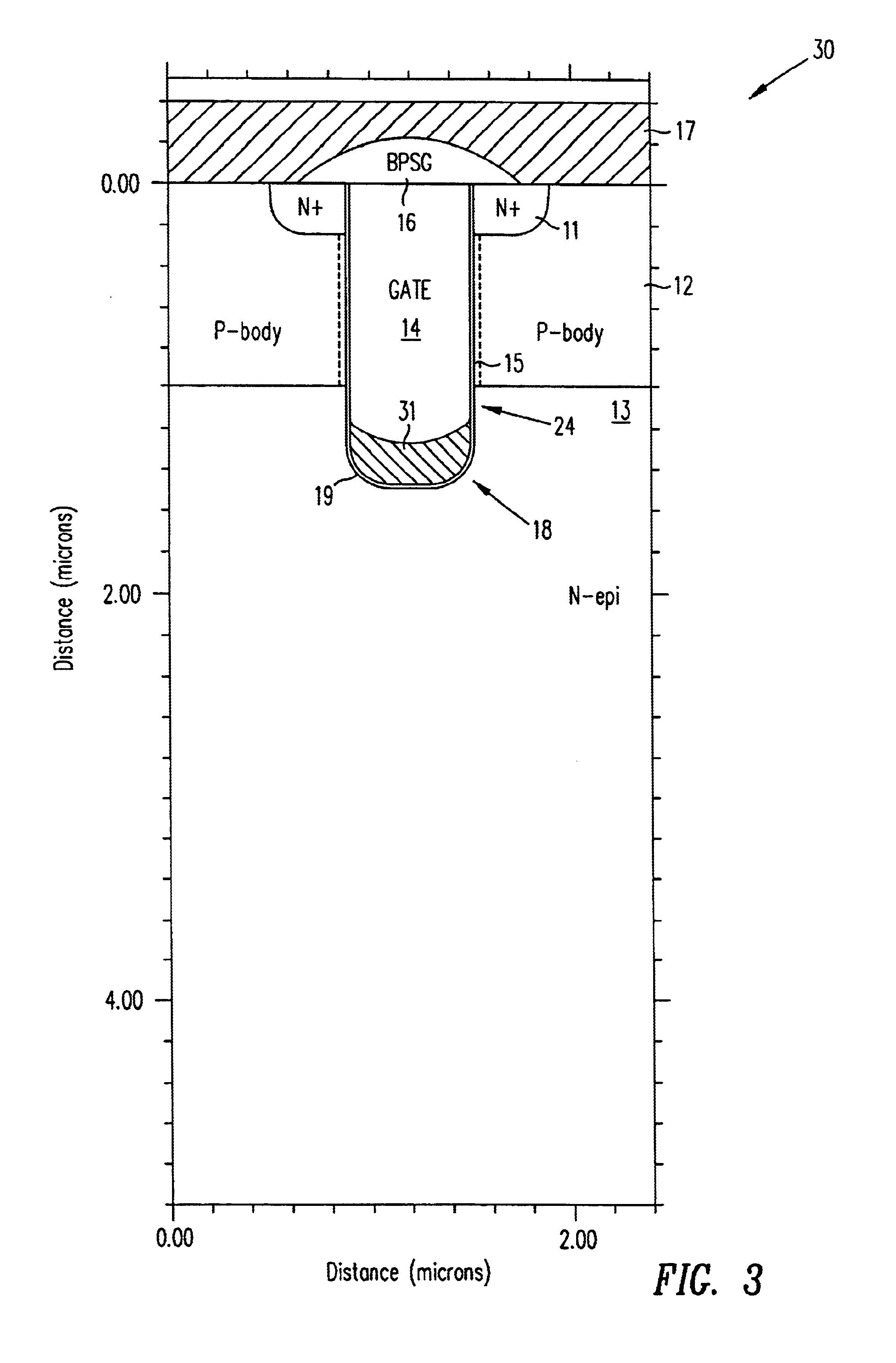

Trench MIS device with active trench corners and thick bottom oxide

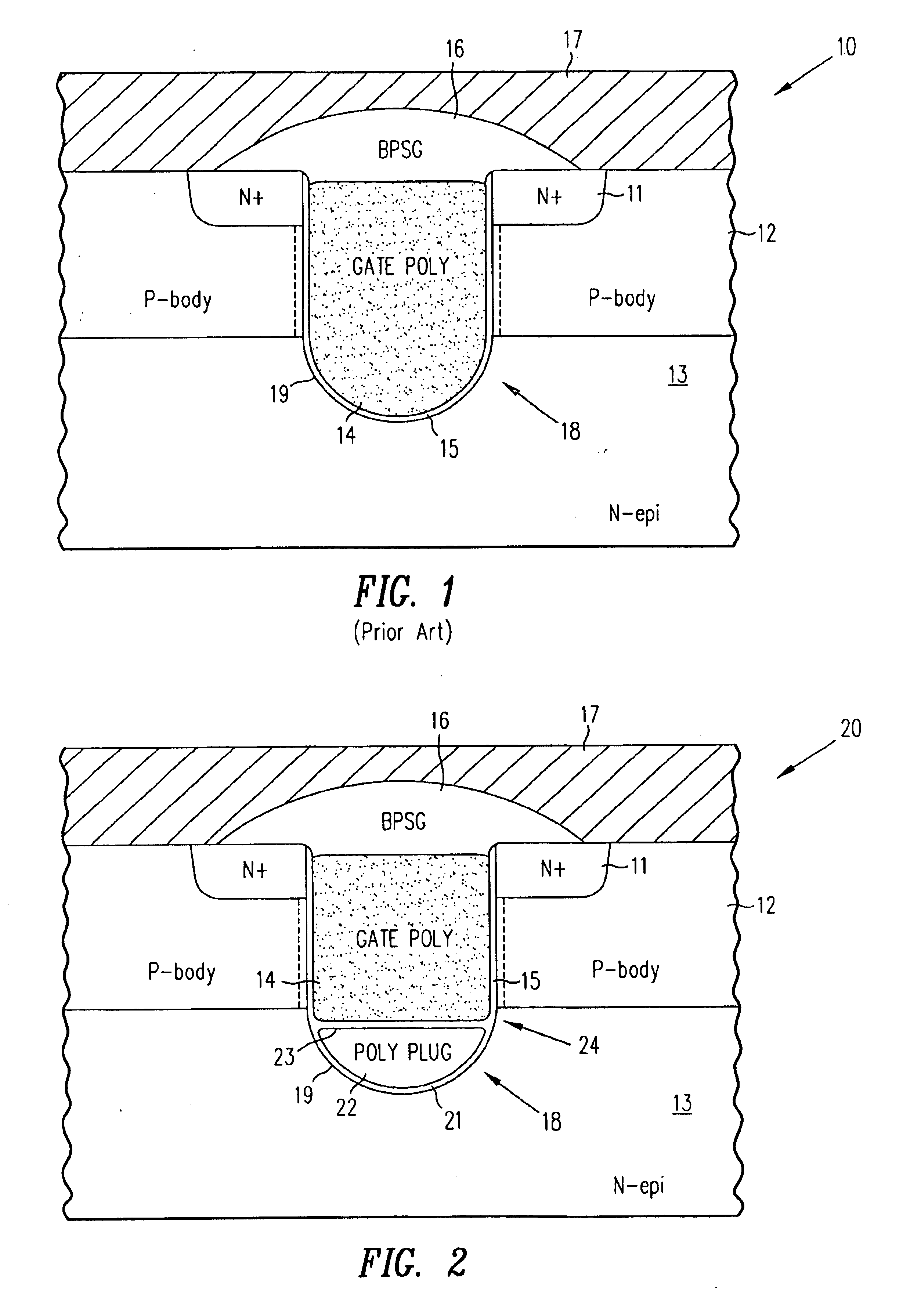

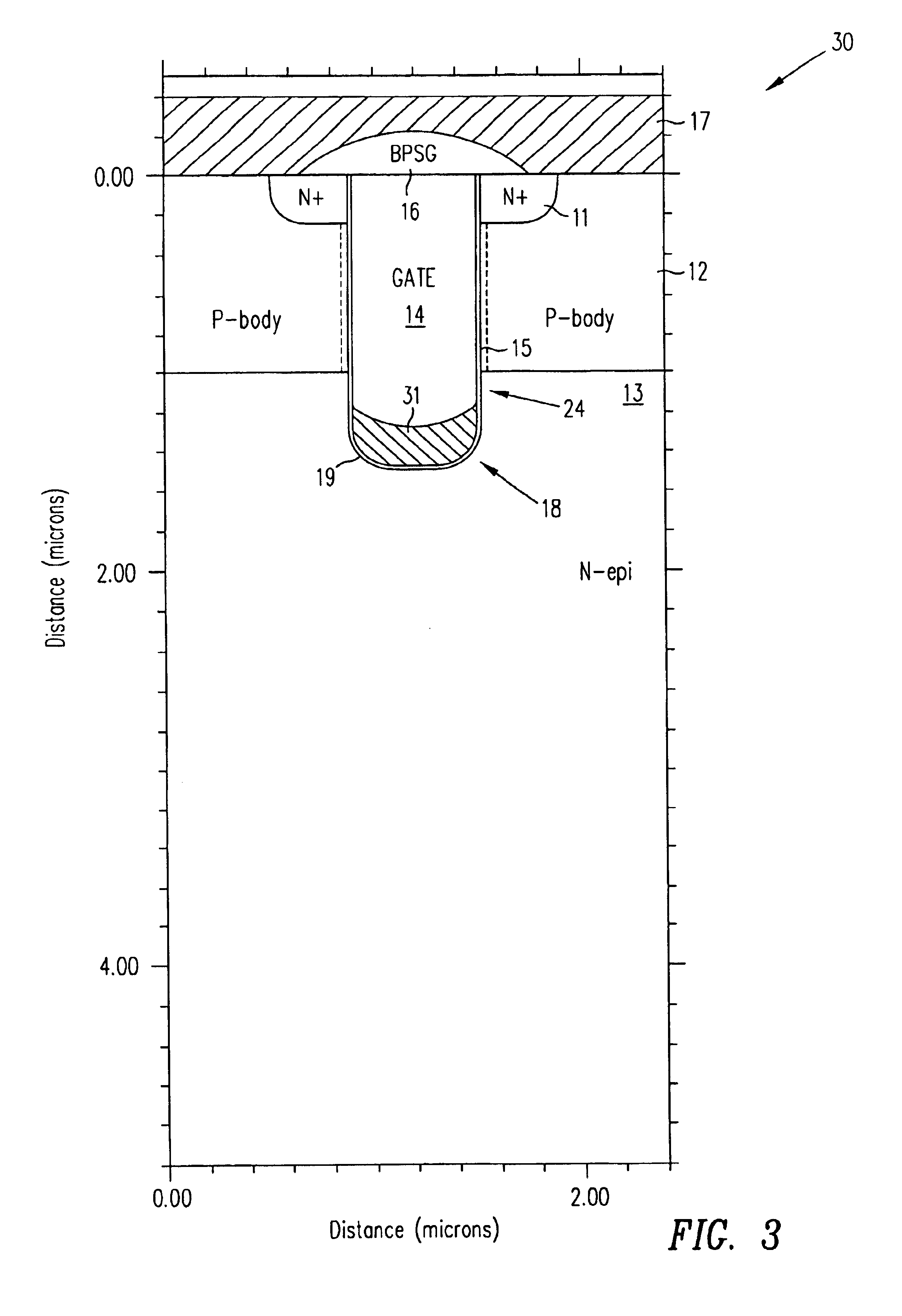

InactiveUS6849898B2Reduce gate-to-drain capacitanceTransistorSolid-state devicesCapacitanceTrench mosfet

Trench MOSFETs including active corner regions and a thick insulative layer at the bottom of the trench are disclosed, along with methods of fabricating such MOSFETs. In an exemplary embodiment, the trench MOSFET includes a thick insulative layer centrally located at the bottom of the trench. A thin gate insulative layer lines the sidewall and a peripheral portion of the bottom surface of the trench. A gate fills the trench, adjacent to the gate insulative layer. The gate is adjacent to the sides and top of the thick insulative layer. The thick insulative layer separates the gate from the drain conductive region at the bottom of the trench yielding a reduced gate-to-drain capacitance making such MOSFETs suitable for high frequency applications.

Owner:SILICONIX

Shield grid DMOS device

ActiveCN109119468AAdjustable Gate-Source CapacitanceReduce switching lossesSemiconductor devicesCapacitanceDielectric layer

The present invention provides a shield grid DMOS device, belonging to the technical field of power semiconductors. An extra floating grid electrode is arranged between a control grid electrode and ashield grid electrode, dielectric layers are configured to mutually isolate the electrodes, the floating grid electrode with an adjustable position is introduced, the grid source capacitance of the device is reduced, the specific value of the grid source capacitance and the grid-drain capacitance is adjustable, and the combination of the floating grid electrode and the earthed shield grid electrode allows an electric field in a first conductive type semiconductor drift region to be more uniformly distributed. The shield grid DMOS device reduces the switching loss of the device, improves the device switching speed and voltage withstand level and improves the contradictory relation of the conduction resistance and the switching loss.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Split gate formation with high density plasma (HDP) oxide layer as inter-polysilicon insulation layer

InactiveUS20080150013A1Improved planar surfaceReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEtching ratePolycrystalline silicon

This invention discloses method of for manufacturing a trenched semiconductor power device with split gate filling a trench opened in a semiconductor substrate wherein the split gate is separated by an inter-poly insulation layer disposed between a top and a bottom gate segments. The method further includes a step of forming the inter-poly layer by applying a RTP process after a HDP oxide deposition process to bring an etch rate of the HDP oxide layer close to an etch rate of a thermal oxide.

Owner:ALPHA & OMEGA SEMICON LTD

A silicon carbide MOSFET device and a manufacturing method thereof

ActiveCN109192779AGood long-term application reliabilityImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeMOSFETHeterojunction

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The invention improves device structure design and finally integrates Schottky contact or heterojunction contact with rectifying characteristics on the basis of traditional silicon carbide UMOSFET structure. At that same time of optimize the basic characteristics of the traditional silicon carbide UMOSFET structure, the improvement realize the integration of multi-sub rectifier devices, greatly optimizes the work performance of the third quadrant of the device, and in addition, the invention also optimizes the dynamic performance of the device, and has shorter switching time; In addition, the invention also has the characteristics of simple process and easy realization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Laterally diffused metal-oxide-semiconductor device

A laterally diffused metal-oxide-semiconductor device includes a substrate, a gate dielectric layer, a gate polysilicon layer, a source region, a drain region, a body region, a first drain contact plug, a source polysilicon layer, an insulating layer, and a source metal layer. The source polysilicon layer disposed on the gate dielectric layer above the drain region can serve as a field plate to enhance the breakdown voltage and to increase the drain-to-source capacitance. In addition, the first drain contact plug of the present invention can reduce the drain-to-source on-resistance and the horizontal extension length.

Owner:SINOPOWER SEMICON

Trench metal oxide semiconductor field effect transistor (MOSFET) with low gate to drain coupled charges (Qgd) structures

ActiveUS8022471B2Coupling chargeReduce chargeSemiconductor/solid-state device manufacturingSemiconductor devicesDopantMOSFET

A trenched semiconductor power device includes a plurality of trenched gates surrounded by source regions near a top surface of a semiconductor substrate encompassed in body regions. The trenched semiconductor power device further comprises tilt-angle implanted body dopant regions surrounding a lower portion of trench sidewalls for reducing a gate-to-drain coupling charges Qgd between the trenched gates and a drain disposed at a bottom of the semiconductor substrate. The trenched semiconductor power device further includes a source dopant region disposed below a bottom surface of the trenched gates for functioning as a current path between the drain to the source for preventing a resistance increase caused by the body dopant regions surrounding the lower portions of the trench sidewalls.

Owner:FORCE MOS TECH CO LTD

Methods for manufacturing trench MOSFET with implanted drift region

ActiveUS20100087039A1Low resistivityReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetBody region

A method to manufacture a trenched semiconductor power device including a plurality of trenched gates surrounded by source regions near a top surface of a semiconductor substrate encompassed in body regions. The method for manufacturing the trenched semiconductor power device includes a step of carrying out a tilt-angle implantation through sidewalls of trenches to form drift regions surrounding the trenches at a lower portion of the body regions with higher doping concentration than the epi layer for Rds reduction, and preventing a degraded breakdown voltage due to a thick oxide in lower portion of trench sidewall and bottom. In an exemplary embodiment, the step of carrying out the tilt-angle implantation through the sidewalls of the trenches further includes a step of carrying out a tilt angle implantation with a tilt-angle ranging between 4 to 30 degrees.

Owner:FORCE MOS TECH CO LTD

Method to manufacture split gate with high density plasma oxide layer as inter-polysilicon insulation layer

ActiveUS20100099230A1Improve configurationReduce gate-to-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityInsulation layer

This invention discloses a method of manufacturing a trenched semiconductor power device with split gate filling a trench opened in a semiconductor substrate wherein the split gate is separated by an inter-poly insulation layer disposed between a top and a bottom gate segments. The method further includes a step of forming the inter-poly layer by applying a RTP process after a HDP oxide deposition process to bring an etch rate of the HDP oxide layer close to an etch rate of a thermal oxide.

Owner:ALPHA & OMEGA SEMICON LTD

Double gate manufactured with locos techniques

InactiveUS20080296673A1Avoid overetchingEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerLOCOS

This invention discloses a trenched semiconductor power device that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The trenched gate further includes at least two mutually insulated trench-filling segments with a bottom insulation layer surrounding a bottom trench-filling segment having a bird-beak shaped layer on a top portion of the bottom insulation attached to sidewalls of the trench extending above a top surface of the bottom trench-filling segment.

Owner:ALPHA & OMEGA SEMICON LTD

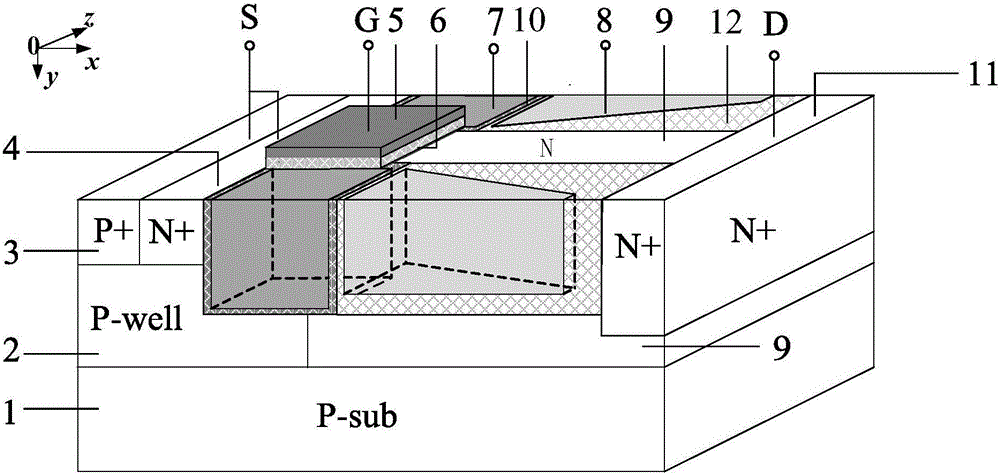

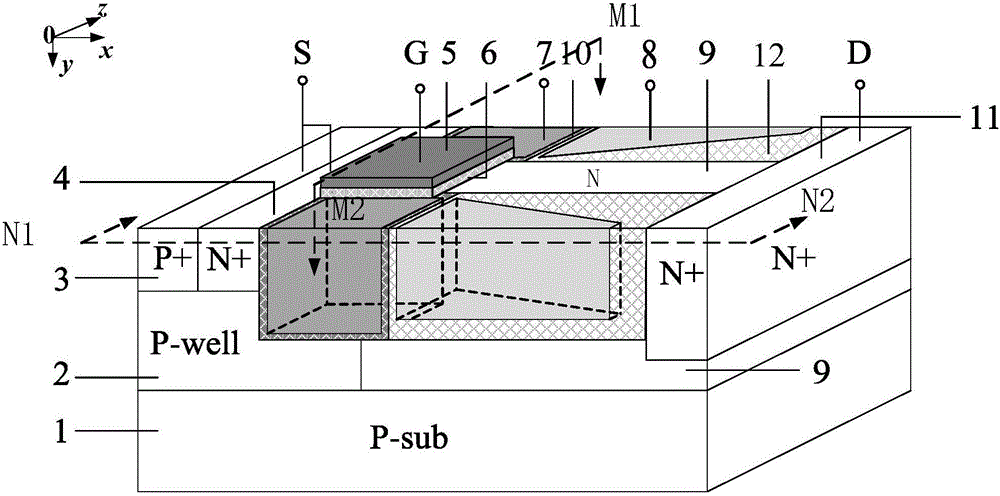

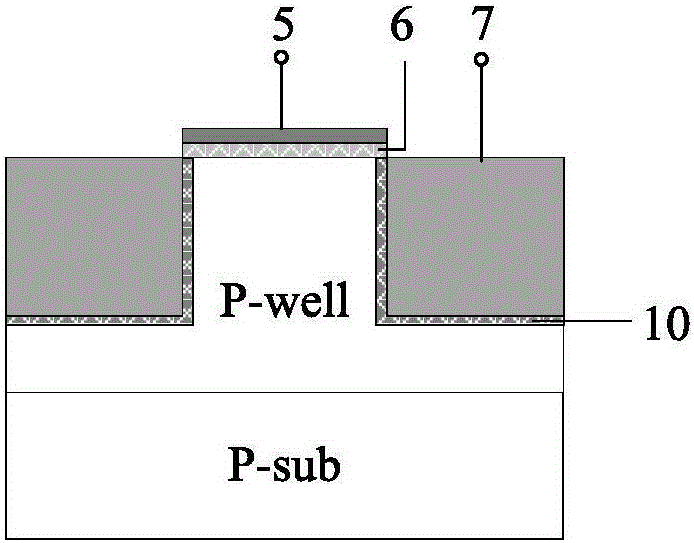

Three-gate power LDMOS

ActiveCN106024897AIncrease the doping concentrationReduce gate-to-drain capacitanceSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the field of power semiconductor devices, and relates to a lateral three-gate power LDMOS based on a bulk silicon technology. The three-gate power LDMOS is mainly characterized by having a three-gate structure and a second conductive material electrically connected with a source or a gate or an external electrode. The three-gate power LDMOS has the main advantages that the three-gate structure increases the channel density and reduces the channel resistance, and thus, the specific on-resistance drops; the second conductive material can freely select the electrode, when the gate electrode is connected, in the positive case, electron accumulation surfaces are formed on the side surface and the bottom surface of a second groove, a multi-dimension low-resistance channel is formed, and the specific on-resistance is greatly reduced, and in the reverse case, assistant depletion of a drift region is carried out, the drift area doping concentration of the device is increased, the specific on-resistance of the device is reduced; when the source electrode is connected, gate-drain overlapping is reduced, the gate-drain capacitance of the device is reduced, and switching loss is reduced; and when the external electrode is electrically connected, multiple effects can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA