Three-gate power LDMOS

A technology of power and the other side, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of small conduction area of low-resistance channels, reduce channel resistance, reduce specific on-resistance, and increase doping concentration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

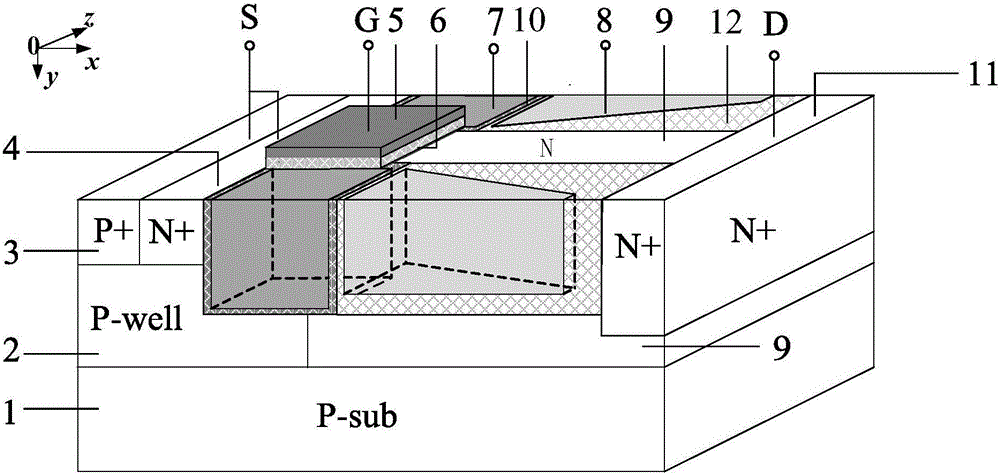

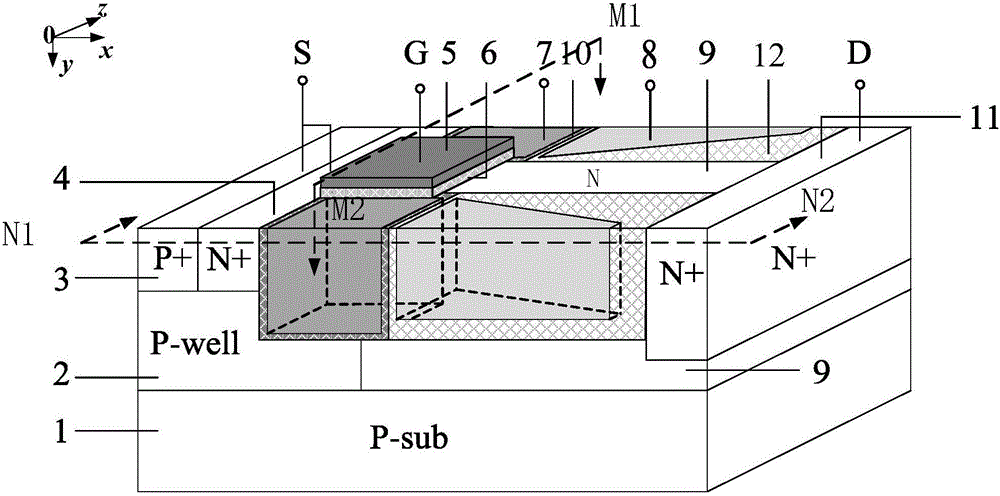

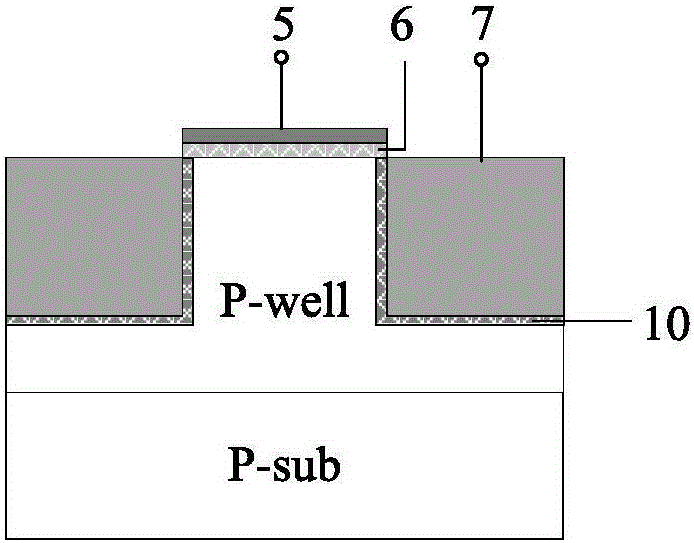

[0028] A tri-gate power LDMOS in this example, such as figure 1 As shown, a substrate layer 1 is included, one end of the upper surface of the substrate layer 1 has a P-type semiconductor body region 2, and the other end has an N-type semiconductor drift region 9, and the P-type semiconductor body region 2 and the N-type semiconductor drift region 9 contacts; the top of the P-type semiconductor body region 2 has a P-type semiconductor contact region 3 and an N-type semiconductor source region 4 on the side away from the N-type semiconductor drift region 9, and the N-type semiconductor source region 4 is located close to the N-type semiconductor drift region One side of 9; the upper surface of the P-type semiconductor body contact region 3 and the N-type semiconductor source region 4 is connected to the source metal; the N-type semiconductor drift region 9 has an N-type semiconductor drain region at one end away from the P-type semiconductor body region 2 11. The upper surface ...

Embodiment 2

[0031] Such as Figure 5 As shown, compared with Embodiment 1, the N-type semiconductor drift region 9 of this embodiment adopts a variable width. The semiconductor drift region 9 with variable width increases multiple sub-conduction paths, further reducing the on-resistance.

Embodiment 3

[0033] Such as Figure 6 As shown, compared with Embodiment 1, the drift region 9 of the N-type semiconductor in this embodiment is laterally doped, and its doping concentration gradually increases from the body region 2 to the N-type semiconductor drain region 11 . The linearly varying doping concentration modulates the electric field distribution in the drift region 9 of the N-type semiconductor, increasing the breakdown voltage.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More