Patents

Literature

1011 results about "N type silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition of: n-type silicon. n-type silicon. The use of n-type and p-type silicon is a foundation concept in the design of transistors. Pure silicon is not conductive. However, it can be made conductive by adding other elements to its crystalline structure, which then become known as "n-type" or "p-type" silicon.

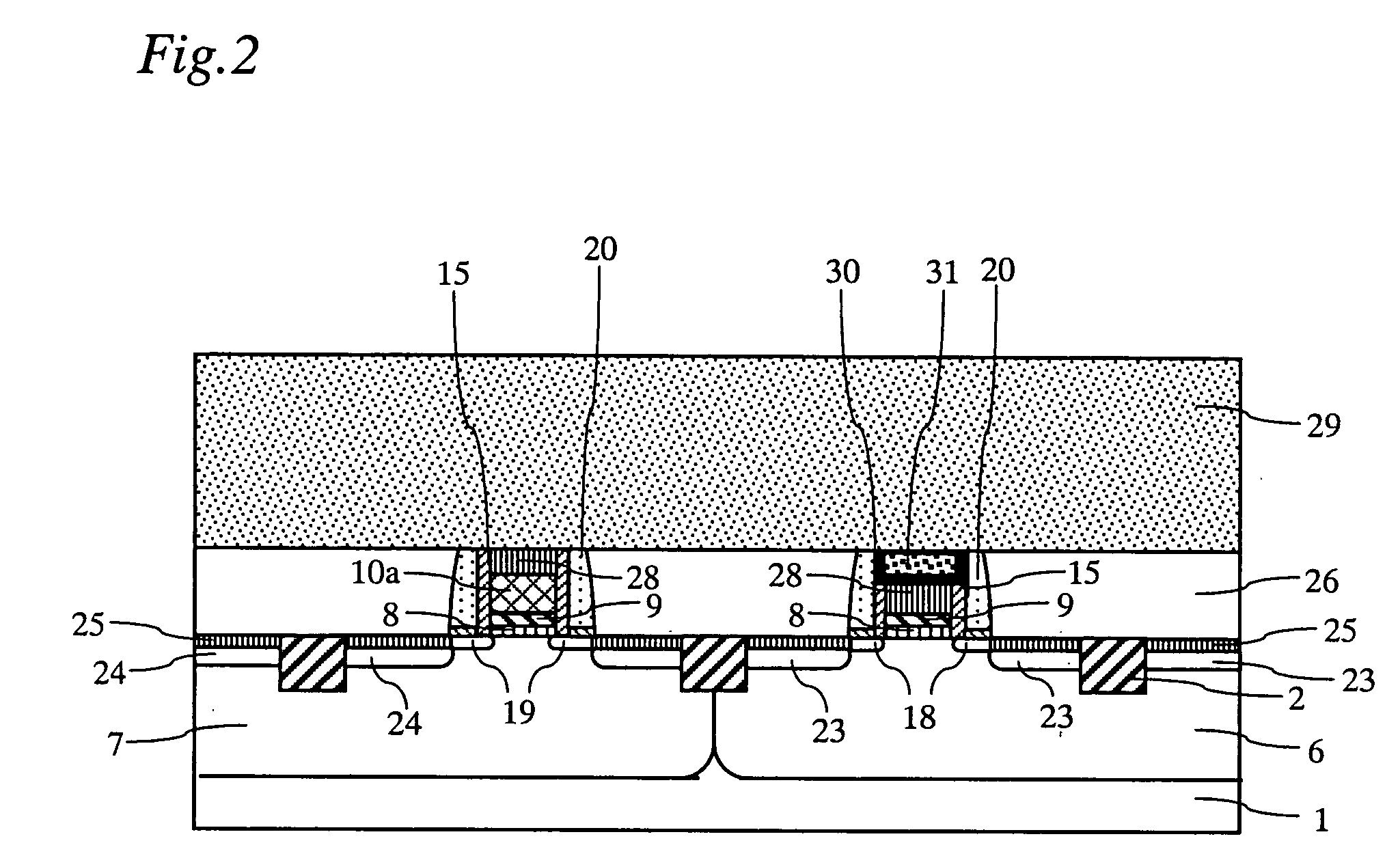

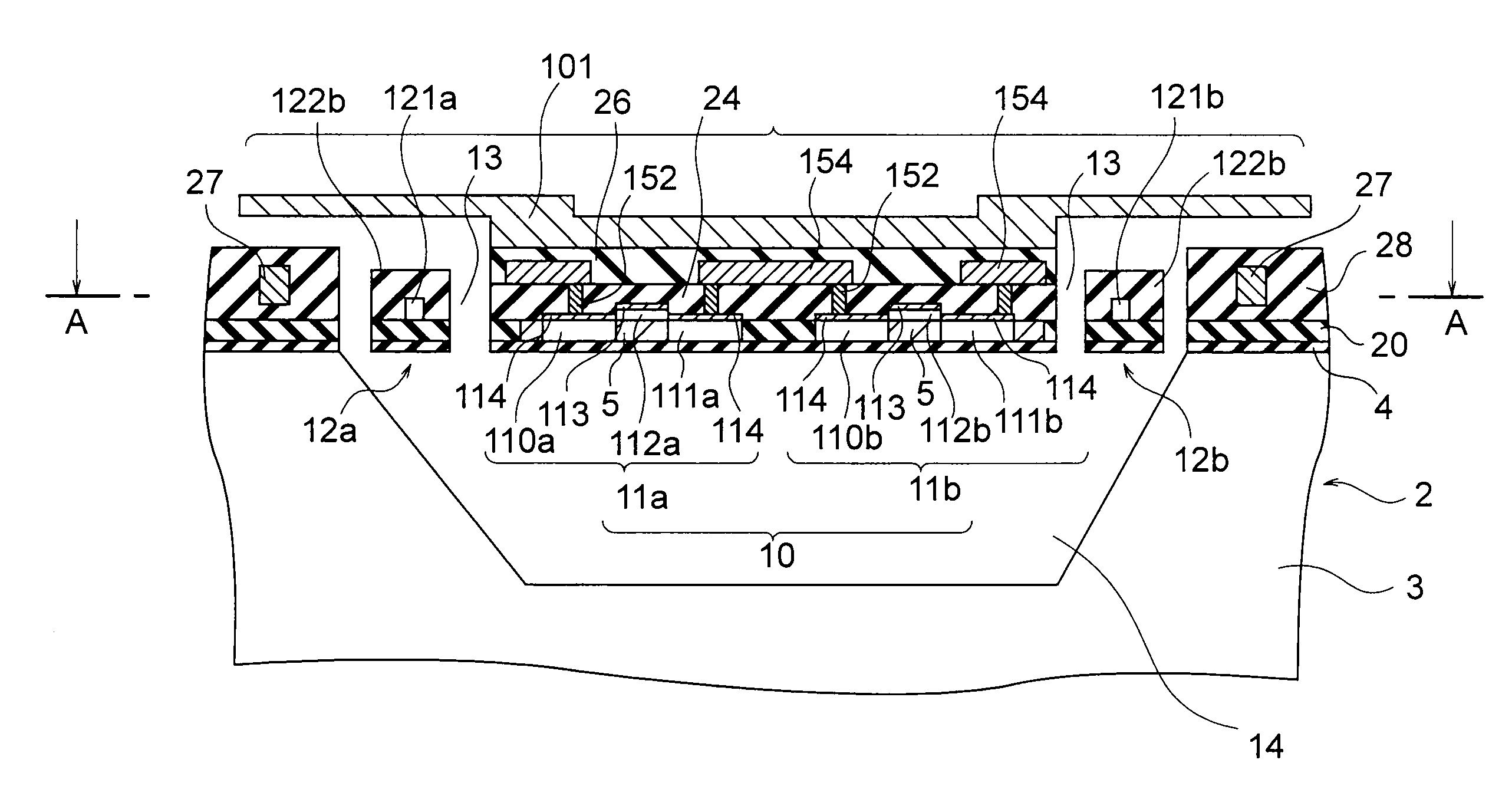

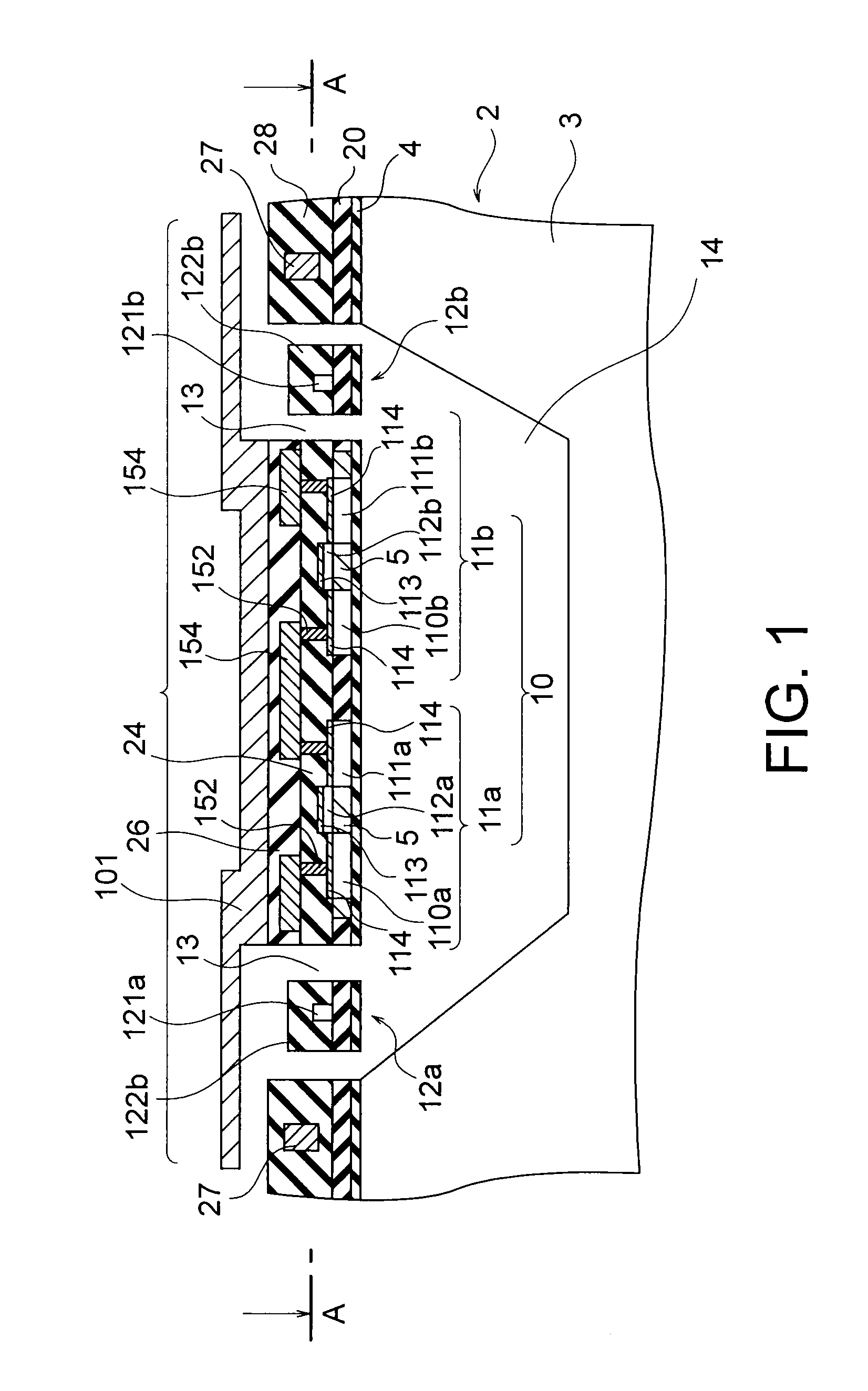

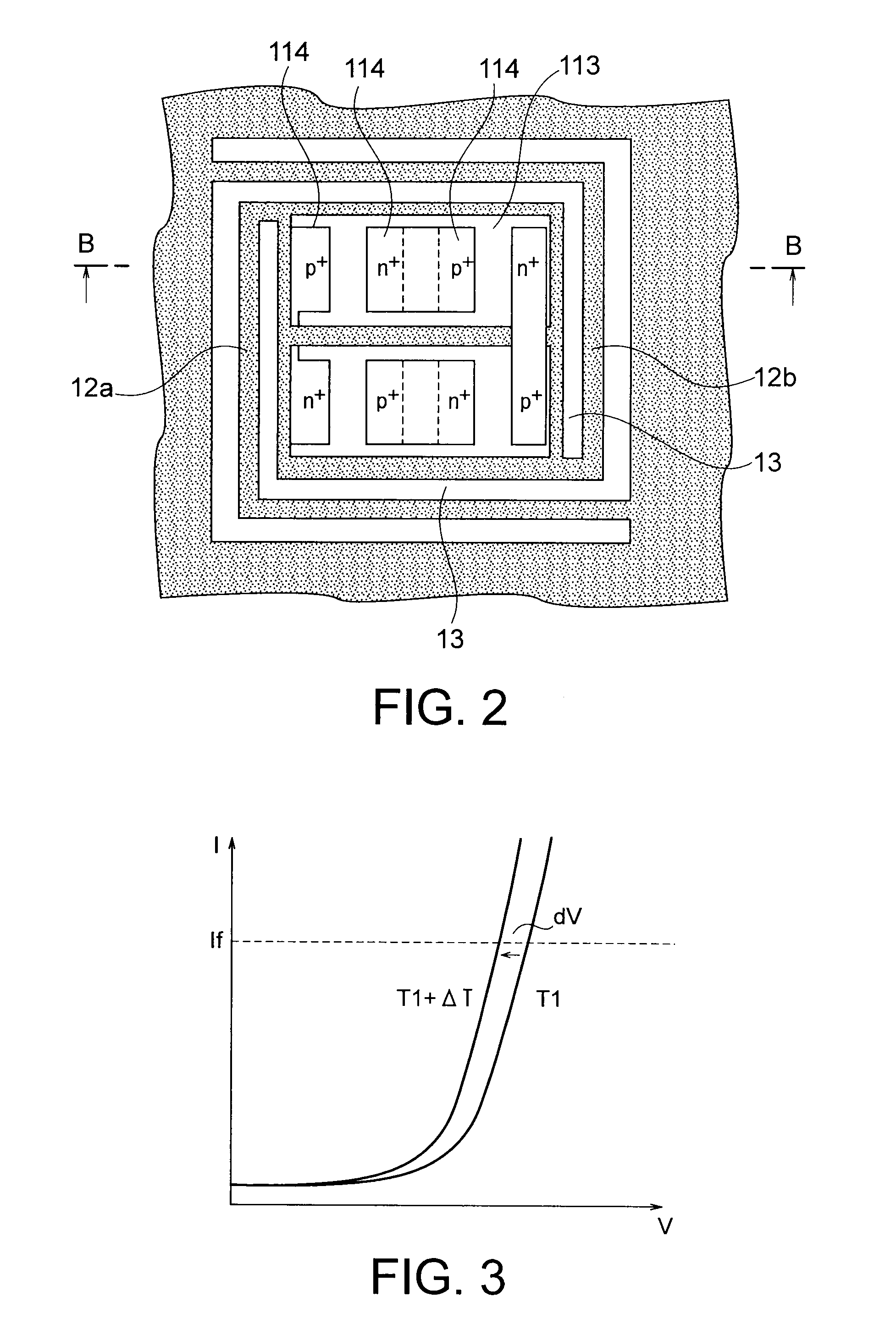

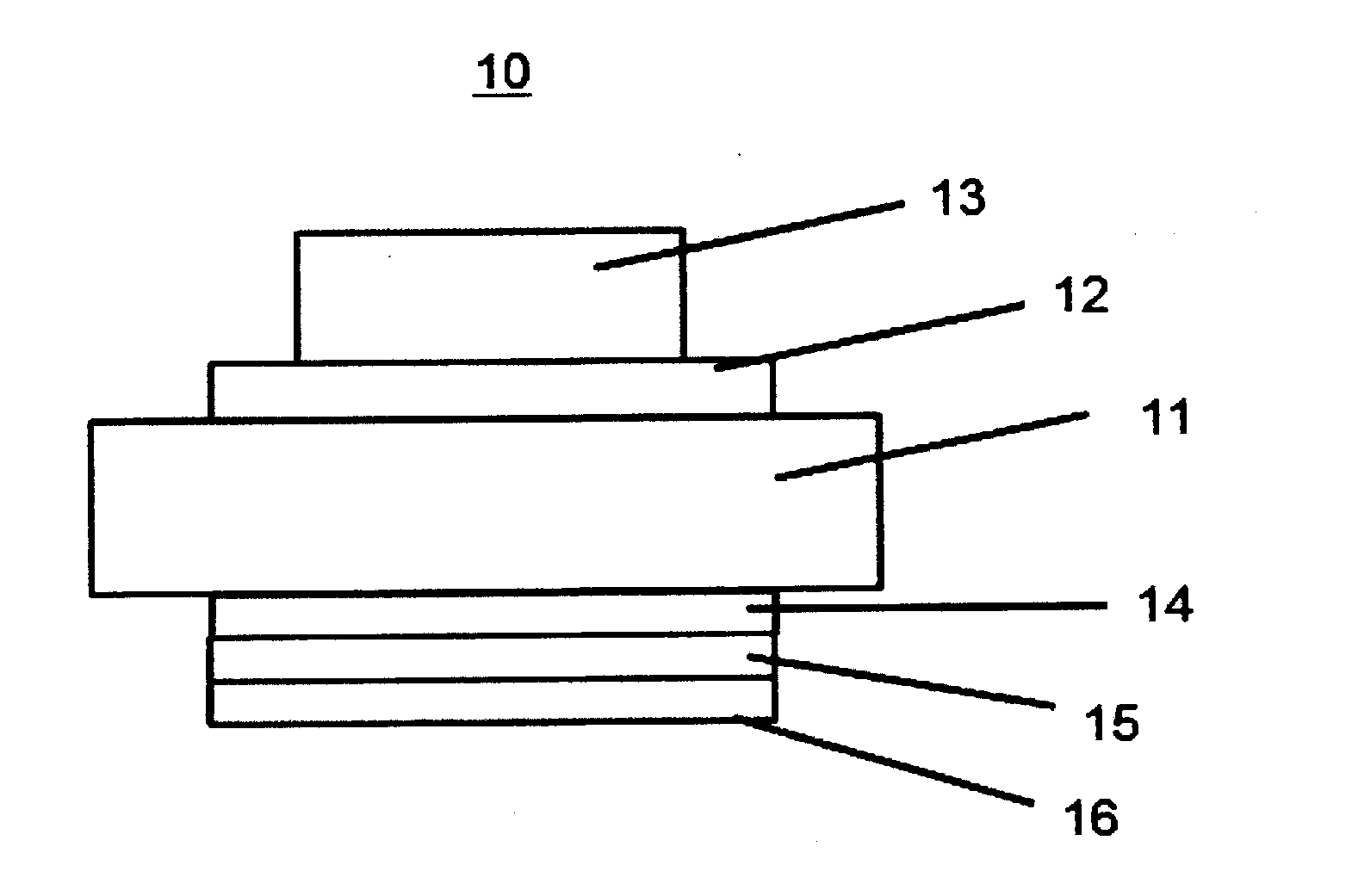

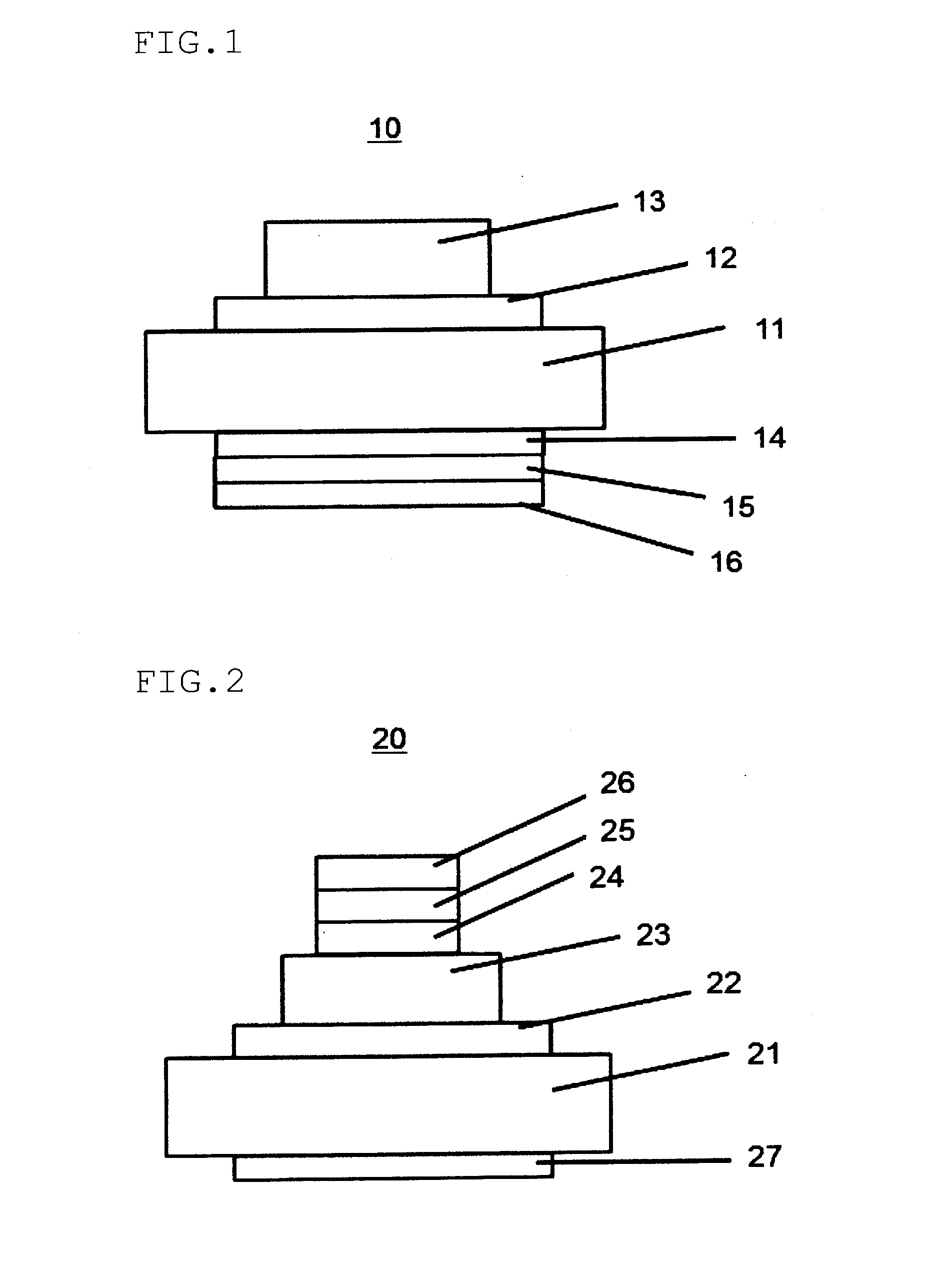

Bidirectional photothyristor chip, optical lighting coupler, and solid state relay

ActiveUS7423298B2Improving luminous sensitivityCoupling device detailsSemiconductor/solid-state device manufacturingOxygenSolid-state relay

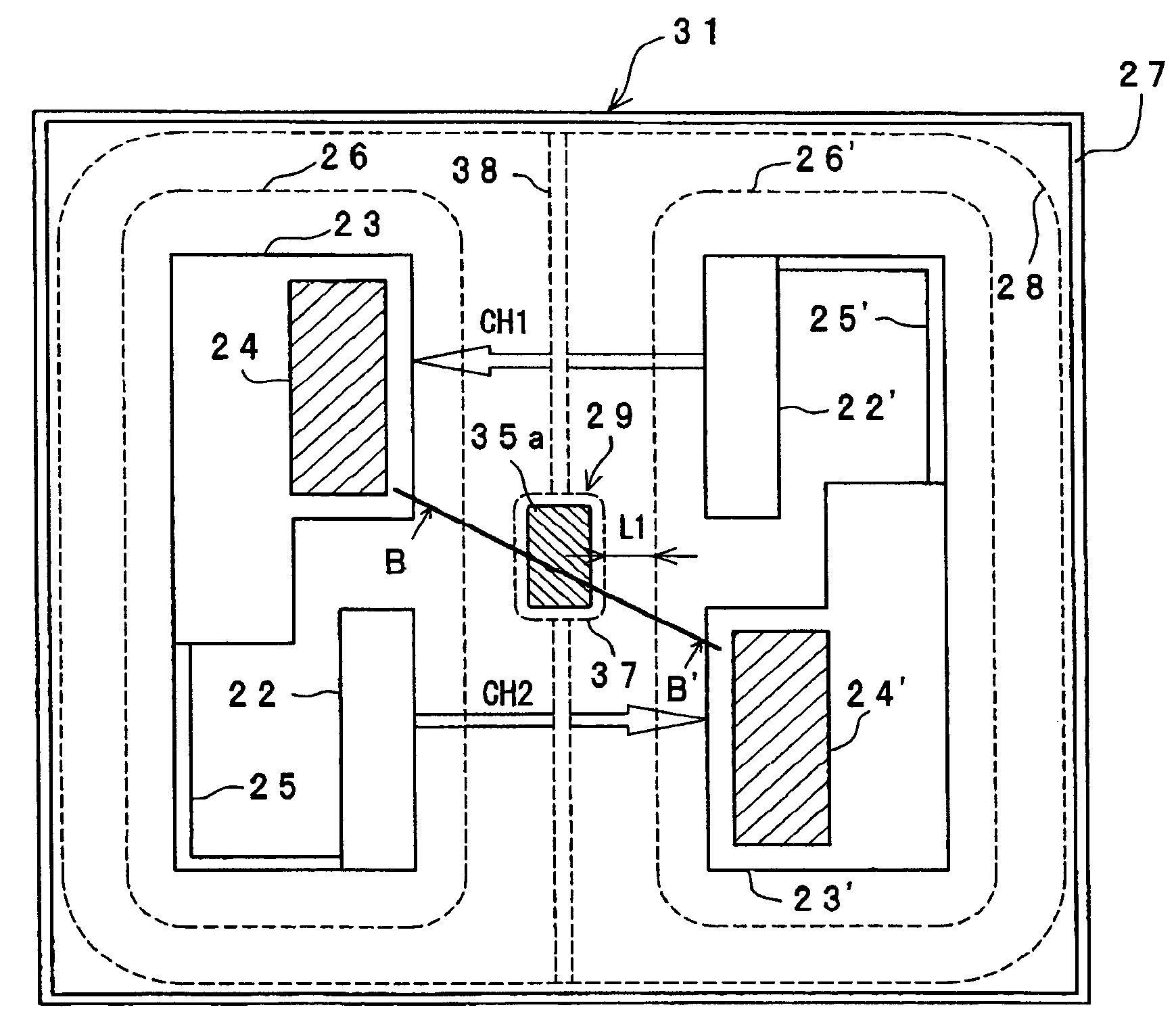

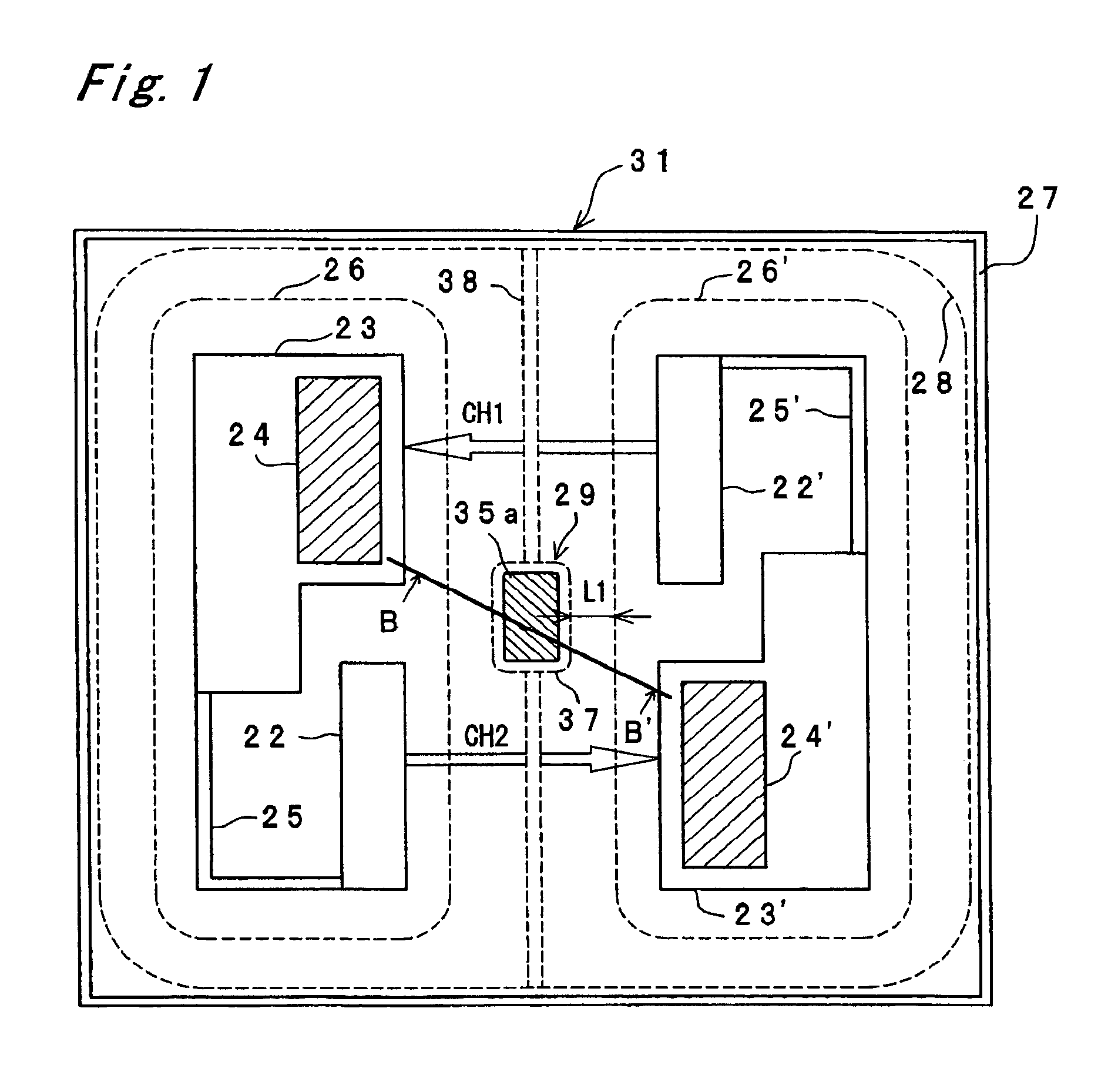

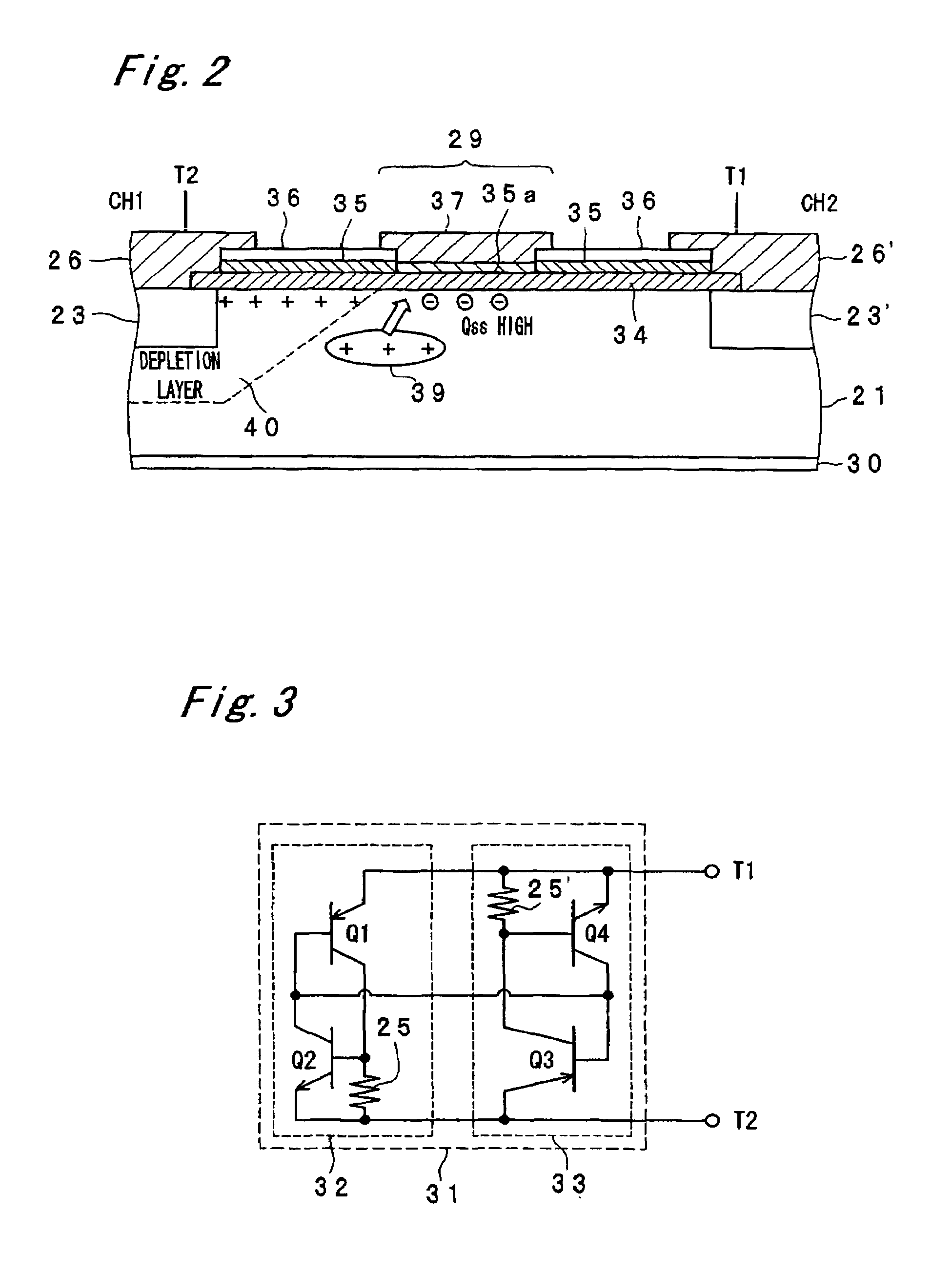

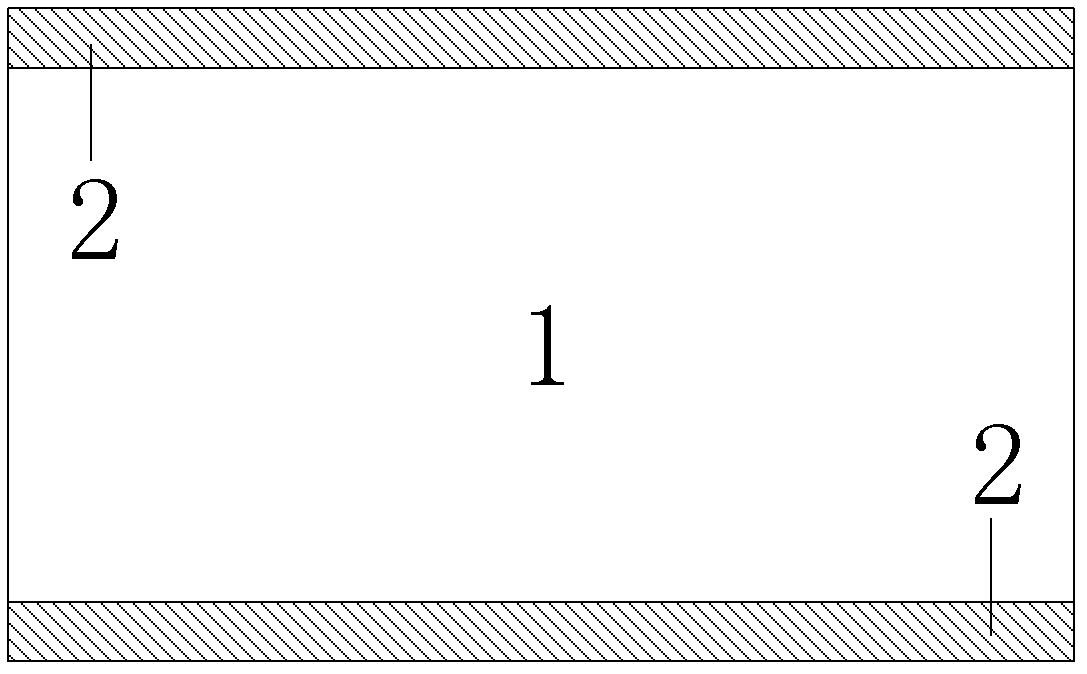

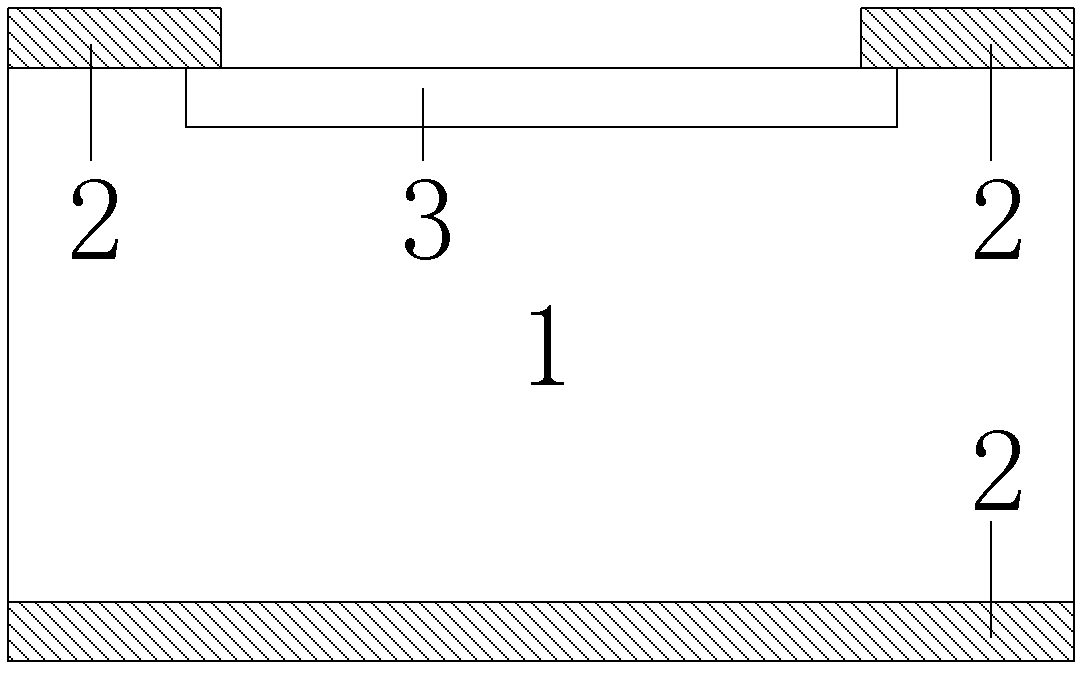

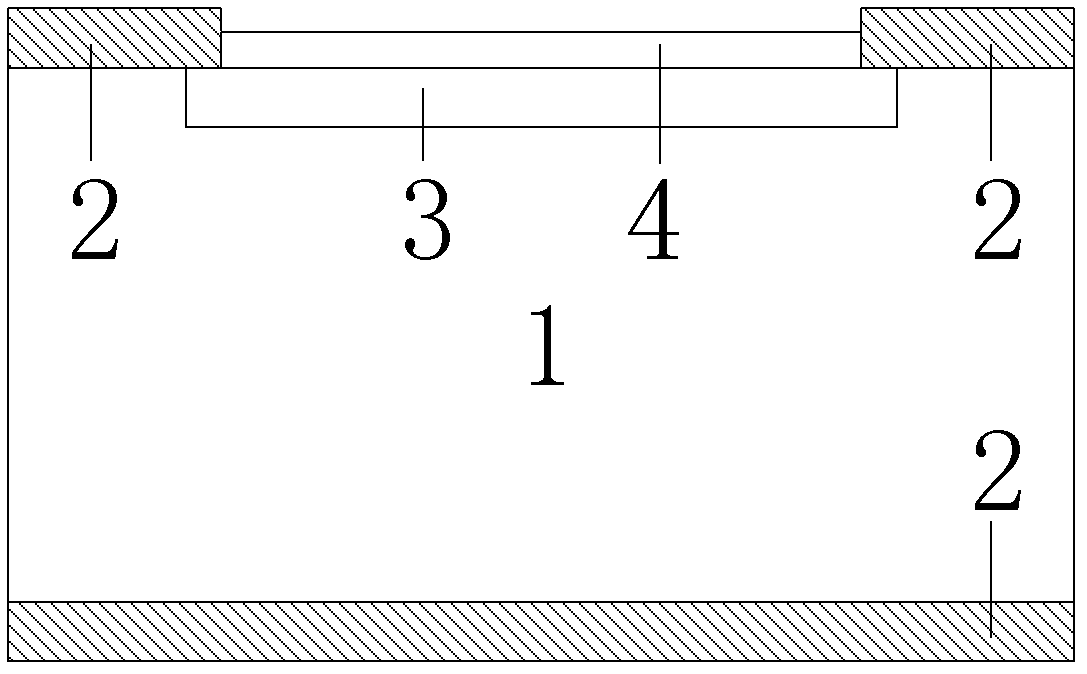

Two operation channels CH1 and CH2 of a bidirectional photothyristor chip 31 are disposed away from each other so as not to intersect with each other. In between a P-gate diffusion region 23 on the left-hand side and a P-gate diffusion region 23′ on the right-hand side on an N-type silicon substrate, and in between the CH1 and the CH2, a channel isolation region 29 comprised of an oxygen doped semi-insulating polycrystalline silicon film 35a doped with phosphorus is formed. Consequently, a silicon interface state (Qss) in the vicinity of the channel isolation region 29 on the surface of the N-type silicon substrate increases, so that holes or minority carriers in the N-type silicon substrate are made to disappear in the region. This makes it possible to prevent such commutation failure that when a voltage of the inverted phase is applied to the CH2 side at the point of time when the CH1 is turned off, the CH2 is turned on without incidence of light, and this allows a commutation characteristic to be enhanced.

Owner:SHARP KK

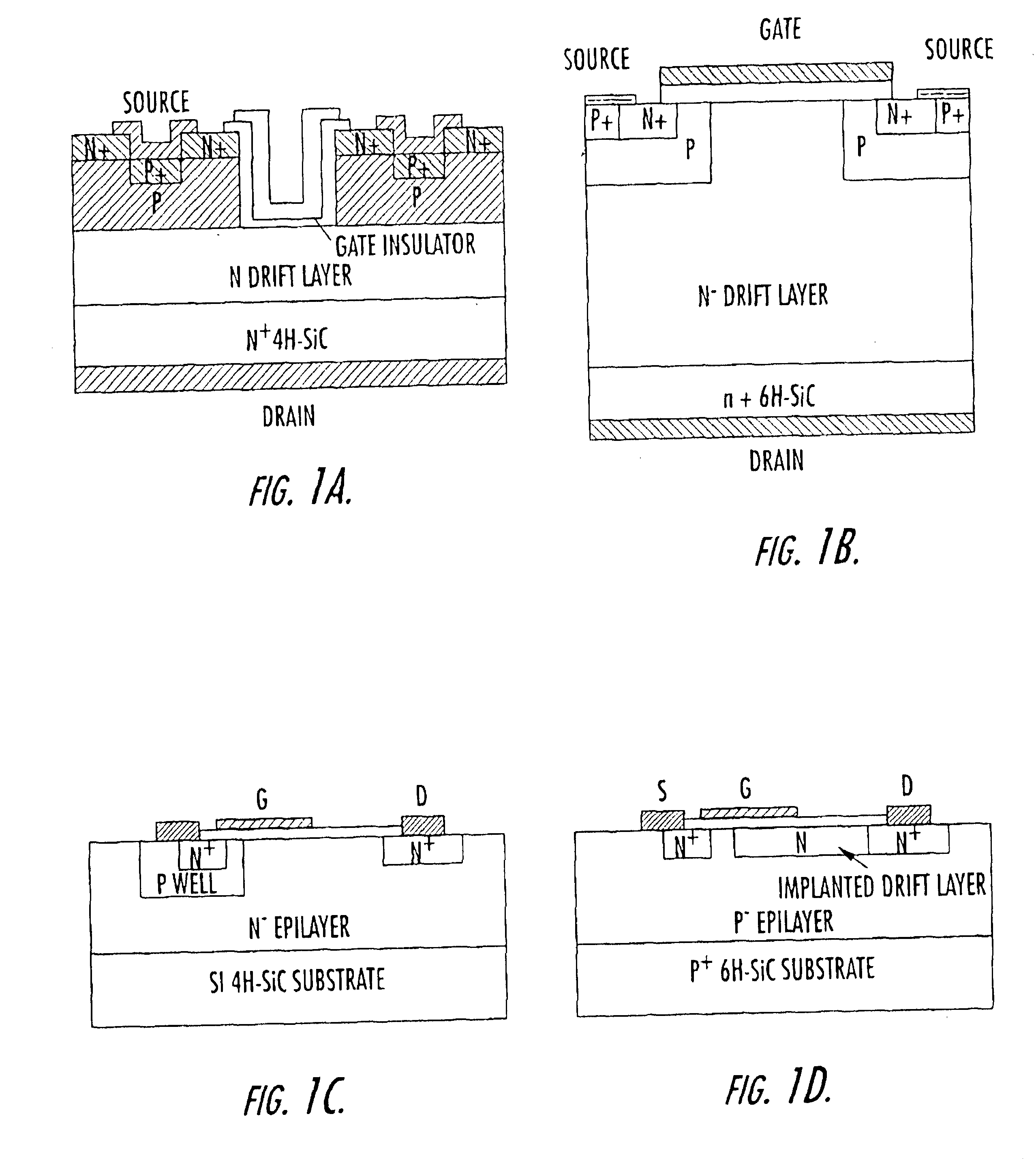

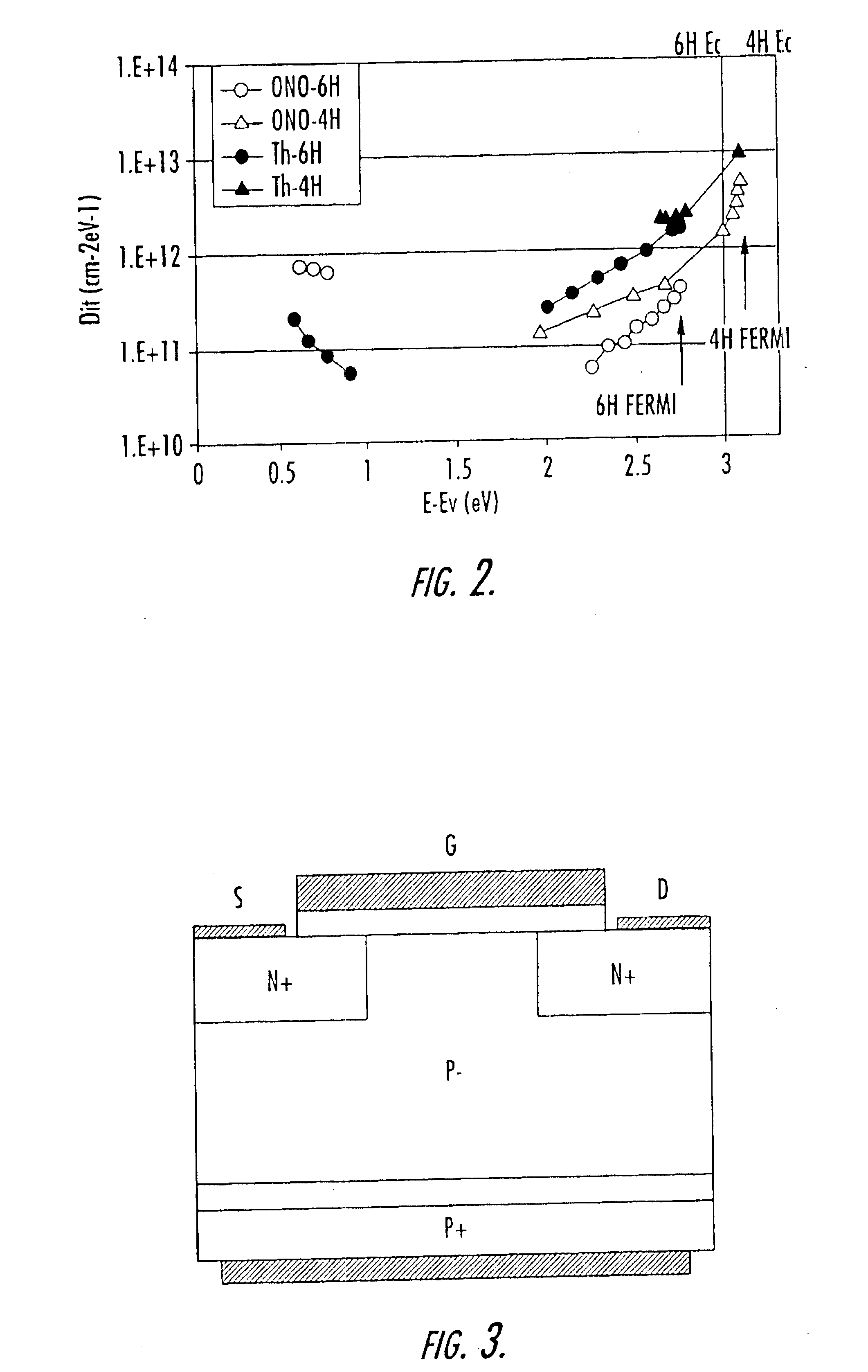

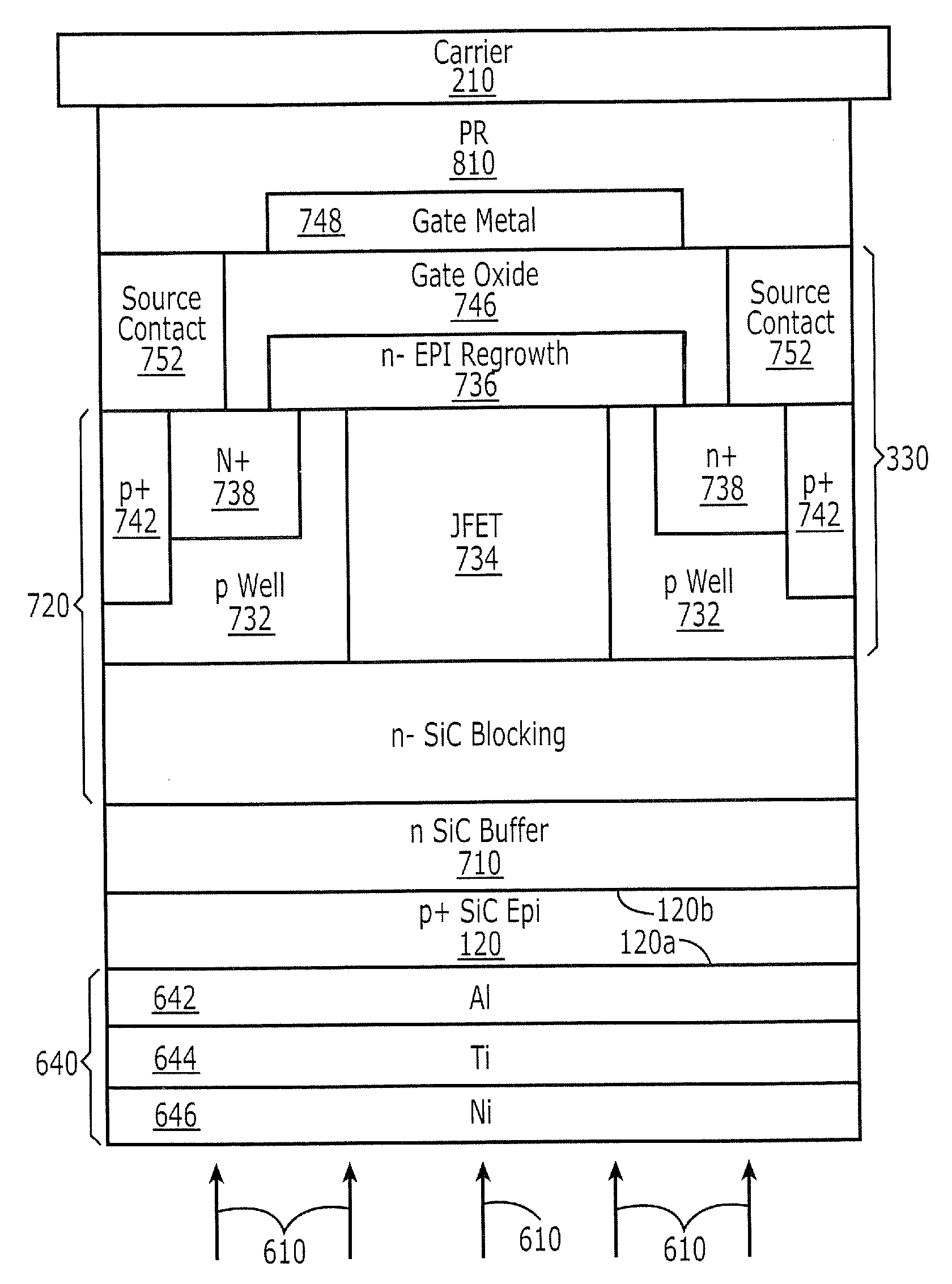

Silicon carbide power metal-oxide semiconductor field effect transistors having a shorting channel and methods of fabricating silicon carbide metal-oxide semiconductor field effect transistors having a shorting channel

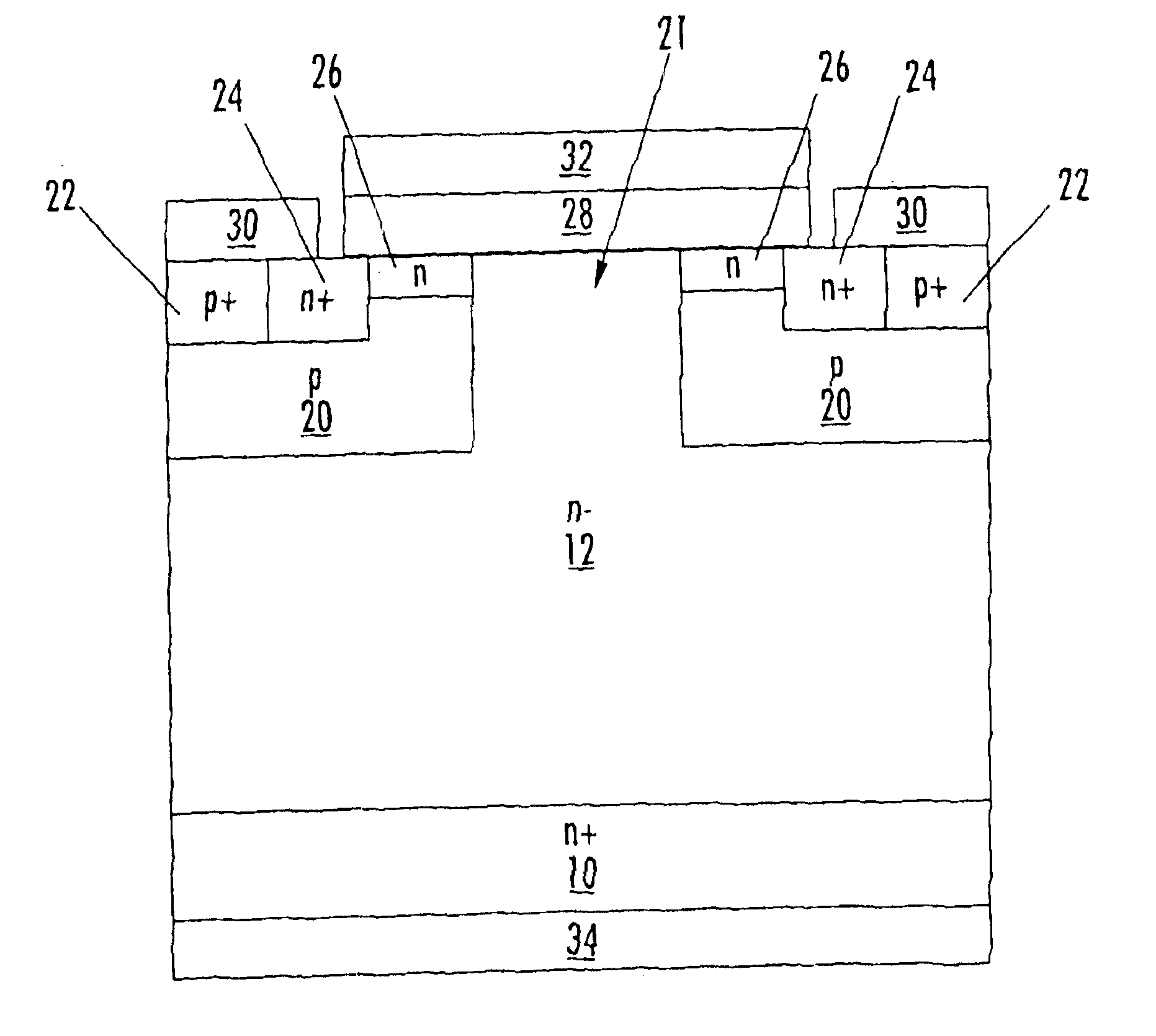

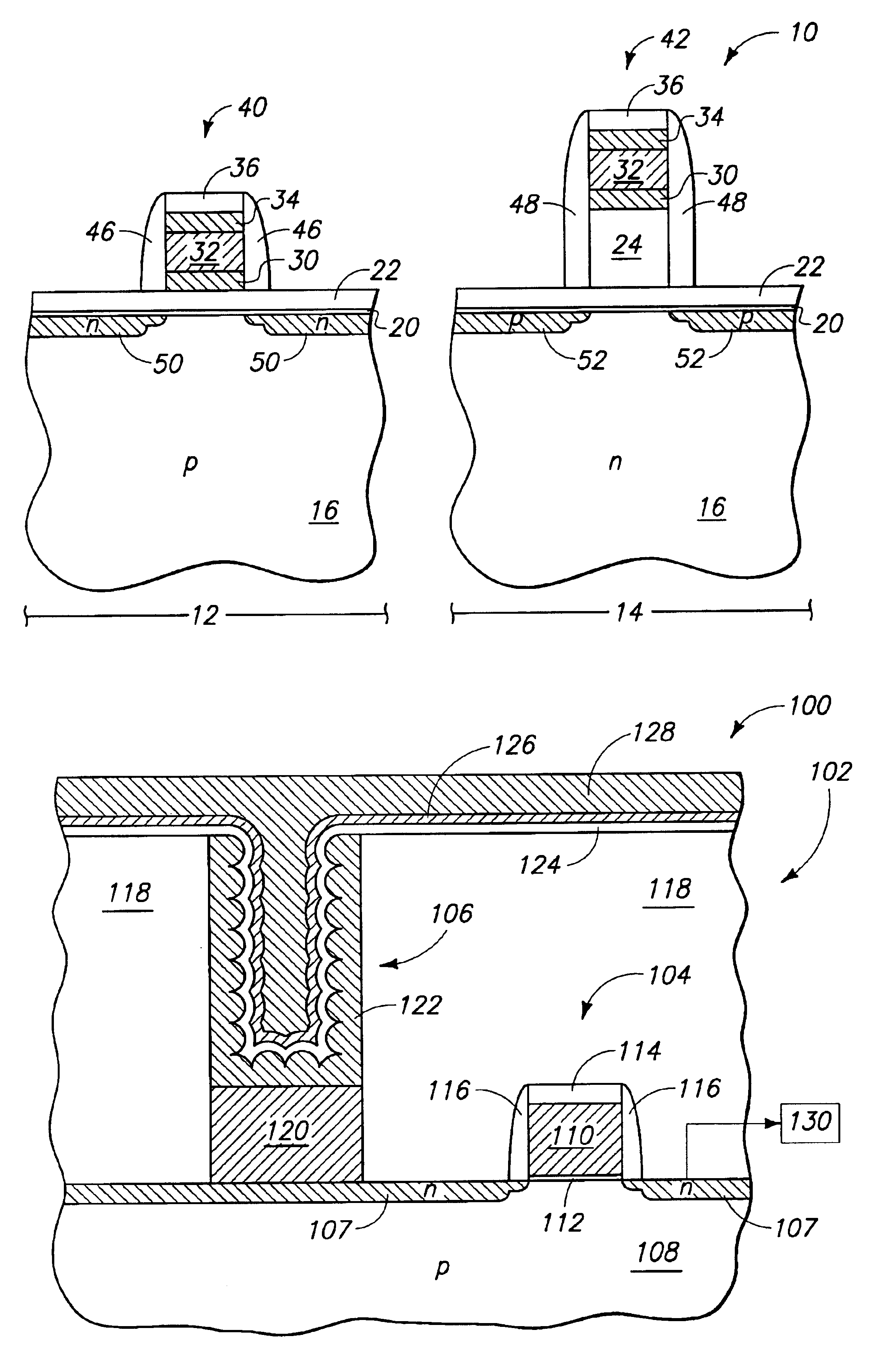

Silicon carbide metal-oxide semiconductor field effect transistors (MOSFETs) and methods of fabricating silicon carbide MOSFETs are provided. The silicon carbide MOSFETs have an n-type silicon carbide drift layer, spaced apart p-type silicon carbide regions in the n-type silicon carbide drift layer and having n-type silicon carbide regions therein, and a nitrided oxide layer. The MOSFETs also have n-type shorting channels extending from respective ones of the n-type silicon carbide regions through the p-type silicon carbide regions to the n-type silicon carbide drift layer. In further embodiments, silicon carbide MOSFETs and methods of fabricating silicon carbide MOSFETs are provided that include a region that is configured to self-deplete the source region, between the n-type silicon carbide regions and the drift layer, adjacent the oxide layer, upon application of a zero gate bias.

Owner:CREE INC

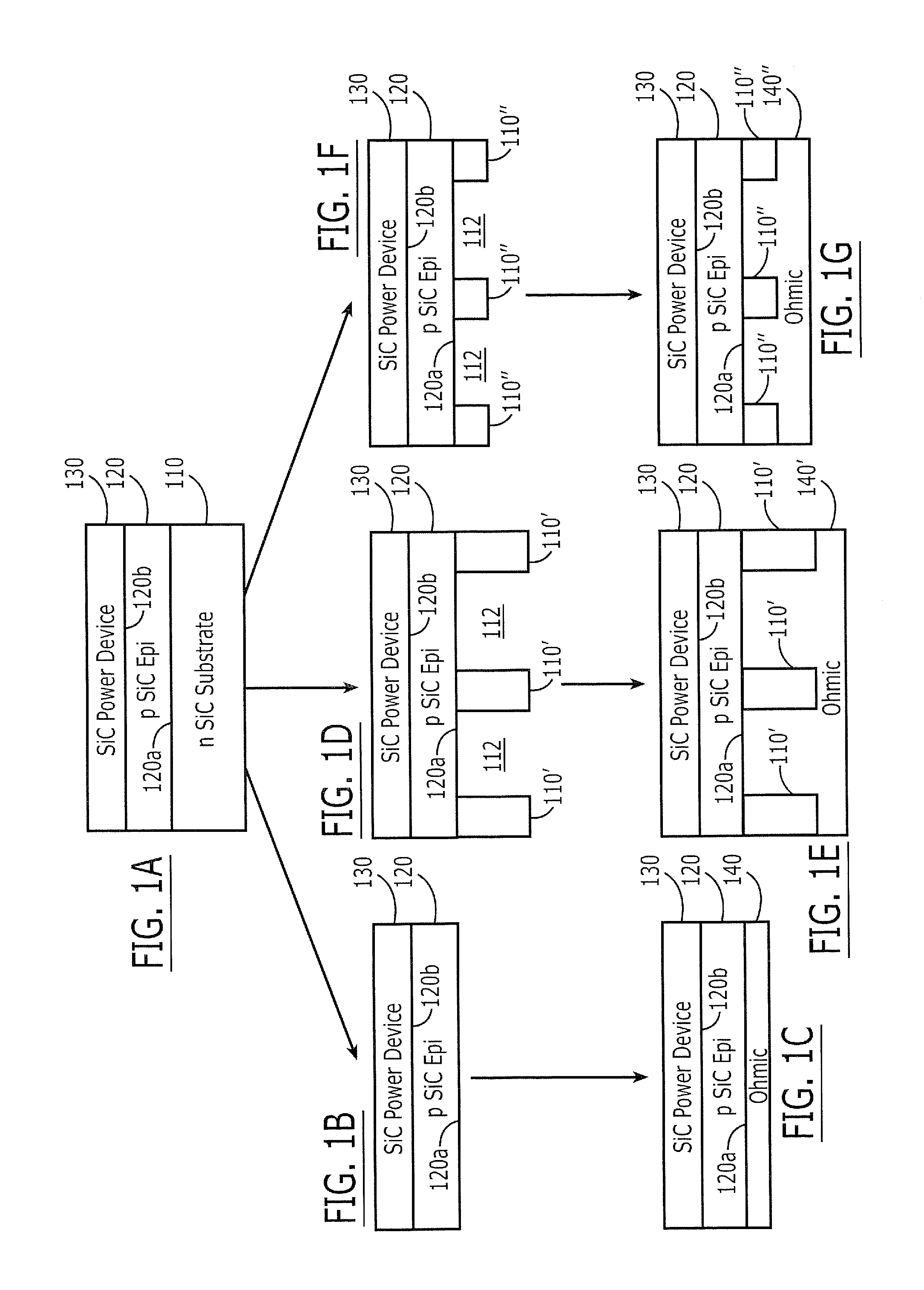

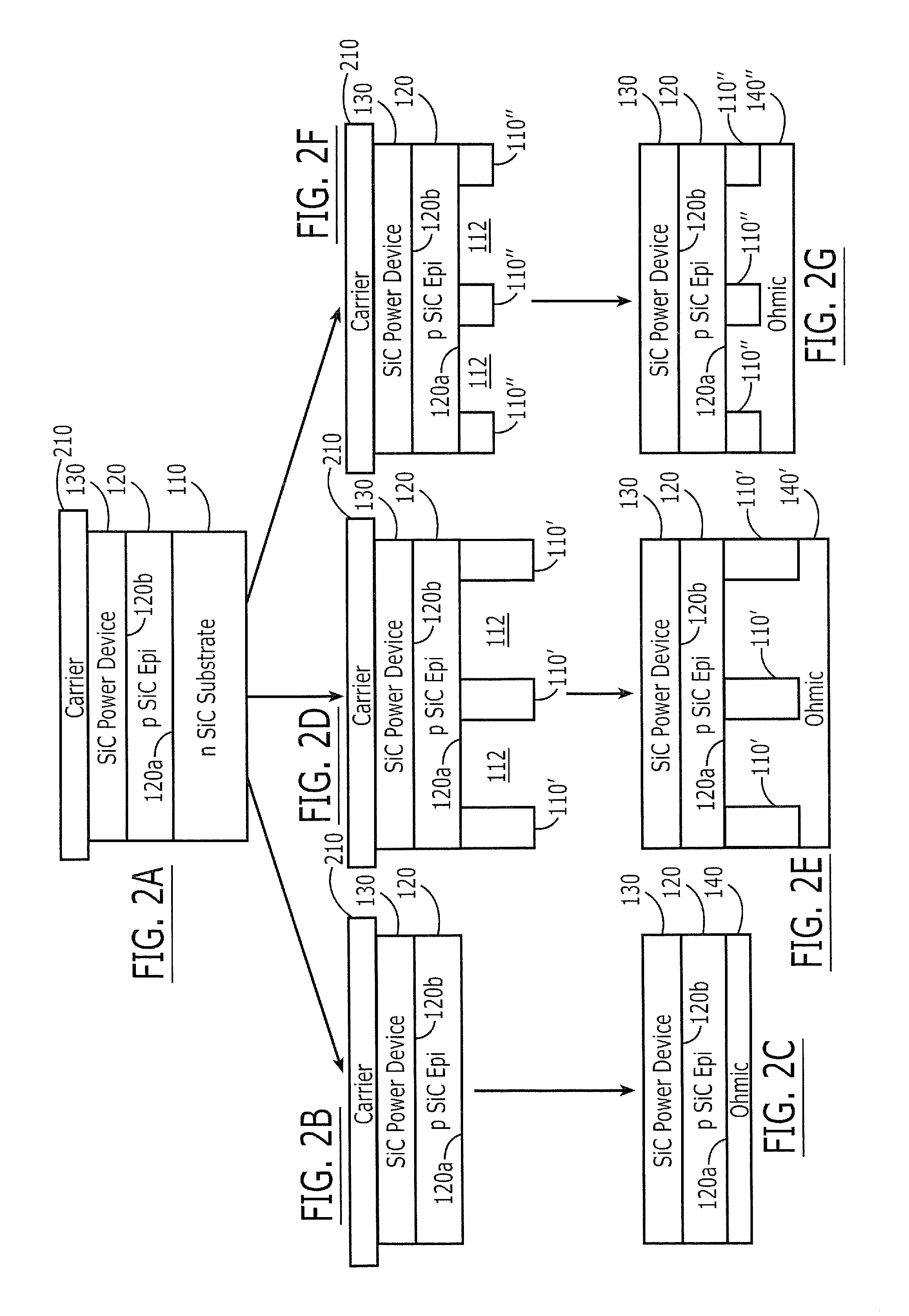

Methods of fabricating silicon carbide power devices by at least partially removing an n-type silicon carbide substrate, and silicon carbide power devices so fabricated

ActiveUS20080296771A1Eliminates and reduces disadvantagePotential disadvantageSemiconductor/solid-state device detailsSolid-state devicesOhmic contactCarbide

A silicon carbide power device is fabricated by forming a p-type silicon carbide epitaxial layer on an n-type silicon carbide substrate, and forming a silicon carbide power device structure on the p-type silicon carbide epitaxial layer. The n-type silicon carbide substrate is at least partially removed, so as to expose the p-type silicon carbide epitaxial layer. An ohmic contact is formed on at least some of the p-type silicon carbide epitaxial layer that is exposed. By at least partially removing the n-type silicon carbide substrate and forming an ohmic contact on the p-type silicon carbide epitaxial layer, the disadvantages of using a p-type substrate may be reduced or eliminated. Related structures are also described.

Owner:CREE INC

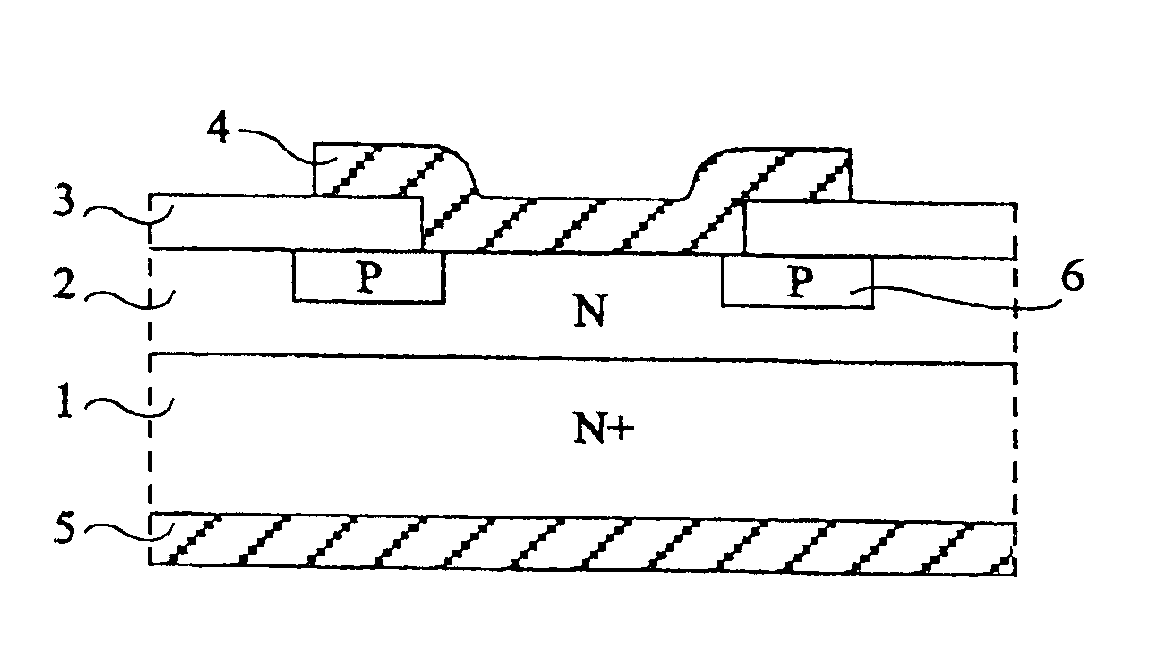

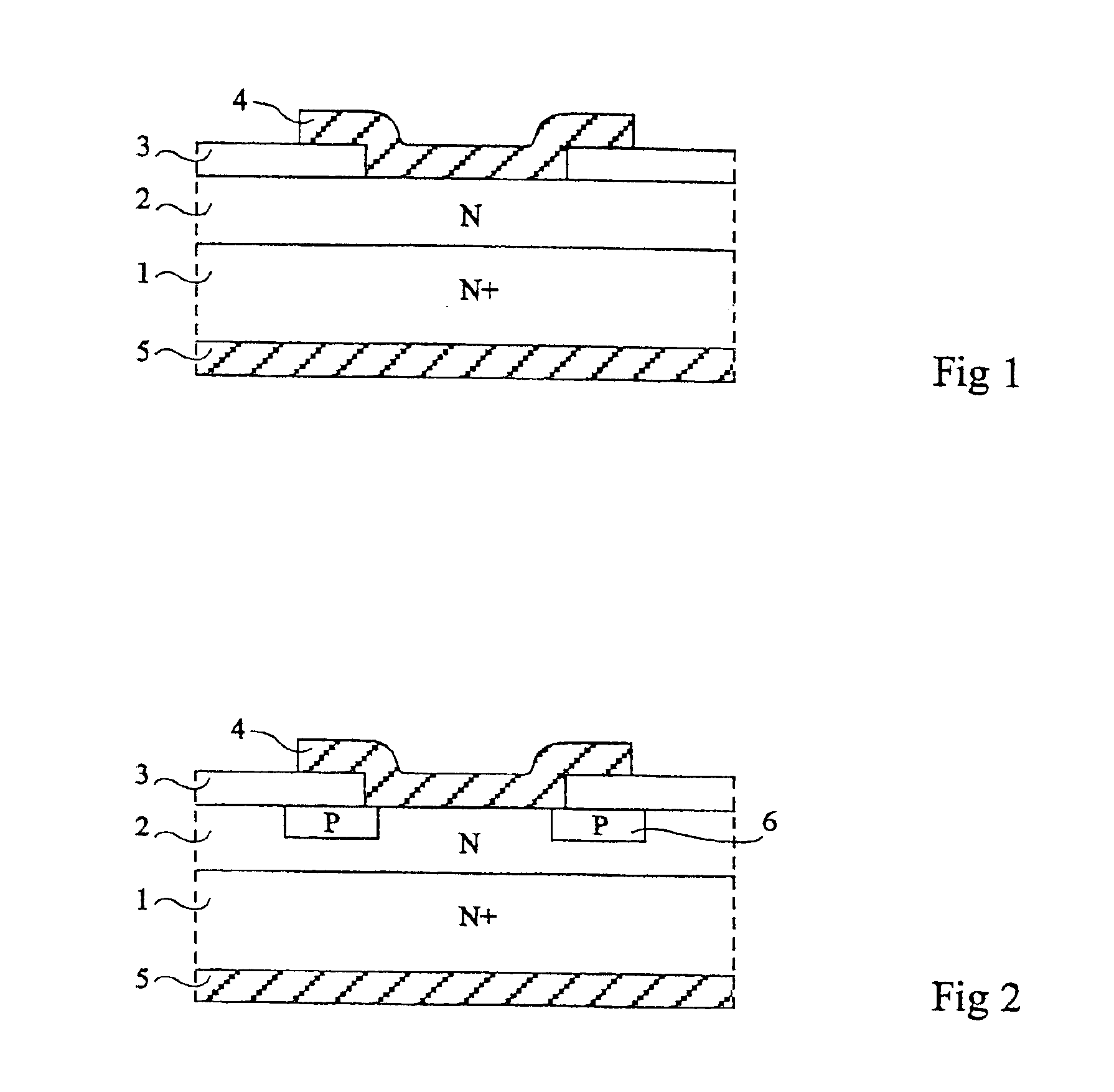

Method for producing a schottky diode in silicon carbide

InactiveUS6897133B2Semiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCarbide

The invention concerns a method for making a vertical Schottky diode on a highly doped N-type silicon carbide substrate (1), comprising steps which consist in forming an N-type lightly doped epitaxial layer (2); etching out a peripheral trench at the active zone of the diode; forming a type P doped epitaxial layer; carrying out a planarization process so that a ring (6) of the P type epitaxial layer remains in the trench; forming an insulating layer (3) on the outer periphery of the component, said insulating layer partly covering said ring; and depositing a metal (4) capable of forming a Schottky barrier with the N type epitaxial layer.

Owner:STMICROELECTRONICS SRL

Transistor devices, and methods of forming transistor devices and circuit devices

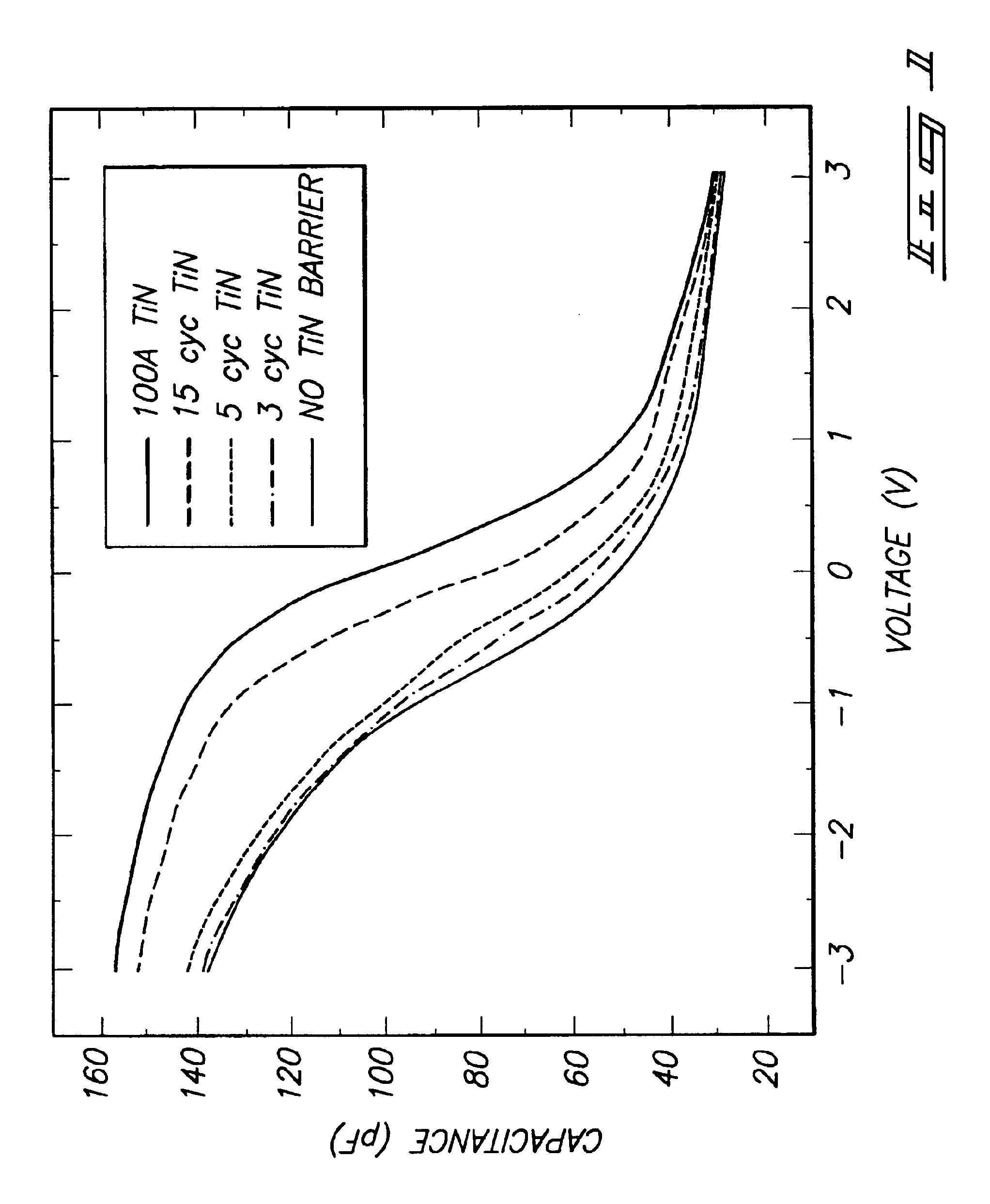

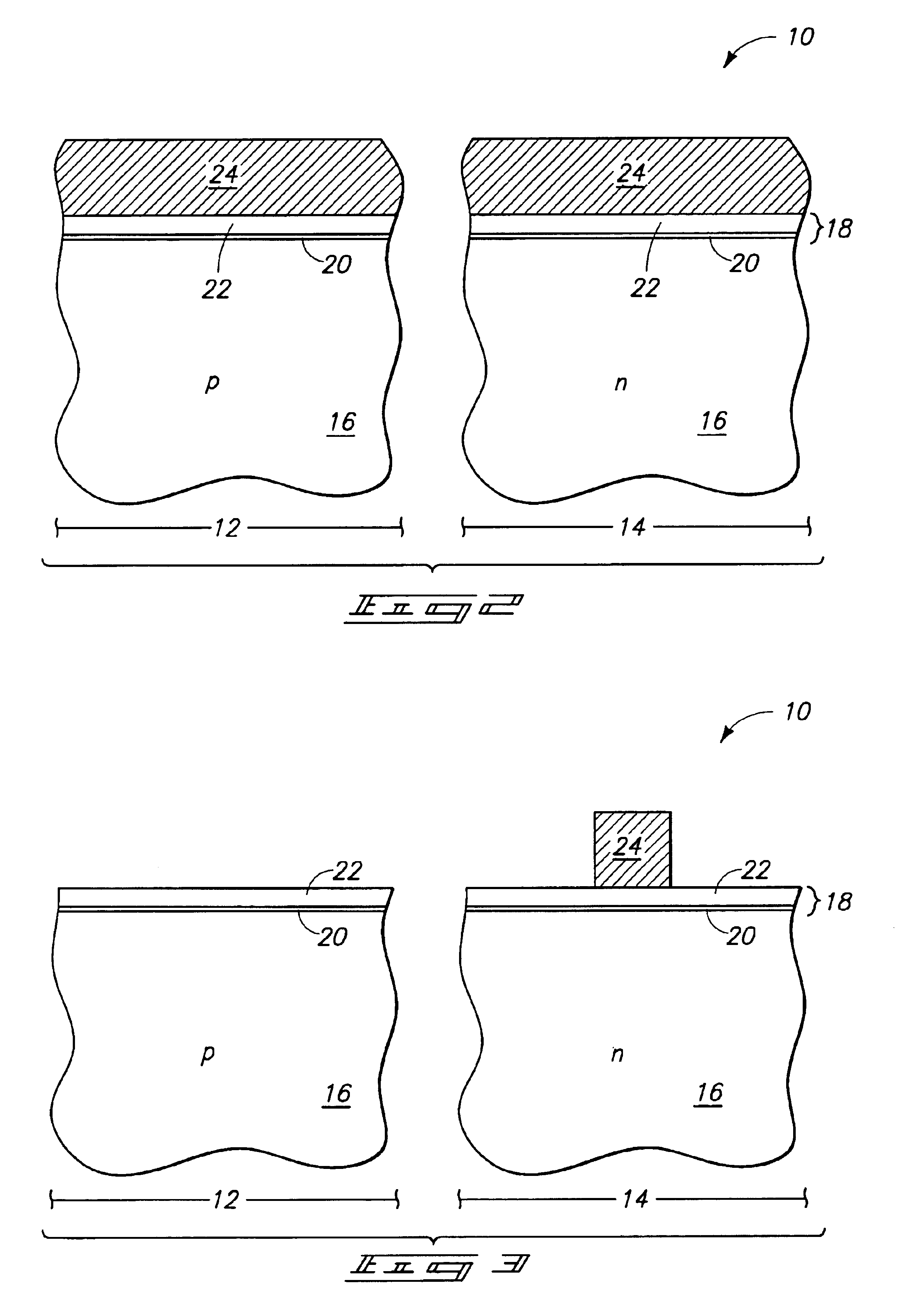

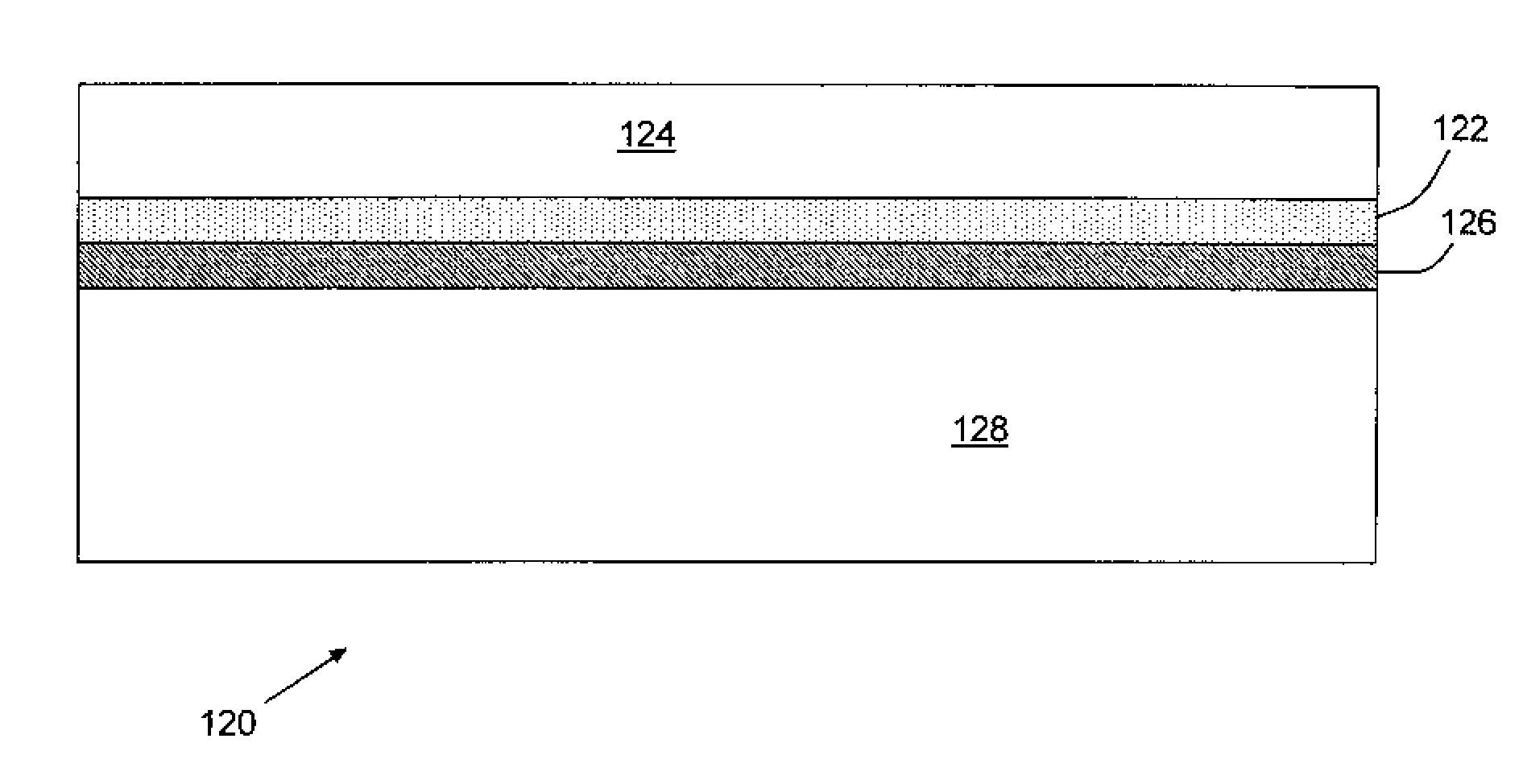

The invention includes methods of forming circuit devices. A metal-containing material comprising a thickness of no more than 20 Å (or alternatively comprising a thickness resulting from no more than 70 ALD cycles) is formed between conductively-doped silicon and a dielectric layer. The conductively-doped silicon can be n-type silicon and the dielectric layer can be a high-k dielectric material. The metal-containing material can be formed directly on the dielectric layer, and the conductively-doped silicon can be formed directly on the metal-containing material. The circuit device can be a capacitor construction or a transistor construction. If the circuit device is a transistor construction, such can be incorporated into a CMOS assembly. Various devices of the present invention can be incorporated into memory constructions, and can be incorporated into electronic systems.

Owner:MICRON TECH INC

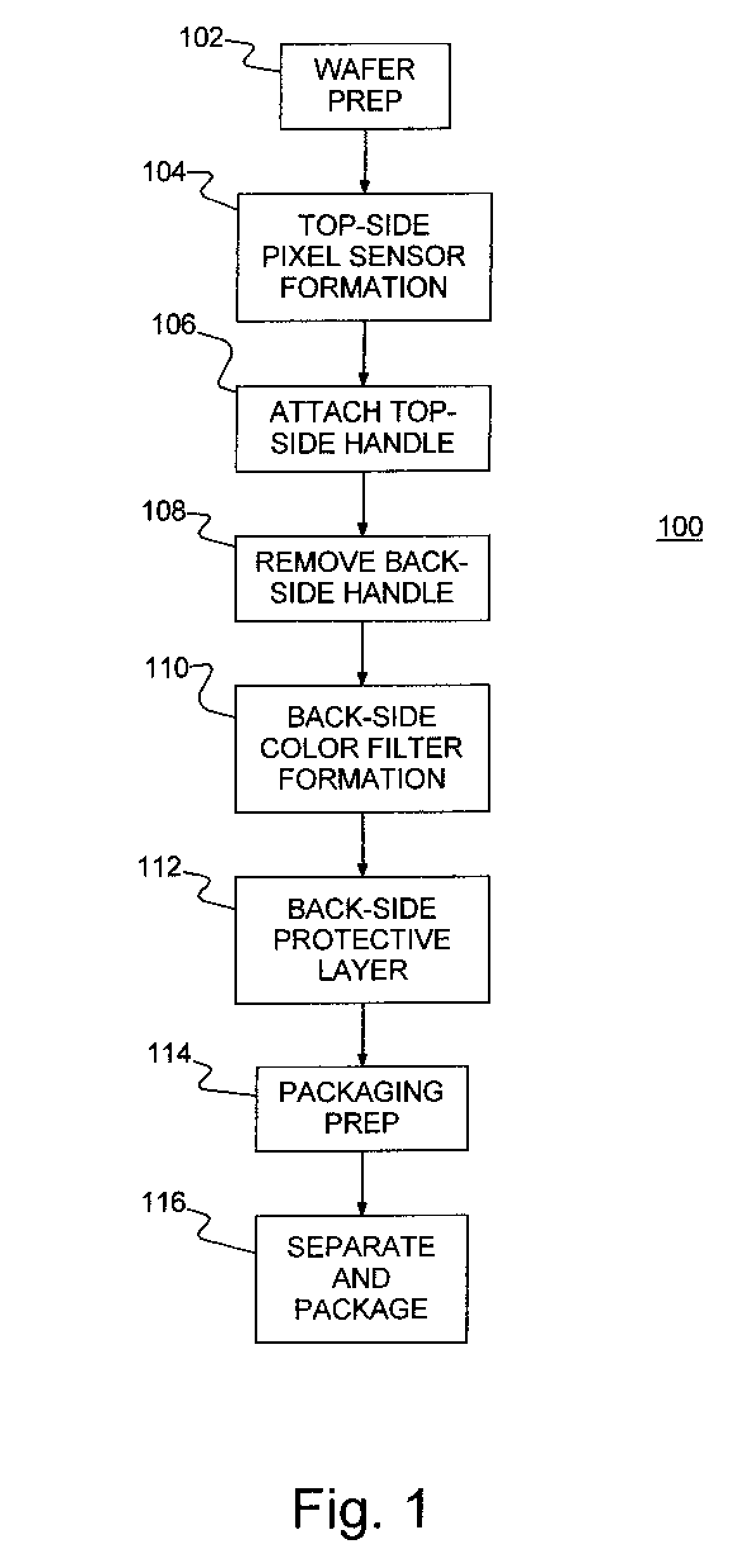

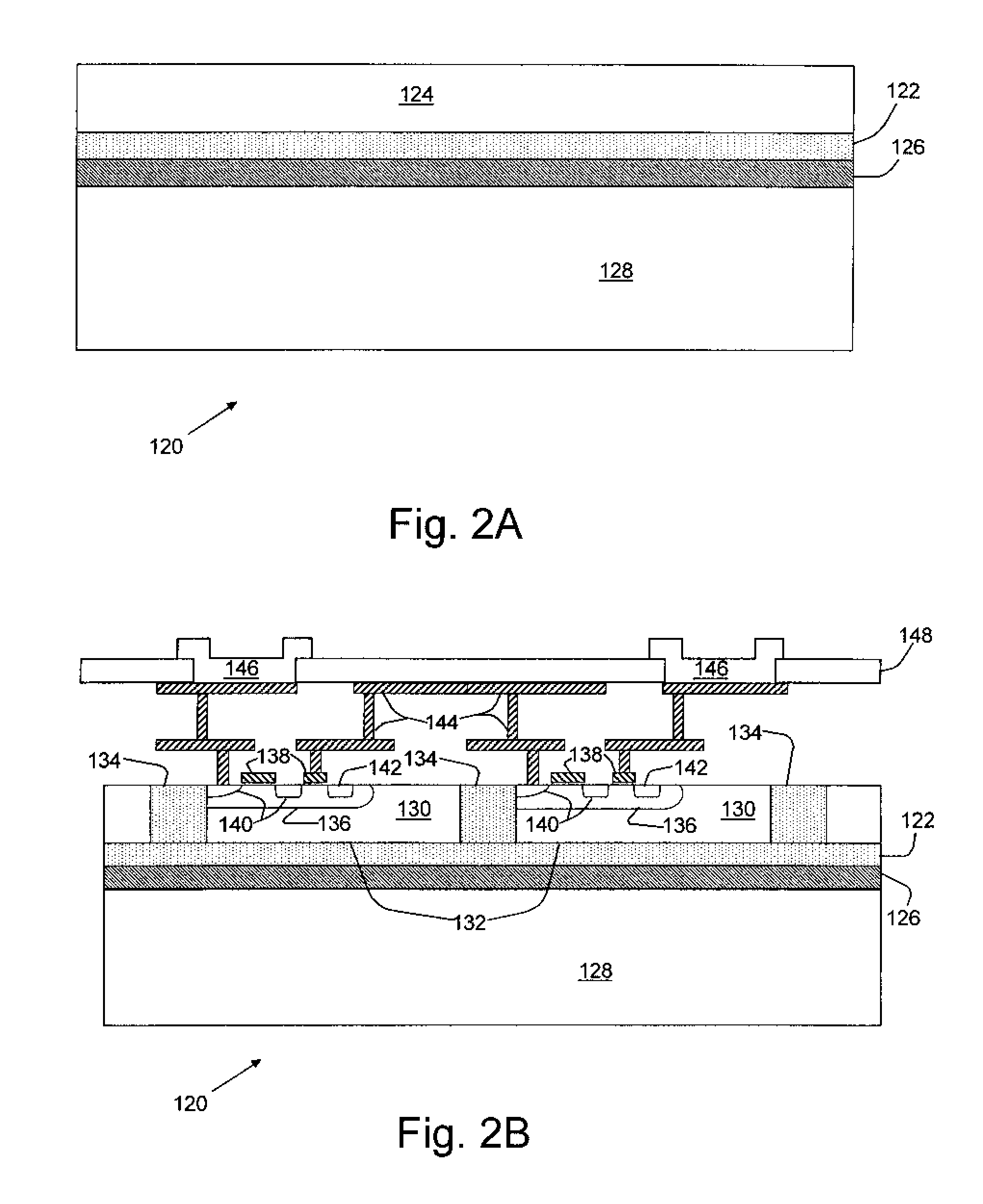

Photo-sensor and pixel array with backside illumination and method of forming the photo-sensor

ActiveUS20070194397A1Maximize signal receptionSolid-state devicesMaterial analysis by optical meansColor gelPhotodiode

Owner:SMARTSENS TECH (HK) CO LTD

Semiconductor device and manufacturing method therefor

InactiveUS20050199963A1High dielectric constantTransistorSolid-state devicesDielectricGate dielectric

An element isolation dielectric film is formed around device regions in a silicon substrate. The device regions are an n-type diffusion region, a p-type diffusion region, a p-type extension region, an n-type extension region, a p-type source / drain region, an n-type source / drain region, and a nickel silicide film. Each gate dielectric film includes a silicon oxide film and a hafnium silicate nitride film. The n-type gate electrode includes an n-type silicon film and a nickel silicide film, and the p-type gate electrode includes a nickel silicide film. The hafnium silicate nitride films are not on the sidewalls of the gate electrodes.

Owner:KK TOSHIBA

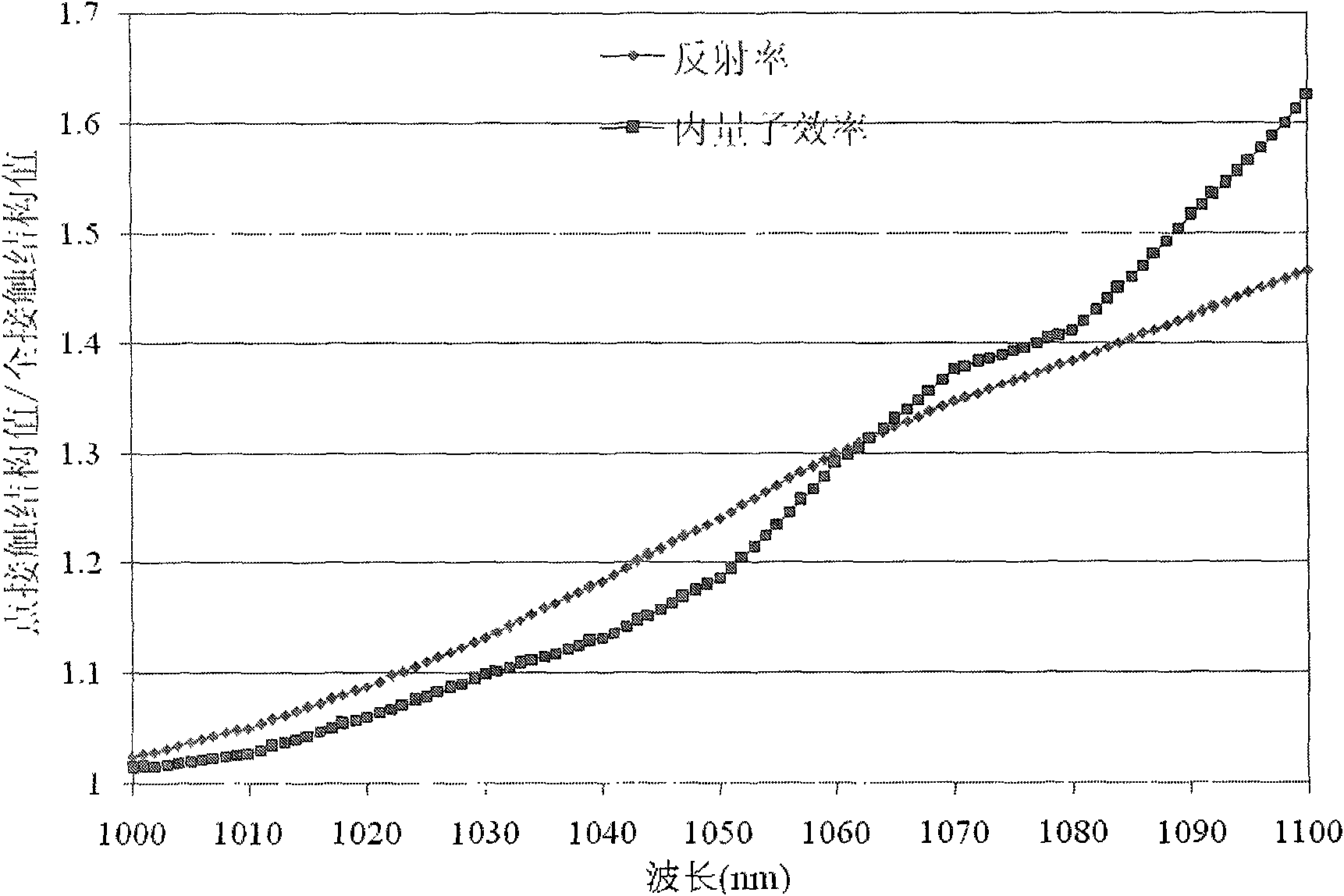

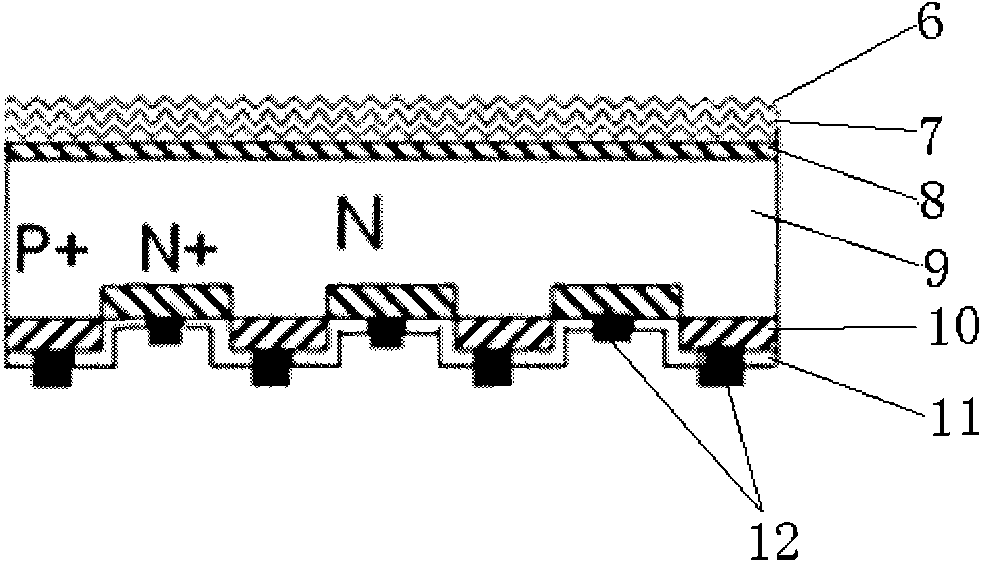

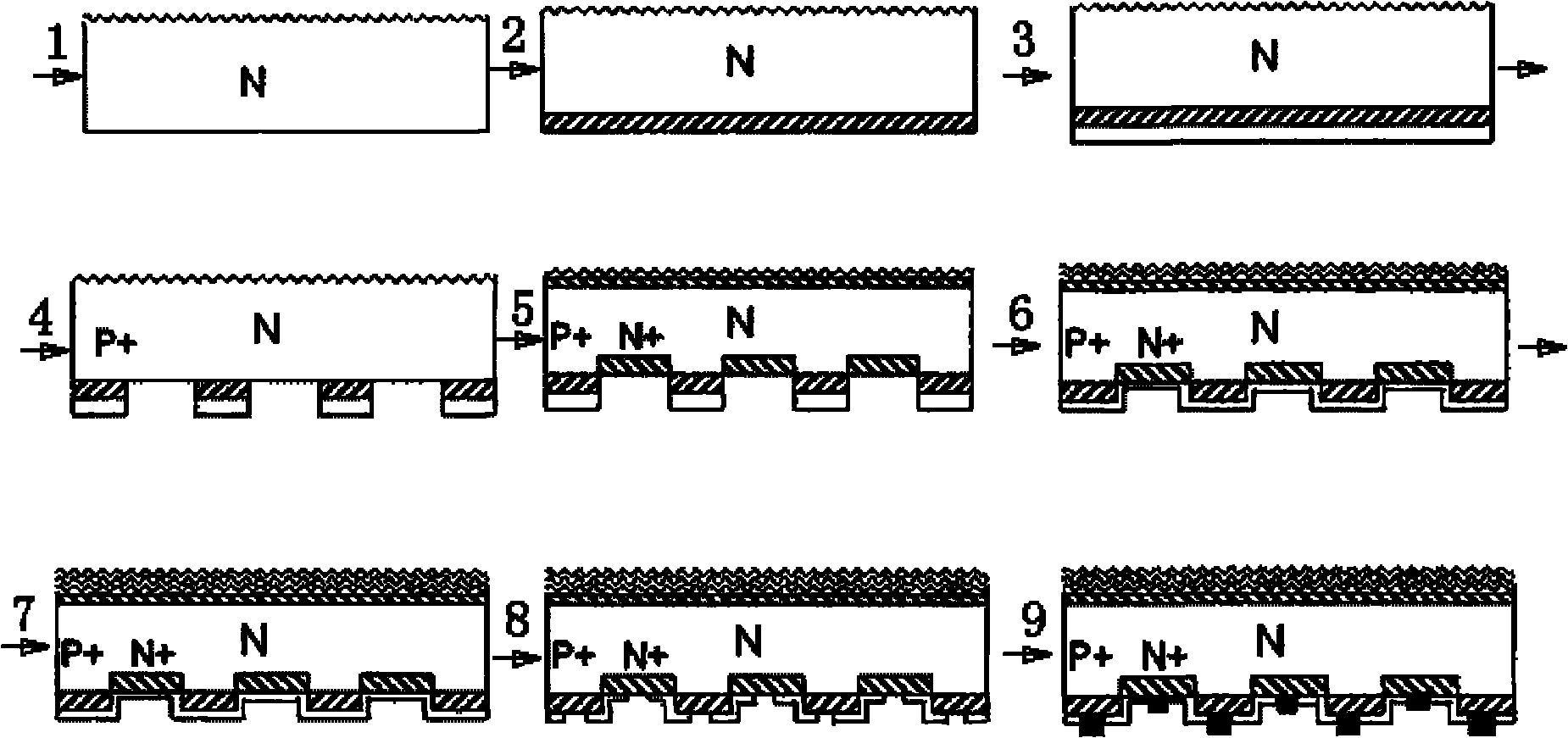

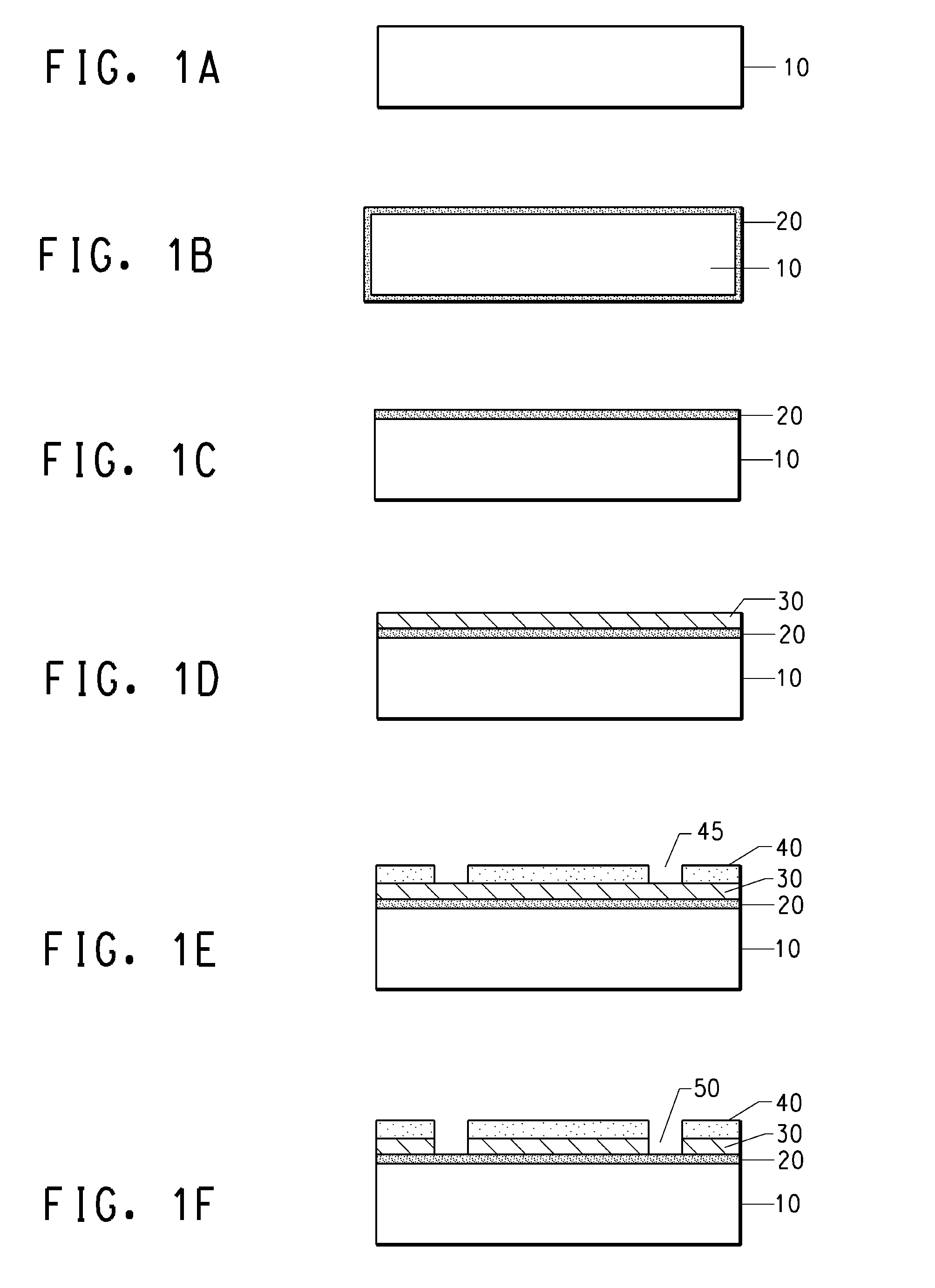

Method for preparing N-type crystalline silicon solar cell with aluminum-based local emitters on back side

InactiveCN101853897AAvoid damageAvoid Edge Leakage SituationsFinal product manufactureSemiconductor devicesP–n junctionMaterials science

The invention provides a method for preparing an N-type crystalline silicon solar cell with aluminum-based local emitters on the back side. The method comprises the following steps: firstly, selecting N-type silicon wafers to carry out the surface-textured etching process; further forming a front surface field through phosphorous diffusion; depositing a passivating film on the front surface after the phosphorosilicate glass is formed during the removal of diffused phosphorous; carrying out the back-side chemical polishing process on the silicon wafers to remove the N+ layer formed on the back side during the phosphorous diffusion; then, sequentially printing an aluminum layer or a silver-aluminum layer through the passivating film deposited on the back side, local holes or grooves on the back side and screens on the back side; then, printing silver paste on the front surface; and finally, carrying out the one-step sintering process to form a local P+ layer on the back side and allowing the P+ layer to coming into ohmic contact with the electrodes on the front and back surfaces. By using the N-type substrate, forming local aluminum-based P-N junctions on the back side and further using the back-side chemical polishing process to remove the edge junctions, the invention can substitute for the conventional stacking-type plasma etching process, simplify the technological procedures and further bring a series of performance improvement to cells.

Owner:JA YANGZHOU SOLAR PHOTOVOLTAIC ENG

Method for manufacturing back contact solar energy batteries

ActiveCN101777603ASimple processEasy to implementFinal product manufactureSemiconductor devicesNon dopedSolar cell

The invention discloses a method for manufacturing back contact solar energy batteries, comprises the following steps of: firstly growing a P type doped silicon dioxide layer on an N type silicon chip; then growing a non-doped silicon dioxide layer on a P type doped layer; after that, printing a corrosive agent or an anti corrosive agent on the non-doped silicon dioxide layer to corrode the P type doped silicon dioxide layer and the non-doped silicon dioxide layer so as to form required patterns; and finally carrying out N type adulteration on the back face and the front face of the silicon chip to form an N type doped layer. The P type doped layer is protected by the non-doped silicon dioxide layer, and an N front surface field on the front face of the battery and a PN alternating doped layer on the back face of the battery are realized in the N type doped step at the same time, thereby reducing the diffusion step, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

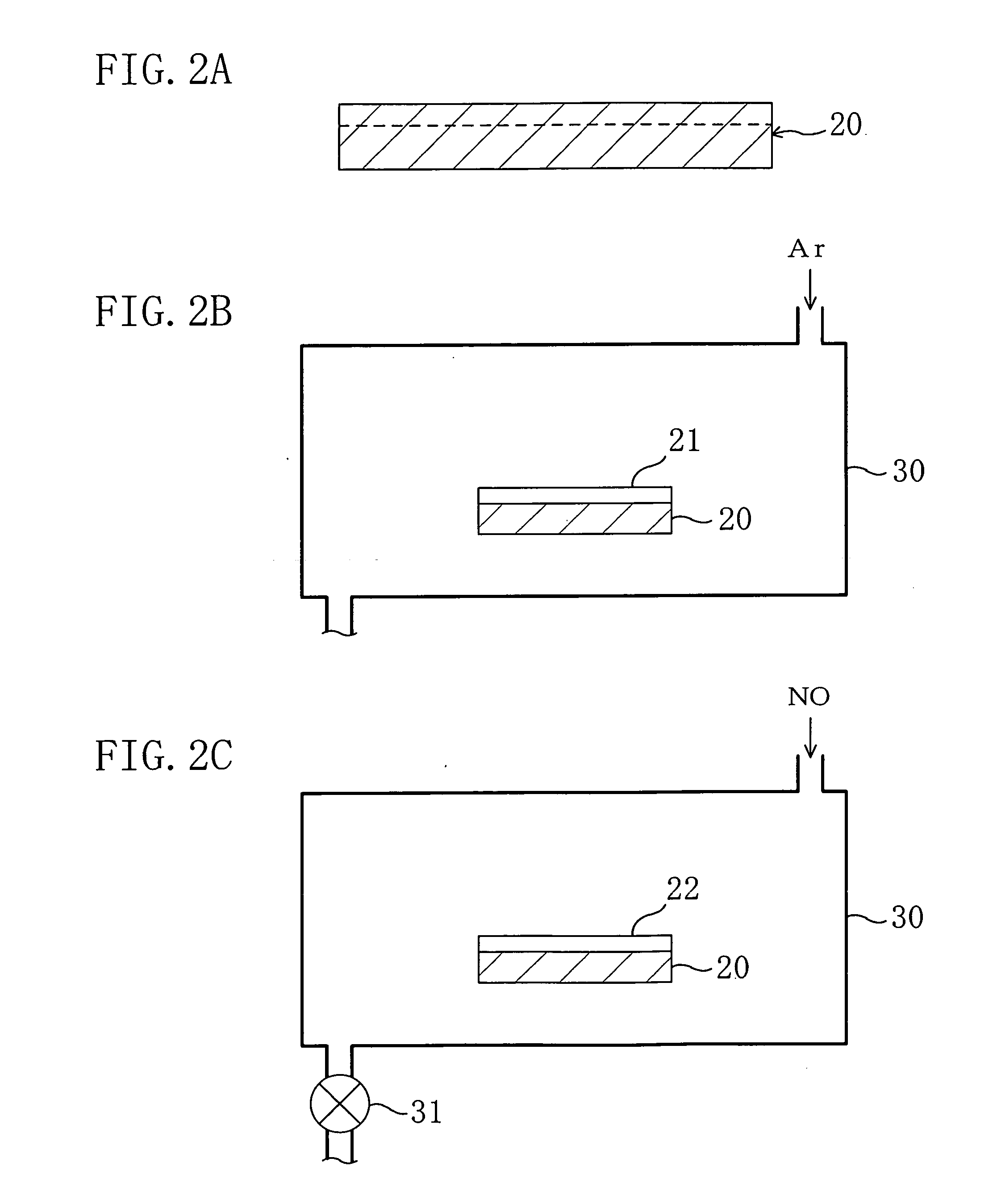

Semiconductor device manufacturing method

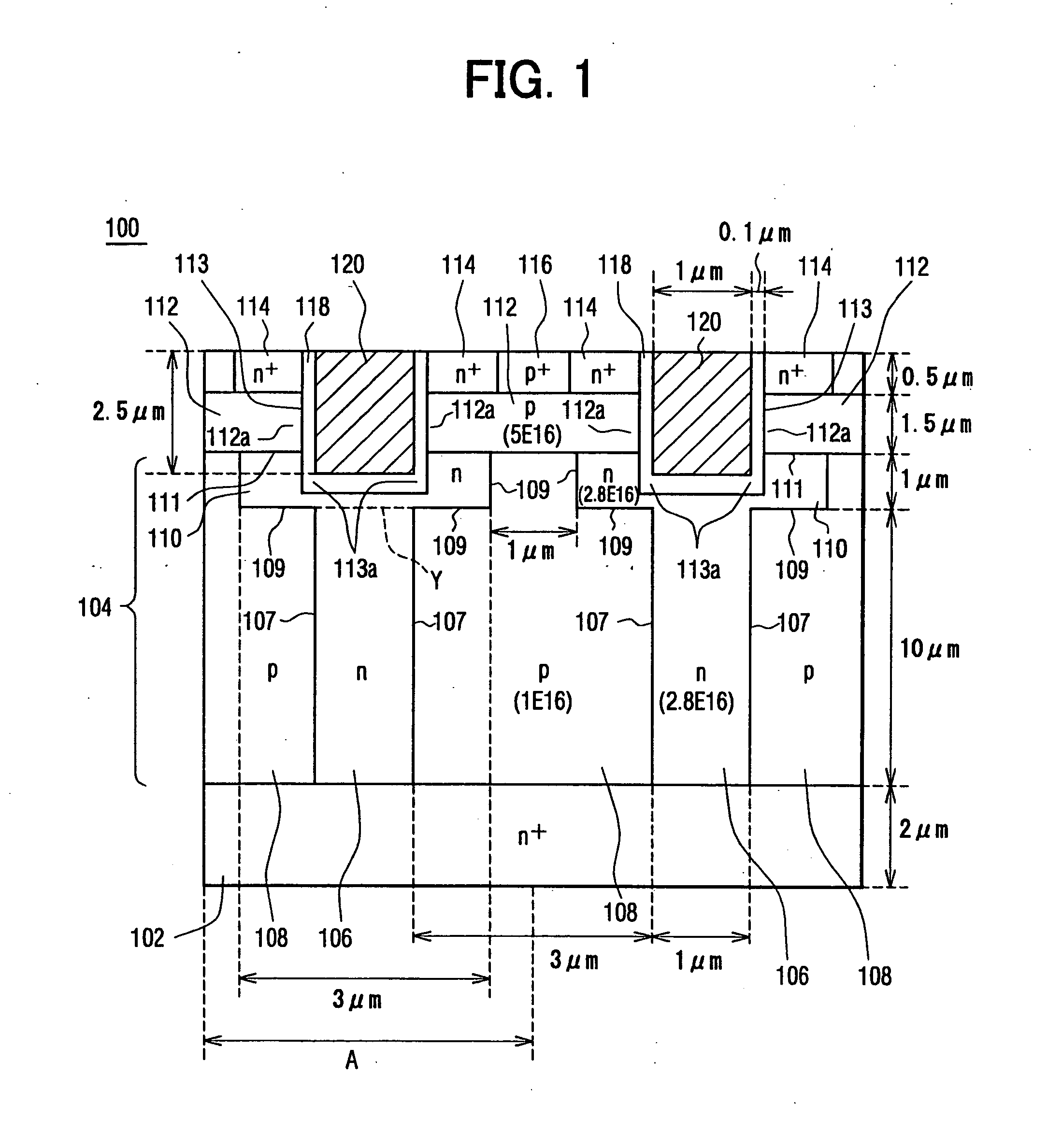

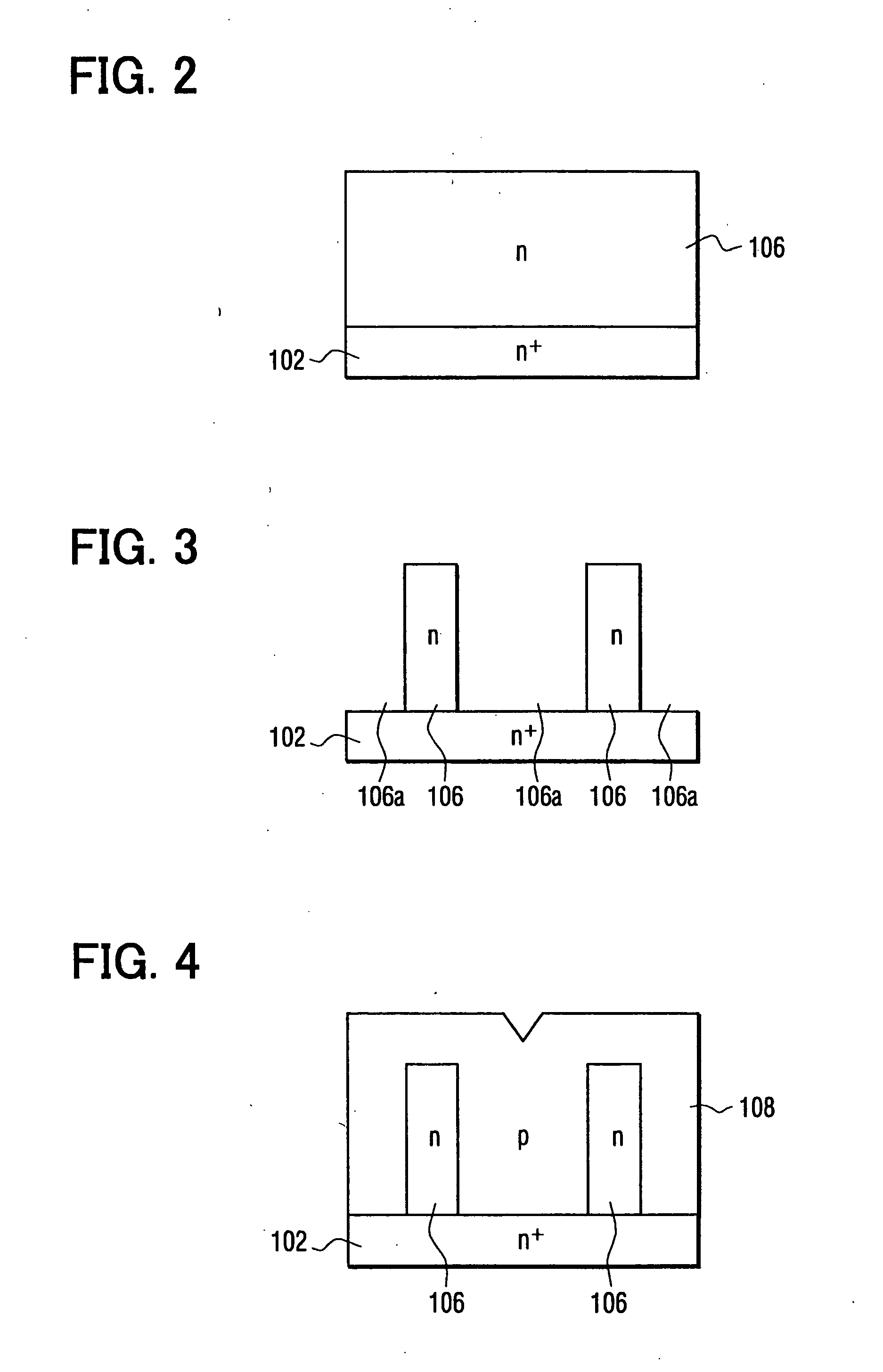

InactiveUS20050035401A1Easy to integrateAvoid resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialP type silicon

A semiconductor device includes: an n+ type drain region; an n type drift region that connects with the n+ type drain region; a p type body region; a n+ type source region that connects with the p type body region; and a gate electrode that is provided, with being covered by a gate insulation film, in a gate trench that penetrates the p type body region. The semiconductor further includes: a p type silicon region that adjoins the n type drift region; and an n type silicon region provided in a region almost including a carrier passage that connects the n type drift region and the p type body region. Here, the p type silicon region and the p type body region directly connect with each other.

Owner:DENSO CORP

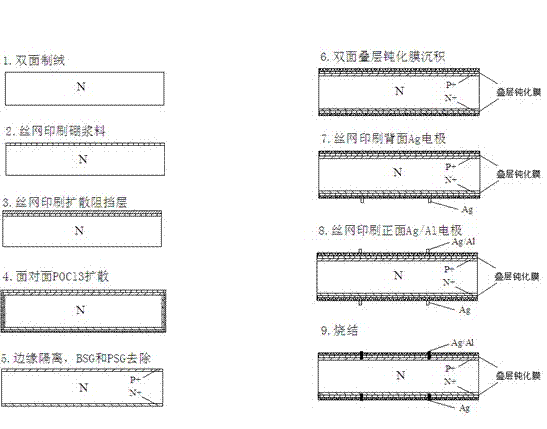

N-type double-sided battery and manufacturing method thereof

InactiveCN104538501AImprove efficiencyIncrease production capacityFinal product manufactureSemiconductor/solid-state device manufacturingScreen printingOptoelectronics

The invention discloses an N-type double-sided battery and a manufacturing method thereof. The manufacturing method comprises the following steps that S1, texturing treatment is performed; S2, a boron source is evenly coated on the upper surface of an N-type silicon wafer in a spin coating or silk-screen printing mode, and boron diffusion is conducted in a furnace tube; S3, a mask is manufactured; S4, phosphorus diffusion is conducted on the lower surface of the N-type silicon wafer, and a high-low-junction structure is formed on the lower surface; S5, phosphorosilicate glass and the mask manufactured in the step S3 are removed; S6, a passivation anti-reflection film made from aluminum oxide and silicon nitride is manufactured on the surface of the diffused boron, and a silicon nitride passivation anti-reflection film is manufactured on the surface of the diffused phosphorus; S7, electrodes are manufactured. The manufacturing method of the N-type double-sided battery is simple in process, and the efficiency of the battery is effectively improved. In addition, a passivation layer manufacturing method of the N-type double-sided battery is a low-temperature process, and a PN junction is not damaged.

Owner:SUZHOU TALESUN SOLAR TECH CO LTD

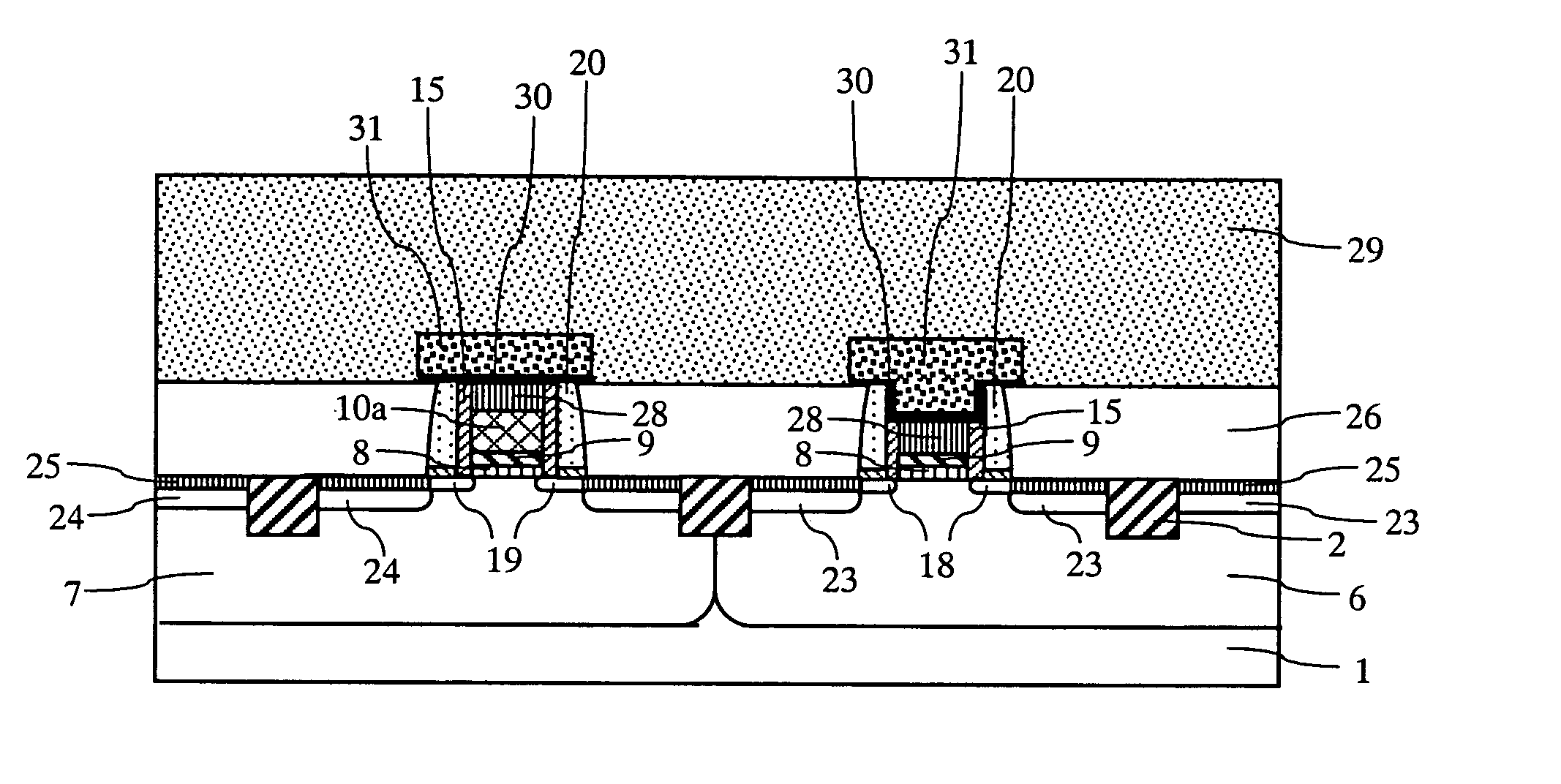

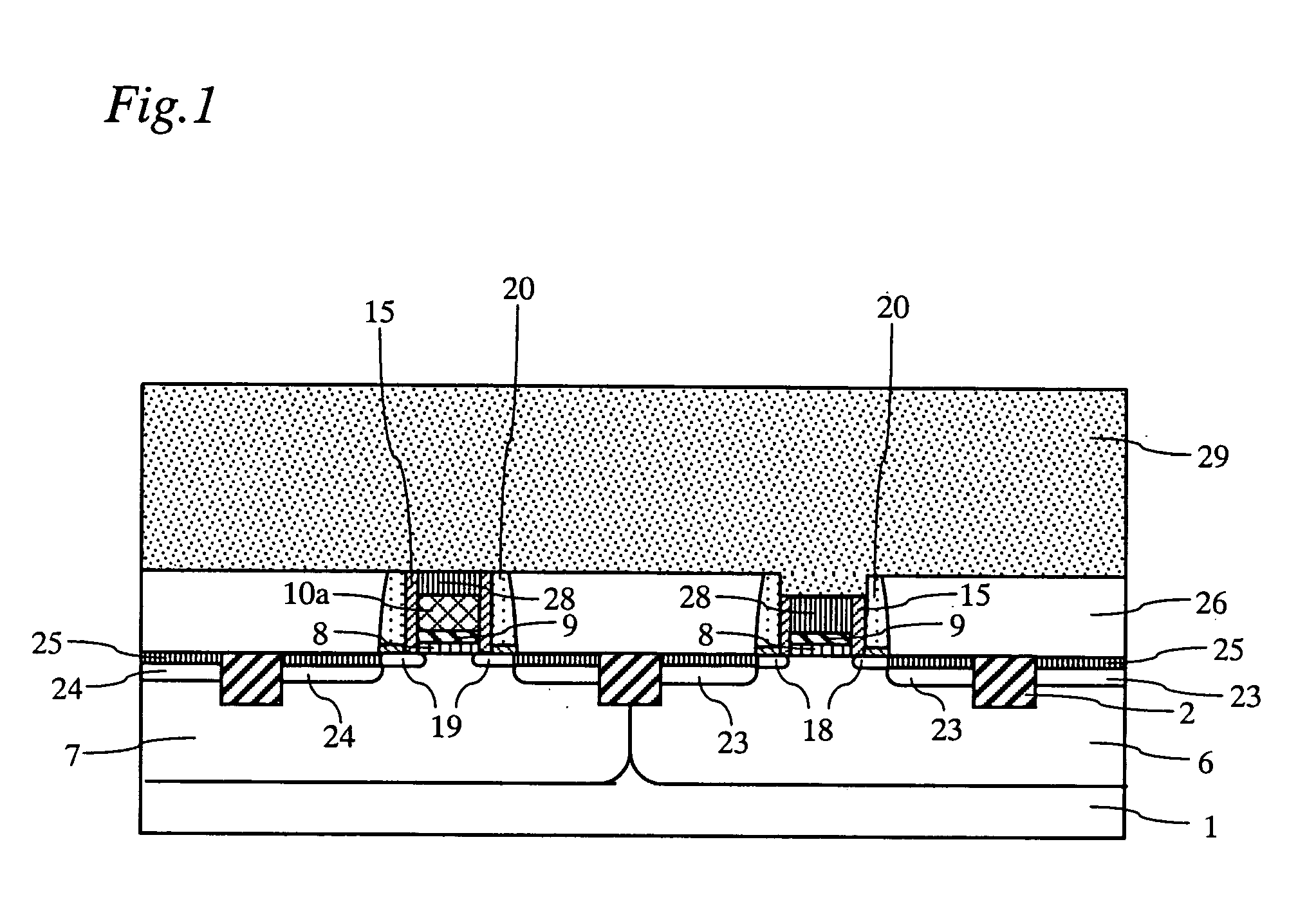

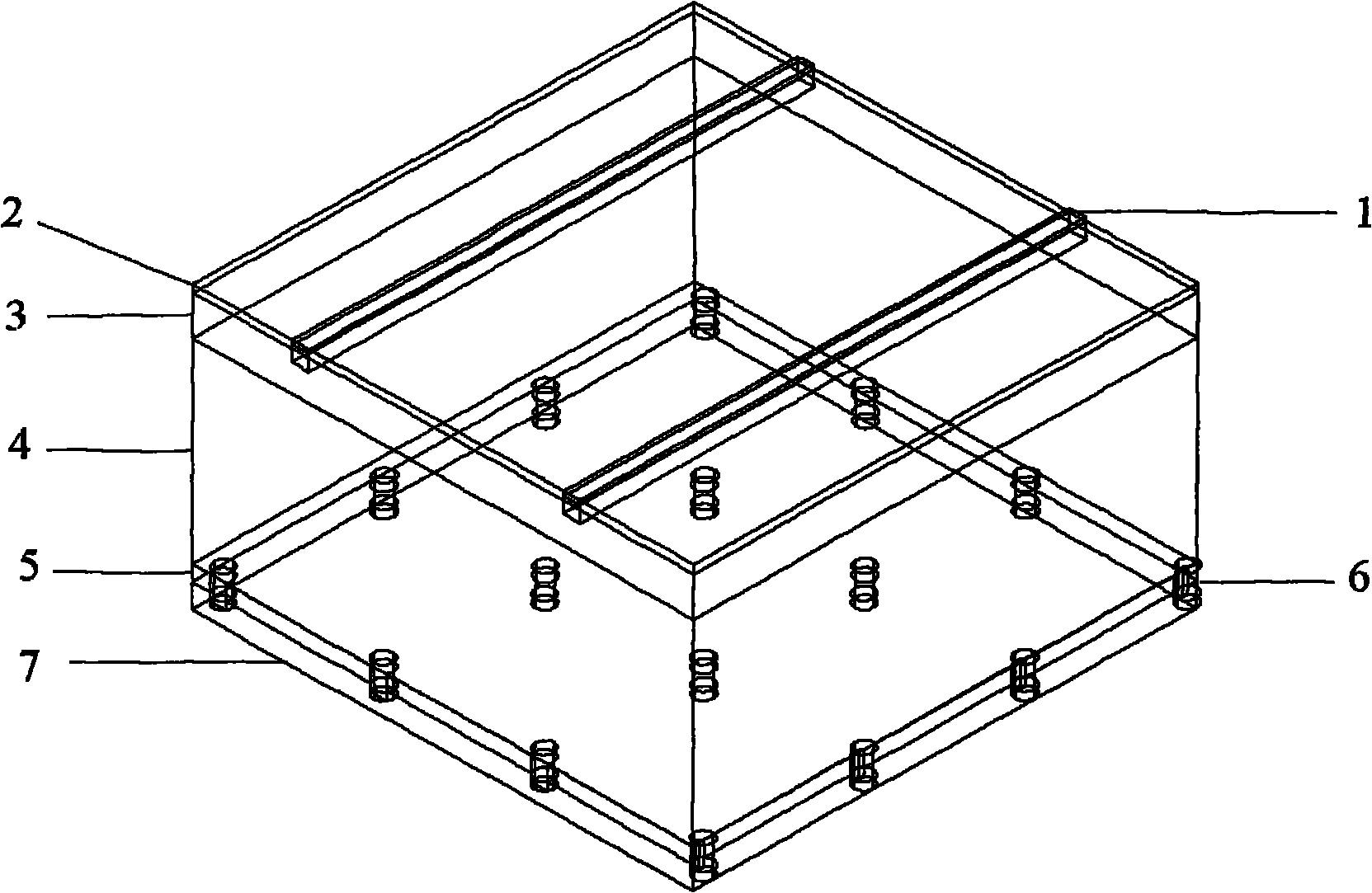

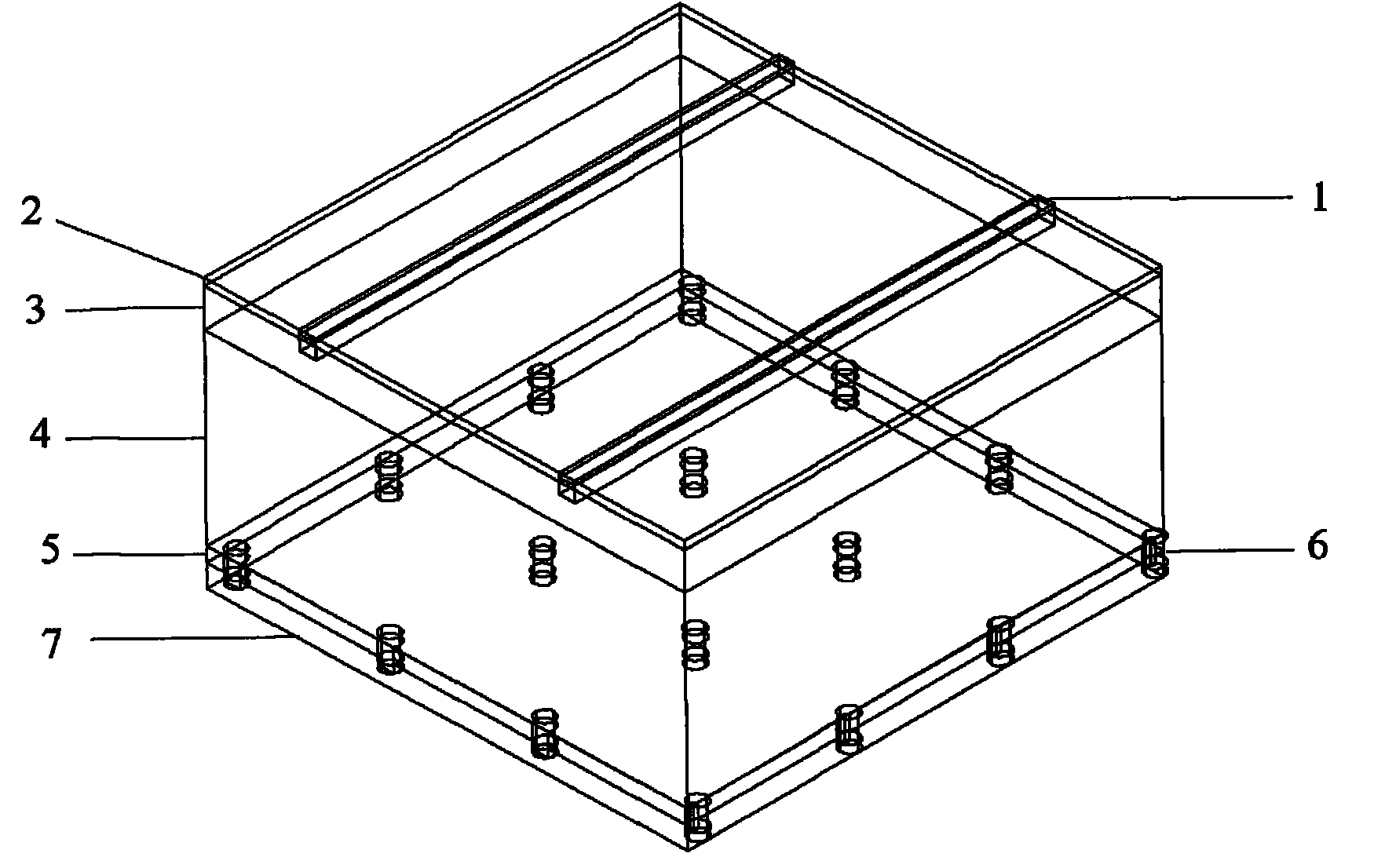

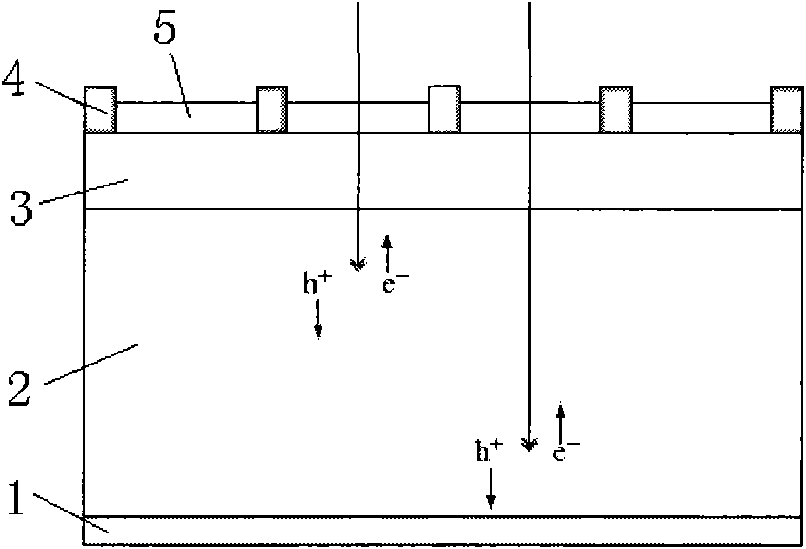

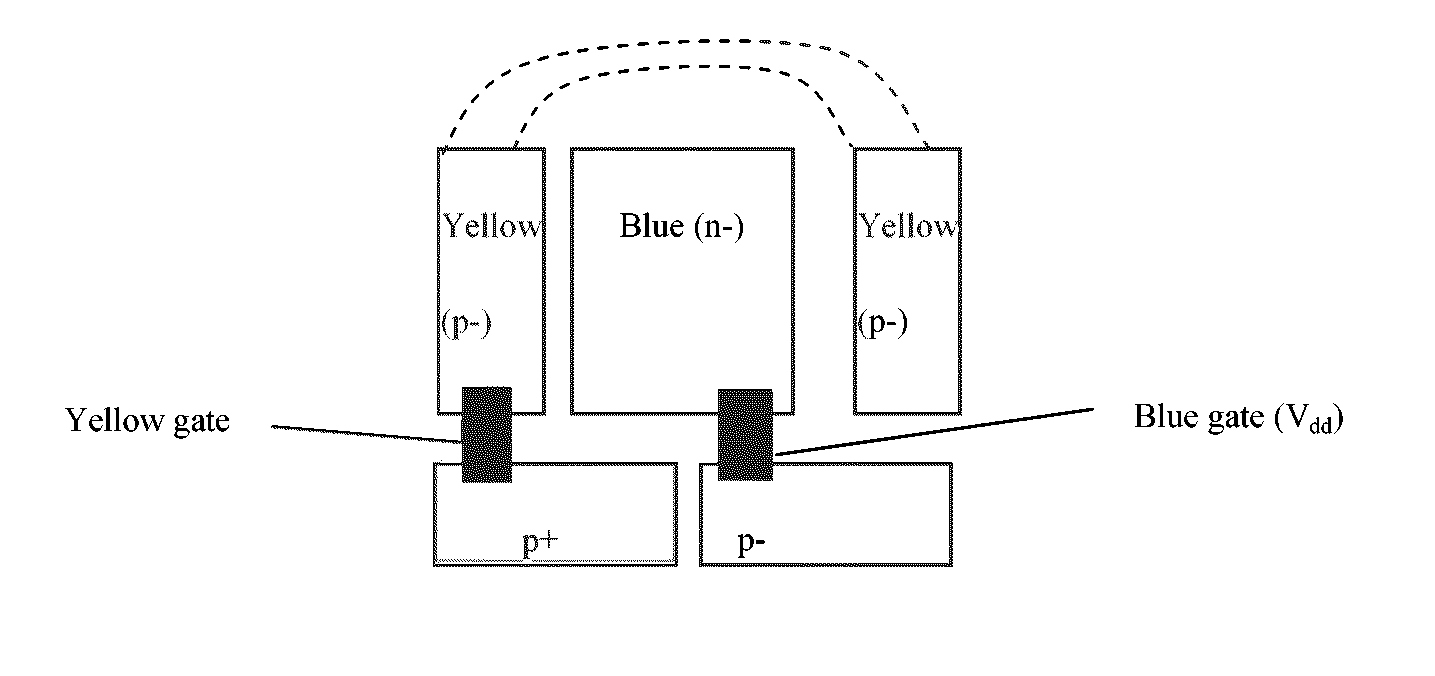

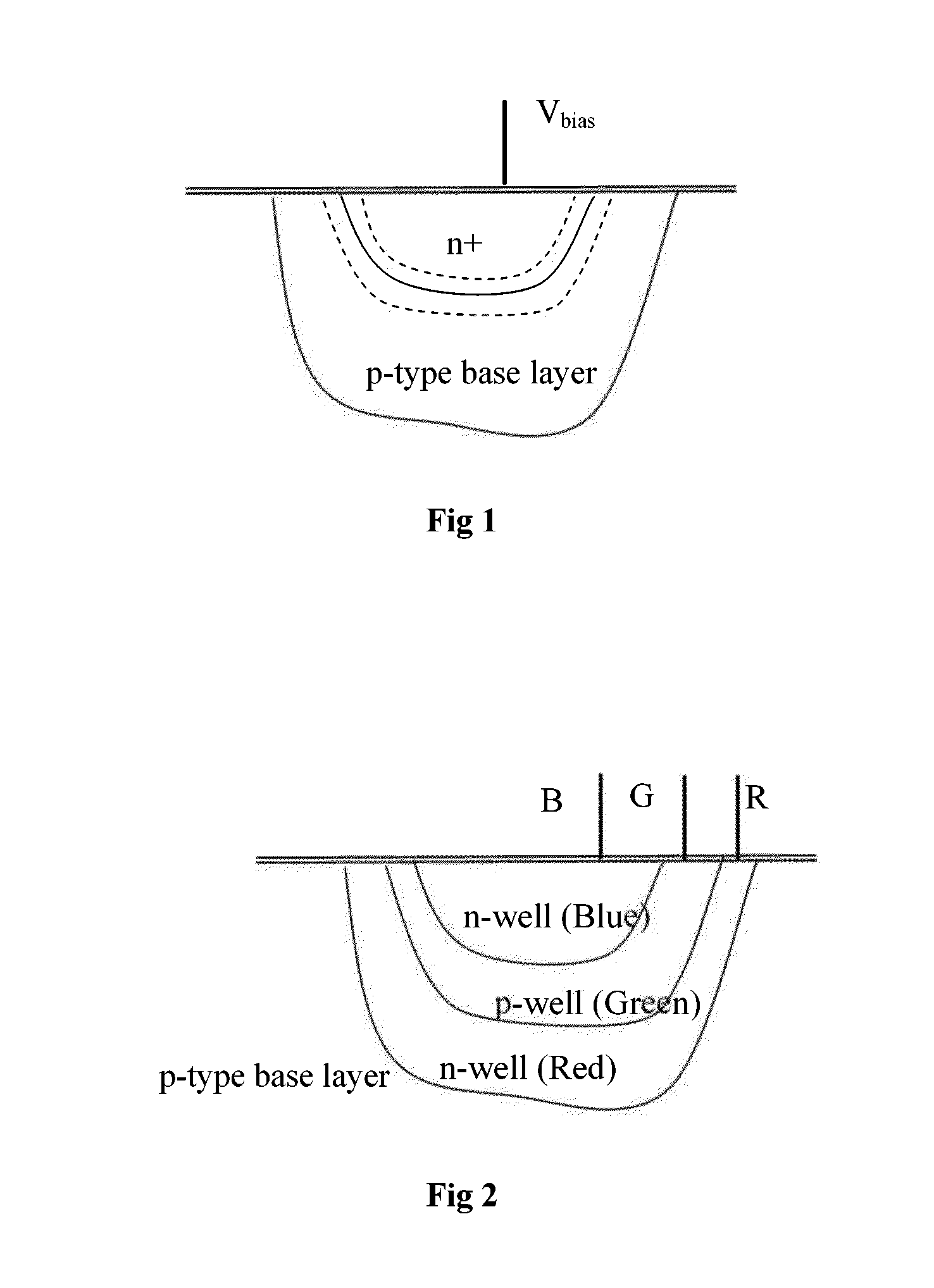

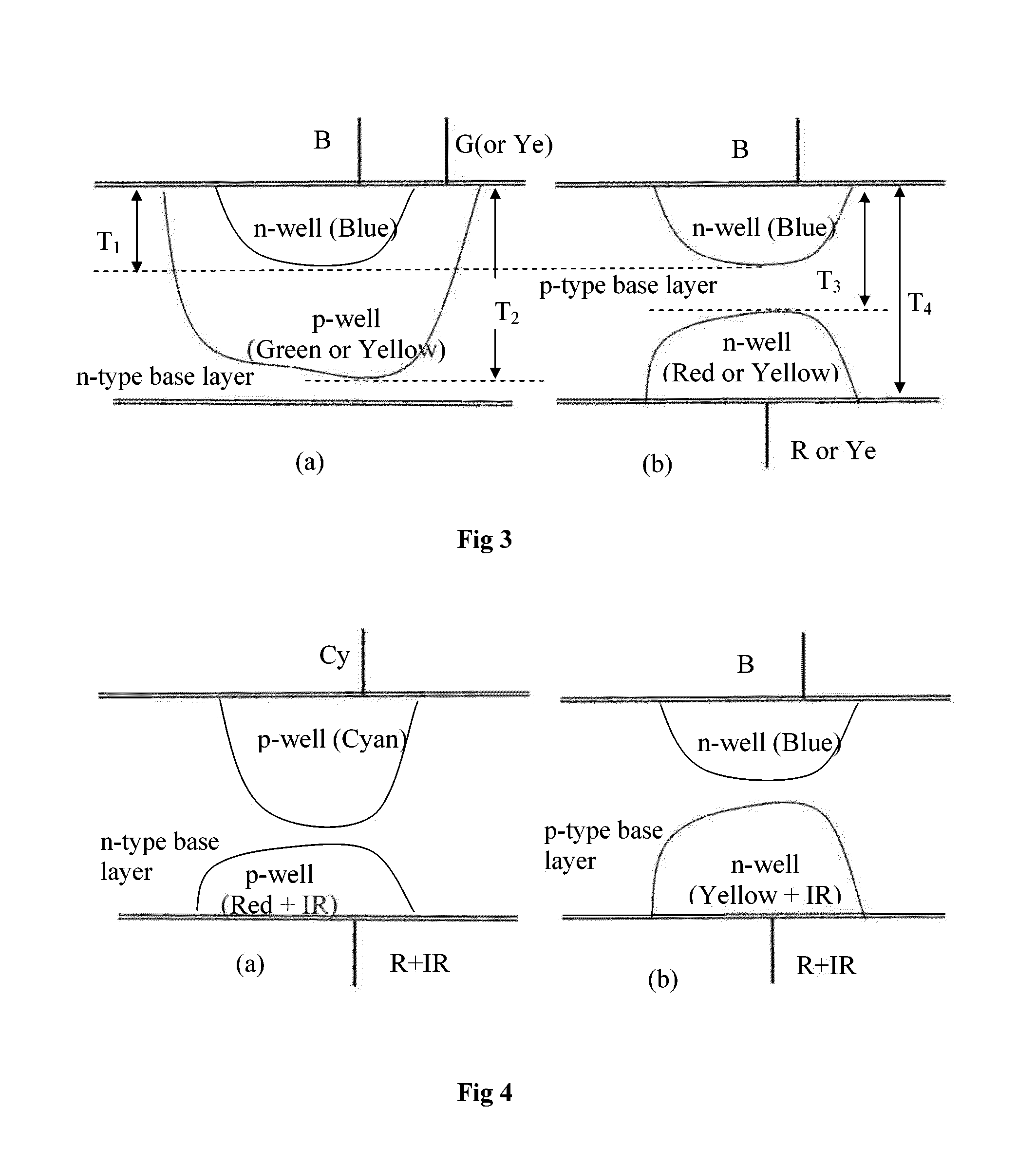

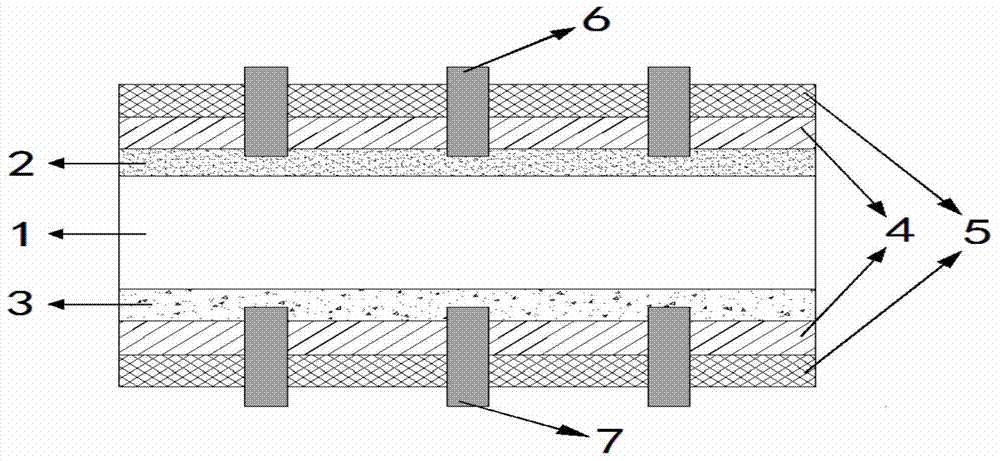

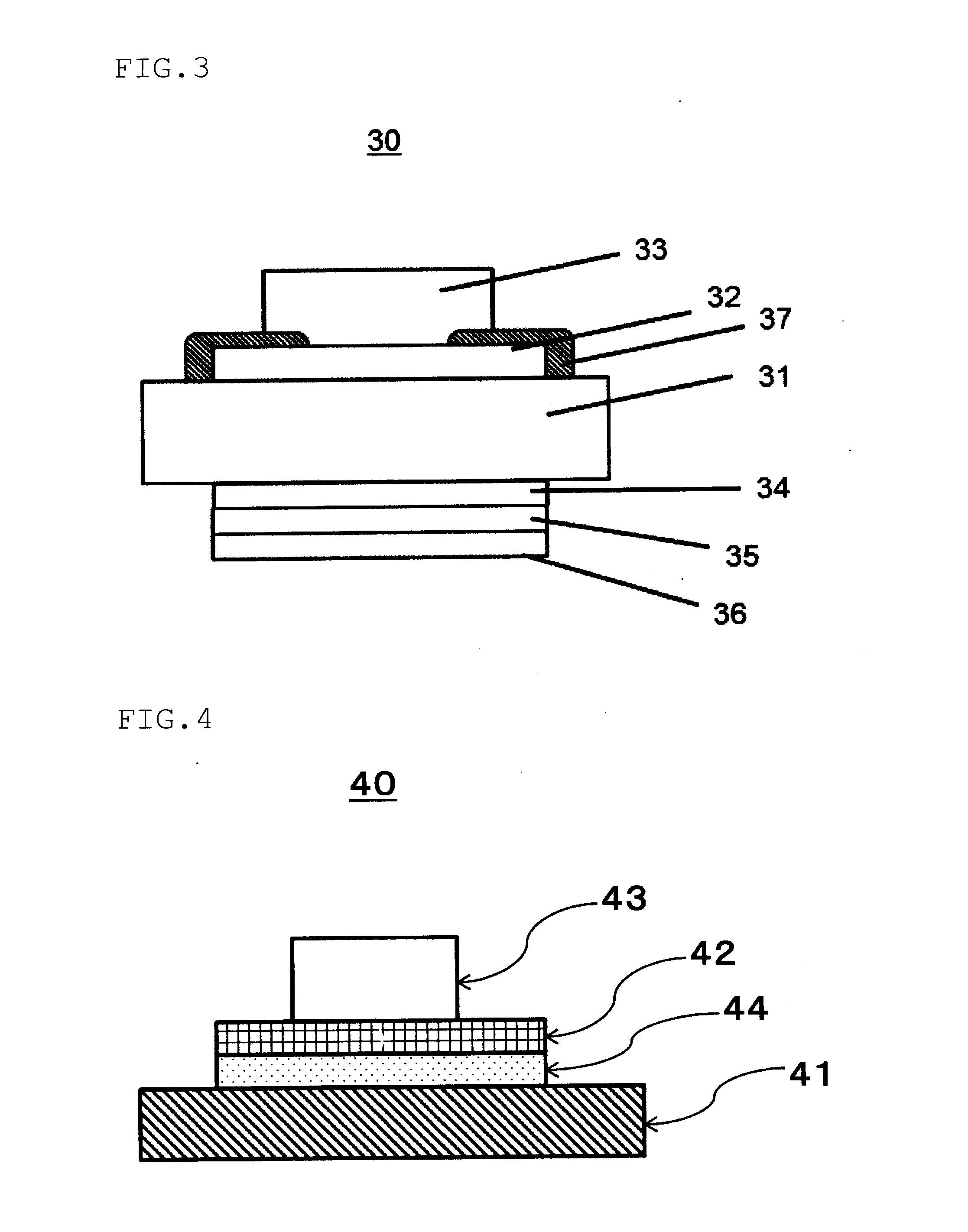

Multi-spectrum photosensitive device

ActiveUS20130062506A1Color sensing performanceGood colorSolid-state devicesMaterial analysis by optical meansN type siliconVisible spectrum

A multi-spectrum photosensitive device comprises two, three, or four composite sensing pixels arranged in layers up and down in a base layer of P-type or N-type silicon by means of single-sided processing or double-sided processing, each composite sensing pixels can sense respectively spectrum orthogonal or complementary to each other in visible light or visible and infrared light. The basic sensing pixels on different layers of the composite sensing pixels can be designed to sense different colors or spectrums, so that a multi-spectrum photosensitive chip can be achieved by repeatedly arranging the macro units consisting of more than one composite sensing pixel. The present disclosure also includes a new multi-layer sensing pixel, and examples of which used in a single-sided double-layer, or a double-sided double-layer, or a double-sided three-layer, or a double-sided four-layer, or a single-sided mixed double-layer, or a double-sided mixed with double-layer or a multi-layer multi-spectrum sensing device. A multi-spectrum photosensitive device according to the present disclosure has the advantage of better color sensing performance, integration of color sensing and infrared sensing, and a simple processing technique.

Owner:BOLY MEDIA COMM SHENZHEN

Silicon wafer and epitaxial silicon wafer

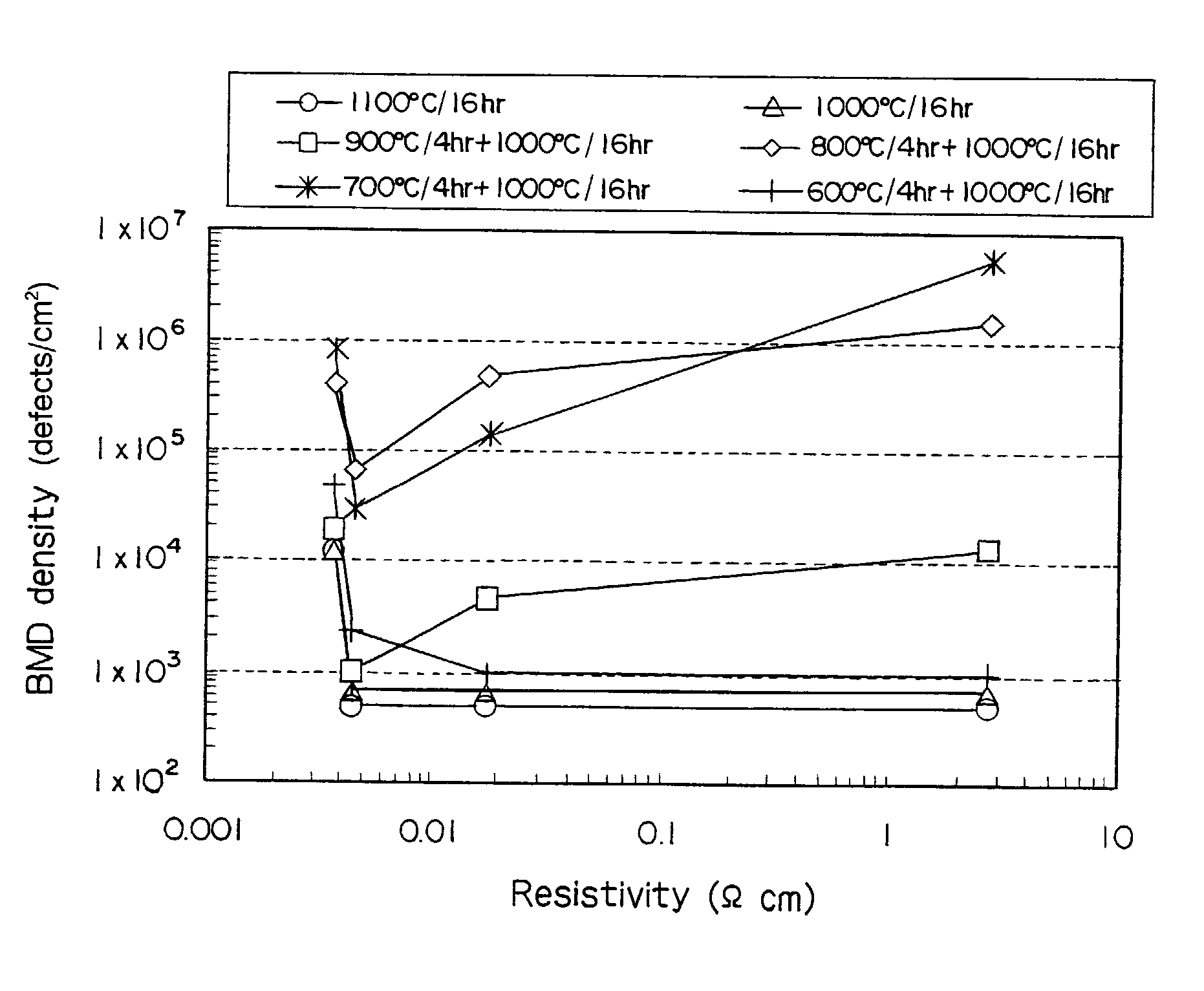

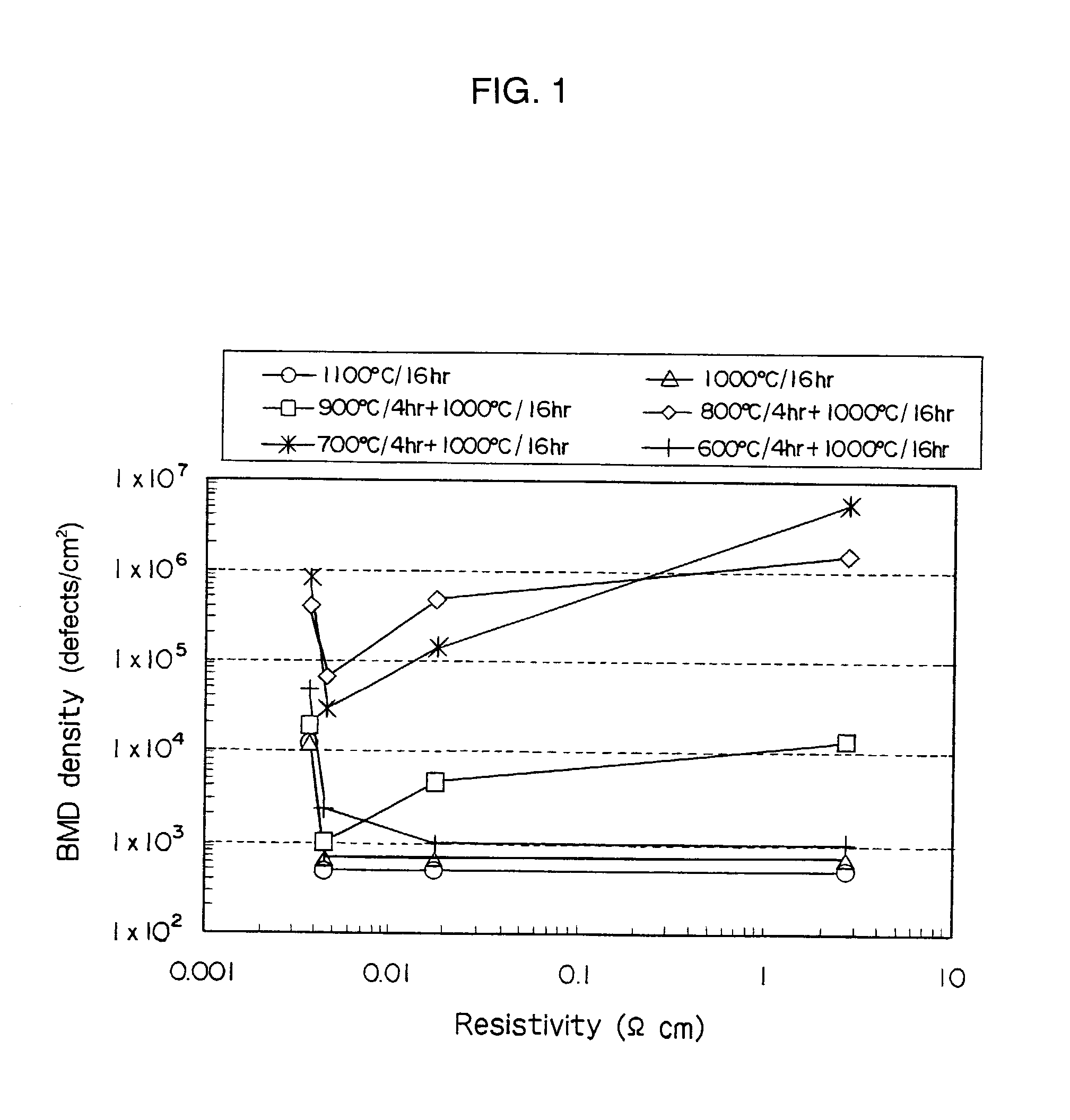

InactiveUS20030104222A1Polycrystalline material growthSemiconductor/solid-state device manufacturingHigh concentrationDopant

The invention relates to a silicon wafer and an epitaxial silicon wafer, which are doped with arsenic (As) as an n-type dopant and are excellent in gettering characteristics. A first silicon wafer has a resistivity of 10 OMEGAcm to 0.001 OMEGAcm as a result of addition of arsenic and has a nitrogen concentration of 1x1013 to 1x1015 atoms / cm3. A second silicon wafer has a resistivity of 0.1 OMEGAcm to 0.005 OMEGAcm and a nitrogen concentration of 1x1014 to 1x1015 atoms / cm3. A third silicon wafer has a resistivity of 0.005 OMEGAcm to 0.001 OMEGAcm and a nitrogen concentration of 1x1013 to 3x1014 atoms / cm3. An epitaxial silicon wafer derived from any of the first to third silicon wafers by forming an epitaxial layer in the surface layer portion is provided. In producing this epitaxial silicon wafer, epitaxial layer formation is desirably carried out after subjecting the silicon wafer to heat treatment for forming oxygen precipitates under conditions of a temperature not lower than 700° C. but lower than 900° C. and a period of 30 minutes to 4 hours. By these, an oxygen precipitate density can be secured and a sufficient gettering effect can be produced in the device producing process in spite of their being n-type silicon wafers doped with a high concentration of arsenic.

Owner:SUMITOMO MITSUBISHI SILICON CORP

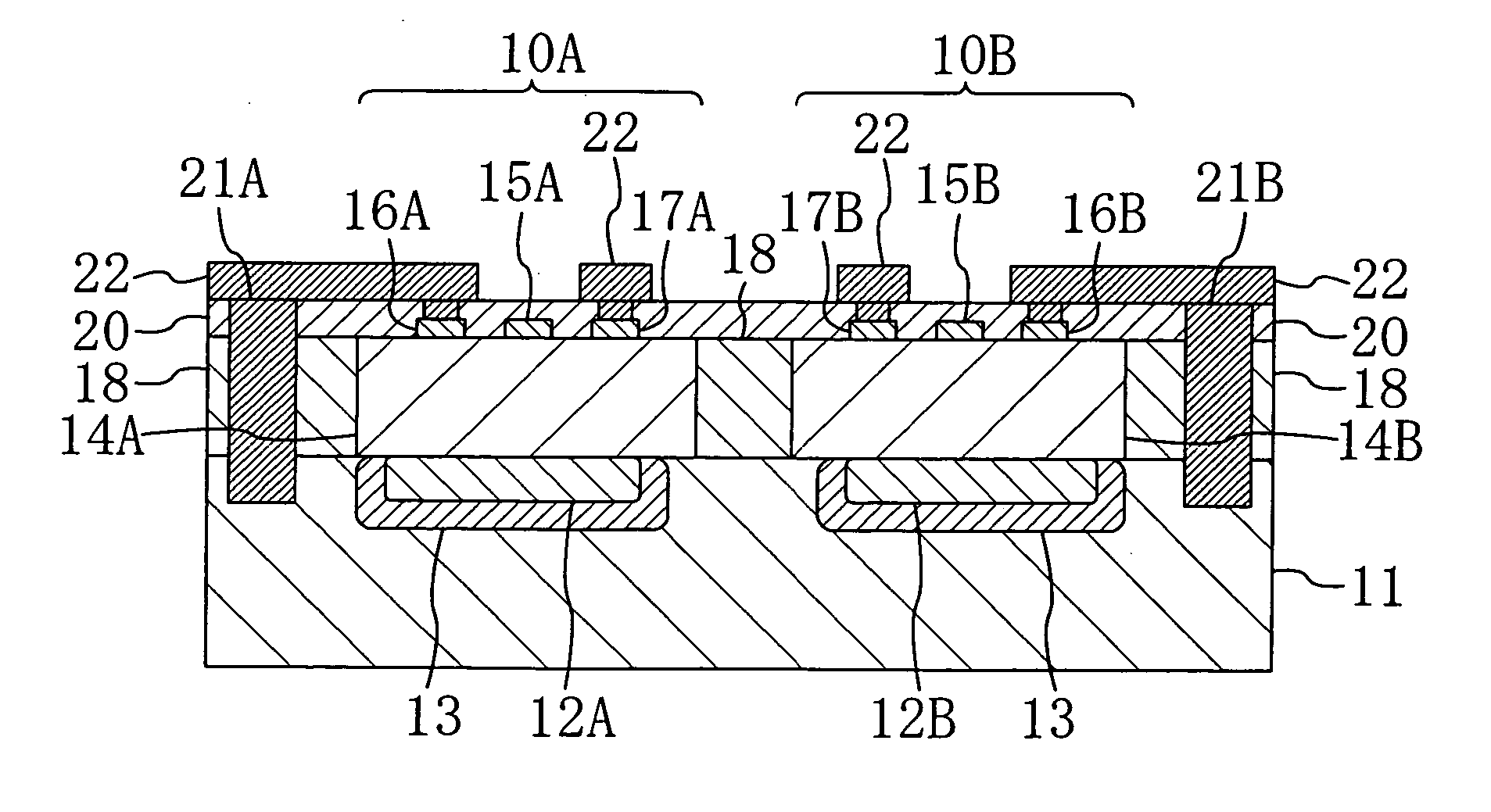

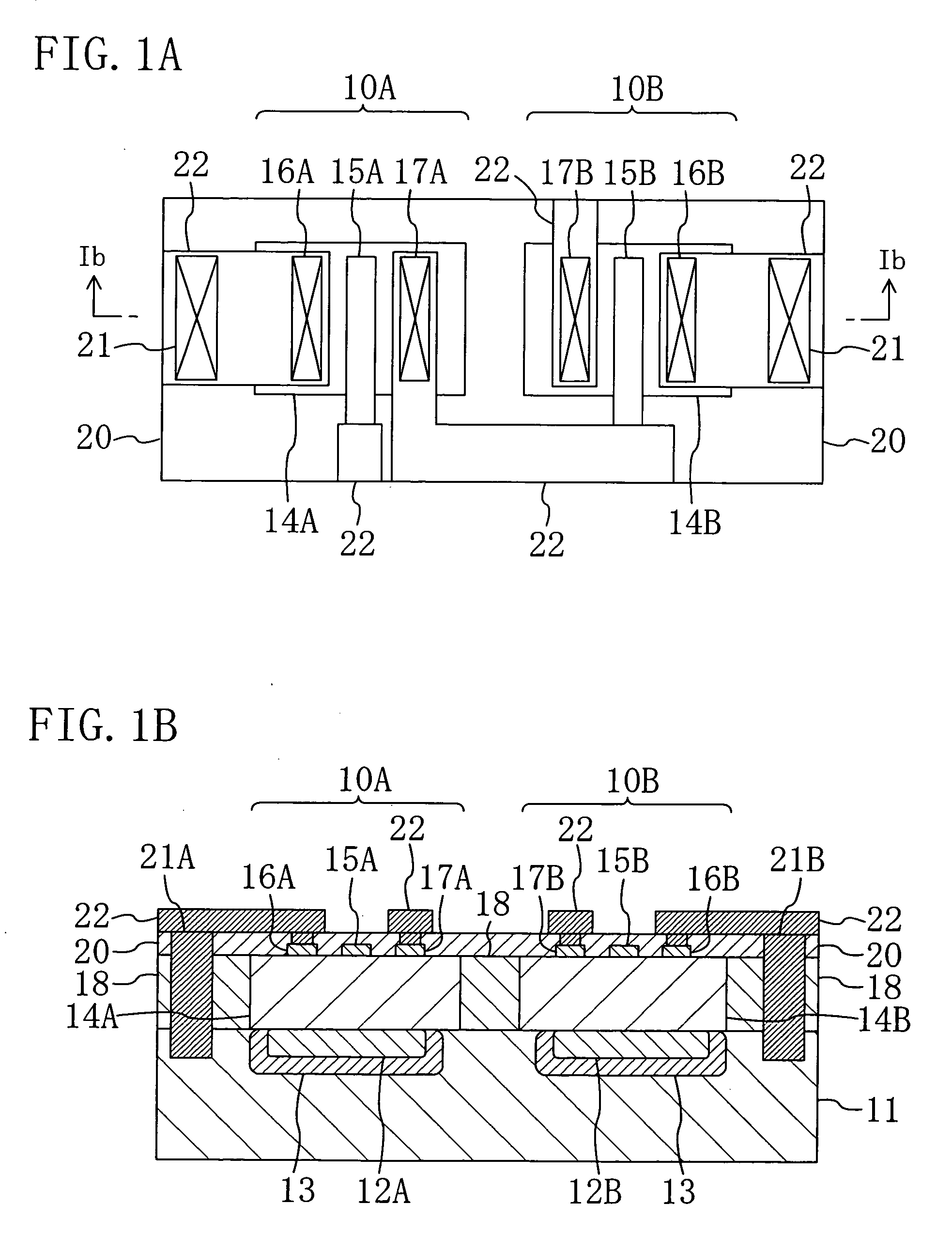

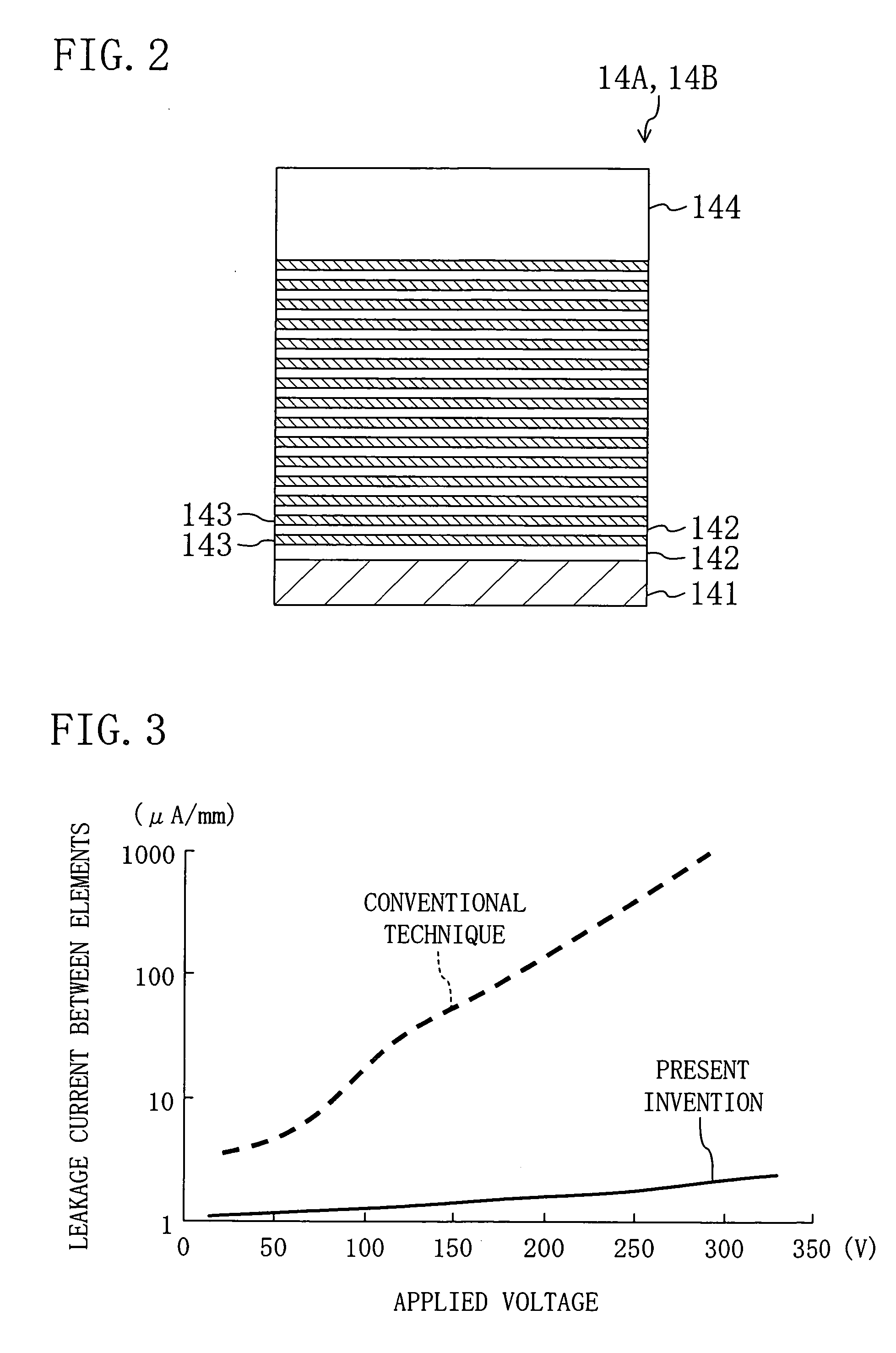

Semiconductor device and method for fabricating the same

ActiveUS20060124960A1High voltageInterconnection resistance can be decreasedSolid-state devicesSemiconductor/solid-state device manufacturingActive layerImpurity

A semiconductor device includes a semiconductor substrate of n-type silicon including, in an upper portion thereof, a first polarity inversion region and a second polarity inversion regions spaced from each other and doped with a p-type impurity. A first HFET including a first active layer and a second HFET including a second active layer both made of a group Ill-V nitride semiconductor are independently formed on the respective polarity inversion regions in the semiconductor substrate, and the HFETs are electrically connected to each other through interconnects.

Owner:PANASONIC CORP

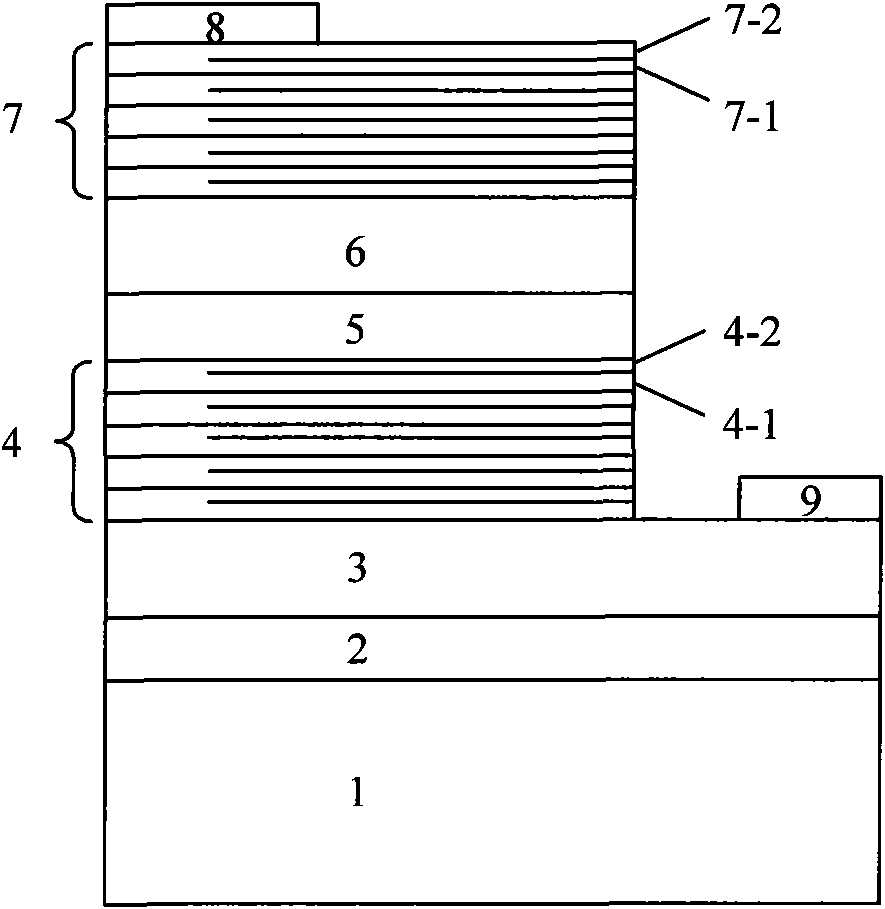

High-brightness light emitting diode with GaN-based multiquantum-well structure and preparation method thereof

InactiveCN101593804AIncrease the degree of spatial overlapImprove luminous efficiencySemiconductor devicesOhmic contactThermal treatment

The invention discloses a high-brightness light emitting diode with a GaN-based multiquantum-well structure and a preparation method thereof, and relates to a light emitting diode. The light emitting diode comprises a substrate, a low temperature buffer layer, an n-type doped GaN layer, 3 to 5 InGaN / GaN multiquantum wells, a p-type doped AlGaN layer, a p-type doped CaN layer, 5 periodic p-InGaN / p-AlGaN superlattice layers, a p-type ohmic contact layer and an n-type ohmic contact layer prepared on the n-type doped GaN layer in turn from bottom to top. The preparation method comprises the following steps: putting the substrate into a reaction chamber to perform thermal treatment for growing a GaN buffer layer, an n-type silicon-doped GaN layer, 3 to 5 periodic InGaN / GaN multiquantum wells with graded components, a p-type Mg-doped AlGaN layer, a p-type Mg-doped GaN layer and 5 periodic Mg-doped p-InGaN / p-AlGaN superlattice layers in turn; performing annealing after epitaxial growth; etching an n-type GaN layer; and preparing the n-type and the p-type ohmic contact layers.

Owner:EPITOP PHOTOELECTRIC TECH

A kind of organic-inorganic hybrid solar cell and preparation method thereof

InactiveCN102263204ALow purity requirementReduce dosageSolid-state devicesSemiconductor/solid-state device manufacturingSolar batteryP–n junction

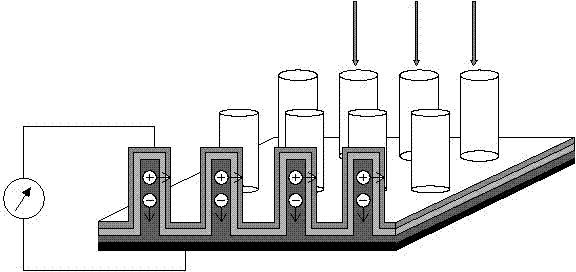

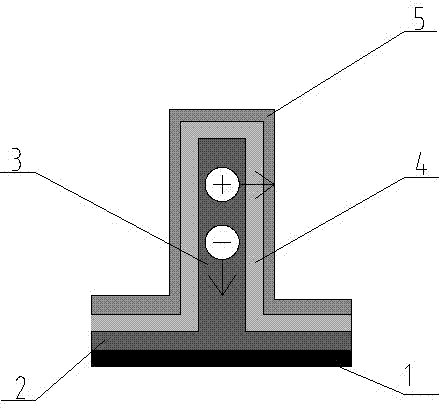

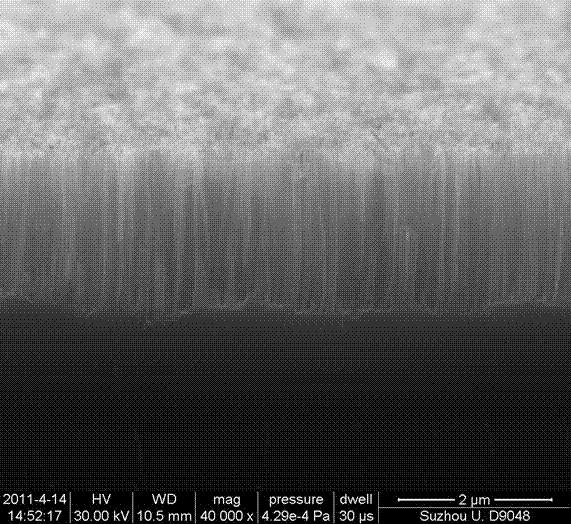

The invention discloses an organic-inorganic hybridization solar battery which comprises a metal backing electrode, an n-type silicon substrate layer, a silicon nanometer wire array and a battery positive electrode and also comprises a p-type cavity transmission shell layer, wherein the p-type cavity transmission shell layer is a conjugated organic matter semiconductor thin film; the metal backing electrode is arranged on the lower surface of the n-type silicon substrate layer; the silicon nanometer wire array is arranged on the upper surface of the n-type silicon substrate layer; the surfaceof a silicon nanometer wire in the silicon nanometer wire array is covered by the layer of p-type cavity transmission shell layer; and the battery positive electrode is arranged on the p-type cavity transmission shell layer. As a three-dimensional radial p-n junction hybridization structure formed by the silicon nanometer wire array and the conjugated organic matter is adopted in the organic-inorganic hybridization solar battery, on one hand, the absorption of light is increased, the usage amount of silicon is reduced, the purify requirement on the silicon is reduced, on the other hand, the transmission range of current carriers is shortened, the problem that the current carriers are easy to combine is reduced, and the photoelectric conversion efficiency is improved.

Owner:SUZHOU UNIV

Compositions and processes for forming photovoltaic devices

InactiveUS20100037941A1Low barrier heightConductive materialSemiconductor/solid-state device manufacturingSalicideSilicon solar cell

Methods and compositions for making photovoltaic devices are provided. A metal that is reactive with silicon is placed in contact with the n-type silicon layer of a silicon substrate. The silicon substrate and reactive metal are fired to form a silicide contact to the n-type silicon layer. A conductive metal electrode is placed in contact with the silicide contact. A silicon solar cell made by such methods is also provided.

Owner:EI DU PONT DE NEMOURS & CO +1

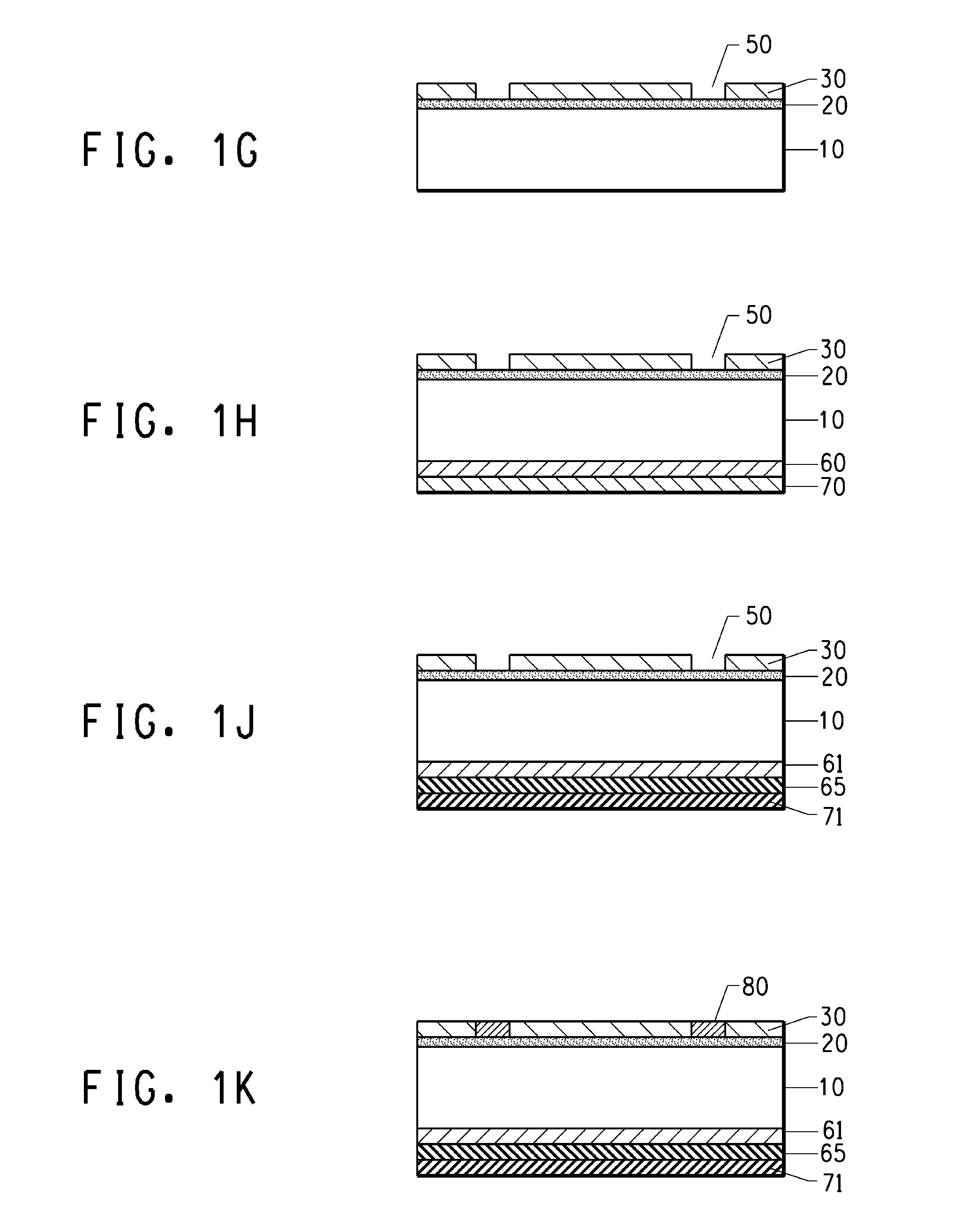

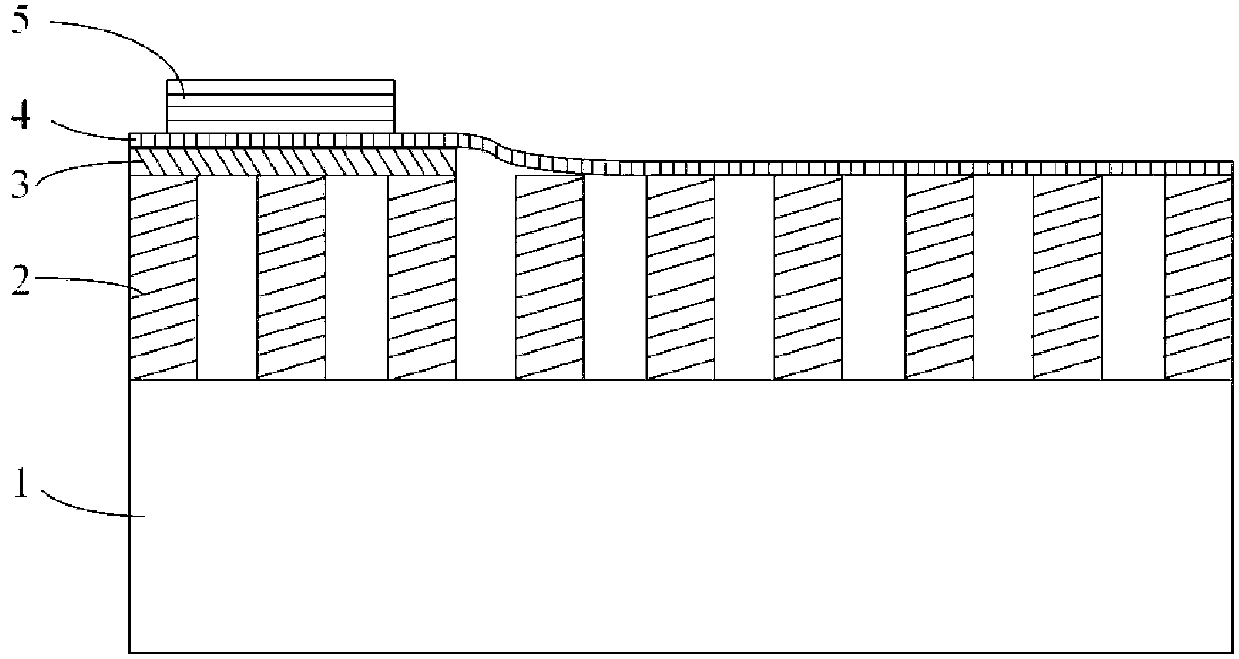

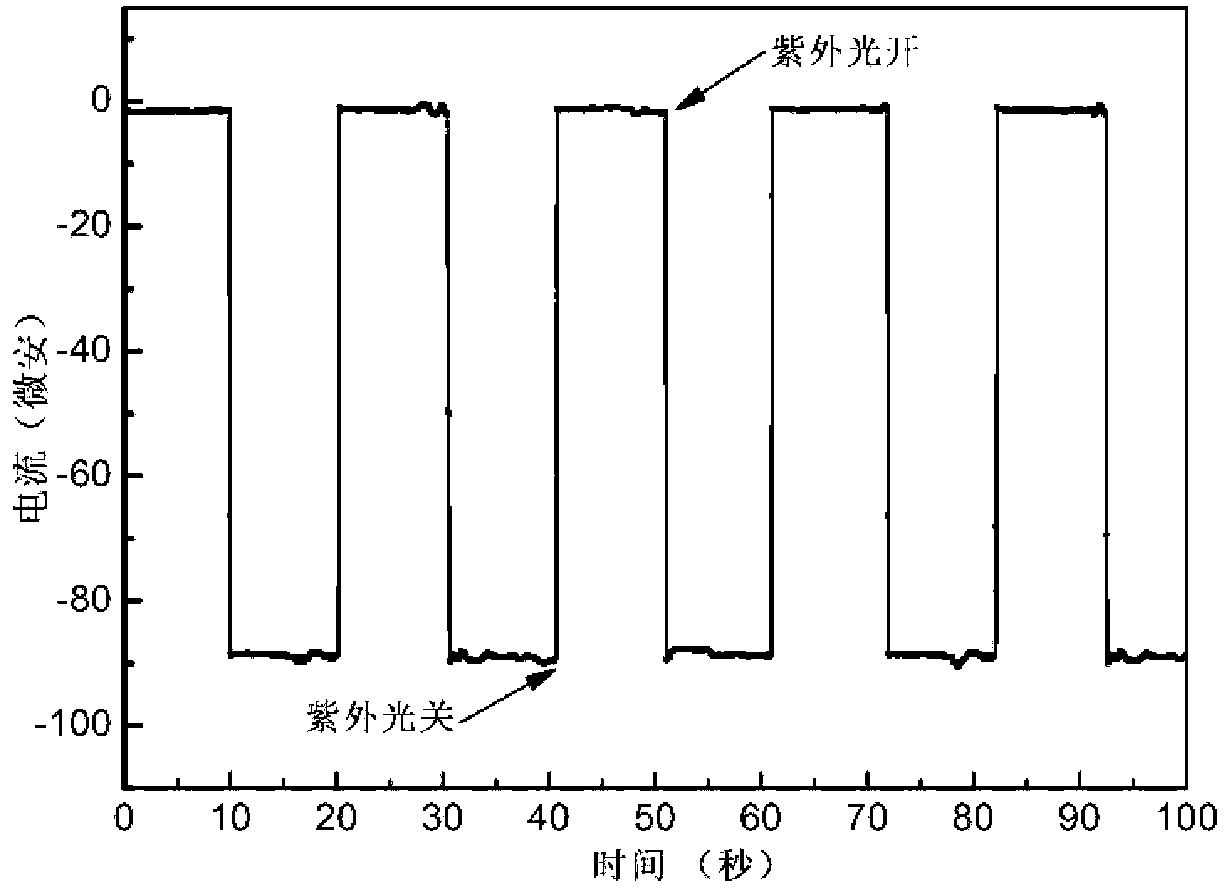

Ultraviolet photoelectric detector and preparation method thereof based on single-layer graphene/zinc oxide nano-rod array schottky junction

InactiveCN103346199ABoundary does not exceedLow costFinal product manufactureSemiconductor devicesInsulation layerUltraviolet

The invention discloses an ultraviolet photoelectric detector and a preparation method of the ultraviolet photoelectric detector based on a single-layer graphene / zinc oxide nano-rod array schottky junction. The ultraviolet photoelectric detector is characterized in that an N-type silicon substrate layer serves as a substrate, a zinc oxide nano-rod array is generated on the upper surface of the substrate in the perpendicular direction, an insulation layer covers the upper surface of the zinc oxide nano-rod array, and the area of the insulation layer is 1 / 4-1 / 3 of that of the zinc oxide nano-rod array; single-layer graphene covers the insulation layer, part of the single-layer graphene is in contact with the insulation layer, and the remaining part covers the zinc oxide nano-rod array; a metal electrode layer is arranged on the single-layer graphene. According to the ultraviolet photoelectric detector and the preparation method of the ultraviolet photoelectric detector based on the single-layer graphene / zinc oxide nano-rod array schottky junction, technology is simple, the ultraviolet photoelectric detector is suitable for large-scale production, and the preparation method of the ultraviolet photoelectric detector is capable of manufacturing the ultraviolet photoelectric detector which is low in manufacturing cost, free in pollution and strong in optical detecting capacity and laying a foundation for the application of a graphene and zinc oxide nanostructure in the ultraviolet photoelectric detector.

Owner:HEFEI UNIV OF TECH

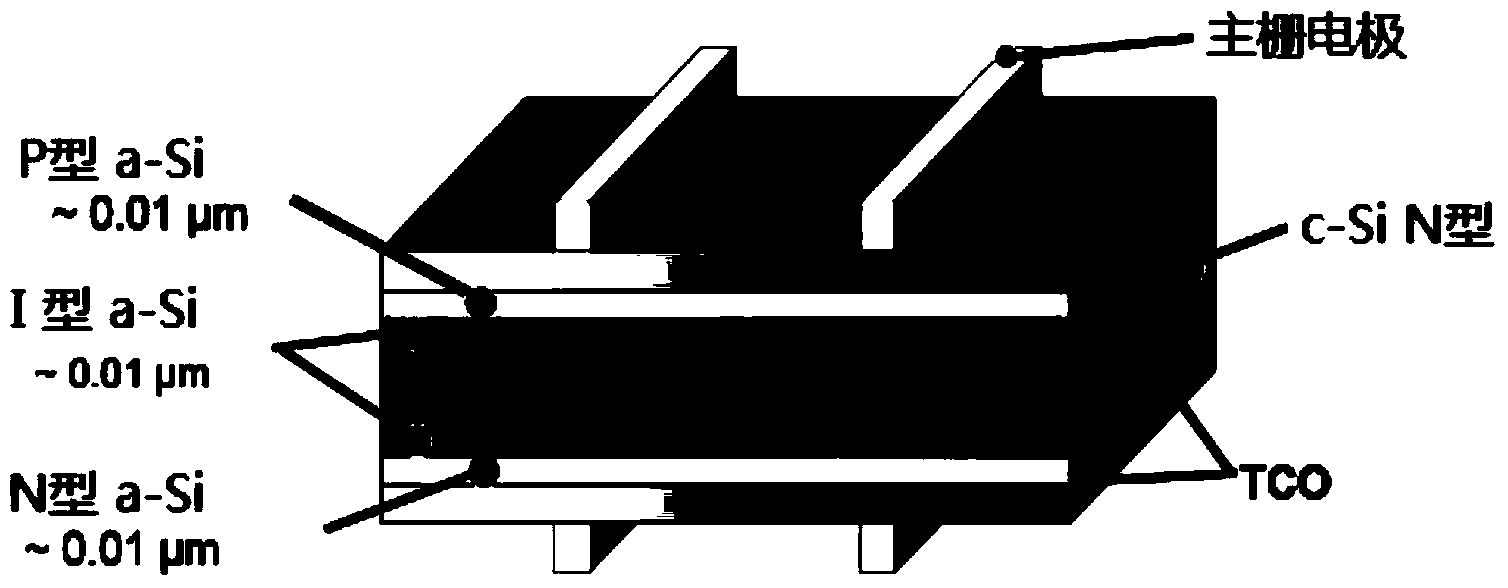

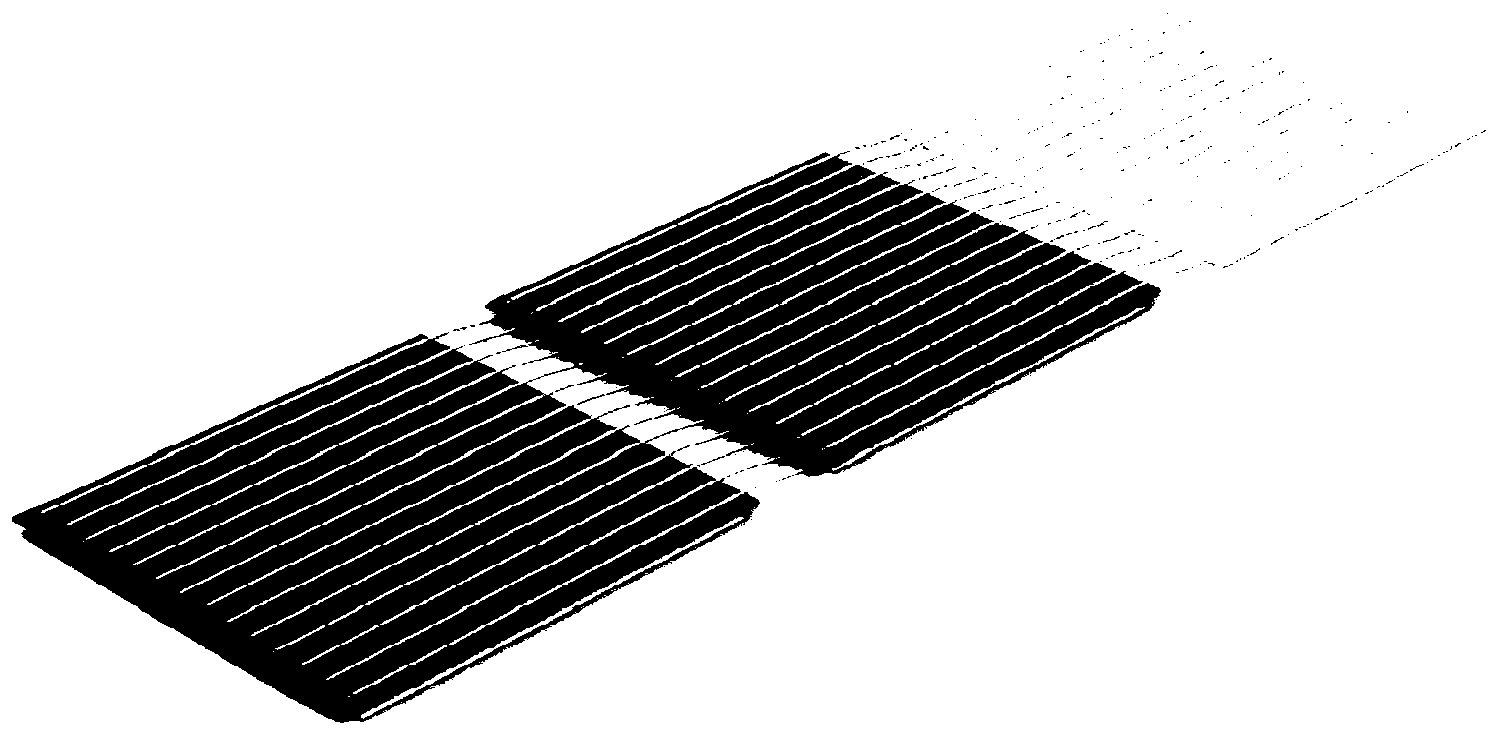

HIT (Heterojunction with Intrinsic Thin Layer) solar cell and electrode preparation and series connection methods thereof

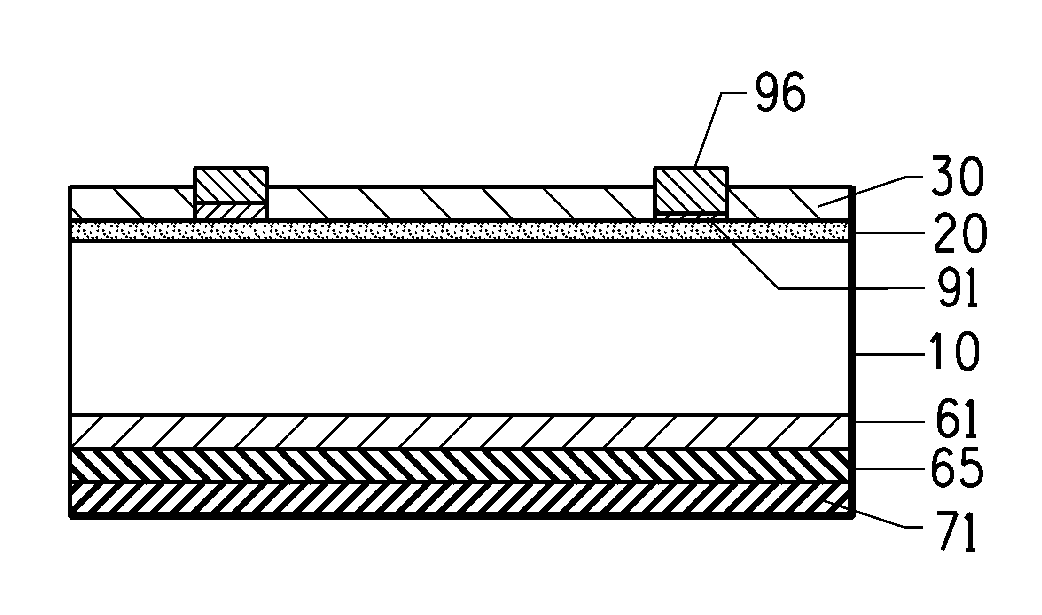

ActiveCN104037265AConductivity advantageReduce surface occlusionFinal product manufacturePhotovoltaic energy generationHeterojunctionAmorphous silicon

The invention discloses a HIT (Heterojunction with Intrinsic Thin Layer) solar cell and electrode preparation and series connection methods thereof. The HIT solar cell comprises a metal wire conduction band and solar cell pieces, wherein each solar cell piece comprises an N type silicon plate; the front side of each N type silicon plate is provided with an intrinsic amorphous silicon film and a P type amorphous silicon film; the back side of each N type silicon plate is provided with an intrinsic amorphous silicon film and an N type amorphous silicon film in sequence; the P type amorphous silicon films and the N type amorphous silicon films are provided with transparent conduction oxide films; one solar cell piece is arranged below the front half portion of the metal wire conduction band; the back half portion of the metal wire conduction band is provided with one solar cell piece. Compared with the conventional HIT solar cell, the method has the advantages that a main gate electrode and a fine gate electrode do not need to be printed, and solar cells can be connected in series without bus bars. On one hand, the metal wire portions of the metal wire conduction band are arranged in parallel on the front side or back side of the solar cell, and current on the surfaces of solar cells is collected and conducted out to realize the functions of a fine gate and a main gate; on the other hand, two solar cells are connected in series to serve as a bus bar.

Owner:陕西众森电能科技有限公司

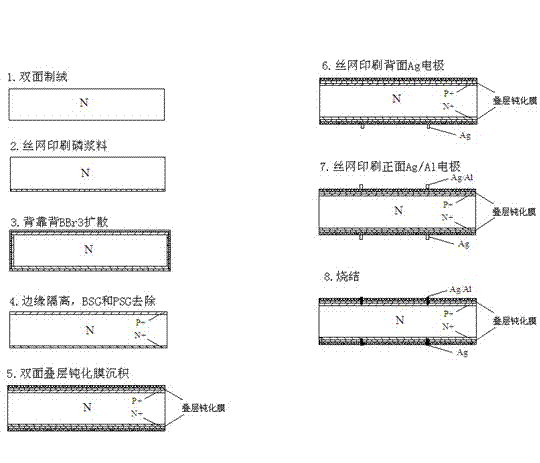

High efficiency N-type double-faced solar cell and preparation method thereof

ActiveCN104733555AIncrease the open circuit voltageInhibited DiffusionFinal product manufacturePhotovoltaic energy generationPhosphorSilicon dioxide

The invention relates to a high efficiency N-type double-faced solar cell and a preparation method thereof. The structure of the solar cell comprises an N-type silicon slice substrate, a front side boron doping layer, a back side phosphor doping layer, double-faced silicon dioxide passivation layers, doubled-faced silicon nitride antireflection layers and double-faced electrodes. The invention further discloses a preparation method for the solar cell, the preparation method particularly comprises the first step that double-faced texturization is conducted; the second step that front side boron diffusion is conducted; the third step that front side film masking is conducted; the fourth step that back side washing is conducted; the fifth step that back side phosphorus diffusion is conducted; the sixth step that a mask film is removed; the seventh step that double-faced passivation is conducted; the eighth step that double-faced film coating is conducted; the ninth step that the front side electrodes and the back side electrodes are formed; the tenth step that laser edge carving is conducted. According to the high efficiency N-type double-faced solar cell and the preparation method thereof, knots are formed on both the front side and the back side of the N-type silicon slice, the front side and the back side both have high photoelectric converting rates, the output power of an assembly of the high efficiency N-type double-faced solar cell is 20% higher than the output power of a common solar cell, and meanwhile the high efficiency N-type double-faced solar cell is applicable to large-scale industrial production due to the fact that the preparation technology is simple and practical.

Owner:常州顺风太阳能科技有限公司

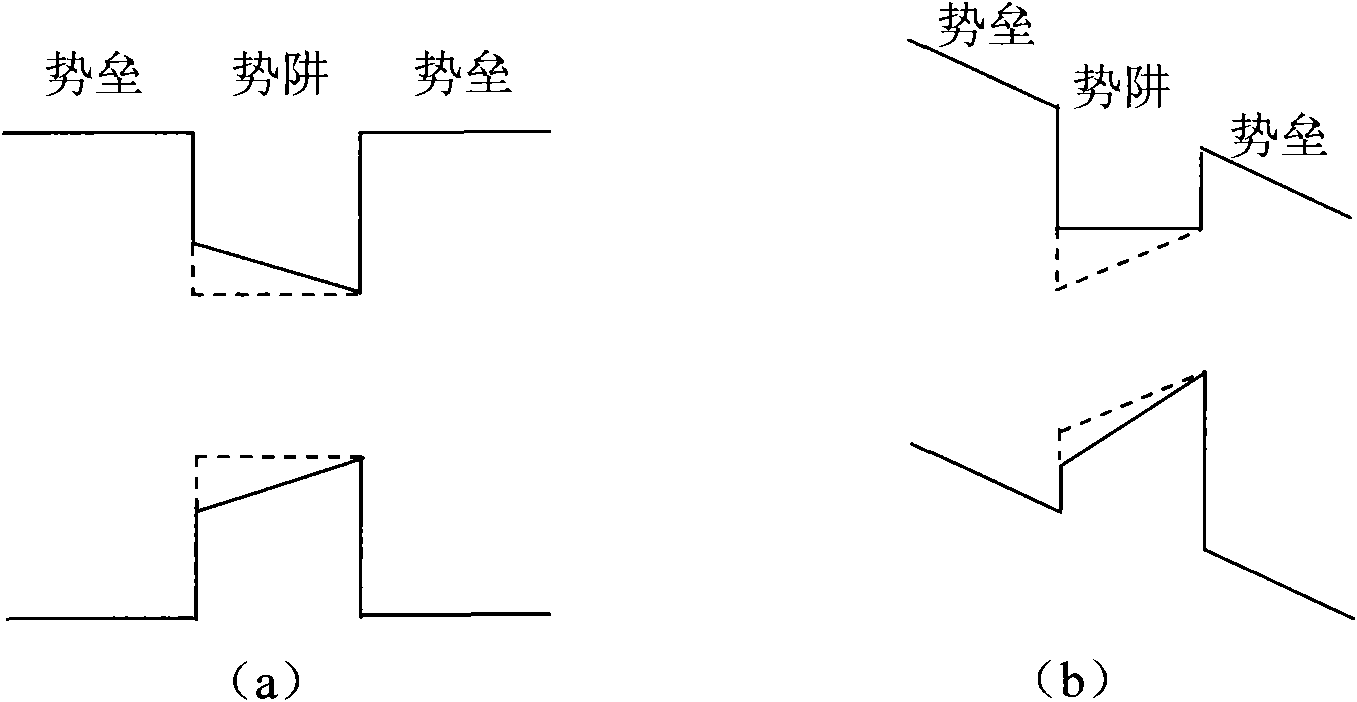

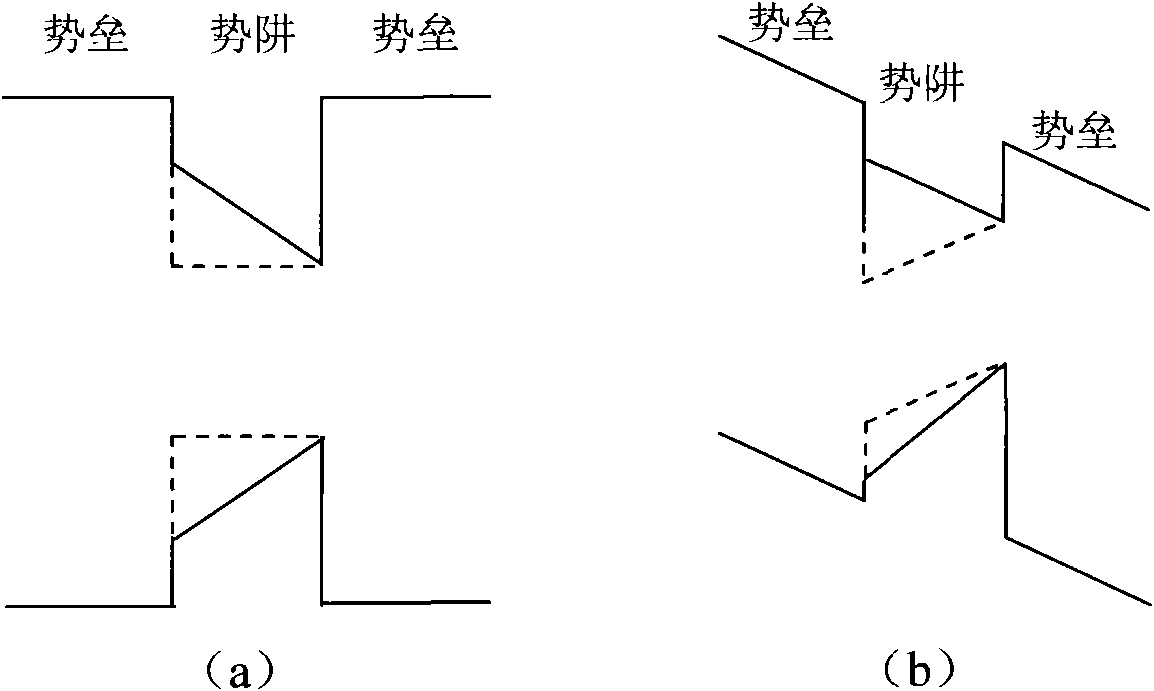

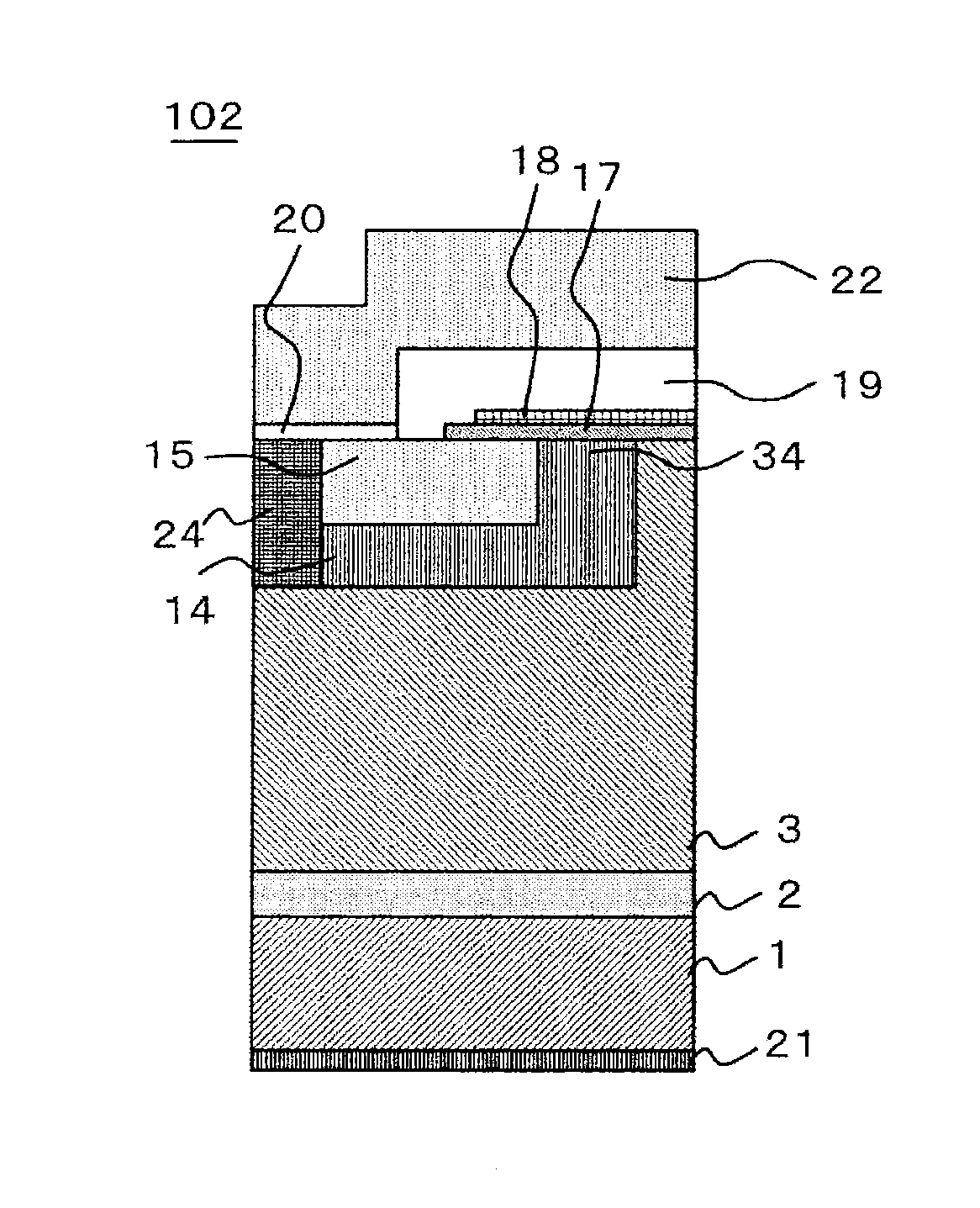

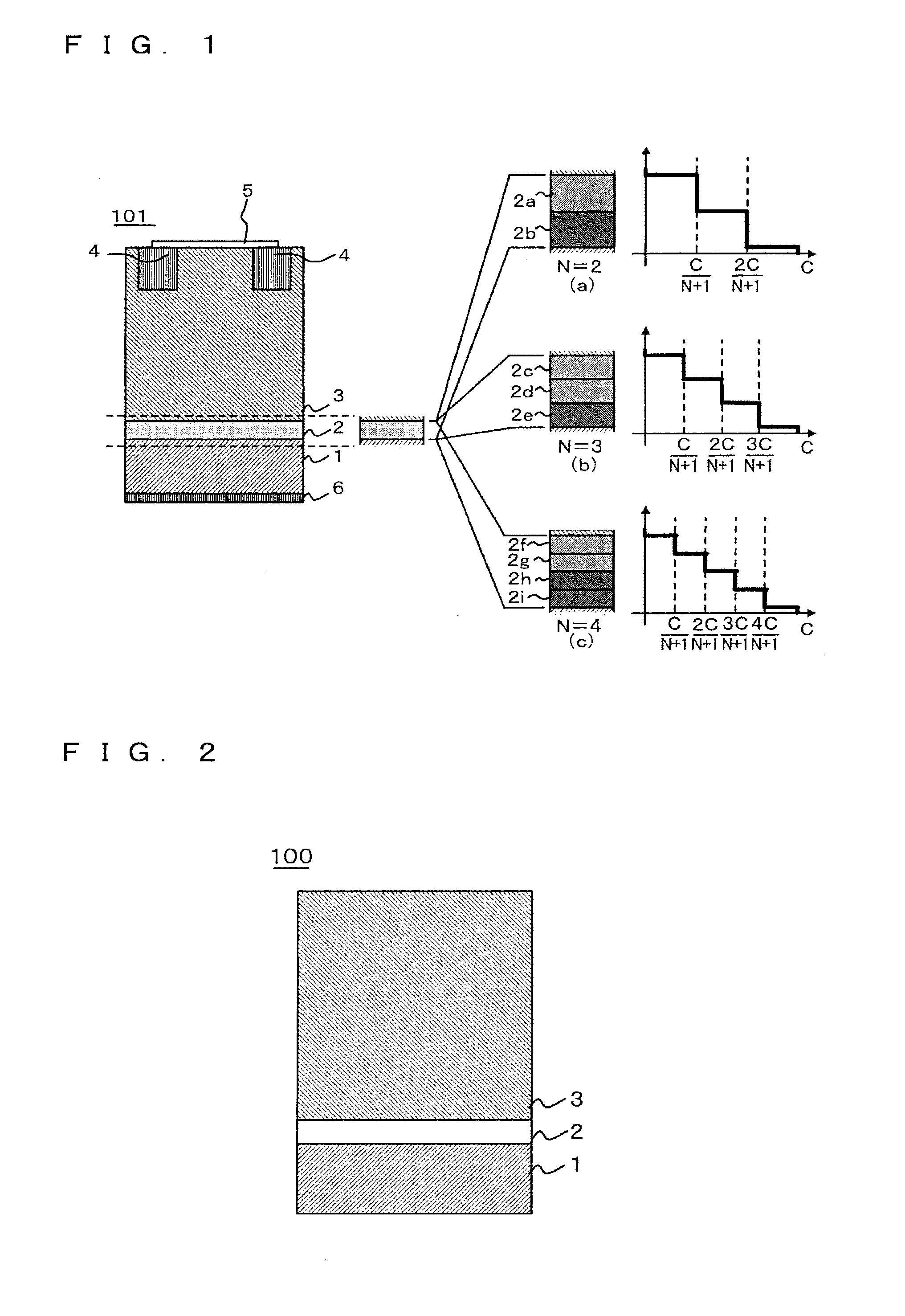

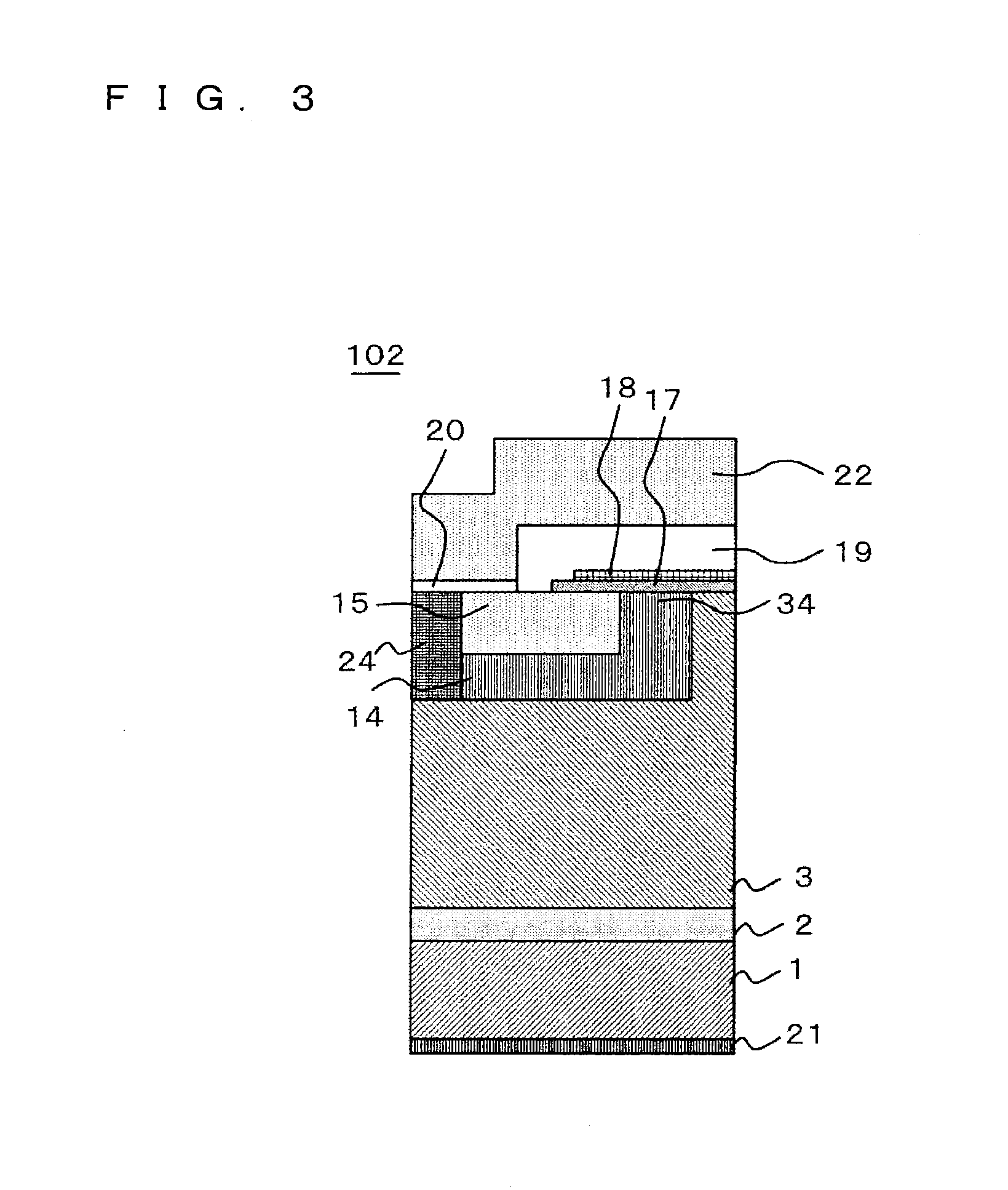

Epitaxial wafer and semiconductor element

ActiveUS20120241766A1High carrier mobilityImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantNitrogen

A silicon carbide semiconductor element, including: i) an n-type silicon carbide substrate doped with a dopant, such as nitrogen, at a concentration C, wherein the substrate has a lattice constant that decreases with doping; ii) an n-type silicon carbide epitaxially-grown layer doped with the dopant, but at a smaller concentration than the substrate; and iii) an n-type buffer layer doped with the dopant, and arranged between the substrate and the epitaxially-grown layer, wherein the buffer layer has a multilayer structure in which two or more layers having the same thickness are laminated, and is configured such that, based on a number of layers (N) in the multilayer structure, a doping concentration of a K-th layer from a silicon carbide epitaxially-grown layer side is C·K / (N+1).

Owner:MITSUBISHI ELECTRIC CORP

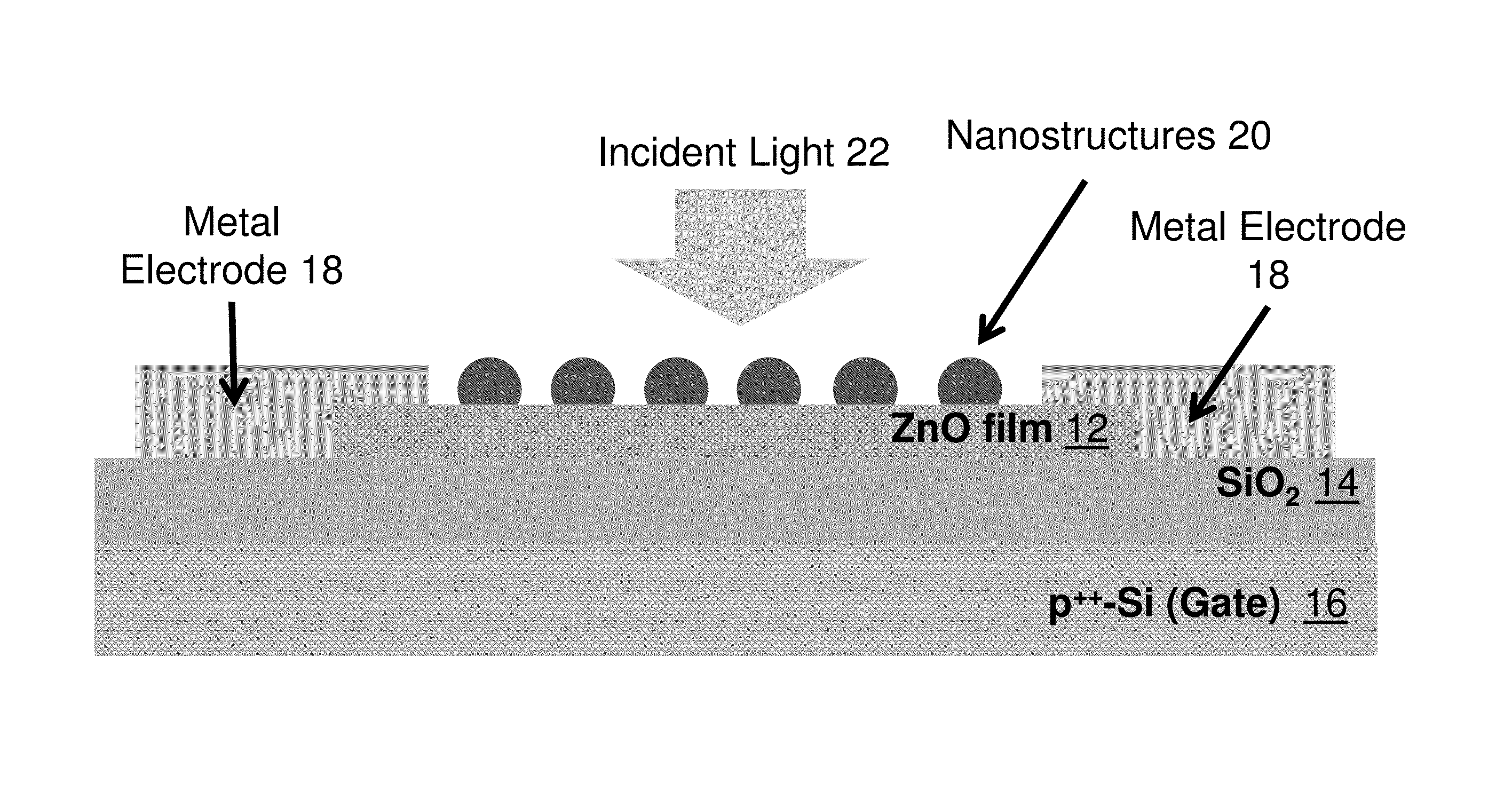

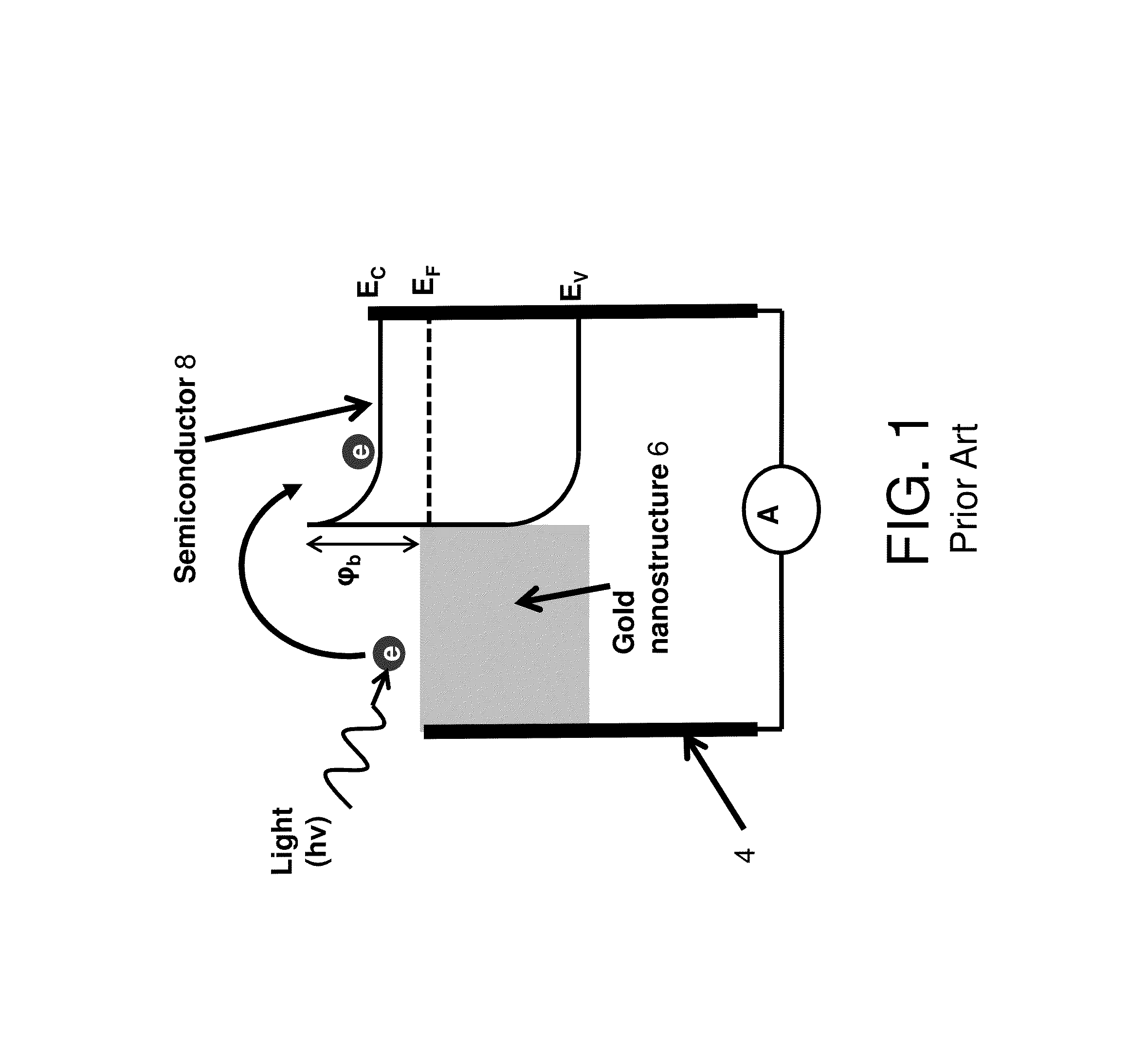

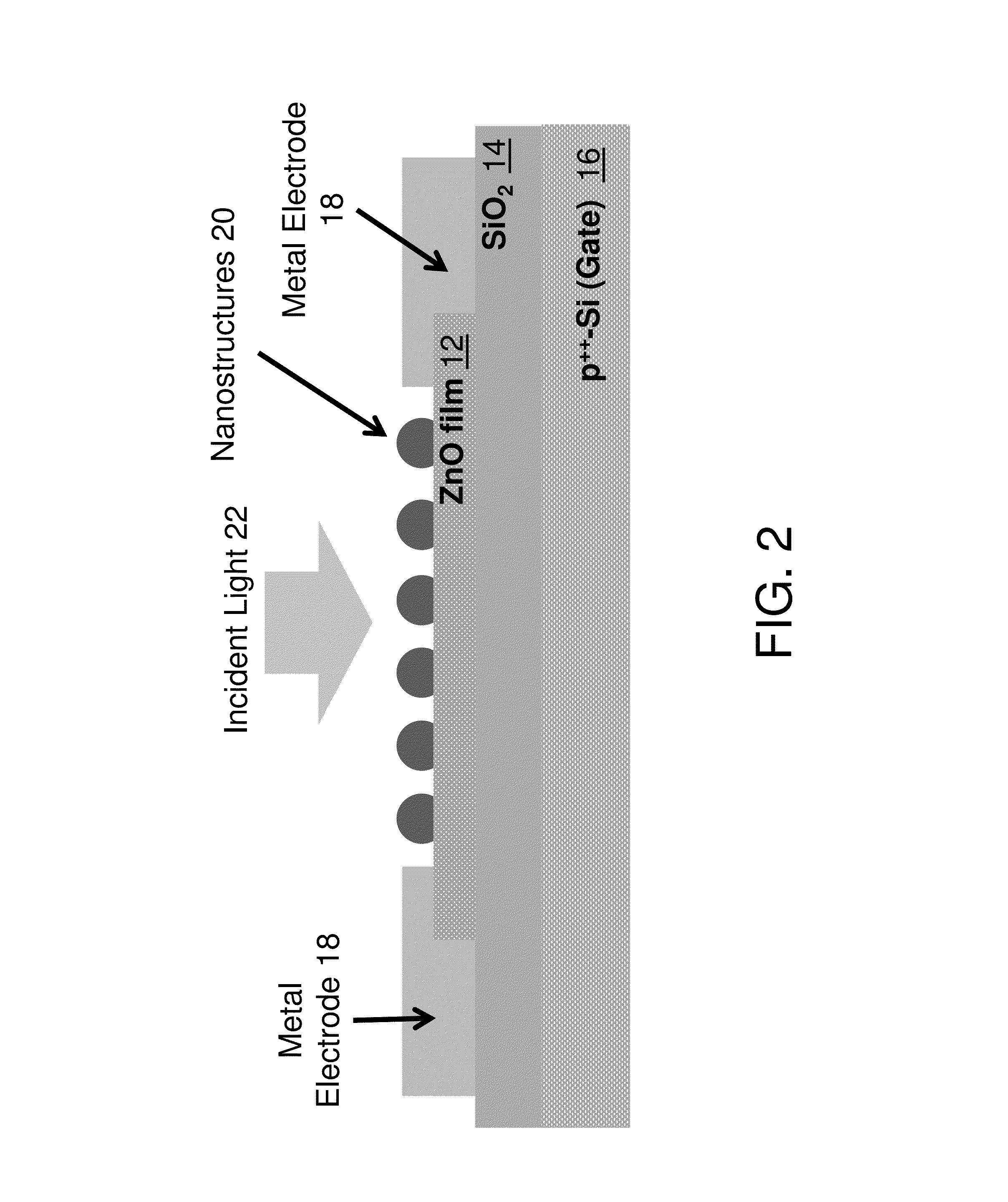

Plasmon field effect transistor

ActiveUS9368667B1Material analysis by electric/magnetic meansMaterial analysis by optical meansDrain currentField-effect transistor

A field effect transistor (FET) is provided. The FET includes a first material layer, second material layer and a third material layer. The third material layer includes an n-type silicon substrate layer and a gate electrode. The gate electrode includes an insulating substrate with at least one conducting metal. The second material layer is disposed on the third material layer. The first material layer is disposed on the second material layer. A source electrode is disposed on the first material layer. A drain electrode is disposed on the first material layer. A plurality of gold nanostructures are disposed on an active channel of the FET. The plurality of gold nanostructures are electrically isolated from the source electrode, drain electrode and gate electrode. The plurality of gold nanostructures contribute to a drain current of the FET based at least in part on plasmonic absorption of photons.

Owner:KIM SUNG JIN

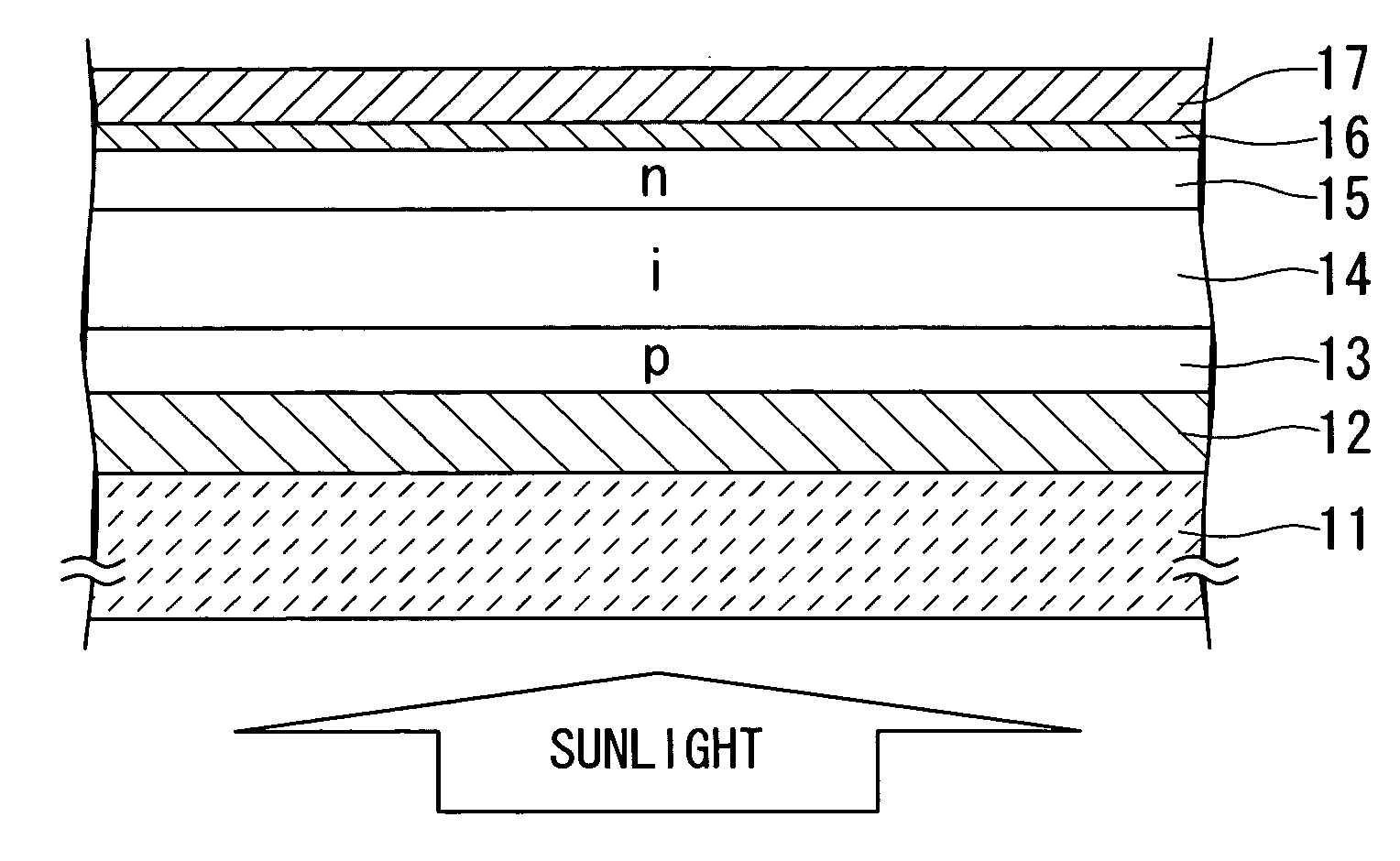

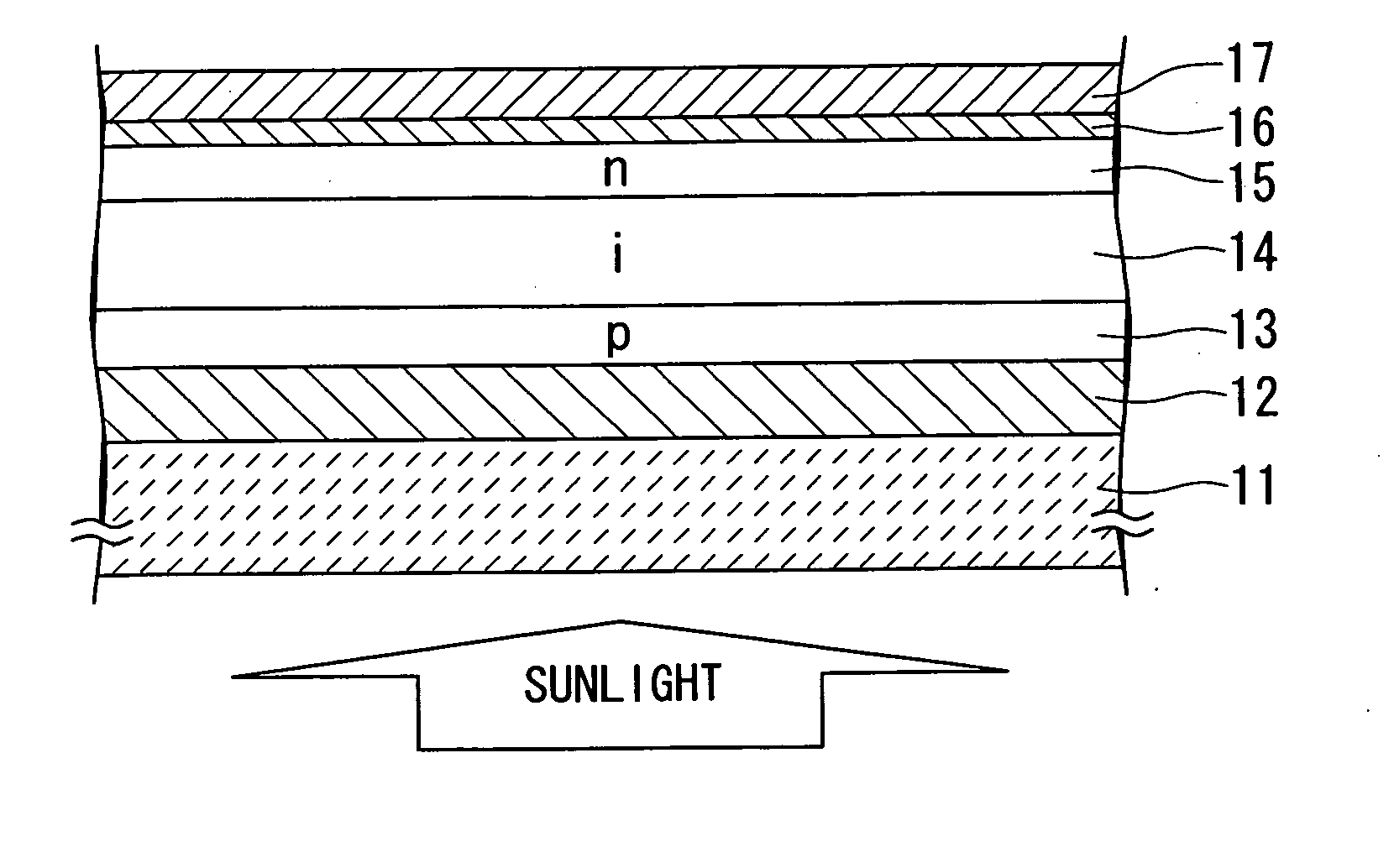

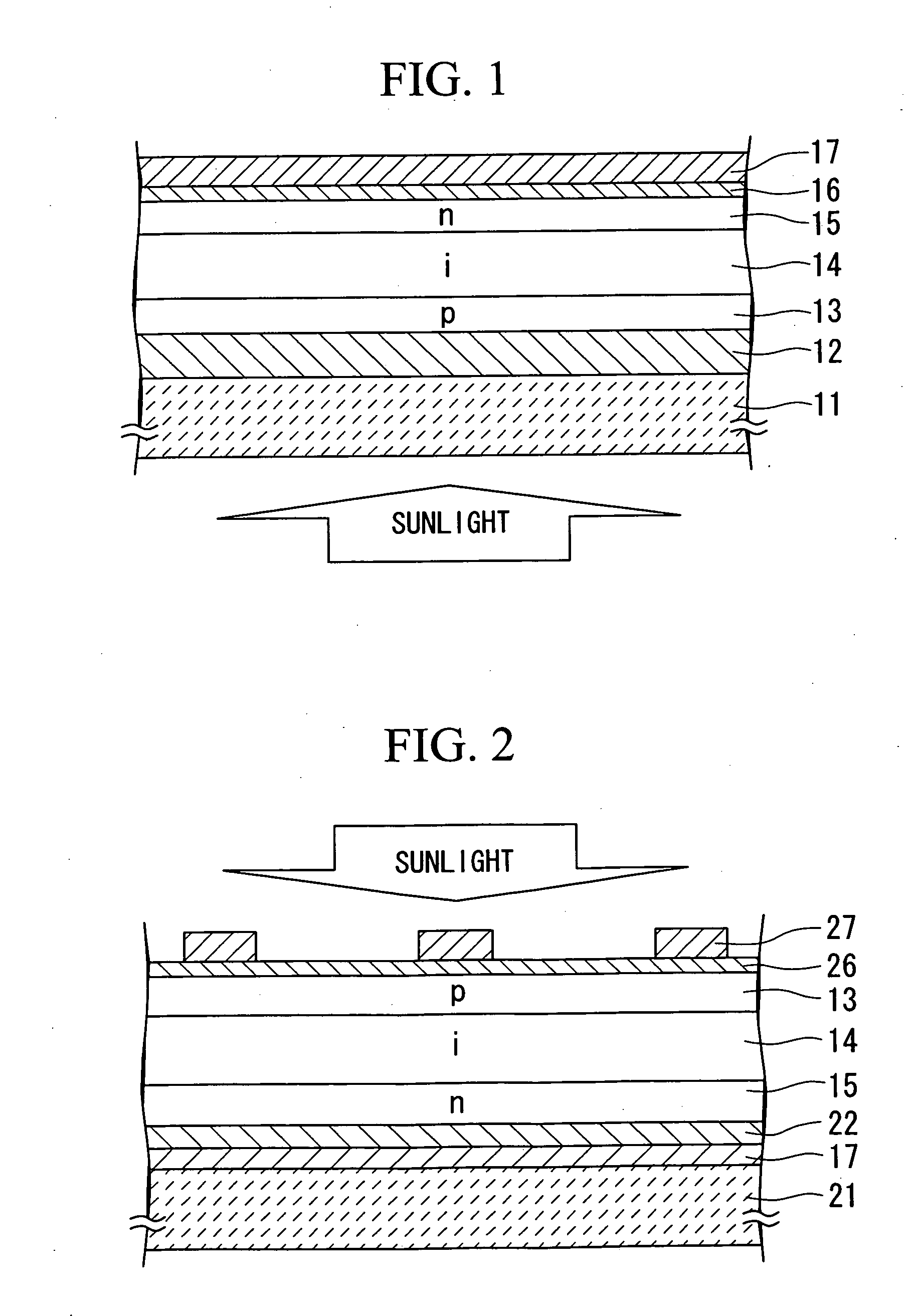

Solar cell and process for producing solar cell

InactiveUS20050103377A1Avoid reorganizationImprove photovoltaic conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingDopantManufacturing technology

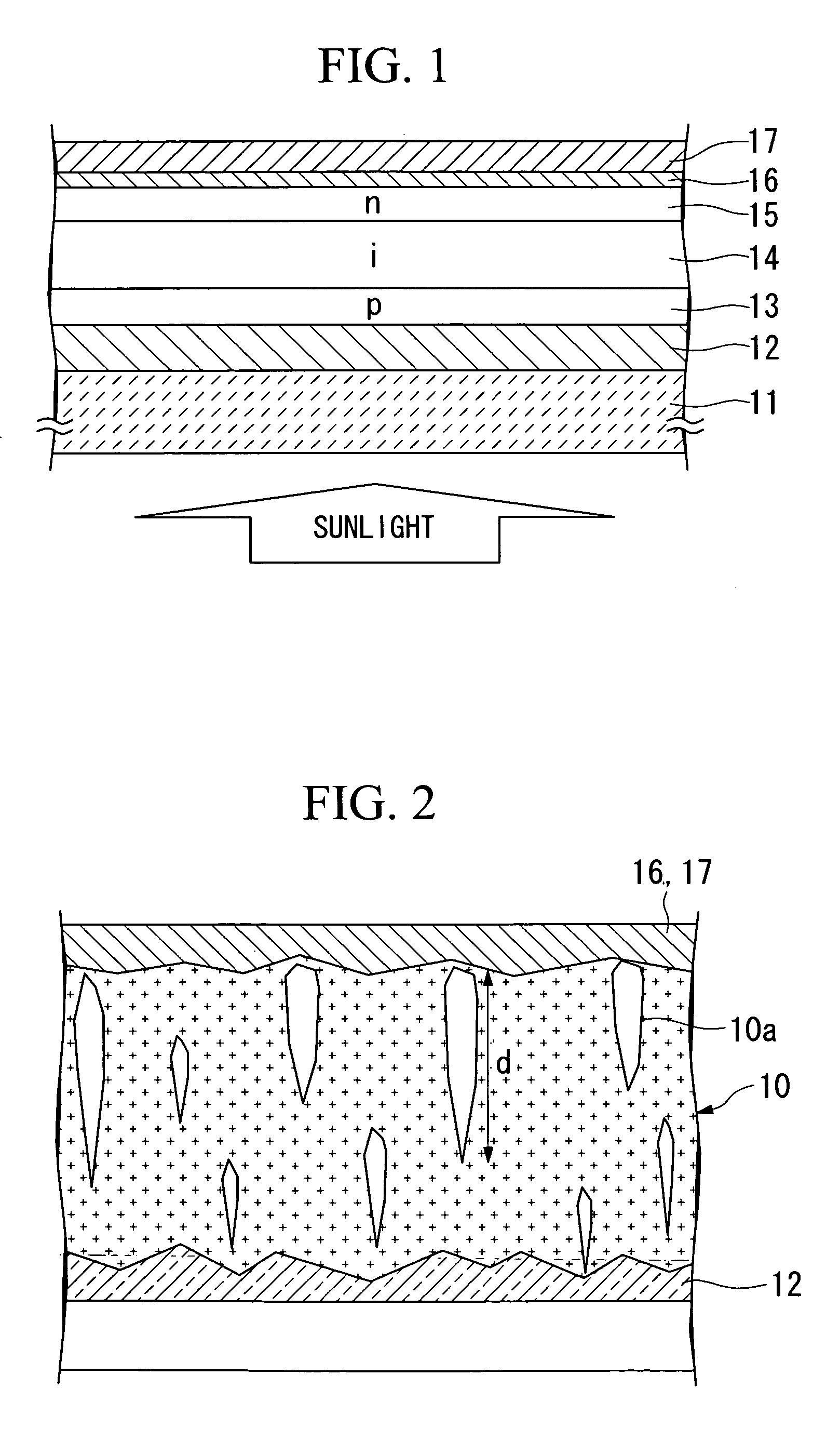

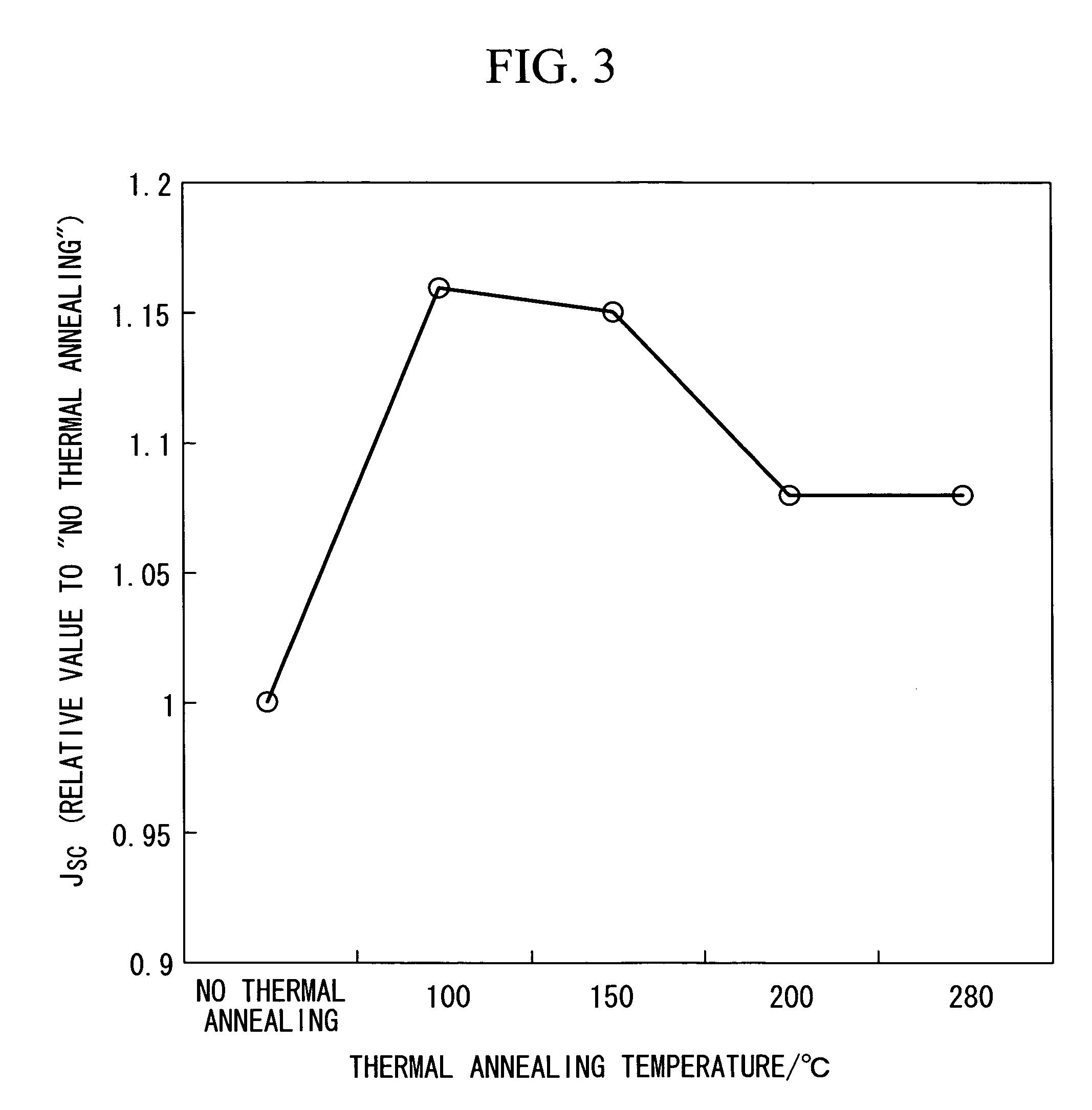

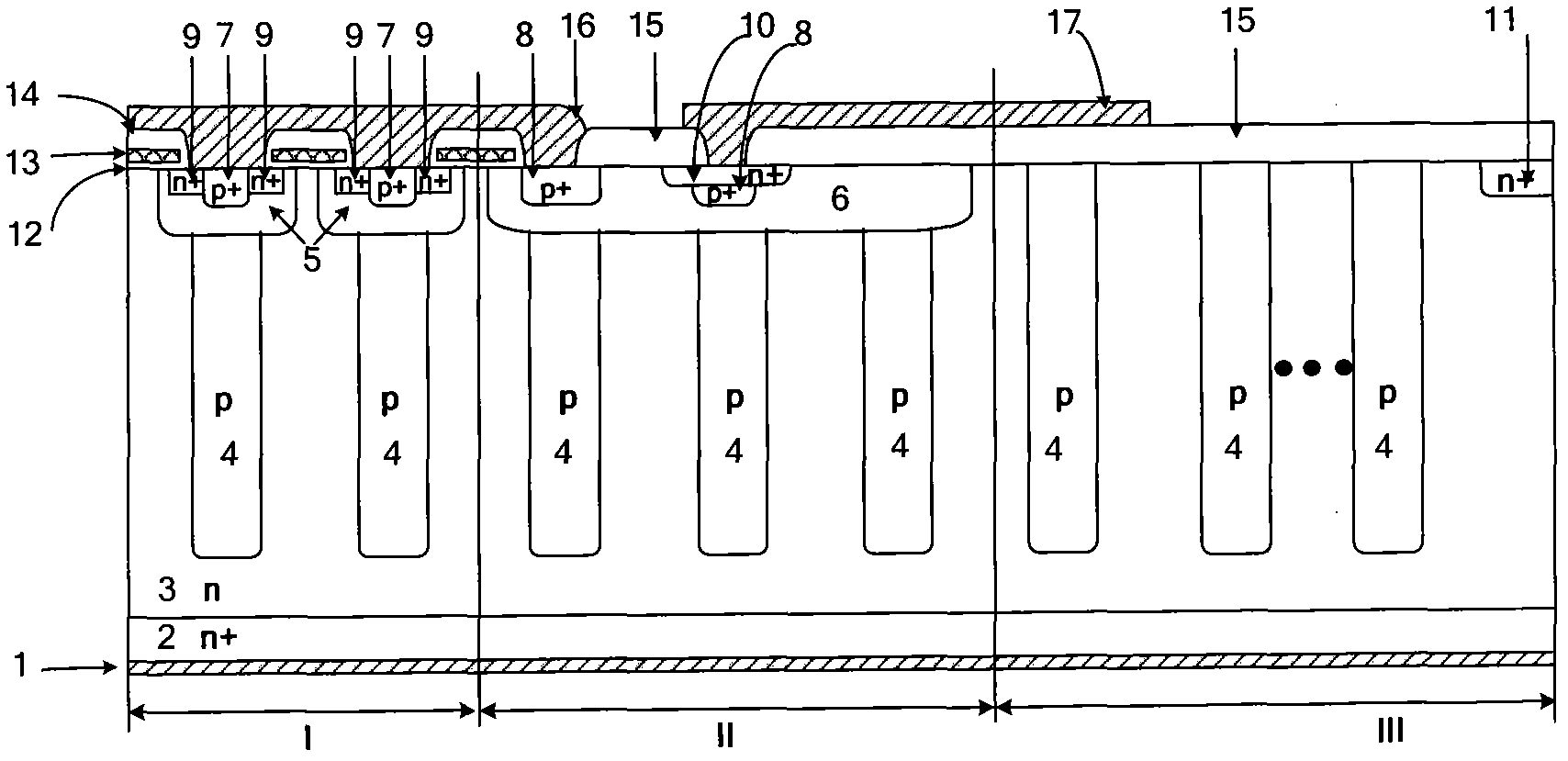

A process for producing a solar cell is provided which can enhance the photovoltaic conversion efficiency by enlarging the grain sizes in the direction of the thickness of an i-layer to reduce grain boundaries, thereby avoiding recombination of carriers and activating the dopant at the same time. A process for producing a solar cell includes depositing at least a first transparent electrode, polycrystalline silicon layers in a PIN structure, and a second electrode in sequence on an electrically insulating substrate, the polycrystalline silicon layers in a PIN structure including a p-type silicon layer, an i-type silicon layer, and an n-type silicon layer, wherein the polycrystalline silicon layers in a PIN structure are formed by: forming a p-type, which is then subjected to thermal annealing; depositing an i-type silicon layer on the p-type silicon layer; and depositing an n-type silicon layer on the i-type silicon layer.

Owner:MITSUBISHI HEAVY IND LTD

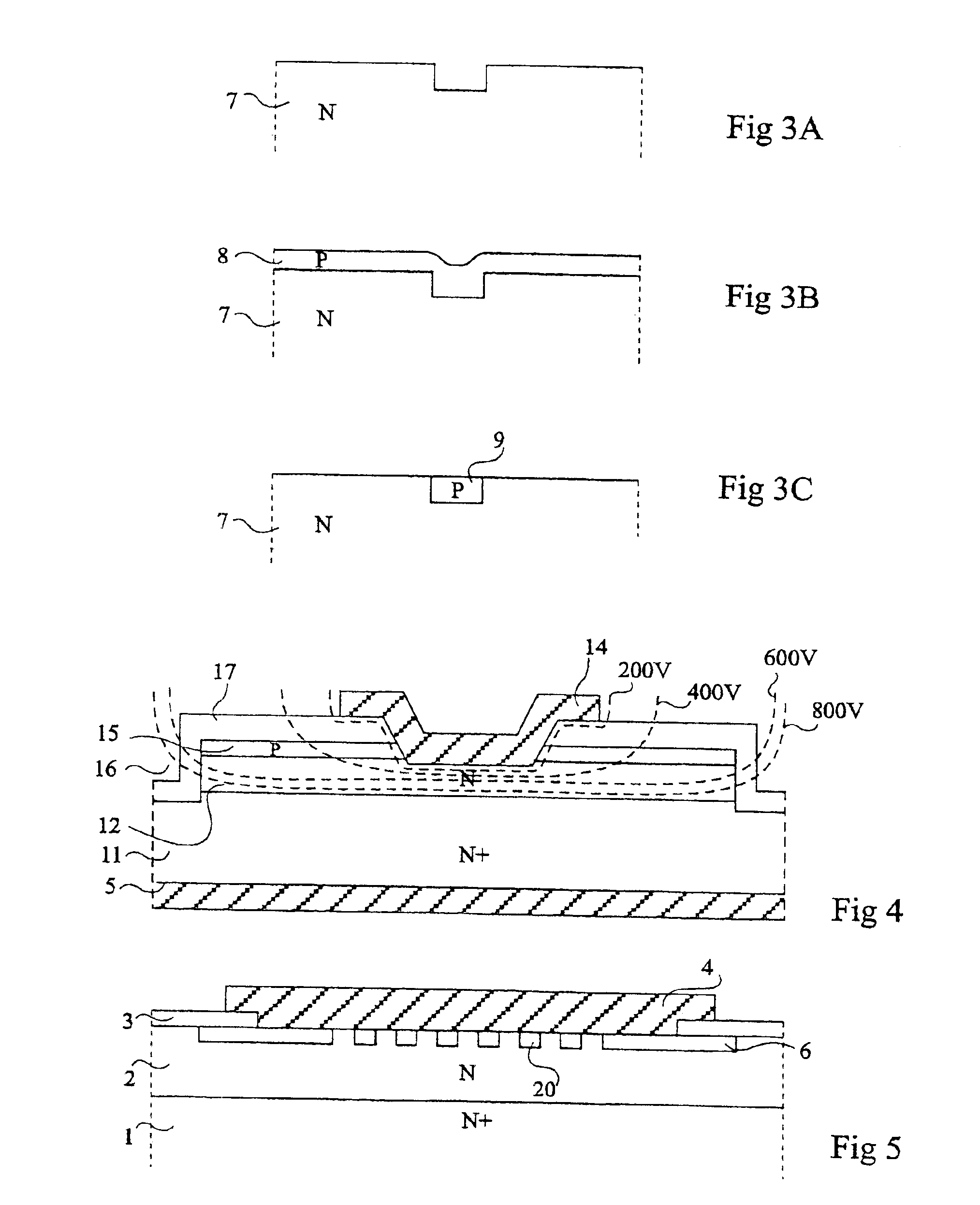

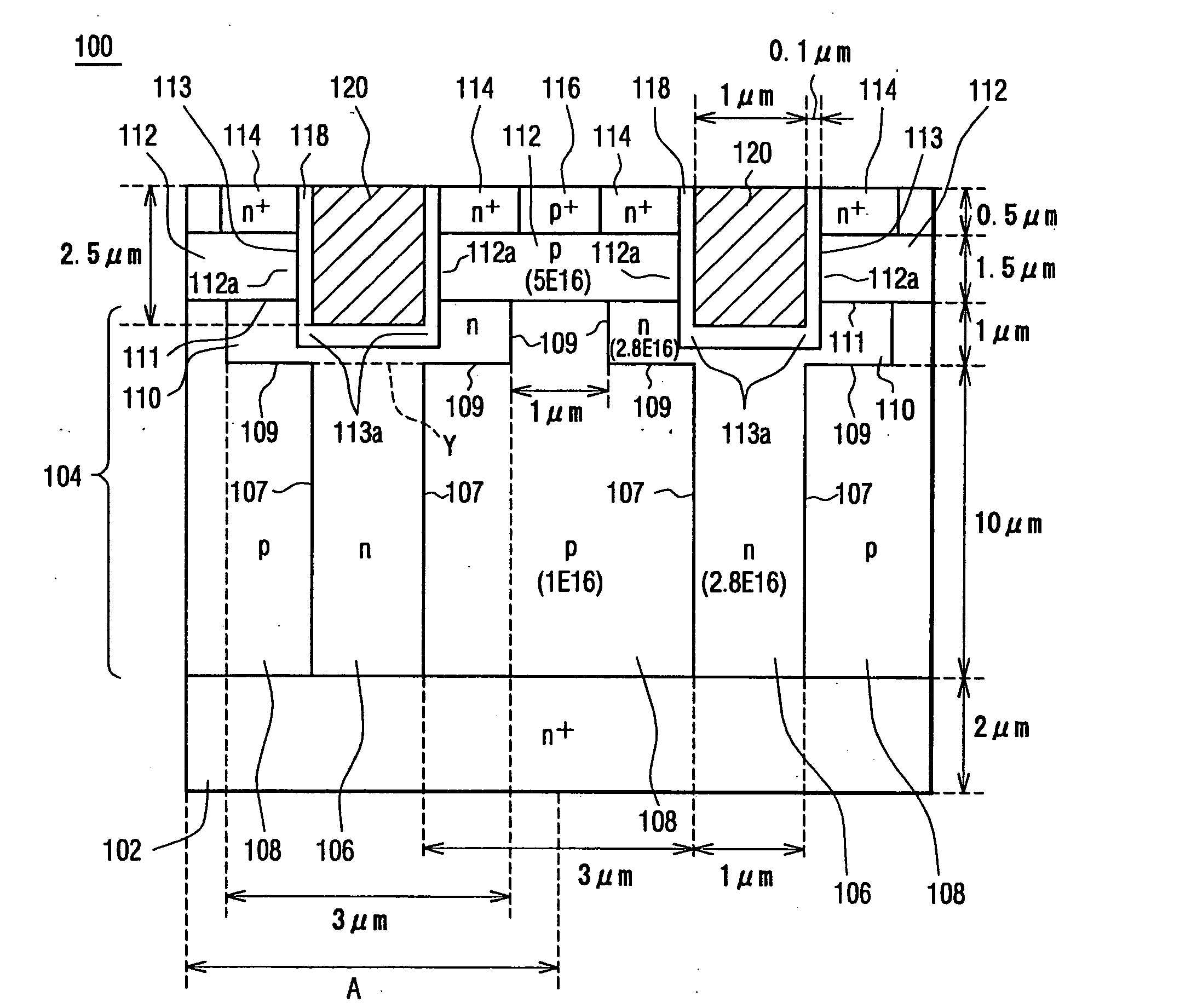

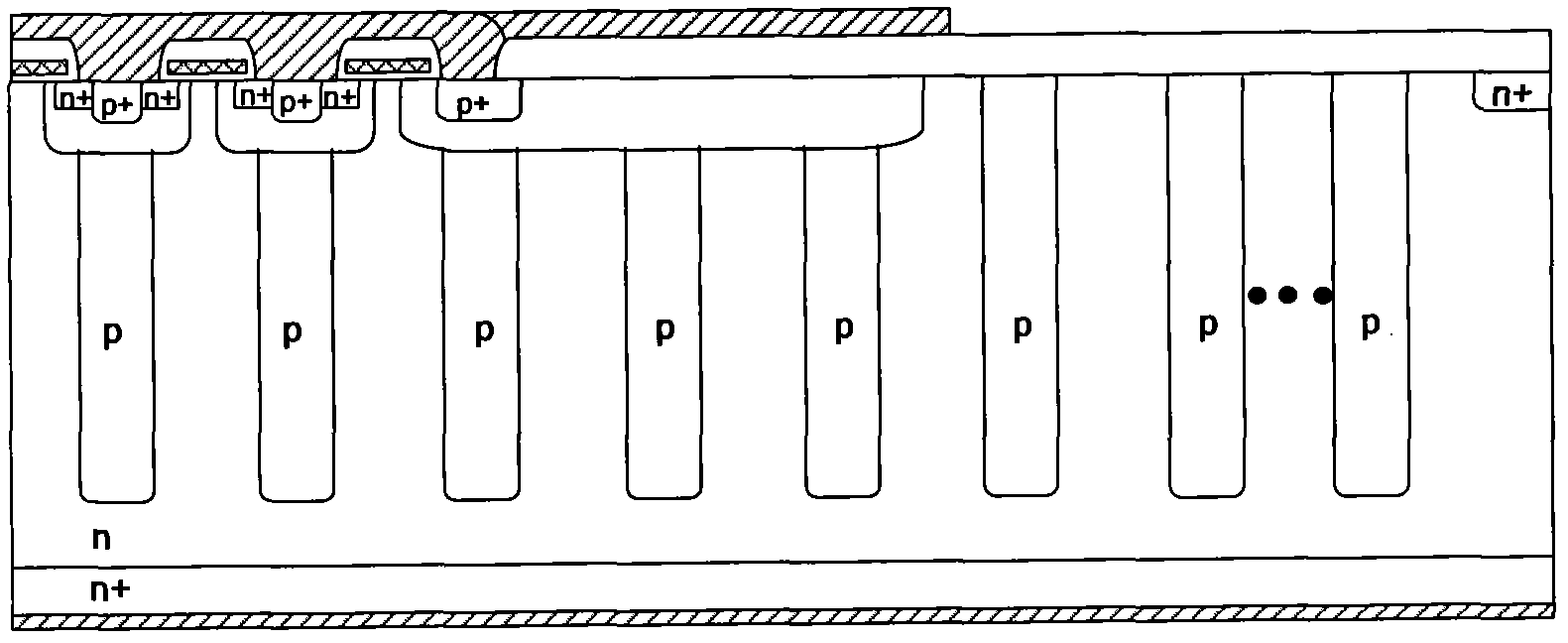

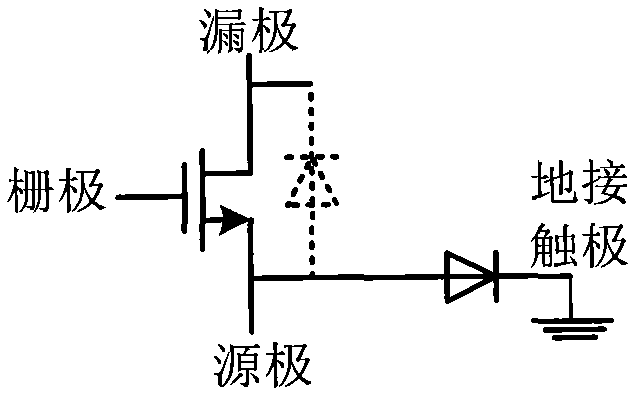

Rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor

InactiveCN101969073AExpand quicklyImprove pressure resistanceSemiconductor devicesDouble diffusionEngineering

The invention relates to a rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor which comprises a cell area, a terminal area and a transition area, wherein the terminal area is arranged at the outermost periphery of a chip; the transition area is positioned between the cell area and the terminal area; the bottoms of the cell area, the transition area and the terminal area (III) are provided with drain electrode metal; a heavy doping n-type silicon substrate is arranged on the drain electrode metal and used as a drain area of the chip; an n-type doping epitaxial layer is arranged on the heavy doping n-type silicon substrate; and a discontinuous p-type doping columnar semiconductor area is arranged in the n-type doping epitaxial layer. The rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor is characterized in that an n-type heavy doping semiconductor area is arranged in a second p-type doping semiconductor area in the transition area, and the surface of the n-type heavy doping semiconductor area is provided with a contact hole which is connected with a metal layer to form a ground contact electrode of the chip. The invention can effectively reduce the reverse recovery charge of a device and improve the reverse recovery characteristics under the conditions of not increasing the process cost or changing the main parameter of the device.

Owner:SOUTHEAST UNIV

Photovoltaic device

InactiveUS20050205127A1High light transmittanceReduce harmPV power plantsPhotovoltaic energy generationMicrocrystalline siliconP type silicon

A photovoltaic device is formed by depositing at least a first transparent electrode, PIN-structured or NIP-structured microcrystalline silicon layers, a second transparent electrode, and a back electrode in sequence on an electrically insulating transparent substrate. The PIN-structured or NIP-structured microcrystalline silicon layers include a p-type silicon layer, an i-type silicon layer, and an n-type silicon layer. At least one of the first transparent electrode and the second transparent electrode is a ZnO layer doped with Ga, and the Ga concentration is 15 atomic percent or less with respect to Zn.

Owner:MITSUBISHI HEAVY IND LTD

Infrared detector and solid state image sensor having the same

InactiveUS20090266987A1Effective absorptionReduce manufacturing costSolid-state devicesMaterial analysis by optical meansEngineeringP type silicon

An infrared detector includes: a readout wiring portion provided on a semiconductor substrate; a support structure portion disposed over a concave portion formed in a surface portion of the semiconductor substrate, the support structure portion having connection wiring connected electrically to the readout wiring portion; and a cell portion disposed over the concave portion and supported by the support structure portion. The cell portion includes: an infrared absorption layer absorbing incident infrared rays; and a plurality of thermoelectric conversion elements connected electrically to the support structure portion and insulated electrically from the infrared absorption layer to generate an electric signal by detecting a temperature change of the cell portion, each of the thermoelectric conversion elements includes a semiconductor layer, a p-type silicon layer and an n-type silicon layer formed with a space between them in the semiconductor layer, and a polysilicon layer formed on the semiconductor layer between the p-type silicon layer and the n-type silicon layer.

Owner:KK TOSHIBA

Oxide semiconductor substrate and schottky barrier diode

ActiveUS20160211386A1Low costImprove batch productivitySemiconductor devicesSchottky barrierP type silicon

A Schottky barrier diode element includes an n-type or p-type silicon (Si) substrate, an oxide semiconductor layer, and a Schottky electrode layer, the oxide semiconductor layer including either or both of a polycrystalline oxide that includes gallium (Ga) as the main component and an amorphous oxide that includes gallium (Ga) as the main component.

Owner:IDEMITSU KOSAN CO LTD

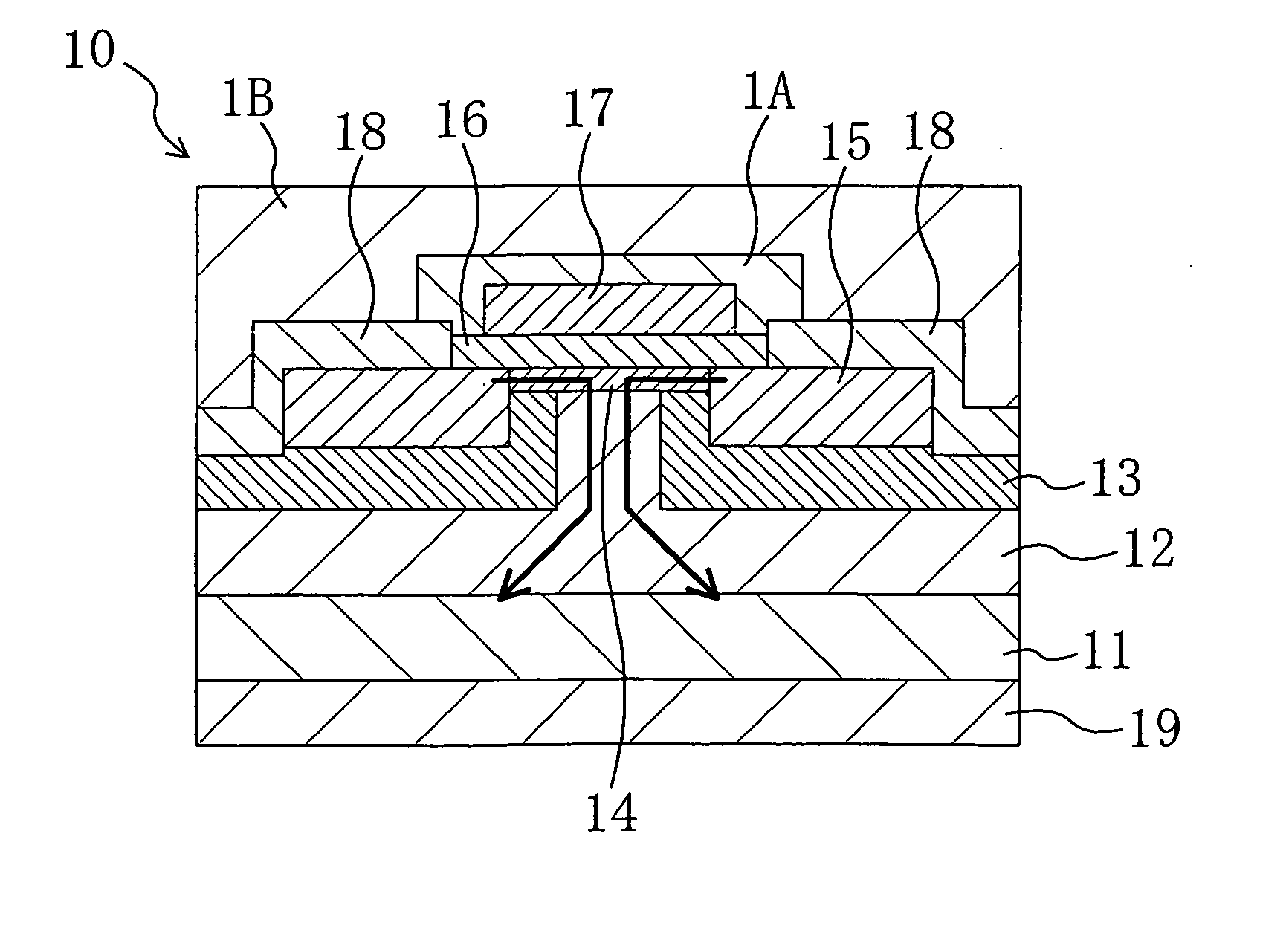

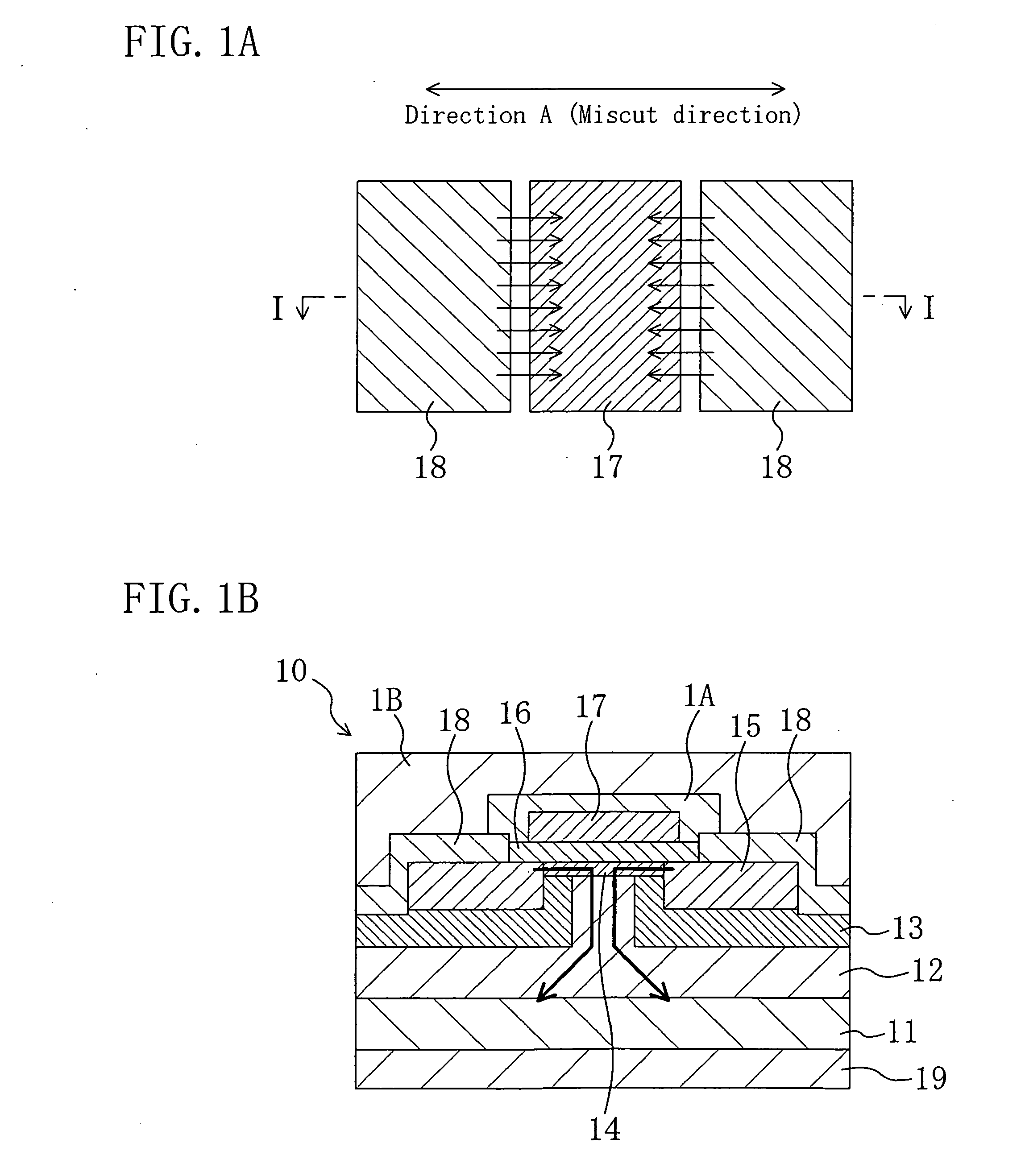

Semiconductor element

InactiveUS20060220026A1Excellent electrical propertiesReduced electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCarbide

In a semiconductor device of the present invention, the top surface of an n-type silicon carbide layer formed on a silicon carbide substrate is miscut from the (0001) plane in the <11-20> direction. A gate electrode, a source electrode and other elements are arranged such that in a channel region, the dominating current flows along a miscut direction. In the present invention, a gate insulating film is formed and then heat treatment is performed in an atmosphere containing a group-V element. In this way, the interface state density at the interface between the silicon carbide layer and the gate insulating film is reduced. As a result, the electron mobility becomes higher in a miscut direction A than in the direction perpendicular to the miscut direction A.

Owner:PANASONIC CORP

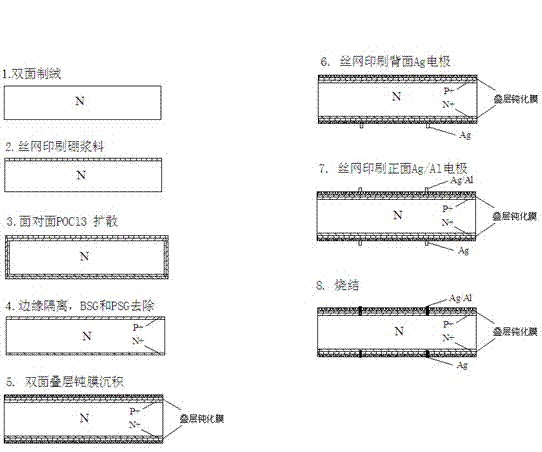

A process for preparing n-type solar cells by co-diffusion of boron and phosphorus

InactiveCN102263159ASimple manufacturing processReduce manufacturing costFinal product manufactureOther printing apparatusScreen printingSlurry

The invention discloses a process for preparing an n-type solar cell by co-diffusion of boron and phosphorus, which comprises the following steps: making surface texture; screen-printing boron slurry or phosphorus slurry on the surface of a silicon chip, and drying at 100-500°C Dry for 5~30 minutes; according to the self-blocking and out-diffusion characteristics of boron slurry or phosphorus slurry at high temperature, you can choose whether to screen print a layer of barrier layer slurry on it; the active layer is back-to-back for high-temperature boron and phosphorus diffusion; for For n-type silicon wafers printed with boron paste, first diffuse at 880-1100°C for 10-60 minutes, then cool down to 800-950°C, and then inject POCl3 source for phosphorus diffusion for 10-60 minutes; for n-type silicon wafers printed with phosphorous paste BBr3 source was passed into the wafer at a temperature of 880-1100°C for boron-phosphorus co-diffusion for 10-60 minutes; edge isolation and removal of BSG, PSG and barrier layers; double-sided passivation; preparation of electrodes.

Owner:JIANGYIN XINHUI SOLAR ENERGY

Silicon detector structure with broad spectral response and method of making same

InactiveCN102290481AWide spectral response rangeImprove absorption rateFinal product manufactureSemiconductor devicesSpectral responseSilicon detector

The invention relates to a silicon detector structure with a wide spectral response range, which comprises an n-type silicon substrate, a silicon dioxide medium masking layer, a p-type doping layer, a front surface contact electrode, an antireflection film layer, a broad-spectrum absorbing black silicon layer, a medium passivating layer and a back surface contact electrode, wherein a circular groove is arranged on the surface of the n-type silicon substrate; the silicon dioxide medium masking layer is formed around the circular groove on the surface of the n-type silicon substrate, and the middle of the silicon dioxide medium masking layer is an annular structure; the p-type doping layer is arranged in the circular groove of the n-type silicon substrate; the front surface contact electrode is produced on the inner wall of the annular structure of the silicon dioxide medium masking layer and covers the partial edge of the surface of the annular structure to form an annular structure; the antireflection film layer is produced in the annular structure of the front surface contact electrode and covers the surface of the p-type doping layer; the broad-spectrum absorbing black silicon layer is produced on the back surface of the n-type silicon substrate; the medium passivating layer is point-type and is formed on the surface of the broad-spectrum absorbing black silicon layer; and the back surface contact electrode is produced on the surface of the broad-spectrum absorbing black silicon layer and covers the point-type medium passivating layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI