Patents

Literature

1059 results about "P type silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The term p-type refers to the fact that the cell is built on a positively charged (hence p-type) silicon base. Indeed, the wafer is doped with boron, which has one electron less than silicium. The top of the wafer is then negatively doped (n-type) with phosphorous, which has one electron more than silicium.

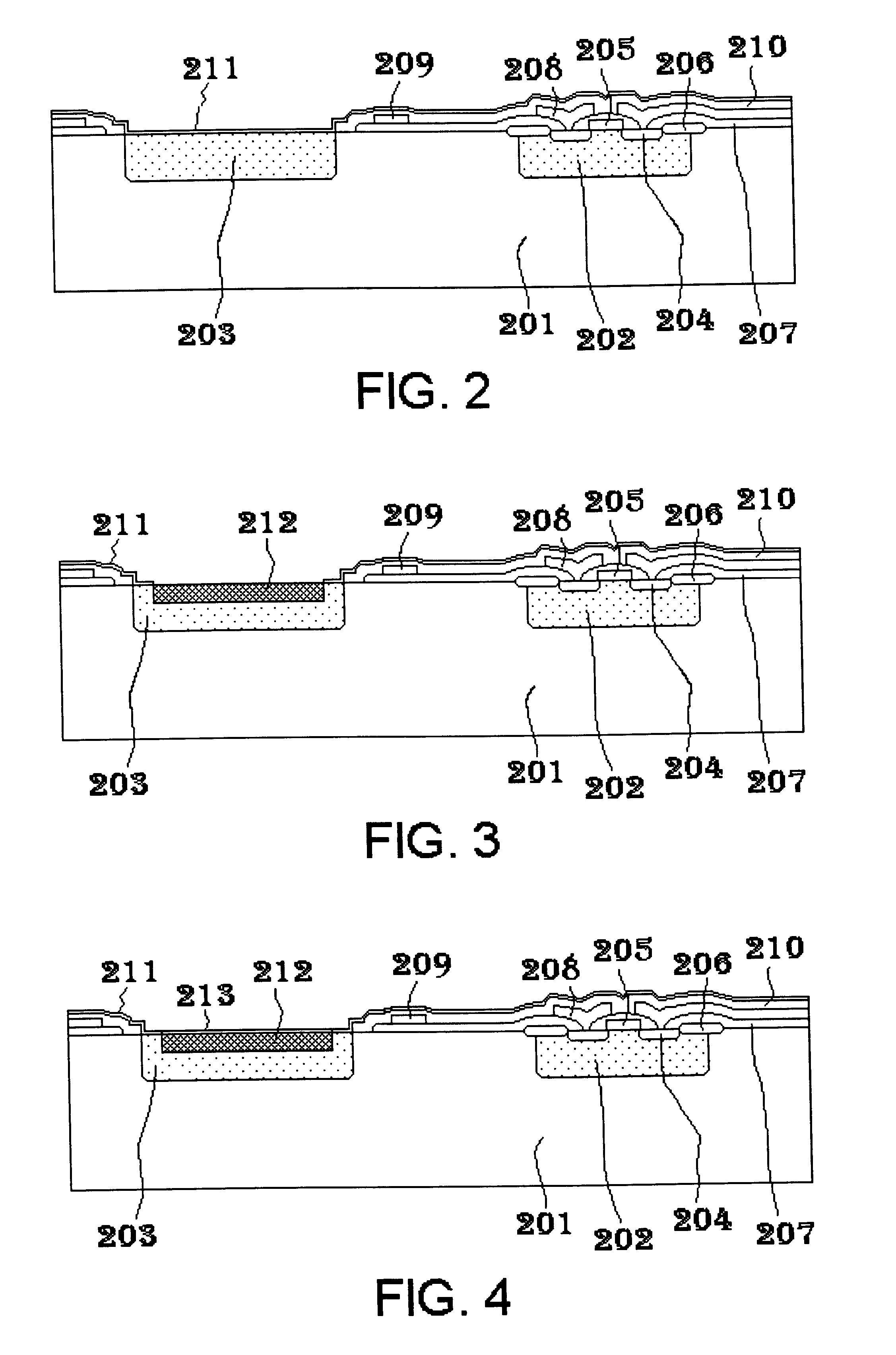

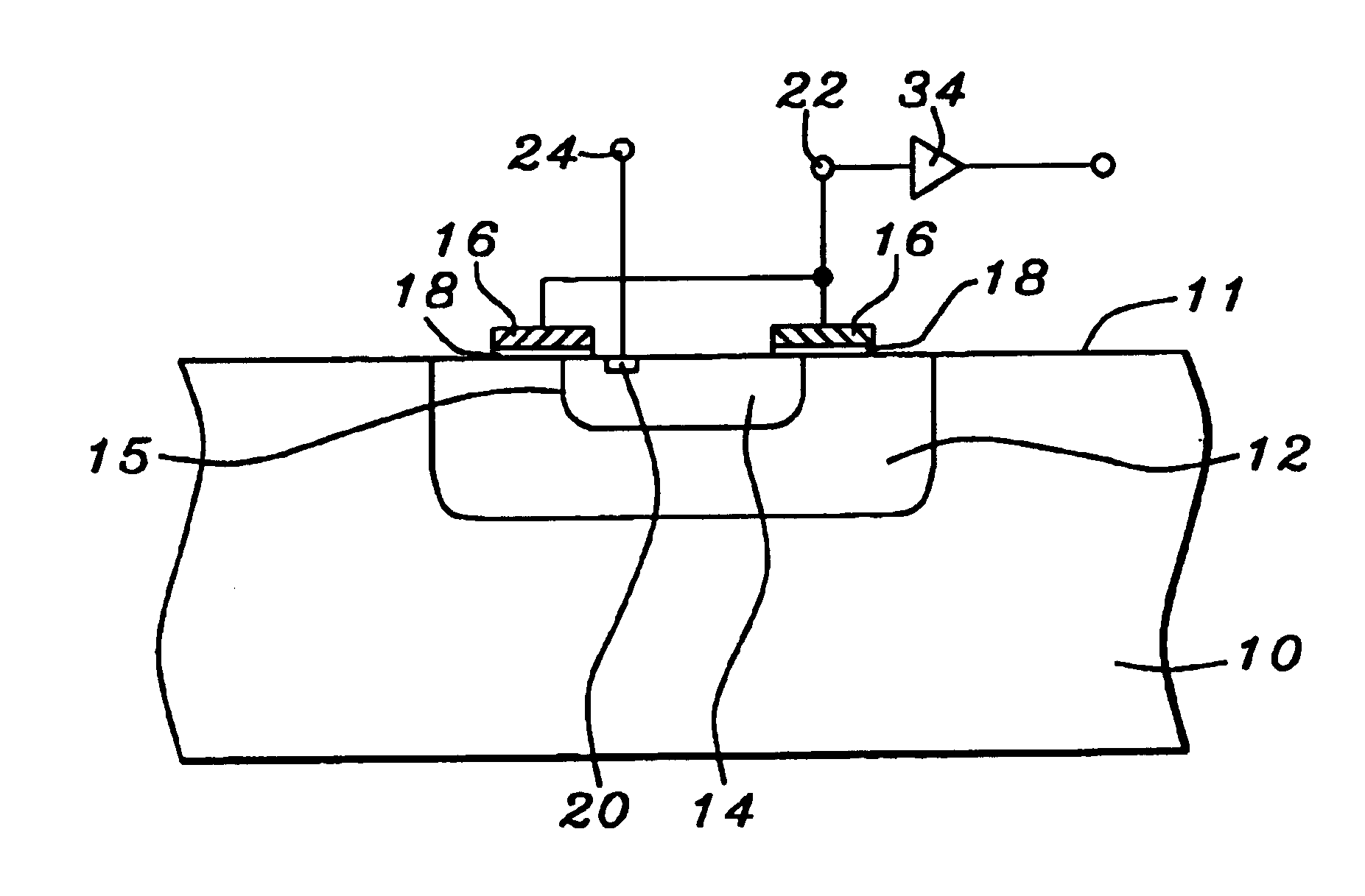

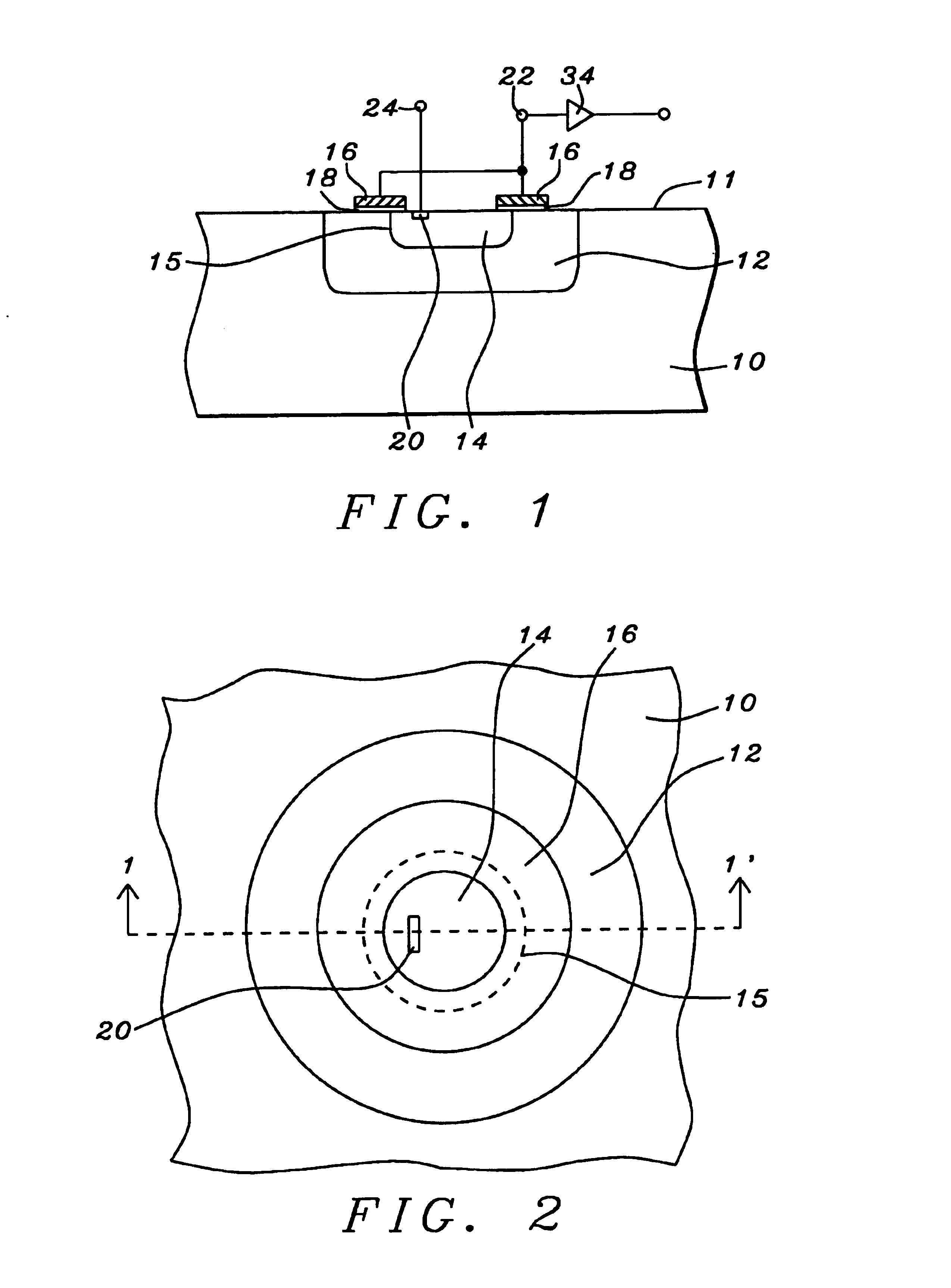

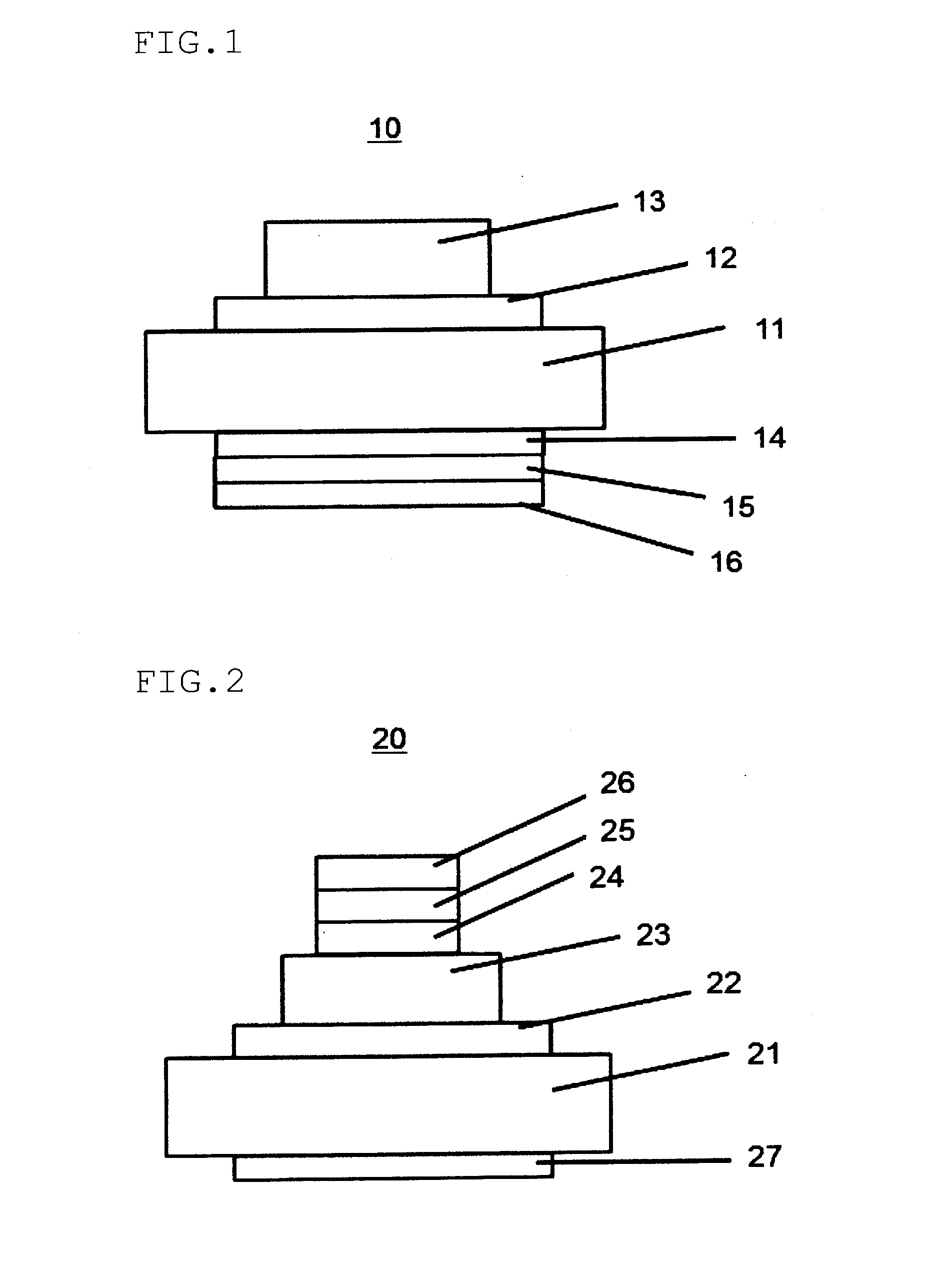

Microbolometer infrared sensors

InactiveUS6359276B1High mechanical strengthReduce residual stressSolid-state devicesMaterial analysis by optical meansThermal isolationMicrobolometer

A microbolometer infrared sensor utilizes a porous silicon bridge as its thermal isolating and mechanical supporting structure. Porous silicon formed from single crystal silicon on lightly doped p-type silicon has a thermal conductivity lower than silicon dioxide and silicon nitride, and, therefore, when used as a mechanical supporting structure, can offer better thermal isolation performance. The porous silicon layer can be fabricated much thicker than silicon dioxide and silicon nitride membranes since there is almost no residual stress therein. A thicker porous silicon bridge has higher mechanical support strength. The porous silicon process is a low temperature process. It facilitates a fabrication strategy of microelectronics first and micromechanics last.

Owner:TU XIANG ZHENG

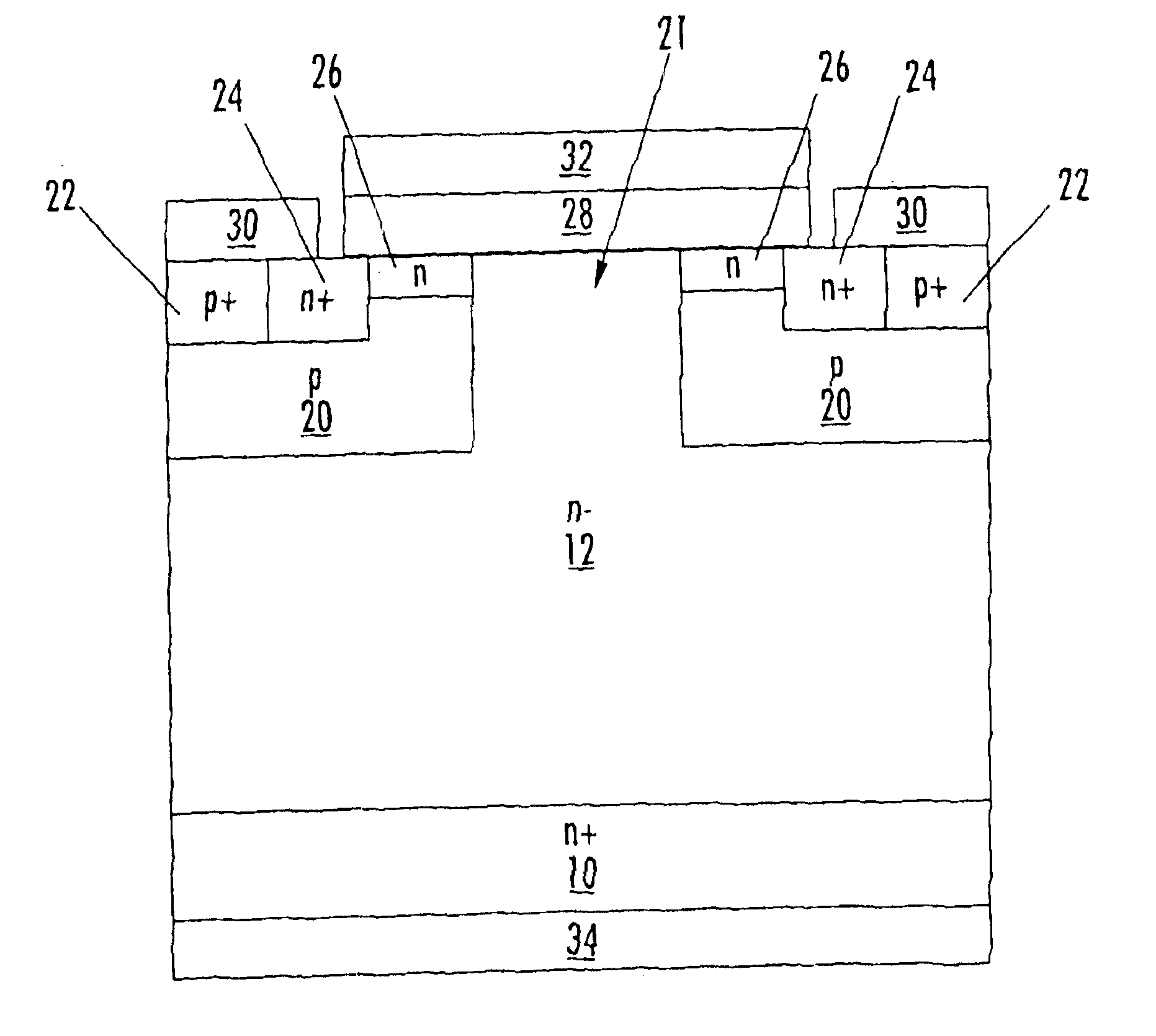

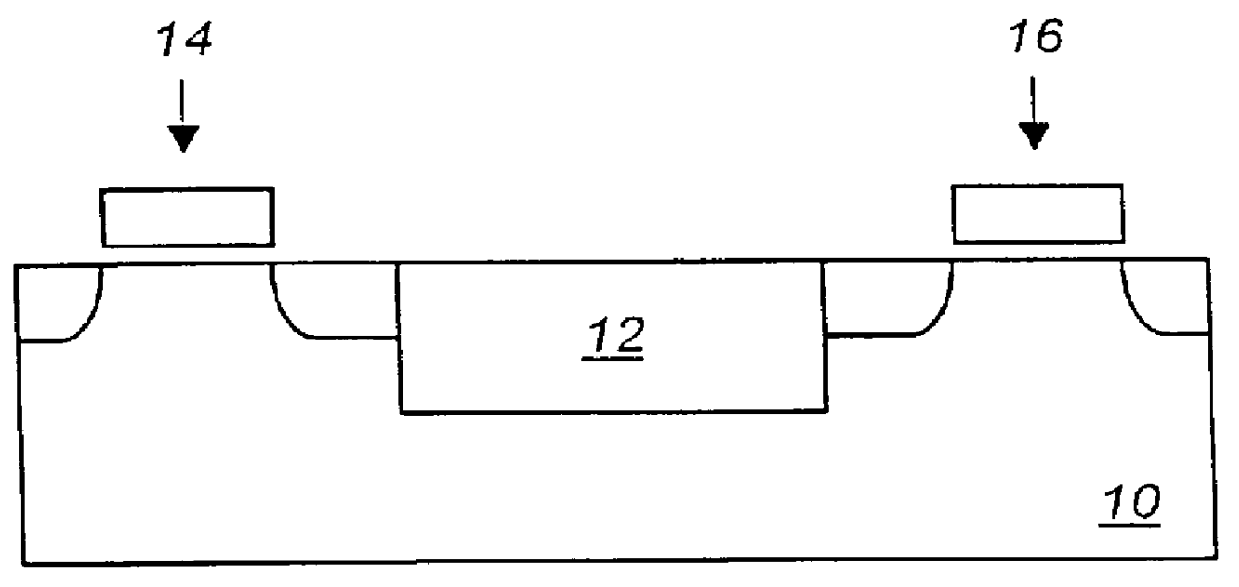

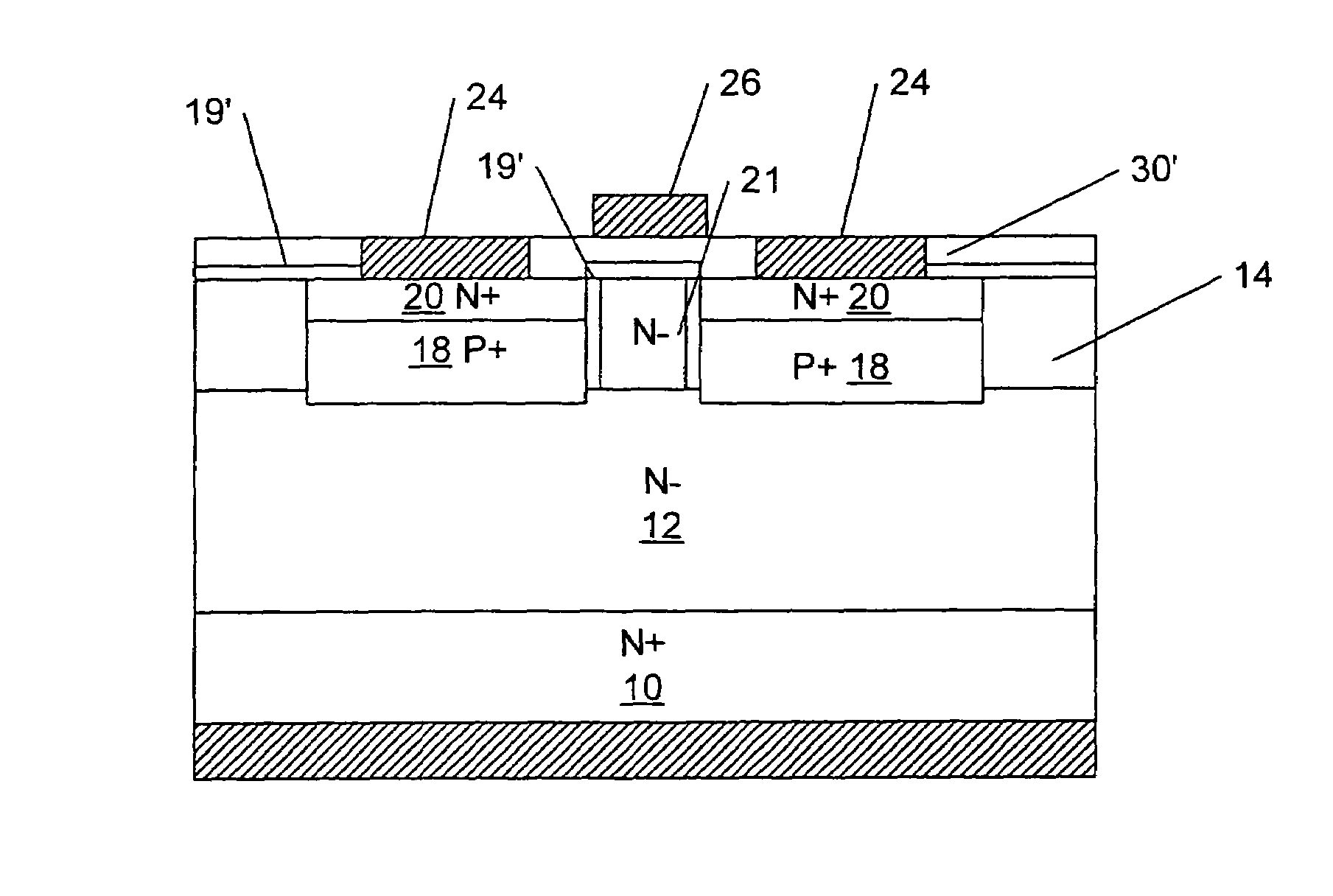

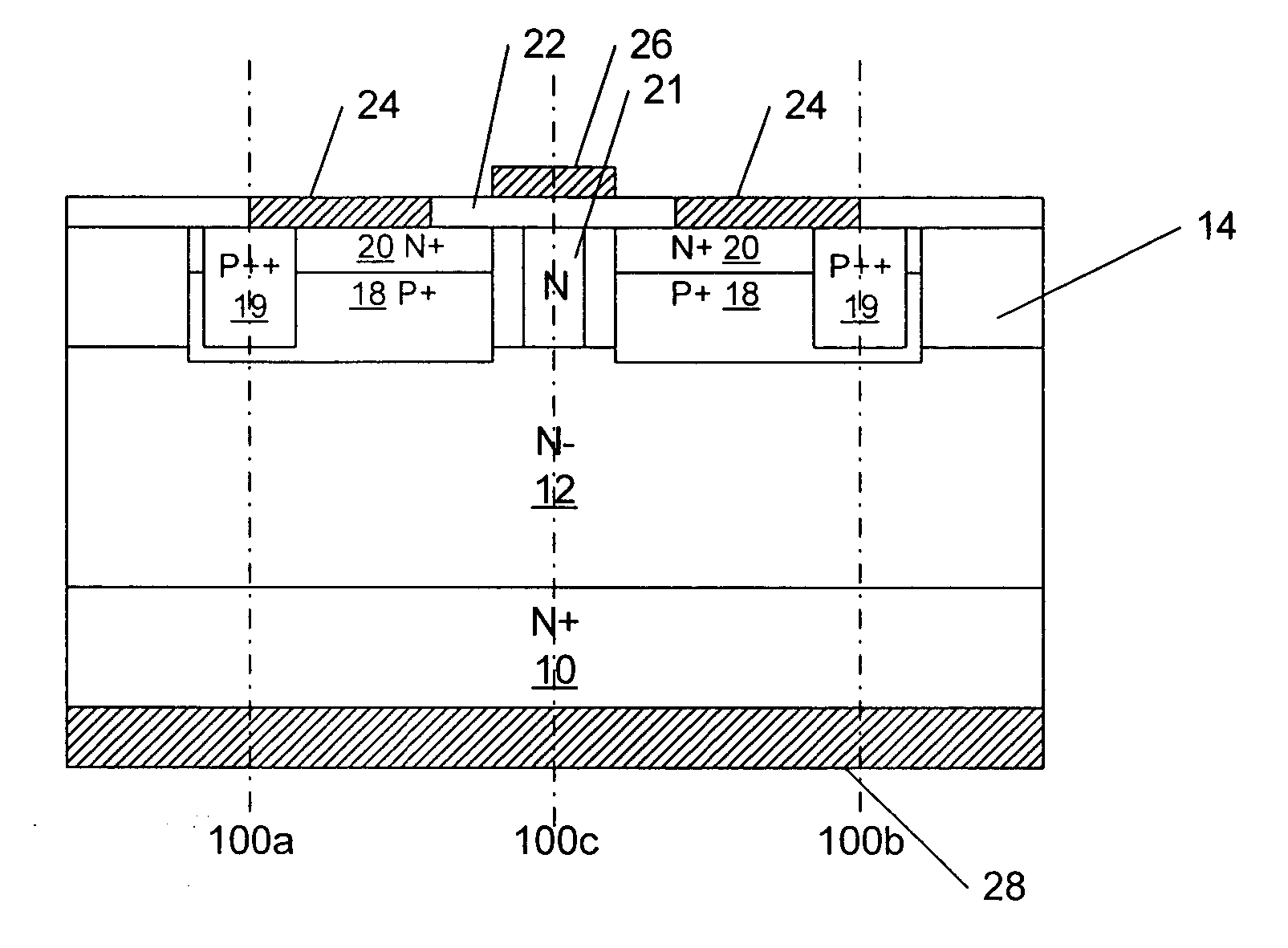

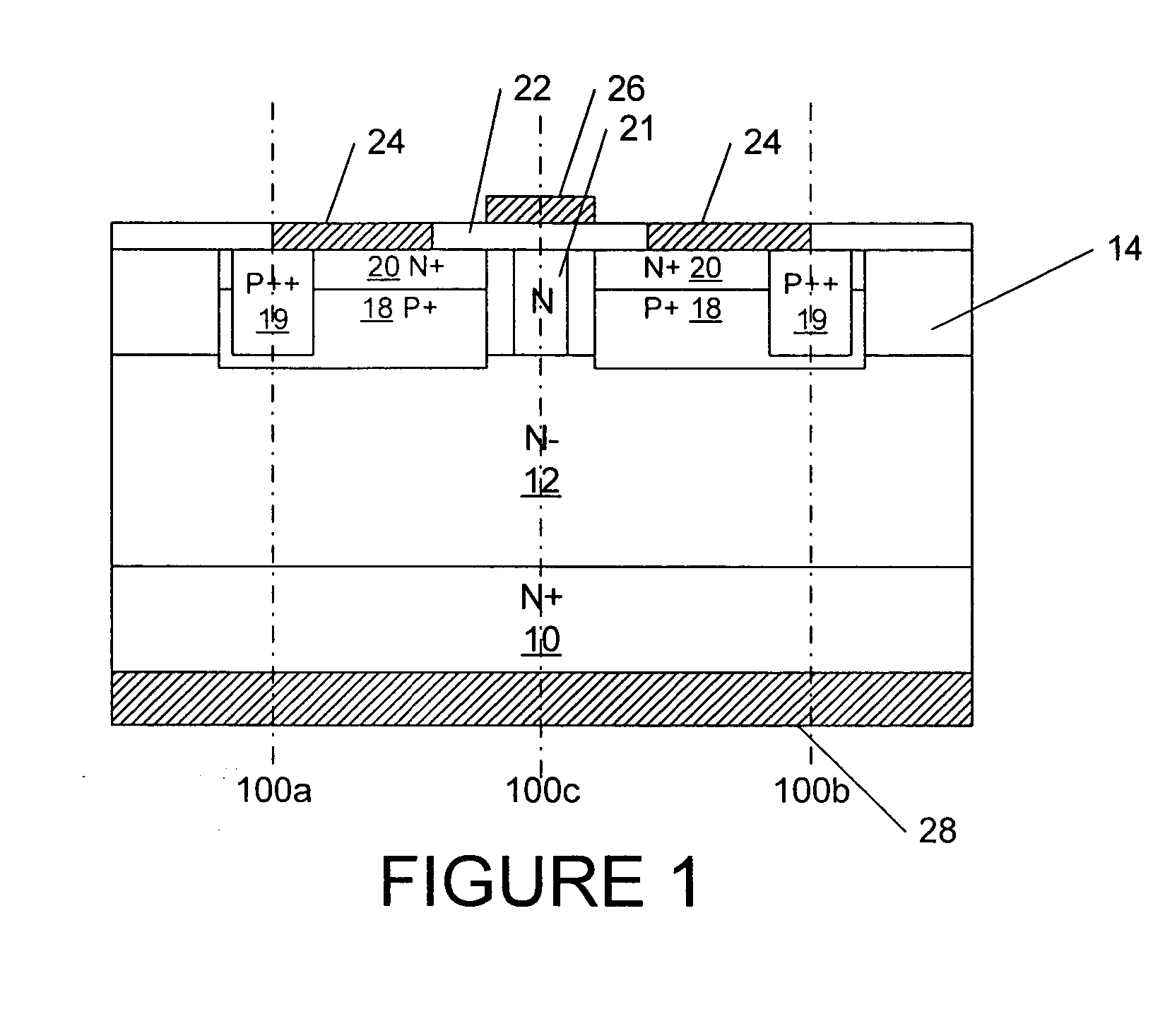

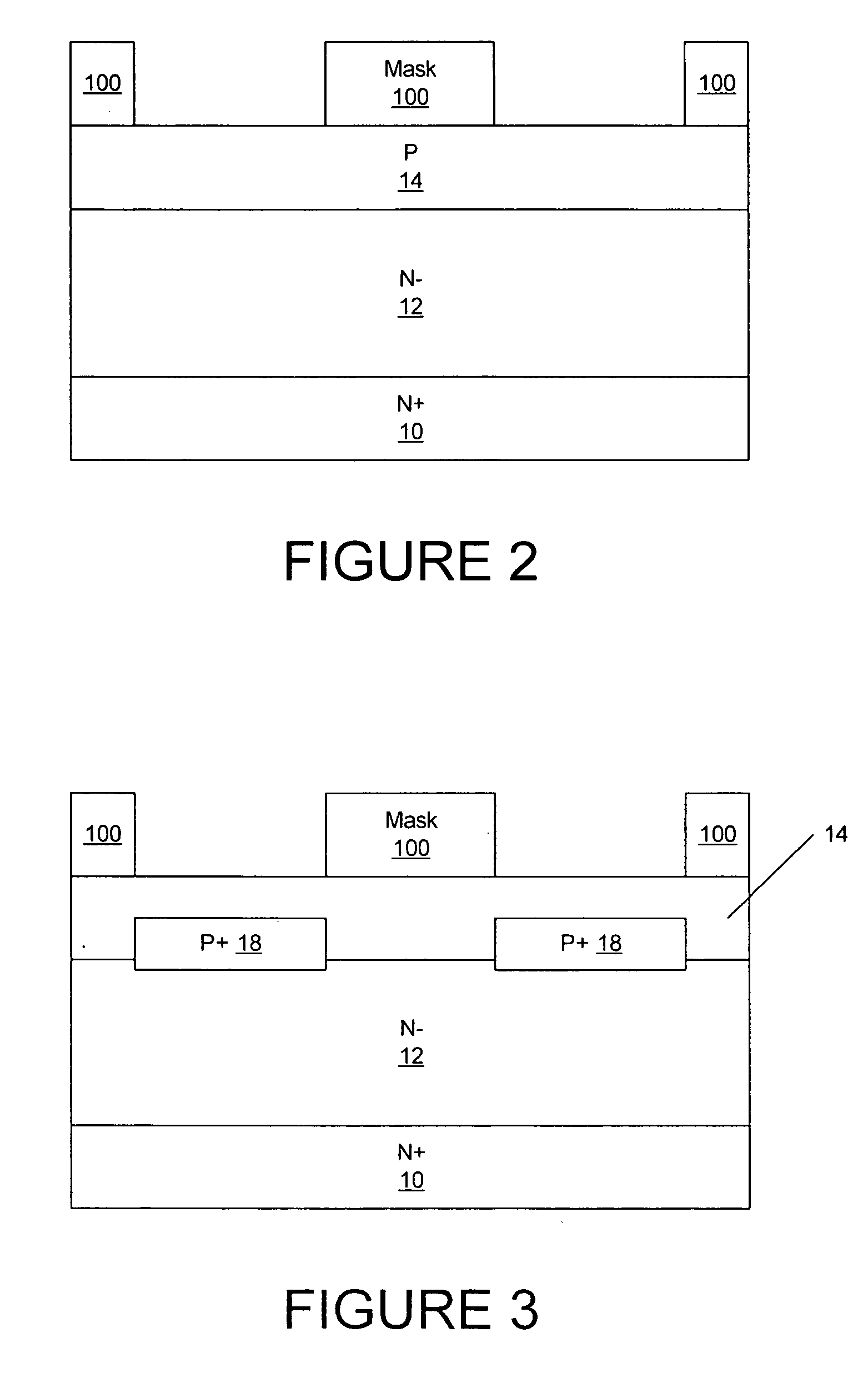

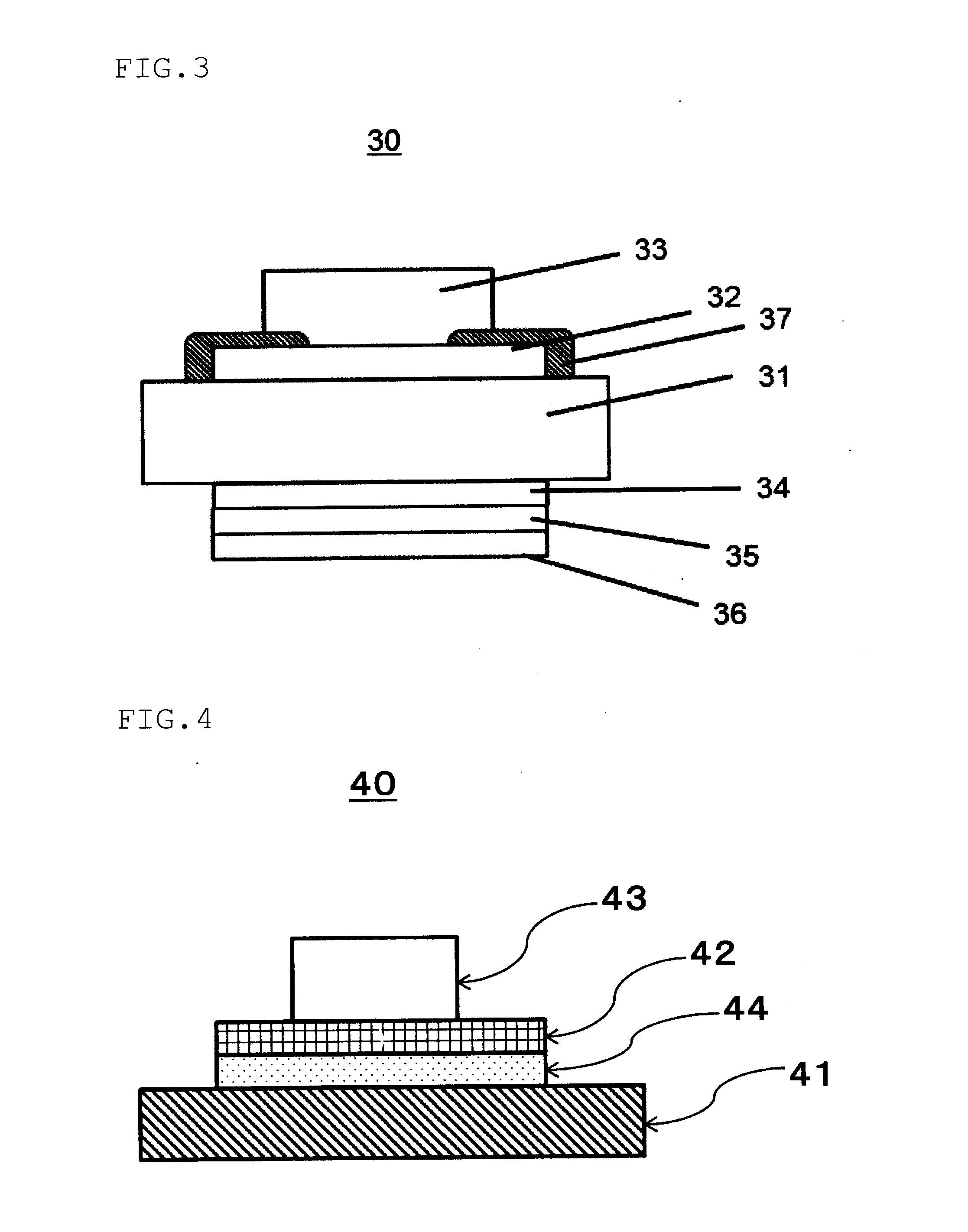

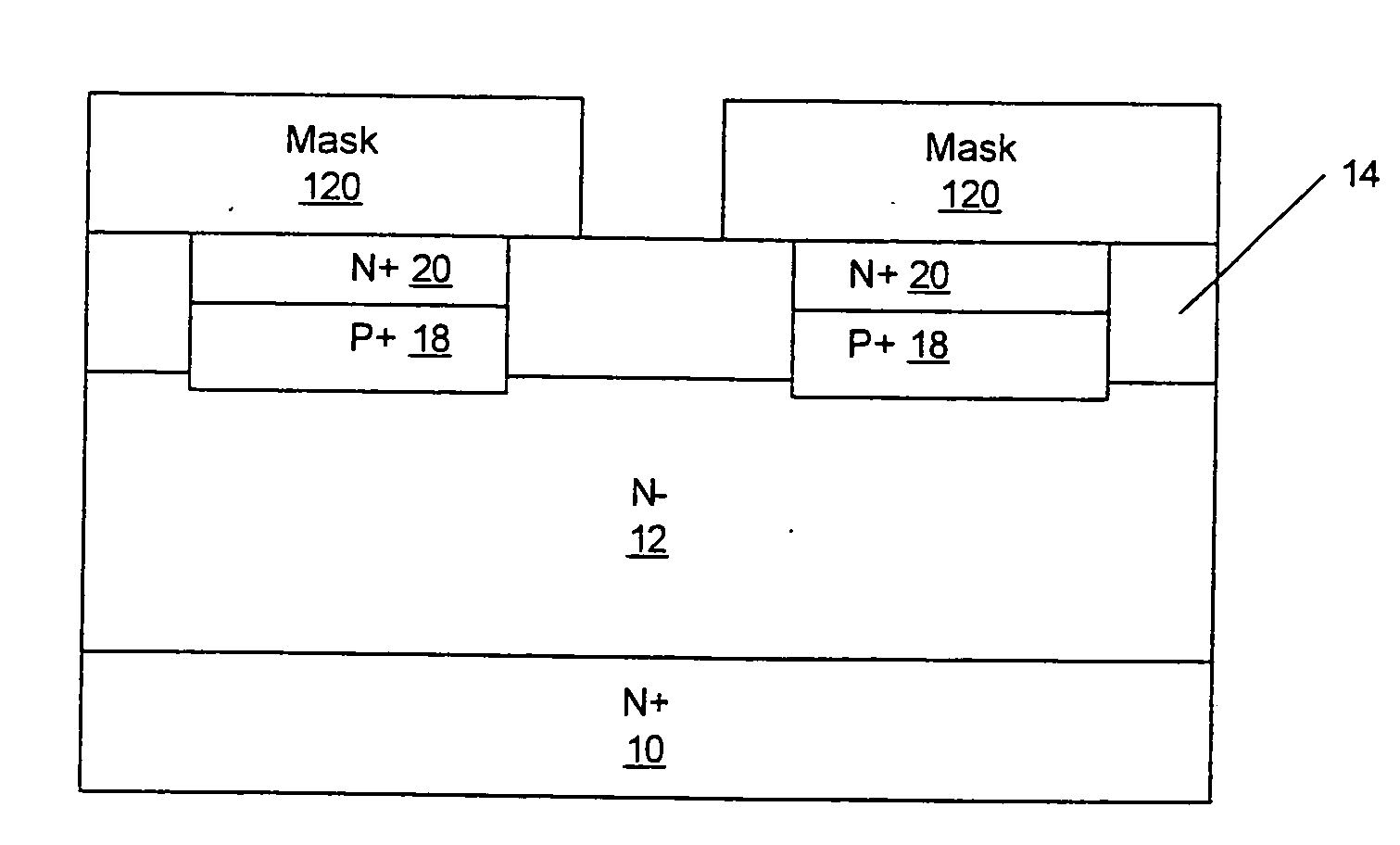

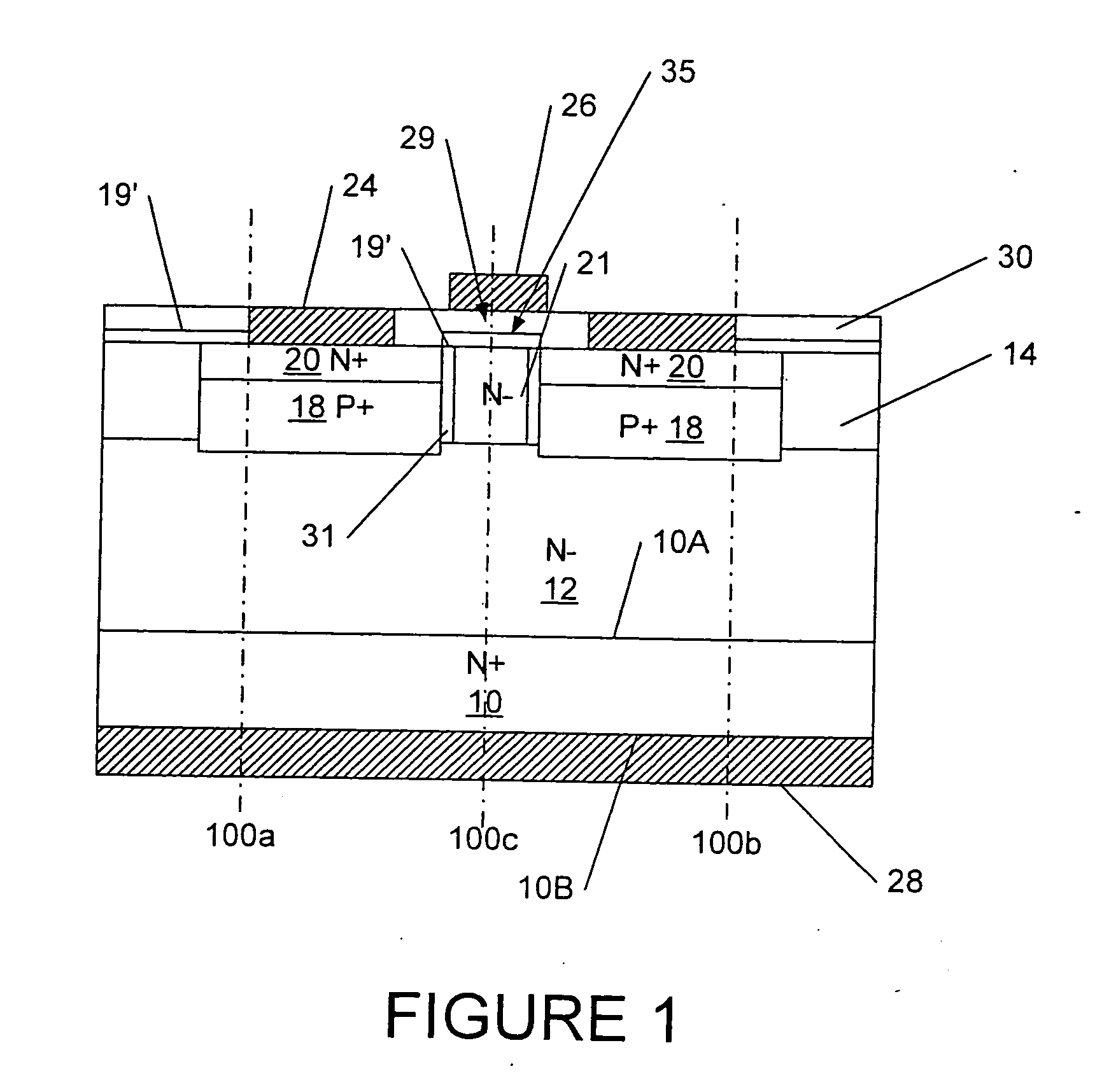

Silicon carbide power metal-oxide semiconductor field effect transistors having a shorting channel and methods of fabricating silicon carbide metal-oxide semiconductor field effect transistors having a shorting channel

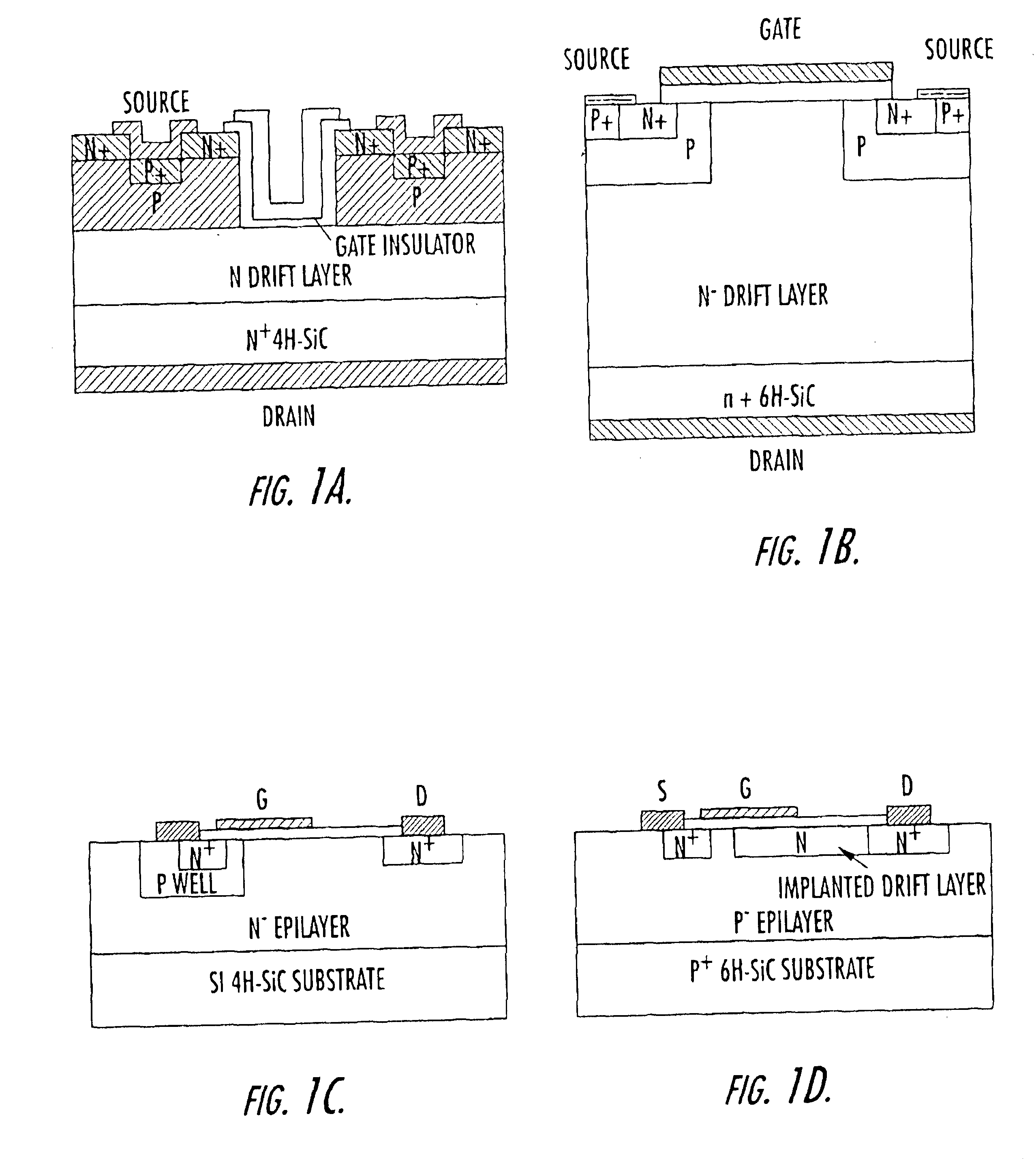

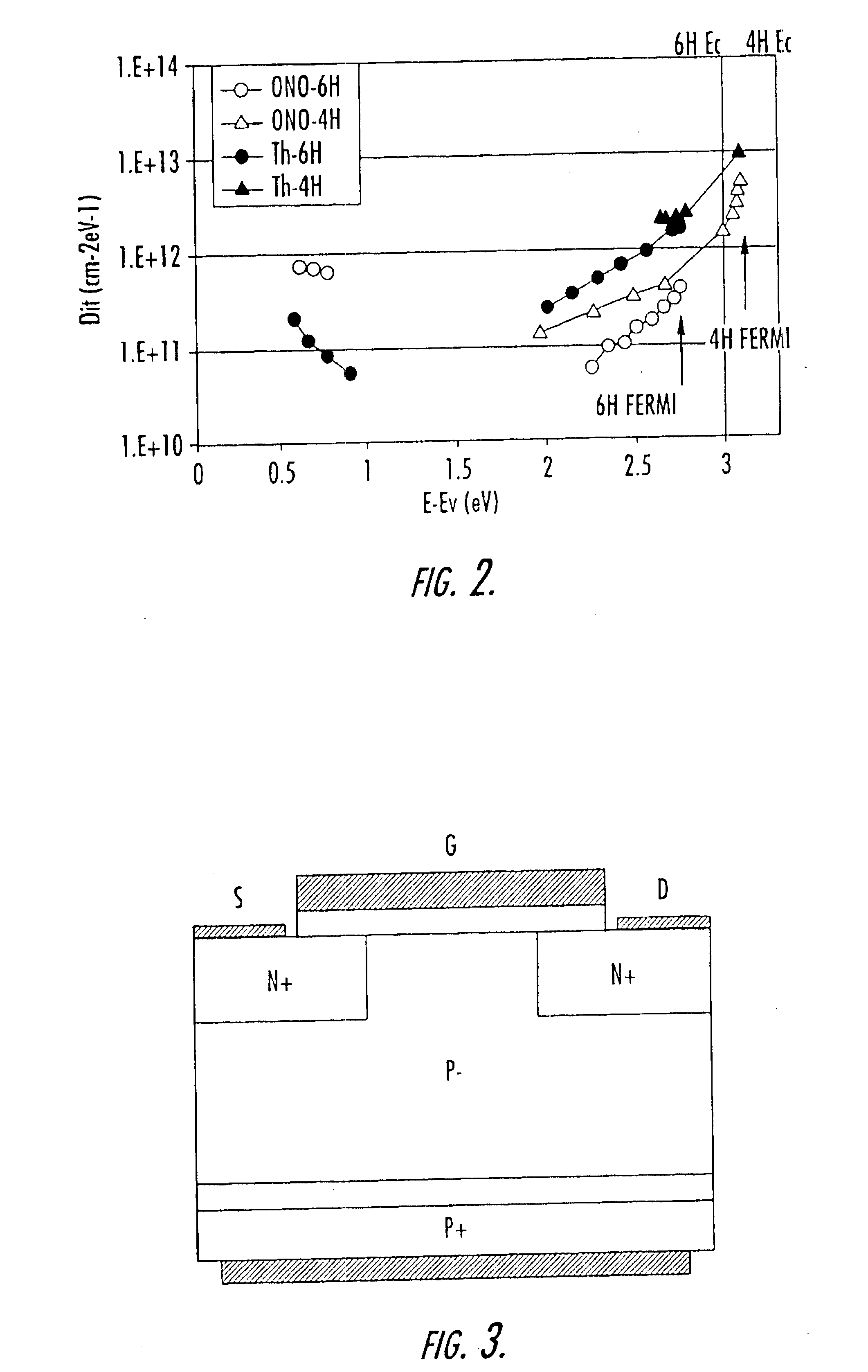

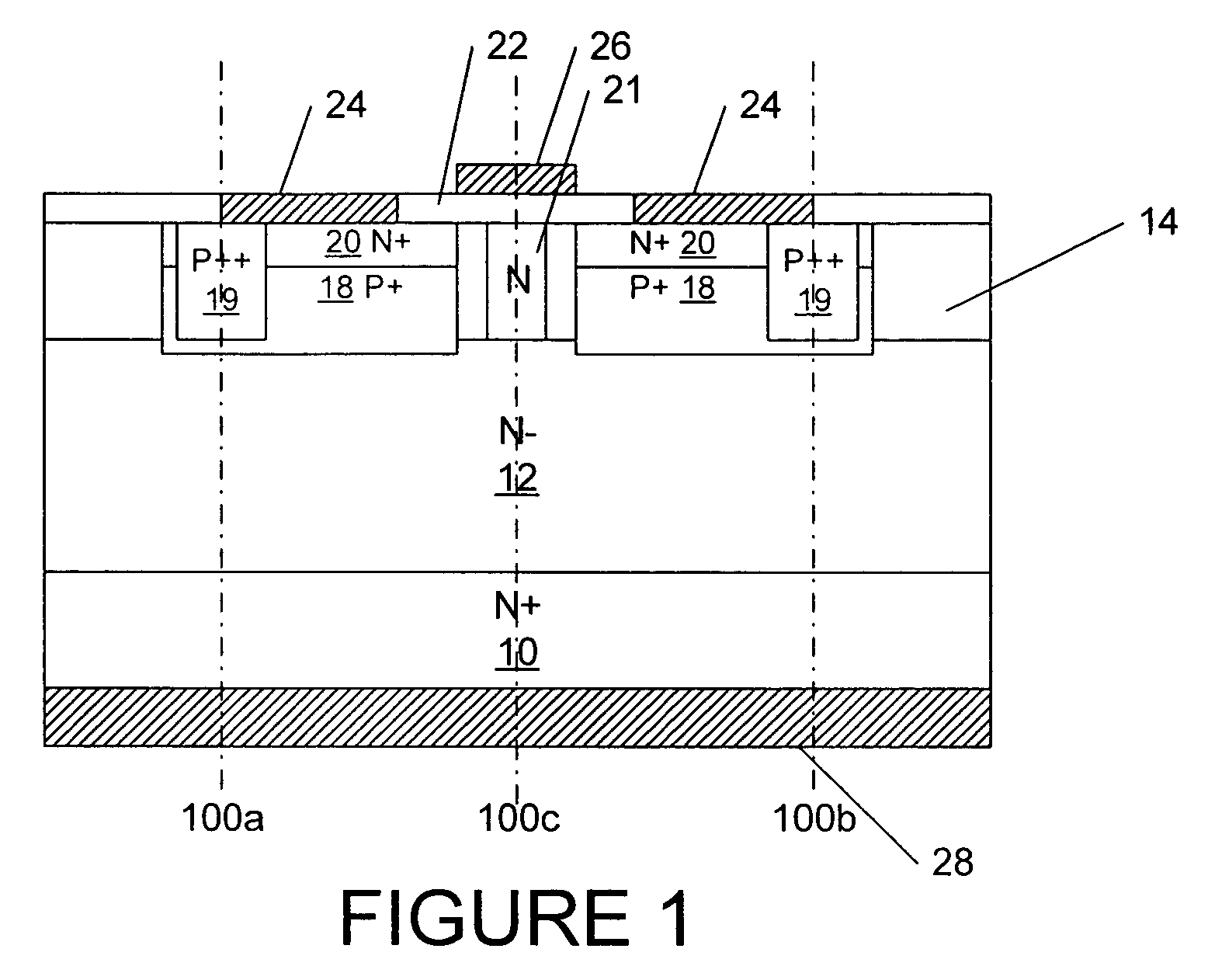

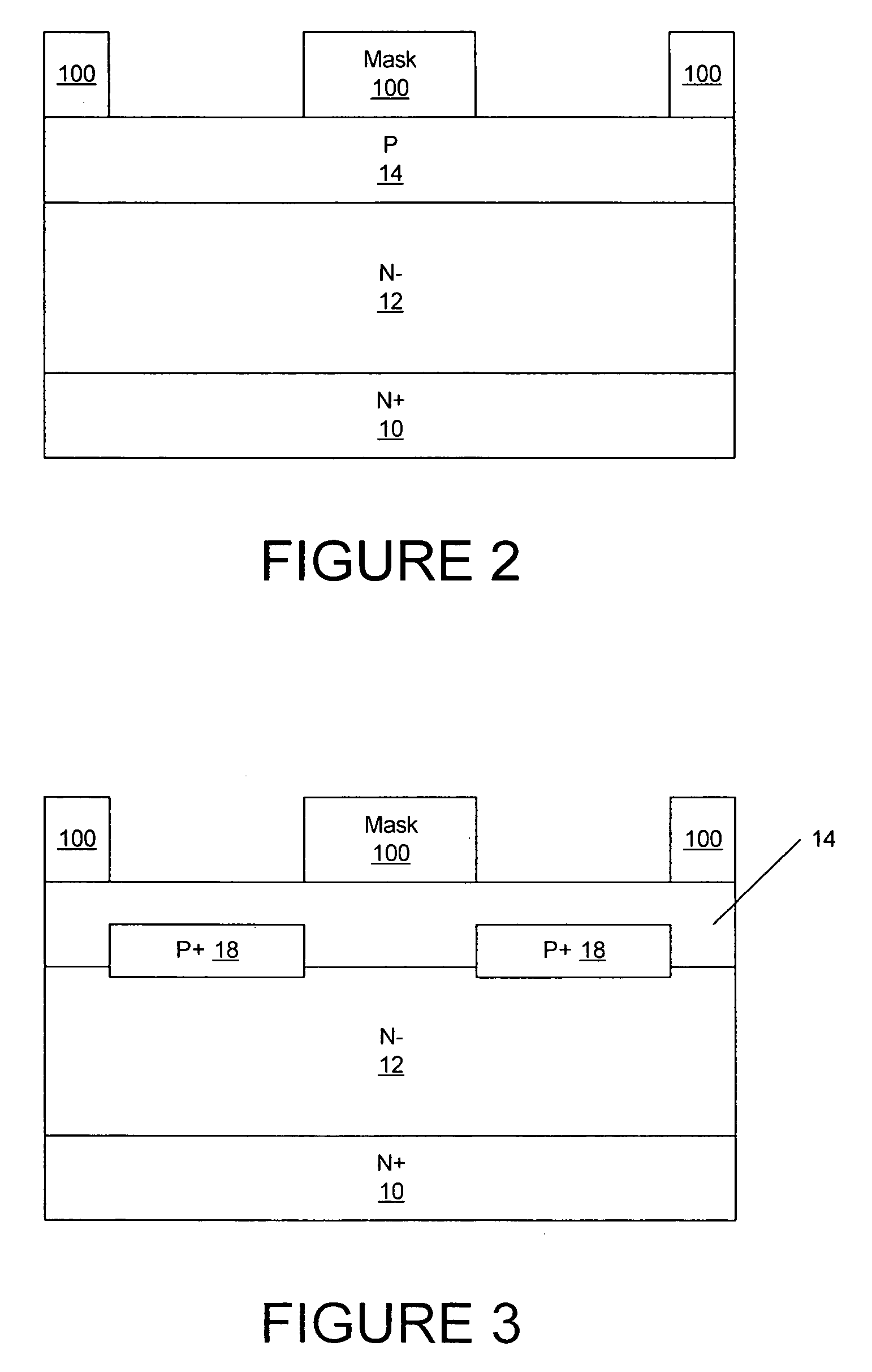

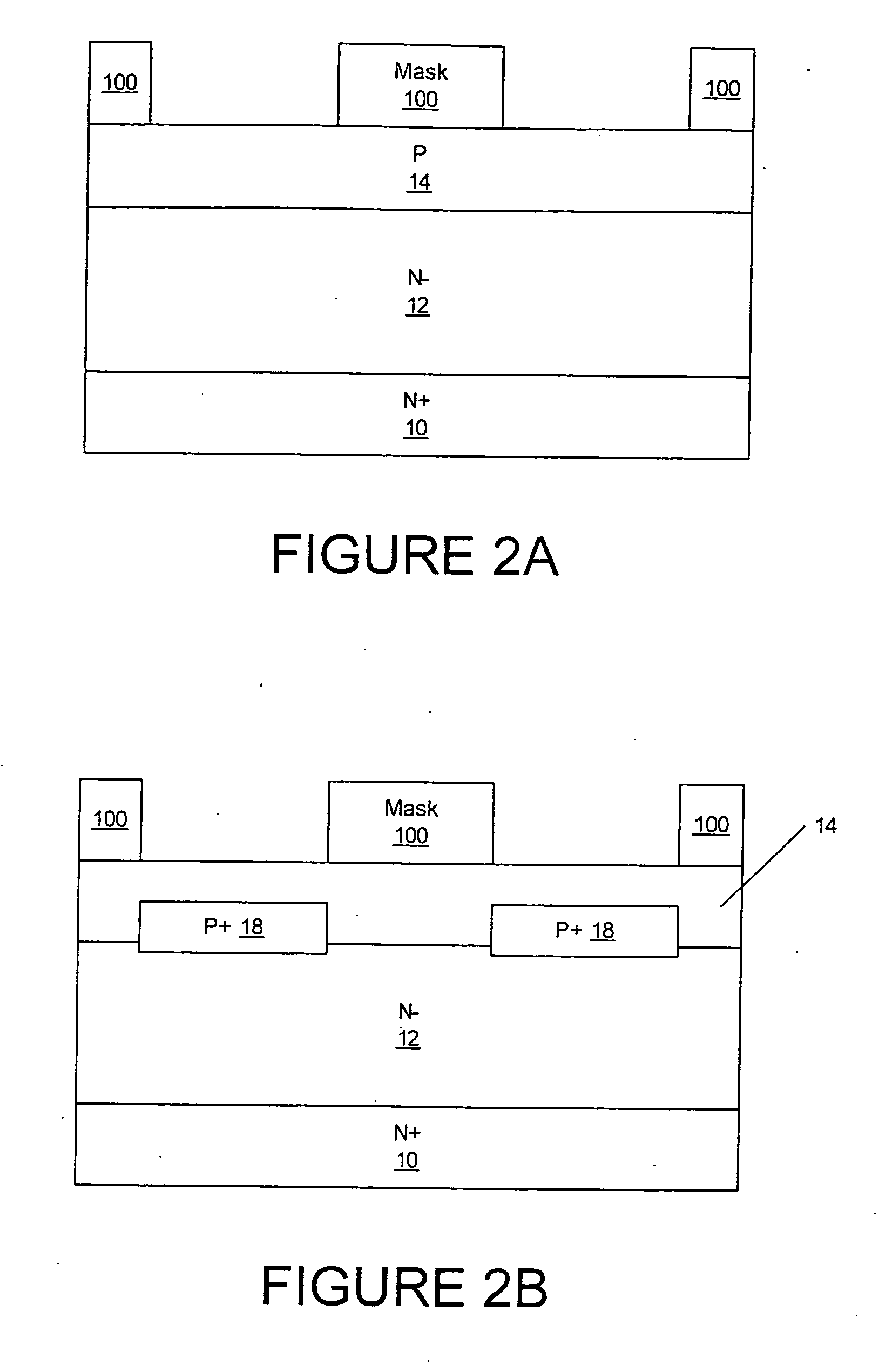

Silicon carbide metal-oxide semiconductor field effect transistors (MOSFETs) and methods of fabricating silicon carbide MOSFETs are provided. The silicon carbide MOSFETs have an n-type silicon carbide drift layer, spaced apart p-type silicon carbide regions in the n-type silicon carbide drift layer and having n-type silicon carbide regions therein, and a nitrided oxide layer. The MOSFETs also have n-type shorting channels extending from respective ones of the n-type silicon carbide regions through the p-type silicon carbide regions to the n-type silicon carbide drift layer. In further embodiments, silicon carbide MOSFETs and methods of fabricating silicon carbide MOSFETs are provided that include a region that is configured to self-deplete the source region, between the n-type silicon carbide regions and the drift layer, adjacent the oxide layer, upon application of a zero gate bias.

Owner:CREE INC

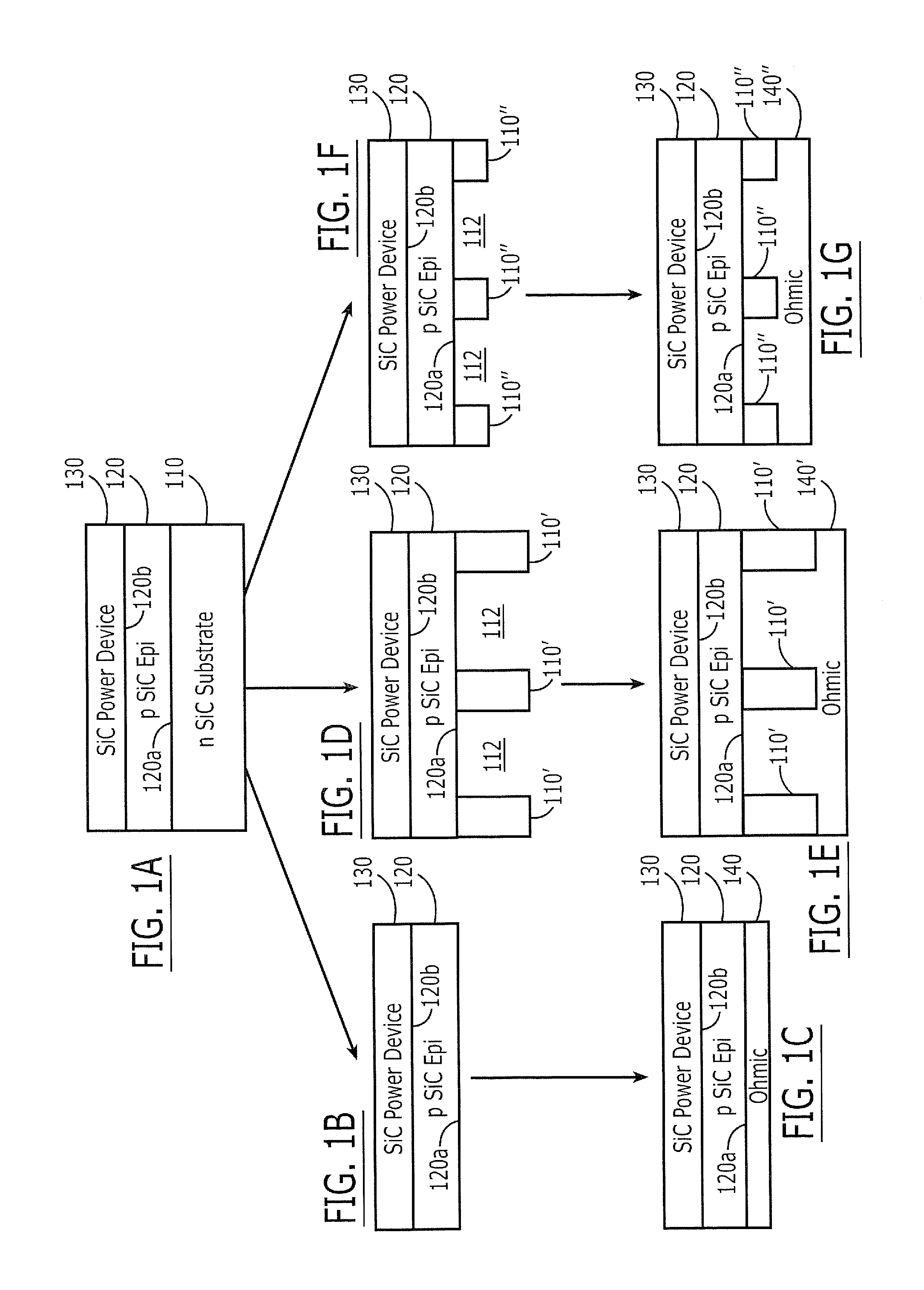

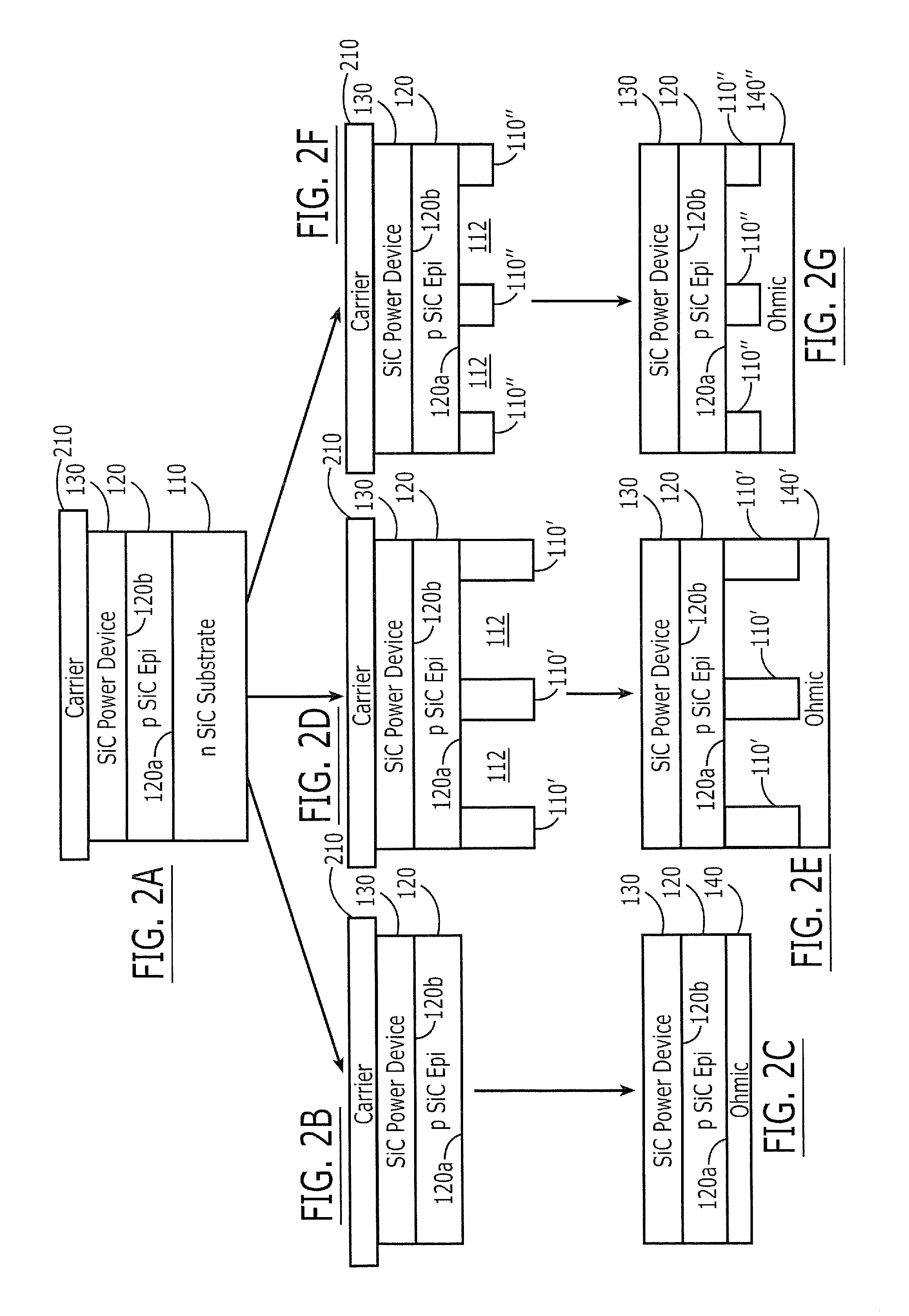

Methods of fabricating silicon carbide power devices by at least partially removing an n-type silicon carbide substrate, and silicon carbide power devices so fabricated

ActiveUS20080296771A1Eliminates and reduces disadvantagePotential disadvantageSemiconductor/solid-state device detailsSolid-state devicesOhmic contactCarbide

A silicon carbide power device is fabricated by forming a p-type silicon carbide epitaxial layer on an n-type silicon carbide substrate, and forming a silicon carbide power device structure on the p-type silicon carbide epitaxial layer. The n-type silicon carbide substrate is at least partially removed, so as to expose the p-type silicon carbide epitaxial layer. An ohmic contact is formed on at least some of the p-type silicon carbide epitaxial layer that is exposed. By at least partially removing the n-type silicon carbide substrate and forming an ohmic contact on the p-type silicon carbide epitaxial layer, the disadvantages of using a p-type substrate may be reduced or eliminated. Related structures are also described.

Owner:CREE INC

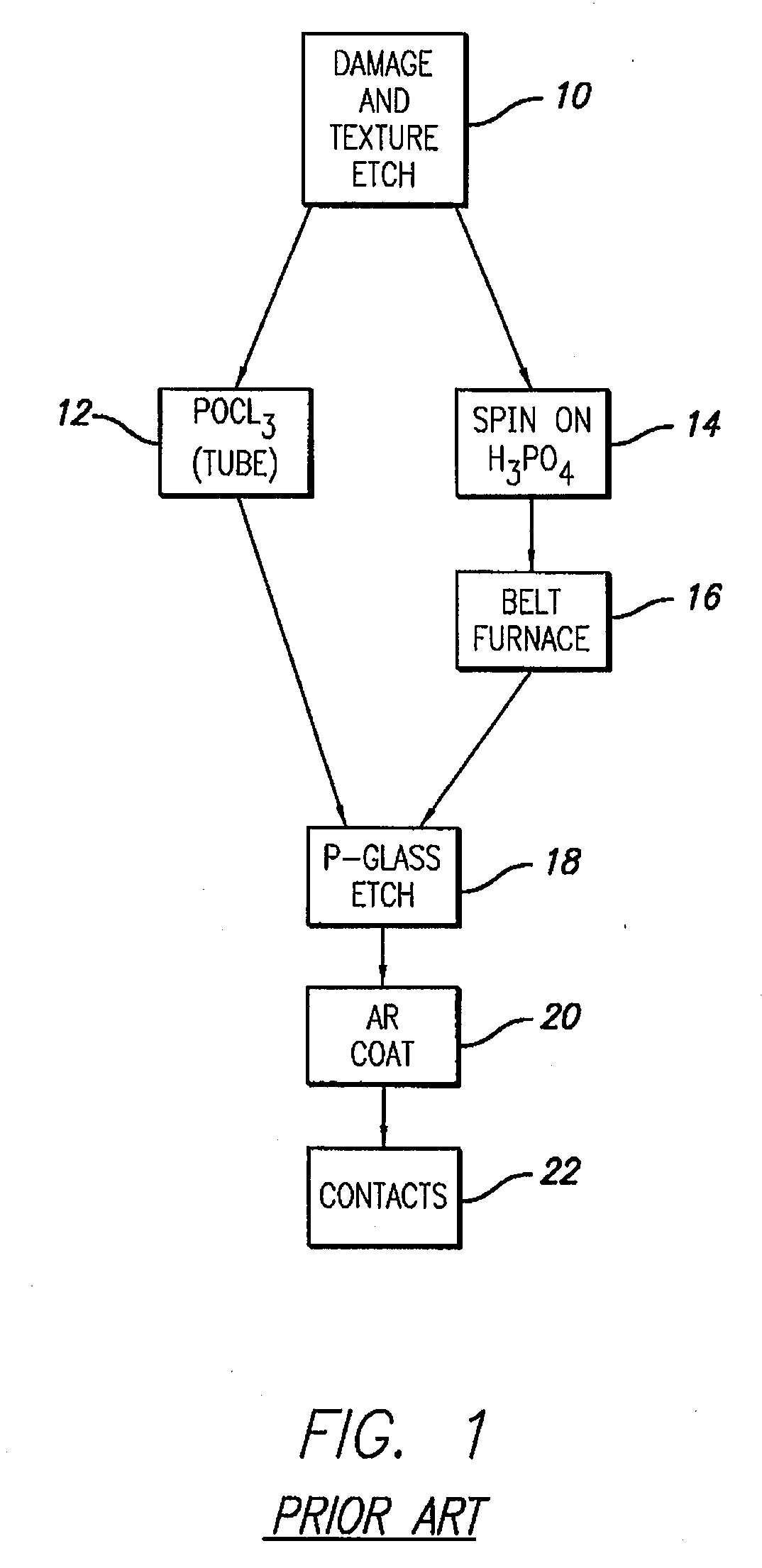

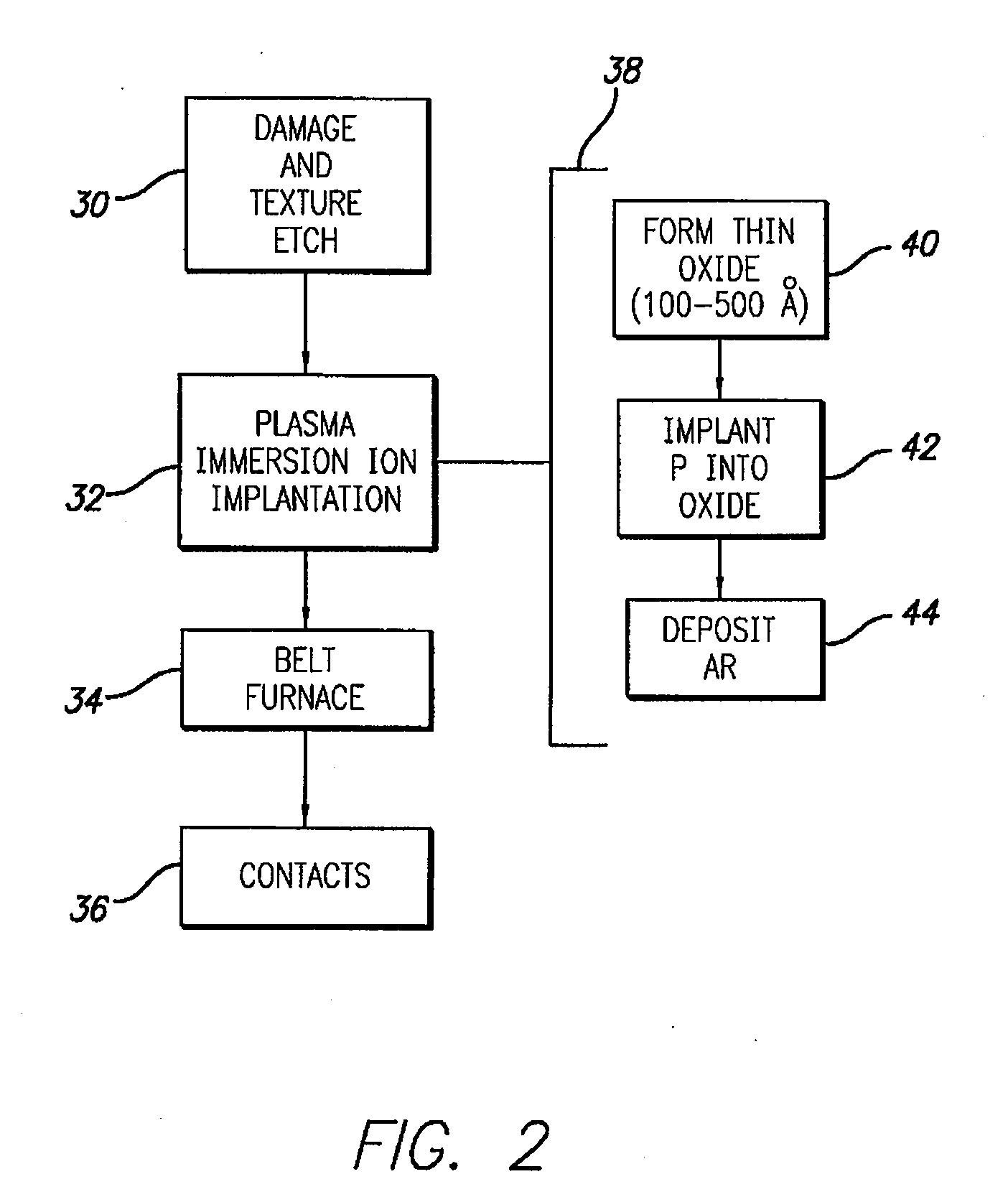

Method of making an improved selective emitter for silicon solar cells

InactiveUS20090142875A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationPlasma-immersion ion implantationSilicon solar cell

A method for forming a selective emitter on a silicon solar cell is provided including forming an oxide layer on a surface of the P-type silicon substrate, implanting phosphorus doping atoms into the oxide layer on the substrate using plasma immersion ion implantation, patterning the oxide layer, annealing the substrate to provide heavily doped regions in the patterned regions and a lightly doped region between the patterned regions, and providing metal contacts to the heavily doped regions.

Owner:APPLIED MATERIALS INC

Process for manufacturing a solar cell

InactiveUS7071018B2Low costFinal product manufactureSemiconductor/solid-state device manufacturingBack surface fieldSilicon solar cell

Process for incorporating a back surface field into a silicon solar cell by depositing a layer of aluminium on the rear surface of the cell, sintering the aluminium at a temperature between 700 and 1000° C., exposing the cell to an atmosphere of a compound of Group V element and diffusing at a temperature of between 950 and 1000°C. so as to dope exposed p-type silicon surfaces with the Group V element. The step of exposing the cell to an atmosphere of a compound of a Group V element is carried separately from the step of sintering the aluminium layer, and subsequent to the step of depositing a layer of aluminium on the rear surface of the cell.

Owner:BP ALTERNATIVE ENERGY INT

Paste composition and solar cell employing the same

ActiveUS20040003836A1Low efficiencyReduce thicknessPV power plantsConductive materialDecompositionInorganic compound

A paste composition for forming an electrically conductive layer on a p-type silicon semiconductor substrate comprises aluminum powder, an organic vehicle and powder of at least one inorganic compound selected from a group consisting of an oxide-based inorganic compound and a non-oxide-based inorganic compound. The oxide-based inorganic compound has a thermal expansion coefficient smaller than the thermal expansion coefficient of aluminum and a melting temperature, a softening temperature and a decomposition temperature each higher than the melting point of aluminum. The non-oxide-based inorganic compound has a thermal expansion coefficient smaller than the thermal expansion coefficient of aluminum and at least one of a melting temperature, a softening temperature or a decomposition temperature higher than the melting point of aluminum. A solar cell comprises an electrically conductive layer formed by applying the paste composition having the aforementioned characteristics onto a p-type silicon semiconductor substrate and thereafter firing the paste composition.

Owner:TOYO ALUMINIUM KK +1

Shallow trench isolation for semiconductor devices

A shallow trench isolation structure is formed by providing a pad layer and a silicon nitride polish stop layer on a surface of a P-type silicon substrate. The silicon nitride polish stop layer and the pad oxide layer are patterned to define openings corresponding to portions of the substrate that will be etched to form trenches. Trenches are defined in the P-type silicon substrate by anisotropic etching. A boron doped oxide or glass is deposited along the walls and floor of the trench. An undoped TEOS oxide is provided over the doped oxide or glass to complete filling of the trench. The device is subjected to a high temperature reflow process, causing the dielectric materials to flow, partially planarizing the device and causing the boron of the first layer to diffuse into the walls and floor of the trench. Chemical mechanical polishing removes excess portions of the dielectric layers. The silicon nitride polish stop layer and the pad oxide layer are removed and conventional processing is performed to complete devices on the substrate. Diffusion of boron into the walls of the trench forms a self-aligned field doping region for the shallow trench isolation structure using relatively few processing steps.

Owner:UNITED MICROELECTRONICS CORP

Methods of fabricating silicon carbide devices with hybrid well regions

ActiveUS7118970B2Semiconductor/solid-state device manufacturingSemiconductor devicesCarbideOptoelectronics

Owner:CREE INC

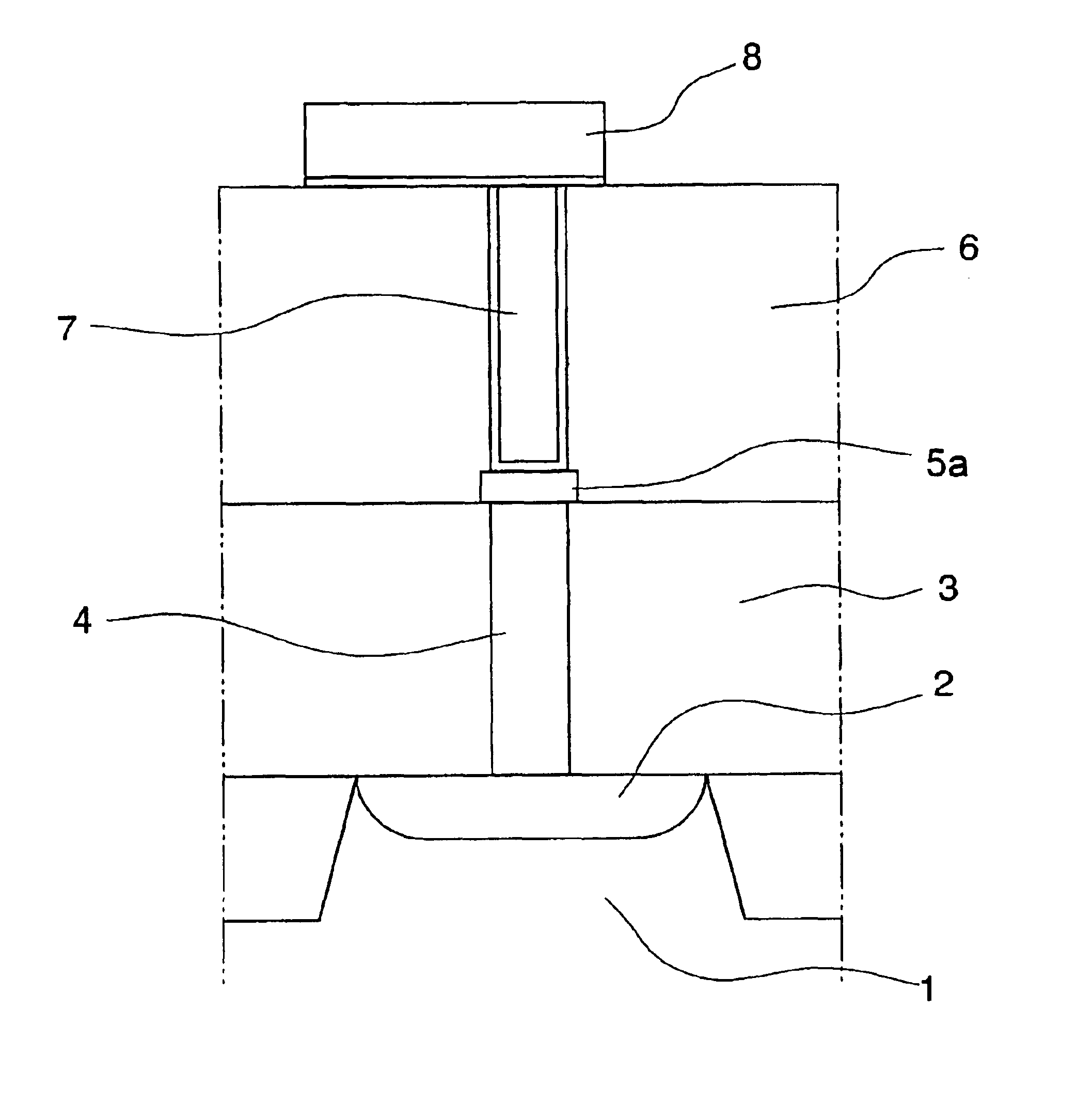

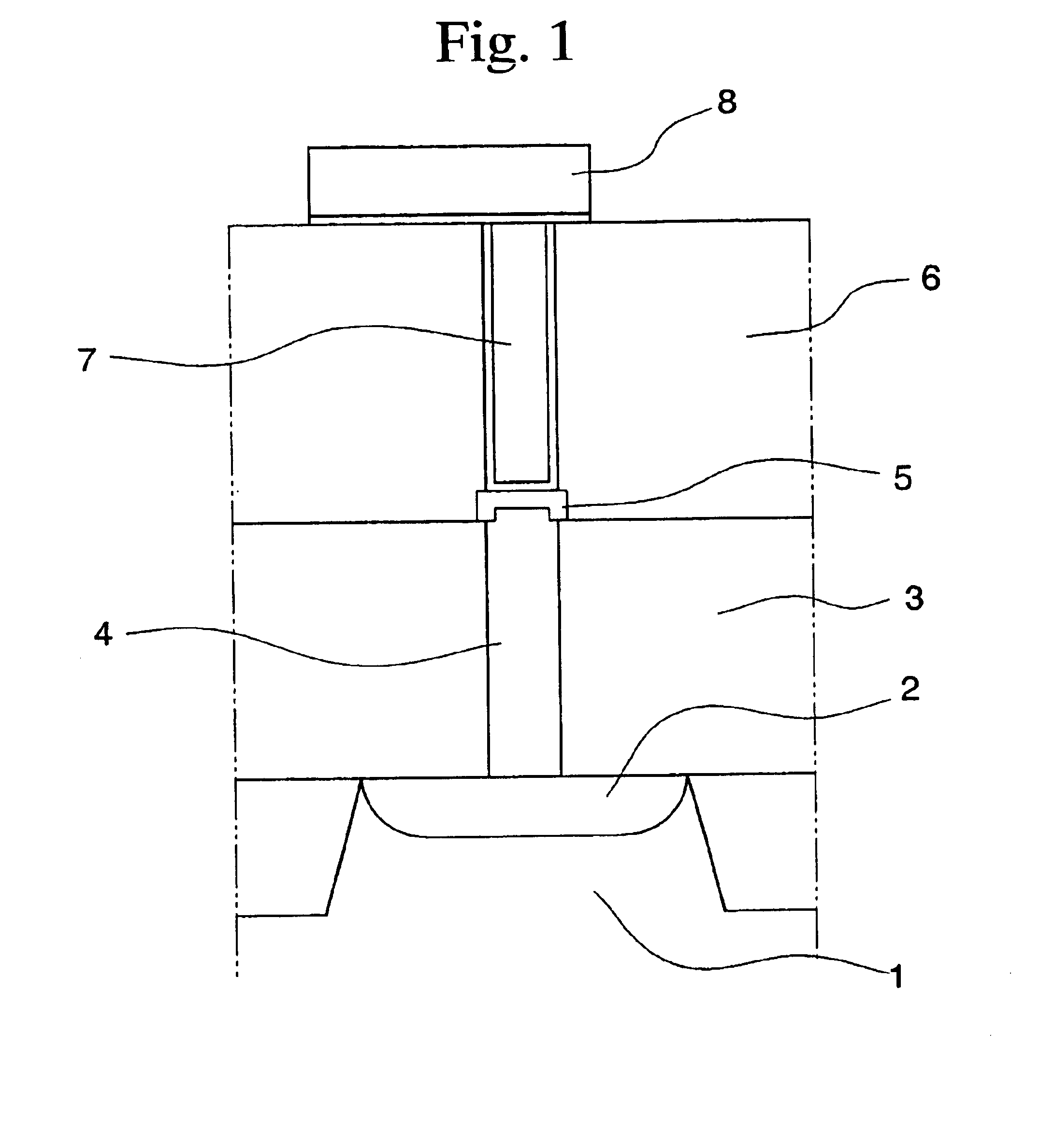

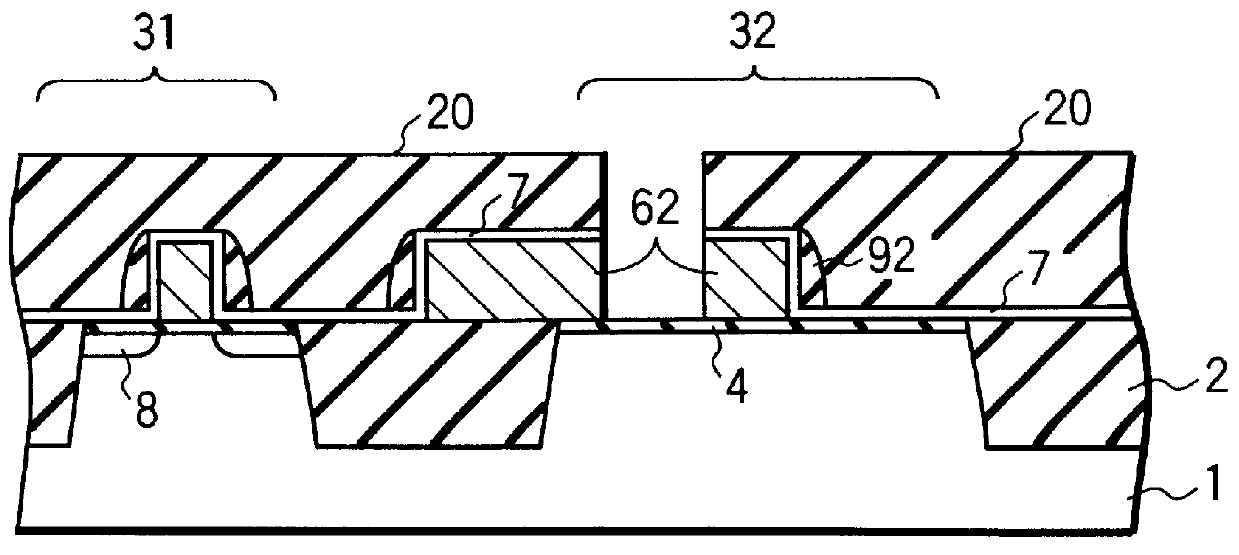

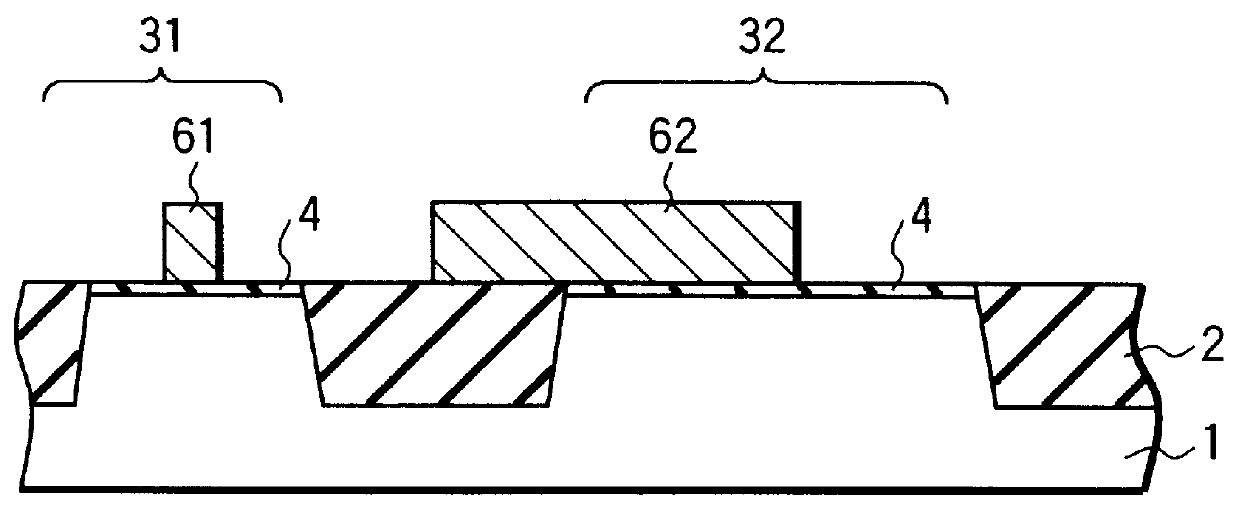

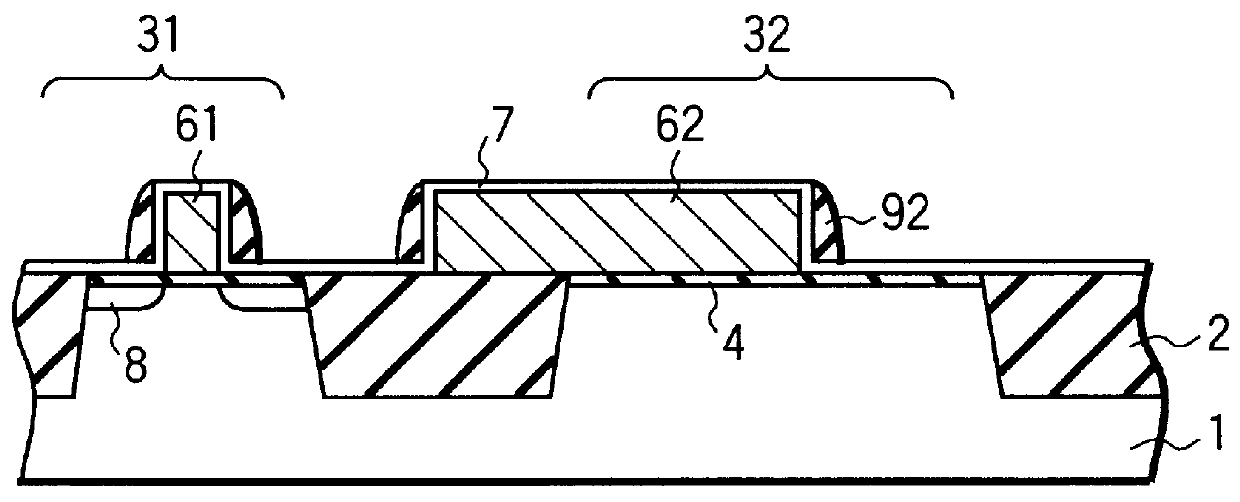

Semiconductor device structure and method for manufacturing the same

InactiveUS6914336B2Reduce connectionsReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesHigh concentrationSilicon oxide

The present invention provides a structure for a semiconductor device, capable of eliminating the generation of defective products due to poor connection. In the present semiconductor device, an n-type high concentration diffusion layer 2 is selectively formed on the P-type silicon substrate 1, and on the diffusion layer 2, a silicon oxide film 3 is formed as a first interlayer insulating film 3. A silicon plug 4 is disposed on the n-type high concentration diffusion layer 2. On the top end surface of the polysilicon plug 4, a silicide pad 5 is formed in a self-aligning manner such that the width of the silicide pad 5 is larger than that of the polysilicon plug 4. A second interlayer insulating film is formed so as to cover the first interlayer insulating film 3 and the silicide pad 5, and a tungsten plug 7 is disposed on the silicide pad 5. On the second interlayer insulating film, wiring 8, made of an aluminum-copper alloy and connected to the tungsten plug, is formed.

Owner:NEC ELECTRONICS CORP

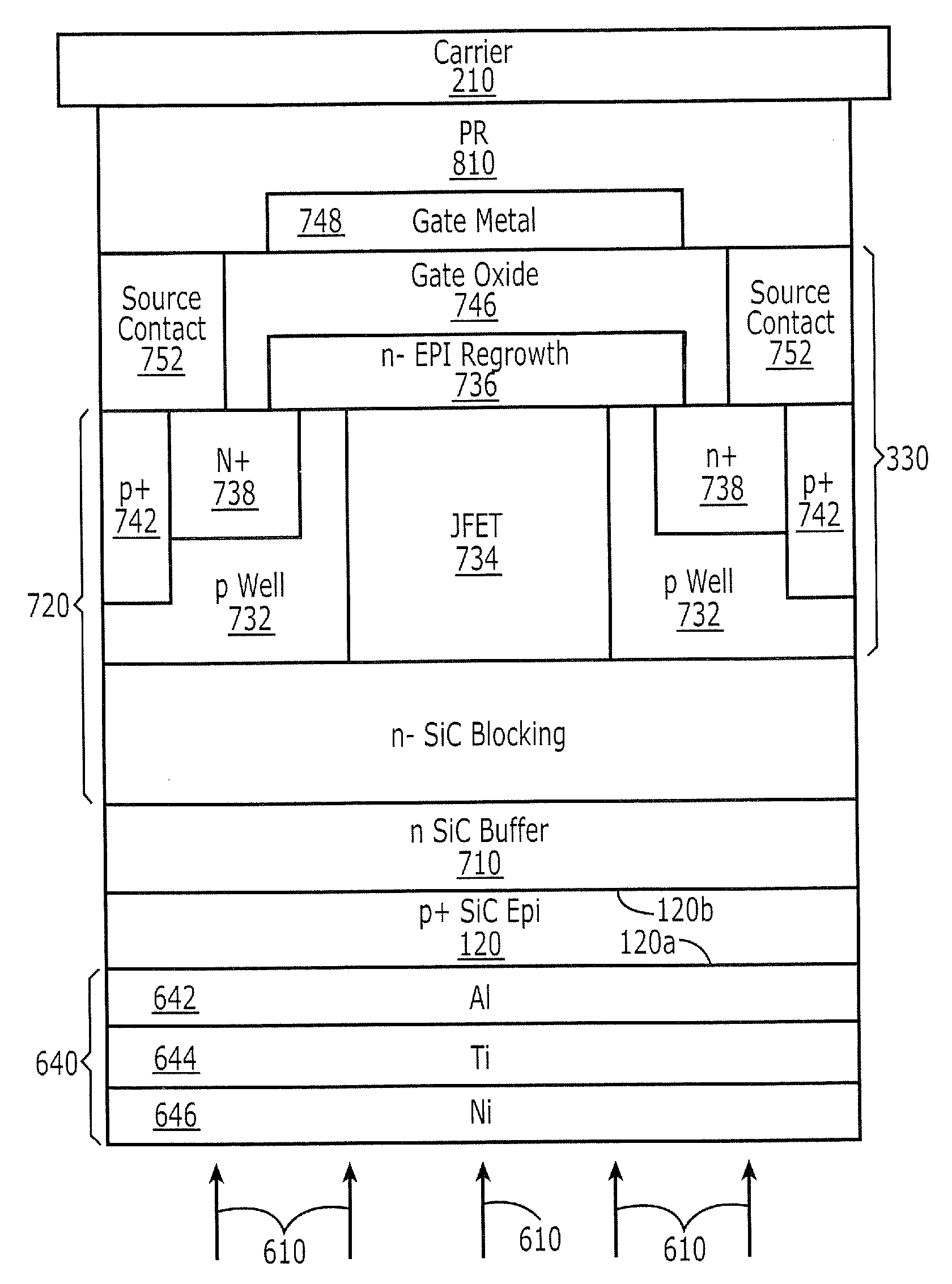

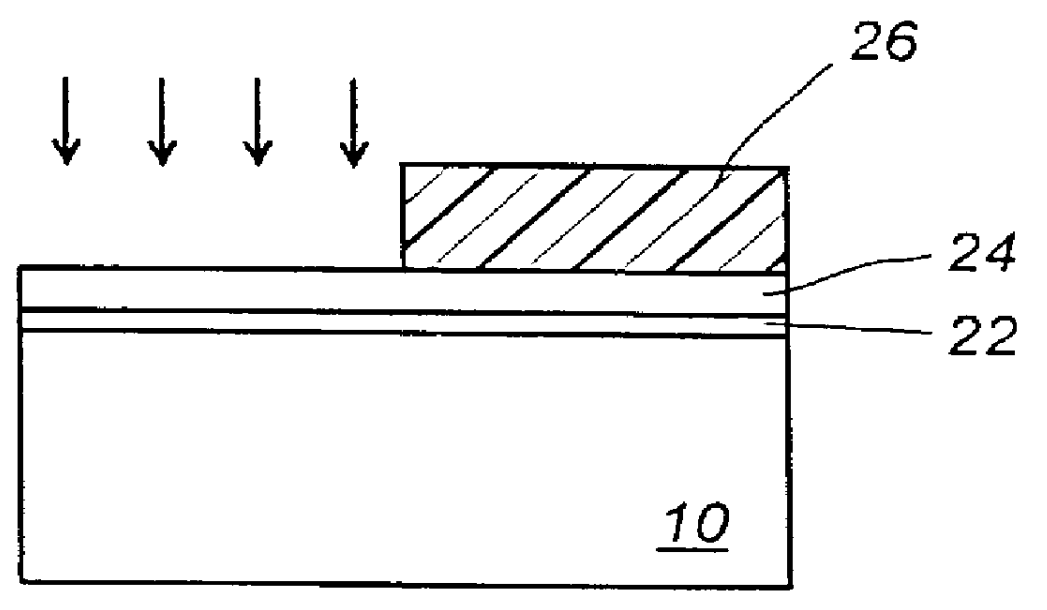

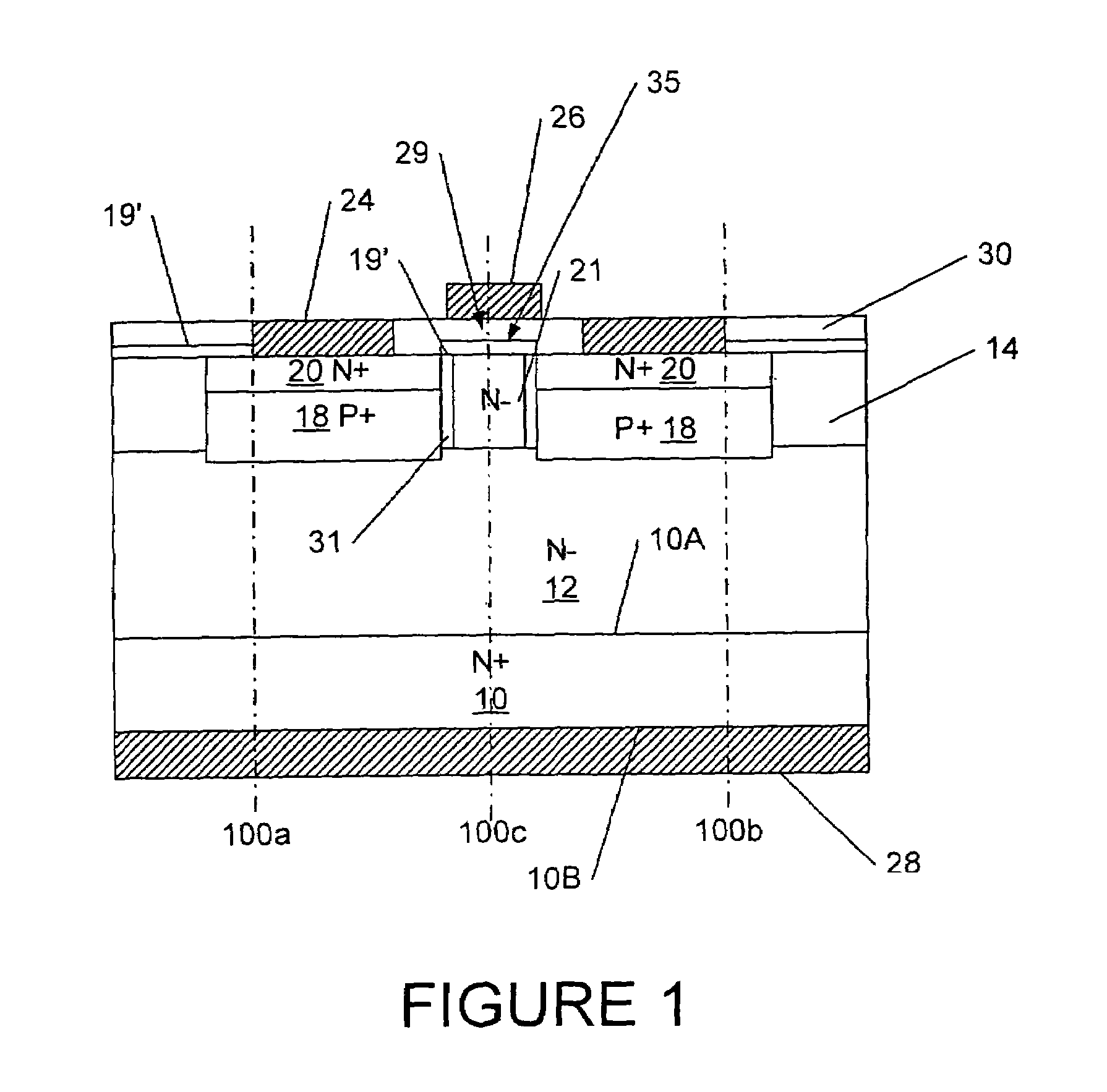

Methods of fabricating silicon carbide devices having smooth channels

ActiveUS7528040B2Semiconductor/solid-state device manufacturingSemiconductor devicesCarbideSurface roughness

Methods of forming silicon carbide power devices are provided. An n− silicon carbide layer is provided on a silicon carbide substrate. A p-type silicon carbide well region is provided on the n− silicon carbide layer. A buried region of p+ silicon carbide is provided on the p-type silicon carbide well region. An n+ region of silicon carbide is provided on the buried region of p+ silicon carbide. A channel region of the power device is adjacent the buried region of p+ silicon carbide and the n+ region of silicon carbide. An n− region is provided on the channel region and a portion of the n− region is removed from the channel region so that a portion of the n− region remains on the channel region to provide a reduction in a surface roughness of the channel region.

Owner:CREE INC

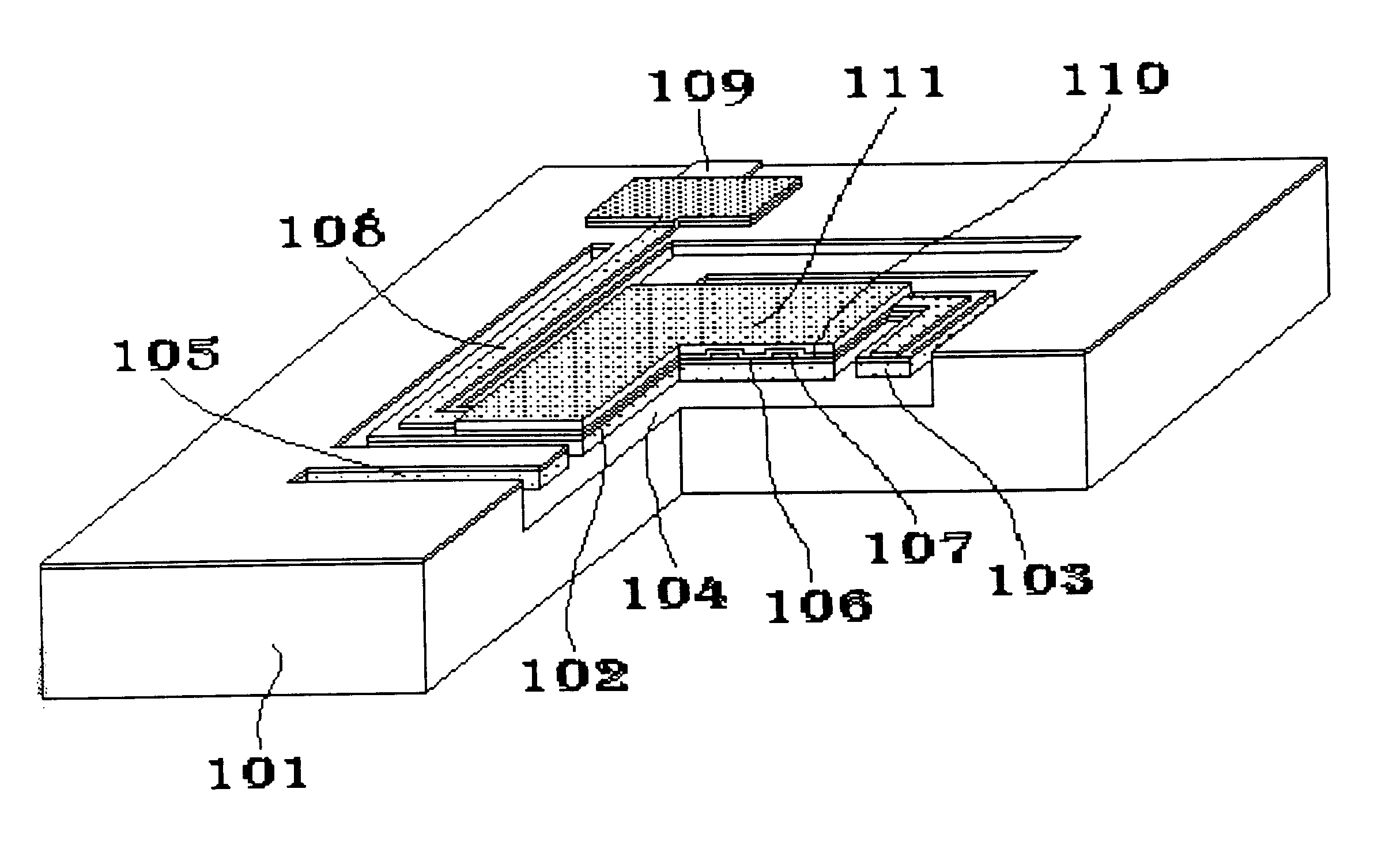

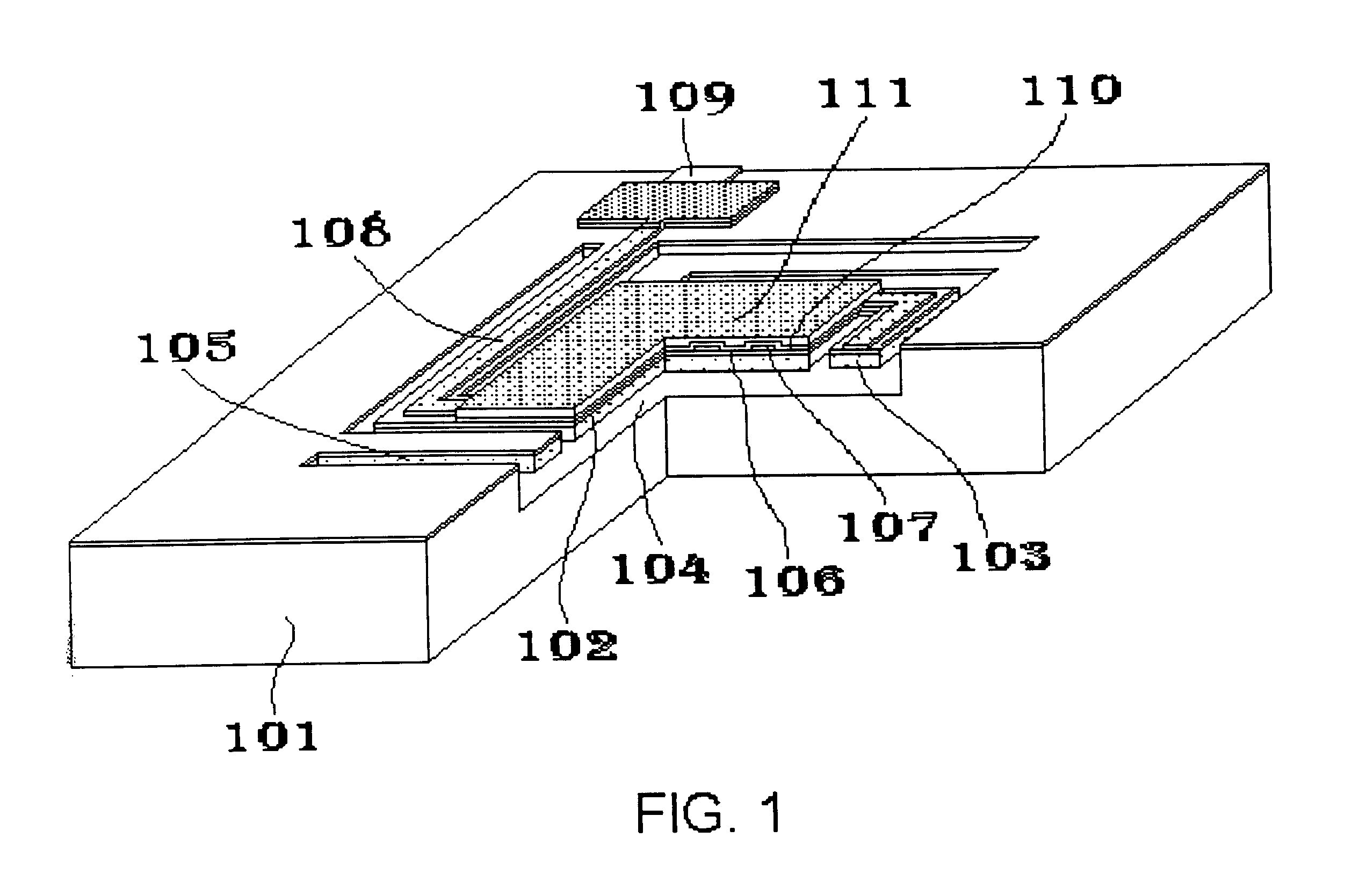

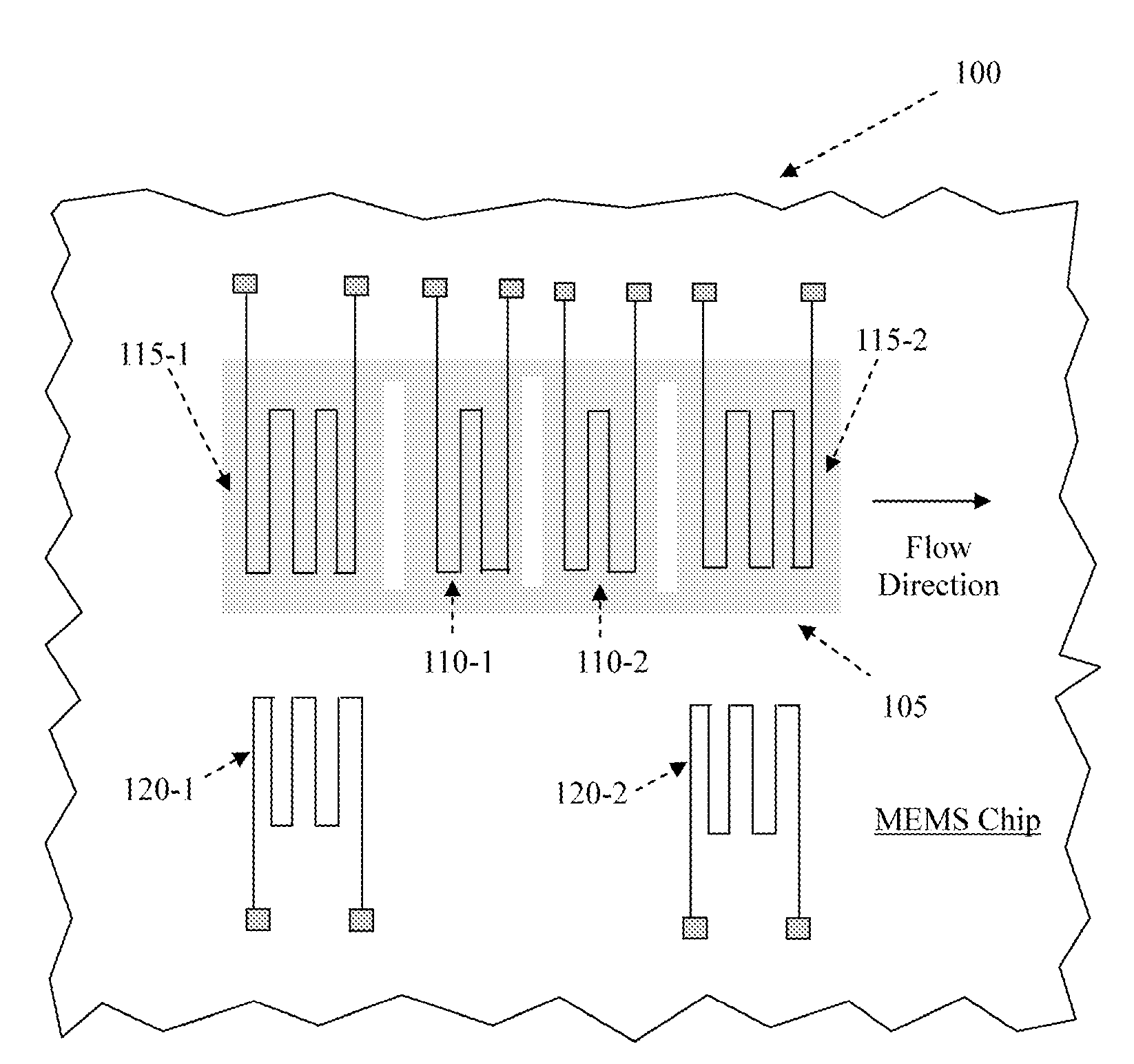

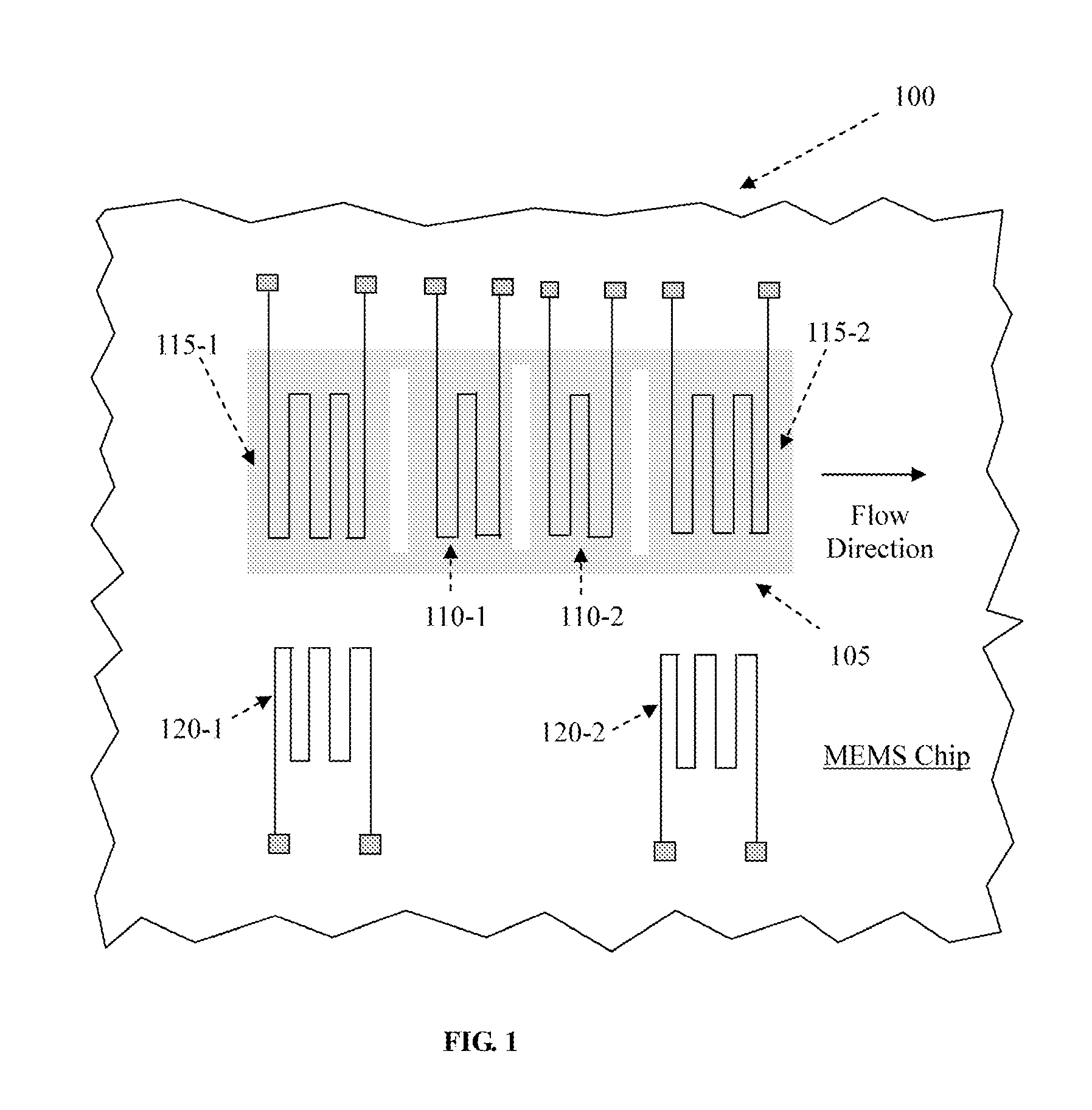

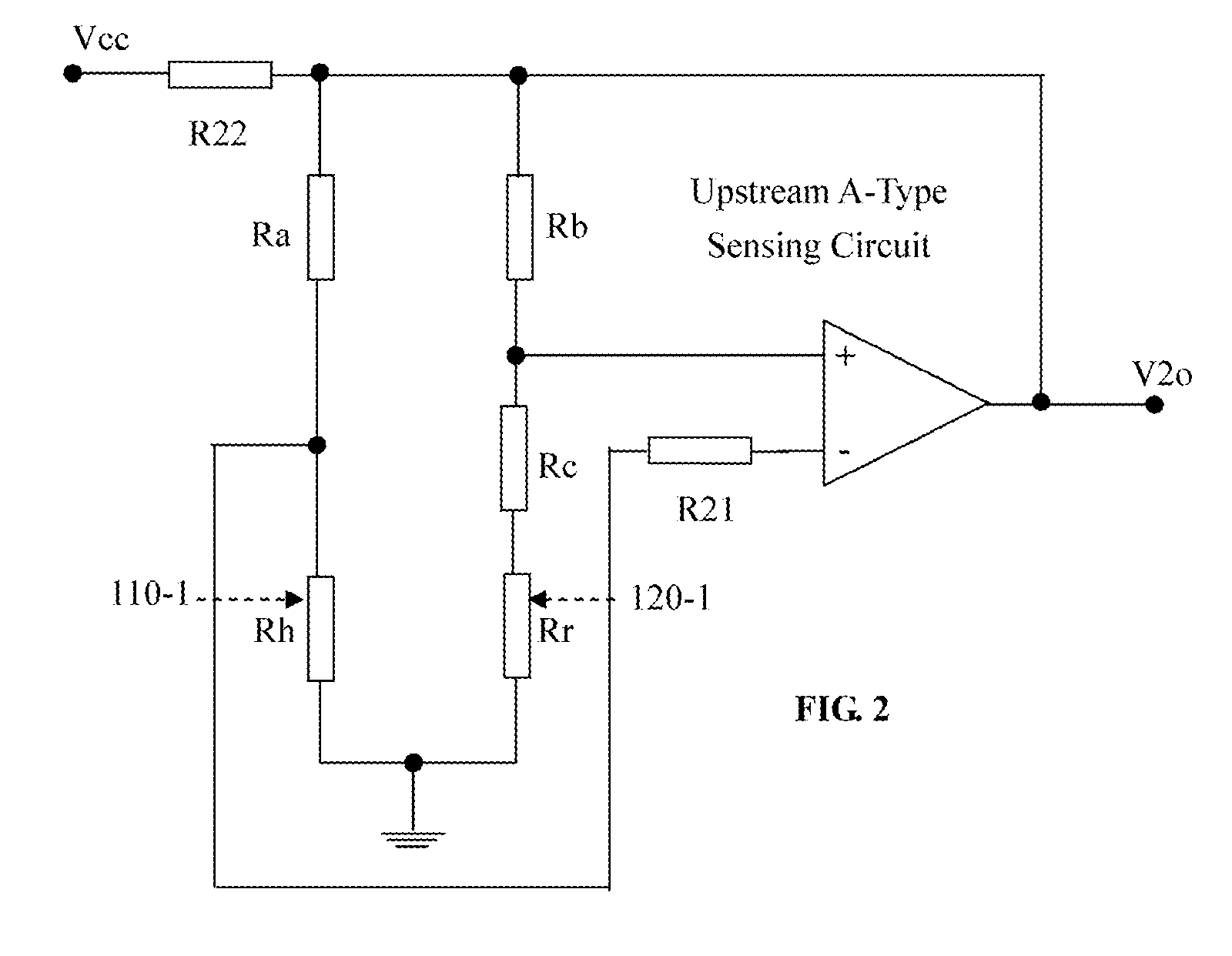

Integrated micromachined thermal mass flow sensor and methods of making the same

ActiveUS20090164163A1Accurate flowIncrease speedTesting/calibration apparatusVolume/mass flow by thermal effectsEngineeringP type silicon

An integrated mass flow sensor is manufactured by a process of carrying out a micro-machining process on an N or P-type silicon substrate with orientation <100>. This mass flow sensor comprises an upstream thin-film heater, an downstream thin-film heater, and a pair of thin-film heat sensing elements, and a thermally isolated membrane for supporting the heaters and the sensors out of contact with the substrate base. This mass flow sensor is operated with three sets of circuits, a first circuit for measuring a flow rate in a first range of flow rates, a second circuit for measuring a flow rate in a second range of flow rates, and a third circuit in a differential configuration for measuring a flow rate in said first range of flow rates or said second range of flow rates, to significantly increase range of flow rate measurements and provide an optional for concentration measurement, while maintains a high degree of measurement accuracy.

Owner:M TECH INSTR HLDG

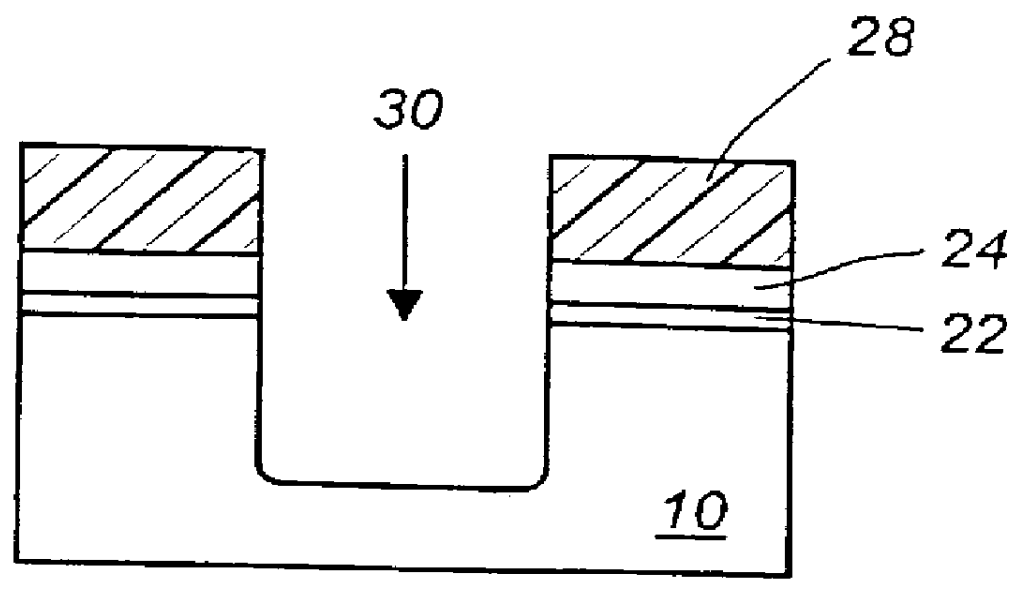

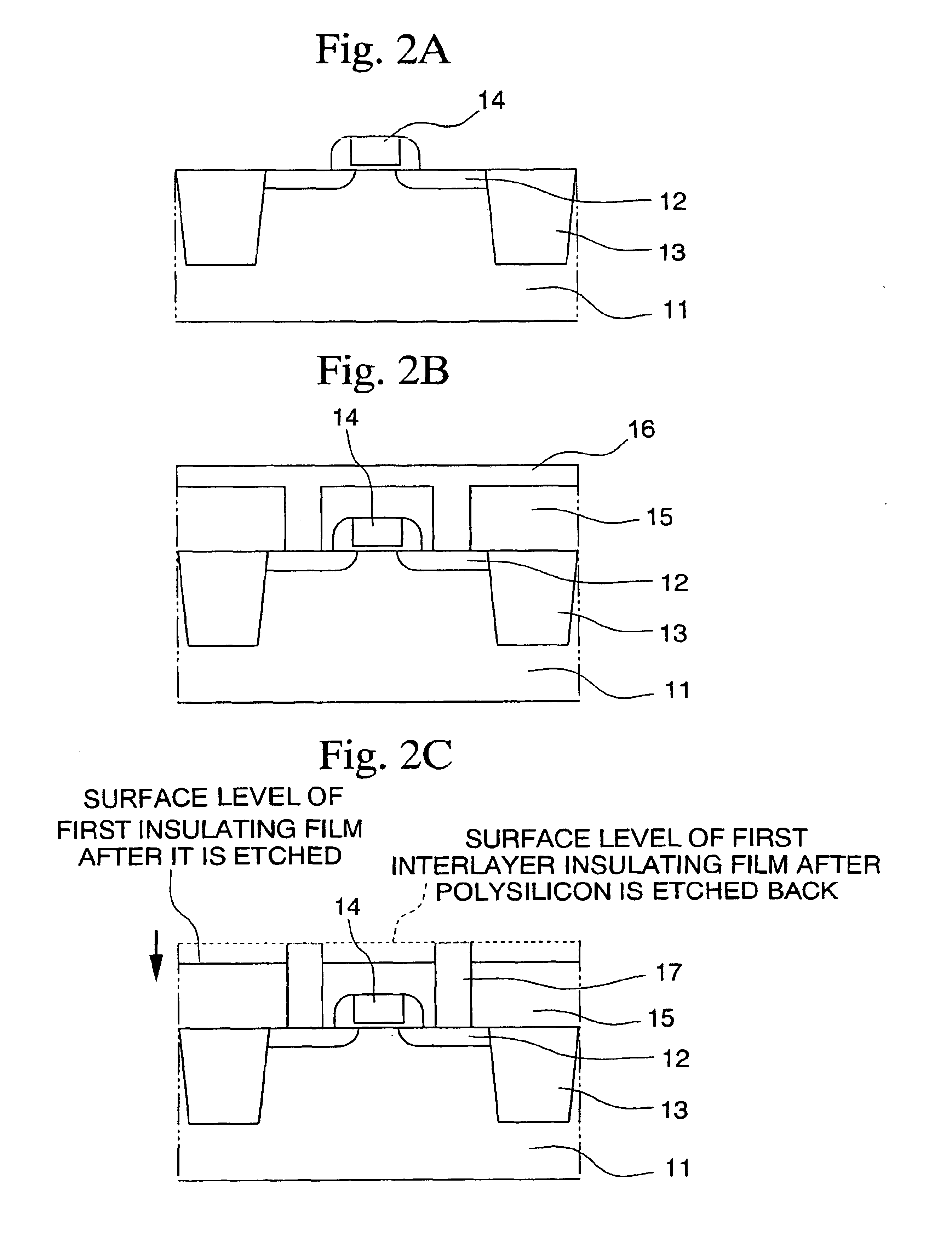

Semiconductor device manufacturing method

InactiveUS20050035401A1Easy to integrateAvoid resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialP type silicon

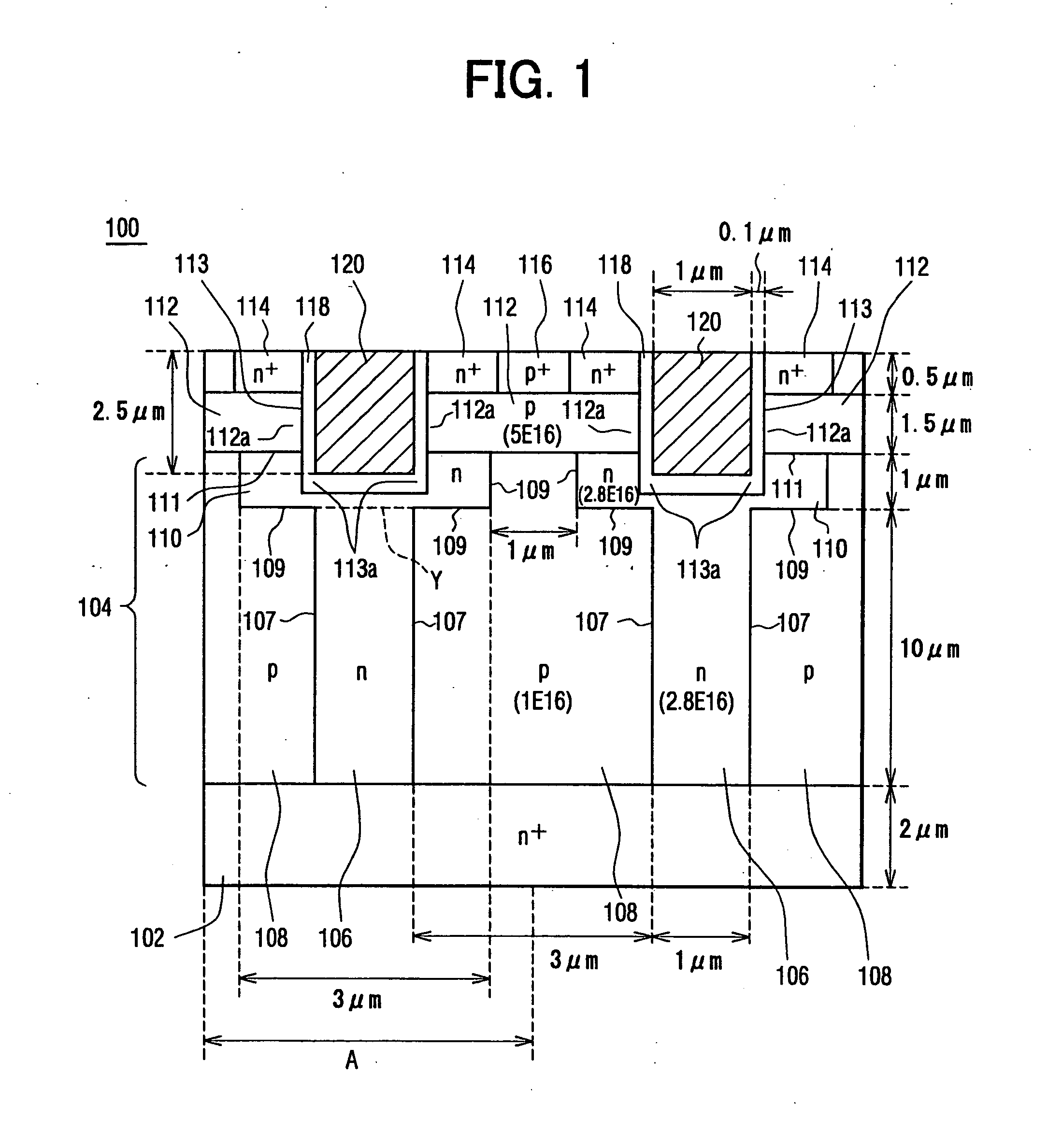

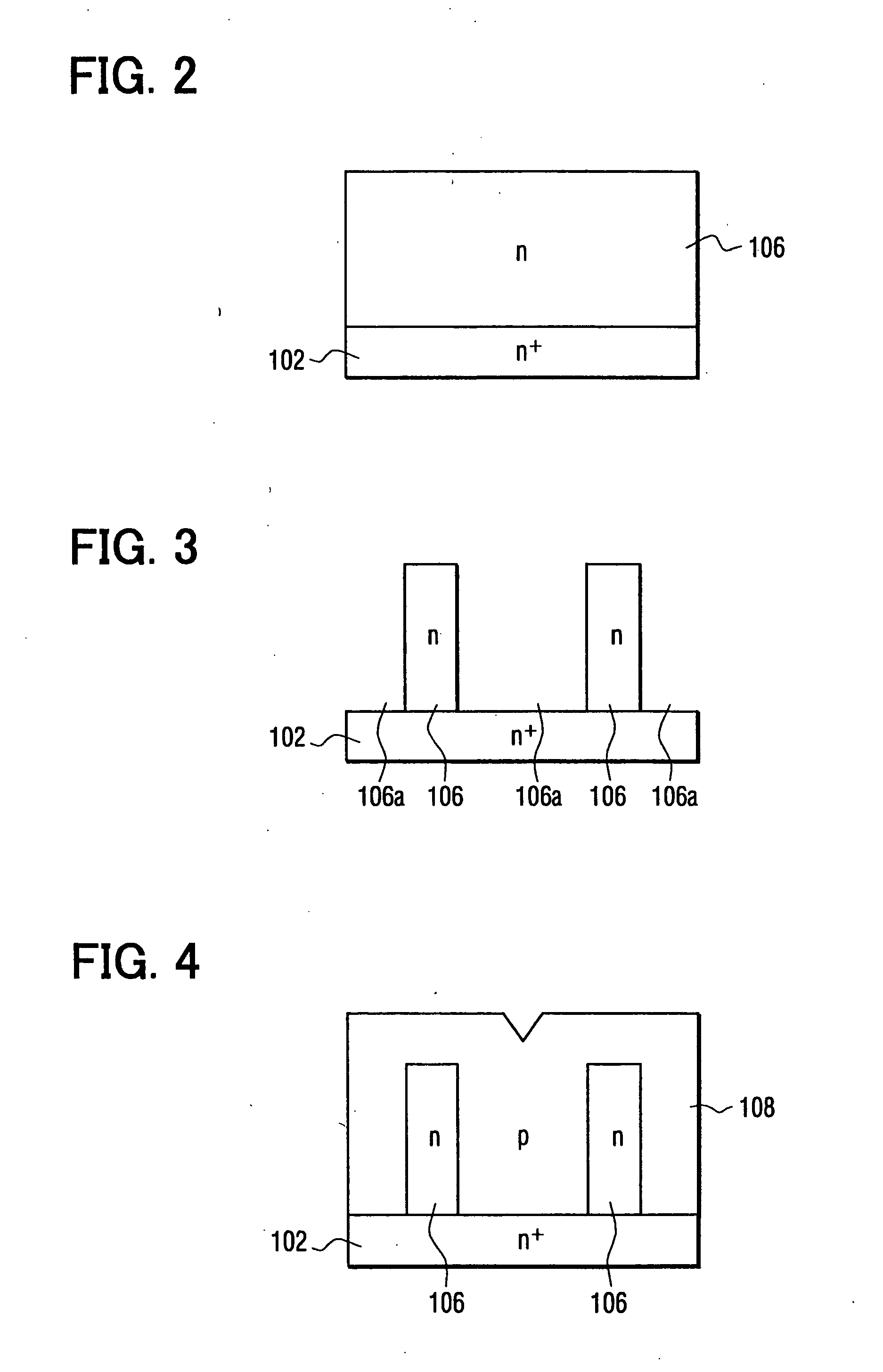

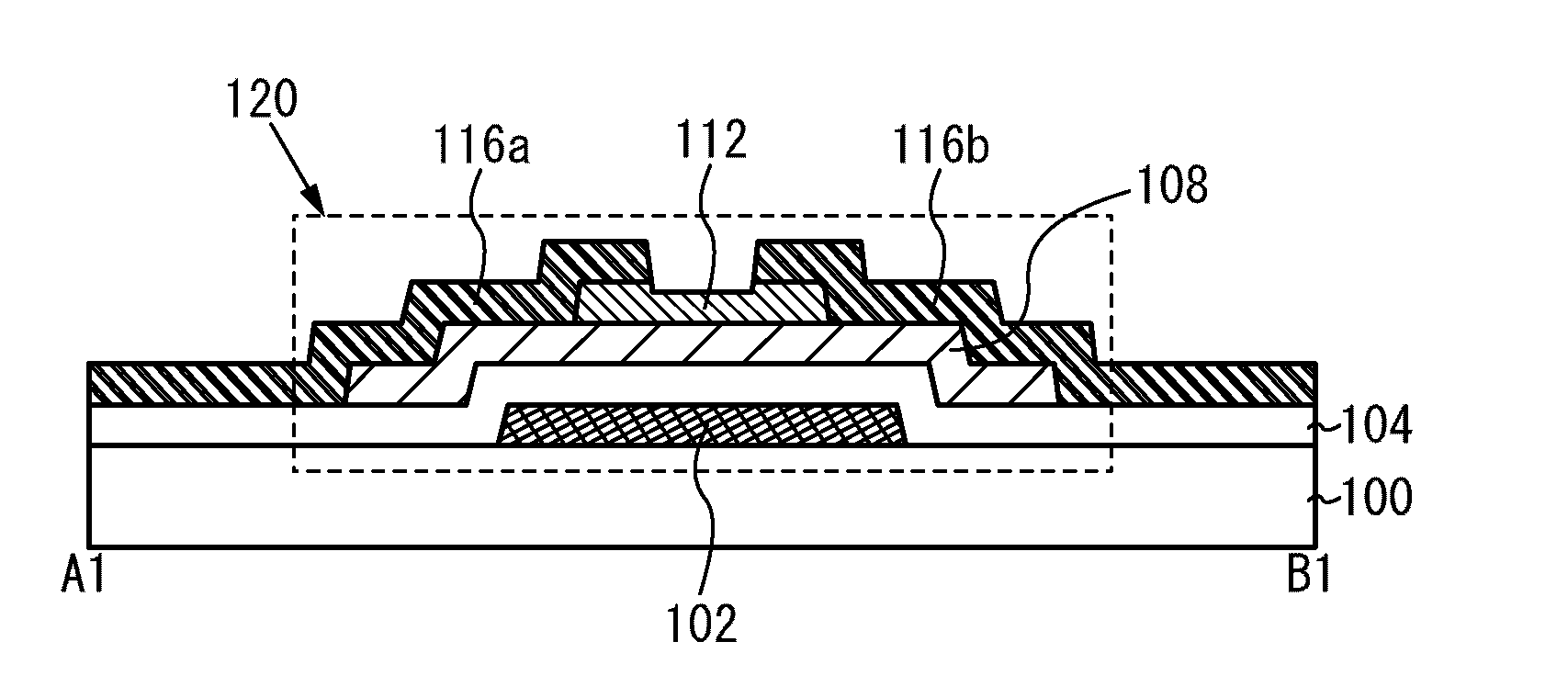

A semiconductor device includes: an n+ type drain region; an n type drift region that connects with the n+ type drain region; a p type body region; a n+ type source region that connects with the p type body region; and a gate electrode that is provided, with being covered by a gate insulation film, in a gate trench that penetrates the p type body region. The semiconductor further includes: a p type silicon region that adjoins the n type drift region; and an n type silicon region provided in a region almost including a carrier passage that connects the n type drift region and the p type body region. Here, the p type silicon region and the p type body region directly connect with each other.

Owner:DENSO CORP

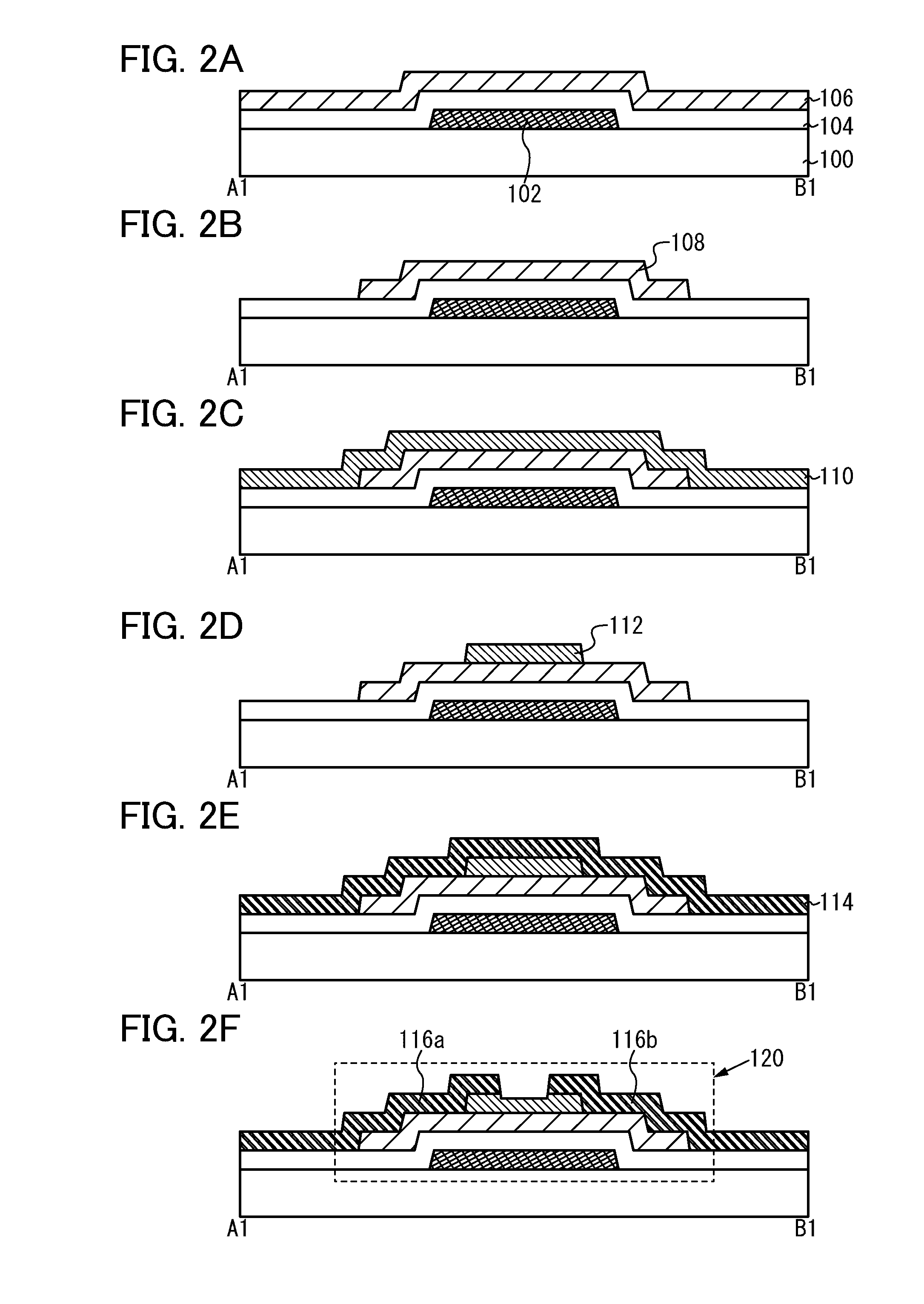

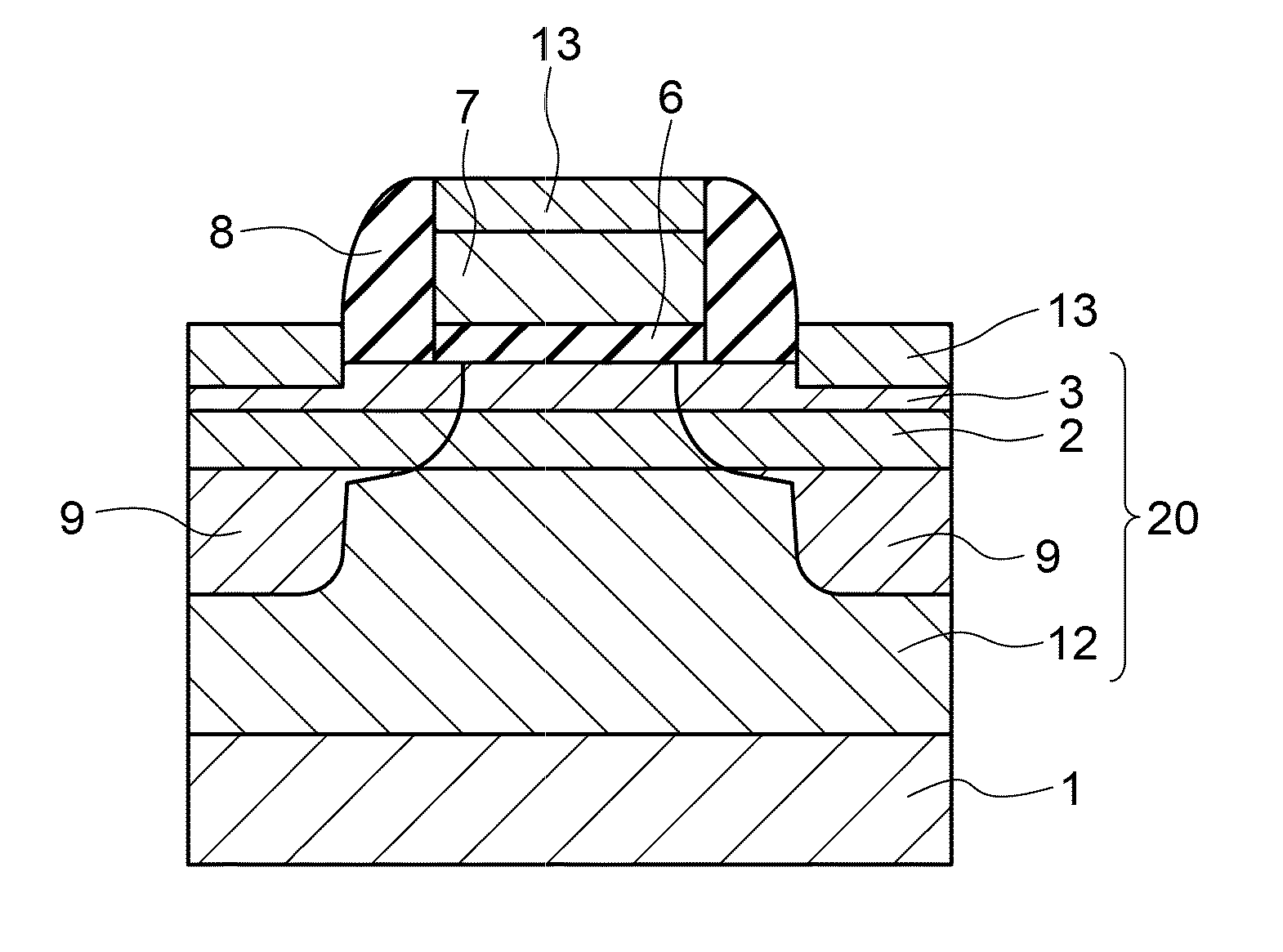

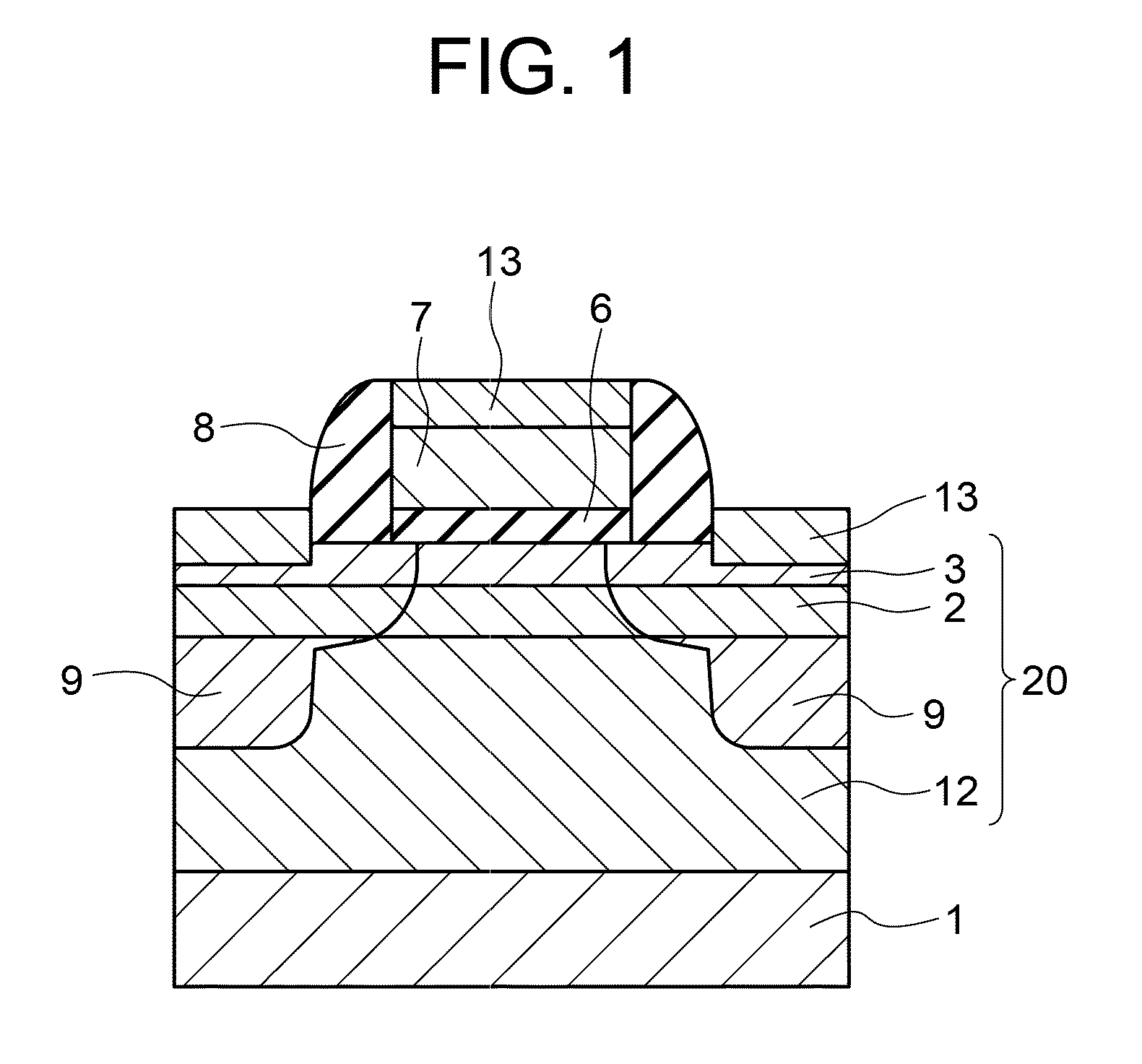

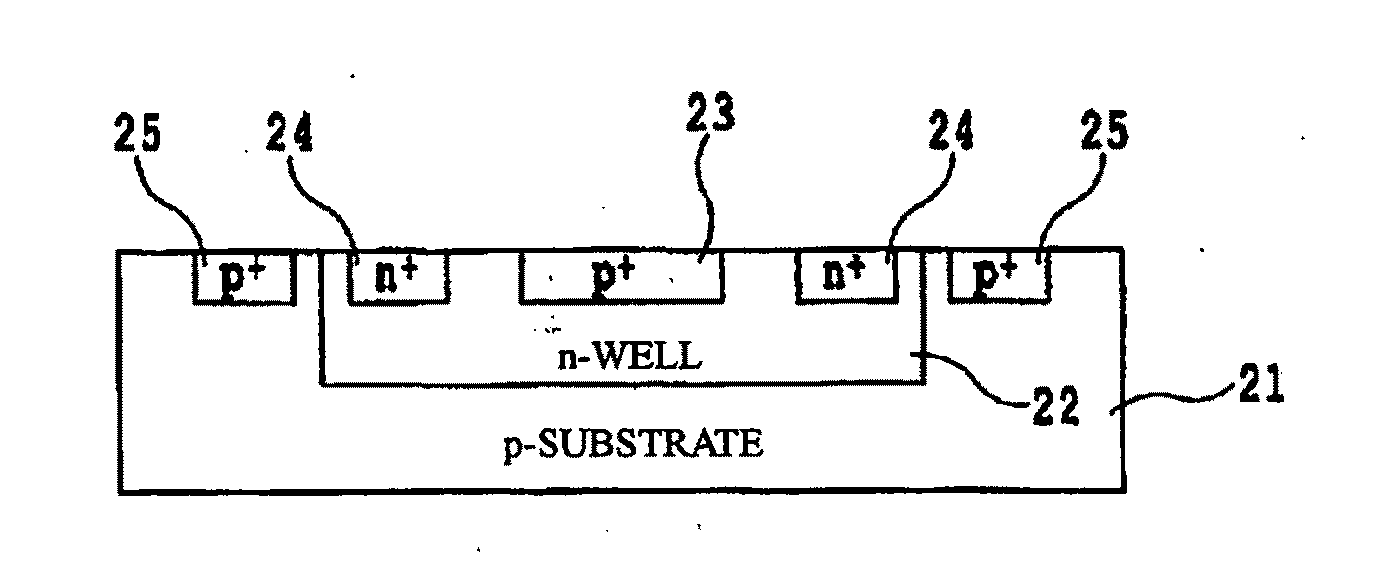

Semiconductor device including a transistor, and manufacturing method of the semiconductor device

ActiveUS20100207119A1Deterioration in characteristic can be suppressedDeterioration of characteristicTransistorElectroluminescent light sourcesOptoelectronicsP type silicon

The object is to suppress deterioration in electrical characteristics in a semiconductor device comprising a transistor including an oxide semiconductor layer. In a transistor in which a channel layer is formed using an oxide semiconductor, a p-type silicon layer is provided in contact with a surface of the oxide semiconductor layer. Further, the p-type silicon layer is provided in contact with at least a region of the oxide semiconductor layer, in which a channel is formed, and a source electrode layer and a drain electrode layer are provided in contact with regions of the oxide semiconductor layer, over which the p-type silicon layer is not provided.

Owner:SEMICON ENERGY LAB CO LTD

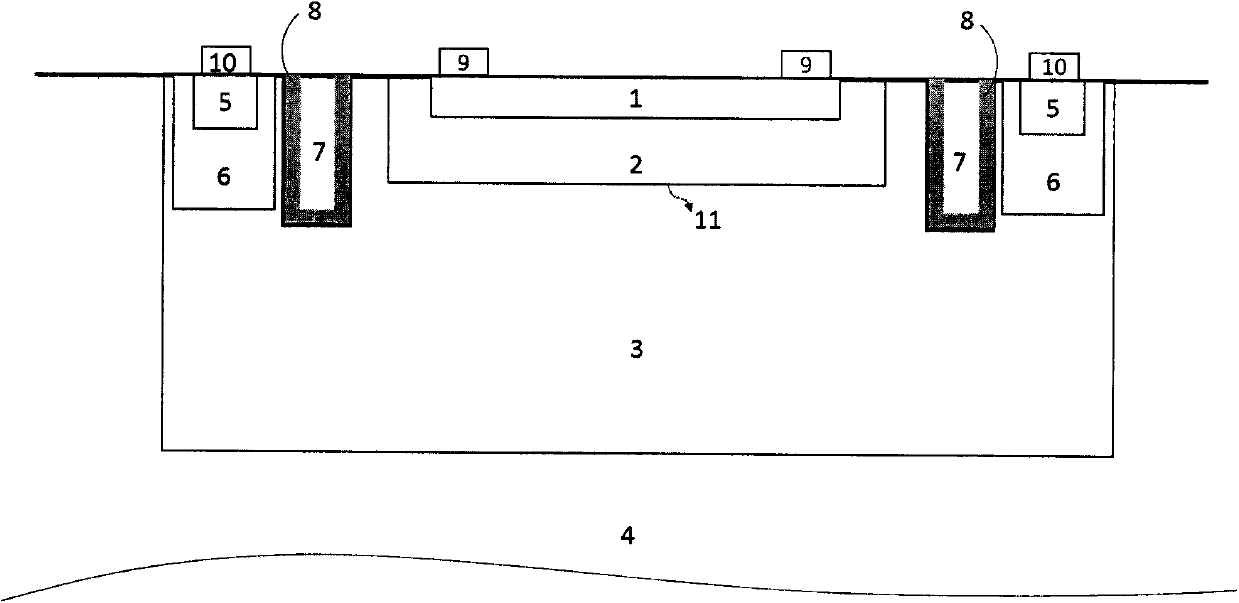

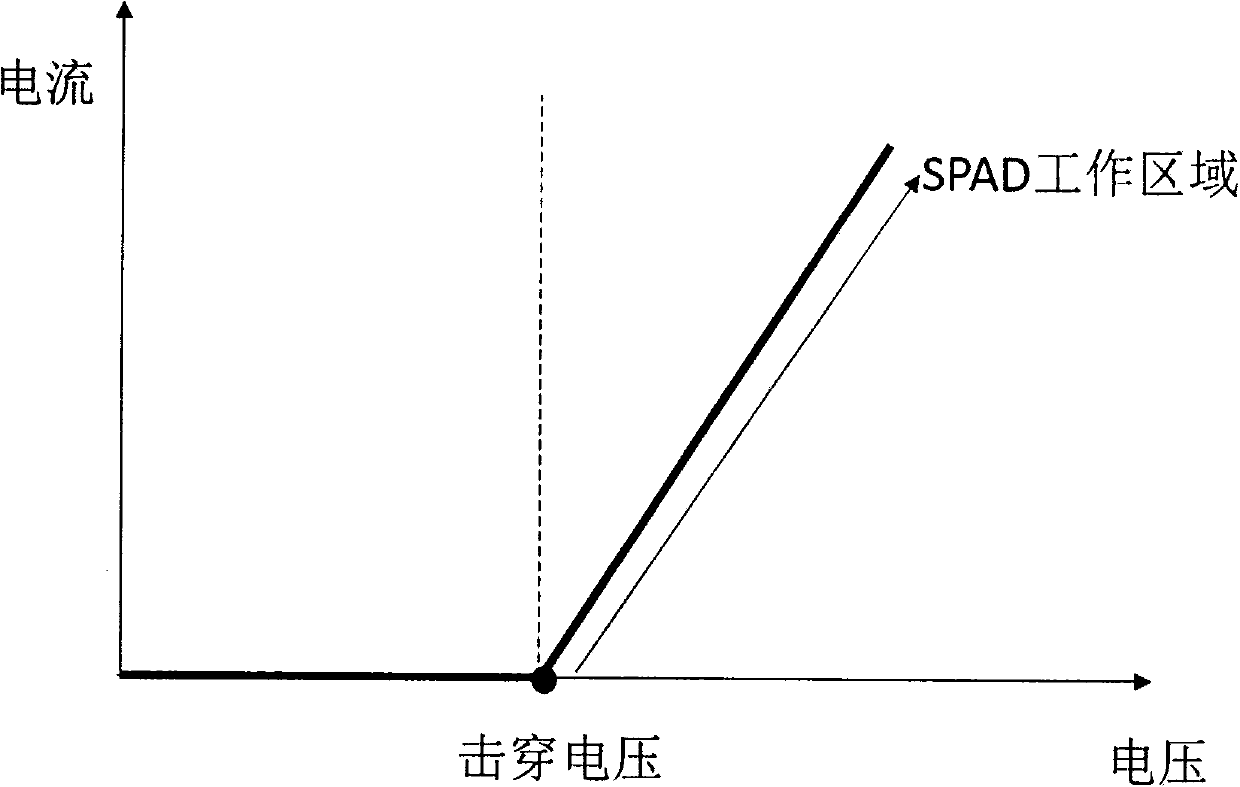

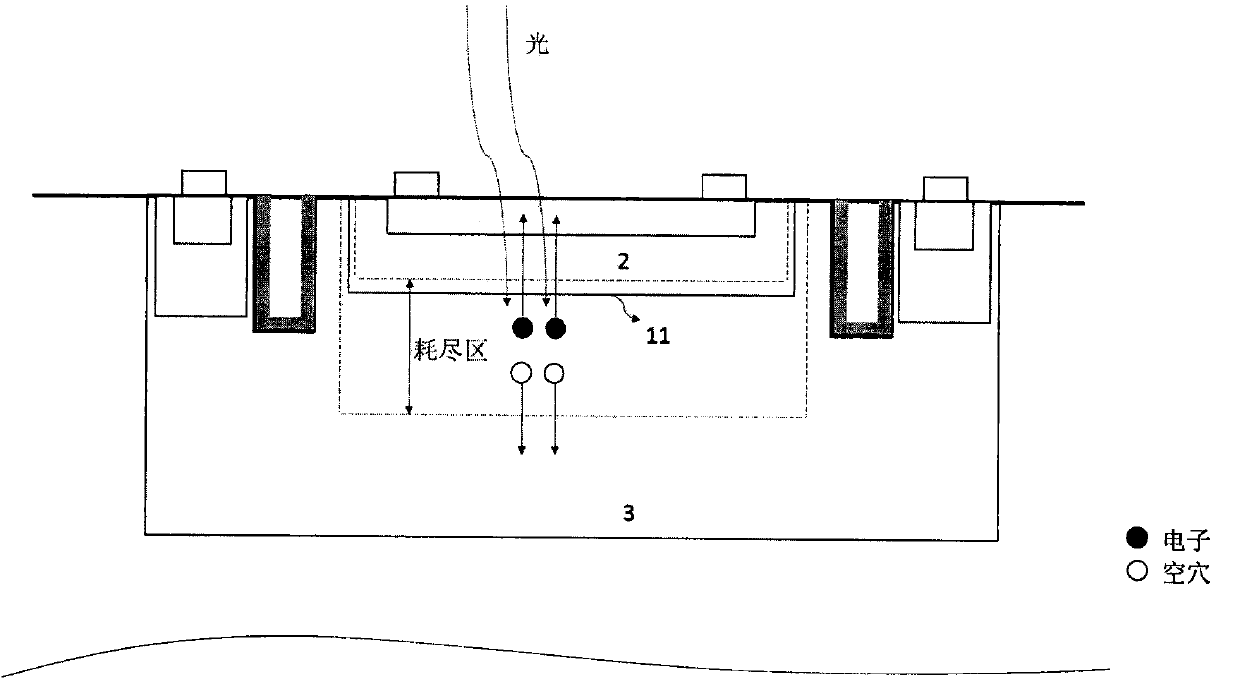

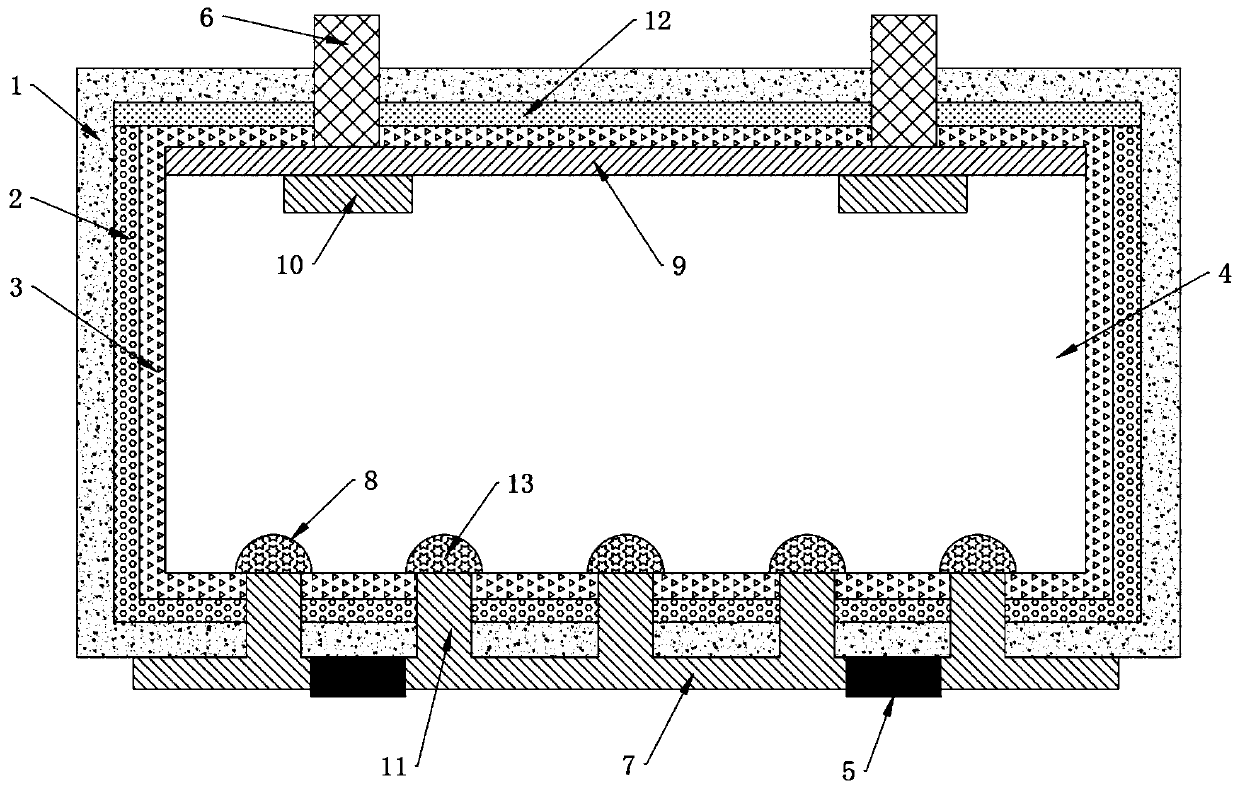

Single-photon-level resolution ratio sensor unit structure based on standard CMOS technology

InactiveCN103779437ASimple structureReduce dark noiseSemiconductor devicesConcentration gradientEngineering

Disclosed is a single-photon-level resolution ratio sensor unit structure based on the standard CMOS technology. The single-photon-level resolution ratio sensor unit structure uses an SPAD. According to the single-photon-level resolution ratio sensor unit structure, basically, a deep N-well (3) is arranged above a P-type silicon substrate (4), a P-well area (2) is formed above the deep N-well (3) and wrapped by the deep N-well (3), an anode contact (9) is connected to the P-well area (2) through a heavy-doping P-well area (1), a cathode contact (10) is connected to an N-well area (6) and the deep N-well (3) through a heavy-doping N-well area (5), a shallow trench isolation area (7) is located between the P-well area (2) and the N-well area (6) to isolate a P-well from an N-well, a P-type doped protection ring (8) surrounds the shallow trench isolation area (7) so as to restrain dark noise caused by defects in shallow trench isolation, and a PN junction (11) is arranged between the bottom of the P-well area (2) and the deep N-well (3); the PN junction generates a high-voltage area when proper bias voltage is applied between the cathode and the anode, and an SPAD multiplication area is formed so as to explore photons; the breakdown voltage of the edge of the PN junction is higher than that of the SPAD plane multiplication area by controlling the concentration gradient of the deep N-well (3).

Owner:苏州超锐微电子有限公司

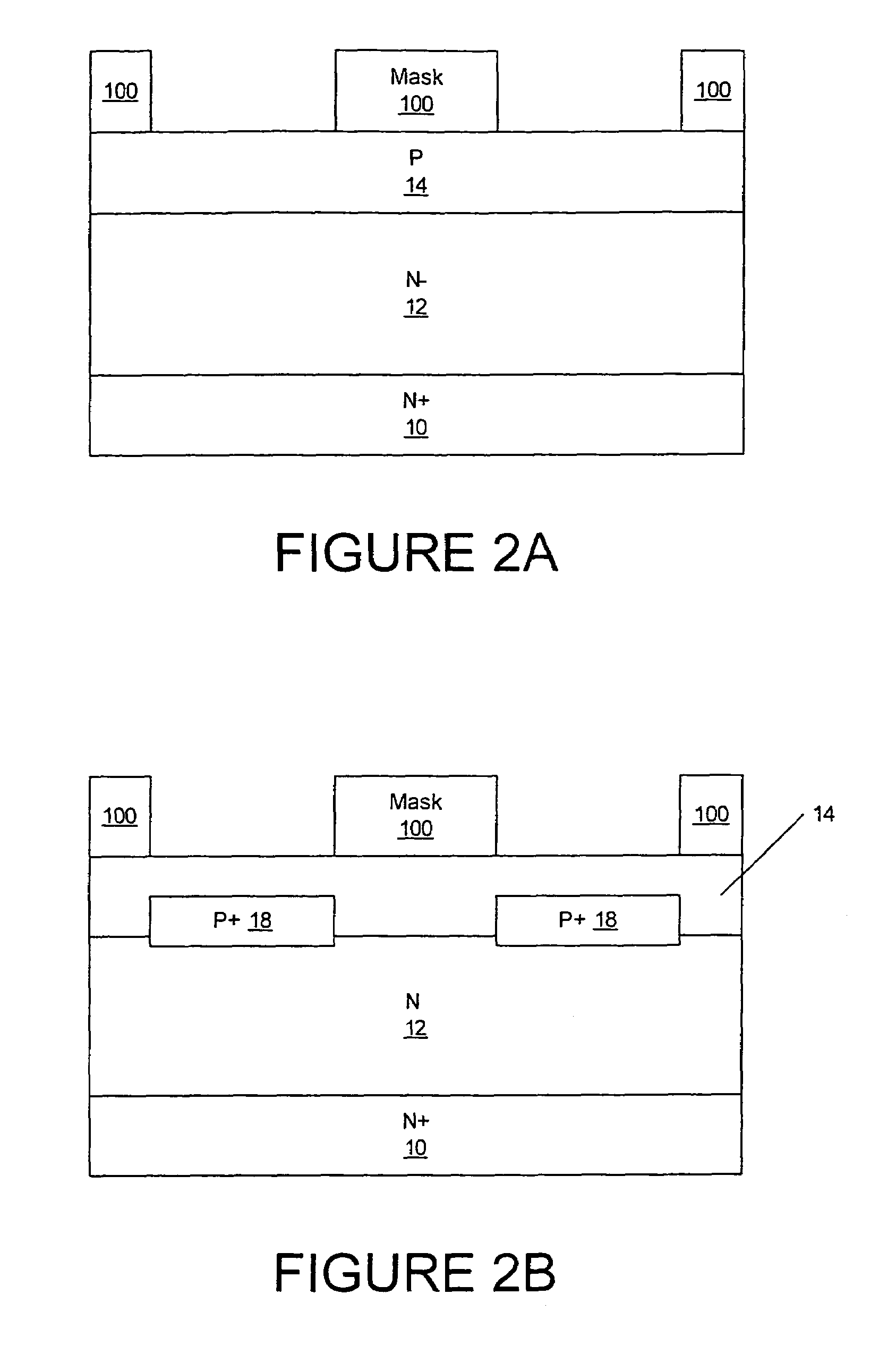

Silicon carbide devices with hybrid well regions and methods of fabricating silicon carbide devices with hybrid well regions

ActiveUS20050280004A1Semiconductor/solid-state device manufacturingSemiconductor devicesCarbideOptoelectronics

MOS channel devices and methods of fabricating such devices having a hybrid channel are provided. Exemplary devices include vertical power MOSFETs that include a hybrid well region of silicon carbide and methods of fabricating such devices are provided. The hybrid well region may include an implanted p-type silicon carbide well portion in a p-type silicon carbide epitaxial layer, an implanted p-type silicon carbide contact portion that contacts the implanted p-type silicon carbide well portion and extends to a surface of the p-type epitaxial layer and / or an epitaxial p-type silicon carbide portion, at least a portion of the epitaxial p-type silicon carbide well portion corresponding to a p-type channel region of the MOSFET.

Owner:CREE INC

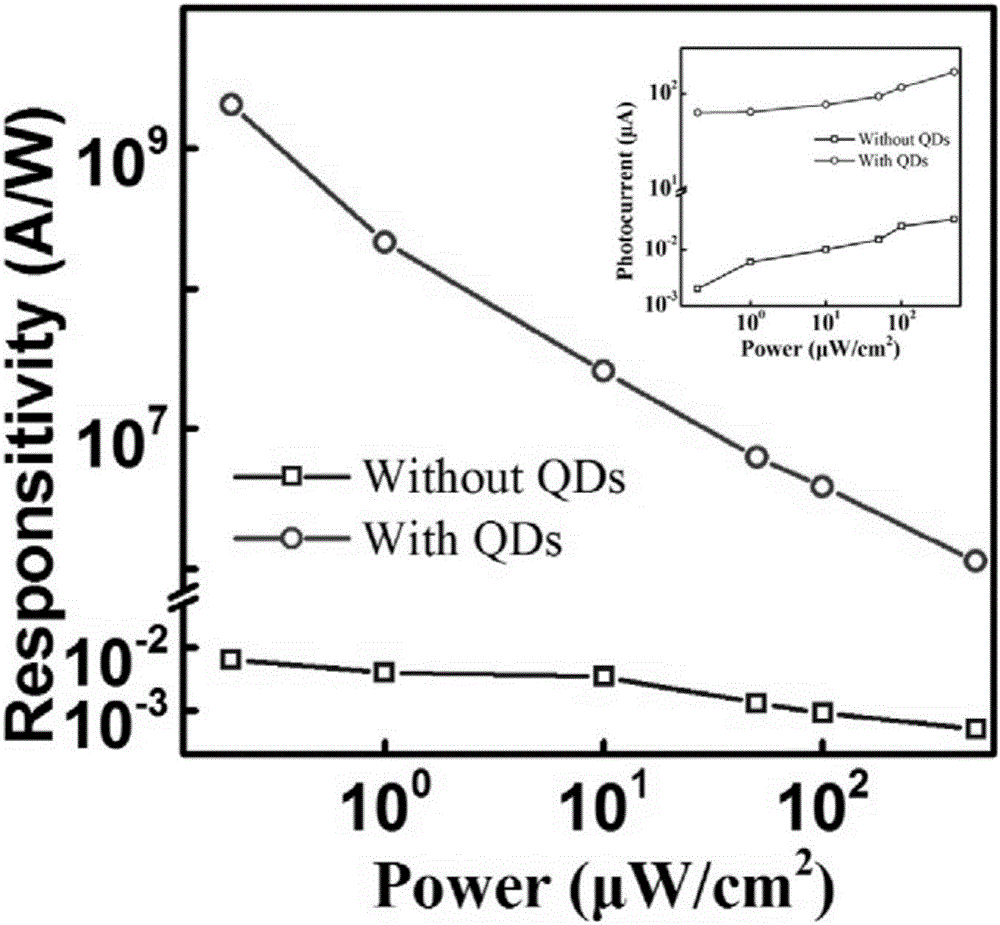

Photoconductive detector based on boron-doped silicon quantum dot/graphene/silicon dioxide and preparation method thereof

ActiveCN106601857ALarge light signal currentHigh gainFinal product manufactureSemiconductor devicesPhotoconductive detectorP type silicon

Owner:ZHEJIANG UNIV

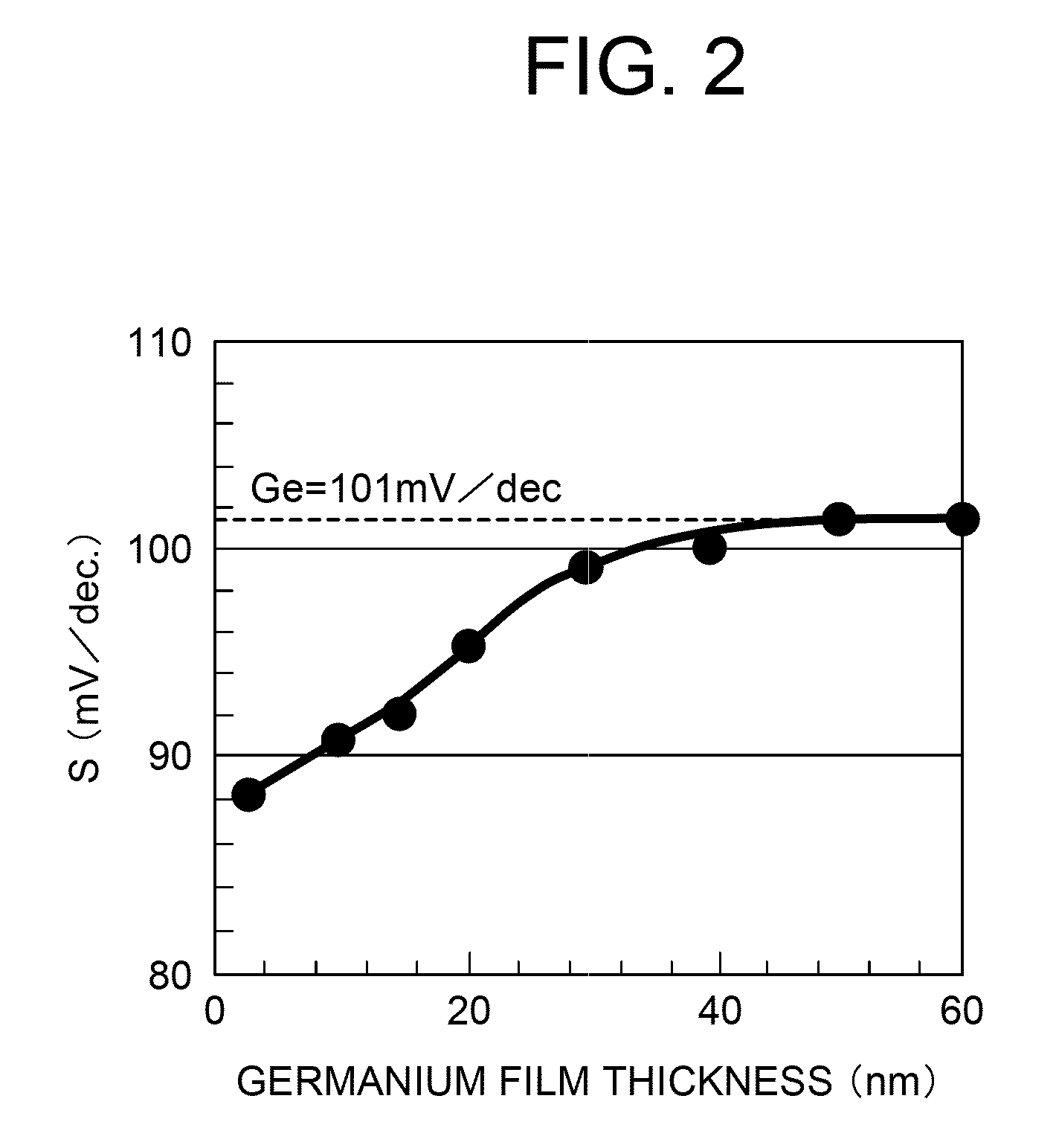

Semiconductor device

ActiveUS20100044781A1Suppression of short channel effectsHigh currentSolid-state devicesSemiconductor devicesDriving currentImpurity diffusion

To suppress short channel effects and obtain a high driving current by means of a semiconductor device having an MISFET wherein a material having high mobility and high dielectric constant, such as germanium, is used for a channel. A p-type well is formed on a surface of a p-type silicon substrate. A silicon germanium layer having a dielectric constant higher than that of the p-type silicon substrate is formed to have a thickness of 30 nm or less on the p-type well. Then, on the silicon germanium layer, a germanium layer having a dielectric constant higher than that of the silicon germanium layer is formed to have a thickness of 3-40 nm by epitaxial growing. The germanium layer is permitted to be a channel region; and a gate insulating film, a gate electrode, a side wall insulating film, an n-type impurity diffusion region and a silicide layer are formed.

Owner:RENESAS ELECTRONICS CORP

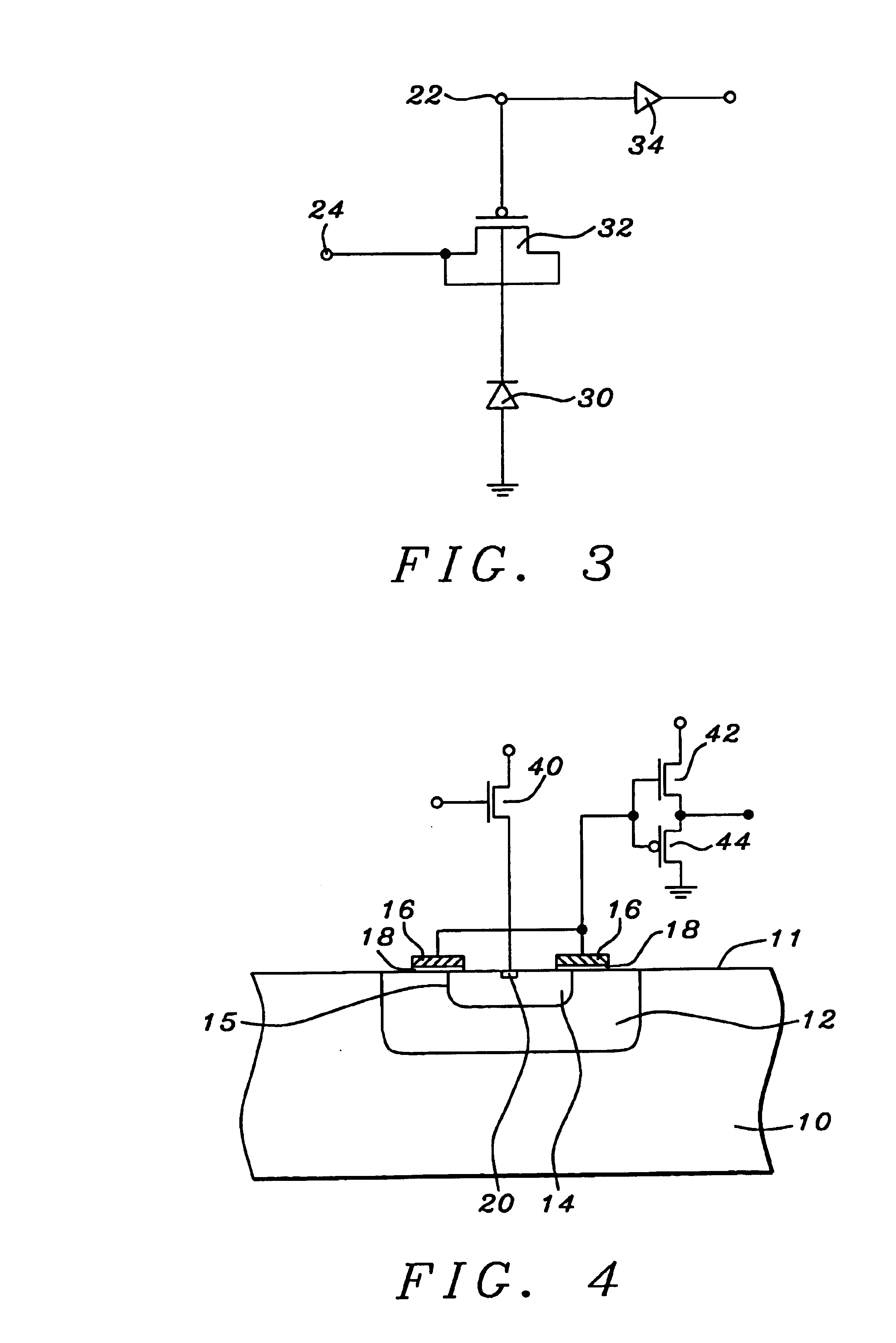

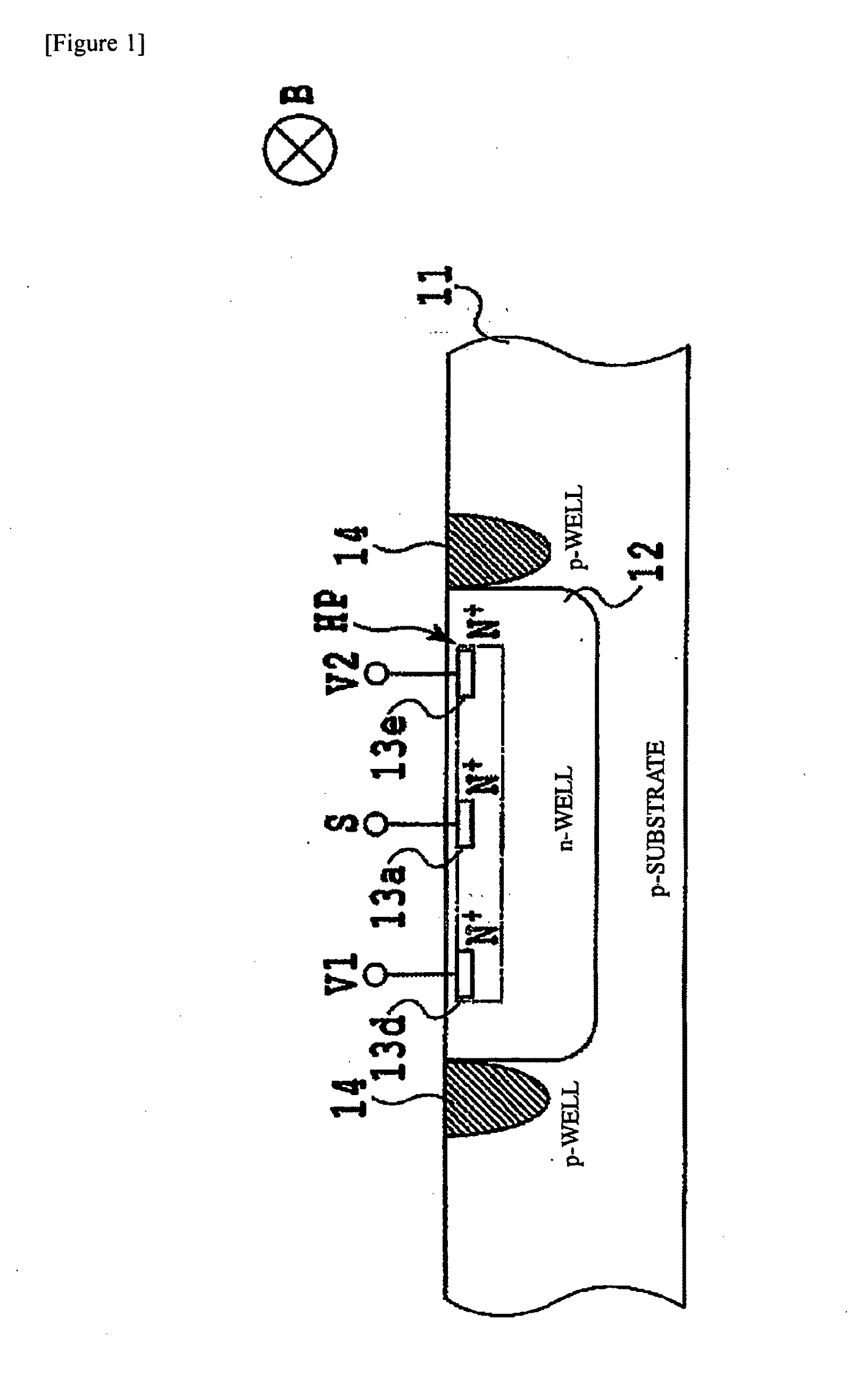

Tunneling floating gate APS pixel

A floating gate pixel is described which is formed by forming an N well in a P type silicon substrate. A P well is formed in the N well A gate is formed over a thin gate oxide, about 25 Angstroms thickness, such that the gate is directly over part of the P well and part of the N well. A P+ contact in the P well allows connection to a reset voltage source, usually through a reset transistor, to reset the pixel. The pixel is reset by setting the potential between the P well and the substrate, which is usually held at ground potential. When the pixel is reset tunneling current through the thin gate oxide sets the voltage of the floating gate. During the charge integration cycle an input signal to the pixel, such as a light signal, changes the potential of the pixel. After the charge integration cycle the tunneling current through the gate oxide changes the potential of the floating gate by an amount related to the input signal to the pixel. The potential of the floating gate can then be read out to determine the input signal to the pixel. The pixel can also be embodied using a P well formed in an N type substrate, an N well formed in the P well, and an N+ contact formed in the N well.

Owner:UNITED MICROELECTRONICS CORP

Metal pastes and use thereof in the production of positive electrodes on p-type silicon surfaces

InactiveUS20100269893A1Reduce weight percentageReduce weightSemiconductor/solid-state device detailsConductive materialAlloyP type silicon

Metal pastes comprising (a) at least one electrically conductive metal powder selected from the group consisting of silver, copper, and nickel, (b) at least one p-type silicon alloy powder, and (c) an organic vehicle, wherein the p-type silicon alloy is selected from the group consisting of alloys comprising silicon and boron, alloys comprising silicon and aluminum and alloys comprising silicon, boron and aluminum.

Owner:EI DU PONT DE NEMOURS & CO

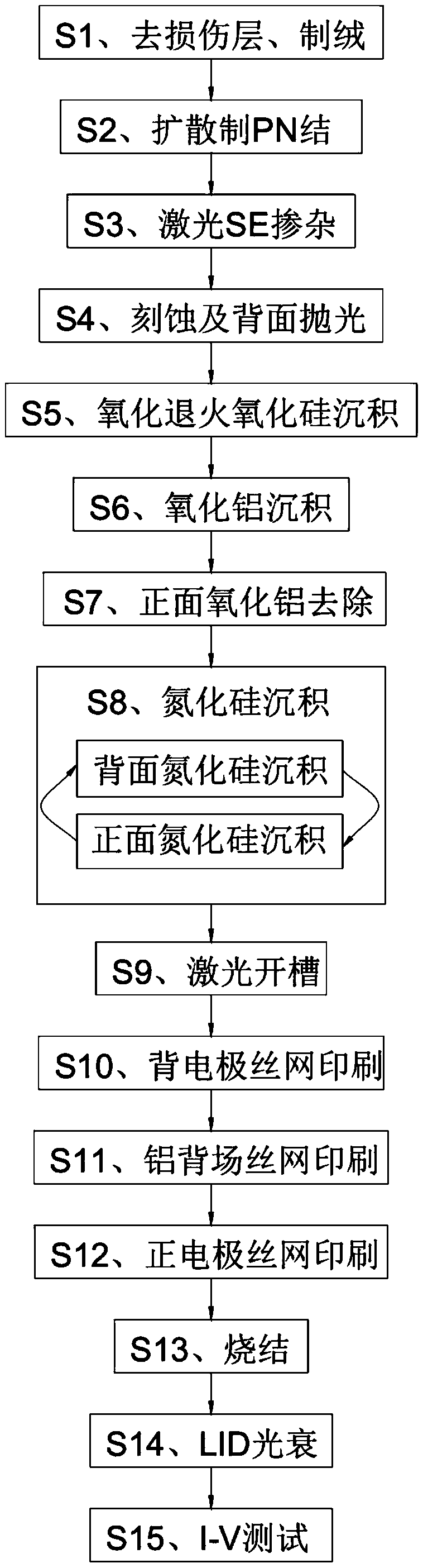

Solar cell with composite dielectric passivation layer structure and preparation process thereof

PendingCN110459615AIncrease short circuit currentIncrease the open circuit voltageFinal product manufacturePhotovoltaic energy generationDielectricRefractive index

The invention discloses a solar cell with a composite dielectric passivation layer structure and a preparation process thereof. A silicon oxide film, an alumina film and a silicon nitride or silicon oxynitride film are deposited in turn on the front, back and sides of a p-type silicon substrate to form a composite dielectric film on the whole surface, and windows are opened locally to lead electrodes out. Through aluminum oxide, silicon dioxide, silicon oxynitride, silicon nitride with different refractive indexes and a back surface passivation layer with a laminated structure of the materials, the back surface recombination rate is greatly reduced, the back reflectivity is improved, the CTM of a module is reduced, and the light attenuation and heat-assisted light attenuation and the anti-PID performance of the cell are improved. The structure can be made on a boron / gallium-doped p-type monocrystalline silicon, p-type polycrystalline silicon or p-type monocrystalline-silicon-like substrate, and a passivation method based on the composite dielectric film passivation structure can be used to manufacture PERC cells, double-sided PERC+ cells and imbricate PERC cells. Based on the preparation process steps and sequence, the corresponding preparation mode and the process parameter range of the laminated structure, the making of the cell can be well completed.

Owner:TONGWEI SOLAR ENERGY CHENGDU CO LID +2

Back point-contact silicon solar cell based on silk-screen printing technology and making method

InactiveCN1815760AImprove performanceSimple manufacturing methodFinal product manufacturePhotovoltaic energy generationGas phaseSilicon solar cell

Phosphorus diffusion formed PN junction is setup on P type silicon chip. There is silicon nitride layer, or surface passivation layer of silica, reflection reducing coating and positive electrode on front face. Characters are that through P type punctual alloy diffusion zone, back metal layer of silicon chip constitutes ohmic contact. Preparing method includes steps: selecting P type chip; preparing knap surface and cleaning; forming PN junction through phosphorus diffusion; etching and corroding edges by using plasma; developing silicon nitride or silica at both sides; preparing point contacted dense P+ zone at back side through screen printing by using solid-solid phase diffusion or selective gaseous phase diffusion; printing and sintering electrode through screen printing; adding metal layer to full back side. The solar cell reaches indexes: open circuit voltage larger than 650mV, current density larger than 38mA / cm2, fill factor as 74úÑ-78úÑ and conversion efficiency 18úÑ-20úÑ.

Owner:WUXI SUNTECH POWER CO LTD

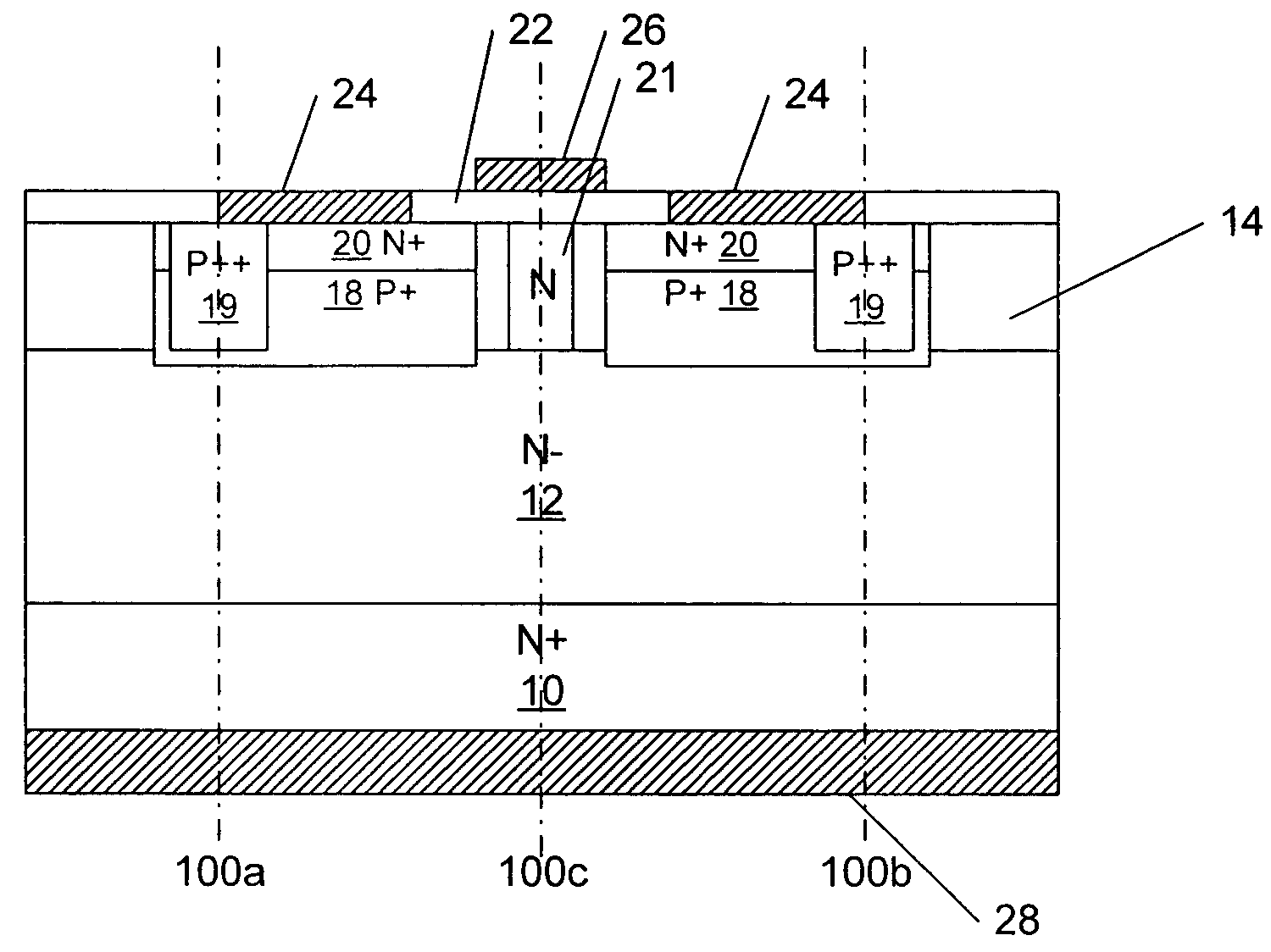

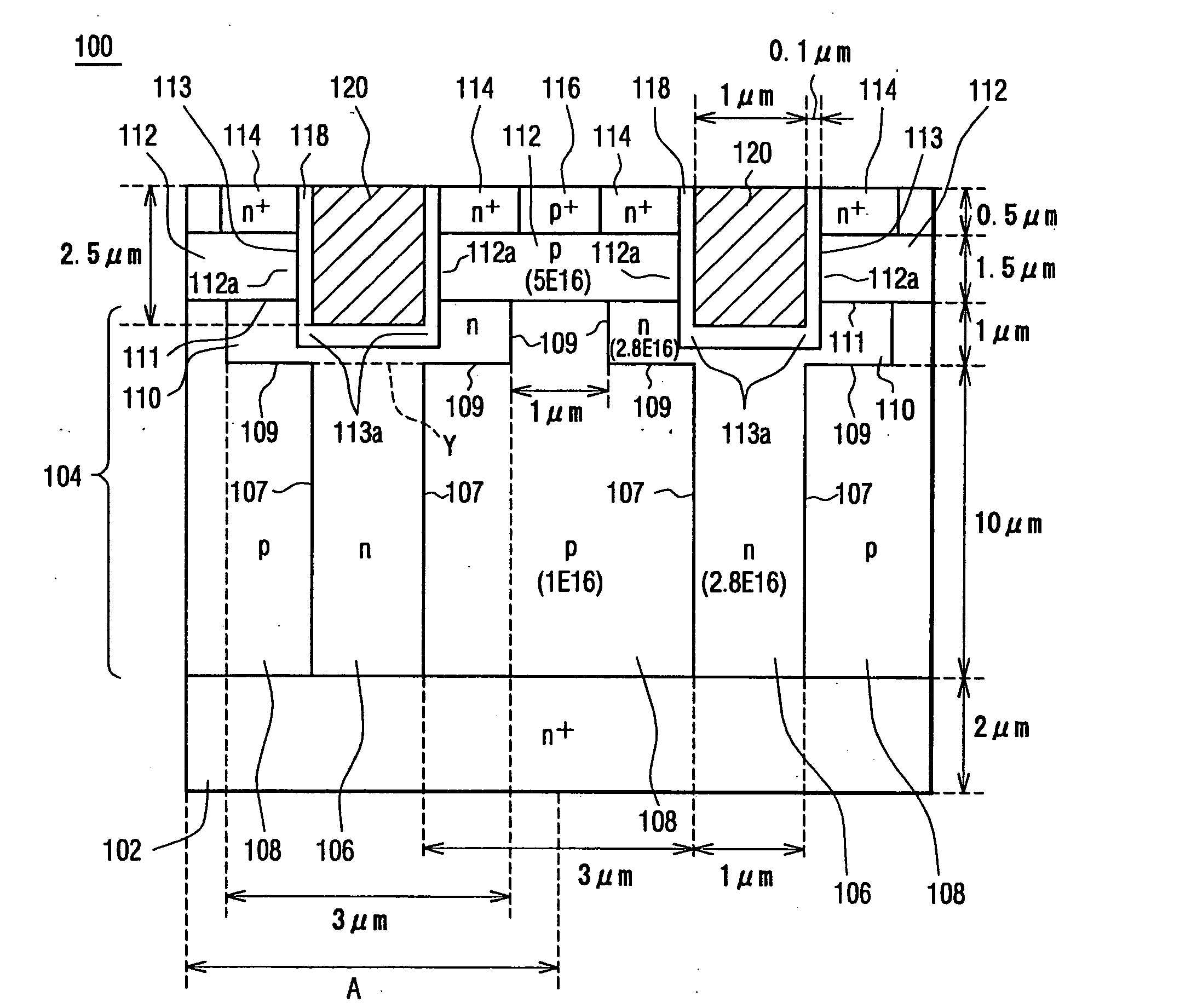

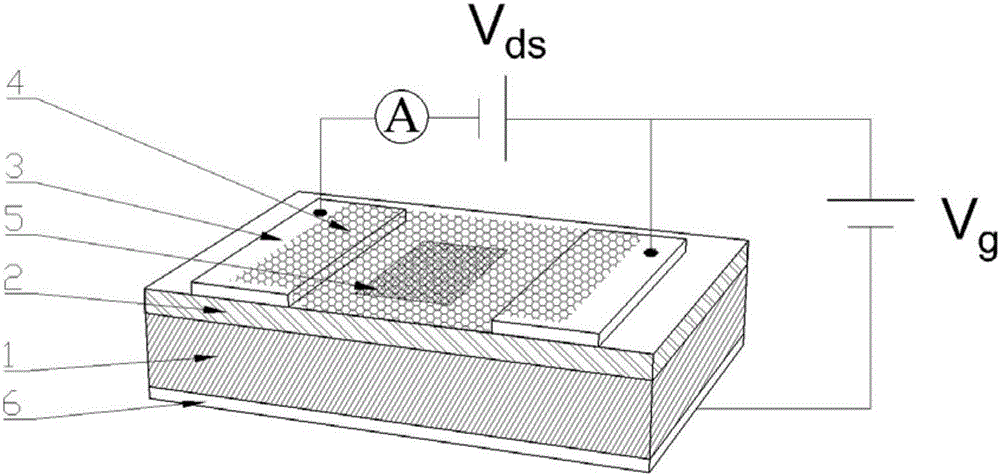

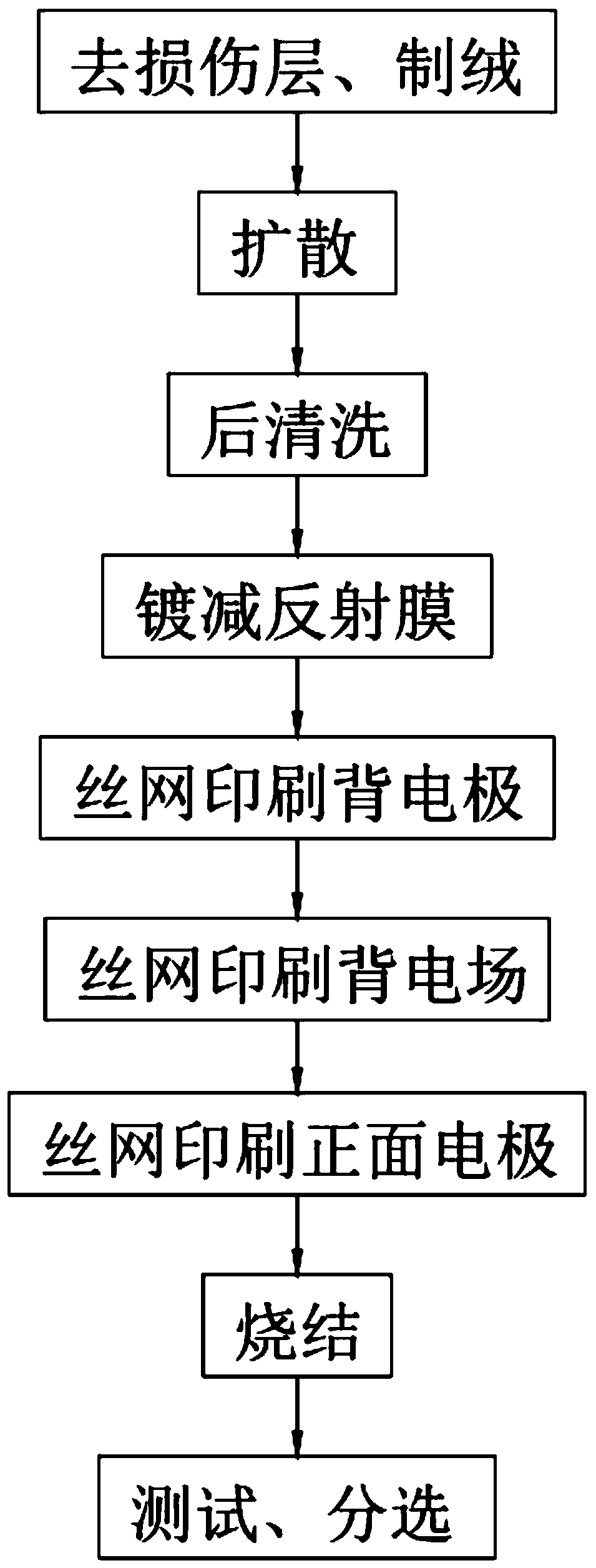

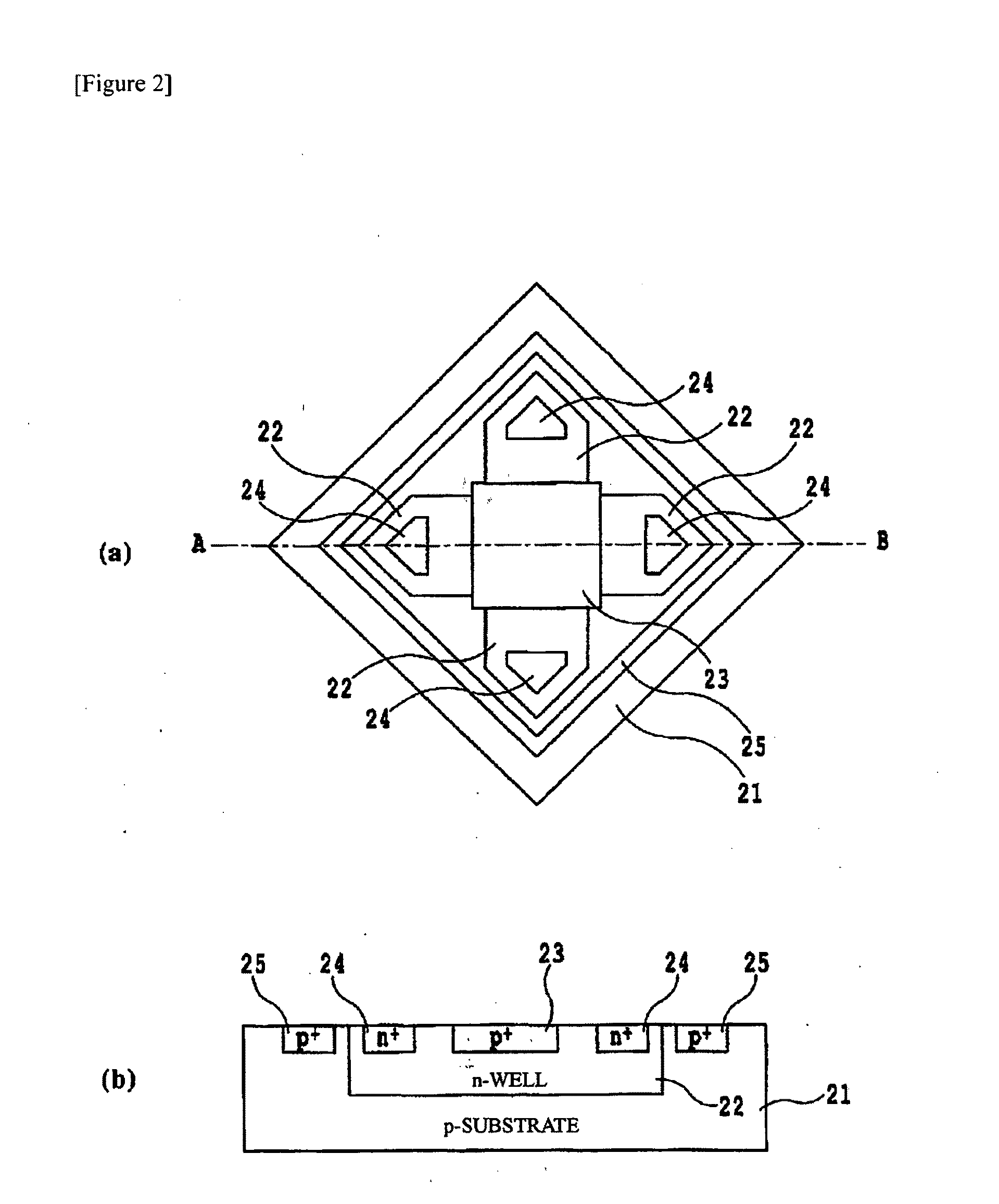

Hall Element and Magnetic Sensor

ActiveUS20100164483A1High sensitivityImprovement in S/N ratio per currentSolid-state devicesMagnetic field measurement using galvano-magnetic devicesHall elementOptoelectronics

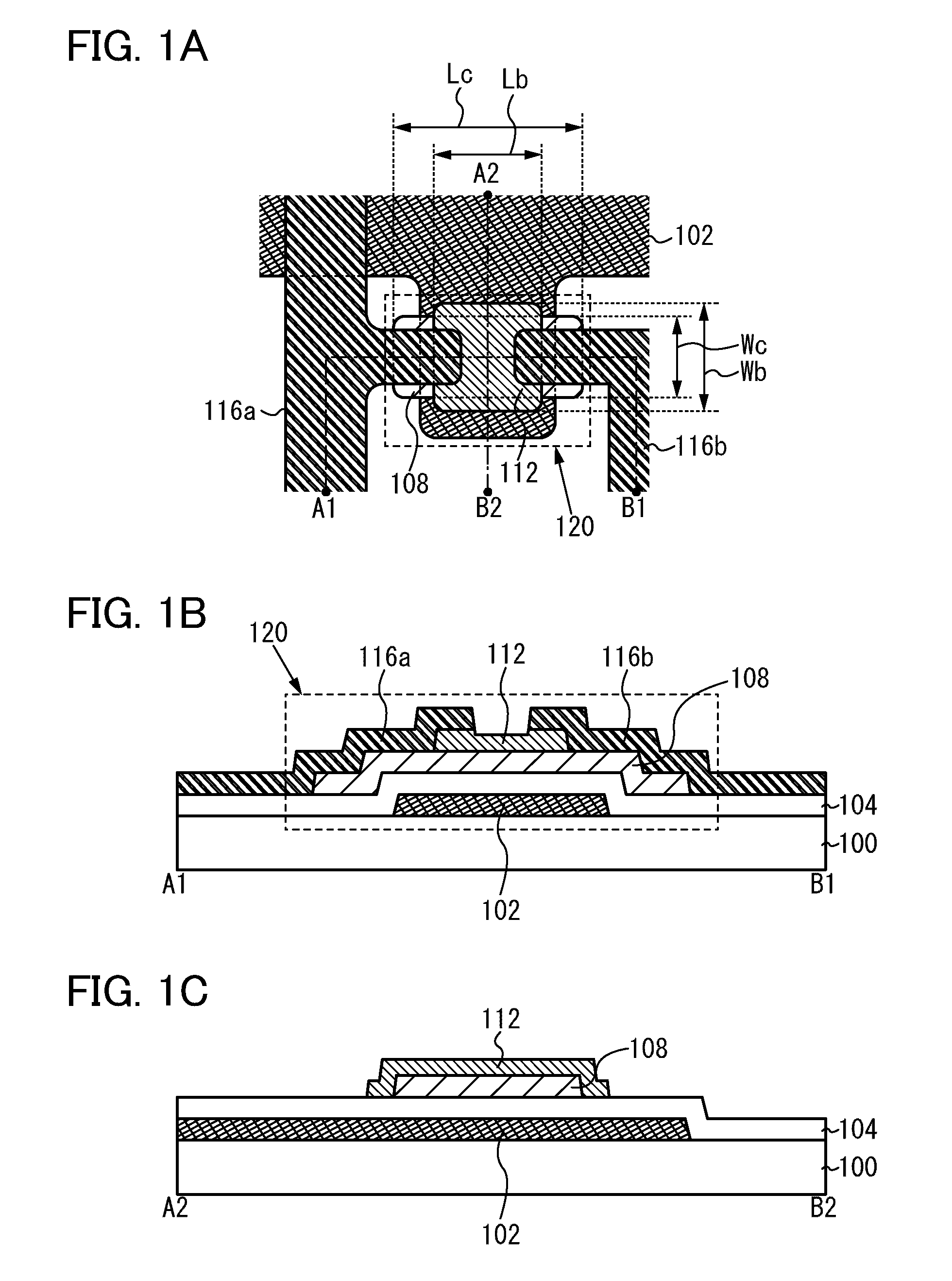

A Hall element is provided which has a high sensitivity and contributes to an improvement in S / N ratio per current by using a low-concentration n-well within a suitable range. The Hall element includes a p-type semiconductor substrate layer 21 of p-type silicon, and an n-type impurity region 22 located in a surface of the p-type semiconductor substrate layer 21, the n-type impurity region 22 functioning as a magnetic sensing part 26. A p-type impurity region 23 is located in a surface of the n-type impurity region 22, and n-type regions 24 are located laterally of the p-type impurity region 23. A p-type substrate region 21a having a resistivity equal to that of the p-type semiconductor substrate layer 21 is located to extend around the n-type impurity region 22. An impurity concentration N in the n-type impurity region 22 functioning as the magnetic sensing part 26 is preferably from 1×1016 to 3×1016 (atoms / cm3), and a distribution depth D of the impurity concentration is preferably from 3.0 μm to 5.0 μm.

Owner:ASAHI KASEI ELECTRONICS CO LTD

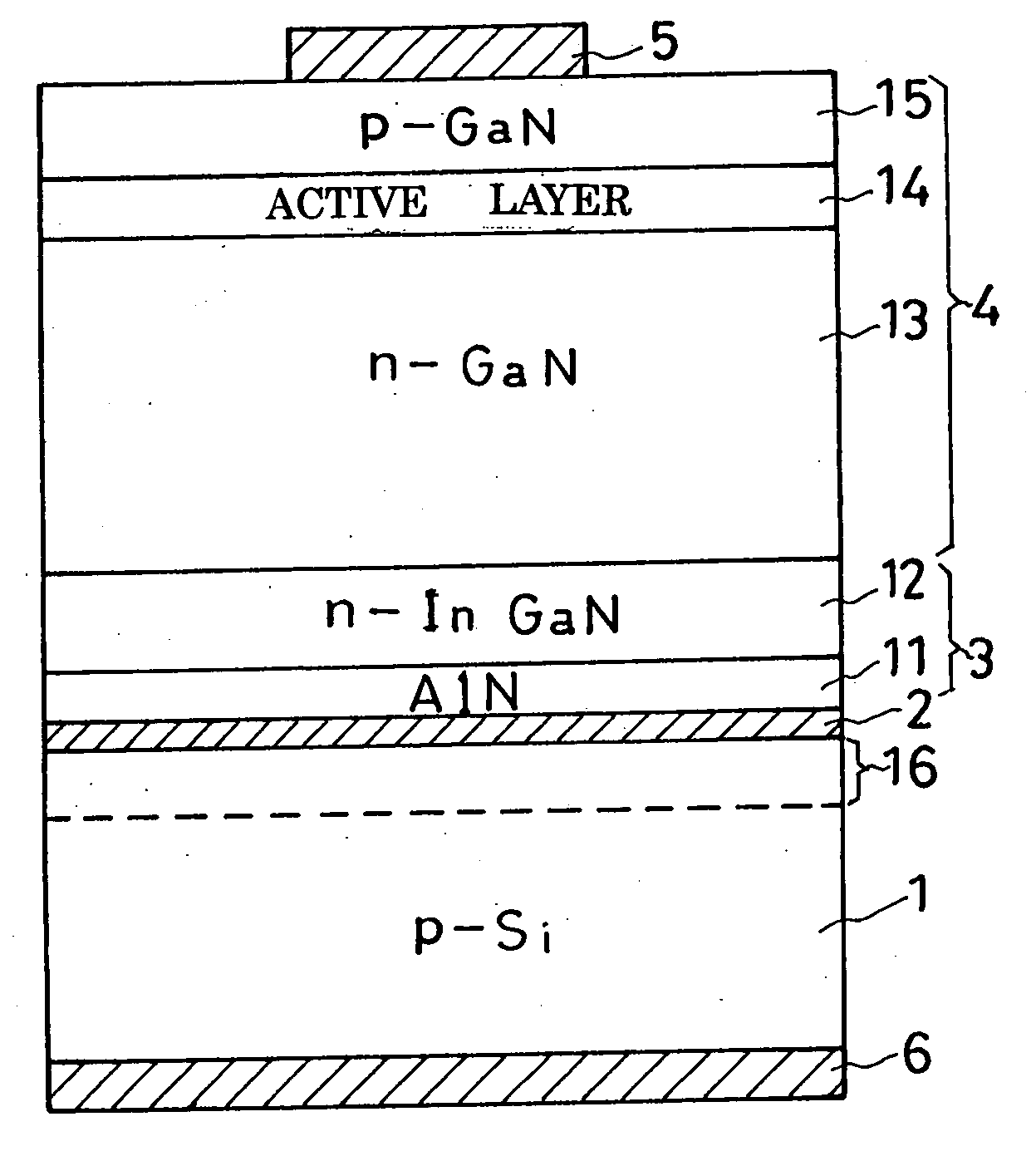

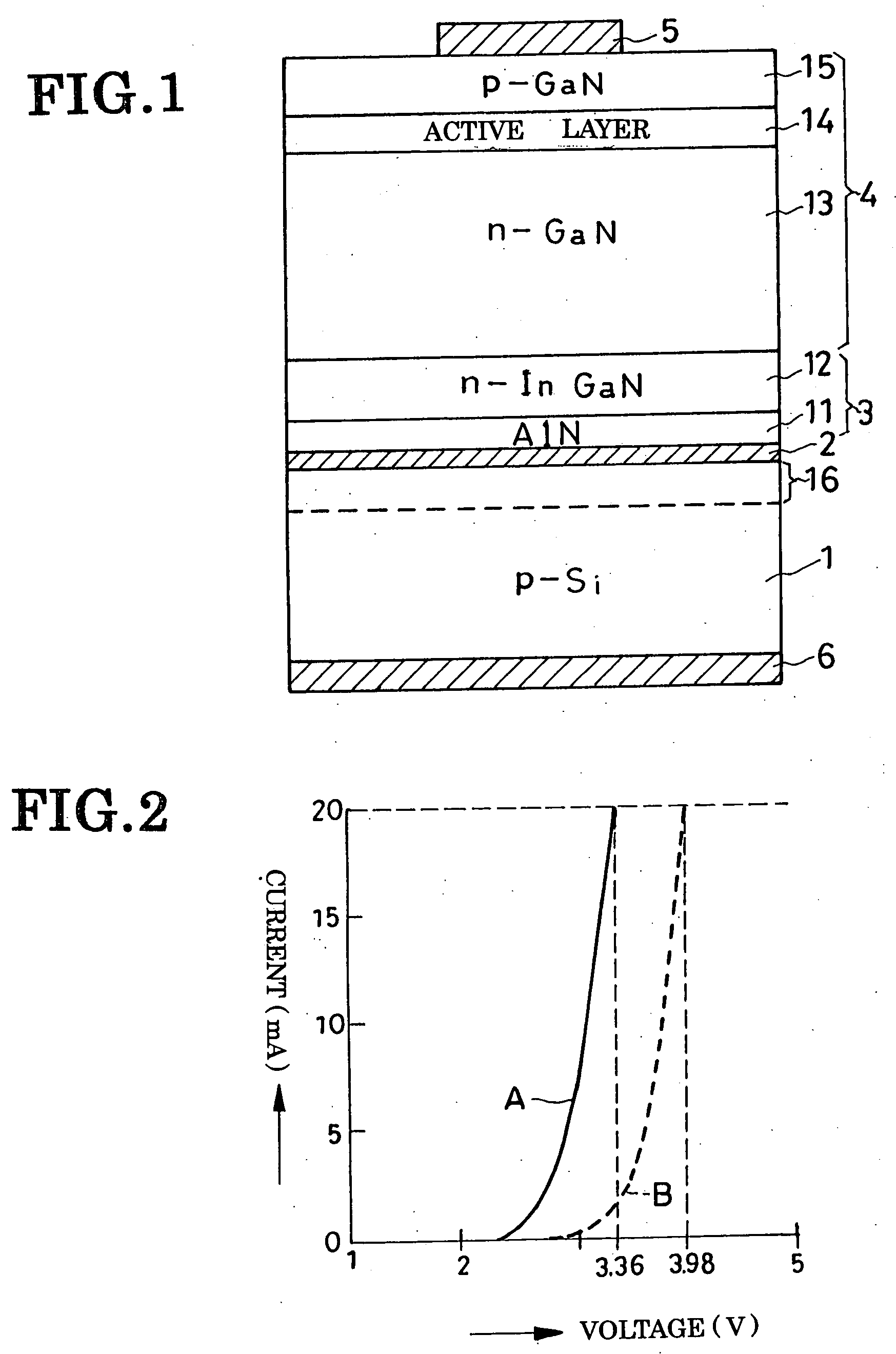

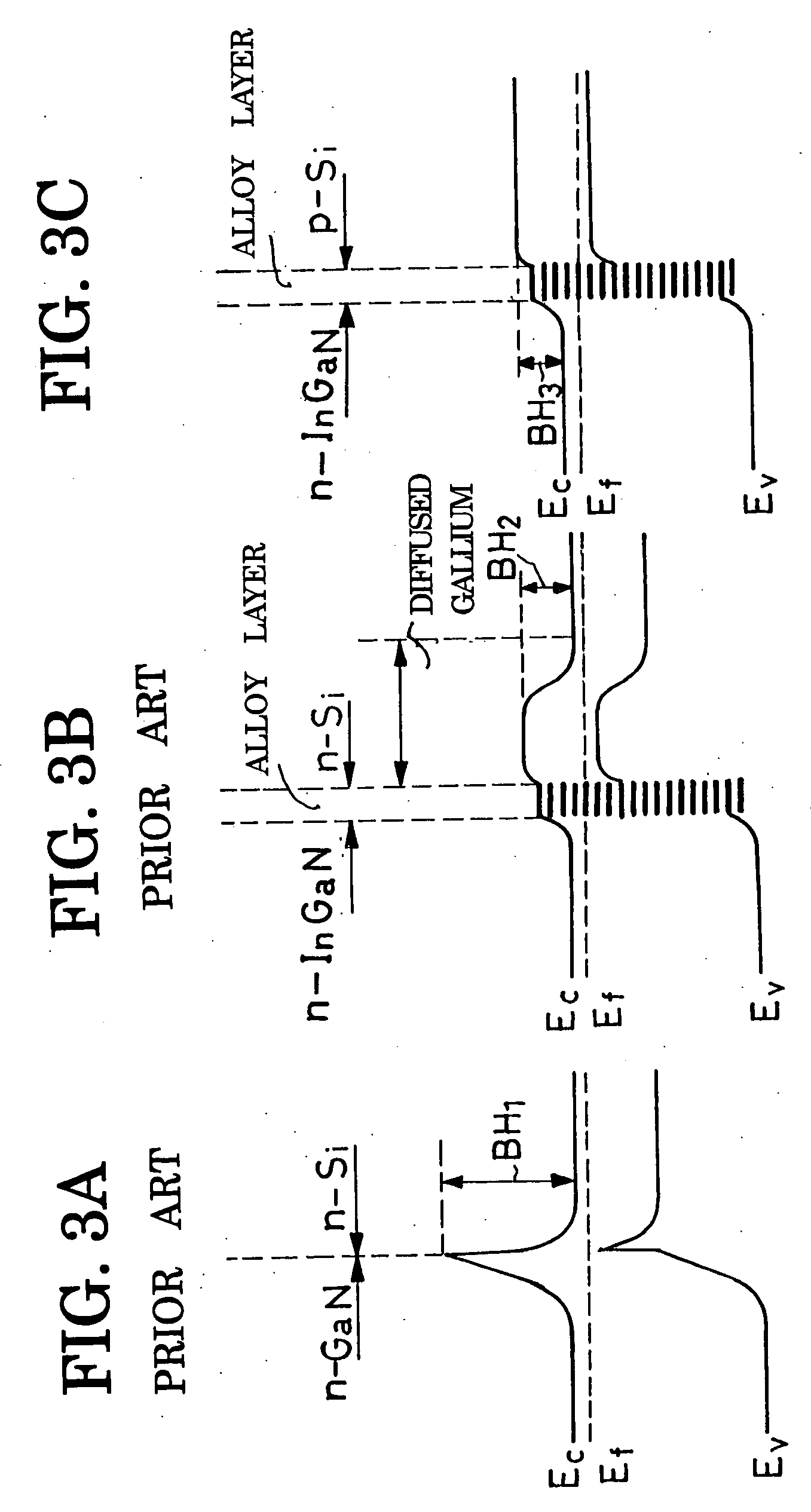

Nitride-based semiconductor device and method of fabrication

ActiveUS20060094145A1Minimize voltage dropLess voltageSemiconductor/solid-state device manufacturingSemiconductor devicesIndiumDevice material

A light-emitting diode is built on a silicon substrate doped with a p-type impurity to possess sufficient conductivity to provide a current path. The p-type silicon substrate has epitaxially grown thereon two superposed buffer layers of aluminum nitride and n-type indium gallium nitride. Further grown epitaxially on the buffer layers is the main semiconductor region of the LED which comprises a lower confining layer of n-type gallium nitride, an active layer for generating light, and an upper confining layer of p-type gallium nitride. In the course of the growth of the main semiconductor region there occurs a thermal diffusion of aluminum, gallium and indium from the buffer layers into the p-type silicon substrate, with the consequent creation of an alloy layer of the diffused metals. Representing p-type impurities in the p-type silicon substrate, these metals do not create a pn junction in the substrate which causes a forward voltage drop.

Owner:SANKEN ELECTRIC CO LTD

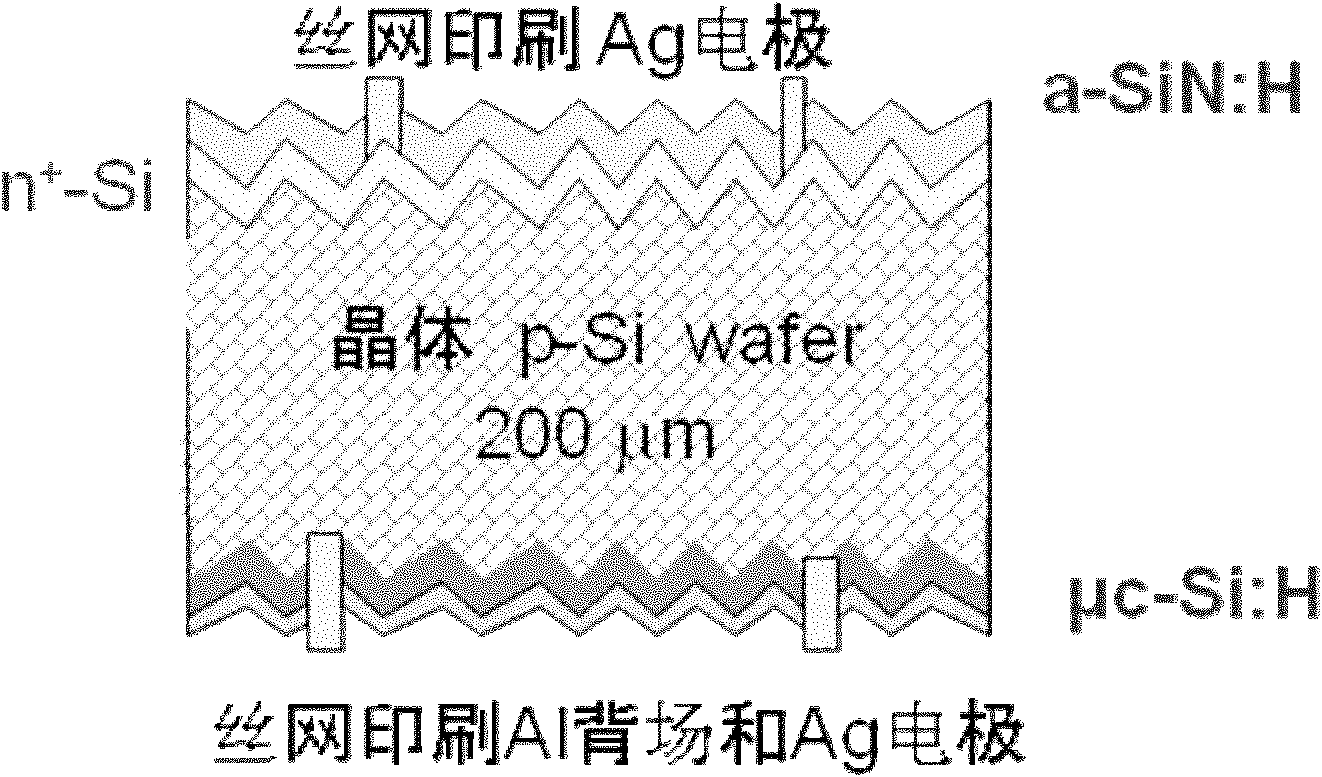

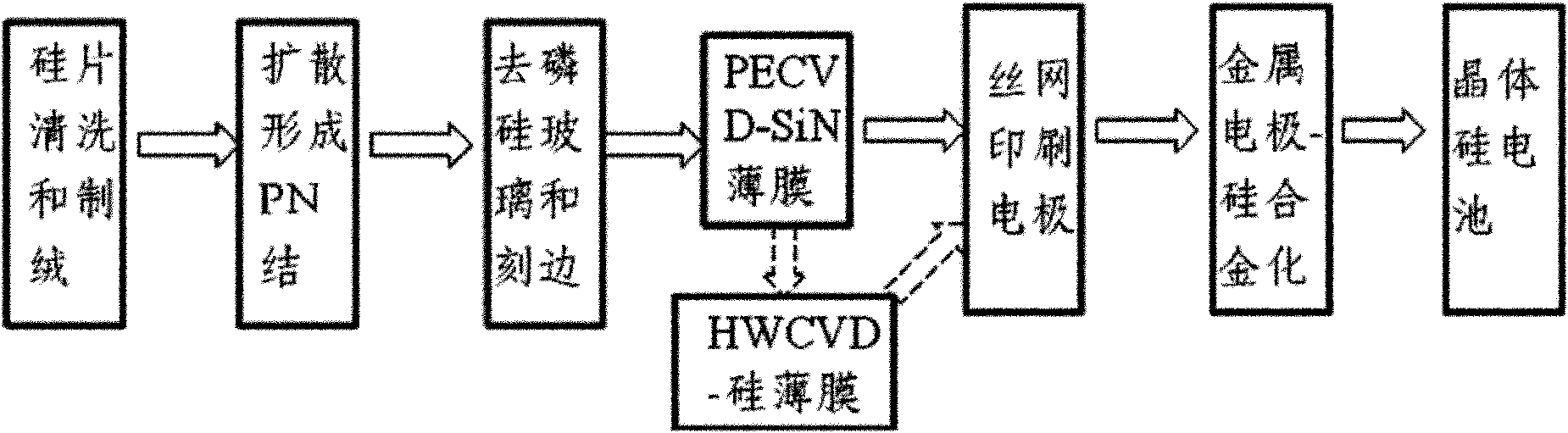

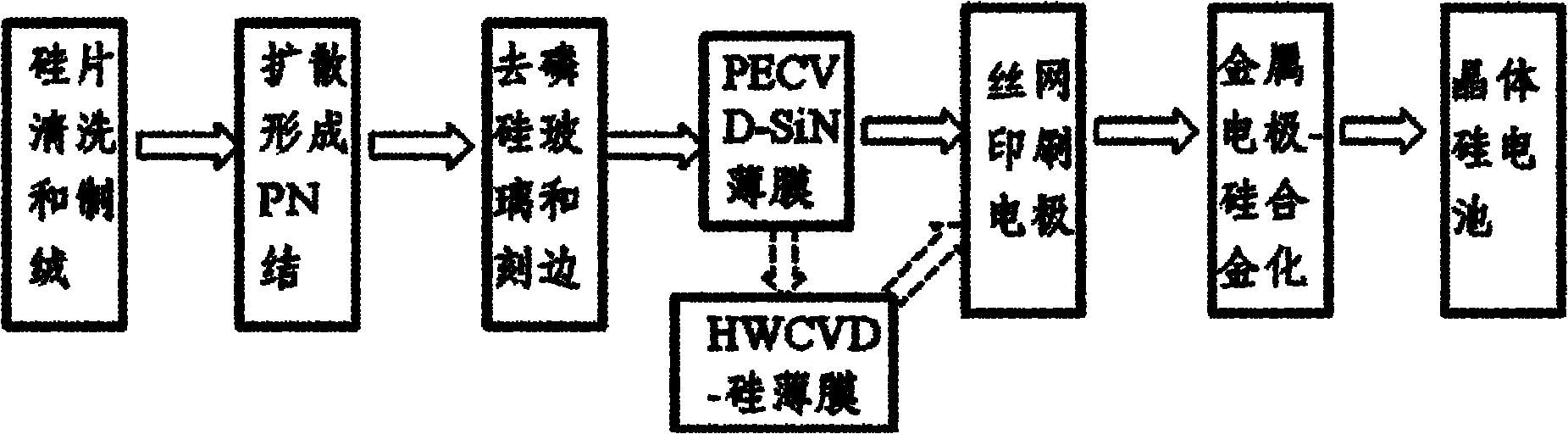

Preparation method of double-sided passivated crystalline silicon solar cell

InactiveCN101937944APrevent escapeAdjustable bandgapSemiconductor devicesP type siliconMicrocrystalline silicon

The invention discloses a preparation method of a double-sided passivated crystalline silicon solar cell, belonging to the technical field of photovoltaic power generation. The preparation method comprises the following steps of: firstly, respectively carrying out surface precleaning and surface texturing on P-shaped single crystal silicon and a polycrystalline silicon wafer by adopting an alkaline solution and an acid solution; secondly, diffusing by using phosphorus oxychloride as a diffusion source to form a PN junction; thirdly, removing a phosphosilicate glass on the surface of the silicon wafer by adopting a chemical wet method, and etching the edge of the silicon wafer by adopting a plasma; fourthly, preparing a silicon nitride film on the surface of an emitting region of a P-type silicon wafer by adopting a plasma enhanced chemical vapor deposition method; fifthly, preparing a mixed phase film material of hydrogenated microcrystalline silicon and amorphous silicon by adopting a hot filament chemical vapor deposition method, depositing a film at one side of the P-type silicon wafer, and passivating the defects and a dangling bond on the surface of the P-type silicon wafer; and sixthly, sintering a screen printing back electrode and a screen printing positive electrode to form the solar cell. The invention lowers the probability of compounding photo-generated minority carriers on the back surface, enhances the long-wave light quantum efficiency and creates the conditions of transportation and collection of the photo-generated carriers.

Owner:SHANGHAI JIAO TONG UNIV

Method of forming a semiconductor device comprising a dummy polysilicon gate electrode short-circuited to a dummy element region in a substrate

InactiveUS6074938AGuaranteed uptimeIncrease wiring areaTransistorSemiconductor/solid-state device detailsEngineeringP type silicon

The present invention relates to a semiconductor device wherein a dummy gate electrode is fixed to the same electric potential as that of a substrate, the stable operation of an LSI is maintained and the process margin is large, and also to a producing method of the semiconductor device, and the semiconductor device comprises a P-type silicon substrate, a dummy element region unnecessary for the actual LSI operation, which is formed on the P-type silicon substrate, and a dummy gate electrode unnecessary for the actual LSI operation, which is formed on at least a part of the dummy element region through a dummy oxide film, wherein by selectively forming titanium silicide on at least a part of a surface of the dummy element region and the dummy gate electrode, a P.sup.+ -diffusion layer and a P.sup.+ -dummy gate electrode of the dummy element region are short-circuited by titanium silicide.

Owner:KK TOSHIBA

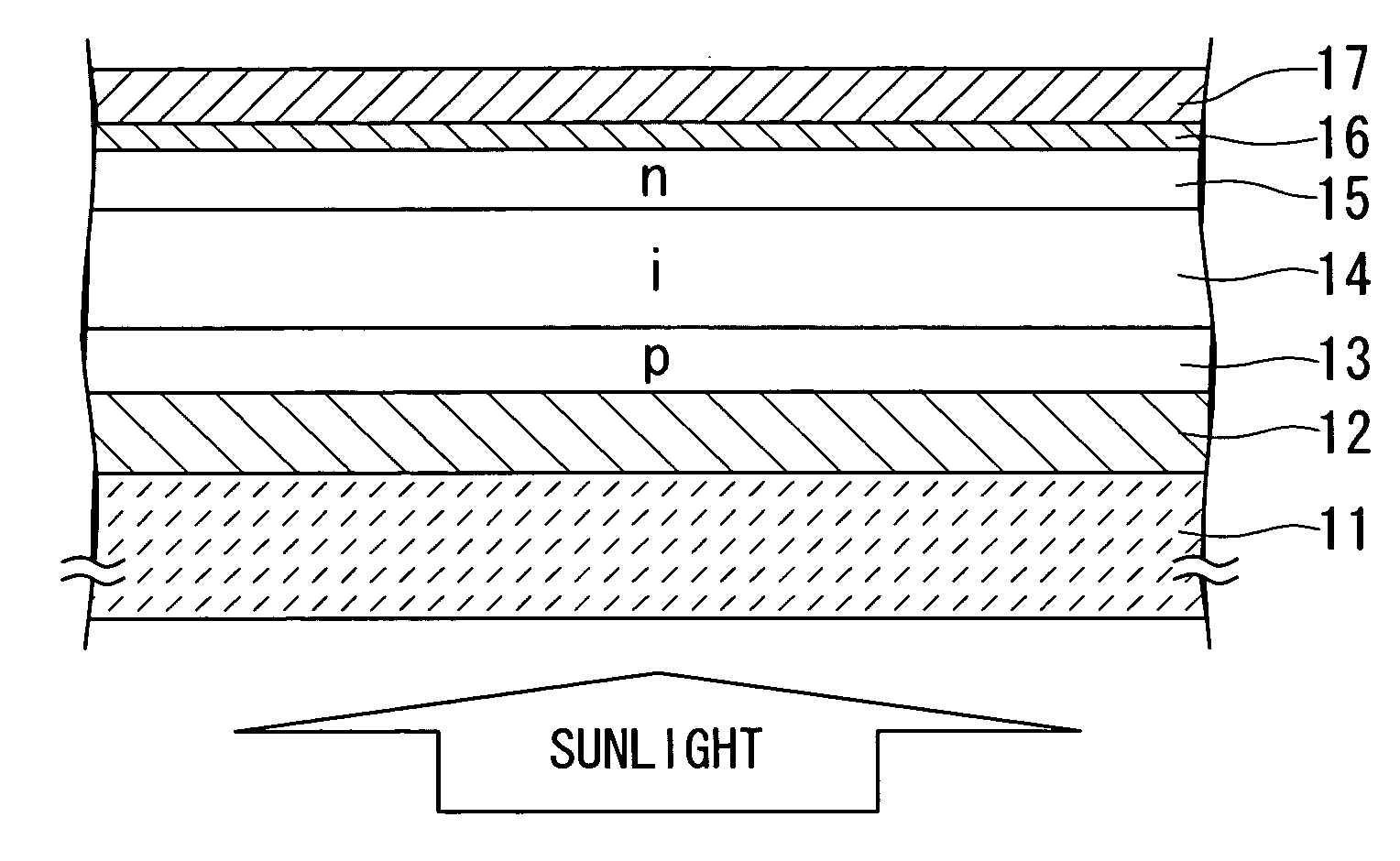

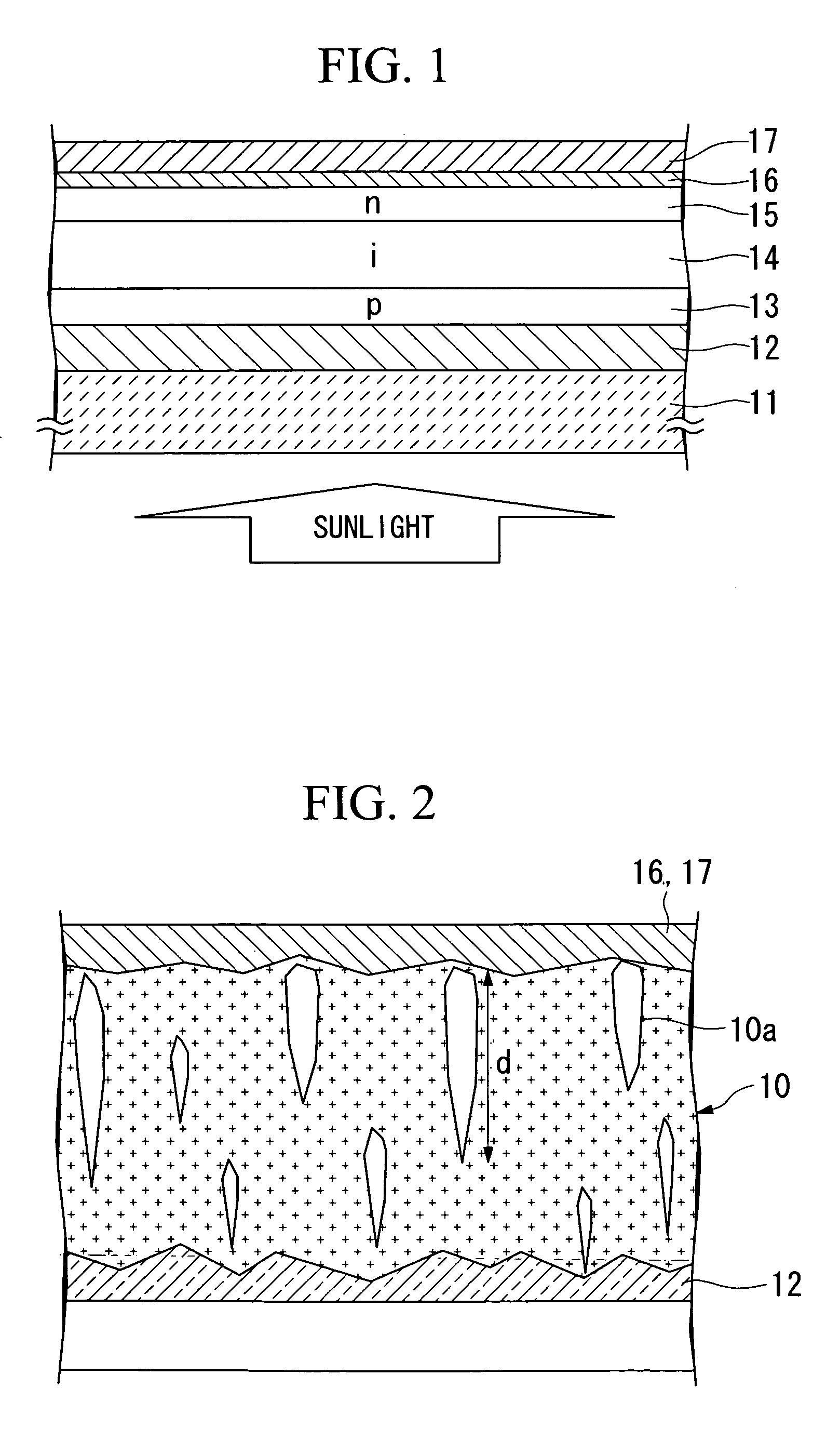

Solar cell and process for producing solar cell

InactiveUS20050103377A1Avoid reorganizationImprove photovoltaic conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingDopantManufacturing technology

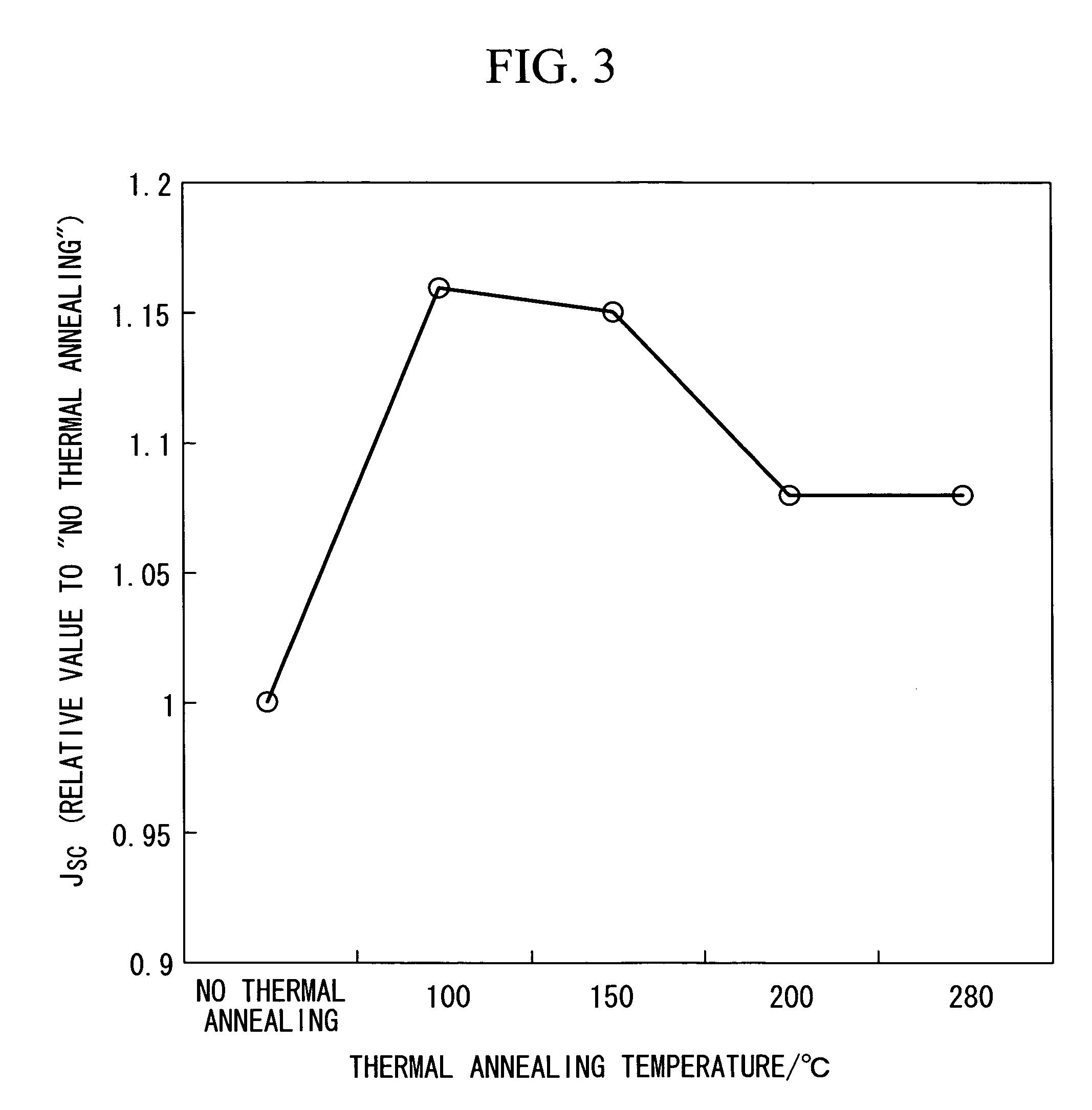

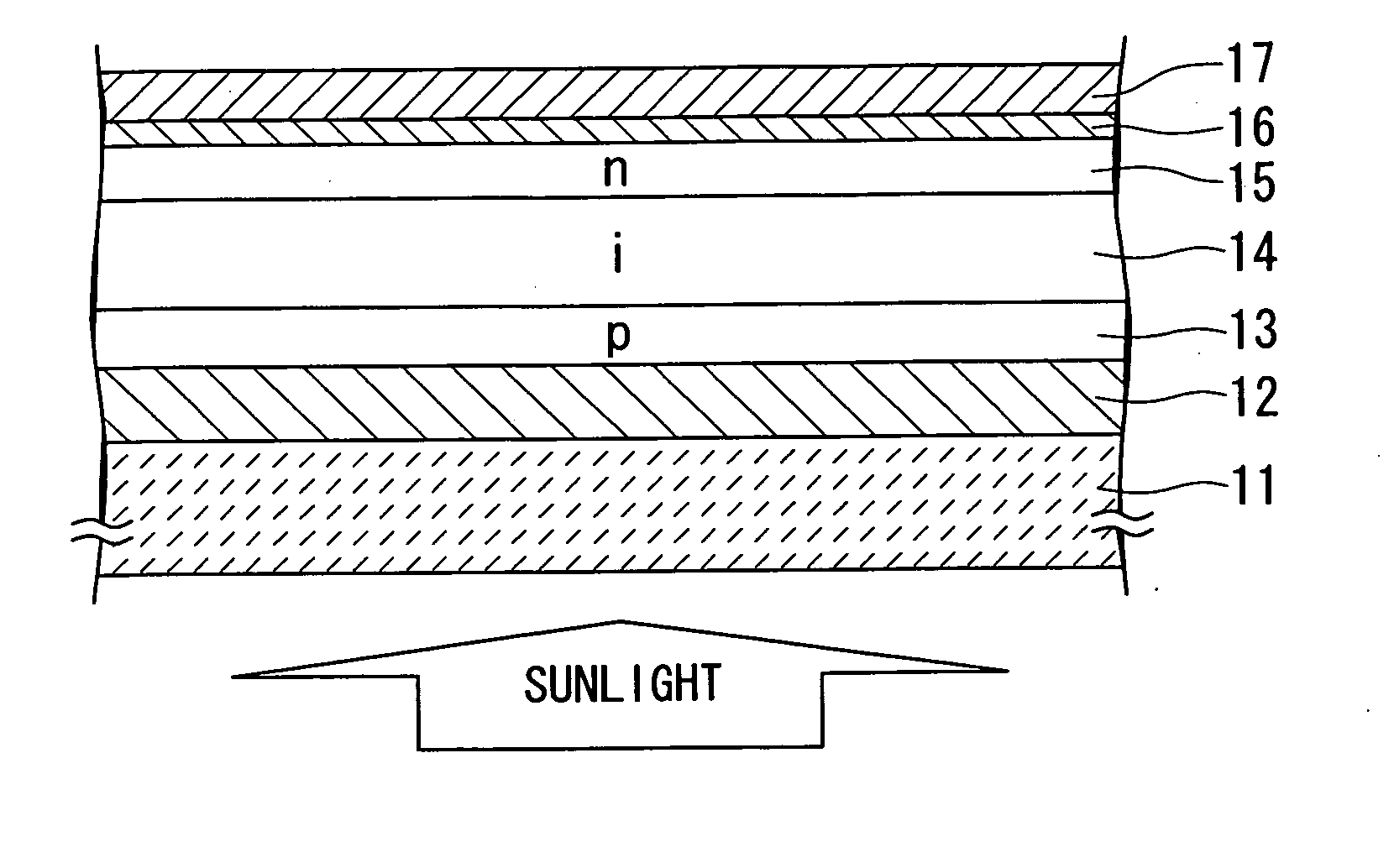

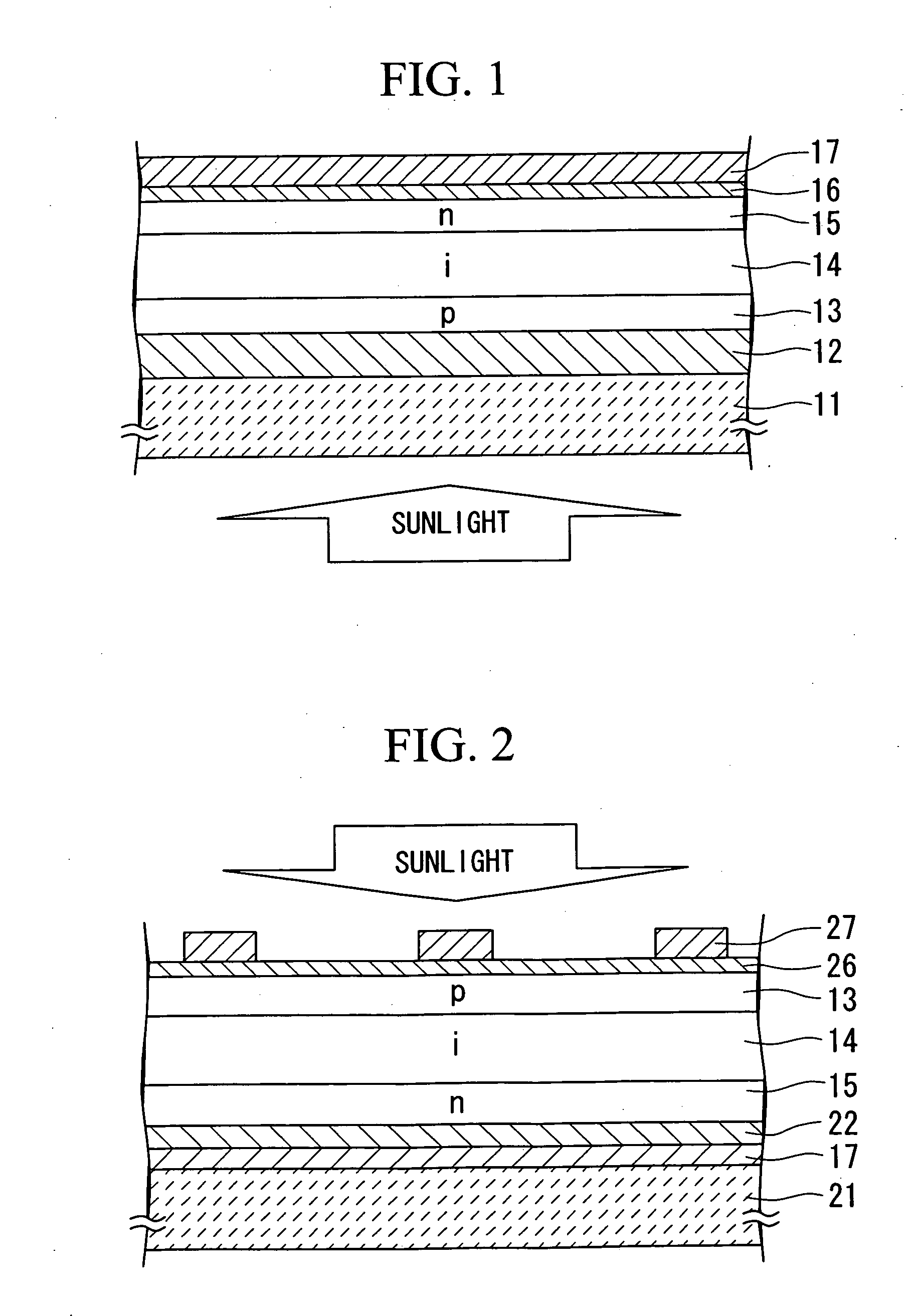

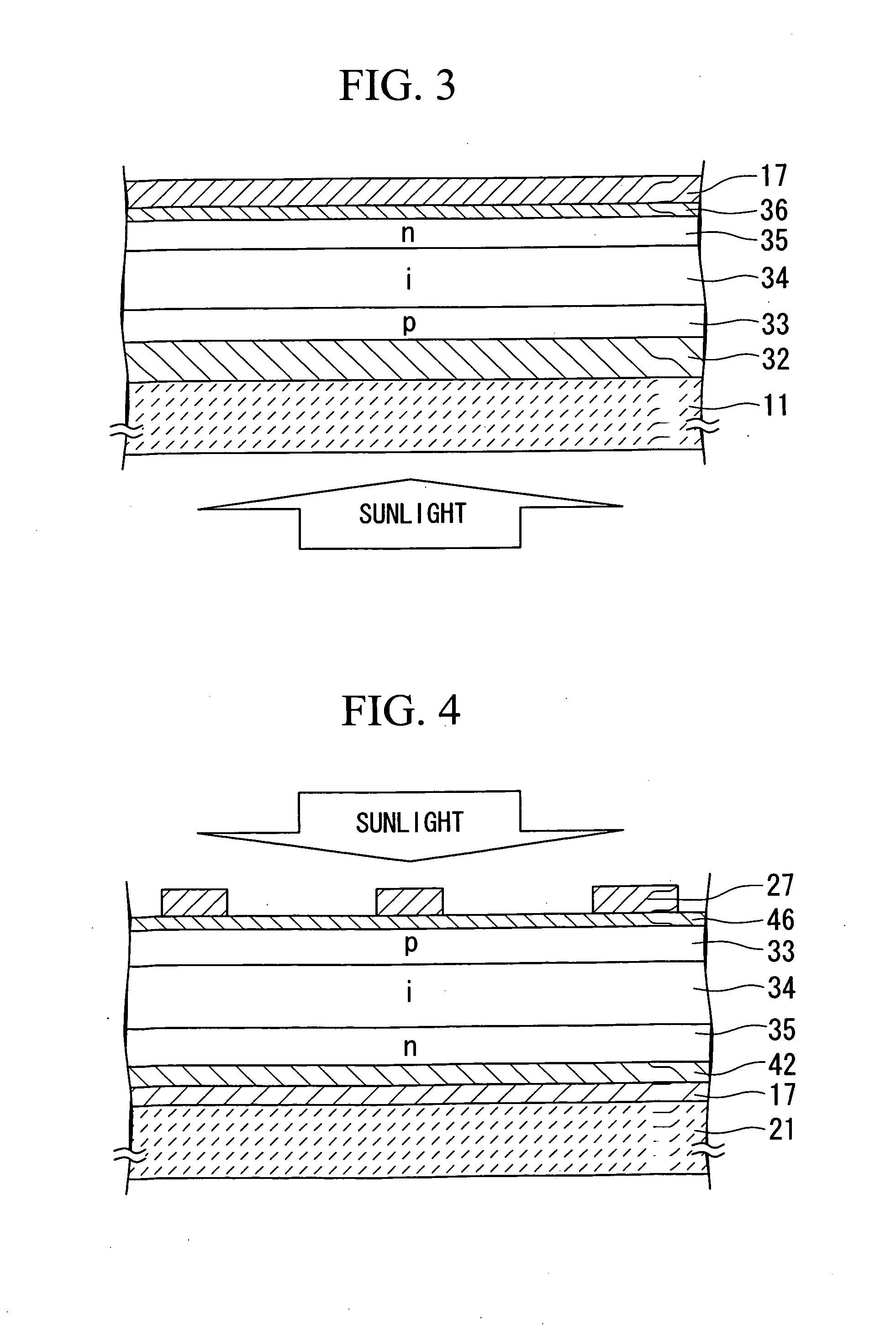

A process for producing a solar cell is provided which can enhance the photovoltaic conversion efficiency by enlarging the grain sizes in the direction of the thickness of an i-layer to reduce grain boundaries, thereby avoiding recombination of carriers and activating the dopant at the same time. A process for producing a solar cell includes depositing at least a first transparent electrode, polycrystalline silicon layers in a PIN structure, and a second electrode in sequence on an electrically insulating substrate, the polycrystalline silicon layers in a PIN structure including a p-type silicon layer, an i-type silicon layer, and an n-type silicon layer, wherein the polycrystalline silicon layers in a PIN structure are formed by: forming a p-type, which is then subjected to thermal annealing; depositing an i-type silicon layer on the p-type silicon layer; and depositing an n-type silicon layer on the i-type silicon layer.

Owner:MITSUBISHI HEAVY IND LTD

Photovoltaic device

InactiveUS20050205127A1High light transmittanceReduce harmPV power plantsPhotovoltaic energy generationMicrocrystalline siliconP type silicon

A photovoltaic device is formed by depositing at least a first transparent electrode, PIN-structured or NIP-structured microcrystalline silicon layers, a second transparent electrode, and a back electrode in sequence on an electrically insulating transparent substrate. The PIN-structured or NIP-structured microcrystalline silicon layers include a p-type silicon layer, an i-type silicon layer, and an n-type silicon layer. At least one of the first transparent electrode and the second transparent electrode is a ZnO layer doped with Ga, and the Ga concentration is 15 atomic percent or less with respect to Zn.

Owner:MITSUBISHI HEAVY IND LTD

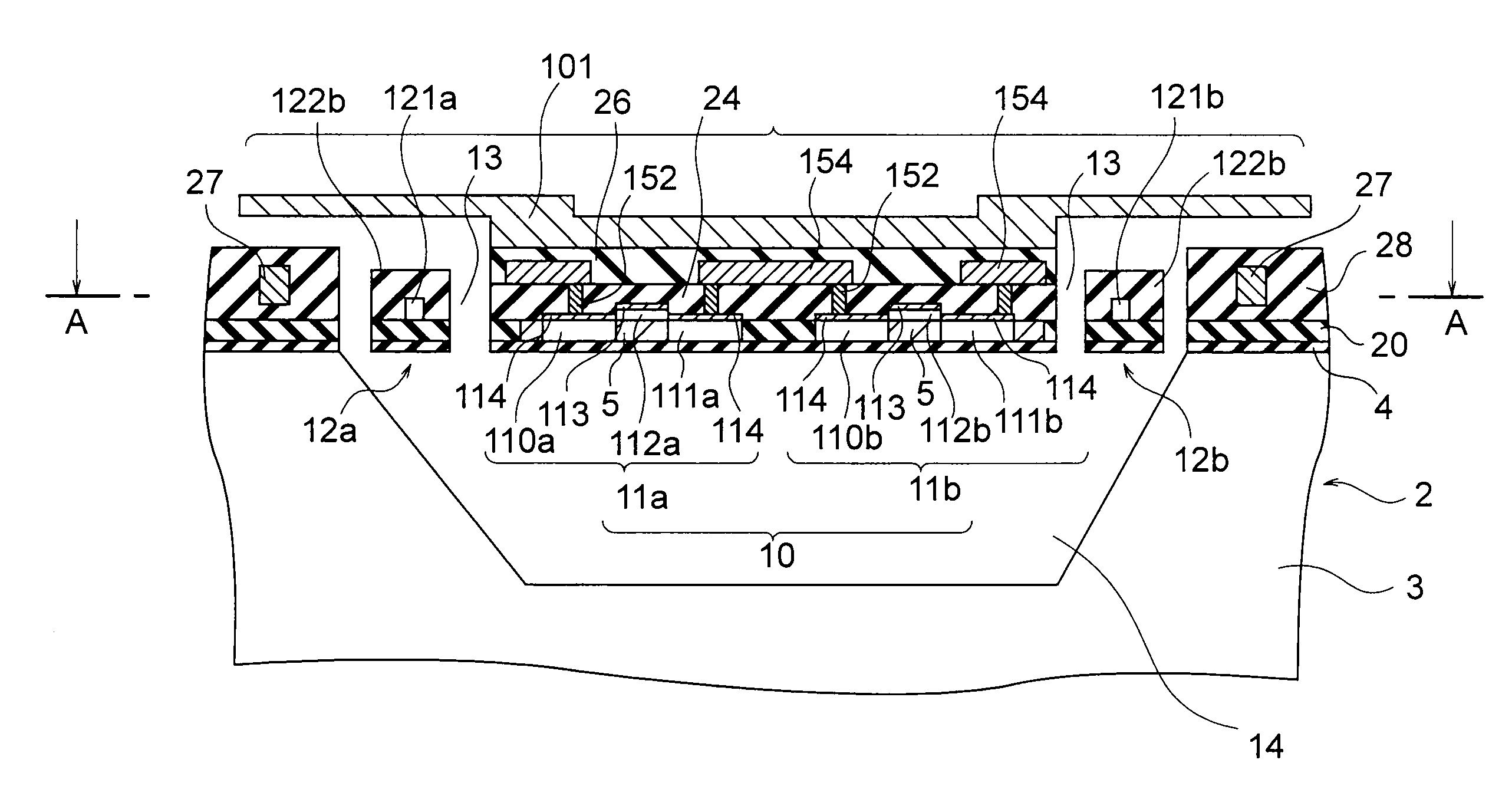

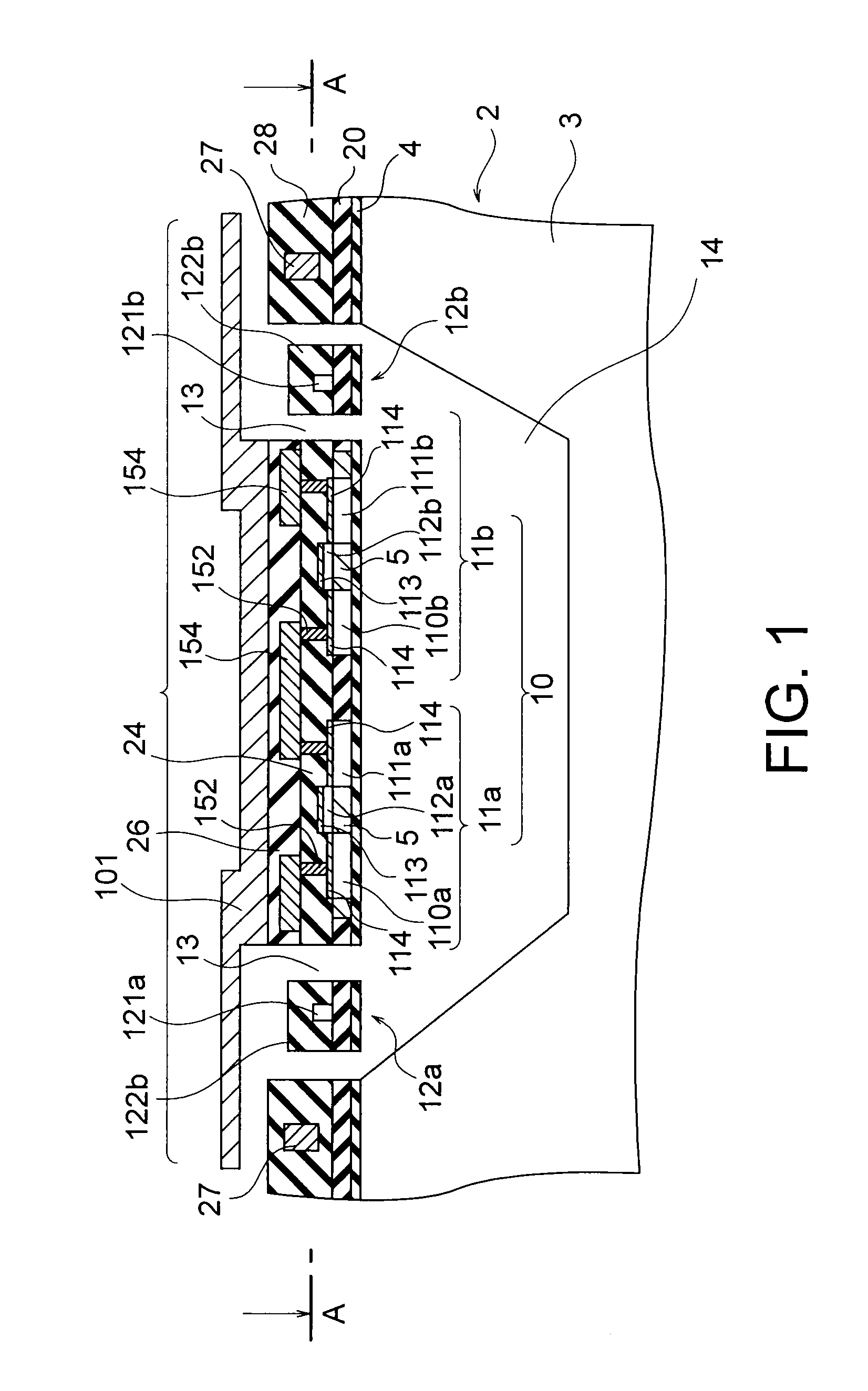

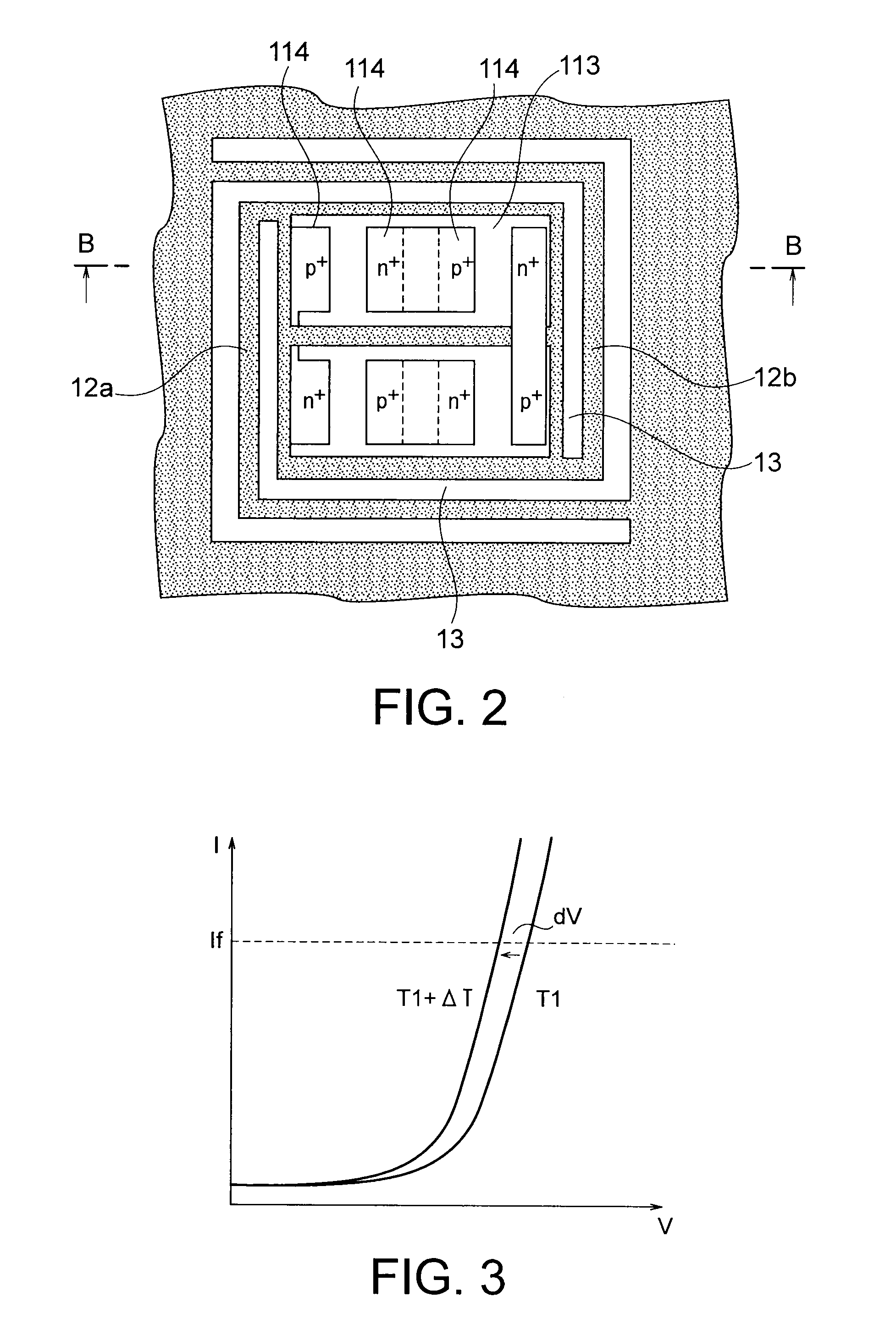

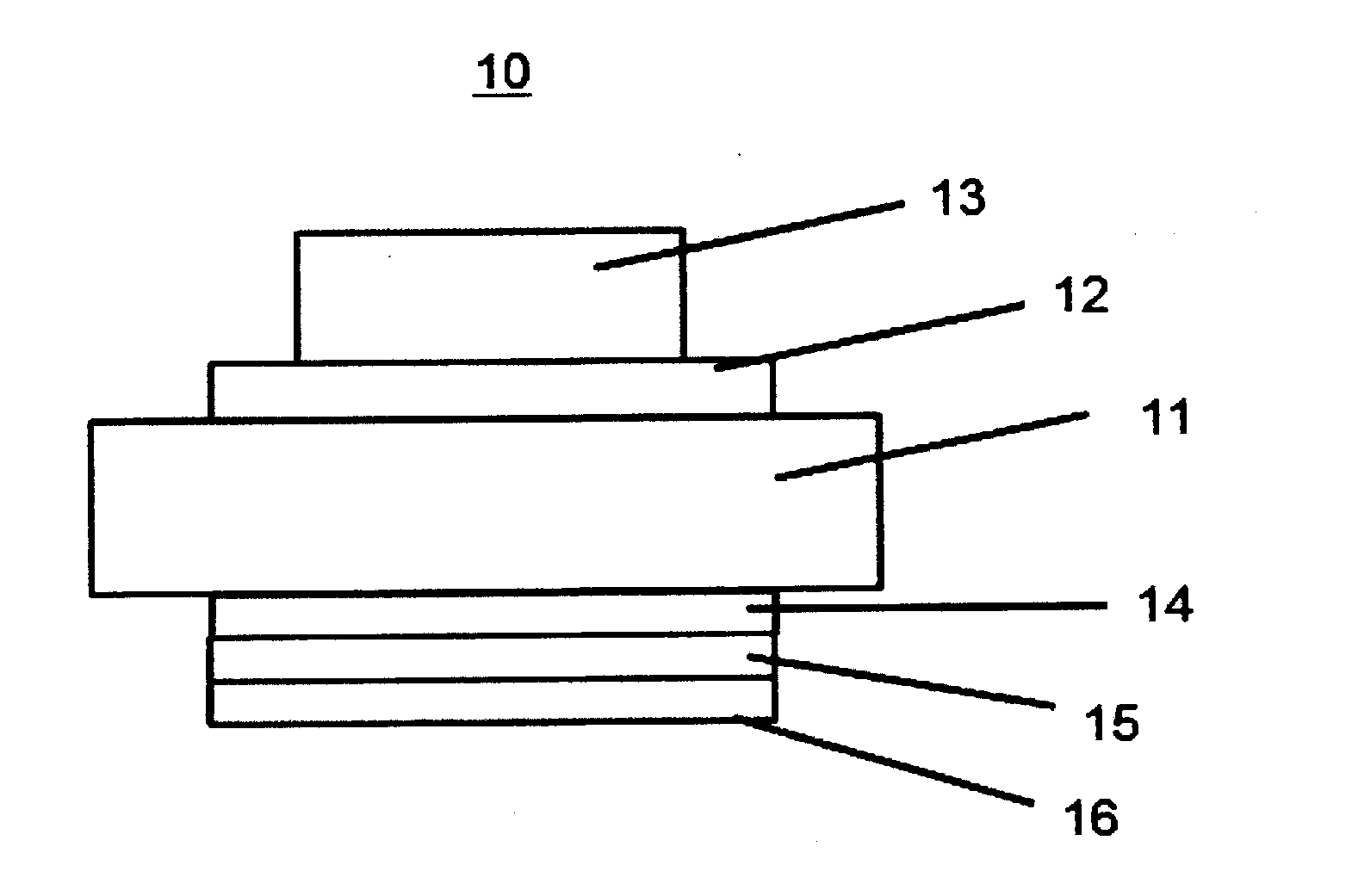

Infrared detector and solid state image sensor having the same

InactiveUS20090266987A1Effective absorptionReduce manufacturing costSolid-state devicesMaterial analysis by optical meansEngineeringP type silicon

An infrared detector includes: a readout wiring portion provided on a semiconductor substrate; a support structure portion disposed over a concave portion formed in a surface portion of the semiconductor substrate, the support structure portion having connection wiring connected electrically to the readout wiring portion; and a cell portion disposed over the concave portion and supported by the support structure portion. The cell portion includes: an infrared absorption layer absorbing incident infrared rays; and a plurality of thermoelectric conversion elements connected electrically to the support structure portion and insulated electrically from the infrared absorption layer to generate an electric signal by detecting a temperature change of the cell portion, each of the thermoelectric conversion elements includes a semiconductor layer, a p-type silicon layer and an n-type silicon layer formed with a space between them in the semiconductor layer, and a polysilicon layer formed on the semiconductor layer between the p-type silicon layer and the n-type silicon layer.

Owner:KK TOSHIBA

Oxide semiconductor substrate and schottky barrier diode

ActiveUS20160211386A1Low costImprove batch productivitySemiconductor devicesSchottky barrierP type silicon

A Schottky barrier diode element includes an n-type or p-type silicon (Si) substrate, an oxide semiconductor layer, and a Schottky electrode layer, the oxide semiconductor layer including either or both of a polycrystalline oxide that includes gallium (Ga) as the main component and an amorphous oxide that includes gallium (Ga) as the main component.

Owner:IDEMITSU KOSAN CO LTD

Methods of fabricating silicon carbide devices having smooth channels

ActiveUS20060270103A1Semiconductor/solid-state device manufacturingSemiconductor devicesCarbideSurface roughness

Methods of forming silicon carbide power devices are provided. An n− silicon carbide layer is provided on a silicon carbide substrate. A p-type silicon carbide well region is provided on the n− silicon carbide layer. A buried region of p+ silicon carbide is provided on the p-type silicon carbide well region. An n+ region of silicon carbide is provided on the buried region of p+ silicon carbide. A channel region of the power device is adjacent the buried region of p+ silicon carbide and the n+ region of silicon carbide. An n− region is provided on the channel region and a portion of the n− region is removed from the channel region so that a portion of the n− region remains on the channel region to provide a reduction in a surface roughness of the channel region.

Owner:CREE INC