Patents

Literature

192 results about "Phosphosilicate glass" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Phosphosilicate glass, commonly referred to by the acronym PSG, is a silicate glass commonly used in semiconductor device fabrication for intermetal layers, i.e., insulating layers deposited between succeedingly higher metal or conducting layers, due to its effect in gettering alkali ions. Another common species of phosphosilicate glass is borophosphosilicate glass (BPSG).

Formulations for cleaning memory device structures

InactiveUS20080125342A1Inorganic/elemental detergent compounding agentsOrganic detergent compounding agentsBorophosphosilicate glassSilicon oxide

A removal composition and process for removing silicon-containing layers from a microelectronic device having said layers thereon. The removal composition selectively removes layers including, but not limited to, silicon oxide, plasma enhanced tetraethyl orthosilicate (P-TEOS), borophosphosilicate glass (BPSG), plasma enhanced oxide (PEOX), high density plasma oxide (HDP), phosphosilicate glass (PSG), spin-on-dielectrics (SOD), thermal oxide, updoped silicate glass, sacrificial oxides, silicon-containing organic polymers, silicon-containing hybrid organic / inorganic materials, organosilicate glass (OSG), TEOS, fluorinated silicate glass (FSG), hemispherical grain (HSQ), carbon-doped oxide (CDO) glass, and combinations thereof, relative to lower electrode, device substrate, and / or etch stop layer materials.

Owner:ADVANCED TECH MATERIALS INC

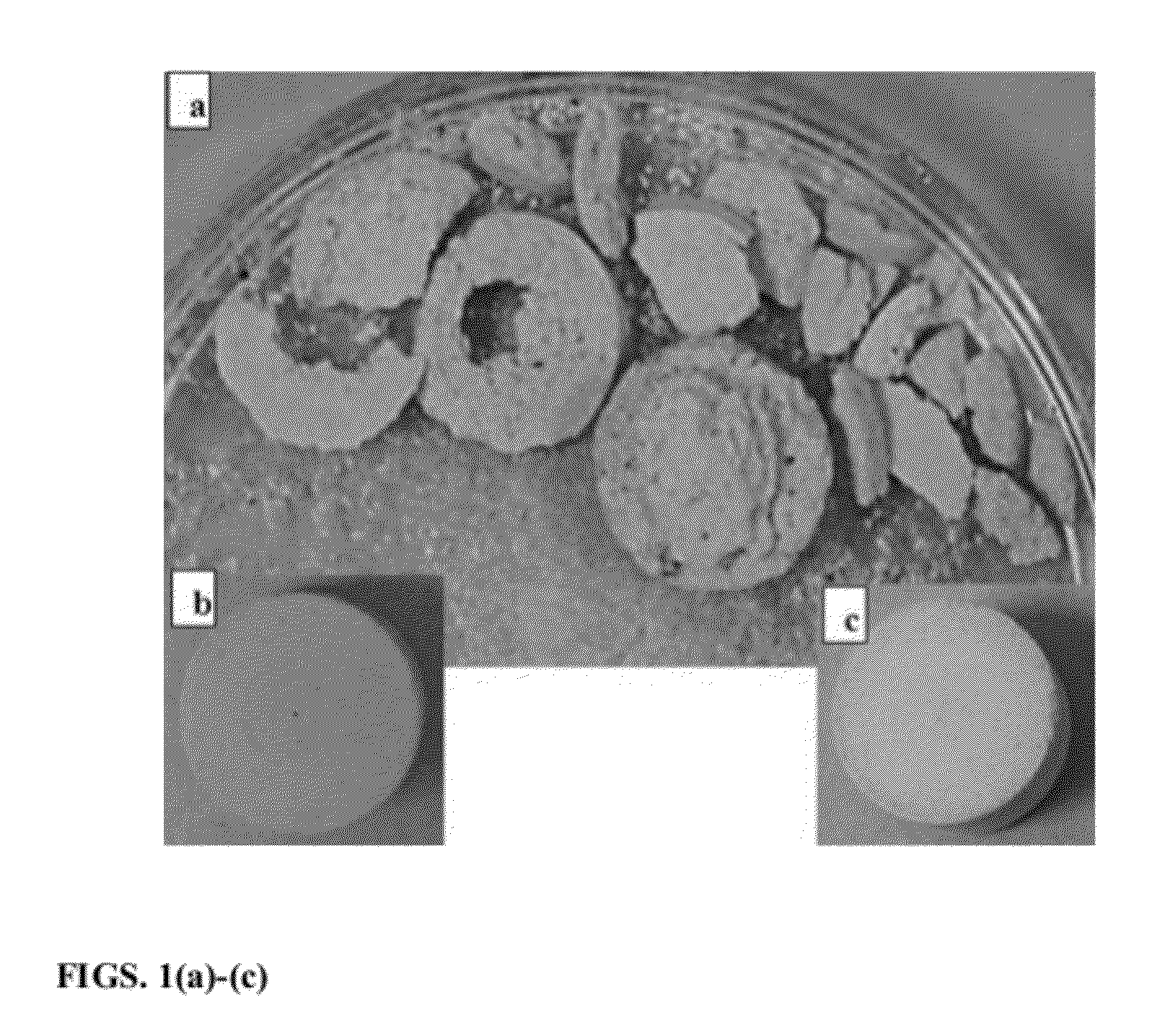

Methods to fabricate nano-macro porous glass using a water soluble pore former

Provided herein are methods for preparing nano-macroporous glass articles, such as bioscaffolds, from starting materials such as phosphosilicate glasses made by melt-quench methods, mixed with a soluble pore former such as a sugar, followed by steps of dissolving, heating, and leaching to yield a glass composition having a highly interconnected system of both macropores and large scale nanoporosity.

Owner:LEHIGH UNIVERSITY

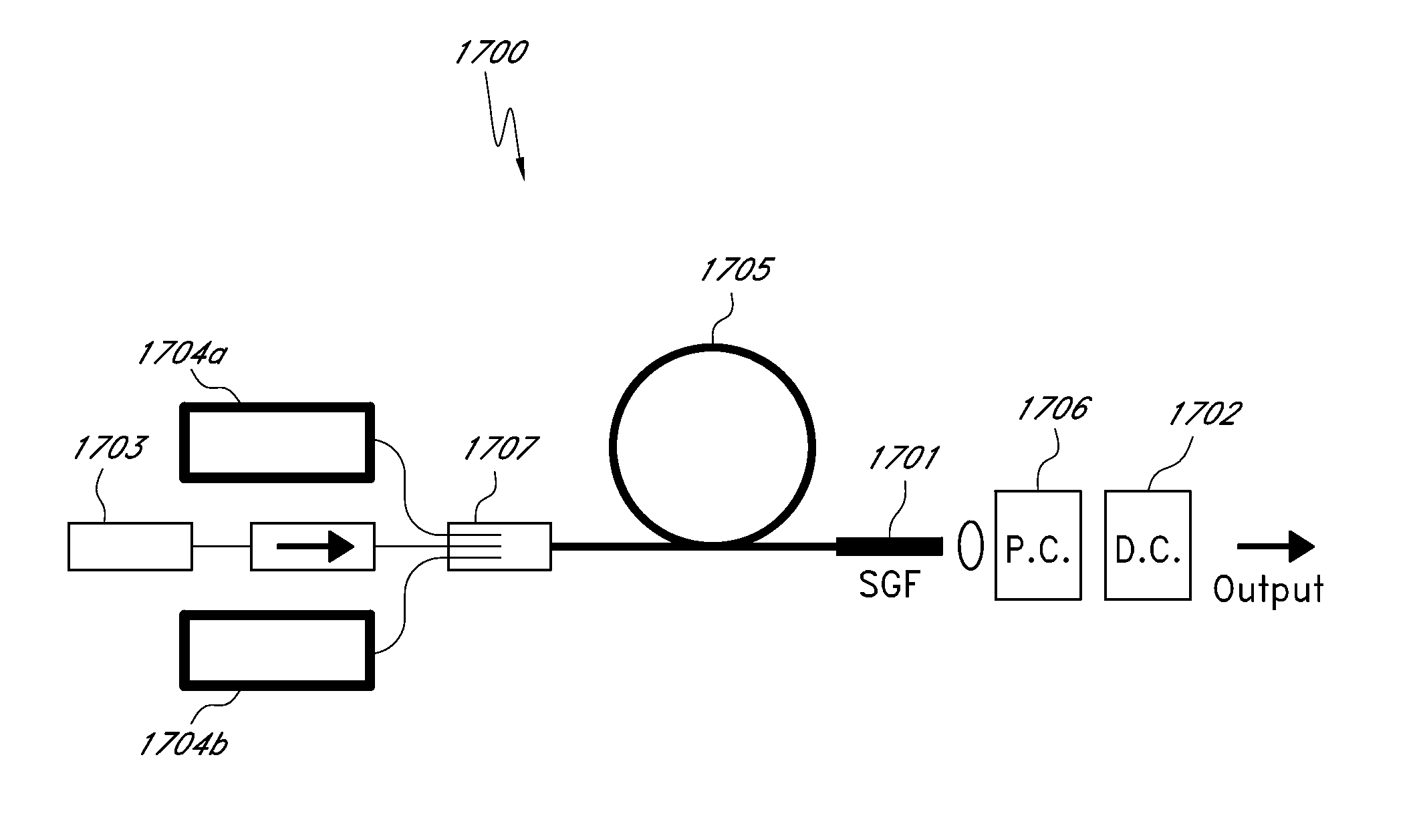

Highly rare-earth-doped optical fibers for fiber lasers and amplifiers

ActiveUS20110069723A1Laser using scattering effectsOptical fibre with multilayer core/claddingAudio power amplifierRare earth

Various embodiments described herein comprise a laser and / or an amplifier system including a doped gain fiber having ytterbium ions in a phosphosilicate glass. Various embodiments described herein increase pump absorption to at least about 1000 dB / m-9000 dB / m. The use of these gain fibers provide for increased peak-powers and / or pulse energies. The various embodiments of the doped gain fiber having ytterbium ions in a phosphosilicate glass exhibit reduced photo-darkening levels compared to photo-darkening levels obtainable with equivalent doping levels of an ytterbium doped silica fiber.

Owner:IMRA AMERICA

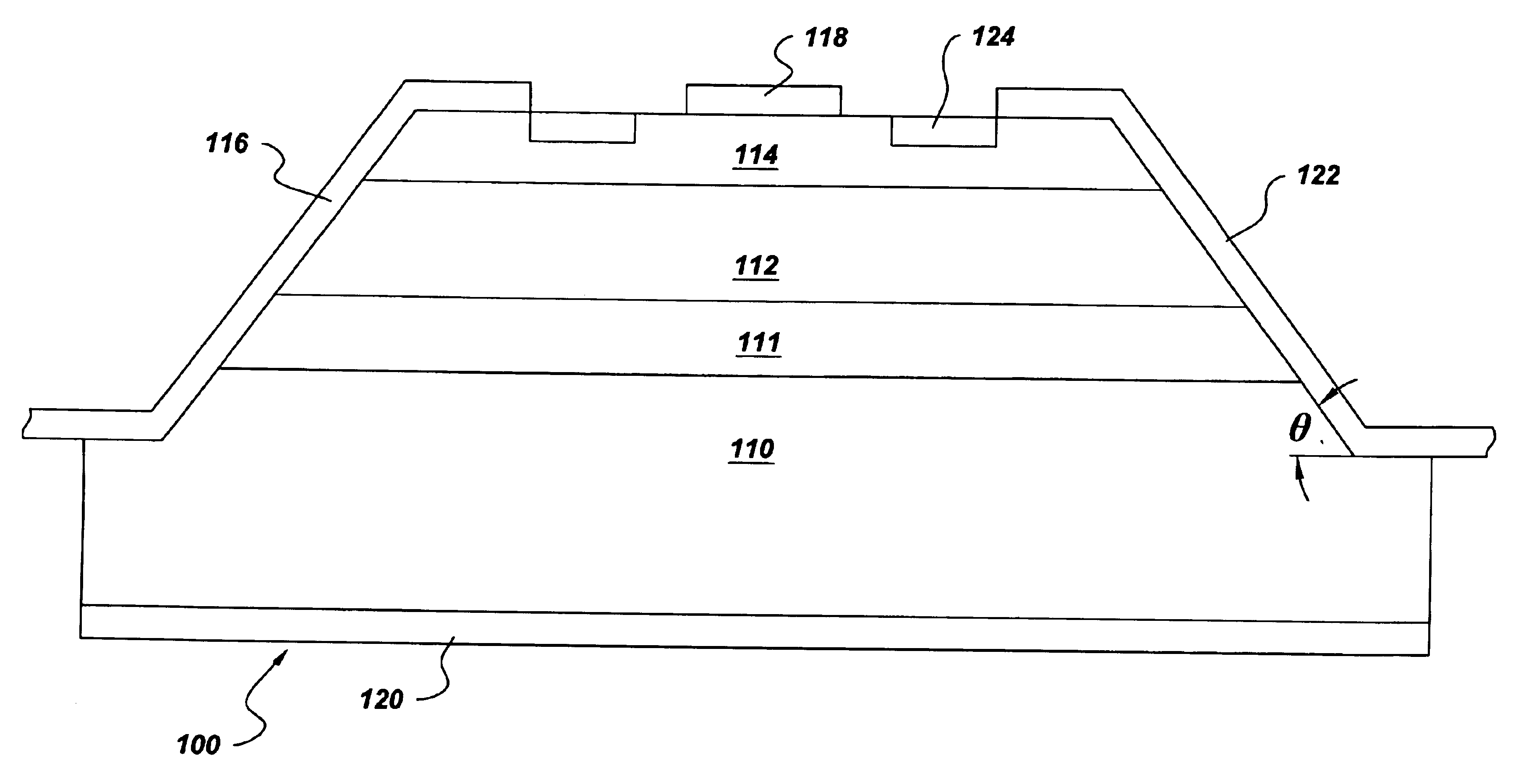

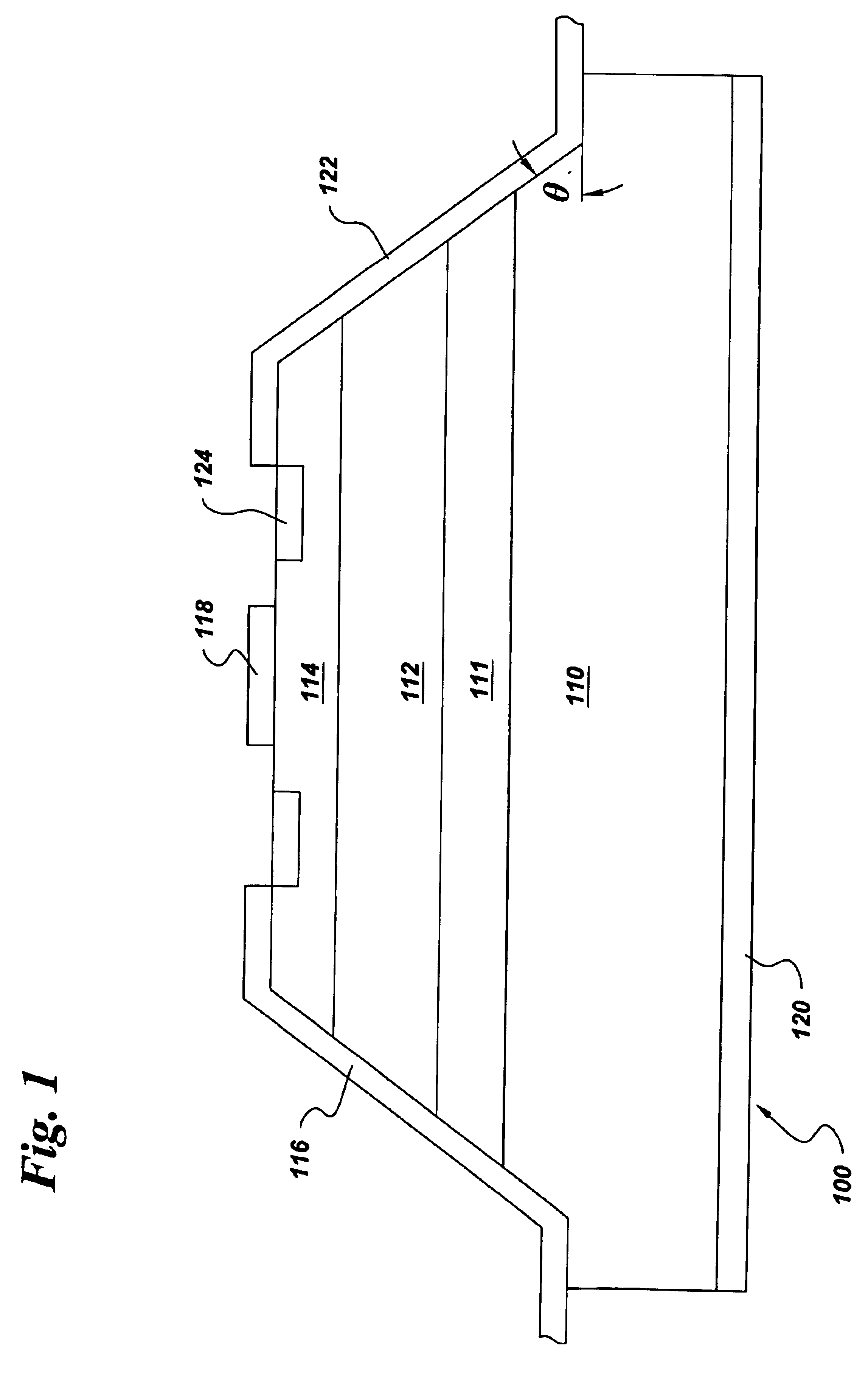

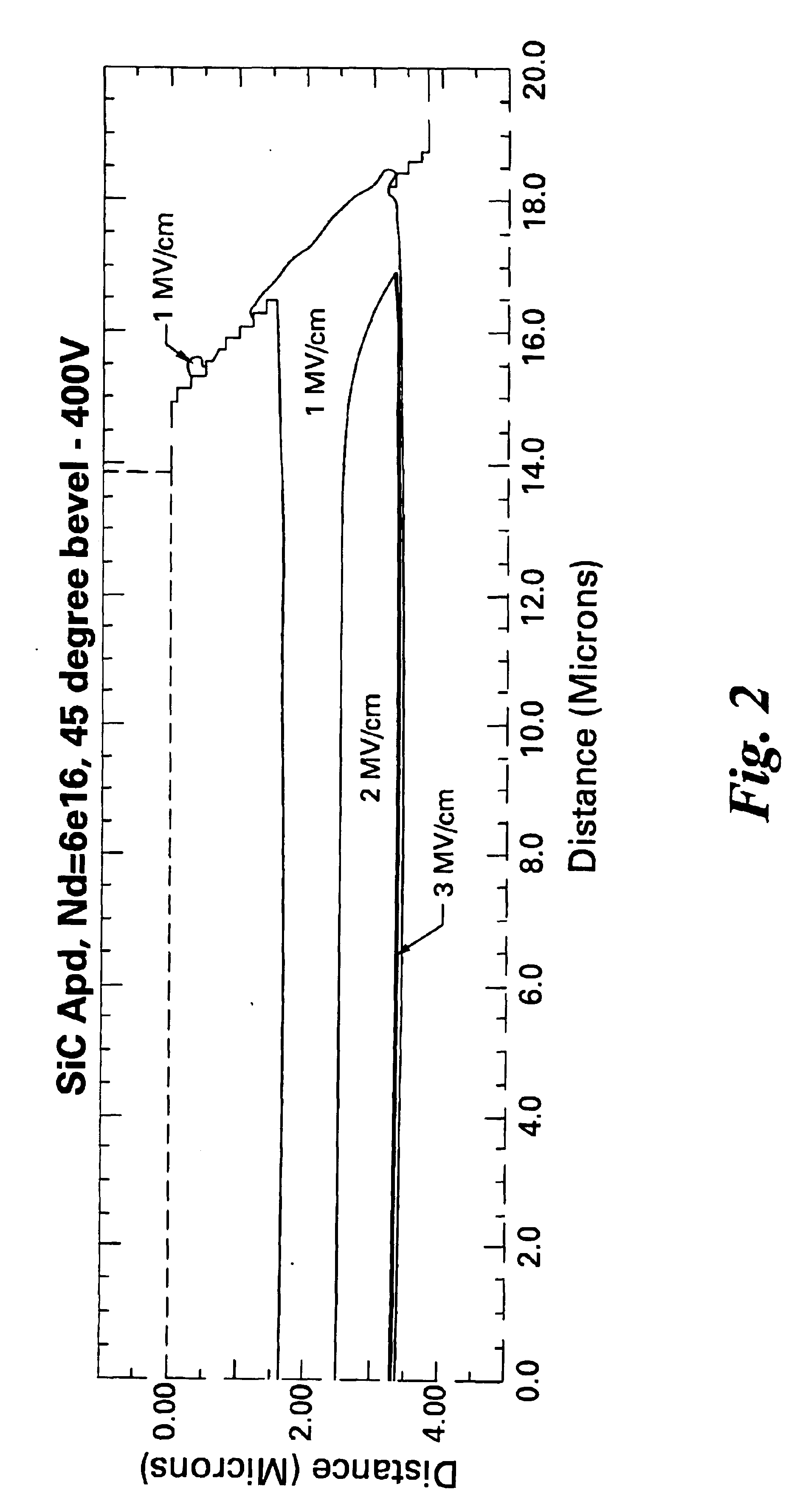

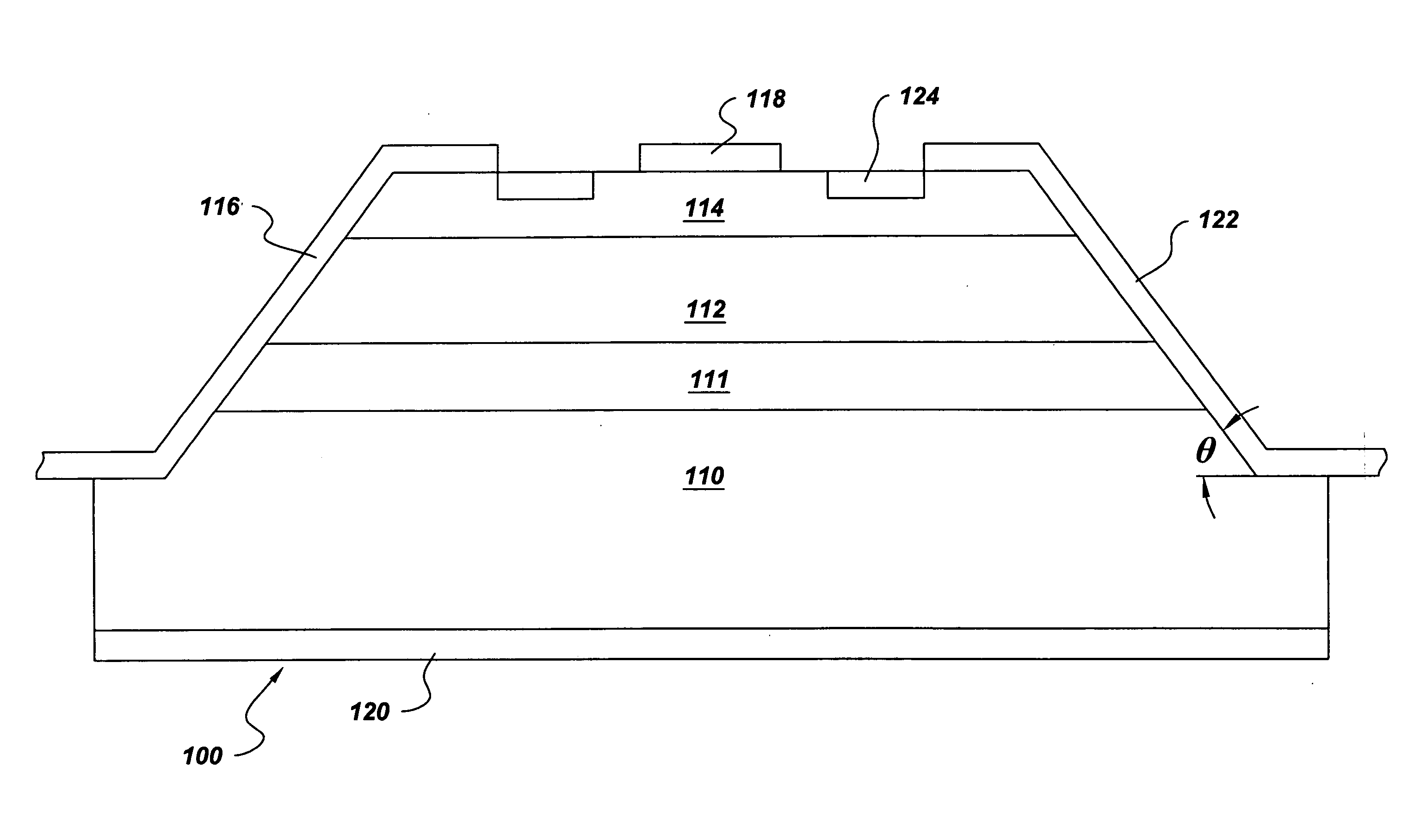

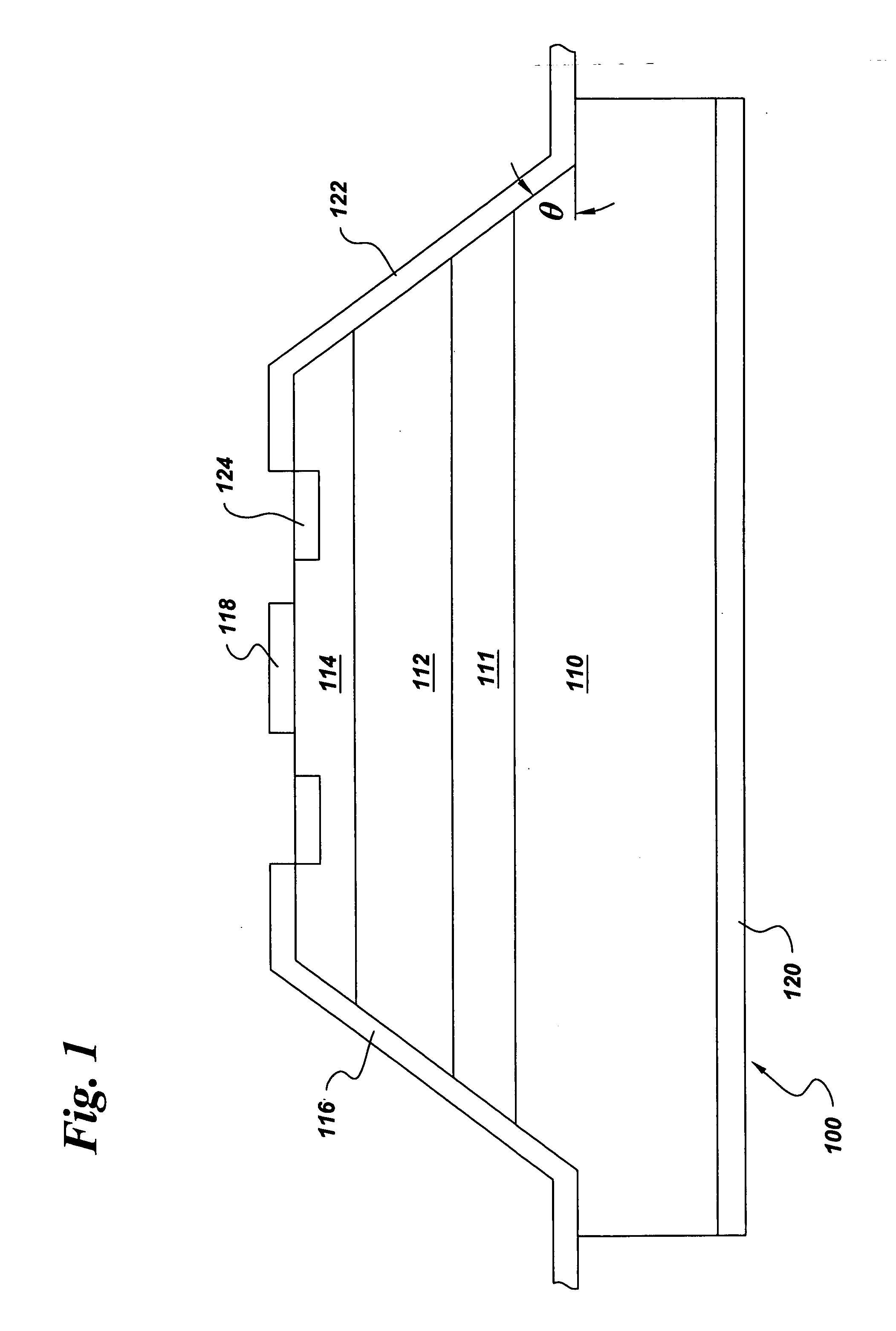

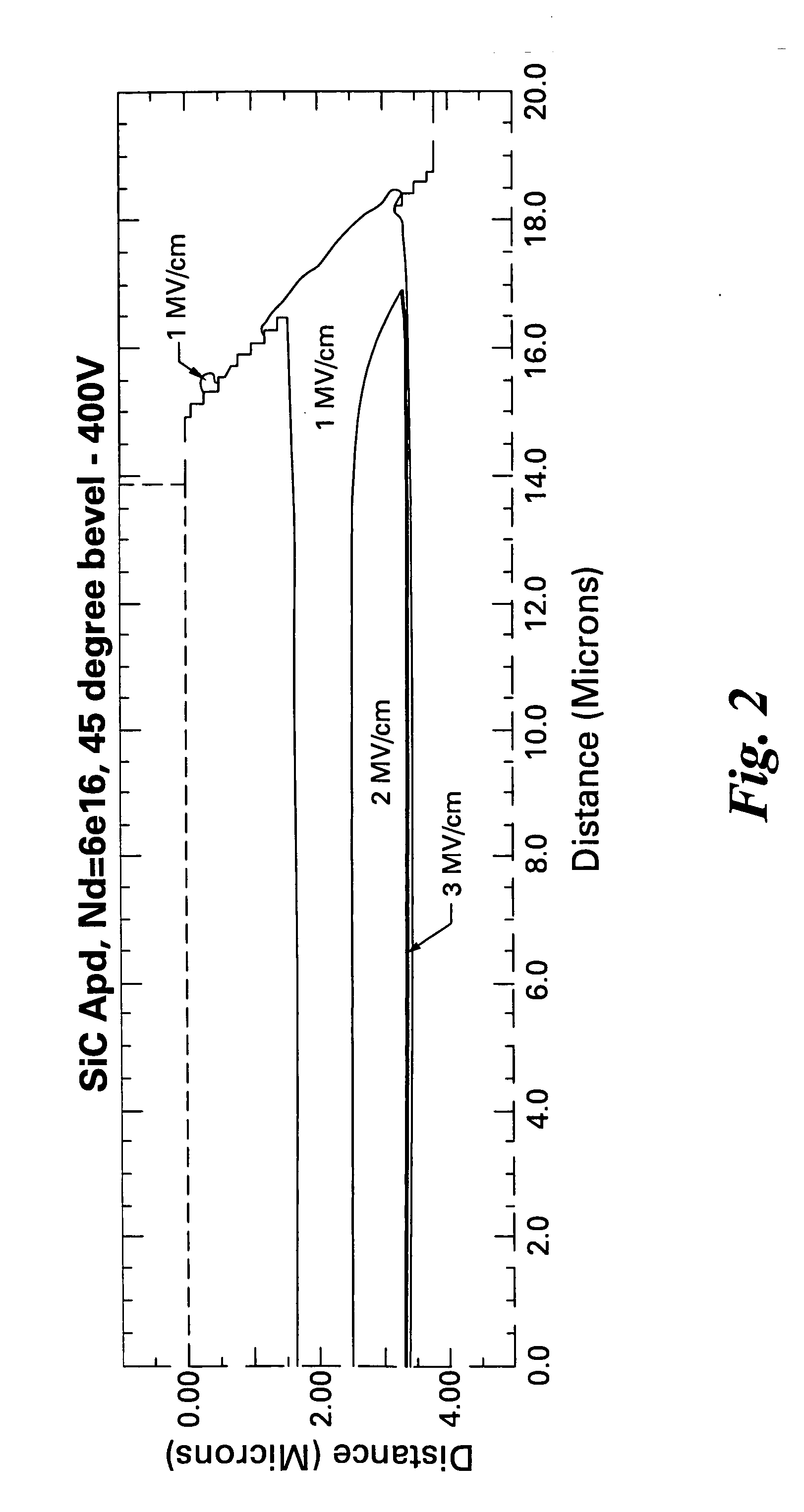

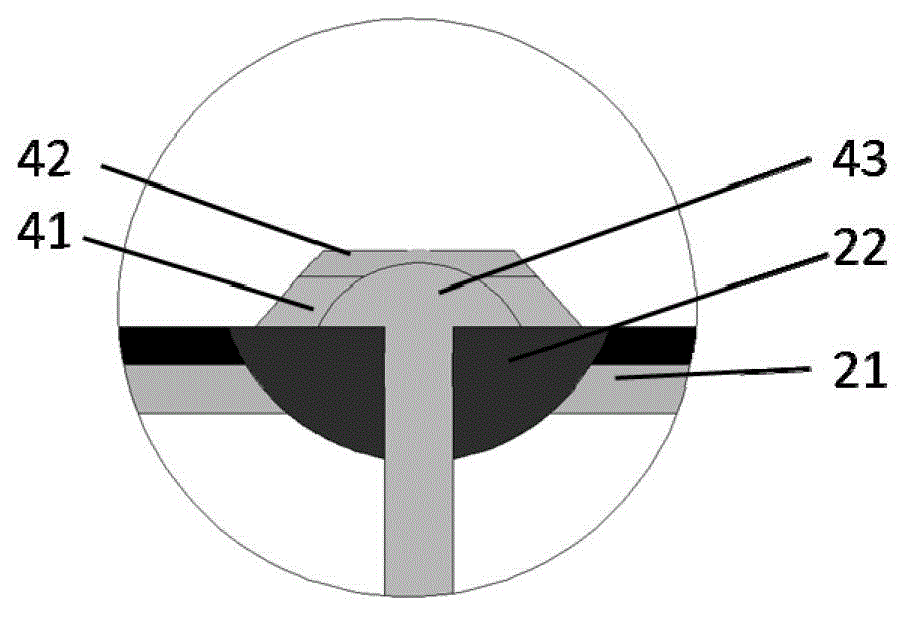

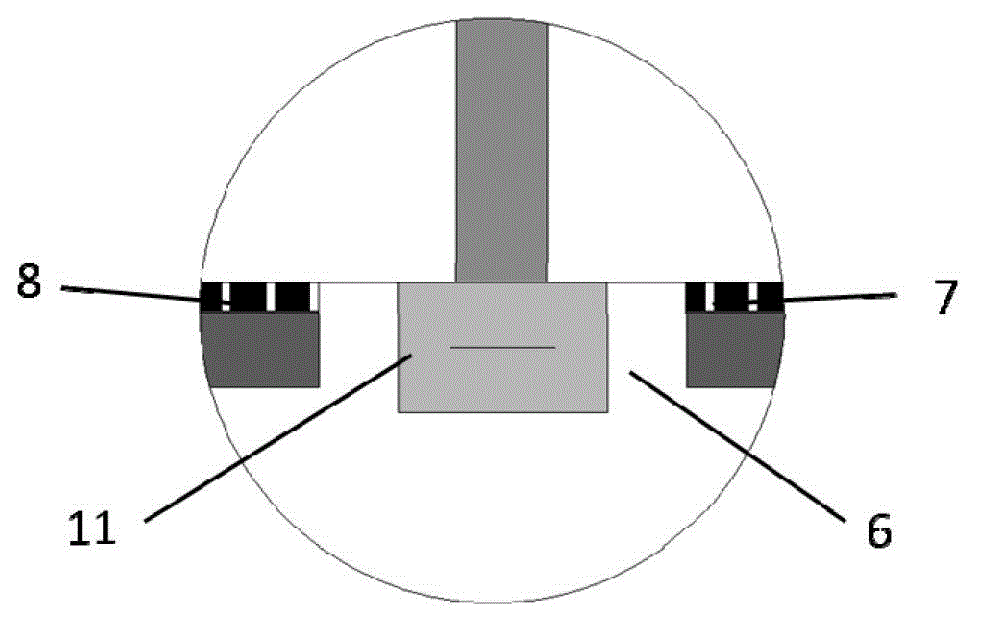

Avalanche photodiode for use in harsh environments

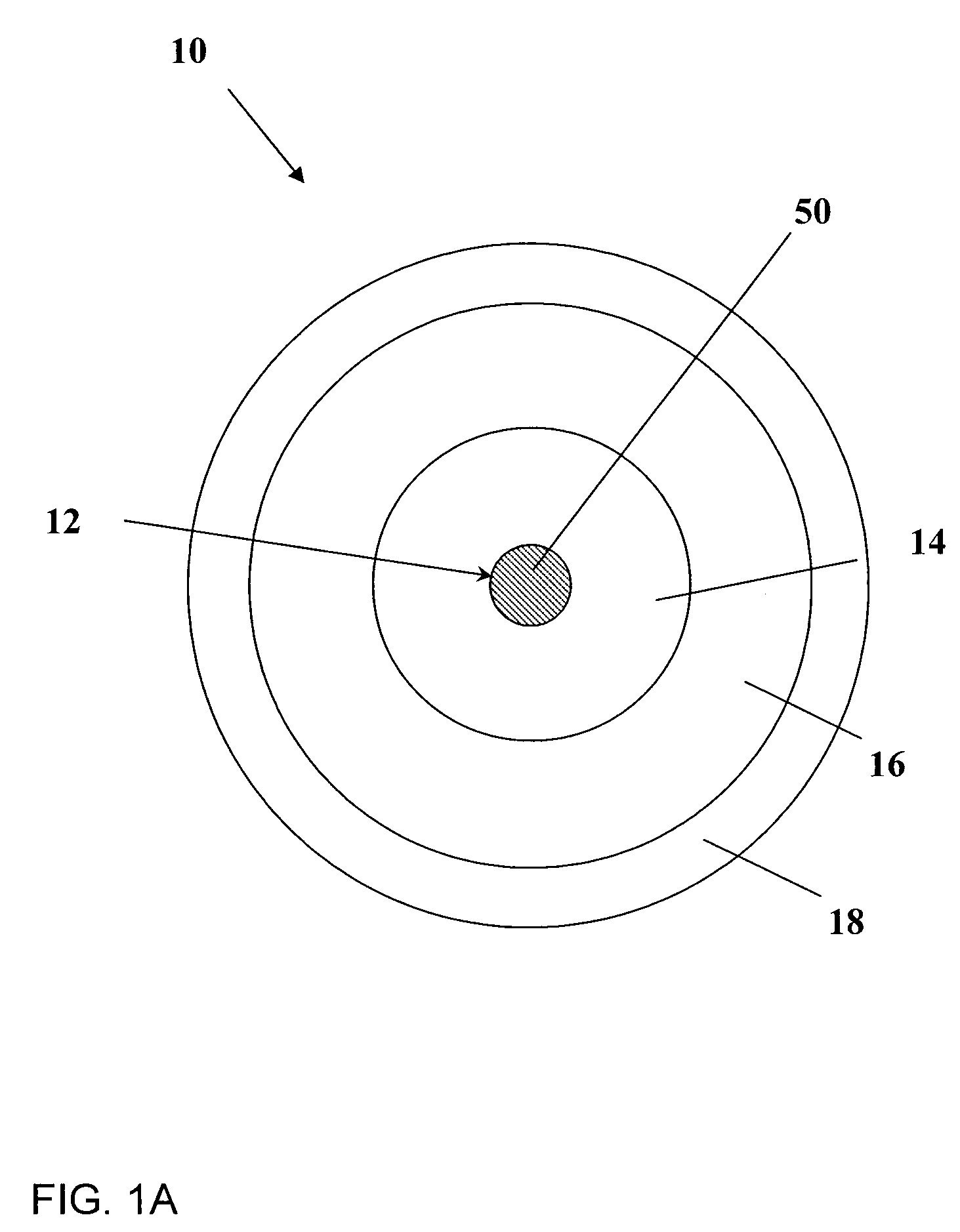

An aspect of the present invention is directed to an avalanche photodiode (APD) device for use in oil well drilling applications in harsh, down-hole environments where shock levels are near 250 gravitational acceleration (G) and / or temperatures approach or exceed 150° C. Another aspect of the present invention is directed to an APD device fabricated using SiC materials. Another aspect of the present invention is directed to an APD device fabricated using GaN materials. According to an embodiment of the present invention, an avalanche photodiode for detecting ultraviolet photons comprises a substrate having a first dopant; a first layer having the first dopant, positioned on top of the substrate; a second layer having a second dopant, positioned on top of the first layer; a third layer having a second dopant, positioned on top of the second layer; a passivation layer for providing electrical passivation on a surface of the avalanche photodiode; a phosphorous silicate glass layer for limiting mobile ion transport, positioned on top of the third layer; and a pair of metal electrodes for providing an ohmic contact wherein a first electrode is positioned below the substrate and a second electrode is positioned above the third layer; wherein the avalanche photodiode comprises a first sidewall and a second sidewall forming a sloped mesa shape; and wherein the avalanche photodiode operates in an environment comprising a temperature approximately equal to 150 degrees Celsius.

Owner:GENERAL ELECTRIC CO

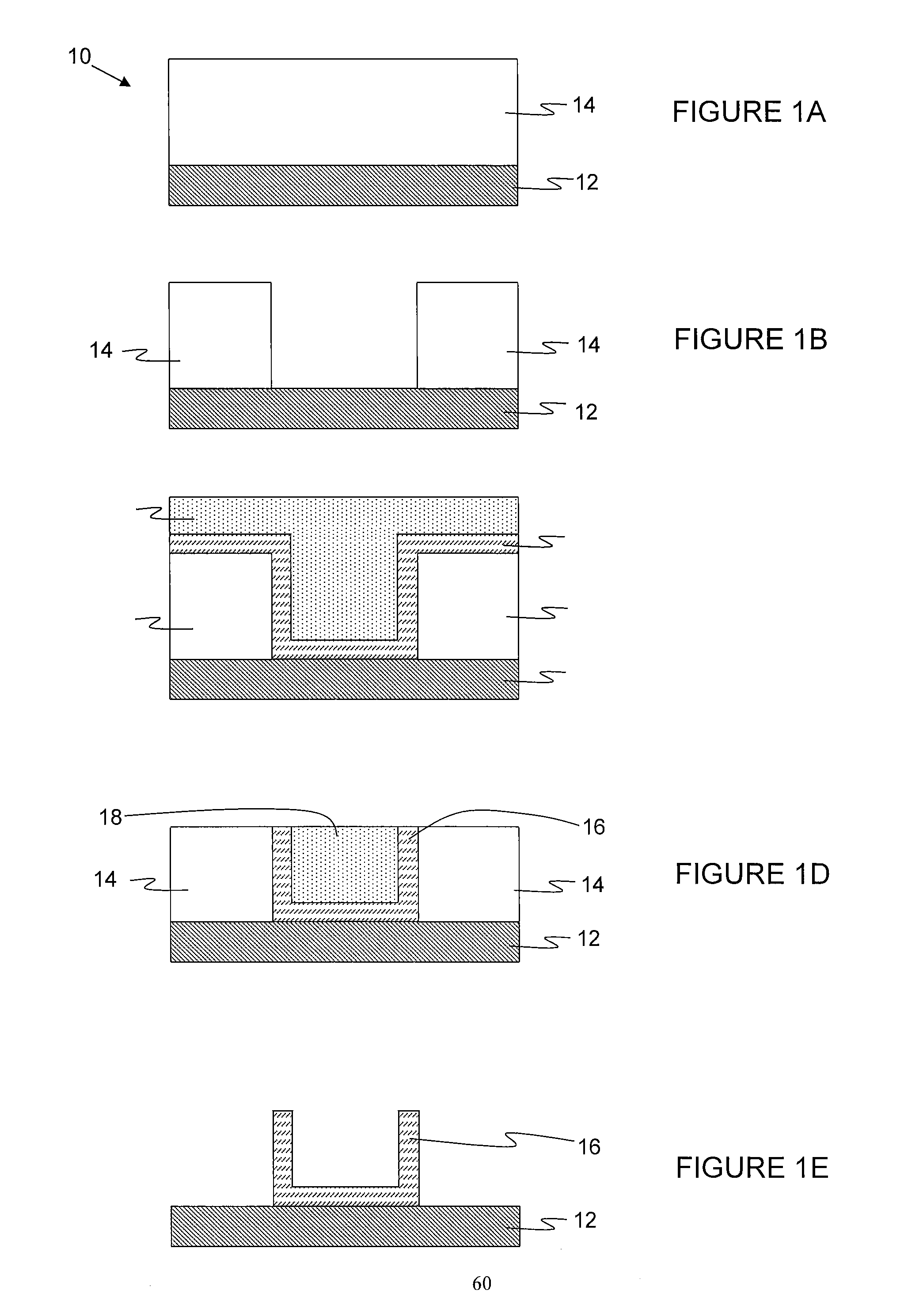

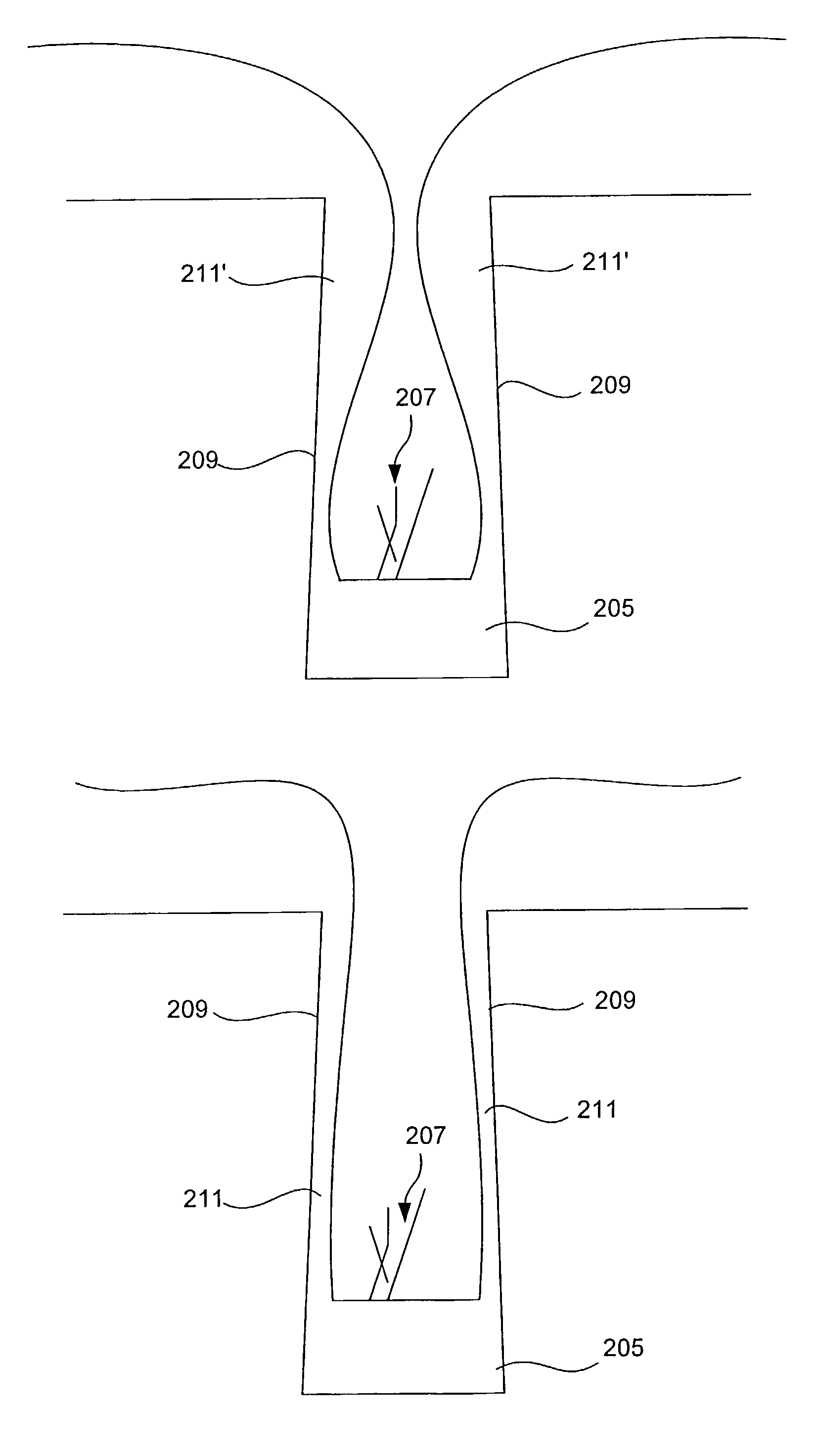

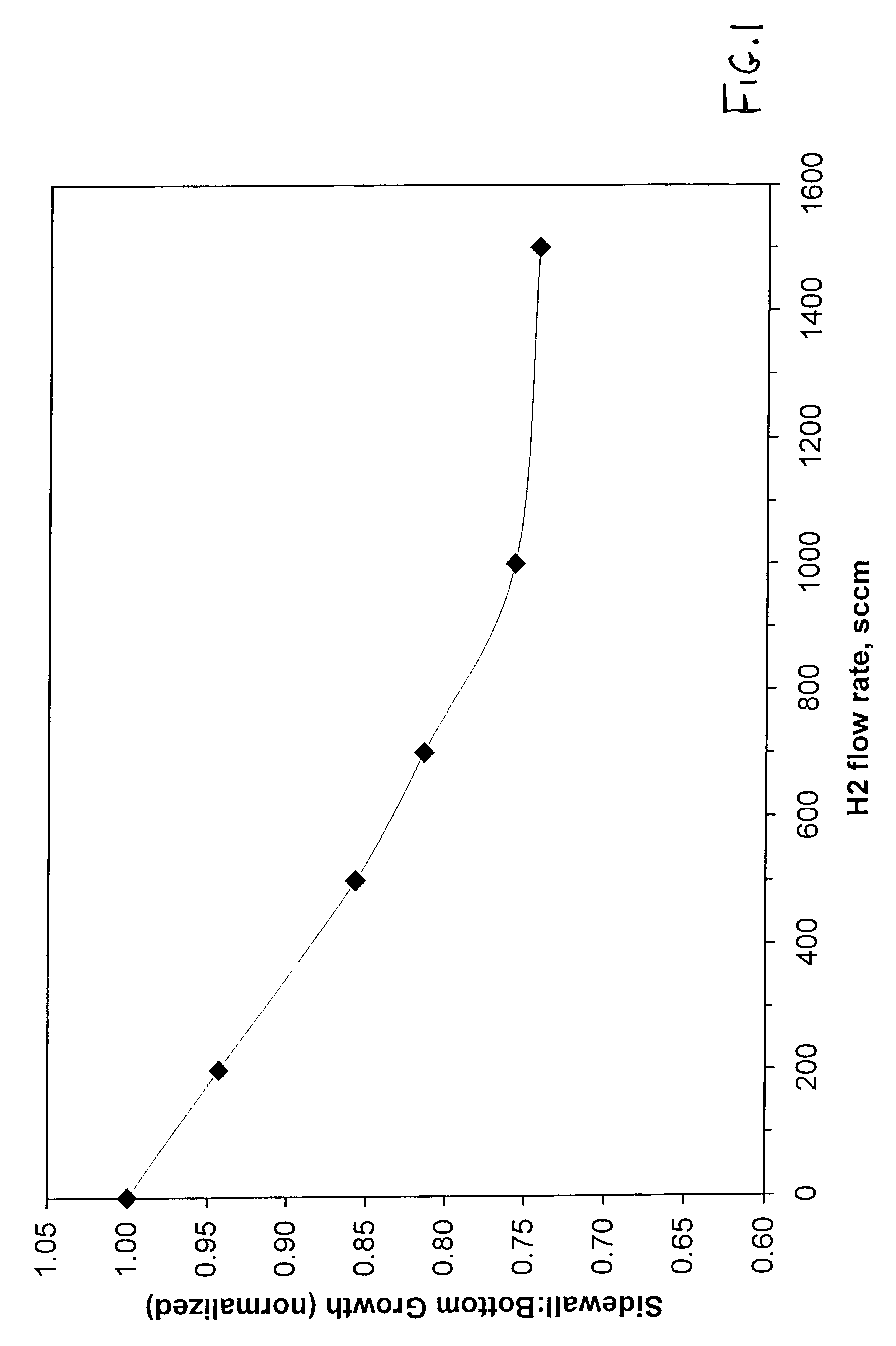

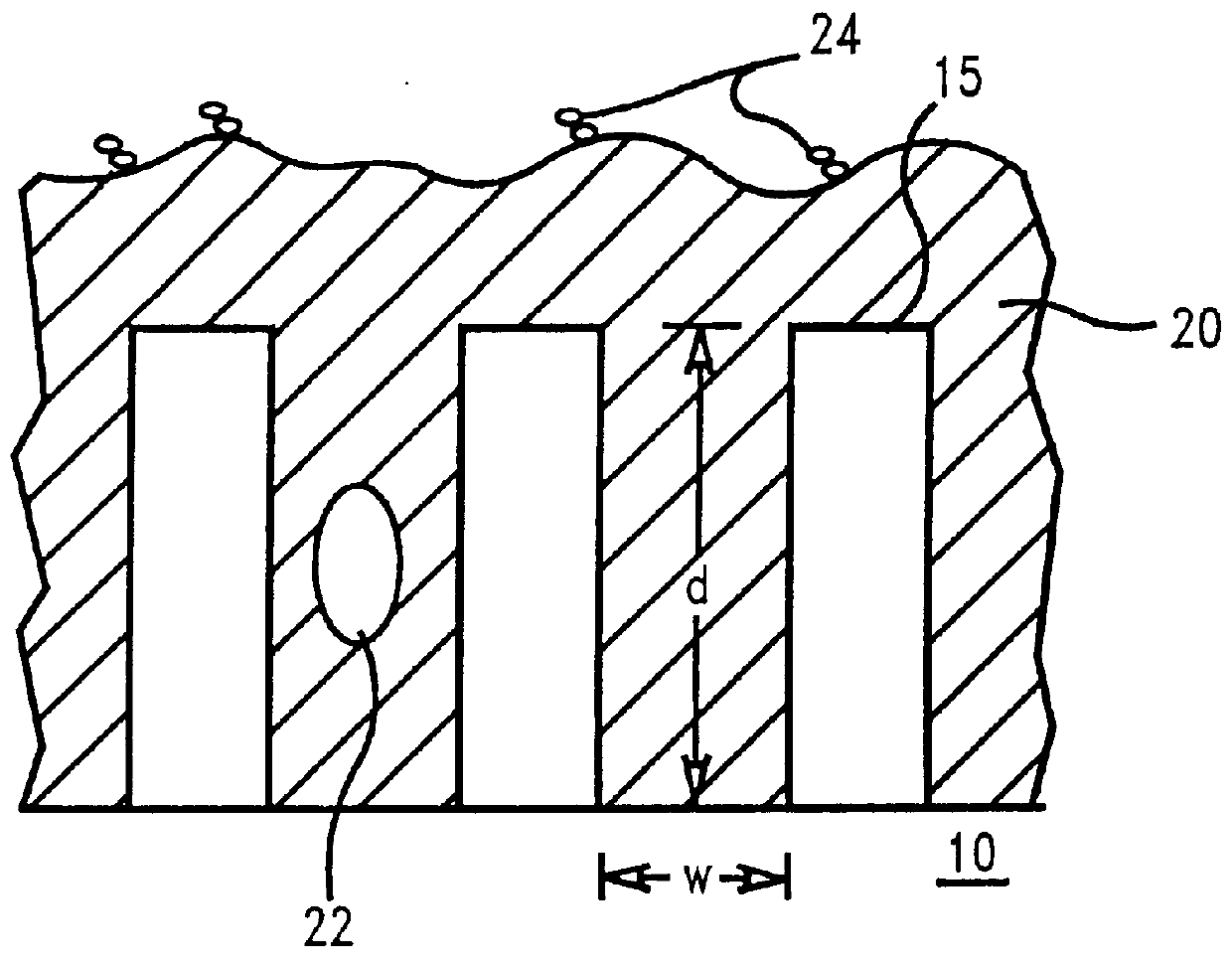

Hydrogen-based phosphosilicate glass process for gap fill of high aspect ratio structures

InactiveUS7001854B1Increase flow rateReduced side-wall dielectric redepositionSemiconductor/solid-state device manufacturingDopantHydrogen

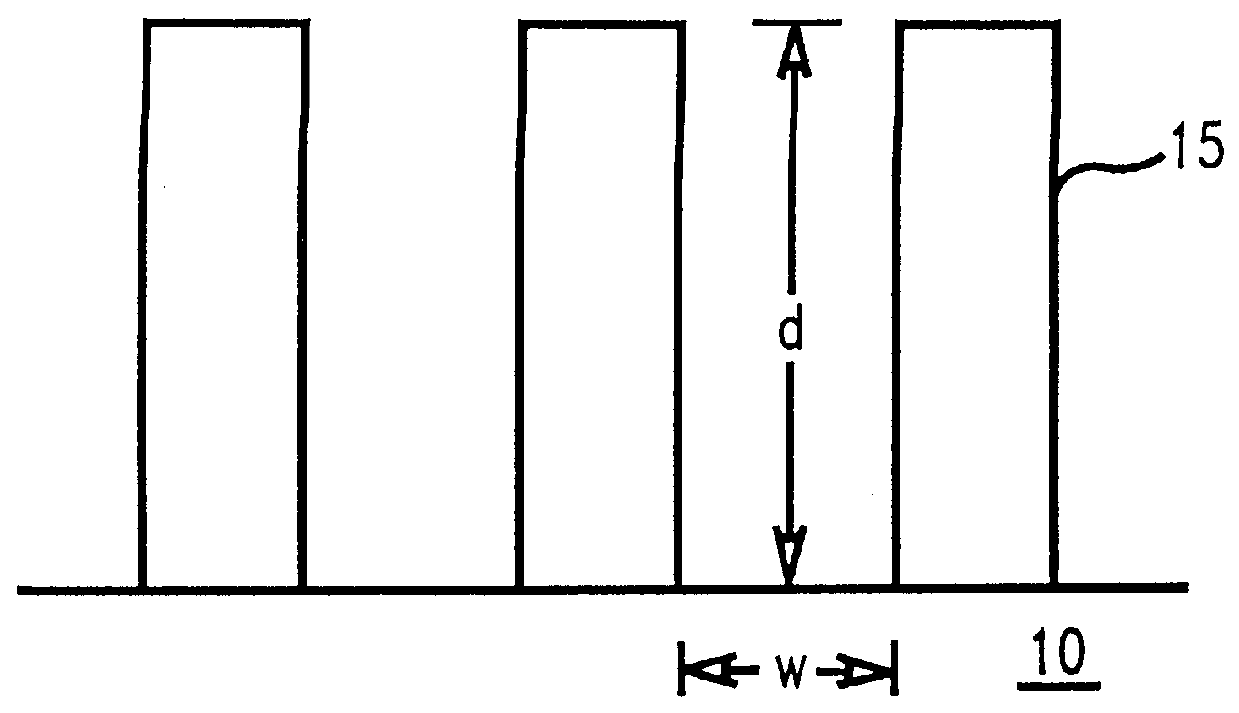

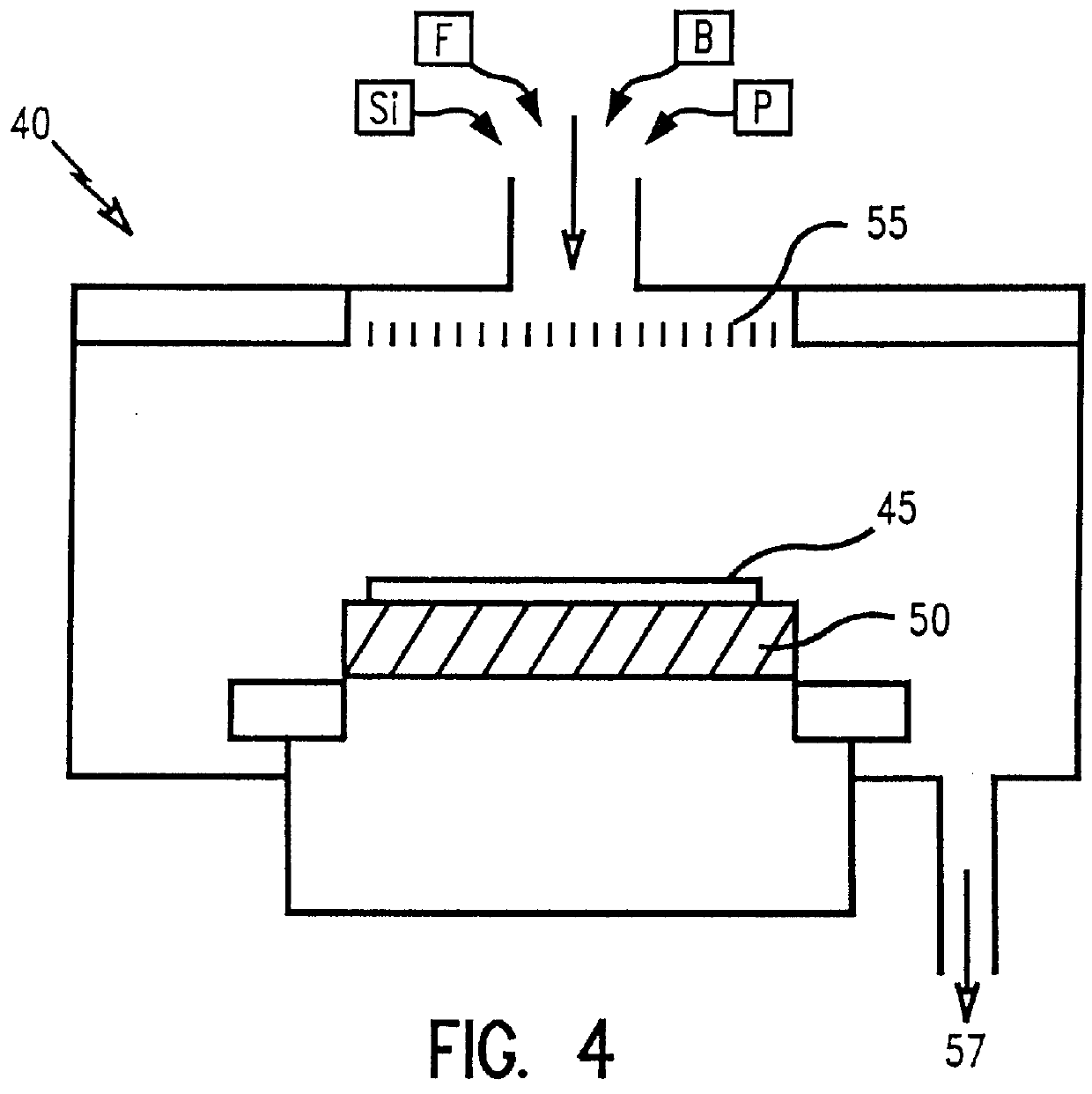

Chemical vapor deposition processes are employed to fill high aspect ratio (typically at least 3:1), narrow width (typically 1.5 microns or less and even sub 0.13 micron) gaps with significantly reduced incidence of voids or weak spots. This deposition process involves the use of hydrogen and a phosphorus dopant precursor as process gasses in the reactive mixture of a plasma containing CVD reactor. The process gas also includes dielectric forming precursor molecules such as silicon and oxygen containing molecules.

Owner:NOVELLUS SYSTEMS

Method for depositing and reflow of a high quality etch resistant gapfill dielectric film

ActiveUS20190259625A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicate glassBorophosphosilicate glass

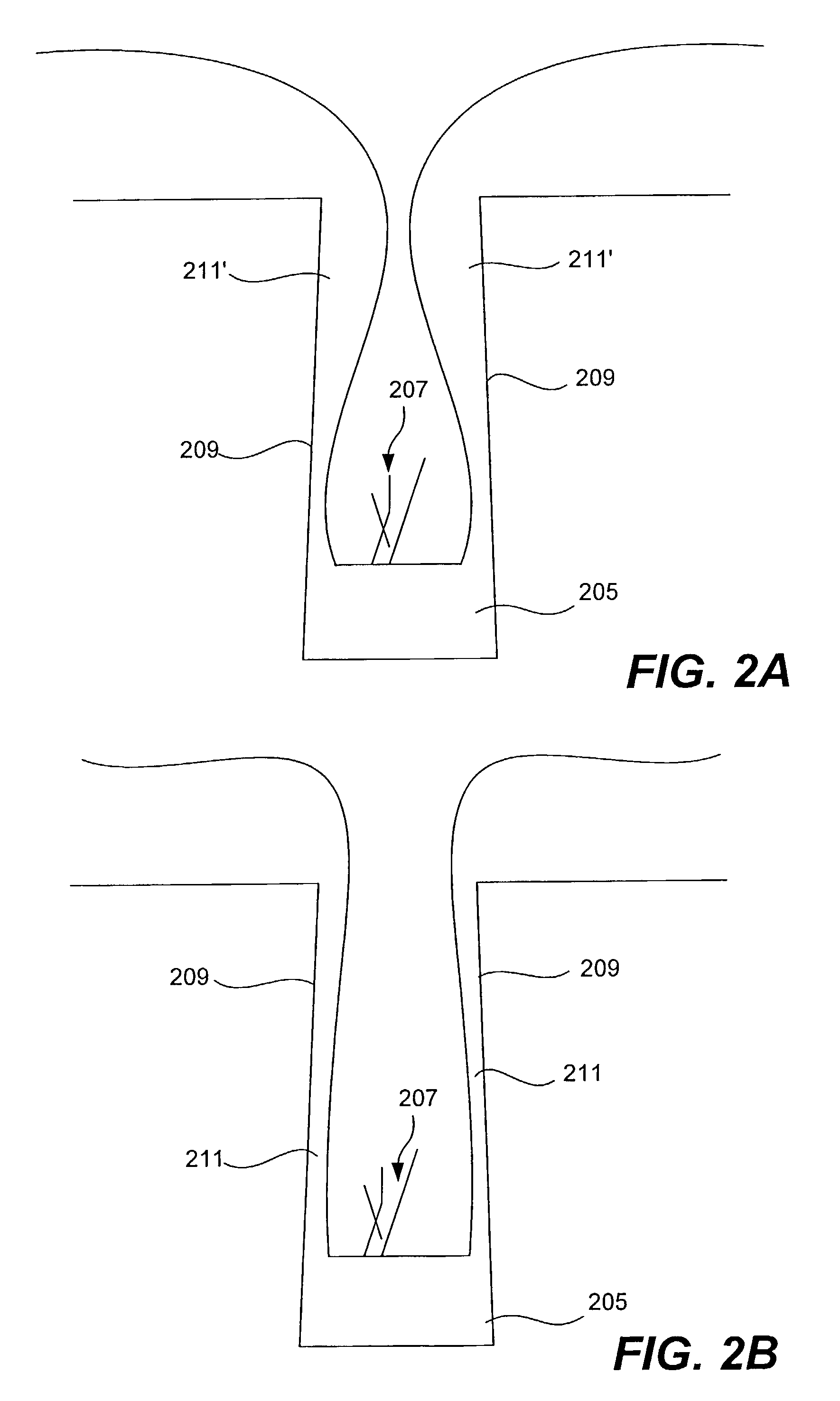

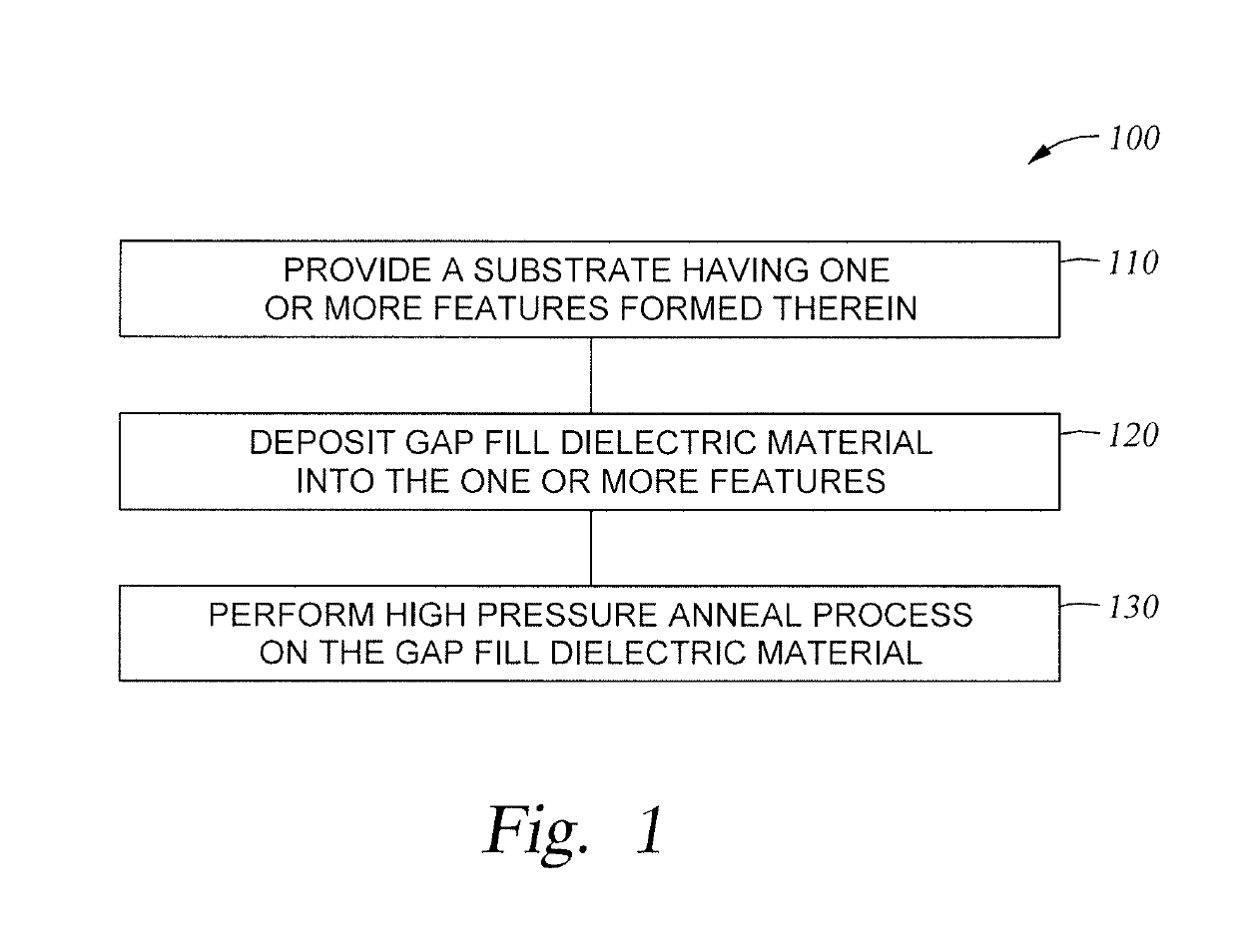

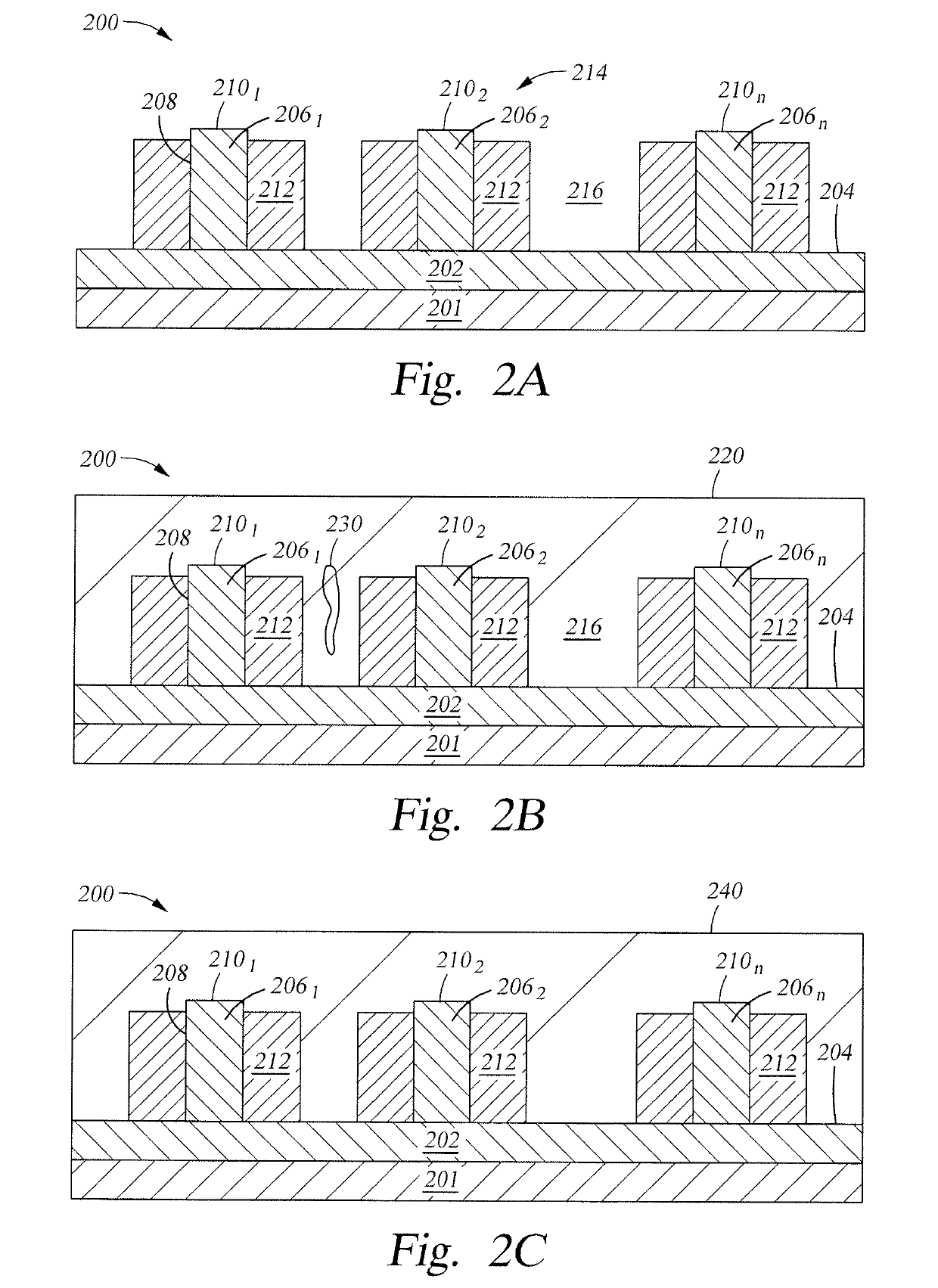

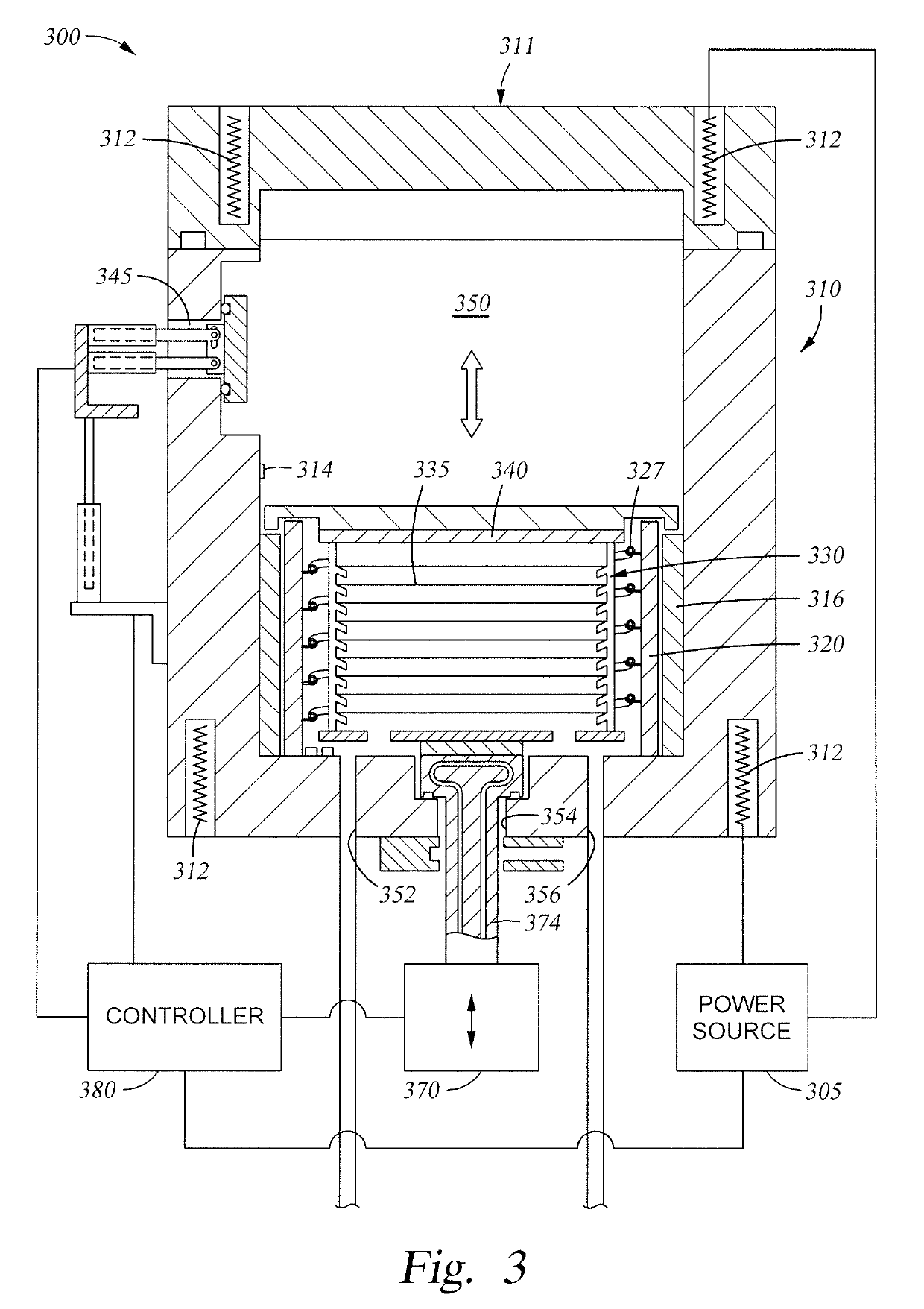

Methods for depositing a gapfill dielectric film that may be utilized for multi-colored patterning processes are provided. In one implementation, a method for processing a substrate is provided. The method comprises filling the one or more features of a substrate with a dielectric material. The dielectric material is a doped silicate glass selected from borophosphosilicate glass (BPSG), phosphosilicate glass (PSG), and borosilicate glass (BSG). The method further comprises treating the substrate with a high-pressure anneal in the presence of an oxidizer to heal seams within the dielectric material. The high-pressure anneal comprises supplying an oxygen-containing gas mixture on a substrate in a processing chamber, maintaining the oxygen-containing gas mixture in the processing chamber at a process pressure at greater than 2 bar and thermally annealing the dielectric material in the presence of the oxygen-containing gas mixture.

Owner:MICROMATERIALS LLC

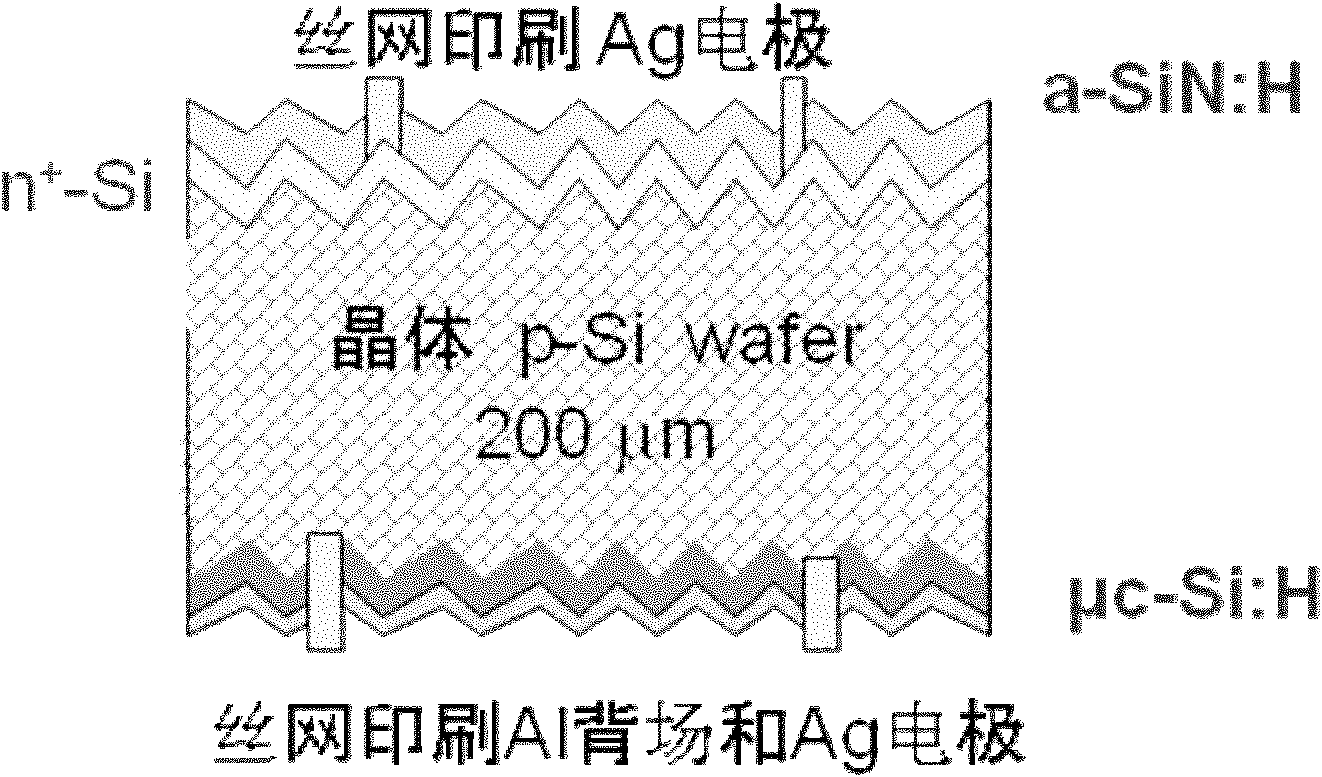

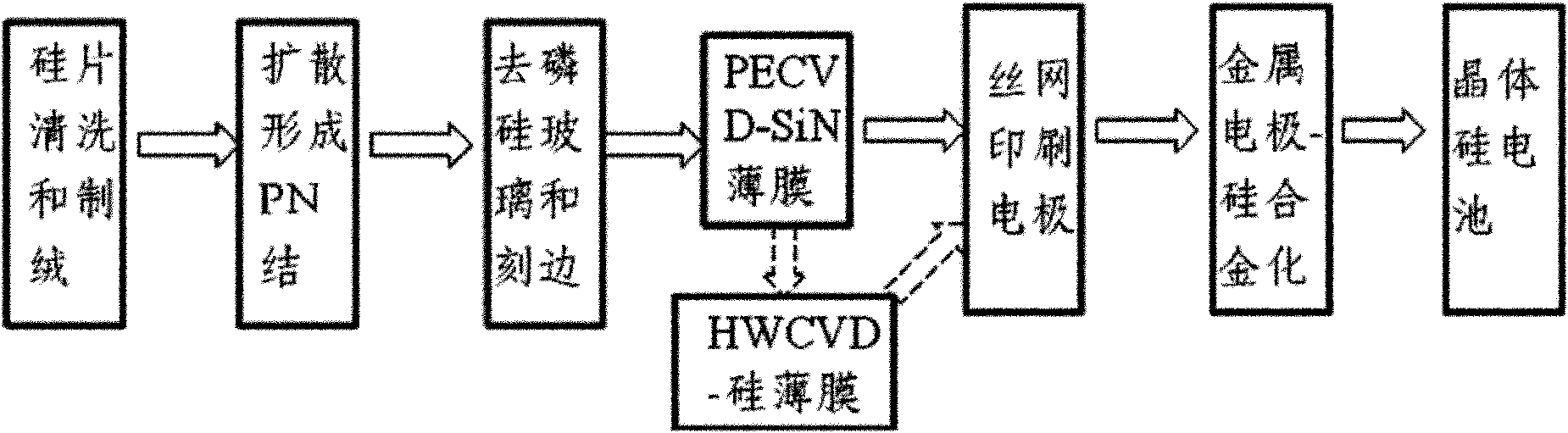

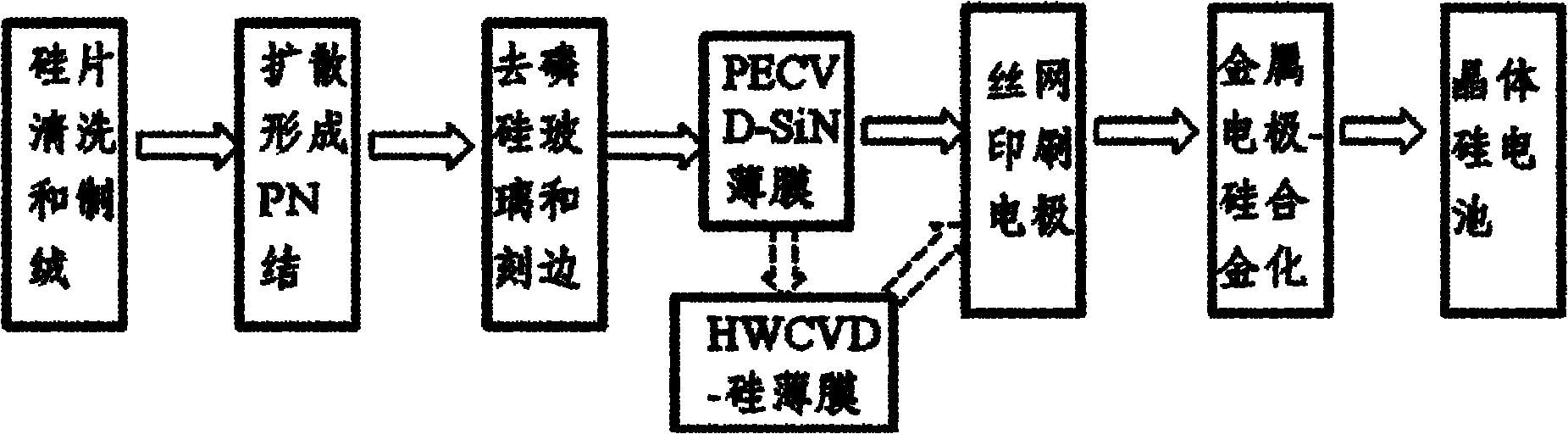

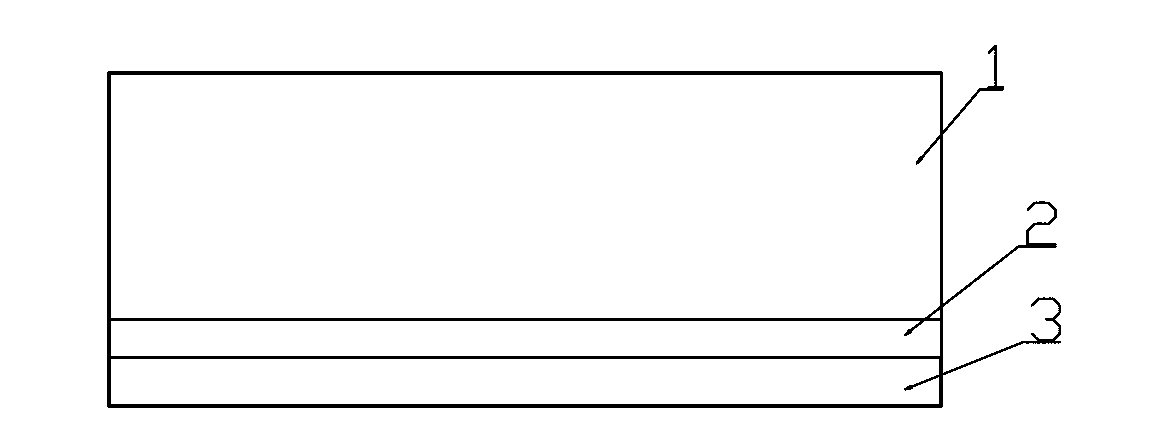

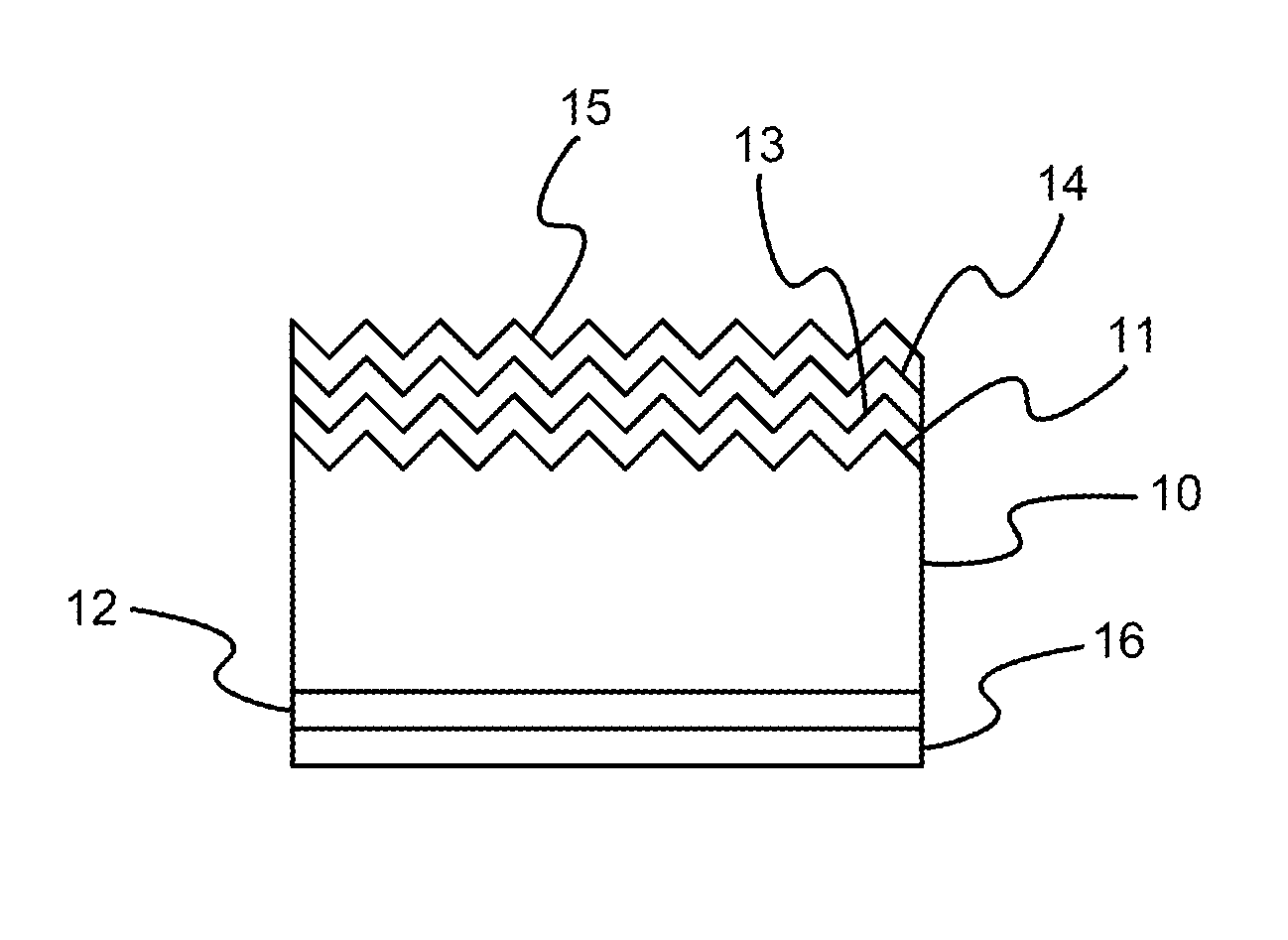

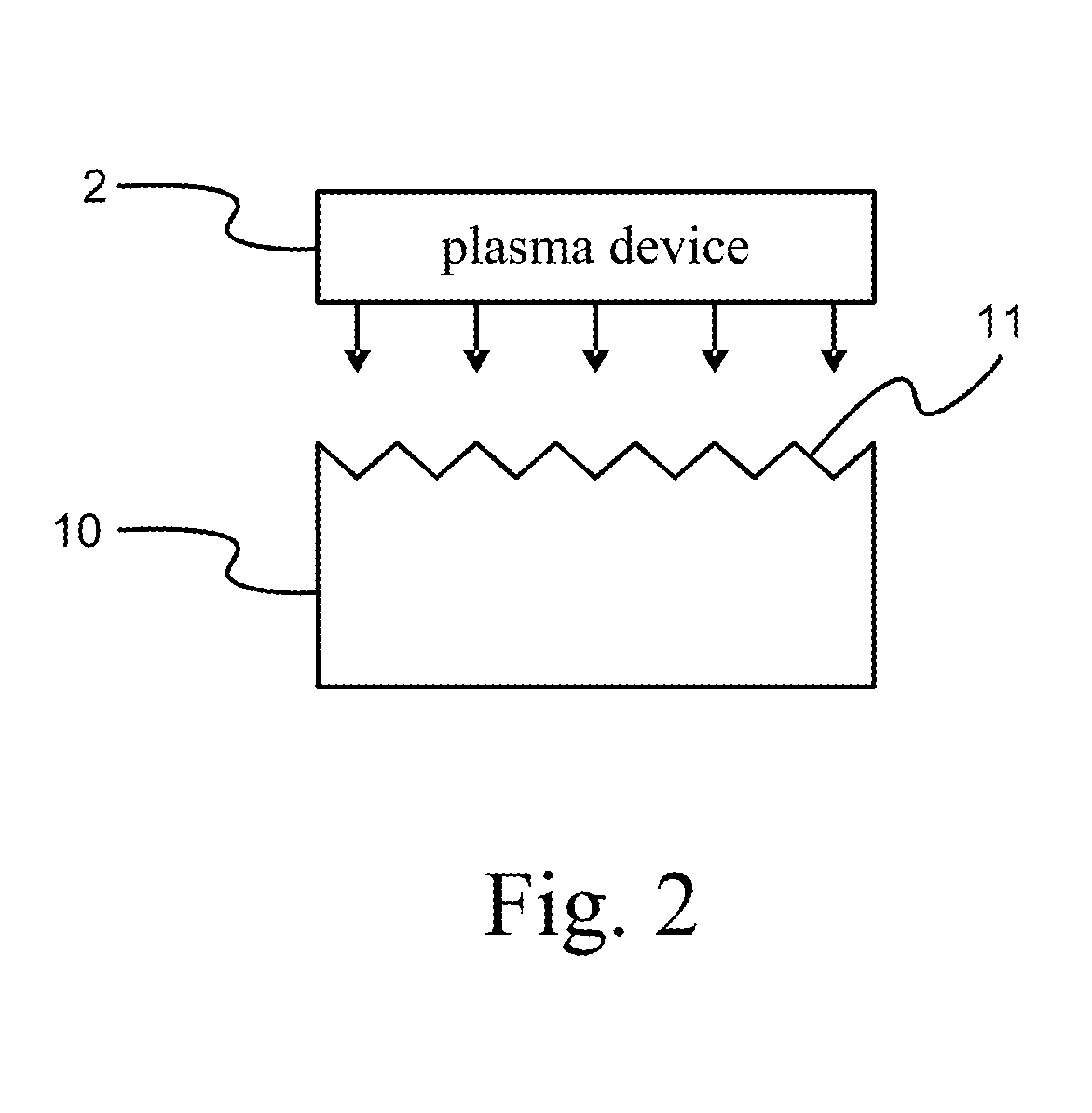

Preparation method of double-sided passivated crystalline silicon solar cell

InactiveCN101937944APrevent escapeAdjustable bandgapSemiconductor devicesP type siliconMicrocrystalline silicon

The invention discloses a preparation method of a double-sided passivated crystalline silicon solar cell, belonging to the technical field of photovoltaic power generation. The preparation method comprises the following steps of: firstly, respectively carrying out surface precleaning and surface texturing on P-shaped single crystal silicon and a polycrystalline silicon wafer by adopting an alkaline solution and an acid solution; secondly, diffusing by using phosphorus oxychloride as a diffusion source to form a PN junction; thirdly, removing a phosphosilicate glass on the surface of the silicon wafer by adopting a chemical wet method, and etching the edge of the silicon wafer by adopting a plasma; fourthly, preparing a silicon nitride film on the surface of an emitting region of a P-type silicon wafer by adopting a plasma enhanced chemical vapor deposition method; fifthly, preparing a mixed phase film material of hydrogenated microcrystalline silicon and amorphous silicon by adopting a hot filament chemical vapor deposition method, depositing a film at one side of the P-type silicon wafer, and passivating the defects and a dangling bond on the surface of the P-type silicon wafer; and sixthly, sintering a screen printing back electrode and a screen printing positive electrode to form the solar cell. The invention lowers the probability of compounding photo-generated minority carriers on the back surface, enhances the long-wave light quantum efficiency and creates the conditions of transportation and collection of the photo-generated carriers.

Owner:SHANGHAI JIAO TONG UNIV

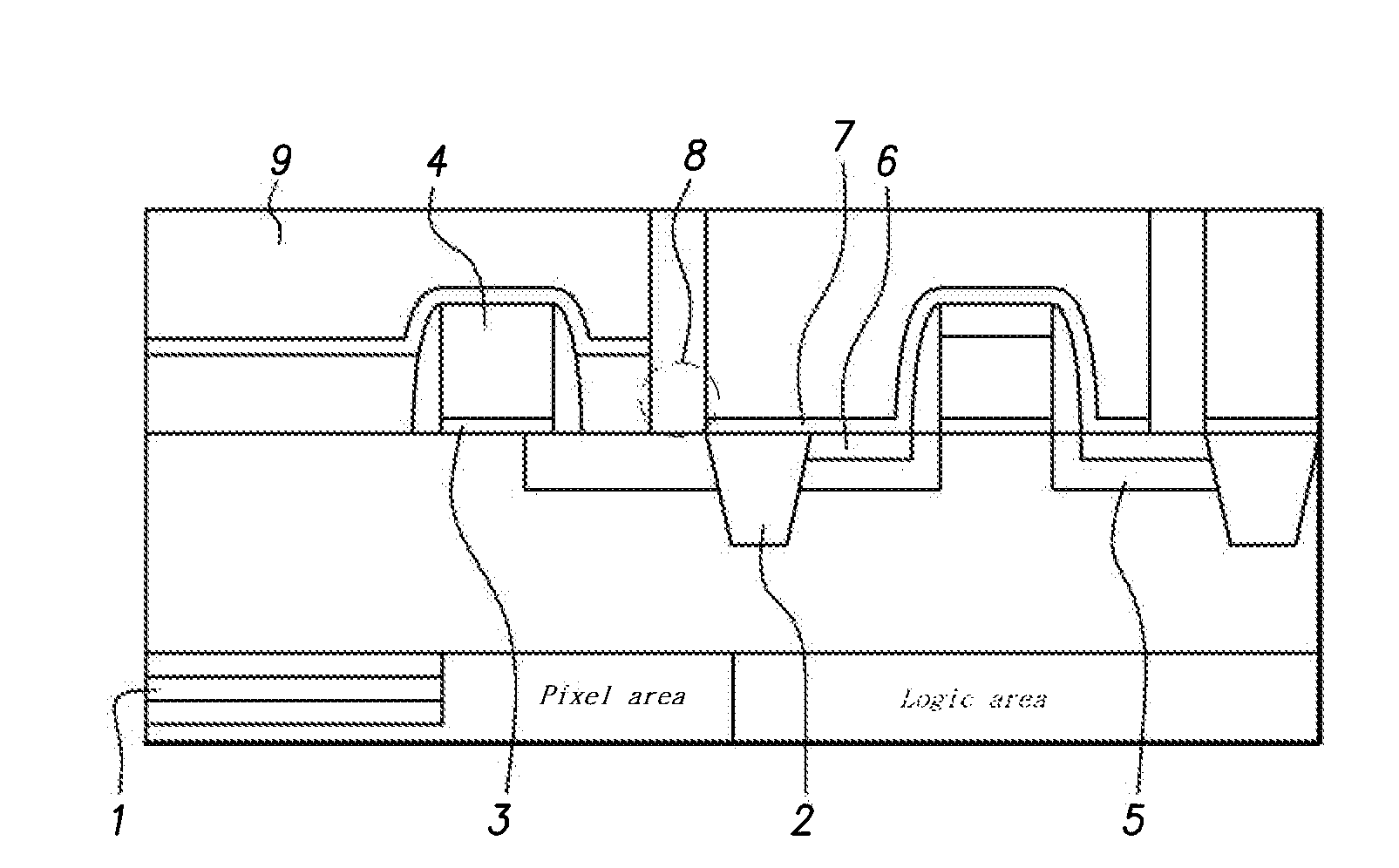

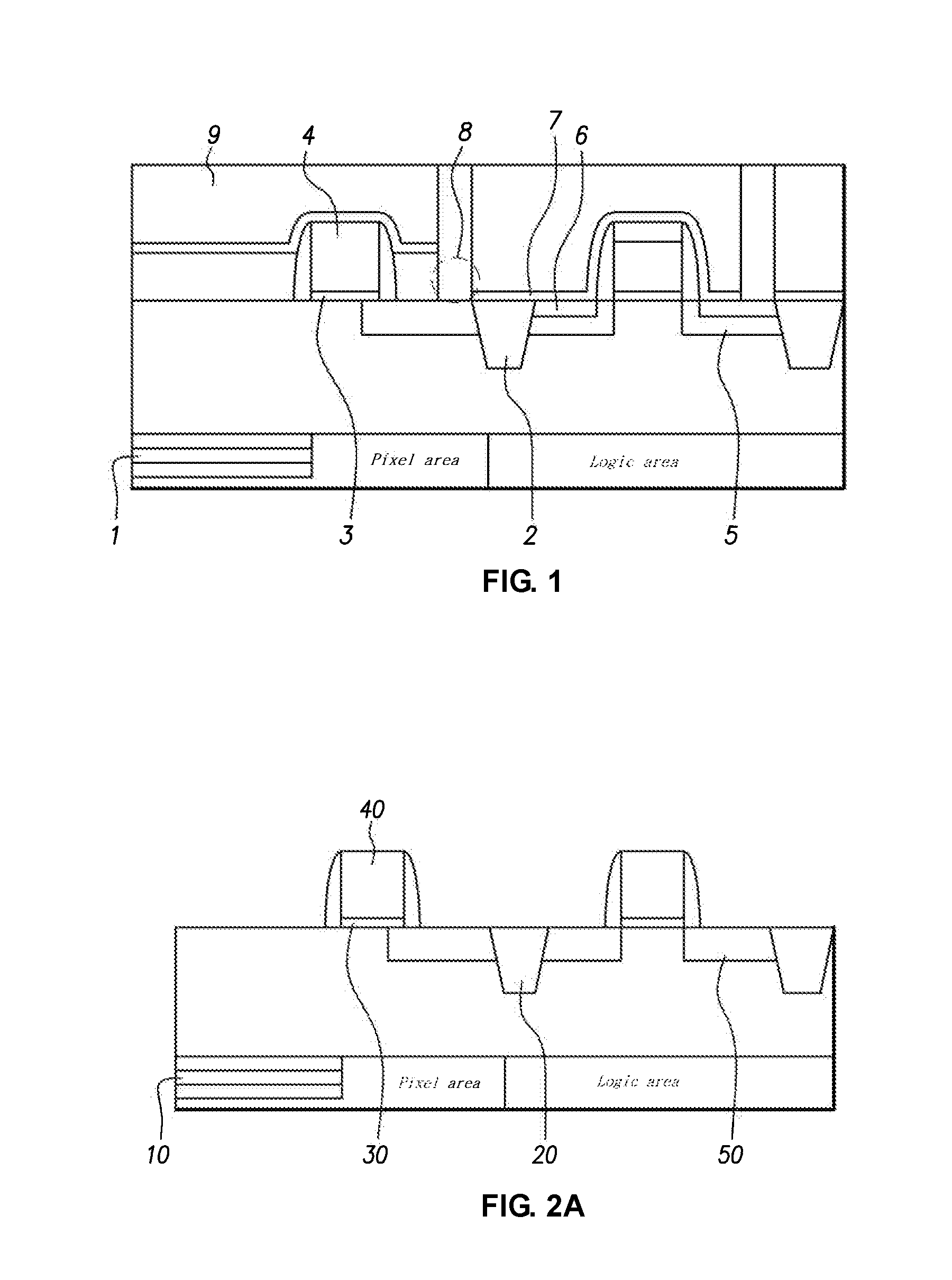

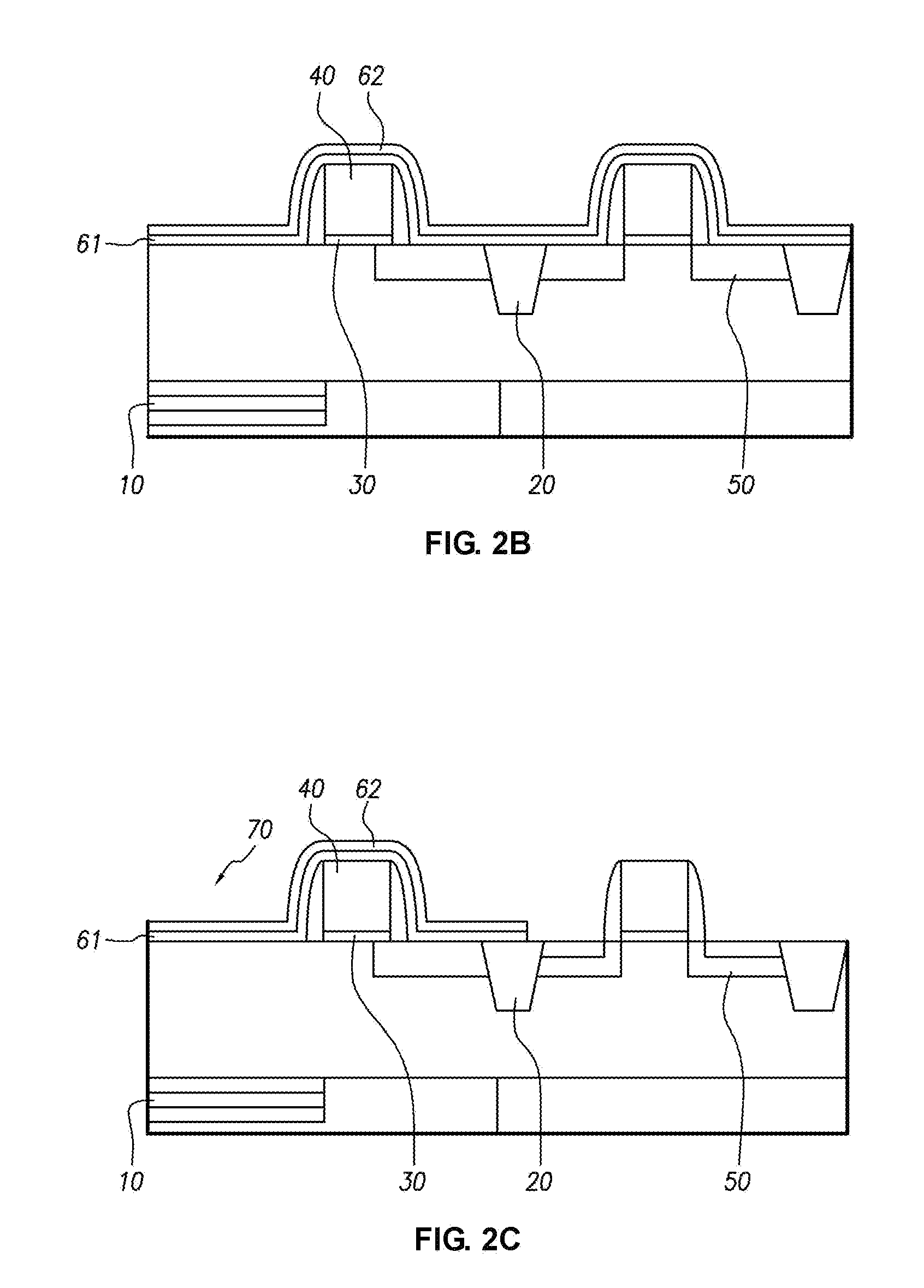

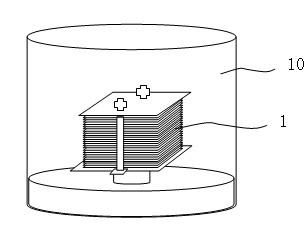

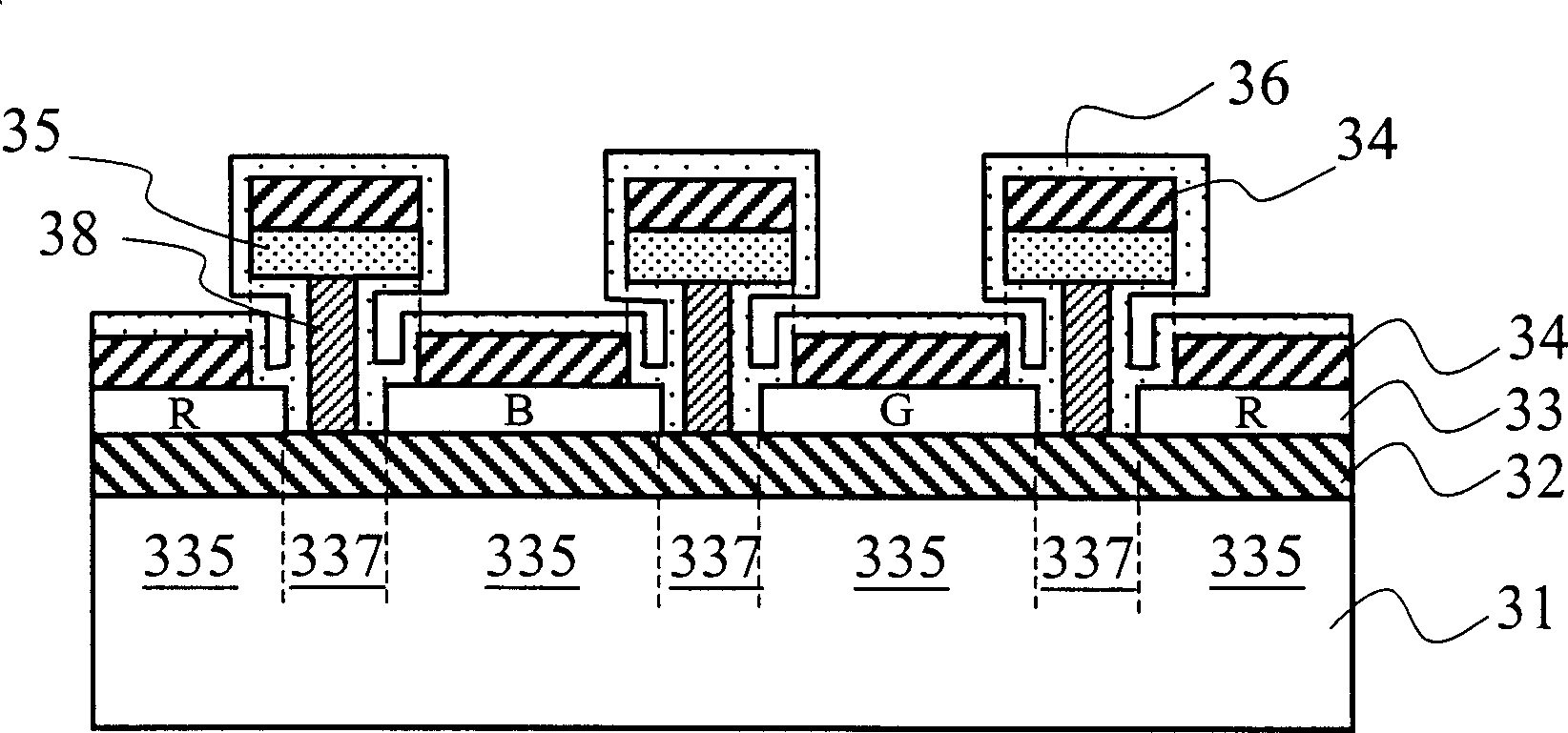

CMOS image sensor and fabricating method thereof

InactiveUS20080157144A1Avoid leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingSalicideCMOS

A method of fabricating a CMOS image sensor comprising forming an epitaxial layer on a semiconductor substrate, the epitaxial layer comprising a pixel and logic area, forming an STI layer in an insulating layer on the epitaxial layer, forming a plurality of wells and a gate pattern having a spacer on the insulating layer, forming a plurality of source and drain regions in the insulating layer using ion implantation, forming a salicide blocking layer on the insulating layer and gate pattern in the pixel area, forming a plurality of silicide layers in the logic area by performing a silicidation process, sequentially forming a PMD liner nitride layer and a PSG (phosphosilicate glass) layer on the salicide blocking layer in the pixel area and the insulating layer and gate pattern in the logic area, and forming a plurality of contacts connecting the PSG layer to the source and drain regions.

Owner:DONGBU HITEK CO LTD

Preparation method of solar cell

InactiveCN101937945AOvercome defilementOvercome defectsFinal product manufactureSemiconductor devicesScreen printingSilicon oxide

The invention discloses a preparation method of a solar cell. The method comprises the following steps: providing a plurality of polycrystalline silicon wafers for texturization; overlapping the textured silicon wafers, depositing a silicon nitride or silicon oxide masking film on the periphery of the silicon wafers, then diffusing a phosphorus doping layer on the front surface of the to-be-prepared positive electrode of the silicon wafers to form a PN junction, wherein the periphery of the silicon wafers can not form the diffusion PN junction owning to the existence of the masking film; removing the peripheral masking film and the surface phosphosilicate glass; preparing a passivation layer and an antireflection layer; and performing screen printing and sintering to form a back Ag electrode, a back Al-back surface and a front Ag electrode. In the preparation method of the solar cell provided by the invention, the masking film is formed before the impurity source diffusion used for preparing the PN junction; owning to the existence of the masking film, the periphery of the silicon wafers can not form the PN junction; and the silicon wafers after diffusion is washed with acid to remove the masking film on the periphery of the silicon wafers and the phosphosilicate glass on the diffusion surface, thus achieving the aim of replacing the etching step.

Owner:百力达太阳能股份有限公司

Detection system including avalanche photodiode for use in harsh environments

An aspect of the present invention is directed to an avalanche photodiode (APD) device for use in oil well drilling applications in harsh, down-hole environments where shock levels are near 250 gravitational acceleration (G) and / or temperatures approach or exceed 150° C. Another aspect of the present invention is directed to an APD device fabricated using SiC materials. Another aspect of the present invention is directed to an APD device fabricated using GaN materials. According to an embodiment of the present invention, an avalanche photodiode for detecting ultraviolet photons comprises a substrate having a first dopant; a first layer having the first dopant, positioned on top of the substrate; a second layer having a second dopant, positioned on top of the first layer; a third layer having a second dopant, positioned on top of the second layer; a passivation layer for providing electrical passivation on a surface of the avalanche photodiode; a phosphorous silicate glass layer for limiting mobile ion transport, positioned on top of the third layer; and a pair of metal electrodes for providing an ohmic contact wherein a first electrode is positioned below the substrate and a second electrode is positioned above the third layer; wherein the avalanche photodiode comprises a first sidewall and a second sidewall forming a sloped mesa shape; and wherein the avalanche photodiode operates in an environment comprising a temperature approximately equal to 150 degrees Celsius.

Owner:GENERAL ELECTRIC CO

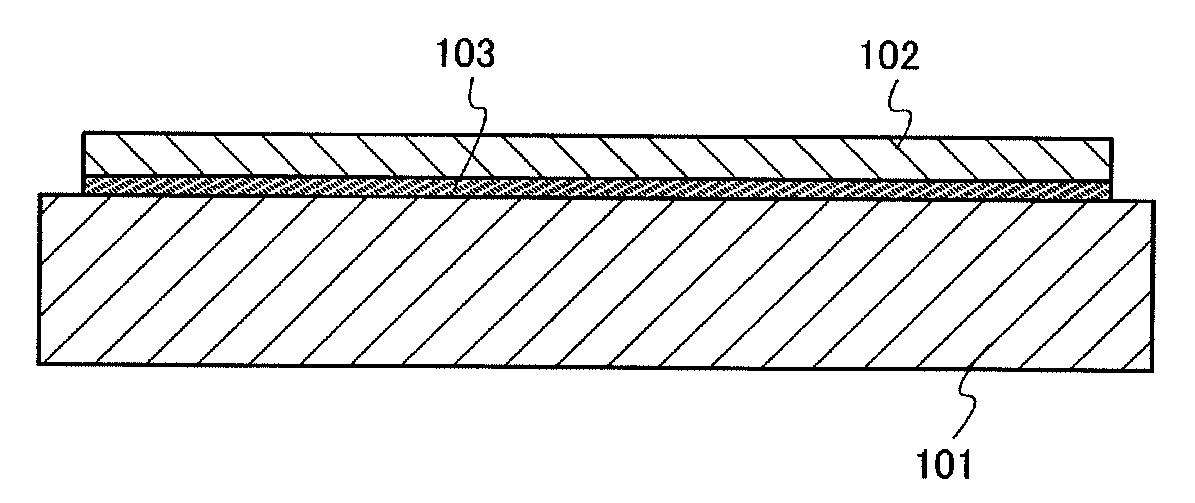

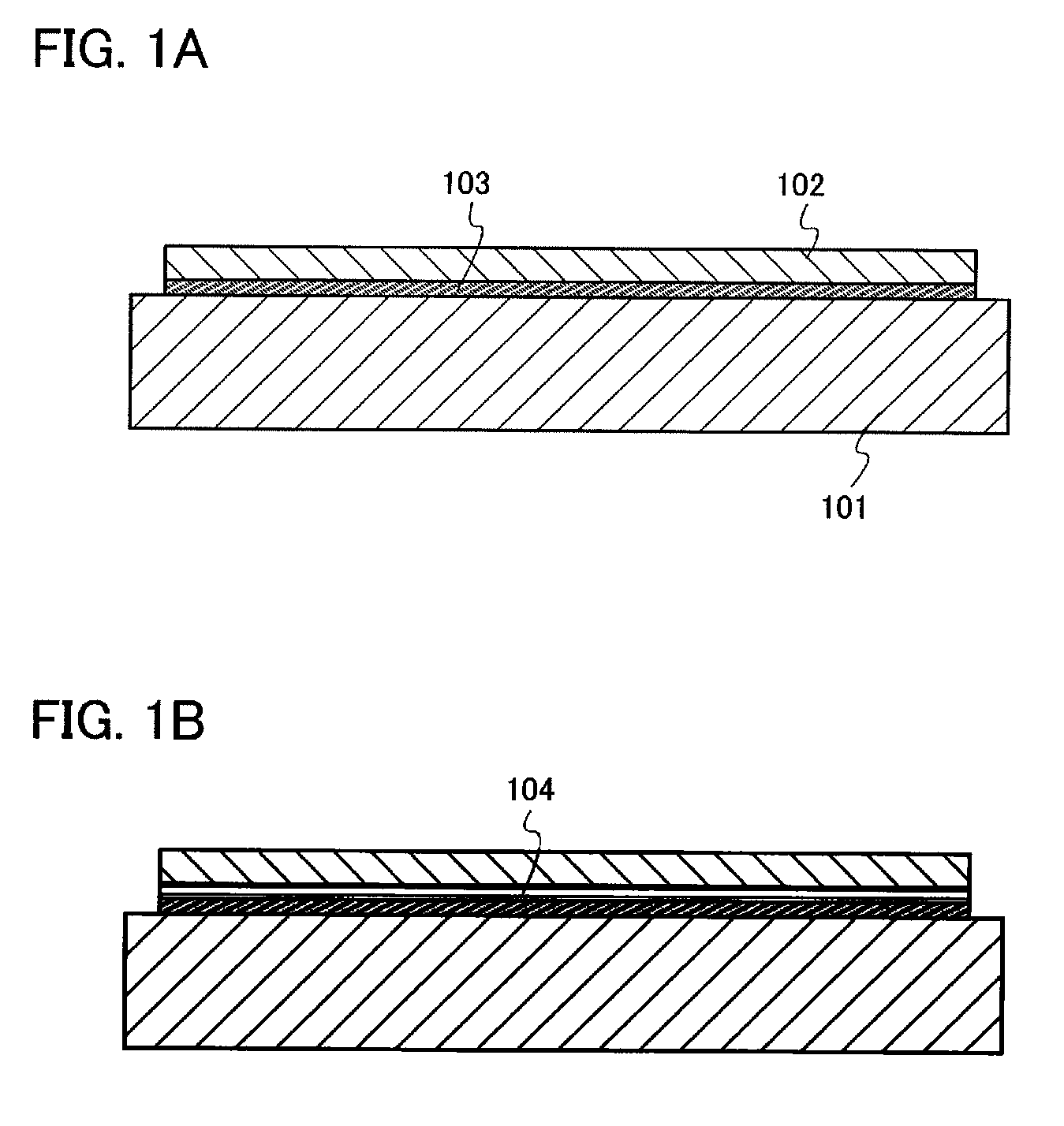

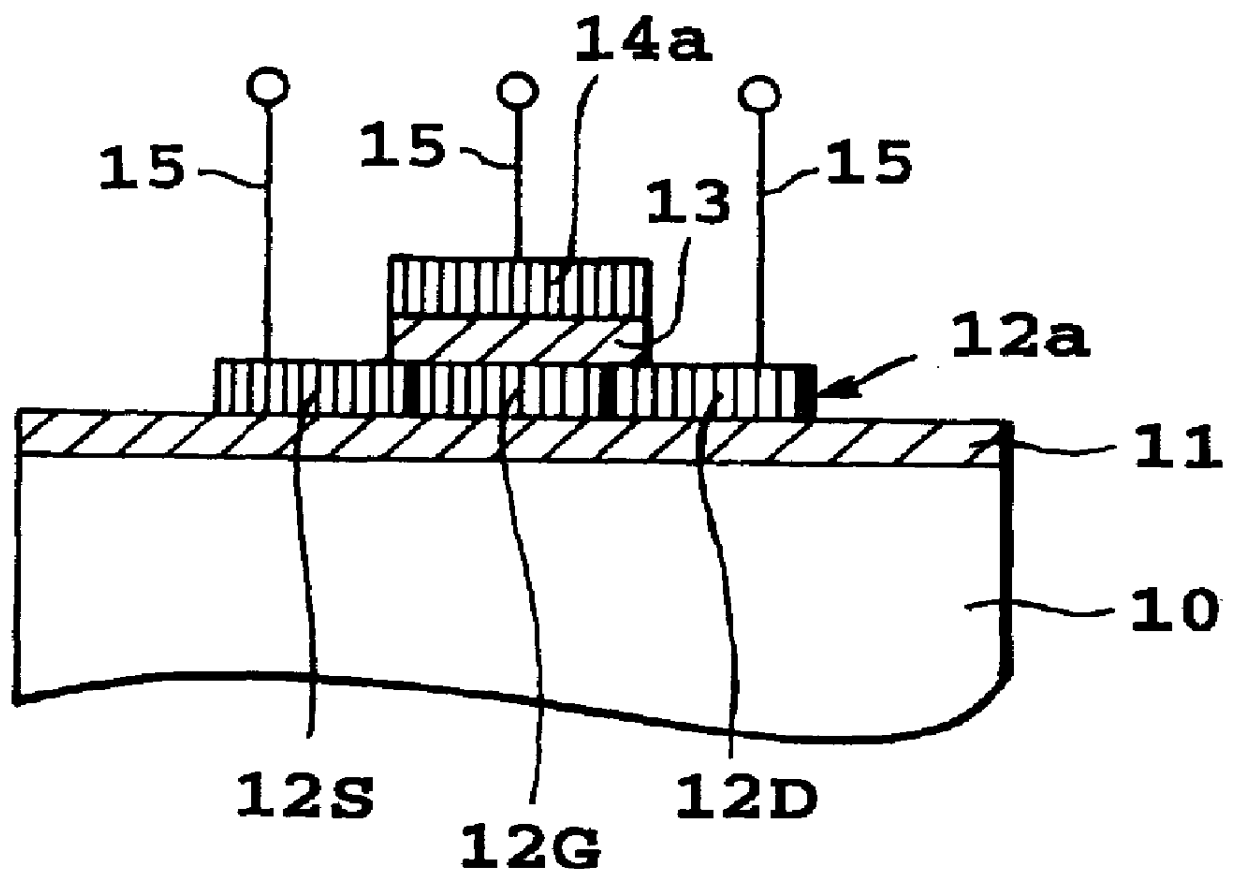

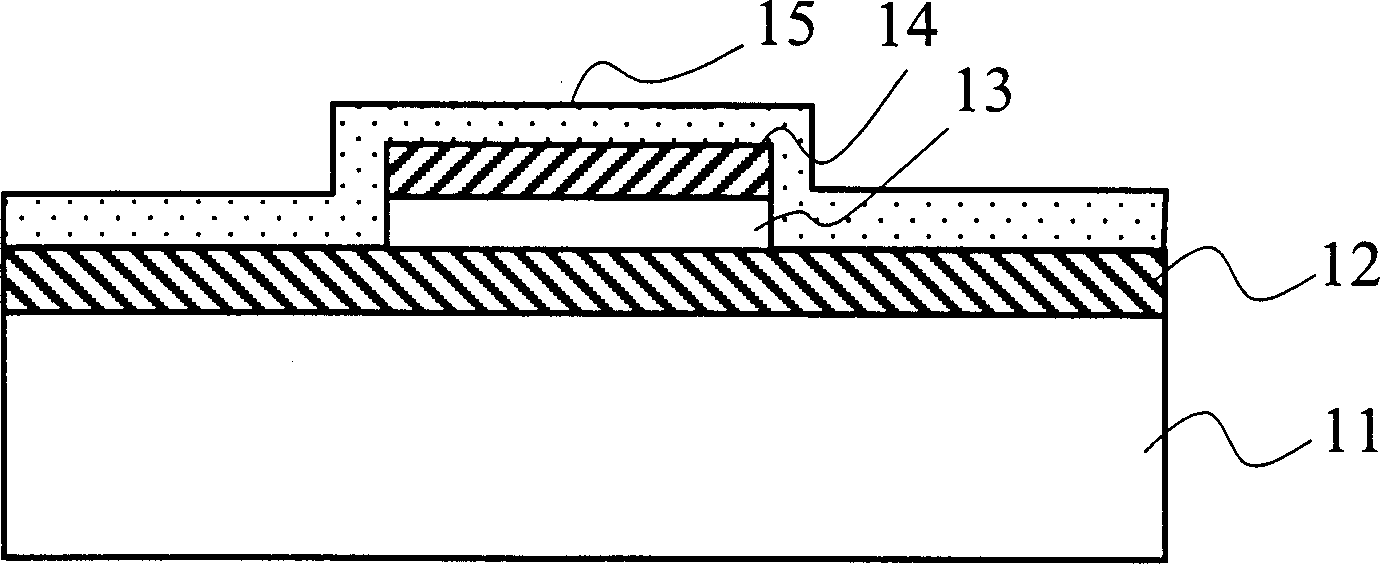

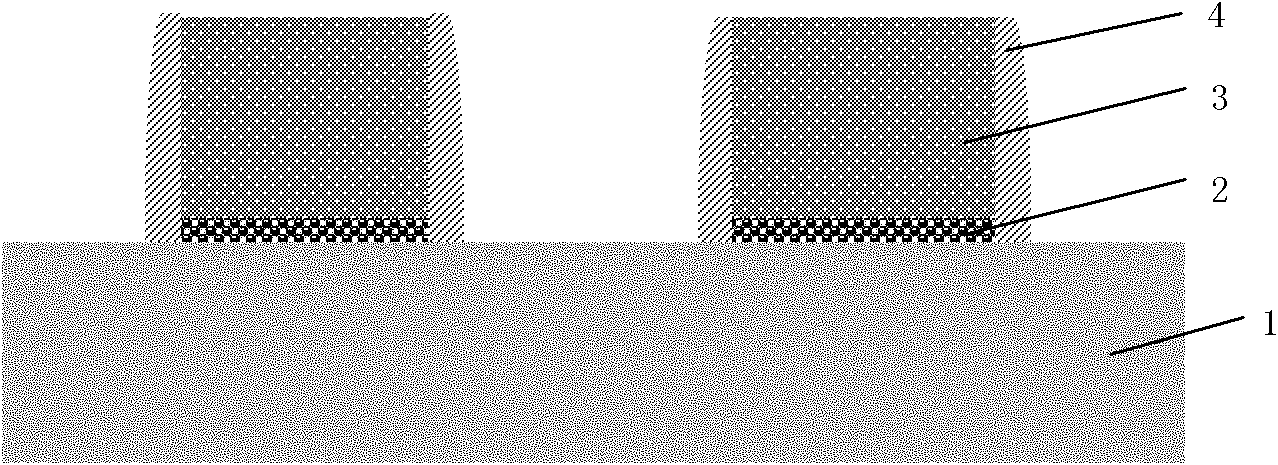

Semiconductor substrate and semiconductor device and manufacturing method of the same

InactiveUS20090102008A1Guaranteed uptimeEasily increased in areaSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSilicate glass

A semiconductor substrate having an SOI layer is provided. Between an SOI layer and a glass substrate, a bonding layer is provided which is formed of one layer or a plurality of layers of phosphosilicate glass, borosilicate glass, and / or borophosphosilicate glass, using organosilane as one material by a thermal CVD method at a temperature of 500° C. to 800° C.

Owner:SEMICON ENERGY LAB CO LTD

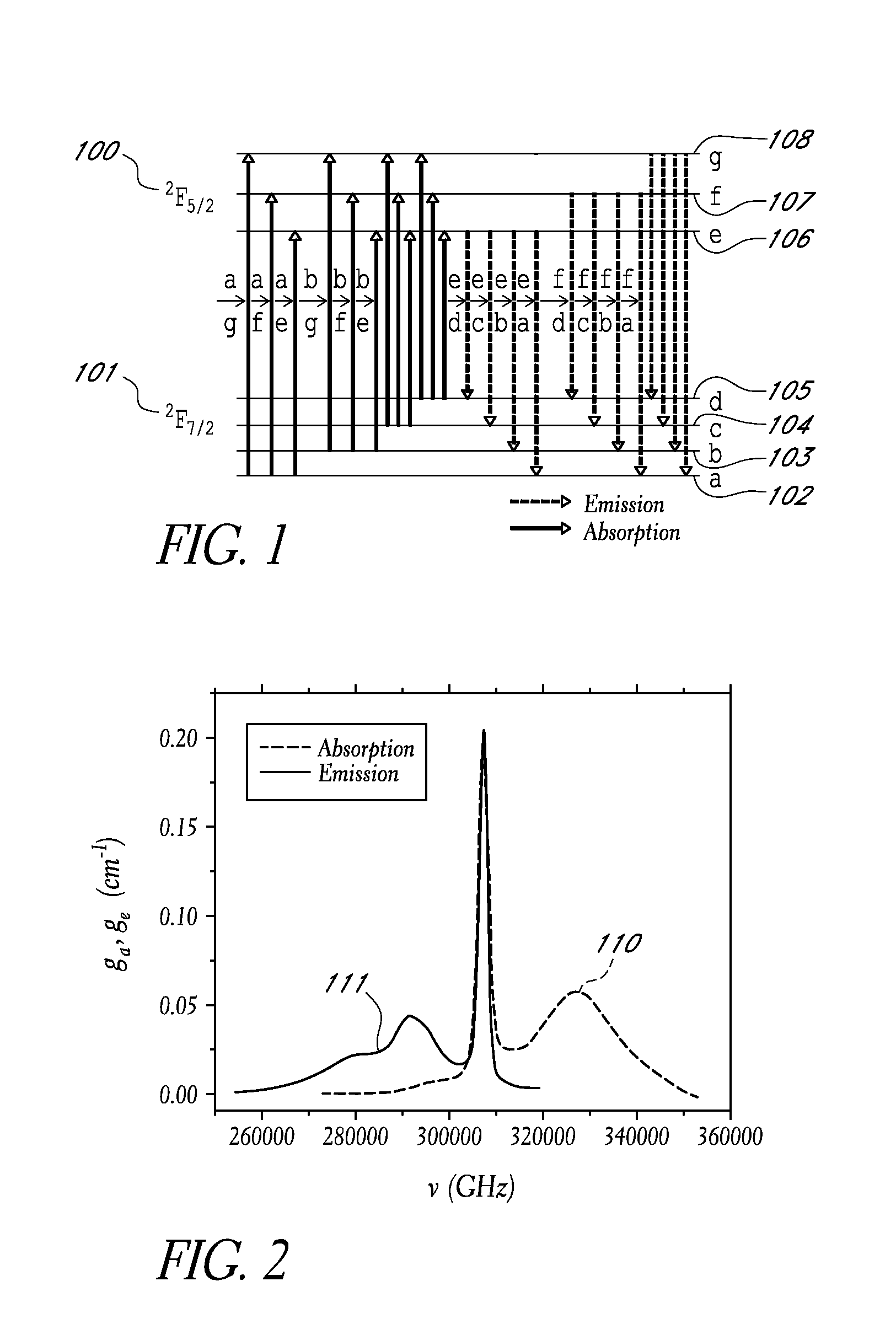

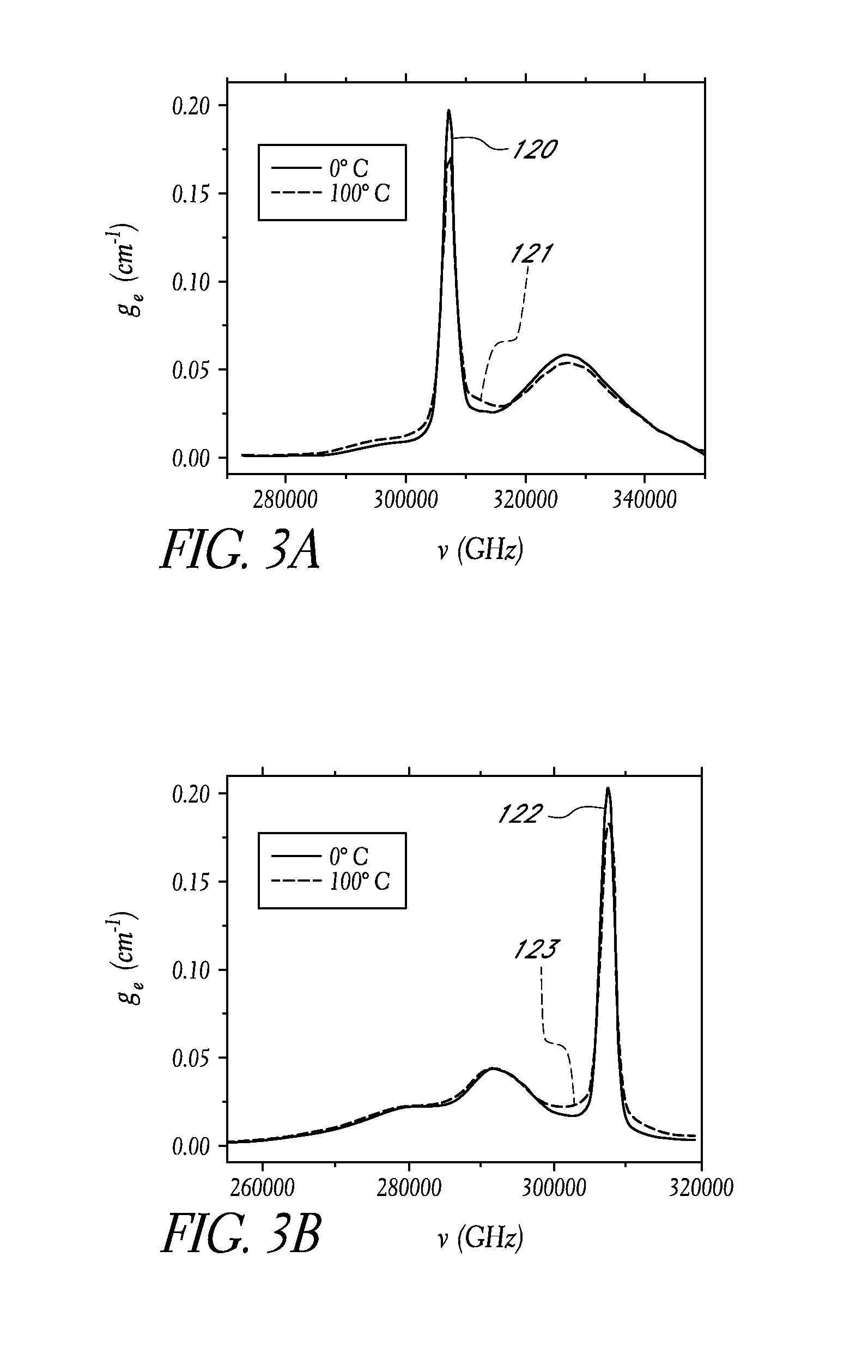

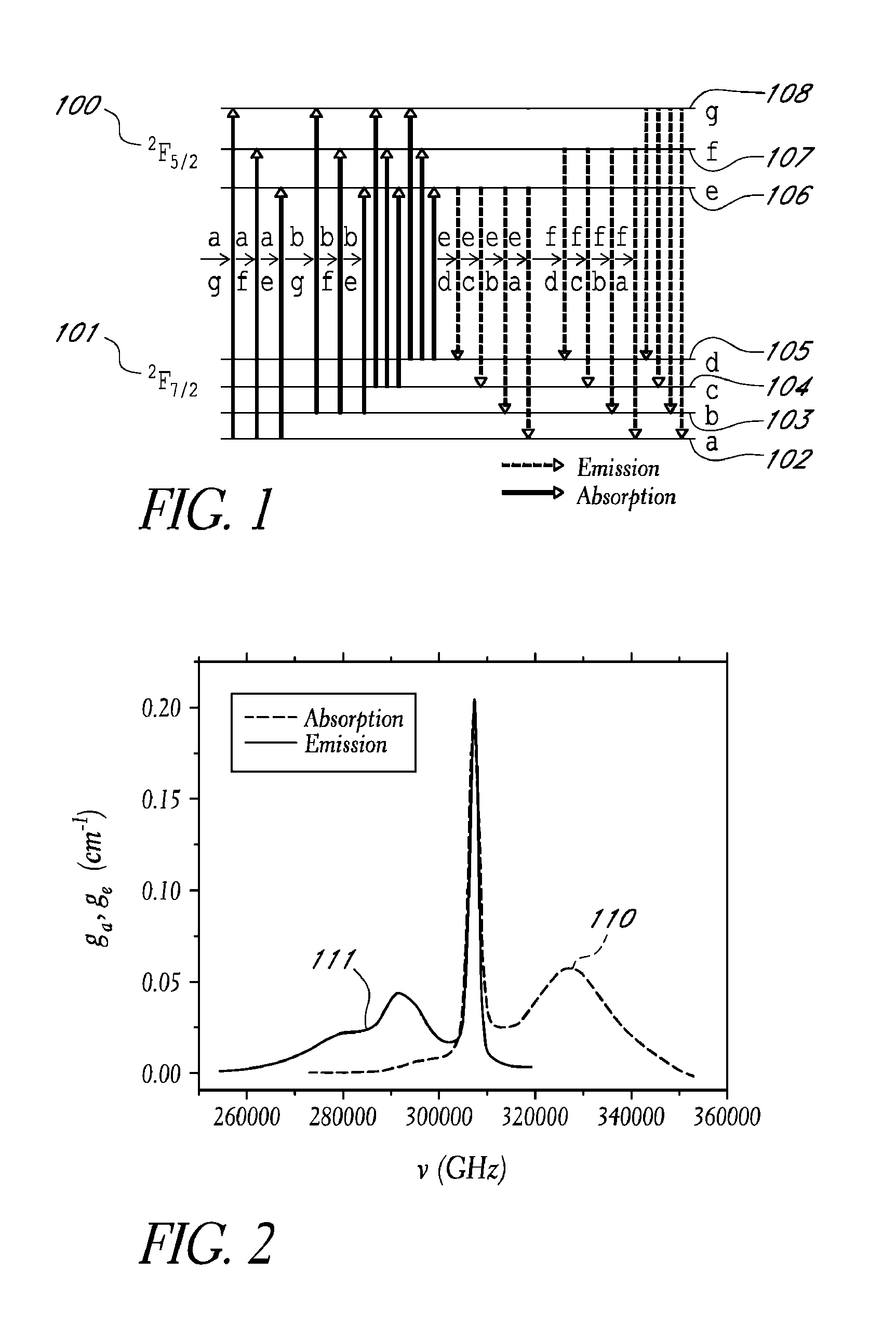

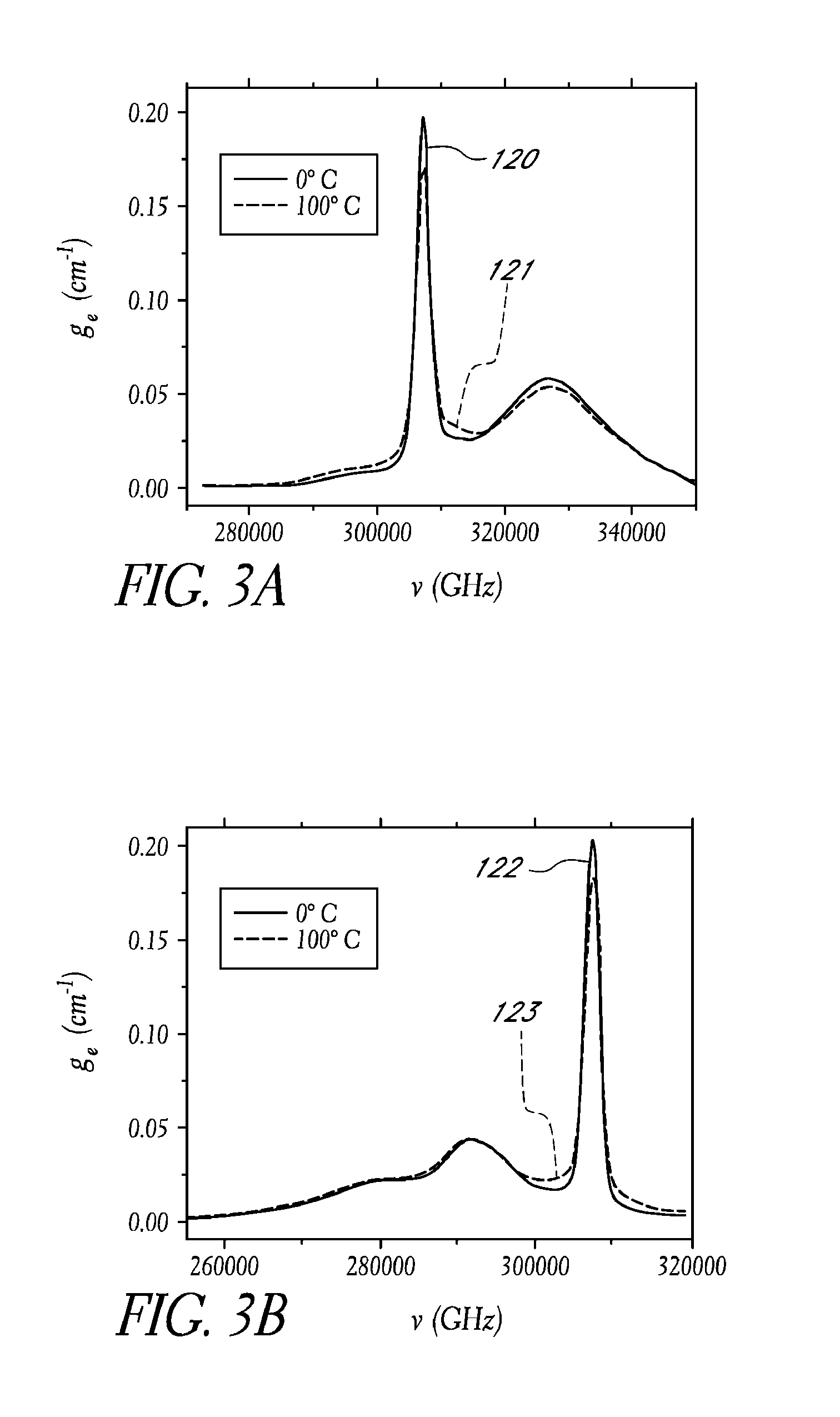

Light emitting devices with phosphosilicate glass

ActiveUS8270445B2Reduce impactLaser using scattering effectsActive medium materialDopantSilicate glass

A light-emitting device is provided which includes a gain medium having an optically-active phosphosilicate glass, wherein the phosphosilicate glass includes at least one active ion dopant and from about 1 to 30 mol % of phosphorus oxide. The phosphorous oxide may be present in an effective amount for reducing any photodarkening effect and increasing the saturation energy of the system. The active ion dopant may be a rare earth dopant. The light-emitting device may include an optical waveguide, the optical waveguide including the gain medium. The optical waveguide may have a core and at least one cladding, and the gain medium having the phosphosilicate glass may be found in the core and / or in one of the cladding.

Owner:CORACTIVE HIGH TECH

Projection having a micro-aperture, probe or multi-probe having such a projection and surface scanner, aligner or information processor comprising such a probe

InactiveUS6376833B2Decorative surface effectsMaterial analysis by optical meansSilicate glassPlastic materials

Owner:CANON KK

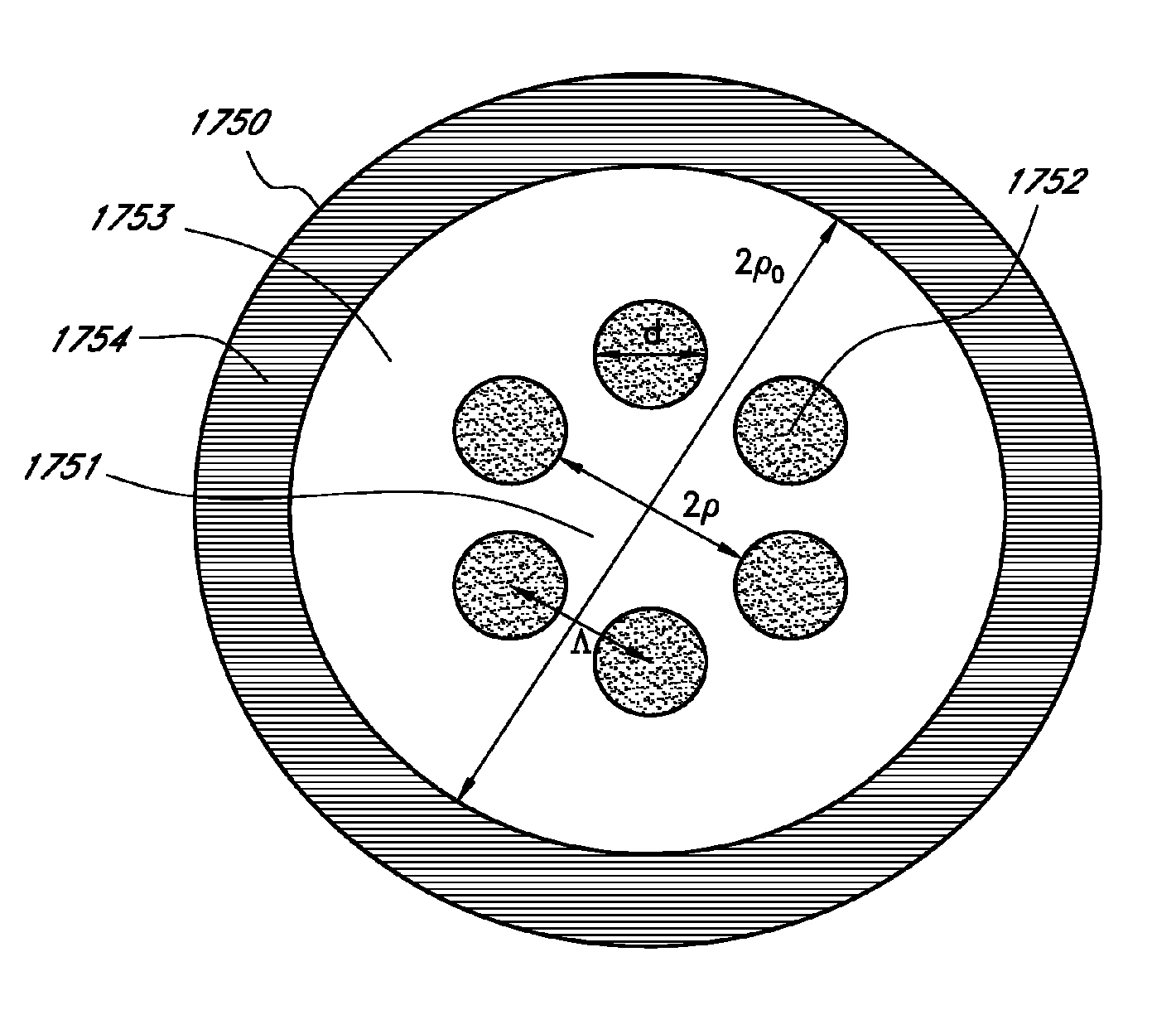

Highly rare-earth-doped optical fibers for fiber lasers and amplifiers

ActiveUS8498046B2Laser using scattering effectsOptical fibre with multilayer core/claddingAudio power amplifierRare earth

Various embodiments described herein comprise a laser and / or an amplifier system including a doped gain fiber having ytterbium ions in a phosphosilicate glass. Various embodiments described herein increase pump absorption to at least about 1000 dB / m-9000 dB / m. The use of these gain fibers provide for increased peak-powers and / or pulse energies. The various embodiments of the doped gain fiber having ytterbium ions in a phosphosilicate glass exhibit reduced photo-darkening levels compared to photo-darkening levels obtainable with equivalent doping levels of an ytterbium doped silica fiber.

Owner:IMRA AMERICA

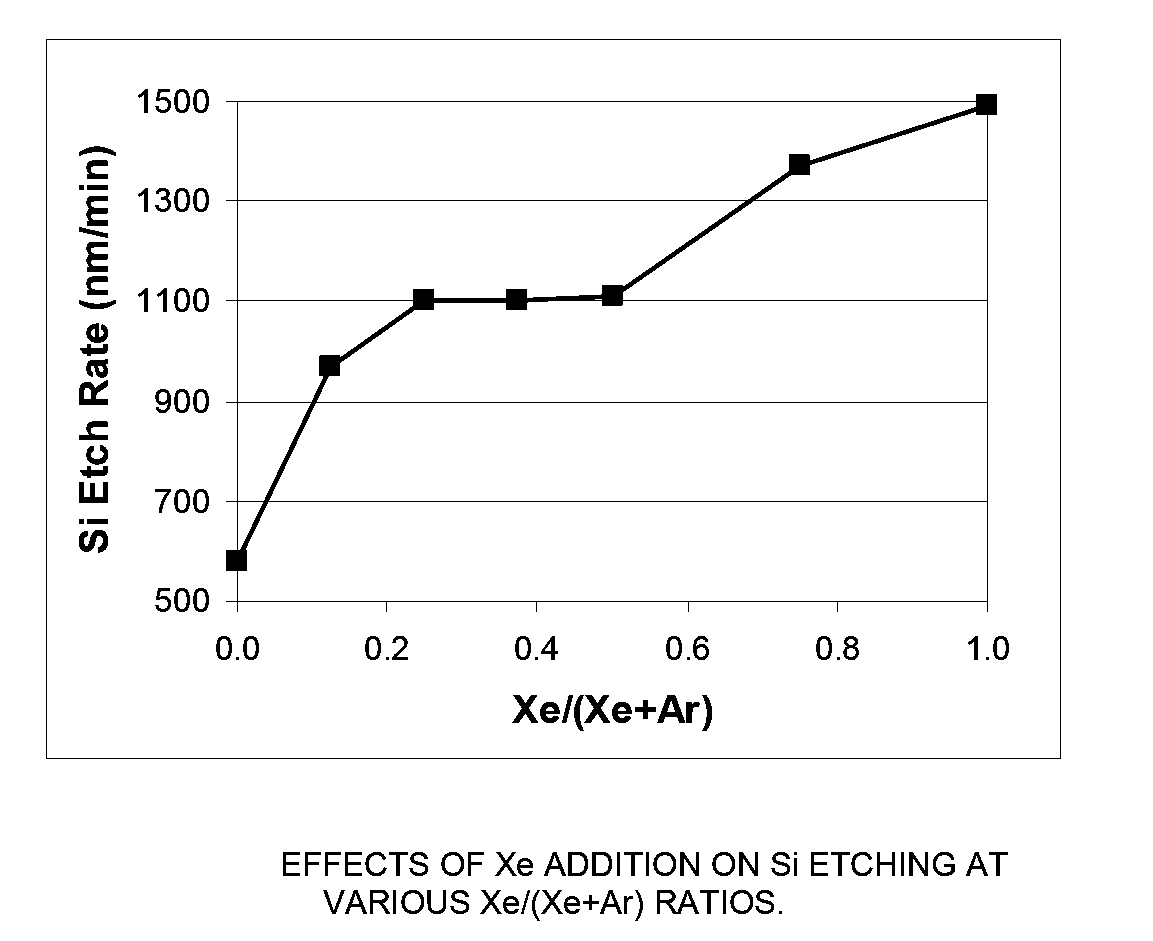

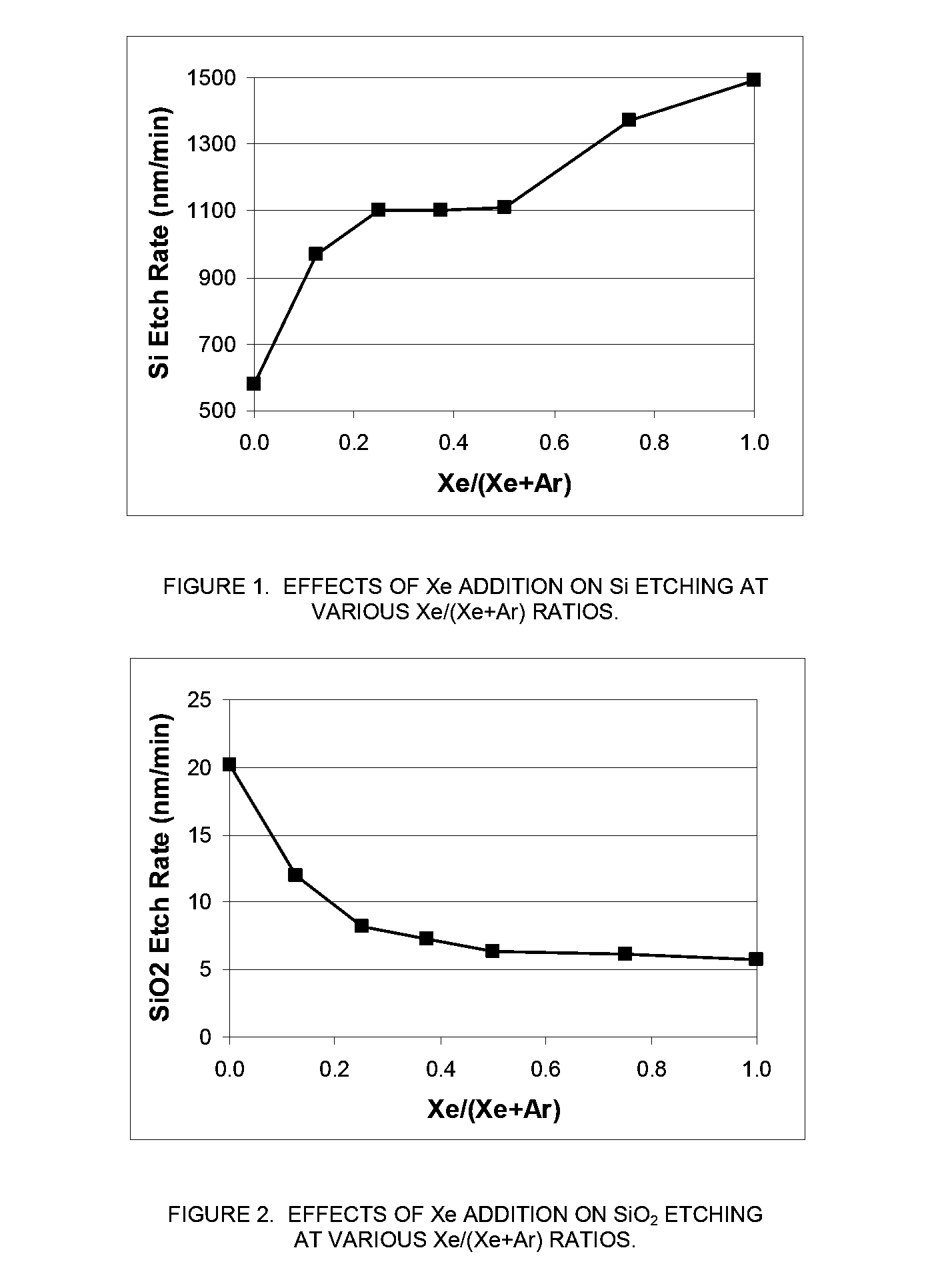

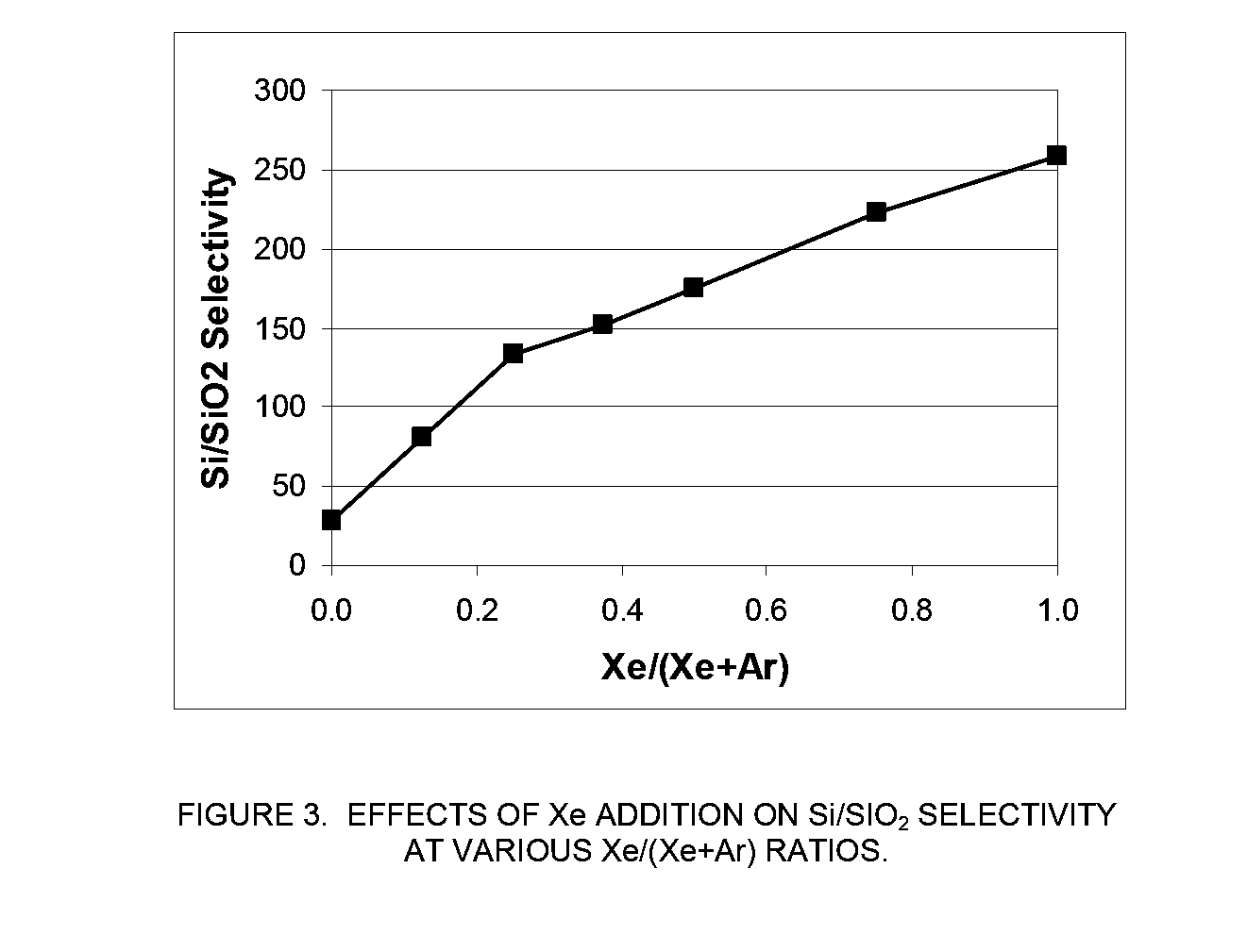

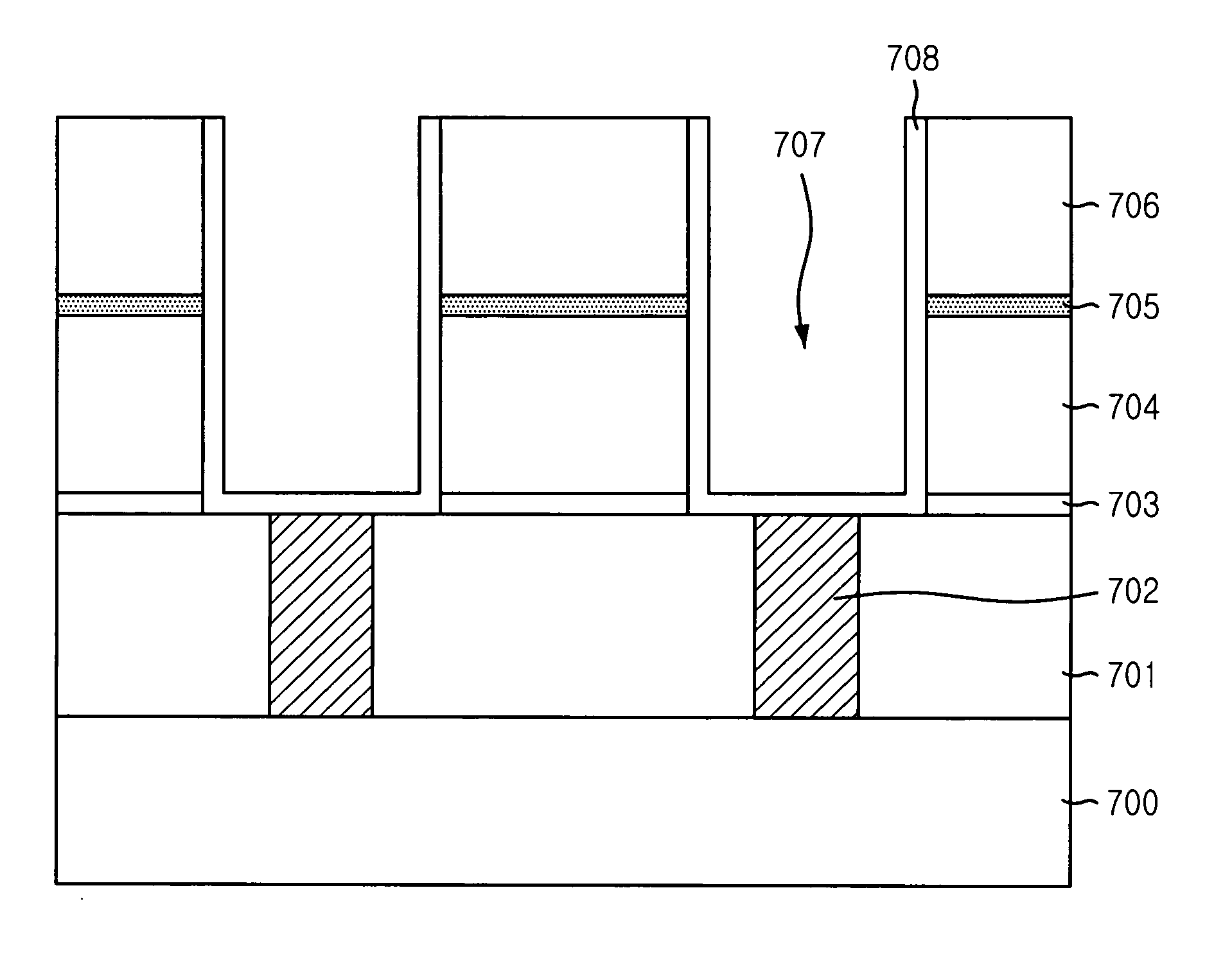

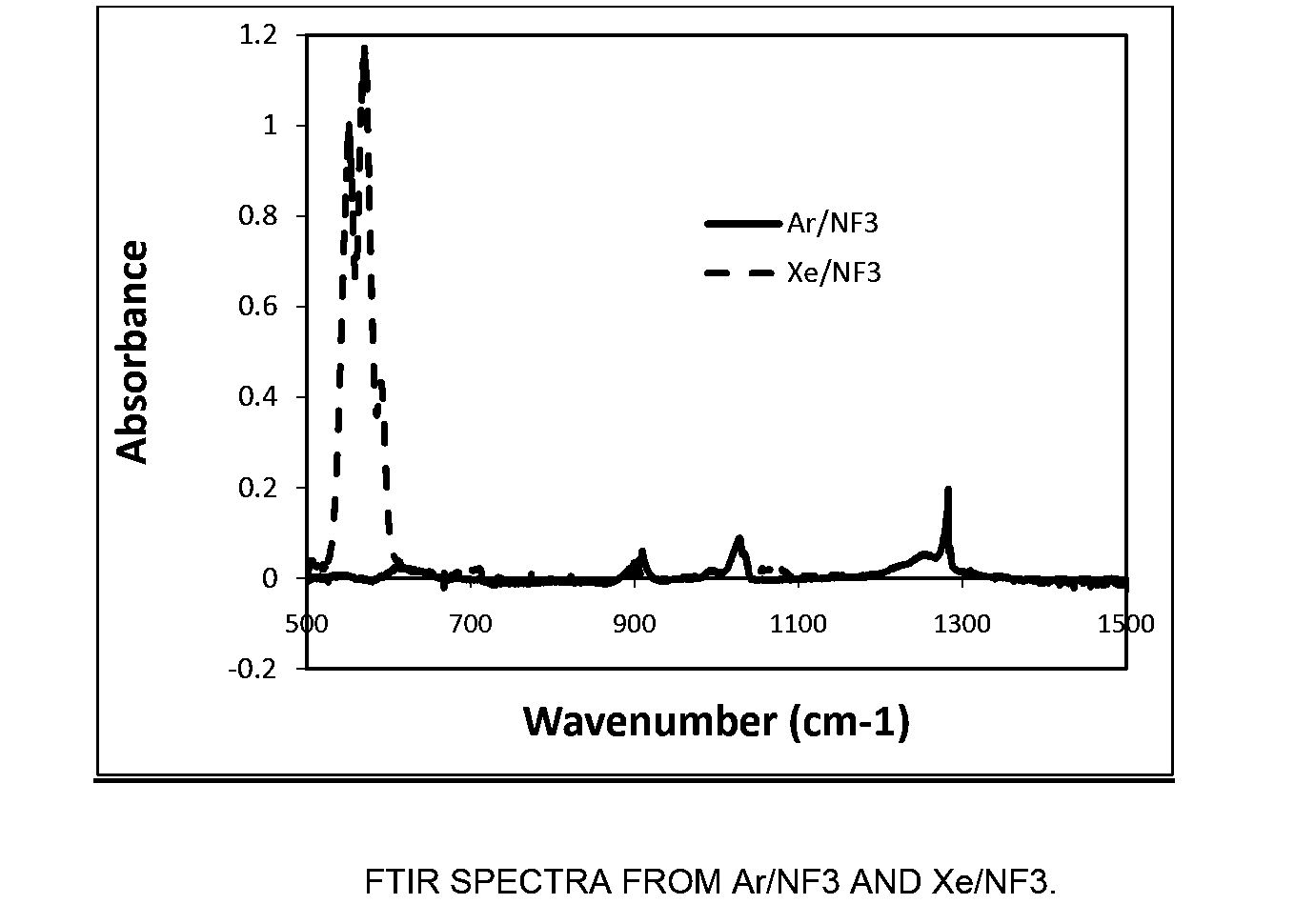

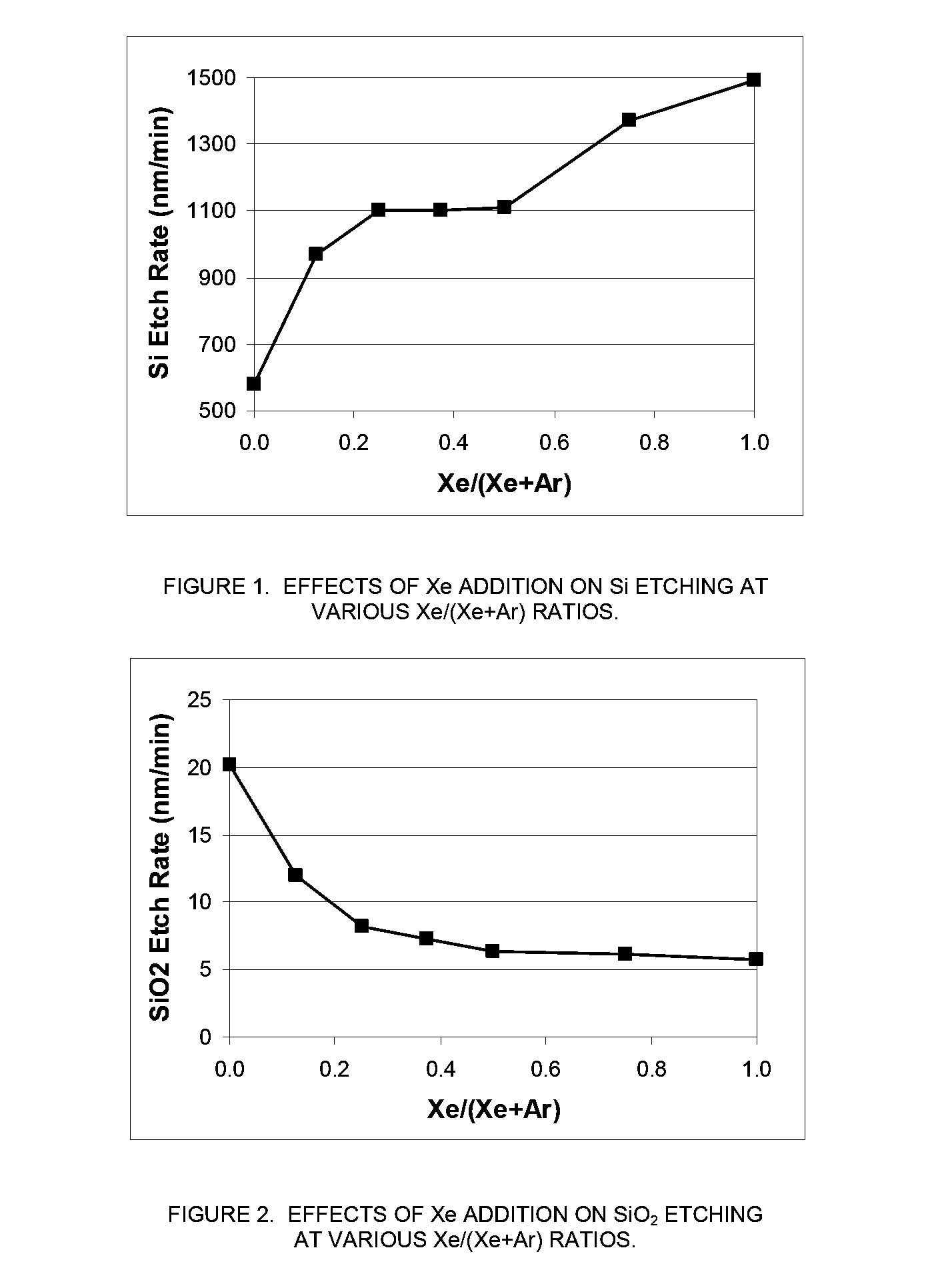

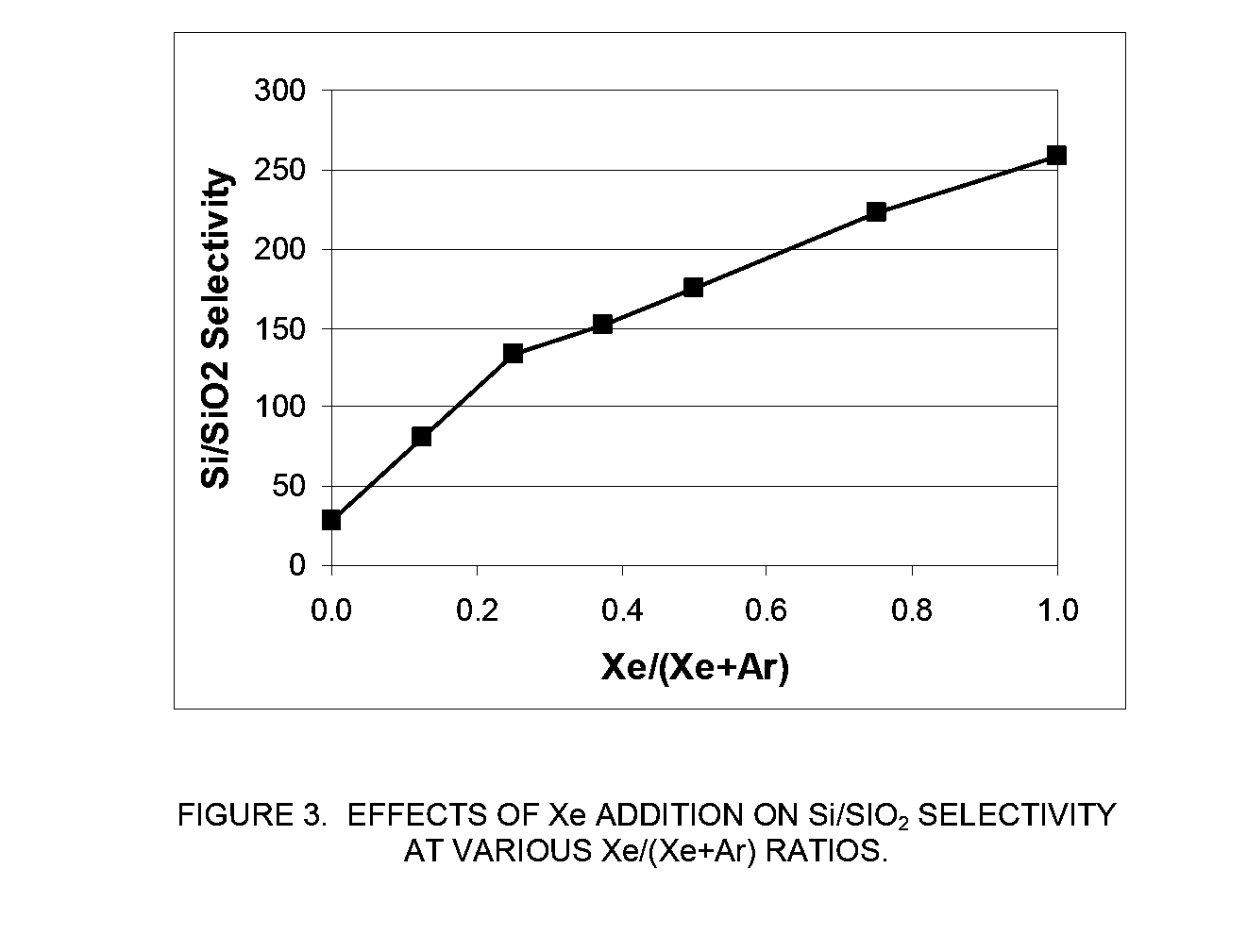

Selective Etching and Formation of Xenon Difluoride

ActiveUS20100022095A1Semiconductor/solid-state device manufacturingNoble gas compoundsEtchingPlasma generator

Owner:VERSUM MATERIALS US LLC

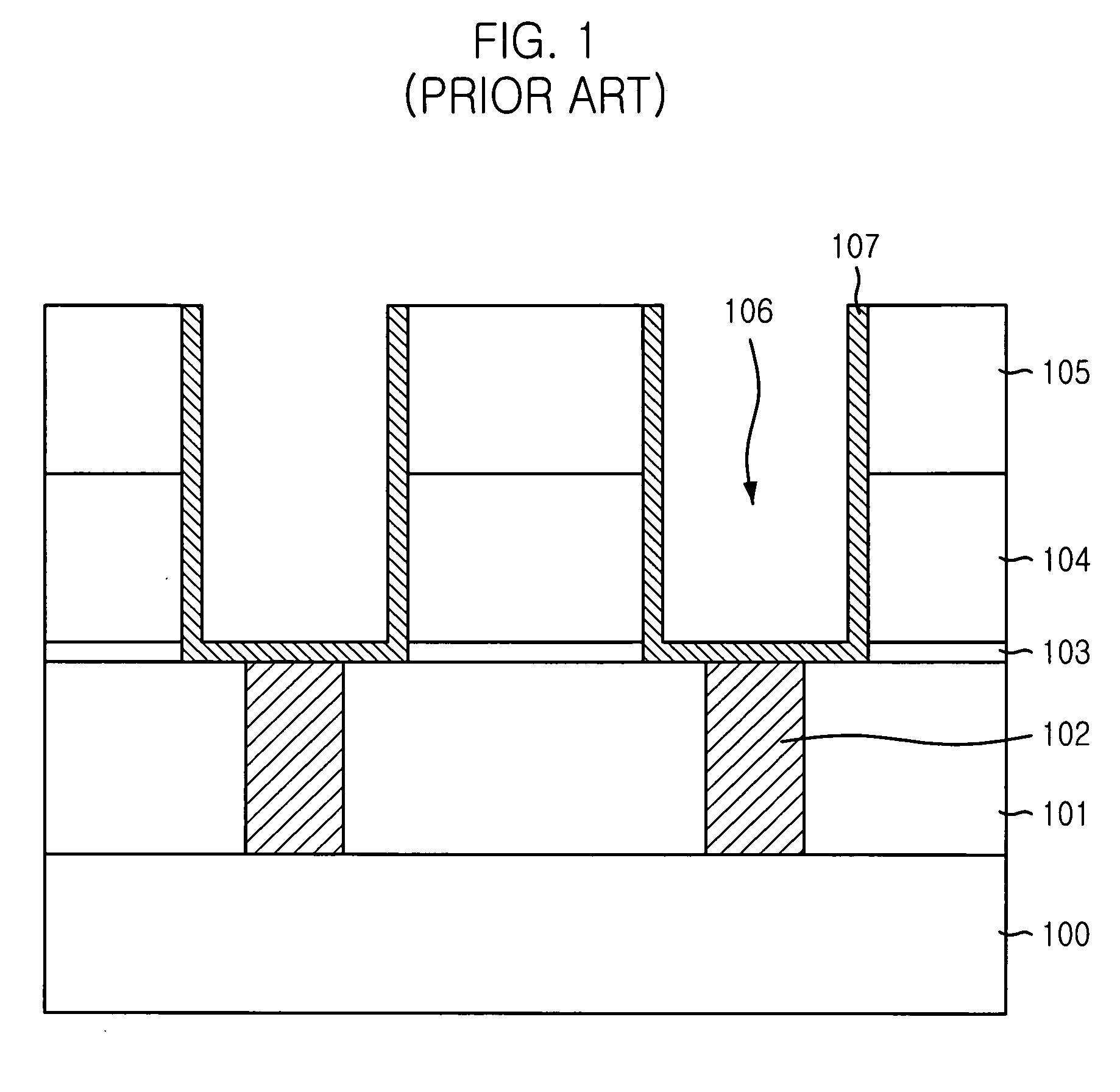

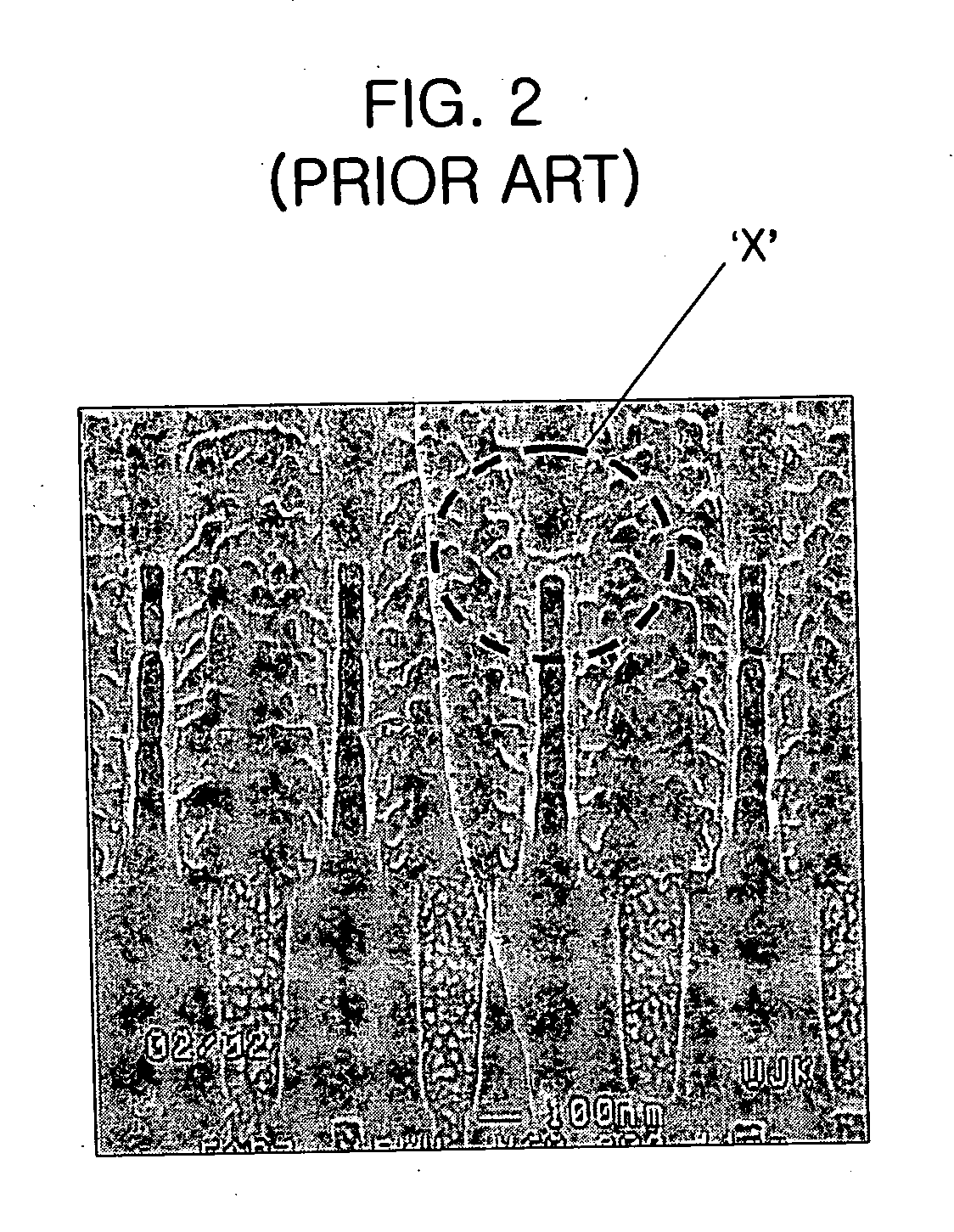

Method for fabricating semiconductor device

ActiveUS20060003582A1Preventing bridge formationLow densitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCapacitor

The present invention relates to a method for fabricating a semiconductor device capable of preventing bridge formation caused by damages to a capacitor oxide structure including a phosphosilicate glass (PSG) layer and a tetraethylorthosilicate (TEOS) layer during a wet cleaning process. The method includes the steps of: forming a PSG layer on a substrate; forming a capping layer on the PSG layer; forming a TEOS layer on the capping layer; selectively etching the TEOS layer, the capping layer and the PSG layer to form a plurality of openings exposing predetermined portions of the substrate; cleaning the openings; forming a conductive layer on the openings; and removing the conductive layer until the TEOS layer is exposed, so that the conductive layer is isolated for each opening.

Owner:CONVERSANT INTPROP MANAGEMENT INC

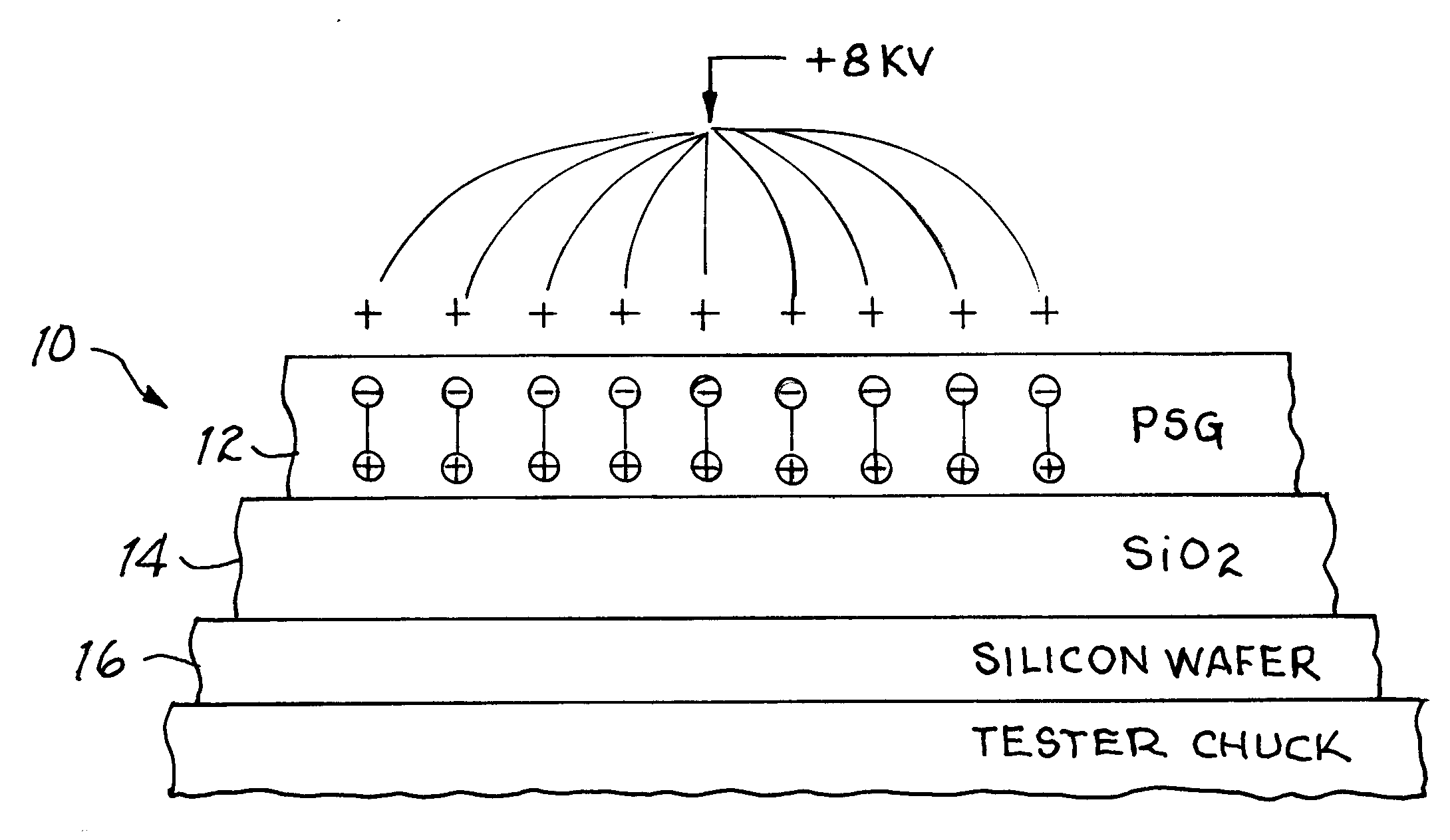

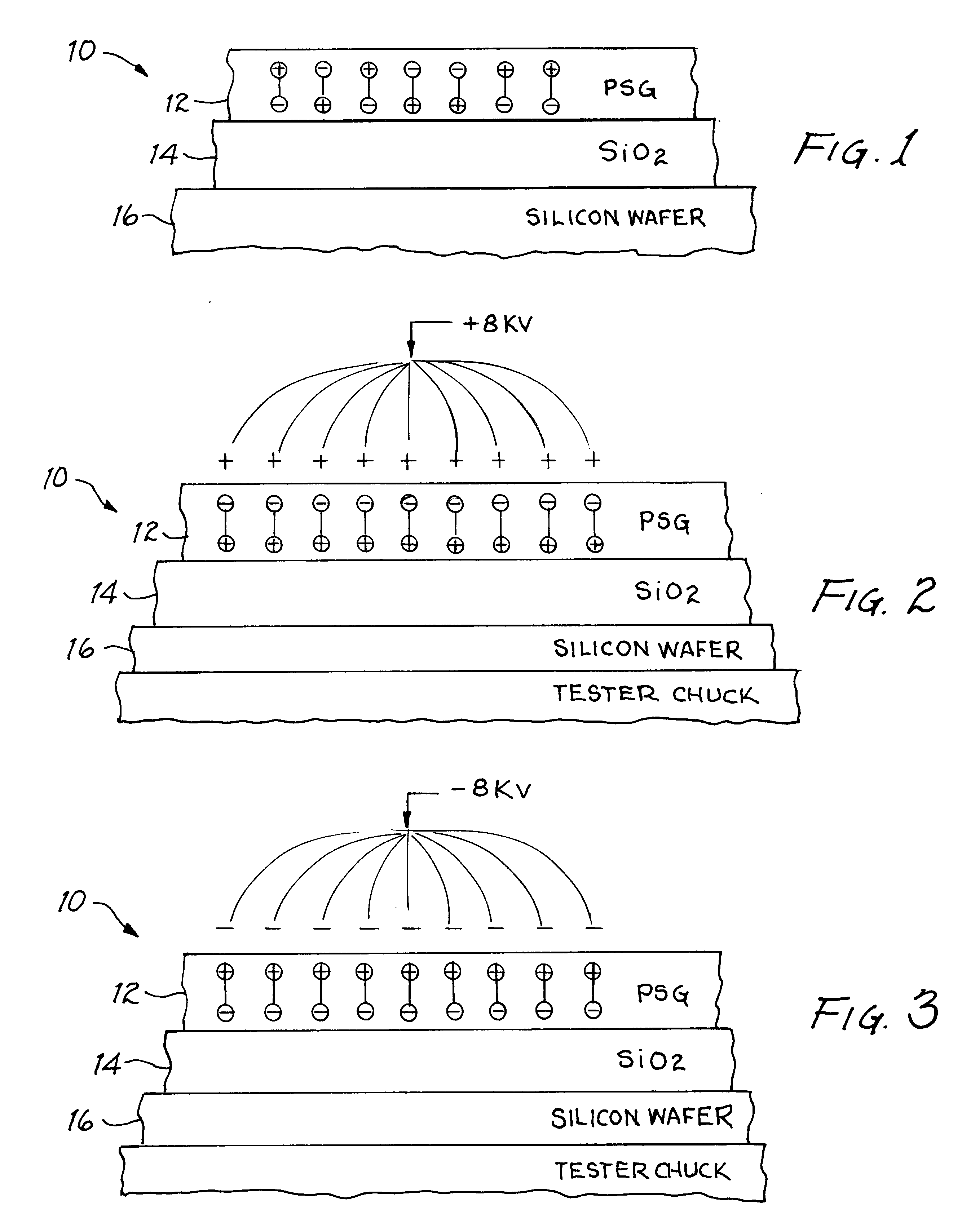

Device for monitoring and calibrating oxide charge measurement equipment and method therefor

InactiveUS6249117B1Quality improvementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsOxygen ionsTest equipment

A stabilized wafer for monitoring and calibrating oxide charge test equipment. The stabilized wafer comprises; a silicon wafer, a SiO2 layer of at least 100 angstroms upon the silicon wafer, and a phosphosilicate glass layer containing phosphorus formed in the SiO2 layer for providing the stabilized wafer by stabilizing an SiO2 interface and containing oxygen ions. The stabilized wafer is used for monitoring and calibrating oxide charge test equipment.

Owner:WAFER STANDARDS

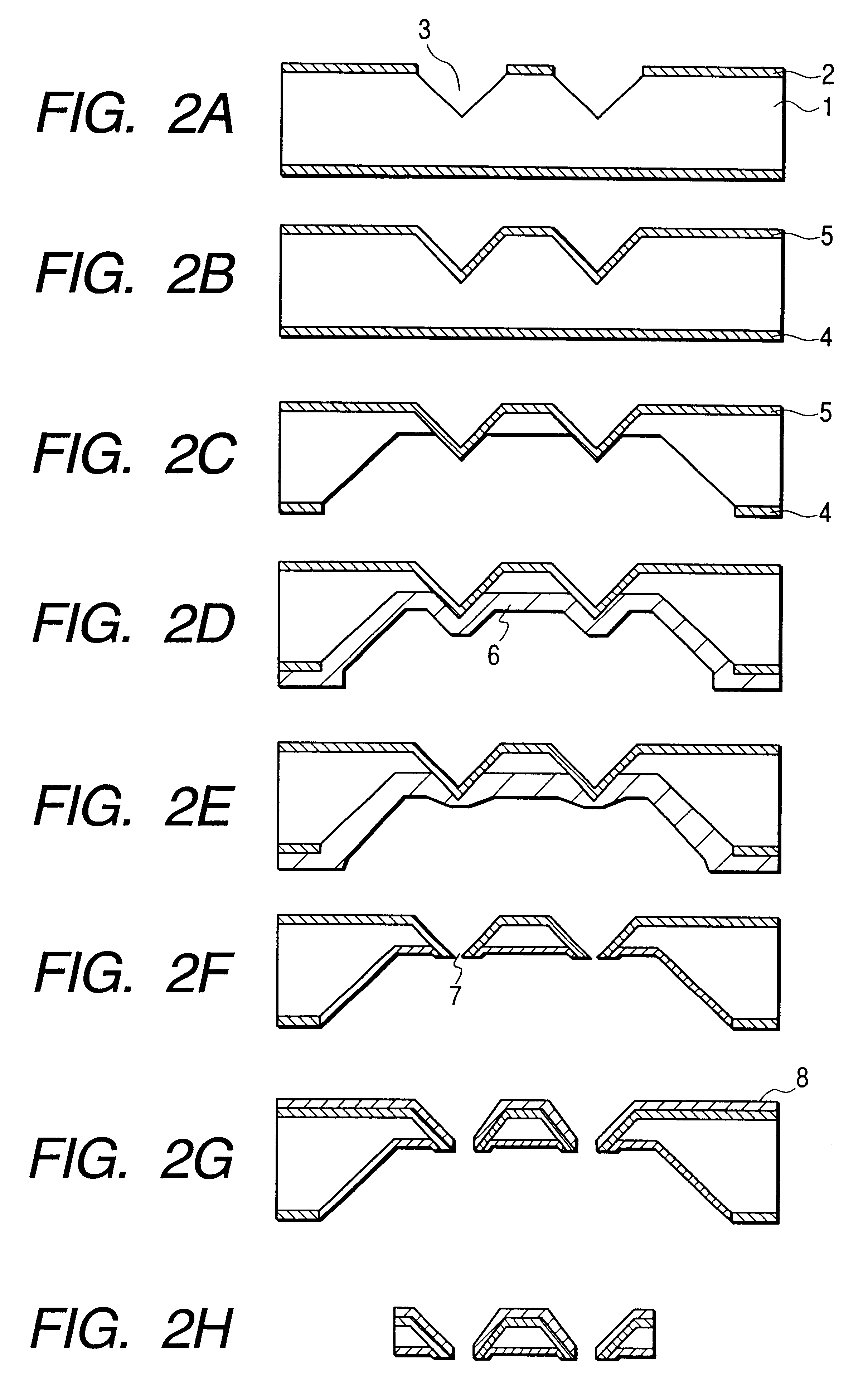

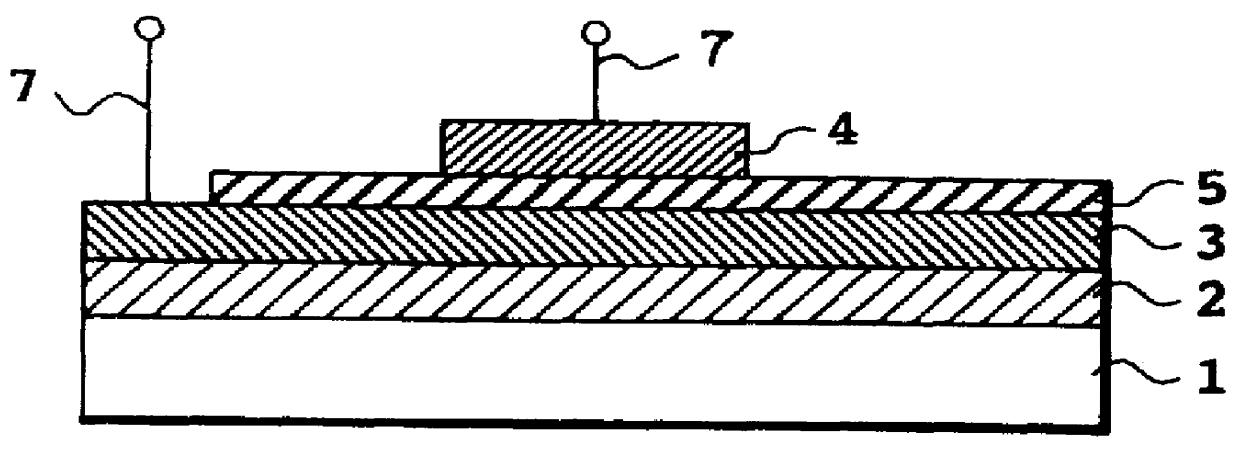

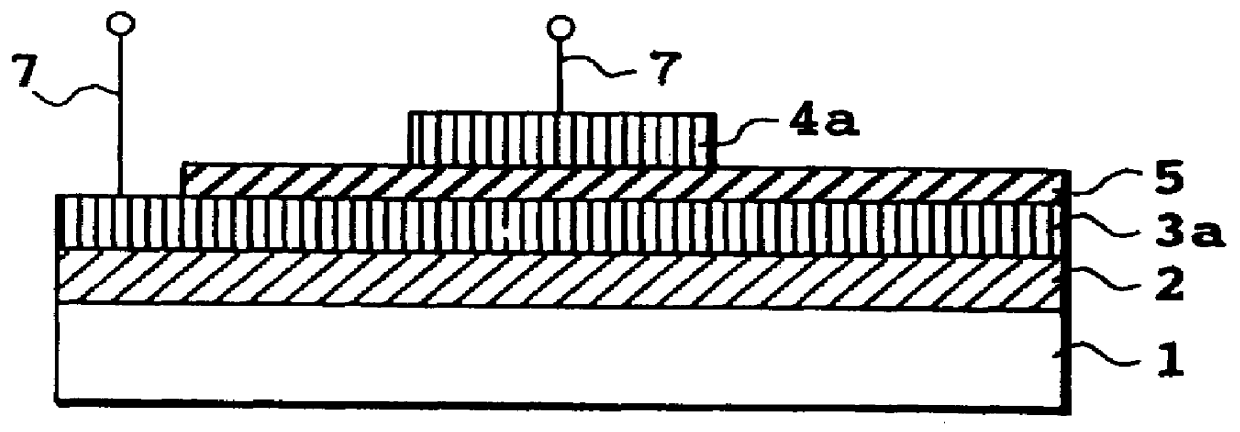

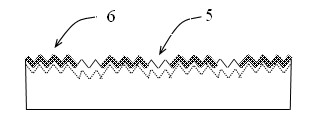

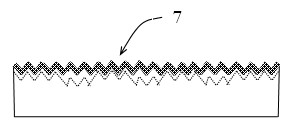

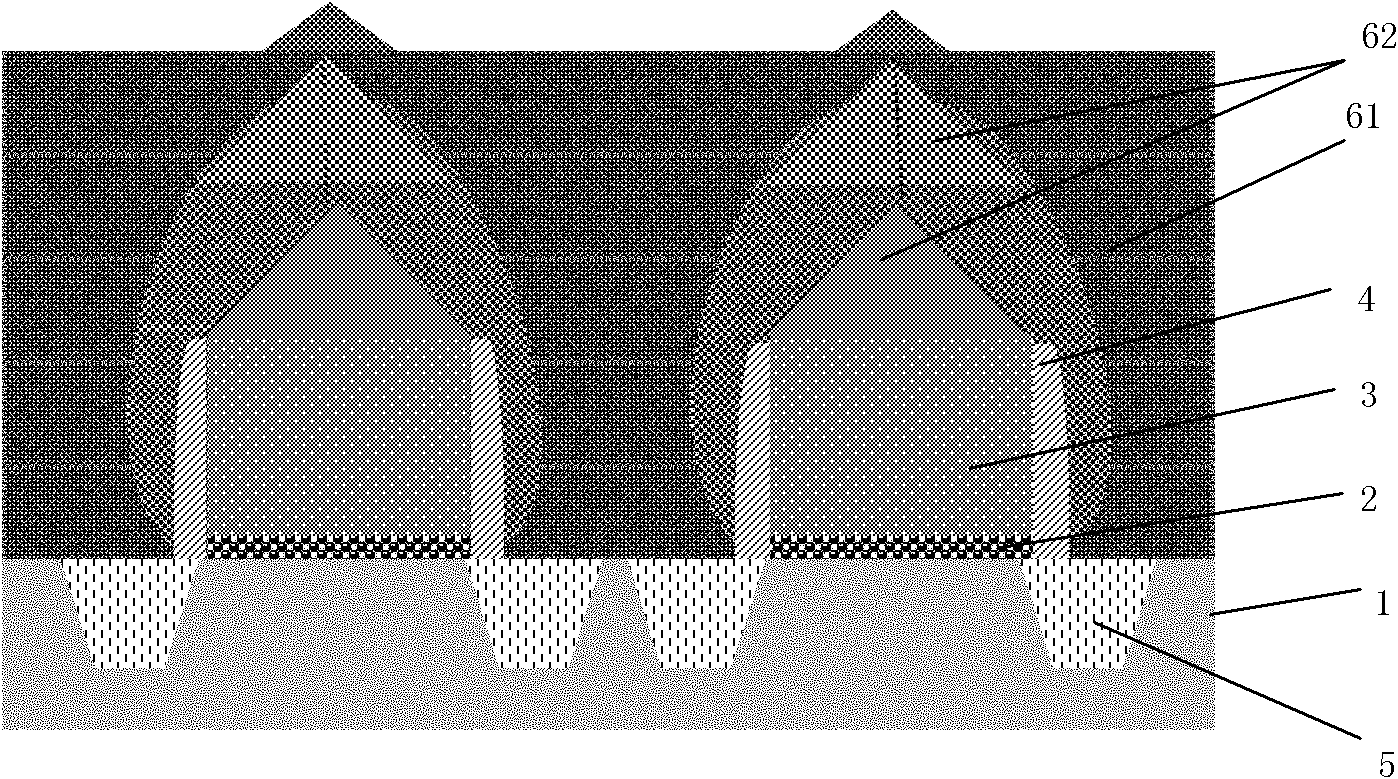

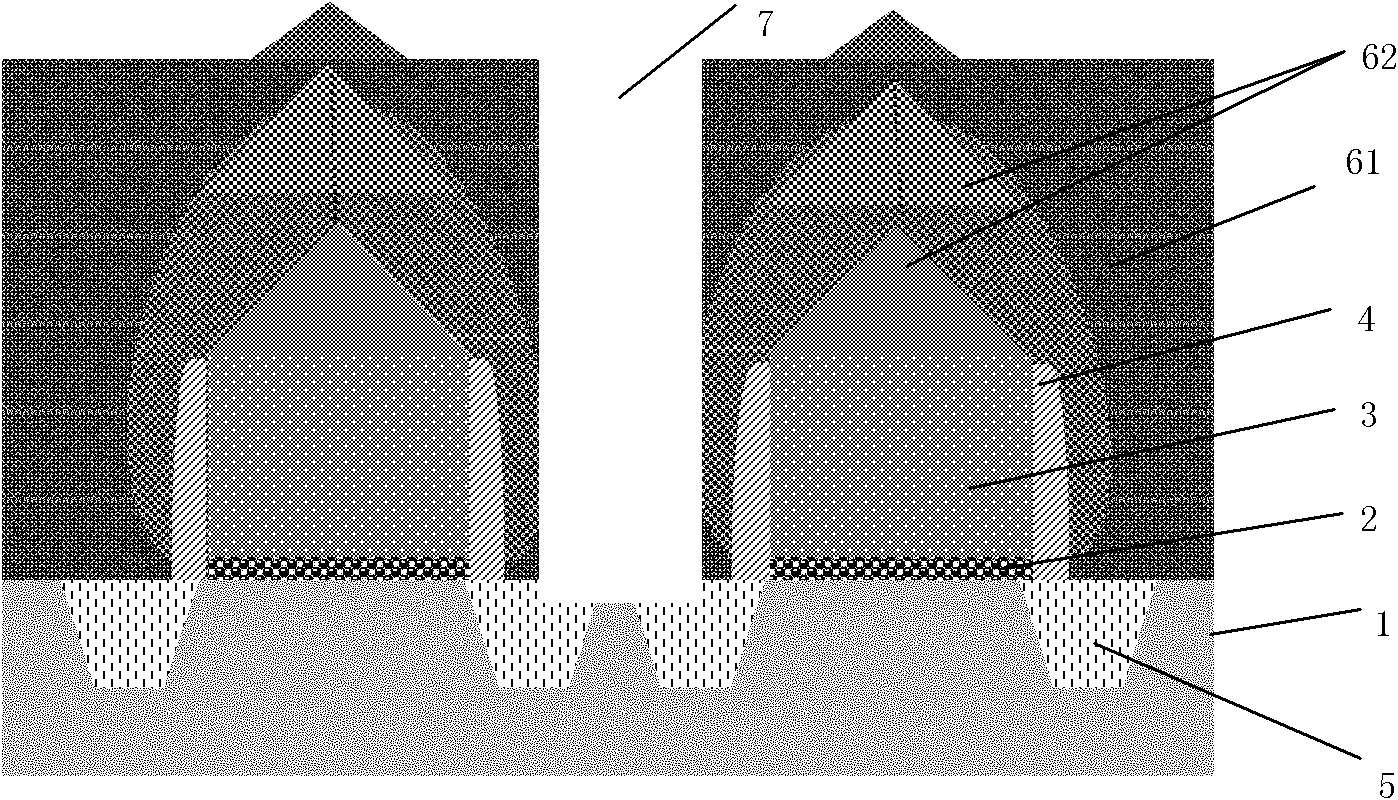

Semiconductor device and production method thereof

InactiveUS6069388AReduce leakage currentMaintain dielectric strengthTransistorFixed capacitor dielectricSilicon oxideDielectric strength

On a silicon substrate 1 is provided a silicon oxide film 2, on which a polycrystalline silicon film 3 is formed by a low pressure CVD method at a monosilane partial pressure of no more than 10 Pa and a film formation temperature of no lower than 600 DEG C. The polycrystalline silicon film is doped with an impurity such as phosphorus in a concentration of 1x1020 atoms / cm3 to 1x1021 atoms / cm3 to form a phosphosilicate glass film 6, and after removing it, the polycrystalline silicon film is thermally oxidized in an oxidative atmosphere to form a dielectric film 5 on the surface. A polycrystalline silicon film 4 is formed on the dielectric film 5, which is treated as the oriented polycrystalline silicon film 3a to form an oriented polycrystalline silicon film 4a. The oriented polycrystalline silicon film 4a as an upper electrode and the oriented polycrystalline silicon film 3a as a lower electrode are wired to obtain a semiconductor device having a capacitor. Further, a thin film transistor of a high dielectric strength can be produced in a short time on the polycrystalline silicon which is oriented in a short time.

Owner:ASAHI KASEI ELECTRONICS CO LTD

Borophosphosilicate glass incorporated with fluorine for low thermal budget gap fill

InactiveUS6159870AStrong Gap Filling CapabilityHigh aspect ratio gapsSemiconductor/solid-state device manufacturingBorophosphosilicate glassChemistry

A method of depositing a fluorinated borophosphosilicate glass (FBPSG) on a semiconductor device as either a final or interlayer dielectric film. Gaps having aspect ratios greater than 6:1 are filled with a substantially void-free FBPSG film at a temperature of about 480 DEG C. at sub-atmospheric pressures of about 200 Torr. Preferably, gaseous reactants used in the method comprise TEOS, FTES, TEPO and TEB with an ozone / oxygen mixture. Dopant concentrations of boron and phosphorus are sufficiently low such that surface crystallite defects and hygroscopicity are avoided. The as-deposited films at lower aspect ratio gaps are substantially void-free such that subsequent anneal of the film is not required. Films deposited into higher aspect ratio gaps are annealed at or below about 750 DEG C., well within the thermal budget for most DRAM, logic and merged logic-DRAM chips. The resultant FBPSG layer contains less than or equal to about 5.0 wt % boron, less than about 4.0 wt % phosphorus, and about 0.1 to 2.0 wt % fluorine.

Owner:IBM CORP

Production method for full back electrode solar cells

ActiveCN102709385AImprove efficiencyReduce manufacturing costFinal product manufactureSemiconductor devicesScreen printingBack surface field

The invention relates to a production method for full back electrode solar cells. The production method includes the steps: 1, performing single-surface boron diffusion to form a P+ layer on the back of an N-type silicon wafer; 2, depositing a texturing mask layer on the P+ layer; 3, performing single-surface texturing; 4, preparing a front surface field on the illuminated surface of the silicon wafer by phosphorus diffusion; 5, removing the texturing mask layer and PSG (phosphosilicate glass); 6, preparing an SiO2 mask layer by thermal oxide growth; 7, slotting in the area of a back surface field on the back of the silicon wafer, wherein the depth of each slot is not less than the junction depth of a P-N plus the depth of the back surface field together; 8, printing a phosphorous doping agent with the height less than the slot depth H minus the P-N junction depth at the bottom of the slotting area; 9, forming N+ layers at the bottom of the slots by the aid of high-temperature diffusion; 10, removing PSG and the SiO2 mask layer; 11, preparing a passive film on each of the front and the back; 12, performing screen printing for metal electrodes; and 13, sintering. The production method for the full back electrode solar cells has the advantages that cell efficiency is improved greatly while production cost is reduced by the aid of height difference of a P+ area and an N- area, namely a matrix N area, and suitability for large-scale production is achieved.

Owner:TRINA SOLAR CO LTD

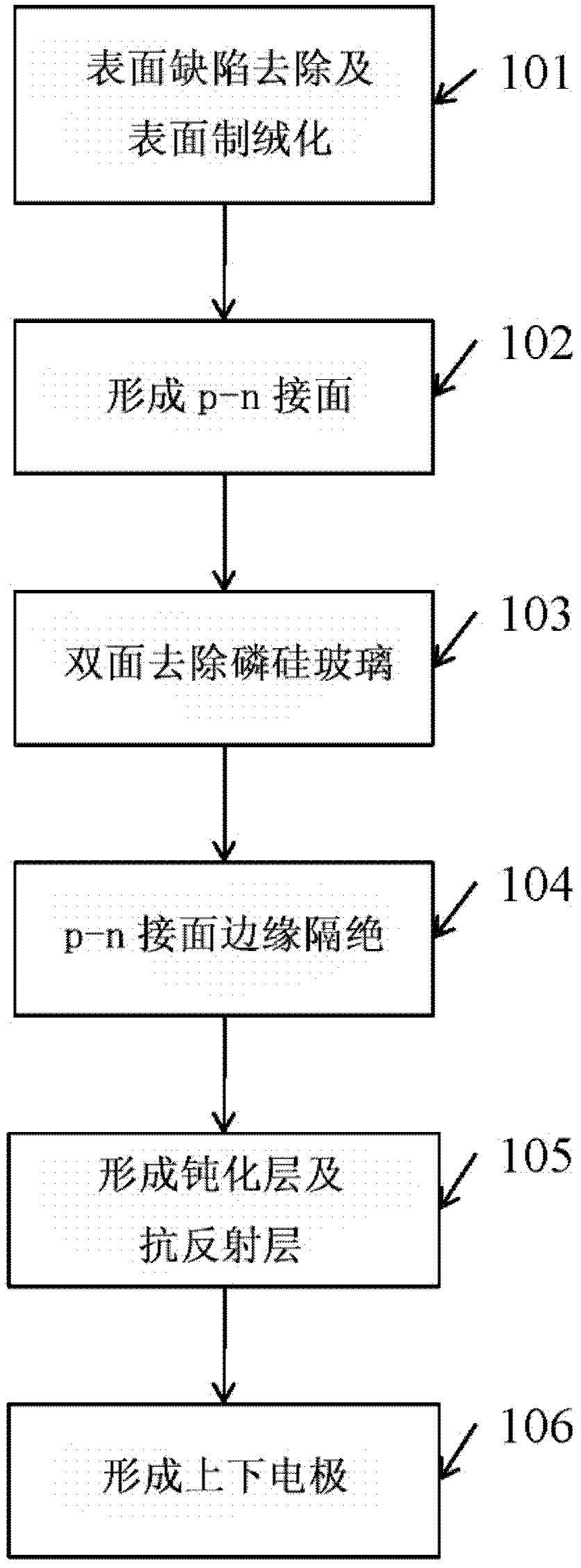

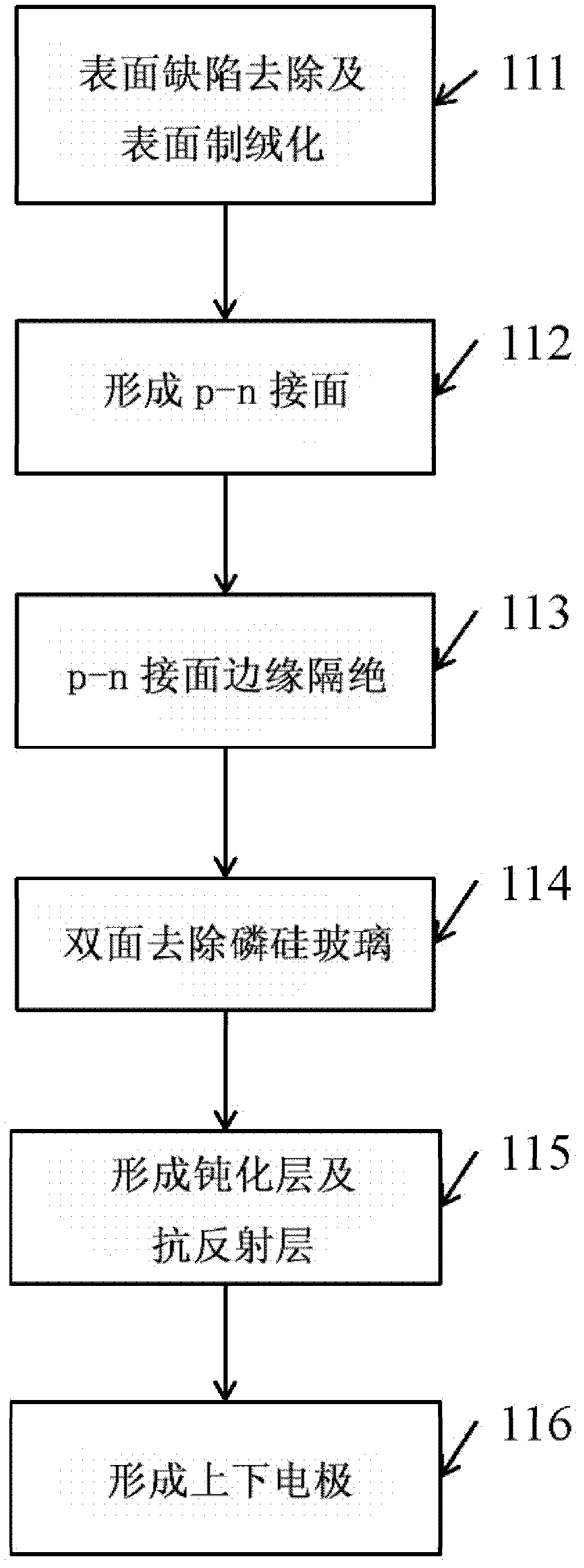

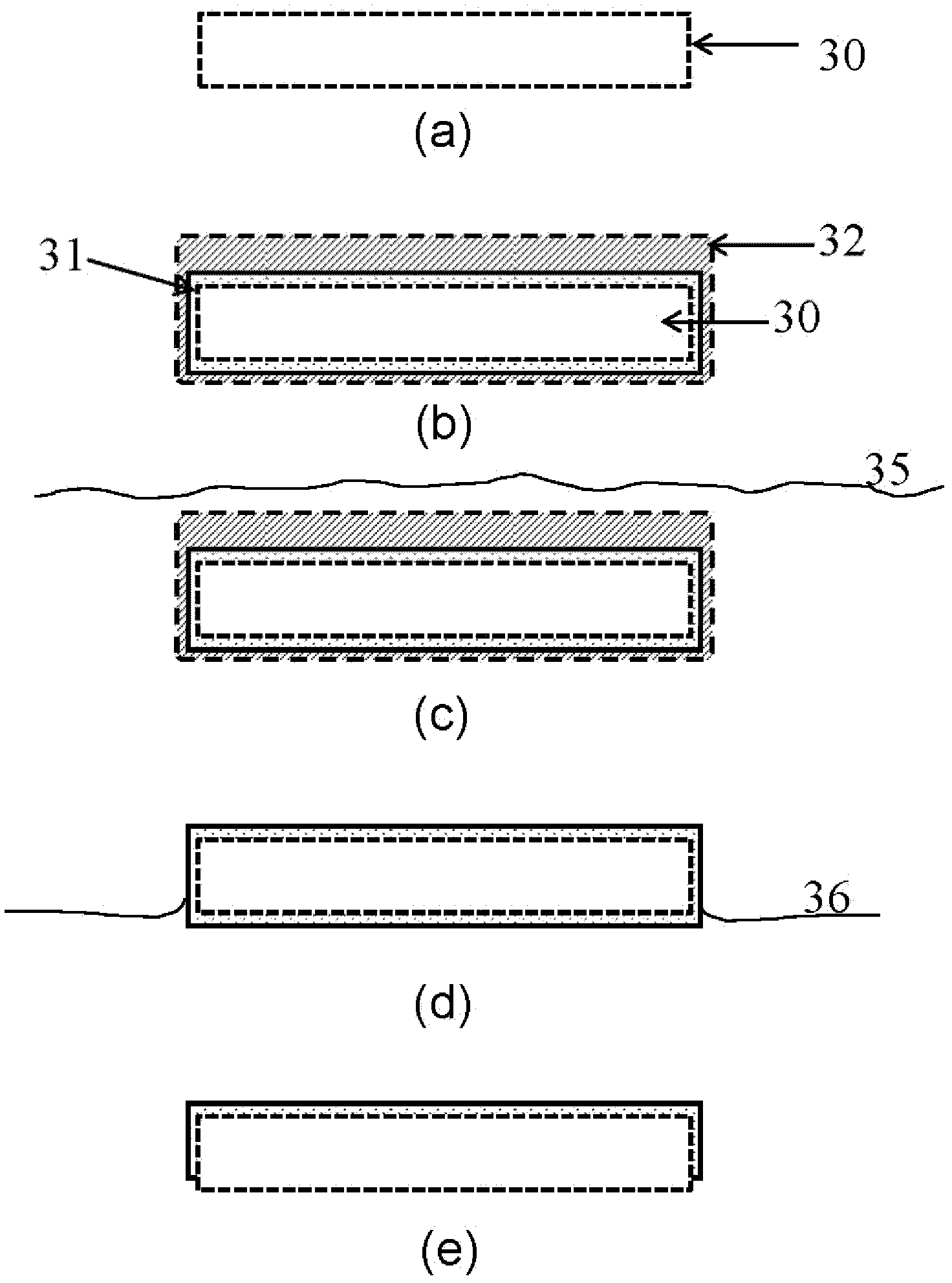

Method for fabricating silicon wafer solar cell

InactiveCN102456771AImprove photoelectric conversion efficiencyIncrease production rateFinal product manufacturePhotovoltaic energy generationCompound (substance)Solar cell

The invention provides a method for fabricating a silicon wafer solar cell, comprising the following steps: texturing a silicon wafer, forming a p-n junction, performing a wet chemical surface treatment, performing a passivation layer formation process, and performing electrodes formation process, wherein the wet chemical surface treatment comprises the following specific process flow: performing a backside phosphosilicate glass (PSG) removal process, performing an edge isolation and backside polish process, performing a double-side phosphosilicate glass and oxide removal process, and performing a front-side shallow junction formation process.

Owner:WAKOM SEMICON CORP

Preparation method of solar cell for reutilizing diffusion oxide layer

InactiveCN102364698AQuick removalShorten manufacturing timeFinal product manufactureSemiconductor devicesHydrofluoric acidSilicate glass

The invention relates to a preparation method of a solar cell for reutilizing a diffusion oxide layer. The method comprises the following steps of: not removing a silicon oxide layer (such as BSG (Boron Silicate Glass) and PSG (Phosphosilicate Glass)) formed by diffusion on a front face immediately but plating a layer of film on the oxide layer after a diffusion process is completed to form a double-layer film for serving as a mask for quickly removing back face junctions subsequently and for use in a procedure for making a back face electric field by back diffusion; and removing the film and the silicon oxide layer on the front face, and a silicon oxide layer on the back face together with hydrofluoric acid in a post cleaning procedure. Due to the adoption of the method, back junctions formed by diffusion can be removed quickly, the production process flow is optimized, the cell producing and manufacturing time is shortened greatly, and mass production is available.

Owner:TRINASOLAR CO LTD

Preparation method of selective emitter solar cell

InactiveCN101950780AReduce one high temperature diffusion processThe process path is simpleFinal product manufactureSemiconductor devicesScreen printingSolar cell

The invention discloses a preparation method of a selective emitter solar cell, comprising the following steps: providing a silicon wafer for carrying out surface texturization; printing a diffusion permeable membrane on the silicon wafer by a first silk-screen printing plate; covering a non-electrode region by using the diffusion permeable membrane printed by the first silk-screen printing plate, exposing an electrode region to be printed; forming a light diffusion layer for the silicon wafer in the non-electrode light-affected region with the permeable membrane, and forming a heavy diffusion layer in the electrode region without the permeable membrane to be printed; carrying out corrosion for removing peripheral PN nodes, washing the membrane, and removing phosphosilicate glasses; preparing a passivation layer and an antireflection layer; and printing by the printing screen printing plate and sintering to form a back Ag electrode, a back Al-BSF and a front Ag electrode. The preparation method for the selective emitter solar cell provided by the invention adopts one-time diffusion to form the light and heavy doping required by the selective emitter solar cell, thereby reducing one-time high-temperature diffusion process, simplifying processes of the technology, and lowering the cost.

Owner:百力达太阳能股份有限公司

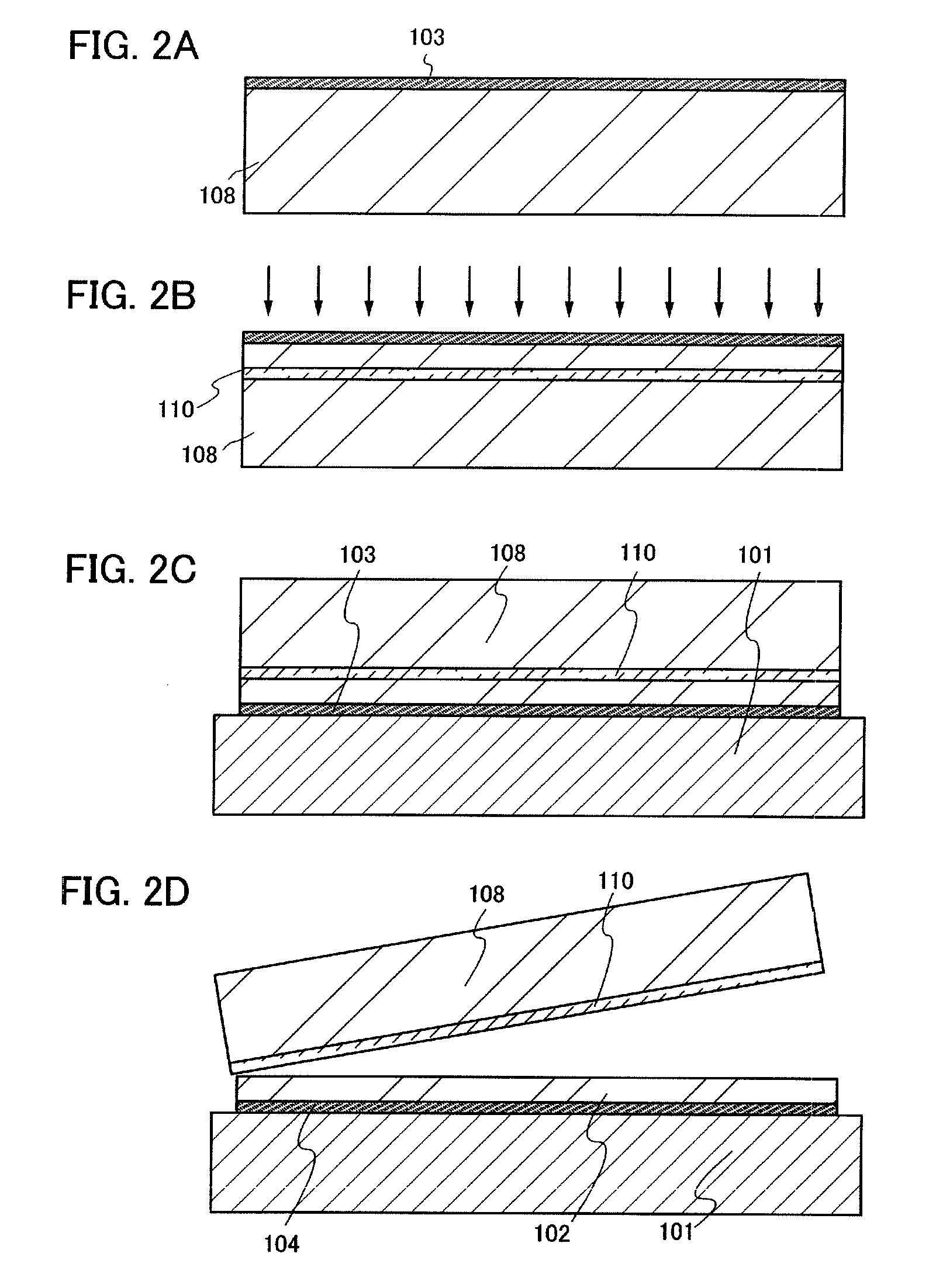

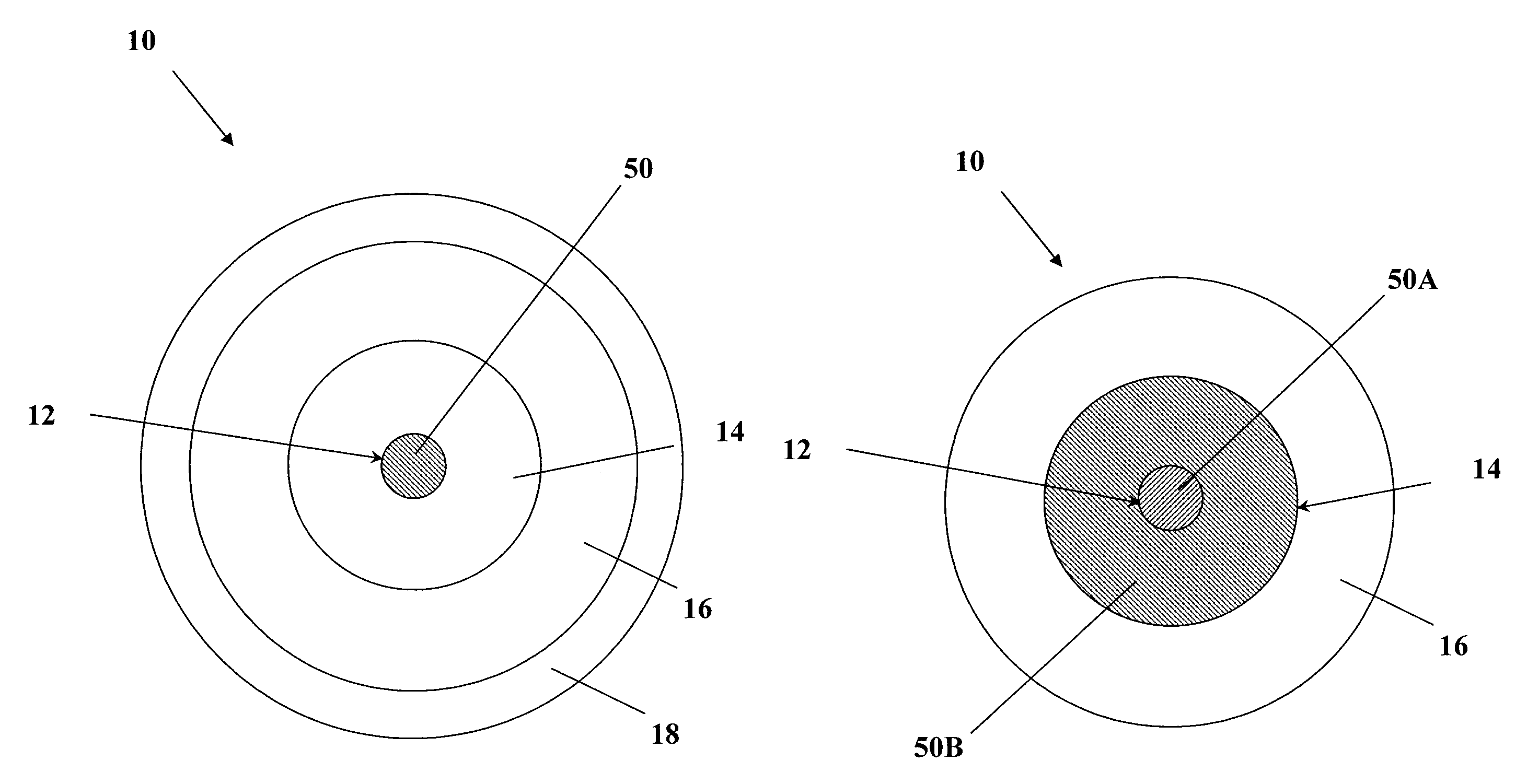

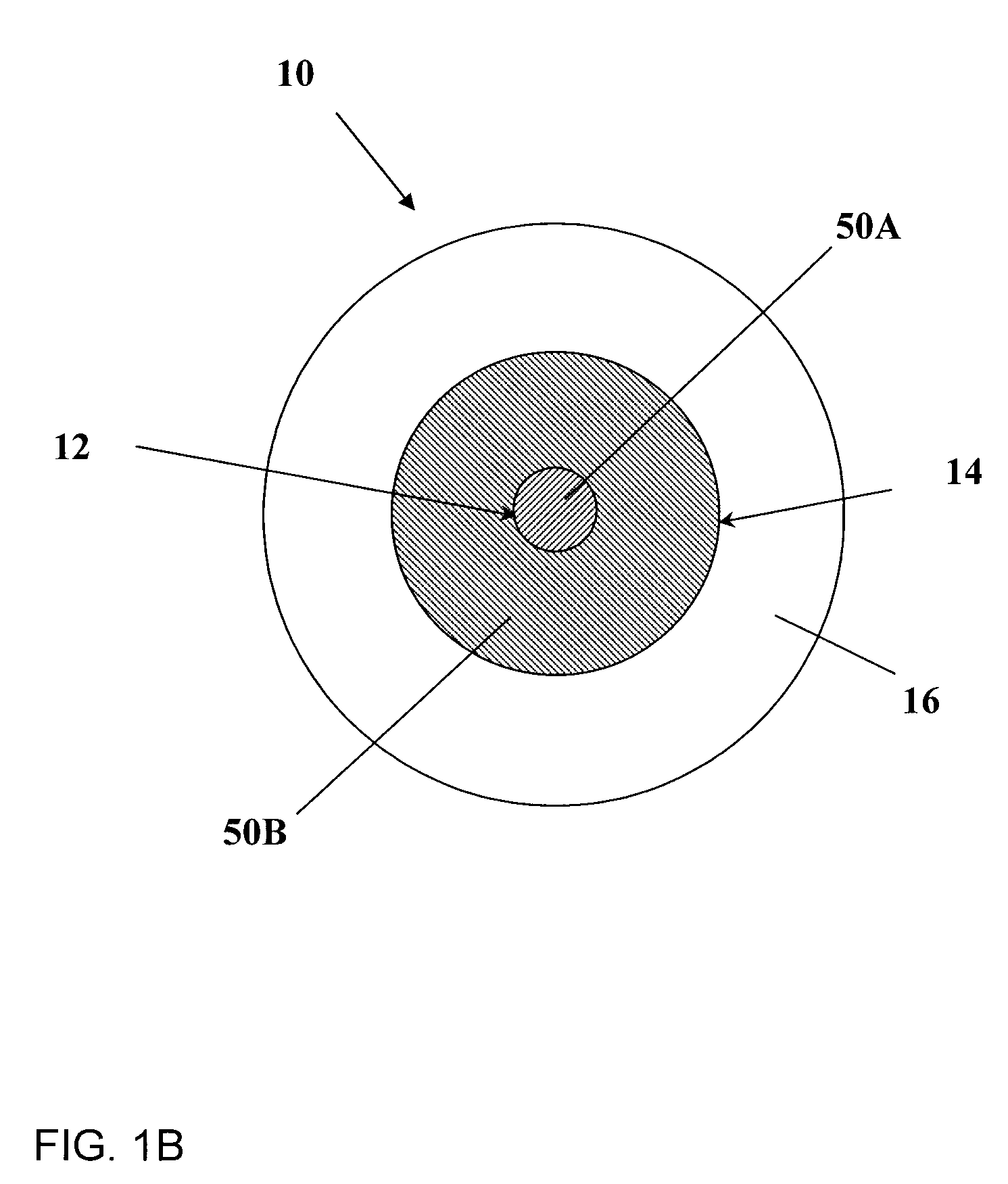

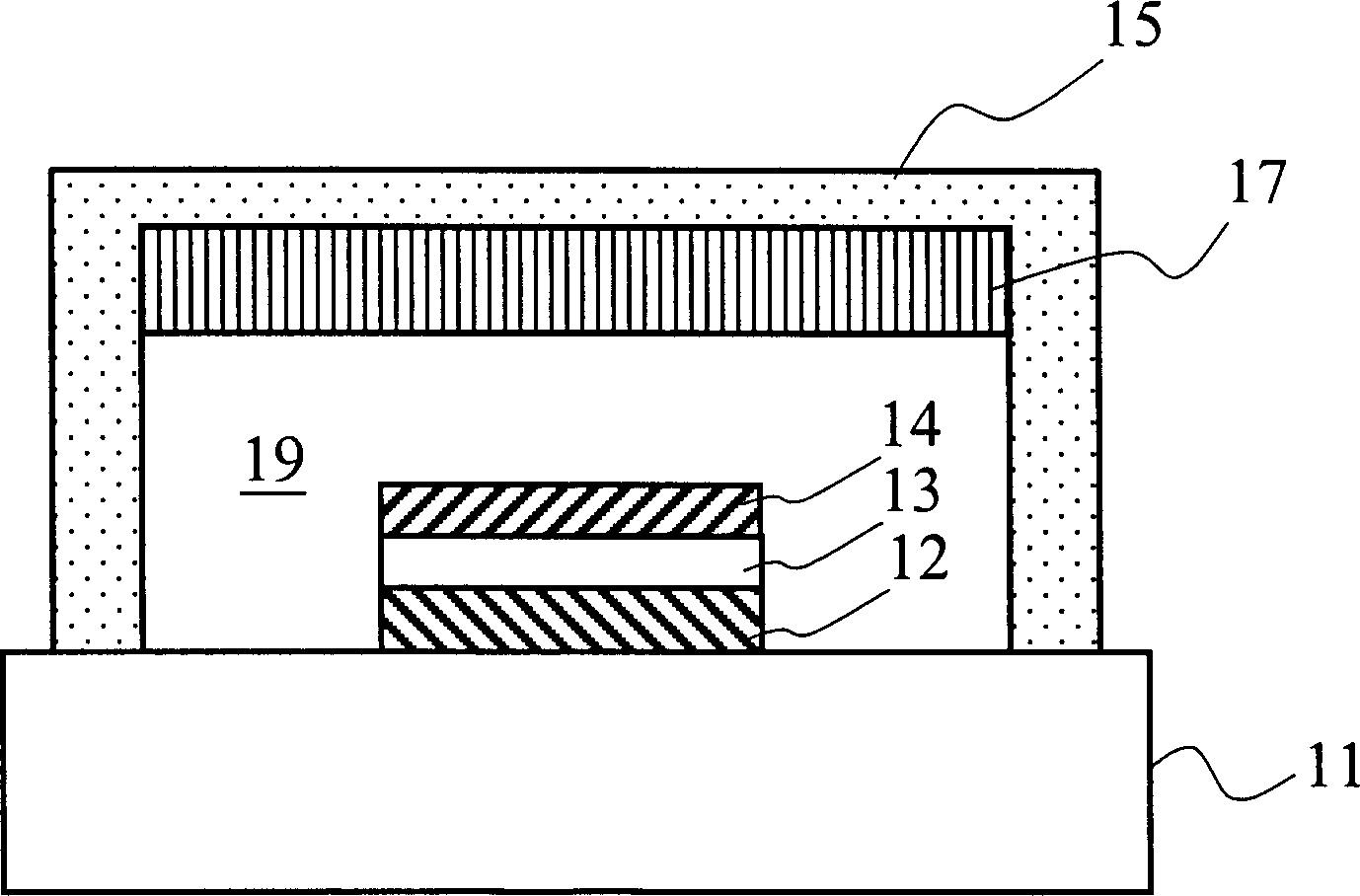

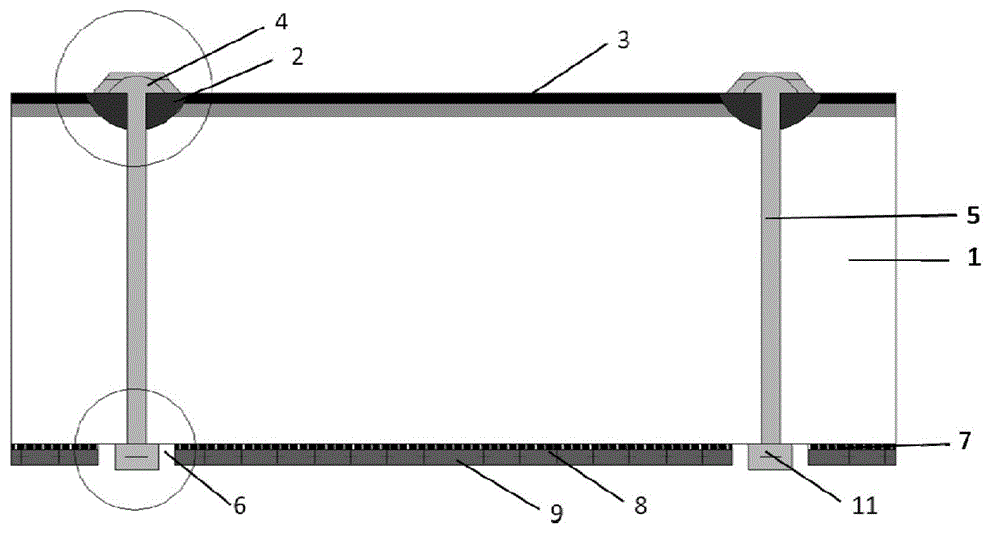

Organic electroluminescent element

InactiveCN1395449AHelp refine requirementsInhibitionElectrical apparatusElectroluminescent light sourcesElectricityOrganic layer

The invention relates to the organic light component excited by electricity, especially the organic light component with the tube added in order to absorb more moisture to restrain the production of the black dot. Thus the quality of the light component is insured. The main structure of the light component includes the base plate, the lower electrode, the multiple insulation bearing ribs, at least one organic layer and the opposite electrodes. The insulation bearing ribs are made from phosphosilicate glass (PSG), which possesses the properties of absorbing moisture and insulating, located on the surface of the lower electrode. Since the ribs absorb the moisture or oxygen around the organic light components effectively, the probability of producing the black sports is reduced.

Owner:OPTO TECH

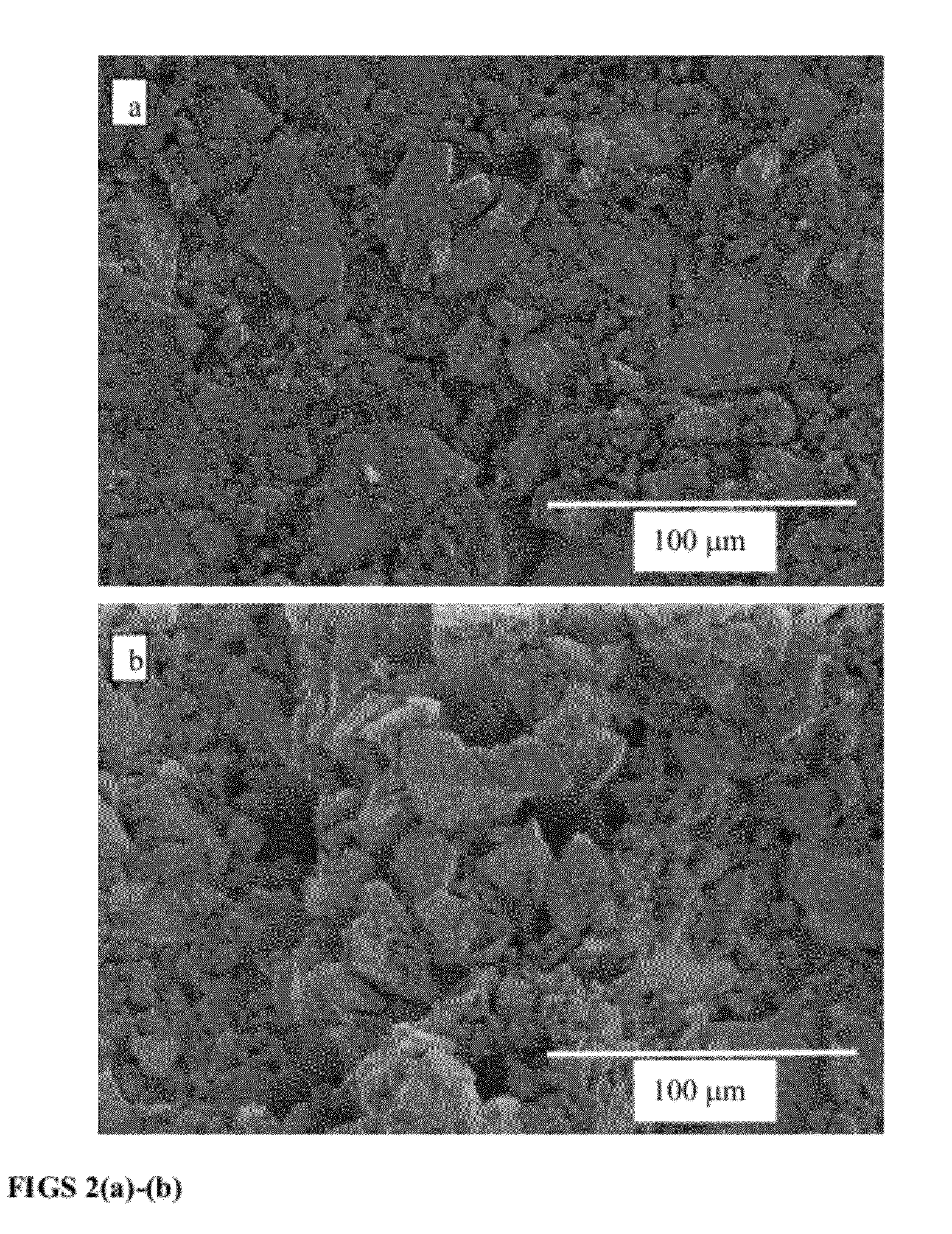

Preparation method for highly-doped phosphorosilicate glass film

InactiveCN102592992AEasy to fillImprove bottom starting positionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEtchingChemical vapor deposition

The invention discloses a preparation method for a highly-doped phosphorosilicate glass film. The preparation method includes the following steps: forming a gate oxide layer, a polycrystalline silicon gate and a side wall on a silicon substrate; injecting a drain source and carrying out rapid thermal annealing; depositing an SACAD PSG (Selected Area Chemical Vapor Deposition Phosphosilicate Glass) film; depositing an HDP PSG (High Density Polyethylene Phosphosilicate Glass) film; and etching a contact hole. According to the preparation method, the phenomenon that the silicon substrate is damaged by over etching of the contact hole can be avoided; and the PSG film prepared by the method has excellent hole-filling performance and a film structure easy to etch. During preparation, firstly, a layer of PSG film is grown by using an SACAD deposition process; and secondly, a highly-doped PSG film is grown by using an HDP CAD deposition process. Due to the utilization of the characteristic that the SACAD PSG film is uniform in the phosphor doping mount, the position of a starting point at the bottom of the HDP PSG film flower-shaped casing is heightened, a process window for selective etching of the contact hole is increased and further the phenomenon that the silicon substrate is damaged caused by the over etching of the contact hole and the performances of the devices are effectively maintained.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Selective etching and formation of xenon difluoride

ActiveUS8278222B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingEtchingPlasma generator

This invention relates to a process for selective removal of materials, such as: silicon, molybdenum, tungsten, titanium, zirconium, hafnium, vanadium, tantalum, niobium, boron, phosphorus, germanium, arsenic, and mixtures thereof, from silicon dioxide, silicon nitride, nickel, aluminum, TiNi alloy, photoresist, phosphosilicate glass, boron phosphosilicate glass, polyimides, gold, copper, platinum, chromium, aluminum oxide, silicon carbide and mixtures thereof. The process is related to the important applications in the cleaning or etching process for semiconductor deposition chambers and semiconductor tools, devices in a micro electro mechanical system (MEMS), and ion implantation systems. Methods of forming XeF2 by reacting Xe with a fluorine containing chemical are also provided, where the fluorine containing chemical is selected from the group consisting of F2, NF3, C2F6, CF4, C3F8, SF6, a plasma containing F atoms generated from an upstream plasma generator and mixtures thereof.

Owner:VERSUM MATERIALS US LLC

Process of manufacturing crystalline silicon solar cell

InactiveUS20140038339A1Improve photoelectric conversion efficiencyMinimal problemFinal product manufactureSemiconductor/solid-state device manufacturingRough surfaceCrystalline silicon

A process of manufacturing a crystalline silicon solar cell includes forming a rough surface on a surface of the crystalline silicon wafer and an Al2O3 film is coated on a non-rough surface thereof. A single-sided n diffusion layer and phosphosilicate glass film are formed. An anti-reflection layer SiNx film is formed on a top surface of the phosphosilicate glass film. An Al metallic film is formed as a back ohmic electrode on the Al2O3 film. The local area of the anti-reflection layer SiNx film and the phosphosilicate glass film is melted and removed to form a local area of n+-Si layer. Then, an Al—Si back ohmic contact electrode is formed between the Al metallic film and the crystalline silicon wafer. A front ohmic contact electrode is formed on the molten and removed area of the antireflection layer SiNx film and the phosphosilicate film by light-induced plating.

Owner:INST NUCLEAR ENERGY RES ROCAEC

High efficient solar cell preparation method

ActiveCN103094419AImprove conversion efficiencyReduce compoundingFinal product manufactureSemiconductor devicesProduction lineManufacturing cell

The invention relates to a high efficient solar cell preparation method. A step of oxidation manufacture procedure is added after the manufacture procedure of removing phosphosilicate glass (PSG) based on manufacturing process of a conventional solar cell, the method is matched with adjusting diffusion manufacture procedure craft, and therefore a layer of silica gettering passivation layer is formed on the surface of a silicon wafer, secondary distribution is carried out on cell N-type layer impurities, compounding of the surface of a cell and an N-type layer is reduced, the cell is enabled to produce high load open-circuit voltage (Uoc ) and a load short-circuit current (Isc), and conversion efficiency of the cell is improved. A high efficient solar cell can be obtained on the basis of improving the conventional solar cell, volume production can be fast achieved, compared with a conventional production line cell, and the manufactured cell has high conversion efficiency and has great market value.

Owner:山东力诺阳光电力科技有限公司

Preparation method of solar cell with elimination of printing wave line

InactiveCN102437241AEasy to operateEasy to industrializeFinal product manufactureOther printing apparatusBack surface fieldSlurry

The invention relates to a preparation method of a solar cell with elimination of a printing wave line. The method is characterized in that the method comprises the following steps that: a silicon wafer is inserted into a petal basket along the downward direction of a cutting trace of the silicon wafer; the monocrystalline silicon wafer is provided and surface texturing is carried out; the processed silicon wafer is inserted into a quartz boat along the downward direction of the cutting trace of the silicon wafer; a diffusion layer is formed on the surface of the silicon wafer that has been processed by texturing; the diffused silicon wafer is placed in a bearing box along a certain direction; etching is carried out to remove PN nodes around the silicon wafer as well as the etched silicon wafer is inserted into the petal basket along the downward direction of the cutting trace of the silicon wafer; pickling is carried out to remove phosphosilicate glass; a passivation and antireflection layer is manufactured; and the silicon wafer that has been processed by film coating is placed in a to-be-printed bearing box along a certain direction, so that after printing, a fine grid line direction is vertical to a cutting line direction; and a cell back side slurry and a right side slurry are successively printed as well as sintering is carried out to form a back side Ag electrode, a back side aluminium back surface field and a right side Ag electrode. According to the invention, the method can be operated simply and conveniently; and compared with a traditional production mode, the industrialized production mode enables no extra production cost to be generated.

Owner:百力达太阳能股份有限公司

Manufacturing method for crystalline silicon solar MWT (metallization wrap-through) cell and manufactured cell

InactiveCN103187482AIncrease short circuit currentReduce compoundingFinal product manufacturePhotovoltaic energy generationSilicon matrixElectrode Contact

The invention discloses a manufacturing method for a crystalline silicon solar MWT (metallization wrap-through) cell. The manufacturing method for the crystalline silicon solar MWT cell comprises the following steps of: producing a conductive through hole; performing wet-method texturization; performing grid line area phosphorous paste printing on a light-receiving surface; diffusing phosphorous; etching the edge of a silicon matrix, and performing PSG (phosphosilicate glass) removal treatment; coating an antireflection film, and printing an emitting electrode contact electrode, a back electrode contact electrode and a base electrode contact electrode; printing the electrode grid line of the light-receiving surface; sintering to form ohmic contact; and electrically insulating the base electrode contact electrode from the emitting electrode contact electrode, so as to finish production for the solar cell. According to the manufacturing method disclosed by the invention, a selective emitting electrode structure is realized on the MWT solar cell; and optical loss is effectively reduced, minority carrier recombination is reduced, various electrode-related resistance losses are reduced, and the short-circuit current ISC, the open-circuit voltage UOC and the filling factor of the cell are remarkable increased by combining with a back passivation technology and a secondary printing technology. The preparation process is easy to operate, capable of being completely compatible with the solar cell production line which is widely applied at present, and suitable for large-scale production.

Owner:EGING PHOTOVOLTAIC TECHNOLOGY CO LTD