Patents

Literature

119 results about "Thermal cvd" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

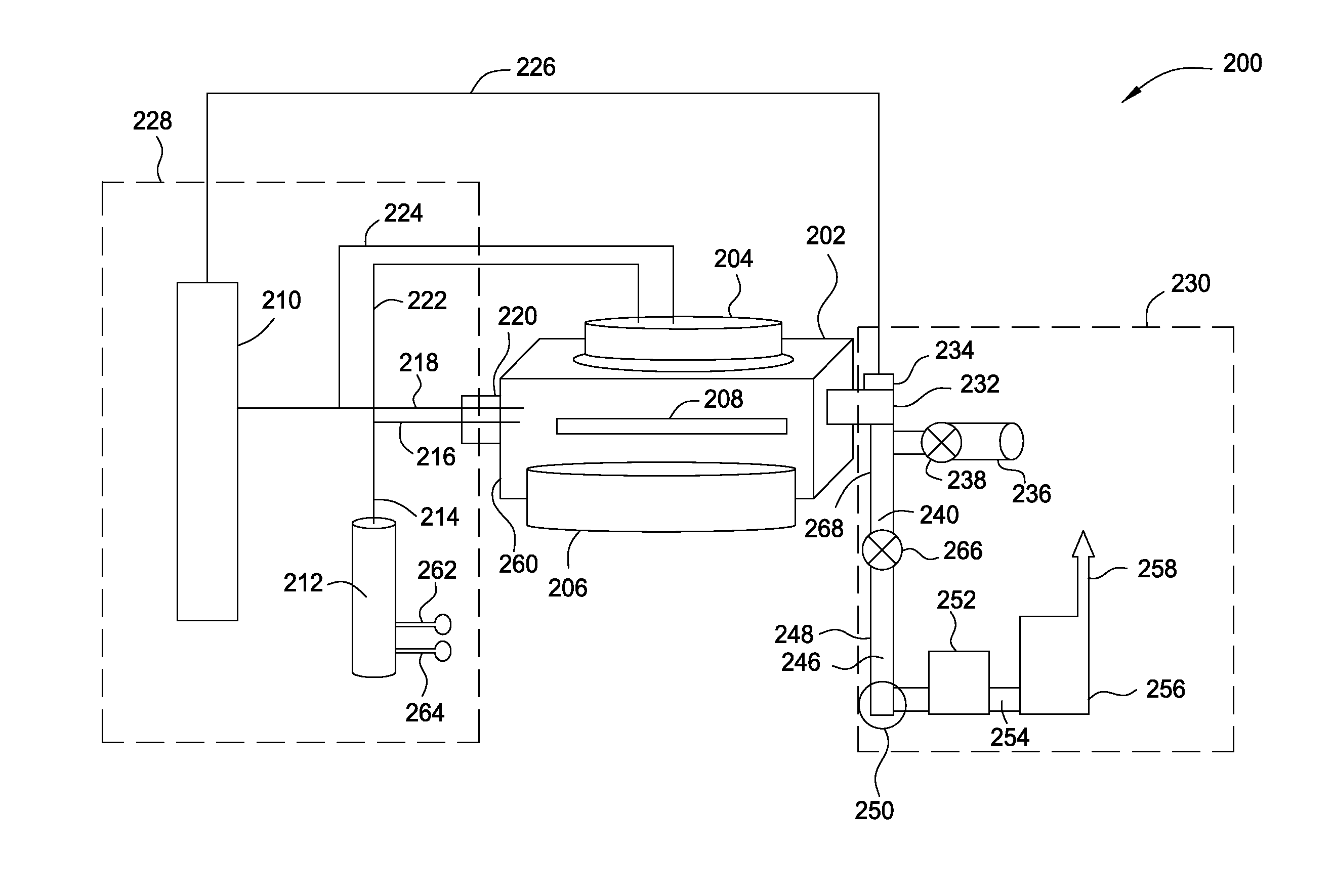

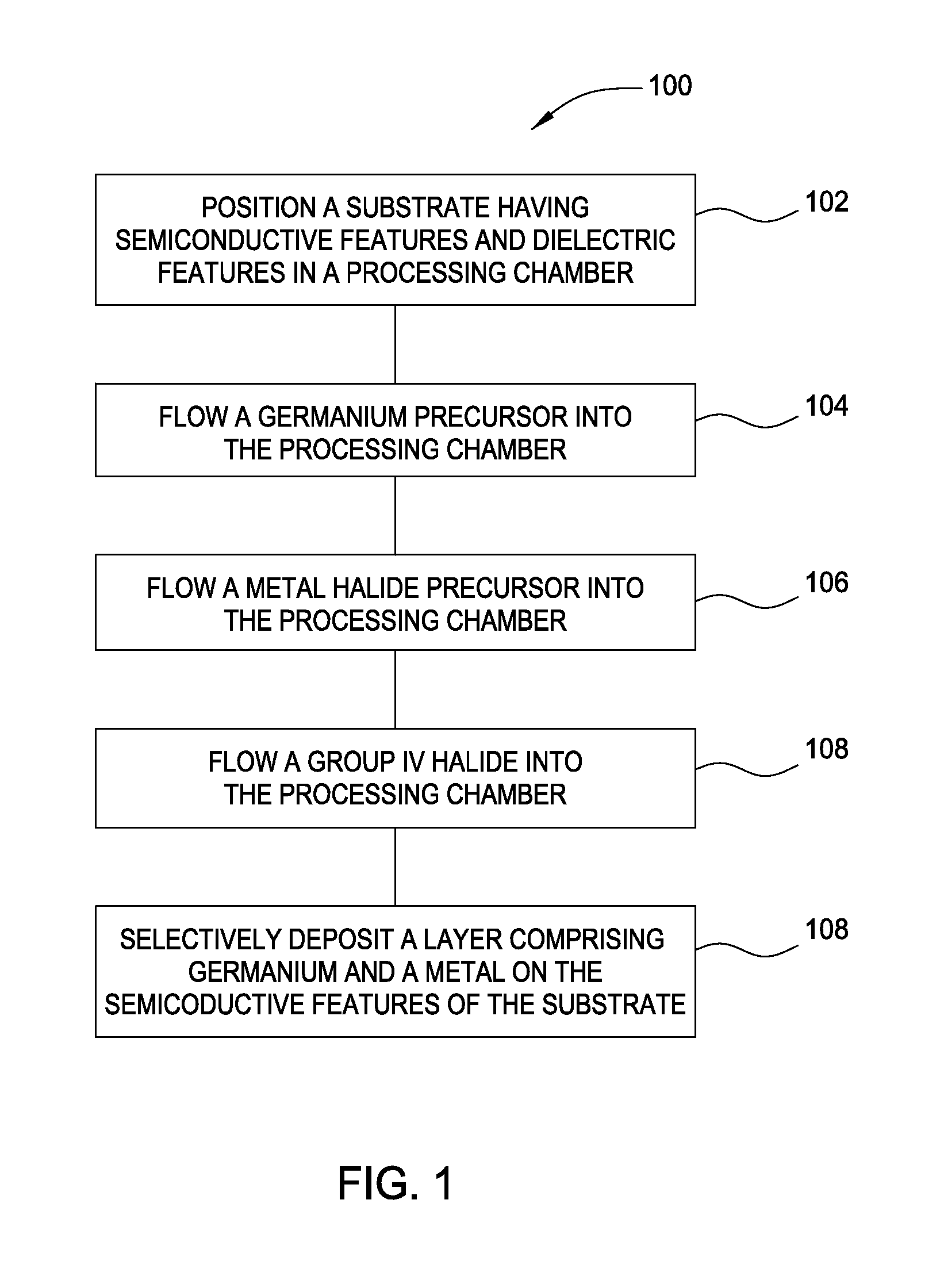

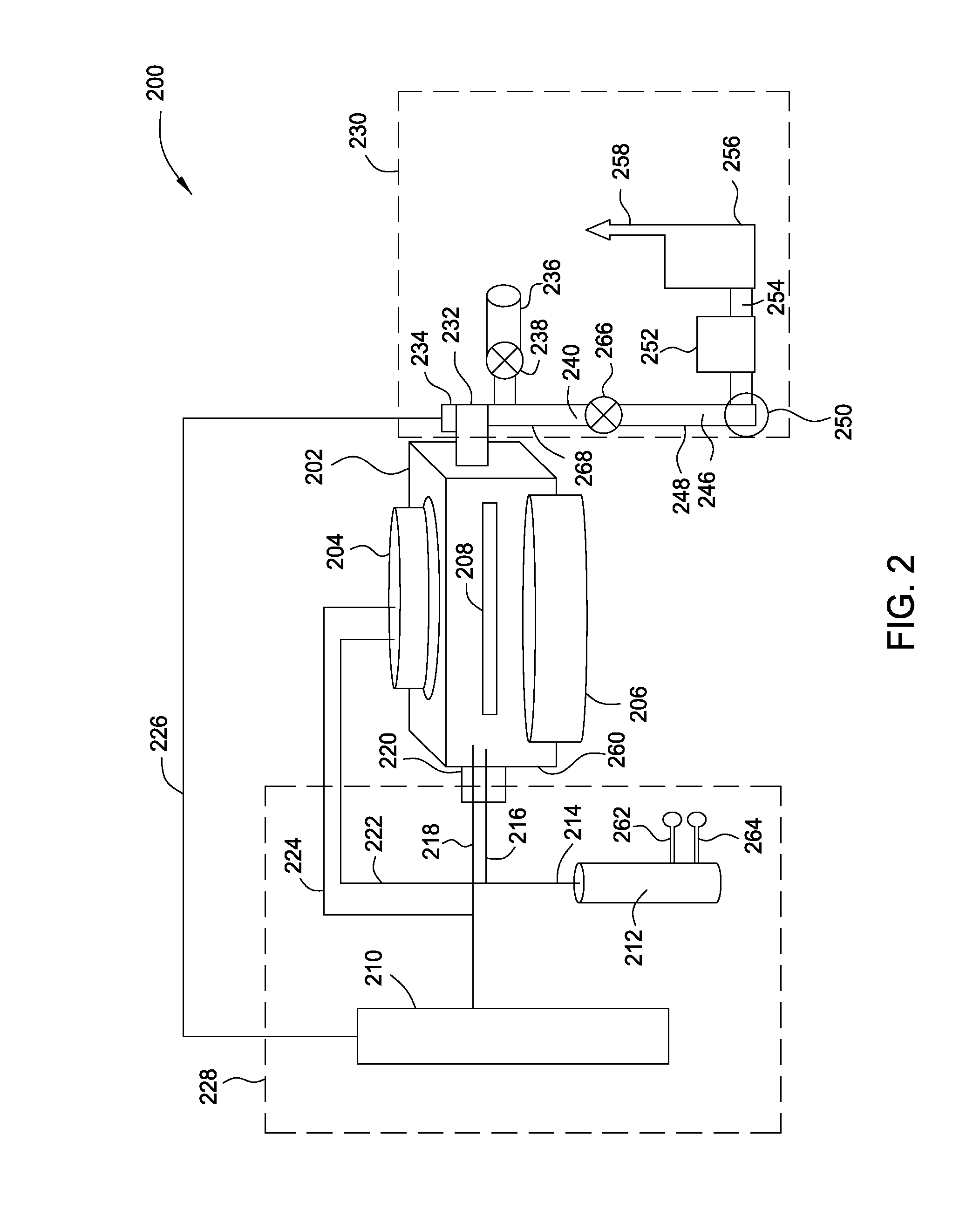

Method and apparatus for germanium tin alloy formation by thermal CVD

InactiveUS20130280891A1Polycrystalline material growthSemiconductor/solid-state device manufacturingSelective depositionLiquid metal

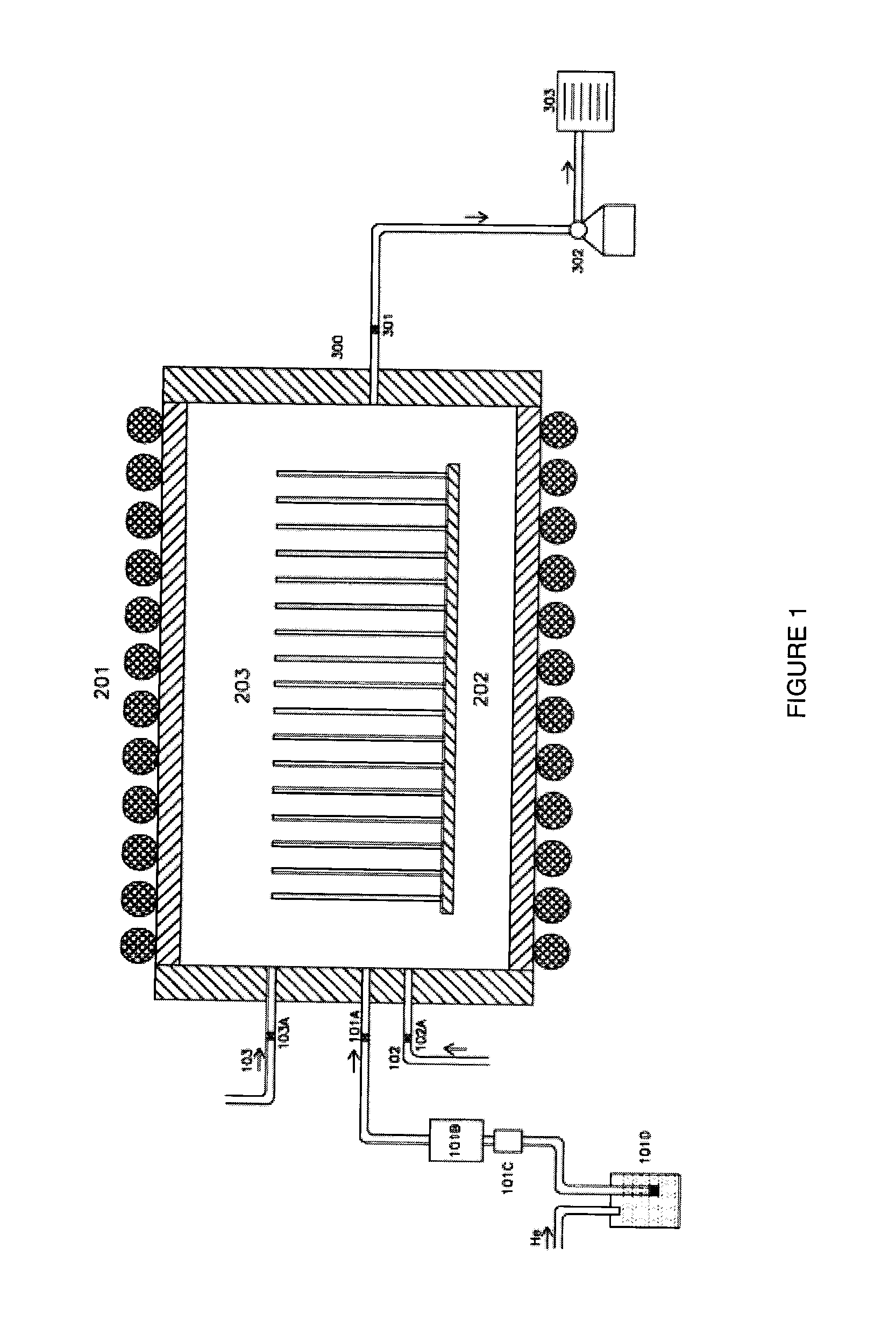

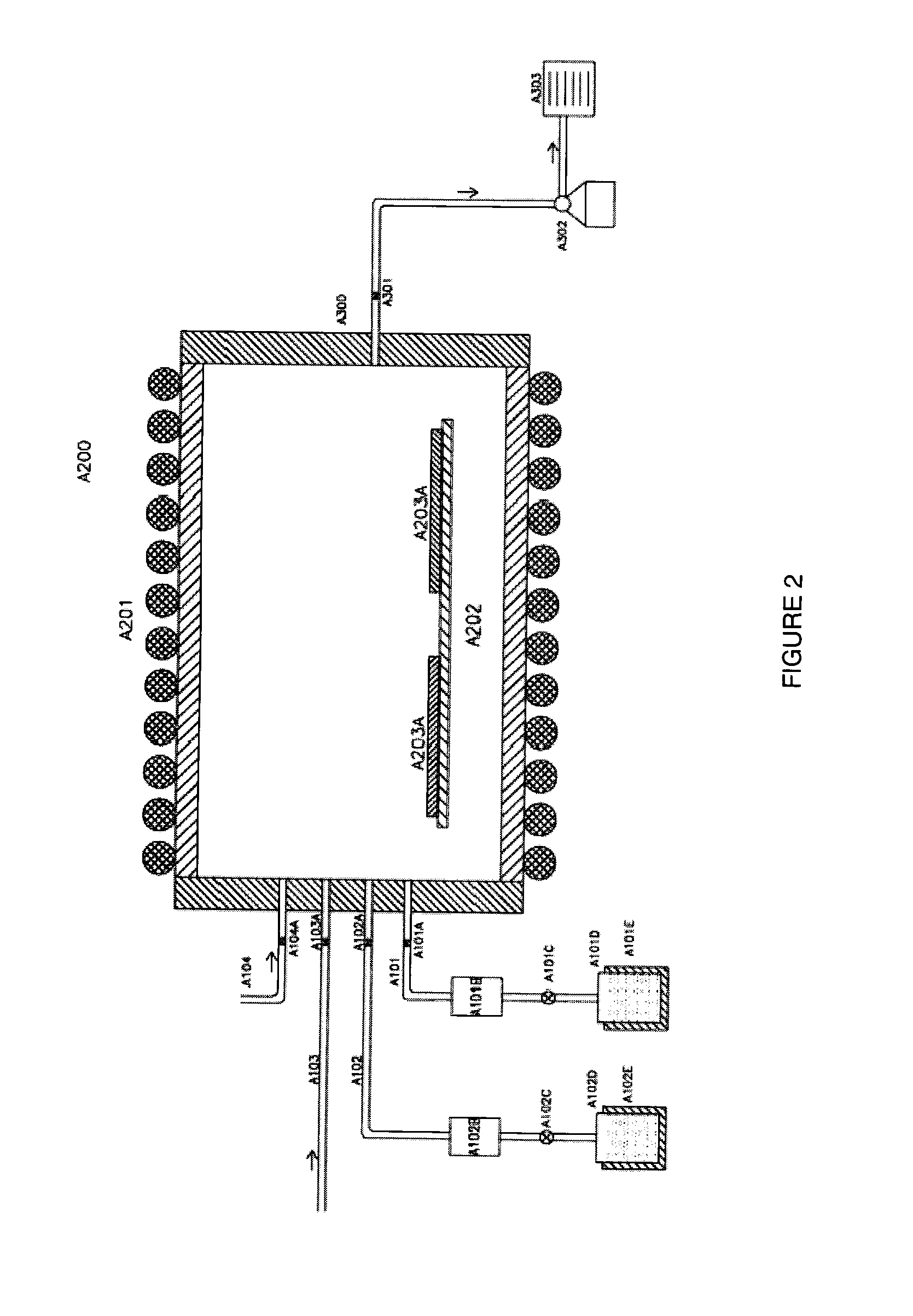

A method and apparatus for forming semiconductive semiconductor-metal alloy layers is described. A germanium precursor and a metal precursor are provided to a chamber, and an epitaxial layer of germanium-metal alloy, optionally including silicon, is formed on the substrate. The metal precursor is typically a metal halide, which may be provided by evaporating a liquid metal halide, subliming a solid metal halide, or by contacting a pure metal with a halogen gas. A group IV halide deposition control agent is used to provide selective deposition on semiconductive regions of the substrate relative to dielectric regions. The semiconductive semiconductor-metal alloy layers may be doped, for example with boron, phosphorus, and / or arsenic. The precursors may be provided through a showerhead or through a side entry point, and an exhaust system coupled to the chamber may be separately heated to manage condensation of exhaust components.

Owner:APPLIED MATERIALS INC

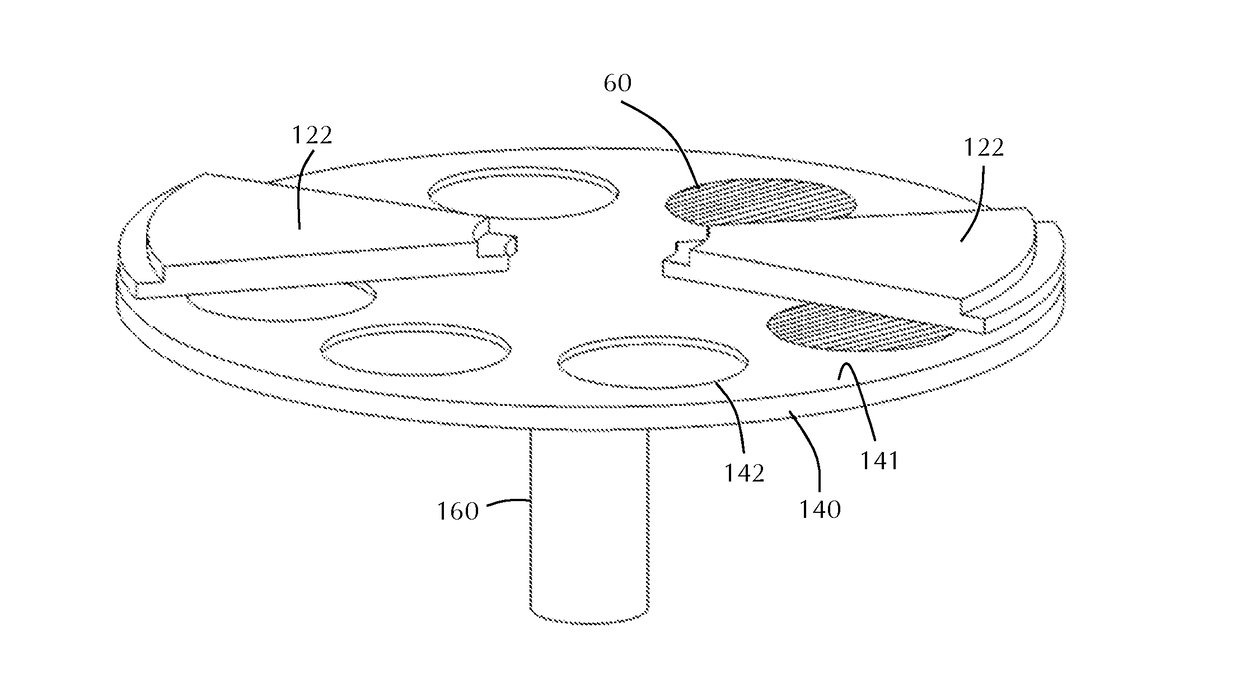

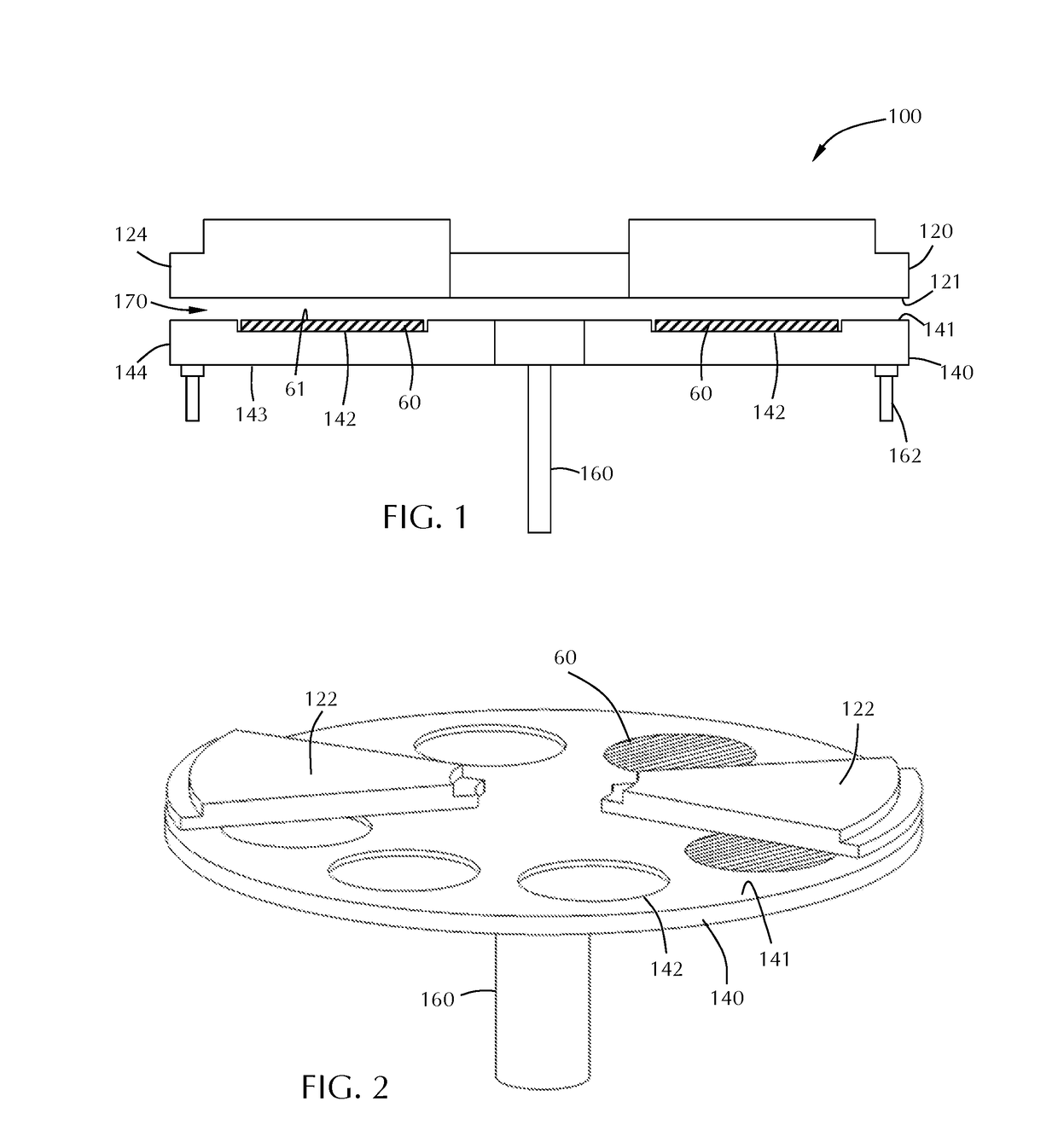

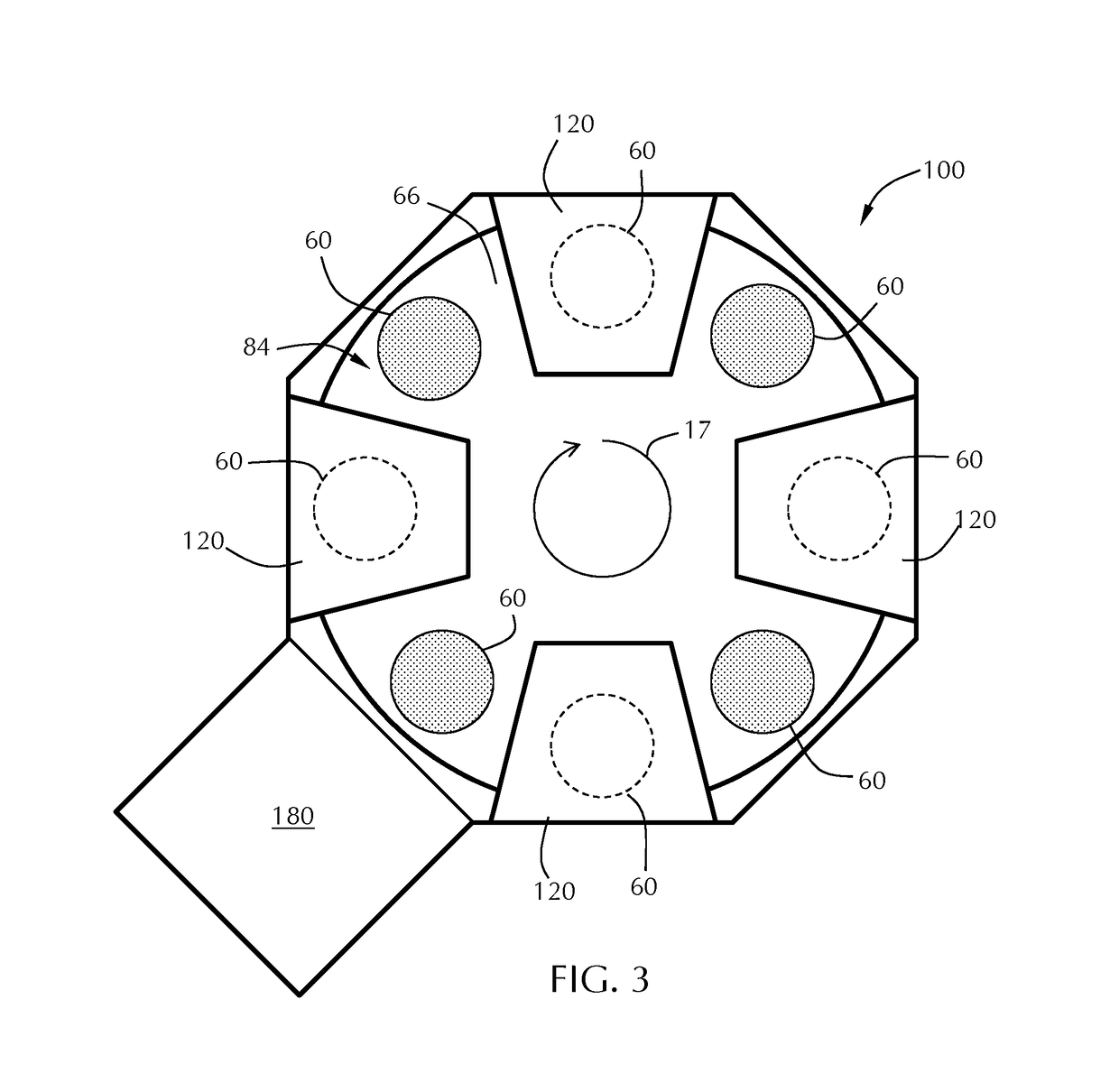

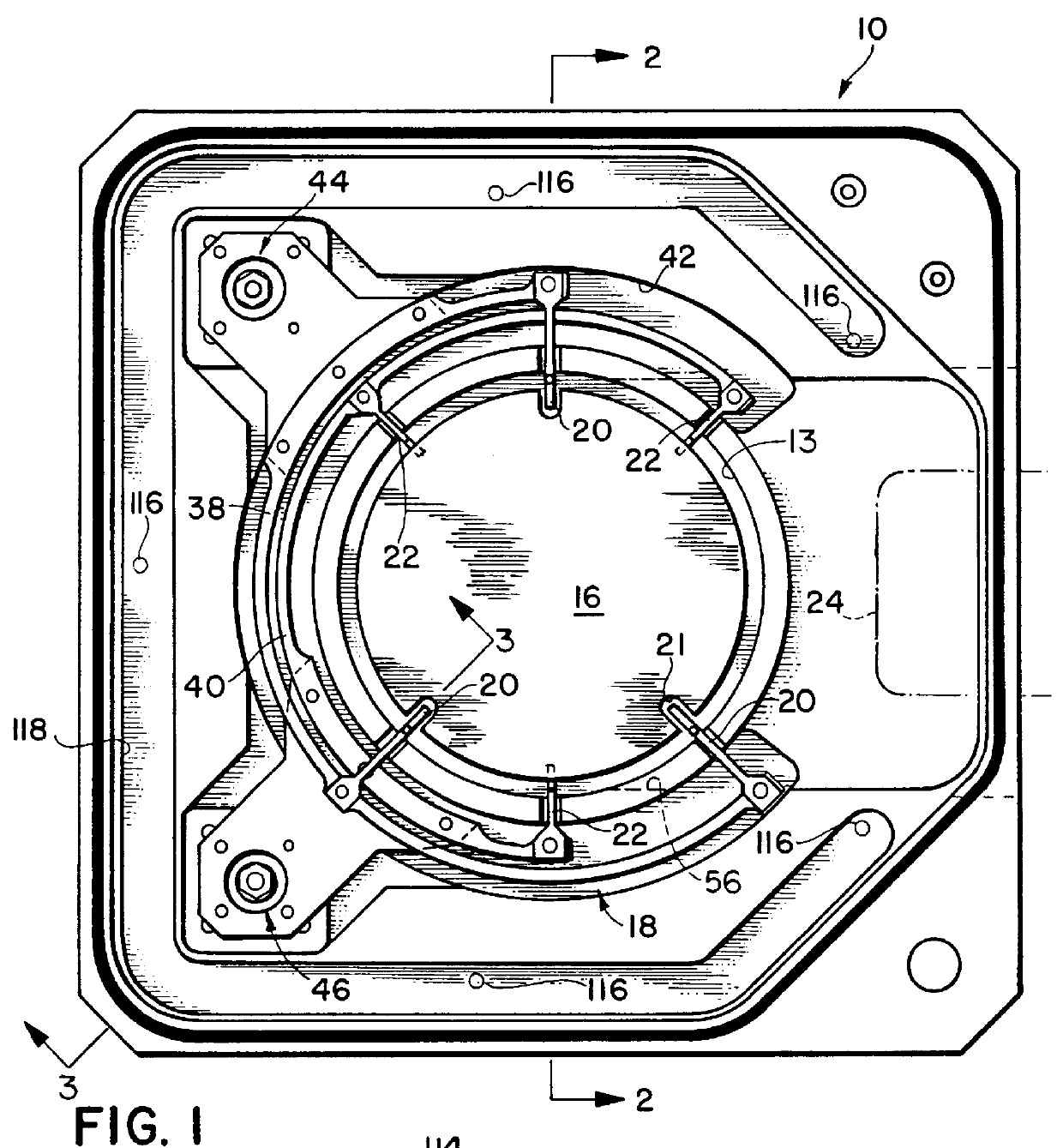

Non-Metallic Thermal CVD/ALD Gas Injector And Purge System

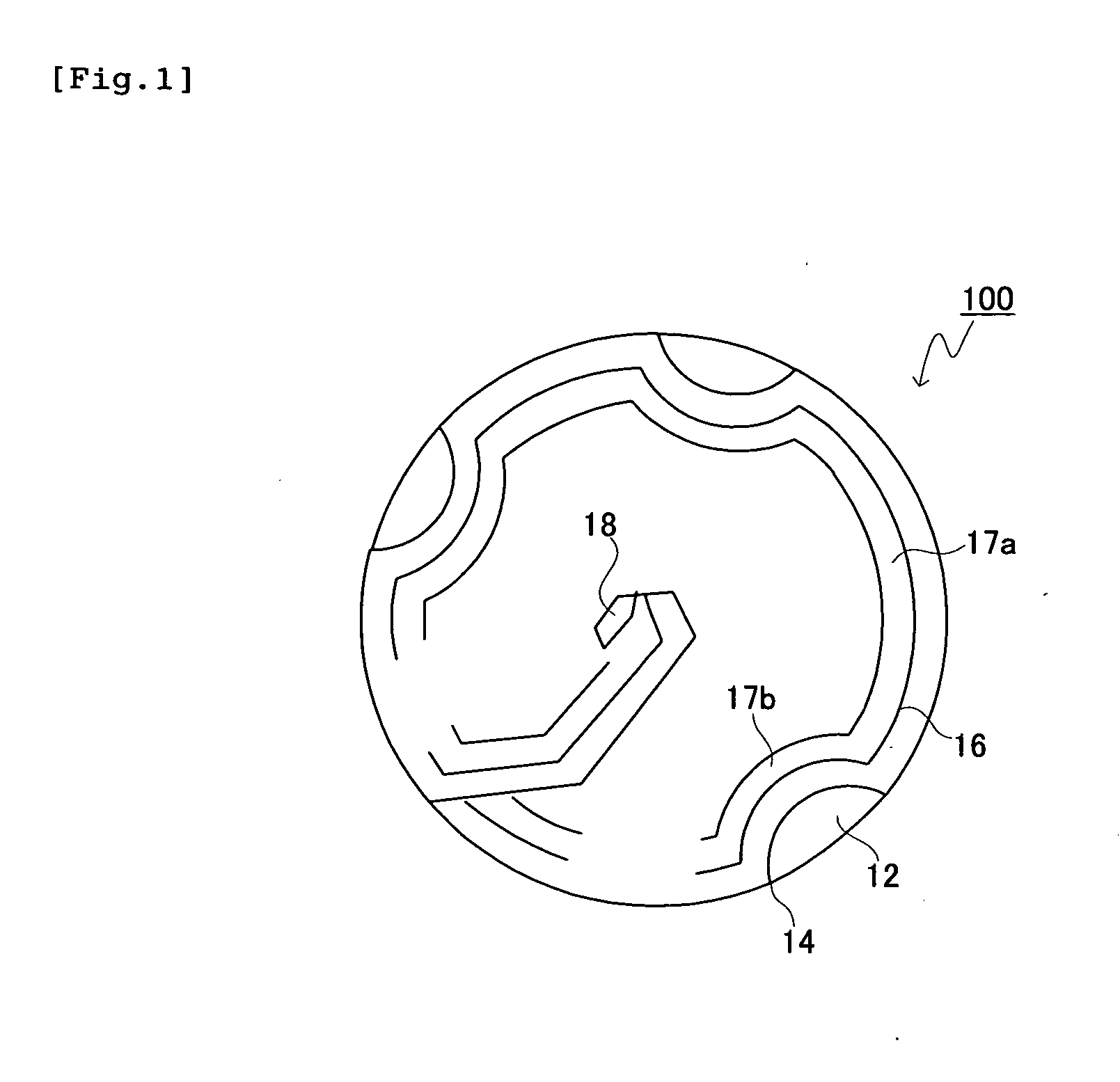

ActiveUS20170191159A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingCircular discReactive gas

Gas distribution assemblies and processing chambers using same are described. The gas distribution assemblies comprise a cooling plate with a quartz puck, a plurality of reactive gas sectors and a plurality of purge gas sectors suspended therefrom. The reactive gas sectors and purge gas sectors having a coaxial gas inlet with inner tubes and outer tubes, the inner tubes and outer tubes in fluid communication with different gas or vacuum ports in the front faces of the sectors. The sectors may be suspended from the cooling plate by a plurality of suspension rods comprising a metal rod body with an enlarged lower end positioned within a quartz frame with a silicon washer around the enlarged lower end.

Owner:APPLIED MATERIALS INC

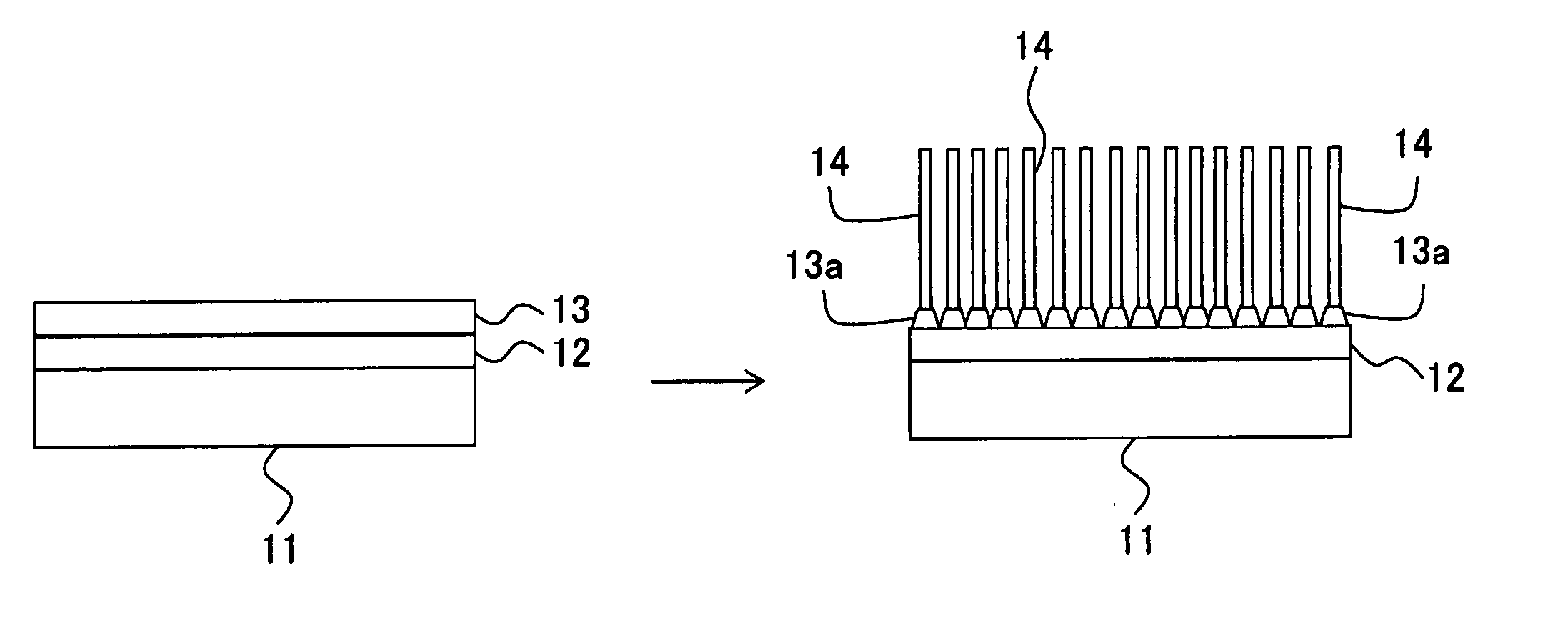

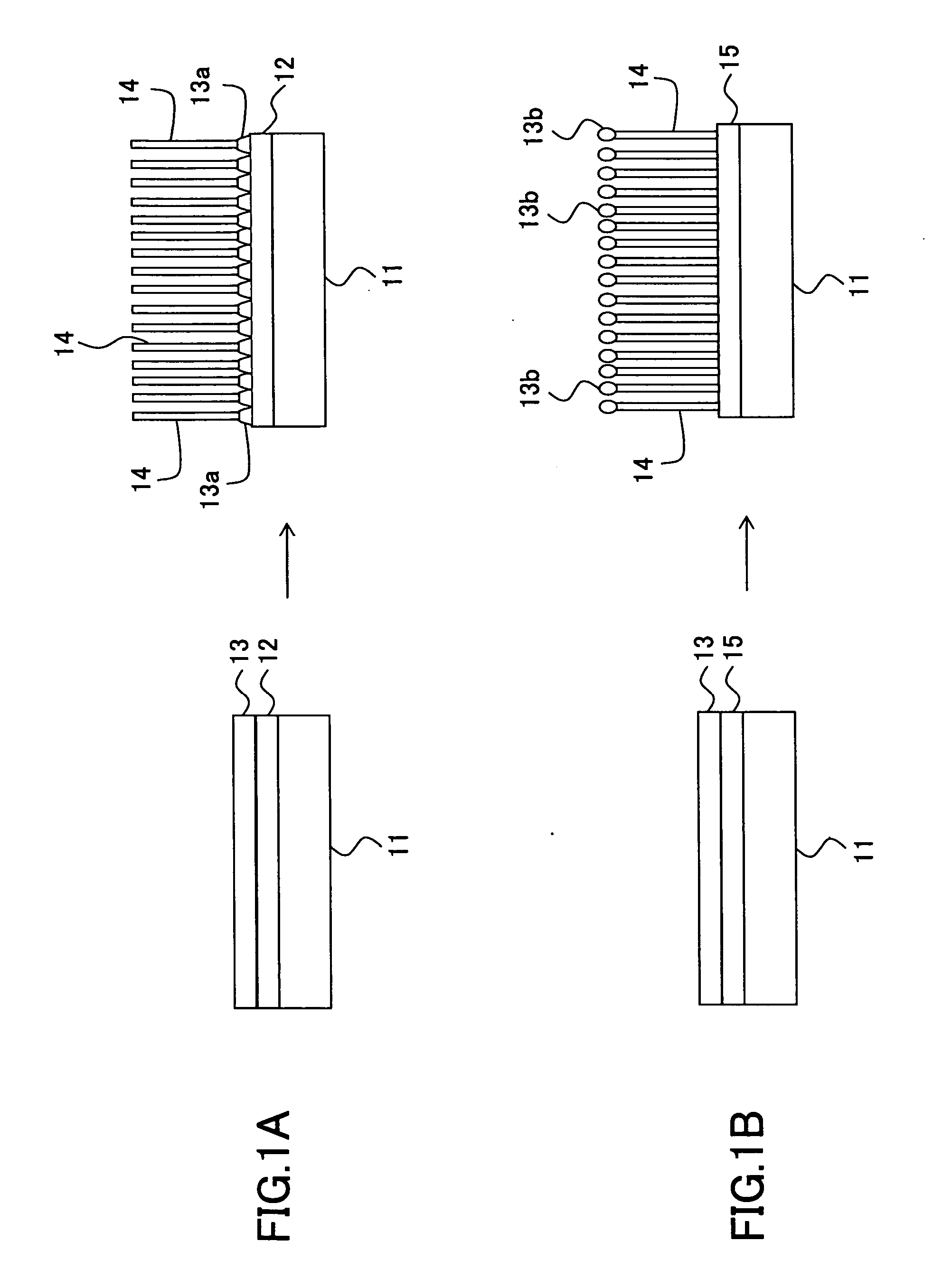

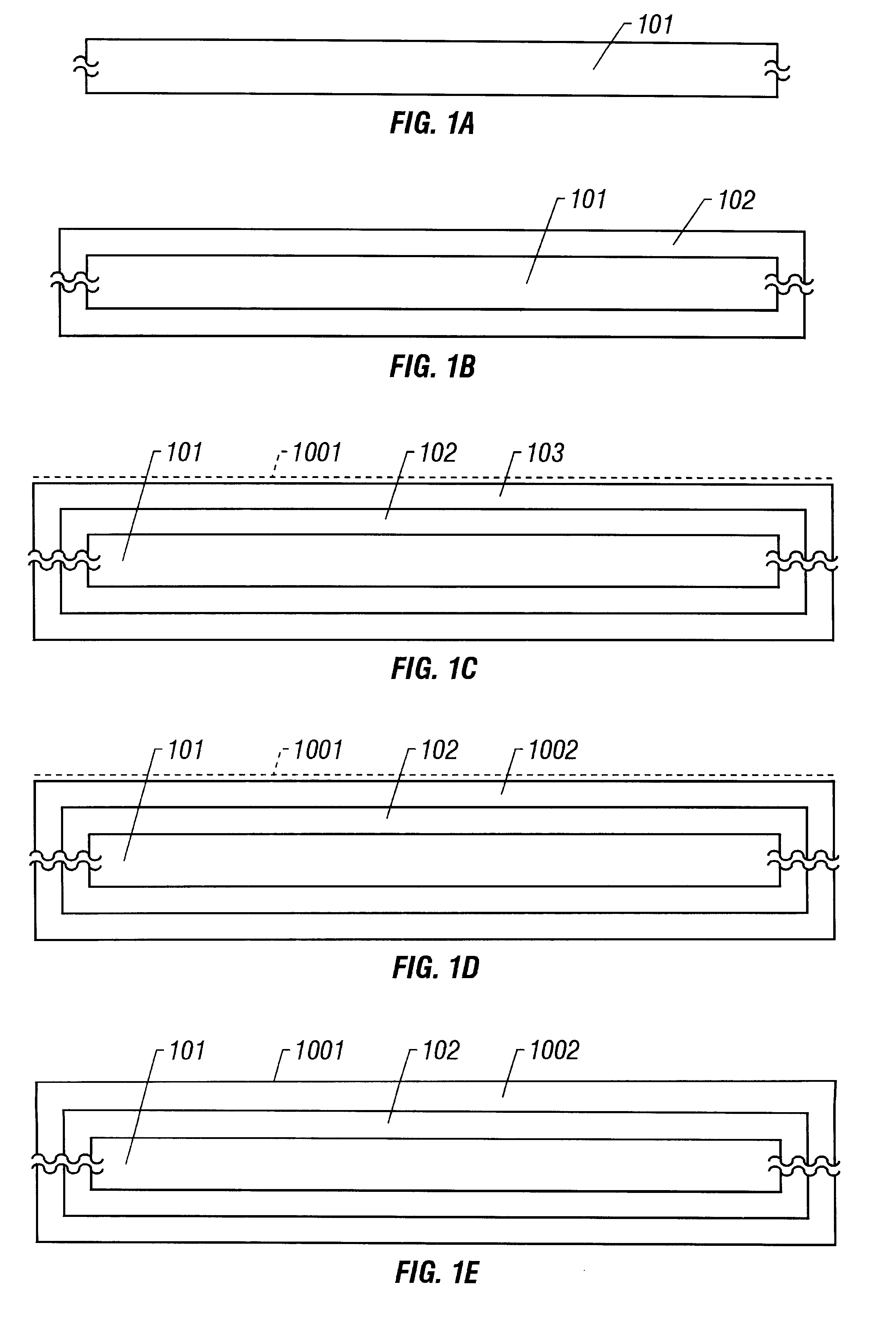

Semiconductor device and method of manufacturing the same

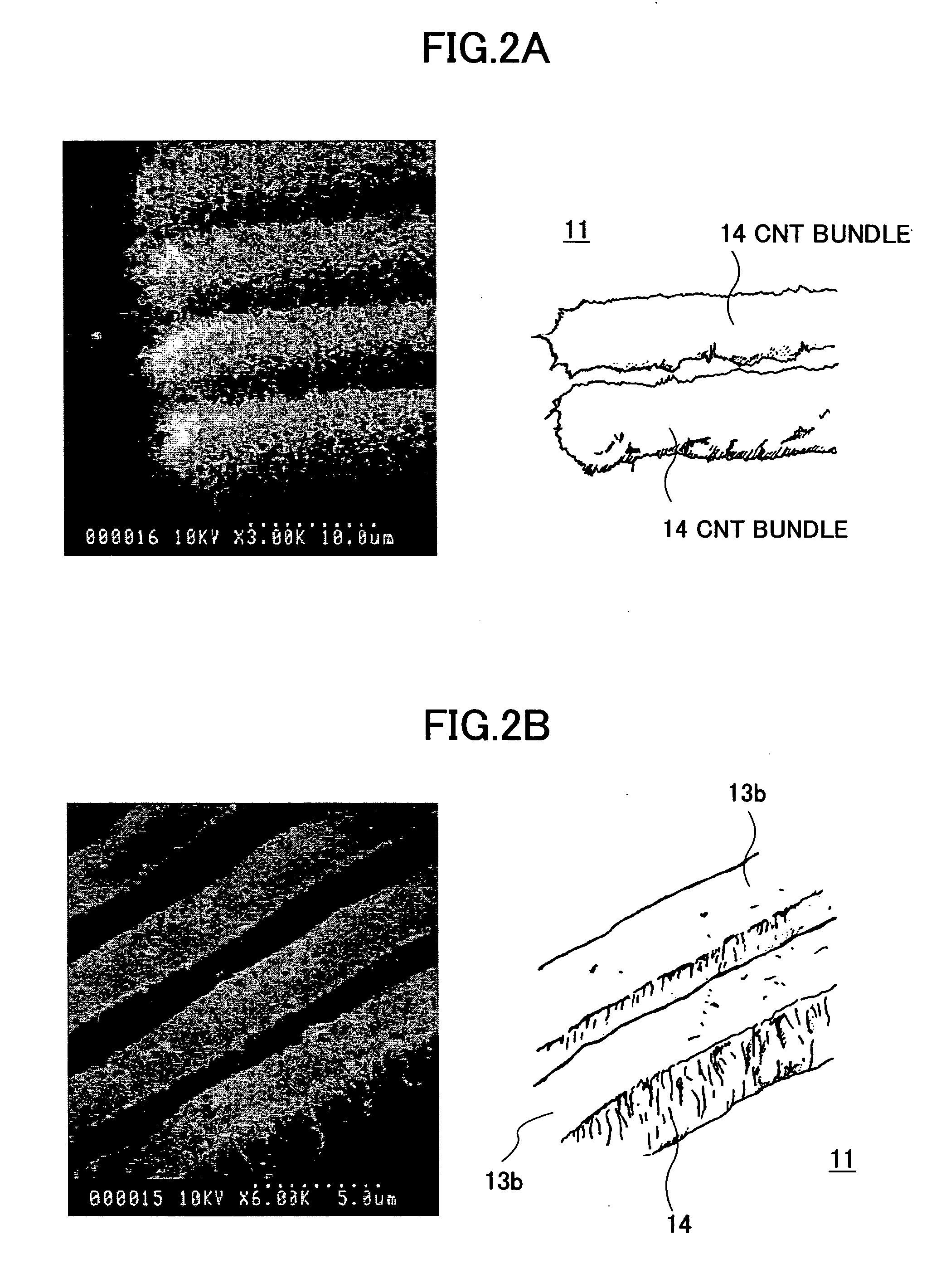

ActiveUS20050215049A1Eliminate disadvantagesSemiconductor/solid-state device detailsNanoinformaticsSputteringDevice material

A method of manufacturing a semiconductor device having an interconnection part formed of multiple carbon nanotubes is disclosed. The method includes the steps of (a) forming a growth mode control layer controlling the growth mode of the carbon nanotubes, (b) forming a catalyst layer on the growth mode control layer, and (c) causing the carbon nanotubes to grow by heating the catalyst layer by thermal CVD so that the carbon nanotubes serve as the interconnection part. The growth mode control layer is formed by sputtering or vacuum deposition in an atmospheric gas, using a metal selected from a group of Ti, Mo, V, Nb, and W. The growth mode is controlled in accordance with a predetermined concentration of oxygen gas of the atmospheric gas.

Owner:FUJITSU LTD

Chemical vapor deposition using organometallic precursors

InactiveUS20020009896A1Solid-state devicesSemiconductor/solid-state device manufacturingPhysical chemistryDielectric layer

A multi-component layer is deposited on a semiconductor substrate in a semiconductor process. The multi-component layer may be a dielectric layer formed from a gaseous titanium organometallic precursor, reactive silane-based gas and a gaseous oxidant. The multi-component layer may be deposited in a cold wall or hot wall chemical vapor deposition (CVD) reactor, and in the presence or absence of plasma. The multi-component layer may also be deposited using other processes, such as radiant energy or rapid thermal CVD.

Owner:MICRON TECH INC

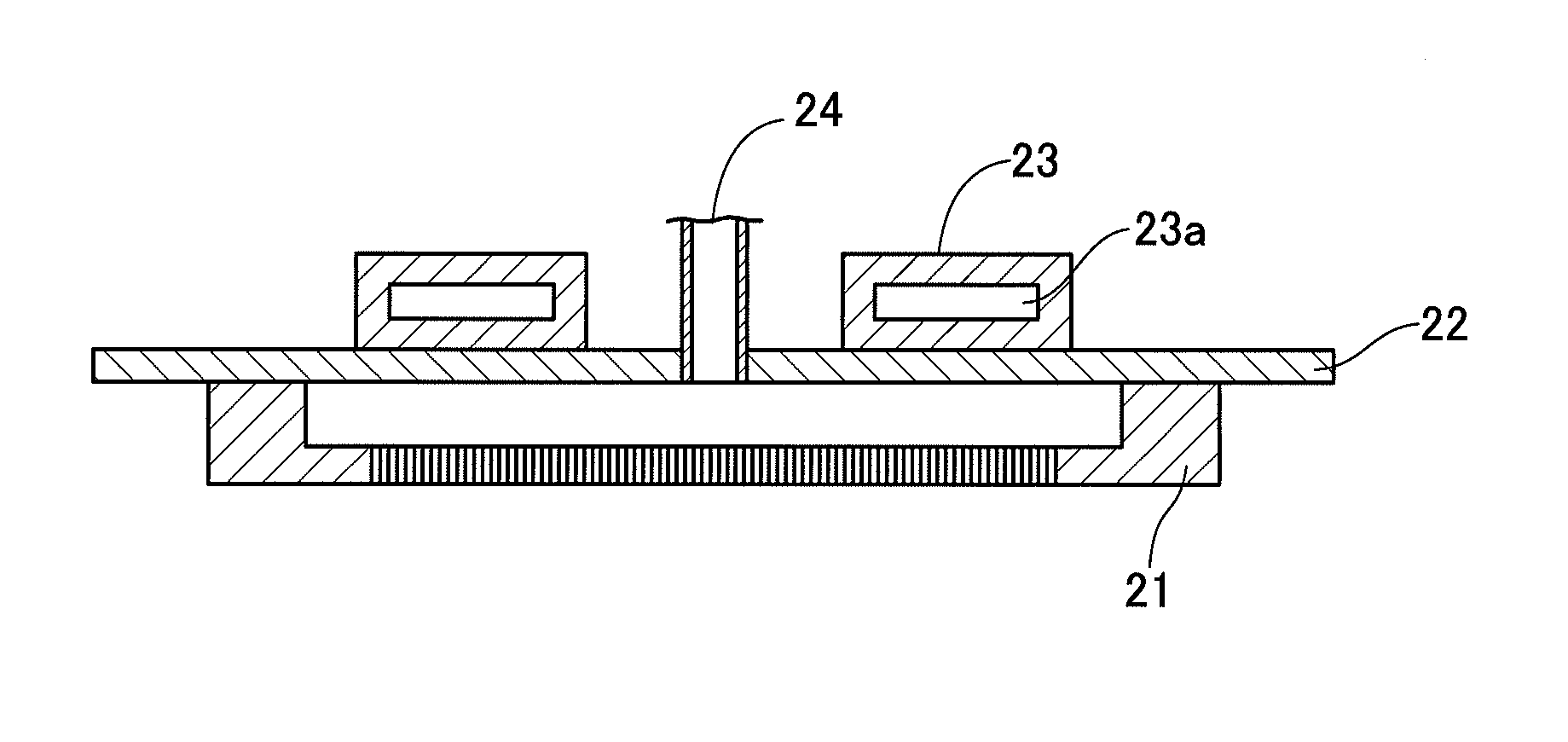

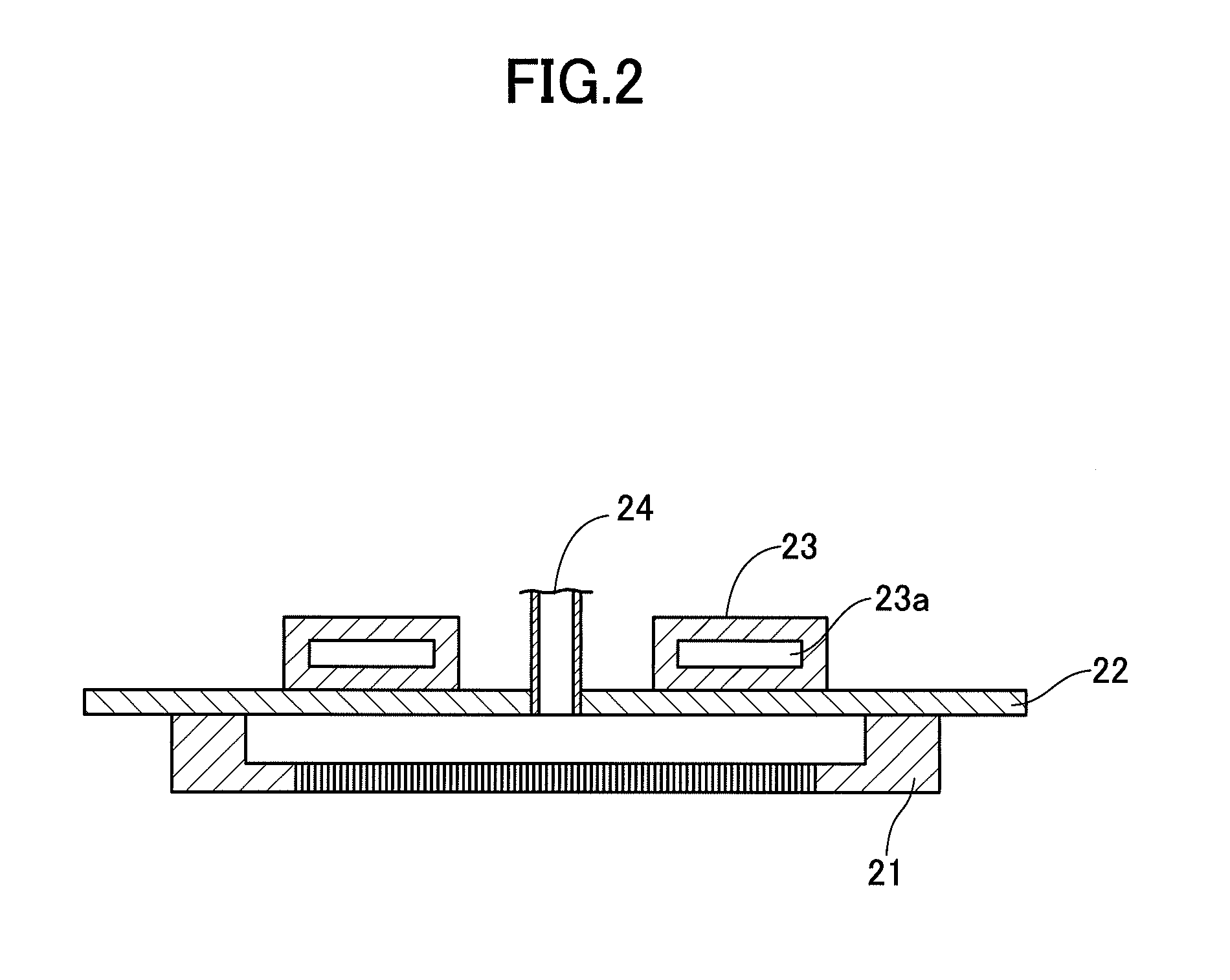

Thin film manufacturing apparatus, thin film manufacturing method and method for manufacturing semiconductor device

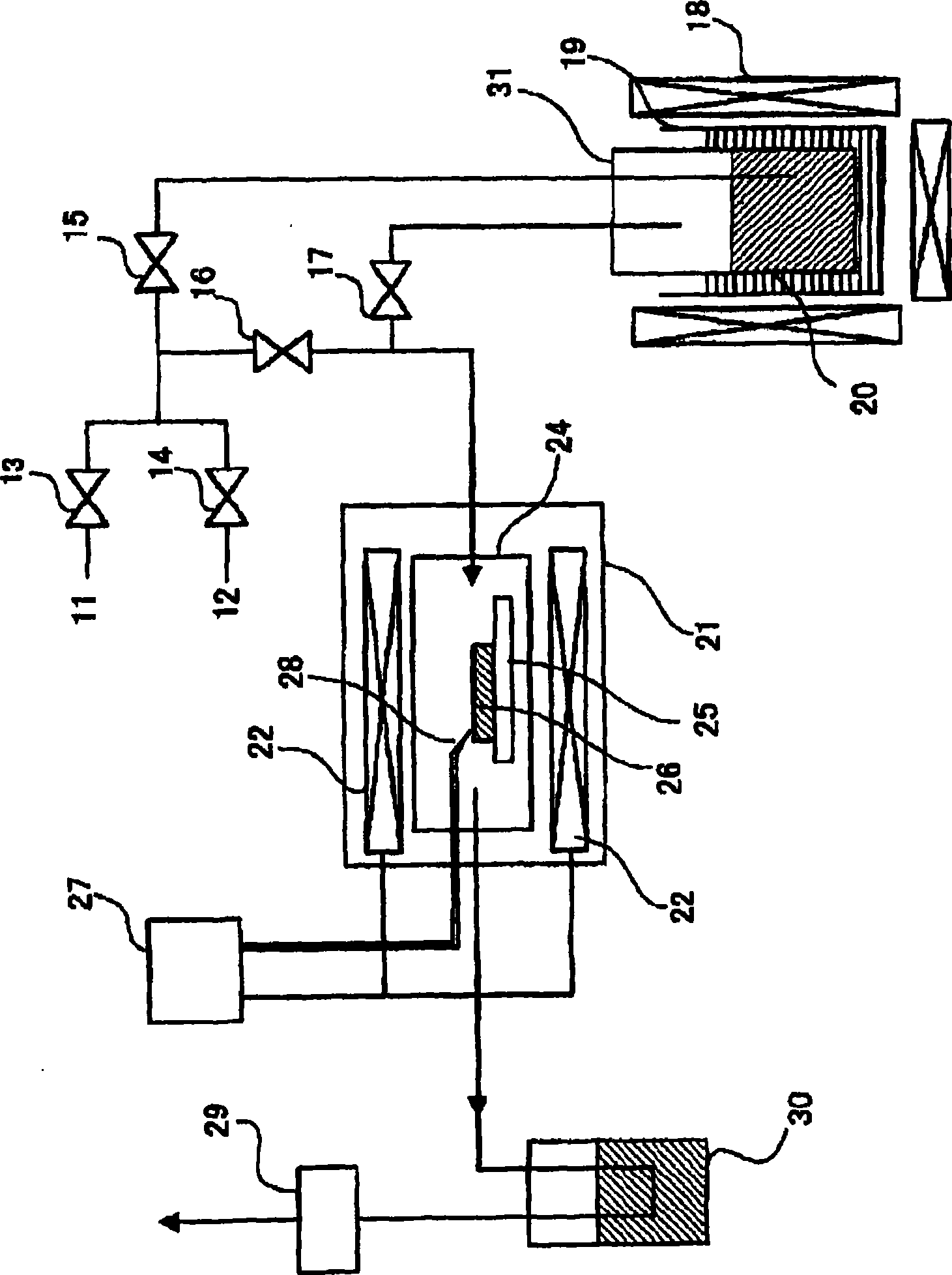

InactiveUS20130023062A1Easy temperature controlGood effectLiquid surface applicatorsSemiconductor/solid-state device manufacturingManufactured apparatusThermal radiation

In an apparatus for manufacturing a ceramic thin film by employing a thermal CVD method, an internal jig, which is provided with a heat radiation material film on the surface, is provided at a position that faces a substrate (S) on which the film is to be formed. The thin film and a semiconductor device are manufactured using such apparatus.

Owner:ULVAC INC

Process for PECVD of silicon oxide using TEOS decomposition

InactiveUSRE36623E1Eliminate depositsAvoid failureElectric discharge tubesPretreated surfacesHigh rateSilicon oxide

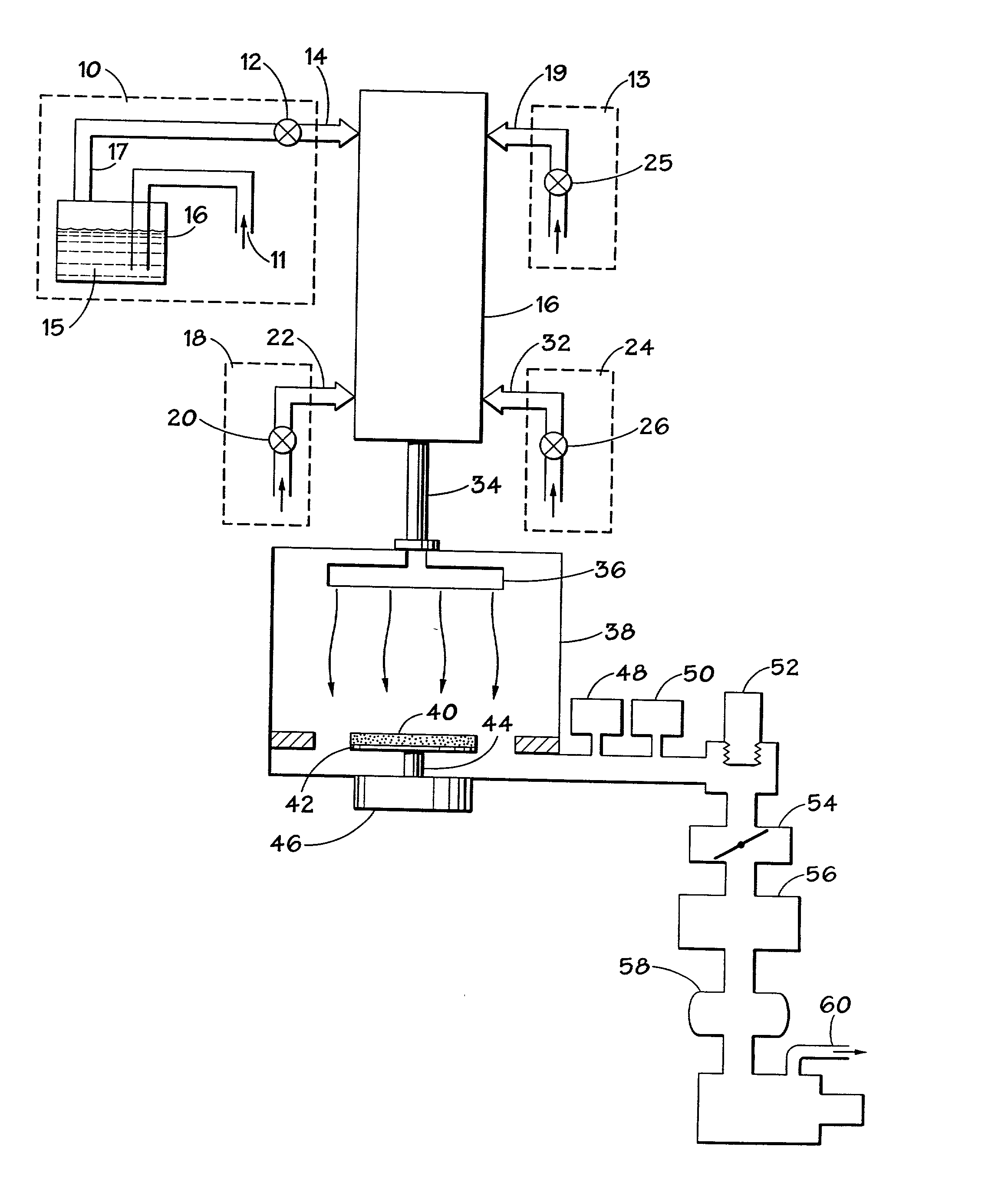

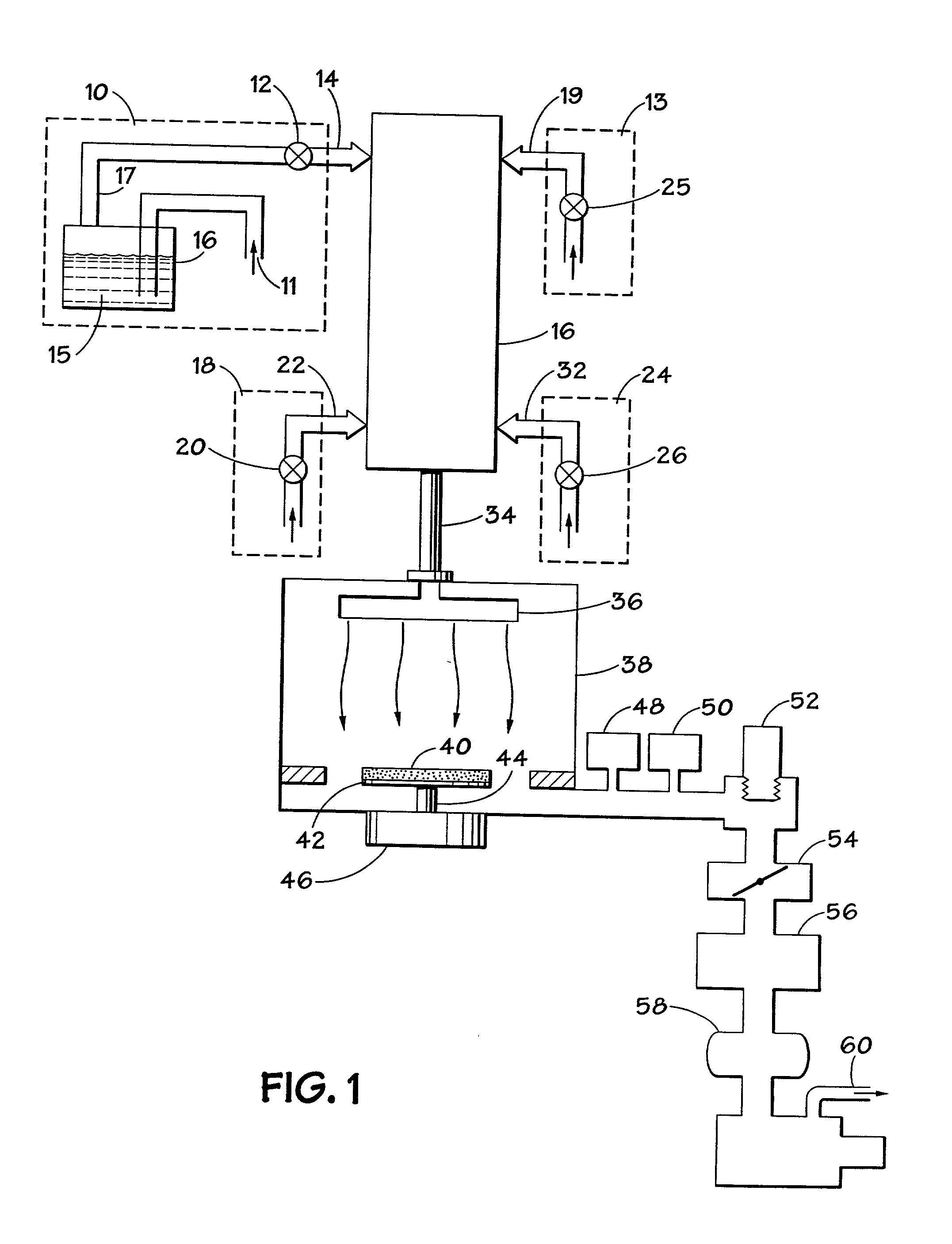

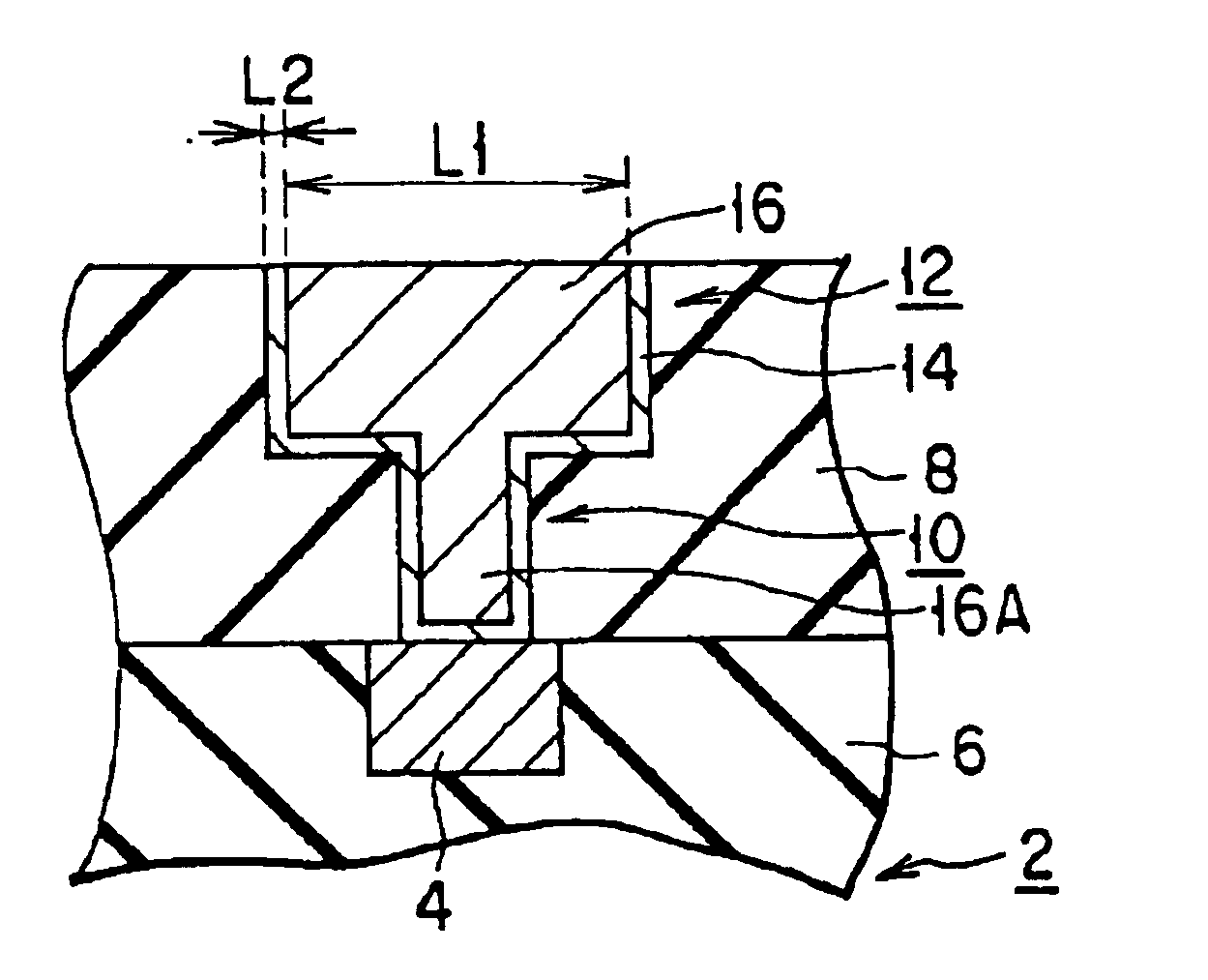

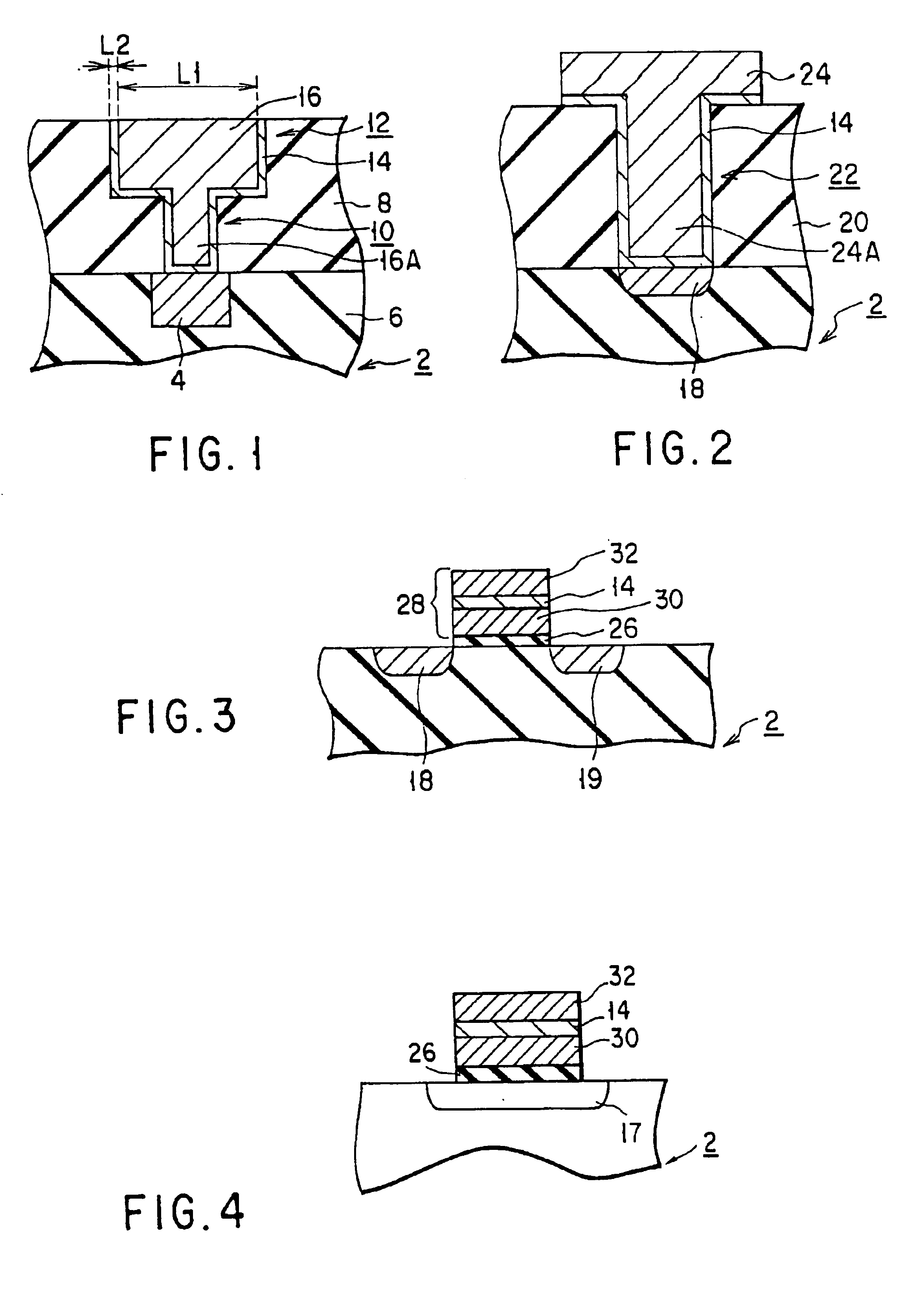

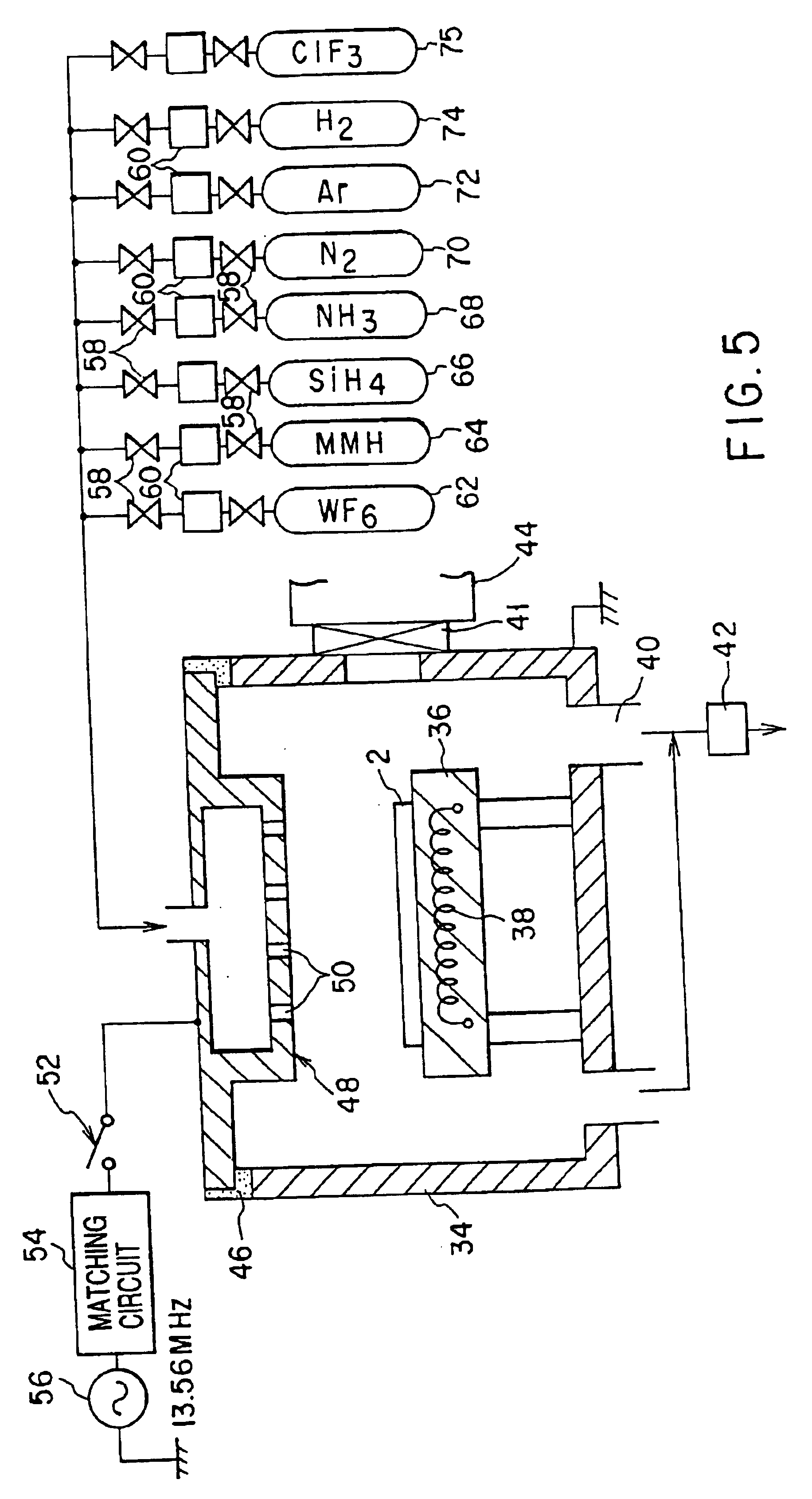

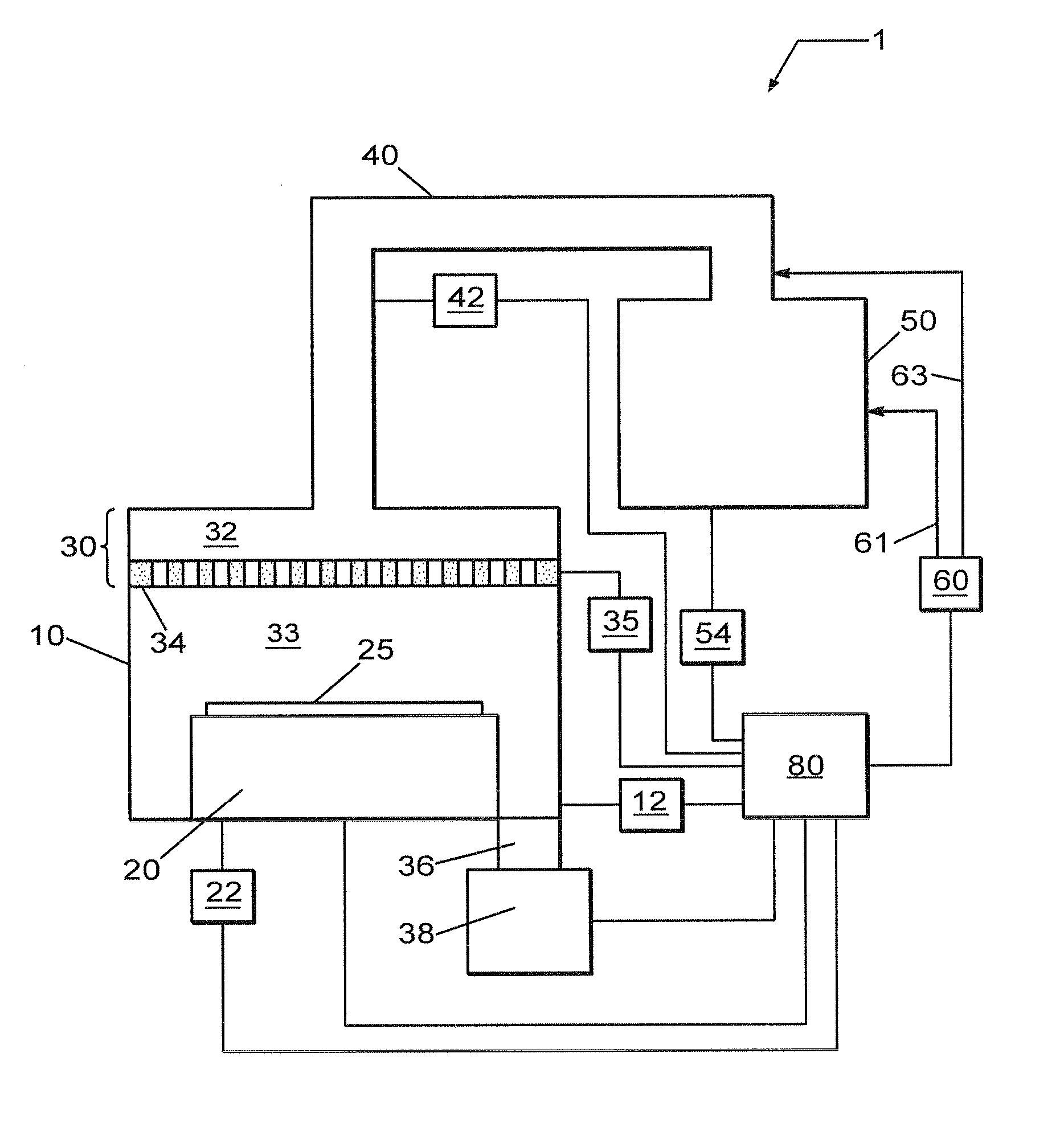

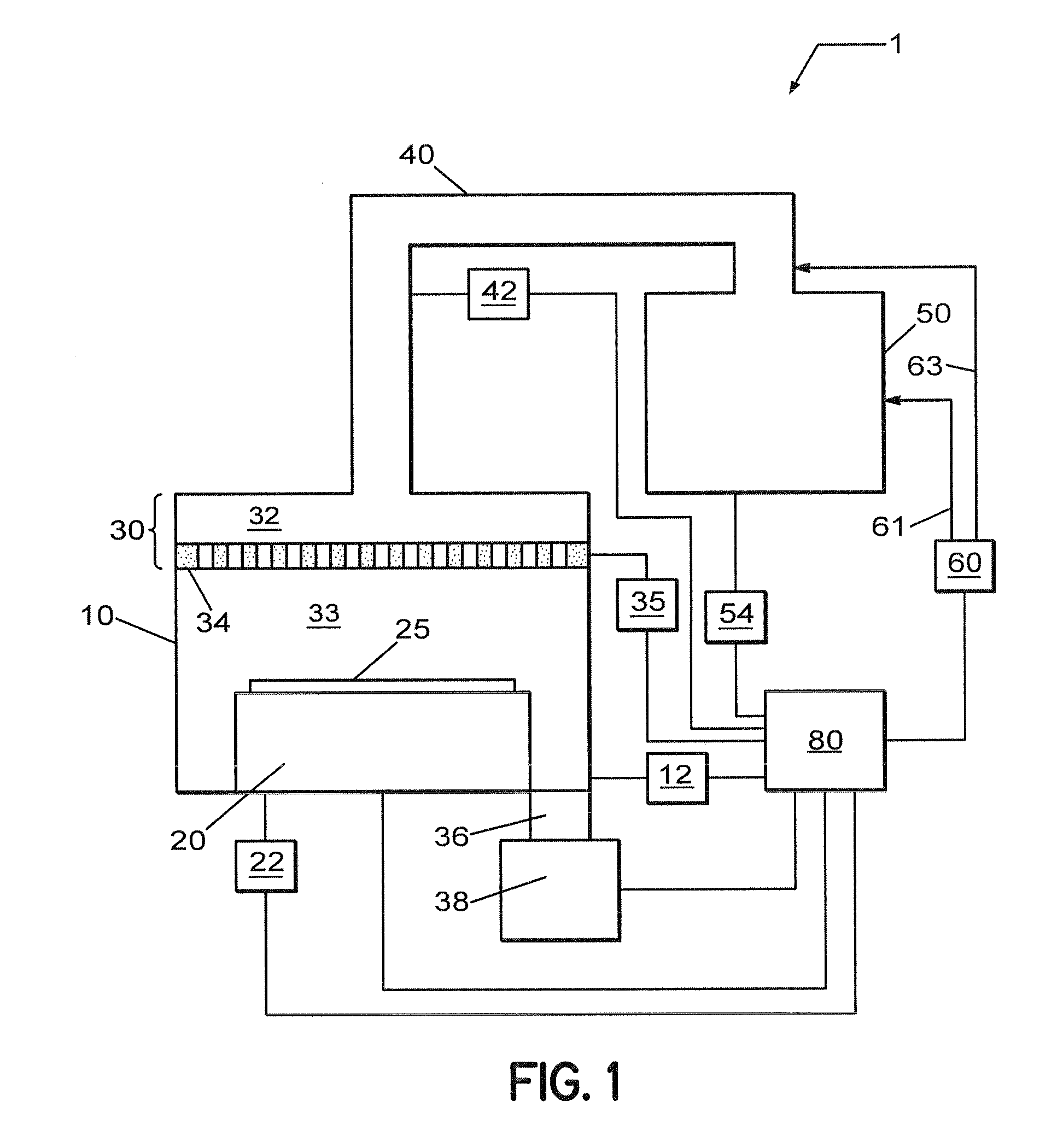

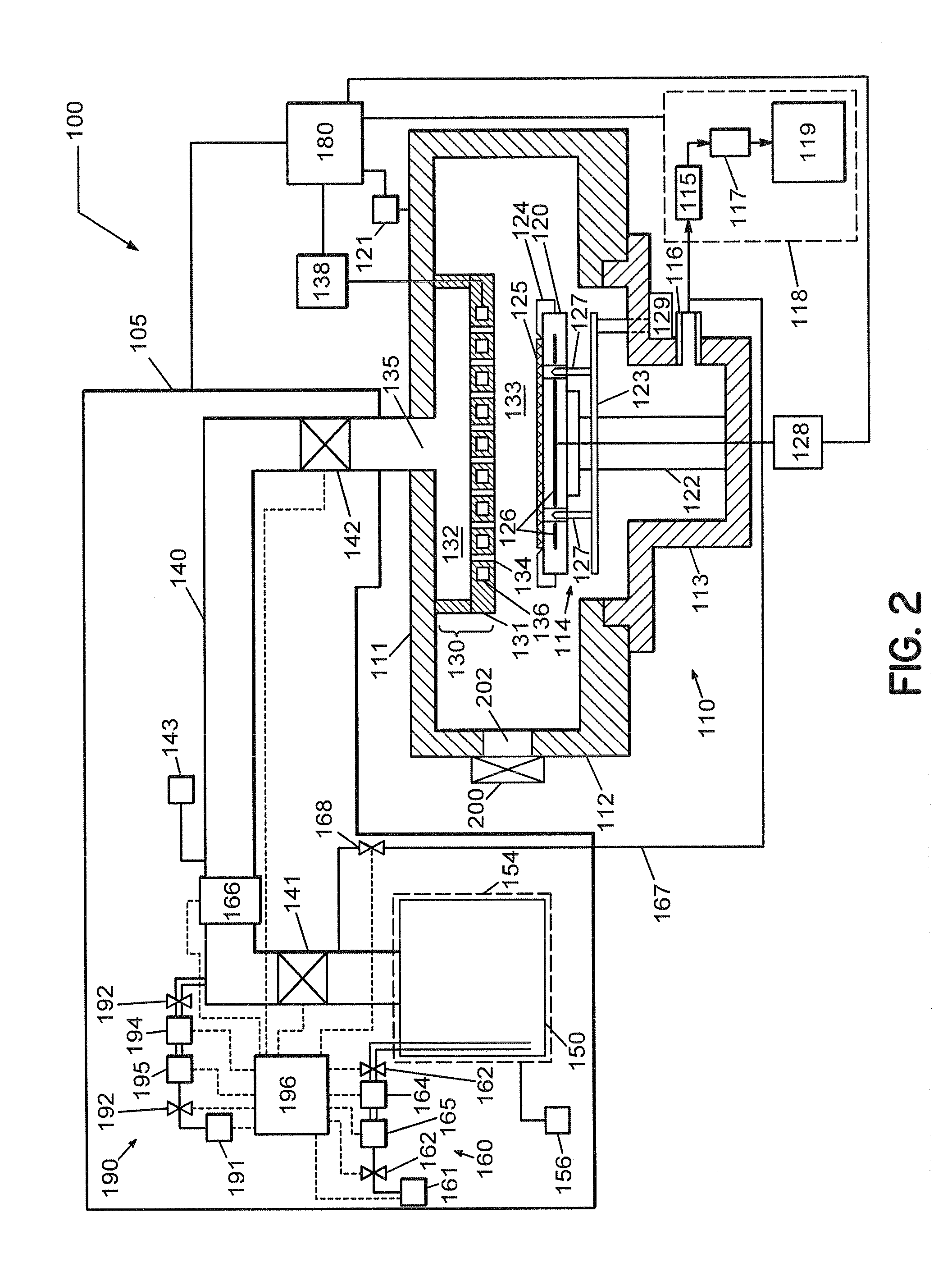

A high pressure, high throughput, single wafer, semiconductor processing reactor is disclosed which is capable of thermal CVD, plasma-enhanced CVD, plasma-assisted etchback, plasma self-cleaning, and deposition topography modification by sputtering, either separately or as part of in-situ multiple step processing. The reactor includes cooperating arrays of interdigitated susceptor and wafer support fingers which collectively remove the wafer from a robot transfer blade and position the wafer with variable, controlled, close parallel spacing between the wafer and the chamber gas inlet manifold, then return the wafer to the blade. A combined RF / gas feed-through device protects against process gas leaks and applies RF energy to the gas inlet manifold without internal breakdown or deposition of the gas. The gas inlet manifold is adapted for providing uniform gas flow over the wafer. Temperature-controlled internal and external manifold surfaces suppress condensation, premature reactions and decomposition and deposition on the external surface. The reactor also incorporates a uniform radial pumping gas system which enables uniform reactant gas flow across the wafer and directs purge gas flow downwardly and upwardly toward the periphery of the wafer for sweeping exhaust gases radially away from the wafer to prevent deposition outside the wafer and keep the chamber clean. The reactor provides uniform processing over a wide range of pressures including very high pressures. A low temperature CVD process for forming a highly conformal layer of silicon dioxide is also disclosed. The process uses very high chamber pressure and low temperature, and TEOS and ozone reactants. The low temperature CVD silicon dioxide deposition step is particularly useful for planarizing underlying stepped dielectric layers, either alone or in conjunction with a subsequent isotropic etch. A preferred in-situ multiple-step process for forming a planarized silicon dioxide layer uses (1) high rate silicon dioxide deposition at a low temperature and high pressure followed by (2) the deposition of the conformal silicon dioxide layer also at high pressure and low temperature, followed by (3) a high rate isotropic etch, preferably at low temperature and high pressure in the sane reactor used for the two oxide deposition steps. Various combinations of the steps are disclosed for different applications, as is a preferred reactor self-cleaning step.

Owner:APPLIED MATERIALS INC

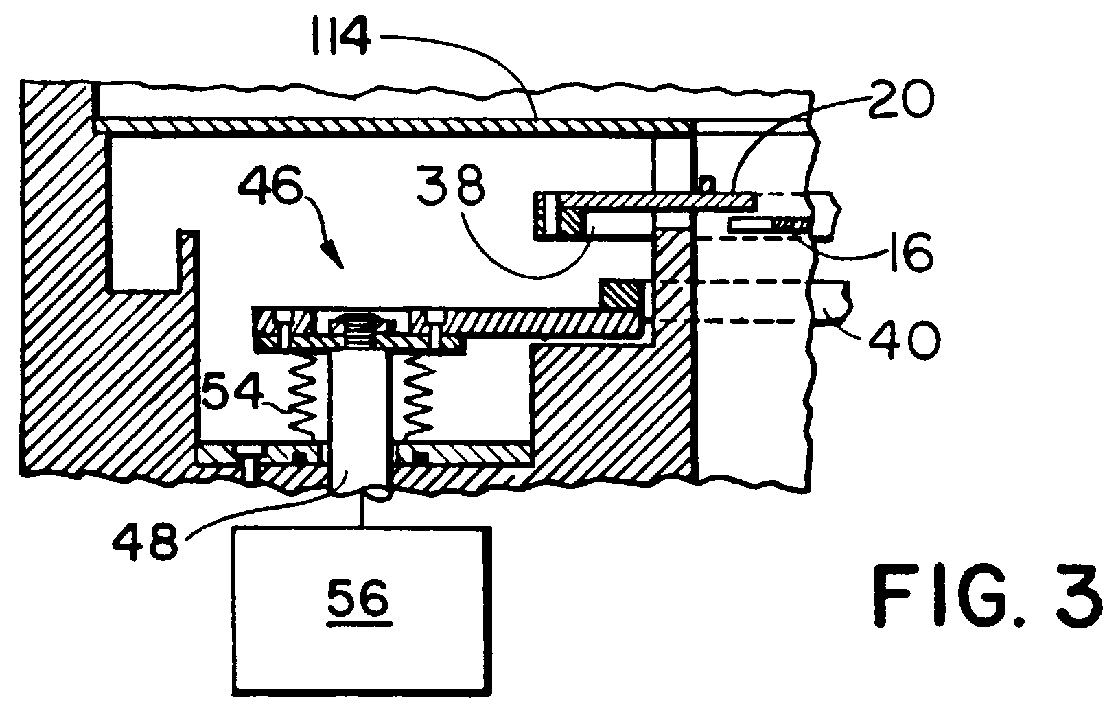

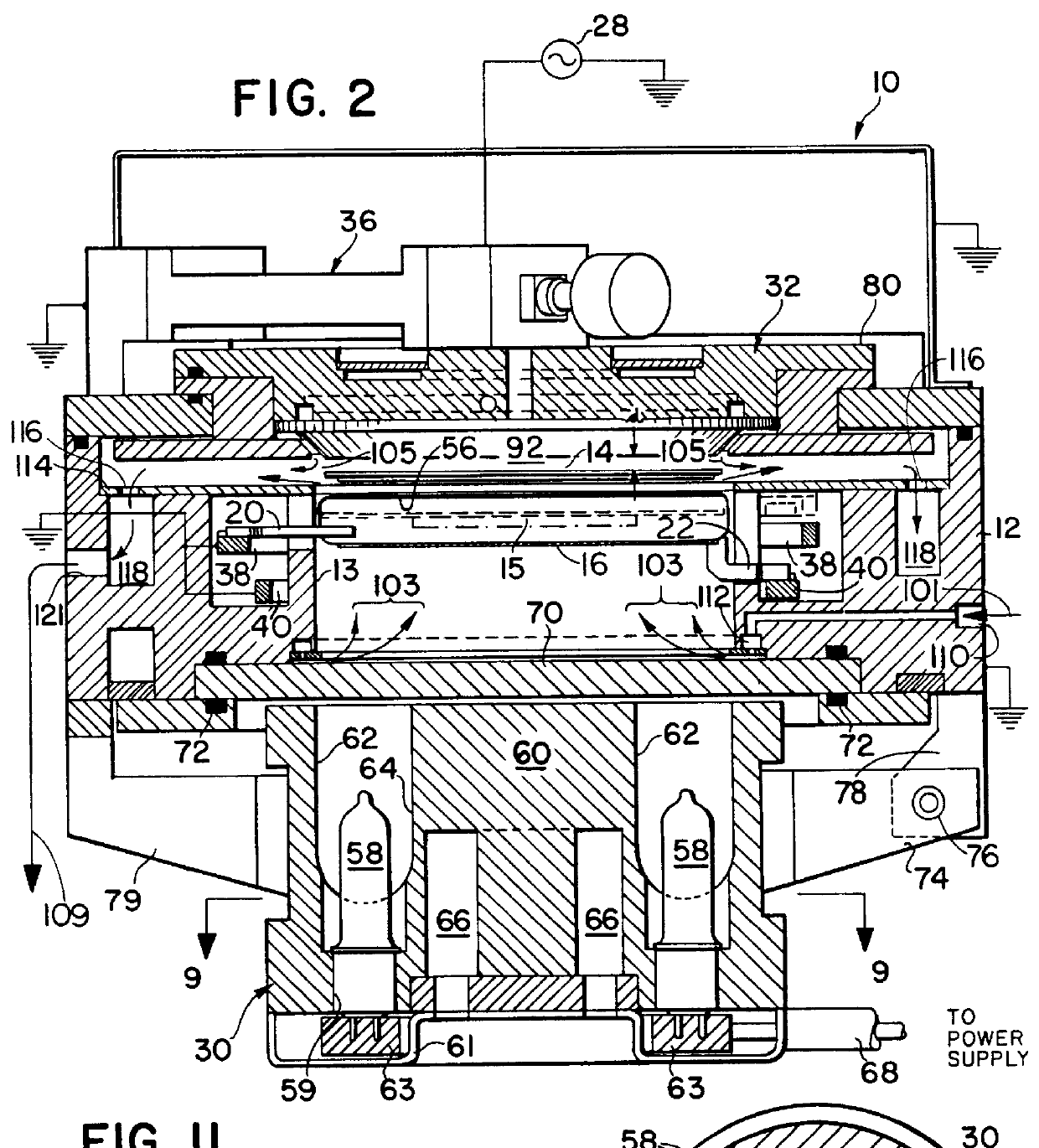

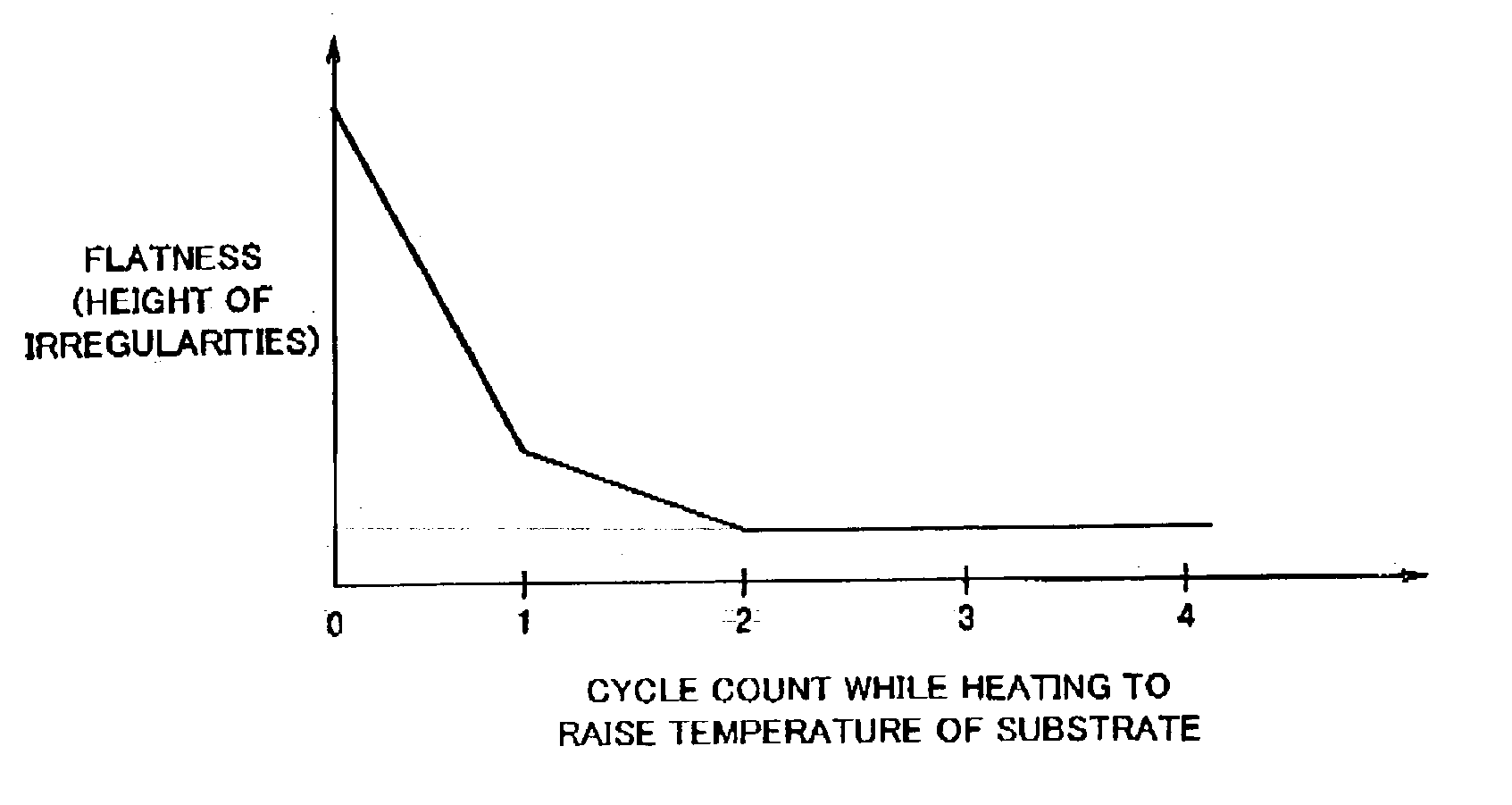

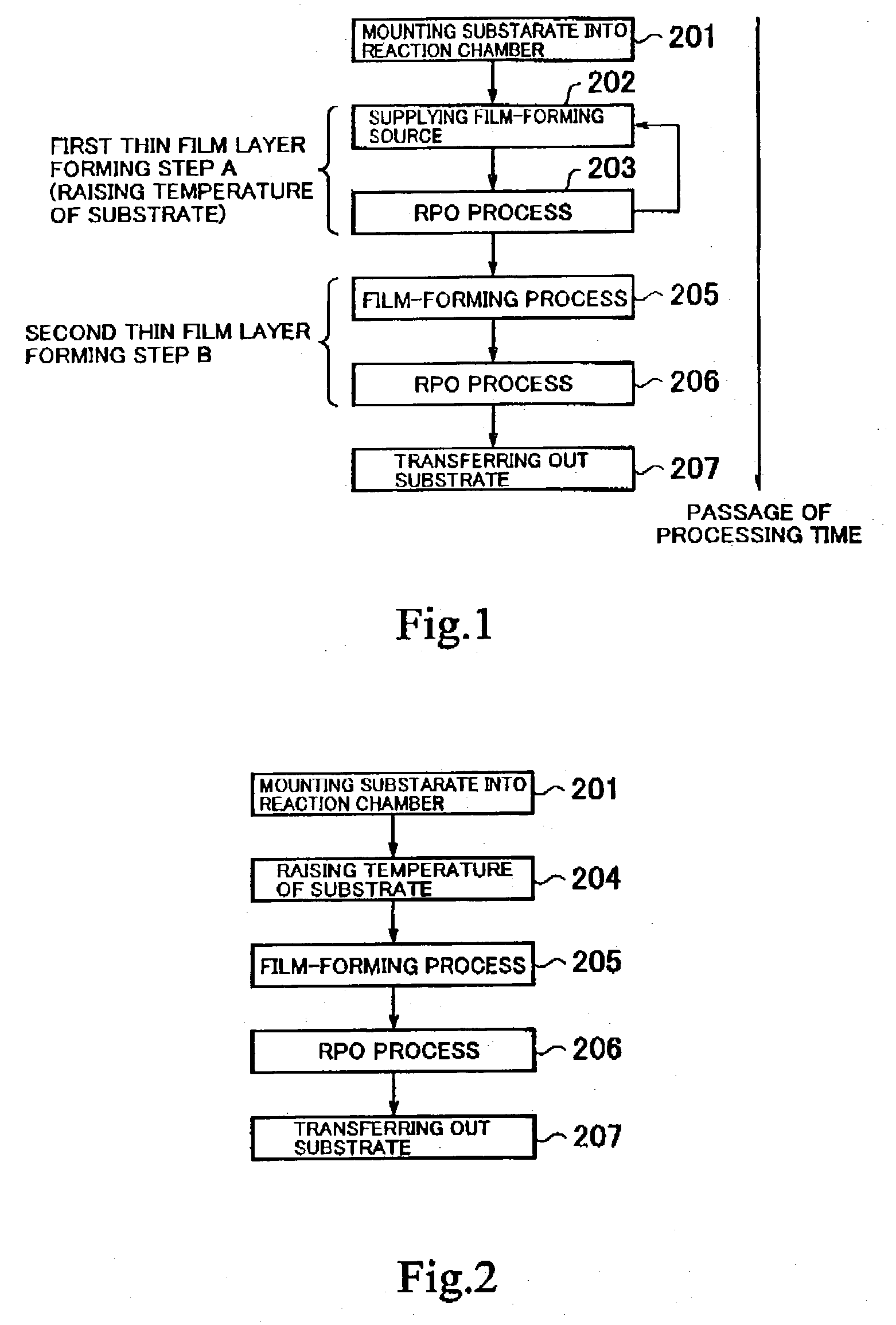

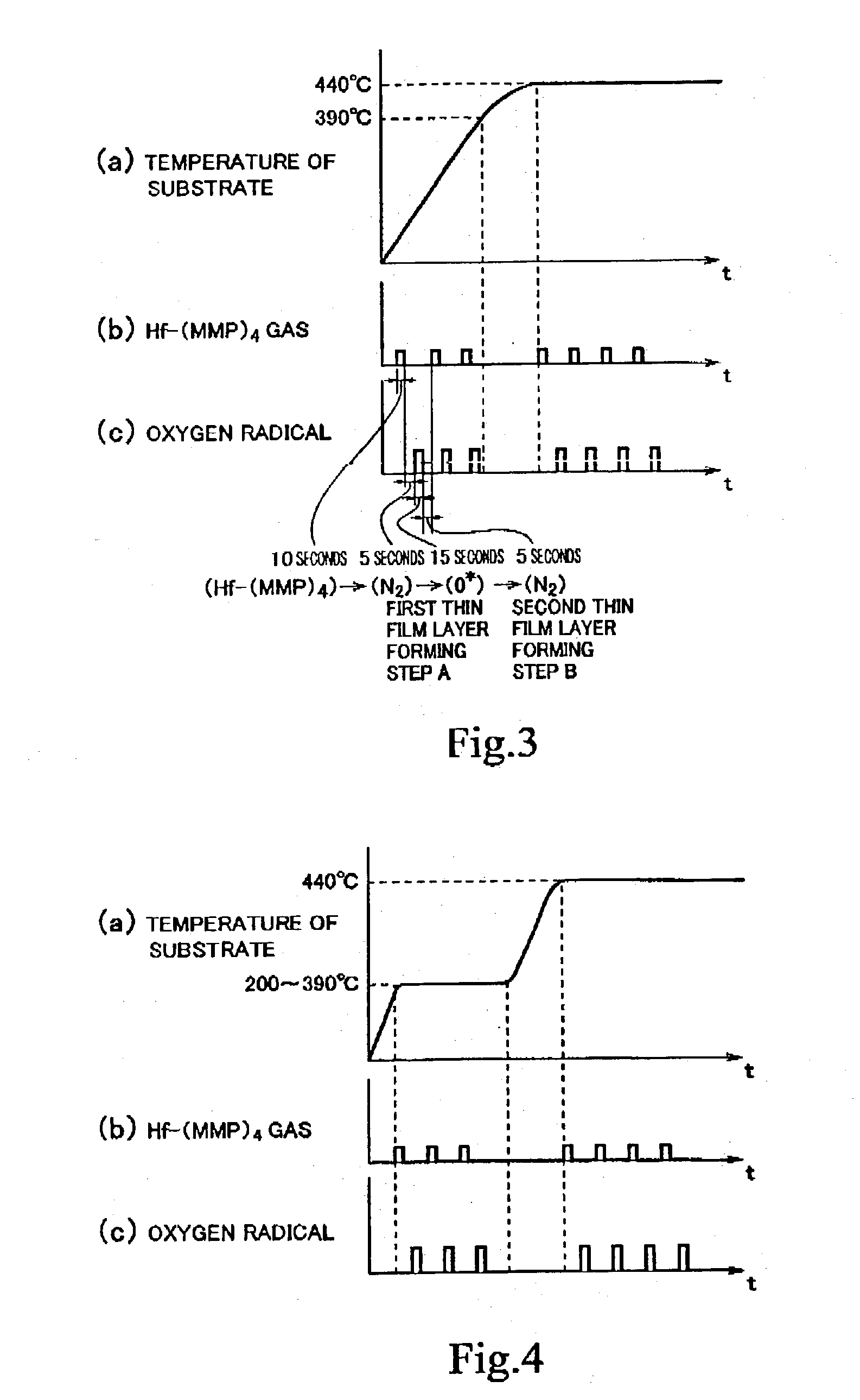

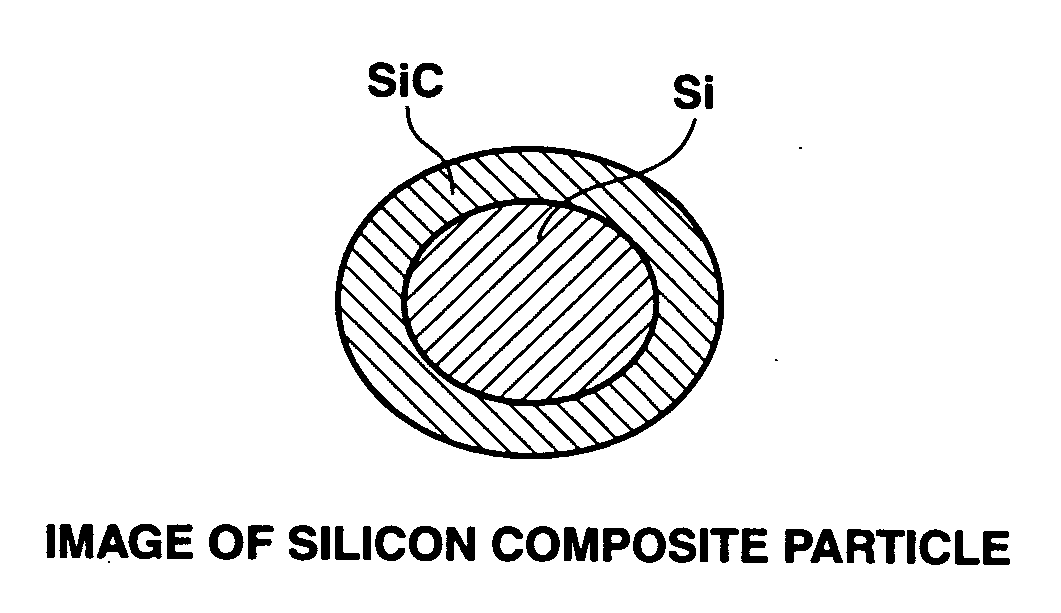

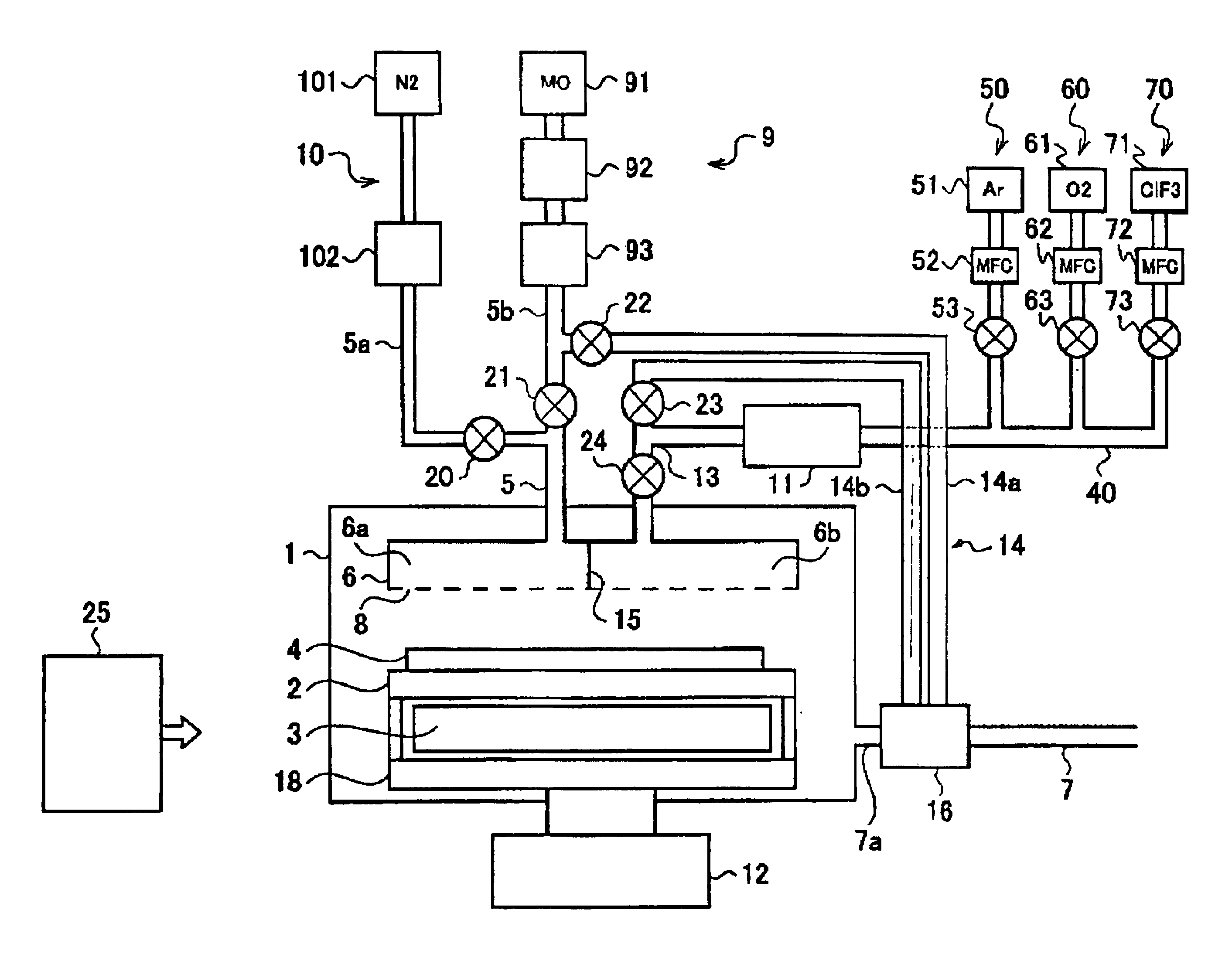

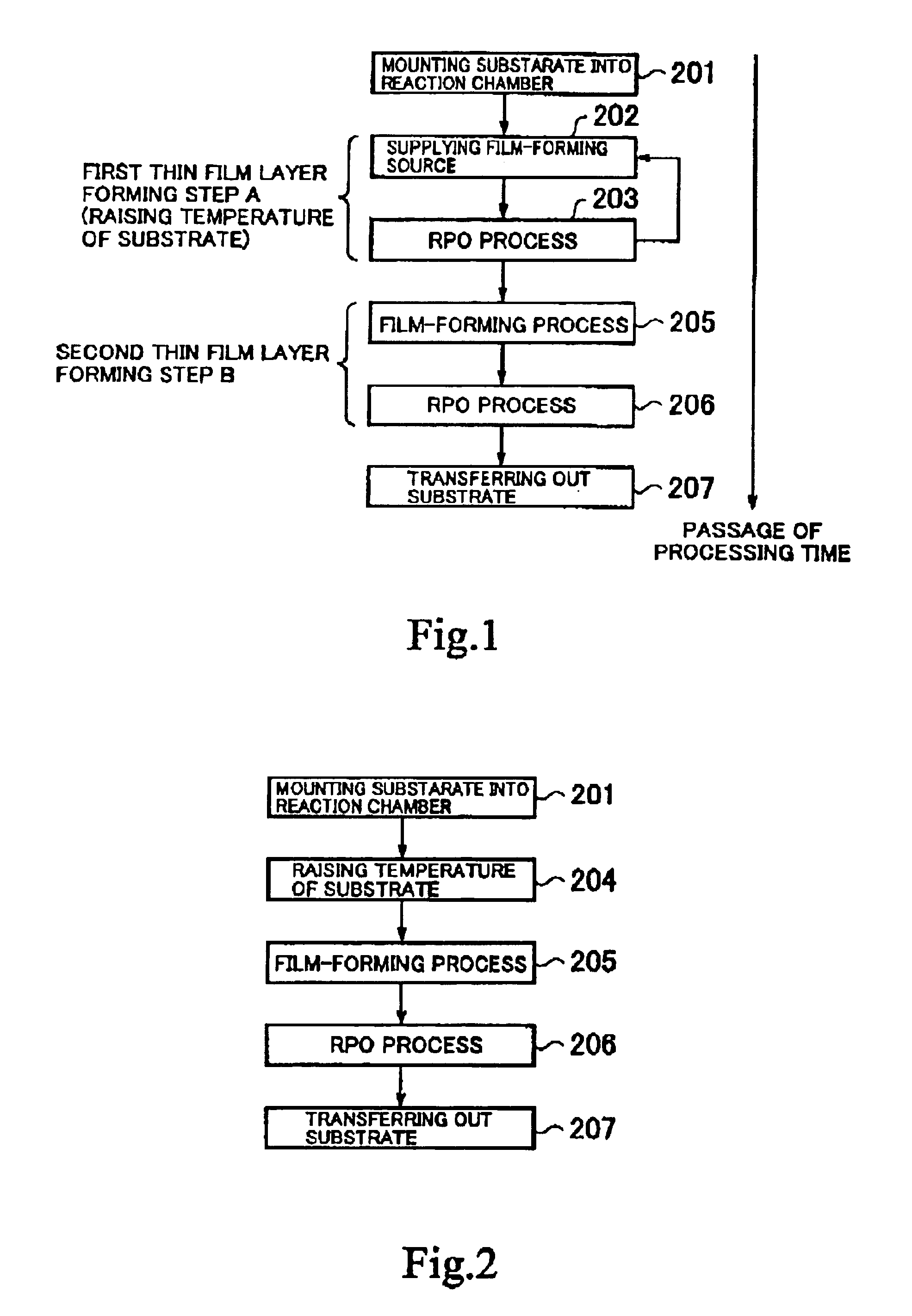

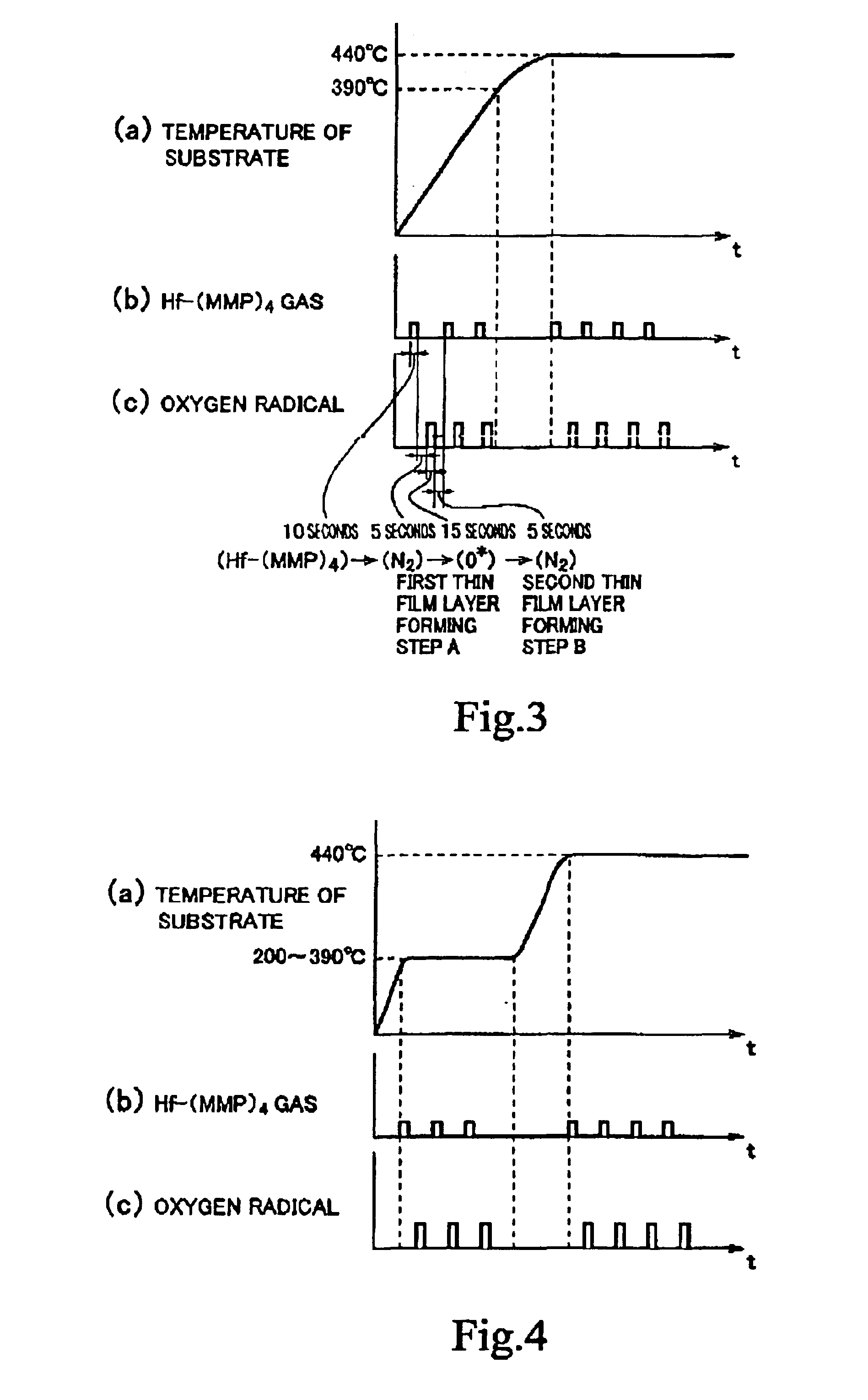

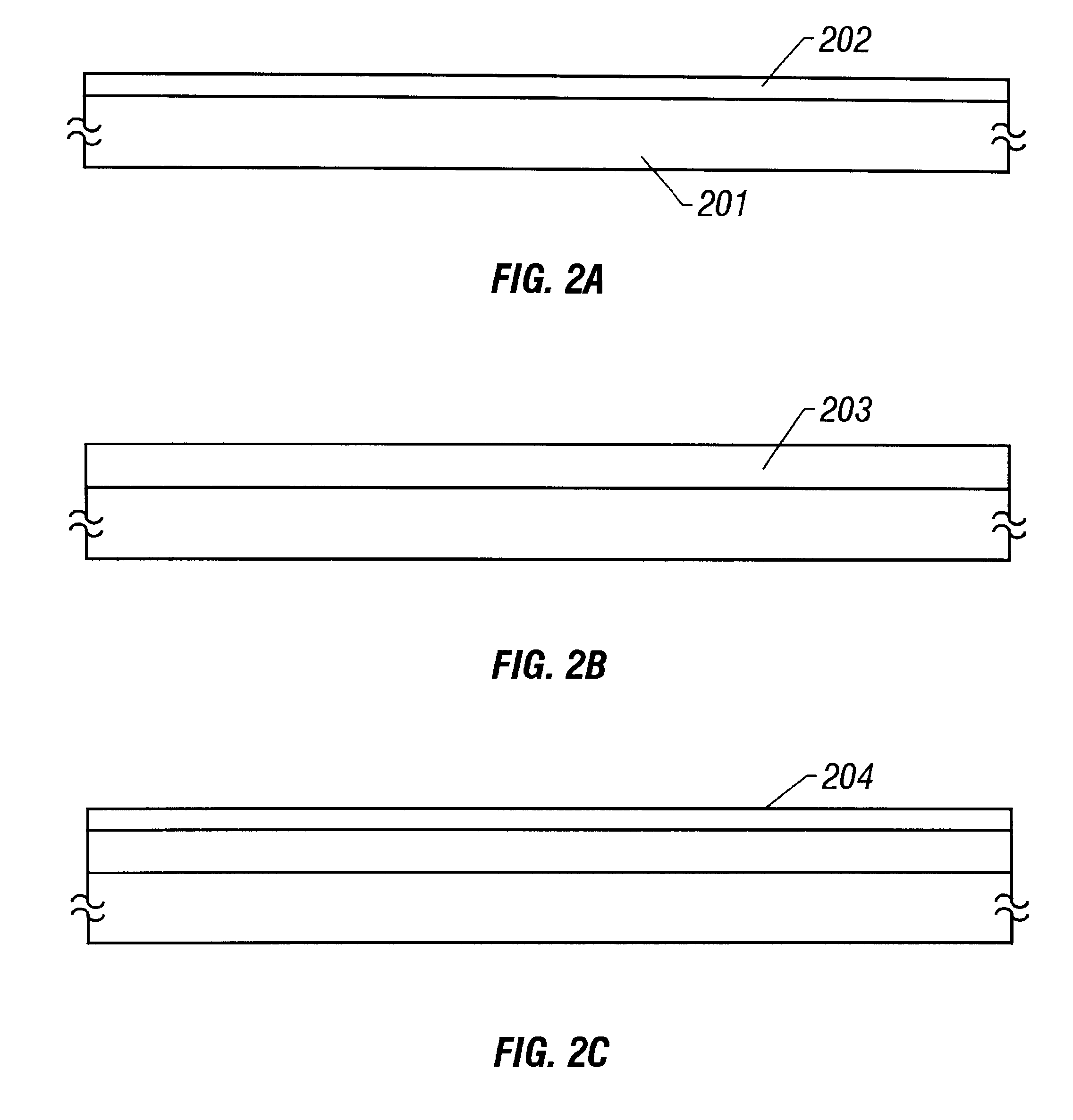

Manufacturing method of semiconductor device and substrate processing apparatus

ActiveUS20030181060A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingProduction rateRemote plasma

According to the present invention, flatness of a thin film formed on a substrate is improved without generating particles and lowering productivity. A method of manufacturing a semiconductor device includes a first thin film layer forming step A and a second thin film layer forming step B. In the first thin film layer forming step A, on the way of heating and raising the temperature of the substrate up to a film-forming temperature, a film-forming source supply in which an organic source gas is made adhere onto the substrate in yet unreacted state is performed (202), and thereafter, a RPO process (Remote Plasma Oxidation) in which an oxygen radical is supplied onto the substrate to form a first thin film layer is performed (203). In this first thin film layer forming step A, it is preferable to repeat the film-forming source supply onto the substrate and the RPO process more than once. In the second thin film layer forming step B, after the source gas is supplied onto the substrate by a thermal CVD method to perform a film-forming process (205) after raising the temperature of the substrate to the film-forming temperature, the RPO process is performed to form a second thin film layer on the first thin film layer with a predetermined film thickness (206).

Owner:KOKUSA ELECTRIC CO LTD

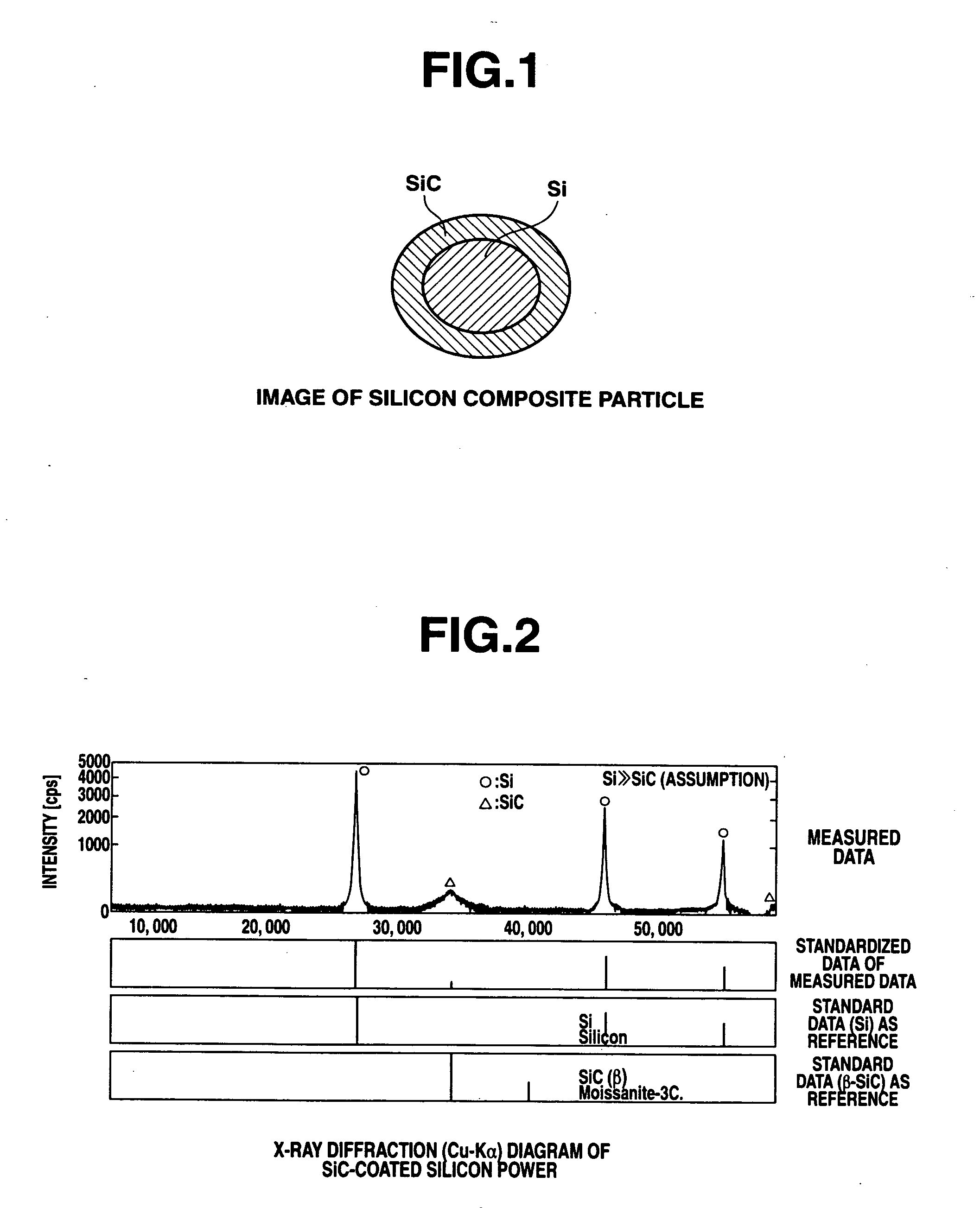

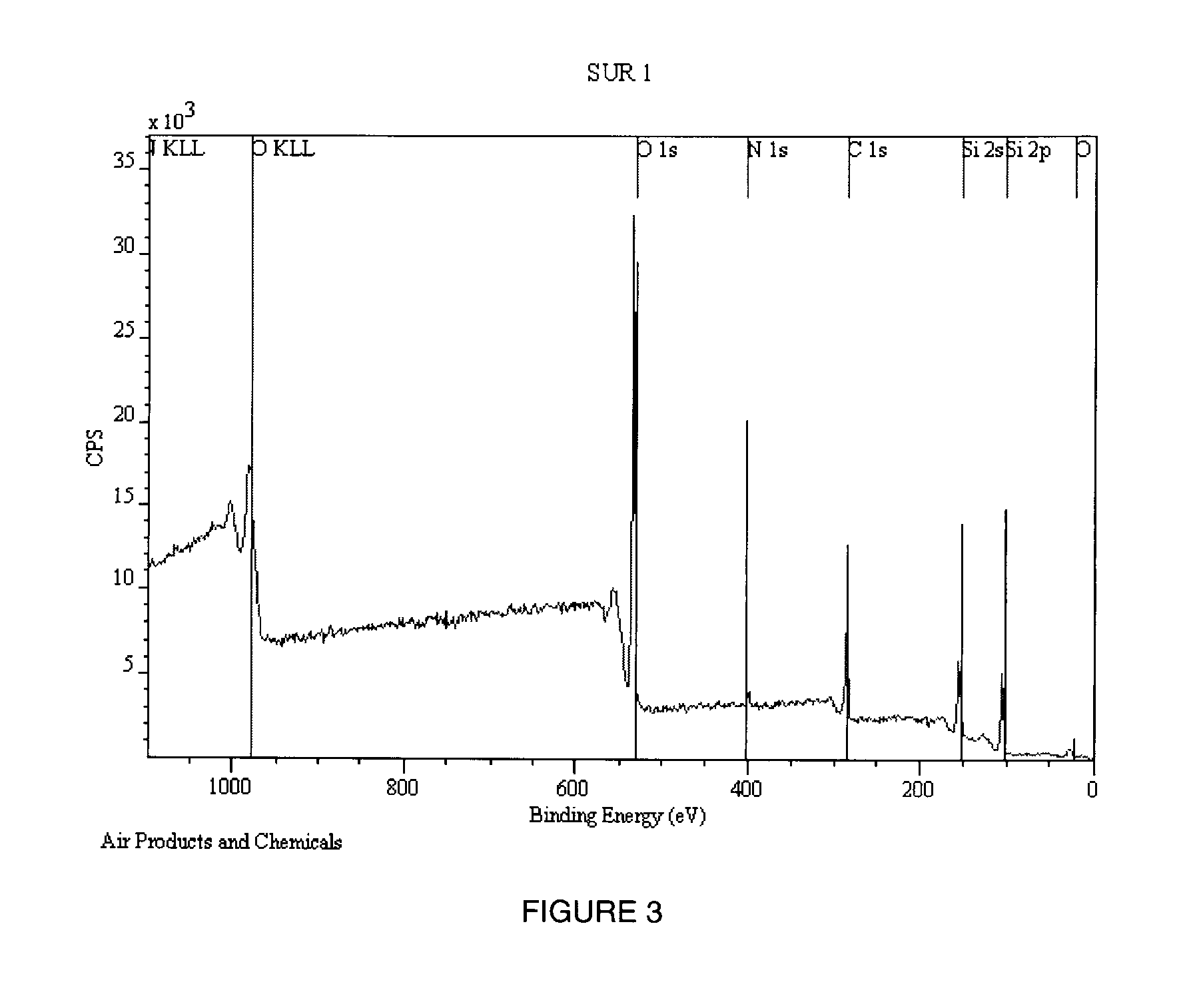

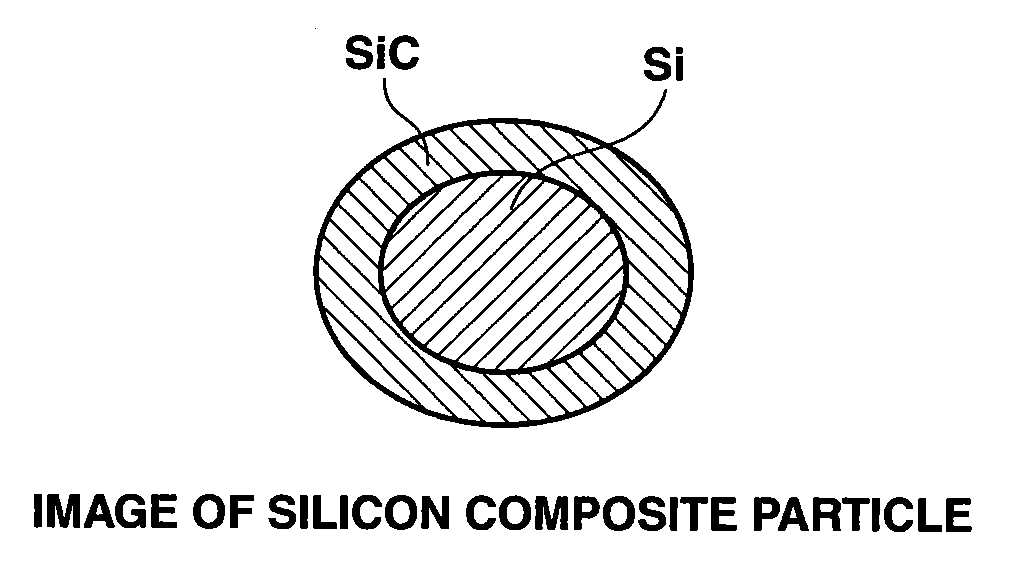

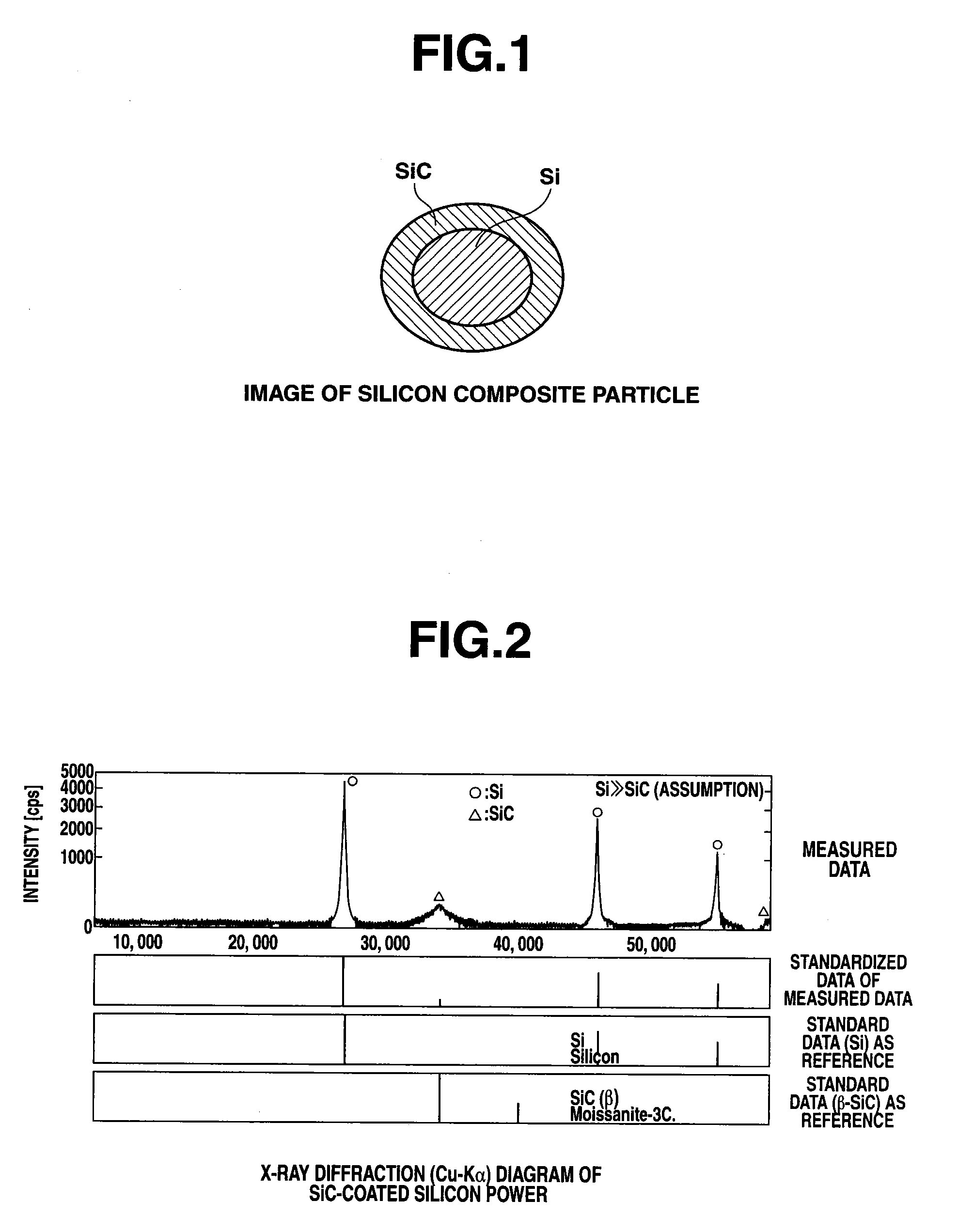

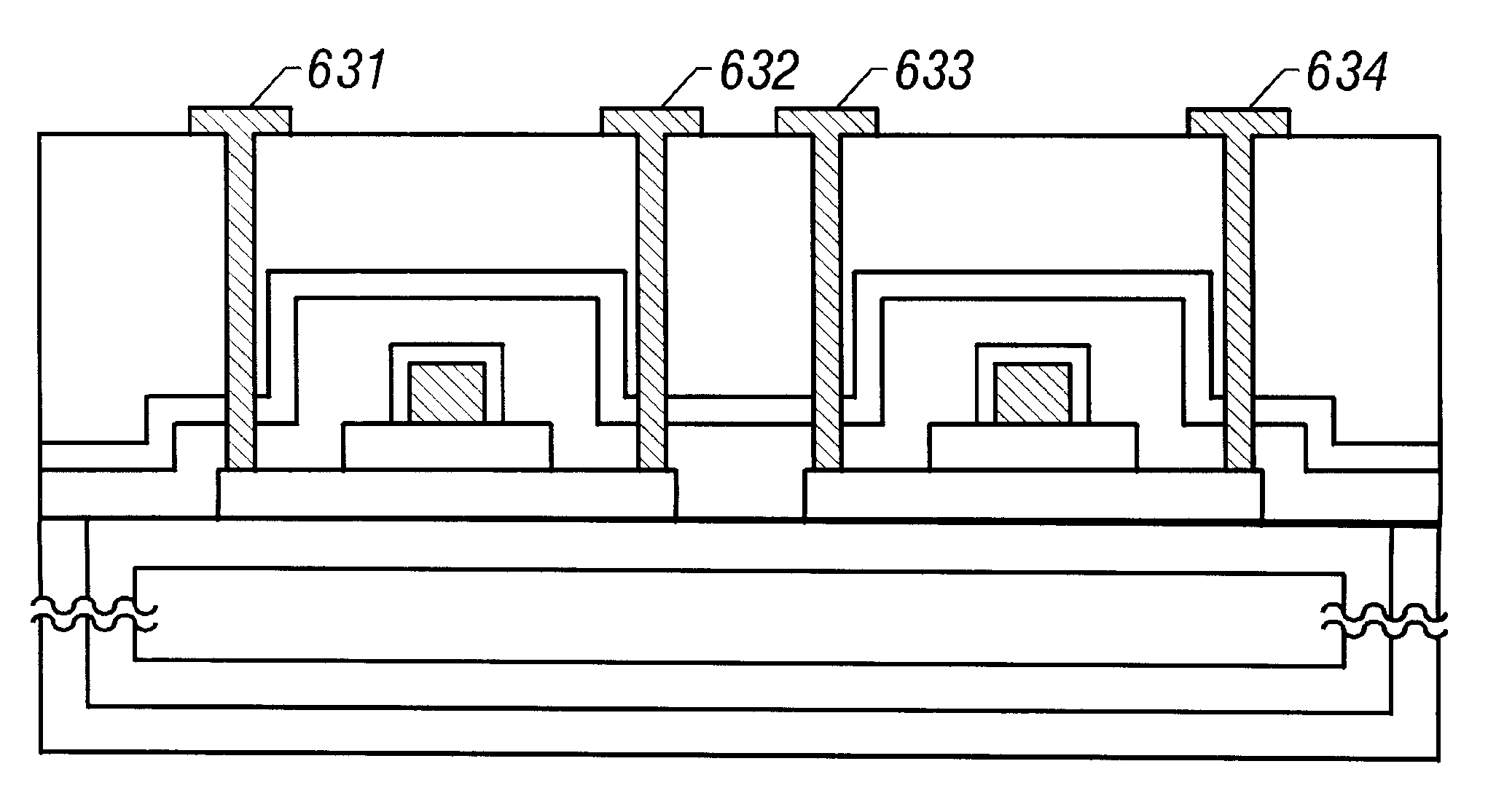

Silicon composite, making method, and non-aqueous electrolyte secondary cell negative electrode material

InactiveUS20060003227A1Improve initial efficiencyImprove cycle performanceFinal product manufactureSecondary cells charging/dischargingCarbon layerDecomposition

A silicon composite comprises silicon particles whose surface is at least partially coated with a silicon carbide layer. It is prepared by subjecting a silicon powder to thermal CVD with an organic hydrocarbon gas and / or vapor at 900-1,400° C., and heating the powder for removing an excess free carbon layer from the surface through oxidative decomposition.

Owner:SHIN ETSU CHEM IND CO LTD

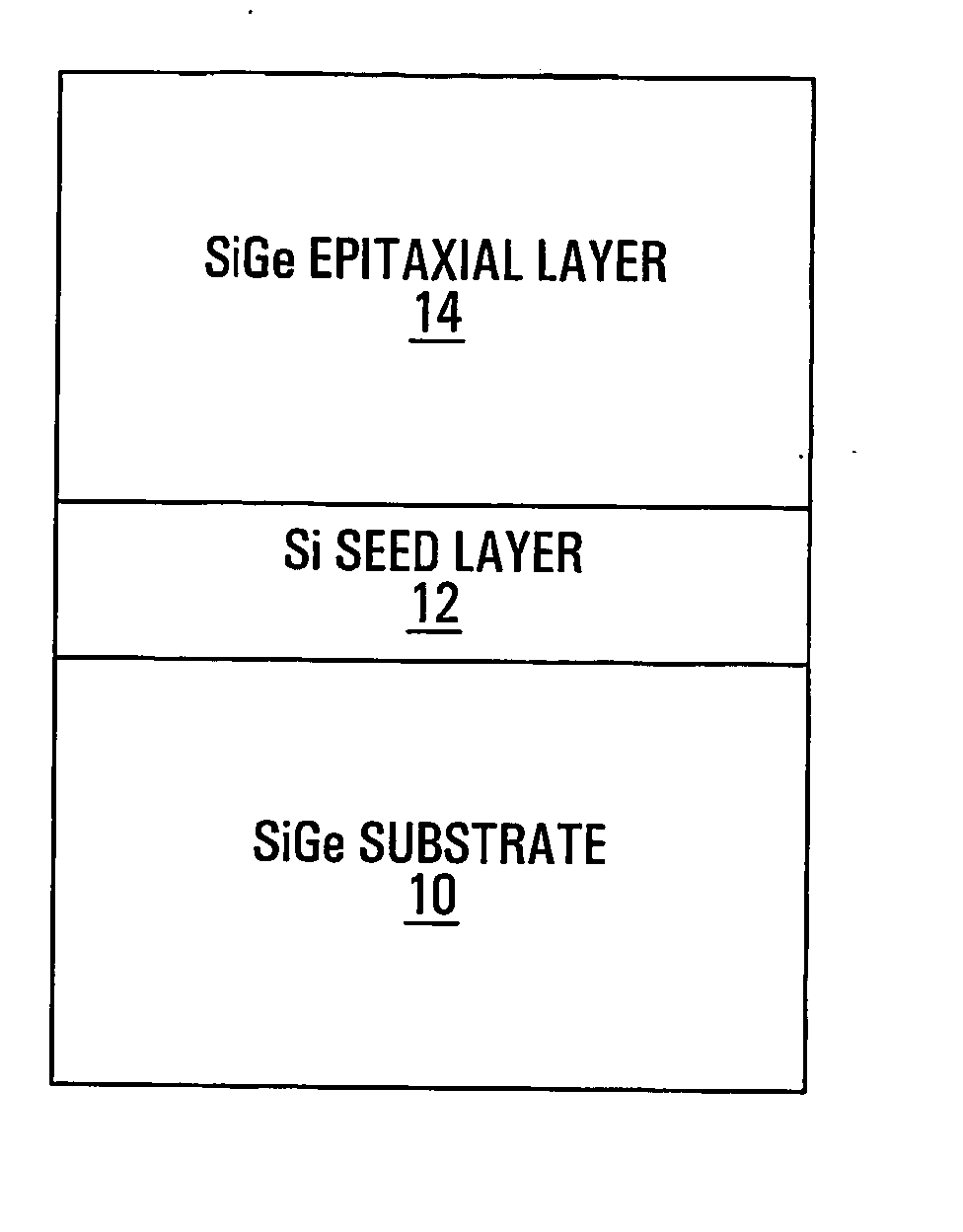

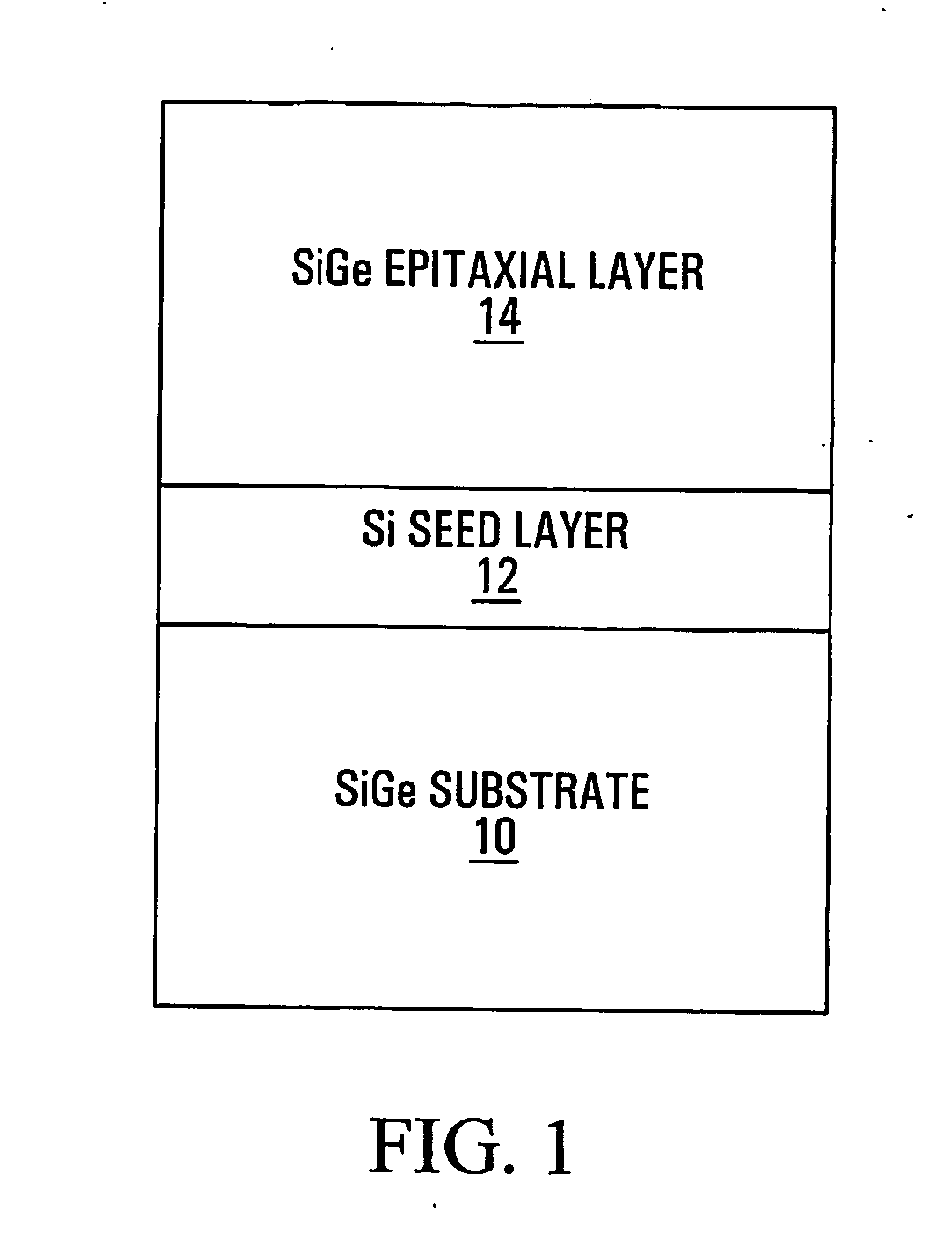

Method of depositing high-quality sige on sige substrates

InactiveUS20050070076A1Polycrystalline material growthFrom solid stateAtomic force microscopyGas phase

This invention provides a method of depositing high-quality Si or SiGe epitaxial layers on SiGe substrates. By first depositing a thin Si seed layer on the SiGe substrate, the quality of the seed layer and of the subsequently deposited layers is greatly improved over what is obtained from depositing SiGe directly onto the SiGe substrate. Indeed, whereas the RMS surface roughness of the deposition of SiGe directly on SiGe, as measured by atomic-force microscopy (AFM), was 3-4 nm, it was more than an order of magnitude better when a thin Si seed layer was employed. This work was performed on an ultra-high-vacuum chemical vapor deposition (UHV / CVD) system; however, the same method would apply to other deposition systems such as atmospheric-pressure, low-pressure and rapid-thermal CVD.

Owner:SIGE SEMICON

Manufacturing method of semiconductor device and substrate processing apparatus

InactiveUS6884738B2Improve flatnessReduce flatness requirementsSemiconductor/solid-state device manufacturingChemical vapor deposition coatingProduction rateRemote plasma

According to the present invention, flatness of a thin film formed on a substrate is improved without generating particles and lowering productivity. A method of manufacturing a semiconductor device includes a first thin film layer forming step A and a second thin film layer forming step B. In the first thin film layer forming step A, on the way of heating and raising the temperature of the substrate up to a film-forming temperature, a film-forming source supply in which an organic source gas is made adhere onto the substrate in yet unreacted state is performed (202), and thereafter, a RPO process (Remote Plasma Oxidation) in which an oxygen radical is supplied onto the substrate to form a first thin film layer is performed (203). In this first thin film layer forming step A, it is preferable to repeat the film-forming source supply onto the substrate and the RPO process more than once. In the second thin film layer forming step B, after the source gas is supplied onto the substrate by a thermal CVD method to perform a film-forming process (205) after raising the temperature of the substrate to the film-forming temperature, the RPO process is performed to form a second thin film layer on the first thin film layer with a predetermined film thickness (206).

Owner:KOKUSA ELECTRIC CO LTD

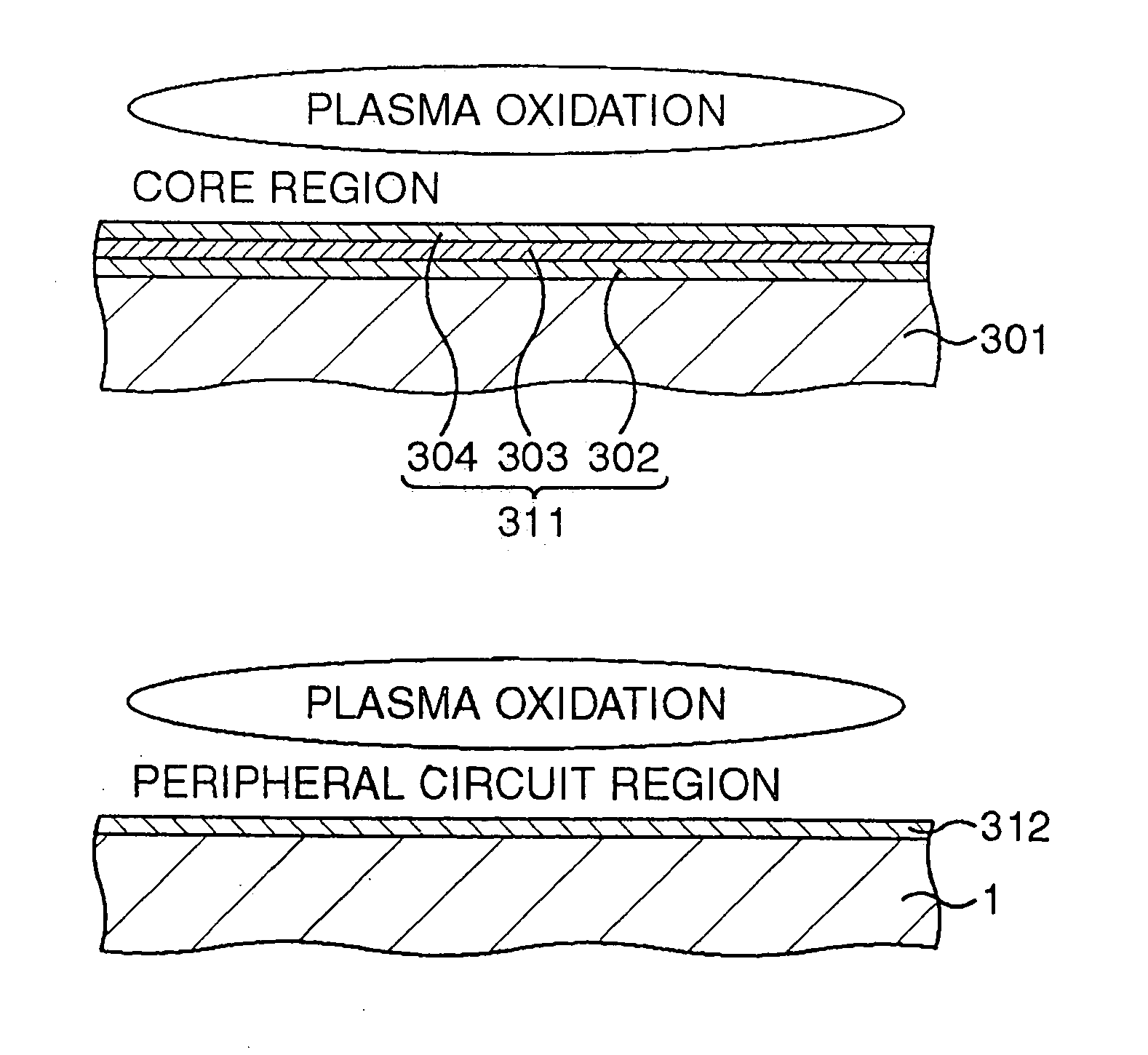

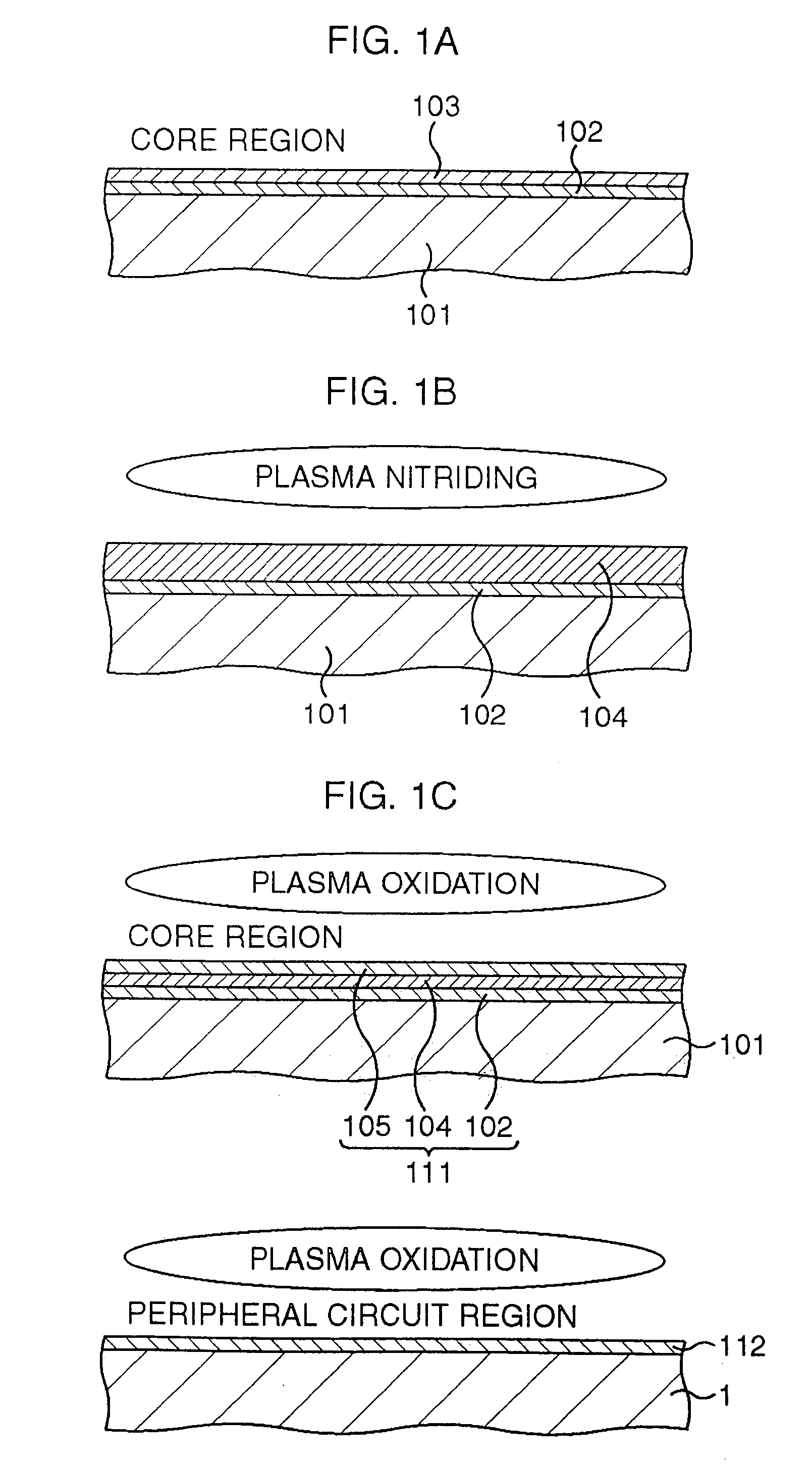

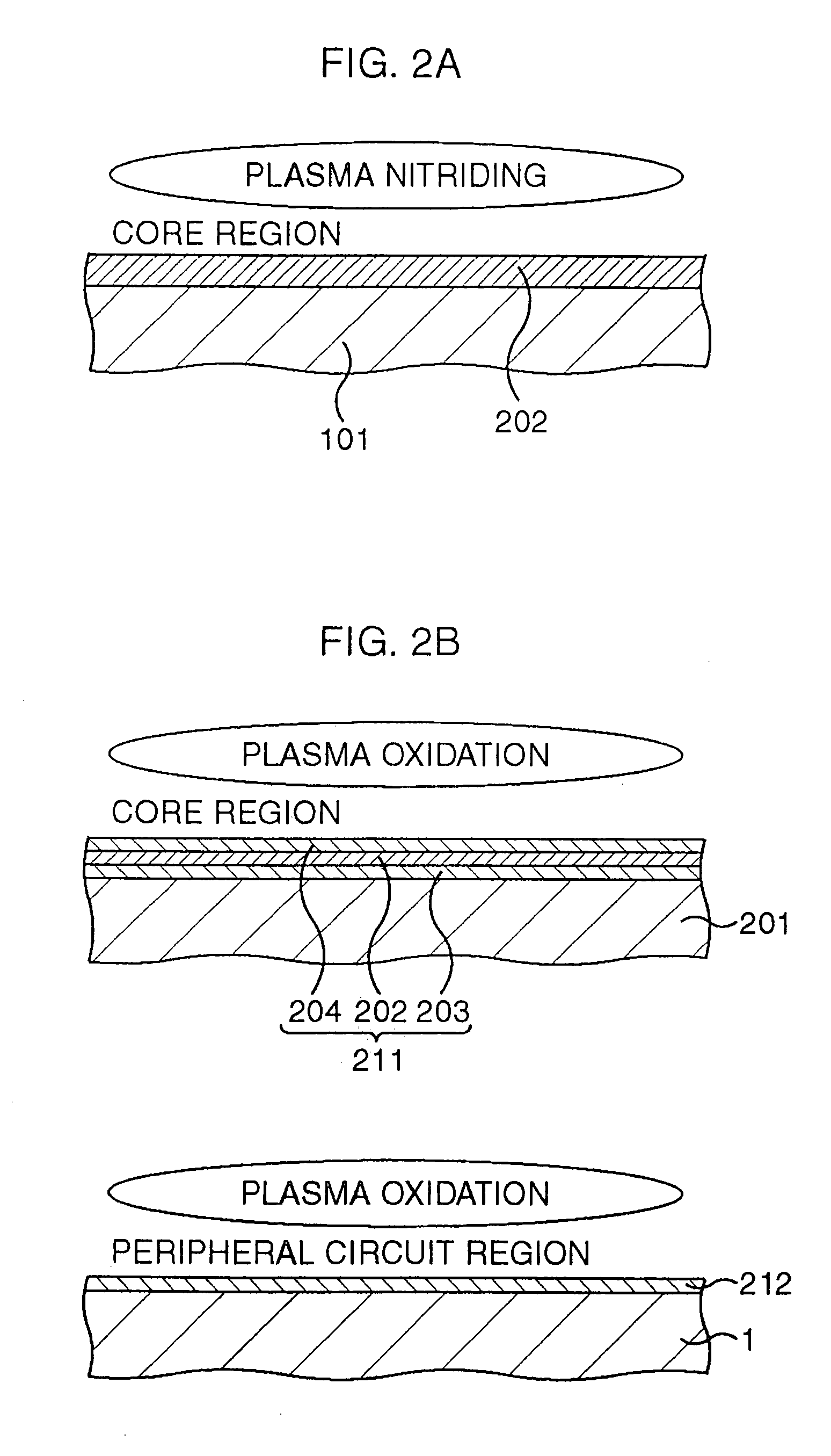

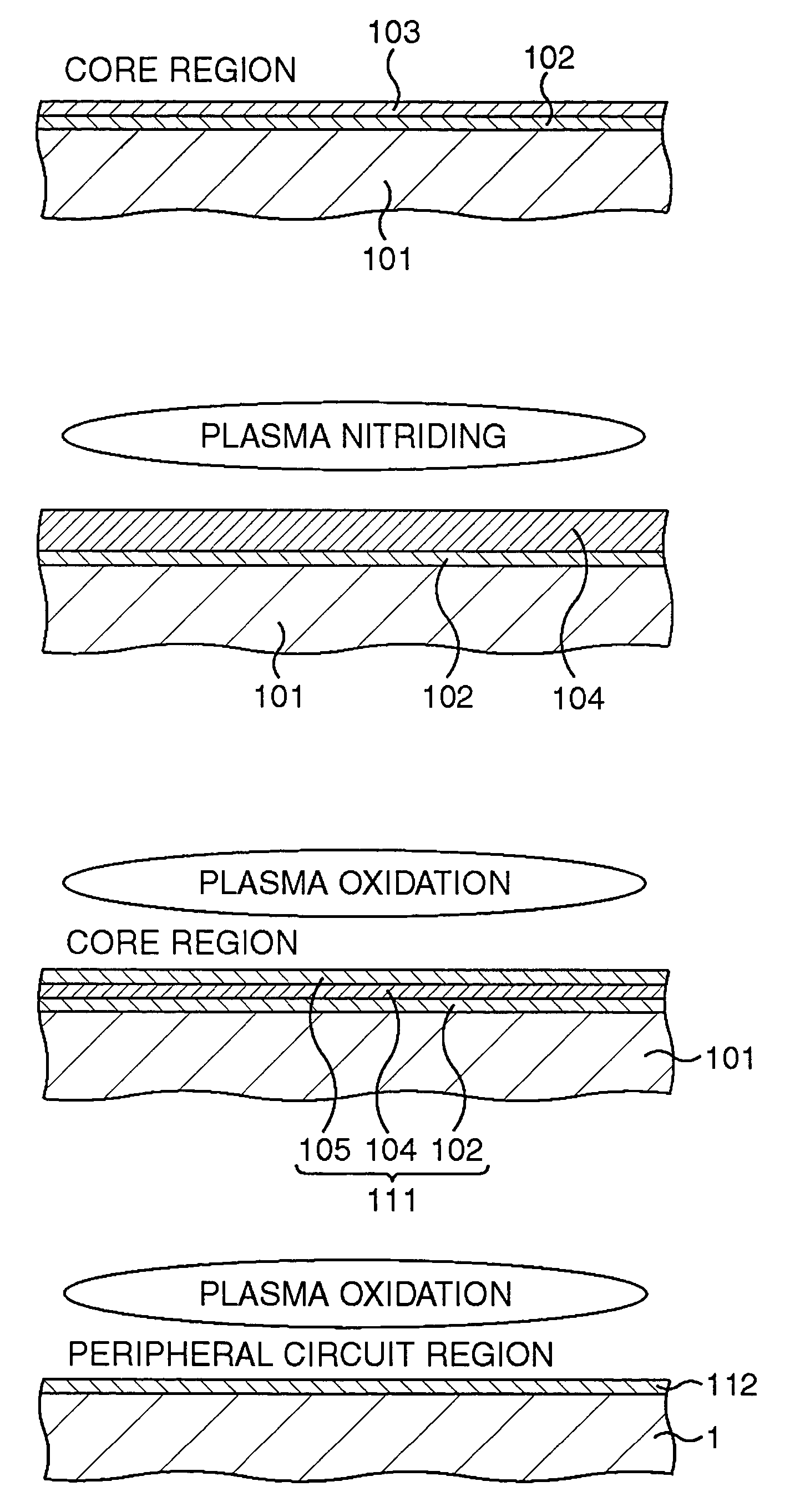

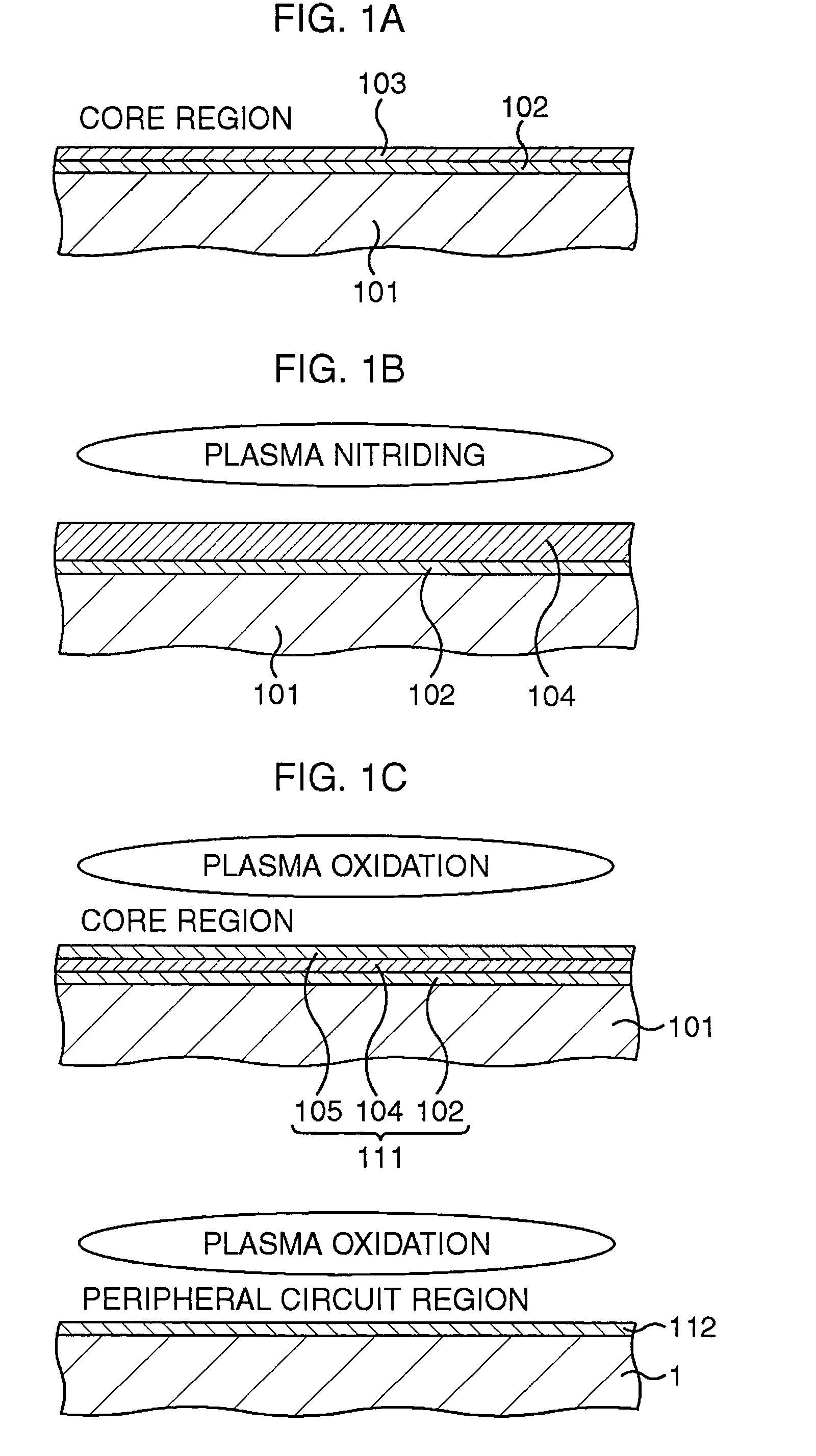

Semiconductor memory device and method for manufacturing semiconductor device

InactiveUS20060228899A1Improve reliabilityQuality improvementTransistorSolid-state devicesSurface layerDevice material

After a lower silicon oxide film is formed on a silicon region, a silicon film is formed on the lower silicon oxide film by, for example, a thermal CVD method. Subsequently, the silicon film is completely nitrided by a plasma nitriding method to be replaced by a silicon nitride film. Subsequently, a surface layer of the silicon nitride film is oxidized by a plasma oxidizing method to be replaced by an upper silicon oxide film. An ONO film as a multilayered insulating film composed of the lower silicon oxide film, the silicon nitride film, and the upper silicon oxide film is formed.

Owner:SPANSION LLC

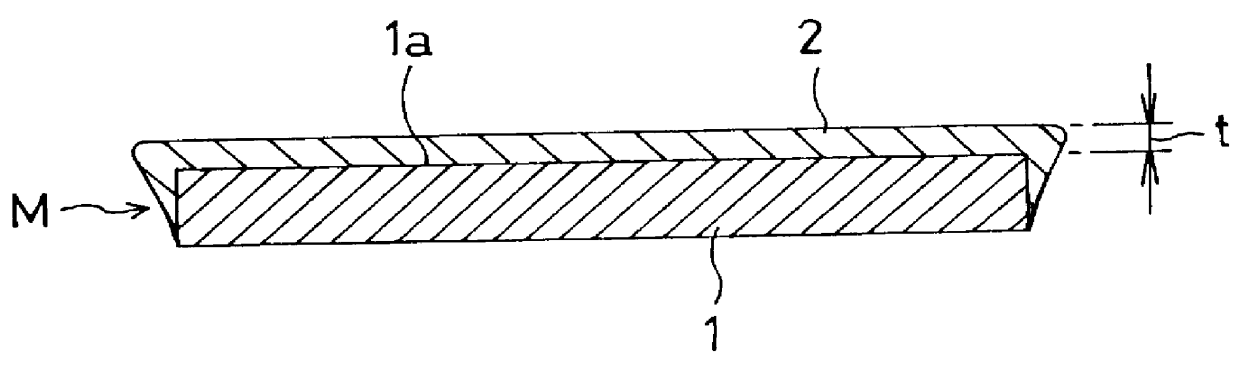

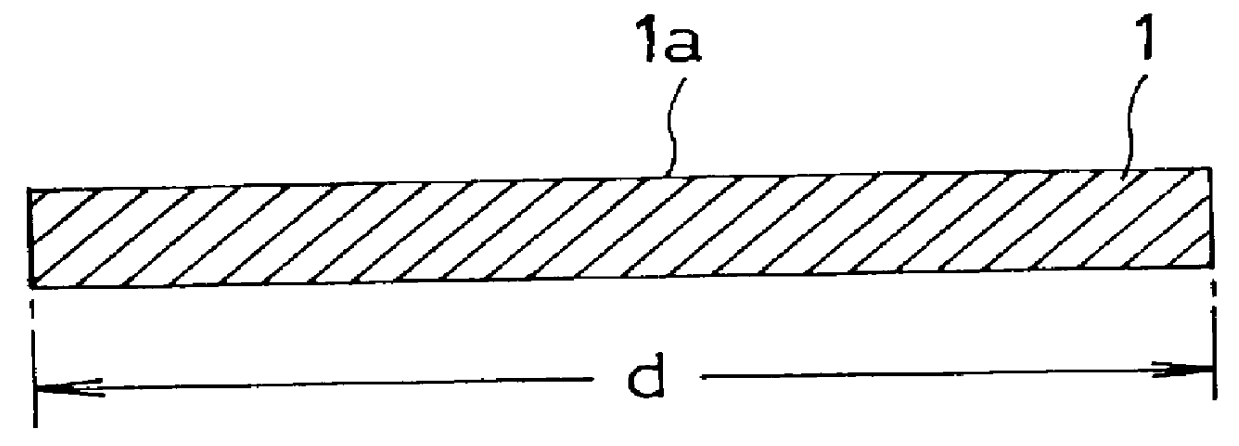

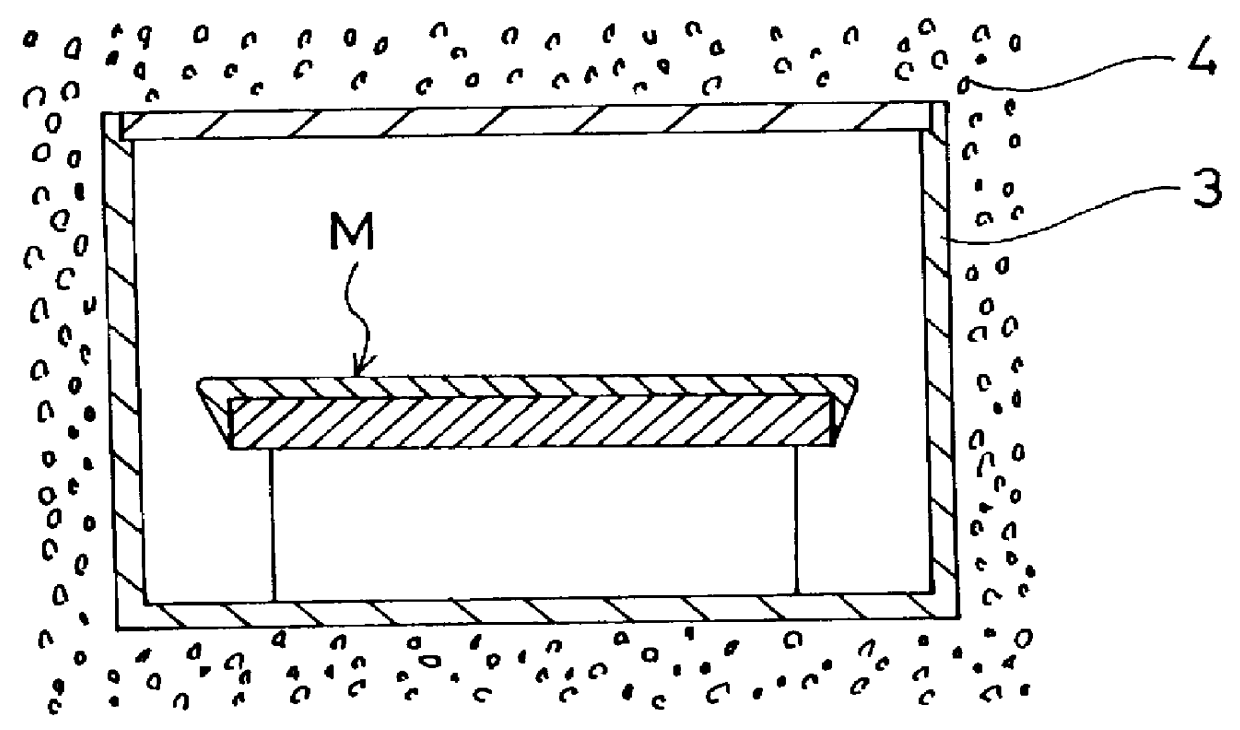

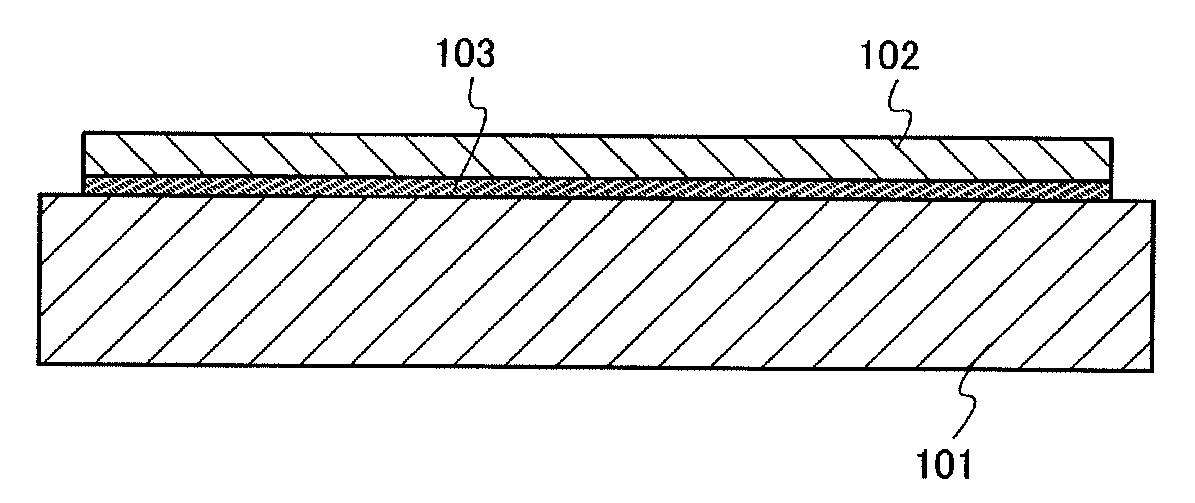

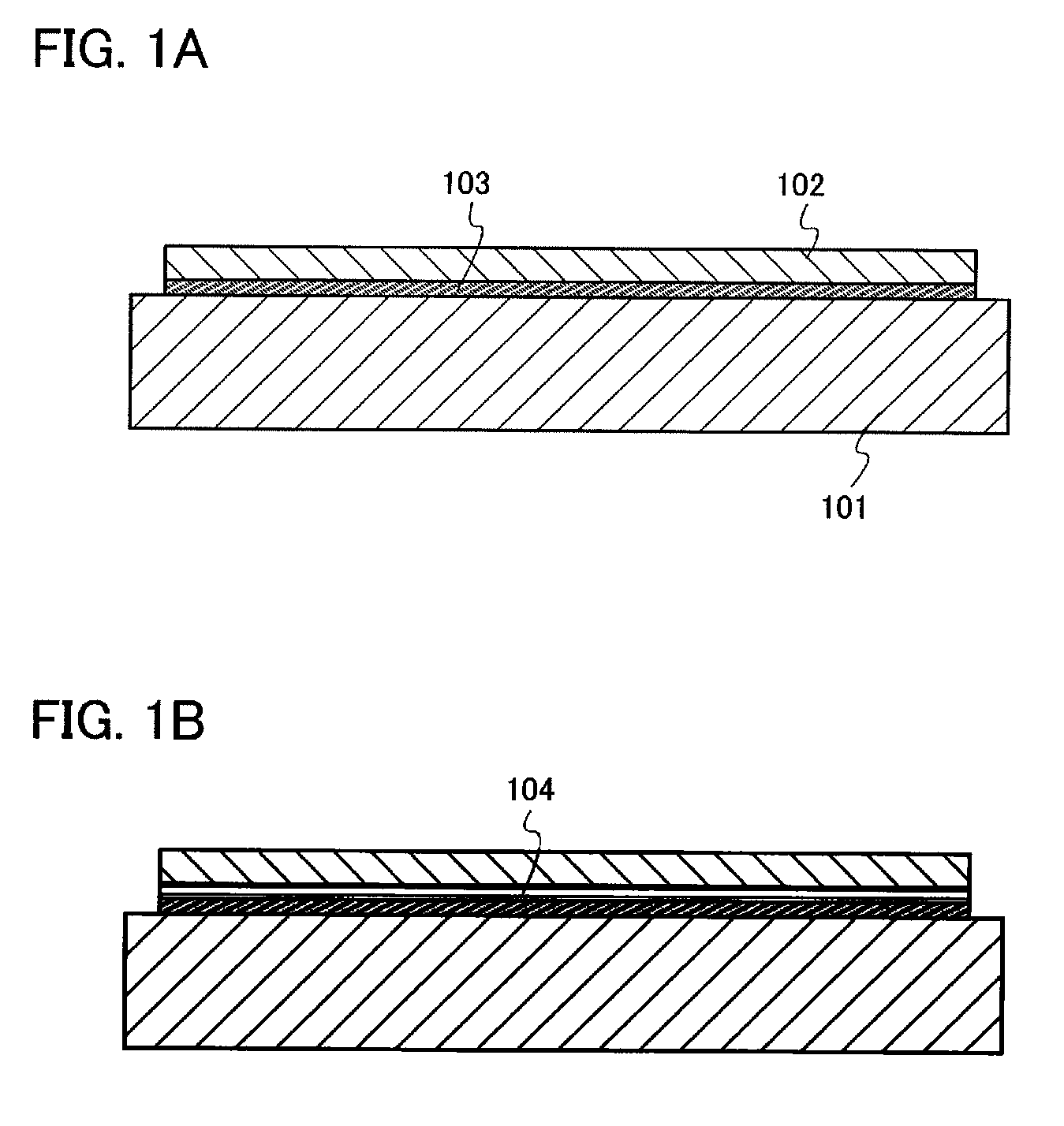

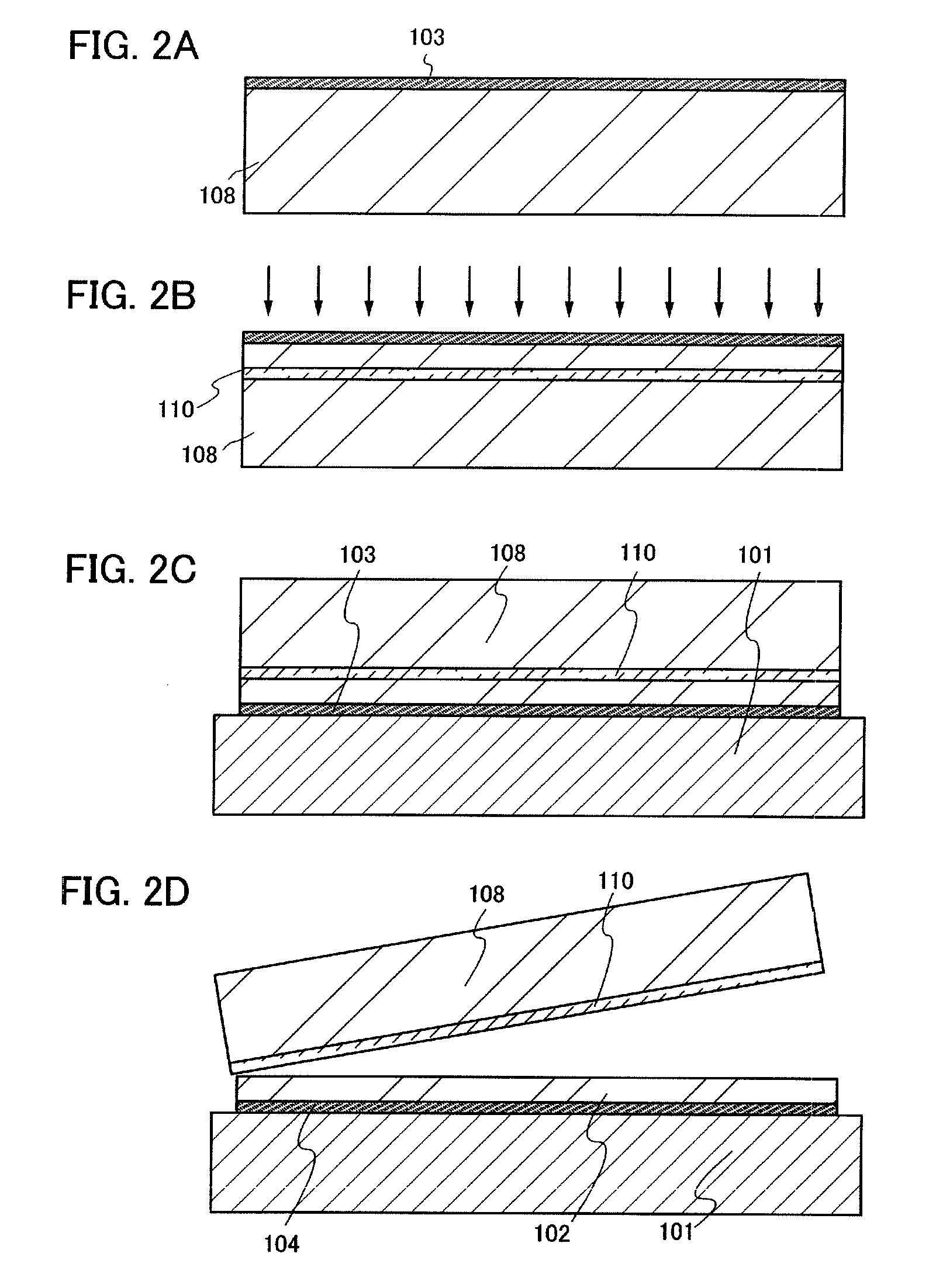

Single crystal SiC and a method of producing the same

InactiveUS6053973AEasily eliminate mismatchStably and efficiently obtainFrom gel statePolycrystalline material growthPorous carbonSurface roughness

The surface 1a of a single crystal alpha -SiC substrate 1 is adjusted so as to have a surface roughness equal to or lower than 2,000 angstroms RMS, and preferably equal to or lower than 1,000 angstroms RMS. On the surface 1a of the single crystal alpha -SiC substrate 1, a polycrystalline alpha -SiC film 2 is grown by thermal CVD to form a complex is placed in a porous carbon container and the carbon container is covered with alpha -SiC powder. The complex is subjected to a heat treatment at a temperature equal to or higher than a film growing temperature, i.e., in the range of 1,900 to 2,400 DEG C. in an argon gas flow, whereby single crystal alpha -SiC is integrally grown on the single crystal alpha -SiC substrate 1 by crystal growth and recrystallization of the polycrystalline alpha -SiC film 2. It is possible to stably and efficiently produce single crystal SiC of a large size which has a high quality and in which any crystal nucleus is not generated.

Owner:NISSIN ELECTRIC CO LTD

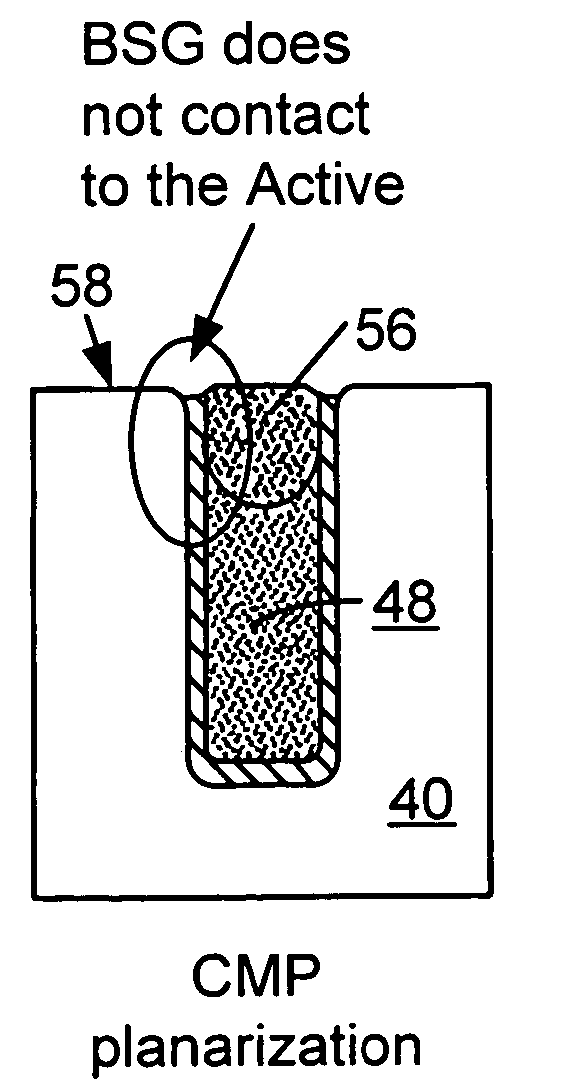

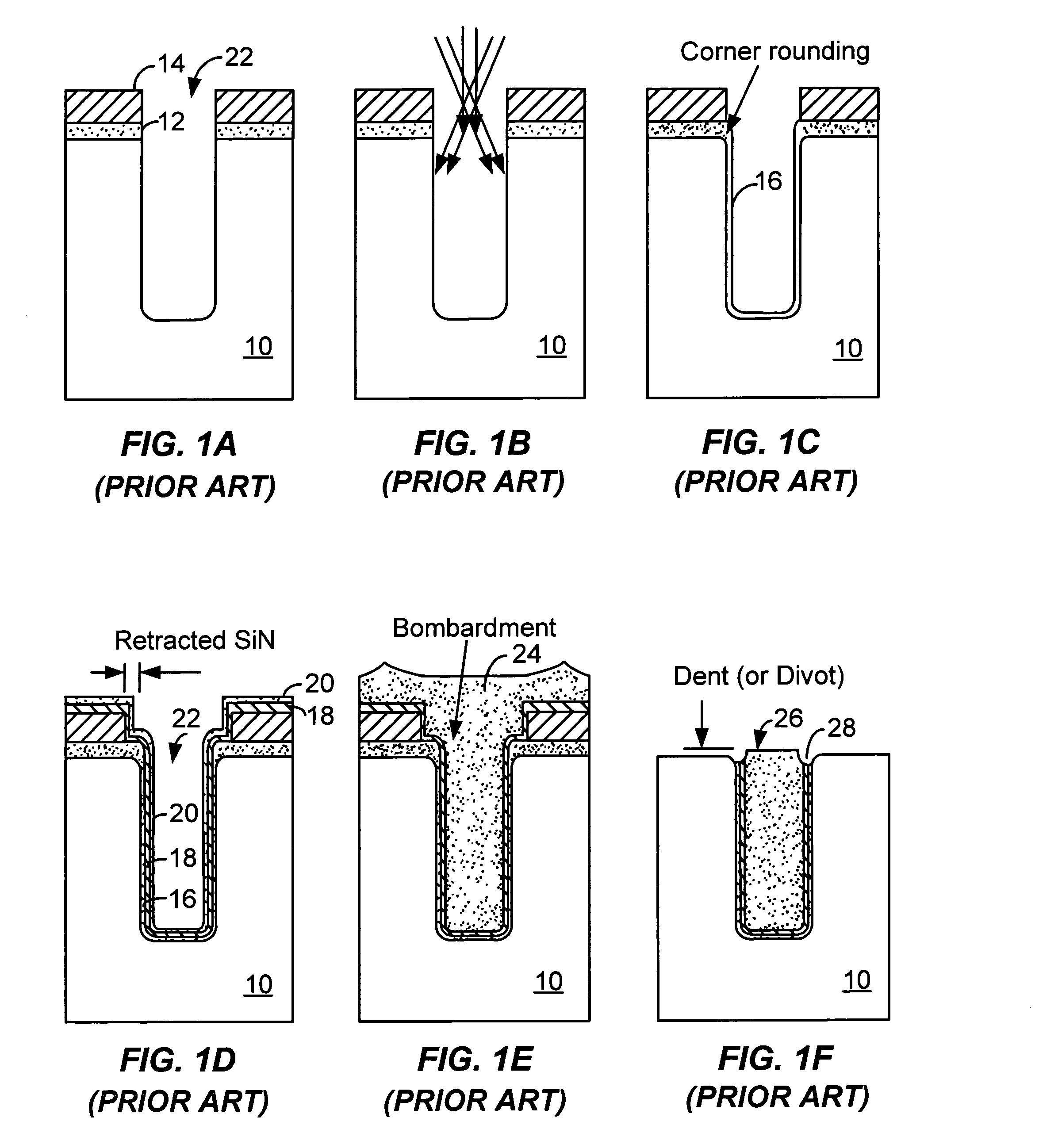

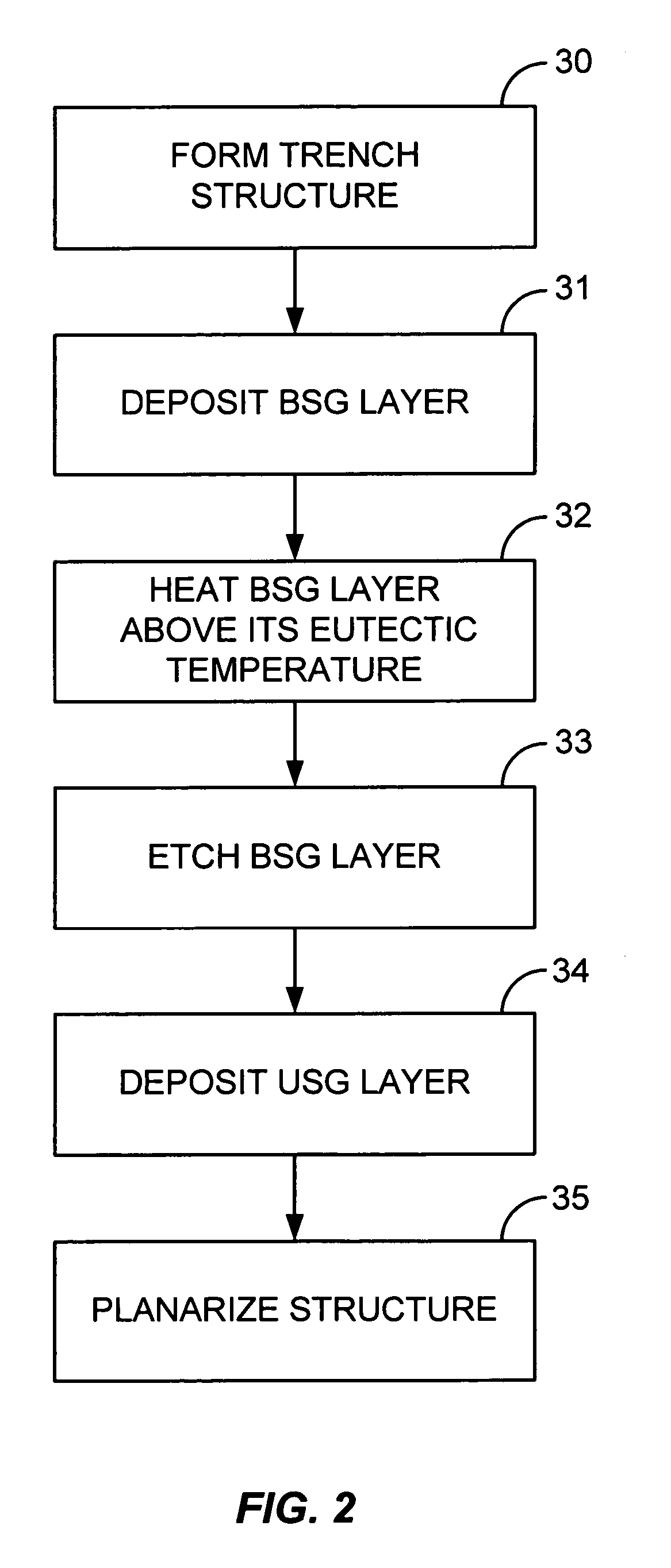

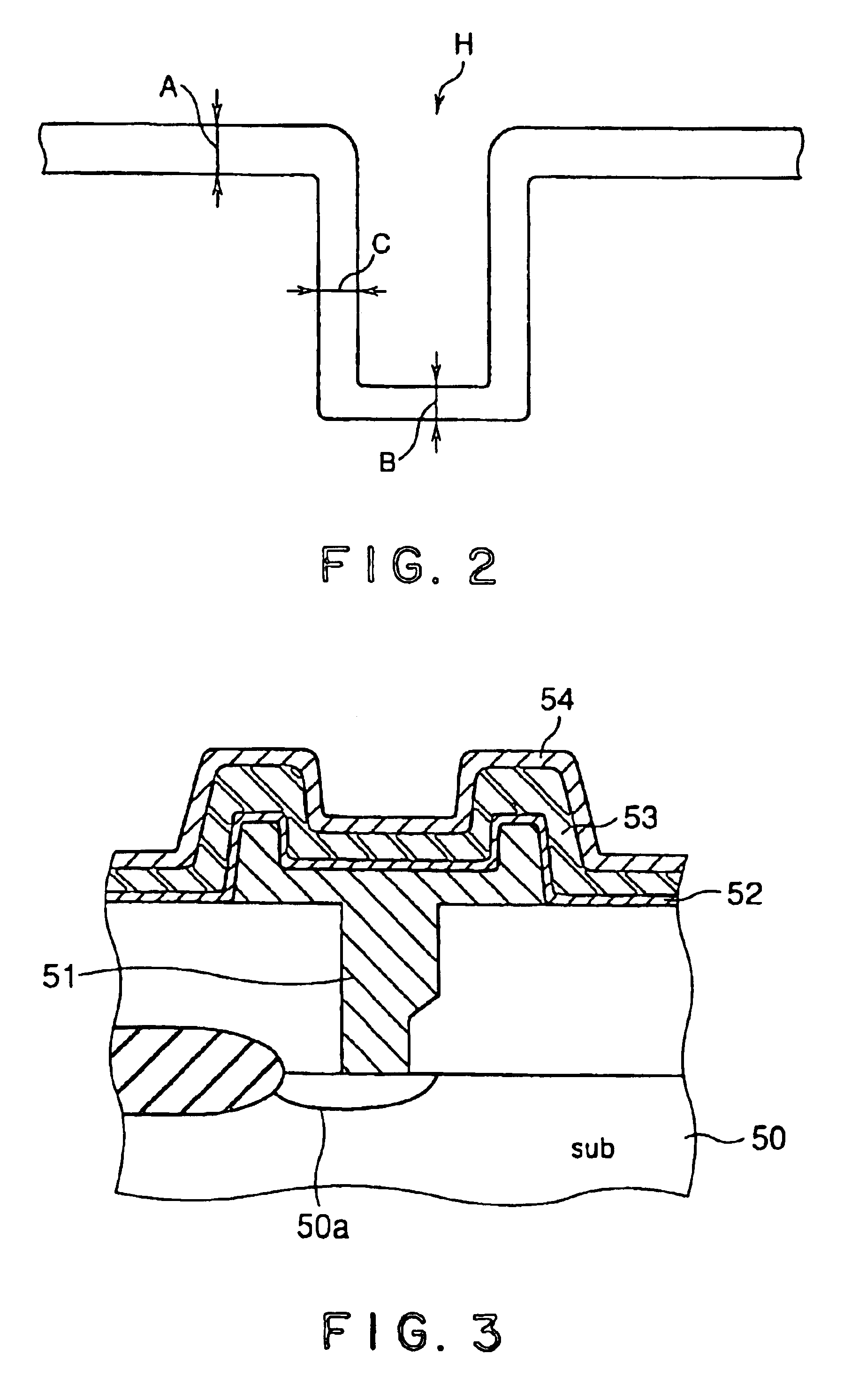

Gap filling with a composite layer

A method of filling a gap formed between adjacent raised surfaces on a substrate. In one embodiment the method comprises depositing a boron-doped silica glass (BSG) layer over the substrate to partially fill the gap using a thermal CVD process; exposing the BSG layer to a steam ambient at a temperature above the BSG layer's Eutectic temperature; removing an upper portion of the BSG layer by exposing the layer to a fluorine-containing etchant; and depositing an undoped silica glass (USG) layer over the BSG layer to fill the remainder of the gap.

Owner:APPLIED MATERIALS INC

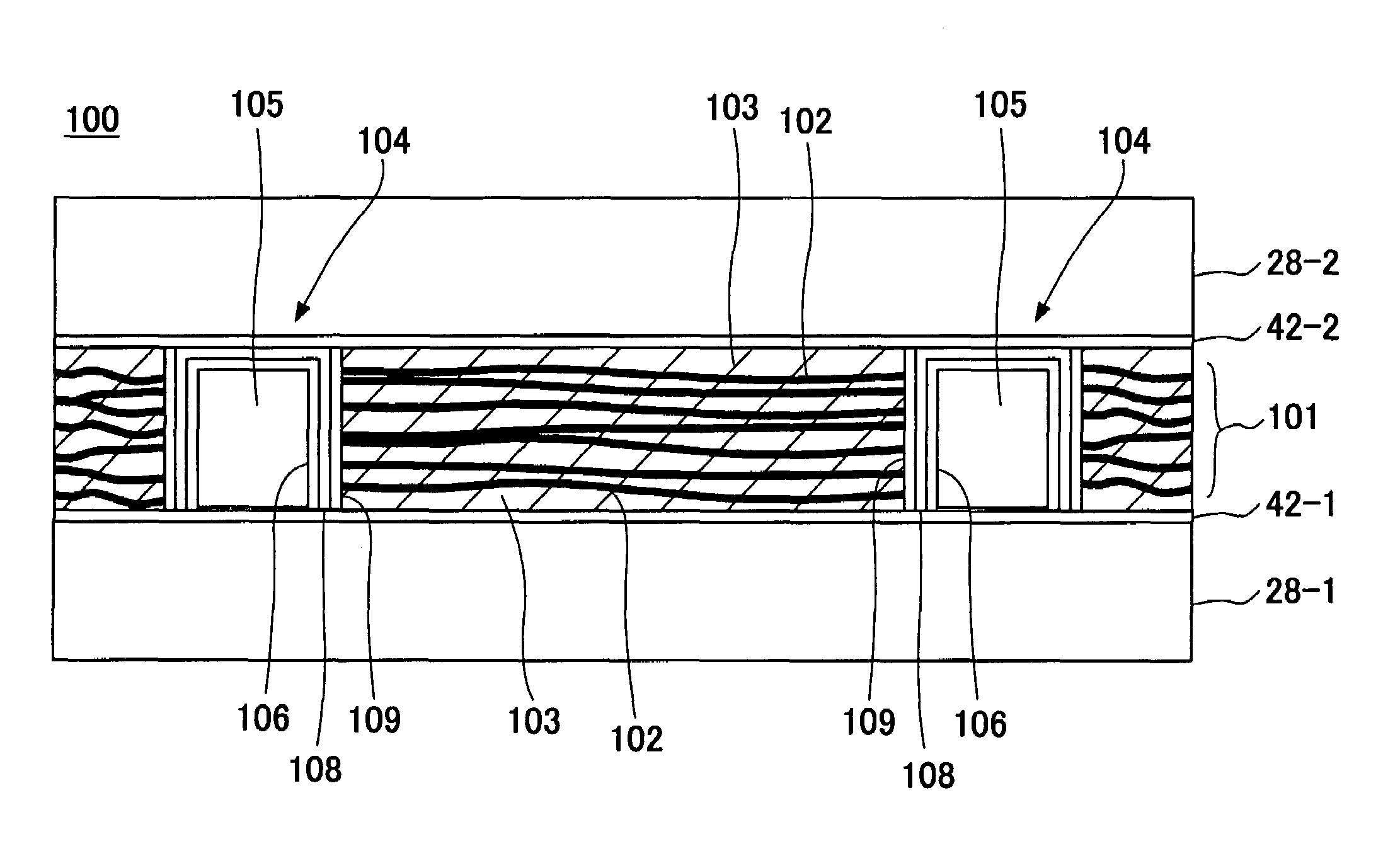

Semiconductor device and method of manufacturing the same

A method of manufacturing a semiconductor device having an interconnection part formed of multiple carbon nanotubes is disclosed. The method includes the steps of (a) forming a growth mode control layer controlling the growth mode of the carbon nanotubes, (b) forming a catalyst layer on the growth mode control layer, and (c) causing the carbon nanotubes to grow by heating the catalyst layer by thermal CVD so that the carbon nanotubes serve as the interconnection part. The growth mode control layer is formed by sputtering or vacuum deposition in an atmospheric gas, using a metal selected from a group of Ti, Mo, V, Nb, and W. The growth mode is controlled in accordance with a predetermined concentration of oxygen gas of the atmospheric gas.

Owner:FUJITSU LTD

Semiconductor memory device and method for manufacturing semiconductor device

InactiveUS7098147B2Improve reliabilityQuality improvementTransistorSolid-state devicesSurface layerPlasma nitridation

After a lower silicon oxide film is formed on a silicon region, a silicon film is formed on the lower silicon oxide film by, for example, a thermal CVD method. Subsequently, the silicon film is completely nitrided by a plasma nitriding method to be replaced by a silicon nitride film. Subsequently, a surface layer of the silicon nitride film is oxidized by a plasma oxidizing method to be replaced by an upper silicon oxide film. An ONO film as a multilayered insulating film composed of the lower silicon oxide film, the silicon nitride film, and the upper silicon oxide film is formed.

Owner:SPANSION LLC

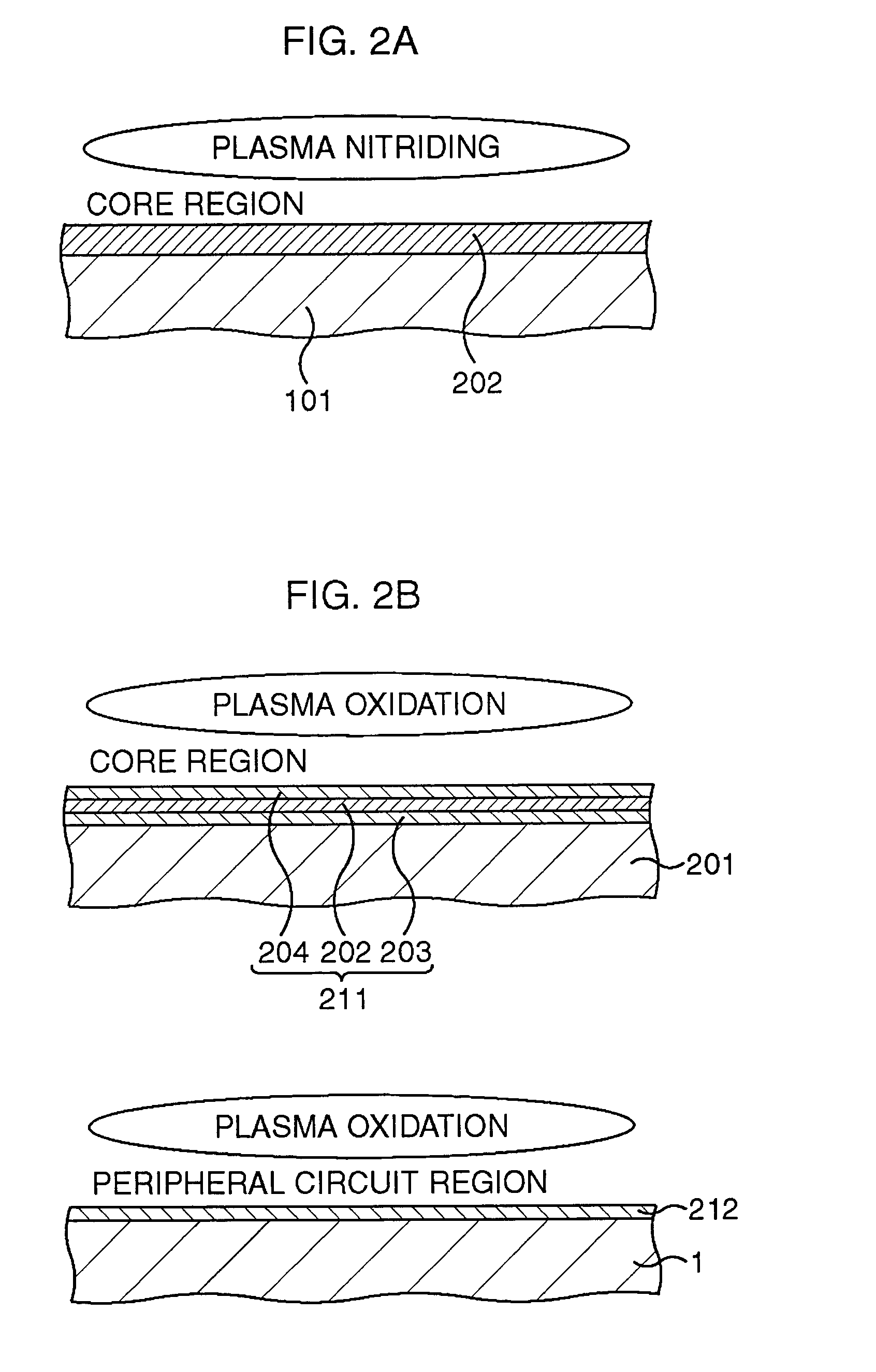

Methods for producing silicon nitride films and silicon oxynitride films by thermal chemical vapor deposition

ActiveUS20050100670A1Quality improvementSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilyleneThermal chemical vapor deposition

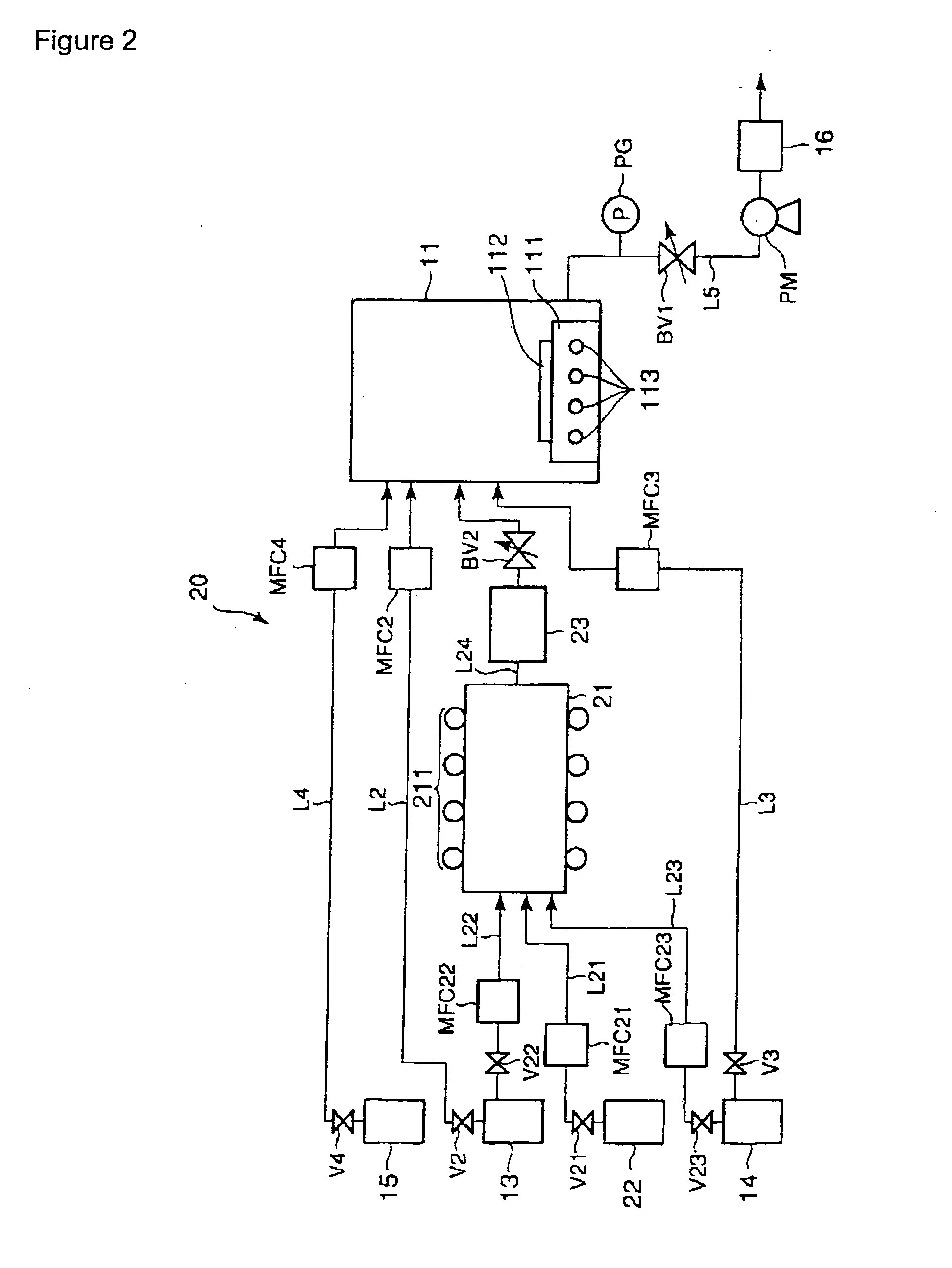

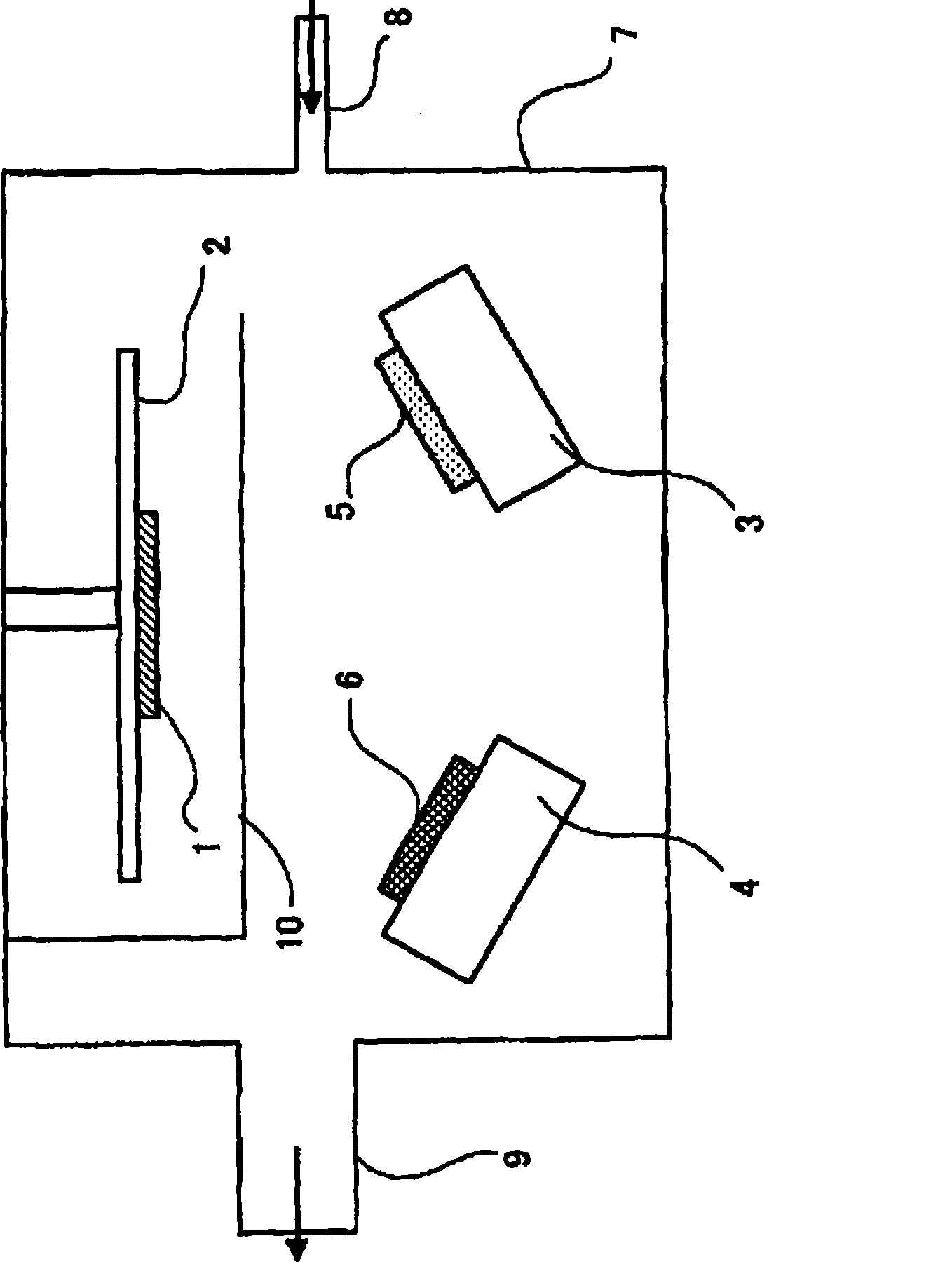

Silicon nitride film is formed on substrate (112) by feeding trisilylamine and ammonia into a CVD reaction chamber (11) that contains a substrate (112). The ammonia gas / trisilylamine gas flow rate ratio is set to a value of at least about 10 and / or the thermal CVD reaction is run at a temperature no greater than about 600° C. Silicon oxynitride is obtained by introducing an oxygen source gas into the CVD reaction chamber (11). This method avoids the production of ammonium chloride and / or the incorporation of carbonaceous contaminants which are detrimental to the quality of the deposited film.

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

Semiconductor substrate and semiconductor device and manufacturing method of the same

InactiveUS20090102008A1Guaranteed uptimeEasily increased in areaSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSilicate glass

A semiconductor substrate having an SOI layer is provided. Between an SOI layer and a glass substrate, a bonding layer is provided which is formed of one layer or a plurality of layers of phosphosilicate glass, borosilicate glass, and / or borophosphosilicate glass, using organosilane as one material by a thermal CVD method at a temperature of 500° C. to 800° C.

Owner:SEMICON ENERGY LAB CO LTD

Method of forming semiconductor wiring structures

InactiveUS6838376B2Improve featuresSemiconductor/solid-state device detailsSolid-state devicesSemiconductorTungsten

A method of forming a barrier metal film formed of a nitride film including tungsten by thermal CVD. The method includes positioning a substrate in a processing vessel and forming a WSi film on one side of the substrate by supplying a process gas including WF6 gas and at least one of SiR4 gas, SiH2Cl2 gas and Si2H6 gas into the processing vessel while a processing pressure in the processing vessel is maintained. The method also includes shutting off the supplying of the process gas into the processing vessel and completely removing the process gas from the processing vessel by supplying a purging gas into the processing vessel after the shutting off the supplying. The WSi film is nitrided by supplying NH3 gas or MMH gas into the processing vessel from which the process gas has been removed, to form a WSixNy film.

Owner:TOKYO ELECTRON LTD

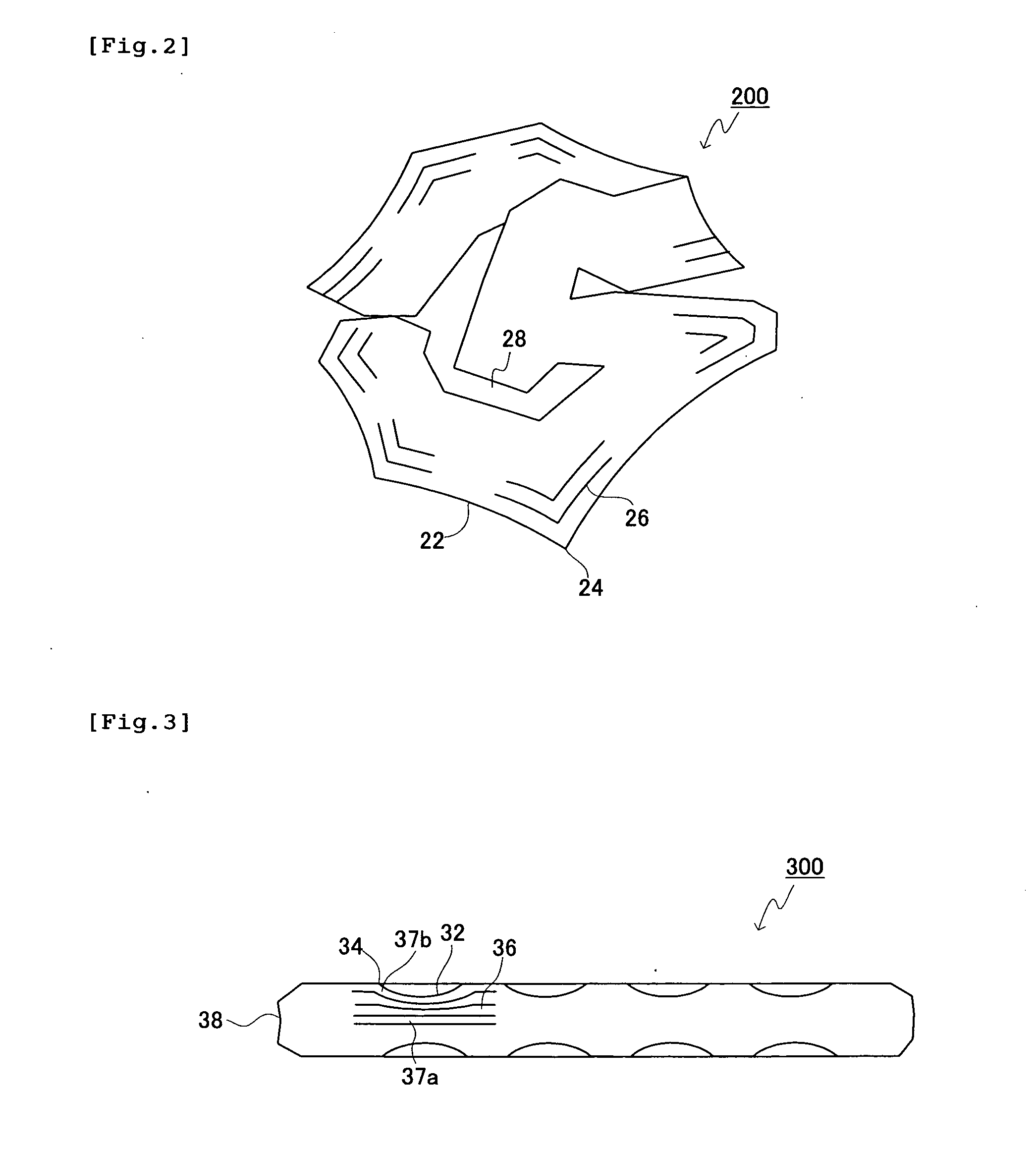

Graphite Particle, Carbon-Graphite Composite Particle and Their Production Processes

ActiveUS20090258298A1Improved cycle life characteristicsLarge capacityGraphiteElectrode carriers/collectorsCarbon layerLithium

The present invention relates to a graphite particle and a carbon-graphite composite particle both suitable for use in electrode for lithium ion secondary battery, as well as to processes for producing these particles.The graphite particle of the present invention has an average particle diameter of 5 to 50 μm, wherein one or more recesses having a depth of 0.1 to 10 μm are formed in the surface. The graphite particle is produced by a mixing step for mixing raw material graphite particles and recess-forming particles, a press molding step for press-molding the mixture composed of the raw material graphite particles and the recess-forming particles to obtain a molded article, a pulverization step for pulverizing the molded article, and a separation step for separating and removing the recess-forming particles from the pulverized molded article. The carbon-graphite composite particle of the present invention is produced by performing a thermal CVD step which comprises covering the surface of the above-mentioned graphite particle with a carbon layer.

Owner:NIPPON POWER GRAPHITE CO LTD

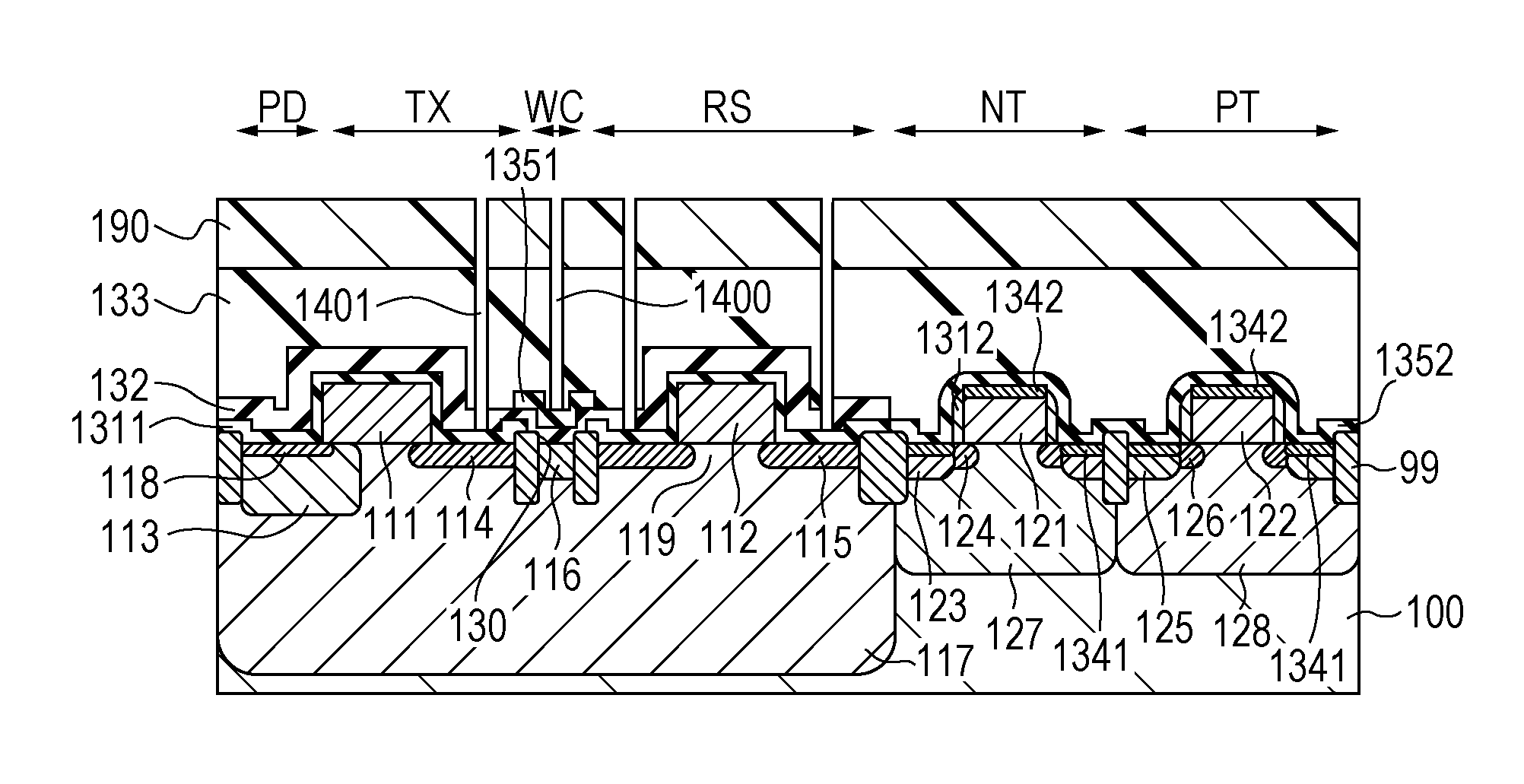

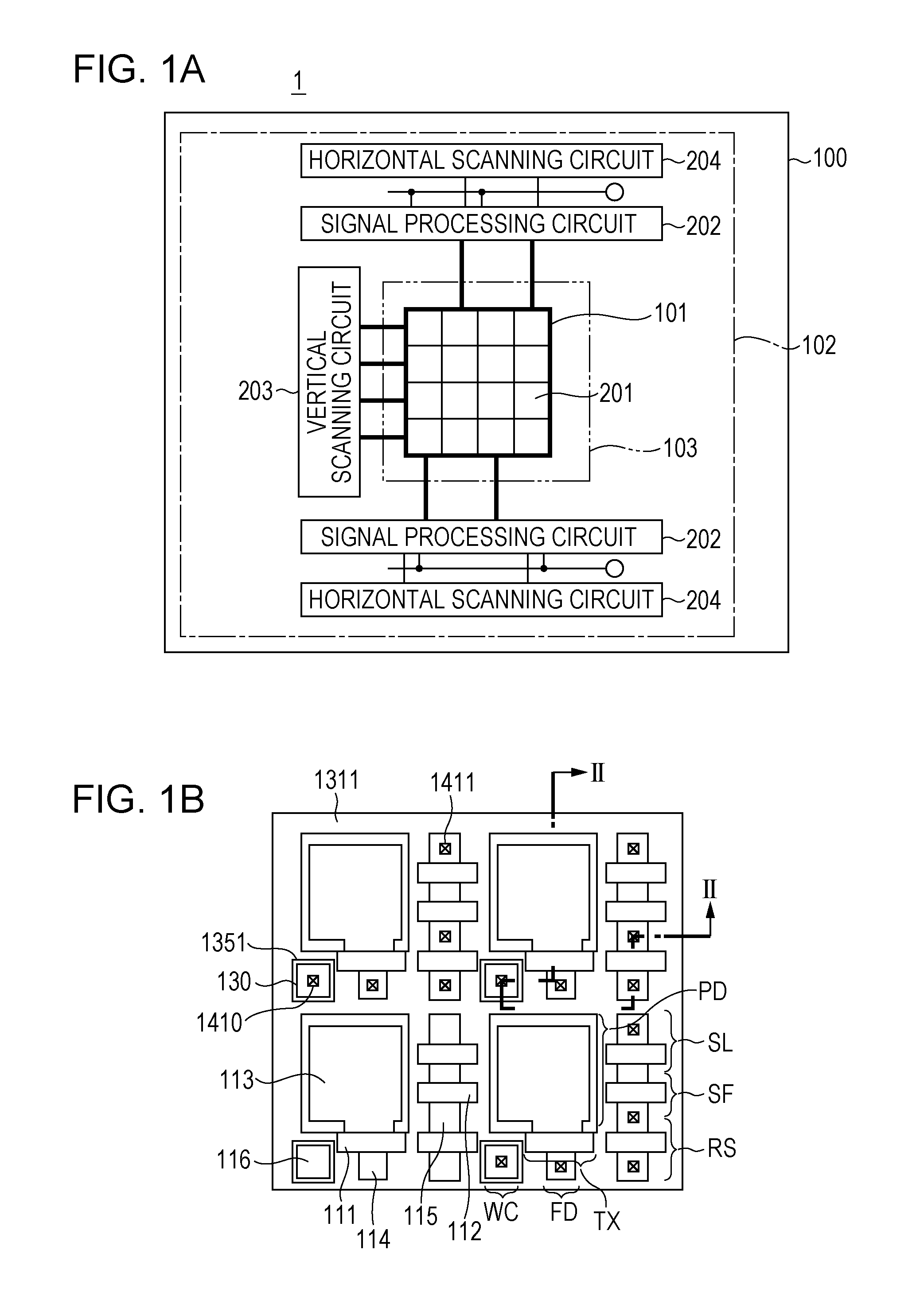

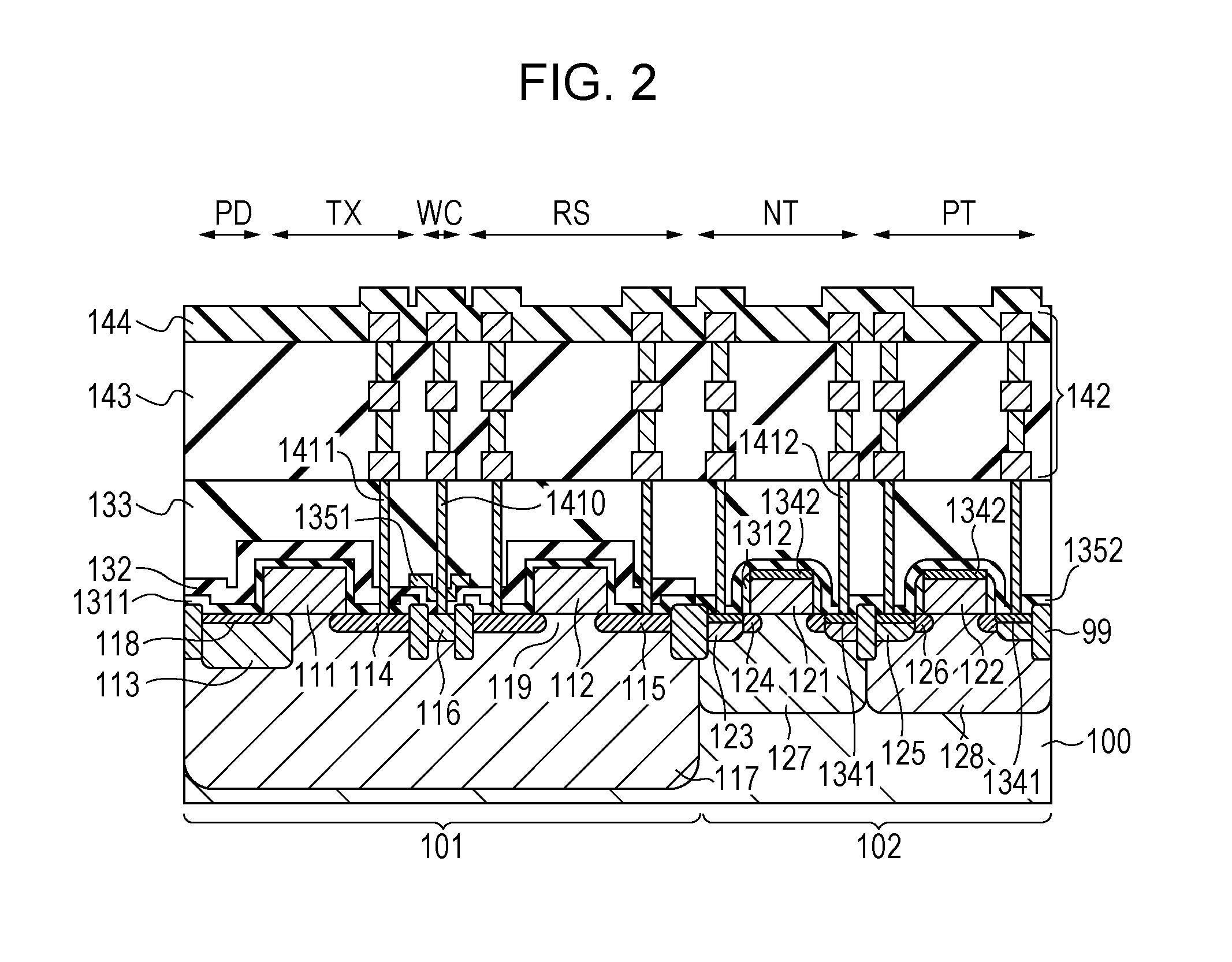

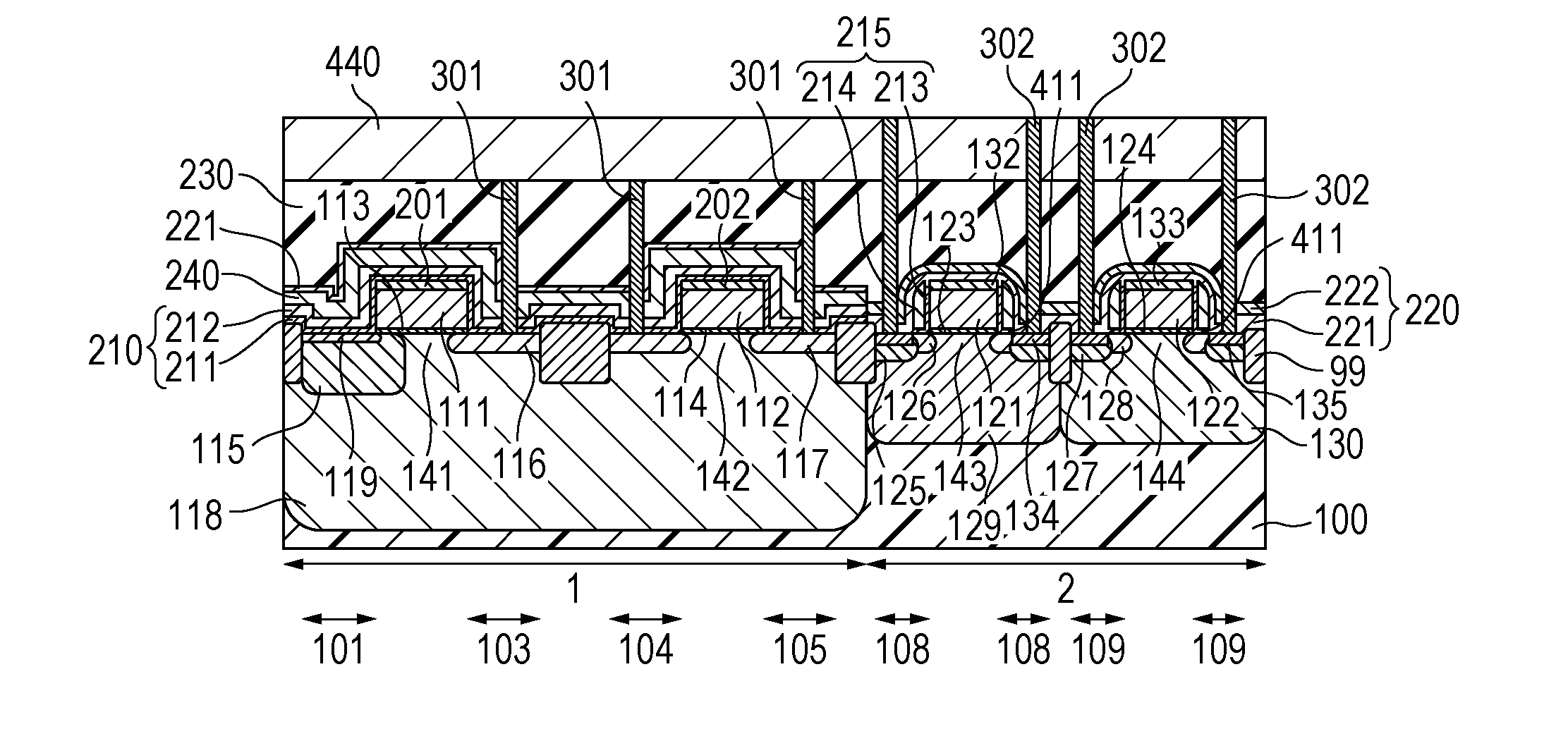

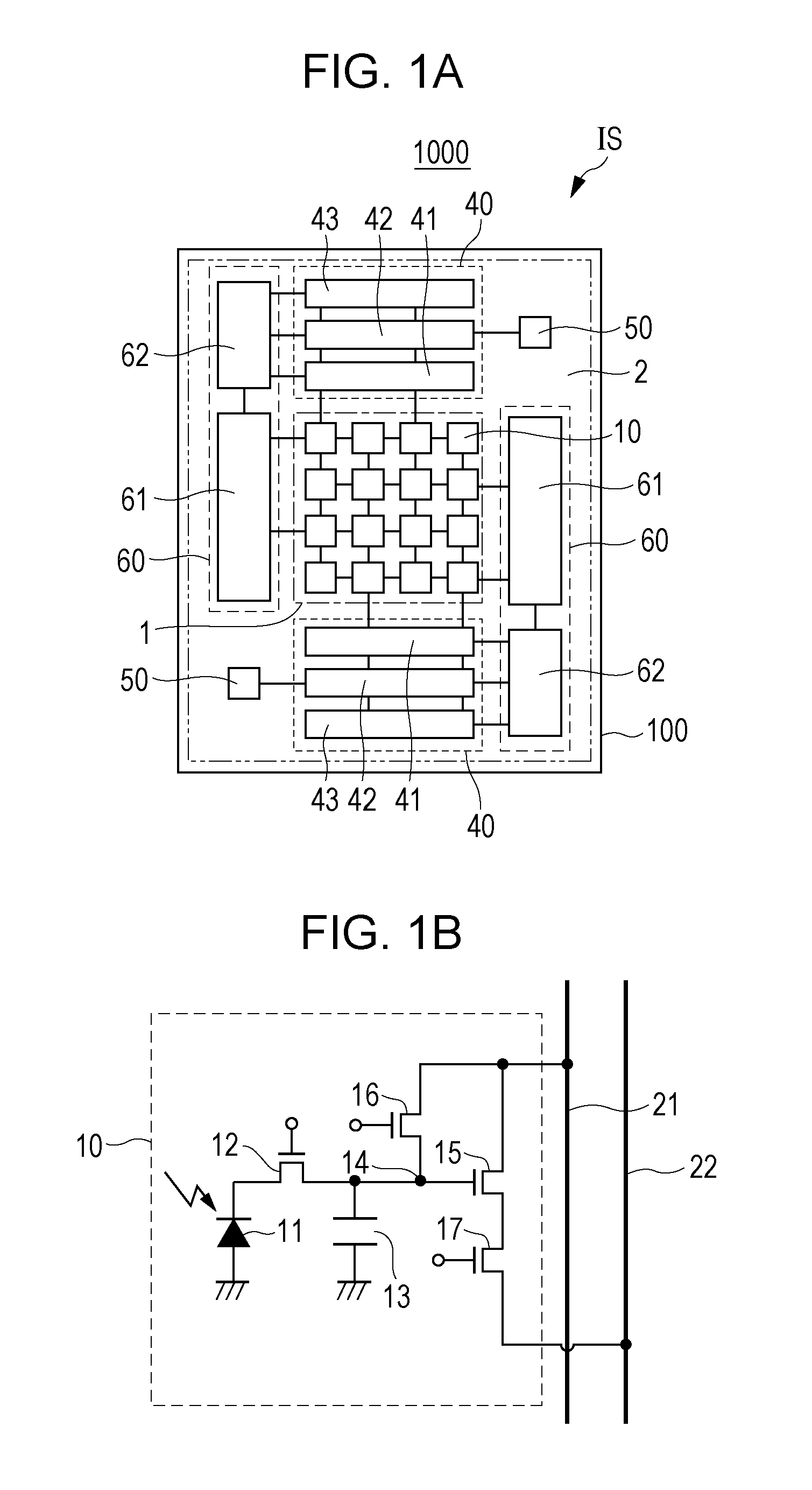

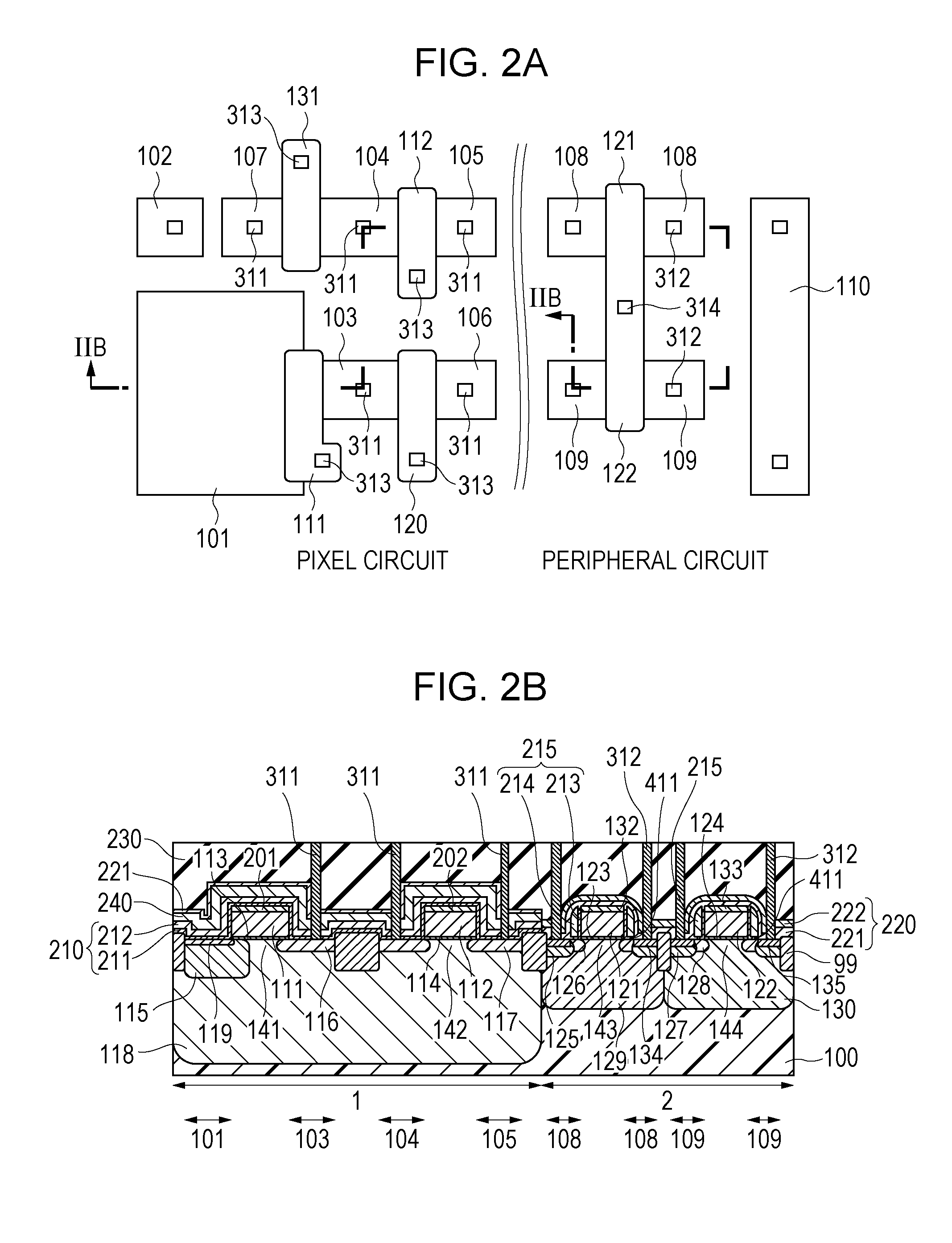

Method of producing image pick-up apparatus and image pick-up apparatus

The method comprises forming a first silicon nitride film covering a pixel circuit section by thermal CVD; forming an opening in the first silicon nitride film by removing a first portion of the first silicon nitride film while remaining a second portion of the first silicon nitride film; forming a second silicon nitride film covering the opening by plasma CVD; forming an insulating film covering the first silicon nitride film and the second silicon nitride film and covering a peripheral transistor in the peripheral circuit section; and forming a contact plug passing through the insulating film and being in contact with the peripheral transistor.

Owner:CANON KK

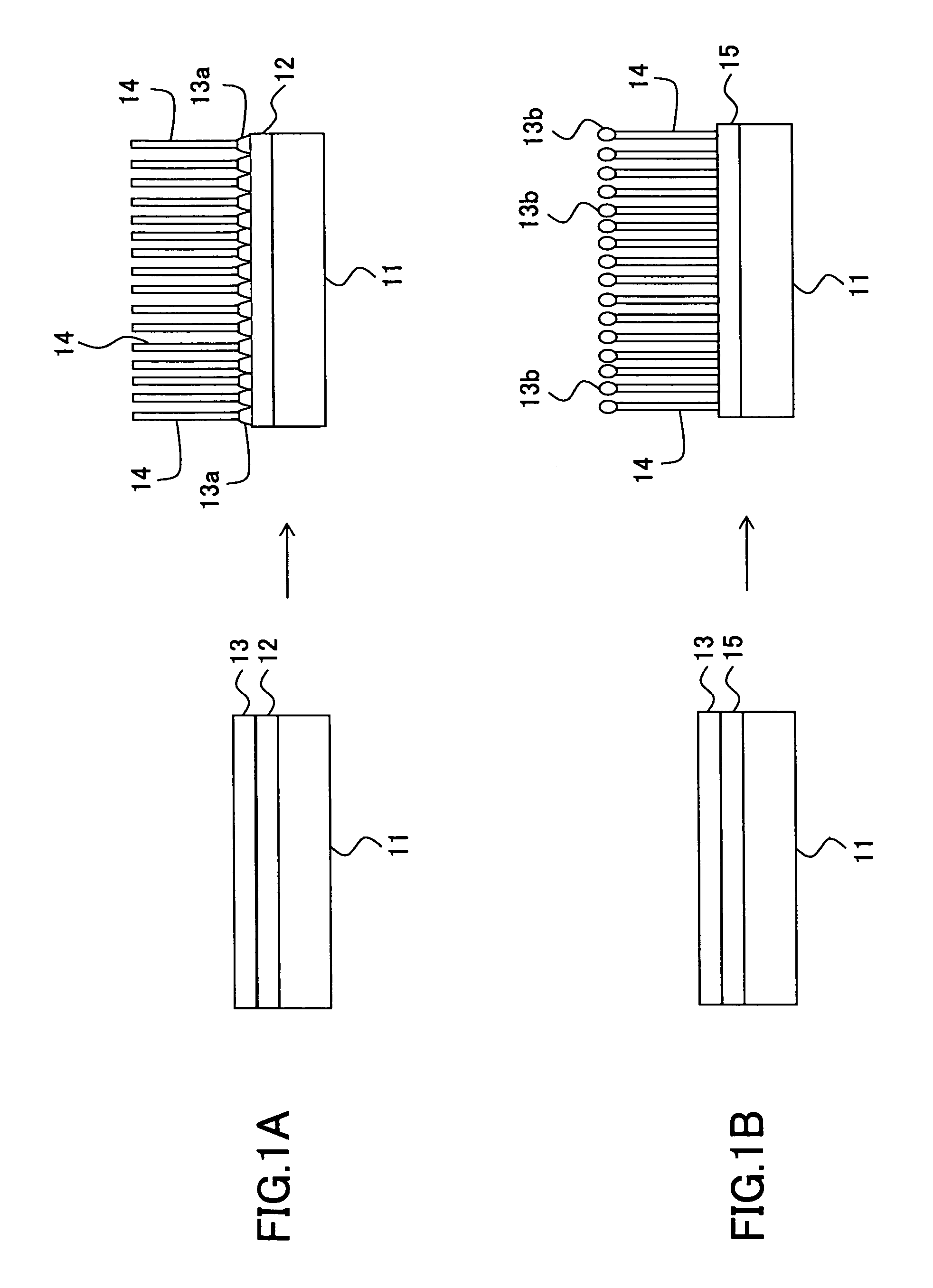

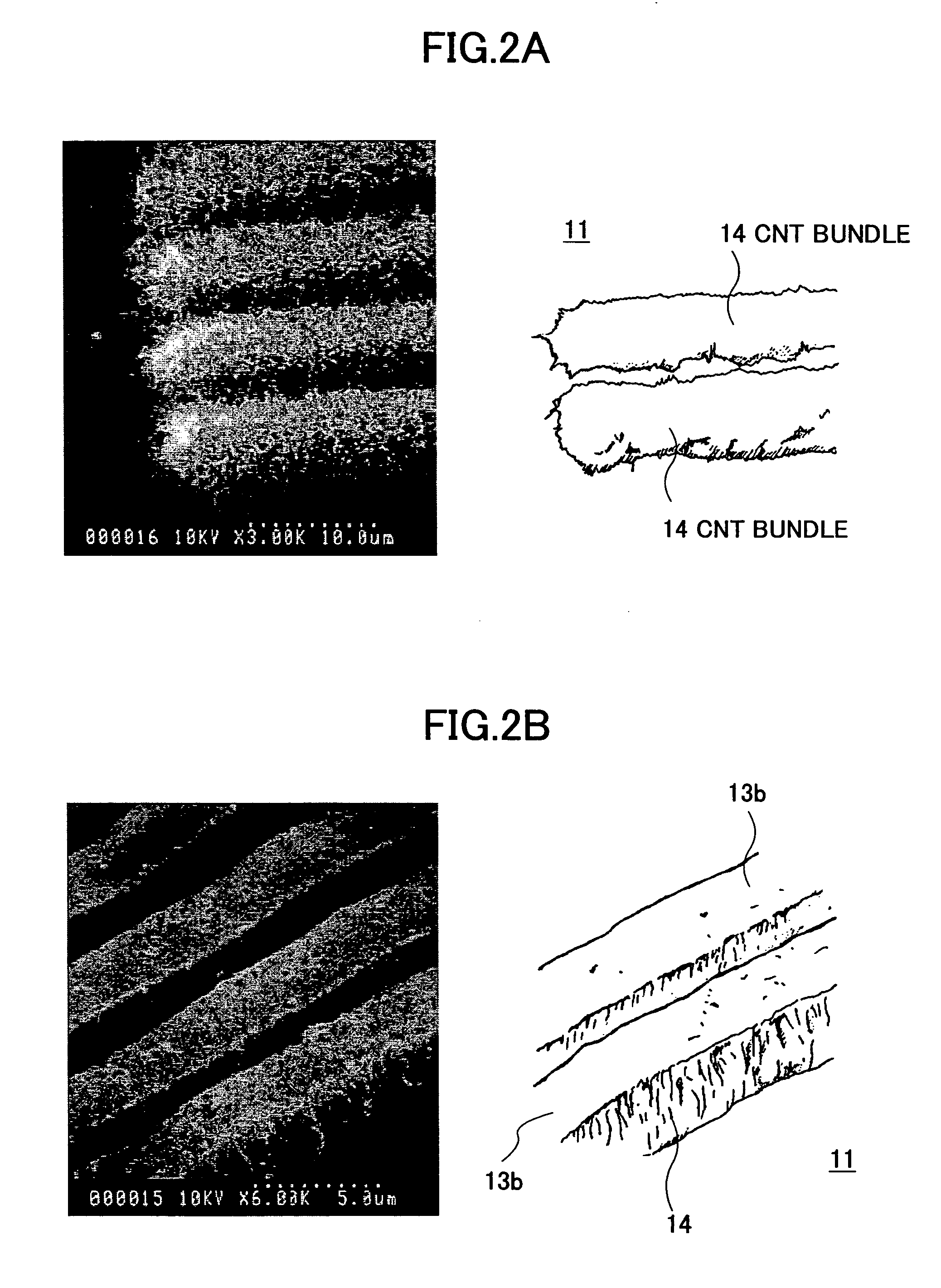

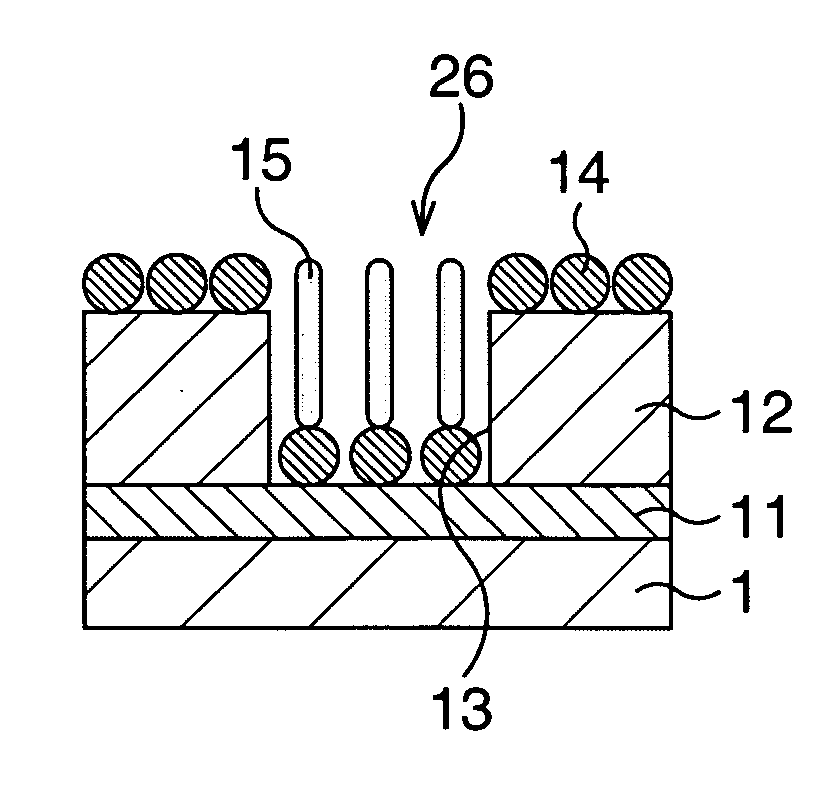

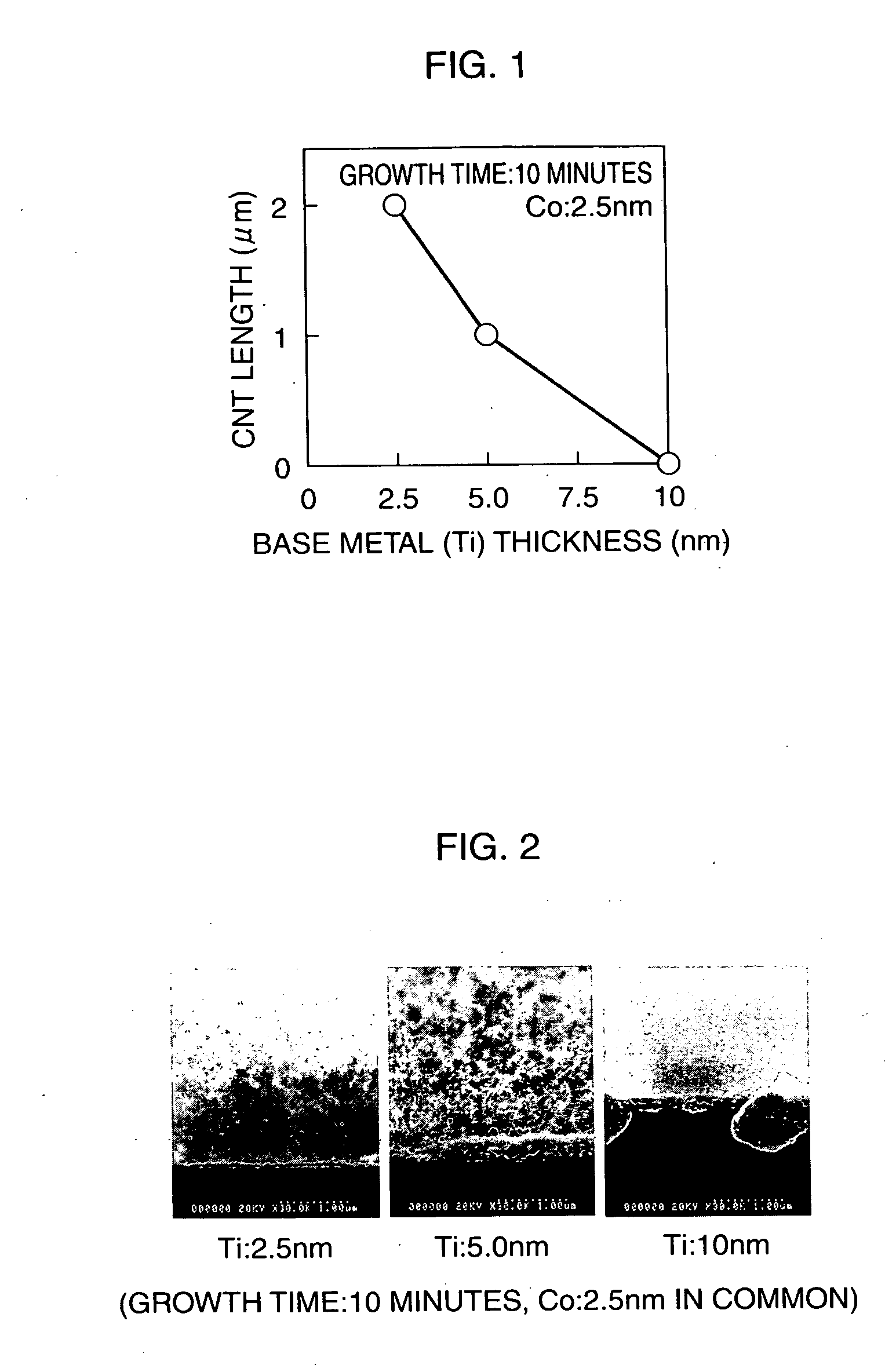

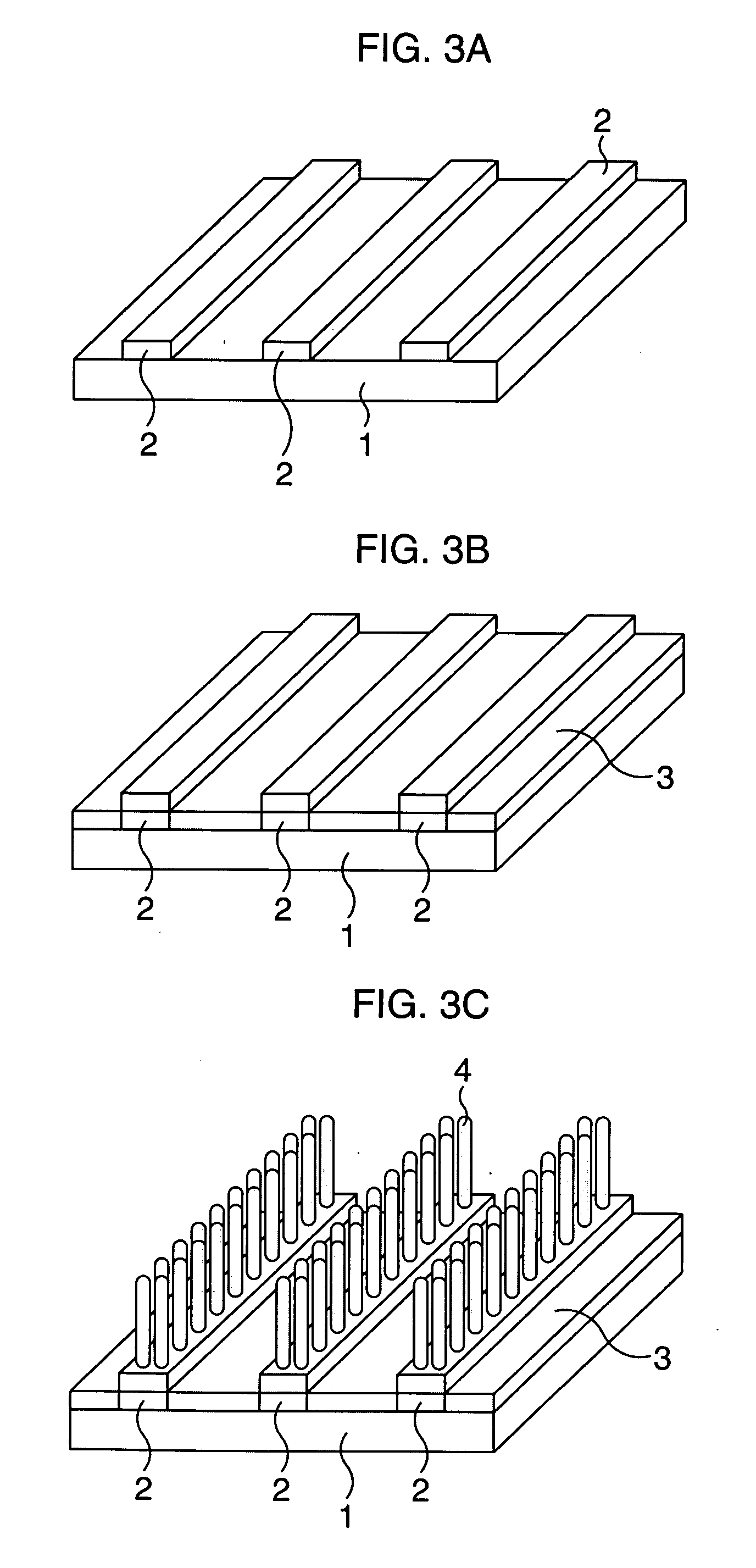

Substrate structure and manufacturing method of the same

ActiveUS20060290003A1Easily and certainly growLinear structureMaterial nanotechnologySemiconductor/solid-state device detailsSiliconThermal cvd

A Ti film is pattern-formed on a desired portion on a silicon substrate, and a Co film is formed on the substrate so as to cover the Ti film. CNTs are formed only on a portion, under which the Ti film is formed, of the surface of the Co film at approximately 600° C. by a thermal CVD method. The length of the CNT can be controlled by adjusting the thickness of the Ti film.

Owner:FUJITSU LTD

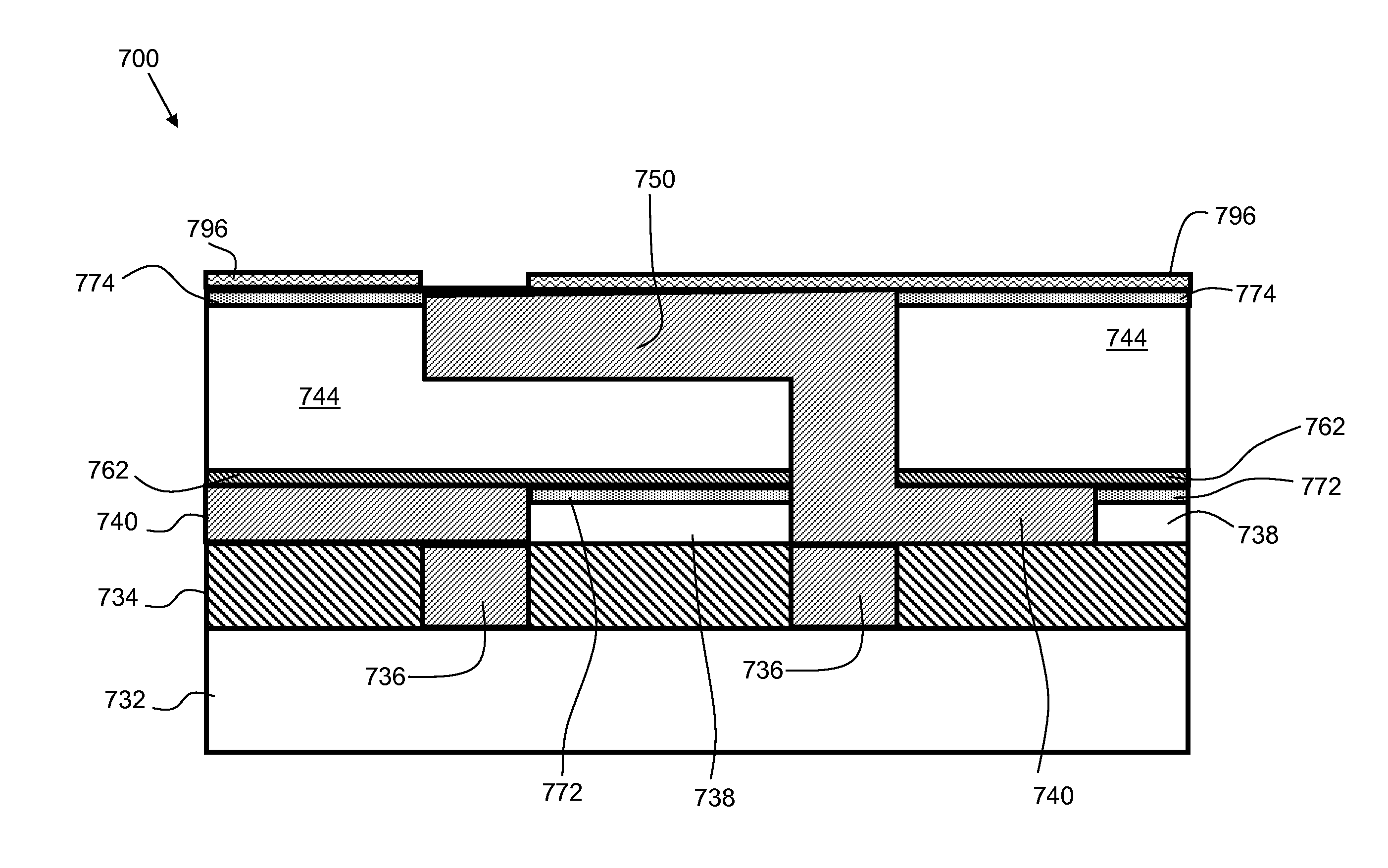

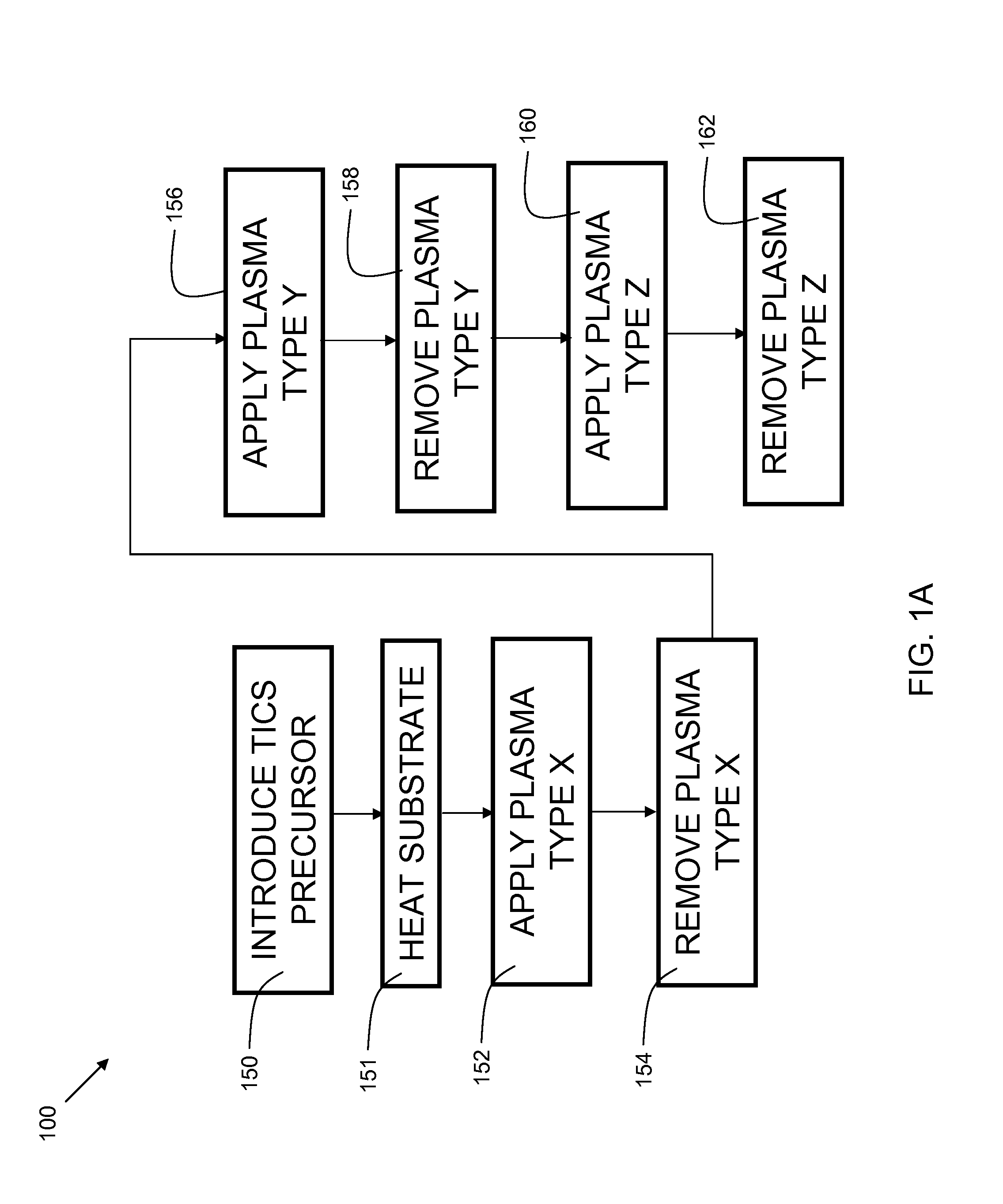

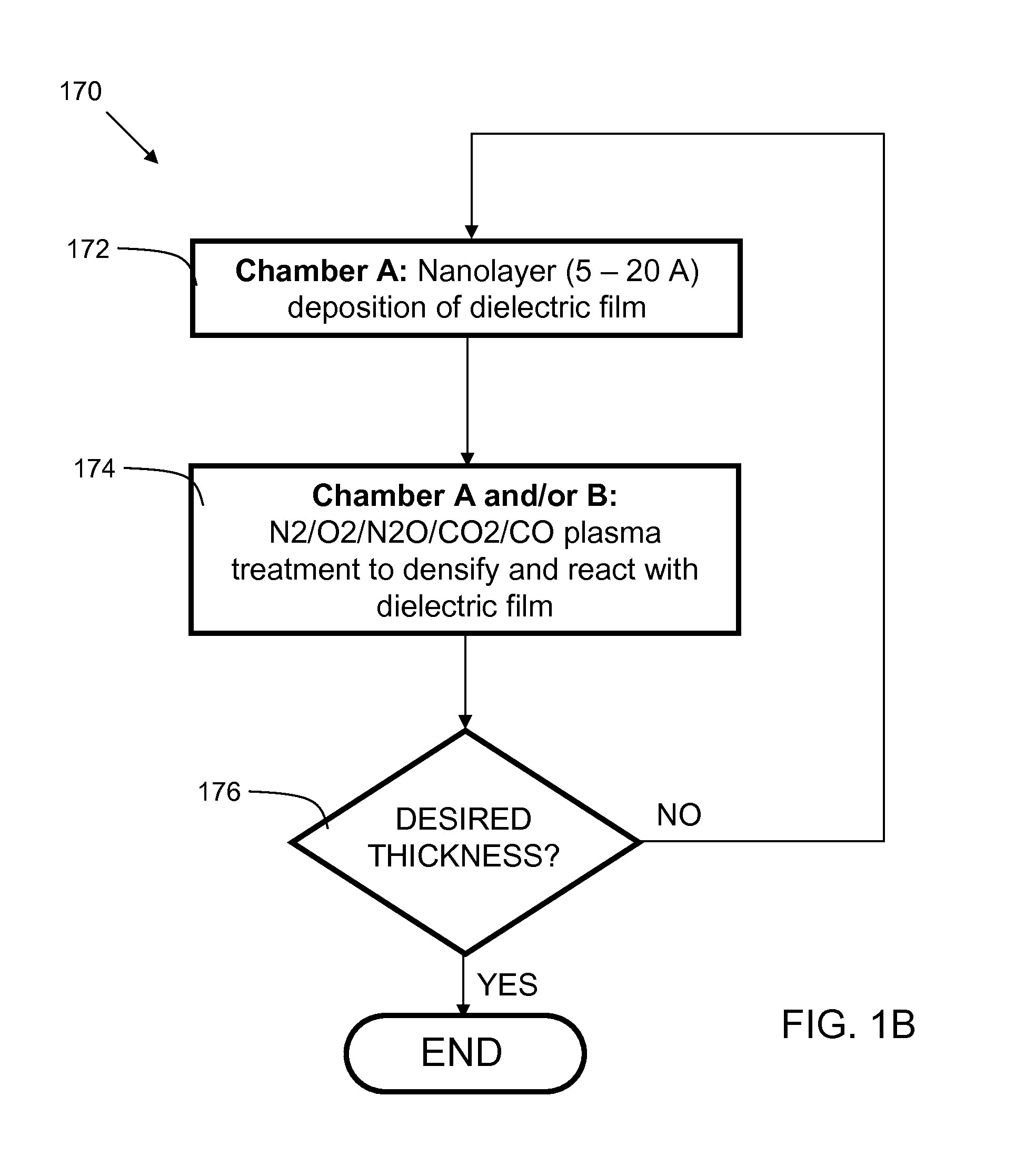

Hydrogen-free silicon-based deposited dielectric films for NANO device fabrication

Embodiments of the present invention provide hydrogen-free dielectric films and methods of fabrication. A hydrogen-free precursor, such as tetraisocyanatosilane, and hydrogen-free reactants, such as nitrogen, oxygen (O2 / O3) and nitrous oxide are used with chemical vapor deposition processes (PECVD, thermal CVD, SACVD, HDP CVD, and PE and Thermal ALD) to create hydrogen-free dielectric films. In some embodiments, there are multilayer dielectric films with sublayers of various materials such as silicon oxide, silicon nitride, and silicon oxynitride. In embodiments, the hydrogen-free reactants may include Tetra Isocyanato Silane, along with a hydrogen-free gas including, but not limited to, N2, O2, O3, N2O, CO2, CO and a combination thereof of these H-Free gases. Plasma may be used to enhance the reaction between the TICS and the other H-free gasses. The plasma may be controlled during film deposition to achieve variable density within each sublayer of the films.

Owner:IBM CORP

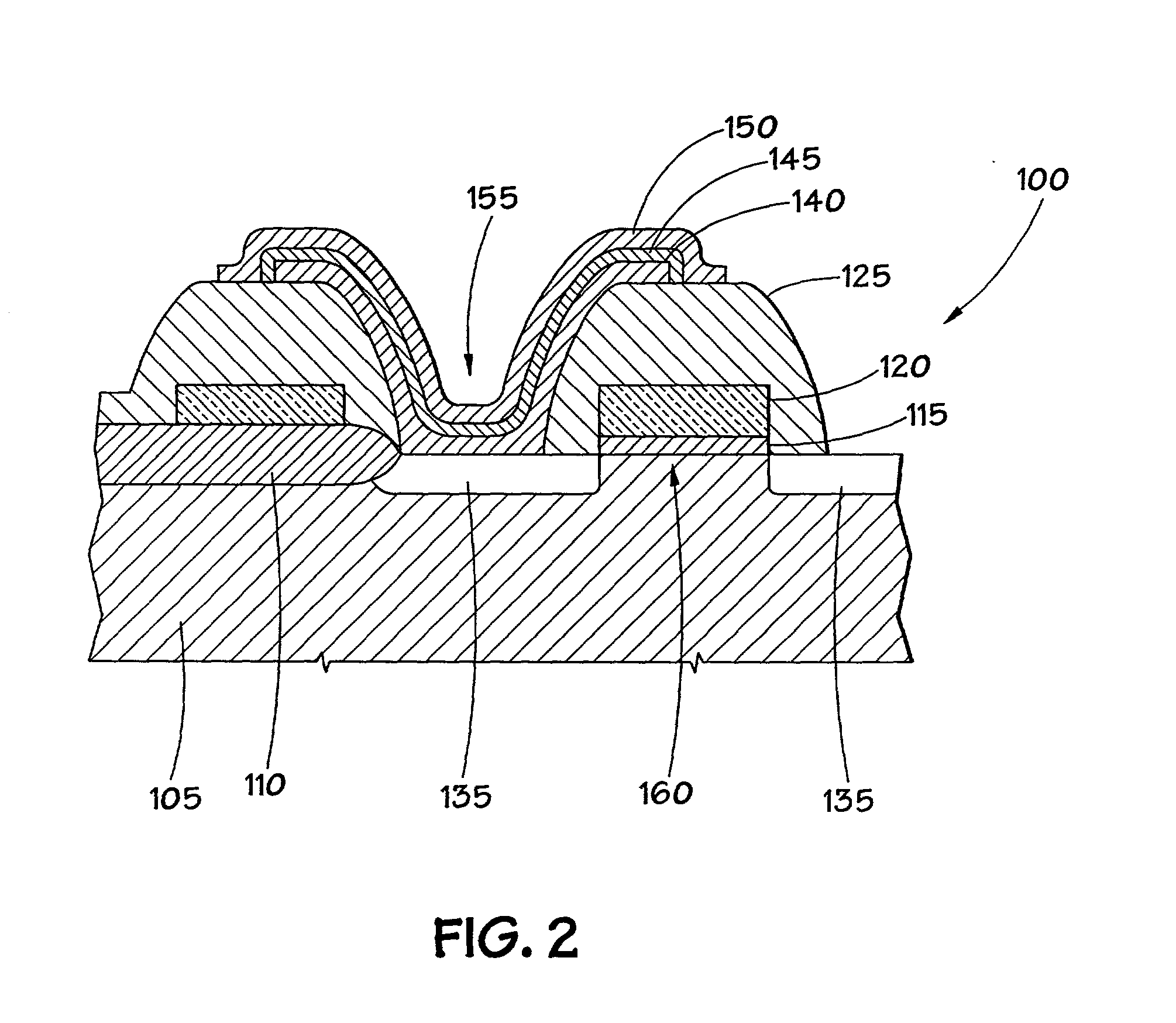

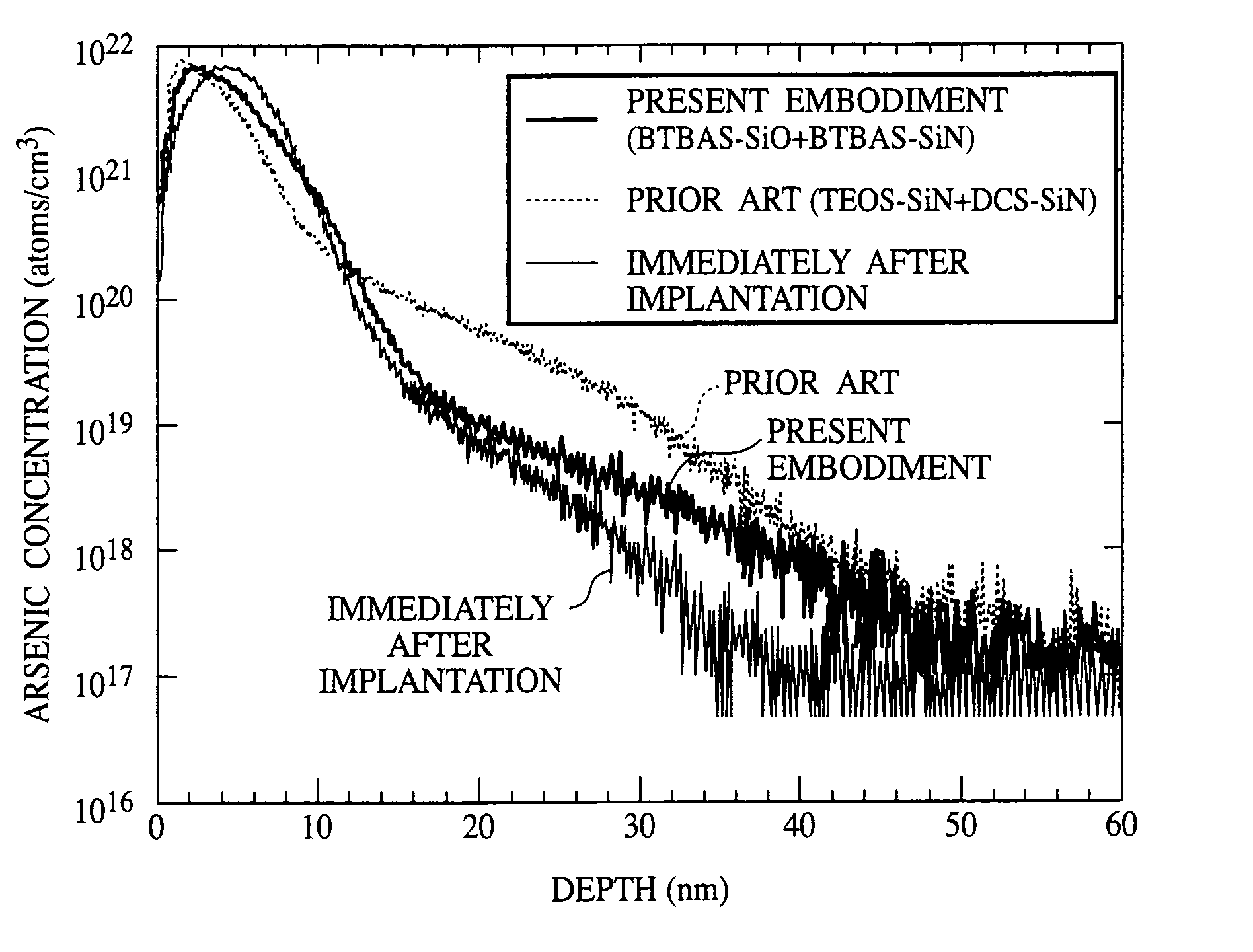

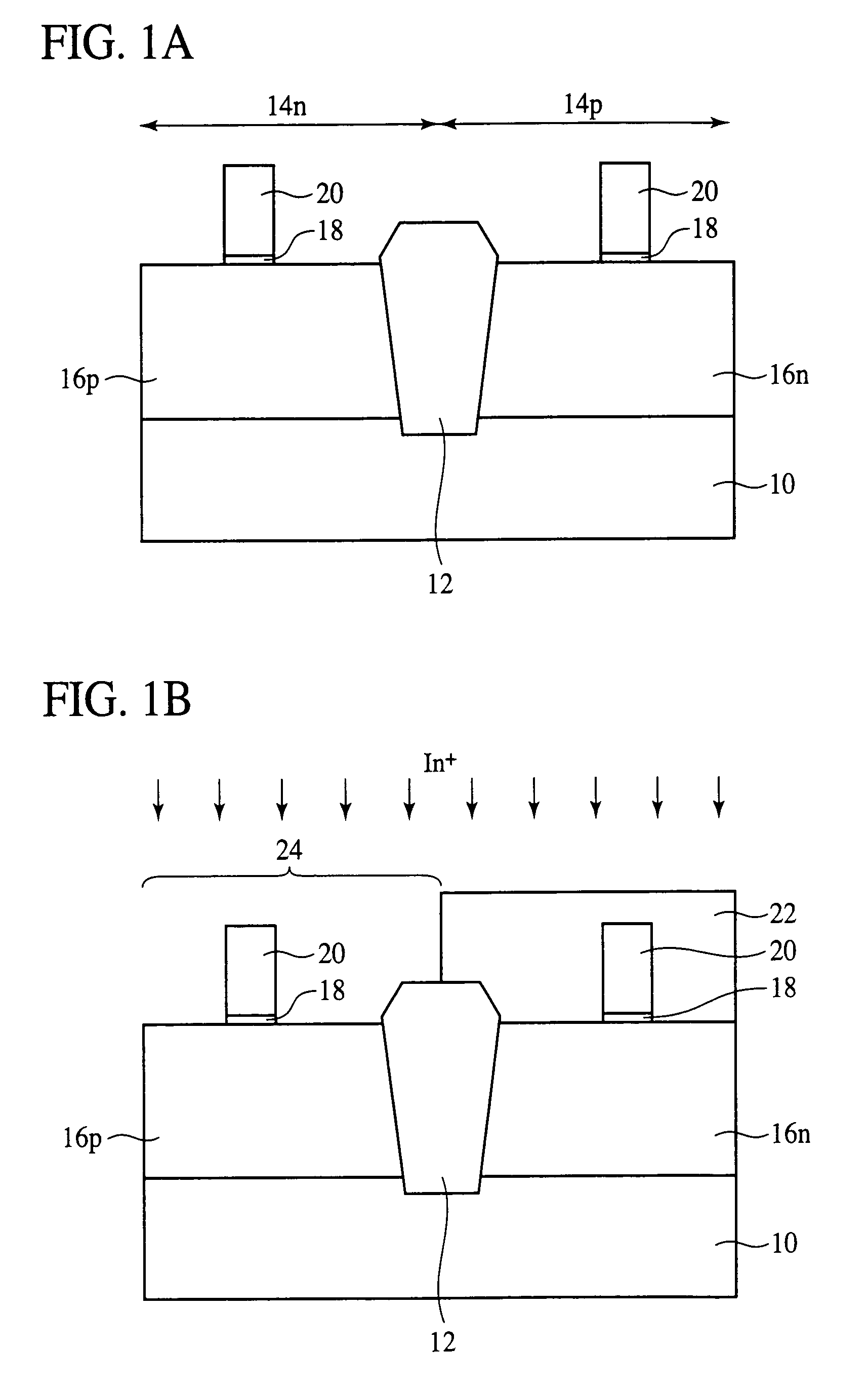

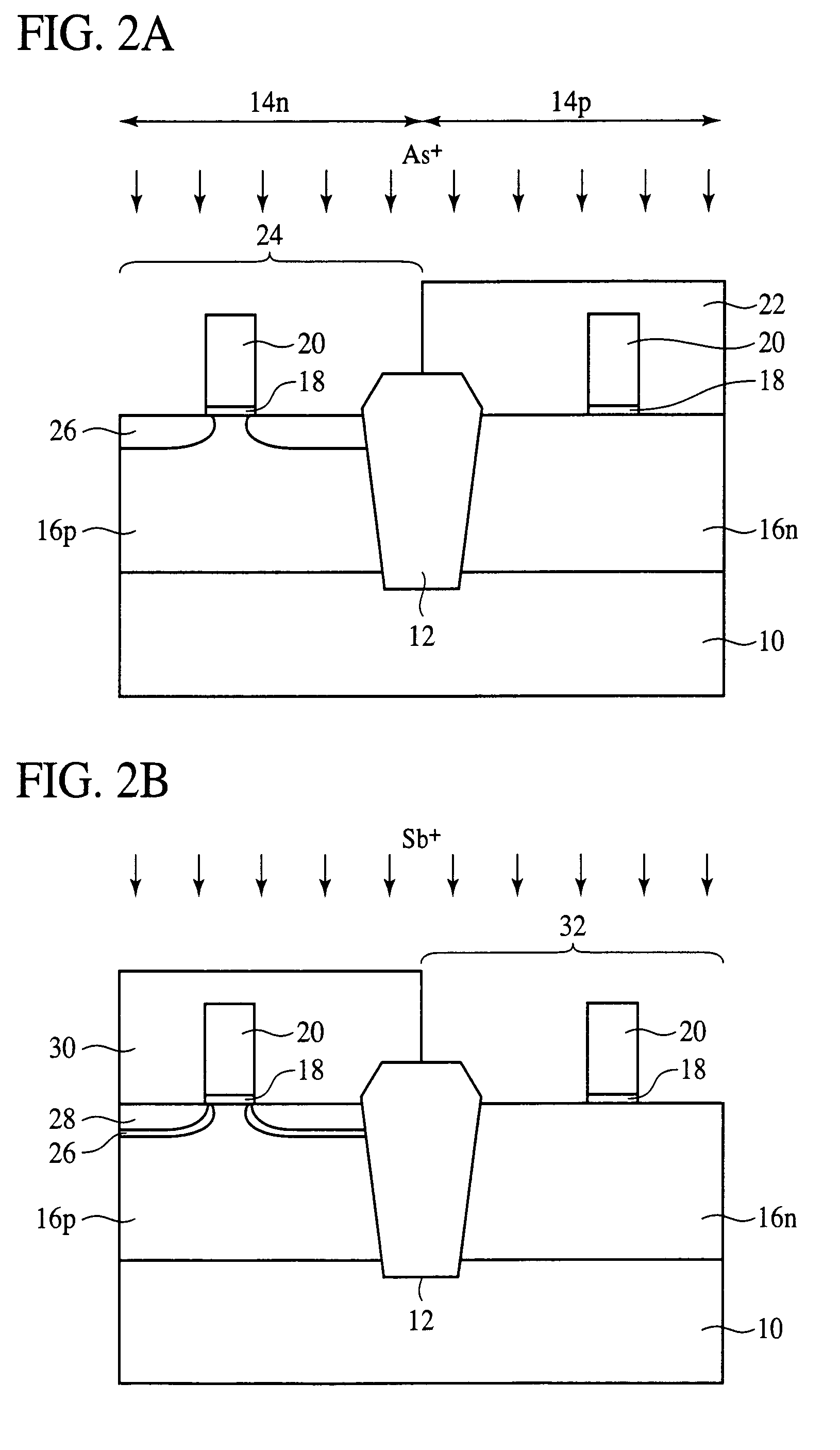

Method for fabricating a semiconductor device including the use of a compound containing silicon and nitrogen to form an insulation film of SiN or SiCN

ActiveUS7166516B2Suppress DiffuseSuppress diffusion of dopantTransistorSemiconductor/solid-state device detailsDopantSilanes

The semiconductor device fabrication method comprises the step of forming gate electrode 20 on a semiconductor substrate 10 with a gate insulation film 18 formed therebetween; the step of implanting dopants in the semiconductor substrate 10 with the gate electrode 20 as the mask to form dopant diffused regions 28, 36; the step of forming a silicon oxide film 38 on the semiconductor substrate 10, covering the gate electrodes 20; anisotropically etching the silicon oxide film 38 to form sidewall spacers 42 including the silicon oxide film 38 on the side walls of the gate electrode 20. In the step of forming a silicon oxide film 38, the silicon oxide film 38 is formed by thermal CVD at a 500–580° C. film forming temperature, using bis(tertiary-butylamino)silane and oxygen as raw materials. Silicon oxide film 38 is formed at a relatively low film forming temperature, whereby the diffusion of the dopant in the doapnt diffused regions 28, 36 forming the shallow region of the extension source / drain structure can be suppressed.

Owner:FUJITSU SEMICON LTD

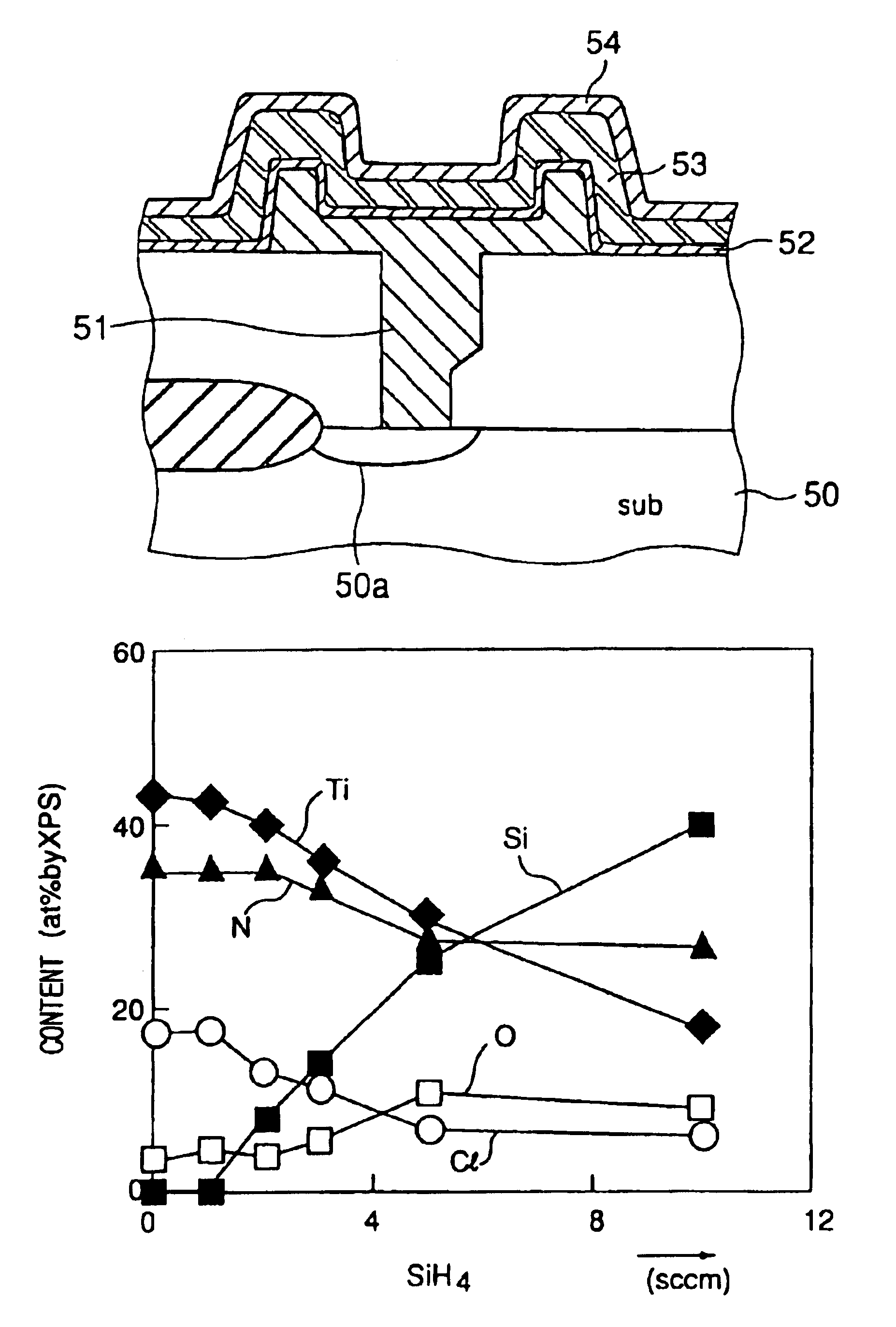

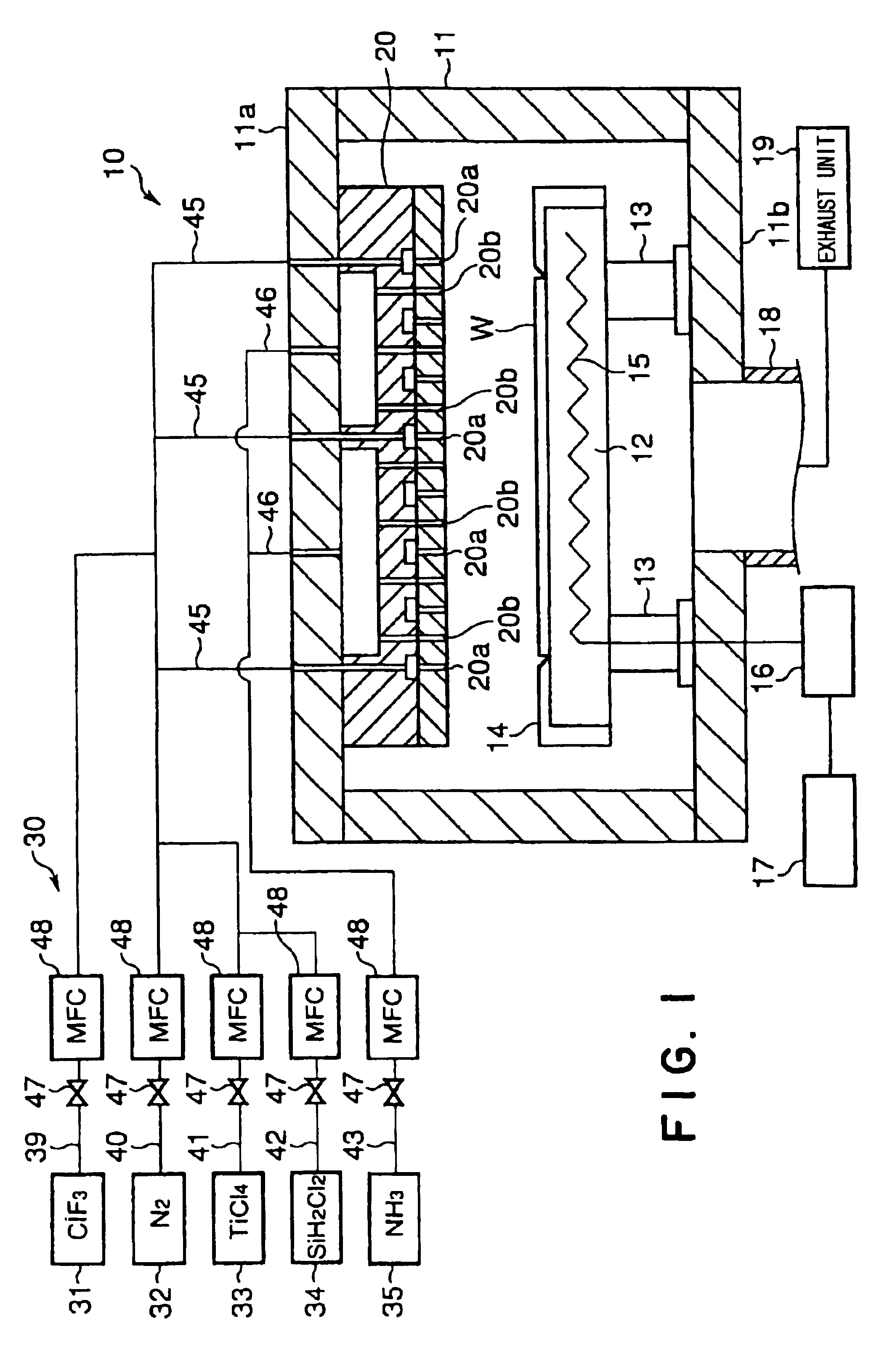

Method for forming TiSiN film, diffusion preventive film comprising TiSiN film, semiconductor device and its production method, and apparatus for forming TiSiN film

A TiSiN film is used as a barrier metal layer for a semiconductor device to prevent the diffusion of Cu. The TiSiN film is formed by a plasma CVD process or a thermal CVD process. TiCl4 gas, a silicon hydride gas and NH3 gas are used as source gases for forming the TiSiN film by the thermal CVD process. TiCl4 gas, a silicon hydride gas, H2 gas and N2 gas are used as source gases for forming a TiSiN film by the plasma CVD process.

Owner:TOKYO ELECTRON LTD

Method for manufacturing semiconductor device

InactiveUS20150155173A1Solid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideSemiconductor

A method includes a step of forming a side wall spacer covering a side surface of a gate electrode of a transistor by etching a first insulator film, and a step of forming a second insulator film covering an upper surface of the gate electrode, the side wall spacer and a source / drain region. The second insulator film is a multilayer film including a silicon oxide layer and a silicon nitride layer. The second step includes forming the silicon oxide layer by thermal CVD so as to come in contact with the side wall spacers, and forming the silicon nitride layer by plasma CVD so as to come in contact with the silicon oxide layer of the second insulator film.

Owner:CANON KK

Methods for depositing silicon dioxide or silicon oxide films using aminovinylsilanes

ActiveUS8460753B2Polycrystalline material growthSemiconductor/solid-state device manufacturingSilazaneSilicon oxide

Described herein are methods to form silicon dioxide films that have extremely low wet etch rate in HF solution using a thermal CVD process, ALD process or cyclic CVD process in which the silicon precursor is selected from one of:R1nR2mSi(NR3R4)4-n-m; and,a cyclic silazane of (R1R2SiNR3)p,where R1 is an alkenyl or an aromatic, such as vinyl, allyl, and phenyl; R2, R3, and R4 are selected from H, alkyl with C1-C10, linear, branched, or cyclic, an alkenyl with C2-C10 linear, branched, or cyclic, and aromatic; n=1-3, m=0-2; p=3-4.

Owner:VERSUM MATERIALS US LLC

Silicon composite, making method, and non-aqueous electrolyte secondary cell negative electrode material

InactiveUS20110001097A1Improve efficiencyImprove cycle performanceNon-metal conductorsFinal product manufactureCarbon layerDecomposition

A silicon composite comprises silicon particles whose surface is at least partially coated with a silicon carbide layer. It is prepared by subjecting a silicon powder to thermal CVD with an organic hydrocarbon gas and / or vapor at 900-1,400° C., and heating the powder for removing an excess free carbon layer from the surface through oxidative decomposition.

Owner:SHIN ETSU CHEM IND CO LTD

Substrate of semiconductor device and fabrication method thereof as well as semiconductor device and fabrication method thereof

There are provided a substrate of a semiconductor device and a fabrication method thereof which allow to suppress impurity from turning around from a glass or quartz substrate in fabrication steps of a TFT. An insulating film is deposited so as to surround the glass substrate by means of reduced pressure thermal CVD. It allows to suppress the impurity from infiltrating from the glass substrate to an active region of the TFT in the later process.

Owner:SEMICON ENERGY LAB CO LTD

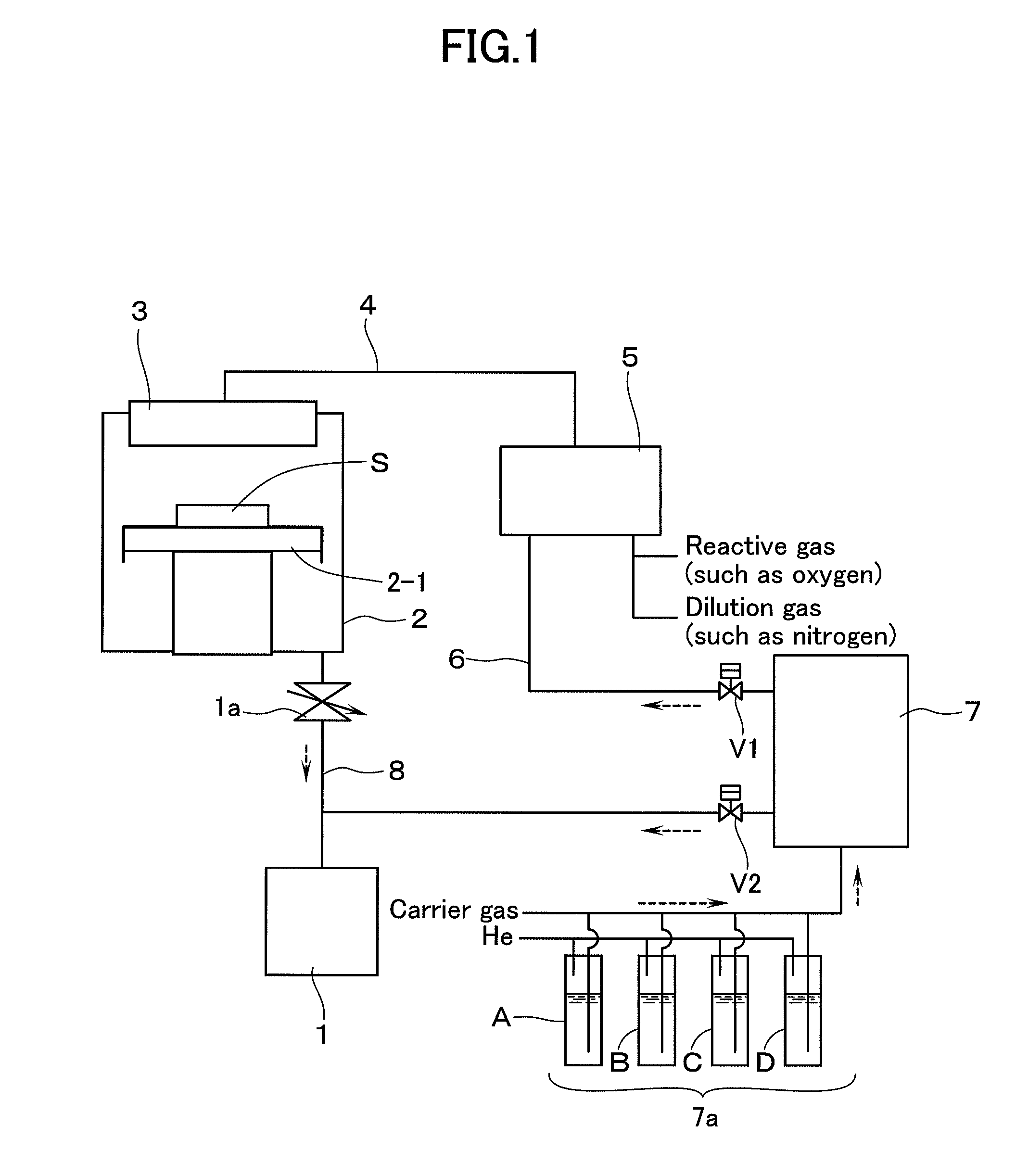

Method for thin film deposition using multi-tray film precursor evaporation system

ActiveUS20070032079A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingEvaporationRuthenium

Owner:TOKYO ELECTRON LTD

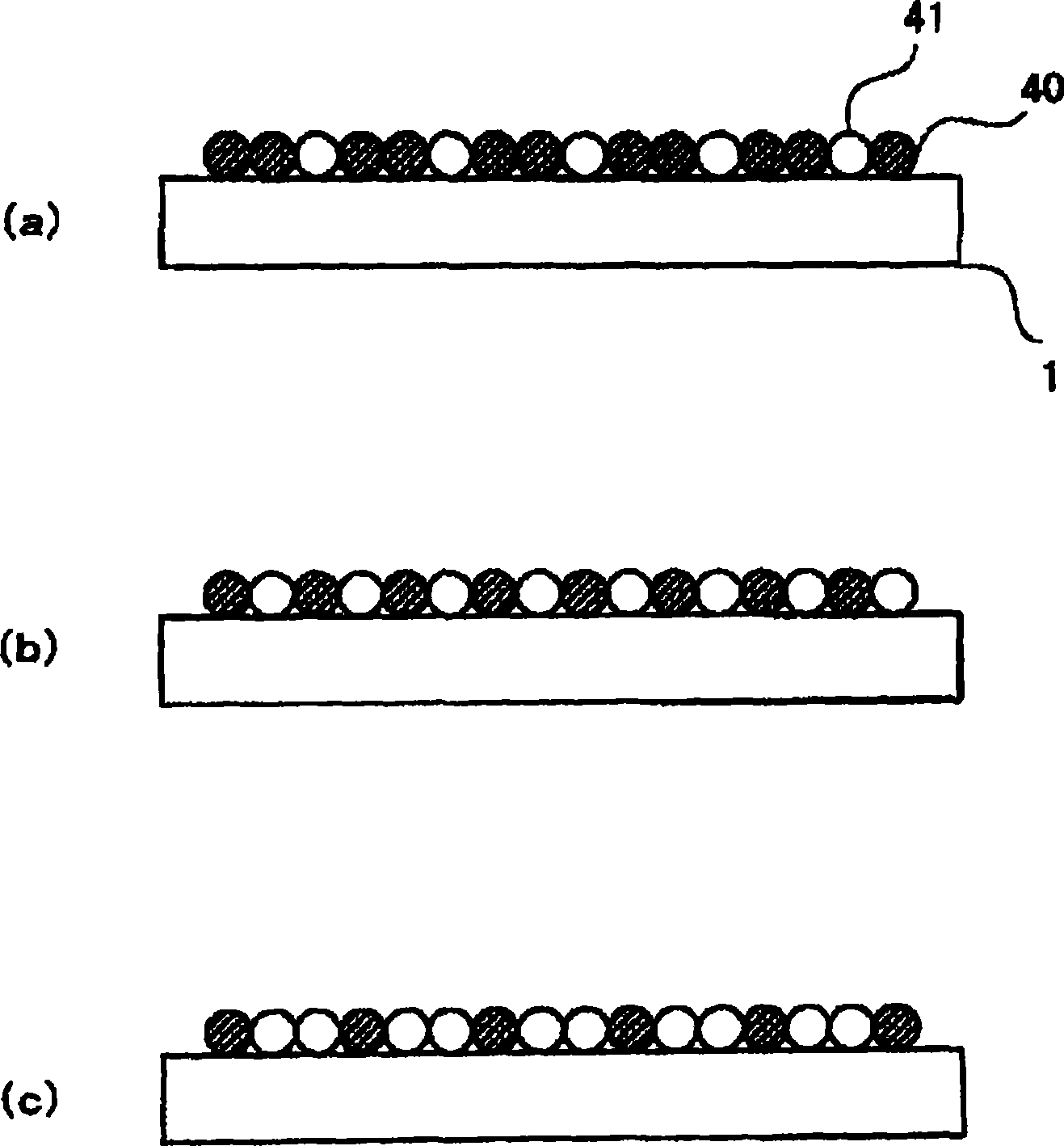

Process for production of carbon nanotube aggregates, carbon nanotube aggregates, catalyst particle dispersion membrane, electron emitters, and field emission displays

InactiveCN101365649AImprove uniformityHigh catalytic efficiencyMaterial nanotechnologyIndividual molecule manipulationMetal catalystDecomposition

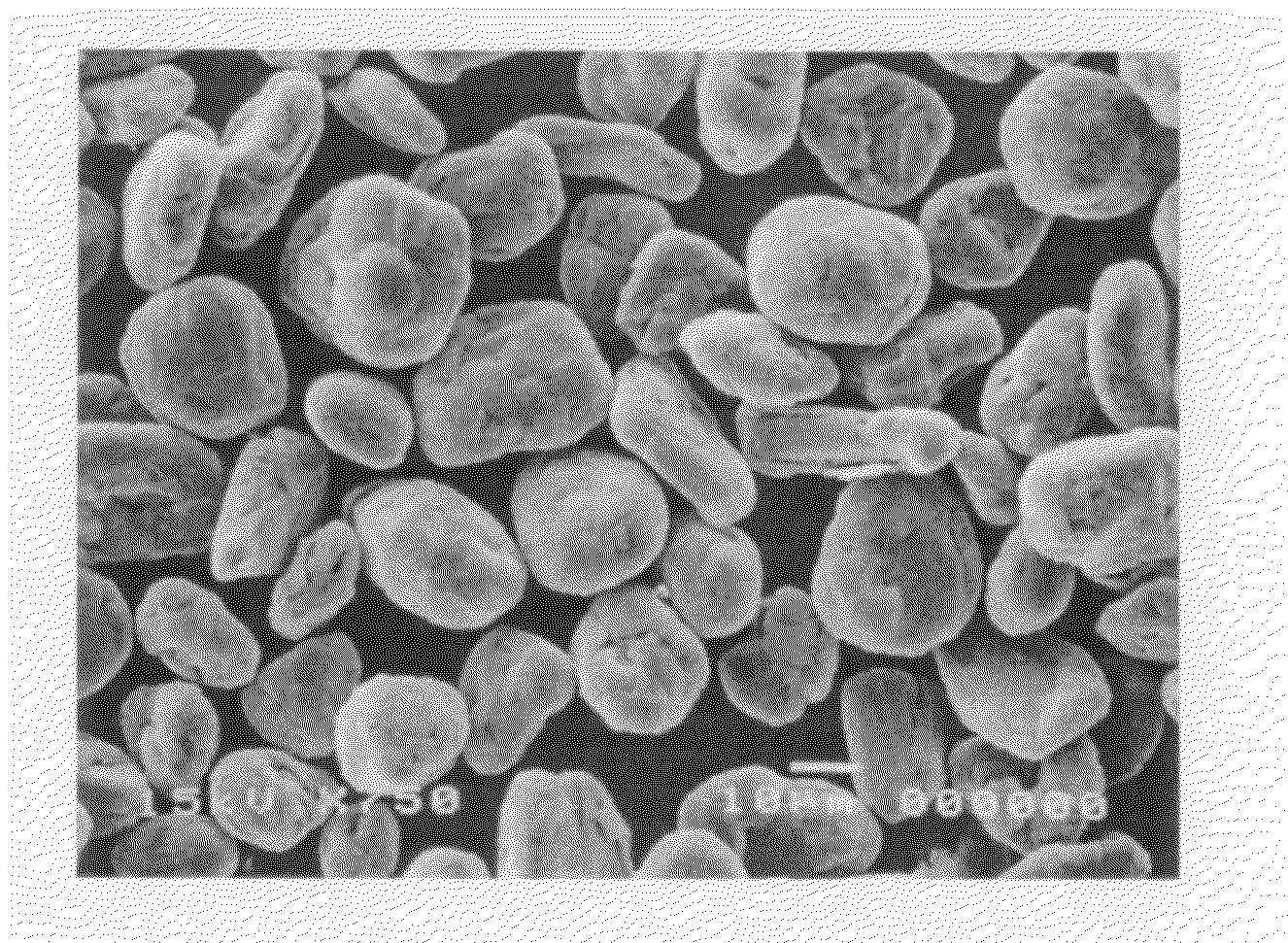

A method for producing a carbon nanotube assembly, the method controlling a growth density of carbon nanotubes on a substrate, includes: a step for preparing a catalyst particle dispersed film-formed substrate including a catalyst particle dispersed film in which metal catalyst particles having a predetermined particle diameter are dispersed among barrier particles; and a thermal CVD step for growing carbon nanotubes from the metal catalyst particles serving as starting points by heat decomposition of an organic compound vapor.

Owner:NIKON CORP