Semiconductor memory device and method for manufacturing semiconductor device

a memory device and semiconductor technology, applied in the direction of semiconductor devices, electrical appliances, transistors, etc., can solve the problems of deterioration of the film quality of the lower silicon oxide film, the increase of the demand for miniaturization and high performance of the semiconductor memory, and the multi-layered insulating film. achieve the effect of high reliability and high quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

specific embodiments

[0086] Specific embodiments are explained below based on the aforementioned basic structure of the present invention.

first embodiment

[0087] In this embodiment, a semiconductor memory device having an embedded bit line type SONOS structure will be disclosed. A structure of the semiconductor memory device is explained with a method for manufacturing thereof as a matter of convenience.

[0088] This semiconductor memory device is so structured that SONOS transistors in a memory cell region are of a planer type and that CMOS transistors are formed in a peripheral circuit region.

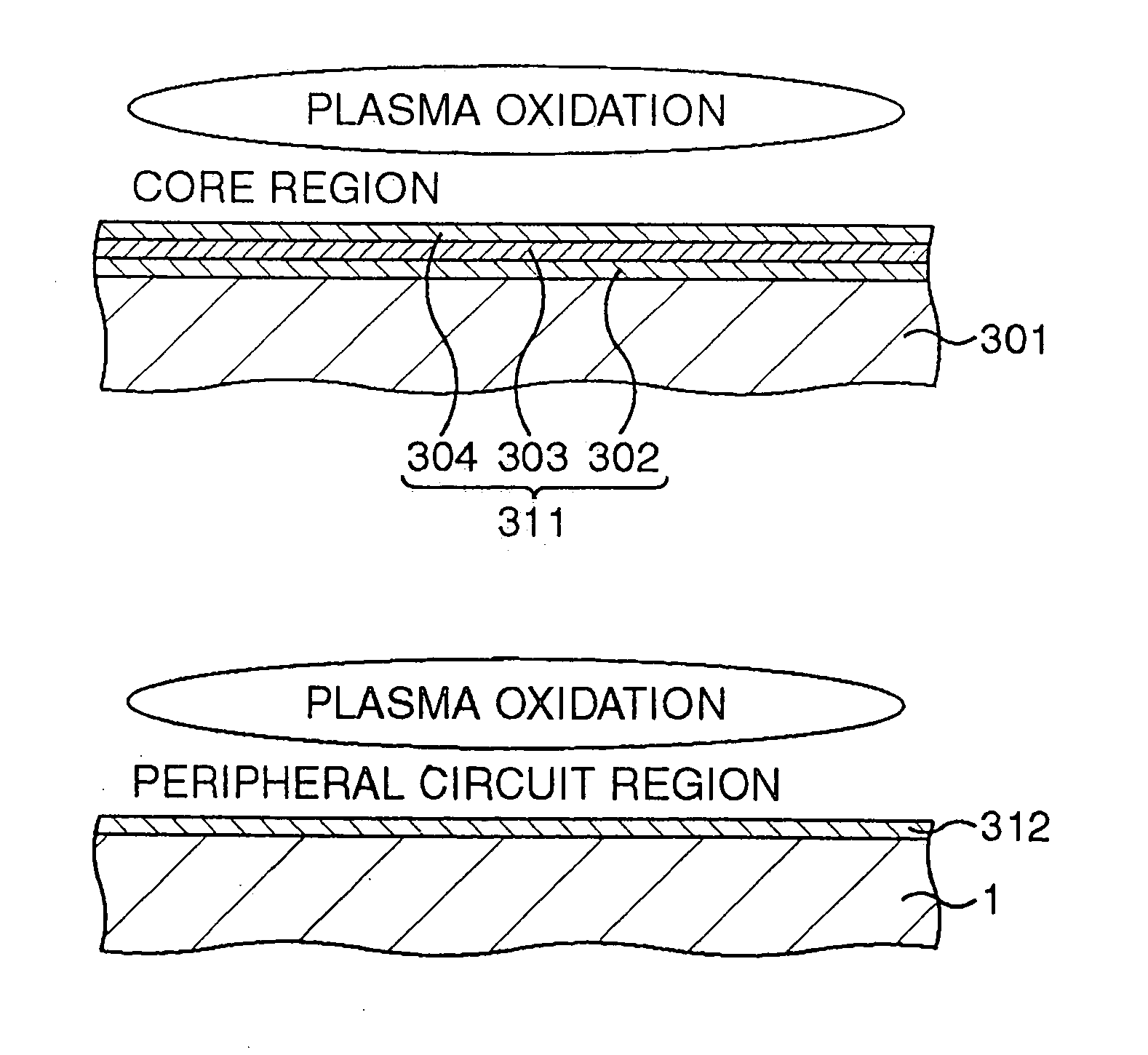

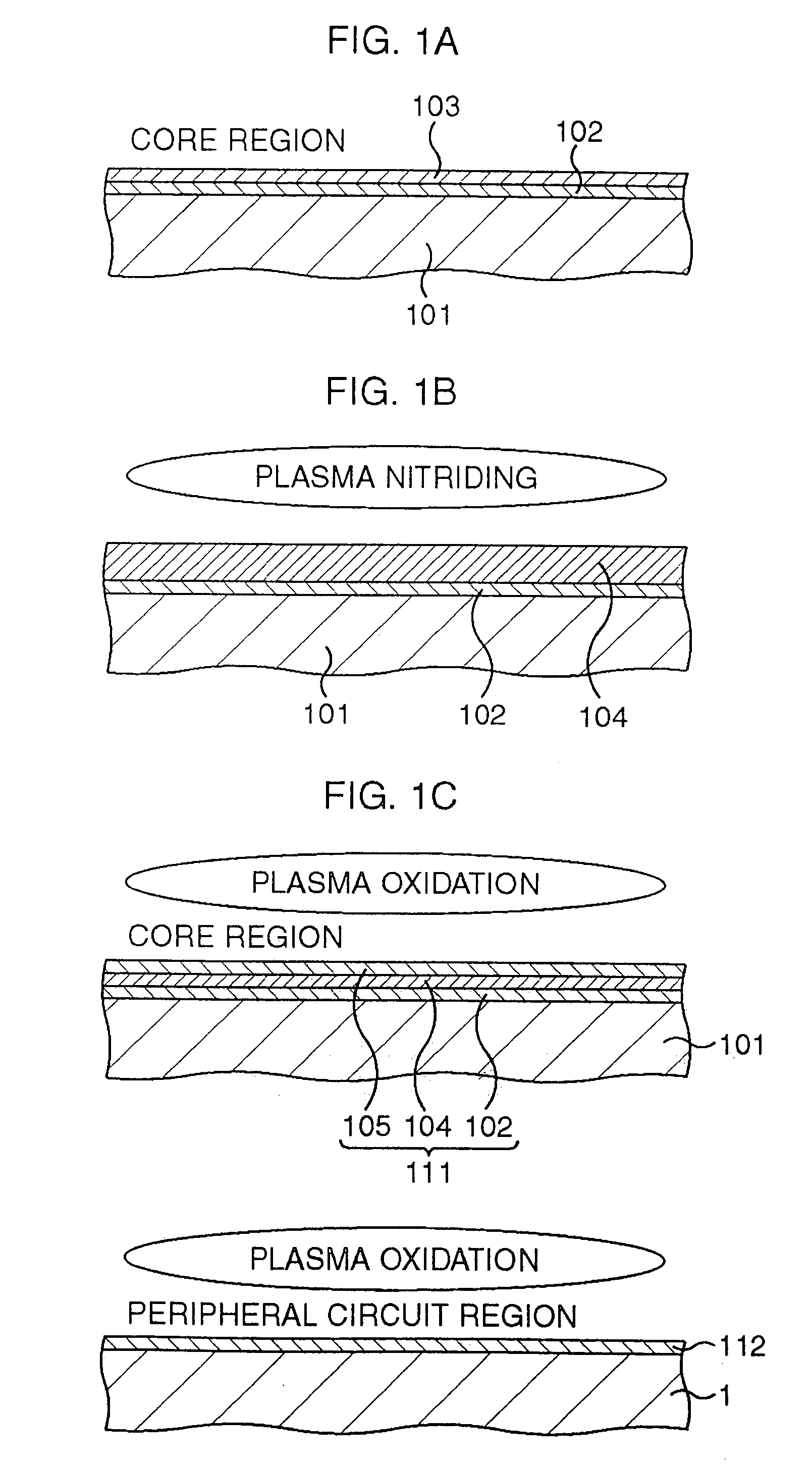

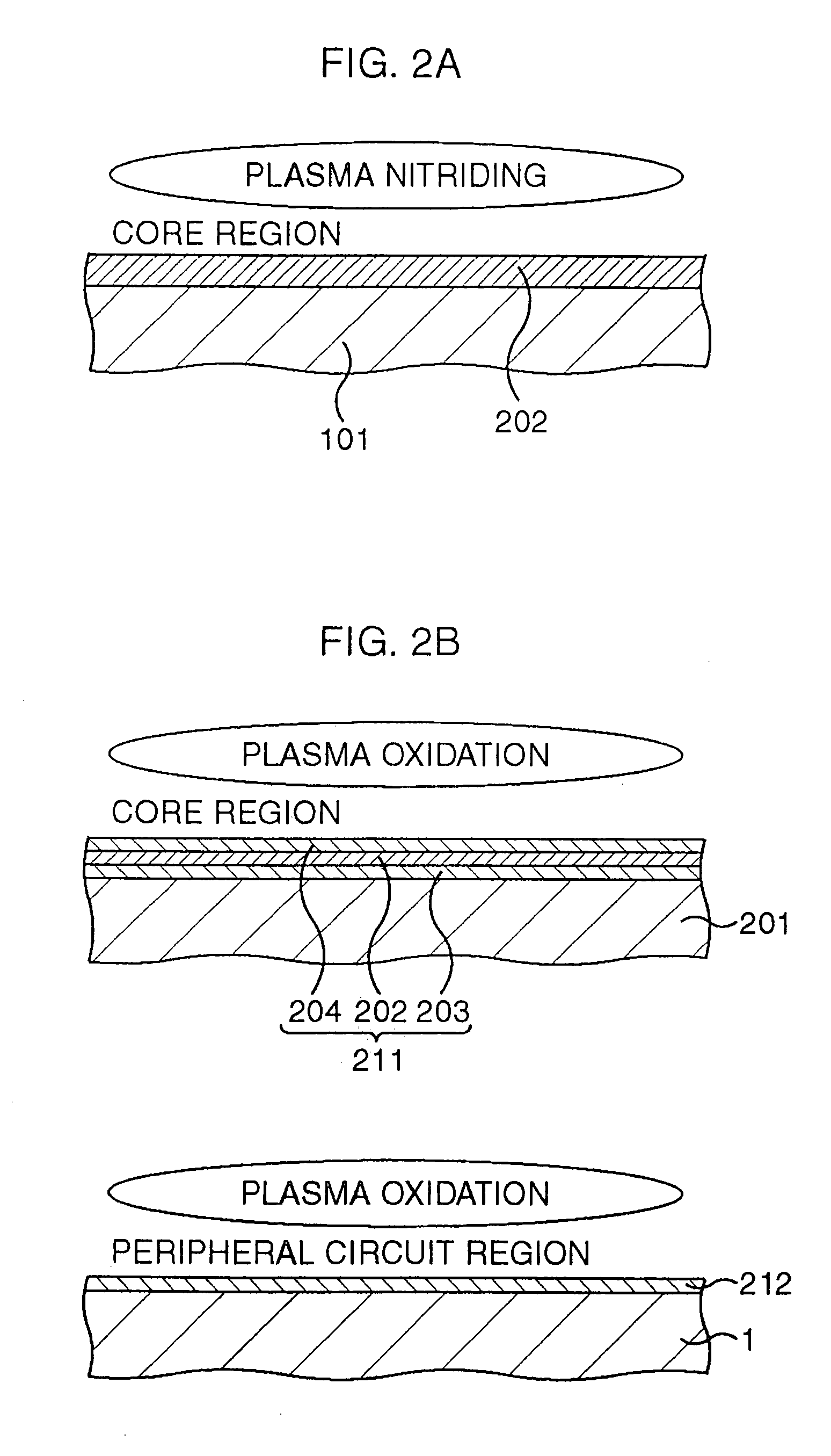

[0089]FIG. 4A to FIG. 13B are schematic cross sectional views showing a method for manufacturing the semiconductor memory device including embedded bit line type SONOS transistors in this embodiment in the order of processes. Here, each A of the drawings shows a memory cell region (a core region), and each B thereof shows a peripheral circuit region. The left side of the A thereof corresponds to a cross section (an X section) taken along the parallel line to a gate electrode (a word line), and the right side corresponds to a cross section (a Y ...

second embodiment

[0122] In this embodiment, a floating gate type semiconductor memory device will be disclosed. A structure of the semiconductor memory device is explained with a method for manufacturing thereof as a matter of convenience.

[0123] The floating gate type transistors are formed in a memory cell region, and CMOS transistors are formed in a peripheral circuit region.

[0124]FIG. 15A to FIG. 26B are schematic cross sectional views showing a method for manufacturing the semiconductor memory device including the floating gate type transistors in this embodiment in the order of processes. It should be noted that, for convenience, the same reference numerals are given to the components or the like explained in the first embodiment. Here, each A of the drawings except FIG. 20 shows a memory cell region (a core region), and each B thereof shows a peripheral circuit region. The left side of the A thereof corresponds to a cross section (an X section) taken along the parallel line to a control gate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More