Process for PECVD of silicon oxide using TEOS decomposition

a technology of pecvd and silicon oxide, which is applied in the direction of chemical vapor deposition coating, coating, plasma technique, etc., can solve the problems of increasing stringent requirements, increasing the difficulty of fabricating the conformal, planar inter-layer materials required, and reducing the efficiency of the process. , to achieve the effect of effective purging and preventing the breakdown of gas

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

I. CVD / PECVD Reactor

A. Overview of CVD / PECVD Reactor

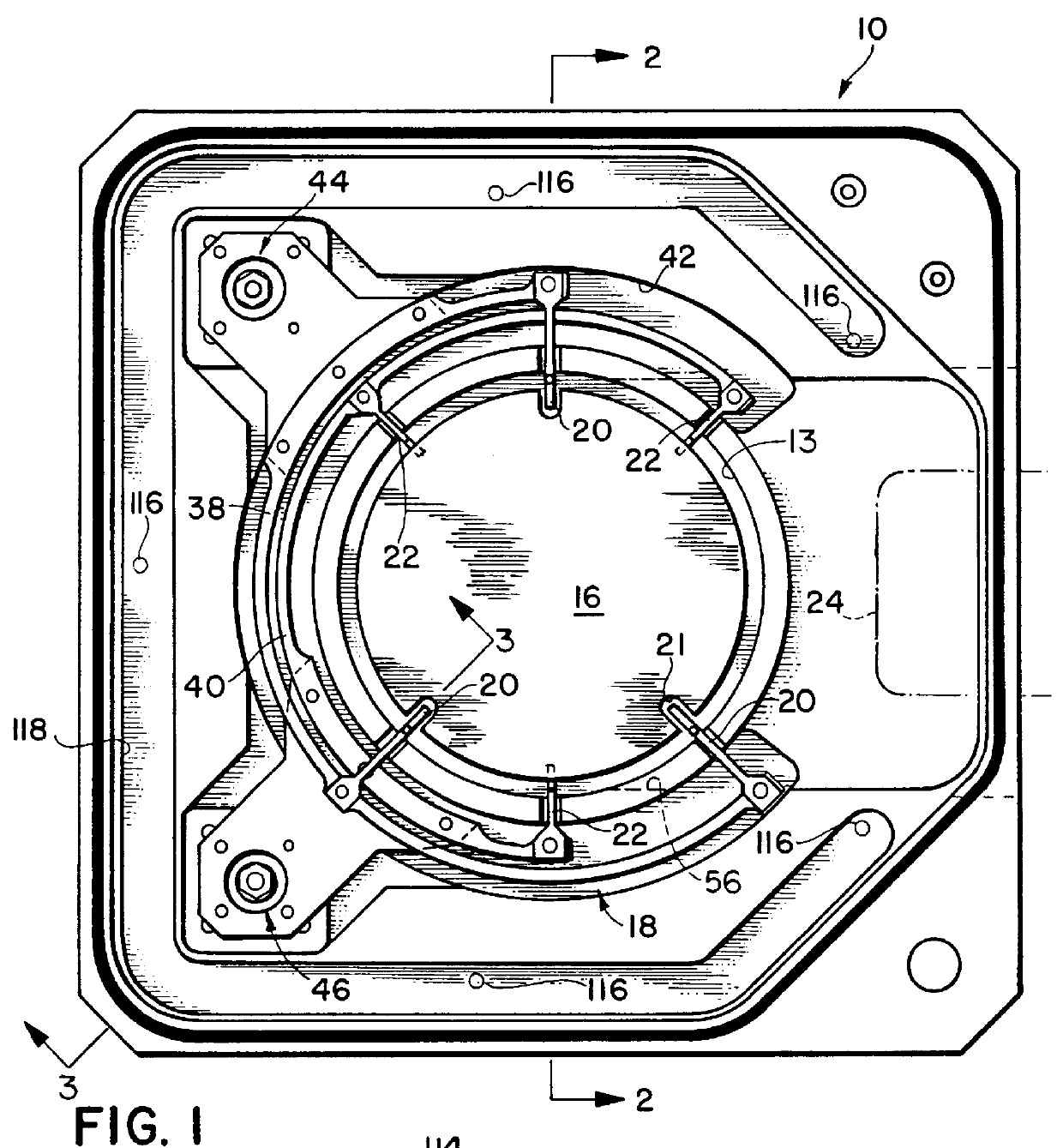

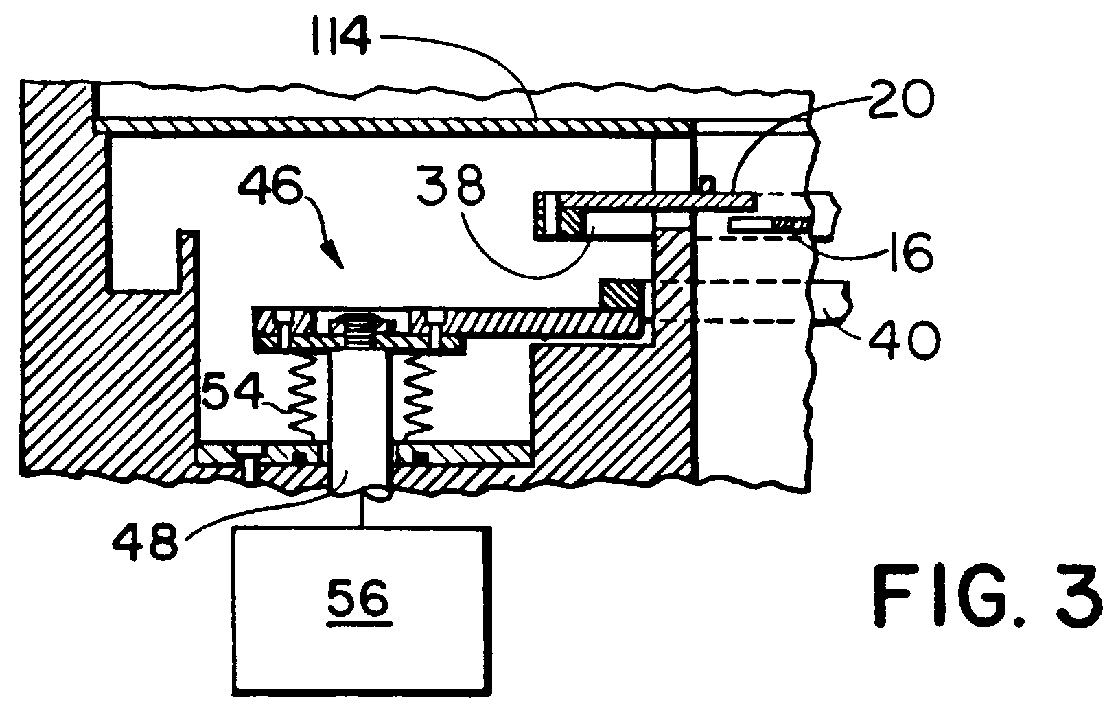

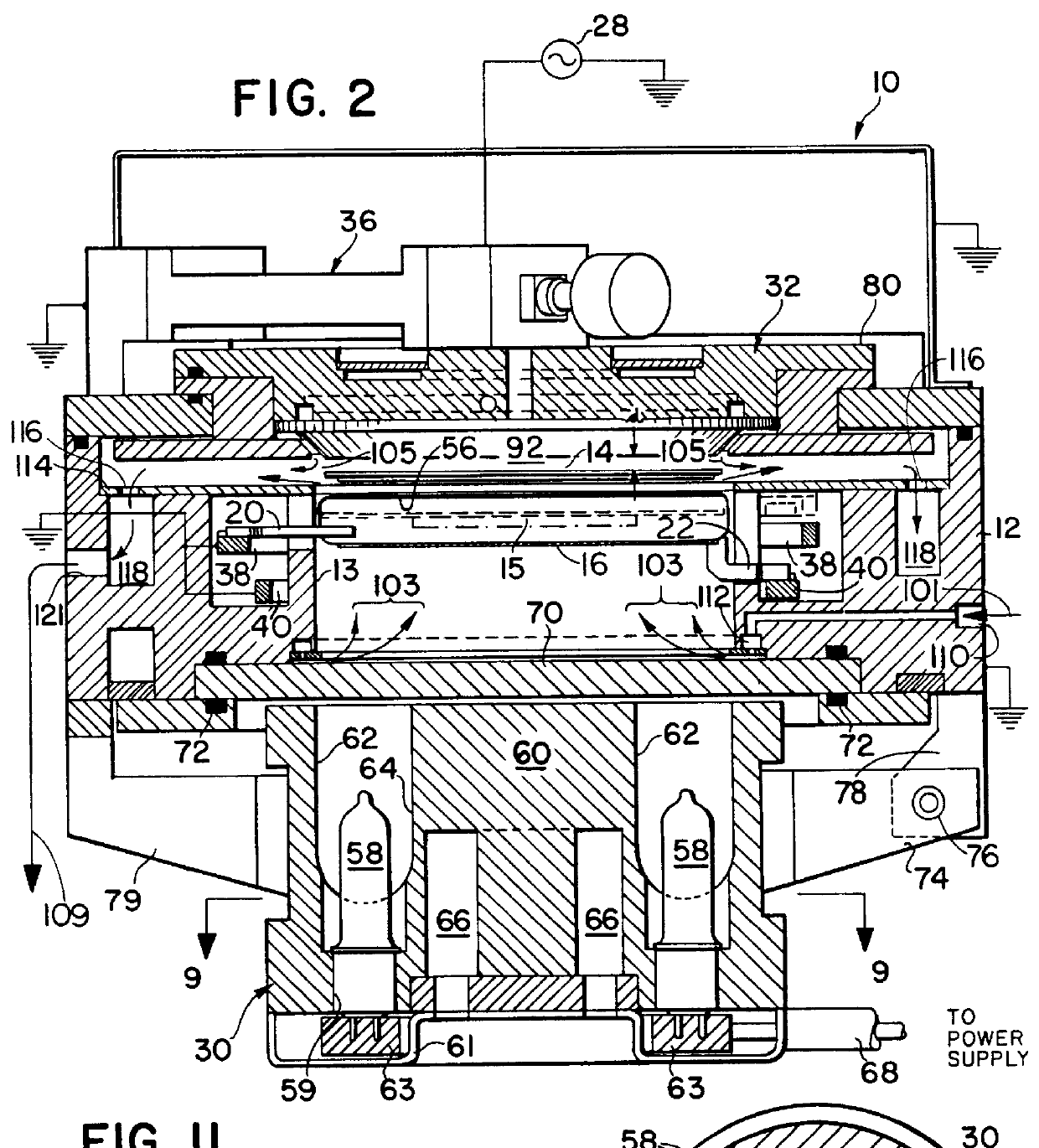

FIGS. 1 and 2 are, respectively, a top plan view of the preferred embodiment of the single wafer, reactor 10 of our present invention, shown with the cover pivoted open, and a vertical cross-section of the reactor 10.

Referring primarily to these two figures and to others indicated parenthetically, the reactor system 10 comprises a housing 12 (also termed a "chamber"), typically made of aluminum, which defines an inner vacuum chamber 13 that has a plasma processing region 14 (FIG. 6). The reactor system 10 also includes a wafer-holding susceptor 16 and a unique wafer transport system 18 (FIG. 1) that includes vertically movable wafer support fingers 20 and susceptor support fingers 22. These fingers cooperate with an external robotic blade 24 (FIG. 1) for introducing wafers 15 into the process legion or chamber 14 and depositing the wafers 15 on the susceptor 16 for processing, then removing the wafers 15 from the susceptor 16 and t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| total pressure | aaaaa | aaaaa |

| chamber pressure | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More