Patents

Literature

719 results about "Glass etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Glass etching or “French Embossing,” is a popular technique developed during the mid-1800s that is still widely used in both residential and commercial spaces today. Glass etching comprises the techniques of creating art on the surface of glass by applying acidic, caustic, or abrasive substances. Traditionally this is done after the glass is blown or cast, although mold-etching has replaced some forms of surface etching. The removal of minute amounts of glass causes the characteristic rough surface and translucent quality of frosted glass.

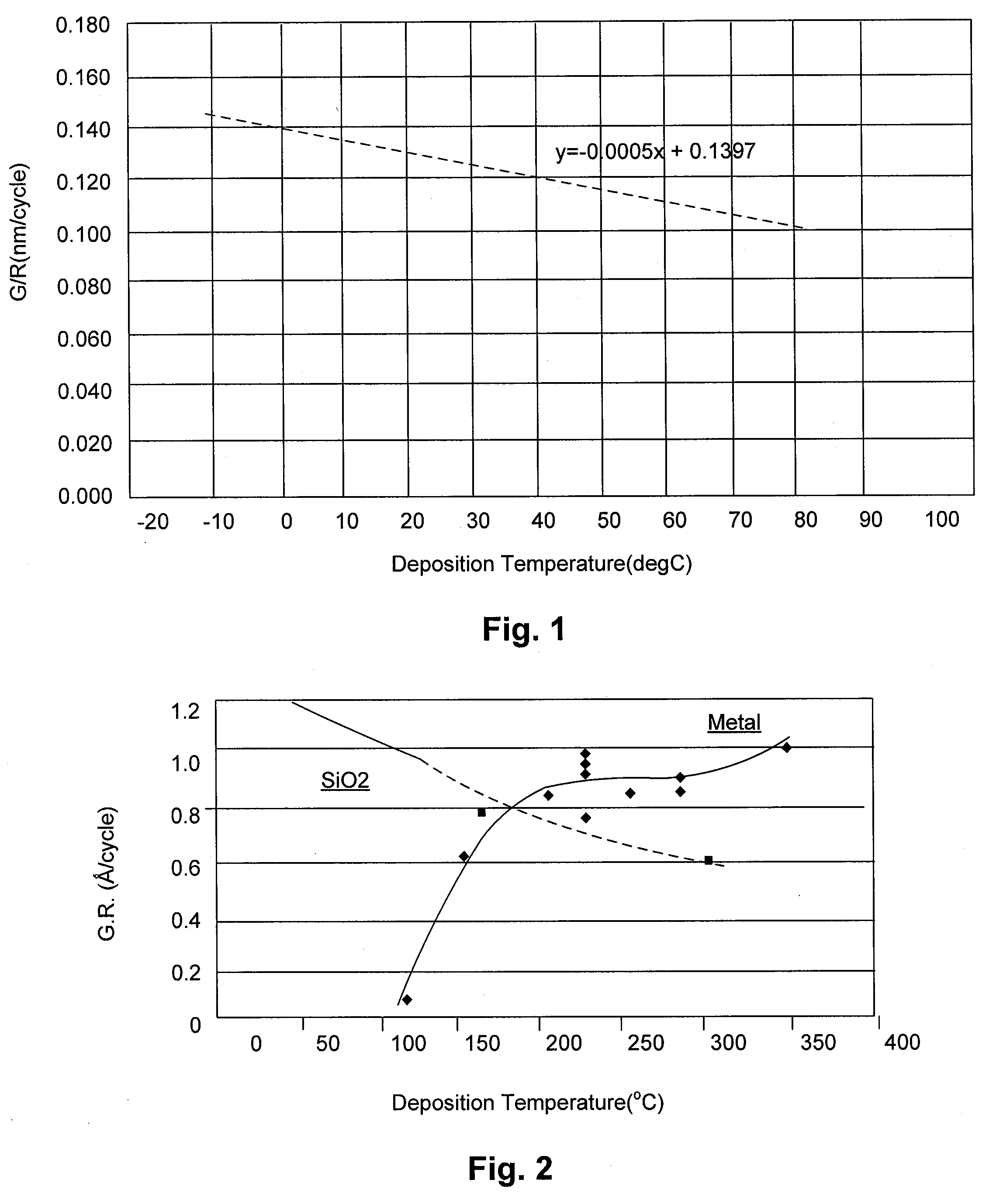

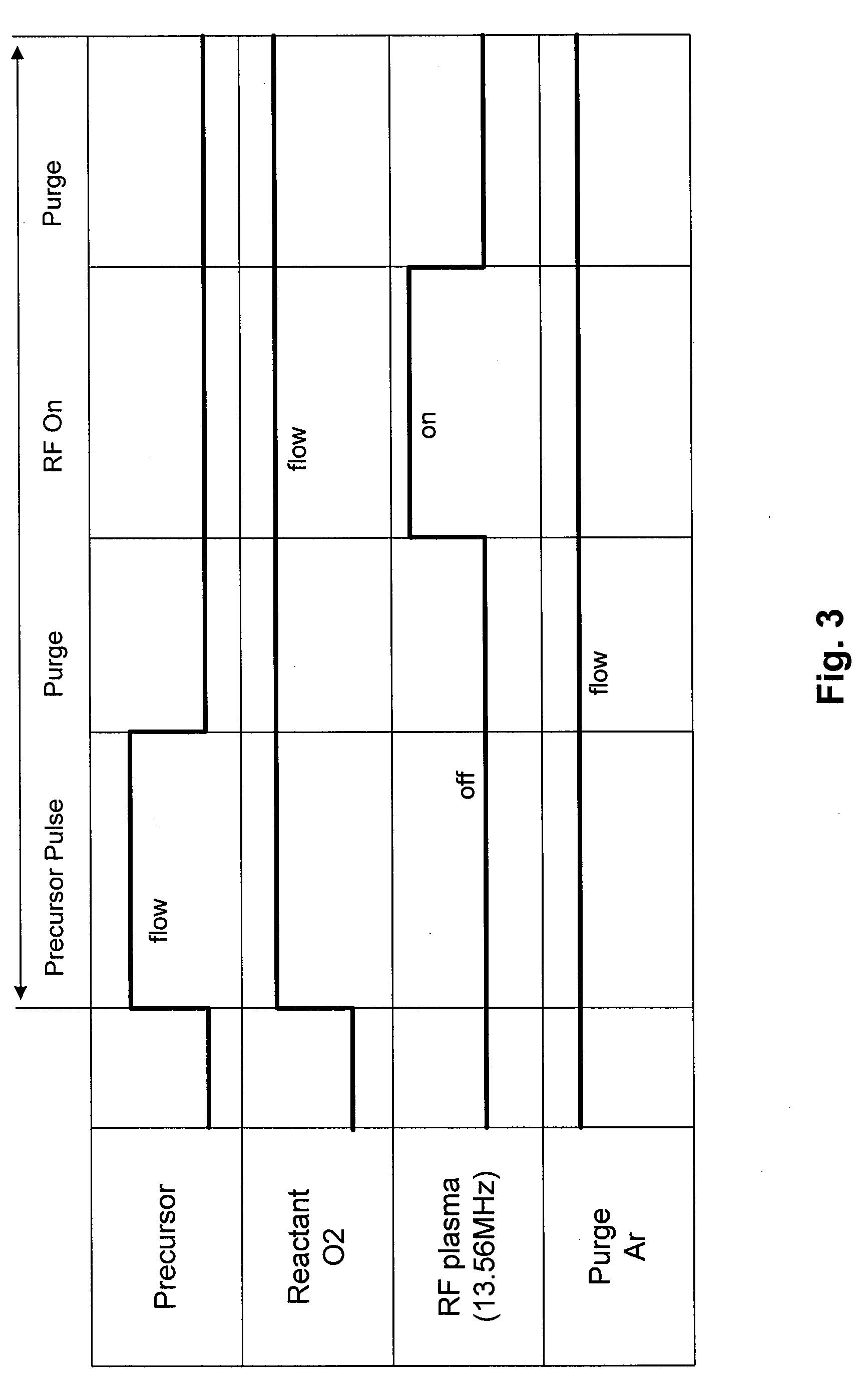

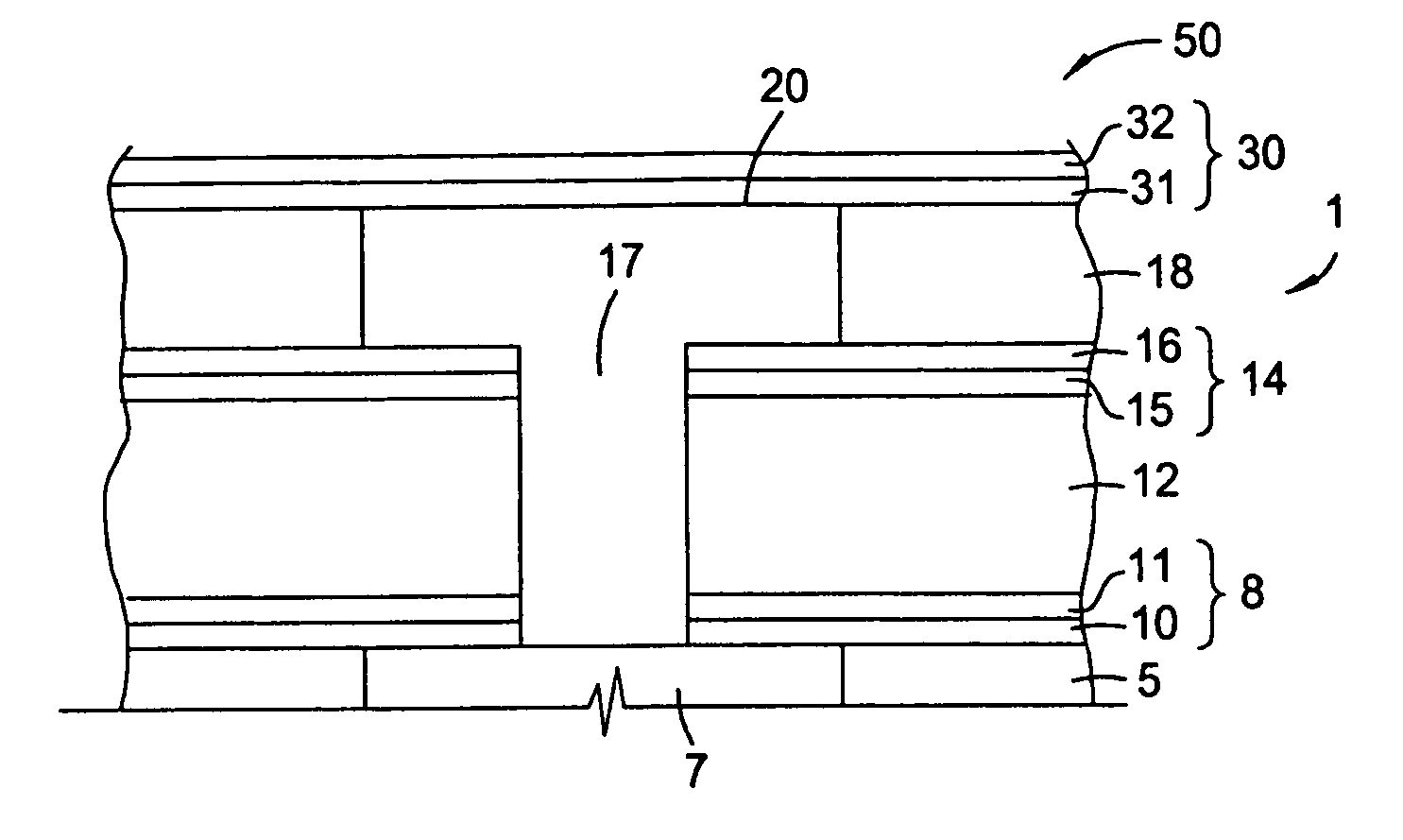

Method of Depositing Silicon Oxide Film by Plasma Enhanced Atomic Layer Deposition at Low Temperature

ActiveUS20100255218A1Increase deposition rateInhibition is effectiveLiquid surface applicatorsSemiconductor/solid-state device manufacturingResistDeposition temperature

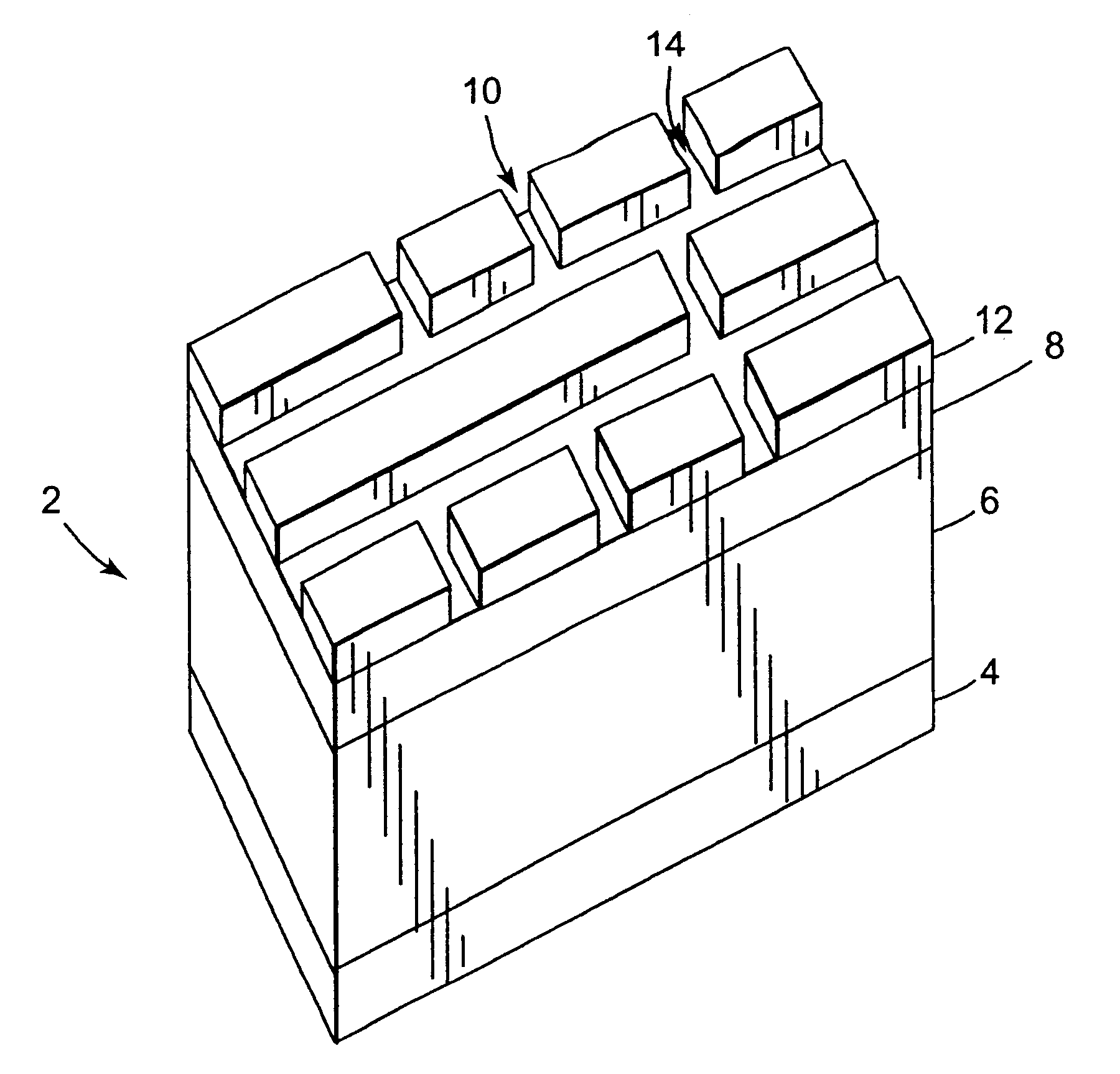

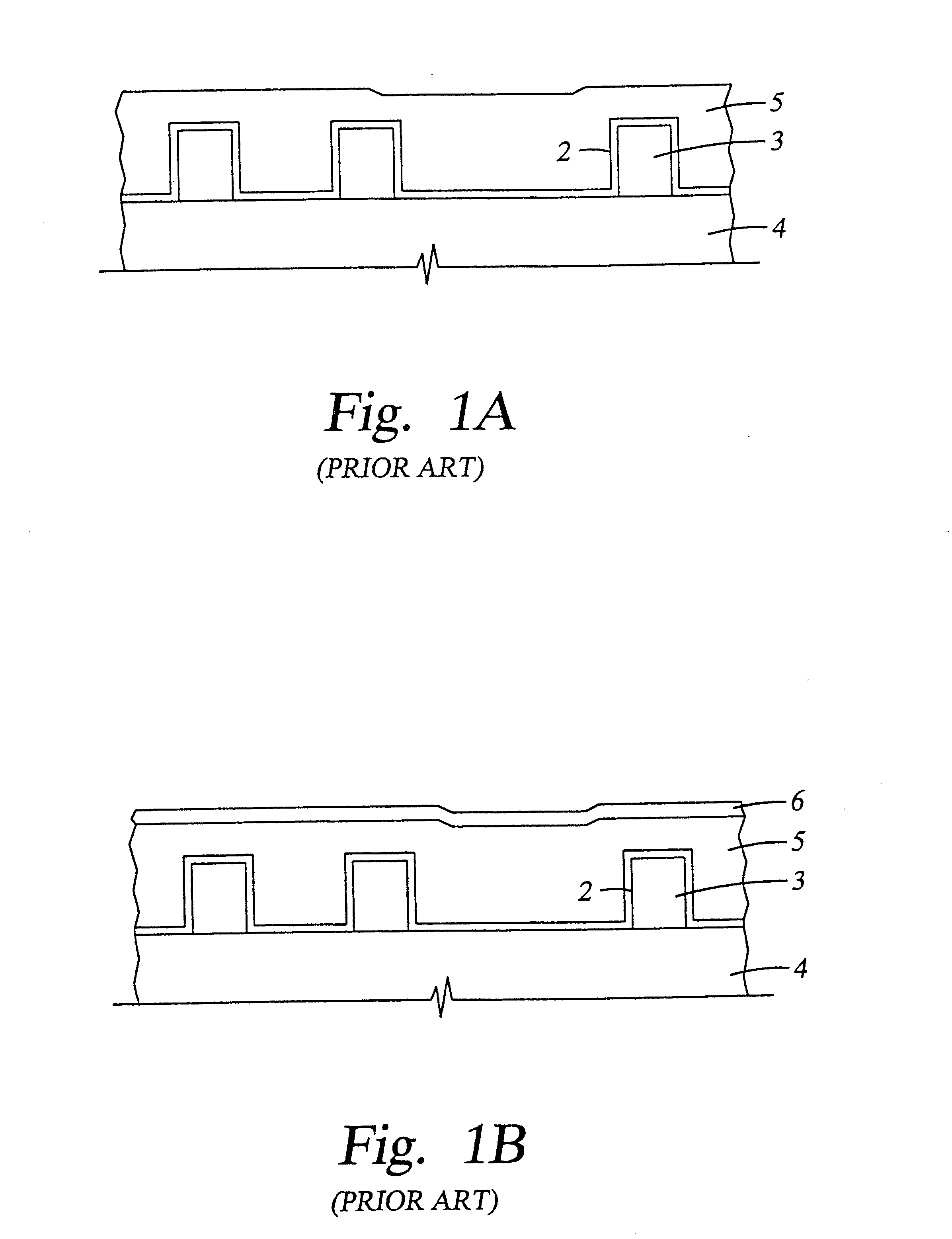

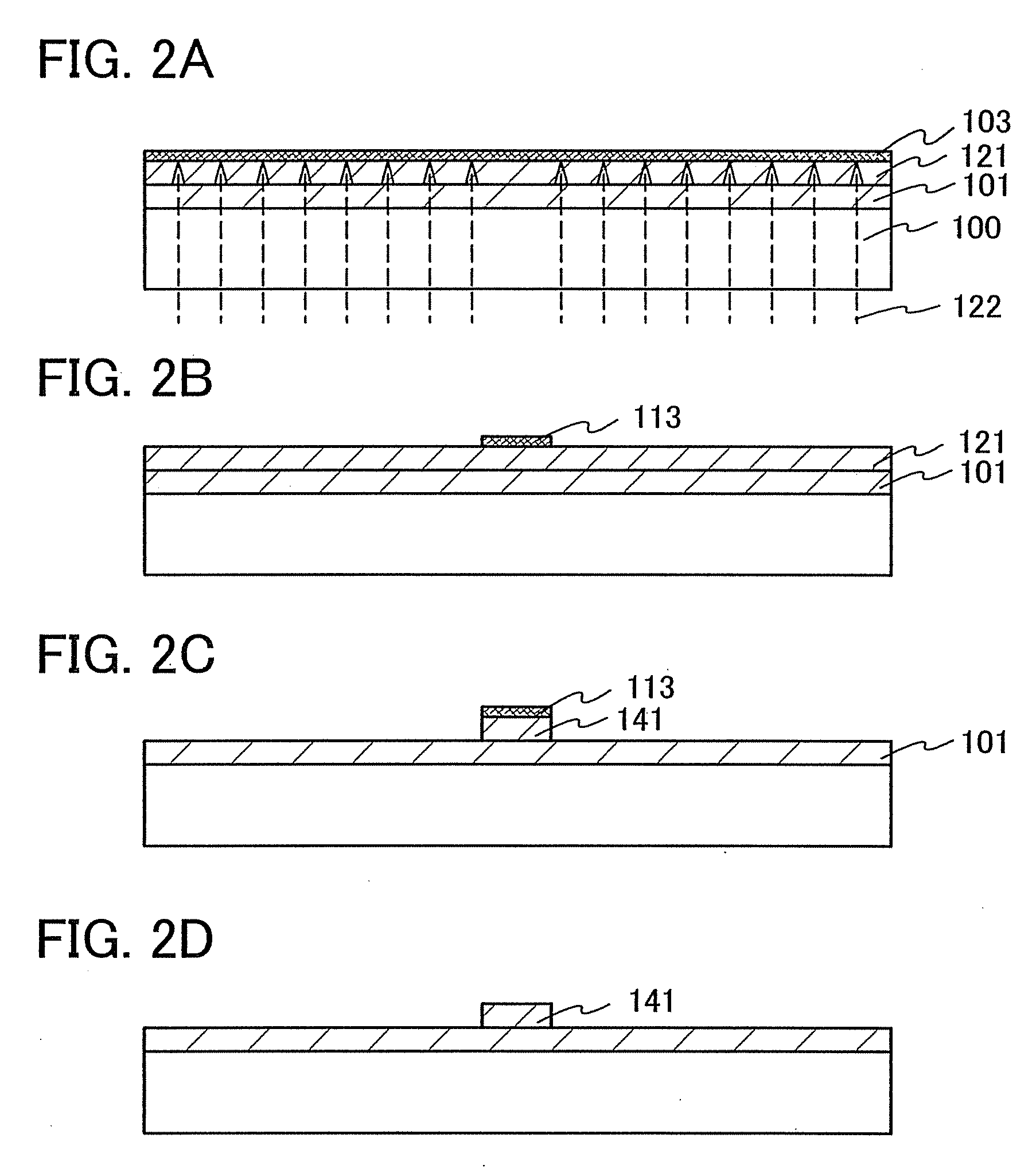

A method of depositing a silicon oxide film on a resist pattern or etched lines formed on a substrate by plasma enhanced atomic layer deposition (PEALD) includes: providing a substrate on which a resist pattern or etched lines are formed in a PEALD reactor; controlling a temperature of a susceptor on which the substrate is placed at less than 50° C. as a deposition temperature; introducing a silicon-containing precursor and an oxygen-supplying reactant to the PEALD reactor and applying RF power therein in a cycle, while the deposition temperature is controlled substantially or nearly at a constant temperature of less than 50° C., thereby depositing a silicon oxide atomic layer on the resist pattern or etched lines; and repeating the cycle multiple times substantially or nearly at the constant temperature to deposit a silicon oxide atomic film on the resist pattern or etched lines.

Owner:ASM JAPAN

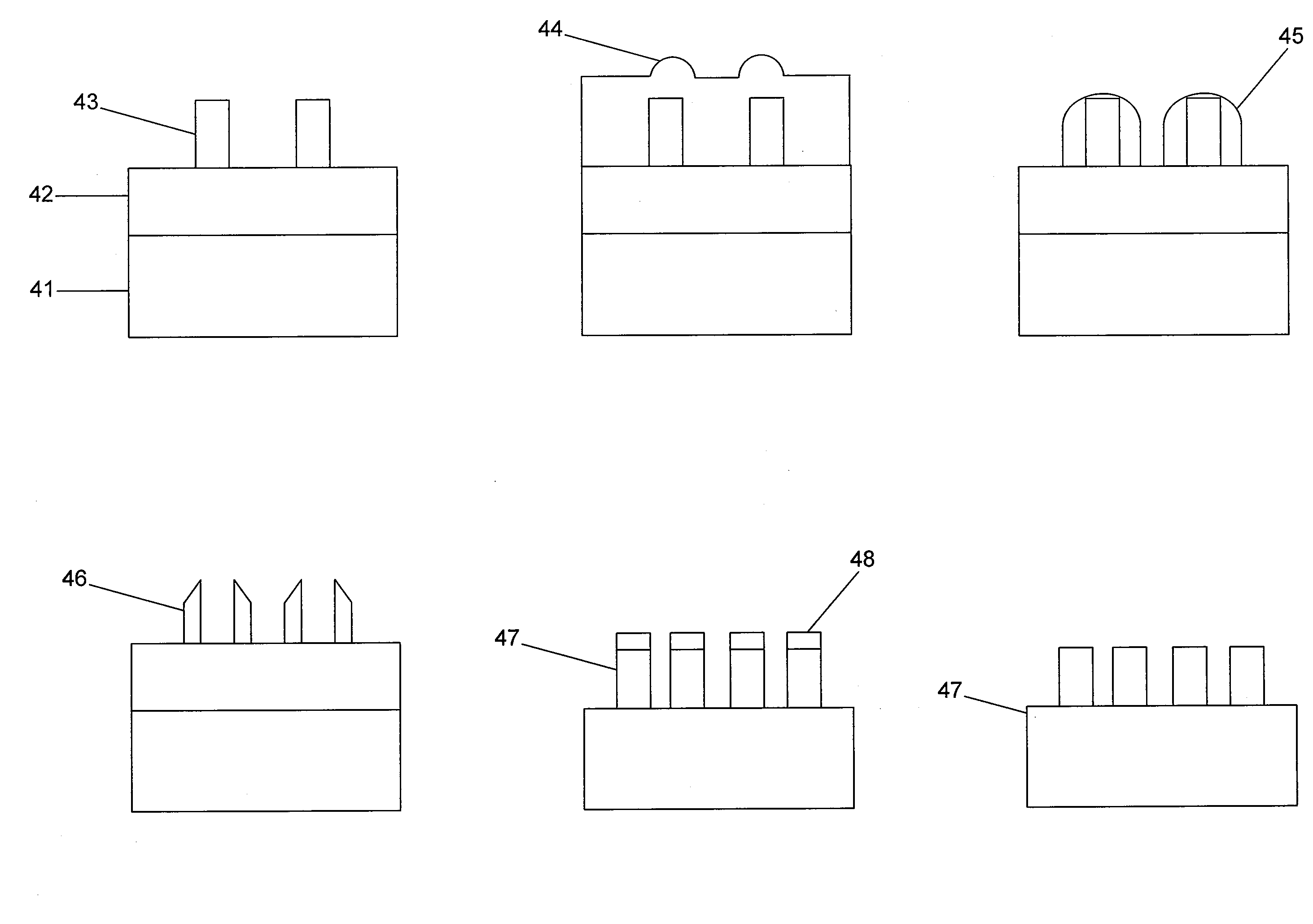

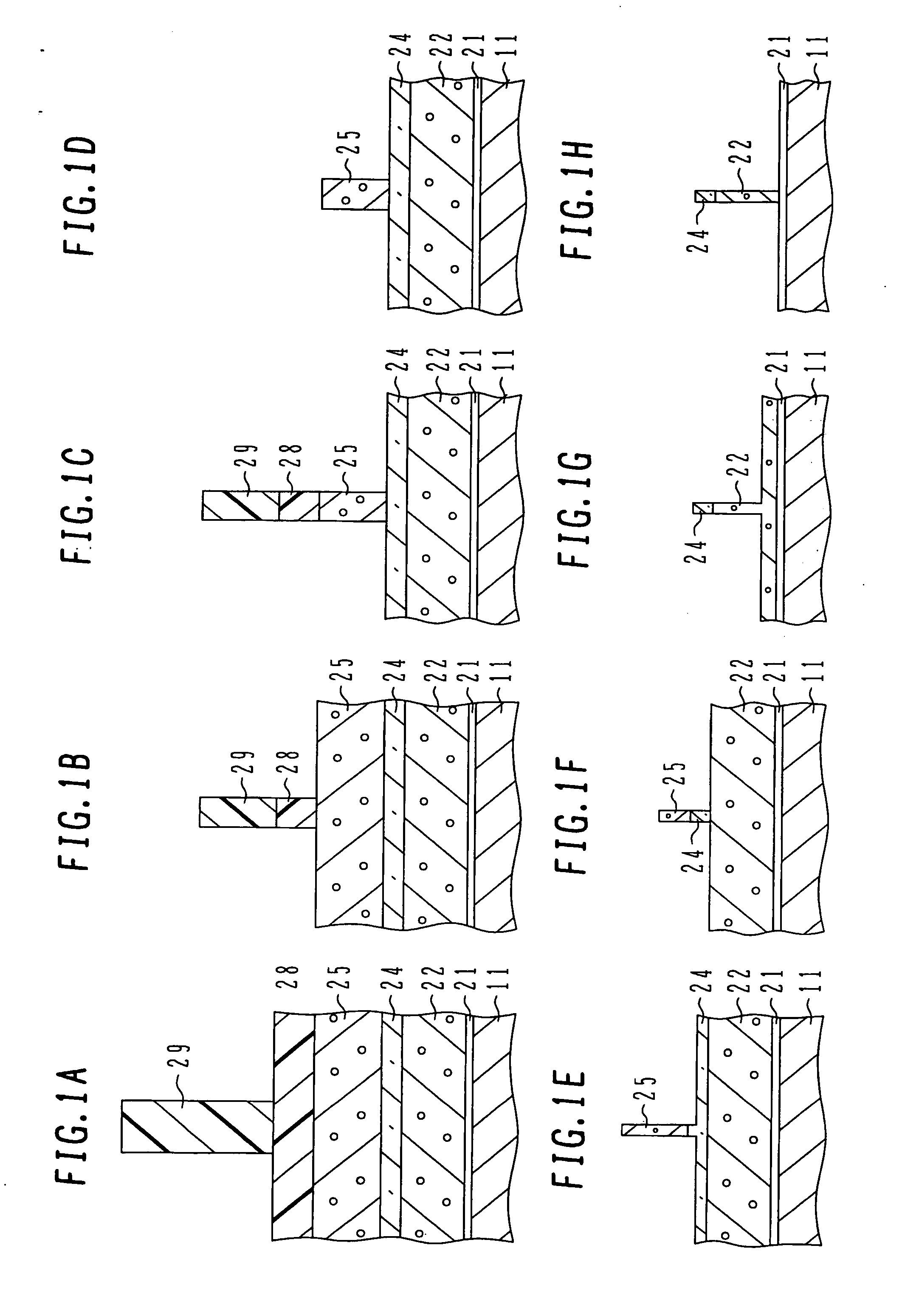

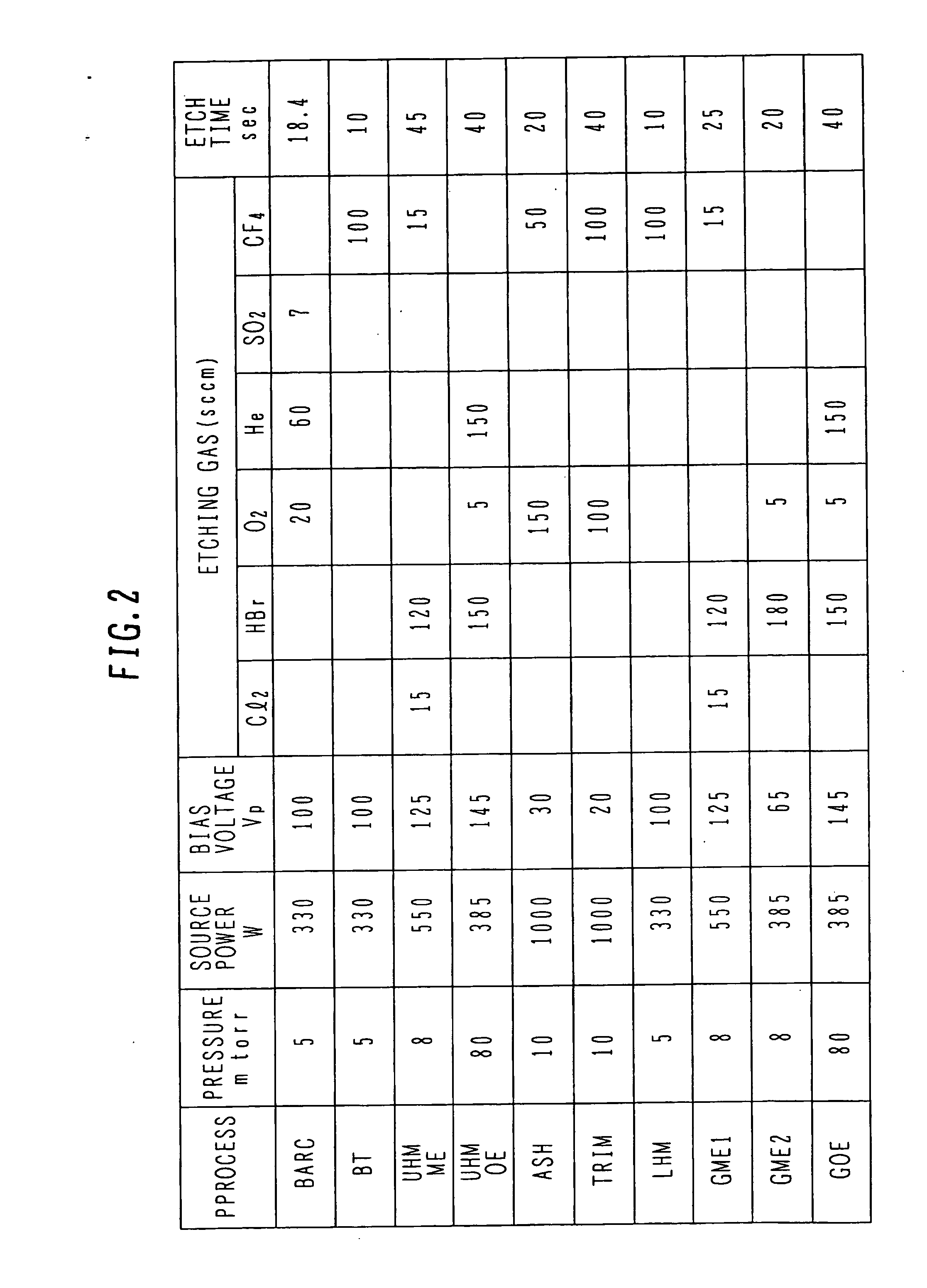

Manufacture method for micro structure

InactiveUS20070037101A1Easy to etchImprove controllabilitySemiconductor/solid-state device manufacturingPhotosensitive material processingResistMicro structure

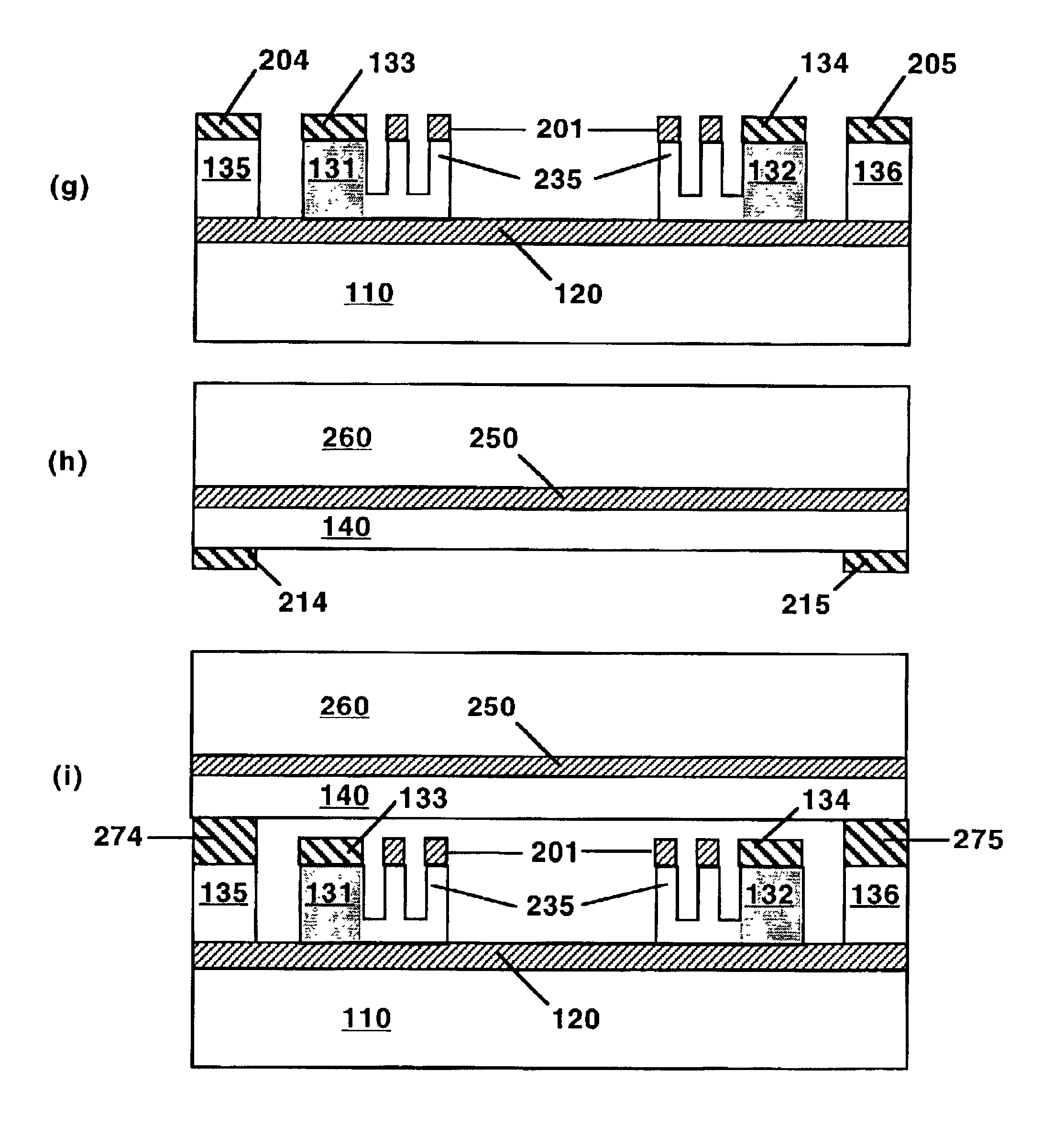

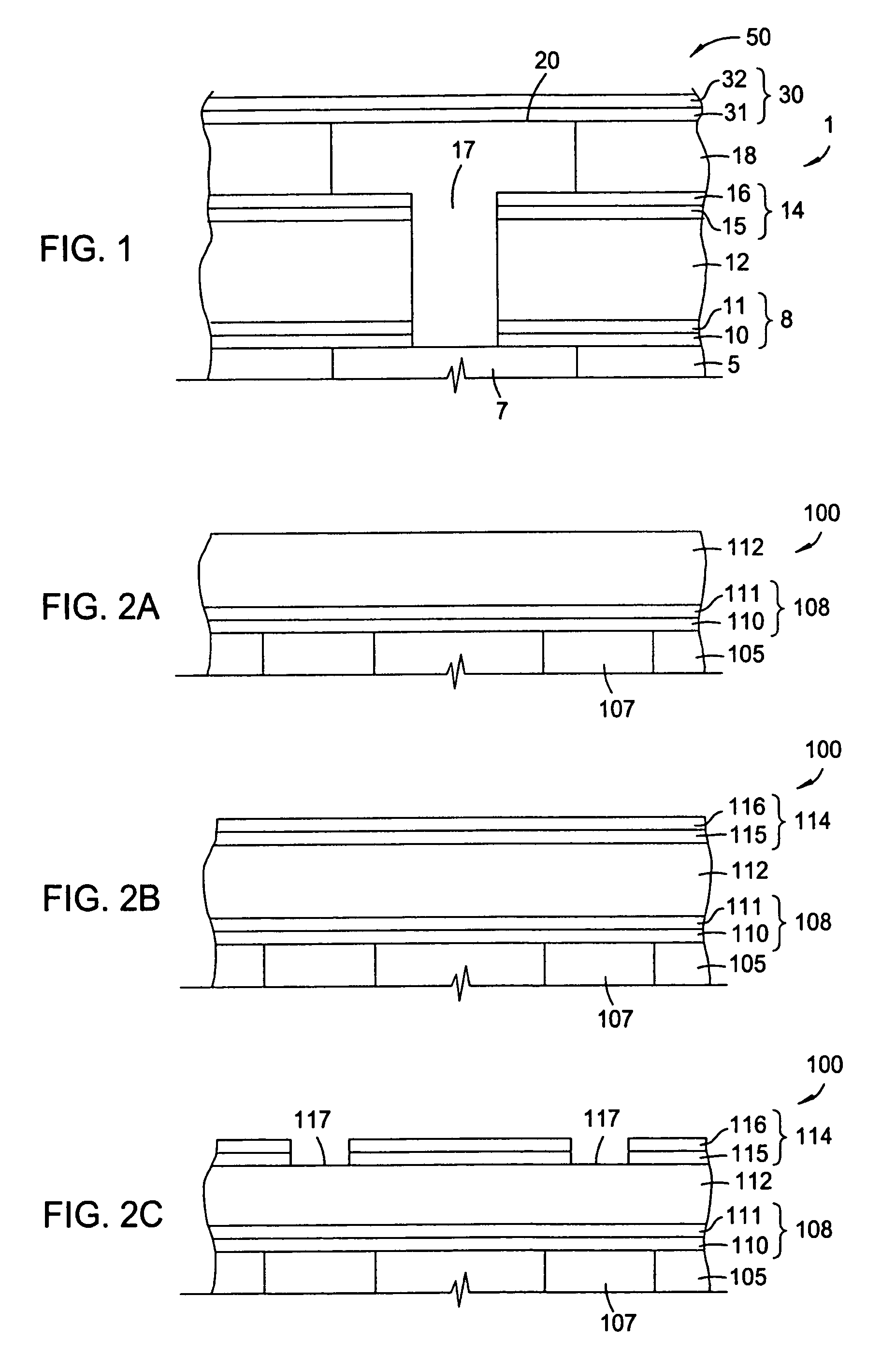

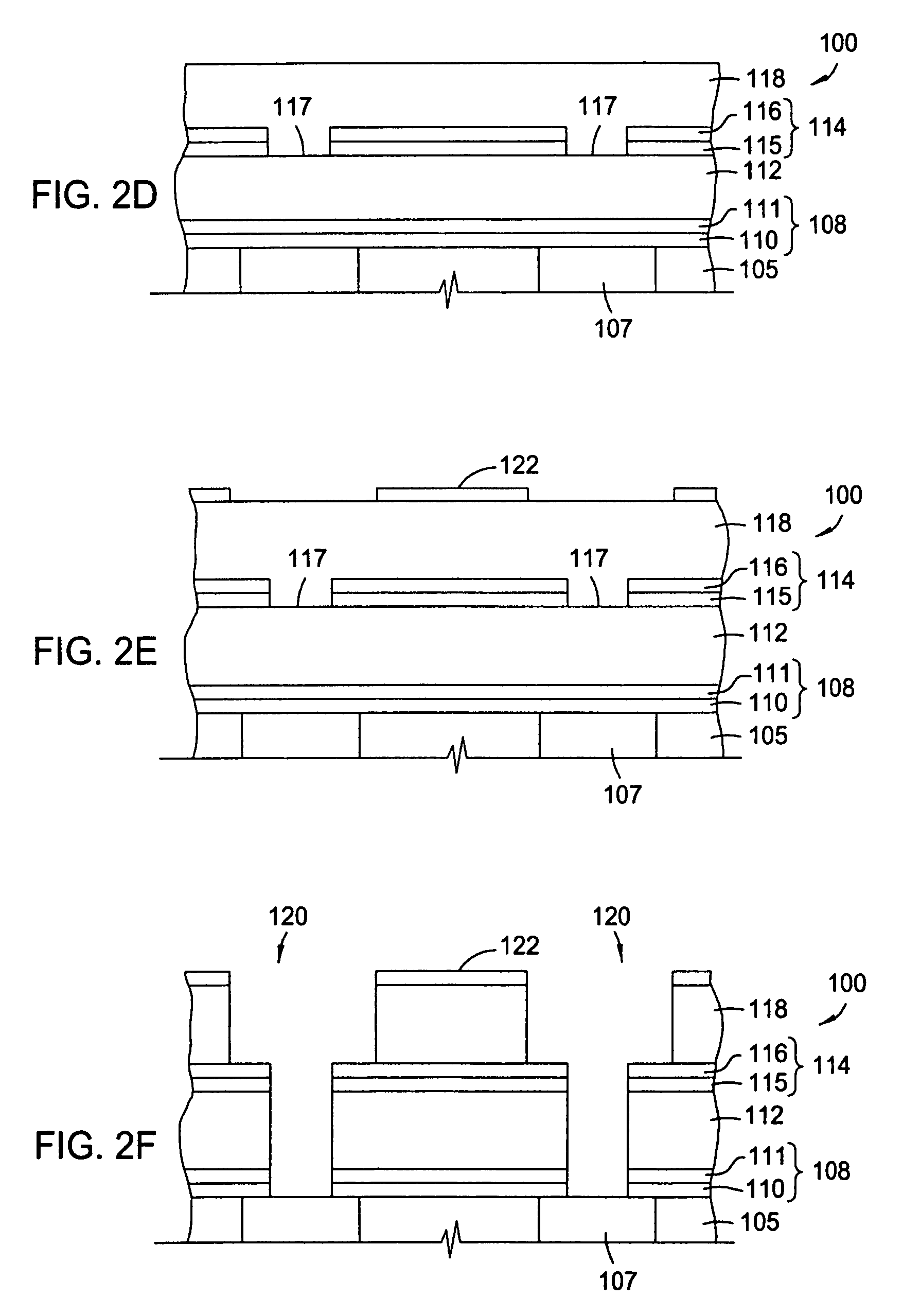

A micro structure manufacture method includes the steps of: (a) preparing an etching object having an etching target film, provided with a lower hard mask layer and an upper hard mask layer stacked on the etching target film; (b) forming a resist pattern above the etching object; (c) etching the upper hard mask film by using the resist pattern as an etching mask to form an upper hard mask; (d) after the step (c), removing the resist pattern; (e) after the step (d), thinning the upper hard mask by etching; (f) etching the lower hard mask film by using the thinned upper hard mask as an etching mask to form a lower hard mask; and (g) etching the etching target film by using the upper hard mask and the lower hard mask as an etching mask, wherein the upper hard mask film is capable of being more easily etched, using the resist pattern as a mask, than the lower hard mask film. The micro structure manufacture method can etch a fine pattern with good yield.

Owner:FUJITSU LTD

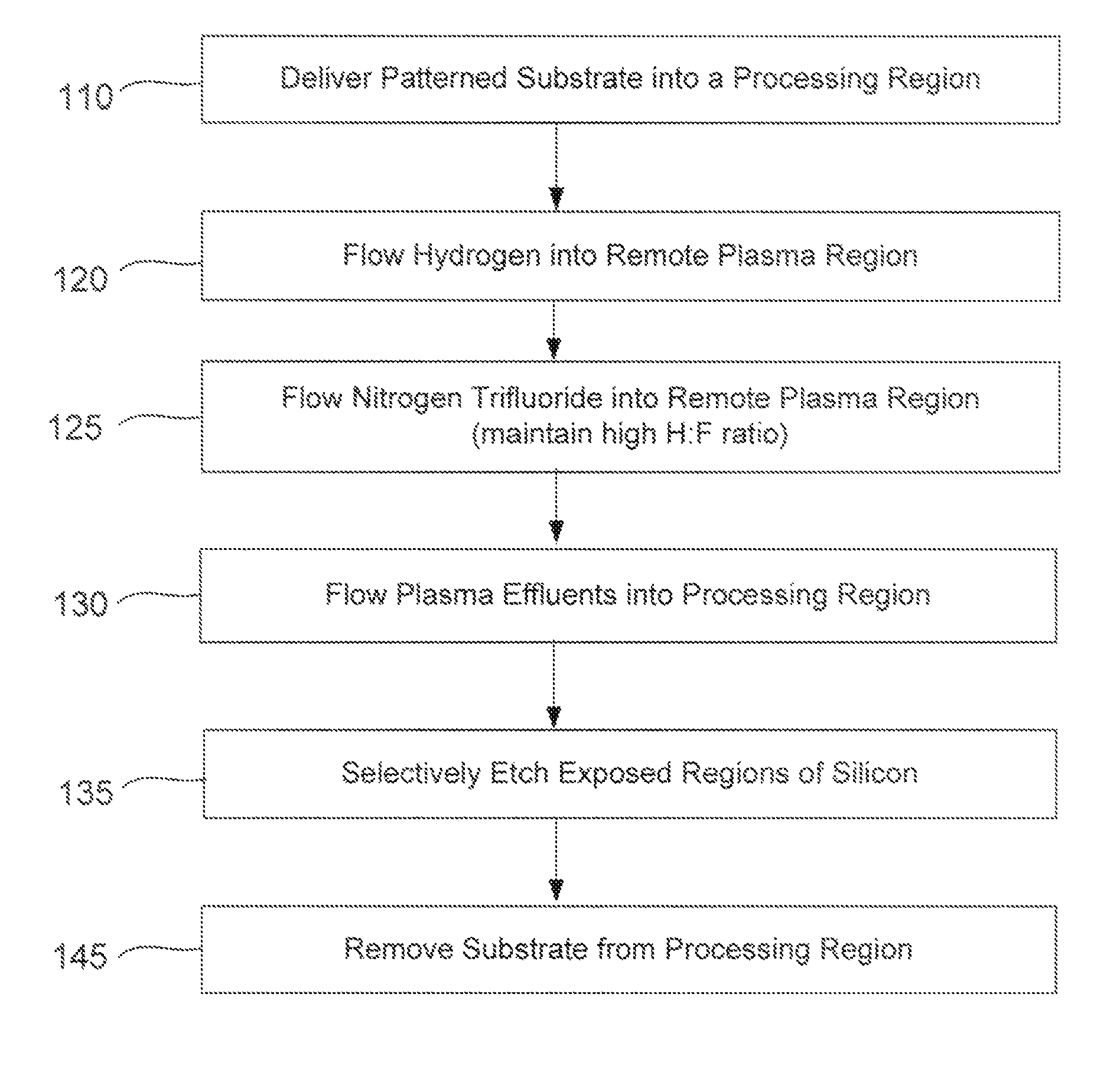

Selective etch of silicon by way of metastable hydrogen termination

ActiveUS8808563B2Easy to disassembleReduces and substantially eliminates numberElectric discharge tubesDecorative surface effectsRemote plasmaHydrogen

Methods of etching exposed silicon on patterned heterogeneous structures is described and includes a remote plasma etch formed from a fluorine-containing precursor and a hydrogen-containing precursor. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents react with the exposed regions of silicon. The plasmas effluents react with the patterned heterogeneous structures to selectively remove silicon while very slowly removing other exposed materials. The silicon selectivity results, in part, from a preponderance of hydrogen-containing precursor in the remote plasma which hydrogen terminates surfaces on the patterned heterogeneous structures. A much lower flow of the fluorine-containing precursor progressively substitutes fluorine for hydrogen on the hydrogen-terminated silicon thereby selectively removing silicon from exposed regions of silicon. The methods may be used to selectively remove silicon far faster than silicon oxide, silicon nitride and a variety of metal-containing materials.

Owner:APPLIED MATERIALS INC

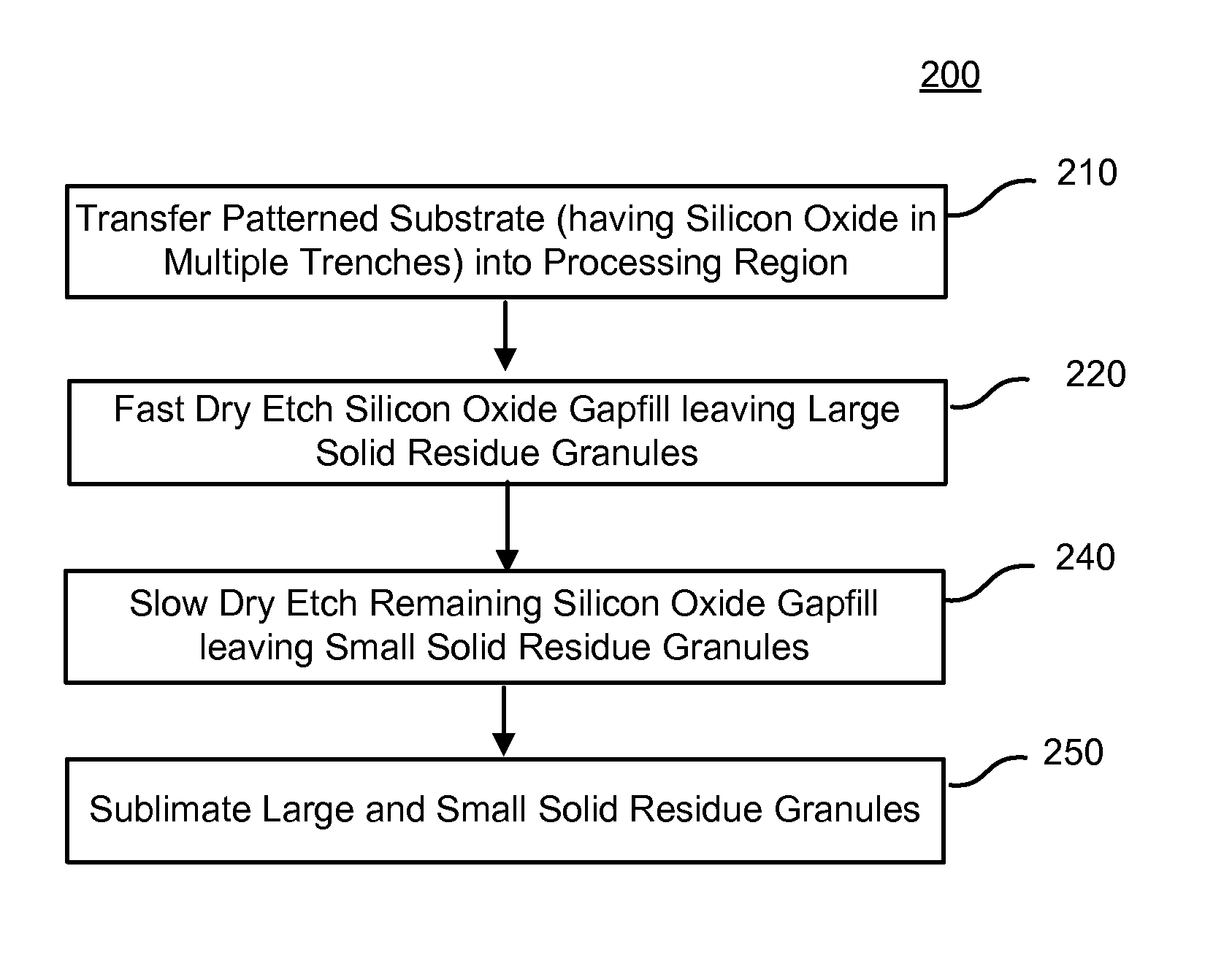

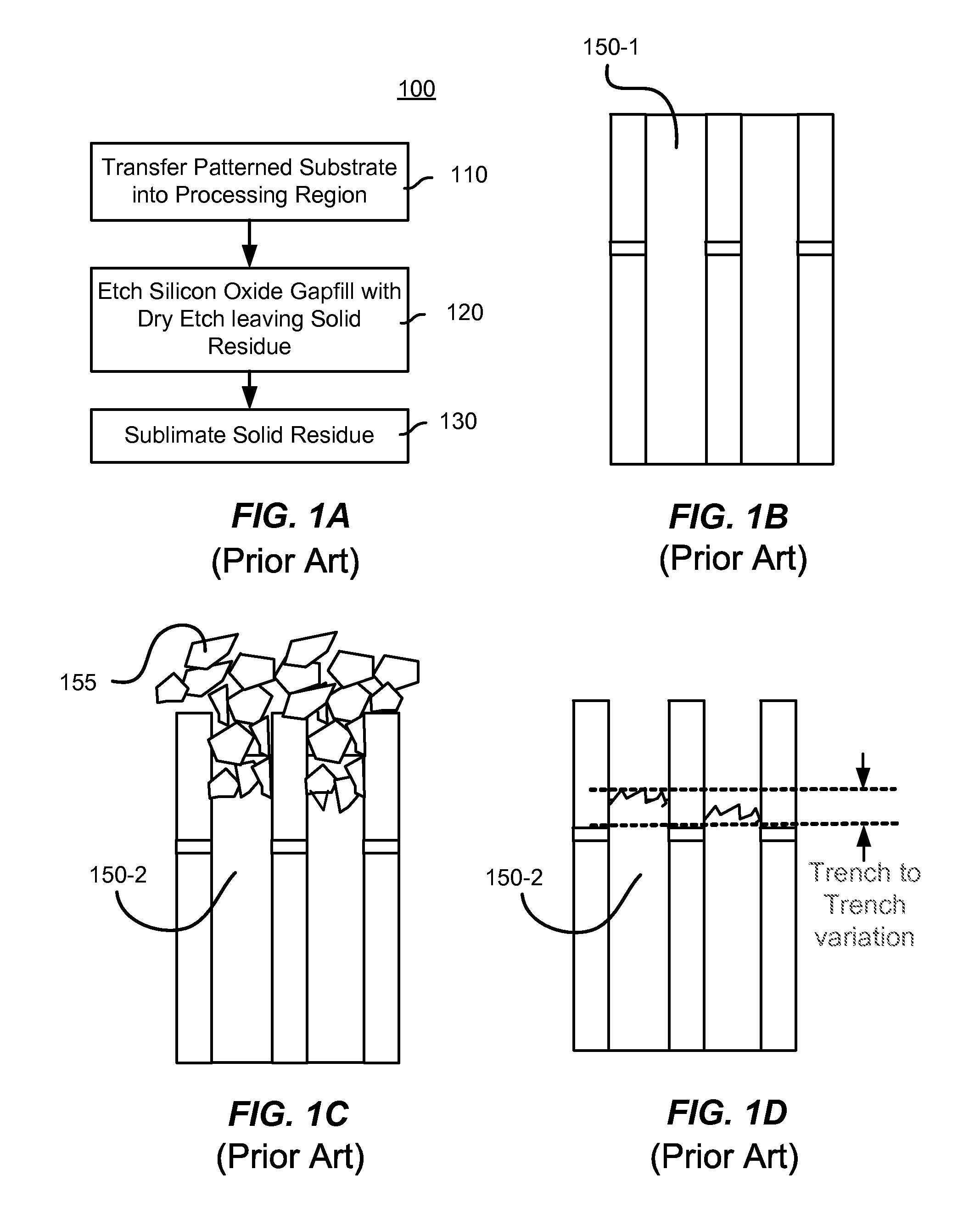

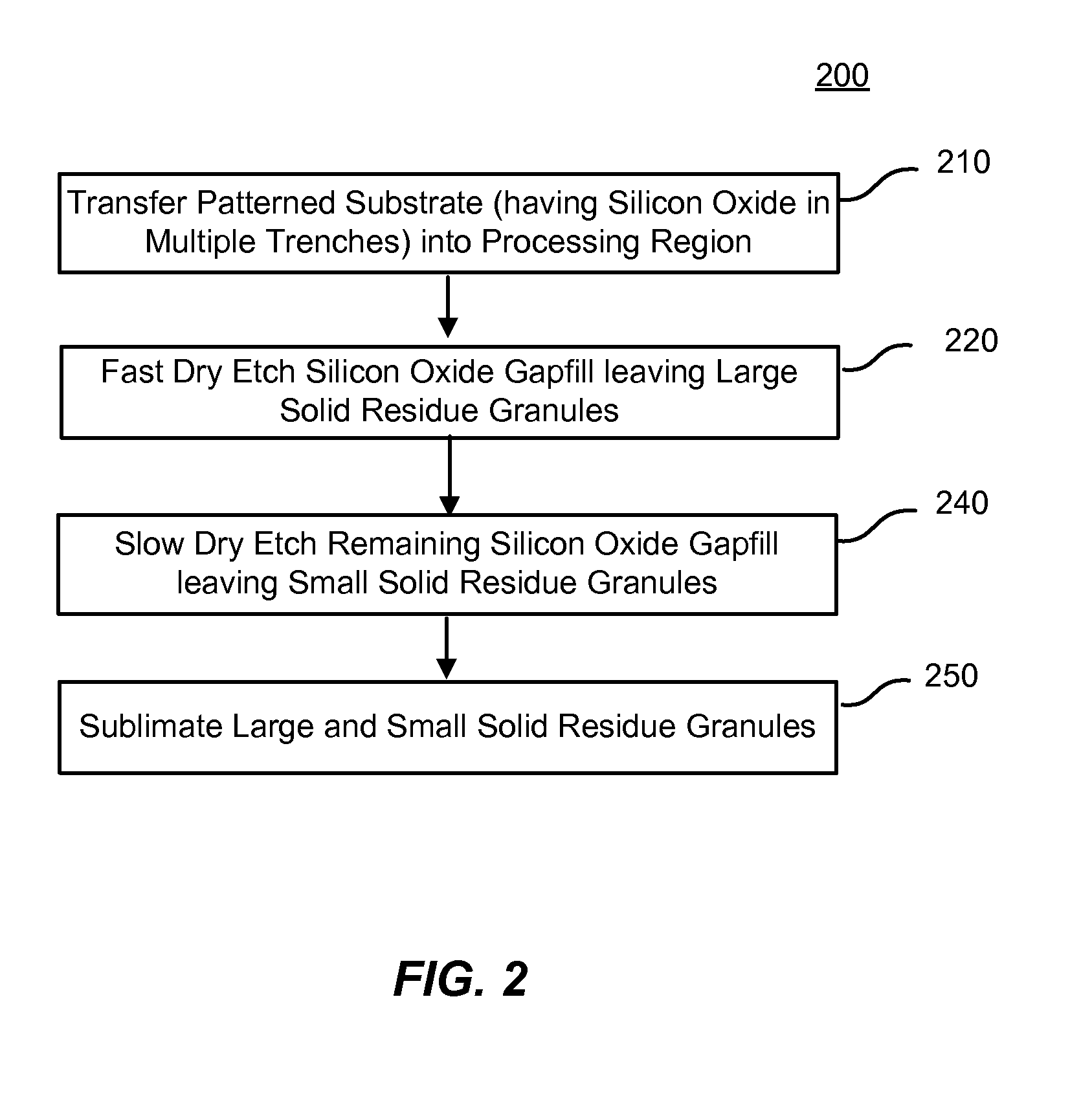

Uniform dry etch in two stages

ActiveUS8741778B2Flat surfaceEasy to removeDecorative surface effectsSemiconductor/solid-state device manufacturingSilicon oxideDry etching

Owner:APPLIED MATERIALS INC

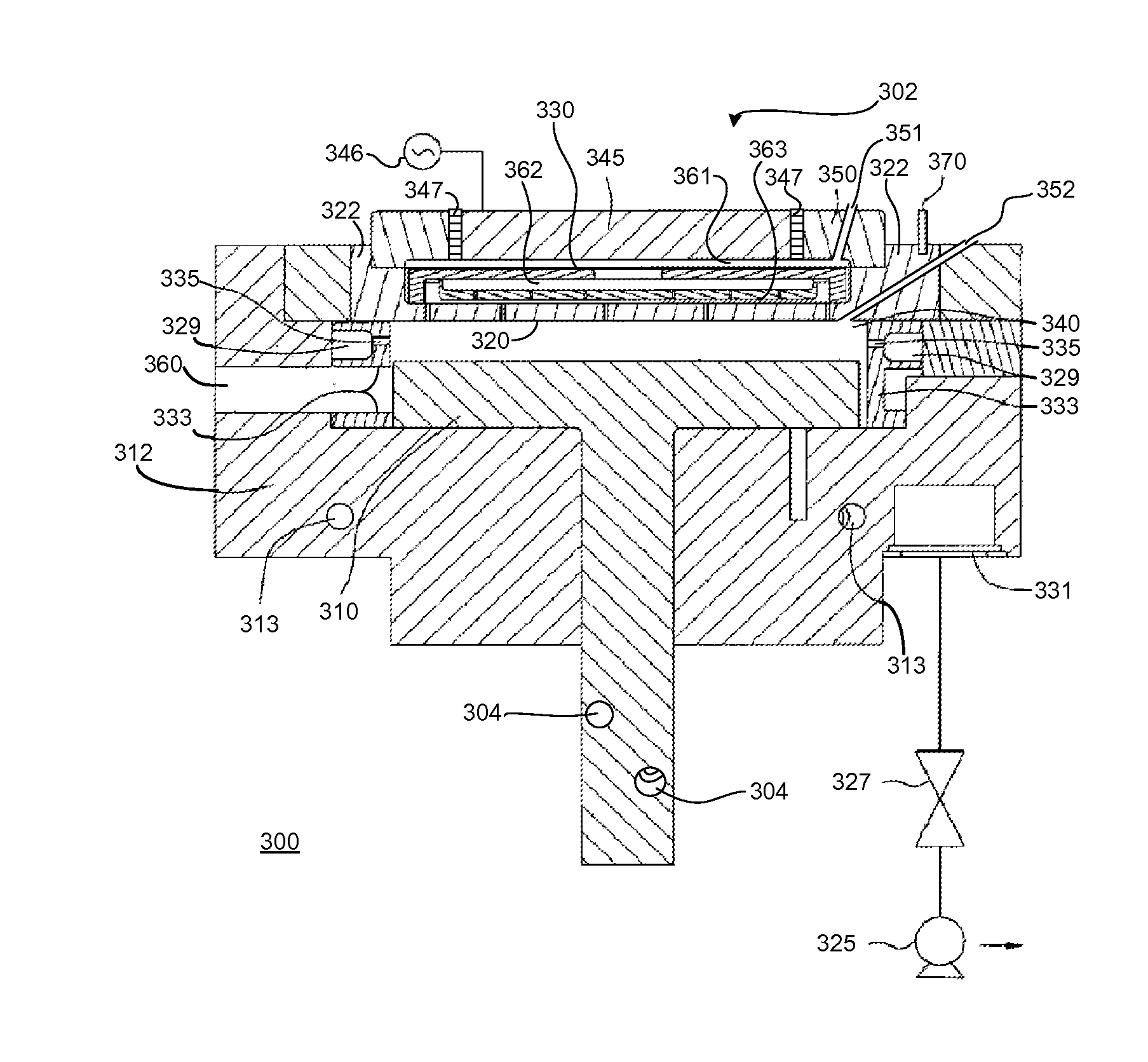

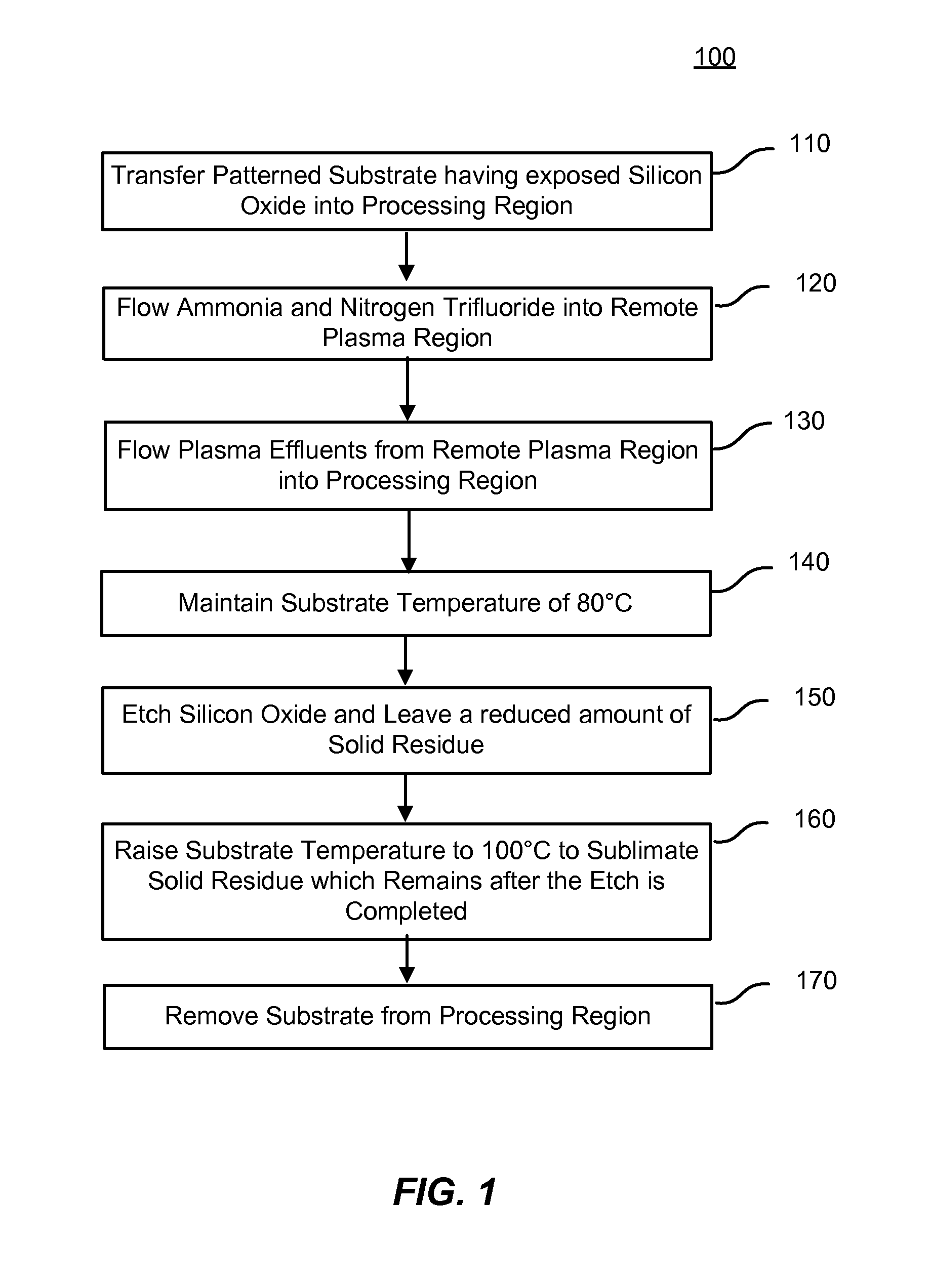

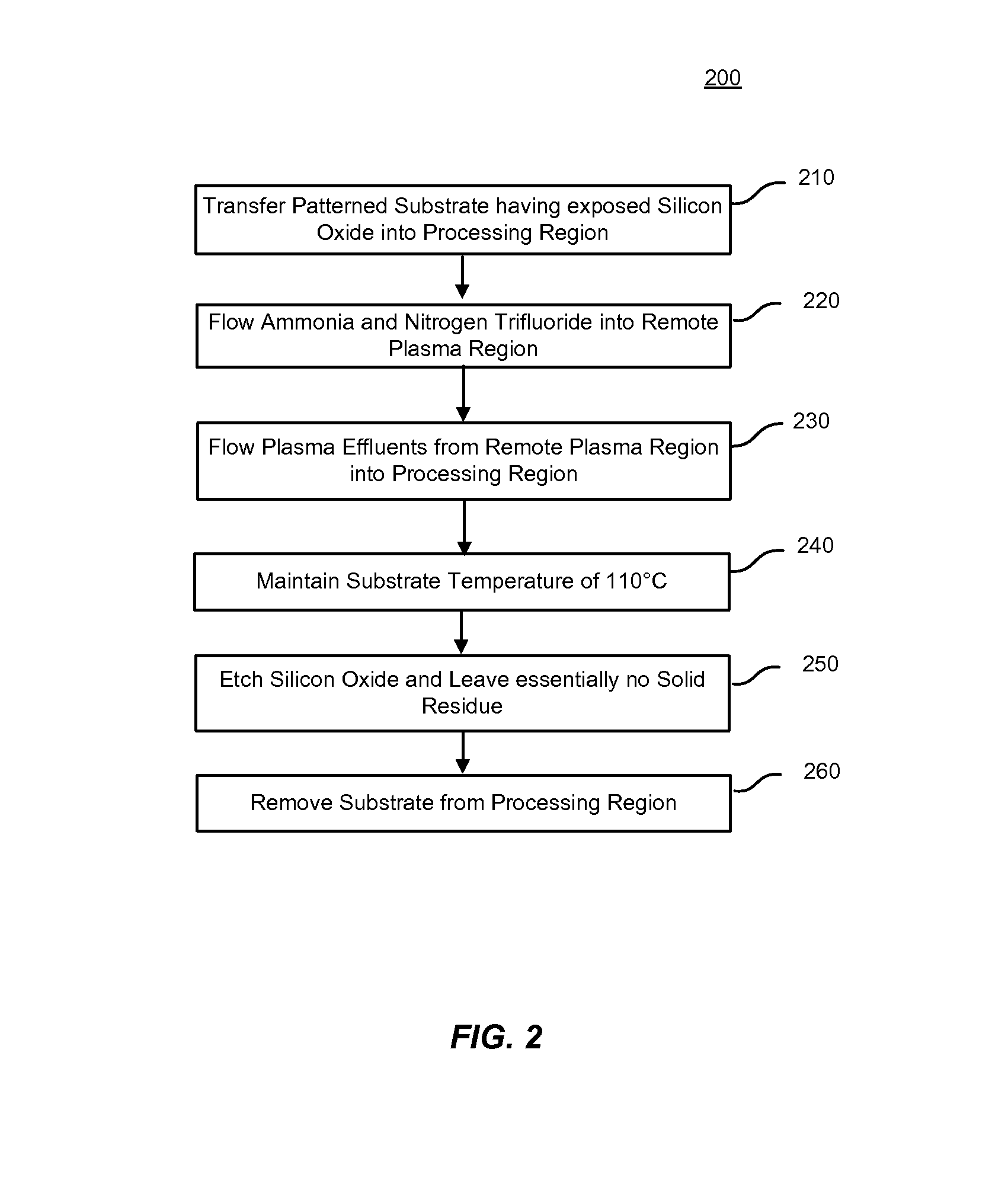

High-temperature selective dry etch having reduced post-etch solid residue

ActiveUS8475674B2Residue reductionHigh temperature of the dielectric filmsElectric discharge tubesDecorative surface effectsDielectricDry etching

Methods of dry etching silicon-containing dielectric films are described. The methods include maintaining a relatively high temperature of the dielectric films while etching in order to achieve reduced solid residue on the etched surface. Partially or completely avoiding the accumulation of solid residue increases the etch rate.

Owner:APPLIED MATERIALS INC

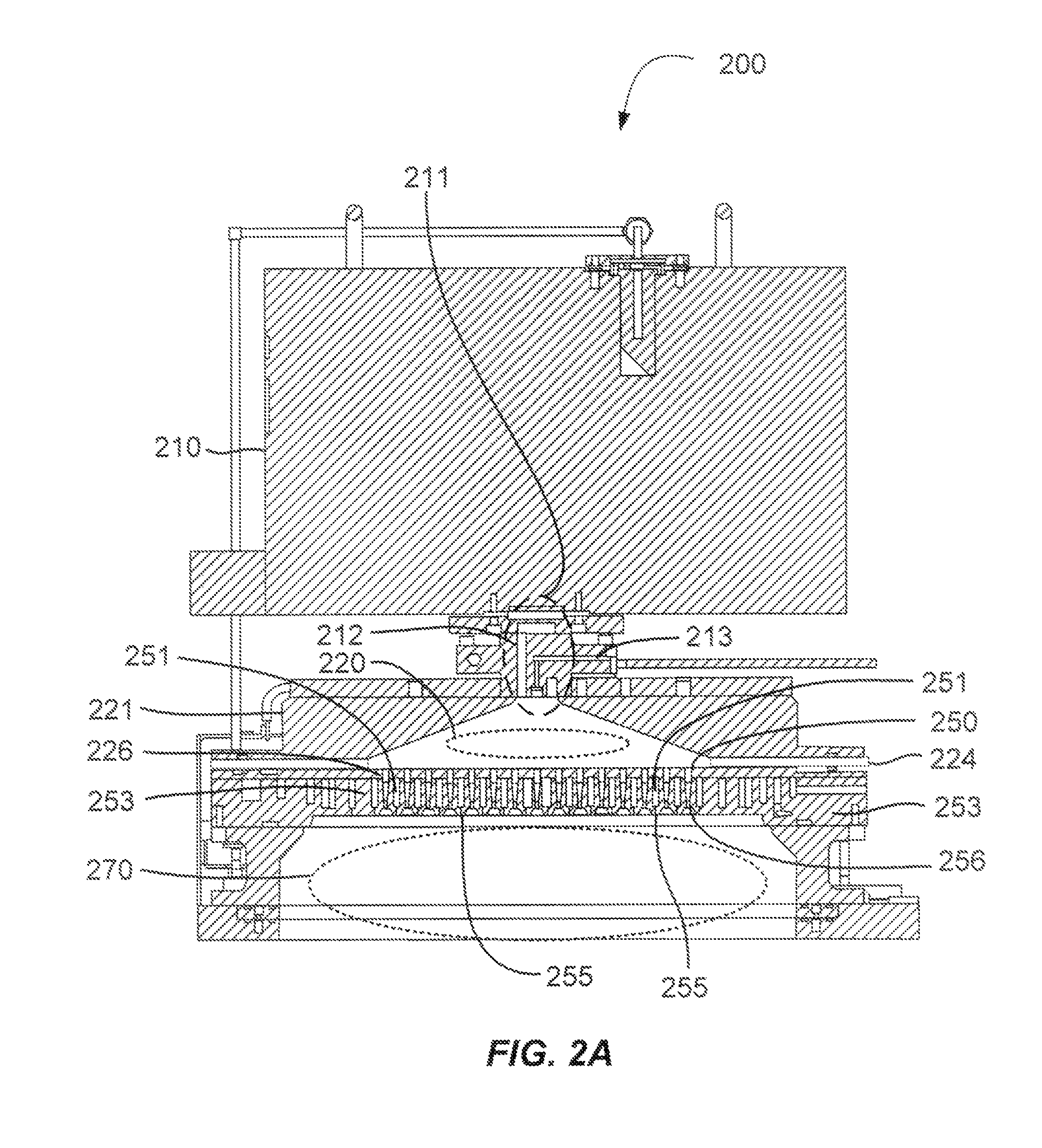

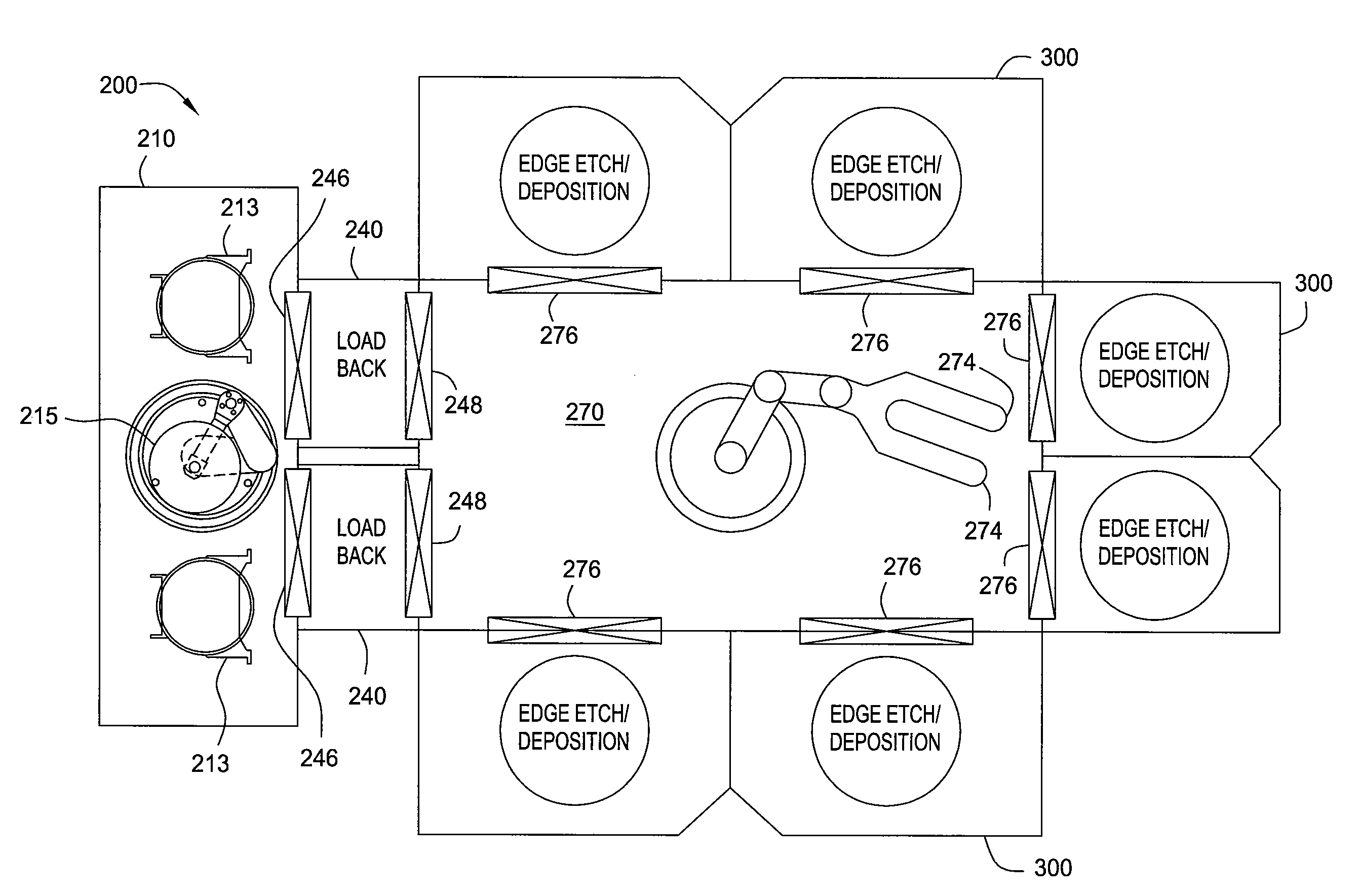

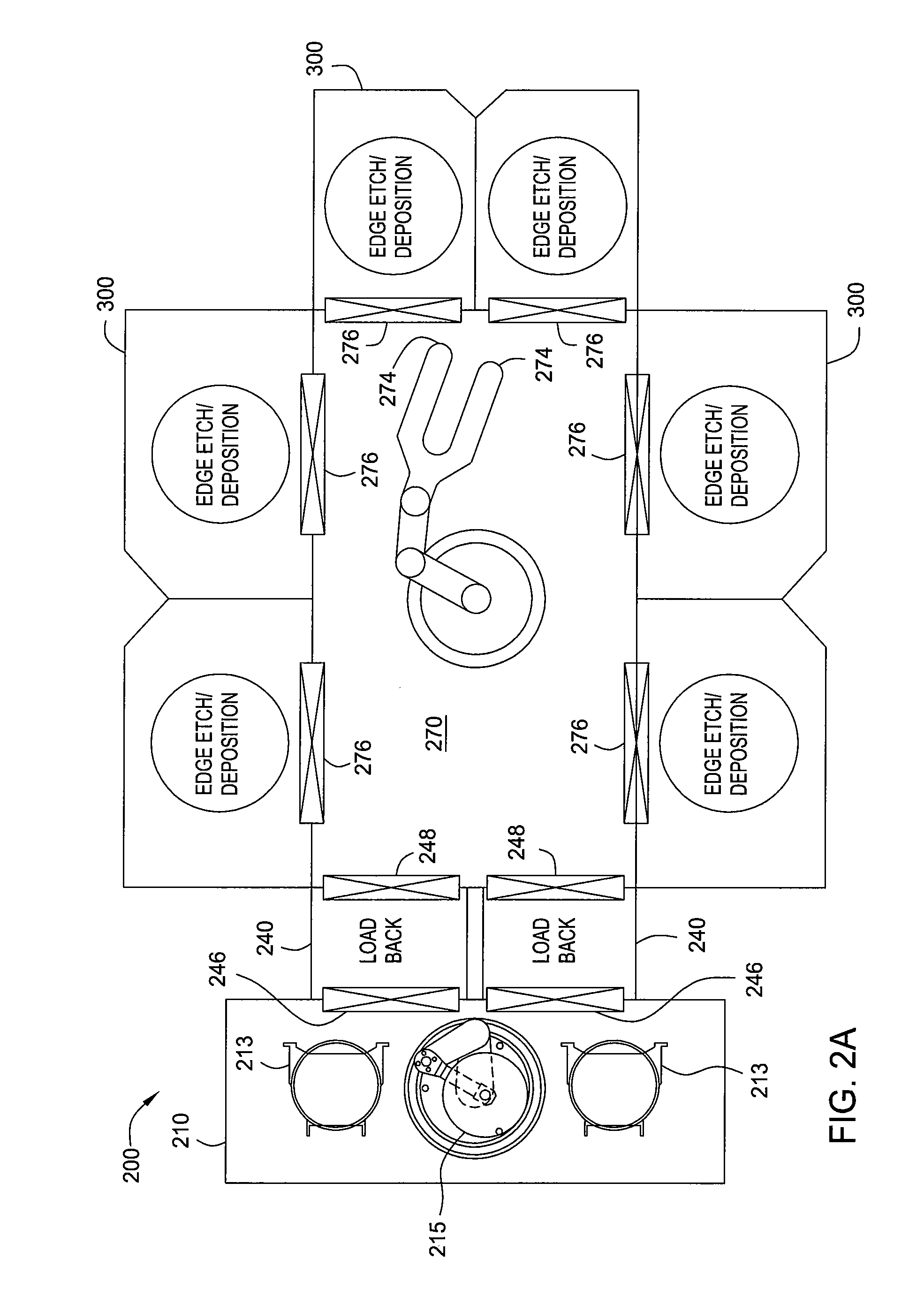

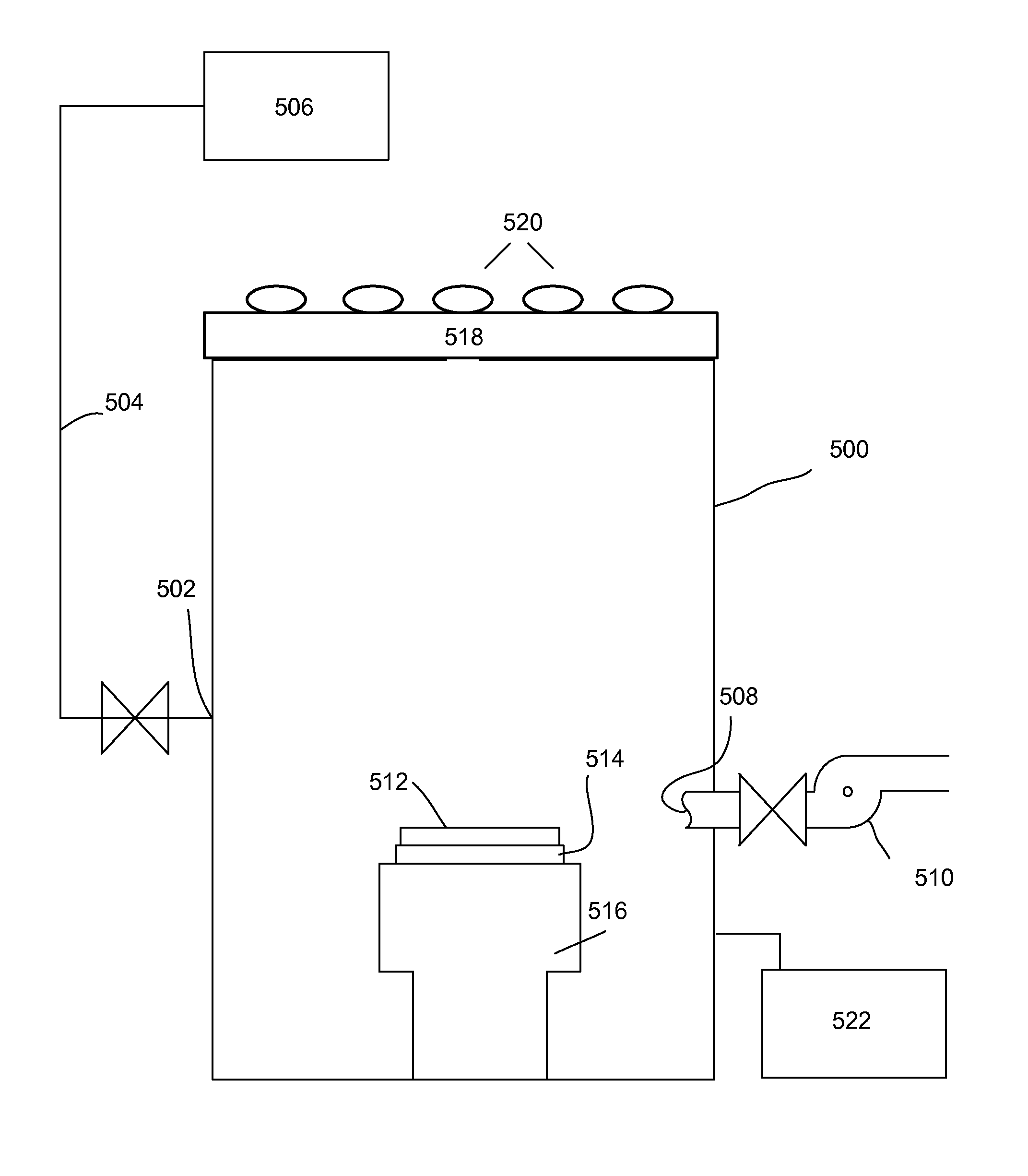

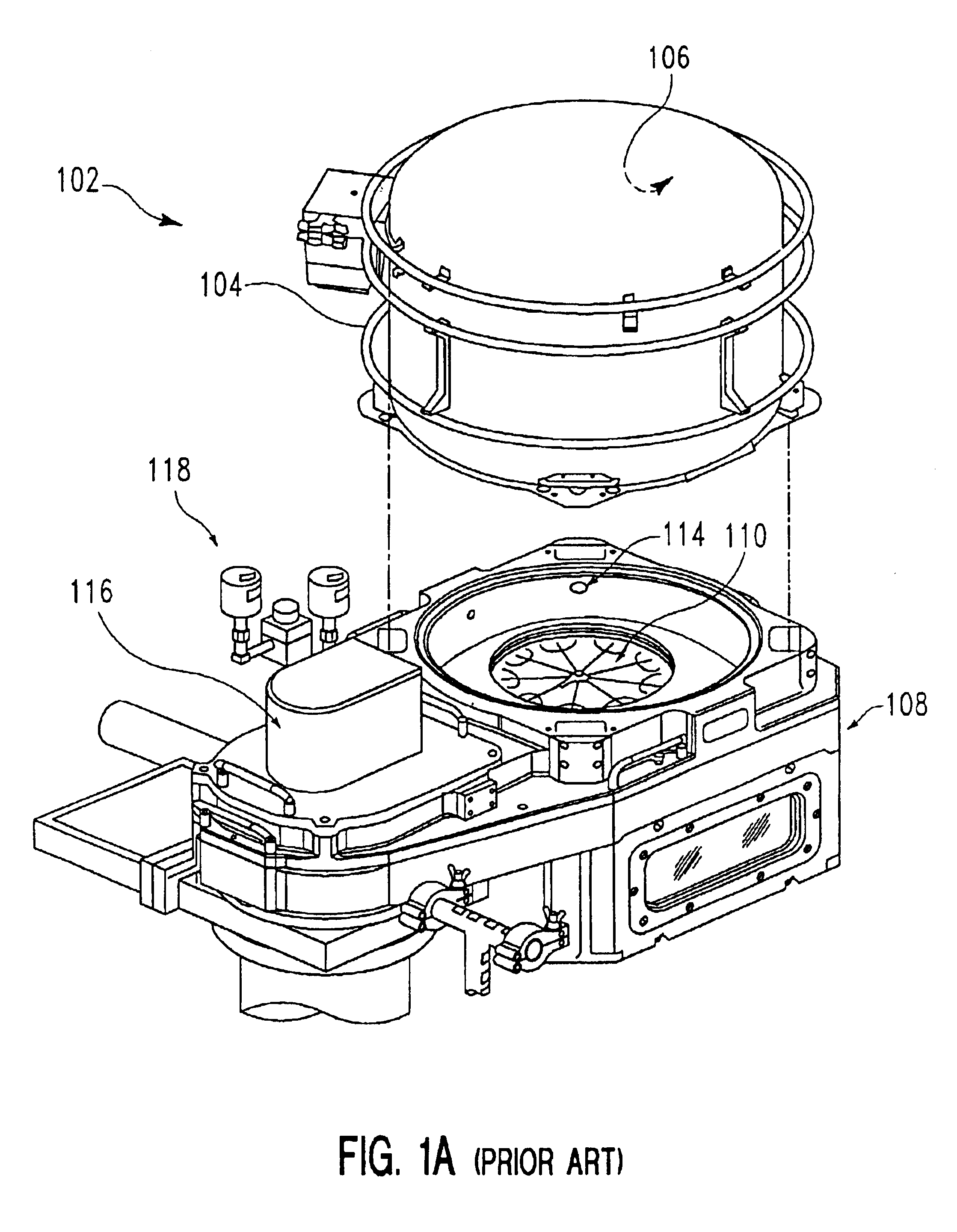

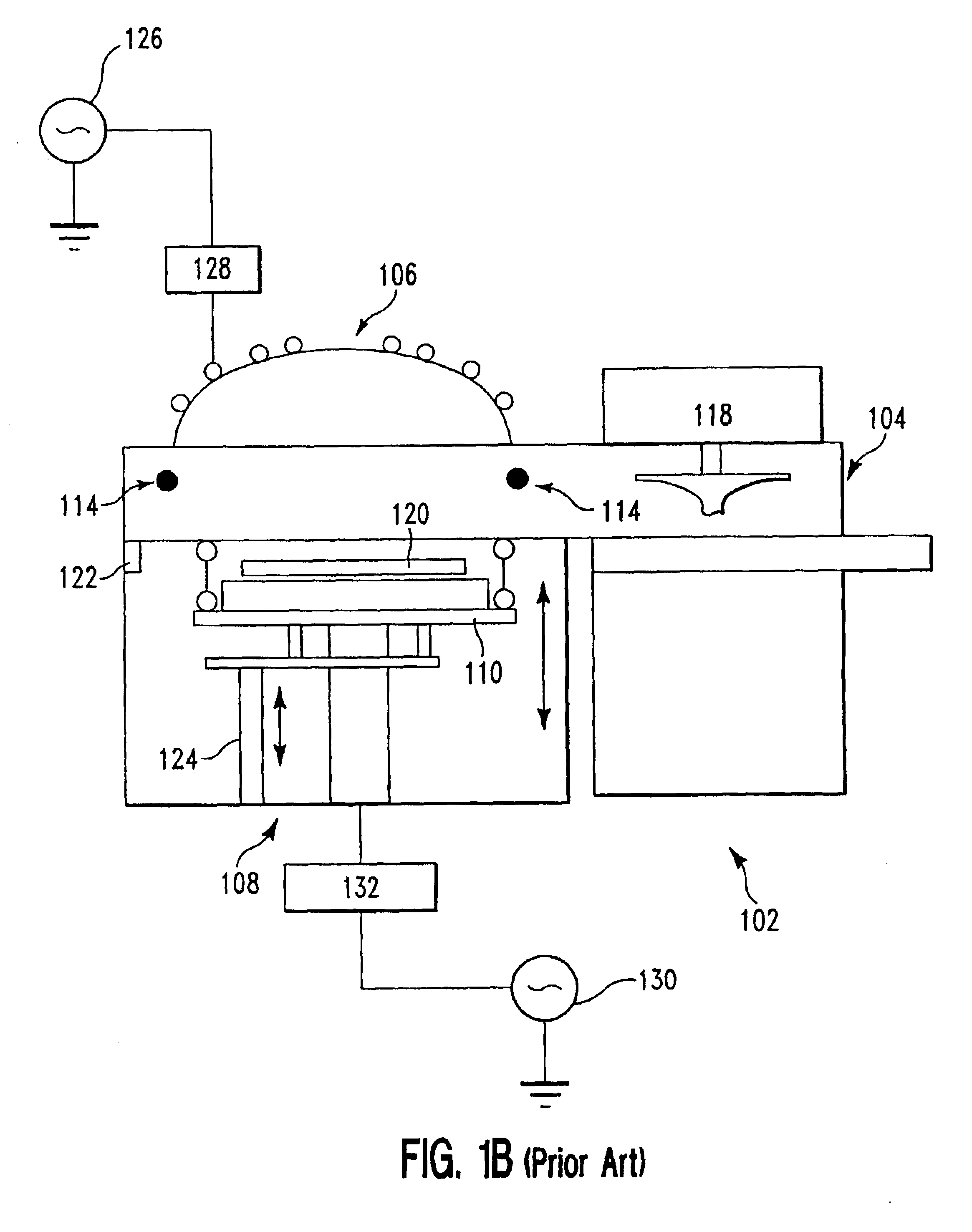

Systems for plasma enhanced chemical vapor deposition and bevel edge etching

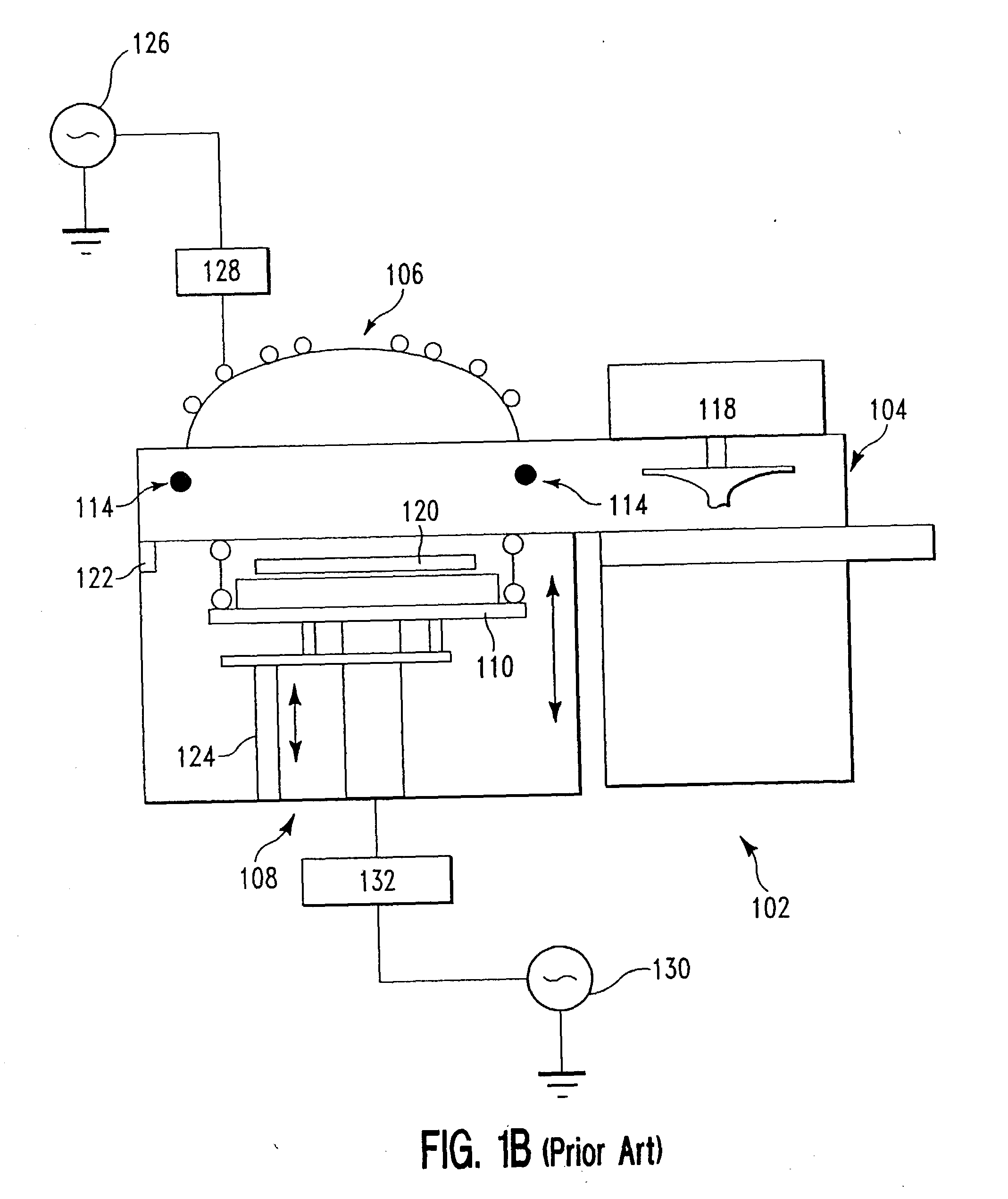

ActiveUS20090014127A1Electric discharge tubesSemiconductor/solid-state device manufacturingGas phaseProcess region

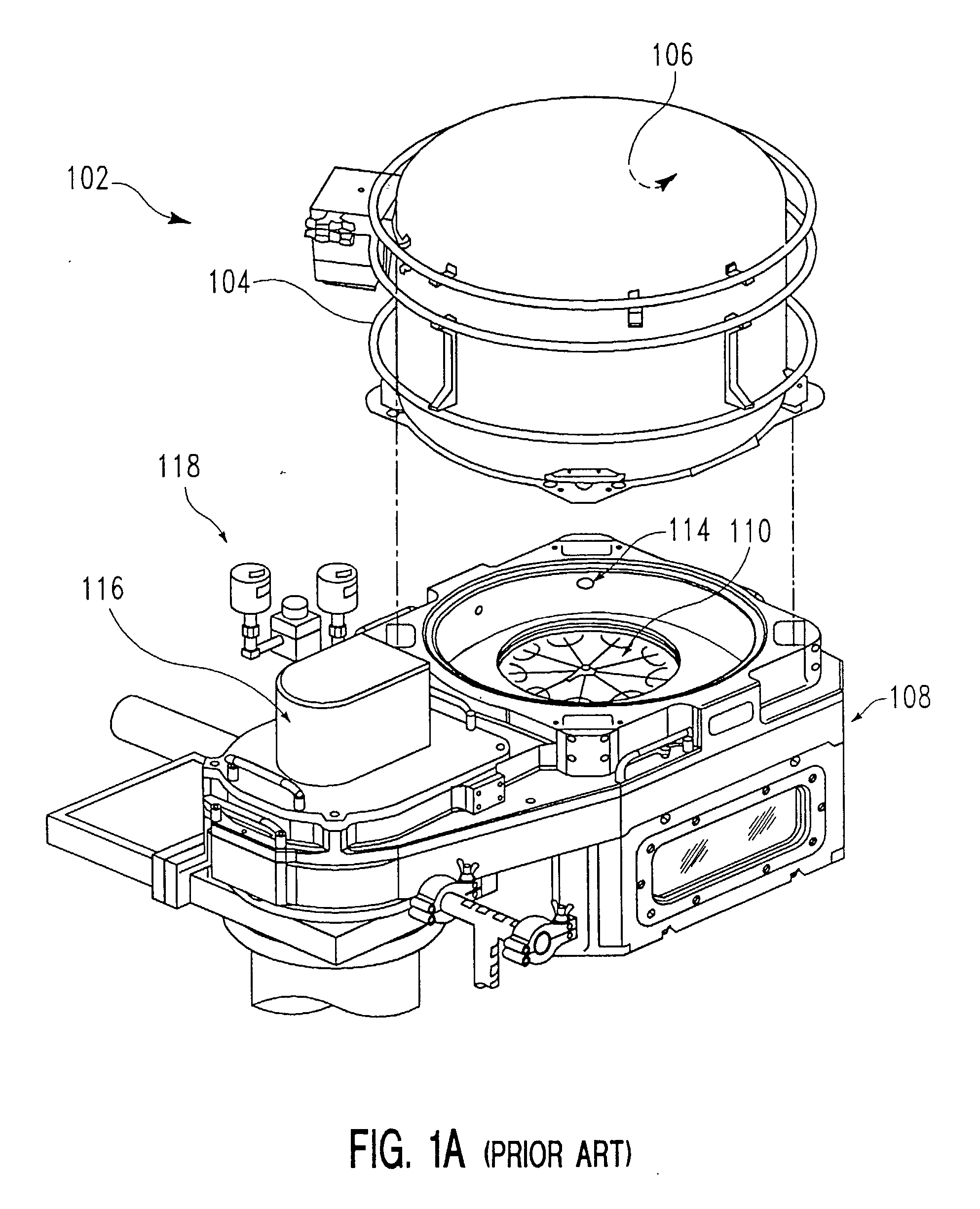

Embodiments described herein relate to a substrate processing system that integrates substrate edge processing capabilities. Illustrated examples of the processing system include, without limitations, a factory interface, a loadlock chamber, a transfer chamber, and one or more twin process chambers having two or more processing regions that are isolatable from each other and share a common gas supply and a common exhaust pump. The processing regions in each twin process chamber include separate gas distribution assemblies and RF power sources to provide plasma at selective regions on a substrate surface in each processing region. Each twin process chamber is thereby configured to allow multiple, isolated processes to be performed concurrently on at least two substrates in the processing regions.

Owner:APPLIED MATERIALS INC

Etching of metallic composite articles

A process for the etching of multiple layers of at least two different metals comprisies:forming a resist pattern over a first layer of metal, said resist pattern having a pattern of openings therein, applying a first etch solution onto said resist pattern so that at least some etch solution contacts exposed areas of the first layer of metal, etching away the majority of the depth of the first metal in exposed areas of metal in the first layer of metal, applying a second etch solution onto the resist pattern the second etch solution having a rate of etch towards the first metal as compared to the first etch solution that is at least 20% less than the millimeter / minute rate of etch of the first etch solution at the same etch solution temperature, removing the second etch solution from said resist pattern after at least the first metal layer has been etched sufficiently to expose areas of a second metal layer underlying the first metal layer by forming an etched first metal layer, and applying a third etch solution to said etched first metal layer, the third etch solution having a faster rate of etch towards the second metal than towards the first metal to etch into said second metal layer without destroying the etched first metal layer.

Owner:BMC INDS

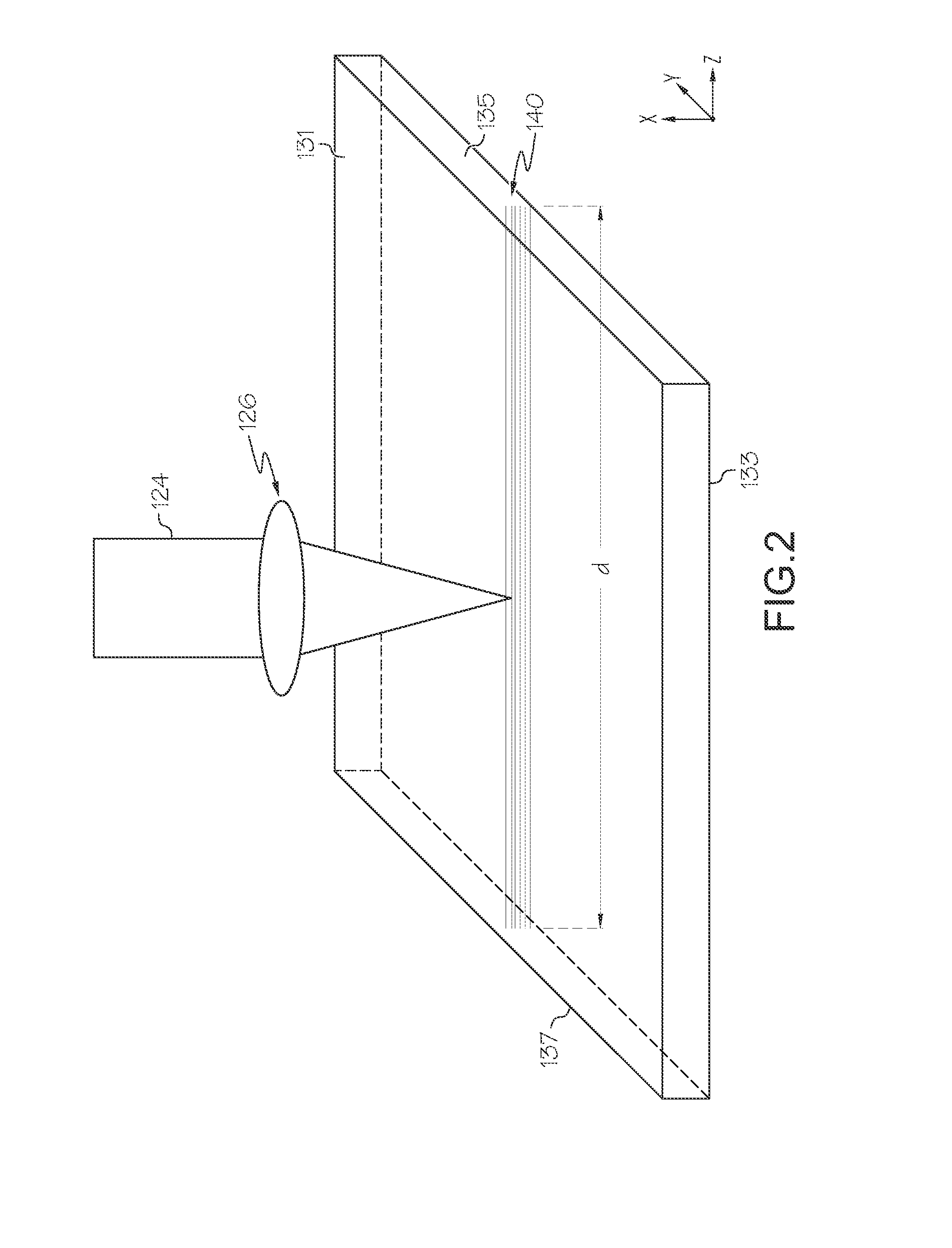

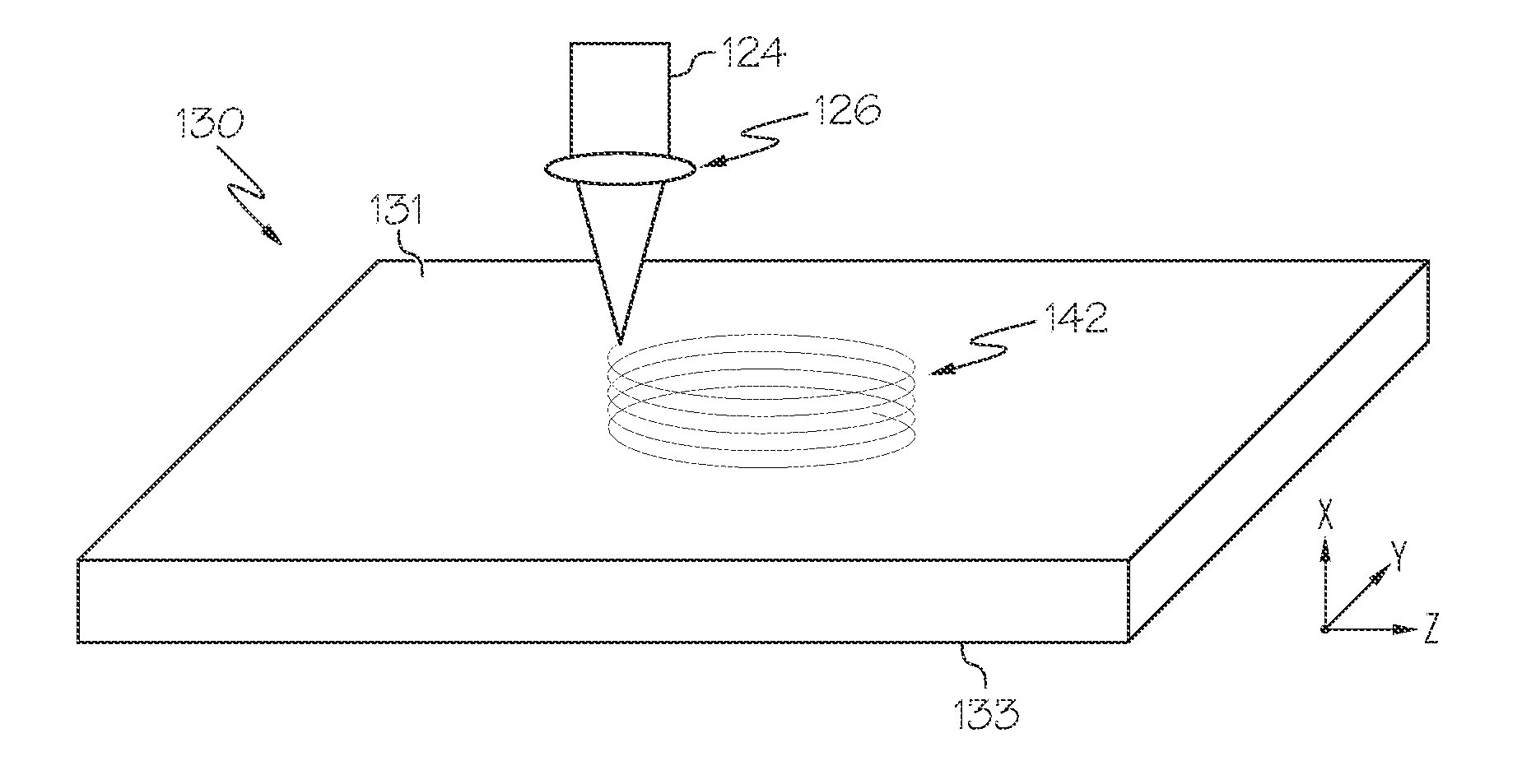

Methods of Fabricating Glass Articles by Laser Damage and Etching

Methods of forming a glass article are disclosed. In one embodiment, a method of forming a glass article includes translating a pulsed laser beam on a glass substrate sheet to form a laser damage region between a first surface and a second surface of the glass substrate sheet. The method further includes applying an etchant solution to the glass substrate sheet to remove a portion of the glass substrate sheet about the laser damage region. The method may further include strengthening the glass substrate sheet by an ion-exchange strengthening process, and coating the glass substrate sheet with an acid-resistant coating. Also disclosed are methods where the laser damage region has an initial geometry that changes to a desired geometry following the reforming of the glass substrate sheet such that the initial geometry of the laser damage region compensates for the bending of the glass substrate sheet.

Owner:CORNING INC

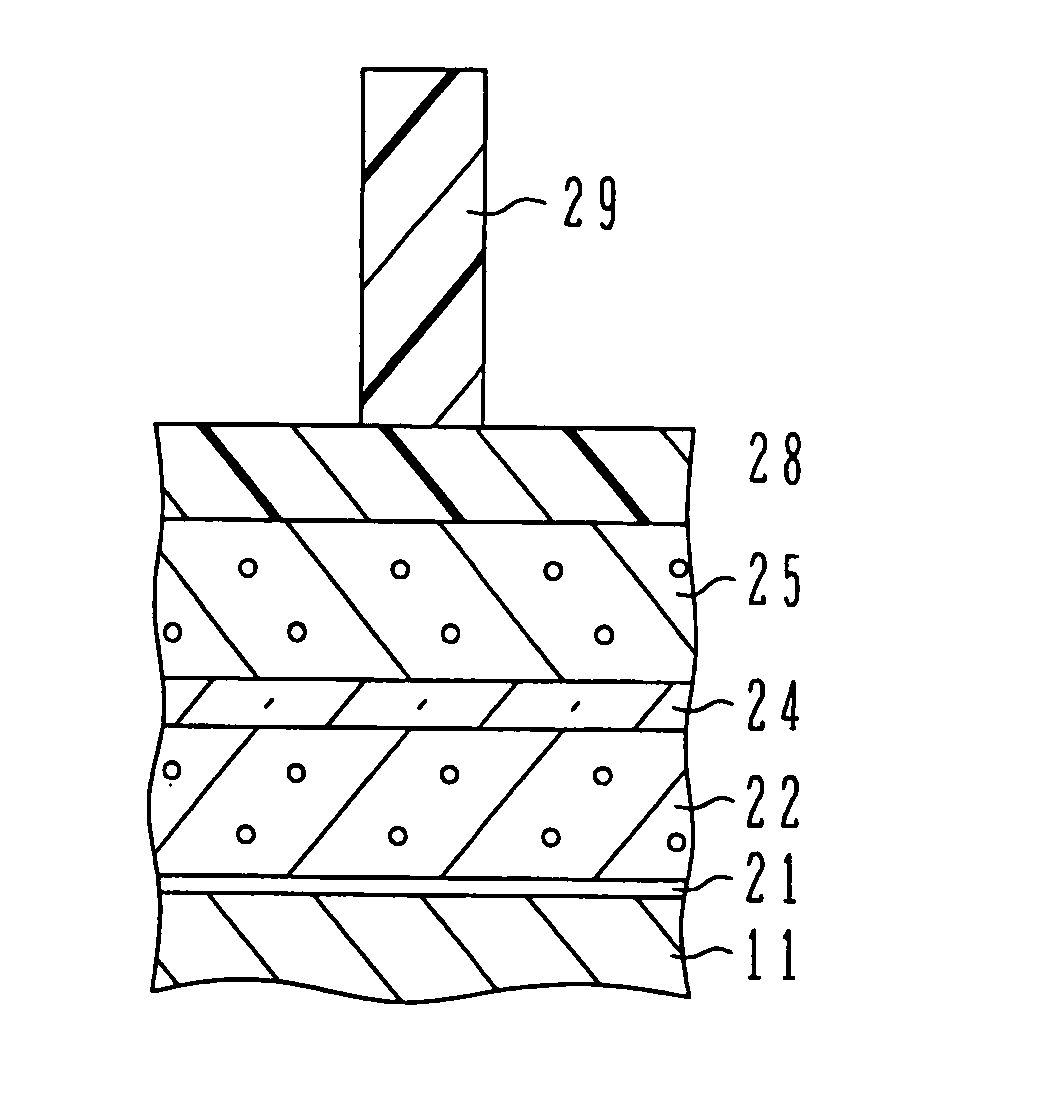

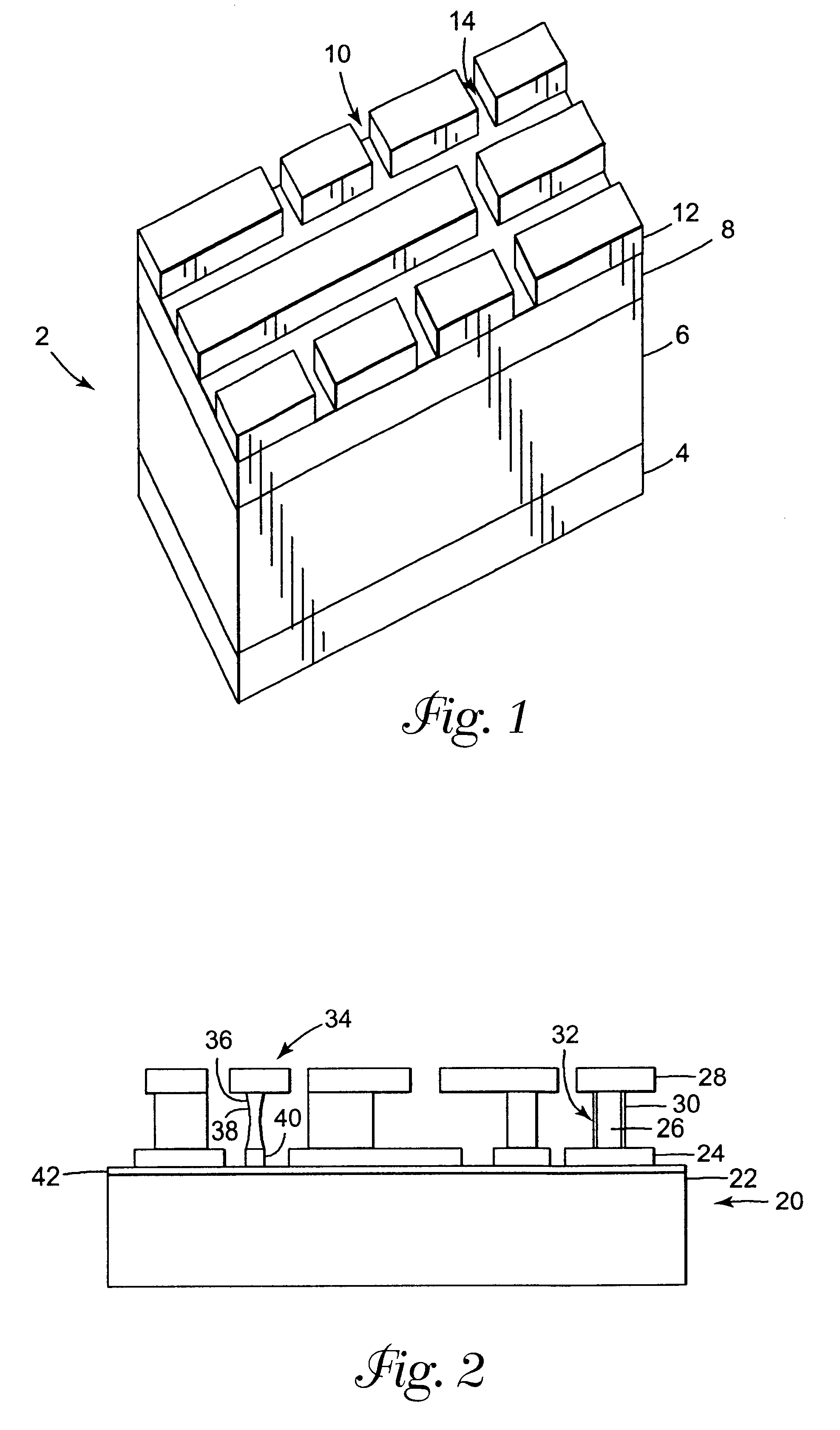

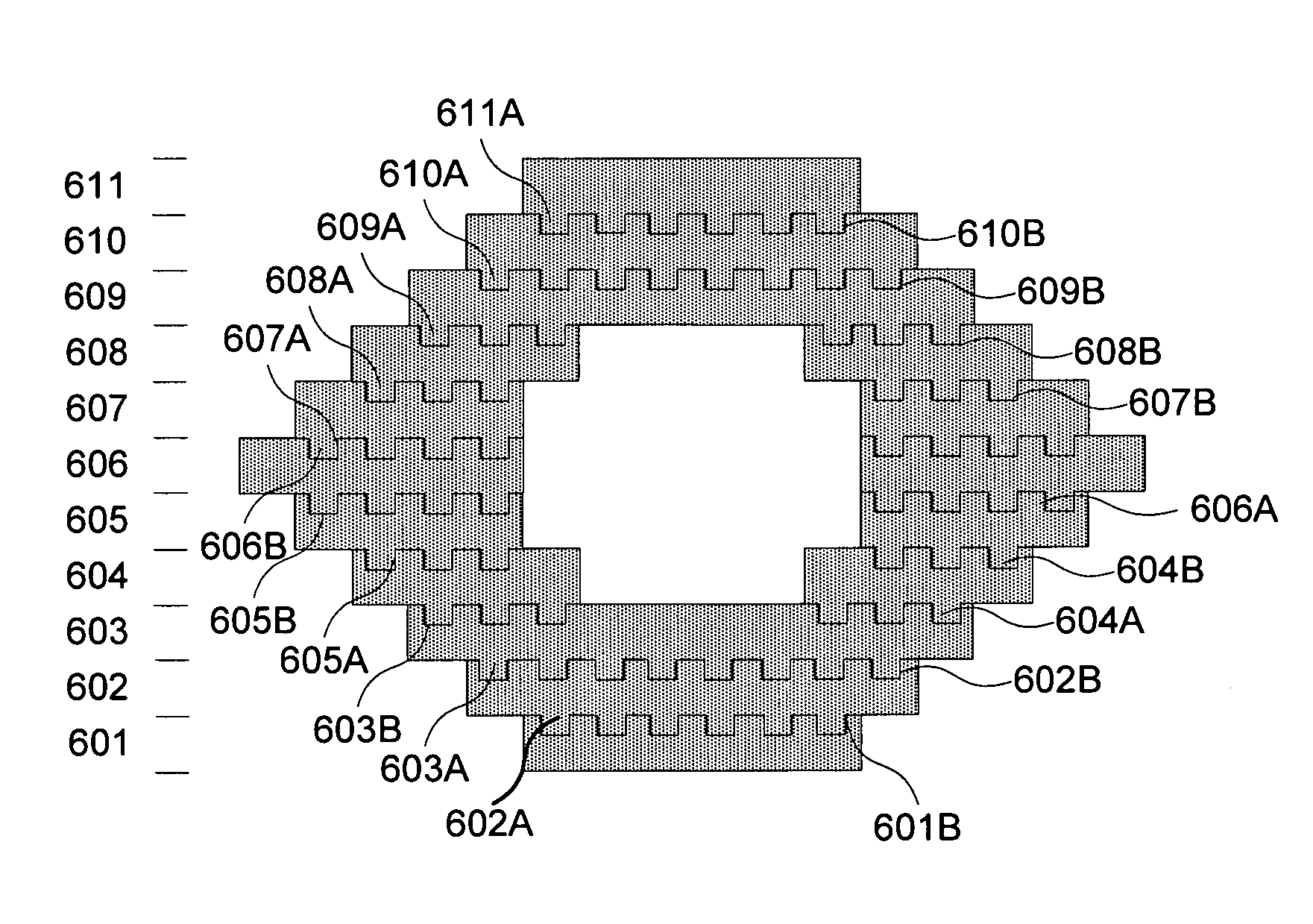

Methods of and apparatus for electrochemically fabricating structures via interlaced layers or via selective etching and filling of voids

ActiveUS7252861B2Advanced manufacturing technologyImprove propertiesAcceleration measurement using interia forcesPretreated surfacesOrder of operationsEngineering

Multi-layer structures are electrochemically fabricated by depositing a first material, selectively etching the first material (e.g. via a mask), depositing a second material to fill in the voids created by the etching, and then planarizing the depositions so as to bound the layer being created and thereafter adding additional layers to previously formed layers. The first and second depositions may be of the blanket or selective type. The repetition of the formation process for forming successive layers may be repeated with or without variations (e.g. variations in: patterns; numbers or existence of or parameters associated with depositions, etchings, and or planarization operations; the order of operations, or the materials deposited). Other embodiments form multi-layer structures using operations that interlace material deposited in association with some layers with material deposited in association with other layers.

Owner:MICROFAB

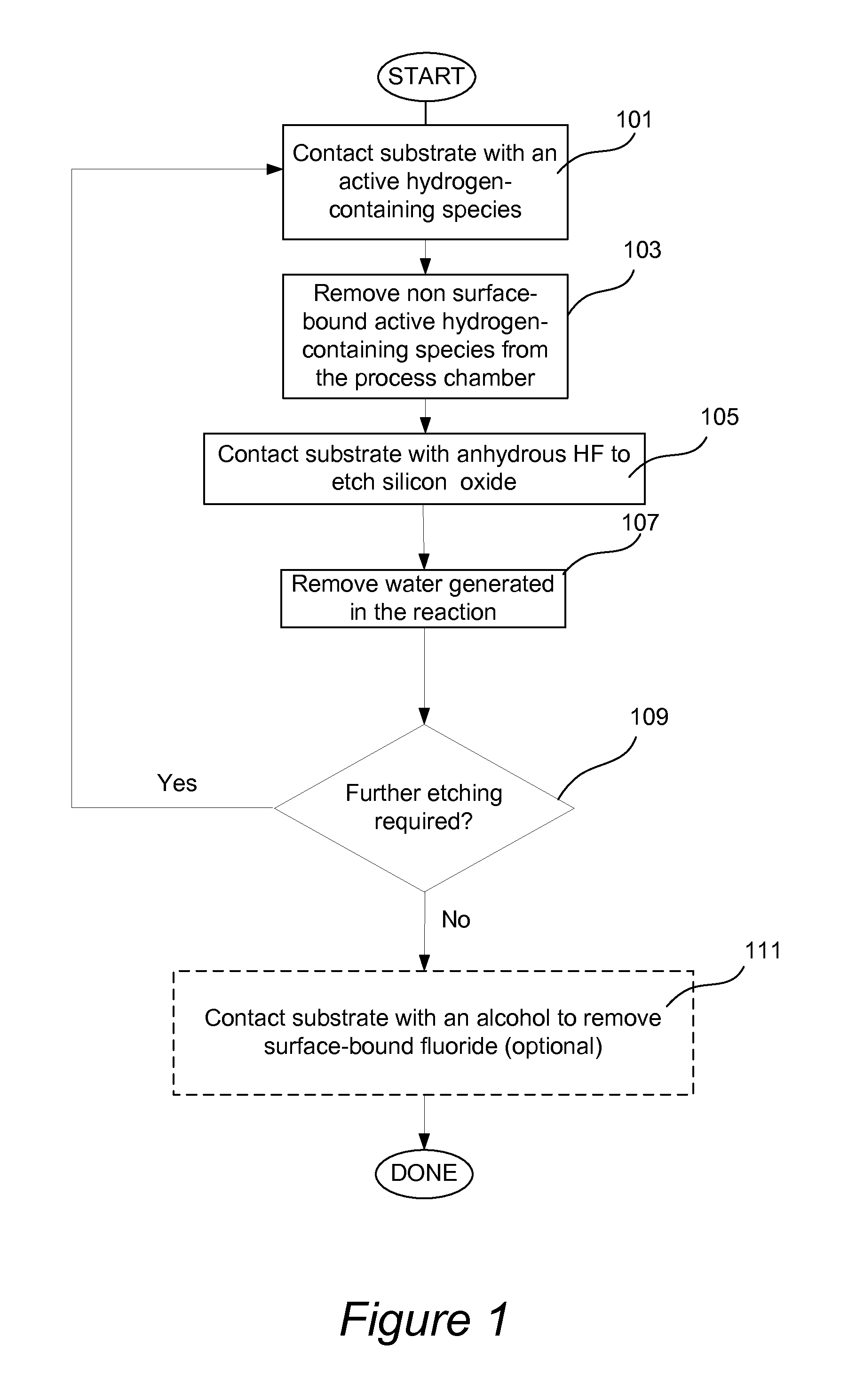

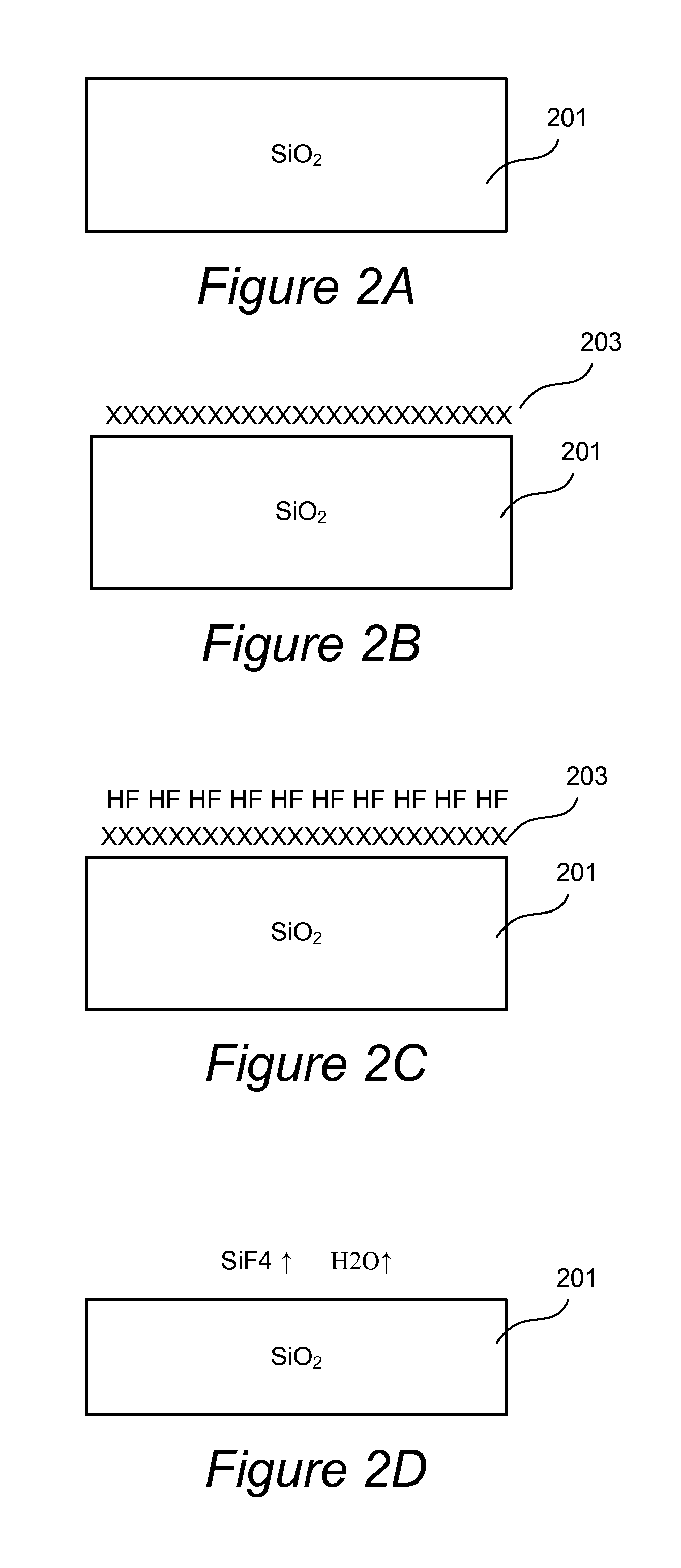

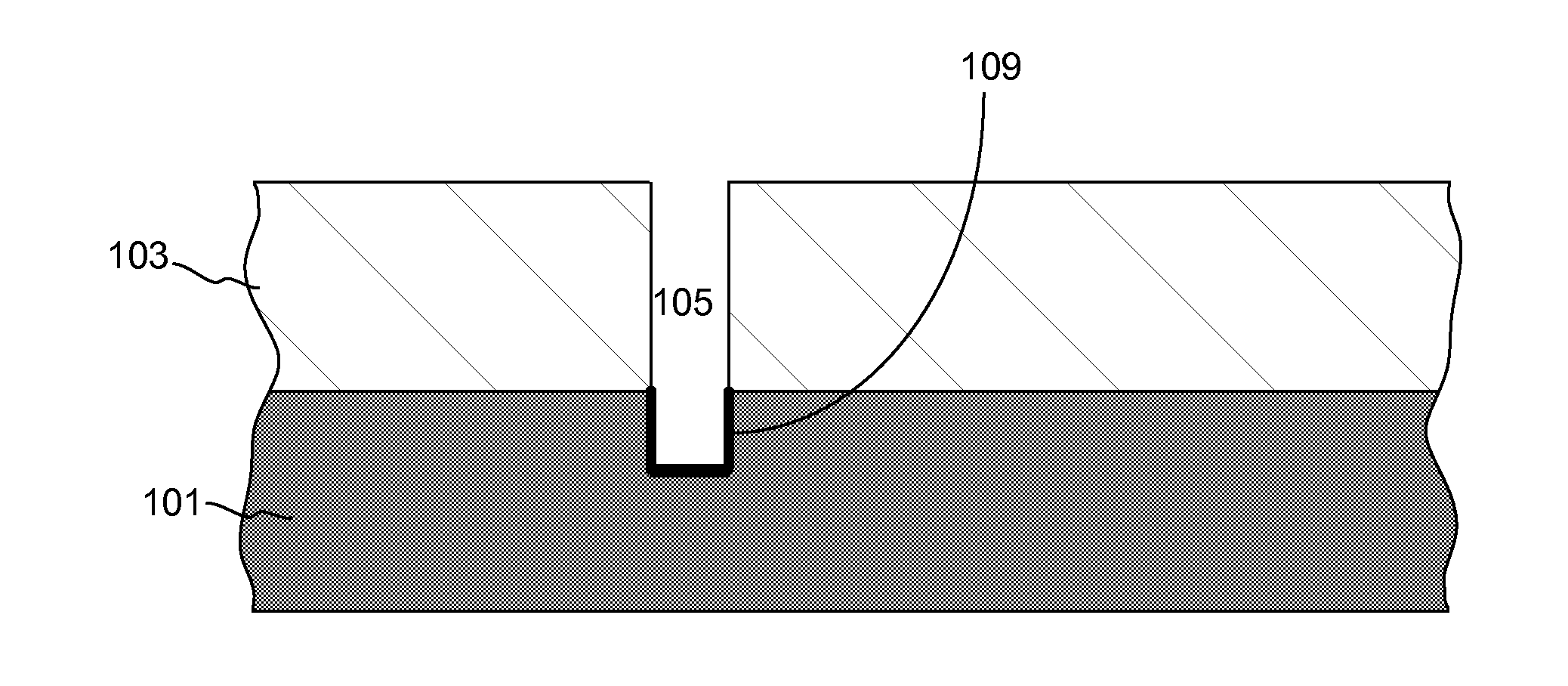

Isotropic atomic layer etch for silicon and germanium oxides

ActiveUS9431268B2Rapid and controlled changeElectric discharge tubesSemiconductor/solid-state device manufacturingAlcoholHydrogen

Methods for controlled isotropic etching of layers of silicon oxide and germanium oxide with atomic scale fidelity are provided. The methods make use of a reaction of anhydrous HF with an activated surface of an oxide, with an emphasis on removal of water generated in the reaction. In certain embodiments the oxide surface is first modified by adsorbing an OH-containing species (e.g., an alcohol) or by forming OH bonds using a hydrogen-containing plasma. The activated oxide is then etched by a separately introduced anhydrous HF, while the water generated in the reaction is removed from the surface of the substrate as the reaction proceeds, or at any time during or after the reaction. These methods may be used in interconnect pre-clean applications, gate dielectric processing, manufacturing of memory devices, or any other applications where accurate removal of one or multiple atomic layers of material is desired.

Owner:LAM RES CORP

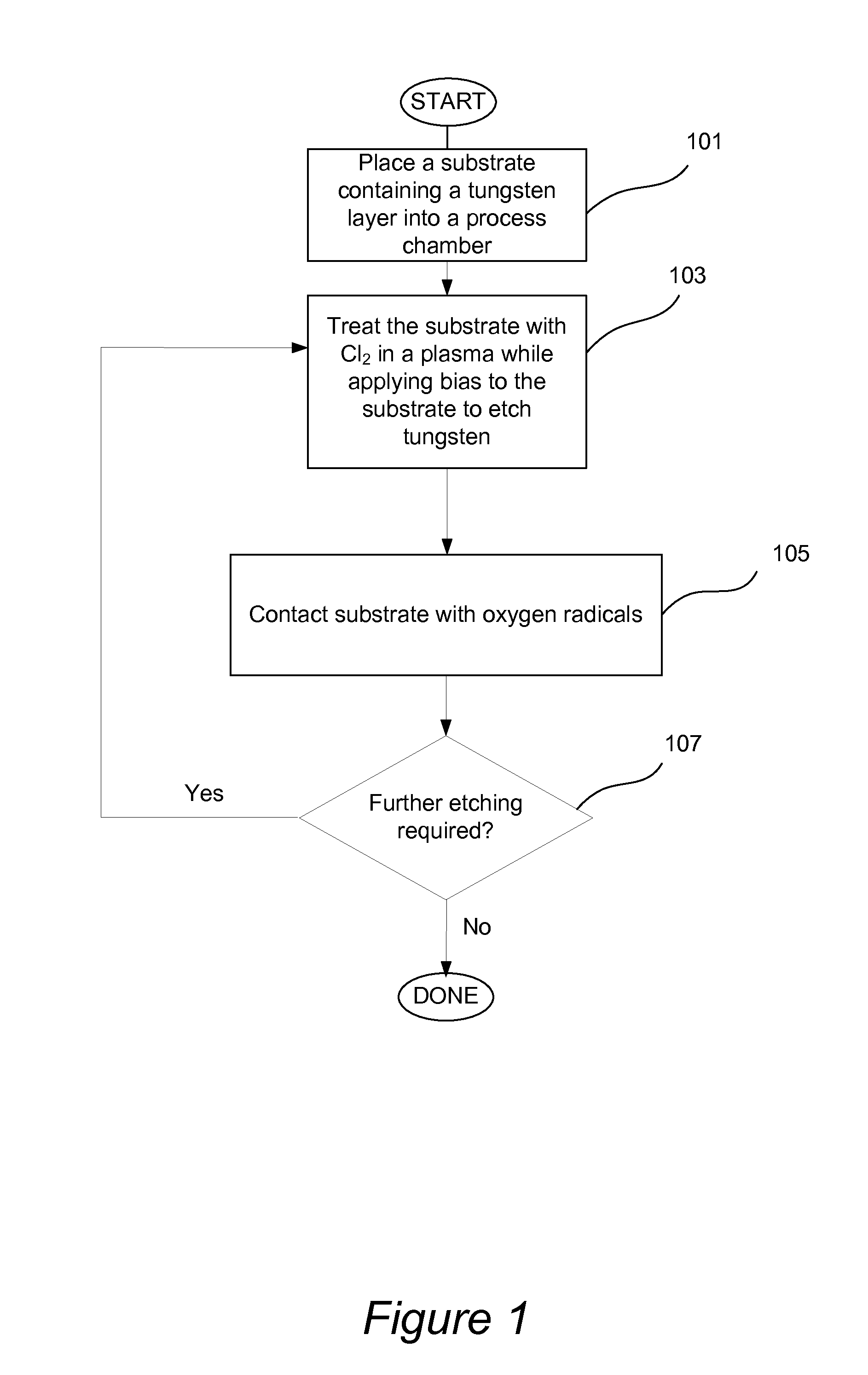

Method and apparatus for anisotropic tungsten etching

ActiveUS20160196985A1Electric discharge tubesSemiconductor/solid-state device manufacturingSilicon oxideOxygen

Methods for anisotropically etching a tungsten-containing material (such as doped or undoped tungsten metal) include cyclic treatment of tungsten surface with Cl2 plasma and with oxygen-containing radicals. Treatment with chlorine plasma is performed while the substrate is electrically biased resulting in predominant etching of horizontal surfaces on the substrate. Treatment with oxygen-containing radicals passivates the surface of the substrate to etching, and protects the vertical surfaces of the substrate, such as sidewalls of recessed features, from etching. Treatment with Cl2 plasma and with oxygen-containing radicals can be repeated in order to remove a desired amount of material. Anisotropic etching can be performed selectively in a presence of dielectric materials such as silicon oxide, silicon nitride, and silicon oxynitride.

Owner:LAM RES CORP

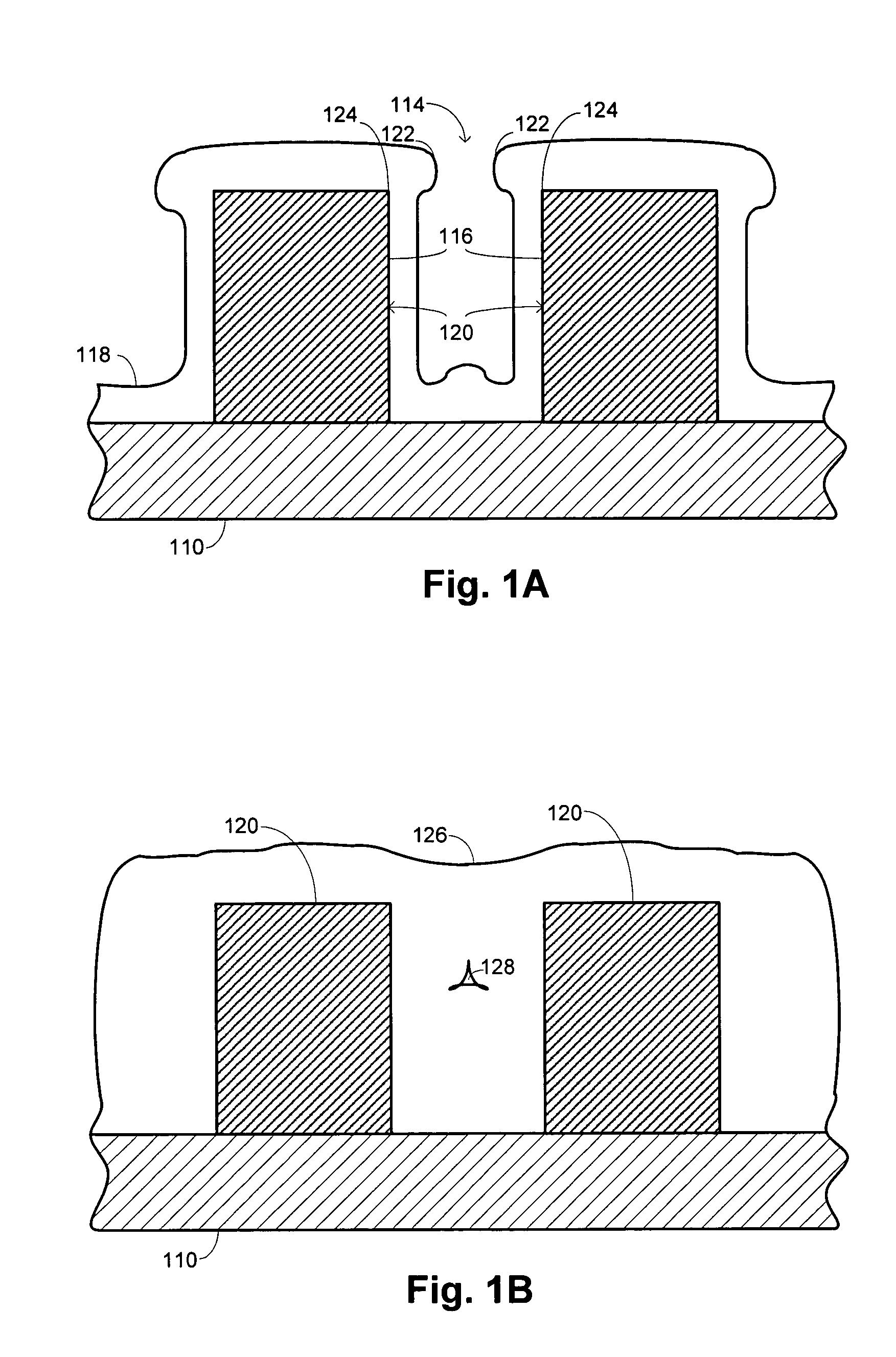

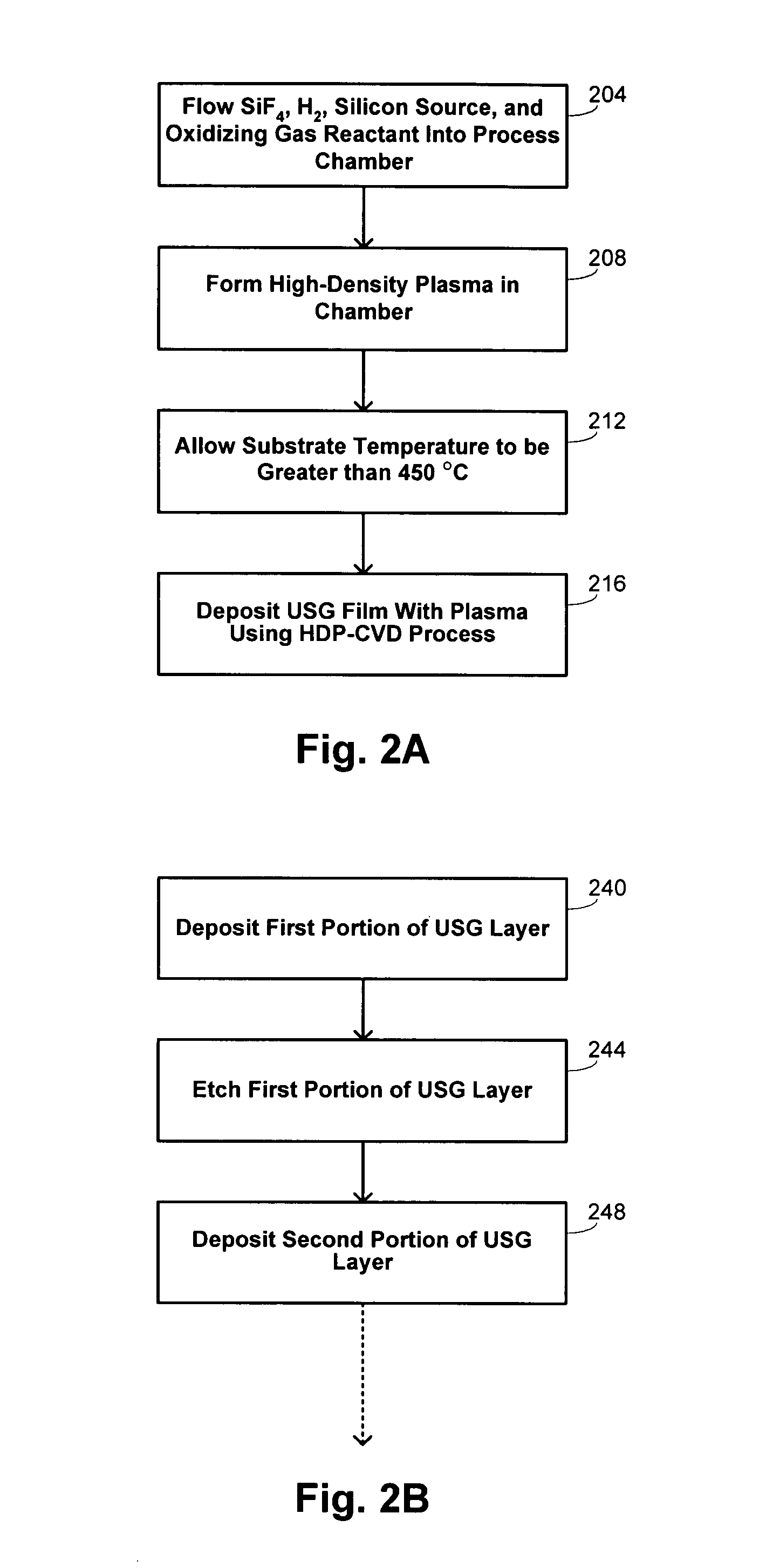

In-situ-etch-assisted HDP deposition using SiF4 and hydrogen

ActiveUS20050048801A1Good gapfill characteristicReduce fluorine concentrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenIon density

A process is provided for depositing an undoped silicon oxide film on a substrate disposed in a process chamber. A process gas that includes SiF4, H2, a silicon source, and an oxidizing gas reactant is flowed into the process chamber. A plasma having an ion density of at least 1011 ions / cm3 is formed from the process gas. The undoped silicon oxide film is deposited over the substrate with the plasma using a process that has simultaneous deposition and sputtering components. A temperature of the substrate during such depositing is greater than 450° C.

Owner:APPLIED MATERIALS INC

Circuit manufacturing using etched tri-metal media

InactiveUS6365057B1Printed circuit aspectsSemiconductor/solid-state device manufacturingElectrical connectionCopper

A process for the formation of an article having multiple electrical circuits comprises:providing a first sub-element comprising in sequence a first metal layer of copper in electrical contact with a second metal layer of aluminum in electrical contact with a third metal layer of copper;etching an electrical circuit design in the first metal layer and in a separate etch step, etching away at least 10%, but less than 100% of the second metal layer to provide electrical connections between the first metal layer and the third metal layer;etching an electrical circuit design into the third metal layer;adhering an etched surface comprising the circuit design of the first or third metal layer to a first surface of a support layer to form a circuit board.The process may etch the first and third metal layers simultaneously or sequentially. After adhering an etched surface comprising the circuit design of the first or third metal layer to a support layer to form a circuit board, an additional step may be performed, which additional step is selected from the group consisting of;a) adhering an etched surface of a second tri-metal subelement to a second surface of the support layer andb) adhering a second support layer to said third or first metal layer, respectively, and adhering an etched surface of a second tri-metal subelement to the second support layer.

Owner:BMC INDS

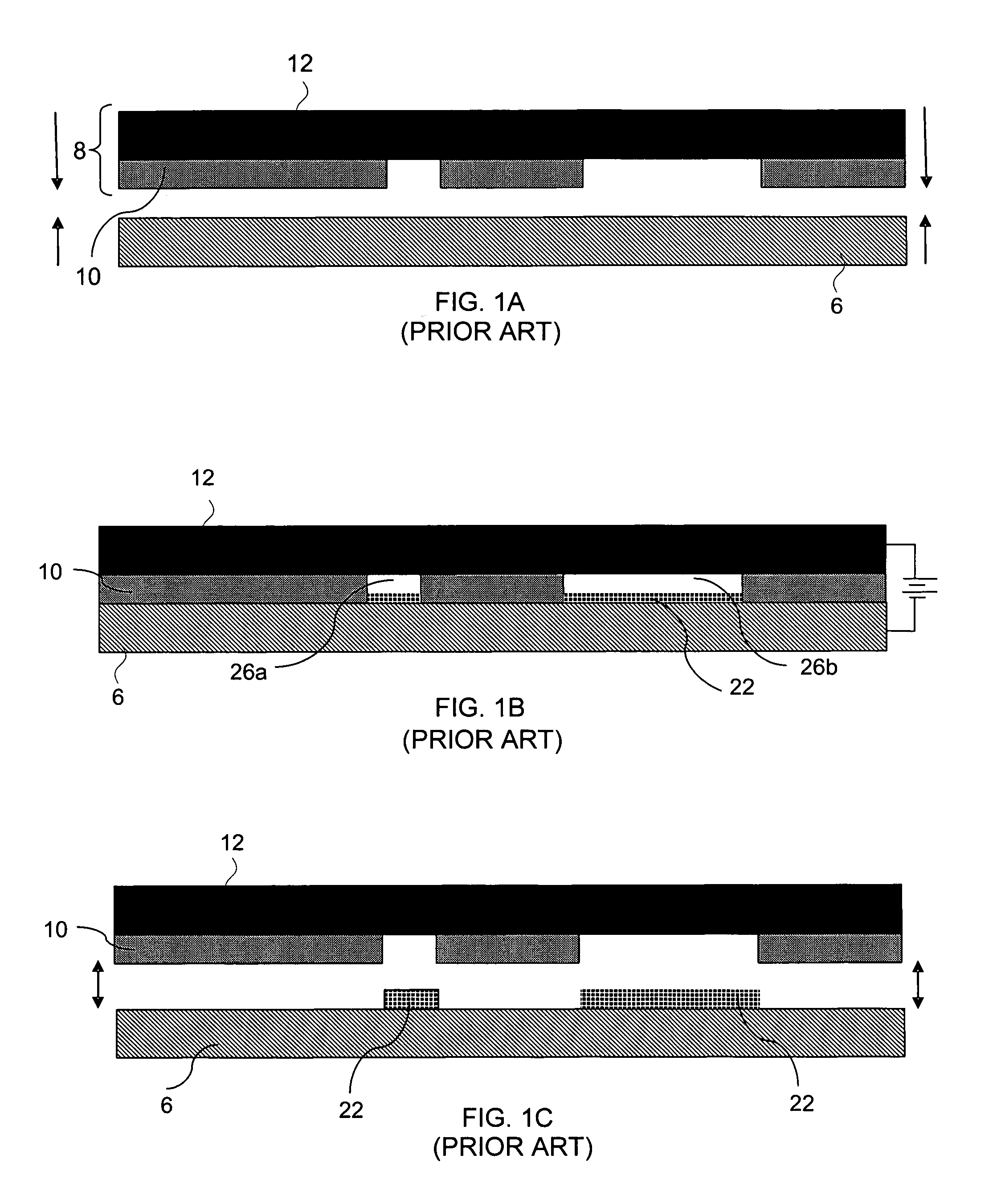

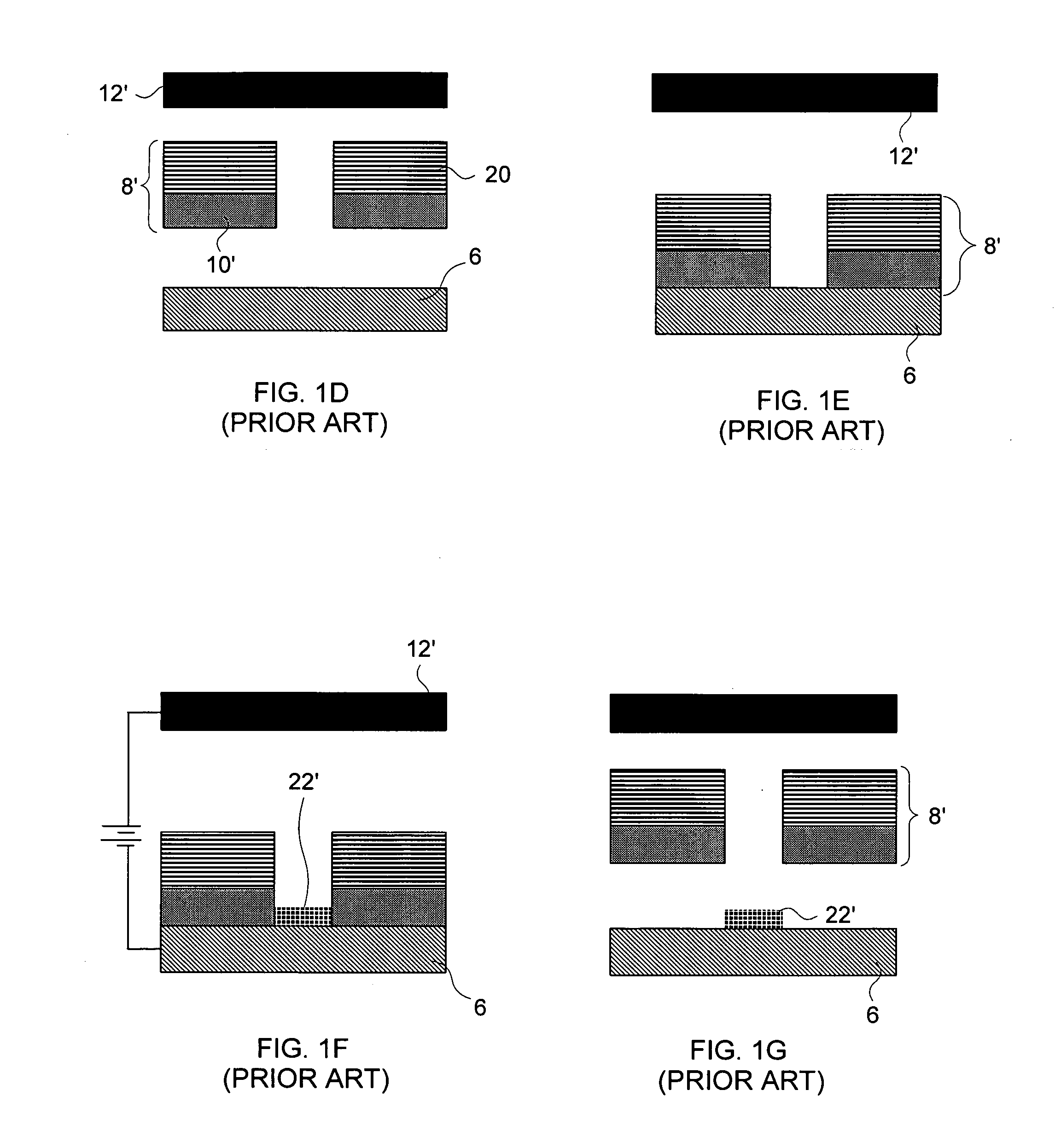

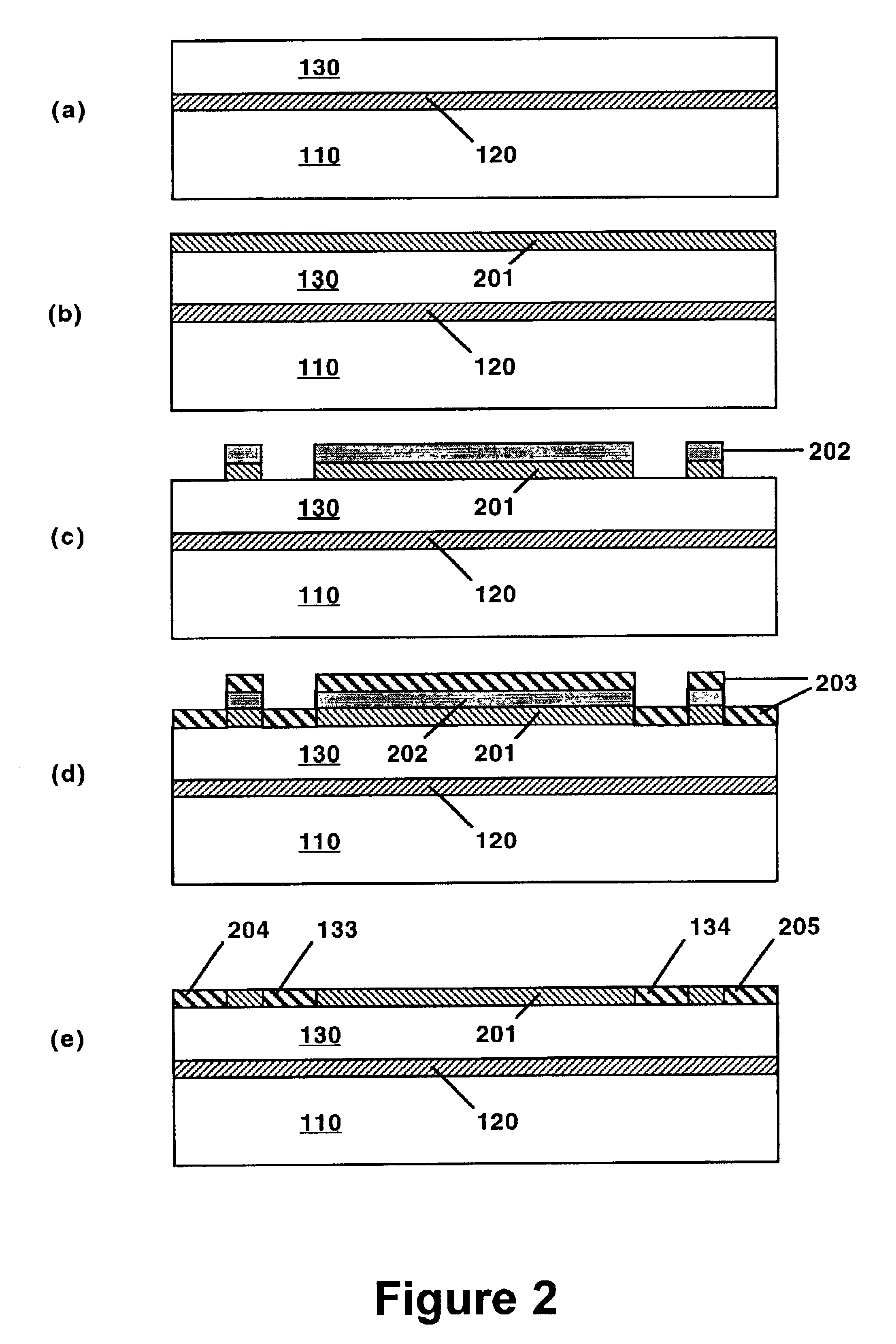

Process for PECVD of silicon oxide using TEOS decomposition

InactiveUSRE36623E1Eliminate depositsAvoid failureElectric discharge tubesPretreated surfacesHigh rateSilicon oxide

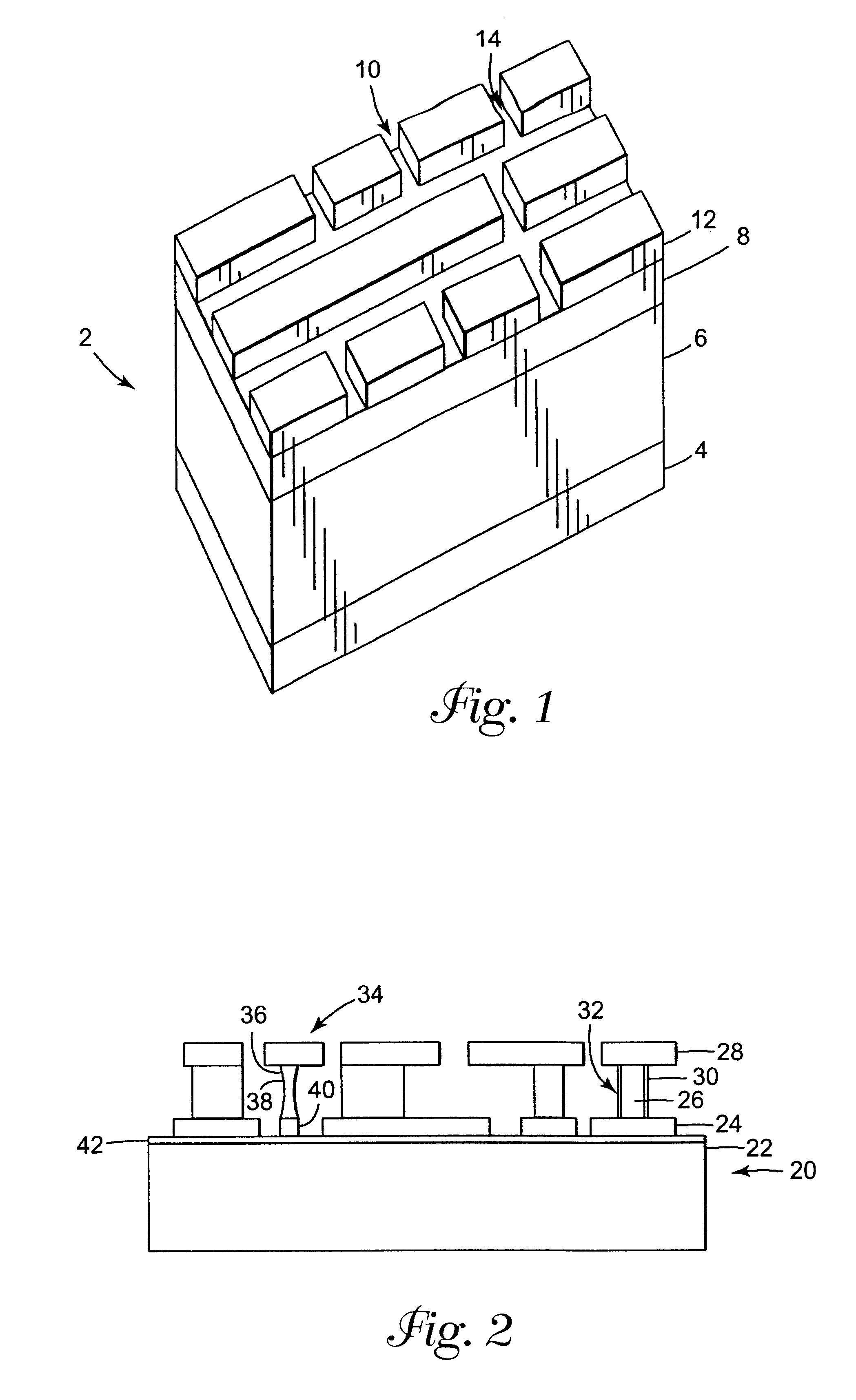

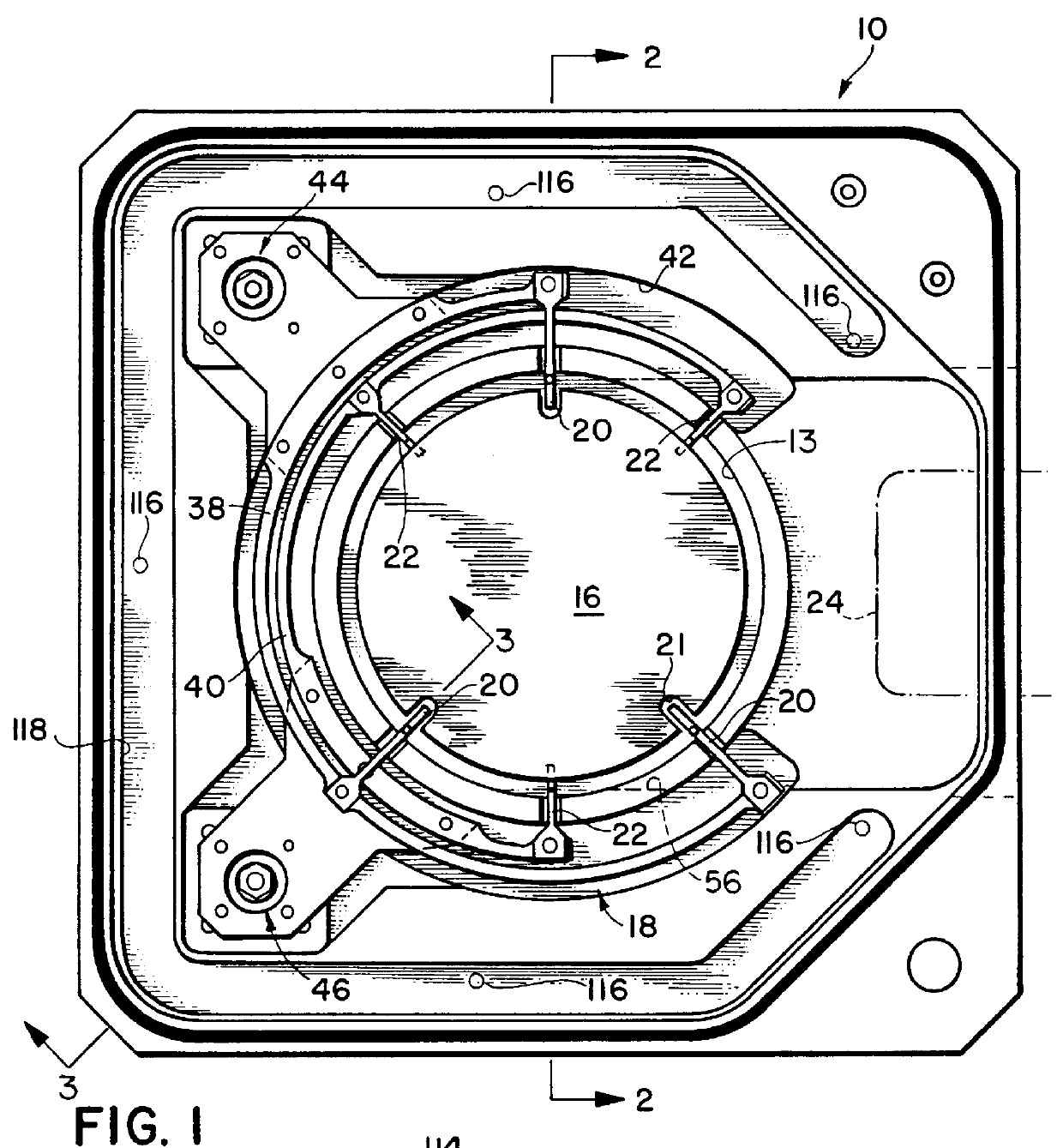

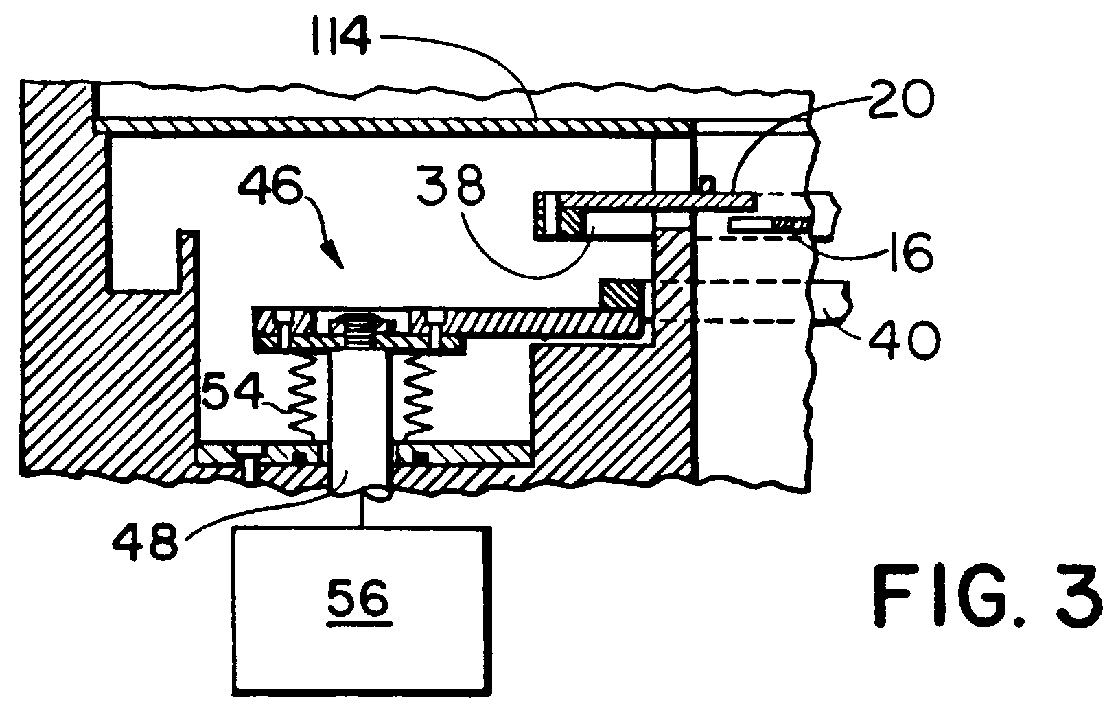

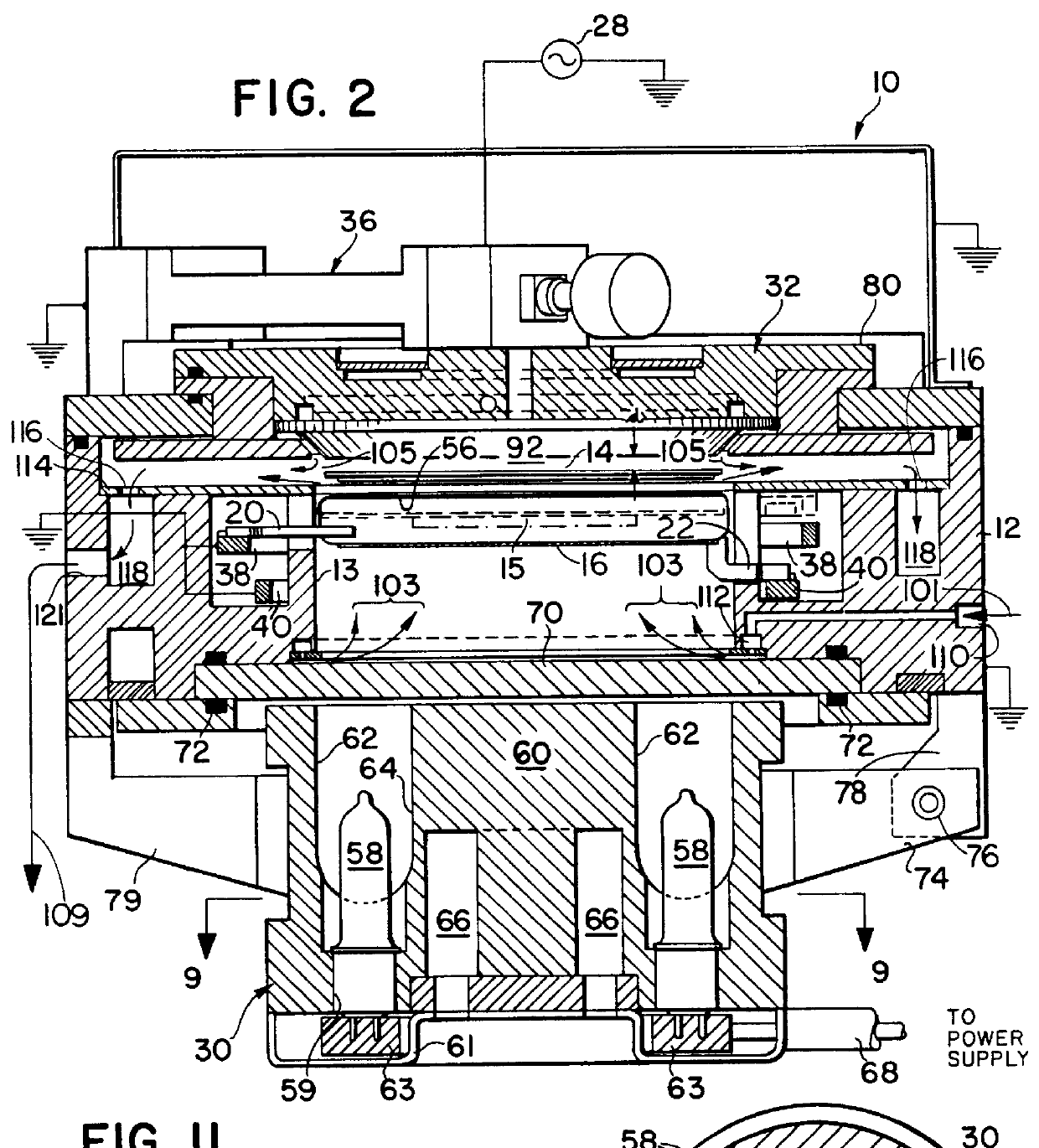

A high pressure, high throughput, single wafer, semiconductor processing reactor is disclosed which is capable of thermal CVD, plasma-enhanced CVD, plasma-assisted etchback, plasma self-cleaning, and deposition topography modification by sputtering, either separately or as part of in-situ multiple step processing. The reactor includes cooperating arrays of interdigitated susceptor and wafer support fingers which collectively remove the wafer from a robot transfer blade and position the wafer with variable, controlled, close parallel spacing between the wafer and the chamber gas inlet manifold, then return the wafer to the blade. A combined RF / gas feed-through device protects against process gas leaks and applies RF energy to the gas inlet manifold without internal breakdown or deposition of the gas. The gas inlet manifold is adapted for providing uniform gas flow over the wafer. Temperature-controlled internal and external manifold surfaces suppress condensation, premature reactions and decomposition and deposition on the external surface. The reactor also incorporates a uniform radial pumping gas system which enables uniform reactant gas flow across the wafer and directs purge gas flow downwardly and upwardly toward the periphery of the wafer for sweeping exhaust gases radially away from the wafer to prevent deposition outside the wafer and keep the chamber clean. The reactor provides uniform processing over a wide range of pressures including very high pressures. A low temperature CVD process for forming a highly conformal layer of silicon dioxide is also disclosed. The process uses very high chamber pressure and low temperature, and TEOS and ozone reactants. The low temperature CVD silicon dioxide deposition step is particularly useful for planarizing underlying stepped dielectric layers, either alone or in conjunction with a subsequent isotropic etch. A preferred in-situ multiple-step process for forming a planarized silicon dioxide layer uses (1) high rate silicon dioxide deposition at a low temperature and high pressure followed by (2) the deposition of the conformal silicon dioxide layer also at high pressure and low temperature, followed by (3) a high rate isotropic etch, preferably at low temperature and high pressure in the sane reactor used for the two oxide deposition steps. Various combinations of the steps are disclosed for different applications, as is a preferred reactor self-cleaning step.

Owner:APPLIED MATERIALS INC

Formulations for removing cooper-containing post-etch residue from microelectronic devices

InactiveUS20090301996A1Decorative surface effectsNon-surface-active detergent compositionsMetal interconnectDiluent

A method and composition for removing copper-containing post-etch and / or post-ash residue from patterned microelectronic devices is described. The removal composition includes a diluent, a solvent and a copper corrosion inhibitor, wherein the diluent may be a dense fluid or a liquid solvent. The removal compositions effectively remove the copper-containing post-etch residue from the microelectronic device without damaging exposed low-k dielectric and metal interconnect materials.

Owner:ADVANCED TECH MATERIALS INC

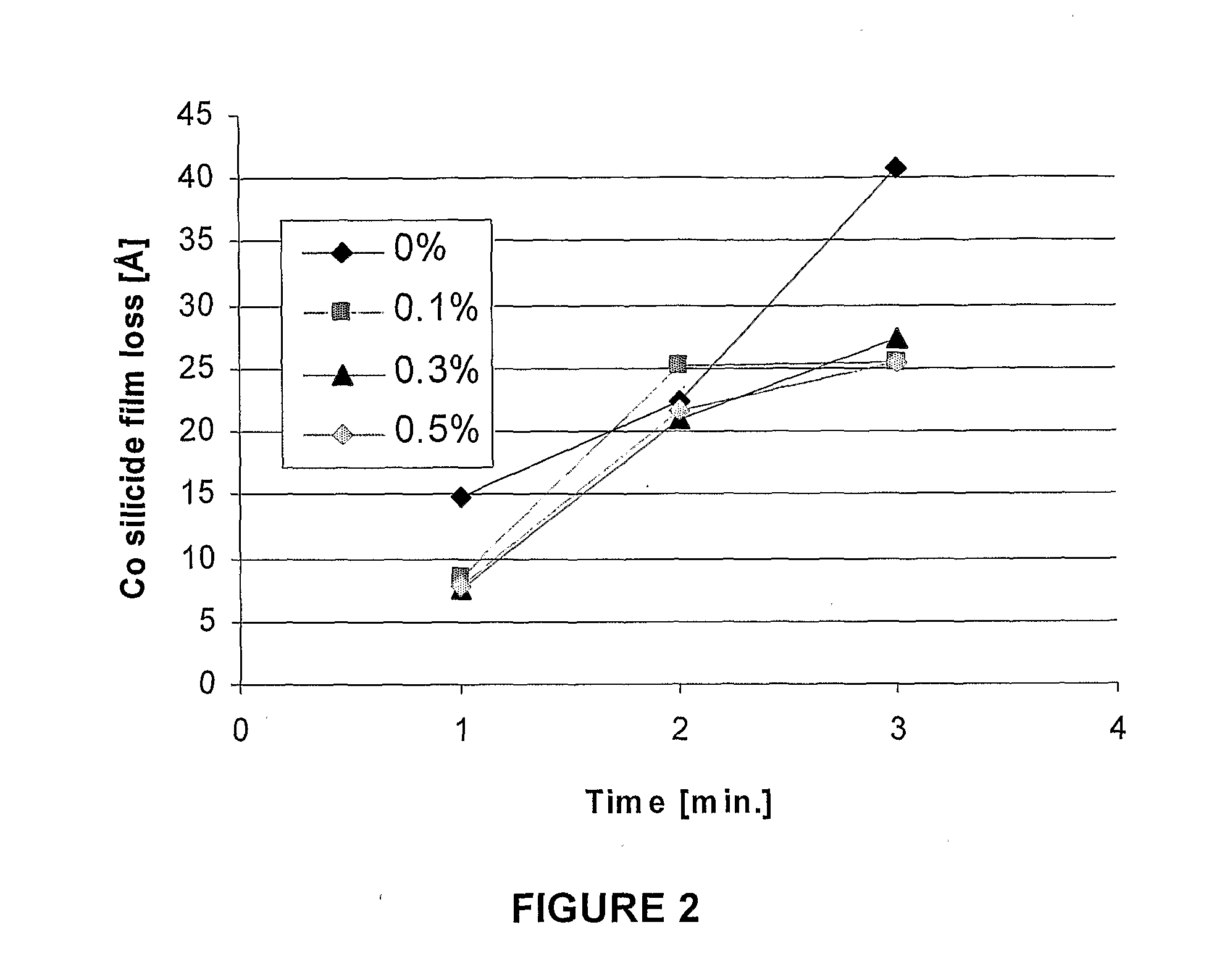

Selective silicon oxide etchant formulation including fluoride salt, chelating agent, and glycol solvent

InactiveUS6280651B1Semiconductor/solid-state device manufacturingSurface treatment compositionsSilicon oxideFluoride

The formulations of the present invention etch doped silicon oxide compounds, such as BPSG and PSG layers, at rates greater than or equal to the etch rate of undoped silicon oxide such as thermal oxide. The formulations have the general composition of a chelating agent, preferably weakly to moderately acidic (0.1-10%; preferably 0.2-2.8%); a fluoride salt, which may be ammonium fluoride or an organic derivative of either ammonium fluoride or a polyammonium fluoride (1.65-7%; preferably 2.25-7%); a glycol solvent (71-98%; preferably 90-98%); and optionally, an amine.

Owner:ENTEGRIS INC

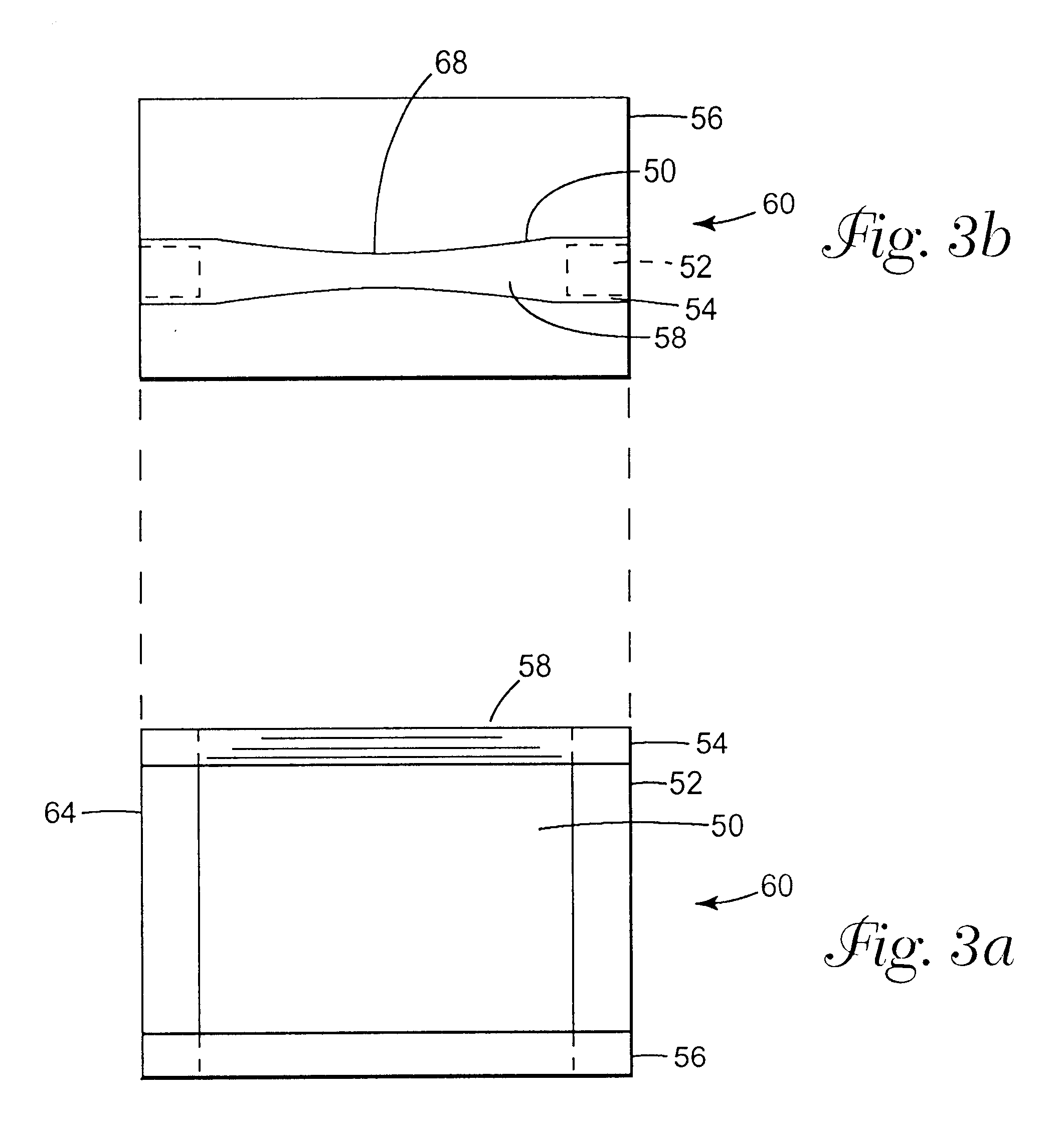

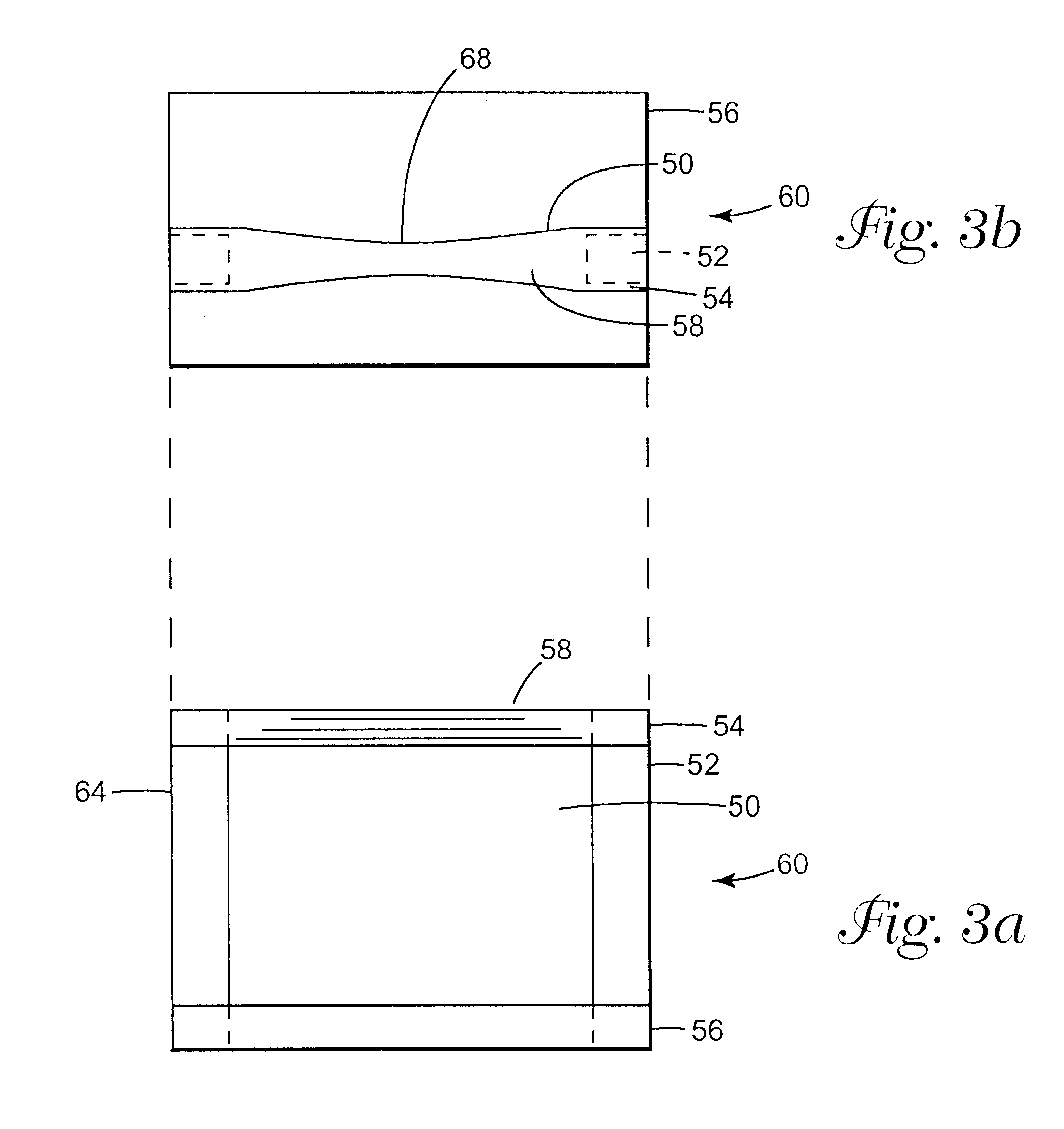

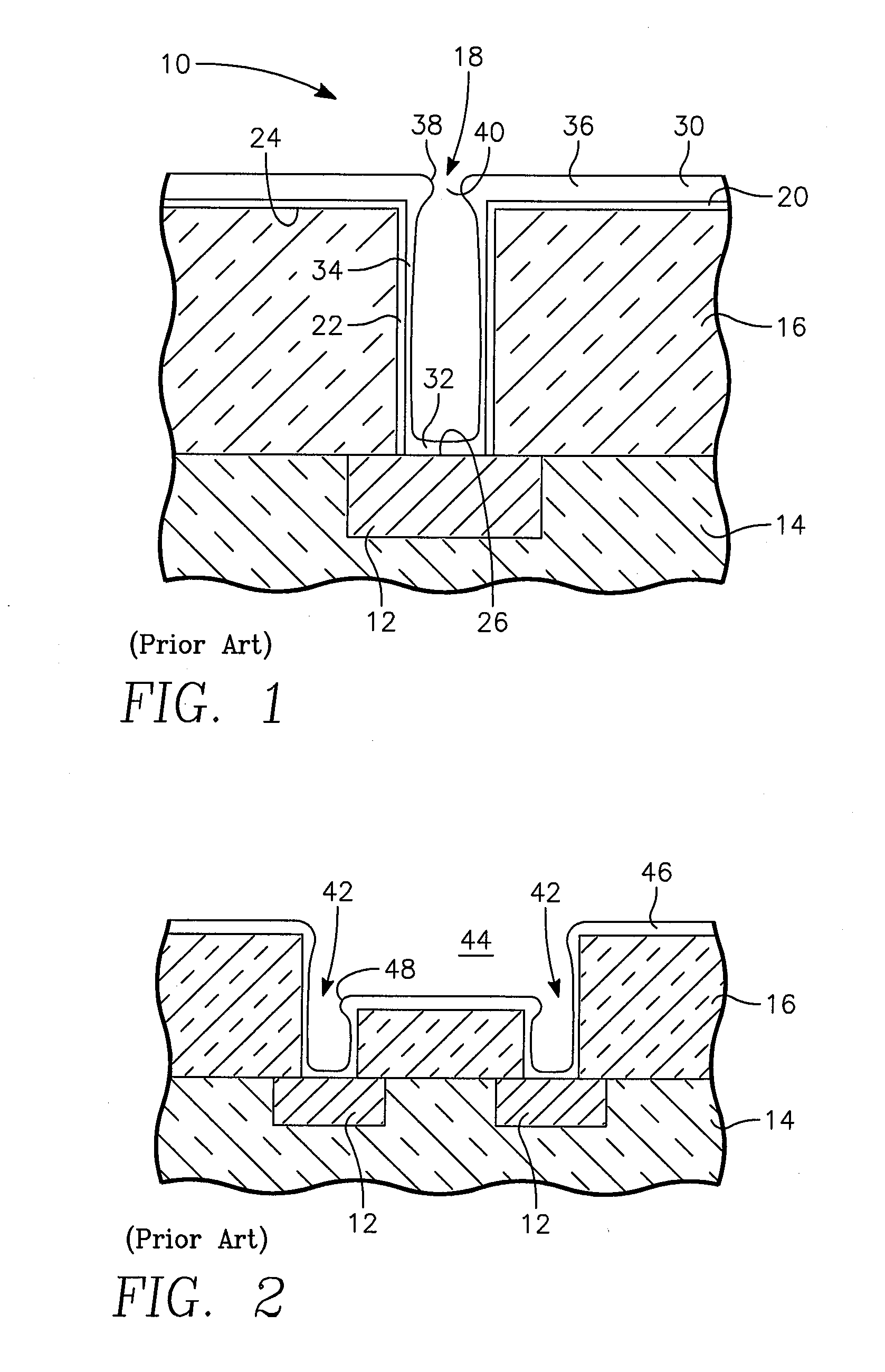

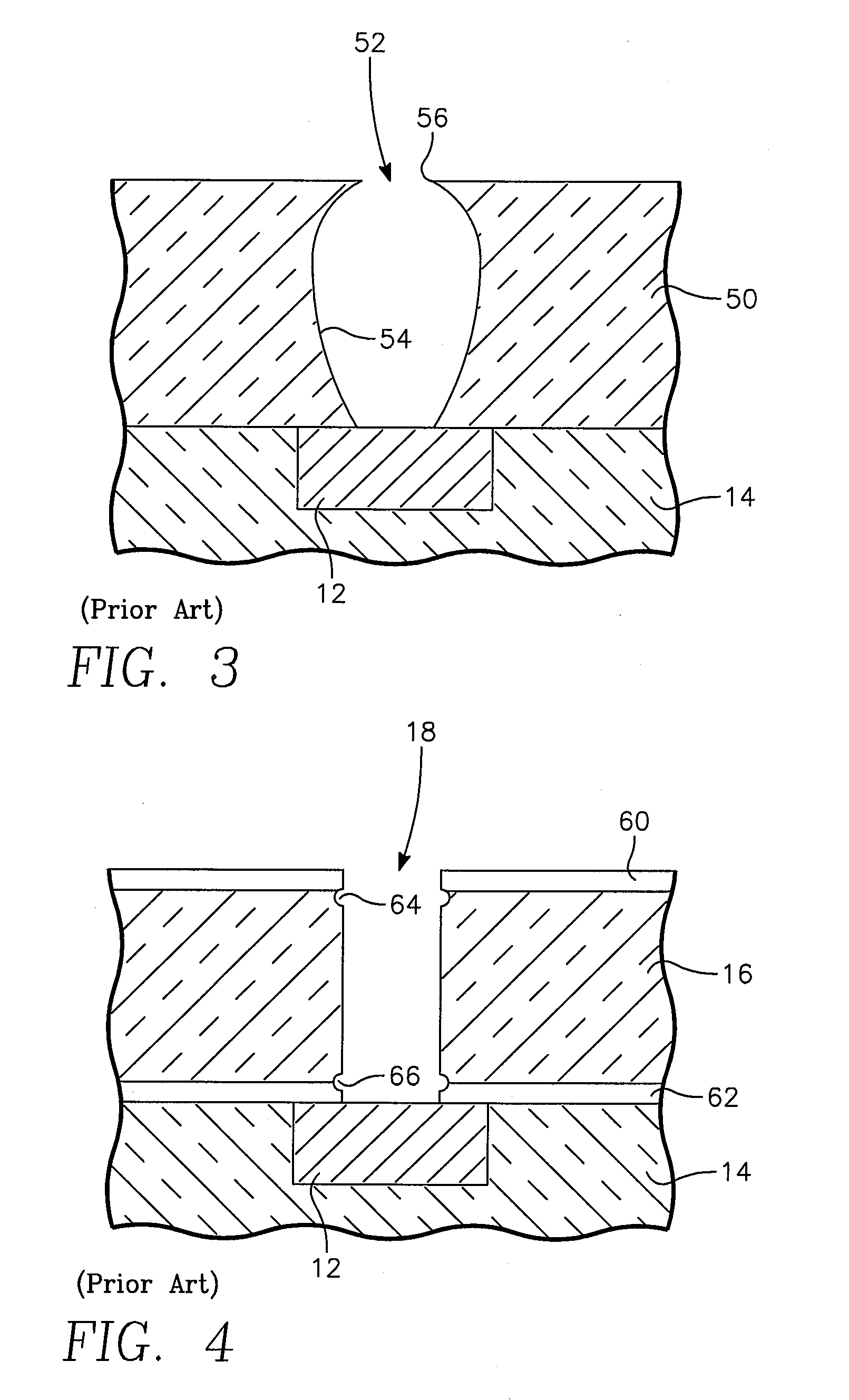

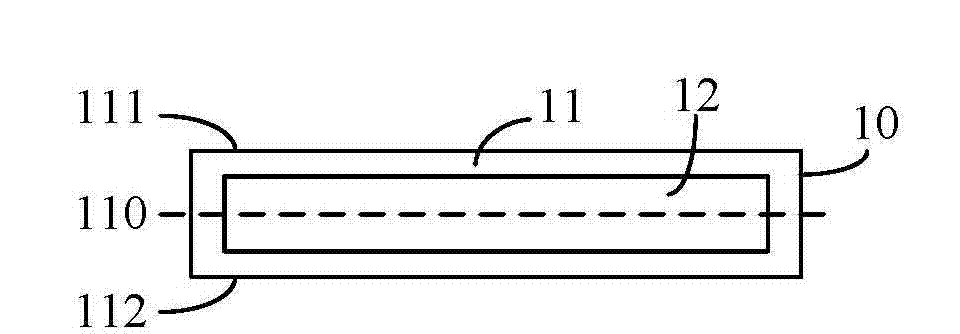

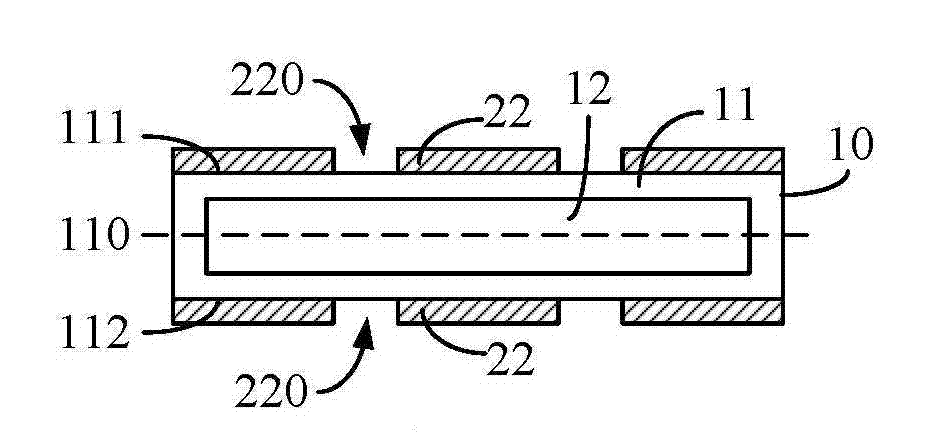

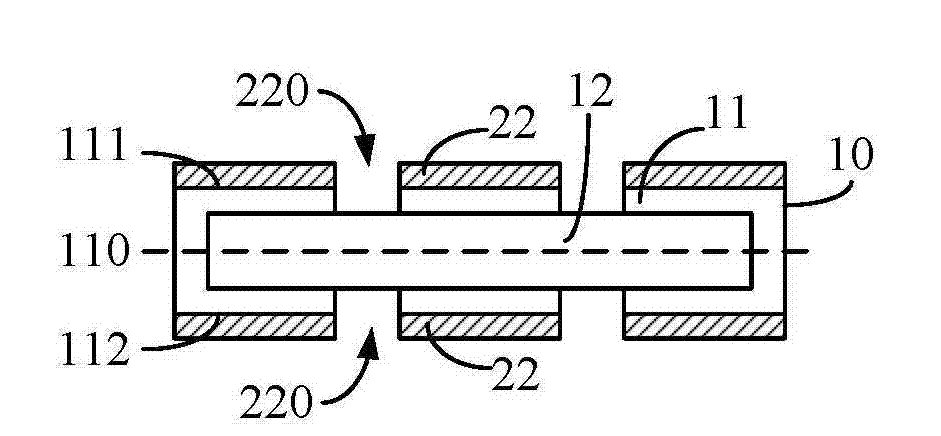

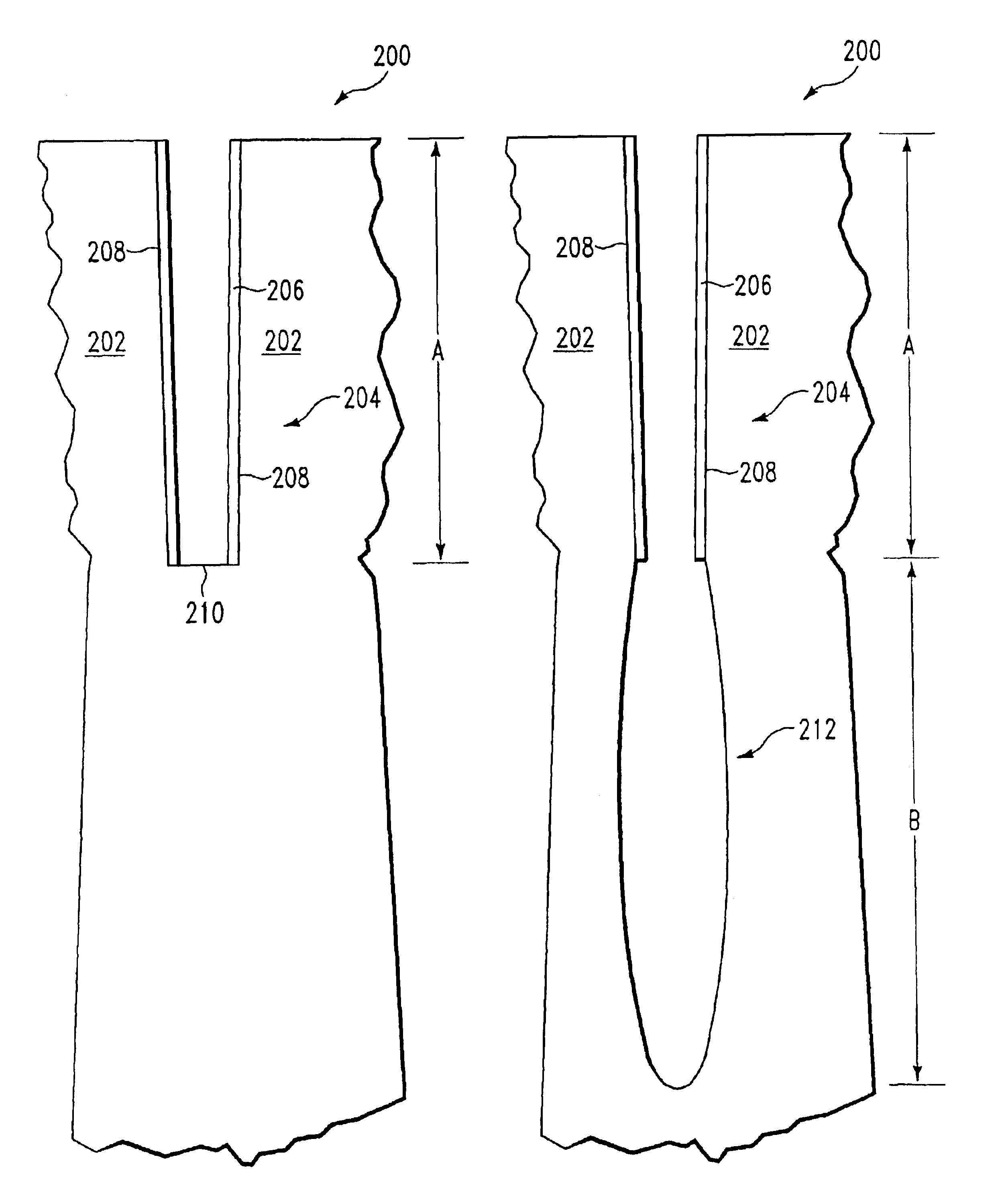

Method of micromachining a multi-part cavity

InactiveUS20020185469A1Decorative surface effectsSolid-state devicesProtection layerMaterials science

The present disclosure pertains to our discovery of a particularly efficient method for etching a multi-part cavity in a substrate. The method provides for first etching a shaped opening, depositing a protective layer over at least a portion of the inner surface of the shaped opening, and then etching a shaped cavity directly beneath and in continuous communication with the shaped opening. The protective layer protects the etch profile of the shaped opening during etching of the shaped cavity, so that the shaped opening and the shaped cavity can be etched to have different shapes, if desired. In particular embodiments of the method of the invention, lateral etch barrier layers and / or implanted etch stops are also used to direct the etching process. The method of the invention can be applied to any application where it is necessary or desirable to provide a shaped opening and an underlying shaped cavity having varying shapes. The method is also useful whenever it is necessary to maintain tight control over the dimensions of the shaped opening.

Owner:APPLIED MATERIALS INC

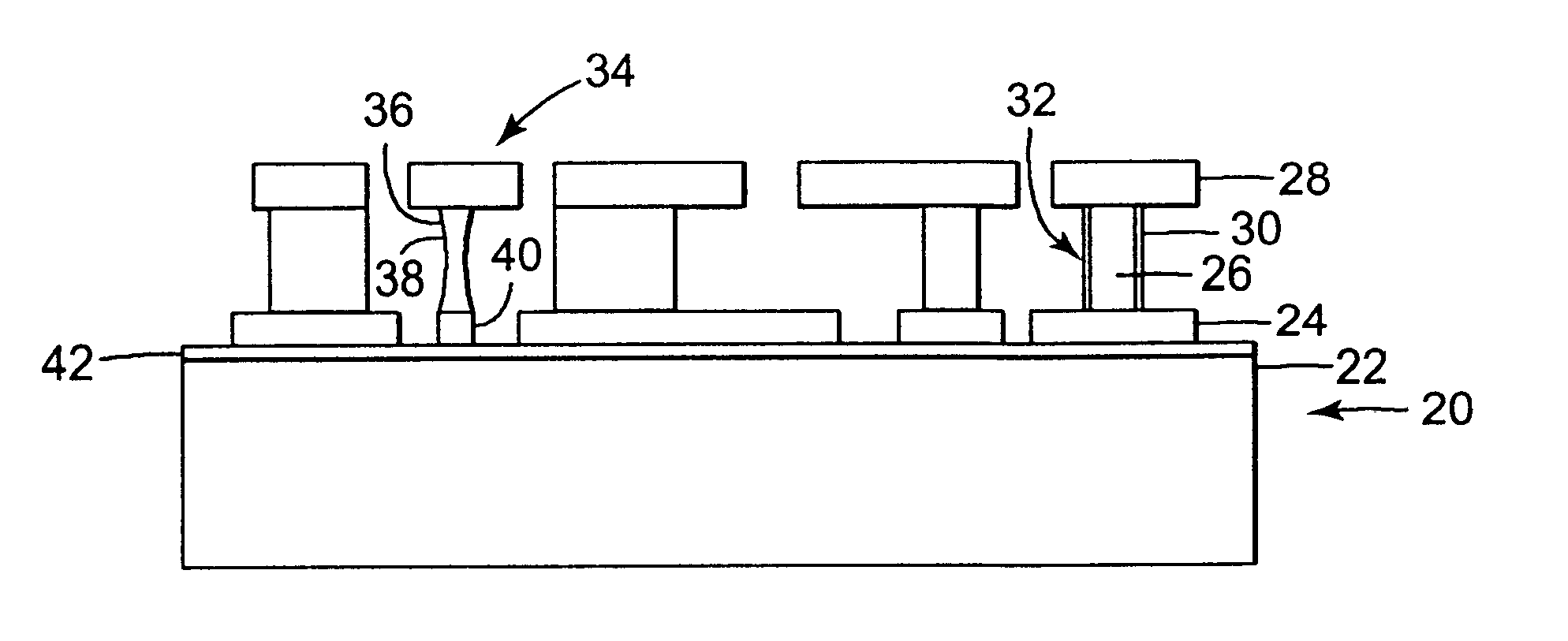

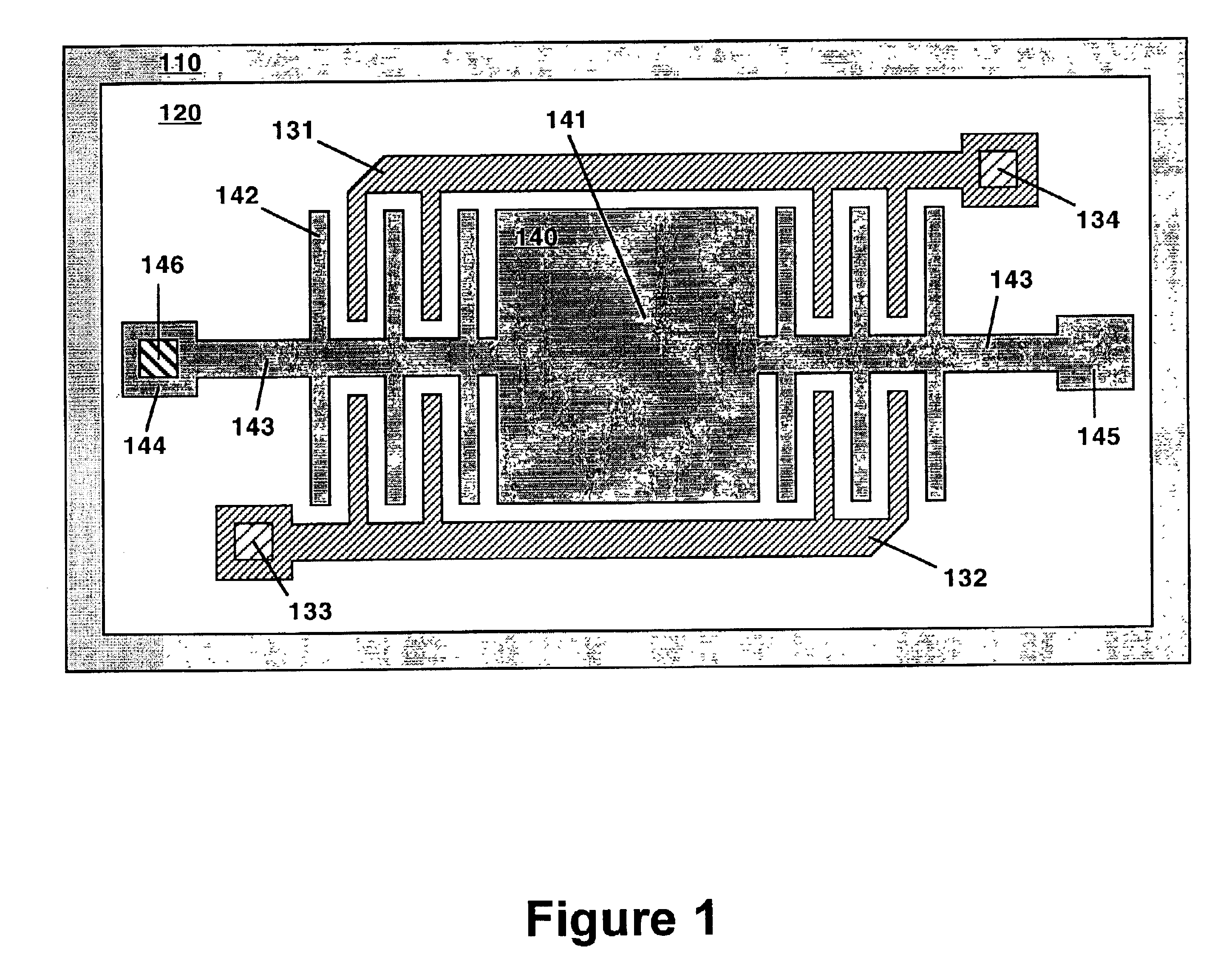

Process for high yield fabrication of MEMS devices

ActiveUS6872319B2Thickness minimizationExceptionally precise layer to layer alignmentSemi-permeable membranesPrecision positioning equipmentEngineeringSilicon

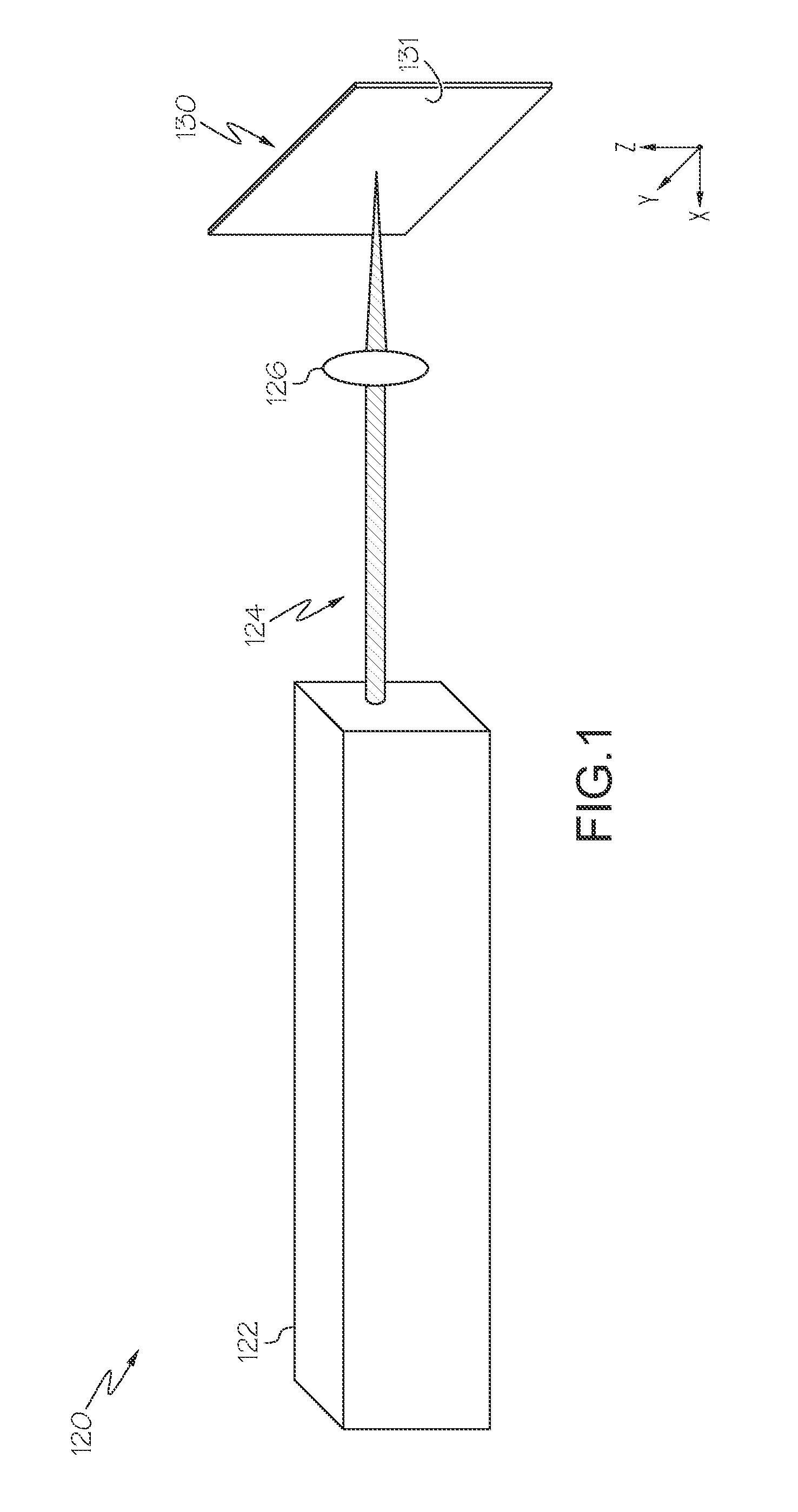

A MEMS fabrication process eliminates through-wafer etching, minimizes the thickness of silicon device layers and the required etch times, provides exceptionally precise layer to layer alignment, does not require a wet etch to release the moveable device structure, employs a supporting substrate having no device features on one side, and utilizes low-temperature metal-metal bonding which is relatively insensitive to environmental particulates. This process provided almost 100% yield of scanning micromirror devices exhibiting scanning over a 12° optical range and a mechanical angle of ±3° at a high resonant frequency of 2.5 kHz with an operating voltage of only 20 VDC.

Owner:TELEDYNE SCI & IMAGING

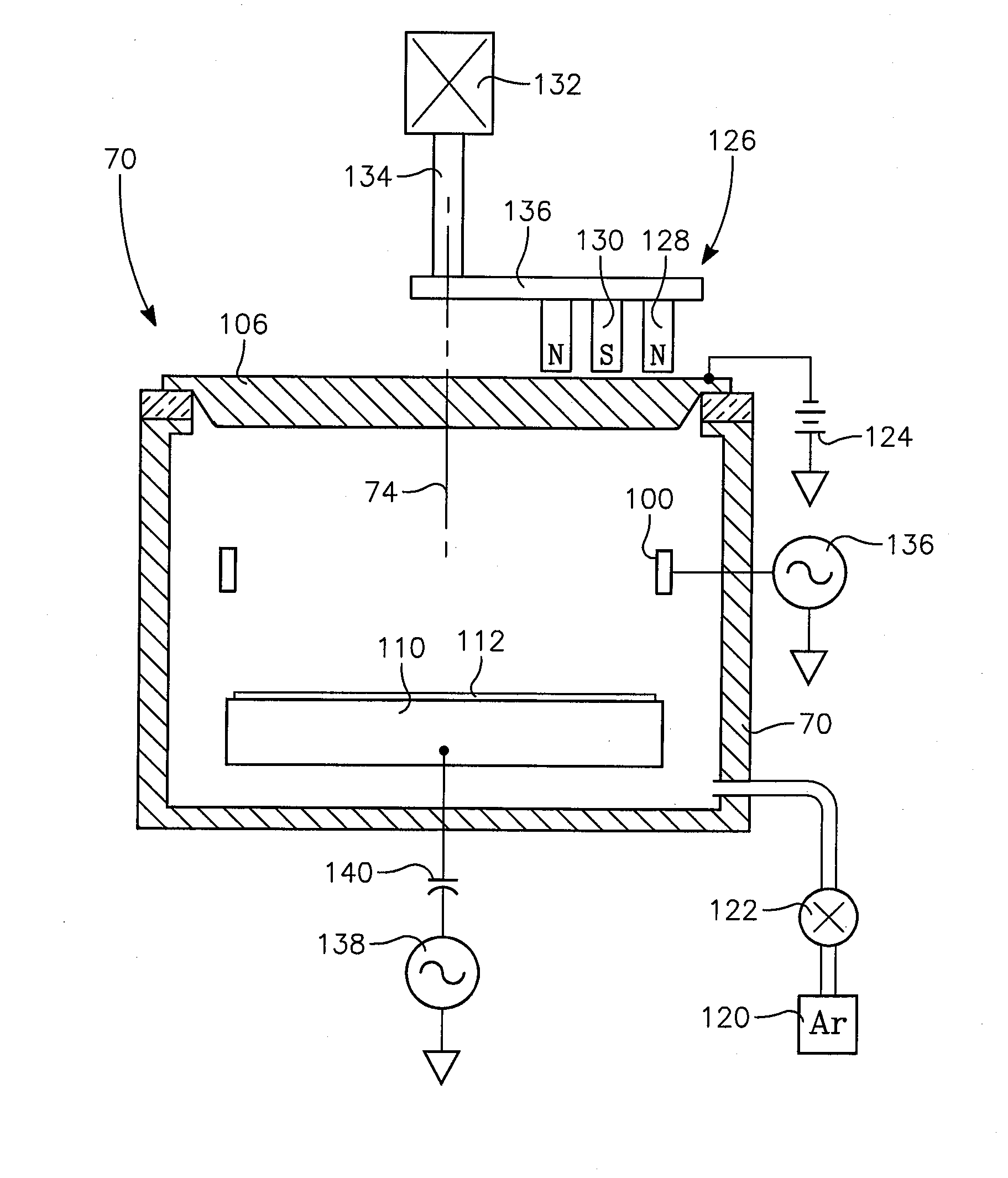

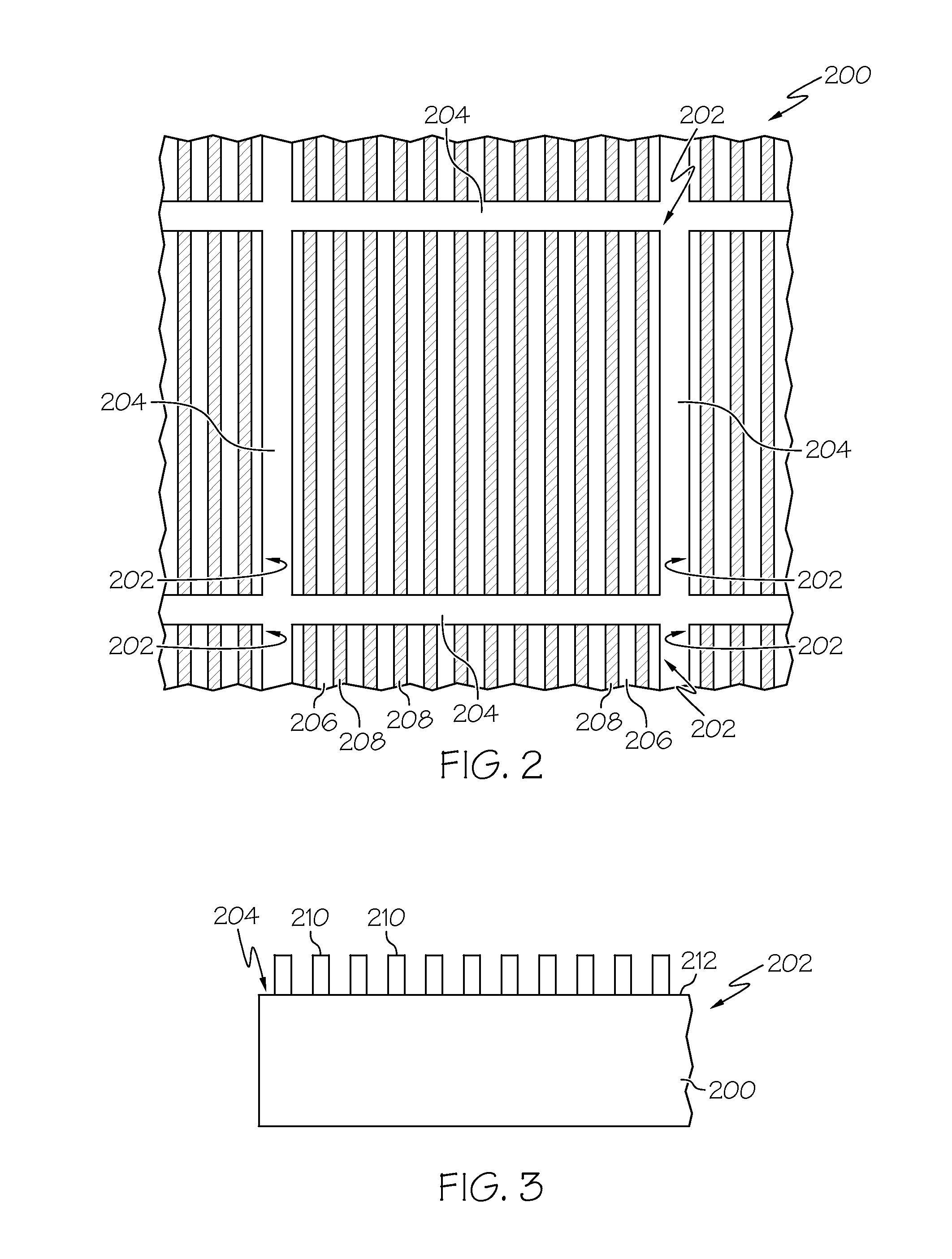

Resputtered copper seed layer

InactiveUS20080190760A1Increase pressureReduce stressElectric discharge tubesVacuum evaporation coatingSputter depositionElectrochemistry

An integrated copper deposition process, particularly useful for forming a copper seed layer in a narrow via prior to electrochemical plating of copper, including at least one cycle of sputter deposition of copper followed by sputter etching of the deposited copper, preferably performed in a same sputter chamber. The deposition is performed under conditions promoting high copper ionization fractions and strong wafer biasing to draw the copper ions into the via. The etching may be done with argon ions, preferably inductively excited by an RF coil around the chamber, or by copper ions, which may be formed with high target power and intense magnetron or by use of the RF coil. Two or more cycles of deposition / etch may be performed. A final flash deposition may be performed with high copper ionization and low wafer biasing.

Owner:APPLIED MATERIALS INC

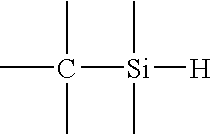

Computer readable medium for holding a program for performing plasma-assisted CVD of low dielectric constant films formed from organosilane compounds

A method and apparatus for depositing a low dielectric constant film by reaction of an organosilane or organosiloxane compound and an oxidizing gas at a low RF power level from 10-250 W. The oxidized organosilane or organosiloxane film has good barrier properties for use as a liner or cap layer adjacent other dielectric layers. The oxidized organosilane or organosiloxane film may also be used as an etch stop or an intermetal dielectric layer for fabricating dual damascene structures. The oxidized organosilane or organosiloxane films also provide excellent adhesion between different dielectric layers. A preferred oxidized organosilane film is produced by reaction of methylsilane, CH3SiH3, or dimethylsilane, (CH3)2SiH2, and nitrous oxide, N2O, at an RF power level from about 10 to 200 W or a pulsed RF power level from about 20 to 250 W during 10-30% of the duty cycle.

Owner:APPLIED MATERIALS INC

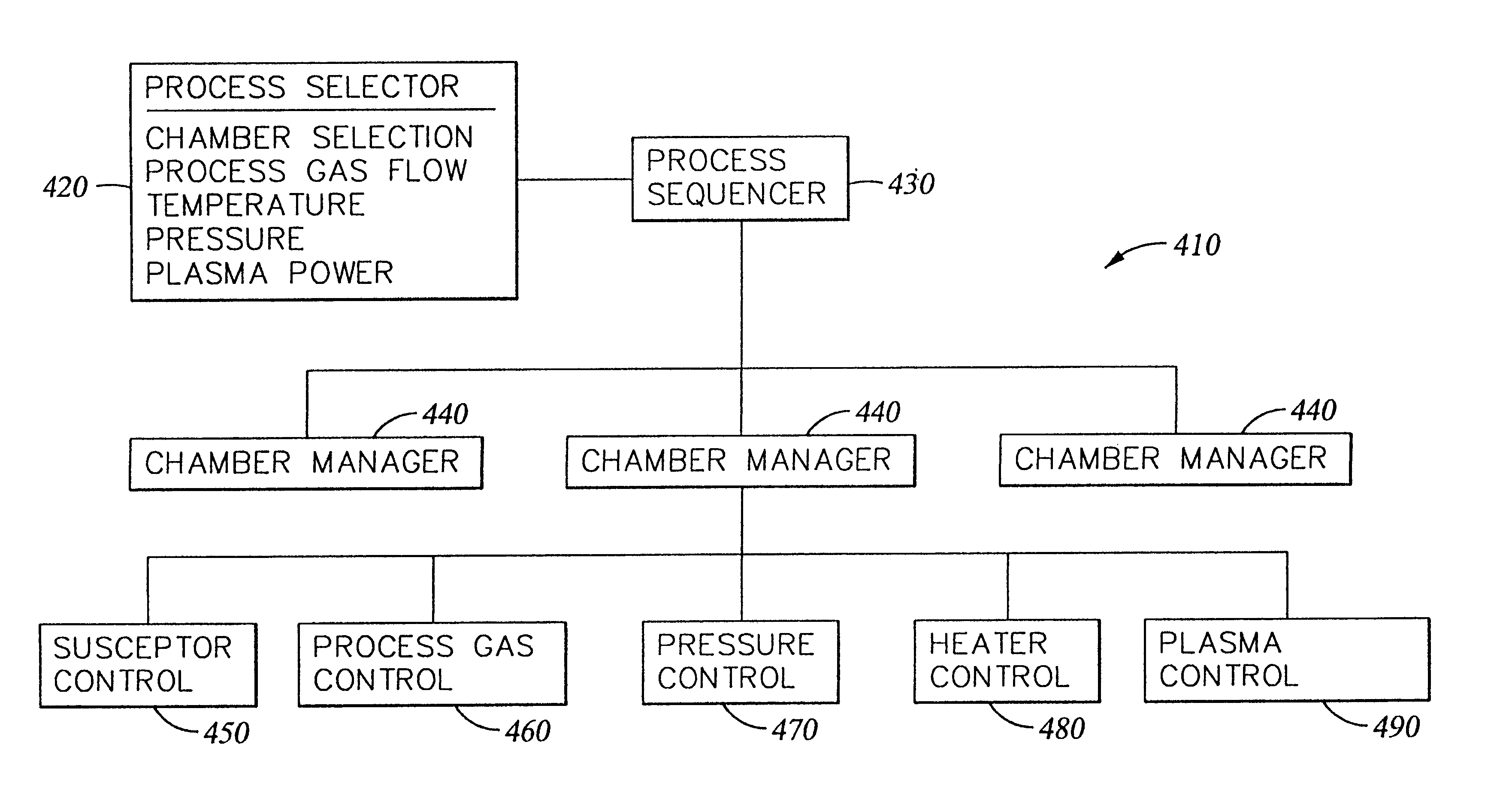

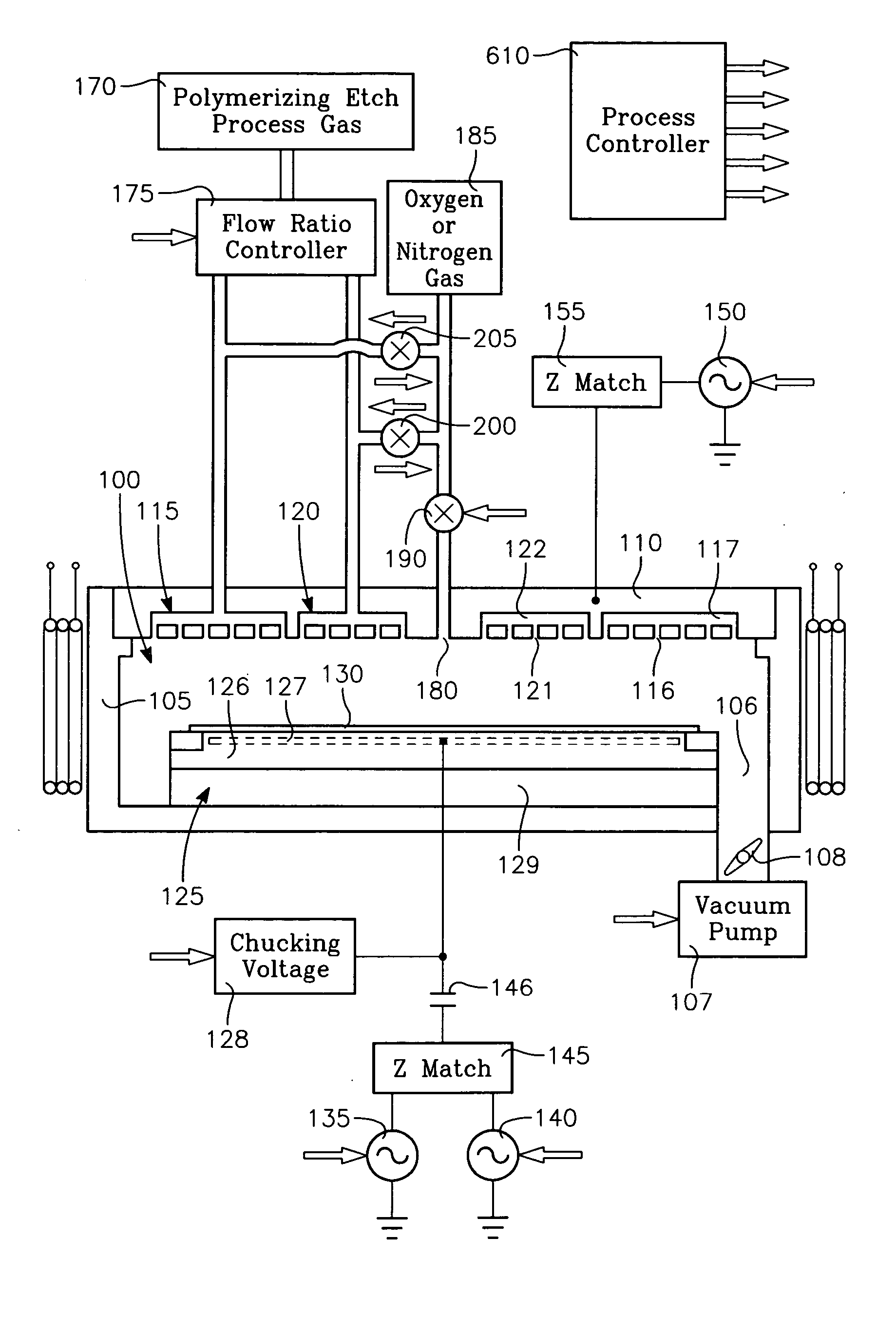

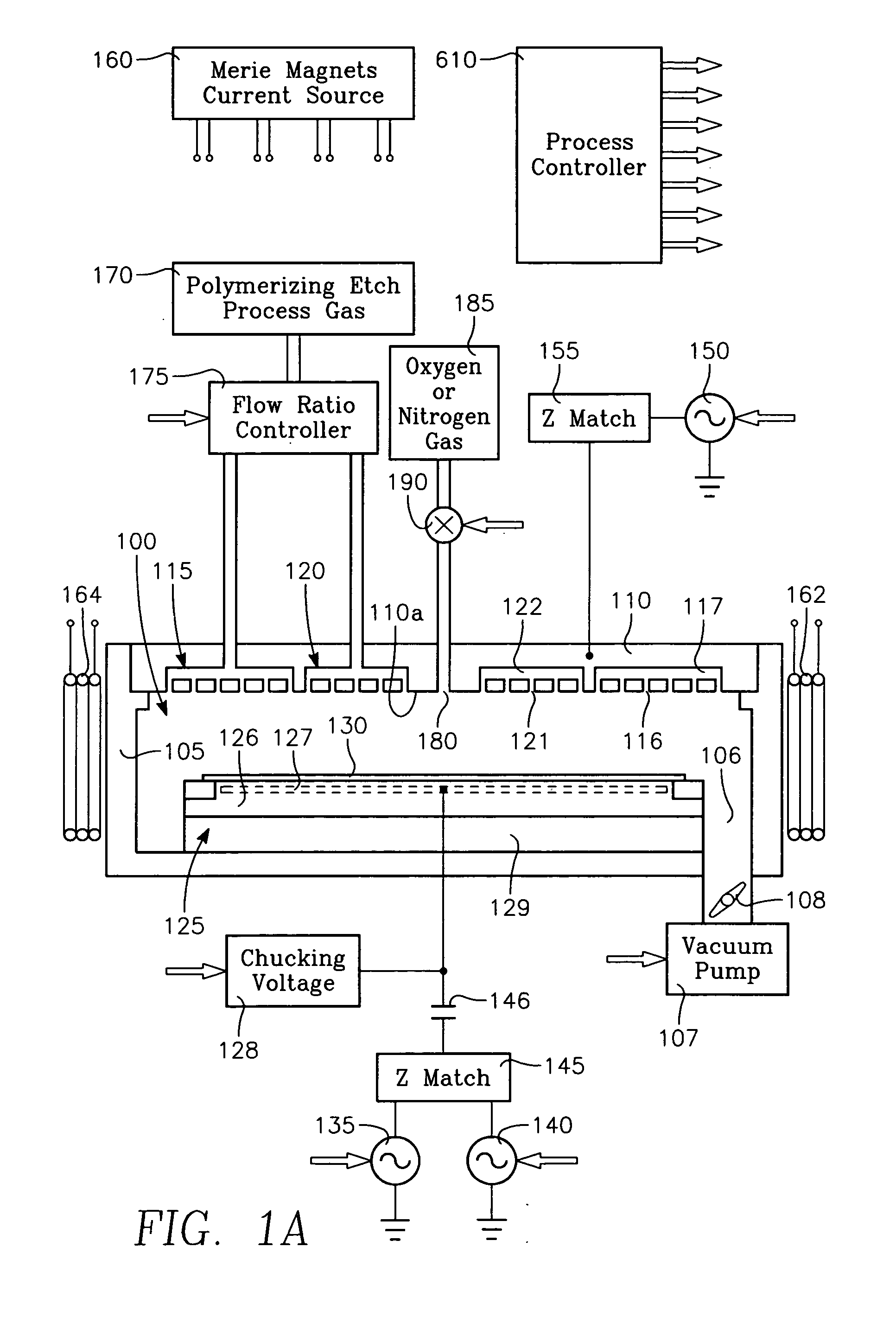

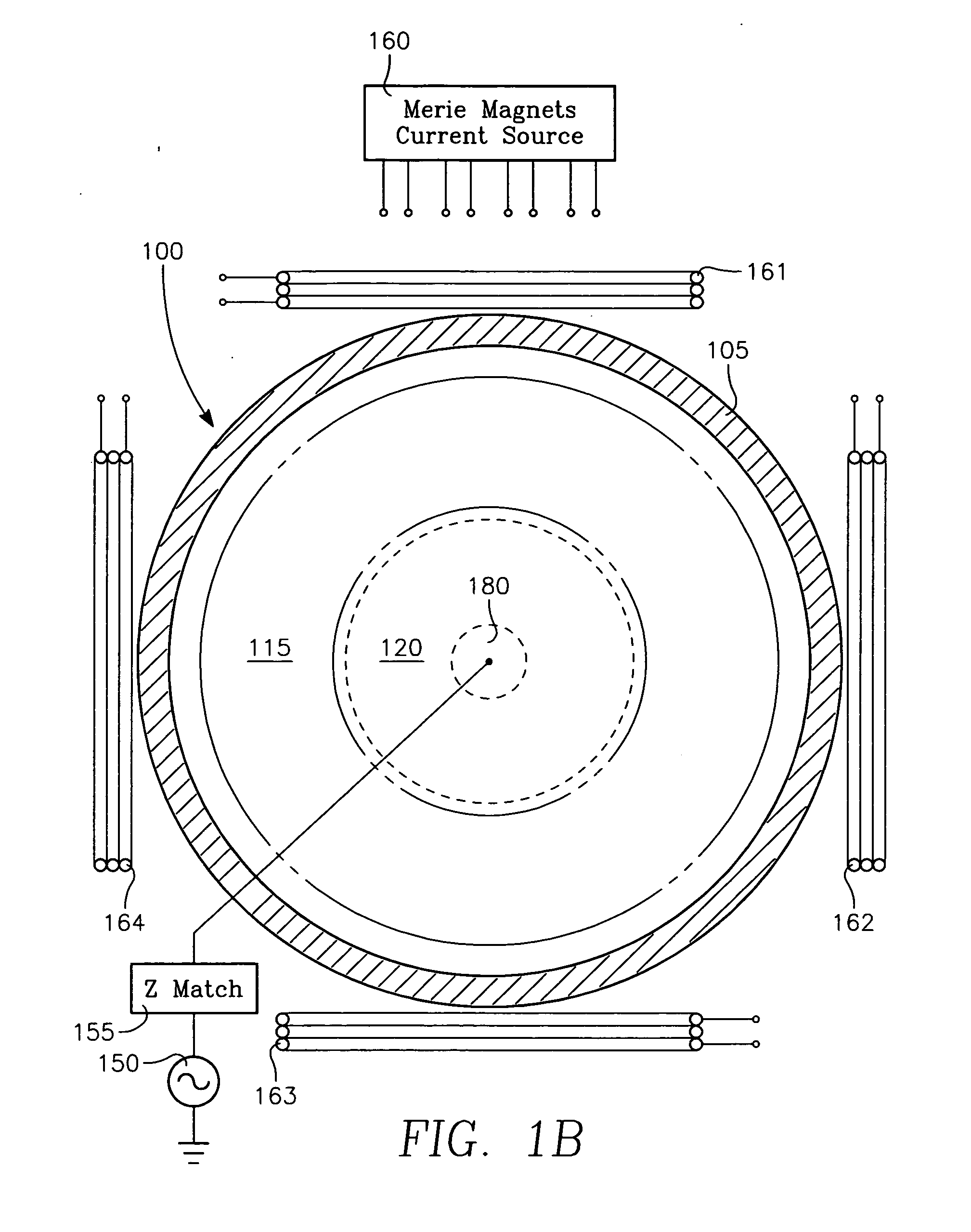

Plasma etch process using polymerizing etch gases across a wafer surface and additional polymer managing or controlling gases in independently fed gas zones with time and spatial modulation of gas content

ActiveUS20070251917A1Slow deposition rateMinimizing etch stopElectric discharge tubesVacuum gauge using ionisation effectsEngineeringOxygen

A plasma etch process etches high aspect ratio openings in a dielectric film on a workpiece in a reactor having a ceiling electrode overlying the workpiece and an electrostatic chuck supporting the workpiece. The process includes injecting a polymerizing etch process gas through an annular zone of gas injection orifices in the ceiling electrode, and evacuating gas from the reactor through a pumping annulus surrounding an edge of the workpiece. The high aspect ratio openings are etched in the dielectric film with etch species derived from the etch process gas while depositing a polymer derived from the etch process gas onto the workpiece, by generating a plasma in the reactor by applying VHF source power and / or HF and / or LF bias power to the electrodes at the ceiling and / or the electrostatic chuck. The process further includes slowing the deposition rate of the polymer, minimizing etch stop and / or increasing the etch rate in a region of the workpiece typically the center by injecting oxygen or nitrogen and / or high-fluorine containing gas through gas injection orifice in the corresponding region of the ceiling electrode, and adjusting the flow rate of the oxygen or nitrogen and / or high-fluorine containing gas through the gas injection orifice to minimize the difference between profiles and etch depths at the workpiece center and the workpiece periphery.

Owner:APPLIED MATERIALS INC

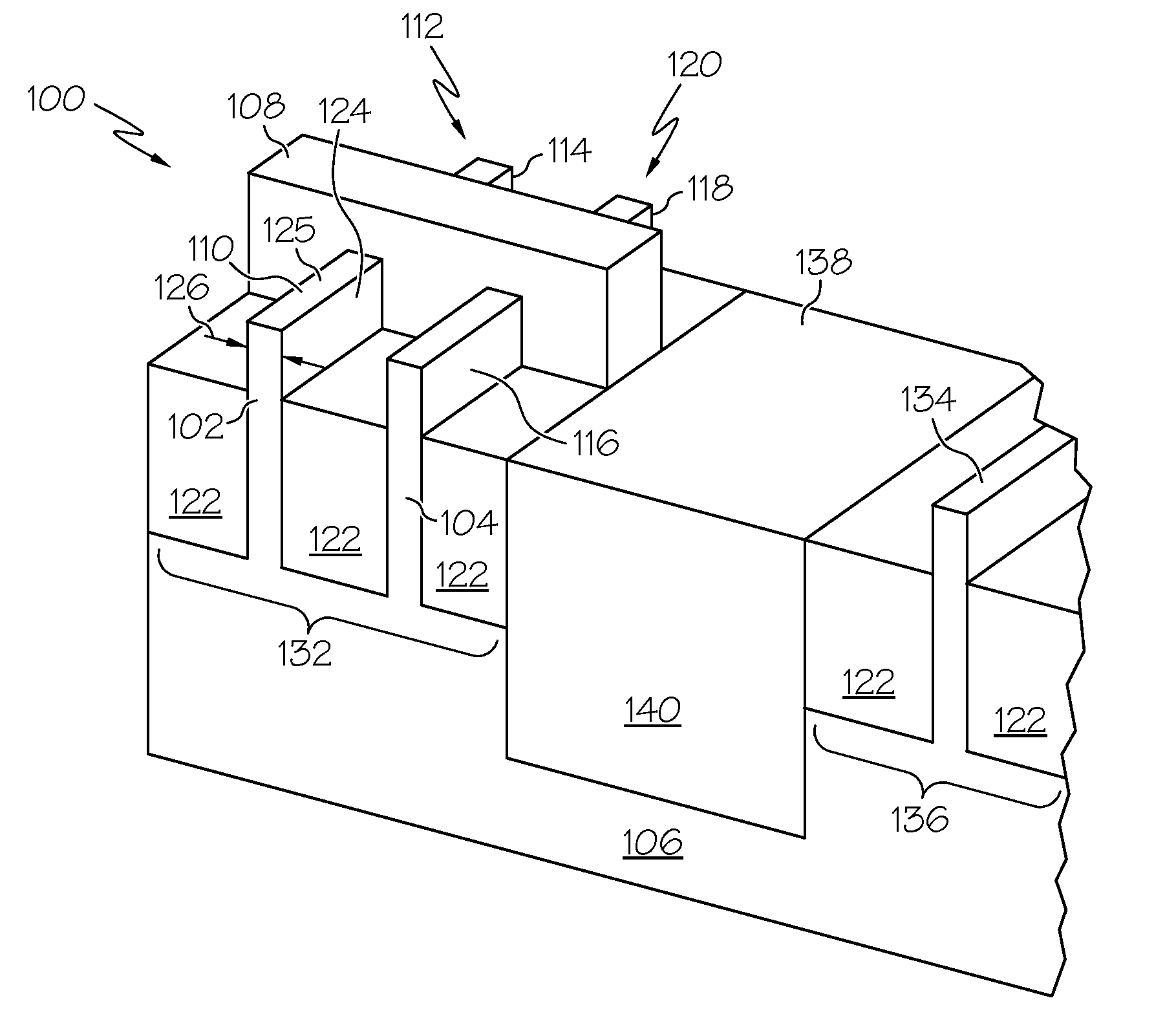

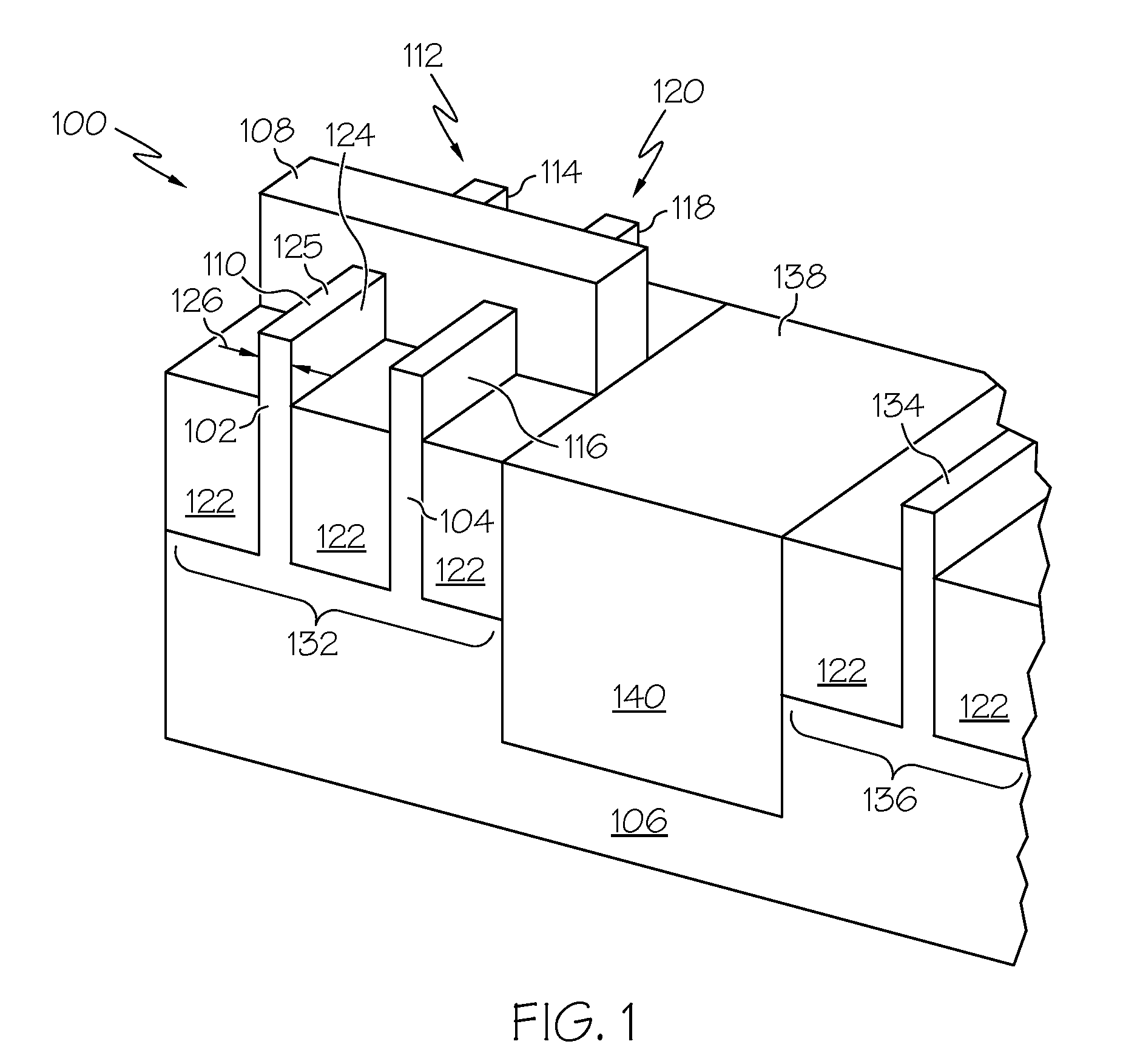

Methods for fabricating finfet integrated circuits in bulk semiconductor substrates

Methods are provided for fabricating FinFETs that avoid thickness uniformity problems across a die or a substrate. One method includes providing a semiconductor substrate divided into a plurality of chips, each chip bounded by scribe lines. The substrate is etched to form a plurality of fins, each of the fins extending uniformly across the width of the chips. An oxide is deposited to fill between the fins and is etched to recess the top of the oxide below the top of the fins. An isolation hard mask is deposited and patterned overlying the plurality of fins and is used as an etch mask to etch trenches in the substrate defining a plurality of active areas, each of the plurality of active areas including at least a portion of at least one of the fins. The trenches are filled with an insulating material to isolate between adjacent active areas.

Owner:TESSERA ADVANCED TECH

Printable etchant compositions for etching silver nanoware-based transparent, conductive film

InactiveUS20140021400A1Less materialFew process stepsInksTransparent dielectricsLiquid-crystal displayDisplay device

The present invention relates to a novel printable paste composition and its use in etching conductive films formed by a plurality of interconnecting silver nano-wires. After etching, the conductive film has a pattern of conductive and non-conductive areas with low visibility. The etched films are suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:SUN CHEM CORP

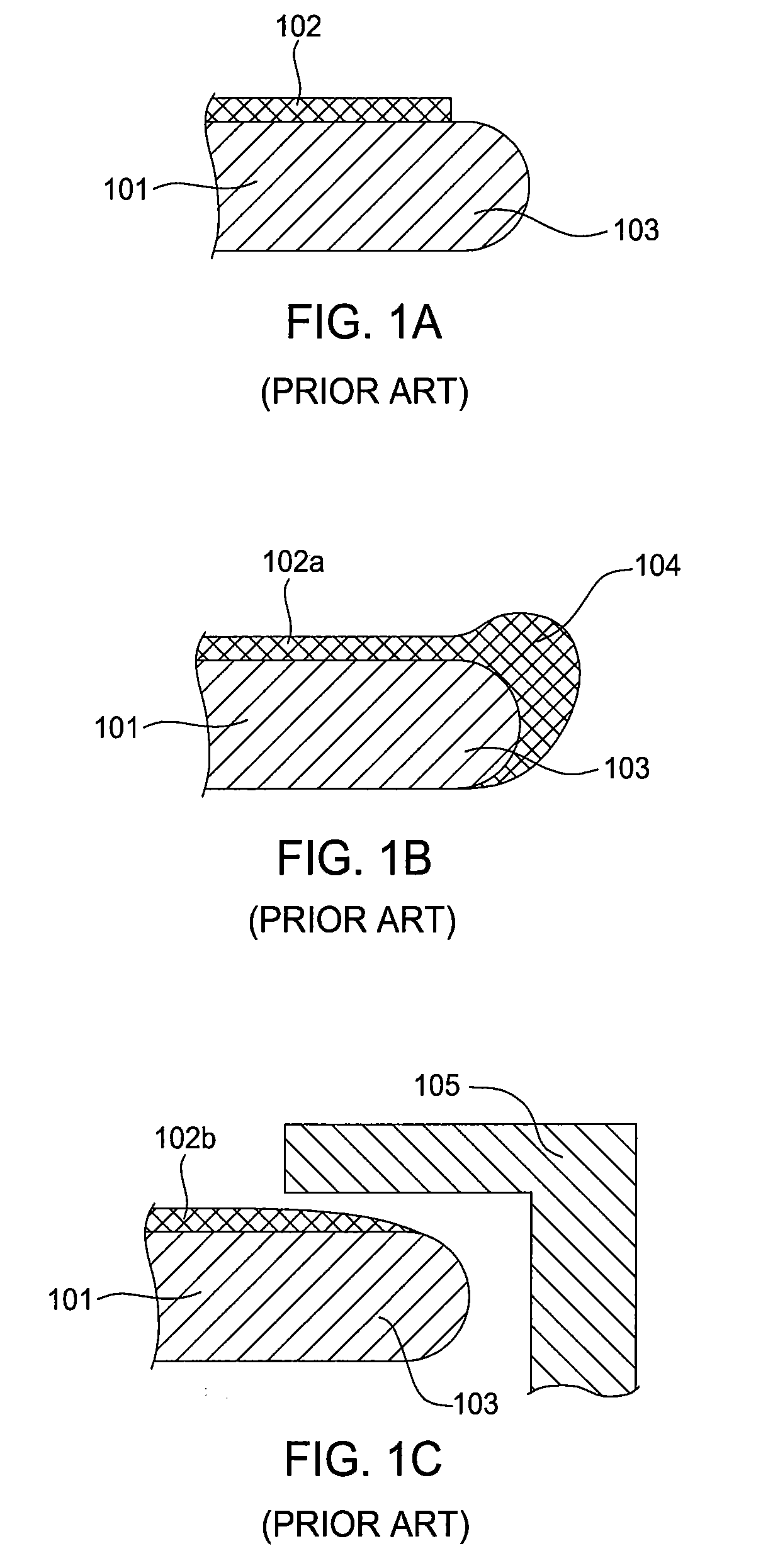

A method for cutting tempered glass

InactiveCN103359947ASolve the costSolve capacity constraintsGlass severing apparatusGlass productionState of artMetallurgy

The invention provides a method for cutting tempered glass. The tempered glass comprises a strengthening layer and a piece of inner glass. The strengthening layer is wrapped around the inner glass. The method for cutting tempered glass comprises following steps: (a) producing a protection layer on the surface of the strengthening layer of the tempered glass, wherein protection layer comprises an area to be cut and the area exposed to a part of the surface of the strengthening layer; (b) executing a etching process in order to remove the part of the strengthening layer corresponding to the area to be cut; and (c) cutting the inner glass along the area to be cut by using a mechanical force cutting manner. The method is capable of resolving problems of high processing cost and limited production capacity caused by cutting the tempered glass using a laser cutting method in the prior art.

Owner:GLOBAL DISPLAY

Methods of fabricating glass articles by laser damage and etching

Methods of forming a glass article are disclosed. In one embodiment, a method of forming a glass article includes translating a pulsed laser beam on a glass substrate sheet to form a laser damage region between a first surface and a second surface of the glass substrate sheet. The method further includes applying an etchant solution to the glass substrate sheet to remove a portion of the glass substrate sheet about the laser damage region. The method may further include strengthening the glass substrate sheet by an ion-exchange strengthening process, and coating the glass substrate sheet with an acid-resistant coating. Also disclosed are methods where the laser damage region has an initial geometry that changes to a desired geometry following the reforming of the glass substrate sheet such that the initial geometry of the laser damage region compensates for the bending of the glass substrate sheet.

Owner:CORNING INC

Method for Manufacturing Semiconductor Device

InactiveUS20080087629A1Improve throughputLow costRadiation applicationsDecorative surface effectsResistLaser beams

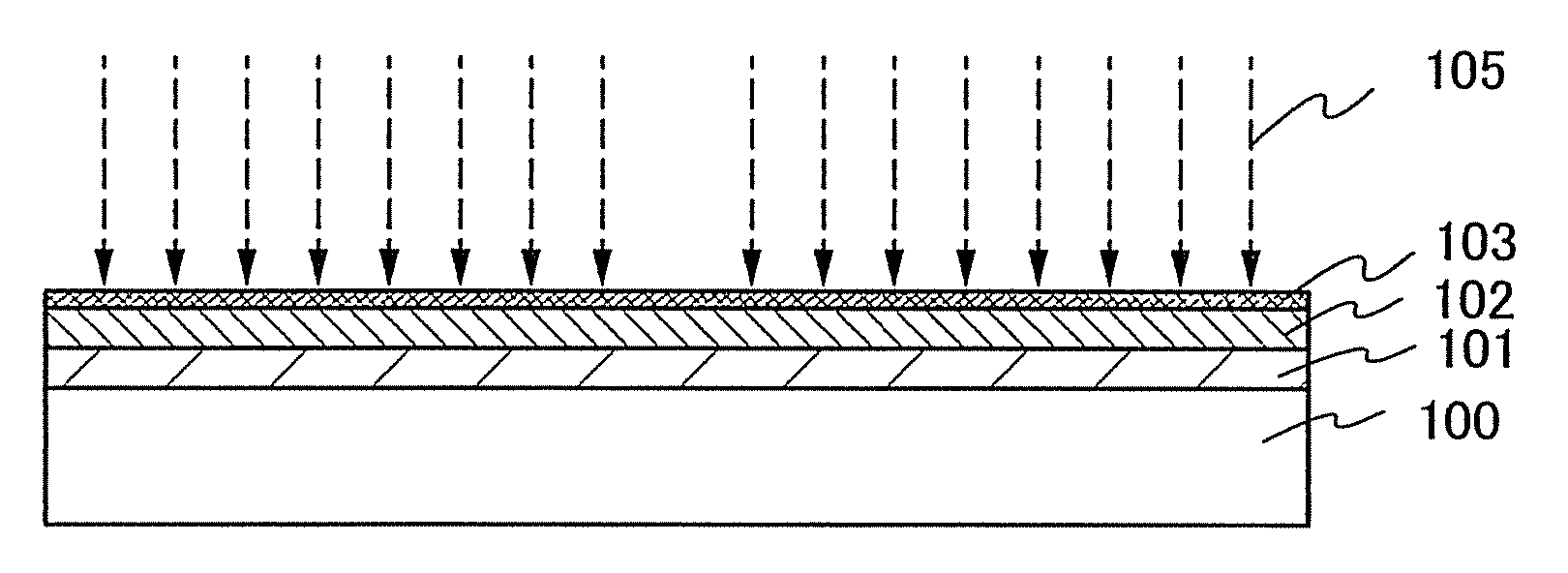

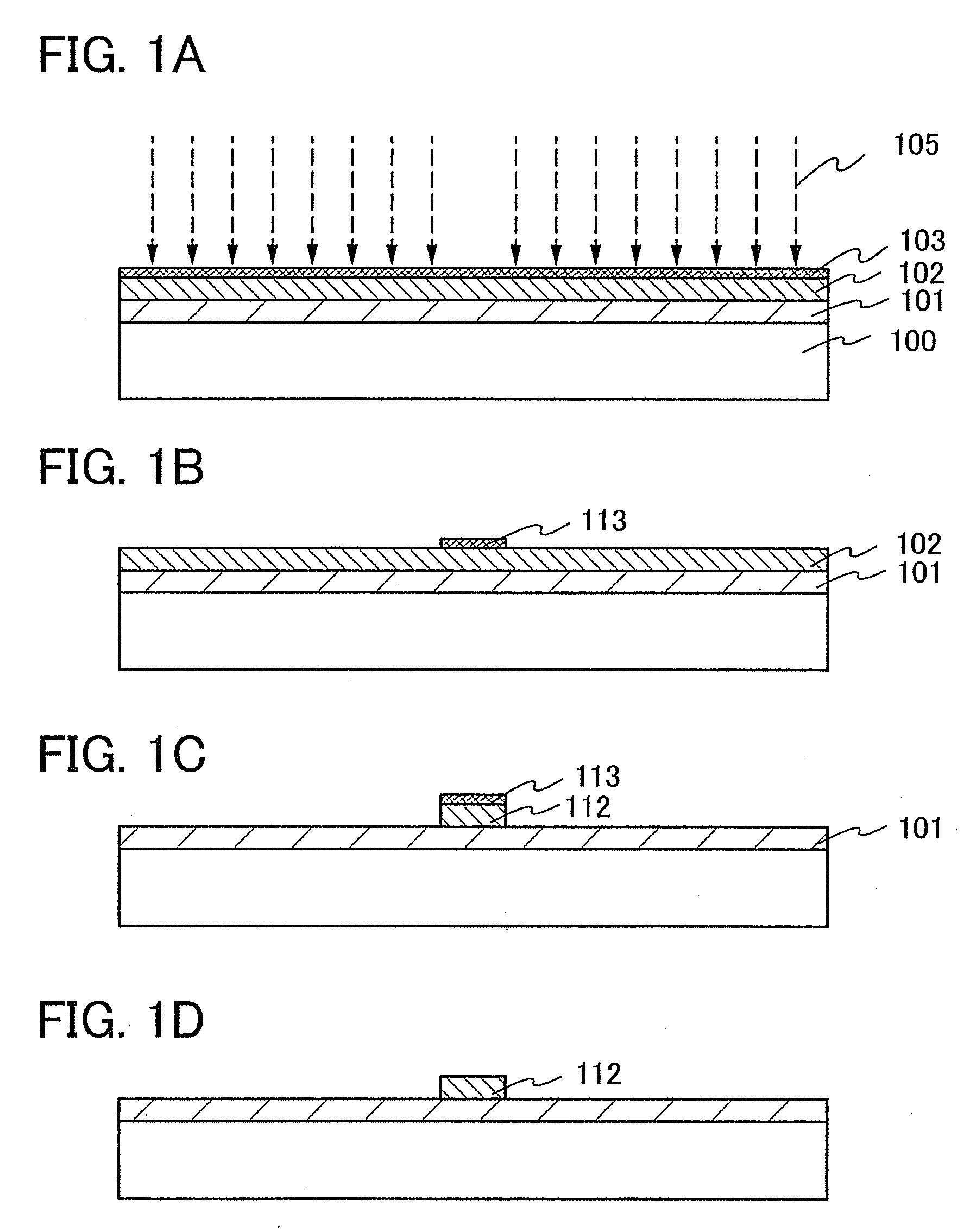

The present invention provides a method by which a thin film process can be conducted simply and accurately without using resist. Further, the present invention provides a method of manufacturing semiconductor devices at low cost. A first layer is formed over a substrate, a peeling layer is formed over the first layer, the peeling layer is selectively irradiated with a laser beam from the peeling layer side to reduce adhesiveness of a part of the peeling layer. Next, the peeling layer in the part with reduced adhesiveness is removed, and the left portion of the peeling layer is used as a mask to selectively etch the first layer.

Owner:SEMICON ENERGY LAB CO LTD

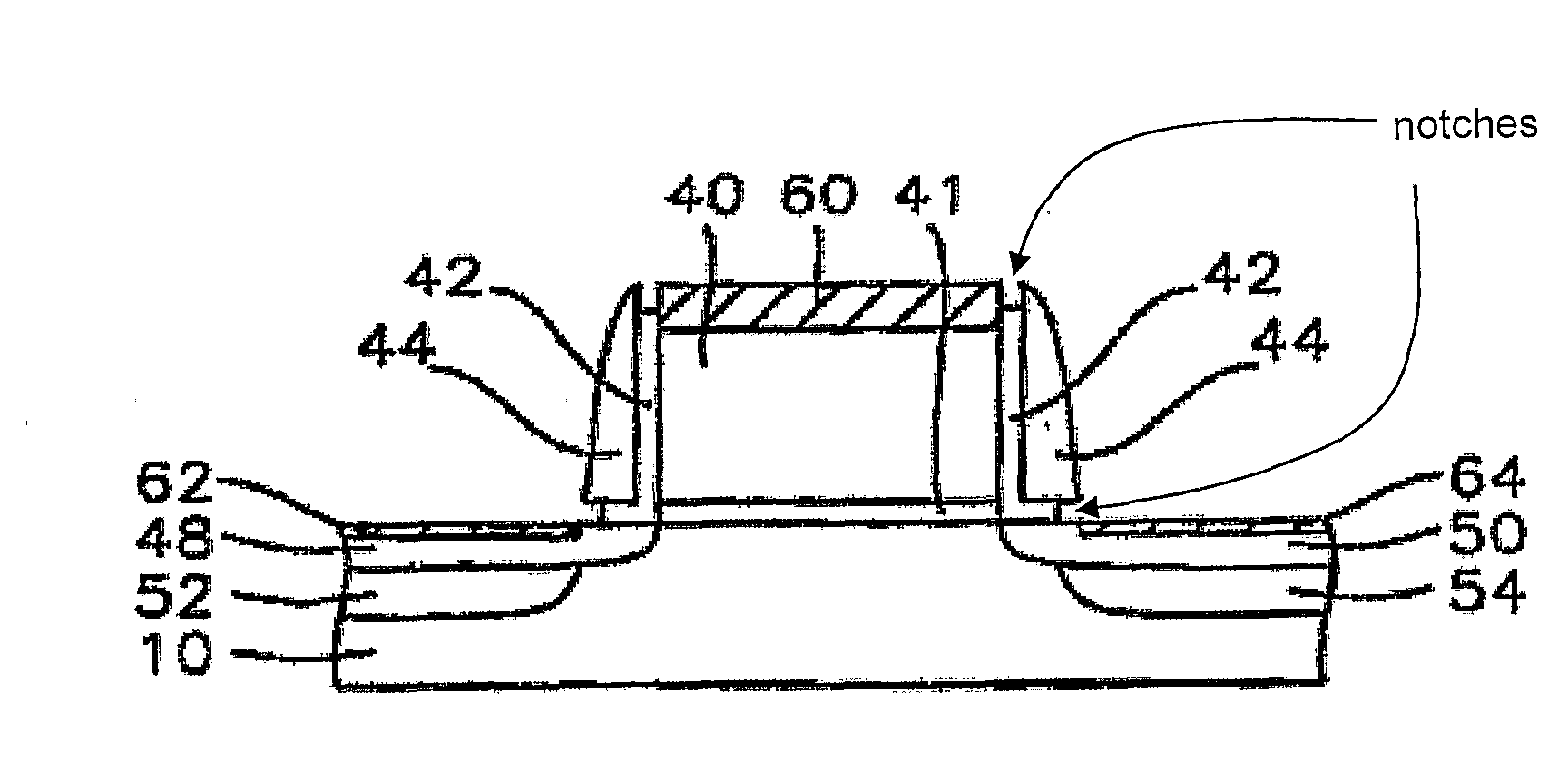

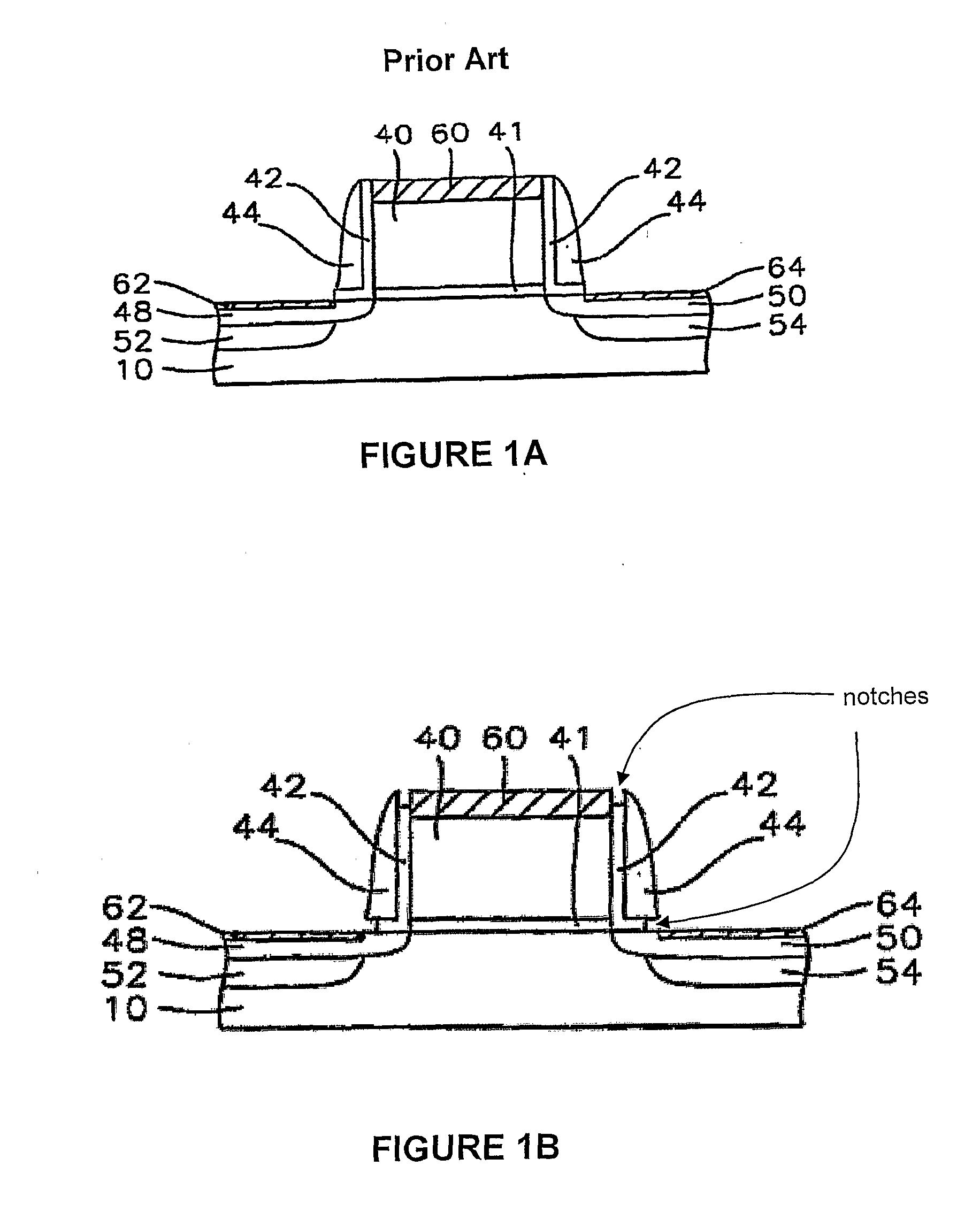

Composition and method for selectively etching gate spacer oxide material

InactiveUS20090032766A1TransistorSemiconductor/solid-state device manufacturingSalicideOrganic solvent

A gate spacer oxide material removal composition and process for at least partial removal of gate spacer oxide material from a microelectronic device having same thereon. The anhydrous removal composition includes at least one organic solvent, at least one chelating agent, a base fluoride:acid fluoride component, and optionally at least one passivator. The composition achieves the selective removal of gate spacer oxide material relative to polysilicon and silicon nitride from the vicinity of the gate electrode on the surface of the microelectronic device with minimal etching of metal silicide interconnect material species employed in the gate electrode architecture.

Owner:ADVANCED TECH MATERIALS INC

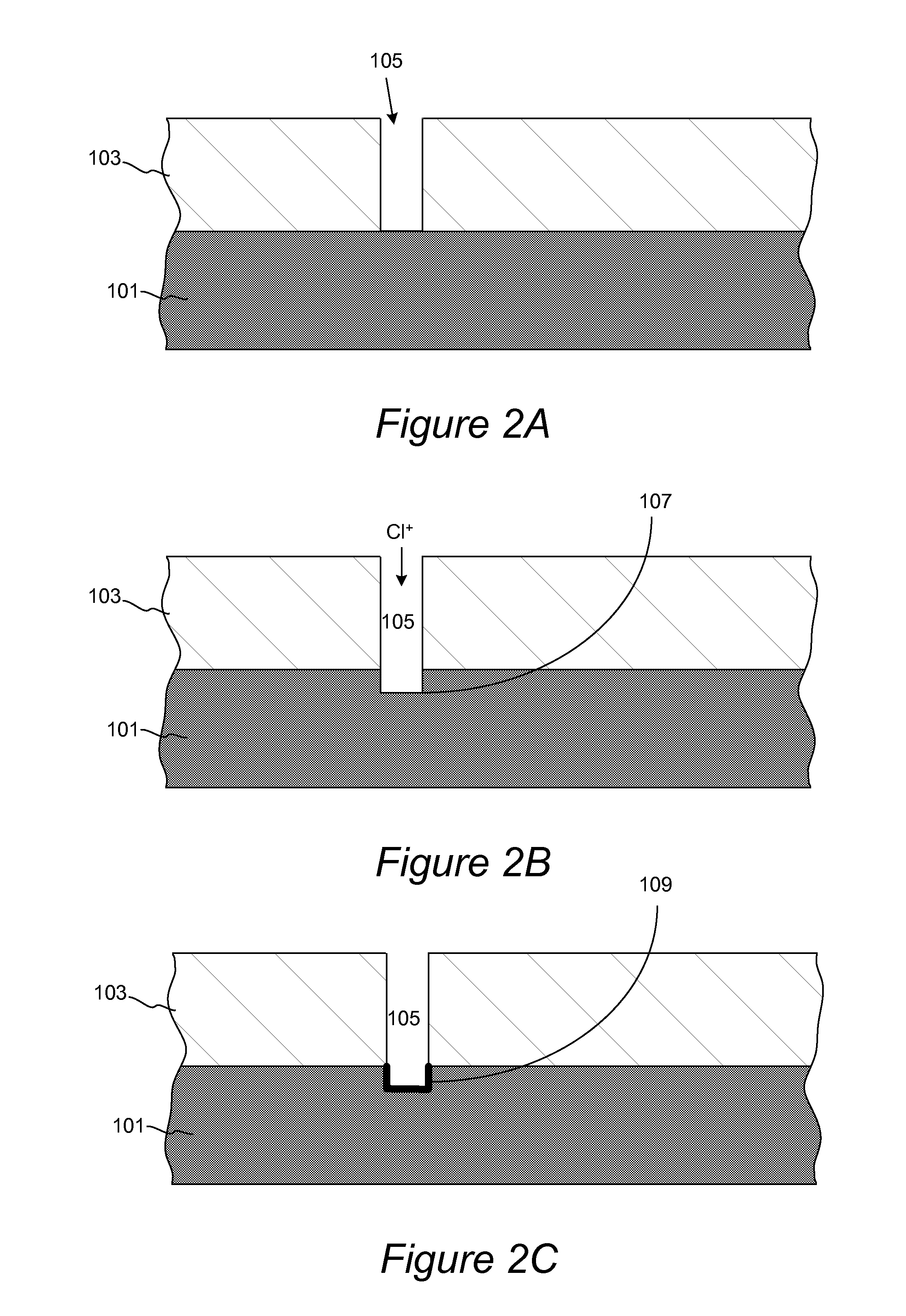

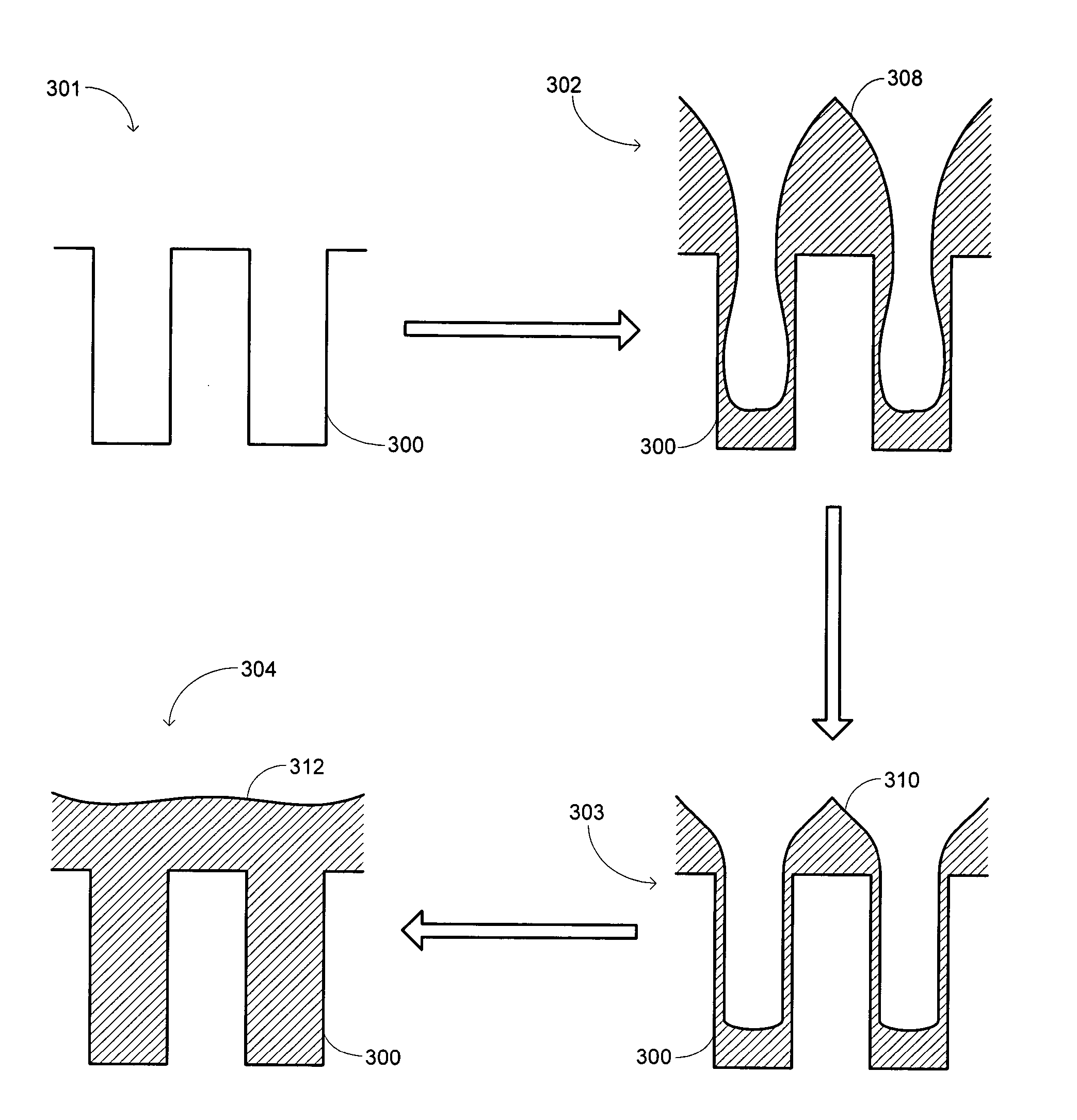

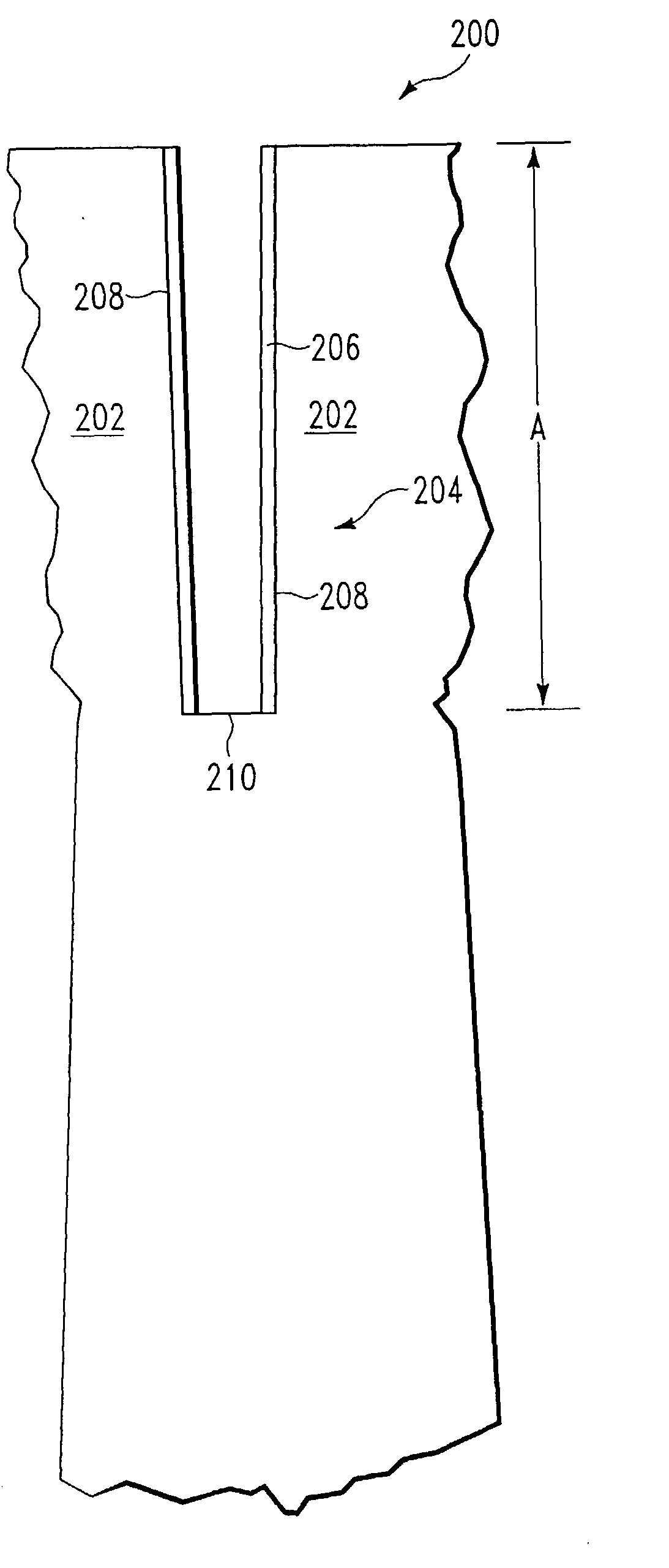

Method of micromachining a multi-part cavity

The present disclosure pertains to our discovery of a particularly efficient method for etching a multi-part cavity in a substrate. The method provides for first etching a shaped opening, depositing a protective layer over at least a portion of the inner surface of the shaped opening, and then etching a shaped cavity directly beneath and in continuous communication with the shaped opening. The protective layer protects the etch profile of the shaped opening during etching of the shaped cavity, so that the shaped opening and the shaped cavity can be etched to have different shapes, if desired. In particular embodiments of the method of the invention, lateral etch barrier layers and / or implanted etch stops are also used to direct the etching process. The method of the invention can be applied to any application where it is necessary or desirable to provide a shaped opening and an underlying shaped cavity having varying shapes. The method is also useful whenever it is necessary to maintain tight control over the dimensions of the shaped opening.

Owner:APPLIED MATERIALS INC

Bi-layer approach for a hermetic low dielectric constant layer for barrier applications

InactiveUS7091137B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingAnti-reflective coatingNitrogen

Methods and apparatus are provided for processing a substrate with a bilayer barrier layer. In one aspect, the invention provides a method for processing a substrate including depositing a nitrogen containing barrier layer on a substrate surface and then depositing a nitrogen free barrier layer thereon. The barrier layer may be deposited over dielectric materials, conductive materials, or both. The bilayer barrier layer may also be used as an etch stop, an anti-reflective coating, or a passivation layer.

Owner:APPLIED MATERIALS INC

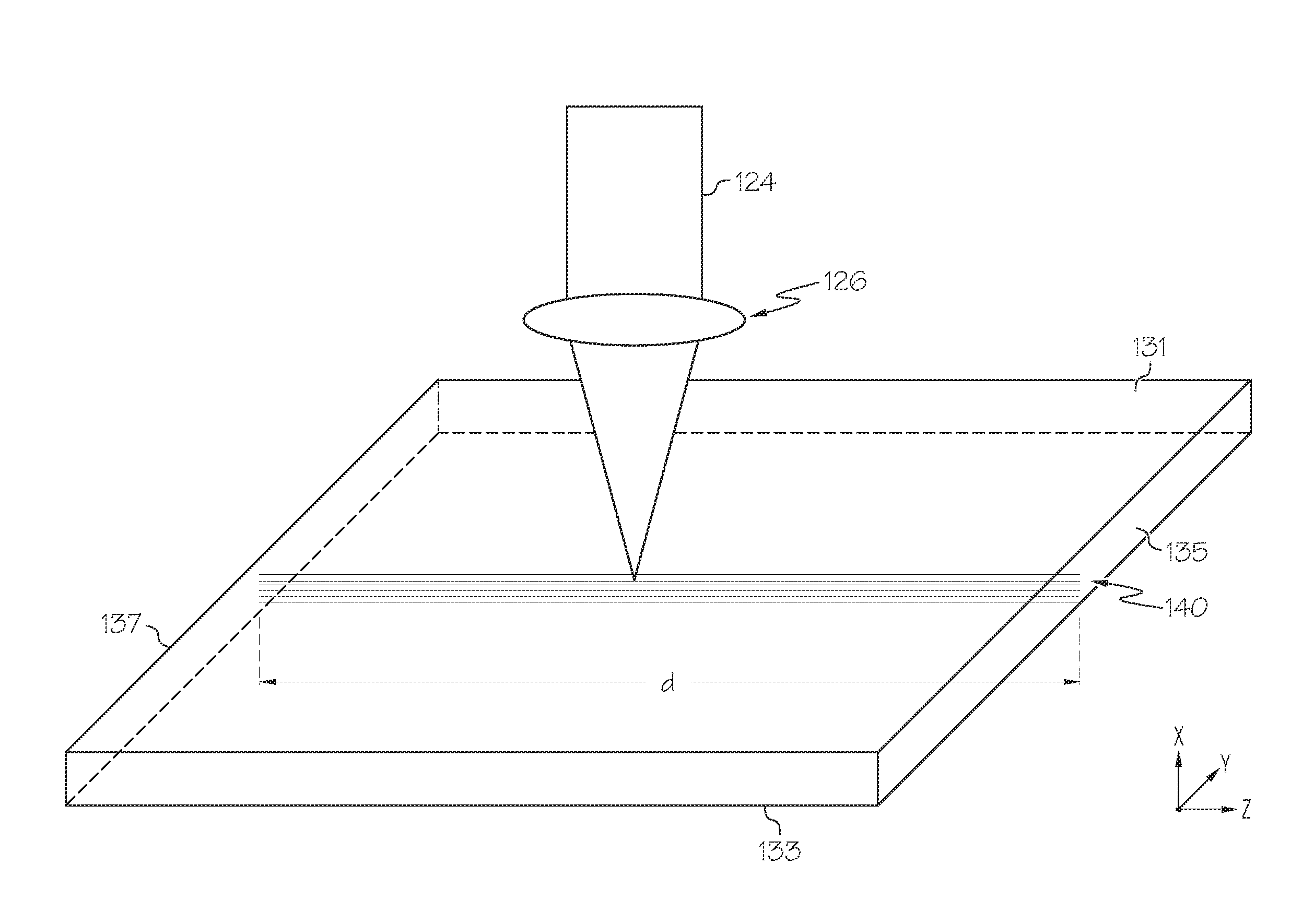

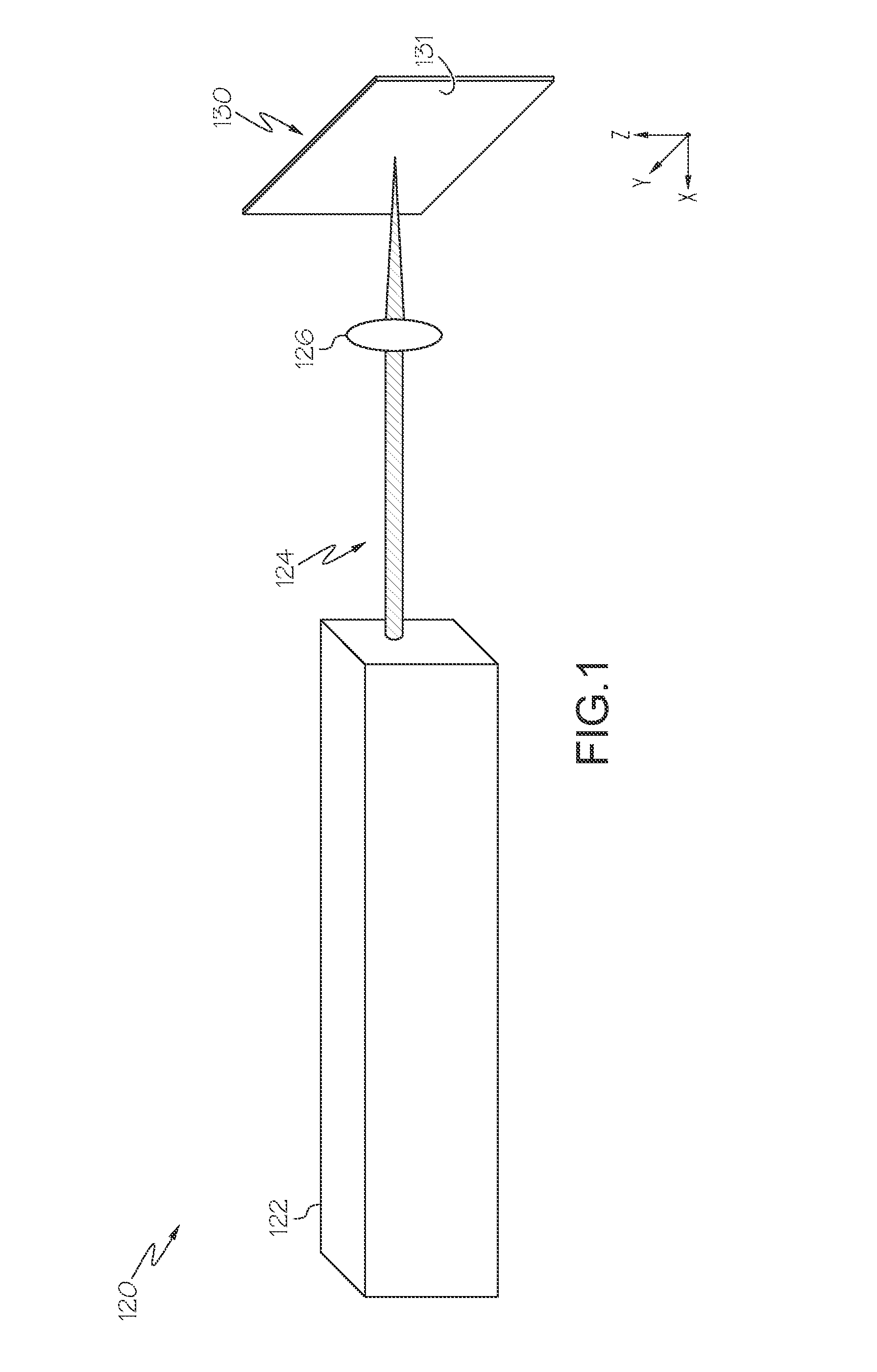

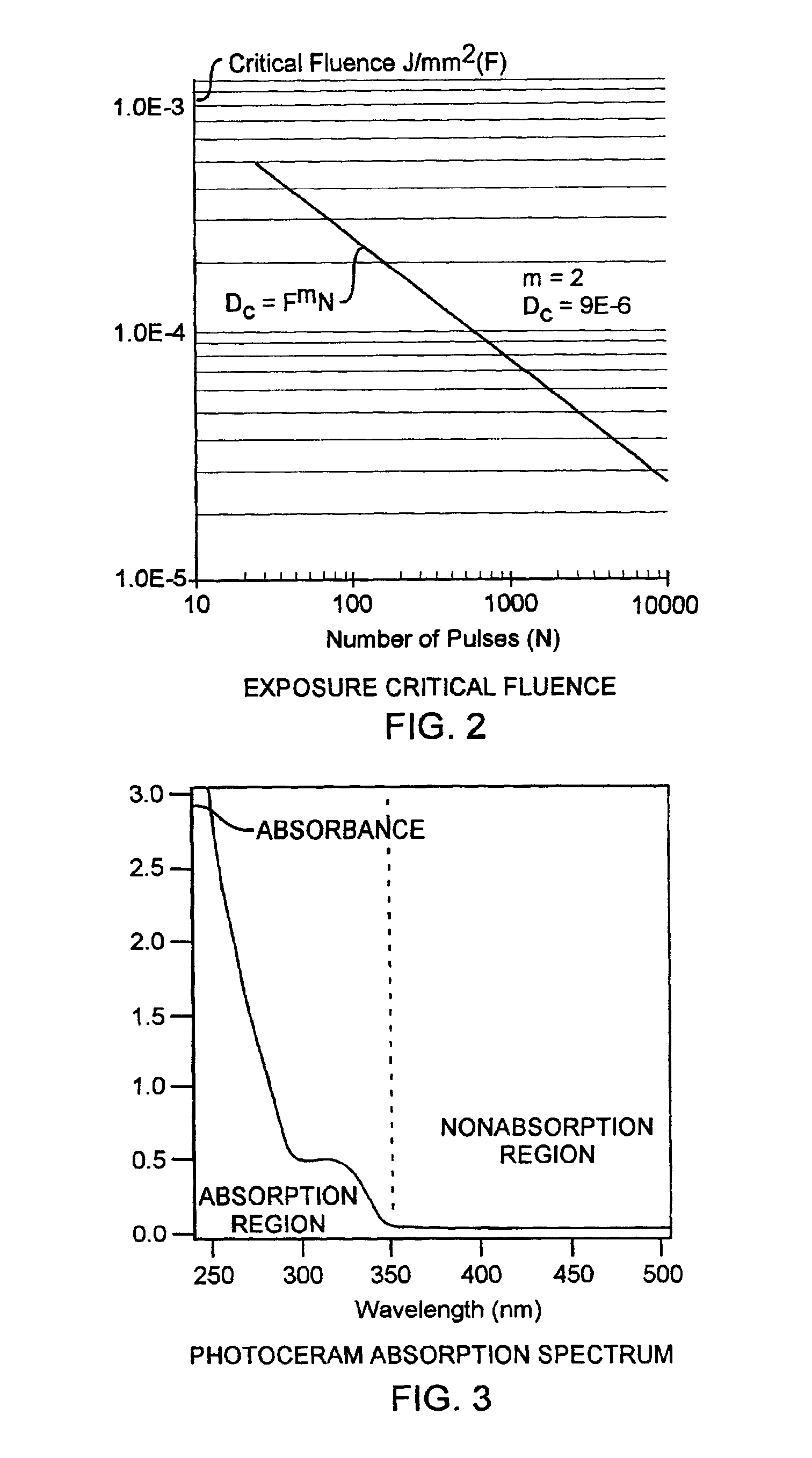

Ultraviolet method of embedding structures in photocerams

InactiveUS6932933B2Fast batch processingEasy to controlDecorative surface effectsPhotomechanical apparatusUltravioletVolumetric Mass Density

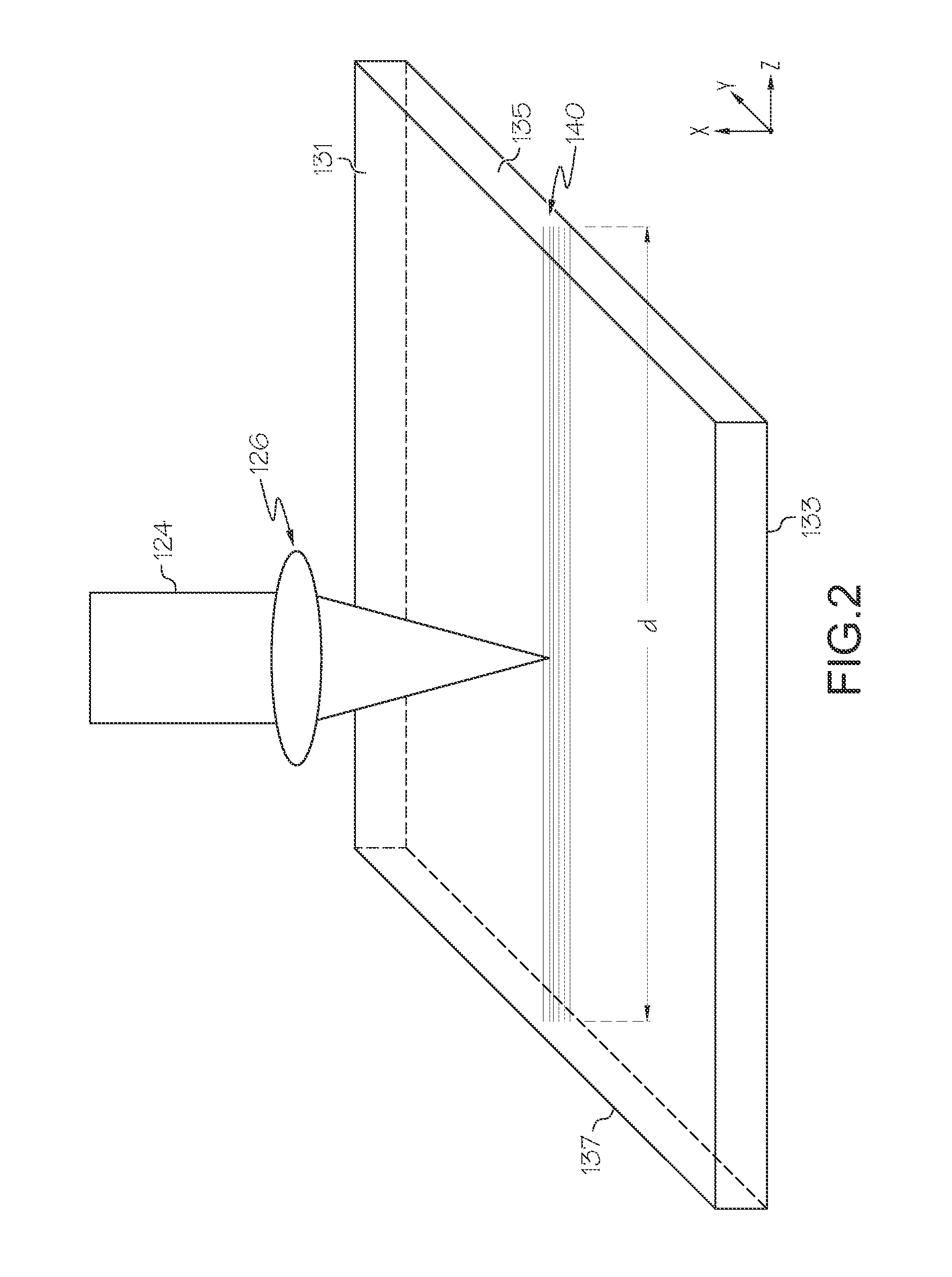

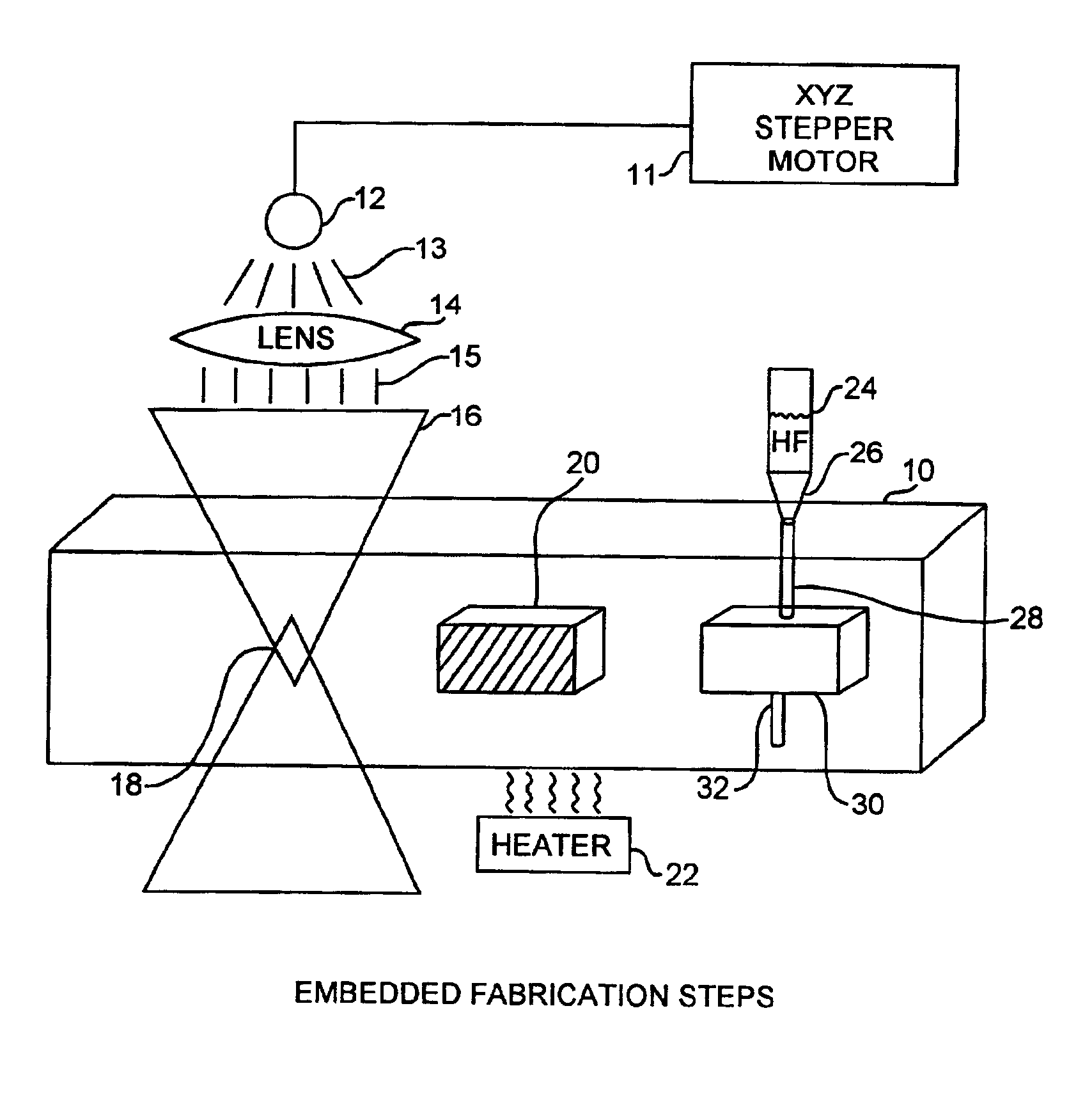

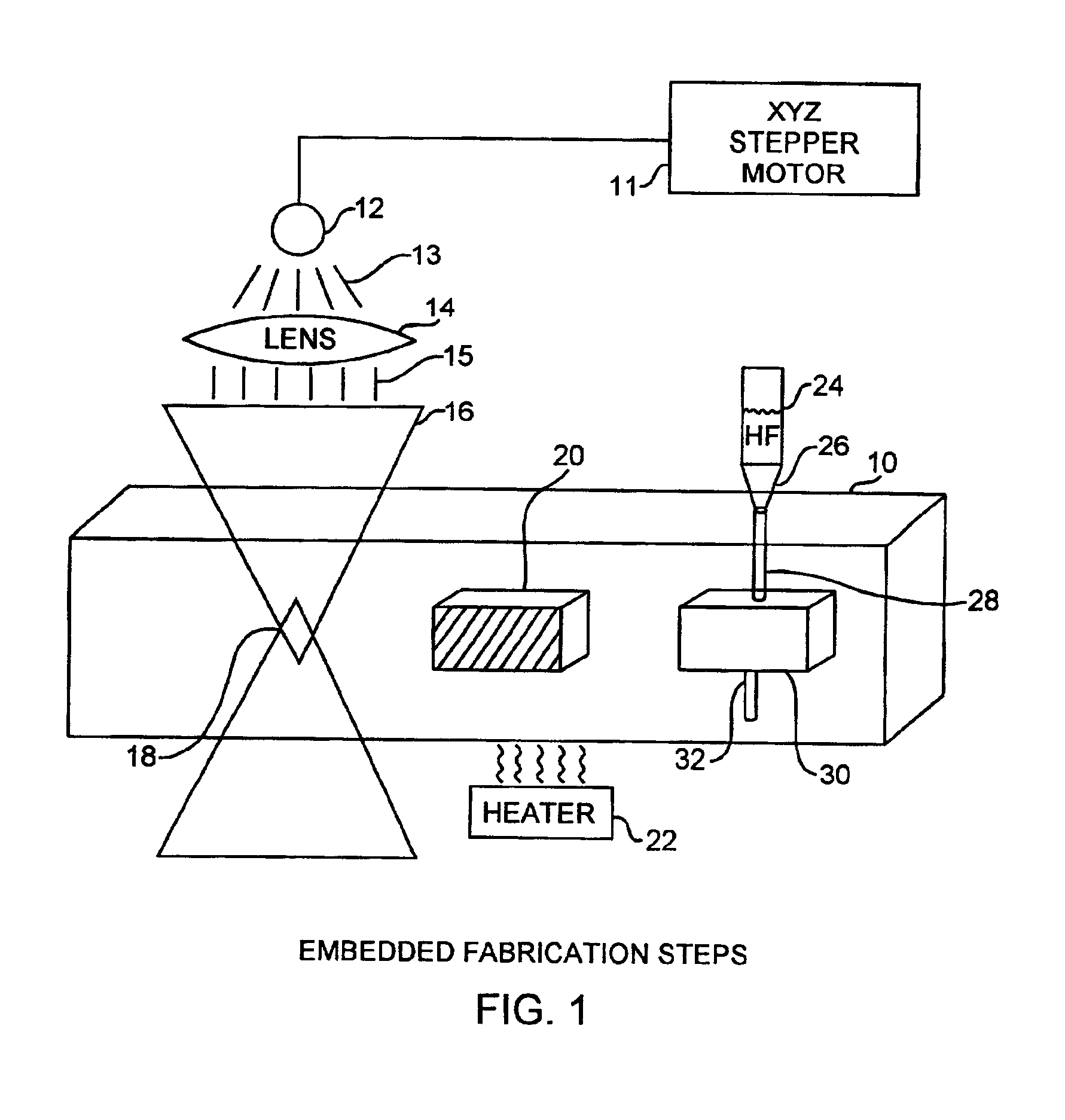

A laser direct write method creates true three dimensional structures within photocerams using an focused pulsed ultraviolet laser with a wavelength in a weakly absorbing region of the photoceram material. A critical dose of focused laser UV light selectively exposes embedded volumes of the material for subsequent selective etching. The photoceram material exposure is nonlinear with the laser fluence and the critical dose depends on the square of the per shot fluence and the number of pulses. The laser light is focused to a focal depth for selective volumetric exposure of the material within a focal volume within the remaining collateral volumes that is critically dosed for selecting etching and batch fabrication of highly defined embedded structures.

Owner:THE AEROSPACE CORPORATION