Patents

Literature

265results about How to "Easy to etch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

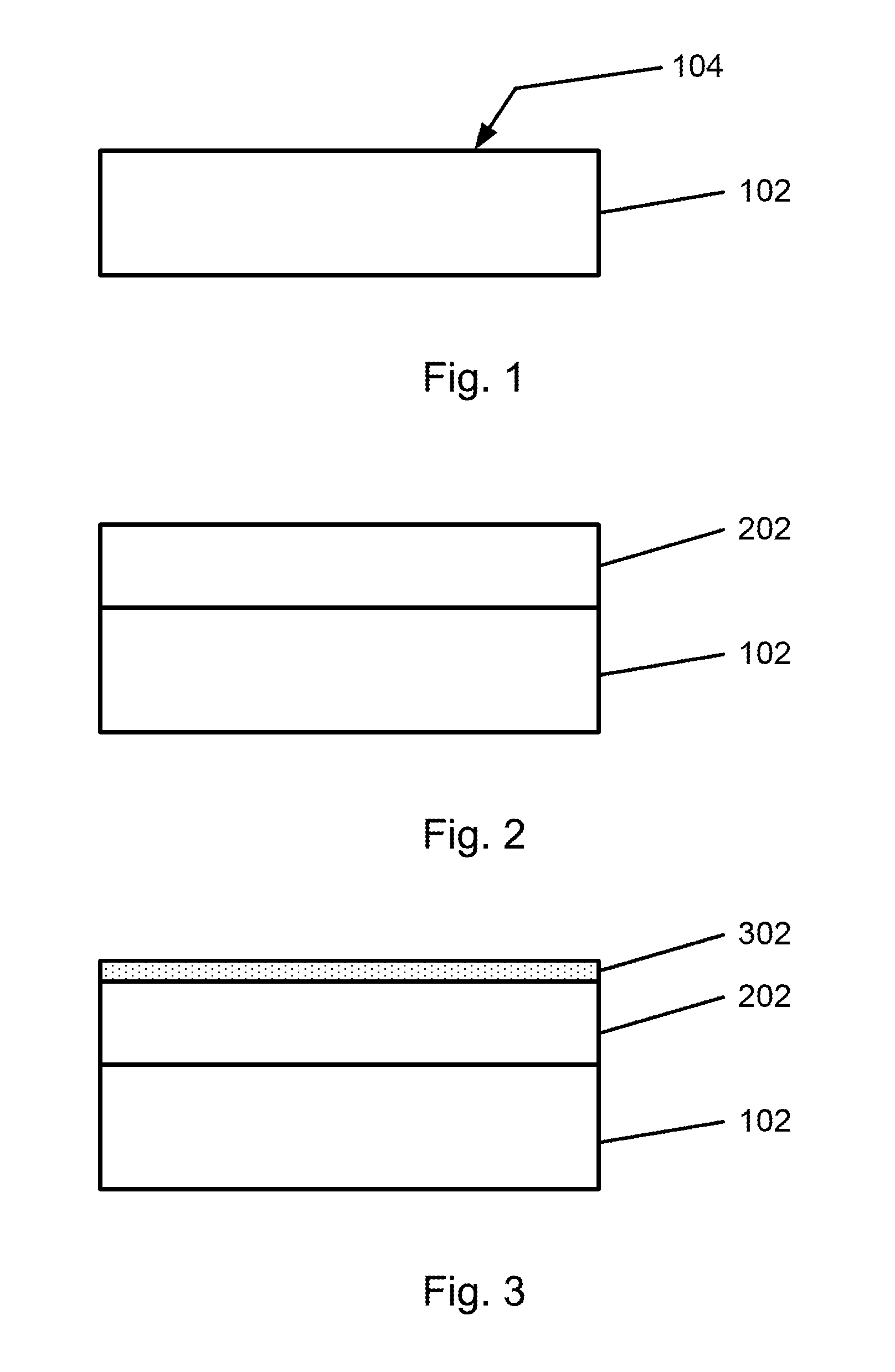

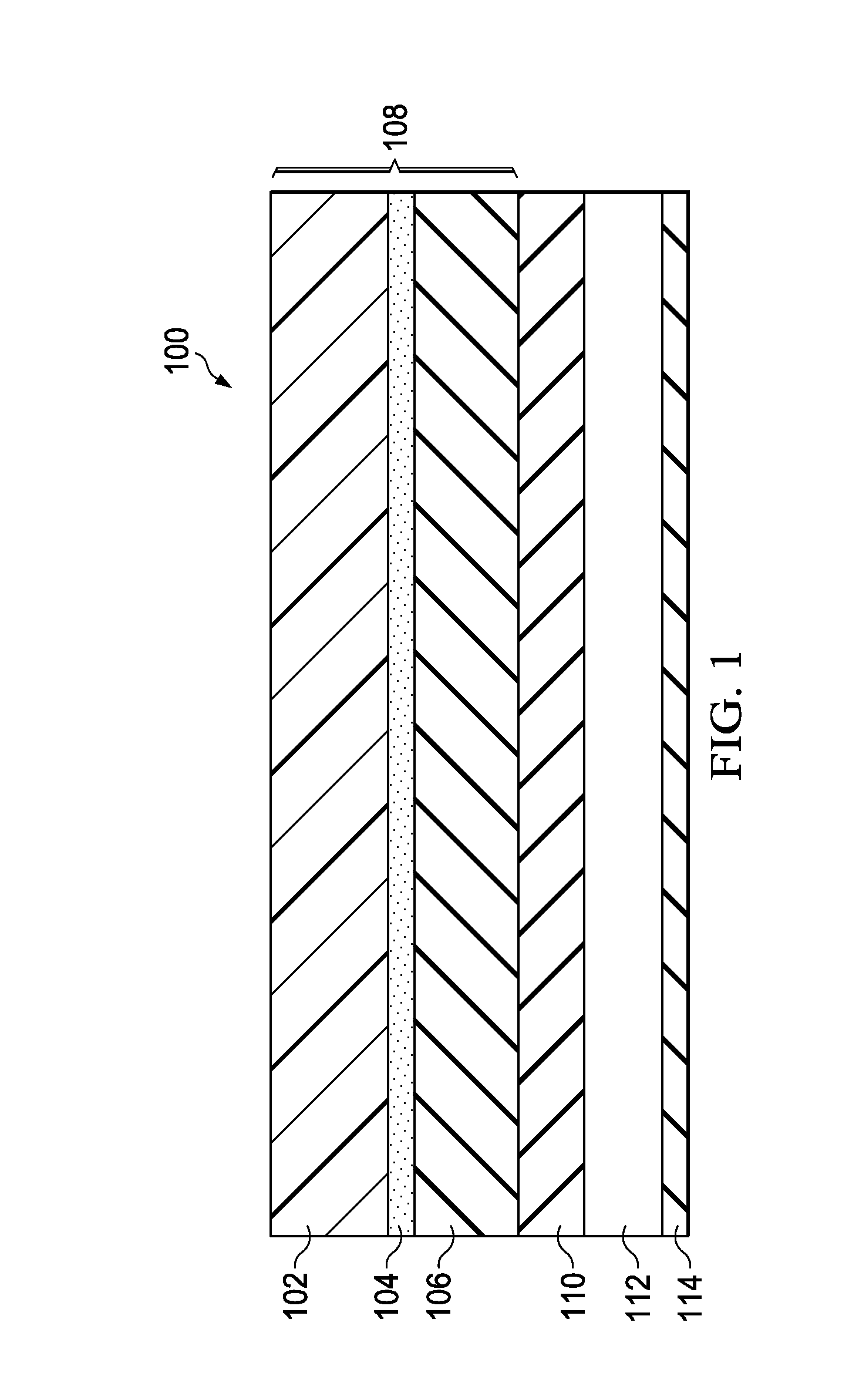

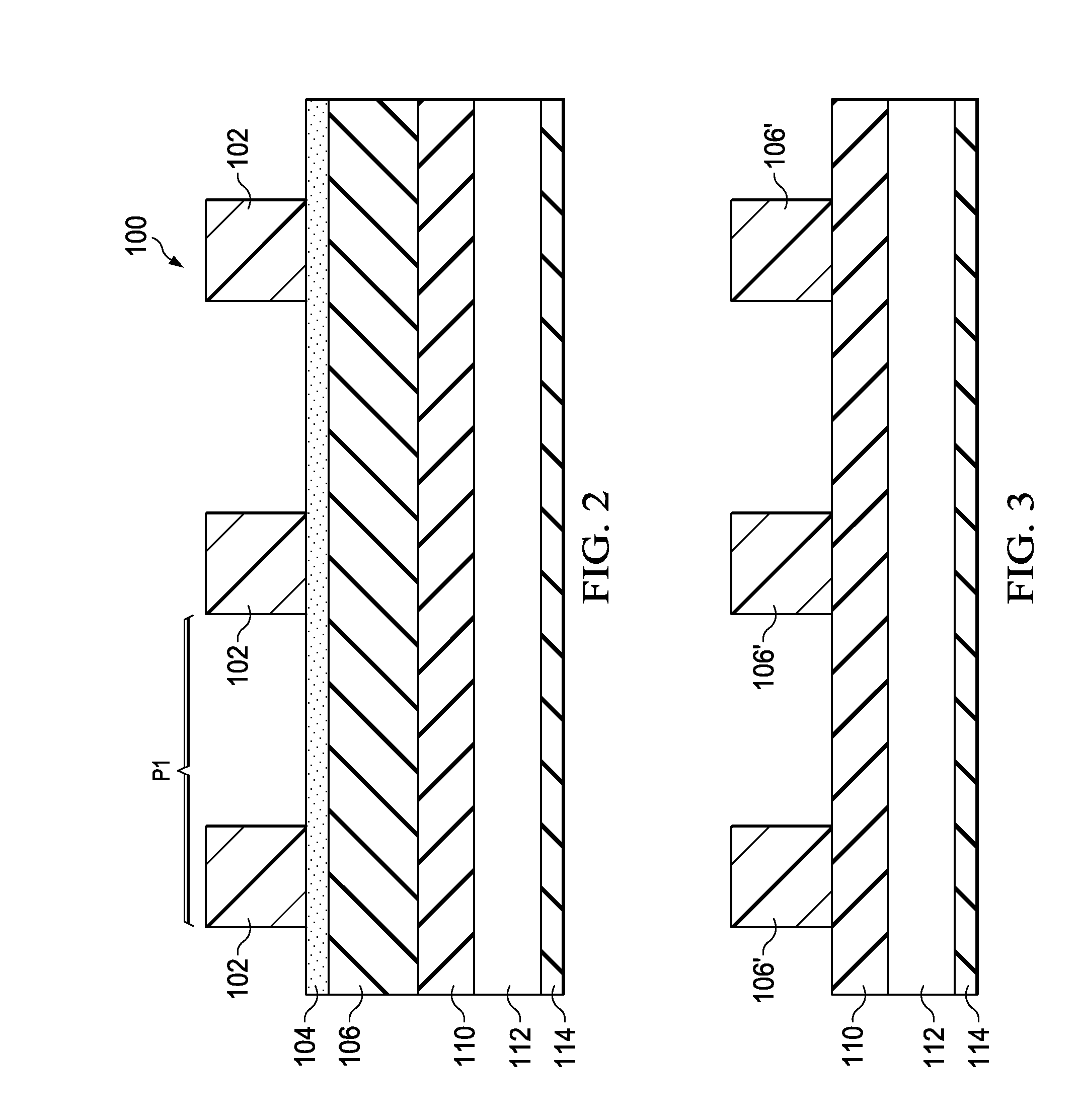

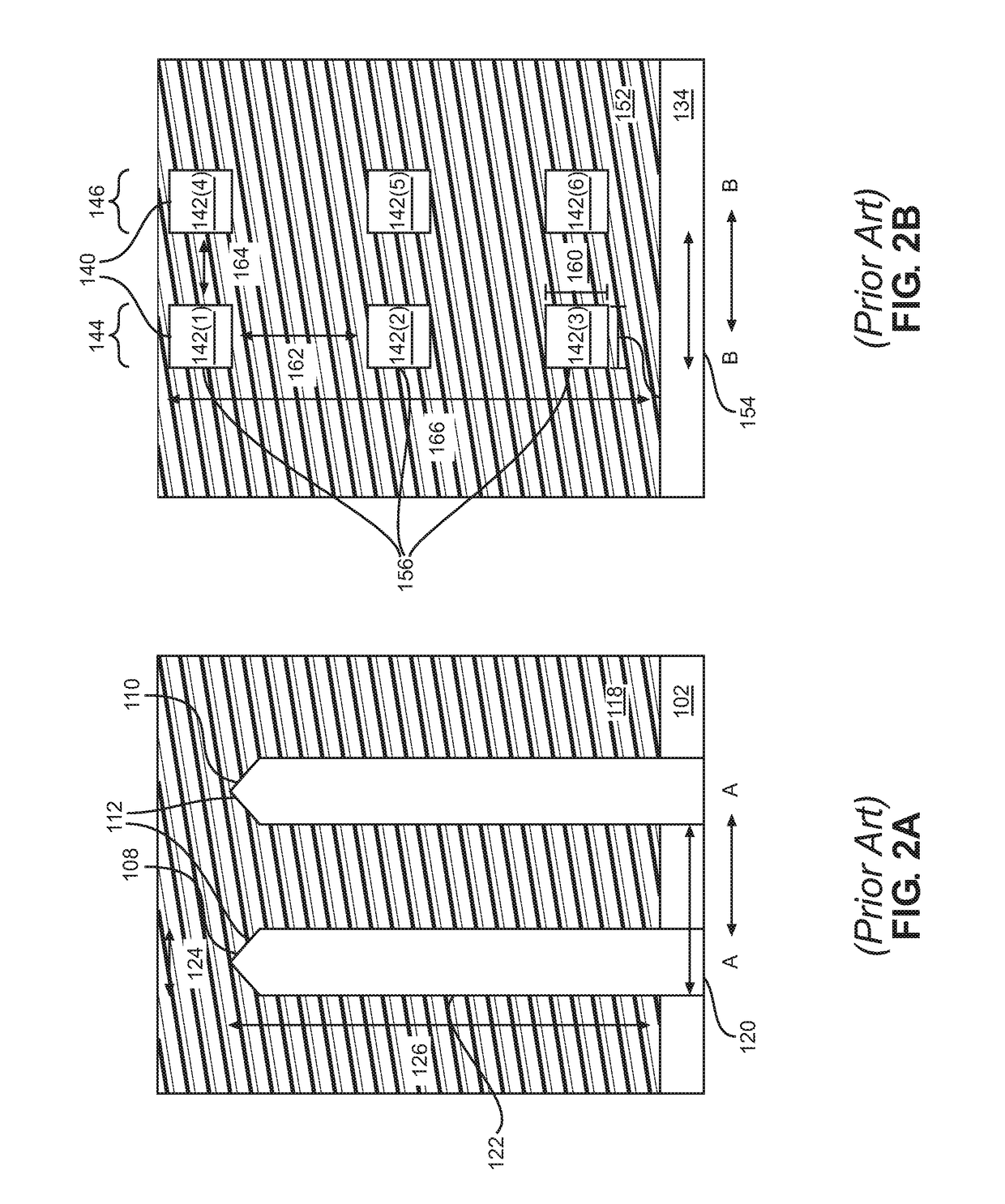

Pillar structure for memory device and method

ActiveUS20110312151A1High densityWide rangeSemiconductor/solid-state device manufacturingConductive materialsEngineering

A method of forming a memory device. The method provides a semiconductor substrate having a surface region. A first dielectric layer is formed overlying the surface region of the semiconductor substrate. A bottom wiring structure is formed overlying the first dielectric layer and a second dielectric material is formed overlying the top wiring structure. A bottom metal barrier material is formed to provide a metal-to-metal contact with the bottom wiring structure. The method forms a pillar structure by patterning and etching a material stack including the bottom metal barrier material, a contact material, a switching material, a conductive material, and a top barrier material. The pillar structure maintains a metal-to-metal contact with the bottom wiring structure regardless of the alignment of the pillar structure with the bottom wiring structure during etching. A top wiring structure is formed overlying the pillar structure at an angle to the bottom wiring structure.

Owner:CROSSBAR INC

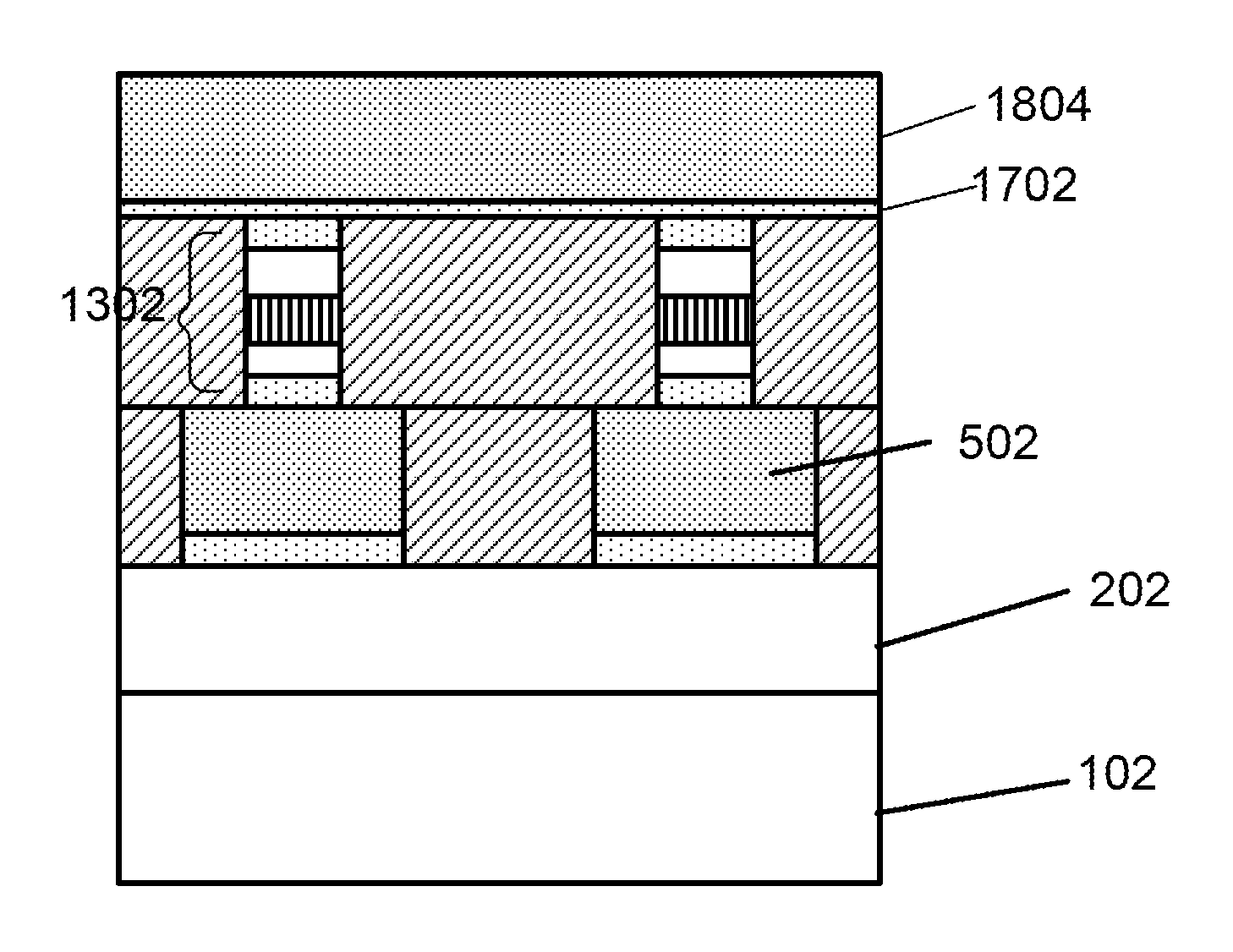

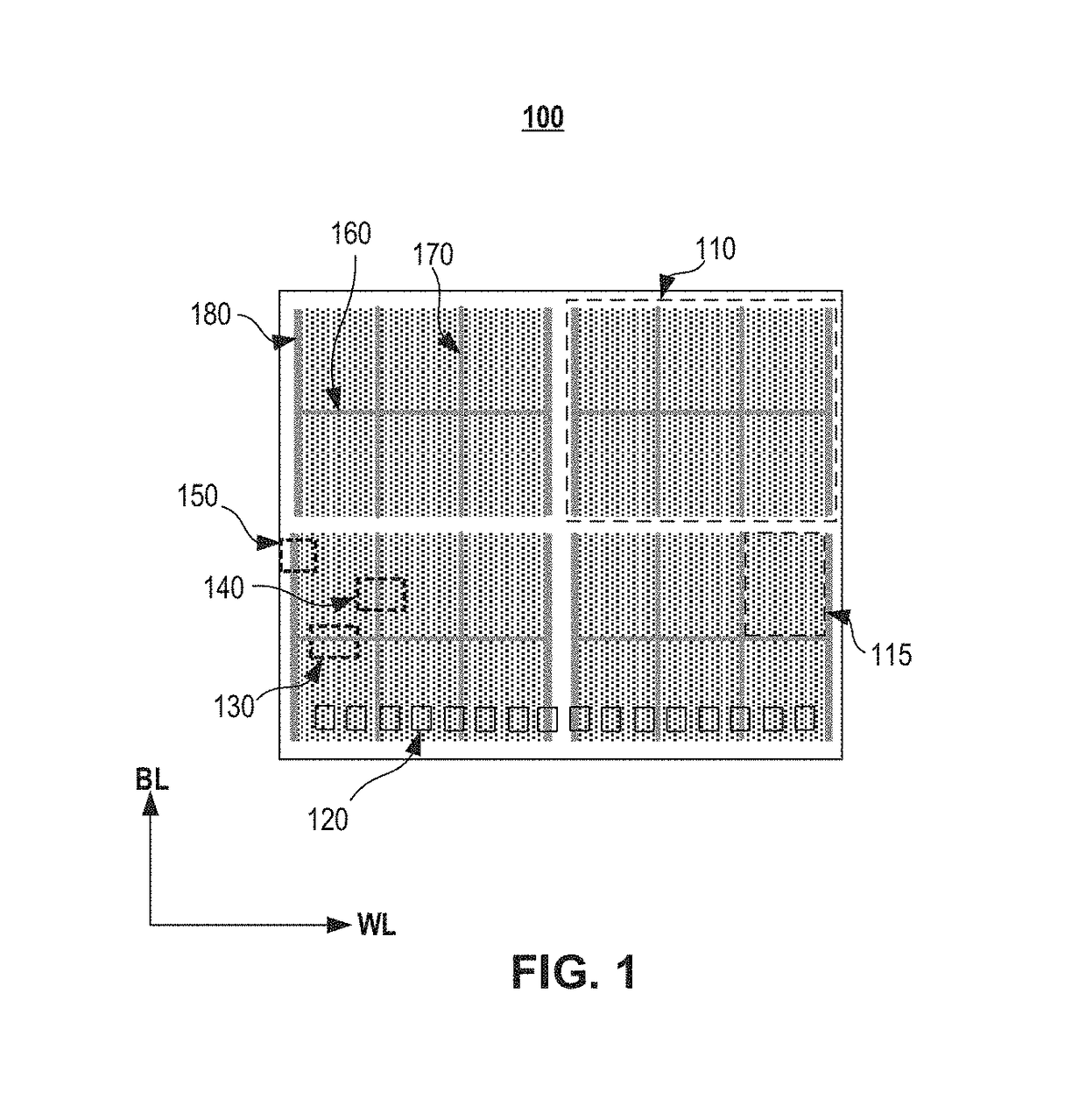

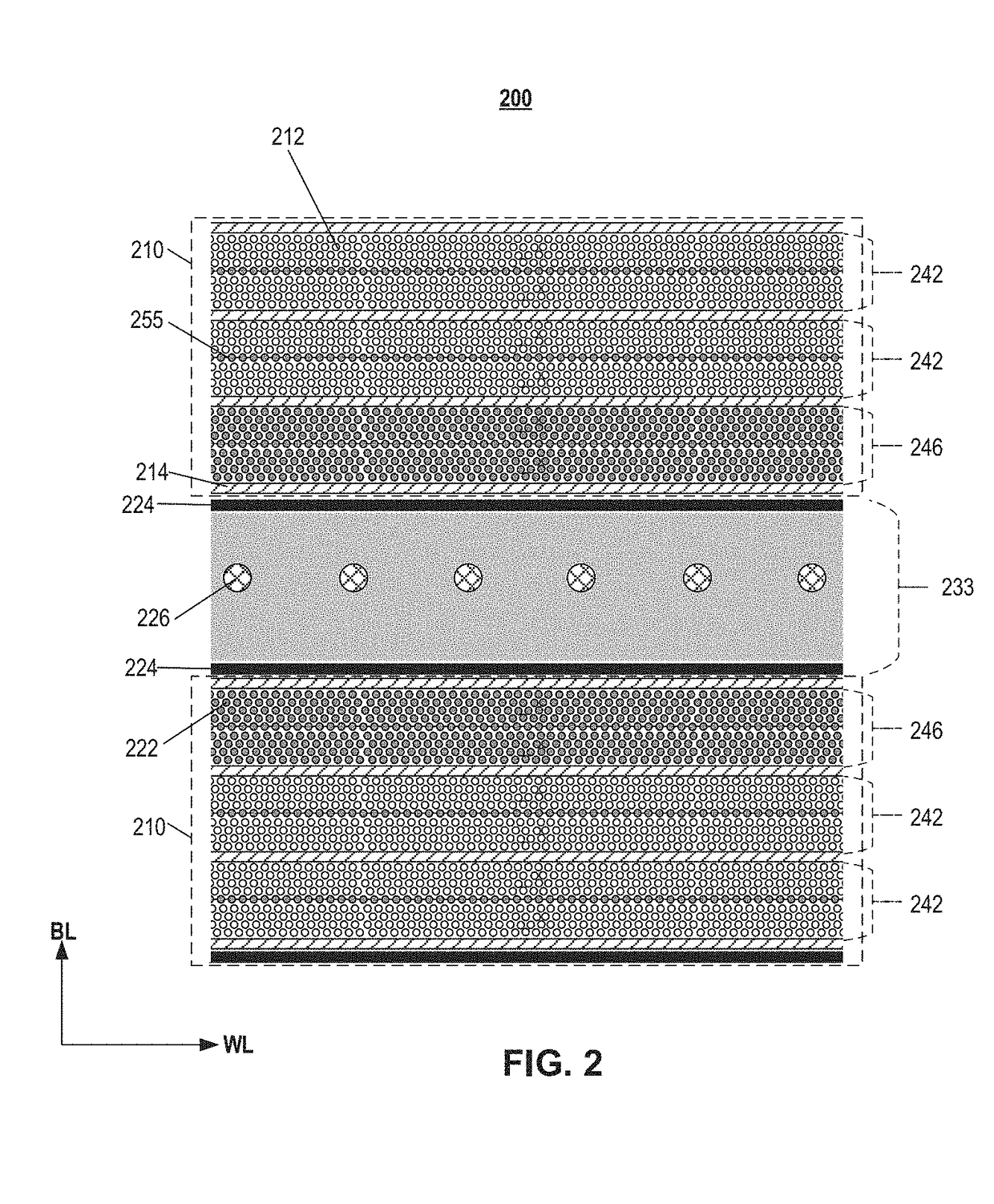

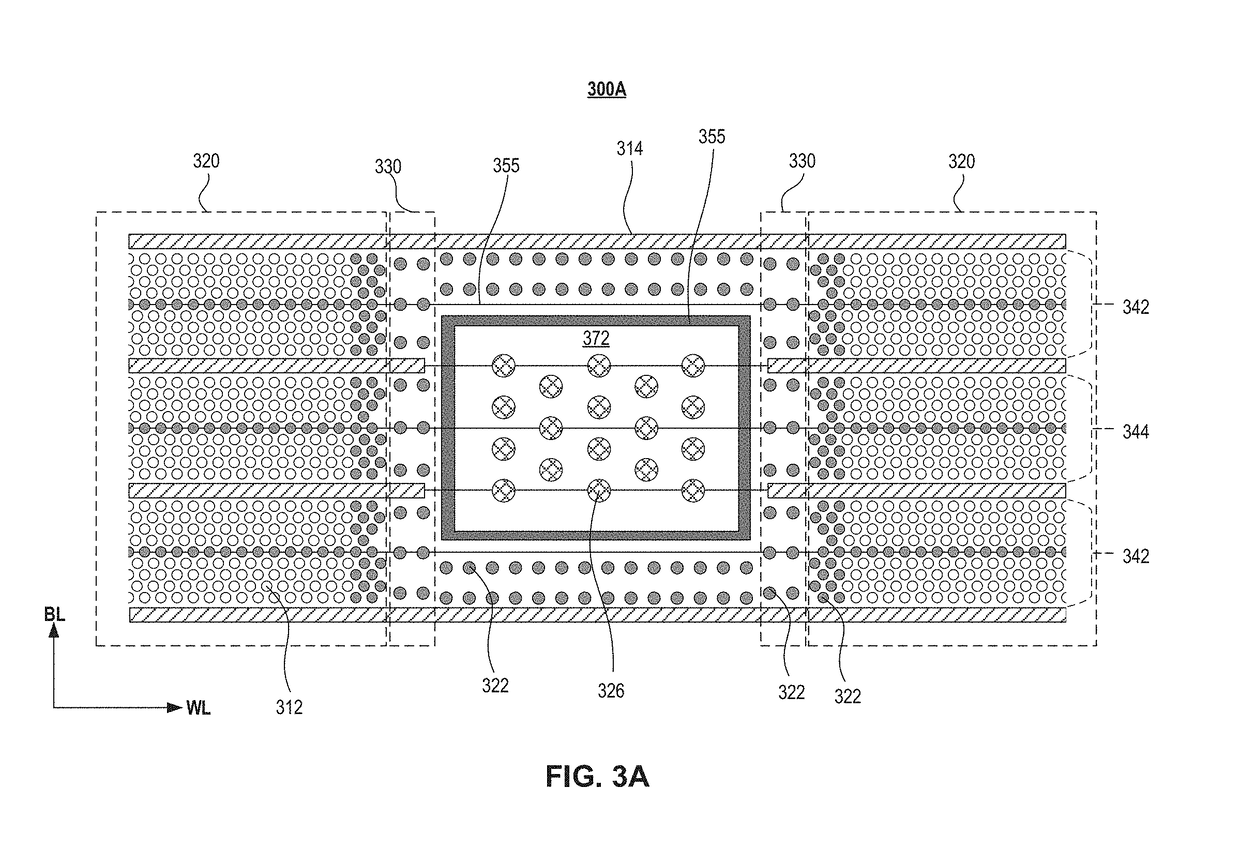

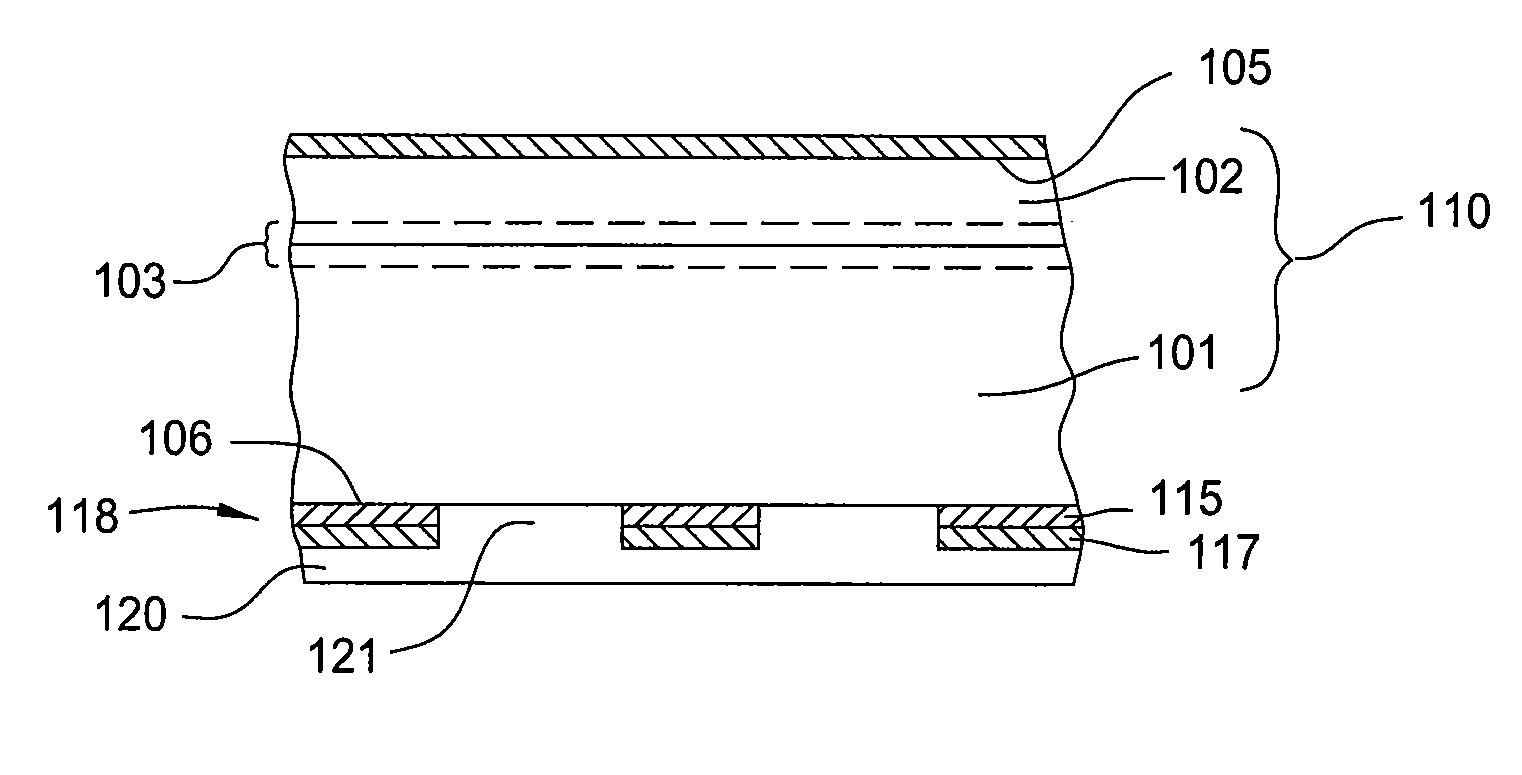

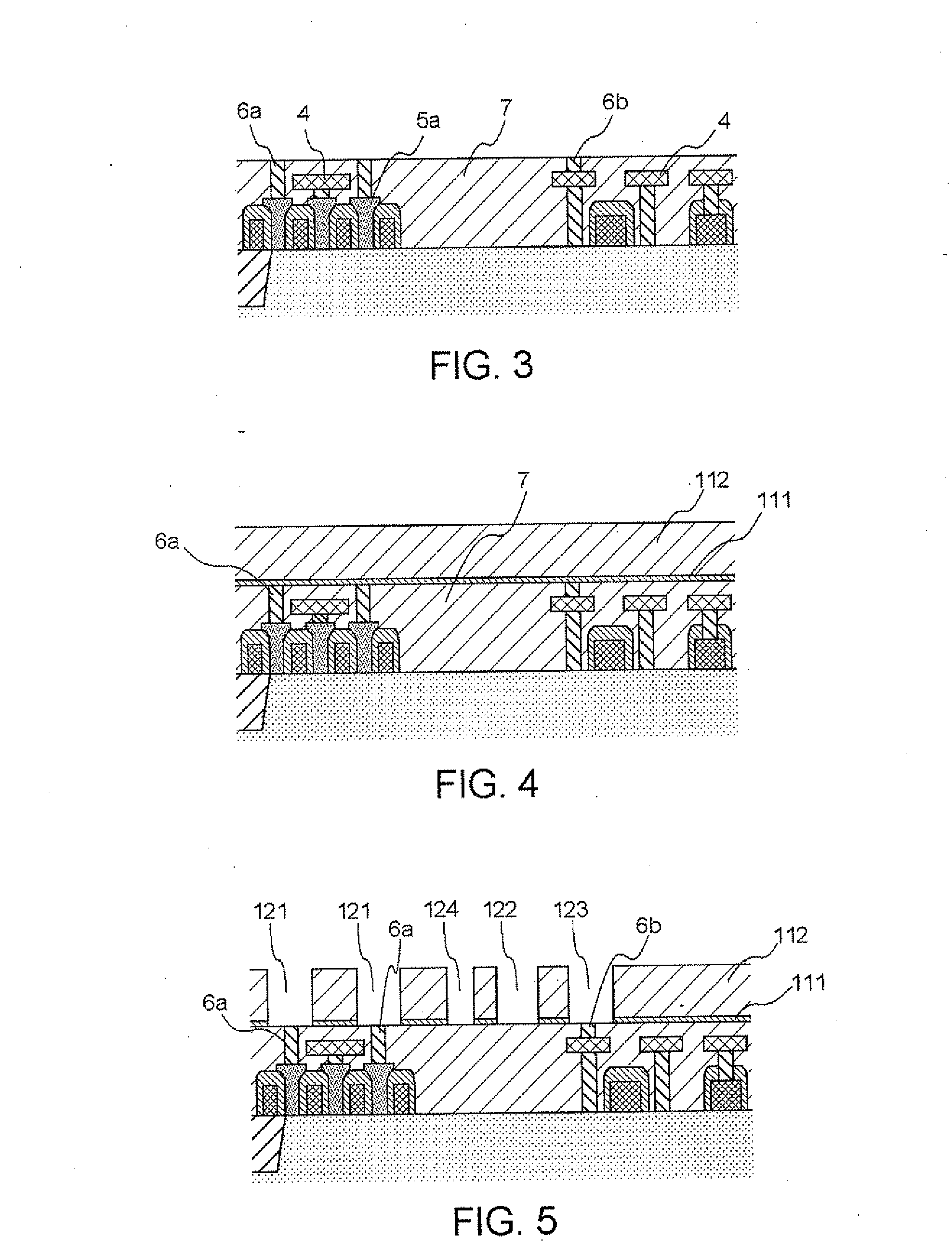

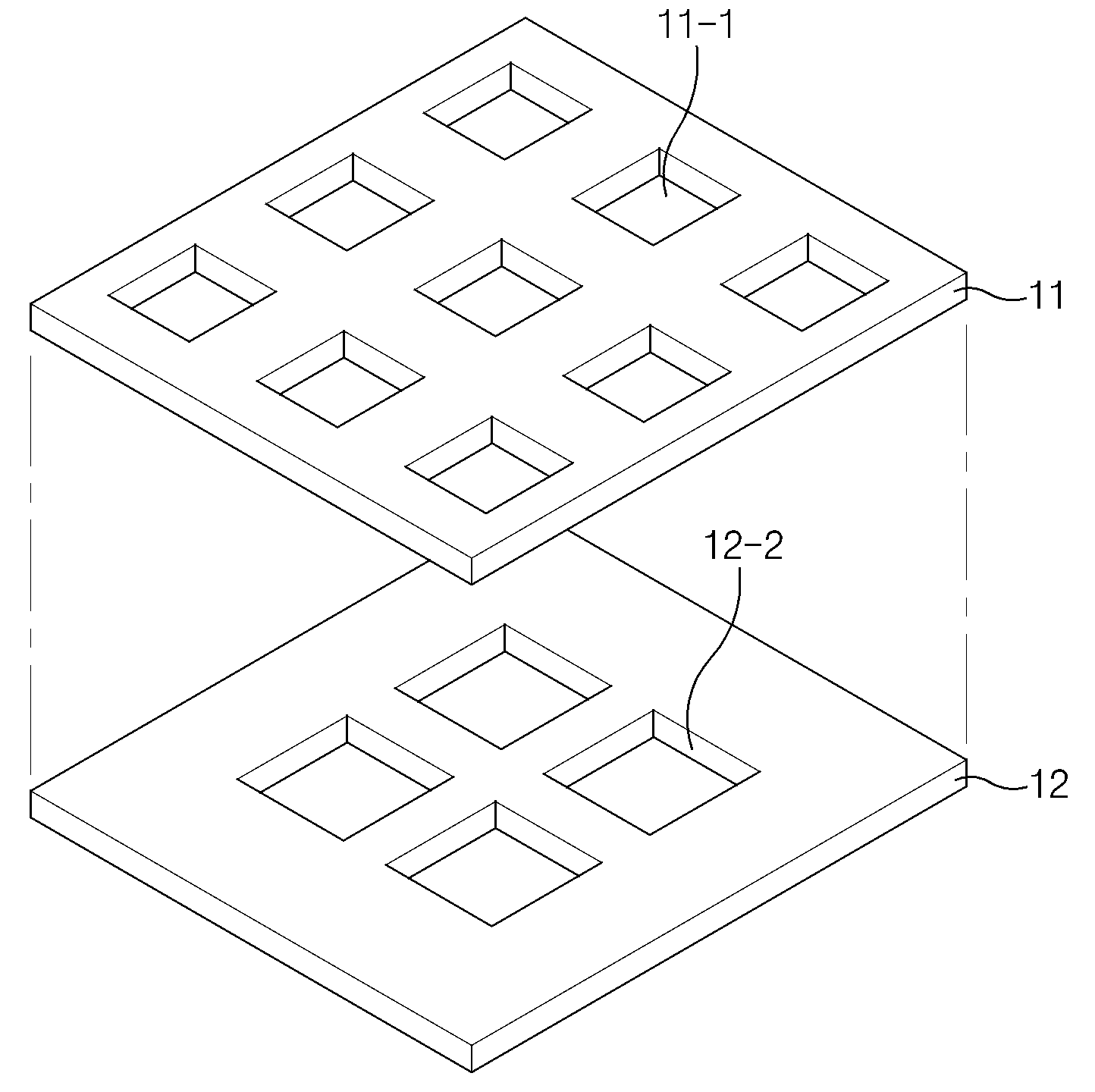

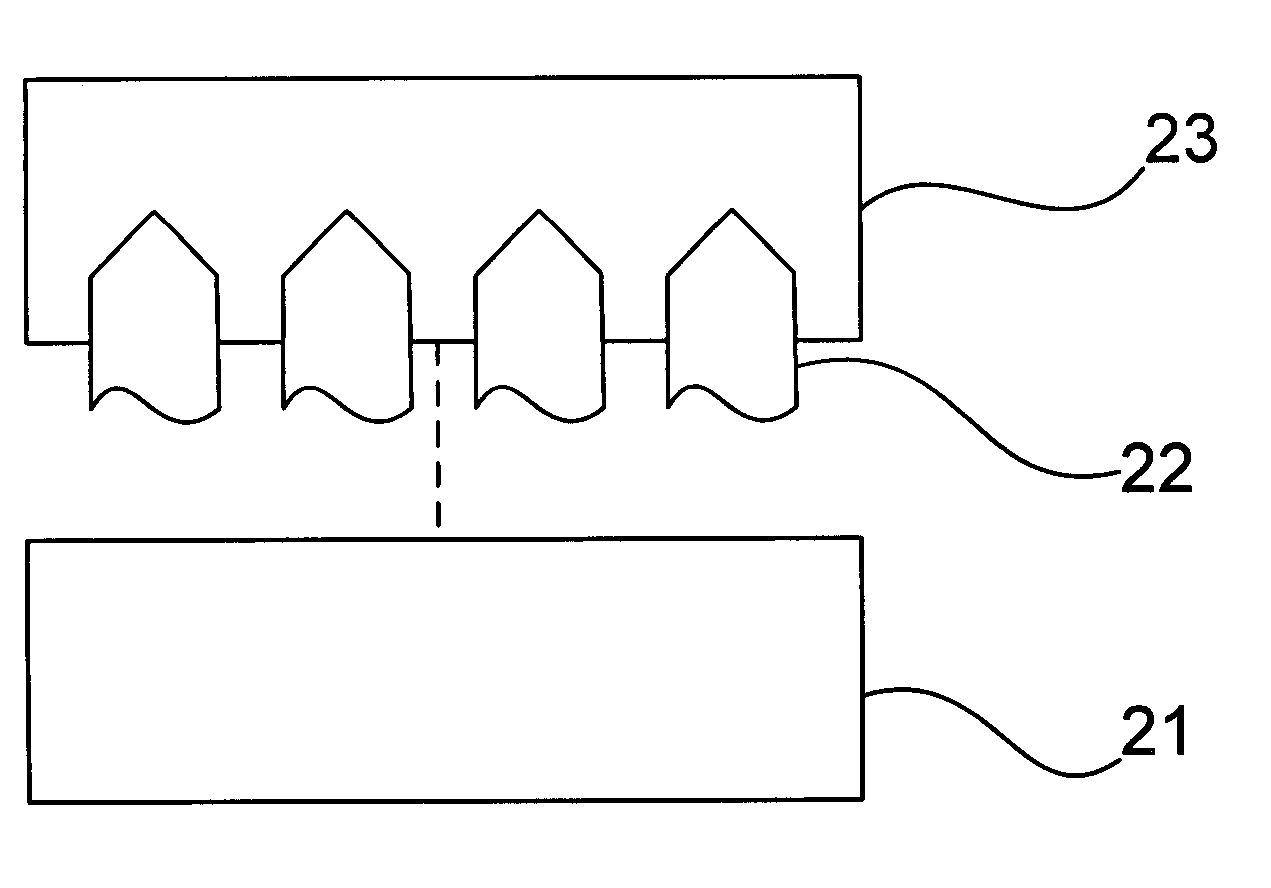

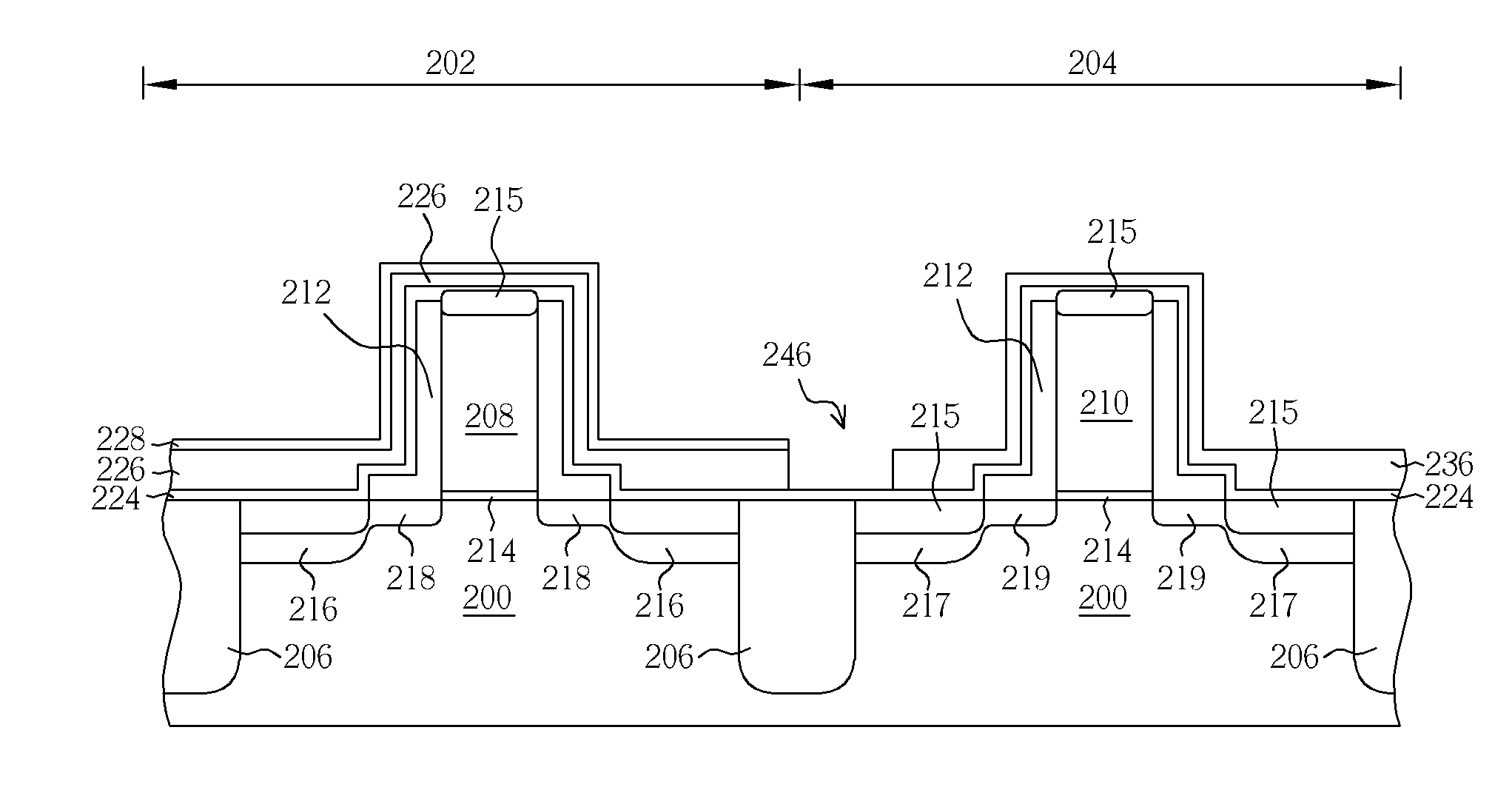

Hybrid bonding contact structure of three-dimensional memory device

ActiveUS20190057974A1Easy to etchLower Level RequirementsSemiconductor/solid-state device detailsSolid-state devicesElectricityArray data structure

Embodiments of through array contact structures of a 3D memory device and fabricating method thereof are disclosed. The memory device includes an alternating layer stack disposed on a first substrate. The alternating layer stack includes a first region including an alternating dielectric stack, and a second region including an alternating conductor / dielectric stack. The memory device further includes a barrier structure extending vertically through the alternating layer stack to laterally separate the first region from the second region, multiple through array contacts in the first region, each through array contact extending vertically through the alternating dielectric stack, an array interconnection layer in contact with the through array contacts, a peripheral circuit formed on a second substrate. and a peripheral interconnection layer on the peripheral circuit. The array interconnection layer is bonded on the peripheral interconnection layer, such that the peripheral circuit is electrically connected with at least one through array contact.

Owner:YANGTZE MEMORY TECH CO LTD

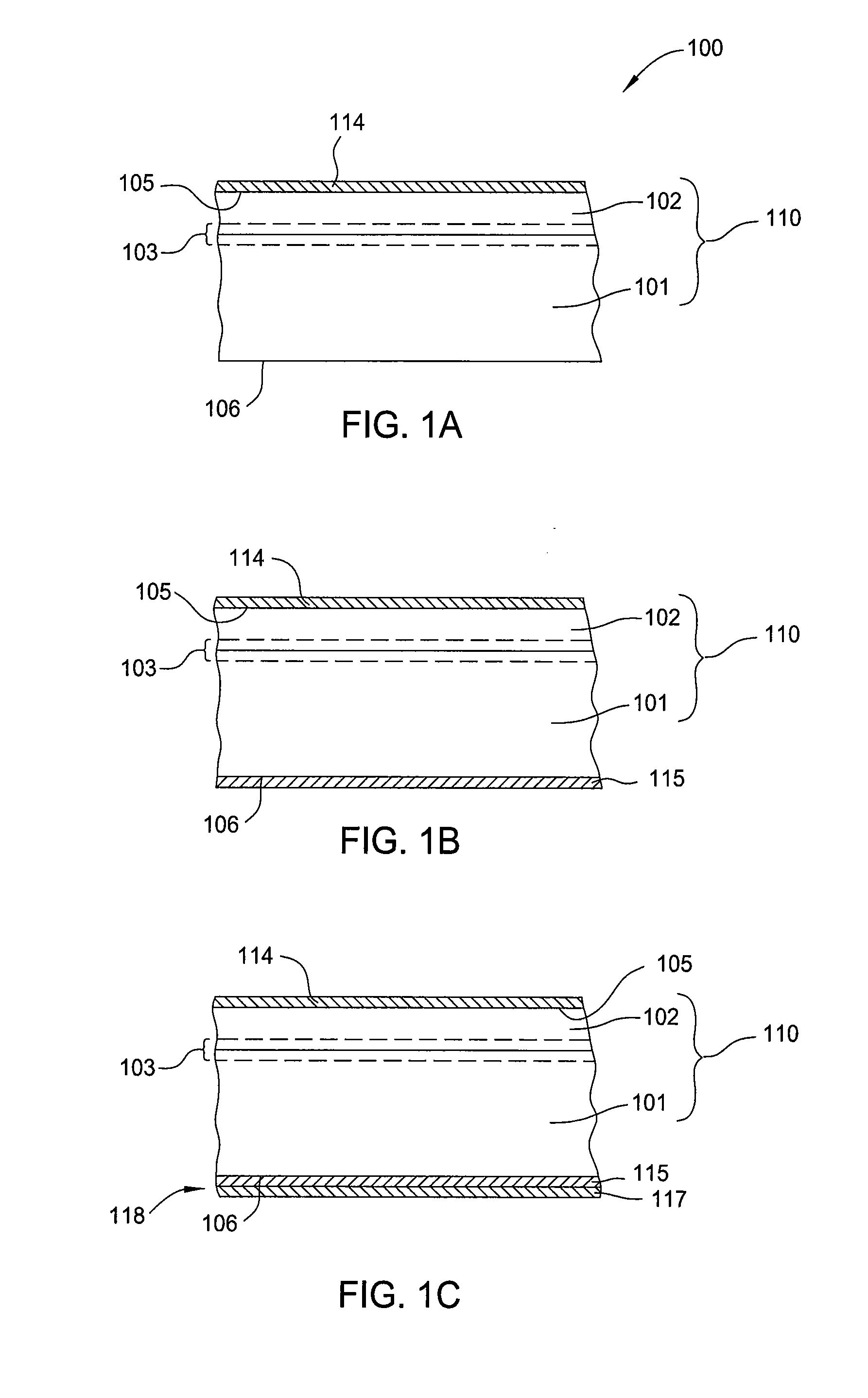

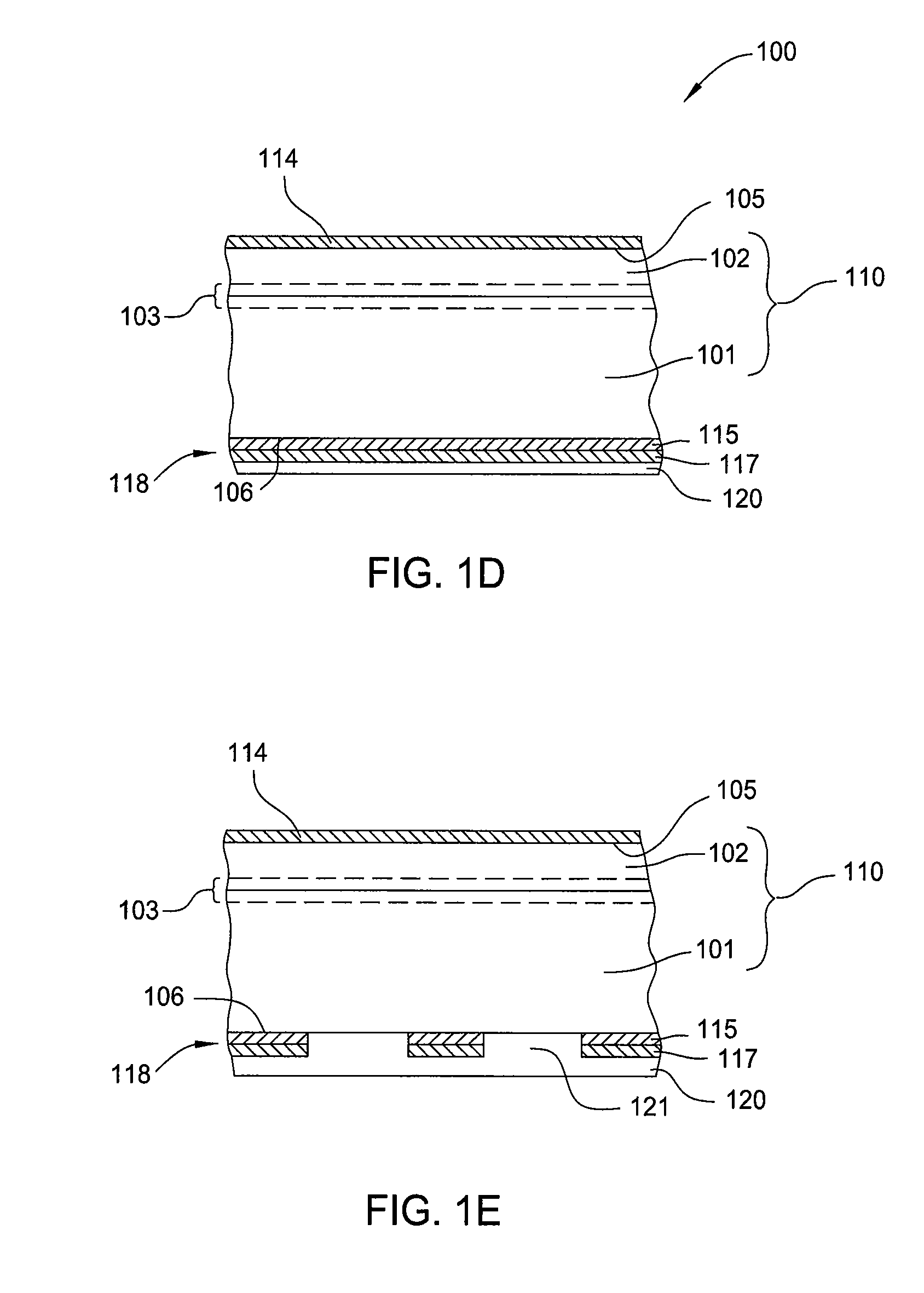

Pillar structure for memory device and method

ActiveUS8198144B2High densityHigh yieldSemiconductor/solid-state device manufacturingConductive materialsDielectric layer

A method of forming a memory device. The method provides a semiconductor substrate having a surface region. A first dielectric layer is formed overlying the surface region of the semiconductor substrate. A bottom wiring structure is formed overlying the first dielectric layer and a second dielectric material is formed overlying the top wiring structure. A bottom metal barrier material is formed to provide a metal-to-metal contact with the bottom wiring structure. The method forms a pillar structure by patterning and etching a material stack including the bottom metal barrier material, a contact material, a switching material, a conductive material, and a top barrier material. The pillar structure maintains a metal-to-metal contact with the bottom wiring structure regardless of the alignment of the pillar structure with the bottom wiring structure during etching. A top wiring structure is formed overlying the pillar structure at an angle to the bottom wiring structure.

Owner:CROSSBAR INC

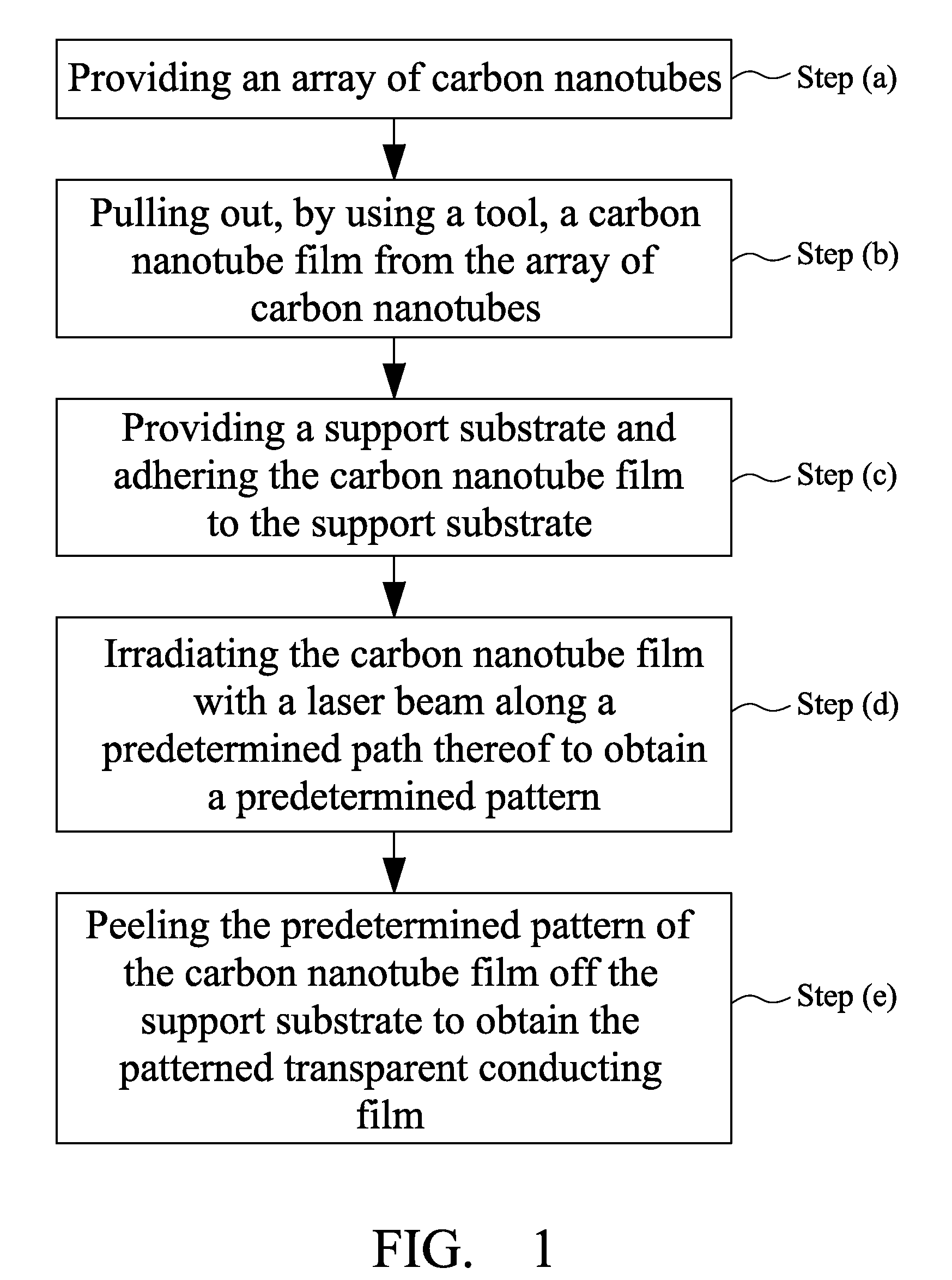

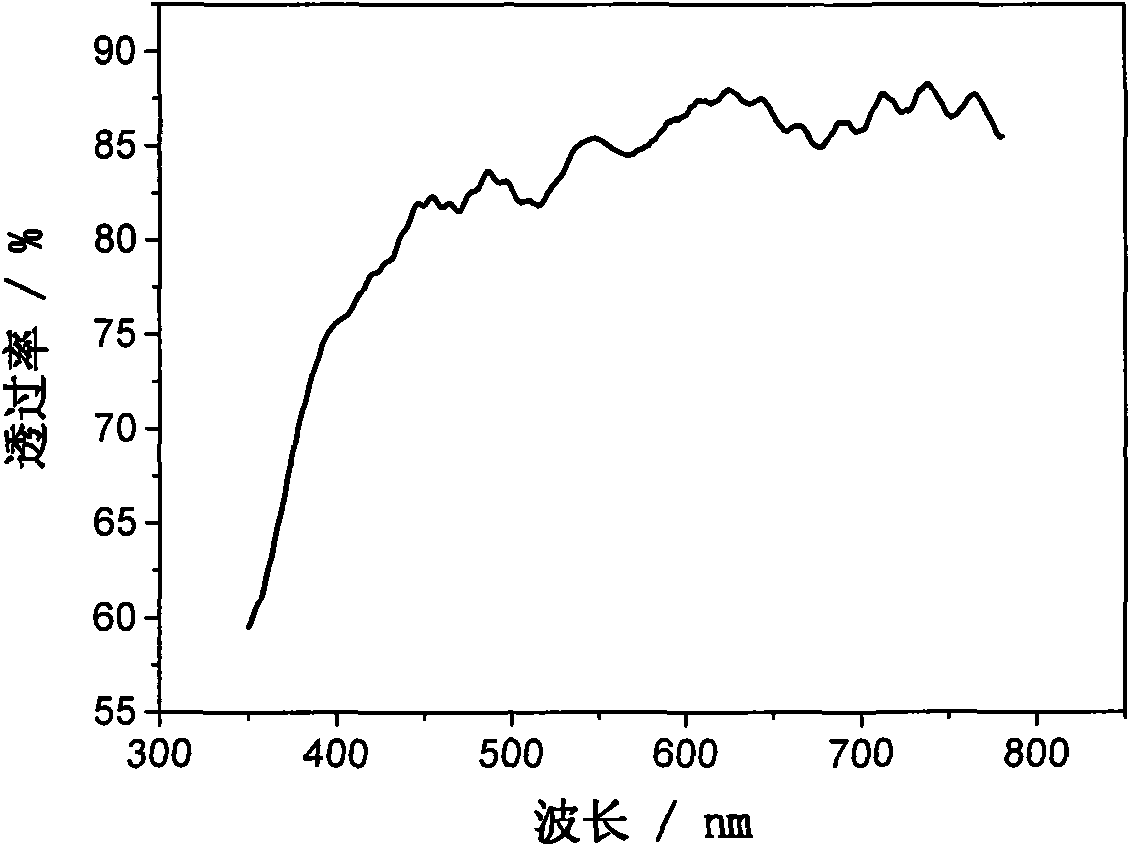

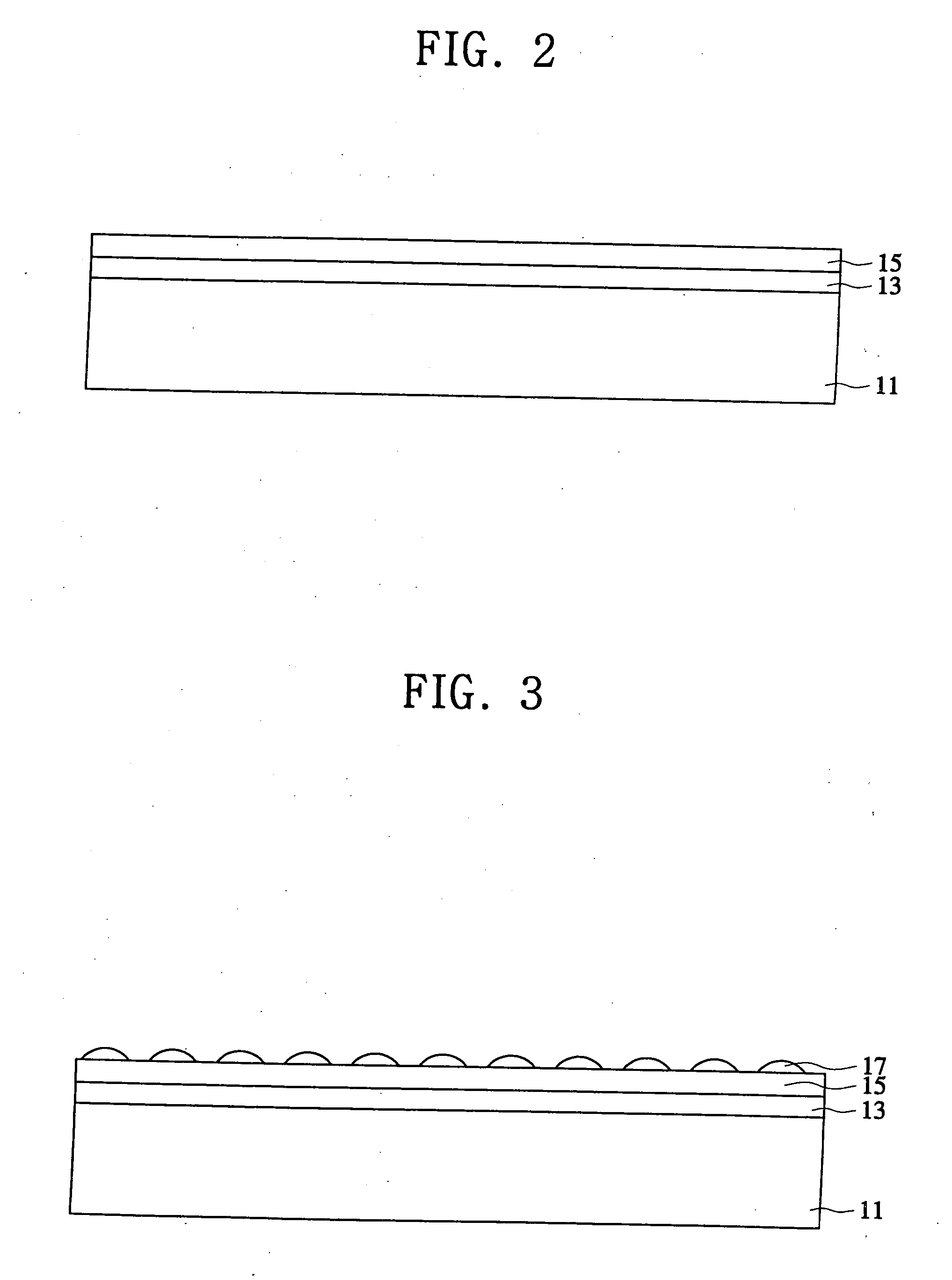

Method of making transparent conductive film

ActiveUS20090267000A1Improve conductivityEasy to etchNanotechCarbon-silicon compound conductorsCarbon nanotubeTransparent conducting film

A method of making a transparent conductive film includes the steps of: providing a carbon nanotube array. At least one carbon nanotube film extracted from the carbon nanotube array. The carbon nanotube films are stacked on the substrate to form a carbon nanotube film structure. The carbon nanotube film structure is irradiated by a laser beam along a predetermined path to obtain a predetermined pattern. The predetermined pattern is separated from the other portion of the carbon nanotube film, thereby forming the transparent conductive film from the predetermined pattern of the carbon nanotube film.

Owner:TSINGHUA UNIV +1

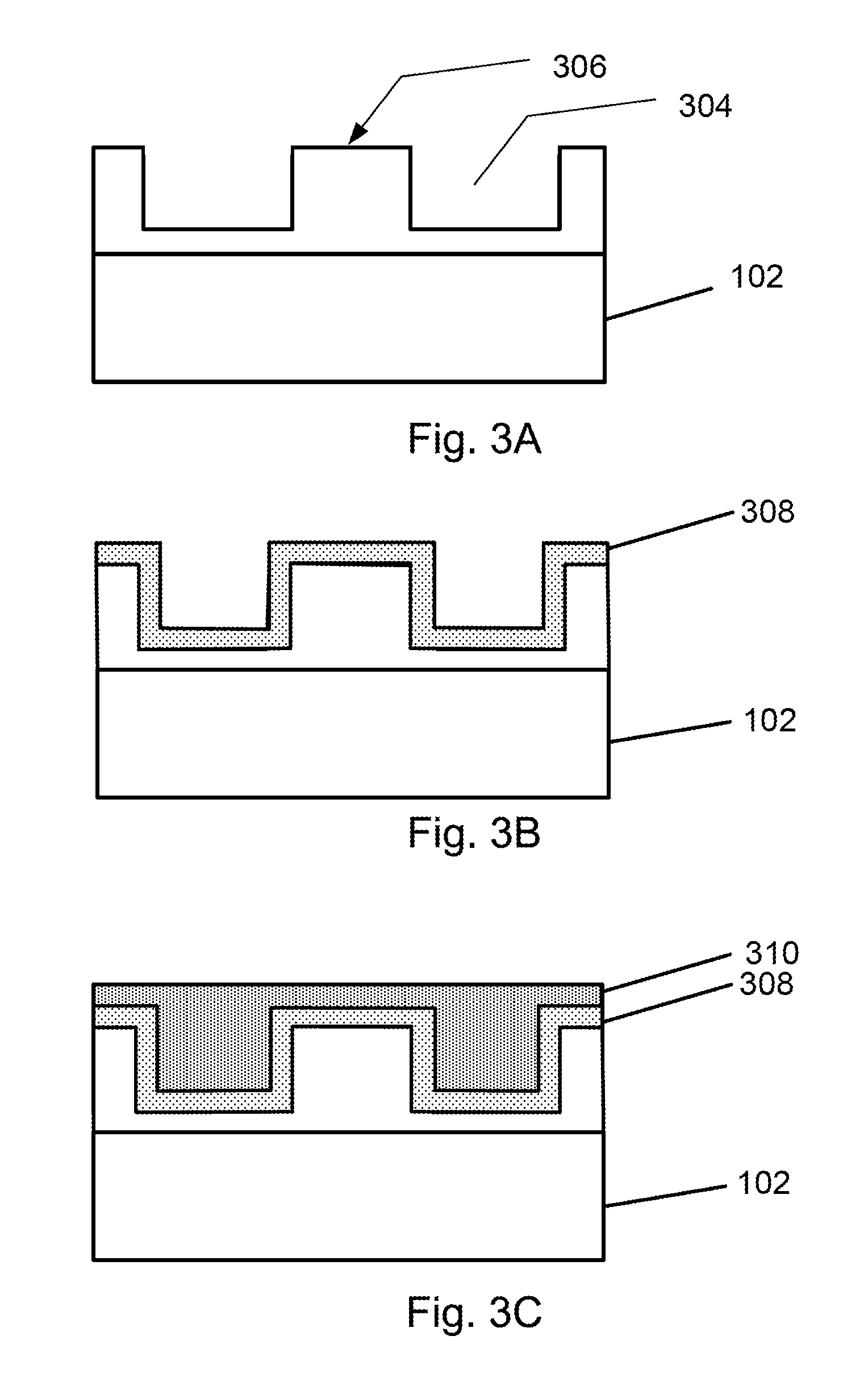

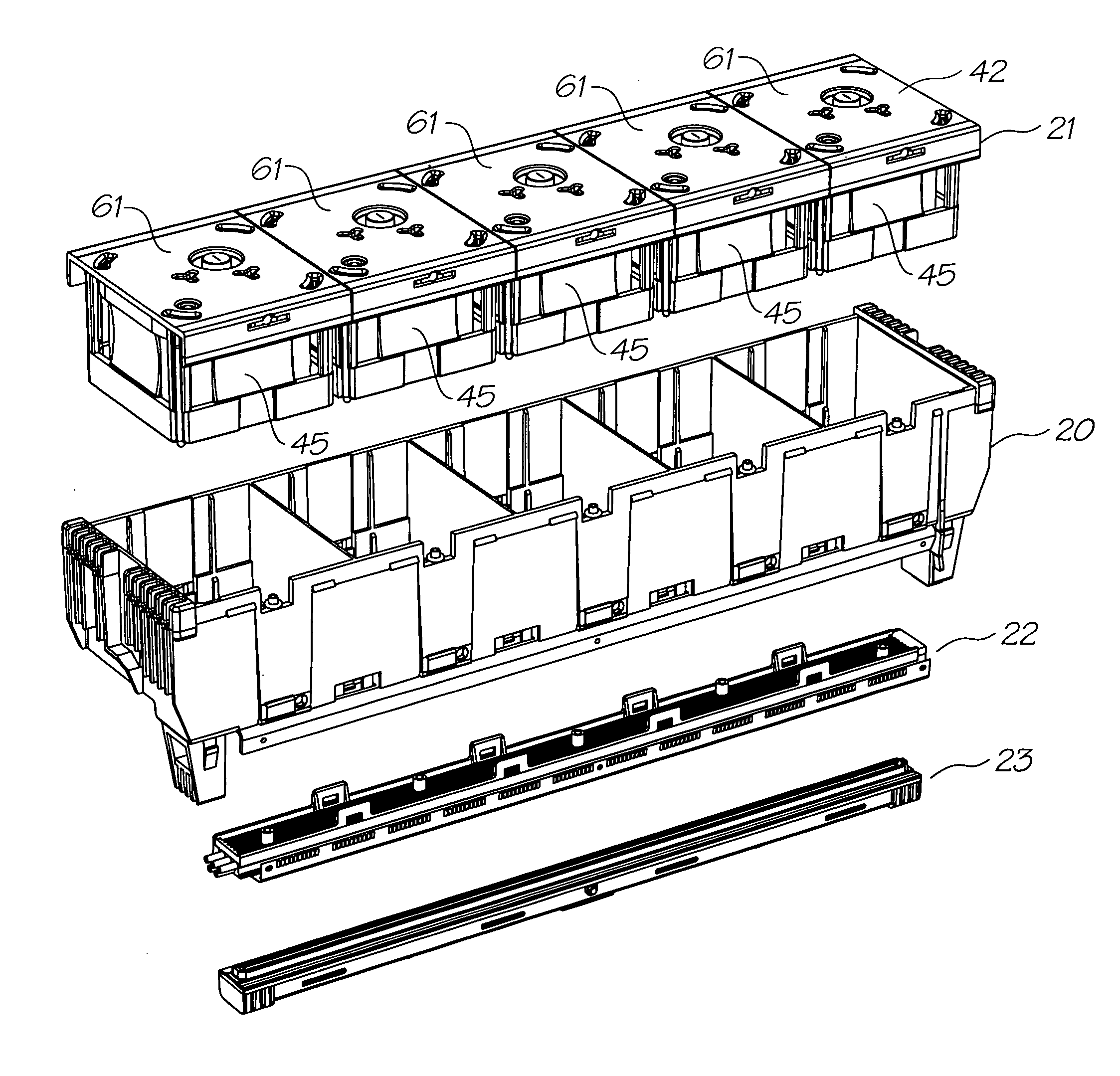

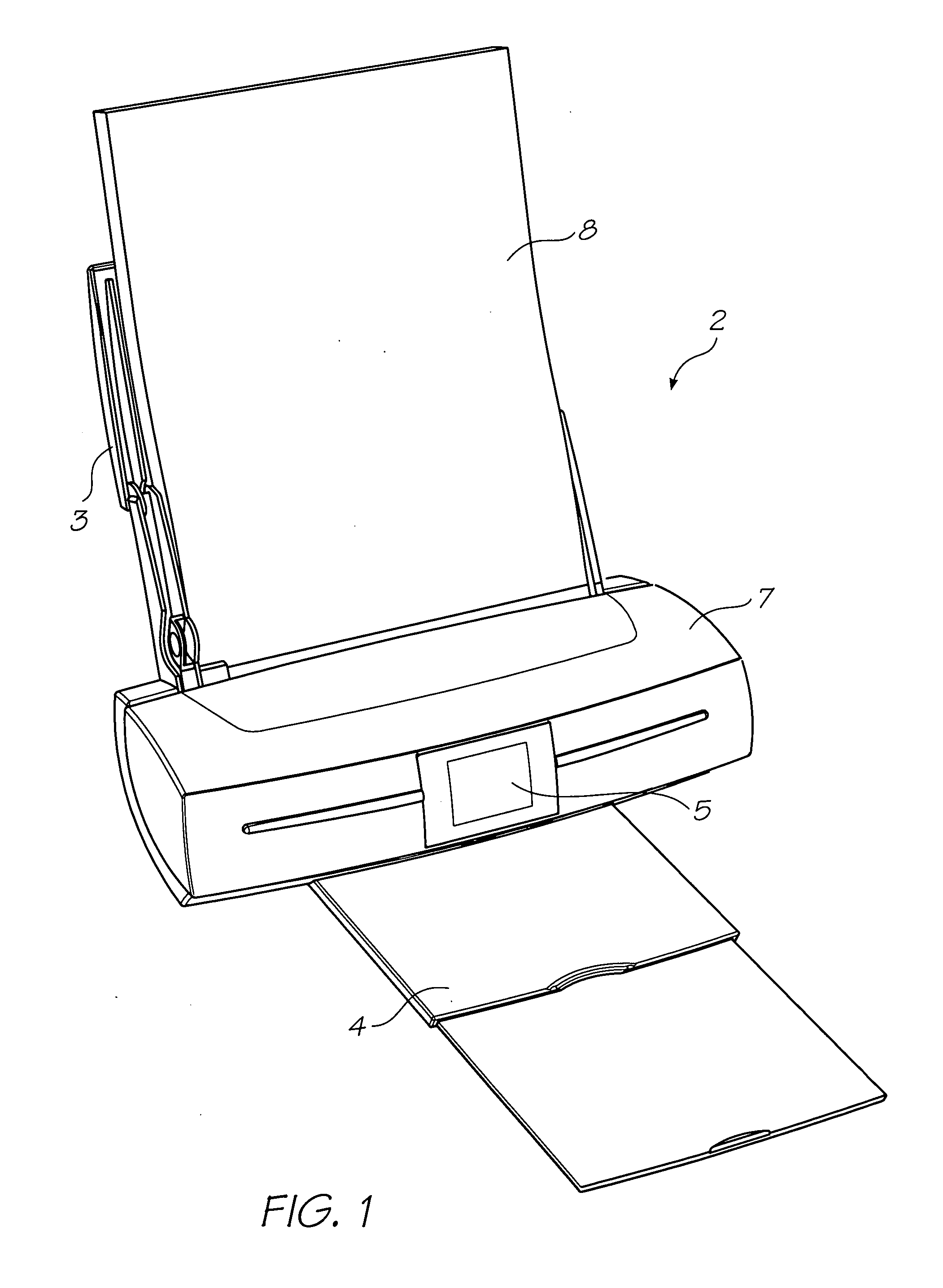

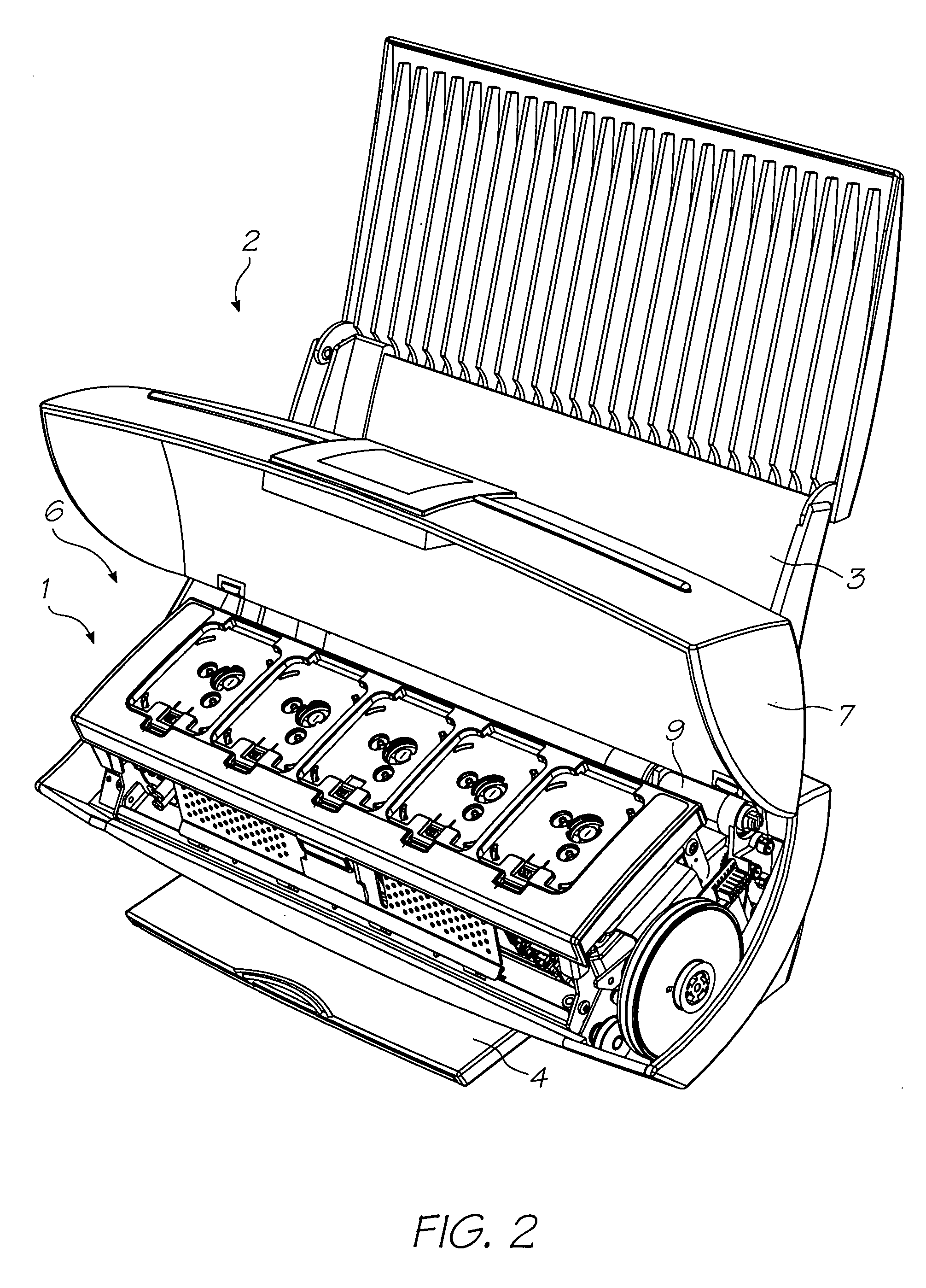

Bonded assembly having improved adhesive bond strength

InactiveUS20060192259A1Advantageous for use in fabricationMaximizing available surface areaRecording apparatusInking apparatusChemistrySemiconductor chip

A bonded assembly is provided. The bonded assembly comprises: (a) a first substrate having a plurality of etched trenches defined in a first bonding surface; and (b) a second substrate having a second bonding surface. The second bonding surface is bonded to the first bonding surface with an adhesive and the adhesive is received, at least partially, in the plurality of etched trenches. Semiconductors chips bonded to a second substrate exemplify the advantages of the invention. The etched trenches allow the adhesive bond to be strengthened whilst avoiding increased surface roughening.

Owner:ZAMTEC

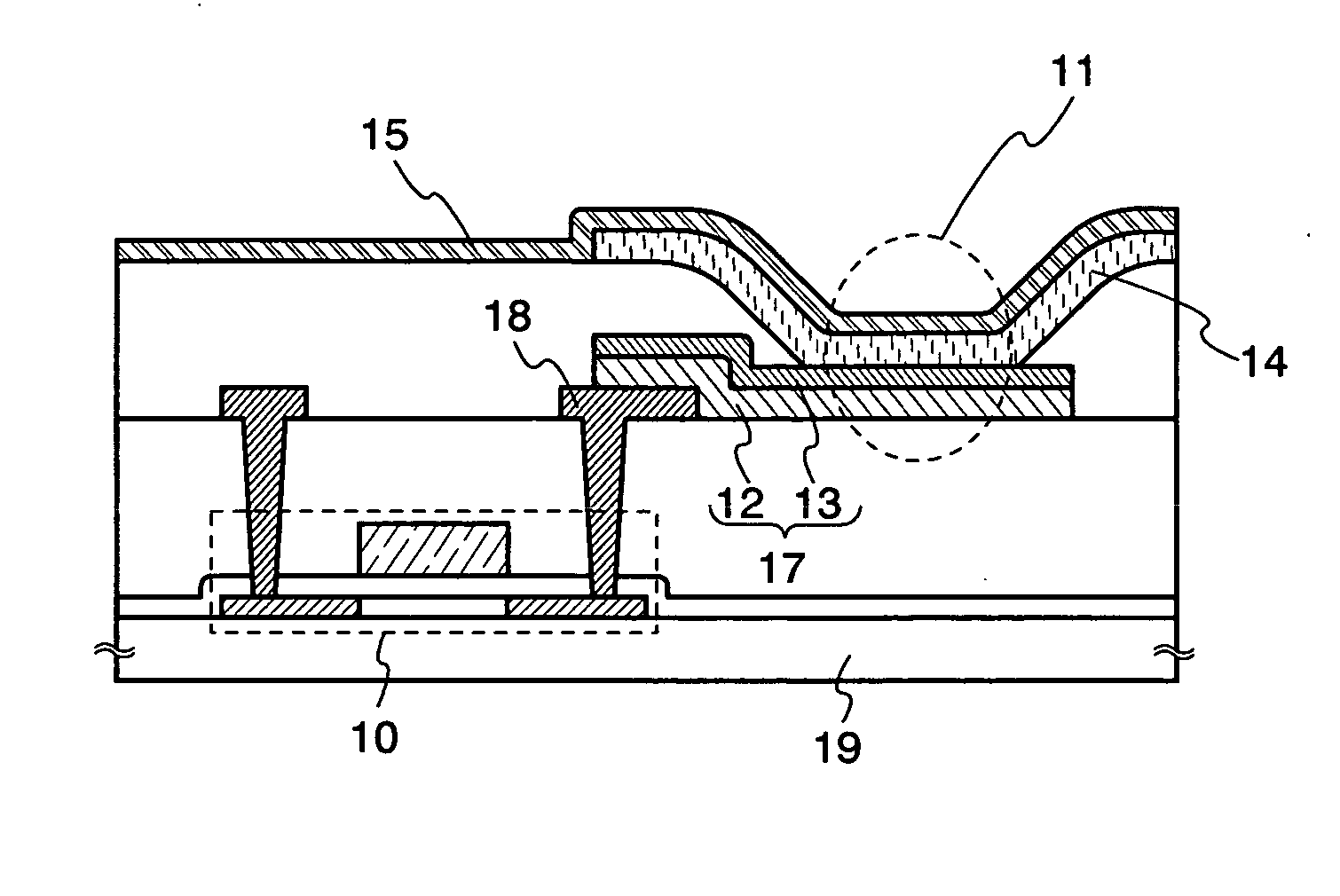

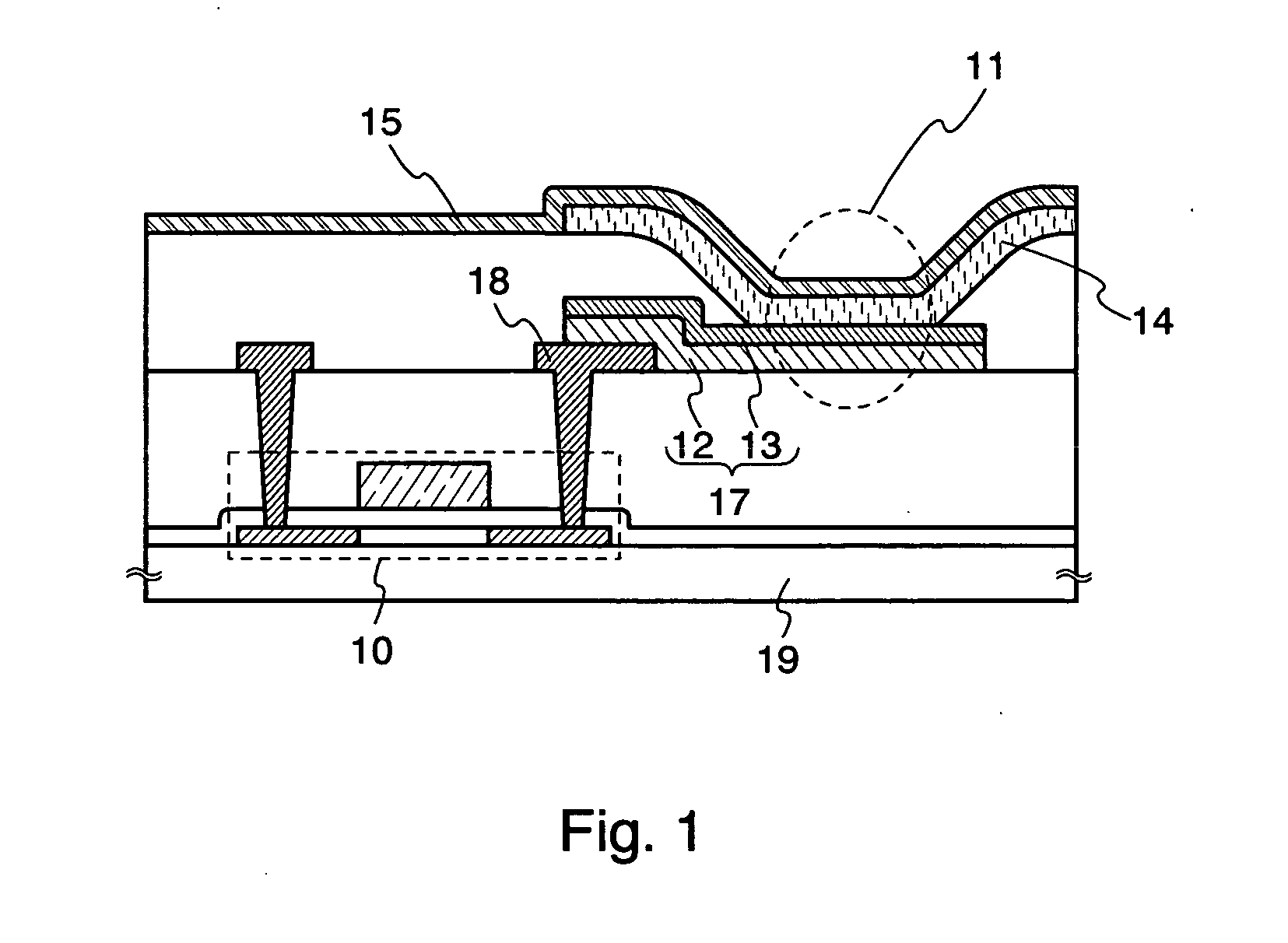

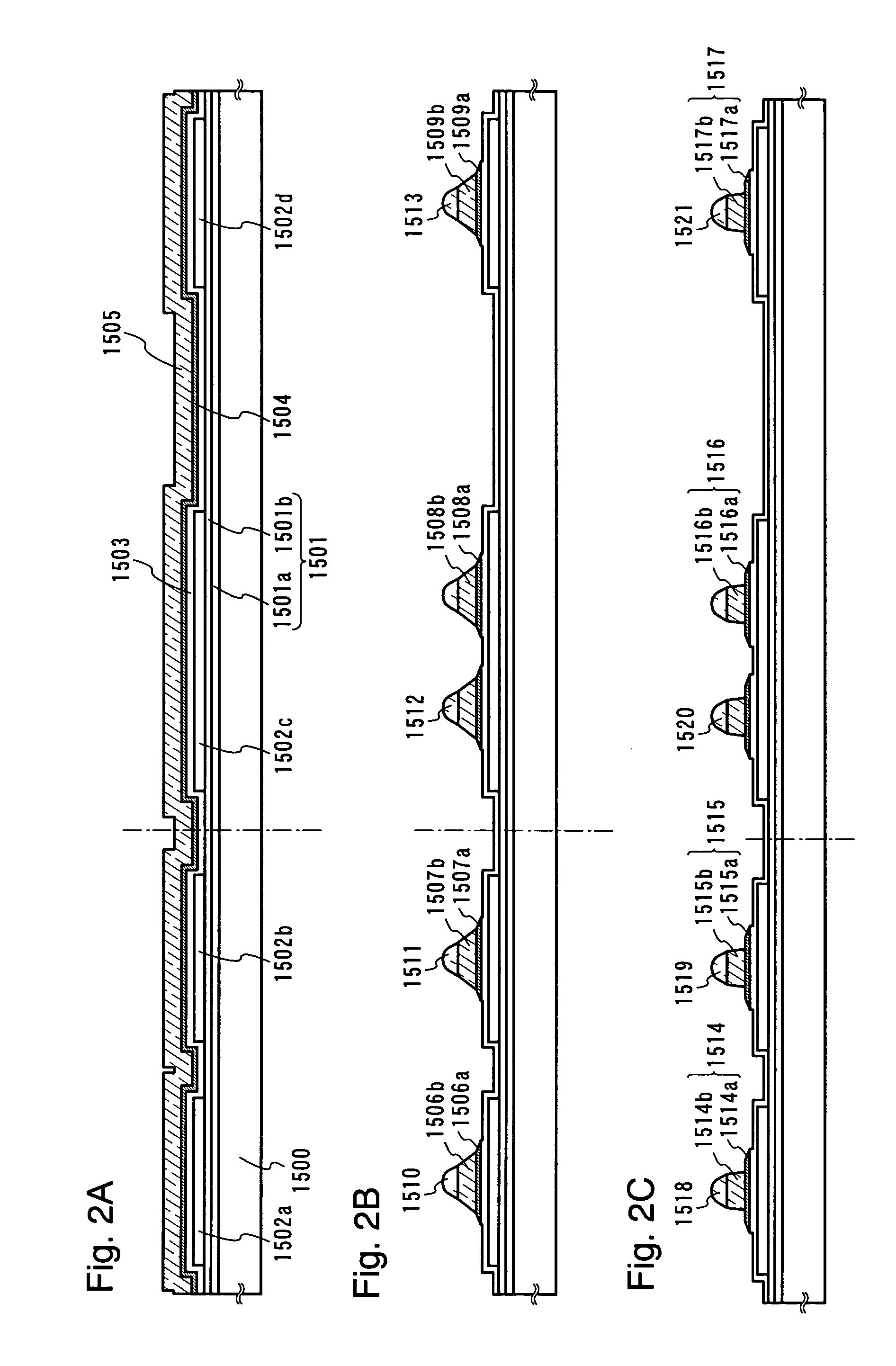

Display device and manufacturing method thereof

ActiveUS20040241931A1Easy to etchEasy to processSolid-state devicesSemiconductor/solid-state device manufacturingEtchingDisplay device

It is an object of the present invention to provide a display device that has a structure of an electrode where a residue of a transparent conductive film is not generated when a weak acid solution is used in etching, which is particularly appropriate for an electrode of a light-emitting element. A display device according to the present invention has an electrode that has a laminated structure of laminated transparent conductive films, and the electrode has a first transparent conductive film as the bottom layer, where no residue is generated when a weak acid solution is used in etching, and a second transparent conductive film as the top layer, which has a work function of 5.0 eV or more.

Owner:SEMICON ENERGY LAB CO LTD

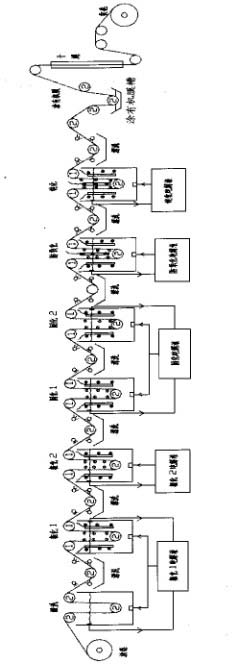

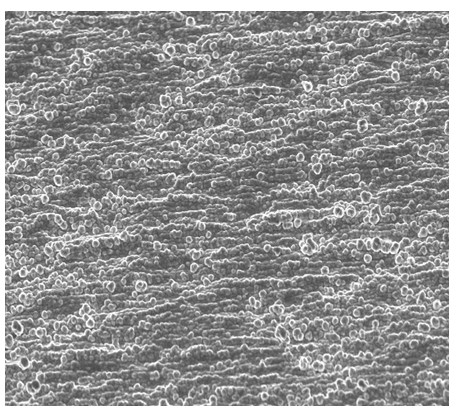

Manufacturing process of smooth roughened electrolytic copper foil

The invention relates to a process for manufacturing smooth surface roughened electrolytic copper foil, which comprises a step of pickling, a step of primary smooth surface roughening, a step of secondary smooth surface roughening, a step of primary smooth surface curing, a step of secondary smooth surface curing, a step of double-size anti-oxidization treatment, a step of double side passivation and a step of smooth surface coupling agent treatment, which are accomplished continuously on the same production line. Compared with the prior art, the smooth surface roughened electric copper foil manufactured by the process for manufacturing the smooth surface roughened electrolytic copper foil has the advantages of short copper teeth, easy etching, and high impedance controllability. When the copper foil is used in production of downstream products, the needs of blackening micro corrosion and toughening treatment are obviated, so the manufacturing process is shortened, and the short circuit rate and open circuit rate are lowered; meanwhile, the copper foil manufactured by the process has the same quality as the conventional high-precision or double-side toughened electrolytic copper foil, is produced at low cost and is more suitable for manufacturing the inner layers of high-precision multilayer plates and high-density fine line printed circuit boards (PCBs).

Owner:合肥铜冠电子铜箔有限公司

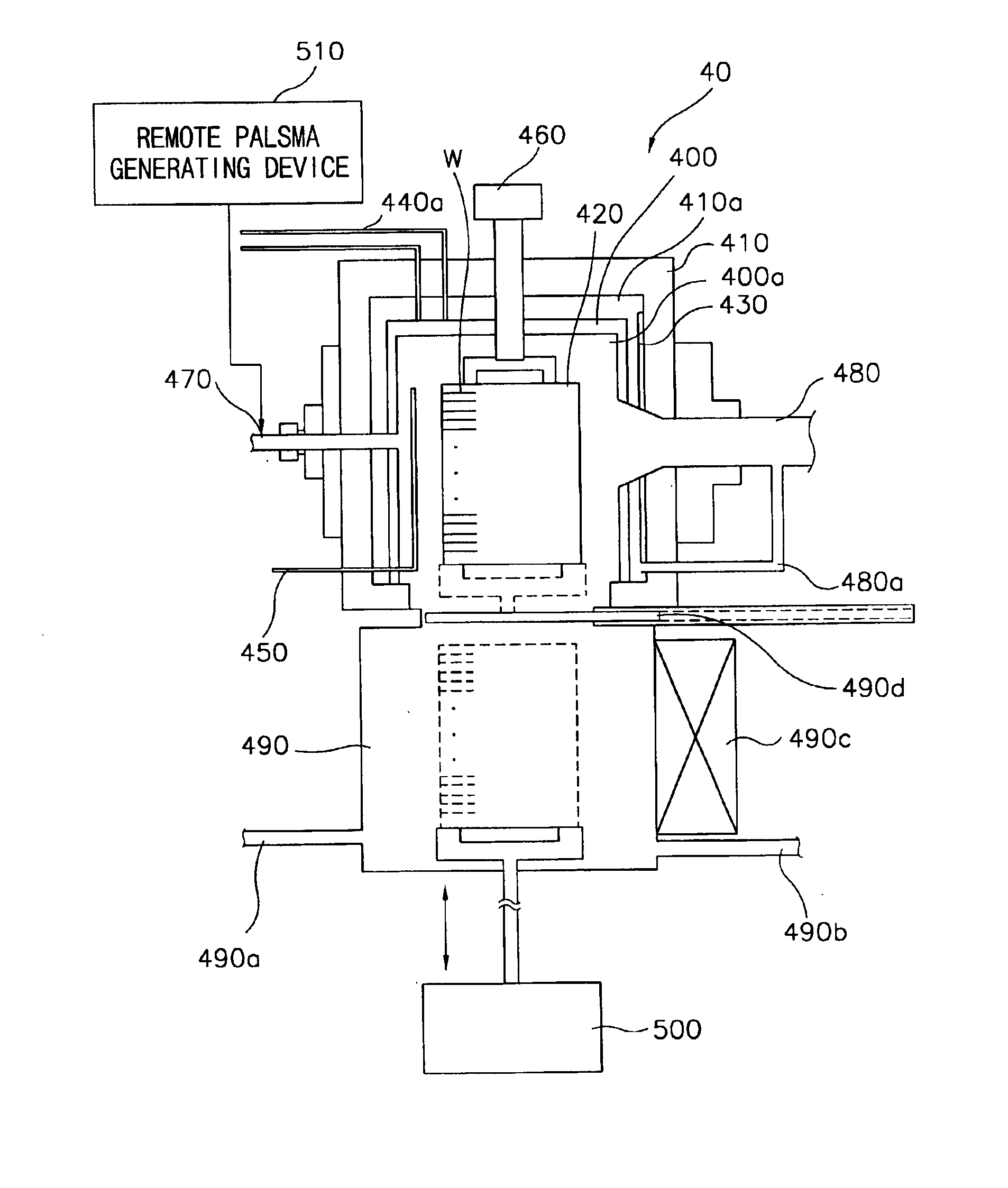

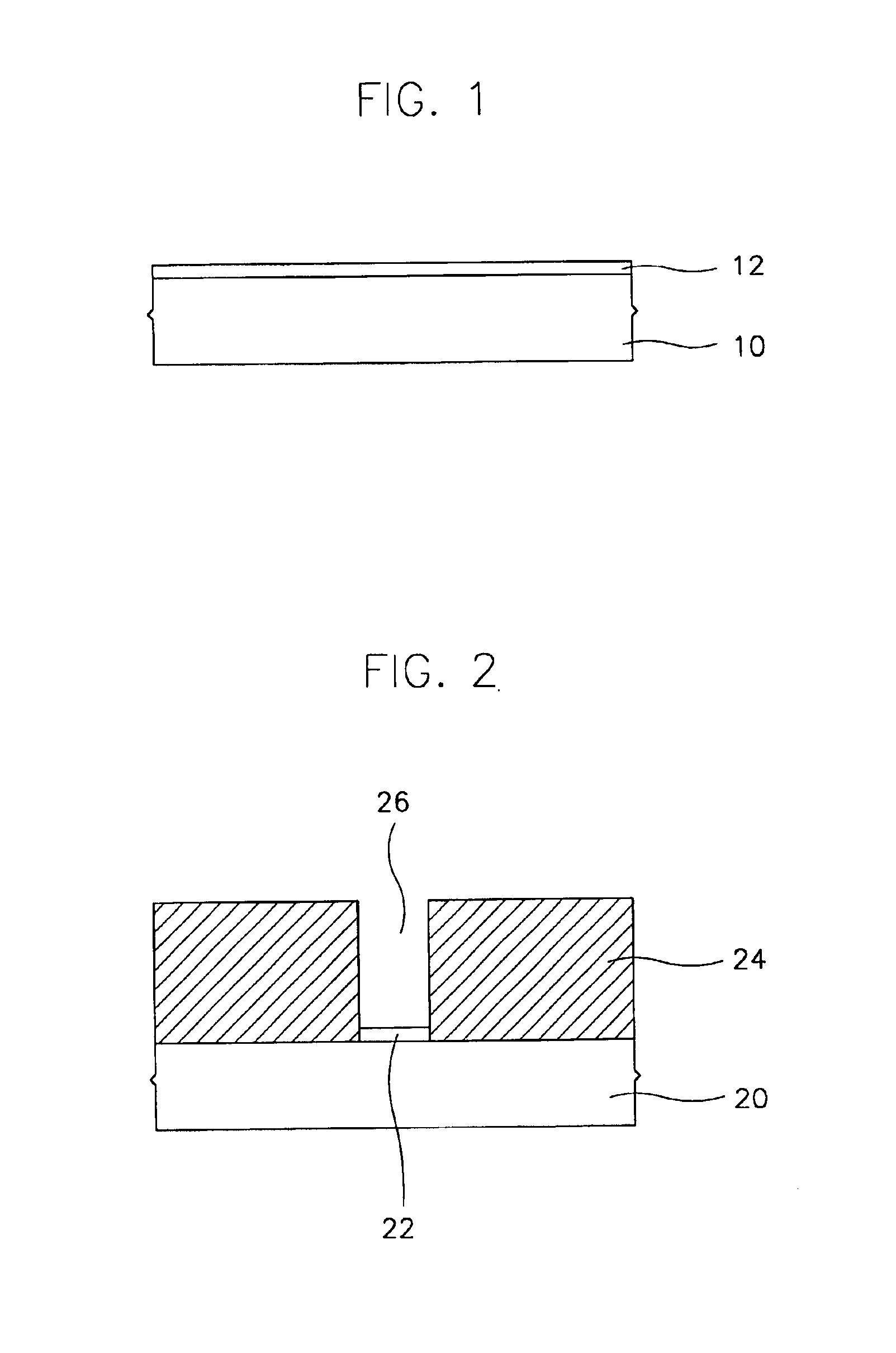

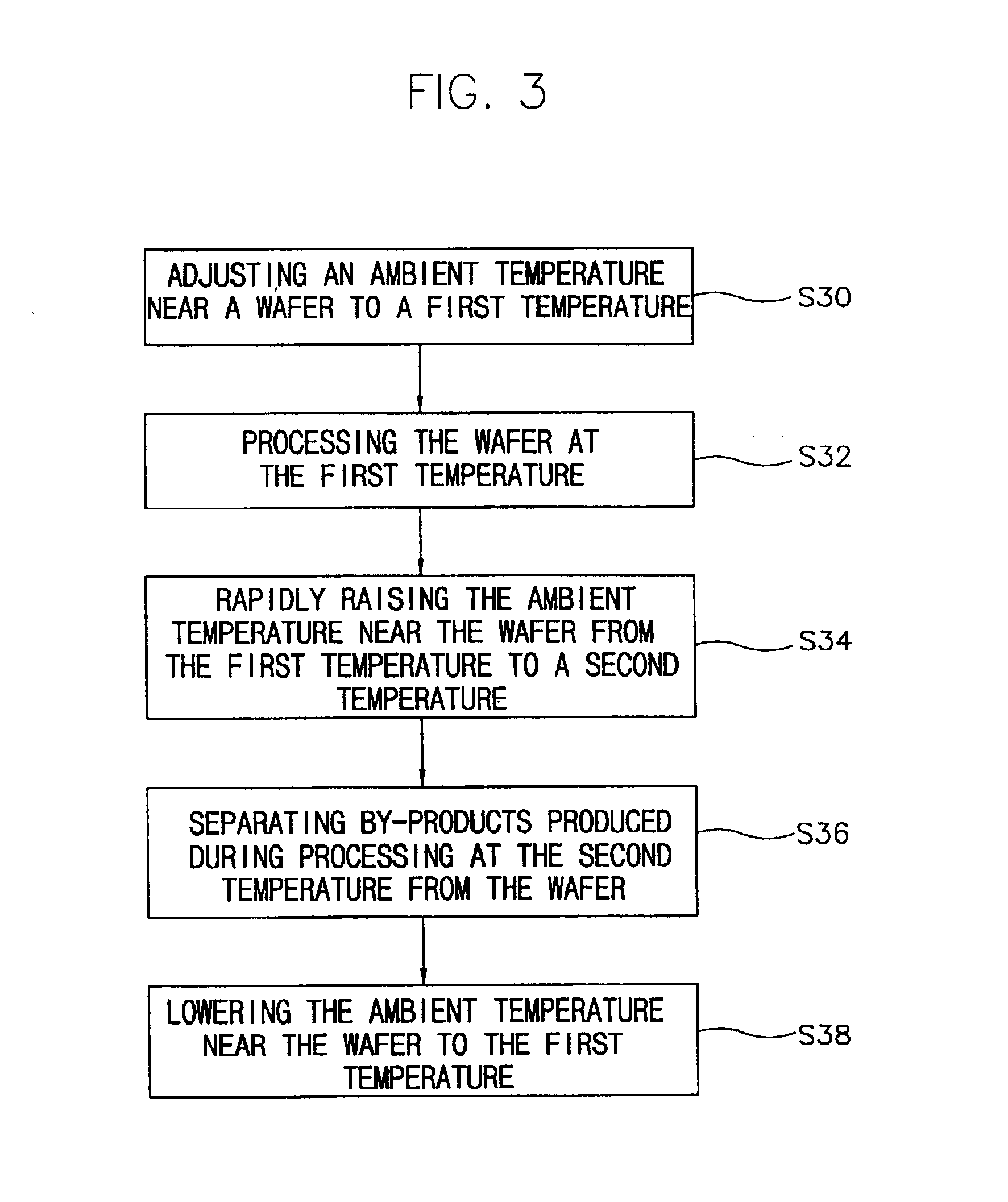

Method for processing a wafer and apparatus for performing the same

InactiveUS6869500B2Producing efficiency can be increasedEasy to etchSemiconductor/solid-state device manufacturingChemical vapor deposition coatingProduction rateDevice material

Disclosed are a method and an apparatus for processing a wafer in manufacturing a semiconductor device and a method and an apparatus for etching a material formed on the wafer, wherein first and second cooling parts adjust an ambient temperature near a plurality of wafers to a first temperature, the wafers are processed by introducing a reaction gas at the first temperature, then, a heating part rapidly raises the temperature of the atmosphere near the wafers from the first temperature to the second temperature to partially separate by-products produced during the processing, the second temperature is maintained to separate most of the by-products from the wafers, and the processing steps are implemented in-situ within the same space. Accordingly, a native oxide layer formed on several wafers can be etched and the reaction by-products can be removed in-situ in the same chamber so productivity is improved.

Owner:SAMSUNG ELECTRONICS CO LTD

Oxide nitride stack for backside reflector of solar cell

InactiveUS20110272008A1Easy to etchEasy to patternSemiconductor/solid-state device manufacturingNanotechnologySemiconductor materialsSilicon oxide

Embodiments of the invention generally provide methods for forming a multilayer rear surface passivation layer on a solar cell substrate. The method includes forming a silicon oxide sub-layer having a net charge density of less than or equal to 2.1×1011 Coulombs / cm2 on a rear surface of a p-type doped region formed in a substrate comprising semiconductor material, the rear surface opposite a light receiving surface of the substrate and forming a silicon nitride sub-layer on the silicon oxide sub-layer. Embodiments of the invention also include a solar cell device that may be manufactured according methods disclosed herein.

Owner:APPLIED MATERIALS INC

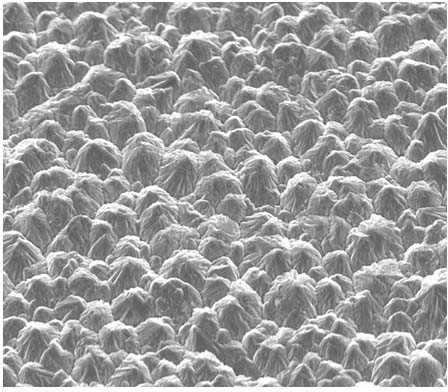

Ultra-thin copper foil with carrier and printed wiring board using ultra-thin copper foil with carrier

InactiveUS20050158574A1High peel strengthEasy wiringInsulating substrate metal adhesion improvementThermometers using material expansion/contactionSurface roughnessCopper foil

To produce an ultra-thin copper foil with a carrier foil that microscopic crystal grains can be deposited without being affected by the surface roughness of a carrier foil, etching can be performed until an ultra-fine width such that line / space is 15 μm or less, and the microscopic line and a wiring board have large peel strength even after line of 15 μm is etched. An ultra-thin copper foil wherein a carrier foil, a peeling layer, an ultra-thin copper foil are laminated in this order, the ultra-thin copper foil (before roughening treatment is performed) is an electrolytic copper foil that surface roughness of 2.5 μm as ten point height of roughness profile, and the minimum distance between peaks of salients of a based material is 5 μm or more. Moreover, the surface of the ultra-thin copper foil is performed roughening treatment.

Owner:FURUKAWA ELECTRIC CO LTD

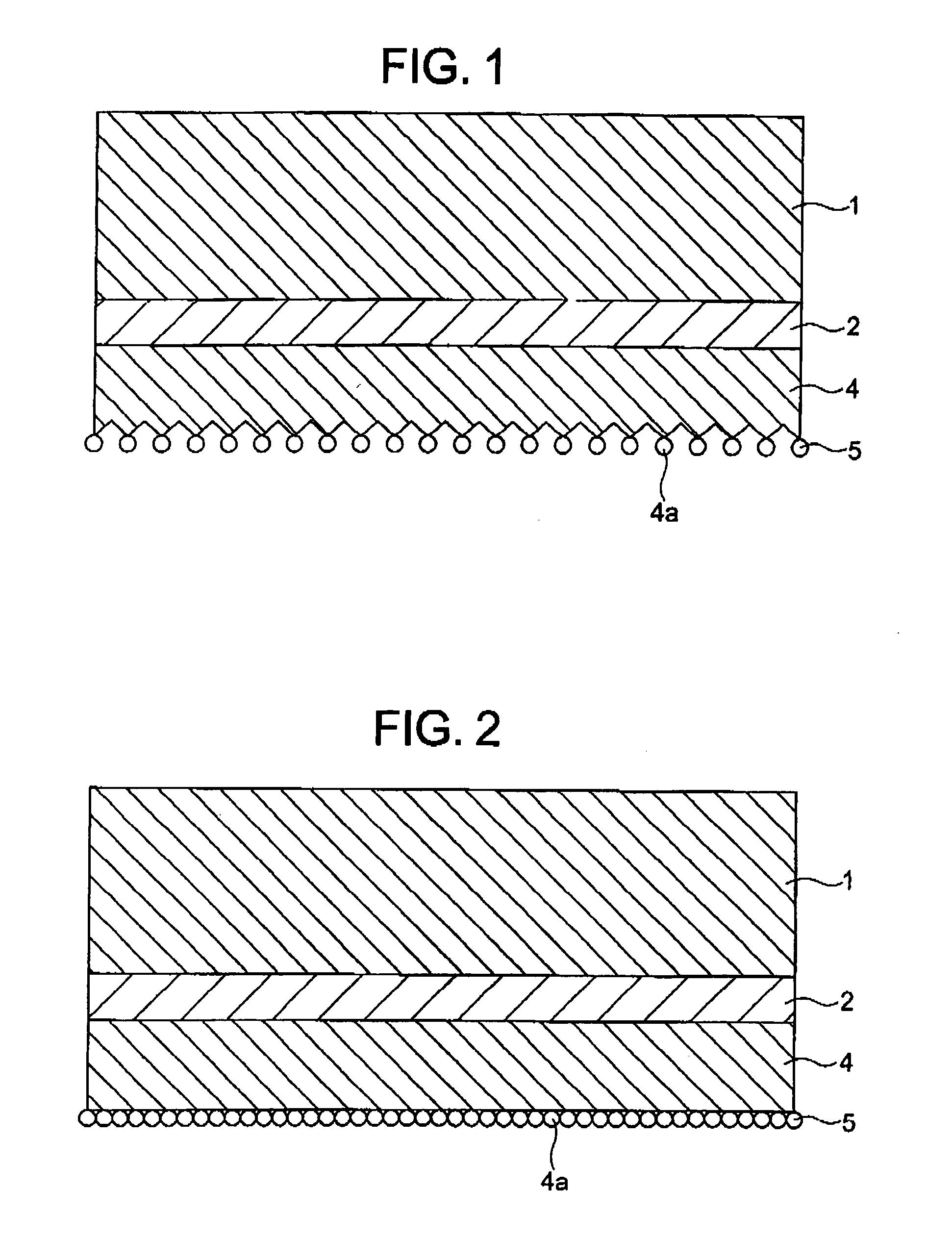

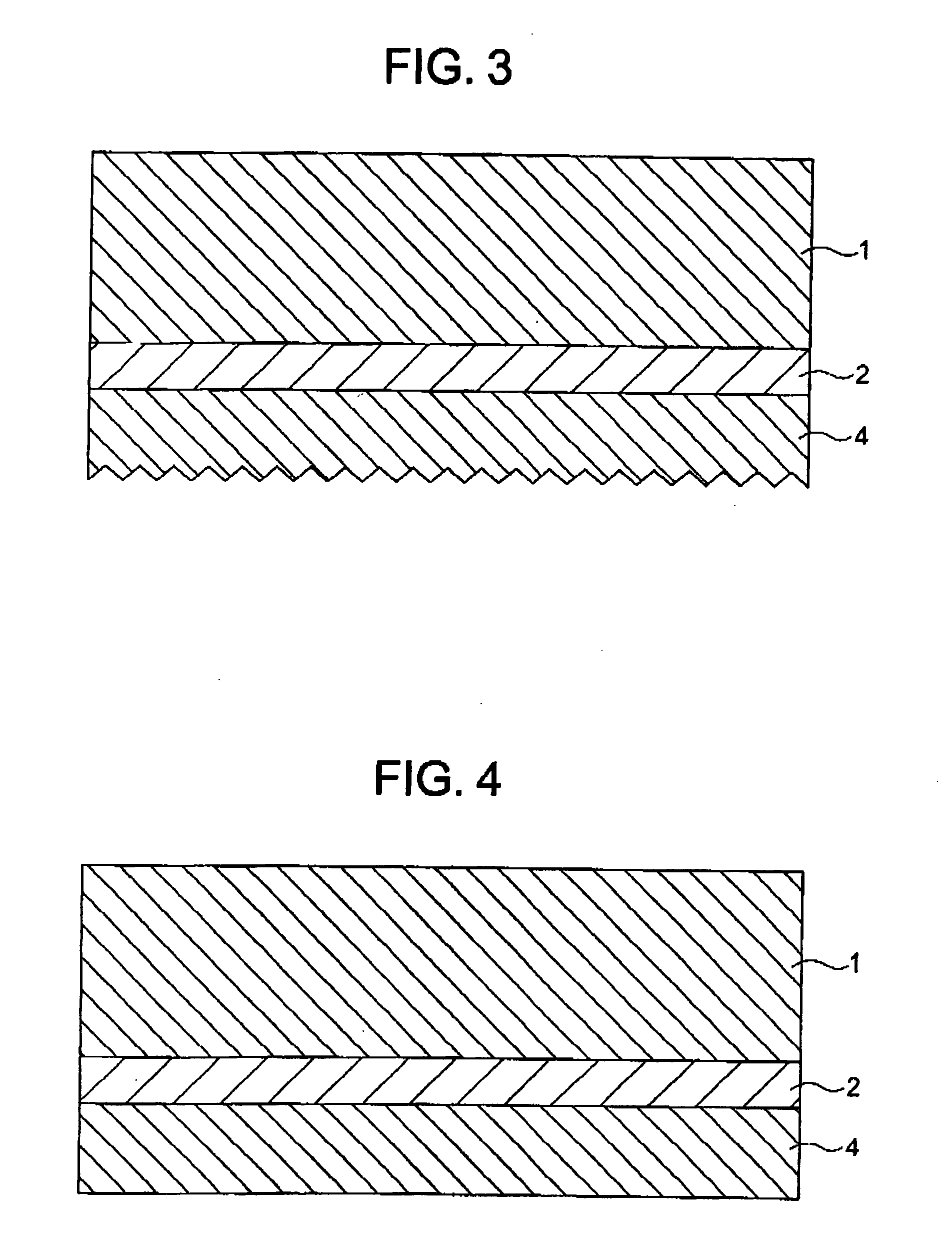

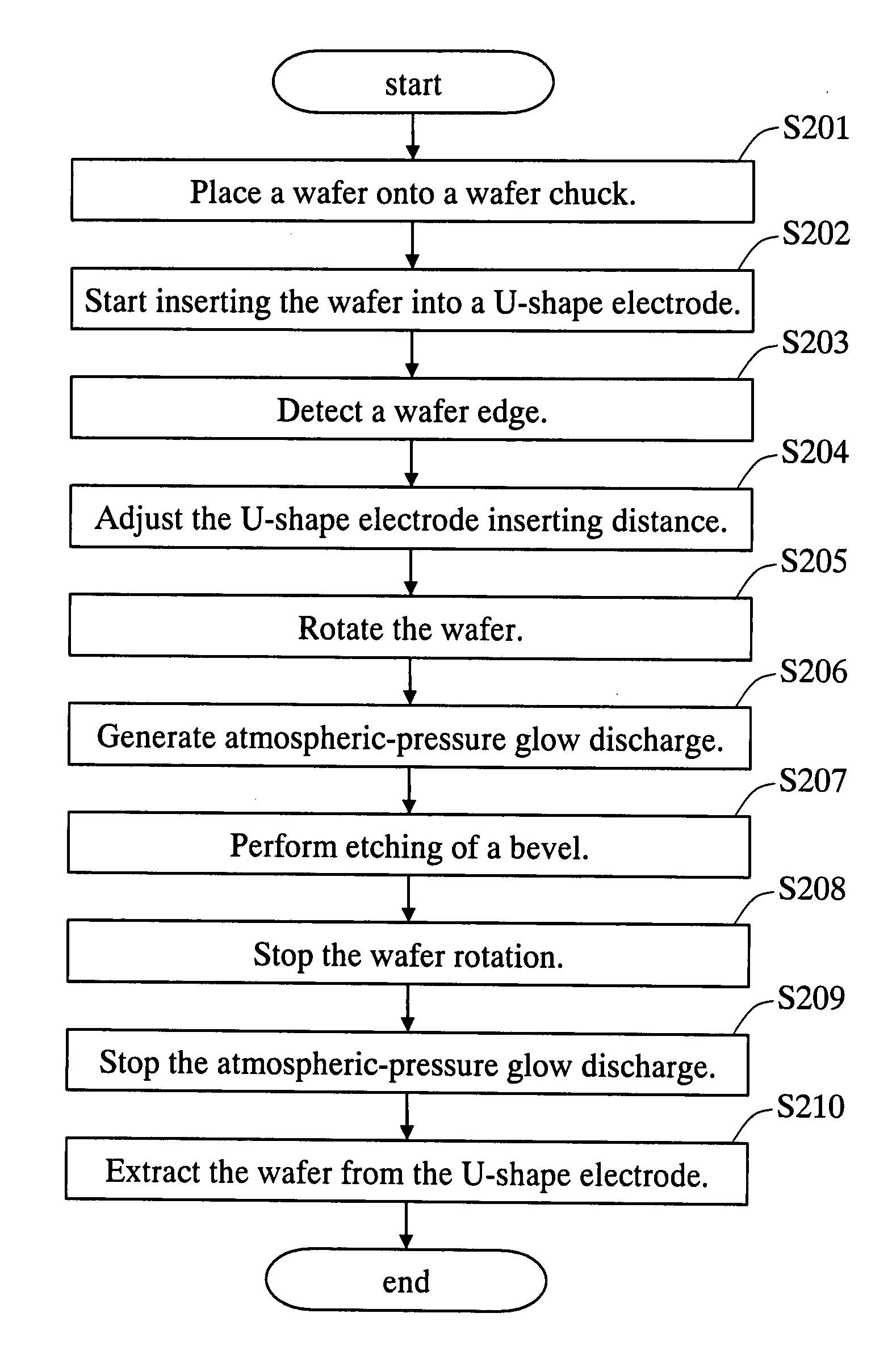

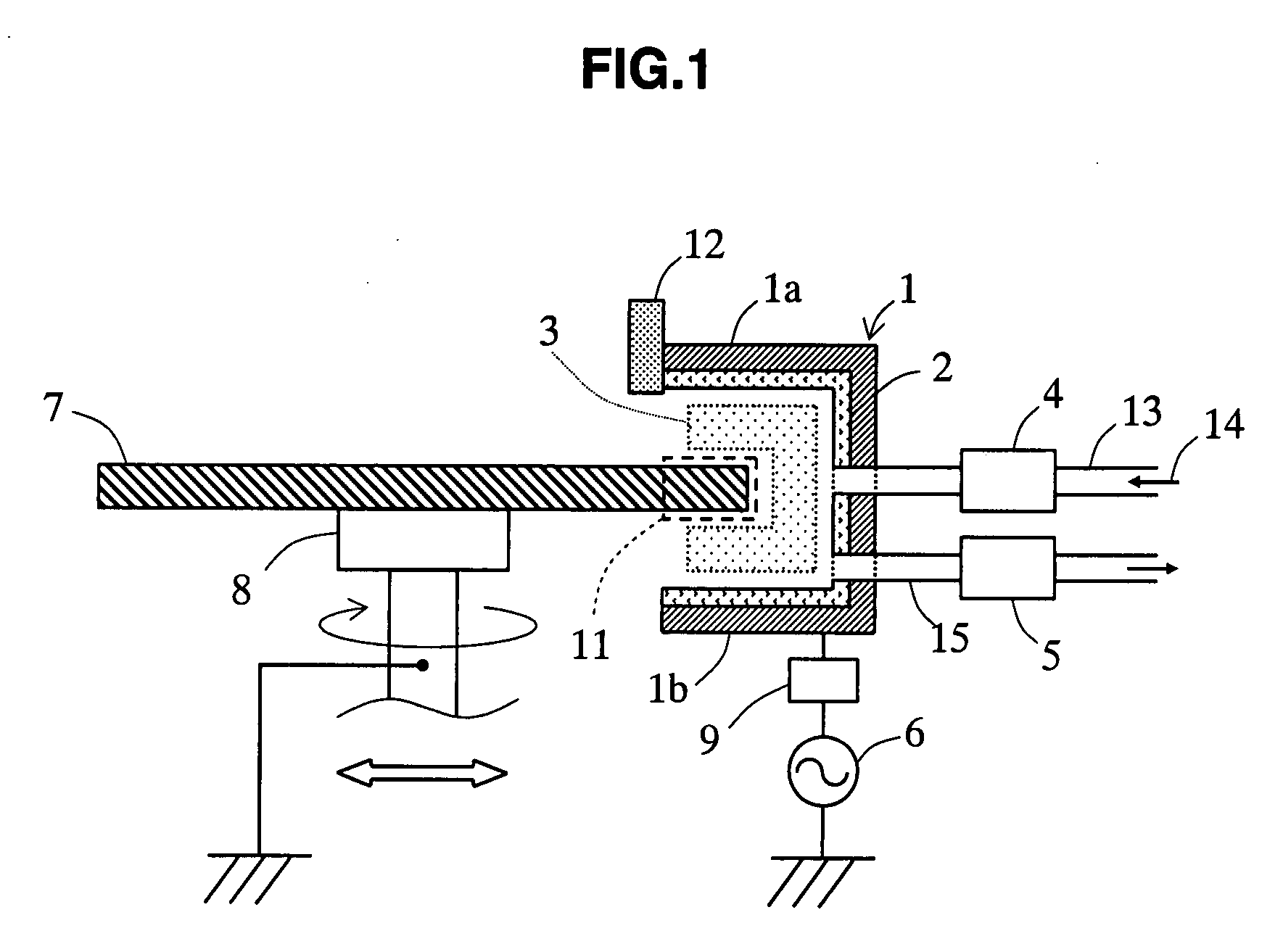

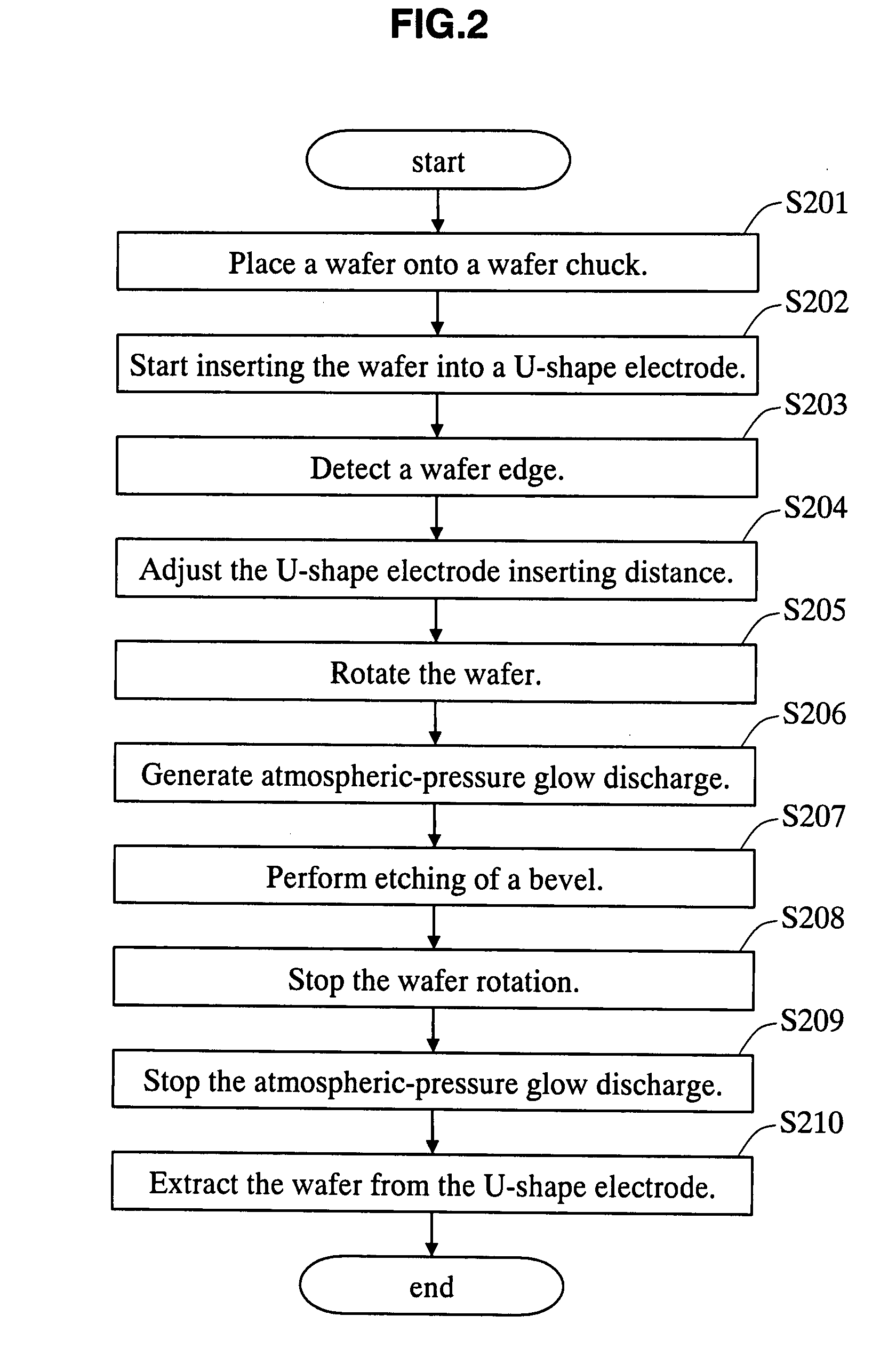

Etching apparatus and etching method for substrate bevel

InactiveUS20070251919A1Prevent redepositionFacilitate bevel etchingElectric discharge tubesVacuum gauge using ionisation effectsElectricityEtching

In the bevel etching apparatus relating to the present invention, a substrate is inserted between electrically connected electrodes. A high-frequency power source is connected to the electrodes, and ground potential is applied to a support unit that supports the substrate. Gas (atmosphere) is supplied to the gap between the electrodes and the application of the high-frequency electric power to the electrodes causes the generation of atmospheric-pressure glow discharge between the electrode and the substrate. Bevel etching is performed by rotating the substrate along the circumferential direction in this condition. According to this construction, the bevel etching can be simultaneously performed to the front surface, the rear surface and the side of the substrate without causing any configuration change in the substrate.

Owner:PANASONIC CORP

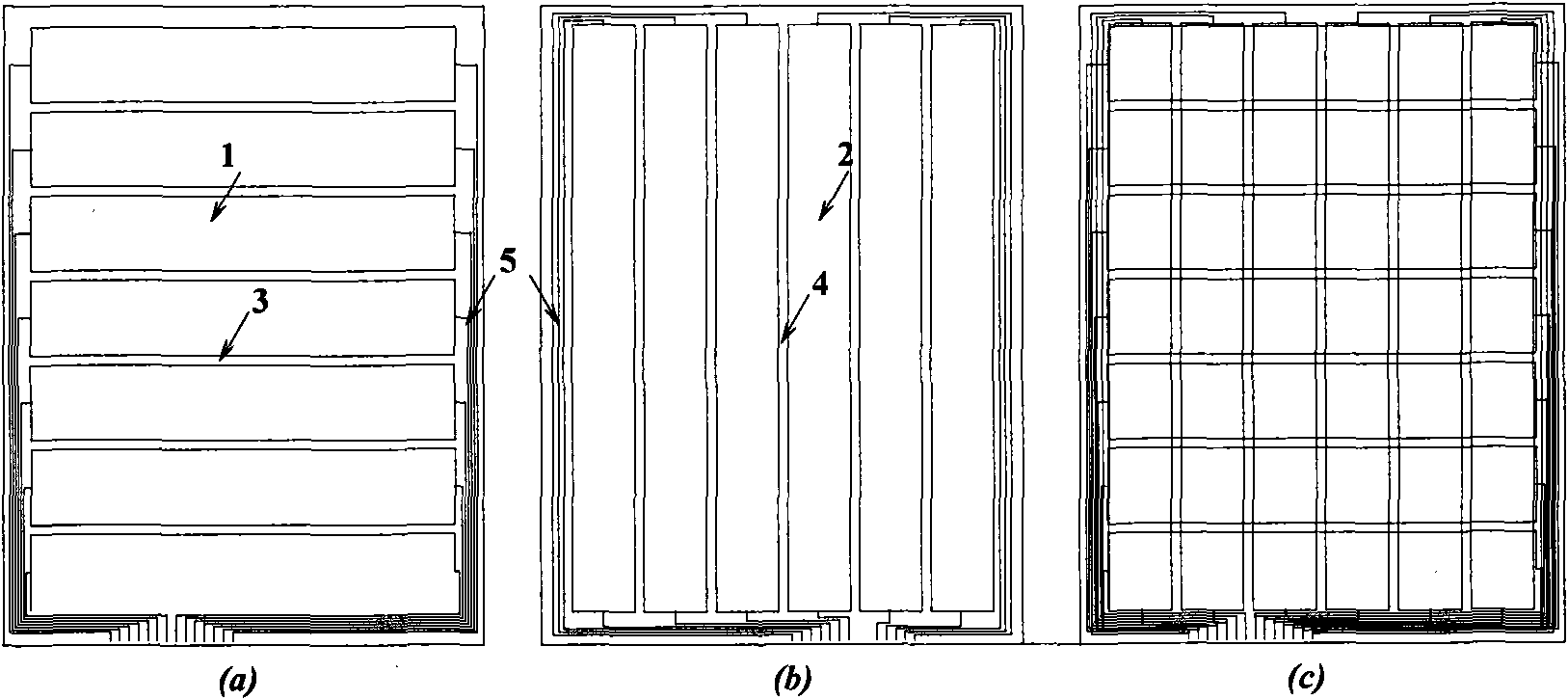

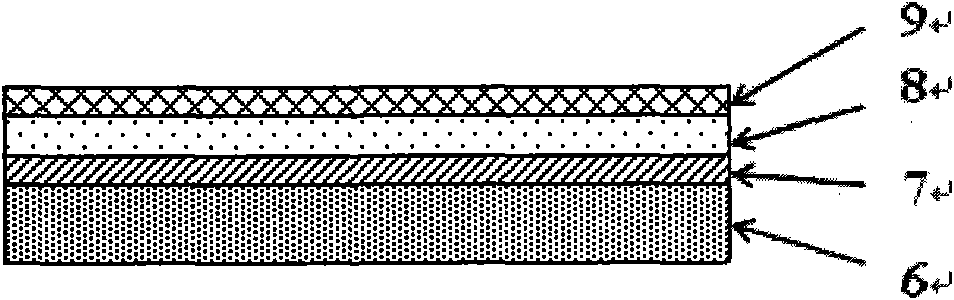

Transparent conducting material for resistive touch panel

InactiveCN101599315AImprove linearityImprove uniformityConductive layers on insulating-supportsSynthetic resin layered productsDielectricElectricity

The invention discloses a transparent conducting material for a resistive touch panel, which comprises a polyethylene terephthalate (PET) substrate and three layers of optical thin films on the surface of the substrate, wherein from the surface of the substrate, the three layers of optical thin films are a high refractive index dielectric optical thin film, a low refractive index dielectric optical thin film and a transparent conducting film sequentially. Through the design of the three layers of optical thin films, the transparent conducting material has an anti-reflection effect on light within a visual wave range of less than 490 nanometers, particularly a range from 400 to 490 nanometers. The sheet resistivity of the transparent conducting material is between 200 and 600 ohms per square. The physical properties of the transparent conducting material facilitate the preparation and quality improvement of the resistive touch panel.

Owner:SHENZHEN O FILM TECH

Preparation method of nanometer metal grating and nanometer metal grating

ActiveCN107479121AEasy to etchSolve the problem that etching cannot be carried outPhotomechanical apparatusPolarising elementsState of artOxygen

The invention provides a preparation method of a nanometer metal grating and a nanometer metal grating. The method includes providing a substrate on which a metal layer is arranged; forming an impression glue layer on the metal layer; impressing the impression glue layer with an impression template with a grating period pattern; solidifying a impression glue layer, removing the impression template after the solidification, forming the impression glue with the grating period pattern, and remaining the impression glue at the bottom of the grating period pattern; removing the residual impression glue by means of oxygen ashing, exposing the metal layer at the bottom of the grating period pattern, and forming a metal oxide film on the surface of the exposed metal layer; removing the impression glue with the grating period pattern; and taking the metal oxide film as a mask layer, and patterning the metal layer to form a nanometer metal grating. The method is advantageous in that the problem that the metal layer in the prior art cannot be etched after the oxidation is solved; and the metal oxide film is taken as the mark layer for the subsequent technology, and can be used as a nanometer metal grating protective layer.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

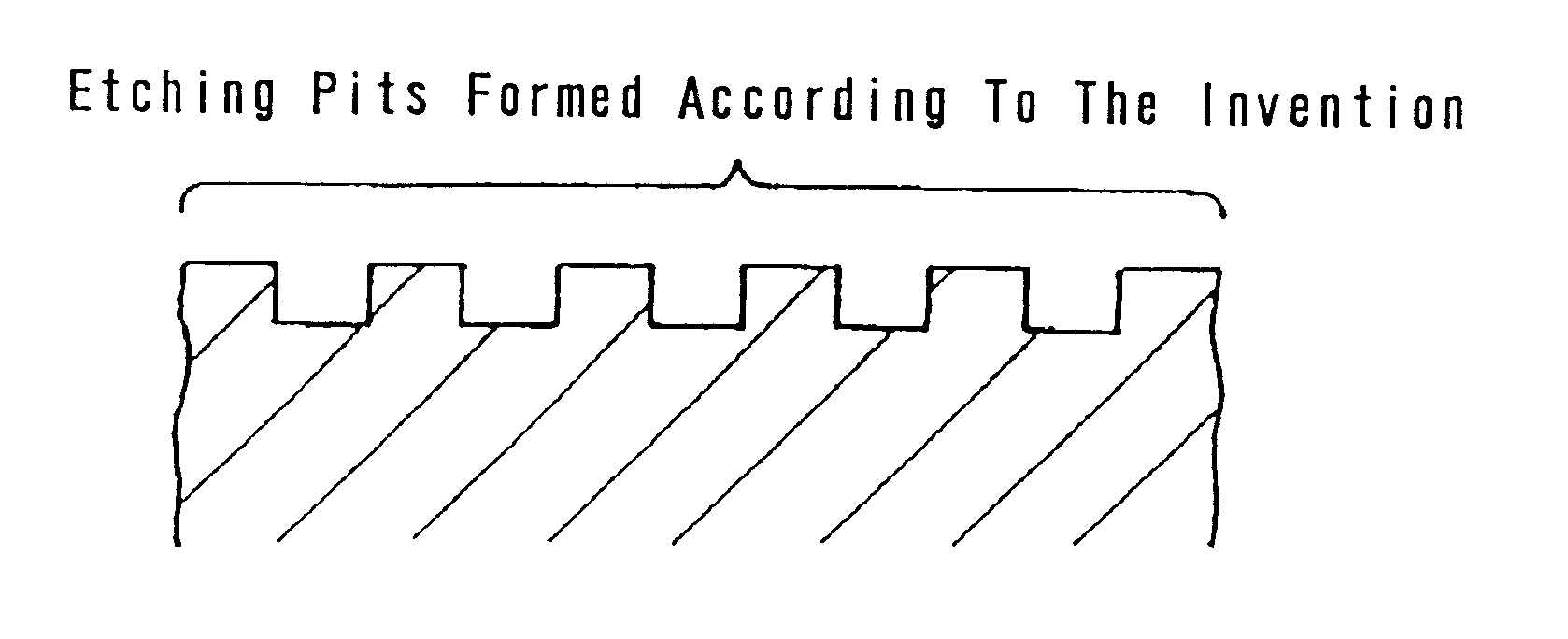

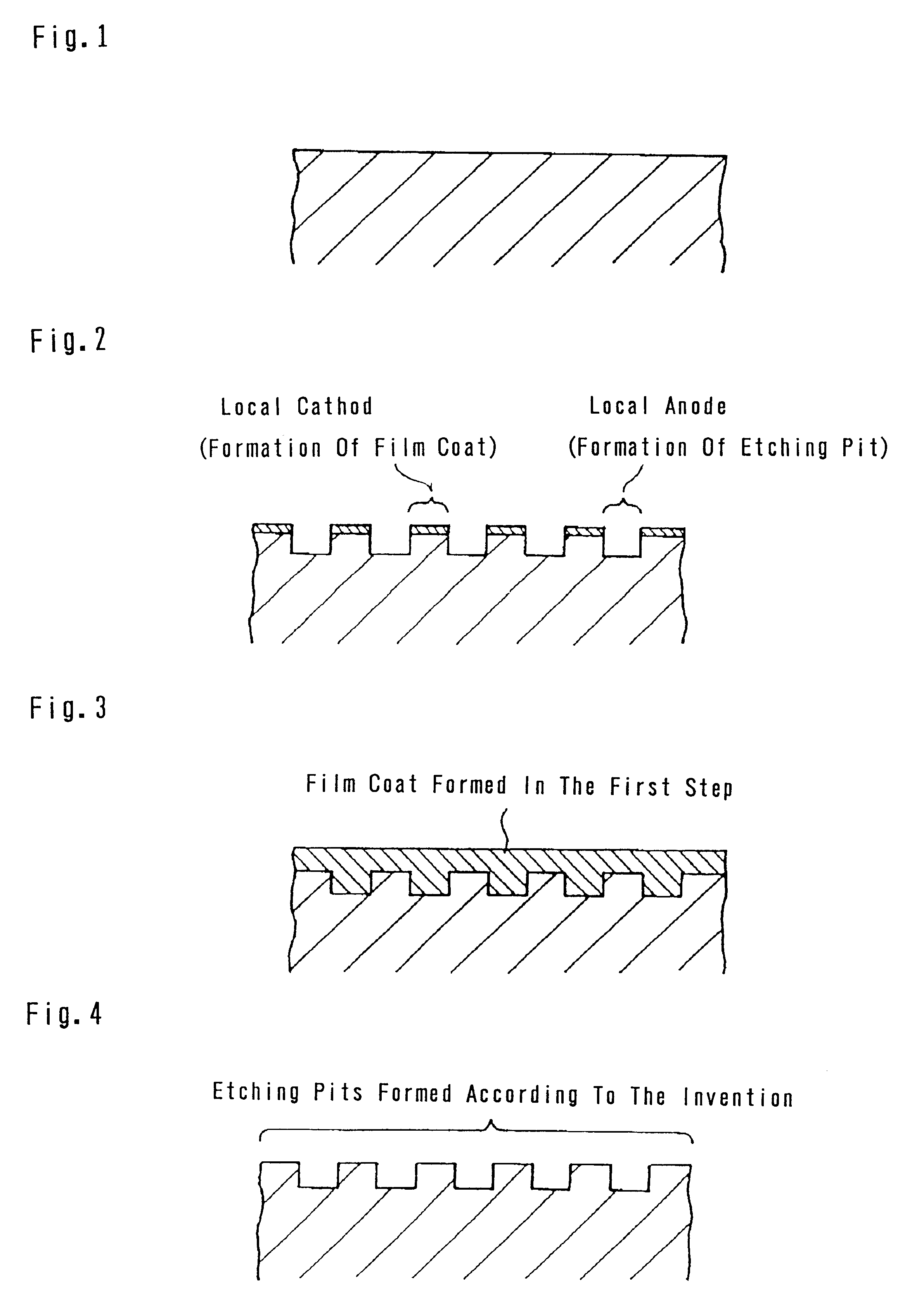

Surface treatment process of metallic material and metallic material obtained thereby

InactiveUS6183570B1Improve adhesionSatisfactory adhesivenessSolid state diffusion coatingThin layerMetallic materials

There is provided a surface treatment method of metal that can endow the surface of a metallic material with strong bonding force in a simple process regardless of the profile and the substance of the metallic material as well as a metallic material obtained by such a method. The method comprises a first step of conducting a chemical etching process accompanied by formation of a film coat on the metal surface and a second step of chemically removing the film coat formed on the metal surface in the first step. If necessary, it may further comprise a third step of forming a thin layer on the metal surface after the second step.

Owner:NIHON PARKERIZING

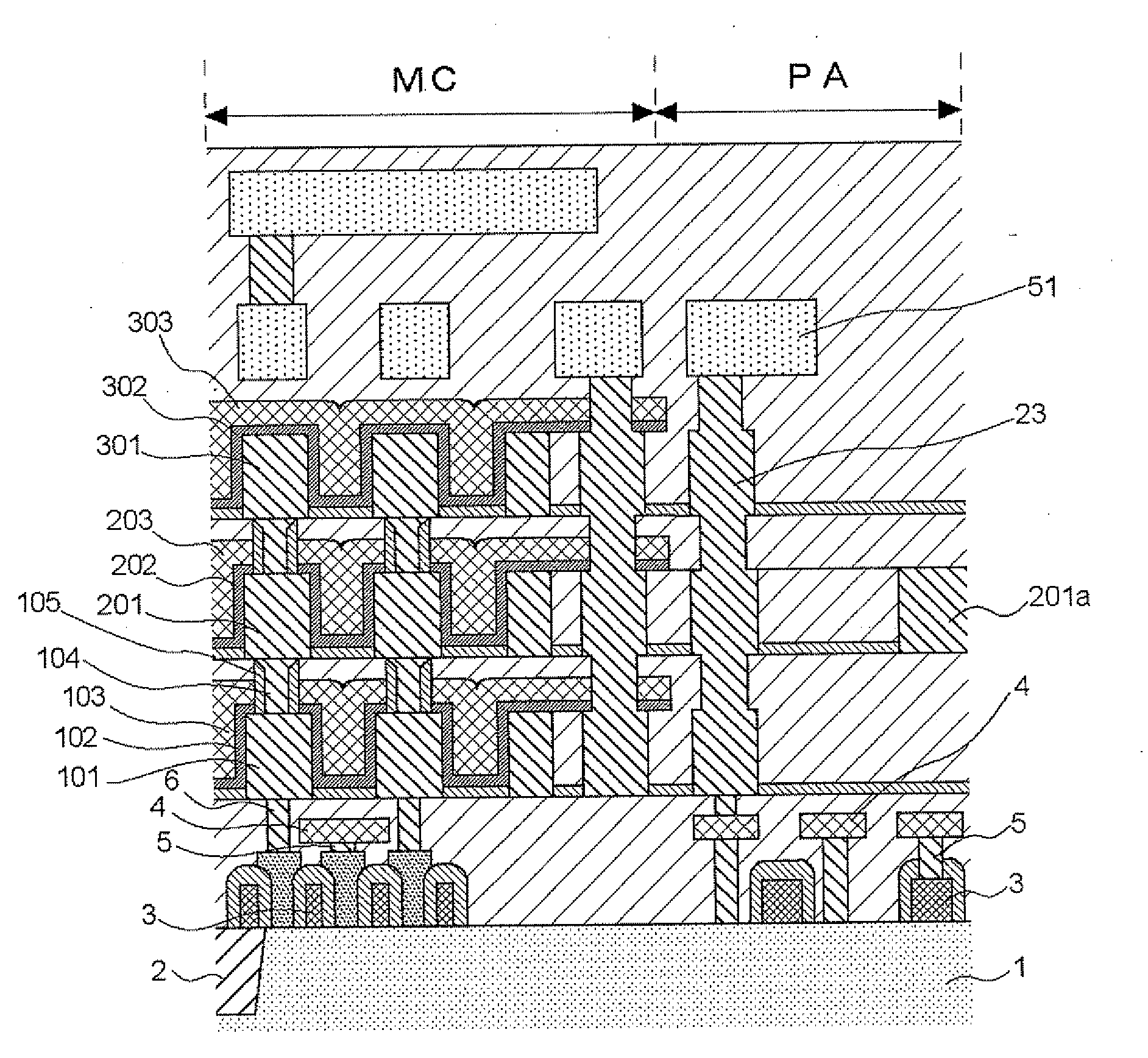

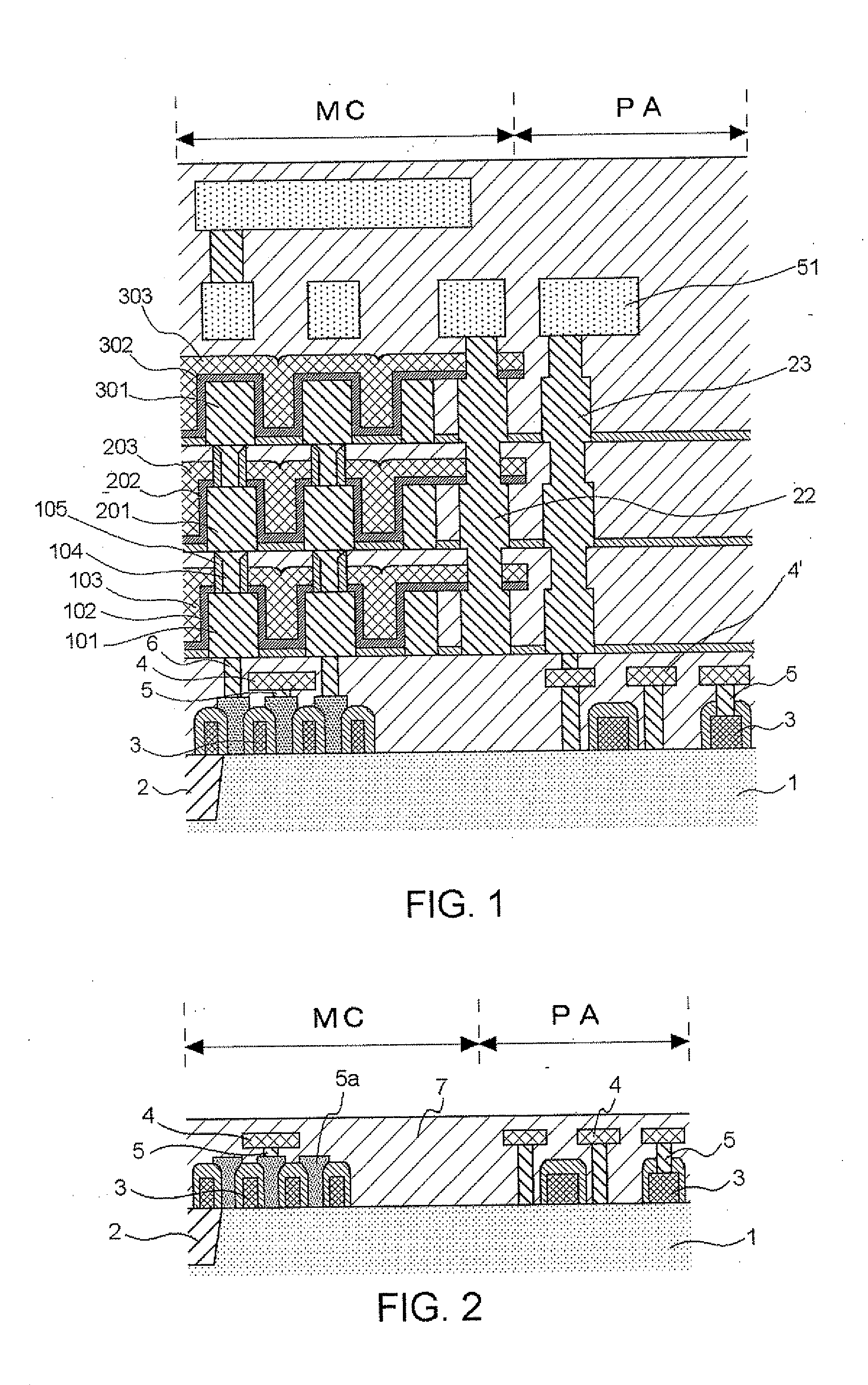

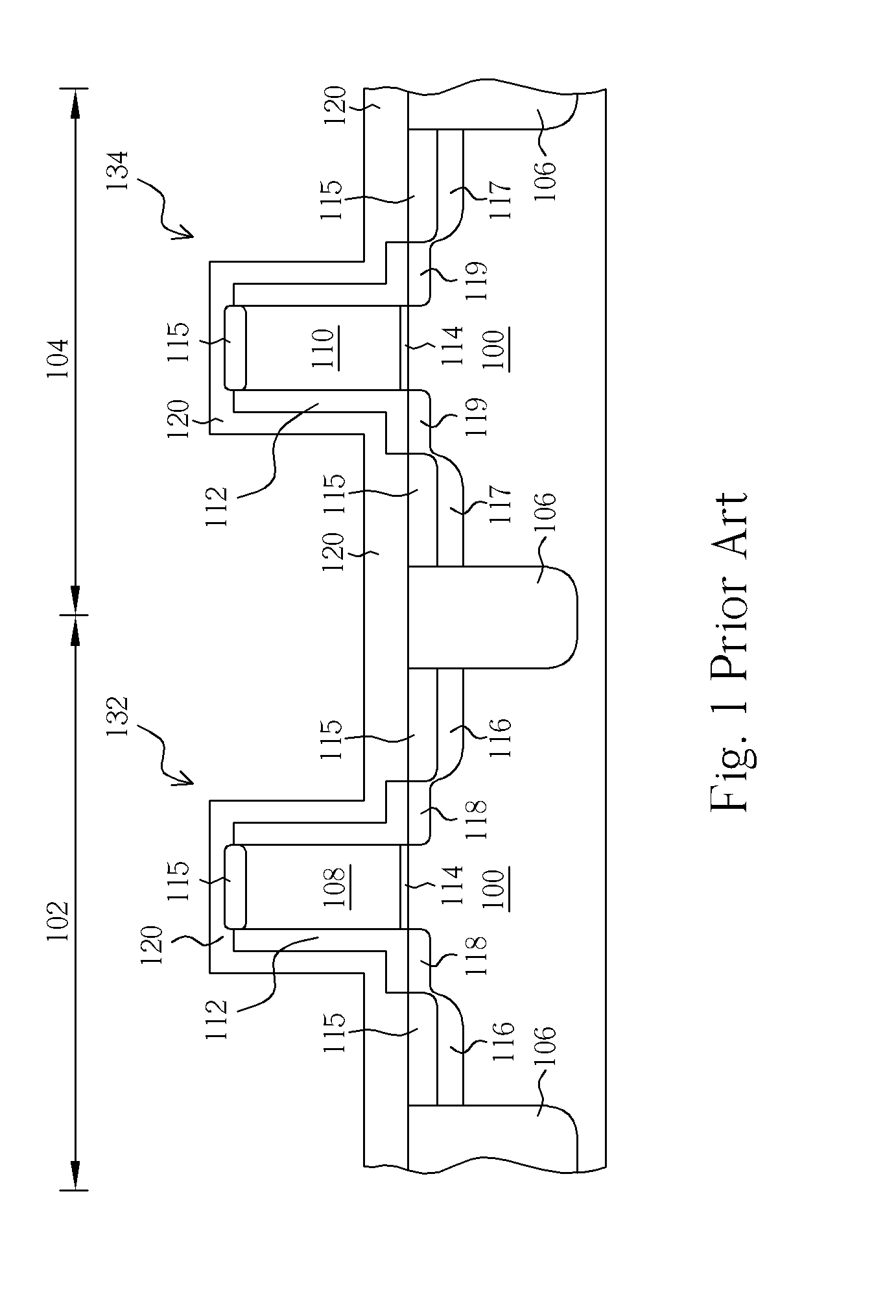

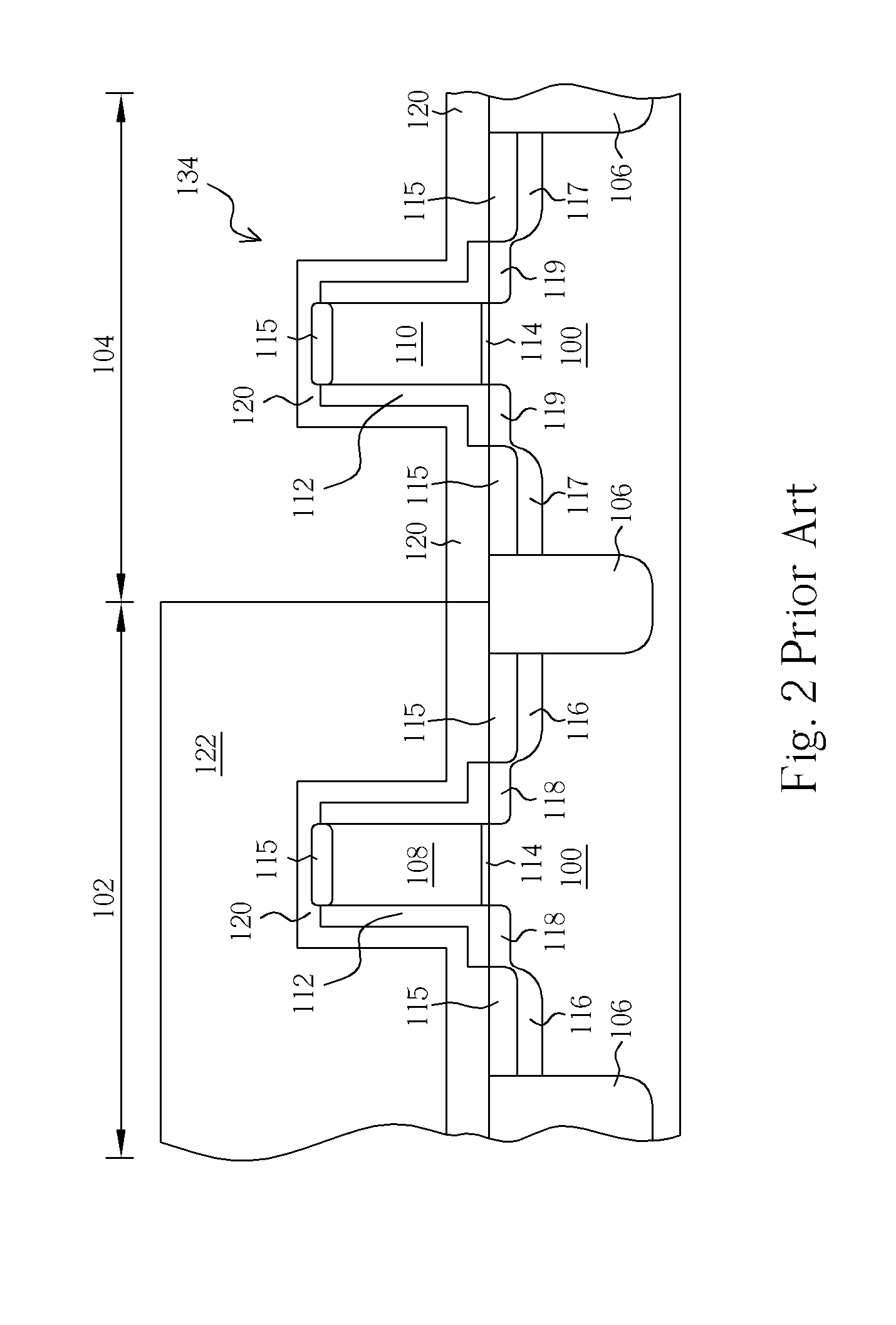

Semiconductor memory device and manufacturing method therefor

A semiconductor memory device in which a plurality of capacitors each including a columnar lower electrode, a capacitor insulation film and an upper electrode are stacked with interlayer films therebetween, a contact plug connects an upper face of each lower electrode of a lower layer with a bottom face of each lower electrode of an upper layer, and another contact plug connects upper electrodes of the capacitors in respective layers with each other.

Owner:LONGITUDE LICENSING LTD

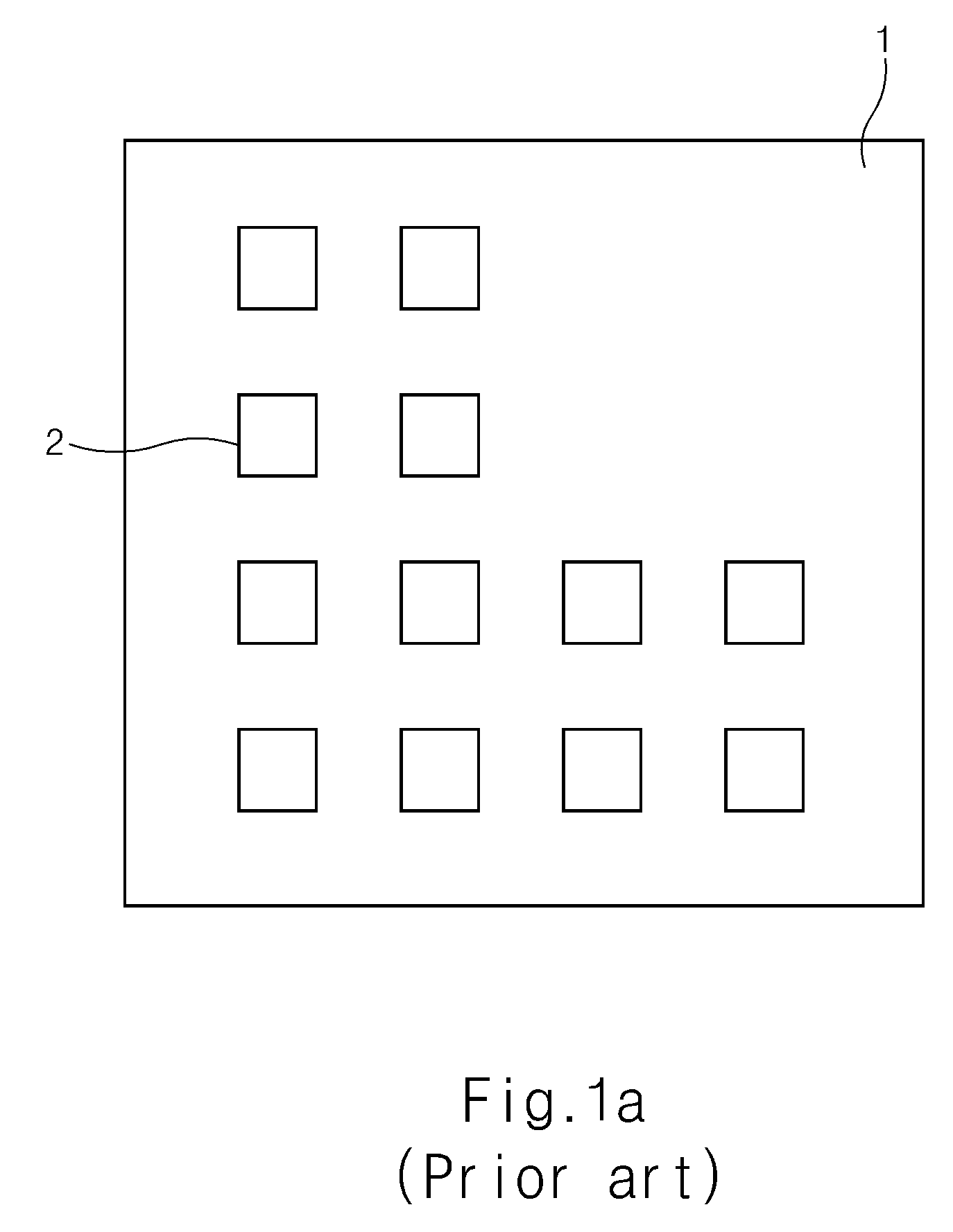

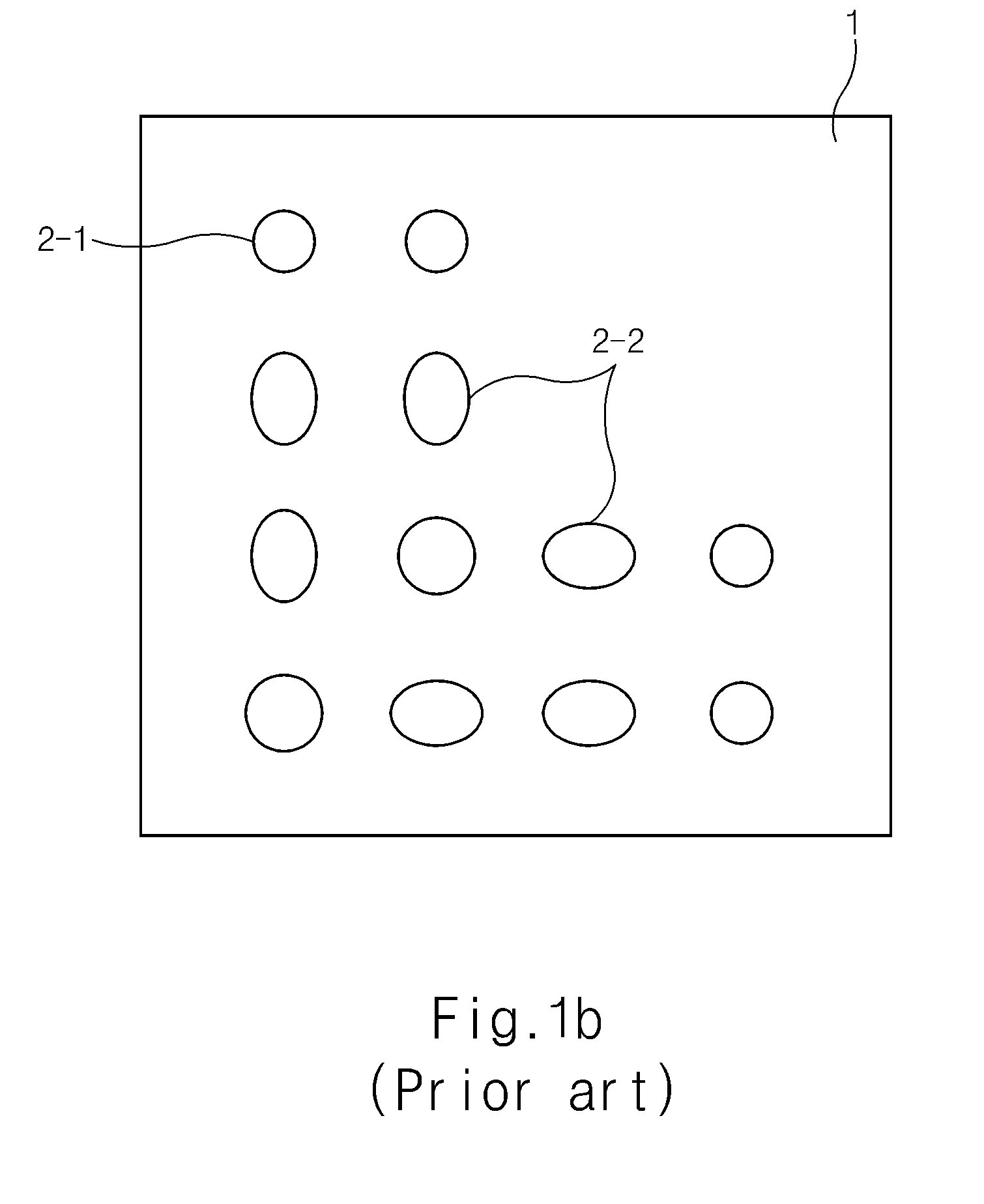

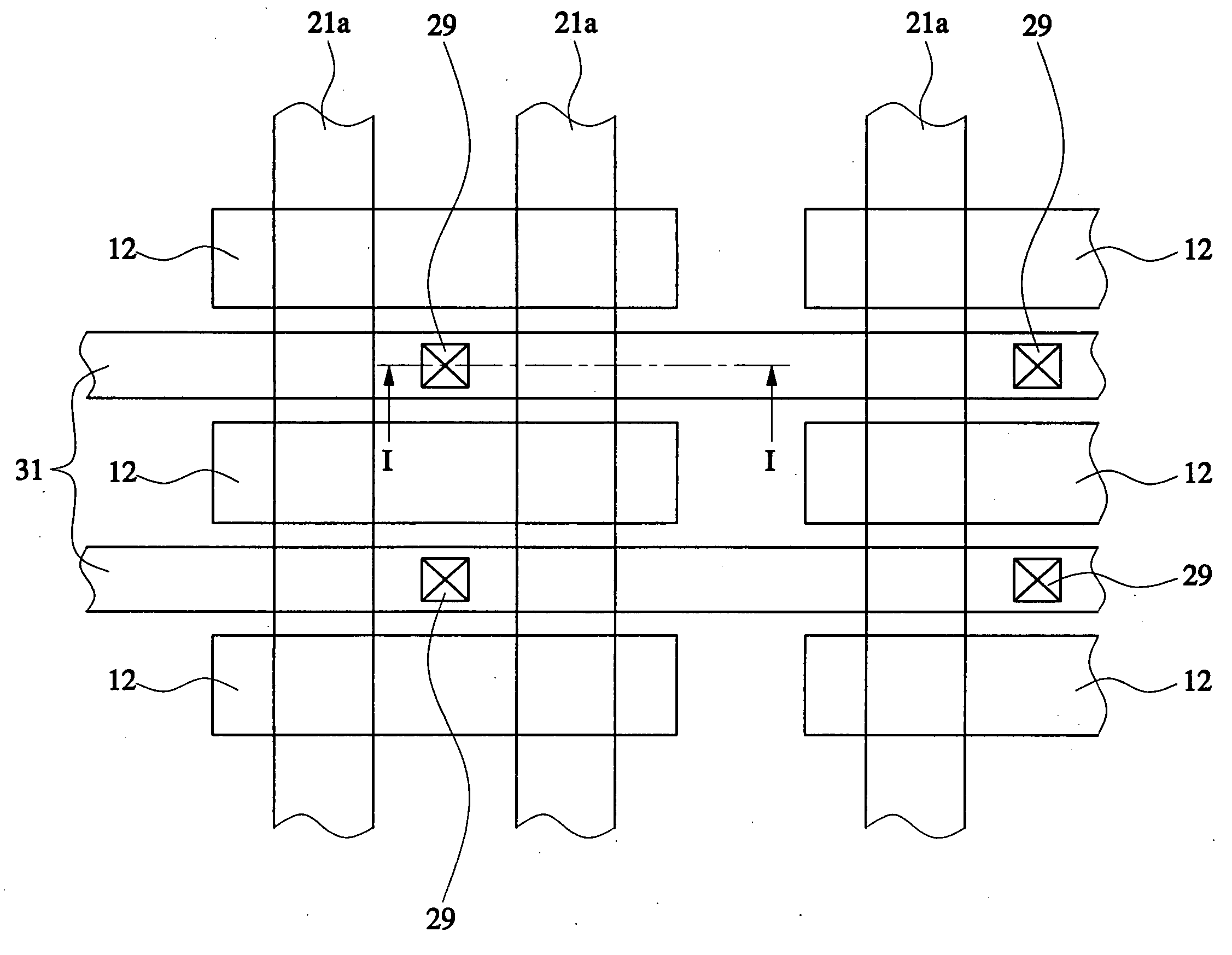

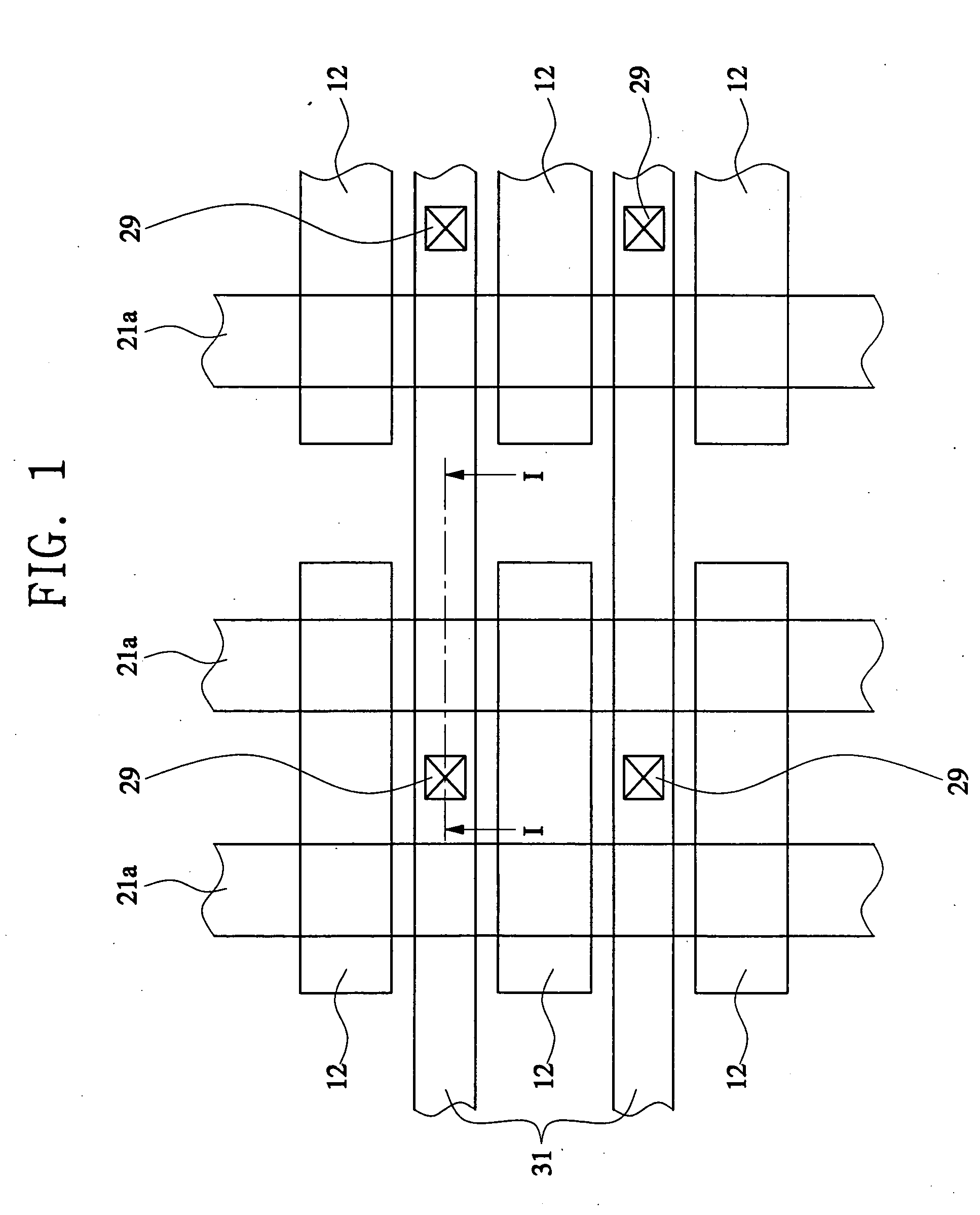

Method for forming fine contact hole pattern of semiconductor device

ActiveUS20100112463A1Reduced minimum pattern pitchEasy to etchSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusTwo stepSemiconductor

A method for forming a fine contact hole of a semiconductor device comprises performing two-step etching processes using a first exposure mask including a plurality of rectangular light transmitting regions each having a given pitch and a second exposure mask including a plurality of rectangular light transmitting regions arranged a shielding region of the first exposure mask with a ‘cross (+)’ shape in the center of rectangular light transmitting regions of the second exposure mask. Each of four corner regions of the light transmitting regions of the first exposure mask is overlapped with four corner regions of rectangular light transmitting regions of the second exposure mask. As a result, the fine contact hole pattern obtained by the method has a uniform size.

Owner:SK HYNIX INC

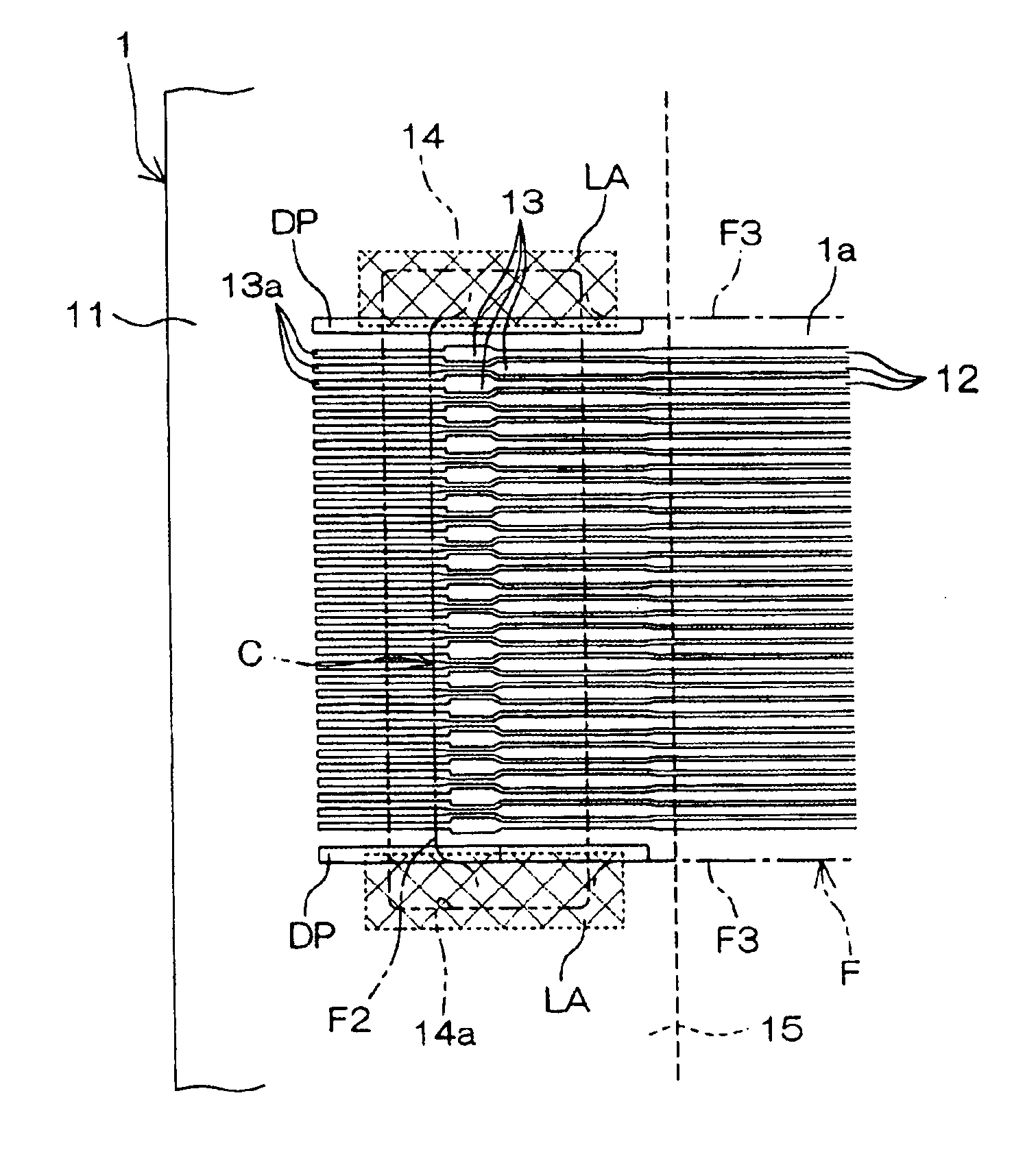

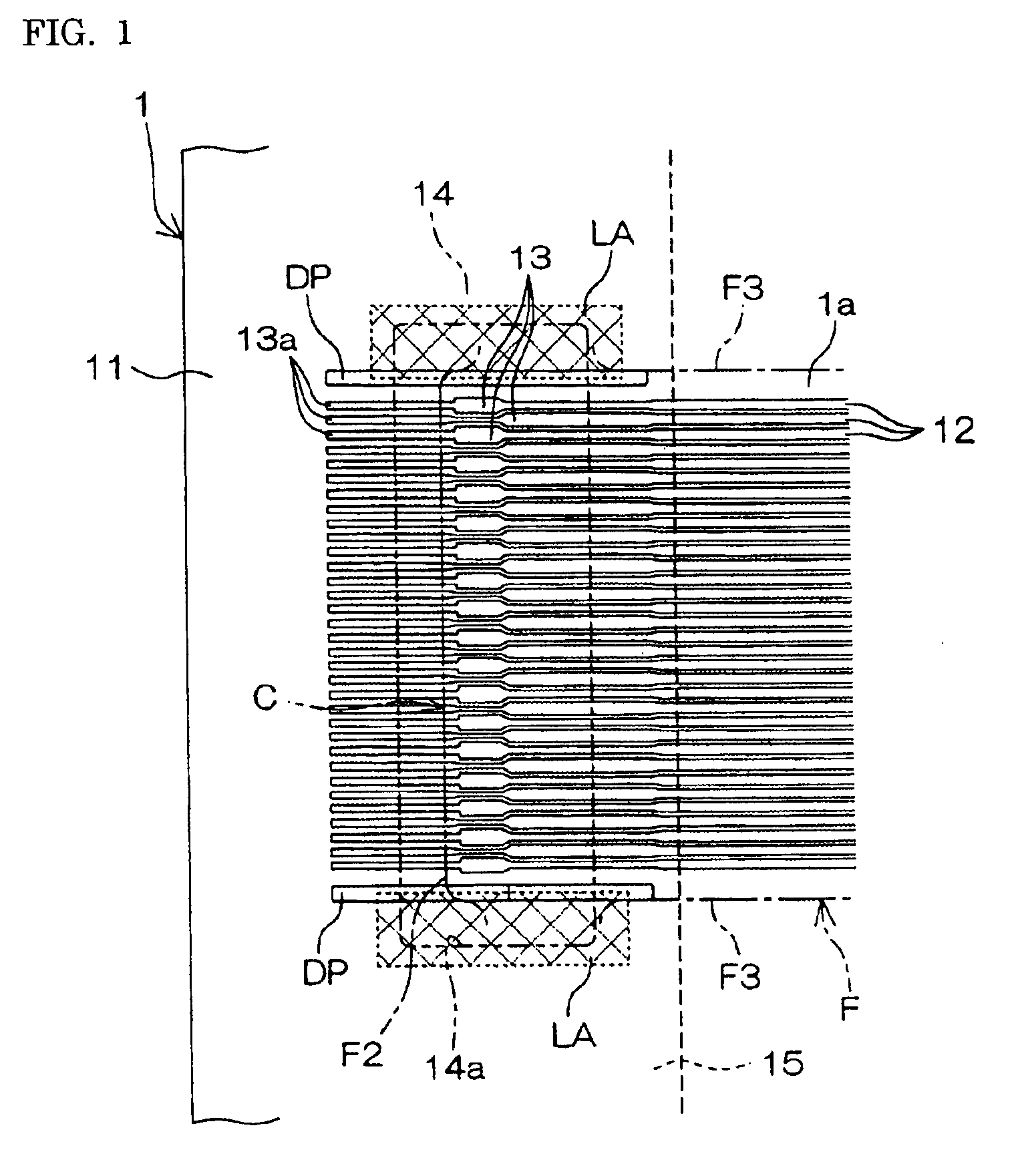

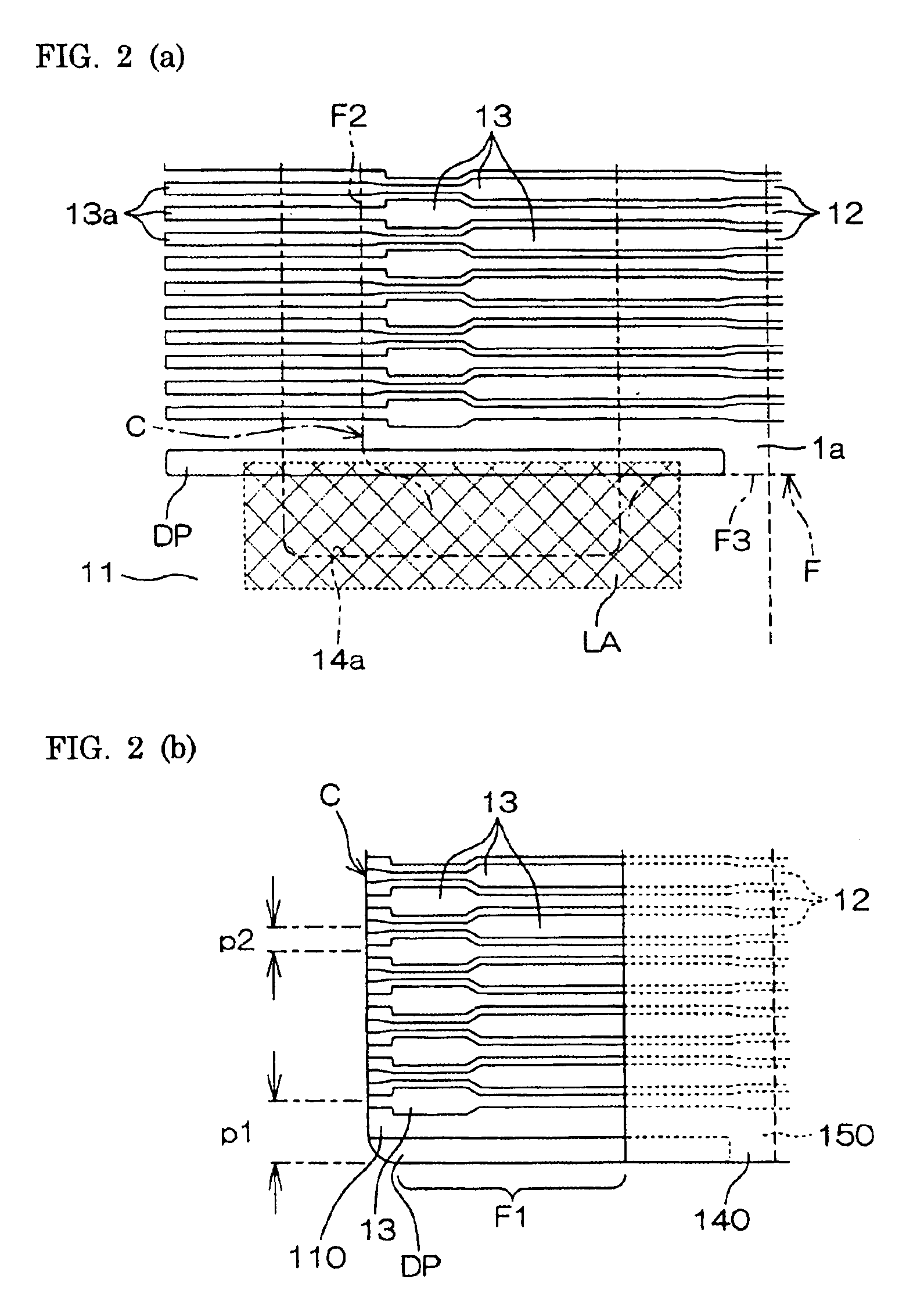

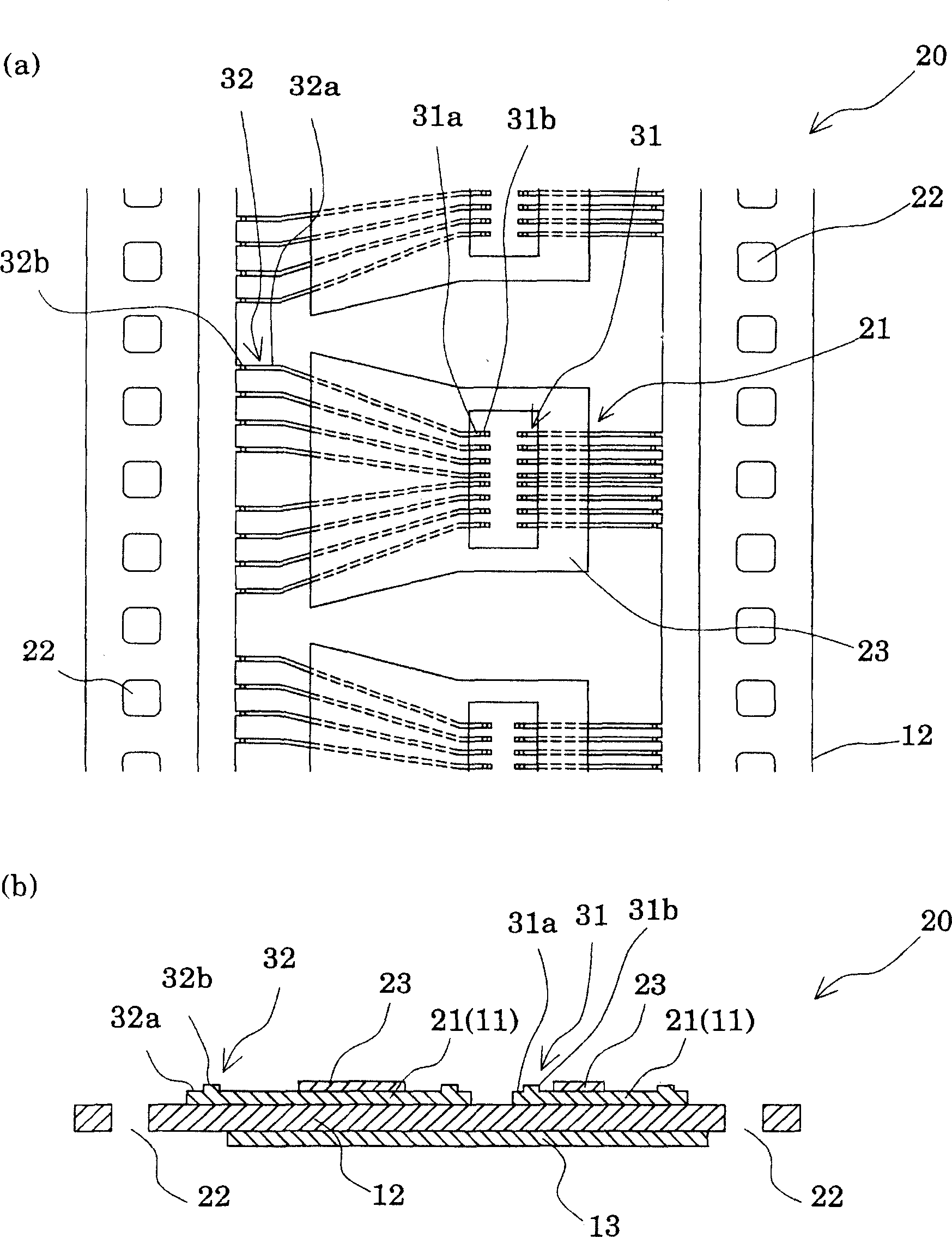

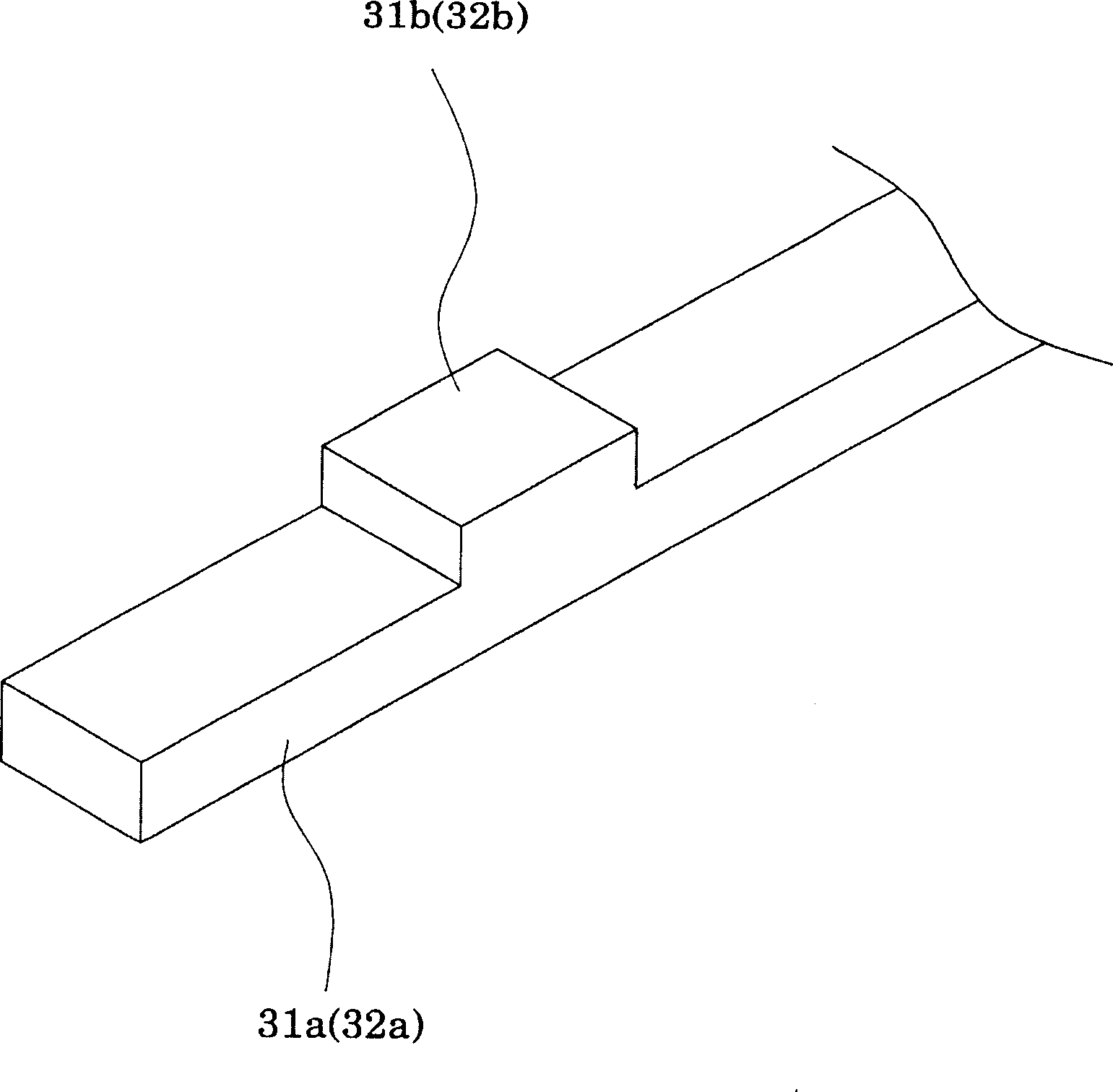

Flexible printed circuit substrate

ActiveUS6858921B2Easy to etchLaser process can be reducedPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringFlexible electronics

A novel flexible printed circuit substrate can be processed into a flexible printed circuit board having a high-accuracy connecting part which does not cause a connection failure when it is connected to a connector even if a pitch between two adjacent terminals is further reduced. The flexible printed circuit substrate has dummy patterns which are formed, simultaneously with the terminals, on the sides of the connecting part, in a shape corresponding to the outline of both sides of connecting part which are used for positioning the terminals when the connecting part is attached to the connector. The dummy patterns are used as masks when a base film is subjected to a laser process.

Owner:SUMITOMO ELECTRIC PRINTED CIRCUITS INC

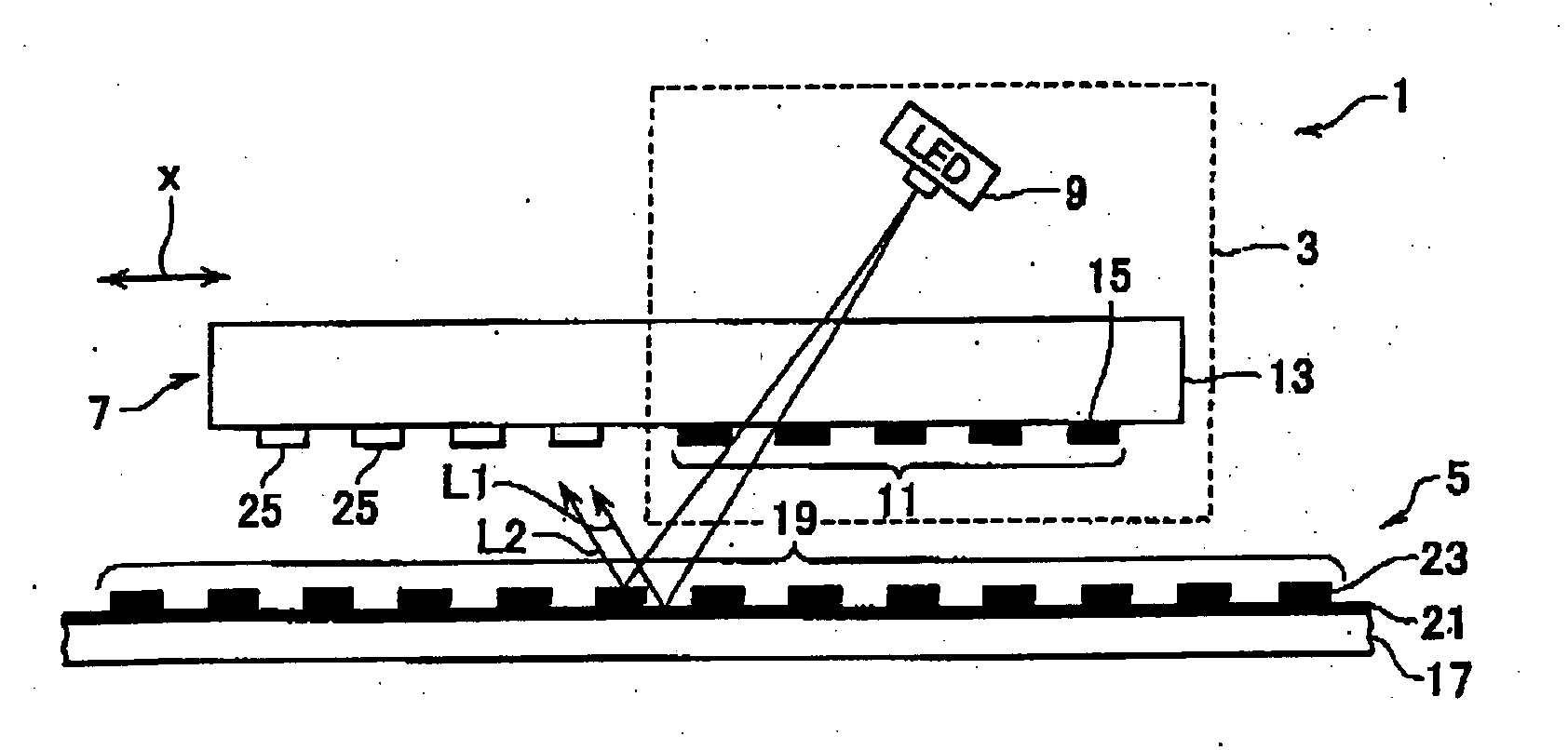

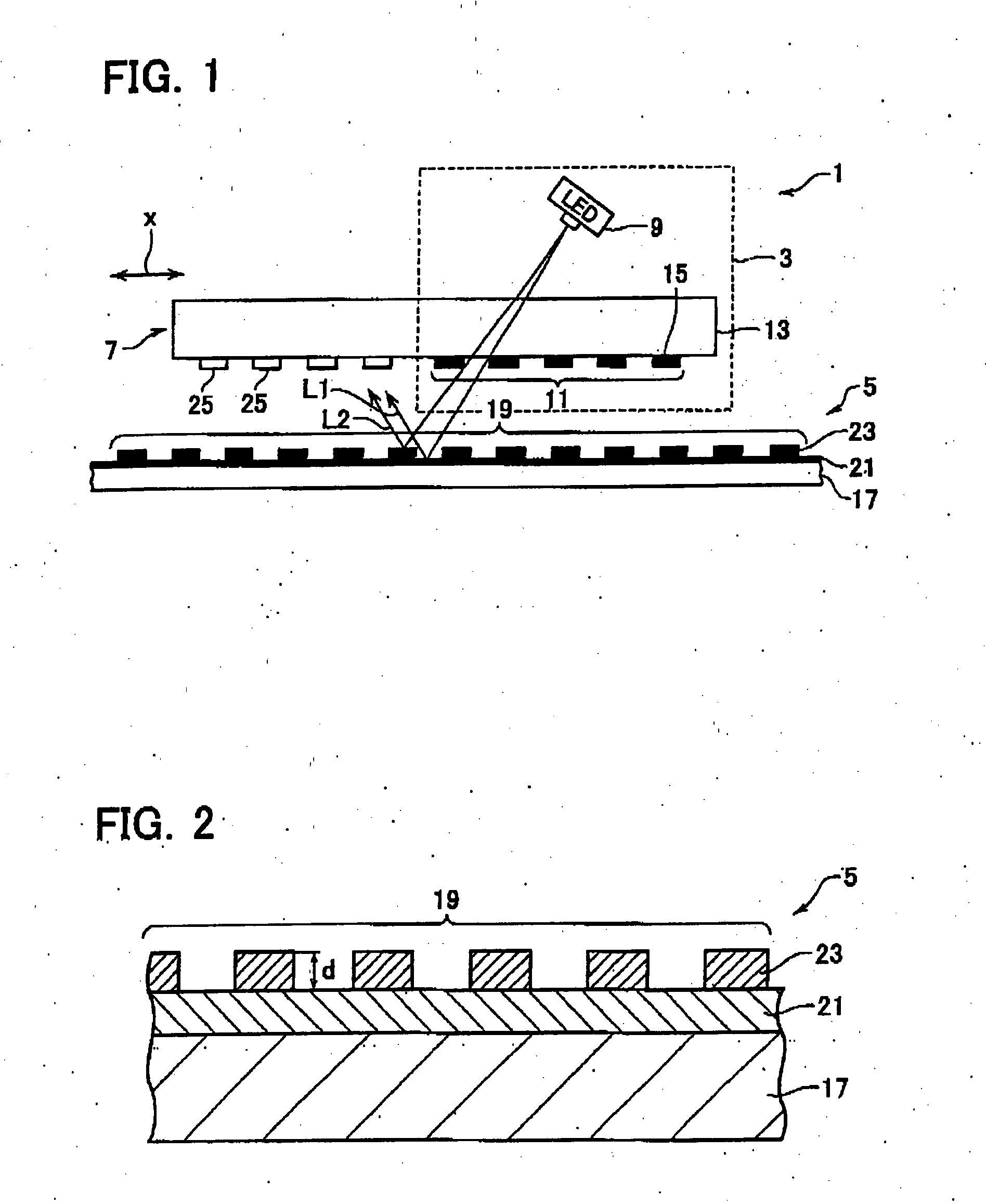

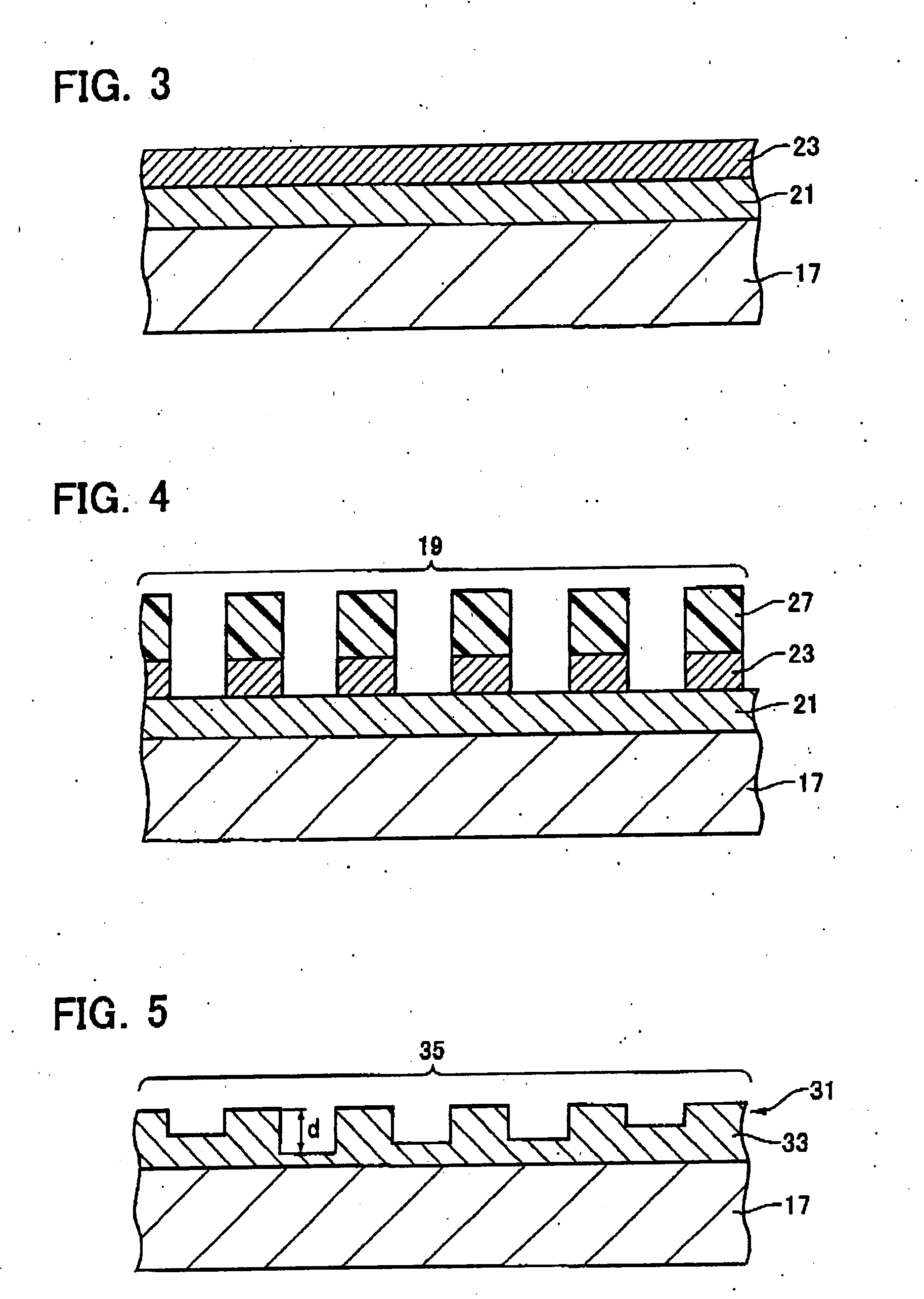

Photoelectric encoder and method of manufacturing scales

InactiveUS20050207013A1Improve controllabilityHigh mechanical strengthBeam/ray focussing/reflecting arrangementsMaterial analysis by optical meansResistGrating

Owner:MITUTOYO CORP

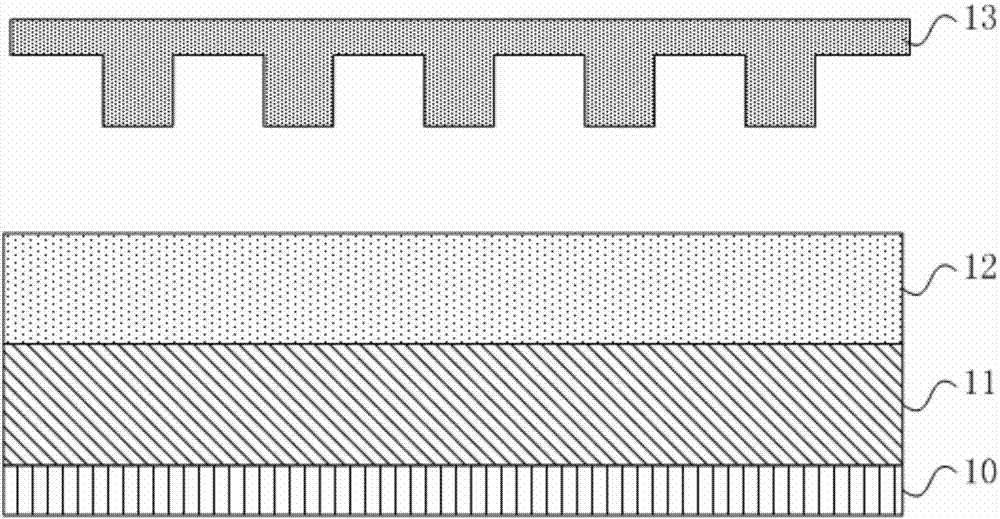

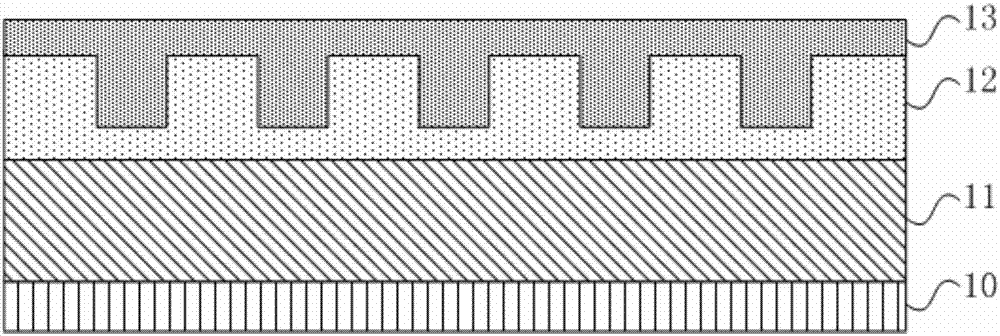

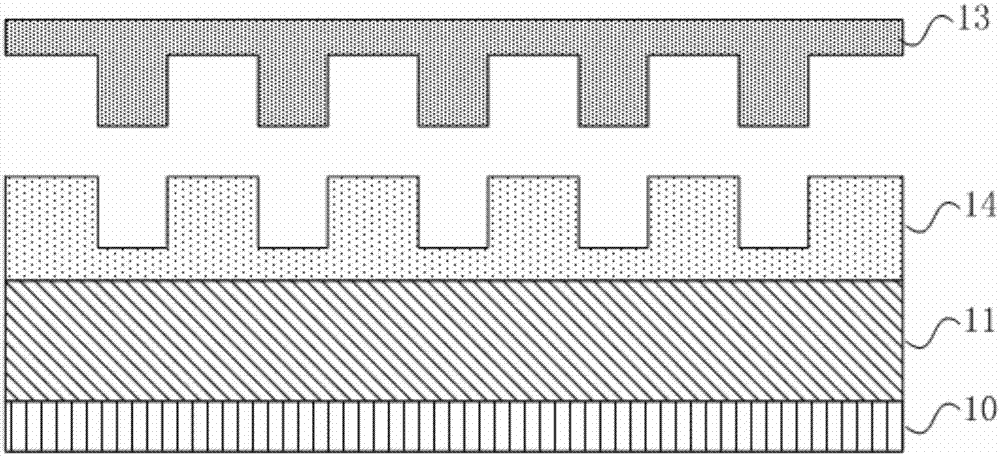

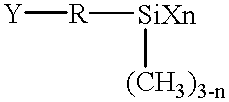

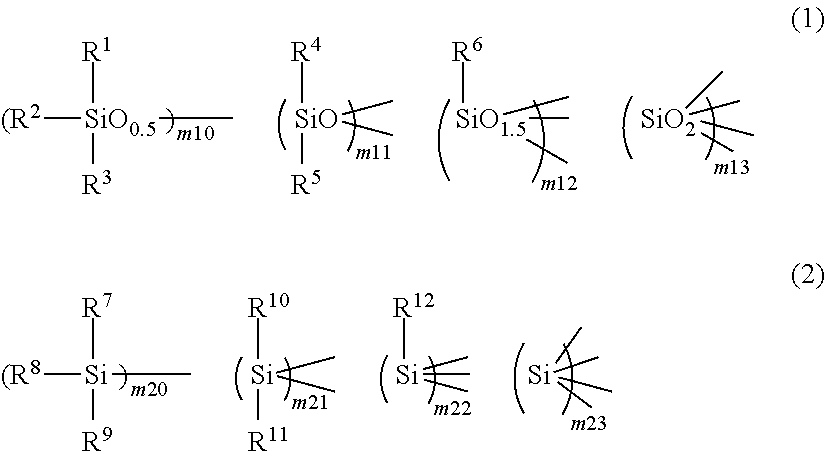

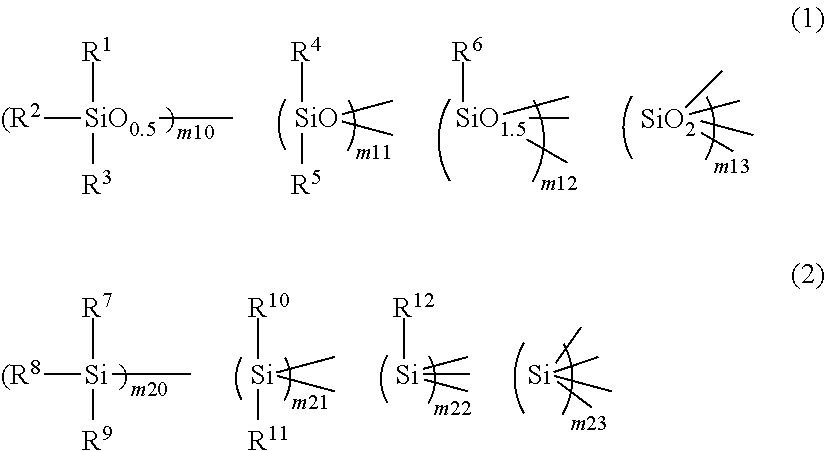

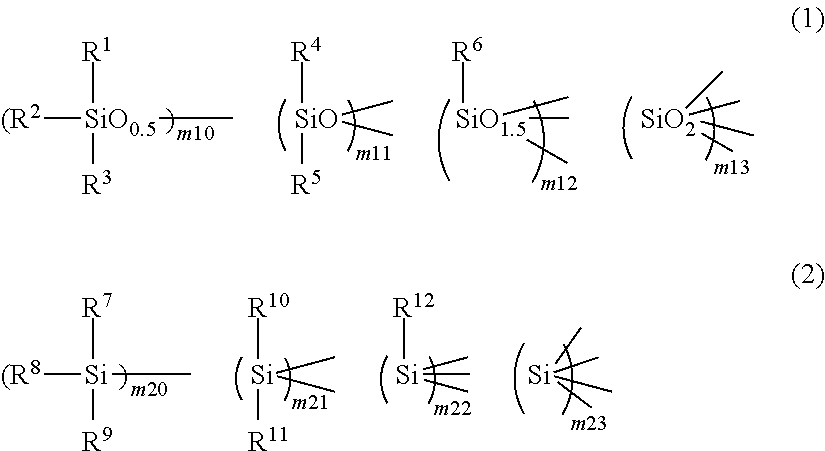

Composition for forming a coating type silicon-containing film, substrate, and patterning process

ActiveUS20160096977A1Improve adhesionEasily wet etchedSemiconductor/solid-state device manufacturingCoatingsOrganic filmSilicic acid

A composition for forming a coating type silicon-containing film, containing one or more silicic acid skeletal structures represented by the formula (1) and one or more silicon skeletal structures represented by the formula (2), wherein the composition contains a coupling between units shown in the formula (2). There can be provided a composition capable of forming a silicon-containing film that has excellent adhesiveness in fine patterning, and can be easily wet etched by a removing liquid which does not cause damage to a semiconductor substrate and a coating type organic film or a CVD film mainly of carbon which is required in the patterning process.

Owner:SHIN ETSU CHEM IND CO LTD

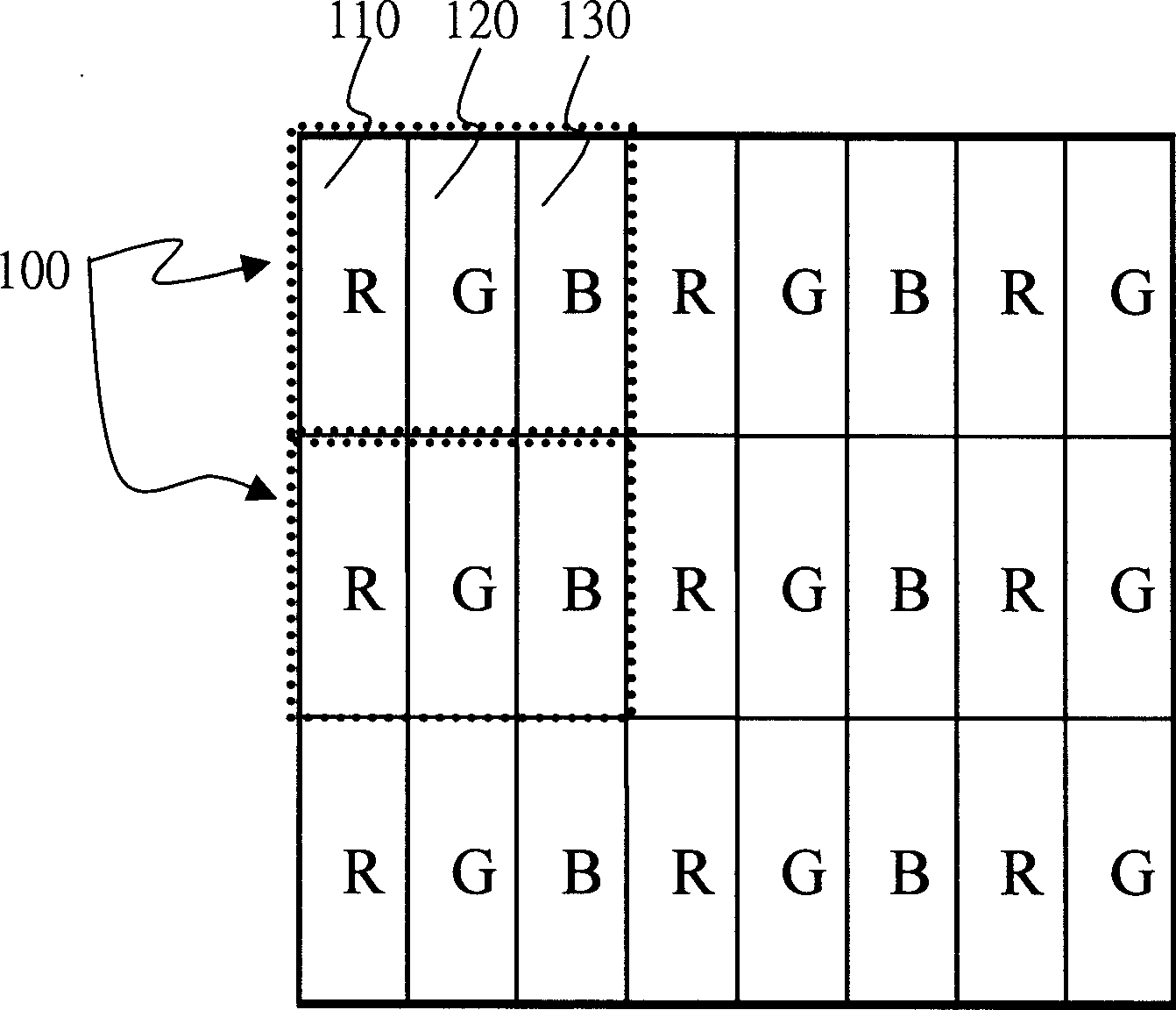

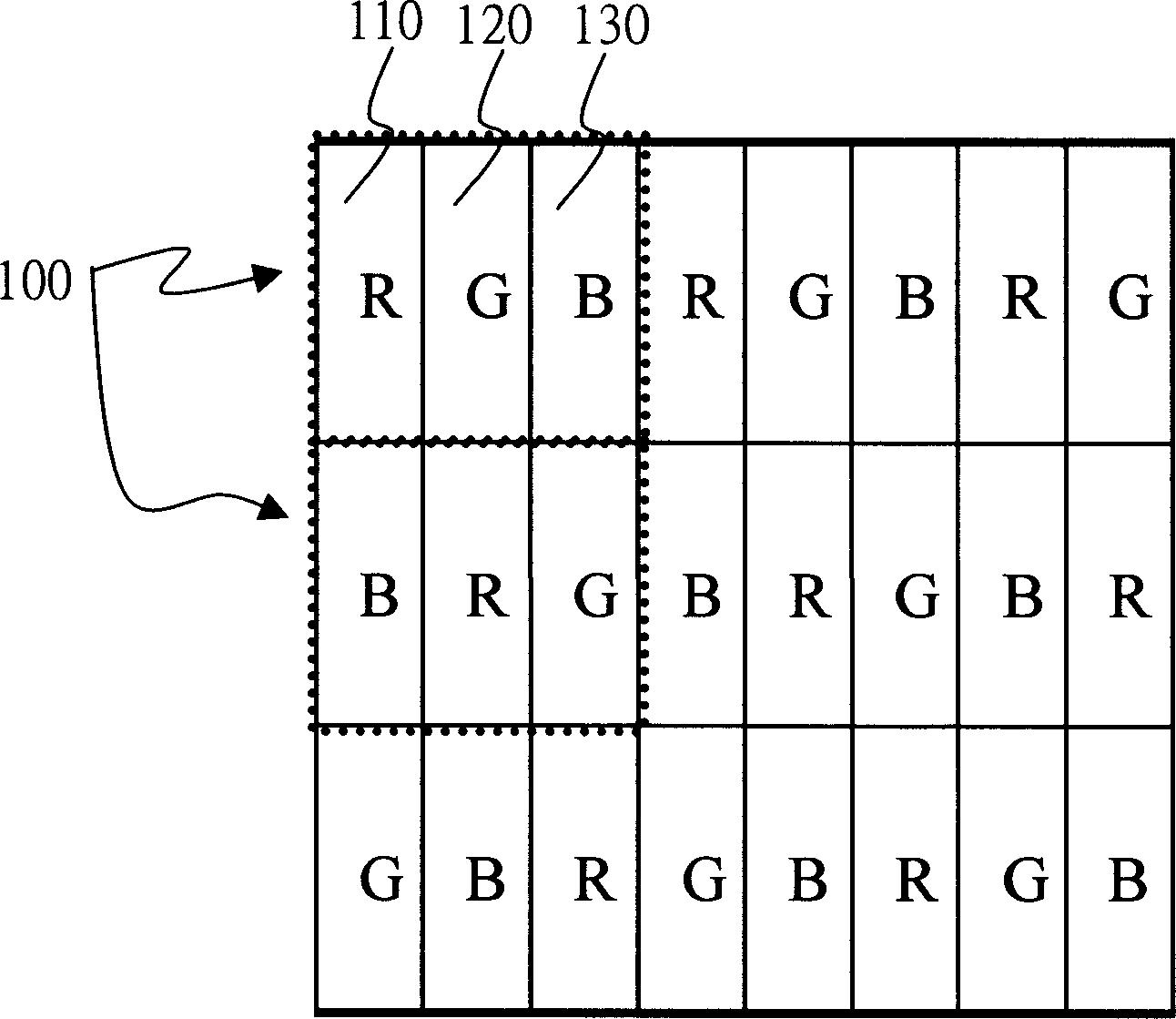

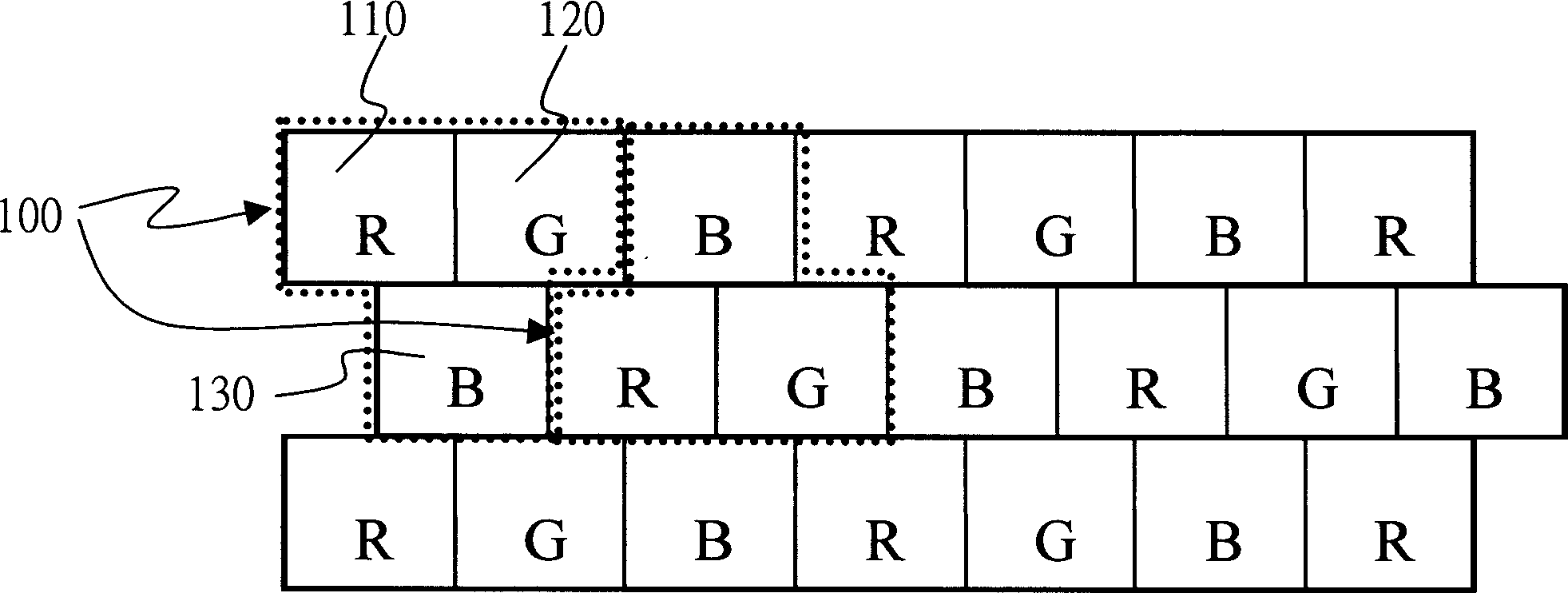

Full color organic electro-luminescent display panel

InactiveCN1738501AReduce manufacturing difficultyWill not overflowElectrical apparatusStatic indicating devicesOrganic electroluminescenceComputer science

The invention discloses a composite color organic electroluminescent display panel, comprising a base panel and several pixel elements arranged in matrix-type on the base panel to form the display panel, while each pixel element comprises a plurality of pixel sub-elements which can emit monochromatic light as red, green or blue. Then, the invention arranges the pixel sub-element near to the adjacent pixel sub-elements which has same monochromatic light side by side via the geometrical arrangement design of pixel sub-elements, to apply the process of manufacturing red, green, blue pixel sub-elements of low molecule organic luminescent diode metallic shield film or the high polymer organic luminescent diode ink-jet of high-definition panel.

Owner:IND TECH RES INST +1

Nonvolatile memory cell employing a plurality of dielectric nanoclusters and method of fabricating the same

InactiveUS20050067651A1Avoid leakage currentMinimizing overeraseNanoinformaticsSolid-state devicesDielectricGate dielectric

A nonvolatile memory cell employing a plurality of dielectric nanoclusters and a method of fabricating the same are disclosed. In one embodiment, the nonvolatile memory cell comprises a semiconductor substrate having a channel region. A control gate is disposed above the channel region. A control gate dielectric layer is disposed between the channel region and the control gate. A plurality of dielectric nanoclusters are disposed between the channel region and the control gate dielectric layer. Each nanocluster may be separated from adjacent nanoclusters by the control gate dielectric layer. A tunnel oxide layer is disposed between the plurality of dielectric nanoclusters and the channel region. Further, a source and a drain are formed in the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

Top covering layer of vertical magnetic resistance element, and manufacturing method of top covering layer

ActiveCN109755382ASimple materialEasy to etchMagnetic-field-controlled resistorsGalvano-magnetic device detailsEtchingMagnetic memory

The invention provides a top covering layer of a vertical magnetic resistance element. The top covering layer sequentially comprises an oxide covering layer and a metal top covering multilayer film, wherein the metal top cover multilayer film is composed of an oxidation prevention layer, a structure transition layer, an etching stop layer, and a hard mask layer; and the lower portion of the oxidation prevention layer is attached to the oxide covering layer. The invention further provides the vertical magnetic resistance element and a manufacturing method thereof; the manufacturing method comprises the following steps that 1, a bottom electrode layer, a seed layer, a vertical magnetic reference layer, a tunnel barrier layer and a magnetic memory layer are gradually grown on the substrate insequence; 2, the oxide covering layer is grown on the magnetic memory layer; 3, the metal top covering multilayer film is grown on the oxide covering layer in sequence; and 4, annealing treatment iscarried out on the magnetic resistance element multilayer film formed in the step 1 to the step 3. The introduction of the oxidation prevention layer and the structure transition layer can help improve the material and magnetoresistance performance of the MTJ multilayer film. Meanwhile, due to the removal of the TA, the etching of the MTJ multilayer film becomes relatively easy.

Owner:SHANGHAI CIYU INFORMATION TECH CO LTD

Organometallic precursor compounds

ActiveUS20050215805A1Easy to depositSpeed up the molding processGroup 8/9/10/18 element organic compoundsGroup 6/16 organic compounds without C-metal linkagesCoatingInorganic chemistry

This invention relates to organometallic precursor compounds represented by the formula (L)M(L′)2(NO) wherein M is a Group 6 metal, L is a substituted or unsubstituted anionic ligand and L′ is the same or different and is a π acceptor ligand, a process for producing the organometallic precursor compounds, and a method for producing a film, coating or powder from the organometallic precursor compounds.

Owner:SAMSUNG ELECTRONICS CO LTD

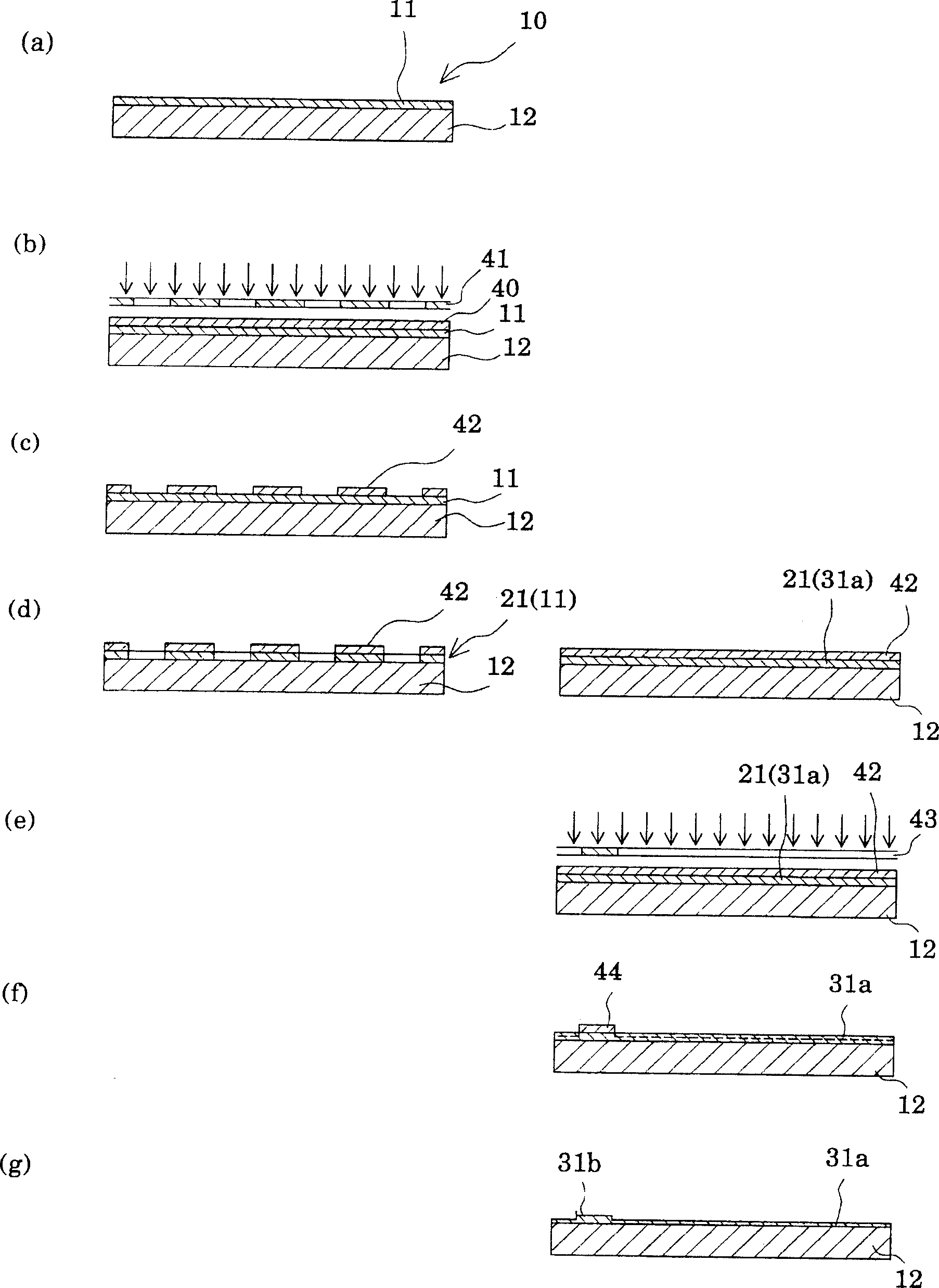

Method for producing flexible printed wiring board, and flexible printed wiring board

InactiveCN1841686AEasy to etchFirmly connectedPrinted circuit detailsSemiconductor/solid-state device detailsResistHigh density

The present invention provides a method for producing a flexible printed wiring board which allows formation of a bump on a wire trace even in a high-density mounting process, and a flexible printed wiring board which realizes high-density mounting with high reliability. In the method for producing a flexible printed wiring board including an insulating layer and a wiring pattern on which a semiconductor chip is to be mounted, the pattern being formed of a conductor layer provided on at least one surface of the insulating layer, the method includes a first etching step including applying a photoresist onto a conductor layer and light-exposing the photoresist by the mediation of a first mask, followed by development, to thereby form a first resist pattern, and etching the conductor layer so as to penetrate the layer in the depth direction, to thereby form a first wiring pattern; and a second etching step including light-exposing the first resist pattern by the mediation of a second mask, followed by development, to thereby form a second resist pattern formed of a remaining portion of the first resist pattern, subsequently, leaving, as a thick portion, a portion of the first wiring pattern covered by the second resist pattern, and half-etching a portion other than the thick portion to an intermediate thickness of the conductor layer, to thereby form a second wiring pattern in the form of a thin portion having a thickness relatively smaller than that of the thick portion.

Owner:MITSUI MINING & SMELTING CO LTD

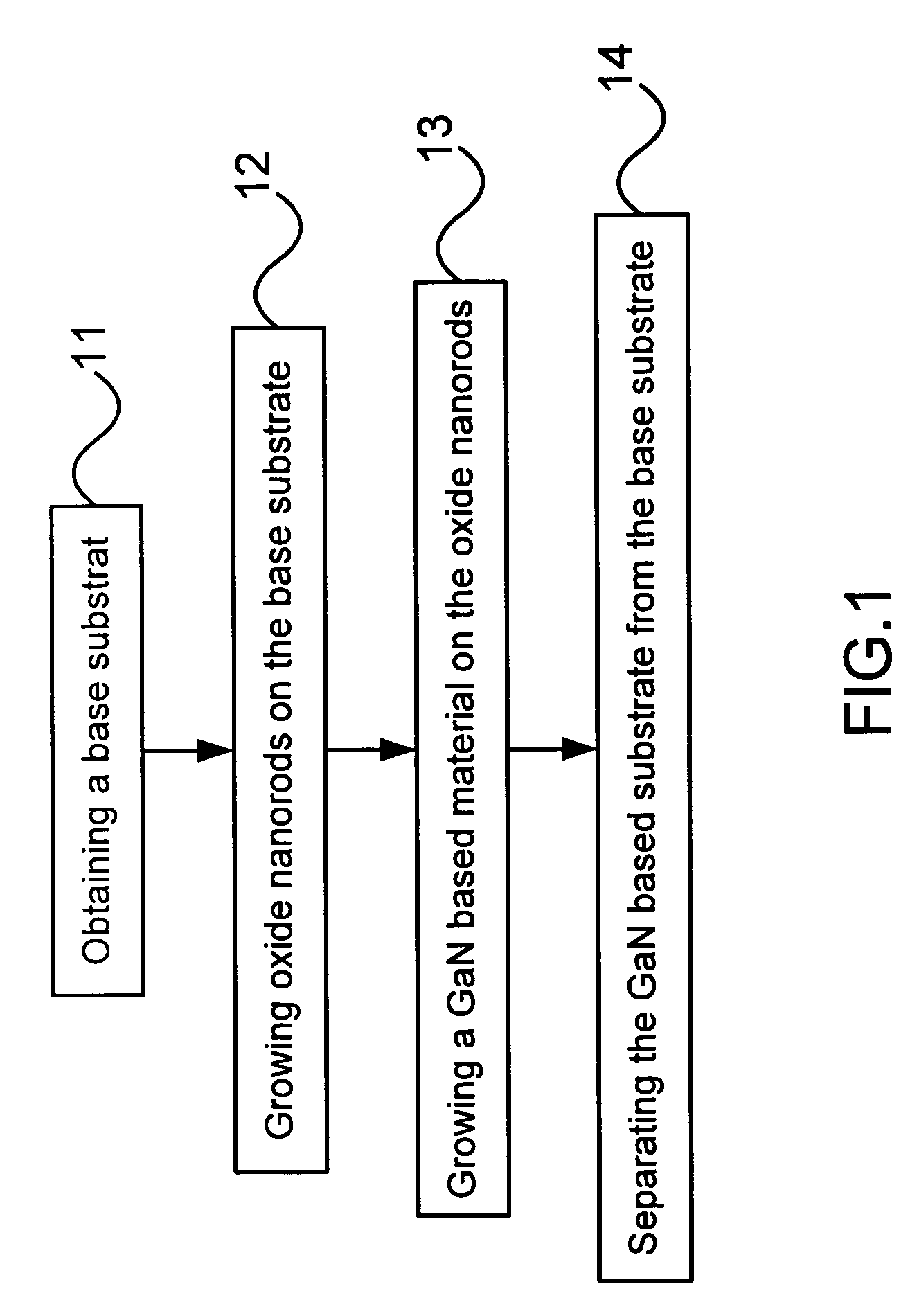

Method for fabricating single-crystal GaN based substrate

InactiveUS20080017100A1Easy to separateEasy to etchPolycrystalline material growthFrom chemically reactive gasesEtchingSingle crystal

A GaN based substrate is obtained with a simple etching. The GaN based substrate is separate from another base substrate with the etching. The whole process is easy and costs low. The substrate is made of a material having a matching lattice length for a lattice structure so that the substrate has good characteristics. And the GaN based substrate has good heat dissipation so that the stability and life-time of GaN based devices on the GaN based substrate are enhanced even when they are constantly operated under a high power.

Owner:NAT CENT UNIV

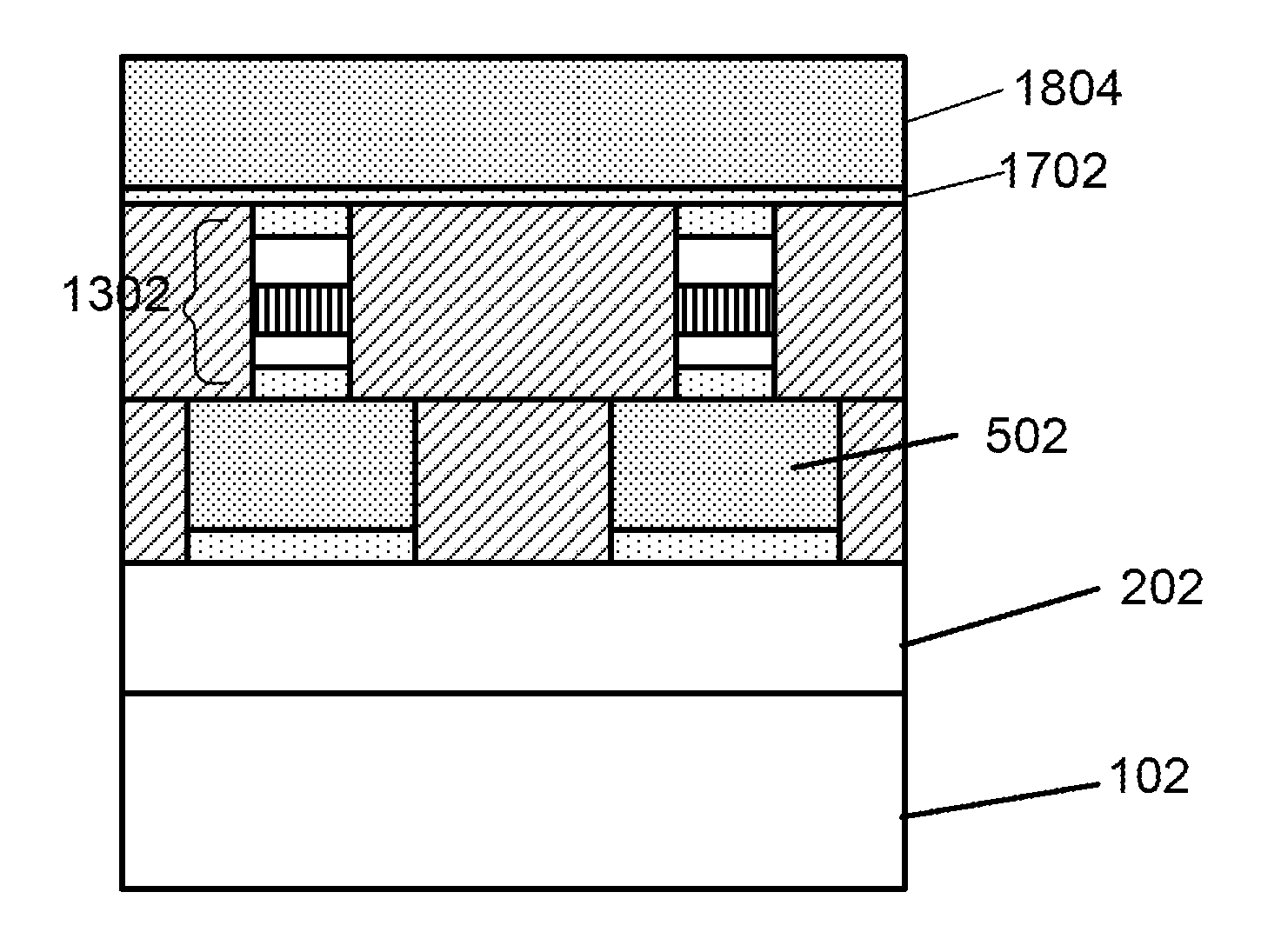

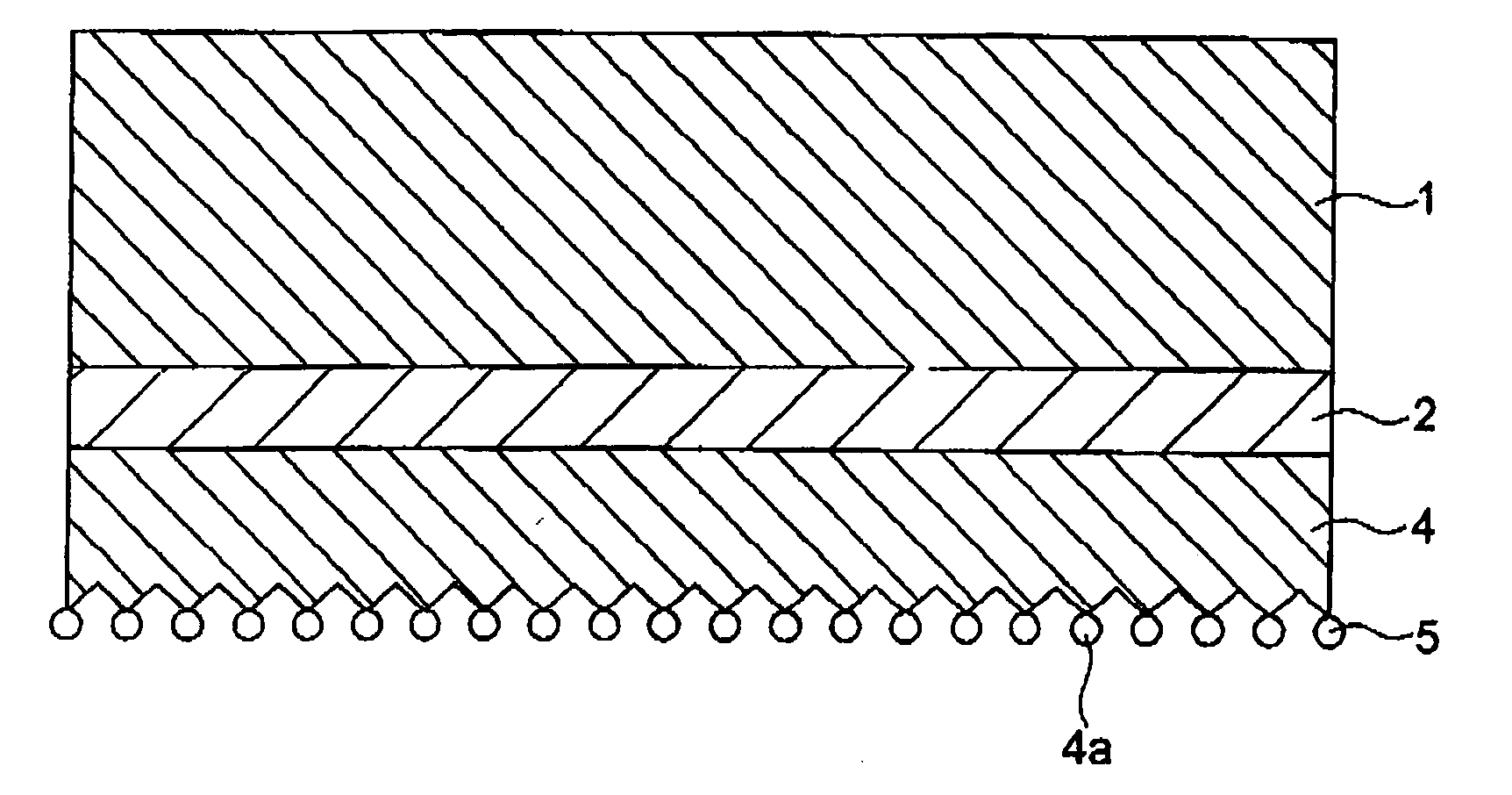

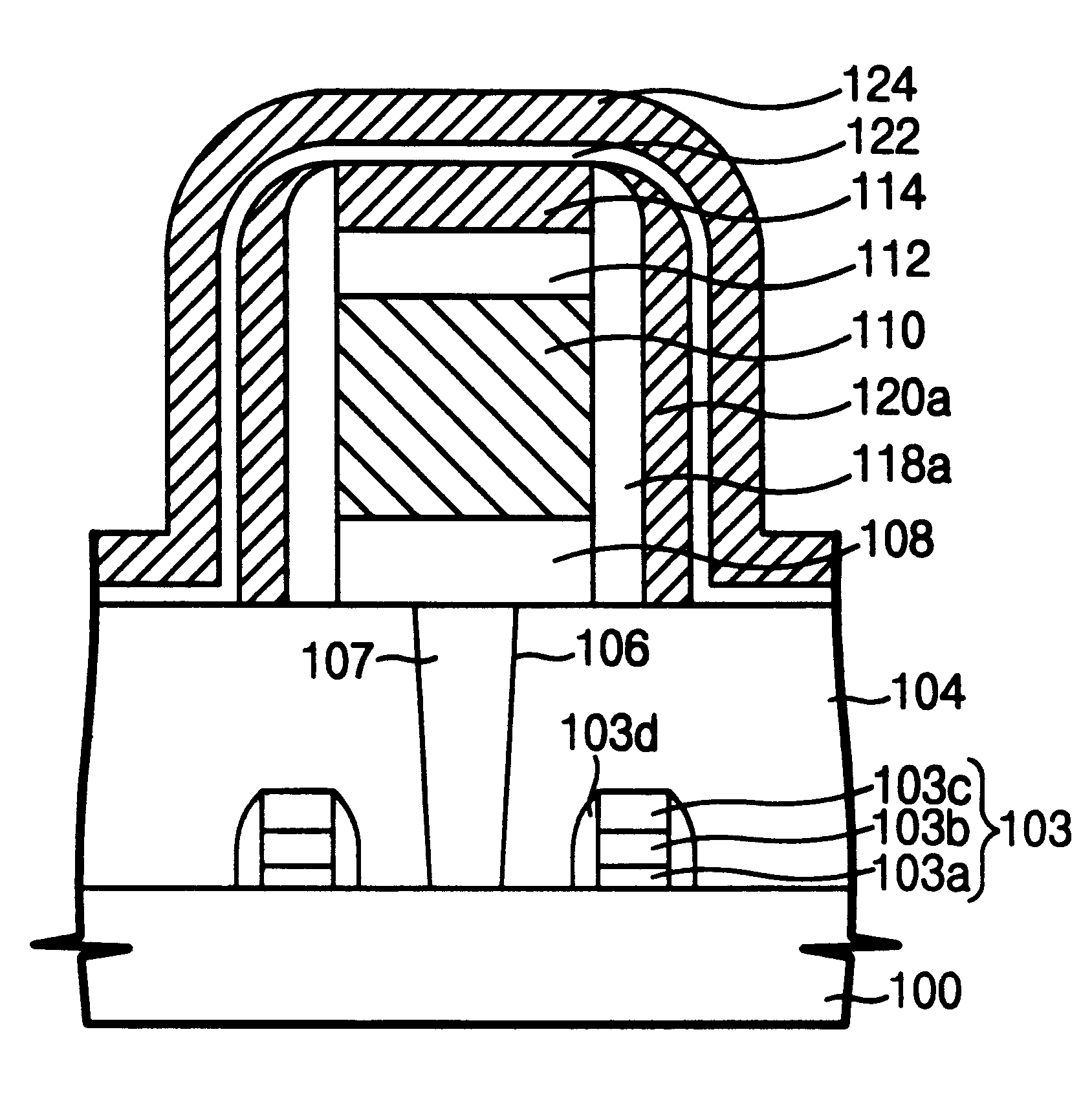

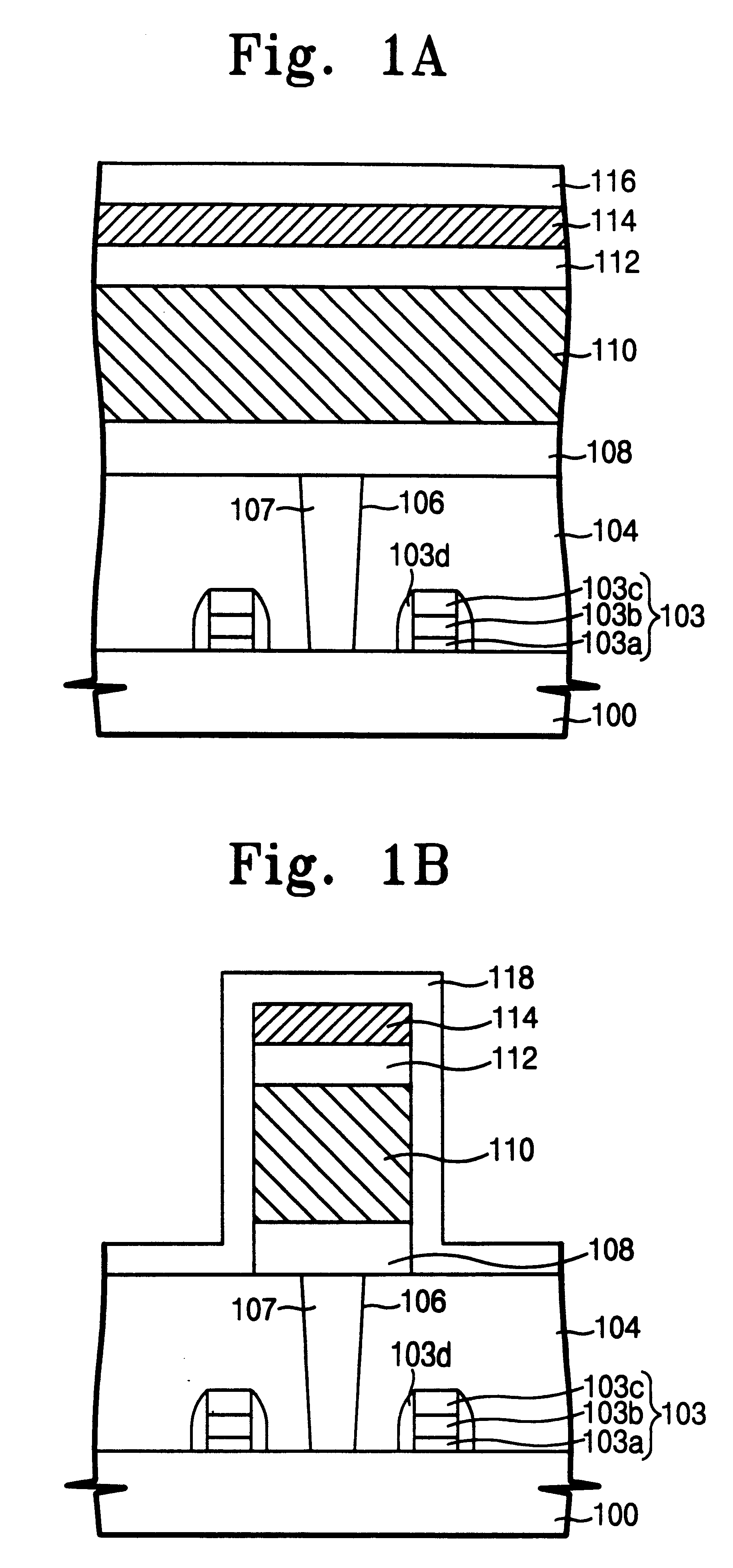

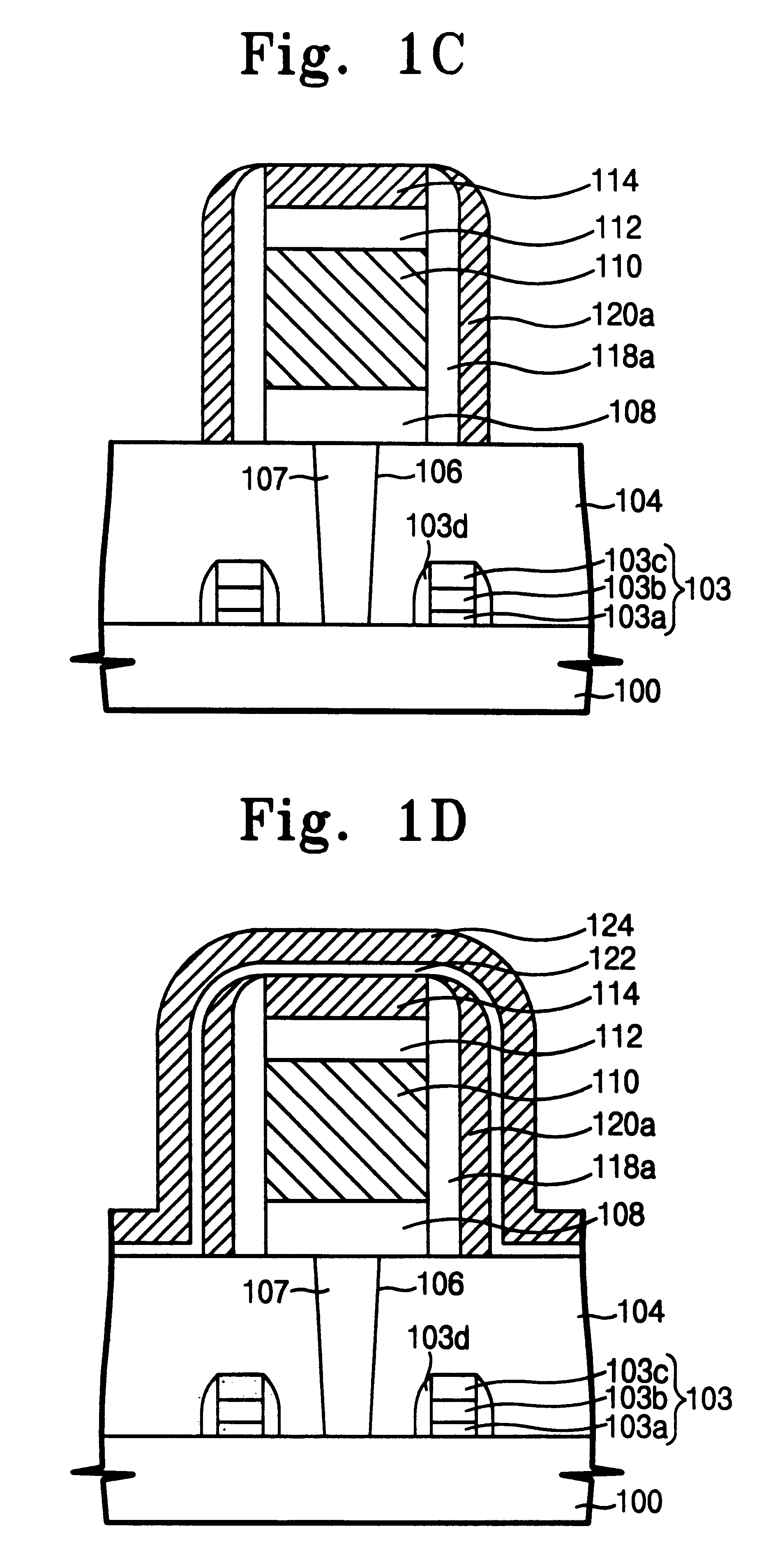

Semiconductor device with pillar-shaped capacitor storage node and method of fabricating the same

A semiconductor device and a method for making a semiconductor device having a pillar-shaped capacitor storage node compatible with a high dielectric film, wherein the pillar-shaped capacitor storage node includes a thick conductive metal layer that is easily etched and a thin conductive layer completely coating the thick conductive metal layer. The thin conductive layer protects the thick conductive metal layer during subsequent high dielectric deposition and annealing and various oxidation process.

Owner:SAMSUNG ELECTRONICS CO LTD

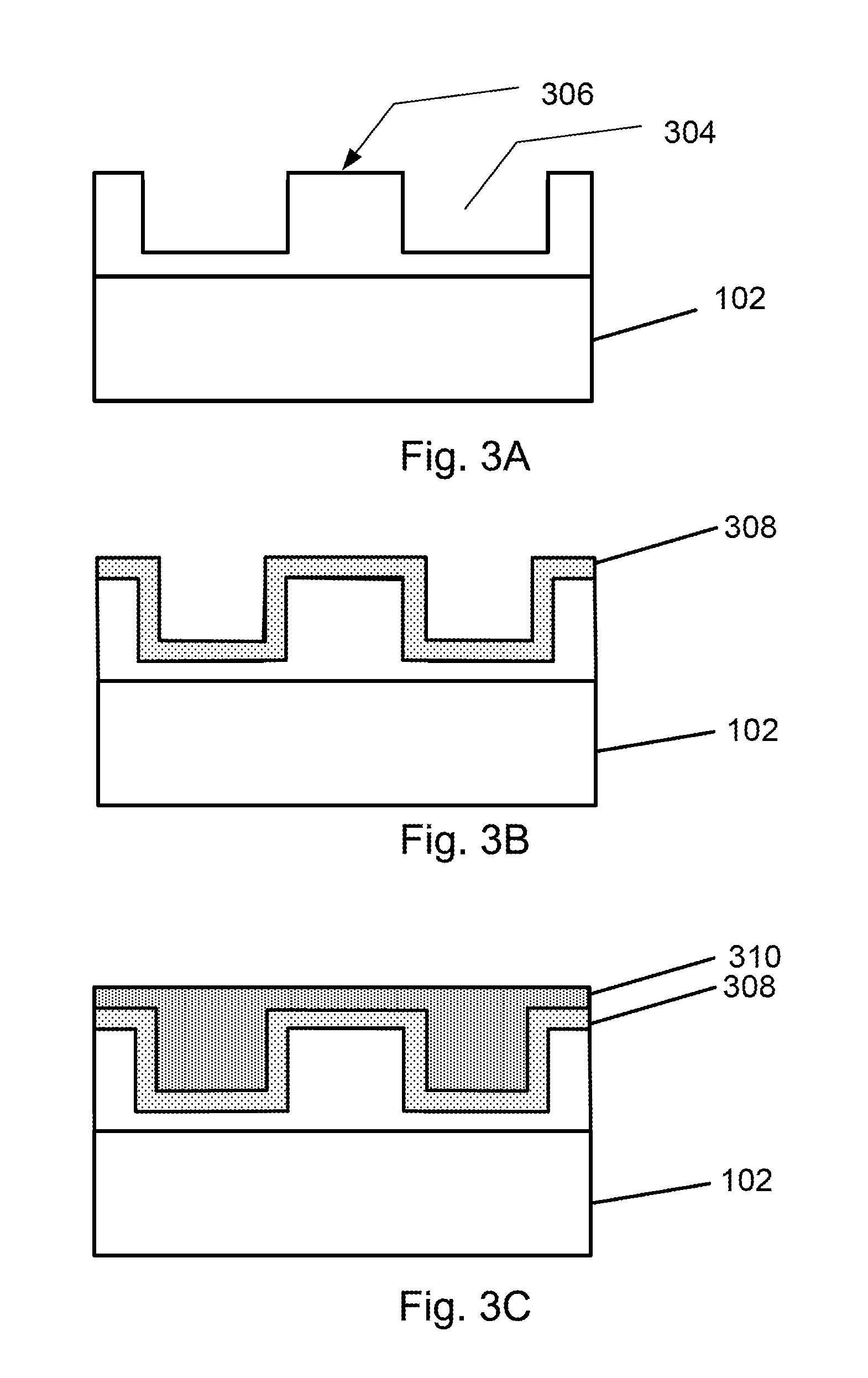

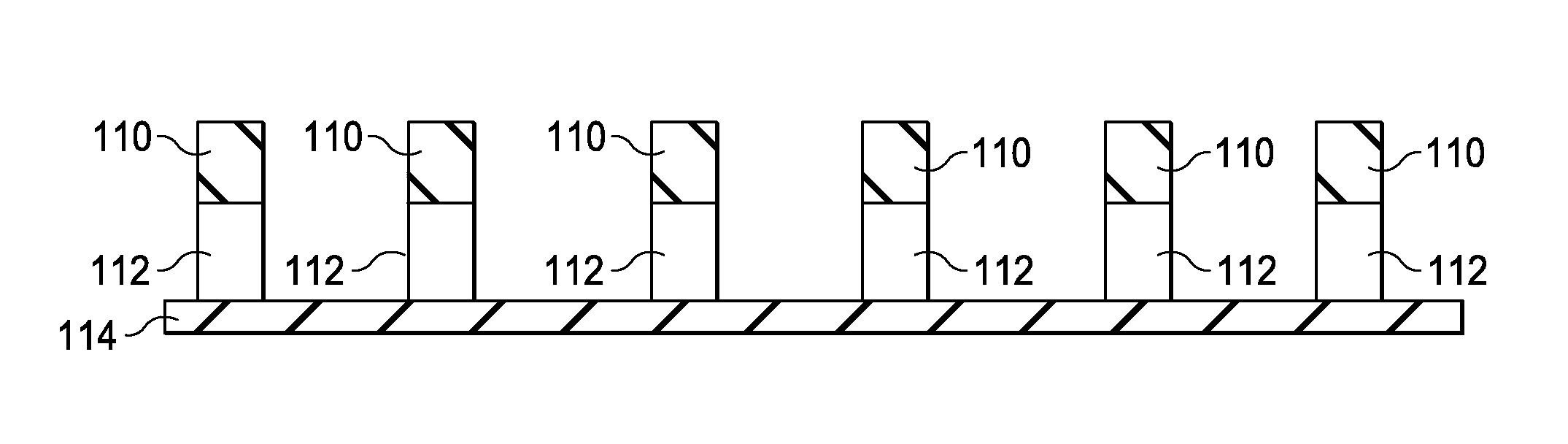

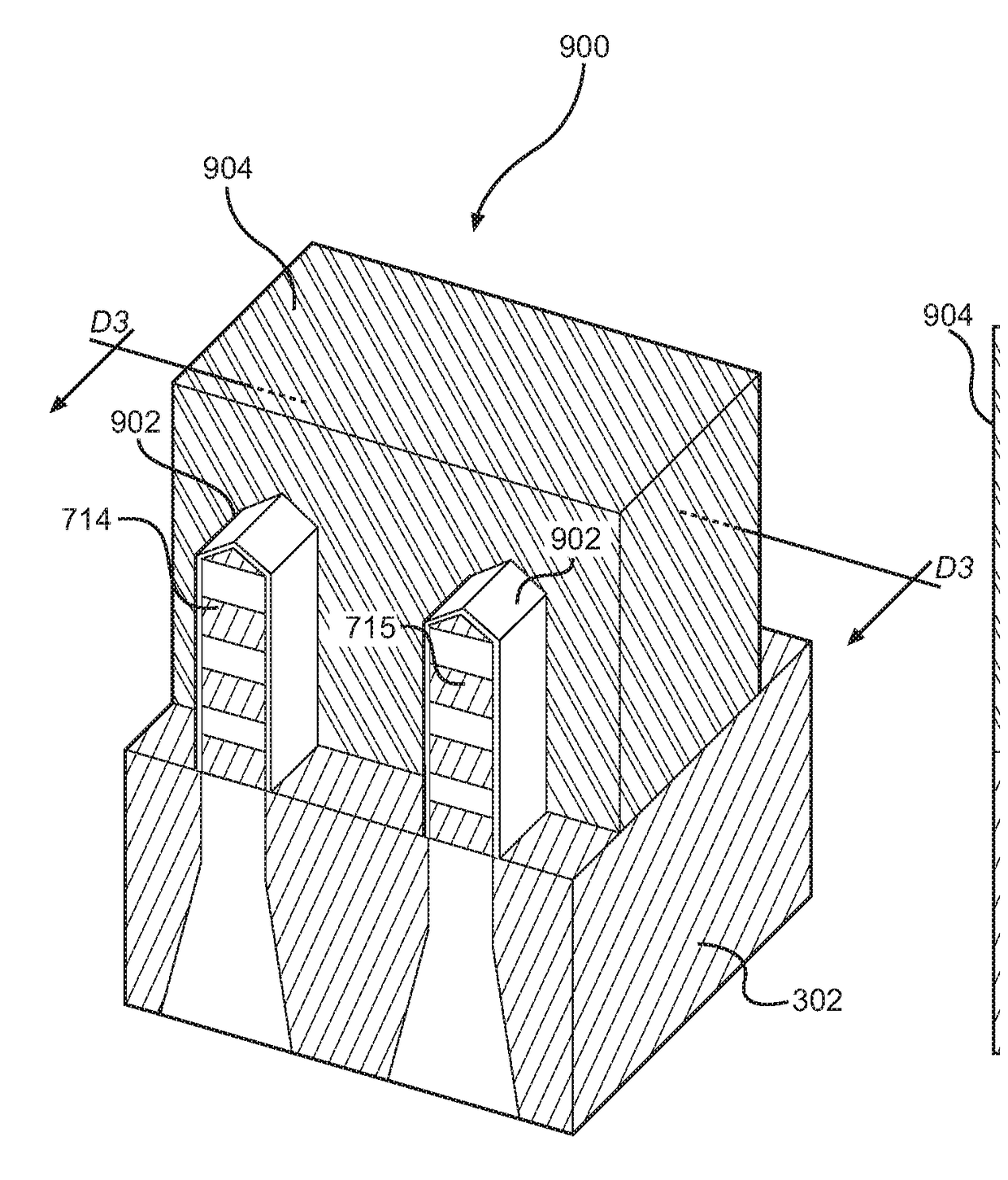

Lithography using Multilayer Spacer for Reduced Spacer Footing

ActiveUS20150118850A1Reduce spacer footingImprove reliabilitySemiconductor/solid-state device manufacturingLithographic artistEngineering

A method embodiment for patterning a semiconductor device includes forming a plurality of mandrels over a substrate, and forming a multilayer spacer layer over the plurality of mandrels. The multilayer spacer layer is formed by conformably depositing a spacer layer over the plurality of mandrels and treating the spacer layer with plasma. The plurality of mandrels is exposed by etching a top portion of the multilayer spacer layer, thereby forming a multilayer spacer.

Owner:TAIWAN SEMICON MFG CO LTD

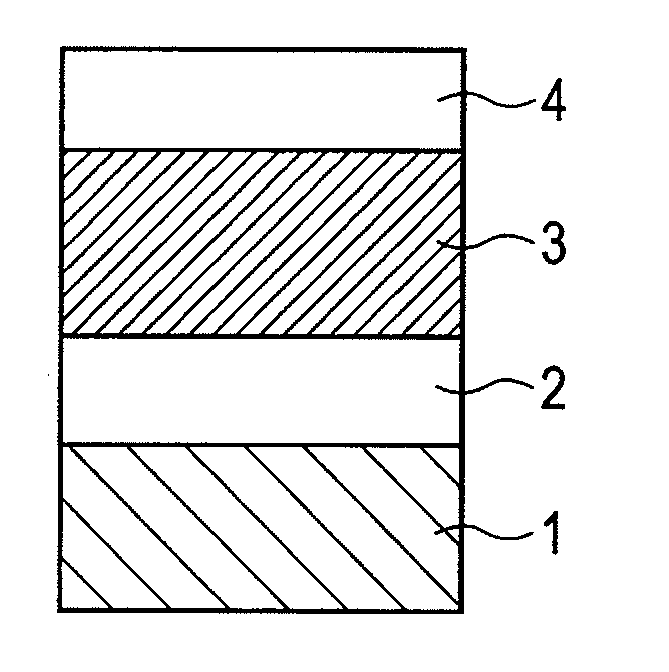

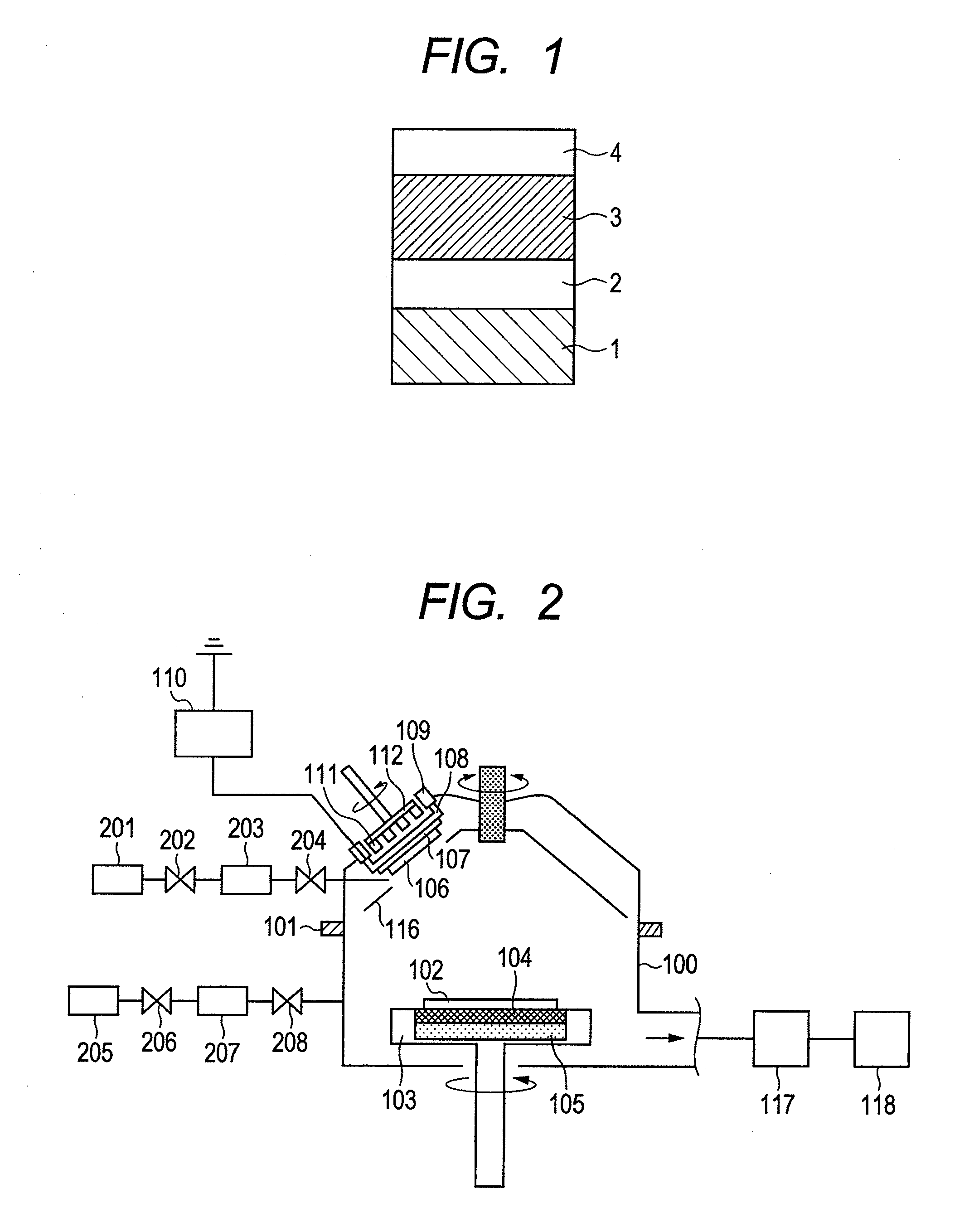

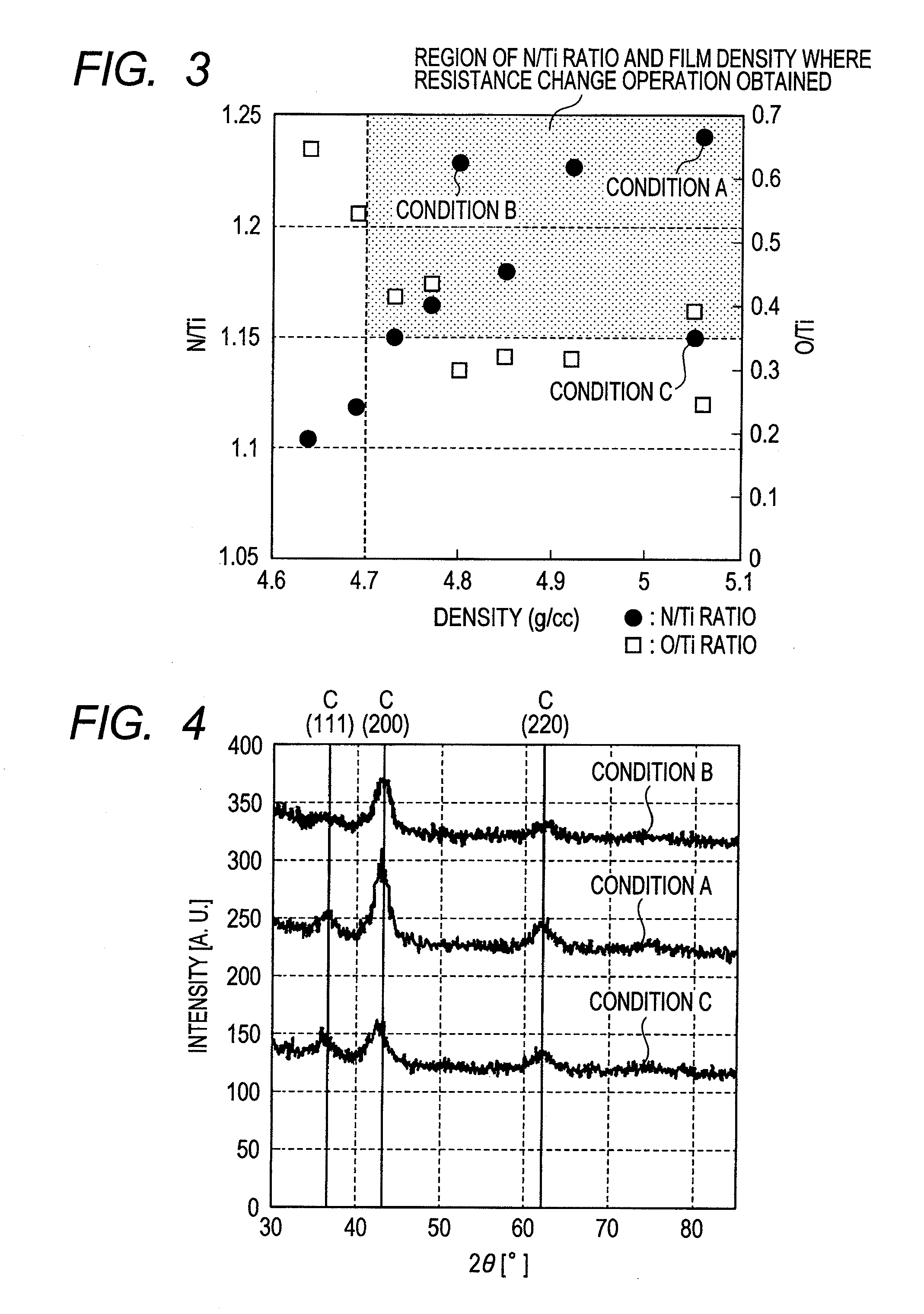

Nonvolatile storage element and manufacturing method thereof

ActiveUS20120248397A1Reduce instabilityReduce material costsBulk negative resistance effect devicesElectrical resistance and conductanceNitride

In a variable resistance nonvolatile storage element, an electrode suitable for a variable resistance operation and formed of a metallic nitride layer containing Ti and N is provided. In a nonvolatile storage device including: a first electrode; a second electrode; and a variable resistance layer which is sandwiched between the first electrode and the second electrode and in which a resistance value changes to two different resistance states, at least one of the first electrode and the second electrode is an electrode including a metallic nitride layer containing at least Ti and N, and a mole ratio (N / Ti ratio) between Ti and N in at least a part of the metallic nitride layer, the part being in contact with the variable resistance layer is 1.15 or more and a film density is 4.7 g / cc or more.

Owner:CANON ANELVA CORP

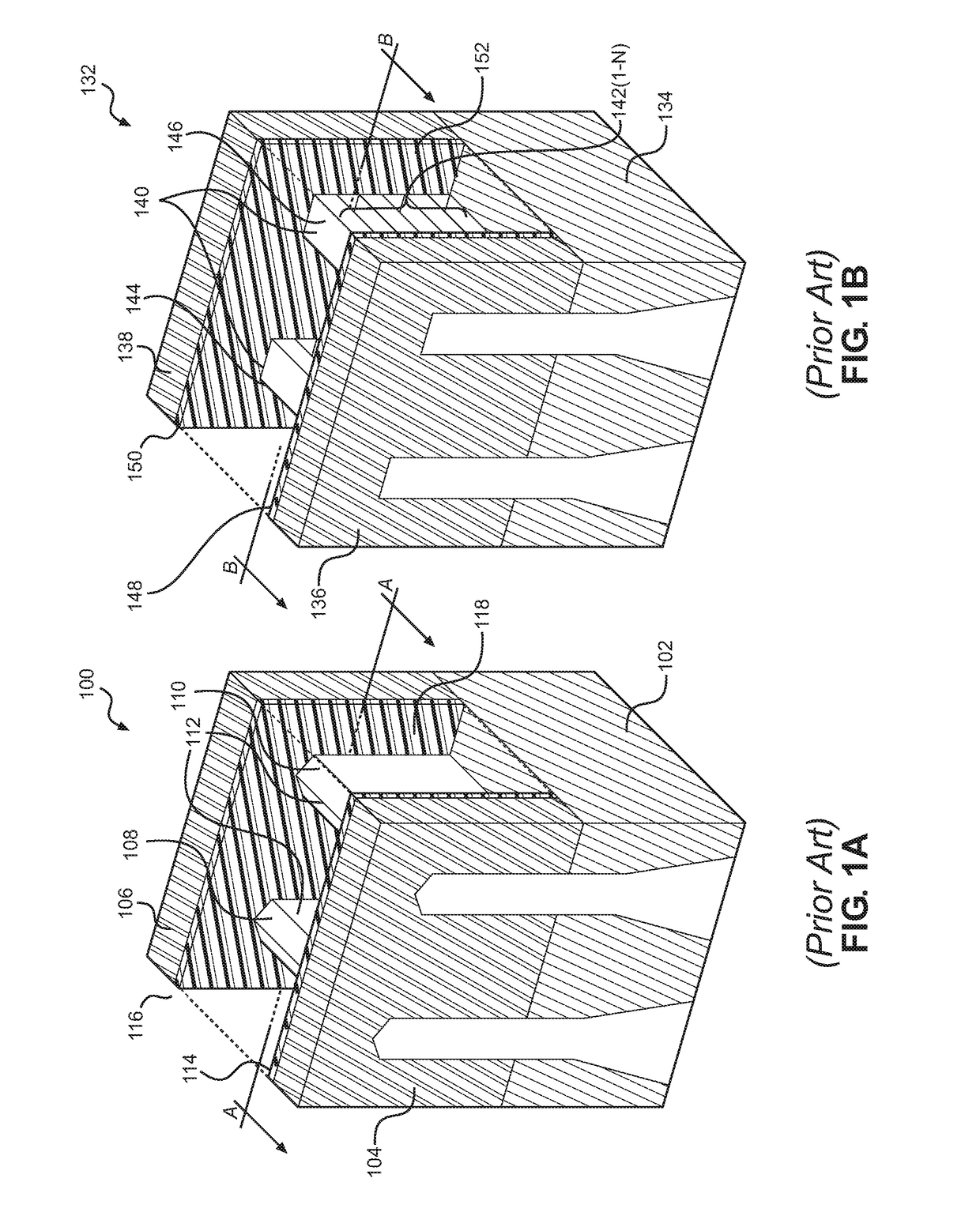

Method for fabricating strained-silicon CMOS transistor

First, a semiconductor substrate having a first active region and a second active region is provided. The first active region includes a first transistor and the second active region includes a second transistor. A first etching stop layer, a stress layer, and a second etching stop layer are disposed on the first transistor, the second transistor and the isolation structure. A first etching process is performed by using a patterned photoresist disposed on the first active region as a mask to remove the second etching stop layer and a portion of the stress layer from the second active region. The patterned photoresist is removed, and a second etching process is performed by using the second etching stop layer of the first active region as a mask to remove the remaining stress layer and a portion of the first etching stop layer from the second active region.

Owner:UNITED MICROELECTRONICS CORP

Nanowire channel structures of continuously stacked heterogeneous nanowires for complementary metal oxide semiconductor (CMOS) devices

InactiveUS20170110541A1Increased gate controlMinimal fabricationTransistorSolid-state devicesParallel plateOxide semiconductor

Aspects disclosed in the detailed description include nanowire channel structures of continuously stacked heterogeneous nanowires for complementary metal oxide semiconductor (CMOS) devices. Each of the nanowires has a top end portion and a bottom end portion that are narrower than a central portion. Furthermore, vertically adjacent nanowires are interconnected at the narrower top end portions and bottom end portions. This allows for connectivity between stacked nanowires and for having separation areas between vertically adjacent heterogeneous nanowires. Having the separation areas allows for gate material to be disposed over a large area of the heterogeneous nanowires and, therefore, provides strong gate control, a shorter nanowire channel structure, low parallel plate parasitic capacitance, and low parasitic channel capacitance. Having the nanowires be heterogeneous, i.e., fabricated using materials of different etching sensitivity, facilitates forming the particular cross section of the nanowires, thus eliminating the use of sacrificial masks / layers to form the heterogeneous nanowires.

Owner:QUALCOMM INC