Patents

Literature

5936 results about "Melting temperature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Down-drawable, chemically strengthened glass for cover plate

An alkali aluminosilicate glass that is chemically strengthened and has a down-drawable composition. The glass has a melting temperature less than about 1650° C. and a liquidus viscosity of at least 130 kpoise and, in one embodiment, greater than 250 kpoise. The glass undergoes ion exchange at relatively low temperatures to a depth of at least 30 μm.

Owner:CORNING INC

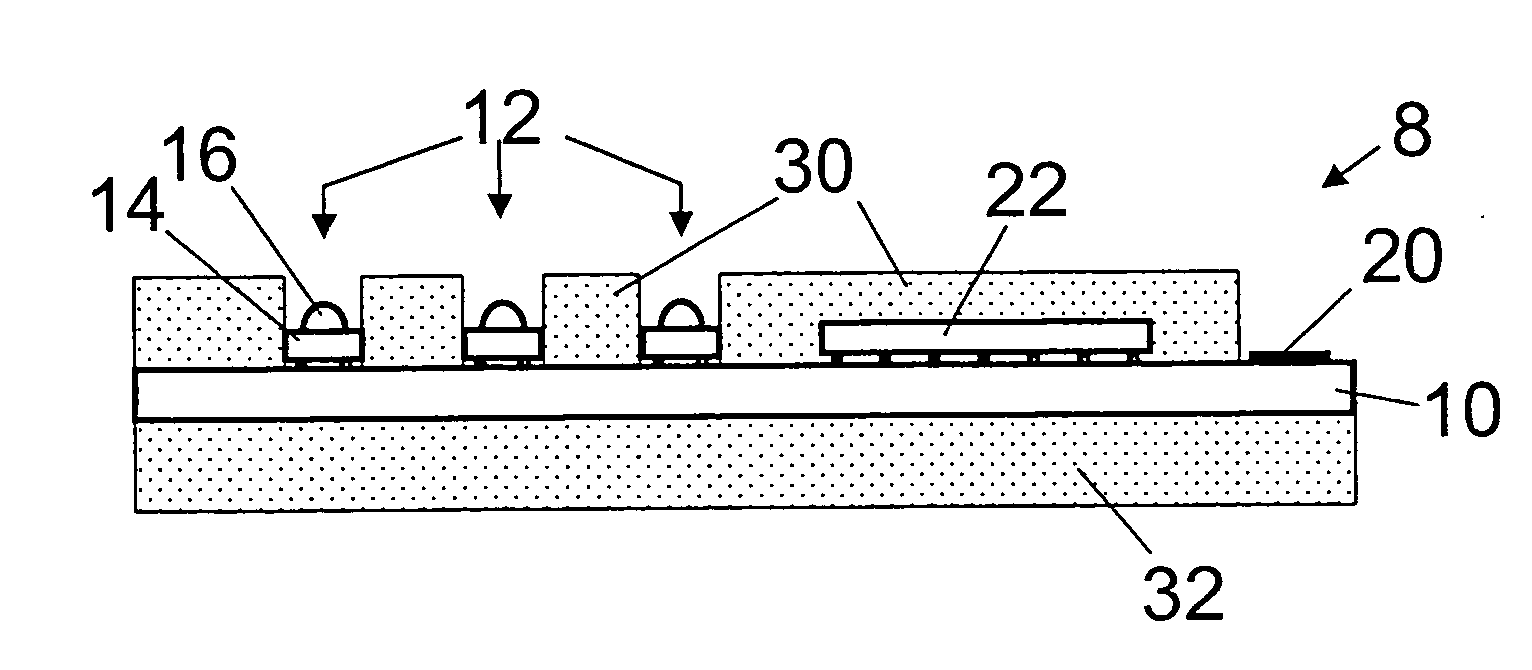

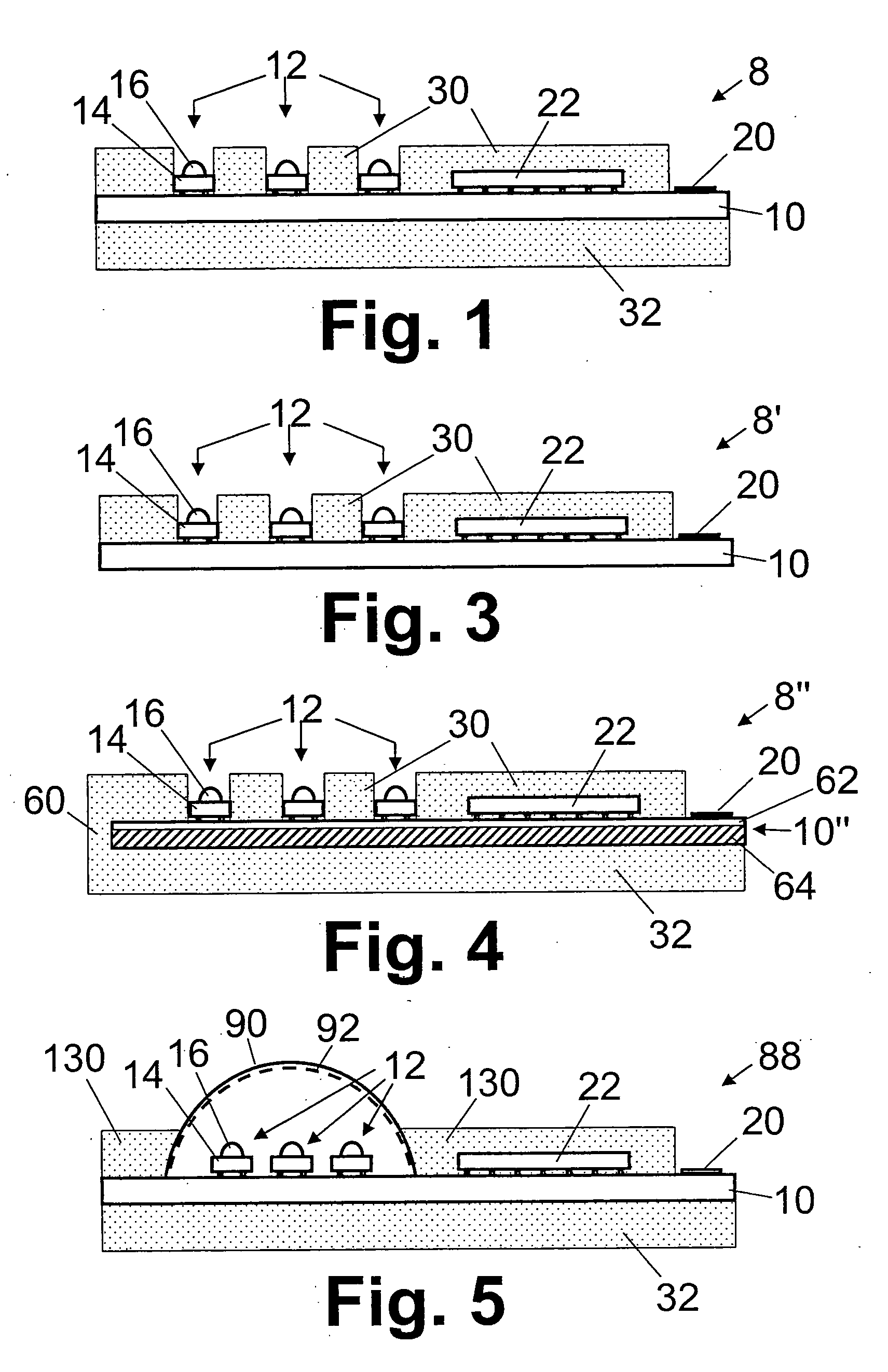

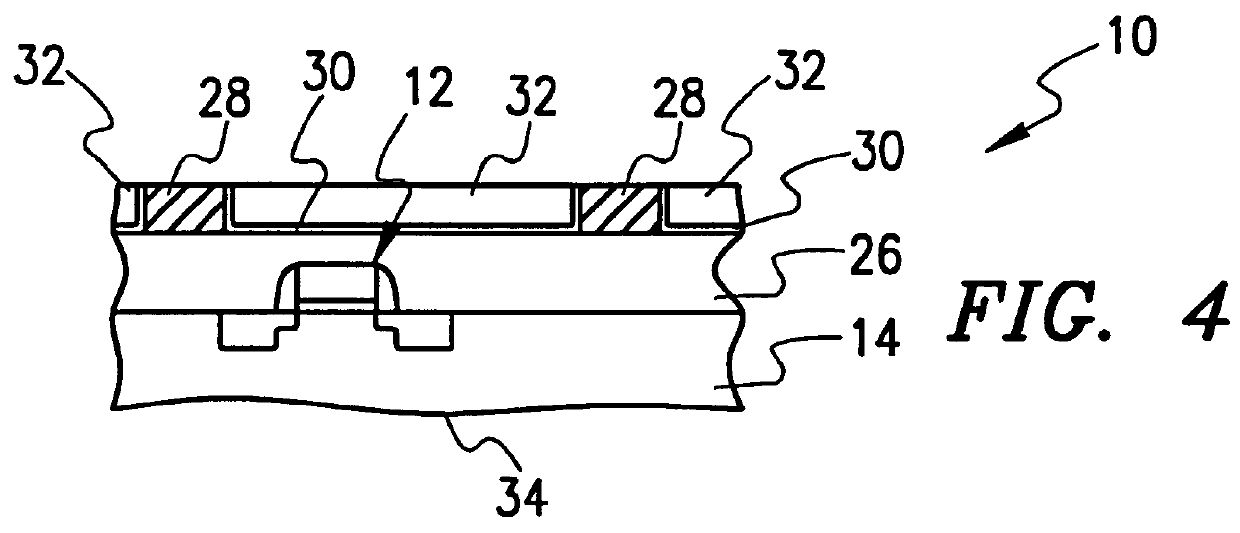

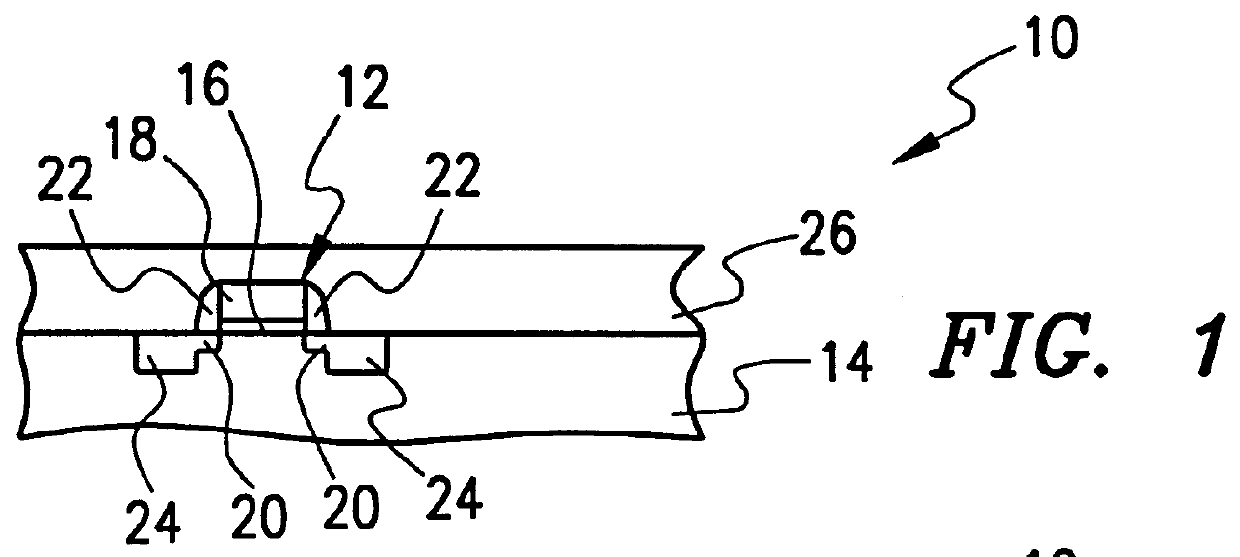

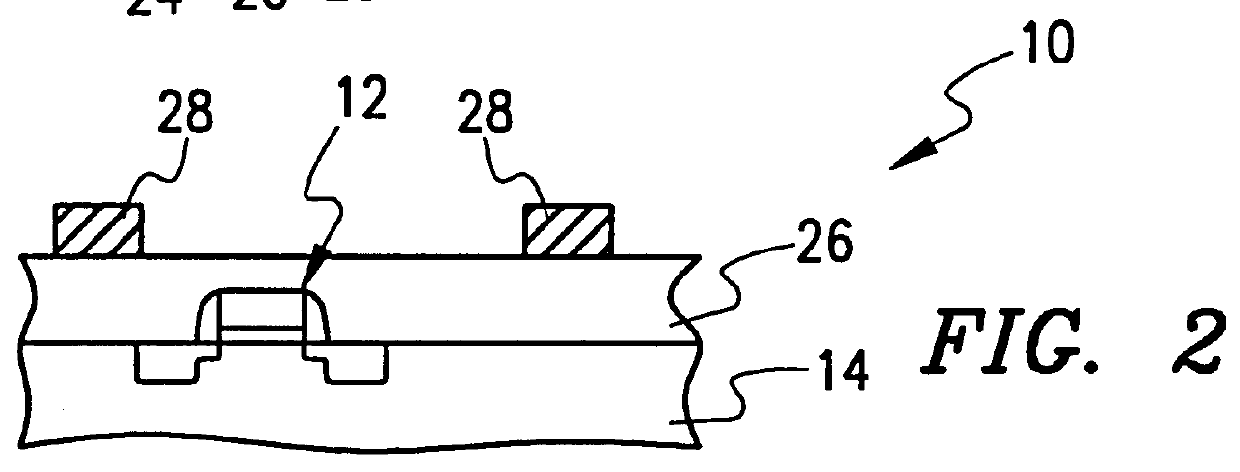

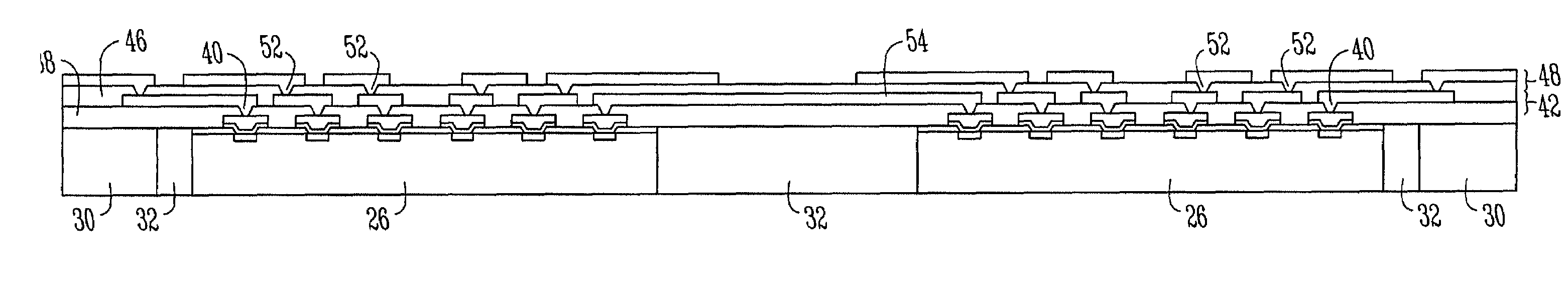

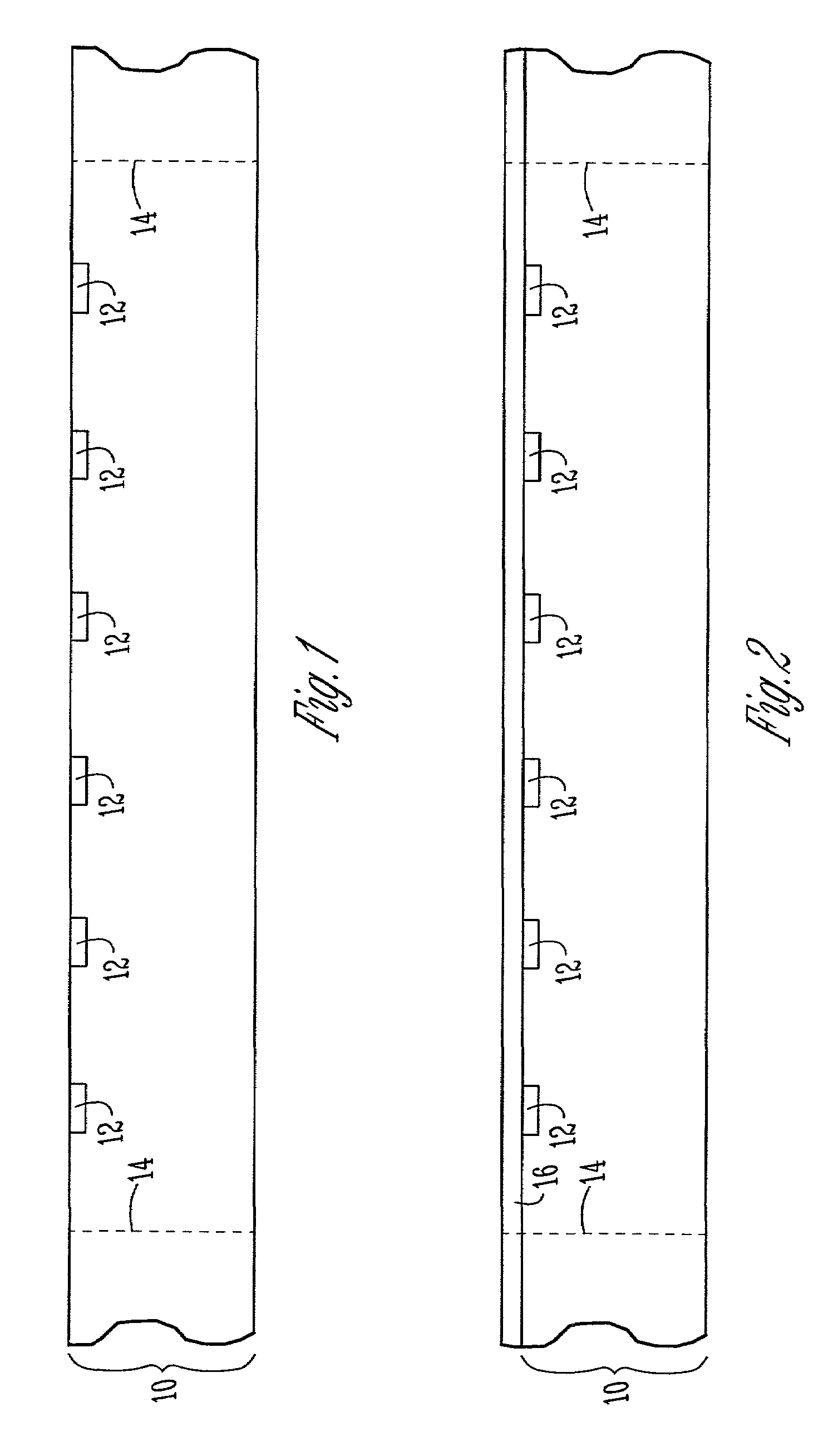

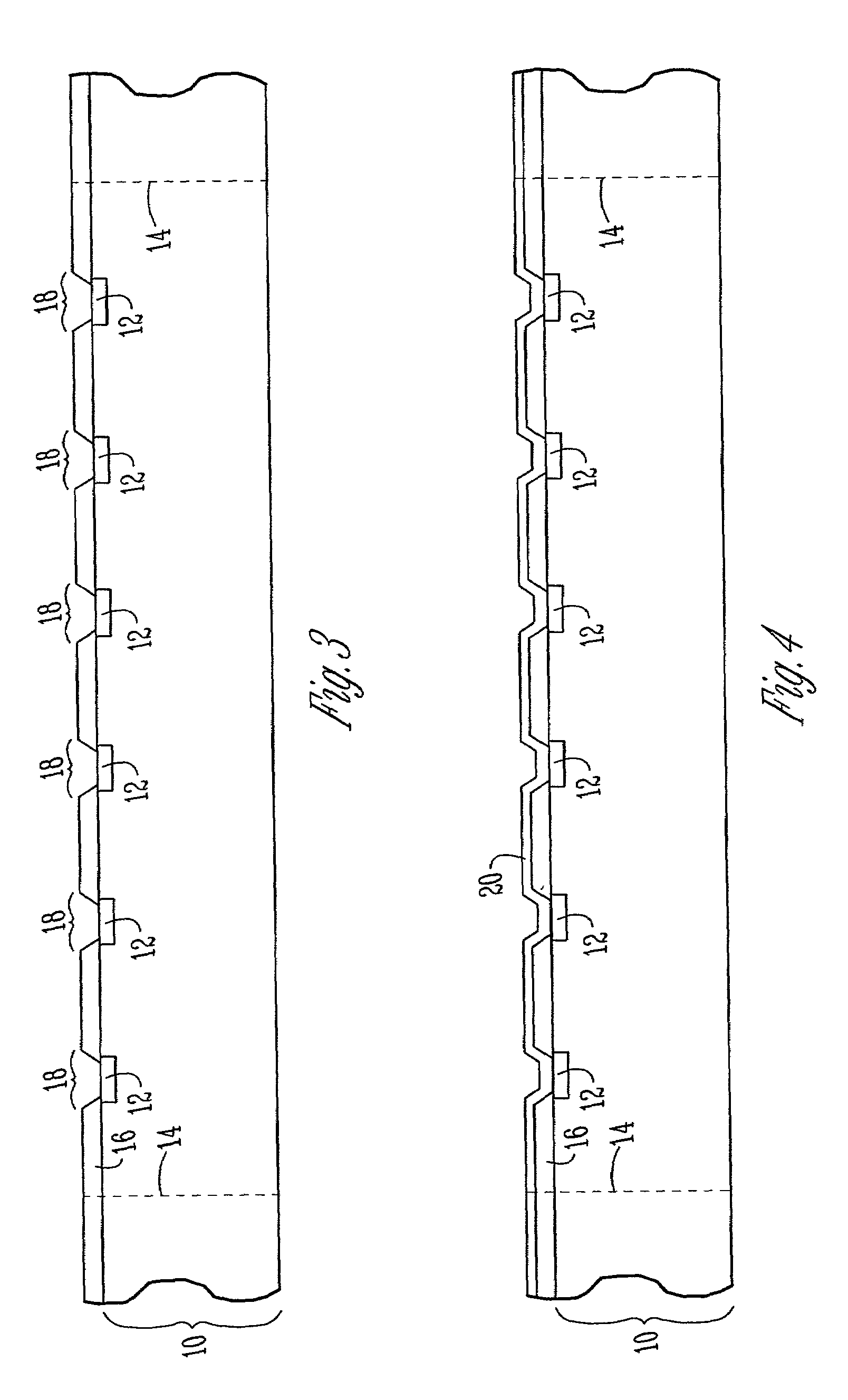

LED lighting assemblies with thermal overmolding

ActiveUS20070121326A1Thermal conductivityPoint-like light sourceElectric circuit arrangementsEffect lightEngineering

One or more light emitting diode diodes (LEDs) are attached to a printed circuit board. The attached LEDs are connectable with a power source via circuitry of the printed circuit board. An overmolding material is insert molded an over at least portions of the printed circuit board proximate to the LEDs to form a free standing high thermal conductivity material overmolding that covers at least portions of the printed circuit board proximate to the LEDs. The free standing high thermal conductivity material has a melting temperature greater than about 100° C. and has a thermal conductivity greater than or about 1 W / m·K. In some embodiments, the free standing high thermal conductivity material is a thermoplastic material.

Owner:GE LIGHTING SOLUTIONS LLC

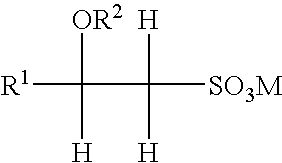

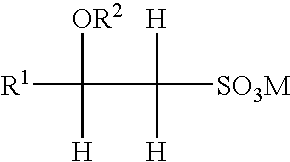

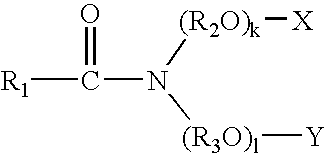

Water-dispersable materials

InactiveUS6211309B1Increase flexibilityGood dispersionMonocomponent polyesters artificial filamentMonocomponent polyamides artificial filamentThermoplasticFiber

The present invention relates to water-dispersible materials (e.g. fibers or films) and to a method of producing same. The materials of the invention comprise a water soluble component, for example, a sulfonated polycondensate thermoplastic, and a modifying auxiliary component, for example, a low melt temperature thermoplastic.

Owner:BASF CORP

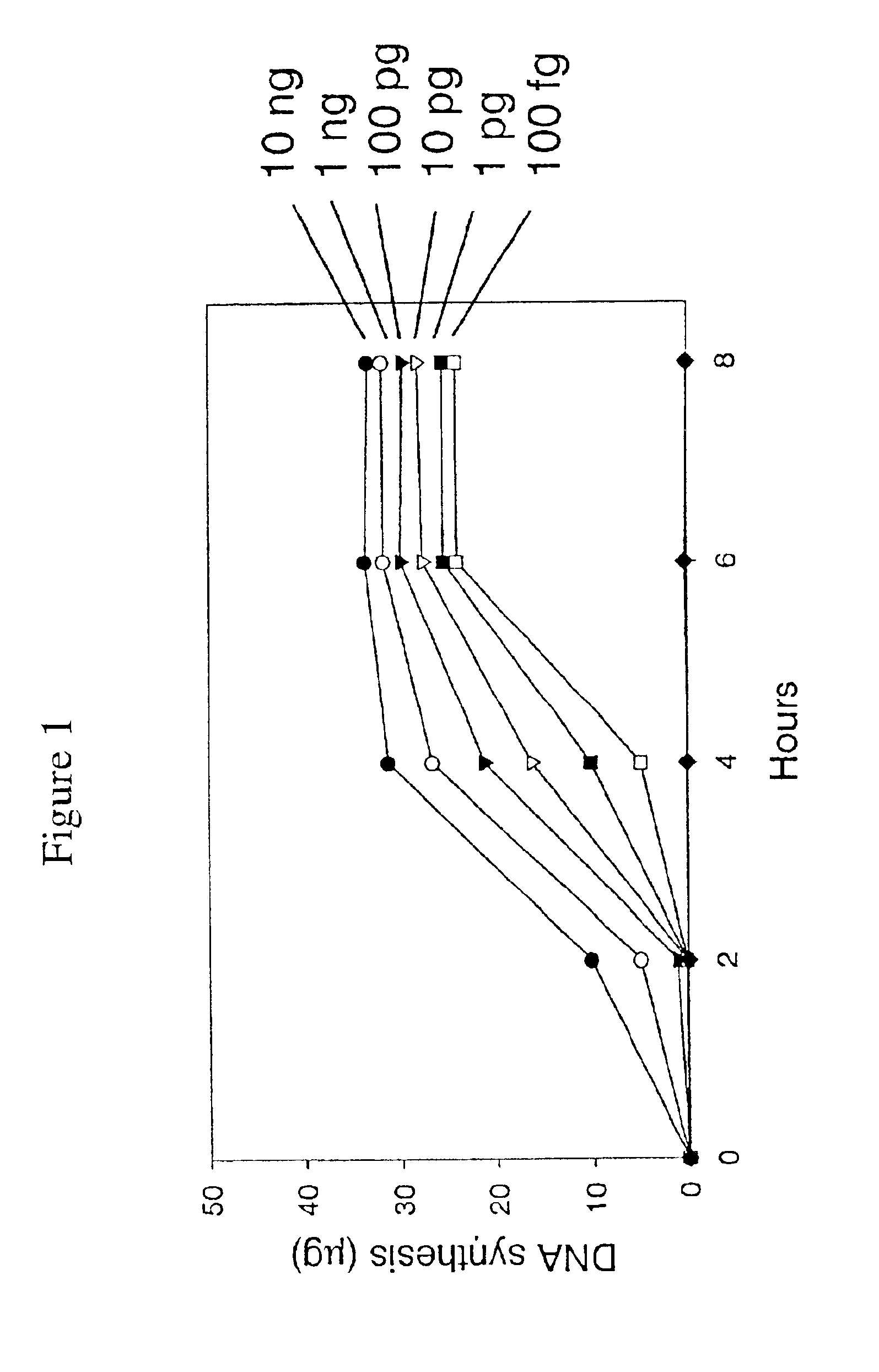

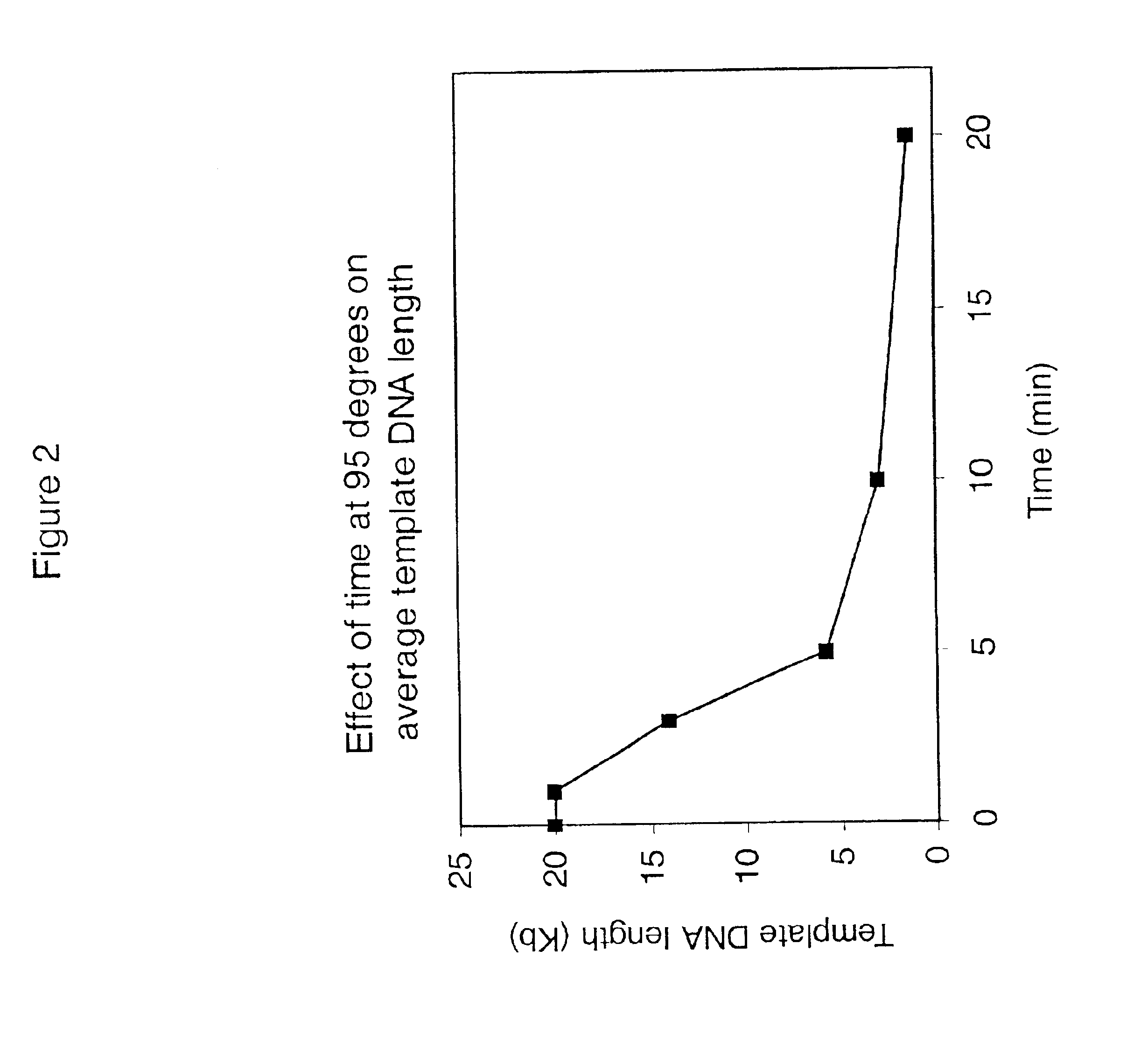

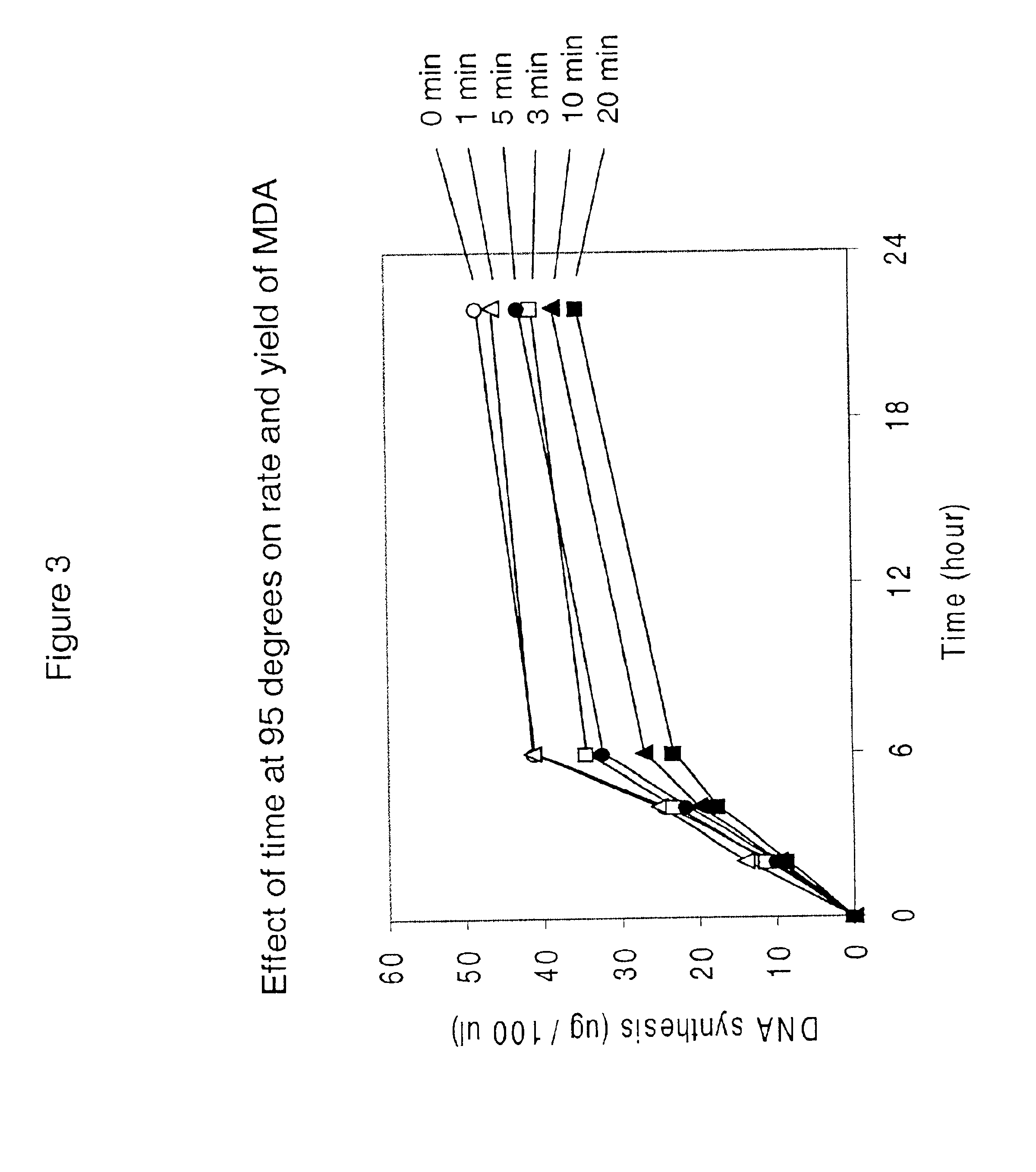

Multiple displacement amplification

InactiveUS6977148B2Consistent outputQuick buildMicrobiological testing/measurementFermentationNucleotideGenomic DNA

Disclosed are compositions and a method for amplification of nucleic acid sequences of interest. The disclosed method generally involves replication of a target sequence such that, during replication, the replicated strands are displaced from the target sequence by strand displacement replication of another replicated strand. In one form of the disclosed method, the target sample is not subjected to denaturing conditions. It was discovered that the target nucleic acids, genomic DNA, for example, need not be denatured for efficient multiple displacement amplification. The primers used can be hexamer primers. The primers can also each contain at least one modified nucleotide such that the primers are nuclease resistant. The primers can also each contain at least one modified nucleotide such that the melting temperature of the primer is altered relative to a primer of the same sequence without the modified nucleotide(s). The DNA polymerase can be φ29 DNA polymerase.

Owner:QIAGEN GMBH

Process for medical implant of cross-linked ultrahigh molecular weight polyethylene having improved balance of wear properties and oxidation resistance

A medical implant of ultrahigh molecular weight polyethylene having an improved balance of wear properties and oxidation resistance is prepared by irradiating a preform of ultrahigh molecular weight polyethylene, annealing the irradiated preform in the absence of oxygen to a temperature at or above the onset of melting temperature, and forming an implant from the stabilized cross-linked polymer. Implants prepared according to the process of the present invention have comparable oxidation resistance and superior wear performance compared to unirradiated ultrahigh molecular weight polyethylene.

Owner:DEPUY ORTHOPAEDICS INC

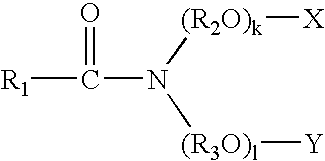

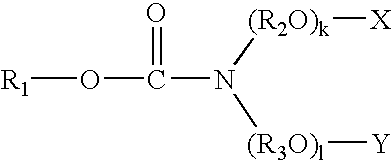

Shampoo containing a gel network

ActiveUS20060024256A1Cosmetic preparationsCationic surface-active compoundsAmphiphileSURFACTANT BLEND

Shampoo compositions comprise (a) from about 5% to about 50% of one or more detersive surfactants, by weight of the shampoo composition; (b) a dispersed gel network phase comprising, by weight of the shampoo composition, (i) at least about 0.05 % of one or more fatty amphiphiles; (ii) at least about 0.01% of one or more secondary surfactants; and (iii) water; and (c) at least about 20% of an aqueous carrier, by weight of the shampoo composition. A process for preparing a shampoo composition comprises the steps of: (a) combining a fatty amphiphile, a secondary surfactant, and water at a temperature sufficient to allow partitioning of the secondary surfactant and the water into the fatty amphiphile to form a pre-mix; (b) cooling the pre-mix below the chain melt temperature of the fatty amphiphile to form a gel network; (c) adding the gel network to one or more detersive surfactants and an aqueous carrier to form a shampoo composition.

Owner:THE PROCTER & GAMBLE COMPANY

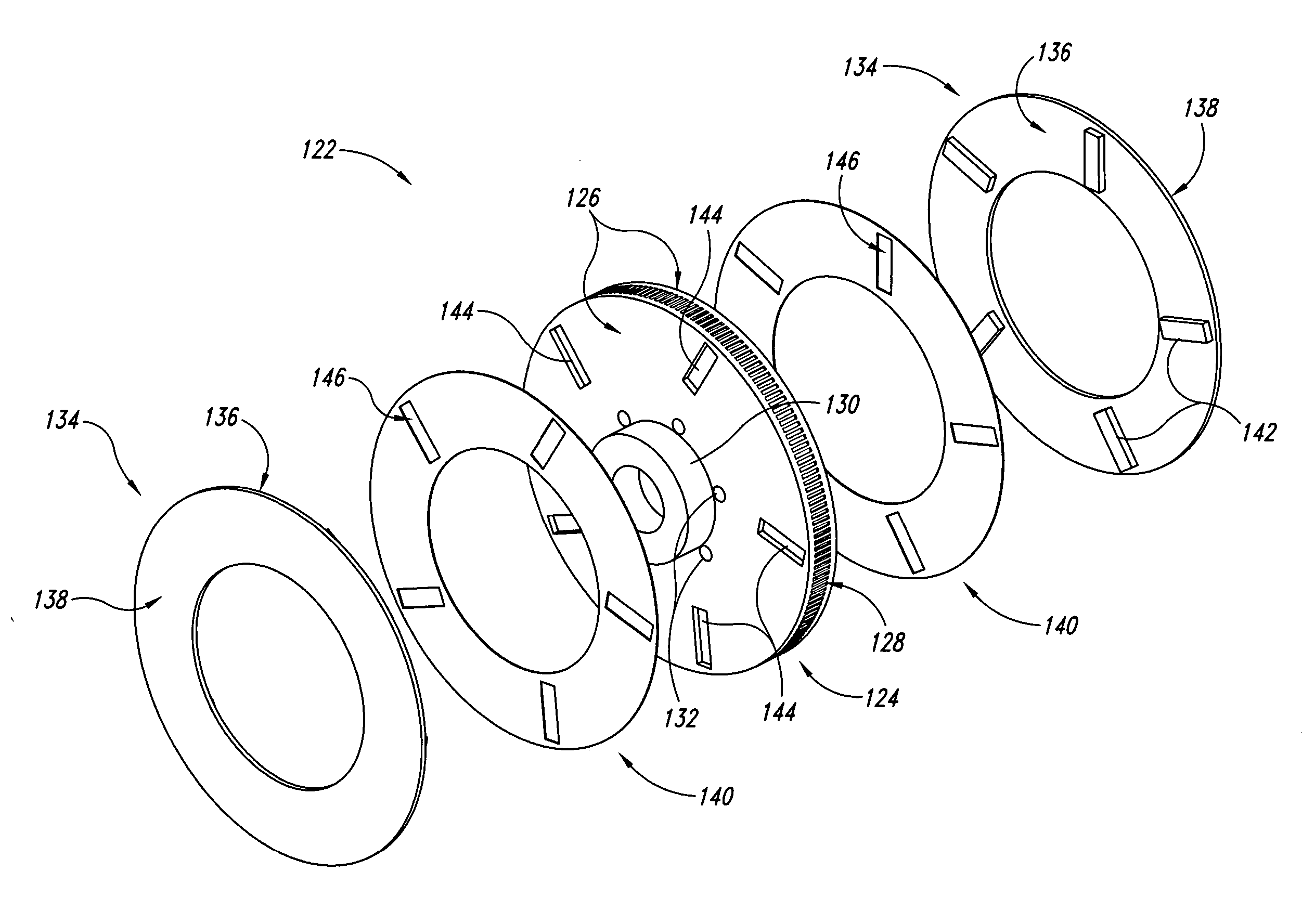

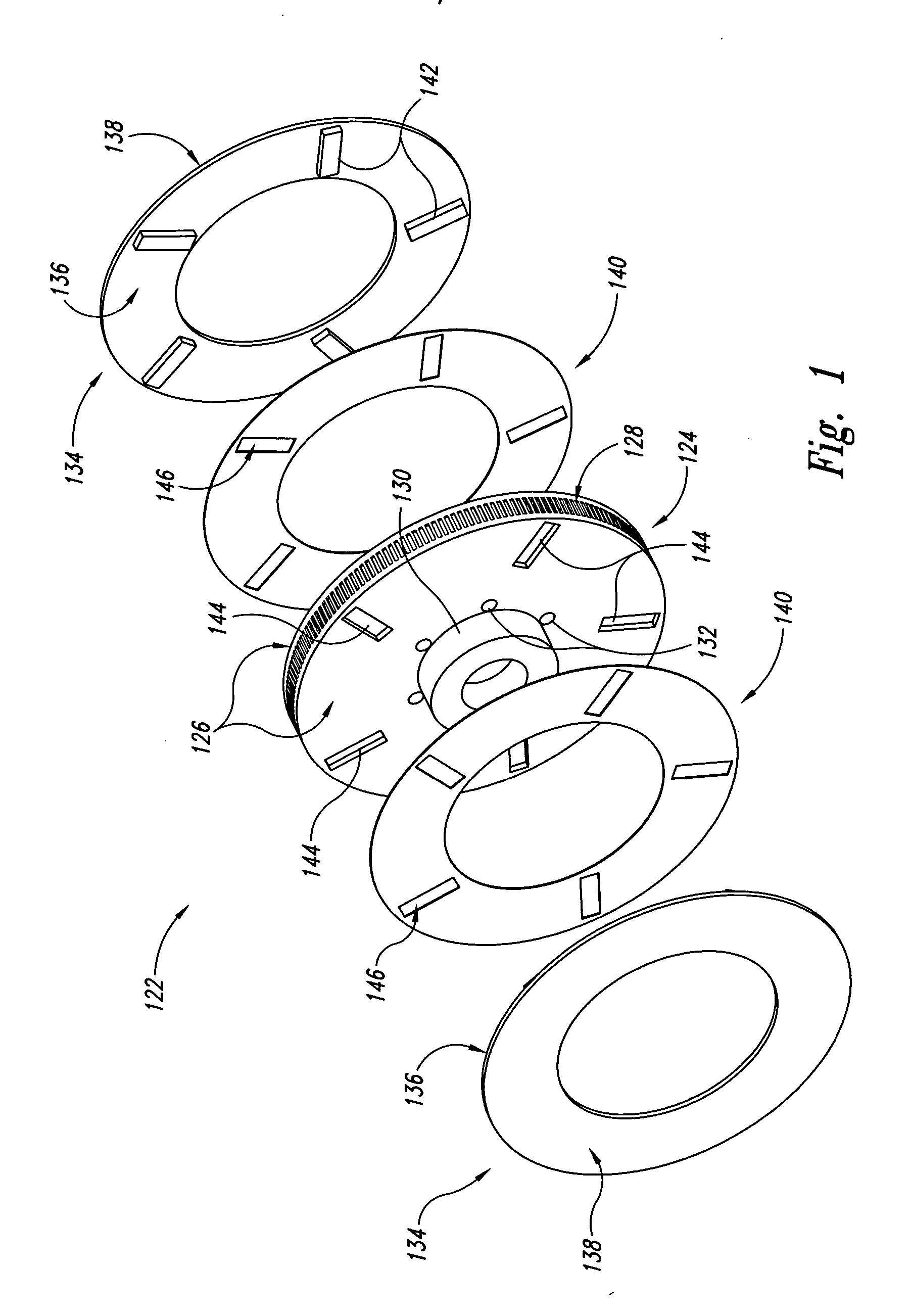

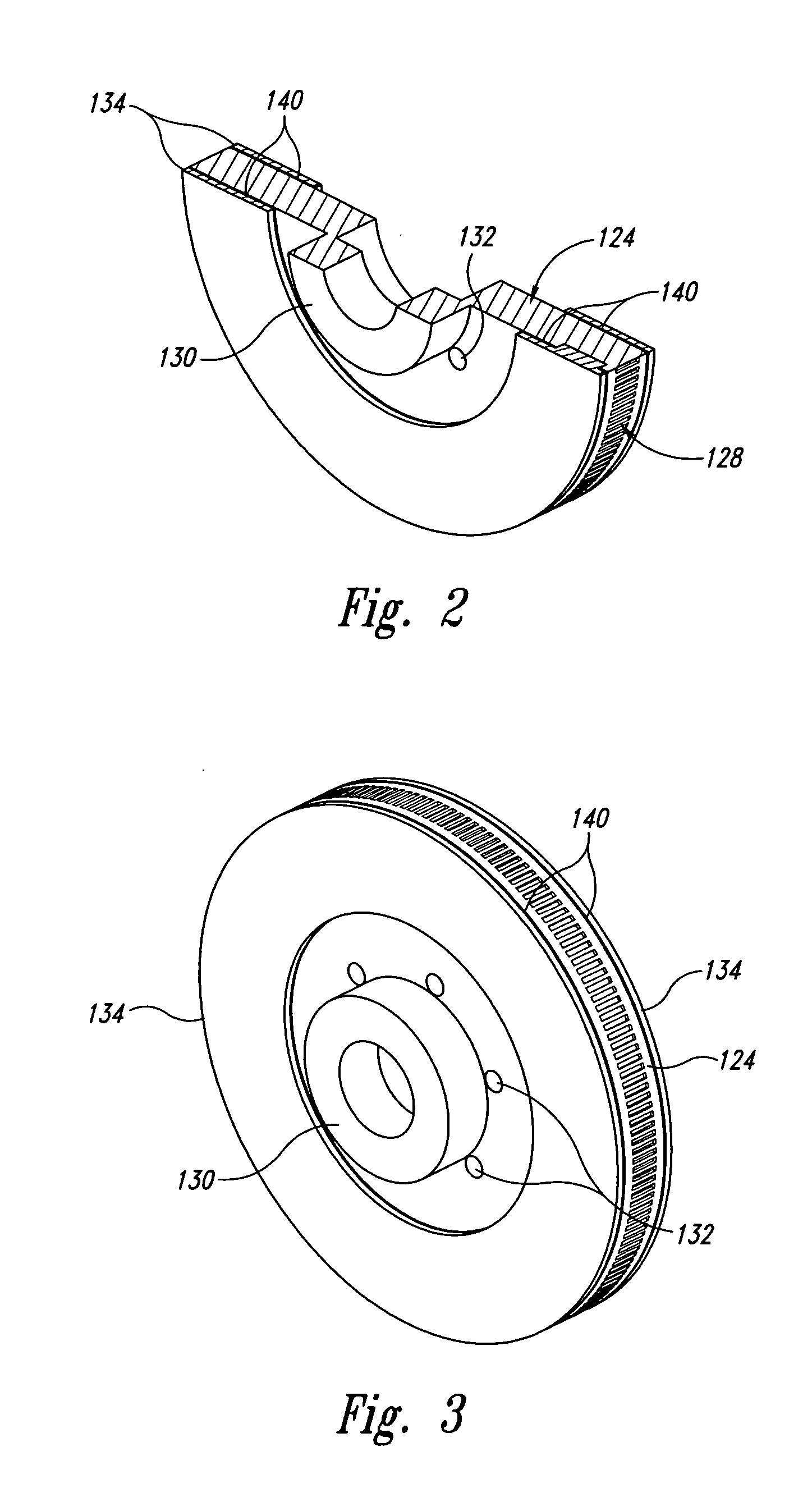

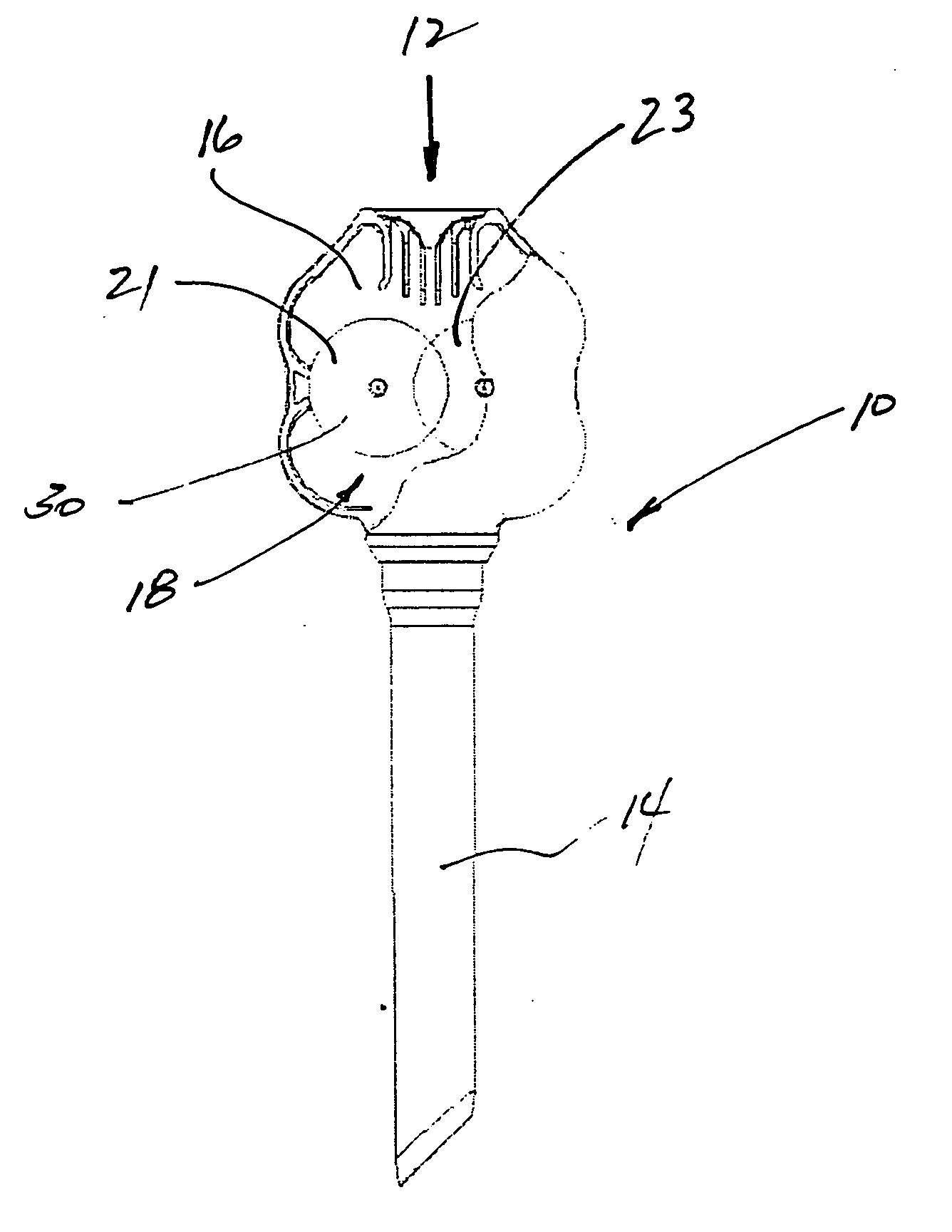

Disc brake rotor assembly and method for producing same

InactiveUS20050183909A1Improve thermal conductivityOptimize acoustic frequency transferBraking element arrangementsNoise/vibration controlAdhesiveMetal alloy

Novel composite disc brake rotor assemblies are provided, along with novel and efficient methods for manufacturing them. Preferably, the rotor assemblies comprise annular wear plates formed of particle reinforced aluminum-based metal matrix composite (MMC), ceramic matrix composite (CMC), or of ‘carbon graphite foam.’ The wear plates, made of a first material, are attached to annular surfaces of a central rotor, made of a second material, by fusing bonding layers between the wear plates and the rotor surfaces. The bonding layers are comprised of at least one of a metal alloy having a melting temperature lower than that of either the first or second materials, and a high-temperature adhesive. Preferably, the wear plates comprise projections that are positioned within adjacent receiving recesses in the center rotor. The bonding layers and projections enhance thermal and acoustical transference between the wear plates and the center rotor section. Carbon graphite foam provides for substantially enhanced heat transference. Use of the fusable binding layer, or adhesive provides for an efficient, low cost method of manufacturing for composite disc brake rotor assemblies.

Owner:BENMAXX

Surgical device with tack-free gel and method of manufacture

InactiveUS20050033246A1Significant drag forceImprove complianceCannulasSurgical needlesMolten stateLow-density polyethylene

A process of making a tack-free gel is disclosed comprising the steps of providing a mold defining a mold cavity, the mold cavity comprising a plastic material; pouring or injecting a molten gel having a high molding temperature into the mold cavity; and forming the tack-free gel as a thin layer of plastic of the mold cavity is melted over the gel. The forming step further comprises cooling the gel from the molten state to a solidified state. The melting temperature of the plastic material is lower than the molding temperature of the gel; and the higher the temperature differential, the greater the melting of the plastic material and the thicker the layer of the plastic material on the surface of the gel. The mold may be formed of low-density polyethylene (LDPE). With the process of the invention, the heat of the molten gel at its molding temperature is transferred to the surface of the LDPE mold so as to melt a thin layer of the LDPE. The mold may comprise a mold base having a plurality of mold holes forming a plurality of mold cavities, each of the mold holes comprising an axial pin to mold an axial hole through a center of the gel, an LDPE cylinder providing a predetermined inside diameter for the mold, and an LDPE disc mounted on the axial pin and disposed at the bottom of each mold cavity in the mold base. The process may further comprise the step of dabbing the gel in a low-friction powder such as polytetrafluoroethylene (PTFE) and a lubricant. The mold may further comprise a mold top disposed axially of the mold base and comprises a plurality of holes forming a plurality of cavities, each of the mold top holes is adapted to receive the LDPE cylinder, and a second LDPE disc disposed at the top of each mold cavity of the mold top.

Owner:APPL MEDICAL RESOURCES CORP

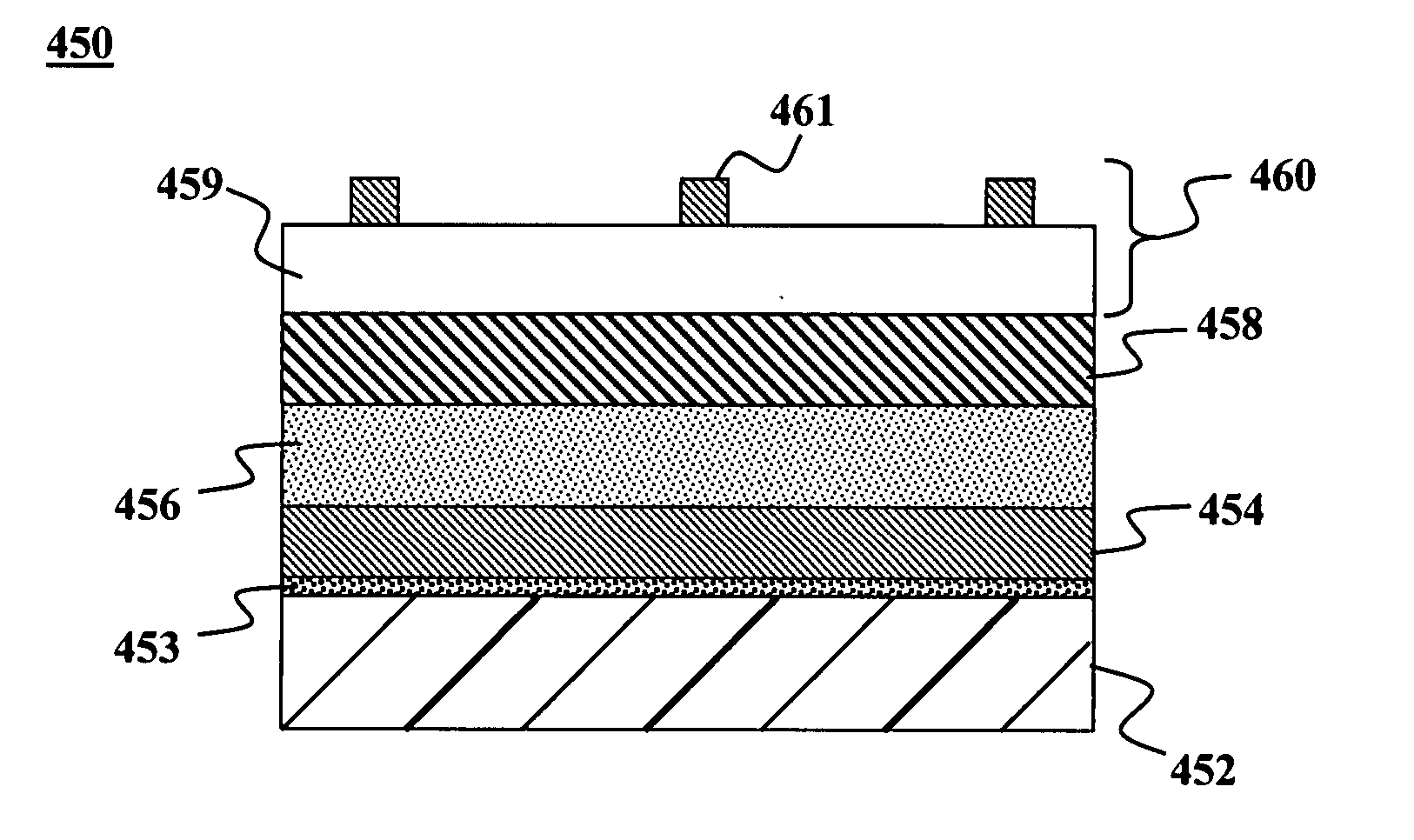

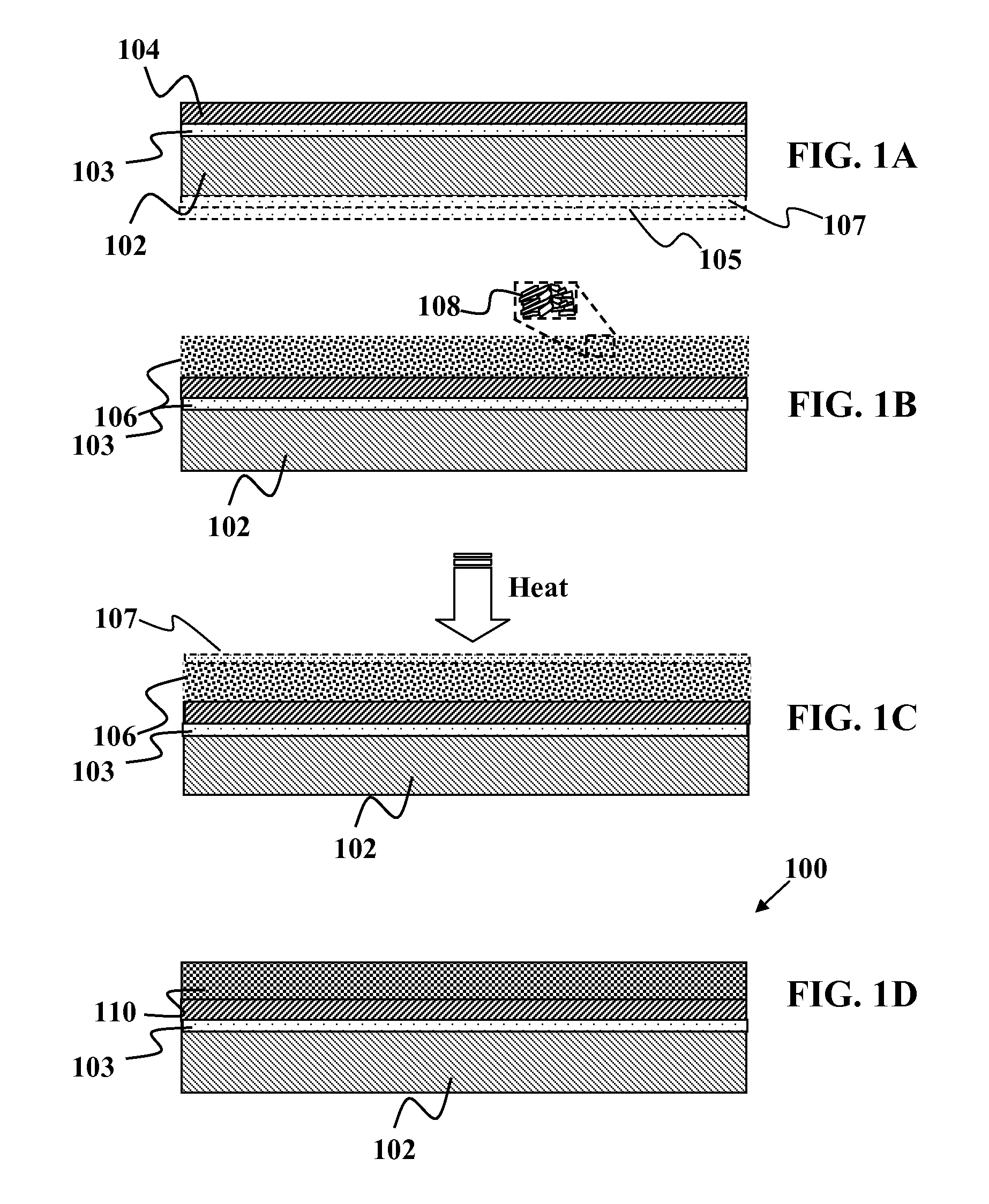

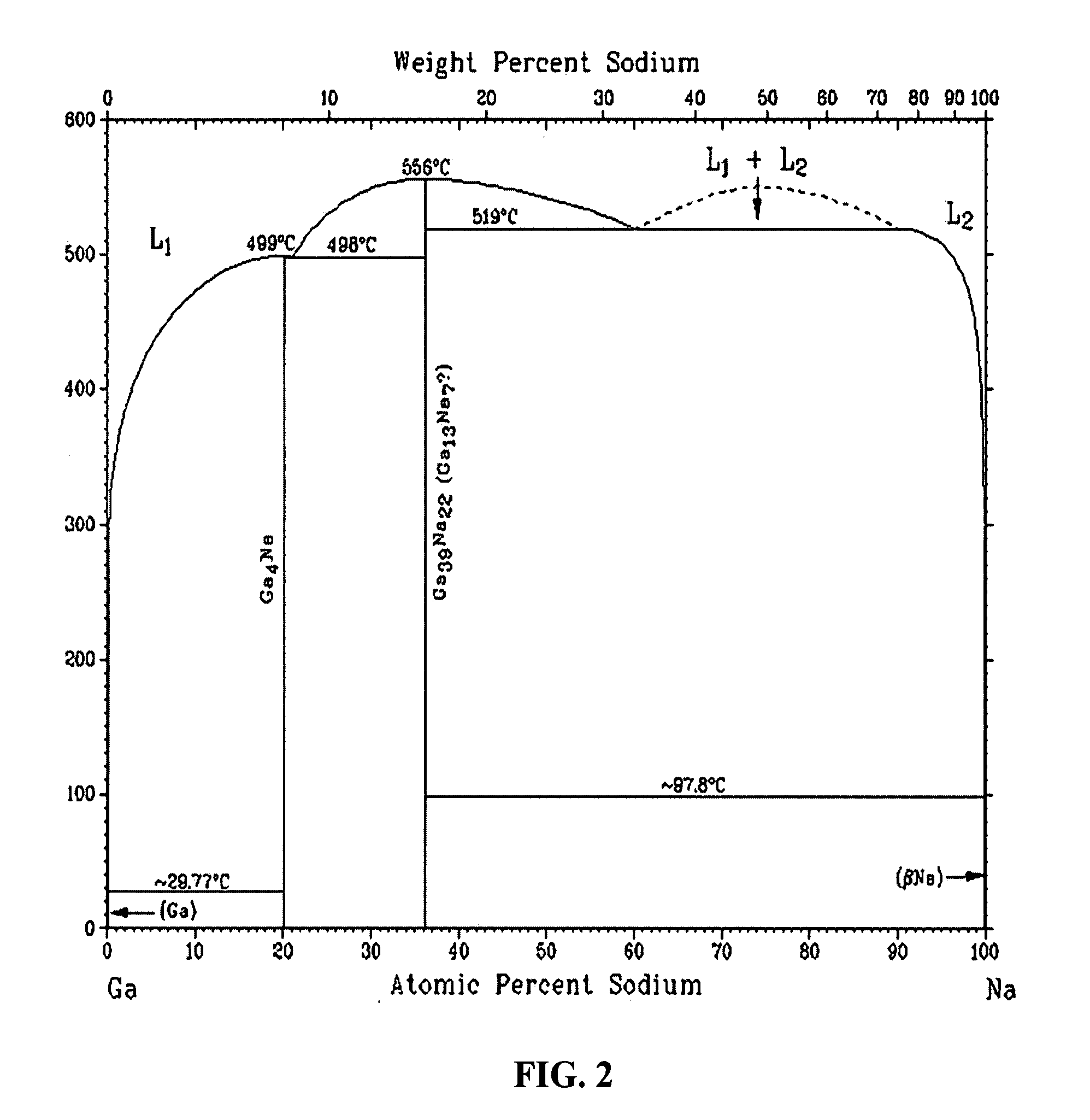

Bandgap grading in thin-film devices via solid group IIIA particles

InactiveUS20080057616A1Efficient and simplified creationPrevent leaching and phase separationSemiconductor/solid-state device manufacturingPhotovoltaic energy generationHigh concentrationBandgap grading

Methods and devices are provided for forming thin-films from solid group IIIA-based particles. In one embodiment, a method is provided for bandgap grading in a thin-film device using such particles. The method may be comprised of providing a bandgap grading material comprising of an alloy having: a) a IIIA material and b) a group IA-based material, wherein the alloy has a higher melting temperature than a melting temperature of the IIIA material in elemental form. A precursor material may be deposited on a substrate to form a precursor layer. The precursor material comprising group IB, IIIA, and / or VIA based particles. The bandgap grading material of the alloy may be deposited after depositing the precursor material. The alloy in the grading material may react after the precursor layer has begun to sinter and thus maintains a higher concentration of IIIA material in a portion of the compound film that forms above a portion that sinters first.

Owner:AERIS CAPITAL SUSTAINABLE IP

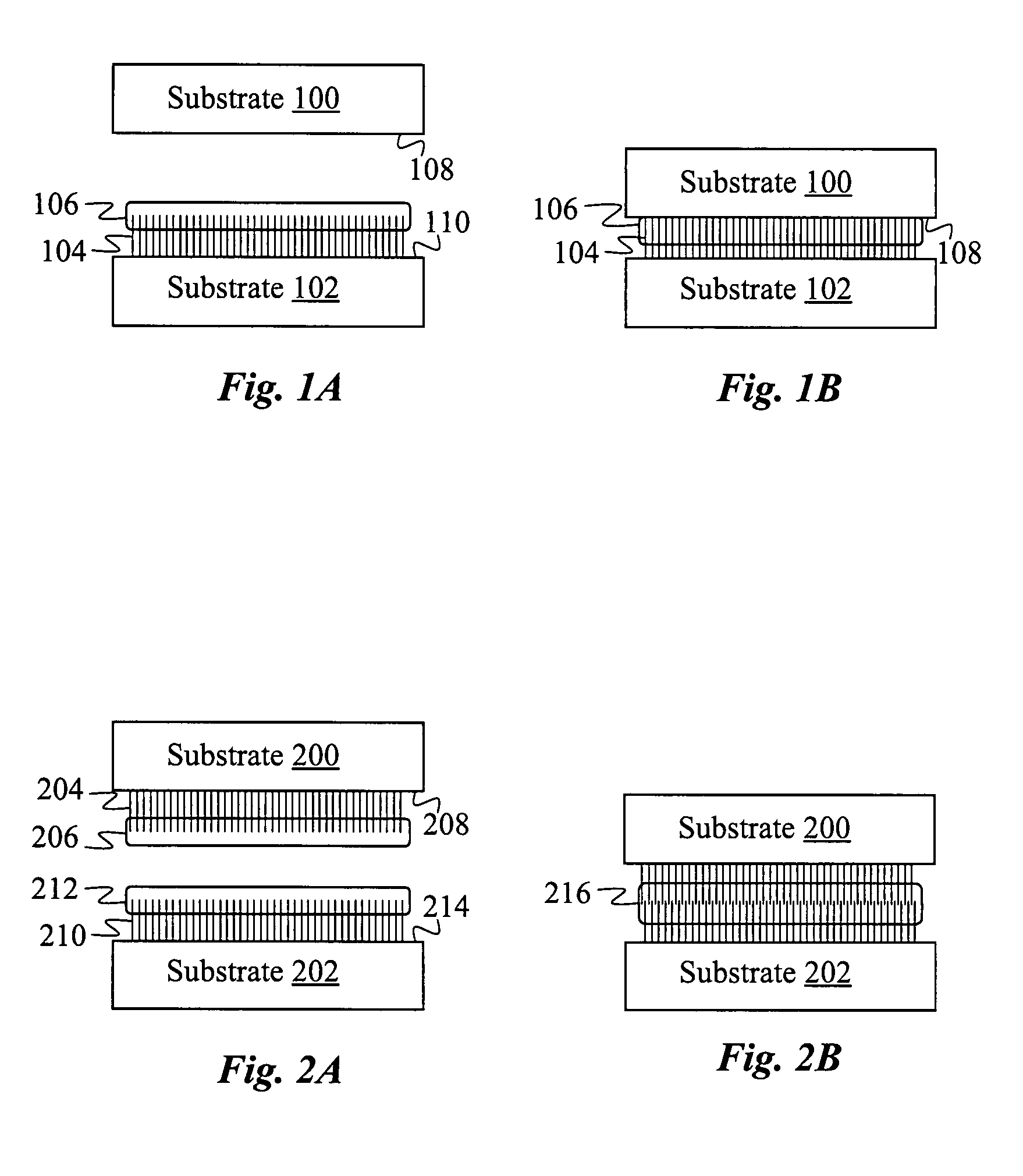

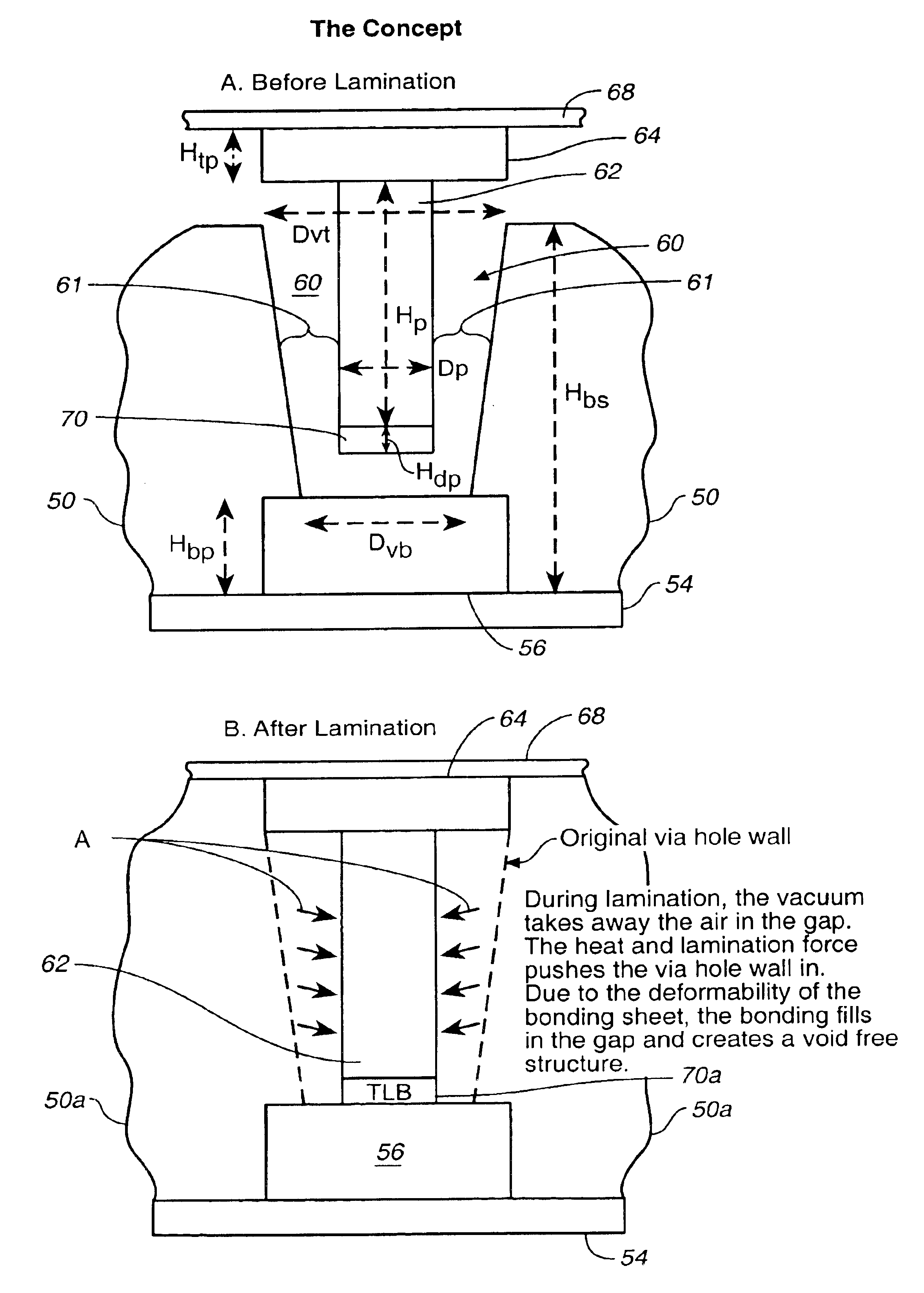

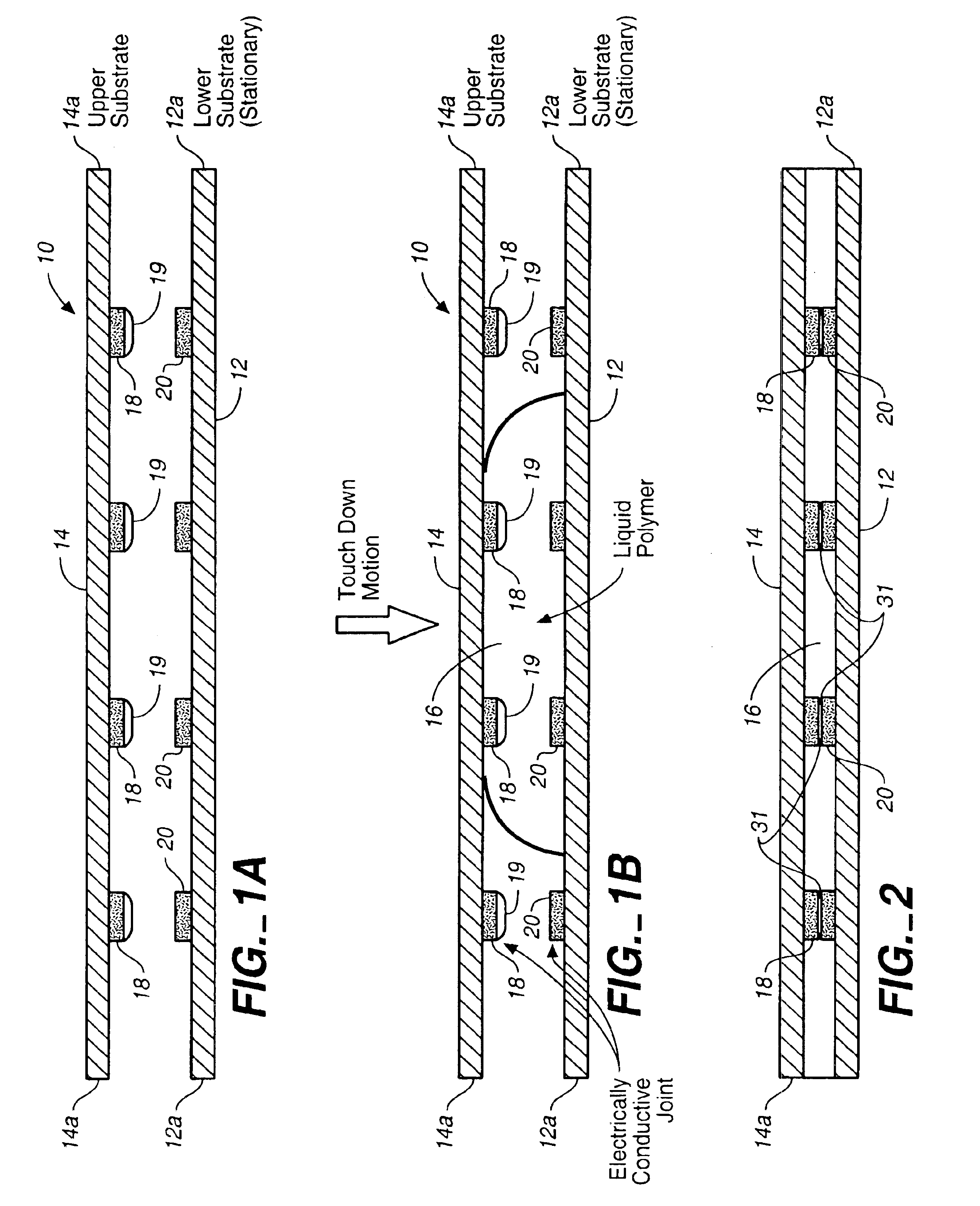

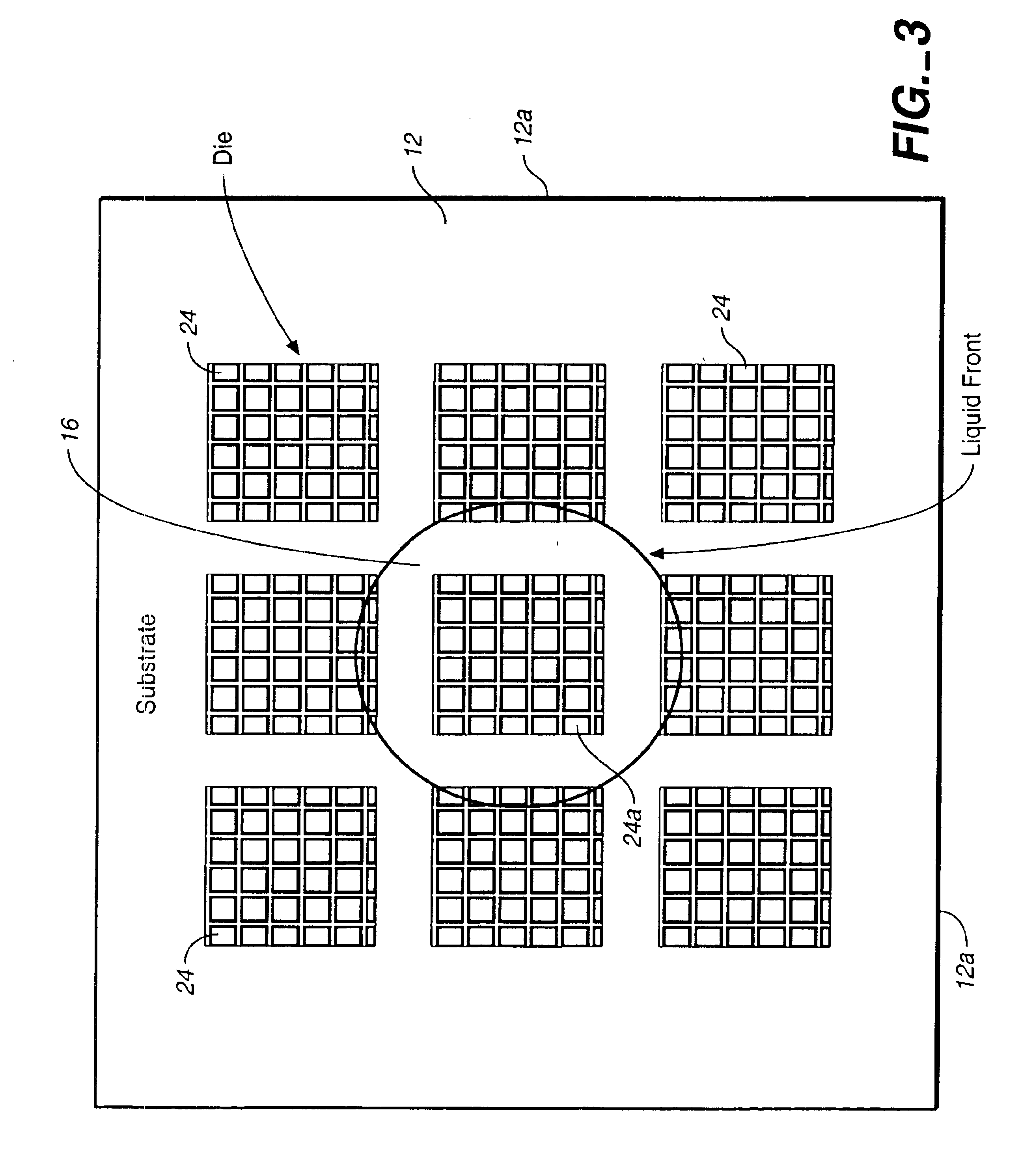

Metal attachment method and structure for attaching substrates at low temperatures

InactiveUS6080640ASemiconductor/solid-state device detailsSolid-state devicesHigh densityMelt temperature

A high density integrated circuit structure and method of making the same includes providing a first silicon substrate structure having semiconductor device formations in accordance with a first circuit implementation and metal interlevel lines disposed on a top surface thereof and a second silicon substrate structure having a second circuit implementation and metal interlevel lines disposed on a top surface thereof. The first substrate structure includes a planarized low-K dielectric disposed between the metal interlevel lines and a protective coating separating the metal interlevel lines from is the low-K dielectric, the metal interlevel lines of the first silicon substrate structure have a melting temperature on the order of less than 500 DEG C. and the low-K dielectric having a dielectric K-value in the range of 2.0-3.8. The second substrate structure also includes a planarized low-K dielectric disposed between the metal interlevel lines and a protective coating separating the metal interlevel lines from the low-K dielectric, the metal interlevel lines having a melting temperature on the order of less than 500 DEG C. and the low-K dielectric having a dielectric K-value in the range of 2.0-3.8. Lastly, the first substrate structure is low temperature bonded to the second substrate structure at respective metal interlevel lines of the first and second substrate structures.

Owner:ADVANCED MICRO DEVICES INC

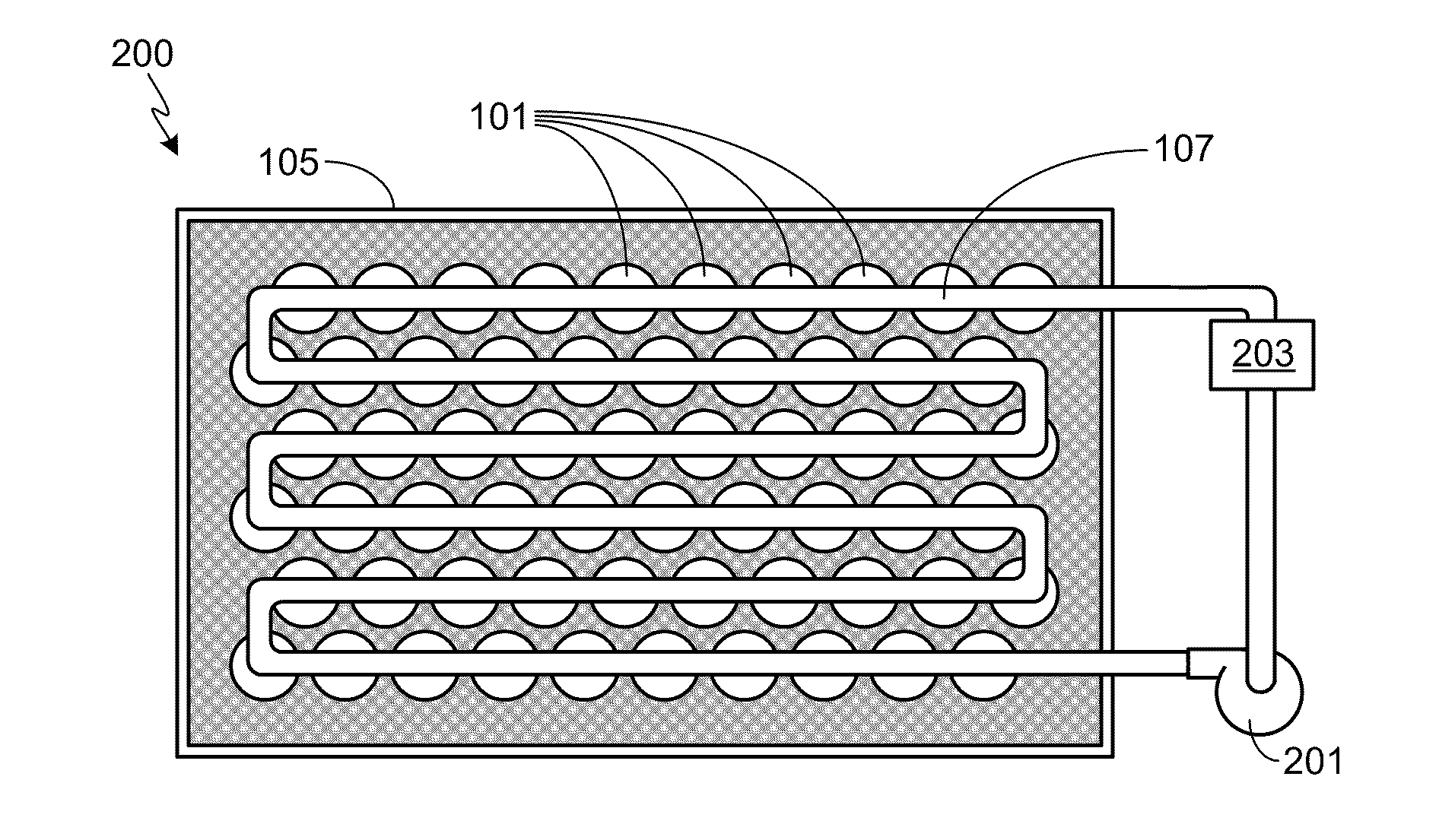

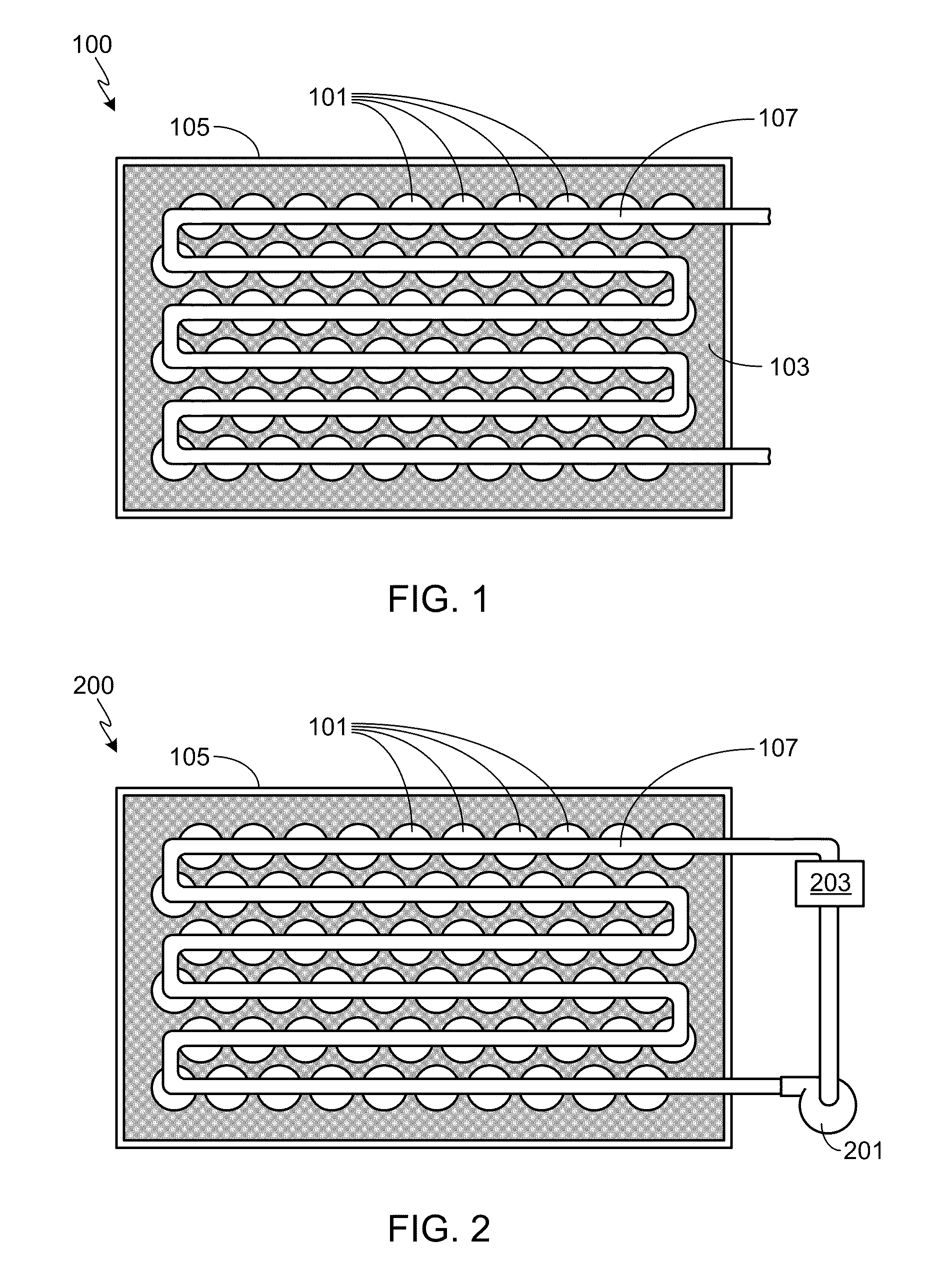

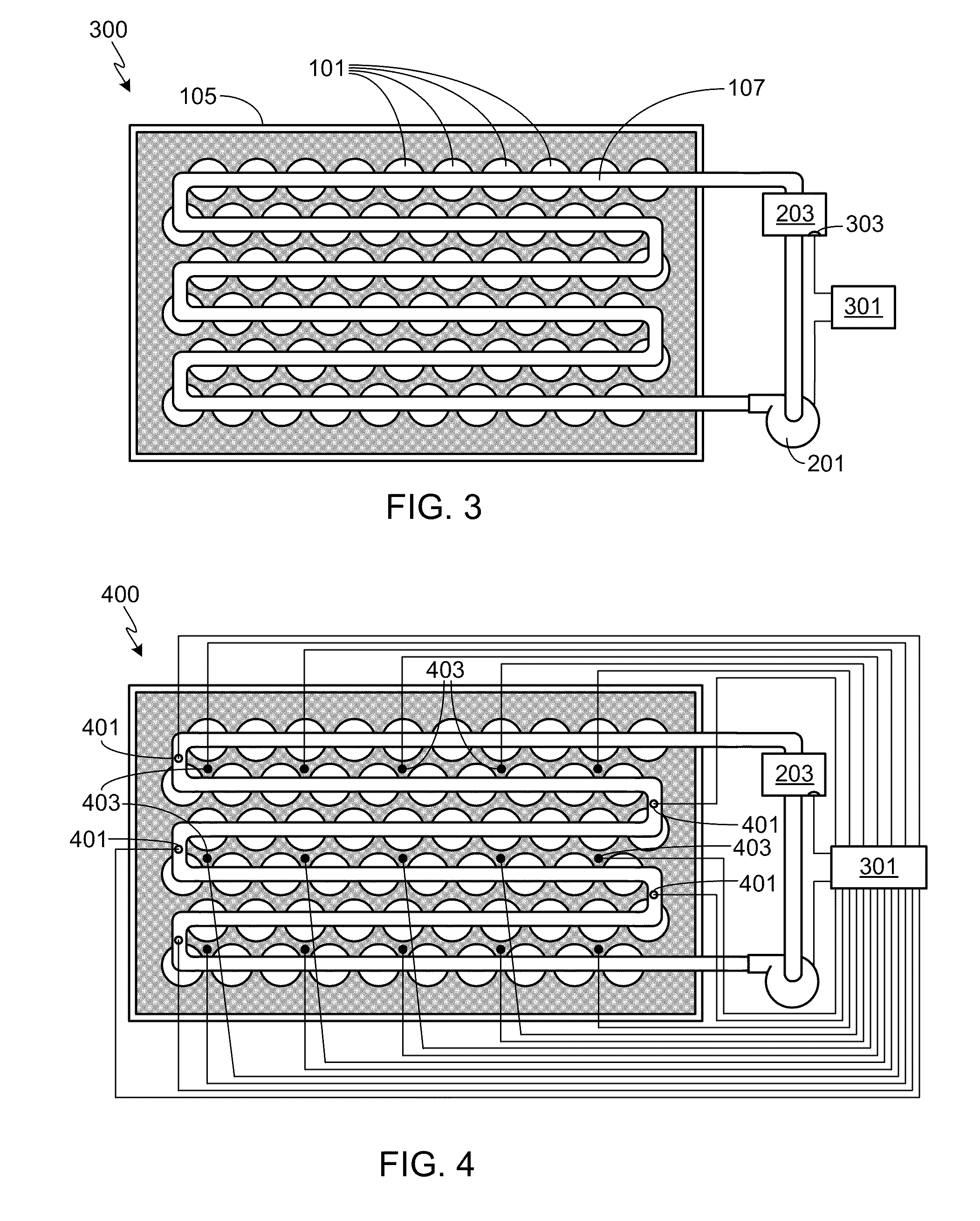

Active Thermal Runaway Mitigation System for Use Within a Battery Pack

ActiveUS20100136391A1Reduce impactHinders its propagationTemperatue controlCell temperature controlEngineeringMelt temperature

An active thermal runaway mitigation system is provided that mitigates the effects of a single cell undergoing thermal runaway, thereby preventing the propagation of the thermal runaway event to neighboring cells within the battery pack. The provided system includes at least one, fluid-containing conduit in proximity to the cells within the battery pack. The conduit includes a plurality of breach points in proximity to the subset of cells, where each breach point is configured to form a breach at a preset temperature that is lower than the melting temperature of the conduit. Once a breach is formed, the fluid contained within the conduit is discharged through the breach.

Owner:TESLA INC

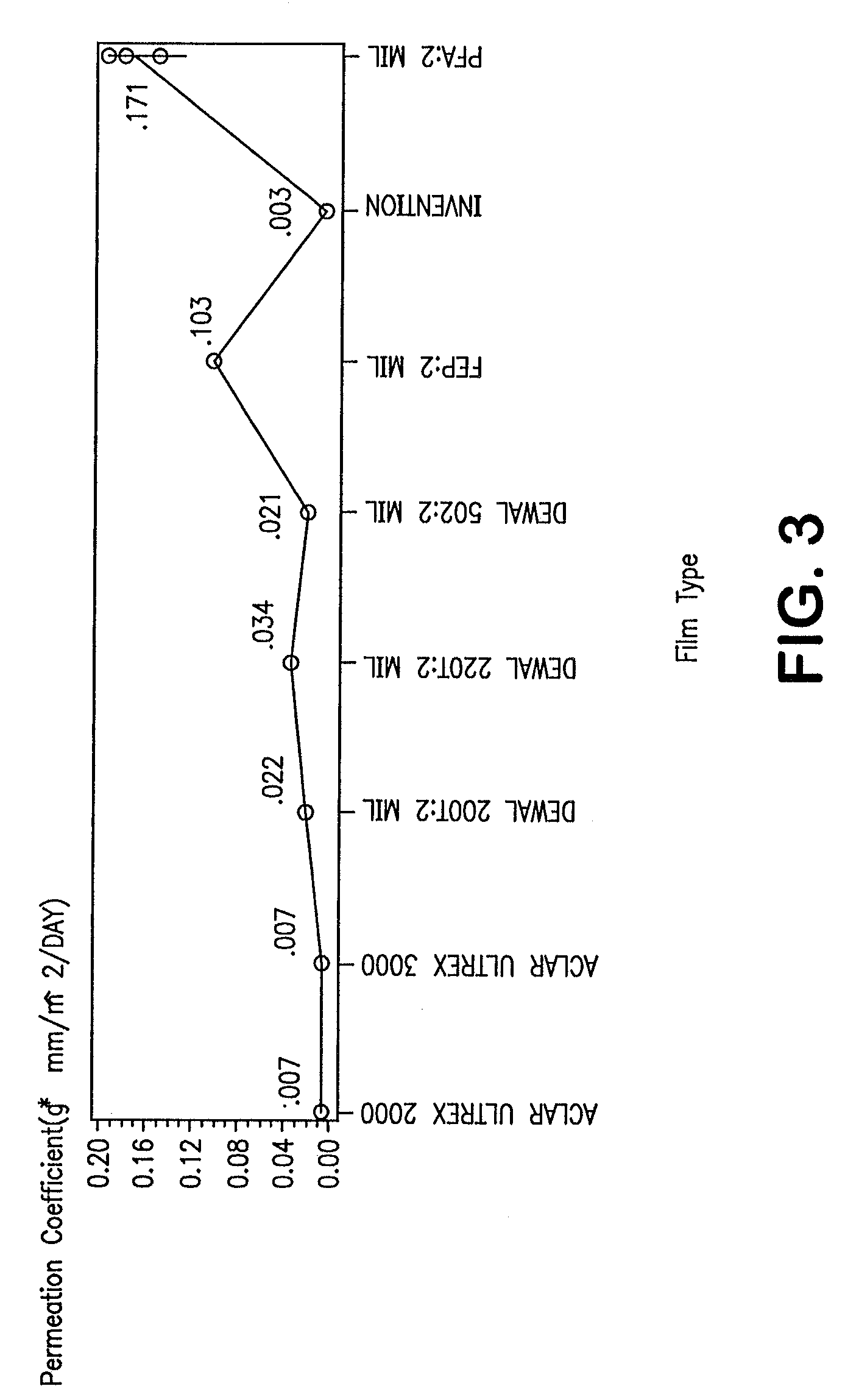

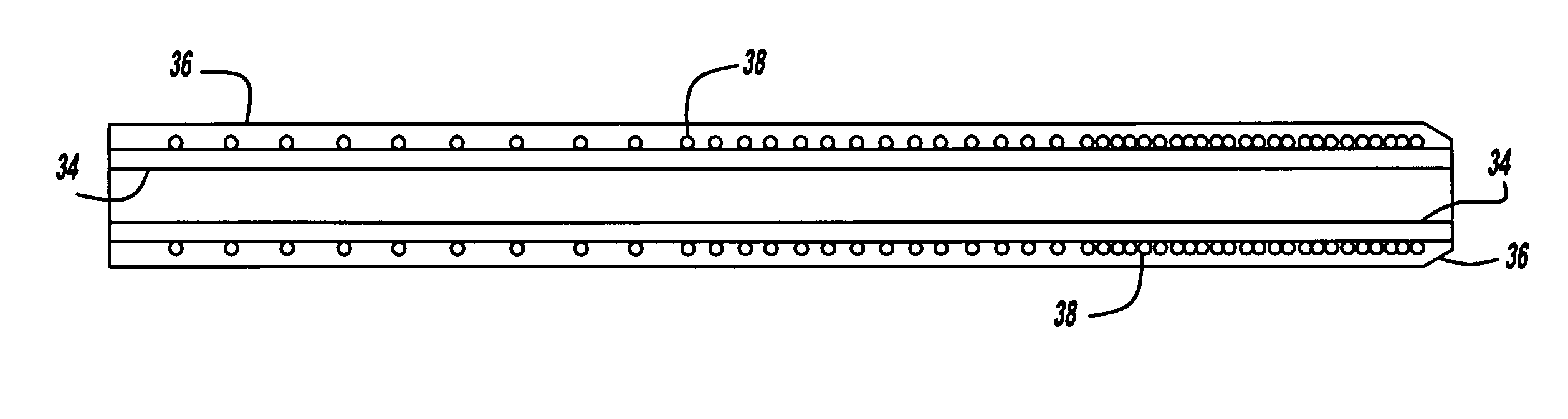

Fluoropolymer barrier material

InactiveUS7521010B2Improve barrier propertiesImprove permeabilitySynthetic resin layered productsCeramic shaping apparatusPolymer scienceWater vapor permeability

A novel densified fluoropolymer article is described which has a water vapor permeation of about 0.015 g-mm / m2 / day or less, and preferably has a matrix tensile strength of at least 10,000 psi in two orthogonal directions. The articles are made by compressing expanded porous PTFE at pressures, temperatures and times which result in elimination of the pores, and subsequent stretching above the crystalline melt temperature.

Owner:WL GORE & ASSOC INC

Thermoset materials with improved impact resistance

The present invention relates to a thermoset material with improved impact resistance comprising:99 to 20% of a thermoset resin, and1 to 80% of an impact modifier comprising at least one copolymer comprising S-B-M, B-M and M-B-M blocks,wherein:each block is connected to the other by means of a covalent bond or of an intermediate molecule connected to one of the blocks via a covalent bond and to the other block via another covalent bond,M is a PMMA homopolymer or a copolymer comprising at least 50% by weight of methyl methacrylate,B is incompatible with the thermoset resin and with the M block and its glass transition temperature Tg is less than the operating temperature of the thermoset material, andS is incompatible with the thermoset resin, the B block and the M block and its Tg or its melting temperature is greater than the Tg of B.S is advantageously polystyrene and B polybutadiene. The thermoset resin advantageously originates from the reaction of a thermosetting epoxy resin and of a hardener.

Owner:ATOFINA

Reinforced polymers

InactiveUS6331265B1Less tangleImprove mechanical propertiesMaterial nanotechnologyWood working apparatusPolymer scienceNanotube

Provided is a method for the production of a reinforced polymer, which method comprises:(a) introducing carbon nanotubes into a polymer to provide a mixture of the polymer and the nanotubes;(b) stretching the mixture at or above the melting temperature (Tm) of the polymer to orient the carbon nanotubes; and(c) stretching the mixture in the solid state to further orient the carbon nanotubes.

Owner:FINA RES SA

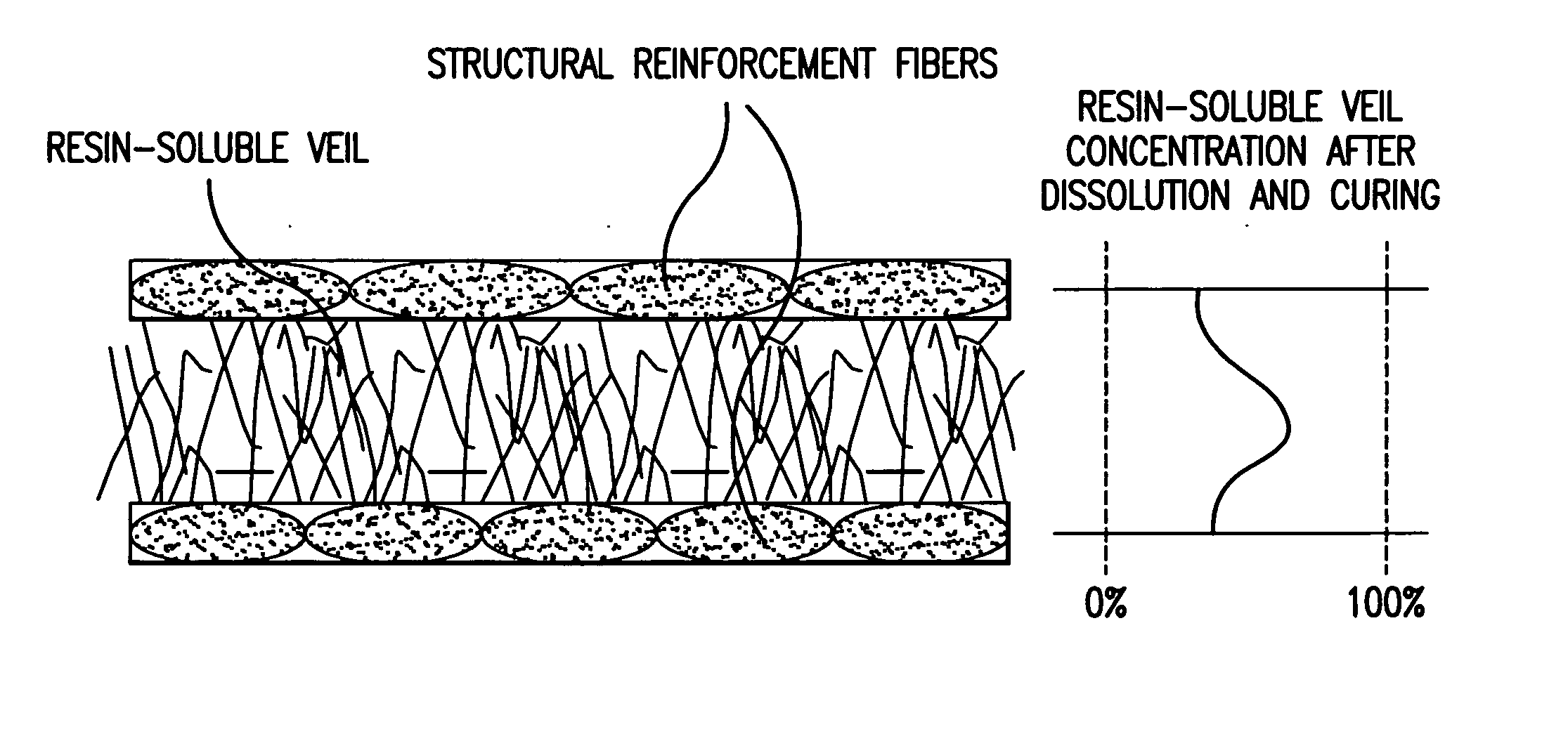

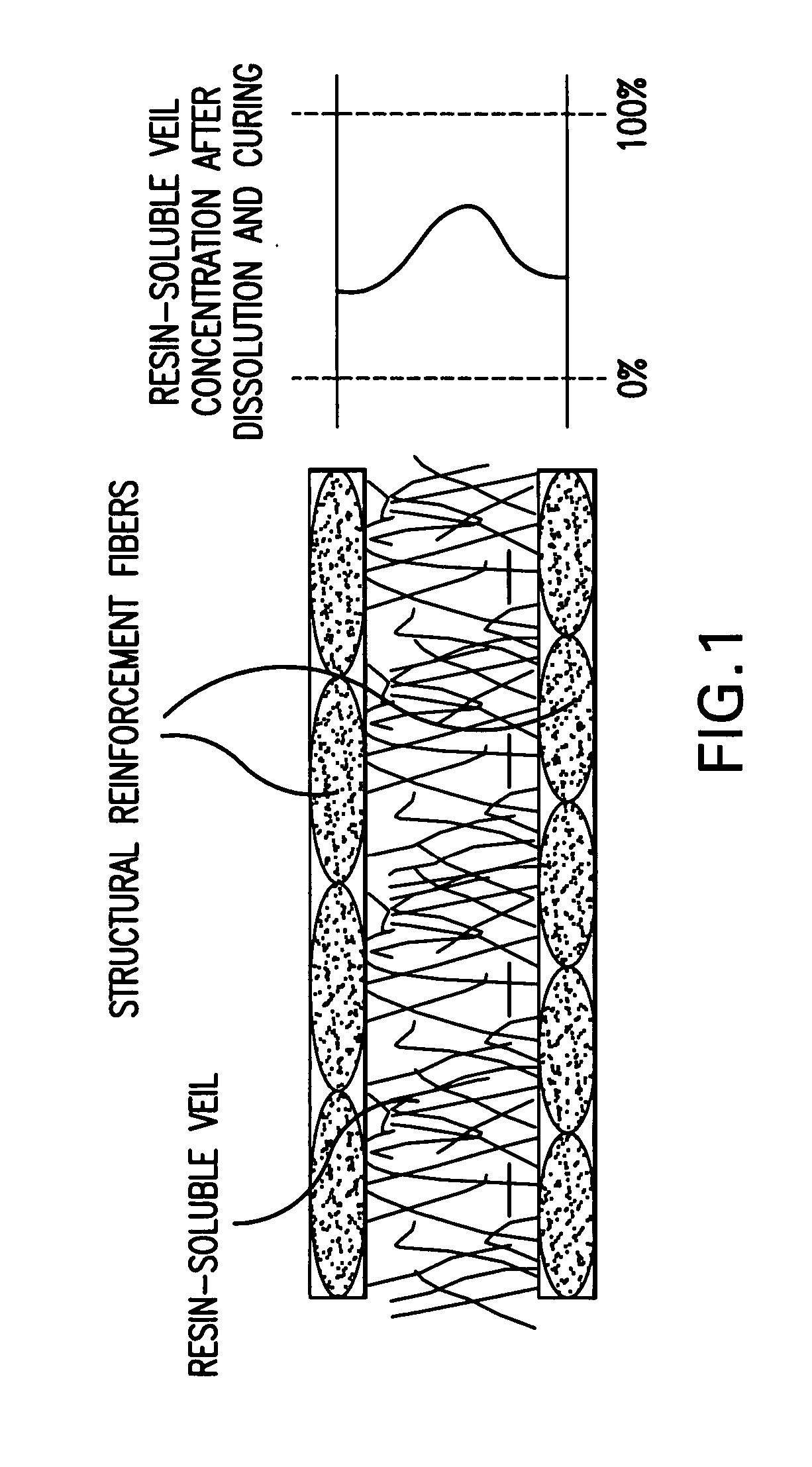

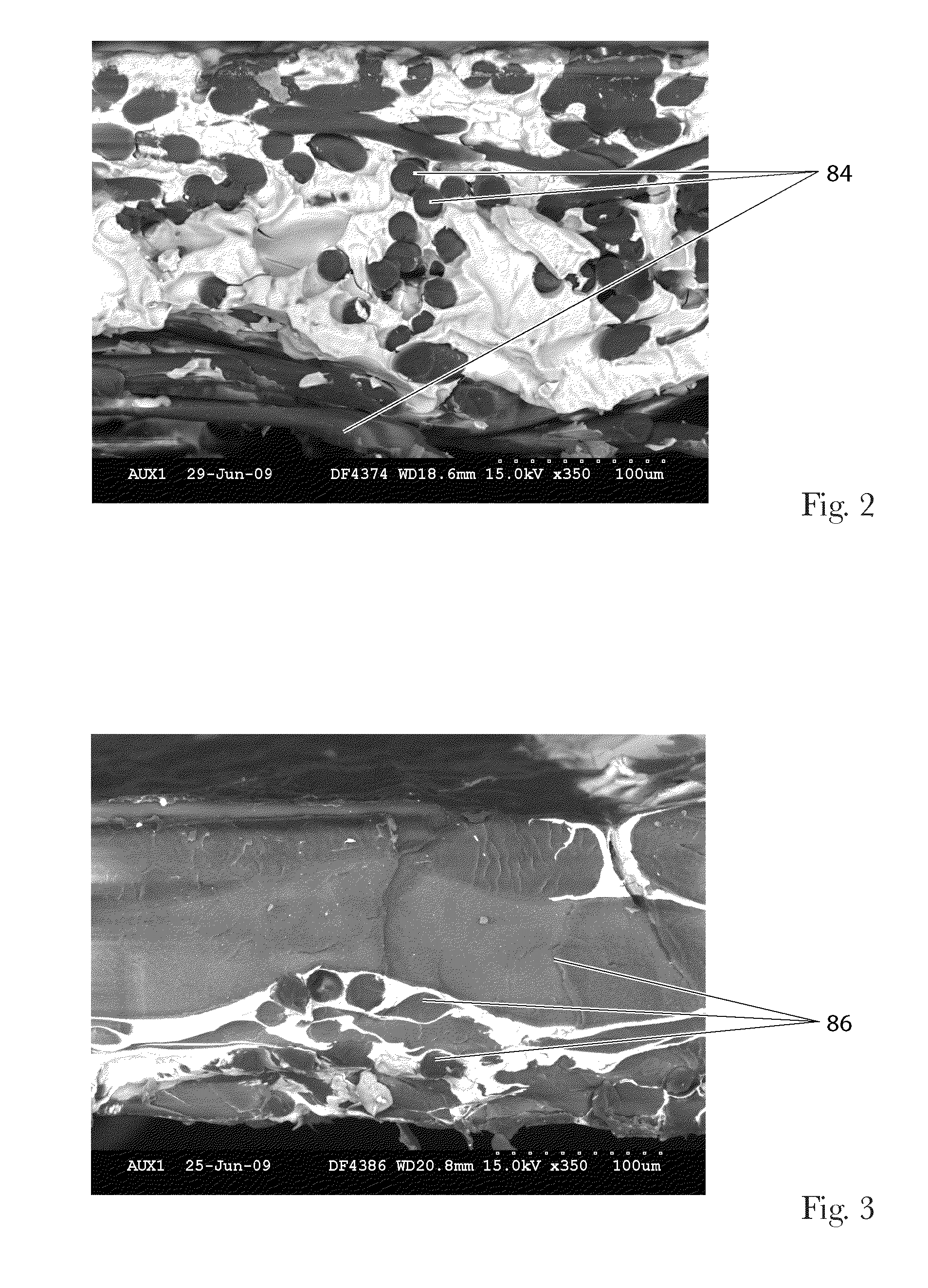

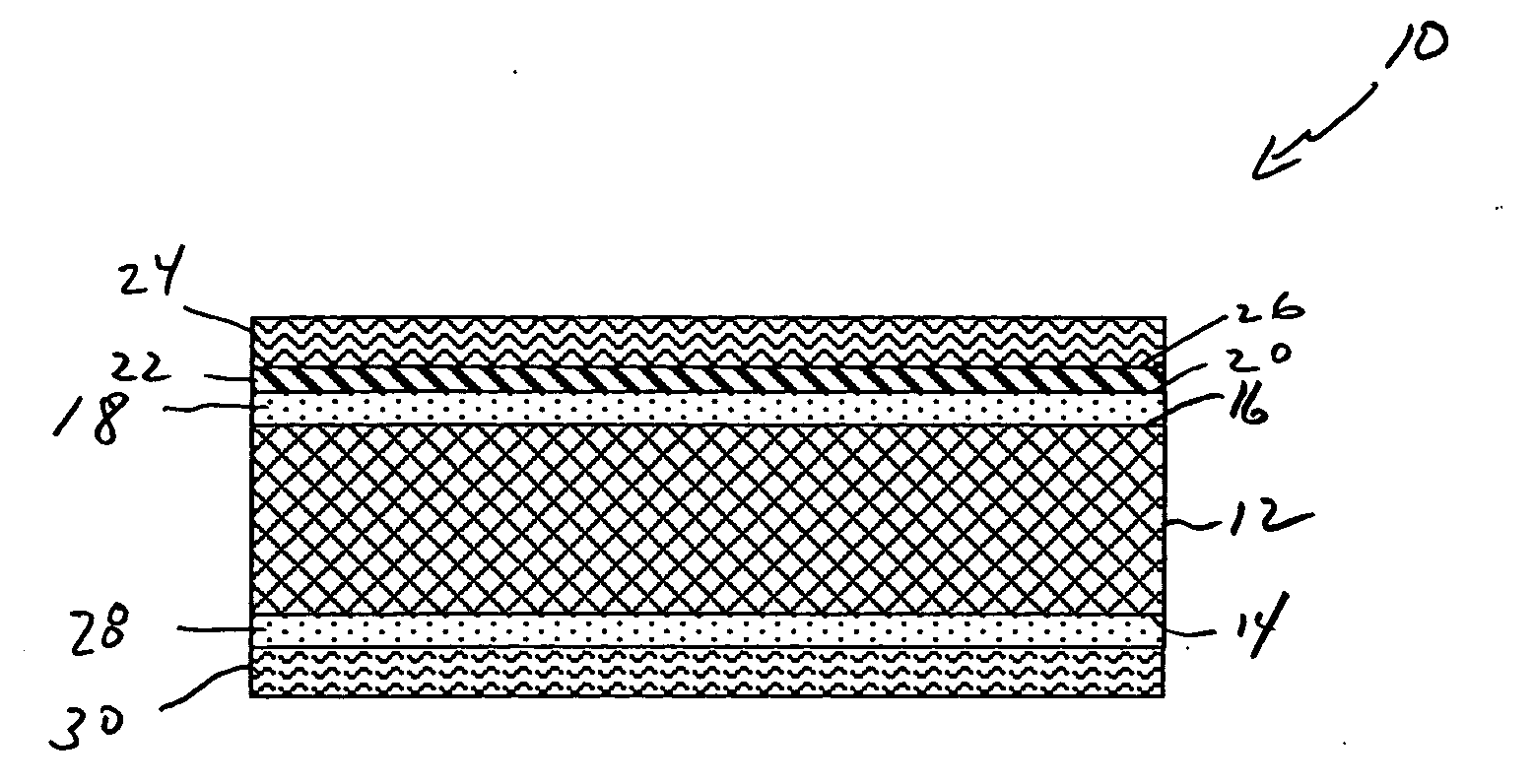

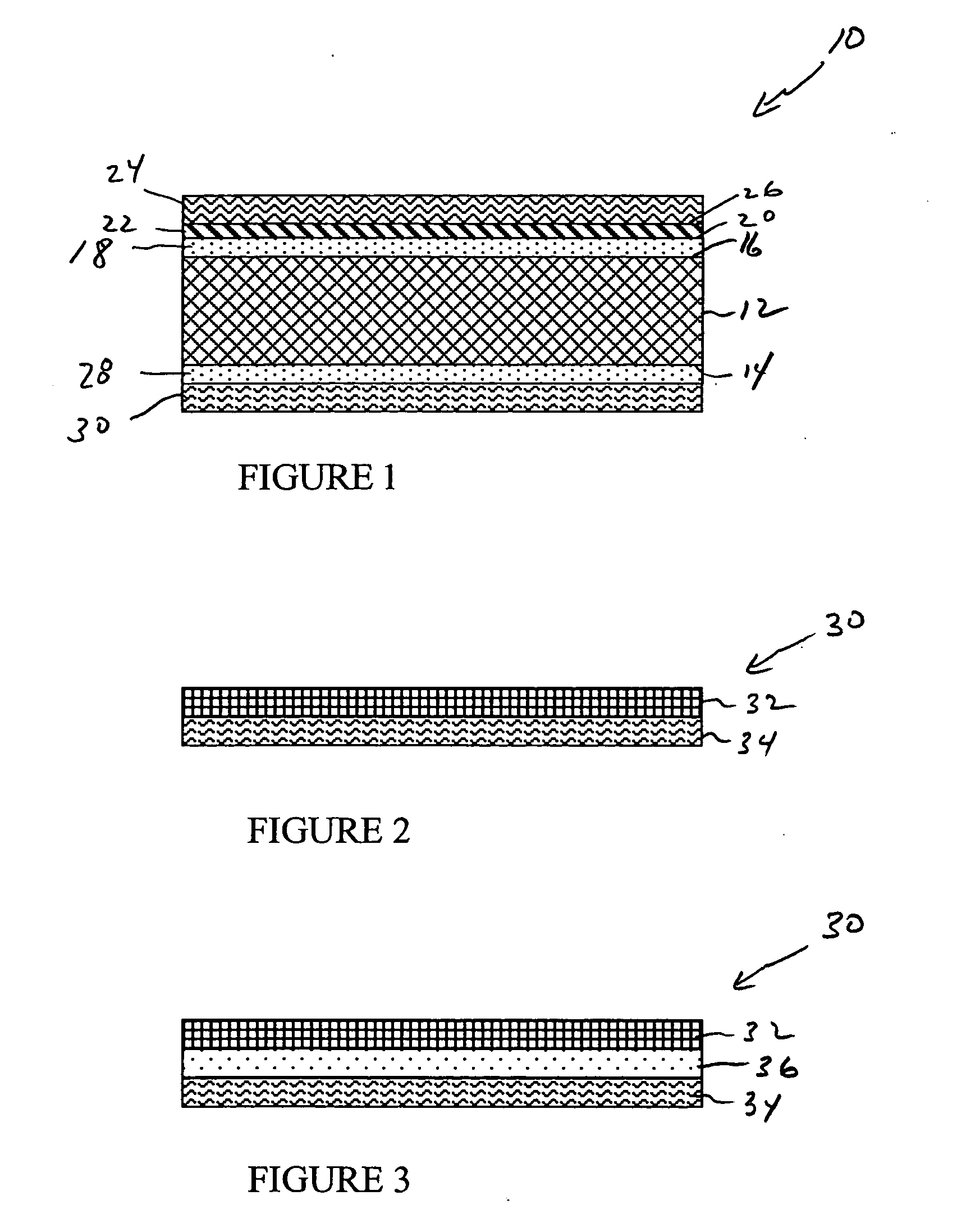

Resin-soluble thermoplastic veil for composite materials

ActiveUS20060252334A1Improve the level ofImprove toughnessWood working apparatusVehicle componentsFiberResin matrix

A resin-soluble thermoplastic polymer veil toughening element for a curable composition wherein the polymer element is a non-woven veil in solid phase adapted to undergo at least partial phase transition to fluid phase on contact with a component of the curable resin matrix composition in which it is soluble at a temperature which is less than the temperature for substantial onset of gelling and / or curing of the curable composition and which temperature is less than the polymer elements melt temperature; a method for the preparation thereof, a preform support structure for a curable composition comprising the at least one thermoplastic veil element together with structural reinforcement fibers, methods for preparation thereof, a curable composition comprising the at least one thermoplastic veil element or the support structure and a curable resin matrix composition, a method for preparation and curing thereof, and a cured composite or resin body obtained thereby, and known and novel uses thereof.

Owner:CYTEC TECH CORP

Shampoo containing a gel network

ActiveUS20070110700A1Cosmetic preparationsCationic surface-active compoundsAmphiphileSURFACTANT BLEND

Shampoo compositions comprise (a) from about 5% to about 50% of one or more detersive surfactants, by weight of the shampoo composition; (b) a dispersed gel network phase comprising, by weight of the shampoo composition, (i) at least about 0.05% of one or more fatty amphiphiles; (ii) at least about 0.01% of one or more secondary surfactants; and (iii) water; and (c) at least about 20% of an aqueous carrier, by weight of the shampoo composition. A process for preparing a shampoo composition comprises the steps of: (a) combining a fatty amphiphile, a secondary surfactant, and water at a temperature sufficient to allow partitioning of the secondary surfactant and the water into the fatty amphiphile to form a pre-mix; (b) cooling the pre-mix below the chain melt temperature of the fatty amphiphile to form a gel network; (c) adding the gel network to one or more detersive surfactants and an aqueous carrier to form a shampoo composition.

Owner:THE PROCTER & GAMBLE COMPANY

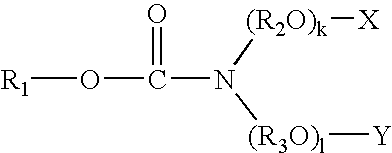

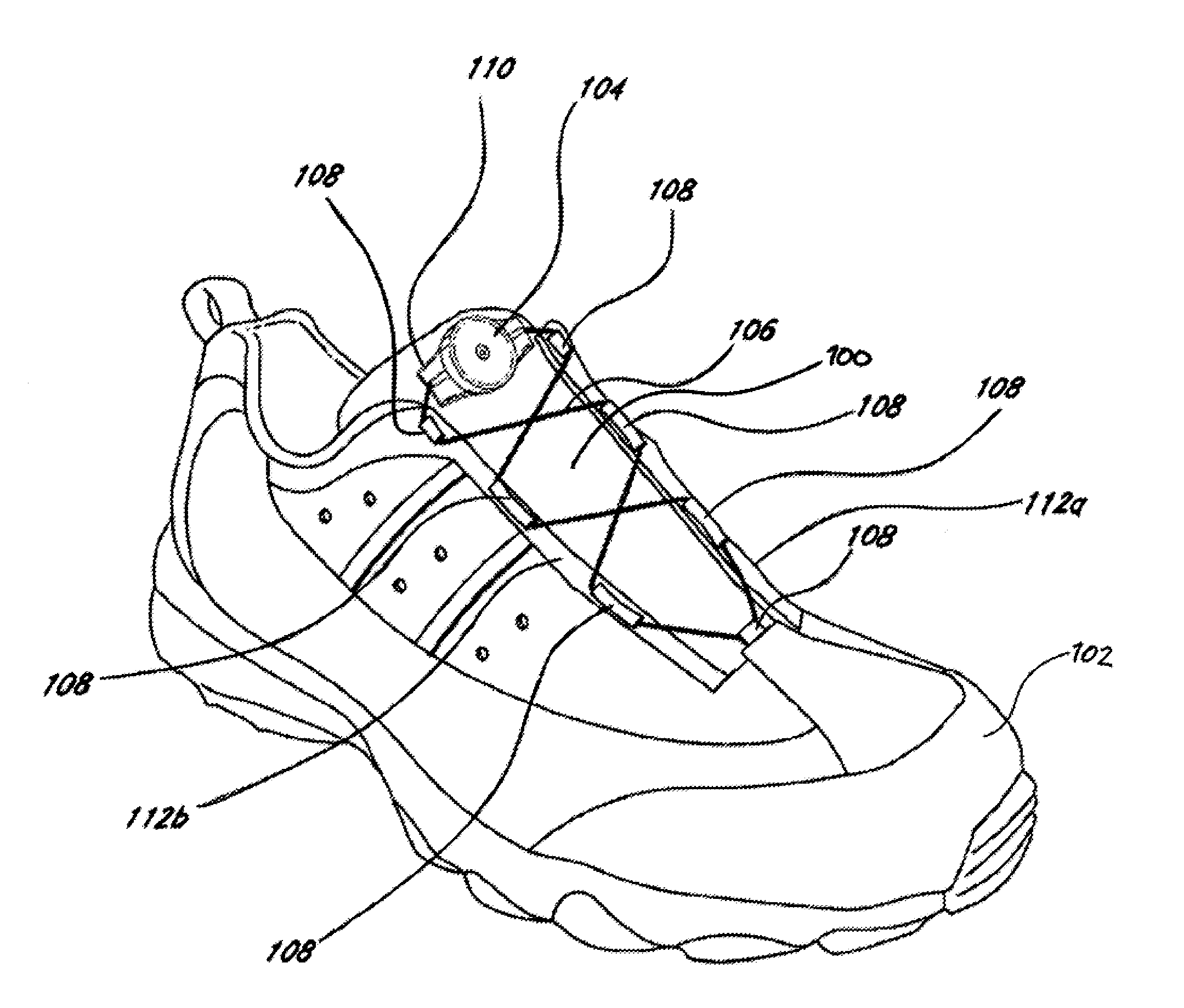

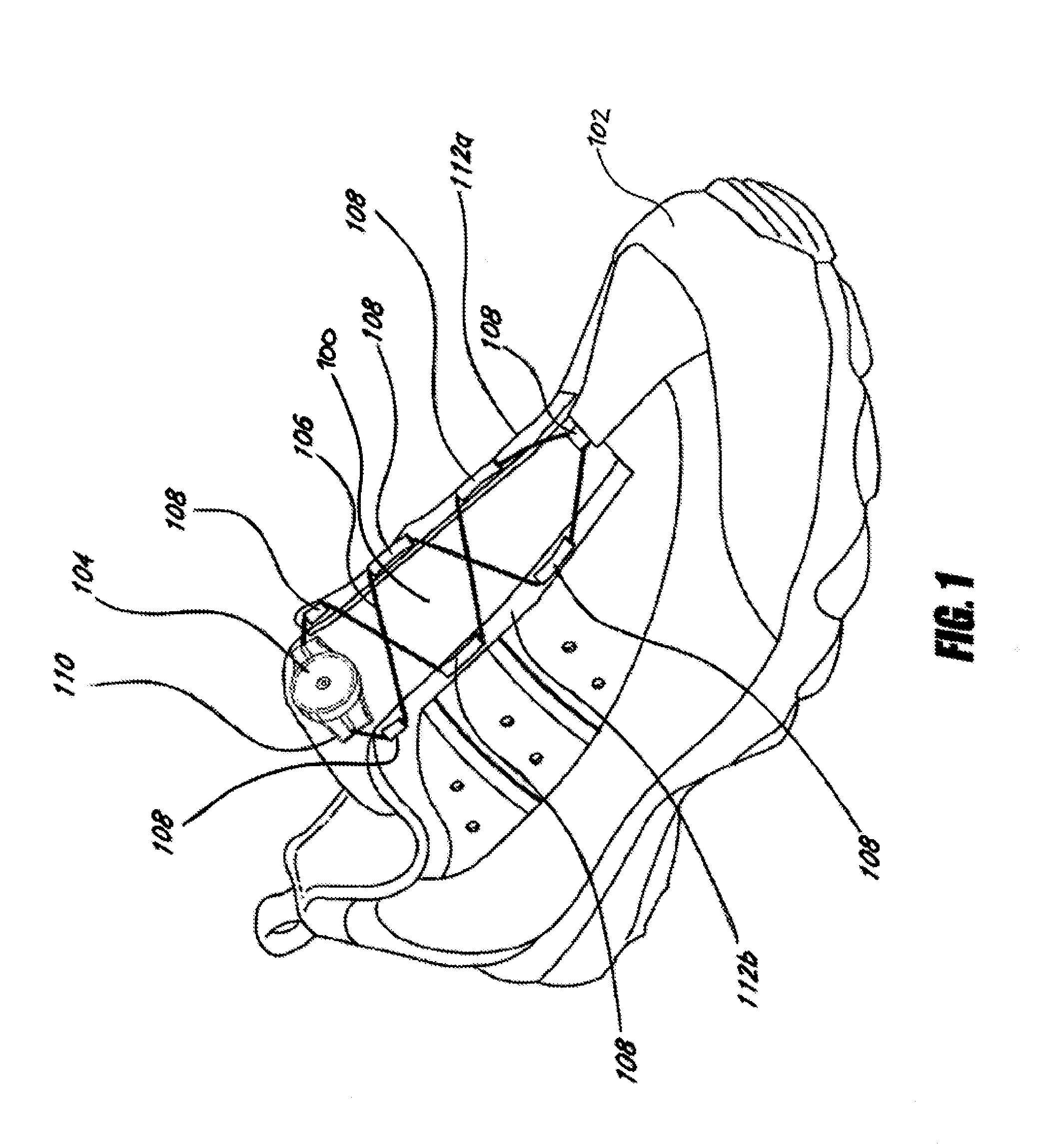

Guides and components for closure systems and methods therefor

ActiveUS20150059206A1Easily and conveniently coupledTighten shoeEyeletsLacing hooksThermoplastic elastomerEngineering

According to an embodiment, a component for attachment to an article includes an upper component that is made of a thermoplastic material having a first melting temperature and a flange member that is molded onto the upper component and made of a thermoplastic elastomer material having a second melting temperature that is lower than the first melting temperature of the upper component. The flange member extends laterally from a bottom end of the upper component so that a bottom surface of the flange member is flush with or positioned axially below a bottom surface of the upper component. The melting temperature of the thermoplastic elastomer material enables the flange member to be directly coupled to the article via heat welding and the like without substantially affecting the upper component.

Owner:BOA TECHNOLOGY

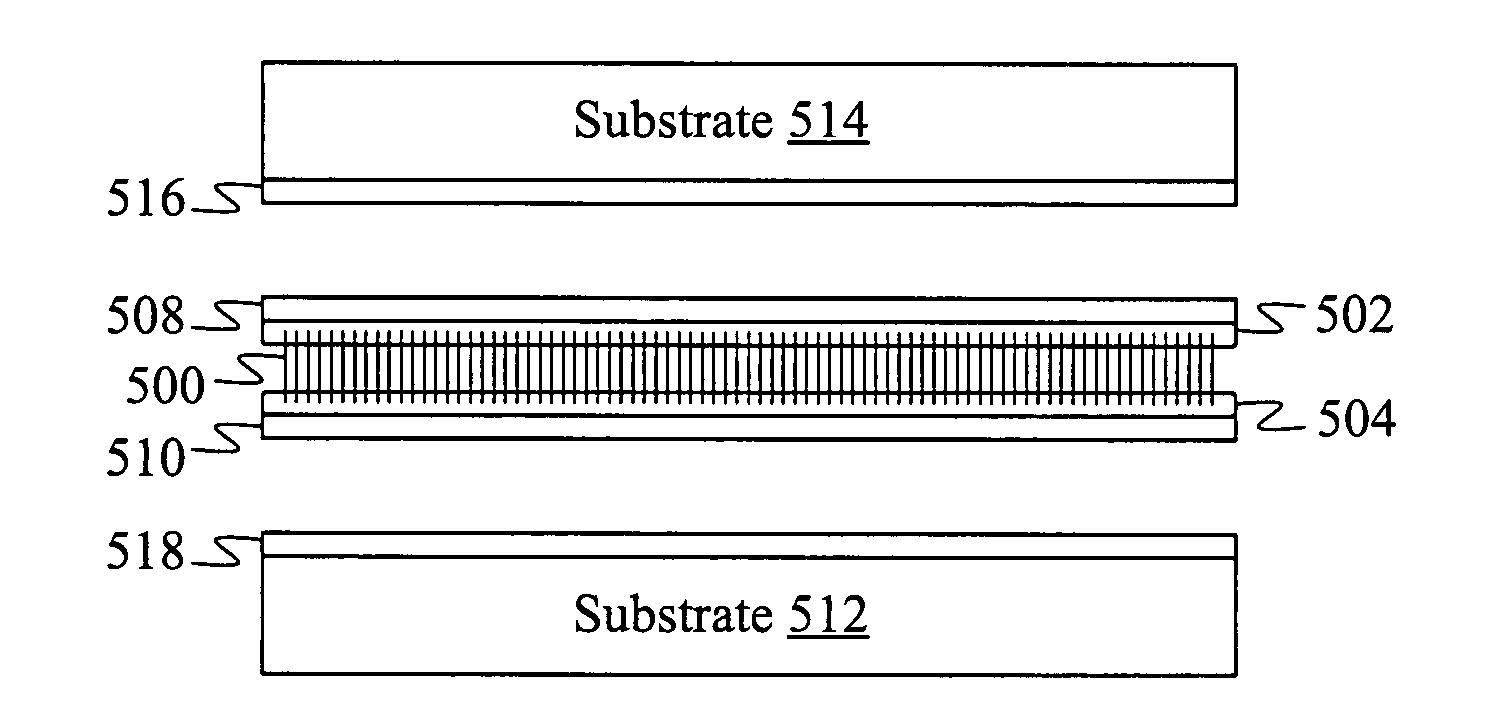

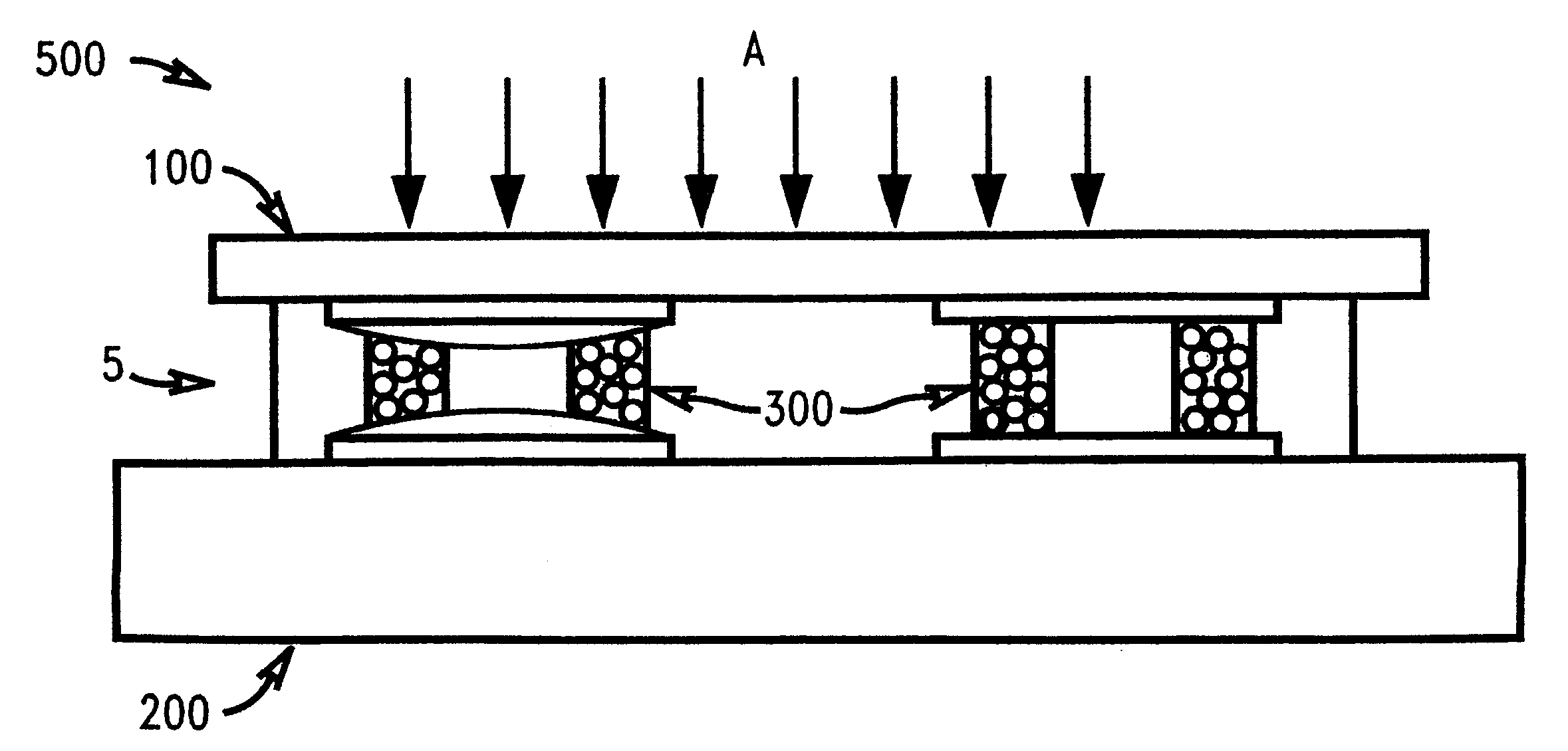

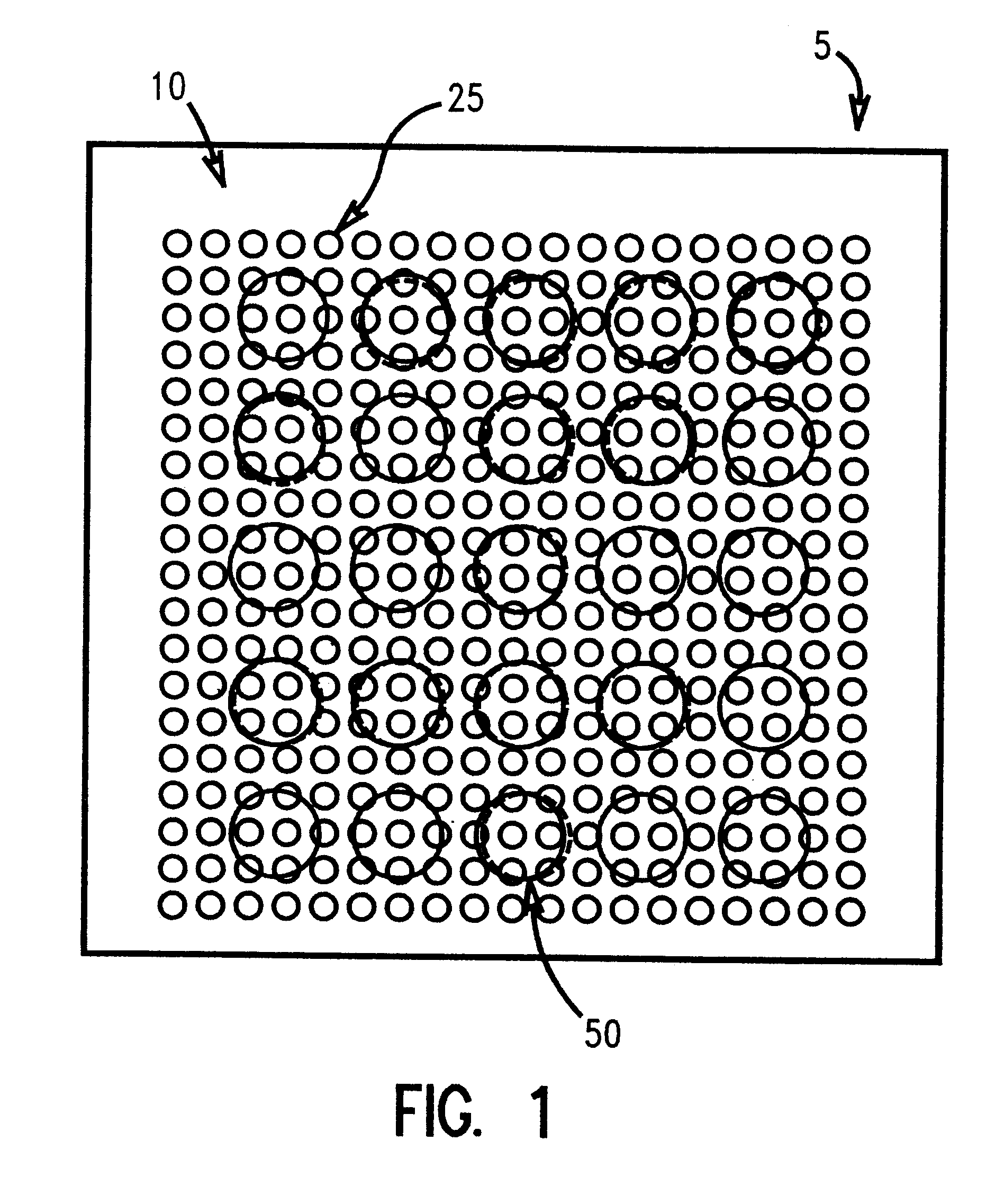

Composite thermal interface material including aligned nanofiber with low melting temperature binder

ActiveUS20090068387A1Improve thermal conductivityMaterial nanotechnologyLamination ancillary operationsFiberAdhesion process

A thermal interface material includes a mechanically compliant vertically aligned nanofiber film and a binder material for joining the nanofibers of the film to the surfaces of two substrates. Preferably, the binder material comprises a non-hydrocarbon-based material such as a metallic eutectic with a melting temperature below a nanofiber thermal damage threshold temperature of the film. The film is grown on a substrate which is then bonded to another substrate by the binder material in an adhesion process that may include pressure and heat. Alternatively, the film may be released from the substrate to produce a stand-alone thermal tape which may later be placed between two substrates and bonded.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Toner processes

ActiveUS20080236446A1Improve blocking propertiesExcellent heat cohesionInksDevelopersPolyesterPolymer chemistry

A toner process comprising the aggregation and coalescence of an amorphous polyester, a crystalline polyester and a colorant, and wherein the coalescence is conducted at a temperature that is about lower than the melting point temperature of the crystalline polyester.

Owner:XEROX CORP

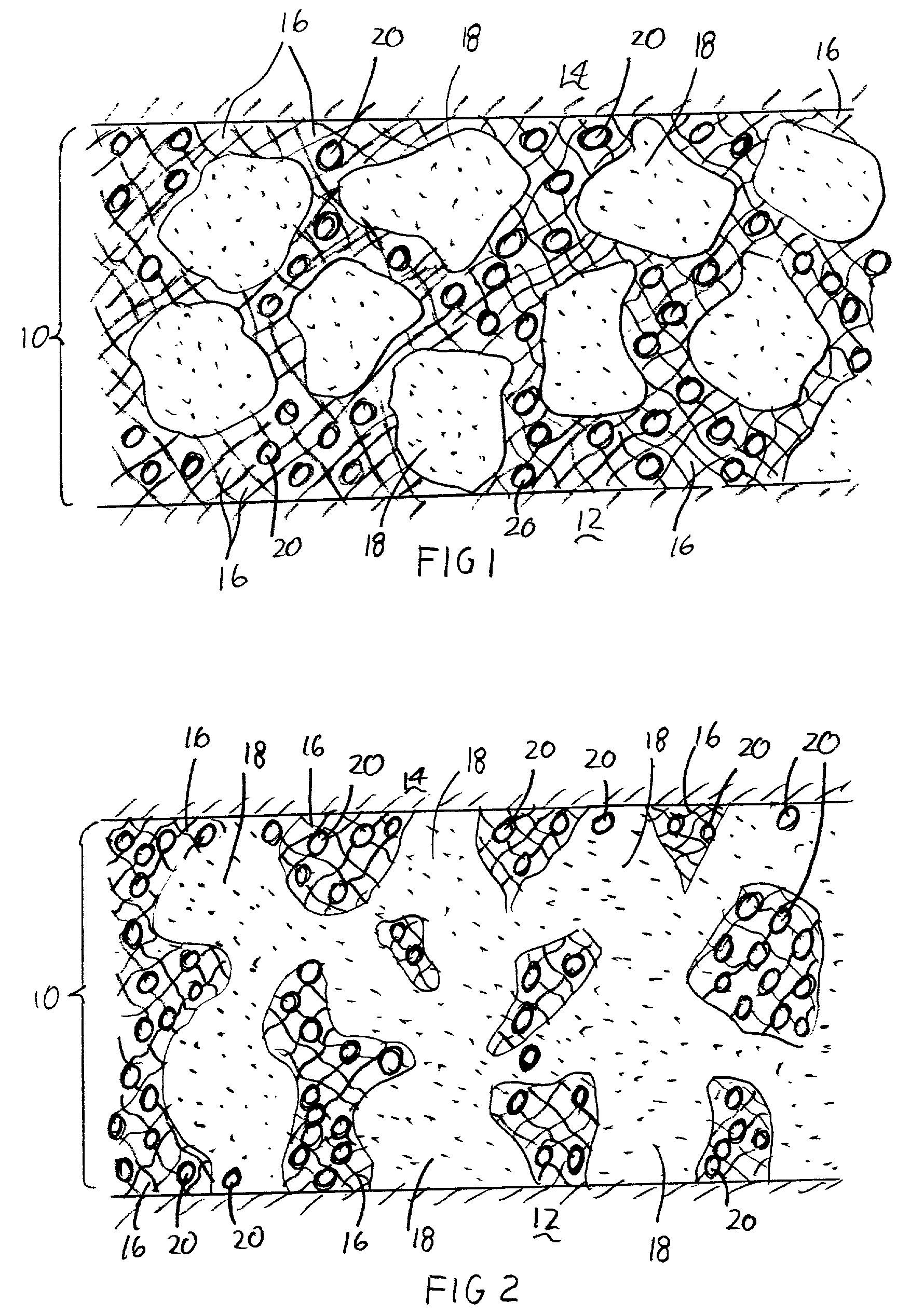

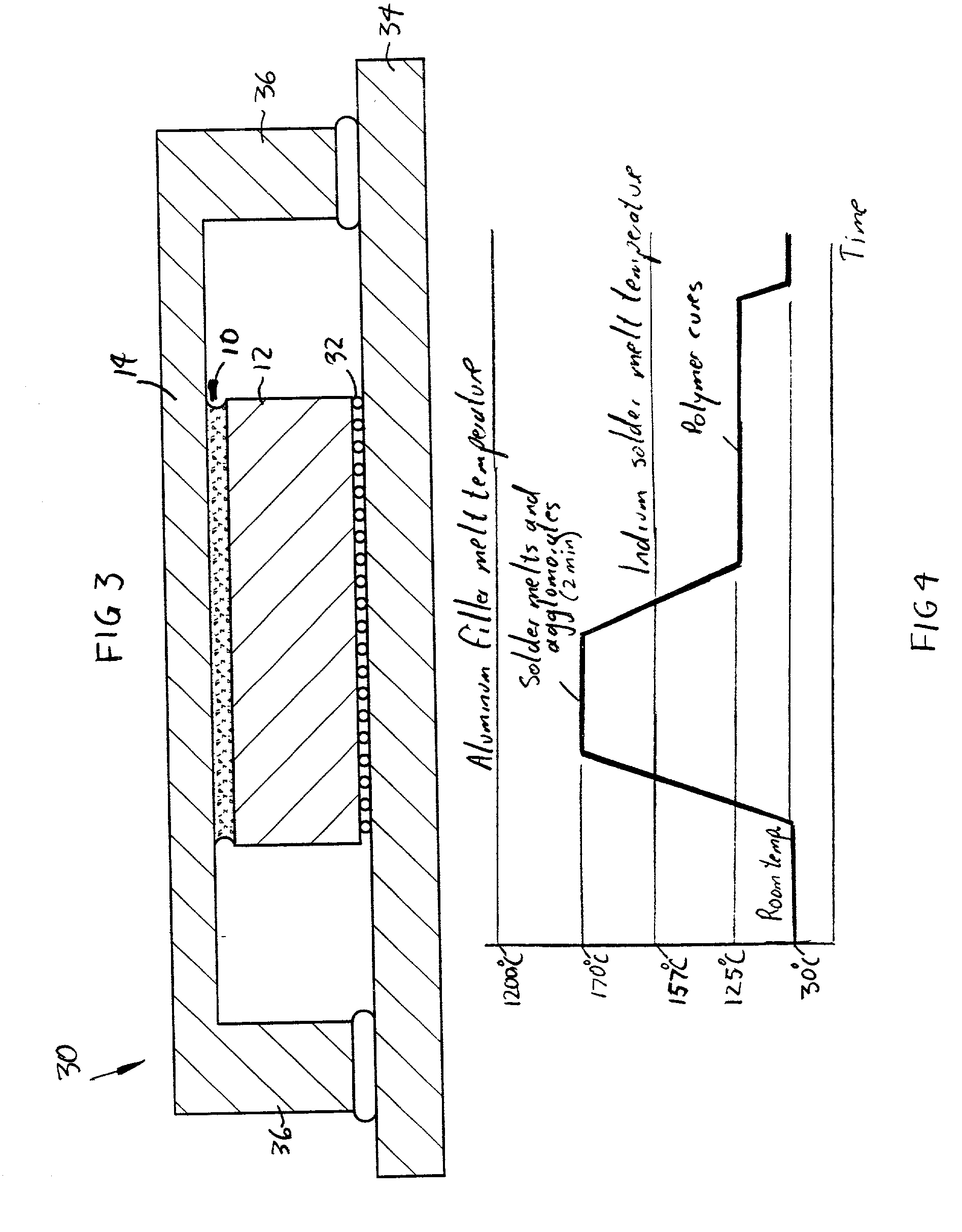

Thermal interface material and electronic assembly having such a thermal interface material

InactiveUS20030077478A1Artificial flowers and garlandsSemiconductor/solid-state device detailsStress conditionsIndium

A thermal interface material is described for thermal coupling of an electronic component to a thermally conductive member. The thermal interface material includes a viscoelastic polymer matrix material, fusible solder particles in the matrix material, and filler particles in the matrix material. The solder particles have a melting temperature below a selected temperature (e.g. 157° C. for indium) and the filler particles have a melting temperature substantially above the selected temperature (e.g. 961° C. for silver). The filler particles keep the thermal interface material intact under adverse thermal and stress conditions.

Owner:INTEL CORP

Seam structure and method for making a seam

A seam comprising two or more porous, at least partially meltable materials, having substantially the same melting temperature. A process for making the seam using heated fluid may be used to join all of the materials at the seam, or to join only selected layers of a laminate in a seam.

Owner:THE PROCTER & GAMBLE COMPANY

Decorative interior sound absorbing panel

A multi-layered fiber reinforced thermoplastic sound absorbing panel includes a porous fiber reinforced thermoplastic core layer having a first surface and a second surface, and includes a thermoplastic material and from about 20 weight percent to about 80 weight percent fibers, a tie layer covering the second surface of the core layer and including a thermoplastic material, and a barrier layer covering the tie layer. The barrier layer includes a thermoplastic material having a melting temperature higher than the melting temperature of the core layer thermoplastic material. The tie layer bonds the barrier layer to the core layer. The panel also includes a non-woven layer including a fabric bonded to the barrier layer. The non-woven layer forms an outer surface of the panel.

Owner:HANWA AZDEL INC

Method for joining conductive structures and an electrical conductive article

Embodiments of the invention include a method comprising disposing a thin metallic layer having a low melting temperature between one end of a conductive post on a substrate and a conducting structure on an opposing substrate. Heated platens in contact with the substrates can apply pressure and heat to the thin metallic layer and cause it to be entirely consumed and subsequently transformed into a bonding layer having a melting temperature higher than the melting temperature of the original thin metallic layer. Prior to, during, or after the conductive post is bonded to the conducting structure, the region around the conductive post and between the substrates may be filled with a dielectric material, such as polyimide.

Owner:FUJITSU LTD

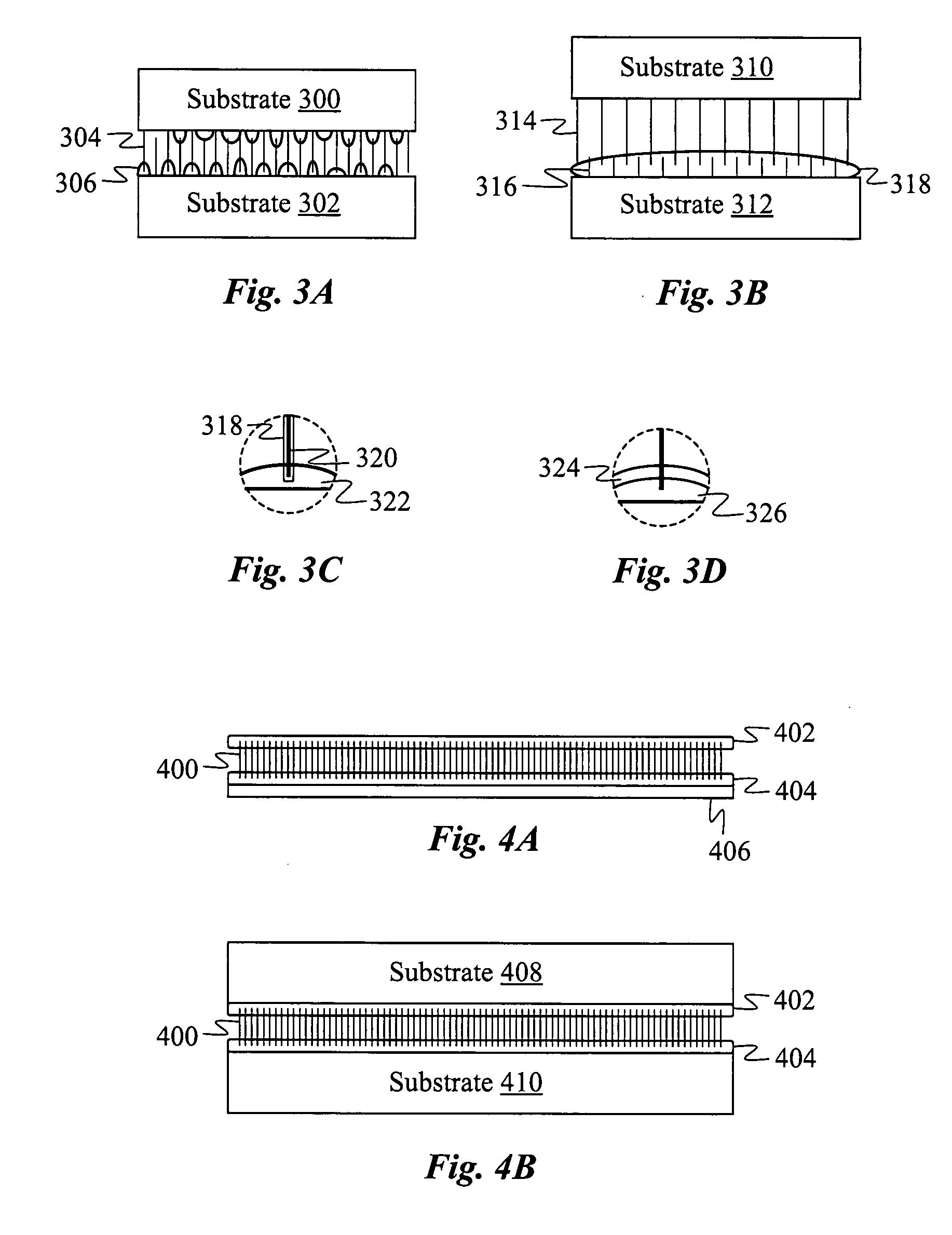

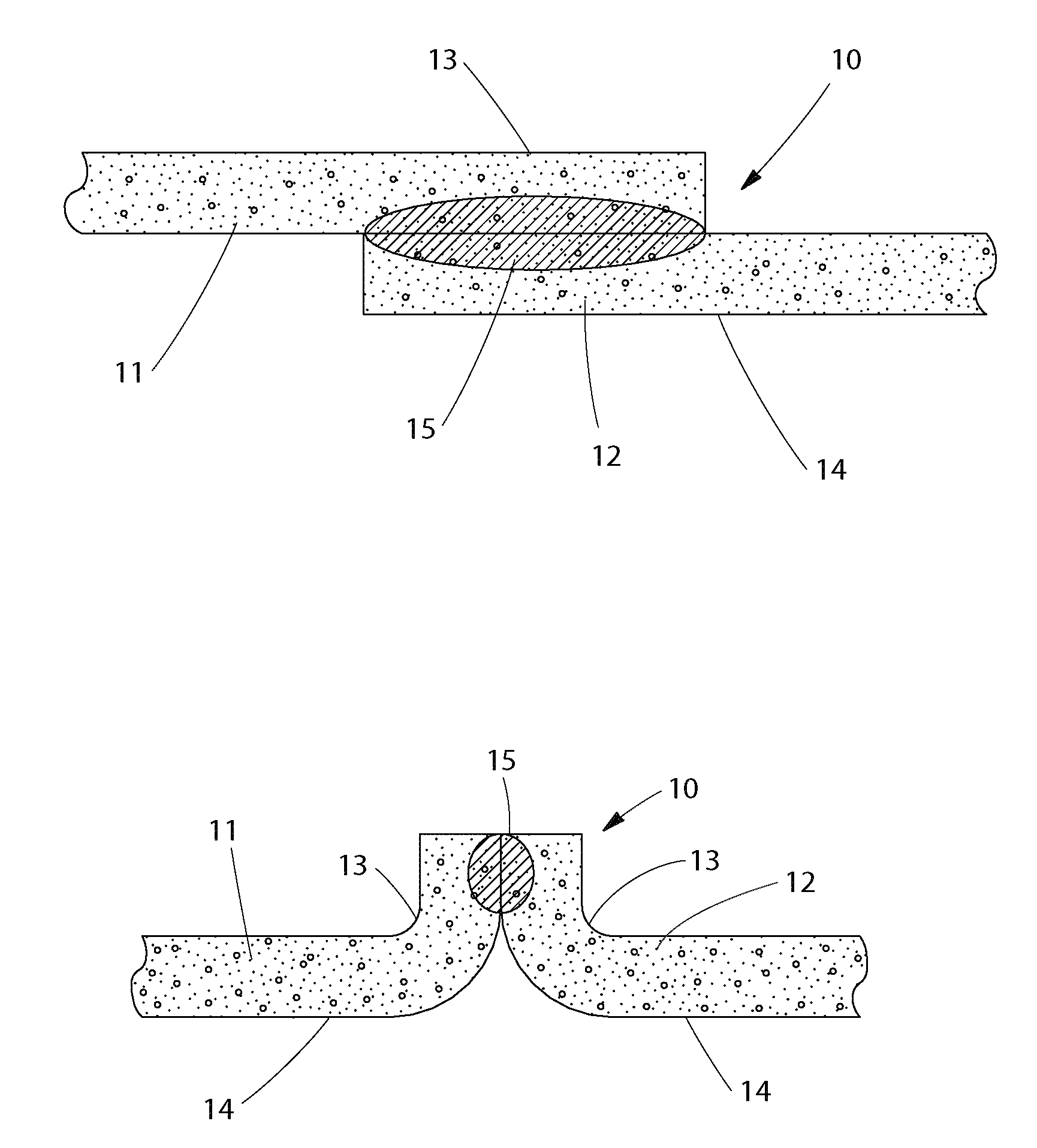

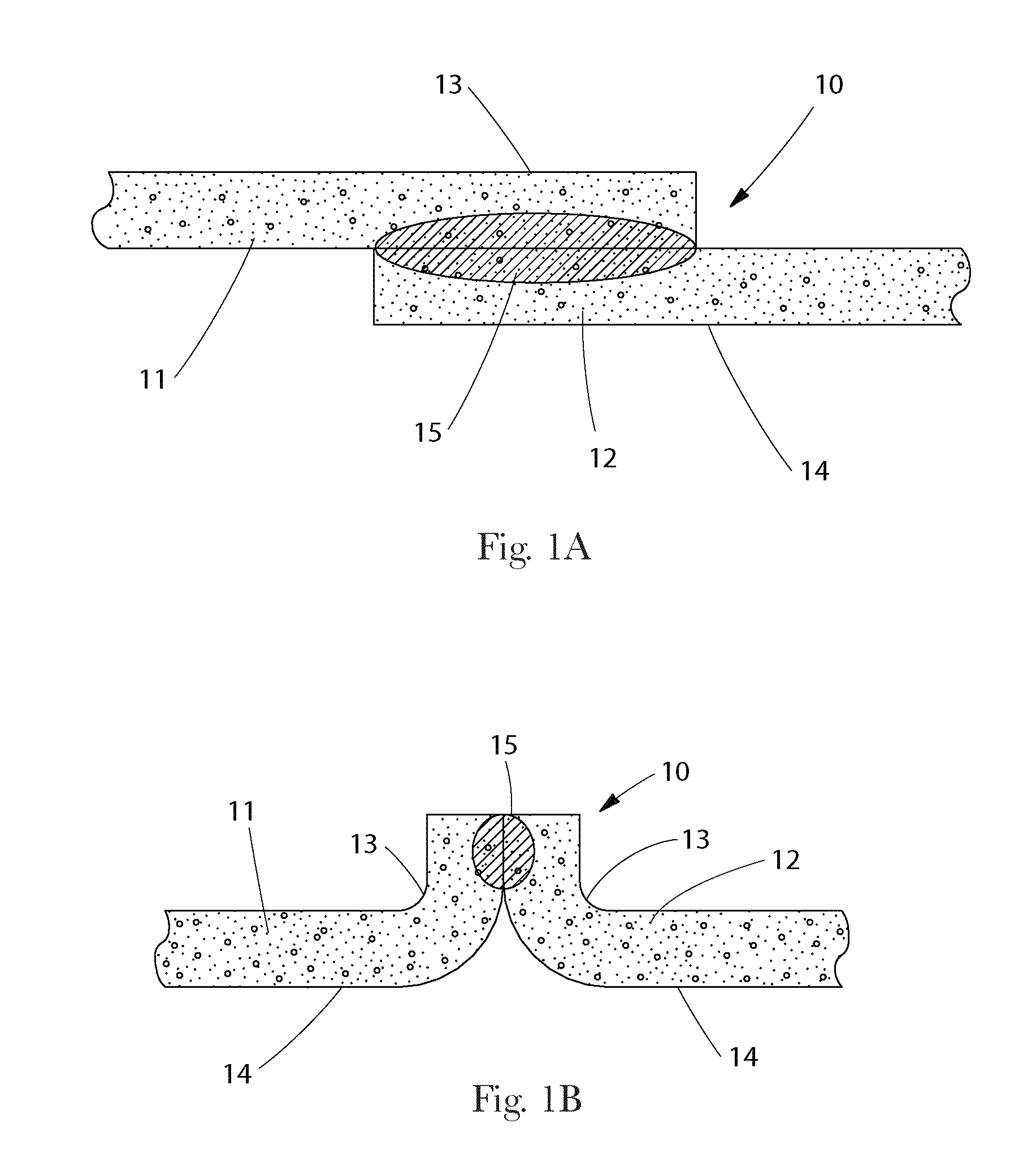

Z-axis compressible polymer with fine metal matrix suspension

InactiveUS6270363B1Reduce openingPrinted circuit assemblingLine/current collector detailsContact padAlloy

A compressible interposer comprising an interposer sheet having a plurality of apertures filled with a dielectric material having a substantially uniform suspension of conductive particles therein forming a plurality of conductive sites. Preferably, the number of conductive sites on the interposer are greater in number than the number of contact pads on the electronic components such that precise alignment of the interposer between the electronic components is not required. The apertures of the interposer sheet confine the conductive particles within the dielectric material such that during compression of the interposer between the electronic components, z-axis conductive pathways are formed without shorting in the x and y directions. Preferably, the interposer sheet comprises polyimide. Preferably, the dielectric material comprises polyimide-siloxane. Preferably, the conductive particles have a diameter of about 2 to about 20 mum and comprise of a material selected from the group consisting of copper, gold, silver, nickel, palladium, platinum, and alloys thereof. The particles may also be coated with an additional conductive material such as solder having a lower melting temperature. Most preferably, the conductive particles comprise solder coated copper particles. The conductive particles are present in an amount of about 30 to about 90 wt. % of the total weight of the conductive particles and the dielectric material.

Owner:IBM CORP

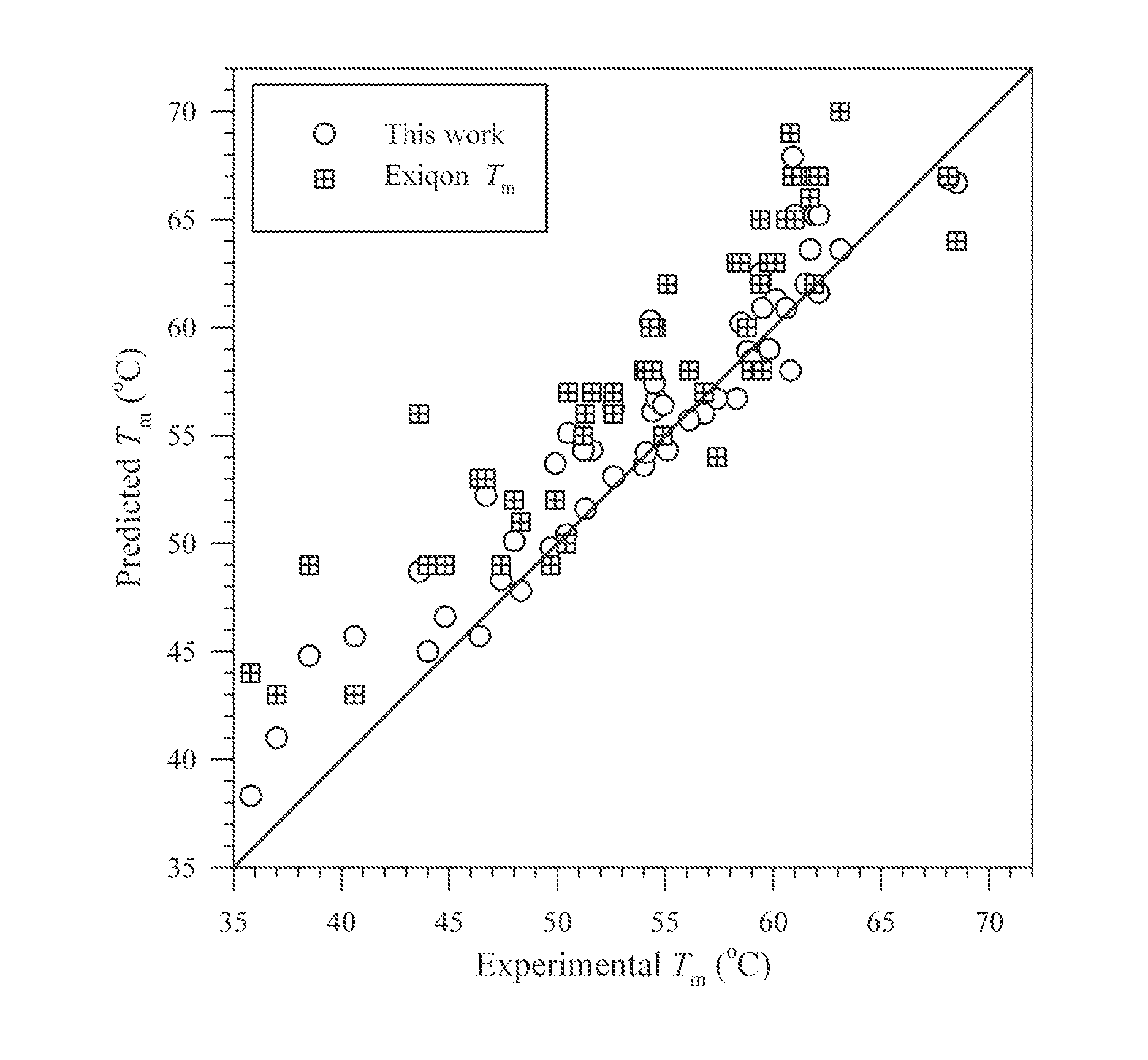

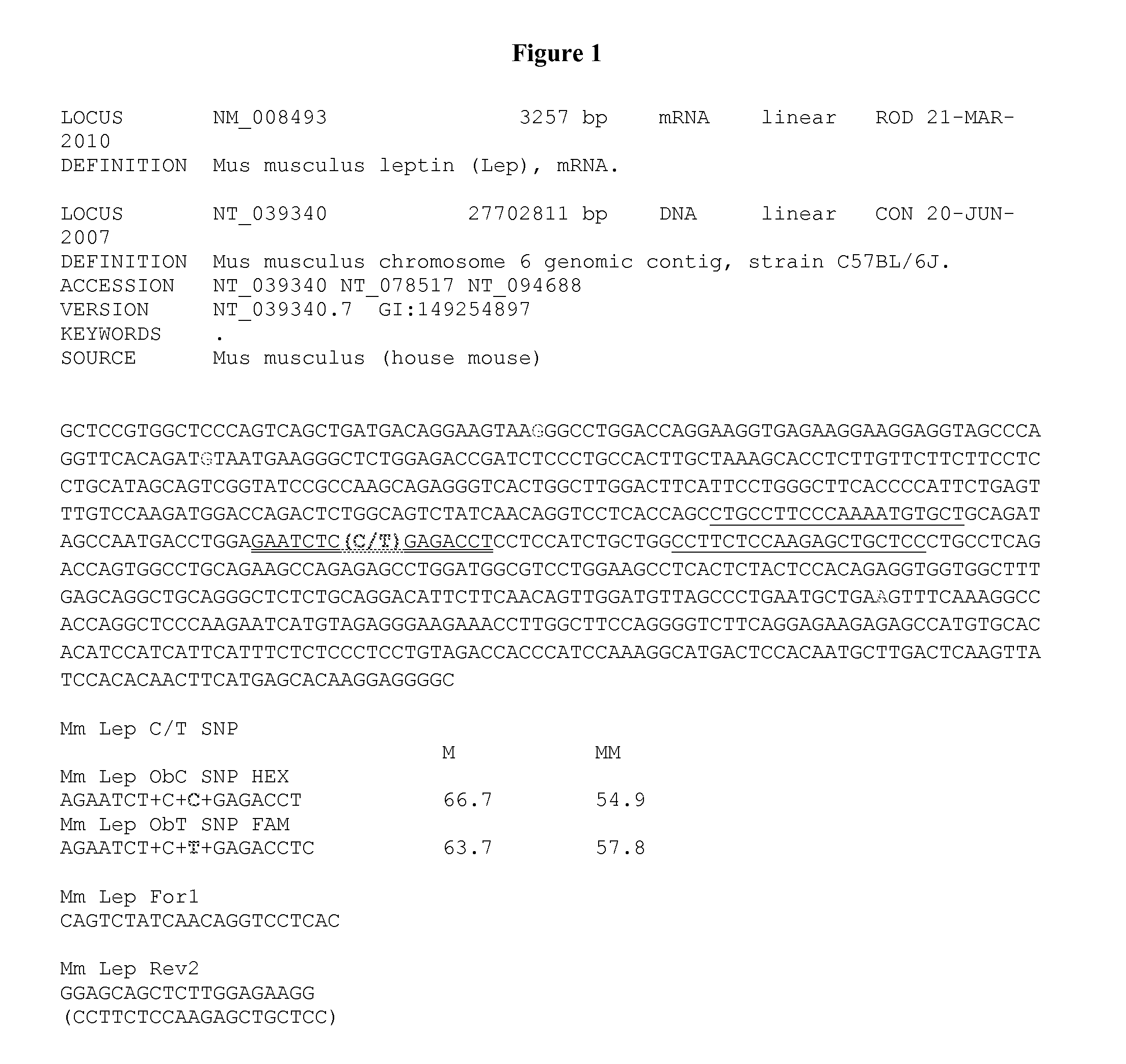

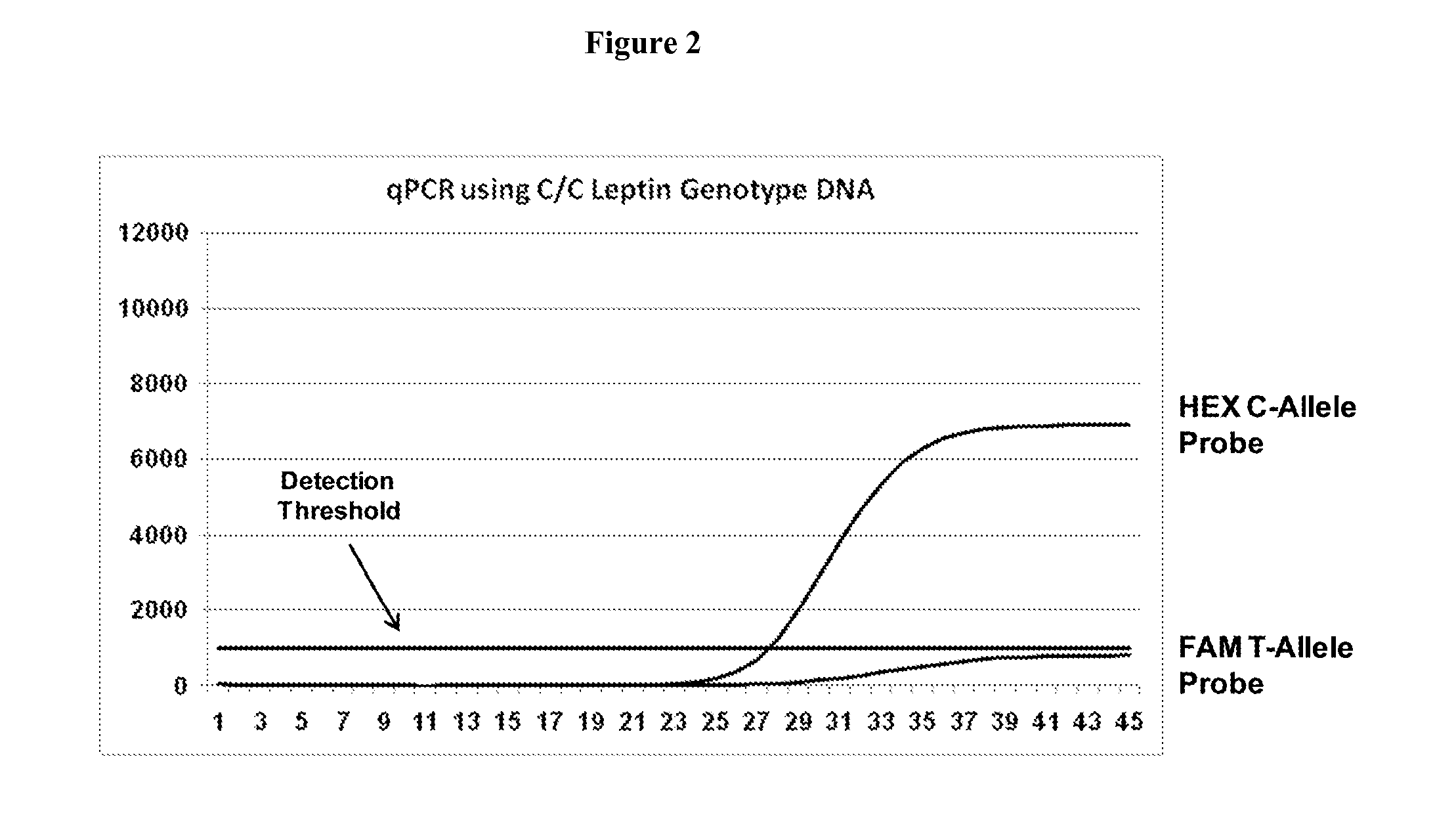

Methods for Predicting Stability and Melting Temperatures of Nucleic Acid Duplexes

ActiveUS20120029891A1Microbiological testing/measurementThermometers using physical/chemical changesOligomerLocked nucleic acid

The present invention provides methods that more accurately predict melting temperatures for duplex oligomers. The invented methods predict the Tm of chimeric duplexes containing various amounts of locked nucleic acid modifications in oligonucleotide strands.

Owner:INTEGRATED DNA TECHNOLOGIES

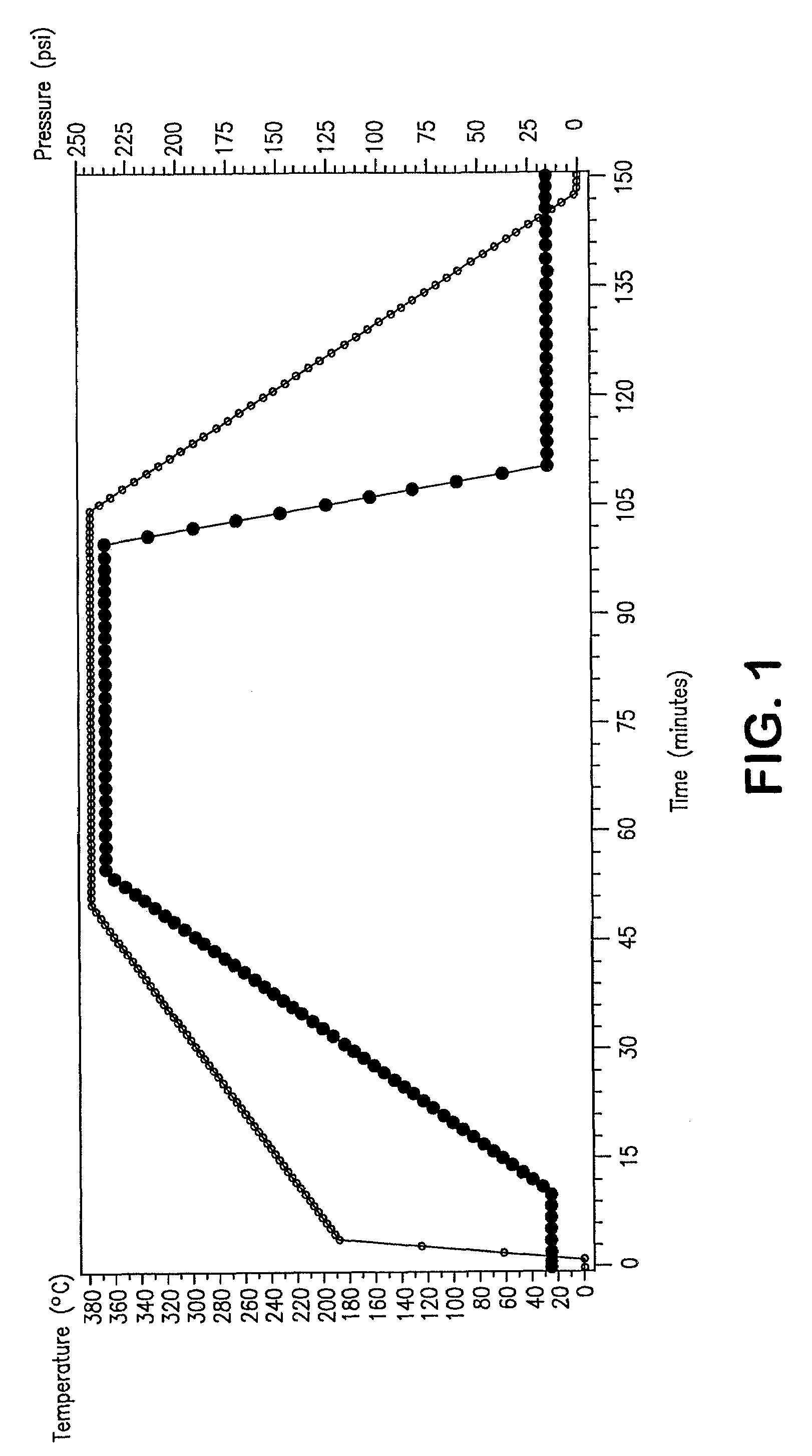

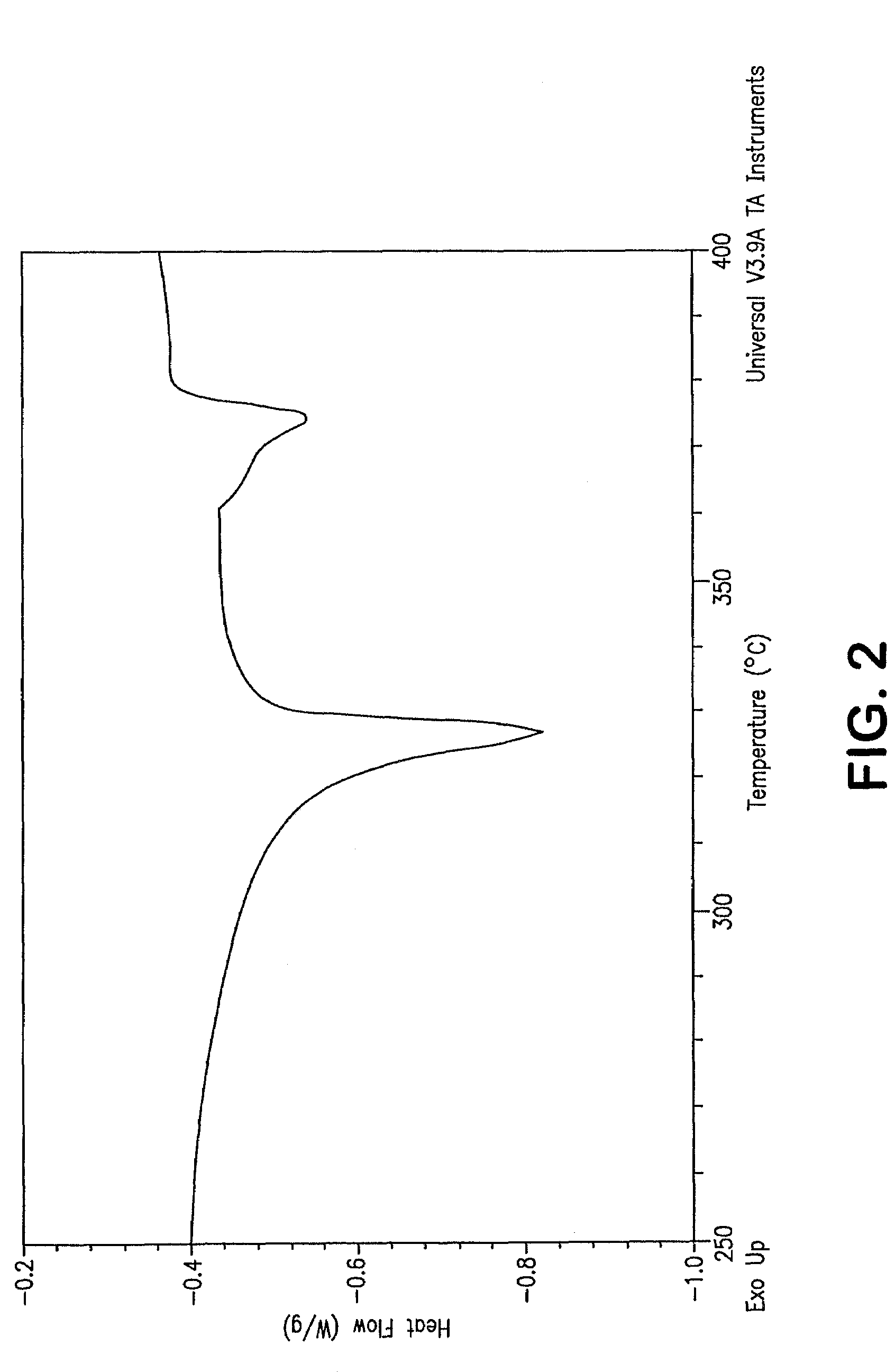

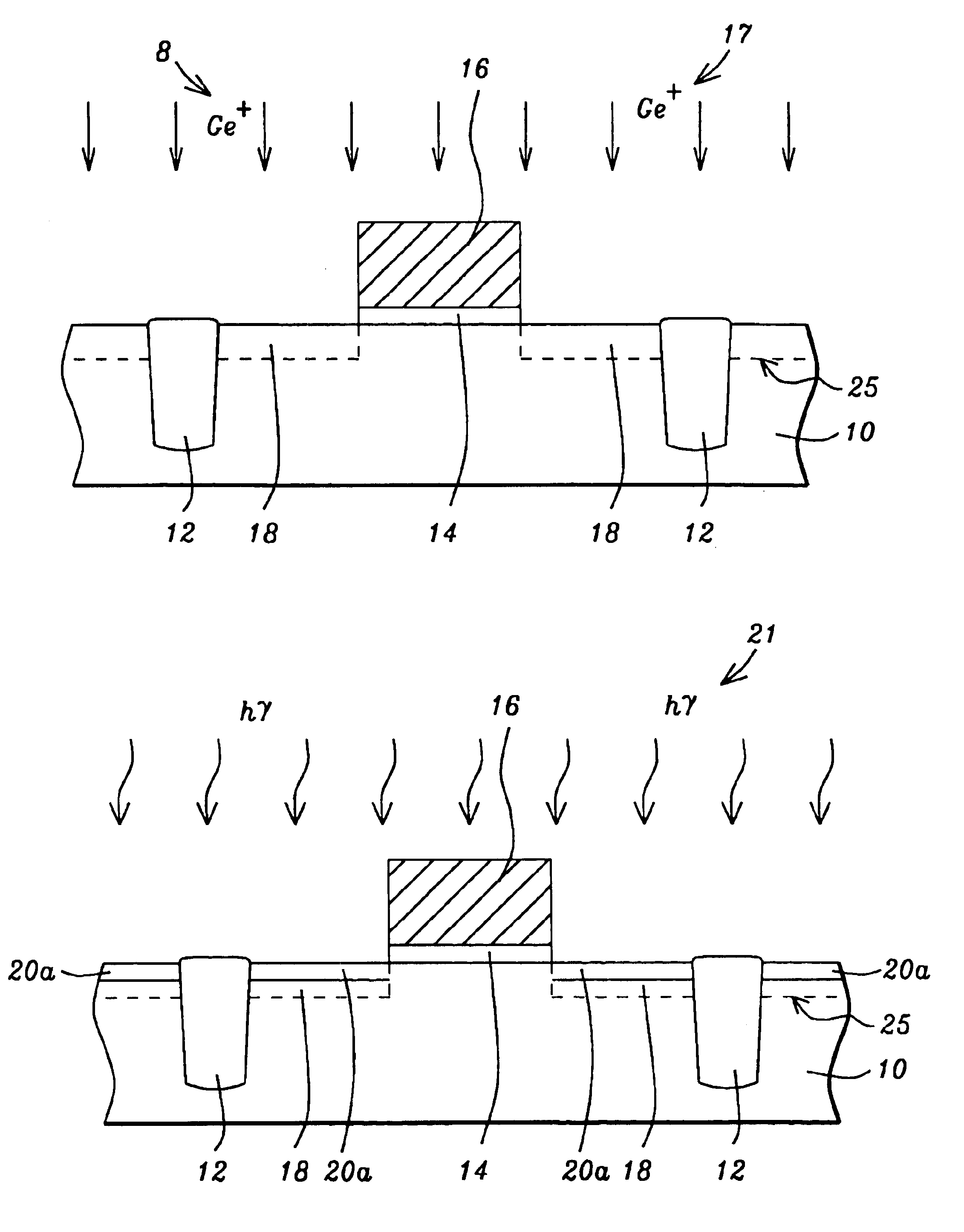

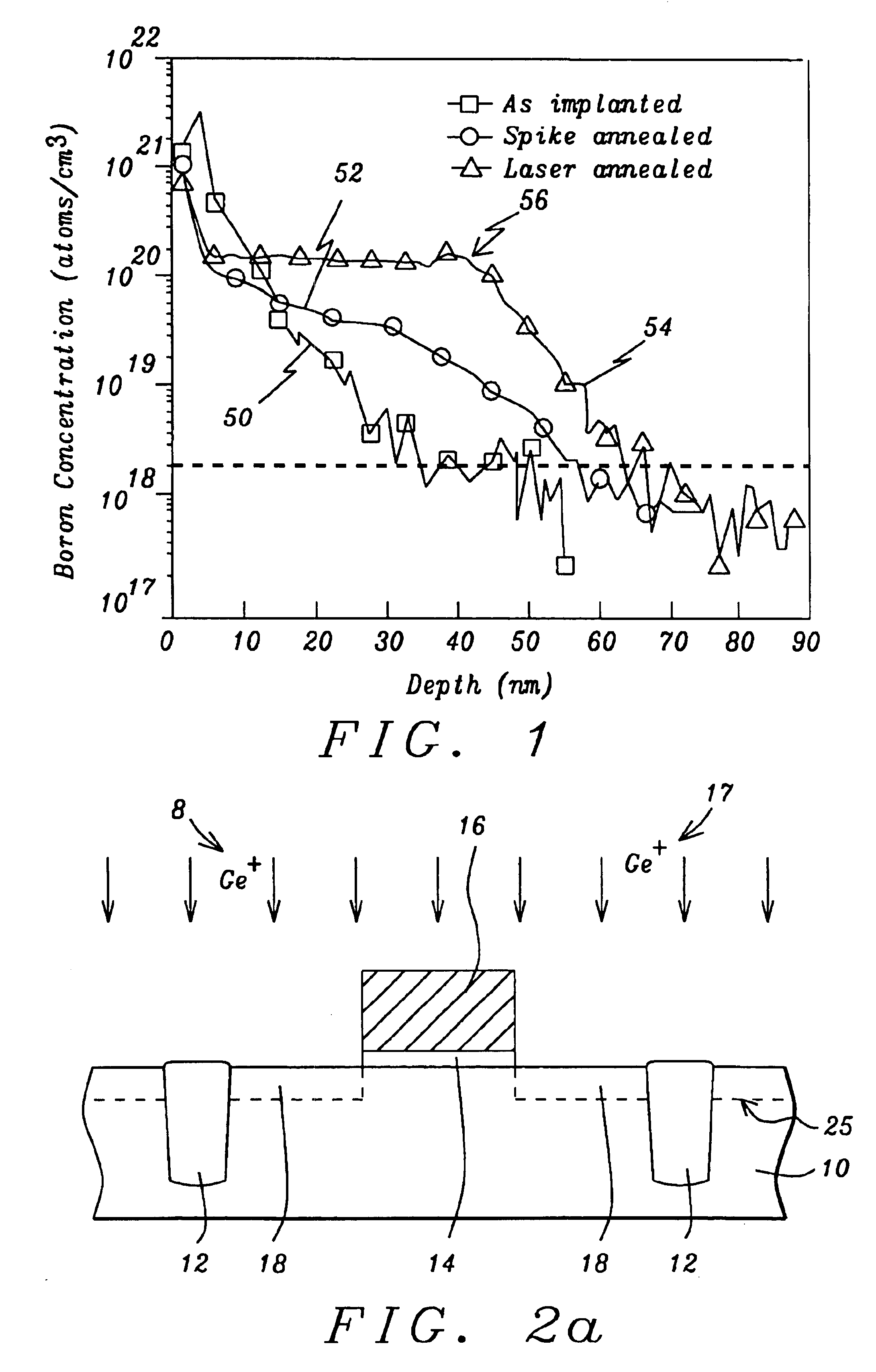

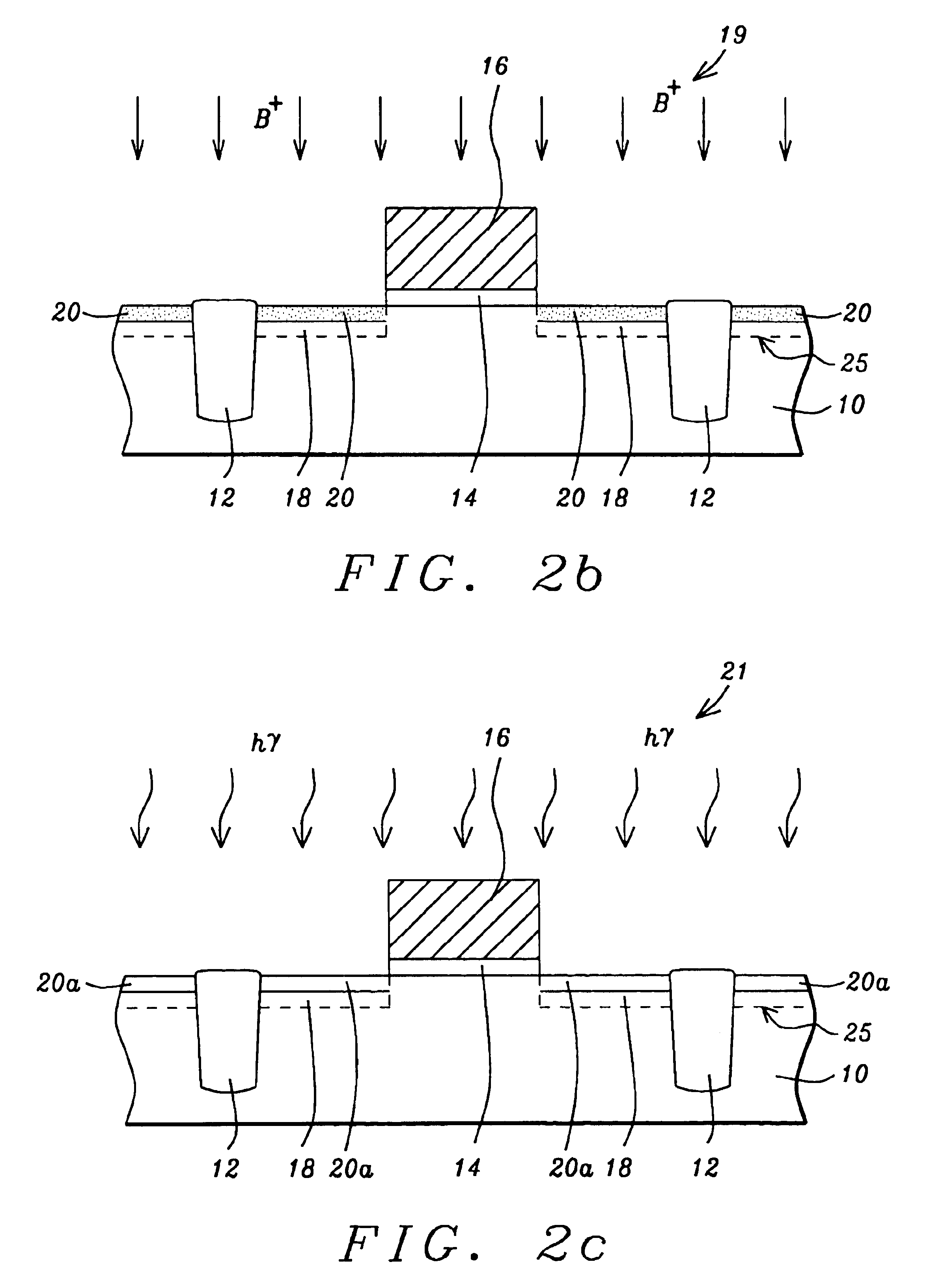

Method of multiple pulse laser annealing to activate ultra-shallow junctions

A method for forming a highly activated ultra shallow ion implanted semiconductive elements for use in sub-tenth micron MOSFET technology is described. A key feature of the method is the ability to activate the implanted impurity to a highly active state without permitting the dopant to diffuse further to deepen the junction. A selected single crystalline silicon active region is first amorphized by implanting a heavy ion such as silicon or germanium. A semiconductive impurity for example boron is then implanted and activated by pulsed laser annealing whereby the pulse fluence, frequency, and duration are chosen to maintain the amorphized region just below it's melting temperature. It is found that just below the melting temperature there is sufficient local ion mobility to secure the dopant into active positions within the silicon matrix to achieve a high degree of activation with essentially no change in concentration profile. The selection of the proper laser annealing parameters is optimized by observation of the reduction of sheet resistance and concentration profile as measured on a test site. Application of the method is applied to forming a MOS FET and a CMOS device. The additional processing steps required by the invention are applied simultaneously to both n-channel and p-channel devices of the CMOS device pair.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

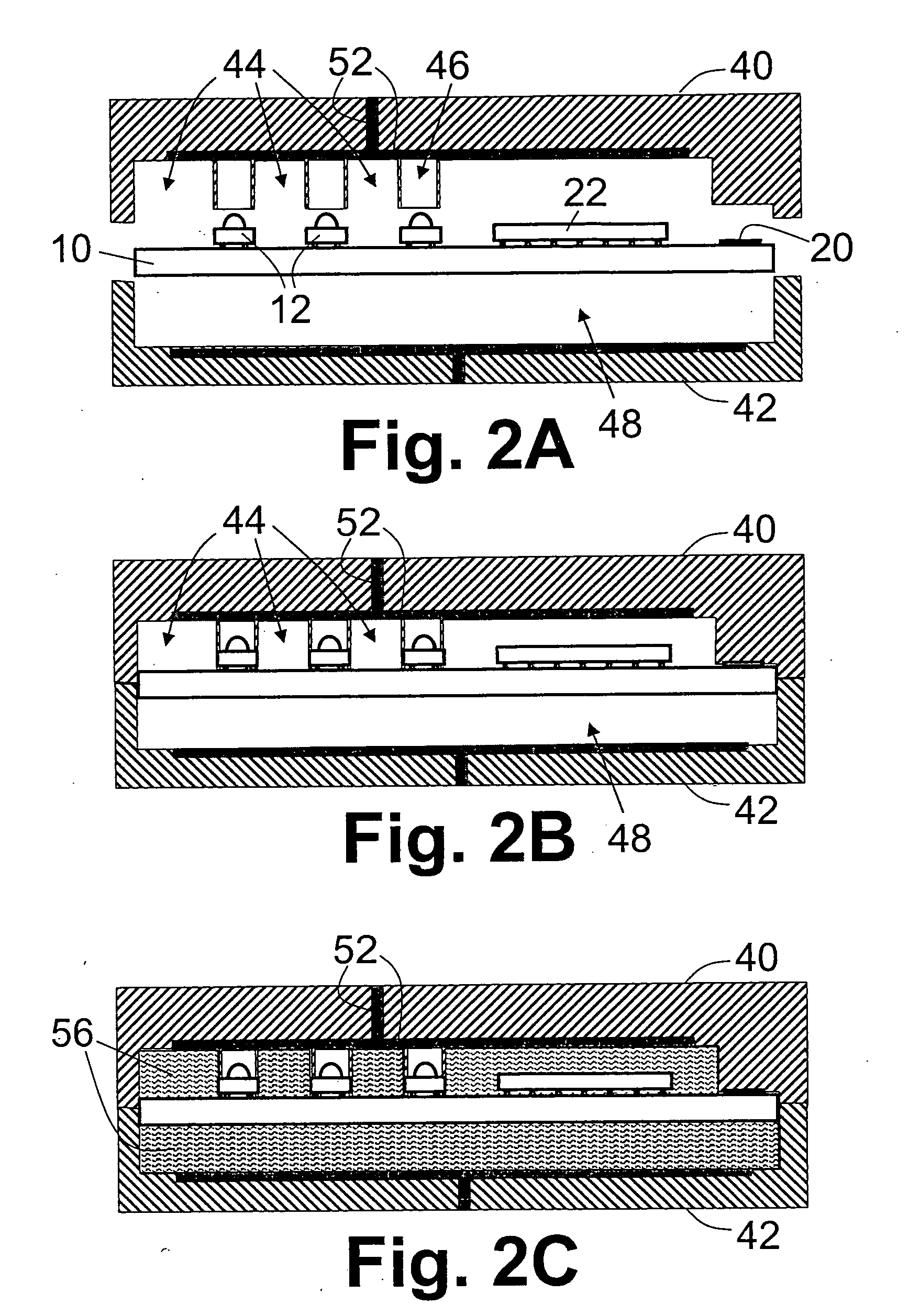

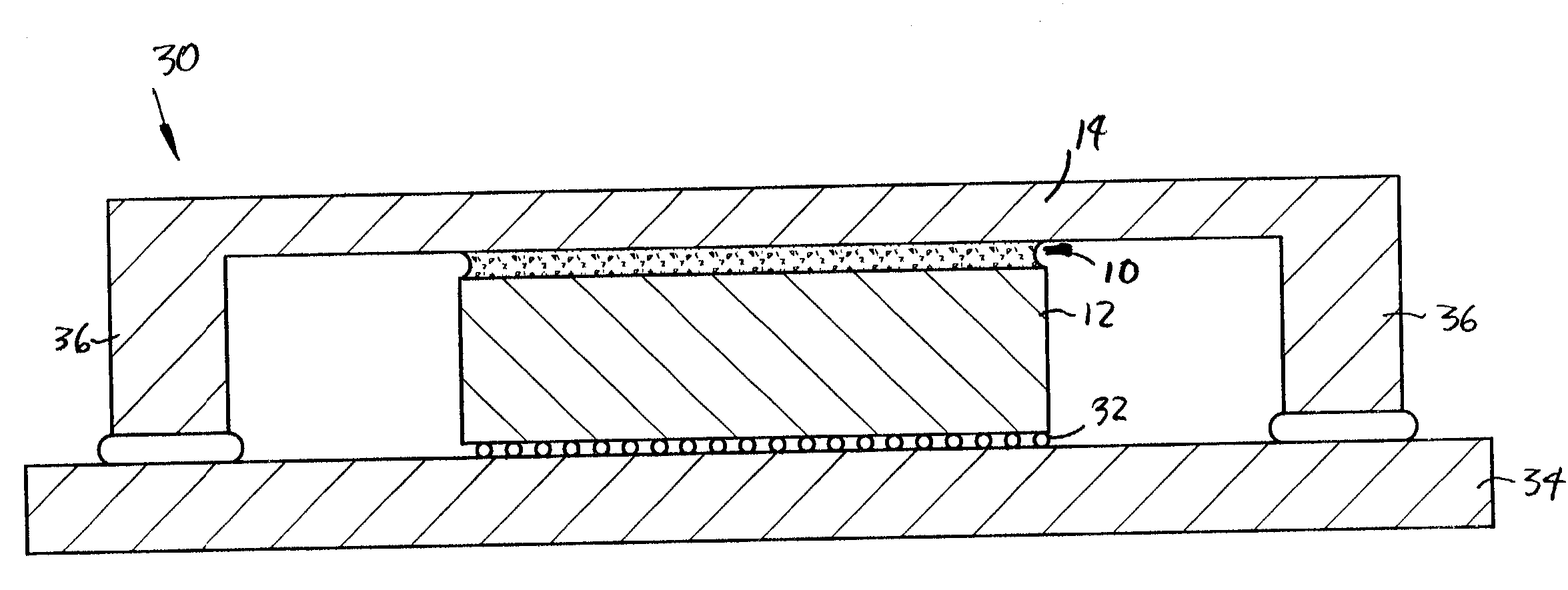

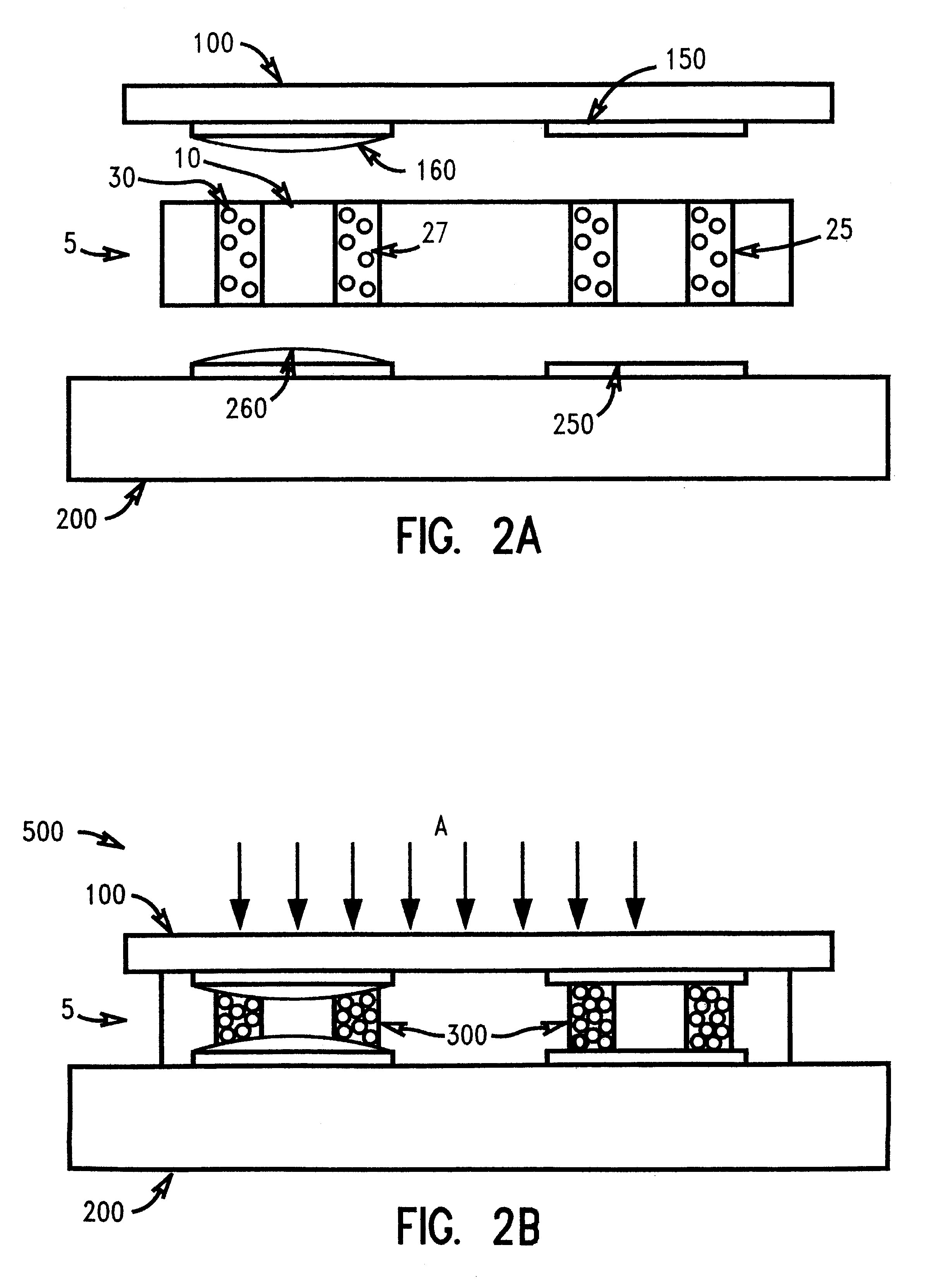

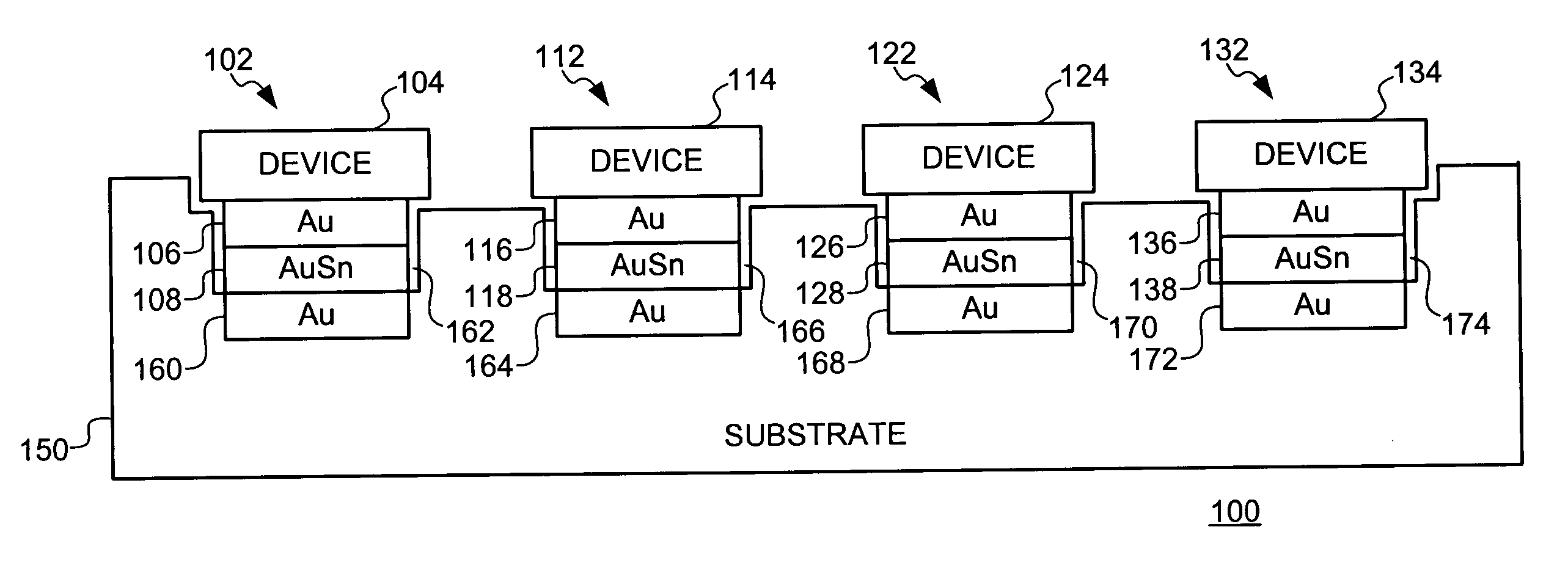

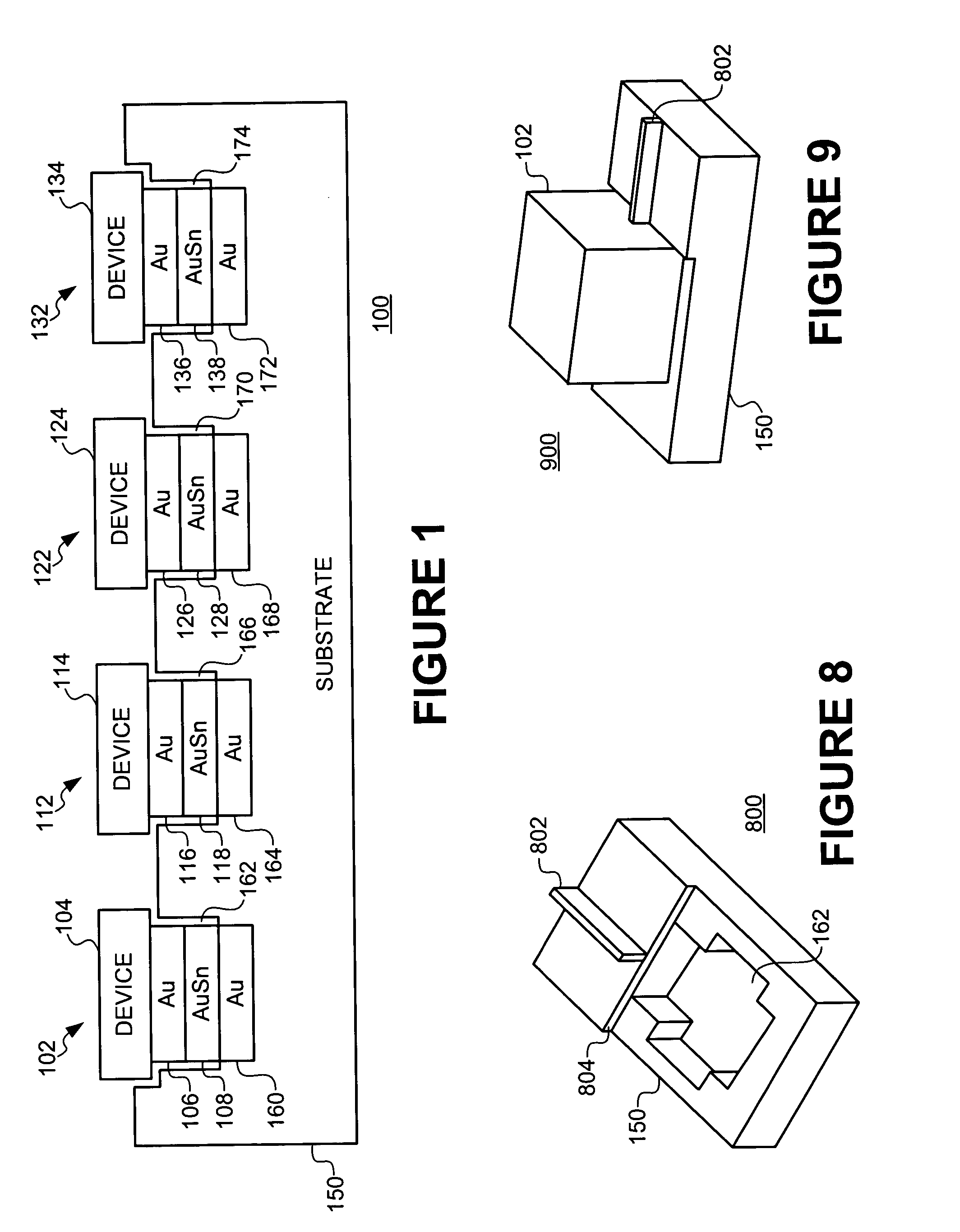

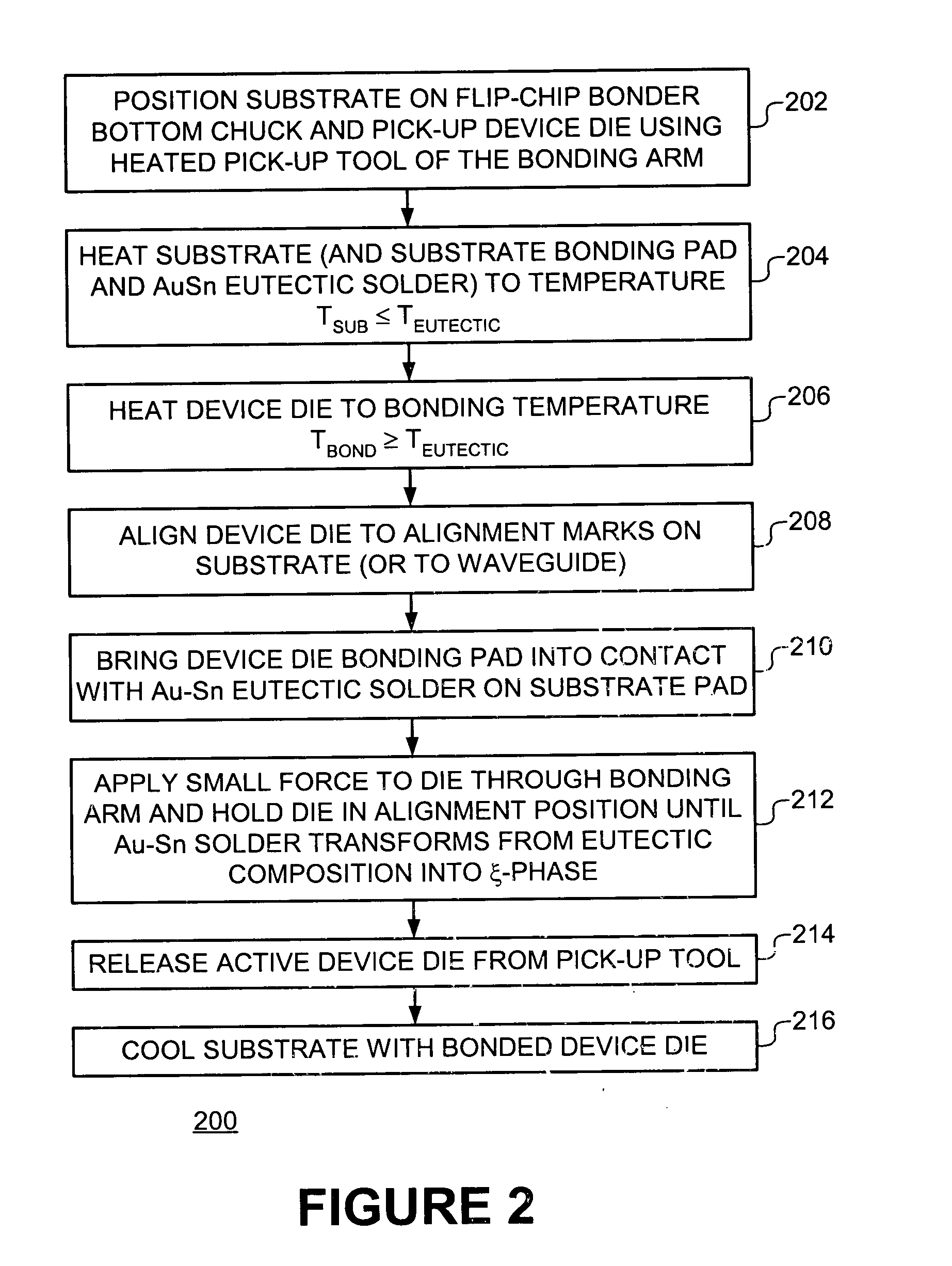

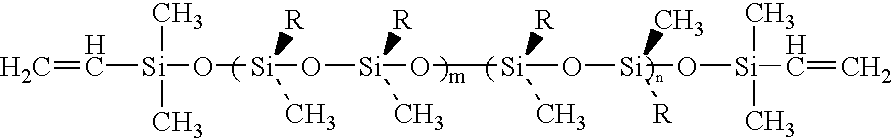

Packaging of multiple active optical devices

InactiveUS20040029304A1Printed circuit assemblingSemiconductor/solid-state device manufacturingEngineeringElectron

A cost effective method is provided for assembly of hybrid optoelectronic circuits requiring flip-chip bonding of multiple active optoelectronic devices onto common substrate or optical bench platform with fine pitch and high accuracy "after-bonding" alignment to the alignment features on substrate and / or to other elements of the hybrid circuit. A Flip-Chip Bonder equipped with high precision Bonding Arm and optical and mechanical system, heated substrate chuck and heated pick-up tool may be used both for alignment and thermal bonding of active component dies to corresponding bonding pads on the common substrate using gold-tin (Au-Sn) solder disposed between die bonding pad and the corresponding substrate bonding pad. During bonding of the first die, tin (Sn) diffuses from a eutectic composition of gold-tin (Au-Sn) solder to (gold (Au) on) the die-bonding pad and / or (gold (Au) on) the substrate bonding-pad resulting in transformation of the Au-Sn eutectic composition to a zeta-phase composition having much higher melting temperature as compared to that of a eutectic composition. As bonding of one or more subsequent dies is performed at temperatures equal to or slightly higher than the melting temperature of a eutectic composition and significantly lower than the melting temperature of a zeta-phase composition, the gold-tin (Au-Sn) solder at the bond of previously attached die does not melt and, consequently, the alignment is not compromised.

Owner:INTEL CORP

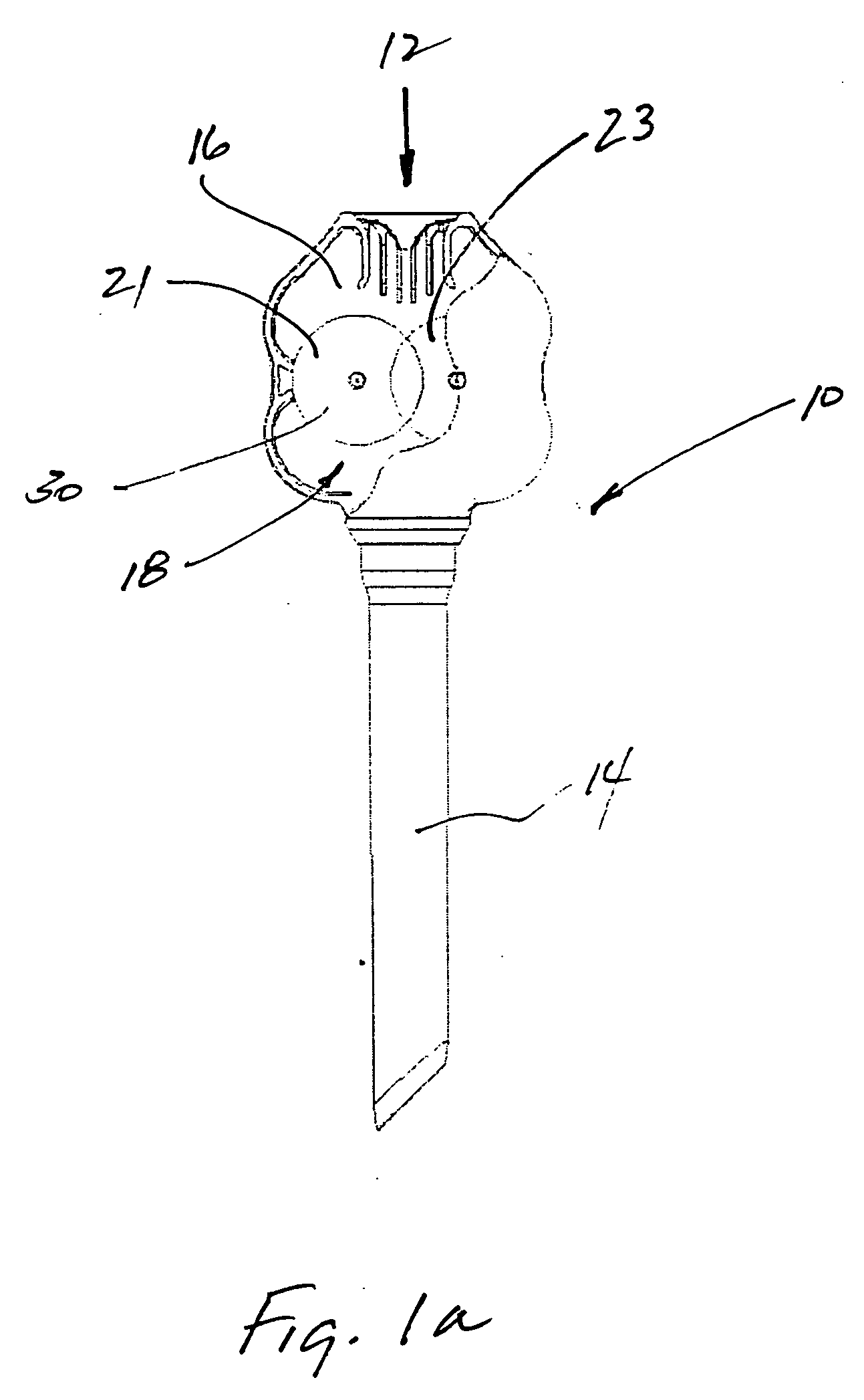

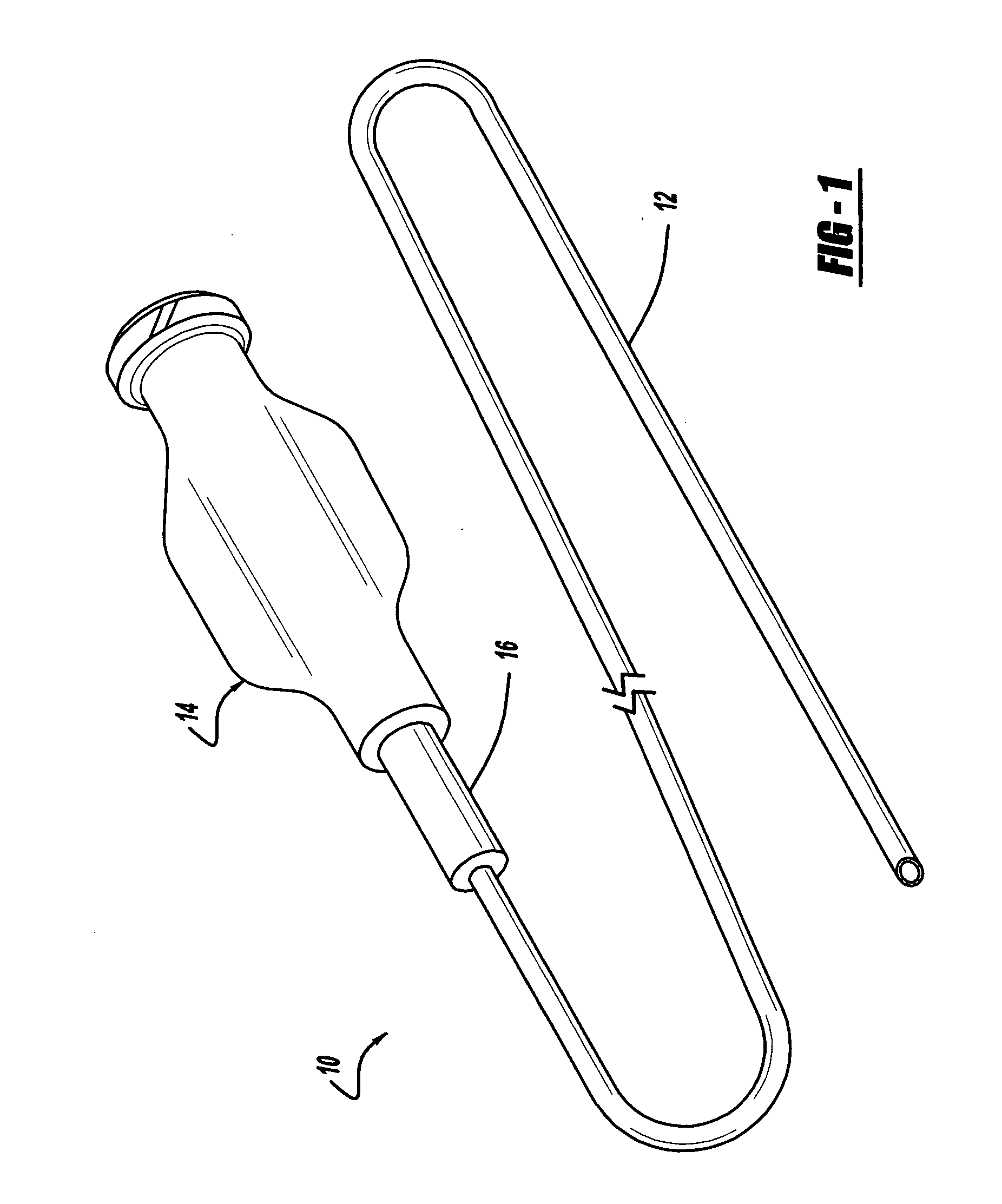

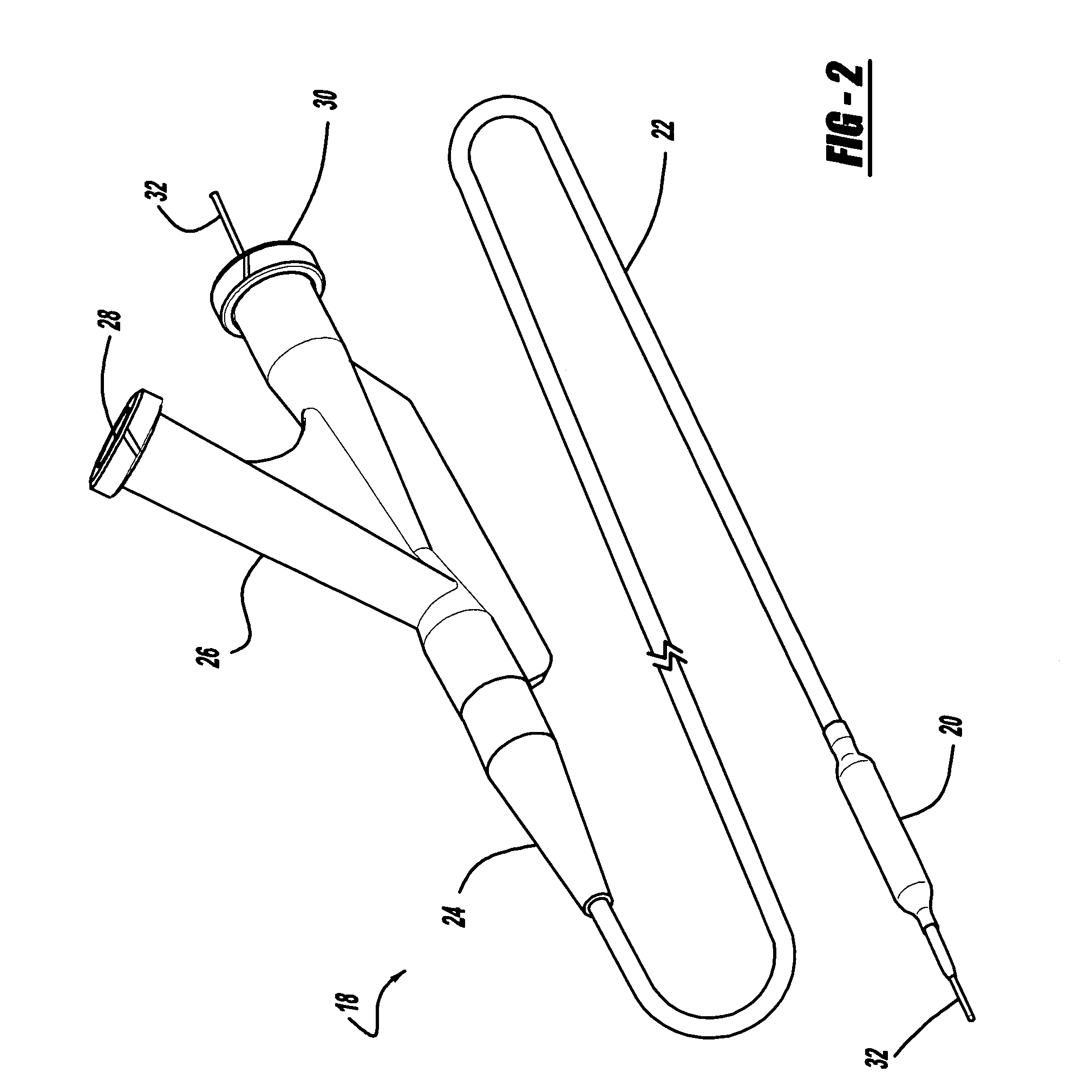

Lumen occluders made from thermodynamic materials

InactiveUS20020129819A1Regain shapeMale contraceptivesPharmaceutical delivery mechanismMelt temperatureMelting temperature

Disclosed are occluders and methods of their use. The occluders comprise shape-memory polymeric materials which, when heated above their crystalline melting temperatures, may be deformed from a first configuration into a second configuration. The occluder is then held in the deformed shape until it cools to a temperature below its crystalline melting temperature (T.sub.m) whereby it holds the deformed shape of the second configuration by virtue of the recrystallization of the polymeric occluder material. Upon reheating the occluder above its T.sub.m, the occluder will resume its original shape. In this manner, an occluder which has been deformed to reduce its diameter may be inserted into and positioned within a target lumen in the body and then allowed to warm to body temperature whereby it resumes its original diameter and results in the occlusion of the lumen. The occluders, according to preferred embodiments, may be used for reversible sterilization of mammals, among other surgical and non-surgical uses.

Owner:NUMED TECH

Method for packaging a microelectronic device using on-die bond pad expansion

InactiveUS7071024B2Semiconductor/solid-state device detailsSolid-state devicesWafer dicingDie bonding

Expanded bond pads are formed over a passivation layer on a semiconductor wafer before the wafer is diced into individual circuit chips. After dicing, the individual chips are packaged by fixing each chip within a package core and building up one or more metallization layers on the resulting assembly. In at least one embodiment, a high melting temperature (lead free) alternative bump metallurgy (ABM) form of controlled collapse chip connect (C4) processing is used to form relatively wide conducting platforms over the bond pads on the wafer.

Owner:INTEL CORP