Patents

Literature

1186 results about "Threshold temperature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

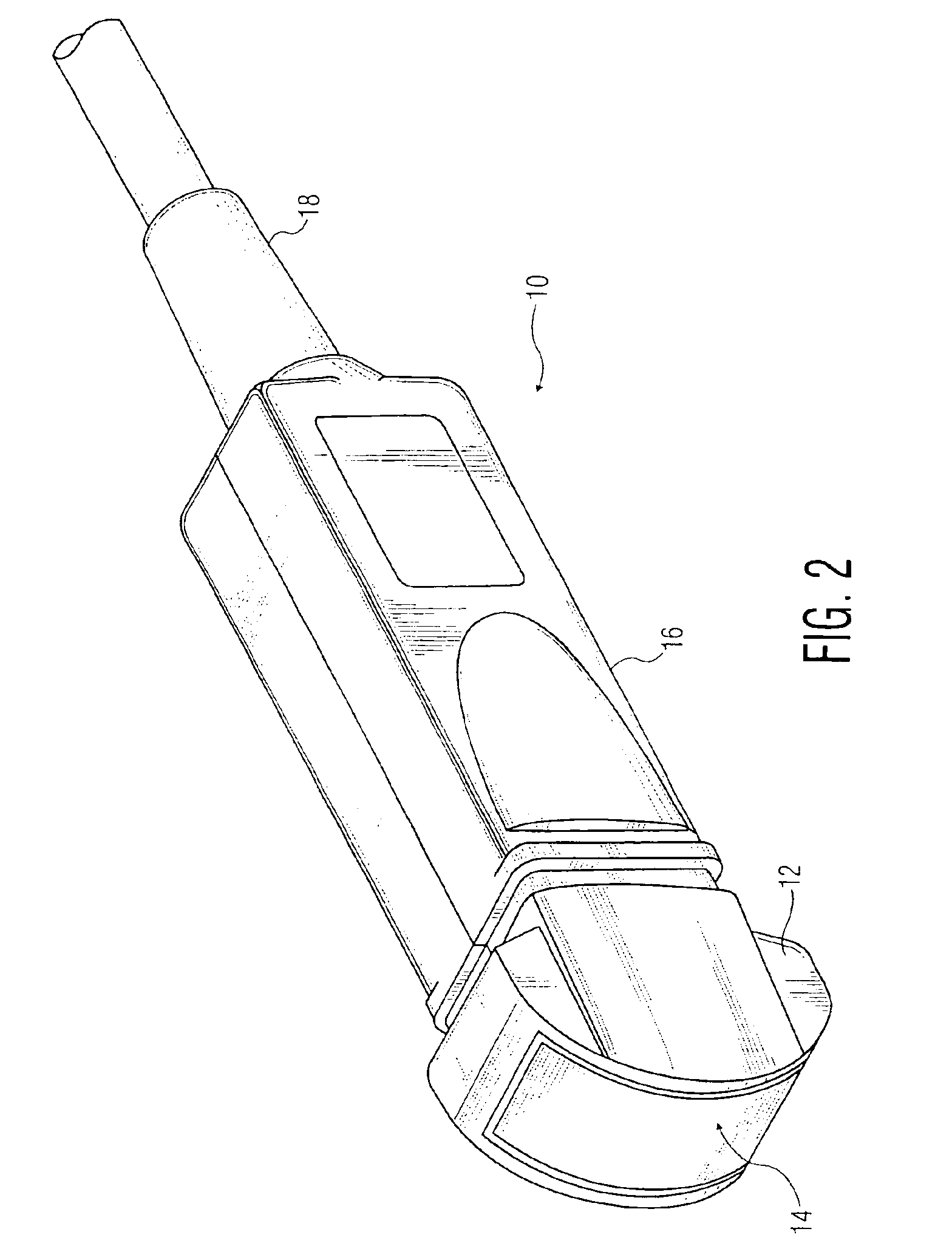

Electrosurgical method and apparatus

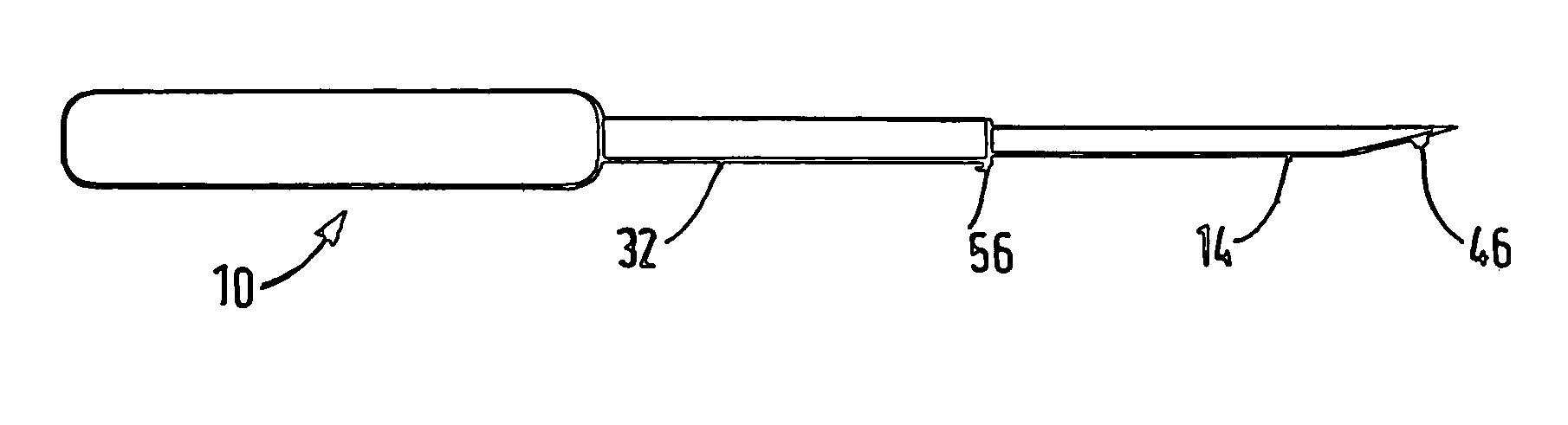

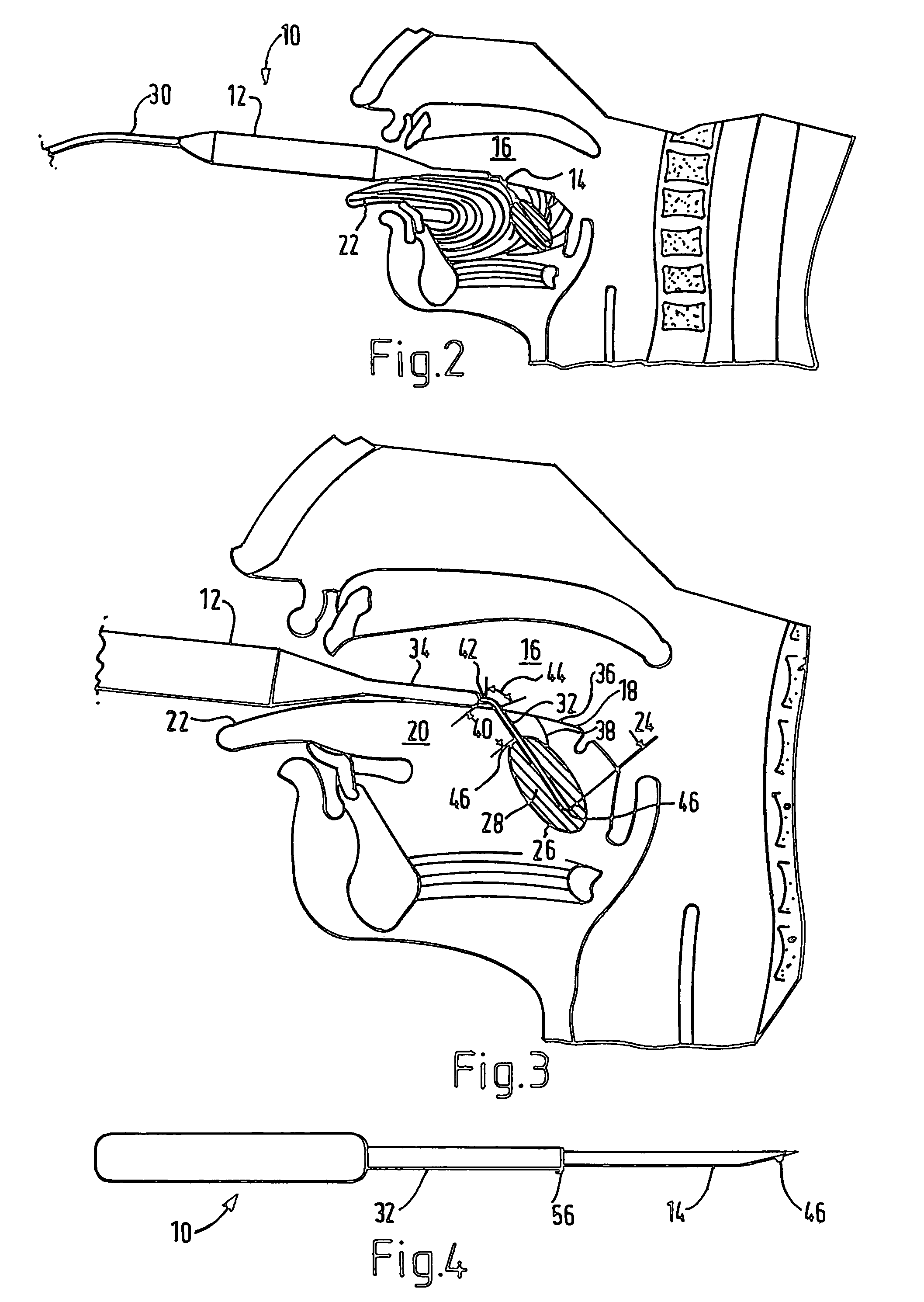

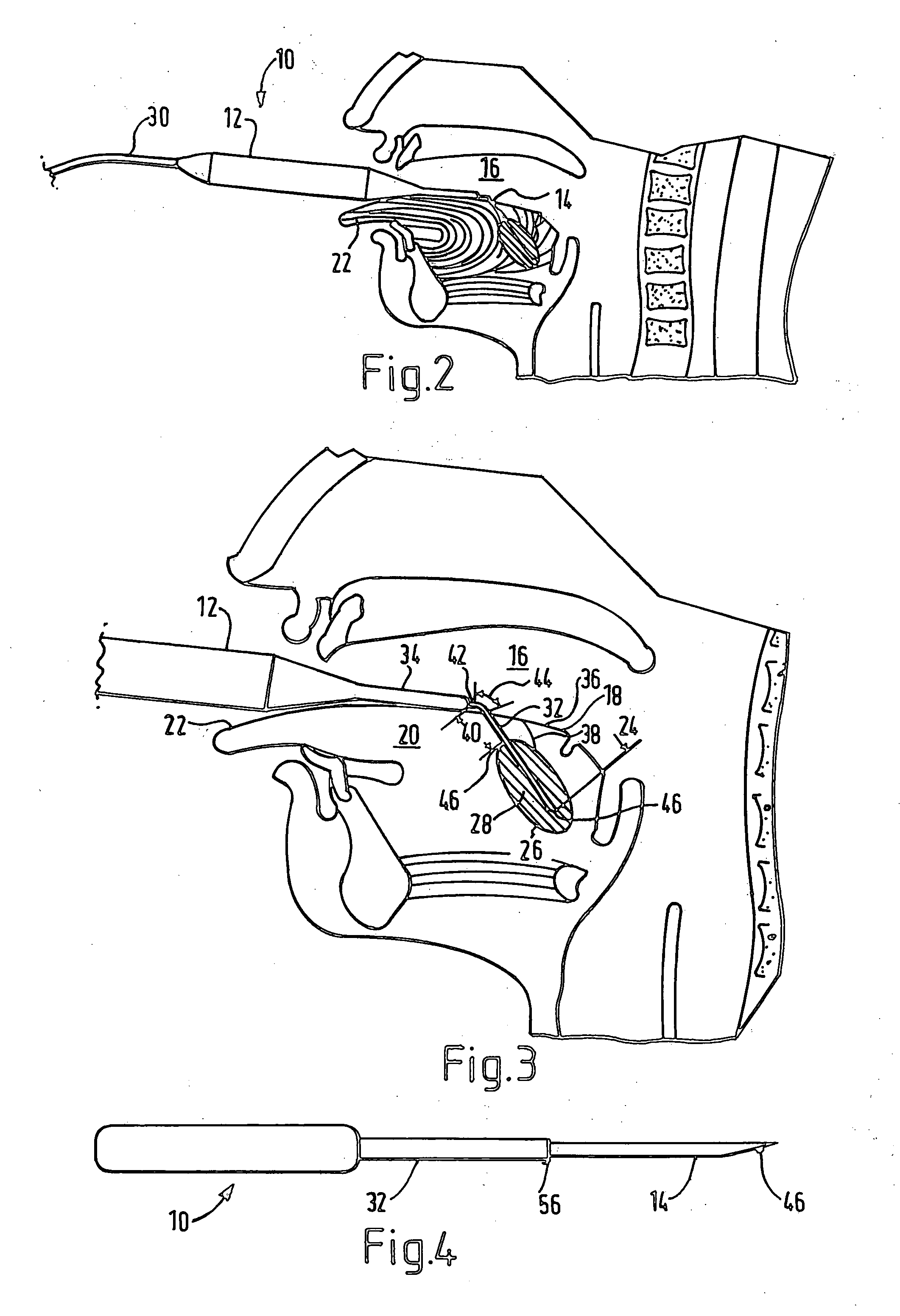

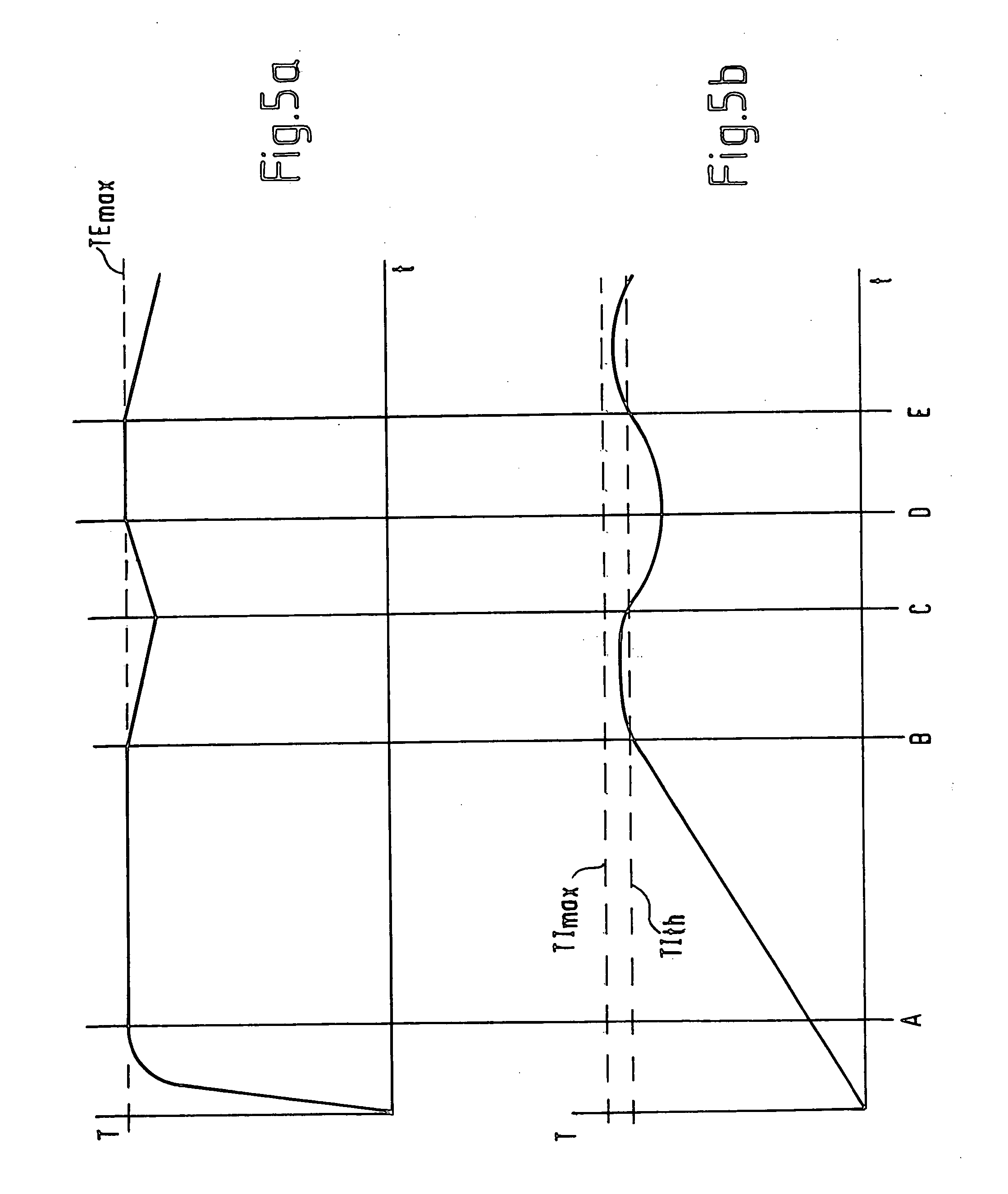

ActiveUS7377918B2Compensation delayIncrease temperatureSurgical needlesSurgical instruments for heatingThreshold temperatureRadio frequency

Owner:GYRUS ENT

Electrosurgical method and apparatus

ActiveUS20050251128A1Compensation delayIncrease temperatureSurgical needlesSurgical instruments for heatingEngineeringRadio frequency

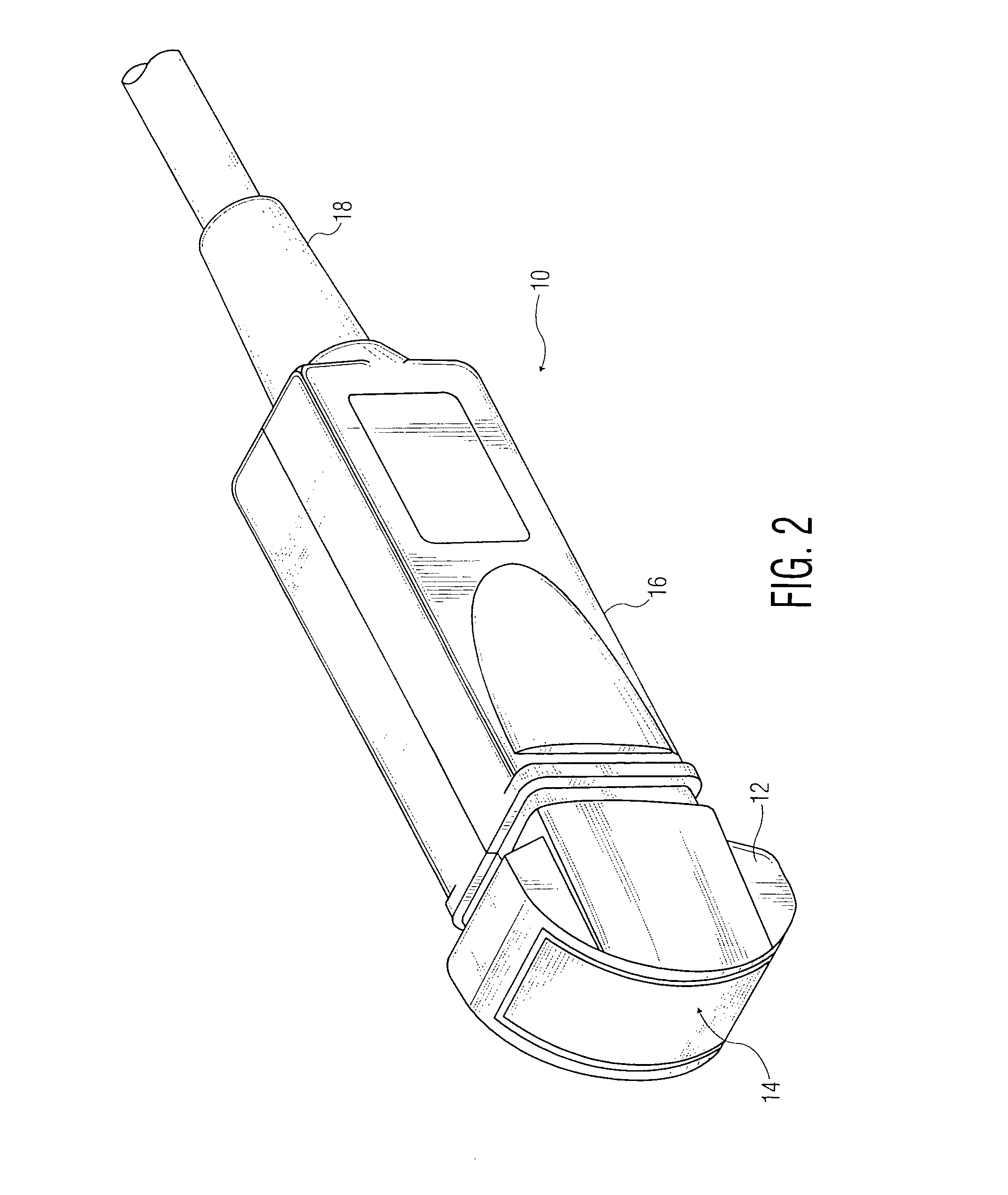

Apparatus for forming a lesion in body tissue includes a probe having an active region with an electrode for contacting tissue to be treated, and an inactive region including an insulative sleeve around a portion of the electrode. The temperature of the inactive region is monitored using a temperature sensor. A controller supplies radio frequency energy to the electrode and samples signals from the temperature sensor. By performing a calculation using the sampled signals and a predetermined inactive region threshold temperature, and by adjusting the supplied radio frequency power, the inactive region of the probe can be maintained at or below an inactive region maximum temperature whilst the controller continues to supply radio frequency energy to the electrode. The probe has a second temperature sensor, mounted at a distal end of the electrode, the controller being configured to reduce the supplied radio frequency power when the electrode temperature reaches a predetermined maximum electrode temperature.

Owner:GYRUS ENT

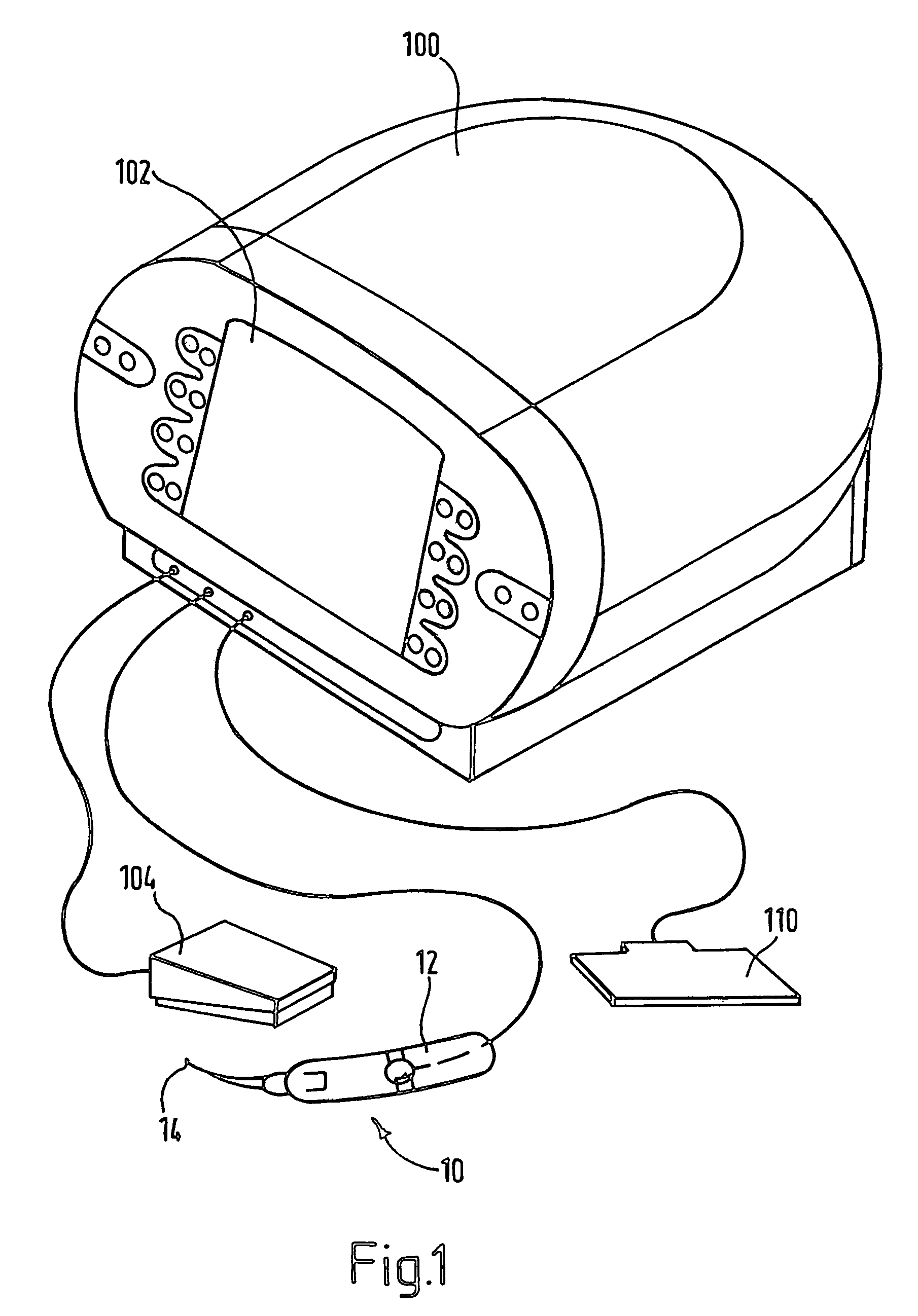

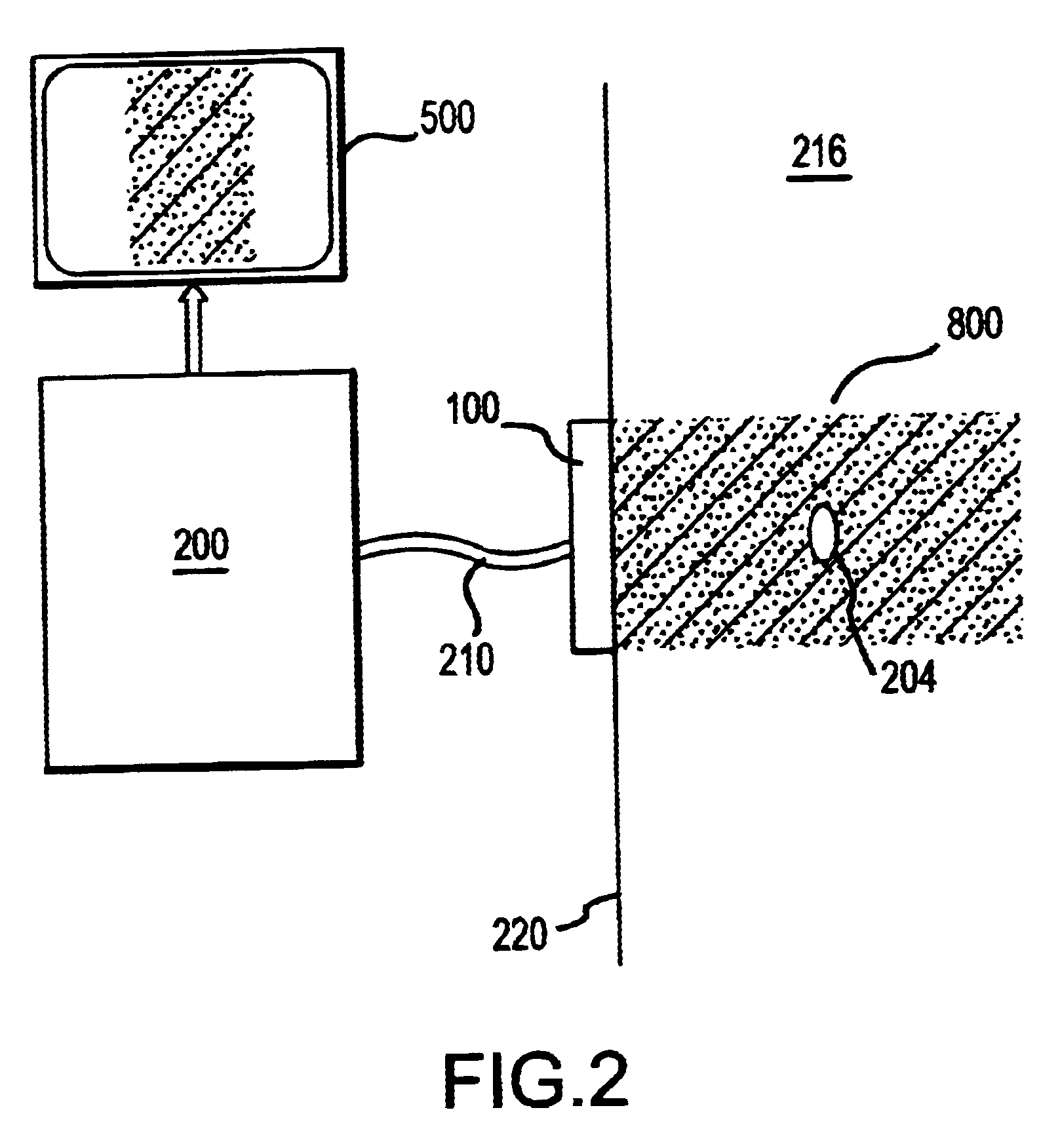

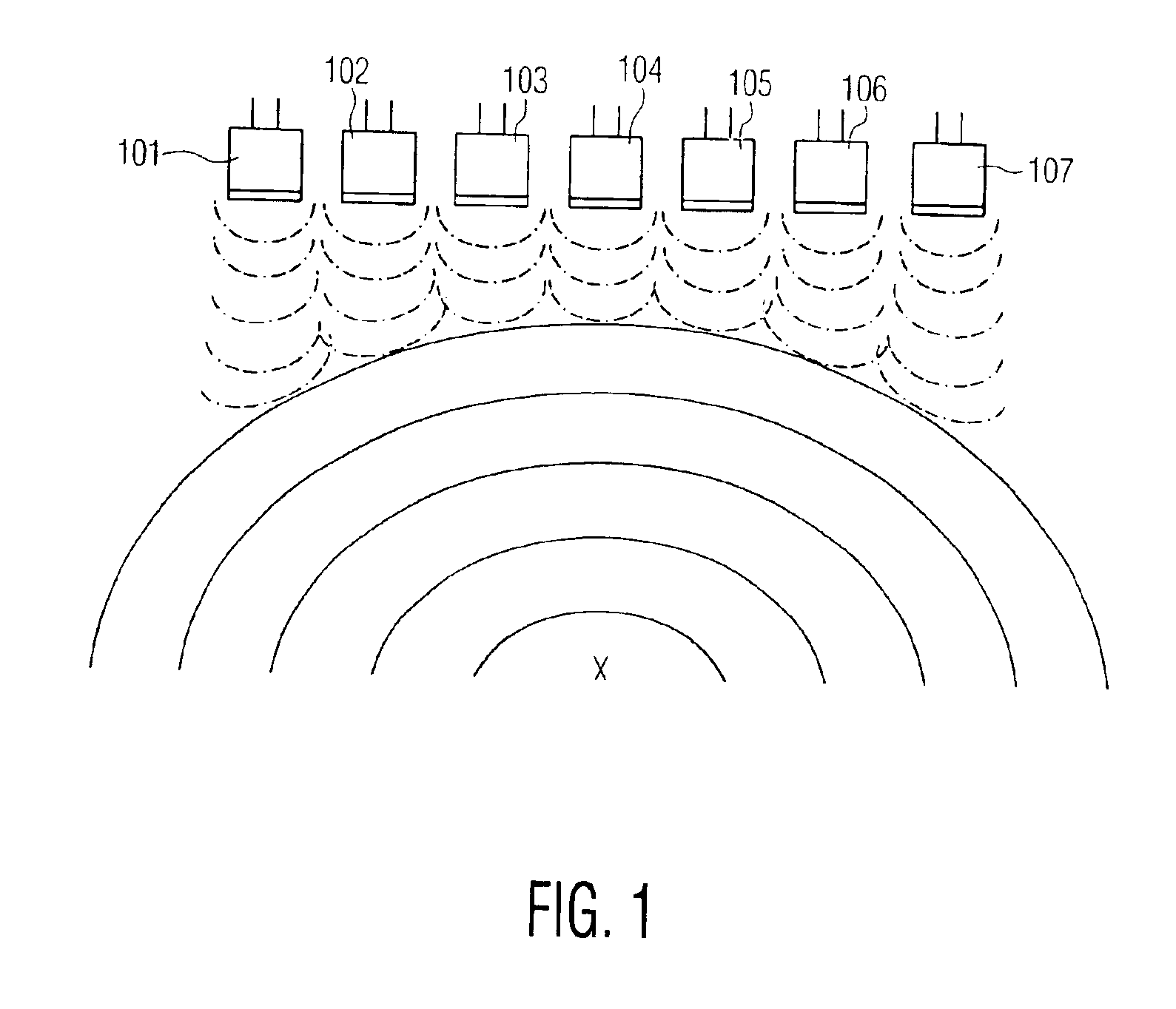

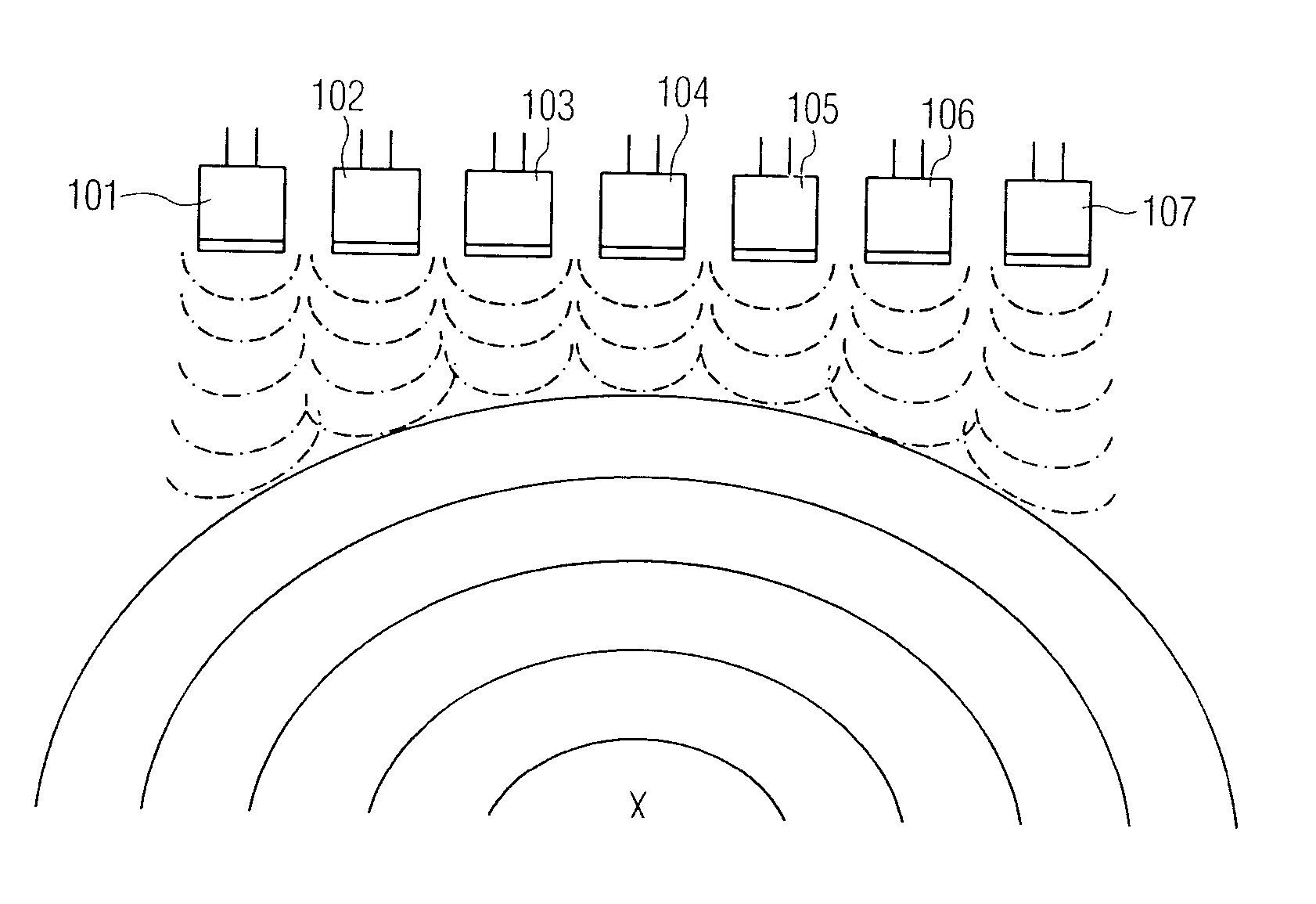

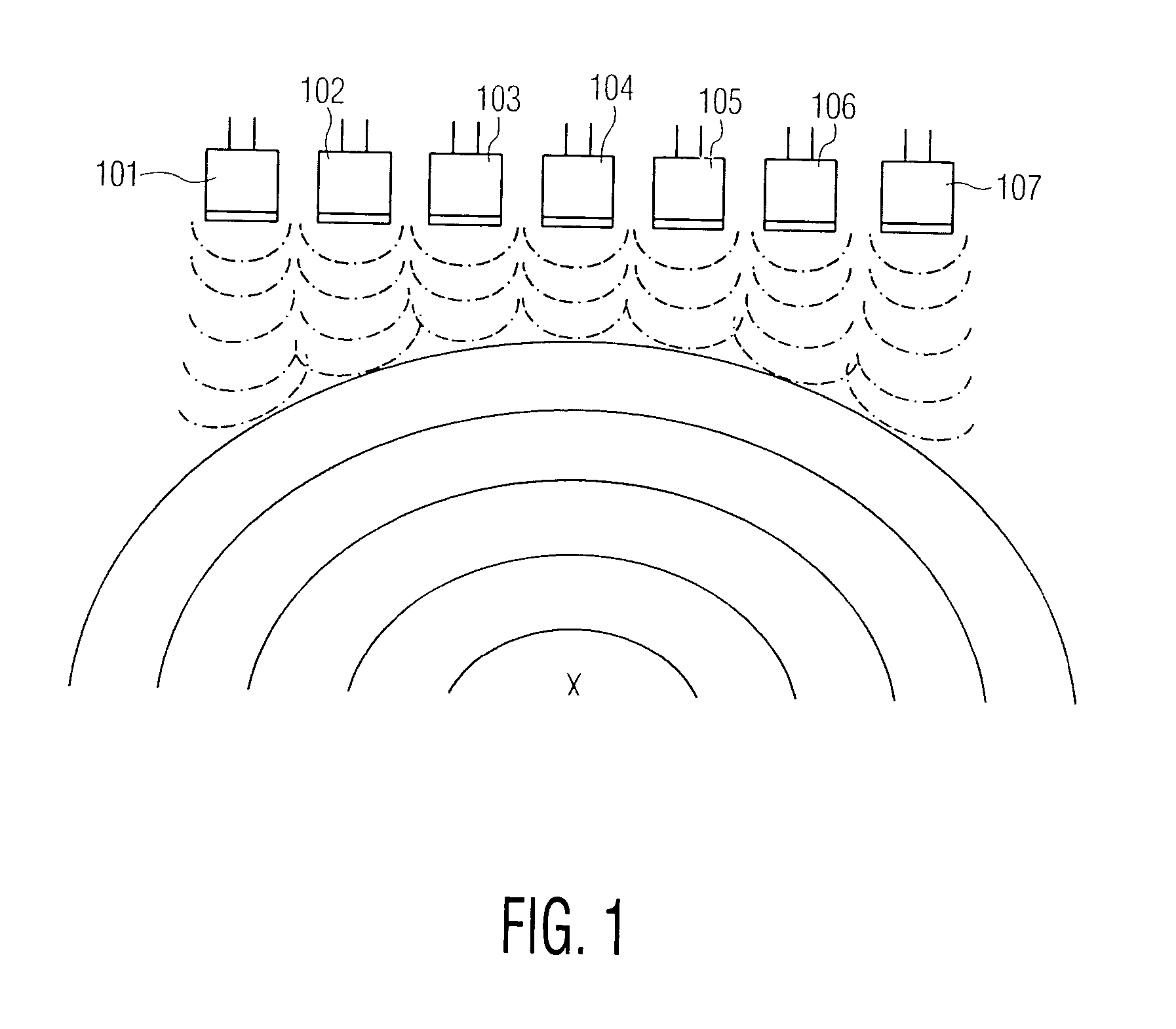

Method and apparatus for safety delivering medicants to a region of tissue using imaging, therapy and temperature monitoring ultrasonic system

A method and apparatus for controlling the safe delivery of thermosensitive liposomes containing medicant to a targeted tissue region using ultrasound. Thermosensitive liposomes containing medicants are delivered to a region of interest, the region of interest is located using ultrasound imaging, ultrasound therapy is applied to heat the region of interest, and the temperature of the region is monitored to determine whether a designated threshold temperature has been reached which allows for the release of medicants from the liposomes. If the threshold temperature is reached, and the liposomes are melted, the treatment stops. If the threshold temperature has not been reached, the application of ultrasound therapy and ultrasound imaging are alternated until the threshold temperature is reached. The ultrasound imaging, temperature monitoring and ultrasound therapy are preferably performed with a single transducer.

Owner:GUIDED THERAPY SYSTEMS LLC

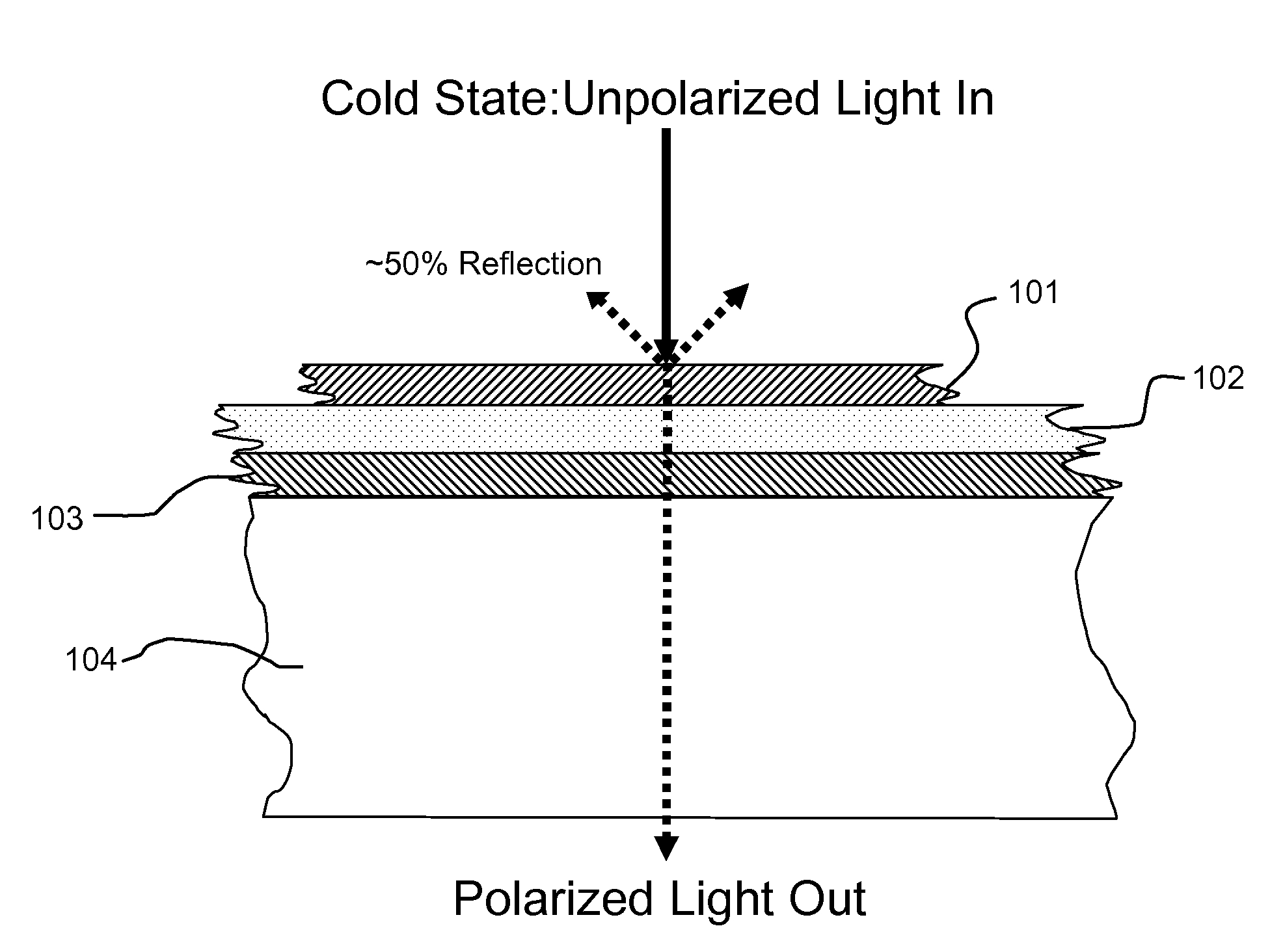

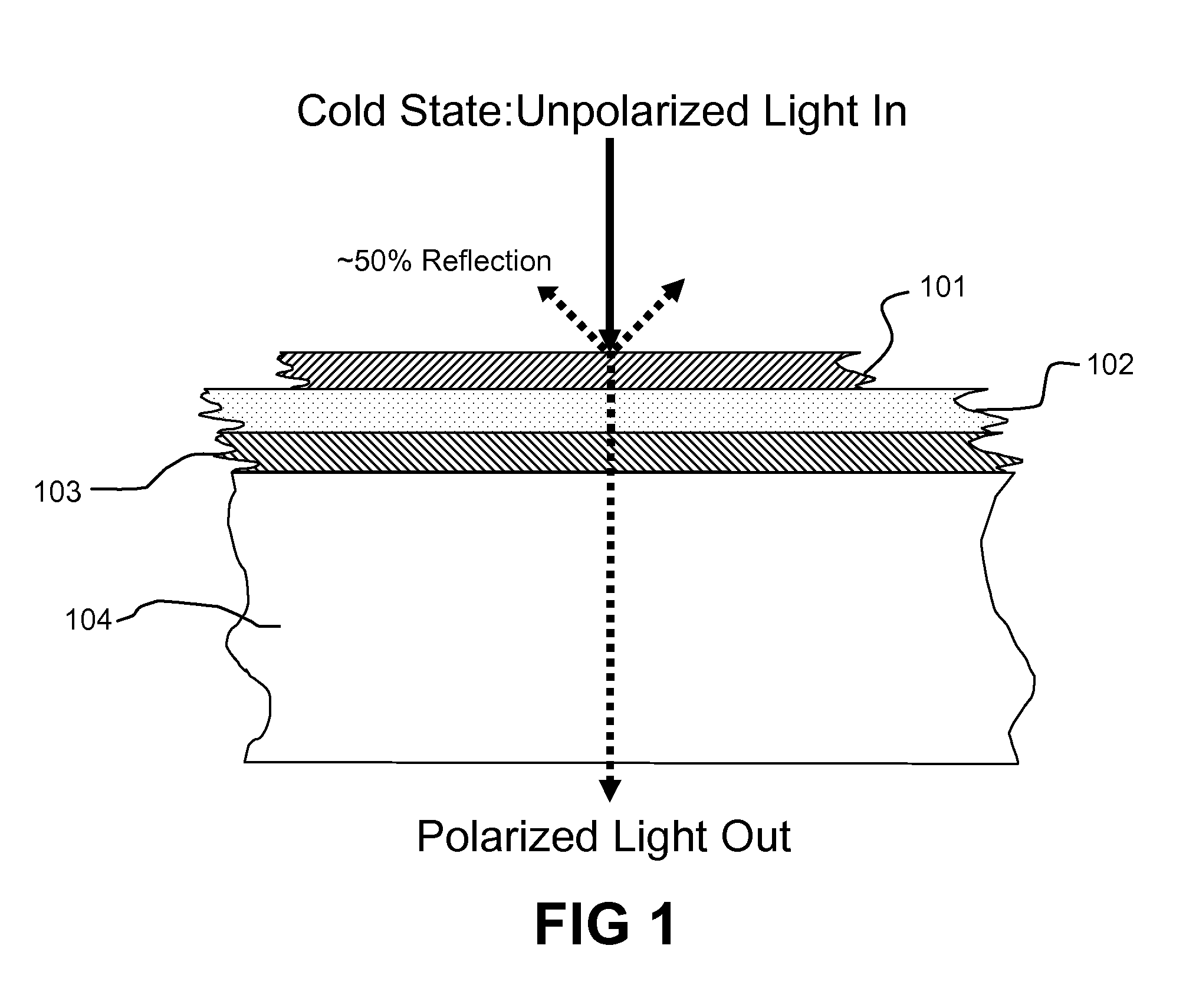

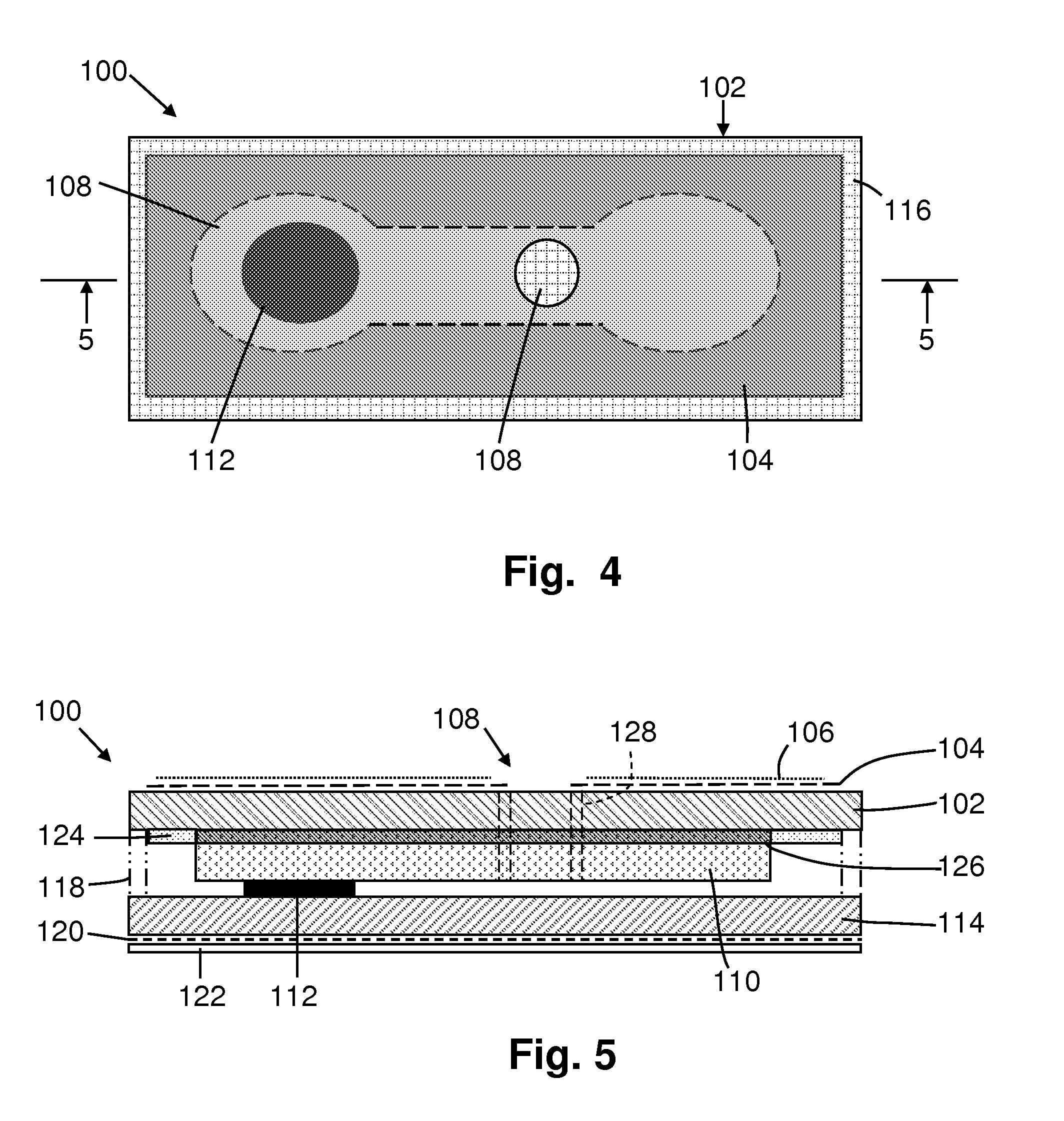

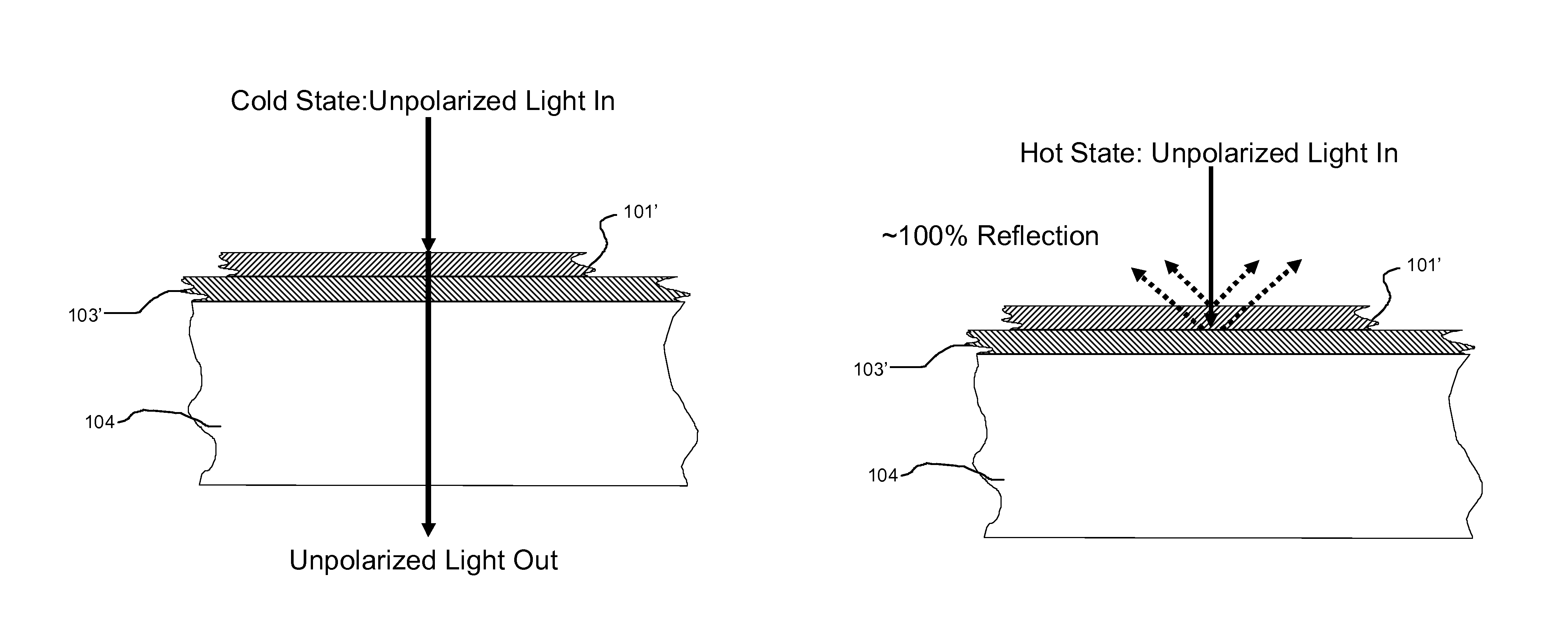

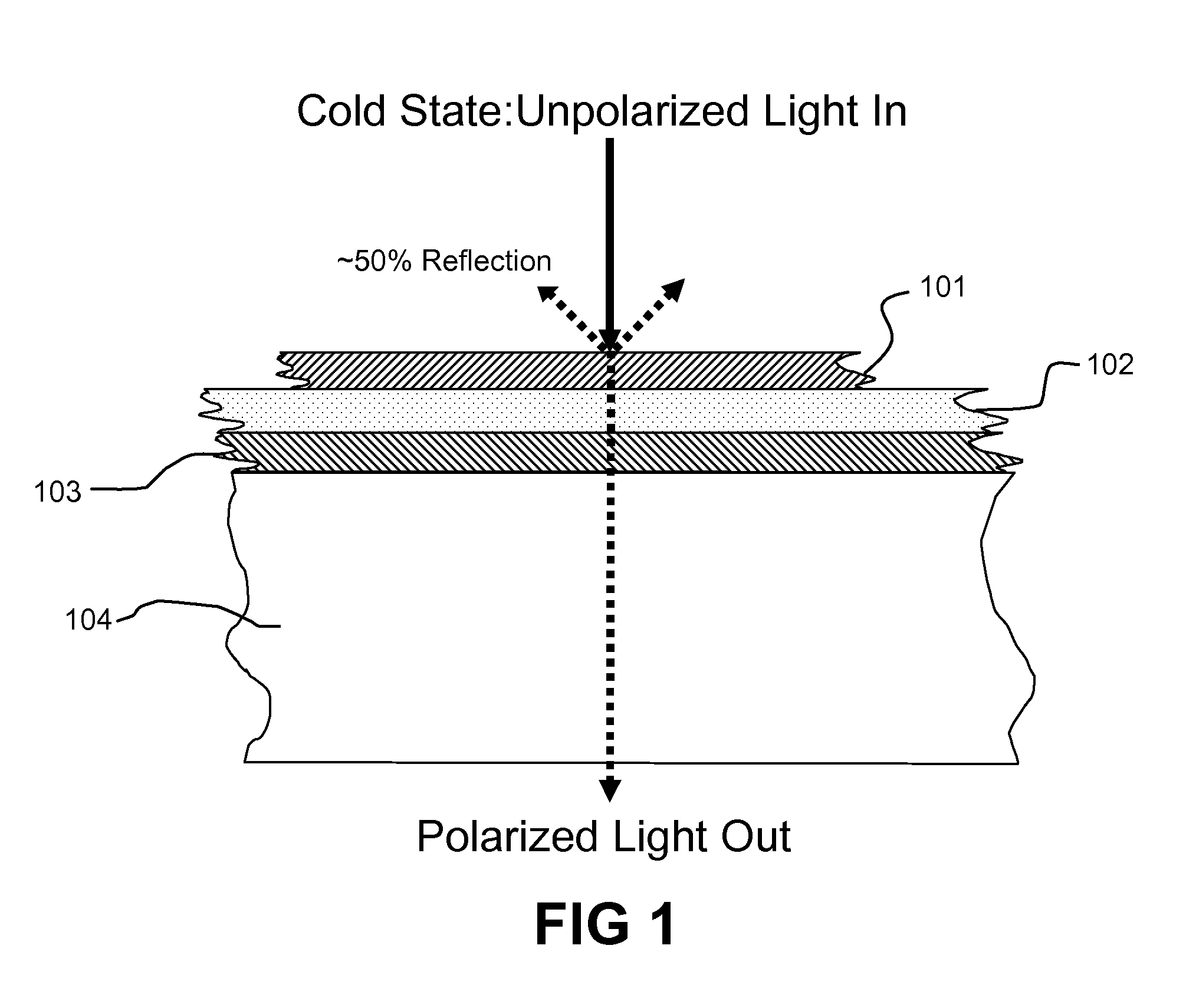

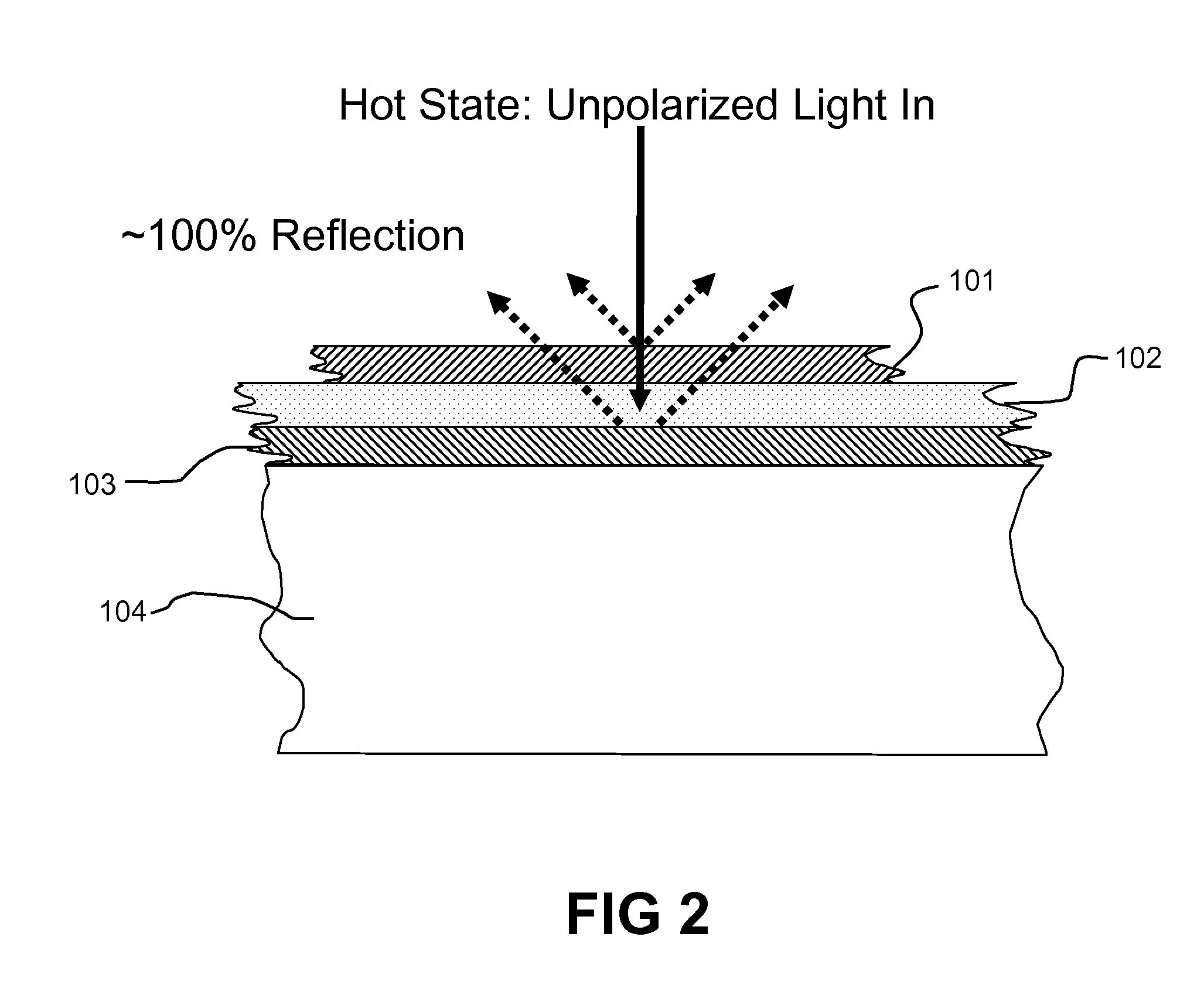

Thermally Switched Reflective Optical Shutter

The thermally switched reflective optical shutter is a self-regulating “switchable mirror” device that reflects up to 100% of incident radiant energy above a threshold temperature, and reflects up to 50% of incident radiant energy below a threshold temperature. Control over the flow of radiant energy occurs independently of the thermal conductivity or insulating value of the device, and may or may not preserve the image and color properties of incoming visible light. The device can be used as a construction material to efficiently regulate the internal temperature and illumination of buildings, vehicles, and other structures without the need for an external power supply or operator signals. The device has unique aesthetic optical properties that are not found in traditional windows, skylights, stained glass, light fixtures, glass blocks, bricks, or walls. The device can be tailored to transmit sufficient visible light to see through in both the transparent and reflective states, while still providing significant control over the total energy transmission across the device.

Owner:RAVENBRICK

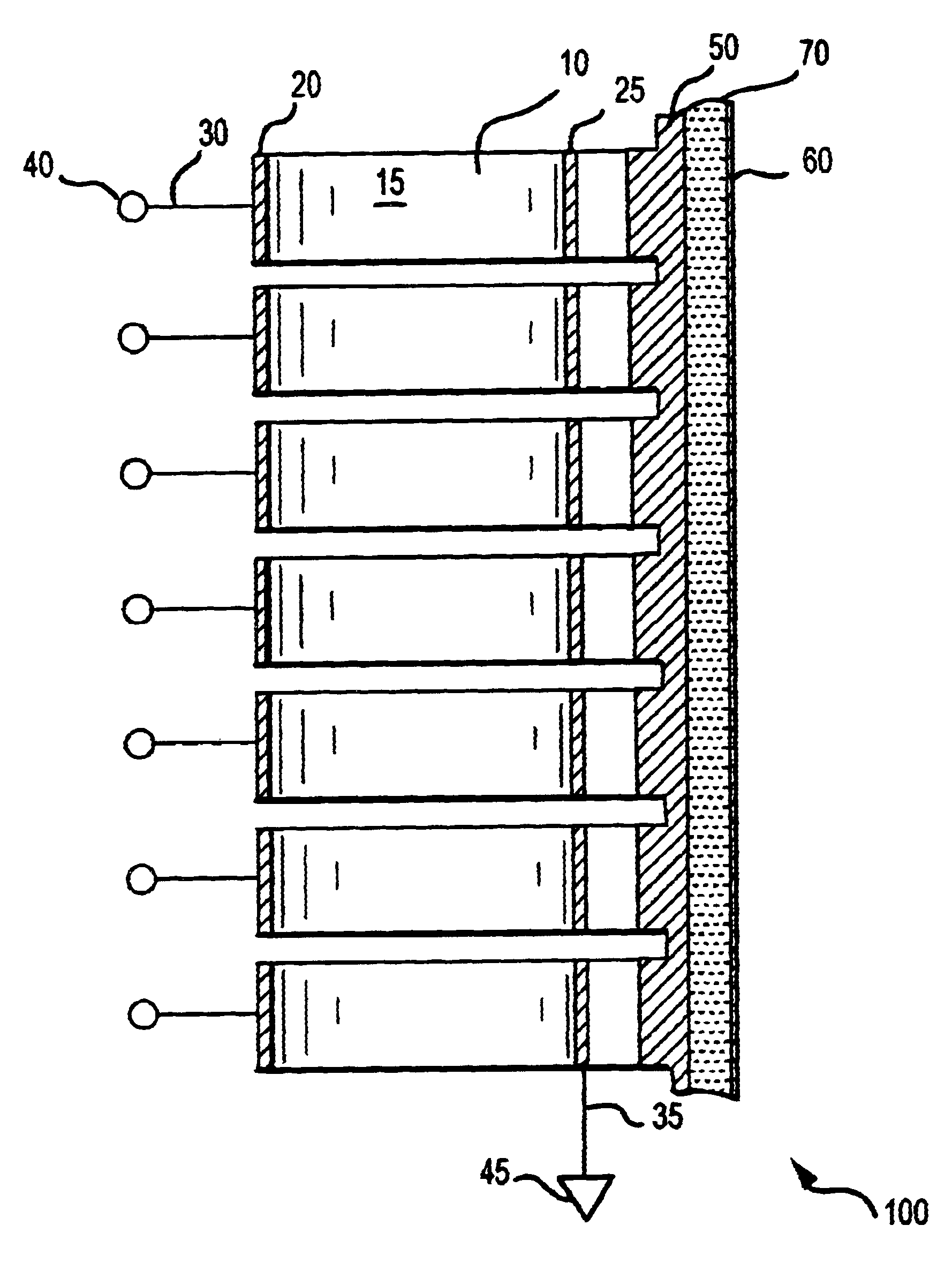

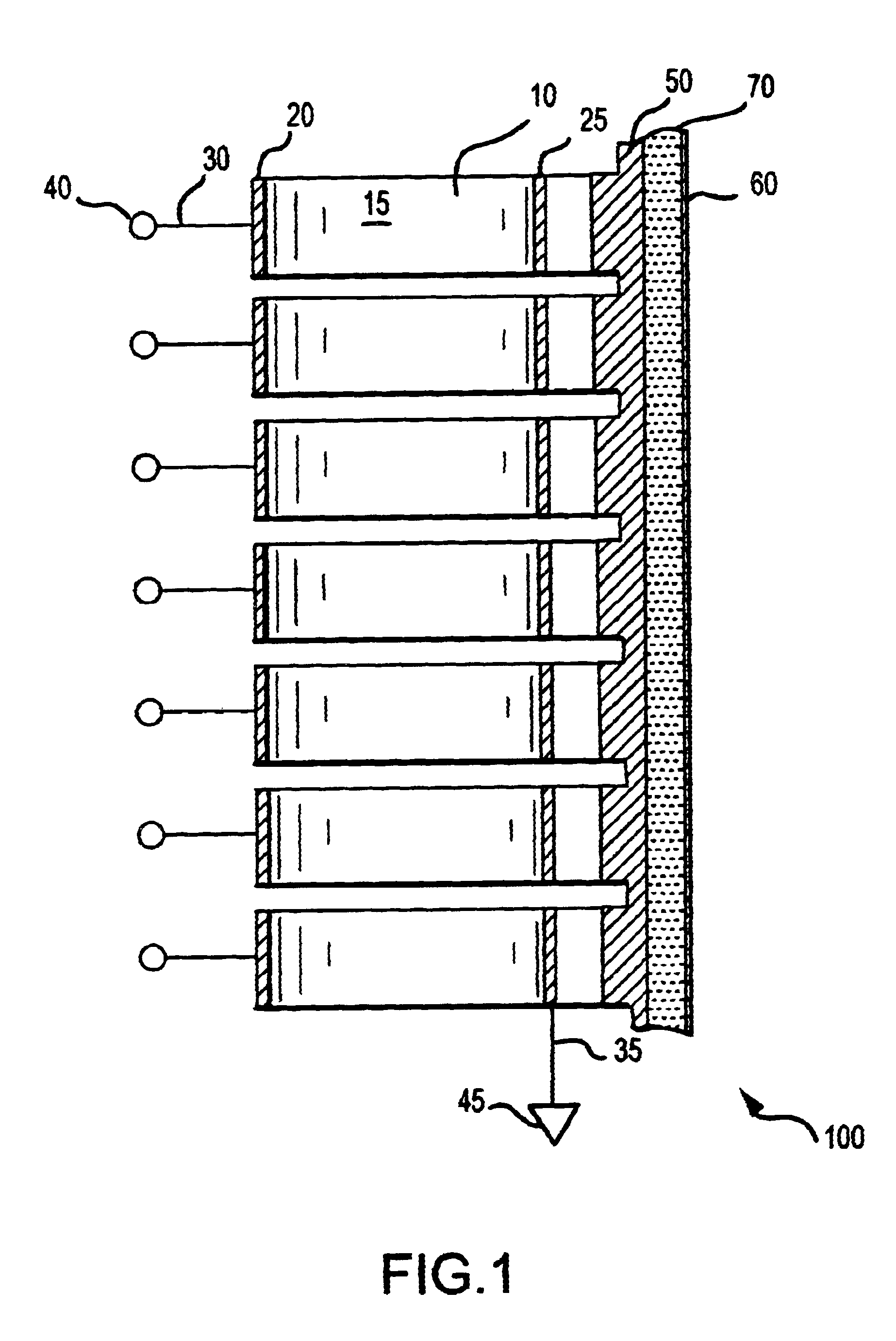

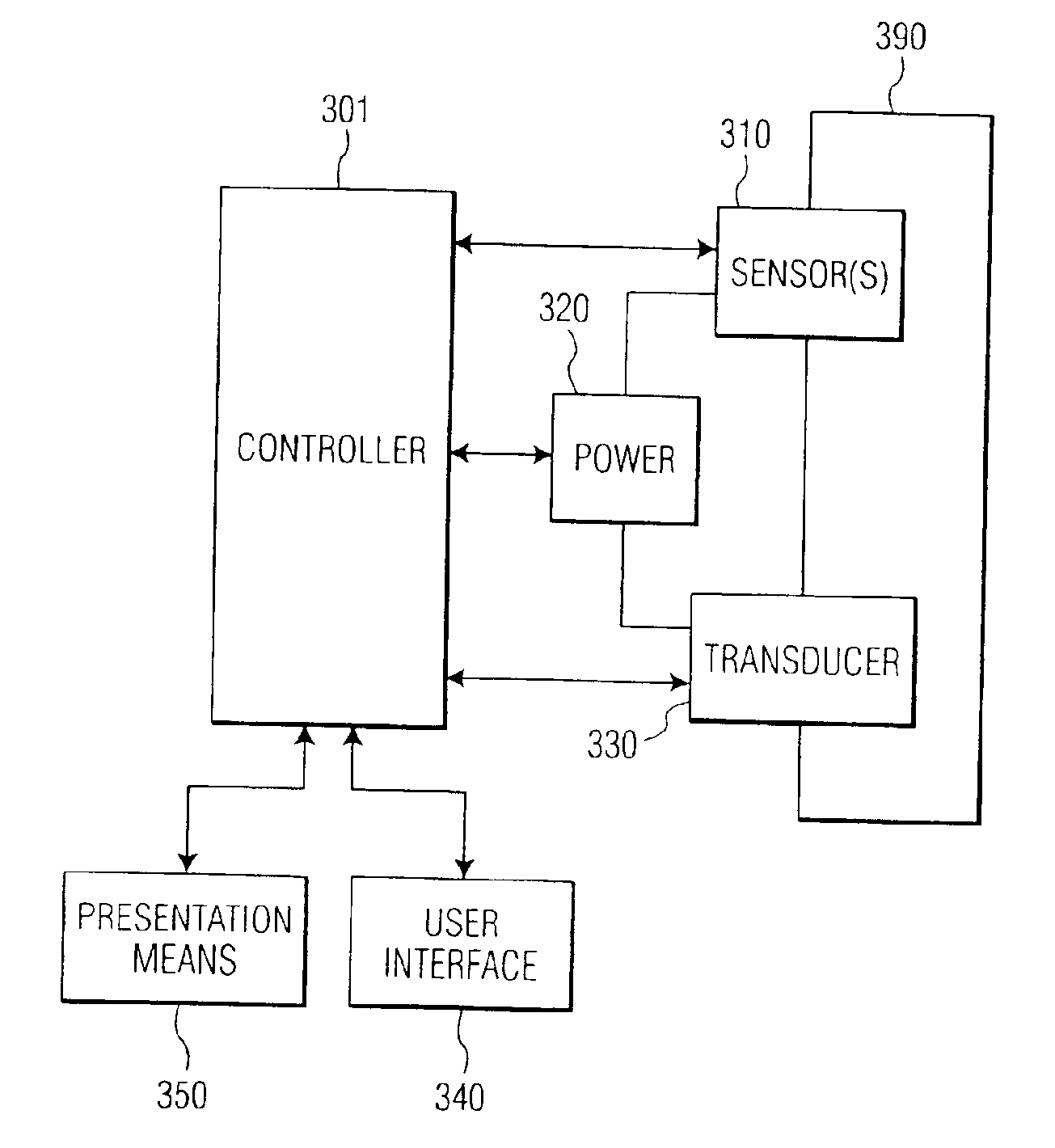

Imaging ultrasound transducer temperature control system and method using feedback

InactiveUS6905466B2Reduce the temperatureReduce temperatureUltrasonic/sonic/infrasonic diagnosticsMaterial analysis using sonic/ultrasonic/infrasonic wavesSonificationOperational system

A system and method for controlling the heat of an ultrasonic transducer is disclosed. In the presently preferred embodiments, the system and method controls the temperature of the transducer by changing operating system parameters based on feedback from temperature sensing elements placed in the transducer. The chosen mutable system parameters may be preset by the construction of the ultrasonic system, under the control of the ultrasonic system user, or a combination of the two. In several exemplary embodiments, the one or more mutable system parameters are altered by an amount proportionate to the difference between the current temperature and a preferred operating temperature. In another exemplary embodiment, the system switches to a lower power imaging mode when the temperature feedback indicates a threshold temperature has been reached.

Owner:KONINK PHILIPS ELECTRONICS NV

Imaging ultrasound transducer temperature control system and method using feedback

InactiveUS20040073113A1Ultrasonic/sonic/infrasonic diagnosticsMaterial analysis using sonic/ultrasonic/infrasonic wavesSonificationOperational system

A system and method for controlling the heat of an ultrasonic transducer is disclosed. In the presently preferred embodiments, the system and method controls the temperature of the transducer by changing operating system parameters based on feedback from temperature sensing elements placed in the transducer. The chosen mutable system parameters may be preset by the construction of the ultrasonic system, under the control of the ultrasonic system user, or a combination of the two. In several exemplary embodiments, the one or more mutable system parameters are altered by an amount proportionate to the difference between the current temperature and a preferred operating temperature. In another exemplary embodiment, the system switches to a lower power imaging mode when the temperature feedback indicates a threshold temperature has been reached.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

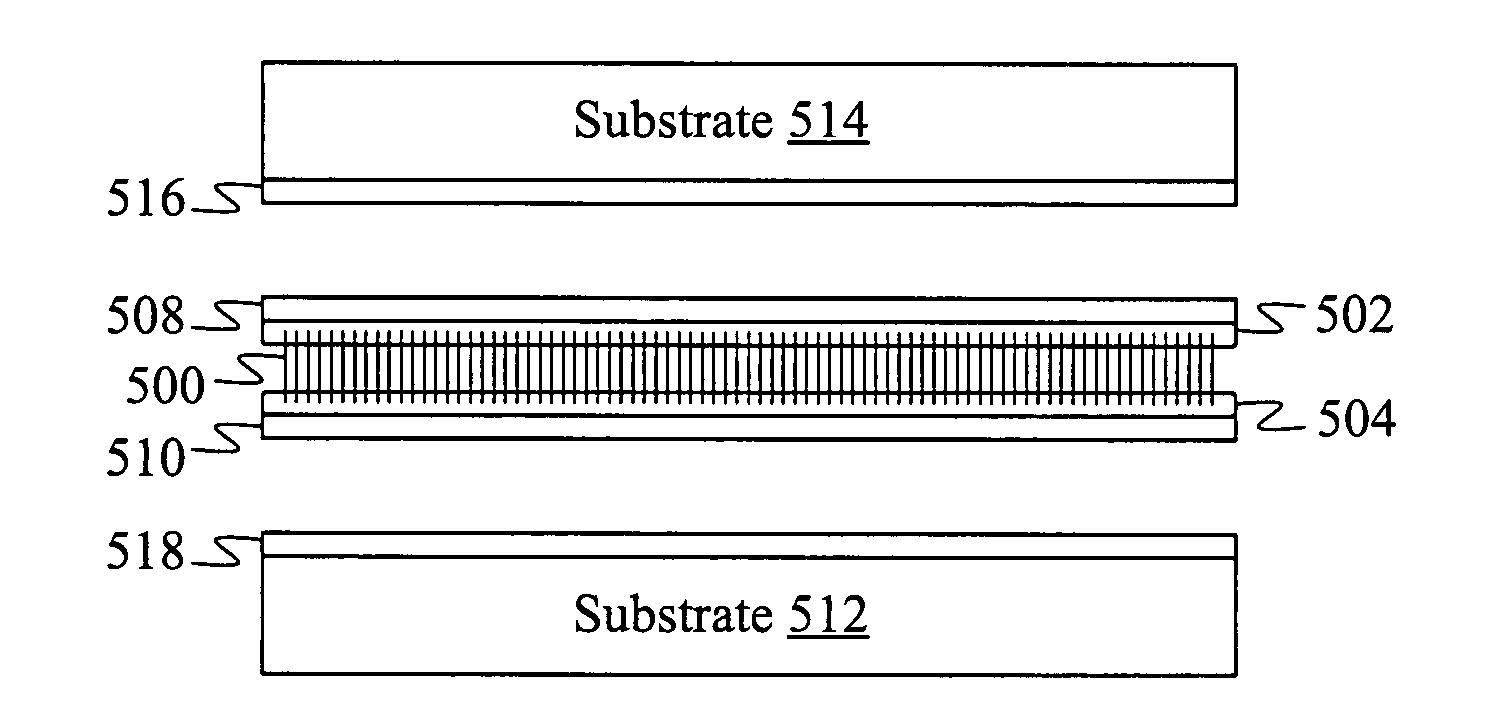

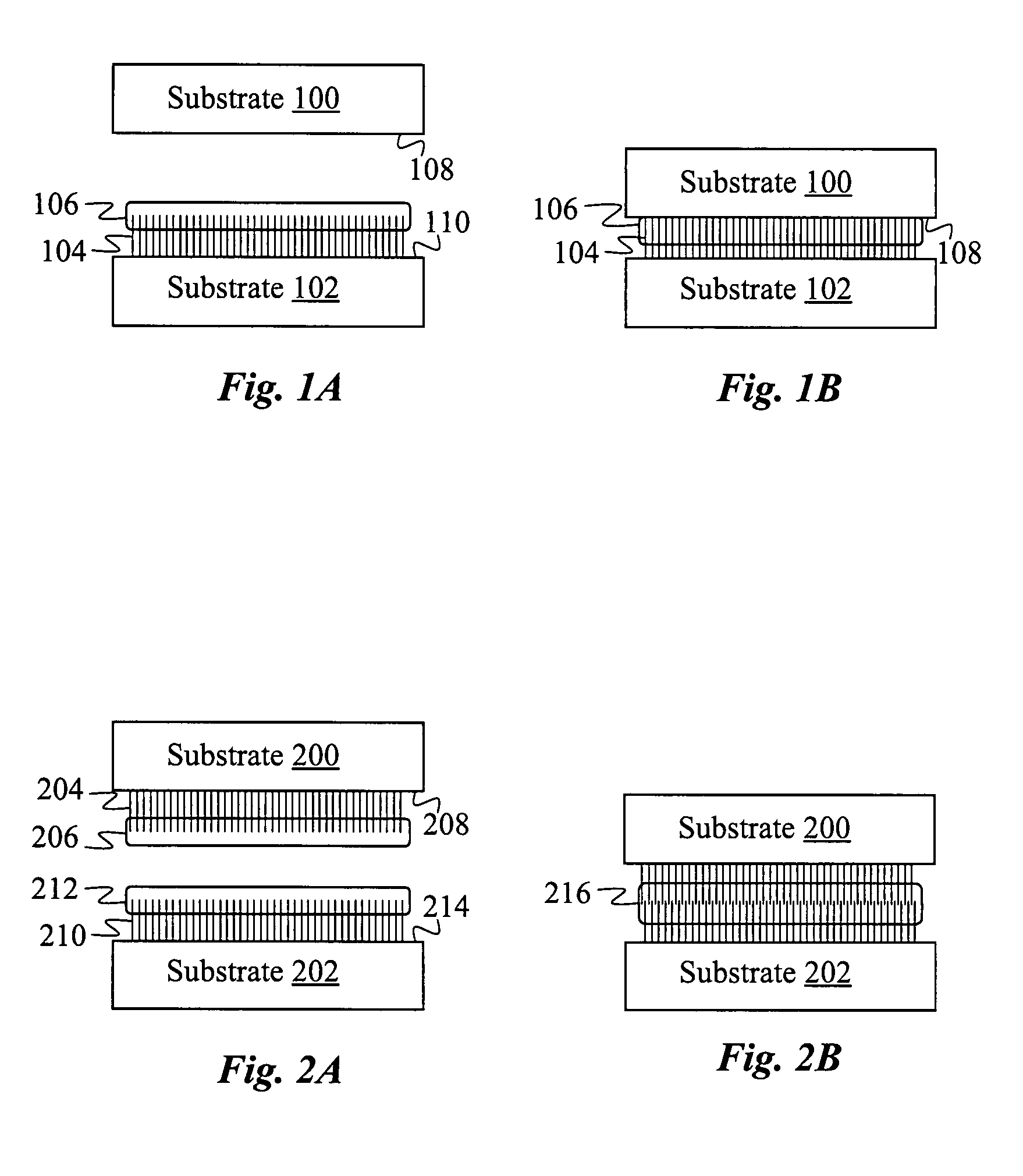

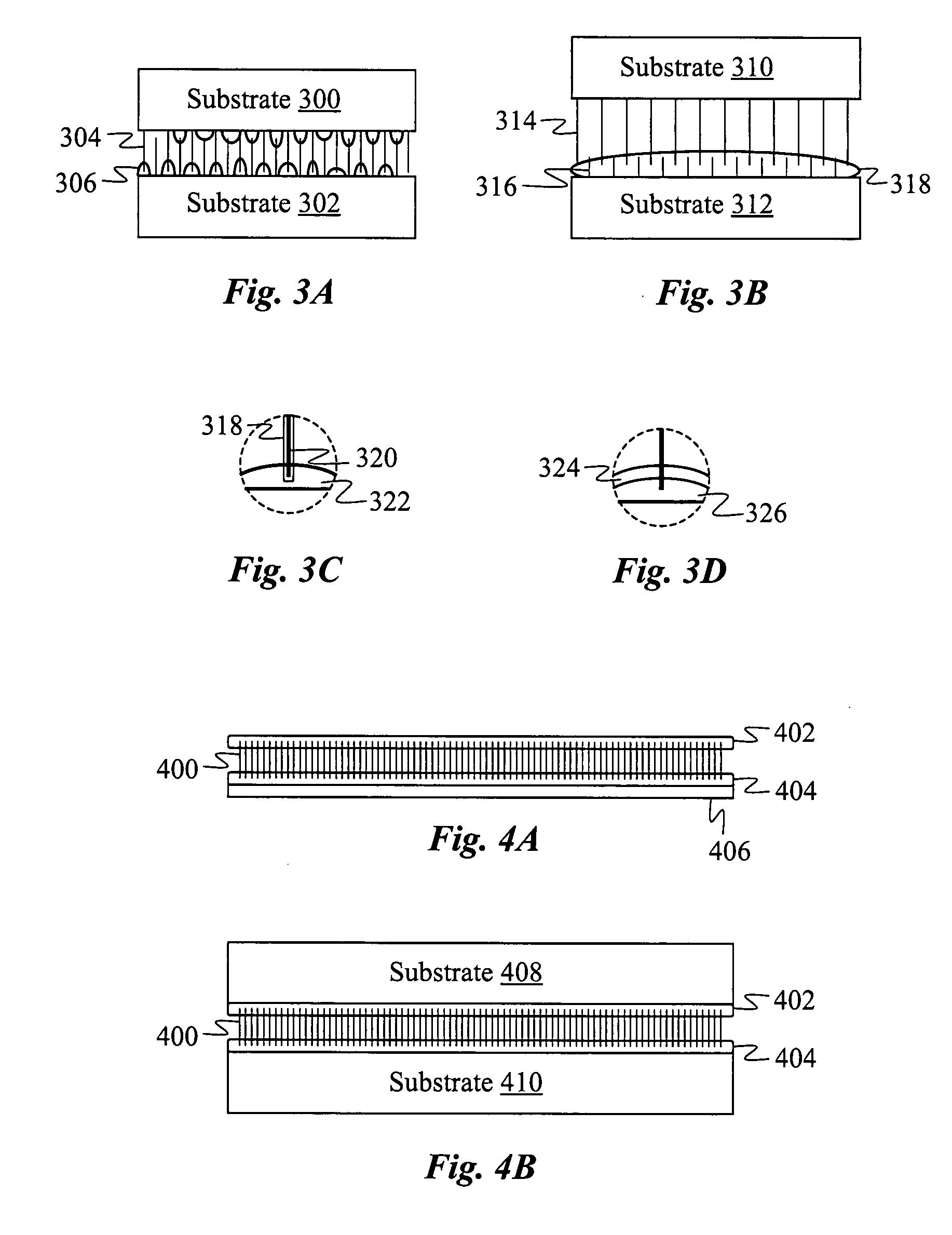

Composite thermal interface material including aligned nanofiber with low melting temperature binder

ActiveUS20090068387A1Improve thermal conductivityMaterial nanotechnologyLamination ancillary operationsFiberAdhesion process

A thermal interface material includes a mechanically compliant vertically aligned nanofiber film and a binder material for joining the nanofibers of the film to the surfaces of two substrates. Preferably, the binder material comprises a non-hydrocarbon-based material such as a metallic eutectic with a melting temperature below a nanofiber thermal damage threshold temperature of the film. The film is grown on a substrate which is then bonded to another substrate by the binder material in an adhesion process that may include pressure and heat. Alternatively, the film may be released from the substrate to produce a stand-alone thermal tape which may later be placed between two substrates and bonded.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

System and method for temperature control of multi-battery systems

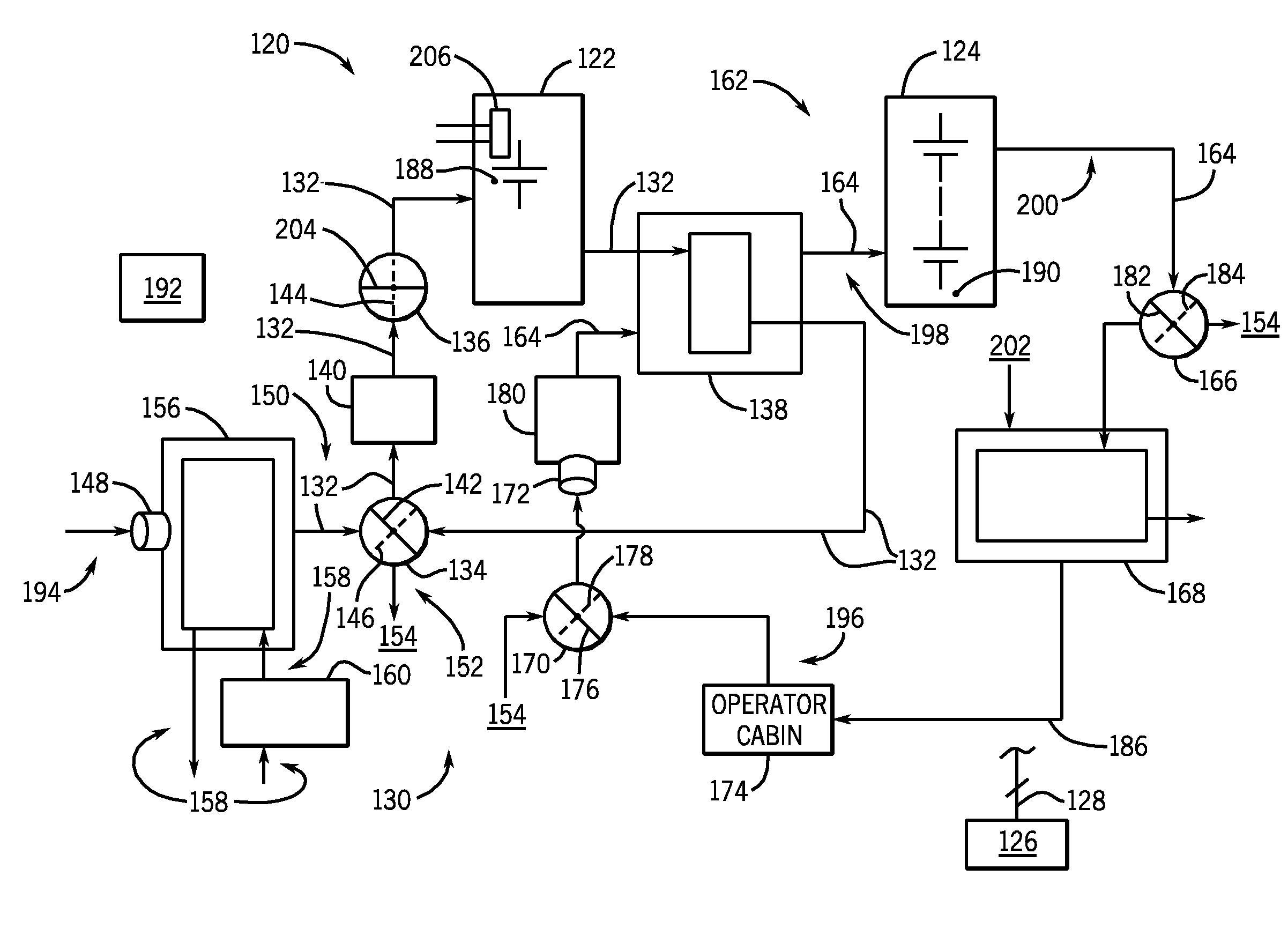

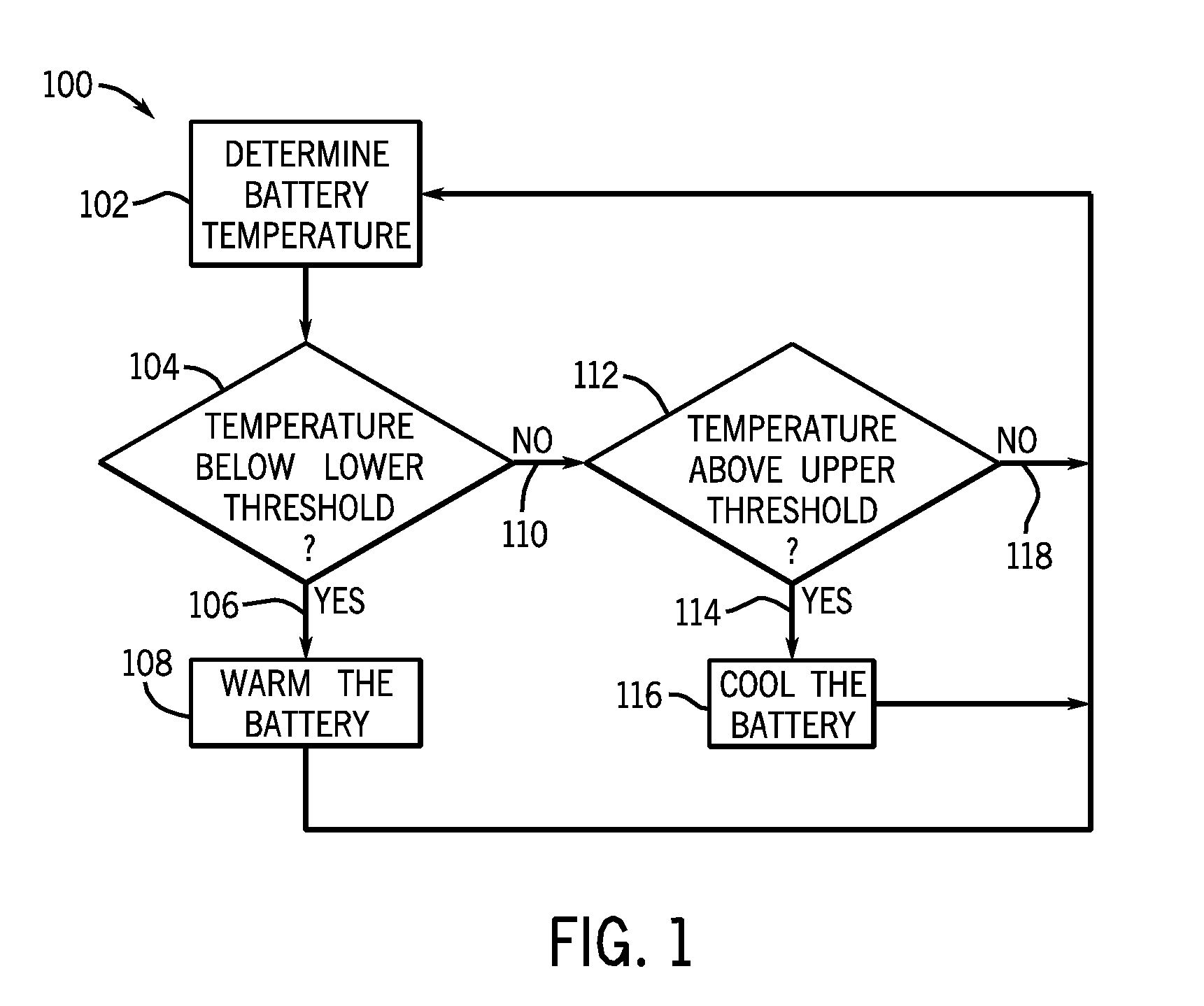

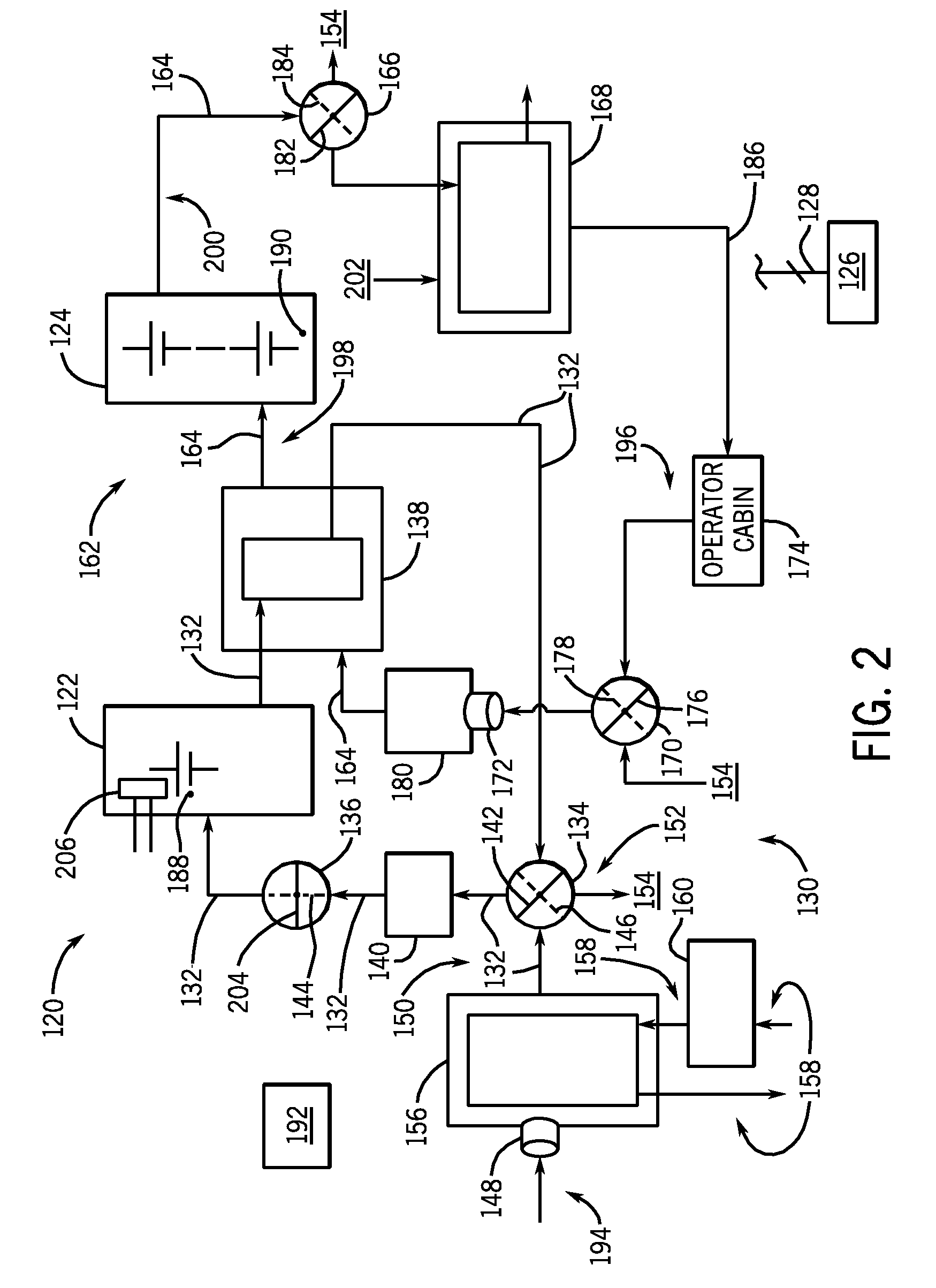

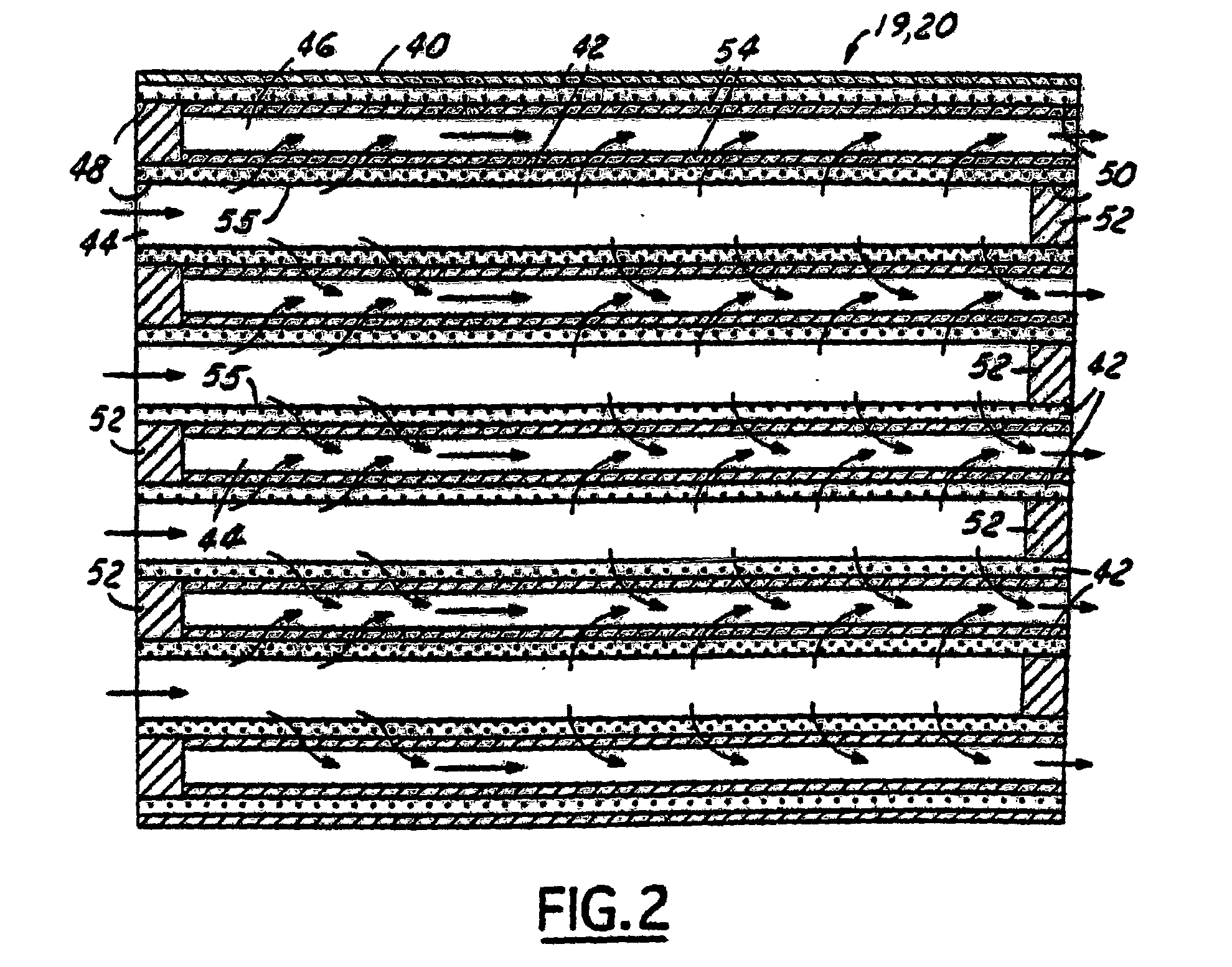

ActiveUS20100089547A1Increase temperatureReduce the temperatureAir-treating devicesRailway heating/coolingTemperature controlControl system

An system includes a first battery having a first desired operating temperature range between a first lower threshold temperature and a first upper threshold temperature and a second battery having a second desired operating temperature range between a second lower threshold temperature and a second upper threshold temperature. The system further includes a temperature control system coupled to the first and second batteries and configured to convey heat energy from the first battery to the second battery when the temperature of the second battery is less than the second lower threshold temperature to increase the temperature of the second battery toward the second desired operating temperature range and to convey heat energy away from the second battery when the temperature of the second battery is greater than the second upper threshold temperature to decrease the temperature of the second battery toward the second desired operating temperature range.

Owner:GENERAL ELECTRIC CO

Color changing cleansing composition

InactiveUS20070142263A1Cosmetic preparationsOrganic detergent compounding agentsThermochromismChange color

A cleansing composition is disclosed that changes color during use. The cleansing composition contains a plurality of thermochromic dyes that cause a color change to occur at a threshold temperature and continue to cause a color change over a temperature range. The range of temperatures corresponds to approximately the amount of time sufficient to properly wash or scrub using the product.

Owner:KIMBERLY-CLARK WORLDWIDE INC

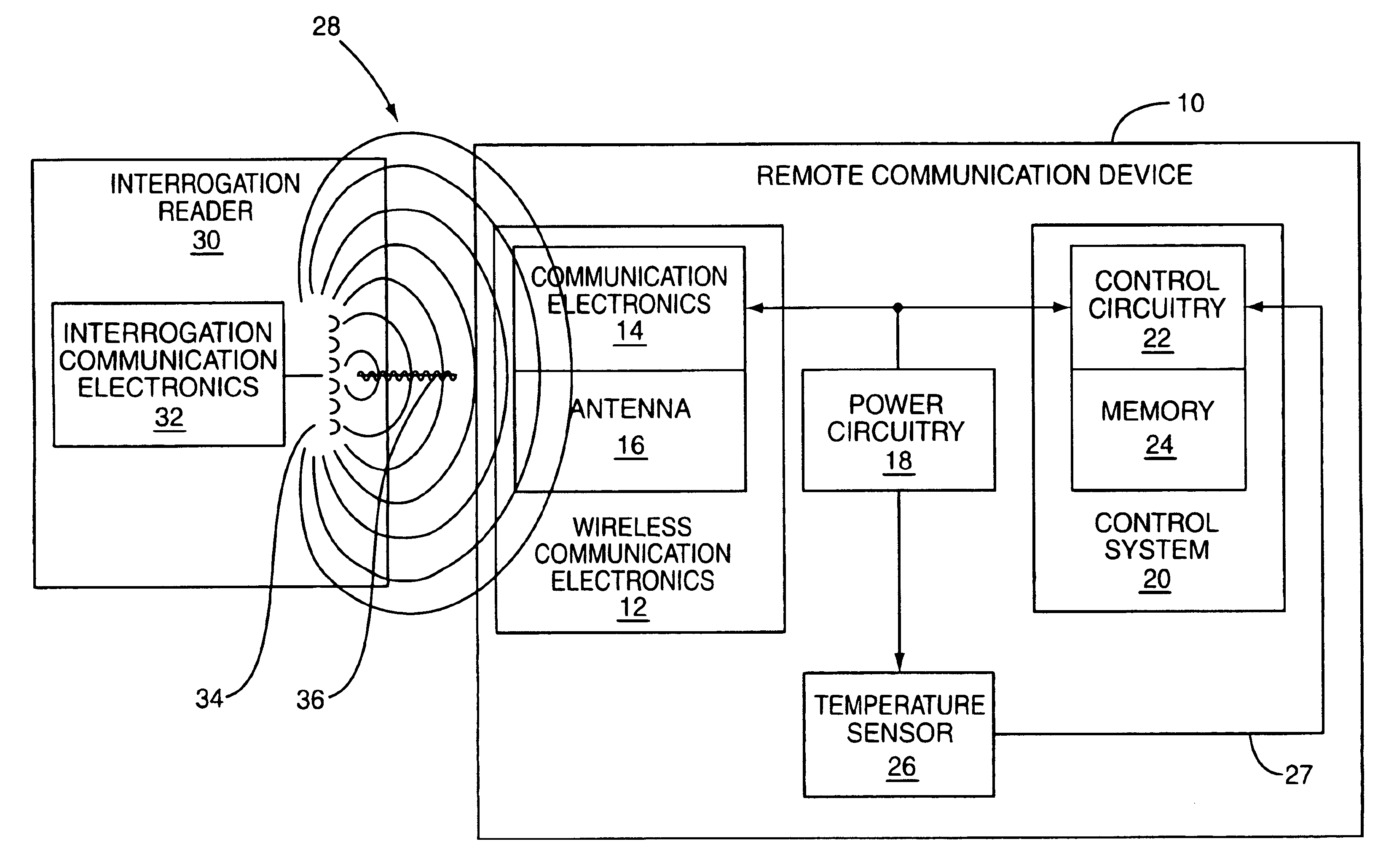

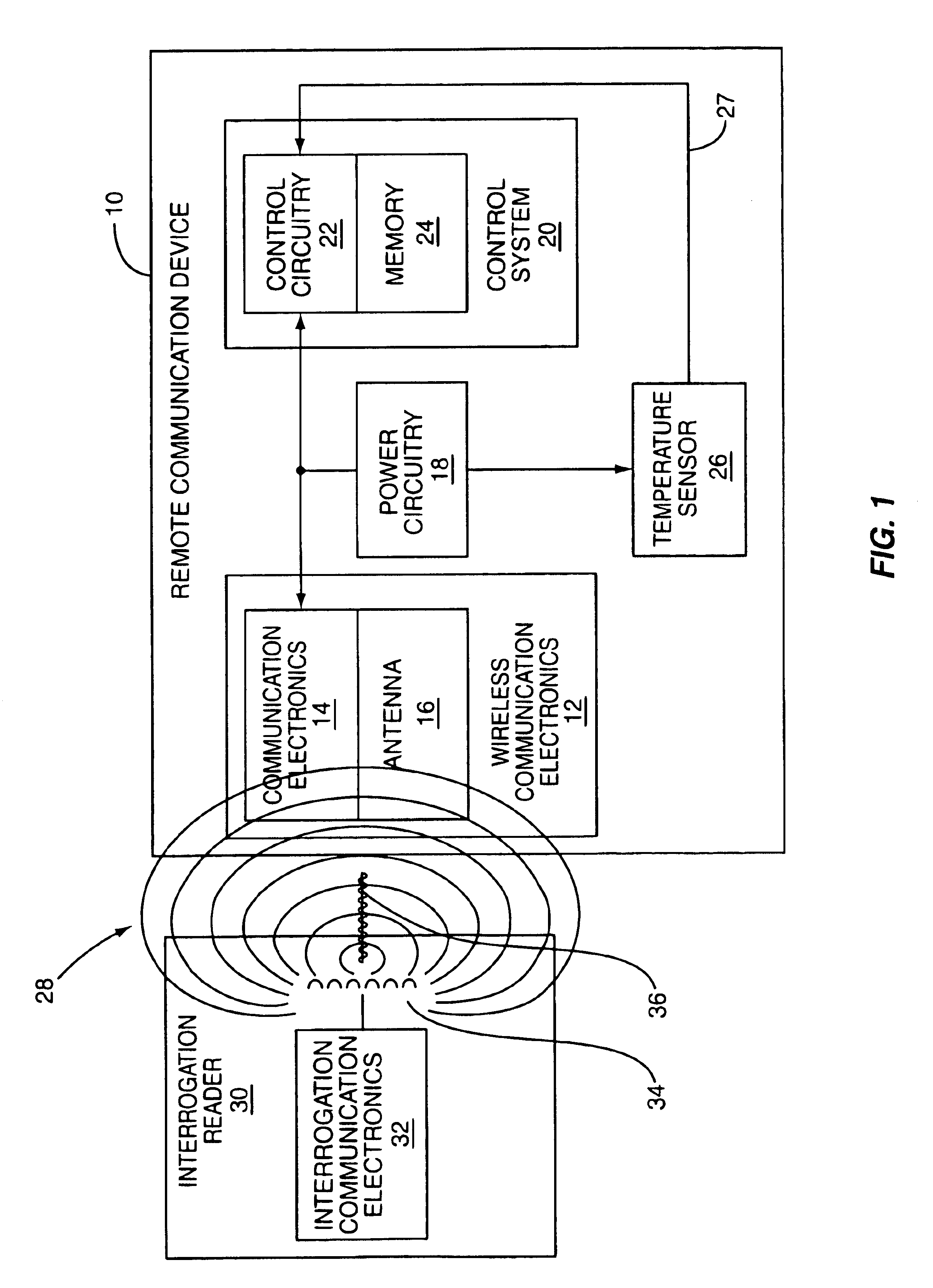

RFID temperature device and method

InactiveUS6847912B2Electric signal transmission systemsPower operated devicesEngineeringThreshold temperature

A remote communication device, that receives temperature indicia concerning a container and / or its contents and communicates such temperature indicia along with an identification indicia to a reader. The remote communication device can measure and communicate temperature indicia associated with a container in a periodic manner. The remote communication device can also measure and communicate temperature indicia associated with a container when such temperature indicia exceed a certain minimum or maximum threshold temperature. The remote communication device can also include power circuitry to store energy when energized in the range of an interrogation reader so that the remote communication device can be powered for temperature indicia measurements when not in the range of an interrogation reader.

Owner:THINKLOGIX LLC

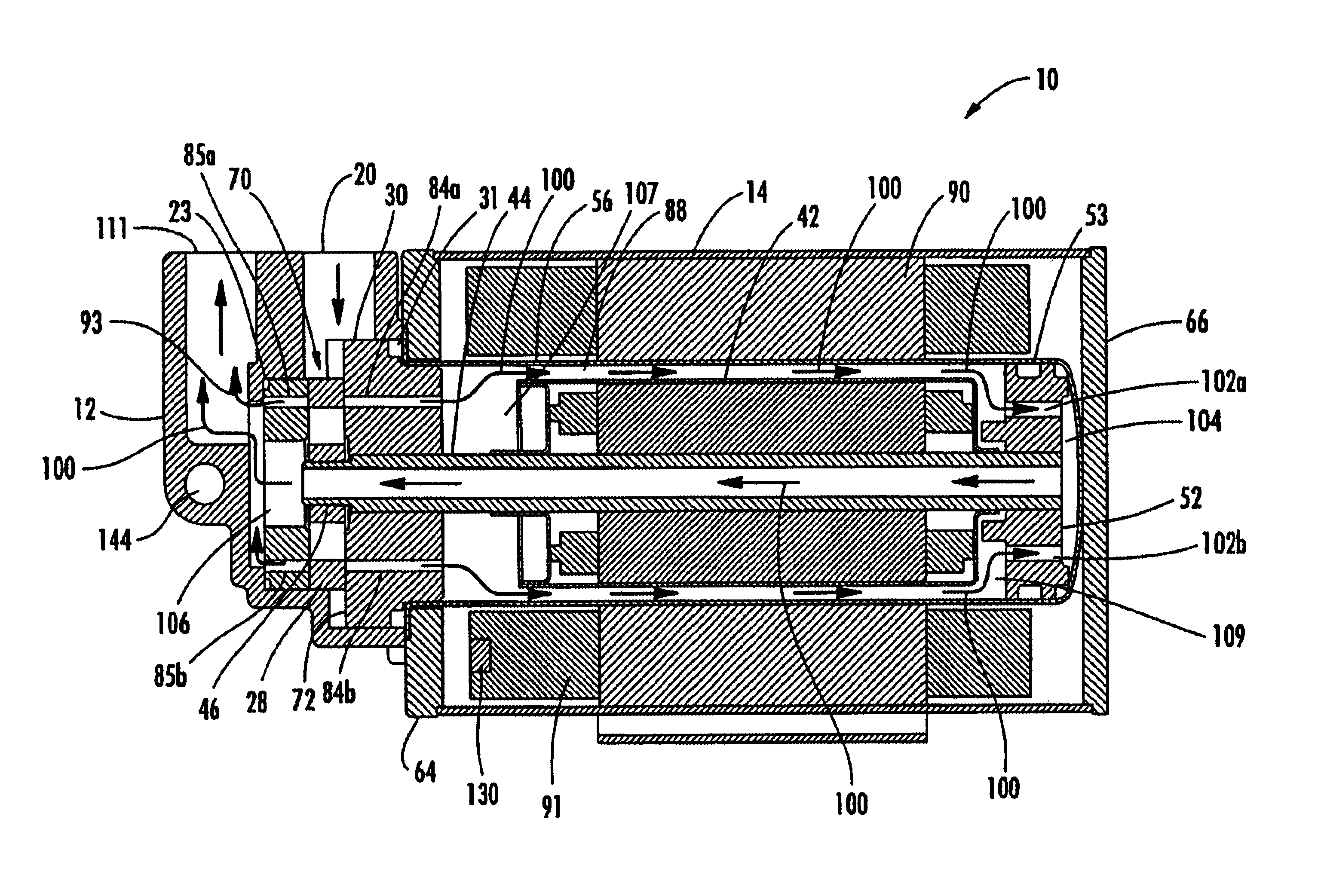

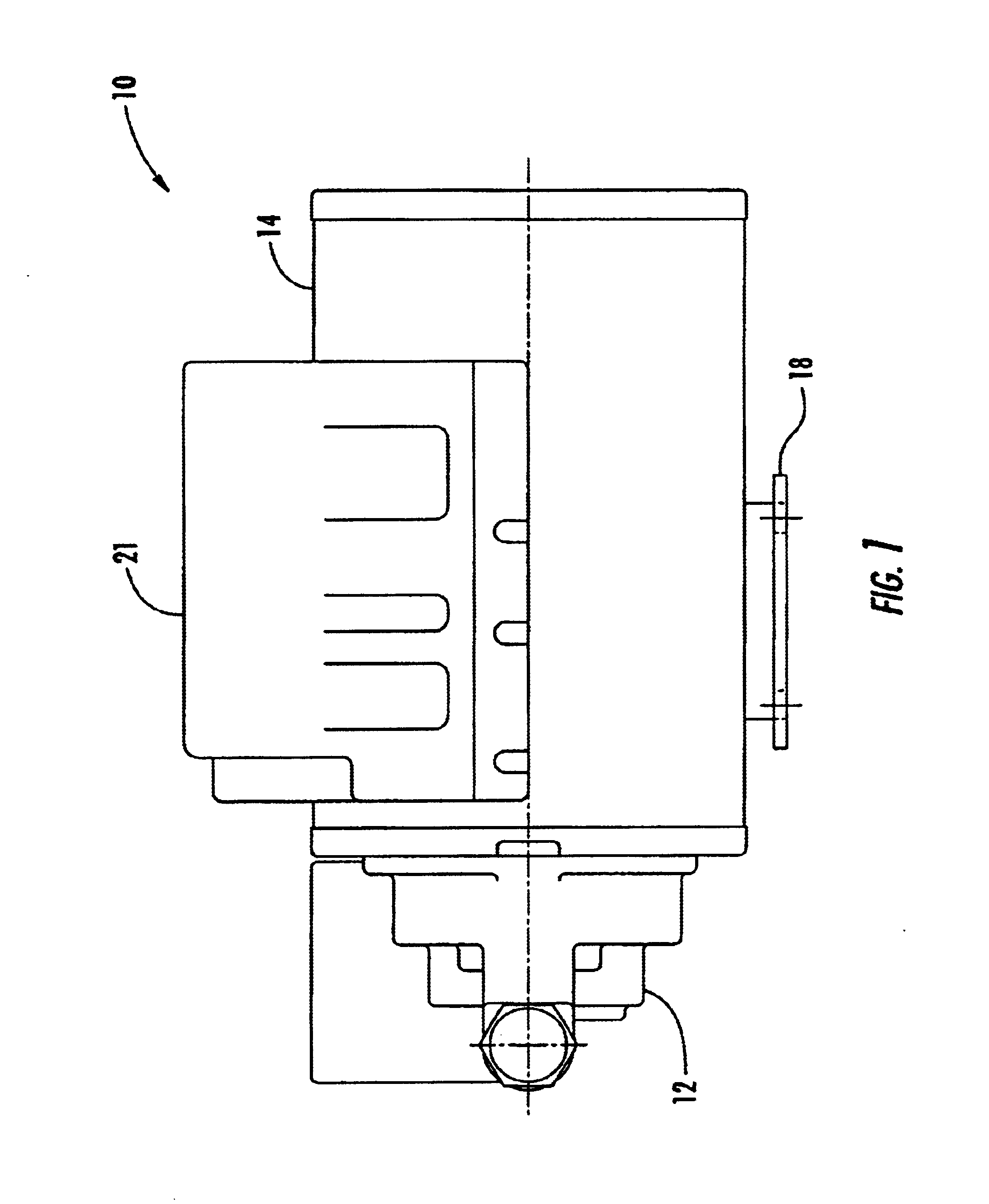

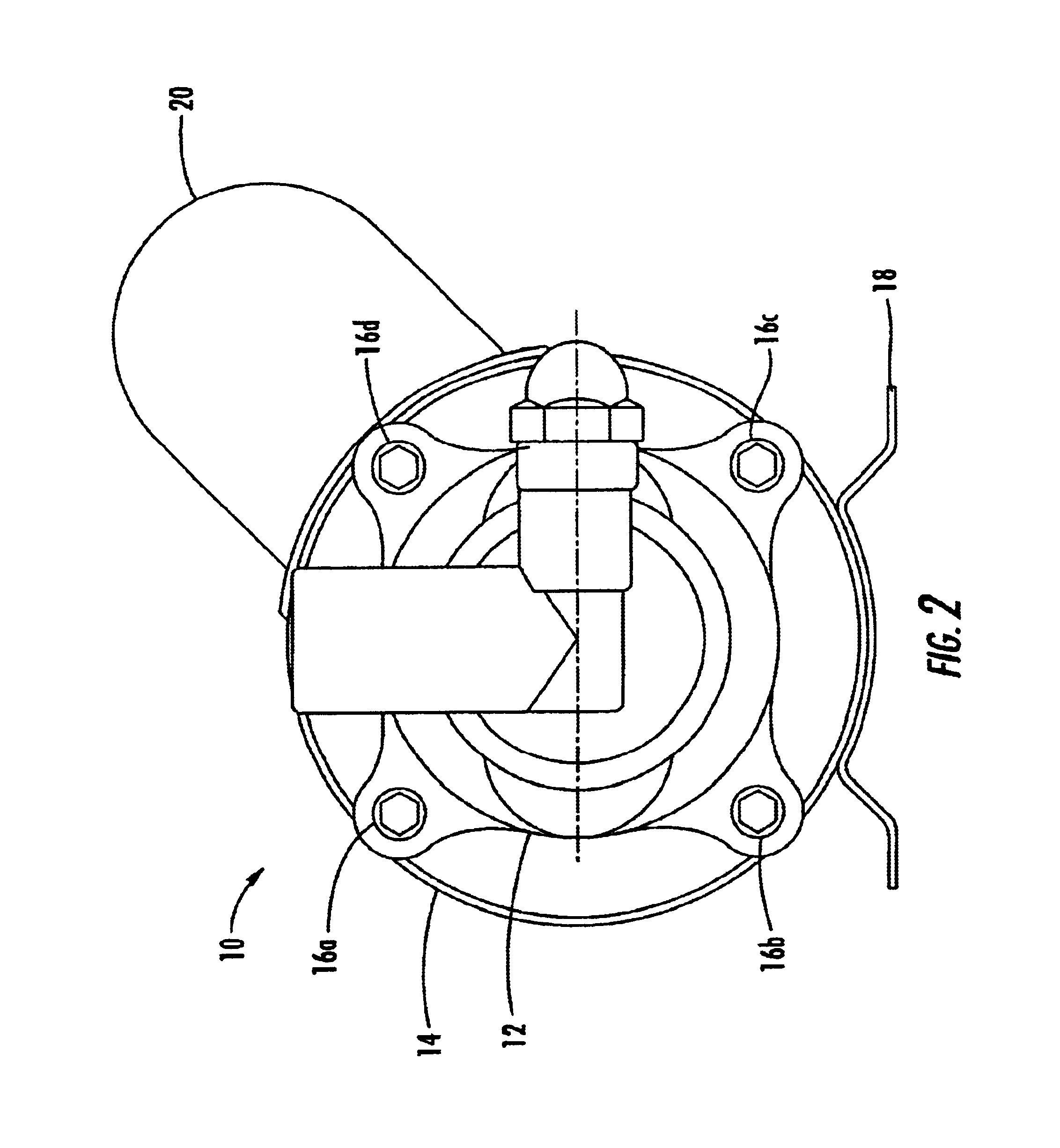

Overheat protection for fluid pump

InactiveUS6837688B2Avoid damageReduce stepsRotary/oscillating piston combinations for elastic fluidsRotary piston pumpsPump headThreshold temperature

An apparatus for detecting the presence of an overheat condition in a fluid pump includes a pump head for receiving a fluid at a first pressure and outputting the fluid at a second pressure that is greater than the first pressure. A motor is positioned adjacent the pump head to drive the pump head to pressurize the fluid. A single overheat sensor senses an overheat condition in the pump head and an overheat condition in the motor. When a threshold temperature is sensed by the overheat sensor, a switch is activated to prevent operation of the motor. In one embodiment, the overheat sensor and switch are integral and may, for example, take the form of a bi-metal switch formed in the stator windings of the motor. In alternate embodiments, the overheat sensor and switch are separate.

Owner:STANDEX INT CORP

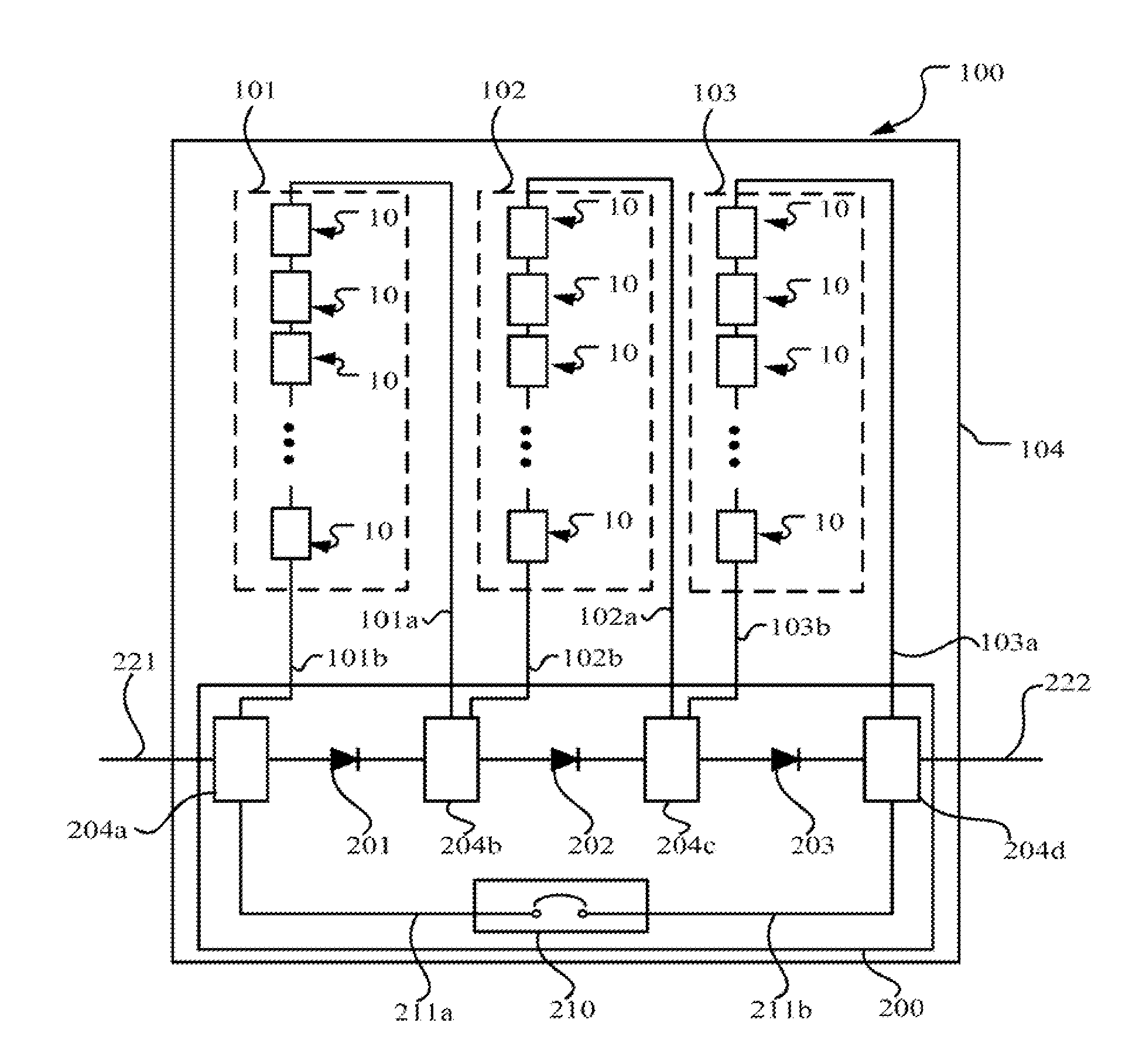

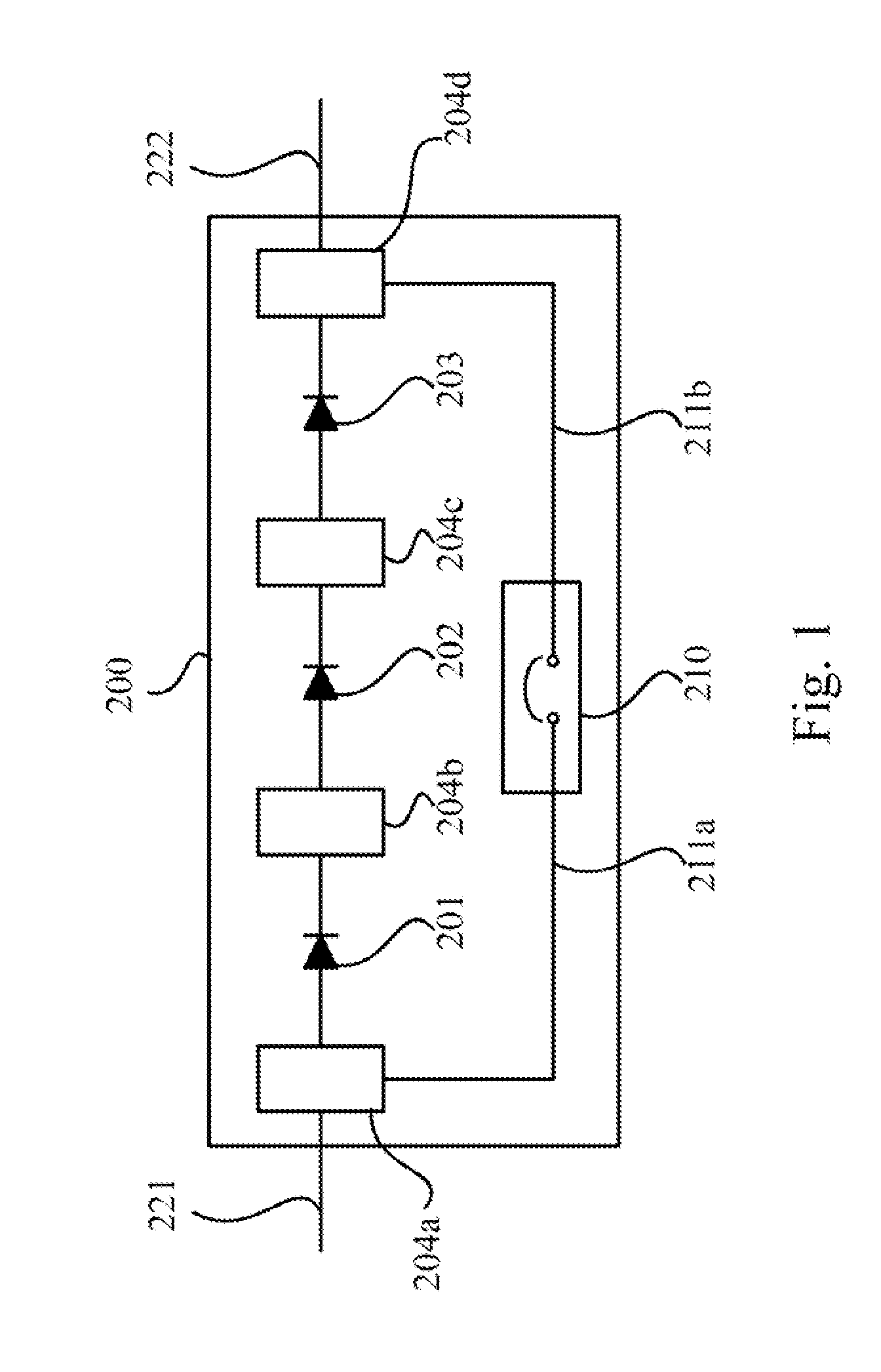

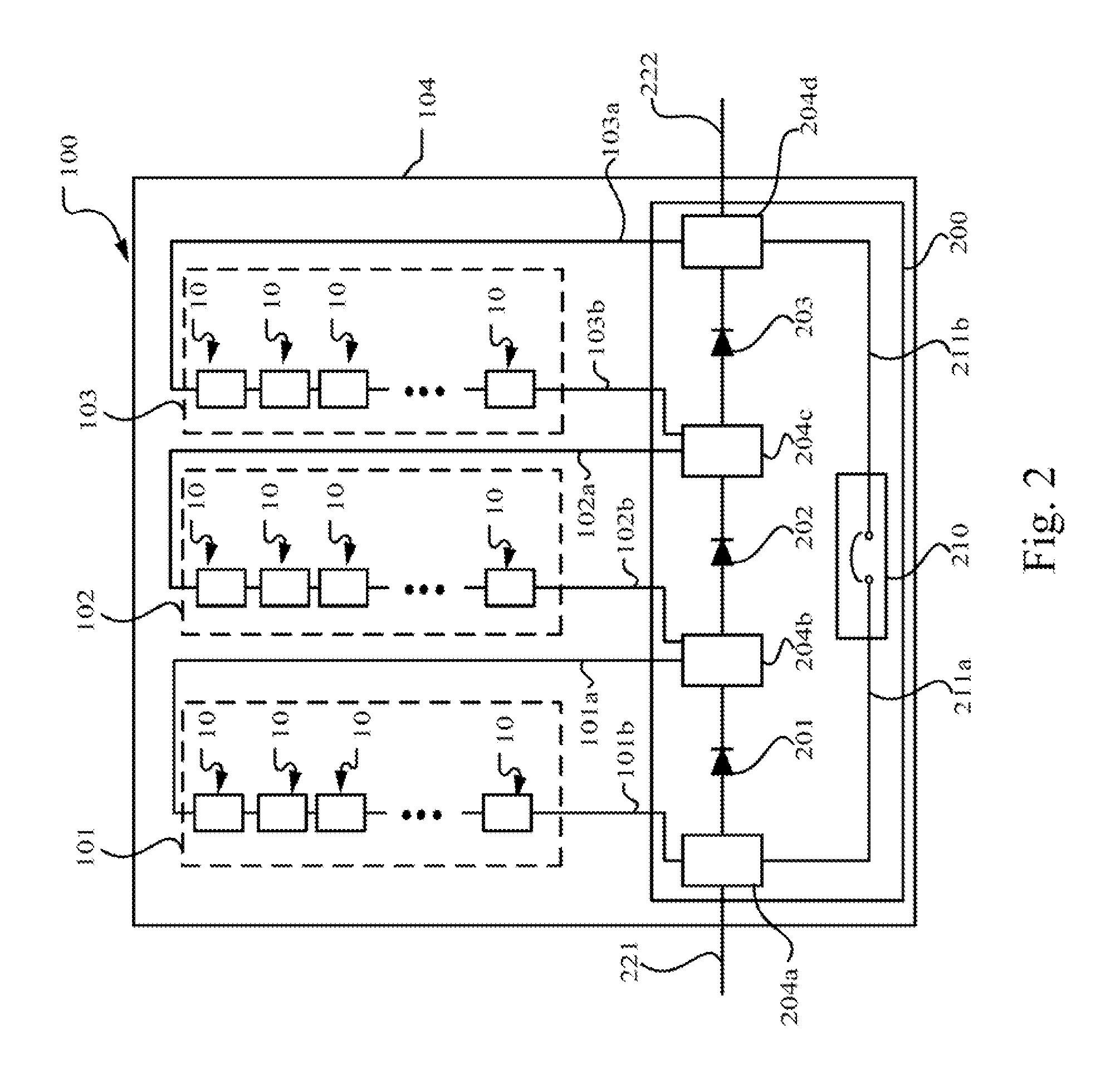

Thermostatically controlled terminal box and photovoltaic power generation system utilizing the same

InactiveUS20110240100A1Reduce voltagePrevent from erroneous short-circuitBoards/switchyards circuit arrangementsPV power plantsEngineeringThreshold temperature

A system comprising a photovoltaic module and a terminal box. Two terminals of the box output voltage generated by the photovoltaic module. A thermal switch shorts the two terminals in response to temperature rise to a threshold temperature and is structured to prevent short-circuit due to the temperature rise of the normally operating photovoltaic module and bypass diodes in the terminal box.

Owner:HON HAI PRECISION IND CO LTD

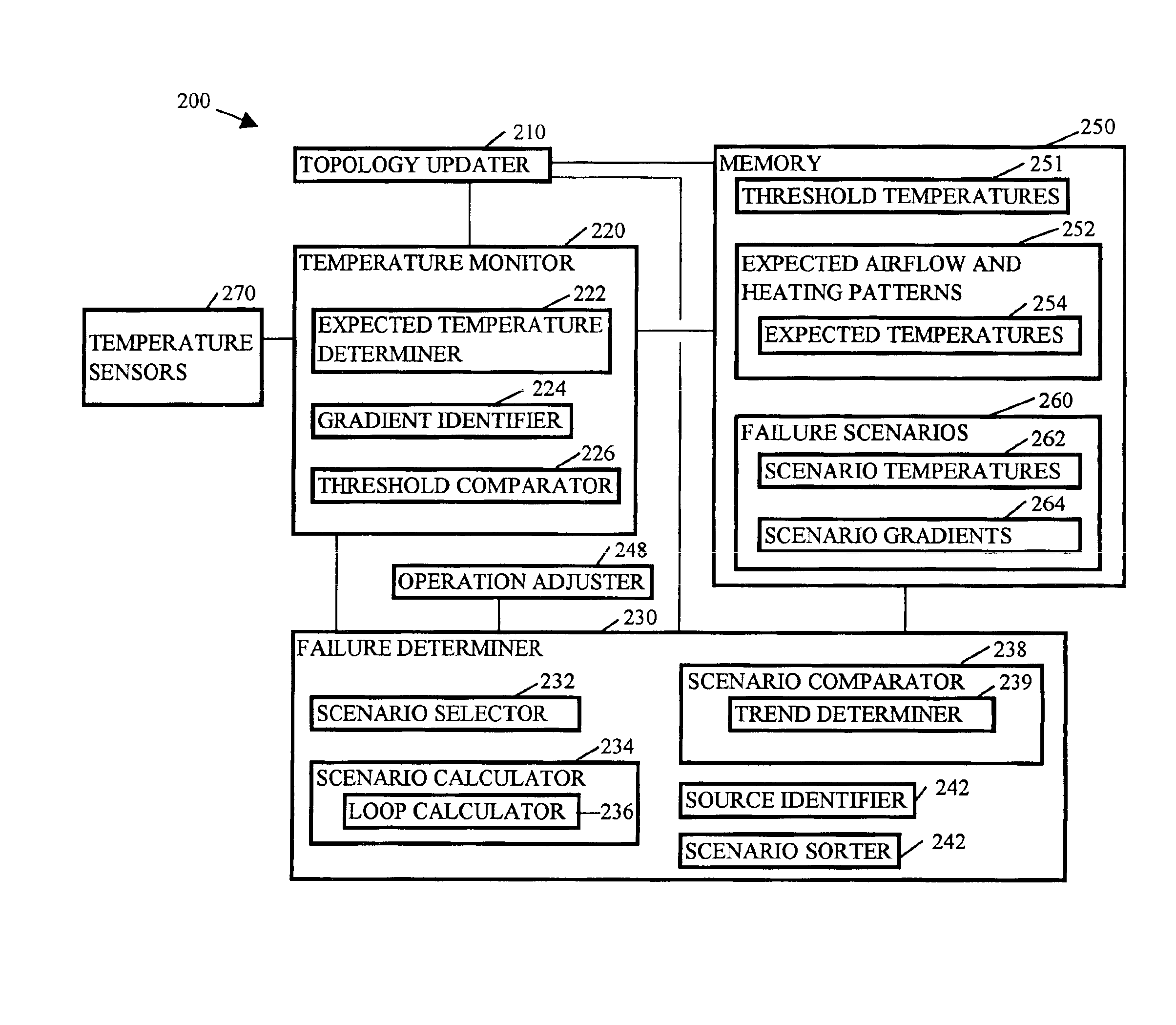

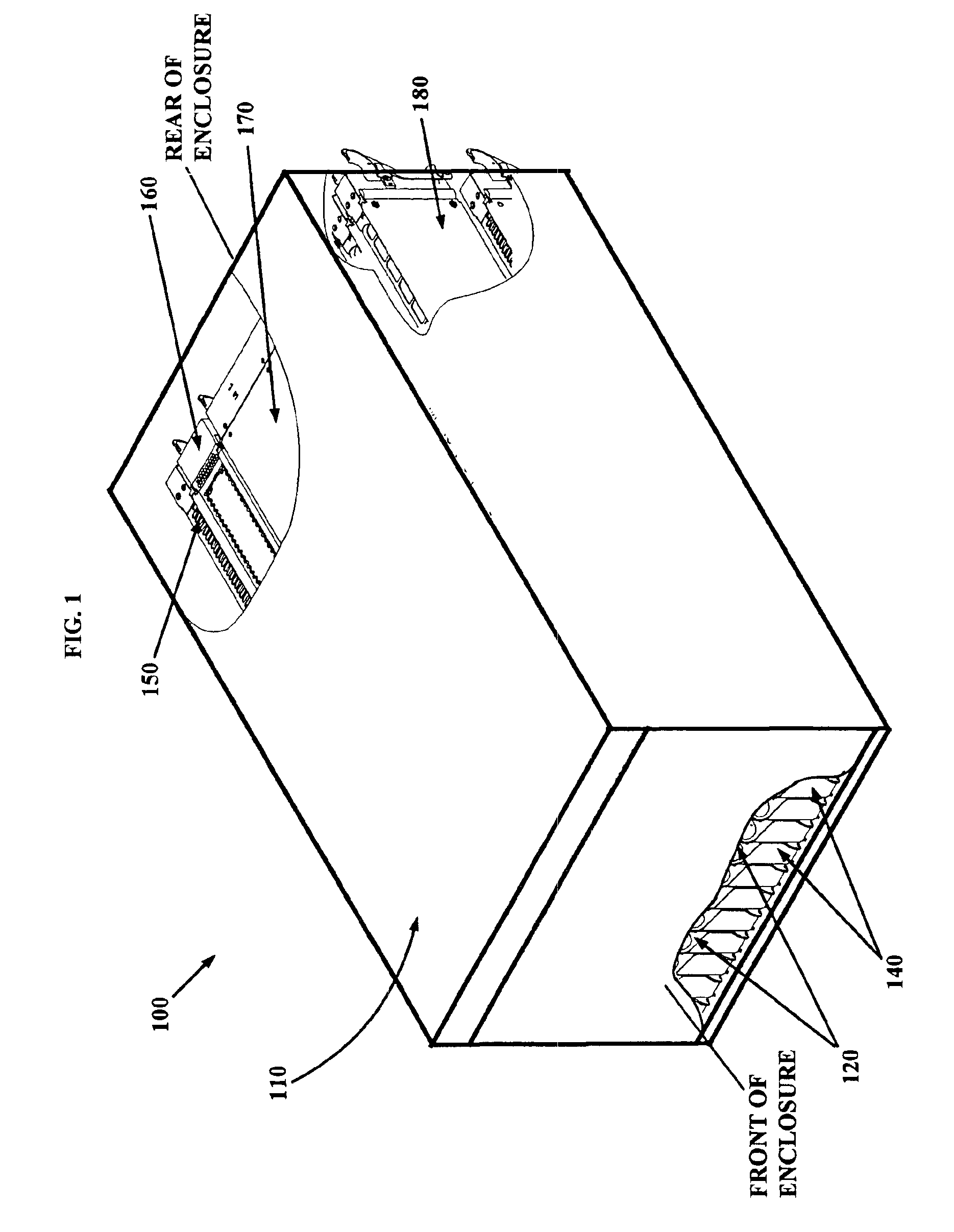

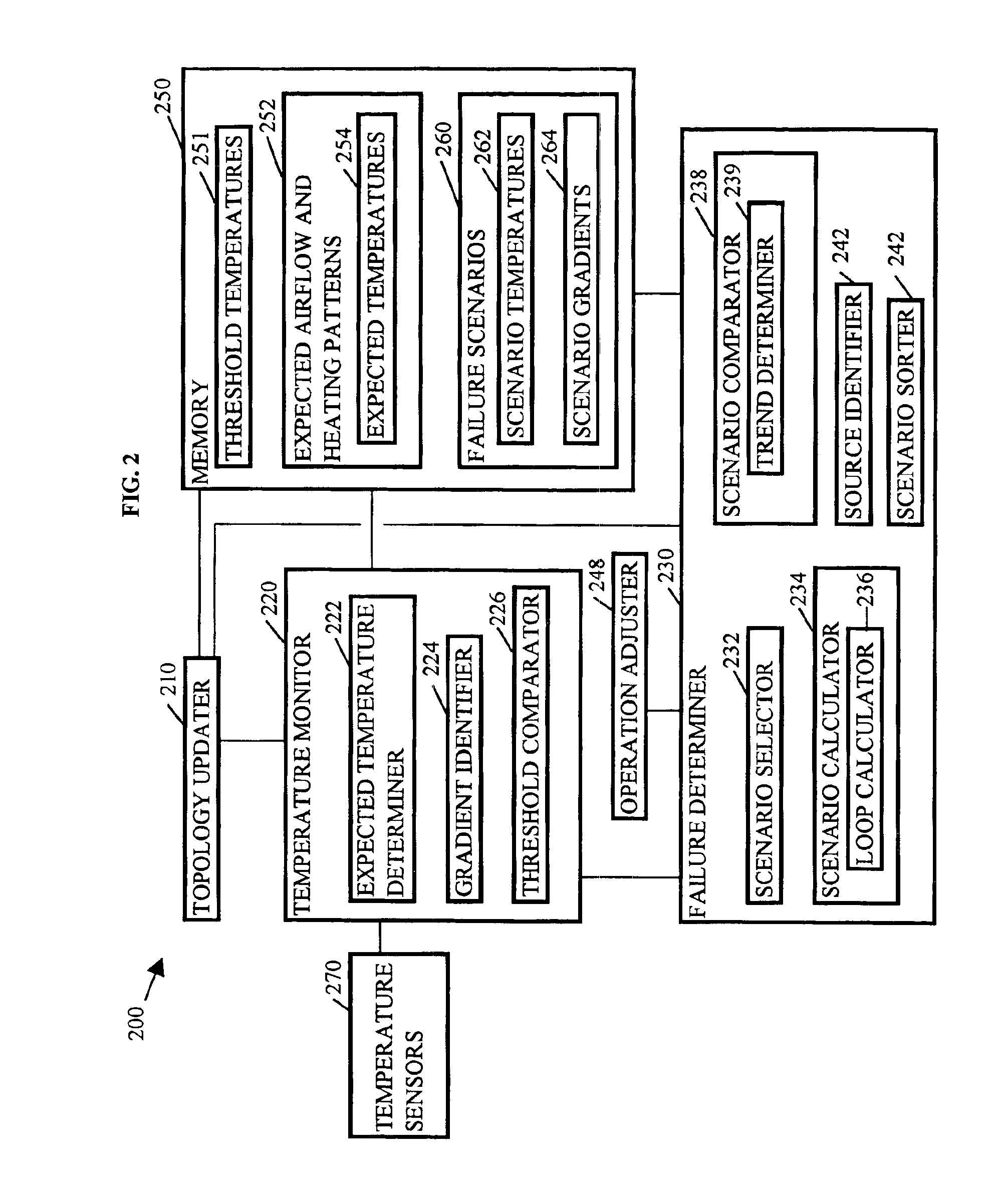

Thermal analysis in a data processing system

InactiveUS6889908B2Mechanical apparatusSpace heating and ventilation safety systemsData processing systemRoot cause

Methods, systems, and media for thermal analysis are disclosed. Embodiments of the invention receive temperatures associated with elements of a system. The temperatures received are dependant upon airflow and heating patterns of the elements. Differences between the temperatures received and expected temperatures are detected. Potential airflow and heating patterns associated with a thermal problem are then determined, the potential airflow and heating patterns being substantially consistent with the temperatures received, to identify a root cause of the thermal problem as a probable source of the differences. More specifically, embodiments collect temperature readings from temperature sensors within an enclosure of the system; identify and upward temperature gradient or temperature that exceeds a threshold temperature; and select a failure scenario associated with a root cause of a thermal problem that is similar to the thermal problem described by the temperature readings collected.

Owner:IBM CORP

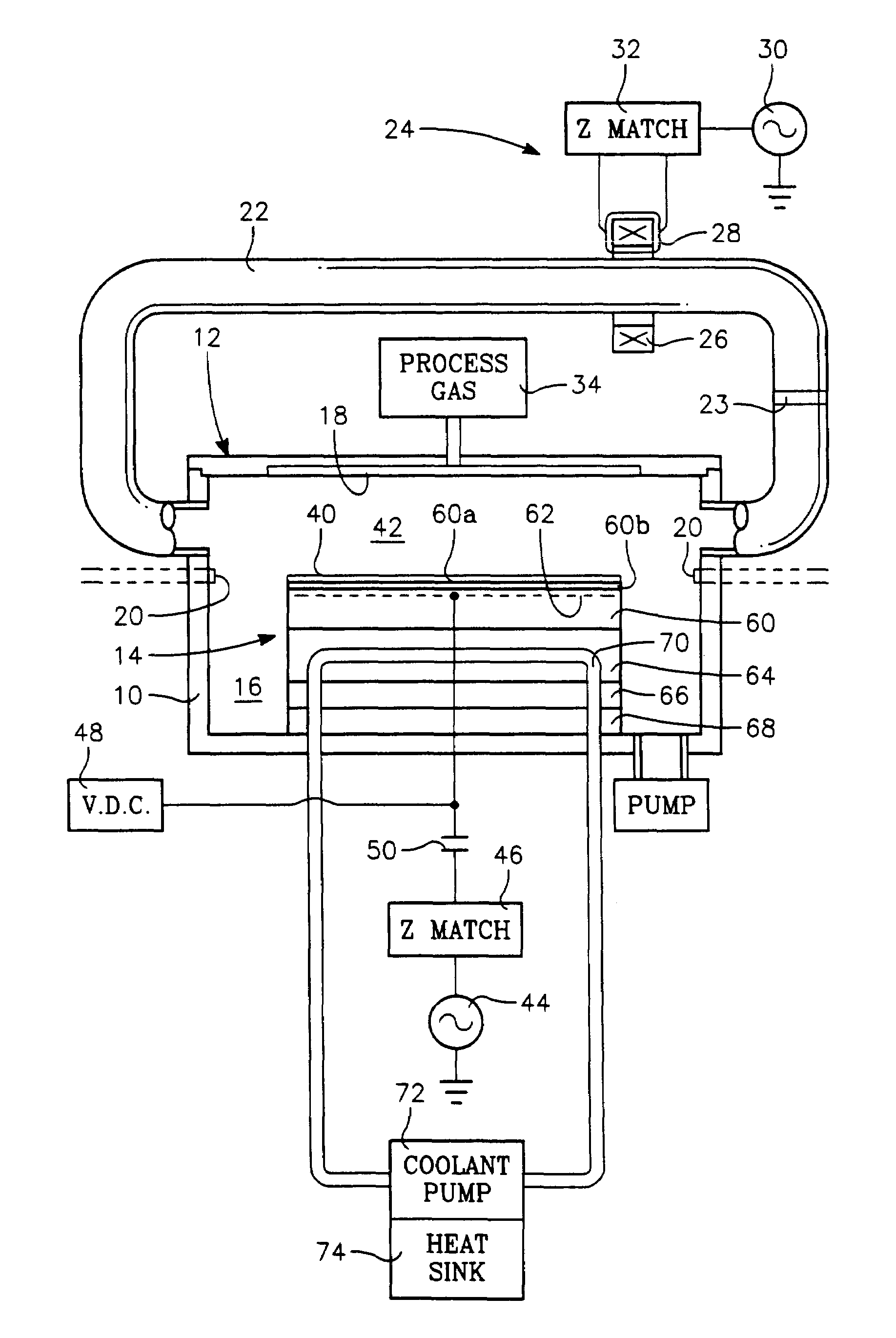

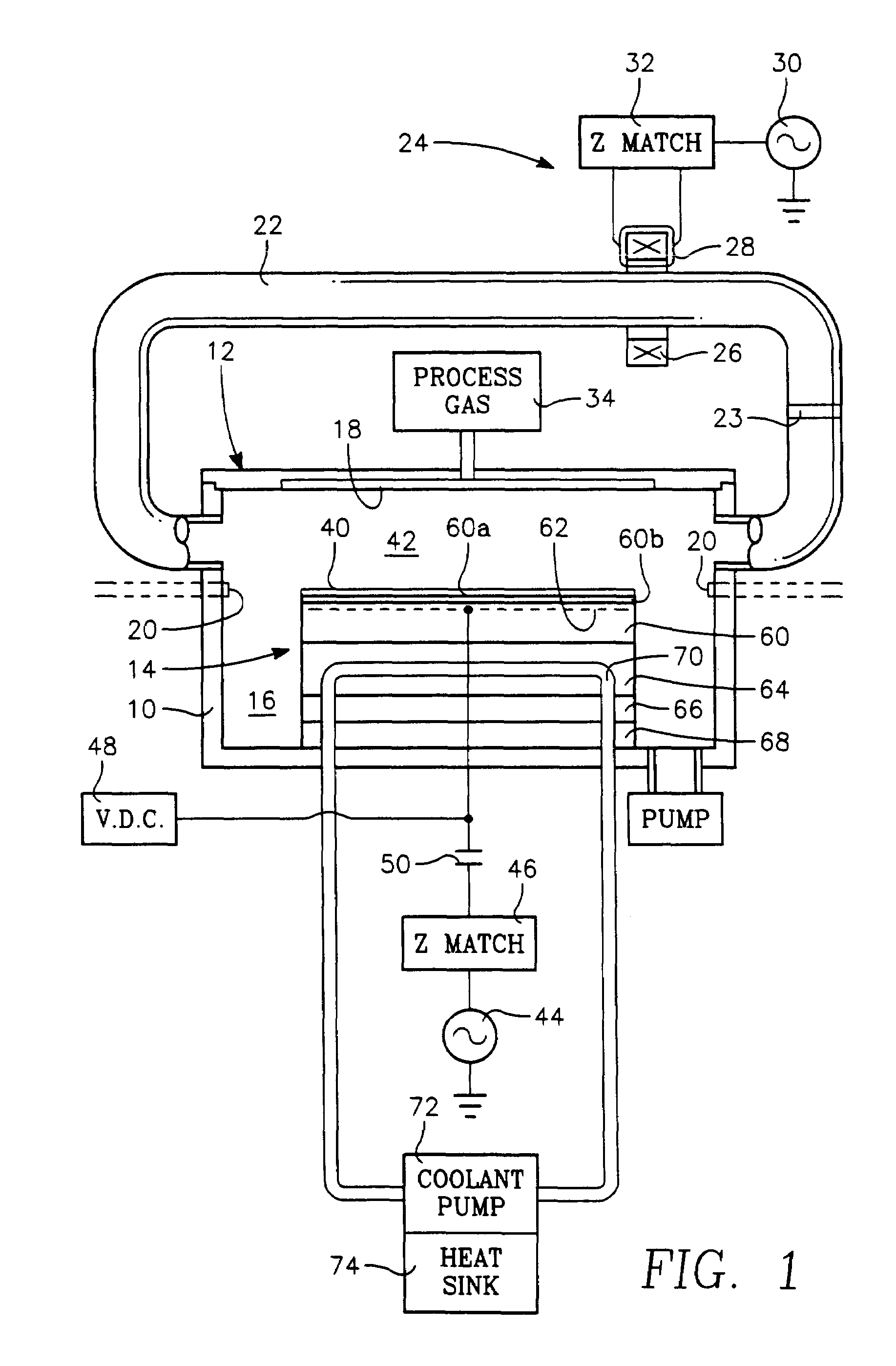

Plasma immersion ion implantation process

InactiveUS7094670B2Electric discharge tubesDecorative surface effectsPlasma-immersion ion implantationThreshold temperature

A method of performing plasma immersion ion implantation on a workpiece in a plasma reactor chamber, includes placing the workpiece on a workpiece support in the chamber, controlling a temperature of the wafer support near a constant level, performing plasma immersion ion implantation on the workpiece by introducing an implant species precursor gas into the chamber and generating a plasma while minimizing deposition and minimizing etching by holding the temperature of the workpiece within a temperature range that is above a workpiece deposition threshold temperature and below a workpiece etch threshold temperature.

Owner:APPLIED MATERIALS INC

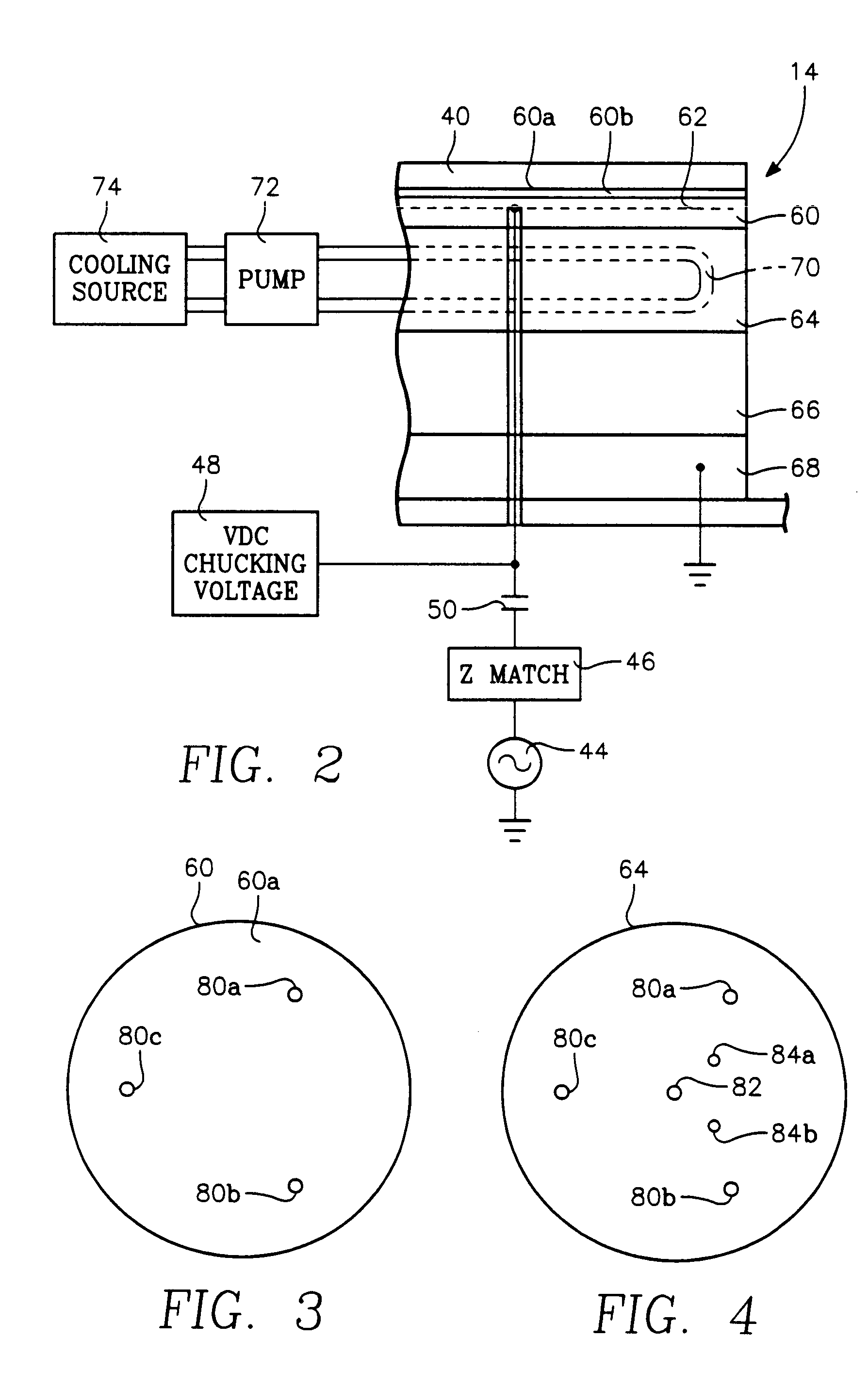

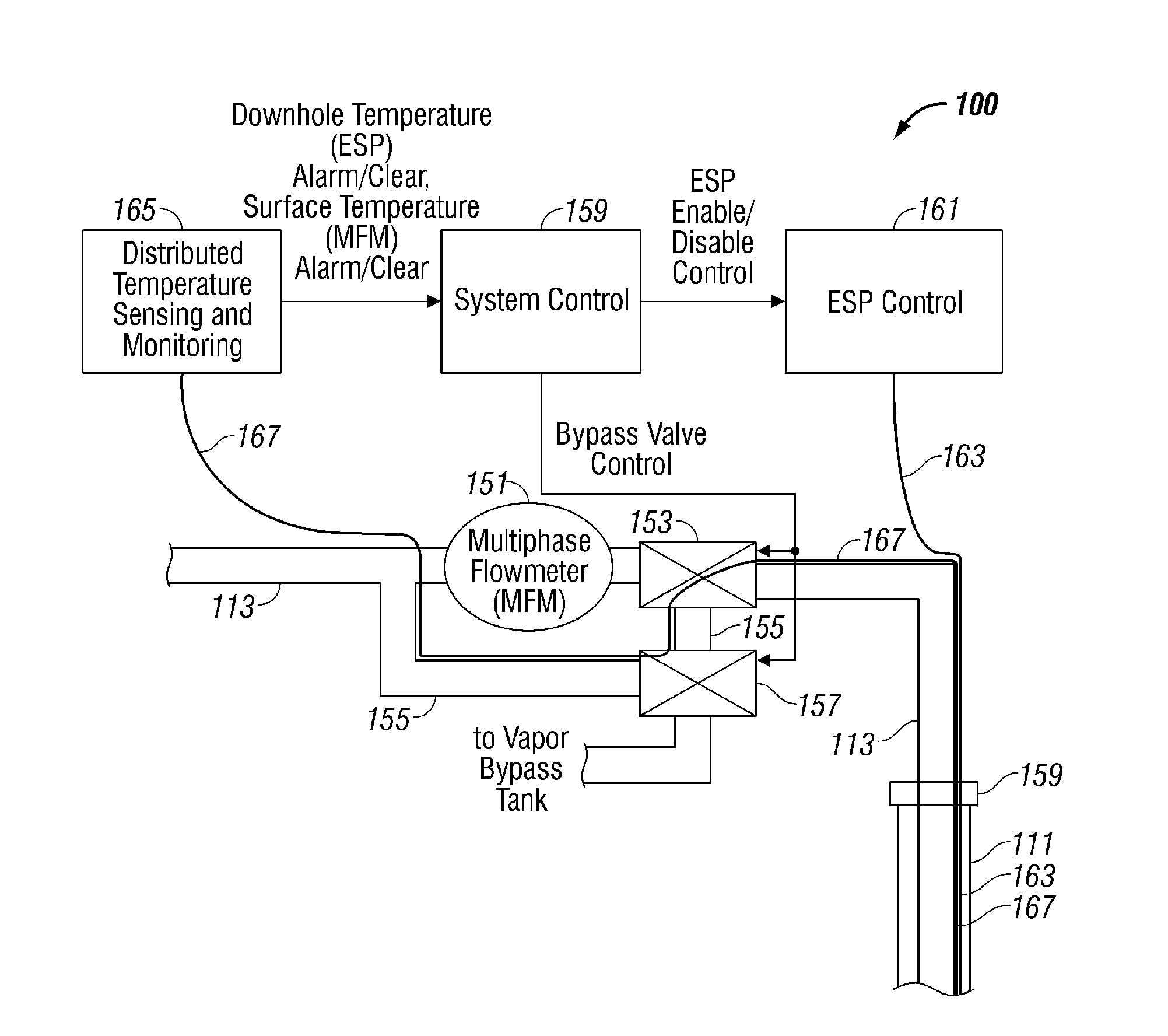

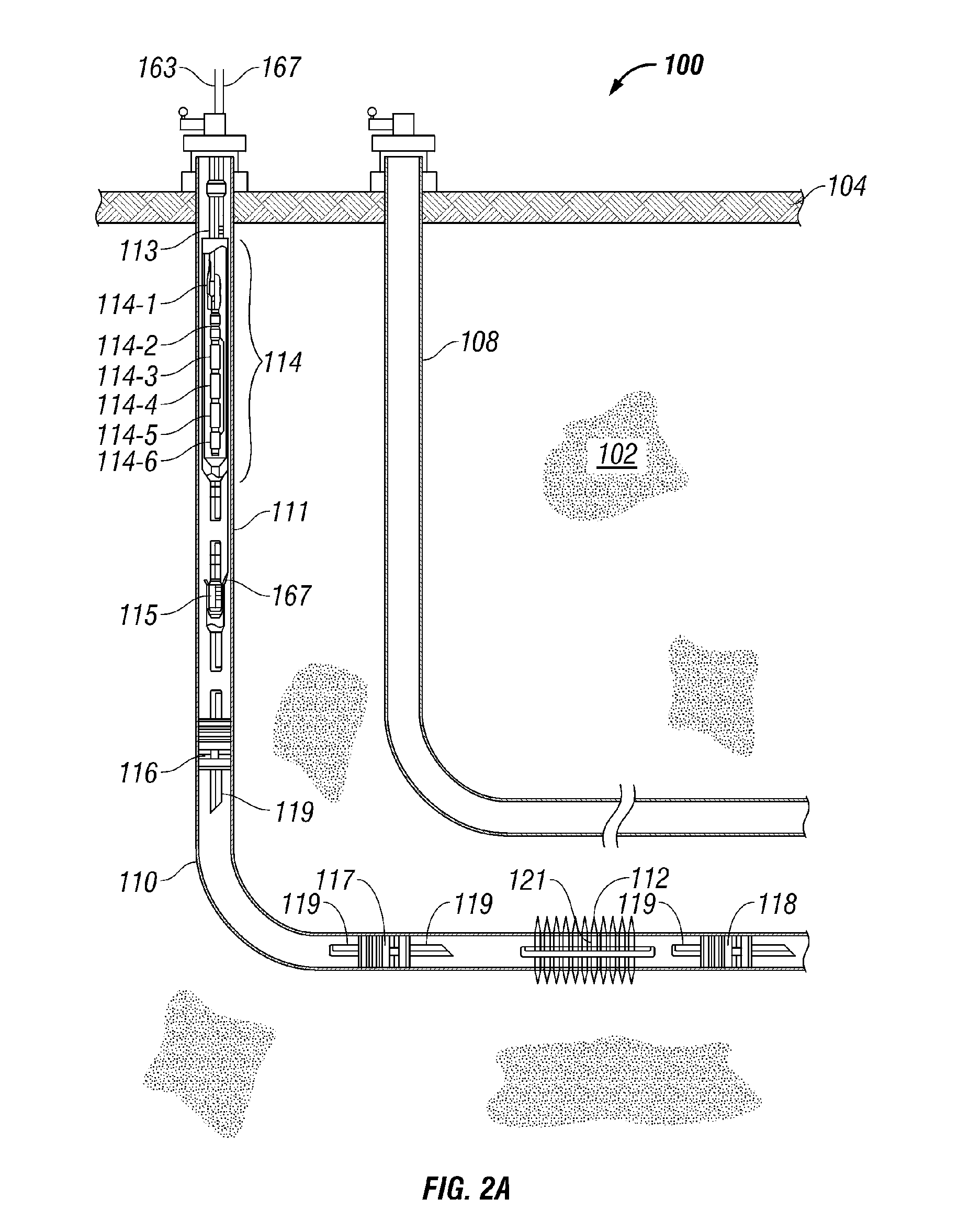

Real-Time Production-Side Monitoring and Control for Heat Assisted Fluid Recovery Applications

An automatic control system that protects downhole equipment and surface equipment from high temperatures resulting from the breakthrough of injection vapor. The system operates to derive an estimate of the temperature of production fluid at a location upstream from the downhole equipment. An alarm signal is generated in the event that this temperature exceeds a threshold temperature characteristic of injection vapor breakthrough. Electric power to the downhole equipment is automatically shut off in response to receiving the alarm signal. A bypass valve selectively directs production fluid to a bypass path. The system operates to derive an estimate of the temperature of the production fluid at a location upstream from the surface equipment. An alarm signal is generated when this temperature exceeds a threshold temperature characteristic of injection vapor breakthrough. The bypass valve is automatically controlled to direct production fluid to the bypass path in response to receiving the alarm signal.

Owner:SCHLUMBERGER TECH CORP

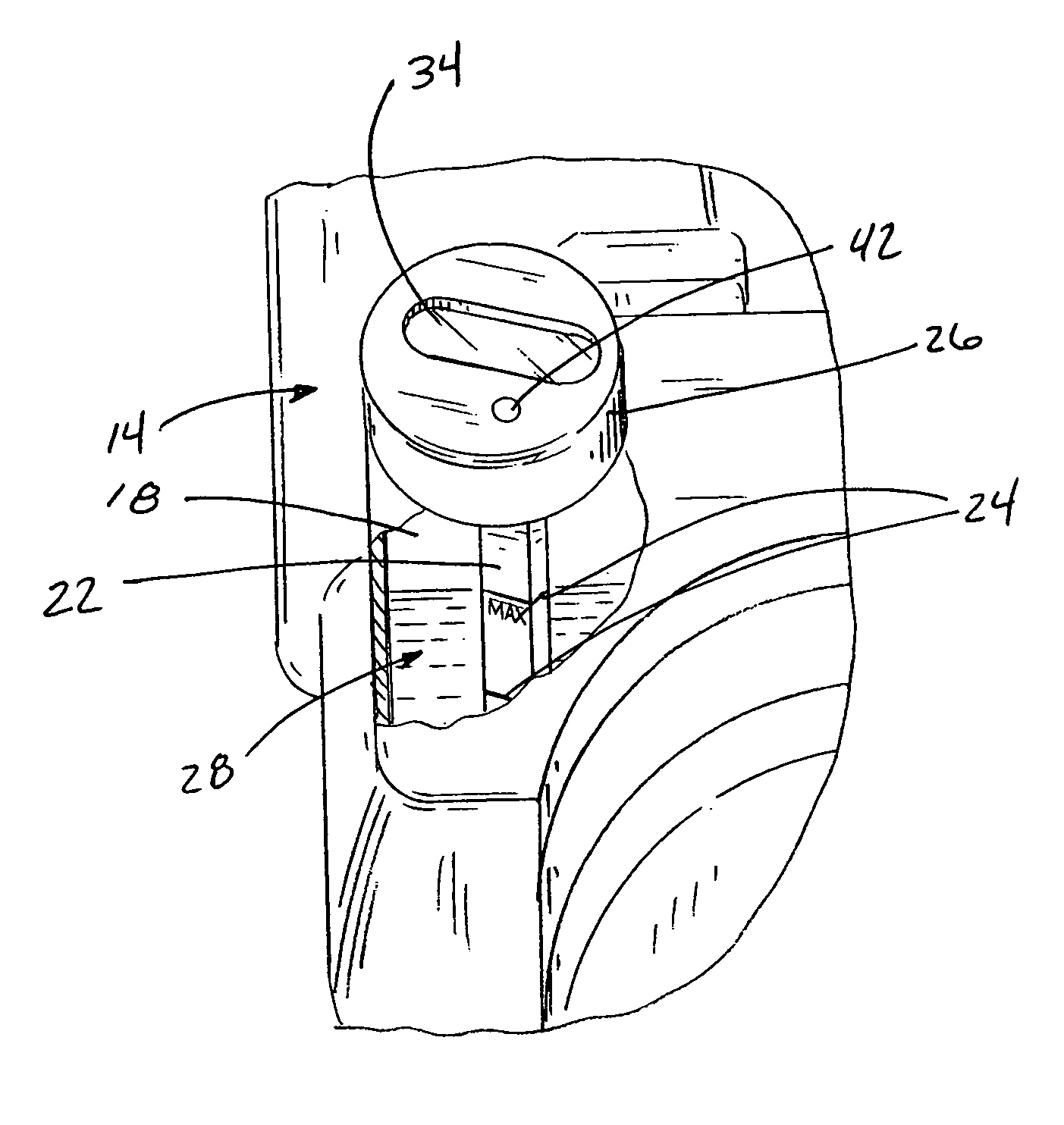

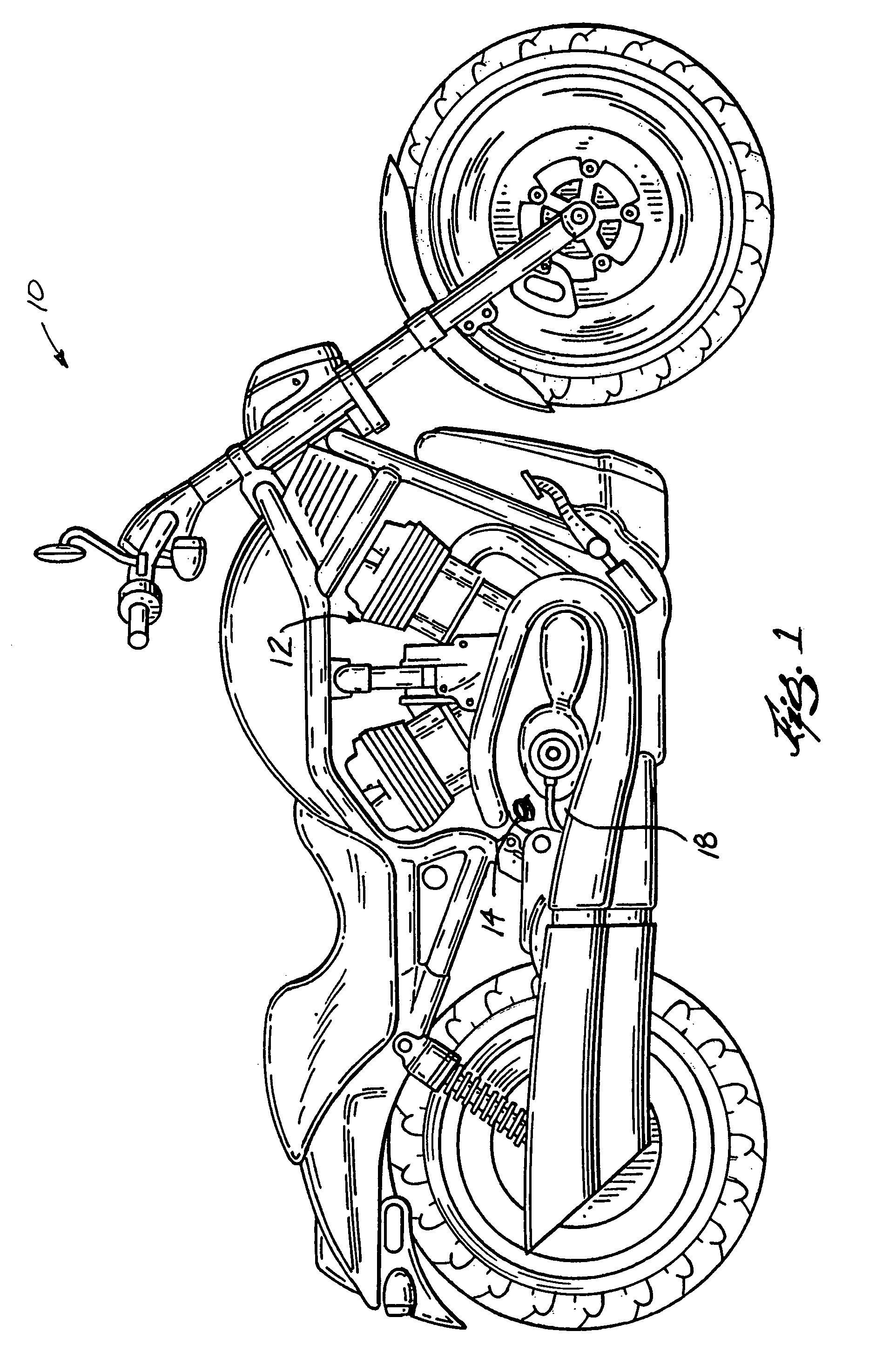

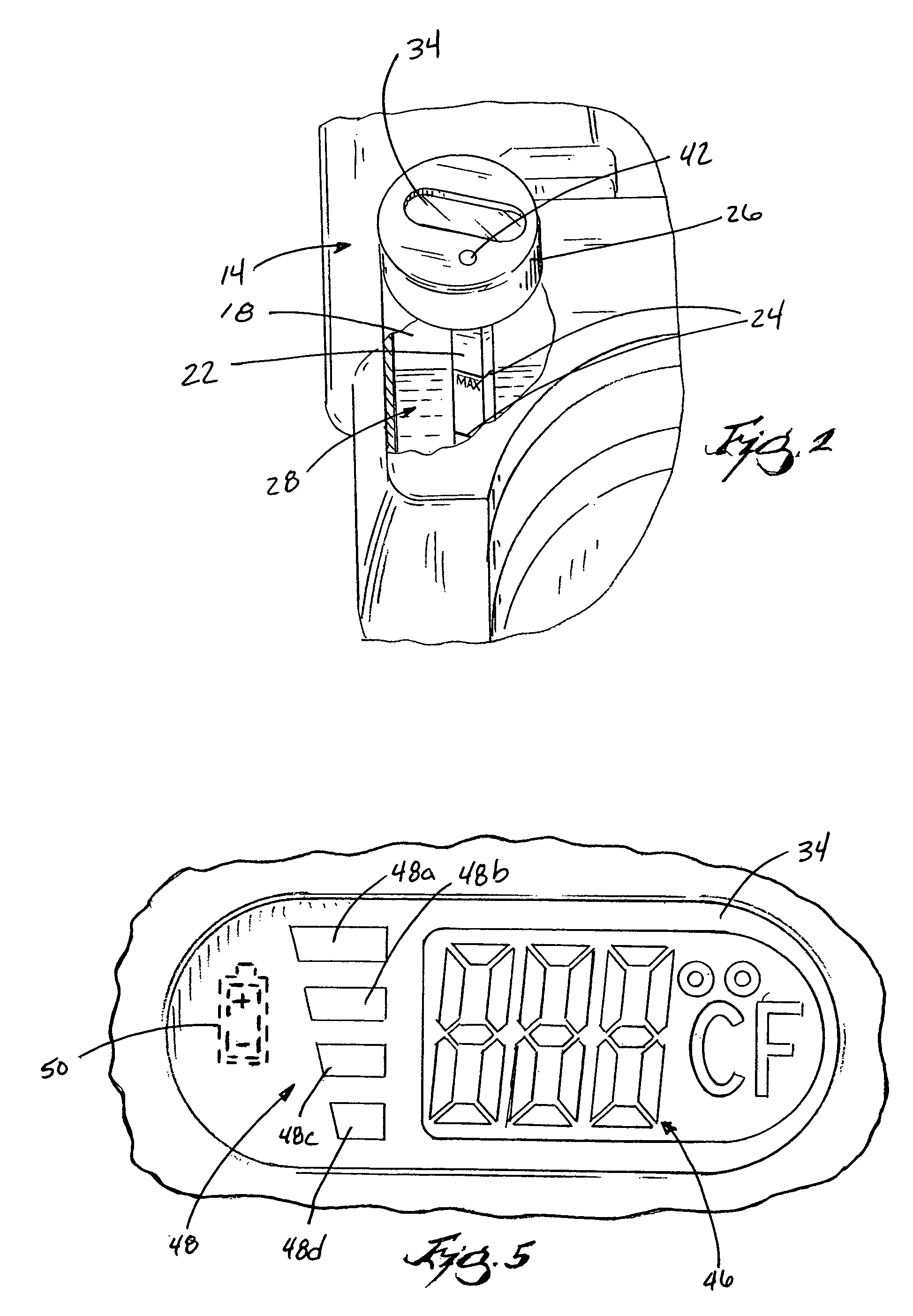

Apparatus for indicating oil temperature and oil level within an oil reservoir

Owner:HARLEY DAVIDSON MOTOR COMPANY GROUP INC

Combination freeze indicators

ActiveUS7490575B2Simple and reliable and inexpensiveThermometer detailsThermometers using mean/integrated valuesEngineeringThreshold temperature

Owner:TEMPTIME CORP

Method of removing MEMS devices from a handle substrate

InactiveUS20080283190A1Short timeLamination ancillary operationsLaminationAdhesiveThreshold temperature

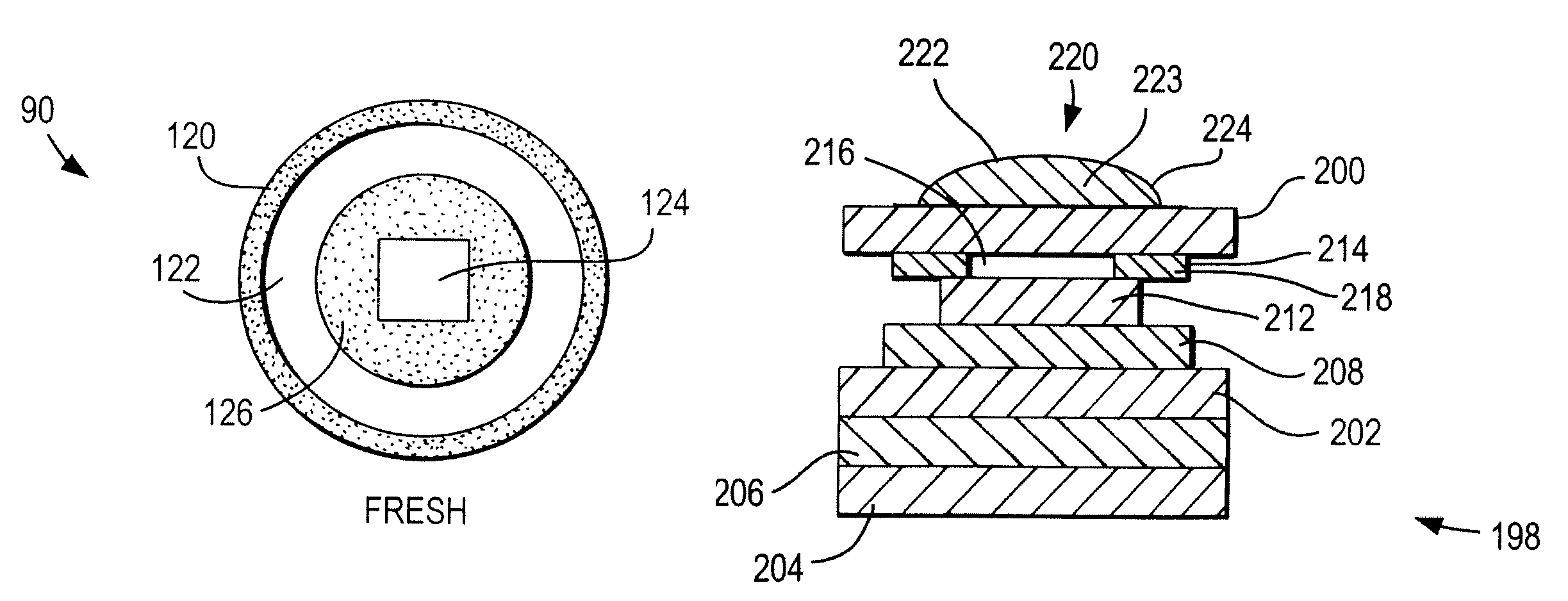

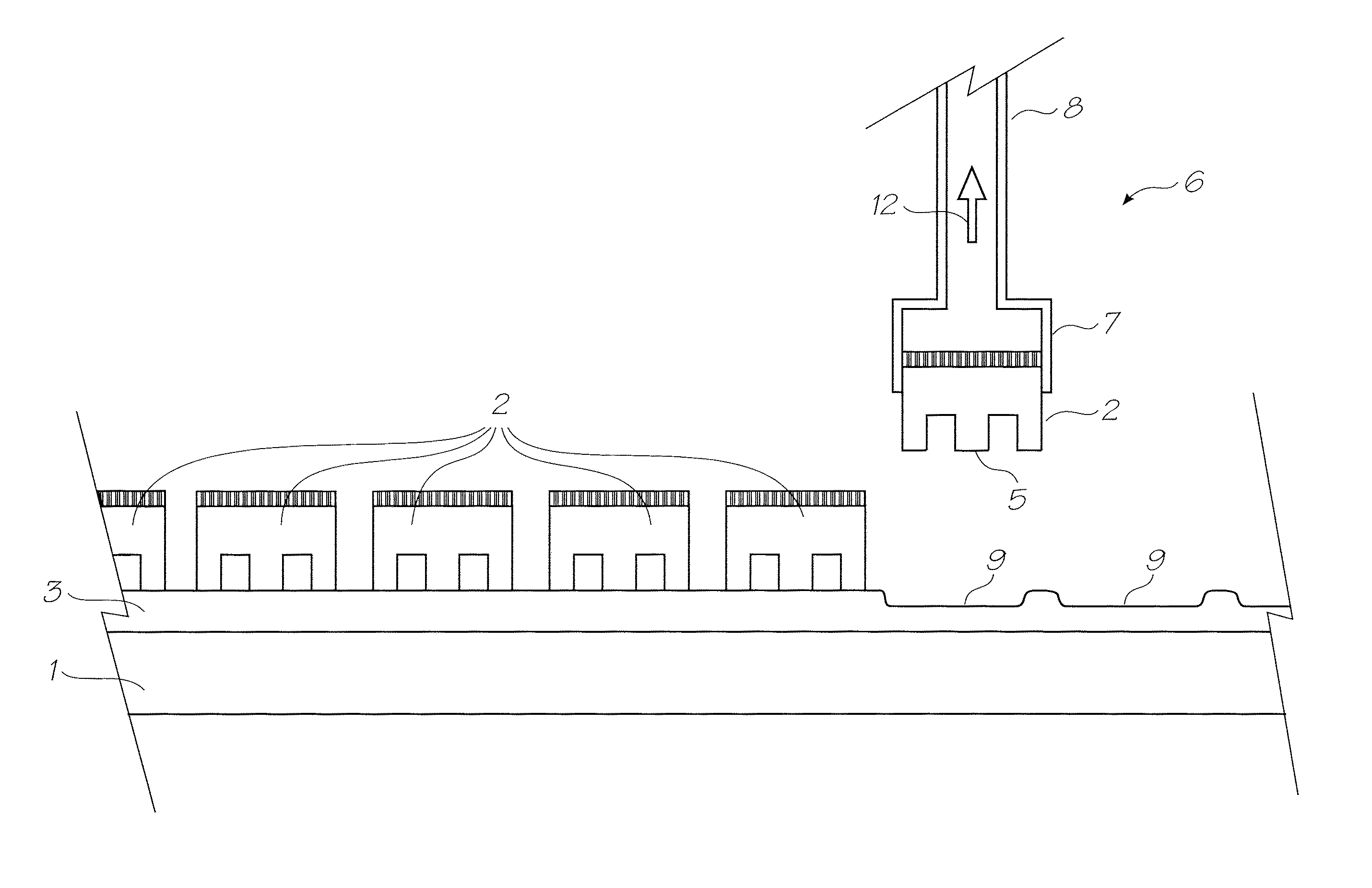

A method of removing MEMS devices (2) from a handle substrate (1), where the MEMS devices are individually bonded to it via a thermal release adhesive (3) that reduces its adhesion when heated above a threshold temperature. The method heats the MEMS devices (2) individually with a heat source (10) to conductively heat the thermal release adhesive (11) above the threshold temperature. With the adhesive (11) directly in contact with the back side (5) of the MEMS device (2) no longer bonding it to the glass handle (1), the devices (2) can be individually removed by a die picker (6). This method quickly heats the adhesive to release each die in about 1 second. This is comparable to UV release adhesive and does not require a prior 30 minute drying bake. Furthermore, heating the die by conduction, will in turn conductively heat the adhesives that only that adhesive which is closely localized to the die is released. The adhesive that bonds the adjacent dies to the glass handle remains unaffected.

Owner:SILVERBROOK RES PTY LTD

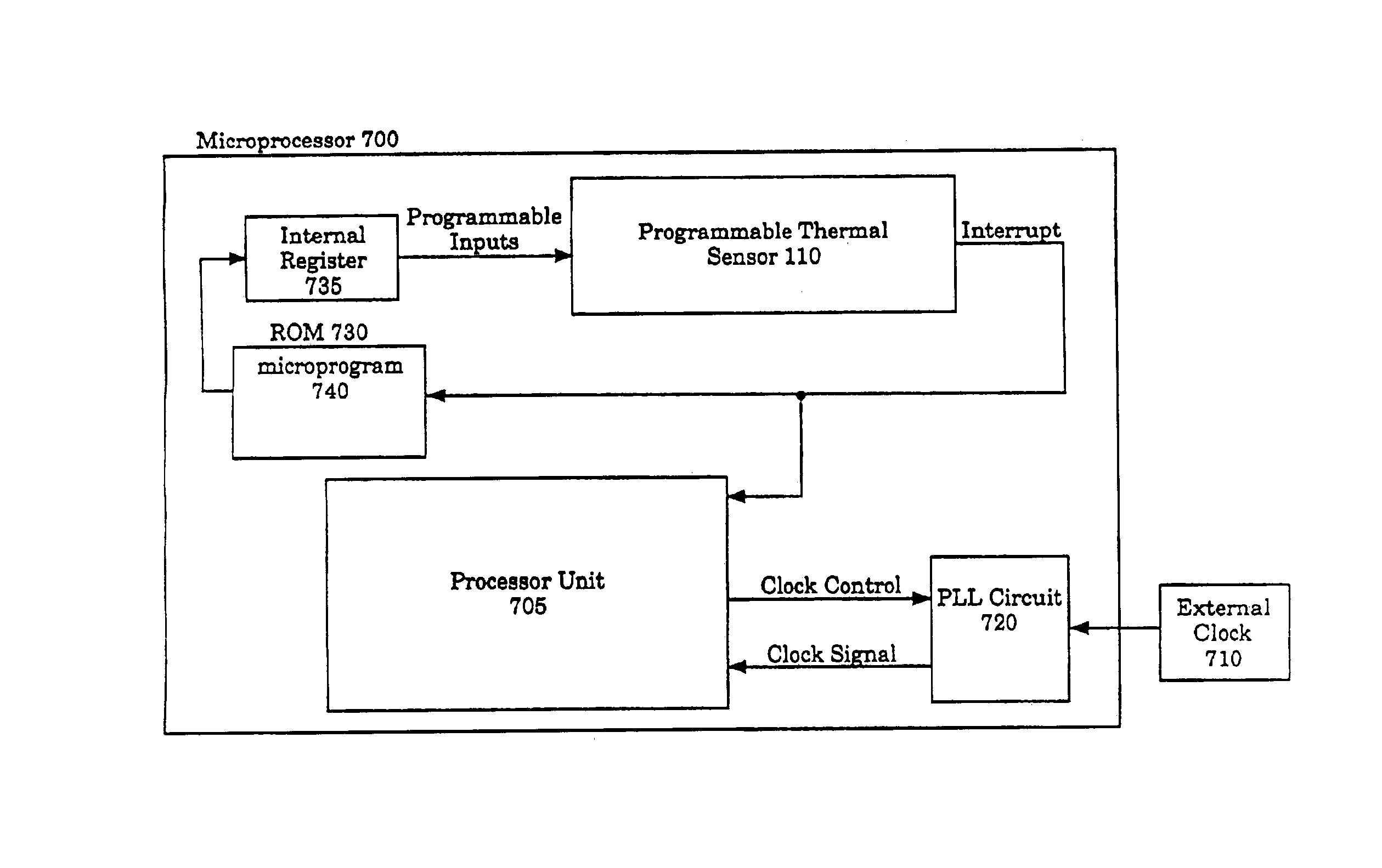

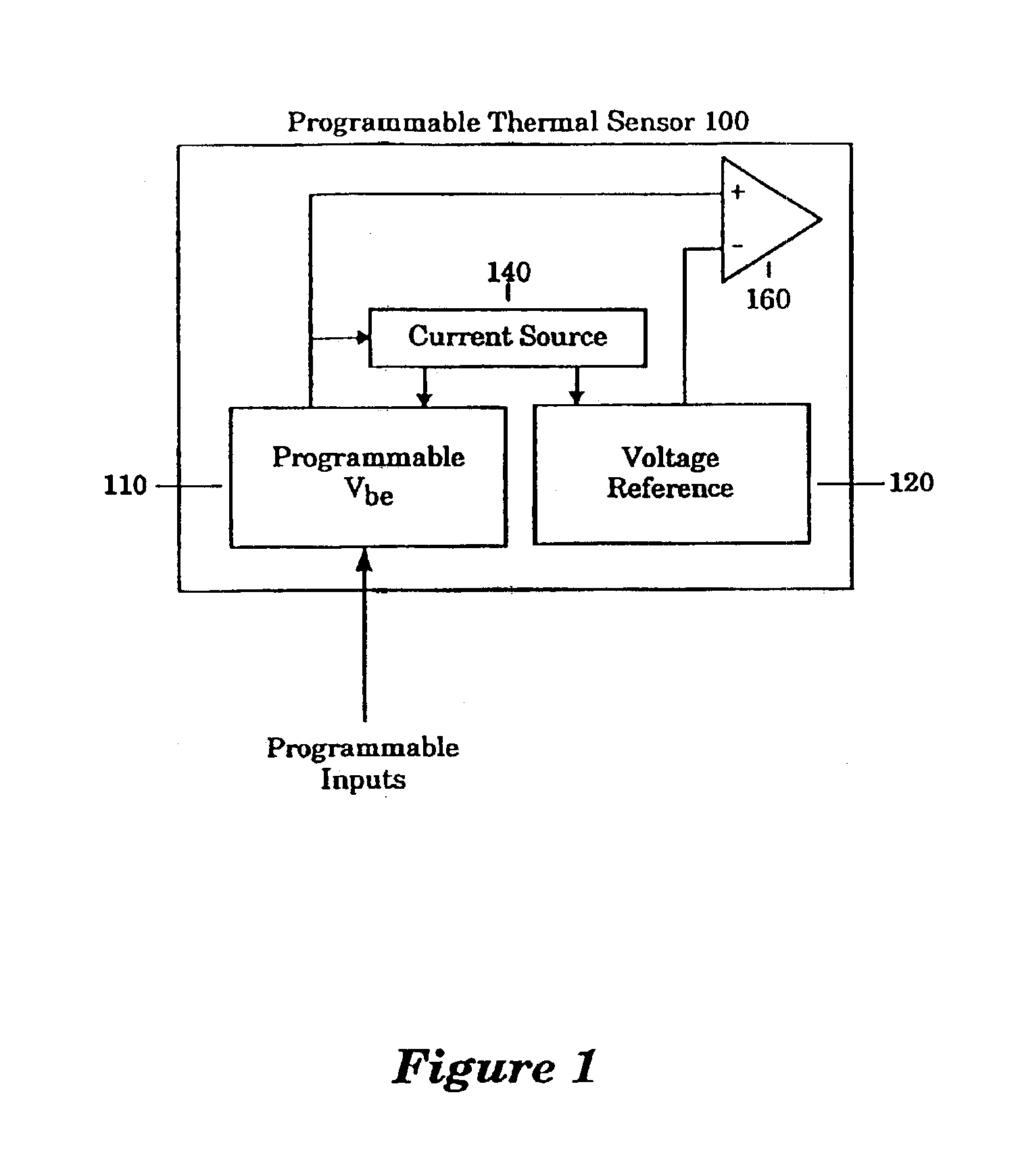

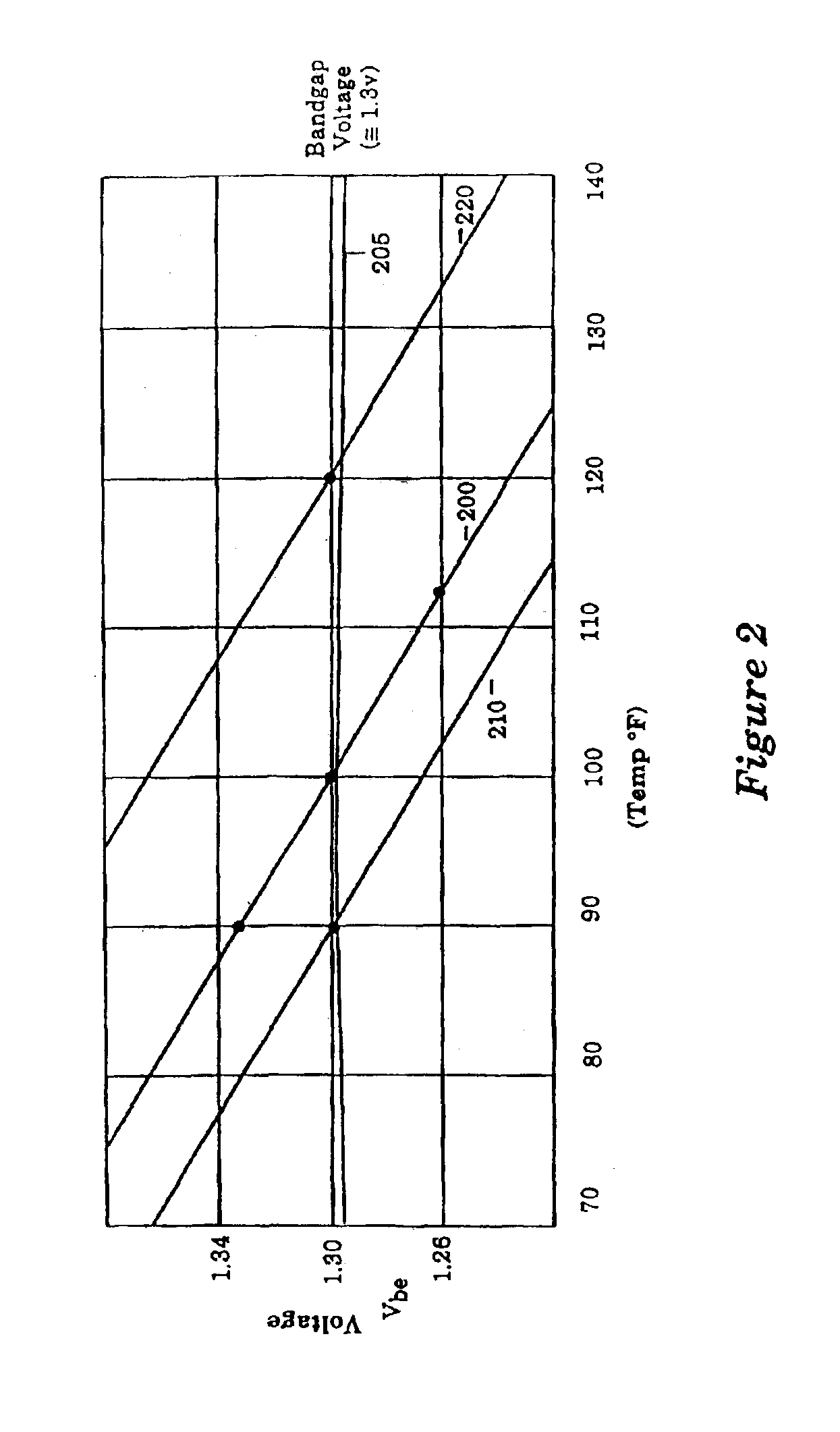

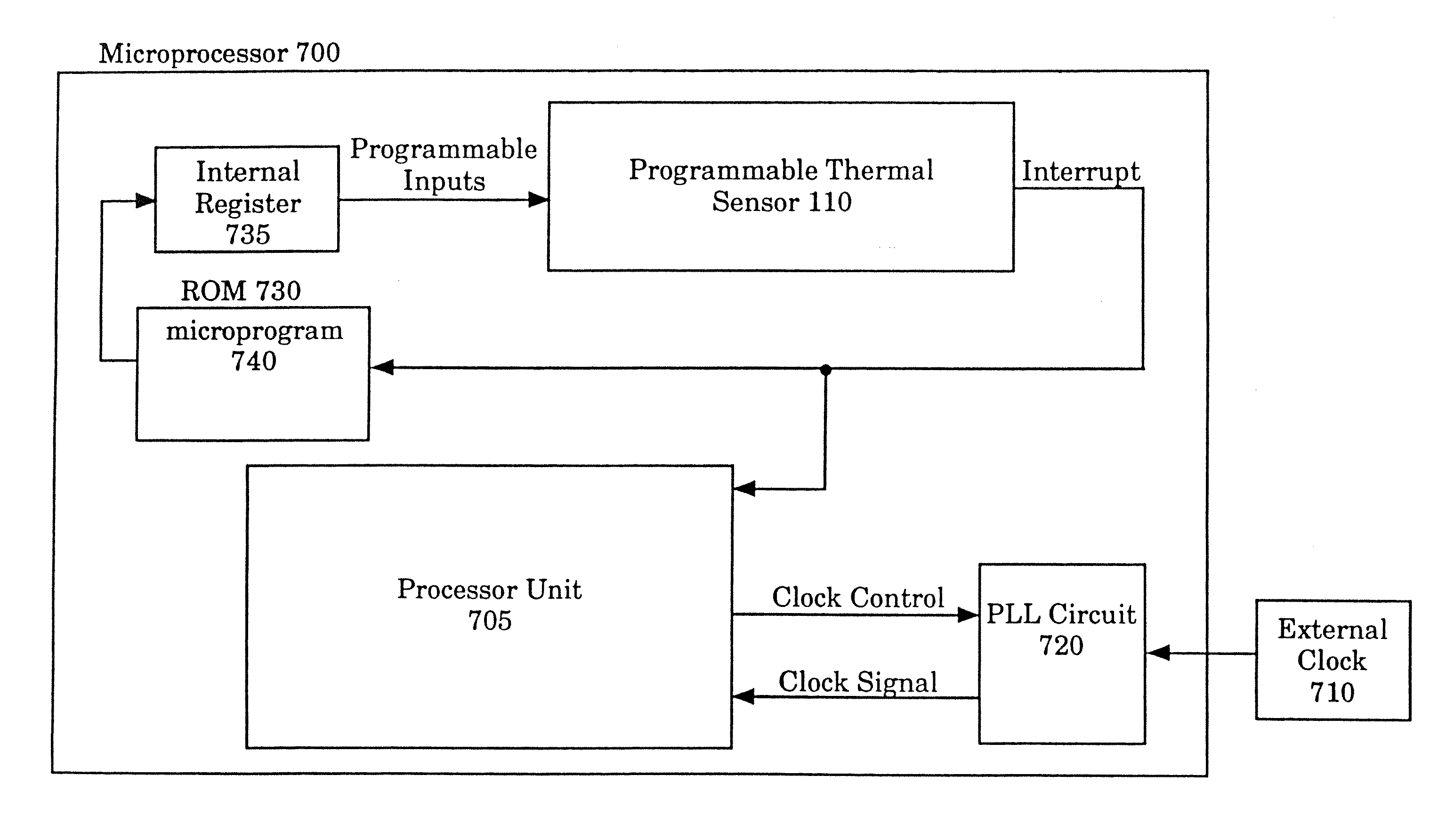

Temperature-based cooling device controller apparatus and method

InactiveUS6975047B2Reduce clock frequencySystem clock frequency is increasedEnergy efficient ICTDigital data processing detailsProcessor registerThreshold temperature

A temperature-based cooling device controller is implemented in an integrated circuit such as a microprocessor. The temperature-based cooling device controller includes a register to store a threshold temperature value, a thermal sensor, and clock adjustment logic to activate a cooling device in response to the thermal sensor indicating that the threshold temperature value has been exceeded. In a microprocessor implementation, the microprocessor contains a plurality of thermal sensors each placed in one of a plurality of different locations across the integrated circuit and an averaging mechanism to calculate an average temperature from the plurality of thermal sensors. Threshold adjustment logic increases the threshold temperature value to a new threshold temperature value in response to the thermal sensor indicating that the threshold temperature value has been exceeded. Threshold adjustment logic further lowers the new threshold temperature to detect decreases in temperature.

Owner:INTEL CORP

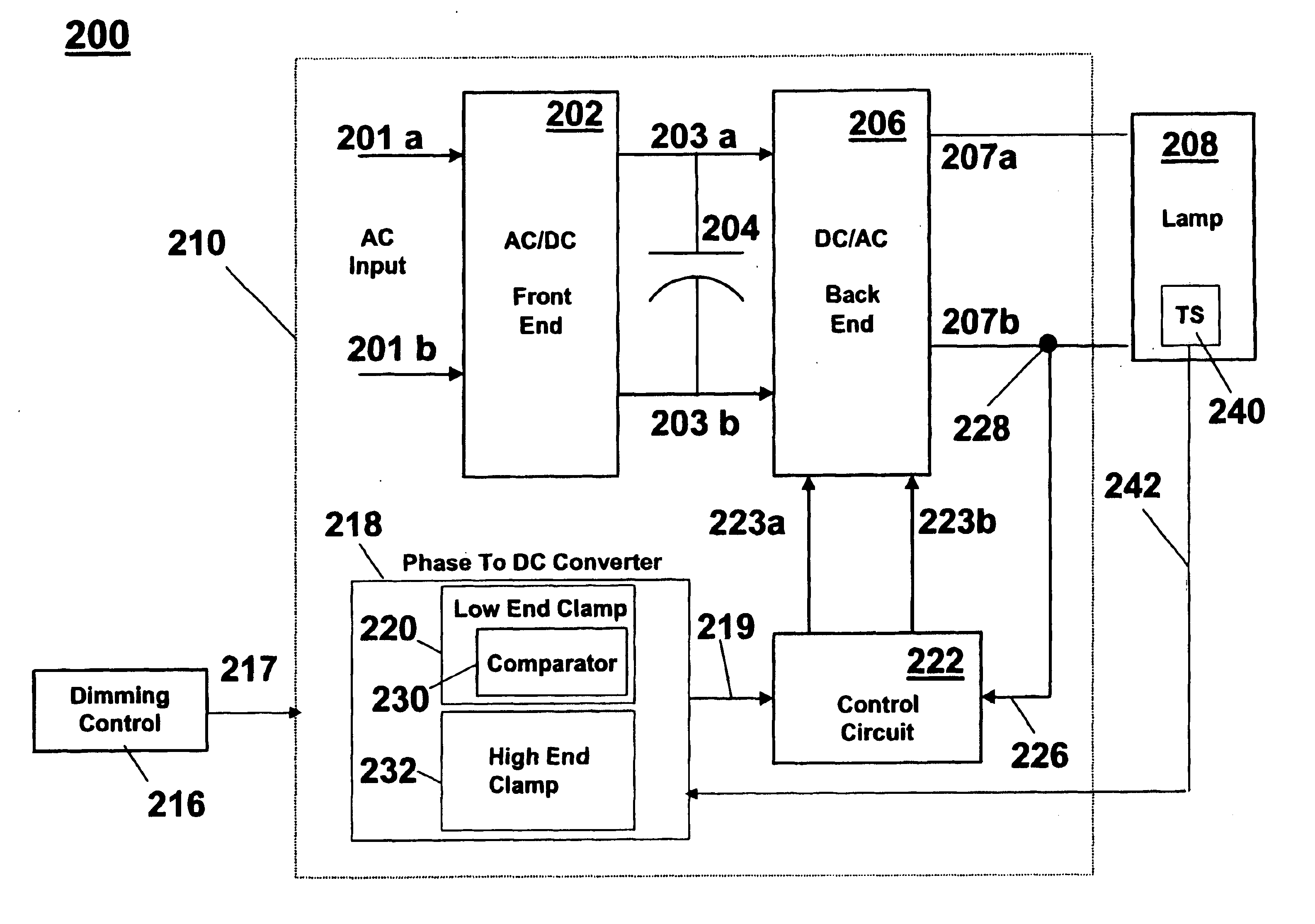

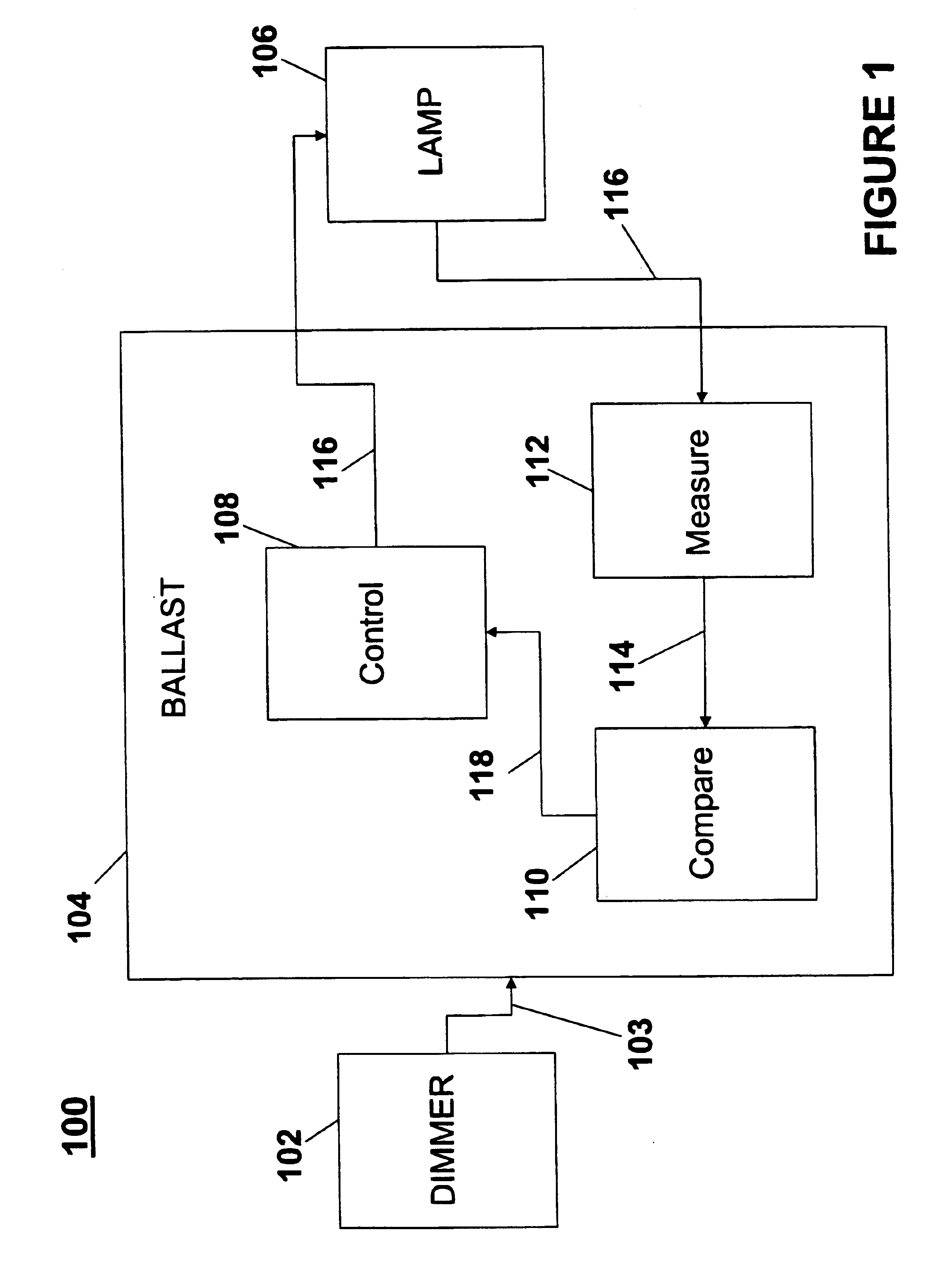

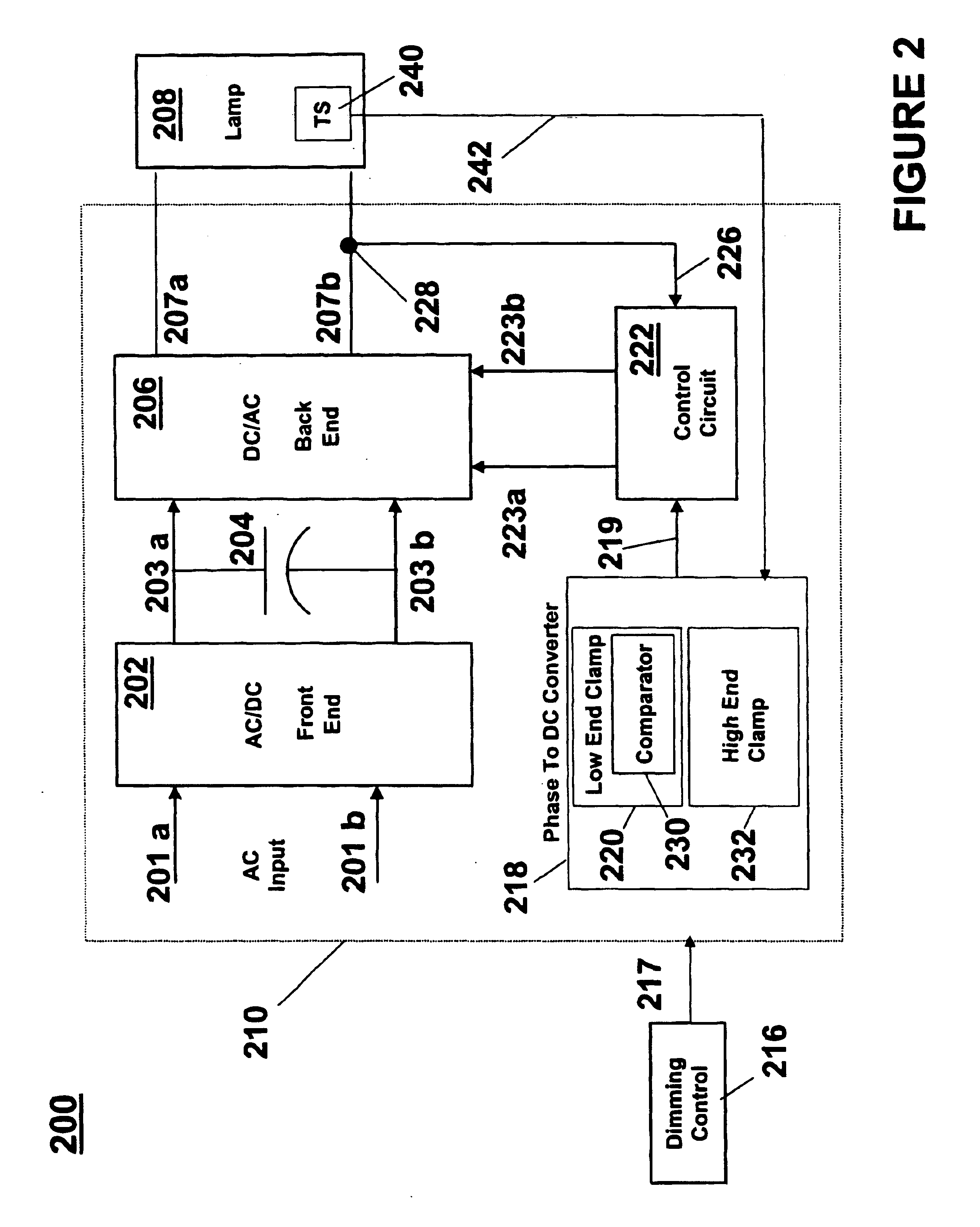

System and method for reducing flicker of compact gas discharge lamps at low lamp light output level

InactiveUS7061191B2Electric light circuit arrangementElectric discharge lampsGas-discharge lampEngineering

Owner:LUTRON TECH CO LLC

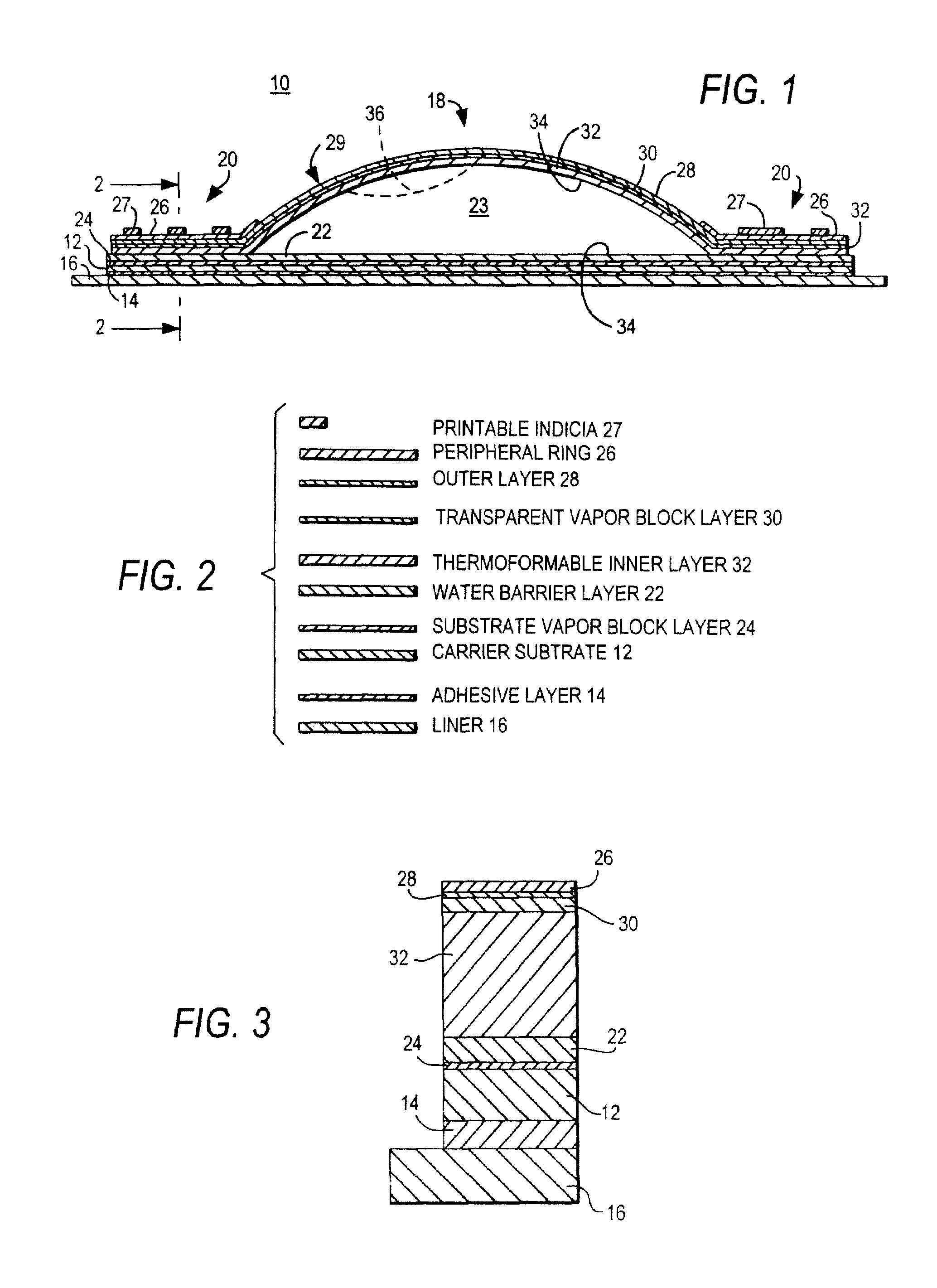

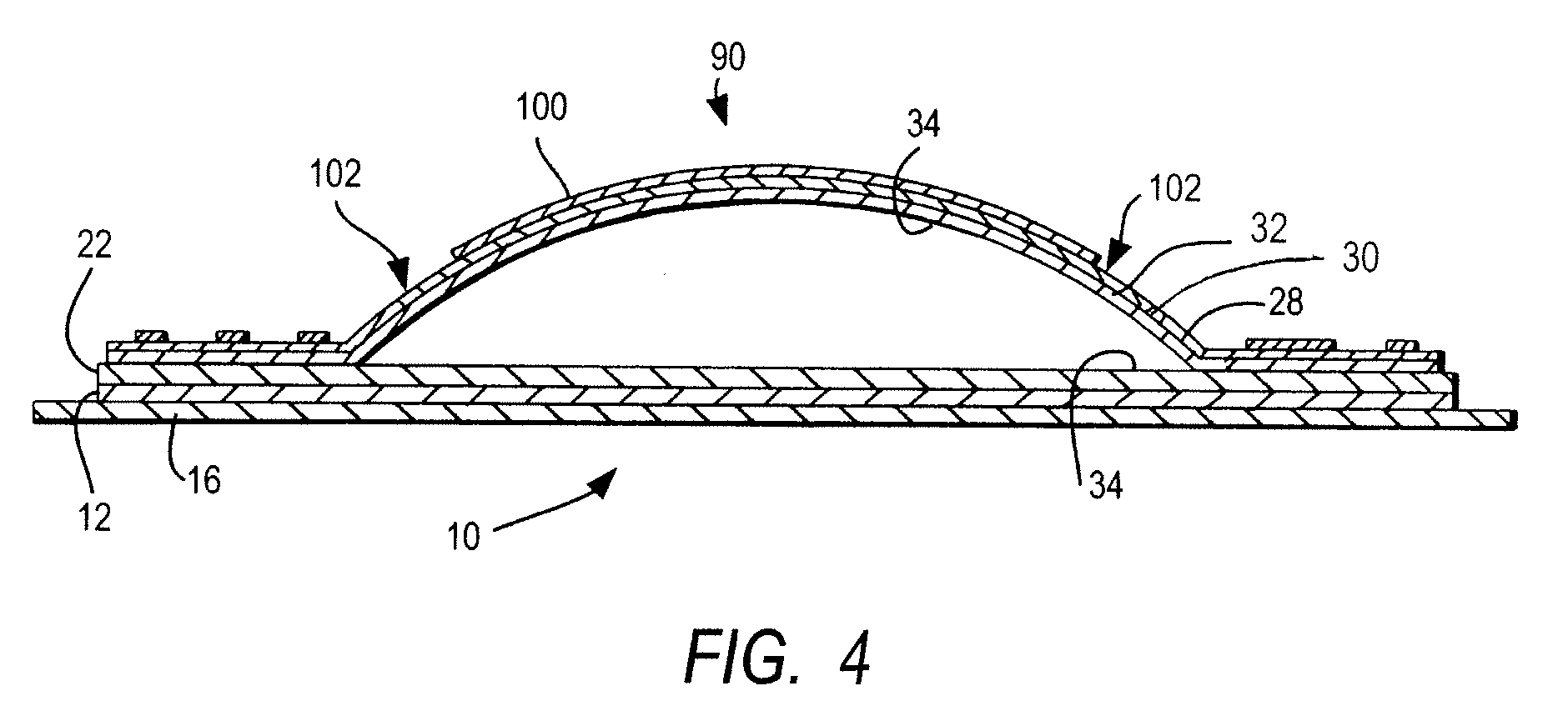

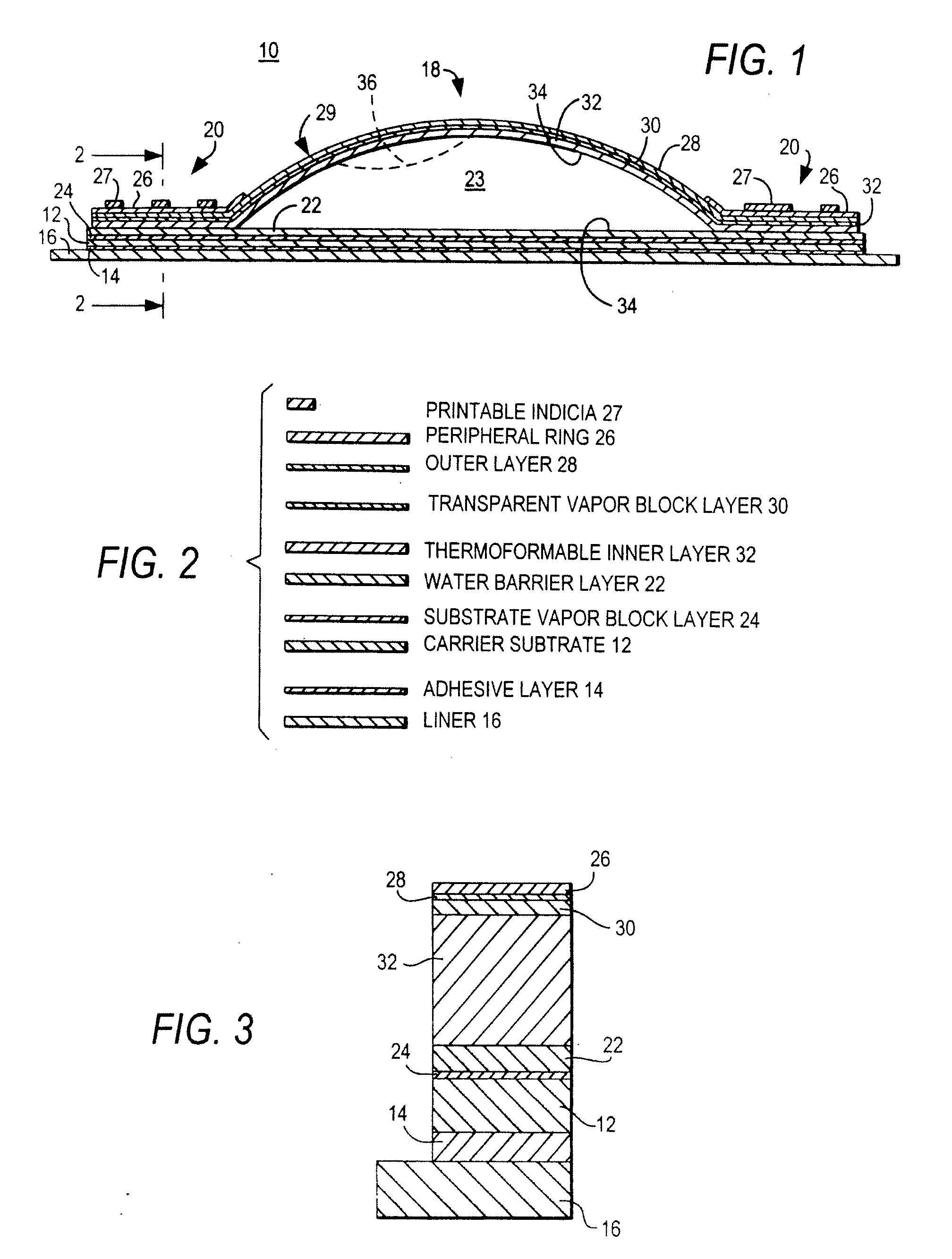

Color-retaining excess-temperature exposure indicator

ActiveUS7517146B2Reduce riskInhibit migrationThermometer detailsThermometers using mean/integrated valuesEngineeringThreshold temperature

An excess temperature indicator can provide a visual indication of past exposure of perishable, maturing and other host products to an elevated temperature exceeding a threshold temperature. The indicator can have an upper layer provided with a viewing window and a wick attached to the upper layer. A reservoir of heat-fusible indicator material can be disposed in contact with the wick, to fuse and move along the wick changing the visual appearance of a first portion of the wick viewable through the window, in response to an excess temperature event. Also, the indicator can have a region of fused upper layer material attaching the wick to the upper layer. Optionally, a window seal can extend around the viewing window to prevent migration of the indicator material. The indicator can be employed to monitor vaccines, foods and other products providing an enduring visual signal of exposure to potentially damaging temperature conditions.

Owner:TEMPTIME CORP

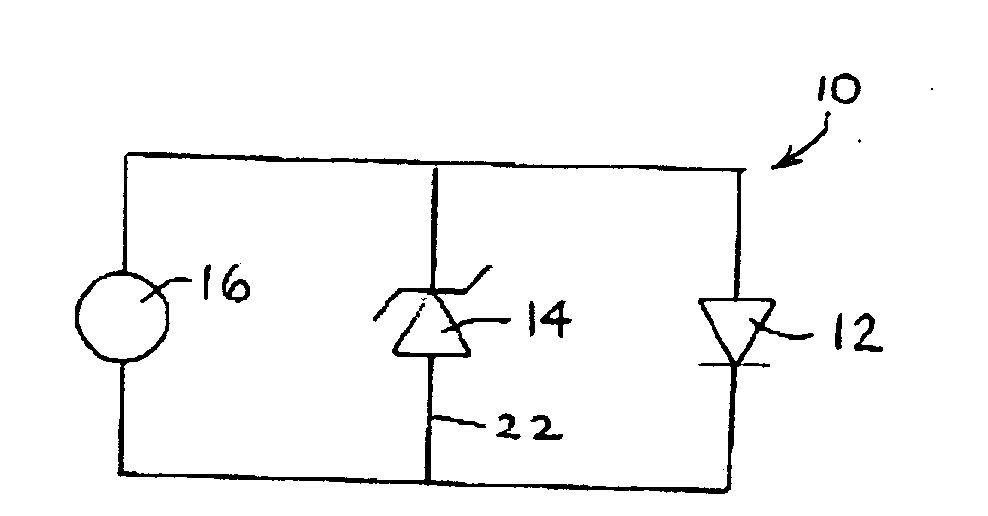

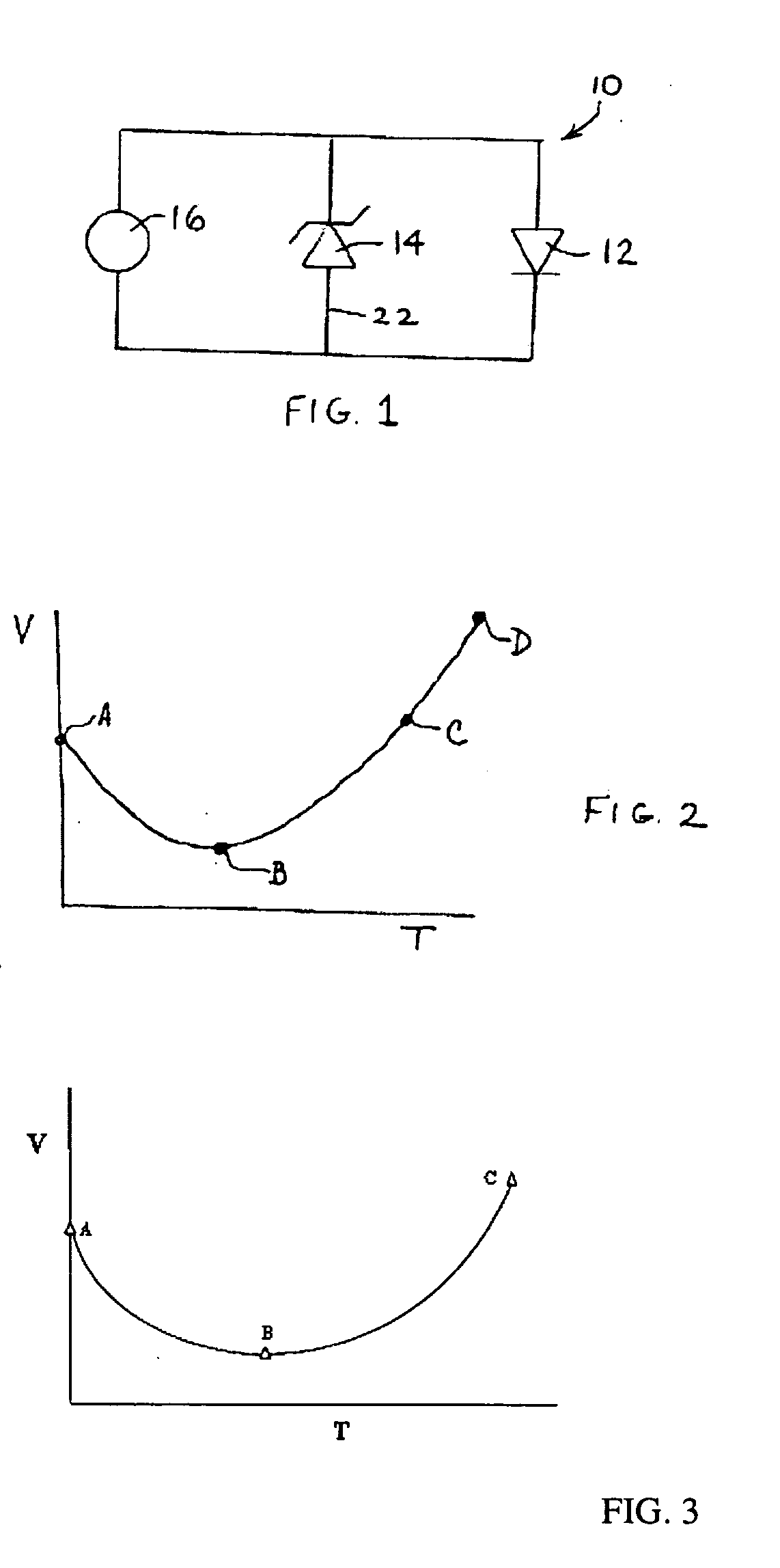

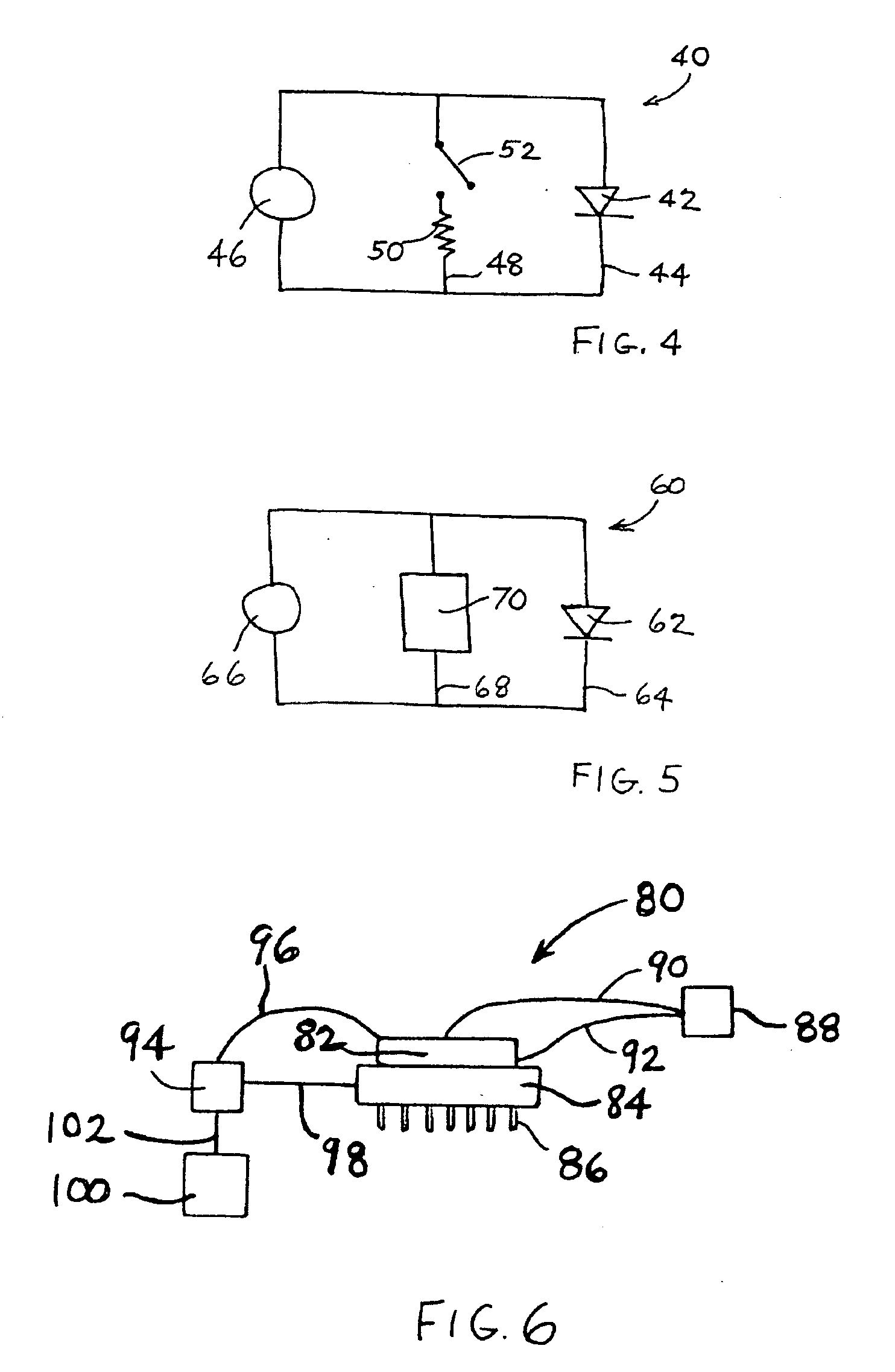

LED thermal management system and method

ActiveUS20100134024A1Low heat generationEasy to operateElectroluminescent light sourcesElectric light circuit arrangementZener diodeEngineering

A thermal management system for reducing or eliminating heat-mediated degradation of LED performance and / or operating life. The system may include a thermal controller arranged to respond to an LED operating condition, and to responsively limit temperature in the LED. The thermal controller in one implementation includes a bypass circuit containing a bypass control element, such as a varistor, Zener diode, or antifuse device, and arranged to divert current from flowing to the LED so that the LED remains in a cool state, e.g., below 75° C. The system may be arranged to (I) at least partially attenuate the power supplied to an LED so as to reduce heat generation in such LED and maintain the LED below a threshold temperature and / or (II) remove heat from the LED to maintain temperature of the LED below a threshold temperature.

Owner:IDEAL IND LIGHTING LLC

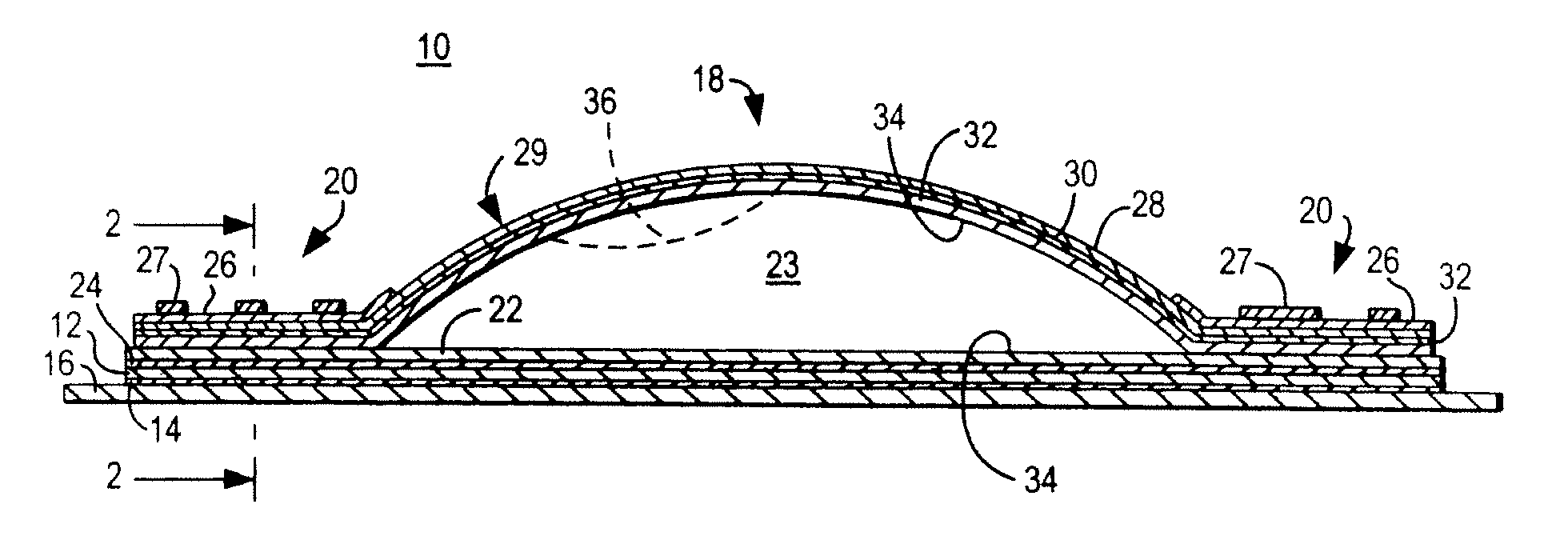

Freeze indicators, flexible freeze indicators and manufacturing methods

ActiveUS20080110391A1Provide flexibilityAvoid lostThermometer detailsThermometers using mean/integrated valuesActive IndicatorColloid

Freeze indicators providing a visual indication of exposure of the freeze indicator to a freezing or near-freezing temperature and their manufacture are disclosed. The freeze indicators employ colloidal dispersions as active elements and include flexible freeze indicators, freeze indicators protected against drying out and freeze indicators employing core shell composites, for example gold coated pigments as active indicator elements. Also disclosed are: a combination freeze indicator and threshold temperature indicator; a combination threshold indicator and cumulative temperature indicator; and three-way combination indicators that can provide indications of cumulative past temperature exposure, exposure to freezing temperatures and exposure to a temperature above a threshold.

Owner:TEMPTIME CORP

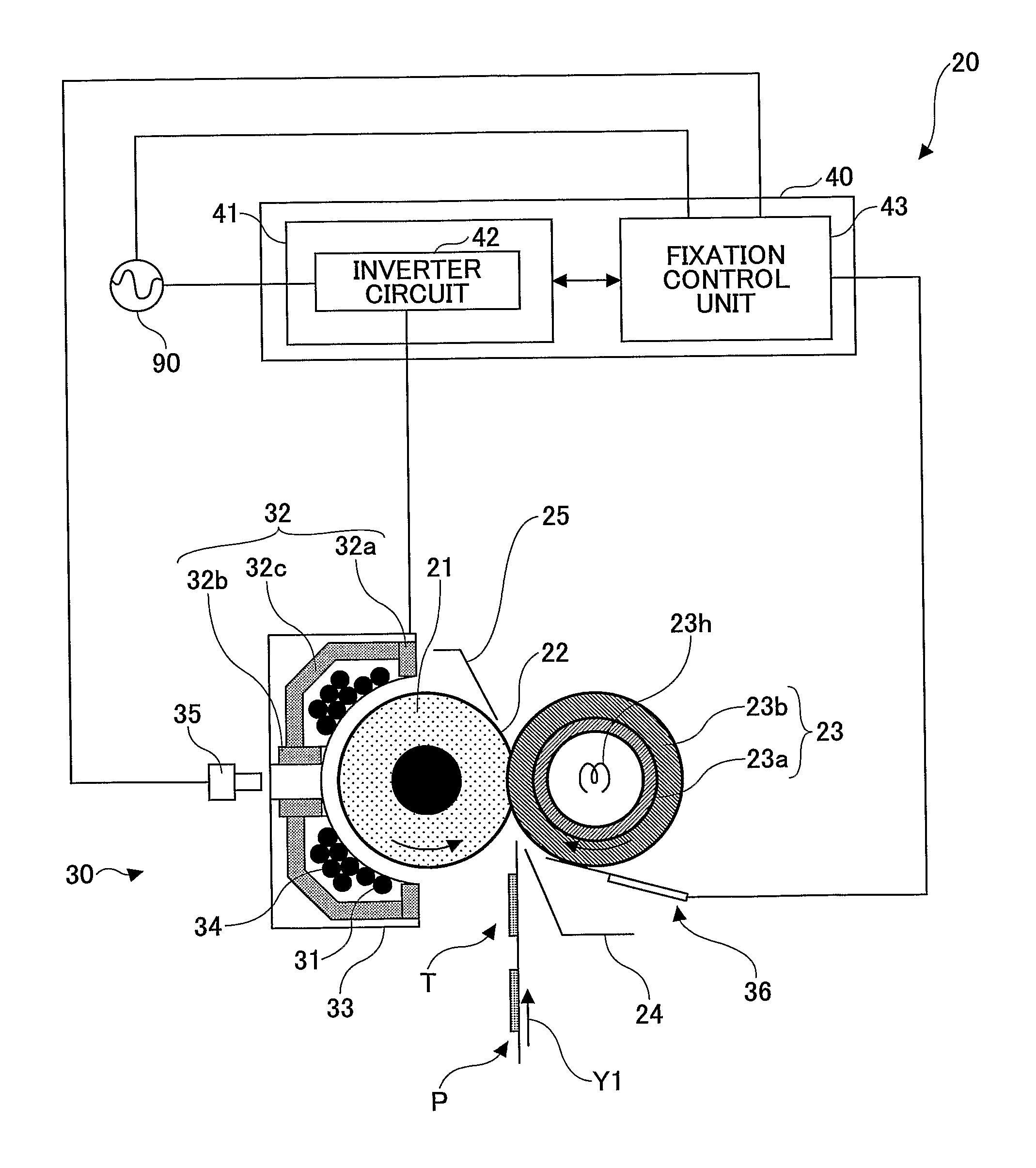

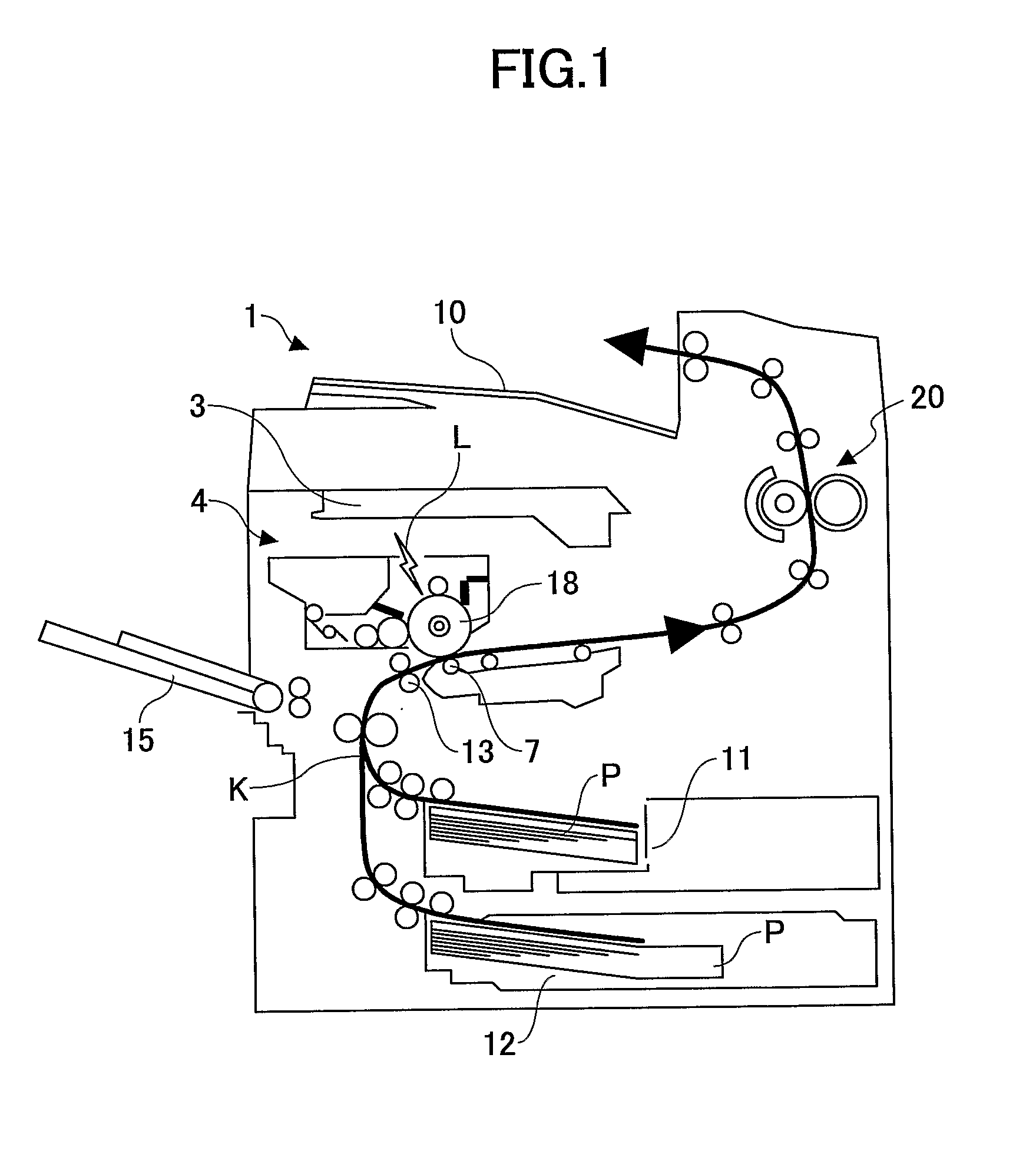

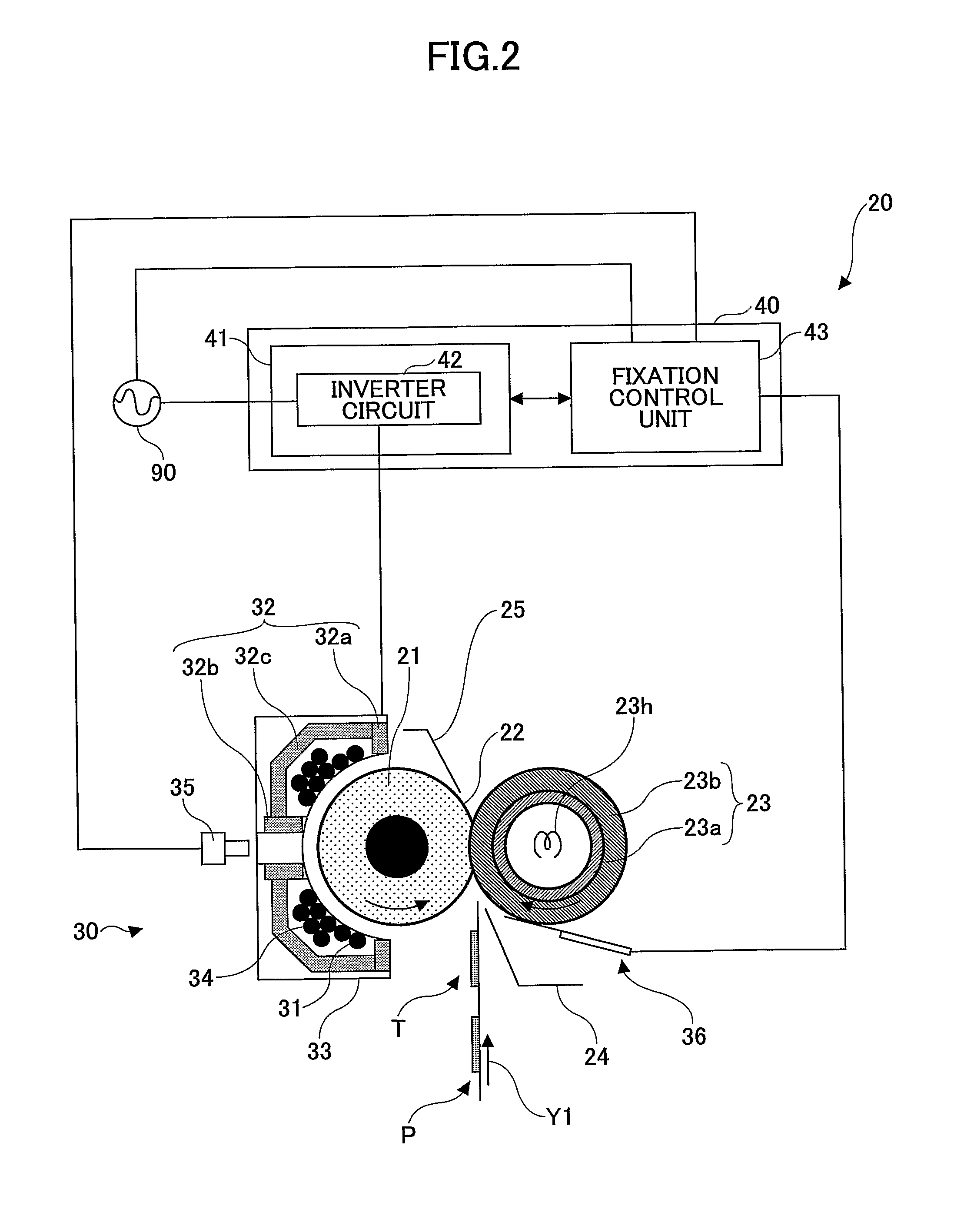

Fixation device and image forming apparatus

InactiveUS20110293309A1Shorten warm-up timeSuppressing overshoot temperatureElectrographic process apparatusMode controlImage formation

A fixation device includes a fixation member including a heating member, a pressure-application member press-contacting the fixation member forming a nip portion, an exciting coil induction-heating the heating member, a first temperature detection unit detecting a first temperature of the pressure-application member or a first ambient temperature of the fixation member, a second temperature detection unit detecting a second temperature of the fixation member, and a control unit selecting a temperature control mode or power control mode controlling power to the exciting coil. When the first temperature exceeds a first threshold temperature or the first ambient temperature exceeds a first ambient threshold temperature, the control unit selects the temperature control mode, and while the first temperature is equal to or lower than the first threshold temperature or the first ambient temperature is equal to or lower than the first ambient threshold temperature, the control unit selects the power control mode.

Owner:RICOH KK

Thermally switched reflective optical shutter

The thermally switched reflective optical shutter is a self-regulating “switchable mirror” device that reflects up to 100% of incident radiant energy above a threshold temperature, and reflects up to 50% of incident radiant energy below a threshold temperature. Control over the flow of radiant energy occurs independently of the thermal conductivity or insulating value of the device, and may or may not preserve the image and color properties of incoming visible light. The device can be used as a construction material to efficiently regulate the internal temperature and illumination of buildings, vehicles, and other structures without the need for an external power supply or operator signals. The device has unique aesthetic optical properties that are not found in traditional windows, skylights, stained glass, light fixtures, glass blocks, bricks, or walls. The device can be tailored to transmit sufficient visible light to see through in both the transparent and reflective states, while still providing significant control over the total energy transmission across the device.

Owner:RAVENBRICK

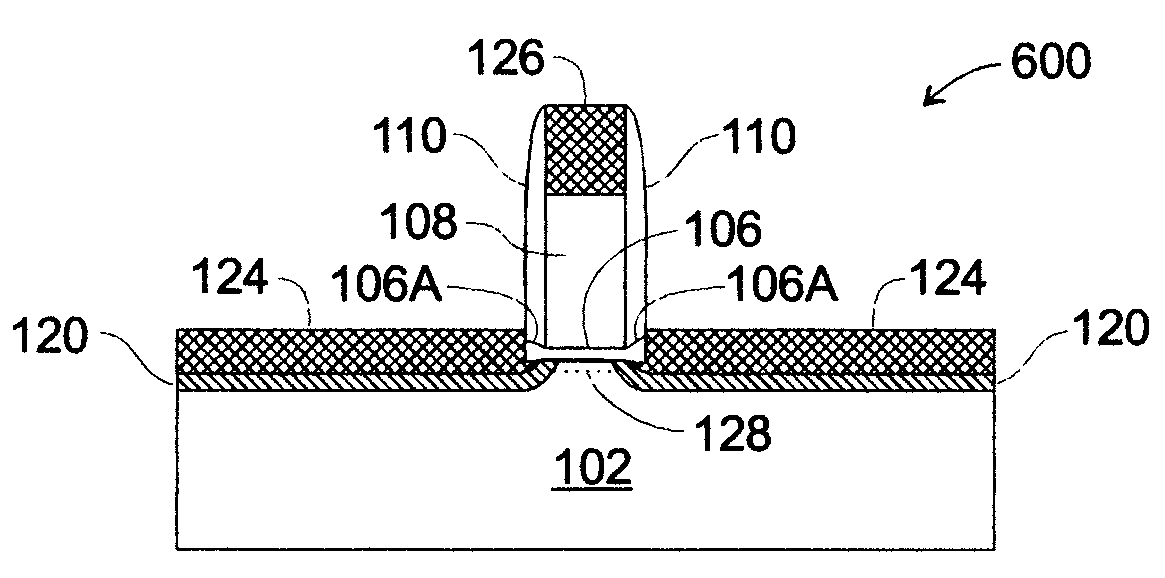

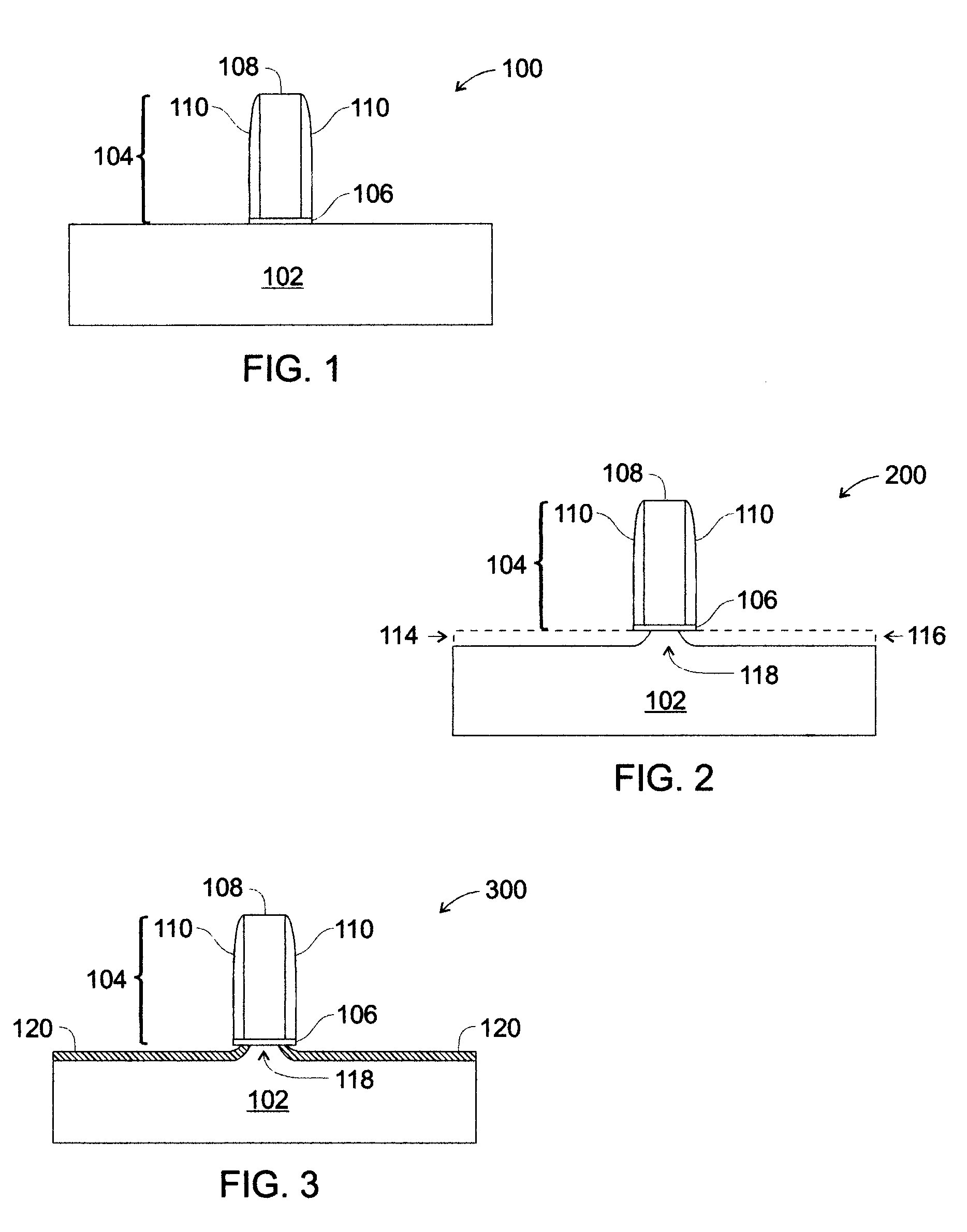

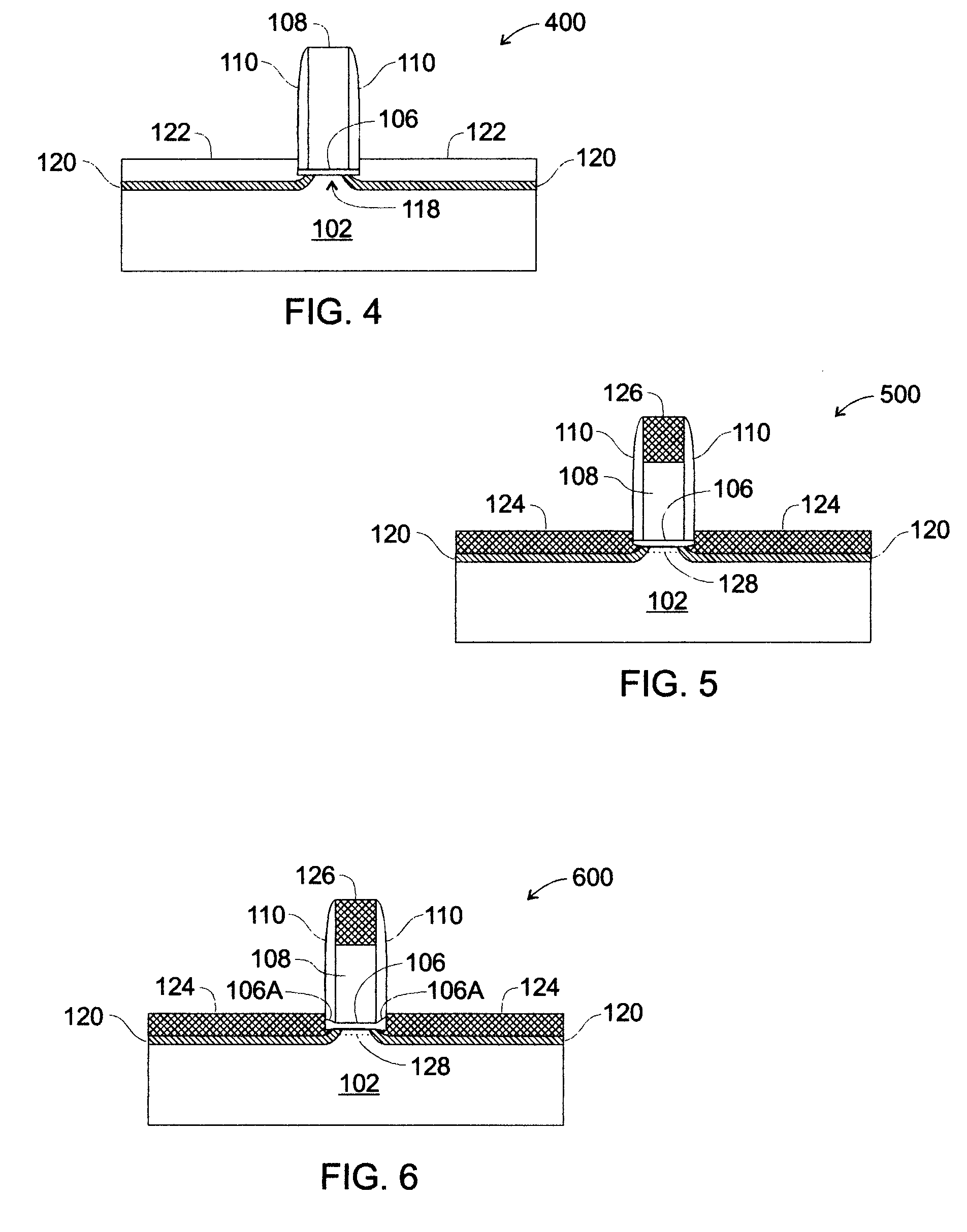

Ultra-thin silicidation-stop extensions in mosfet devices

ActiveUS20050112857A1Prevent breachTransistorSemiconductor/solid-state device manufacturingMOSFETFilling materials

Very low resistance, scaled in MOSFET devices are formed by employing thin silicidation-stop extension that act both as a silicidation “stop” barriers and as thin interface layers between source / drain silicide regions and channel region of the MOSFET. By acting as silicidation stops, the silicidation-stop extensions confine silicidation, and are not breached by source / drain silicide. This permits extremely thin, highly-doped silicidation-stop extensions to be formed between the silicide and the channel, providing an essentially ideal, low series resistance interface between the silicide an the channel. On an appropriately prepared substrate, a selective etching process is performed to expose the sides of the channel region (transistor body). A very thin layer of a silicidation-stop material, e.g., SiGe, is disposed in the etched away area, coating the exposed sides of the channel region. The silicidation-stop material is doped (highly) appropriately for the type of MOSFET being formed (n-channel or p-channel). The etched away areas are then filled with silicon, e.g., by an Si epi process. Silicidation is then performed (to form, e.g., CoSi2) on the newly filled areas. The silicidation stop material constrains silicidation to the silicon fill material, but prevents silicide expansion past the silicidation stop material. Because the germanium (Ge) in SiGe is insoluble in CoSi2, the SiGe acts as a barrier to silicidation, permitting silicidation to go to completion in the Si fill but stopping silicidation at the SiGe boundary when silicidation is performed at a temperature above a silicidation threshold temperature for Si, but below a silicidation threshold temperature for SiGe. This results in a very compact, well-defined lateral junction characterized by a thin layer of SiGe disposed between silicide lateral extensions and the sides of the channel region. Because of the thin, highly-doped SiGe layer between the channel and the silicide lateral extensions, the extension resistance is very low.

Owner:GLOBALFOUNDRIES US INC

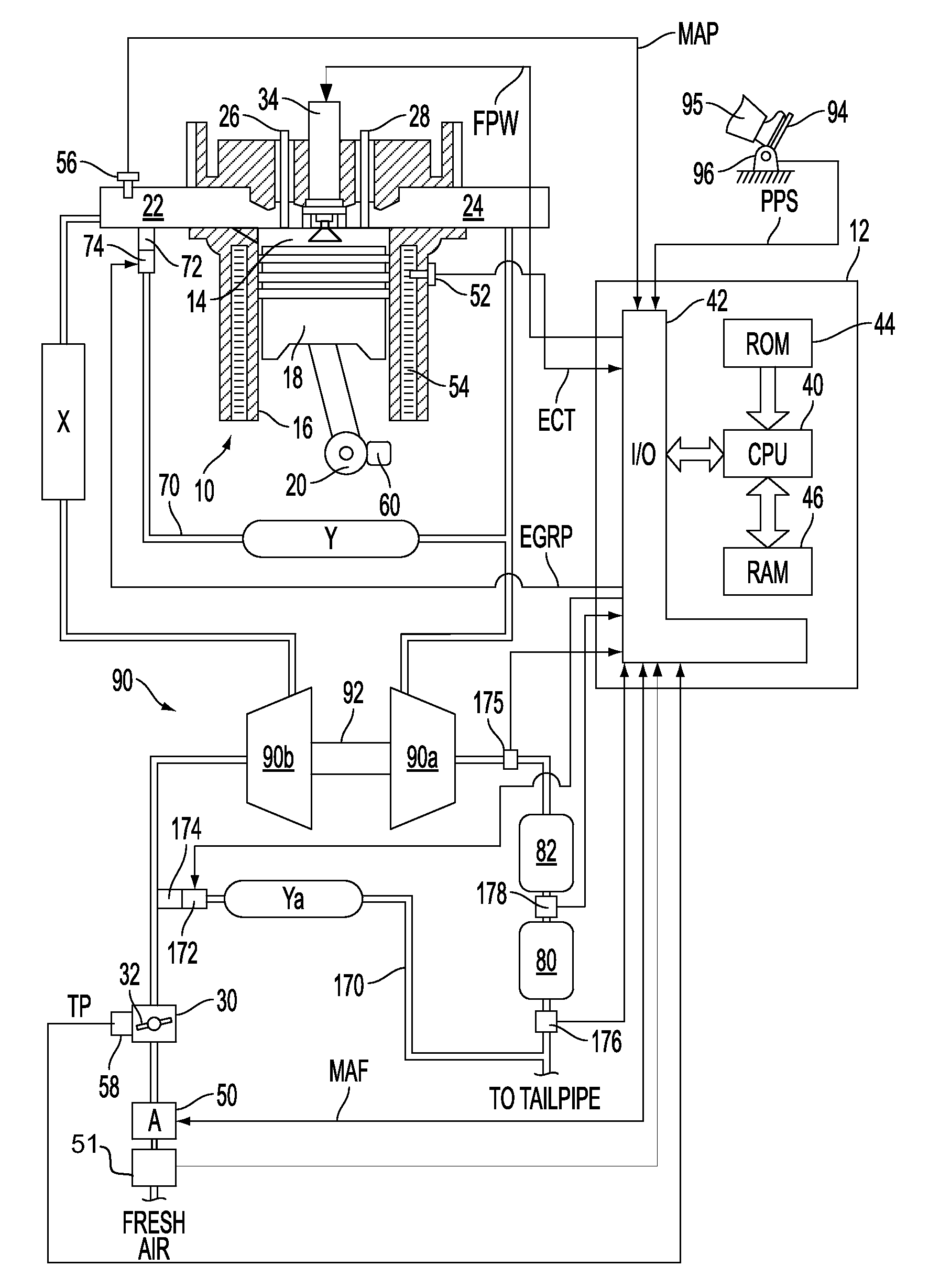

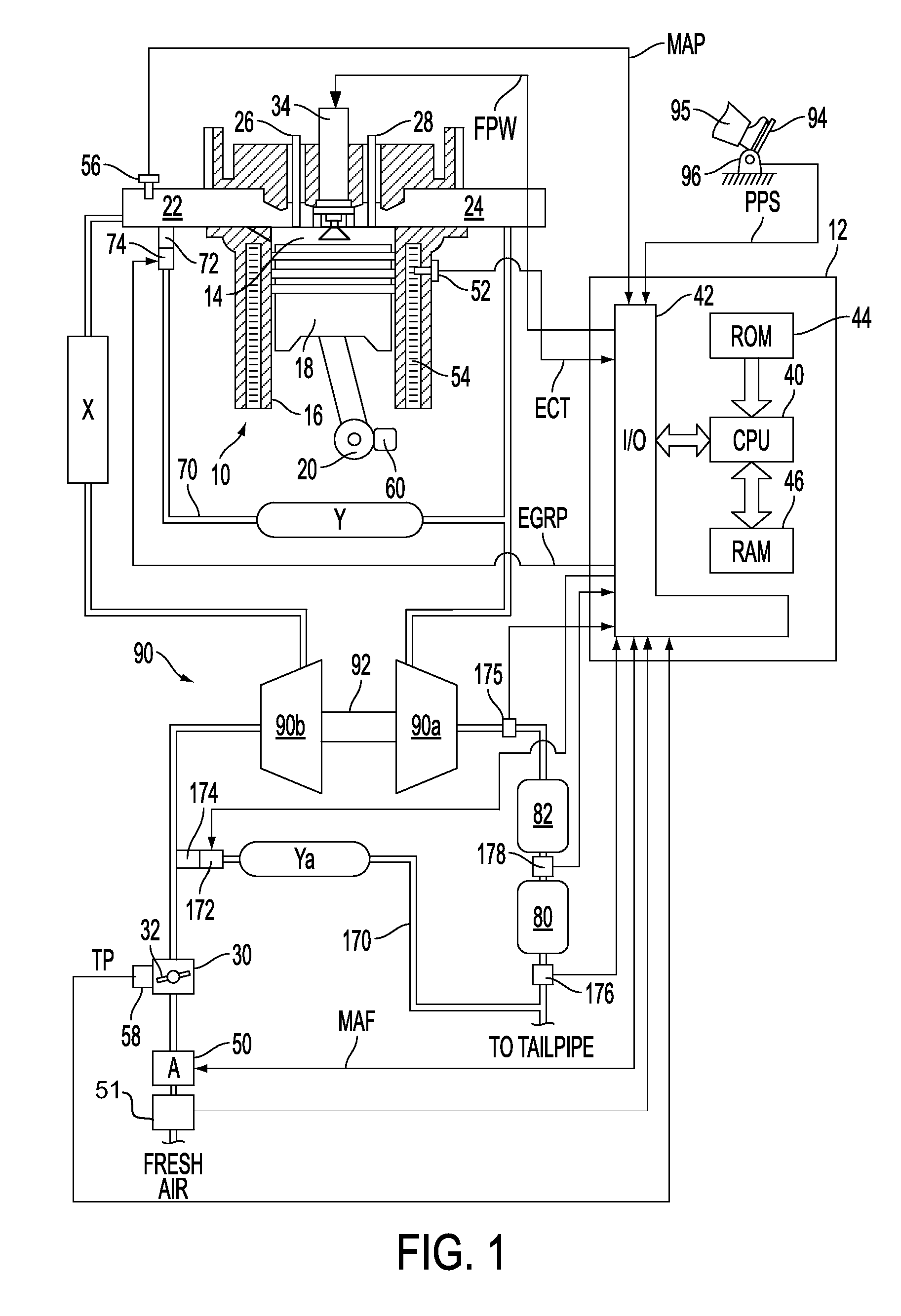

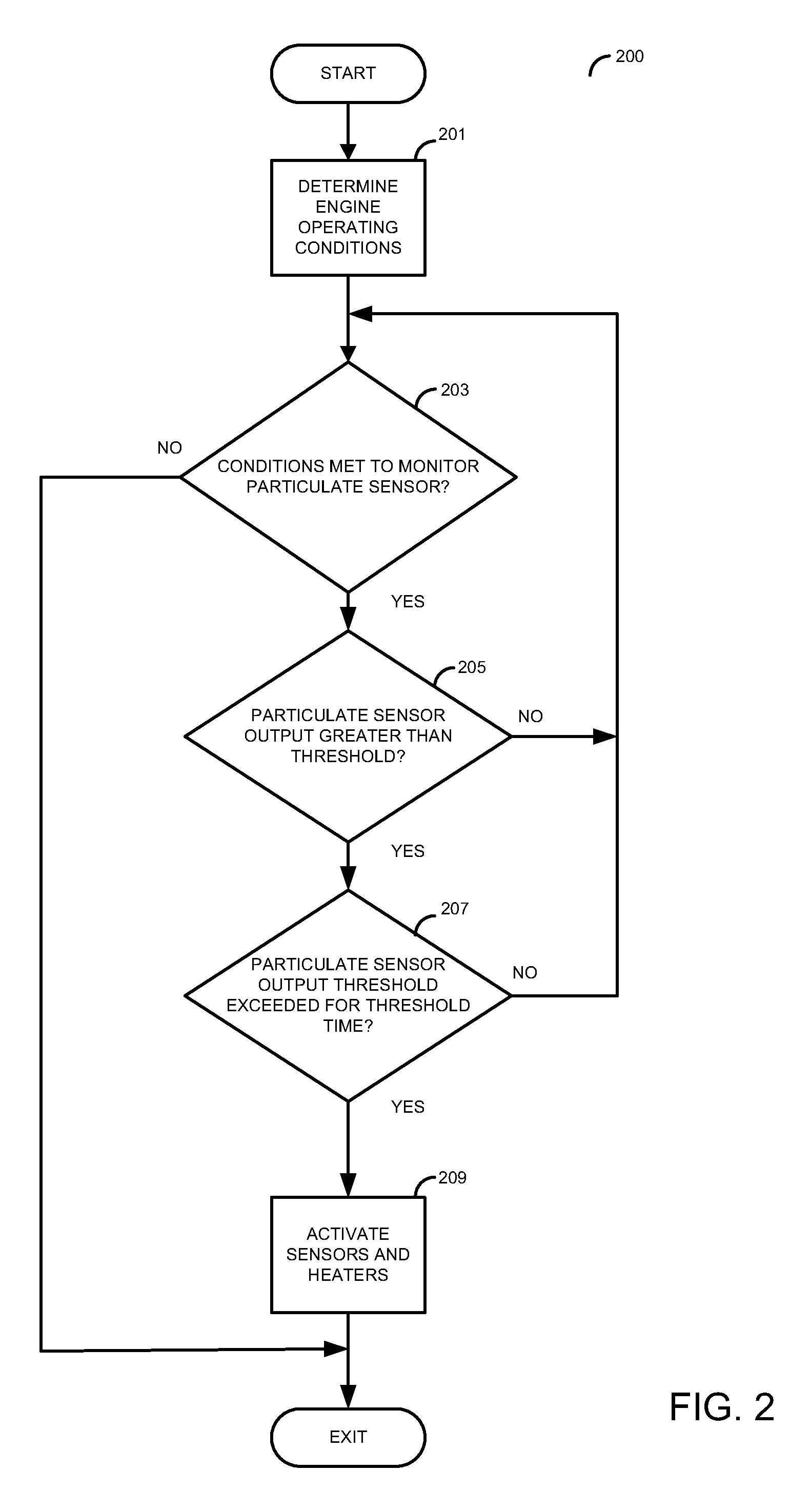

Method for evaluating degradation of a particulate matter sensor

ActiveUS20110047978A1Emission reductionAccelerate emissionsVehicle testingElectrical controlParticulatesIn vehicle

A system for improving operation of an engine having a particulate matter sensor is presented. The system may be used to improve engine operation during cold starts especially under conditions where water vapor or entrained water droplets are present in vehicle exhaust gases. In one embodiment, degradation of a particulate matter sensor is indicated after a temperature of a substrate of the particulate matter sensor exceeds a threshold temperature and an output of the particulate matter sensor is below a threshold value.

Owner:FORD GLOBAL TECH LLC

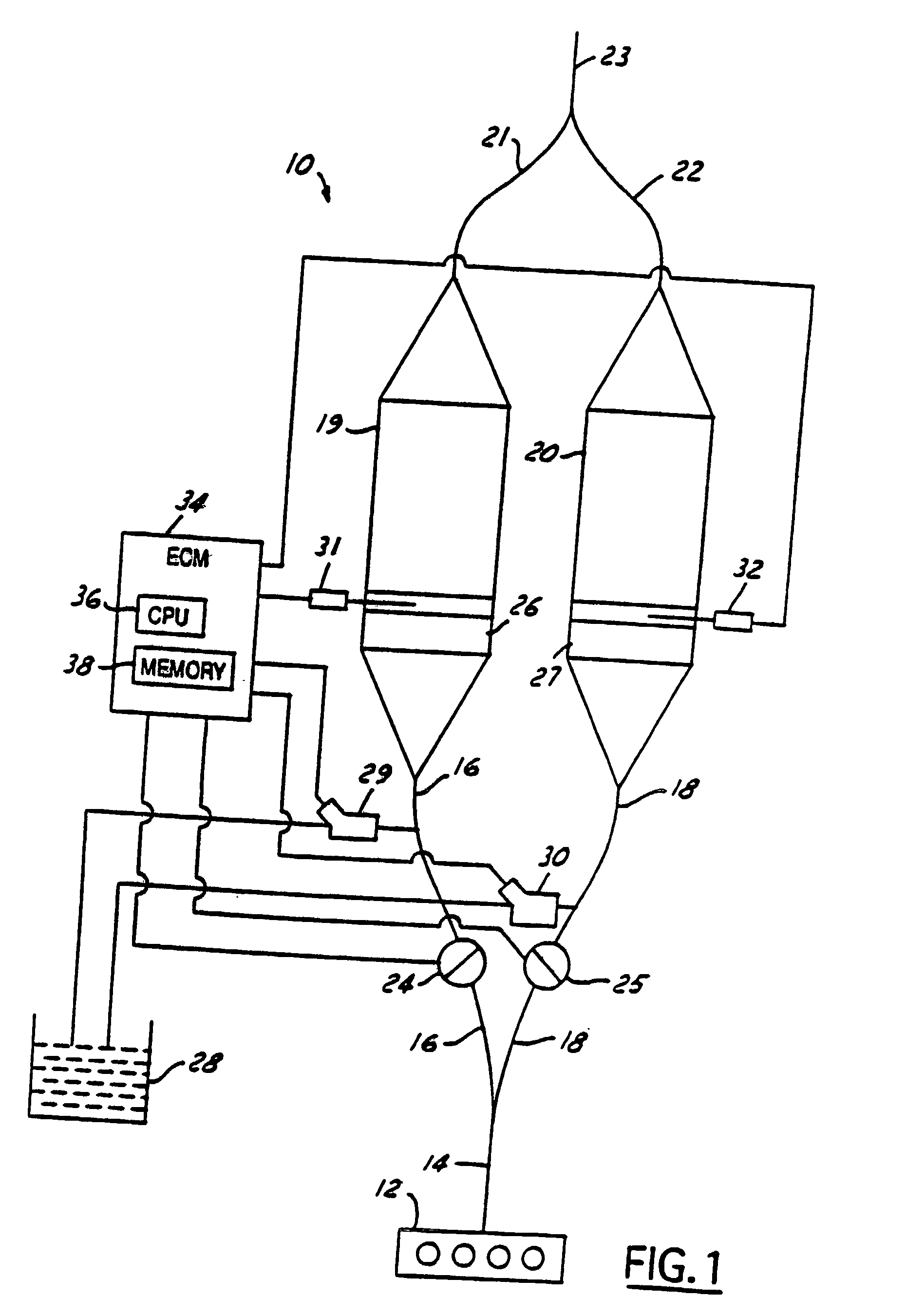

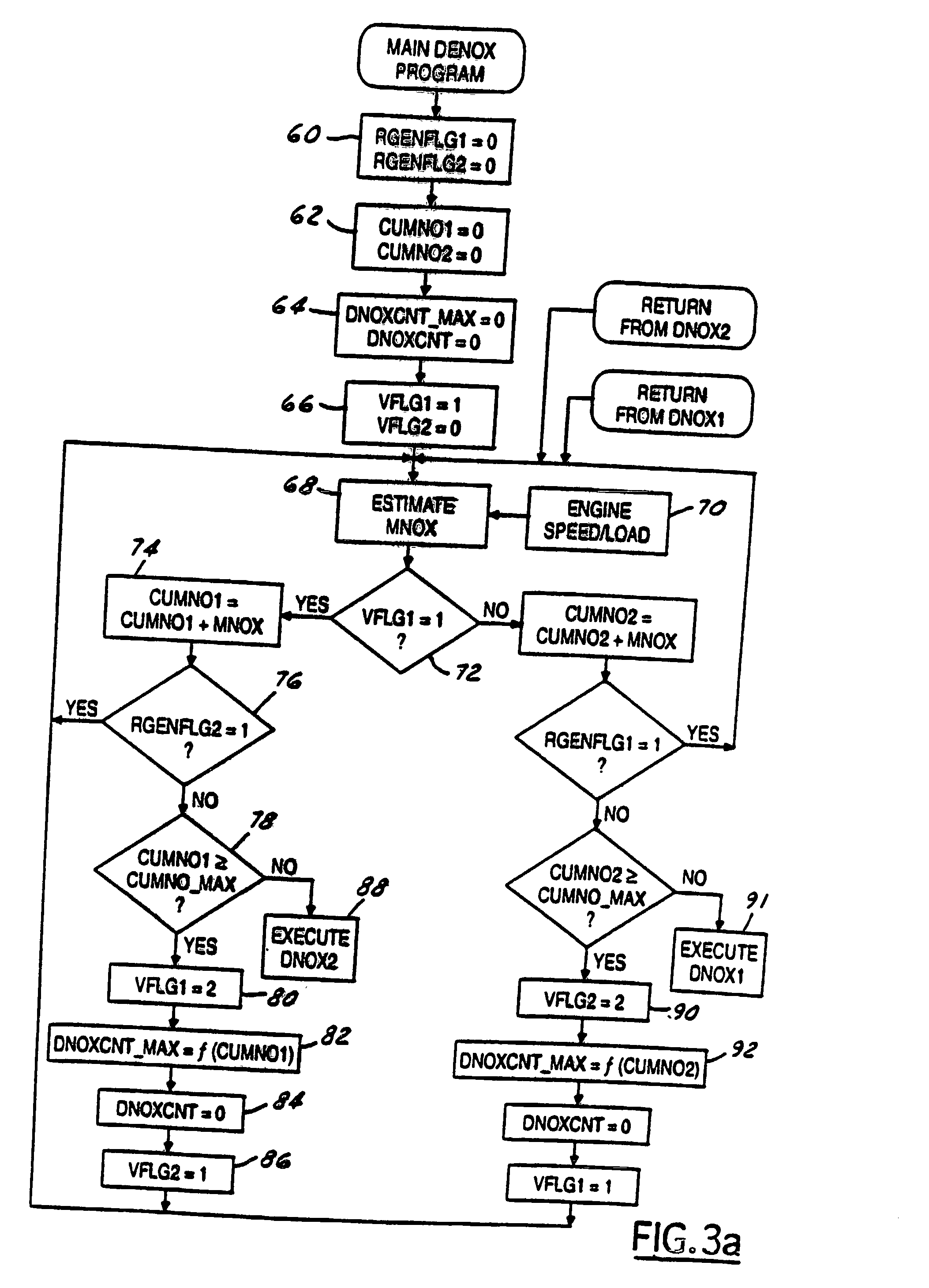

System and method for removing SOx and particulate matter from an emission control device

InactiveUS20030113249A1Combination devicesInternal combustion piston enginesParticulatesExhaust fumes

A system and method for removing SOx and particulate matter from an emission control device receiving exhaust gases from an engine is provided. The method includes adding a reductant to the exhaust gases to increase a temperature of the emission control device above a threshold temperature. The method further includes ceasing adding the reductant to the exhaust gases to remove particulate matter from the device. The method further includes adding additional reductant to the exhaust gases to remove SOx from the device.

Owner:FORD GLOBAL TECH LLC

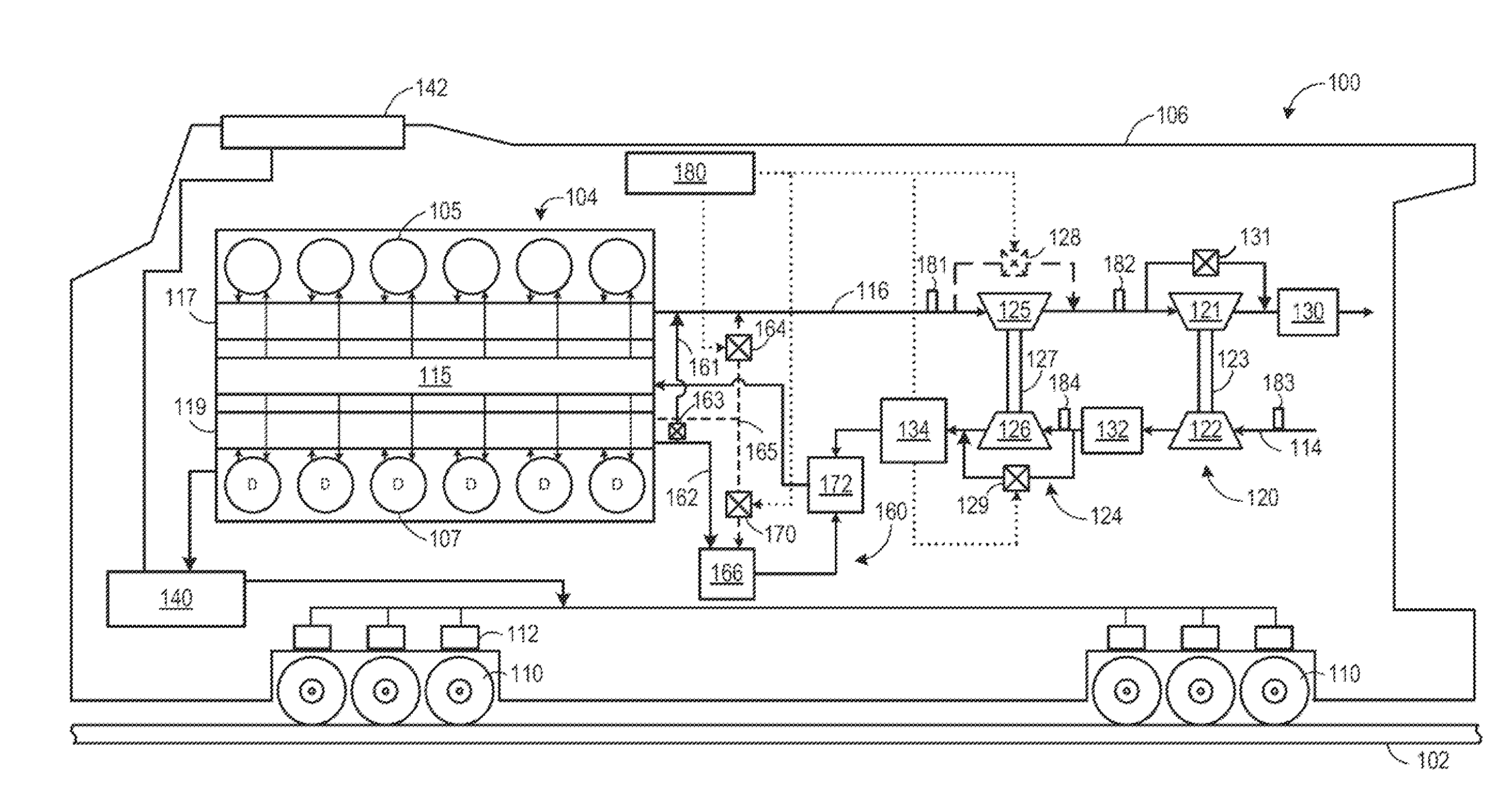

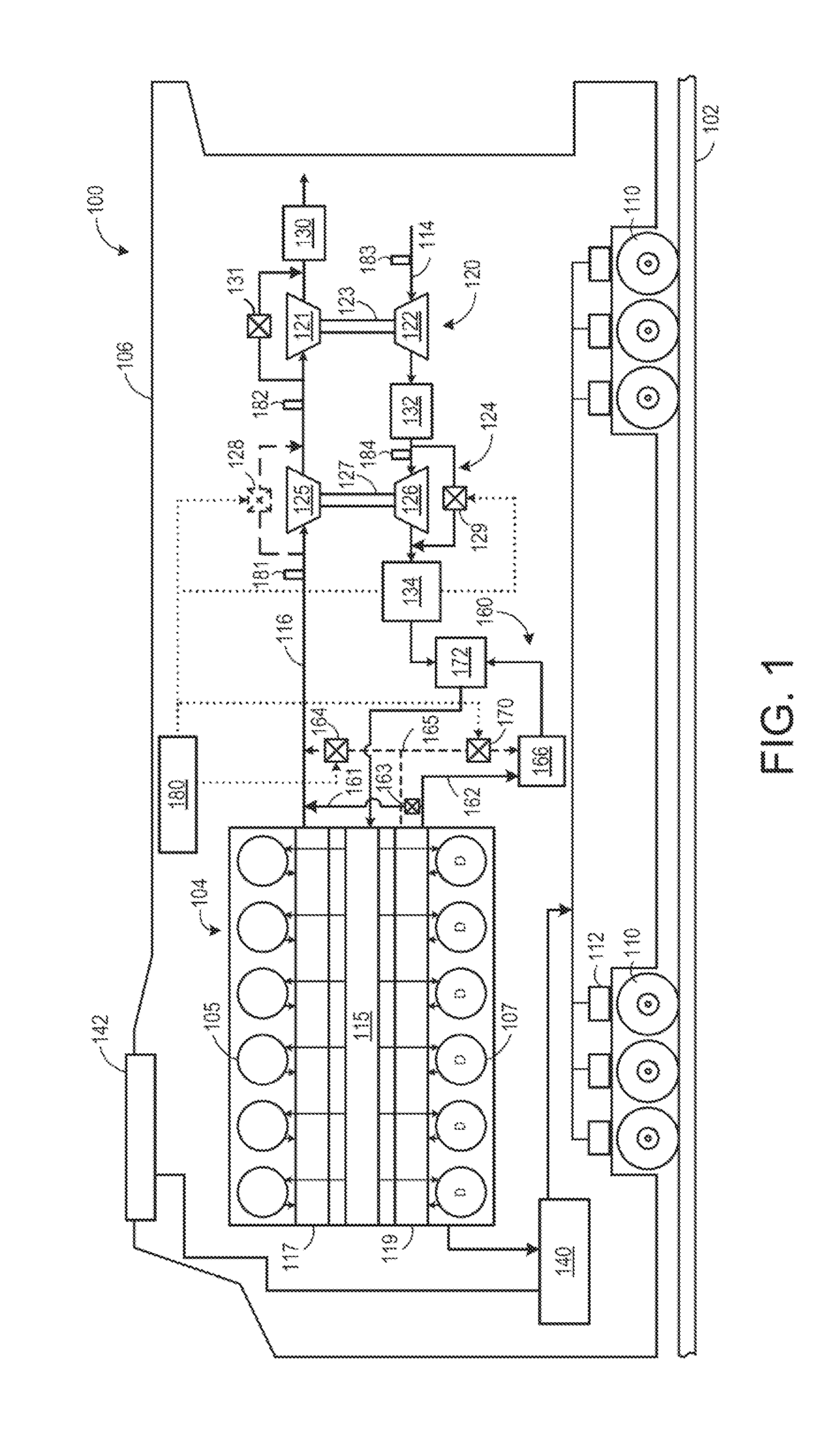

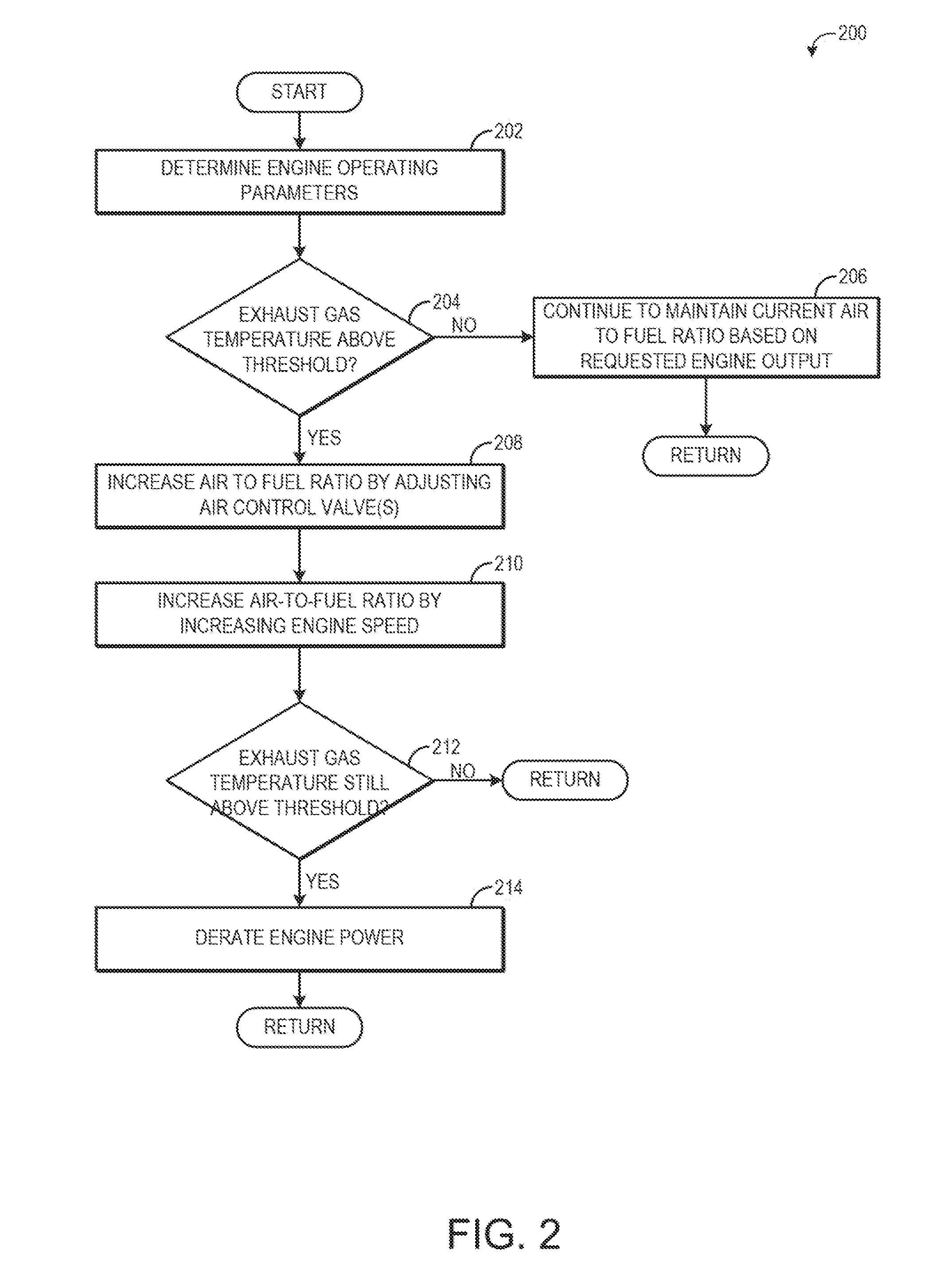

Methods and system to prevent exhaust overheating

ActiveUS20140067236A1Lower exhaust gas temperatureIncrease the air-fuel ratioElectrical controlInternal combustion piston enginesProcess engineeringThreshold temperature

Various methods and systems are provided for lowering exhaust gas temperature. In one embodiment, a method comprises increasing an air-to-fuel ratio of an engine in response to an exhaust gas temperature exceeding a threshold temperature value to lower the exhaust gas temperature to a temperature below the threshold temperature value.

Owner:GE GLOBAL SOURCING LLC