Patents

Literature

403 results about "Tunneling current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The tunneling current to the tip measures the density of electrons at the surface of the sample, and this information is displayed in the image. In semiconductors, such as silicon, the electron density reaches a maximum near the atomic sites.

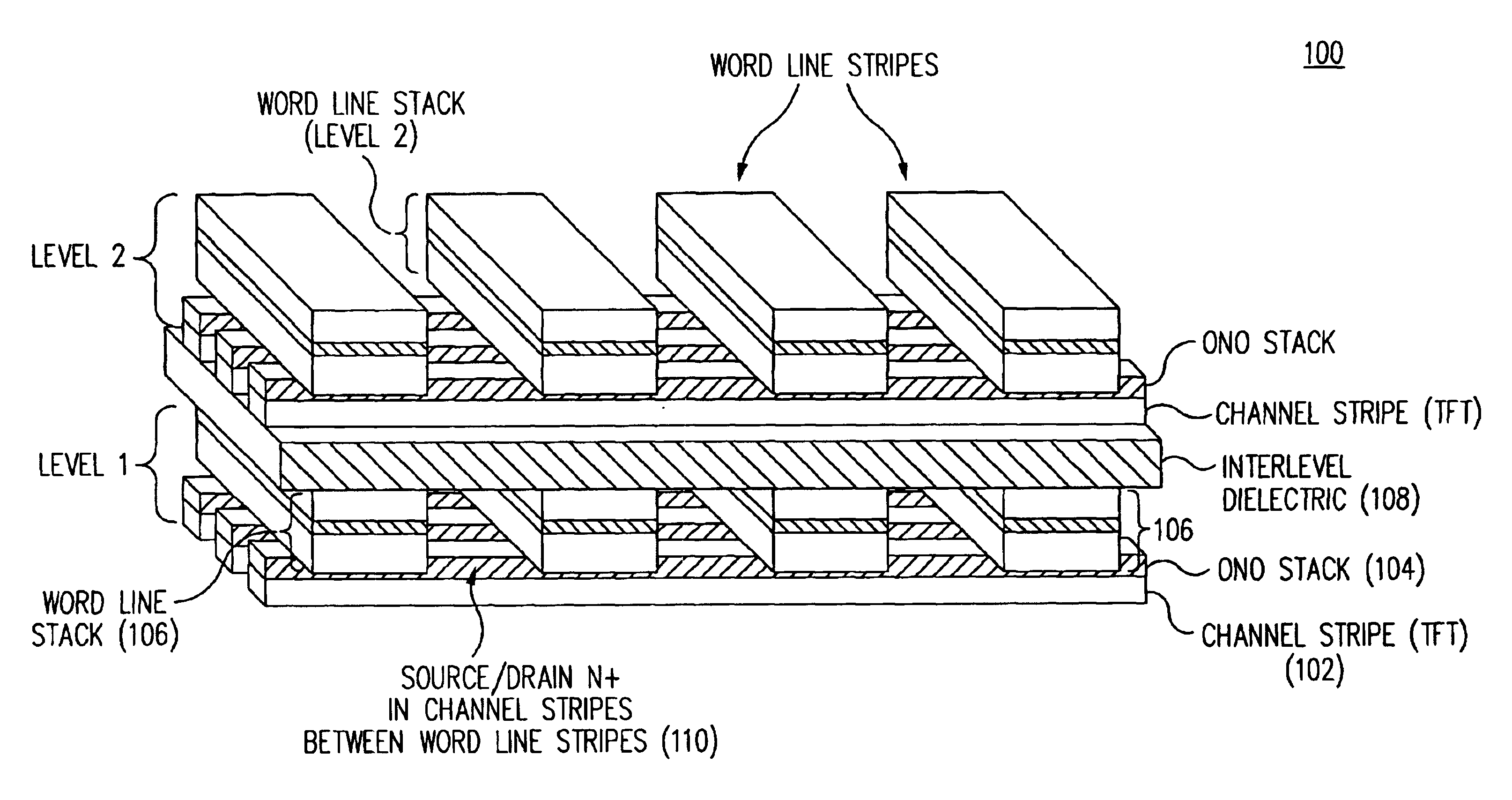

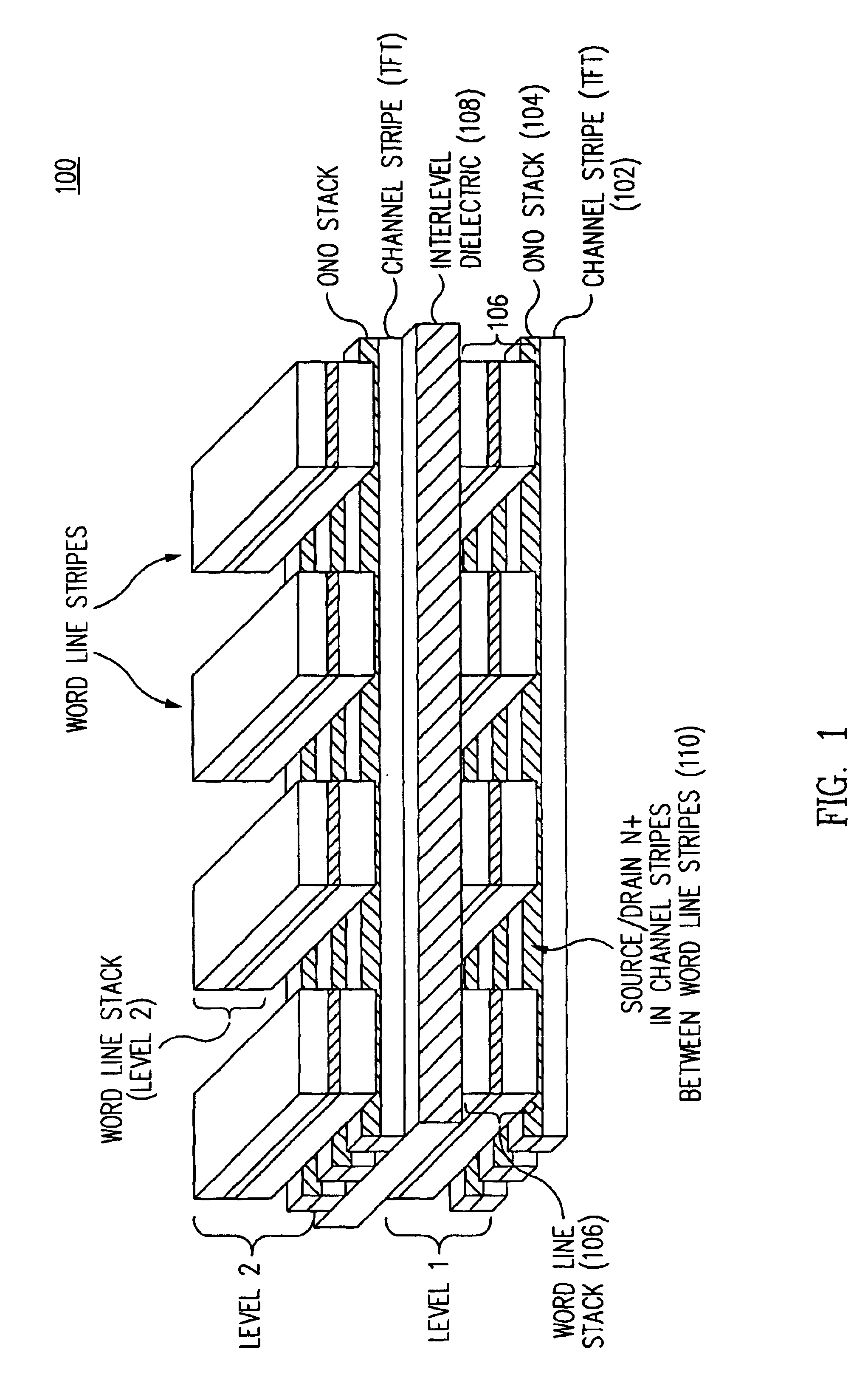

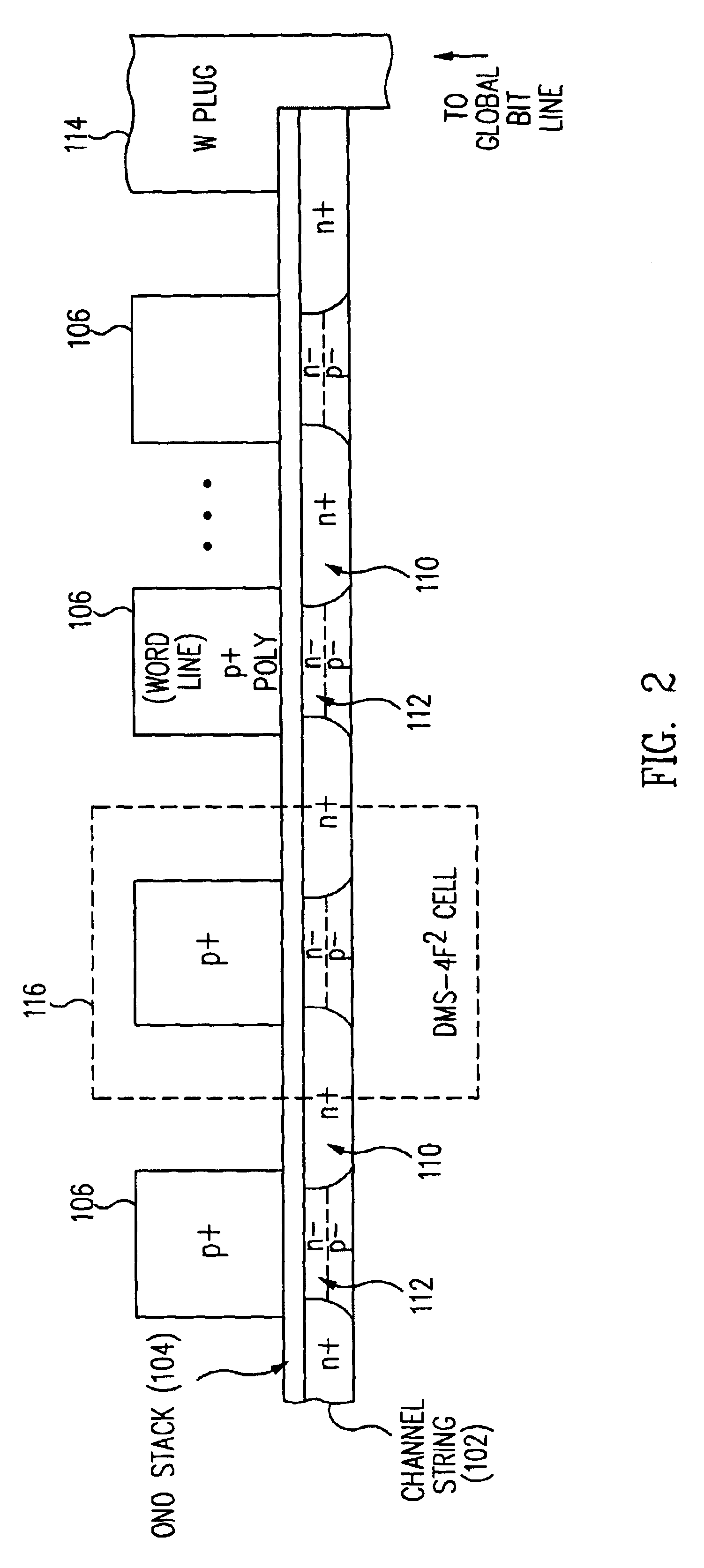

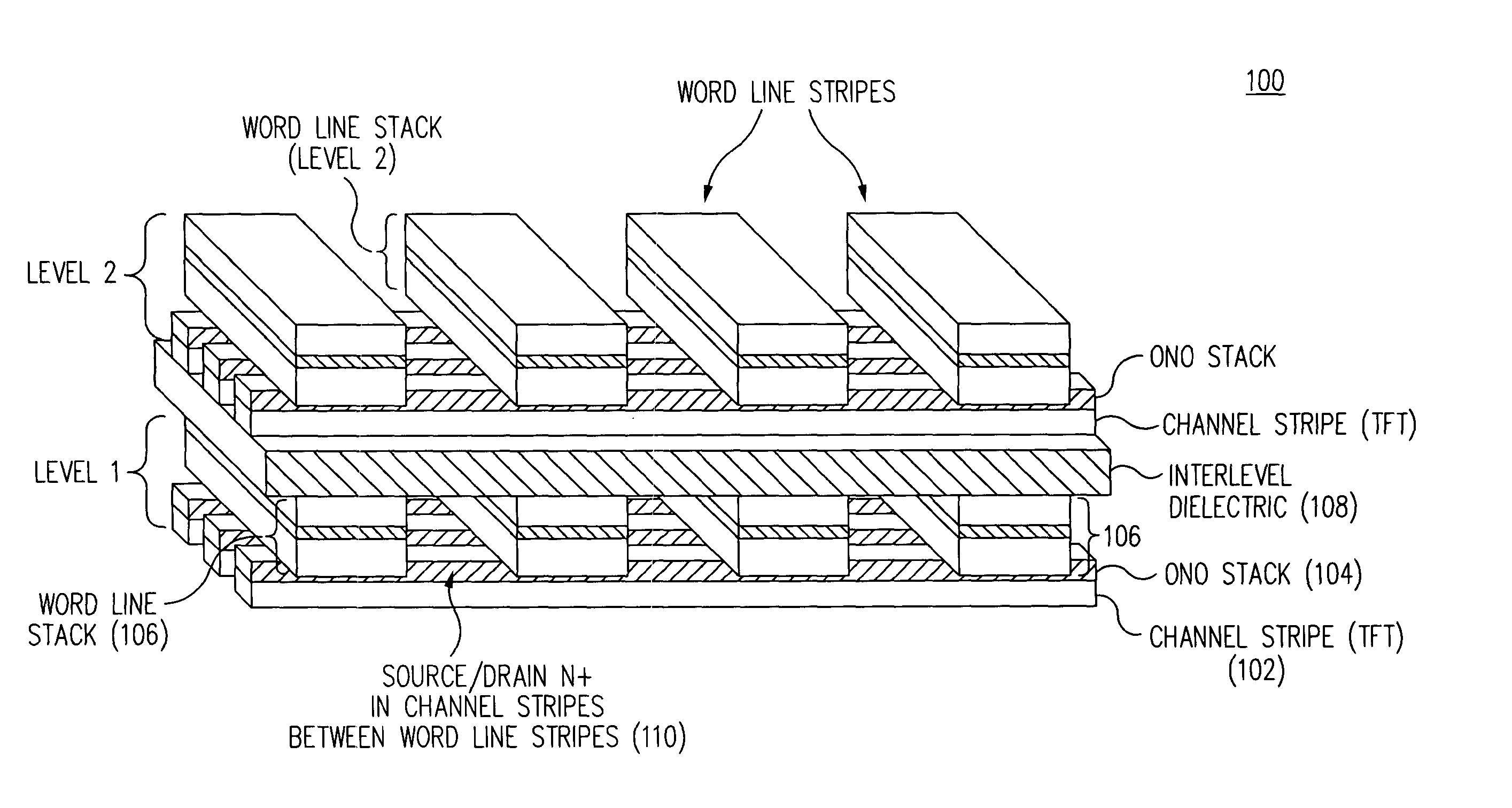

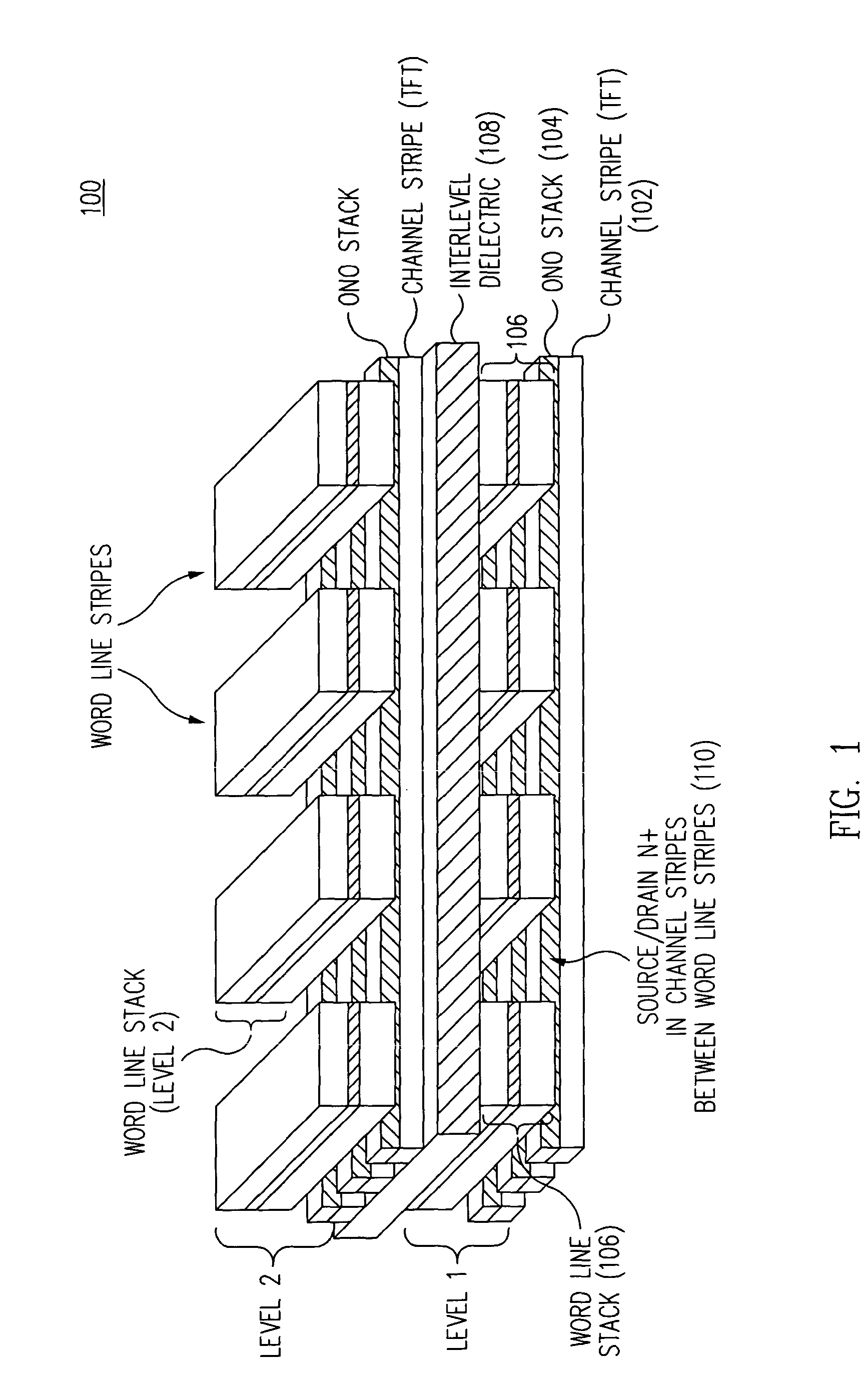

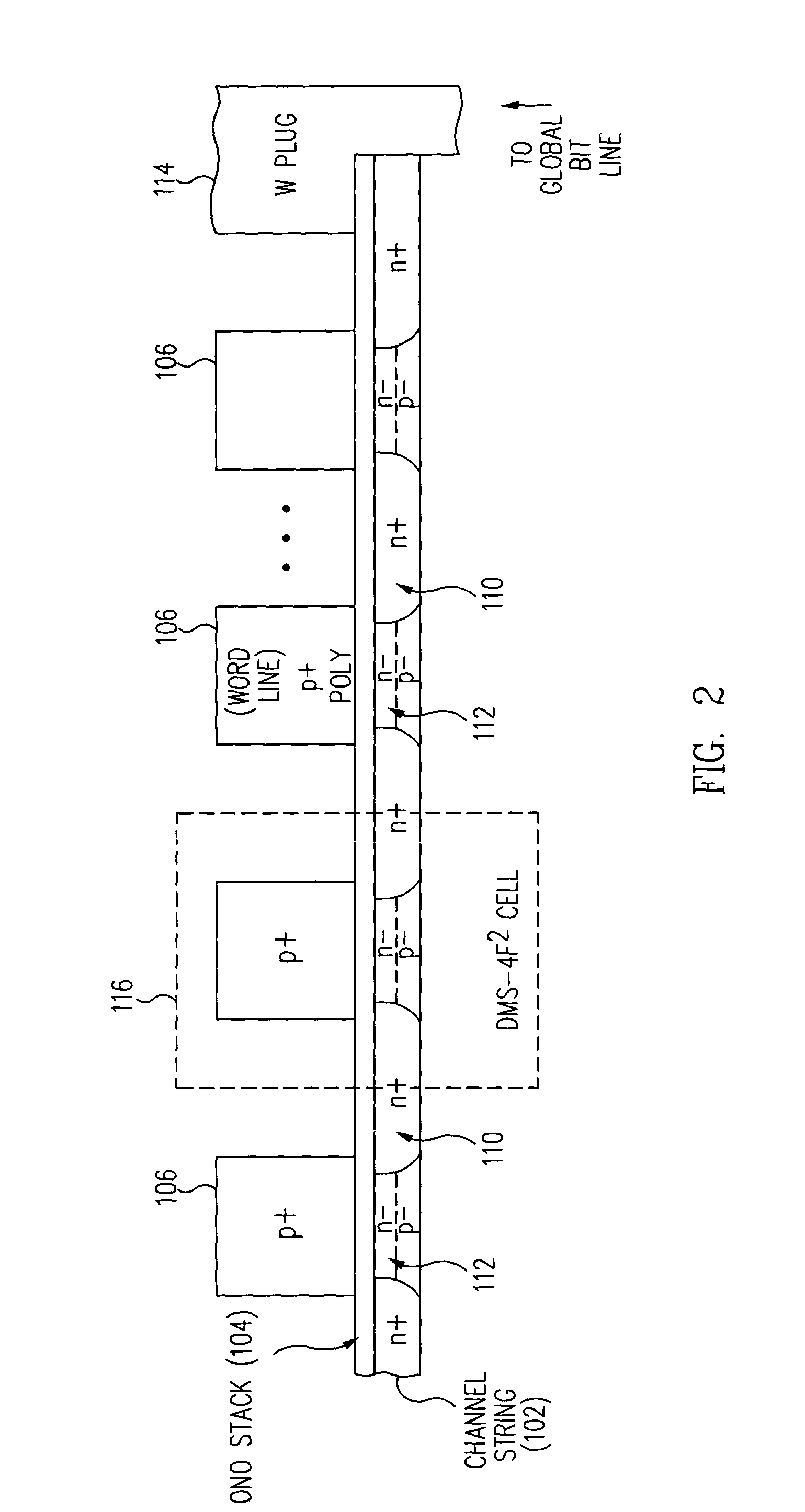

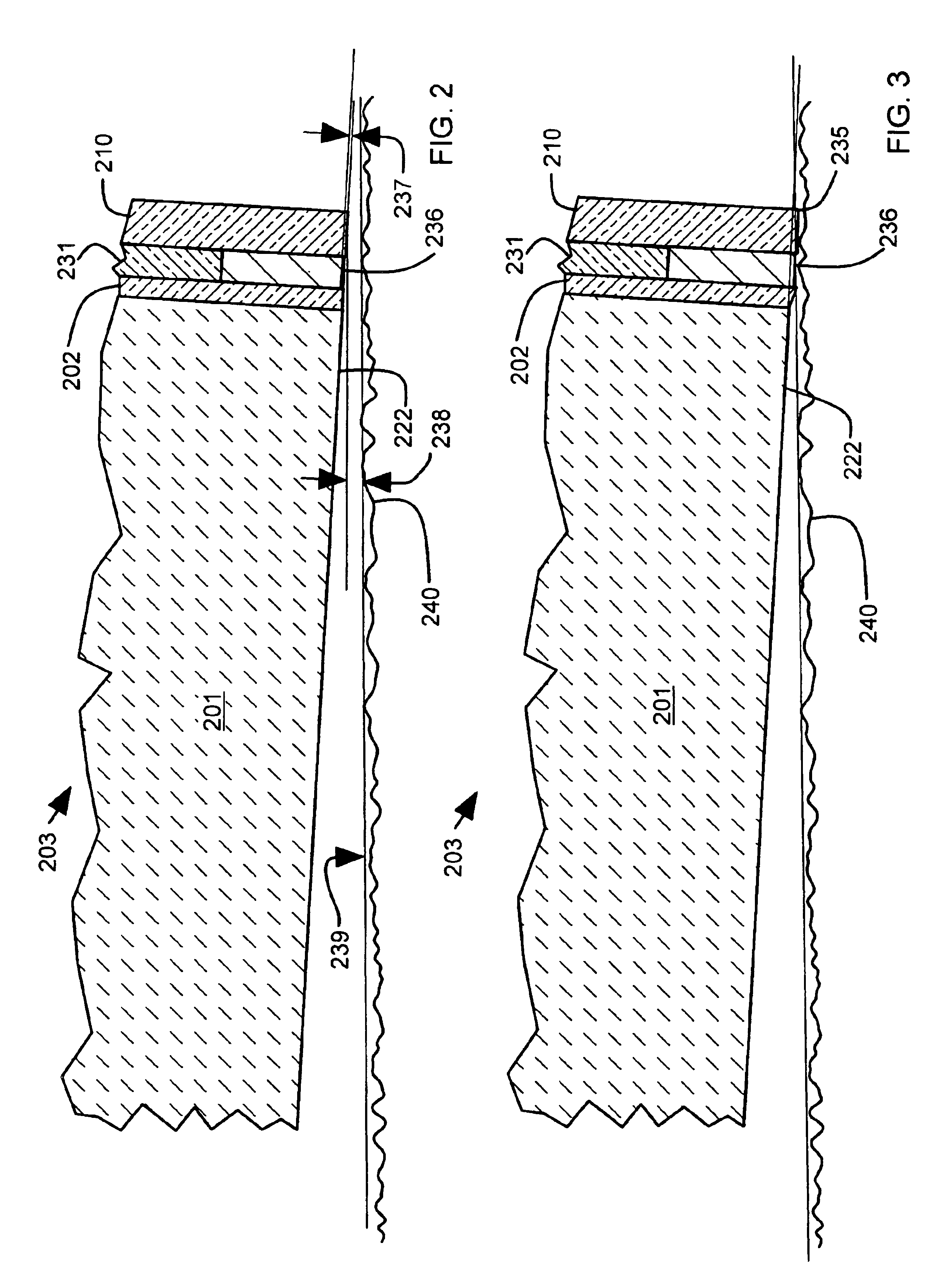

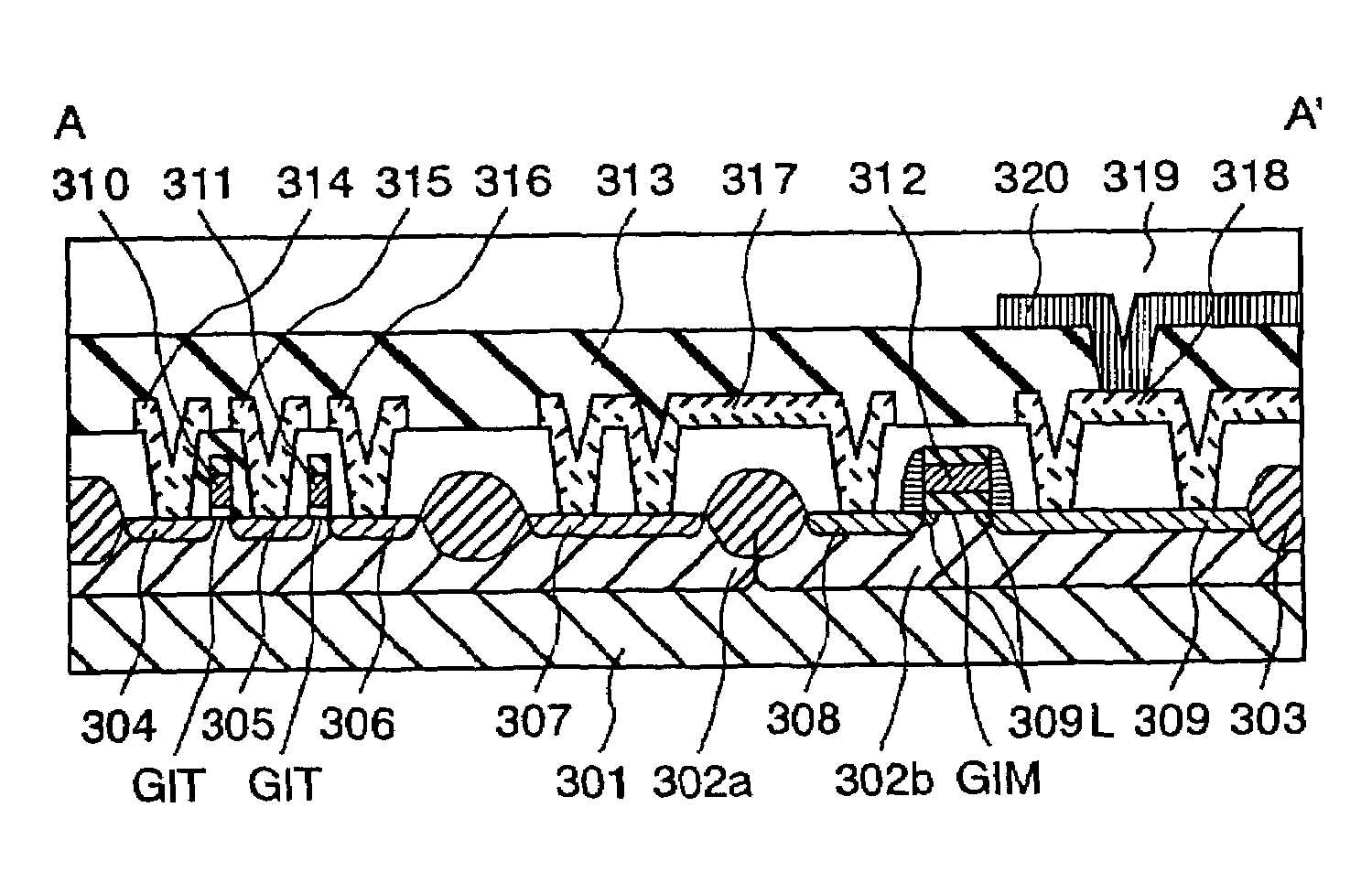

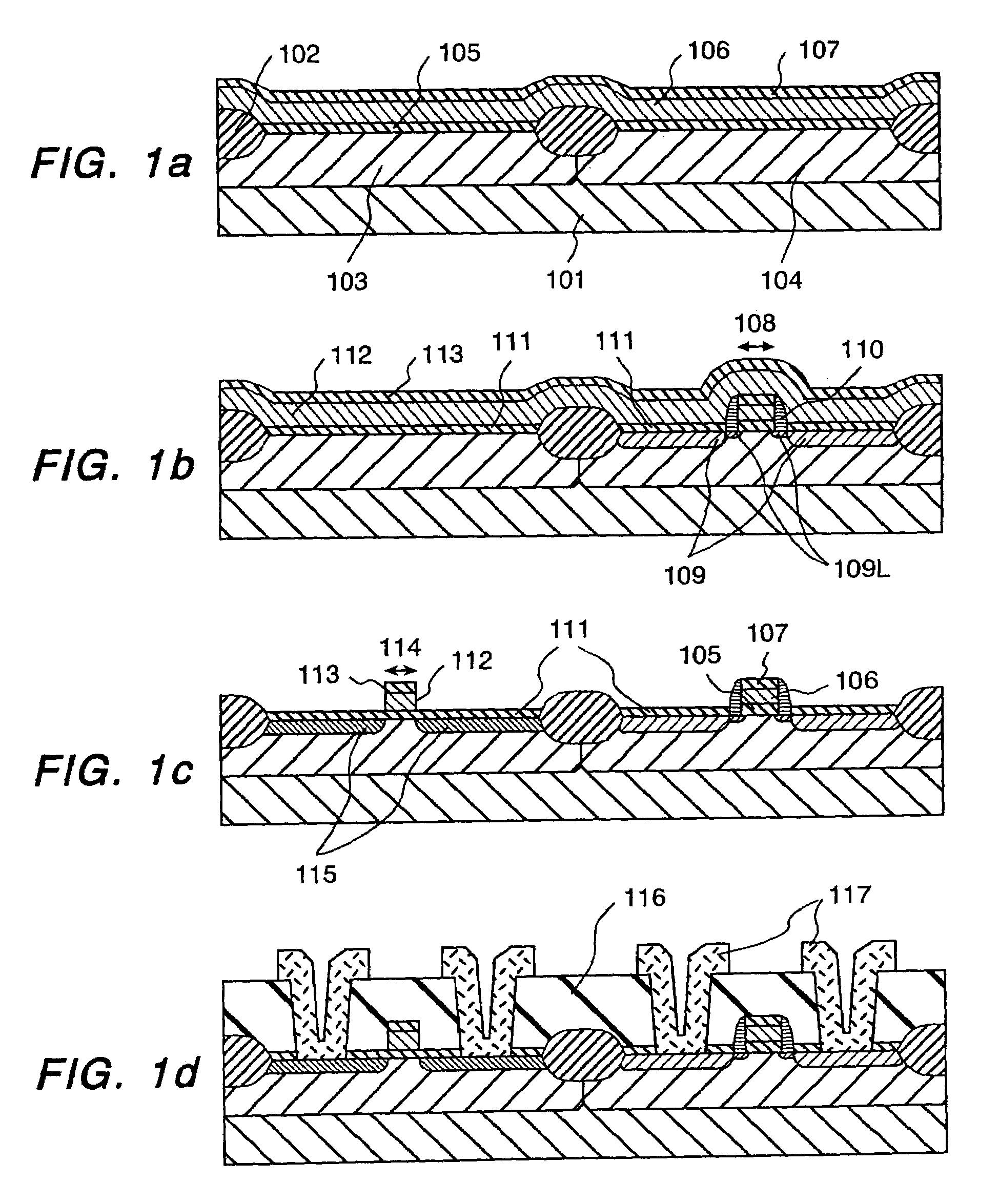

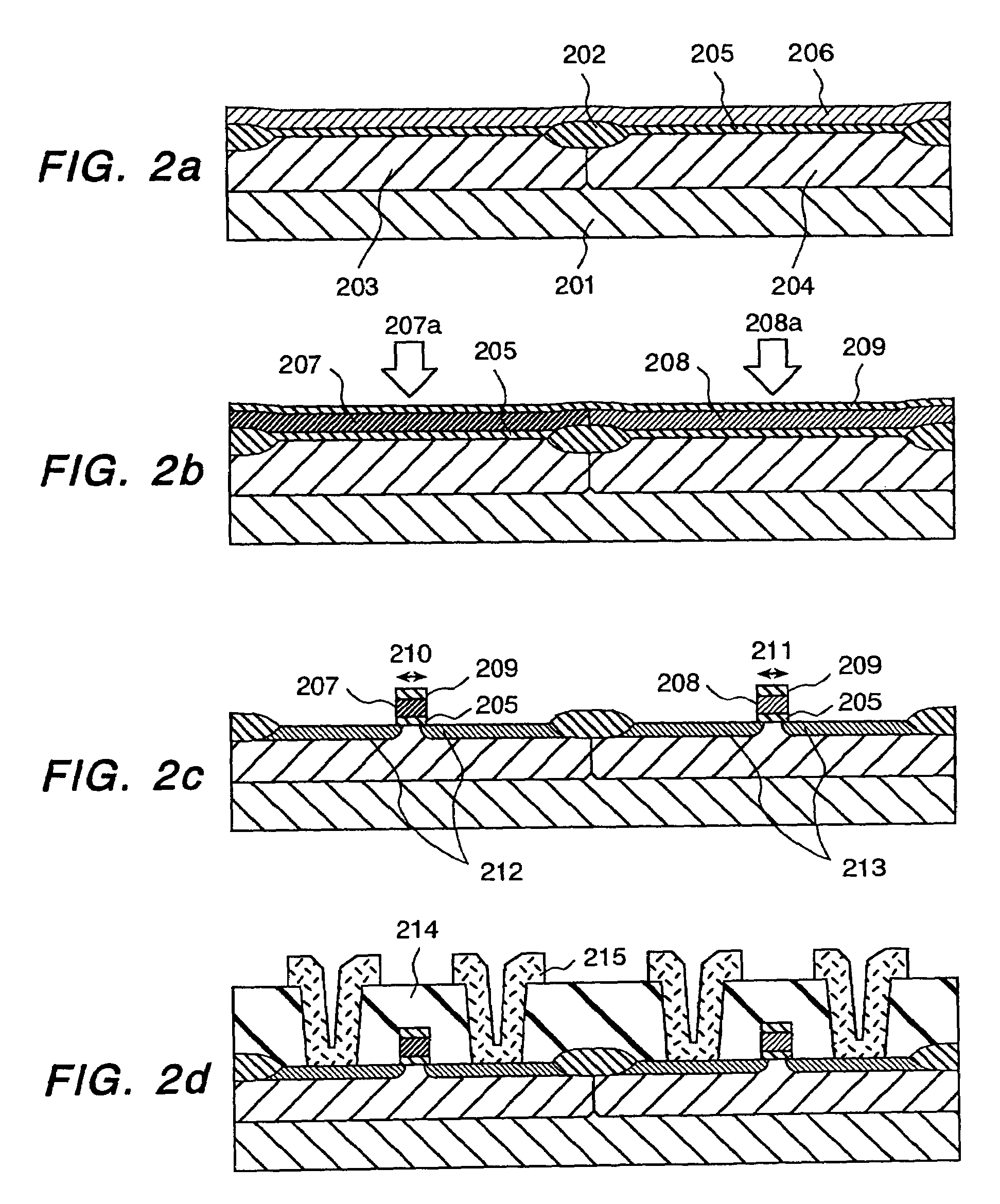

Method for fabricating programmable memory array structures incorporating series-connected transistor strings

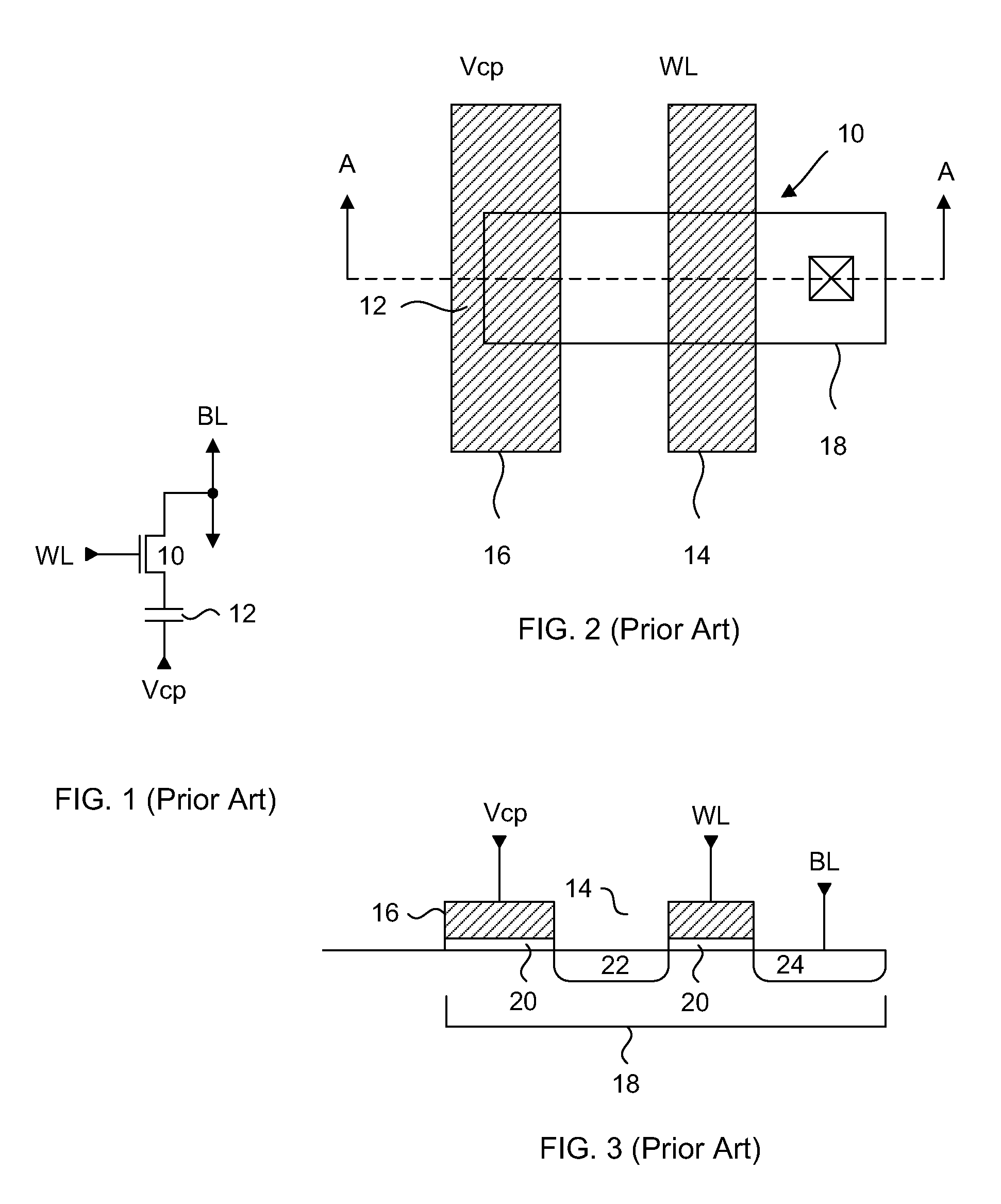

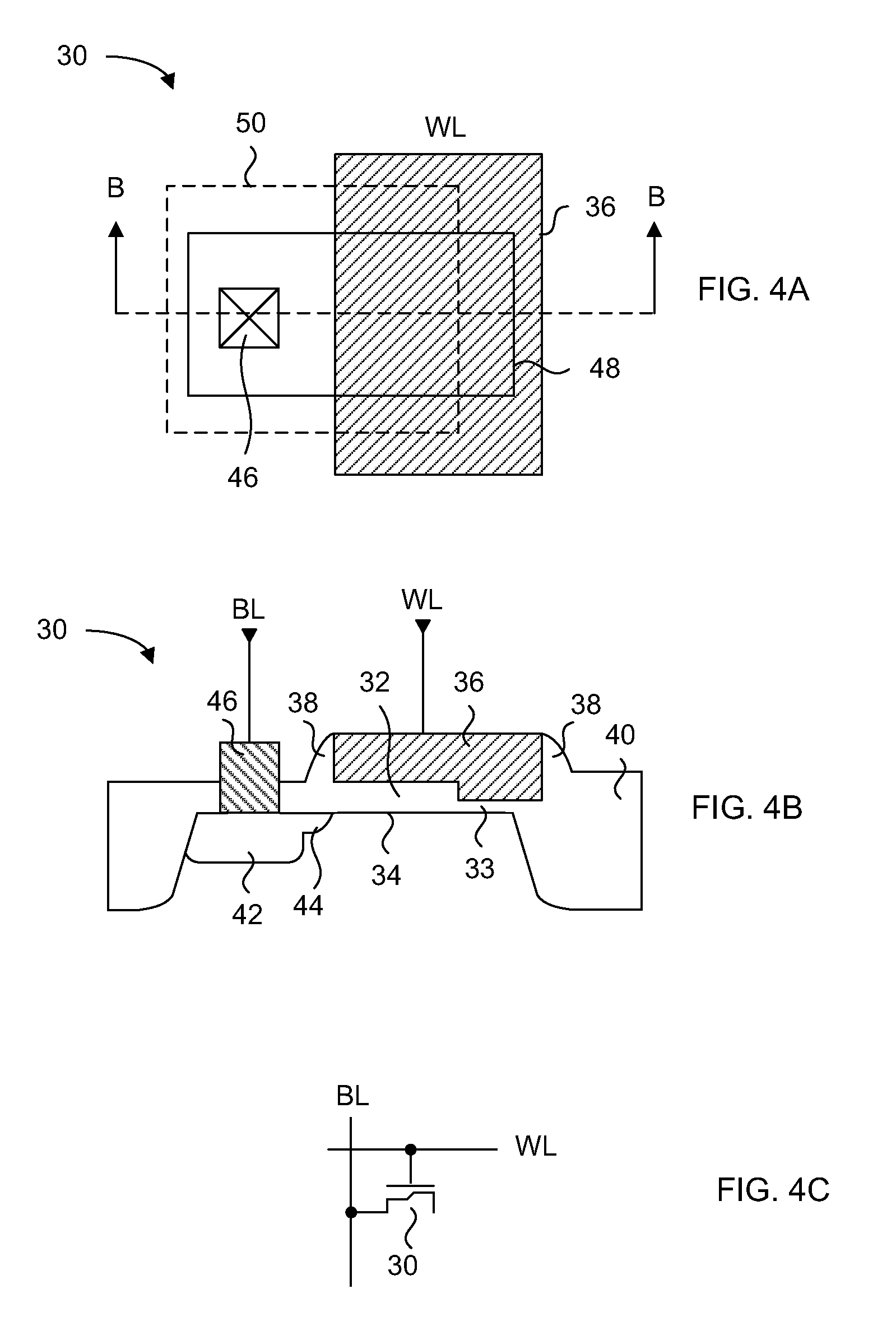

InactiveUS7005350B2Reduce in quantityDense memory arraySolid-state devicesRead-only memoriesBit lineComputer architecture

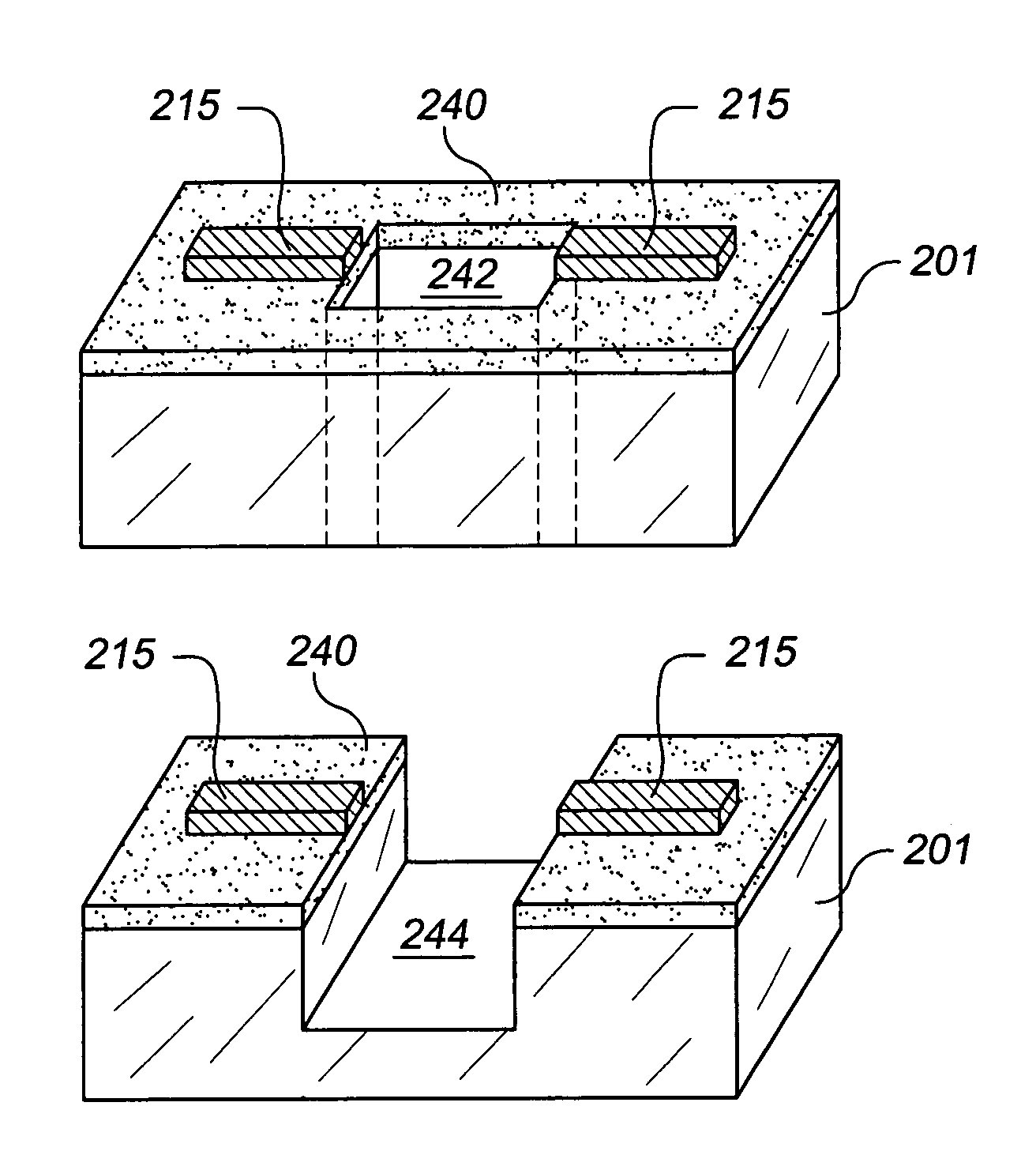

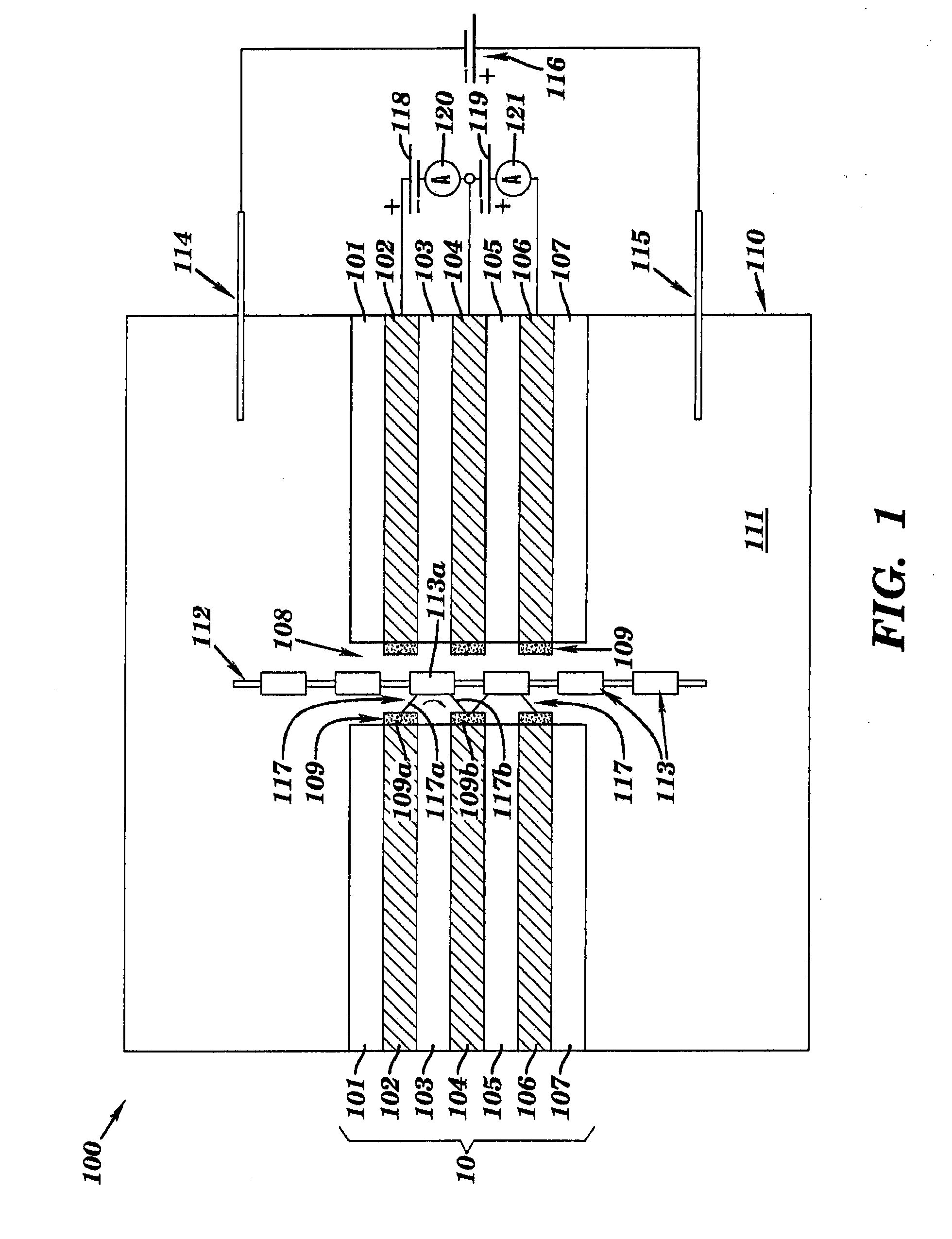

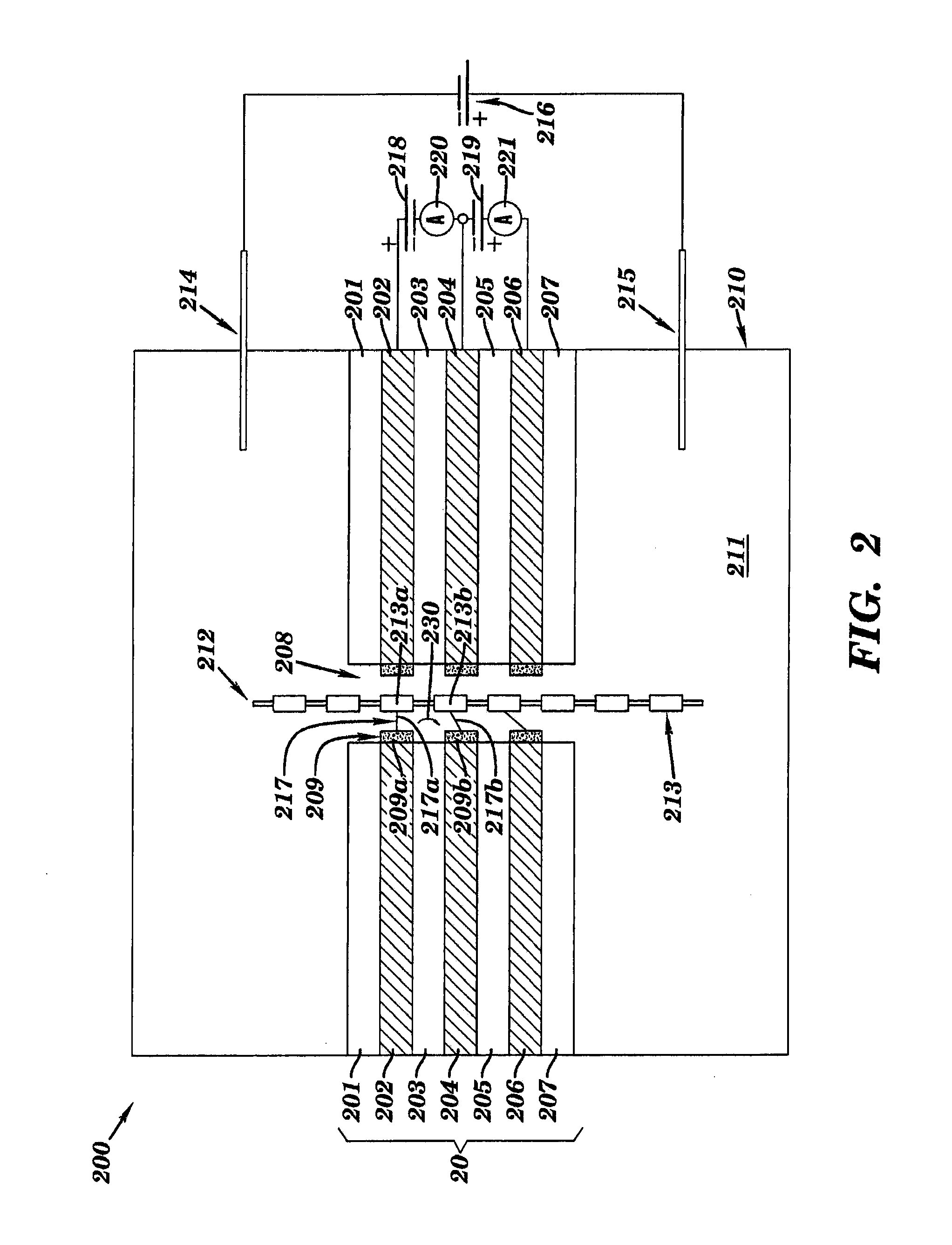

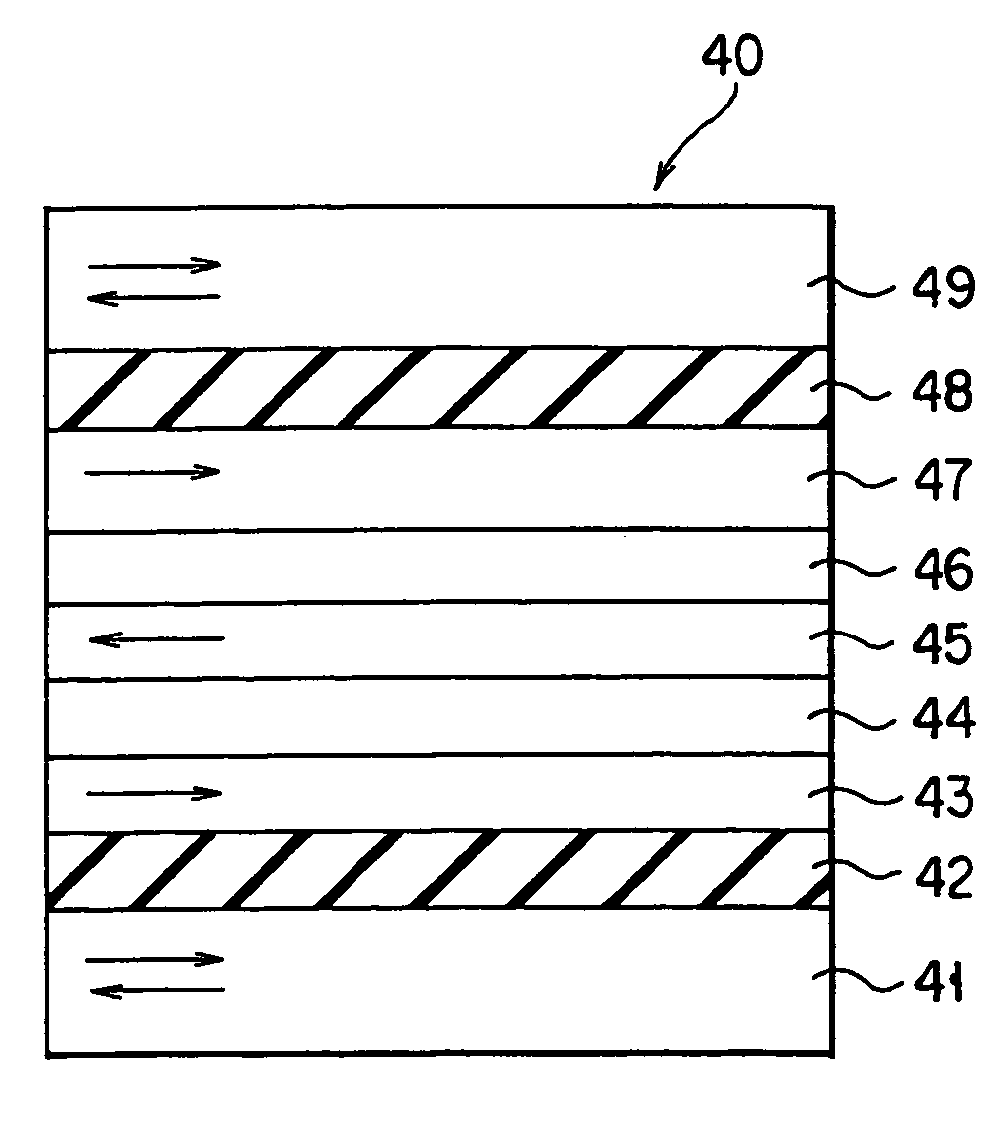

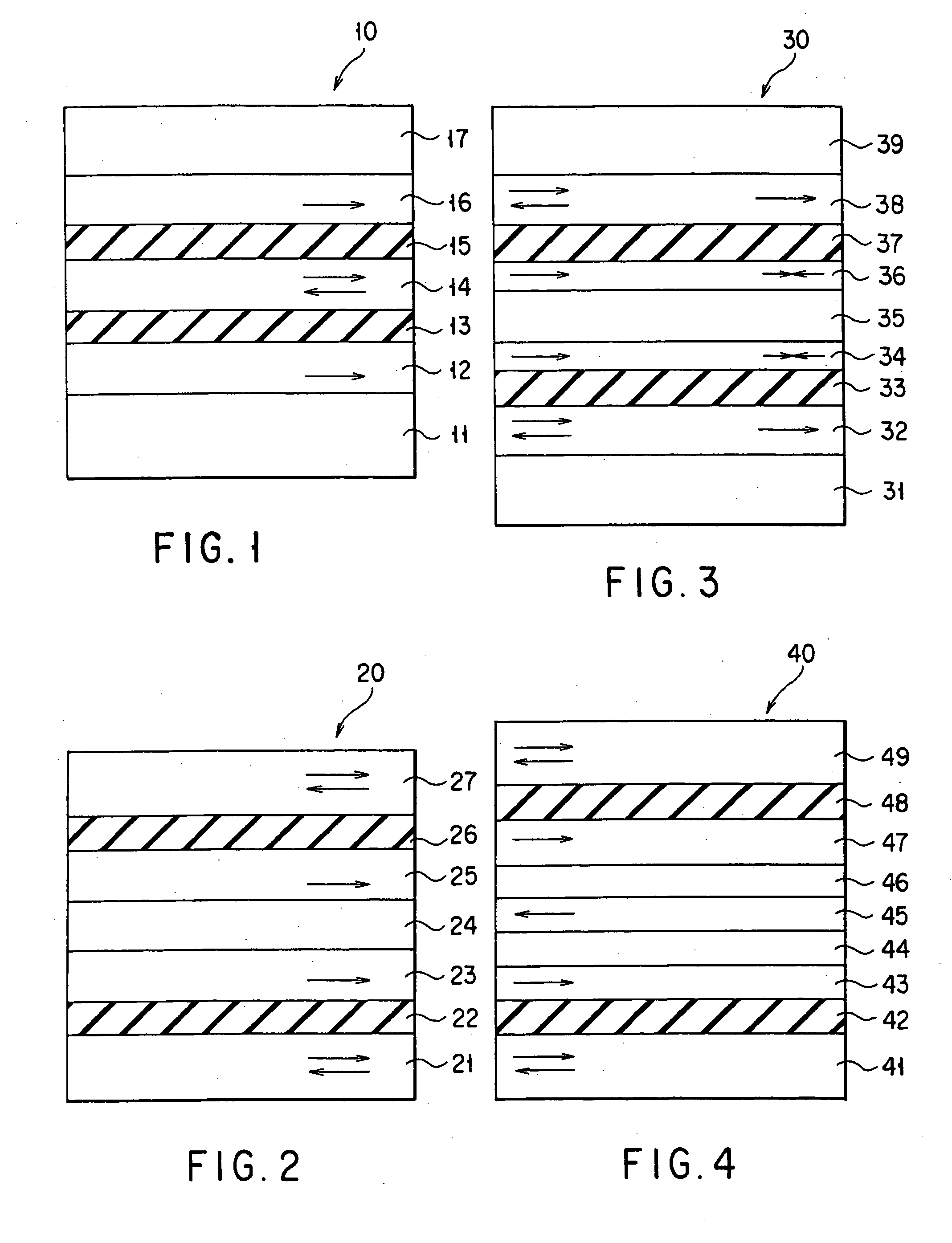

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F2 memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

Method for fabricating programmable memory array structures incorporating series-connected transistor strings

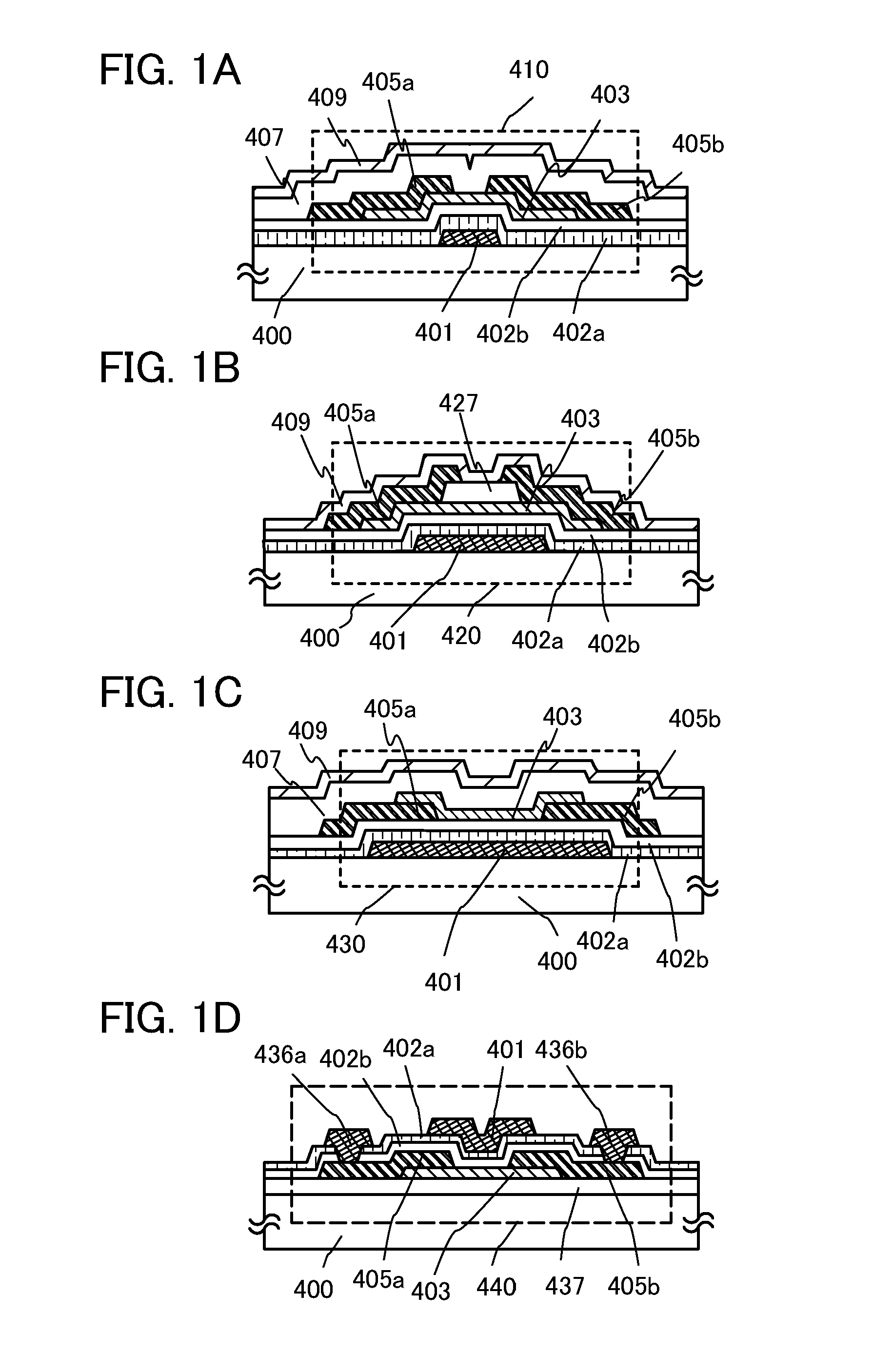

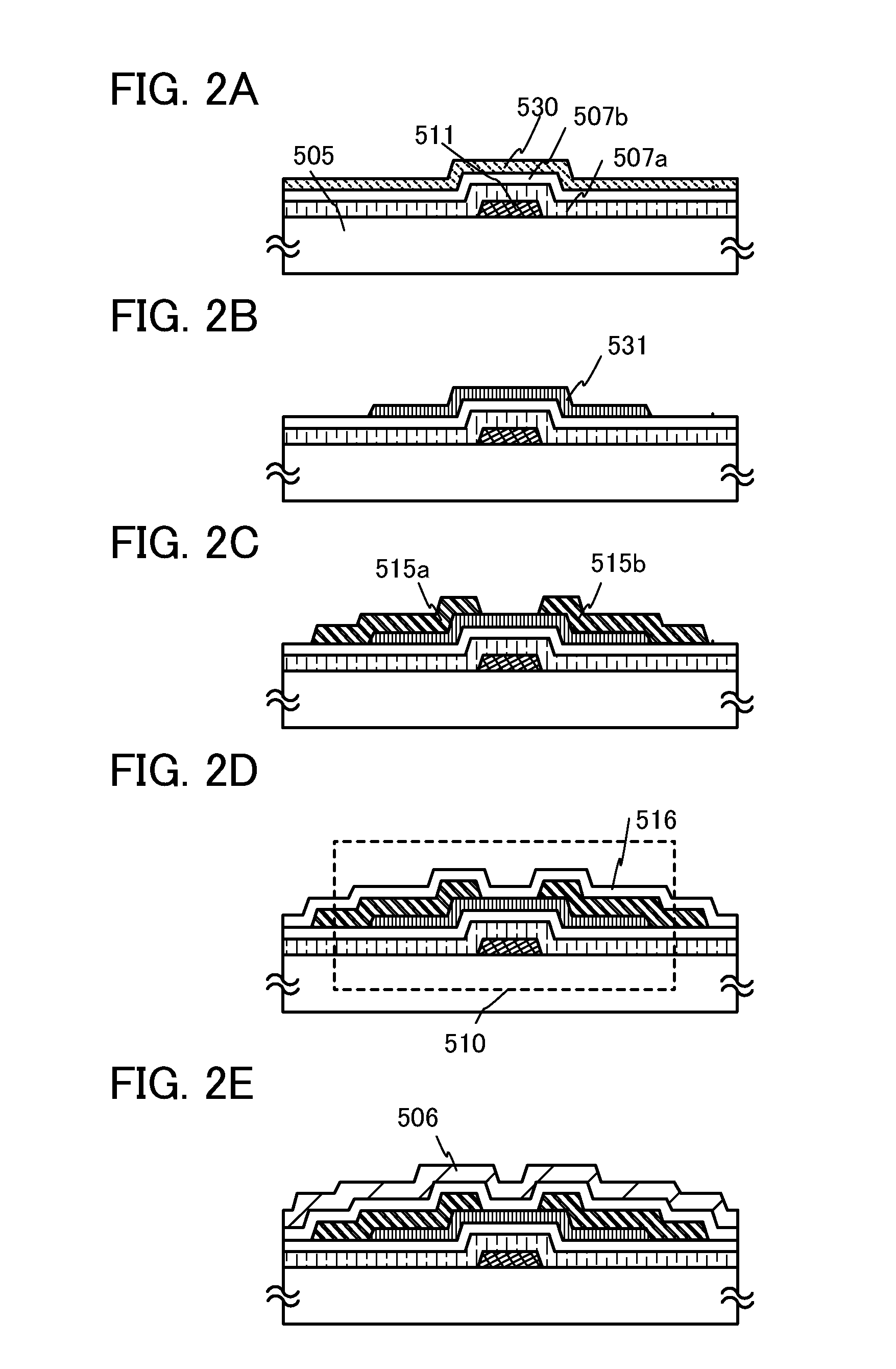

A three-dimensional flash memory array incorporates thin film transistors having a charge storage dielectric arranged in series-connected NAND strings to achieve a 4F<2 >memory cell layout. The memory array may be programmed and erased using only tunneling currents, and no leakage paths are formed through non-selected memory cells. Each NAND string includes two block select devices for respectively coupling one end of the NAND string to a global bit line, and the other end to a shared bias node. Pairs of NAND strings within a block share the same global bit line. The memory cells are preferably depletion mode SONOS devices, as are the block select devices. The memory cells may be programmed to a near depletion threshold voltage, and the block select devices are maintained in a programmed state having a near depletion mode threshold voltage. NAND strings on more than one layer may be connected to global bit lines on a single layer. By interleaving the NAND strings on each memory level and using two shared bias nodes per block, very little additional overhead is required for the switch devices at each end of the NAND strings. The NAND strings on different memory levels are preferably connected together by way of vertical stacked vias, each preferably connecting to more than one memory level. Each memory level may be produced with less than three masks per level.

Owner:SANDISK TECH LLC

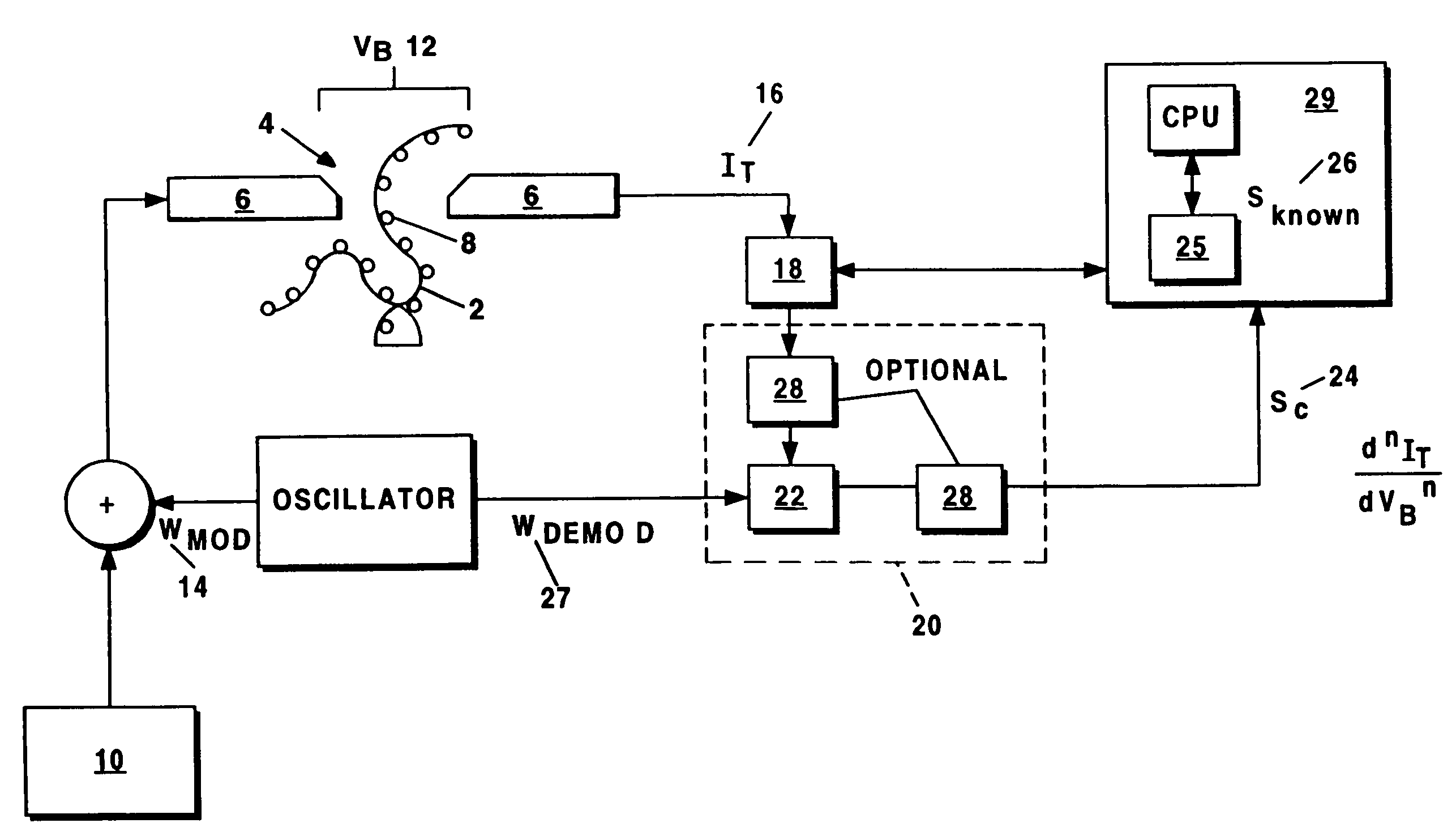

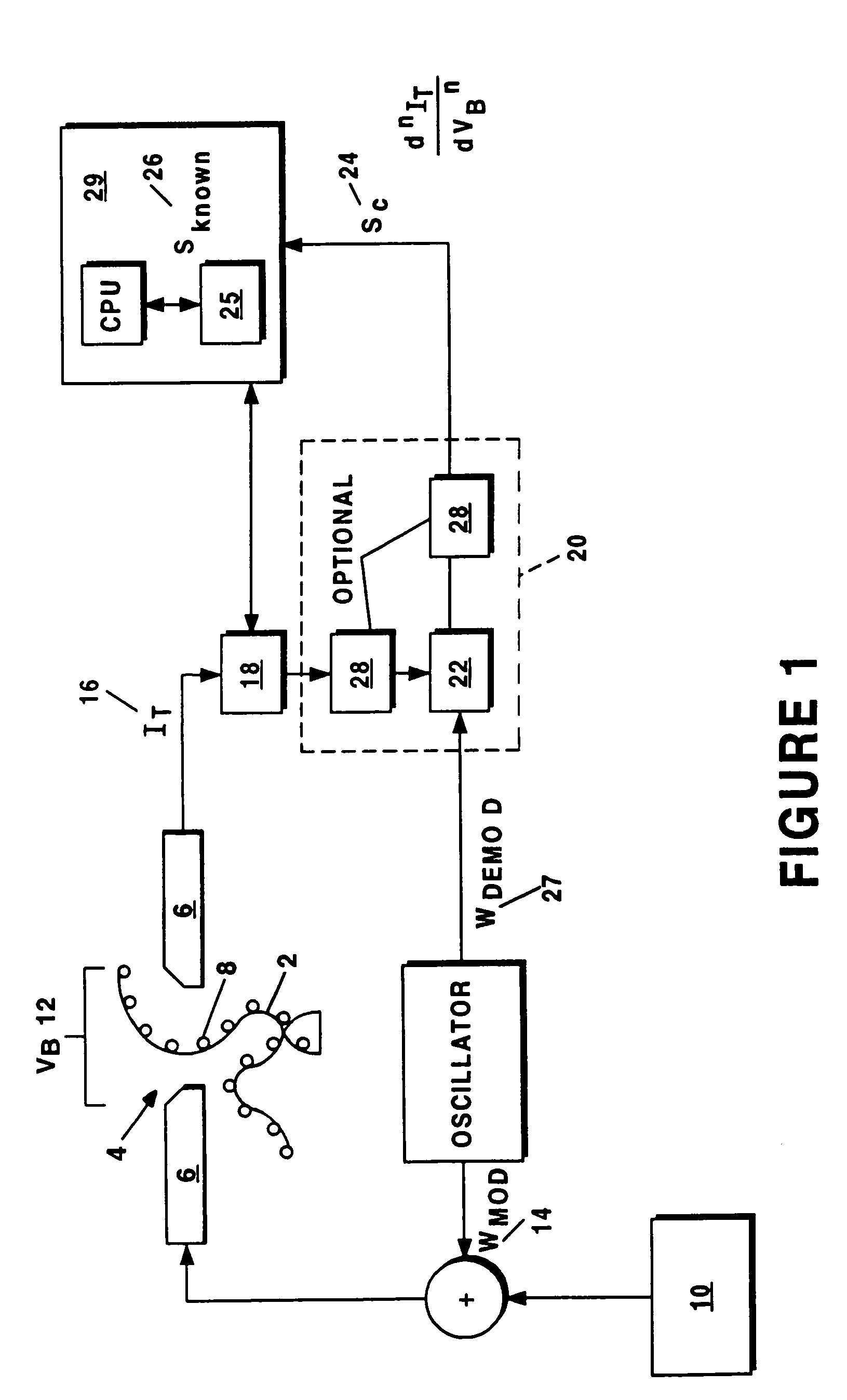

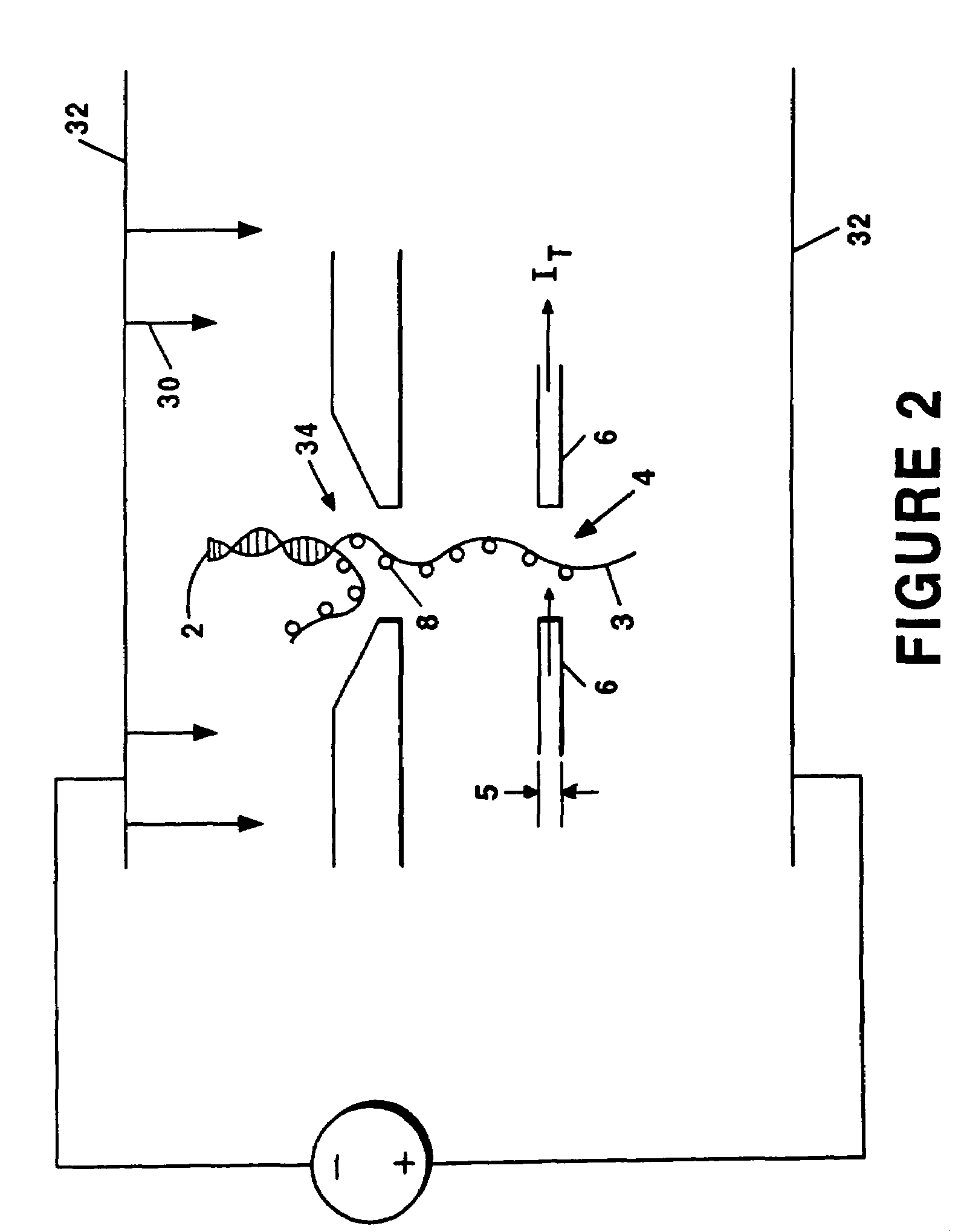

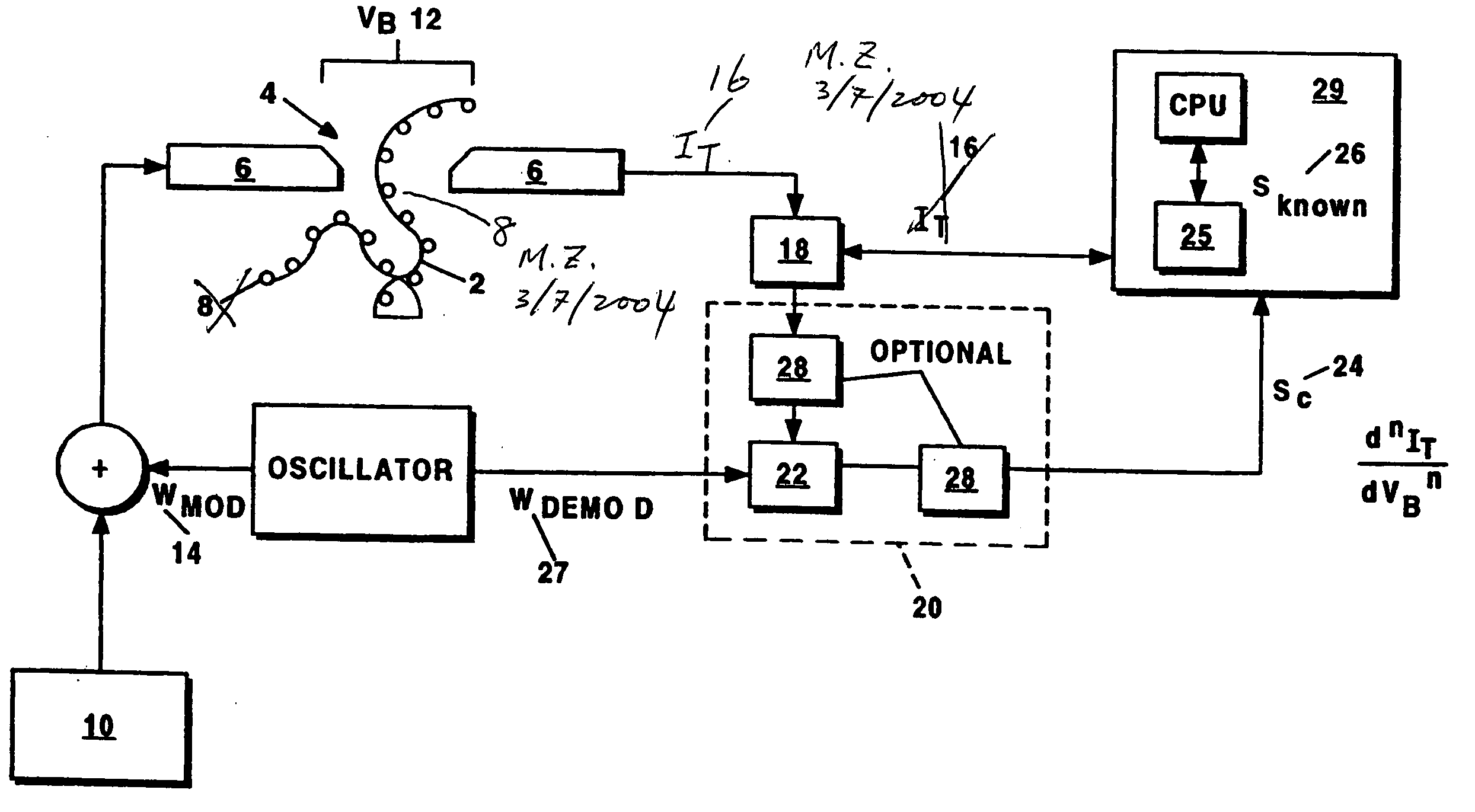

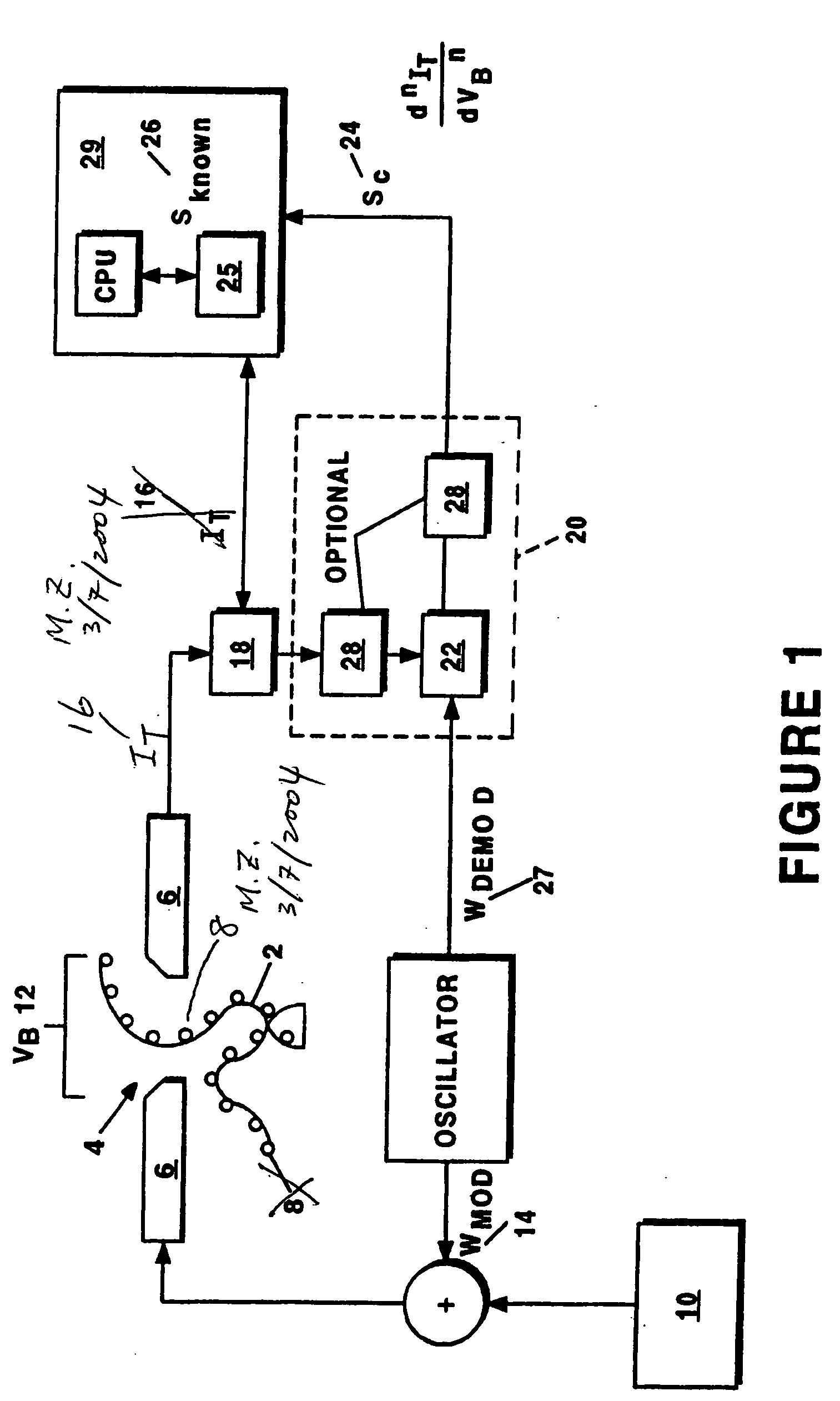

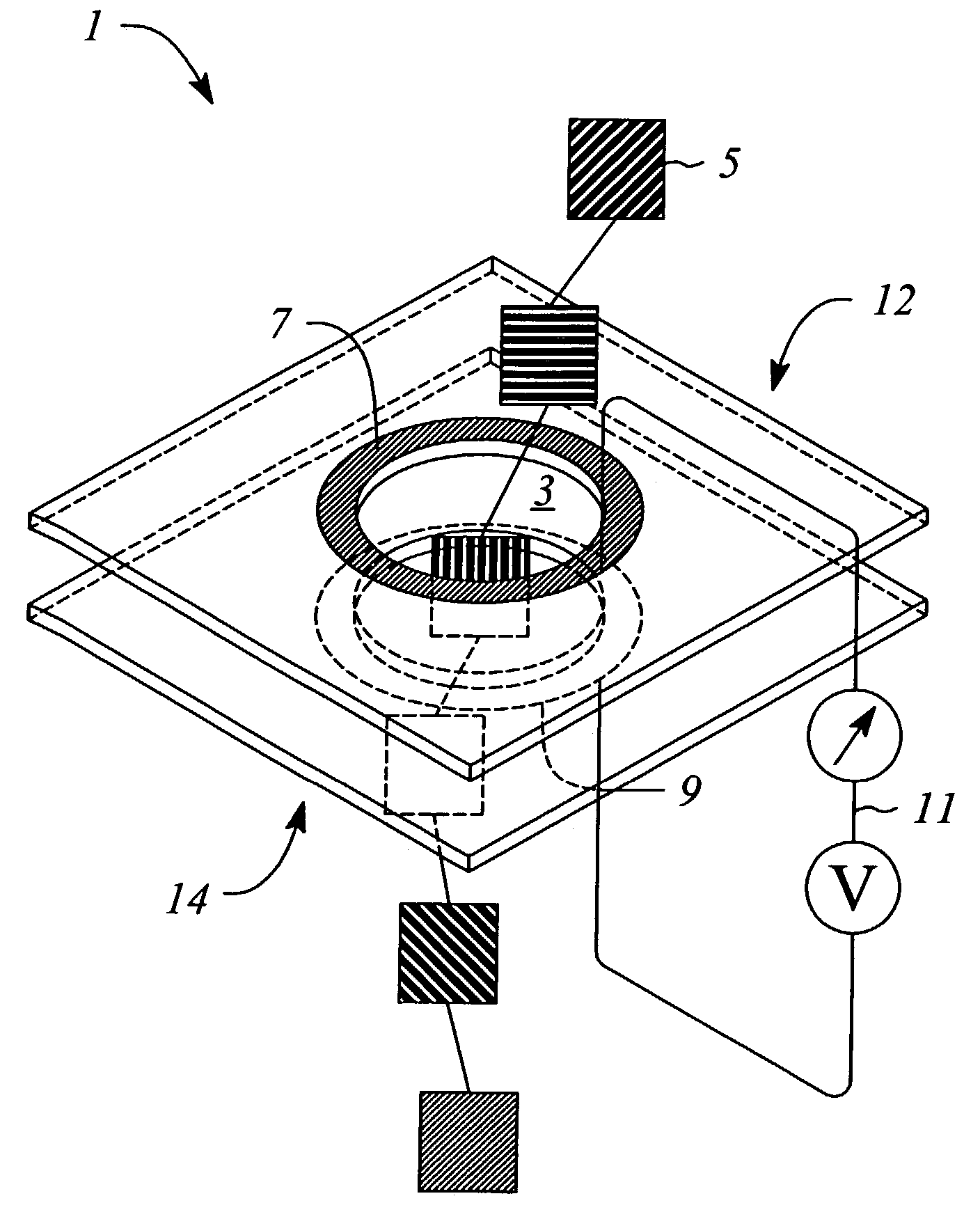

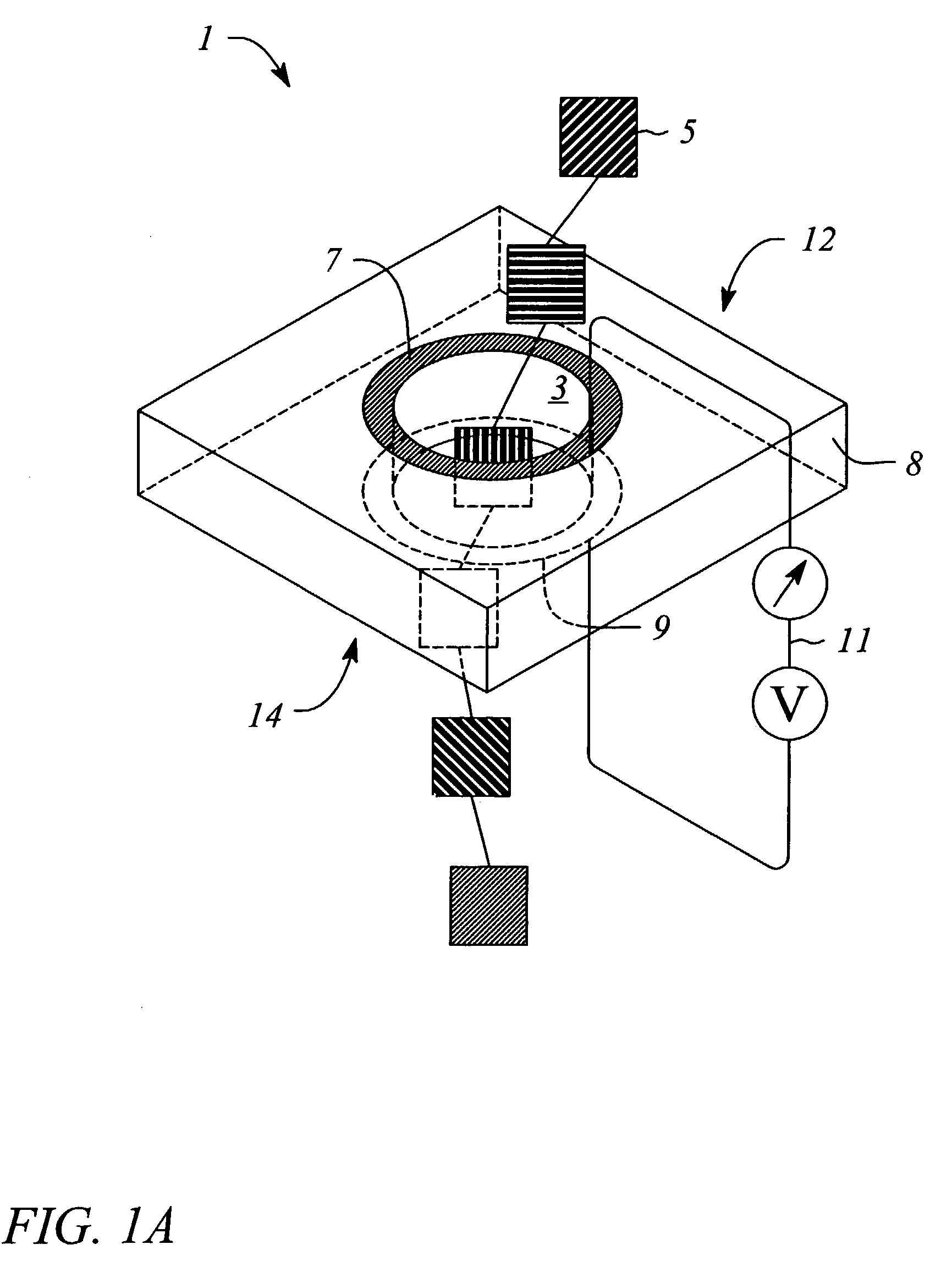

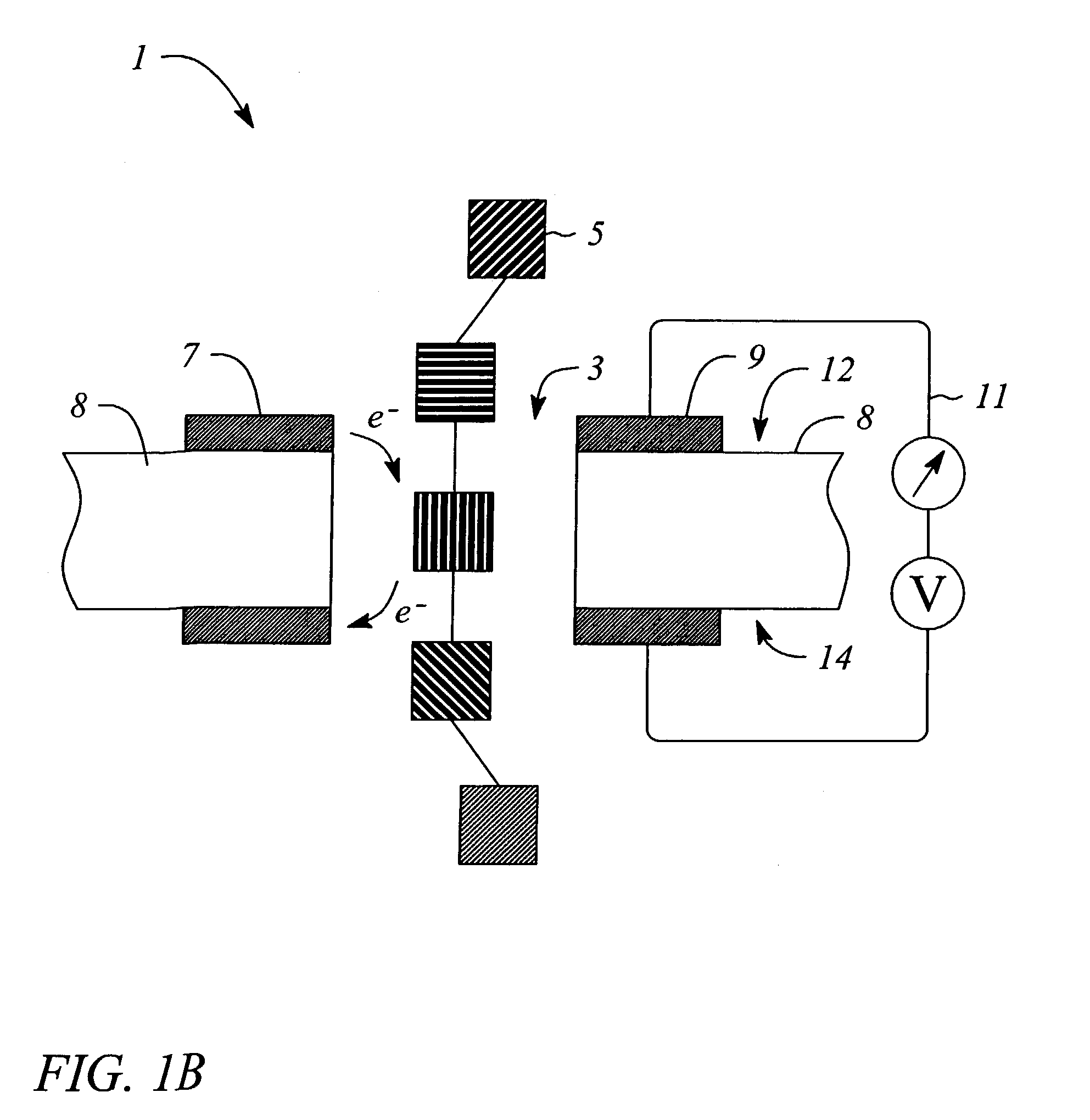

Method and apparatus for sequencing polymers through tunneling conductance variation detection

ActiveUS7279337B2Easy to detectHarmonic suppressionImmobilised enzymesBioreactor/fermenter combinationsElectric conductanceInternal energy

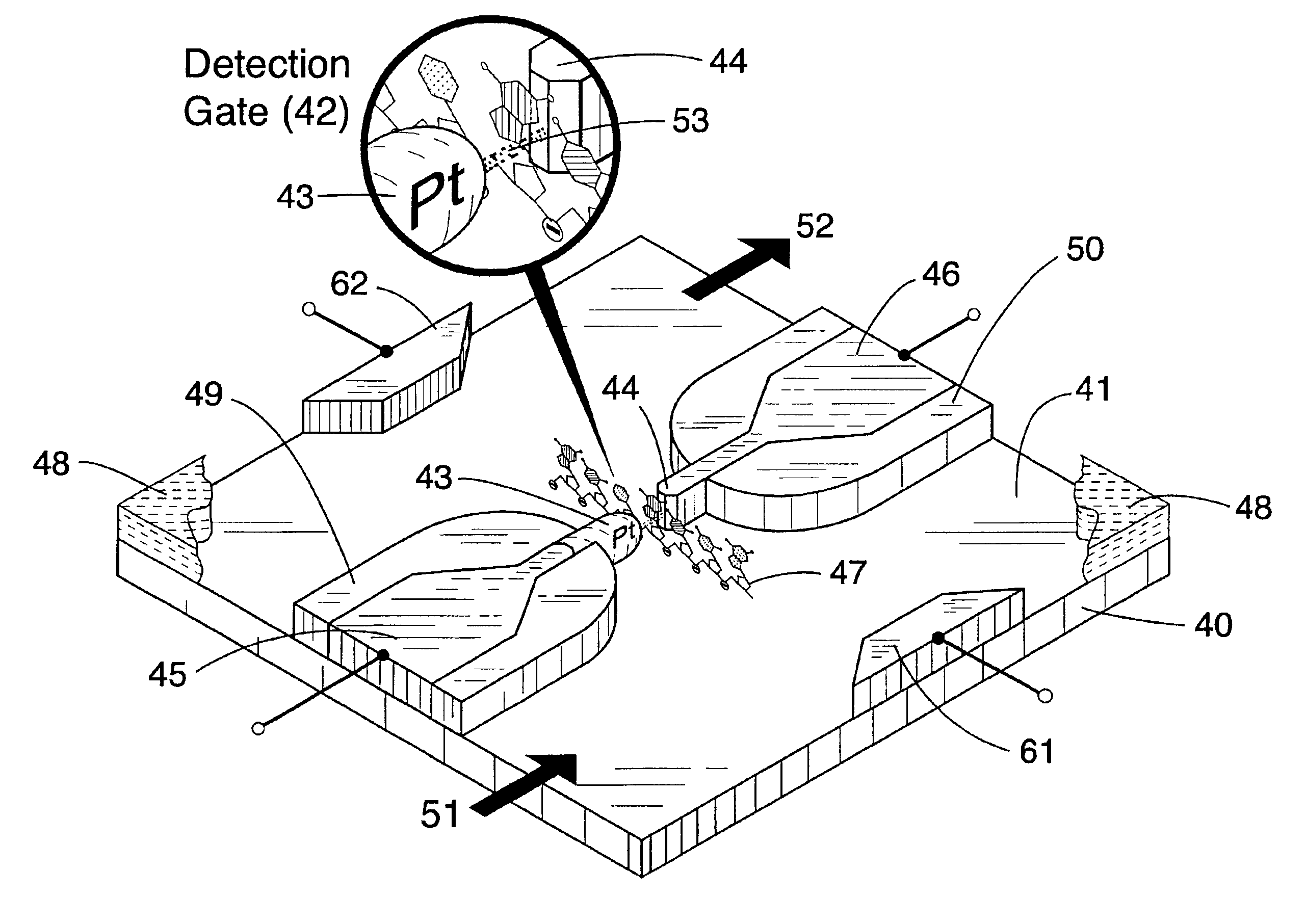

Systems and methods of identifying molecules of polymers such as, for example, a nucleic acid, are described. The method involves centering a bias voltage across a pair of nanoelectrodes separated by a channel that corresponds to one of any of the energy differences between any two internal energy levels of a molecule of interest, and modulating the bias voltage with a modulation waveform while the molecule of interest is in the channel. An electrical signal characteristic of the molecule of interest is derived from the tunneling current between the nanoelectrodes, and the characteristic electrical signal is compared with known values of the signal for chemically-known molecules in order to identify the molecule of interest. Multiple pairs of nano-electrodes may be employed to identify more reliably a single molecule or multiple molecules.

Owner:AGILENT TECH INC

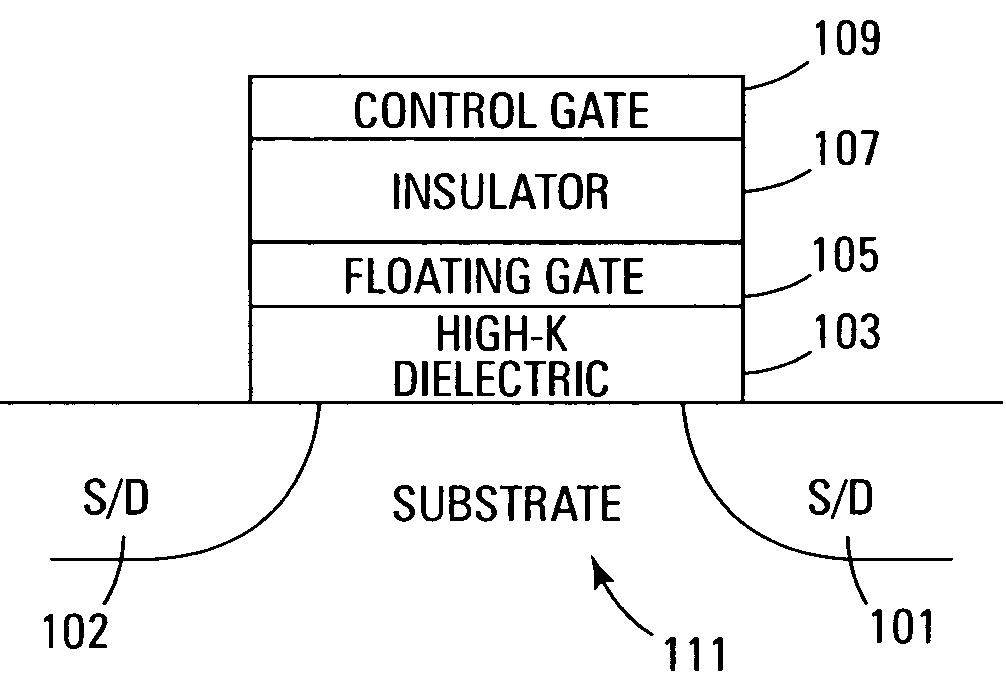

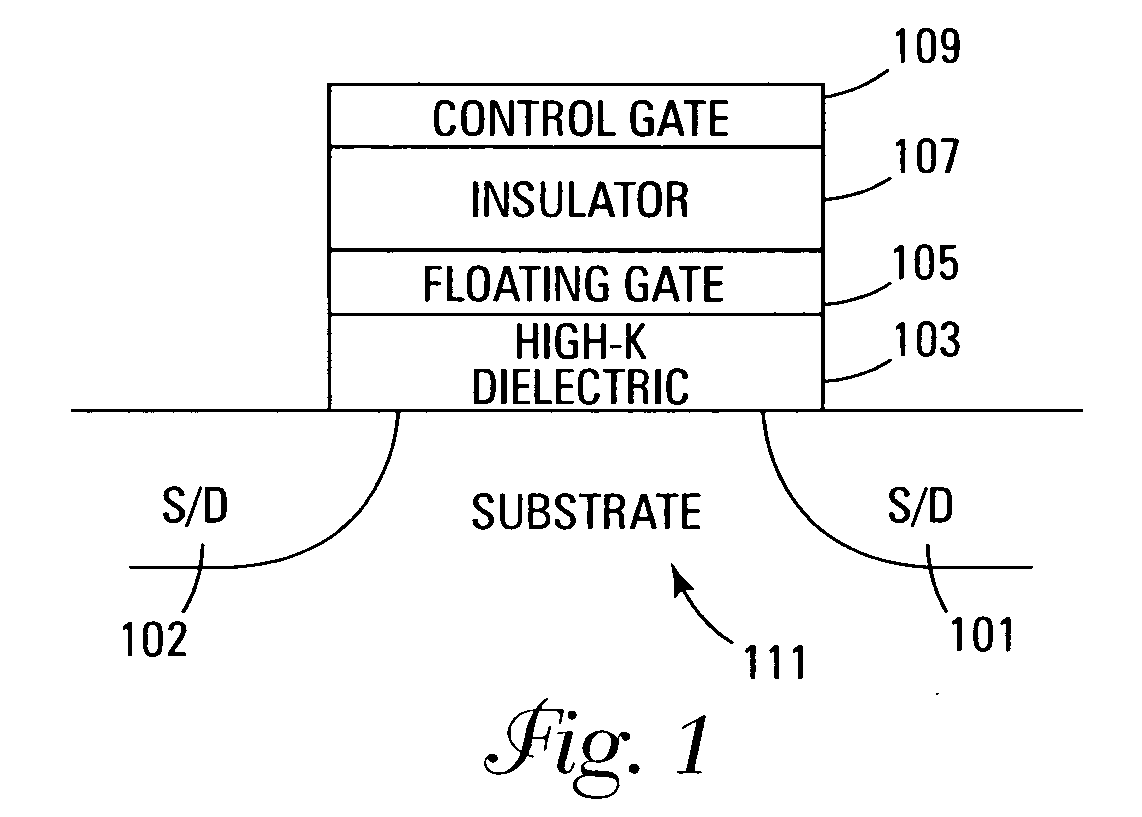

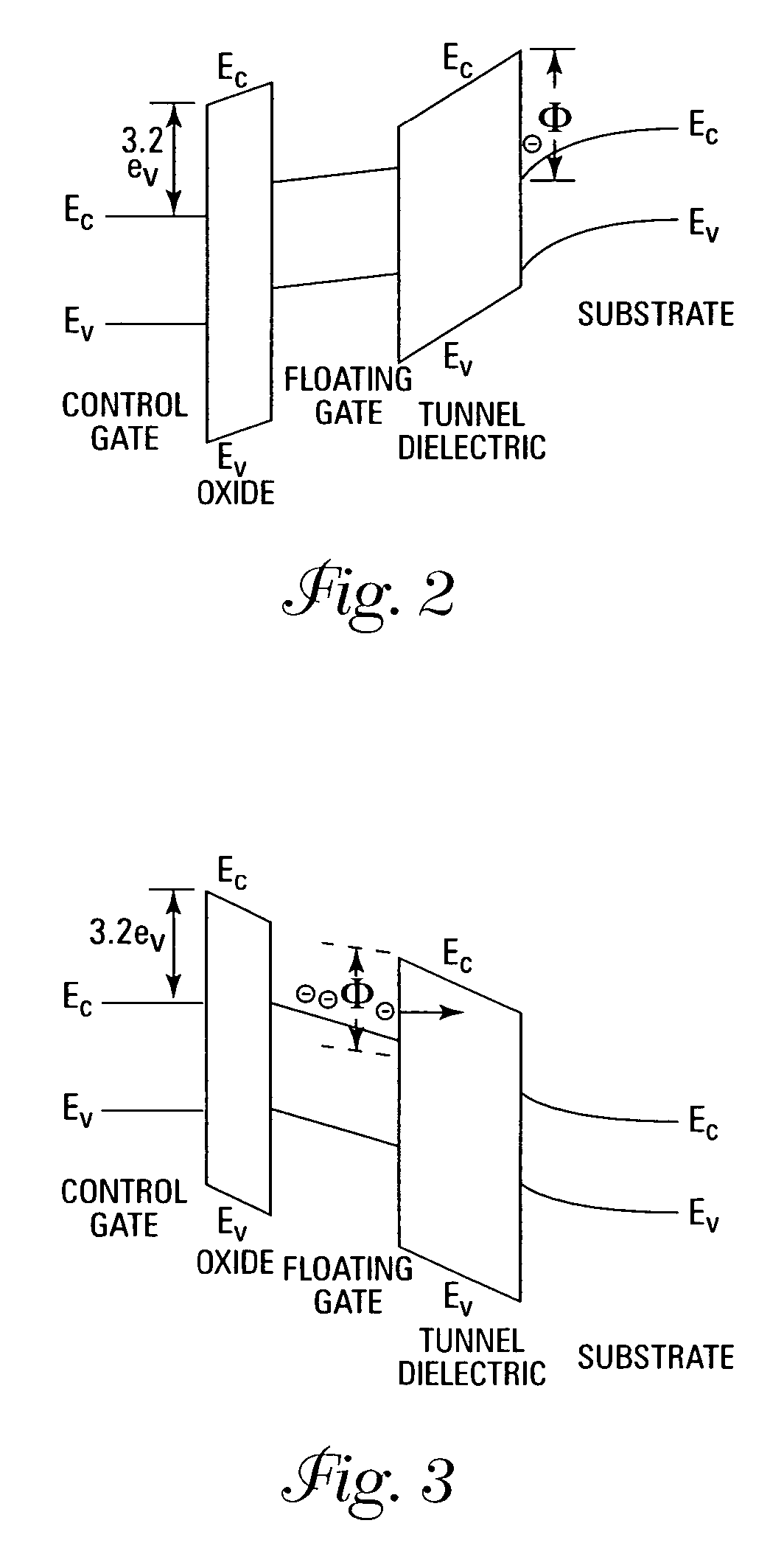

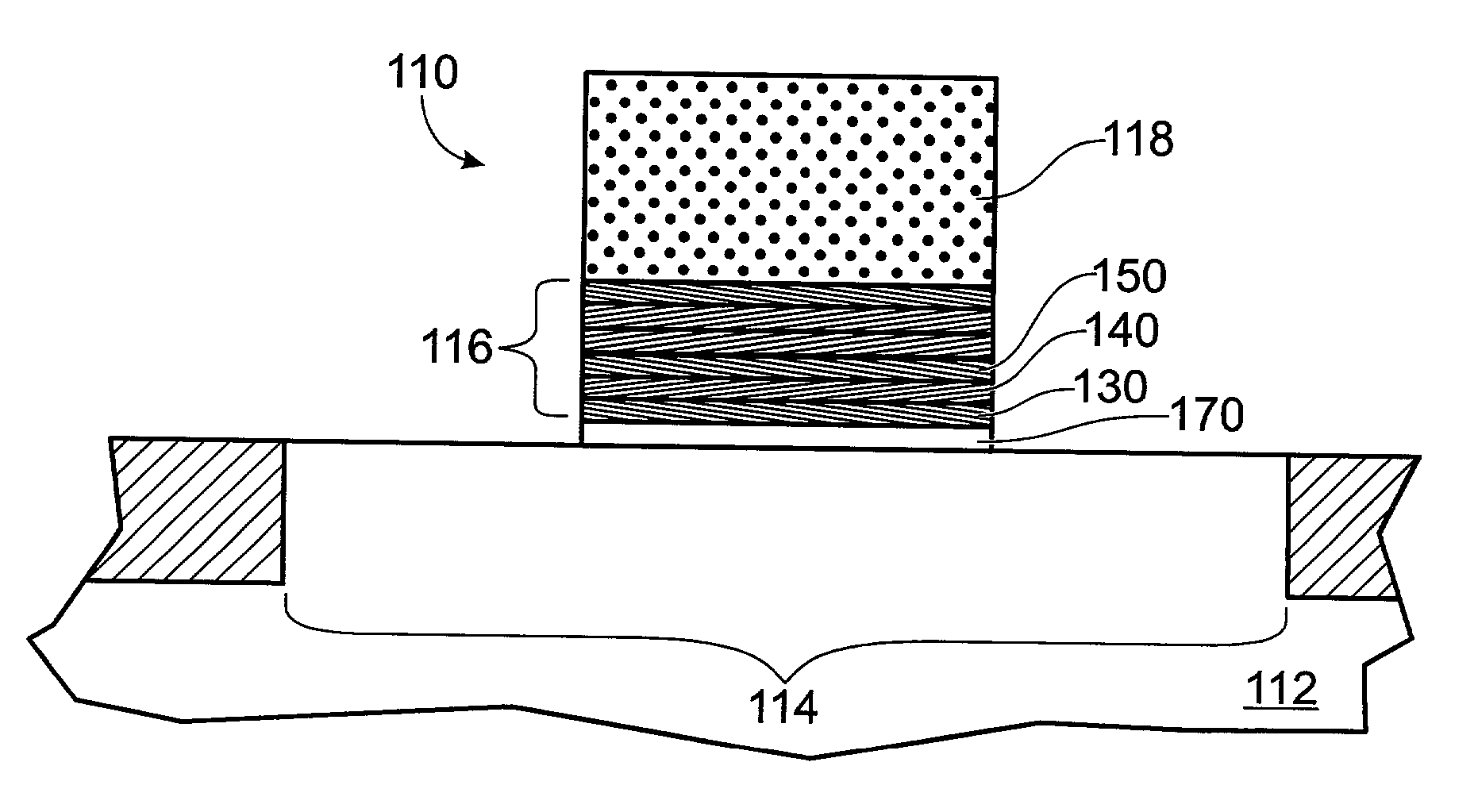

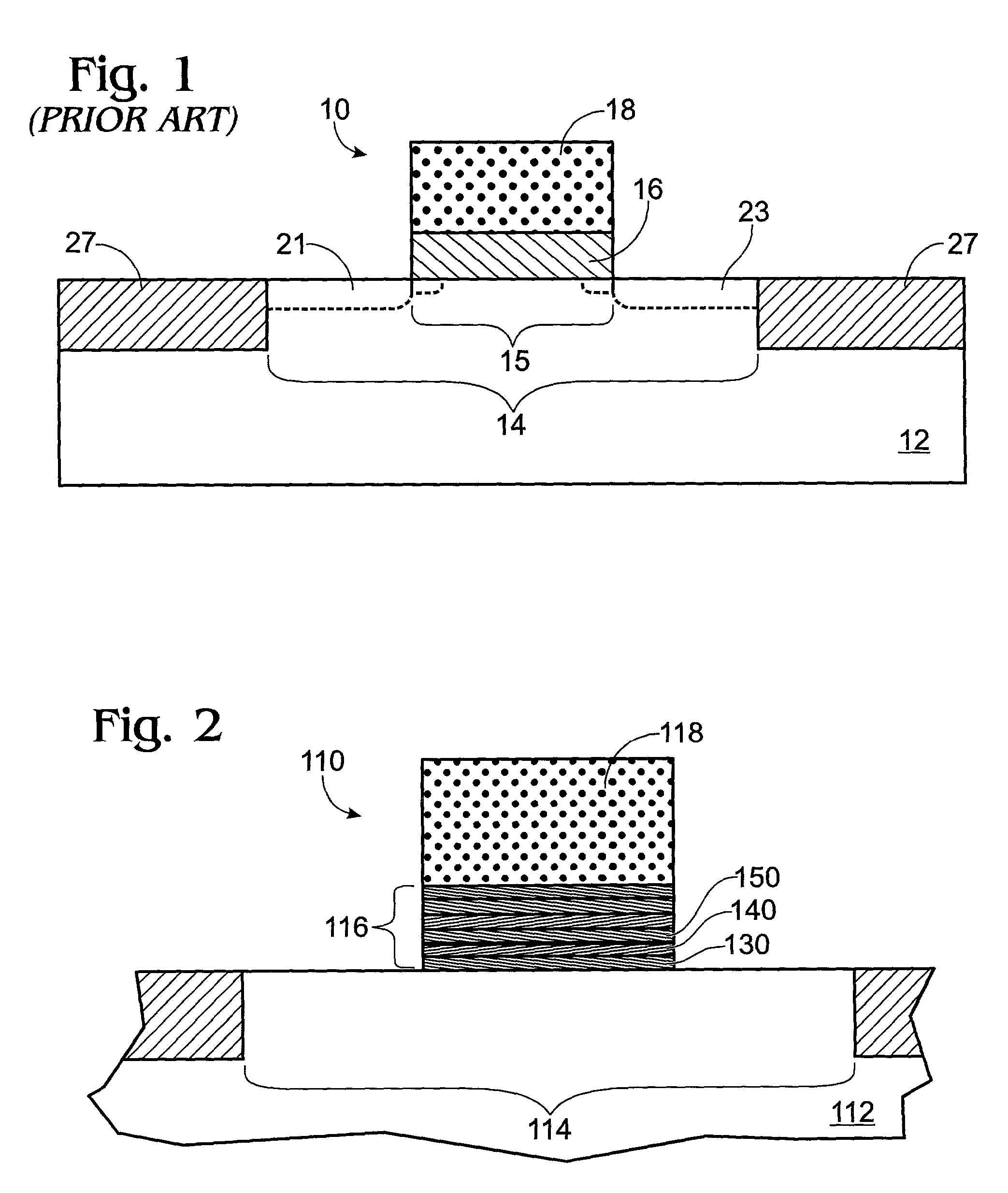

Flash memory having a high-permittivity tunnel dielectric

A high permittivity tunneling dielectric is used in a flash memory cell to provide greater tunneling current into the floating gate with smaller gate voltages. The flash memory cell has a substrate with source / drain regions. The high-k tunneling dielectric is formed above the substrate. The high-k tunneling dielectric can be deposited using evaporation techniques or atomic layer deposition techniques. The floating gate is formed on top of the high-k dielectric layer with an oxide gate insulator on top of that. A polysilicon control gate is formed on the top gate insulator.

Owner:MICRON TECH INC

High sensitivity magnetic built-in current sensor

InactiveUS7619431B2Improve sensor sensitivityHigh sensitivityMagnetic measurementsDigital storageElectrical conductorEngineering

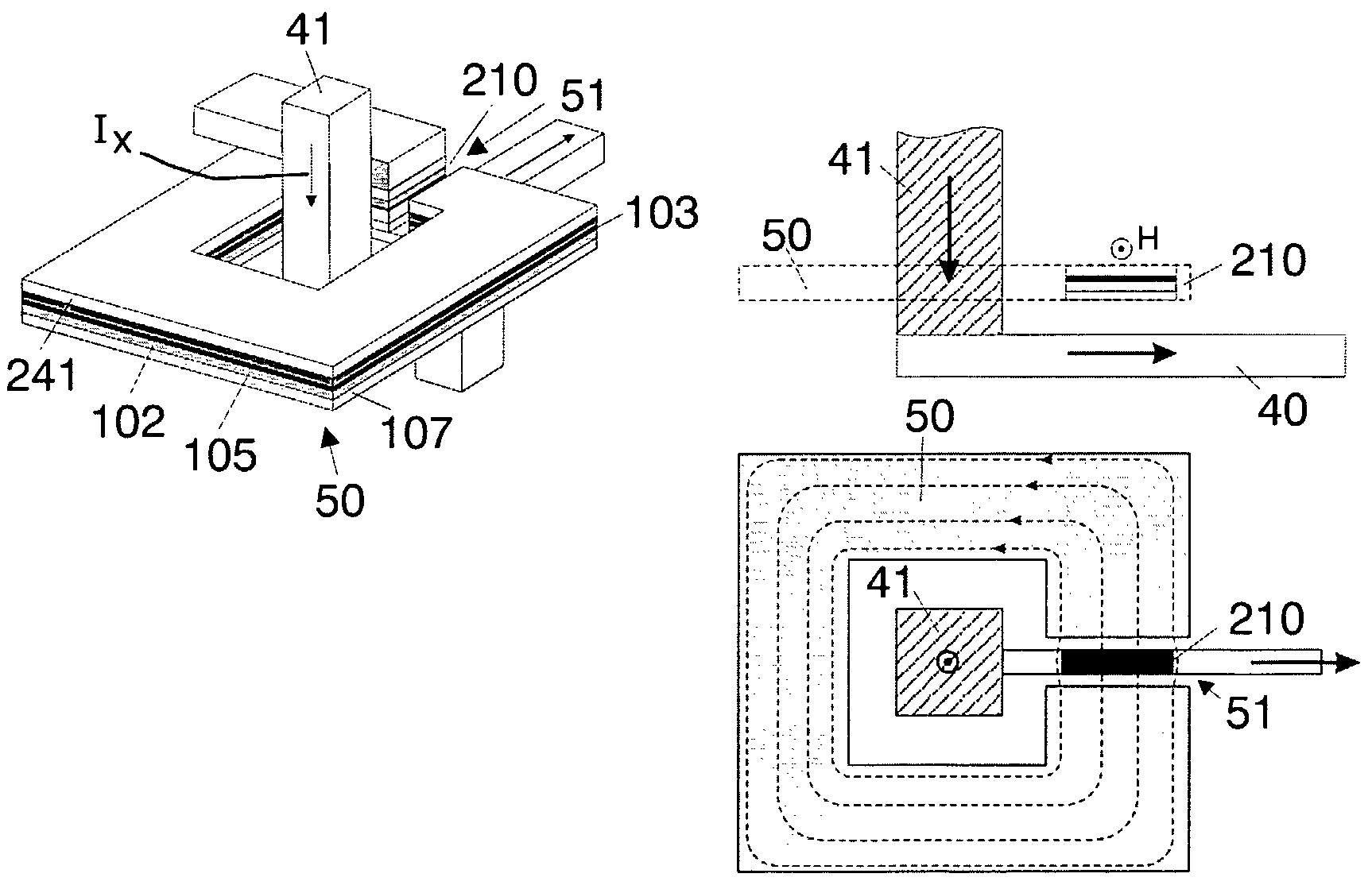

A sensor for contactlessly detecting currents, has a sensor element having a magnetic tunnel junction (MTJ), and detection circuitry, the sensor element having a resistance which varies with the magnetic field, and the detection circuitry is arranged to detect a tunnel current flowing through the tunnel junction. The sensor element may share an MTJ stack with memory elements. Also it can provide easy integration with next generation CMOS processes, including MRAM technology, be more compact, and use less power. Solutions for increasing sensitivity of the sensor, such as providing a flux concentrator, and for generating higher magnetic fields with a same current, such as forming L-shaped conductor elements, are given. The greater sensitivity enables less post processing to be used, to save power for applications such as mobile devices. Applications include current sensors, built-in current sensors, and IDDQ and IDDT testing, even for next generation CMOS processes.

Owner:ELIPOSKI REMOTE

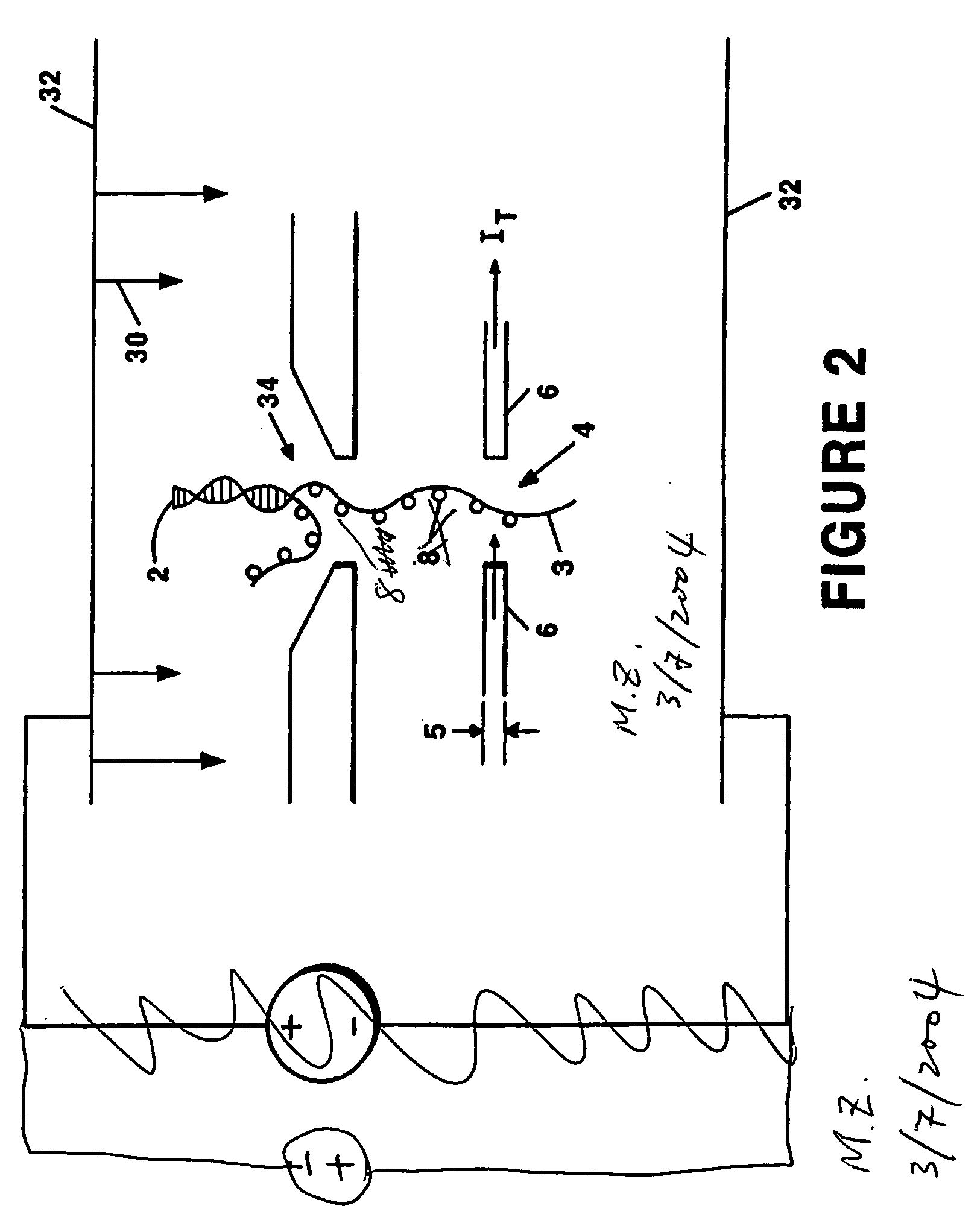

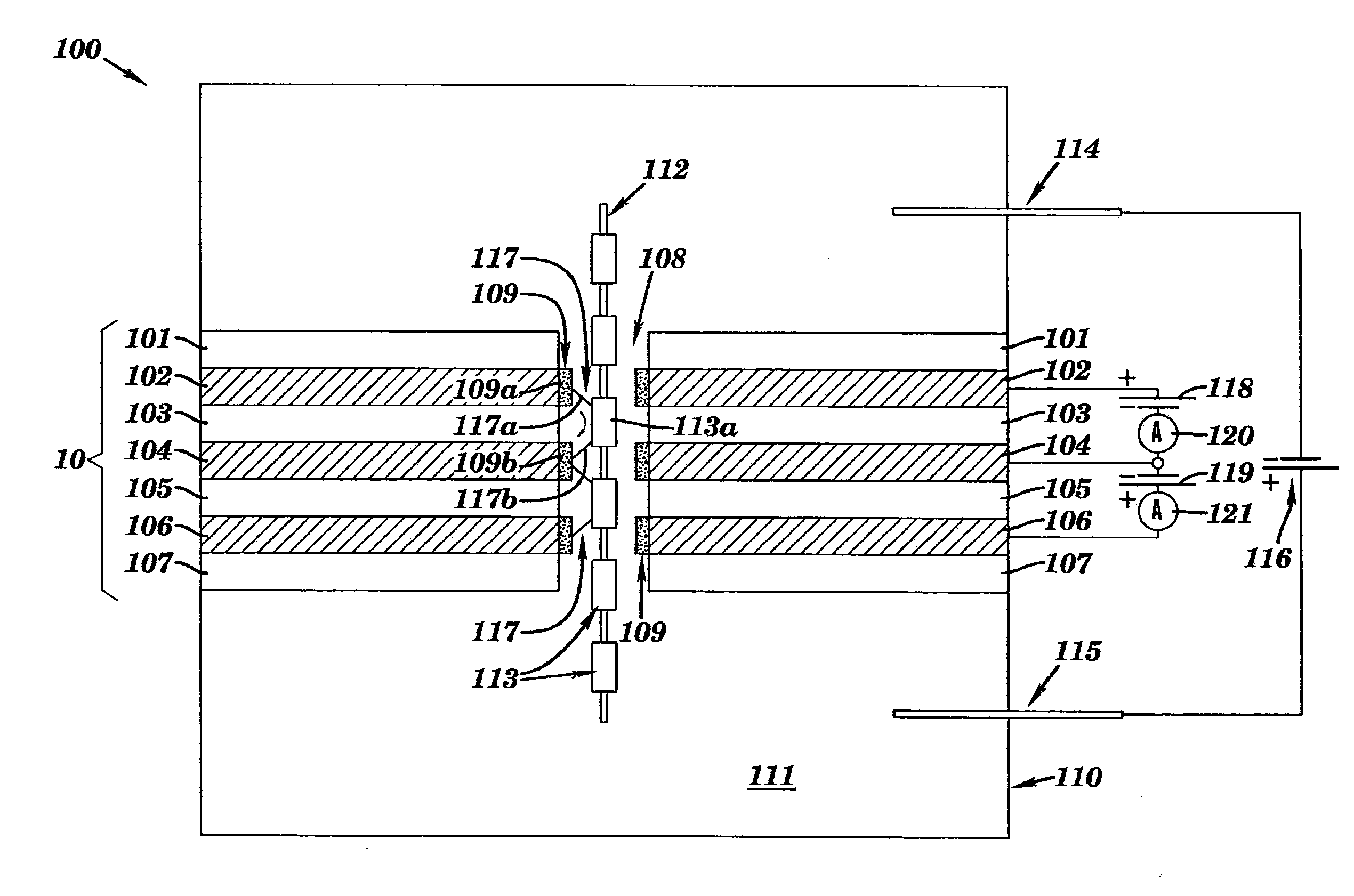

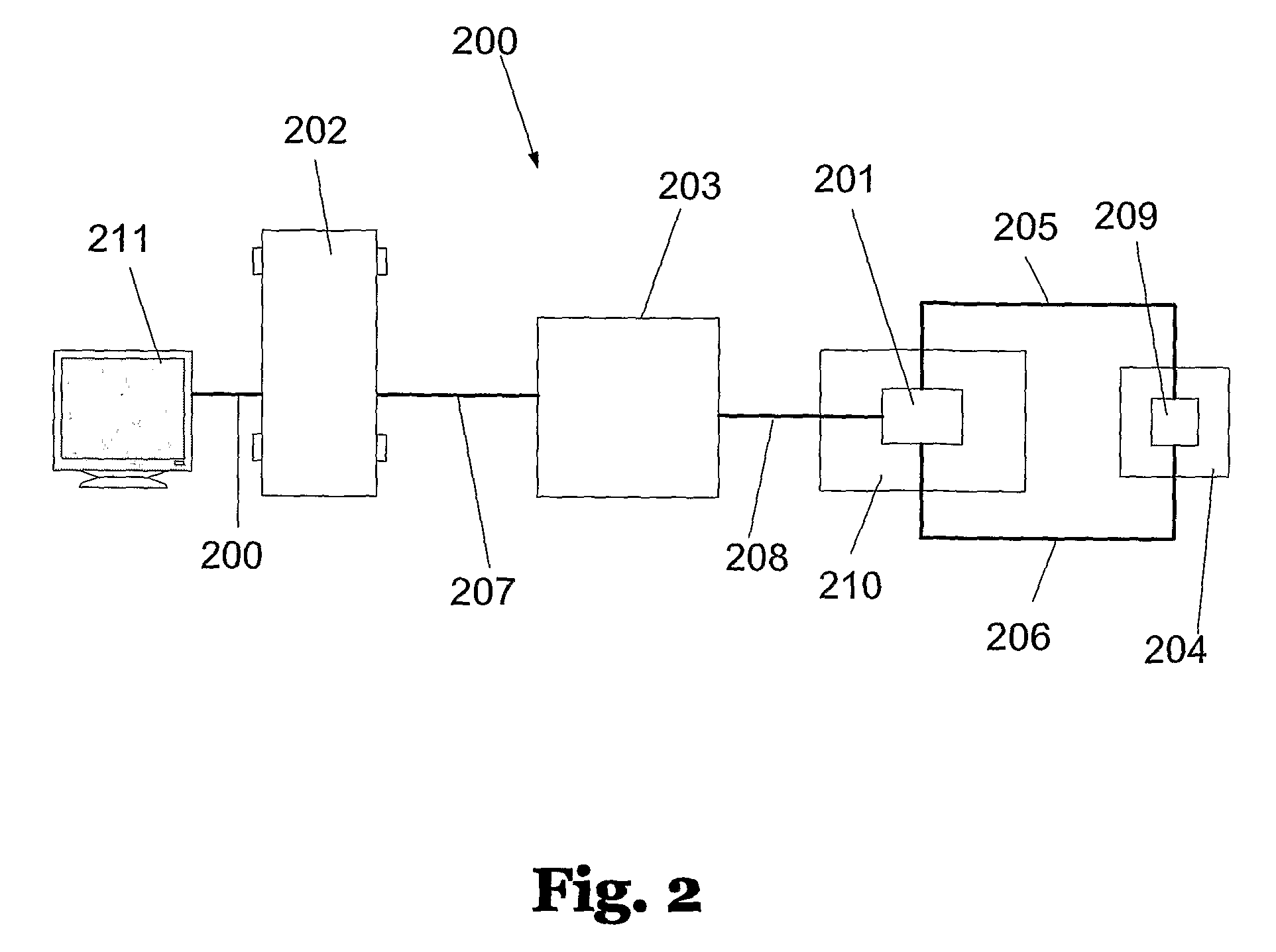

DNA and RNA sequencing by nanoscale reading through programmable electrophoresis and nanoelectrode-gated tunneling and dielectric detection

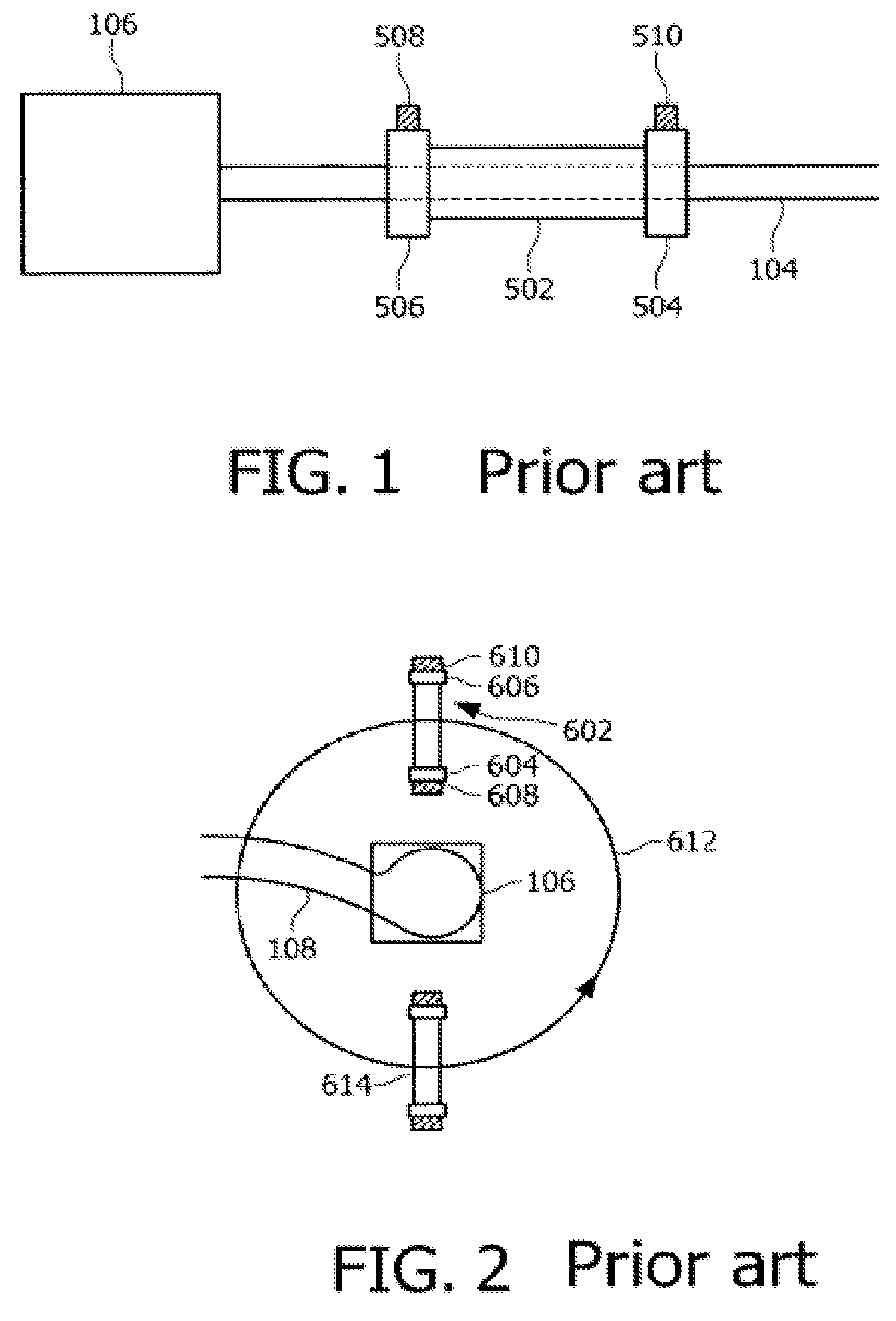

An apparatus and method for performing nucleic acid (DNA and / or RNA) sequencing on a single molecule. The genetic sequence information is obtained by probing through a DNA or RNA molecule base by base at nanometer scale as though looking through a strip of movie film. This DNA sequencing nanotechnology has the theoretical capability of performing DNA sequencing at a maximal rate of about 1,000,000 bases per second. This enhanced performance is made possible by a series of innovations including: novel applications of a fine-tuned nanometer gap for passage of a single DNA or RNA molecule; thin layer microfluidics for sample loading and delivery; and programmable electric fields for precise control of DNA or RNA movement. Detection methods include nanoelectrode-gated tunneling current measurements, dielectric molecular characterization, and atomic force microscopy / electrostatic force microscopy (AFM / EFM) probing for nanoscale reading of the nucleic acid sequences.

Owner:UT BATTELLE LLC

Method and apparatus for sequencing polymers through tunneling conductance variation detection

ActiveUS20050202444A1Improve signal-to-noise ratioRestricts passageImmobilised enzymesBioreactor/fermenter combinationsInternal energyPolymer

Systems and methods of identifying molecules of polymers such as, for example, a nucleic acid, are described. The method involves centering a bias voltage across a pair of nano-electrodes separated by a channel that corresponds to one of any of the energy differences between any two internal energy levels of a molecule of interest, and modulating the bias voltage with a modulation waveform while the molecule of interest is in the channel. An electrical signal characteristic of the molecule of interest is derived from the tunneling current between the nano-electrodes, and the characteristic electrical signal is compared with known values of the signal for chemically-known molecules in order to identify the molecule of interest. Multiple pairs of nano-electrodes may be employed to identify more reliably a single molecule or multiple molecules.

Owner:AGILENT TECH INC

Apparatus and method for biopolymer identification during translocation through a nanopore

The present invention provides an apparatus and method for identifying and sequencing a biopolymer translocating a nanopore. The apparatus of the present invention provides a first electrode, a second electrode and a potential means for applying a bias ramping potential across the electrodes to produce resonant tunneling of current carriers between the two electrodes. As the bias potential is ramped across the electrodes the increase in tunneling current occurs as the carrier energy sequentially matches the conduction band energies of the translocating biopolymer. This technique allows for real-time identification and sequencing of a biopolymer as the band energy spectra of the individual portions of the bipolymer are recorded, differentiated and identified. A method for identifying the biopolymer is also disclosed.

Owner:AGILENT TECH INC

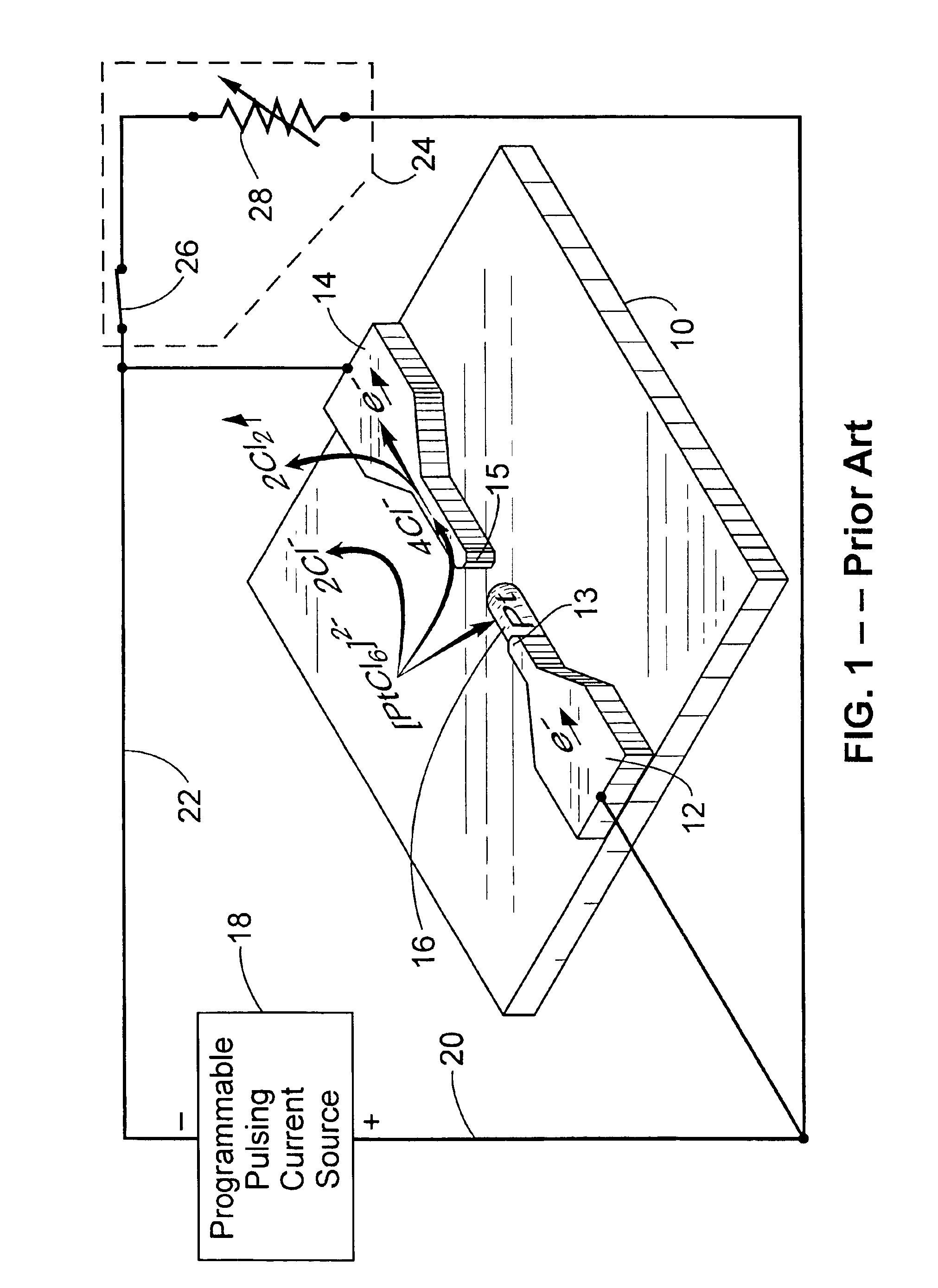

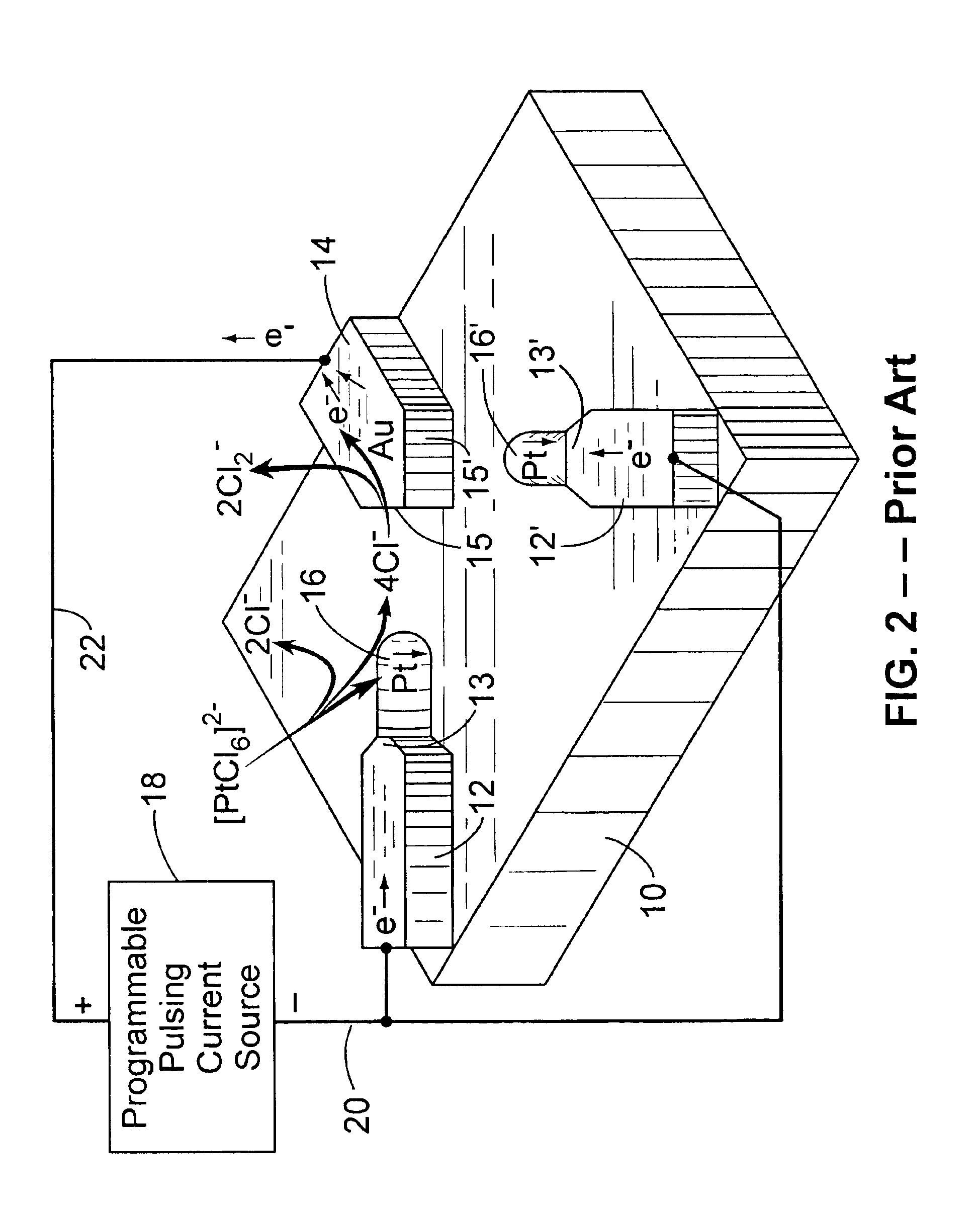

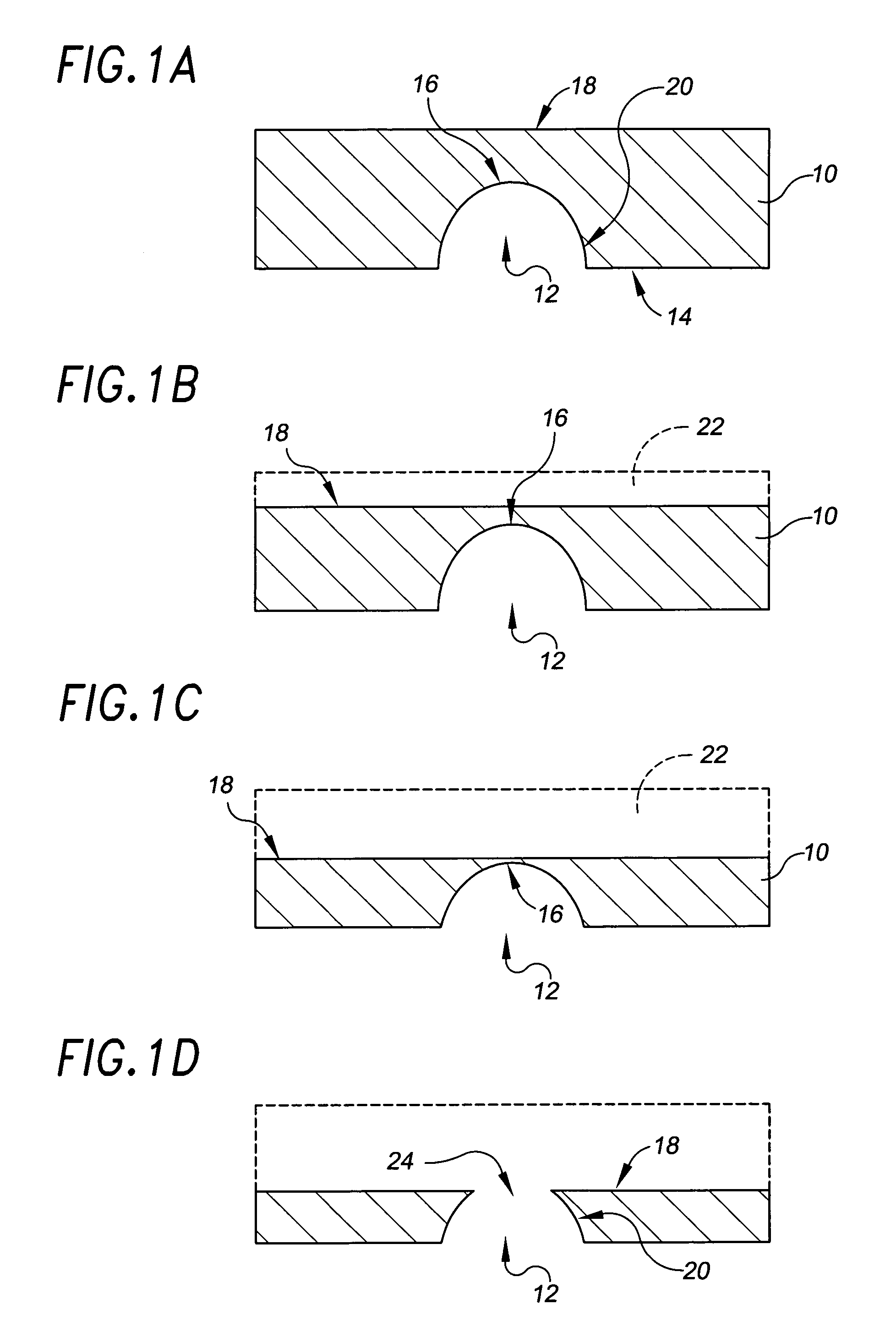

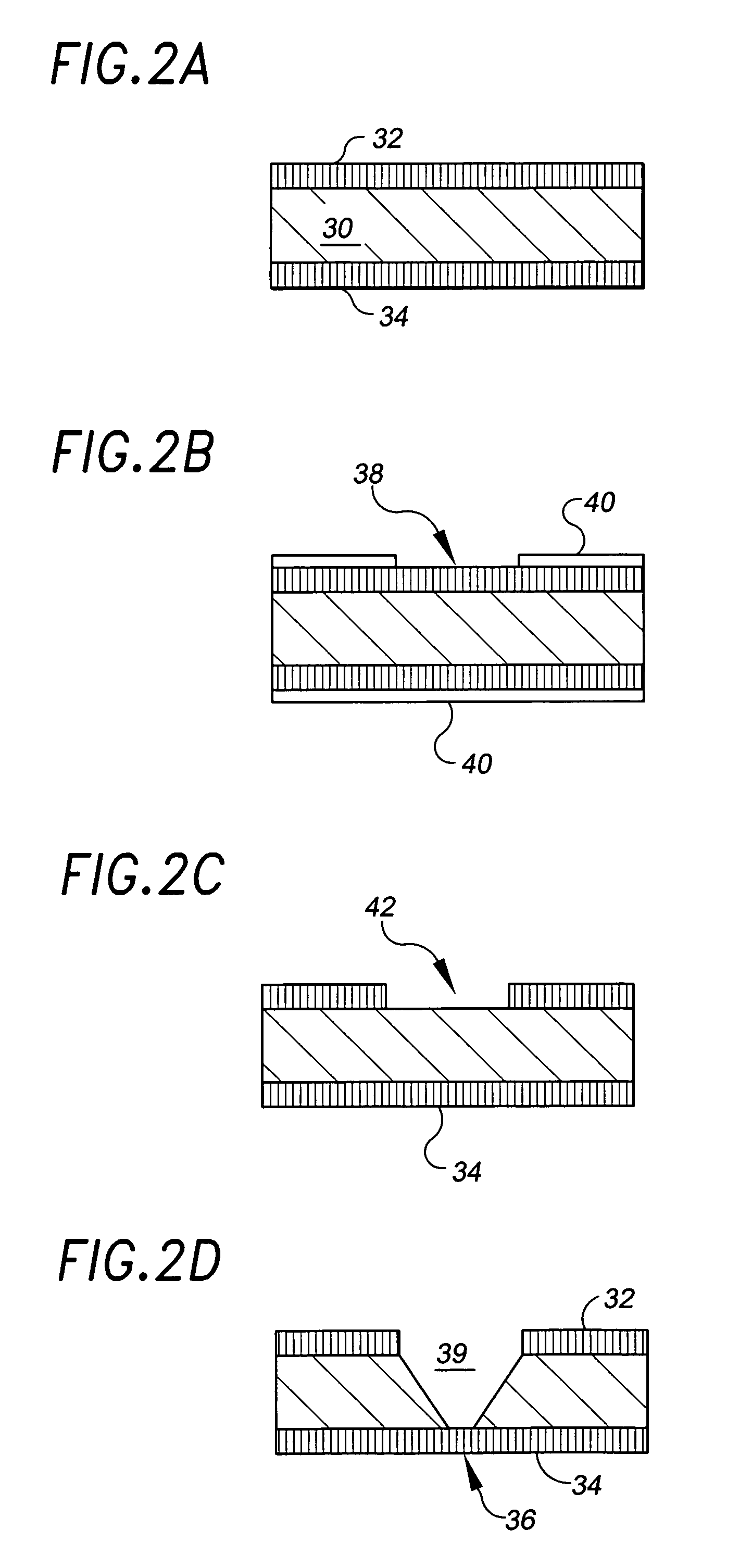

Controlled fabrication of gaps in electrically conducting structures

InactiveUS7582490B2Leveling precisionAccurate repeatabilityDecorative surface effectsSolid-state devicesSolid state structureEngineering

A method for controlling a gap in an electrically conducting solid state structure provided with a gap. The structure is exposed to a fabrication process environment conditions of which are selected to alter an extent of the gap. During exposure of the structure to the process environment, a voltage bias is applied across the gap. Electron tunneling current across the gap is measured during the process environment exposure and the process environment is controlled during process environment exposure based on tunneling current measurement. A method for controlling the gap between electrically conducting electrodes provided on a support structure. Each electrode has an electrode tip separated from other electrode tips by a gap. The electrodes are exposed to a flux of ions causing transport of material of the electrodes to corresponding electrode tips, locally adding material of the electrodes to electrode tips in the gap.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

DNA sequencing using multiple metal layer structure with organic coatings forming transient bonding to DNA bases

A nanodevice is provided. A reservoir is filled with an ionic fluid. A membrane separates the reservoir, and the membrane includes electrode layers separated by insulating layers in which the electrode layers have an organic coating. A nanopore is formed through the membrane, and the organic coating on the electrode layers forms transient bonds to a base of a molecule in the nanopore. When a first voltage is applied to the electrode layers a tunneling current is generated by the base in the nanopore, and the tunneling current travels through the transient bonds formed to the base to be measured as a current signature for distinguishing the base.

Owner:IBM CORP

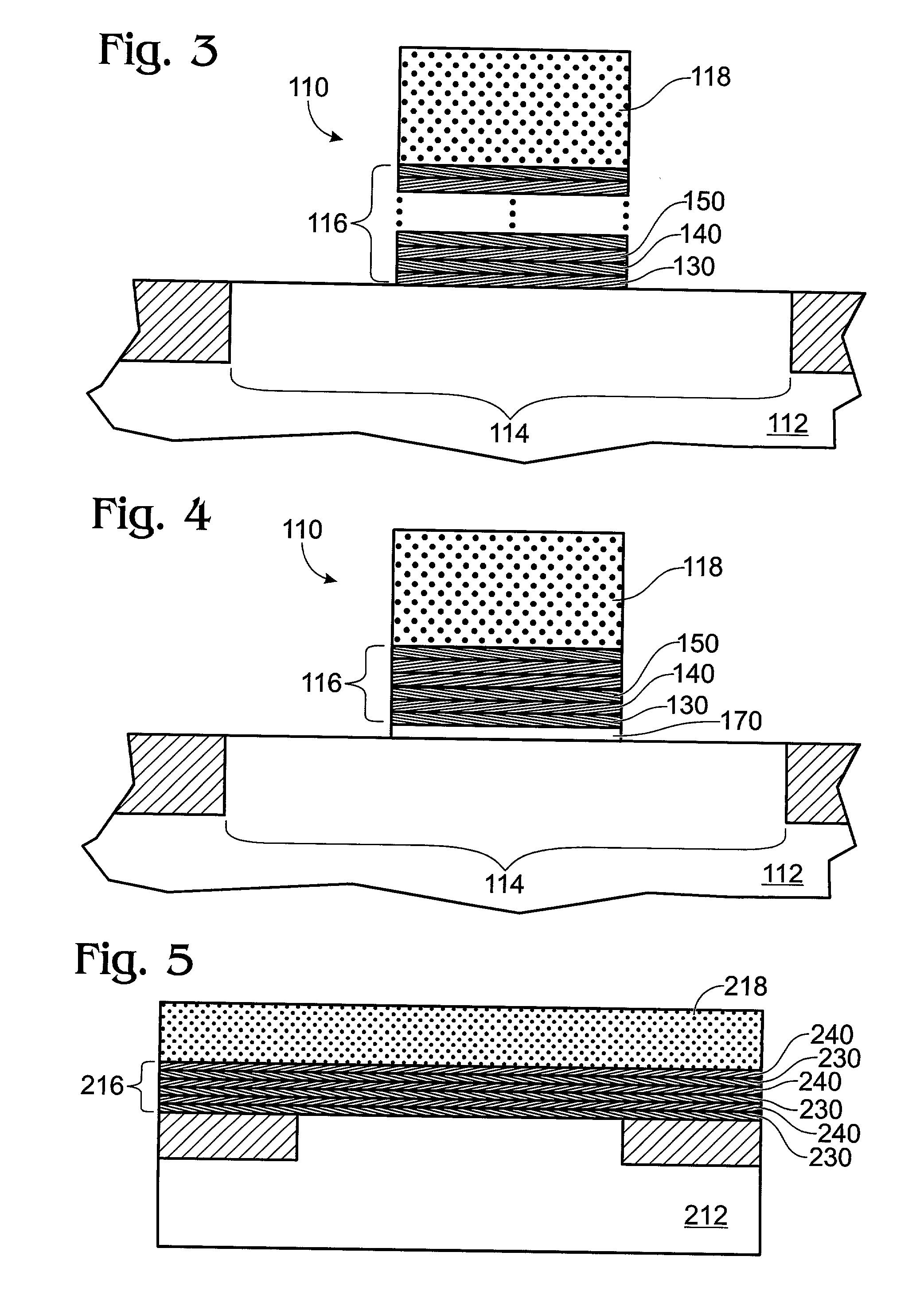

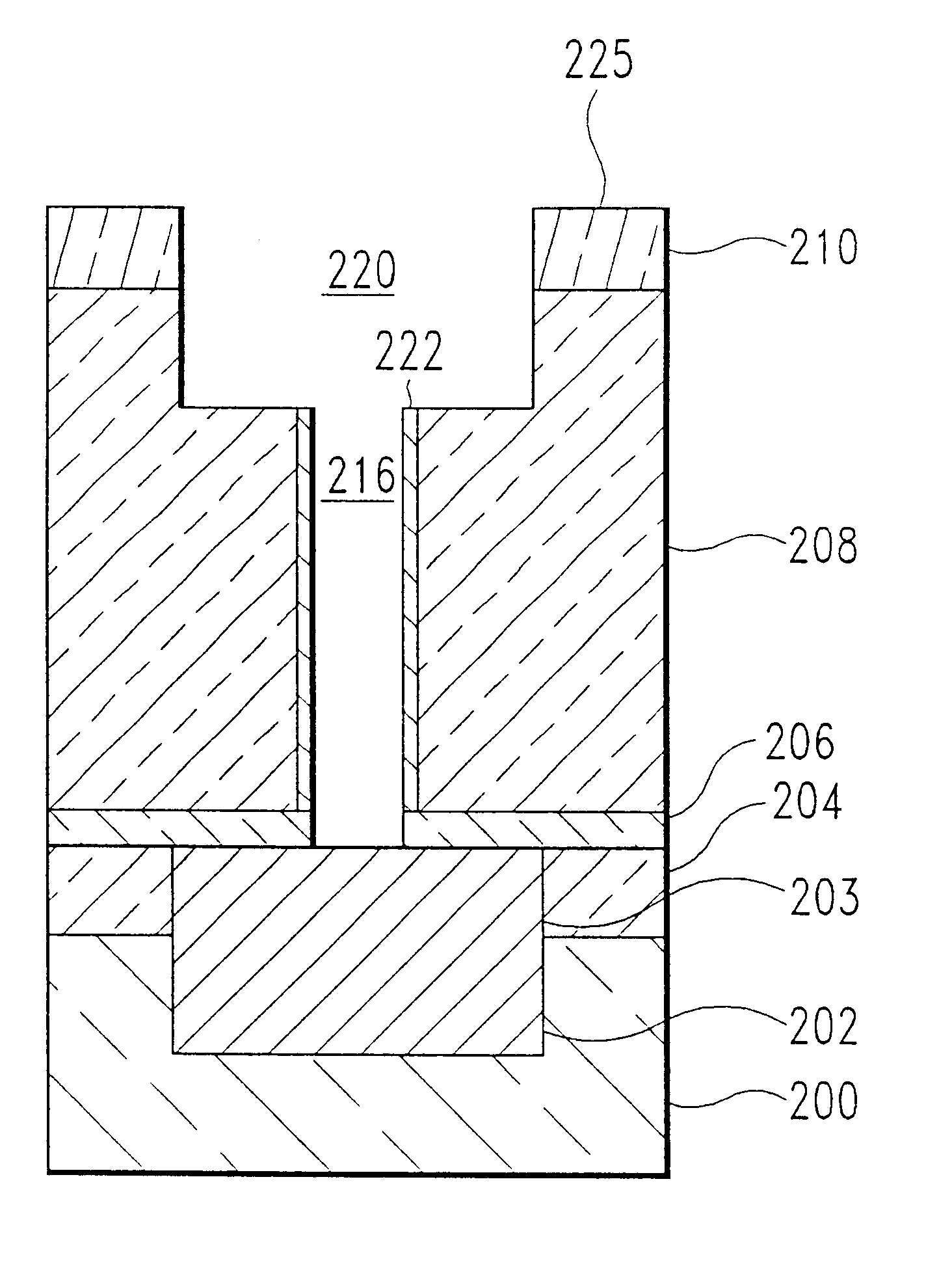

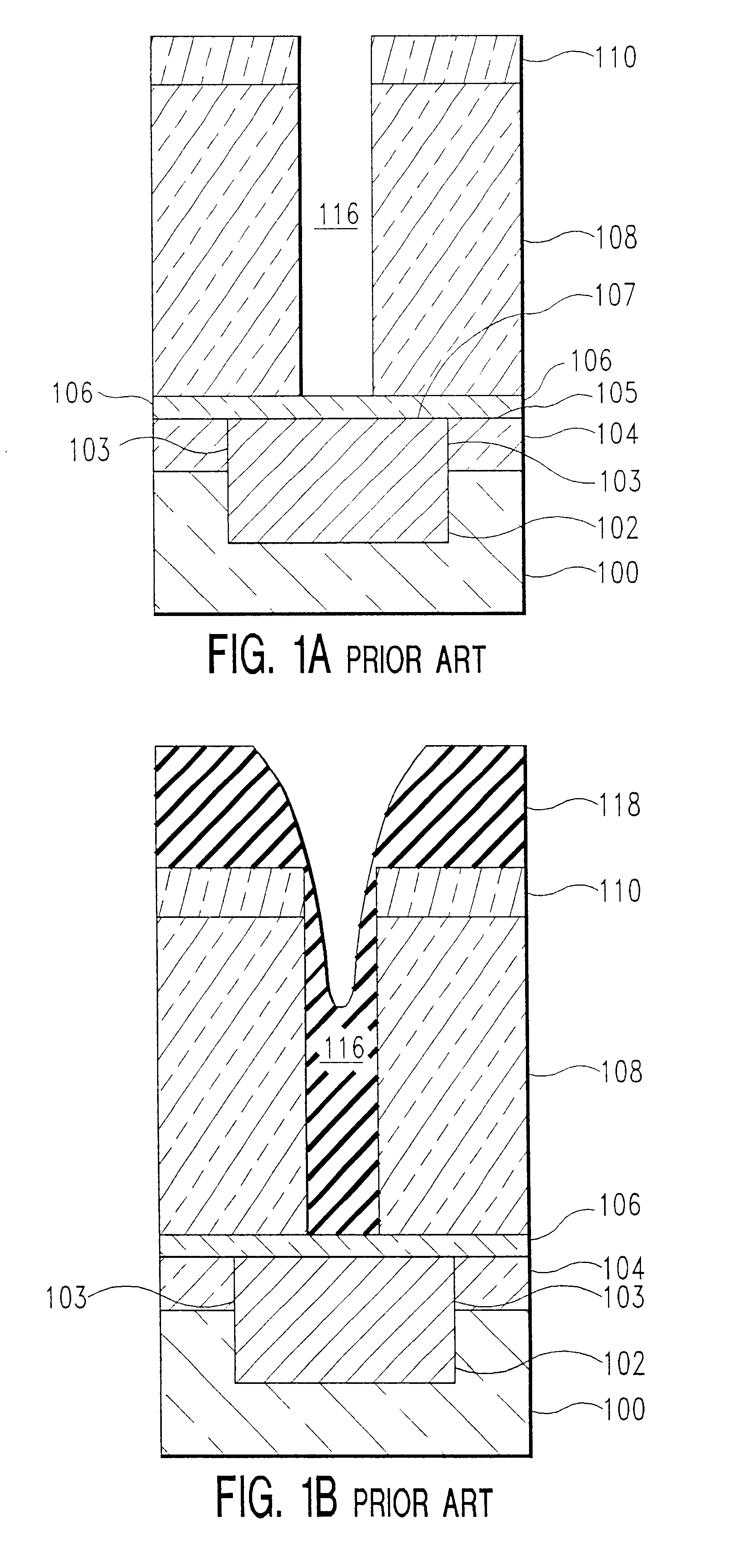

Method of forming a multilayer dielectric stack

InactiveUS20020130340A1Reduces and eliminates formationImprove device performanceIndividual molecule manipulationSolid-state devicesEvaporationHafnium

A multilayer dielectric stack is provided which has alternating layers of a high-k material and an interposing material. The presence of the interposing material and the thinness of the high-k material layers reduces or eliminate effects of crystallization within the high-k material, even at relatively high annealing temperatures. The high-k dielectric layers are a metal oxide of preferably zirconium or hafnium. The interposing layers are preferably amorphous aluminum oxide, aluminum nitride, or silicon nitride. Because the layers reduce the effects of crystalline structures within individual layers, the overall tunneling current is reduced. Also provided are atomic layer deposition, sputtering, and evaporation as methods of depositing desired materials for forming the above-mentioned multilayer dielectric stack.

Owner:SHARP LAB OF AMERICA INC

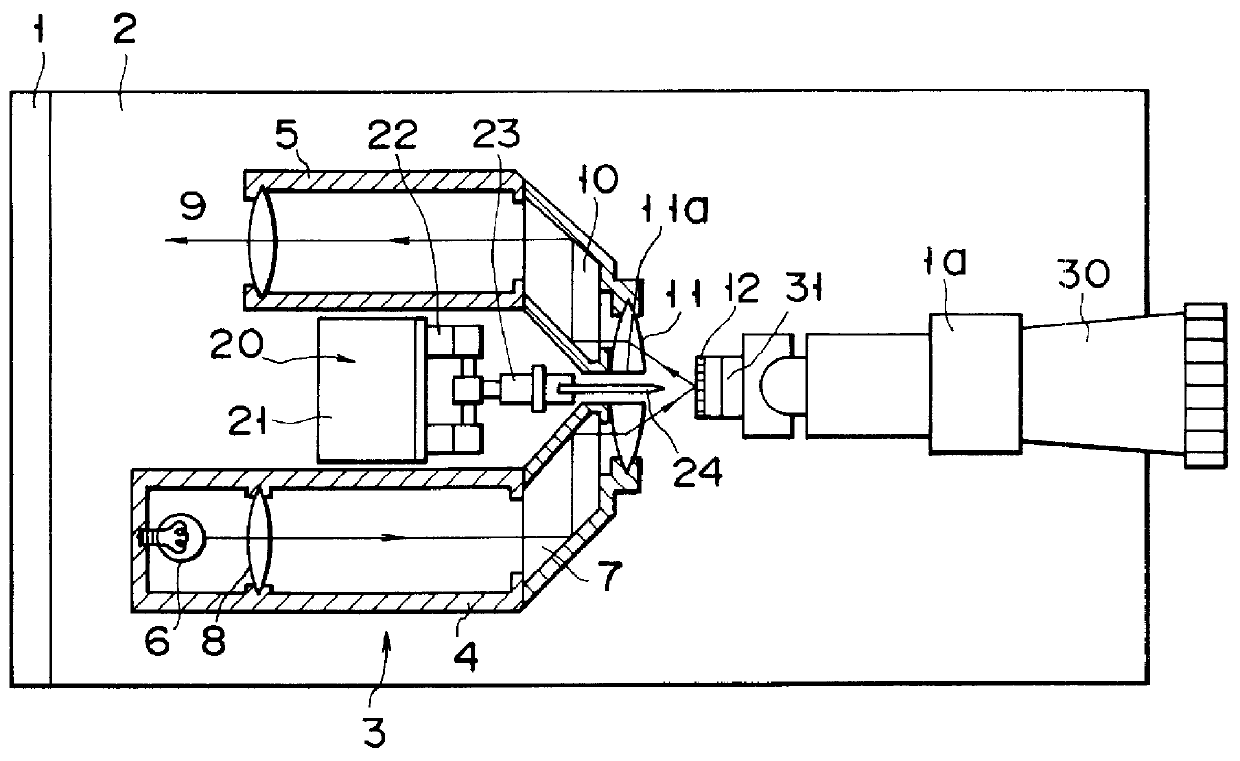

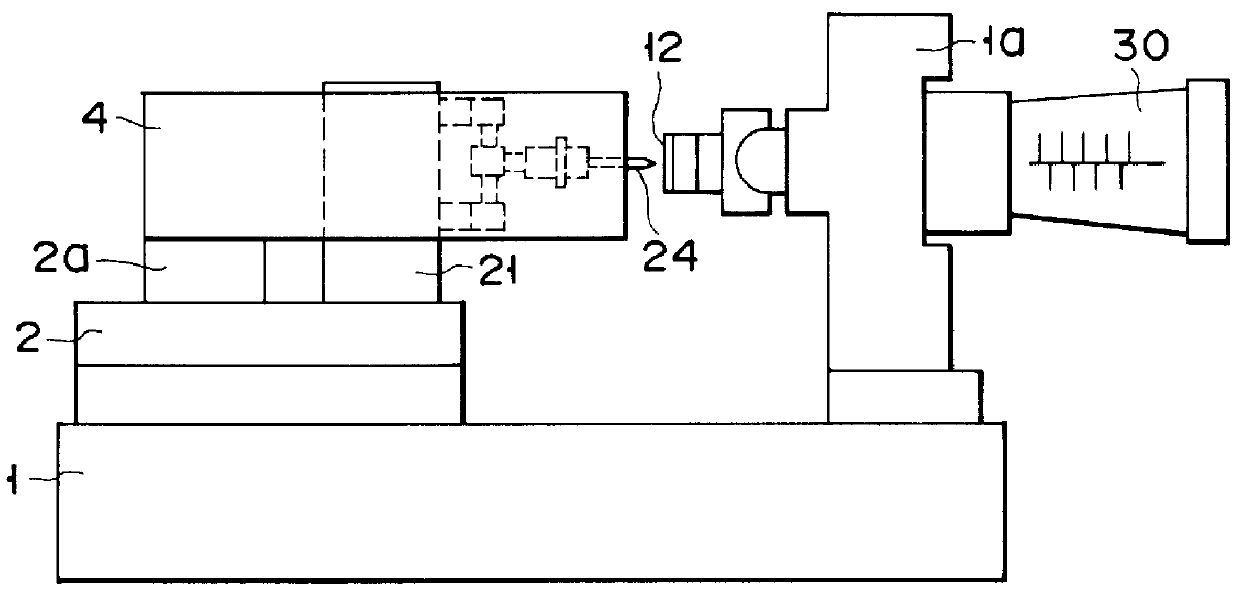

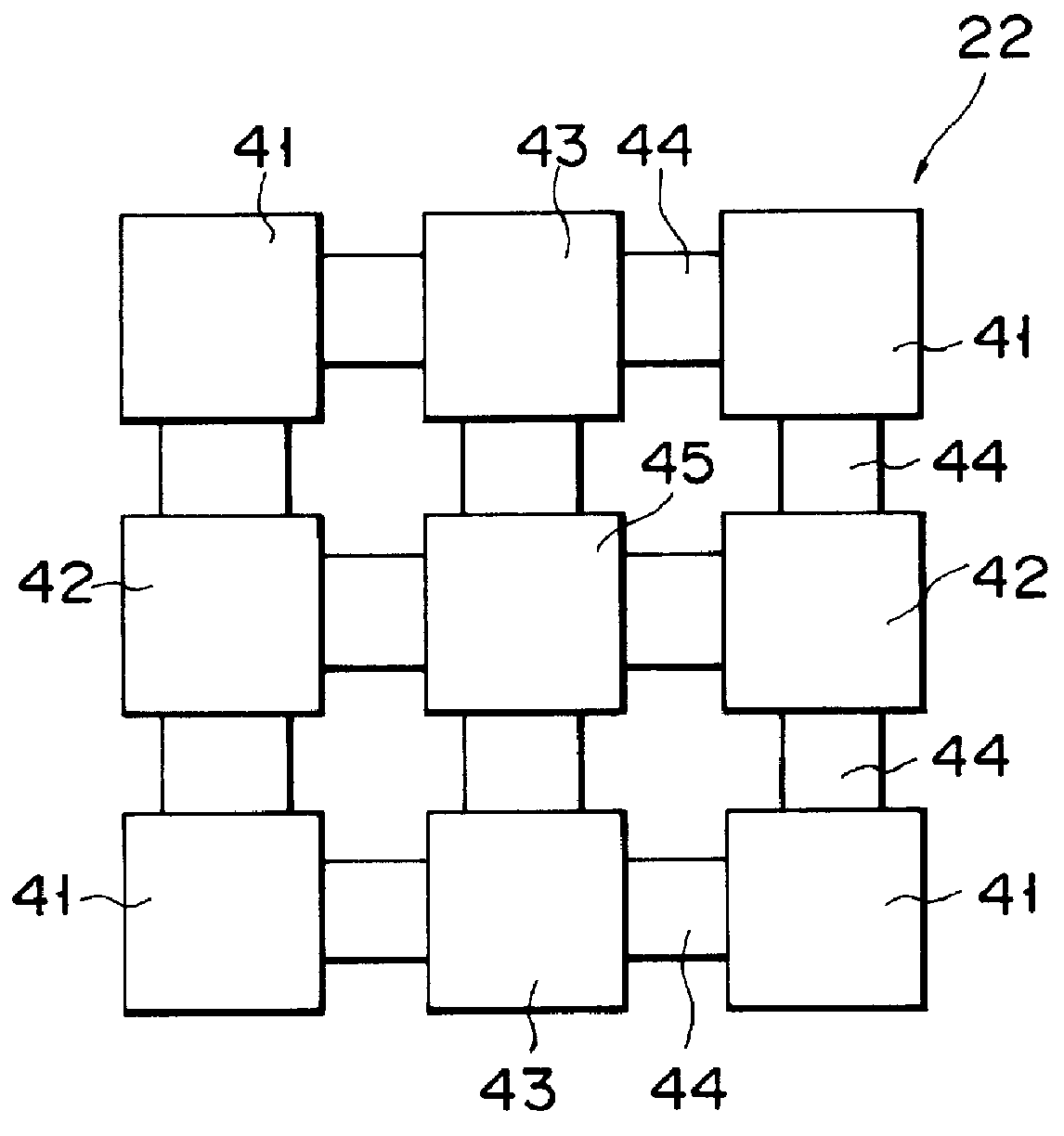

Scanning tunnel microscope

PCT No. PCT / JP88 / 00804 Sec. 371 Date Feb. 5, 1990 Sec. 102(e) Date Feb. 5, 1990 PCT Filed Aug. 12, 1988 PCT Pub. No. WO89 / 01603 PCT Pub. Date Feb. 23, 1989A scanning tunnel microscope is arranged by a combination of an optical microscope and a tunnel scanning unit. The scanning tunnel unit includes a probe held to be spaced apart from a sample placed on a sample table by a predetermined interval in an axial direction, and an actuator for axially moving the sample table and the probe to a tunnel region and relatively and three-dimensionally driving the sample table and the probe. An objective lens and the probe are arranged such that the axis of the probe of the scanning tunnel unit is aligned with an optical axis of the objective lens of the optical microscope. The sample and the probe are axially moved and brought into the tunnel region, and the sample is scanned in its surface direction while the sample and the probe are finely moved in the axial direction and a tunnel current is kept constant, thereby performing an STM observation of an observation surface of the sample. The objective lens of the optical microscope is axially moved to obtain an in-focus state, and the field of the STM observation surface is observed as an optical microscopic image through an eyepiece lens.

Owner:OLYMPUS OPTICAL CO LTD

Layers that impede diffusion of metals in group vi element-containing materials

InactiveUS20080251119A1Improve efficiencyContact stabilityFinal product manufactureSemiconductor/solid-state device manufacturingElectrical resistance and conductanceCadmium fluoride

A method of making thermodynamically stable, diffusion-impeded barrier layers within, for example, a photovoltaic cell with a metal-containing electrical contact using exposure to fluorine. Exposing the cadmium telluride surface to fluorine creates a Te-poor barrier layer of cadmium fluoride. Once that barrier layer is formed, the metal-containing electrical contact may be applied or formed. The barrier layer allows tunneling current to occur between the p-type layer and the metal-containing electrical contact establishing a low-resistance, highly uniform, and thermally stable electrical contact.

Owner:FOREHAND DAVID

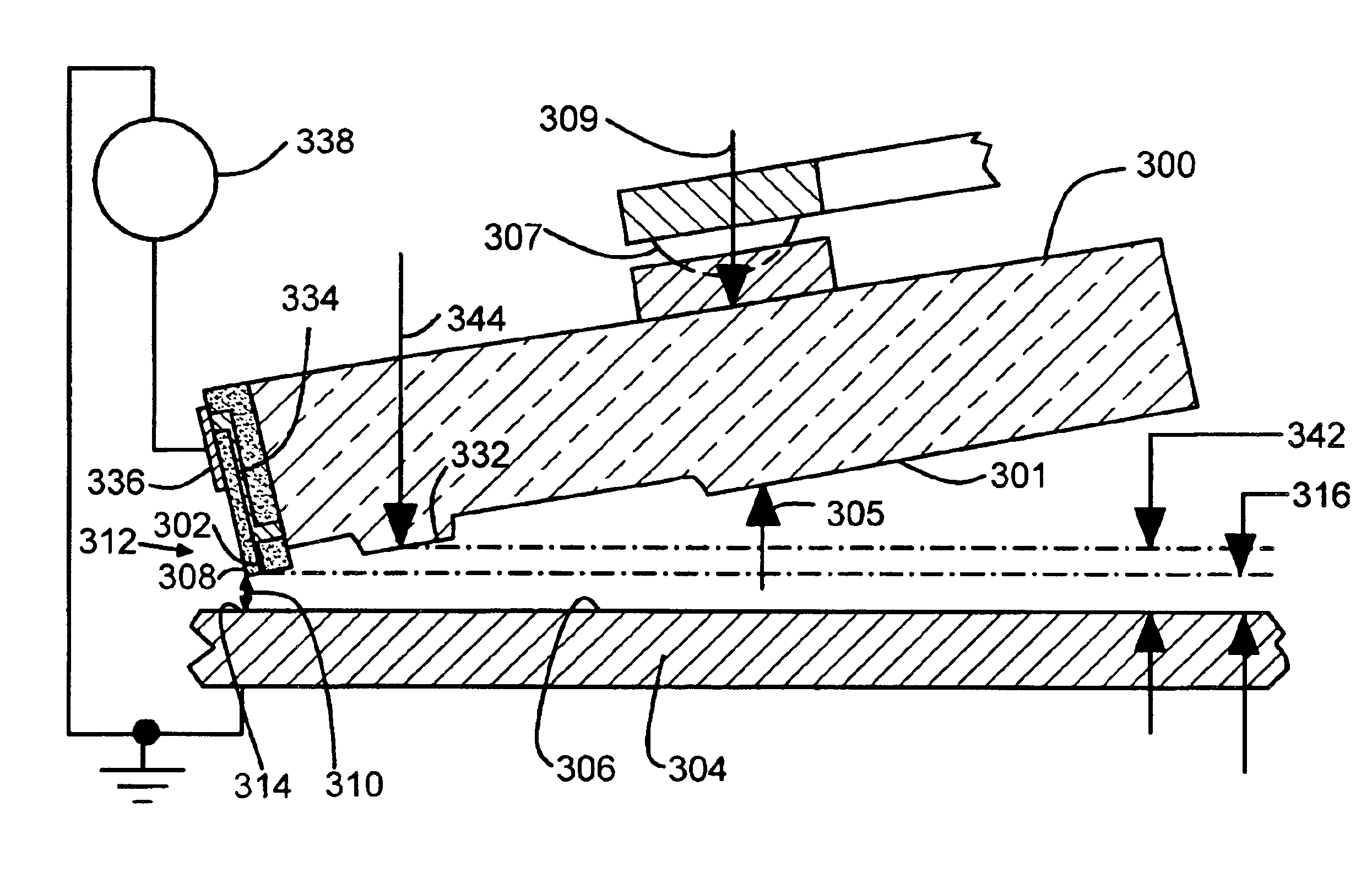

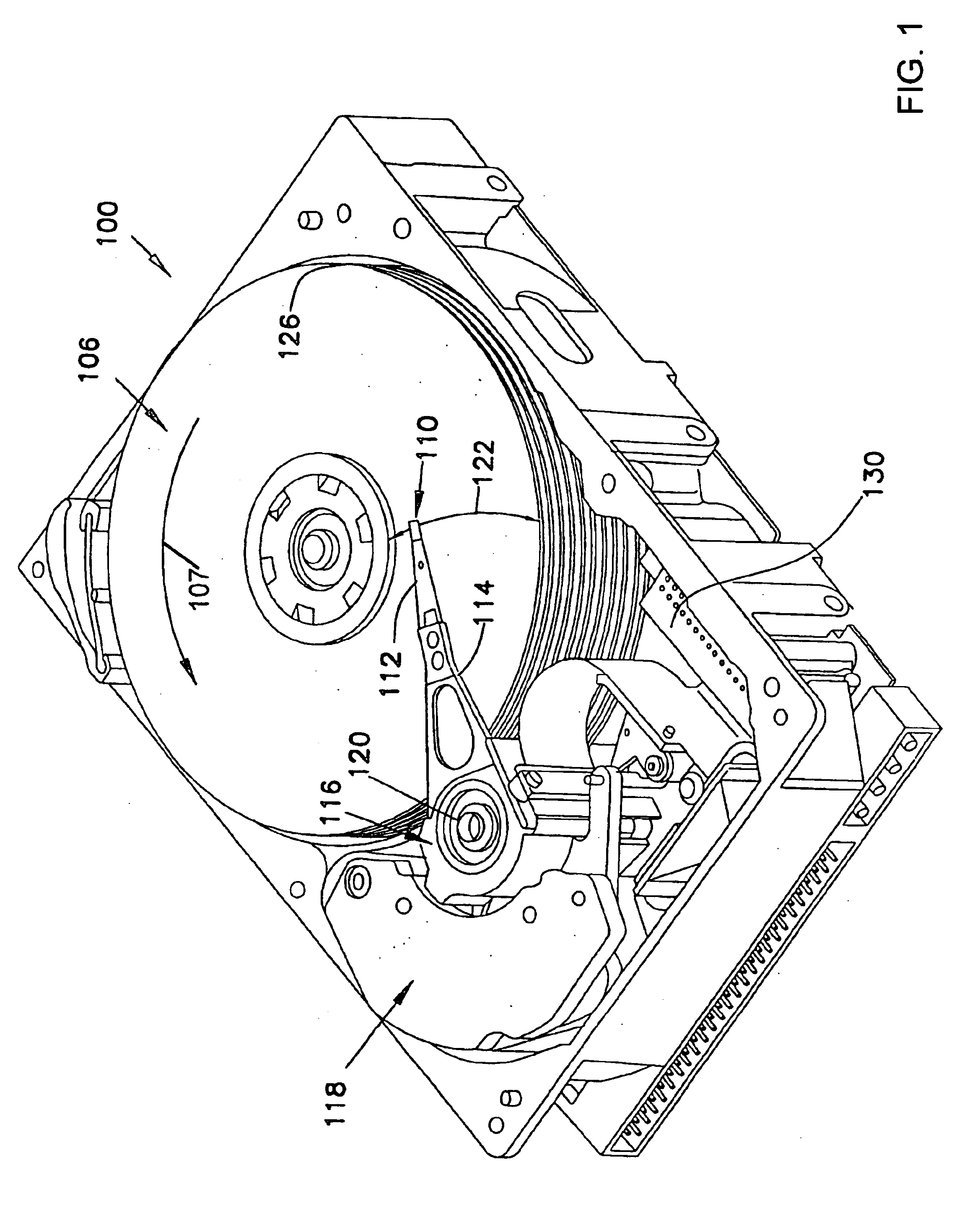

Integrated electrostatic slider fly height control

A disc drive that includes a slider with a field emission sensor that senses fly height. The sensor has an electrode tip disposed on the slider. The electrode tip faces a media surface across a gap. The sensor conducts a tunneling current through the gap and provides an output representing the length of the gap. An actuator adjusts the fly height spacing. A feedback circuit provides an actuator electrical input as a feedback function of the sensor output to control the fly height spacing.

Owner:SEAGATE TECH LLC

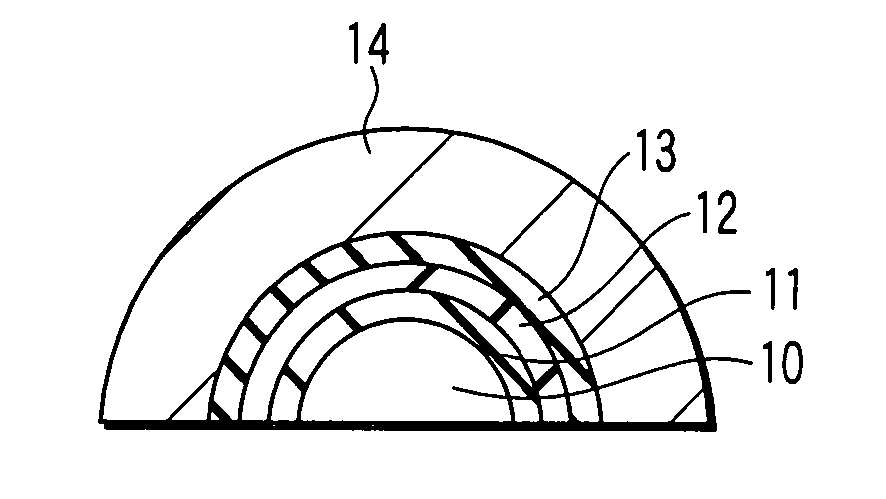

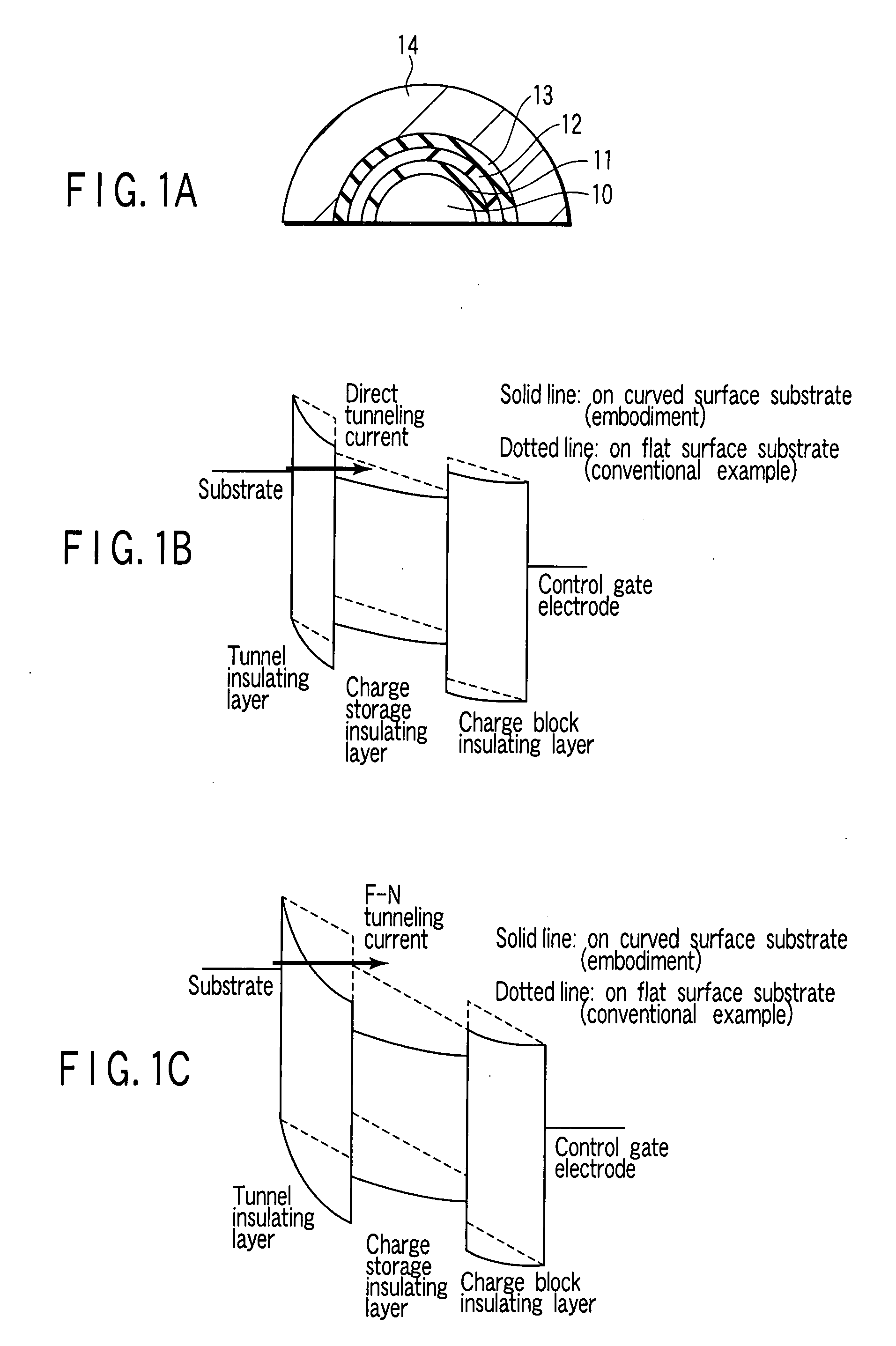

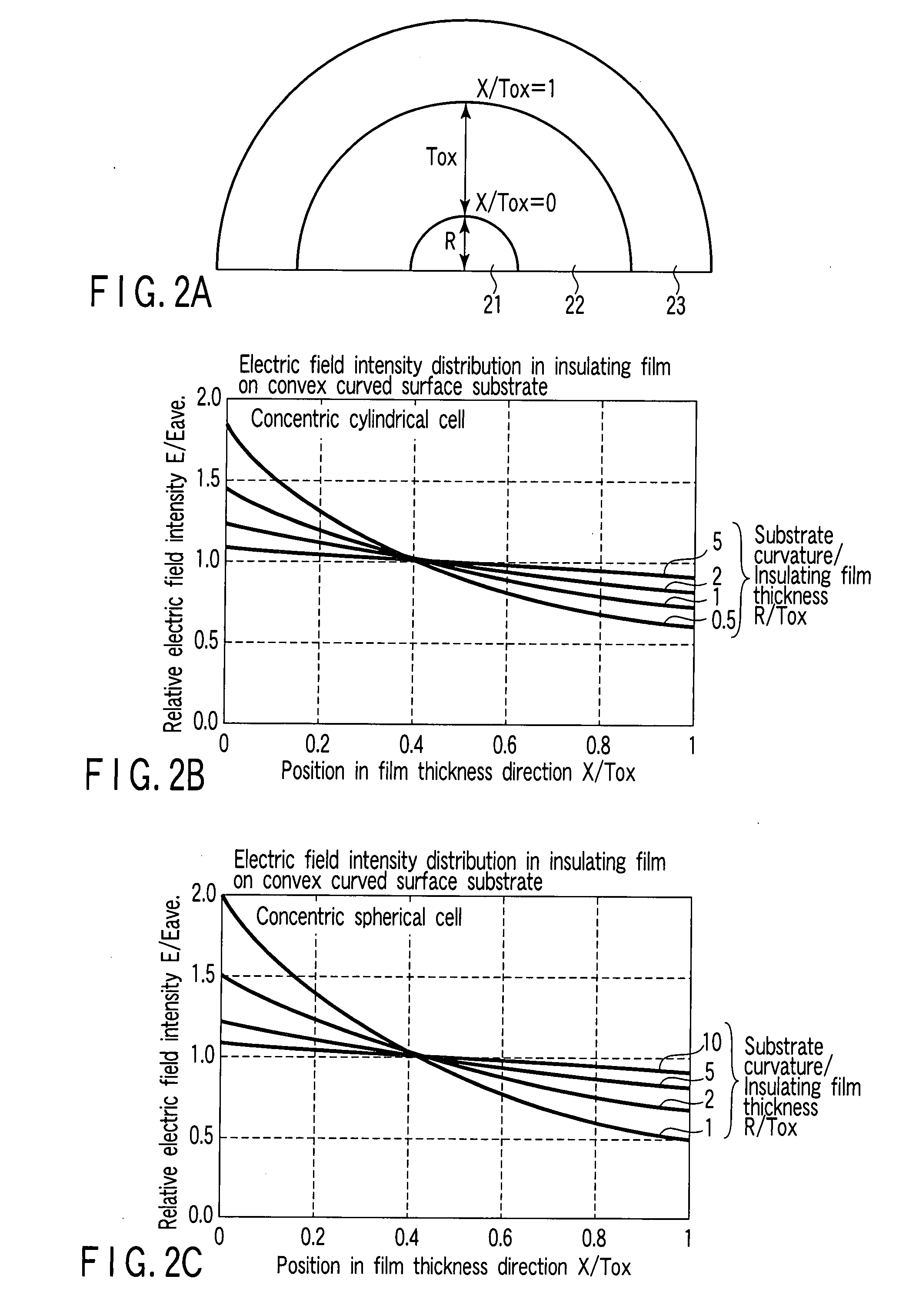

MONOS type nonvolatile memory cell, nonvolatile memory, and manufacturing method thereof

A MONOS type nonvolatile memory cell is structured such that a laminated insulating film which is formed by sequentially laminating a tunnel insulating layer, a charge storage insulating layer, and a charge block insulating layer is provided on a convex curved surface portion of a semiconductor substrate, and a control gate electrode is further formed thereon. A thickness of the tunnel insulating layer is set to be 4 to 10 nm, and data writing / data erasing operations are carried out by making an F-N tunneling current flow in the tunnel insulating layer.

Owner:KK TOSHIBA

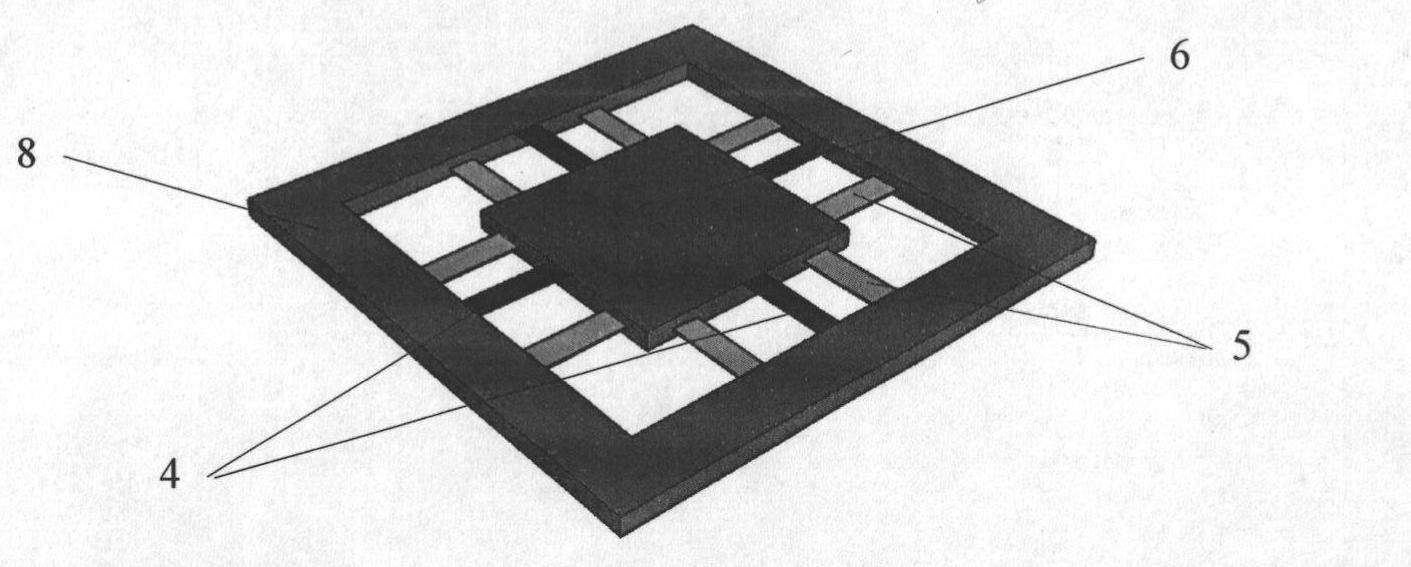

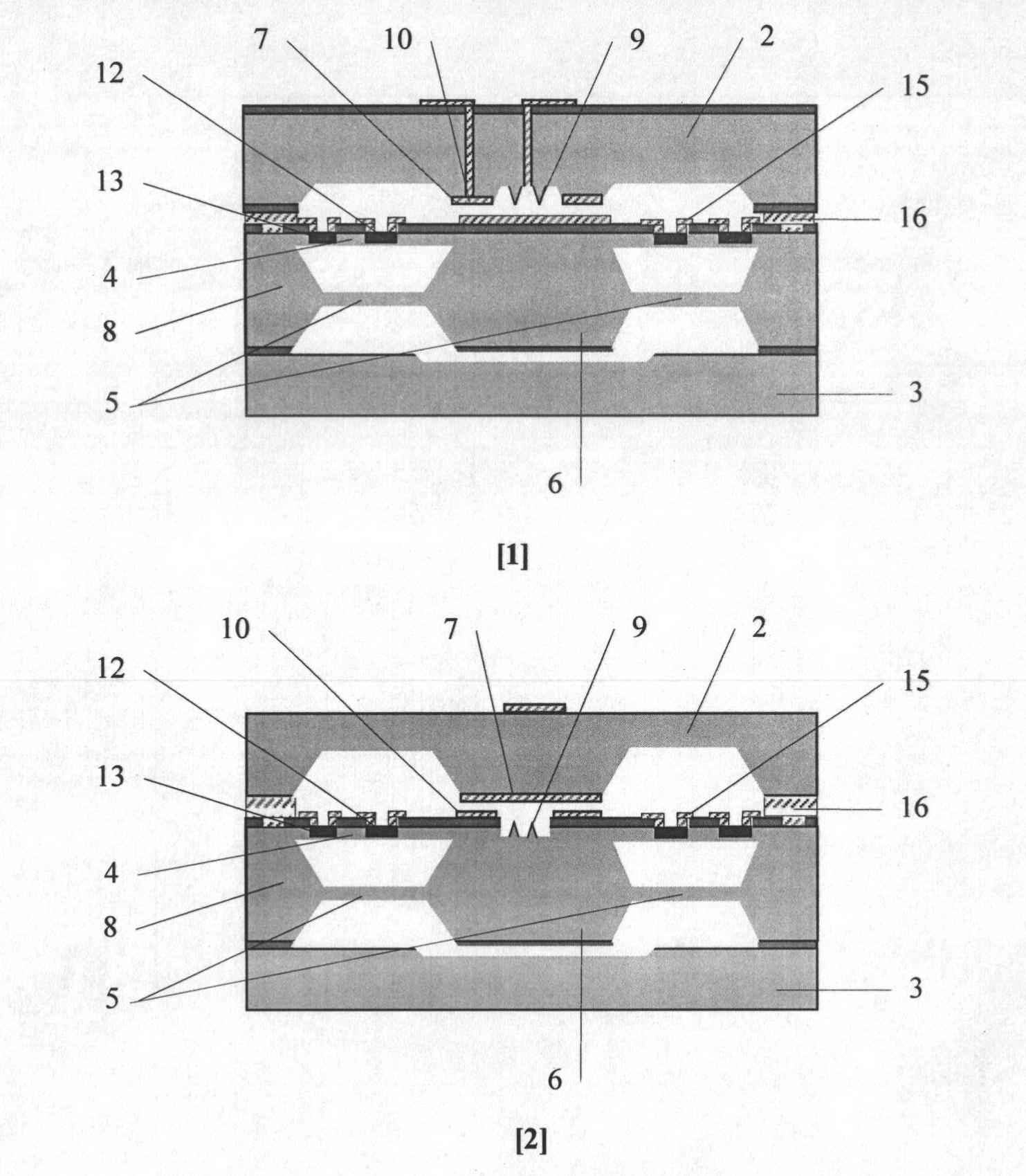

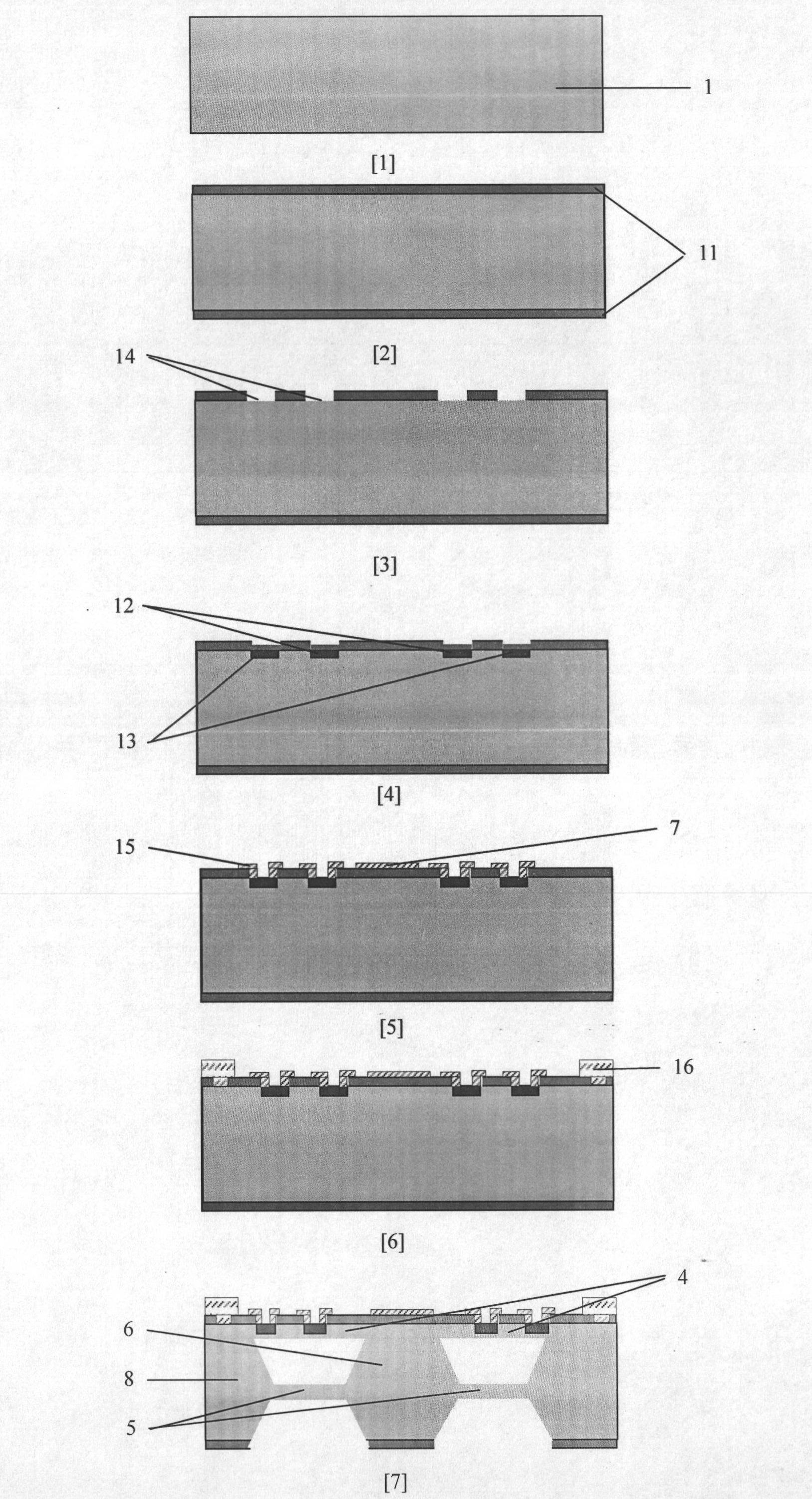

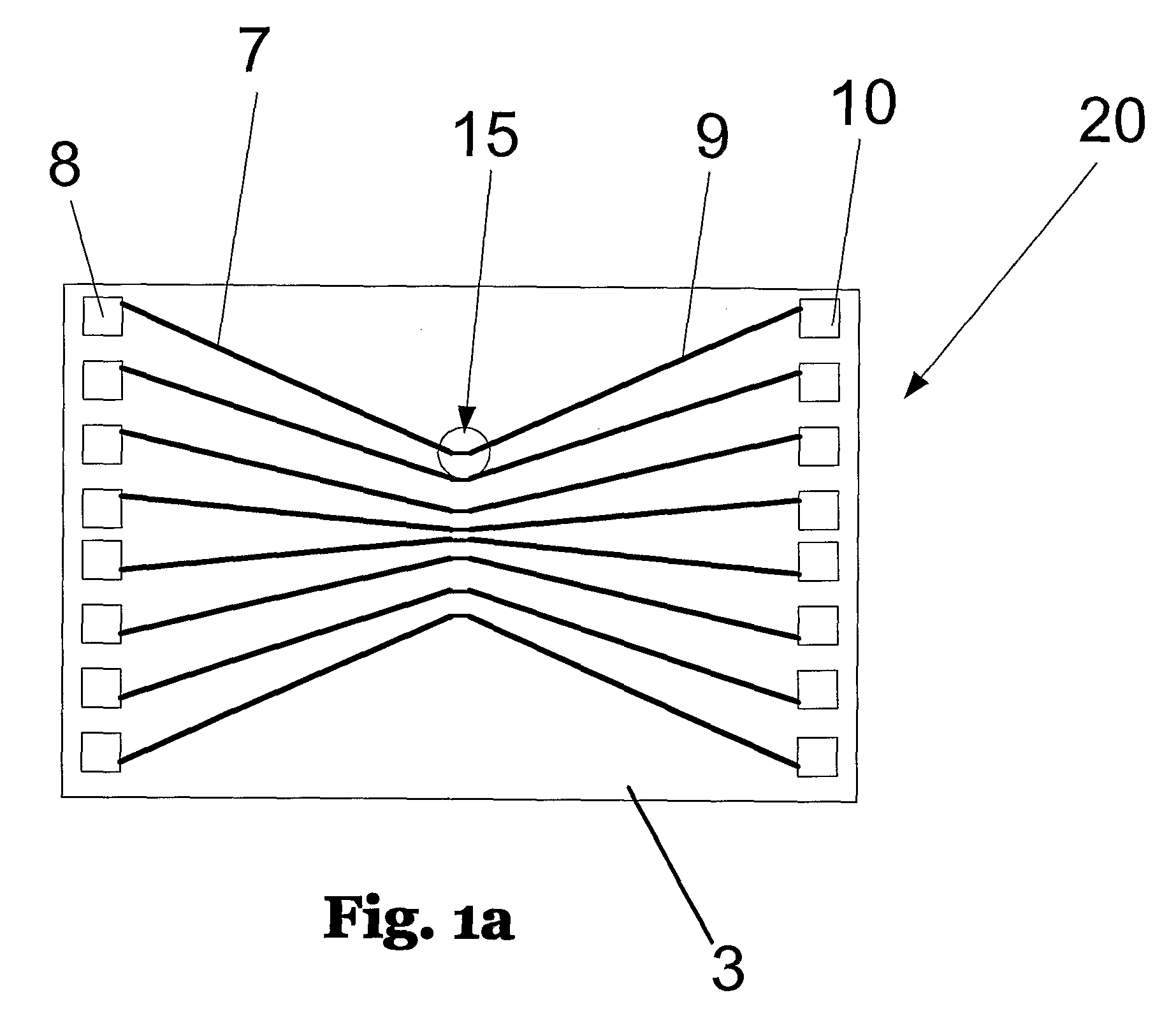

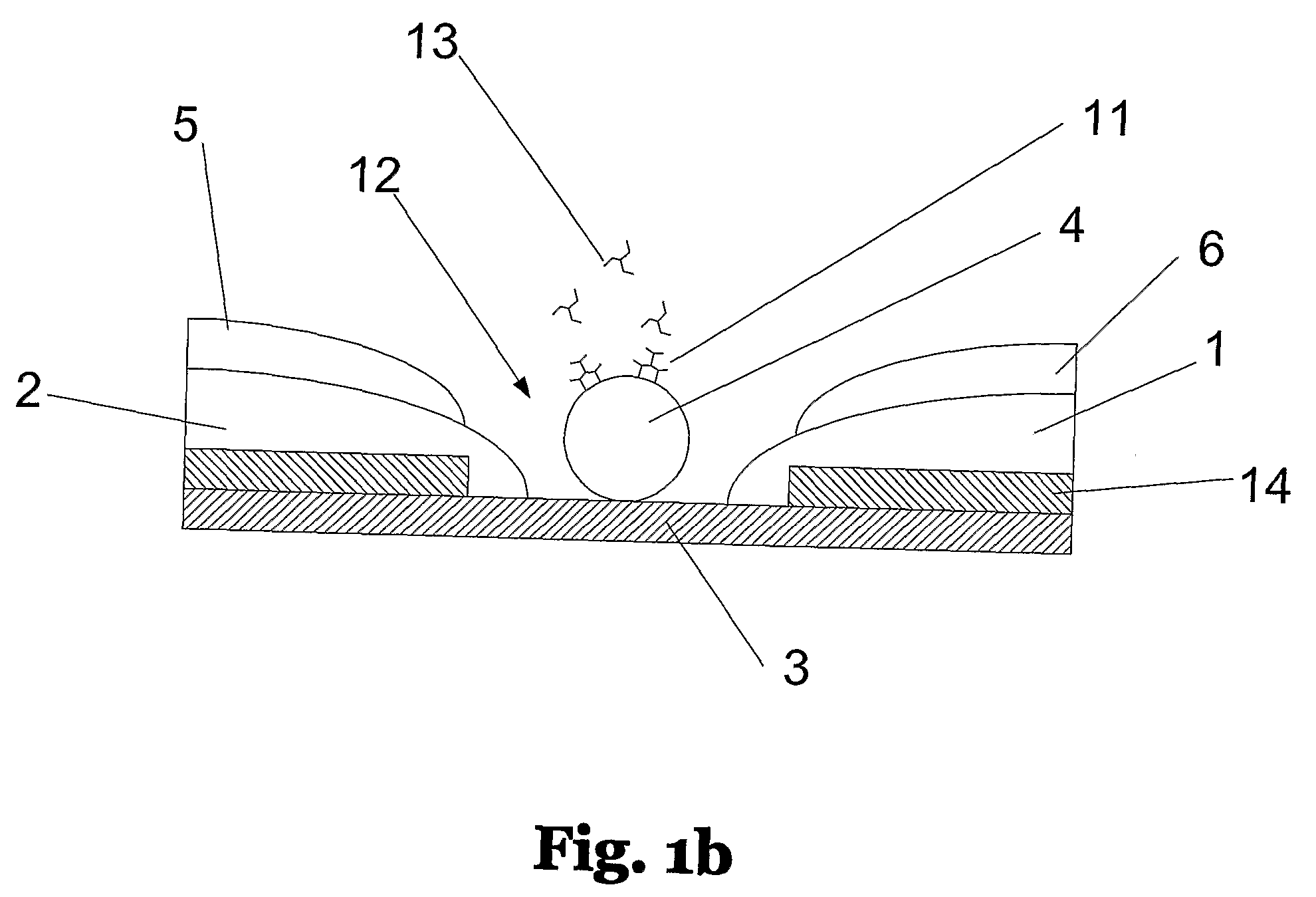

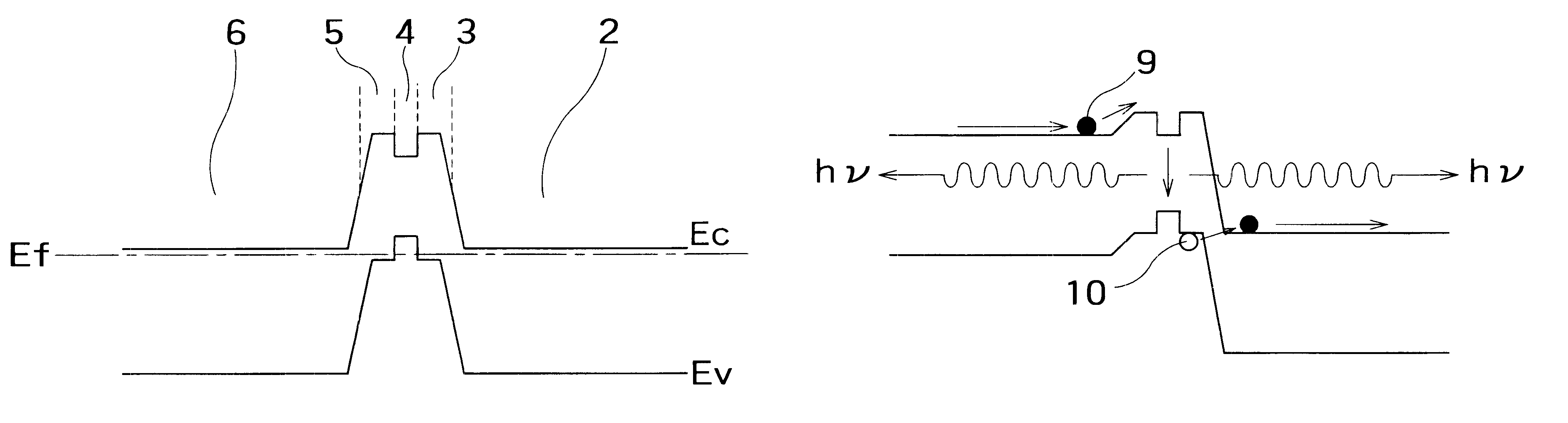

Resonance-equilibrium tunnel current type three-axis acceleration transducer and manufacturing method thereof

InactiveCN102608355AMeet high performance requirementsReduce cross-interferenceAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsResonanceClosed loop

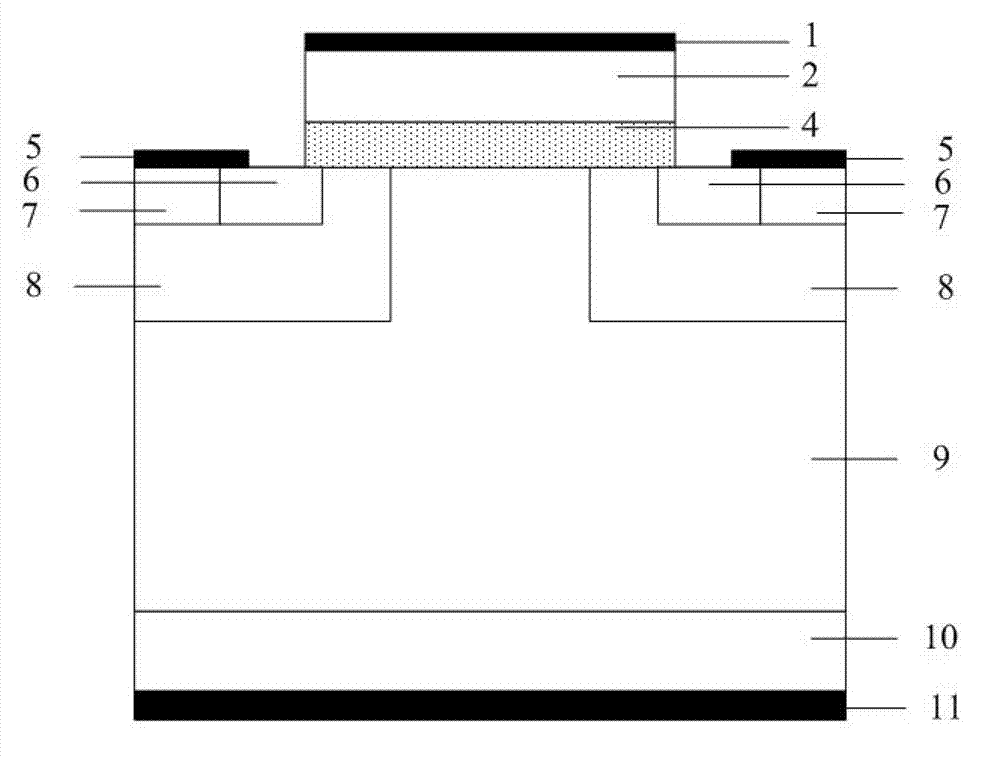

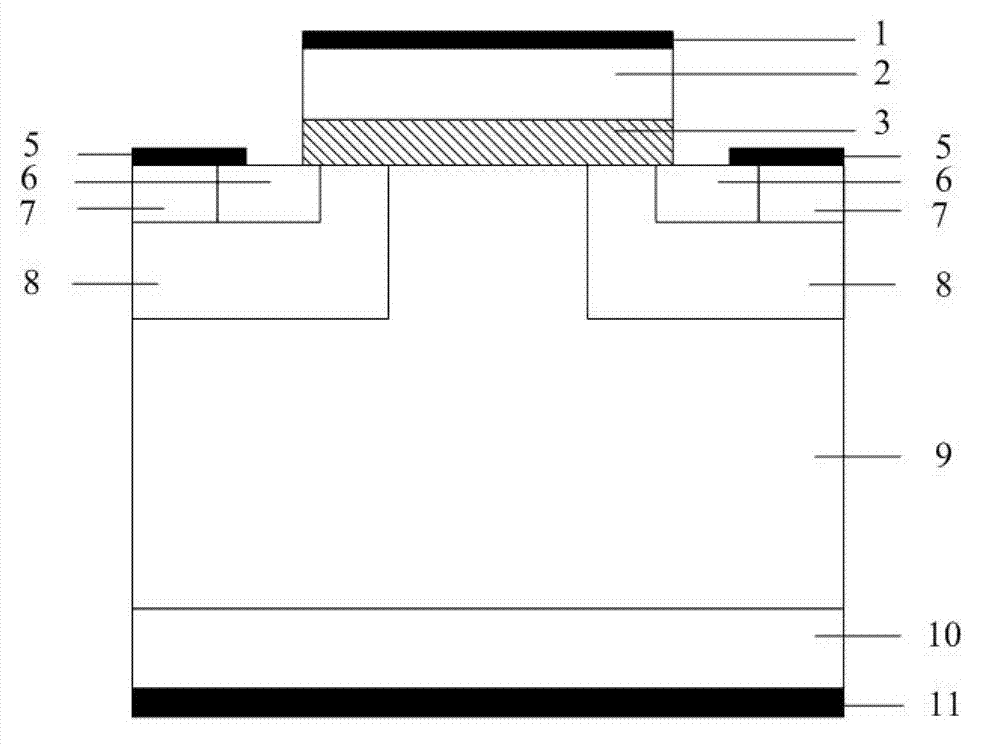

The invention discloses a resonance-equilibrium tunnel current type three-axis acceleration transducer and a manufacturing method thereof, which belong to the field of microelectronic mechanical systems. The resonance-equilibrium tunnel current type three-axis acceleration transducer is structurally characterized in that the three-axis transducer comprises an intermediate silicon wafer (1), a top cover plate (2) and a bottom plate (3), and double-end fixing beam resonators (4), a mass block (6) and supporting beams (5) are manufactured on the intermediate silicon wafer (1). Besides, in the aspect of the detection principle, acceleration signals of the X-axis and the Y-axis in the plane of the chip are detected by the double-end fixing beam resonators (4), variation of resonant frequency of the double-end fixing beam resonators (4) reflects acceleration and direction thereof, a tunnel tip (9), a control electrode (10) and a biased electrode (7) form a portion for detecting acceleration signal of the Z-axis, detection is realized according to the tunnel current type sensitive principle, and the transducer works in a closed-loop equilibrium mode. Besides, the normal displacement of the mass block (6) on the chip is small, and the cross interference introduced by the acceleration signals of the Z-axis to detection of X-axis acceleration and Y-axis acceleration is low.

Owner:CHINA JILIANG UNIV

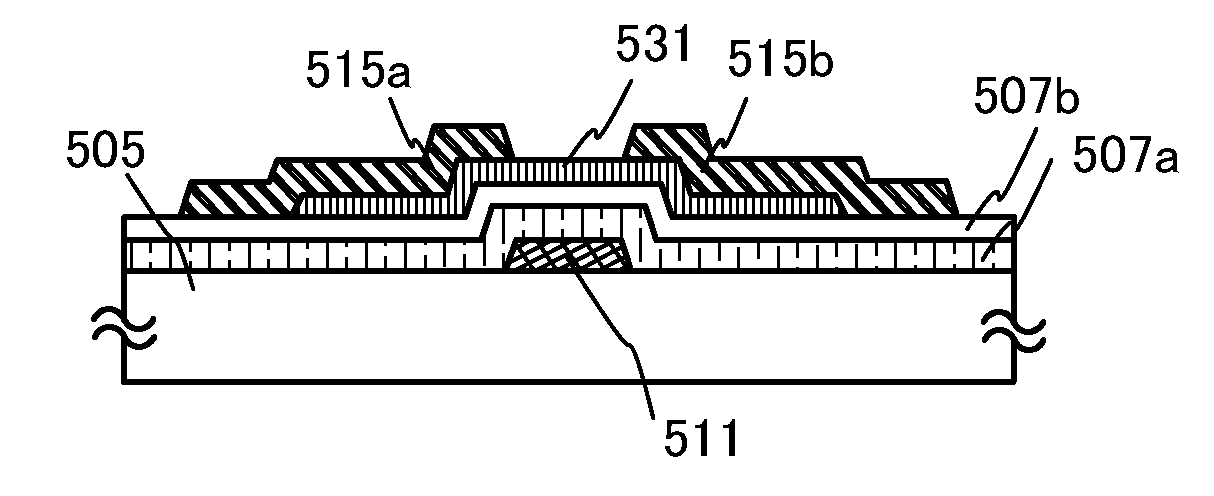

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20110193079A1Reduce manufacturing costReduce hydrogen concentrationSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceGate leakage current

In a miniaturized transistor, a gate insulating layer is required to reduce its thickness; however, in the case where the gate insulating layer is a single layer of a silicon oxide film, a physical limit on thinning of the gate insulating layer might occur due to an increase in tunneling current, i.e. gate leakage current. With the use of a high-k film whose relative permittivity is higher than or equal to 10 is used for the gate insulating layer, gate leakage current of the miniaturized transistor is reduced. With the use of the high-k film as a first insulating layer whose relative permittivity is higher than that of a second insulating layer in contact with an oxide semiconductor layer, the thickness of the gate insulating layer can be thinner than a thickness of a gate insulating layer considered in terms of a silicon oxide film.

Owner:SEMICON ENERGY LAB CO LTD

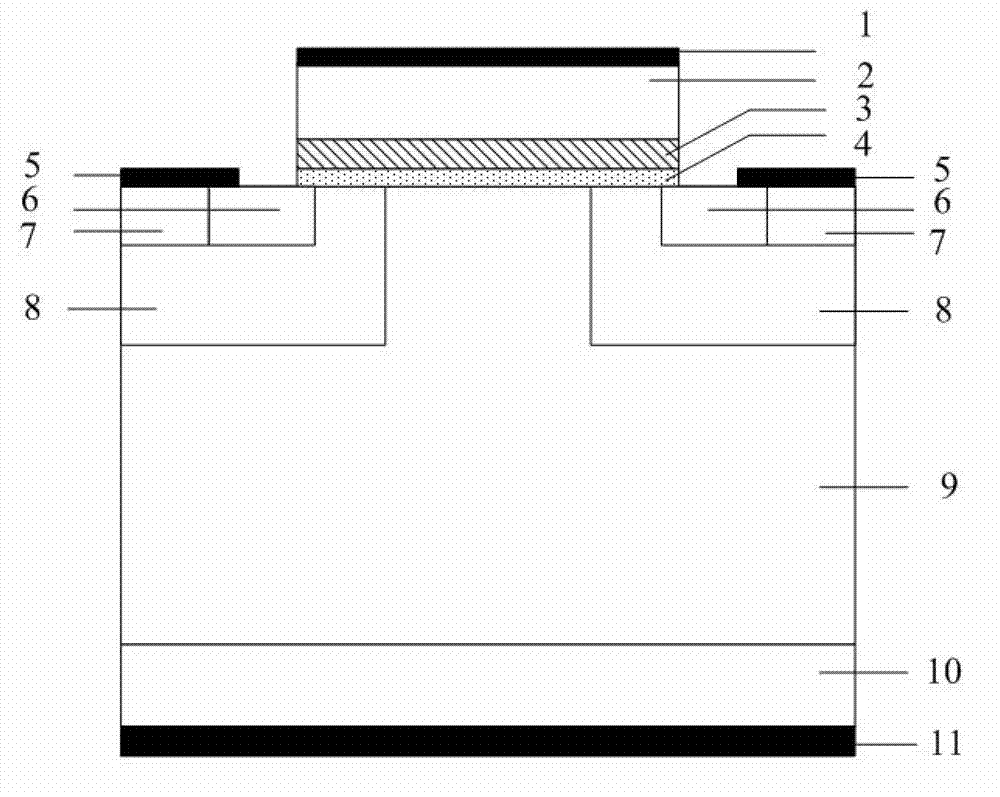

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

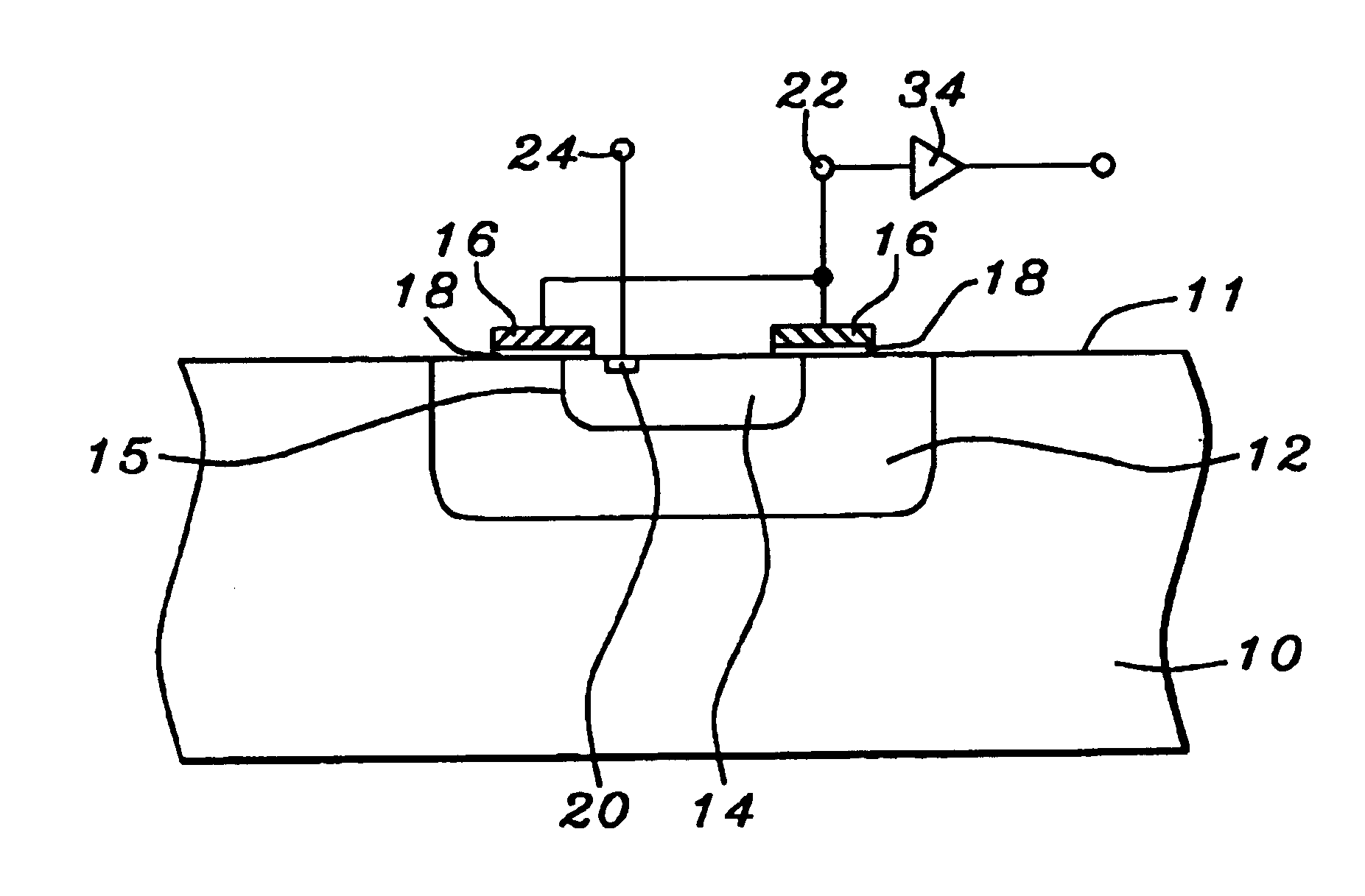

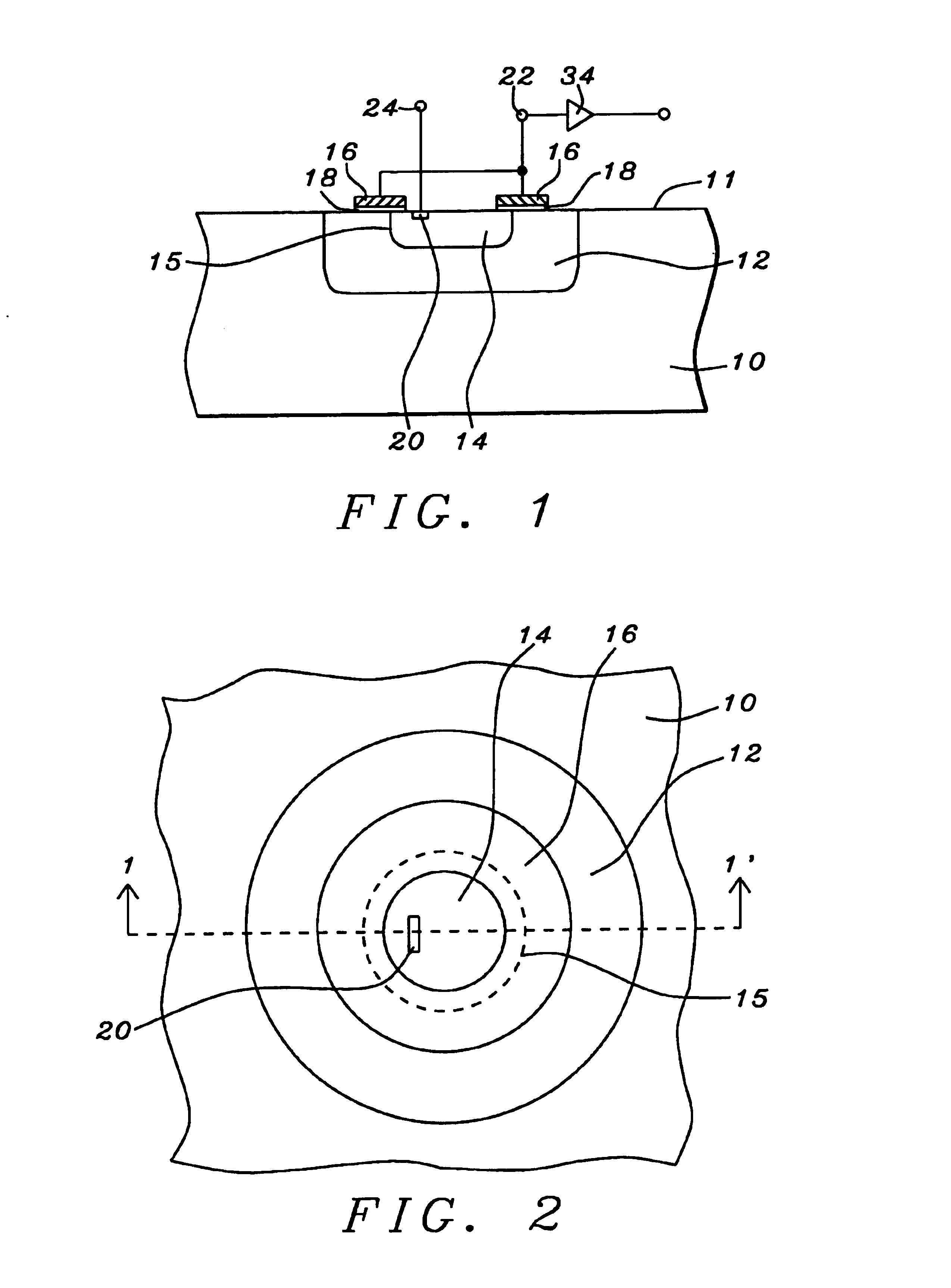

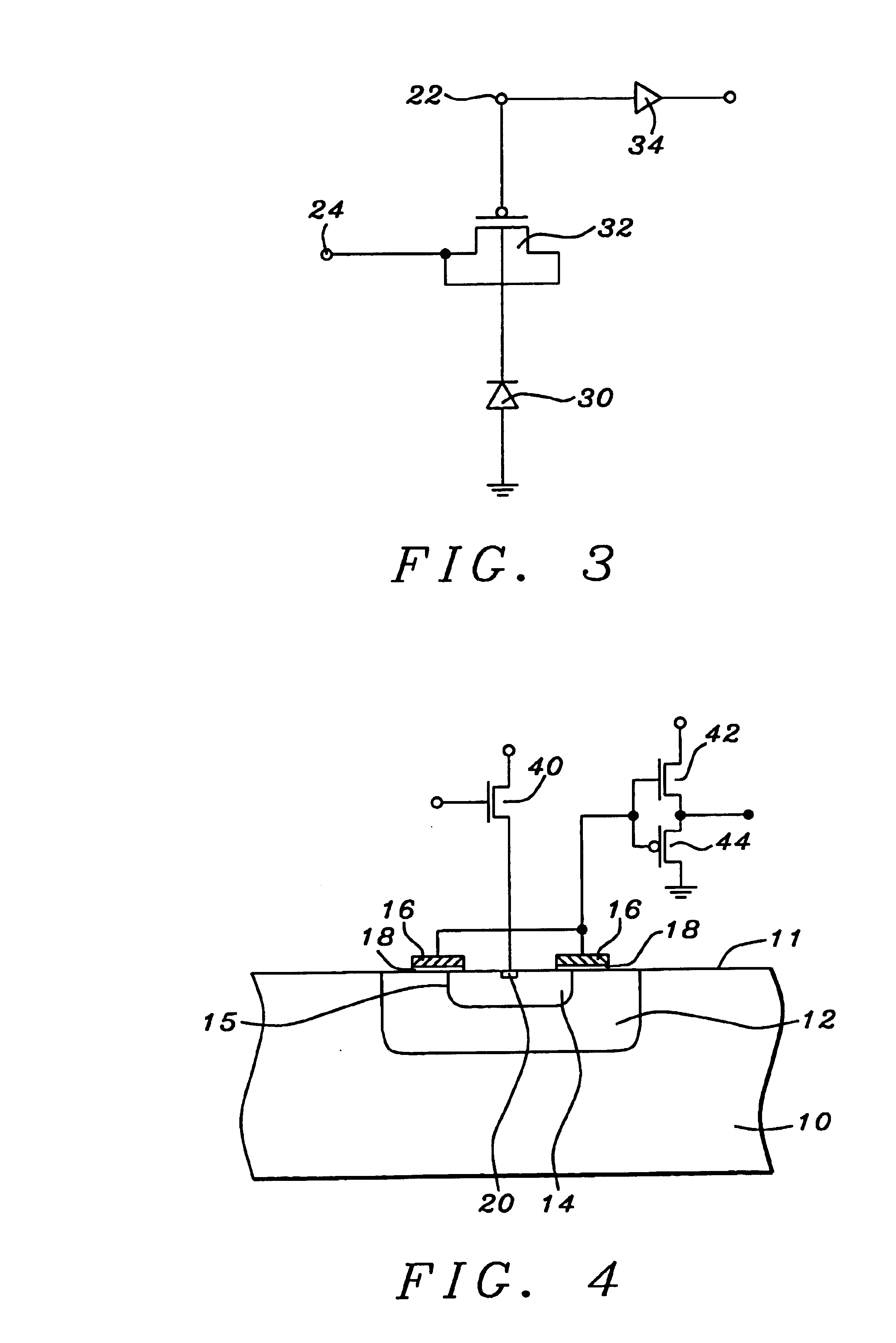

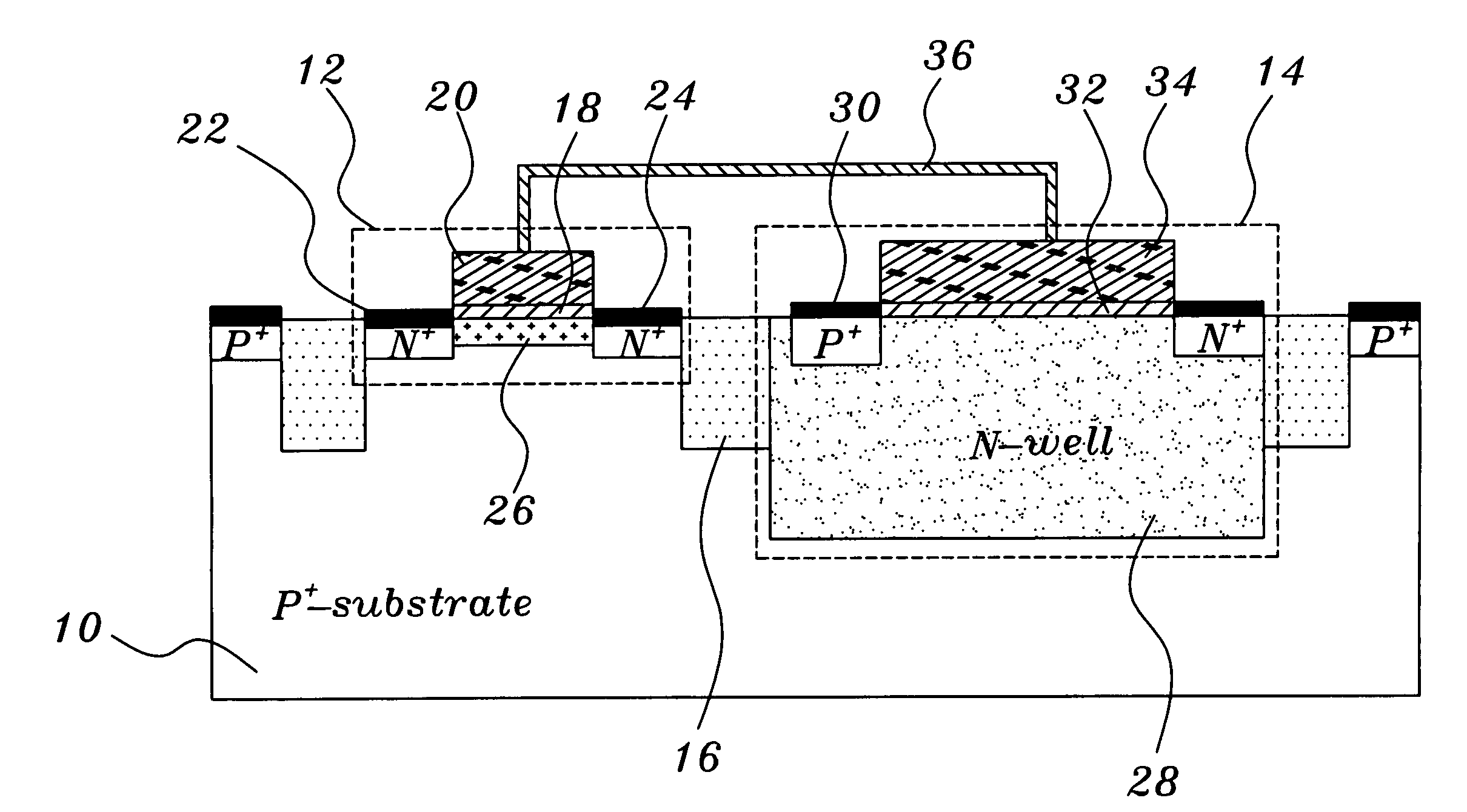

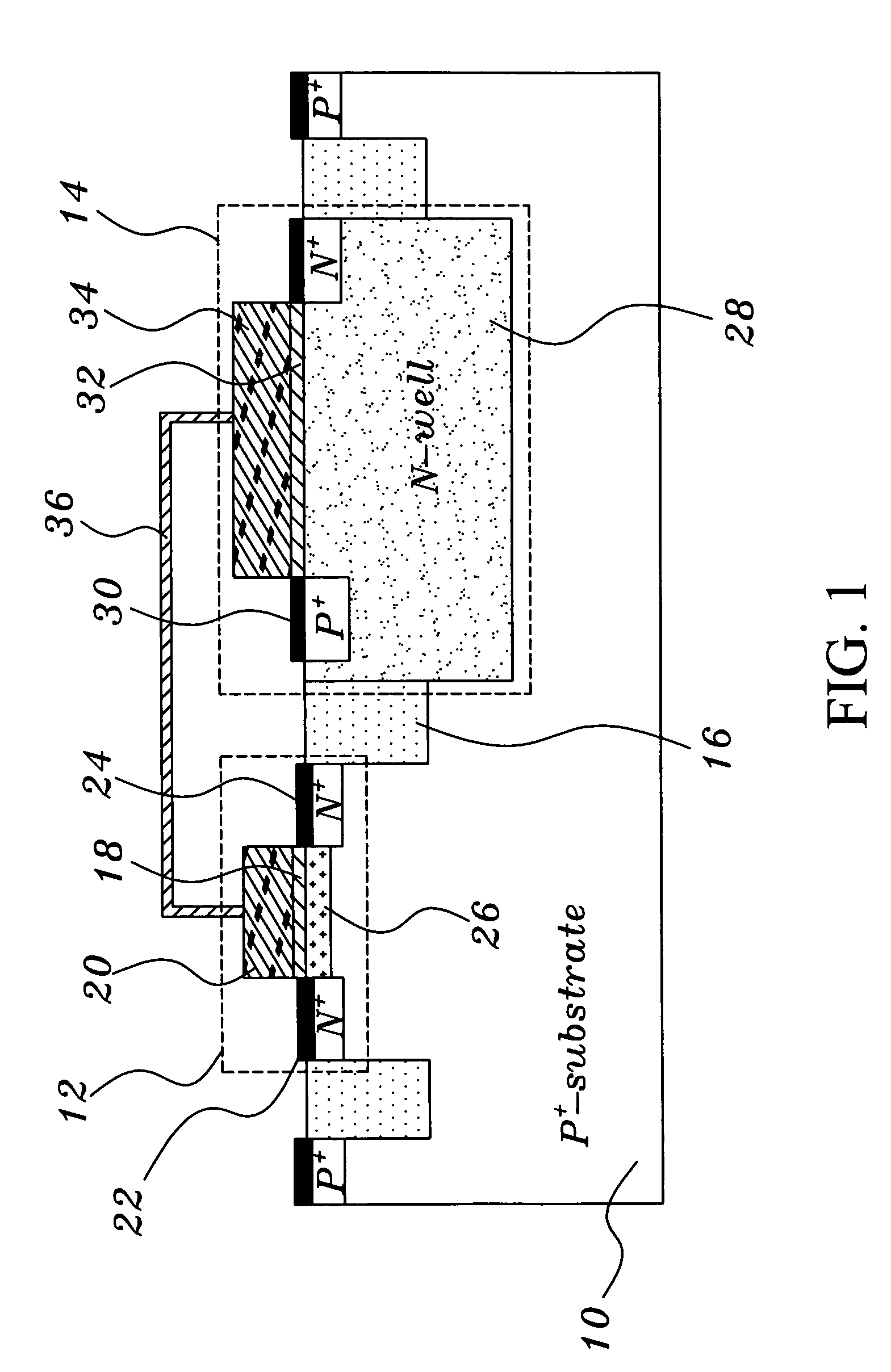

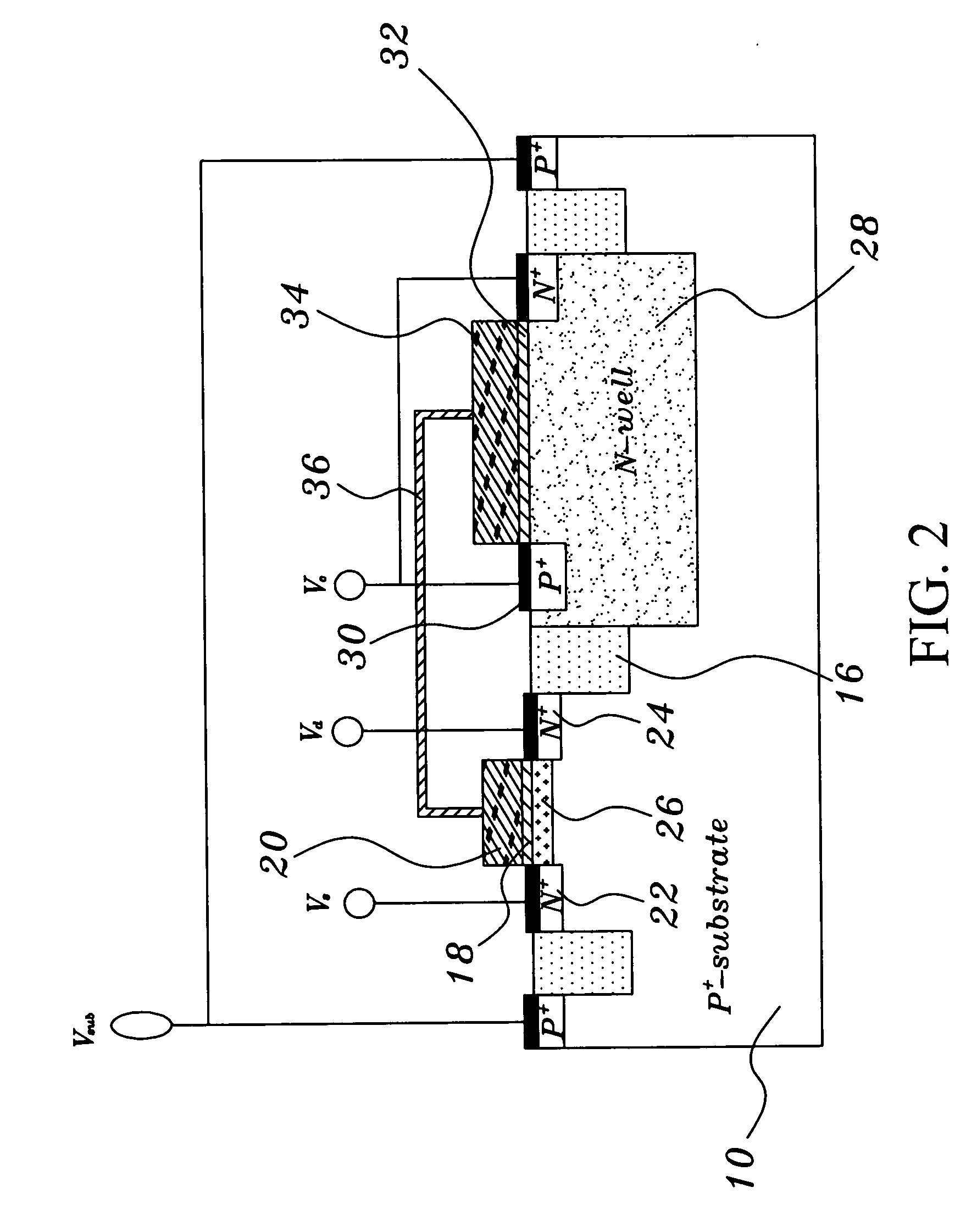

Tunneling floating gate APS pixel

A floating gate pixel is described which is formed by forming an N well in a P type silicon substrate. A P well is formed in the N well A gate is formed over a thin gate oxide, about 25 Angstroms thickness, such that the gate is directly over part of the P well and part of the N well. A P+ contact in the P well allows connection to a reset voltage source, usually through a reset transistor, to reset the pixel. The pixel is reset by setting the potential between the P well and the substrate, which is usually held at ground potential. When the pixel is reset tunneling current through the thin gate oxide sets the voltage of the floating gate. During the charge integration cycle an input signal to the pixel, such as a light signal, changes the potential of the pixel. After the charge integration cycle the tunneling current through the gate oxide changes the potential of the floating gate by an amount related to the input signal to the pixel. The potential of the floating gate can then be read out to determine the input signal to the pixel. The pixel can also be embodied using a P well formed in an N type substrate, an N well formed in the P well, and an N+ contact formed in the N well.

Owner:UNITED MICROELECTRONICS CORP

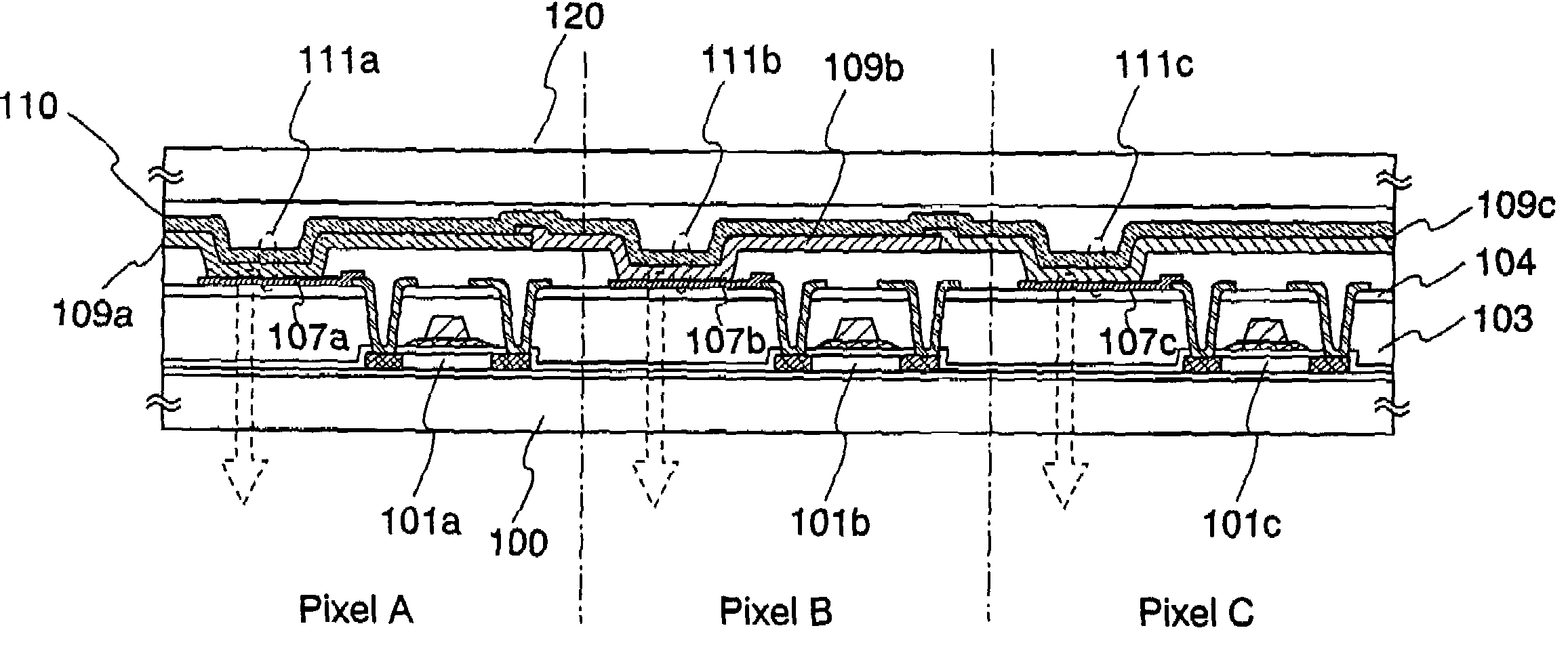

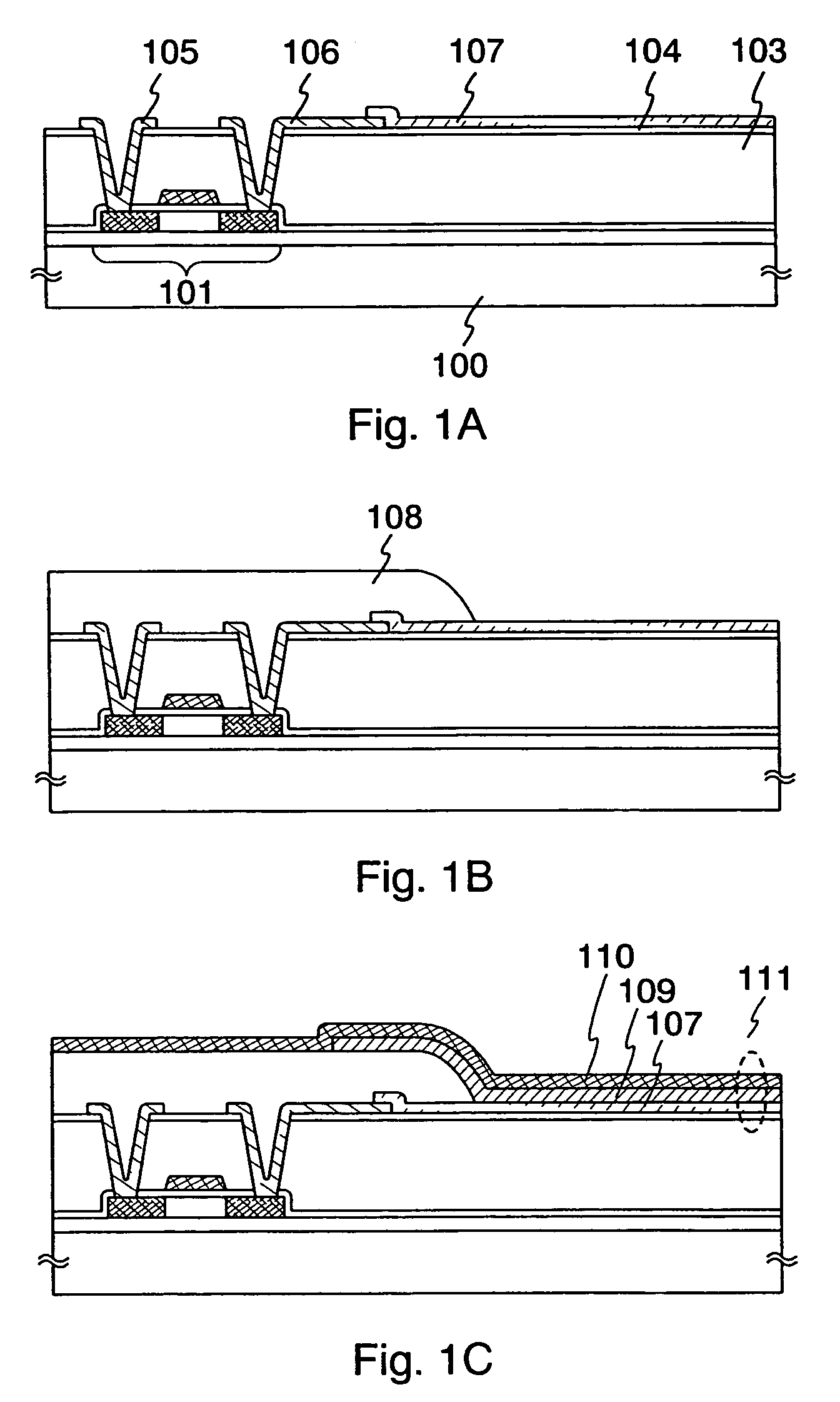

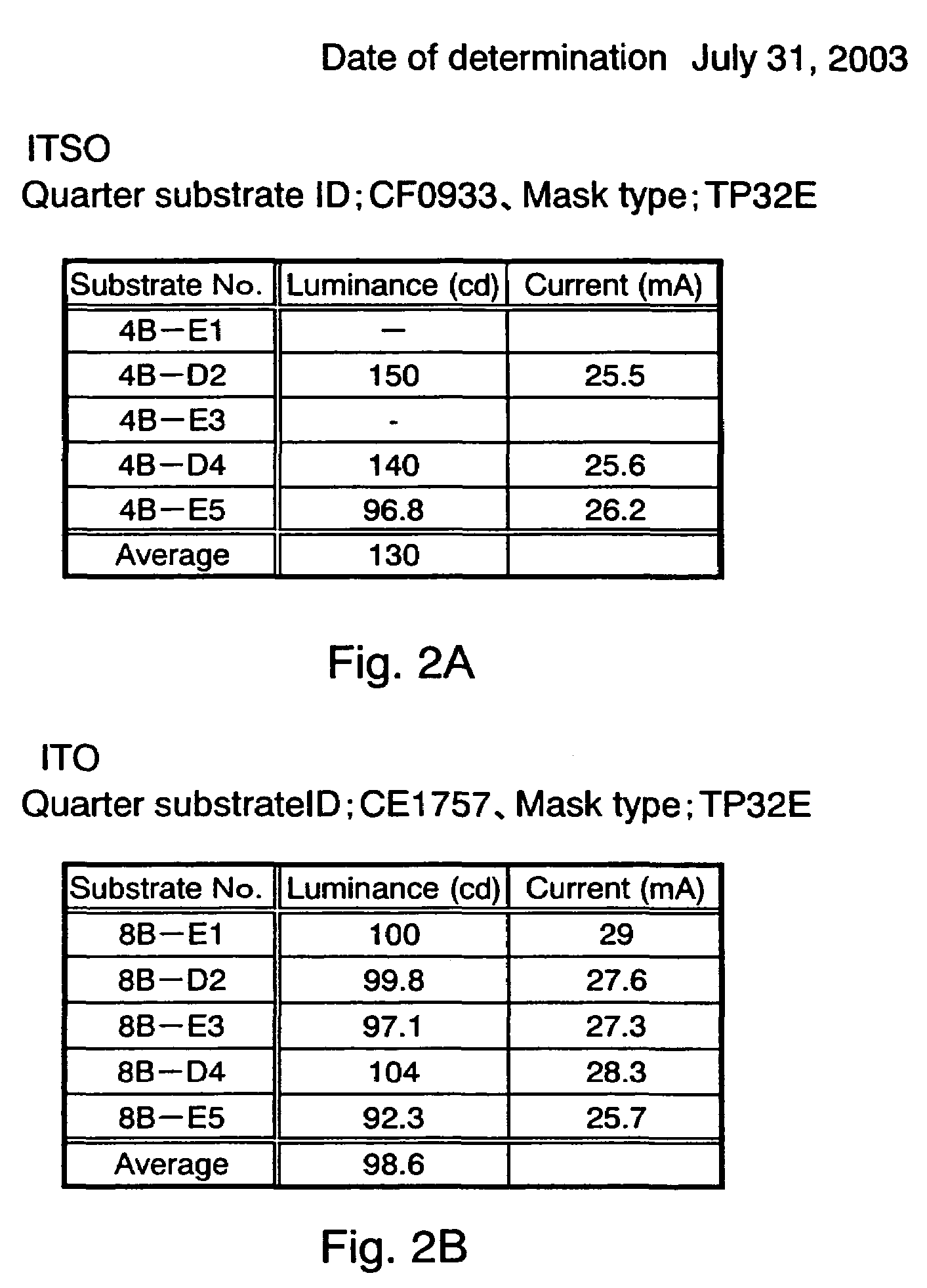

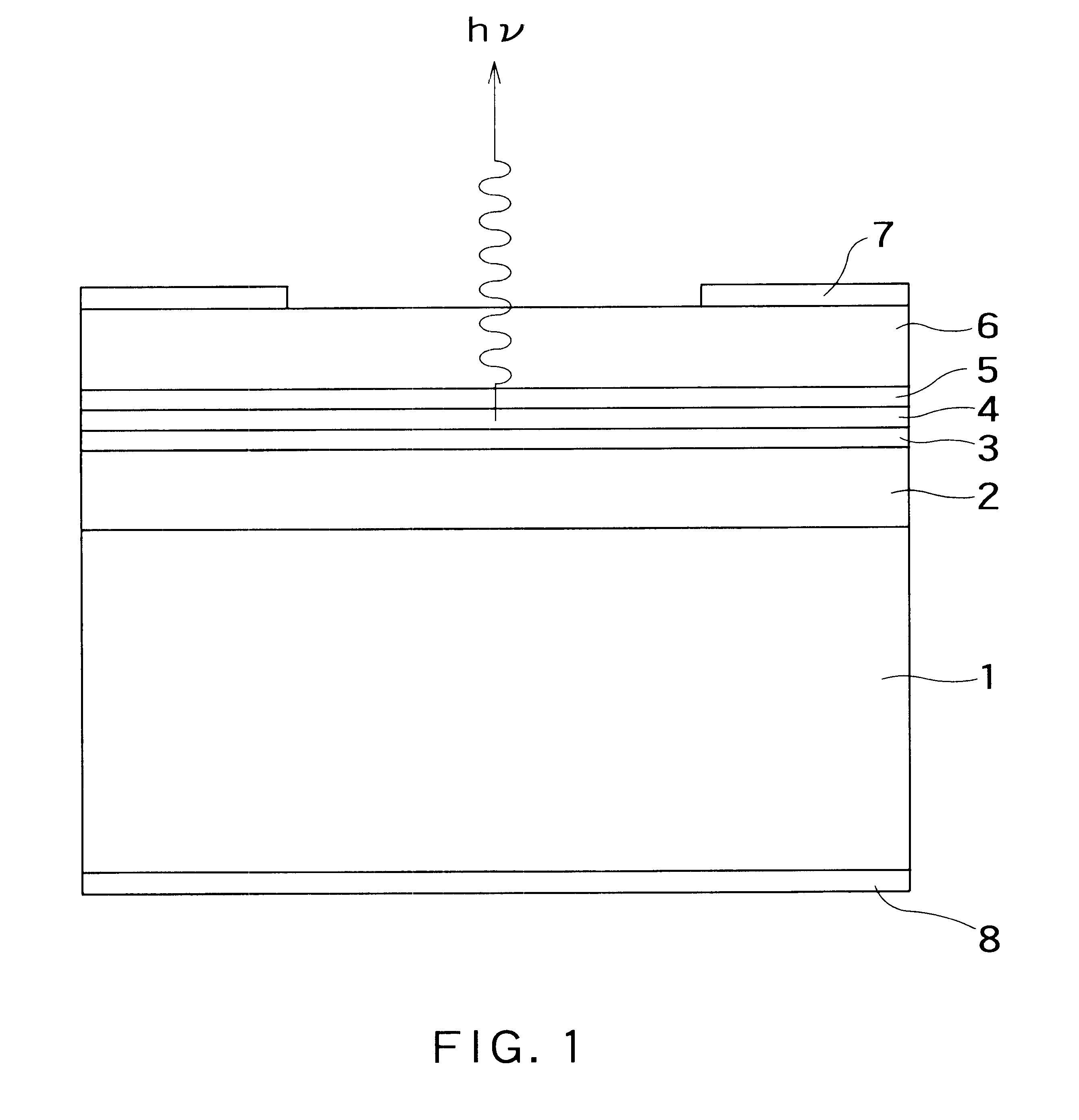

Light emitting element including a barrier layer and a manufacturing method thereof

InactiveUS7291967B2Improve stabilityExcellent luminous propertiesDischarge tube luminescnet screensElectroluminescent light sourcesHole injection layerSilicon oxide

According to the invention, an insulating or semi-insulating barrier layer which has a thickness where a tunnel current can flow through is provided between a hole injection electrode and an organic compound layer with hole transport characteristics (a hole injection layer or a hole transport layer). Specifically, a thin insulating or semi-insulating barrier layer which contains silicon or silicon oxide; silicon or silicon oxide and a light transmitting conductive oxide material; or silicon or silicon oxide, a light transmitting conductive oxide material, and carbon may be provided between a light transmitting conductive oxide film formed of a light transmitting conductive oxide material, such as ITO and a hole injection layer containing an organic compound.

Owner:SEMICON ENERGY LAB CO LTD

Non-volatile flash memory structure and method for operating the same

InactiveUS20070241392A1Increase capacitanceReduce areaTransistorSolid-state devicesCapacitanceBack bias

A non-volatile memory structure and a method for operating the same are proposed. The non-volatile memory structure makes use of a single floating gate structure and a capacitor structure including a pair of regions doped with different type impurities to increase the capacitance and shrink the area. When performing programming operations to this memory structure, a voltage is applied to the source or a back bias is applied to the substrate of the transistor to greatly reduce the current requirement of a single-gate EEPROM device. When performing erase operations, the drain voltage is raised, and a small voltage is added to the gate to increase the F-N tunneling current, thereby accomplishing the effect of fast erase.

Owner:YIELD MICROELECTRONICS CORP

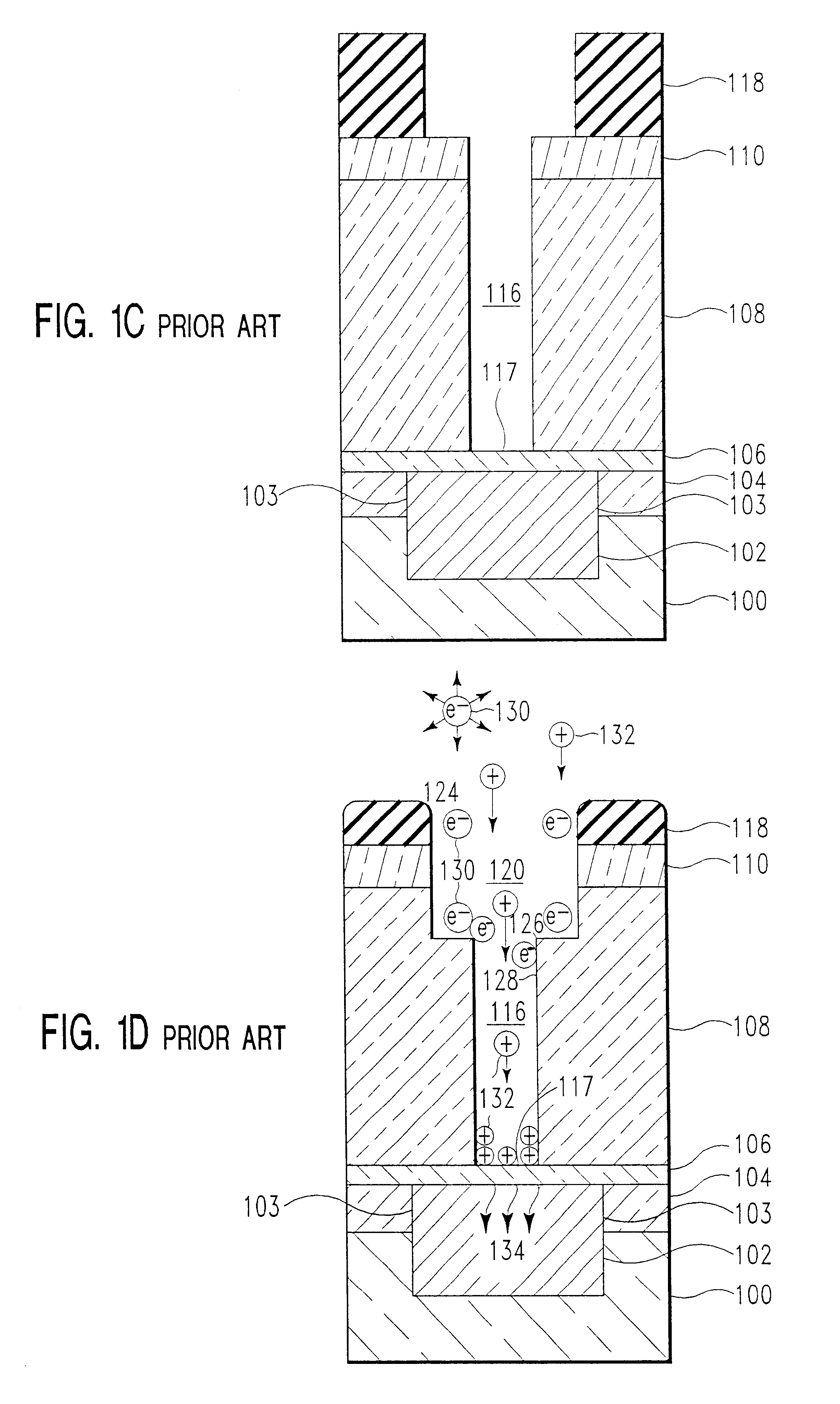

Method of reducing plasma charging damage during dielectric etch process for dual damascene interconnect structures

Charging damage, caused by electron shading during plasma etching in a dual damascene structure, is alleviated by first depositing a protective conductive layer which provides a conductive path for maintaining charge balance in the etched structures. This conductive layer reduces the buildup of unbalanced positive charge in the contact opening, and the damage done to underlying layers caused by the resultant tunneling current. Further, if the protective conductive layer comprises a material which can also serve as an interdiffusion barrier layer for the contact opening fill material, a separate subsequent step to deposit such a barrier layer on the contact opening sidewall is avoided. Further, in the process of doing lithography on the trench etch resist layer, the protective conductive layer also functions as an antireflective coating, permitting the stepper to accurately focus the desired pattern.

Owner:APPLIED MATERIALS INC

Sensor for Detection of Single Molecules

InactiveUS20080149479A1High sensitivityReduce distortion problemsImmobilised enzymesMaterial nanotechnologySingle electronNano manufacturing

A single electron transistor device for sensing at least one particle, includes at least two electrodes positioned with a gap formed between the electrodes and an activation object positioned in the gap with an insulating layer between the activation object and each electrode. The activation object which is able to transfer electrons is arranged with at least one binding structure bonded to it for receiving the at least one particle. The electrodes are formed with an inter distance of less than 50 nm and the electrodes are connectable directly or indirectly to a signal acquisition system. The sensing device is arranged to allow a tunnelling current proportional to the presence of the at least one particle in the binding structure, to flow through the activation object. A method, and system using a single electron transistor device fabricated with micro / nano fabrication methods are also disclosed.

Owner:MIDORION

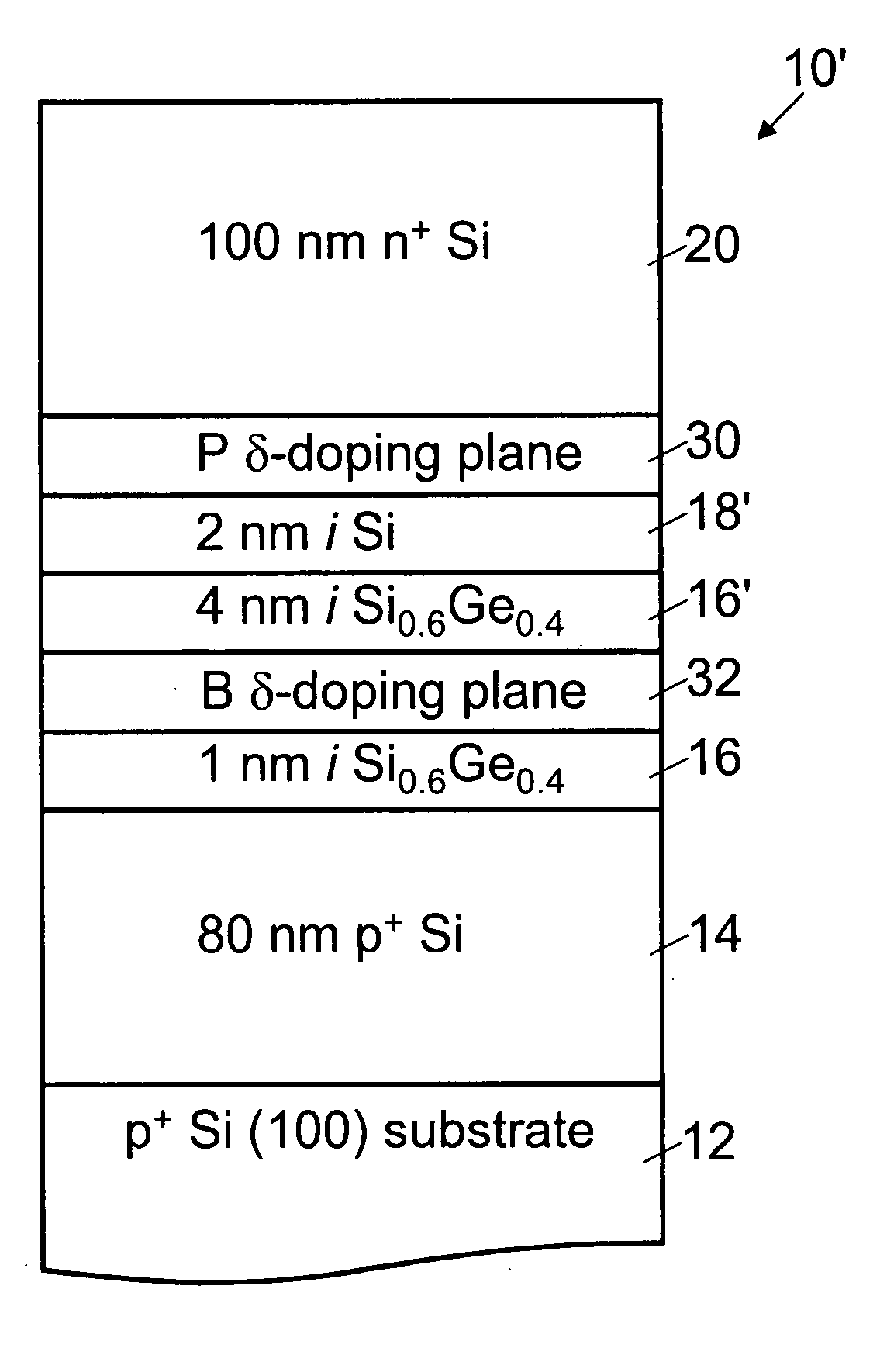

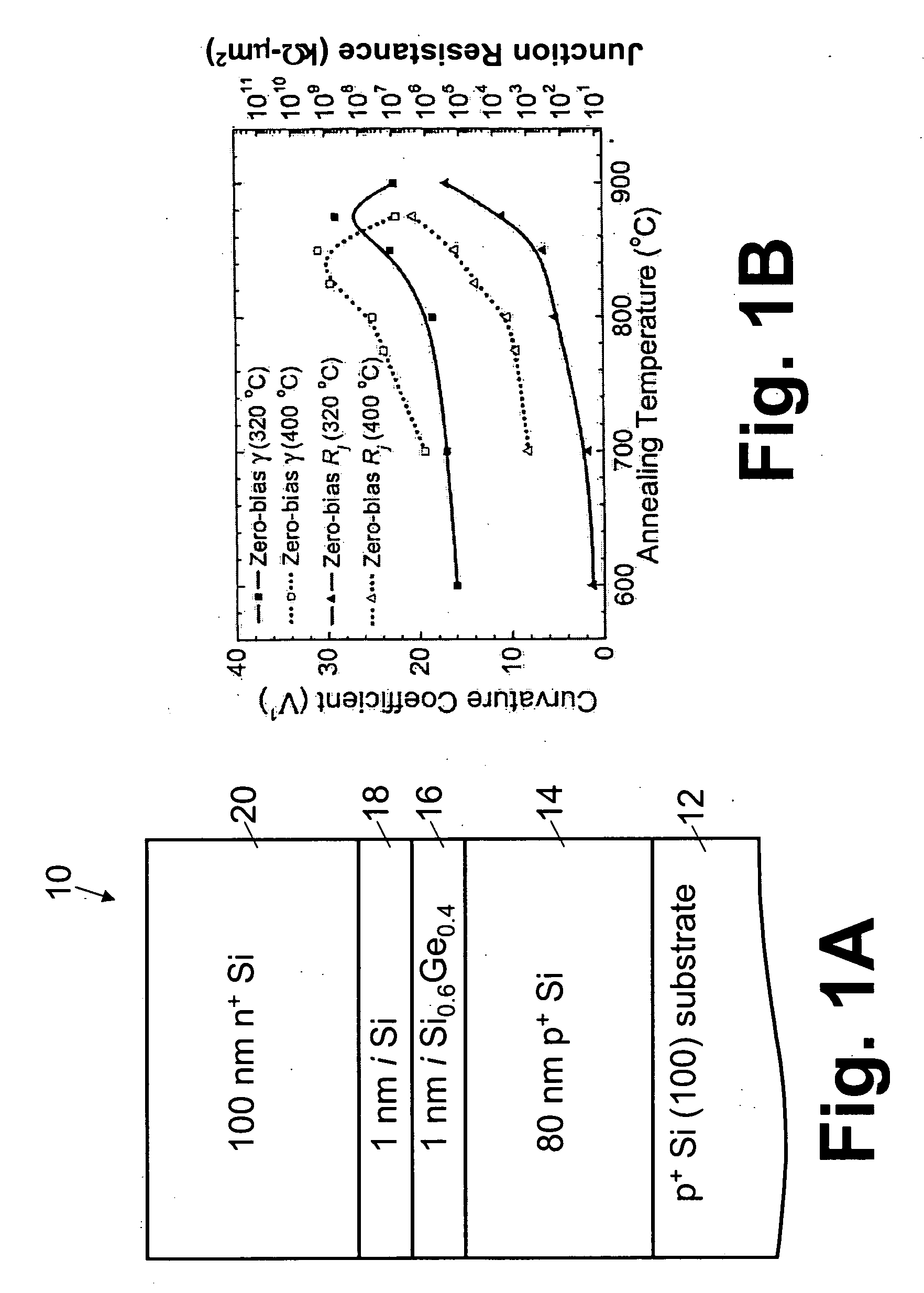

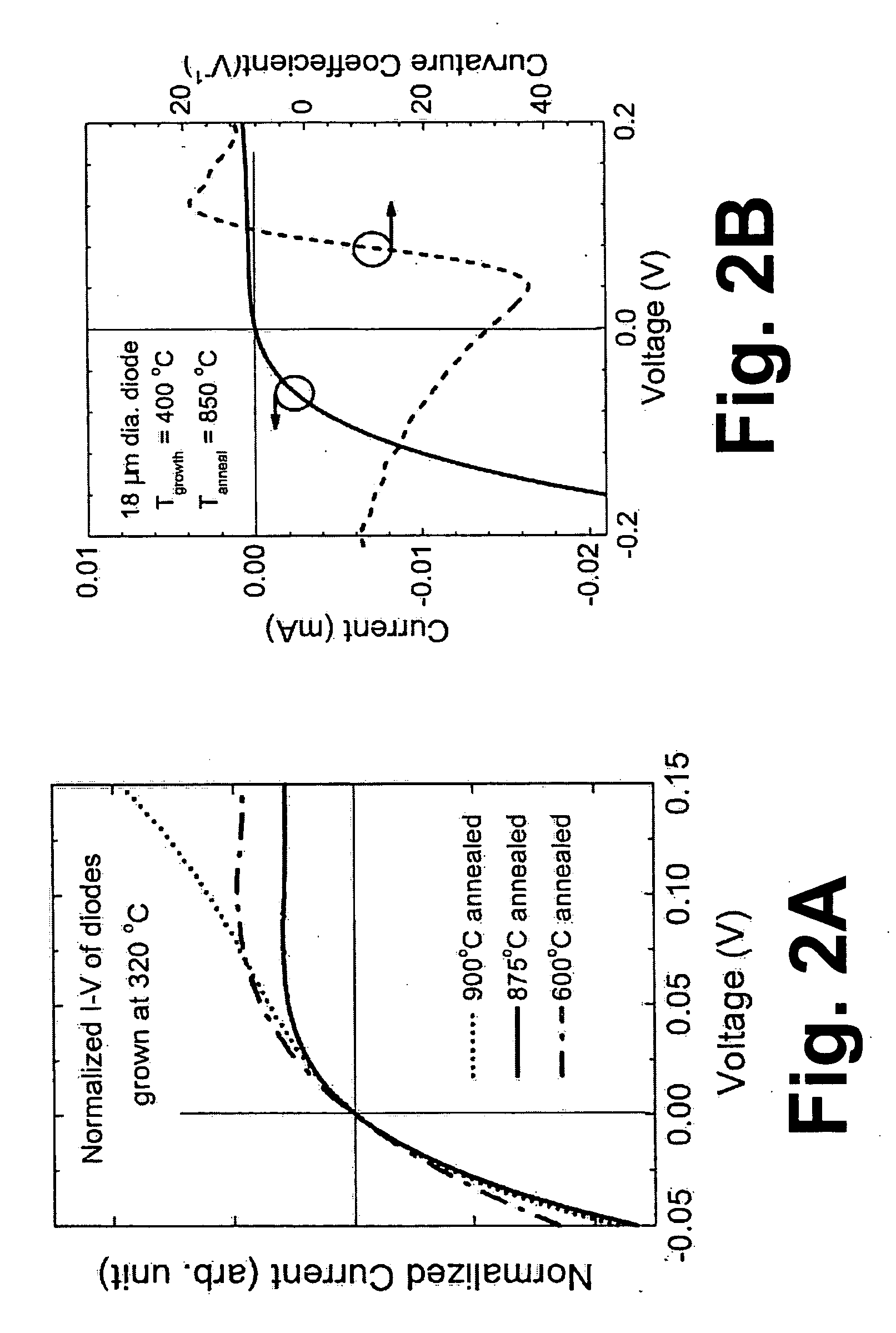

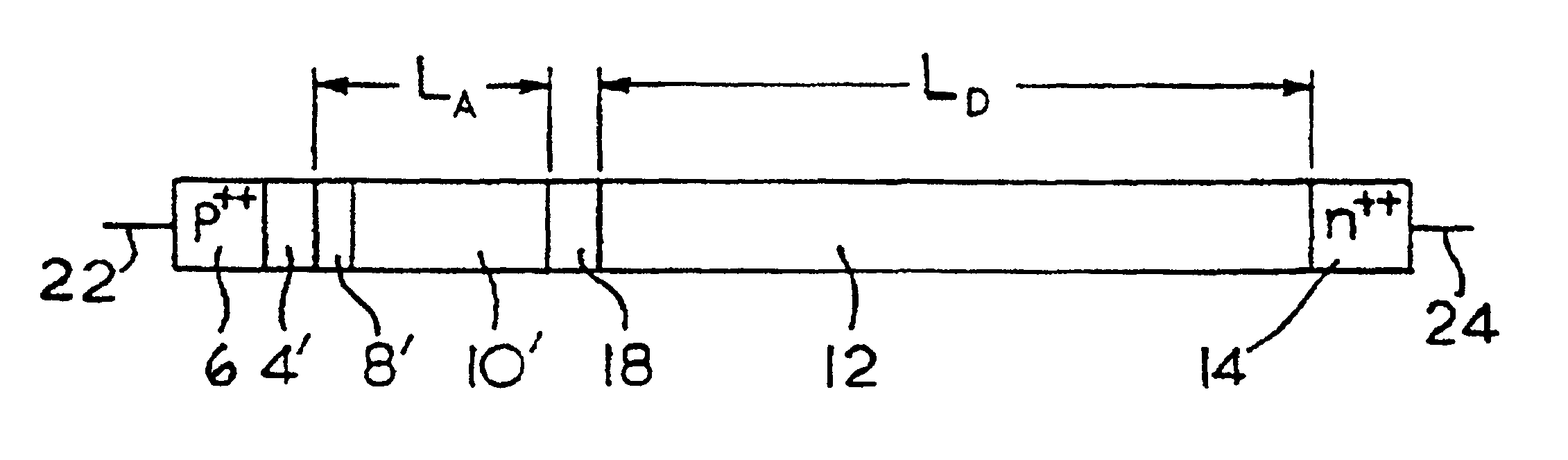

Silicon-based backward diodes for zero-biased square law detection and detector arrays of same

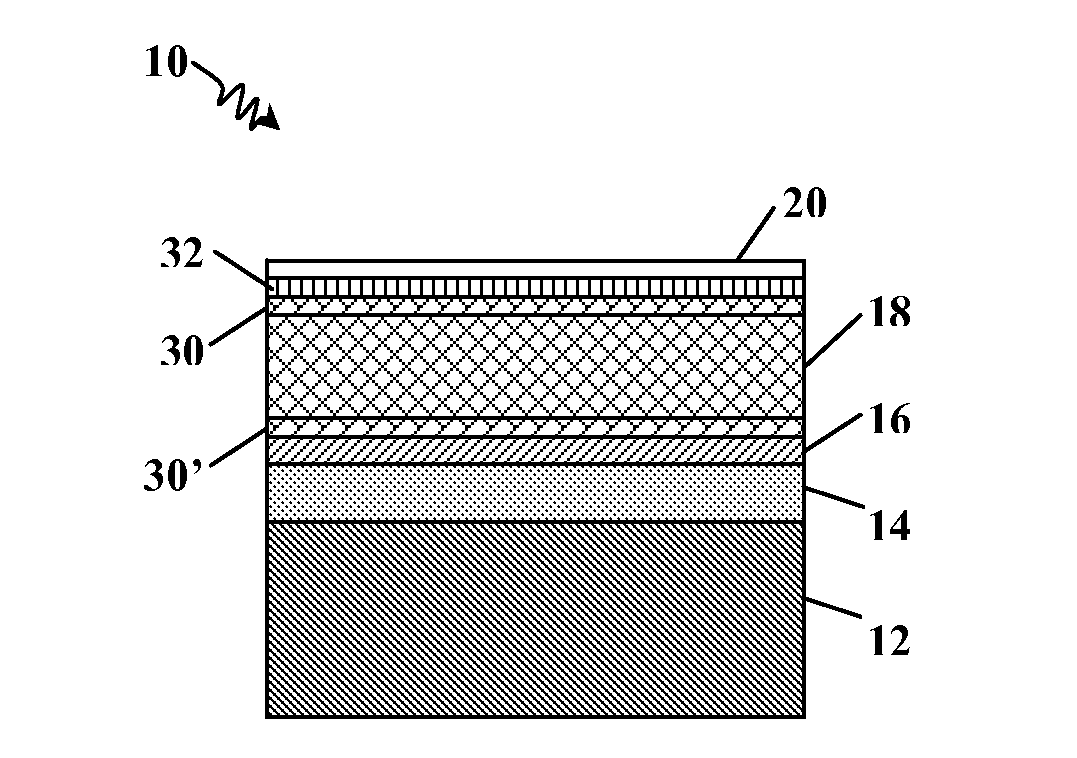

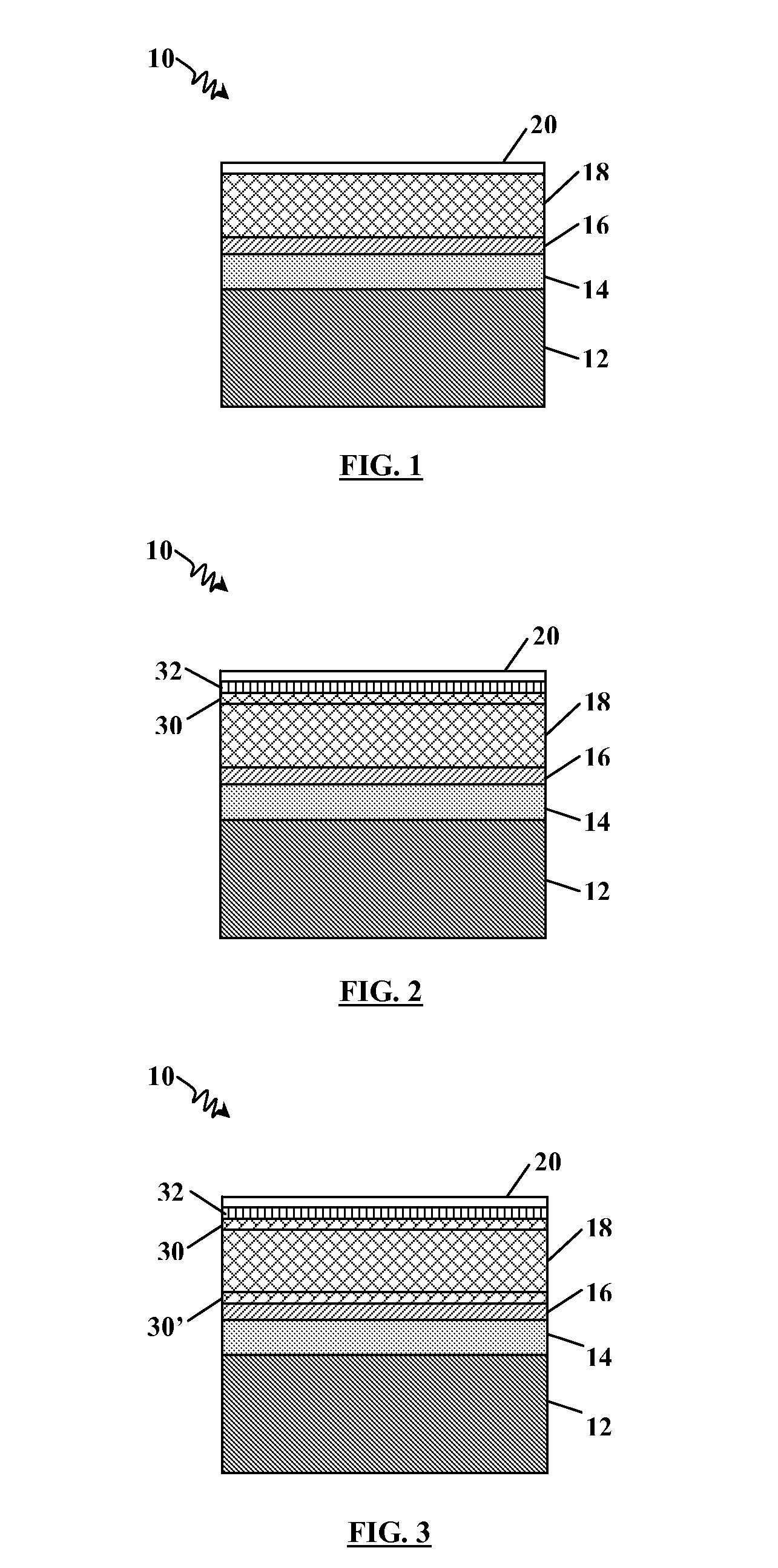

A Si-based diode (10, 10′, 100) is formed by epitaxially depositing a Si-based diode structure on a silicon substrate. The Si-based diode structure includes a Si-based pn junction (16, 16′, 18, 18′, 30, 32, 160, 161) having a backward diode current-voltage characteristic in which the forward tunneling current is substantially smaller than the backward tunneling current at comparable voltage levels. In some embodiments, the Si-based pn junction includes at least one non-silicon or silicon alloy layer such as at least one SiGe layer (16, 16′, 160, 161). In some embodiments, at least one delta doping (30, 32) is disposed on the silicon substrate in or near the pn junction, that together with the Si-based pn junction define an electrical junction having the backward diode current-voltage characteristic. A large area detector array may include a plurality of such Si-based diodes (10, 10′, 100).

Owner:THE OHIO STATES UNIV +1

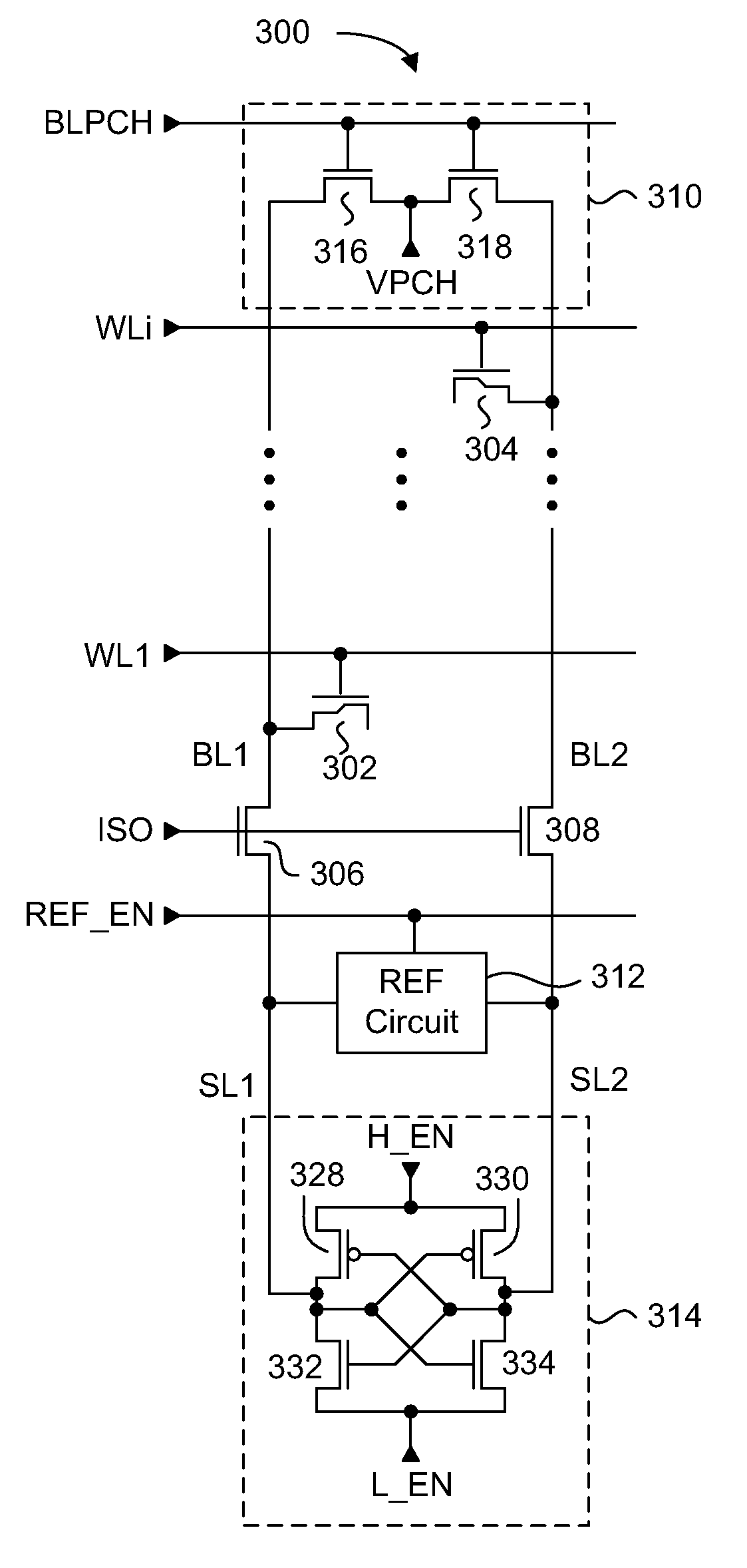

Low power antifuse sensing scheme with improved reliability

ActiveUS20100220511A1Reduce oxide breakdownReduce disadvantagesSemiconductor/solid-state device detailsSolid-state devicesBit lineAudio power amplifier

Generally, a method and circuit for improving the retention and reliability of unprogrammed anti-fuse memory cells. This is achieved by minimizing the tunneling current through the unprogrammed anti-fuse memory cells which can cause eventual gate oxide breakdown. The amount of time a read voltage is applied to the anti-fuse memory cells is reduced by pulsing a read voltage applied to a wordline connected to the unprogrammed anti-fuse memory cells, thereby reducing the tunneling current. Further tunneling current can be reduced by decoupling the unprogrammed anti-fuse memory cells from a sense amplifier that can drive the corresponding bitline to VSS.

Owner:SYNOPSYS INC

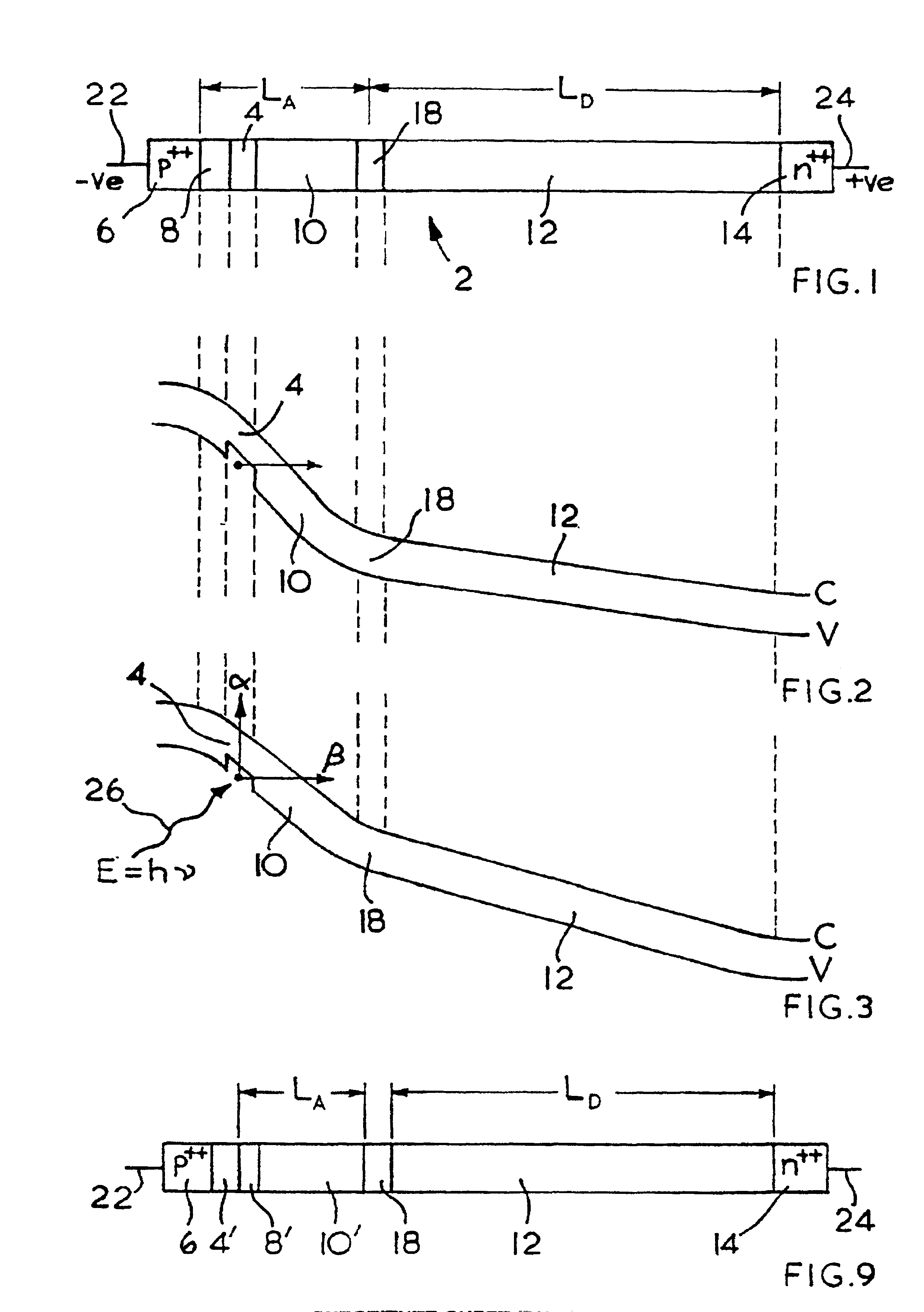

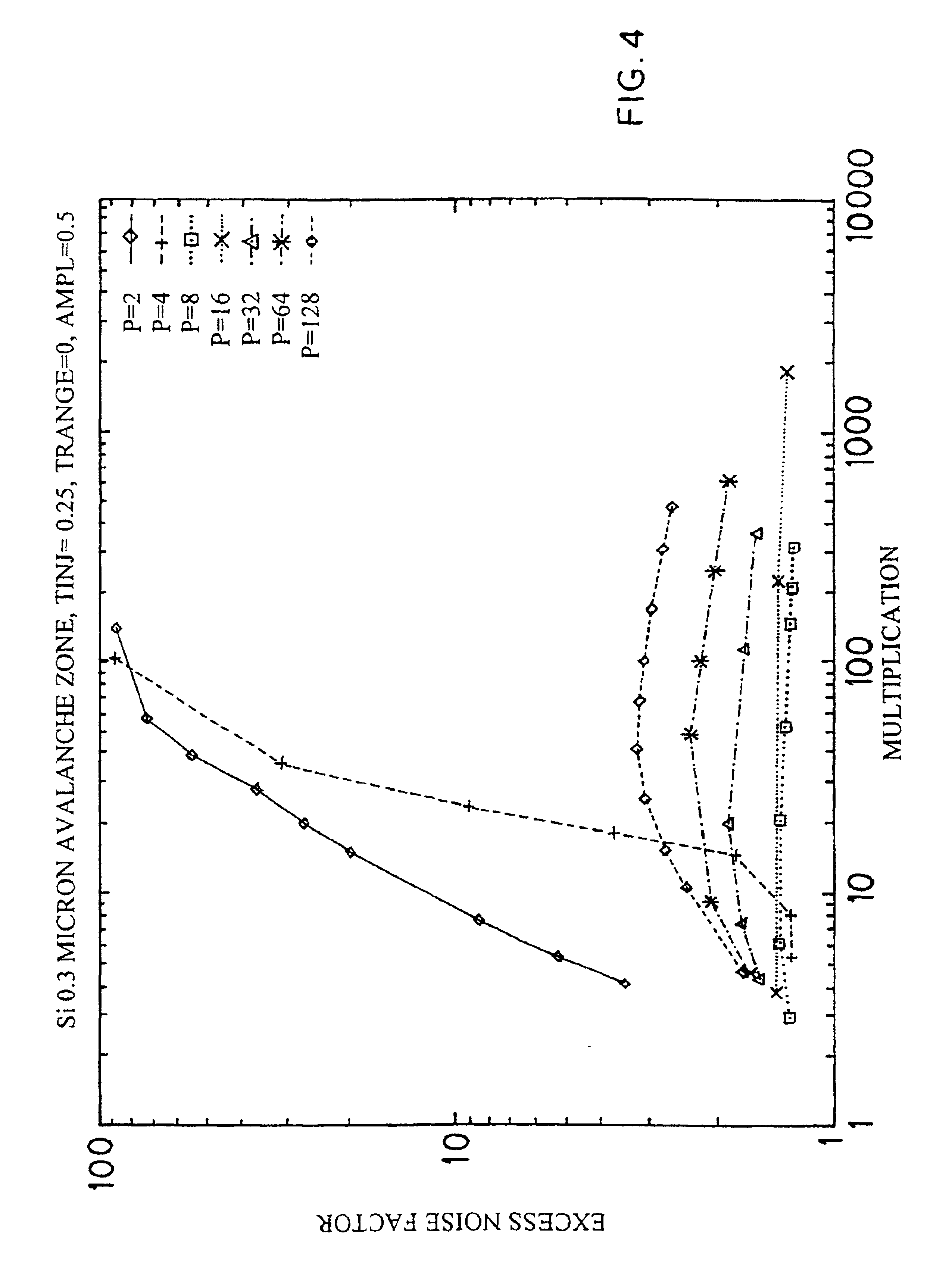

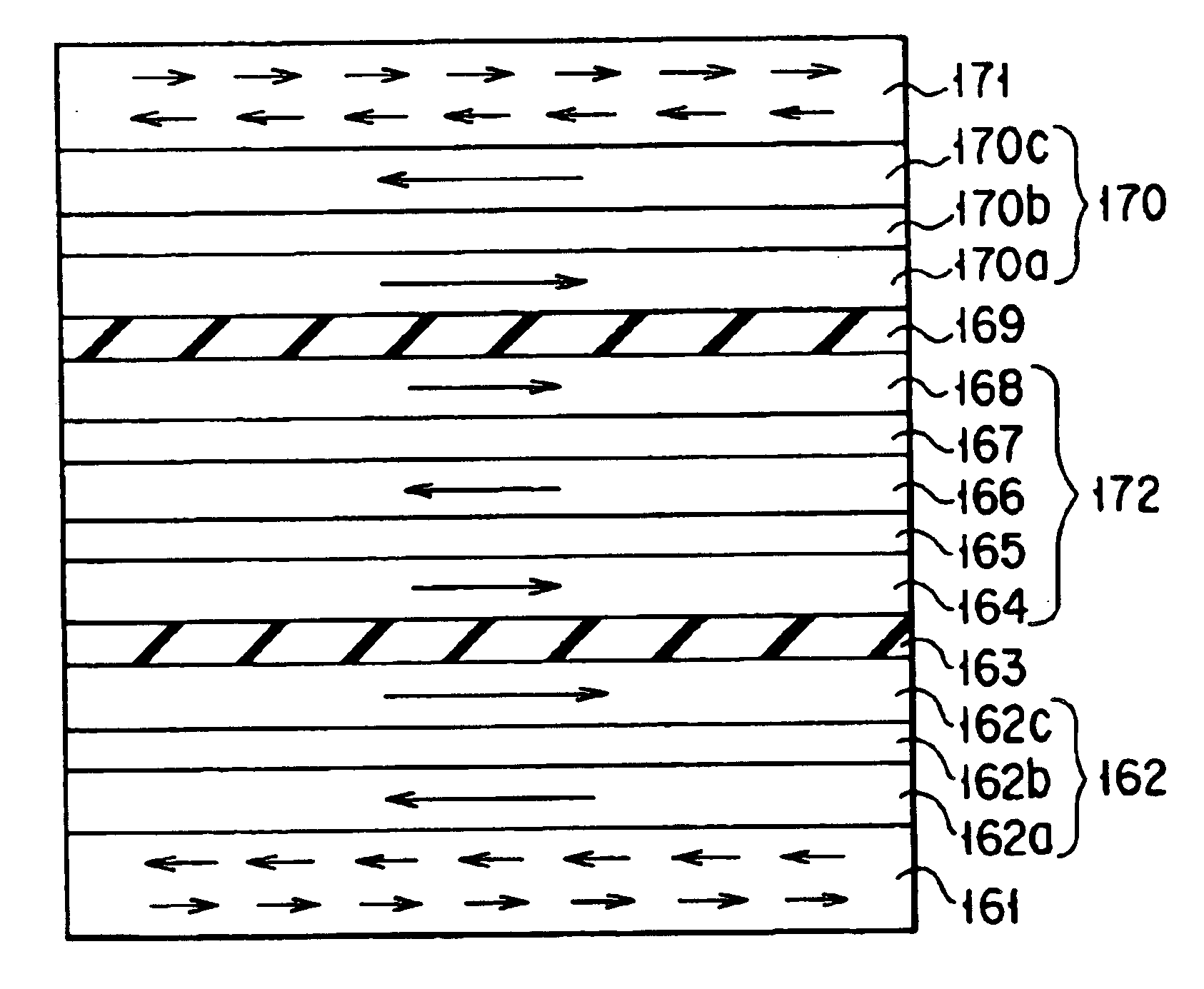

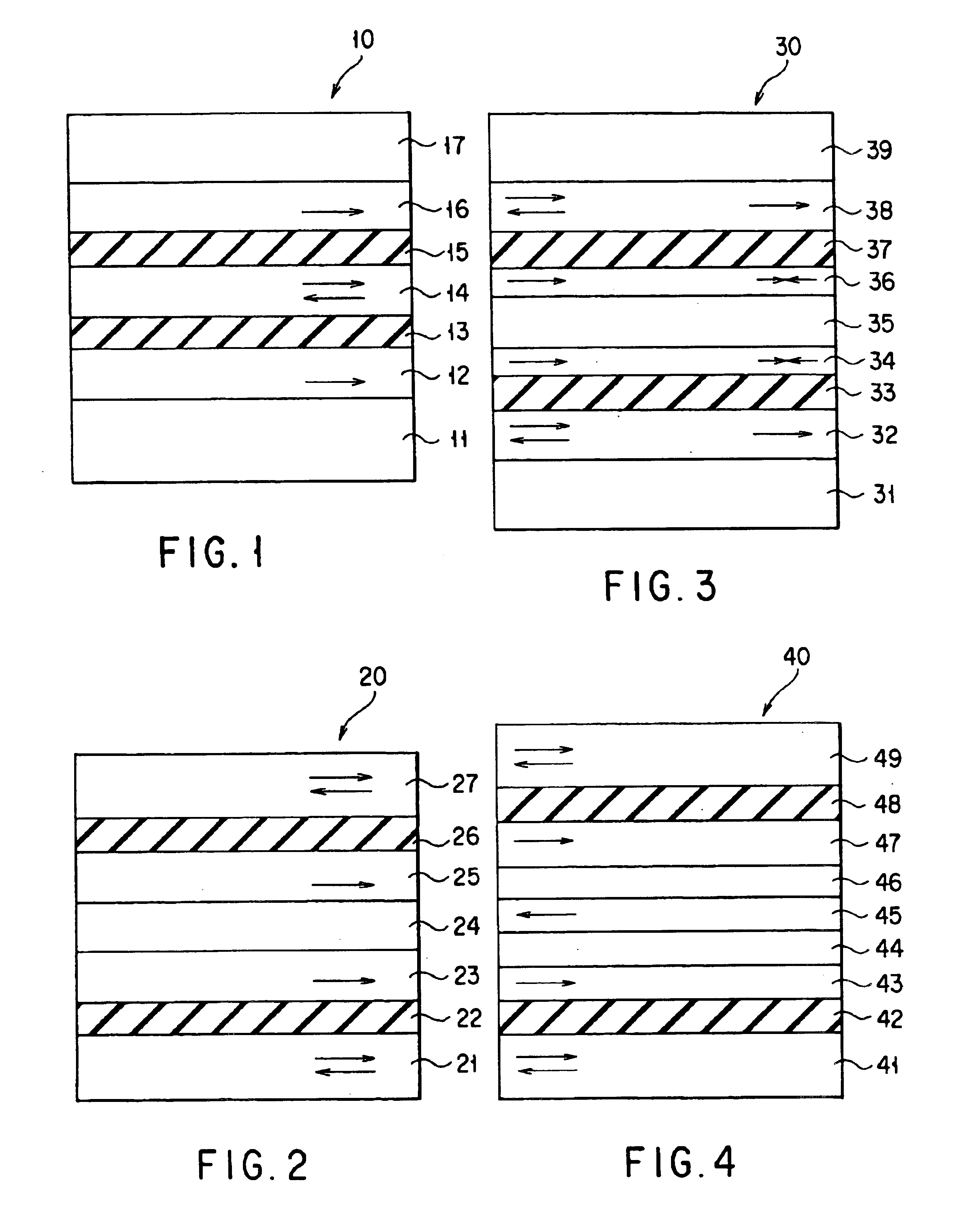

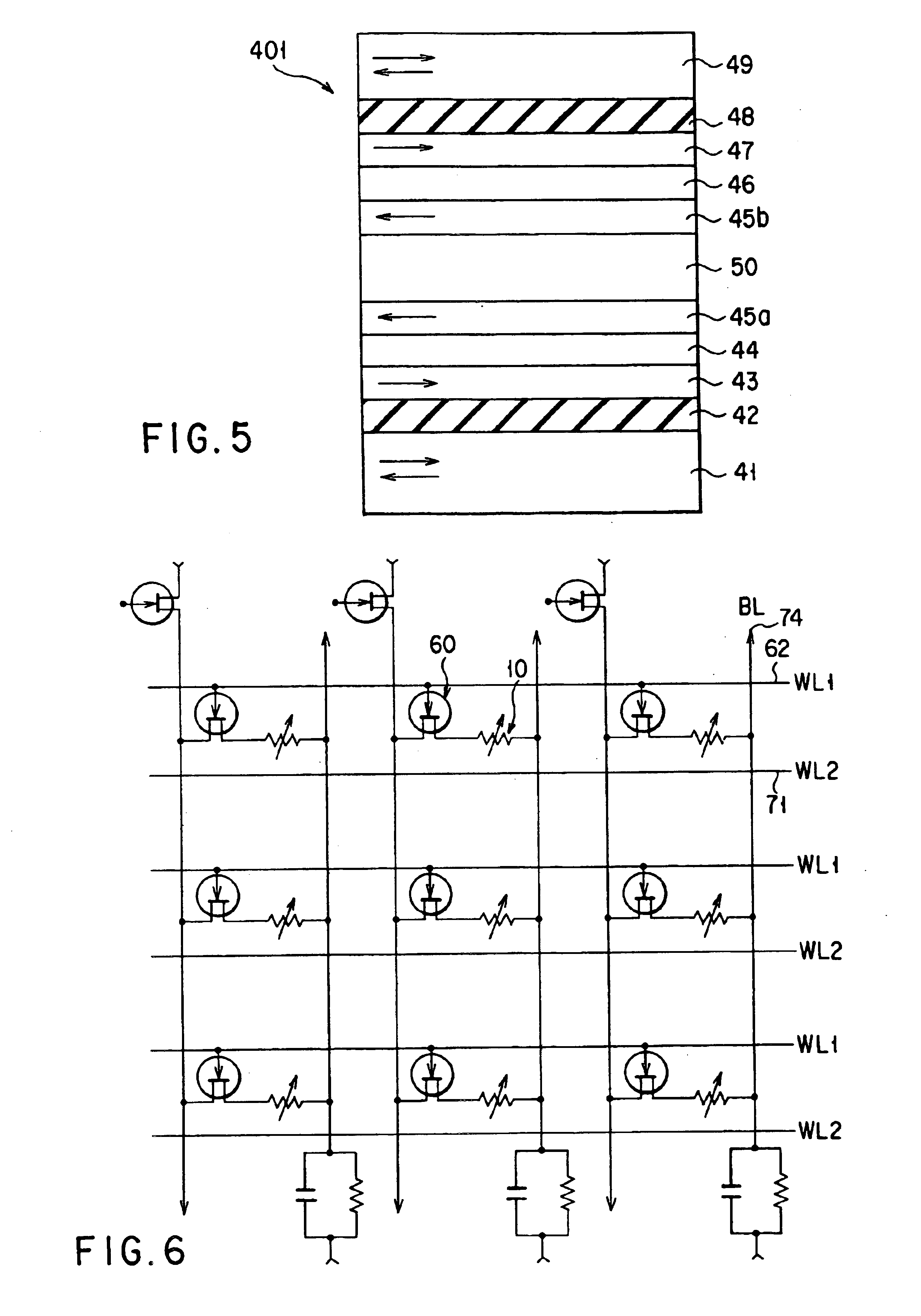

IMPATT diodes

InactiveUS6774460B1Improve predictabilityReduce noiseSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueImpact ionization

The present invention relates to an impact ionisation avalanche transit time (IMPATT) diode device comprising an avalanche region and a drift region, wherein at least one narrow bandgap region, with a bandgap narrower than the bandgap in the avalanche region, is located adjacent to or within the avalanche region in order to generate within the narrow bandgap region a tunnel current which is injected into the avalanche region. This improves the predictability with which a current can be injected into the avalanche region and enables a relatively narrow pulse of current to be injected into the avalanche region in order to enable a relatively noise free avalanche multiplication. The narrow bandgap region may be located between a heavily doped contact region and the avalanche region and is preferably arranged to generate a tunnel current at the peak reverse bias applied to the diode.

Owner:CHEMTRON RES

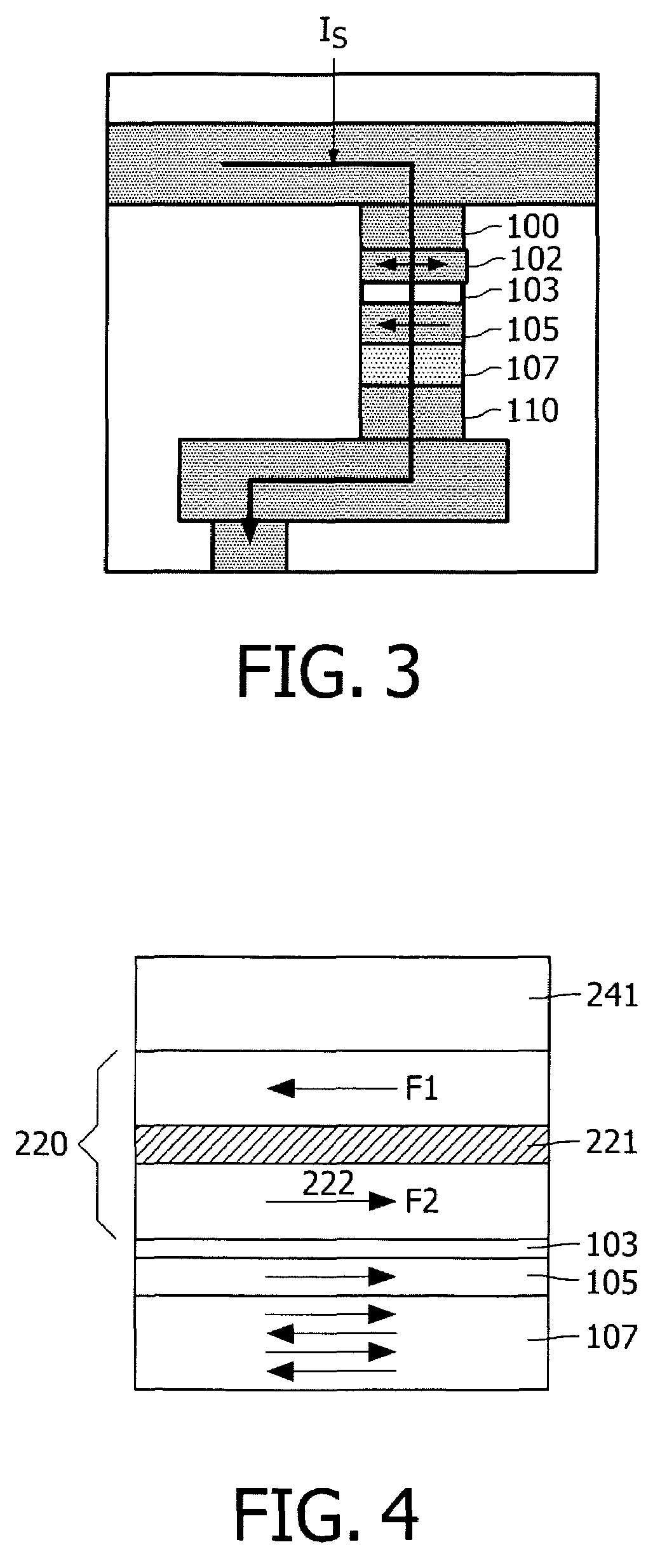

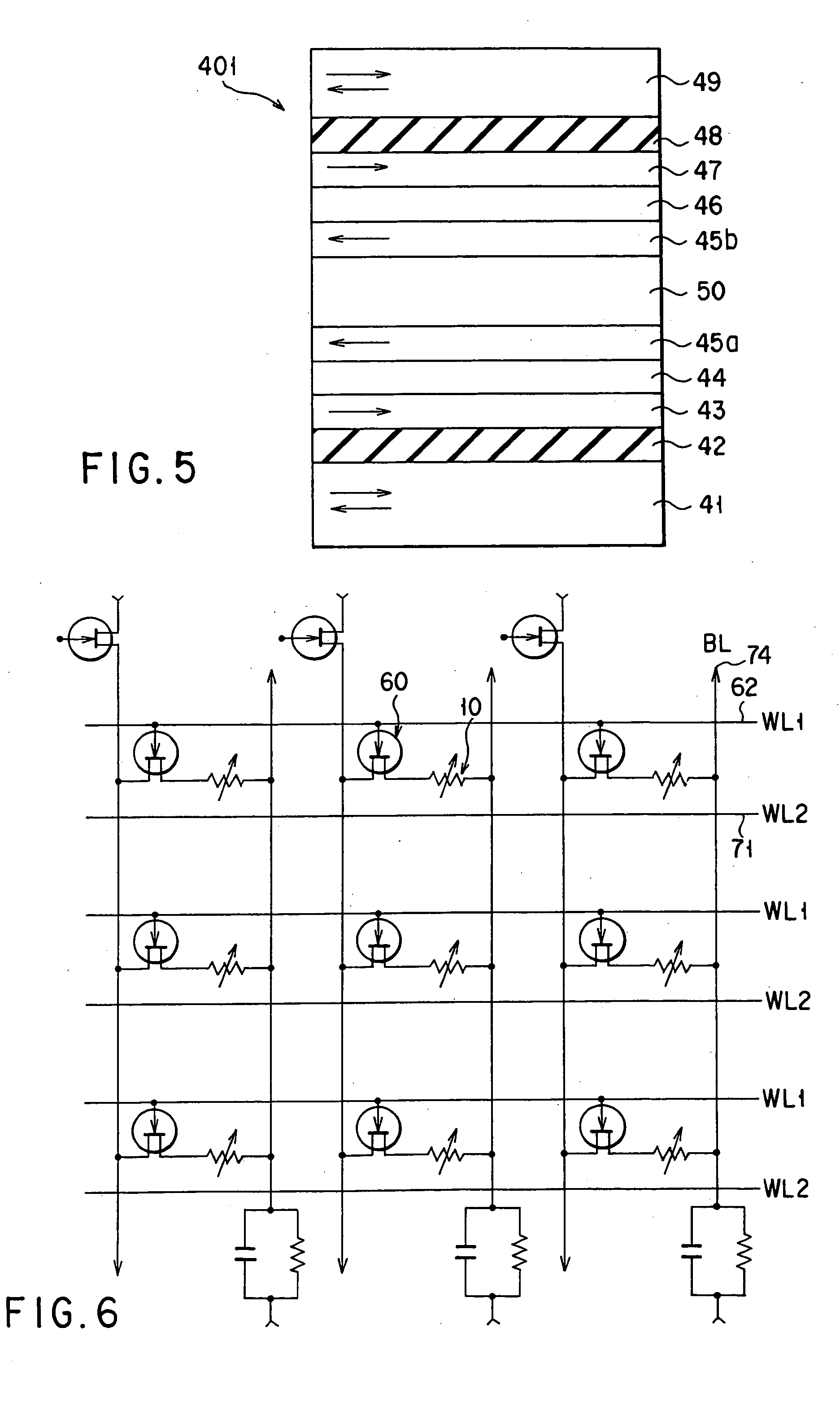

Magnetoresistive element and magnetic memory device

InactiveUS6987653B2Slow changeDesign freedomNanomagnetismMagnetic measurementsMagnetic memoryMagnetic reluctance

A magnetoresistive element has a ferromagnetic double tunnel junction having a stacked structure of a first antiferromagnetic layer / a first ferromagnetic layer / a first dielectric layer / a second ferromagnetic layer / a second dielectric layer / a third ferromagnetic layer / a second antiferromagnetic layer. The second ferromagnetic layer that is a free layer consists of a Co-based alloy or a three-layered film of a Co-based alloy / a Ni—Fe alloy / a Co-based alloy. A tunnel current is flowed between the first ferromagnetic layer and the third ferromagnetic layer.

Owner:TOSHIBA MEMORY CORP

Method of forming a CMOS structure having gate insulation films of different thicknesses

InactiveUS7427791B2Reduce standby power consumptionRaise the thresholdTransistorNanotechCMOSEngineering

The semiconductor integrated circuit device employs on the same silicon substrate a plurality of kinds of MOS transistors with different magnitudes of tunnel current flowing either between the source and gate or between the drain and gate thereof. These MOS transistors include tunnel-current increased MOS transistors at least one of which is for use in constituting a main circuit of the device. The plurality of kinds of MOS transistors also include tunnel-current reduced or depleted MOS transistors at least one of which is for use with a control circuit. This control circuit is inserted between the main circuit and at least one of the two power supply units.

Owner:TESSERA ADVANCED TECH

Magnetoresistive element and magnetic memory device

InactiveUS20050185347A1Reduction in MR changeDesign freedomNanomagnetismMagnetic measurementsNuclear magnetic resonanceTunneling current

A magnetoresistive element has a ferromagnetic double tunnel junction having a stacked structure of a first antiferromagnetic layer / a first ferromagnetic layer / a first dielectric layer / a second ferromagnetic layer / a second dielectric layer / a third ferromagnetic layer / a second antiferromagnetic layer. The second ferromagnetic layer that is a free layer consists of a Co-based alloy or a three-layered film of a Co-based alloy / a Ni—Fe alloy / a Co-based alloy. A tunnel current is flowed between the first ferromagnetic layer and the third ferromagnetic layer.

Owner:TOSHIBA MEMORY CORP

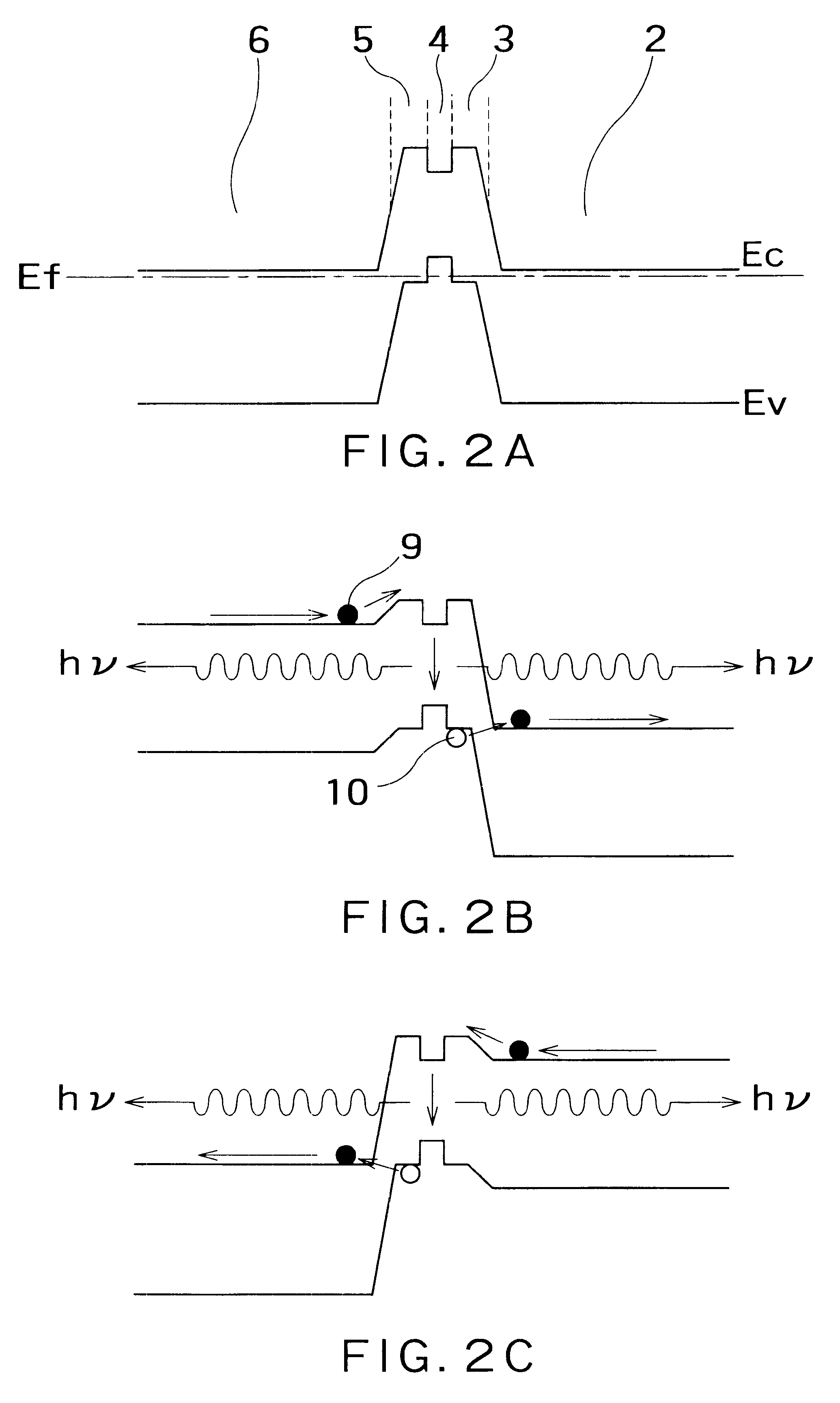

Bidirectional semiconductor light-emitting element and optical system

According to the invention, a bidirectional semiconductor light emitting element is provided, which comprises: a first semiconductor region of a first type of conductivity; a second semiconductor region of a second type of conductivity provided on the first semiconductor region; a third semiconductor region of a first conductivity type provided on the second semiconductor region; and a semiconductor light emitting layer interposed in the second semiconductor region, the light emitting layer emitting light by an injection of a tunneling current generated at a reverse-biased p-n junction between the first and second regions or between the second and third regions under an application of a voltage of a first polarity across the first and third semiconductor regions, and the light emitting layer emitting light by an injection of a tunneling current generated at another reverse-biased p-n junction between the first and second regions or between the second and third regions under an application of a voltage of a second polarity, which is opposite to the first polarity, across the first and third semiconductor regions.

Owner:KK TOSHIBA