Patents

Literature

346 results about "Double diffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Double diffusion. A type of convective transport in fluids that depends on the difference in diffusion rates of at least two density-affecting components. Also, it is necessary to have an unstable or top-heavy distribution of one component.

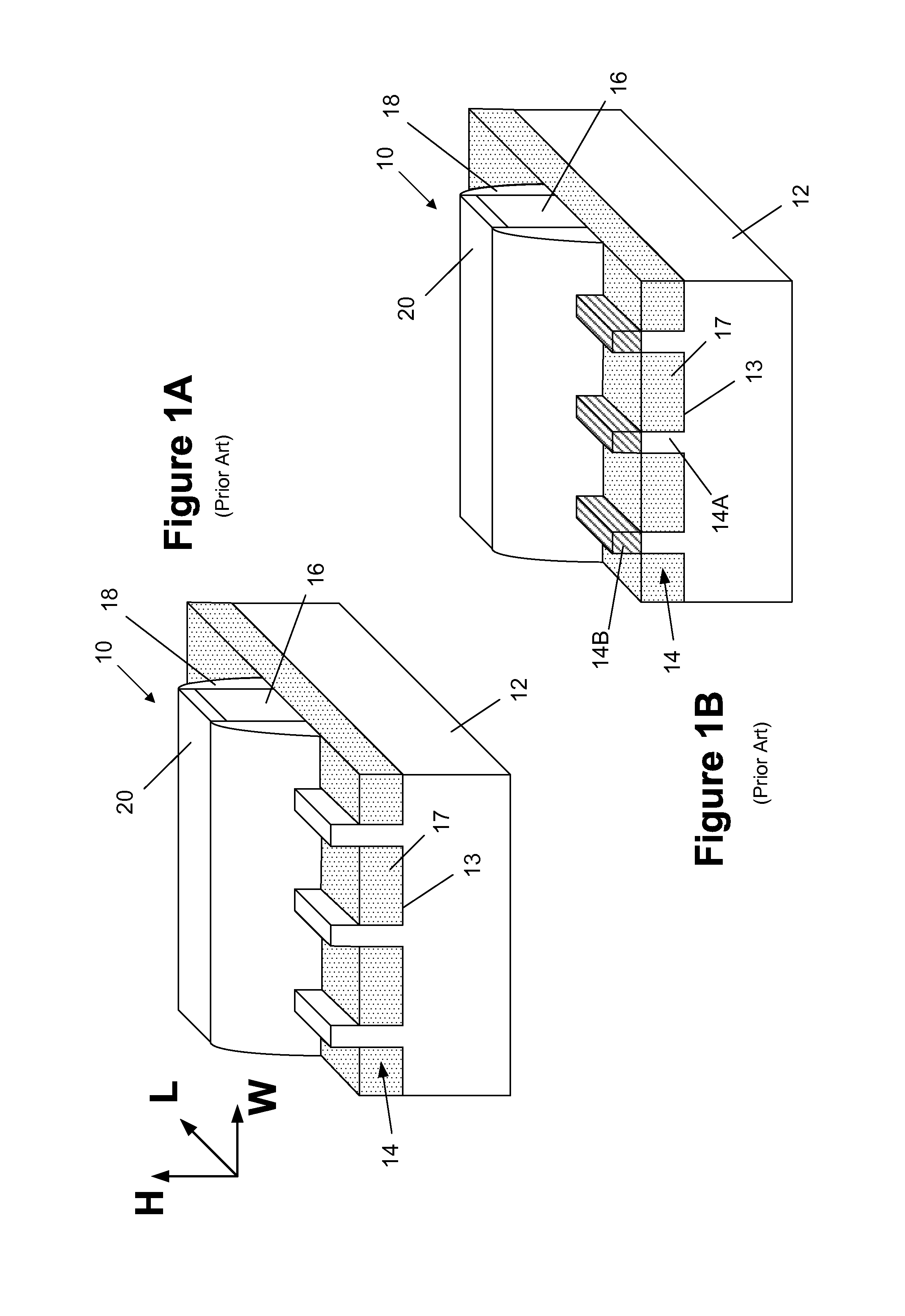

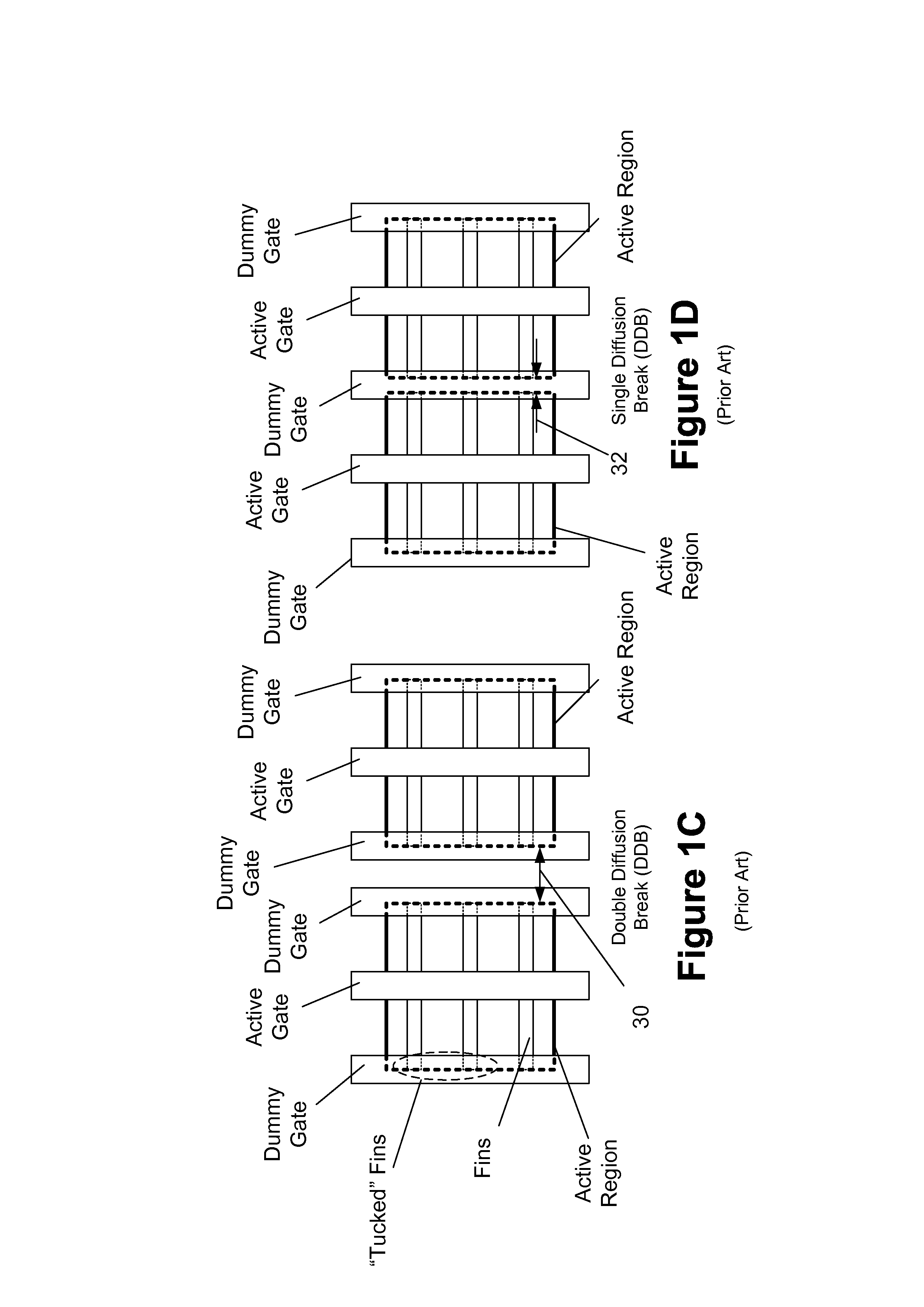

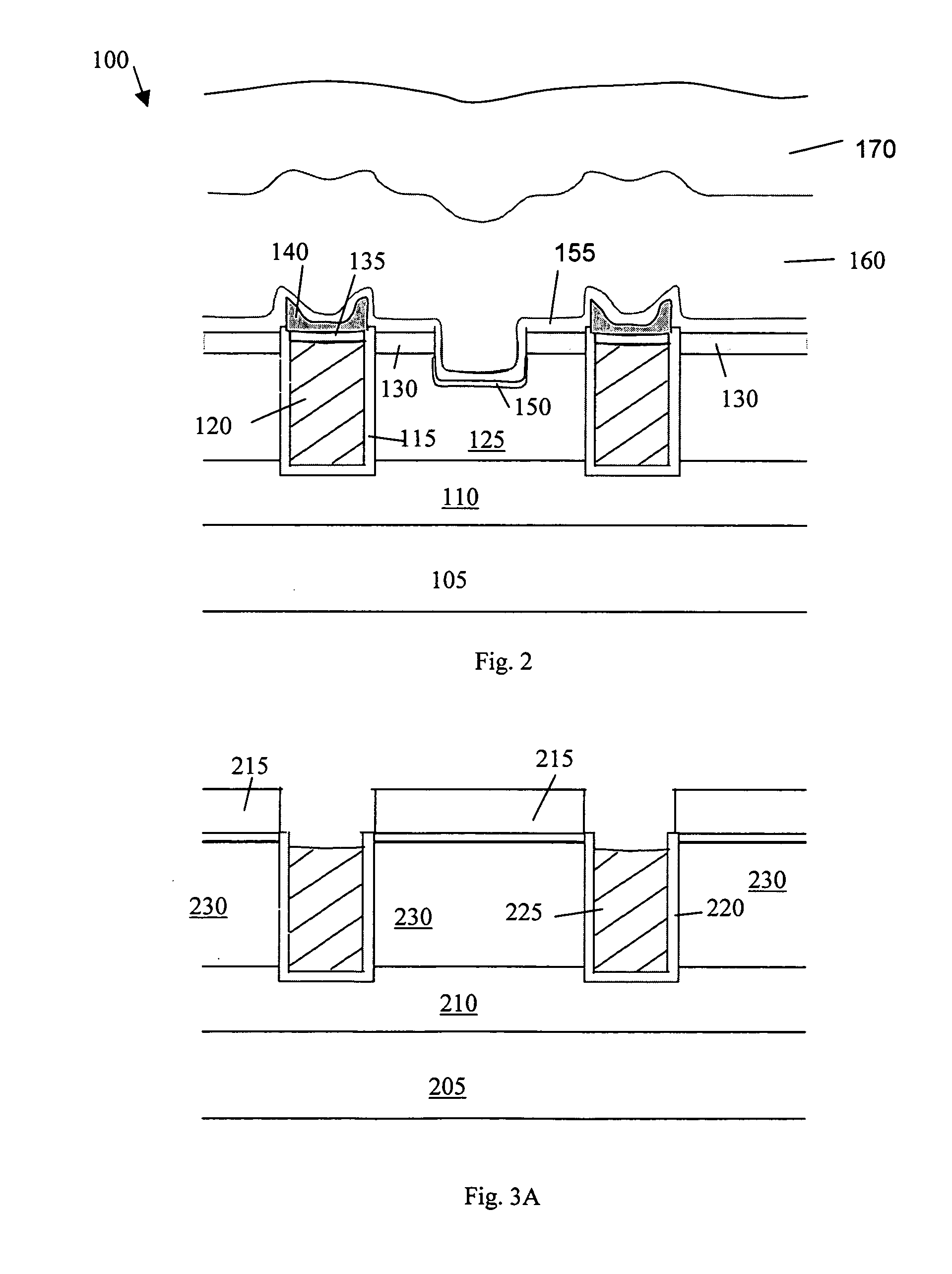

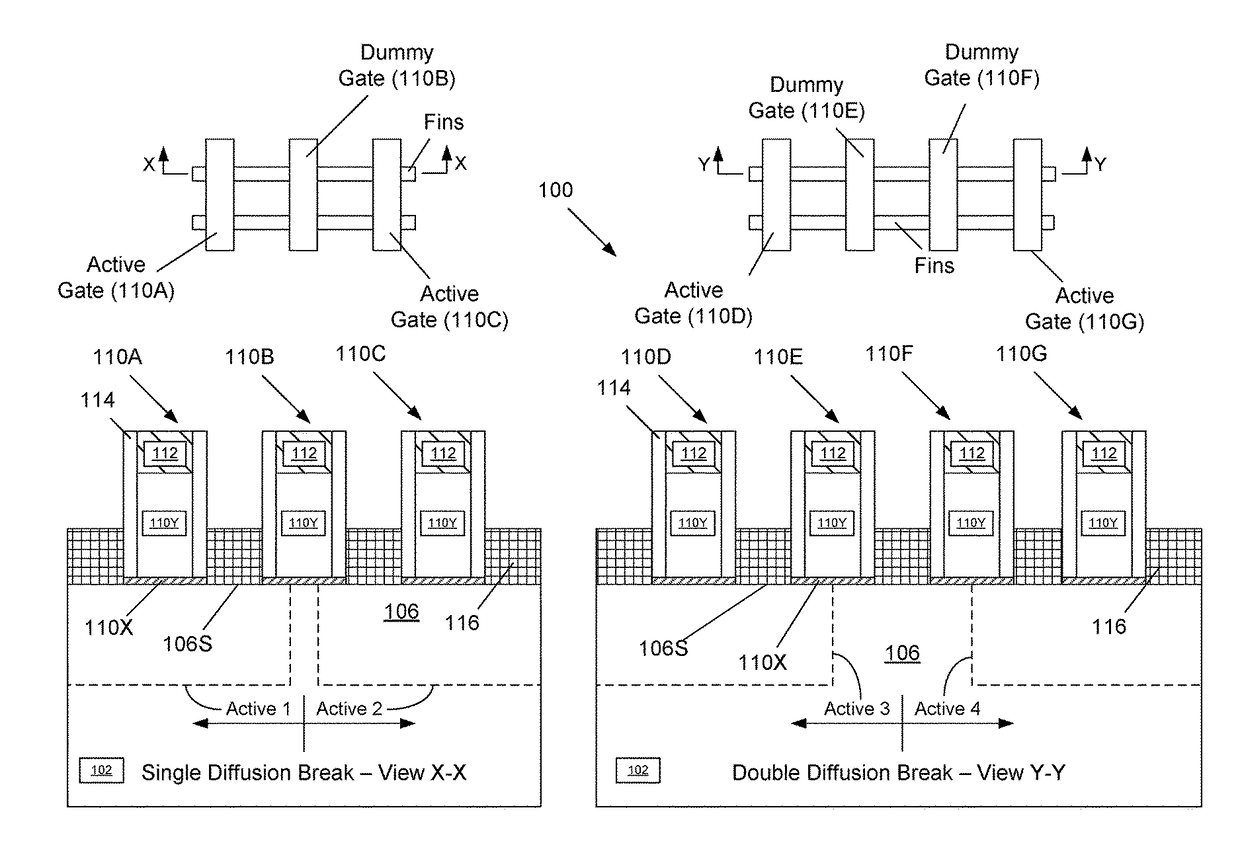

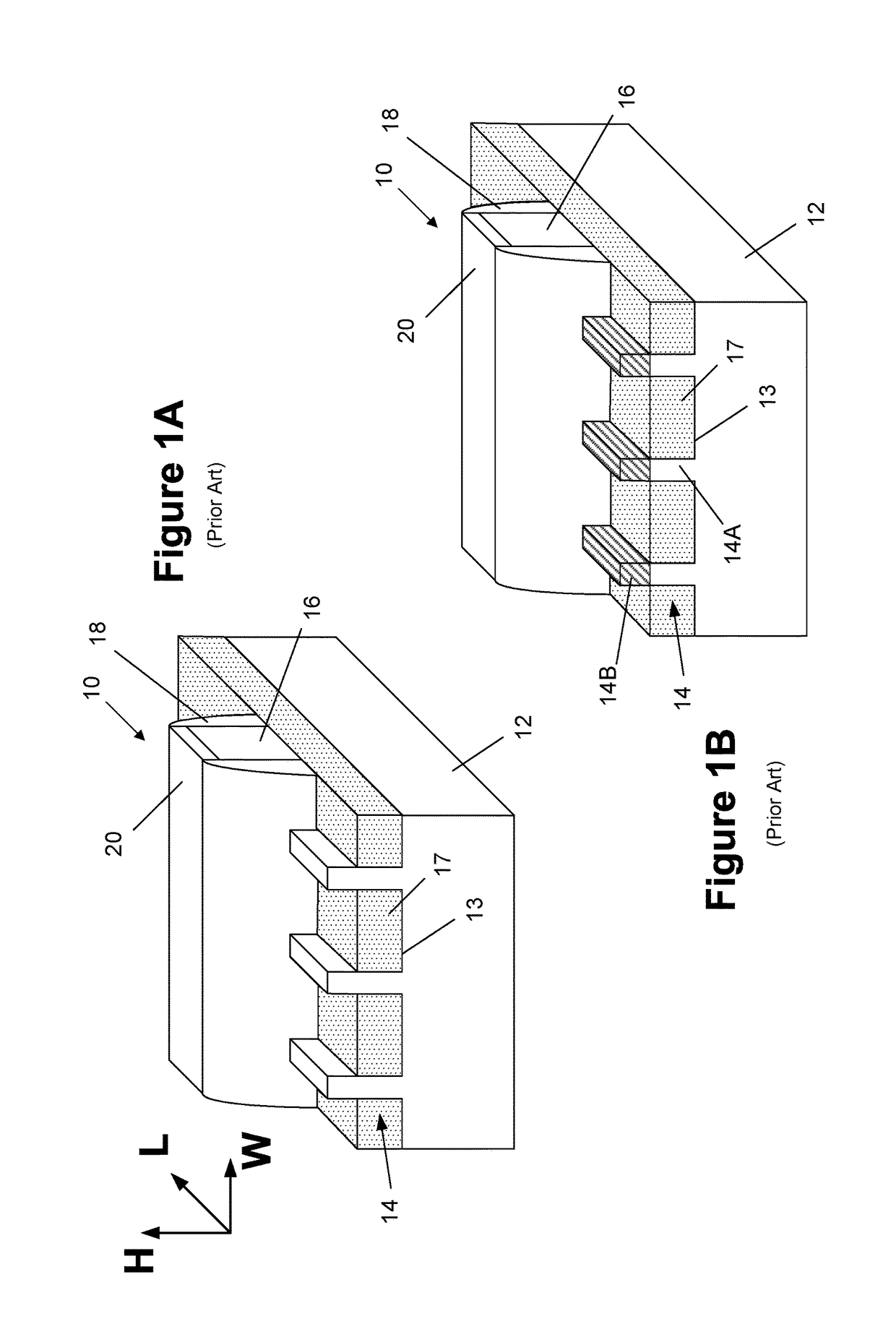

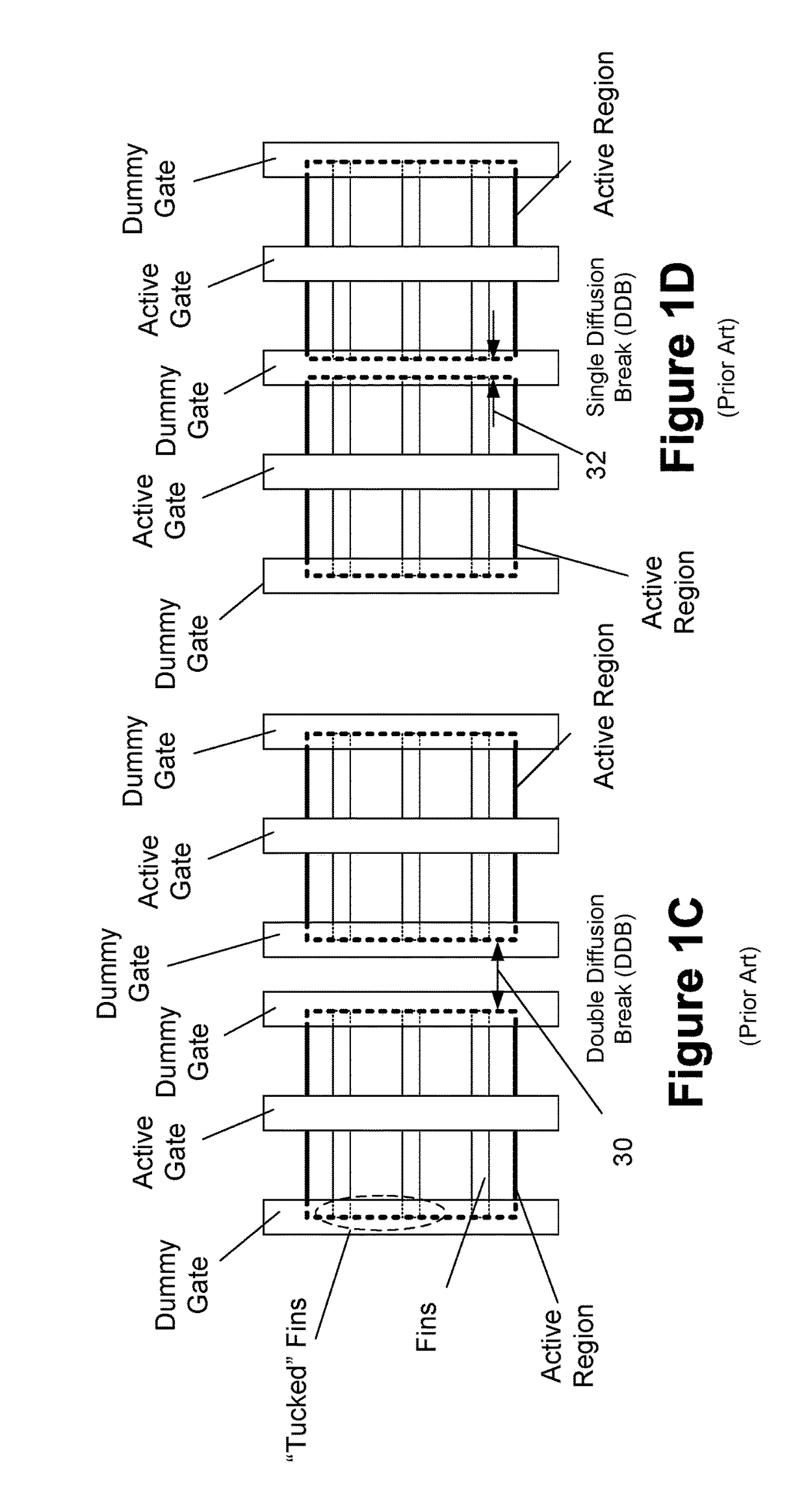

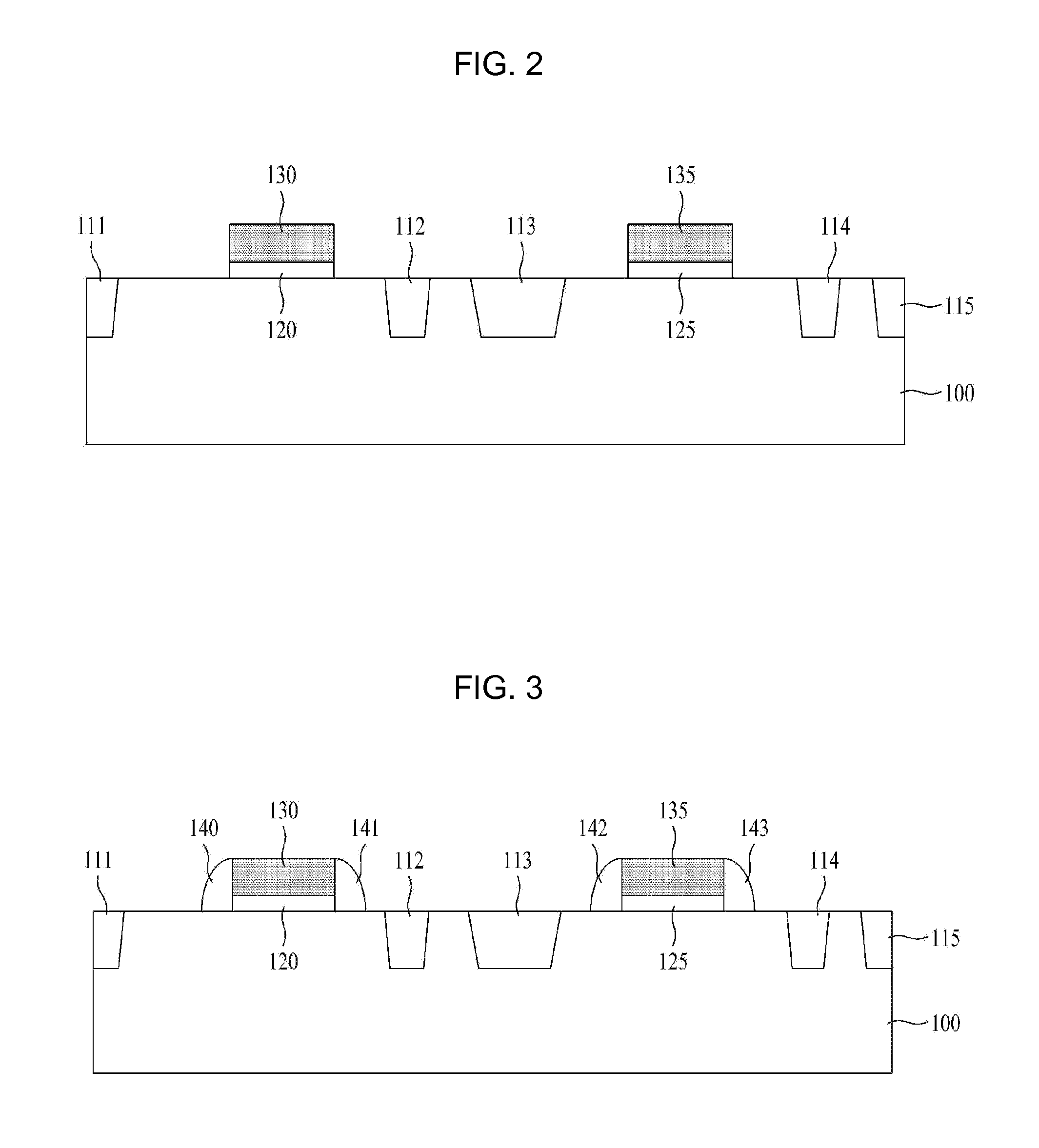

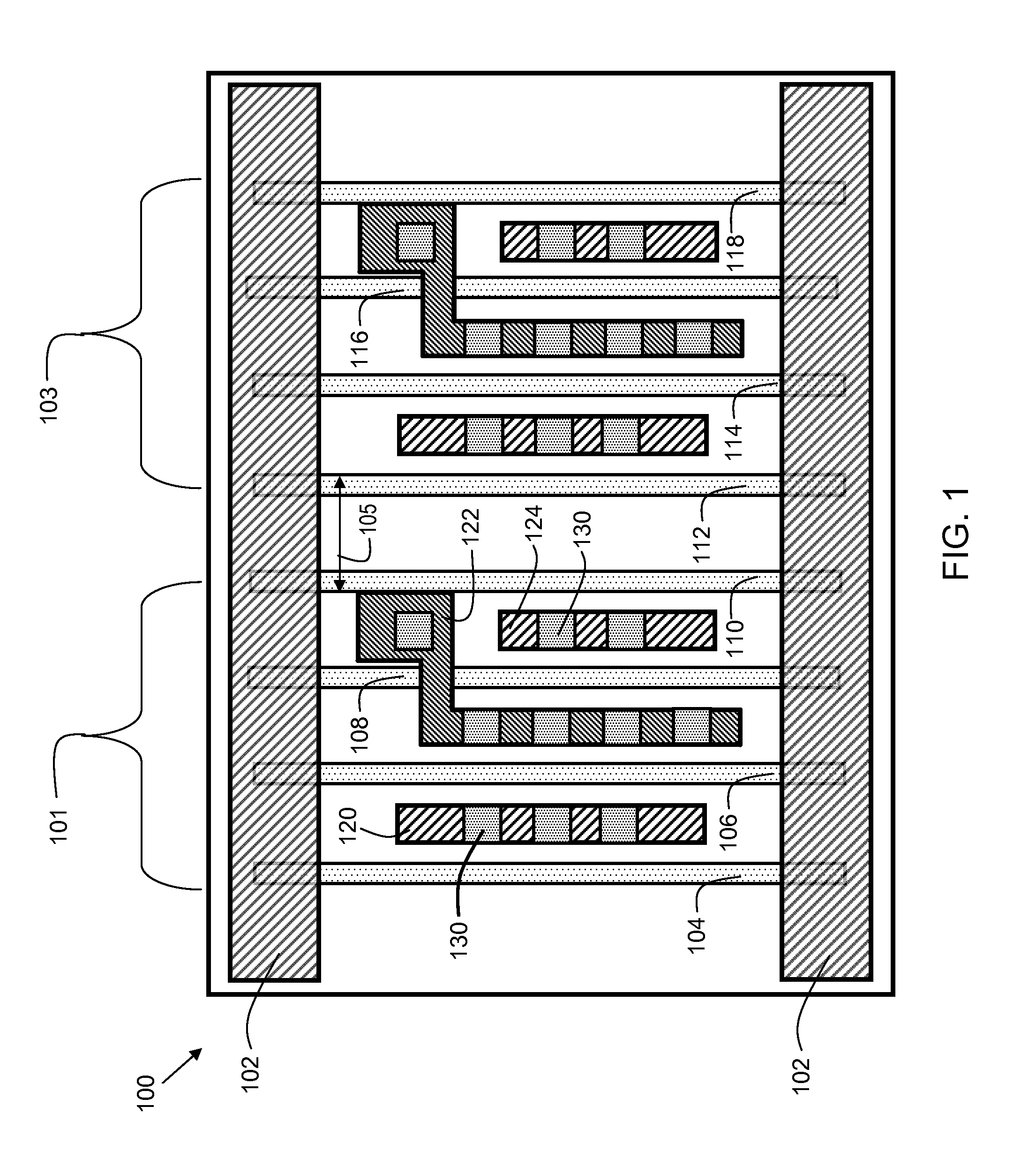

Methods of forming single and double diffusion breaks on integrated circuit products comprised of FinFET devices and the resulting products

ActiveUS9412616B1Well formedSolid-state devicesSemiconductor/solid-state device manufacturingDouble diffusionIntegrated circuit layout

One illustrative method disclosed herein includes, among other things, forming a multi-layer patterned masking layer comprised of first and second layers of material and first and second openings that extend through both of the first and second layers of material, wherein the first opening is positioned above a first area of the substrate where the DDB isolation structure will be formed and the second opening is positioned above a second area of the substrate where the SDB isolation structure will be formed. The method also includes performing a first process operation through the first opening to form the DDB isolation structure, performing a second process operation to remove the second layer of material and to expose the first opening in the first layer of material, and performing a third process operation through the second opening to form the SDB isolation structure.

Owner:GLOBALFOUNDRIES US INC

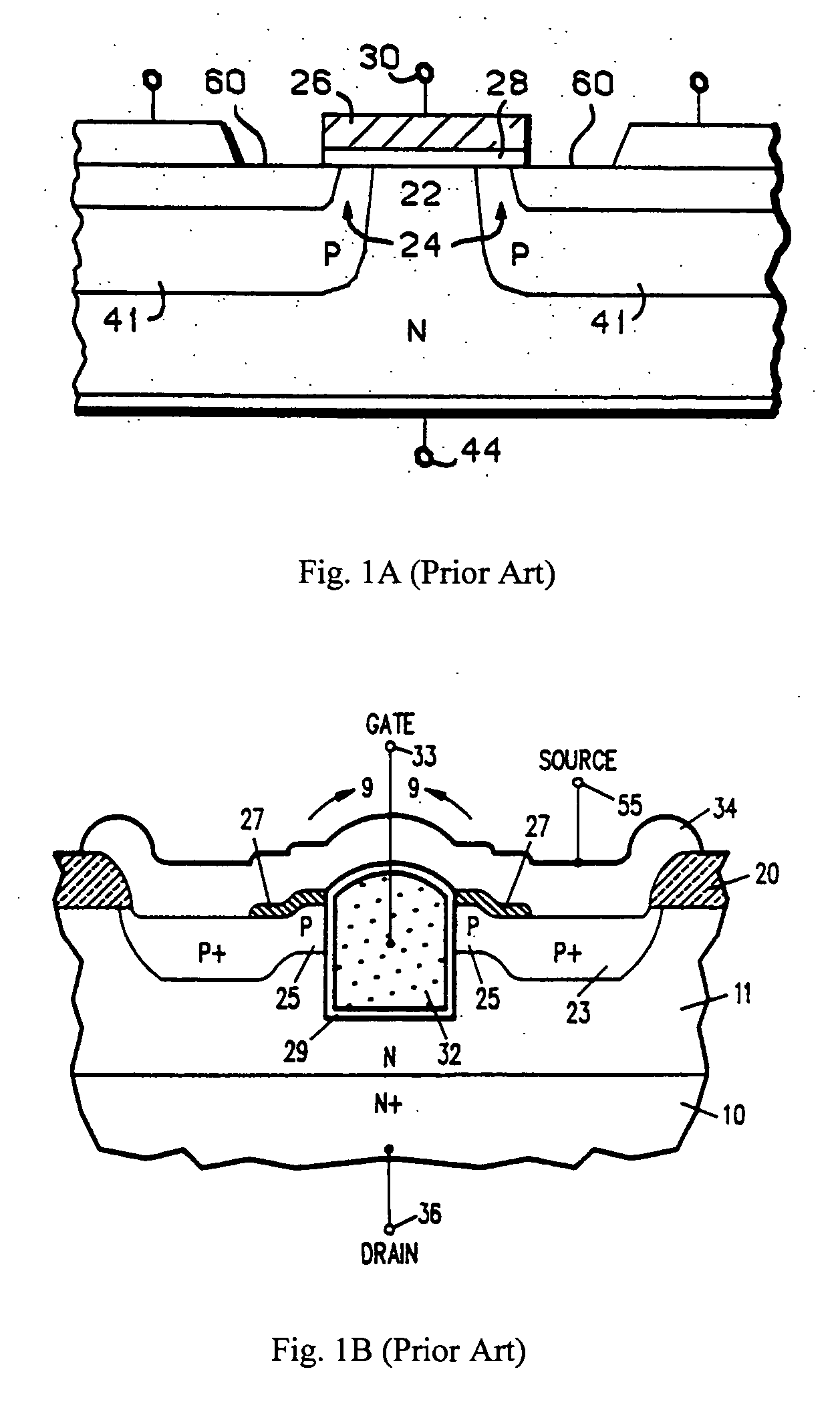

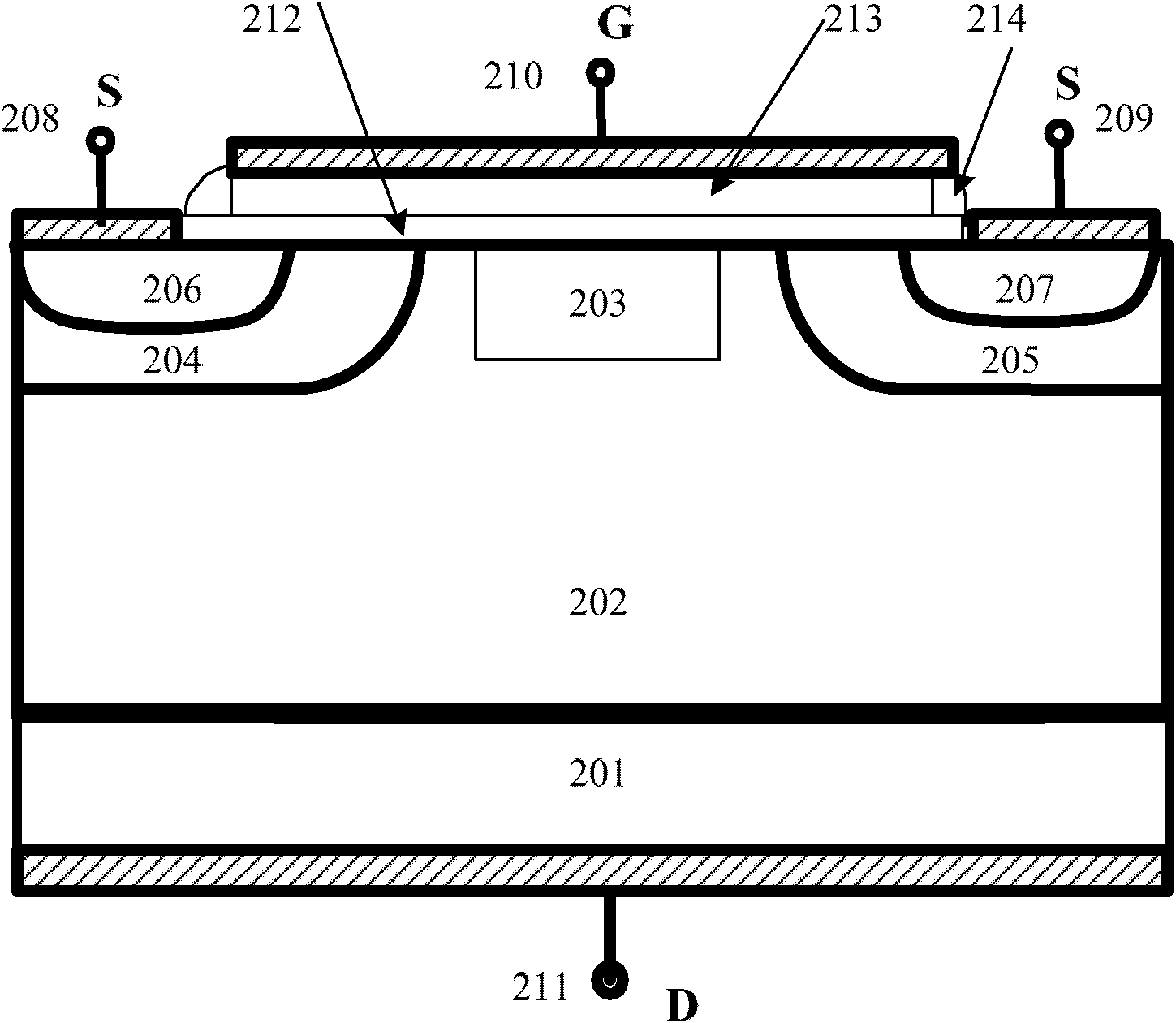

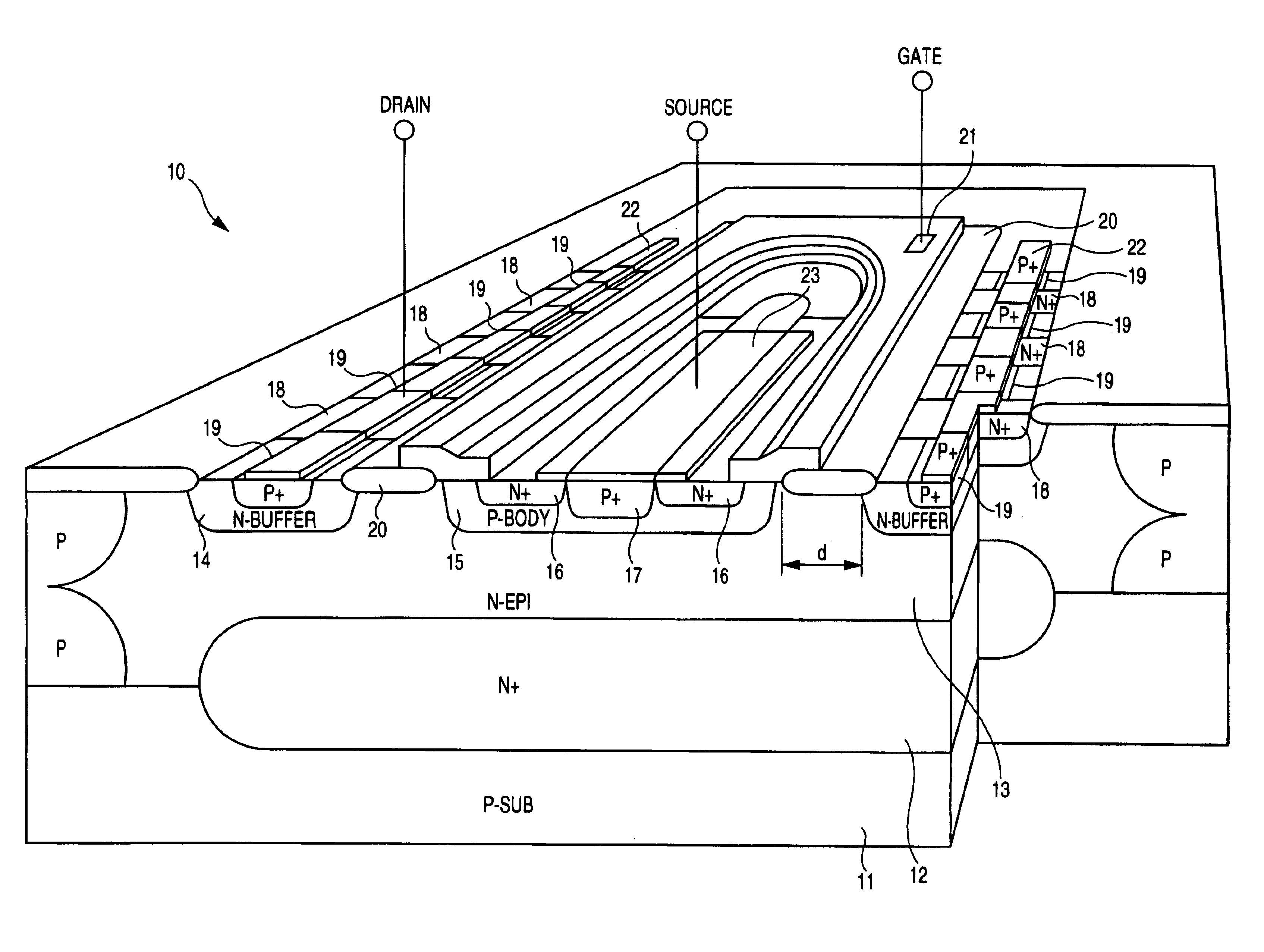

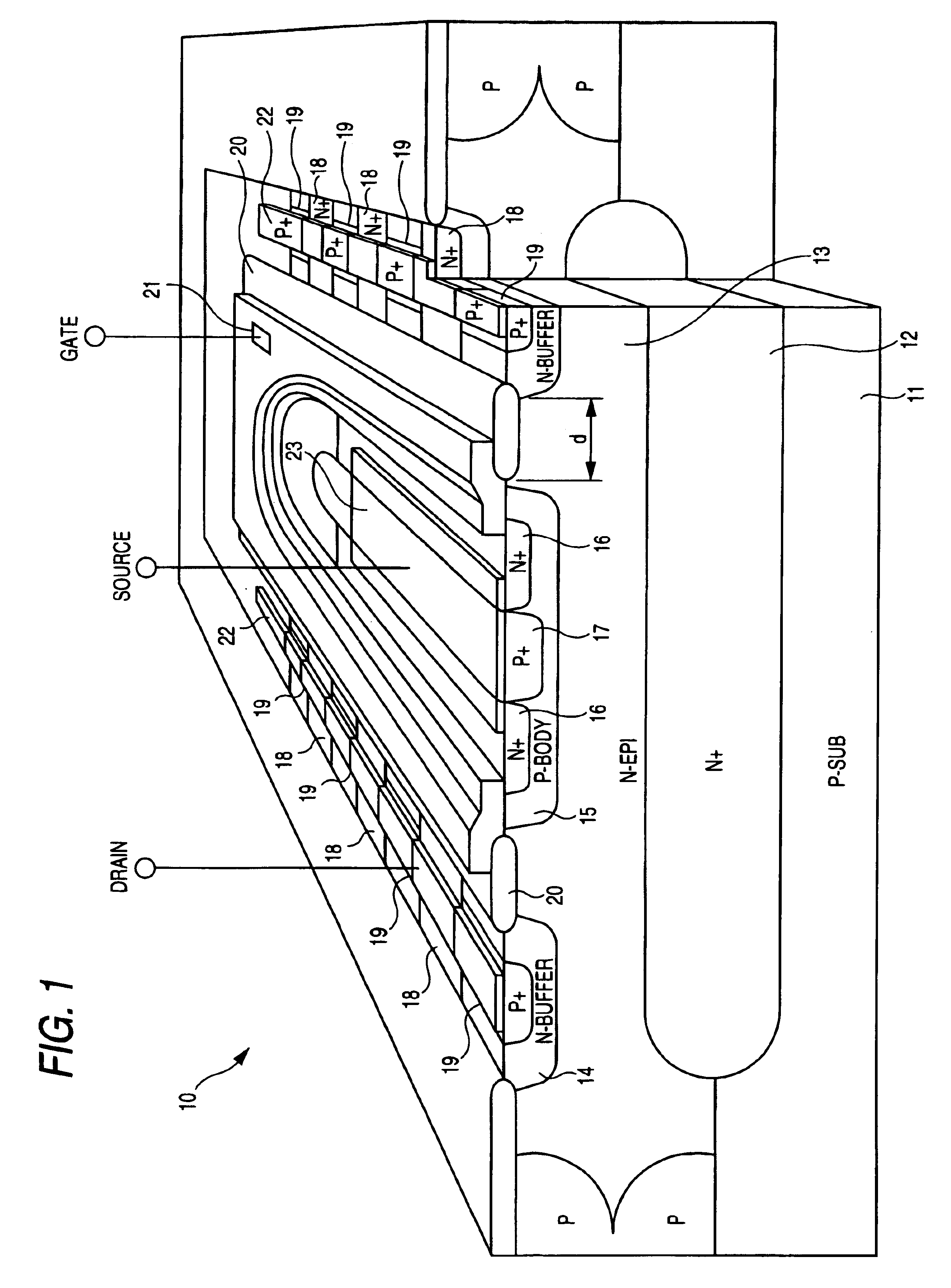

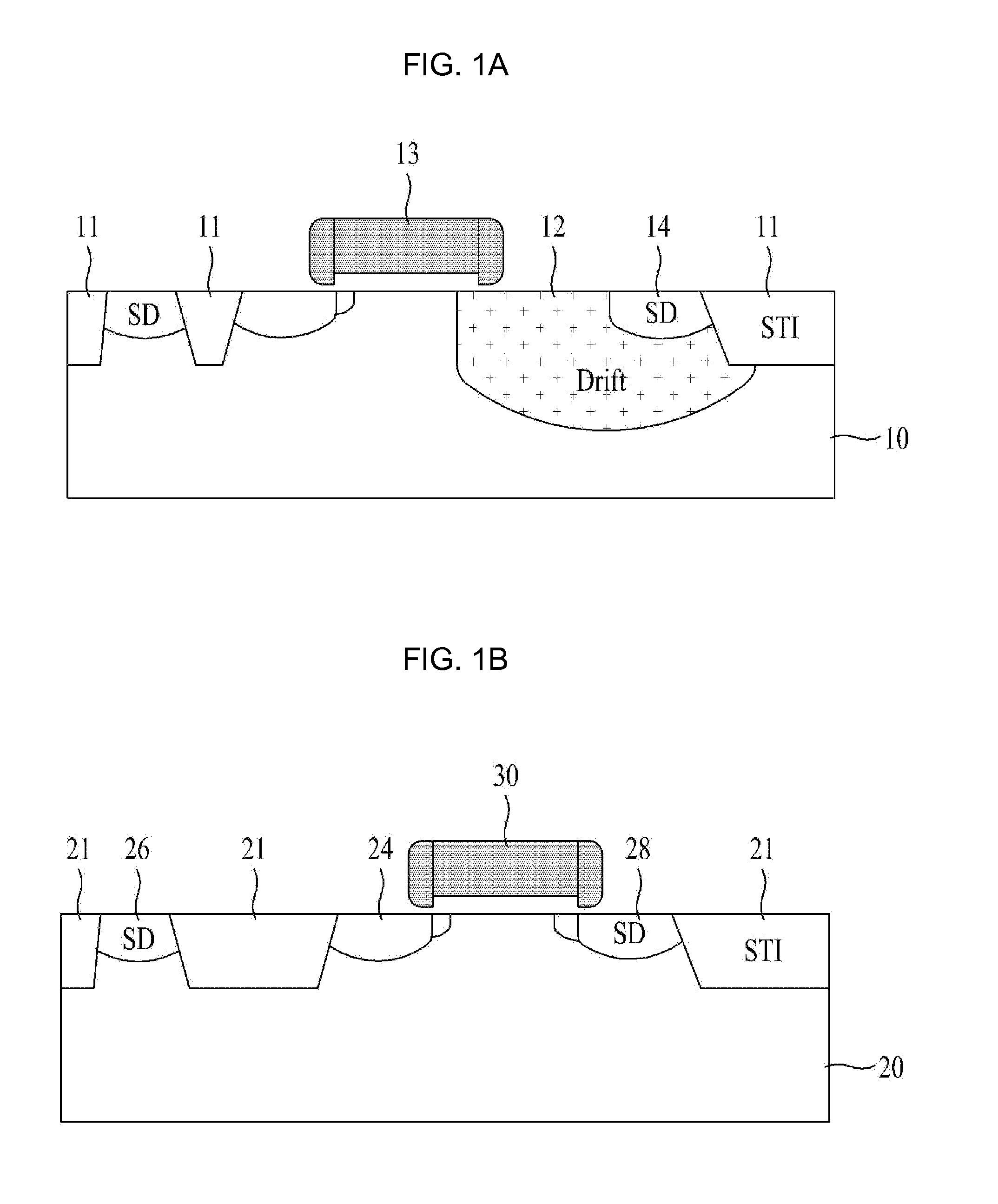

Method of fabrication and device configuration of asymmetrical DMOSFET with Schottky barrier source

ActiveUS20070187751A1Much-reduced contact resistanceTransistorSemiconductor/solid-state device detailsInsulation layerSchottky barrier

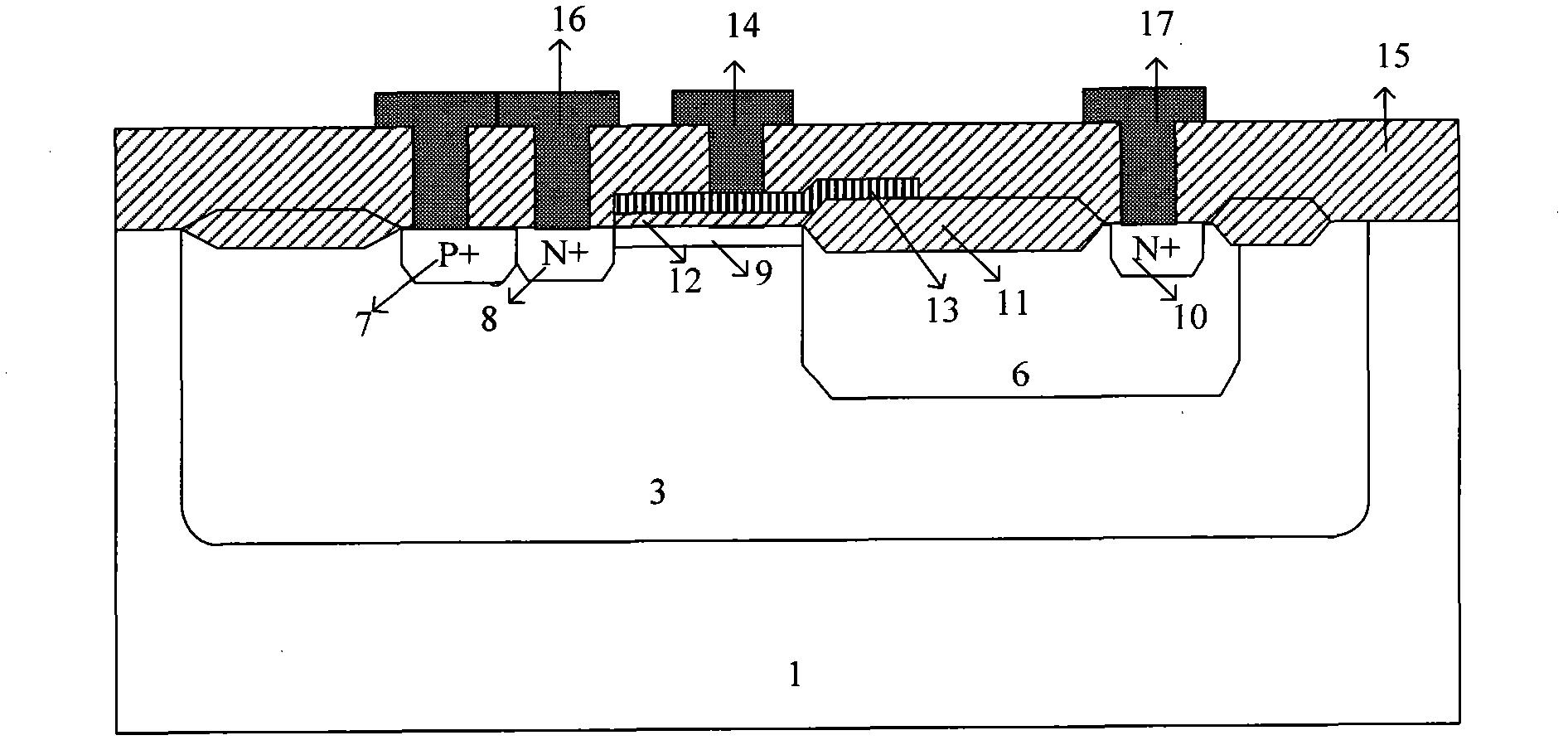

A trenched semiconductor power device includes a trenched gate insulated by a gate insulation layer and surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a semiconductor substrate. The source region surrounding the trenched gate includes a metal of low barrier height to function as a Schottky source. The metal of low barrier height further may include a PtSi or ErSi layer. In a preferred embodiment, the metal of low barrier height further includes an ErSi layer. The metal of low barrier height further may be a metal silicide layer having the low barrier height. A top oxide layer is disposed under a silicon nitride spacer on top of the trenched gate for insulating the trenched gate from the source region. A source contact disposed in a trench opened into the body region for contacting a body-contact dopant region and covering with a conductive metal layer such as a Ti / TiN layer. In a preferred embodiment, the semiconductor power device constitutes an asymmetrical double diffusion metal oxide semiconductor field effect transistor (DMOSFET) device.

Owner:ALPHA & OMEGA SEMICON LTD

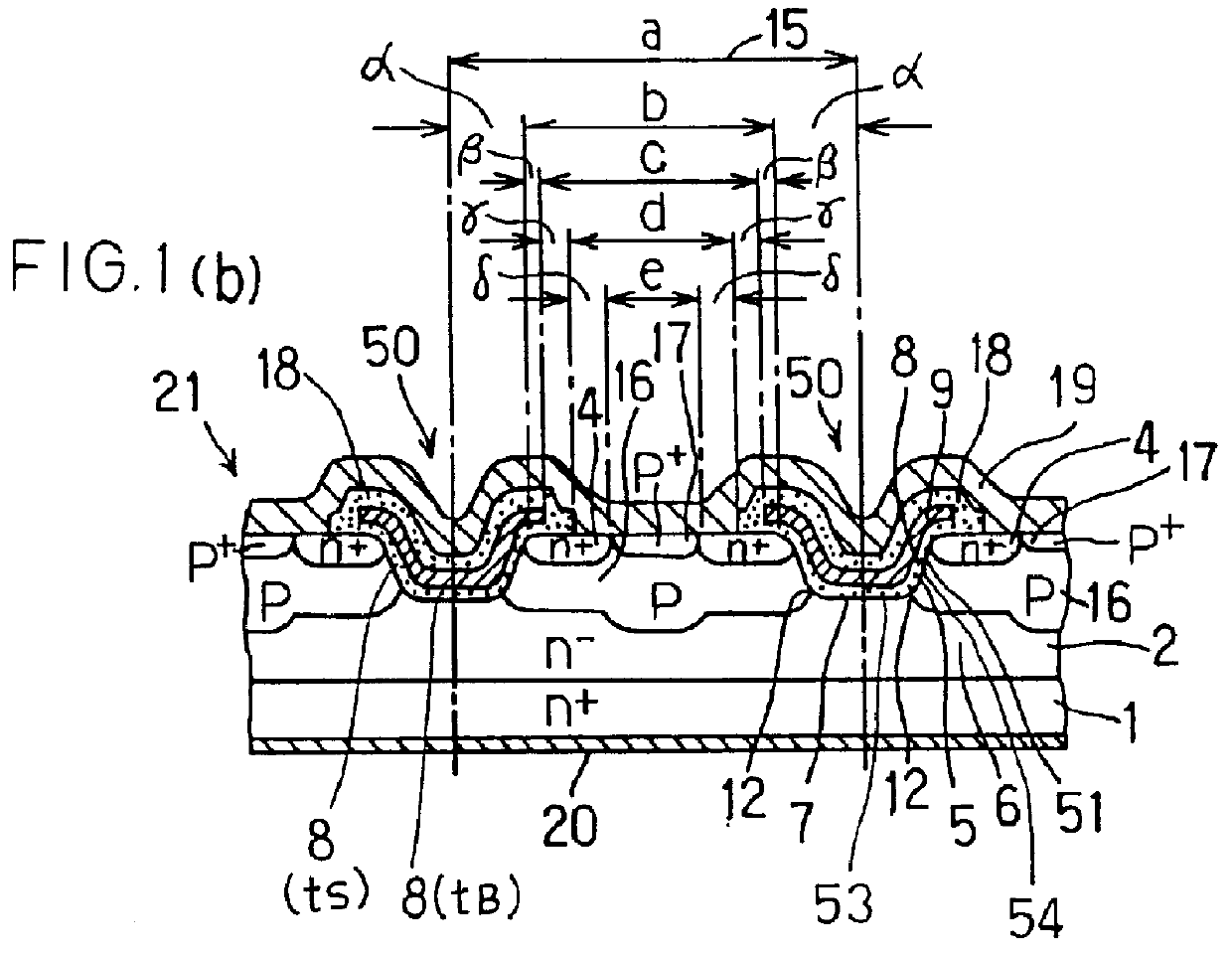

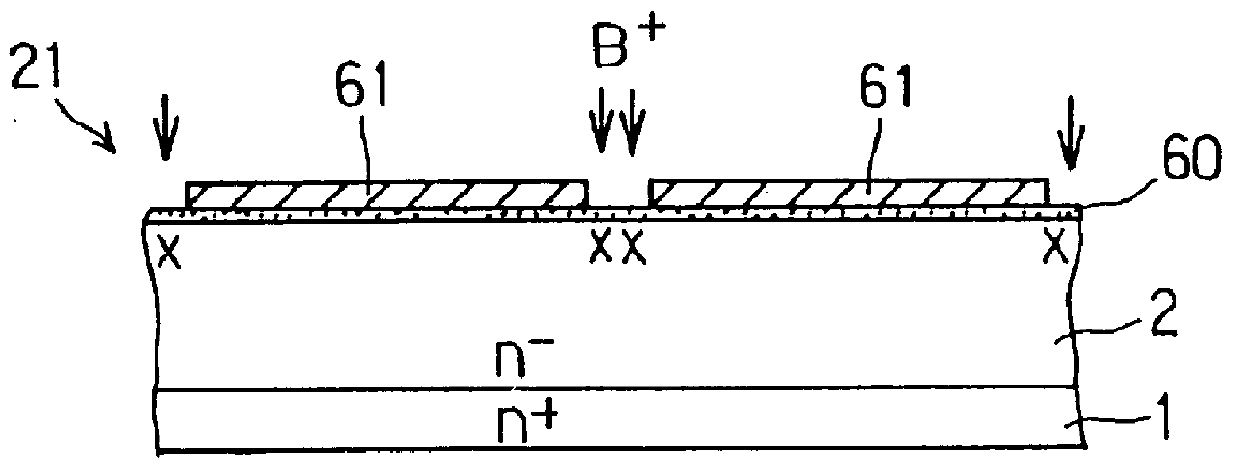

Production method of a vertical type MOSFET

InactiveUS6015737AMade smallSmall on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionLOCOS

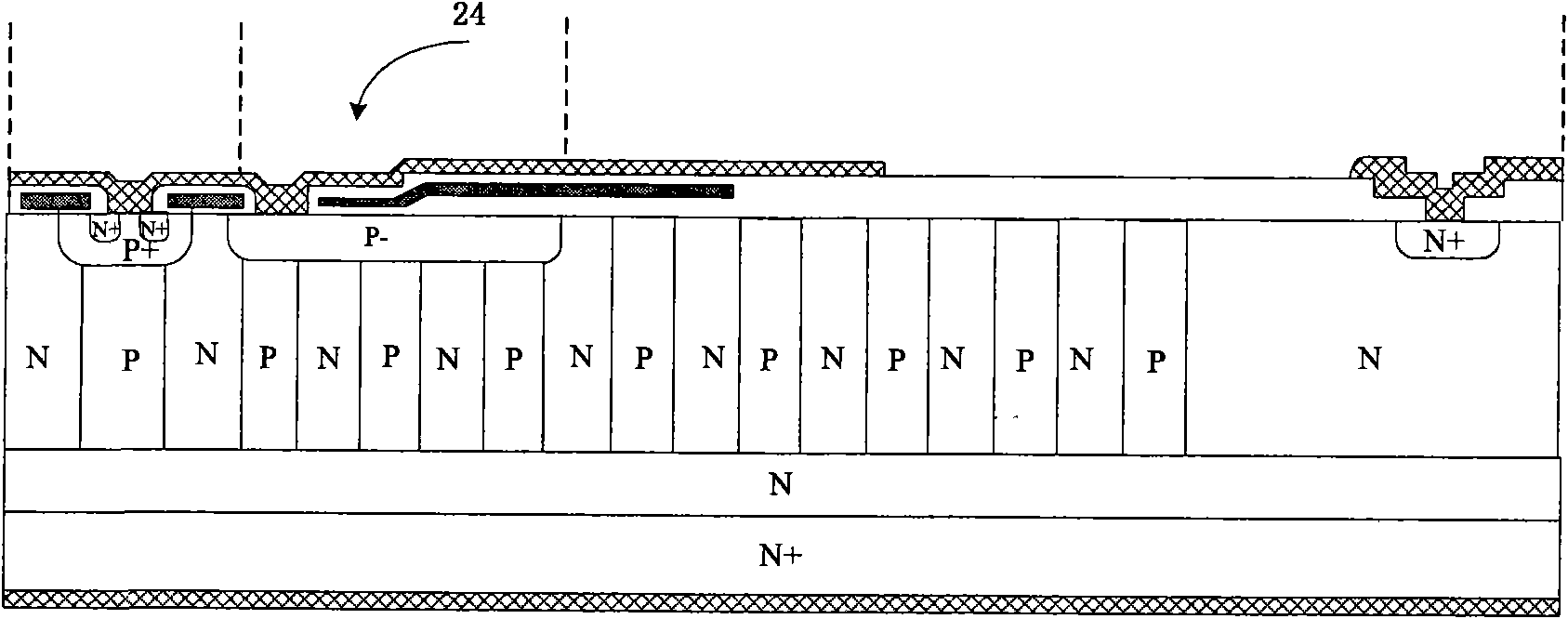

A vertical type power MOSFET remarkably reduces its ON-resistance per area. A substantial groove formation in which a gate structure is constituted is performed beforehand utilizing the LOCOS method before the formation of a p-type base layer and an n+-type source layer. The p-type base layer and the n+-type source layer are then formed by double diffusion in a manner of self-alignment with respect to a LOCOS oxide film, simultaneously with which channels are set at sidewall portions of the LOCOS oxide film. Thereafter the LOCOS oxide film is removed to provide a U-groove so as to constitute the gate structure. Namely, the channels are set by the double diffusion of the manner of self-alignment with respect to the LOCOS oxide film, so that the channels, which are set at the sidewall portions at both sides of the groove, provide a structure of exact bilateral symmetry, there is no positional deviation of the U-groove with respect to the base layer end, and the length of the bottom face of the U-groove can be made minimally short. Therefore, the unit cell size is greatly reduced, and the ON-resistance per area is greatly decreased.

Owner:DENSO CORP

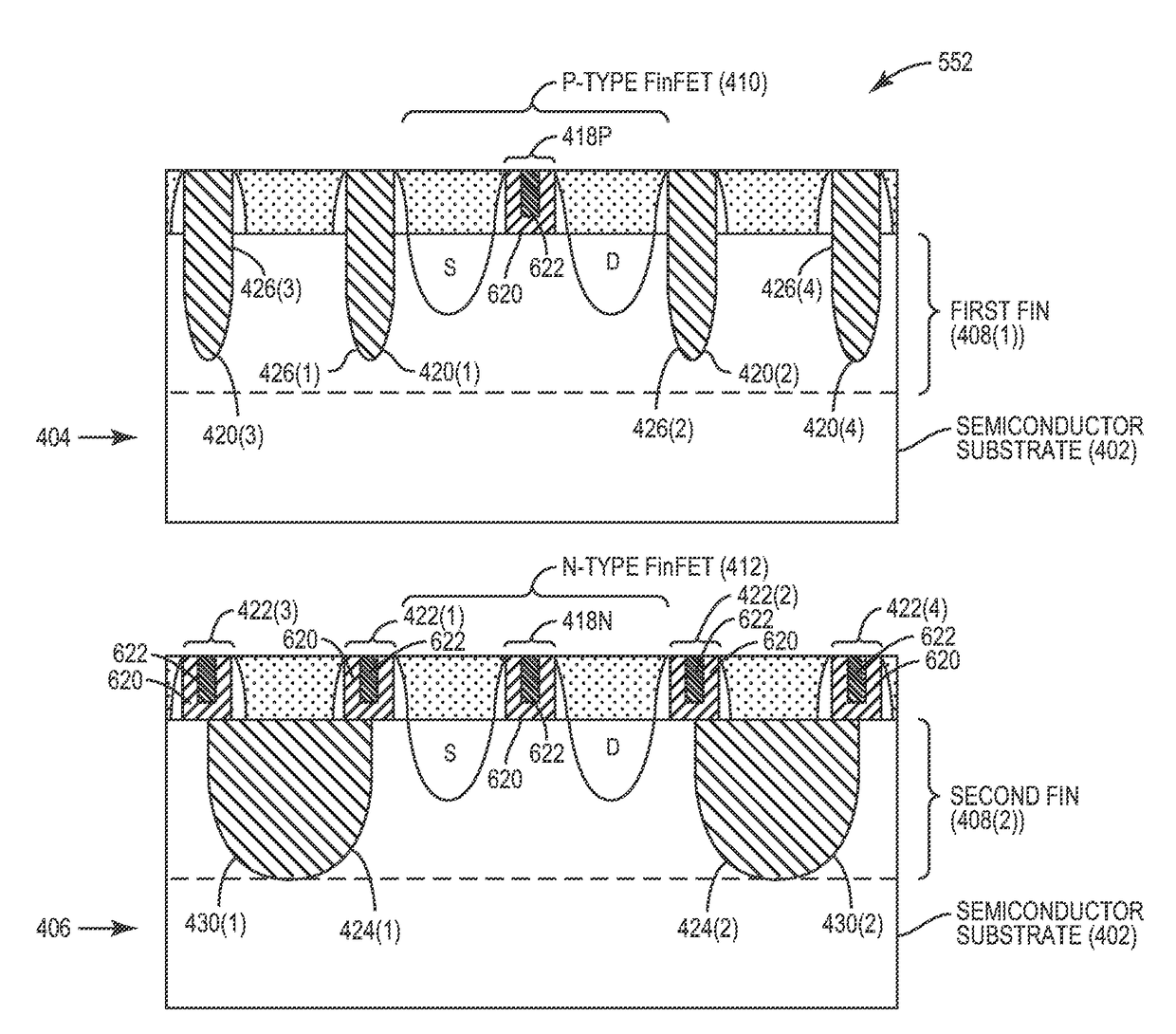

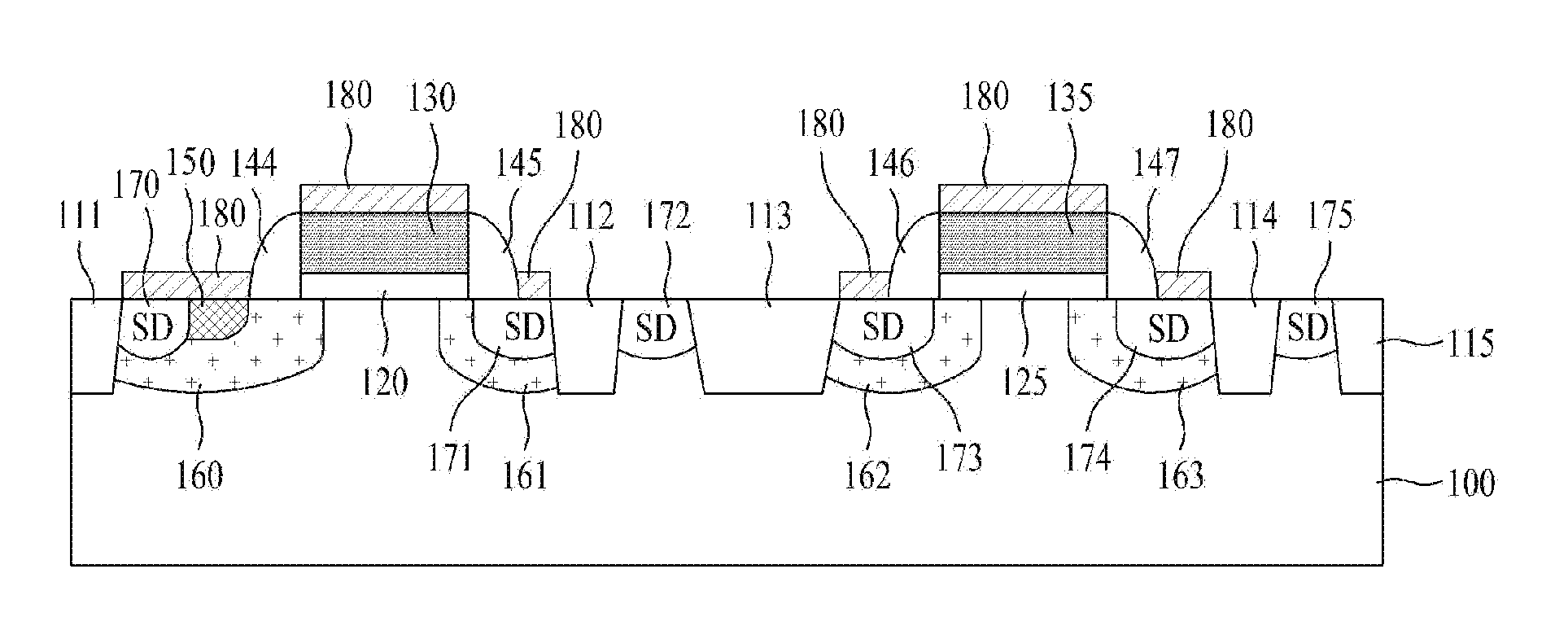

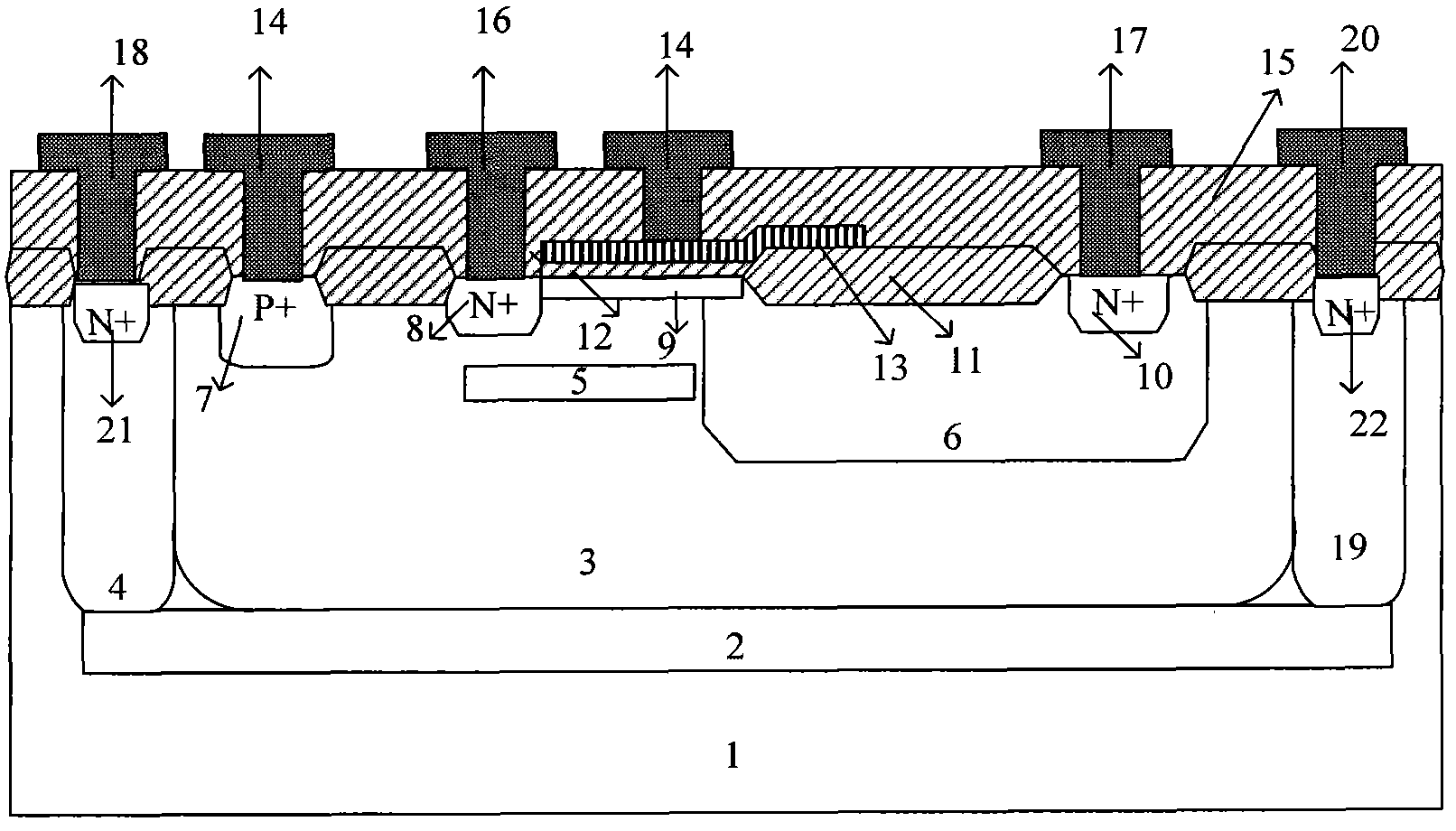

Single and double diffusion breaks on integrated circuit products comprised of finfet devices

One illustrative integrated circuit product disclosed herein includes, among other things, a plurality of FinFET devices, each of which comprises a gate structure comprising a high-k gate insulation material and at least one layer of metal, a single diffusion break (SDB) isolation structure positioned in a first trench defined in a semiconductor substrate between first and second active regions, the SDB isolation structure comprising the high-k insulating material and the at least one layer of metal, and a double diffusion break (DDB) isolation structure positioned in a second trench defined in a semiconductor substrate between third and fourth active regions, the DDB isolation structure comprising a first insulating material that substantially fills the second trench.

Owner:GLOBALFOUNDRIES US INC

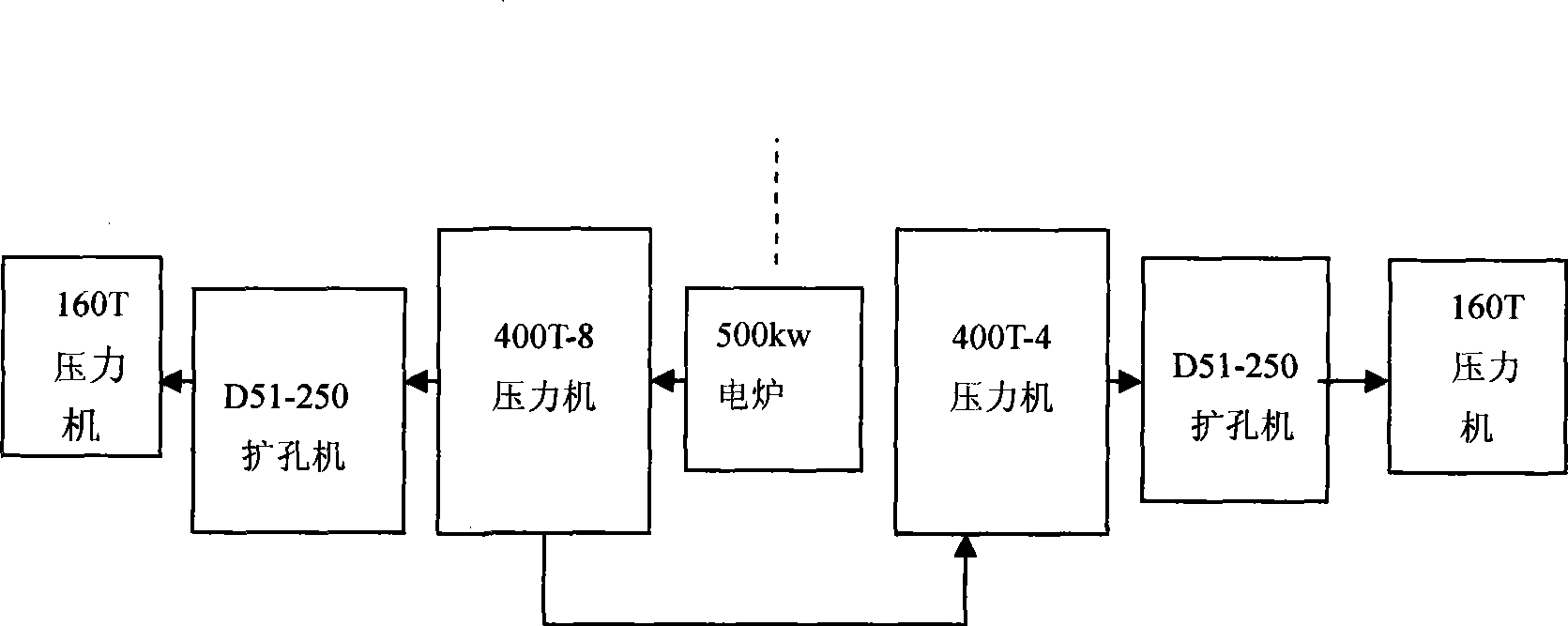

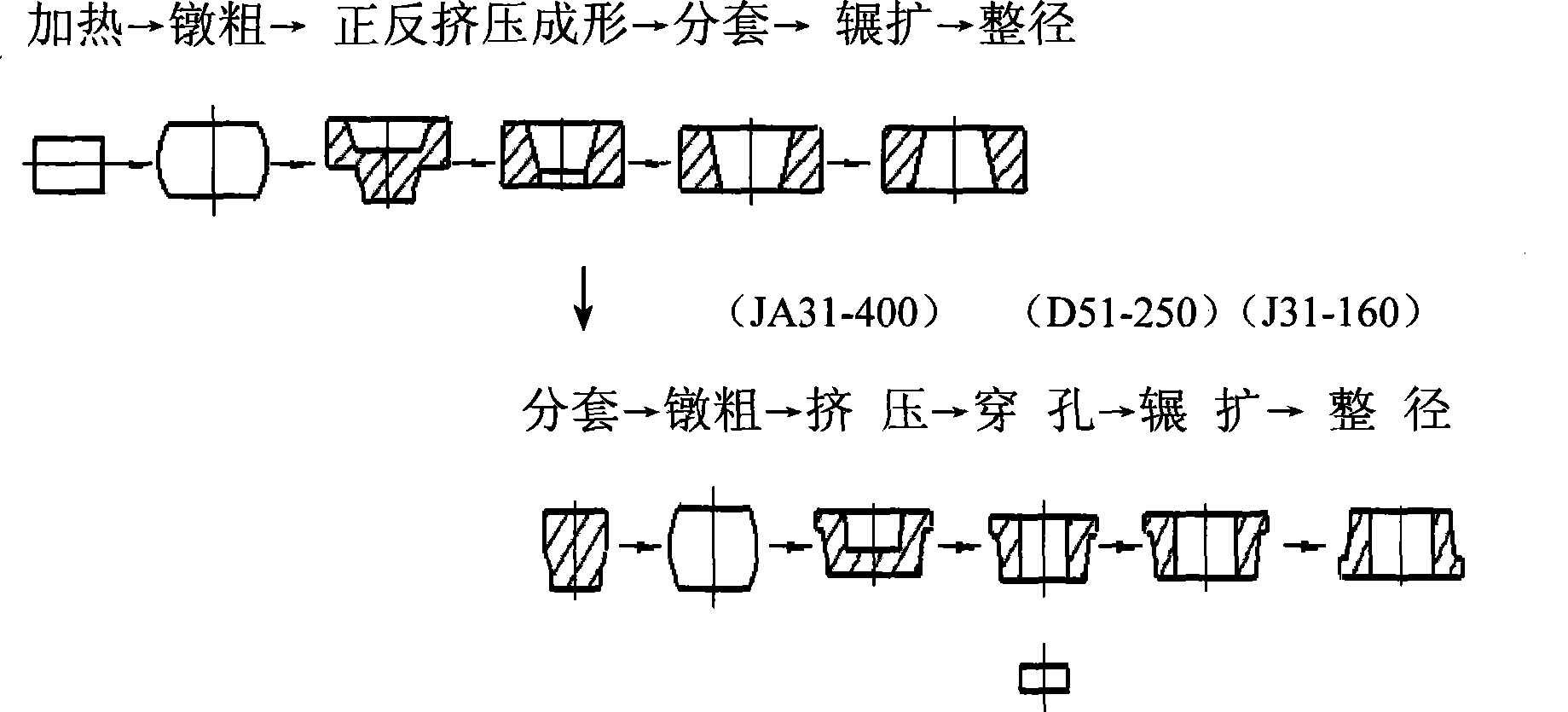

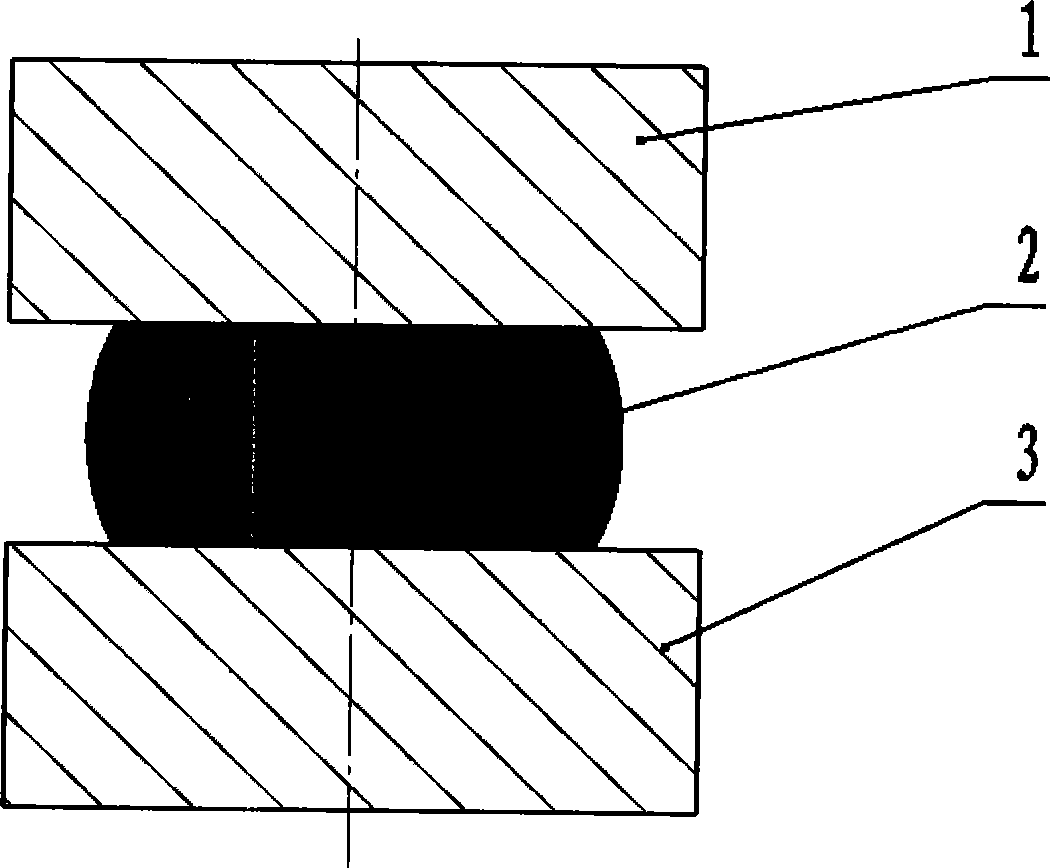

Tapered roller bearing ring double extension-sleeve forging technique

ActiveCN101417379AReduce labor intensityIncrease profitMetal rollingHigh volume manufacturingDouble diffusion

The invention relates to a double diffusion intussusception forge technique of a bearing ring of a tapered roller, belongs to the technical field of forging of the bearing ring of the tapered roller and mainly aims at solving the problems that the existing ring forging technique is not suitable for various bearing rings of the large and medium size tapered rollers. The technique is mainly characterized in that: (1) a GCr15 steel material section is heated to 1050 DEG C on a medium frequency induction furnace, then upset on a press, extruded backward and forward, formed, sheathed respectively and is separated into an outer sleeve and an inner sleeve or a small outer sleeve blank; (2) the outer sleeve blank is ring-rolled on a ring rolling machine, then reeled on the press and cooled into an outer sleeve forged parts of a bearing; and (3) the inner sleeve or the small outer sleeve blank is placed on the press, upset again, extruded and punched and then a ring part is obtained which is ring-rolled on the ring rolling machine, then an inner sleeve hot forged part after being ring-rolled is reeled on the press and then cooled to obtain the inner sleeve forged part of the bearing. The technique is mainly used for manufacturing the inner and outer ring forged parts of the bearing of the large and medium size tapered roller with various types, small batch or large batch.

Owner:XIANGYANG AUTOMOBILE BEARING CO LTD

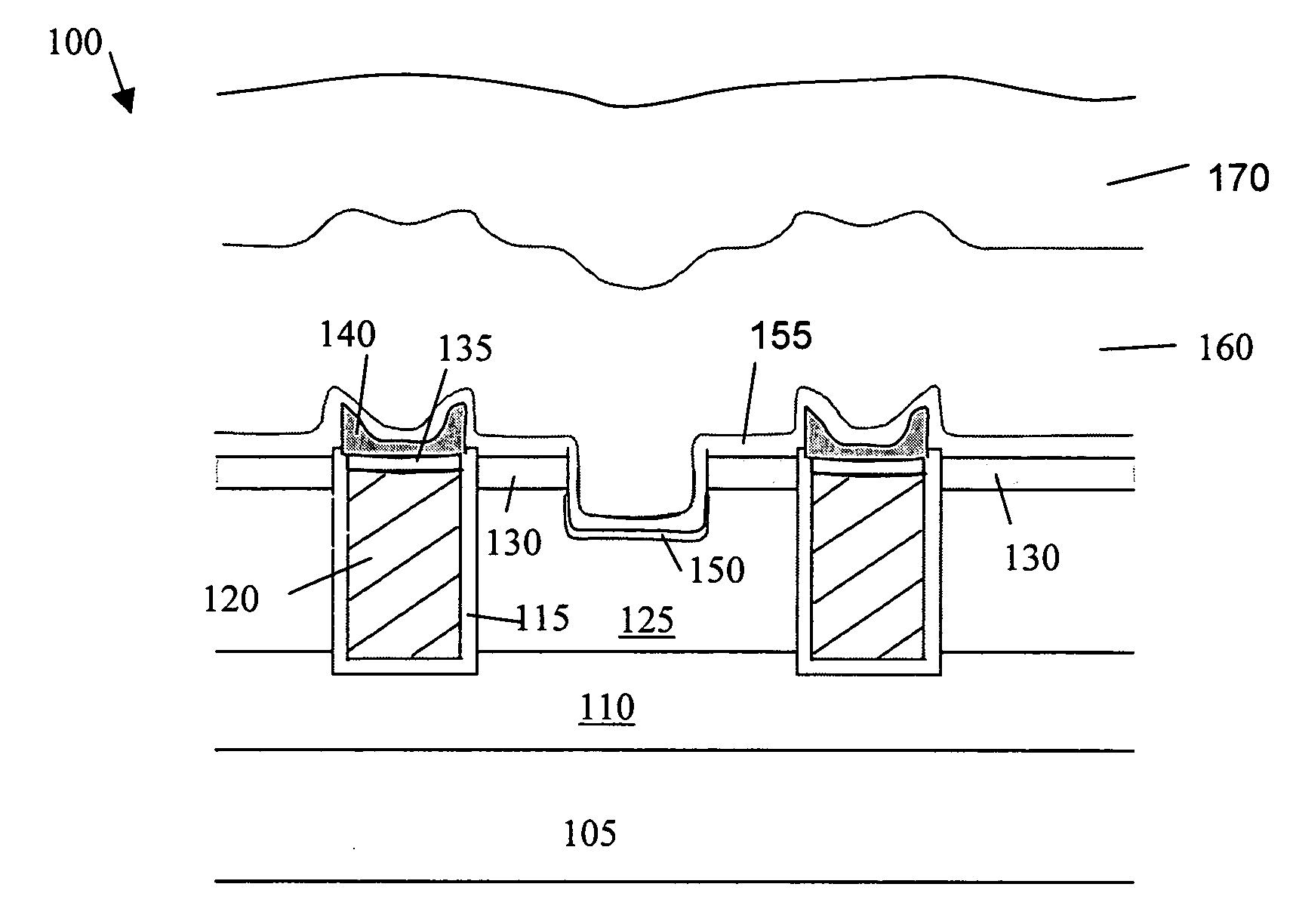

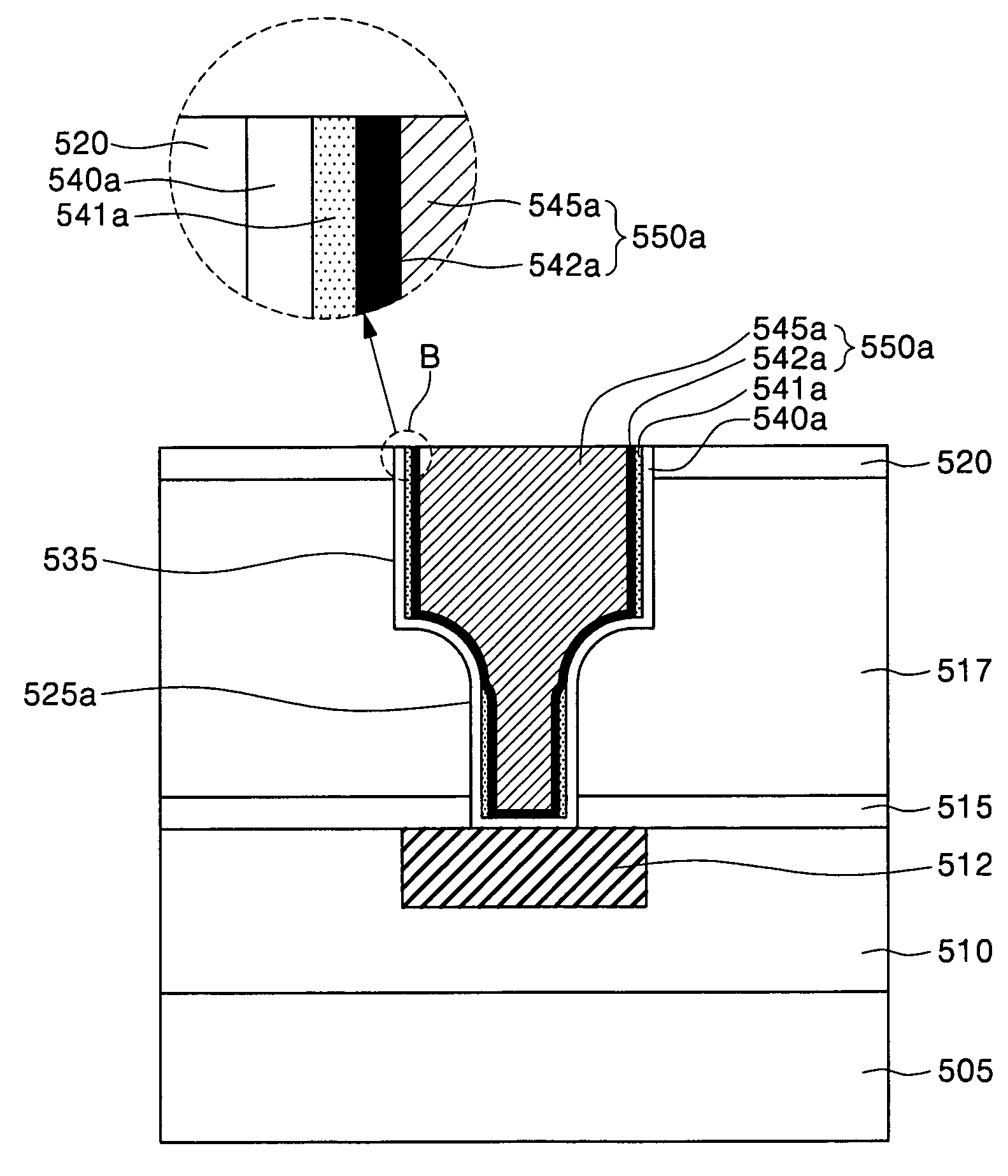

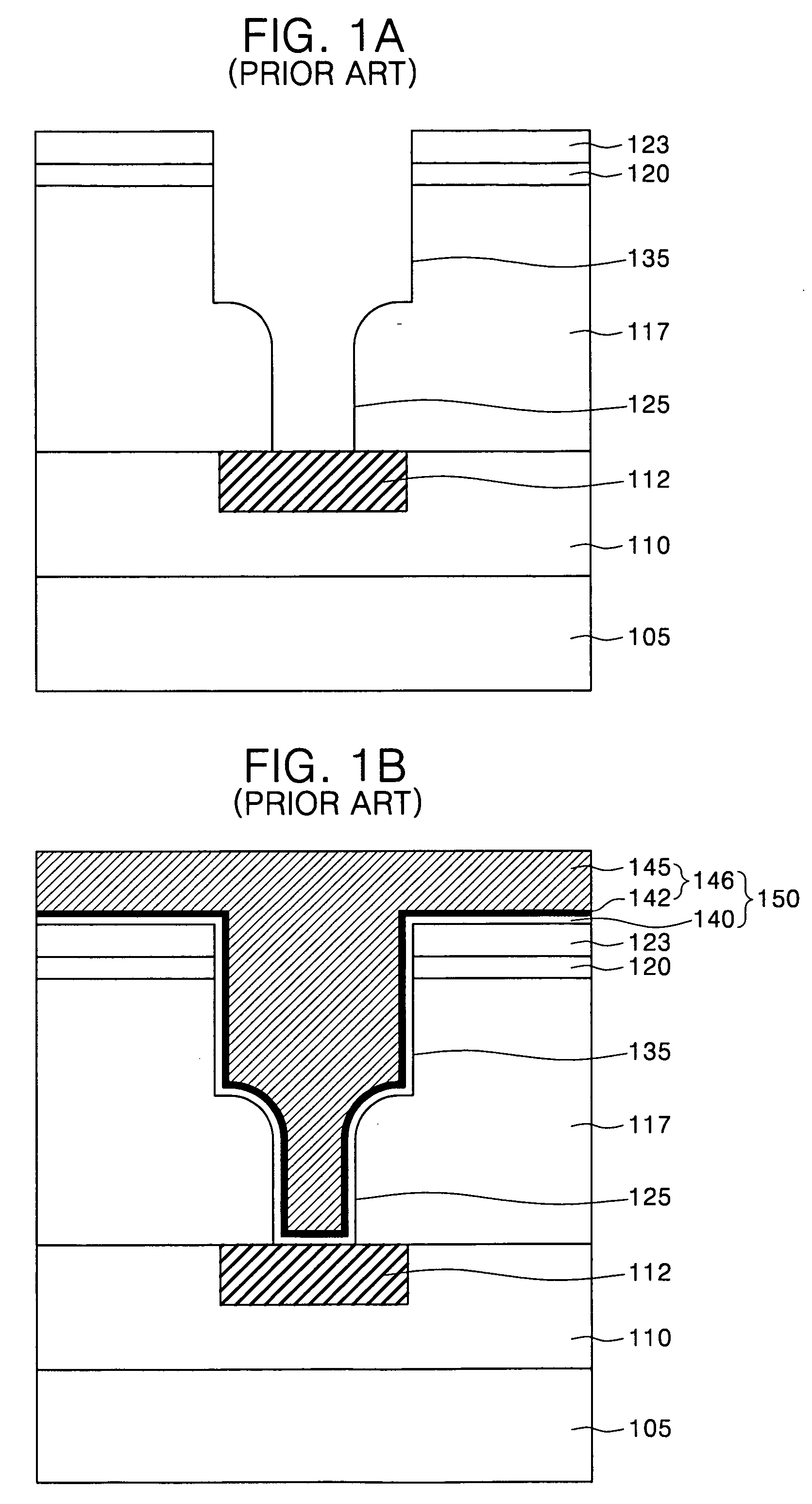

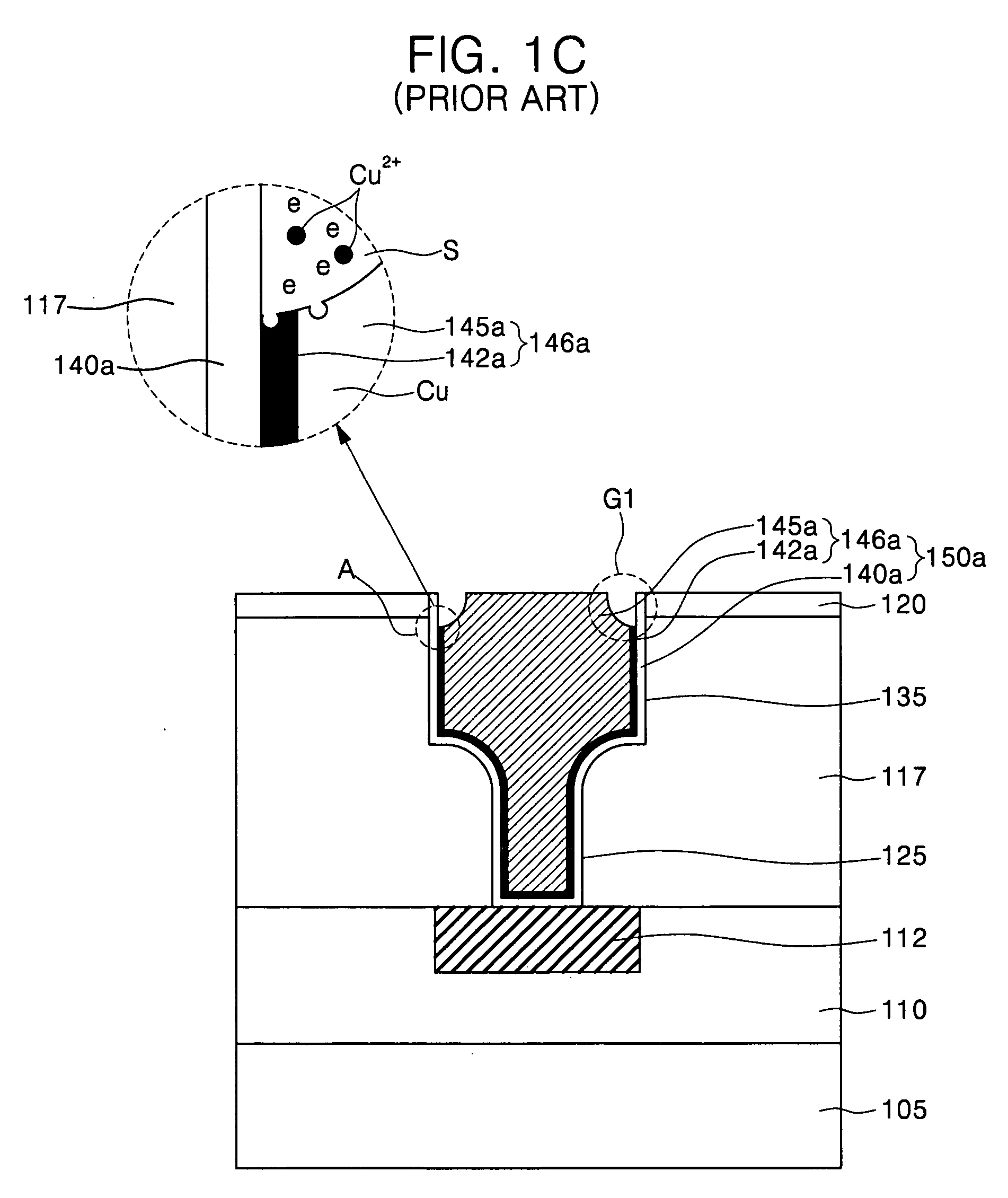

Interconnection structure having double diffusion barrier layer and method of fabricating the same

InactiveUS20060151887A1Semiconductor/solid-state device detailsSolid-state devicesDouble diffusionEngineering

An interconnection structure and a method of fabricating the same are provided. The interconnection structure includes an interlayer insulating layer having a structure comprising a via hole structure or a trench-shaped line structure. A conformal metal diffusion barrier layer is disposed inside the via hole structure or the trench-shaped line structure of the interlayer insulating layer. An insulating diffusion barrier spacer is disposed to cover the metal diffusion barrier layer on the sidewalls of the via hole structure or the trench-shaped line structure of the interlayer insulating layer. In addition, a copper interconnection is disposed to fill the inside of the via hole structure or the trench-shaped line structure of the interlayer insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

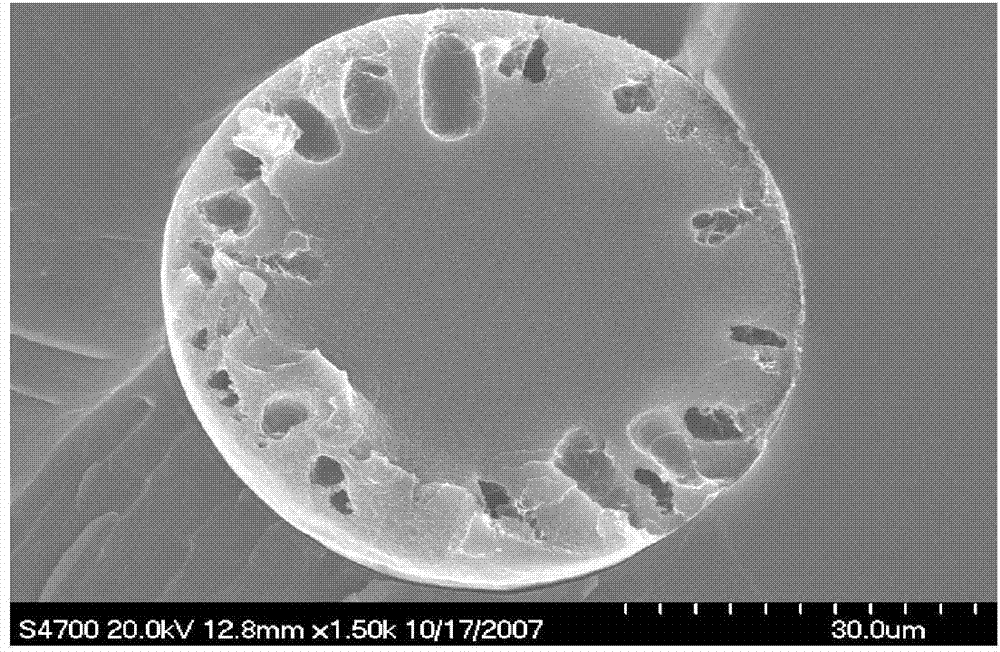

Polyvinylidene fluoride hollow fiber membrane and preparation method thereof

InactiveCN101954248AImprove anti-pollution performanceGuaranteed high temperature performanceSemi-permeable membranesFibre treatmentChemical industryDouble diffusion

The invention relates to a polyvinylidene fluoride hollow fiber membrane and a preparation method thereof, belonging to the field of chemical industry. The pore size of the membrane is 0.02-0.5 micrometers, the thickness is 0.2-0.5 millimeters, and the external diameter of membrane wires is 1-2 millimeters. A membrane making liquid comprises the following components in percentage by weight: 15-30% of polyvinylidene fluoride resin, 1-10% of hydrophilic polymer, 0.5-5% of functional polymer or polymer monomer, 0.1-5% of surfactant, 0.1-15% of inorganic or organic polymer pore-forming agent, 0.1-5% of nano additive and 40-71% of solvent. The preparation method of the polyvinylidene fluoride hollow fiber membrane comprises the following step of: effectively controlling the interfacial tension between the membrane making liquid and a solidifying liquid and the double diffusion permeation speed of the solidifying agent and the solution on the interface by properly adjusting the ratio of all components and using the surface moistening and dispersing actions of the surfactant, the dispersing and thickening actions of the pore-forming agent and the hydrophilic action of the hydrophilic substance. Thus, the hydrophilic polyvinylidene fluoride hollow fiber membrane with high permeability is prepared.

Owner:QINGDAO SEACON WATER SERVICE TECH

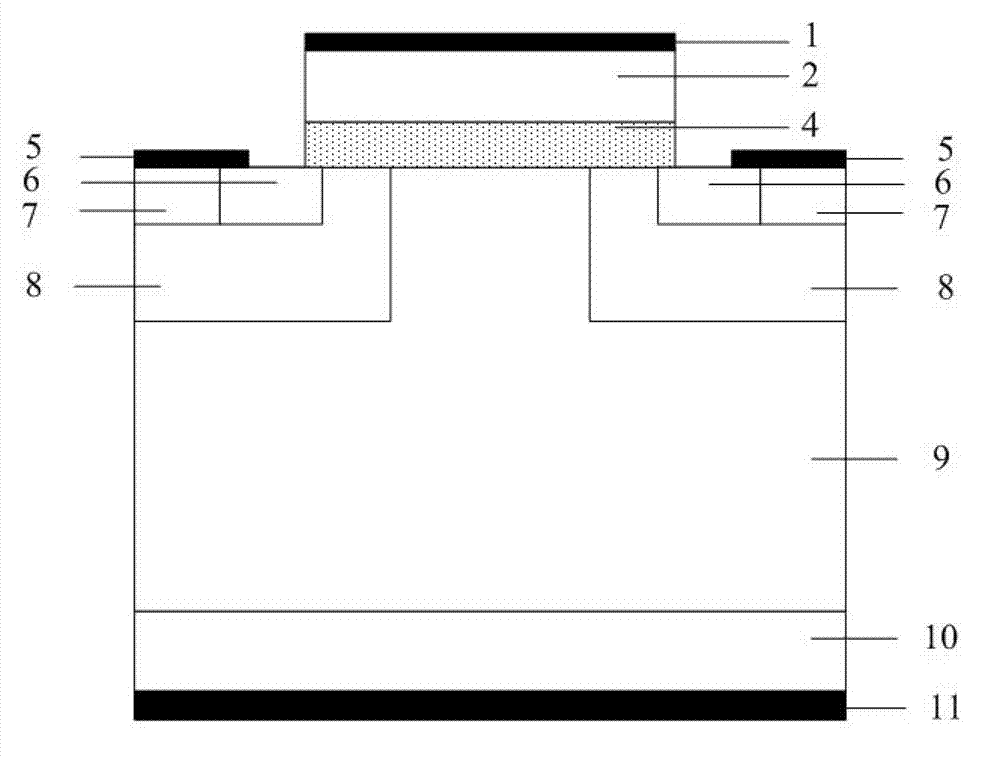

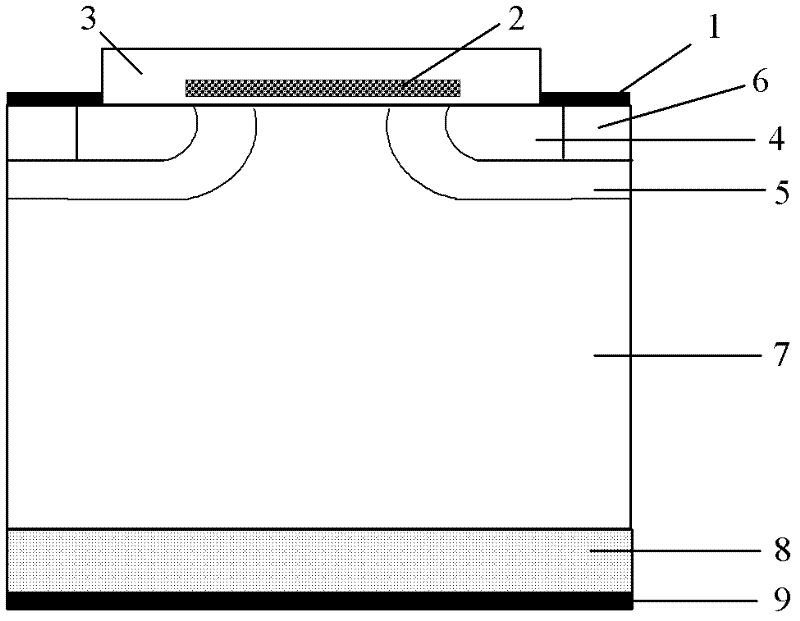

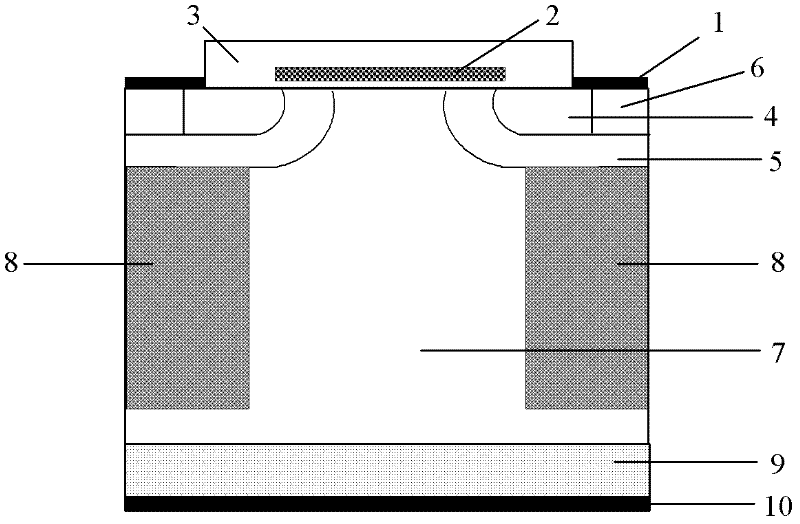

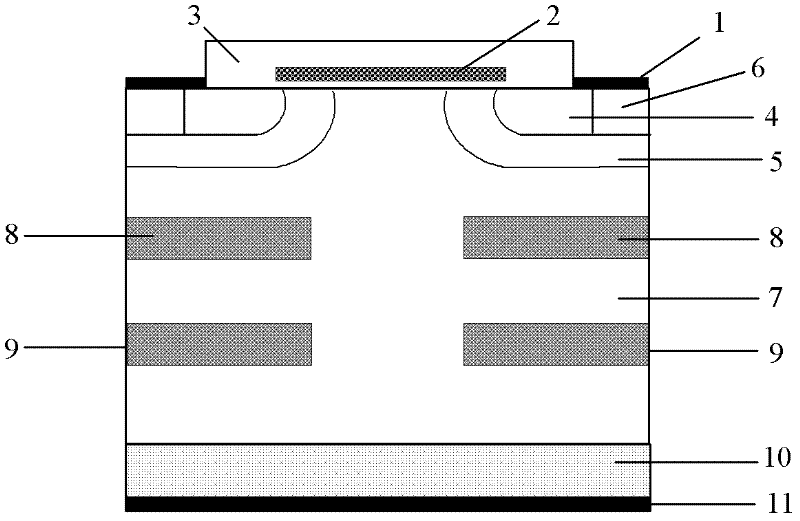

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

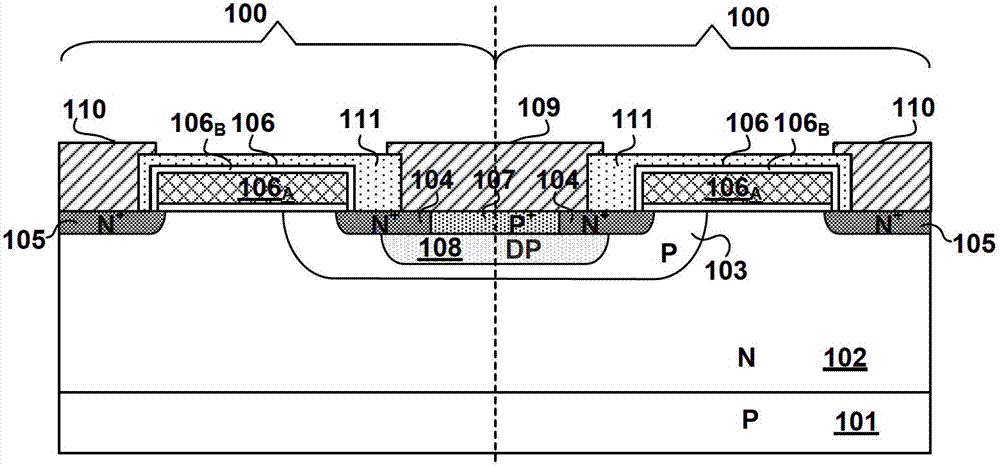

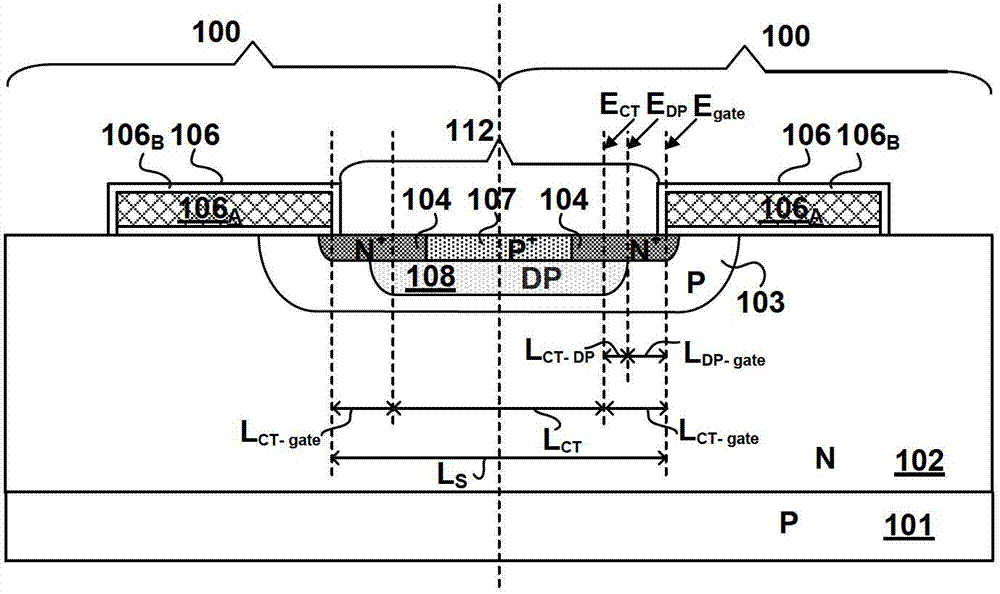

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

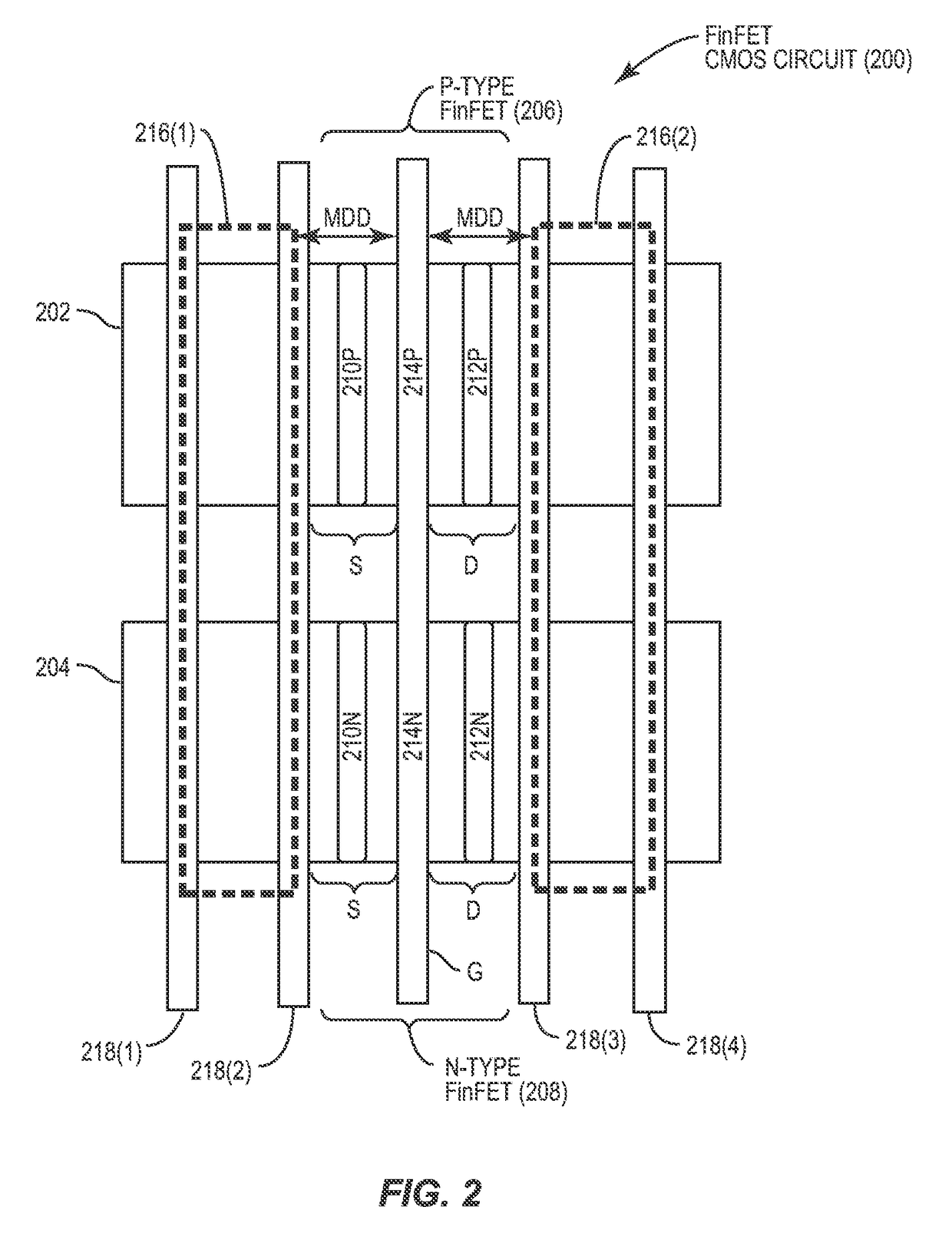

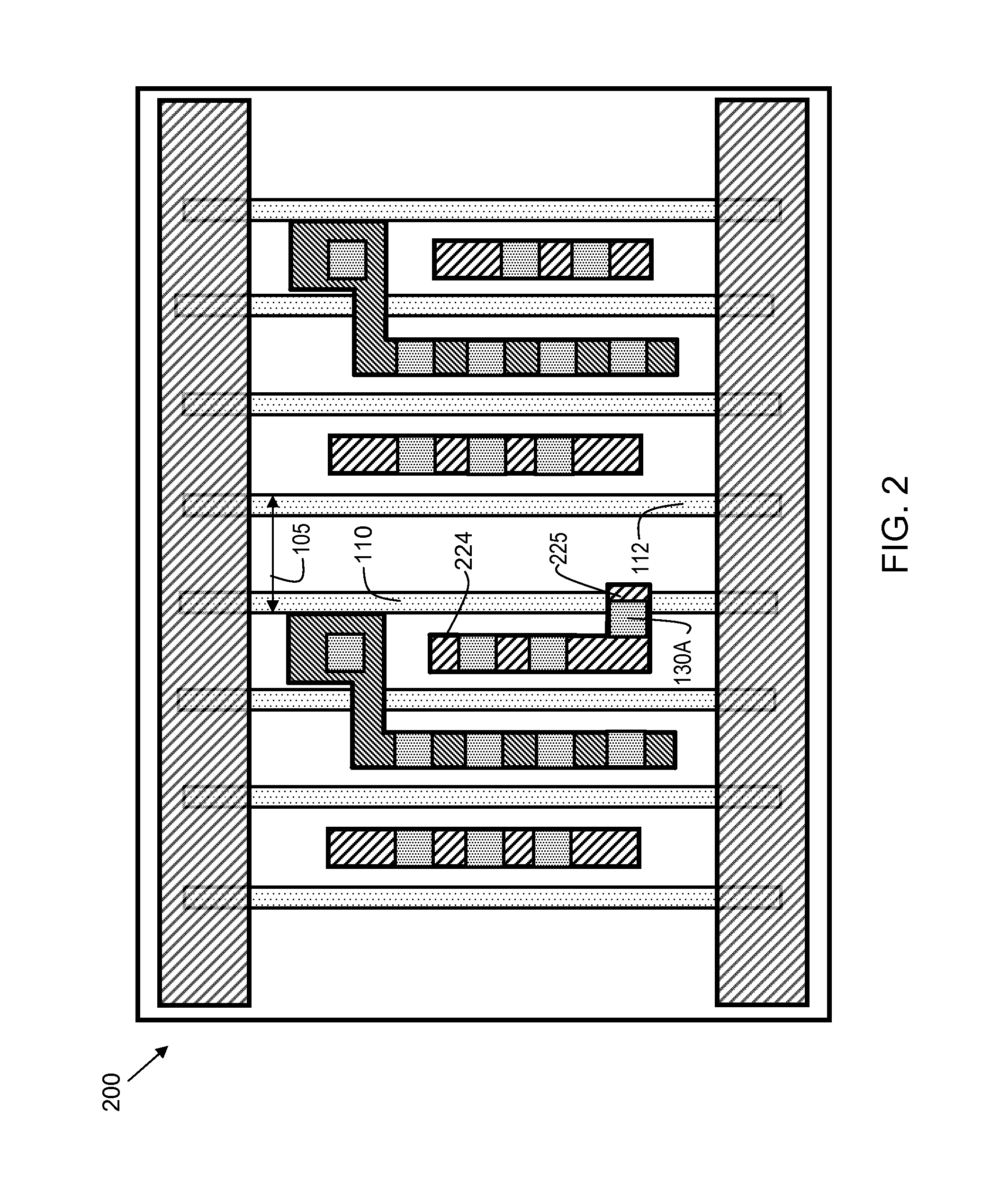

Fin field effect transistor (FET) (finfet) complementary metal oxide semiconductor (CMOS) circuits employing single and double diffusion breaks for increased performance

ActiveUS20180006035A1Improve performanceAvoiding increased fabrication costTransistorSolid-state devicesCMOSDouble diffusion

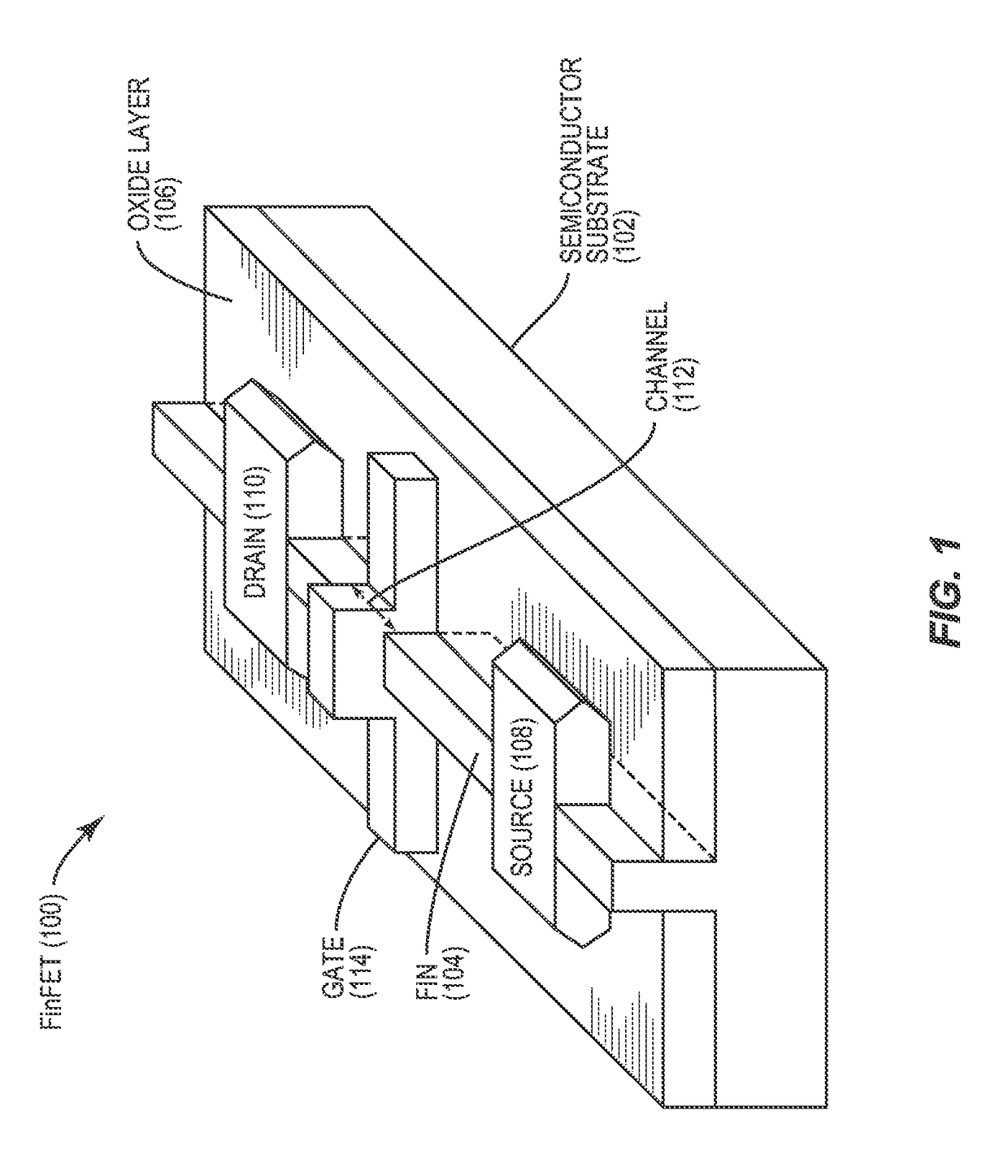

Fin Field Effect Transistor (FET) (FinFET) complementary metal oxide semiconductor (CMOS) circuits with single and double diffusion breaks for increased performance are disclosed. In one aspect, a FinFET CMOS circuit employing single and double diffusion breaks includes a P-type FinFET that includes a first Fin formed from a semiconductor substrate and corresponding to a P-type diffusion region. The FinFET CMOS circuit includes an N-type FinFET that includes a second Fin formed from the semiconductor substrate and corresponding to an N-type diffusion region. To electrically isolate the P-type FinFET, first and second single diffusion break (SDB) isolation structures are formed in the first Fin on either side of a gate of the P-type FinFET. To electrically isolate the N-type FinFET, first and second double diffusion break (DDB) isolation structures are formed in the second Fin on either side of a gate of the N-type FinFET.

Owner:QUALCOMM INC

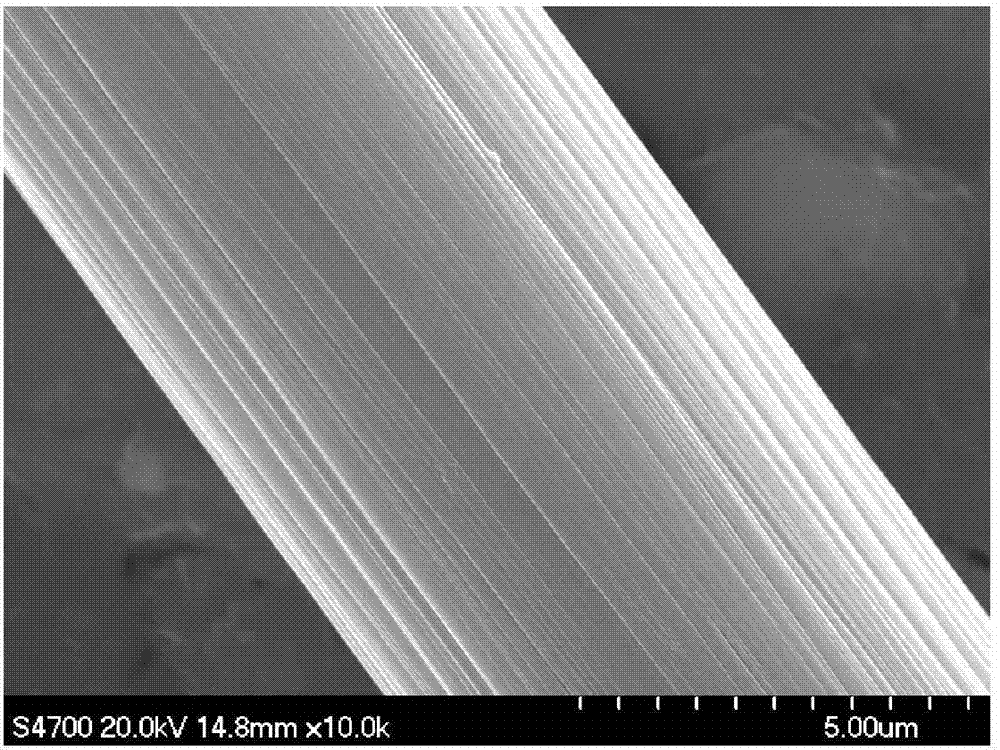

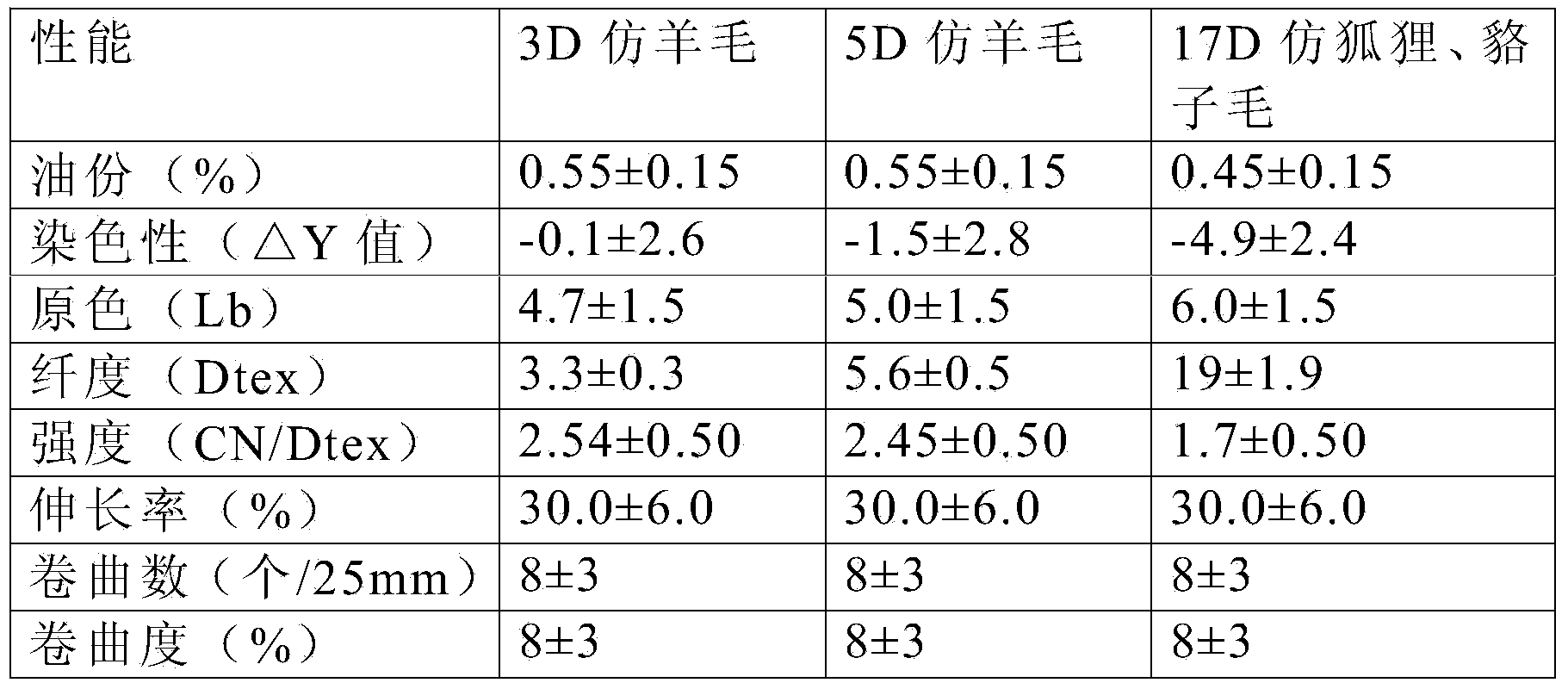

High strength polyacrylonitrile-base carbon fibers having structured surface grooves, and preparation method thereof

ActiveCN102733009AAggregation control is easyHigh tensile strengthMonocomponent synthetic polymer artificial filamentWet spinning methodsCarbon fibersDouble diffusion

The present invention relates to high strength carbon fibers having structured surface grooves, and a preparation method thereof. According to the present invention, a wet spinning technology is adopted, and a solvent adopted by polymerization and solidification molding is modified, such that the solvent and the modifying agent form a complex structure so as to improve solidification double-diffusion in the wet spinning solidification molding process to prepare a polyacrylonitrile precursor having a axial structured surface groove structure and a uniform and dense radial structure; and then pre-oxidation structure control is adopted in a pre-oxidation process to prepare the high strength polyacrylonitrile-base carbon fibers having the structured surface groove structure. The carbon fibers of the present invention have high tensile strength and high modulus, and are easily compounded with other materials so as to improve performances of the composite material.

Owner:BEIJING UNIV OF CHEM TECH

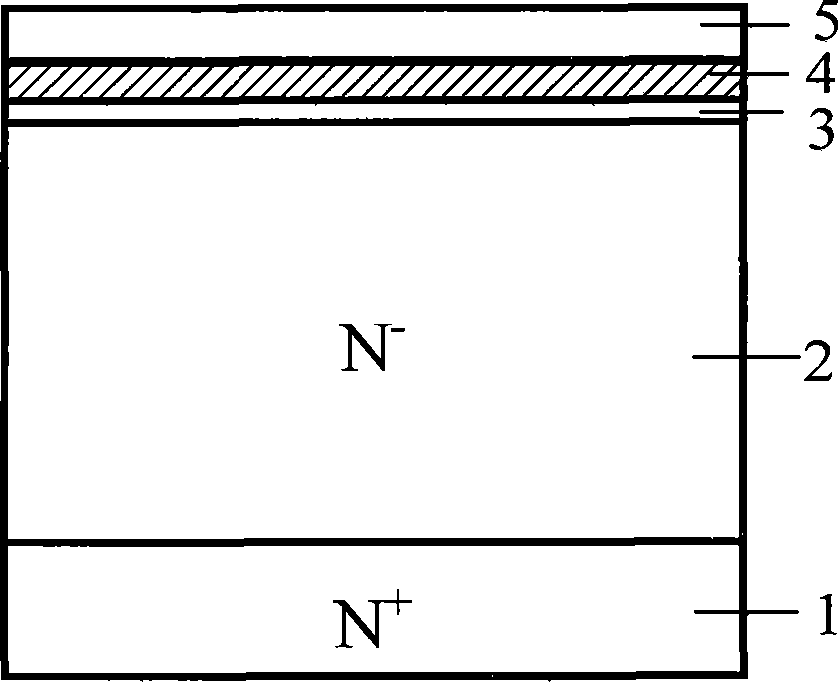

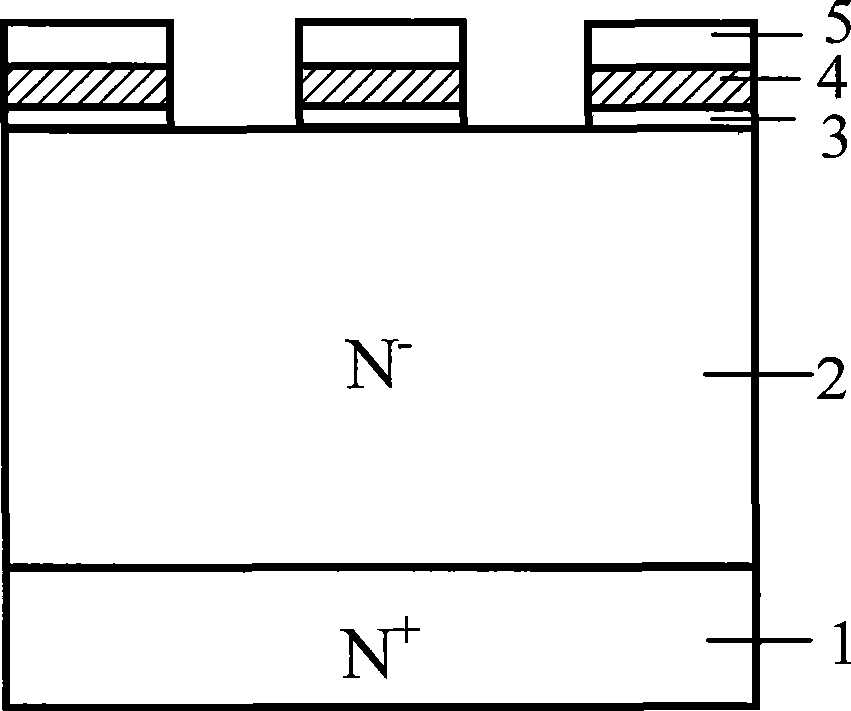

Manufacturing method for vertical DMOS device

InactiveCN101383287AThe parasitic transistor effect is weakenedReduce parasitic resistanceSemiconductor/solid-state device manufacturingHigh concentrationDouble diffusion

The invention relates to a method for preparing a vertical double-diffusion metal oxide semiconductor device, which belongs to the technical preparation field of a semiconductor. The method comprises the main preparing steps: preparing a N<+> substrate, extending and growing N<->, oxidizing gate oxidation, depositing and adulterating polysilicon, depositing silicon dioxide, etching polysilicon windows, injecting and pushing a P trap, injecting high-concentration deep P<+>, injecting a N<+> source, oxidizing and forming a contact hole, etching a groove-shaped window by using an oxidizing layer as a mask, depositing metal, etching metal, passivating and back metalizing. The invention can manufacture a VDMOS device by only using two mask plates, the manufacturing cost of the device is greatly reduced, and meanwhile, the parasitic transistor effect of the device is weakened for the existence of a P<+> layer and the introduction of groove-shaped source contact metal, and the resistance among drain sources is reduced. The invention can be used for the production and the manufacture of the VDMOS device, other semiconductor devices (such as an insulating gate double-pole transistor) and an integrated circuit.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

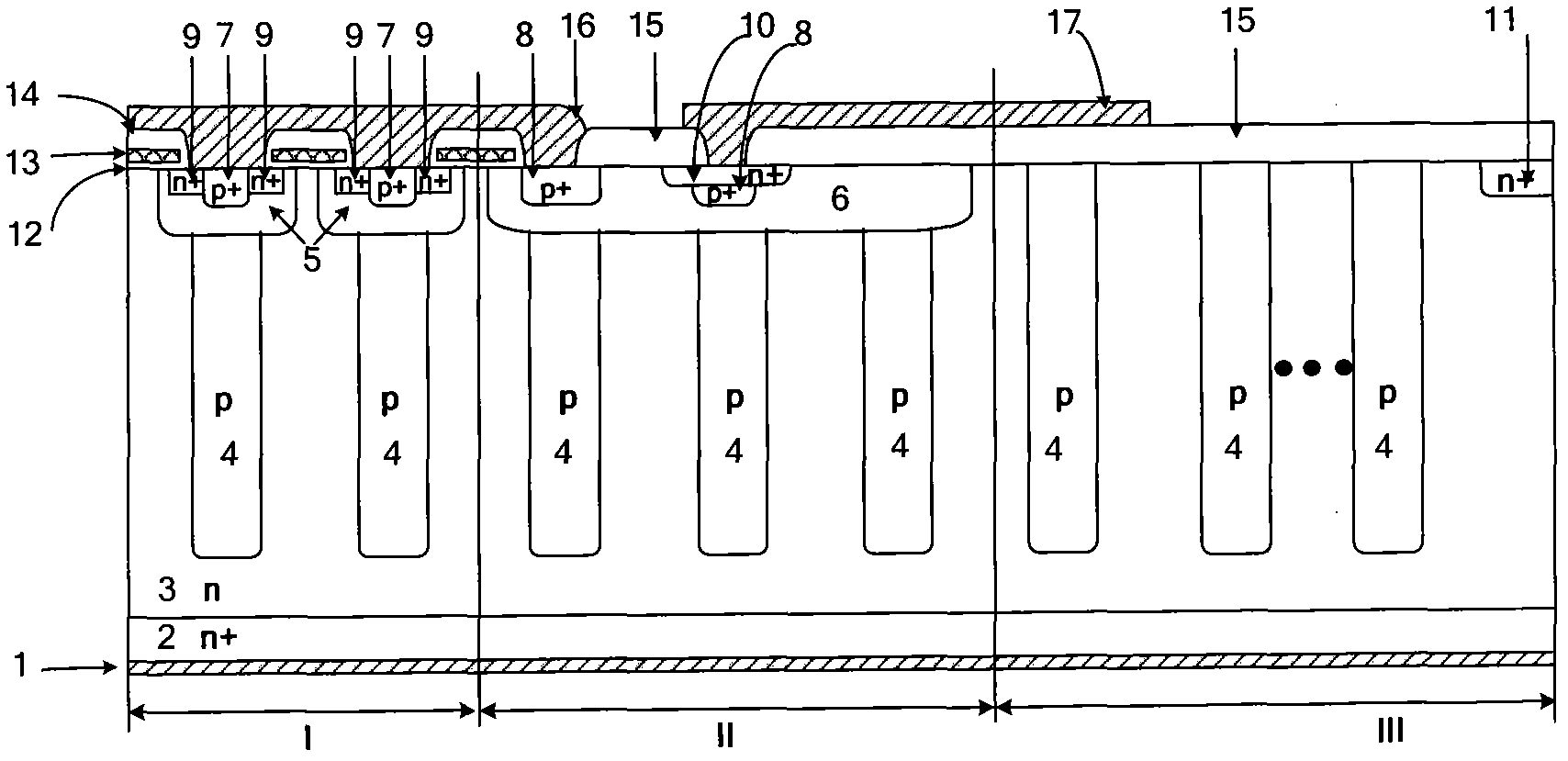

Rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor

InactiveCN101969073AExpand quicklyImprove pressure resistanceSemiconductor devicesDouble diffusionEngineering

The invention relates to a rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor which comprises a cell area, a terminal area and a transition area, wherein the terminal area is arranged at the outermost periphery of a chip; the transition area is positioned between the cell area and the terminal area; the bottoms of the cell area, the transition area and the terminal area (III) are provided with drain electrode metal; a heavy doping n-type silicon substrate is arranged on the drain electrode metal and used as a drain area of the chip; an n-type doping epitaxial layer is arranged on the heavy doping n-type silicon substrate; and a discontinuous p-type doping columnar semiconductor area is arranged in the n-type doping epitaxial layer. The rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor is characterized in that an n-type heavy doping semiconductor area is arranged in a second p-type doping semiconductor area in the transition area, and the surface of the n-type heavy doping semiconductor area is provided with a contact hole which is connected with a metal layer to form a ground contact electrode of the chip. The invention can effectively reduce the reverse recovery charge of a device and improve the reverse recovery characteristics under the conditions of not increasing the process cost or changing the main parameter of the device.

Owner:SOUTHEAST UNIV

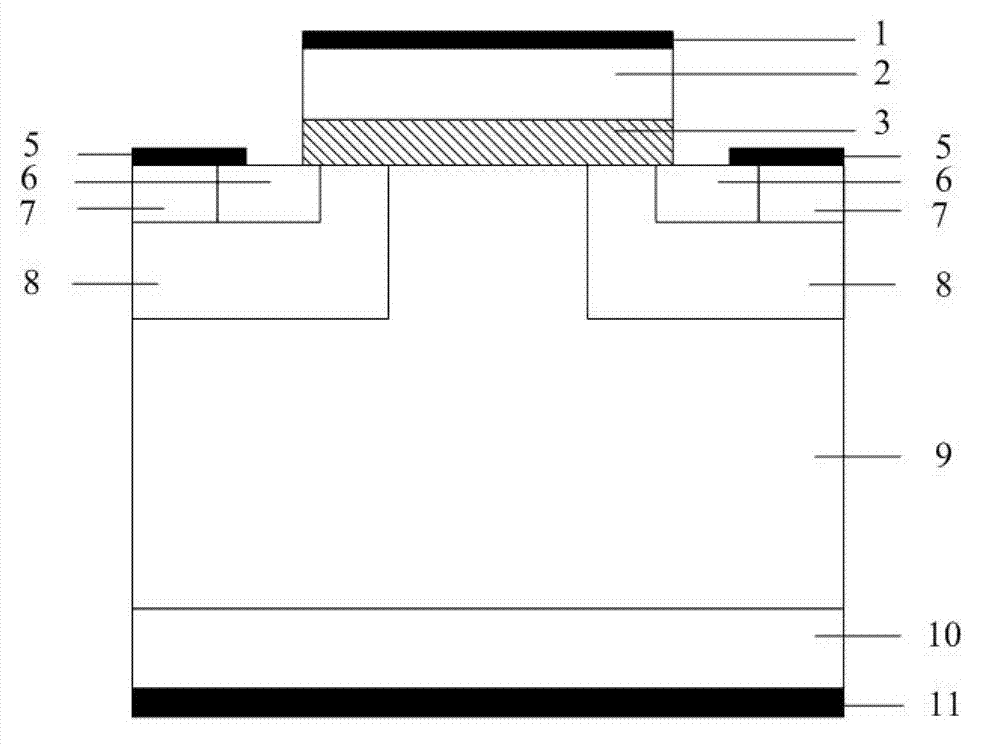

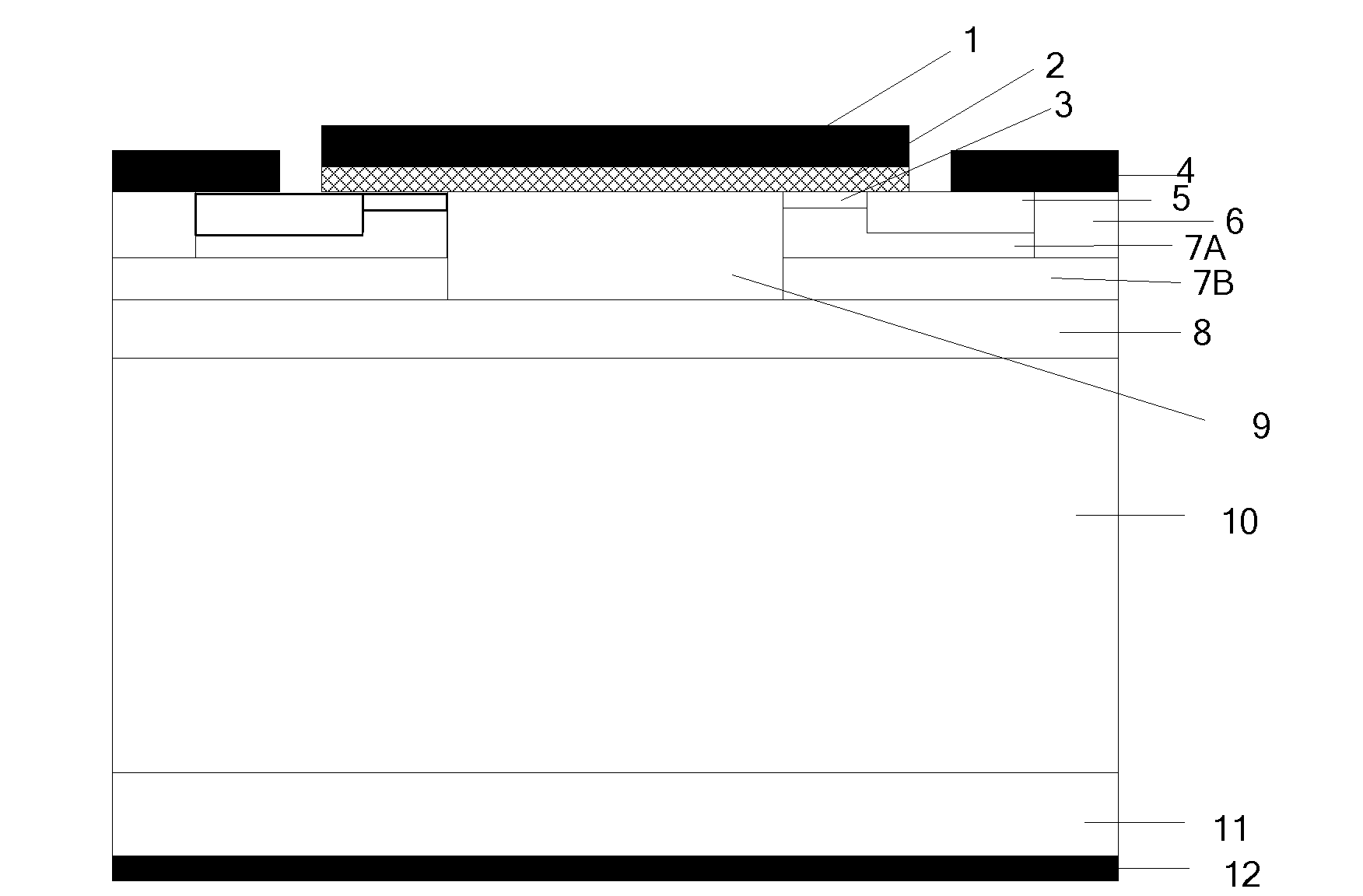

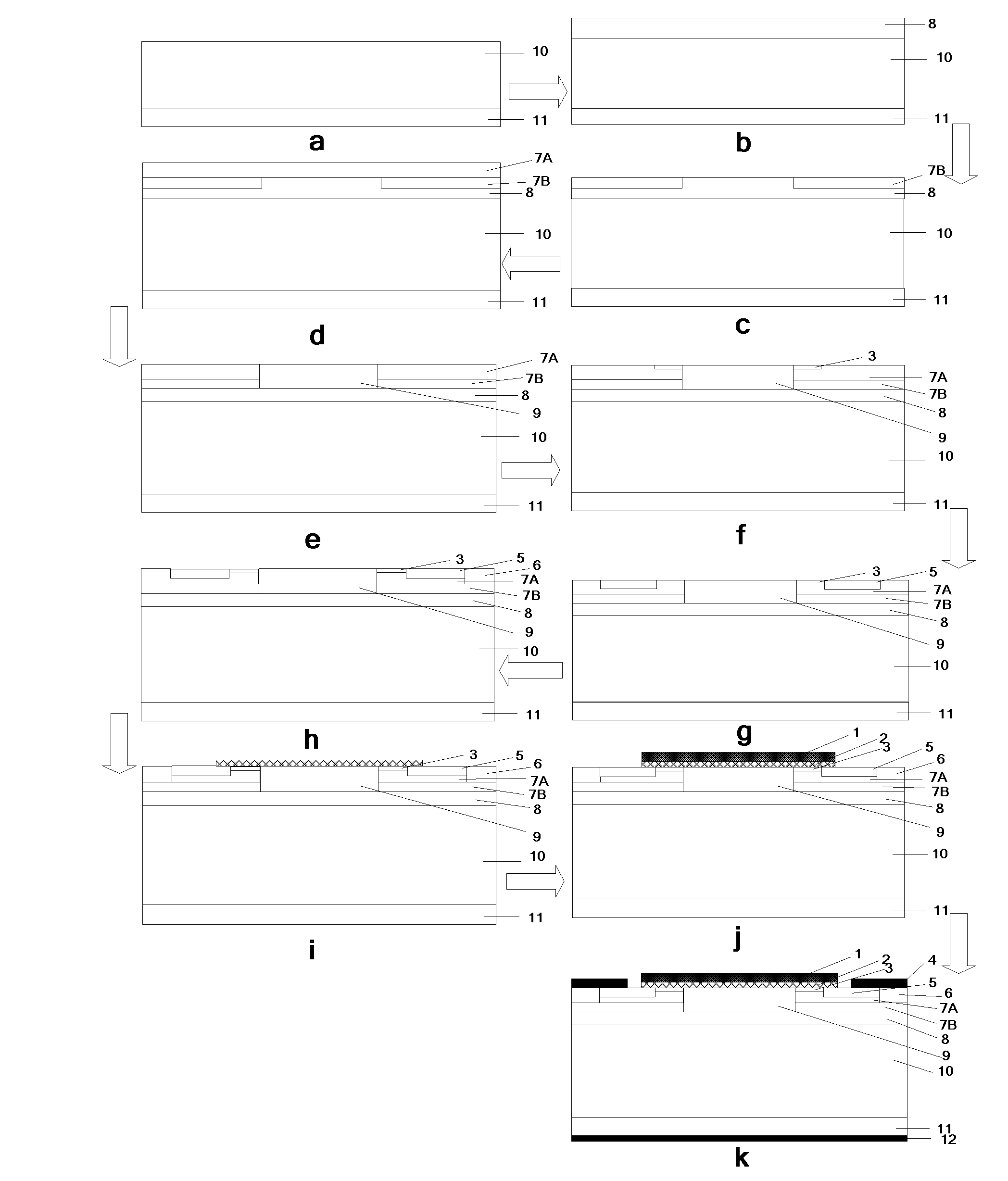

N-type buried-channel silicon carbide metal oxide semiconductor field effect transistor (DEMOSFET) device and preparation method thereof

ActiveCN102194885AInto the uniformIncrease the areaSemiconductor/solid-state device manufacturingSemiconductor devicesAluminum IonMOSFET

The invention discloses an N-type buried-channel silicon carbide metal oxide semiconductor field effect transistor (DEMOSFET) device and a preparation method thereof and mainly solves the problems of low inversion layer electron mobility of the silicon carbide (MOSFET) device and contradiction between reduction in on resistance and improvement on breakdown voltage in the prior art. The device is characterized in that: an N- buried channel layer (3) which has the thickness of 0.1 mu m and the nitrogen ion doped concentration of 5*10<15>cm<-3> is introduced between a SiO2 isolation medium (2) and a P<-> layer (7A) of the traditional vertical double-diffusion metal oxide semiconductor (VDMOS) device structure; an N-type current diffusion layer (8) which has the thickness of 0.5 to 0.6 mu m and the nitrogen ion doped concentration of between 5*10<16>cm<-3> and 1*10<17>cm<-3> is introduced between a P<+> layer (7B) and an N<-> epitaxial layer (10); a P well is divided into two layers, namely the P<-> layer (7A) and the P<+> layer (7B); the P<-> layer (7A) has the thickness of 0.5 mu m and the aluminum ion doped concentration of between 1*10<15>cm<-3> and 5*10<15>cm<-3>; and the P<+> layer (7B) has the thickness of 0.2 mu m and the aluminum ion doped concentration of 3*10<18>cm<-3>. The device has the advantages of high inversion layer electron mobility, high switching reaction speed and low power consumption, and can be used for high-power electrical equipment, solar modules and hybrid fuel electric vehicles.

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

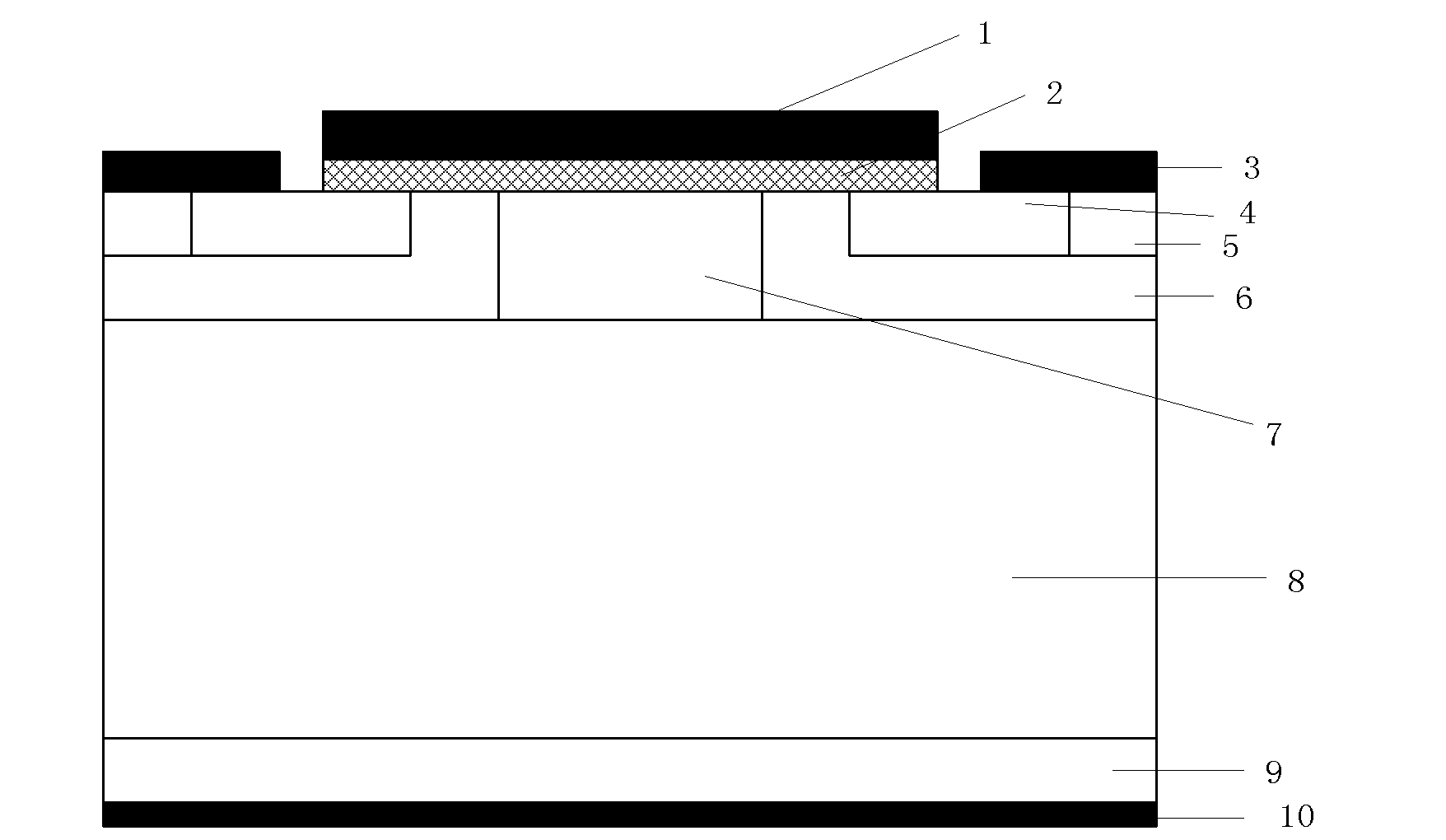

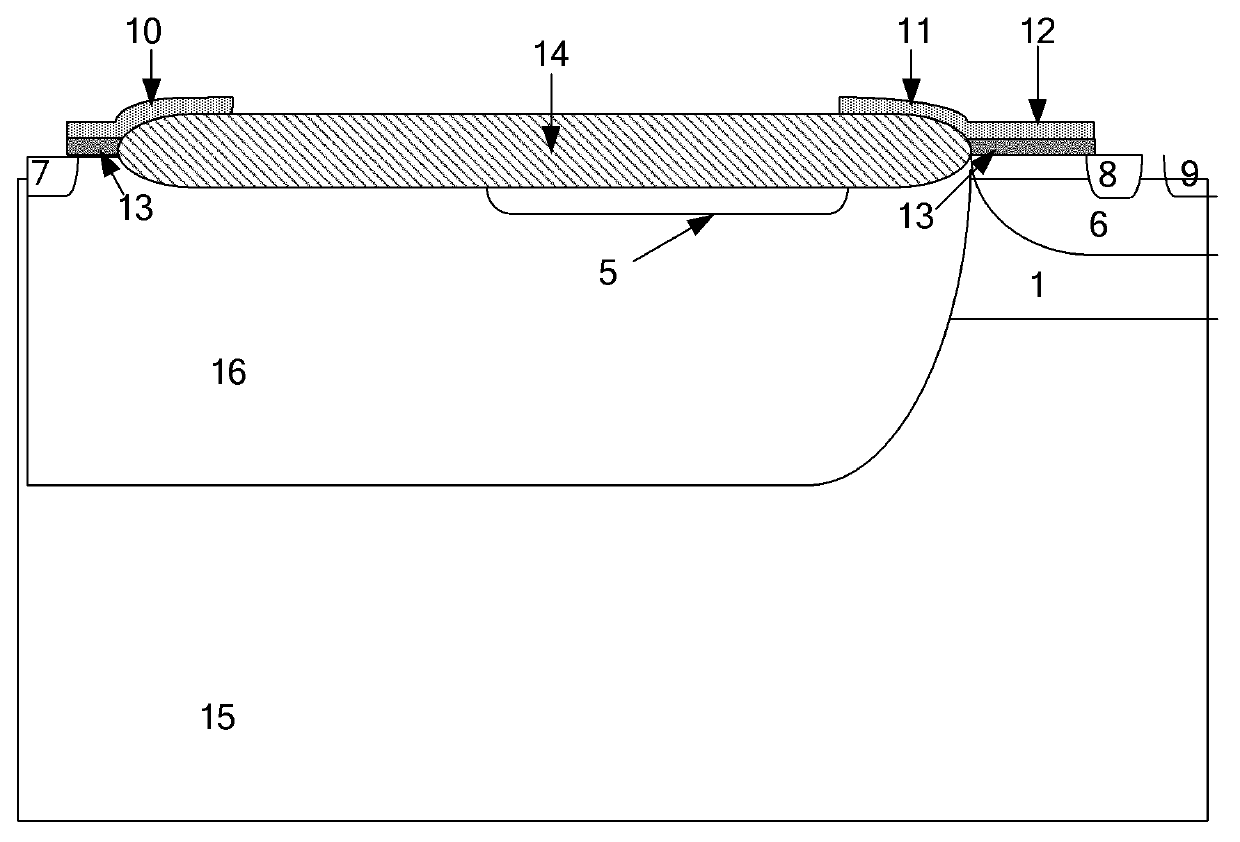

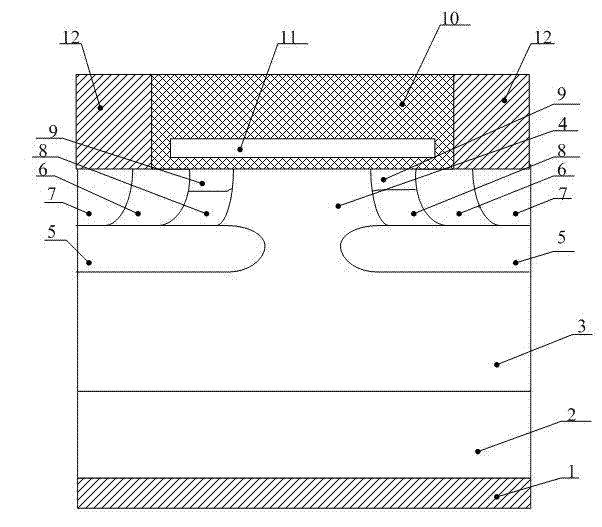

VDMOS (Vertical Double-diffusion Metal Oxide Semiconductor Structure) device and manufacturing method thereof

ActiveCN102468334AEliminate parasitic resistanceLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionBody area

The embodiment discloses a VDMOS (Vertical Double-diffusion Metal Oxide Semiconductor Structure) device and a manufacturing method thereof. The device comprises a substrate, an isolating area, a first body area, a second body area, a first source area, a second source area and a gate area, wherein the substrate comprises a body layer and an epitaxial layer positioned above the body layer; the body layer comprises a drain area; the isolating area is positioned in the epitaxial layer; the first body area and the second body area are positioned in the epitaxial layer at two sides of the isolating area; the first source area is positioned in the first body area; the second source area is positioned in the second body area; and the gate area is positioned between the first source area and the second source area and above the isolating area. The insulated isolating area is formed in the epitaxial layer between the first body area and the second body area, a transition zone where a conductive channel diffuses toward the epitaxial layer area between the first body area and the second body area is eliminated, a parasitic resistor of the VDMOS device is eliminated, the total conduction resistor of the device is reduced, and the electricity of the device is improved. In addition, because of the disappearance of the parasitic resistor, the occupation area of the device cell is reduced, and the utilization ratio of the substrate surface is improved.

Owner:CSMC TECH FAB2 CO LTD

High-voltage low-on-resistance LDMOS device and manufacturing method thereof

InactiveCN102005480ALower on-resistanceImprove electric field distributionSemiconductor/solid-state device manufacturingSemiconductor devicesDouble diffusionLow voltage

The invention relates to a high-voltage low-on-resistance lateral double-diffusion metal oxide semiconductor (LDMOS) device and a manufacturing method thereof. The high-voltage low-on-resistance LDMOS device comprises P-epitaxy, a P-well region, an N+ anode, an N+ cathode, a P+ cathode end, an anode multi-crystal field board, a cathode multi-crystal field board, gate polycrystal, a gate oxide, a field oxide layer, a P-substrate, an N-well region and a P-type region, and also comprises the P-type region and a P-buried layer, wherein the P-type region is positioned on the surface of the N-well region; and the P-buried layer is positioned in the N-well region; the P-type region is isolated from the P-well region and the N+ anode, the P-type region is isolated from the field oxide layer; the P-type region and the N-well region form a PN junction; and the N-well region is segmented into a second N-well region and a first N-well region which are positioned above the P-buried layer by using the P-buried layer; and the P-buried layer forms PN junctions with the first N-well region and the second N-well region respectively. The high-voltage low-on-resistance LDMOS device has the advantages that: on one hand, the compatibility of the LDMOS device and a conventional low-voltage Bipolar+metal oxide semiconductor (CMOS)+double-diffusion metal-oxide-semiconductor (DMOS) (BCD) process is improved, on the other hand, the on-resistance of the LDMOS device is reduced on the premise of the same voltage resistance.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

crosswise double diffusion MOFET and manufacturing method thereof

ActiveCN102738215ALower base resistanceImprove stabilityTransistorSemiconductor/solid-state device manufacturingDouble diffusionBody area

The invention provides a crosswise DMOS with cupped source electrode contact and a method for forming the crosswise DMOS. The crosswise DMOS comprises a cupped source electrode contact, wherein the cupped source electrode contact comprises a cupped part which longitudinally extends and penetrates the source area of the crosswise DMOS and contacts the body area,and the cupped part is electrically coupled with the source area and the body area. The crosswise DMOS not only has smaller size, but also is low in production cost.

Owner:CHENGDU MONOLITHIC POWER SYST

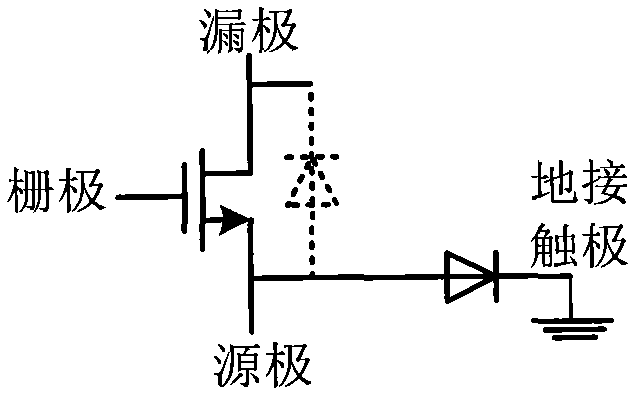

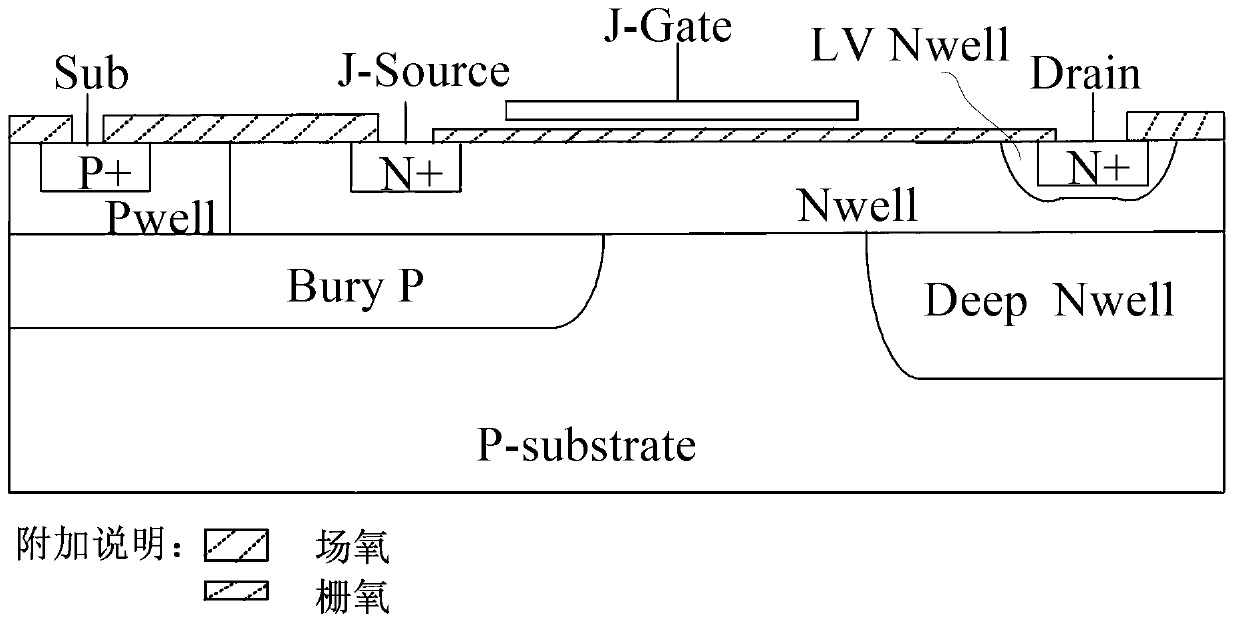

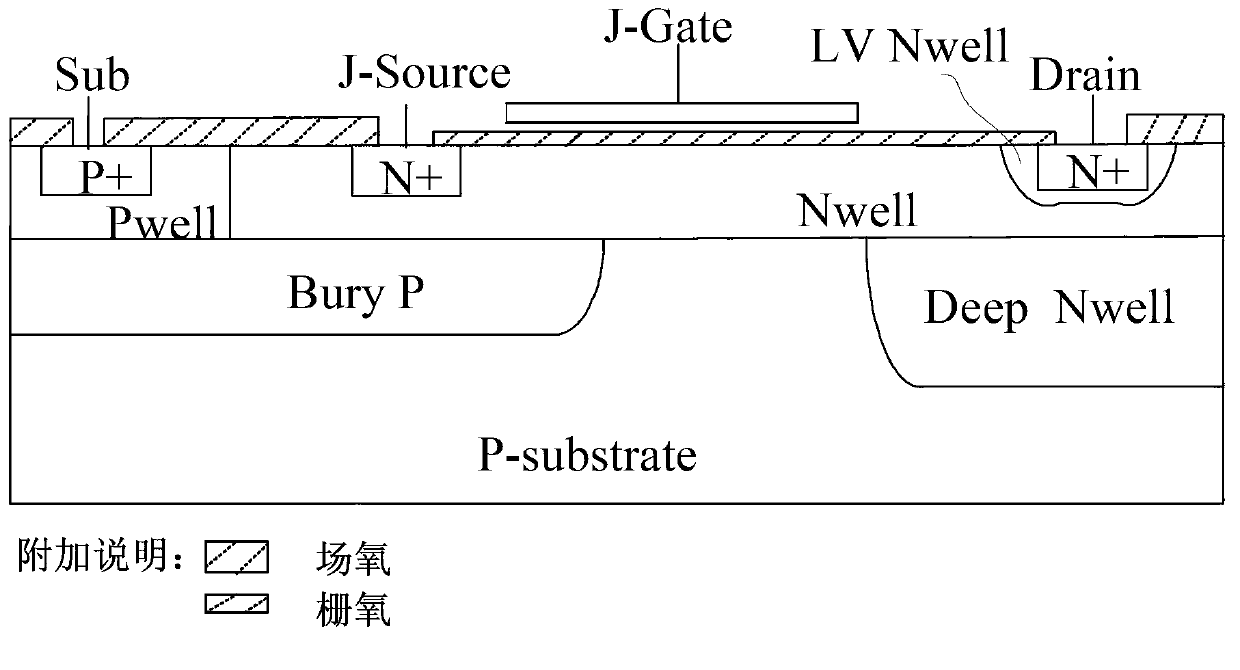

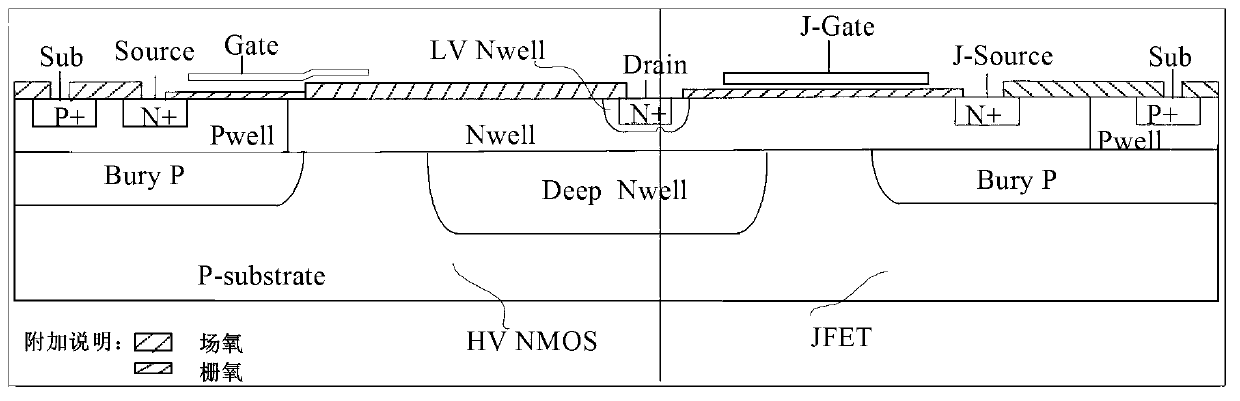

High-voltage device in composite structure and starting circuit

An embodiment of the invention provides a high-voltage device in a composite structure. The high-voltage device in the composite structure comprises a high-voltage power tube HVNMOS and a JFET tube. The high-voltage power tube HVNMOS comprises a drain electrode, a source electrode, a grid electrode and a substrate, and a P-type well region P well arranged between the source electrode and the drain electrode is adopted as a conducting channel. The JFET tube comprises a drain electrode, a source electrode, a grid electrode and a substrate, and an N-type well region N well arranged between the source electrode and the drain electrode is adopted as a conducting channel. The high-voltage power tube HVNMOS and the JFET tube share the same drain electrode, and the N-type double diffusion process is adopted for the drain electrode. A starting circuit provided with the high-voltage device in the composite structure is further provided. By adopting the high-voltage device in the composite structure, chip area is effectively saved and chip cost is reduced.

Owner:SHENZHEN SUNMOON MICROELECTRONICS

Method for manufacturing double diffusion type optical avalanche diode with incident light on back surface by adopting epitaxial equipment

The invention relates to a method for manufacturing a double diffusion type optical avalanche diode with incident light on a back surface by adopting epitaxial equipment. MOCVD epitaxial equipment is used for carrying out epitaxial treatment once on an avalanche photodiode on an indium phosphide substrate; a double diffusion method of the MOCVD epitaxial equipment is used for doping; a sputtering method is used for manufacturing a P-surface electrode; the substrate is thinned and polished; a wet corrosion method is used for manufacturing a light incidence window and an anti-reflection layer; the sputtering method is used for manufacturing a N-surface electrode; and the N-surface electrode is alloyed. By using the double diffusion method, in the diffusion process, the invention realizes gradient doping of different regions and different concentration by controlling the flow rate of a diffusion source; and an abrupt junction is formed in diffusion. The invention has good diffusion uniformity and high rate of finished products of pieces; and the manufactured avalanche photodiode with incident light on the back surface has the characteristics of small dark current, high sensitivity, small series resistance, high reliability and the like.

Owner:WUHAN HUAGONG GENUINE OPTICS TECH

Preparation method of hollow fiber nanofiltration membrane

ActiveCN103041713AAvoid the problem that it is difficult to distribute fully and evenly on the surface of the membrane filamentHigh affinitySemi-permeable membranesDouble diffusionSolvent

The invention discloses a preparation method of a hollow fiber nanofiltration membrane, and provides the preparation method of the hollow fiber nanofiltration membrane continuous in technical process, uniform in nanofiltration functional layer and few in deficiencies. The method comprises the following steps of: using polyelectrolyte aqueous alkali as an outer coagulating bath and a mixed liquor of water and a solvent for the coagulating bath as an inner coagulating bath, spinning and forming a hollow fiber nanofiltration membrane spinning and membrane forming system through a hollow spinning nozzle and a double diffusion process, and initially curing and forming a hollow fiber membrane; and adding the initially cured hollow fiber nanofiltration membrane into an aqueous liquor of polyamine, erasing the suspended liquid on the surface, adding the membrane into an organic liquor of polyacyl chloride, and drying and curing the membrane to obtain the hollow fiber nanofiltration membrane. The method provided by the invention is continuous in technical process, uniform and controllable in nanofiltration functional layer and few in defects, and has a wide prospect in the fields of seawater and brackish water desalination, treatment and recovery of sewage and wastewater, preparation of ultrapure water and the like.

Owner:ZHEJIANG JINMO ENVIRONMENT TECH CO LTD

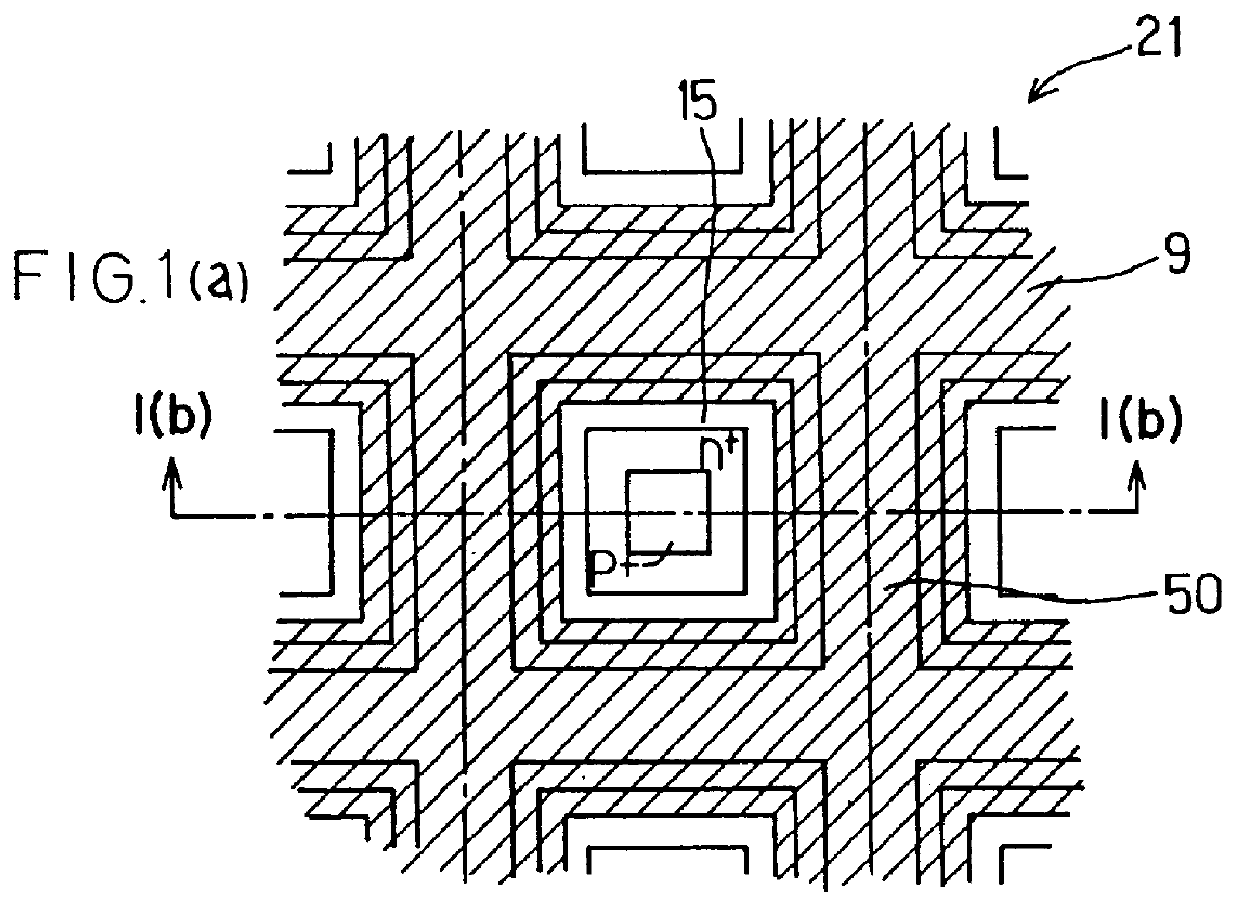

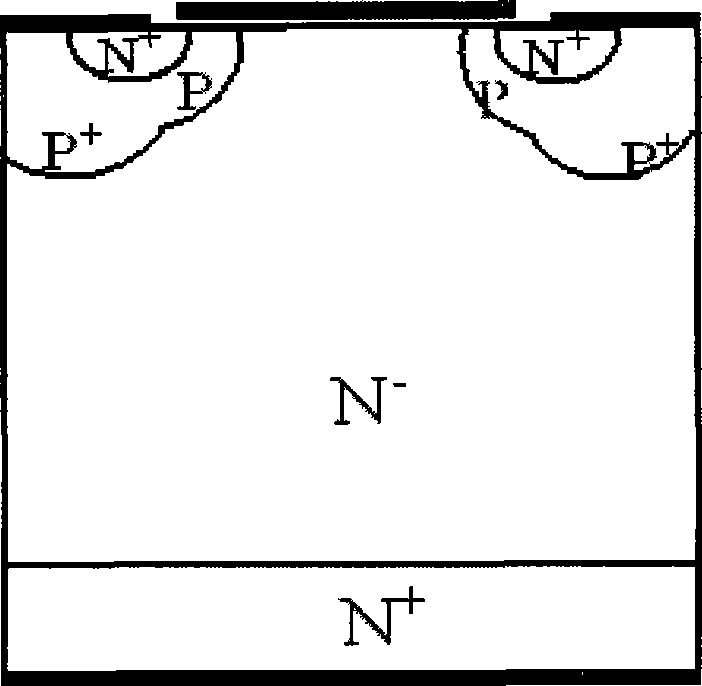

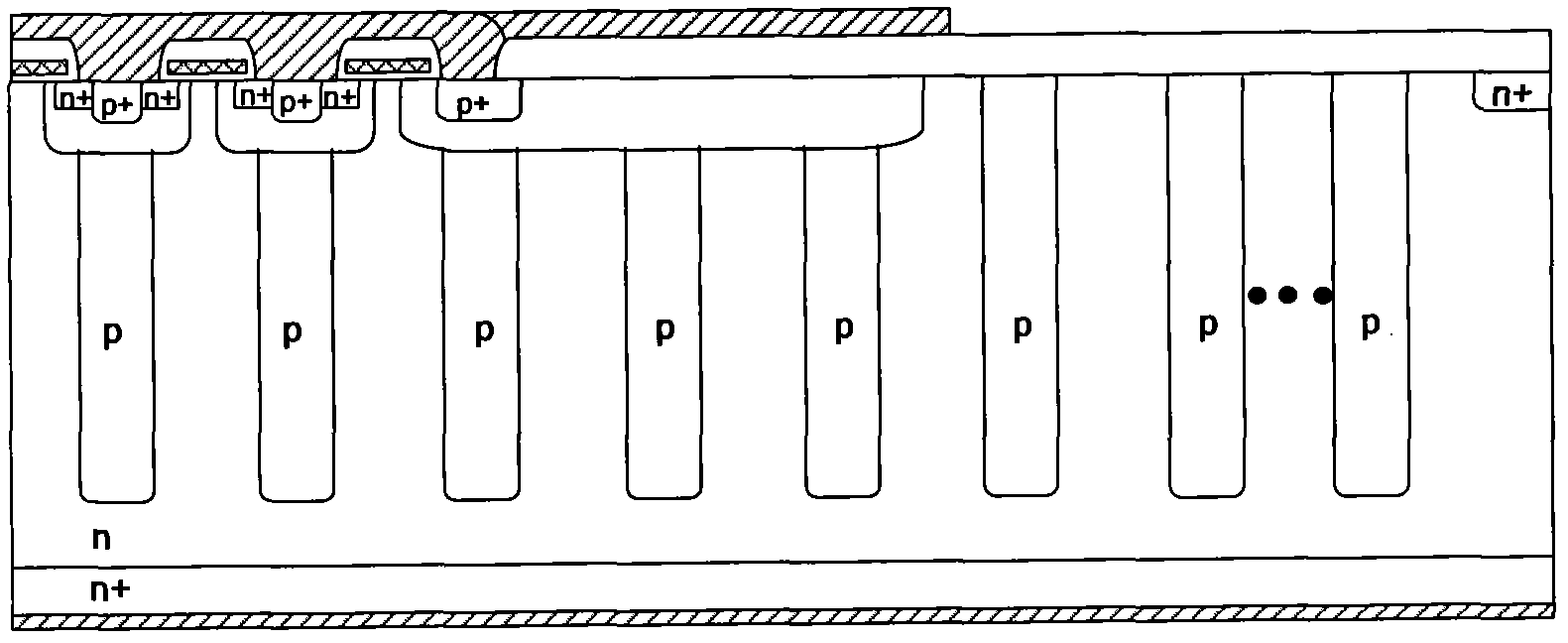

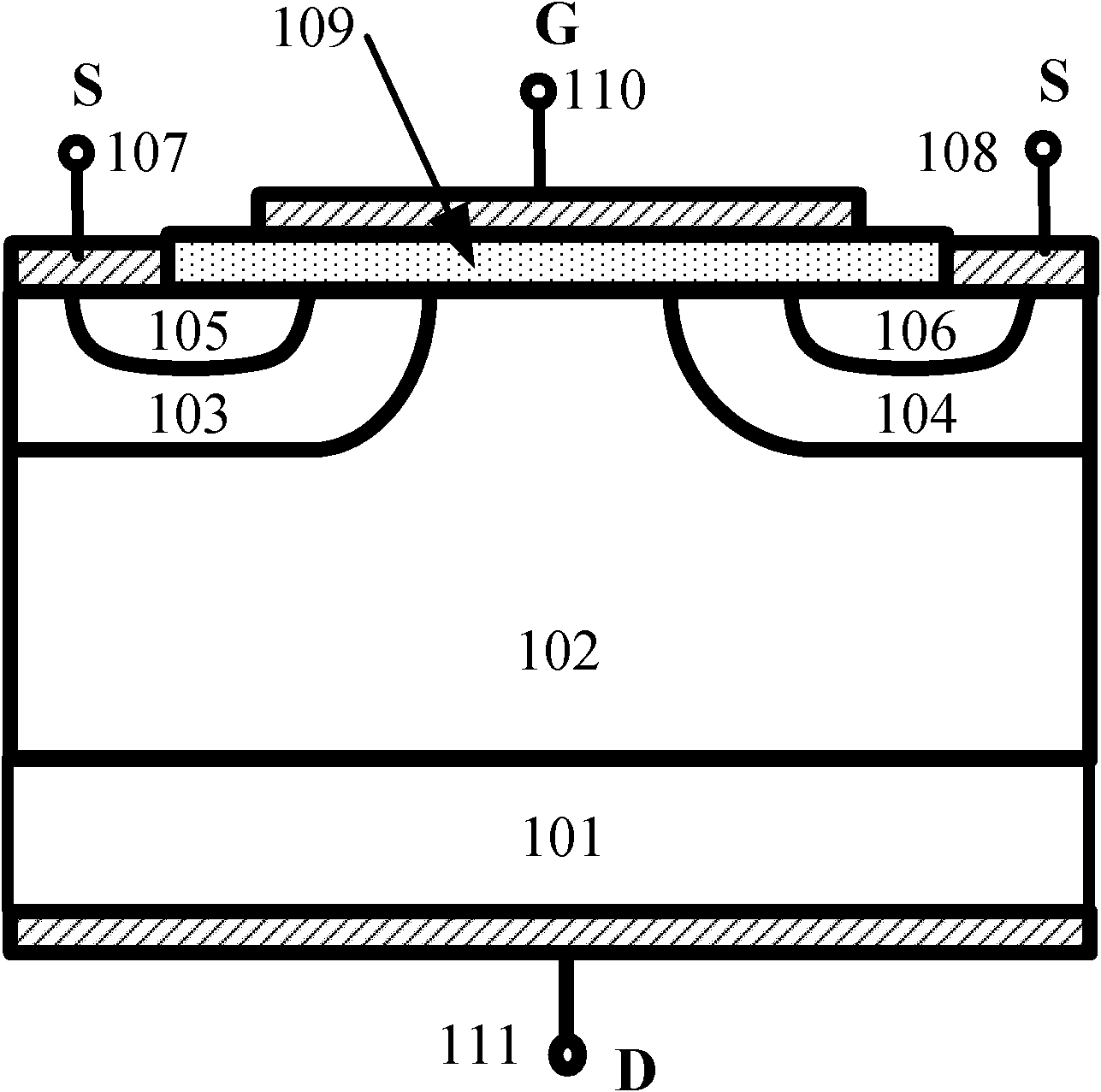

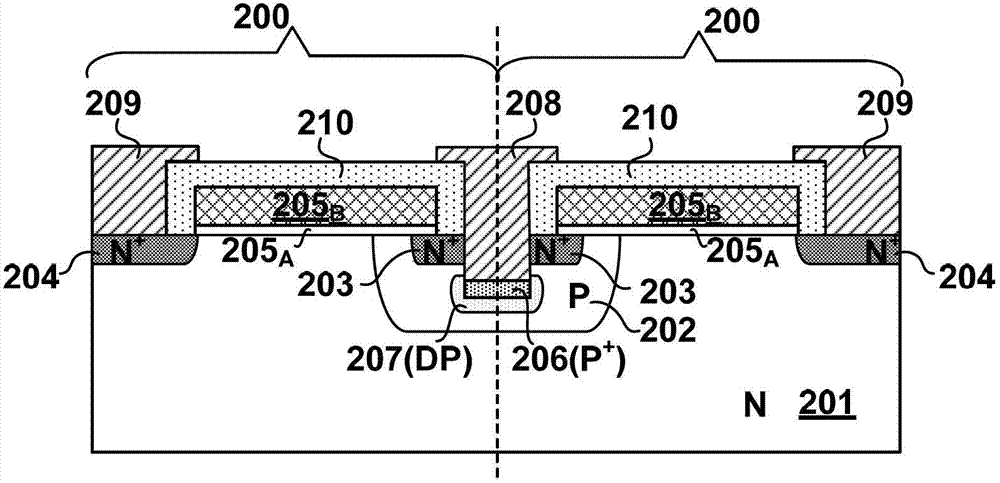

Double diffusion MOSFET with N+ and P+ type regions at an equal potential

InactiveUS6914298B1Easy to adjustHigh dielectric breakdown resistance quantitySemiconductor/solid-state device detailsSolid-state devicesMOSFETDouble diffusion

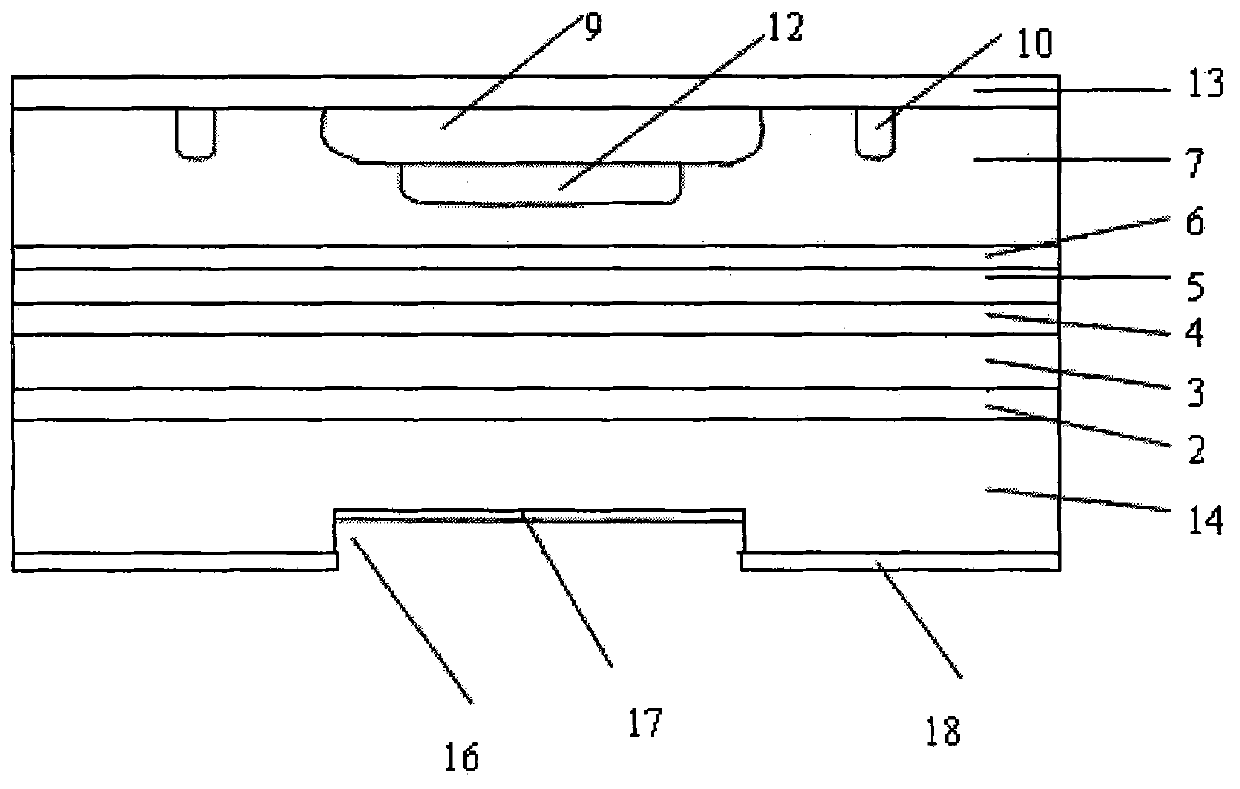

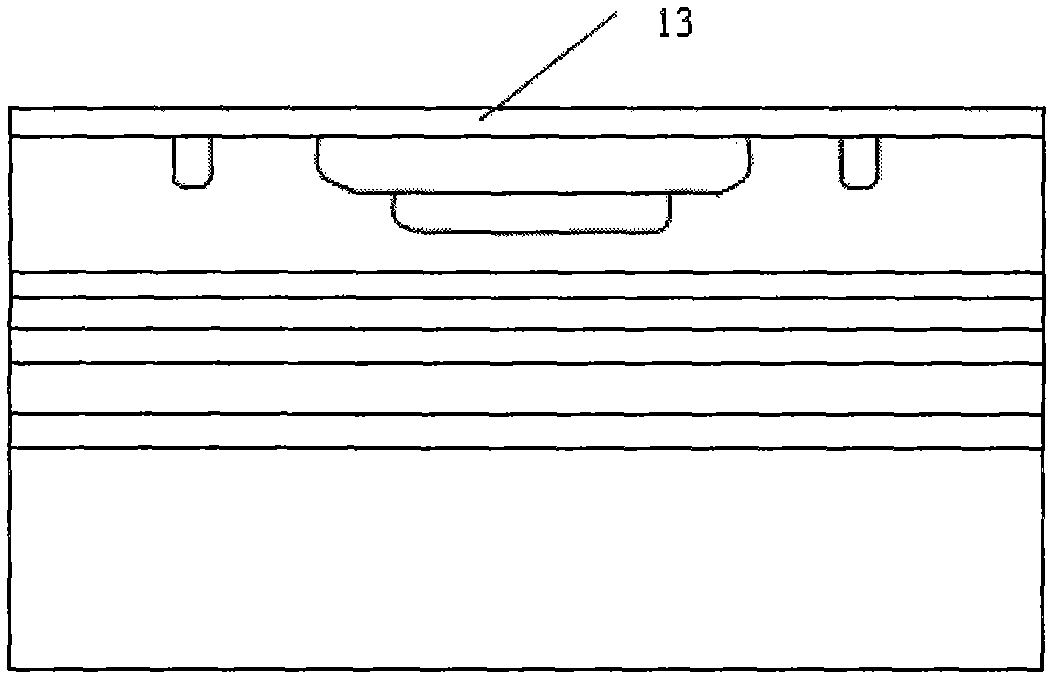

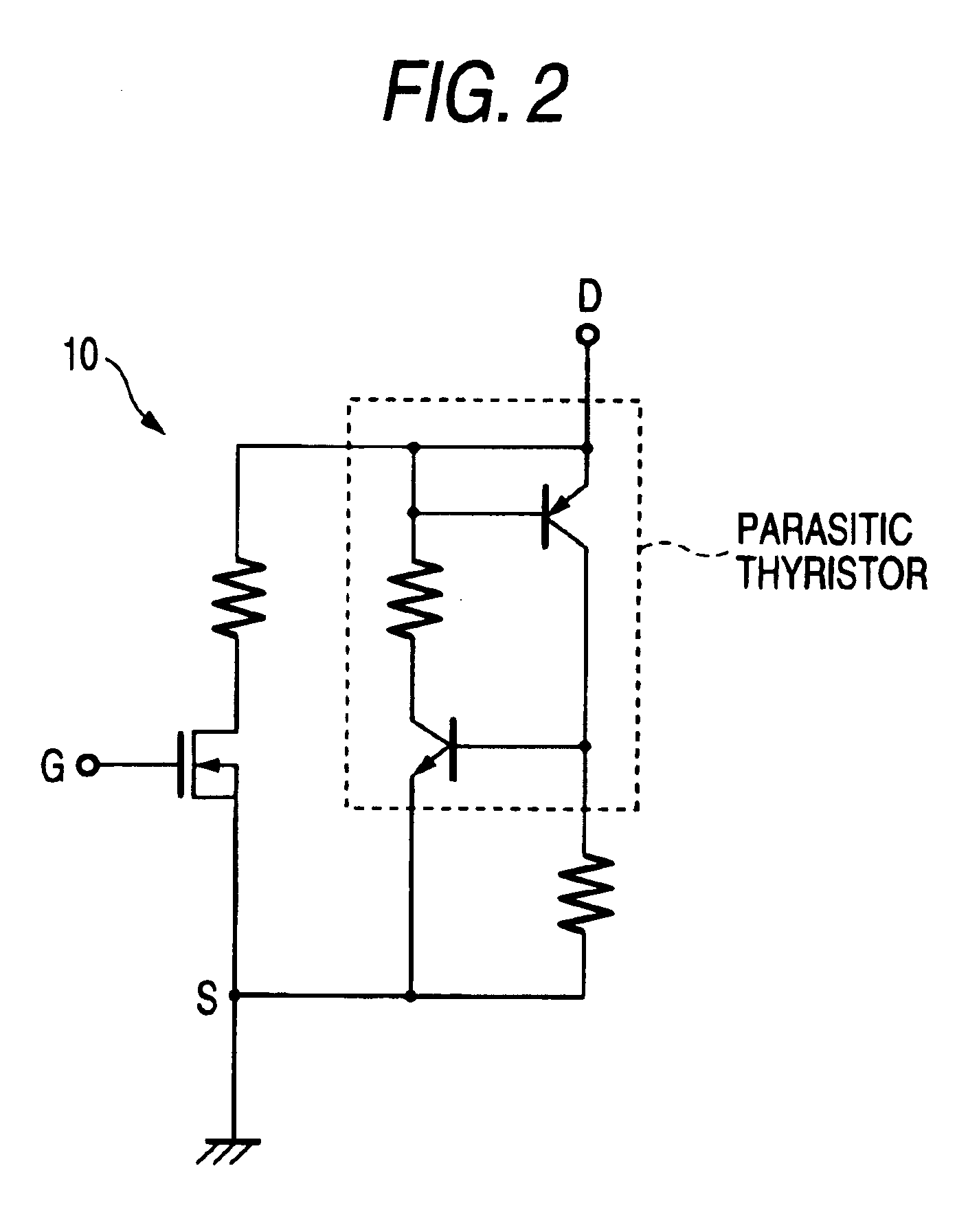

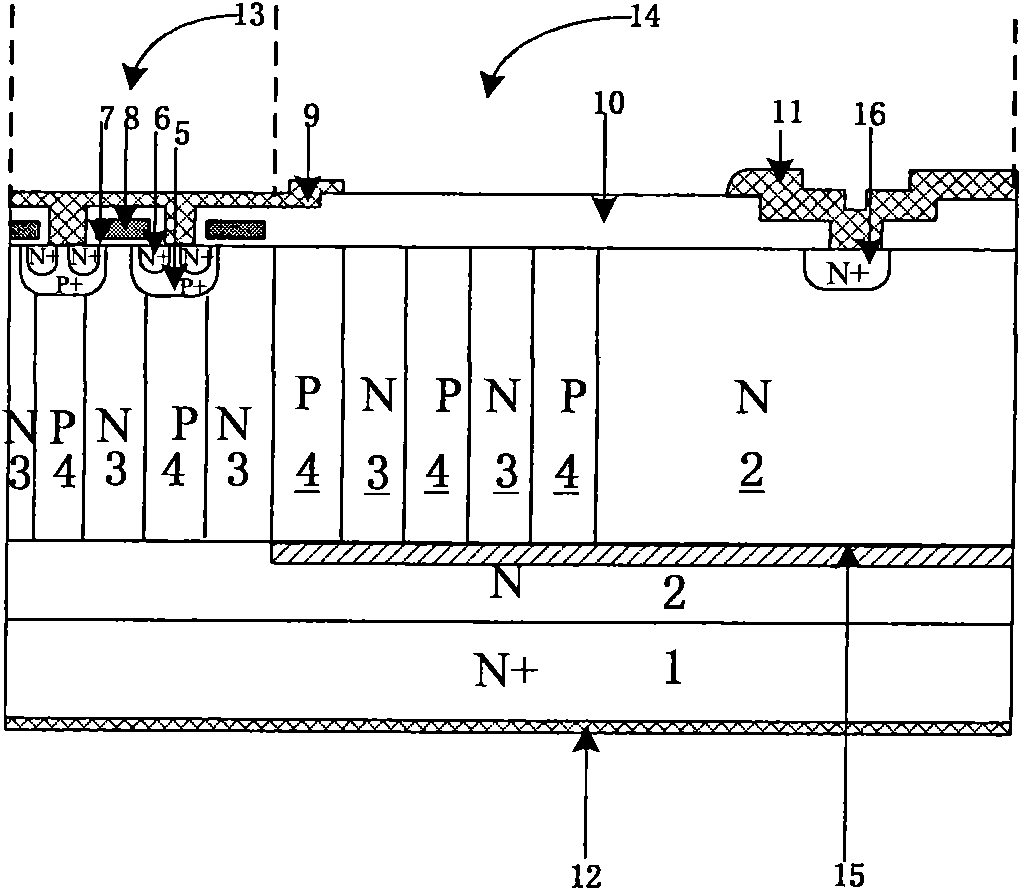

A double diffusion MOSFET is disclosed which comprises: a drain region 13 of an N-type semiconductor layer formed on a semiconductor substrate 11; a body region 15 of a P-type semiconductor region formed in the drain region 13; an N-type source region 16 formed in the body region 15; and a gate electrode 21 formed on a surface of the body region 15, wherein the drain region 13 contains N+ type drain contact regions 18 and P+ type regions 19 such that those are put at an equal potential.

Owner:ROHM CO LTD

Semiconductor tube of hyperconjugation longitudinal double diffusion metal oxide with N channels

InactiveCN101552291AIncrease working currentGuaranteed withstand voltage levelSemiconductor devicesDouble diffusionHyperconjugation

The invention relates to a semiconductor tube of hyperconjugation longitudinal double diffusion metal oxide with N channels, comprising an N-type doped silicon substrate which is also used as a drain region, an N-type doped silicon epitaxial layer, a primitive cell region and a terminal region arranged at the periphery of the primitive cell region; the N-type doped silicon epitaxial layer is arranged on the N-type doped silicon substrate; the primitive cell region and the terminal region are arranged on the N-type doped silicon epitaxial layer; the terminal region comprises a first hyperconjugation structure and an N-type silicon doped semiconductor region, wherein the first hyperconjugation structure comprises a P-type column and a N-type column; an N-type heavily doped semiconductor region is arranged in the N-type silicon doped semiconductor region; the first hyperconjugation structure and the N-type silicon doped semiconductor region are respectively provided with a field oxidation layer; and the N-type heavily doped semiconductor region is connected with a metal layer. The semiconductor tube is characterized in that the first hyperconjugation structure and the N-type silicon doped semiconductor region are respectively provided with the field oxidation layer.

Owner:SOUTHEAST UNIV

VDMOS (Vertical Double-Diffusion Metal-Oxide-Semiconductor) device with non-uniform floating island structure

InactiveCN102420251AImprove pressure resistanceGood reverse recovery characteristicsSemiconductor devicesElectrical resistance and conductanceDouble diffusion

A VDMOS (Vertical Double-Diffusion Metal-Oxide-Semiconductor) device with a non-uniform floating island structure belongs to the technical field of semiconductor power. For the VDMOS device, the non-uniform floating island structure is drawn into a first conductive type semiconductor drift region of a common VDMOS and comprises at least two layers of second conductive type semiconductor floating islands which are respectively an upper layer of second conductive type semiconductor floating island and a lower layer of second conductive type semiconductor floating island, wherein the upper layer of second conductive type semiconductor floating island is larger in transverse width dimension and lower in doping density, and the lower layer of second conductive type semiconductor floating island is smaller in transverse width dimension and higher in doping density. Compared with the common VDMOS, the VDMOS with the non-uniform floating island, provided by the invention, can adopt higher electrical resistivity of an epitaxial layer under the condition the same puncture voltage, thereby the on-resistance is greatly reduced; compared with a VDMOS with a uniform floating island, the VDMOS with the non-uniform floating island is wider in current path and also can lead the on-resistance to be reduced; and compared with a super-junction VDMOS, the VDMOS is better in the reverse recovery characteristic of a body diode and is relatively simple in process.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

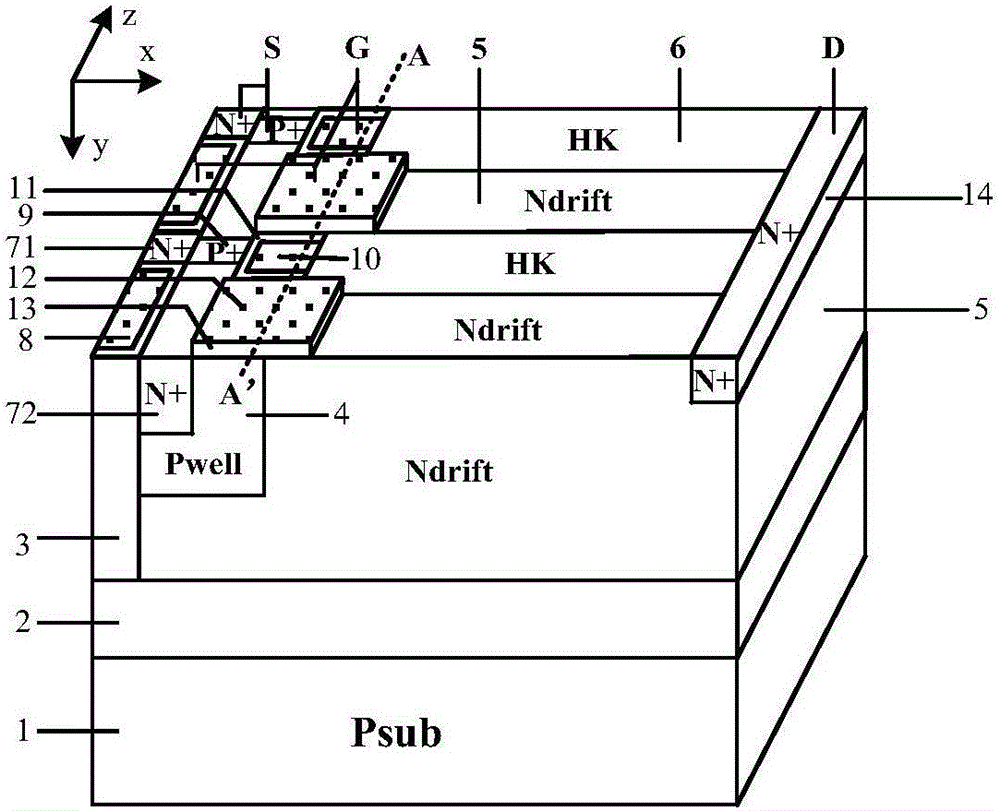

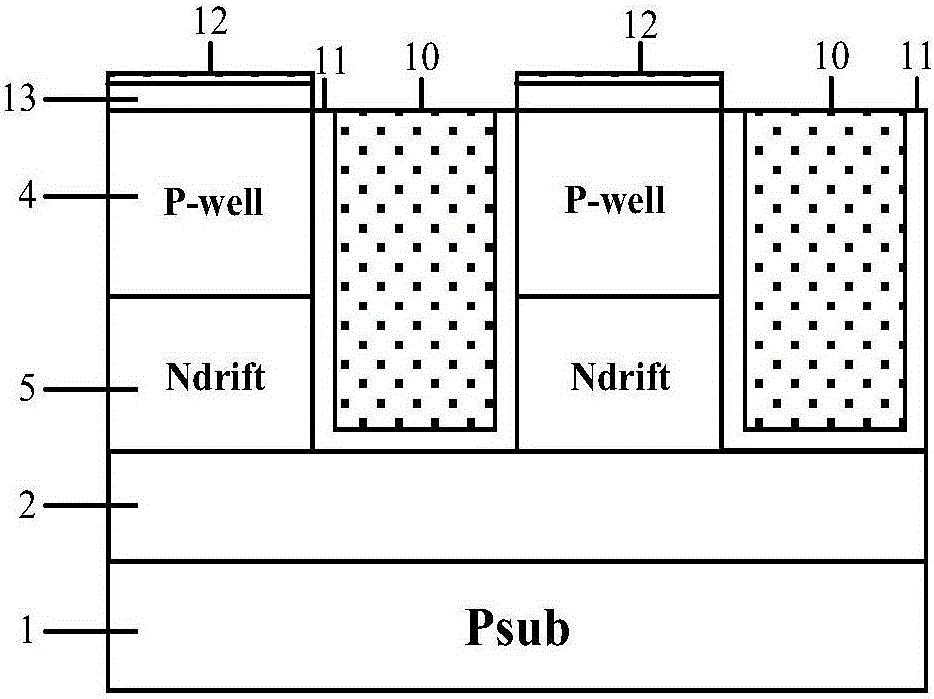

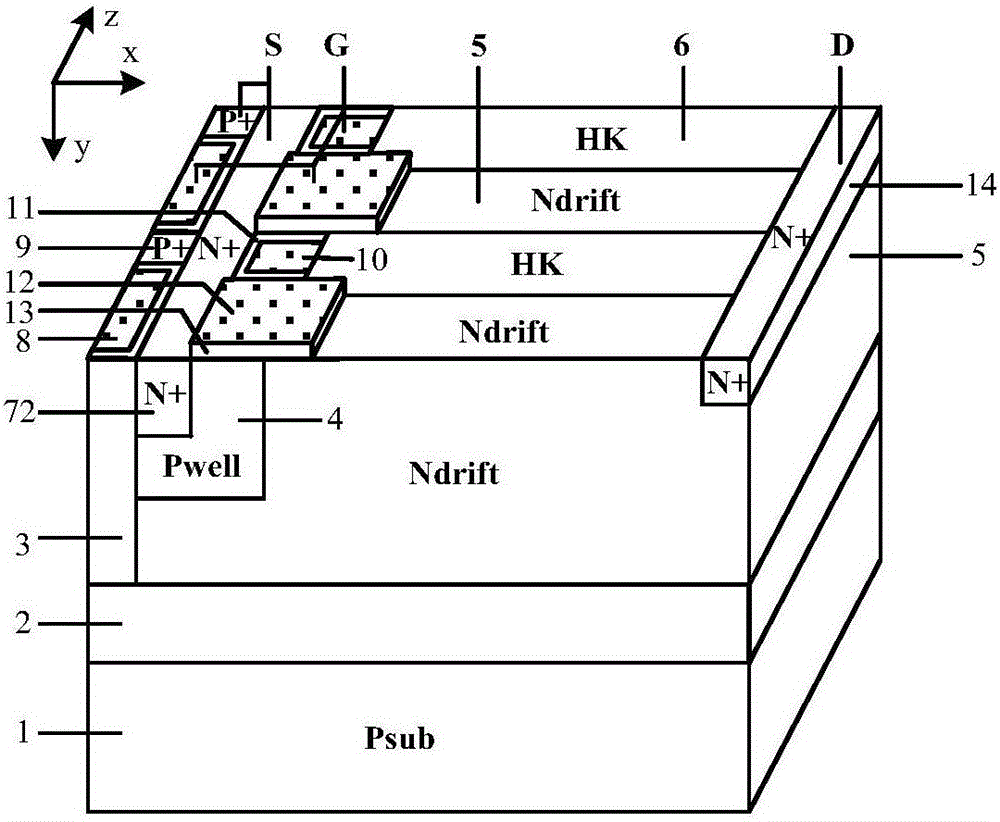

HK SOI LDMOSdevice having three-grating structure

The invention belongs to a field of semiconductor technology and specifically relates to an HK SOI LDMOS (Lateral Double-Diffusion Metal Oxide Semiconductor) device. The device has the following characteristics. First, the device has three separated grating structures including a plane grate and two channel grates. In an open state, the three-grating structure an form a plurality of crosswise and longitudinal channels, thus increasing channel density, increasing current and reducing specific on-resistance. Second, high K mediums are embedded into drifting zones adjacent to a semiconductor zone and are arranged in alternation with the drifting zones. In the open state, electron accumulation layers are formed on side walls of the drifting zones adjacent to the high K mediums, so that low resistance channels are provided and the specific on-resistance is reduced. In a closed state, the high K mediums assist to drain the drifting zones, so that the drifting zone doping is improved, the electric field is improved and the specific on-resistance is reduced and the voltage holding performance is improved further. Third, an SOI structure is adopted, so that longitudinal voltage holding performance is improved, leakage current is reduced and a latch-up effect is eliminated.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

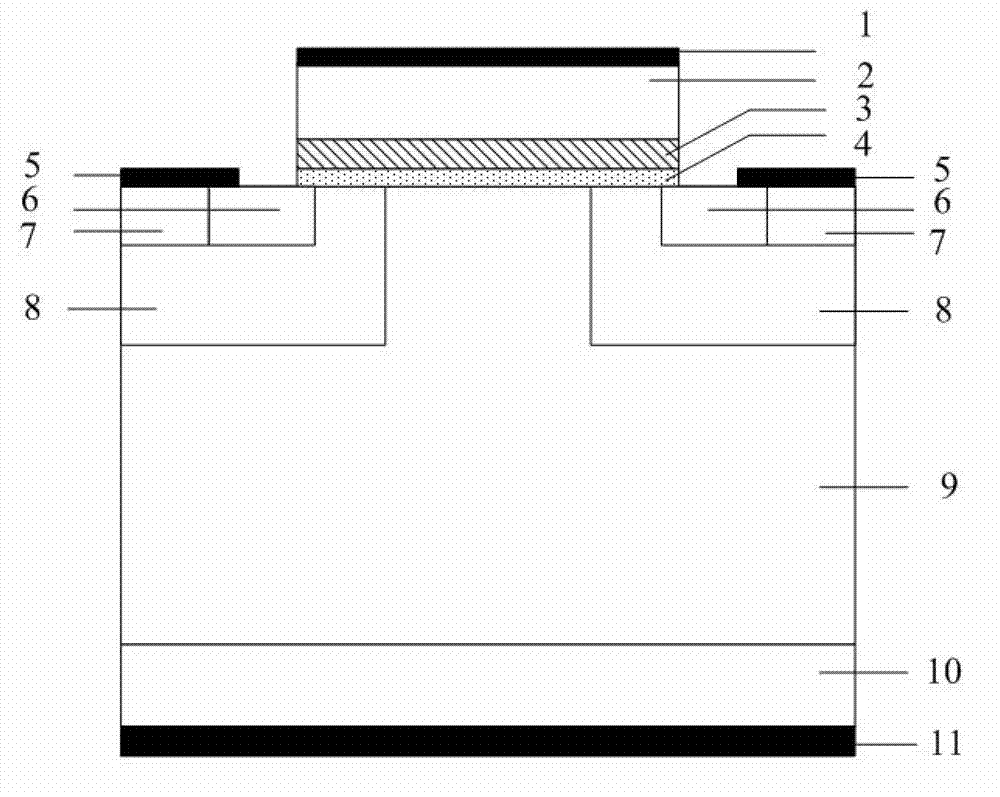

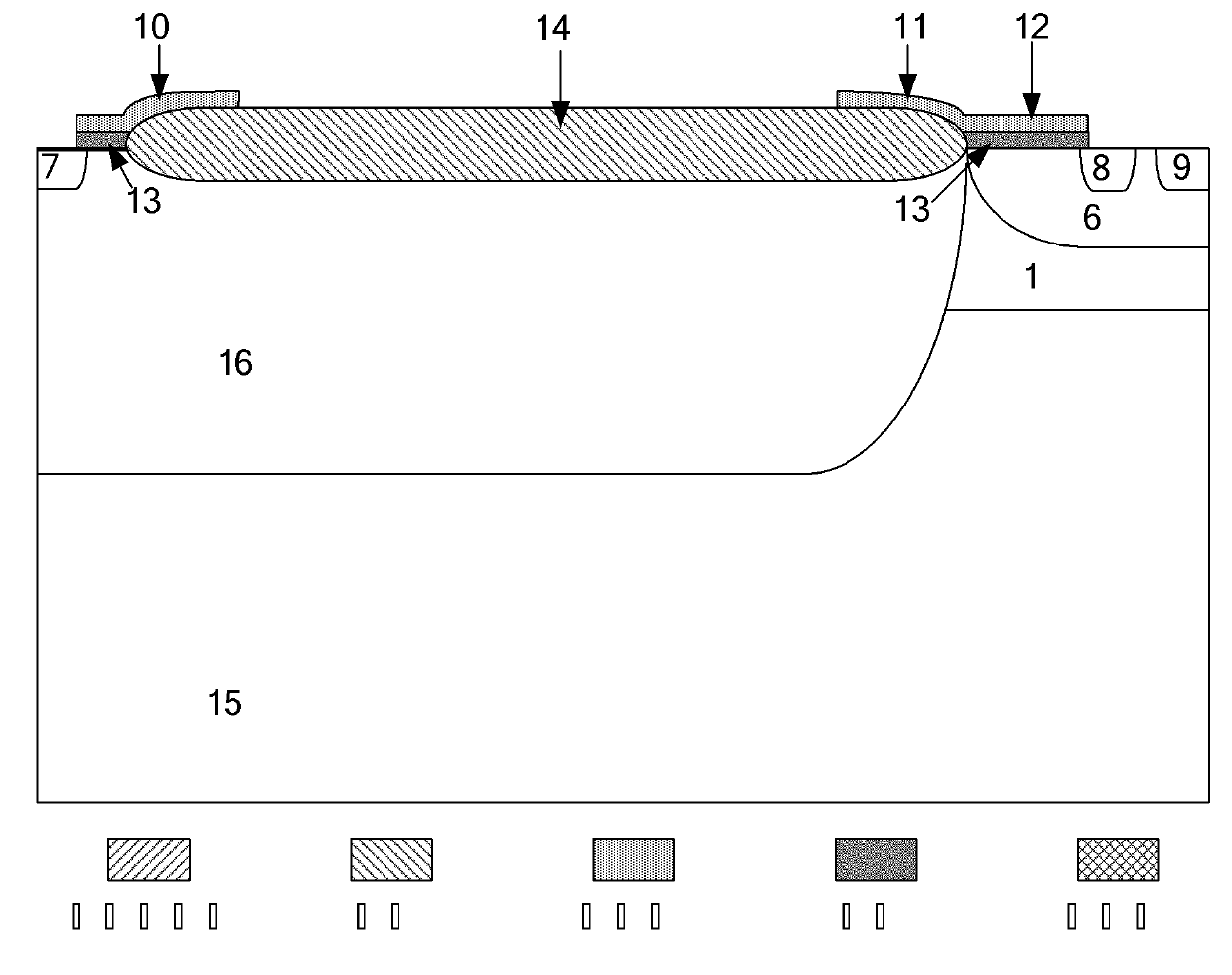

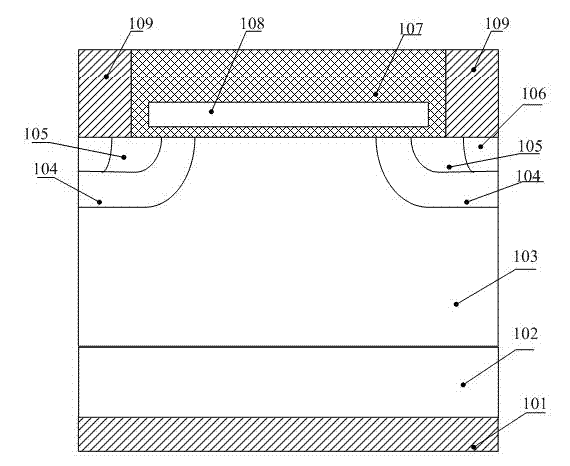

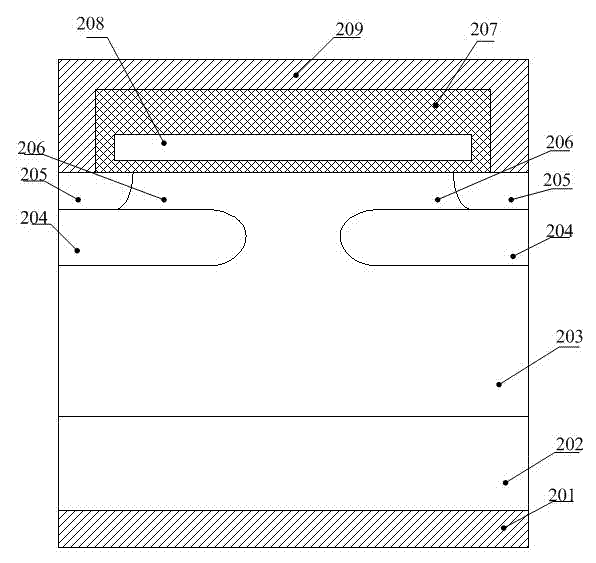

Vertical double-diffusion metal oxide semiconductor field effect transistor (MOSFET)

InactiveCN102364688ALower on-resistanceImprove the withstand voltage levelSemiconductor devicesMOSFETDouble diffusion

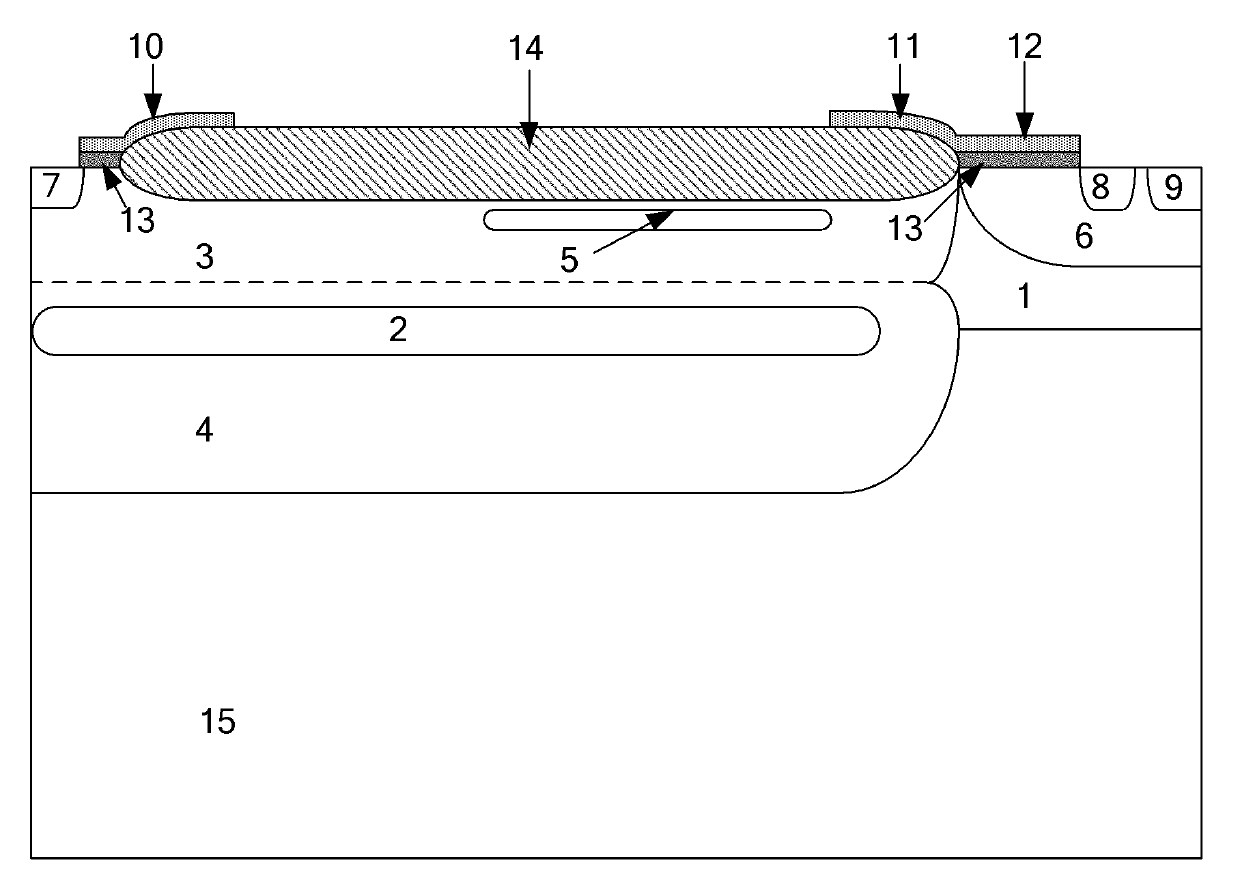

The invention discloses a vertical double-diffusion metal oxide semiconductor field effect transistor (MOSFET), which comprises a metallization drain 1, an N<+> substrate 2, an N<-> drift region 3, a deep P body region 5, an N type heavy doping source region 6, a P type heavy doping region 7, an N type buried layer channel 8, a P type epitaxial layer 9, a gate oxidation layer 10, a polysilicon gate electrode 11 and a metallization source 12. When the vertical double-diffusion MOSFET is switched on, the switch-on resistance of a device is greatly reduced through the common electricity conducting mechanism of two channels; and when the vertical double-diffusion MOSFET is switched off, electric fields of the channels are shielded through a P+N junction barrier, so that a higher voltage-resisting level of more than 1,000V is realized.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

A homogeneous coagulation molding method for polyacrylonitrile precursor

InactiveCN102260919AAchieve homogenizationImprove performanceWet spinning methodsPolymer scienceDouble diffusion

The invention discloses a method for homogenizing, solidifying and forming polyacrylonitrile precursor. By adopting a wet spinning technology, a polyacrylonitrile spinning solution trickles in a coagulating bath to be subjected to double diffusions through solvent and precipitator and then solidified and separated so that the polyacrylonitrile precursor is formed. According to the method disclosed by the invention, an ammonia-containing compound is added in the a coagulating bath; the ammonia-containing compound is served as a third component and can be used for retarding the double-diffusion speed in the solidification process of the polyacrylonitrile spinning solution; therefore, the solidifying and forming homogenization is realized; and the high-performance polyacrylonitrile precursor and carbon fibre can be obtained.

Owner:ZHEJIANG TAIXIAN NEW MATERIAL

Semiconductor Device and Method for Fabricating the Same

ActiveUS20100163983A1TransistorSemiconductor/solid-state device manufacturingDouble diffusionEngineering

Semiconductor devices and methods for fabricating the same are disclosed. The semiconductor device includes gate electrodes having sidewall spacers on a semiconductor substrate, double diffusion drain regions in the semiconductor substrate adjacent to the sidewall spacers, double diffusion junction regions aligned with the gate electrodes, and source / drain regions in the double diffusion junction regions.

Owner:DONGBU HITEK CO LTD

Consumption type N-type lateral double-diffusion metal-oxide semiconductor for reducing voltage

ActiveCN101969072ASolve the disadvantage of limited threshold voltageLower threshold voltageSemiconductor devicesLow voltage circuitsDouble diffusion

The invention relates to a consumption type N-type lateral double-diffusion metal-oxide semiconductor for reducing voltage, which comprises a P-type semiconductor substrate, wherein an N-type buried layer, a P-type well region, an N-type well region and an N-type drift region are arranged on the P-type semiconductor substrate; a P-type contact region, an N-type source region and an N-type channelinjection region are arranged near the left side of the surface of the P-type well region; a P-type injection region is arranged in the P-type well region; the left end boundary of the P-type injection region is arranged below the N-type source region; the right end boundary of the P-type injection region is adjacent to the N-type drift region on a drain terminal; and the P-type contact region and a polycrystalline silicon electrode are connected through an interconnection metal cable to be used as a grid. The structure of the invention greatly reduces the threshold voltage of the consumptiontype N-type lateral double-diffusion metal-oxide semiconductor; a metal cable of a drain is directly connected to a high-voltage power supply in circuit application; the metal cable of the grid is grounded; and the metal cable of the drain is directly connected to a low-voltage circuit so as to provide a low-voltage power supply for the low-voltage circuit.

Owner:SOUTHEAST UNIV

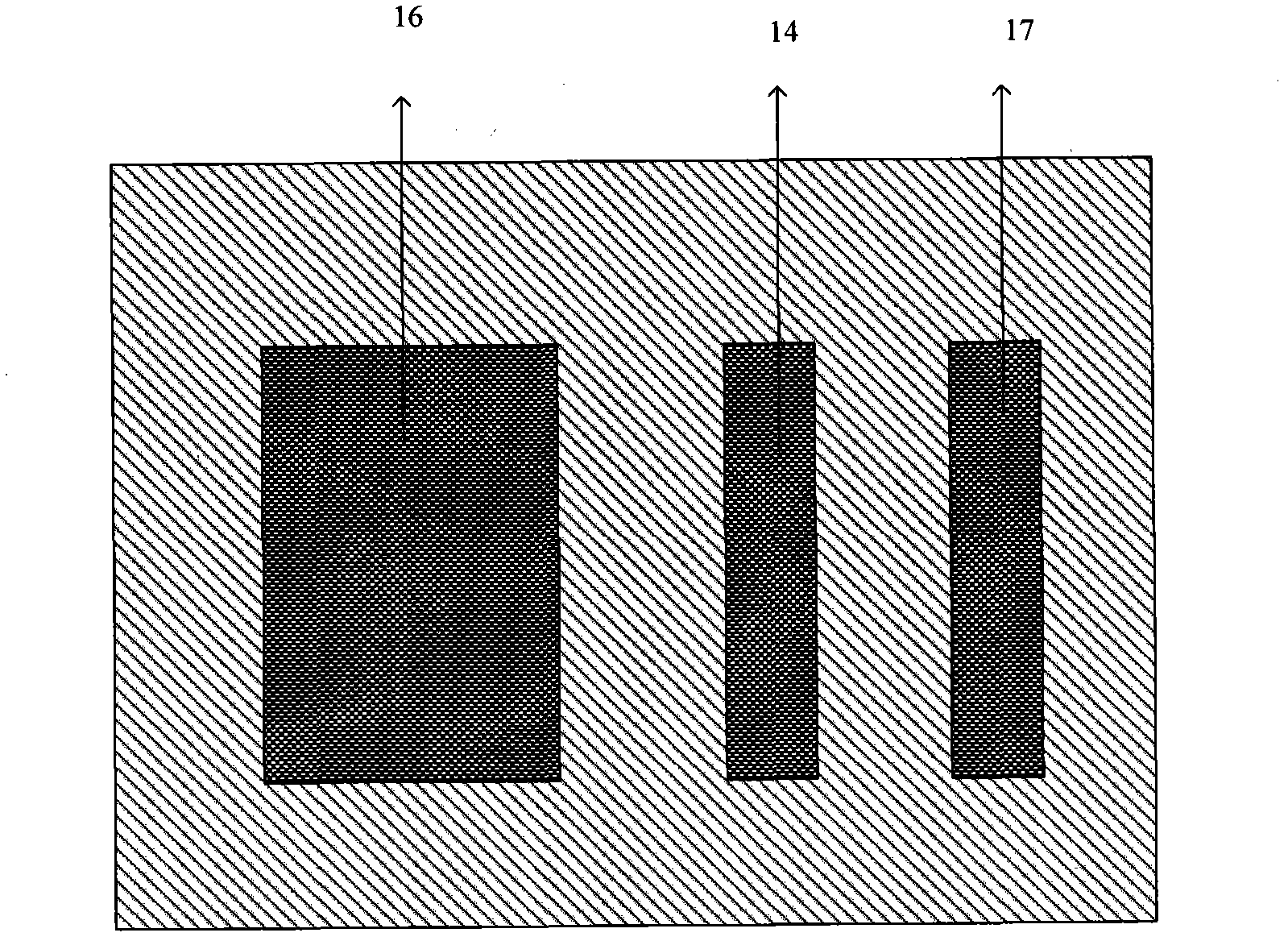

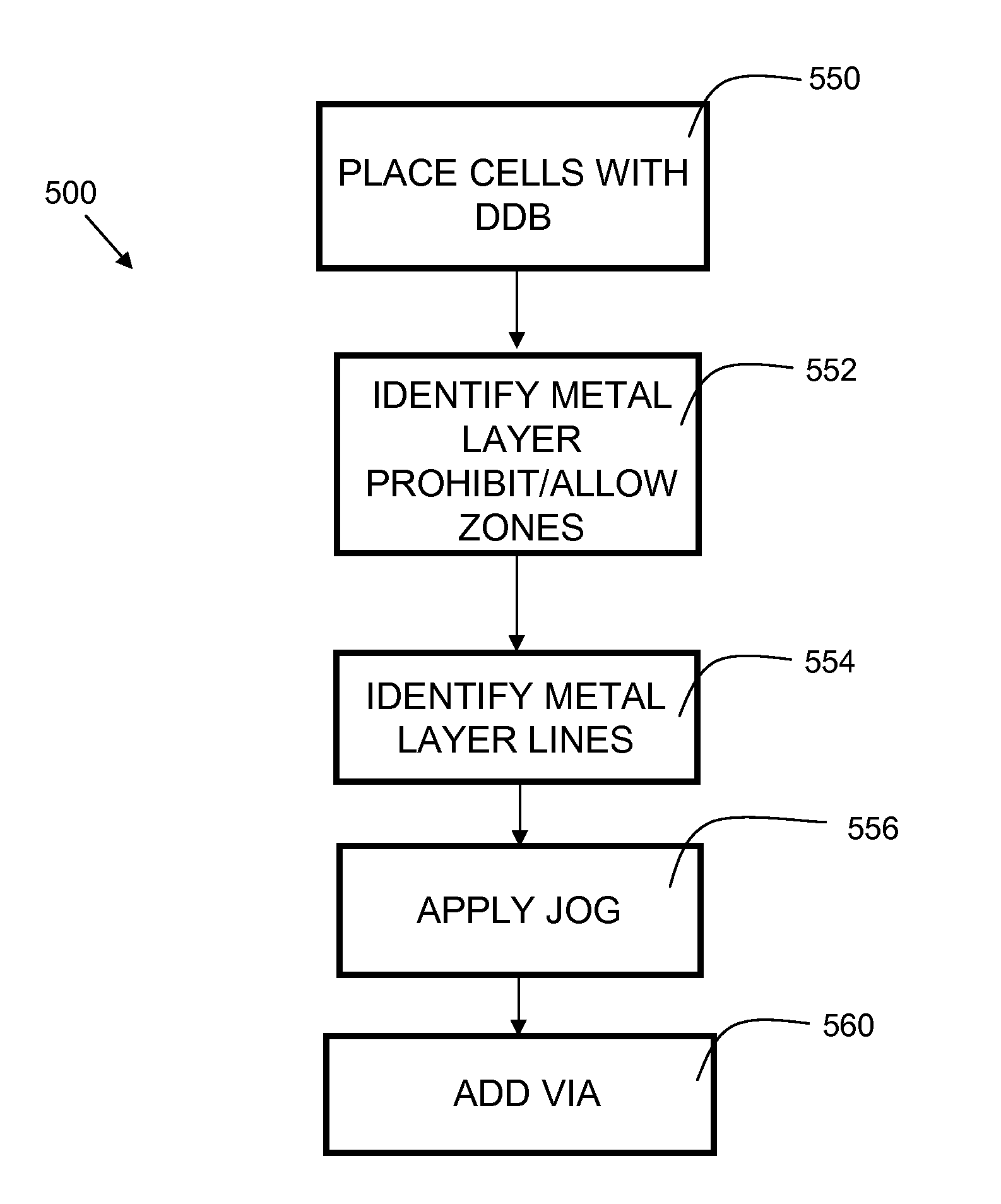

Methods for improving double patterning route efficiency

InactiveUS8881083B1Semiconductor/solid-state device detailsSolid-state devicesIntegrated circuitDouble diffusion

A design methodology for routing for an integrated circuit is disclosed. The method includes placement of cells having double diffusion breaks, which create an extended intercell region. Metal layer prohibit zones are defined to prohibit any M1 structures in the prohibit zones. Metal layer allow zones are placed adjacent to outer metal lines, and jogs are formed in the metal layer allow zones. Vias and viabars may then be applied on the jogs.

Owner:GLOBALFOUNDRIES INC

Flat acrylic fiber and production method thereof

ActiveCN103882547ALower glass transition temperatureGood flexibilitySpinnerette packsArtificial filament heat treatmentPolymer scienceDouble diffusion

The invention relates to a flat acrylic fiber and a production method thereof. The flat acrylic fiber consists of the following components in percentage by weight: 91-94 percent of acrylonitrile and 6-9 percent of vinyl acetate, wherein the length-width ratio of the flat acrylic fiber is (2-13):1. The method for producing the flat acrylic fiber comprises the following steps: carrying out copolymerization reaction on the acrylonitrile and the vinyl acetate to prepare dried polyacrylonitrile powder, dissolving the powder in a solvent to form a stock solution, extruding from a rectangular hole of a spinneret plate after heating, and performing double diffusion to form a nascent fiber in a coagulating bath; washing the nascent fiber by water, and drawing the fiber through a drawing machine; oiling tows; and drying the tows and setting, so as to obtain the flat acrylic fiber. The contents of the acrylonitrile and the vinyl acetate in a copolymer, the molecular weight of the copolymer and a specific process flow are adjusted, so that the prepared flat acrylic fiber is good in handfeel, the softness and handfeel of the fiber can be improved, the rebound resilience, hydrophobicity and spinnability of the fiber can be guaranteed, and the acrylic fiber is easy to color.

Owner:NINGBO ZHONGXIN ACRYLIC FIBERS

Method suitable for carrying out consolidation forming on polyacrylonitrile carbon fiber precursor by dry-wet method

ActiveCN104264286AImprove applicabilityPositive supportArtificial filament chemical after-treatmentDouble diffusionResidence time

The invention relates to a method suitable for carrying out consolidation forming on a polyacrylonitrile carbon fiber precursor by a dry-wet method. The method comprises the following preparation steps: in a low-temperature low-concentration coagulating bath with a consolidation temperature of 20 DEG C below zero to 25 DEG C and mass concentration of 5 to 40 percent, enabling spinning solution to pass through a spinneret plate and jetting the spinning solution by an air layer so as to enable the spinning solution to enter the coagulating bath, wherein residence time in the coagulating bath is 2 to 10s; rapidly quenching the surface of stock solution to generate a hard film; by the hard film and the conditions of low temperature, low concentration and the like, slowing down a double diffusion rate, improving the orientation degree of nascent fibers by the hard film to realize homogenizing of consolidation forming and avoid a skin-core structure so as to obtain the nascent fibers with pre-draft times of 2.3 to 4.0 times, wherein the nascent fibers have orientation degree of 65 to 70 percent. The protofilament prepared by the method disclosed by the invention has high homogeneity; high-quality protofilaments and carbon filaments can be obtained; moreover, in the dry-wet technology, the method has strong universality and can be popularized and used in the dry-wet production.

Owner:ZHONGFU SHENYING CARBON FIBER