Patents

Literature

1136 results about "Source area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition of Source area. Source area means a component of urban land use in- cluding rooftops, sidewalks, driveways, parking lots, storage areas, streets and lawns from which urban runoff pollutants are generated during periods of snow melt and rainfall runoff.

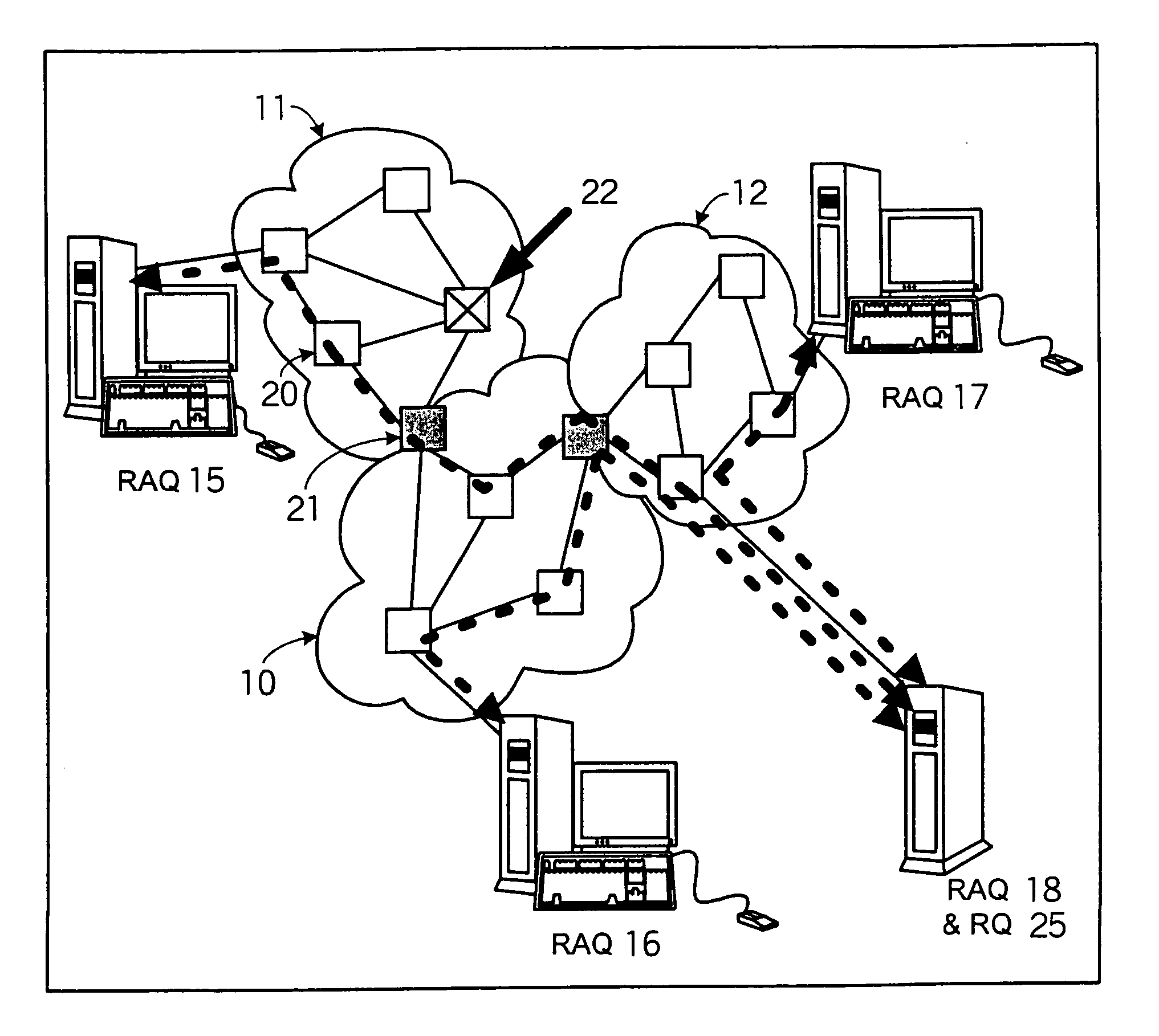

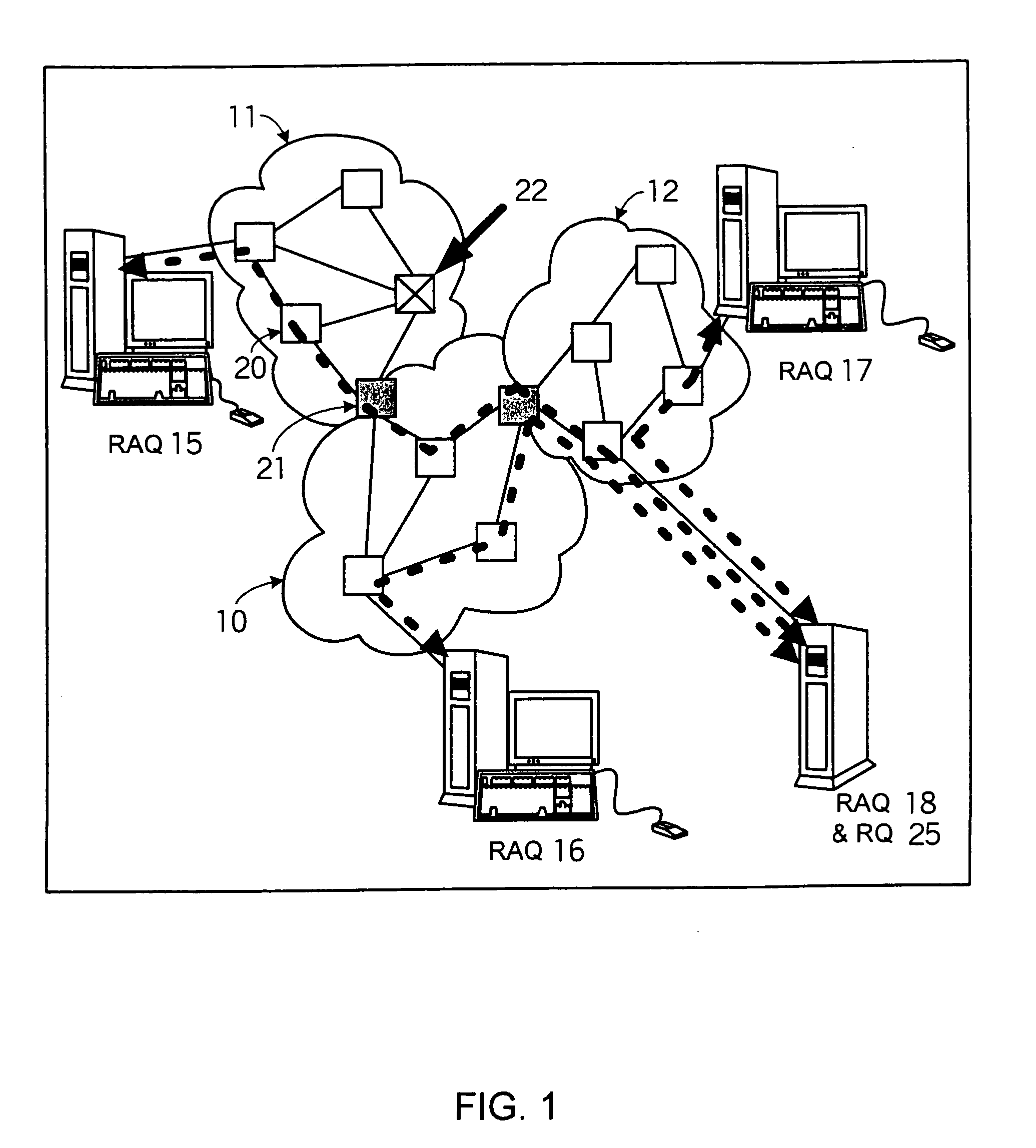

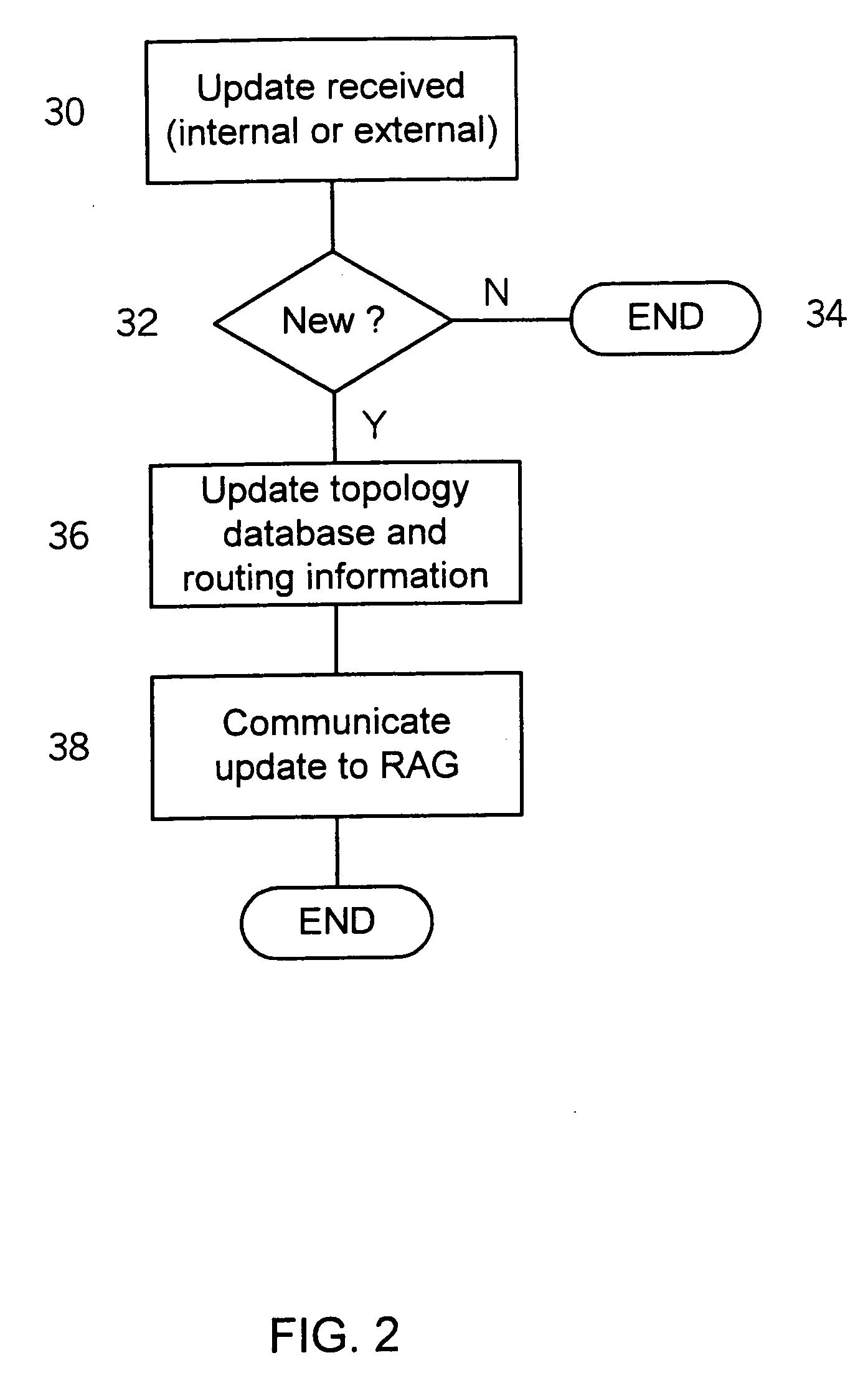

Method and system for path identification in packet networks

ActiveUS20050025059A1Simple methodColor television with pulse code modulationError preventionEntry pointSource area

A method and system for extracting and building end-to-end route information in a multi-area Internet protocol (IP) autonomous system (AS) is disclosed. The method and system enable a user, such as a network administrator, to explicitly identify a full set of paths (links and routers) that a given IP packet would potentially traverse from its entry point in the source area of the AS where it originates until its exit point in its intended destination area.

Owner:SONS OF INNOVATION LLC

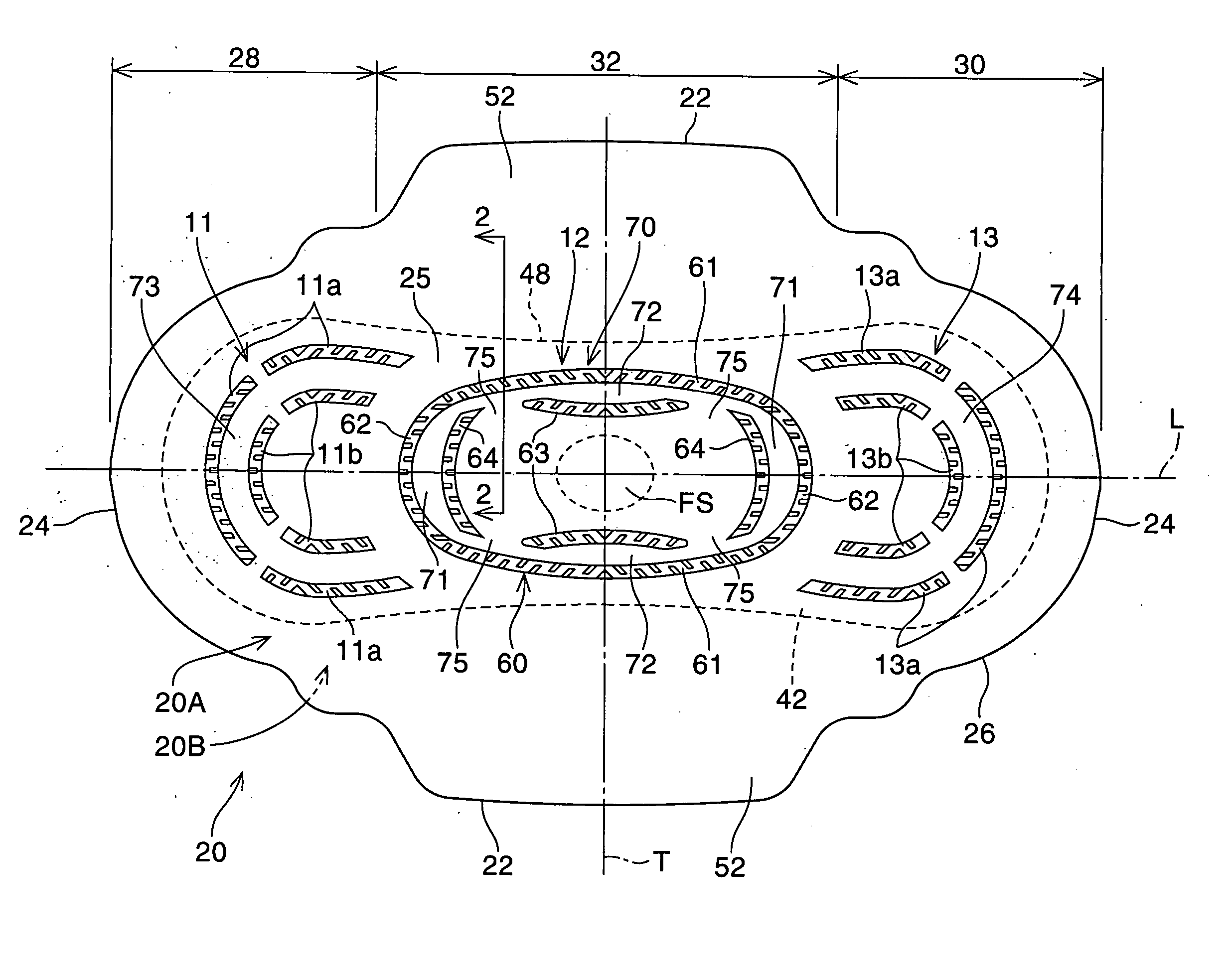

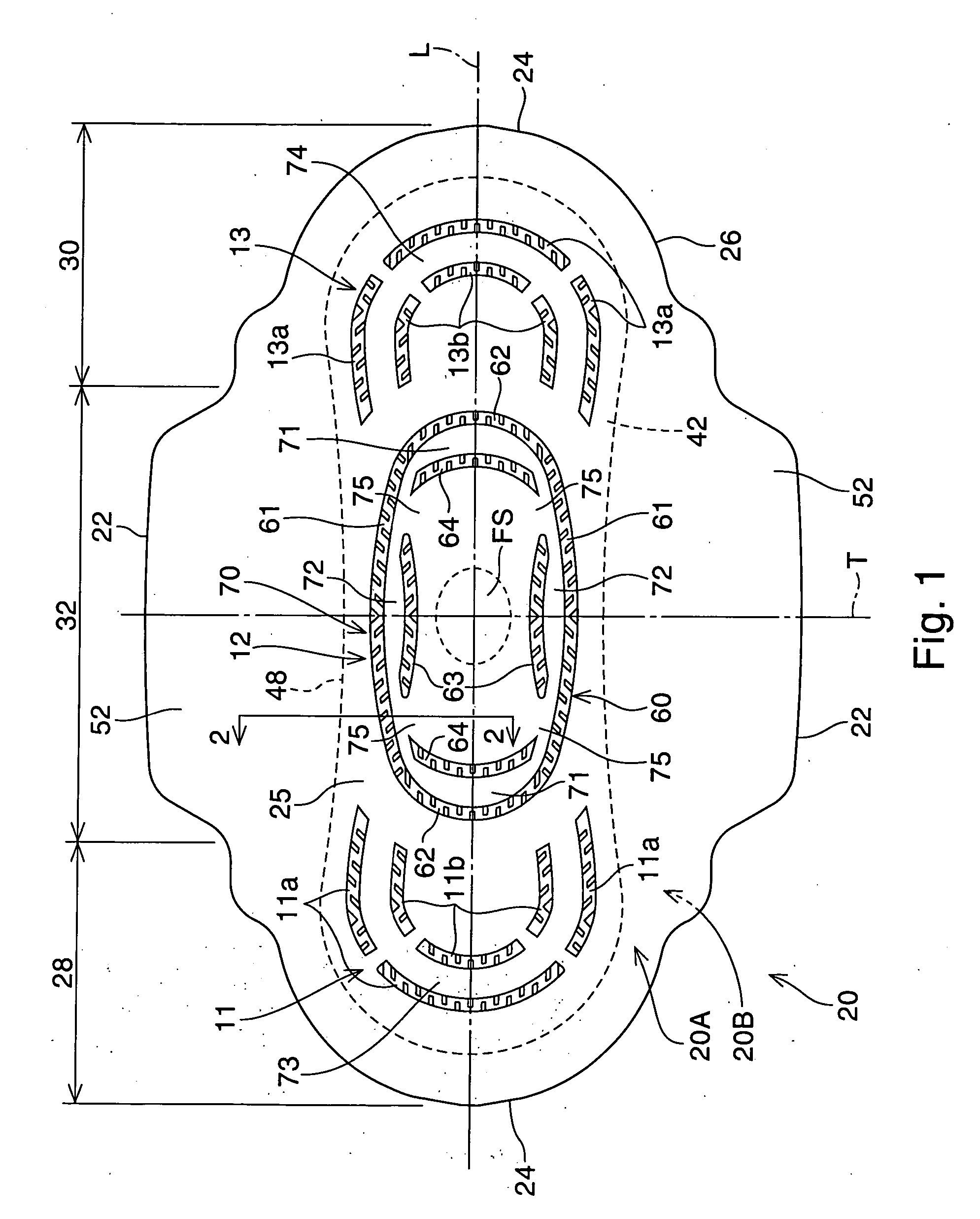

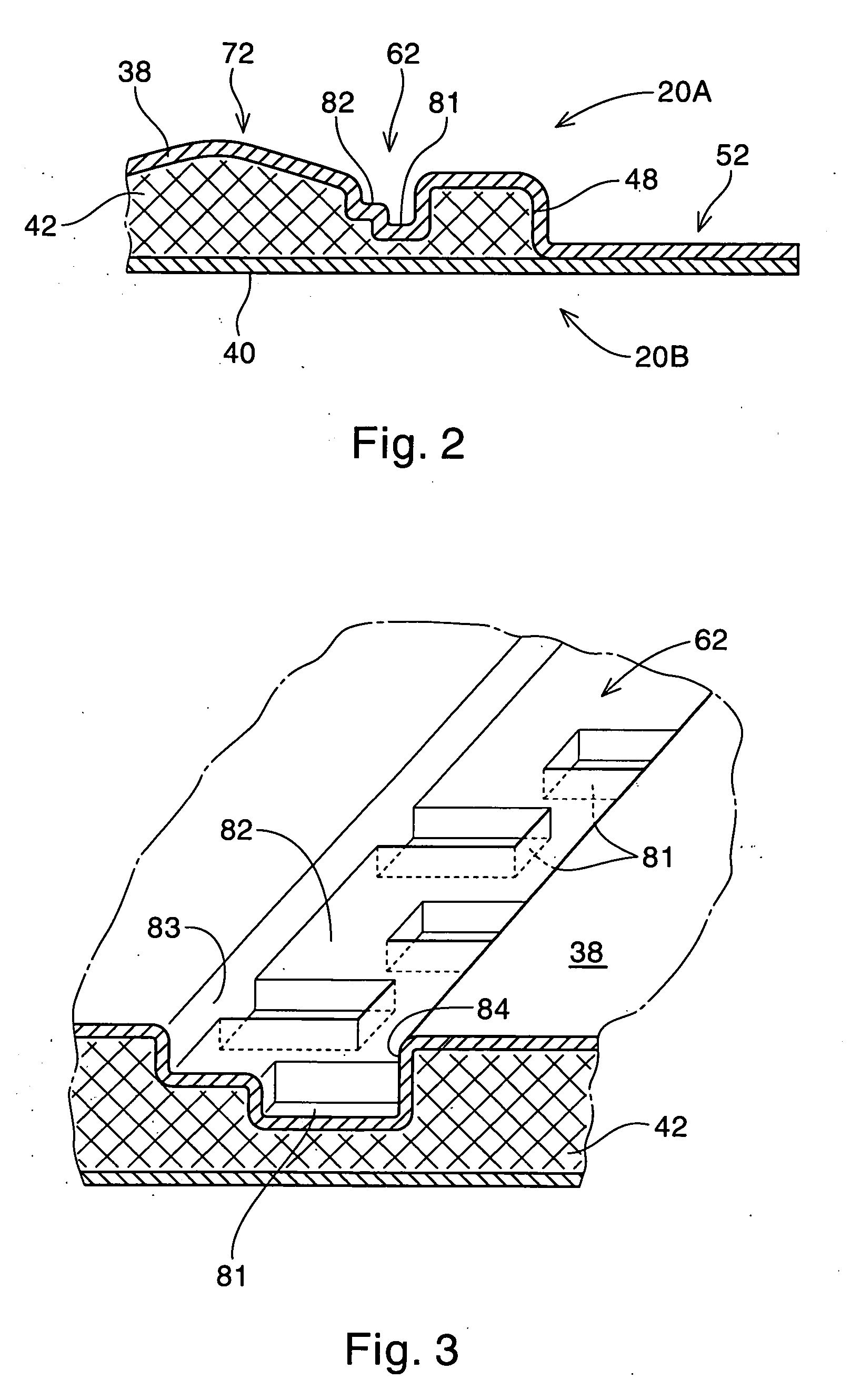

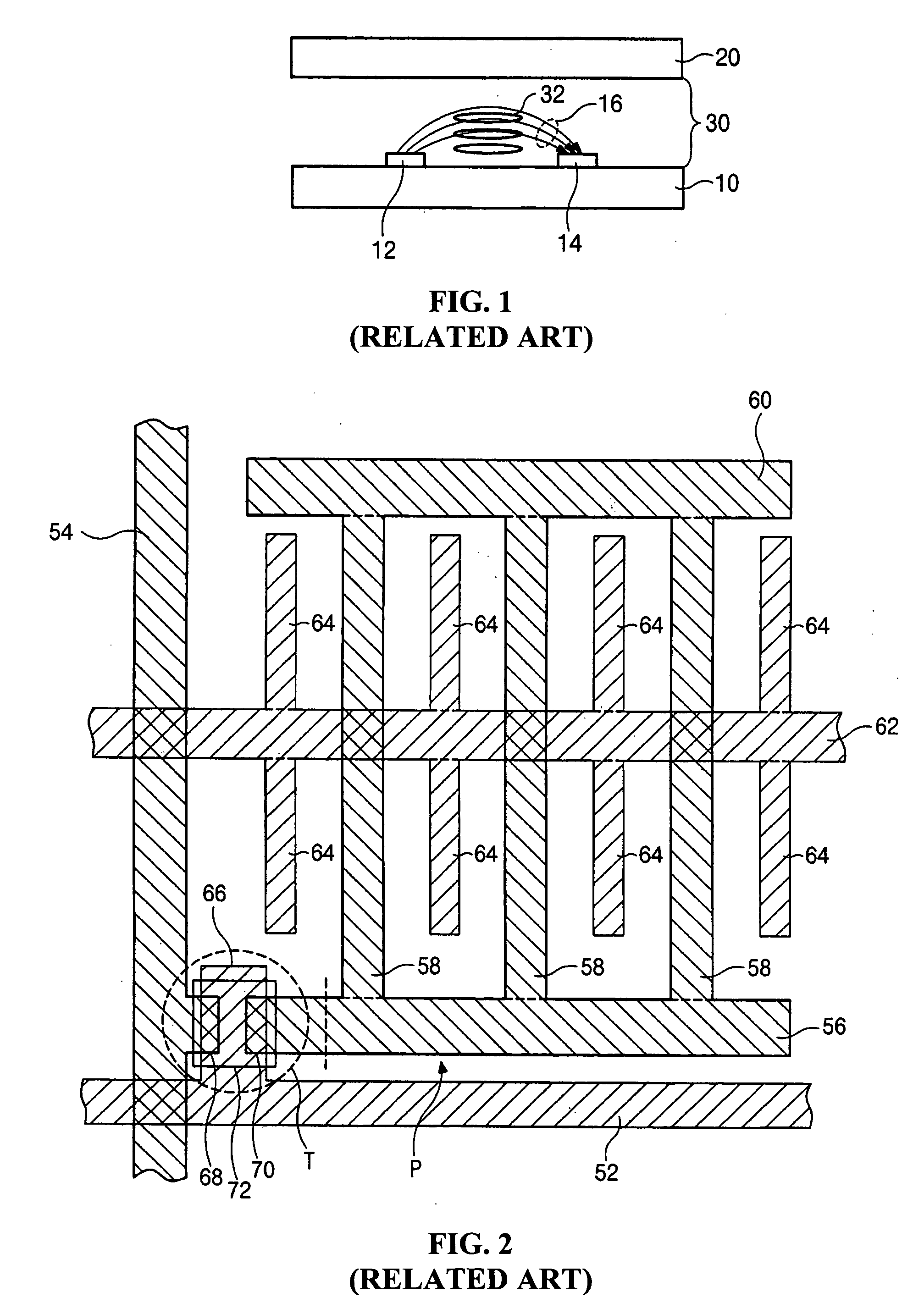

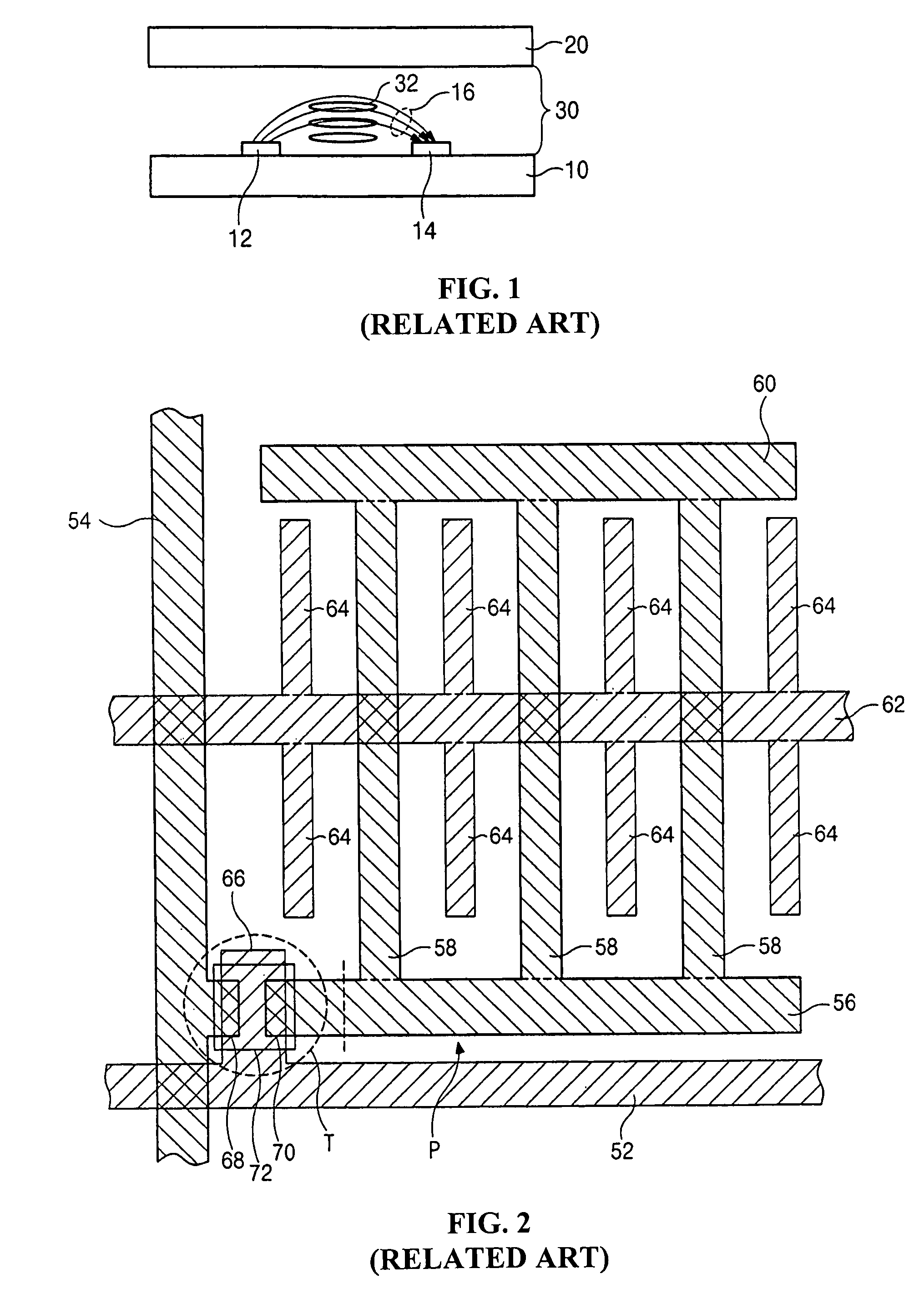

Absorbent article having traverse reinforcing element

An absorbent article having a front end region, a rear end region, a central region disposed between the front and rear end regions, a fluids source area, and a transverse axis and a longitudinal axis. The absorbent article includes a topsheet, a backsheet, an absorbent core disposed between the topsheet and the backsheet, and a reinforcing structure disposed within the central region. In one aspect of the invention, the reinforcing structure includes a pair of traverse reinforcing elements each of which is formed by two traverse channels. The two traverse channels may be disposed generally parallel to the transverse axis with a reinforcement distance such that the absorbent core has an average density of in the range of about 5% to about 500% higher at the traverse reinforcing element than the fluids source area.

Owner:THE PROCTER & GAMBLE COMPANY

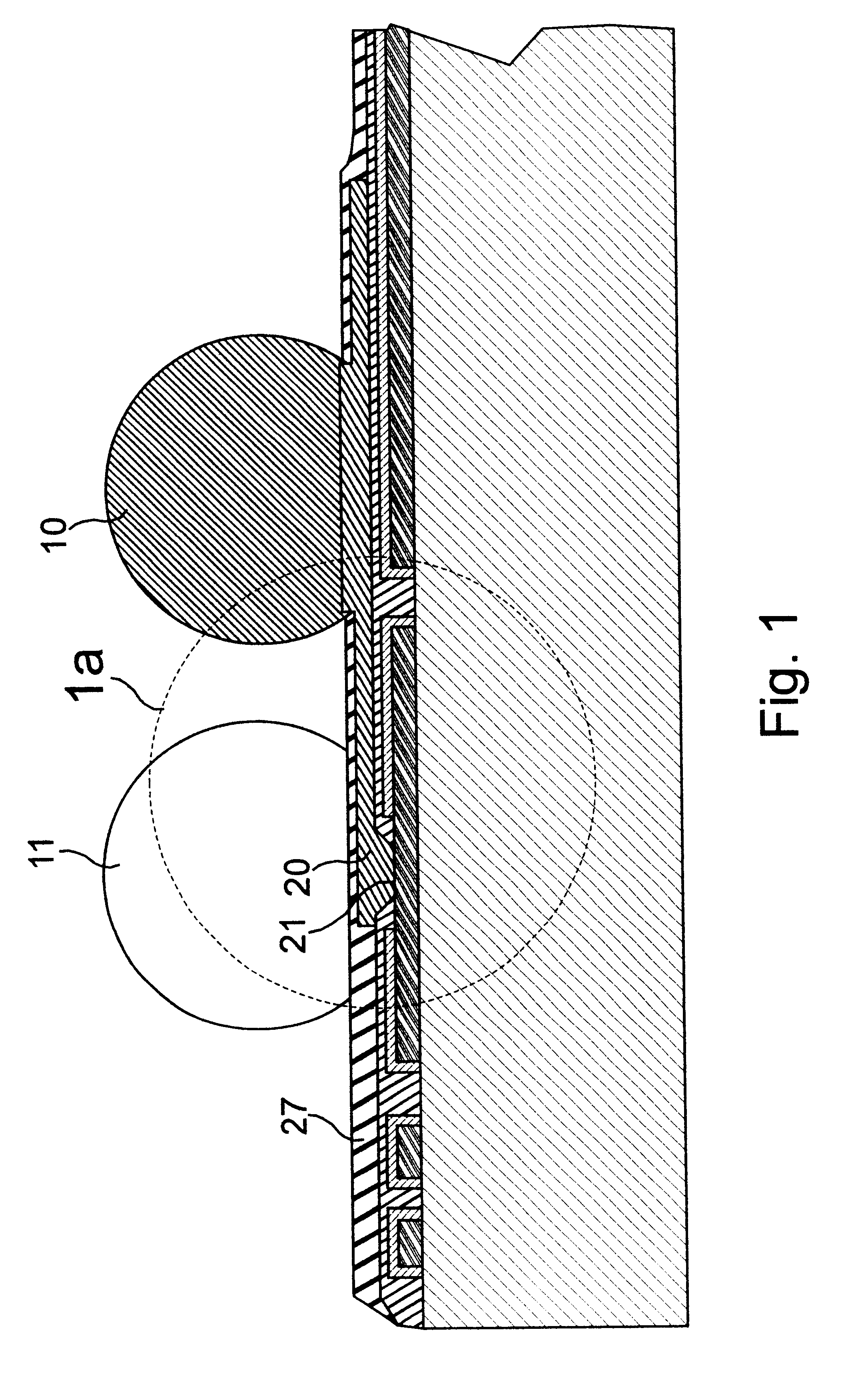

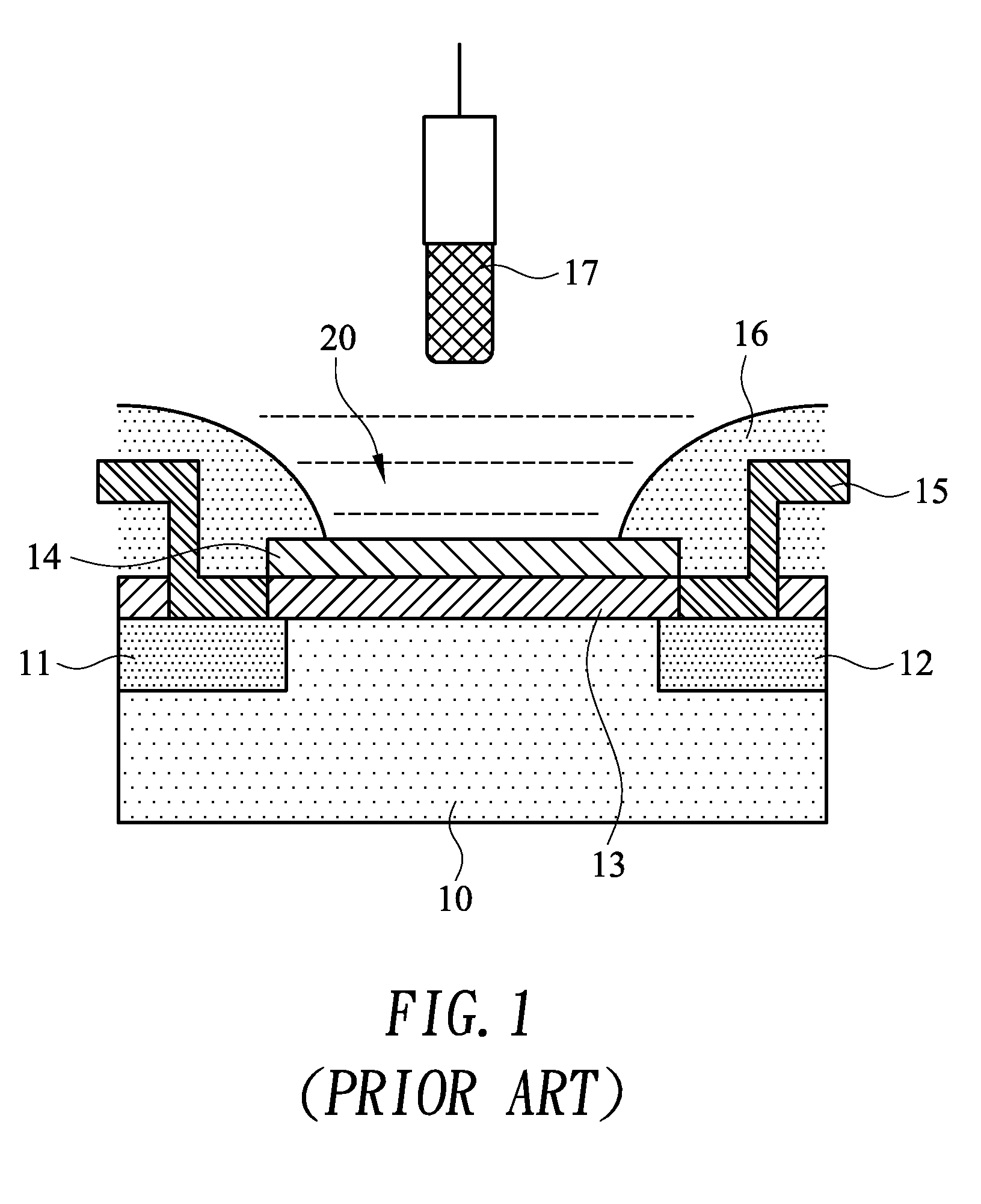

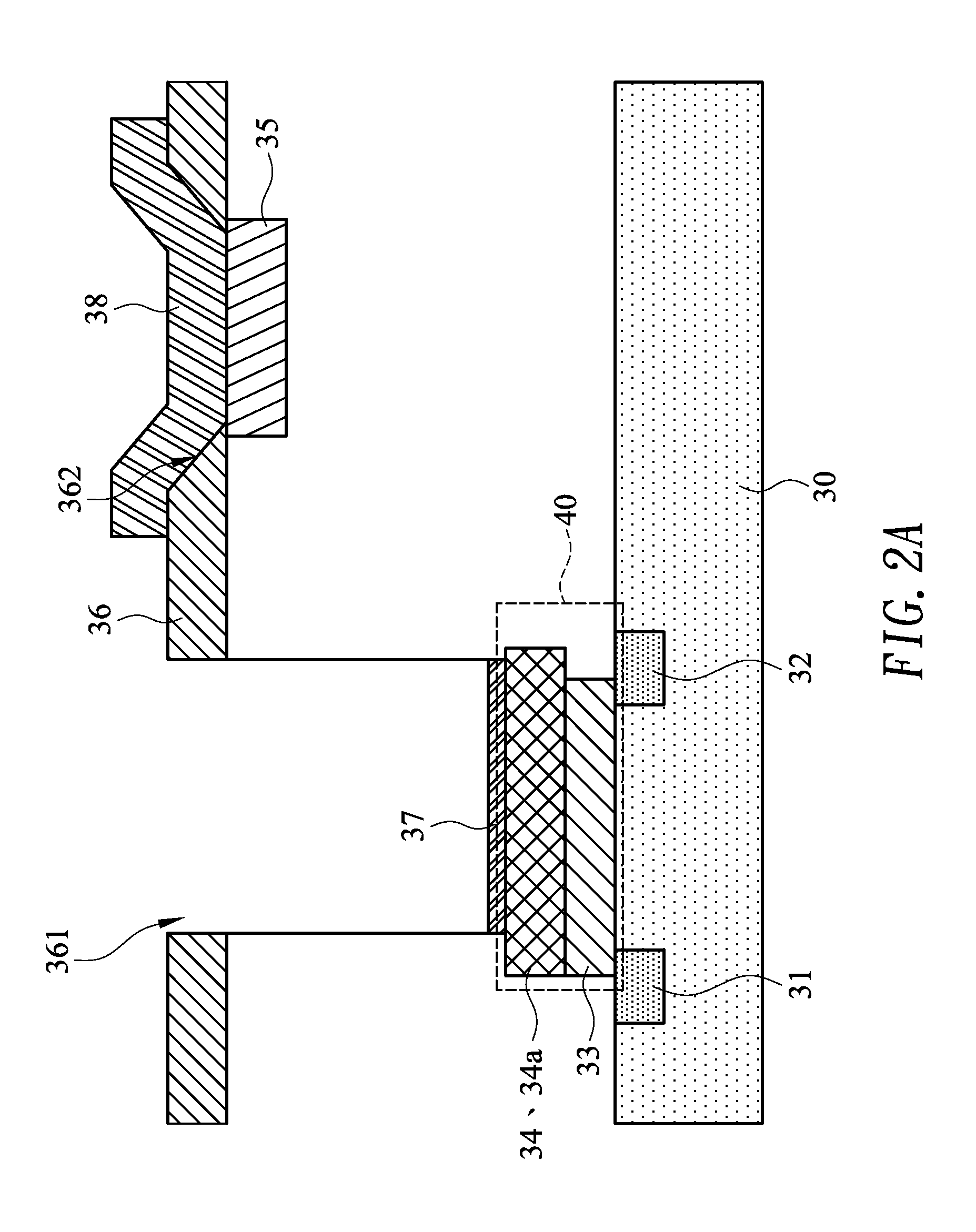

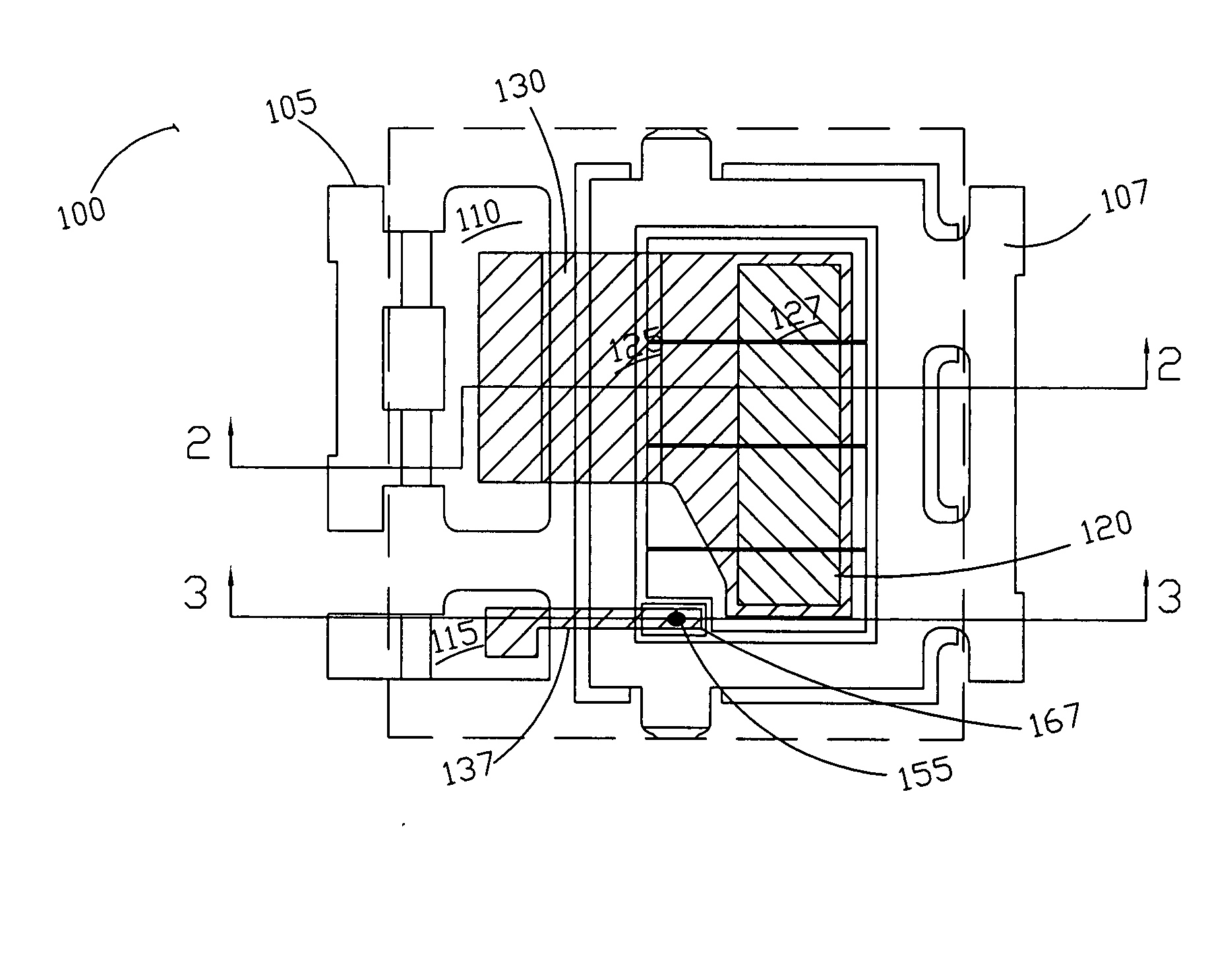

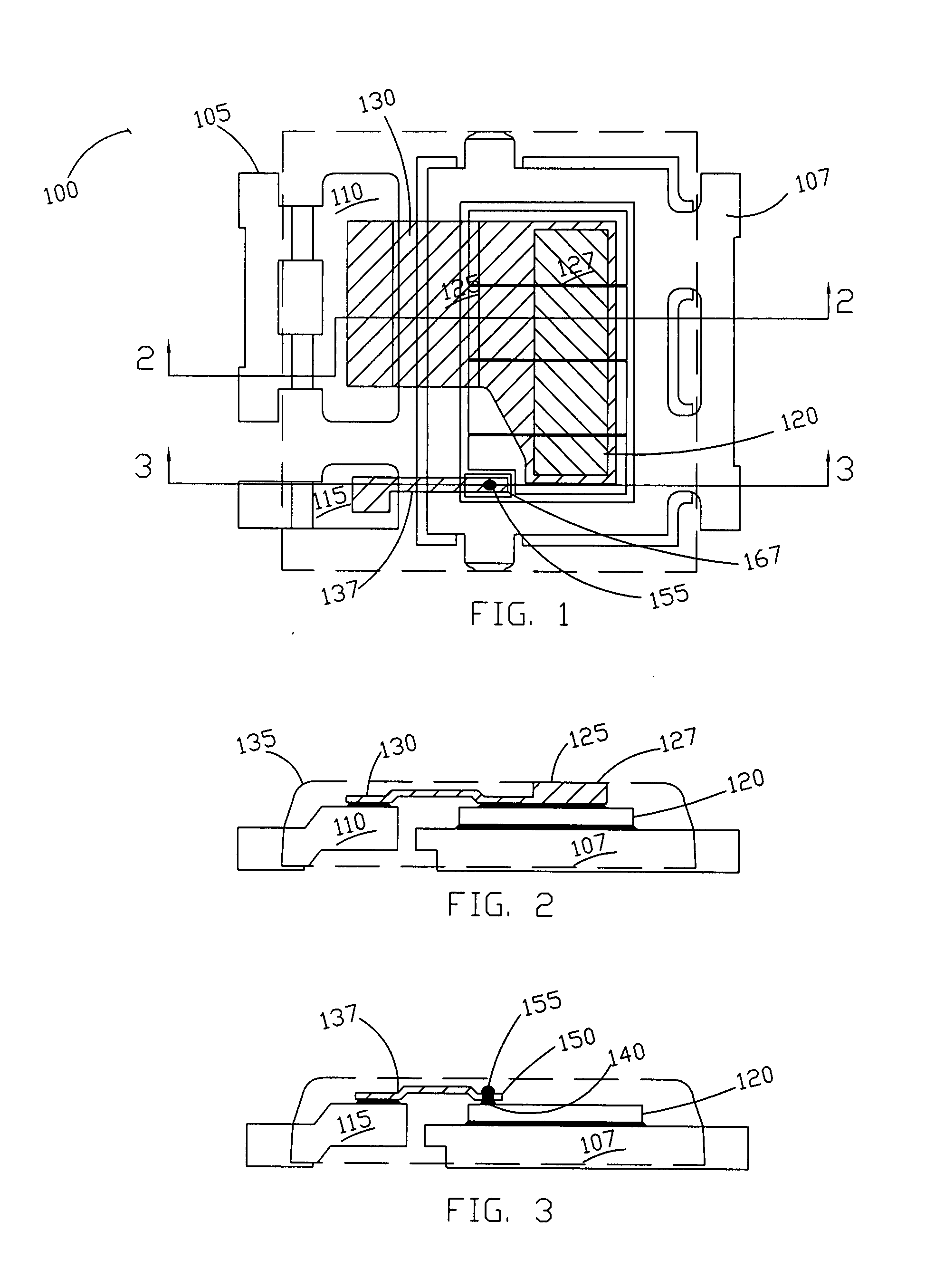

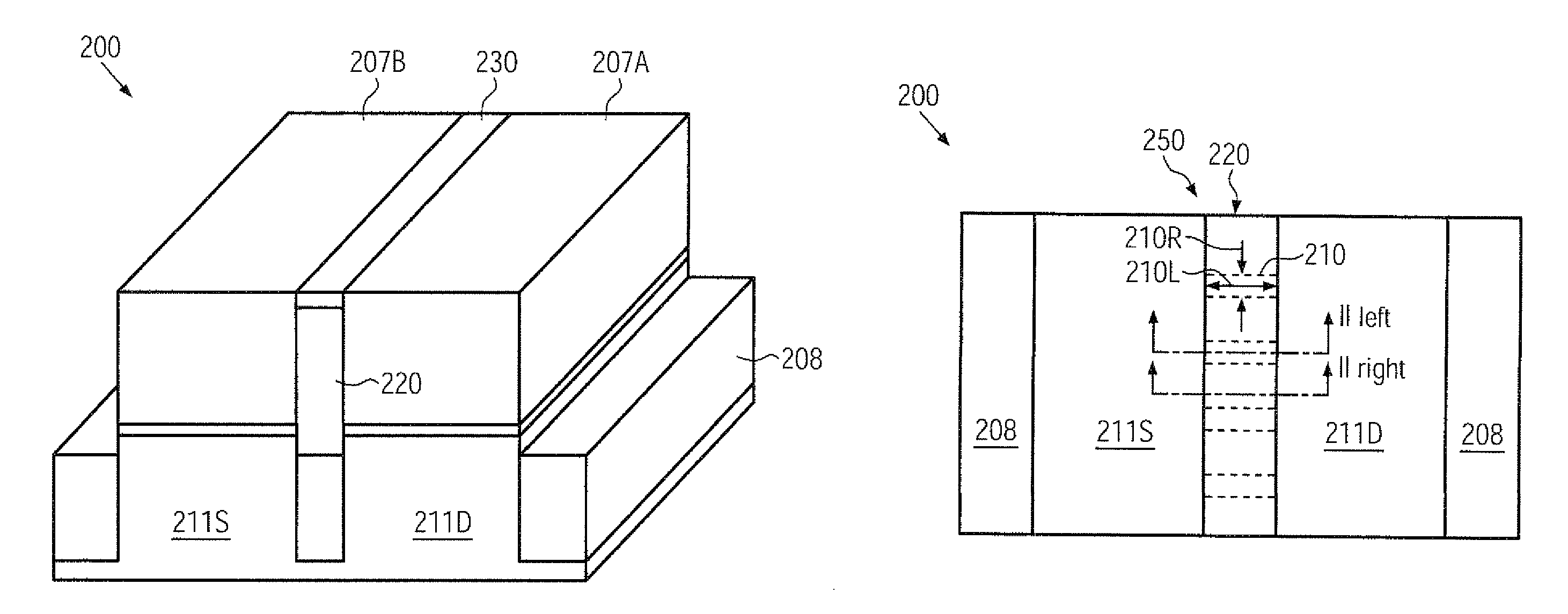

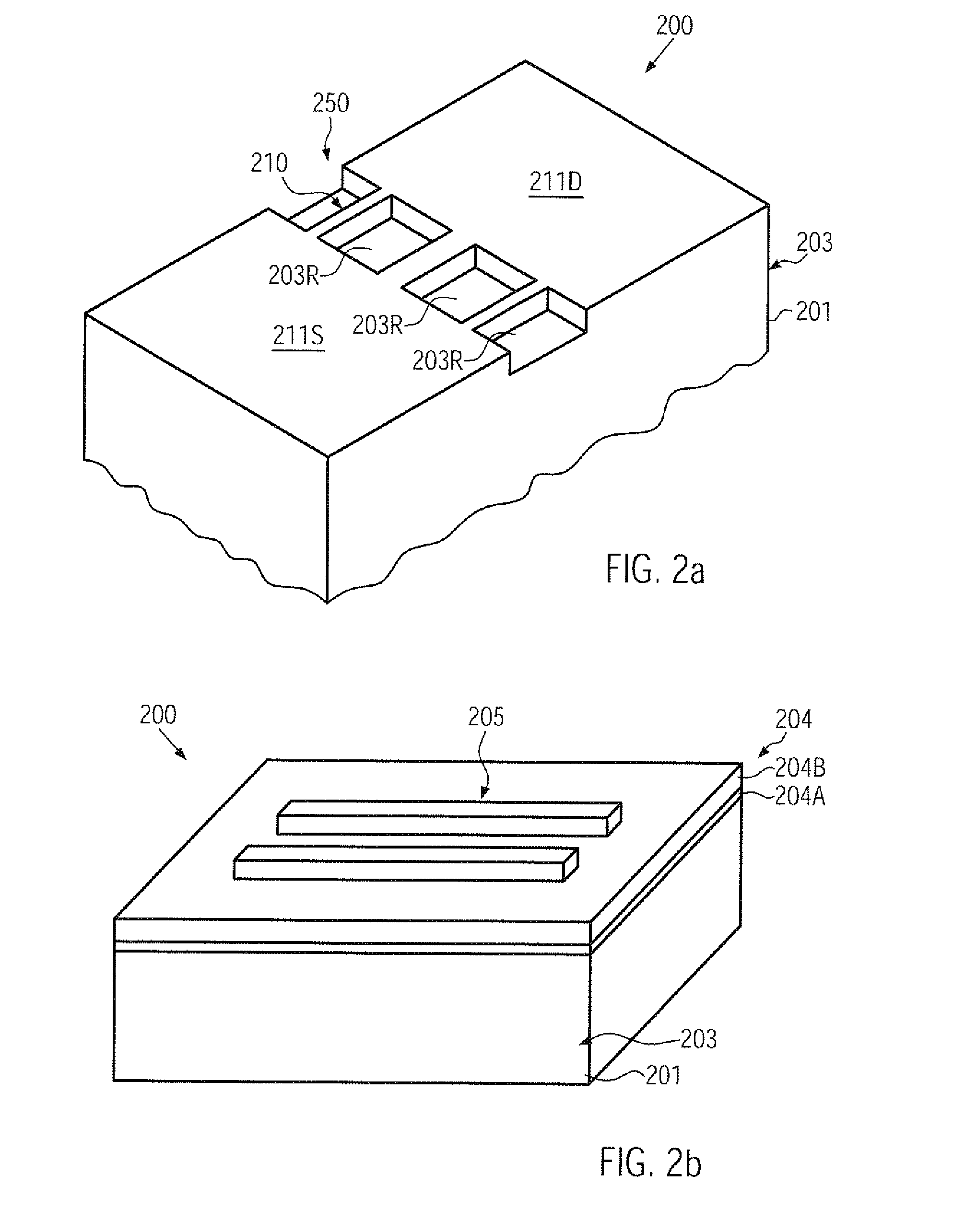

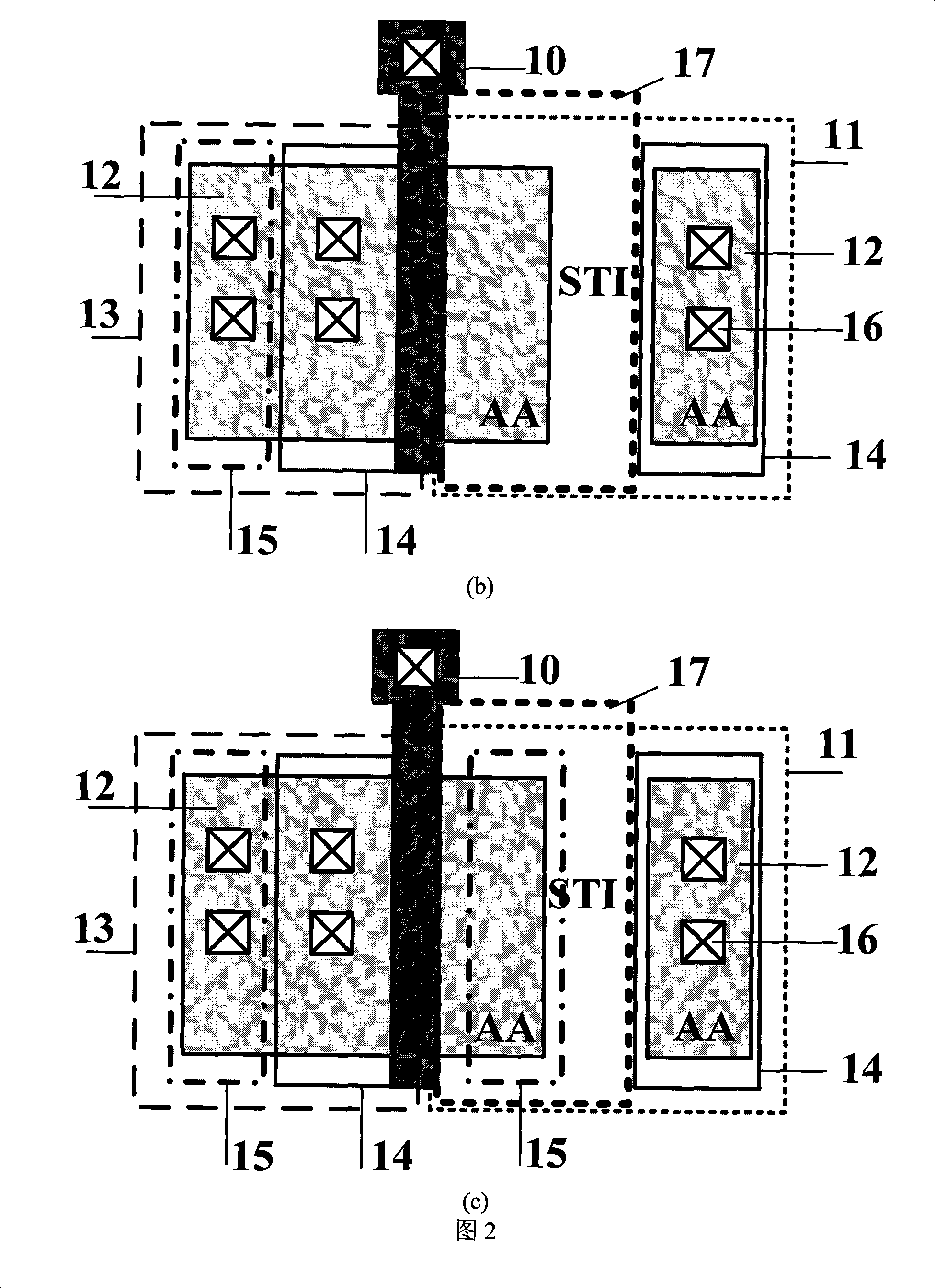

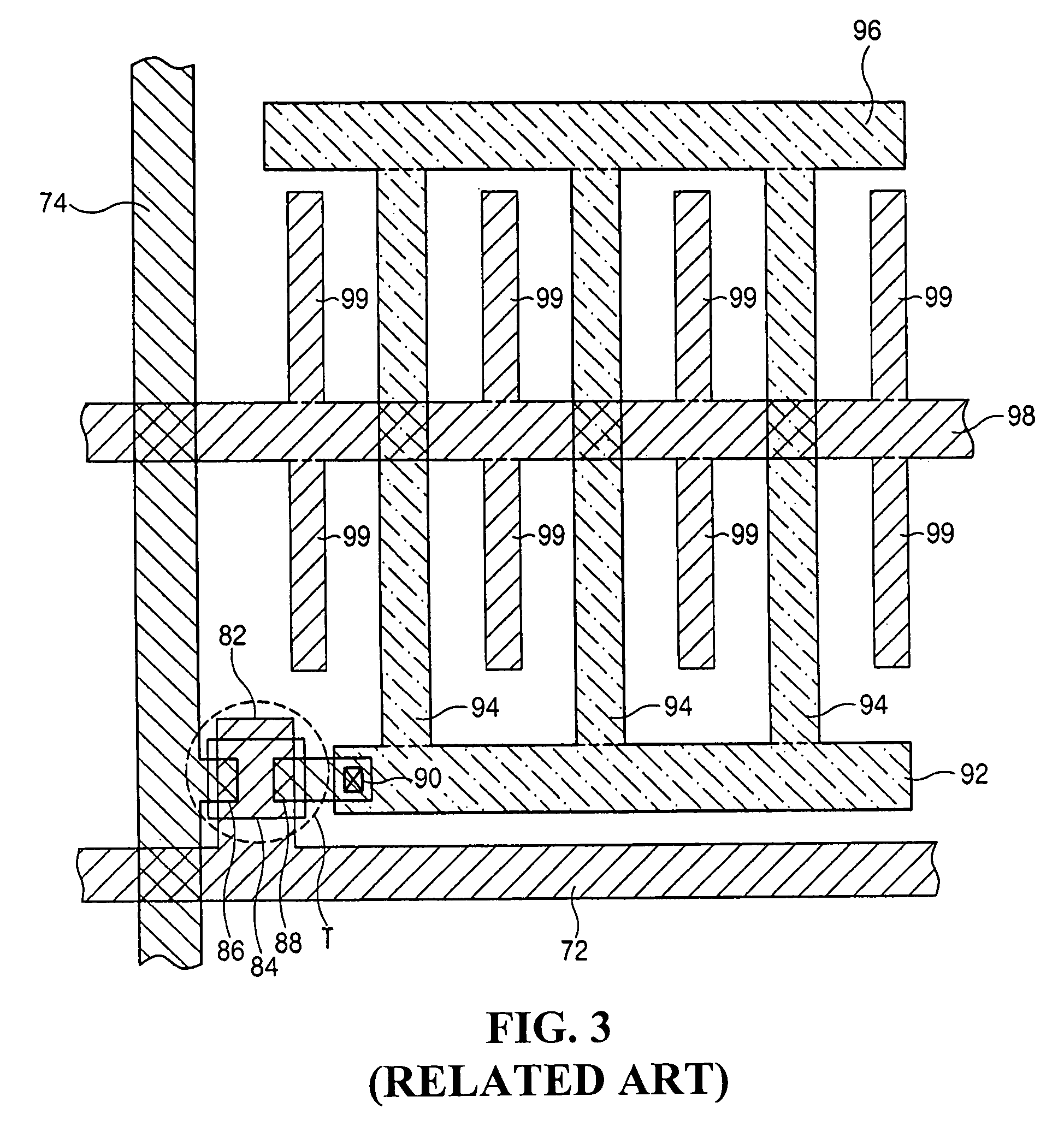

MOSFET device with multiple gate contacts offset from gate contact area and over source area

Careful repositioning of MOSFET gate contacts and increasing of their number makes MOSFET gate contacts more durable and reliable without requiring changes in either the leadframe design or the assembly process. Extension of the under-bump metal laterally from the gate contact with the gate pad metallization out to two or more gate pads not overlying the gate pad metallization minimizes the risk of delamination of the metallization due to thermal and mechanical stresses in assembly and operation. Use of more than one gate pad further reduces such failure risks. Positioning the gate pads sufficiently close to the original gate contact permits use of the same leadframe design and assembly process as would be used for a single gate pad placed directly over the gate contact. The result is a reliable, durable MOSFET gate contact compatible with current assembly methods.

Owner:SEMICON COMPONENTS IND LLC

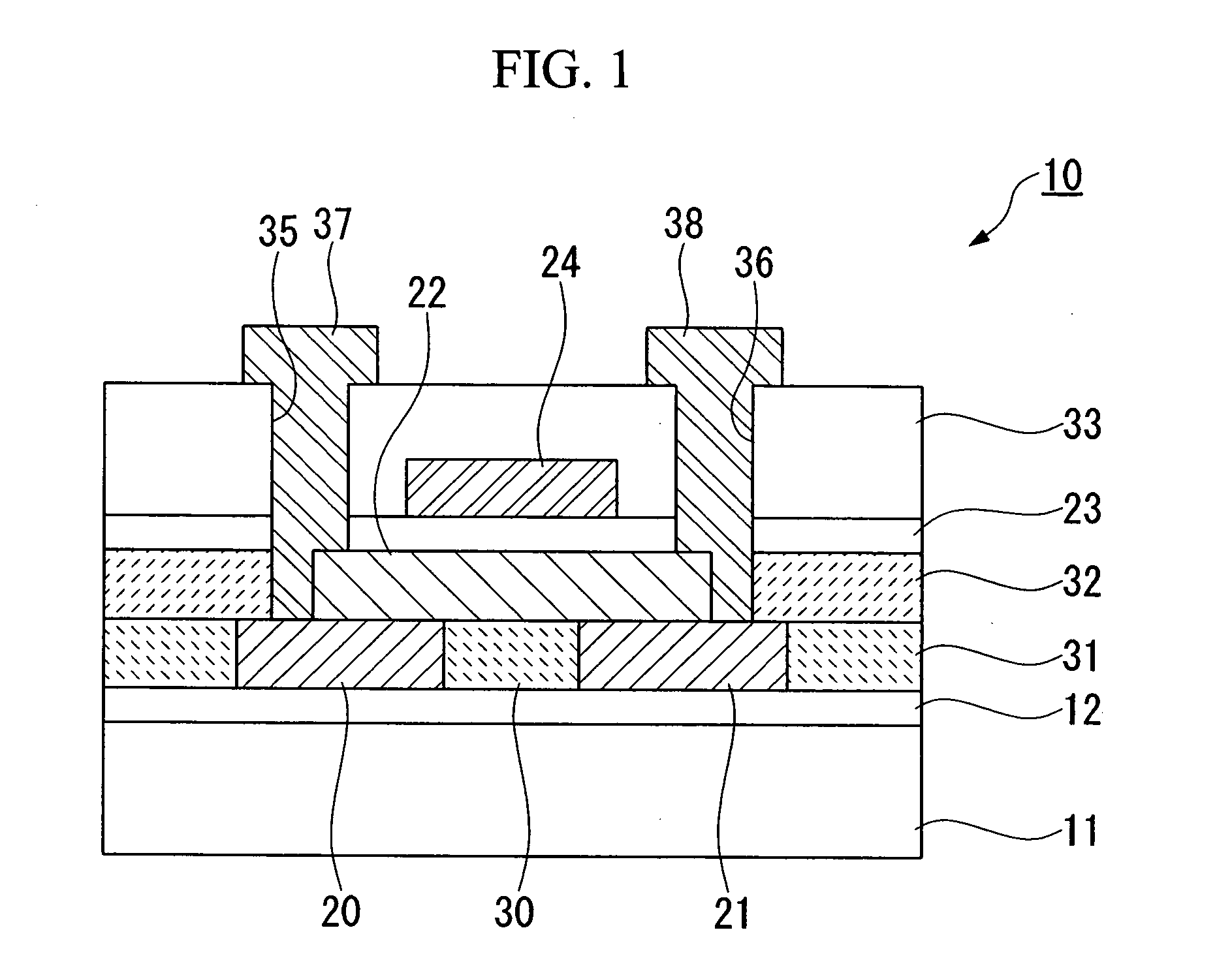

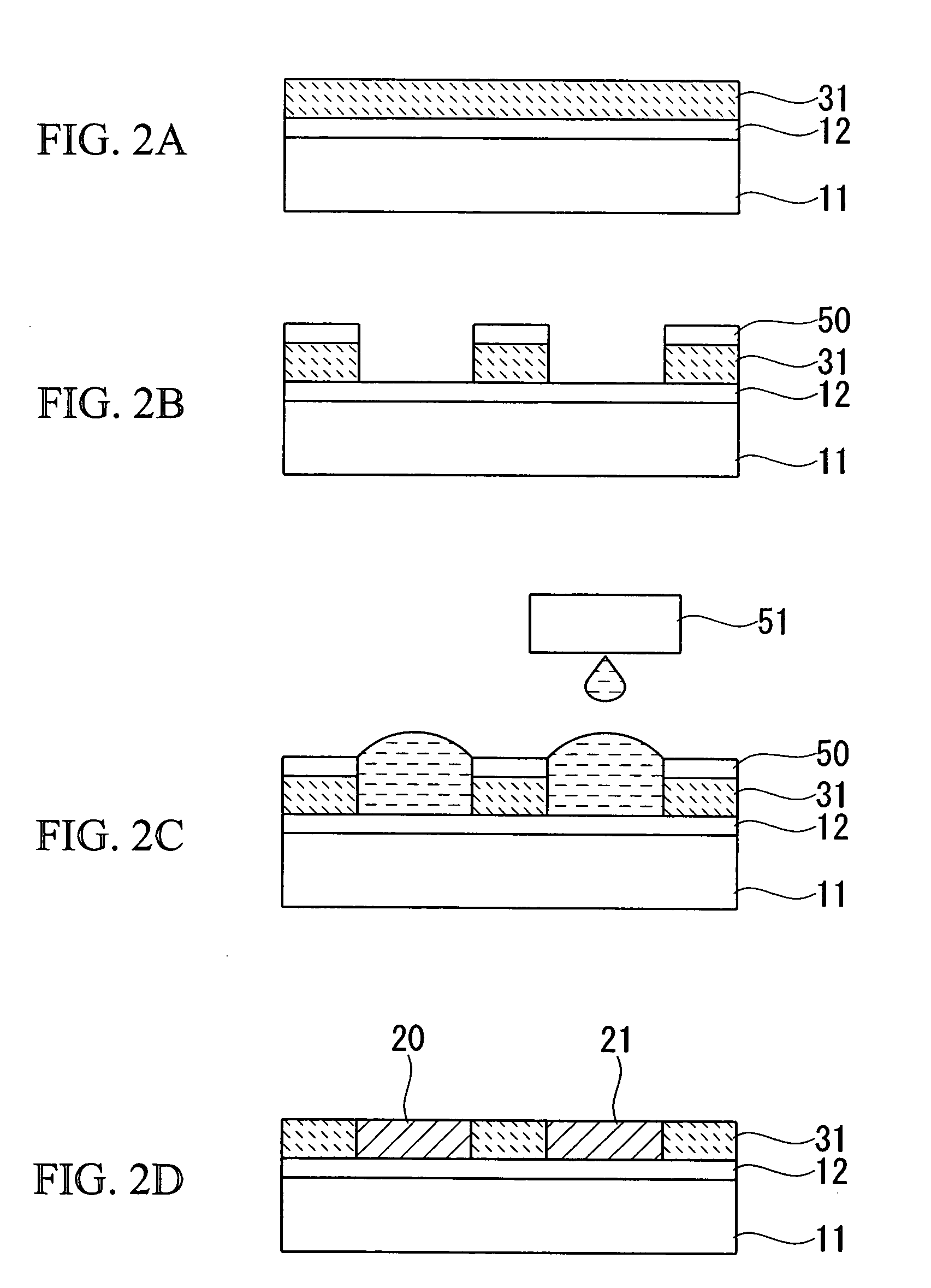

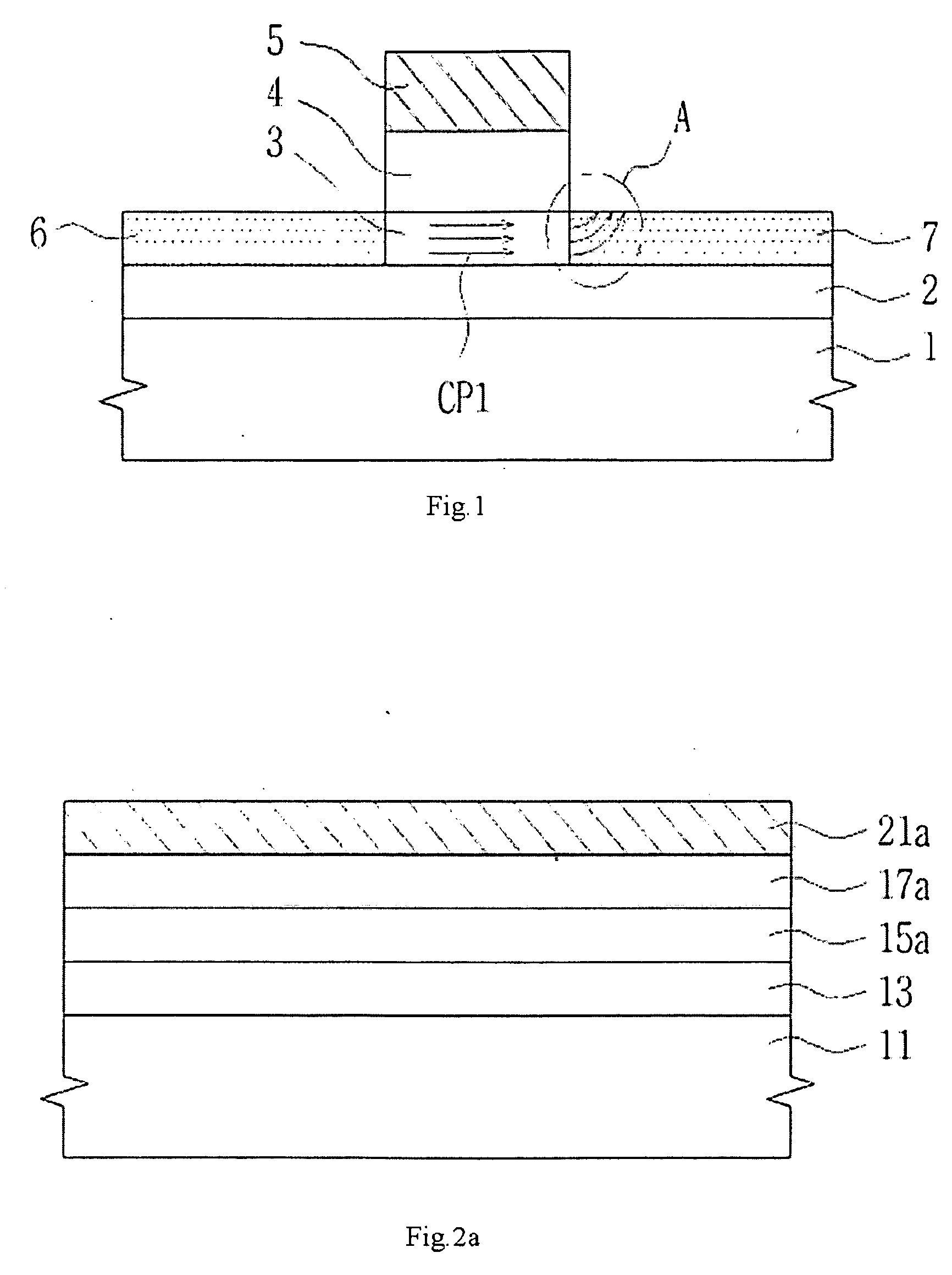

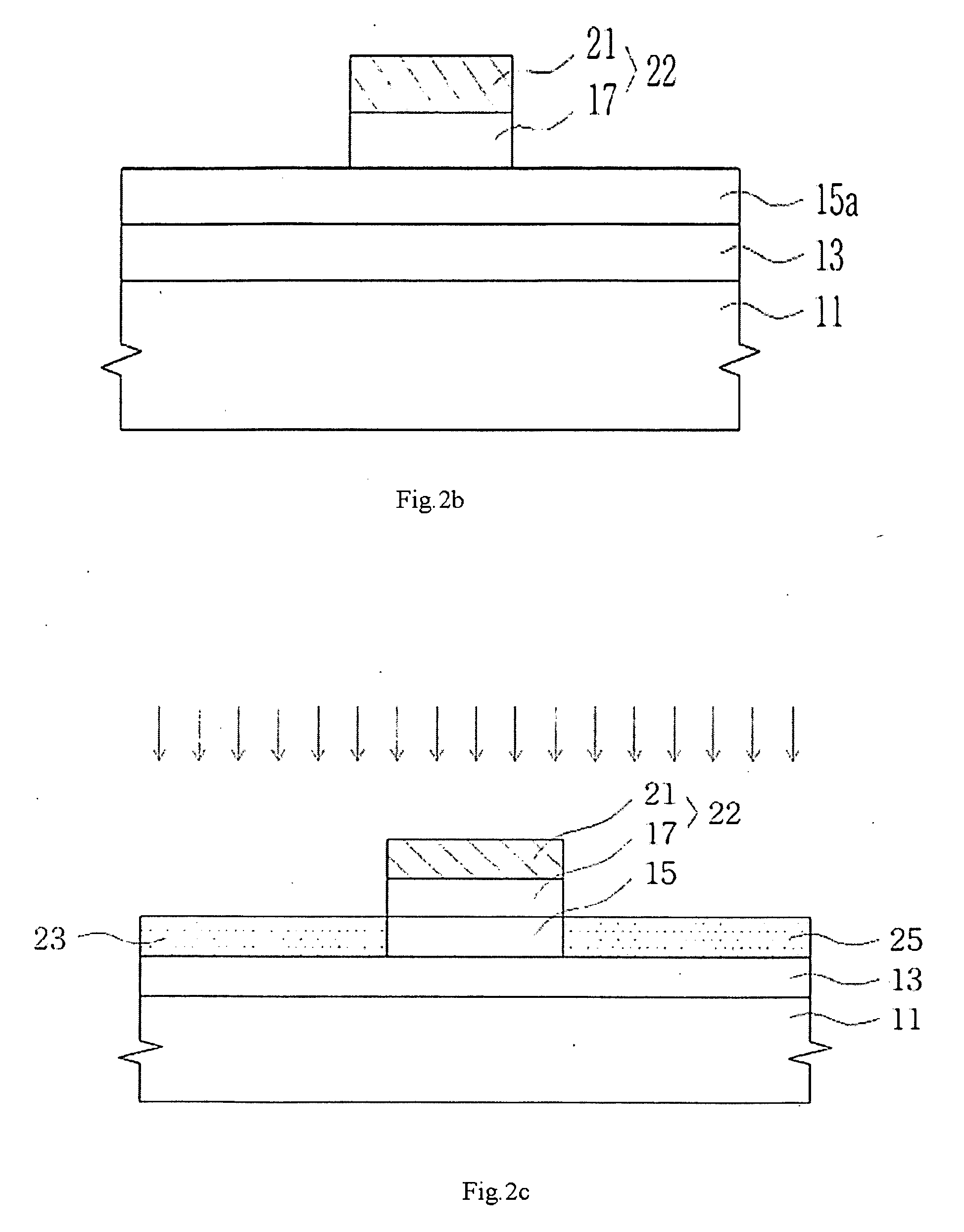

Hydrogen ion-sensitive field effect transistor and manufacturing method thereof

ActiveUS20110169056A1Thin and compactThin layerSemiconductor/solid-state device detailsSolid-state devicesEngineeringSource area

A hydrogen ion-sensitive field effect transistor and a manufacturing method thereof are provided. The hydrogen ion-sensitive field effect transistor includes a semiconductor substrate, an insulating layer, a transistor gate, and a sensing film. A gate area is defined on the semiconductor substrate having a source area and a drain area. The insulating layer is formed within the gate area on the semiconductor substrate. The transistor gate is deposited within the gate area and includes a first gate layer. Further, the first gate layer is an aluminum layer, and a sensing window is defined thereon. The sensing film is an alumina film formed within the sensing window by oxidizing the first gate layer. Thus, the sensing film is formed without any film deposition process, and consequently the manufacturing method is simplified.

Owner:NAT APPLIED RES LAB

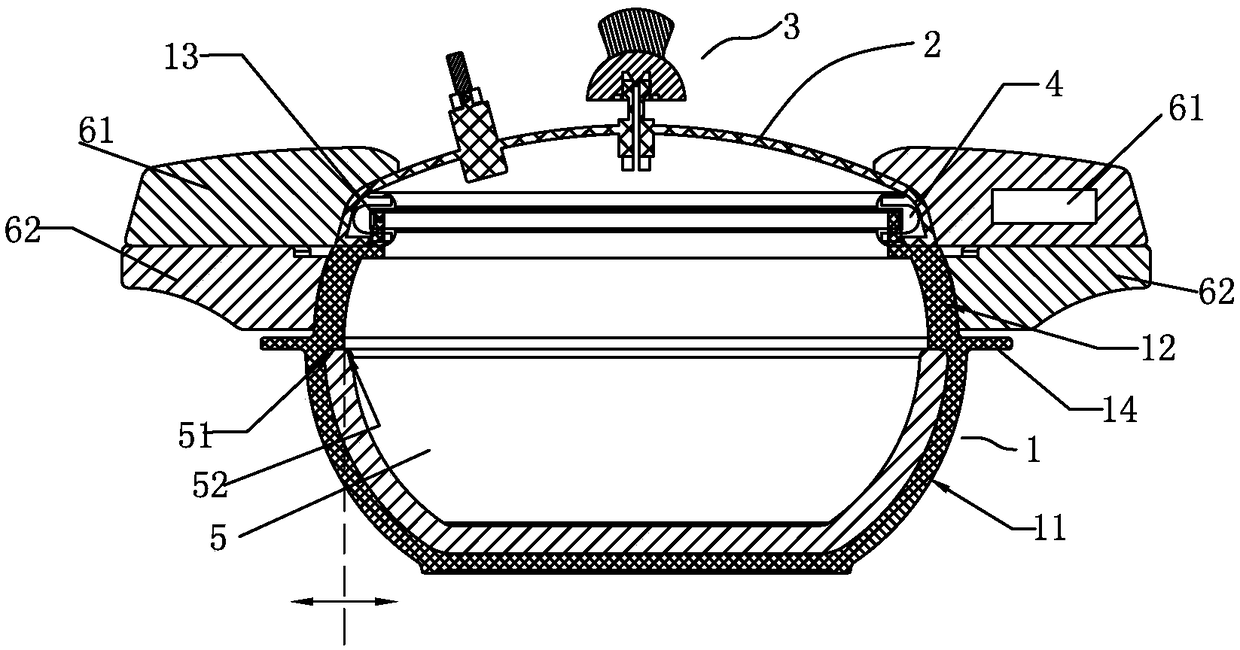

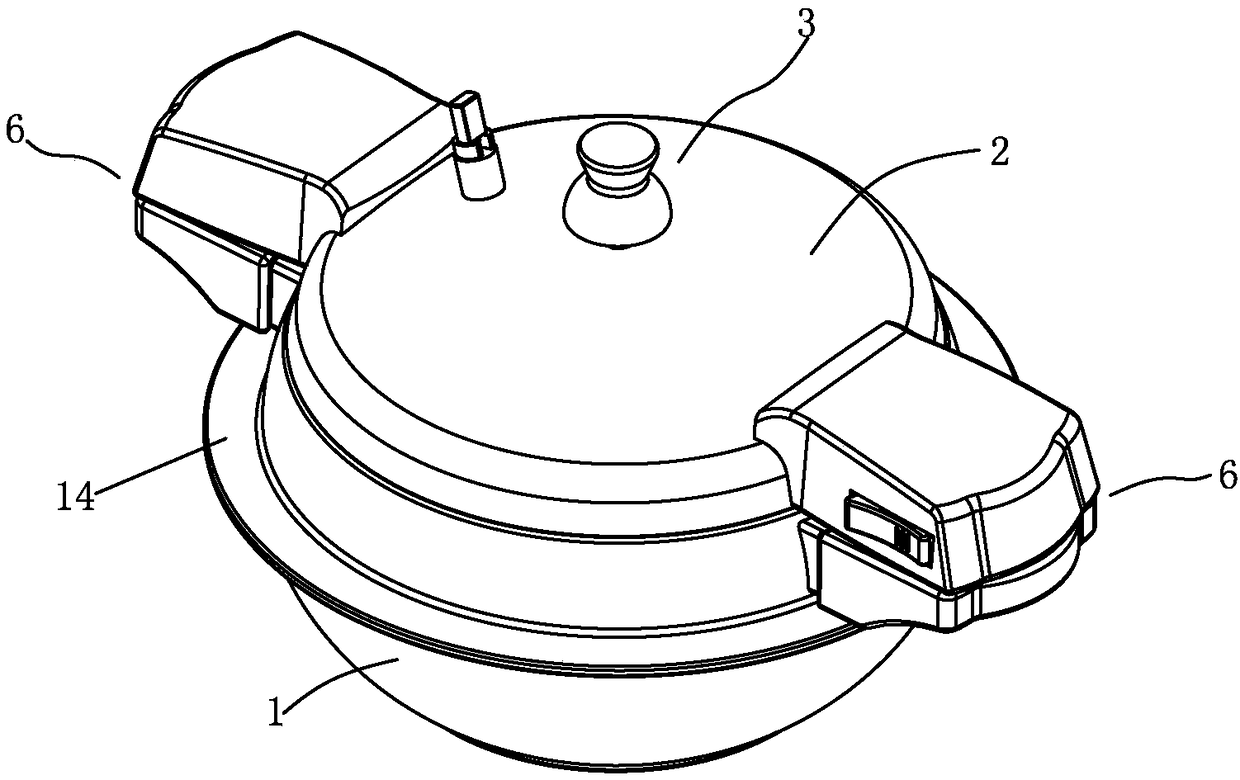

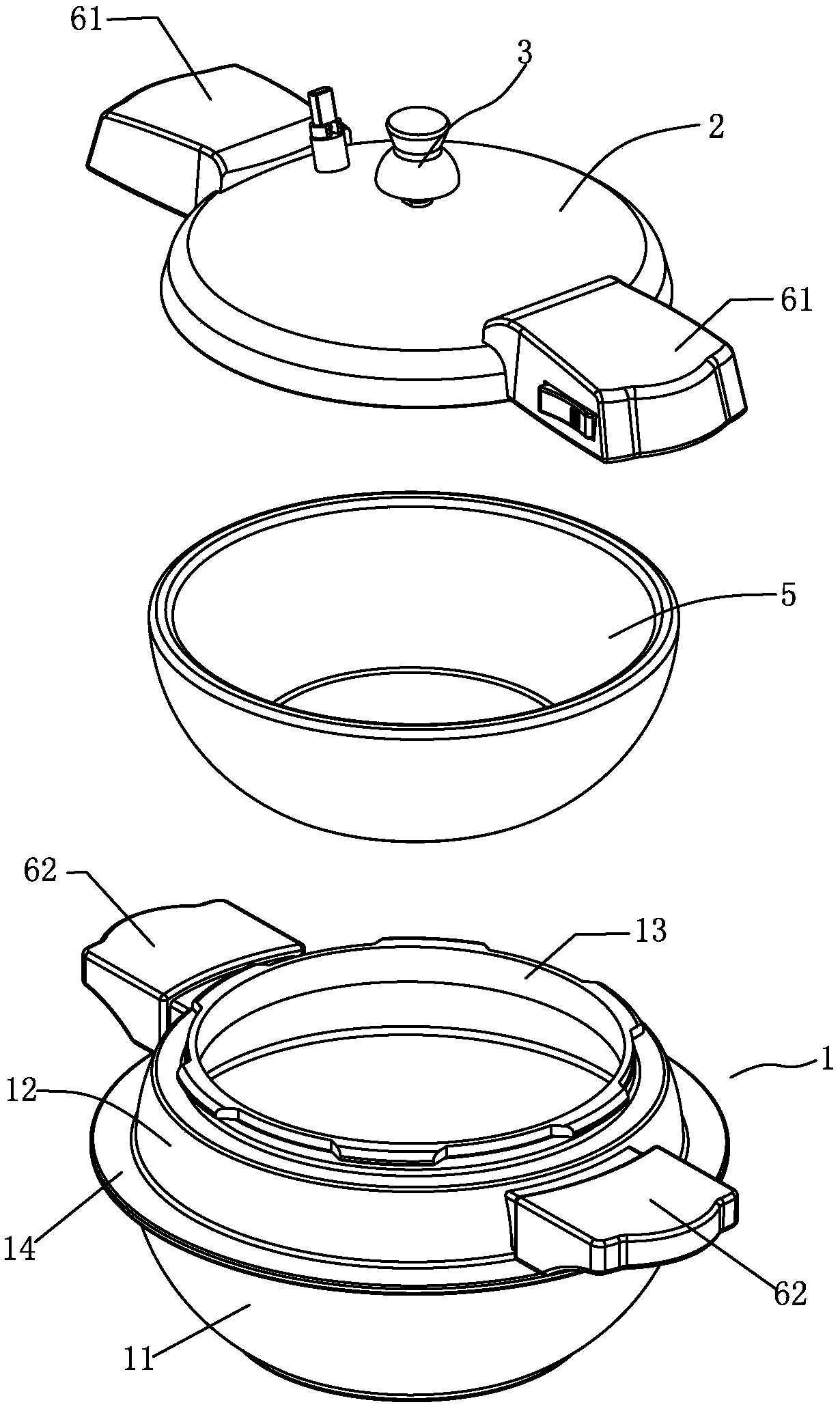

Pressure cooker

PendingCN108652431AKeep the smellPlay a role in breaking the wallCooking-vessel materialsPressure-cookersCooking & bakingMetallic materials

A pressure cooker comprises a body, a lid, a pressure relief valve arranged on the lid and a sealing ring arranged on the lid. Upper fastening threads of the lid are in screw fit with lower fasteningthreads on an opening in the body. The cooker further comprises an inner pot opening up and made of a non-metallic material and a heat conductive material. The body is made of aluminum or aluminum alloy with certain ductility, and comprises a lower wrapping portion, a steam chamber portion and an upper interface portion. The upper interface portion is provided with the lower fastening threads. Theinner pot is embedded in the lower wrapping portion. During use, a food material is located in the inner pot, a high temperature cooking area is formed in the inner pot, a high pressure high temperature heat source area is formed in the steam chamber portion, and a secondary high pressure and high temperature area is formed in the lid. During use, the high temperature cooking area is formed in the inner pot, a high temperature high pressure hot baking area is formed in a steam chamber, and a secondary high temperature high pressure hot baking area is formed in the lid. The inner pot is heatedto emit infrared rays, and the infrared rays break the long starch protein in the food material and achieve a wall-breaking effect. The original flavor of the food material can be effectively maintained, and the taste is effectively improved.

Owner:中山市家冠电气有限公司

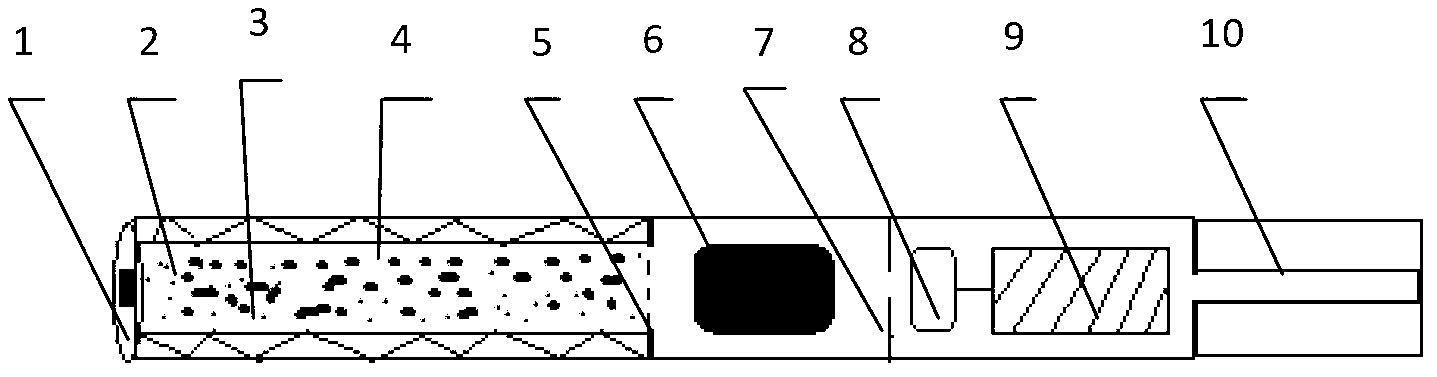

Visible heating atomizing cigarette

The invention discloses a visible heating atomizing cigarette which comprises a cigarette body and a cigarette holder. The cigarette body comprises a heating area, an atomizing area and a power source area. The heating area, the atomizing area and the power source area of the cigarette body are sequentially communicated with the cigarette holder through an airflow channel. A case of the heating area is made of heat-insulating transparent materials. Tobacco shreds or remanufactured tobacco leaves are filled in the heating area. Heating wires are arranged between the case and the tobacco shreds. A liquid storing cavity is formed in the atomizing area. The liquid storing cavity is connected with an atomizer in the power source area. The power source area is formed by electrically connecting a battery, a control circuit, a pneumatic inductive switch and the atomizer. When the visible heating atomizing cigarette is burnt and smoked, a user can breathe mixed smoke which is generated after heating of the tobacco shreds and atomizing of fragrance into the mouth through suction, and the sucking effect which is the same as that of a common cigarette is achieved. The visible heating atomizing cigarette has the dual advantages of electronic cigarettes and electrical heating cigarettes and is large in smoke amount, the amount of released harmful ingredients can be reduced greatly, tar cannot be generated, harm of passive smoking and the smoke of side flowing are avoided, and the visible heating atomizing cigarette is an effective substitute of a traditional combustible cigarette.

Owner:HONGYUN HONGHE TOBACCO (GRP) CO LTD

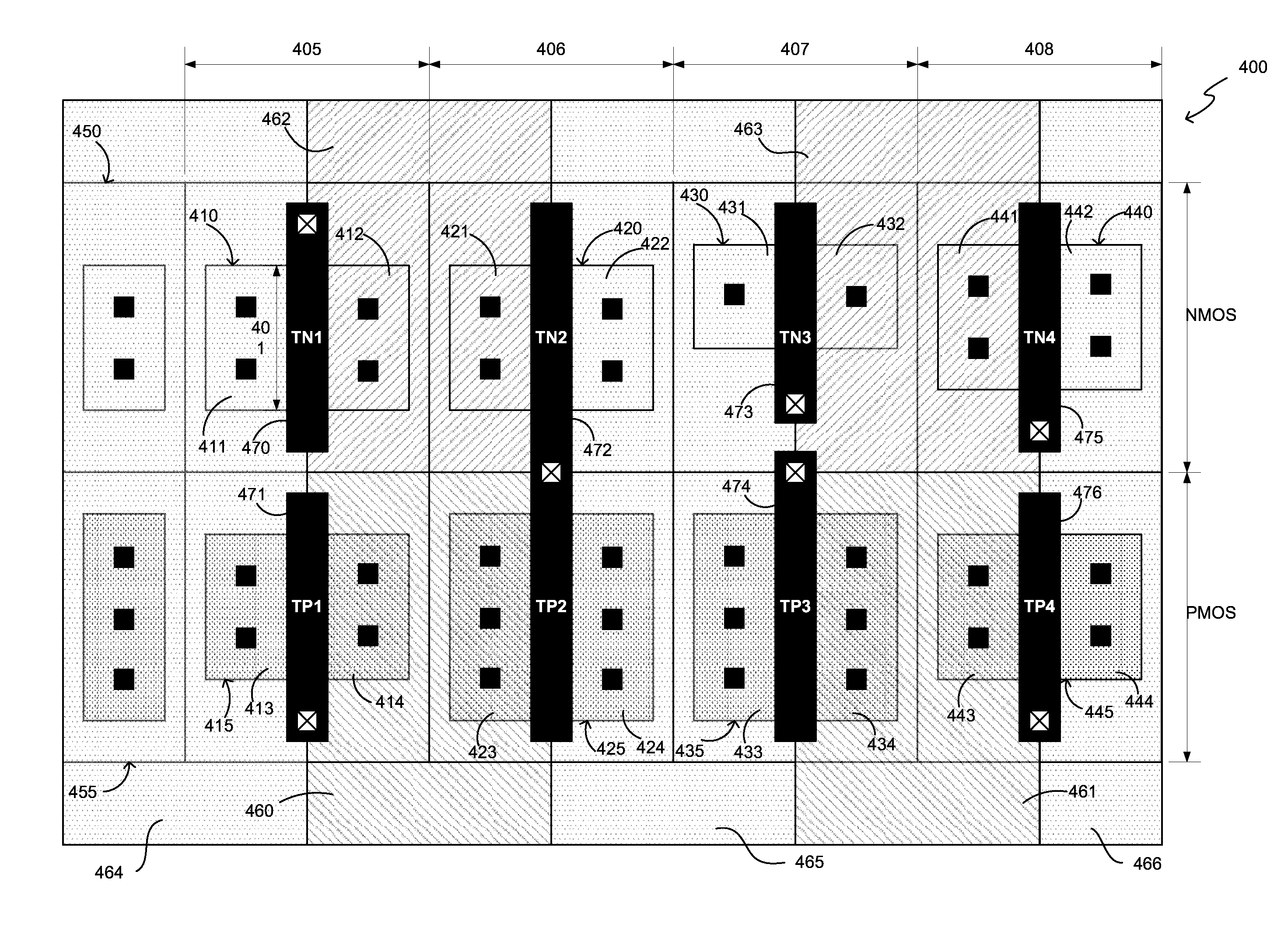

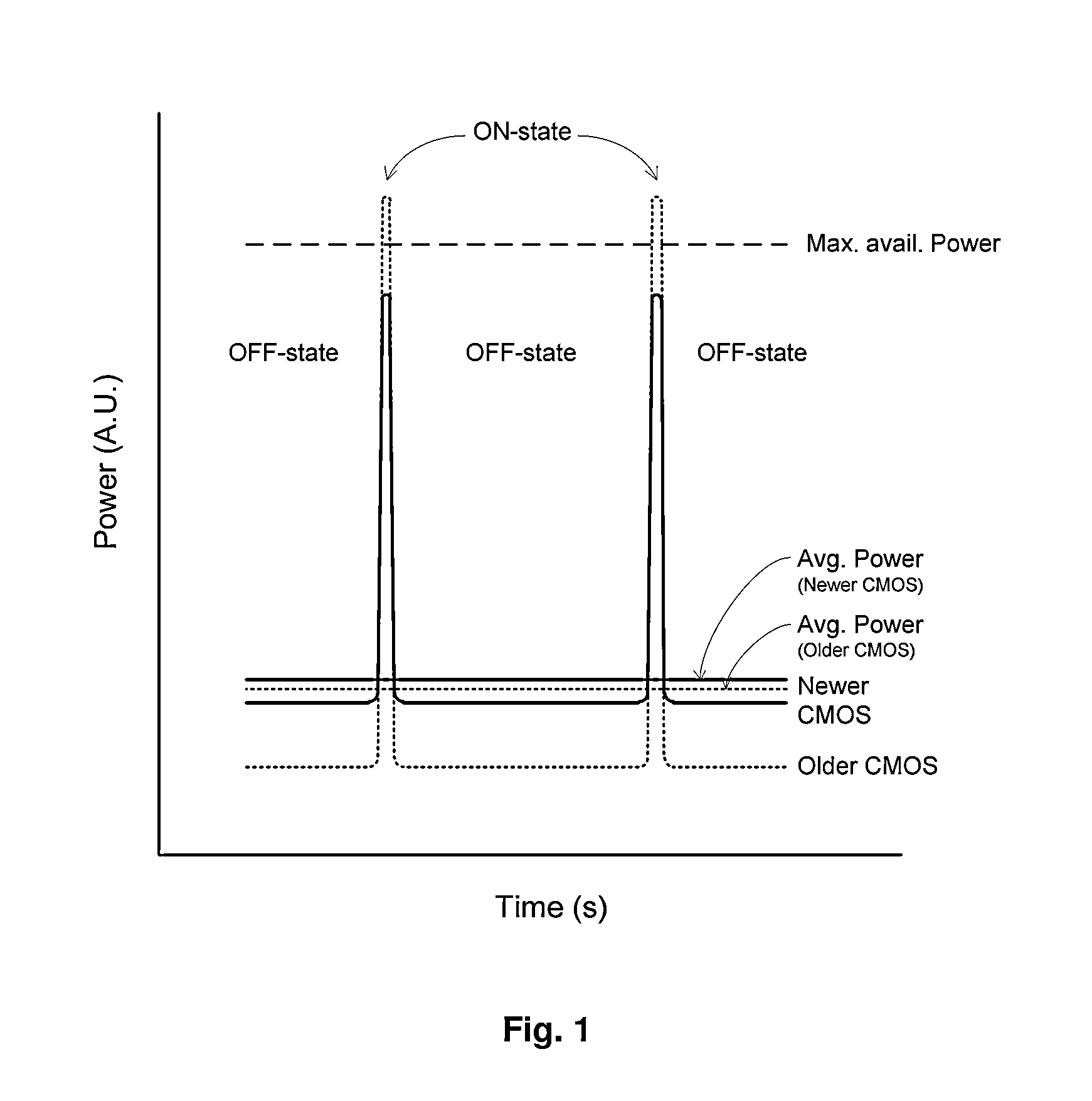

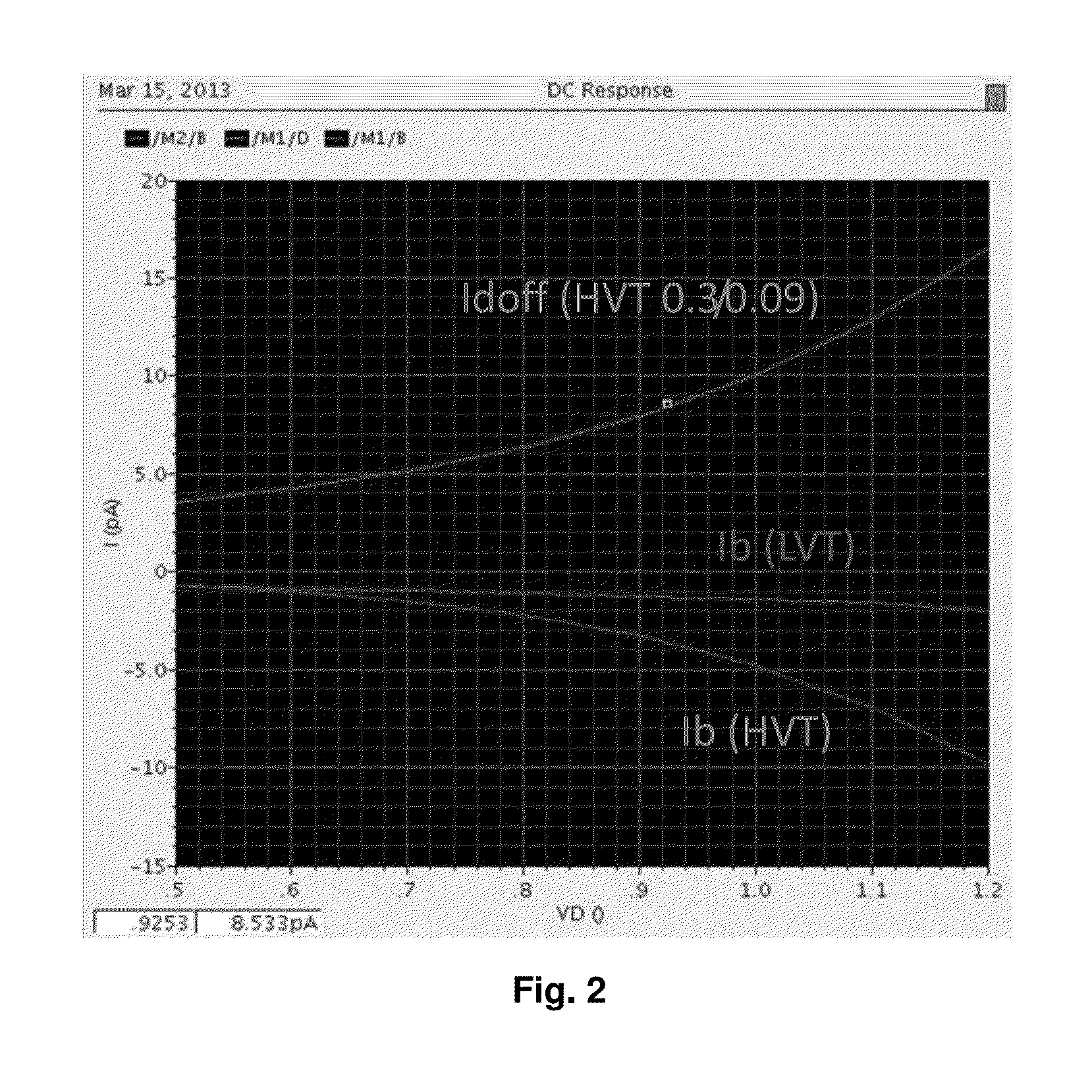

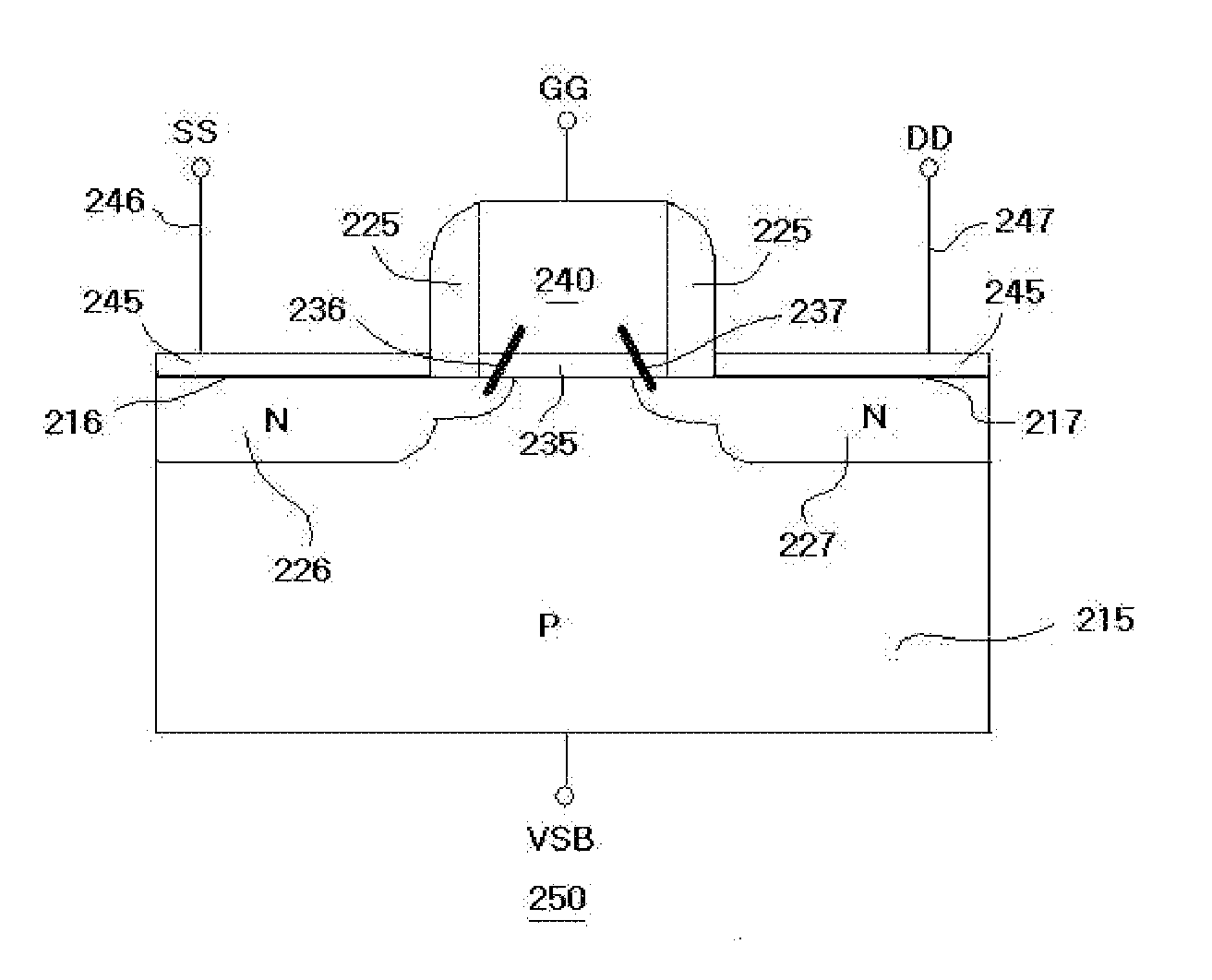

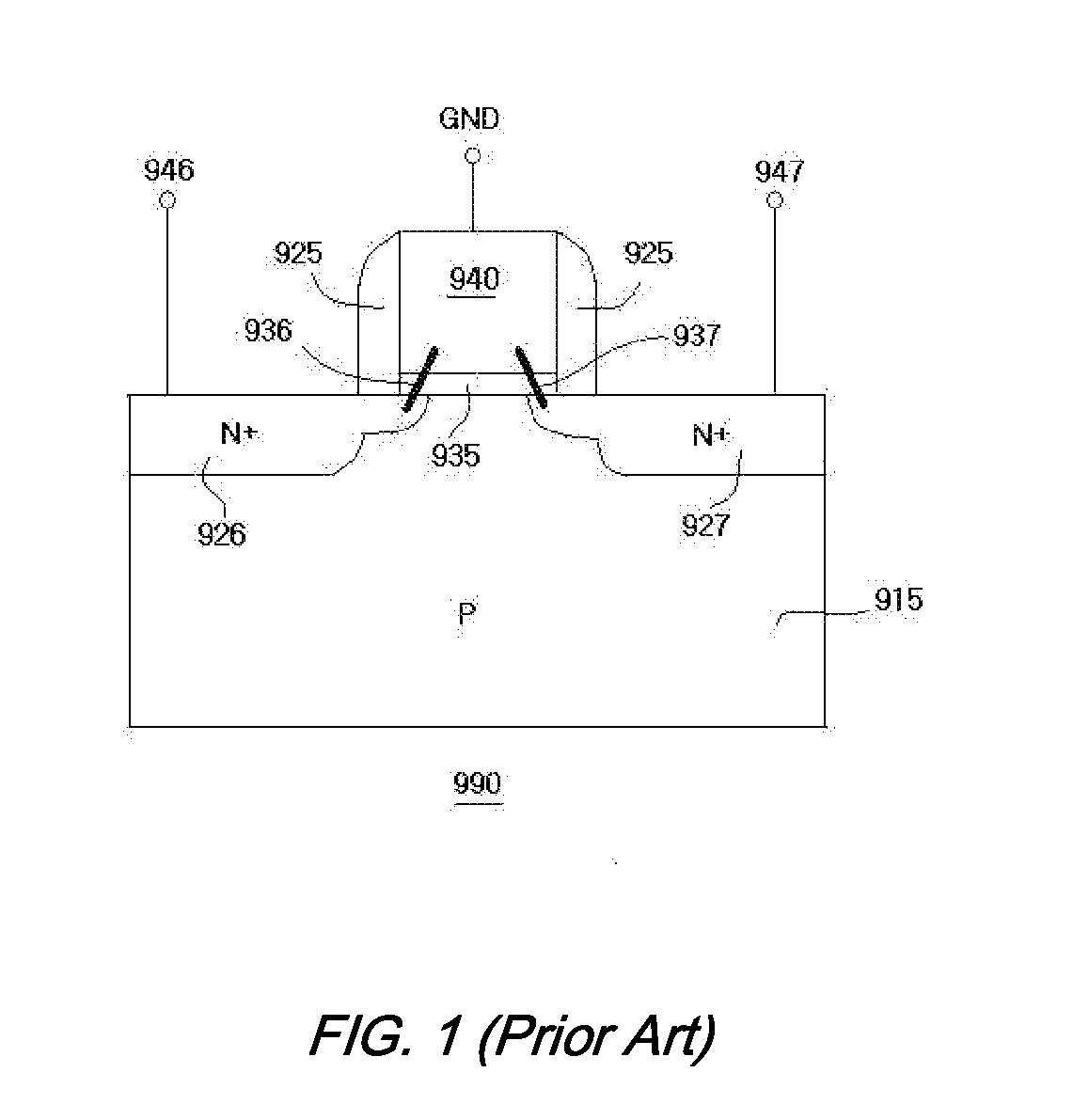

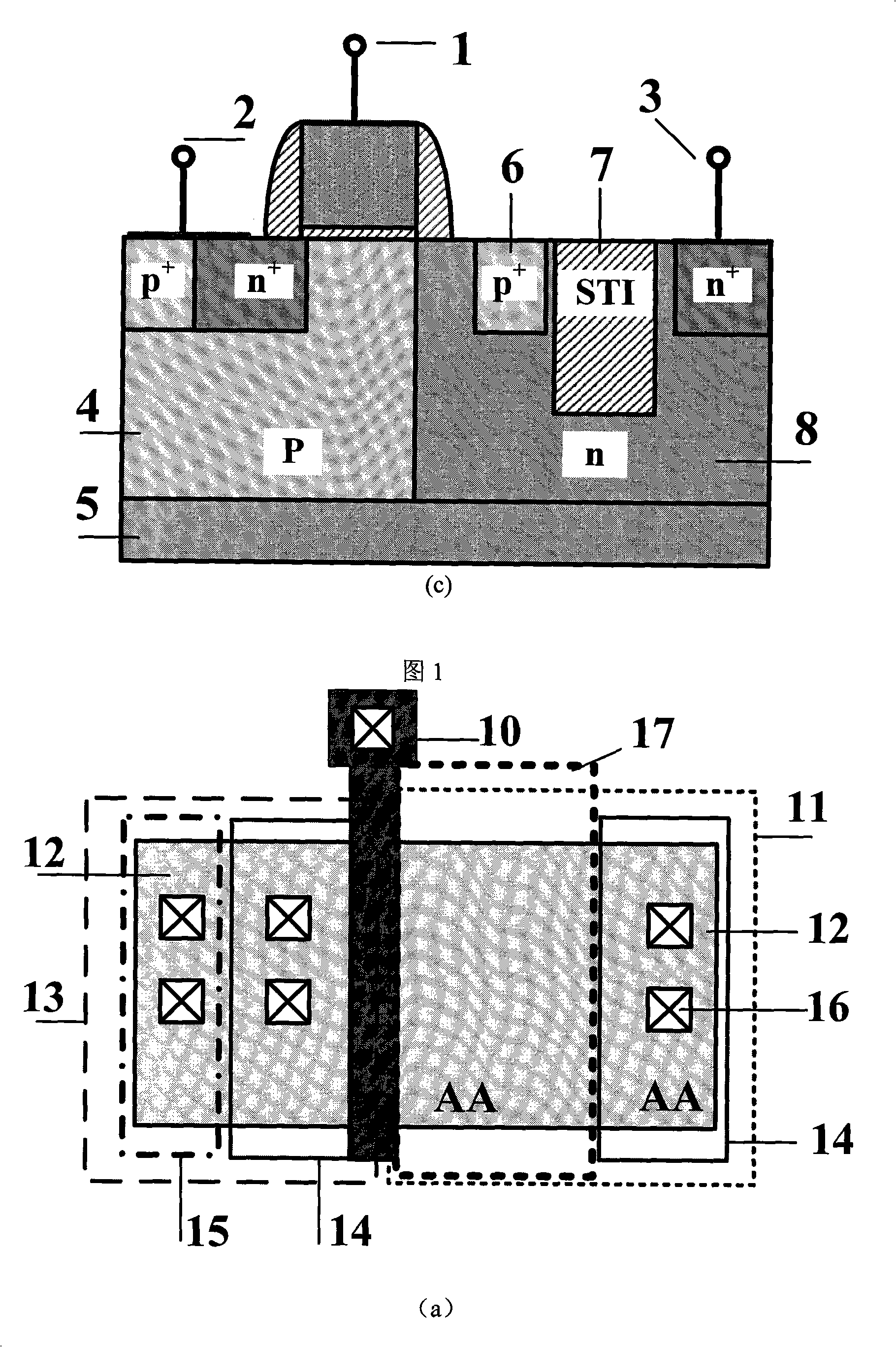

Integral fabrication of asymmetric CMOS transistors for autonomous wireless state radios and sensor/actuator nodes

InactiveUS20150213180A1TransistorSemiconductor/solid-state device detailsElectrical junctionActuator

A method of arranging asymmetrically doped CMOS transistors in a semiconductor wafer that forms base cells within a plurality of logic standard cells in a CMOS process technology that includes conventional symmetric CMOS transistors having different threshold voltages. The asymmetrically doped CMOS transistors have a gate length exceeding 1.5 times the minimum gate length of the symmetric CMOS transistors. Regions defined by electrical junctions directly adjacent to the gate of the asymmetric transistors are formed by an implant mask exposing an area of the wafer on the source side of the transistor to receive the junction implant of the symmetric CMOS transistors with a higher threshold voltage while shielding the drain area, and a further implant mask exposing an area of the wafer on the drain side of the transistor to receive the junction implant of the symmetric CMOS transistors with a lower threshold voltage while shielding the source area.

Owner:QUALCOMM TECH INT

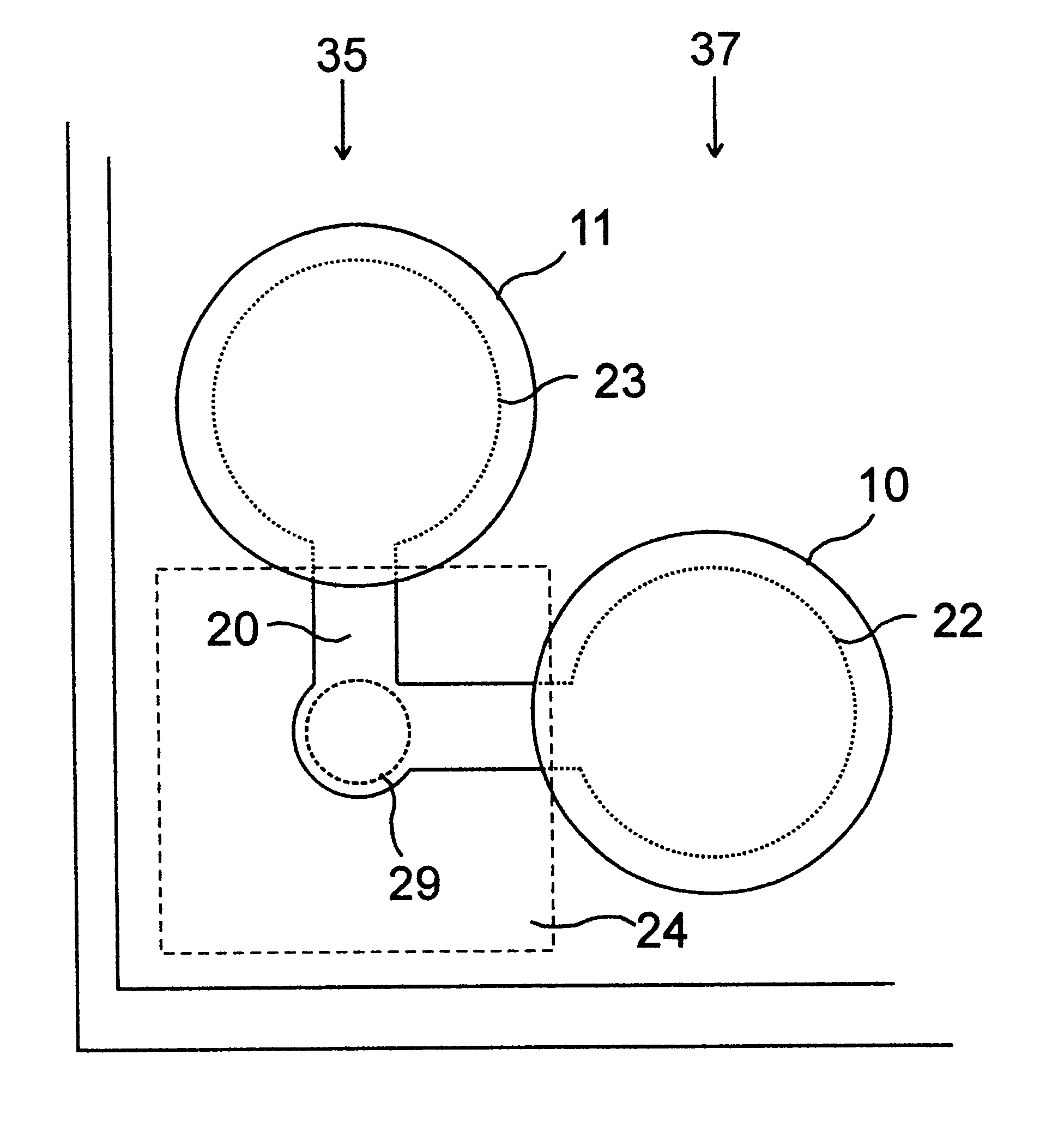

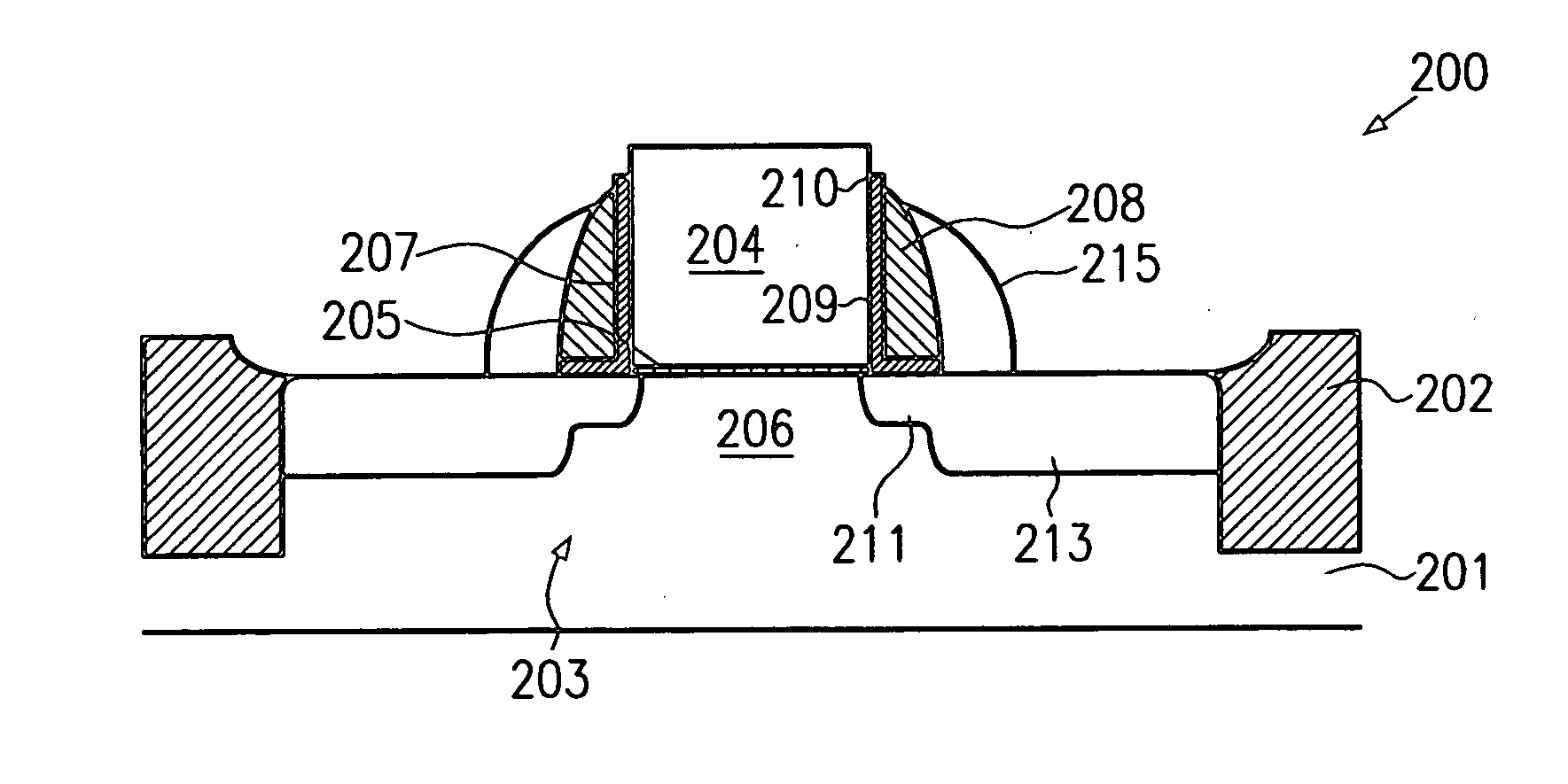

Semiconductor package having dimpled plate interconnections

ActiveUS20070290336A1Improve cooling effectOvercome limitationsSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageInterconnection

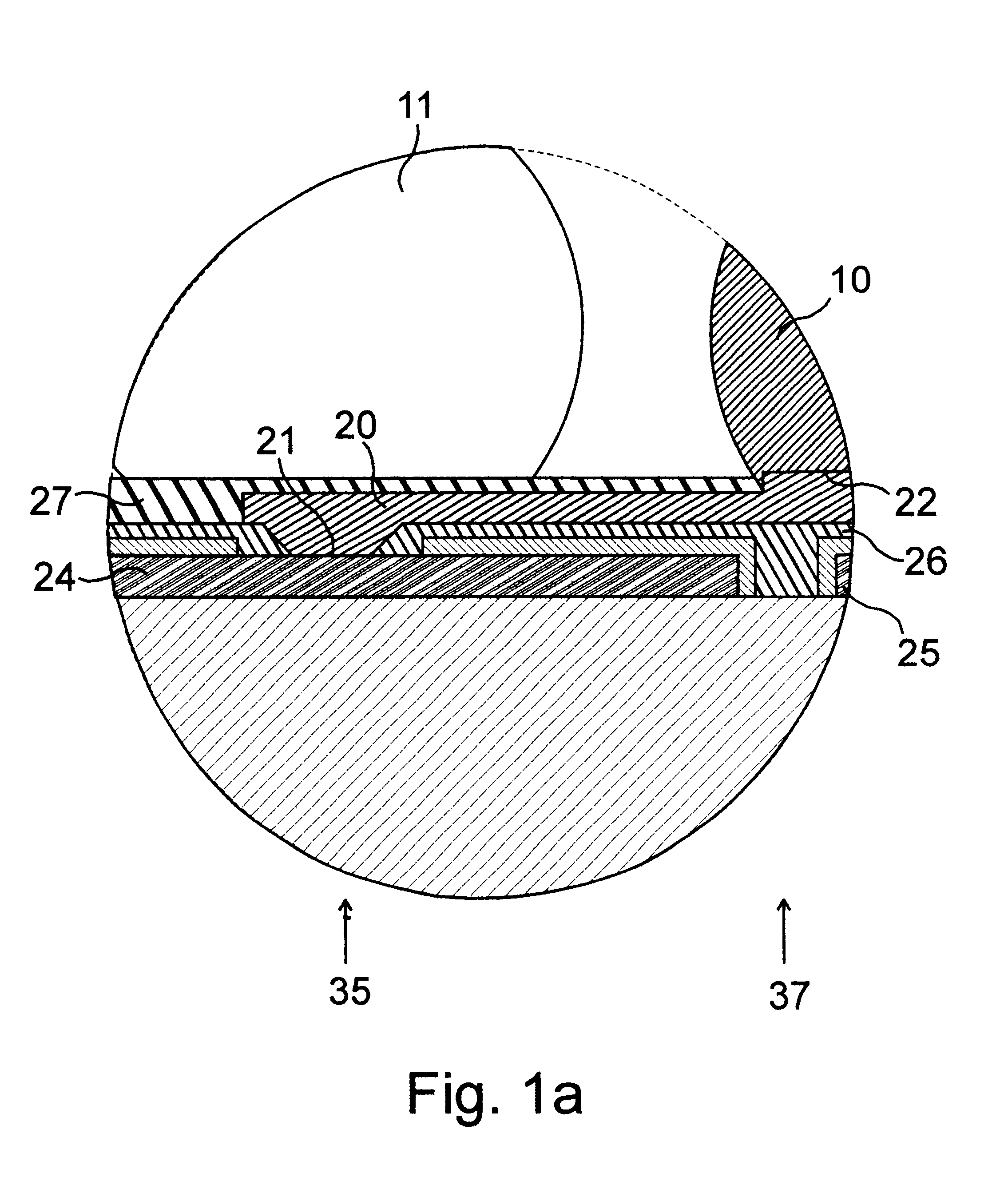

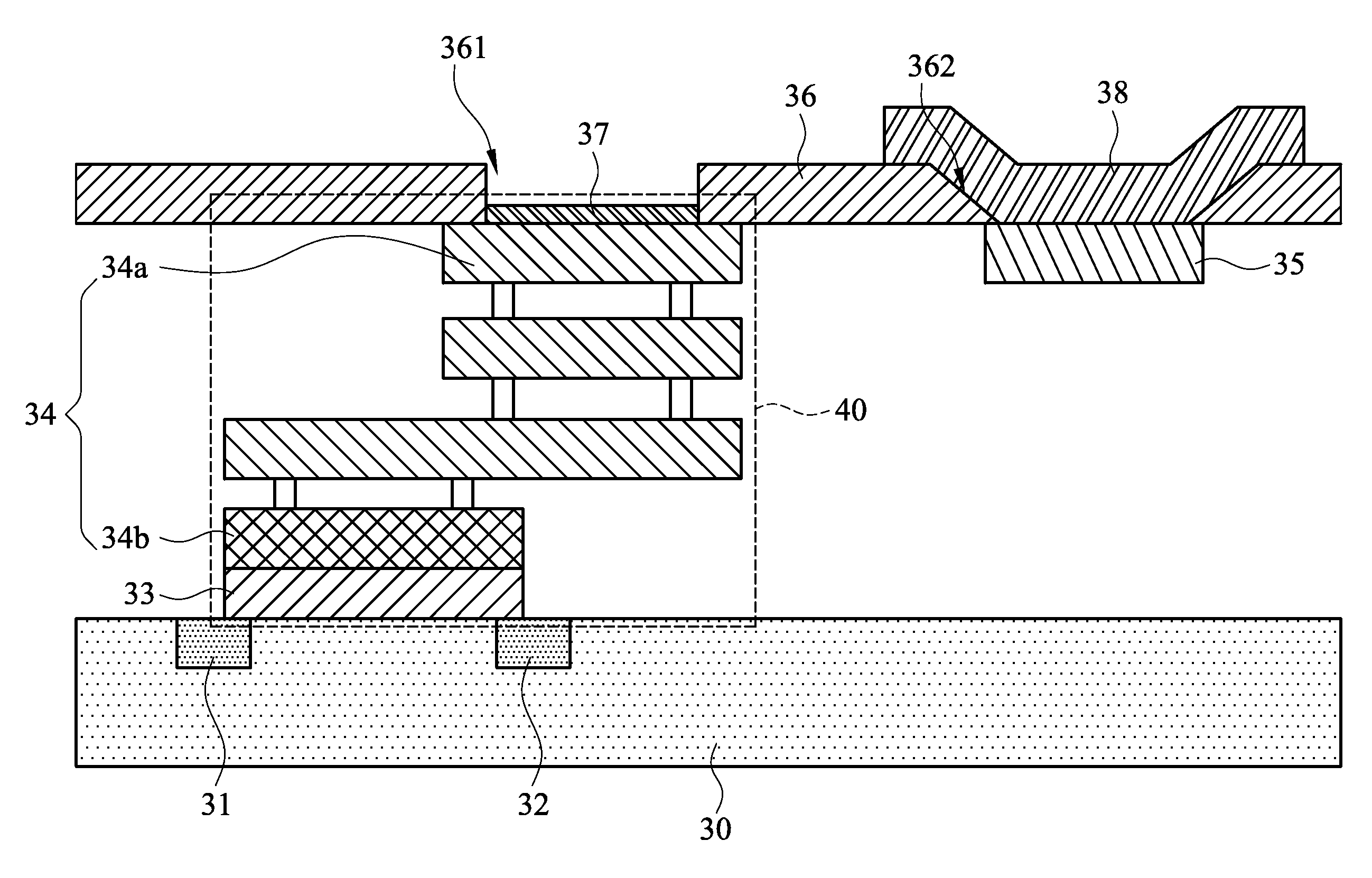

A semiconductor package is disclosed. The package includes a leadframe having drain, source and gate leads, a semiconductor die coupled to the leadframe, the semiconductor die having a plurality of metalized source areas and a metalized gate area, a patterned source connection having a plurality of dimples formed thereon coupling the source lead to the semiconductor die metalized source areas, a patterned gate connection having a dimple formed thereon coupling the gate lead to the semiconductor die metalized gate area, a semiconductor die drain area coupled to the drain lead, and an encapsulant covering at least a portion of the semiconductor die and drain, source and gate leads.

Owner:ALPHA & OMEGA SEMICON INC

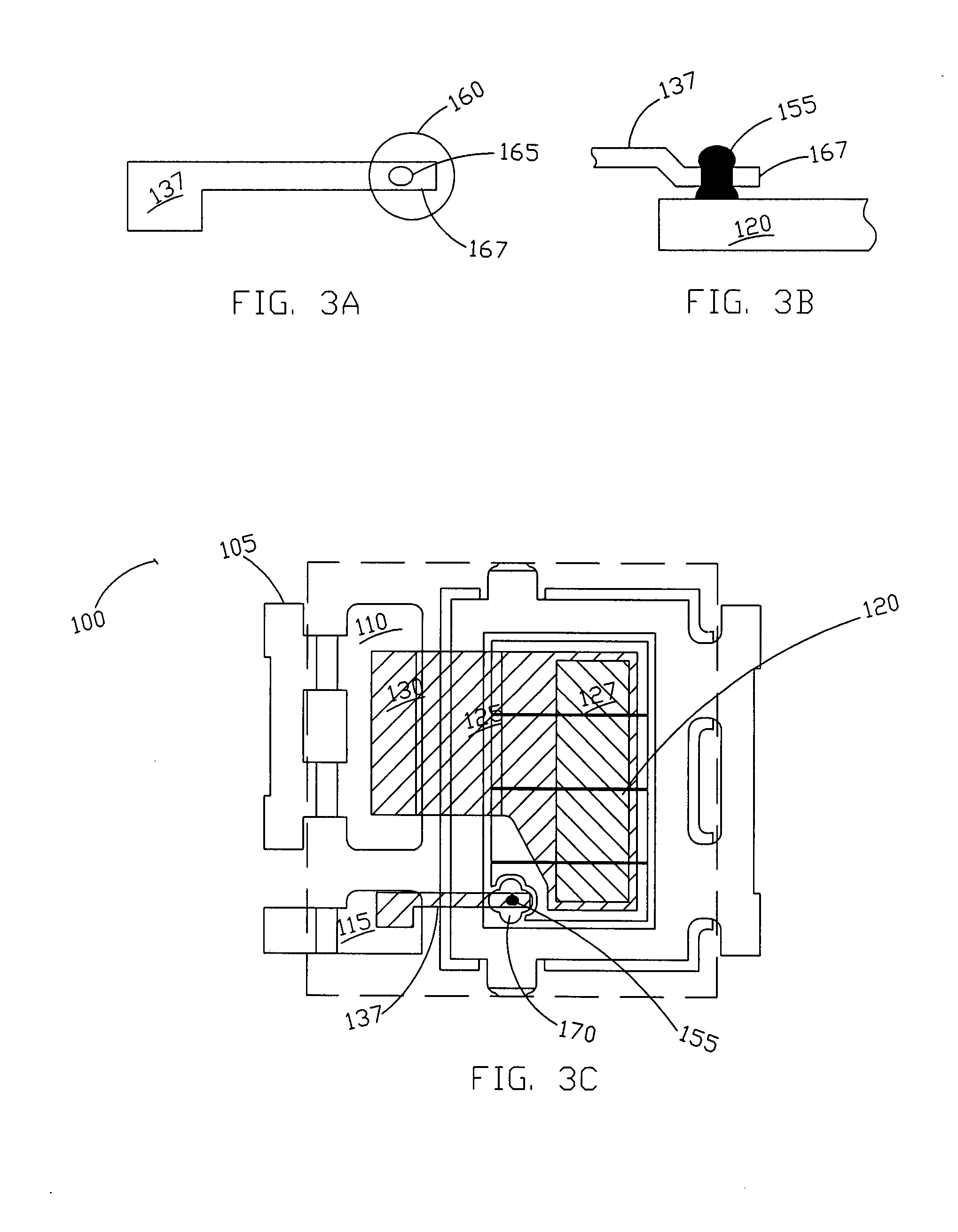

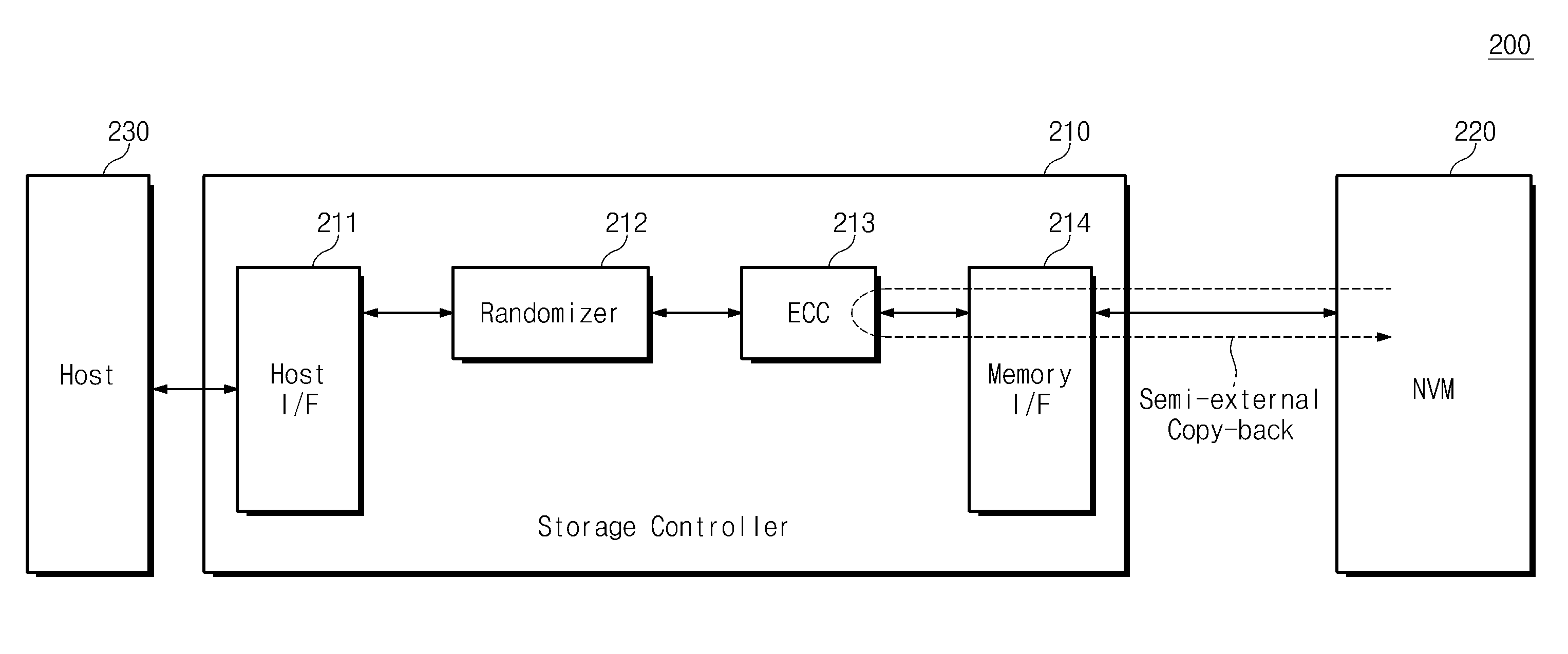

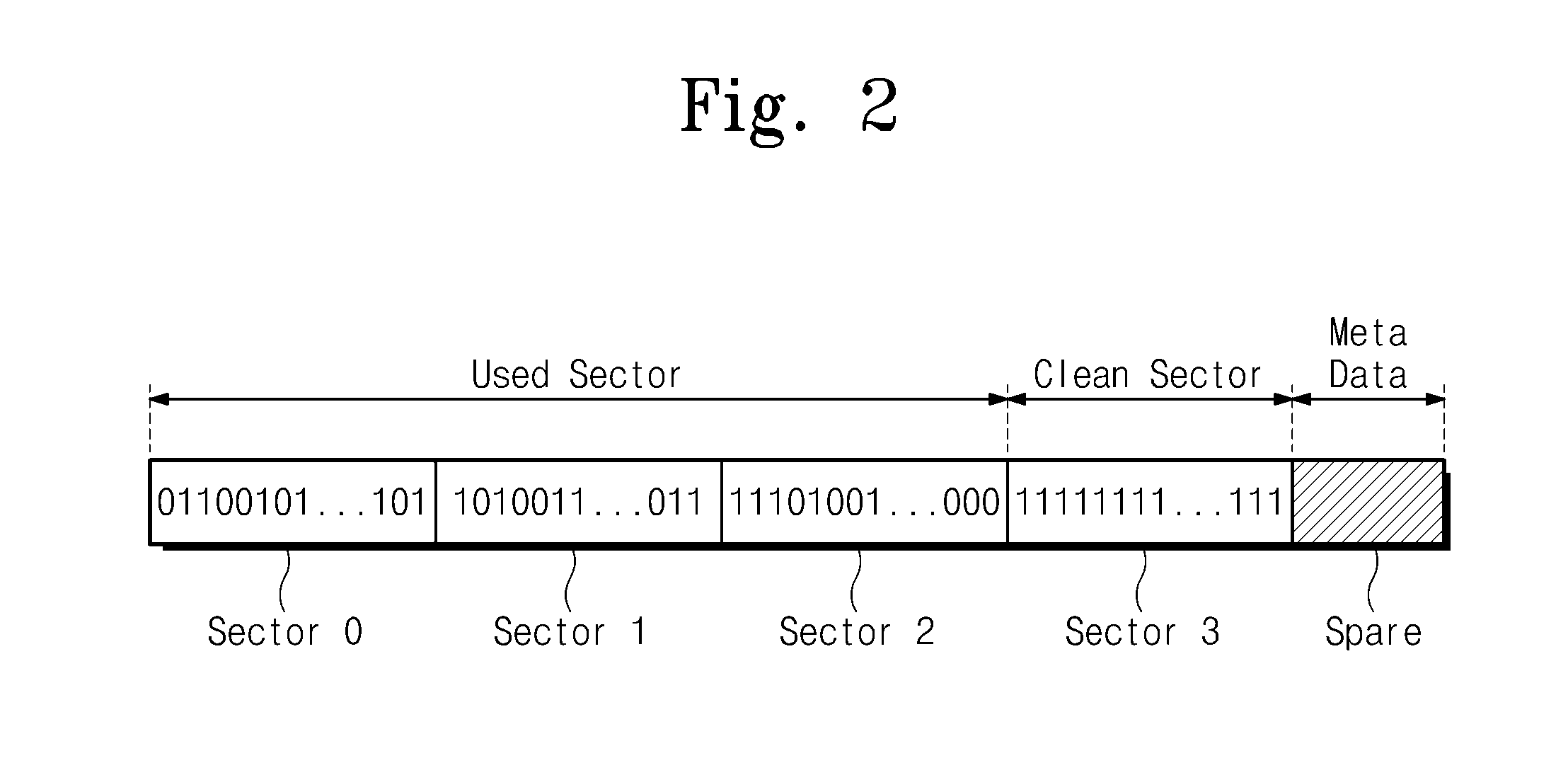

Storage device having a non-volatile memory device and copy-back method thereof

A storage device includes a non-volatile memory device outputting read data from a source area and a memory controller configured to execute an ECC operation on a plurality of vectors in the read data and to write the error-corrected read data into target area of the non-volatile memory device. The memory controller declares that a vector corresponding to a clean area is decoding pass without using a flag bit among the plurality of vectors during the error correction operation.

Owner:SAMSUNG ELECTRONICS CO LTD

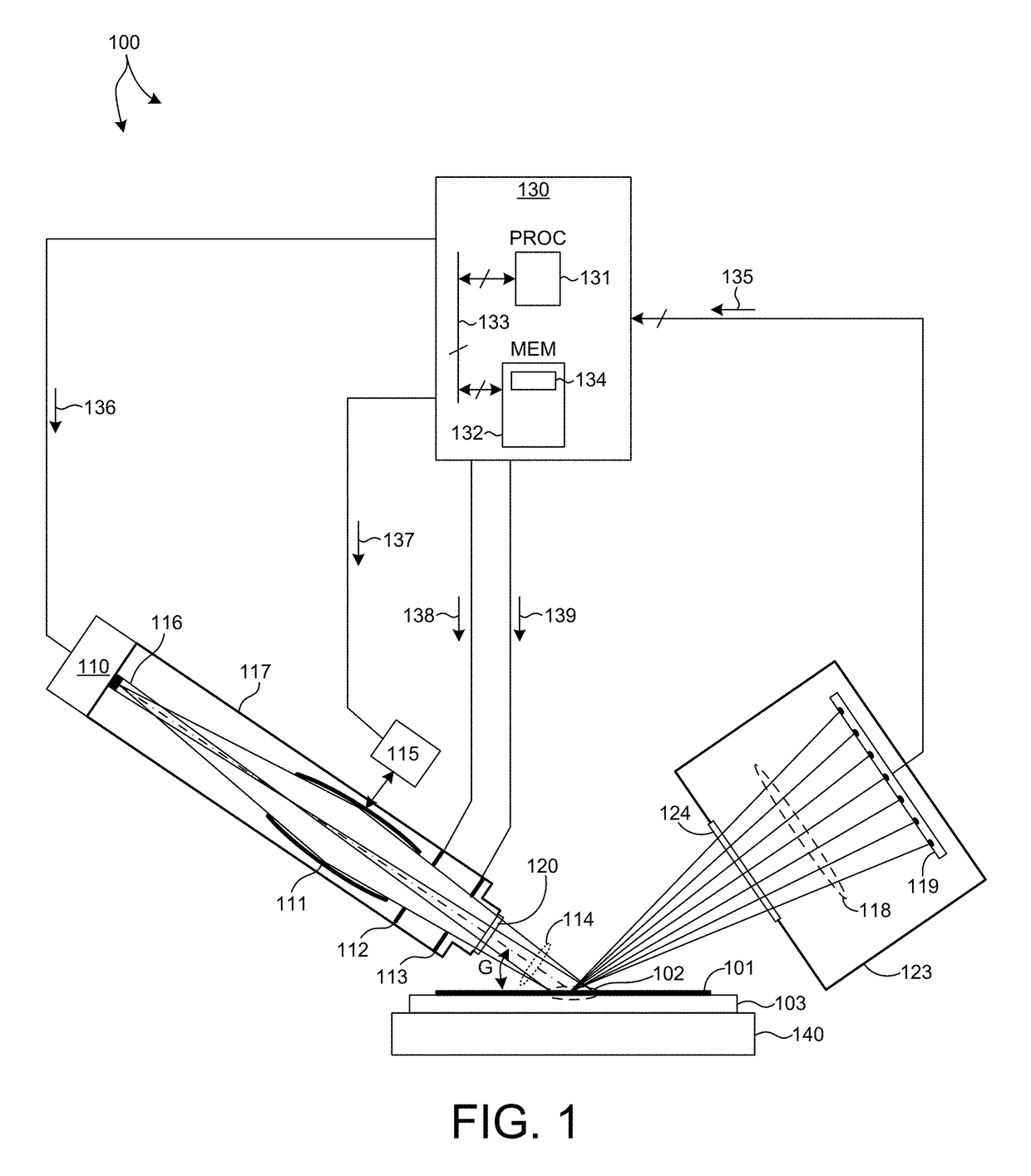

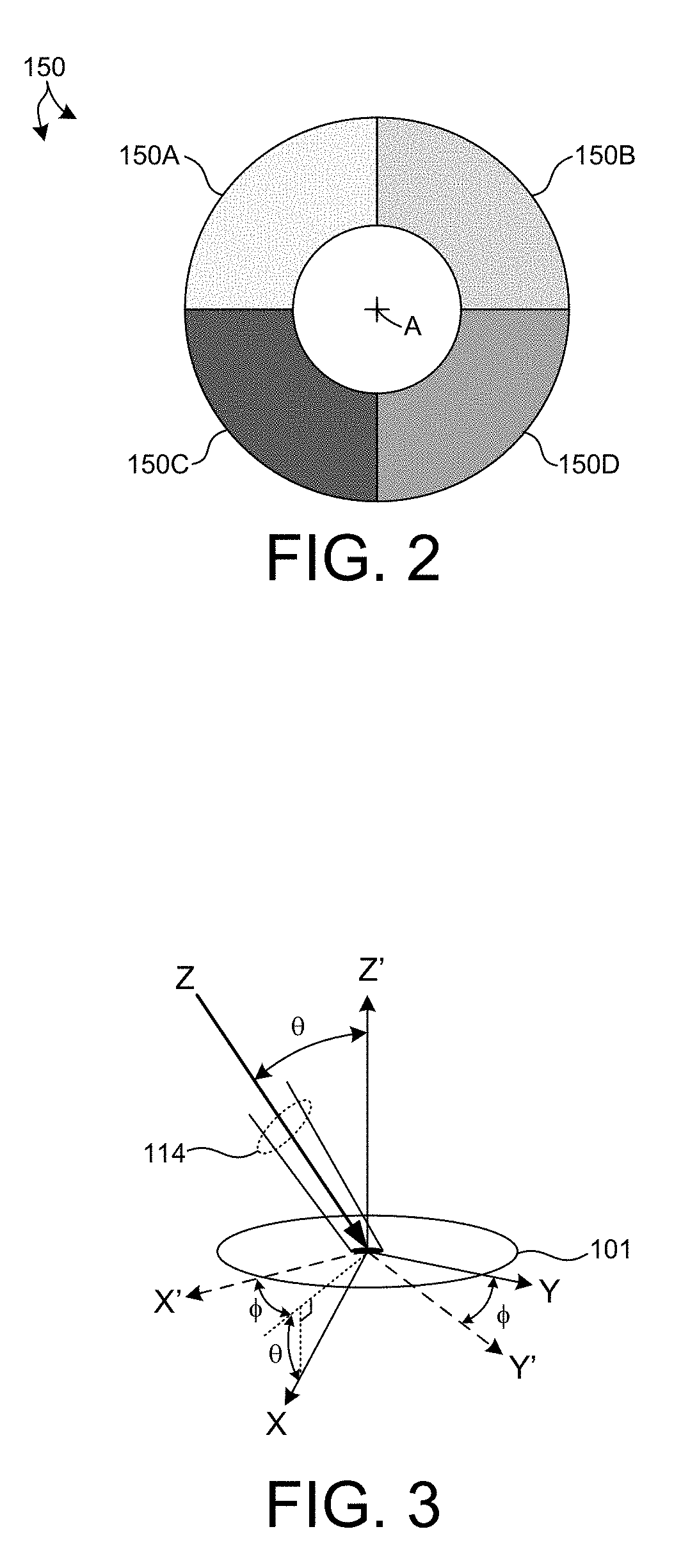

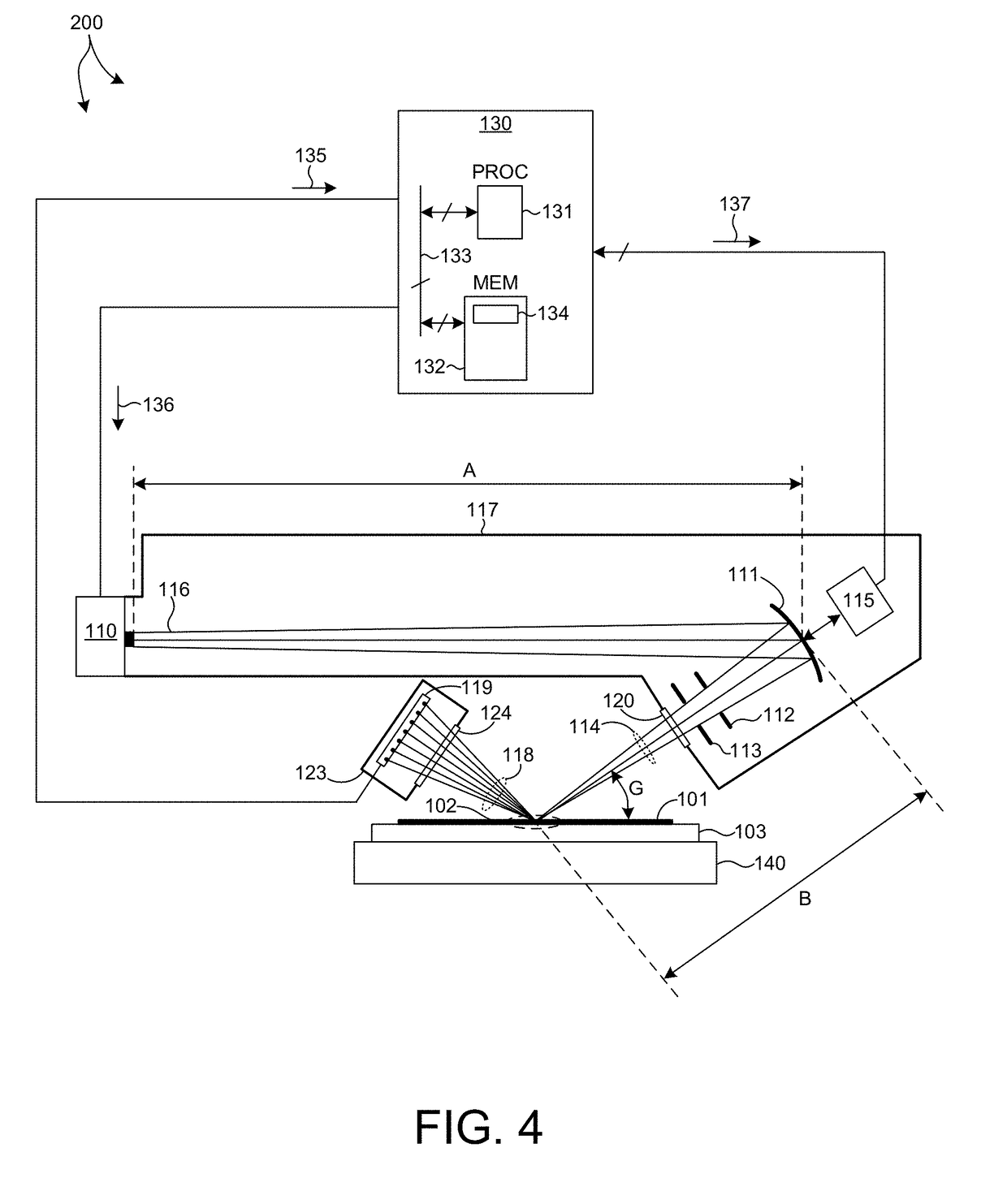

Methods And Systems For Semiconductor Metrology Based On Polychromatic Soft X-Ray Diffraction

ActiveUS20190017946A1Increase measurement throughputSimultaneous measurementMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementMetrologyAngle of incidence

Methods and systems for performing measurements of semiconductor structures based on high-brightness, polychromatic, reflective small angle x-ray scatterometry (RSAXS) metrology are presented herein. RSAXS measurements are performed over a range of wavelengths, angles of incidence, and azimuth angles with small illumination beam spot size, simultaneously or sequentially. In some embodiments, RSAXS measurements are performed with x-ray radiation in the soft x-ray (SXR) region at grazing angles of incidence in the range of 5-20 degrees. In some embodiments, the x-ray illumination source size is 10 micrometers or less, and focusing optics project the source area onto a wafer with a demagnification factor of 0.2 or less, enabling an incident x-ray illumination spot size of less than two micrometers. In another aspect, active focusing optics project programmed ranges of illumination wavelengths, angles of incidence, and azimuth angles, or any combination thereof, onto a metrology area, either simultaneously or sequentially.

Owner:KLA TENCOR TECH CORP

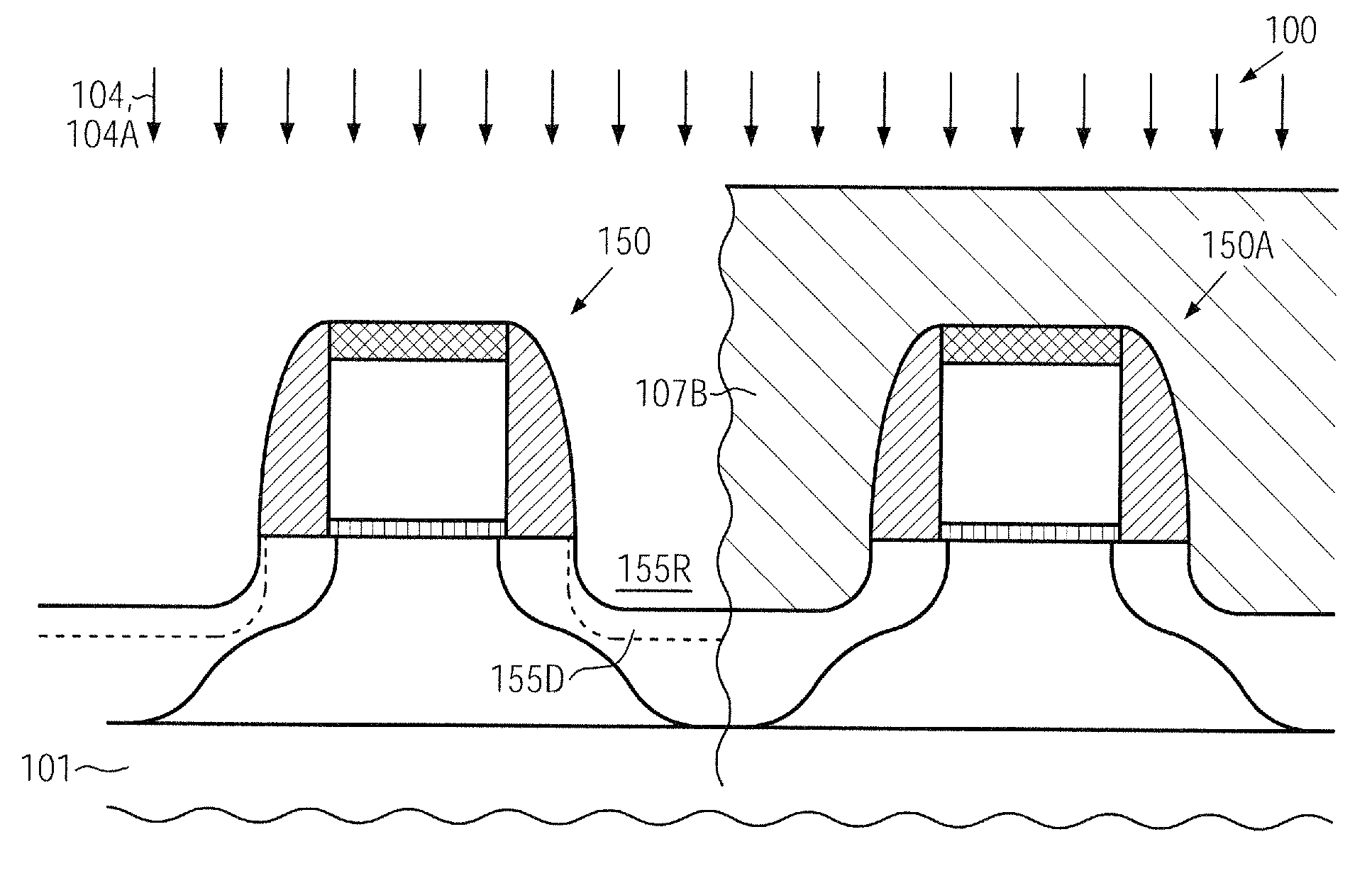

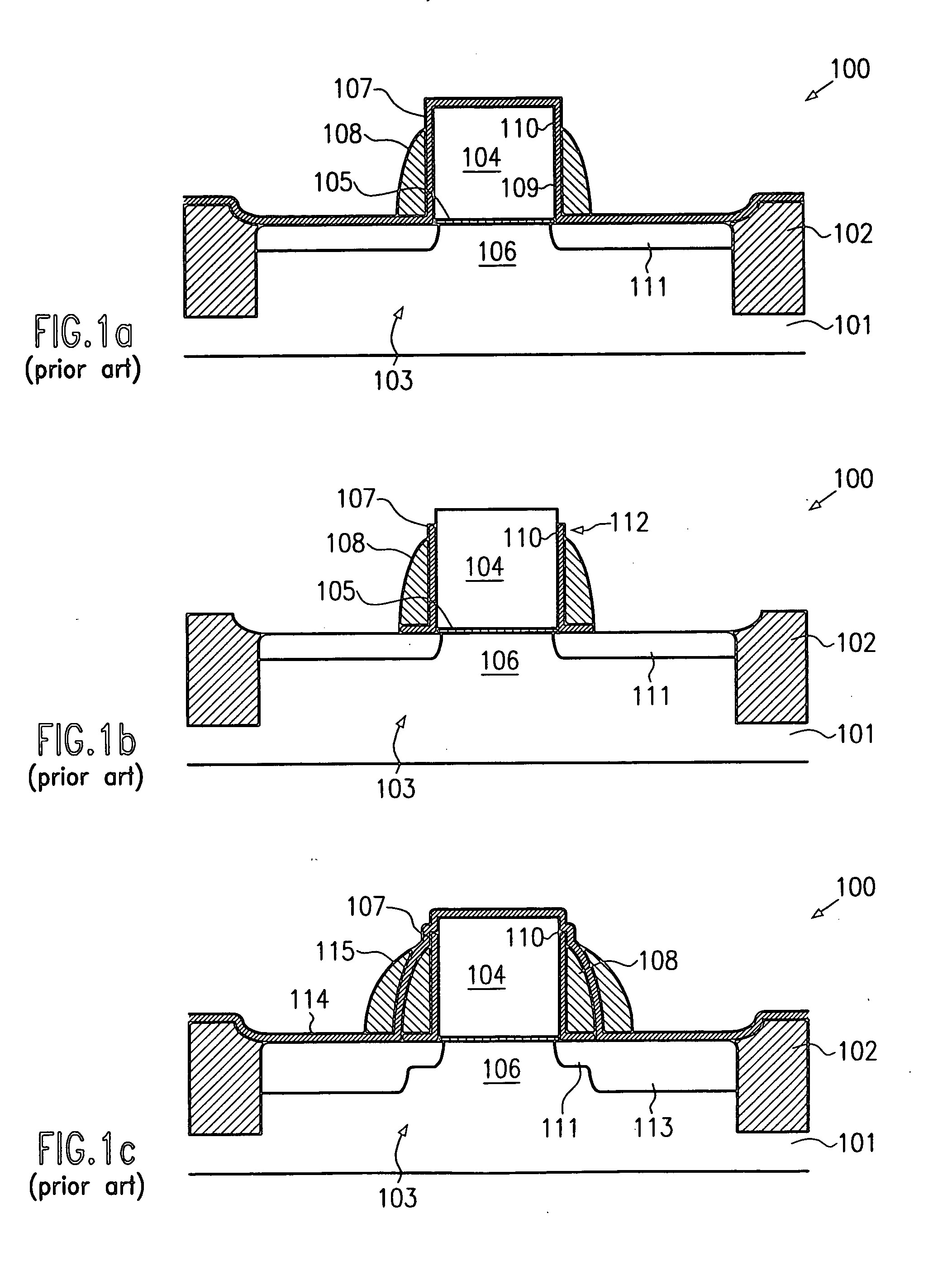

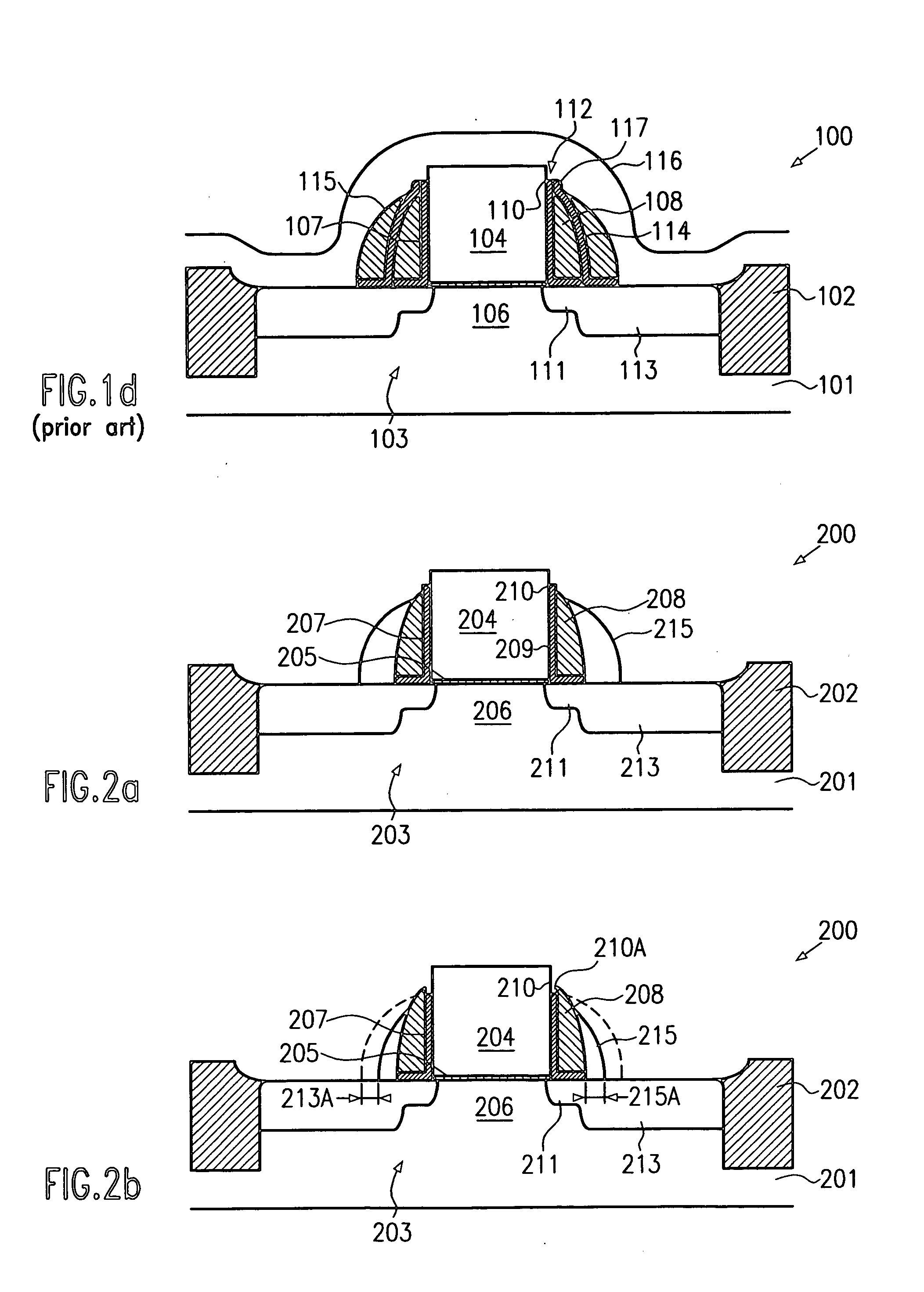

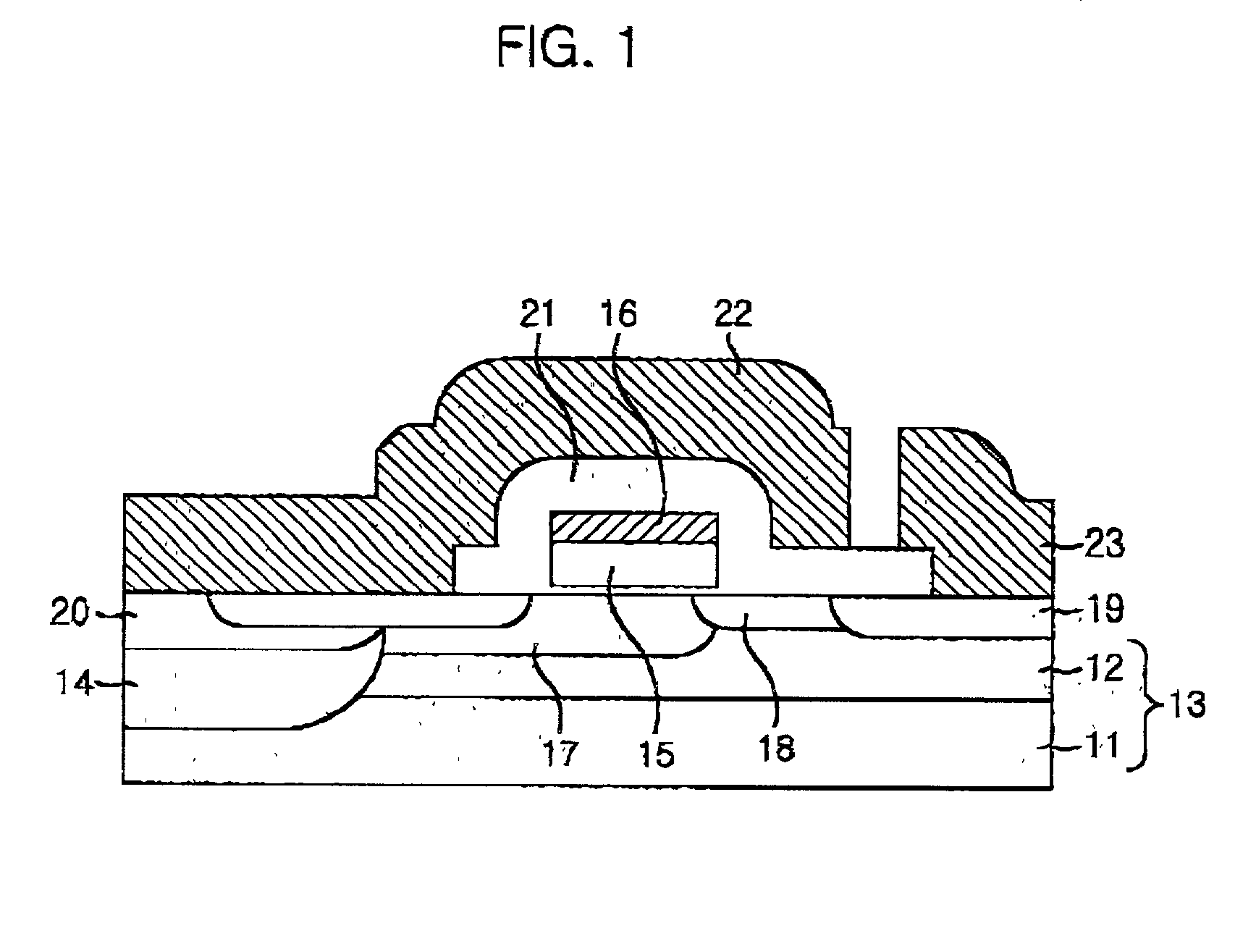

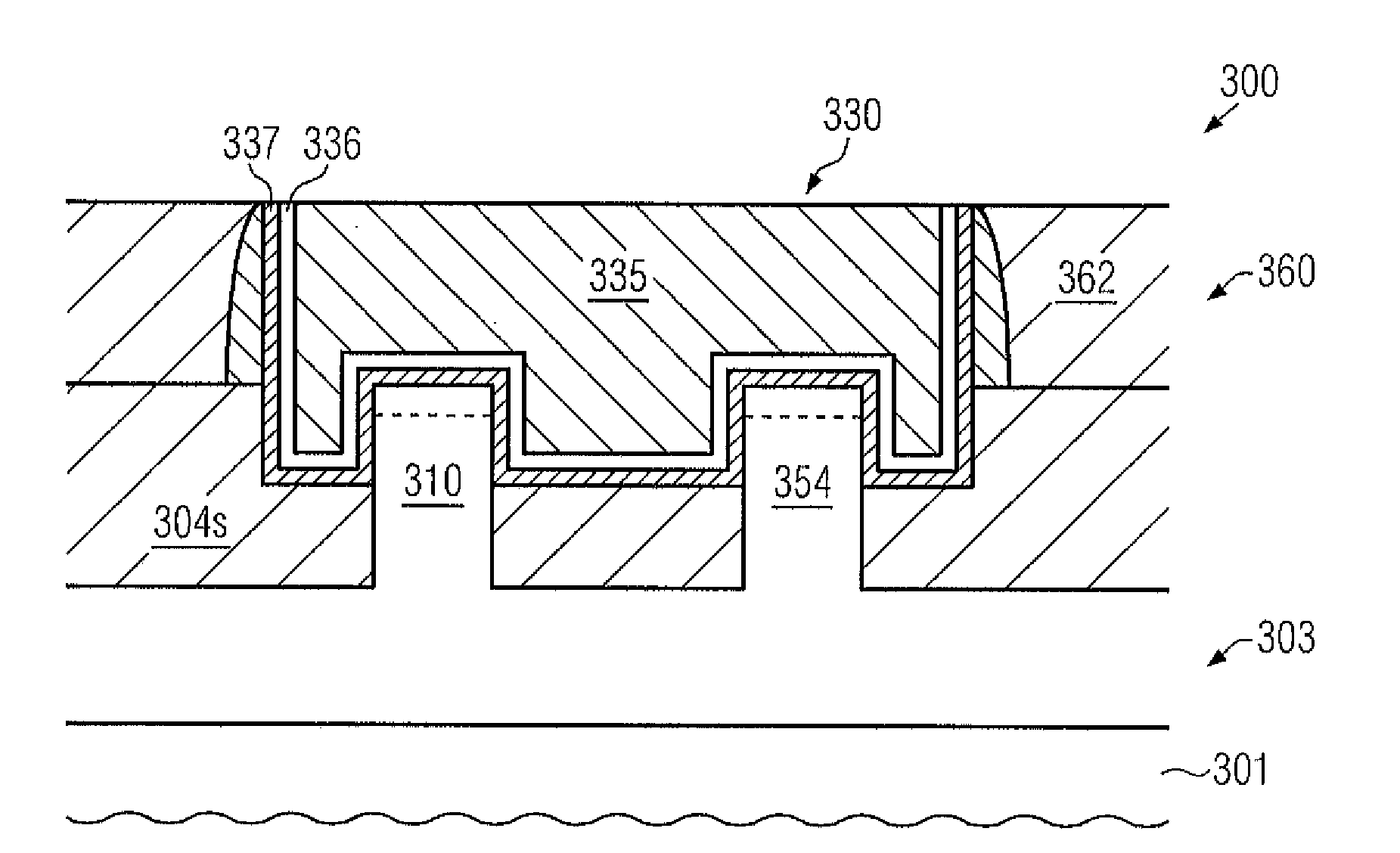

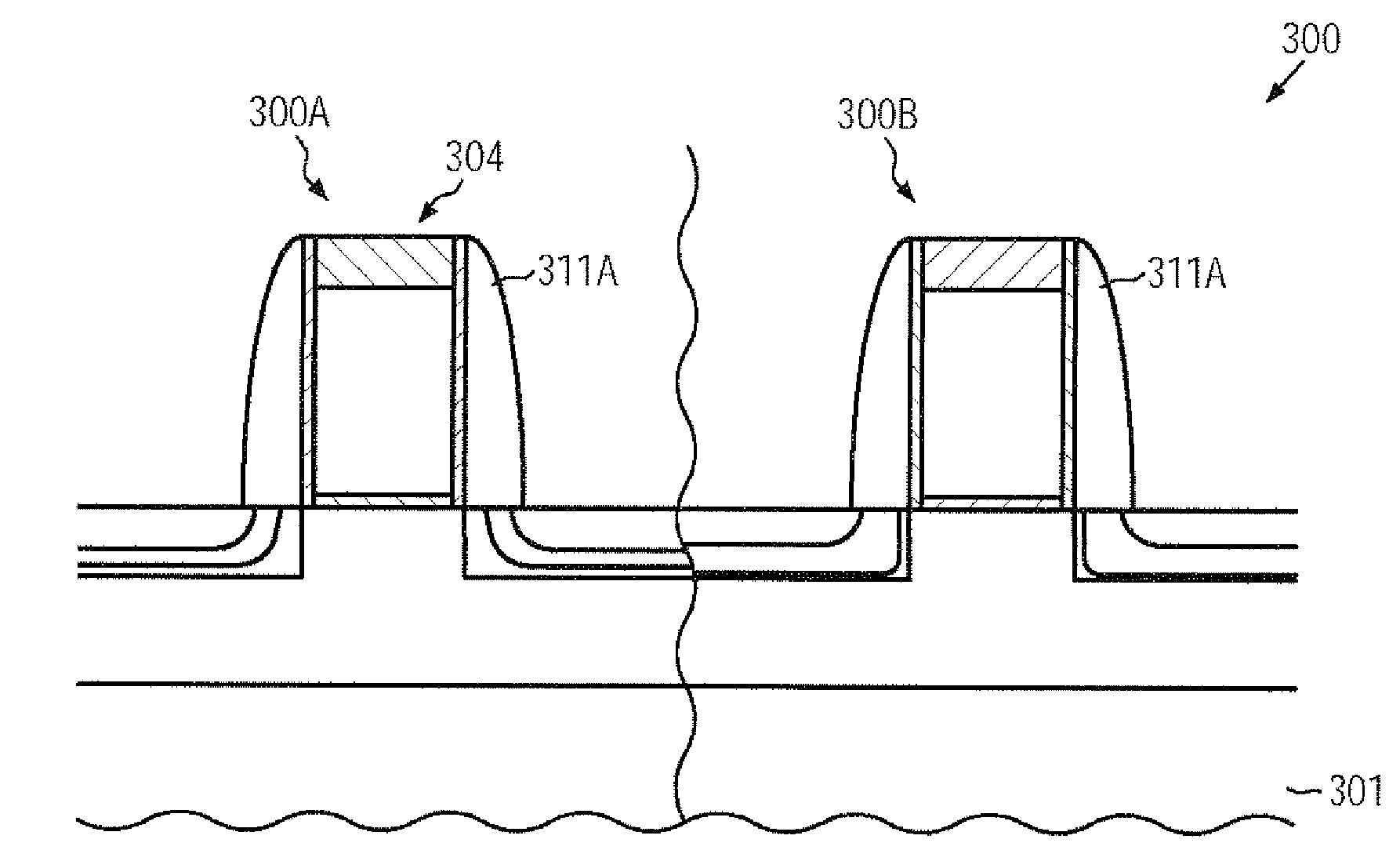

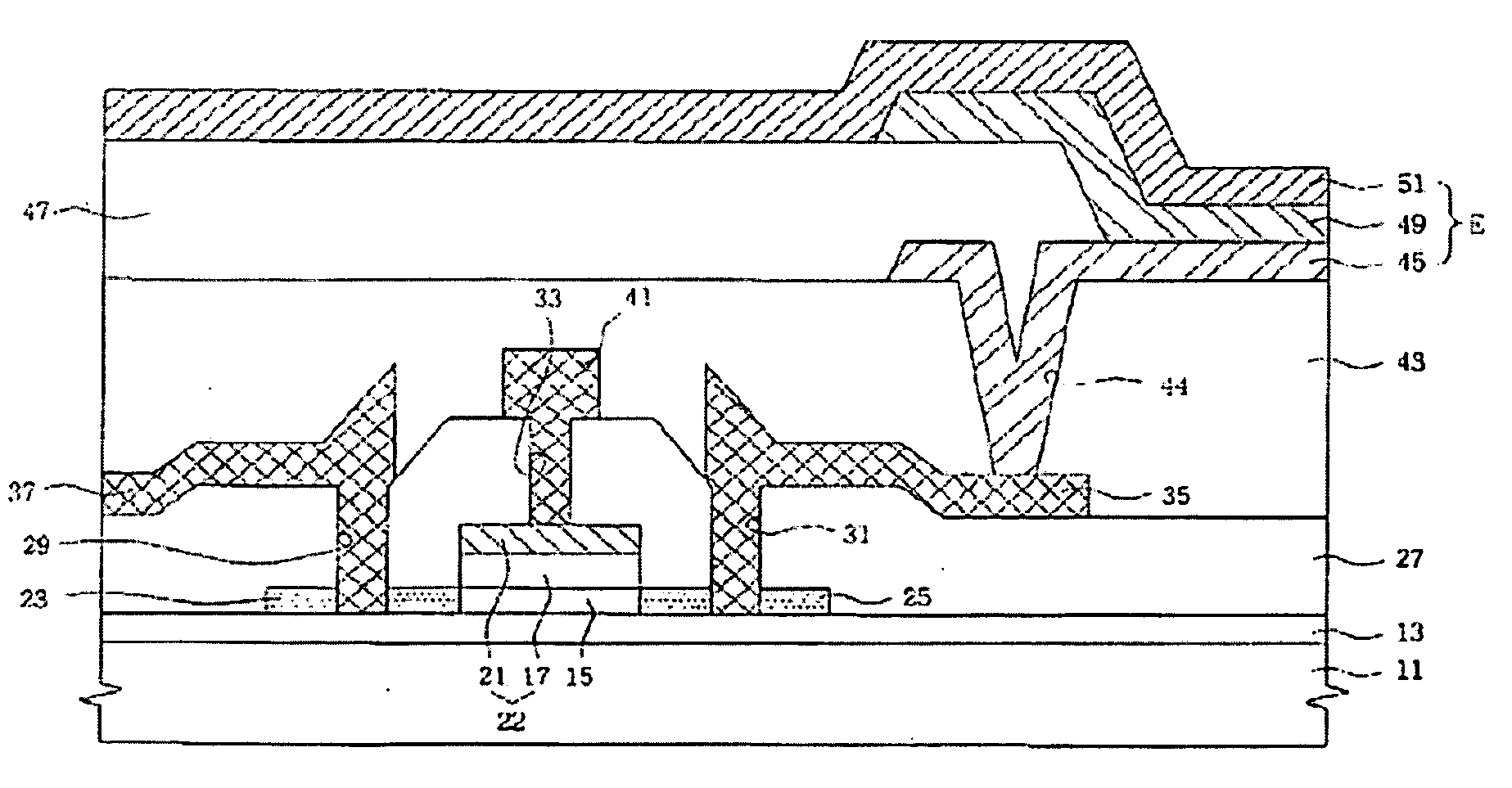

CMOS device comprising mos transistors with recessed drain and source areas and non-conformal metal silicide regions

InactiveUS20090321841A1Reduction of metal silicide thicknessIncreasing the thicknessTransistorSemiconductor/solid-state device manufacturingCMOSMetal silicide

A non-conformal metal silicide in a transistor of recessed drain and source configuration may provide enhanced efficiency with respect to strain-inducing mechanisms, drain / source resistance and the like. For this purpose, in some cases, an amorphizing implantation process may be performed prior to the silicidation process, while in other cases an anisotropic deposition of the refractory metal may be used.

Owner:ADVANCED MICRO DEVICES INC

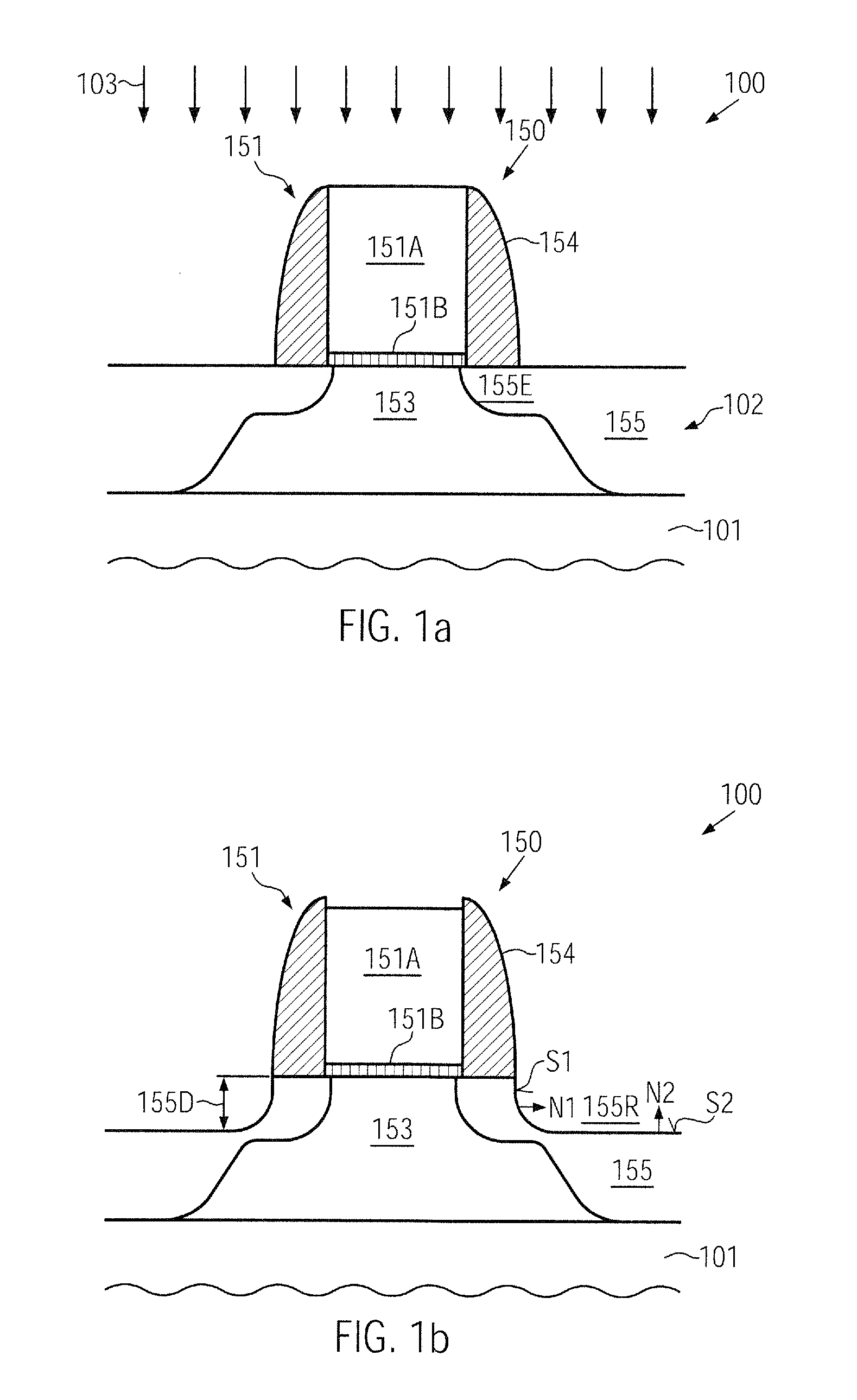

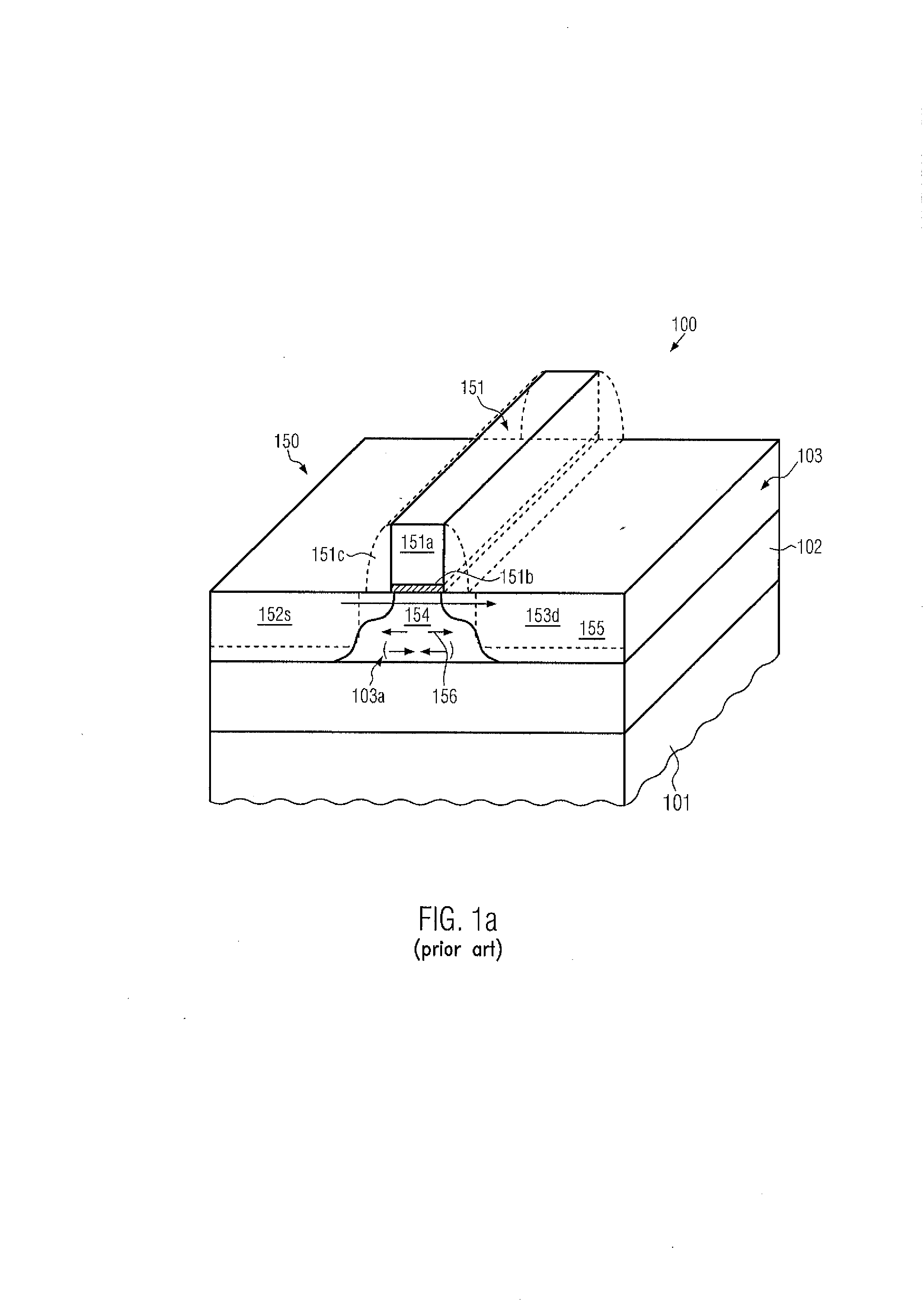

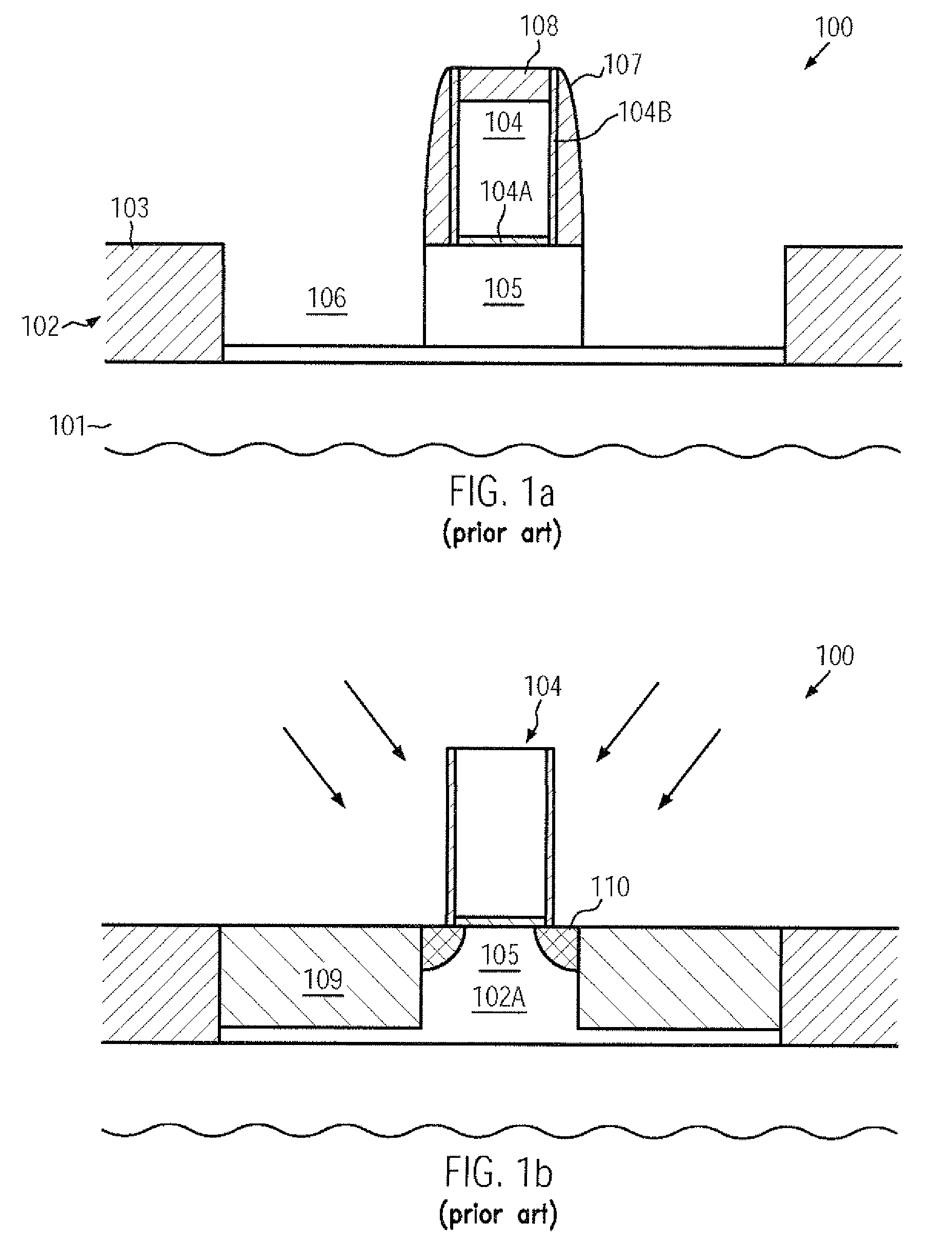

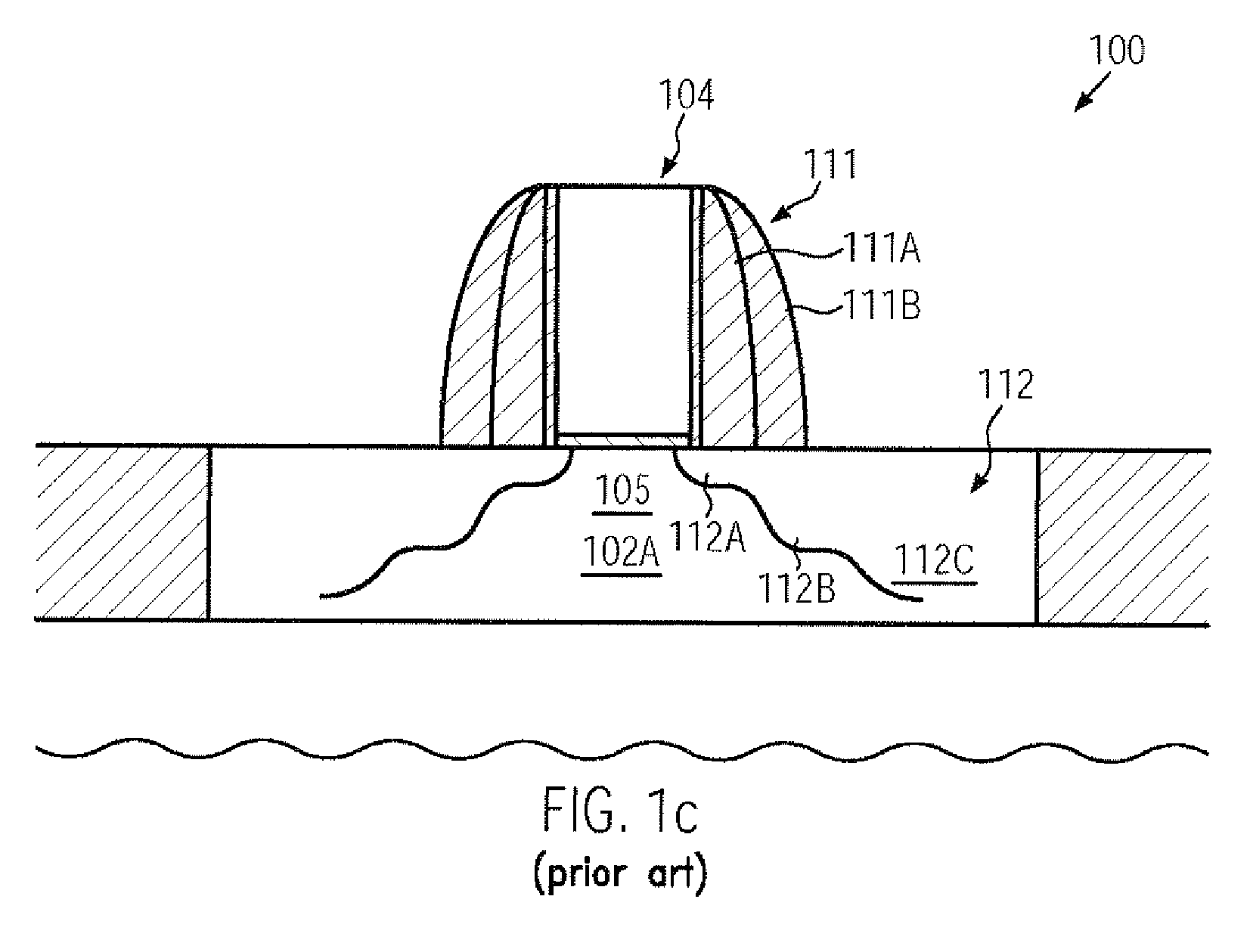

Technique for forming recessed sidewall spacers for a polysilicon line

ActiveUS20050026380A1Promotes metal diffusionFacilitated DiffusionTransistorSemiconductor/solid-state device manufacturingEngineeringLateral extension

In a double-spacer or multi-spacer approach to the formation of sophisticated field effect transistors, an upper sidewall portion of a gate electrode may be effectively exposed during recessing of an outer spacer element, since the outer spacer is substantially comprised of the same material as the liner material. Consequently, the anisotropic etch process for recessing the outer sidewall spacer also efficiently removes liner residues on the upper sidewall portion and provides an increased diffusion path for a refractory metal. Additionally, the lateral extension of the silicide regions on the drain and source area may be increased by correspondingly controlling an isotropic etch process for removing oxide residues.

Owner:CONVERSANT INTPROP MANAGEMENT INC

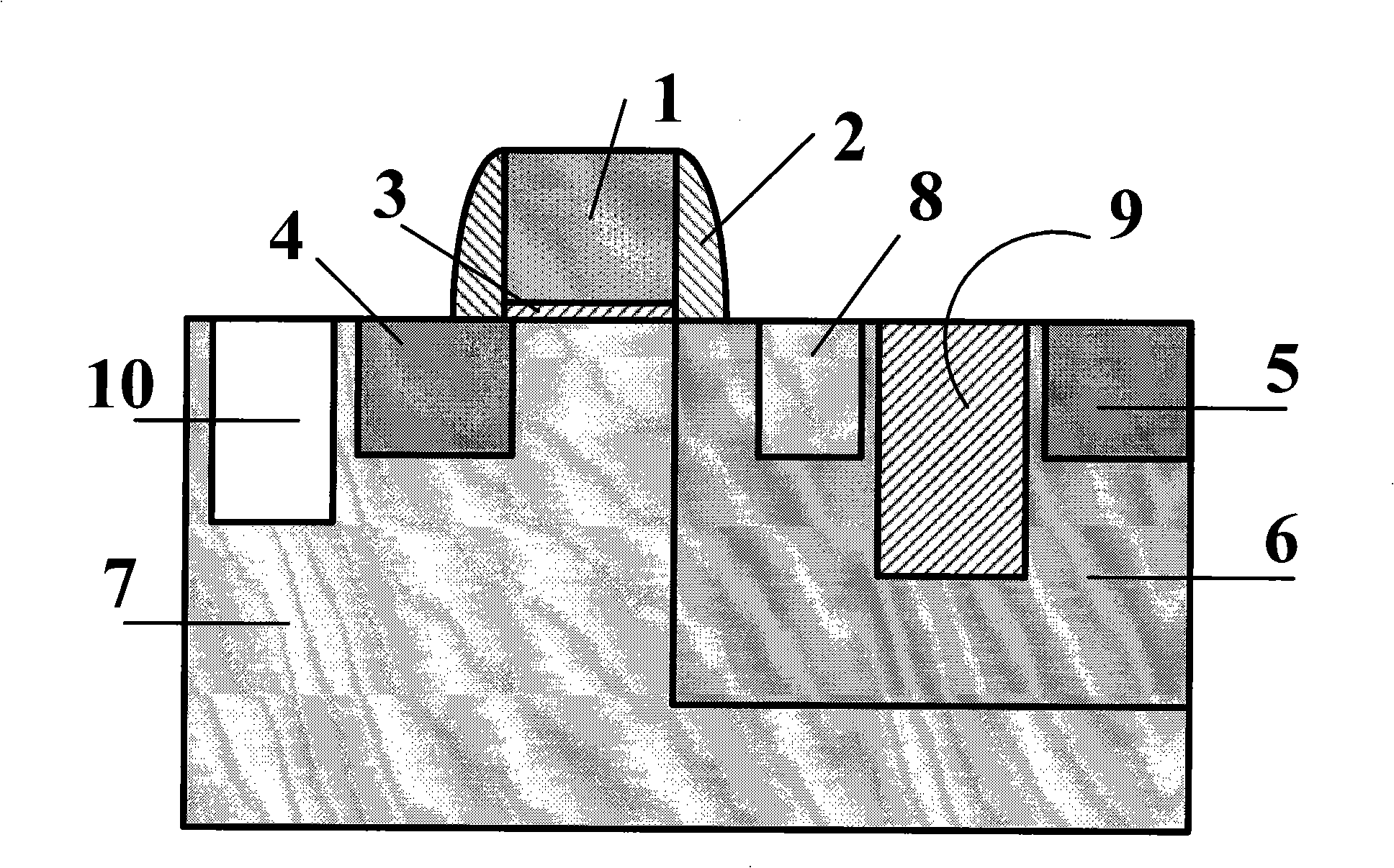

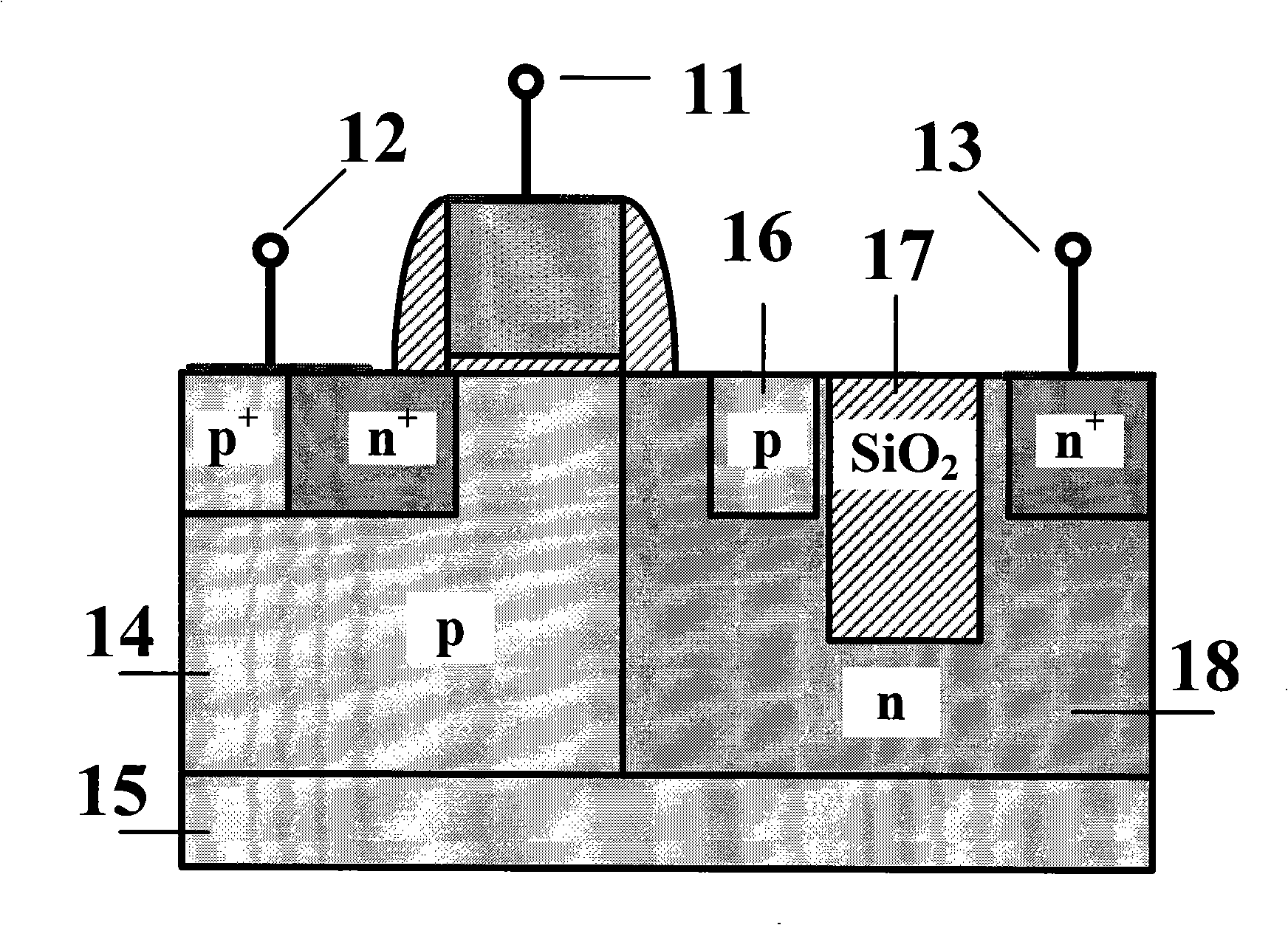

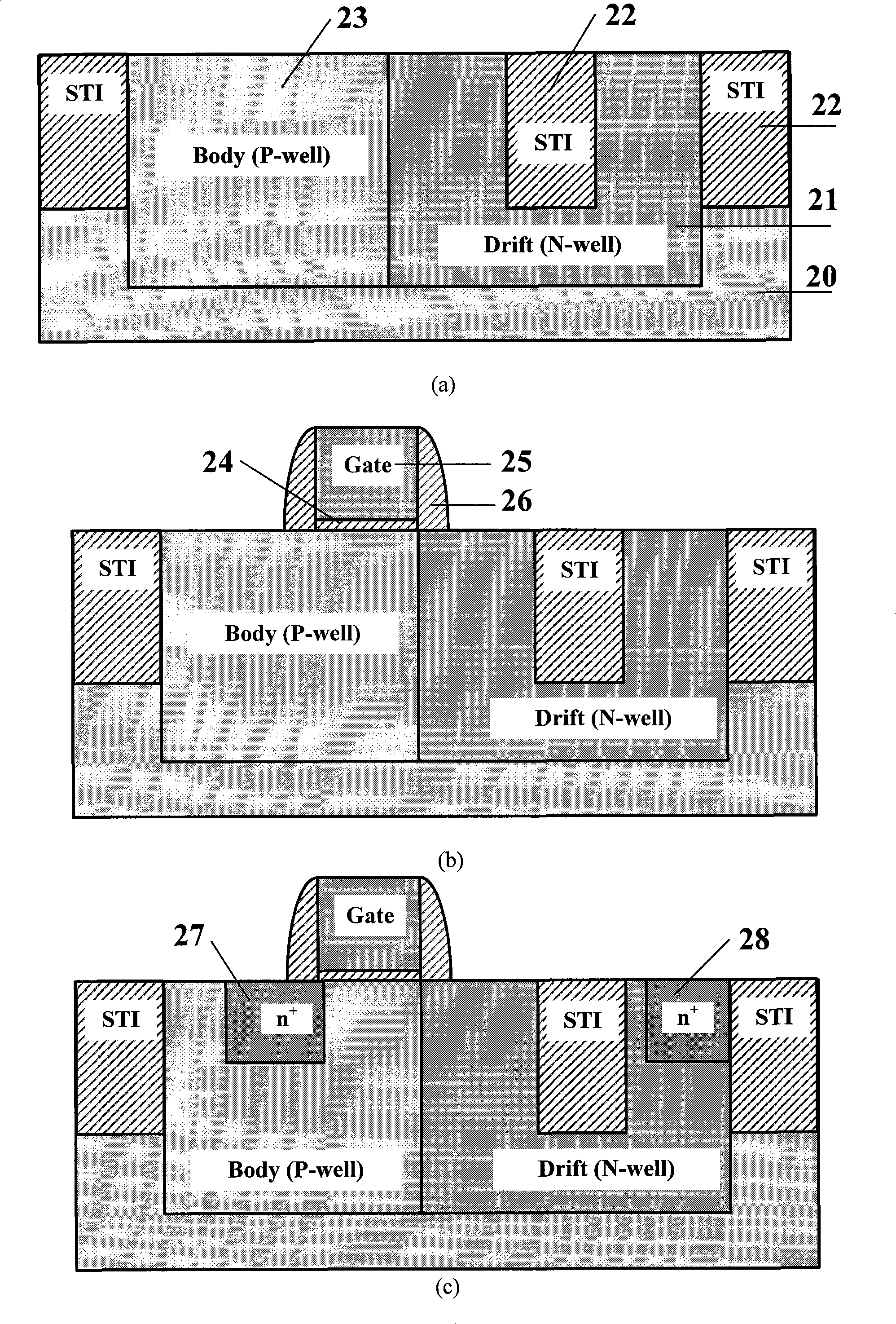

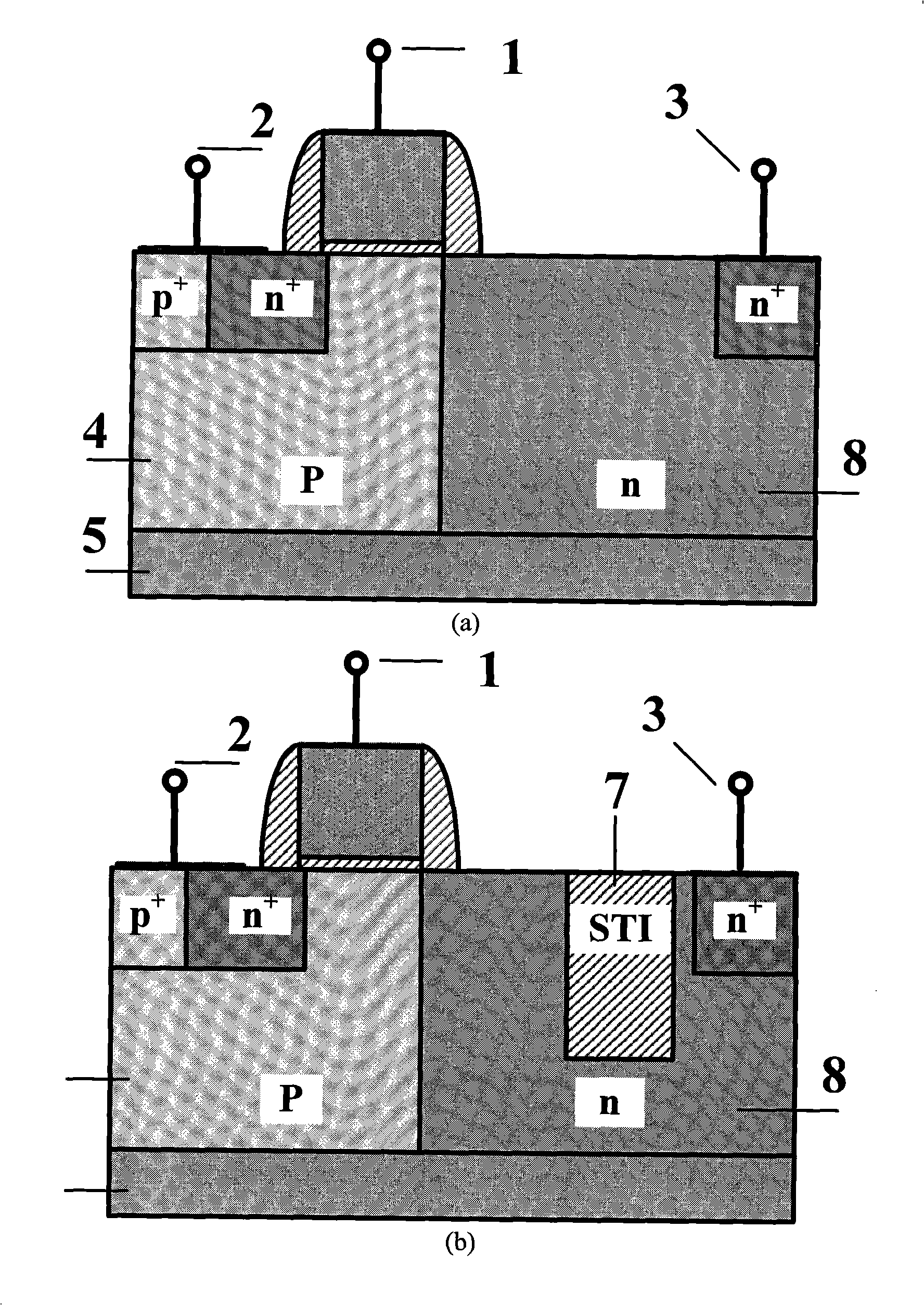

High pressure resistant lateral direction bilateral diffusion MOS transistor

InactiveCN101257047AImprove breakdown voltageIncrease the doping concentrationSemiconductor devicesEngineeringHigh pressure

The present invention discloses a transversal bilateral diffusion MOS transistor with high pressure resistant, which belongs to micro-electronics semi-conductor device field. The device includes a gate region, a source area, a drain region, a tagma, a gate medium and a drift region, the setting drift region is placed between the tagma and the drain region, and the doping type is opposite to the tagma, an insulating medium region and a doping region which is opposite to the doping type of the drift region are equipped in the drift region, and the doping concentration of the doping region is higher than that of the drift region, the doping region is adjacent to the tagma, however the insulating medium region is adjacent to the drain region. Because the insulating medium region and the doping region are inducted into the drift region at the same time, the effective depth of the drift region is reduced effectively to make the electric field more uniform and increase the equivalent length of the drift region, the resistant high Voltage characteristic of the transversal bilateral diffusion MOS transistor device of the present invention is good.

Owner:PEKING UNIV

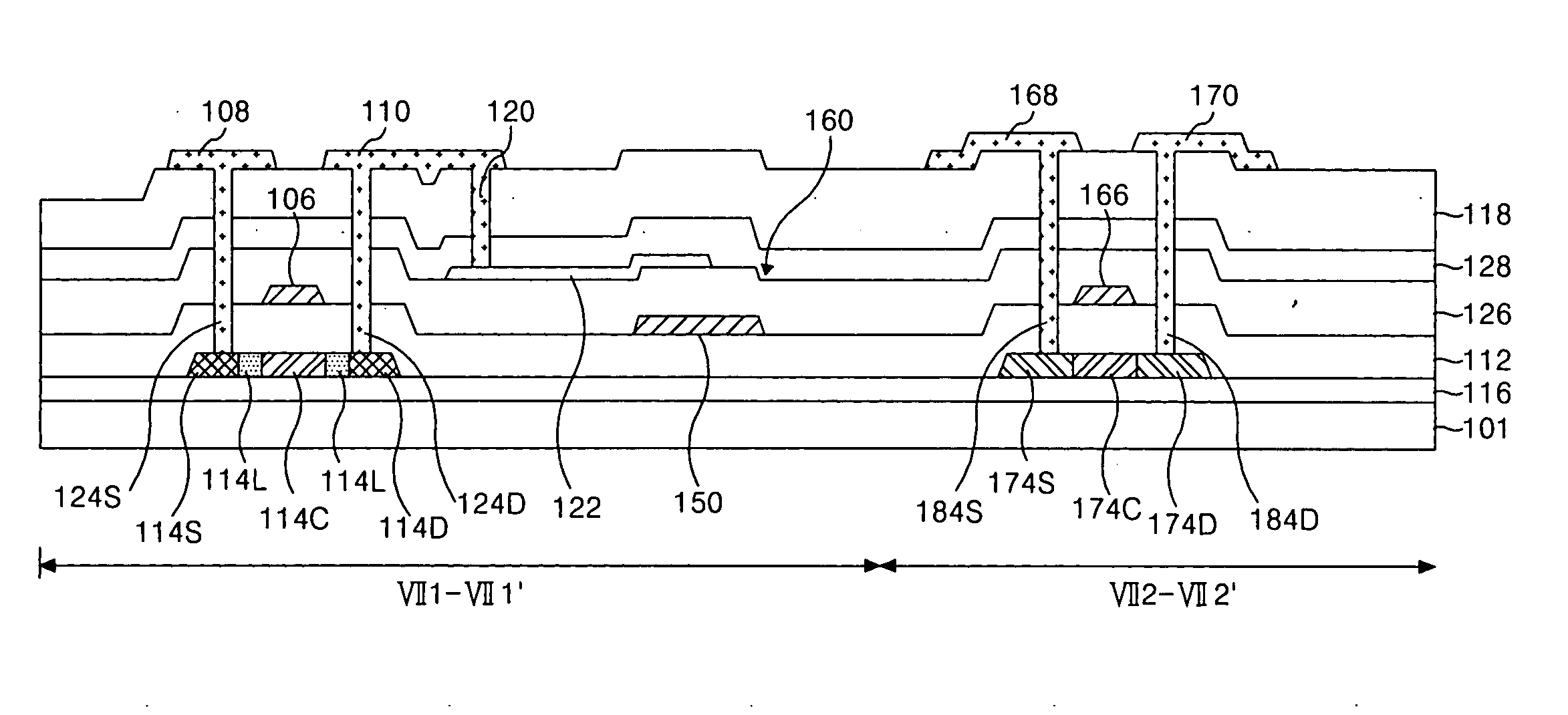

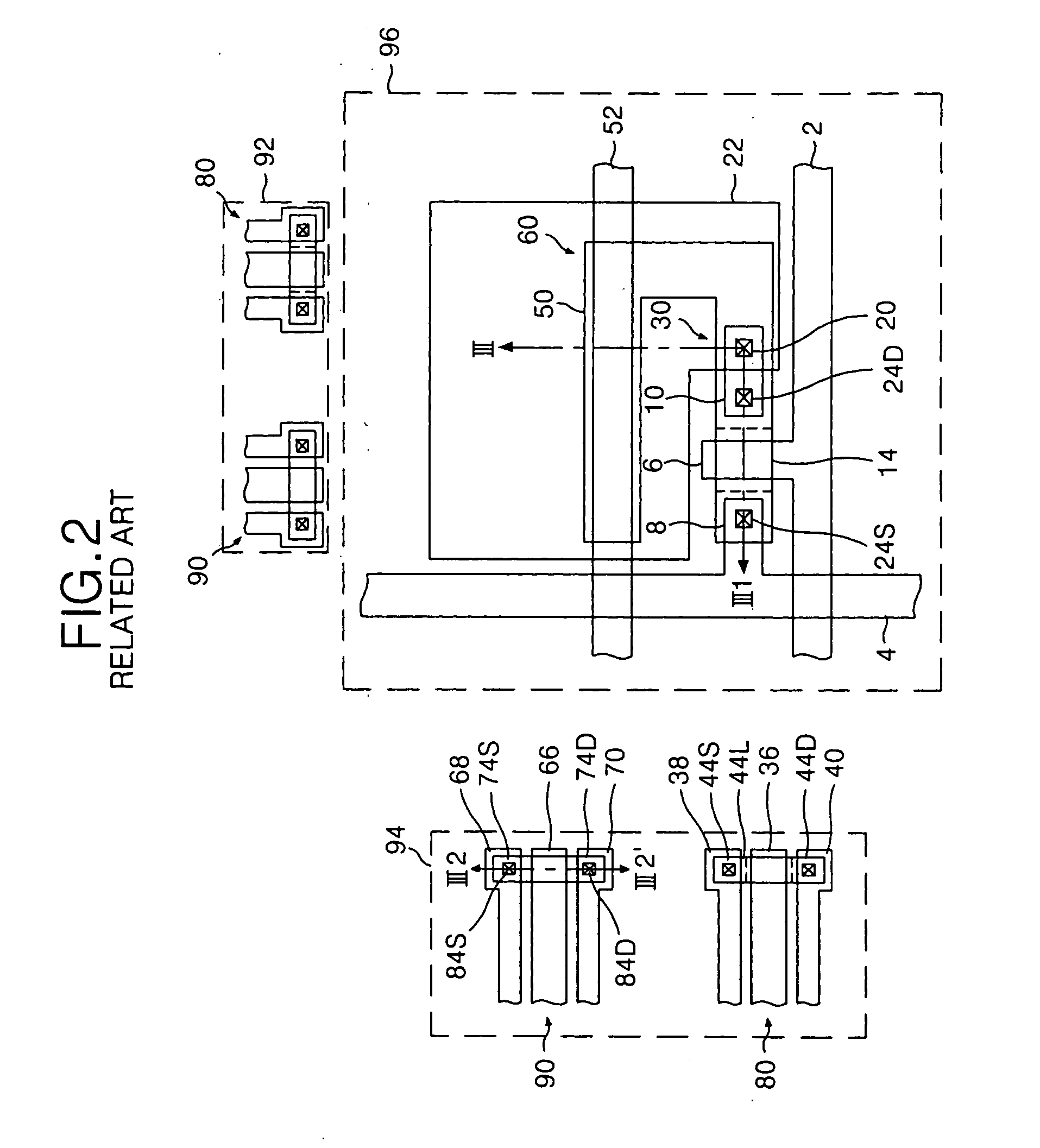

Method of fabricating liquid crystal display device

ActiveUS20050134754A1Simplify the manufacturing processTransistorSolid-state devicesLiquid-crystal displaySource area

A method of fabricating a liquid crystal display device includes forming a first active layer on a substrate, forming a first gate insulating film on the first active layer, forming a first gate electrode on the first gate insulating film, forming a first interlayer insulating layer on the first gate electrode, forming a pixel electrode on the first interlayer insulating layer, forming at least one insulating film to cover the pixel electrode, forming a first plurality of contact holes in the first interlayer insulating layer and the at least one insulating film, the first plurality of contact holes including a first source contact hole to expose a first source area of the first active layer and a first drain contact hole to expose a first drain area of the first active layer, forming a pixel contact hole in the at least one insulating film to expose the pixel electrode, performing a hydrogenating treatment to the substrate including the first source contact hole, the first drain contact hole, and the pixel contact hole, and forming a first source electrode contacting the first source area of the first active layer, and a first drain electrode contacting the direct drain area of the first active layer and connected to the pixel electrode.

Owner:LG DISPLAY CO LTD

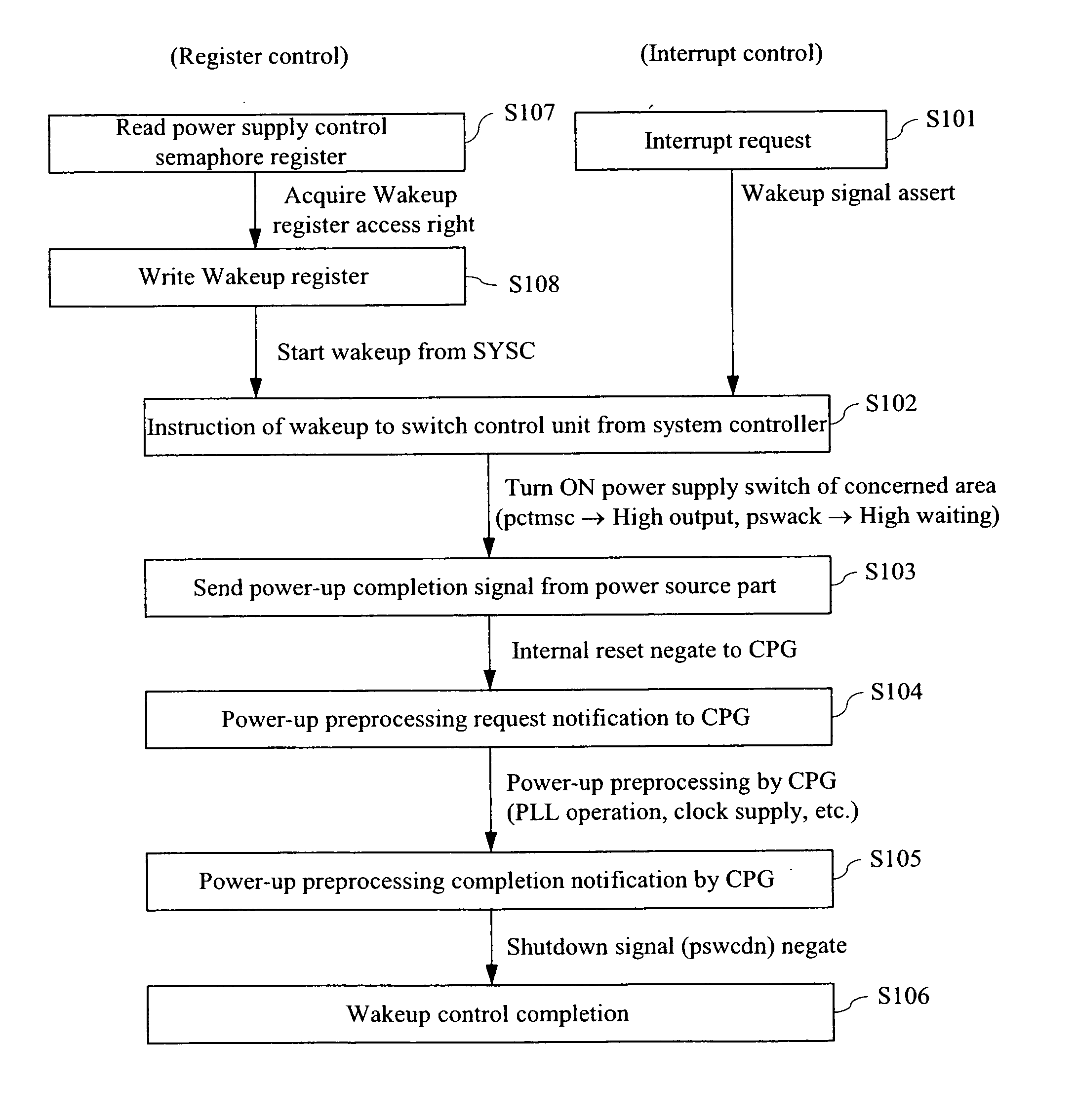

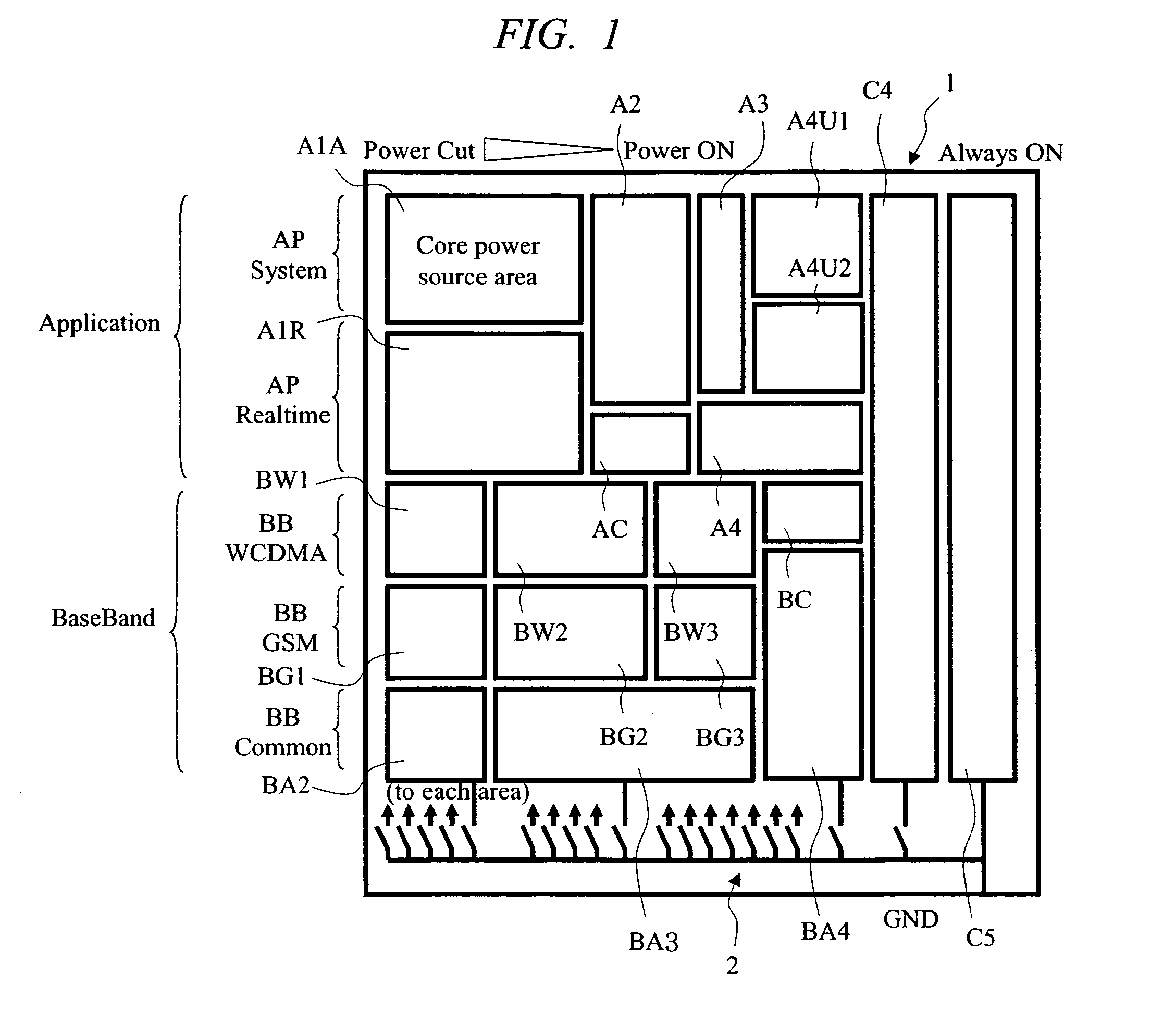

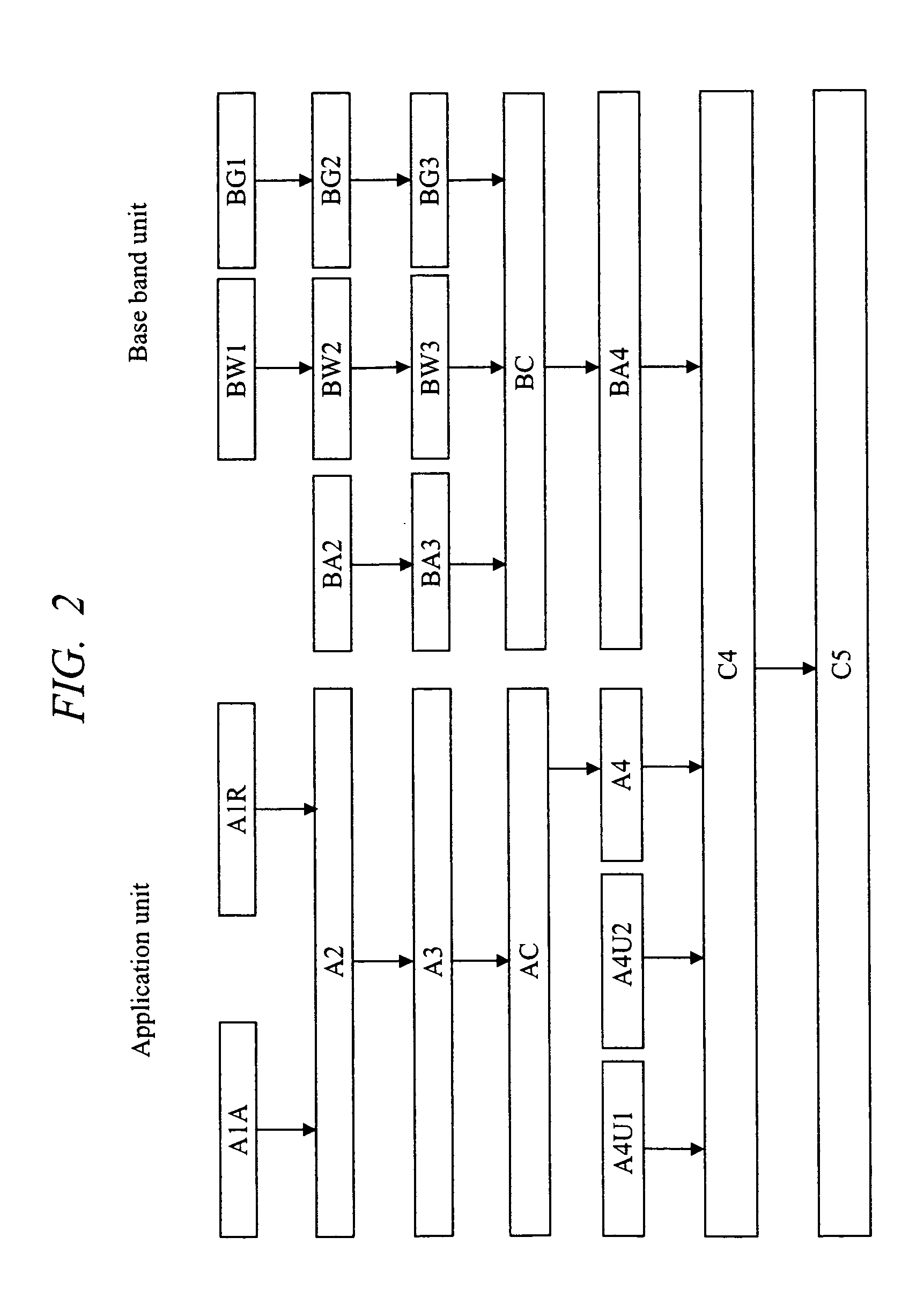

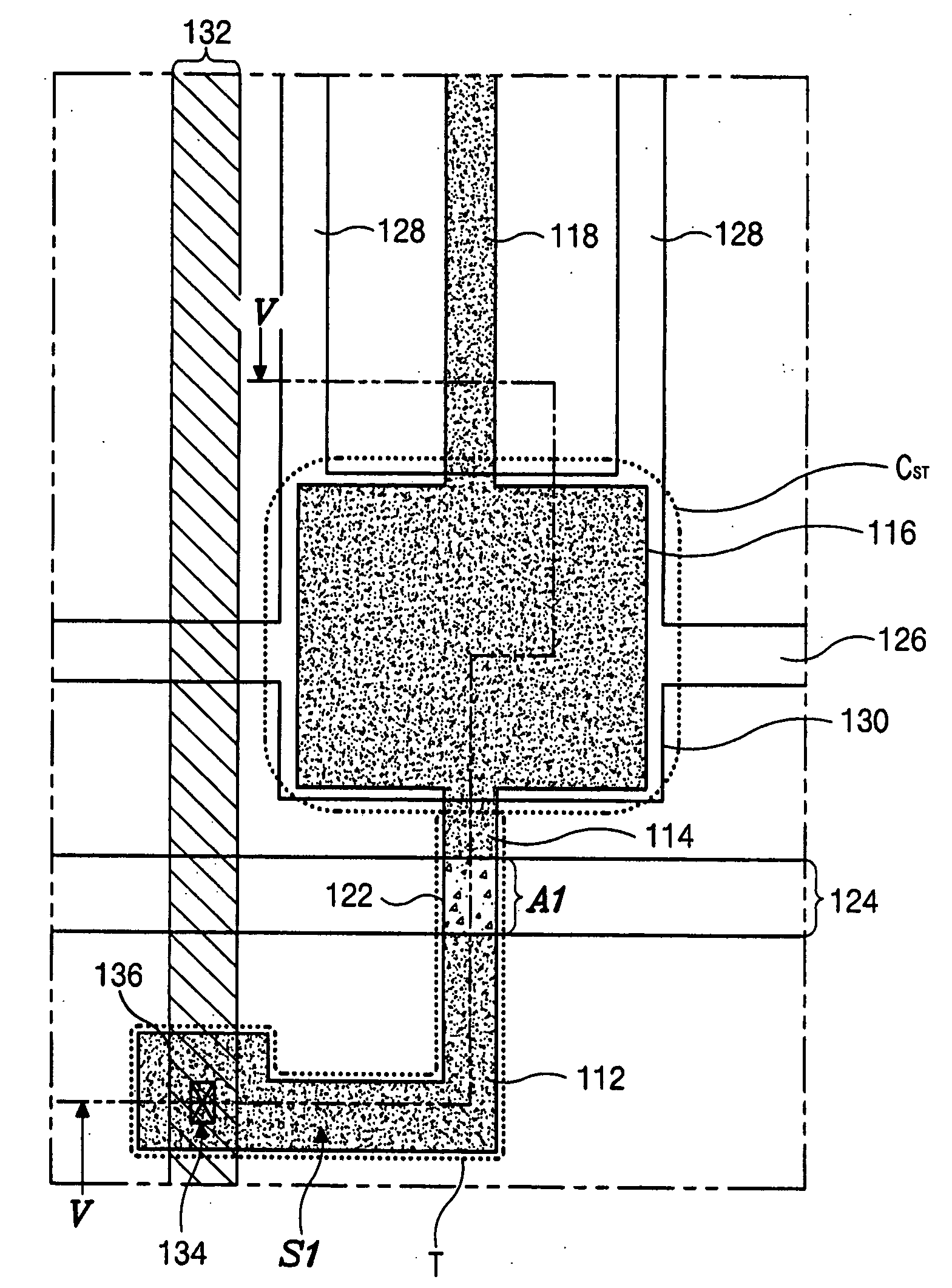

Semiconductor integrated circuit device

ActiveUS20070101174A1Efficient power supply controlLow power operationVolume/mass flow measurementPower supply for data processingControl powerPower switching

The power supply is effectively controlled in a semiconductor integrated circuit device having a multi domain structure so as to reduce the power consumption. When an interrupt signal is inputted, the system controller makes an instruction of wakeup to the corresponding switch control unit. At this moment, the system controller controls power supply so as to be supplied sequentially from the core power source area belonging to the lower hierarchical level dependent on the core power source area to which power is supplied. The system controller outputs the power supply switch-on request signal to the switch control unit. The switch control unit turns ON the power supply switch and sends the power-on completion signal back to the system controller. Similarly, the system controller supplies power sequentially to core power source areas in the dependency relation one after another from the lower hierarchy to the upper hierarchy.

Owner:RENESAS ELECTRONICS CORP

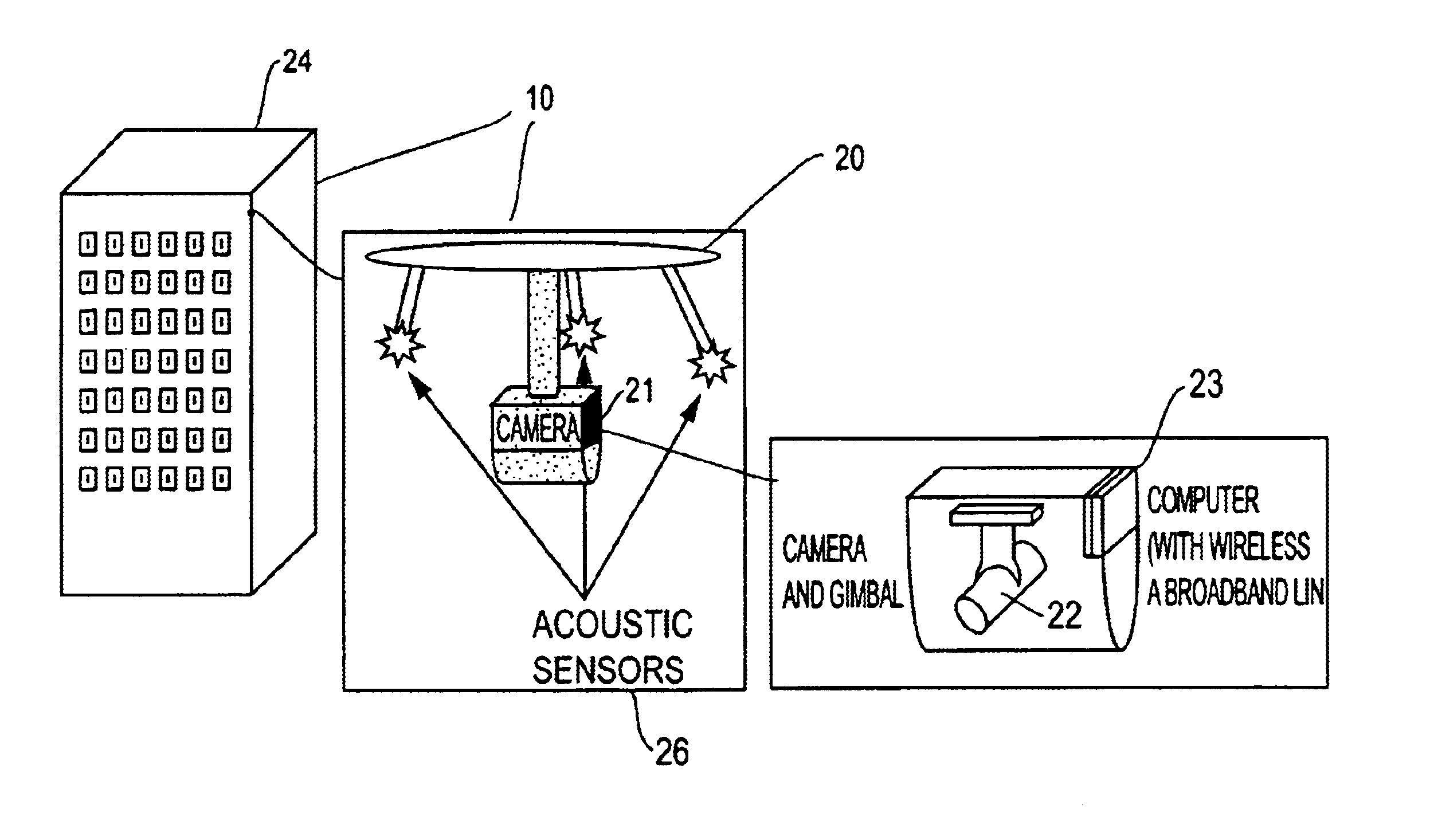

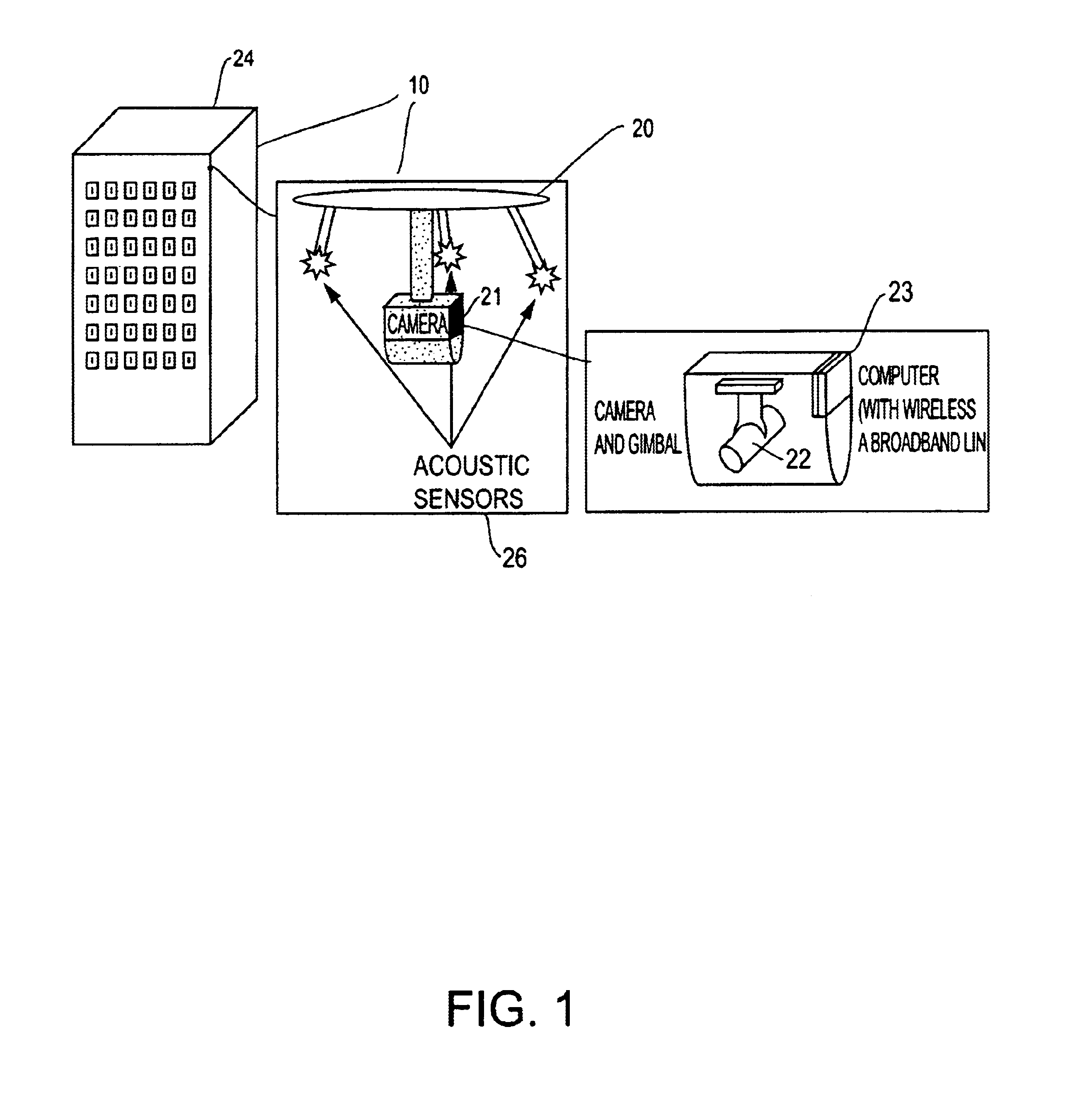

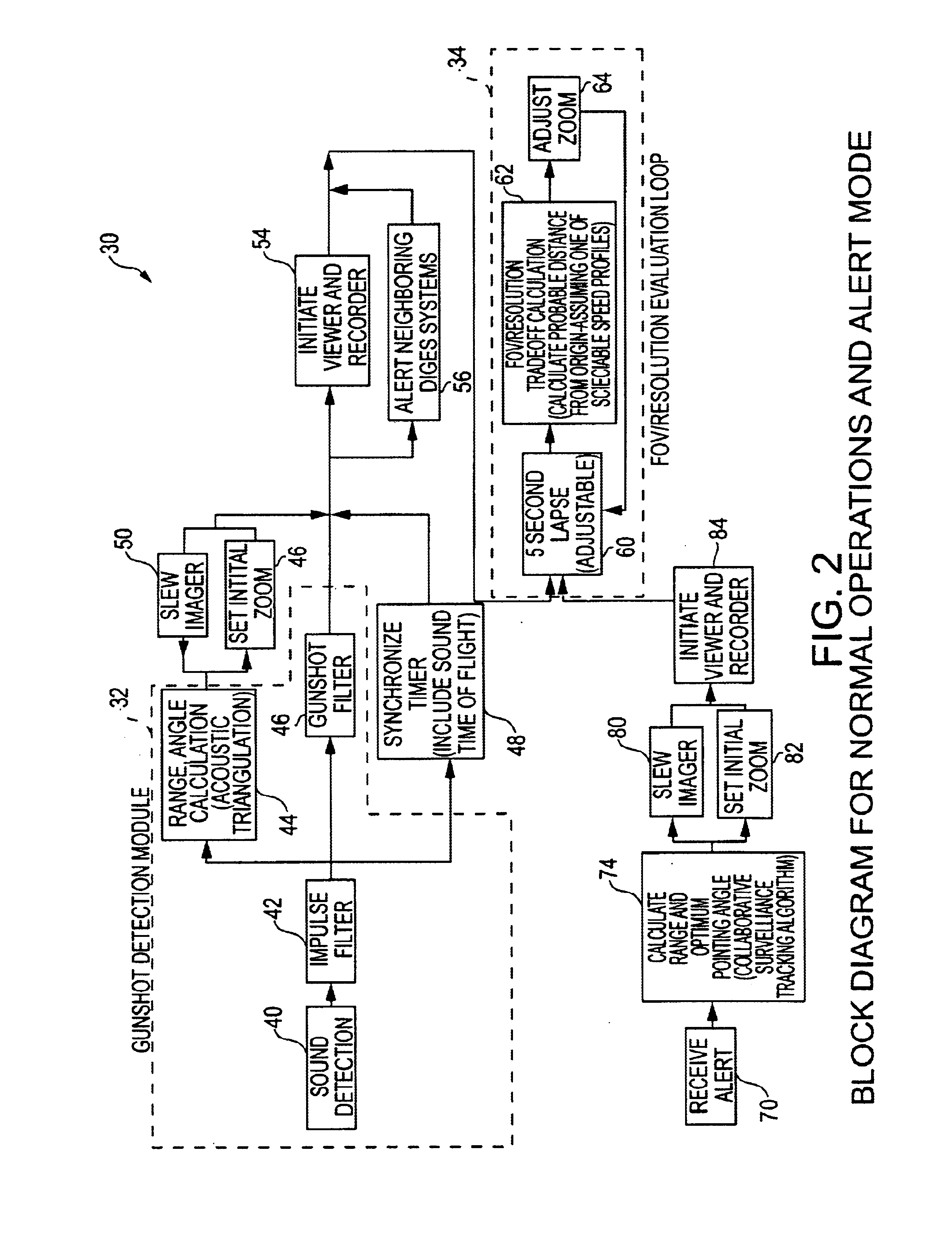

Gun shot digital imaging system

InactiveUS6965541B2Rapid detection and imaging and trackingPosition fixationDiversity direction findingDigital imagingSound sources

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

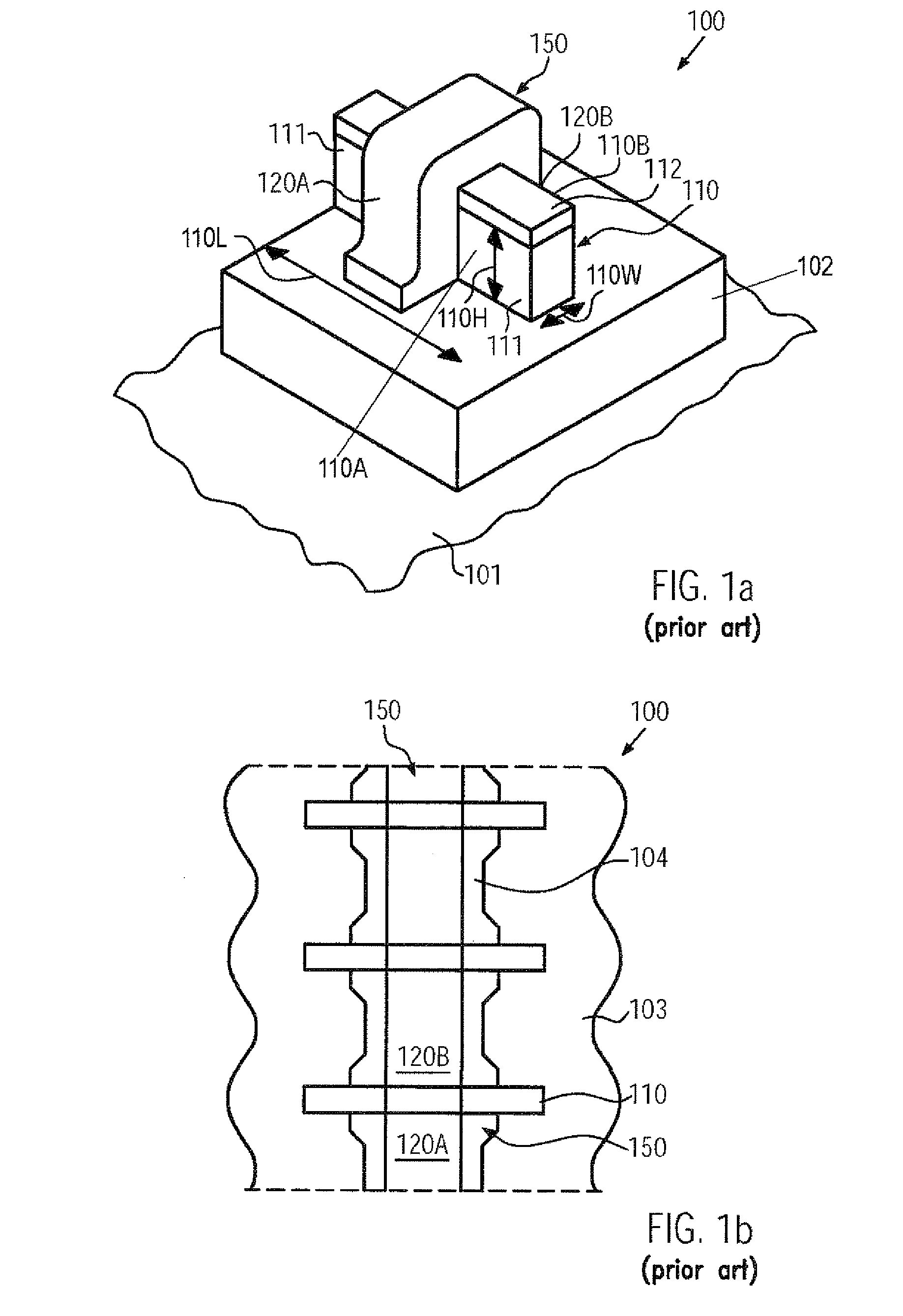

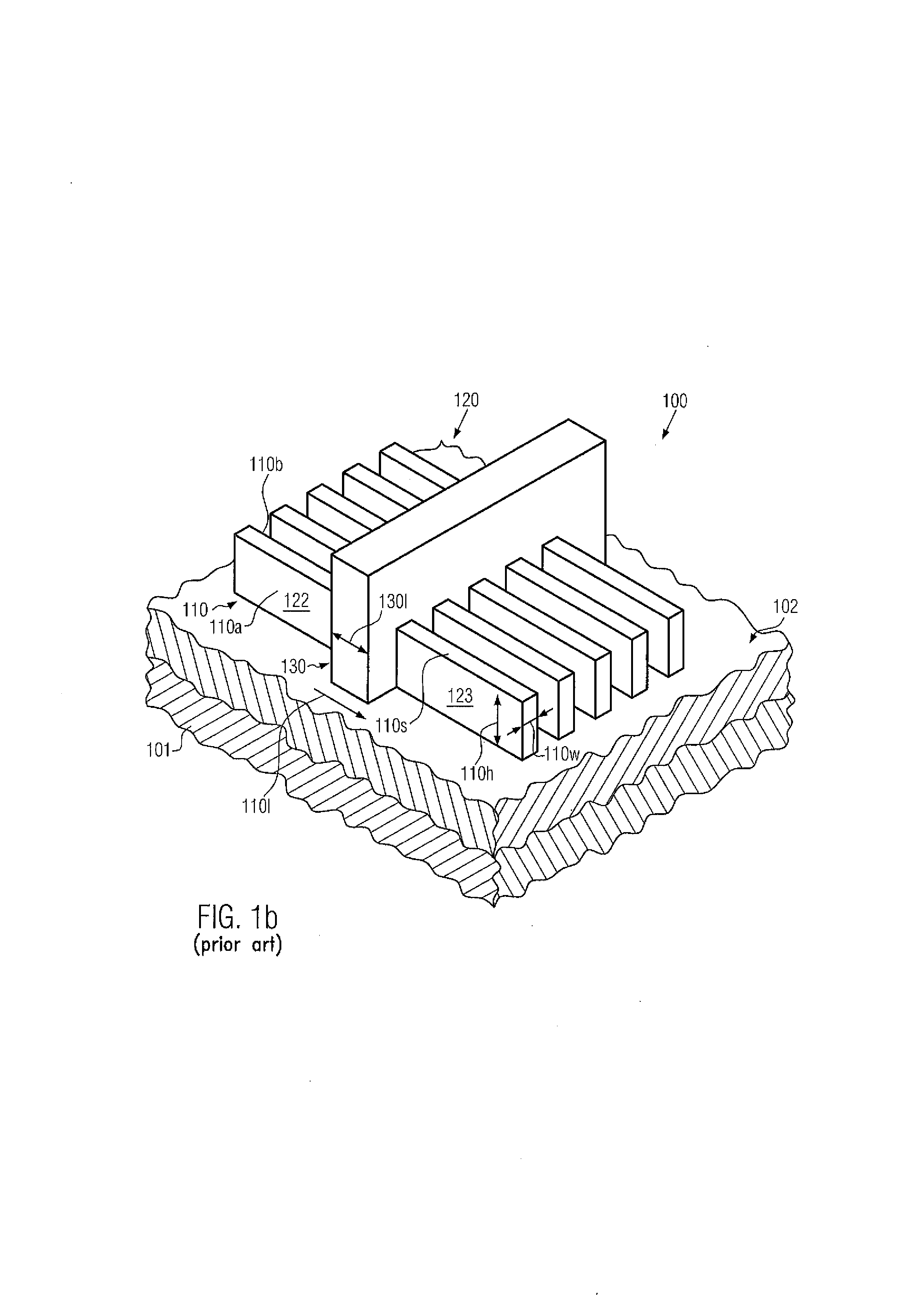

Method for forming double gate and tri-gate transistors on a bulk substrate

ActiveUS8114746B2Increase volumeReduced series resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

Owner:ADVANCED MICRO DEVICES INC

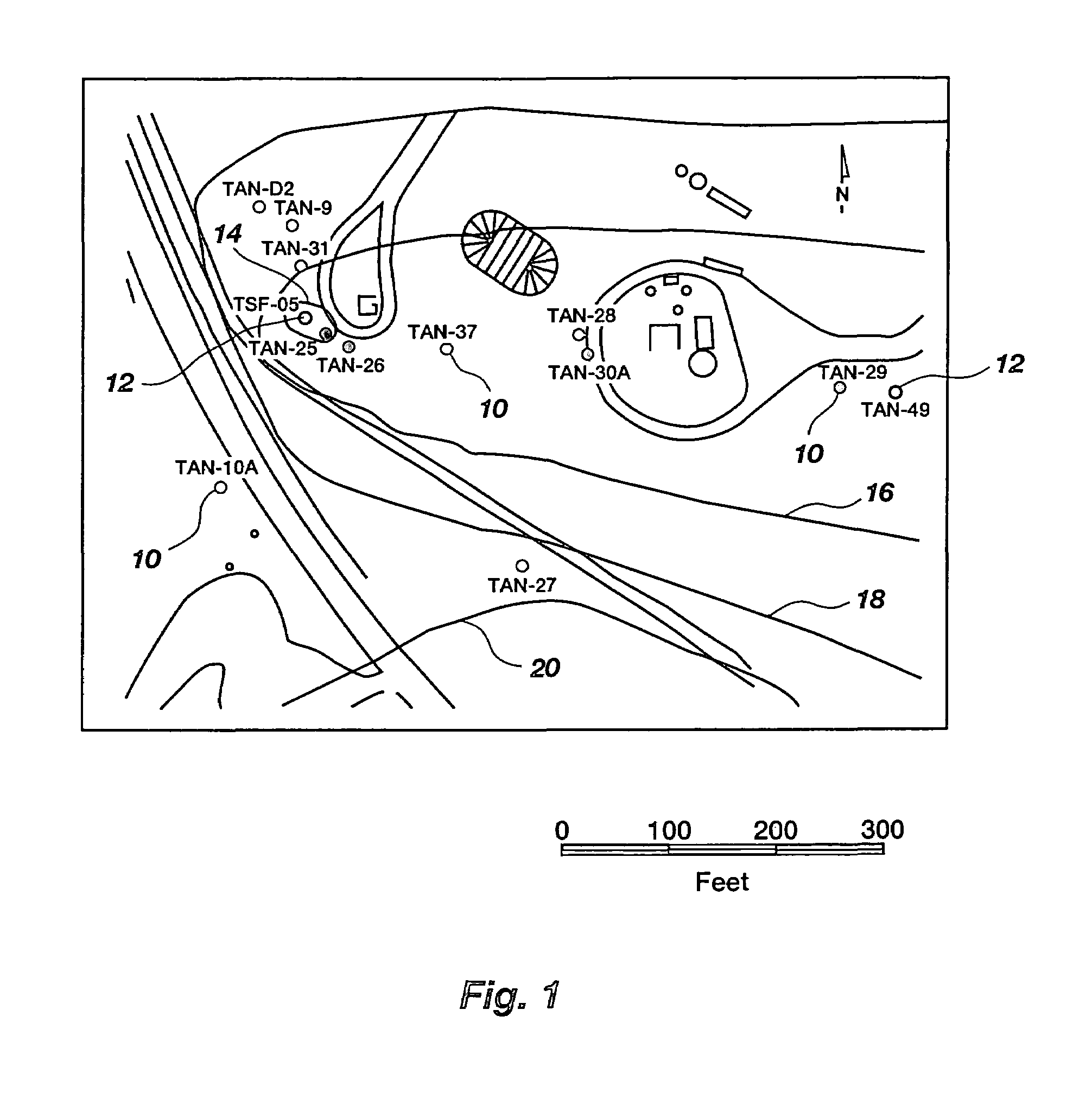

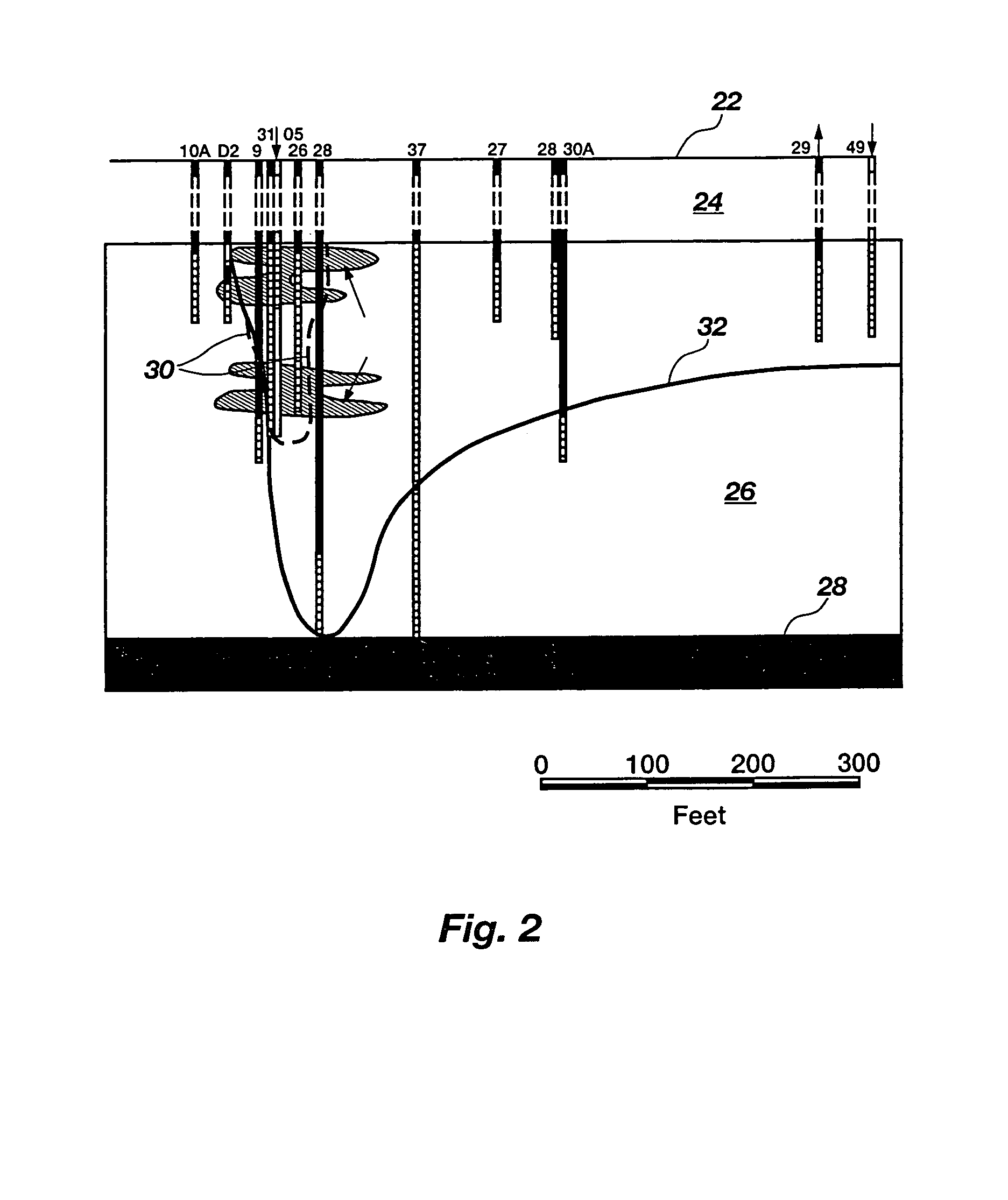

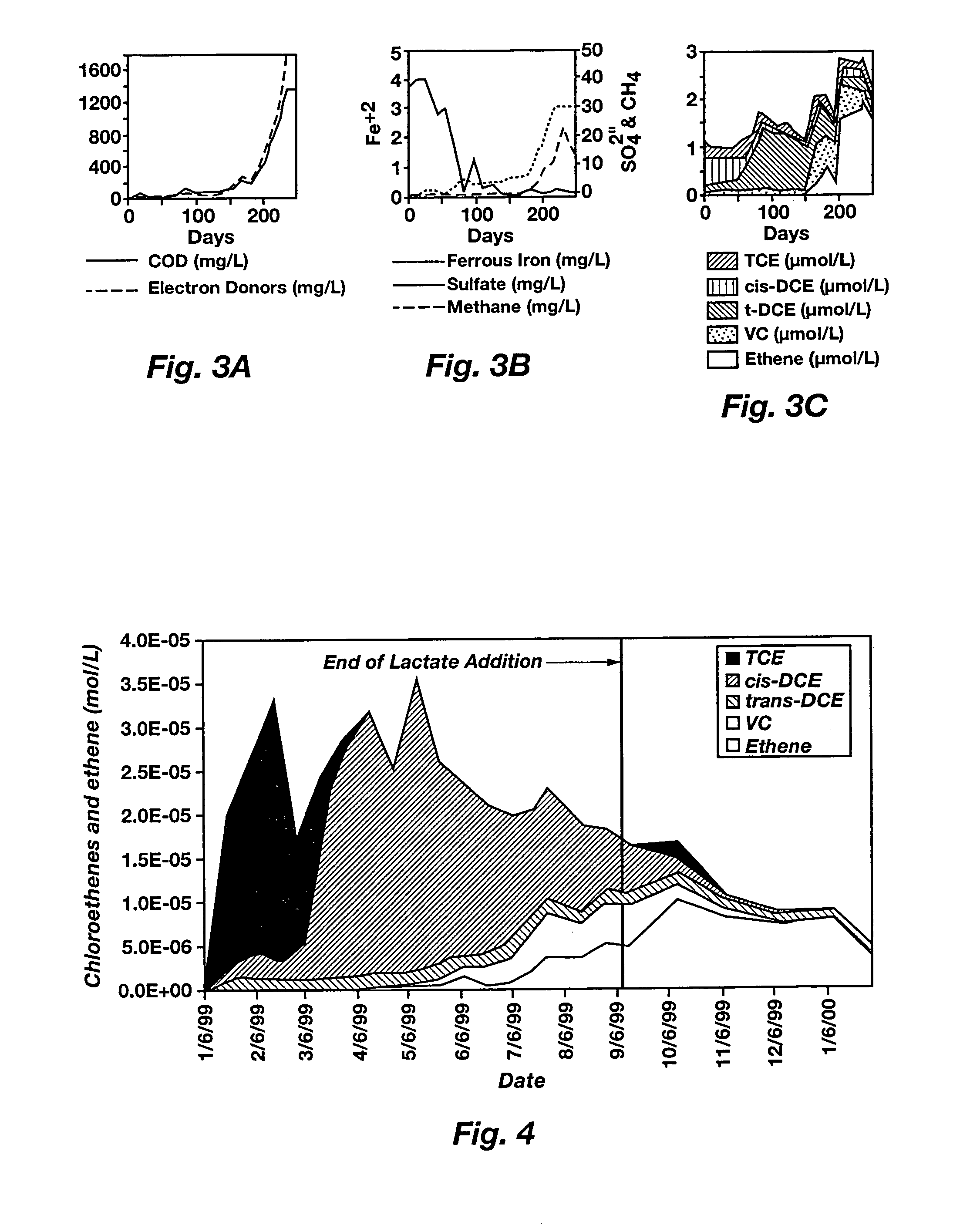

Electron donors for chlorinated solvent source area bioremediation

InactiveUS7045339B2Lower cost of capitalQuality improvementTreatment using aerobic processesSolid waste disposalSodium lactateElectron donor

Methods for enhancing bioremediation of ground water contaminated with nonaqueous halogenated solvents are disclosed. An illustrative method includes adding a composition to the ground water wherein the composition is an electron donor for microbe-mediated reductive dehalogenation of the halogenated solvents and enhances mass transfer of the halogenated solvents from residual source areas into the aqueous phase of the ground water. Illustrative compositions effective in these methods include surfactants such as C2–C4 carboxylic acids and hydroxy acids, salts thereof, esters of C2–C4 carboxylic acids and hydroxy acids, and mixtures thereof. Other illustrative compositions according to the present invention include oleyl lactylic acid and, optionally, oleic acid and lactic acid or salts thereof. Especially illustrative compositions for use in these methods include lactic acid, salts of lactic acid, such as sodium lactate, lactate esters, and mixtures thereof. The microbes are either indigenous to the ground water, or such microbes can be added to the ground water in addition to the composition.

Owner:JRW BIOREMEDIATION +1

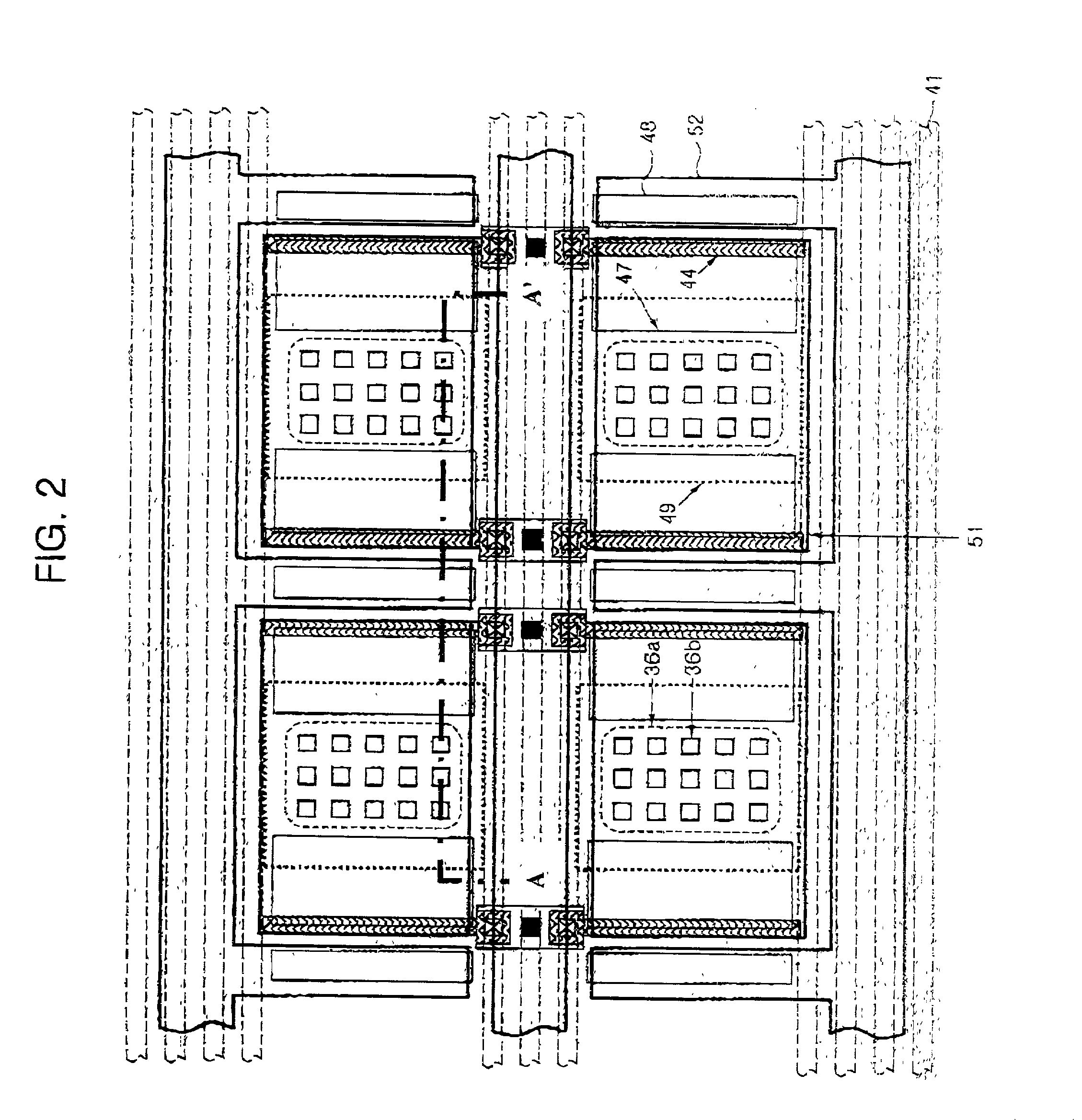

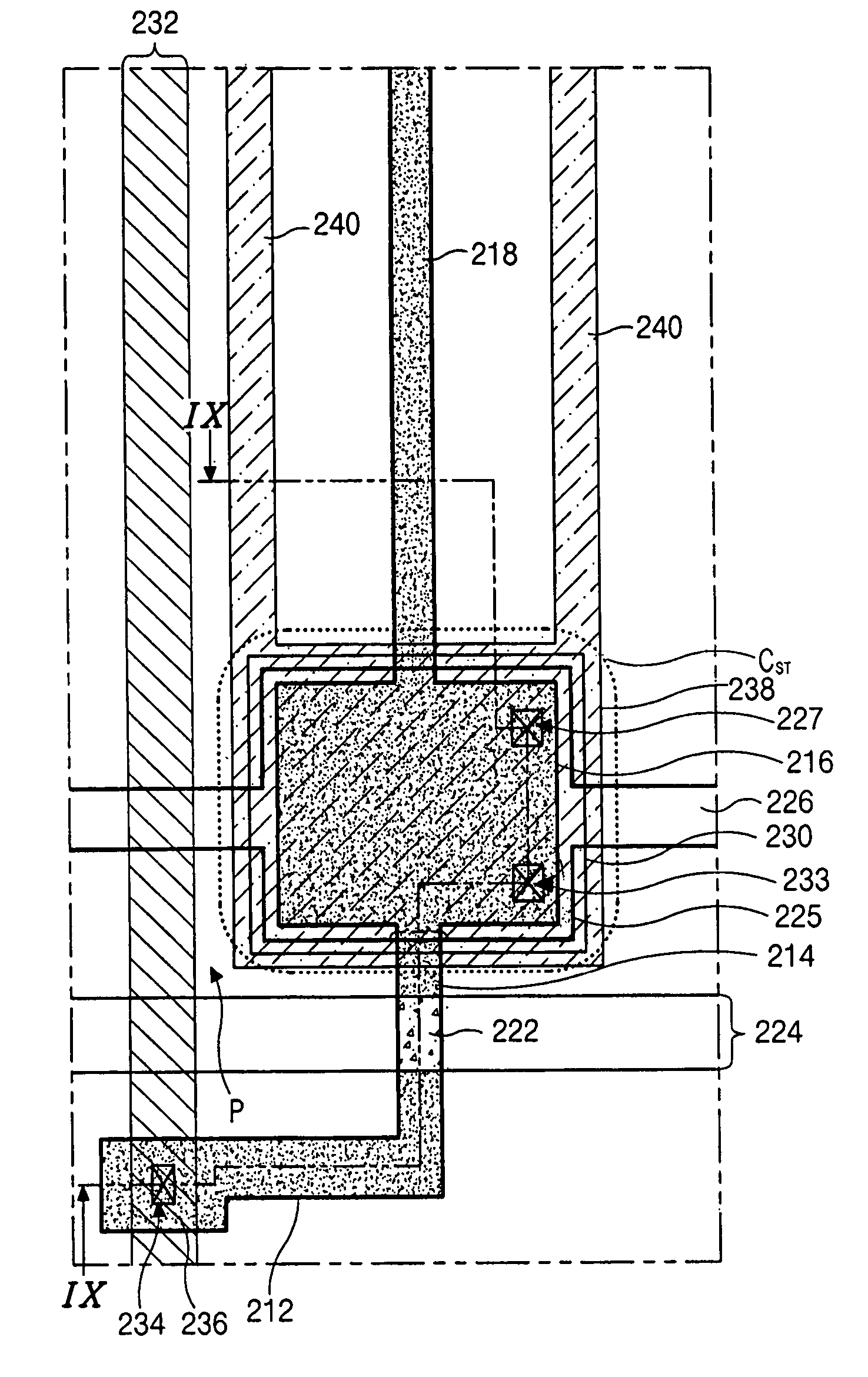

Array substrate for in-plane switching liquid crystal display device with polycrystalline silicon pixel electrode and method of manufacturing the same

ActiveUS20070013820A1Increase the aperture ratioUniform dimensionsNon-linear opticsCapacitanceIn plane

Owner:LG DISPLAY CO LTD

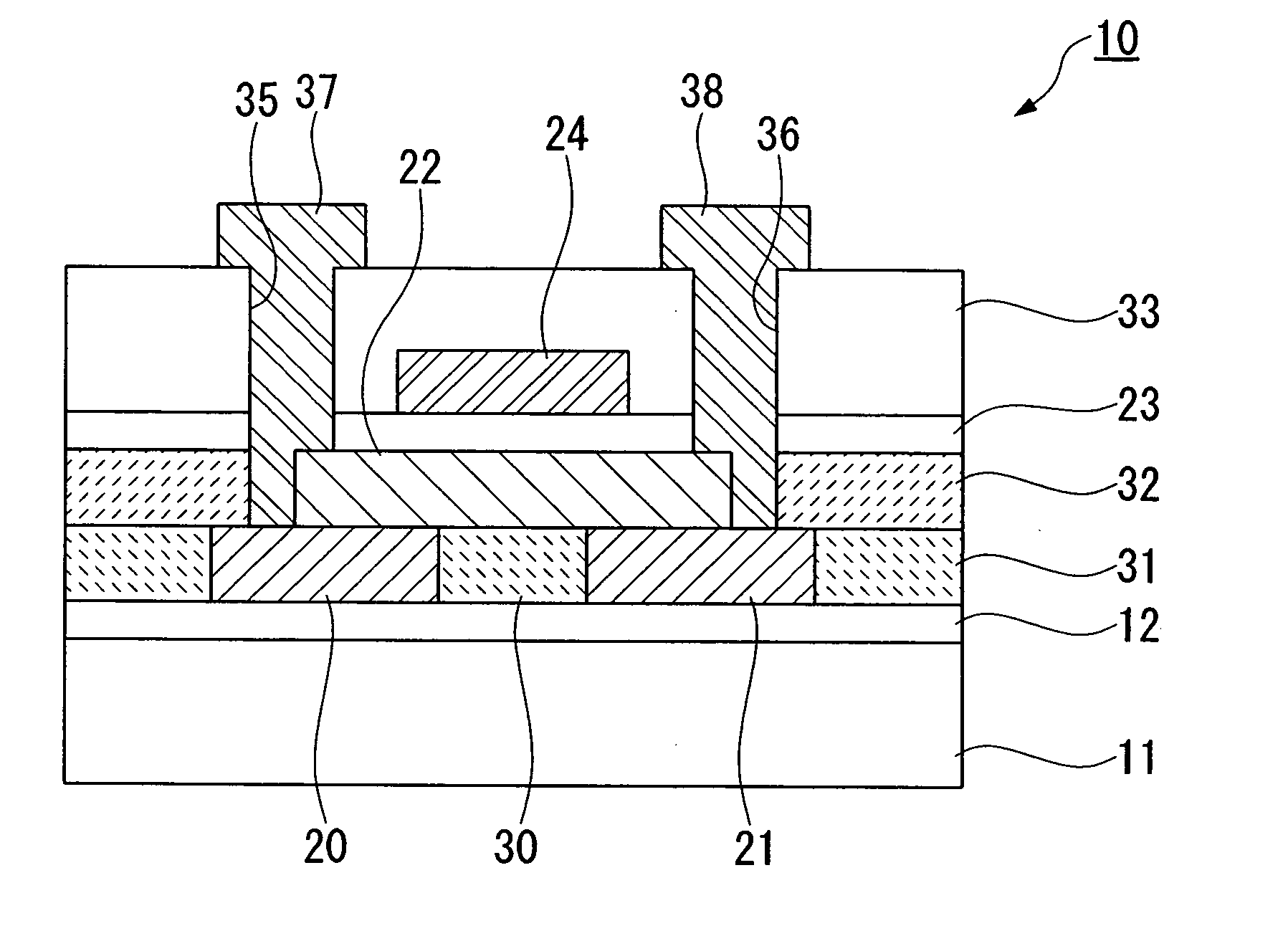

Transistor, integrated circuit, electro-optic device, electronic instrument and method of manufacturing a transistor

InactiveUS20050029591A1Little wastagePrecise positioningTransistorSolid-state devicesElectronic instrumentSource area

There is provided a transistor and a method of manufacturing this transistor that allow a high degree of freedom when designing a wiring structure and also allow an improvement in product quality to be achieved. The transistor includes a source area, a drain area, and a channel area, each of which are formed by semiconductor films, and also a gate insulating film and a gate electrode. The semiconductor film containing the source area and the semiconductor film containing the drain area are formed separately sandwiching both sides of an insulating member. The semiconductor film containing the channel area is formed on top of the insulating member.

Owner:SEIKO EPSON CORP

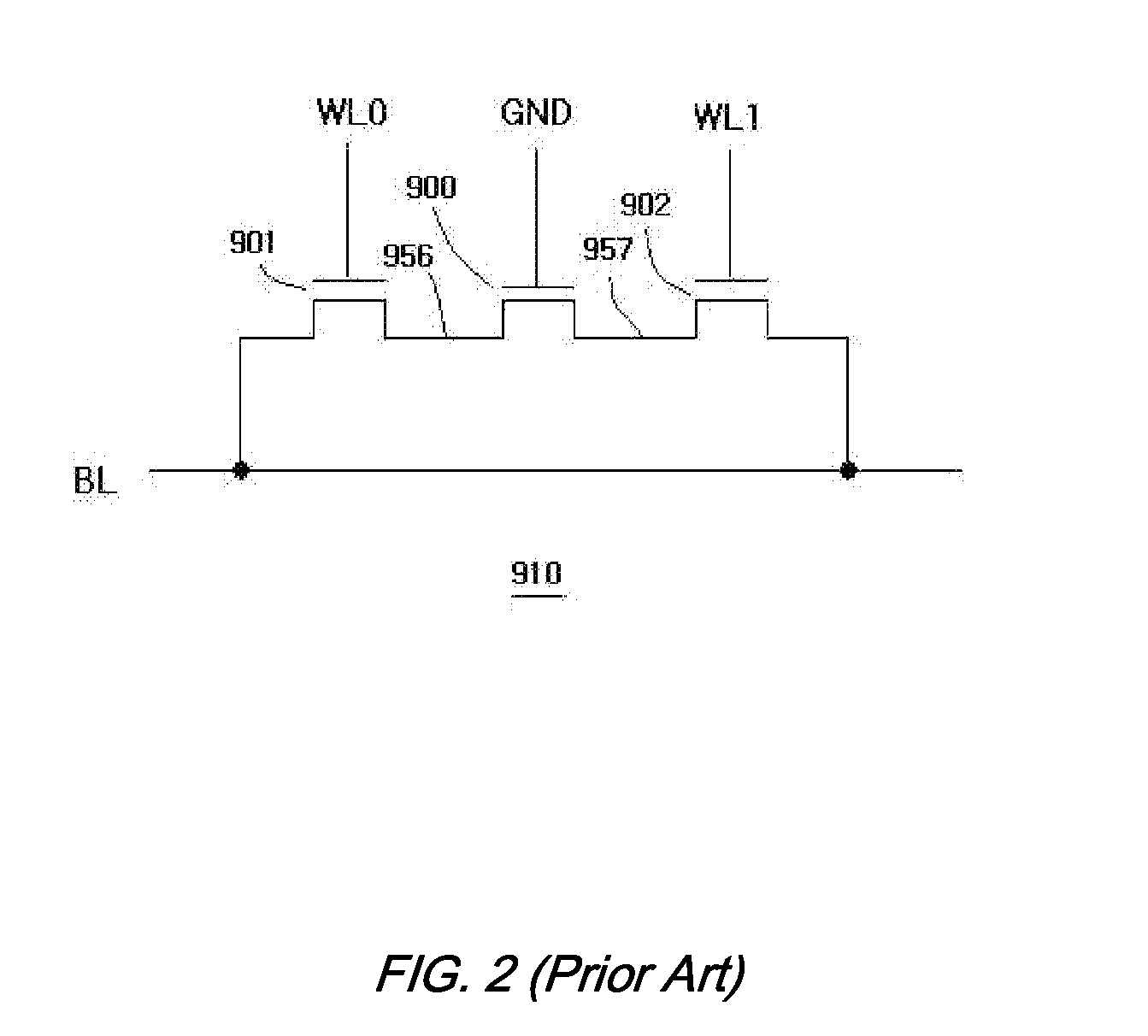

Programmable non-volatile memory

ActiveUS20130051113A1Improve integration densityEasy to processTransistorSolid-state devicesEngineeringAntifuse

A programmable non-volatile memory including a memory cell includes a transistor acting as an anti-fuse and two diodes for access. The memory cell that can store two bits and includes a transistor acting as an anti-fuse and two diodes for access, wherein the cell transistor includes: the source electrode formed by a metal; the first diode as the source region contact structure; the drain electrode formed by a metal; and the second diode as the drain region contact structure wherein the cell transistor, the oxide layer between the source area and the gate is the first anti-fuse the first storage; the oxide layer between the drain area and the gate is the second anti-fuse the second storage; the two diodes are connected in series to access the two anti-fuses.

Owner:RANGDURU

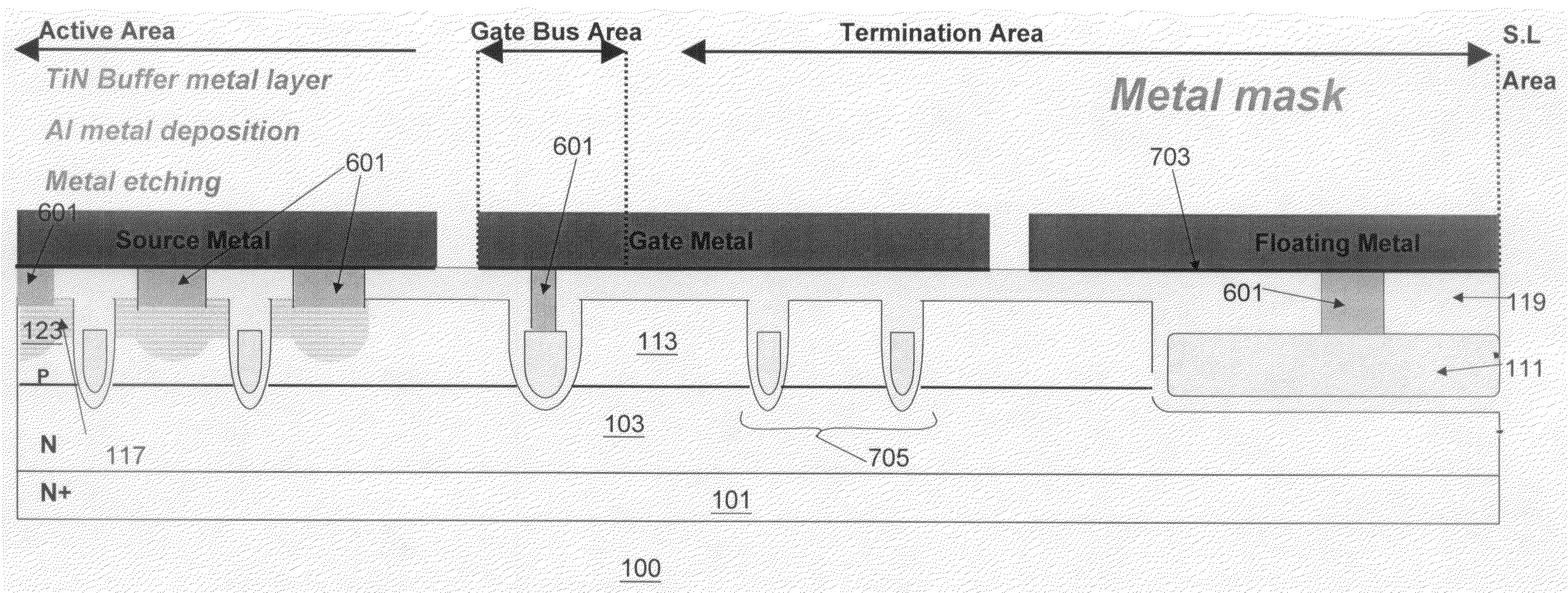

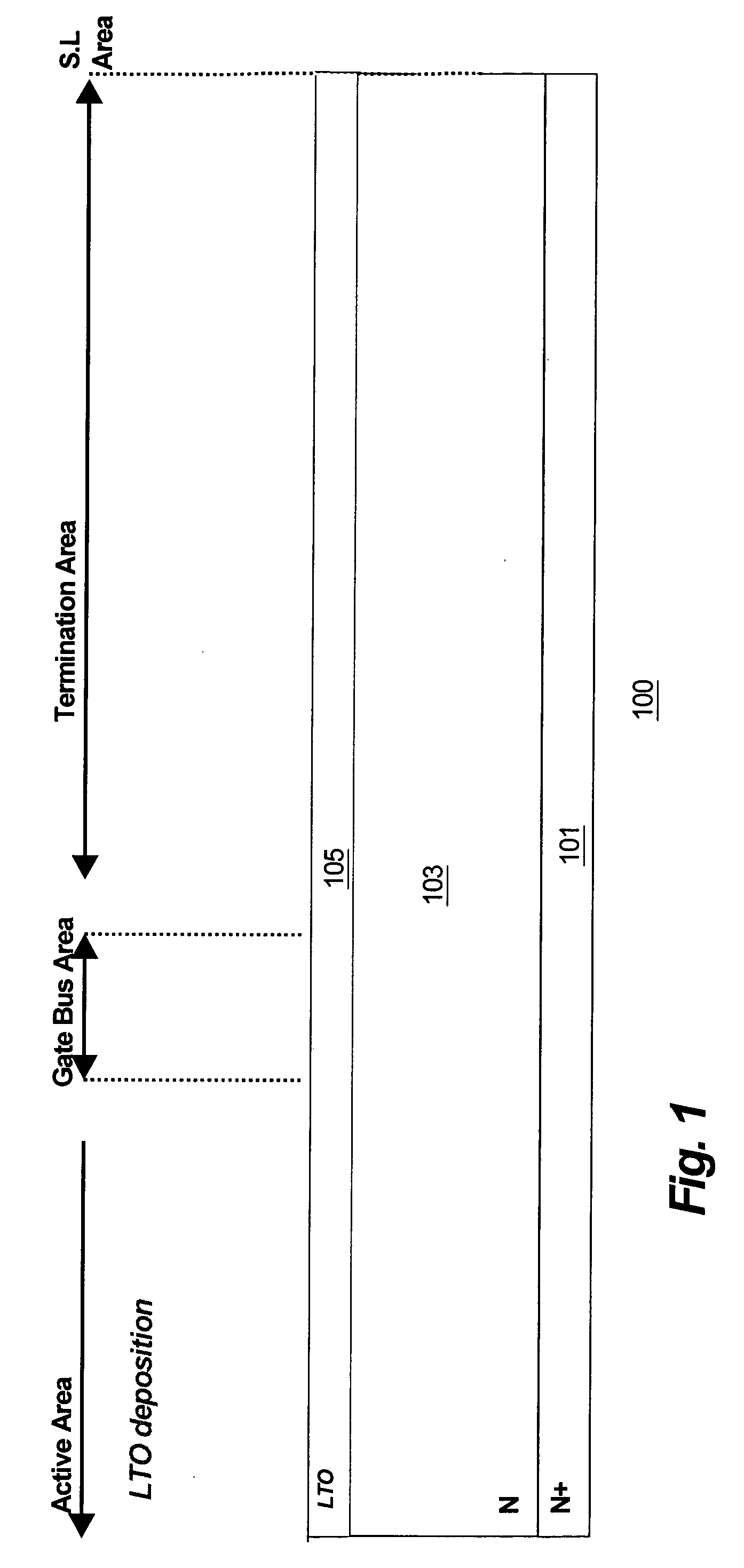

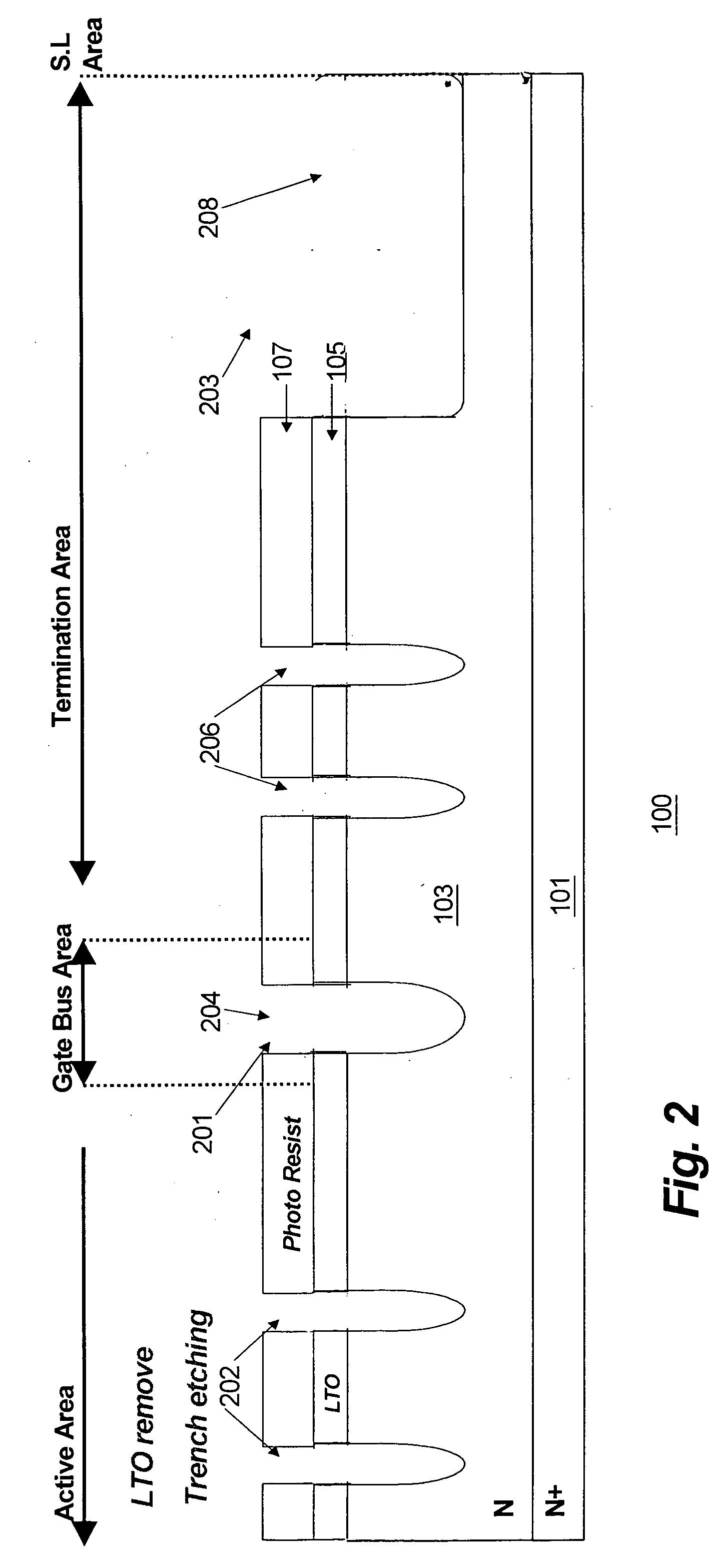

Trench mosfet and method of manufacture utilizing two masks

InactiveUS20090085105A1Improved cell pitchReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesThin metalTrench mosfet

A method for manufacturing a trench MOSFET semiconductor device comprises: providing a heavily doped N+ silicon substrate; forming an N type epitaxial layer; forming a thick SiO2 layer; creating P body and source area formations by ion implantation without any masks; utilizing a first mask to define openings for a trench gate and a termination; thermally growing a gate oxide layer followed by formation of a thick poly-Silicon refill layer without a mask to define a gate bus area; forming sidewall spacers; forming P+ areas; removing the sidewall spacers; depositing tungsten to fill contacts and vias; depositing a first thin barrier metal layer; depositing a first thick metal layer; utilizing a second metal mask to open a gate bus area; forming second sidewall spacers; depositing a second thin barrier metal layer; depositing a second thick metal layer; and planarizing at least the second thick metal layer and the second thin metal layer to isolate the source metal portions from gate metal portions, whereby the trench MOSFET semiconductor device is manufactured utilizing only first and second masks.

Owner:INPOWER SEMICON

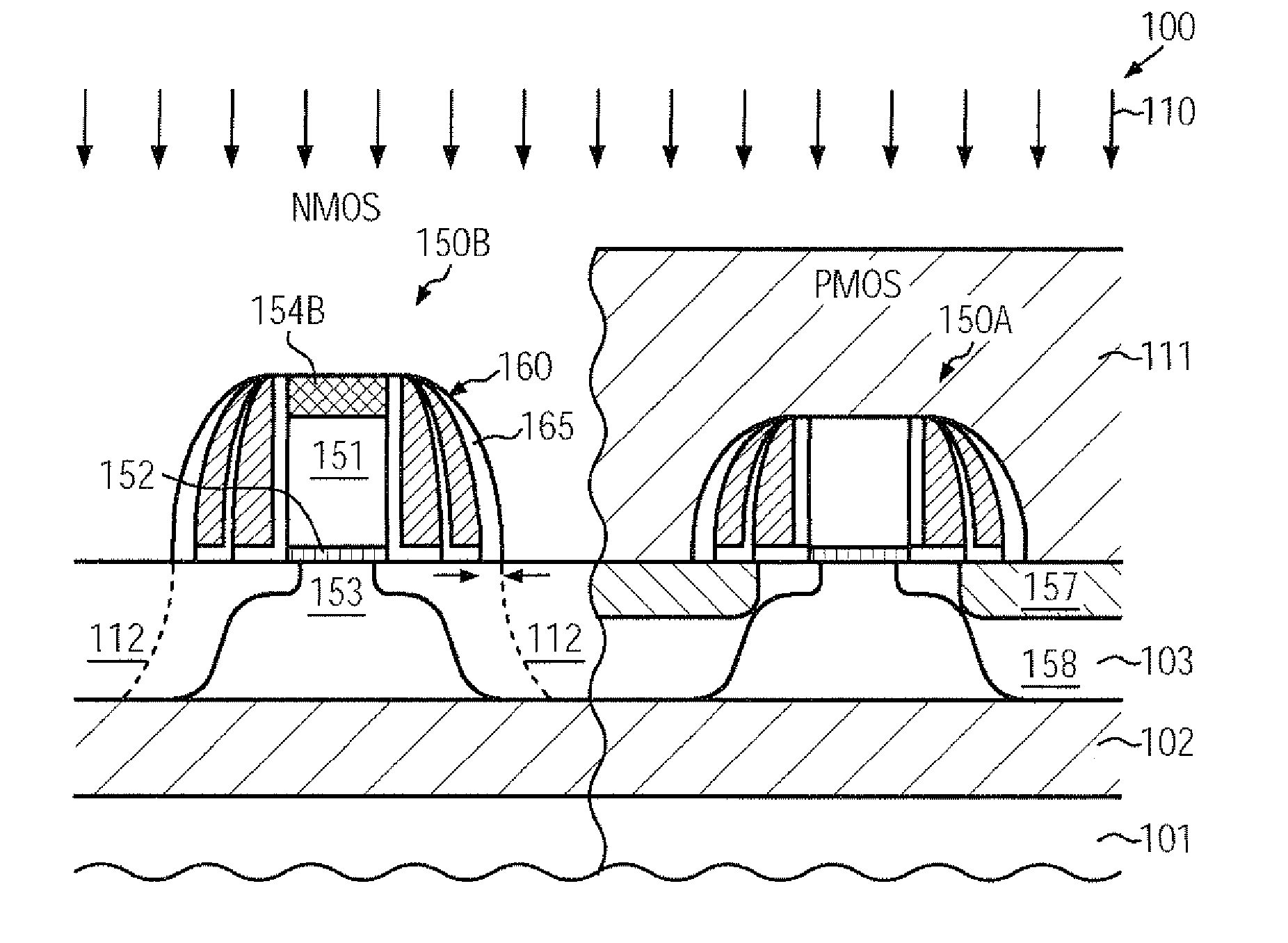

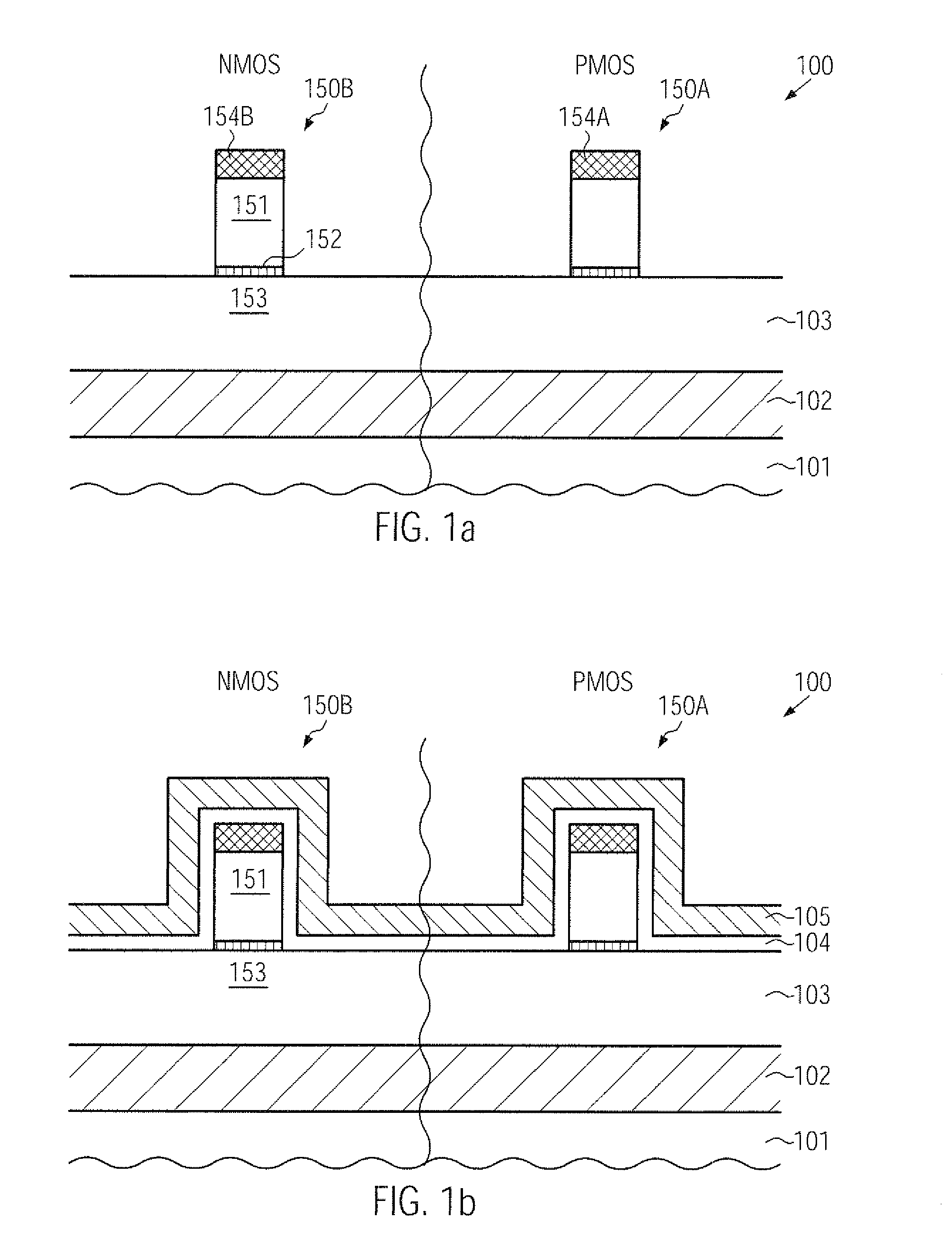

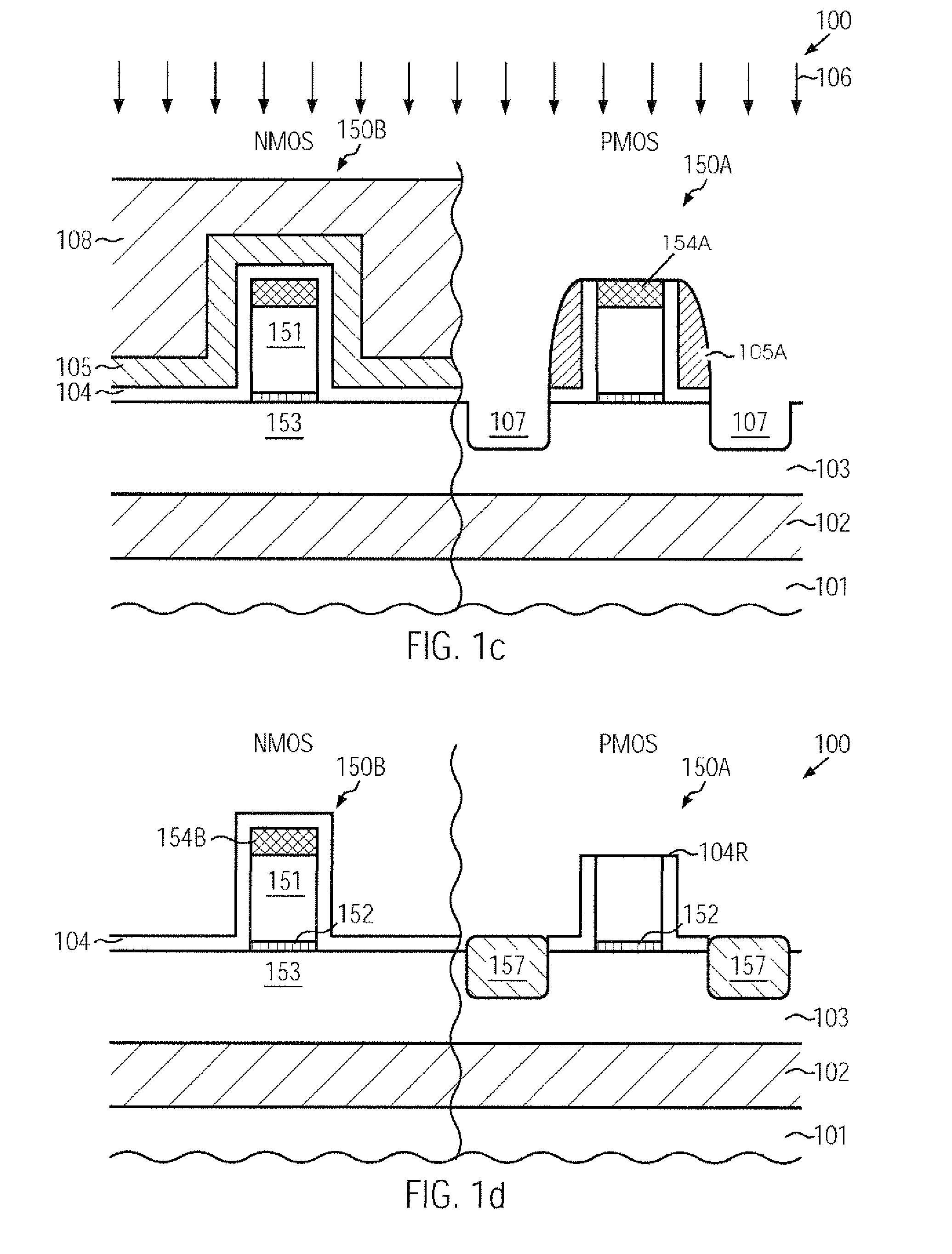

CMOS device comprising an nmos transistor with recessed drain and source areas and a pmos transistor having a silicon/germanium material in the drain and source areas

InactiveUS20090218633A1Enhanced transistor performanceImprove compatibilityTransistorSolid-state devicesCMOSSemiconductor alloys

A recessed transistor configuration may be provided selectively for one type of transistor, such as N-channel transistors, thereby enhancing strain-inducing efficiency and series resistance, while a substantially planar configuration or raised drain and source configuration may be provided for other transistors, such as P-channel transistors, which may also include a strained semiconductor alloy, while nevertheless providing a high degree of compatibility with CMOS techniques. For this purpose, an appropriate masking regime may be provided to efficiently cover the gate electrode of one transistor type during the formation of the corresponding recesses, while completely covering the other type of transistor.

Owner:ADVANCED MICRO DEVICES INC

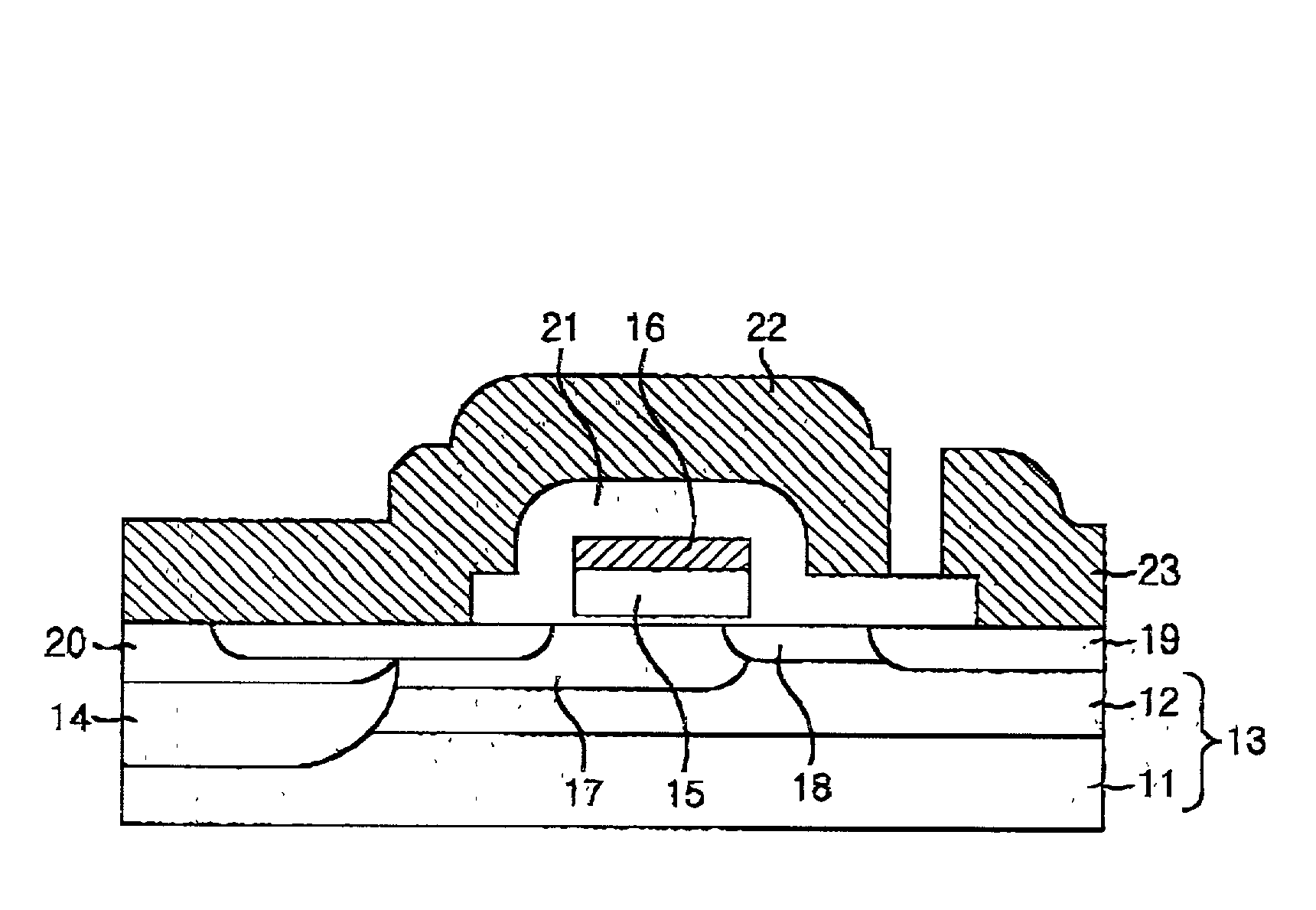

RF power device and method of manufacturing the same

InactiveUS20020053699A1Deterioration degreeSemiconductor/solid-state device detailsSolid-state devicesSource areaMetal electrodes

An HF power device in an HF transistor includes a semiconductor layer as a first conductive type, a field area formed in a trench structure on one side of the semiconductor layer, gate electrode formed on a given surface of the semiconductor layer, a channel layer as a second conductive type laterally diffused from the field area to a width containing both sides of the gate electrode, and formed on the surface of the semiconductor layer, a source area as the second conductive type formed within the channel layer between one side of the gate electrode and the field area, a drain area as the second conductive type formed on the surface of the semiconductor layer with a given interval from another side of the gate electrode, a sinker as the first conductive type provided as a column shape of a trench structure for dividing into two source areas by a piercing through the source area, and connected to the semiconductor layer, an LDD area as the second conductive type formed on the surface of the semiconductor layer between the drain area and the gate electrode, first metal electrode contacted with the source area divided into two source areas and electrically connected to the semiconductor layer through the sinker, and second metal electrode coupled with the drain area.

Owner:ELECTRONICS & TELECOMM RES INST

A method for making horizontal dual pervasion field effect transistor

ActiveCN101266930ALow costExpand the ability to prepare special devicesSemiconductor/solid-state device manufacturingLDMOSCMOS

The invention discloses a method for manufacturing a laterally dual-diffused FET (field effect transistor), belonging to FET manufacturing field, the method is achieved by using the method for manufacturing LDMOS according to standard CMOS manufacturing processes, to realize LDMOS via chart design as following: defining a active layout to form a body extracting area, a source area, a drain area, a channel area, a drift area and a grid area of a LDMOS element; the source area, grid area and drain area are formed according to a re-doping injection layout; the drift area is disposed between the drain area and the channel area; both of the body extracting area and the source area are in grounding connection; using a N well layout to form a low-doping drift area of a N type LDMOS, or using P well layout to form a P type low-doping drift are of a P type LDMOS; using anti-silicification board to prevent the drift area from being silicified; the design of the source area, the drain area and the grid area complies with the normal MOS. The invention can be applied on any standard process, effectively reducing costs, and improving the capability of standard process for manufacturing special elements.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

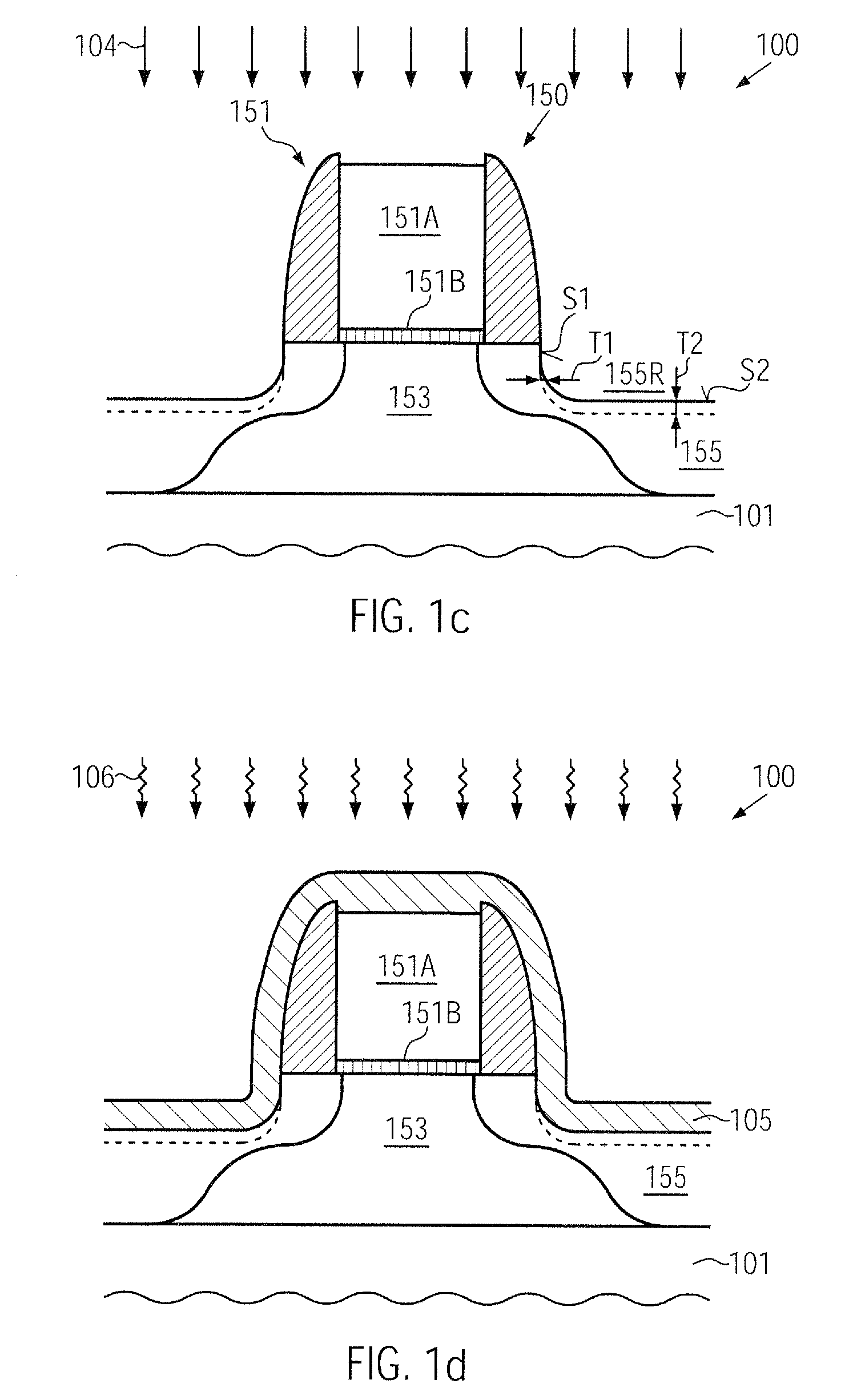

Strain Engineering in Three-Dimensional Transistors Based on Strained Isolation Material

InactiveUS20130181299A1Well formedSuperior strain conditionTransistorSolid-state devicesEngineeringSource area

In a three-dimensional transistor configuration, a strain-inducing isolation material is provided, at least in the drain and source areas, thereby inducing a strain, in particular at and in the vicinity of the PN junctions of the three-dimensional transistor. In this case, superior transistor performance may be achieved, while in some illustrative embodiments even the same type of internally stressed isolation material may result in superior transistor performance of P-channel transistors and N-channel transistors.

Owner:GLOBALFOUNDRIES US INC

In situ formed drain and source regions in a silicon/germanium containing transistor device

By repeatedly applying a process sequence comprising an etch process and a selective epitaxial growth process during the formation of drain and source areas in a transistor device, highly complex dopant profiles may be generated on the basis of in situ doping. Further-more, a strain material may be provided while stress relaxation mechanisms may be reduced due to the absence of any implantation processes.

Owner:TAIWAN SEMICON MFG CO LTD

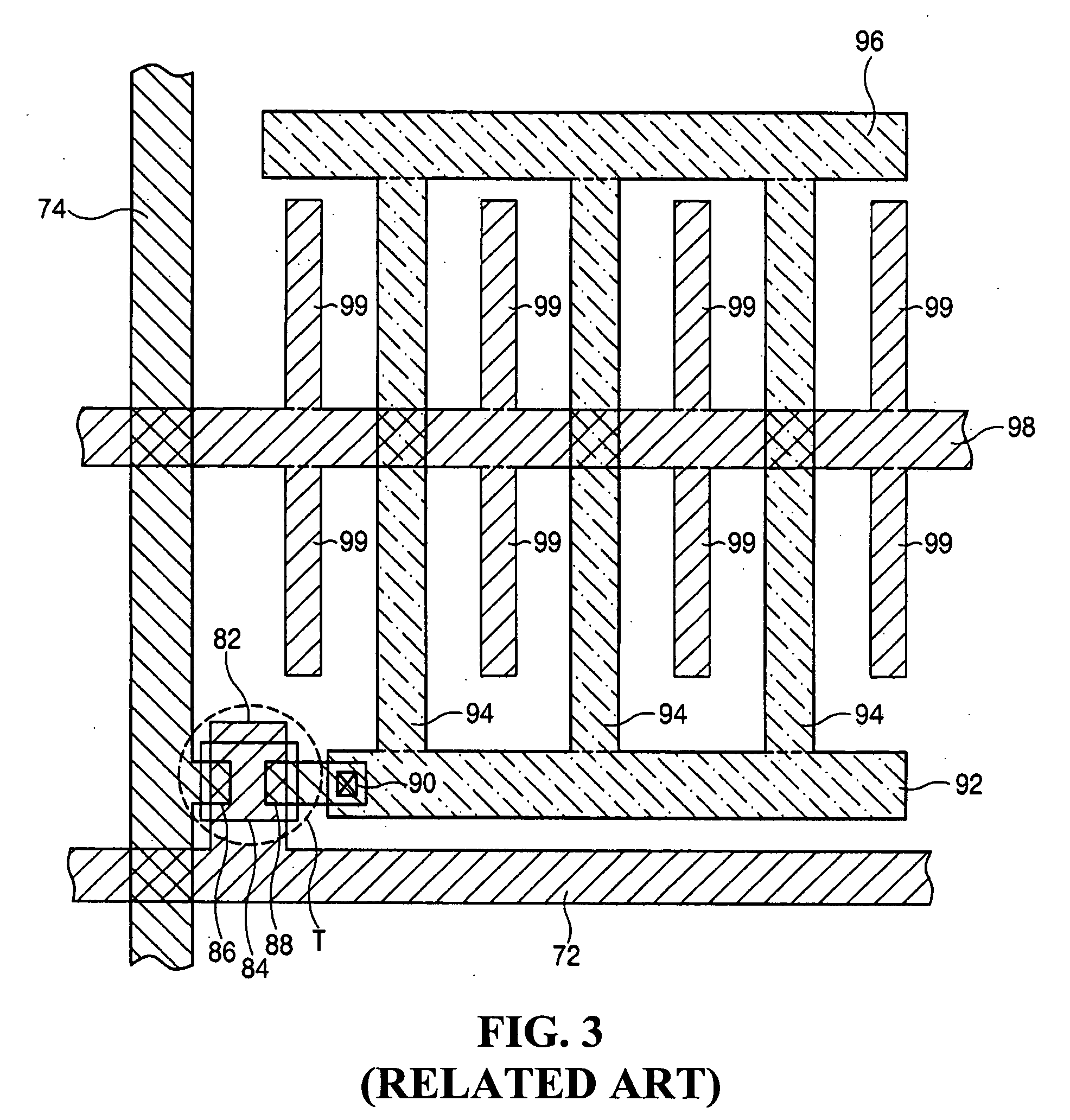

Array substrate for in-plane switching liquid crystal display device and method of fabricating the same with polycrystalline silicon pixel electrode

ActiveUS7130010B2Increase the aperture ratioUniform critical dimensionNon-linear opticsIn planeLiquid-crystal display

An array substrate for in-plane switching liquid crystal display device includes a gate line on a substrate, a data line crossing the gate line to define a pixel region, a semiconductor layer including an active area and a source area, wherein the active area overlaps the gate line and the source area overlaps the data line, a drain electrode connected to the semiconductor layer, a first capacitor electrode in the pixel region and connected to the drain electrode, a pixel electrode connected to the first capacitor electrode and substantially in parallel to the data line, a common line substantially parallel to the gate line, a second capacitor electrode connected to the common line and overlapping the first capacitor electrode, and a common electrode connected to the common line and alternatively arranged with the pixel electrode, wherein the source area of the semiconductor layer, the drain electrode, the first capacitor electrode and the pixel electrode include doped polycrystalline silicon.

Owner:LG DISPLAY CO LTD

Thin film transistor, method of forming the same and flat panel display device having the same

InactiveUS20100148155A1Increase charge mobilityExtend your lifeTransistorSolid-state devicesEngineeringFlat panel display

A thin film transistor (TFT), a method of forming the same and a flat panel display device having the same are disclosed. The TFT includes a buffer layer and a semiconductor layer which are sequentially disposed on a substrate, a gate pattern including an insulating pattern and a gate electrode pattern which are sequentially disposed on the semiconductor layer, source and drain regions defining a portion of the semiconductor layer below the gate pattern as a channel area, formed by doping the semiconductor layer disposed at both sides of the gate pattern with impurities, and extending from both sides of the channel area, a passivation layer which covers the entire surface of the substrate having the gate pattern, a first metal electrode which penetrates a portion of the passivation layer disposed on the source area and a portion of the source region below the portion of the passivation layer to be electrically connected with the source region, and a second metal electrode which penetrates a portion of the passivation layer disposed on the drain area and a portion of the drain region below the portion of the passivation layer to be electrically connected with the drain region. According to the present invention, a metal is infiltrated into source and drain regions to disperse an electric current when a TFT operates, and thus charge mobility is improved, and damage of a drain region caused by the excessive current density is prevented, leading to the long lifespan and excellent performance.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

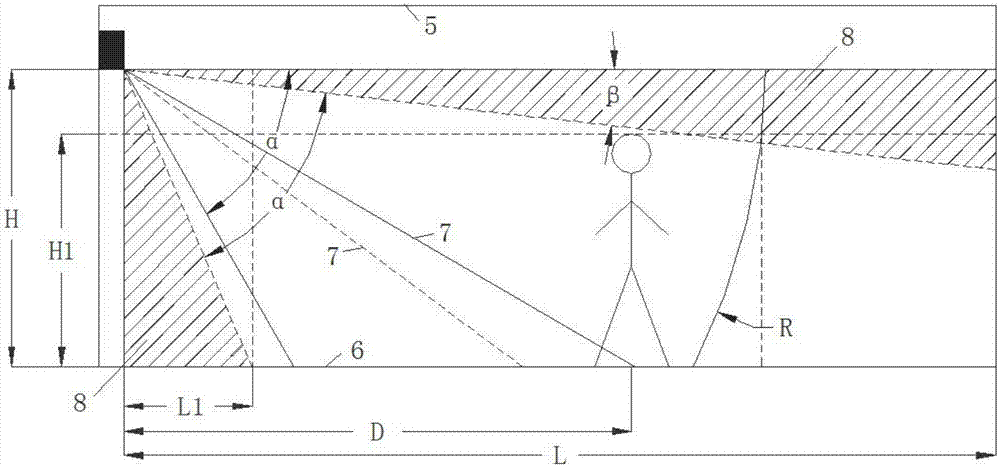

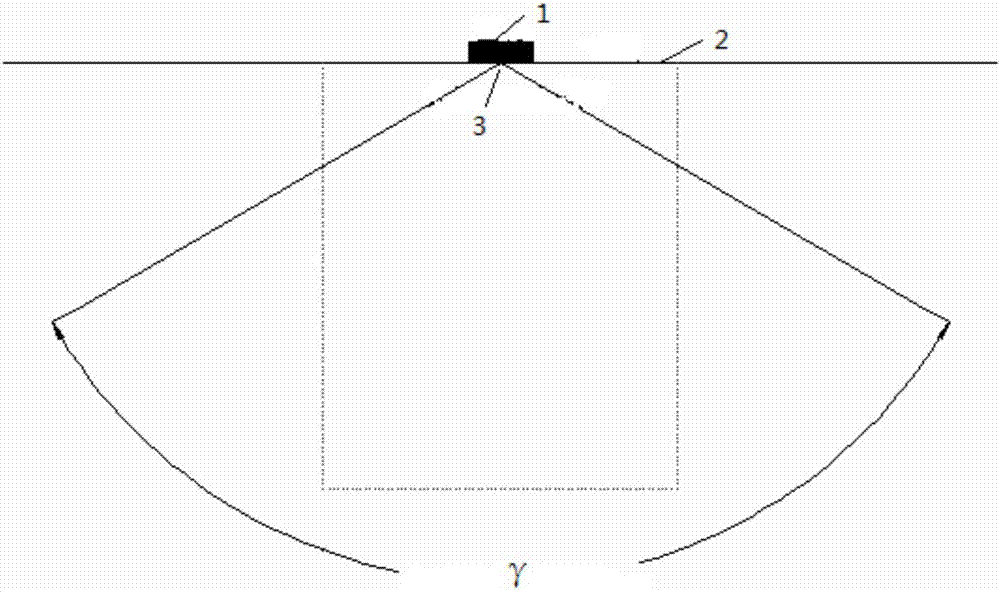

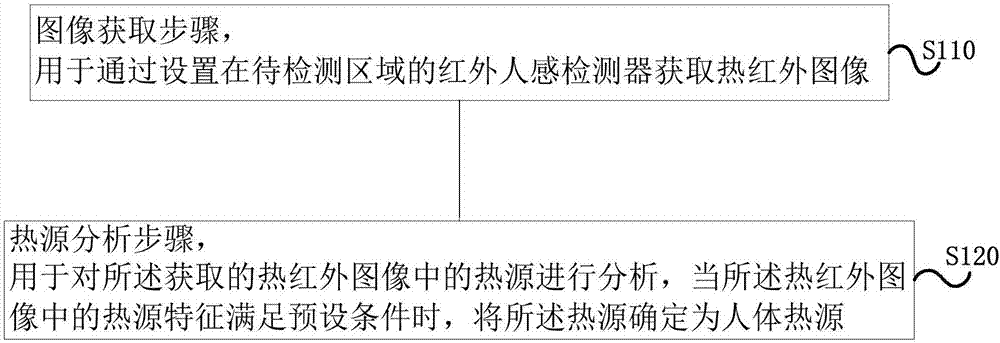

Human body heat source recognition method and device and equipment having device

ActiveCN107084795AAccurate identificationAccurate feedbackMechanical apparatusSpace heating and ventilation safety systemsLower limitHuman body

The invention provides a human body heat source recognition method and device and equipment having the device. The human body heat source recognition method comprises an image acquisition step which is used for acquiring a thermal infrared image through an infrared human sensing detector arranged in an area to be detected; and a heat source analysis step which is used for analyzing the heat source in the acquired thermal infrared image and determining the heat source as a human body heat source when the heat source characteristics in the thermal infrared image meet the preset conditions, wherein the preset conditions include that the temperature of the heat source is greater than or equal to the lower limit value of normal human body temperature and less than or equal to the upper limit value of the normal human body temperature, and the difference value of the heat source core temperature and the background temperature is greater than or equal to a preset temperature difference threshold. According to the technical scheme, the human body heat source can be accurately recognized, the human body position is monitored in real time and the recognition accuracy is high so that the position information of the human body heat source can be accurately fed back and the human body heat source area is constantly maintained to have great comfort level experience effect.

Owner:GREE ELECTRIC APPLIANCES INC