A method for making horizontal dual pervasion field effect transistor

A field effect transistor, lateral double diffusion technology, applied in semiconductor/solid state device manufacturing, electrical components, circuits, etc., can solve problems such as increasing costs, and achieve the effect of expanding capacity and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in further detail below in conjunction with the specific implementation manner of accompanying drawing and N-type LDMOS device:

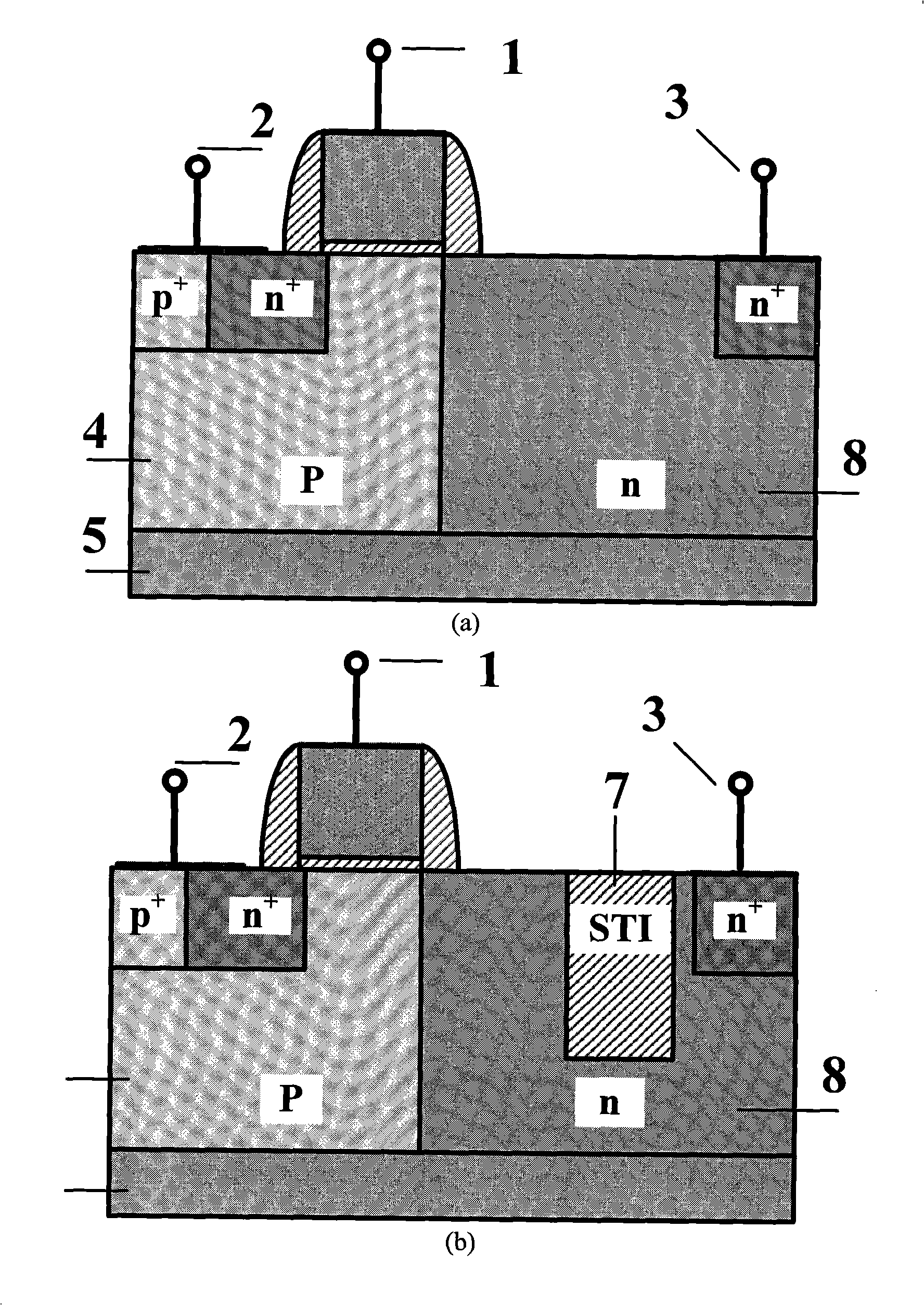

[0024] Figure 1 shows three LDMOS structures prepared by this method. The main difference between LDMOS and conventional MOS field effect transistors is that there is a low-doped drift region (Figure 1(a)). The drift region of LDMOS can be further optimized by introducing a doped implant region or an insulating impurity region, as shown in Figure 1(b) and Figure 1(c). However, the LDMOS structure shown in Fig. 1 can be realized only by using the standard CMOS process through the method of layout design.

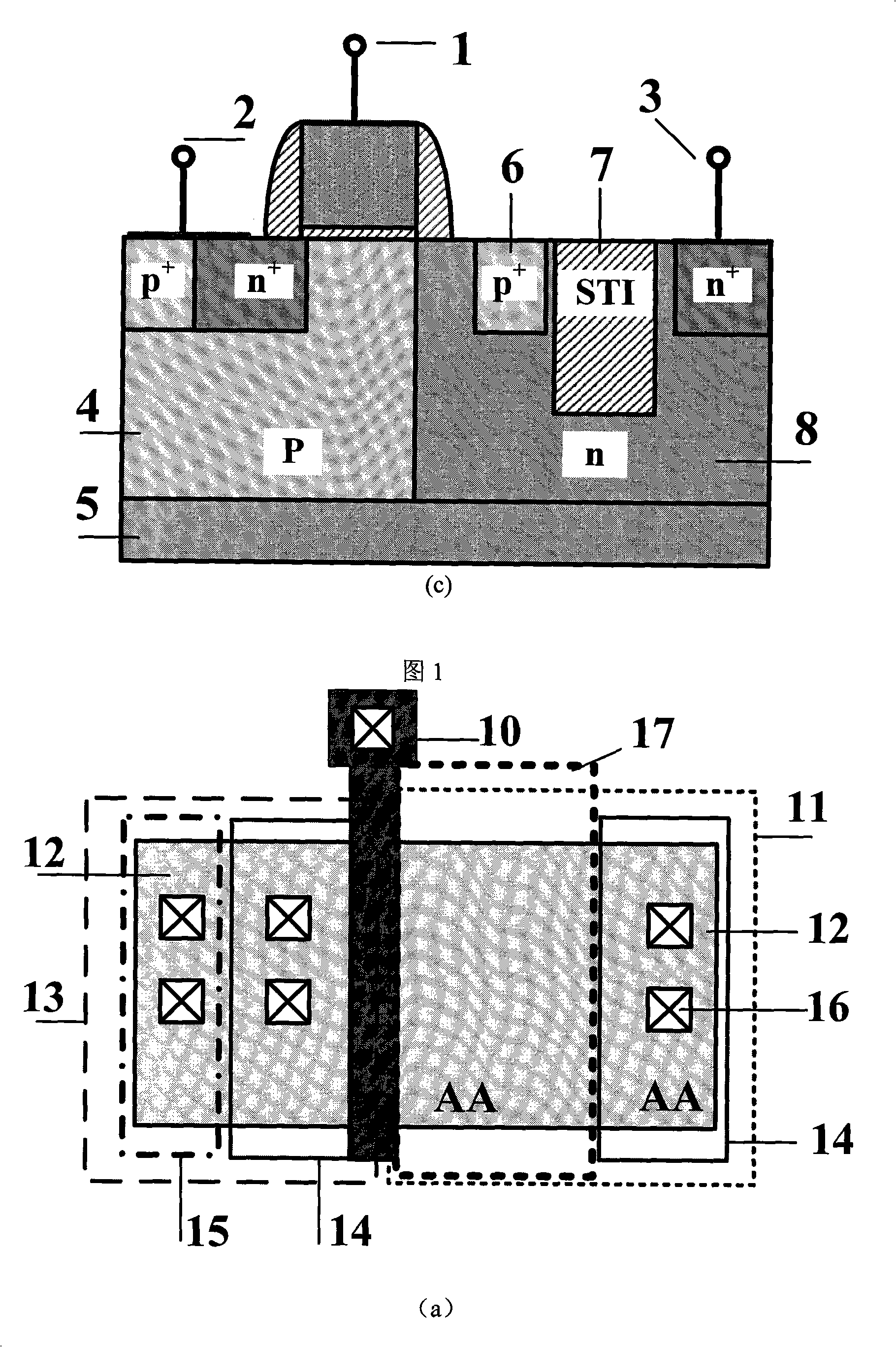

[0025] Figure 2 shows a schematic diagram of the layout design for preparing the structure shown in Figure 1(c). In the figure: the layout of the N well is used in the layout to form the low-doped drift region of the N-type LDMOS, the layout of the P well forms the body region, and the body lead-out ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Horizontal length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More