Patents

Literature

381 results about "In situ doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

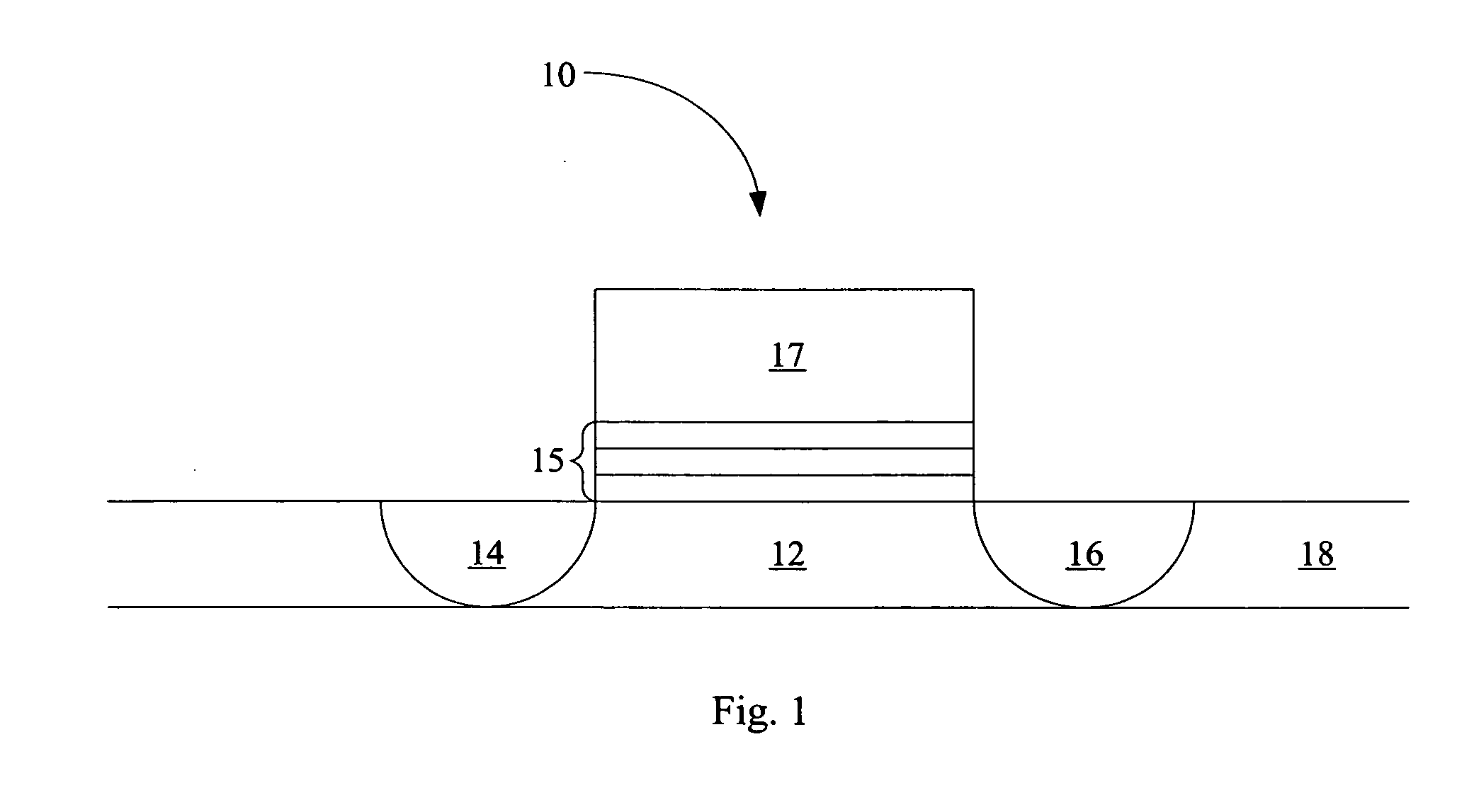

Method for forming an integrated circuit

ActiveUS7402872B2Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

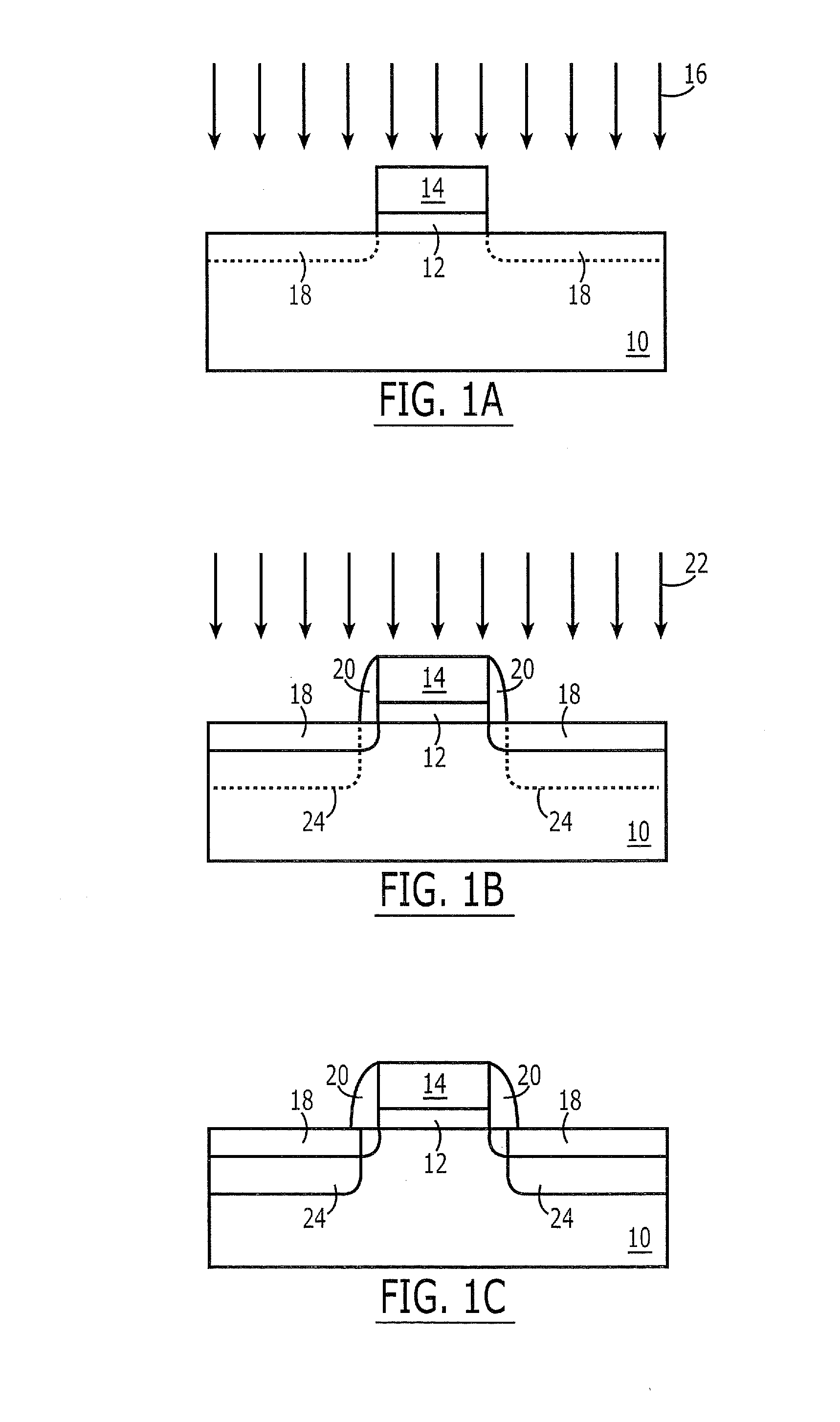

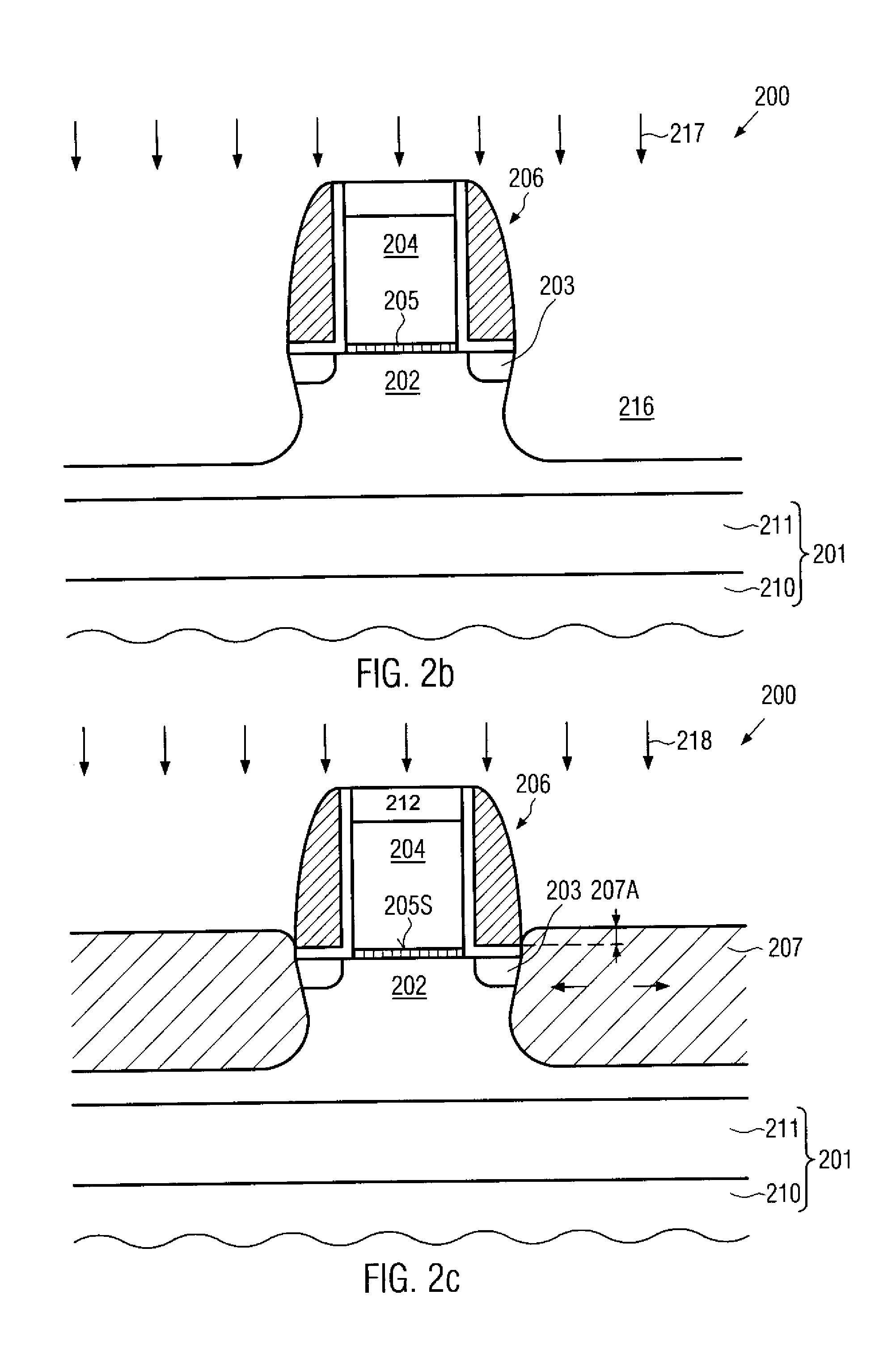

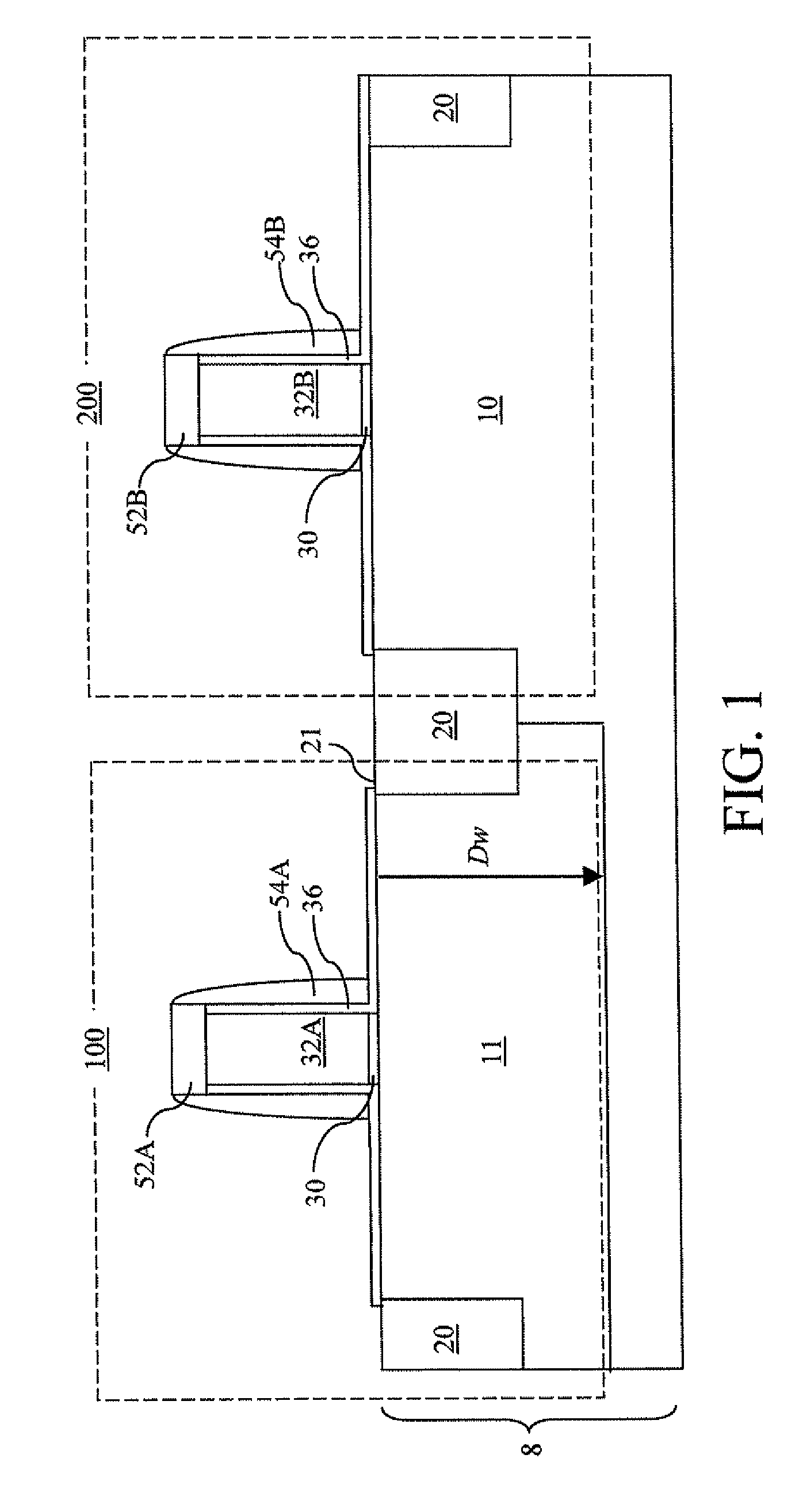

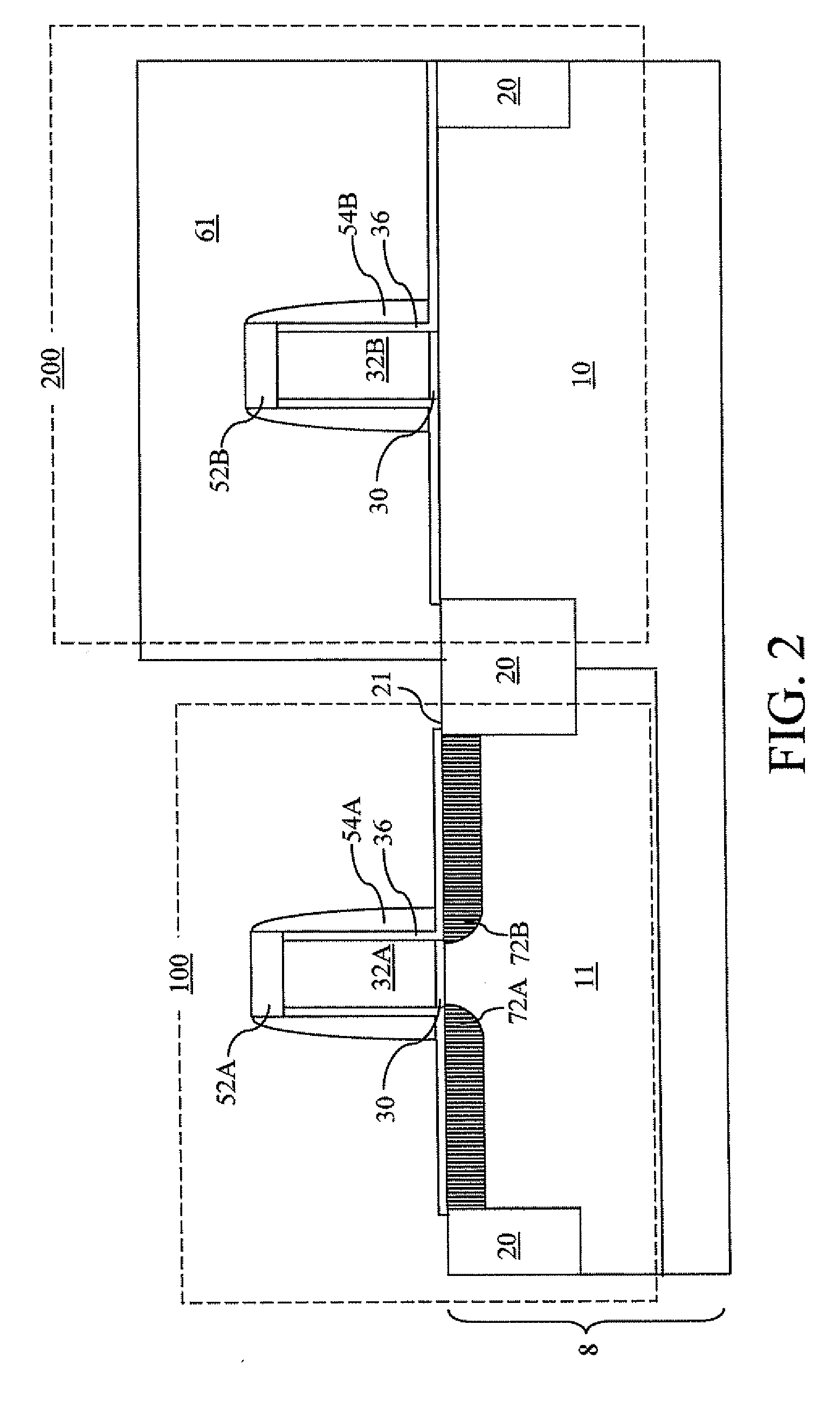

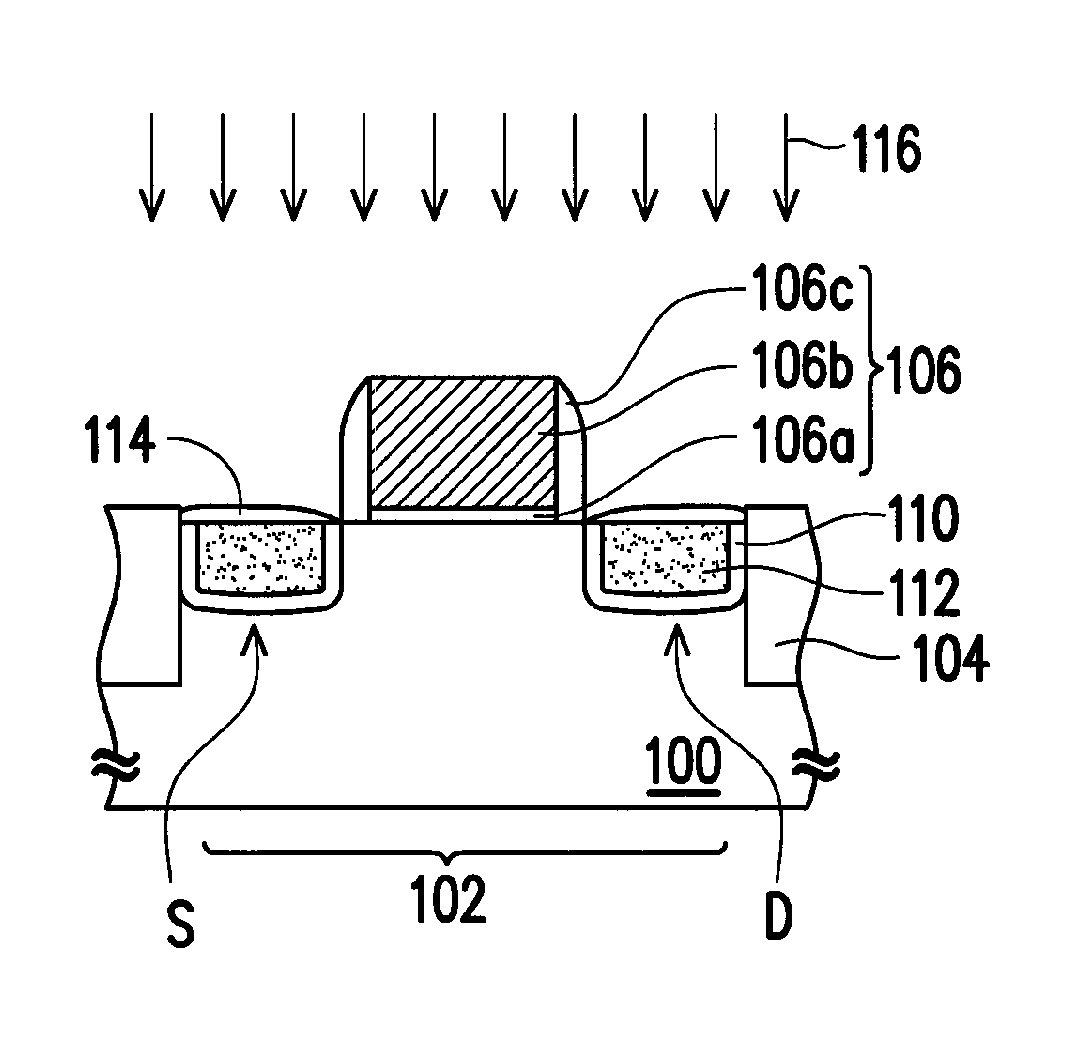

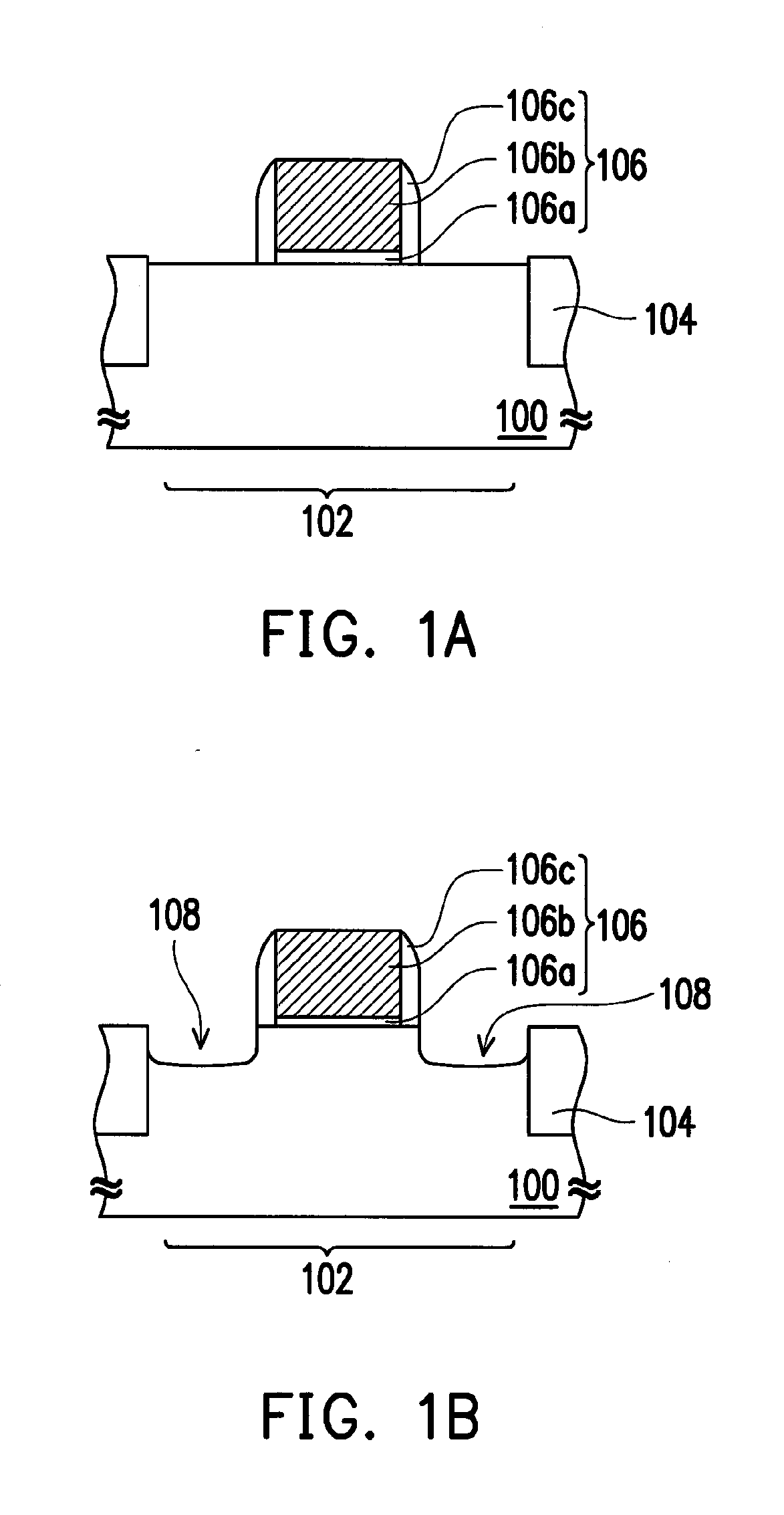

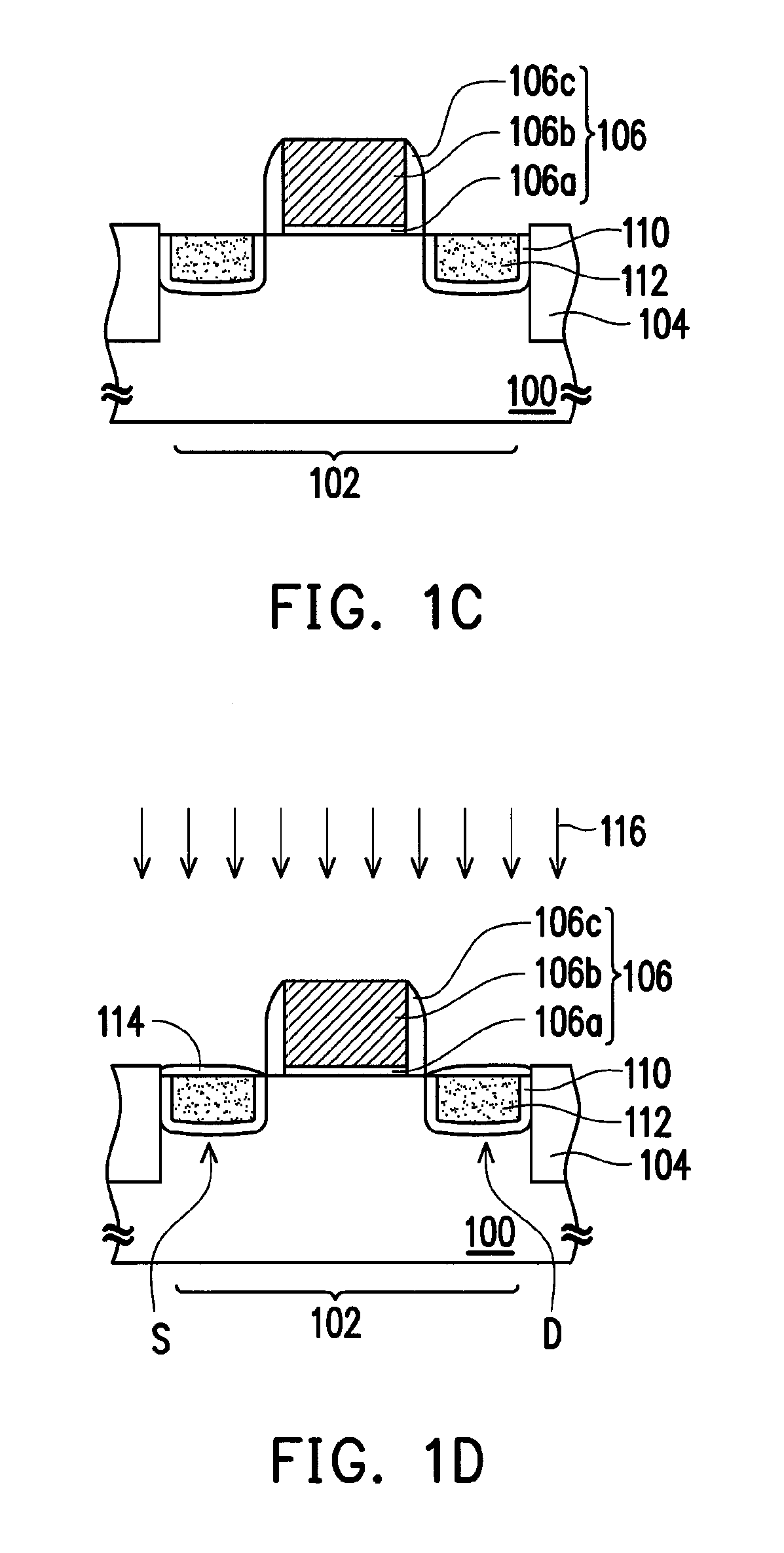

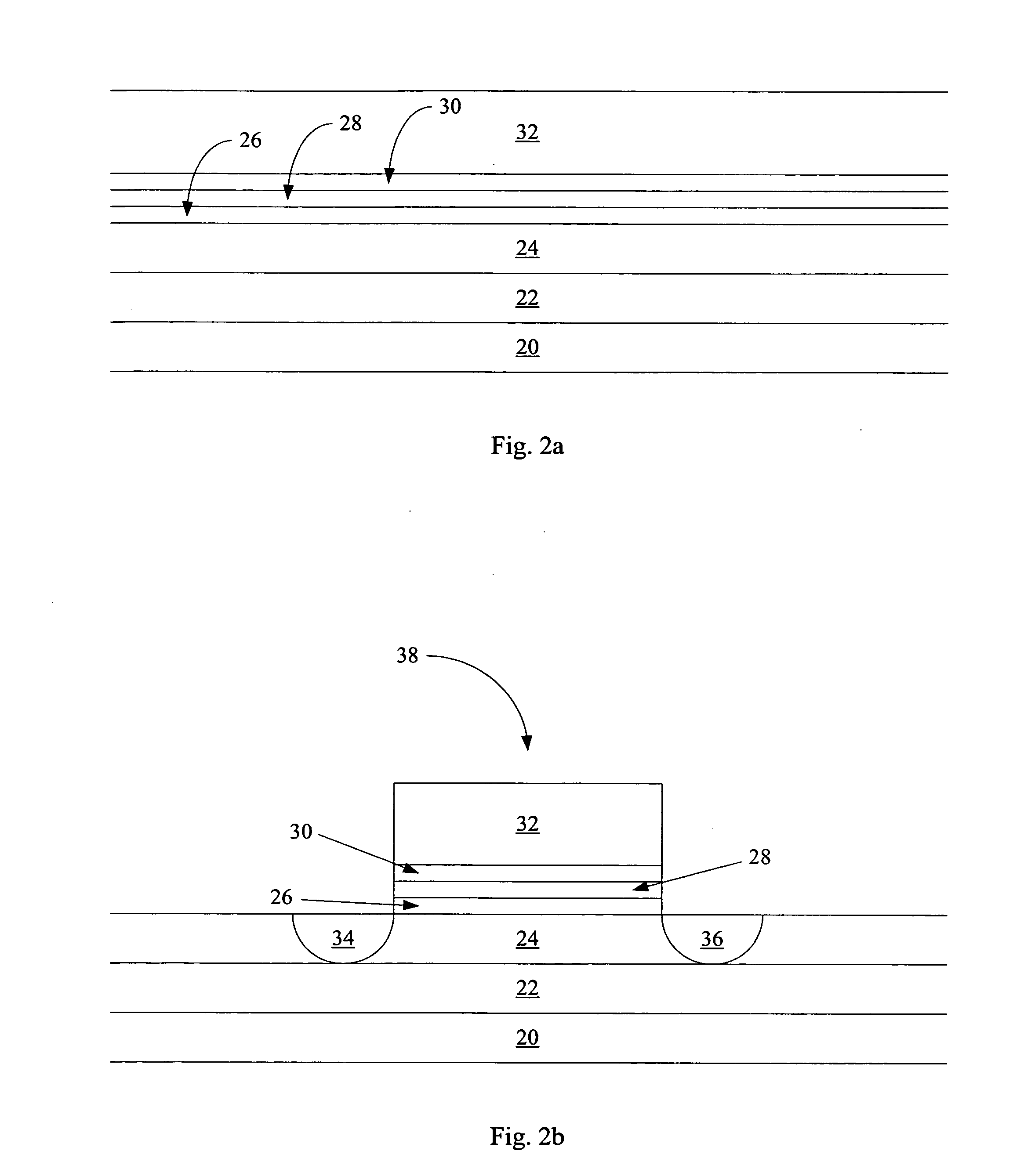

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

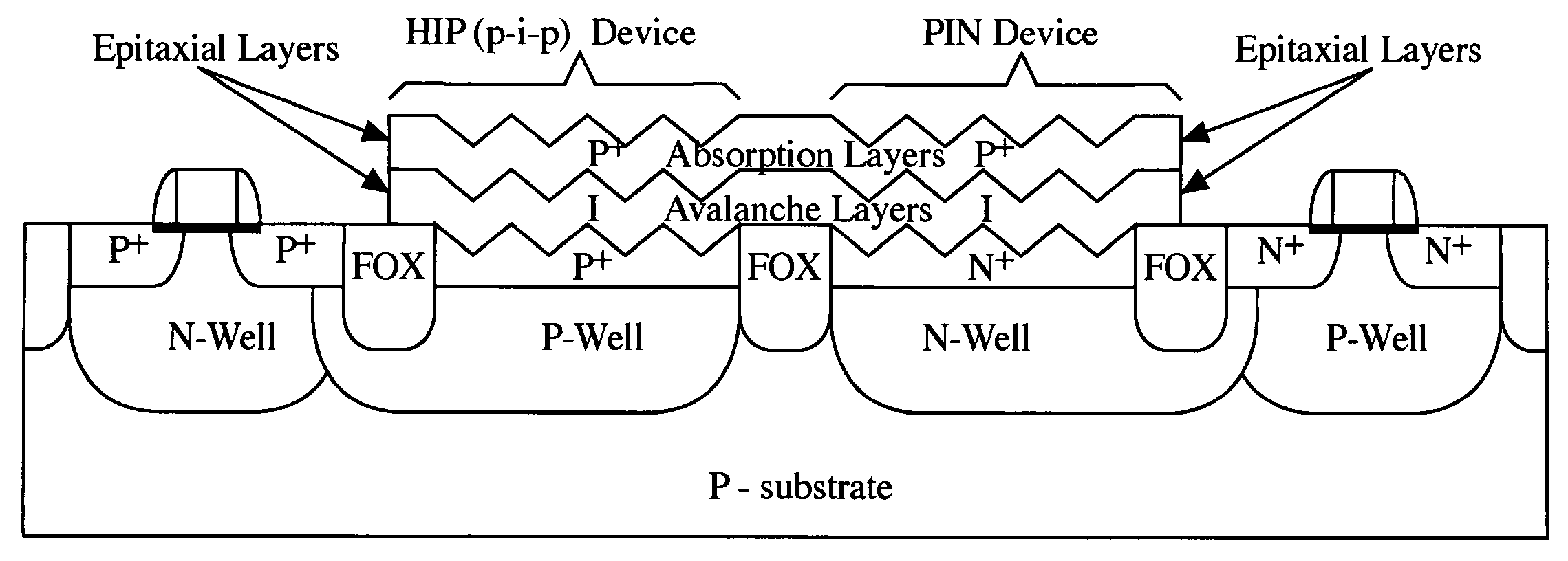

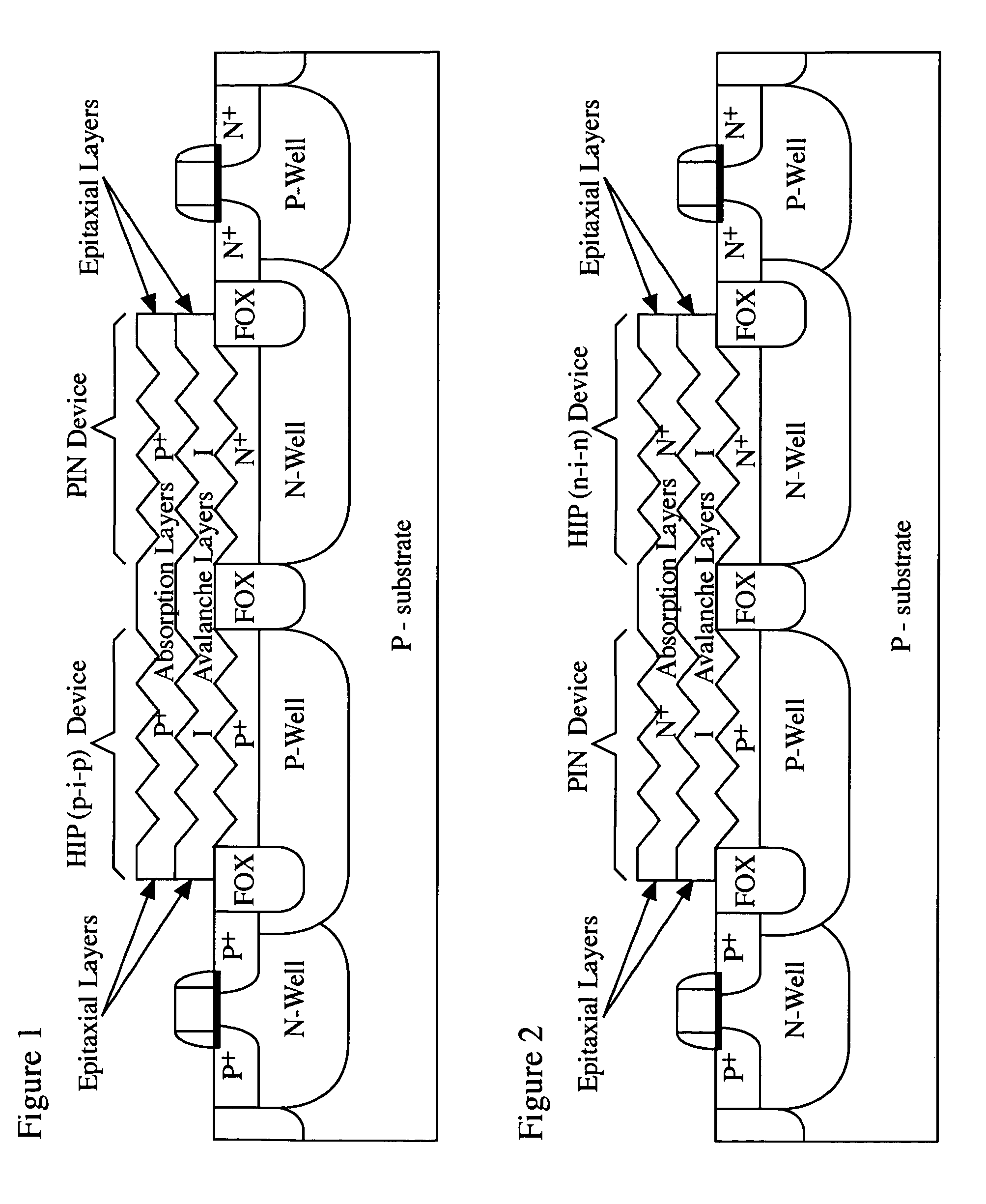

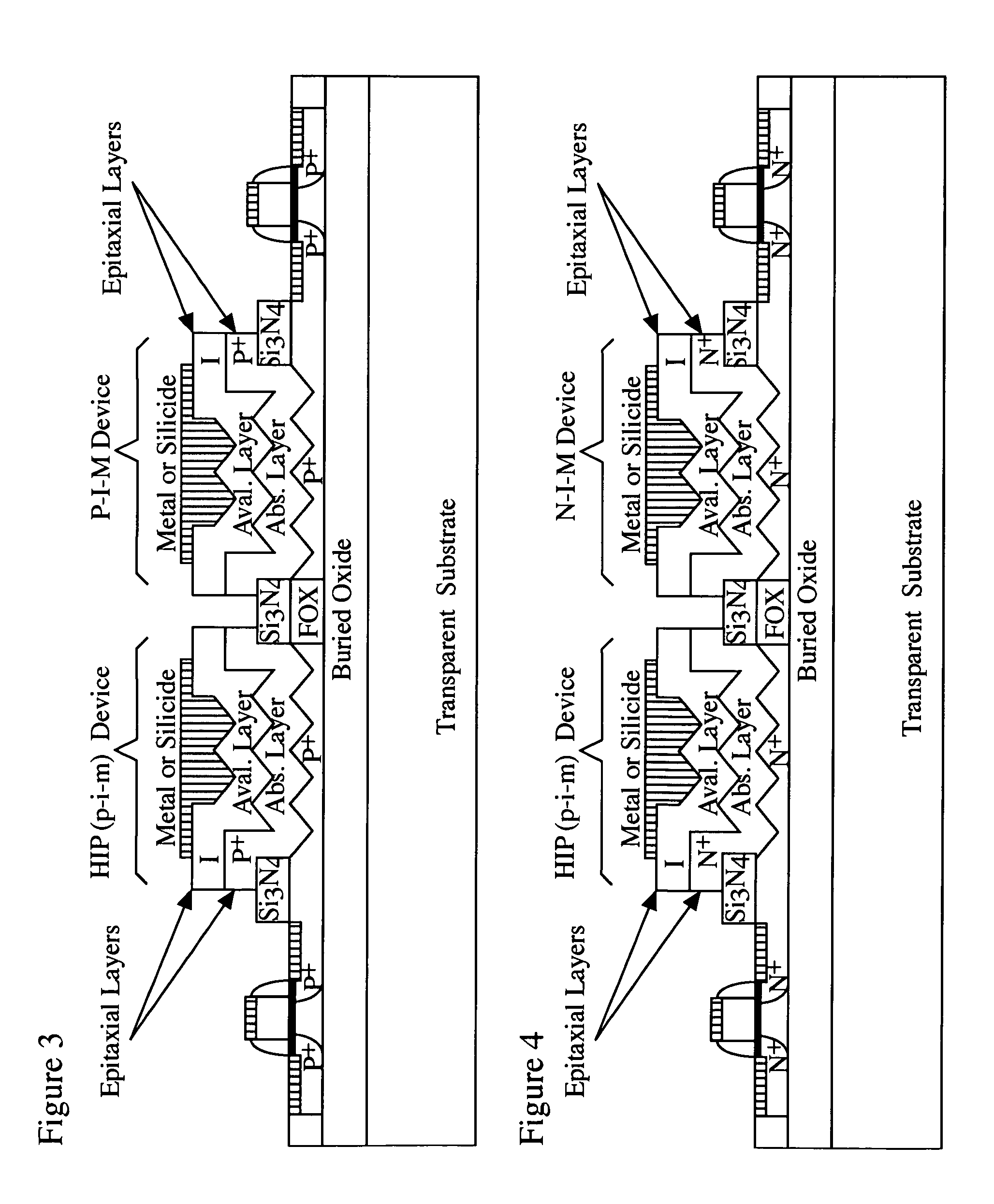

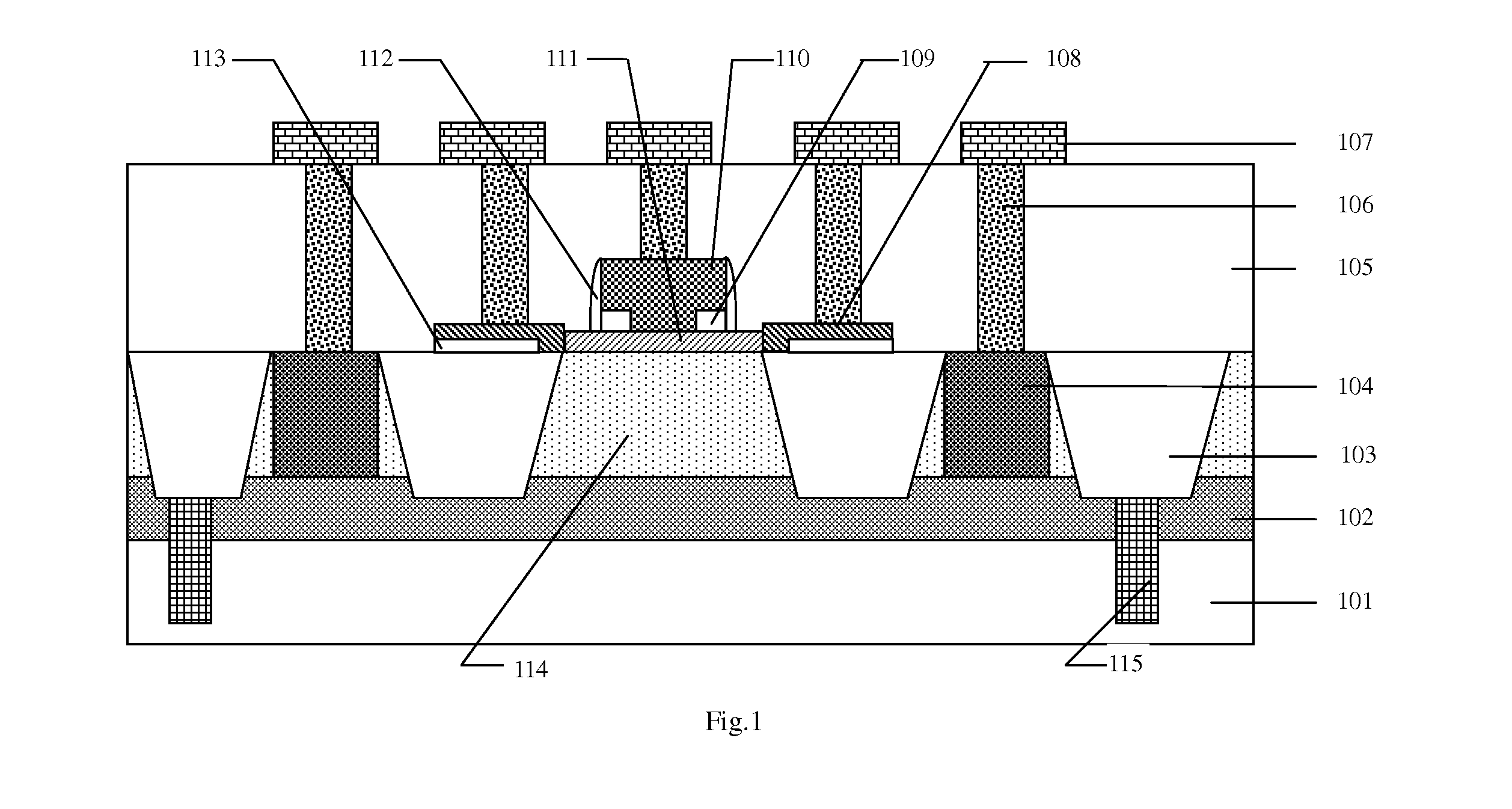

Light-sensing device

ActiveUS7521737B2Solid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionPixel density

A method of fabricating light-sensing devices including photodiodes monolithically integrated with CMOS devices. Several types of photodiode devices (PIN, HIP) are expitaxially grown in one single step on active areas implanted in a common semiconductor substrate, the active areas having defined polarities. The expitaxially grown layers for the photodiode devices may be either undoped or in-situ doped with profiles suitable for their respective operation. With appropriate choice of substrate materials, device layers and heterojunction engineering and process architecture, it is possible to fabricate silicon-based and germanium-based multi-spectral sensors that can deliver pixel density and cost of fabrication comparable to the state of the art CCDs and CMOS image sensors. The method can be implemented with epitaxially deposited films on the following substrates: Silicon Bulk, Thick-Film and Thin-Film Silicon-On-Insulator (SOI), Germanium Bulk, Thick-Film and Thin-Film Geranium-On-Insulator (GeOI).

Owner:QUANTUM SEMICON

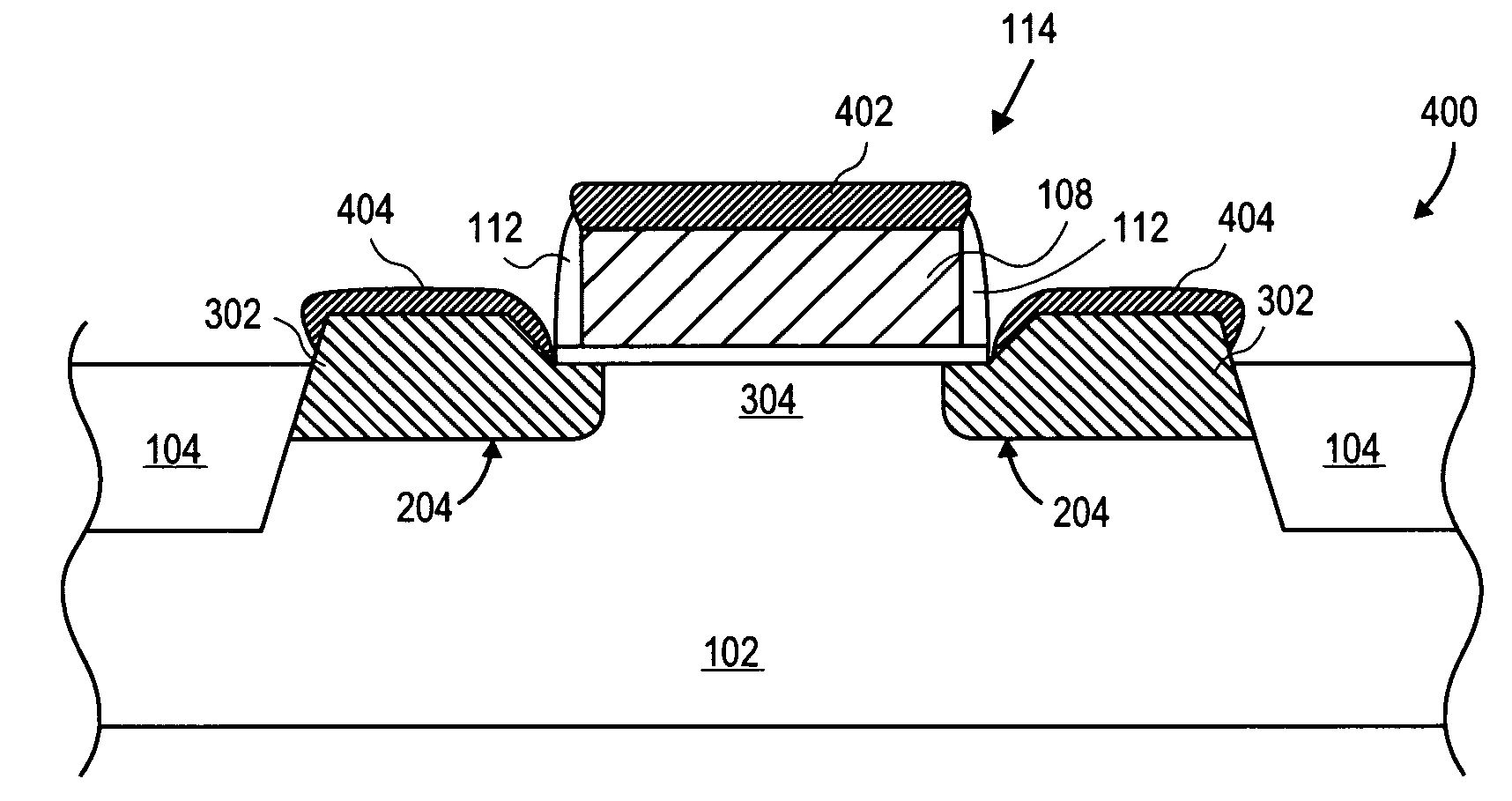

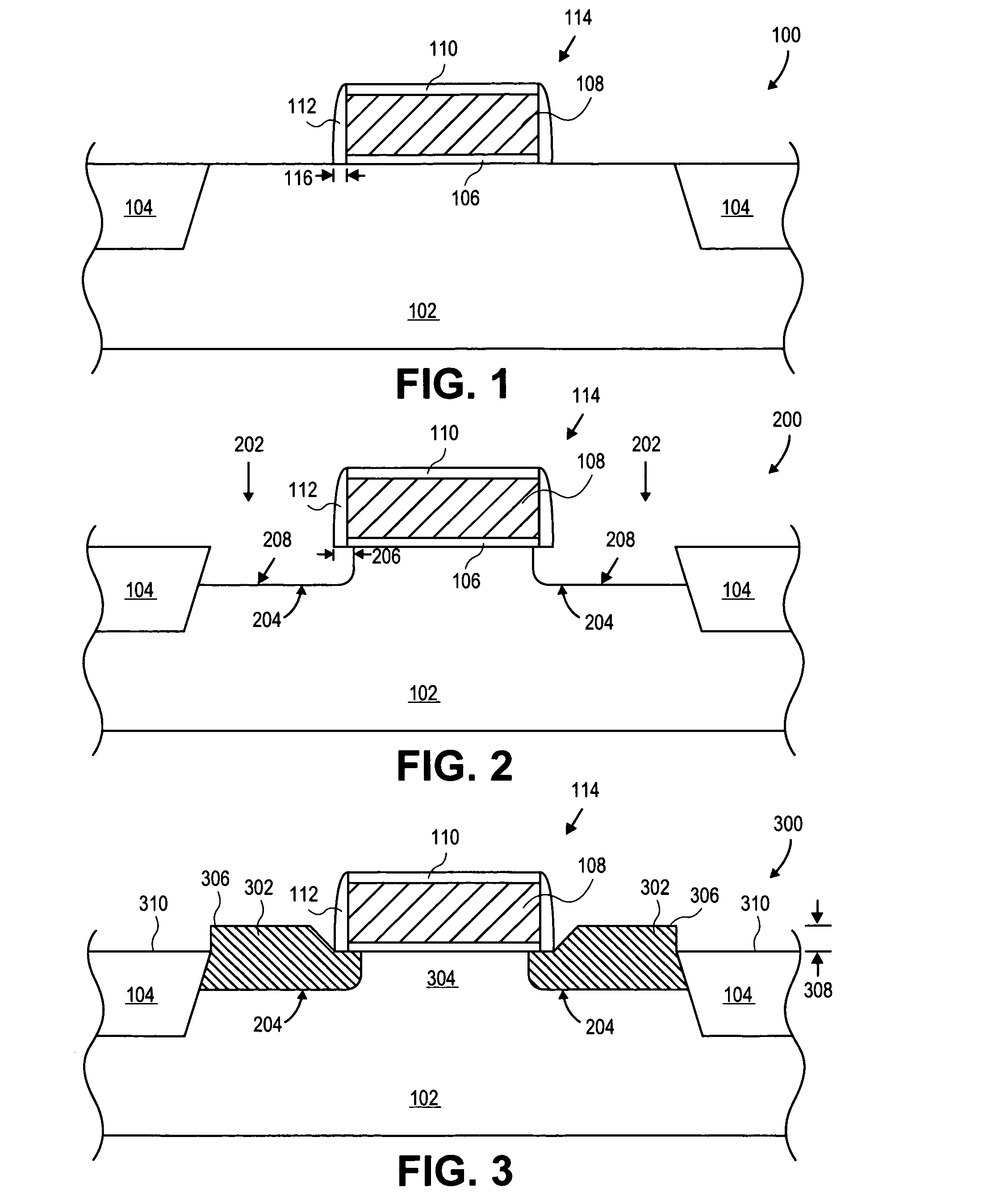

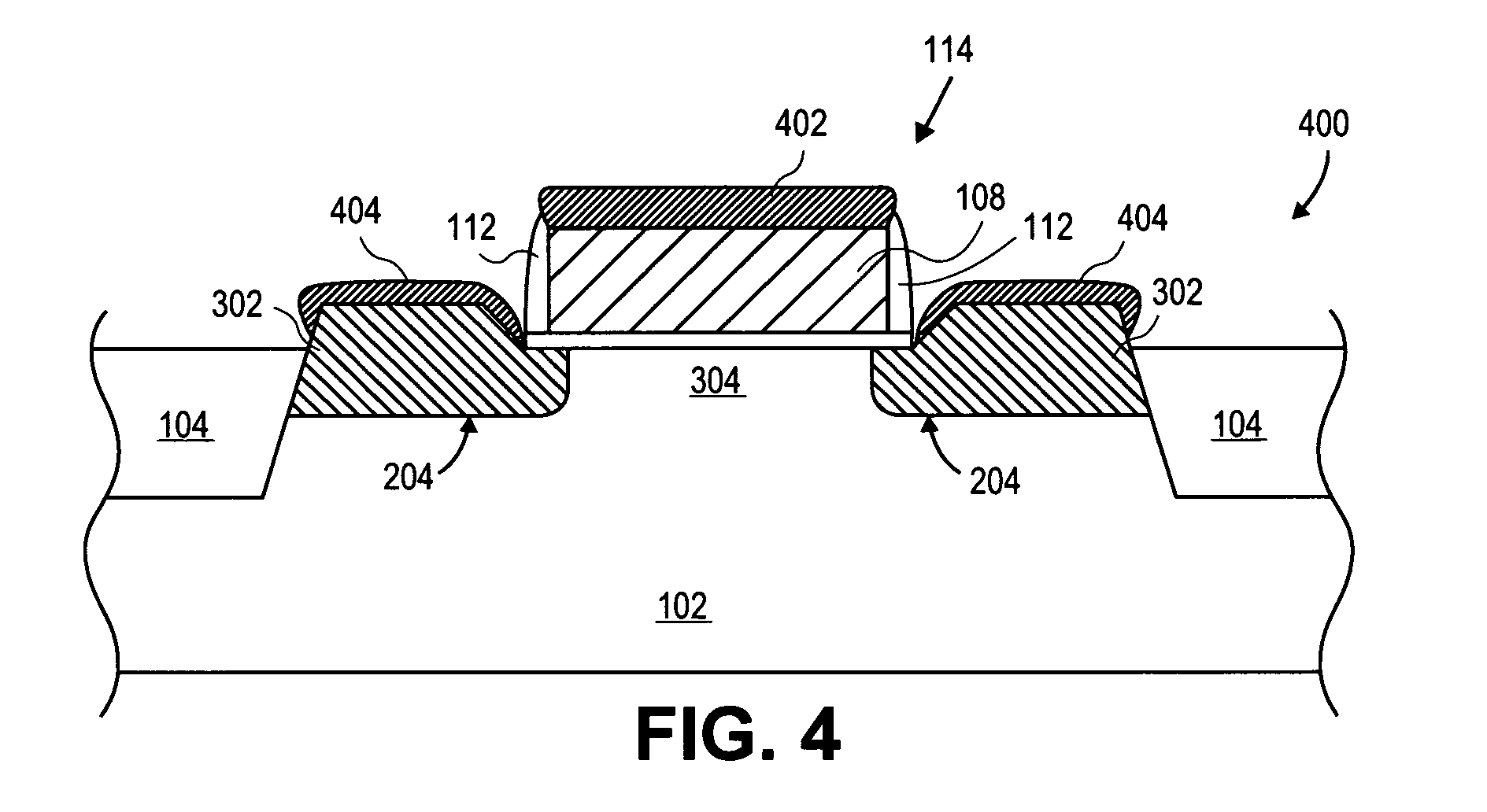

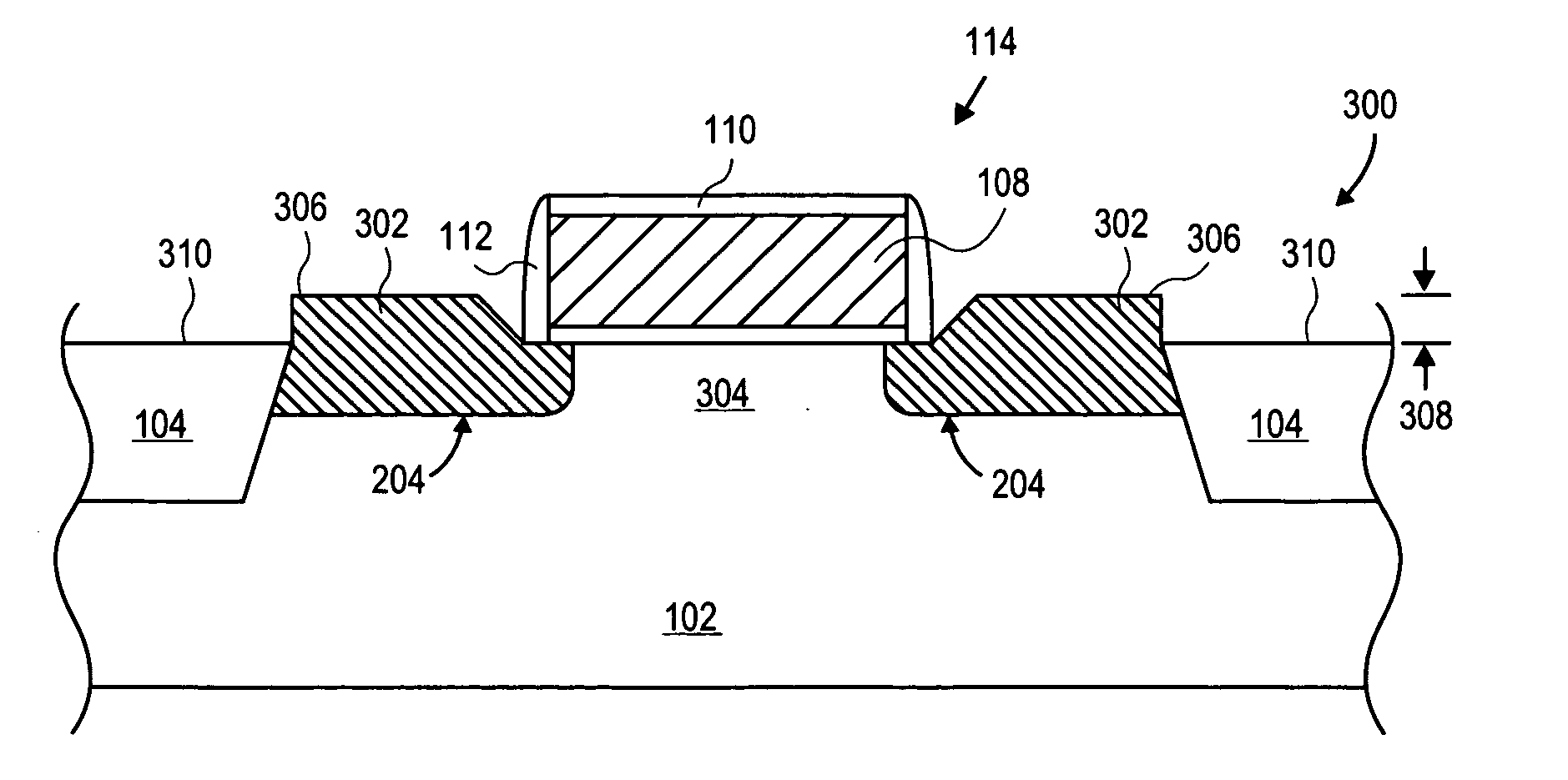

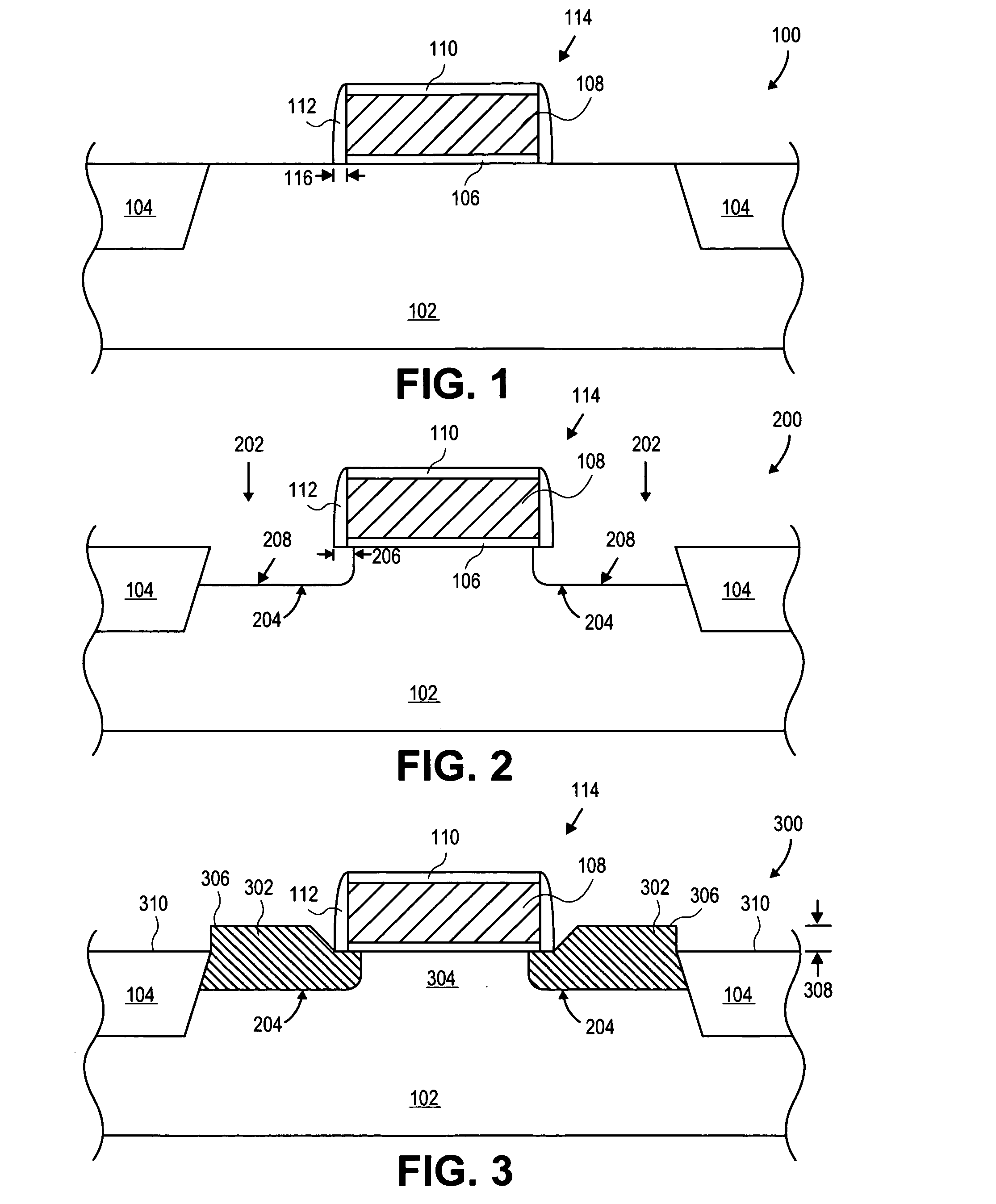

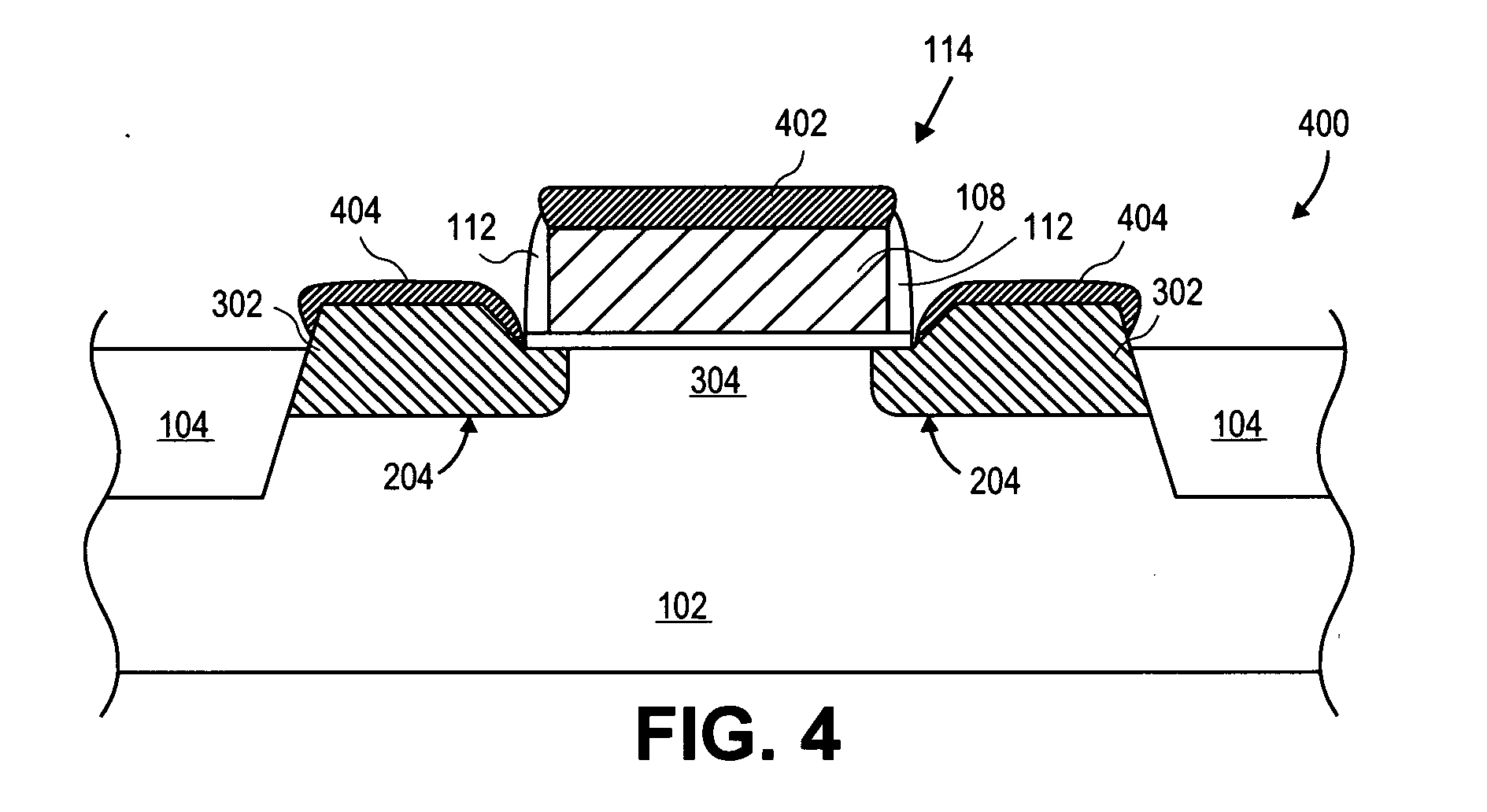

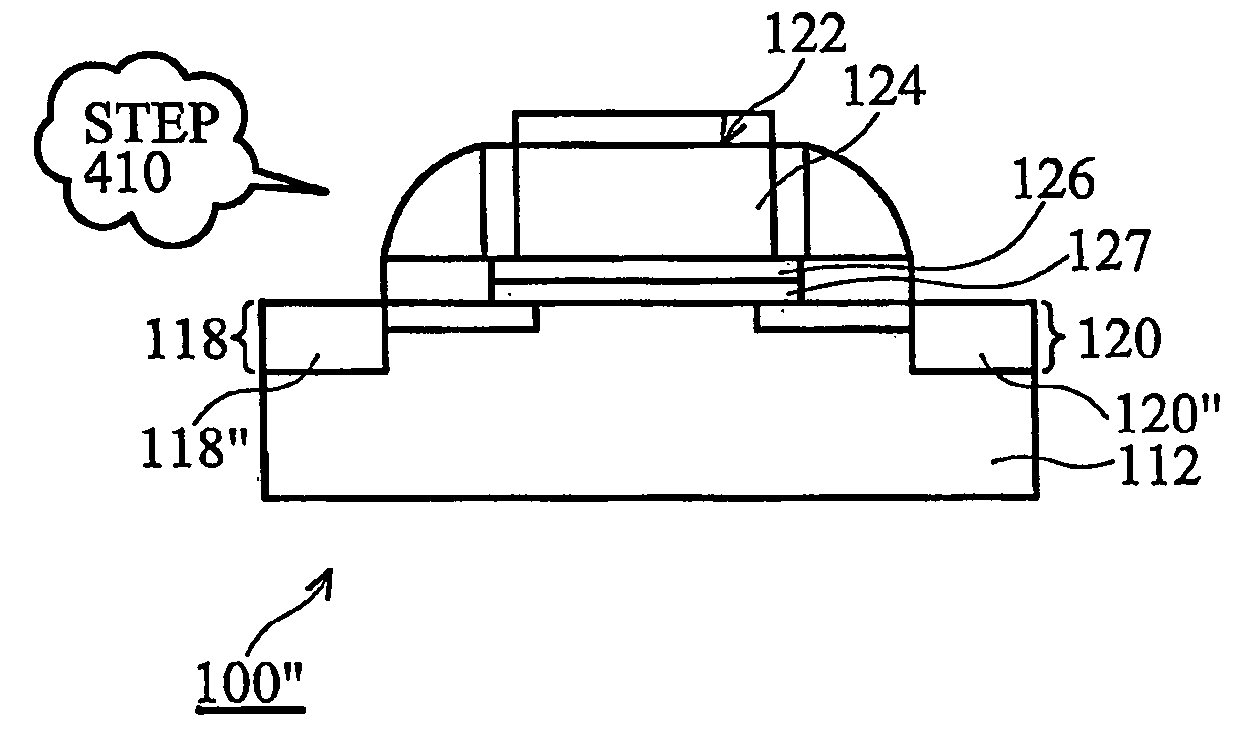

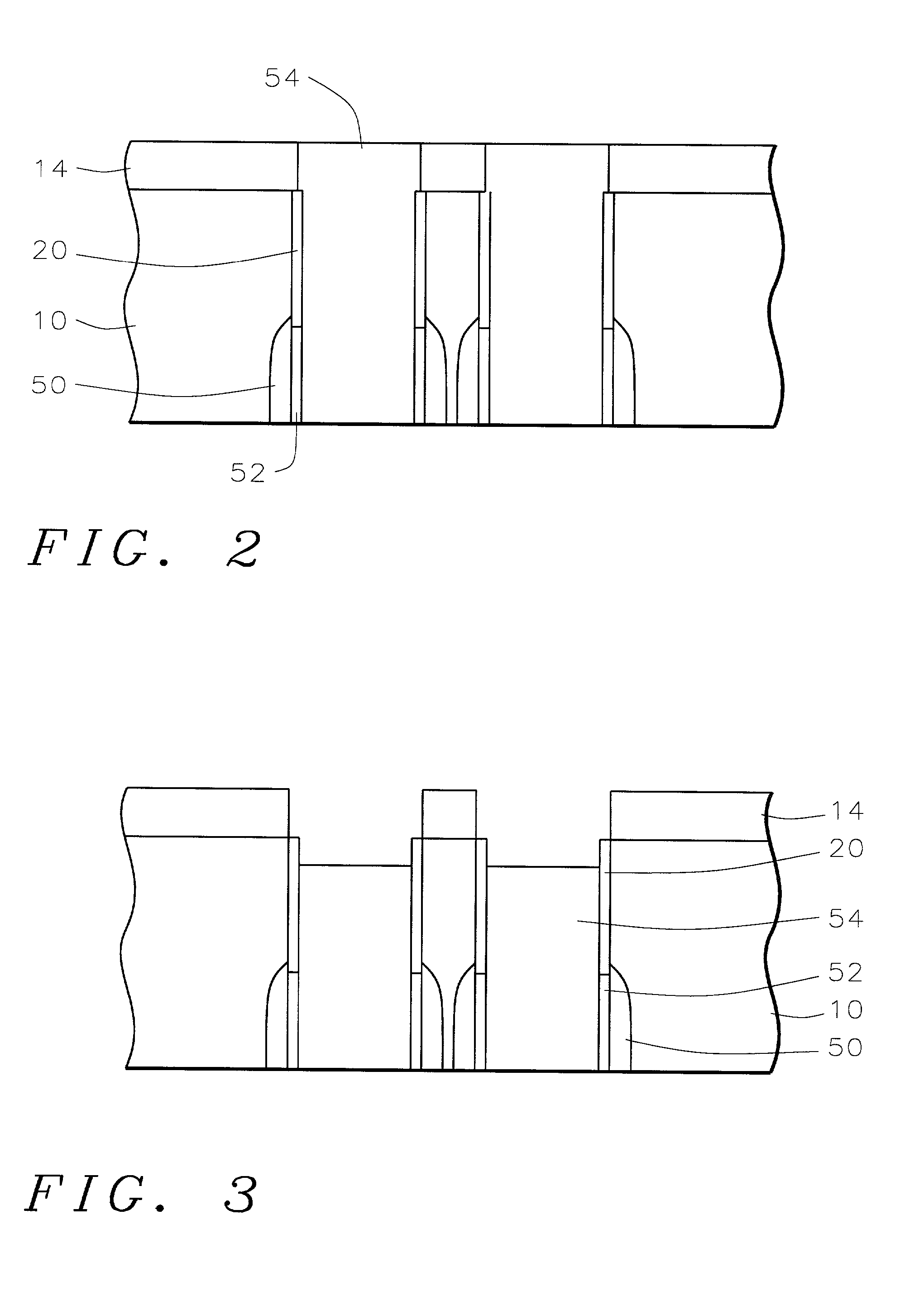

Method for forming an integrated circuit

ActiveUS20060131665A1Semiconductor/solid-state device manufacturingSemiconductor devicesContact resistanceEpitaxial silicon

A method is described for manufacturing an n-MOS semiconductor transistor. Recesses are formed in a semiconductor substrate adjacent a gate electrode structure. Silicon is embedded in the recesses via a selective epitaxial growth process. The epitaxial silicon is in-situ alloyed with substitutional carbon and in-situ doped with phosphorus. The silicon-carbon alloy generates a uniaxial tensile strain in the channel region between the source and drain, thereby increasing electron channel mobility and the transistor's drive current. The silicon-carbon alloy decreases external resistances by reducing contact resistance between source / drain and silicide regions and by reducing phosphorous diffusivity, thereby permitting closer placement of the transistor's source / drain and channel regions.

Owner:TAHOE RES LTD

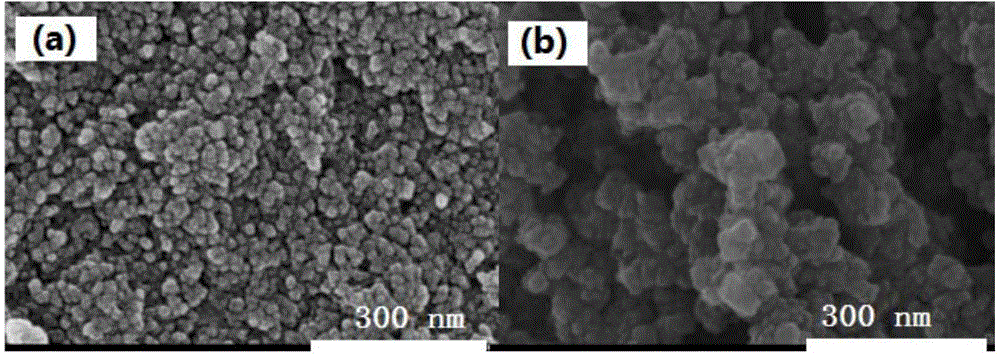

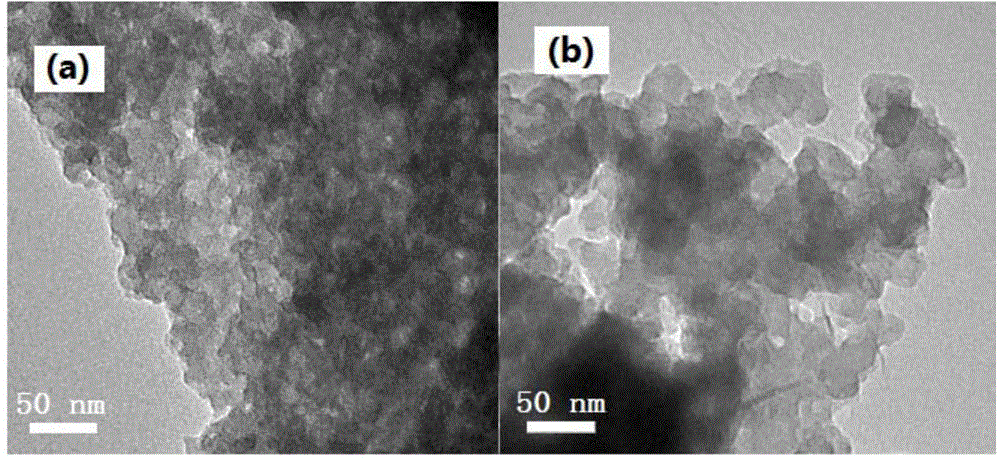

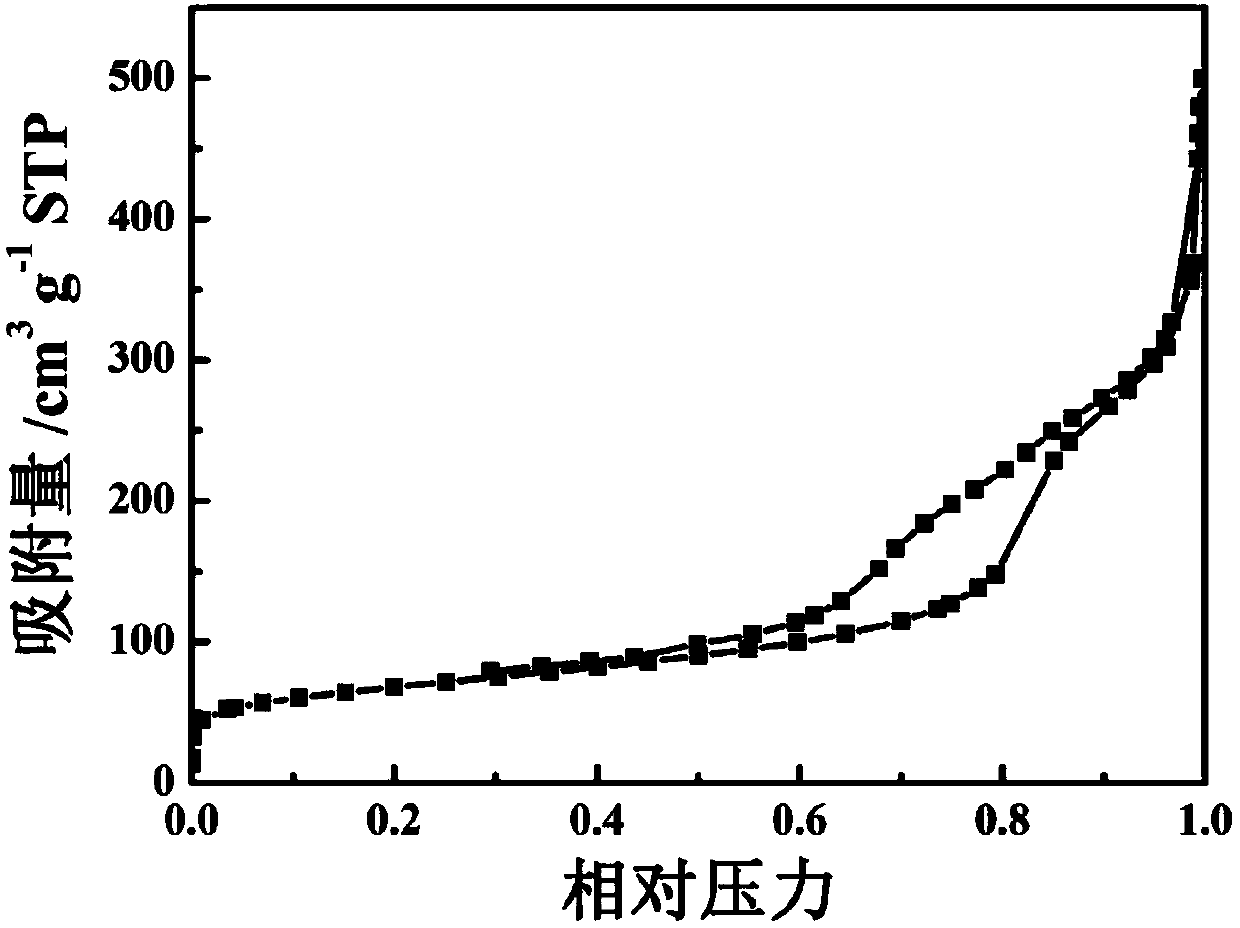

Preparing method for nitrogen-doped porous carbon material, catalyst comprising material and application of material

ActiveCN104689857AGood dispersionHigh bonding strengthCatalyst carriersOrganic compound preparationDispersityIn situ doping

The invention relates to a novel preparing method for an in-situ nitrogen-doped porous carbon material, the application of the in-situ nitrogen-doped porous carbon material serving as a carrier of a load type catalyst, the load type catalyst comprising the in-situ nitrogen-doped porous carbon material, and the application of the load type catalyst in the water phase alcohol condensation reaction. Cheap micromolecule nitrogen substances serve as a nitrogen source of the in-situ nitrogen-doped porous carbon material, nitrogen atom in-situ doping is achieved in the carbon material preparing process, the doping content of the in-situ nitrogen-doped porous carbon material is controllable, the in-situ nitrogen-doped porous carbon material is distributed evenly, the dispersity of metal in the carrier and the combining strength with the carrier can be improved through doping of nitrogen atoms, and therefore the catalytic activity of the nitrogen-doped porous carbon material can be improved, and the service life of the nitrogen-doped porous carbon material can be prolonged.

Owner:QINGDAO INST OF BIOENERGY & BIOPROCESS TECH CHINESE ACADEMY OF SCI

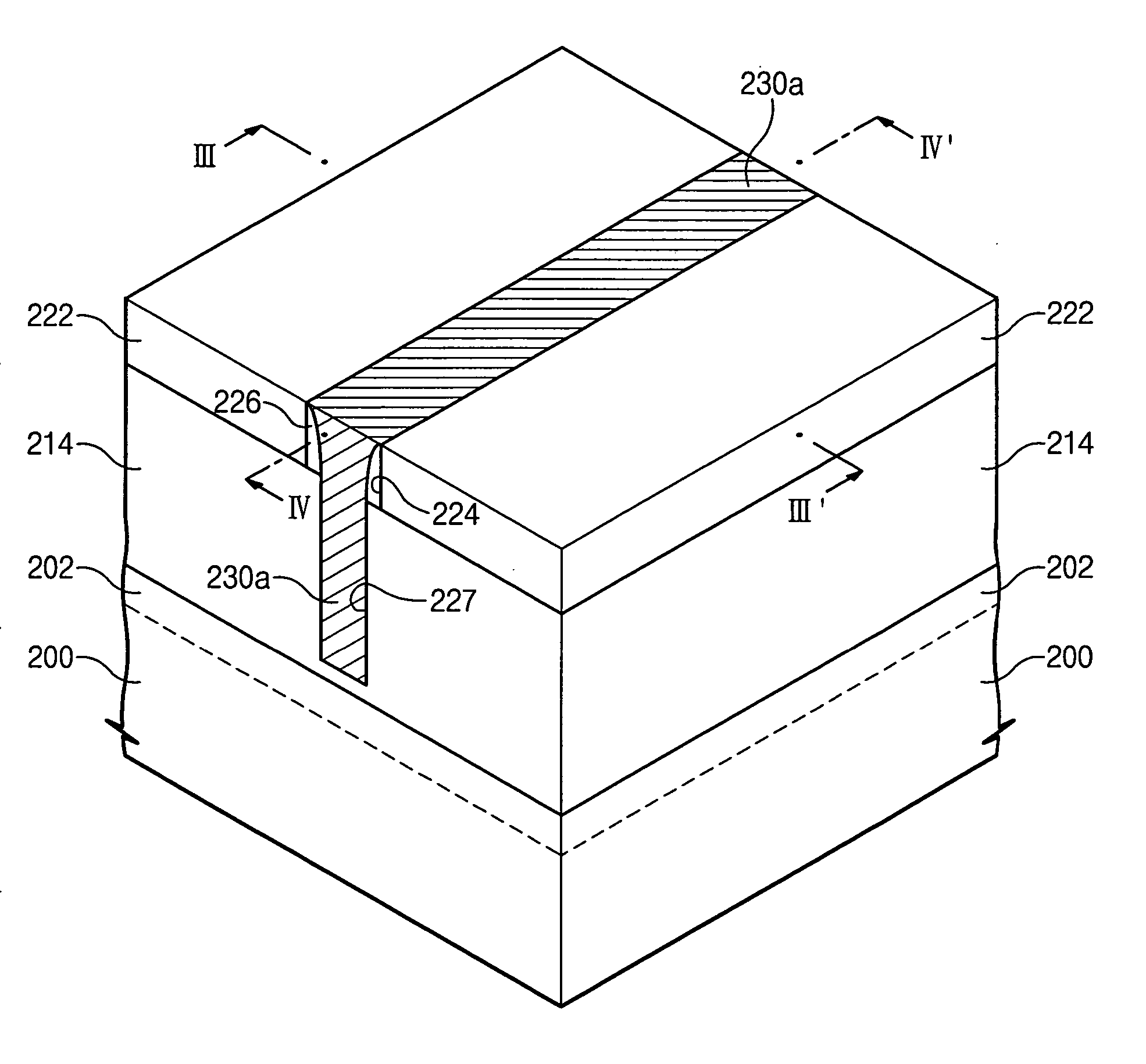

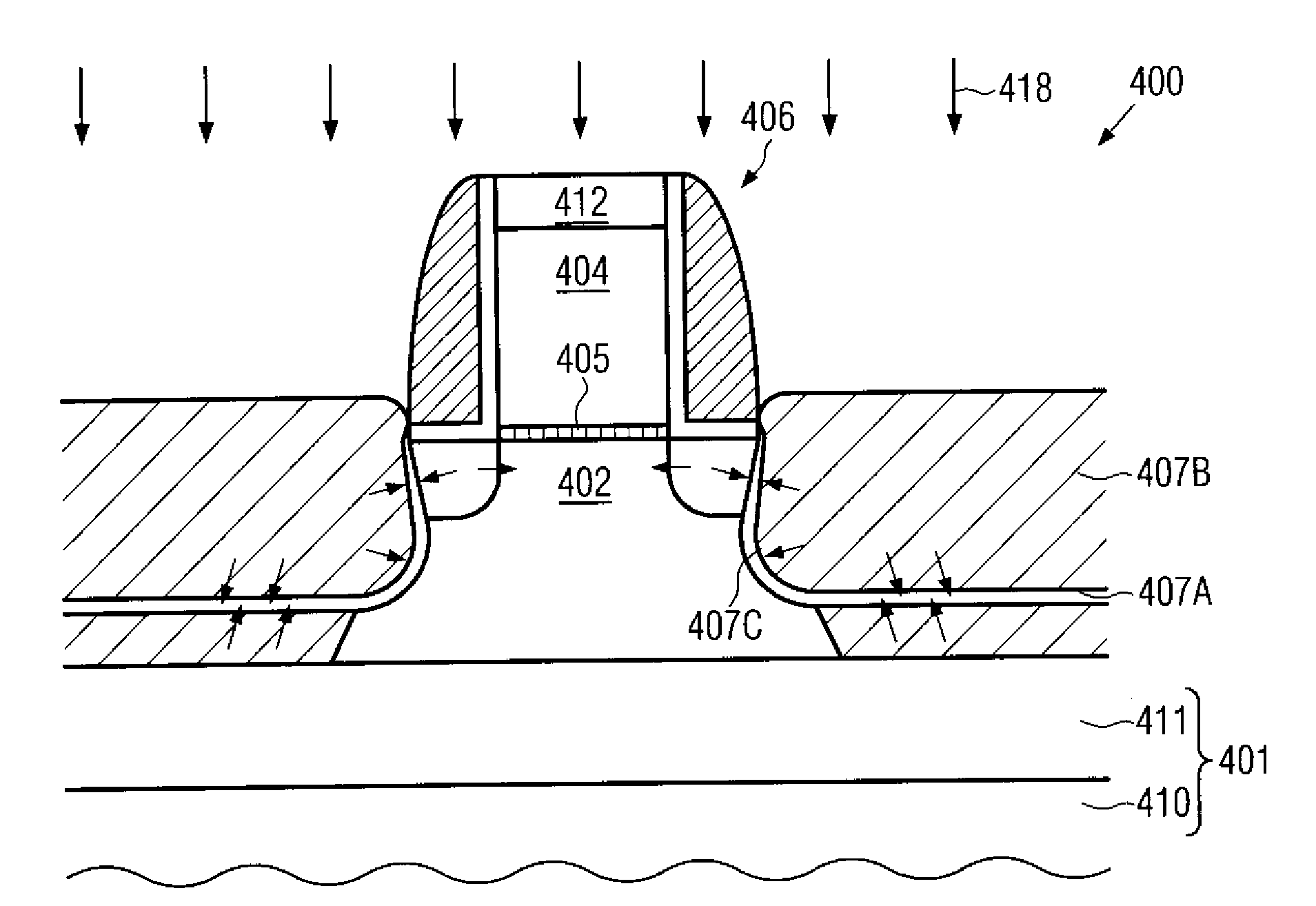

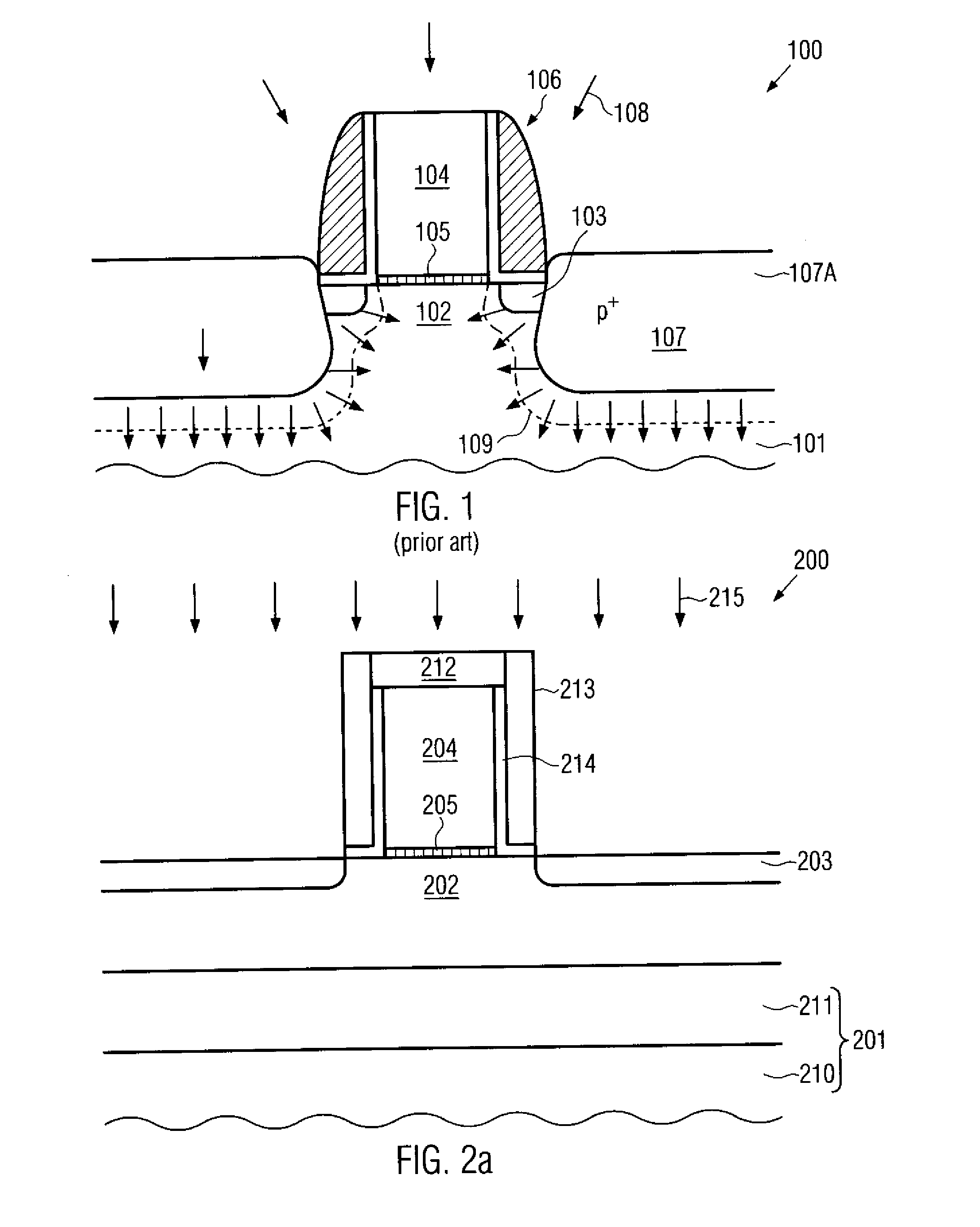

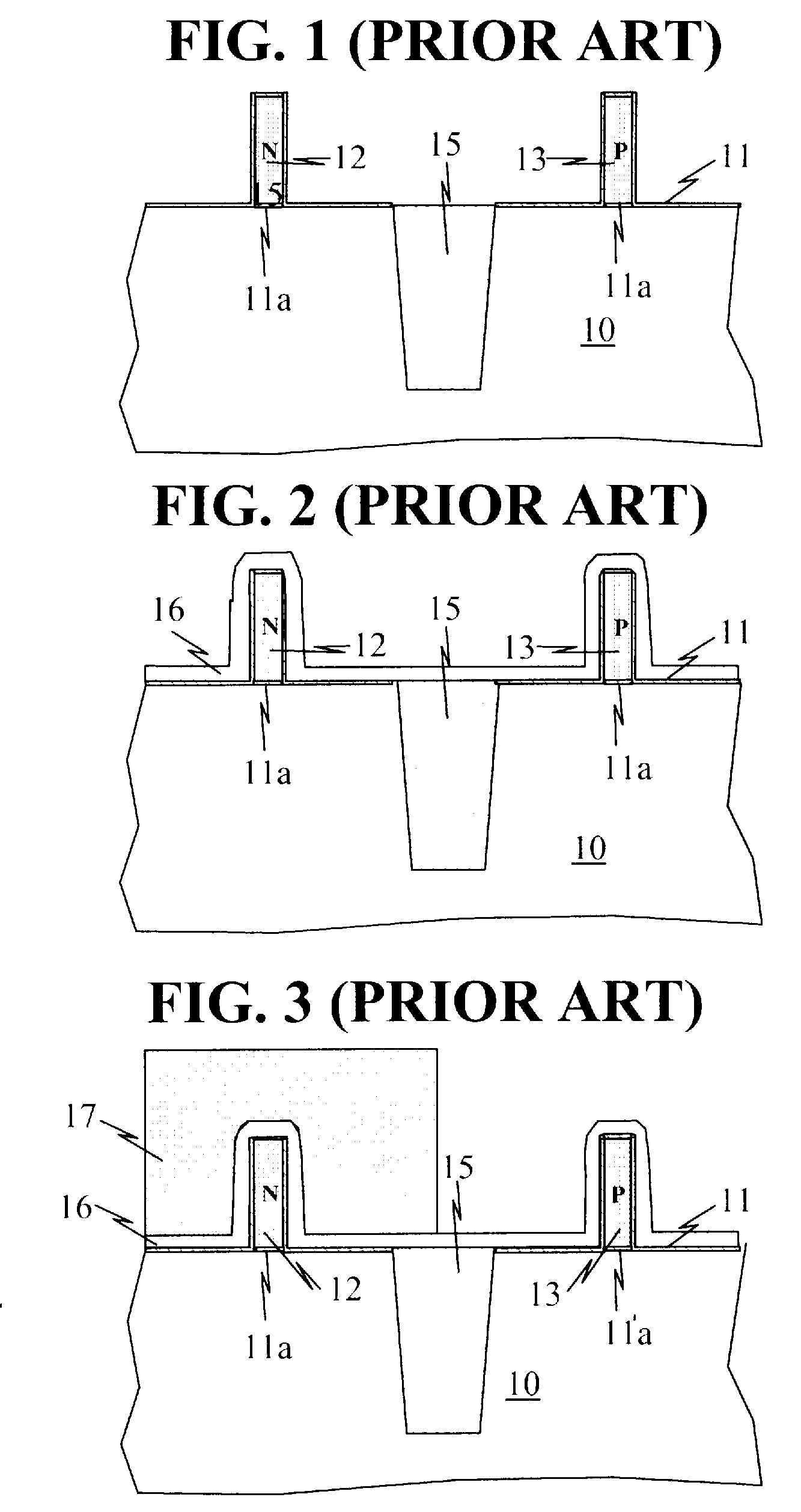

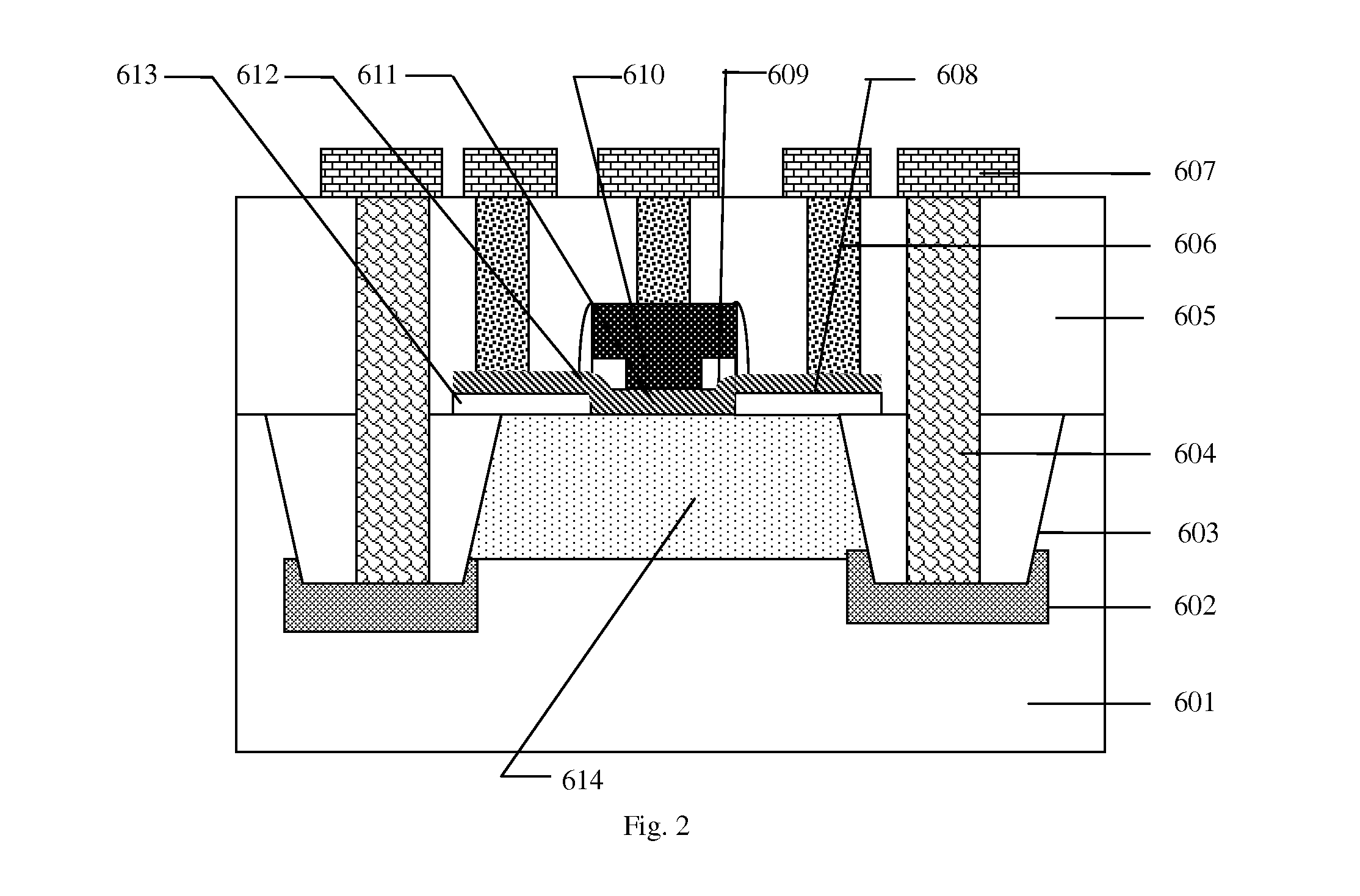

Ultra-shallow junction MOSFET having a high-k gate dielectric and in-situ doped selective epitaxy source/drain extensions and a method of making same

ActiveUS20050093084A1Eliminates and ameliorates leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

A MOSFET includes a gate having a high-k gate dielectric on a substrate and a gate electrode on the gate dielectric. The gate dielectric protrudes beyond the gate electrode. A deep source and drain having shallow extensions are formed on either side of the gate. The deep source and drain are formed by selective in-situ doped epitaxy or by ion implantation and the extensions are formed by selective, in-situ doped epitaxy. The extensions lie beneath the gate in contact with the gate dielectric. The material of the gate dielectric and the amount of its protrusion beyond the gate electrode are selected so that epitaxial procedures and related procedures do not cause bridging between the gate electrode and the source / drain extensions. Methods of fabricating the MOSFET are described.

Owner:TAIWAN SEMICON MFG CO LTD

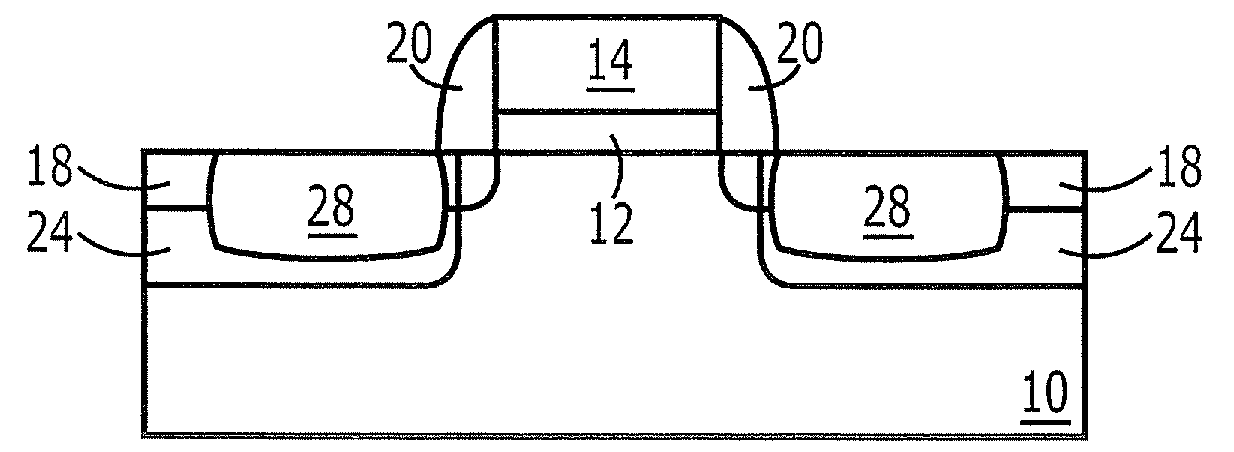

Methods of Forming Field Effect Transistors Having Silicon-Germanium Source and Drain Regions

InactiveUS20080124874A1TransistorSemiconductor/solid-state device manufacturingIn situ dopingAmmonium hydroxide

Methods of forming field effect transistors include forming an insulated gate electrode on a non-SiGe semiconductor substrate and then selectively etching the semiconductor substrate to define source and drain region trenches on opposite sides of the insulated gate electrode. A step is performed to remove native oxide layers from sidewalls of the source and drain region trenches. The removal of the native oxide is followed by recessing the sidewalls of the source and drain region trenches by selectively wet etching the sidewalls of the source and drain region trenches. This step of wet etching the sidewalls of the source and drain region trenches may include exposing the sidewalls to a cleaning solution including ammonium hydroxide (NH4OH). A step is then performed to epitaxially grow SiGe source and drain regions in the source and drain region trenches. This step of epitaxially growing SiGe source and drain regions may include epitaxially growing in-situ doped SiGe source and drain regions of first conductivity type in the source and drain region trenches.

Owner:SAMSUNG ELECTRONICS CO LTD

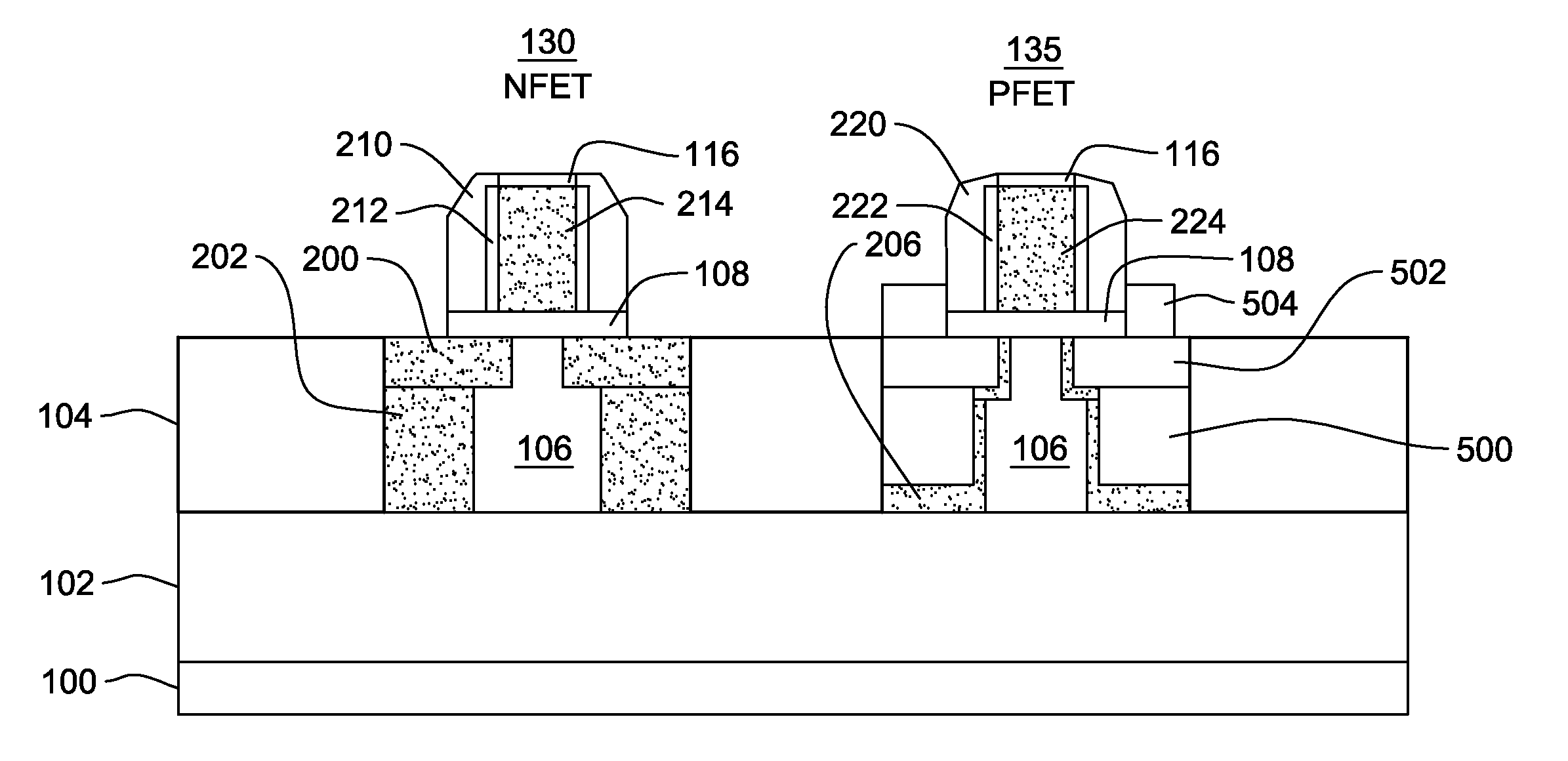

In Situ Doping and Diffusionless Annealing of Embedded Stressor Regions in PMOS and NMOS Devices

ActiveUS20130178024A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesDopantIn situ doping

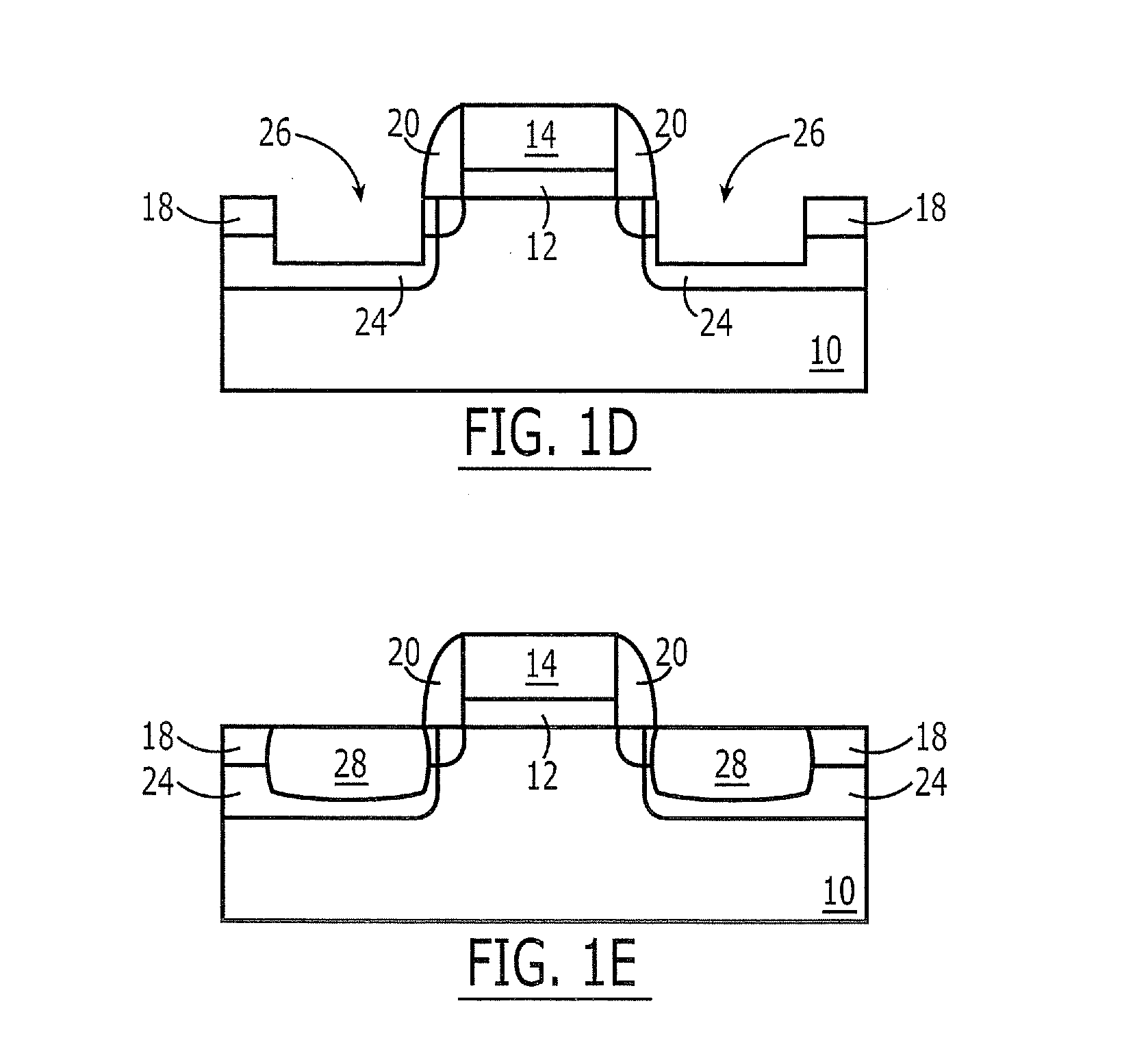

Generally, the present disclosure is directed to methods for forming dual embedded stressor regions in semiconductor devices such as transistor elements and the like, using in situ doping and substantially diffusionless annealing techniques. One illustrative method disclosed herein includes forming first and second cavities in PMOS and NMOS device regions, respectively, of a semiconductor substrate, and thereafter performing first and second epitaxial deposition processes to form in situ doped first and second embedded material regions in the first and second cavities, respectively. The method further includes, among other things, performing a single heat treating process to activate dopants in the in situ doped first and second embedded material regions.

Owner:TAIWAN SEMICON MFG CO LTD

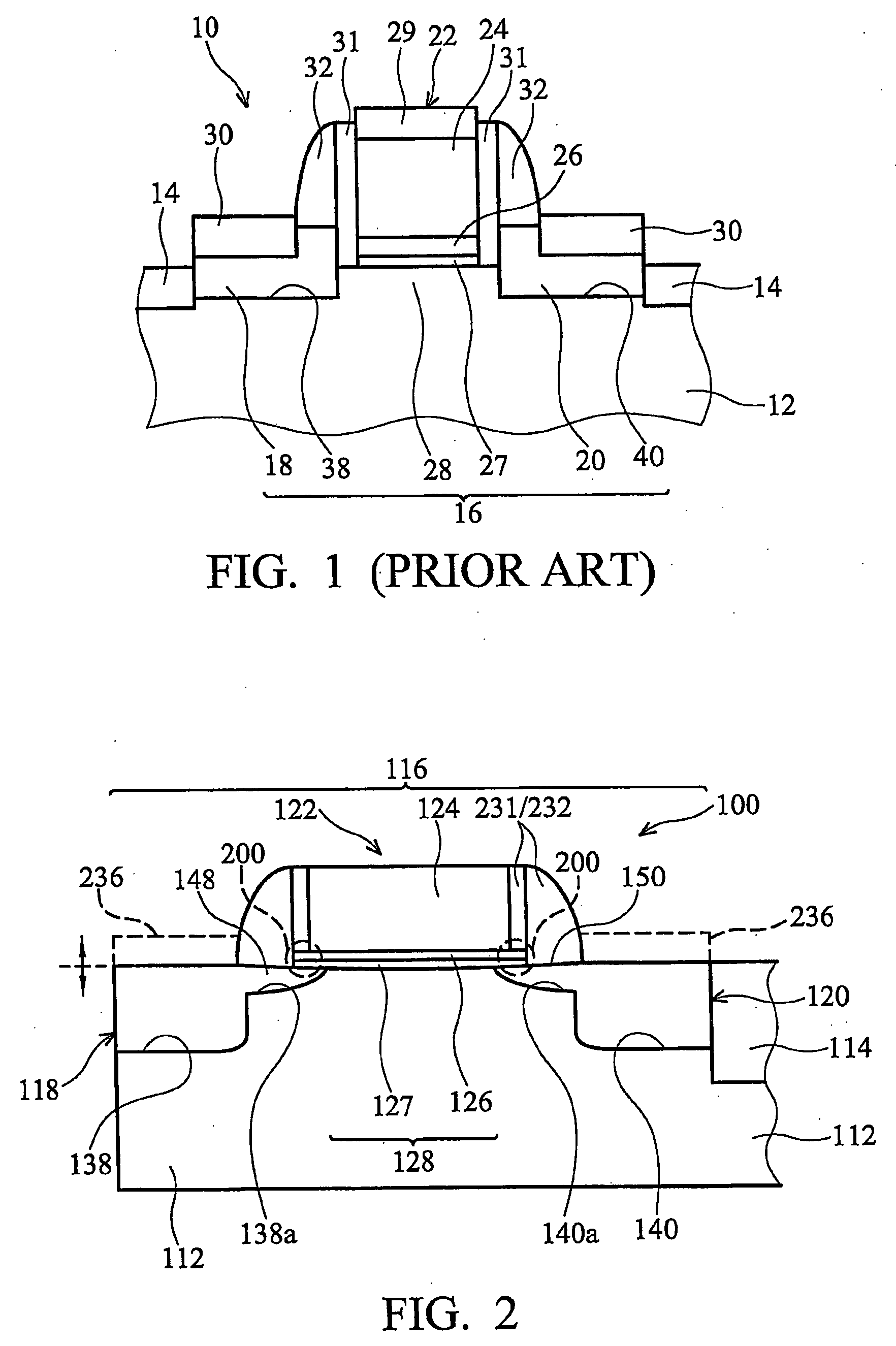

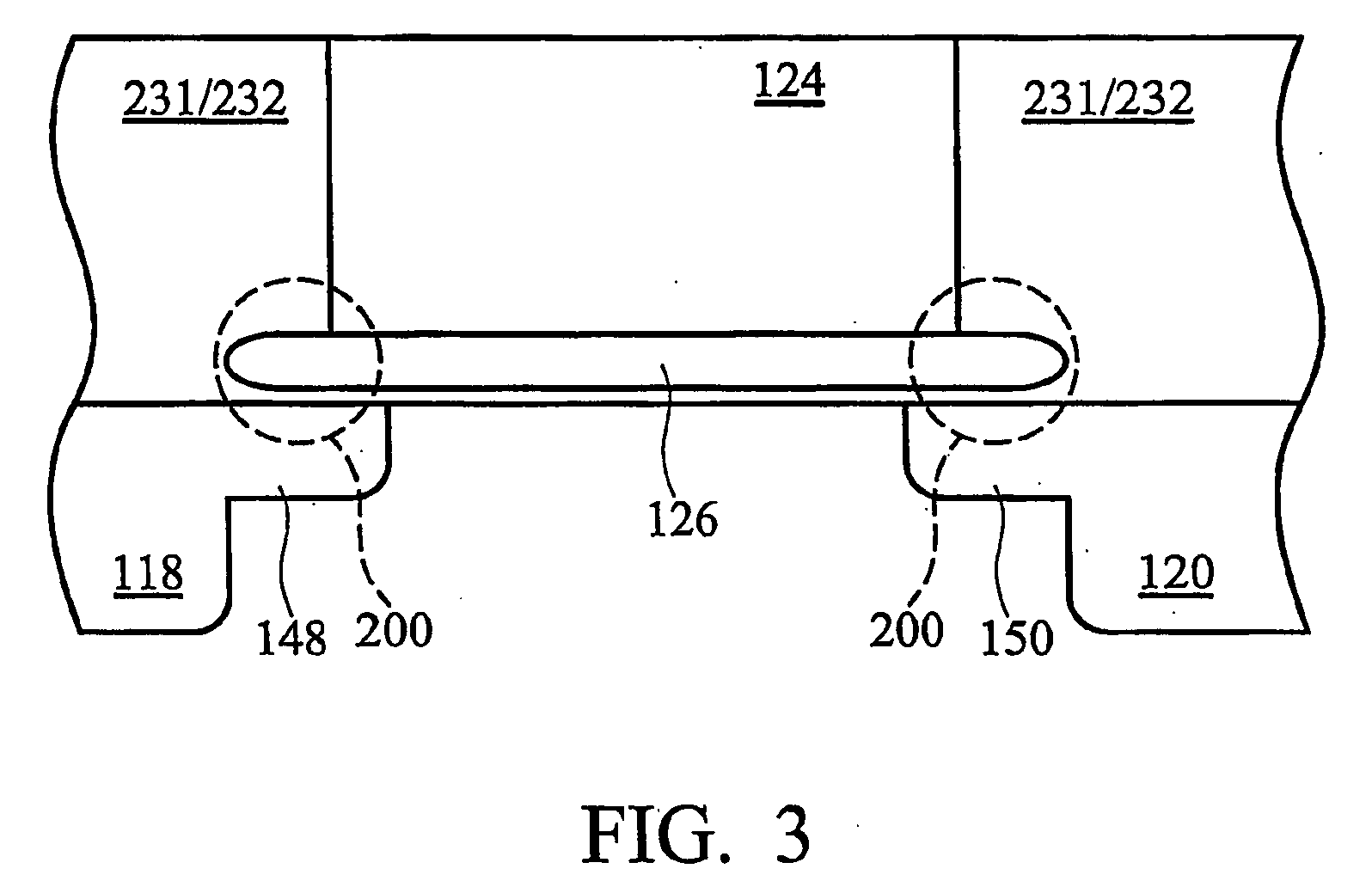

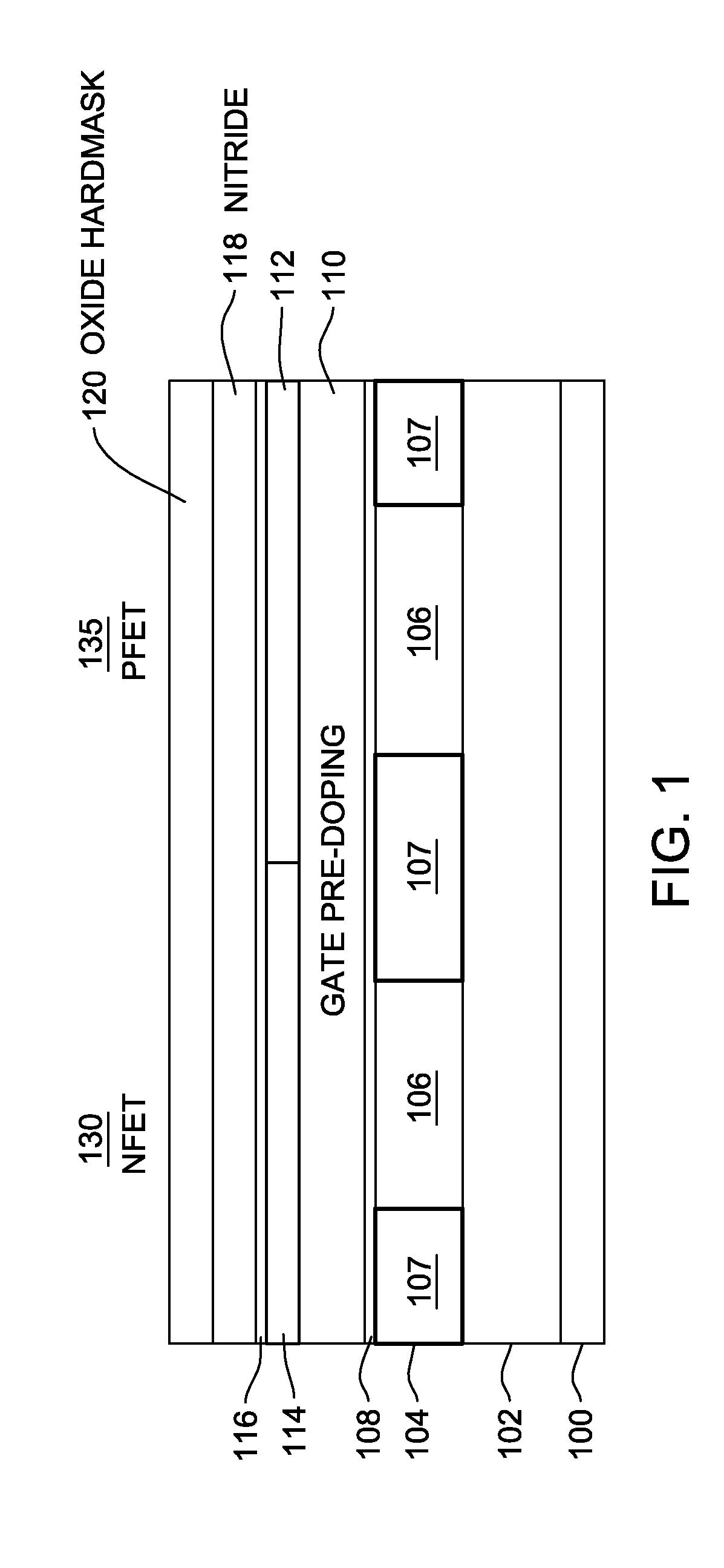

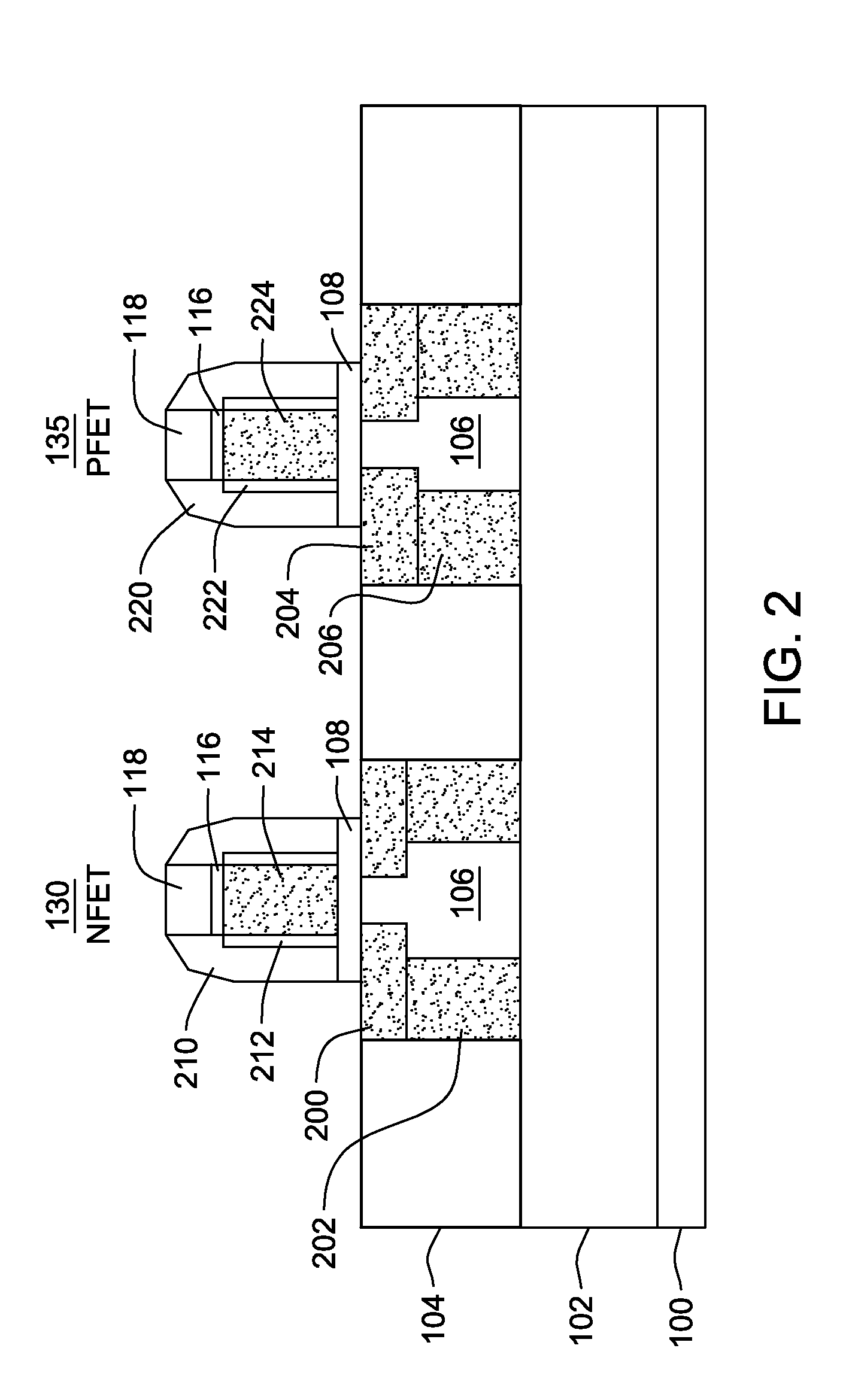

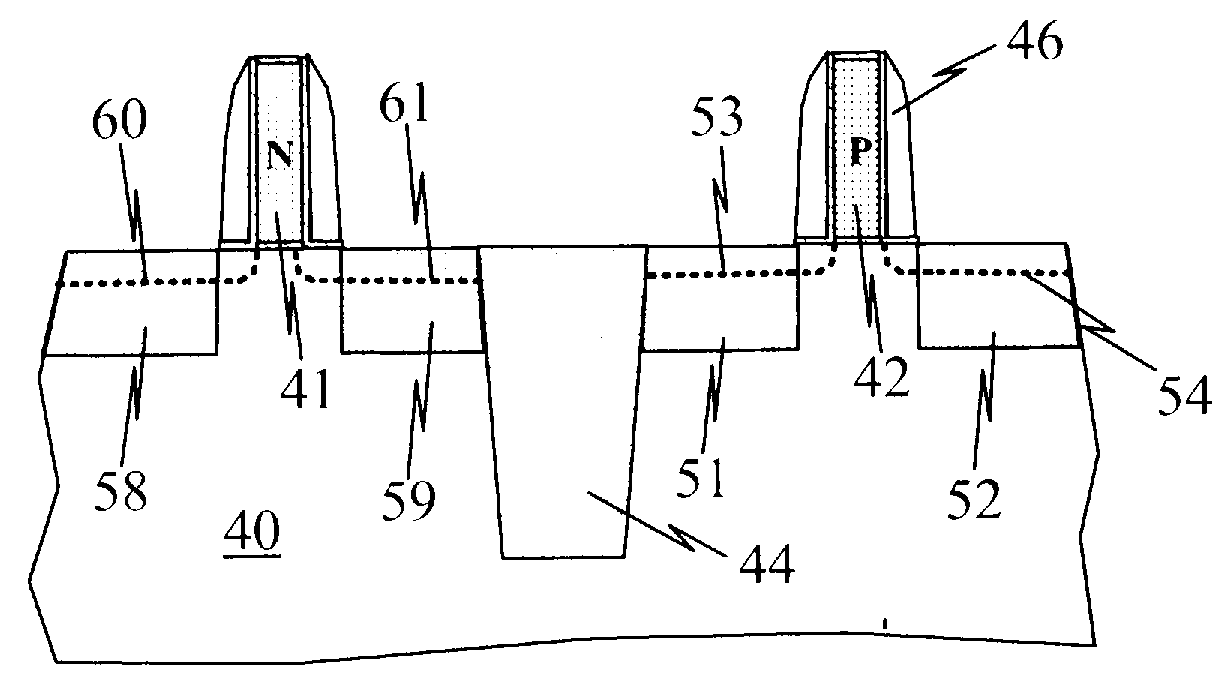

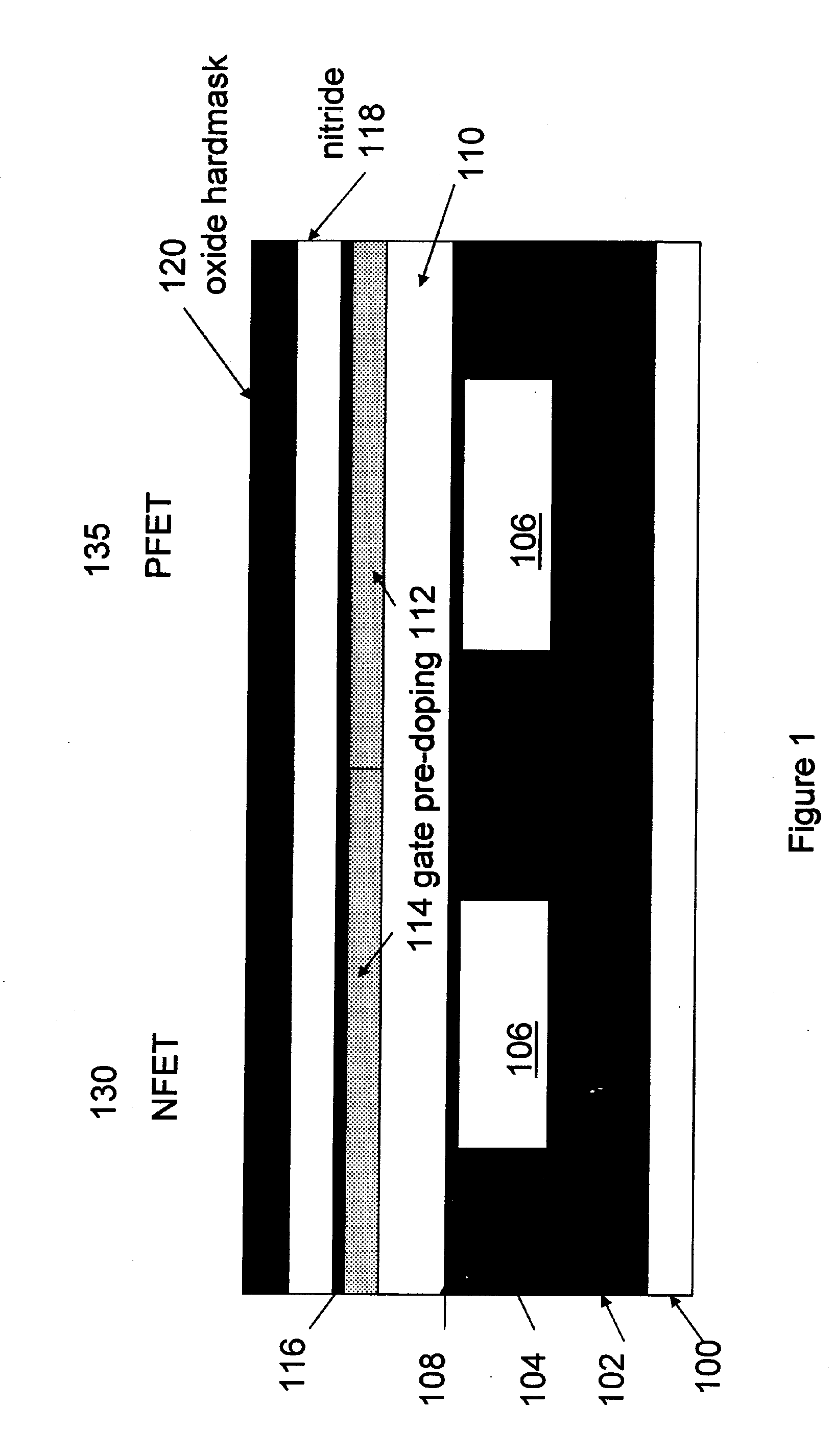

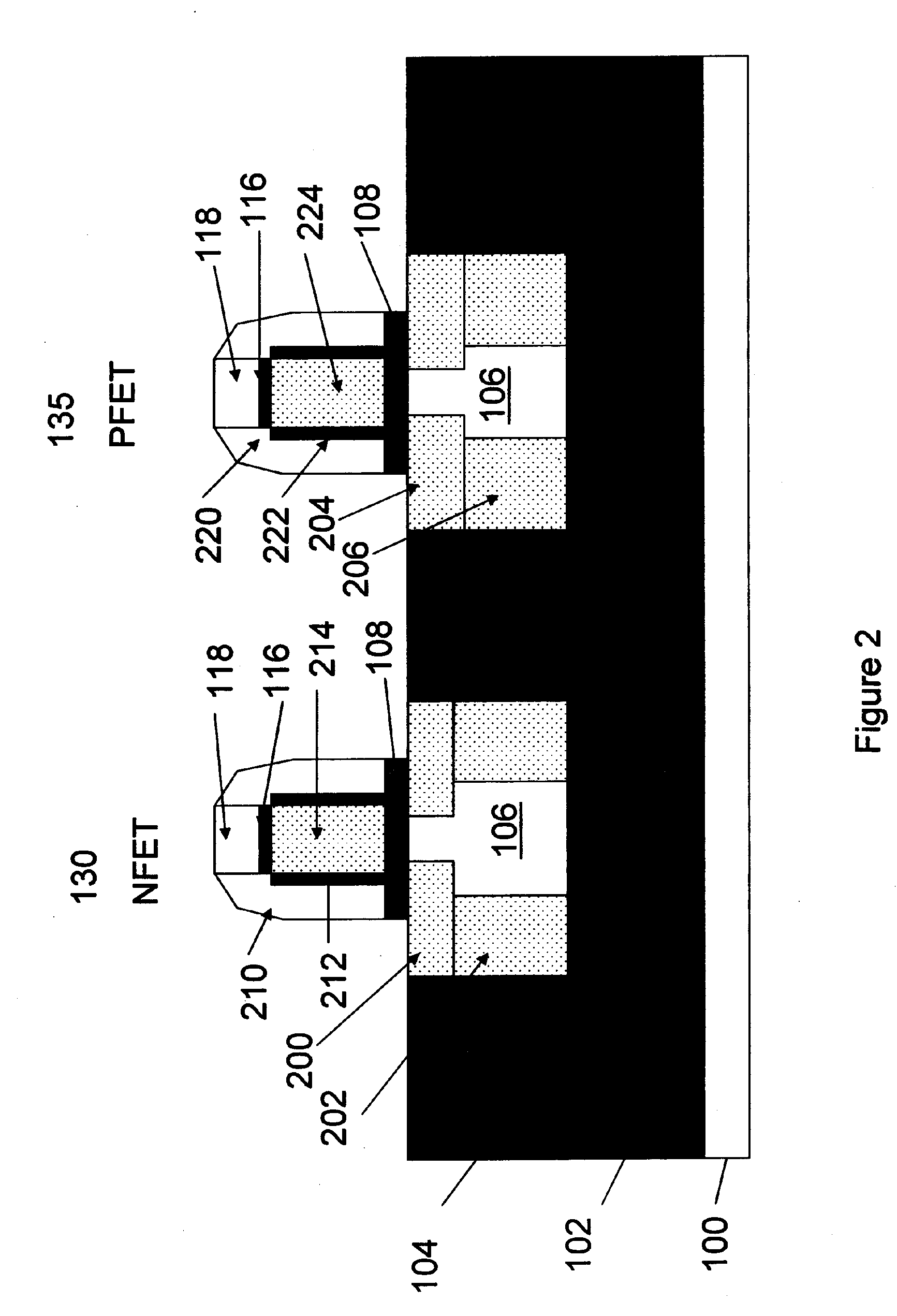

In situ doped embedded sige extension and source/drain for enhanced PFET performance

ActiveUS7176481B2Growth inhibitionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIn situ doping

Disclosed is an integrated circuit structure and a method of making such a structure that has a substrate and P-type and N-type transistors on the substrate. The N-type transistor extension and source / drain regions comprise dopants implanted into the substrate. The P-type transistor extension and source / drain regions partially include a strained epitaxial silicon germanium, wherein the strained silicon germanium comprises of two layers, with a top layer that is closer to the gate stack than the bottom layer. The strained silicon germanium is in-situ doped and creates longitudinal stress on the channel region.

Owner:MICROSOFT TECH LICENSING LLC

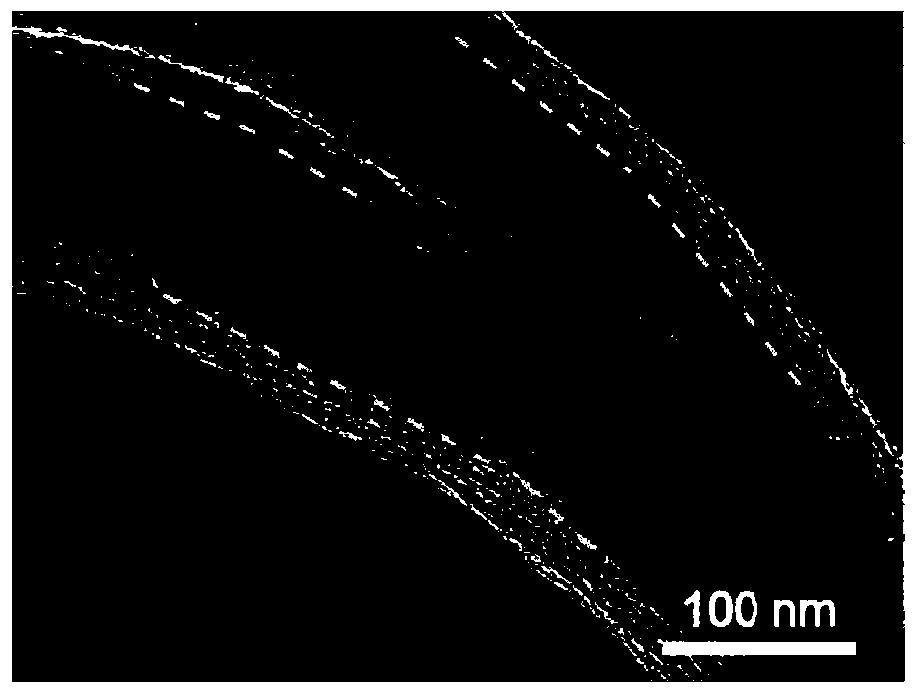

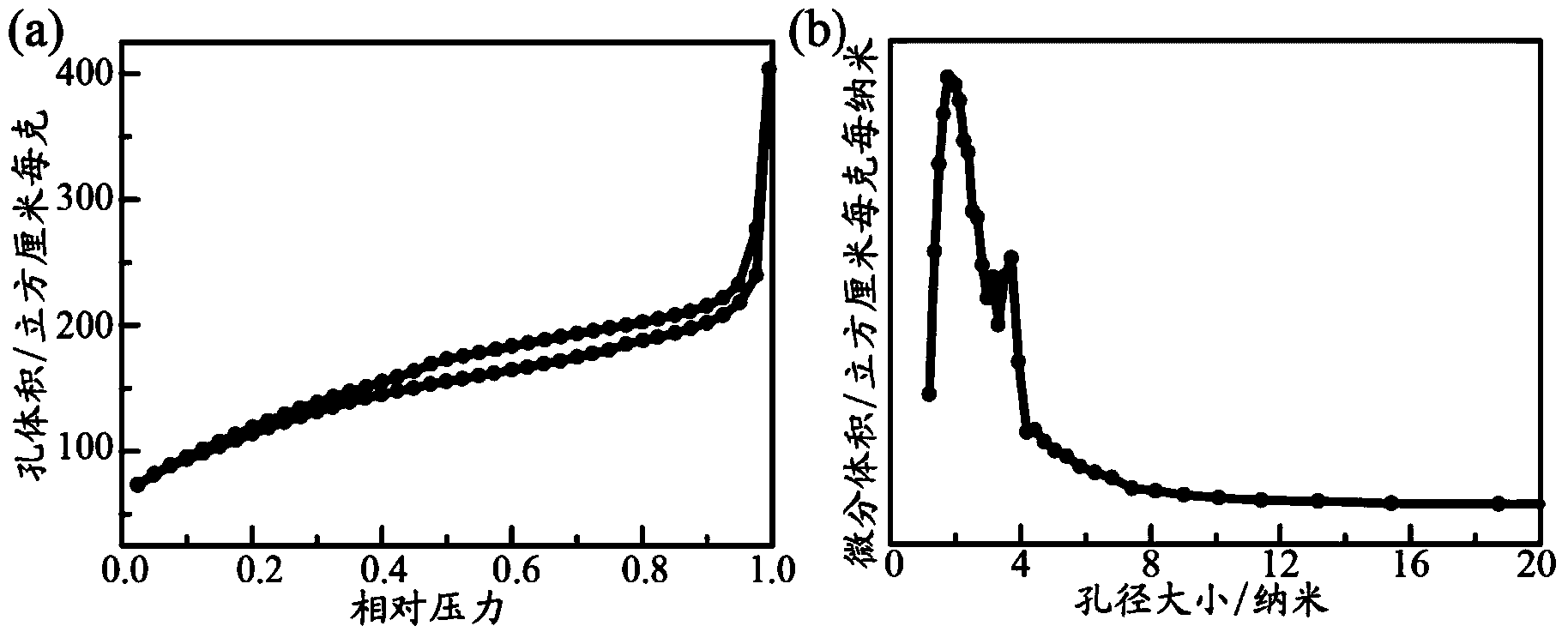

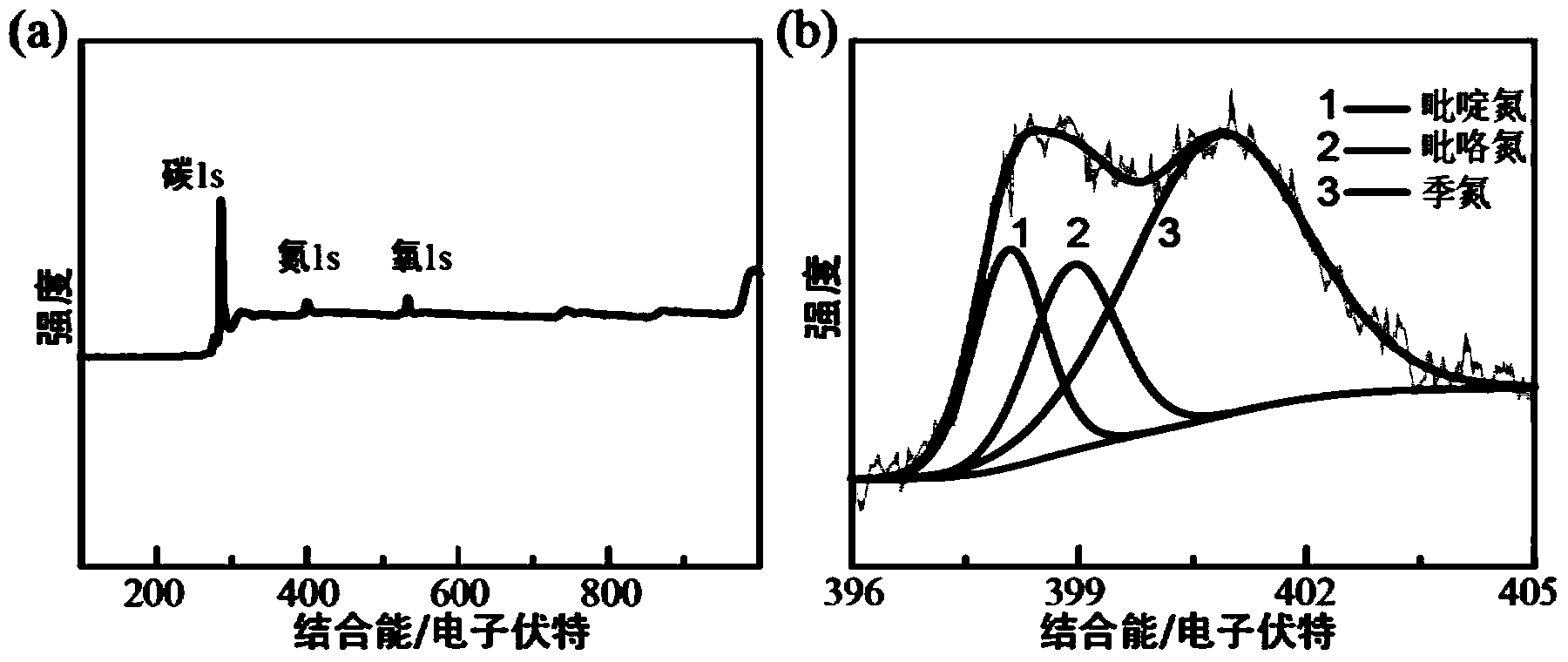

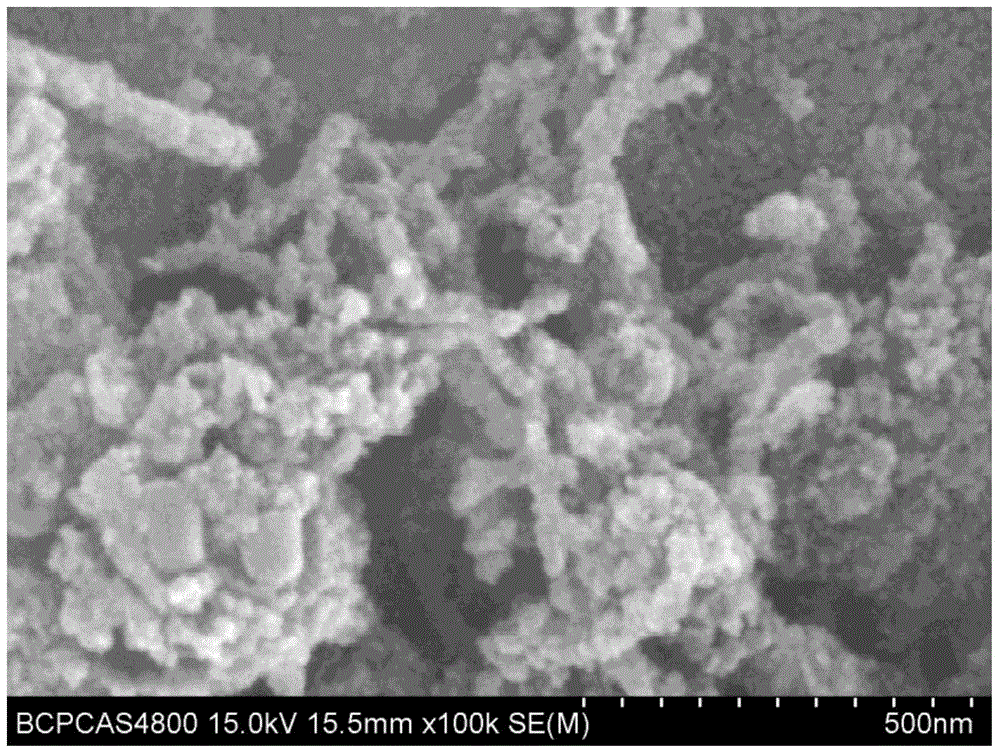

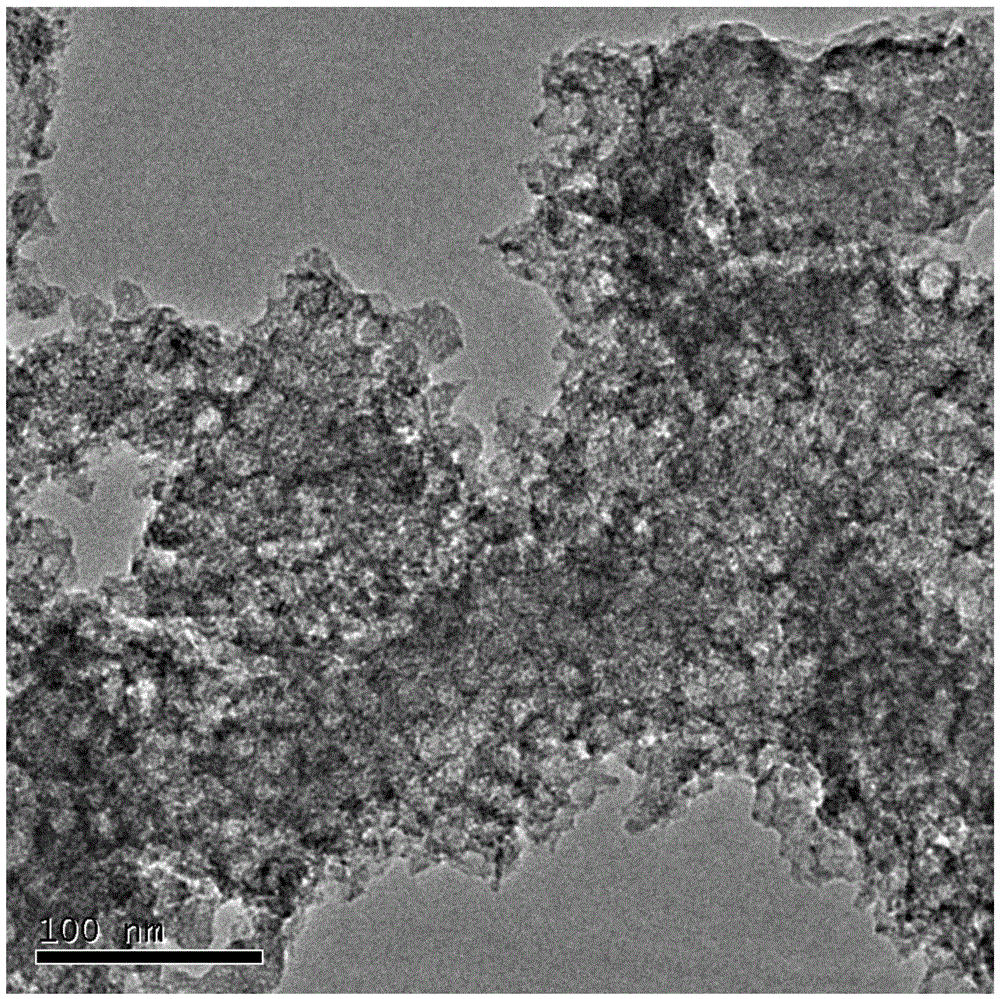

Composite material of nitrogen-doped porous carbon-wrapped carbon nano tube as well as preparation method and application of material

ActiveCN103706388AEasy to prepareEconomical method of preparationMaterial nanotechnologyPhysical/chemical process catalystsCarbon layerPorous carbon

The invention relates to a composite material of a nitrogen-doped porous carbon-wrapped carbon nano tube as well as a preparation method and an application of the composite material. The preparation method comprises the following steps: dispersing the carbon nano tube in water, adding a carbon source to obtain a reaction system, subsequently performing hydrothermal reaction, performing thermal treatment on the carbon nano tube wrapped with a carbon layer on the surface, and a nitrogen source at the high temperature so as to obtain the composite material of the nitrogen-doped porous carbon-wrapped carbon nano tube. According to the preparation method, the carbon source is polymerized under a hydrothermal reaction condition so as to obtain the carbon layer, the outer surface of the carbon nano tube is wrapped with the carbon layer, subsequently the carbon layer is carbonized and decomposed to generate a porous structure under high temperature treatment, and at the same time, the gasified nitrogen source is diffused to the carbon layer through ducts to be subjected to in-situ doping. The composite material provided by the invention can be used as a cathode oxidation reduction catalyst of a fuel battery, is excellent in catalysis, and is high in oxidation activity when being compared with other nitrogen-doped materials reported in documents. The preparation method provided by the invention is simple and economic in process, convenient to operate and easy to achieve the large-scale production.

Owner:INST OF CHEM CHINESE ACAD OF SCI

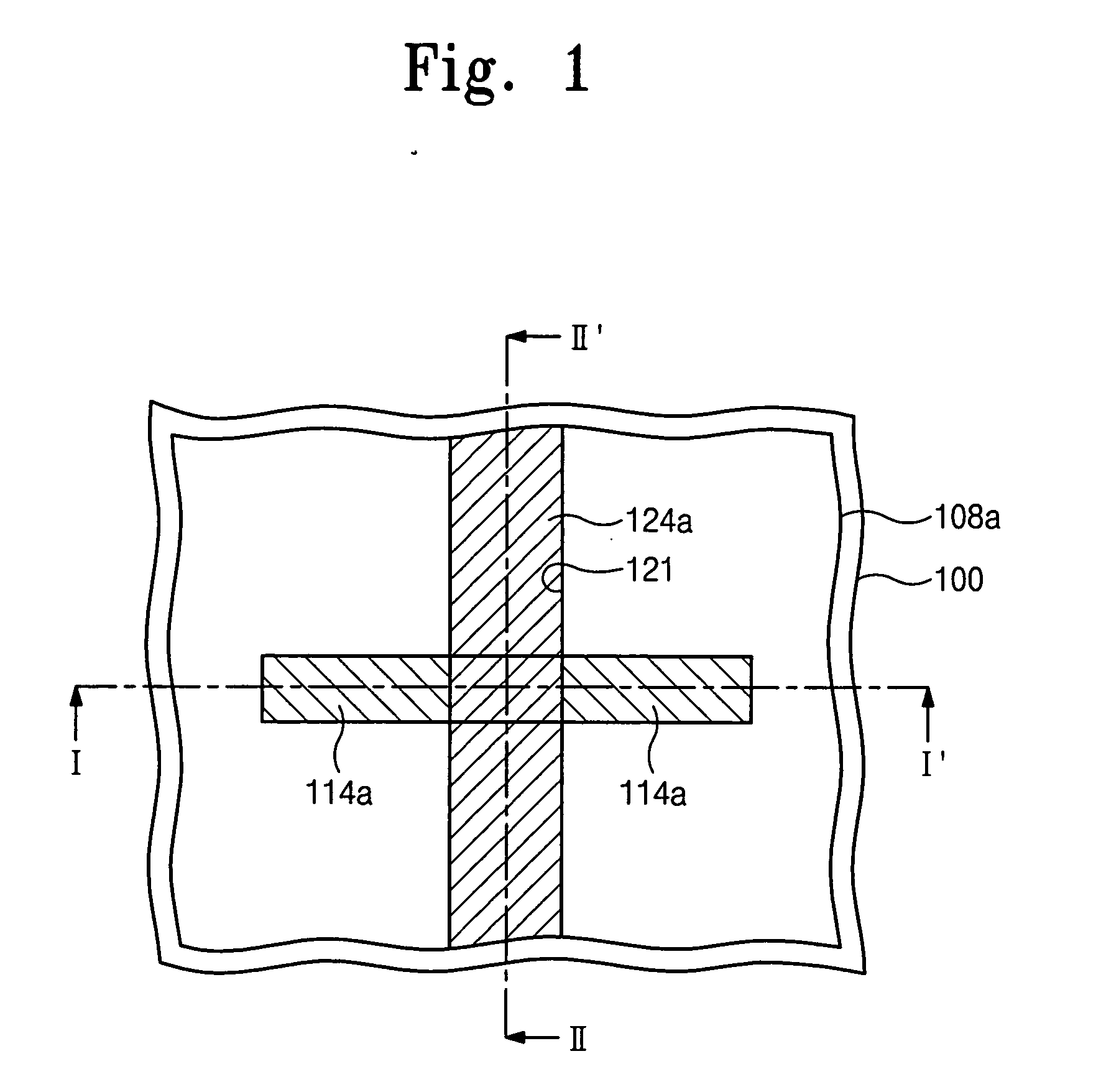

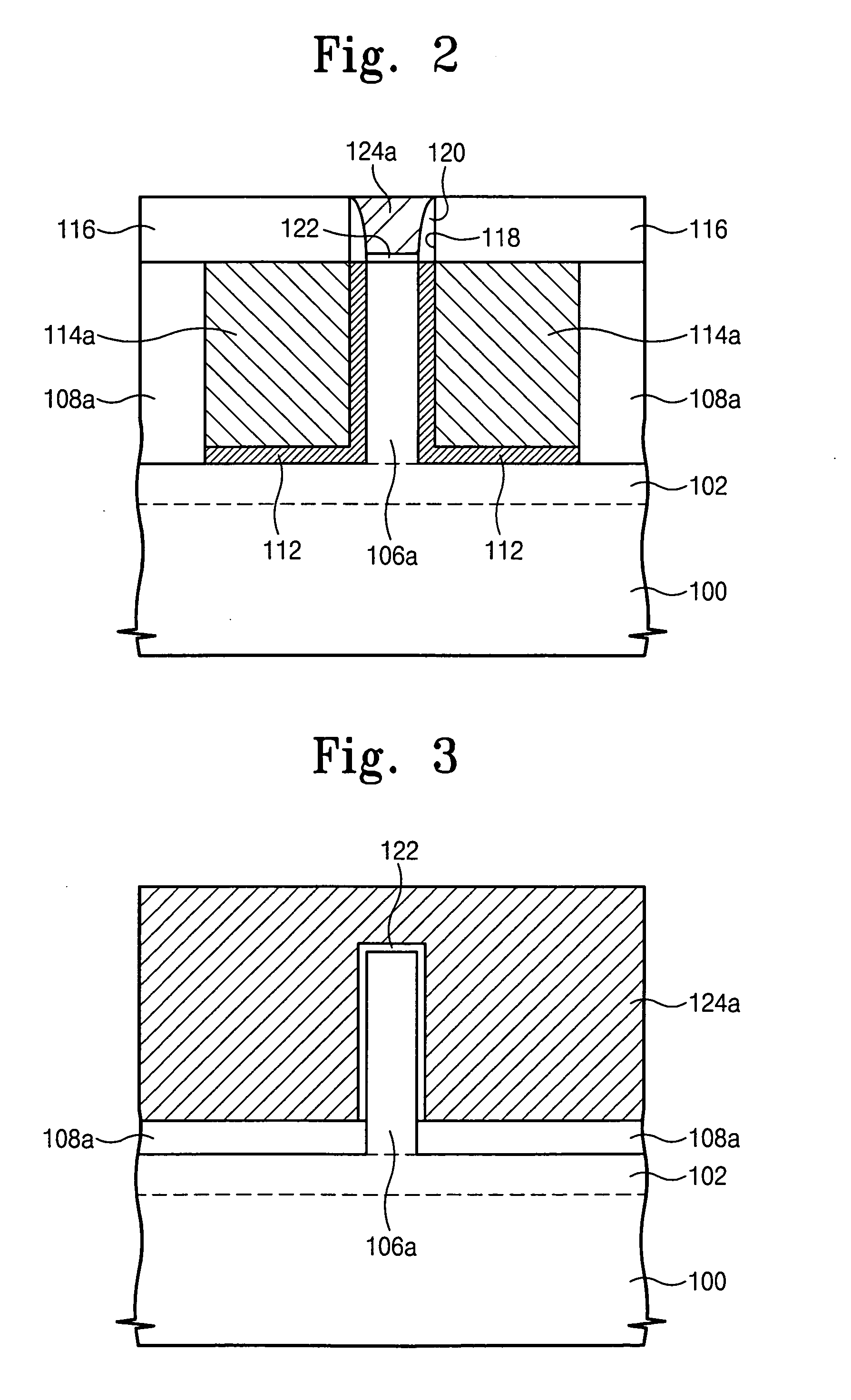

Semiconductor devices having field effect transistors and methods of fabricating the same

A semiconductor device having a field effect transistor and a method of fabricating the same. In-situ doped epitaxial patterns are respectively formed at both sidewalls of a protruded channel pattern from a substrate by performing an in-situ doped epitaxial growth process. The in-situ doped epitaxial pattern has a conformal impurity concentration throughout. Accordingly, source / drain regions with a conformal impurity concentration are connected throughout a channel width of a channel region including both sidewalls of a protruded channel pattern. As a result, it is possible to maximize a driving current of the filed effect transistor, and an on-off characteristic can be highly stabilized.

Owner:SAMSUNG ELECTRONICS CO LTD

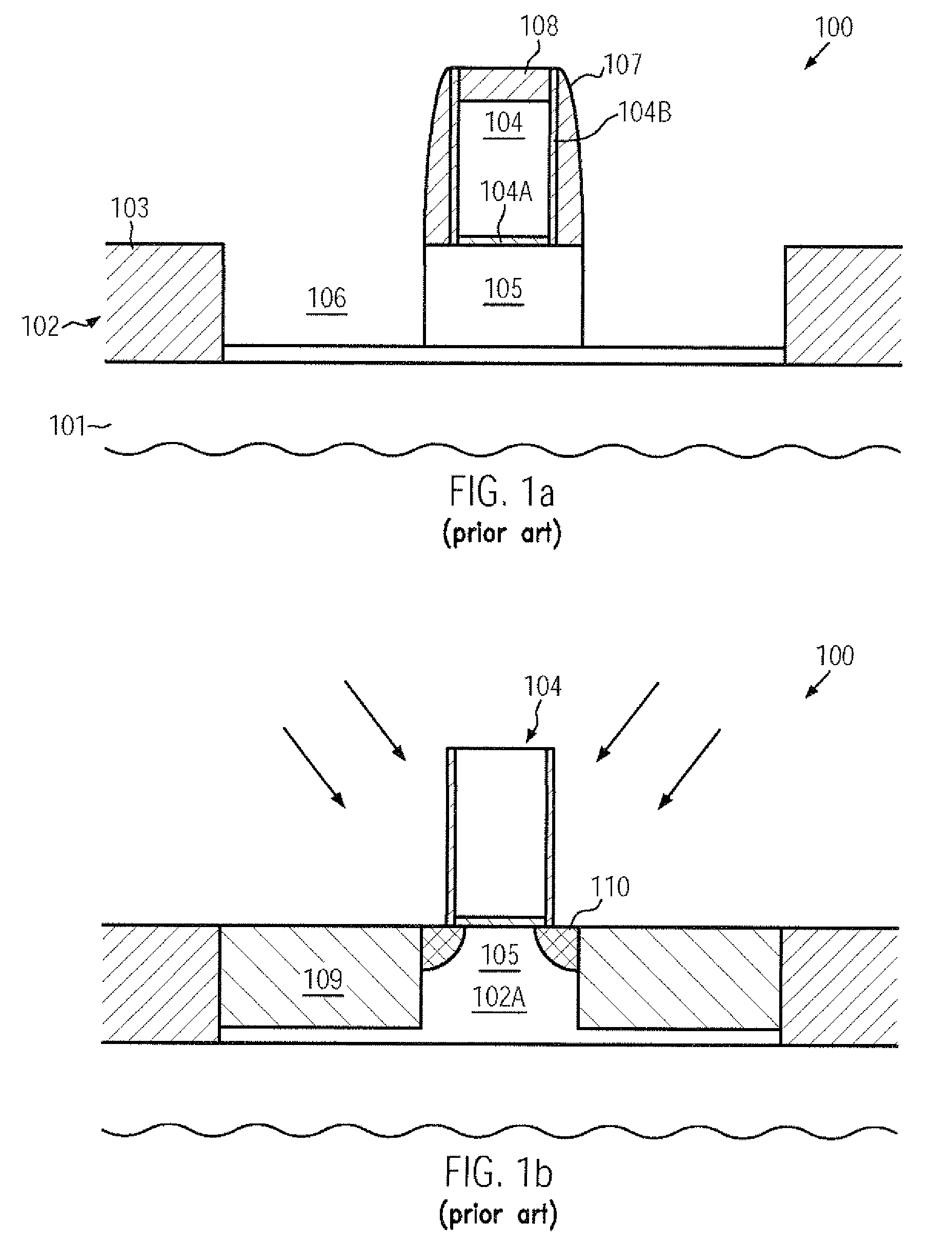

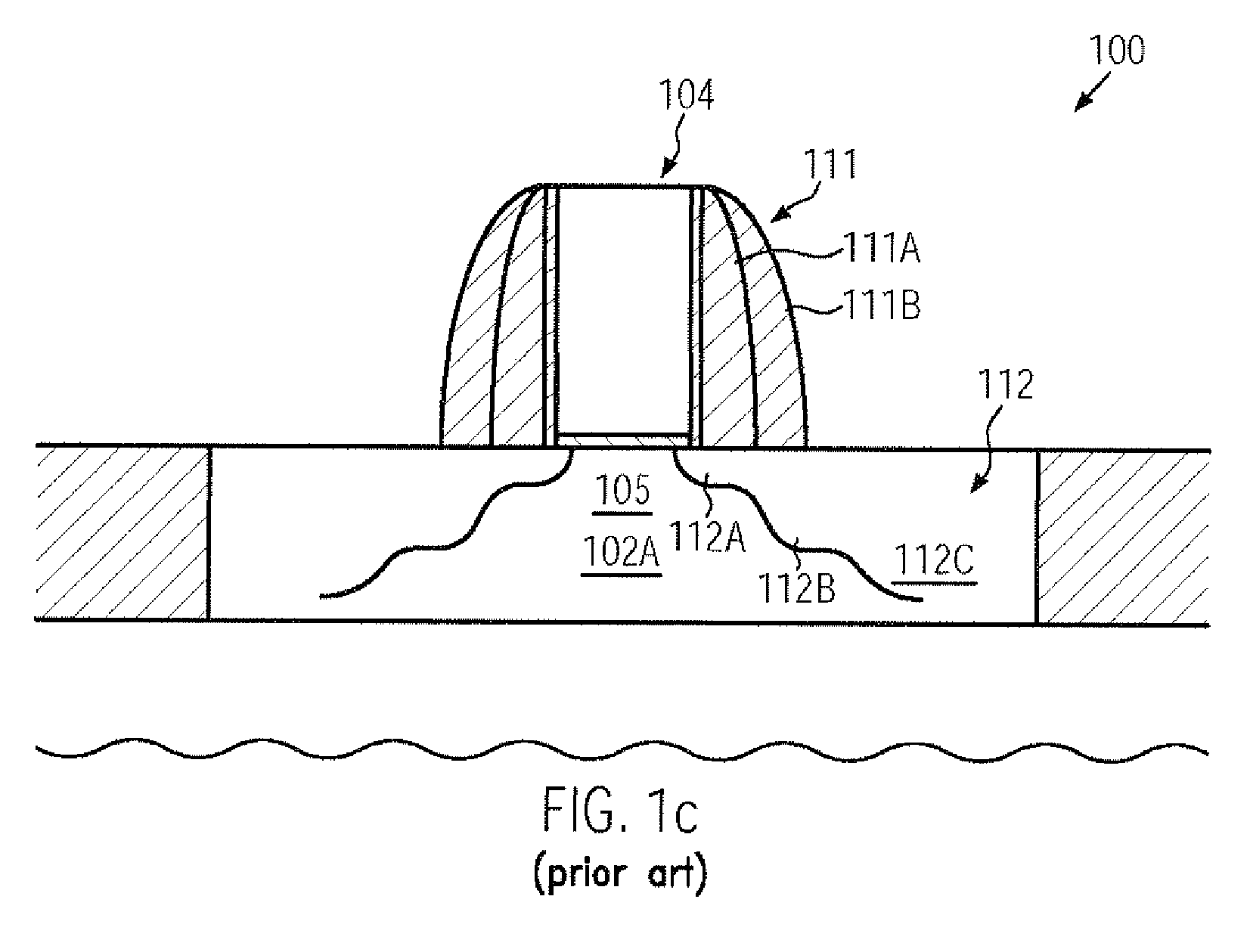

Soi transistor having an embedded strain layer and a reduced floating body effect and a method for forming the same

InactiveUS20070252204A1Improve performanceEfficient dischargeTransistorSolid-state devicesDriving currentFloating body effect

By forming a portion of a PN junction within strained silicon / germanium material in SOI transistors with a floating body architecture, the junction leakage may be significantly increased, thereby reducing floating body effects. The positioning of a portion of the PN junction within the strained silicon / germanium material may be accomplished on the basis of implantation and anneal techniques, contrary to conventional approaches in which in situ doped silicon / germanium is epitaxially grown so as to form the deep drain and source regions. Consequently, high drive current capability may be combined with a reduction of floating body effects.

Owner:ADVANCED MICRO DEVICES INC

Composite-coated lithium iron phosphate and preparation method therefor, and lithium ion battery

ActiveUS20180097228A1Improve conductivityHigh activityMaterial nanotechnologyElectrode thermal treatmentNanonetworkConductive polymer

A composite-coated lithium iron phosphate in a three-dimensional nanonetwork layered structure and a preparation method therefor, and a lithium ion battery, wherein a composite is prepared by compounding a conducting polymer, graphene and a carbon nano tube. The preparation method for the coated lithium iron phosphate comprises the following steps: doping the composite and anhydrous ferric phosphate in situ in the process of preparing the anhydrous ferric phosphate, serving as a lithium iron phosphate precursor, then mixing the composite in-situ doped anhydrous ferric phosphate, a lithium source, a traditional carbon material and a solvent to obtain slurry, spray drying the slurry, and calcining to obtain the composite-coated lithium iron phosphate in a three-dimensional nanonetwork layered structure. The preparation method is simple and has a wide raw material source, low cost and very broad practical application prospect. Serving as an anode material of the lithium ion battery, the coated lithium iron phosphate has higher electrical conductivity and cycling stability, and more excellent comprehensive electrochemical performance.

Owner:INST OF PROCESS ENG CHINESE ACAD OF SCI

In situ doped epitaxial films

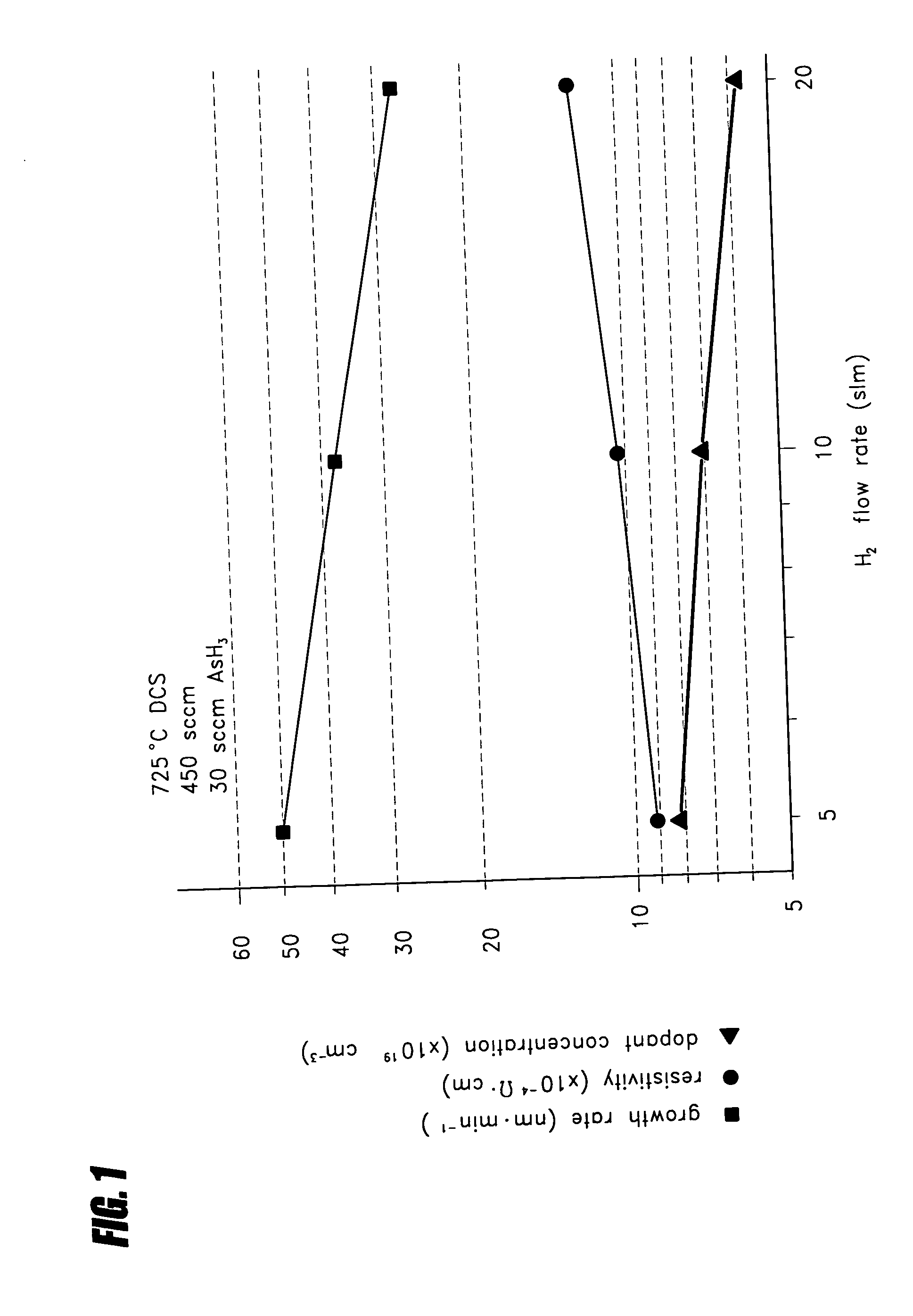

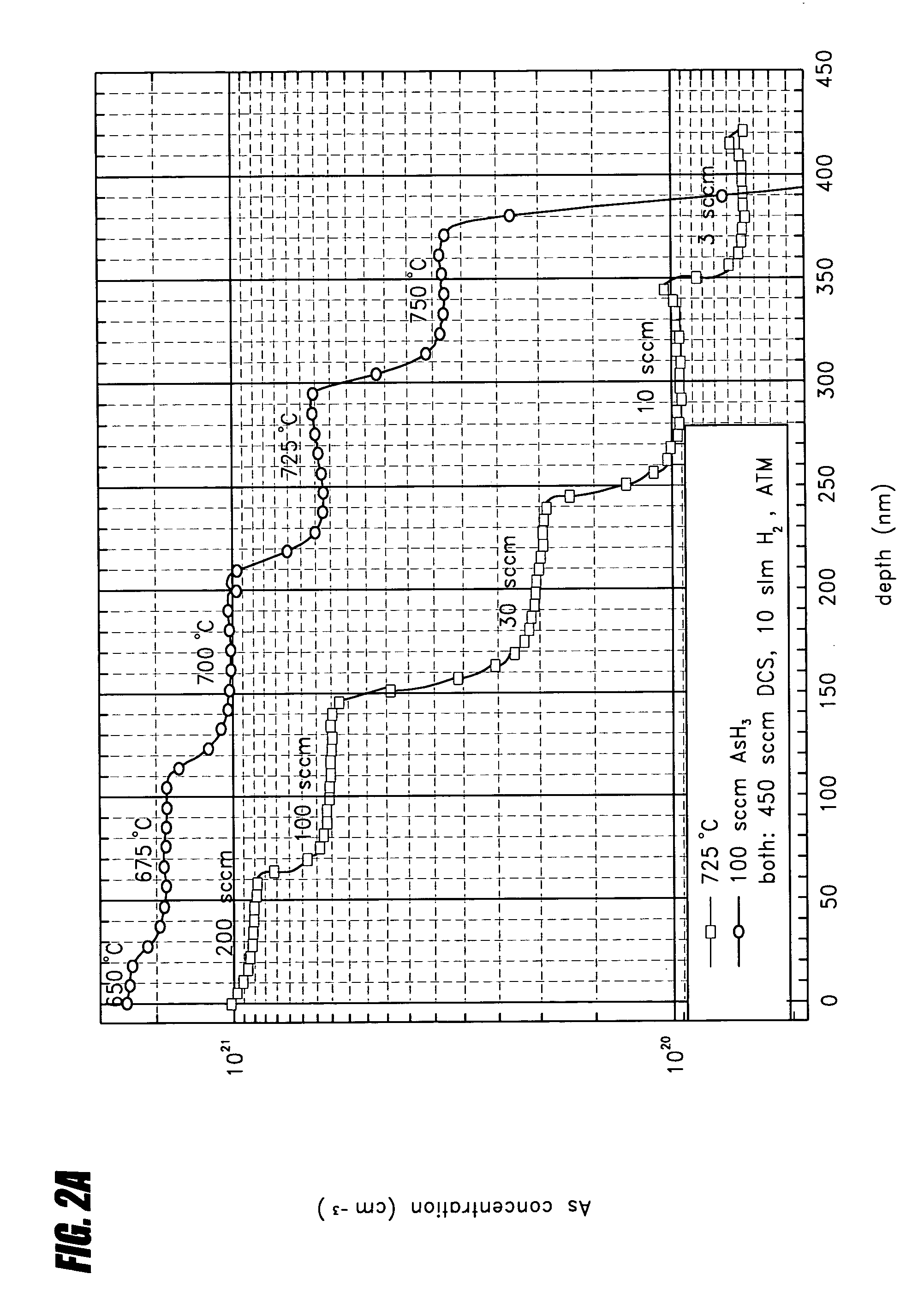

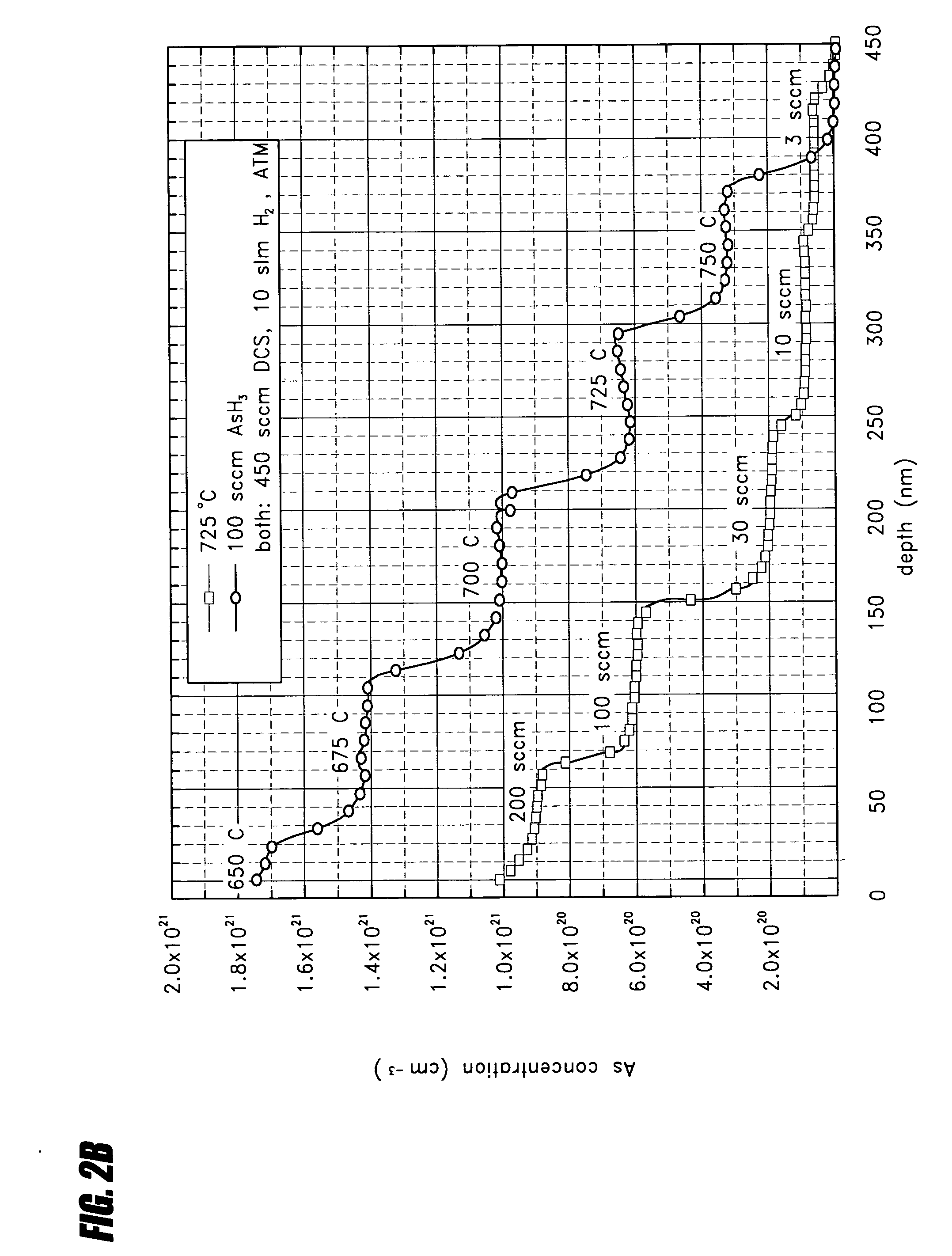

InactiveUS20050250298A1Slow deposition rateReduce the probability of depositionPolycrystalline material growthFrom solid stateDopantIn situ doping

A method for depositing an in situ doped epitaxial semiconductor layer comprises maintaining a pressure of greater than about 80 torr in a process chamber housing a patterned substrate. The method further comprises providing a flow of dichlorosilane to the process chamber. The method further comprises providing a flow of a dopant hydride to the process chamber. The method further comprises selectively depositing the epitaxial semiconductor layer on single crystal material on the patterned substrate at a rate of greater than about 3 nm min−1.

Owner:ASM AMERICA INC

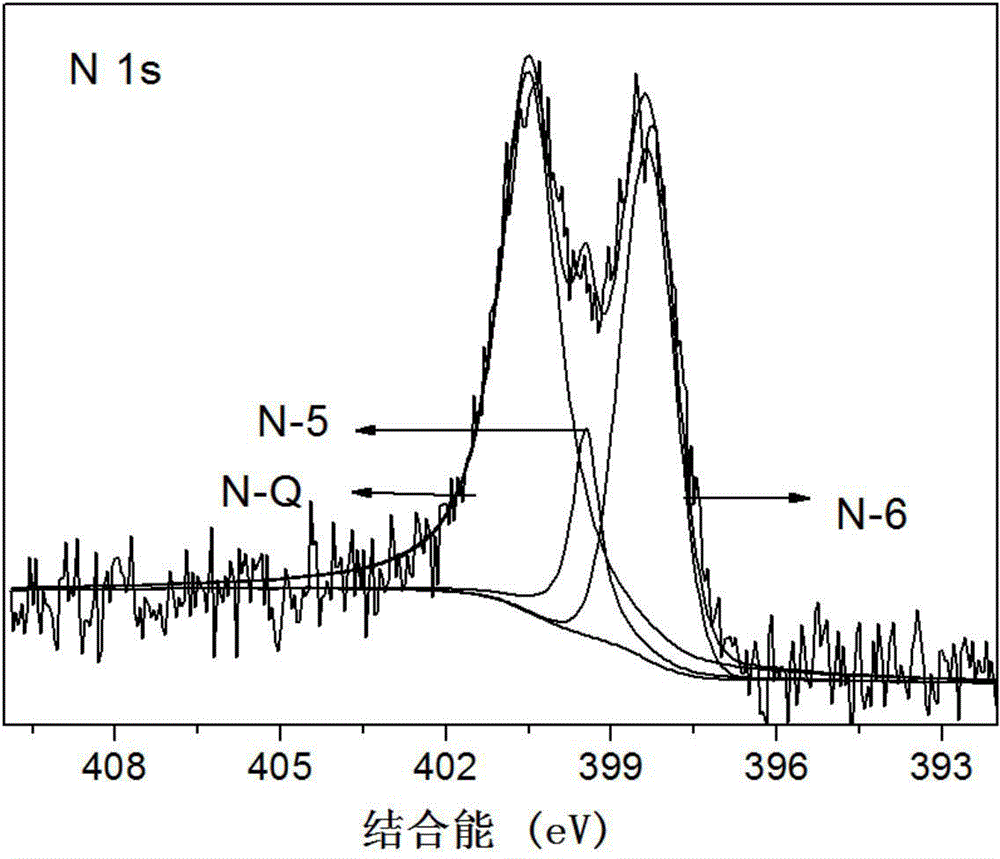

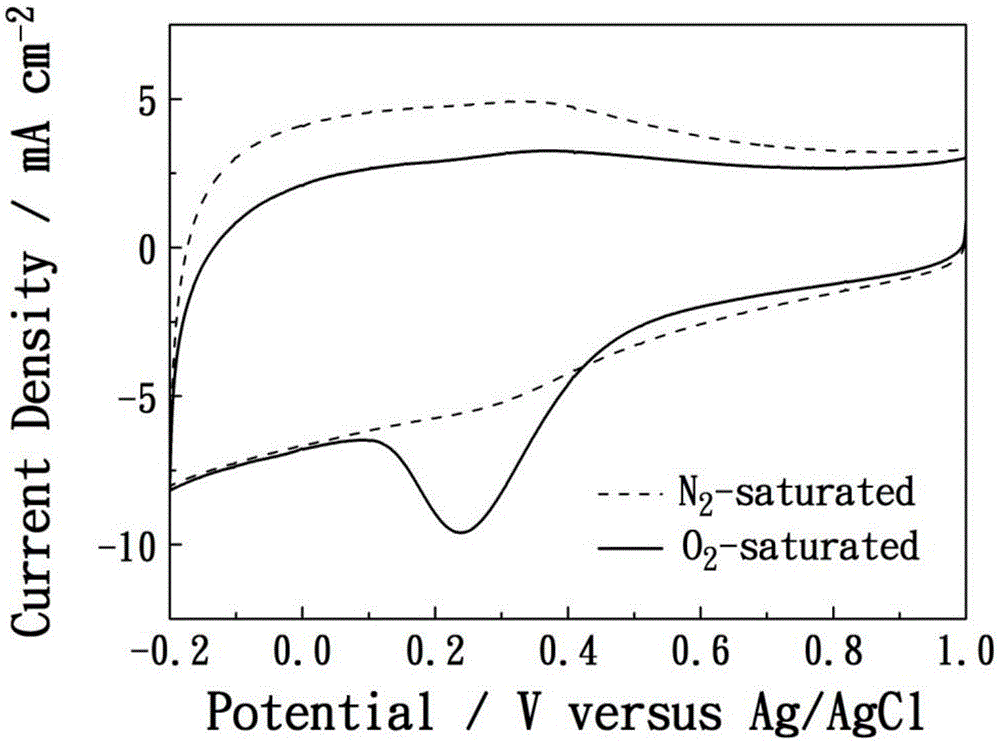

Nitrogen and phosphorus co-doped porous carbon catalyst and preparation method thereof

InactiveCN105457666AAperture controllableImprove adsorption capacityPhysical/chemical process catalystsCell electrodesPorous carbonAniline

The invention provides a preparation method and an application of a nitrogen and phosphorus co-doped porous carbon catalyst and belongs to the field of oxygen reduction catalysts for a fuel cell cathode. Nitrogen and phosphorus are introduced with an in-situ doping method, and the nitrogen and phosphorus doping amount is changed by adjusting the content of a nitrogen and phosphorus precursor. Besides, nitrogen and phosphorus co-doped porous carbon is prepared with a hard template method, and controllability of pore diameters of the porous carbon is realized by adjusting a hard template. The method comprises steps as follows: an earlier polymer of aniline monomers, a phosphorus precursor, a silica-based hard template and non-precious metal salt is prepared; the earlier polymer is calcined, and solids are obtained; the solids are etched, cleaned and dried, and the carbon material is obtained. More importantly, the prepared nitrogen and phosphorus co-doped porous carbon material has an excellent oxygen reduction electro-catalytic property under the acid condition and has huge application potential.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

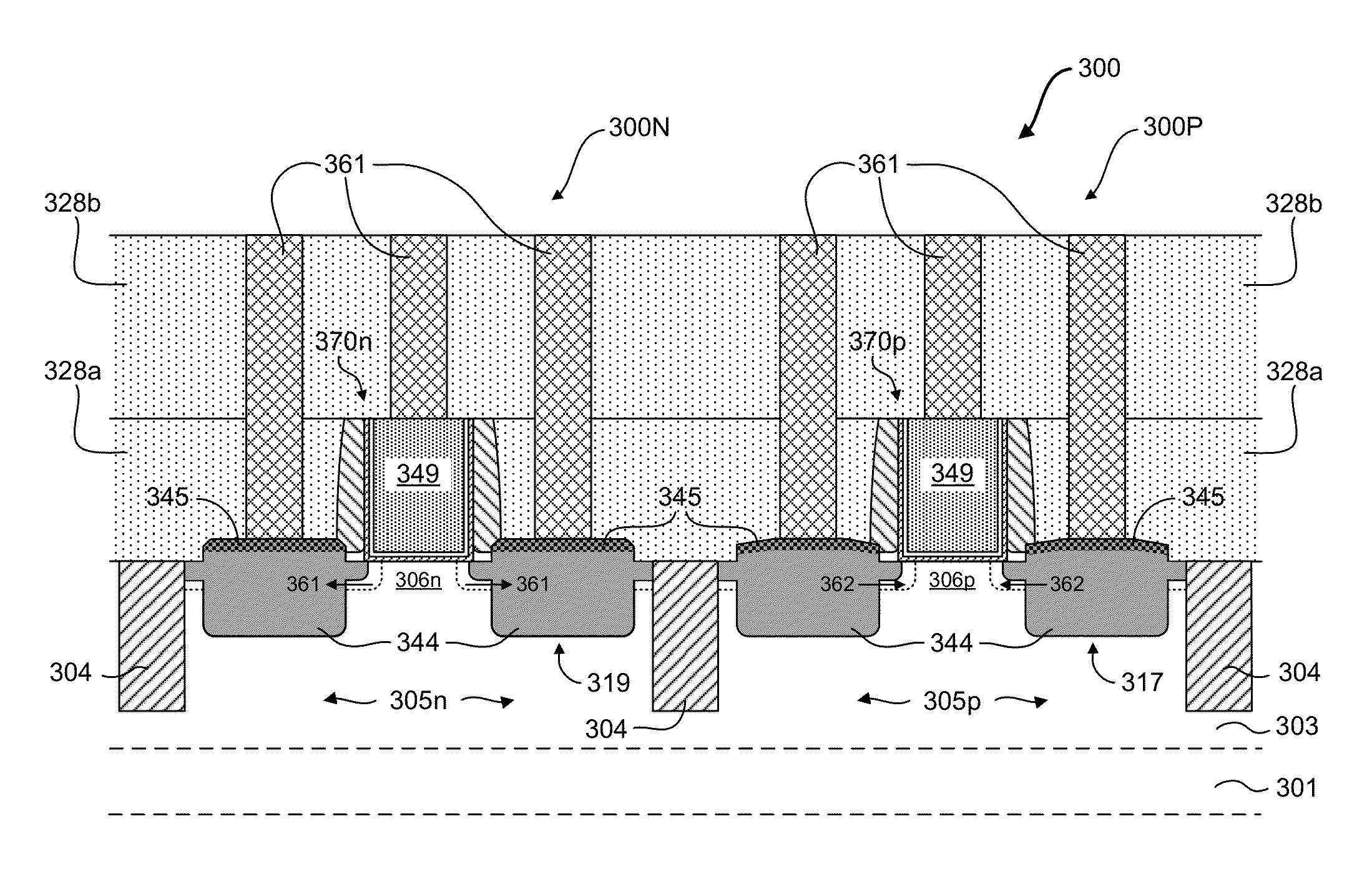

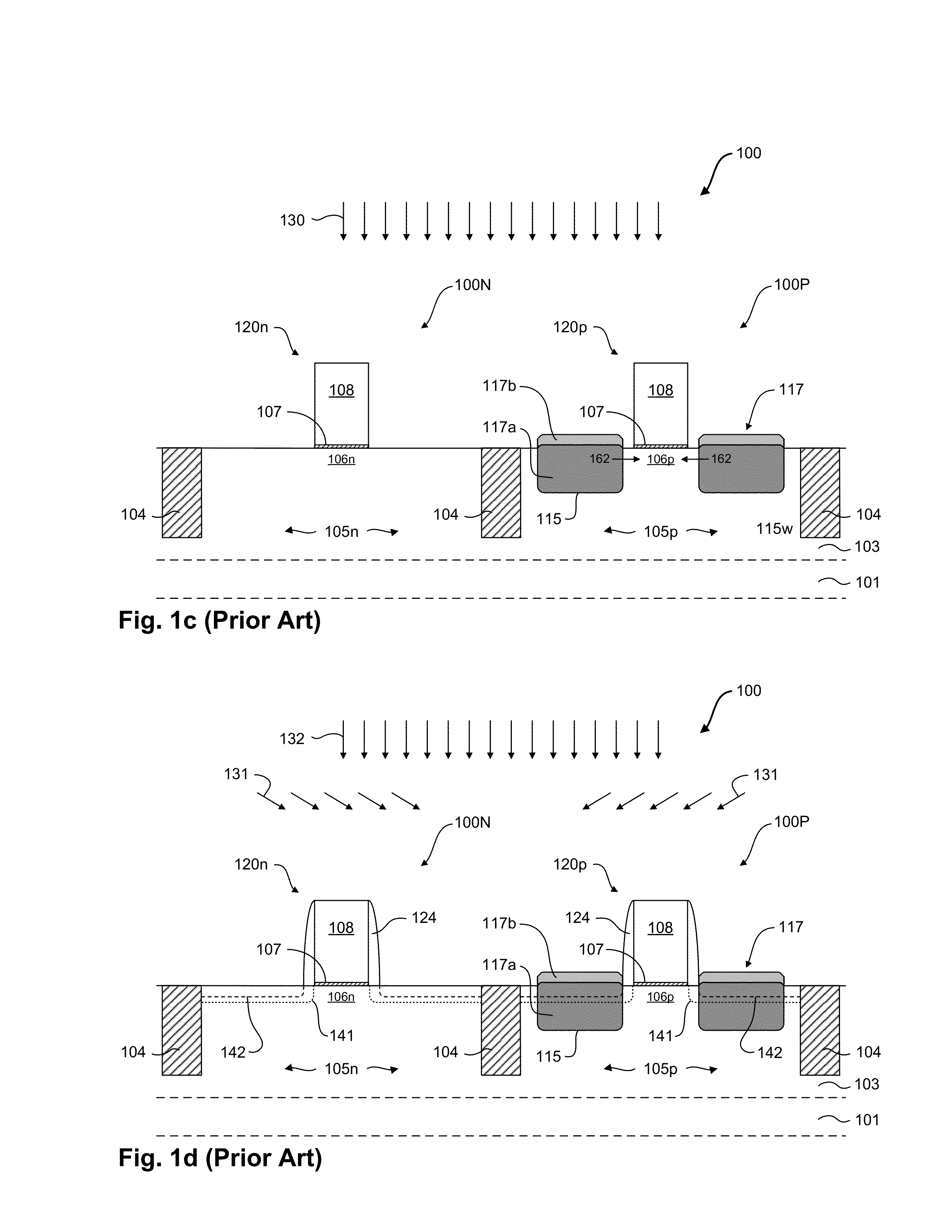

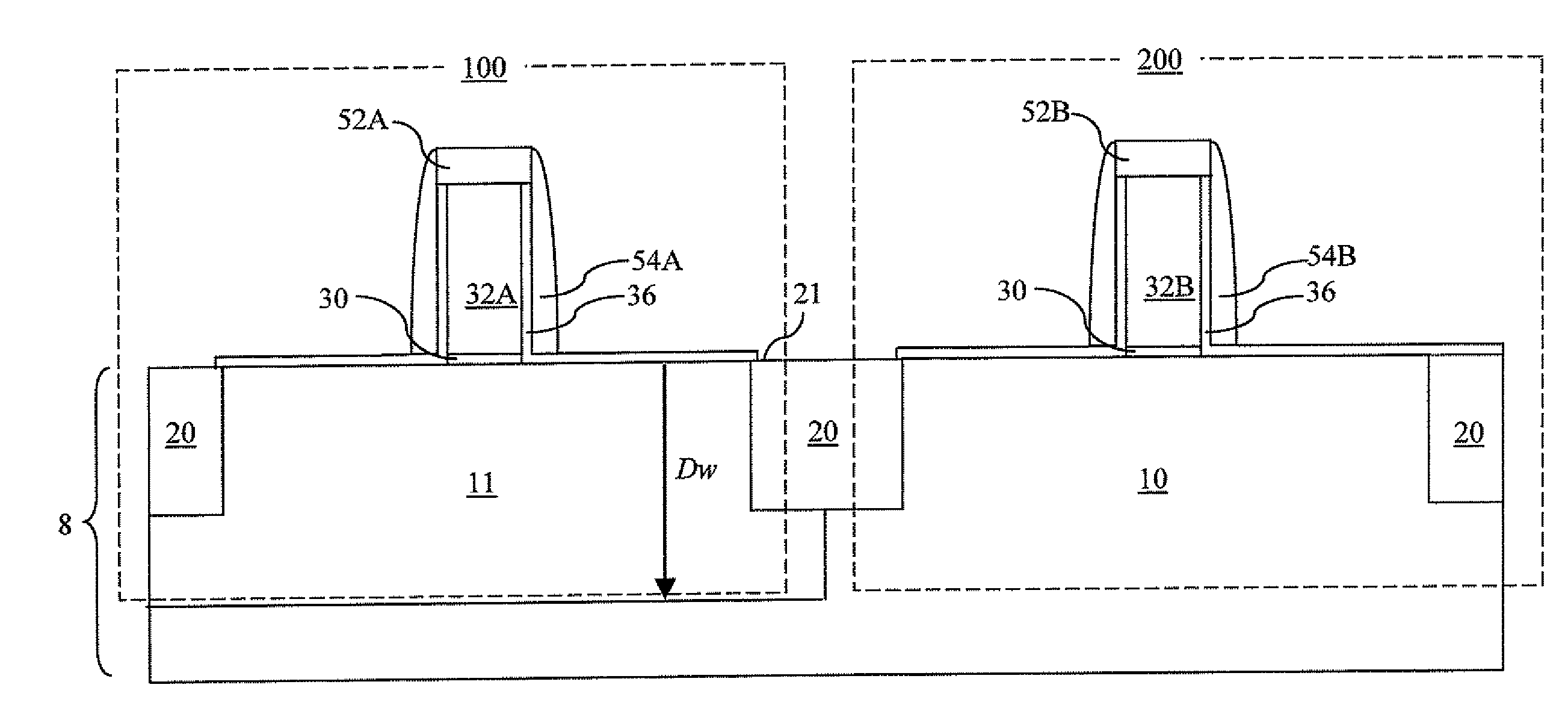

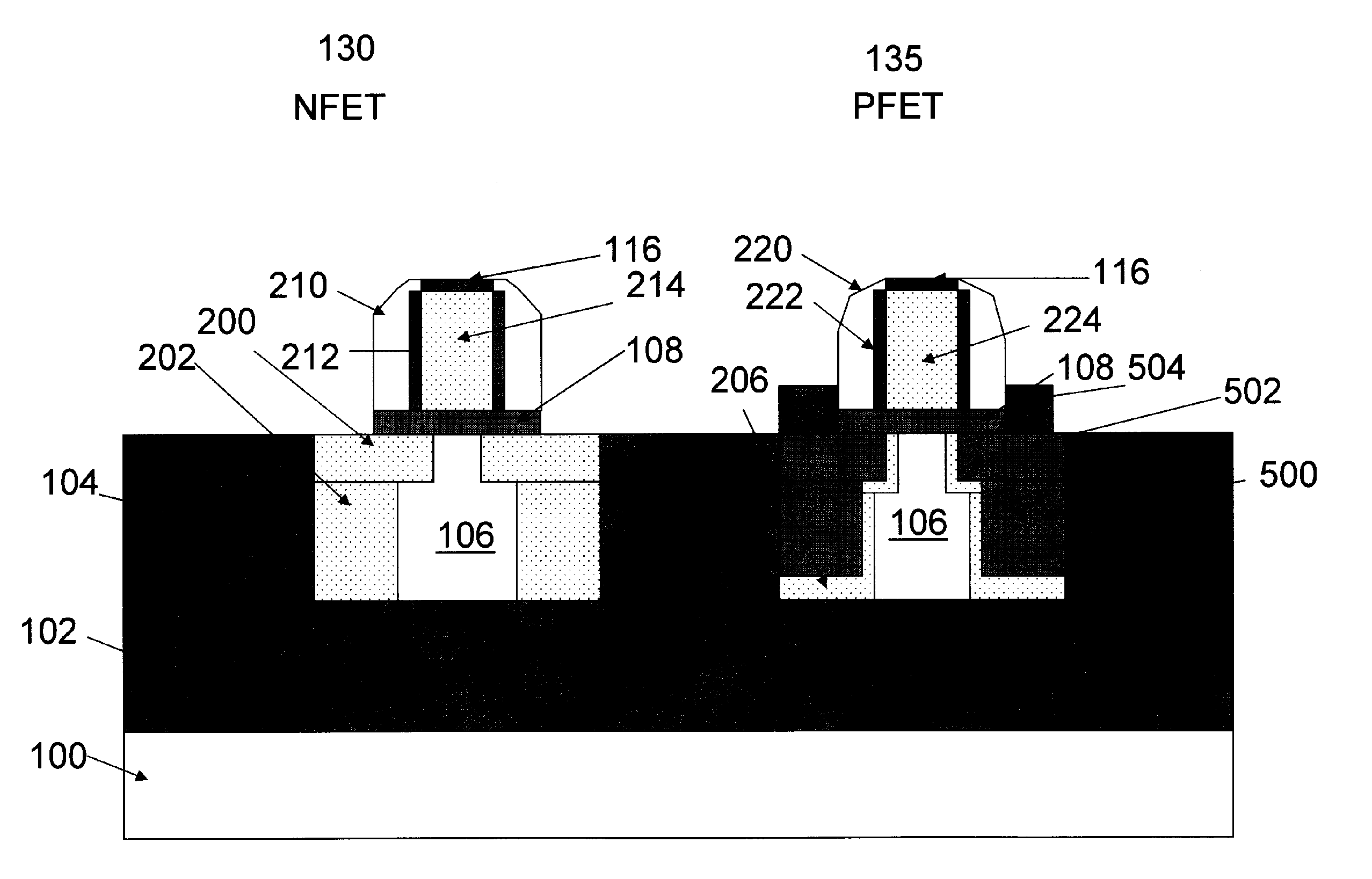

Local stress engineering for CMOS devices

A first dielectric layer is formed over a PFET gate and an NFET gate, and lithographically patterned to expose a PFET area, while covering an NFET area. Exposed PFET active area is etched and refilled with a SiGe alloy, which applies a uniaxial compressive stress to a PFET channel. A second dielectric layer is formed over the PFET gate and the NFET gate, and lithographically patterned to expose the NFET area, while covering the PFET area. Exposed NFET active area is etched and refilled with a silicon-carbon alloy, which applies a uniaxial tensile stress to an NFET channel. Dopants may be introduced into the SiGe and silicon-carbon regions by in-situ doping or by ion implantation.

Owner:GLOBALFOUNDRIES US INC

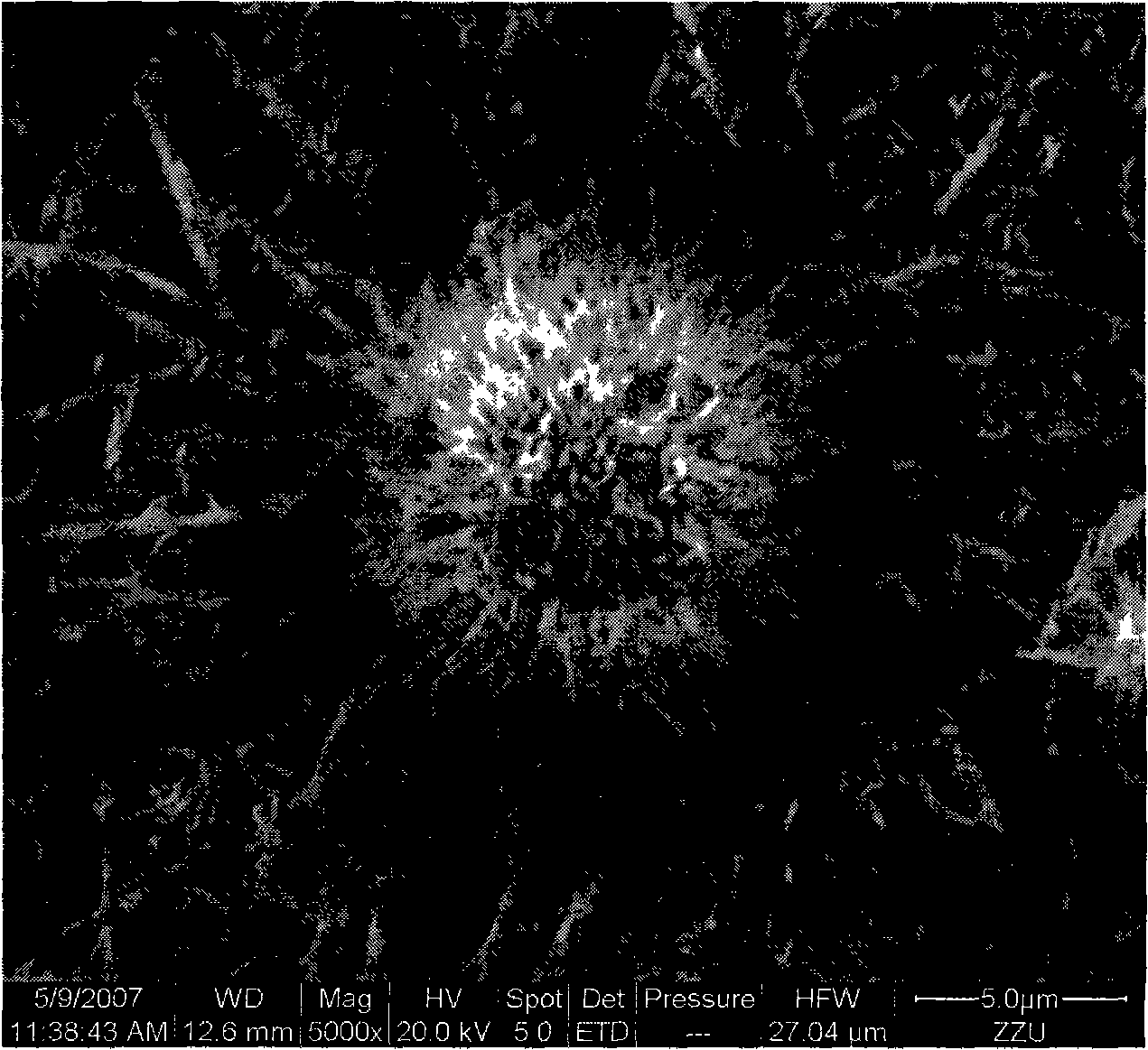

Preparation of nano-HAP coating/magnesium alloy composite biological material

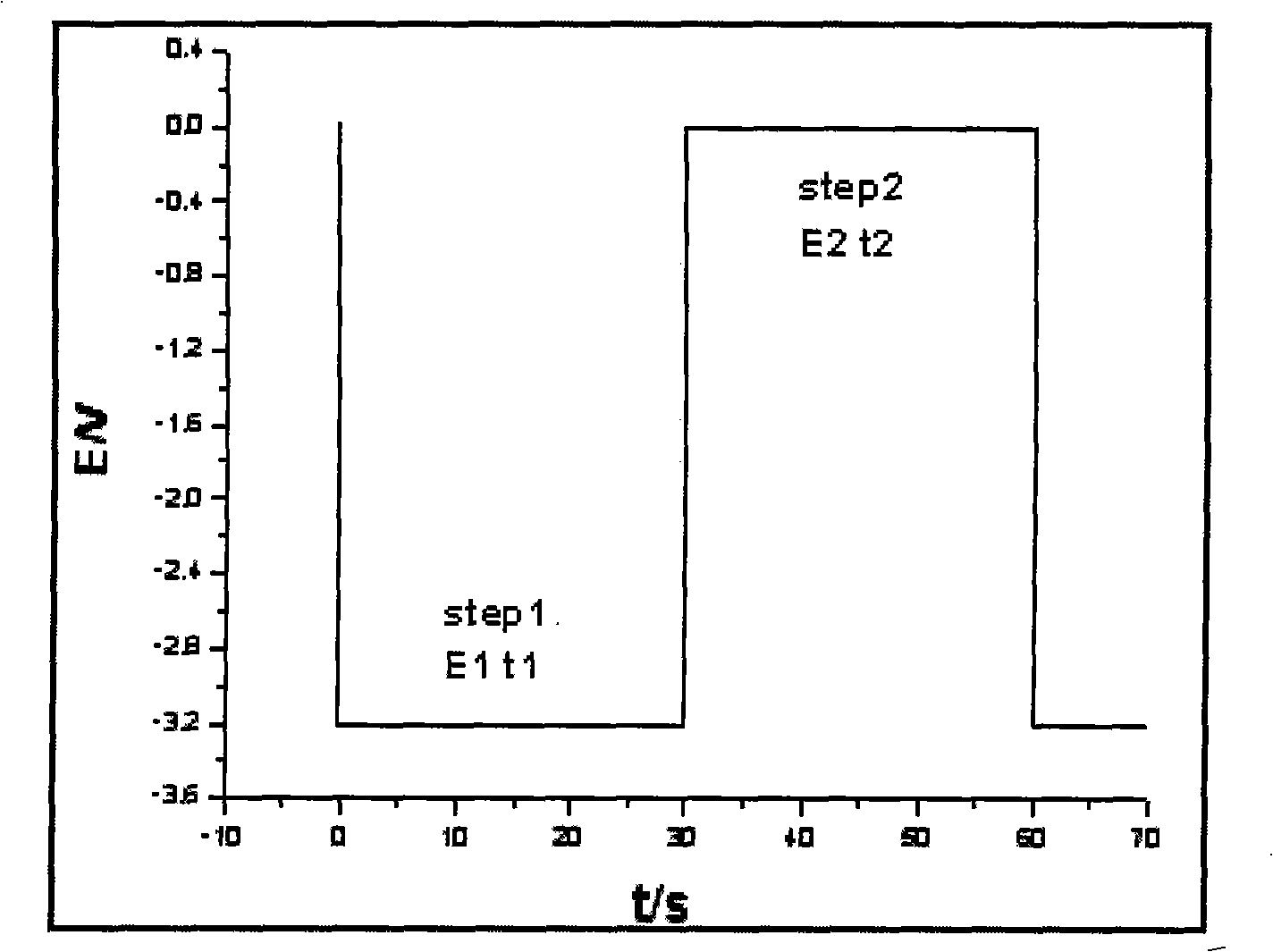

InactiveCN101302638AHigh bonding strengthImprove biological activityElectrolytic inorganic material coatingProsthesisMagnesium phosphateBiocompatibility Testing

The invention provides a method for making a nano HAP coating / magnesium alloy composite biomaterial. The method is as follows: the method takes a magnesium alloy as a cathode and graphite as an anode; the magnesium alloy and the graphite are placed in electrolyte containing NH4H2PO4, NaHO3 and Ca(OH3)2.4H2O so as to carry out stepped electrodeposition at a temperature of between 60 and 95 DEG C and a voltage of between minus 5 V to minus 1 V and 0 V, thereby effectively improving the interface bonding between a coating and a matrix and reducing hydrogen evolution during electrodeposition; meanwhile, the increase of magnesium ions at an interface can realize in-situ doping of magnesium ions and hydroxyapatite so as to generate a magnesium phosphate transition layer on the surface of the magnesium alloy and to increase bonding strength; thus, a degradable nano acicular hydroxyapatite / magnesium alloy coating composite biomaterial with excellent mechanical property, biocompatibility and corrosion resistance can be obtained. Meanwhile, the method also has the advantages of low cost of raw materials and simple technological operation, etc.

Owner:ZHENGZHOU UNIV

Semiconductor device and method for fabricating the same

InactiveUS20130069172A1Improve film qualityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesIn situ dopingStress relaxation

A semiconductor device and a method for fabricating the same are provided. The semiconductor device includes a gate structure, a source region and a drain region. The gate structure is disposed on a substrate. The source and drain regions disposed at respective sides of the gate structure include a boron-doped silicon germanium (SiGeB) layer substantially without stress relaxation. The boron-doped silicon germanium (SiGeB) layer has a germanium concentration greater than 30 at % and an in-situ doping concentration of boron ranging between 2.65×1020 / cm3 and 1×1021 / cm3.

Owner:UNITED MICROELECTRONICS CORP

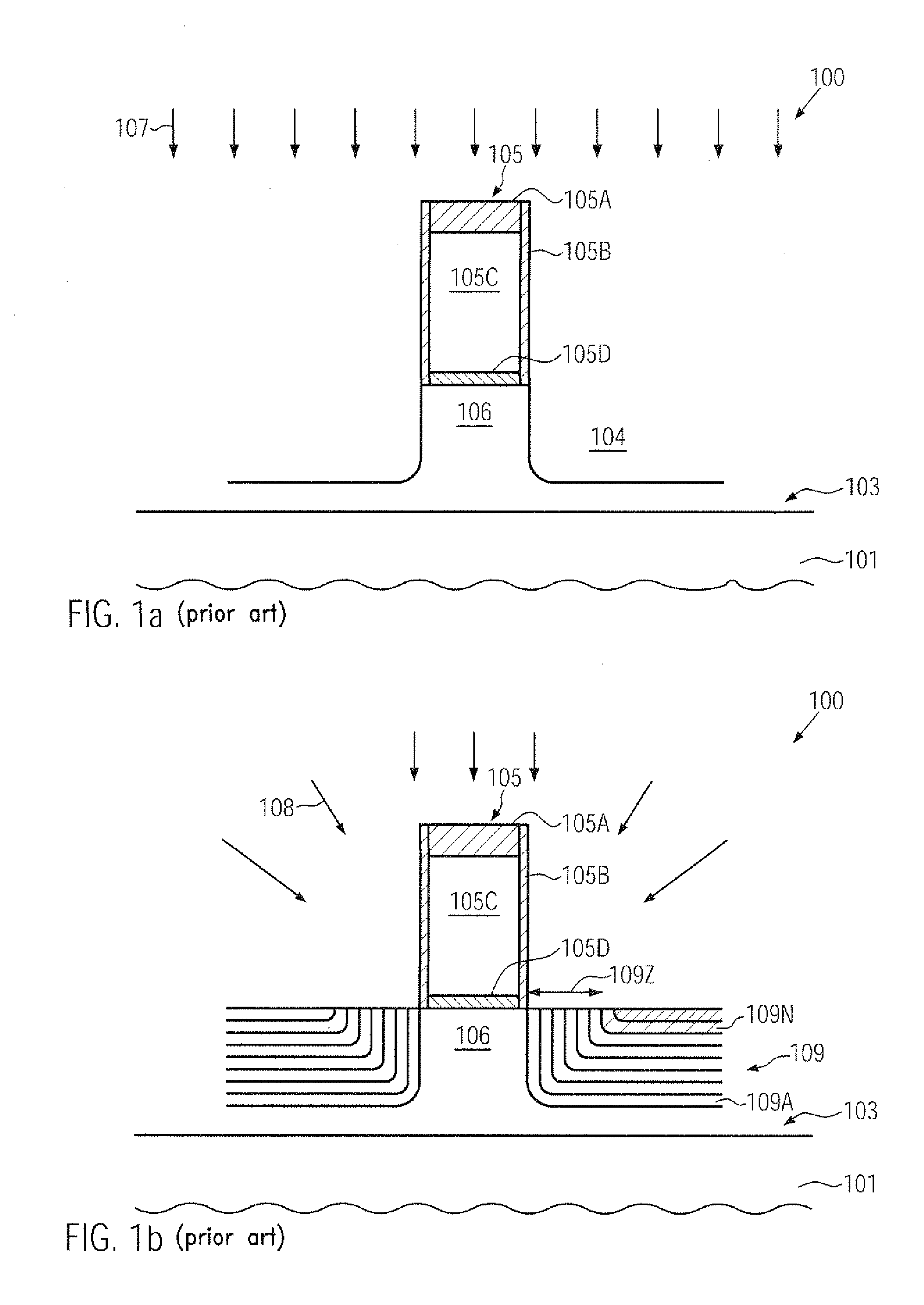

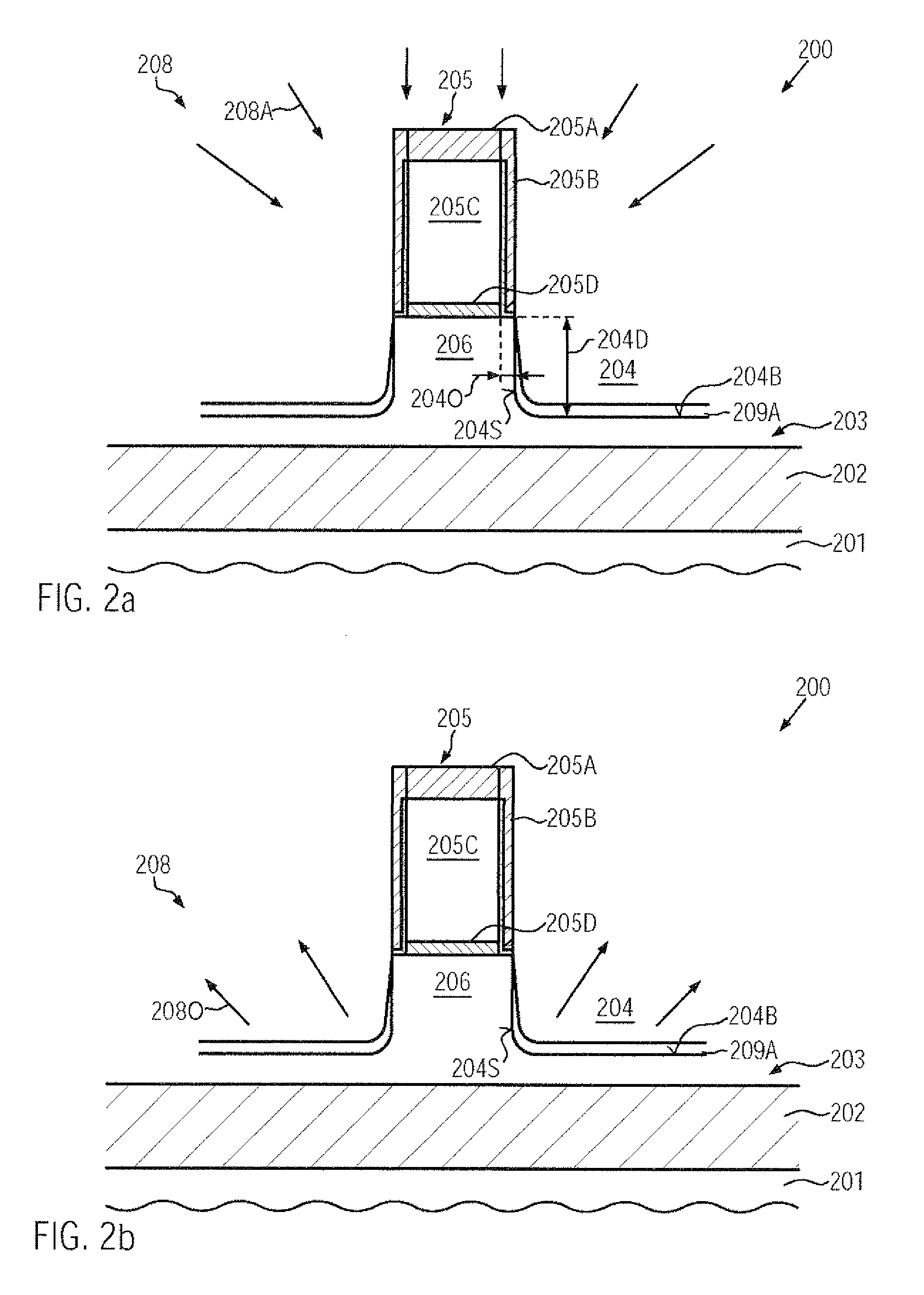

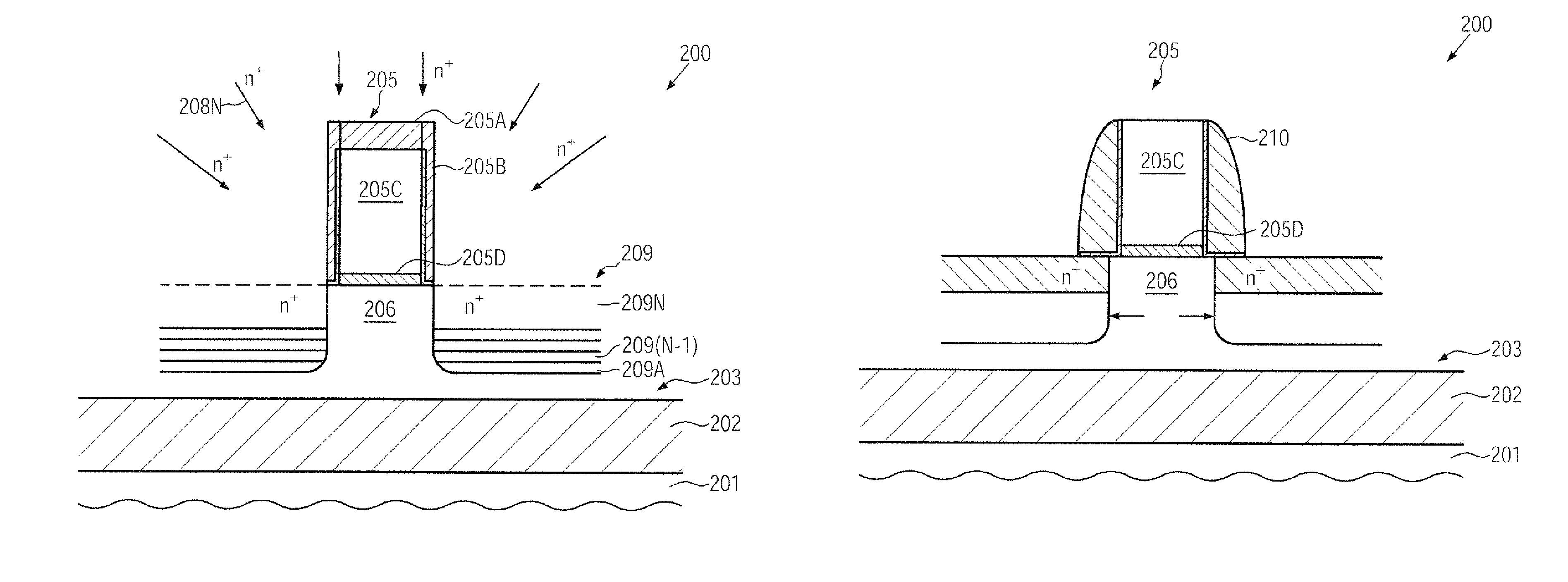

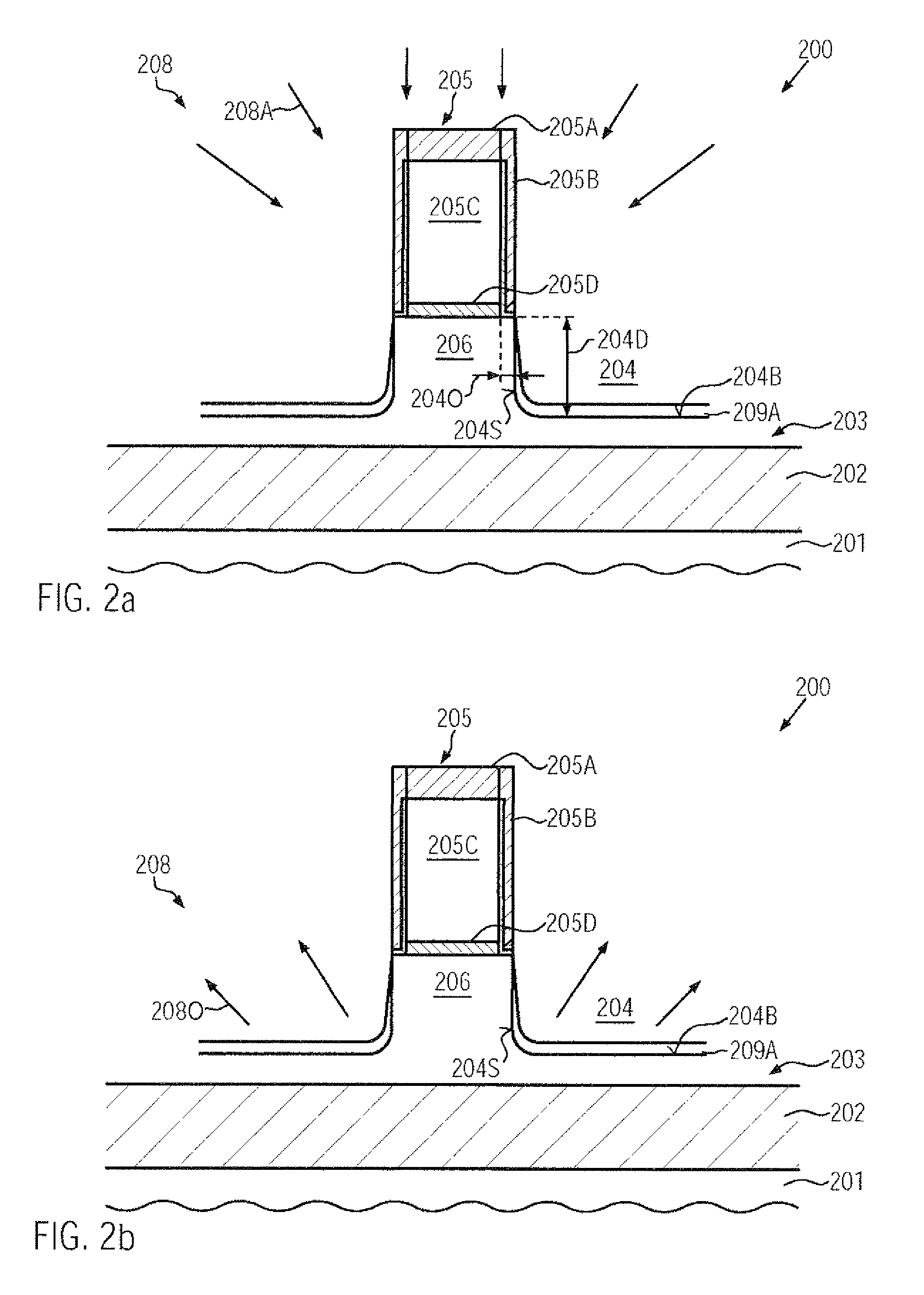

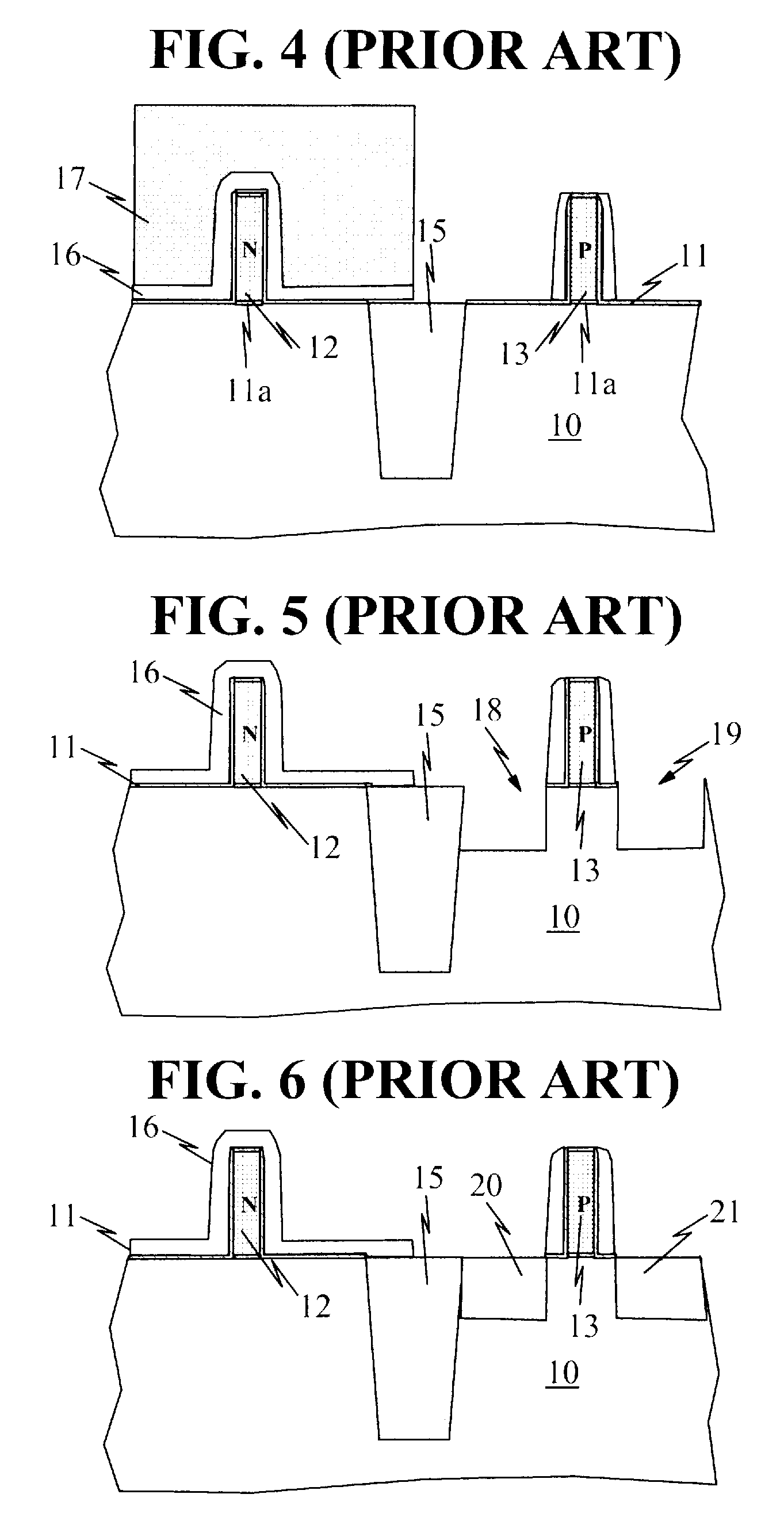

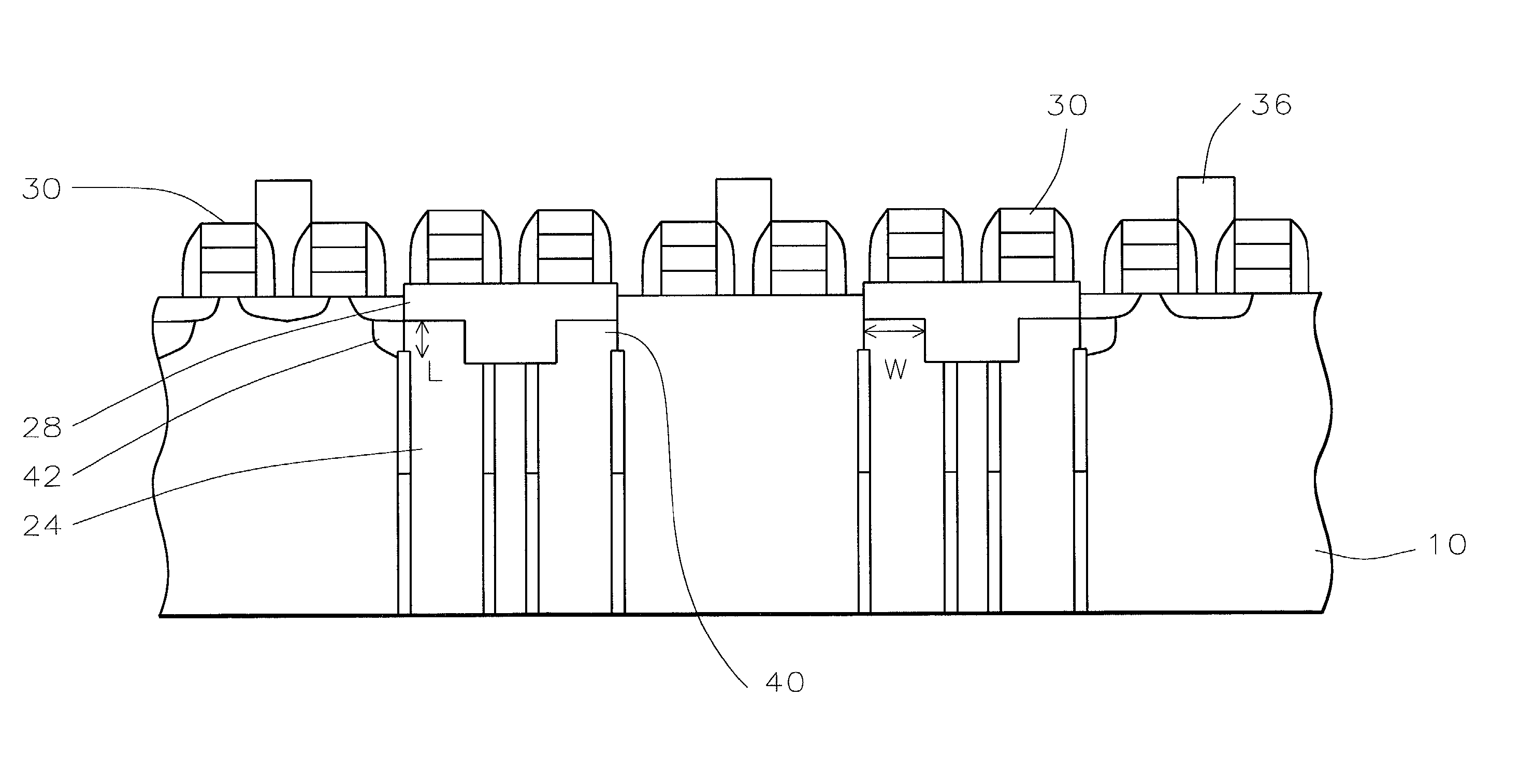

Shallow pn junction formed by in situ doping during selective growth of an embedded semiconductor alloy by a cyclic growth/etch deposition process

ActiveUS20100025779A1Increase strainImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingIn situ dopingUltra-high vacuum

A silicon / carbon alloy may be formed in drain and source regions, wherein another portion may be provided as an in situ doped material with a reduced offset with respect to the gate electrode material. For this purpose, in one illustrative embodiment, a cyclic epitaxial growth process including a plurality of growth / etch cycles may be used at low temperatures in an ultra-high vacuum ambient, thereby obtaining a substantially bottom to top fill behavior.

Owner:ADVANCED MICRO DEVICES INC

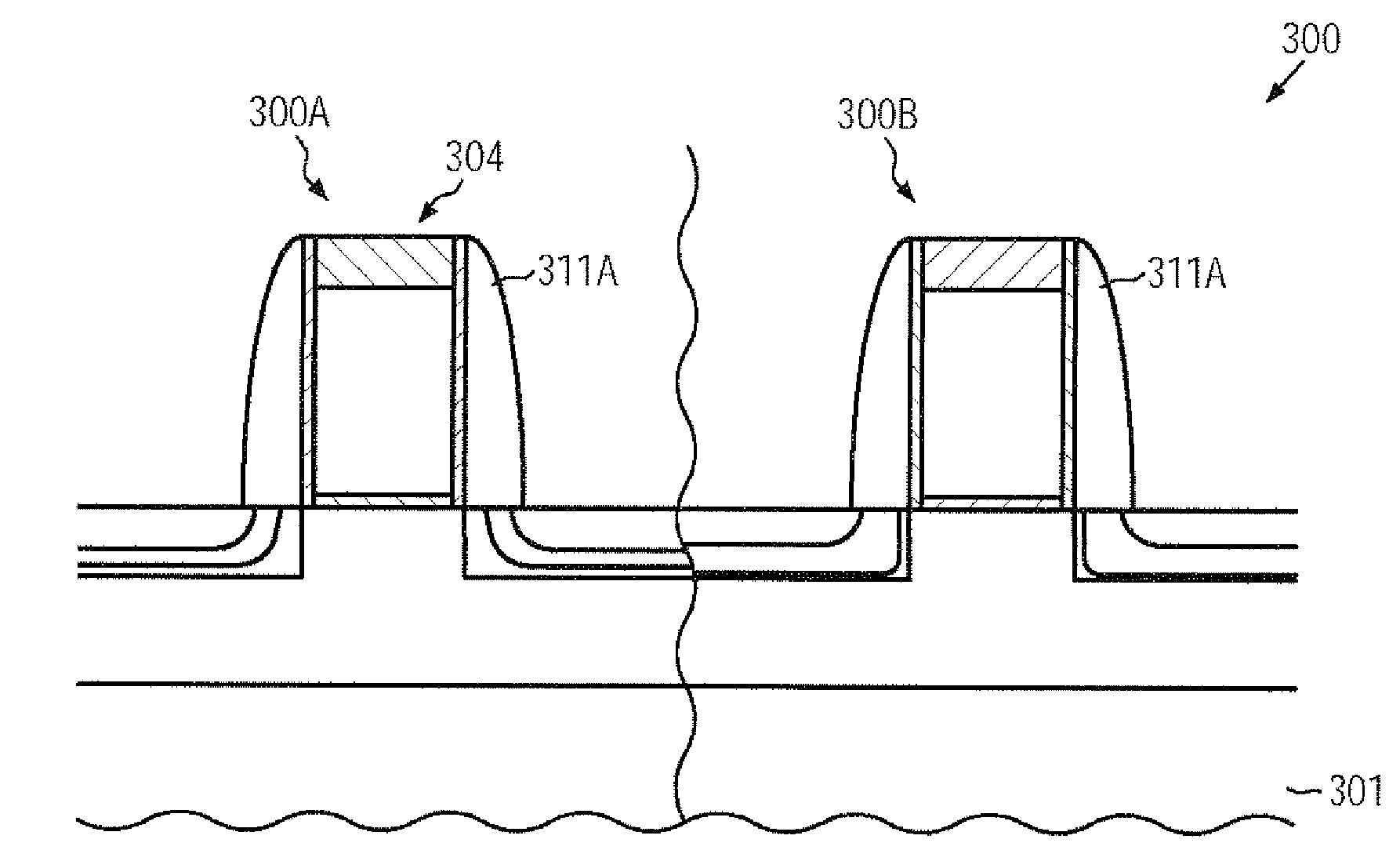

In situ formed drain and source regions in a silicon/germanium containing transistor device

By repeatedly applying a process sequence comprising an etch process and a selective epitaxial growth process during the formation of drain and source areas in a transistor device, highly complex dopant profiles may be generated on the basis of in situ doping. Further-more, a strain material may be provided while stress relaxation mechanisms may be reduced due to the absence of any implantation processes.

Owner:TAIWAN SEMICON MFG CO LTD

Shallow PN junction formed by in situ doping during selective growth of an embedded semiconductor alloy by a cyclic growth/etch deposition process

ActiveUS8053273B2Increase strainImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingIn situ dopingUltra-high vacuum

A silicon / carbon alloy may be formed in drain and source regions, wherein another portion may be provided as an in situ doped material with a reduced offset with respect to the gate electrode material. For this purpose, in one illustrative embodiment, a cyclic epitaxial growth process including a plurality of growth / etch cycles may be used at low temperatures in an ultra-high vacuum ambient, thereby obtaining a substantially bottom to top fill behavior.

Owner:ADVANCED MICRO DEVICES INC

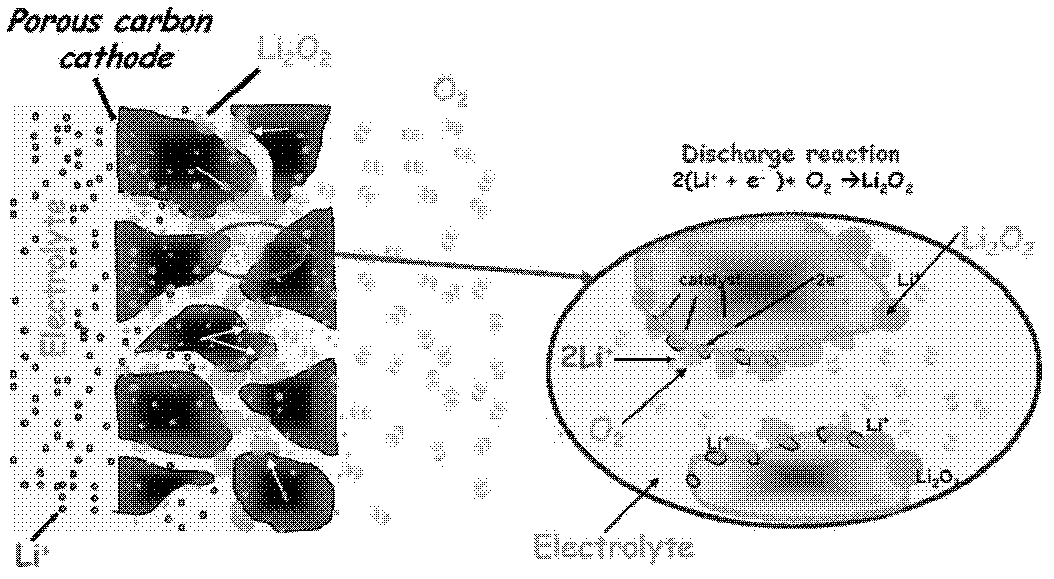

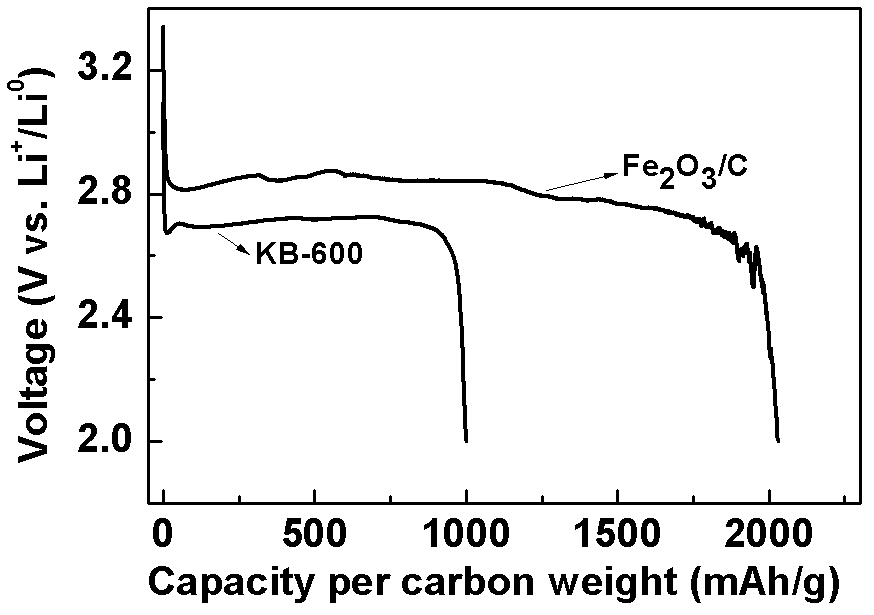

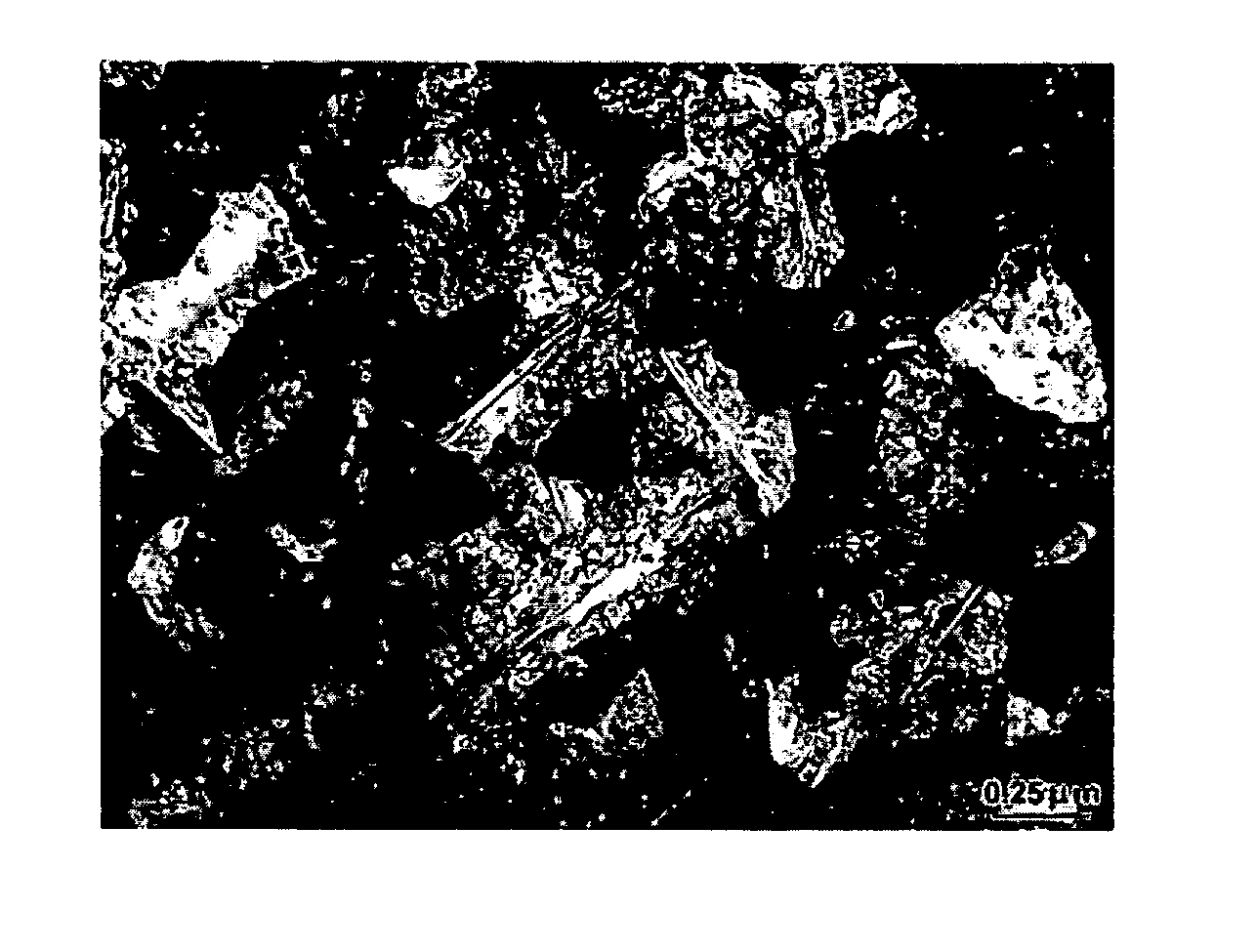

Application of carbon material containing in-situ doped component with catalytic activity to lithium-air battery

InactiveCN103050702AEvenly dispersedGood dispersionCell electrodesMetal/metal-oxides/metal-hydroxide catalystsIn situ dopingLithium–air battery

The invention relates to an application of a carbon material containing an in-situ doped component with catalytic activity to a lithium-air battery. The carbon material containing the in-situ doped component with catalytic activity is used as an electrode material in the lithium-air battery, the component with catalytic activity is doped in the carbon material in situ, and the component with catalytic activity is 1-80wt% of the carbon material. The component with catalytic activity is doped in situ in the preparation process of the carbon material and controllable in content, and the component with the catalytic activity is uniformly dispersed in the prepared carbon material, so that the dispersibility and coverage degree of the component with catalytic activity on the surface of the carbon material are greatly improved, the utilization ratio of the component with catalytic activity is increased in the charging and discharging processes, the discharging and discharging polarization potentials are reduced, and the energy efficiency of the lithium-air battery is increased.

Owner:DALIAN INST OF CHEM PHYSICS CHINESE ACAD OF SCI

Large-grain p-doped polysilicon films for use in thin film transistors

ActiveUS20060051911A1Semiconductor/solid-state device manufacturingSemiconductor devicesHydrogenIn situ doping

A method is disclosed to form a large-grain, lightly p-doped polysilicon film suitable for use as a channel region in thin film transistors. The film is preferably deposited lightly in situ doped with boron atoms by an LPCVD method at temperatures sufficiently low that the film is amorphous as deposited. After deposition, such a film contains an advantageous balance of boron, which promotes crystallization, and hydrogen, which retards crystallization. The film is then preferably crystallized by a low-temperature anneal at, for example, about 560 degrees for about twelve hours. Alternatively, crystallization may occur during an oxidation step performed, for example at about 825 degrees for about sixty seconds. The oxidation step forms a gate oxide for a thin film transistor device, for example a tunneling oxide for a SONOS memory thin film transistor device.

Owner:SANDISK TECH LLC

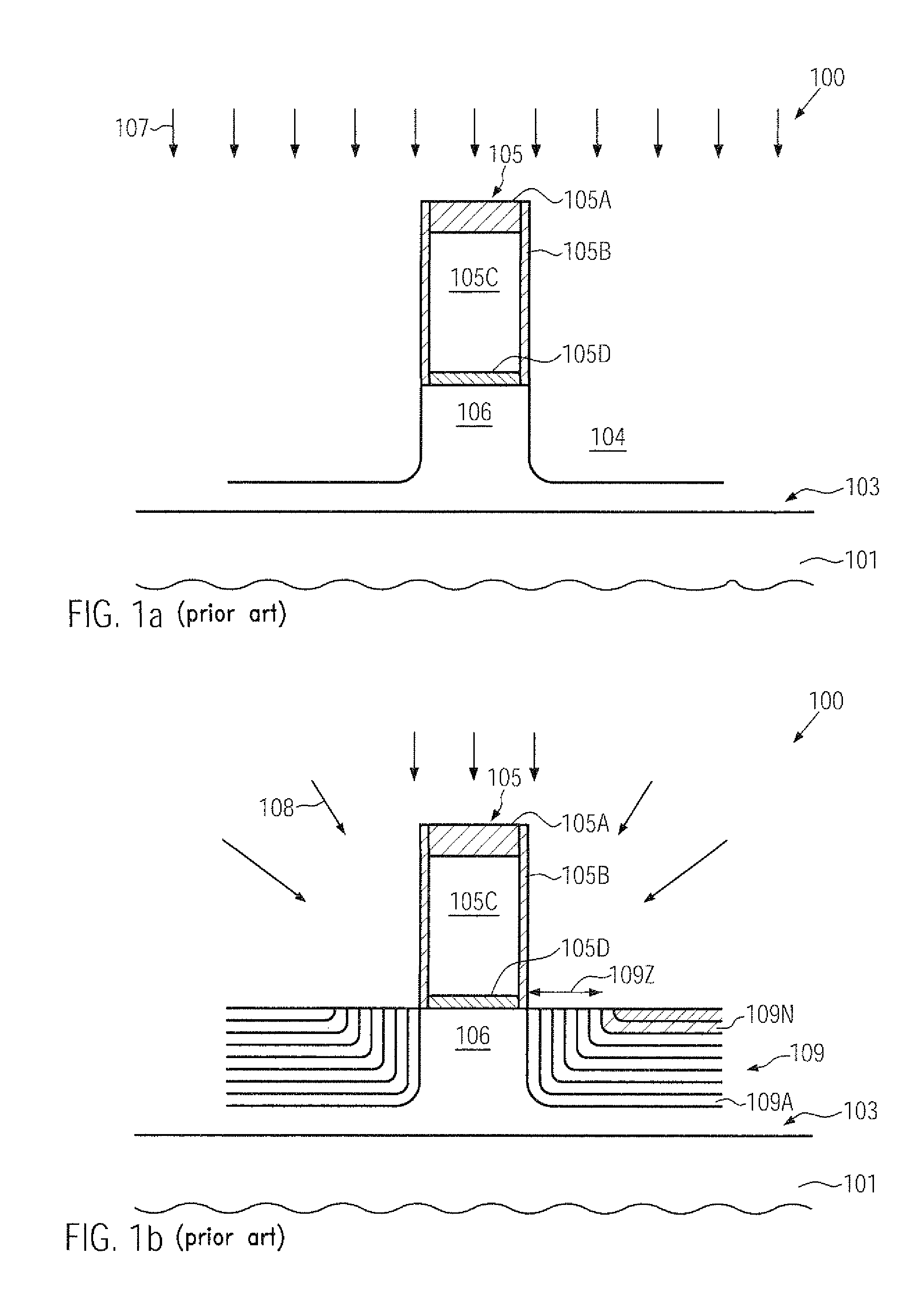

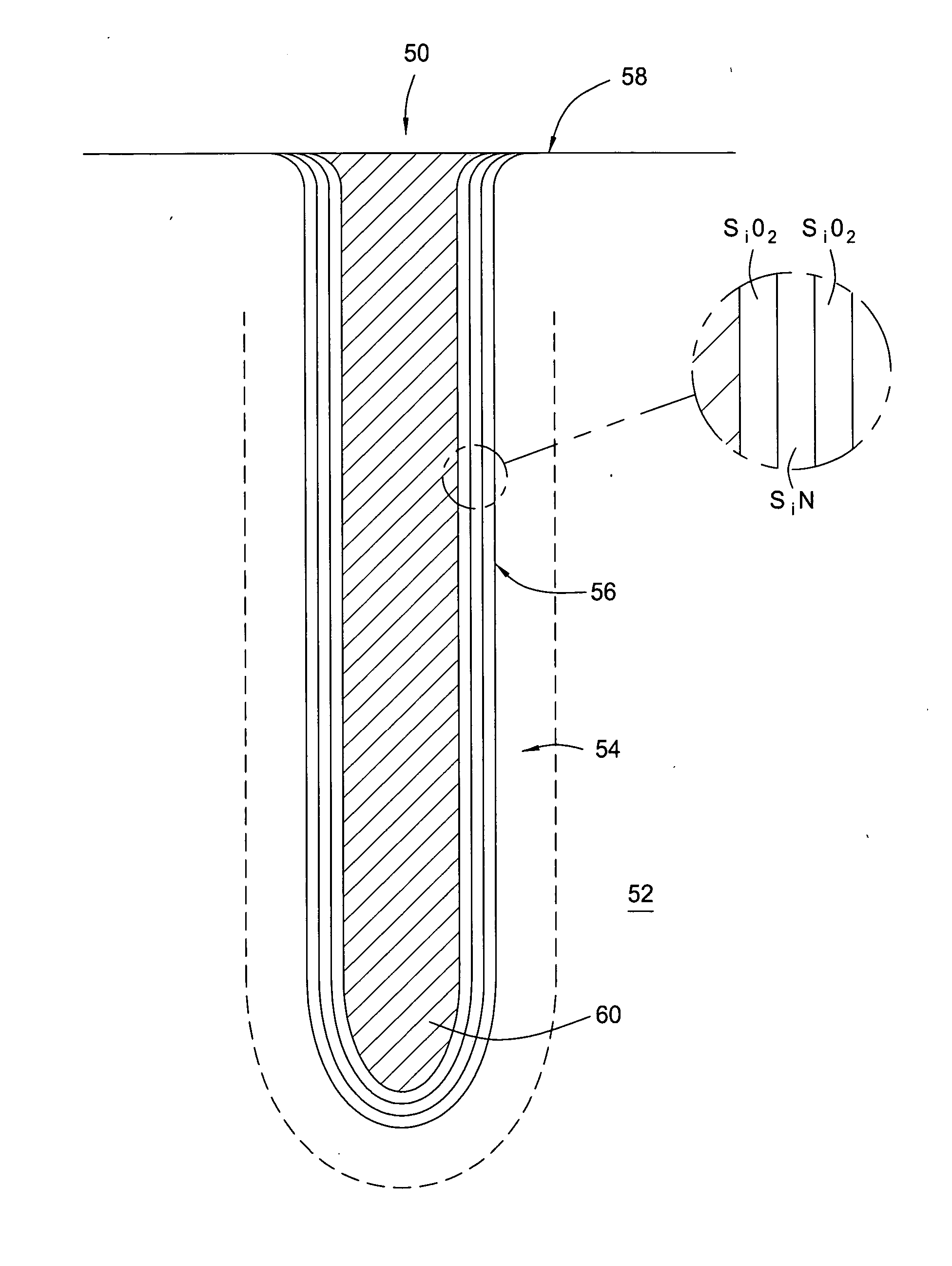

Process sequence for doped silicon fill of deep trenches

InactiveUS20060128139A1Increase deposition rateShort staySolid-state devicesSemiconductor/solid-state device manufacturingDopantFirst Fill

A method for void free filling with in-situ doped amorphous silicon of a deep trench structure is provided in which a first fill is carried out in at a temperature, pressure and dopant to silane ratio such that film deposition occurs from the bottom of the trench upwards. By way of this first fill, step coverages well in excess 100% are achieved. In the second fill step, deposition is carried out under changed conditions so as to reduce the impact of dopant on deposition rate, whereby trench fill is completed at a deposition rate which exceeds the deposition rate of the first fill. In an application of this method to the formation of deep trench capacitor structures, the intermediate steps further including the capping of the void free filled trench with a thick layer of amorphous silicon, planarization of the wafer thereafter, followed by a thermal anneal to re-distribute the dopant within the filled trench. Thereafter, additional steps can be performed to complete the formation of the capacitor structure.

Owner:APPLIED MATERIALS INC

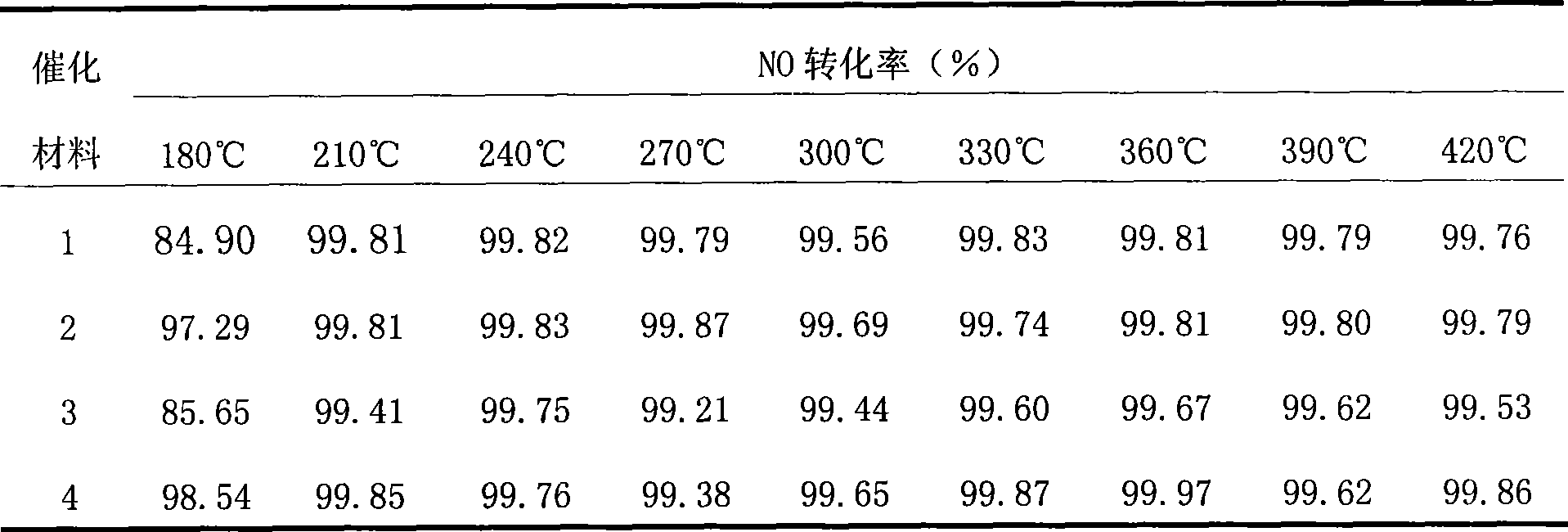

Vanadium-doped titanium-base flue gas denitration catalyst material and preparation method thereof

InactiveCN101480611ALarge specific surface areaImprove thermal stabilityDispersed particle separationCatalyst activation/preparationVanadium dopingActive agent

The invention relates to a vanadium doping type titanium base fume denitration catalytic material and a preparation method thereof. The material is characterized in that a surface active agent is used as a pore structure guiding agent, a water solution system sol-gel method is used for preparing the vanadium doping type titanium base catalytic material, and the doping content of active component vanadium is 0.5 to 20wt percent measured by V2O5. Because an in-situ doping loading mode is adopted in the sol-gel process, the preparation method is simple, and the production cost is low; in addition, the prepared denitration catalytic material has larger specific surface area, higher heat stability, higher denitration efficiency and wider active temperature window, and is suitable for the field of removal of coal-fired fume nitrogen oxide. The laboratory simulation fume evaluation shows that when the air speed is 10,000 / h, and under the condition that the content of NO is 1000ppm, the removal rate of NO achieves more than 95 percent at the temperature of 180 to 420 DEG C.

Owner:UNIV OF SCI & TECH BEIJING

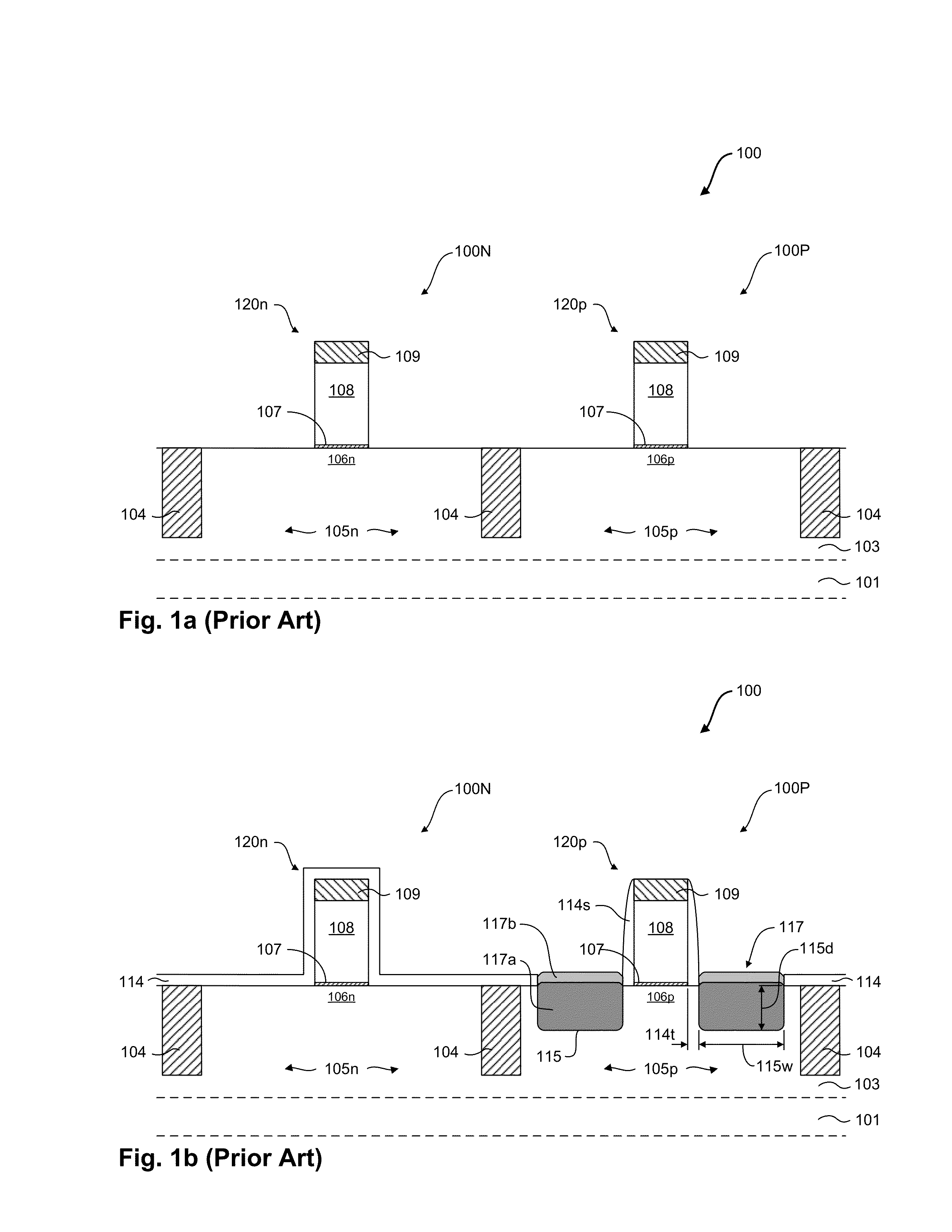

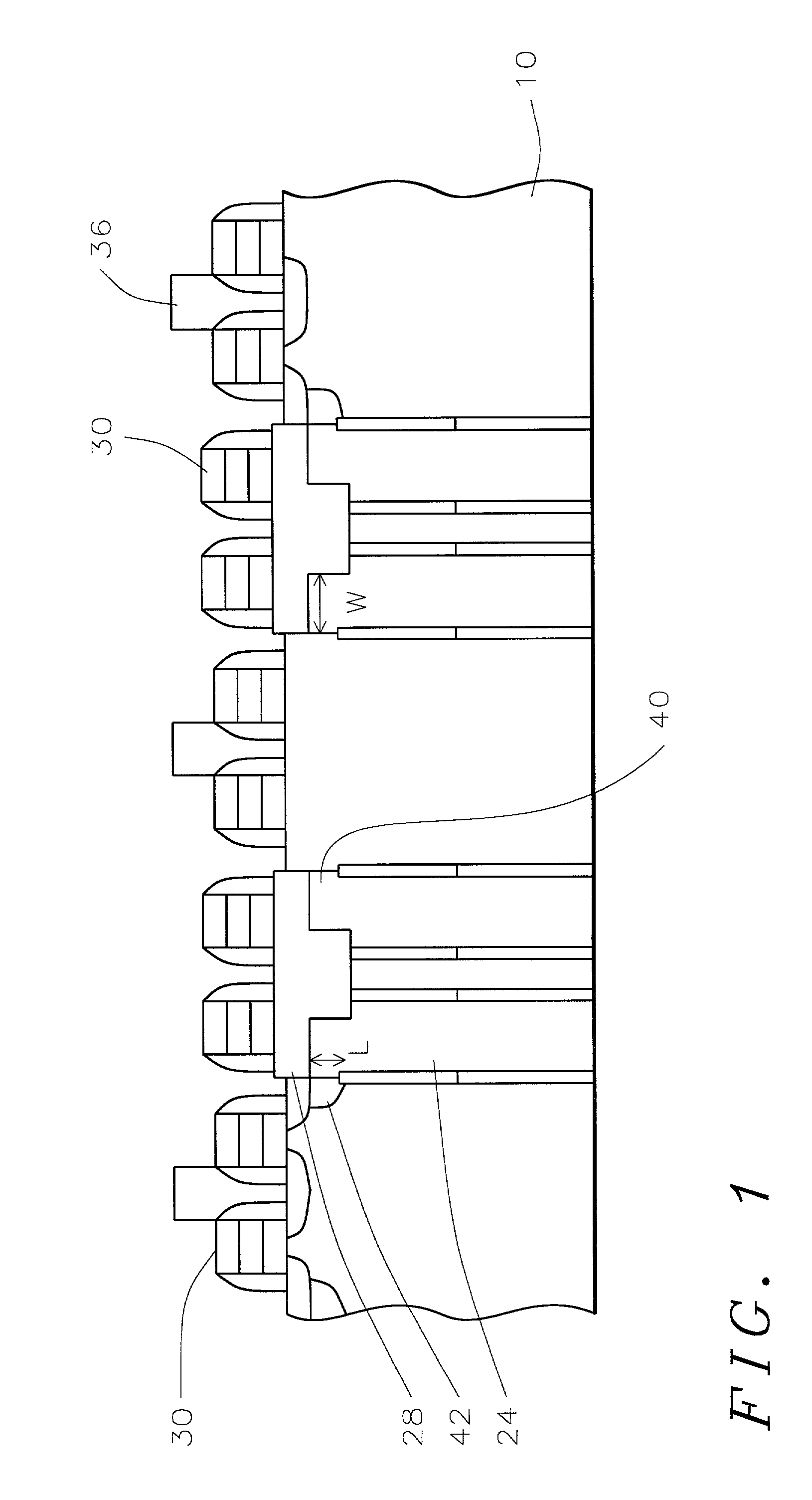

METHOD OF DOPING FIELD-EFFECT-TRANSISTORS (FETs) WITH REDUCED STRESS/STRAIN RELAXATION AND RESULTING FET DEVICES

InactiveUS20090001413A1Reducing stress/strain relaxationHigh activationSemiconductor/solid-state device manufacturingSemiconductor devicesDopantIn situ doping

A method for fabricating a FET transistor for an integrated circuit by the steps of forming recesses in a substrate on both sides of a gate on the substrate, halo / extension ion implanting into the recesses, and filling the recesses with embedded strained layers comprising dopants for in-situ doping of the source and drain of the transistor. The stress / strain relaxation of the resulting transistor is reduced.

Owner:GLOBALFOUNDRIES US INC

In situ doped embedded sige extension and source/drain for enhanced pfet performance

ActiveUS20060151837A1Growth inhibitionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIn situ doping

Disclosed is an integrated circuit structure and a method of making such a structure that has a substrate and P-type and N-type transistors on the substrate. The N-type transistor extension and source / drain regions comprise dopants implanted into the substrate. The P-type transistor extension and source / drain regions partially include a strained epitaxial silicon germanium, wherein the strained silicon germanium comprises of two layers, with a top layer that is closer to the gate stack than the bottom layer. The strained silicon germanium is in-situ doped and creates longitudinal stress on the channel region.

Owner:MICROSOFT TECH LICENSING LLC

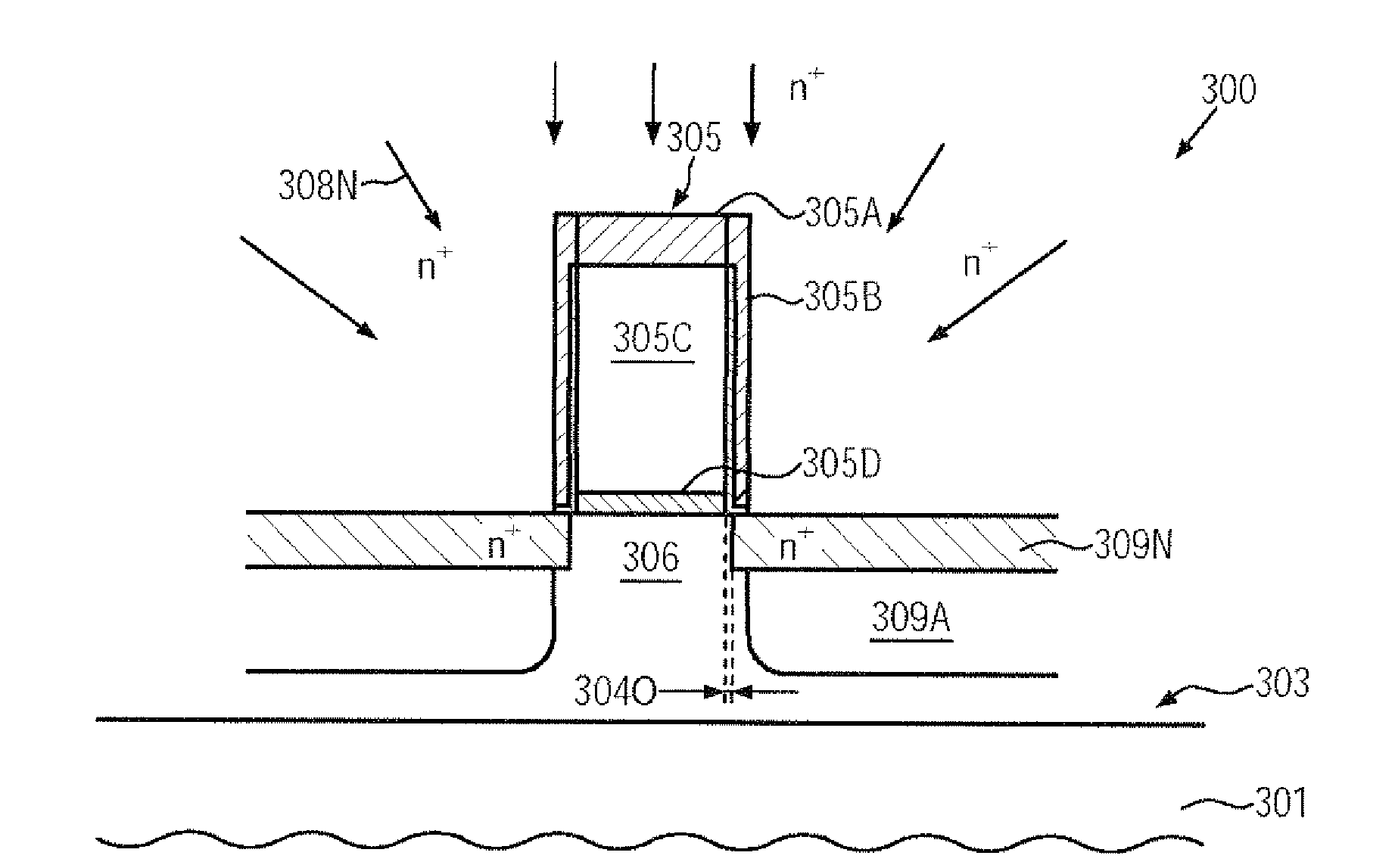

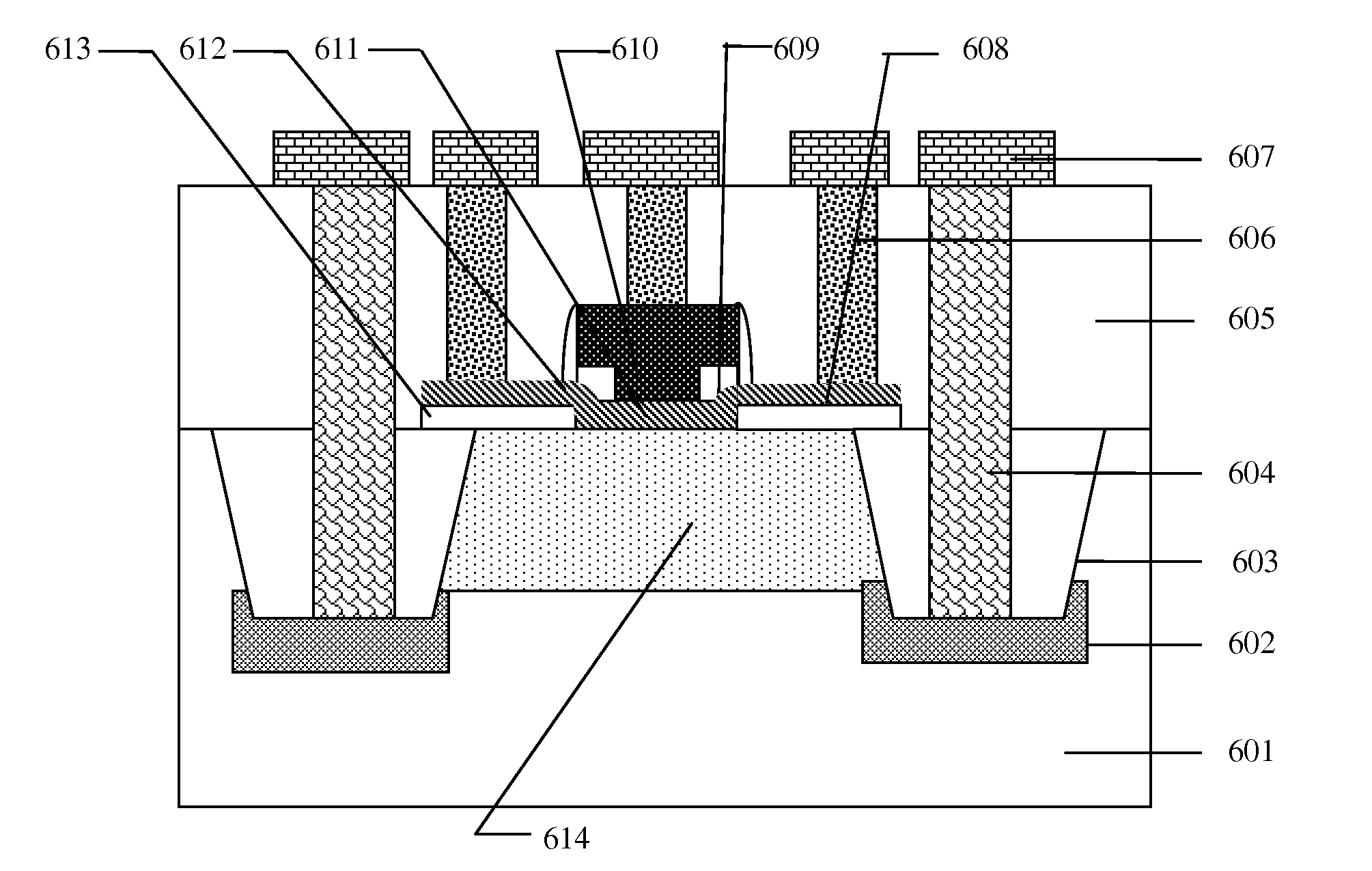

High Voltage Bipolar Transistor with Pseudo Buried Layers

ActiveUS20110140239A1Low costImprove breakdown voltageTransistorSemiconductor/solid-state device manufacturingHigh dosesEngineering

A high voltage bipolar transistor with shallow trench isolation (STI) comprises the areas of a collector formed by implanting first electric type impurities into active area and connected with pseudo buried layers at two sides; Pseudo buried layers which are formed by implanting high dose first type impurity through the bottoms of STI at two sides if active area, and do not touch directly; deep contact through field oxide to contact pseudo buried layers and pick up the collectors; a base deposited on the collector by epitaxial growth and in-situ doped by second electric type impurity, in which the intrinsic base touches local collector and extrinsic base is used for base pick-up; a emitter which is a polysilicon layer deposited on the intrinsic base and doped with first electric type impurities. This invention makes the depletion region of collector / base junction from 1D (vertical) distribution to 2D (vertical and lateral) distribution. The bipolar transistor's breakdown voltages are increased by only enlarge active critical dimension (CD). This is low-cost process.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Buried strap formation method for sub-150 nm best DRAM devices

InactiveUS20030109140A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

An improved buried strap method in the fabrication of a DRAM integrated circuit device is described. A deep trench is etched into a substrate. A collar is formed on an upper portion of the deep trench. A buried plate is formed by doping around a lower portion of the deep trench and a capacitor dielectric layer is formed within the deep trench. The deep trench is filled with a silicon layer wherein the silicon layer forms a deep trench capacitor and covers the collar. The silicon layer is recessed below a top surface of the substrate to leave a recess. A top portion of the collar is etched away to leave a collar divot. A hemispherical grain polysilicon layer is selectively deposited into the deep trench and filling the collar divot. The HSG layer is doped in-situ or by post plasma doping. The doped hemispherical grain polysilicon layer forms a buried strap in the fabrication of a deep trench DRAM integrated circuit device.

Owner:CHANG LIAO HLDG

Process for manufacture of proton conductive polymer gel useful as backfill for sacrificial and impressed current anode systems

InactiveUS20040186221A1Conveniently insertedImprove efficiencyEmulsion paintsPolymer scienceConductive polymer

The process of the present invention provides for the manufacture of a novel proton conductive polymer gel useful as backfill for sacrificial and impressed current anode systems The process of the present invention is carried out in aqueous phase thus providing a cheaper option besides the use of ingredients readily available in the international markets. The polymer used as backfill is transformed into a proton conducting form in the gelated network through an in-situ doping process during gelation. The gel product produced can be sliced to sheet of any desired size suitable and compatible to concrete or soil medium. The novelty of the product of the present invention is that it can be used as backfill between any anode such as sacrificial or impressed current mode and is adaptable to the concrete surface both in the presence of moisture or absence of moisture, which is not hitherto been achieved in prior art. Further, the specialty of the utility of this product, is its compatibility with all the sacrificial anodes such Mg, Al, Zn which is not hitherto been realized with any of the earlier chemical backfill known for this application.

Owner:COUNCIL OF SCI & IND RES

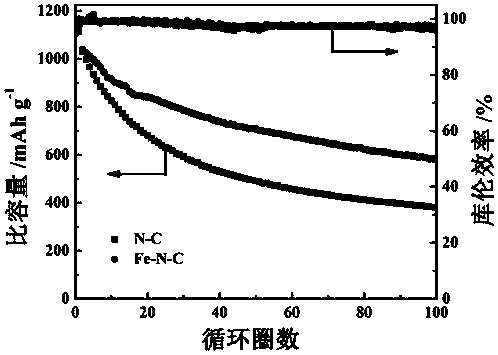

Lithium sulfur battery anode material and lithium sulfur battery utilizing same

InactiveCN107768638AInhibit shuttleImprove performanceCell electrodesLi-accumulatorsArgon atmospherePorous carbon

The invention discloses a lithium sulfur battery anode material and a lithium sulfur battery utilizing same. By adopting an in-situ doping method, iron and nitrogen are jointly added, and an iron-nitrogen exotic atom dual-doped porous carbon material is prepared by adopting a hard template method. The method comprises the following steps: preparing a precursor, a catalyst and a previous polymer ofa hard template; calcining the previous polymer to obtain solids; and etching, cleaning and drying the solids to obtain the carbon material of the invention. The prepared carbon material is uniformlymixed with sulfur powder to be heated in an argon atmosphere to form a carbon sulfur composite material which is applied to the lithium sulfur battery. The obtained carbon material is relatively highin content of nitrogen and iron, relatively high in specific surface area and yield, simple in preparation step and easy in operation. When the lithium sulfur battery anode material is applied to thelithium sulfur battery, the electrochemical performance is relatively good, compared with the iron-free carbon material, the performance is apparently improved, the sulfur can be well fixed by addingthe iron catalyst, the shuttle of the poly-sulfide can be inhibited, and the reaction dynamics can be accelerated, so that the cycling stability of the lithium sulfur battery can be improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY