Patents

Literature

162 results about "Channel pattern" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Channel patterns are found in rivers, streams, and other bodies of water that transport water from one place to another. Systems of branching river channels dissect most of the sub-aerial landscape, each in a valley proportioned to its size. Whether formed by chance or necessity, by headward erosion or downslope convergence, whether inherited or newly formed. Depending on different geological factors such as weathering, erosion, depositional environment, and sediment type, different types of channel patterns can form.

Methods of forming a multi-bridge-channel MOSFET

ActiveUS7402483B2Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

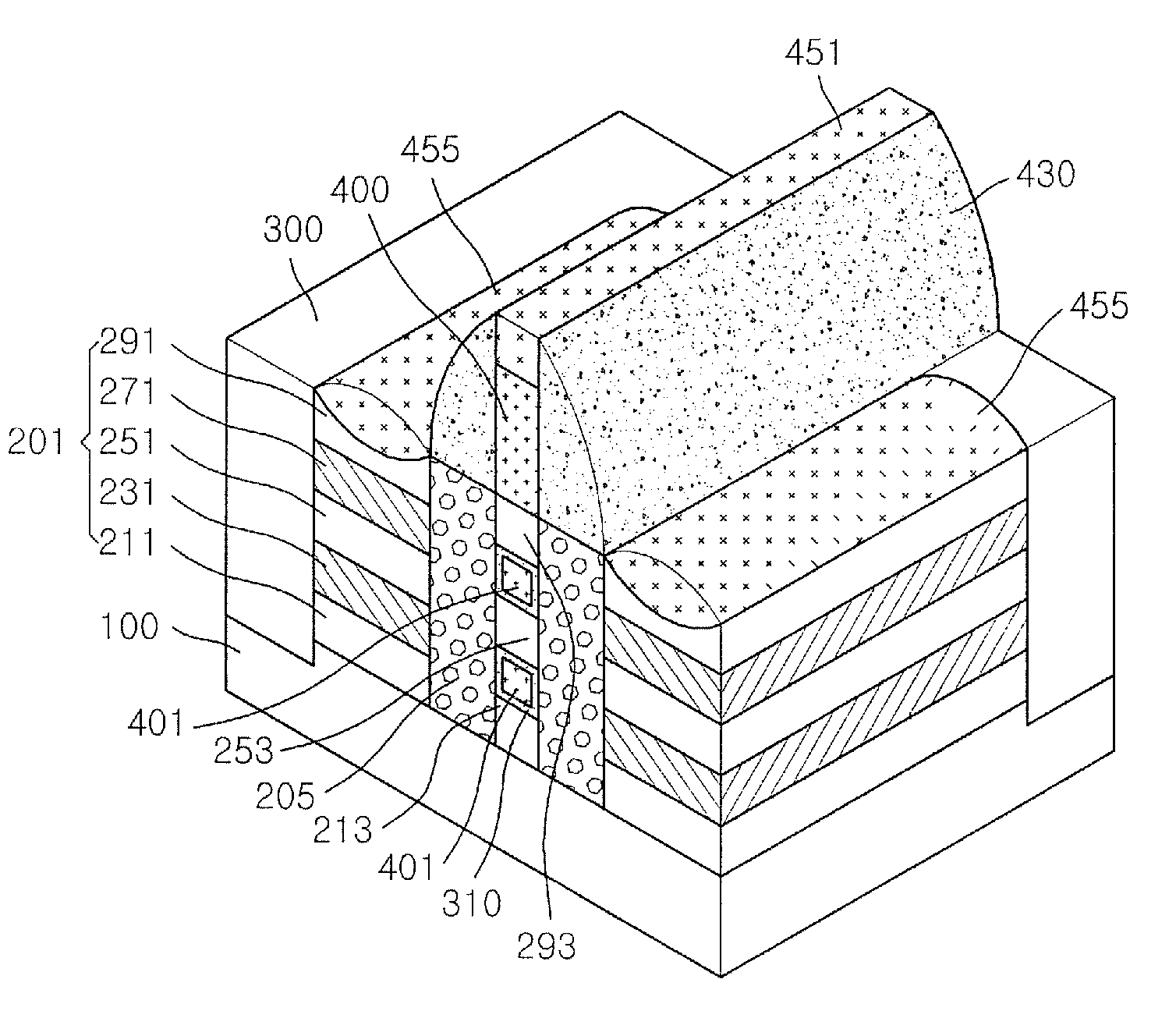

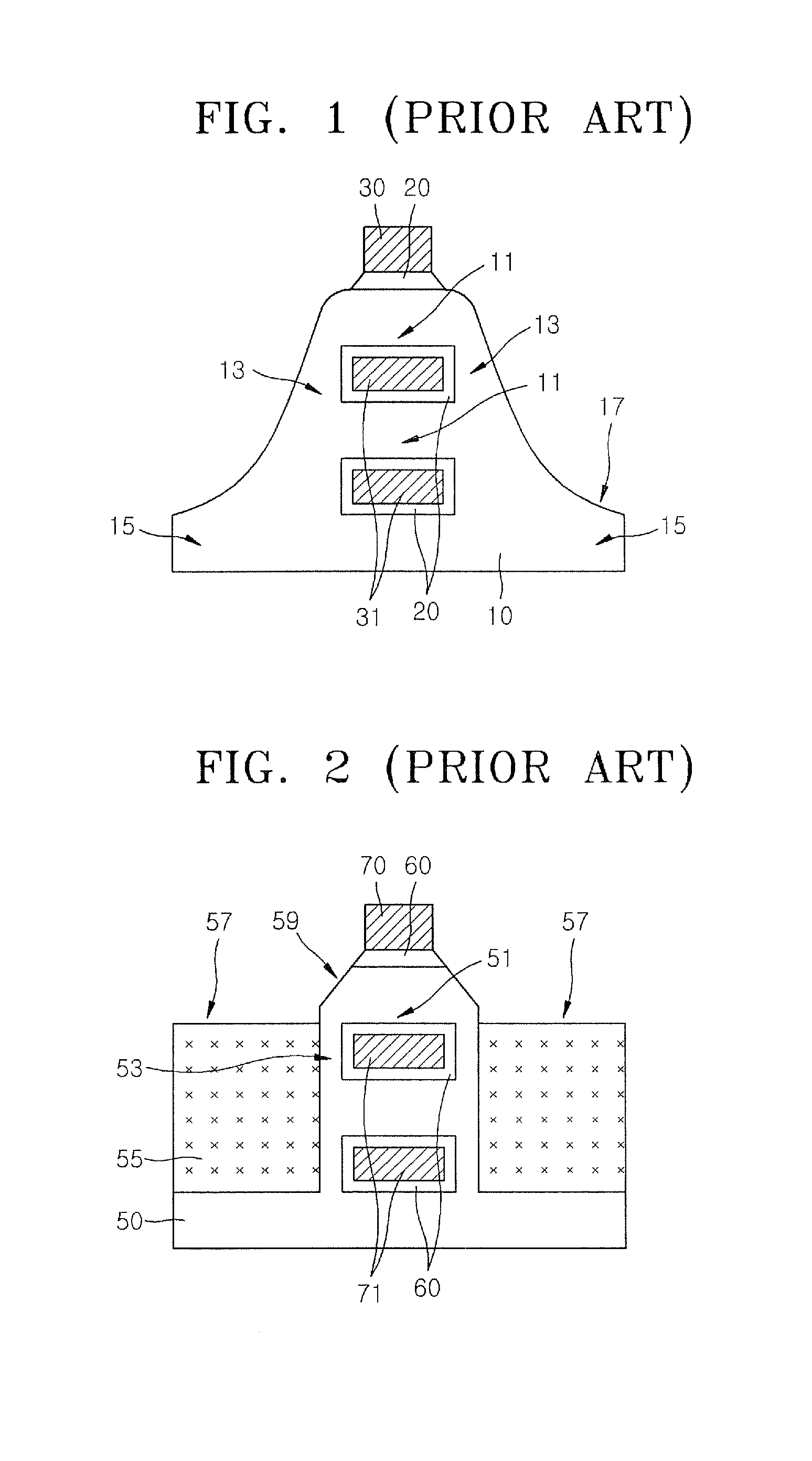

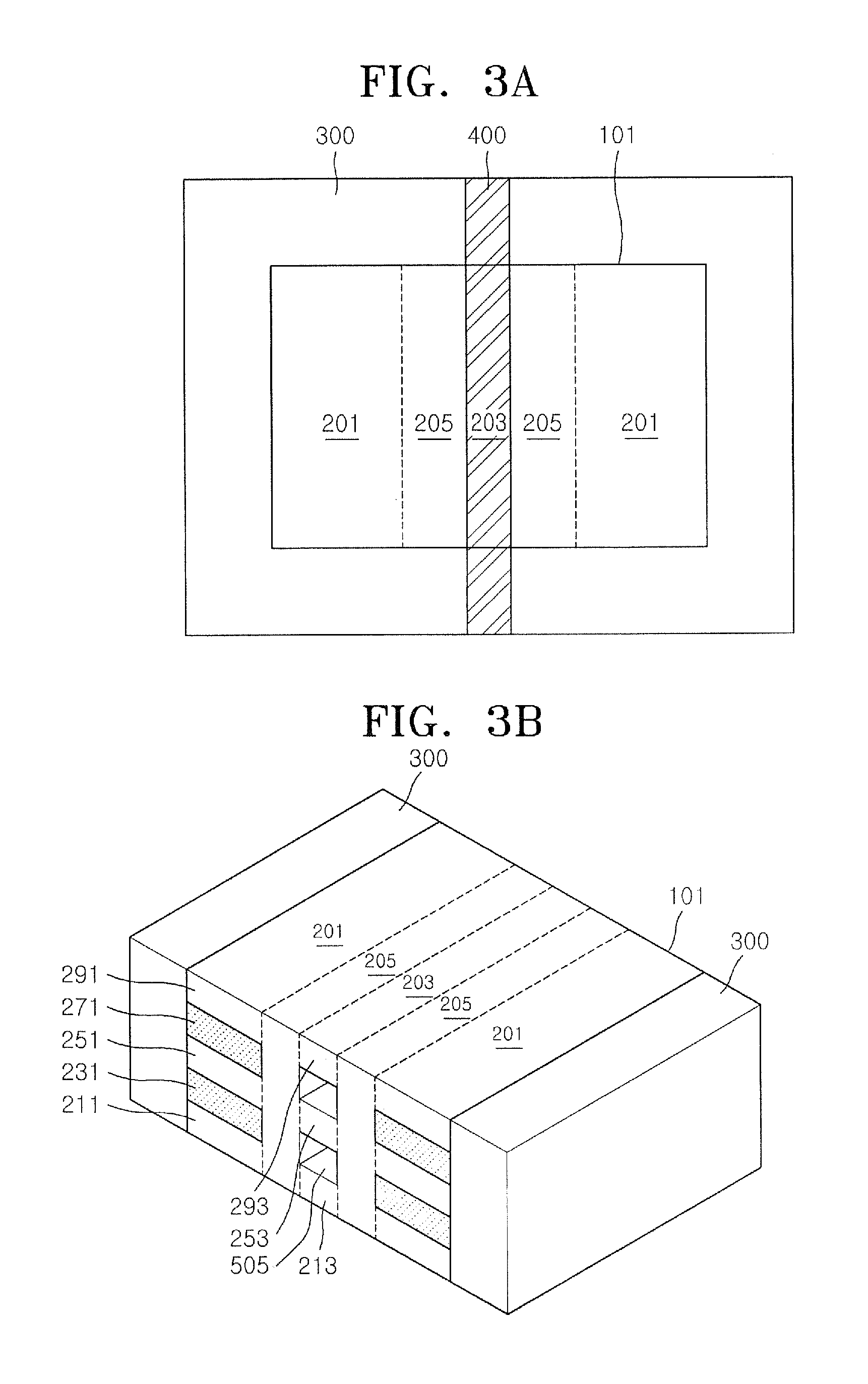

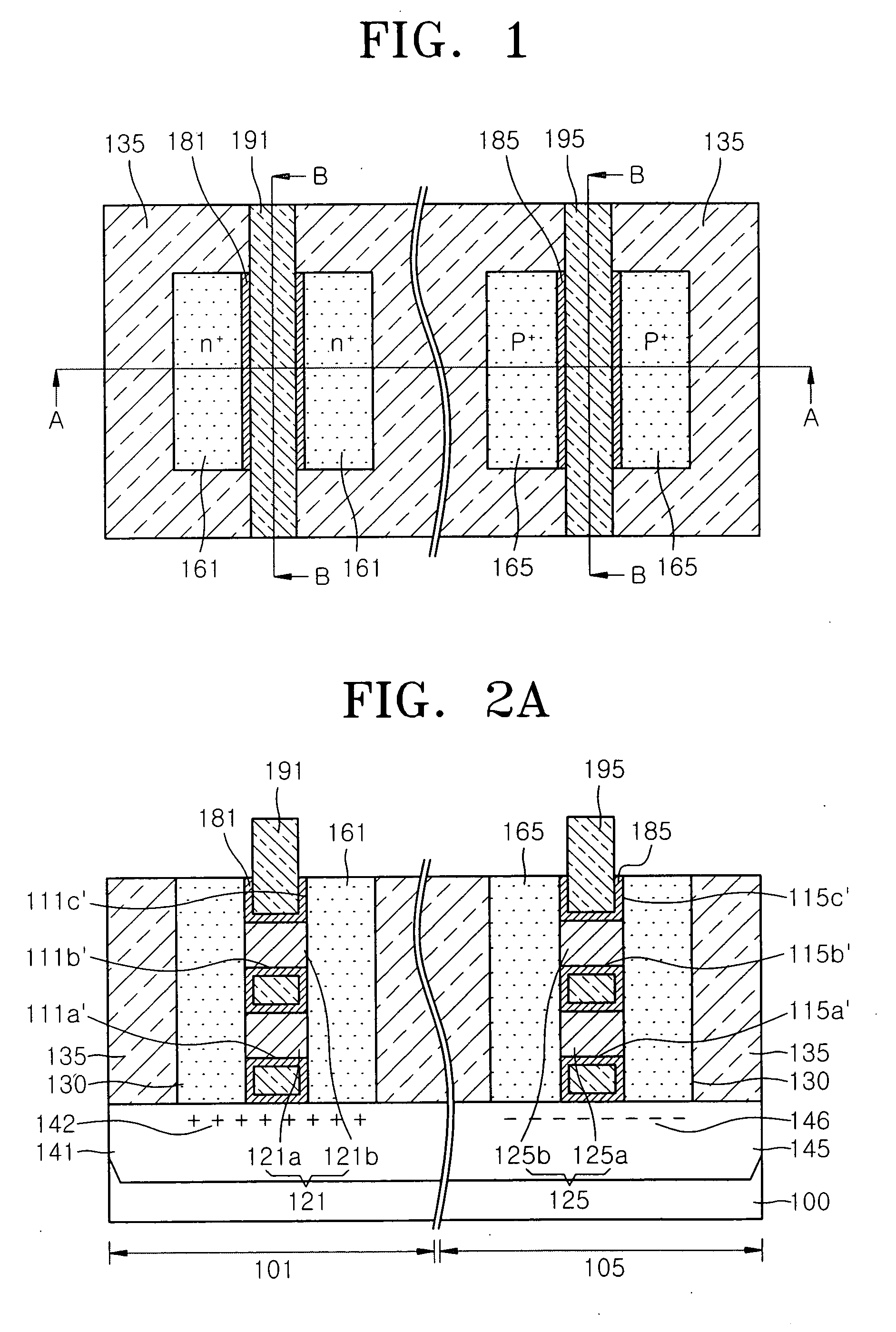

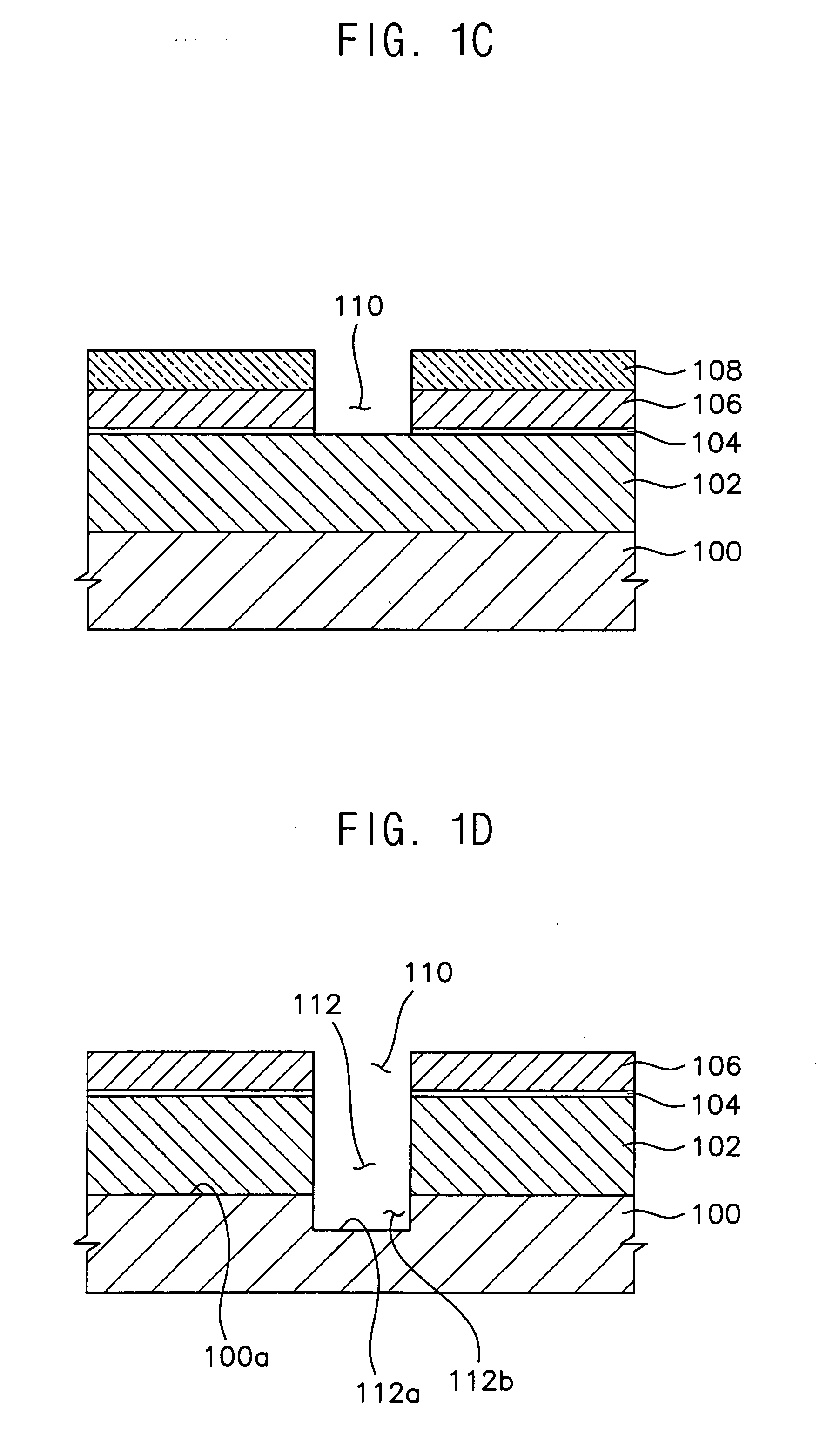

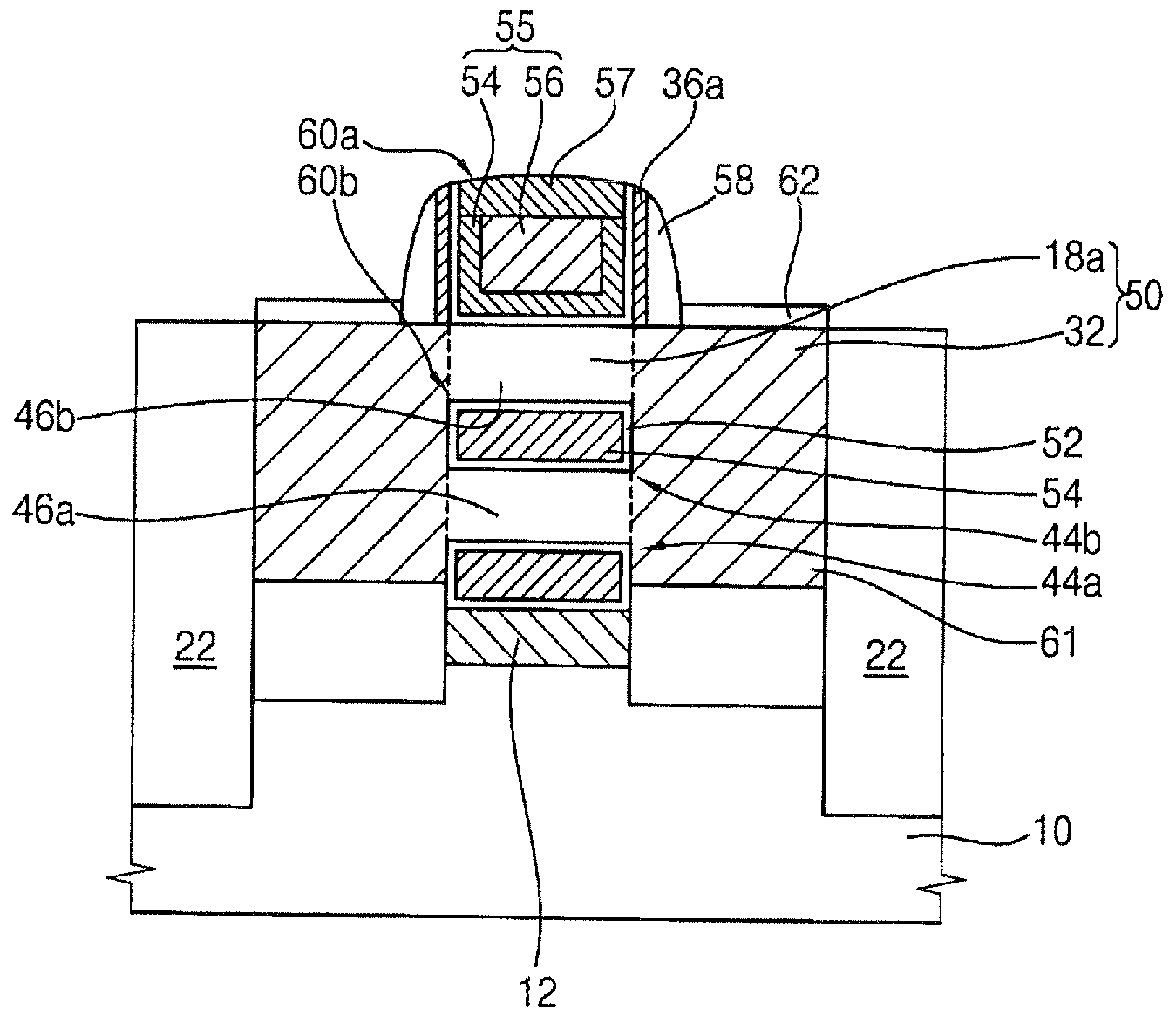

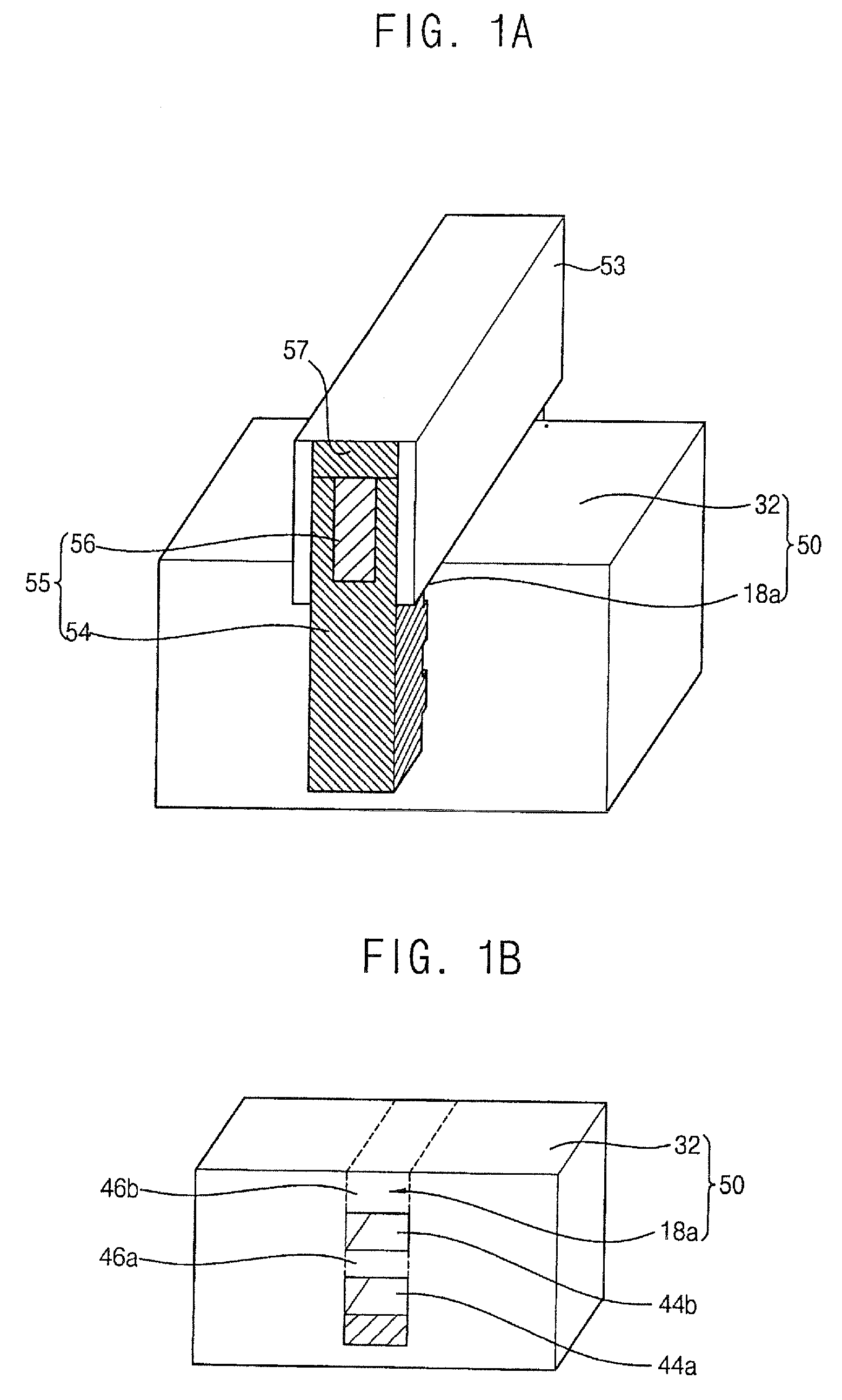

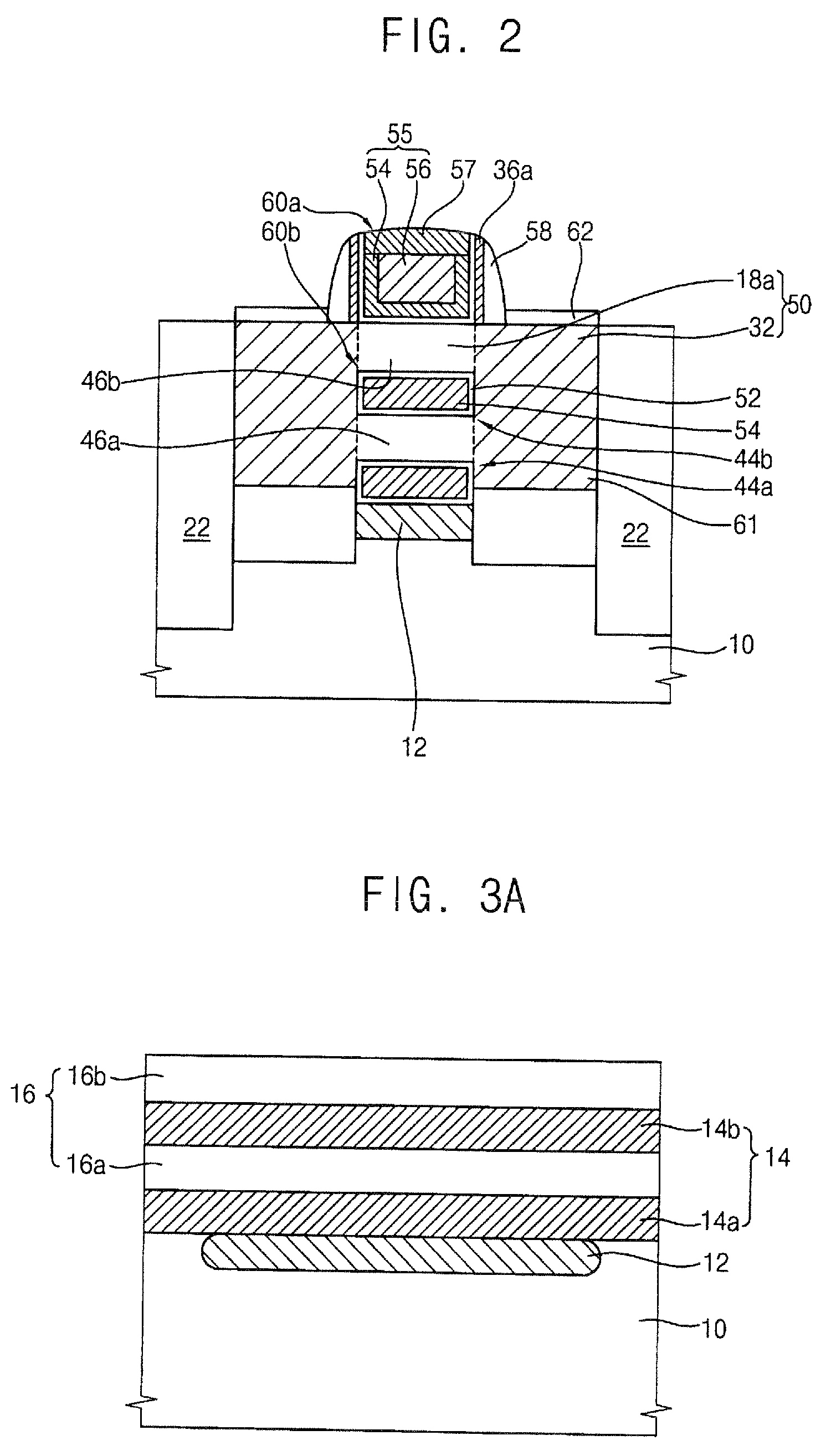

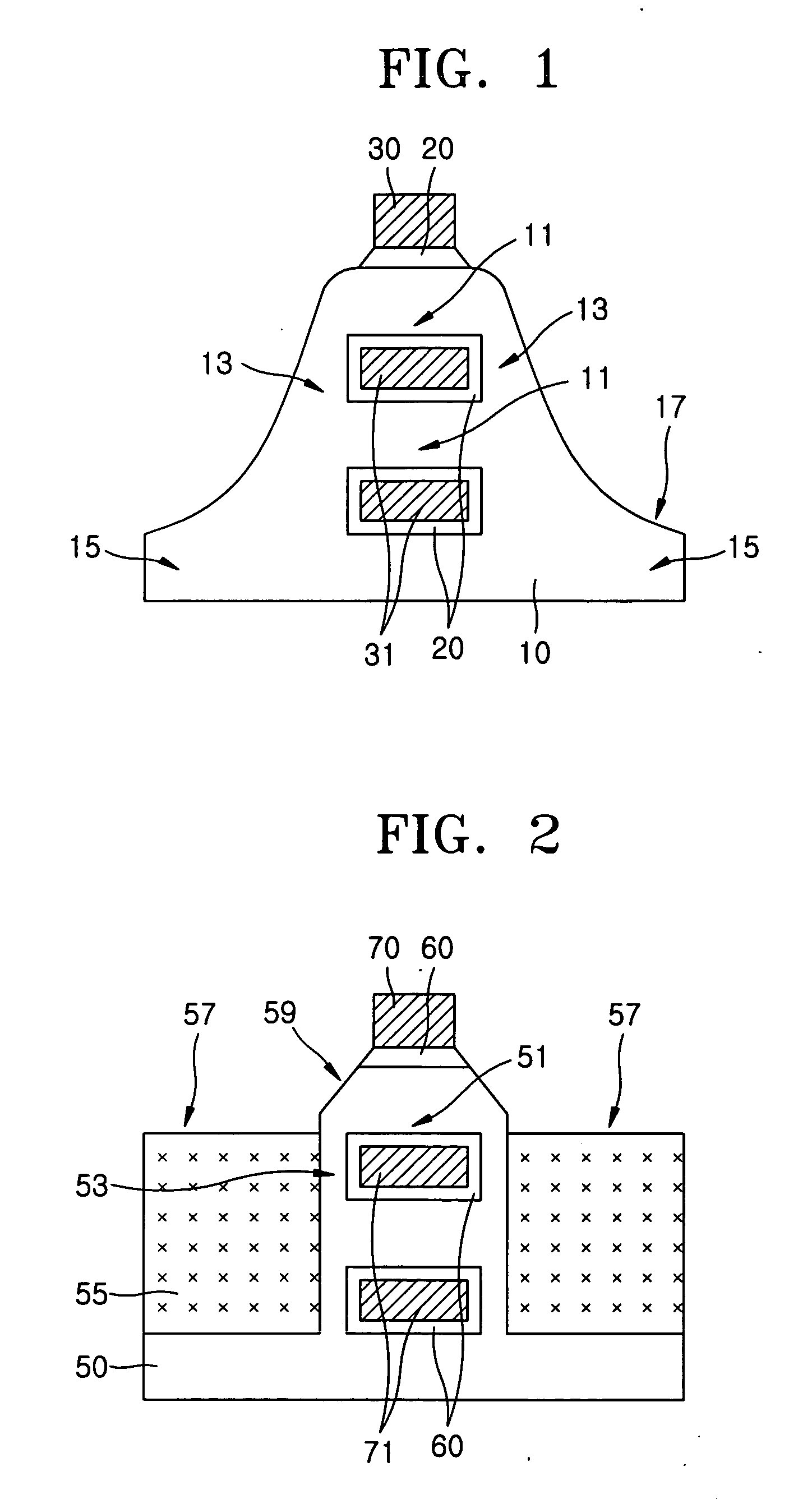

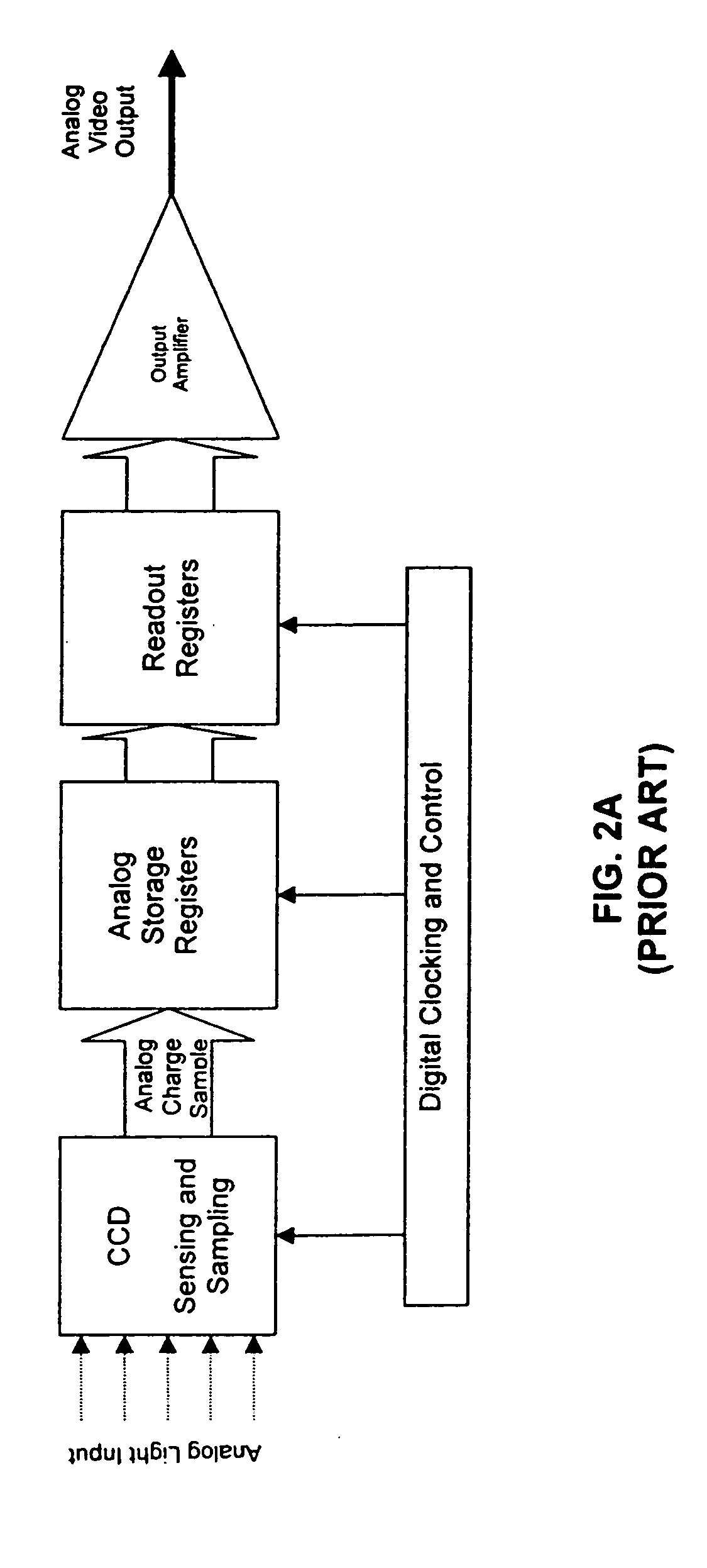

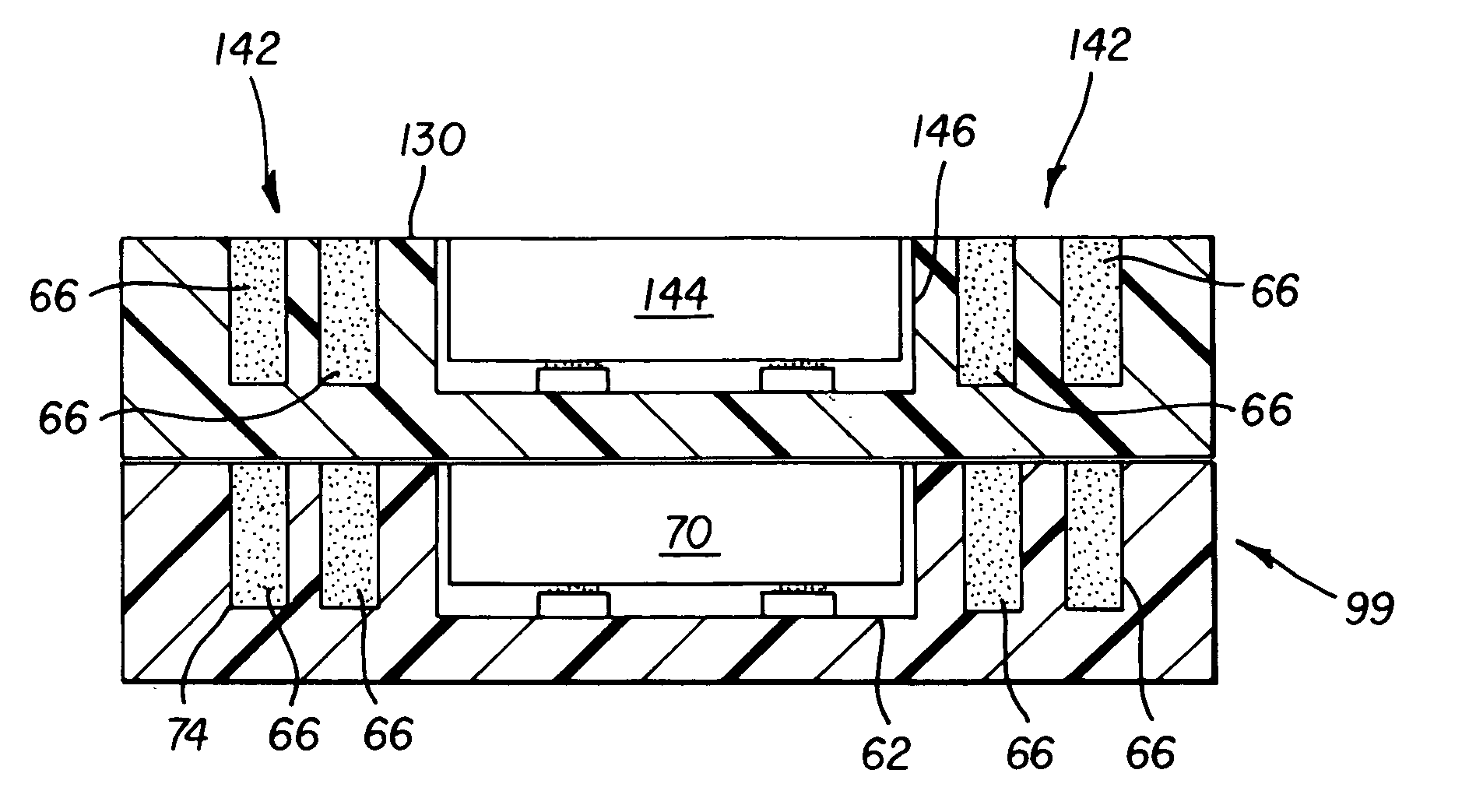

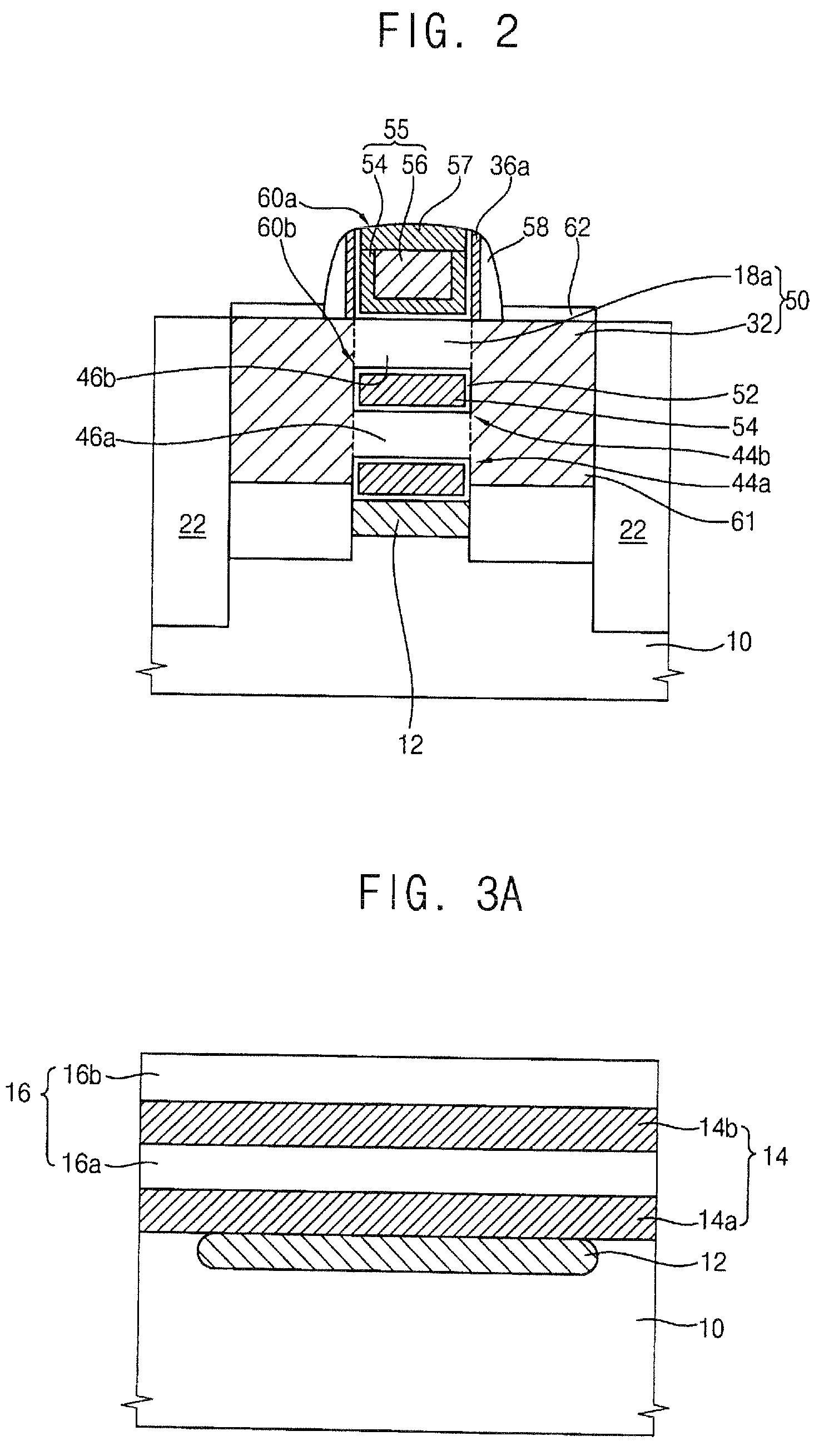

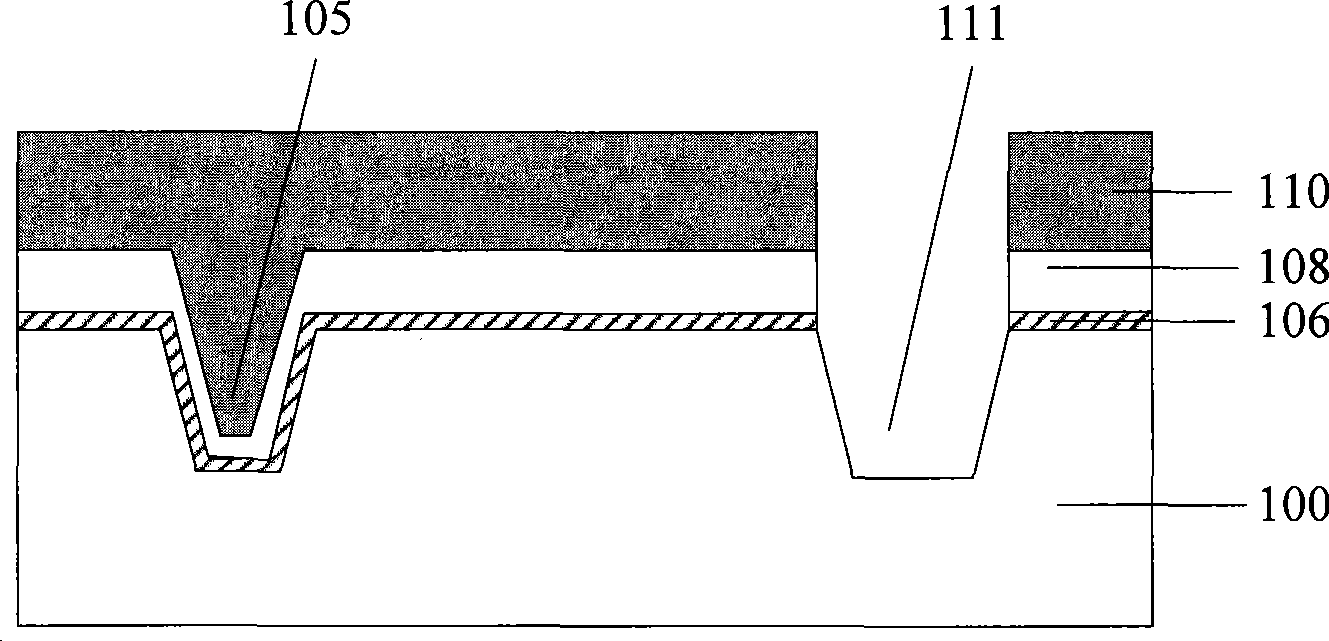

A multi-bridge-channel MOSFET (MBCFET) may be formed by forming a stacked structure on a substrate that includes channel layers and interchannel layers interposed between the channel layers. Trenches are formed by selectively etching the stacked structure. The trenches run across the stacked structure parallel to each other and separate a first stacked portion including channel patterns and interchannel patterns from second stacked portions including channel and interchannel layers remaining on both sides of the first stacked portion. First source and drain regions are grown using selective epitaxial growth. The first source and drain regions fill the trenches and connect to second source and drain regions defined by the second stacked portions. Marginal sections of the interchannel patterns of the first stacked portion are selectively exposed. Through tunnels are formed by selectively removing the interchannel patterns of the first stacked portion beginning with the exposed marginal sections. The through tunnels are surrounded by the first source and drain regions and the channel patterns. A gate is formed along with a gate dielectric layer, the gate filling the through tunnels and extending onto the first stacked portion.

Owner:SAMSUNG ELECTRONICS CO LTD

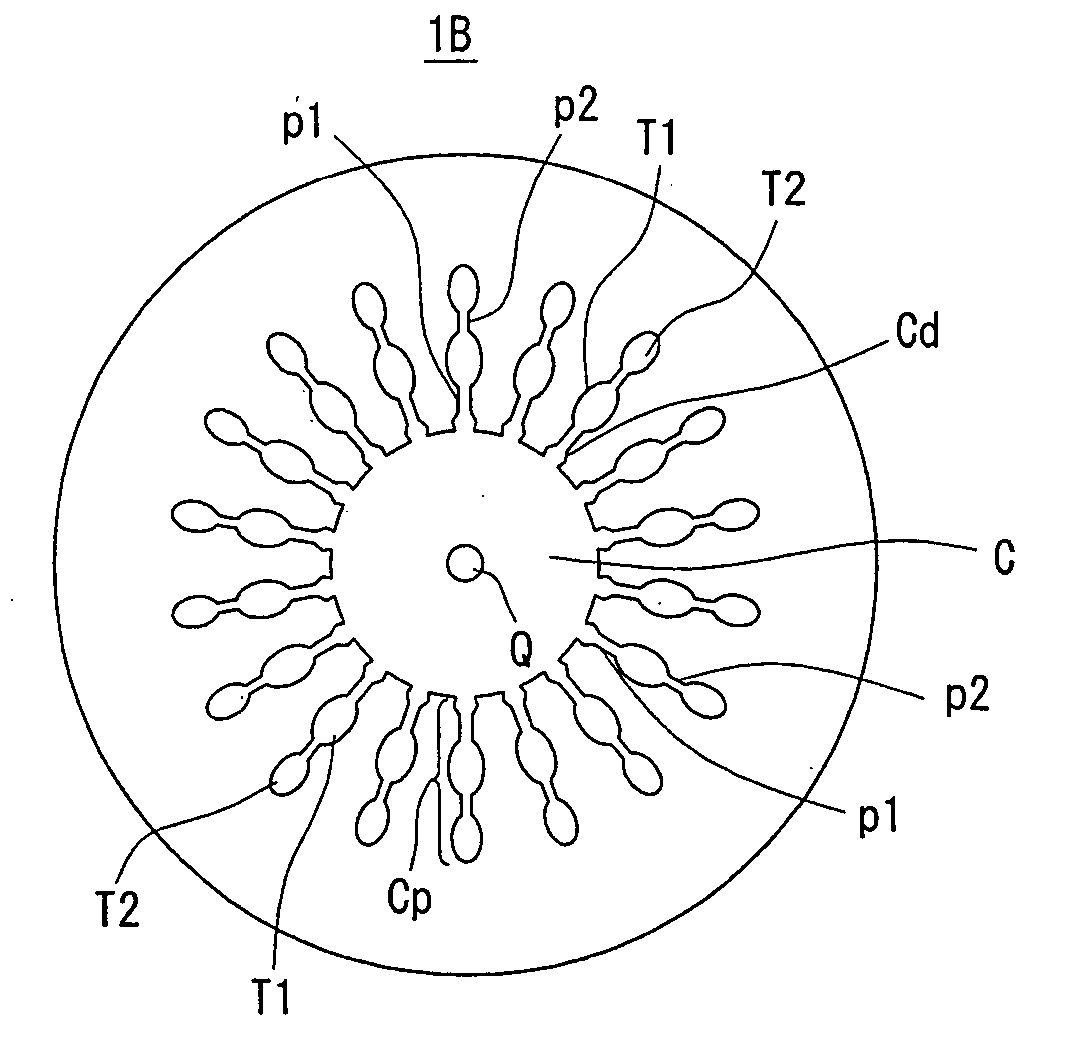

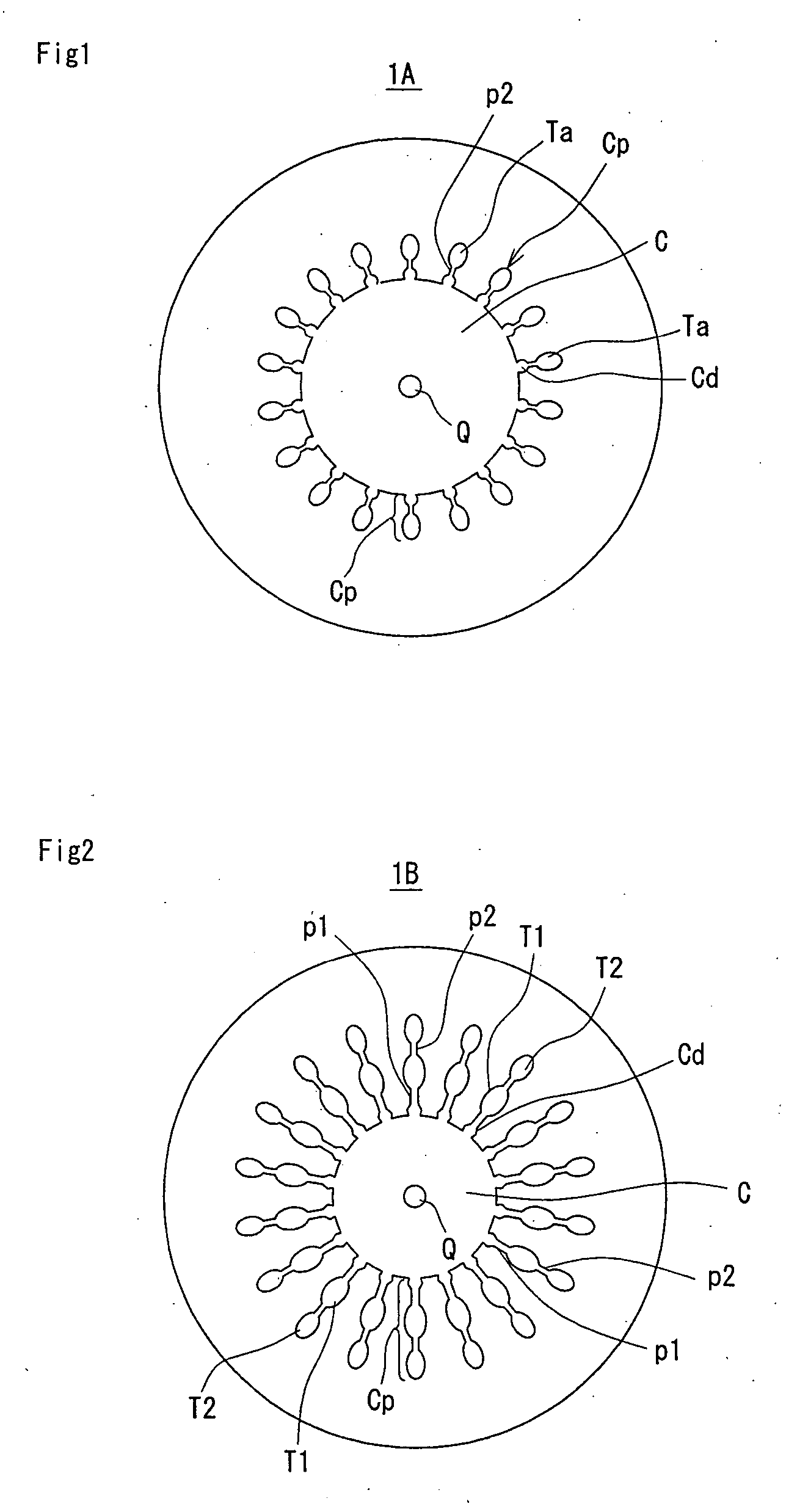

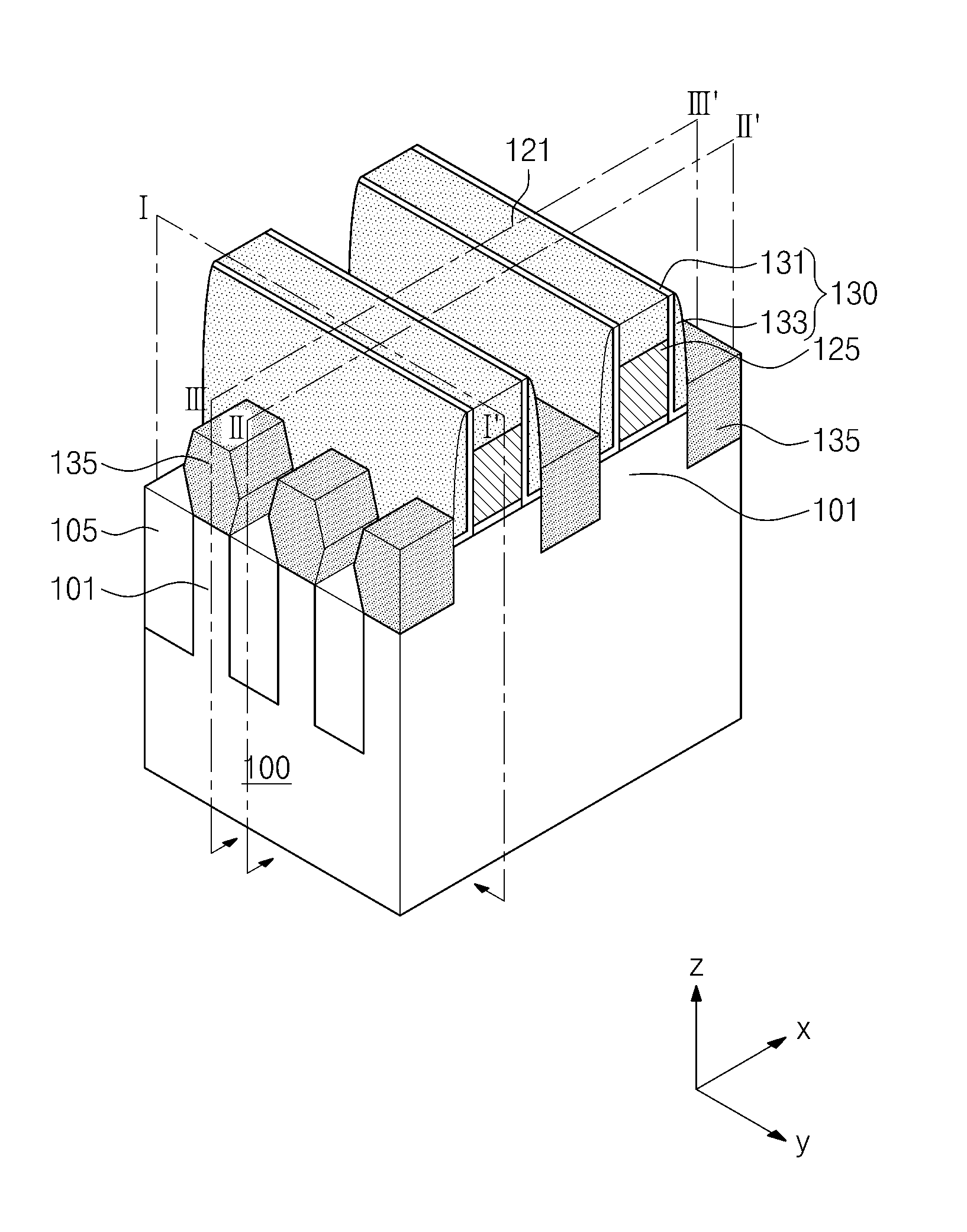

Multi-channel semiconductor device and method of manufacturing the same

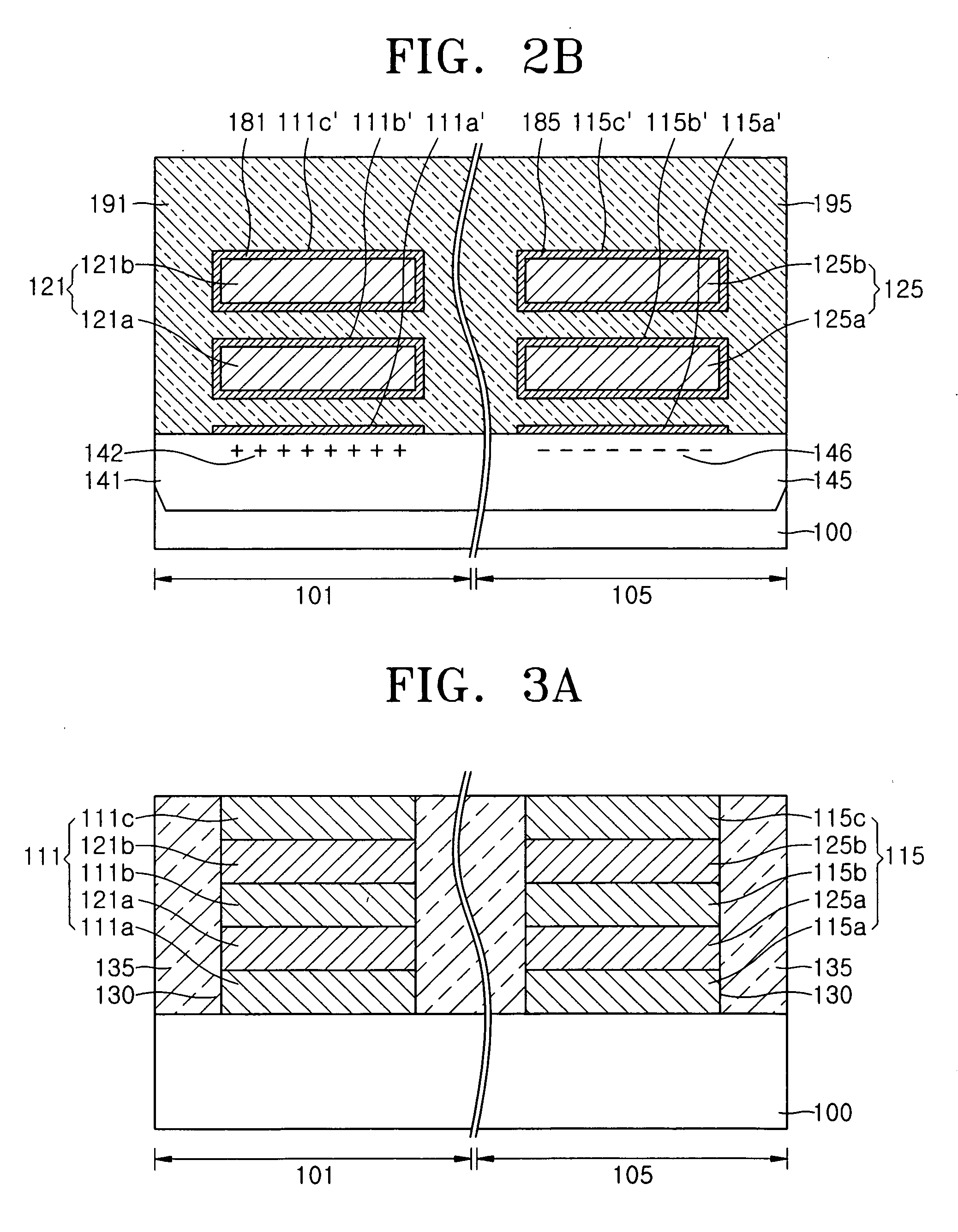

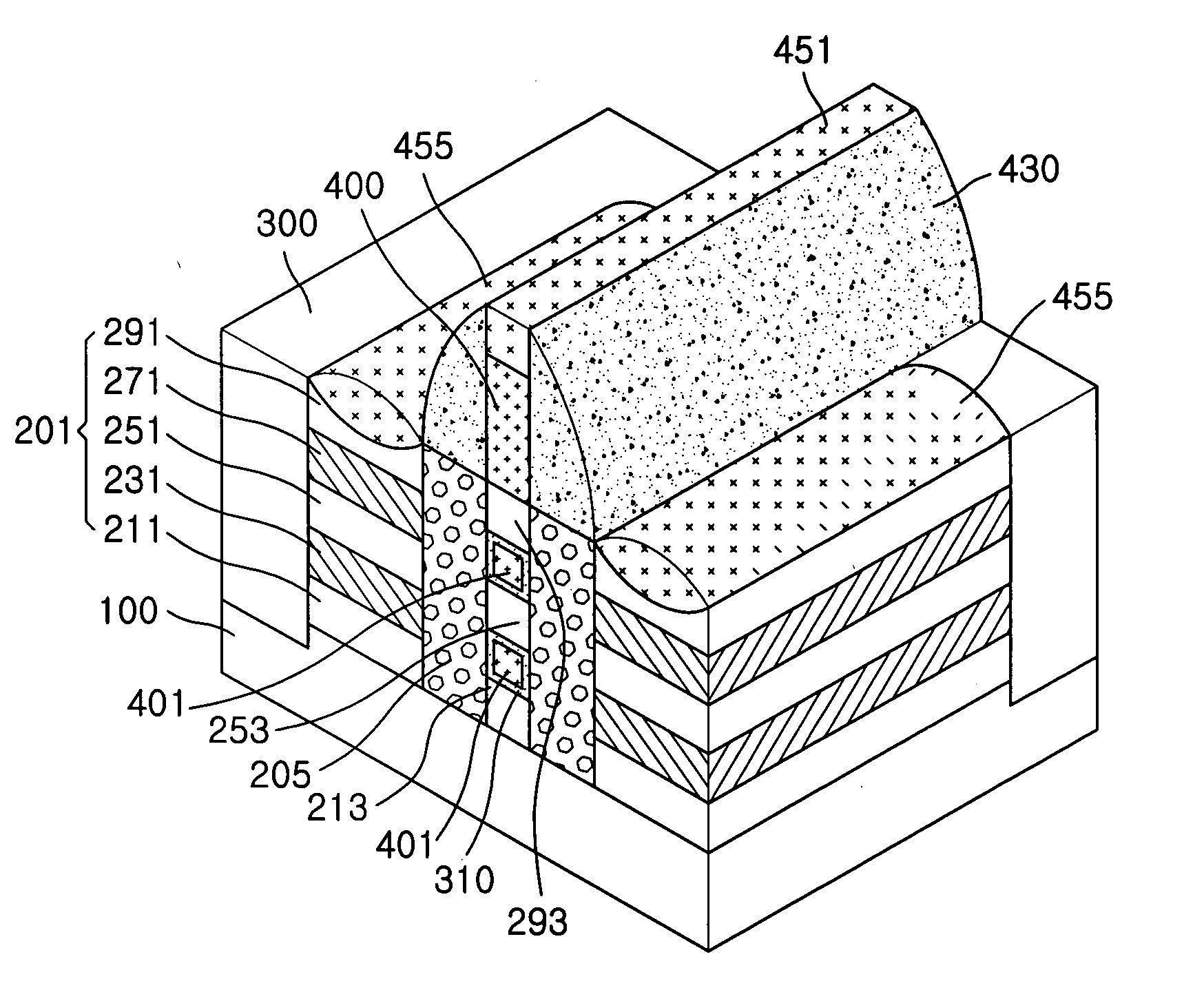

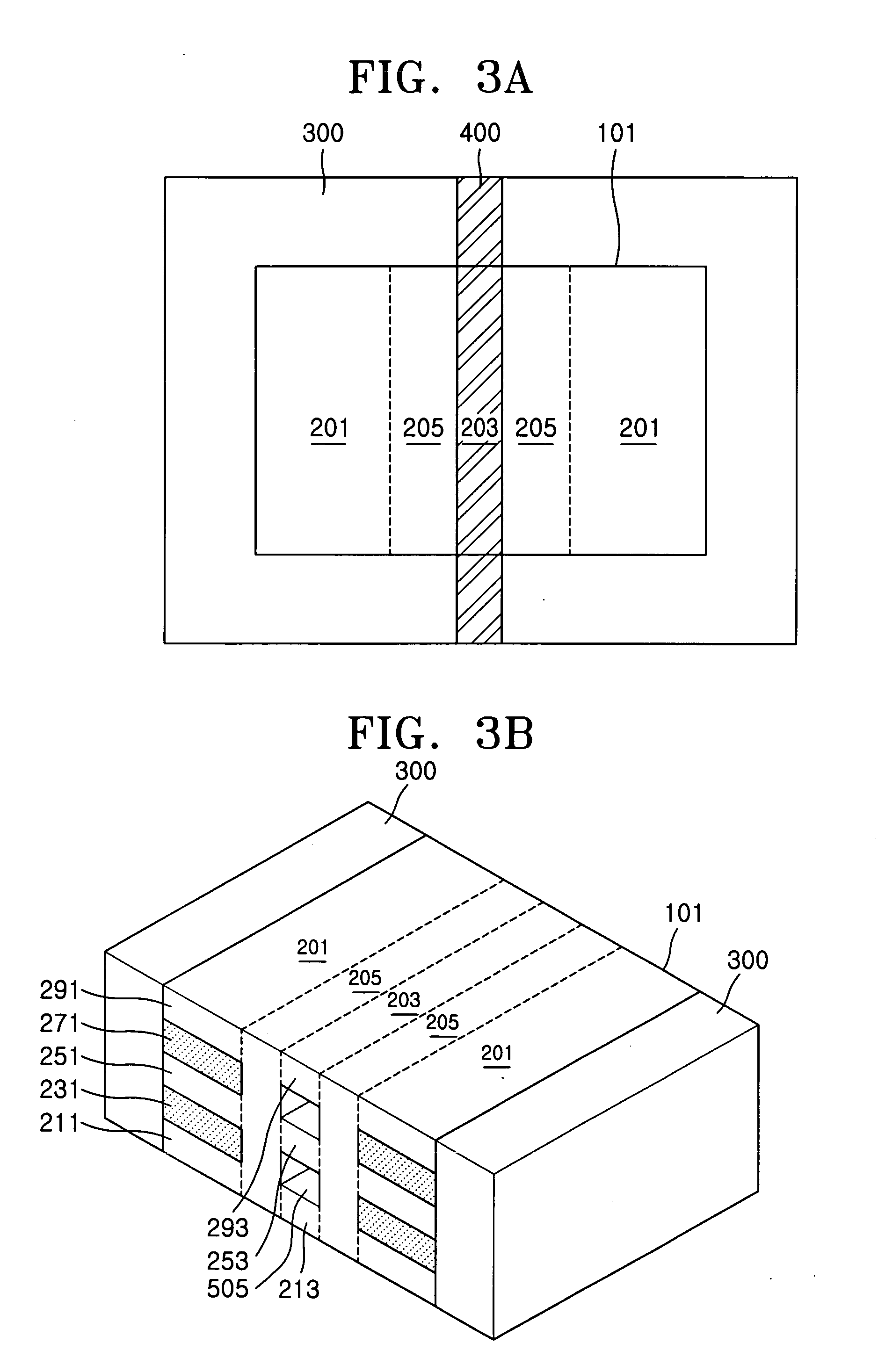

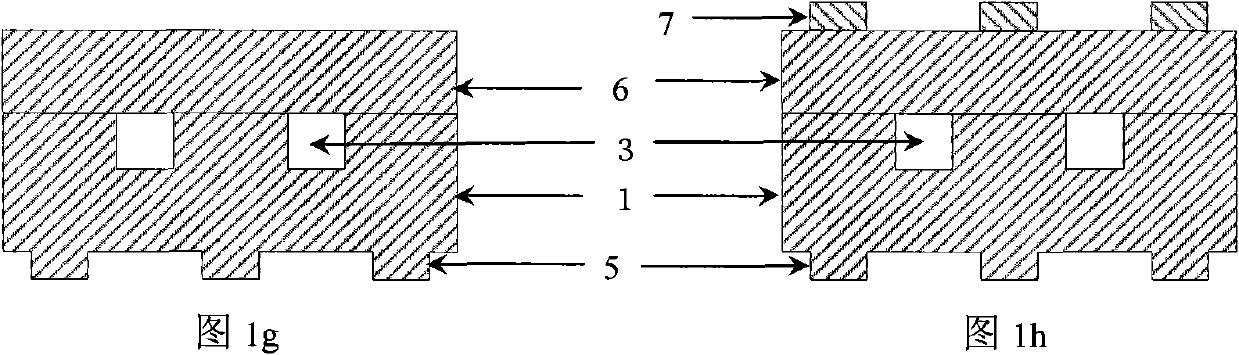

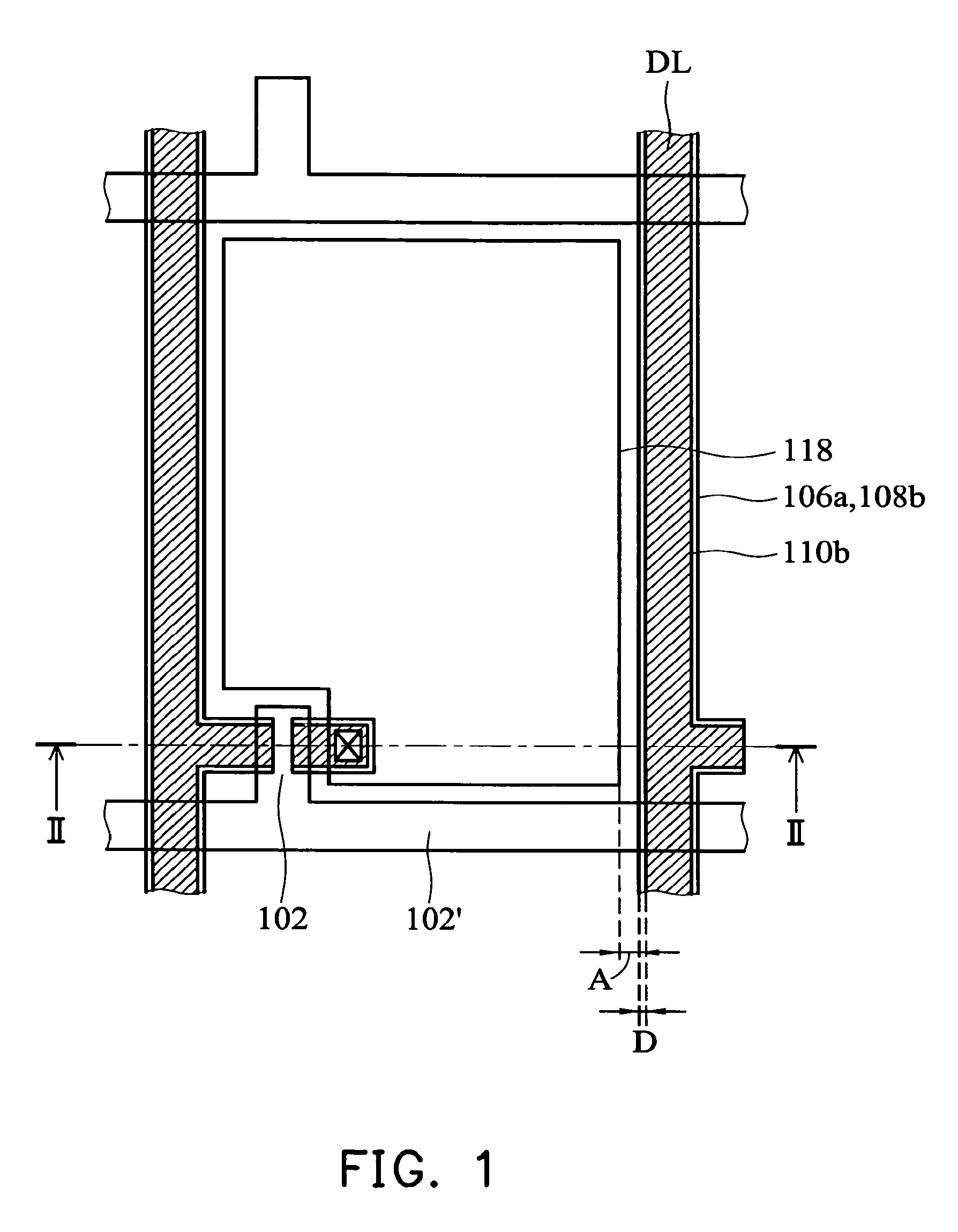

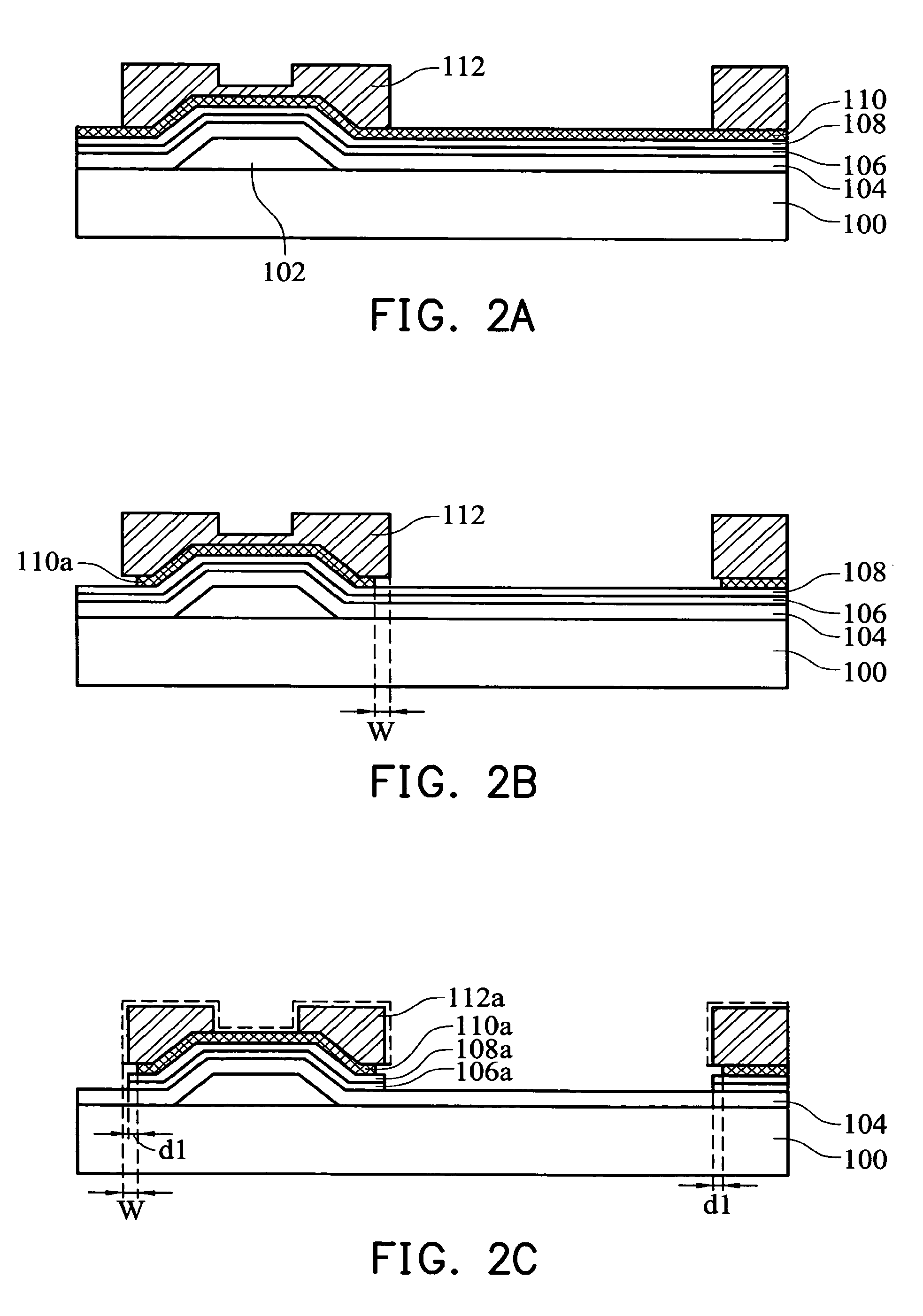

Provided are a multi-channel semiconductor device and a method for manufacturing the semiconductor device through a simplified process. A sacrificial layer and a channel layer are alternately stacked on a semiconductor substrate. Thereafter, the sacrificial layer and the channel layer are etched to form a separated active pattern, and a device isolation layer is formed to cover sidewalls of the active pattern. Dopant ions are implanted into the entire semiconductor substrate, thereby forming a channel separation region under the active pattern. A portion of the active pattern is etched to separate the active pattern from a pair of facing sidewalls of the device separation layer, thereby forming a channel pattern having a pair of first exposed sidewalls. Source / drain semiconductor layers are formed on the first sidewalls of the channel pattern, and a part of the device isolation layer is removed to expose a pair of second sidewalls of the channel pattern contacting with the device separation layer. Thereafter, the sacrificial layer included in the channel pattern is remove, and a conductive layer for a gate electrode is formed to cover the channel layer exposed by the removing of the sacrificial layer.

Owner:SAMSUNG ELECTRONICS CO LTD

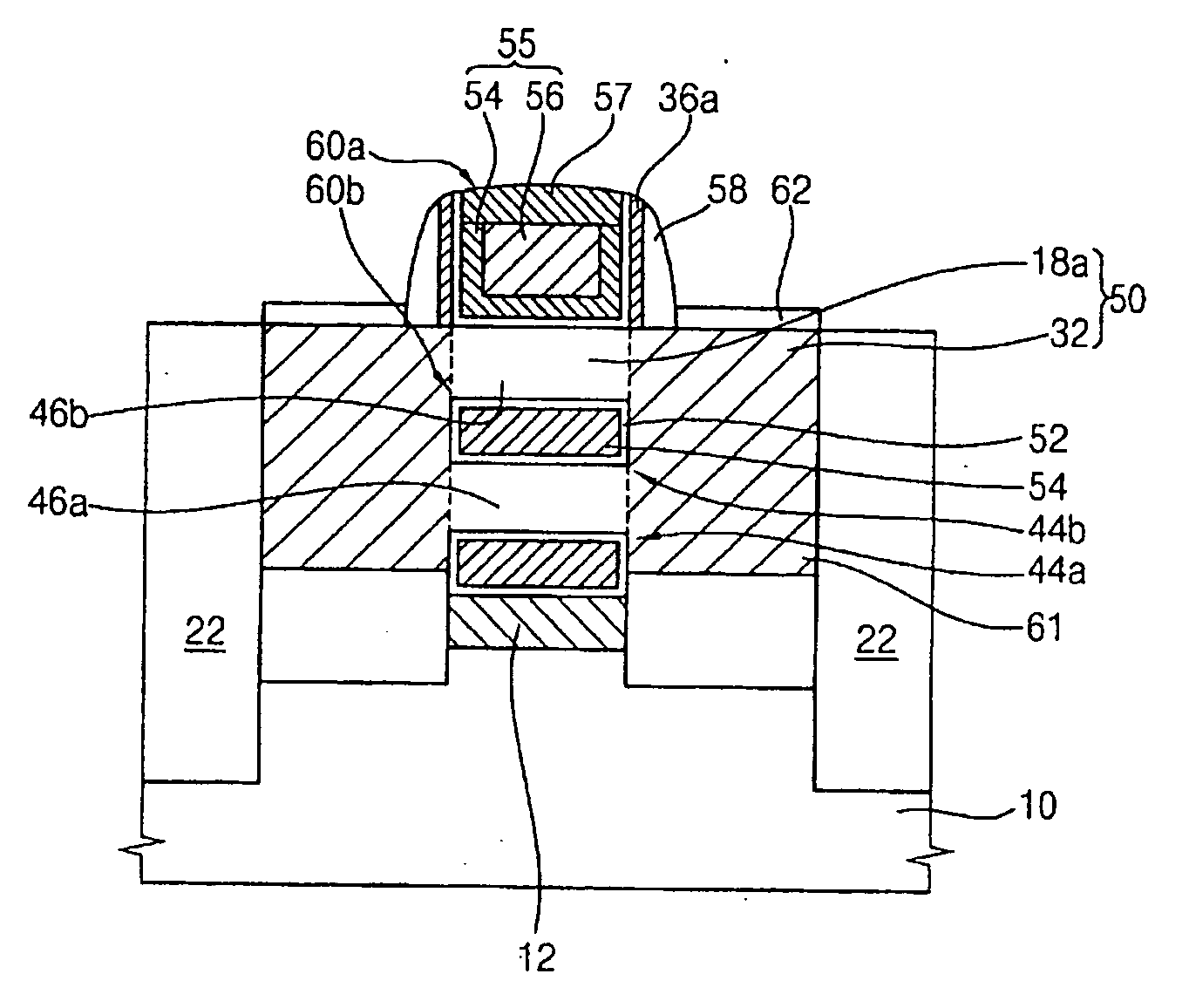

Semiconductor device gate structure and method of forming the same

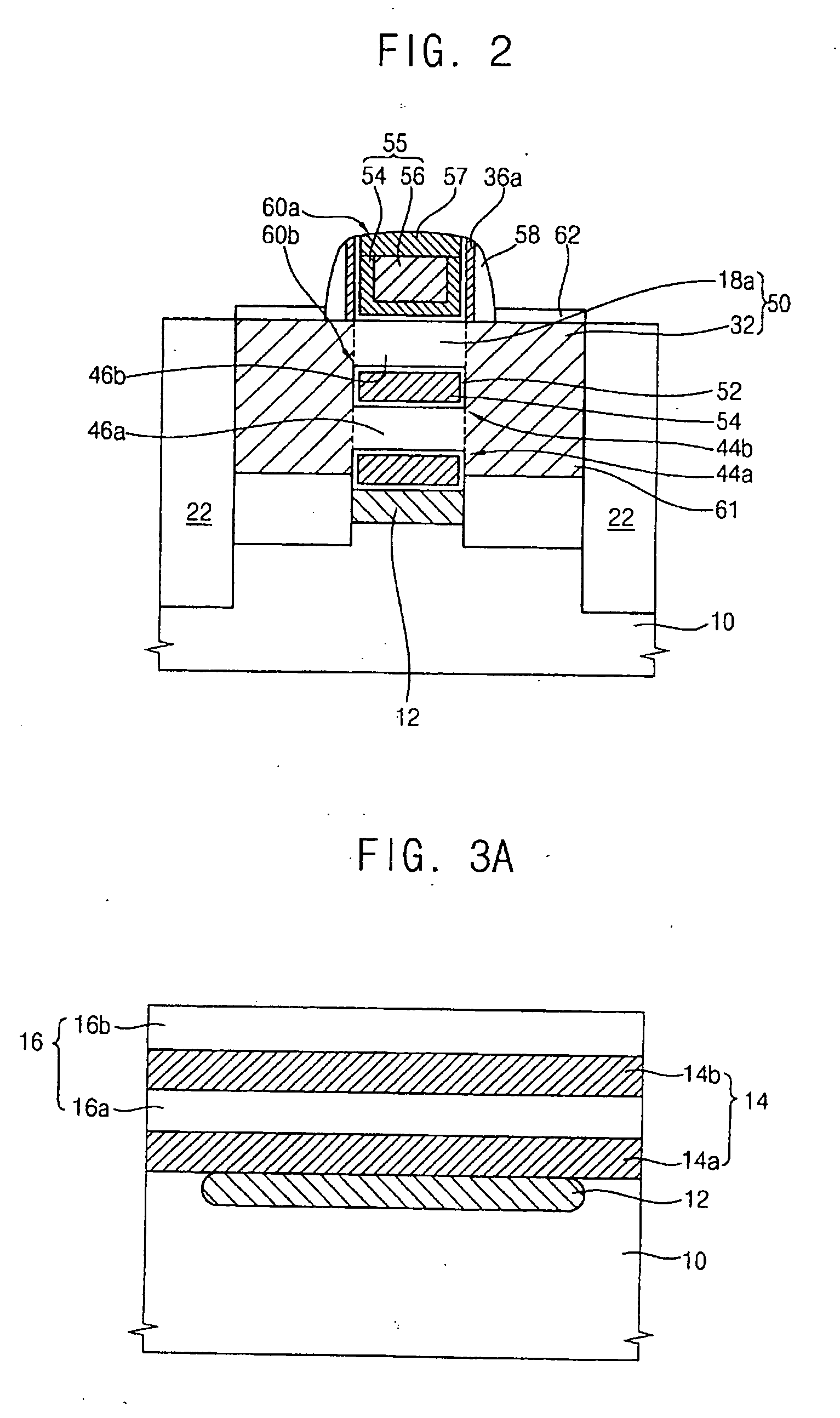

InactiveUS20050184348A1Effective preventionEffectively preventTransistorSolid-state devicesInsulation layerDevice material

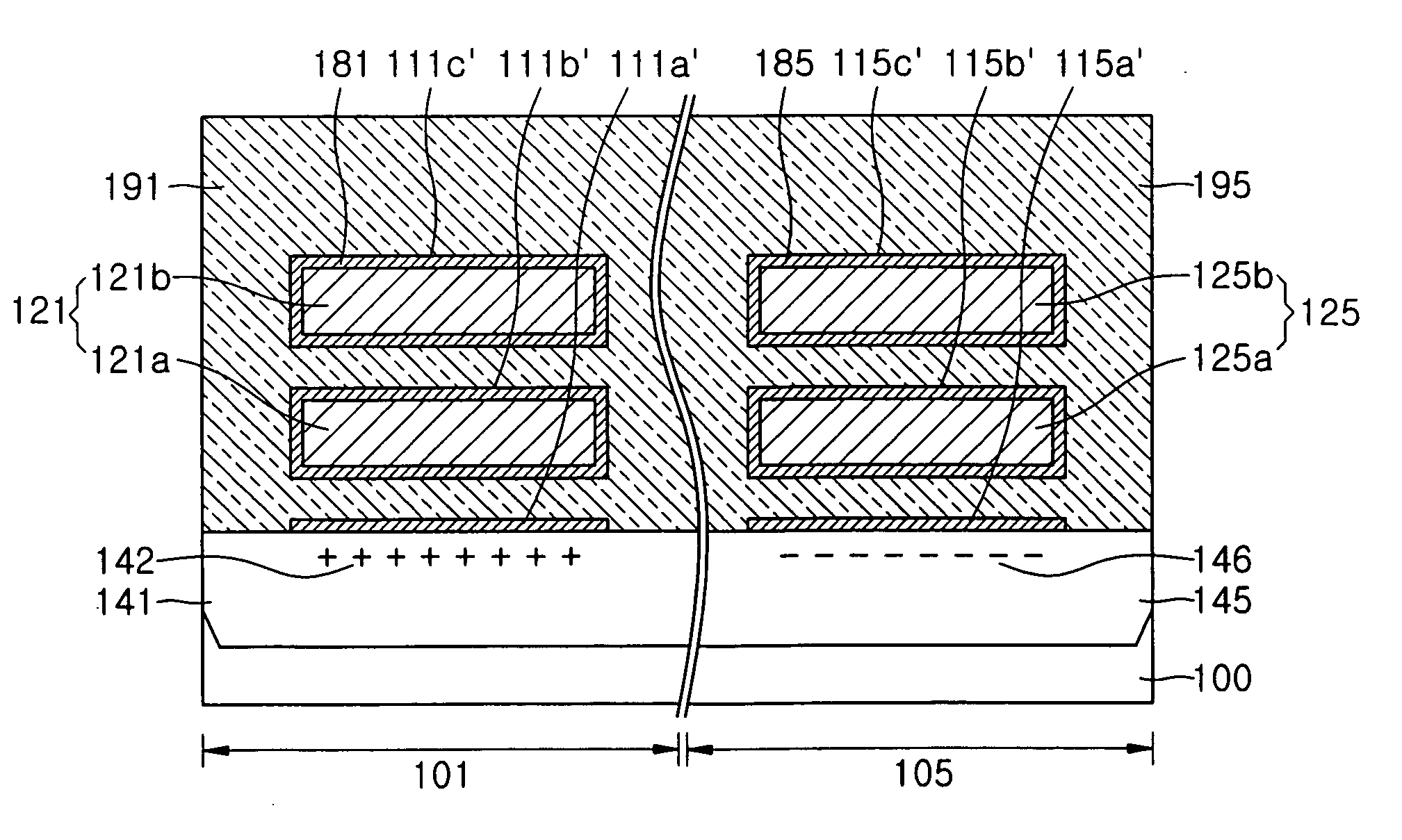

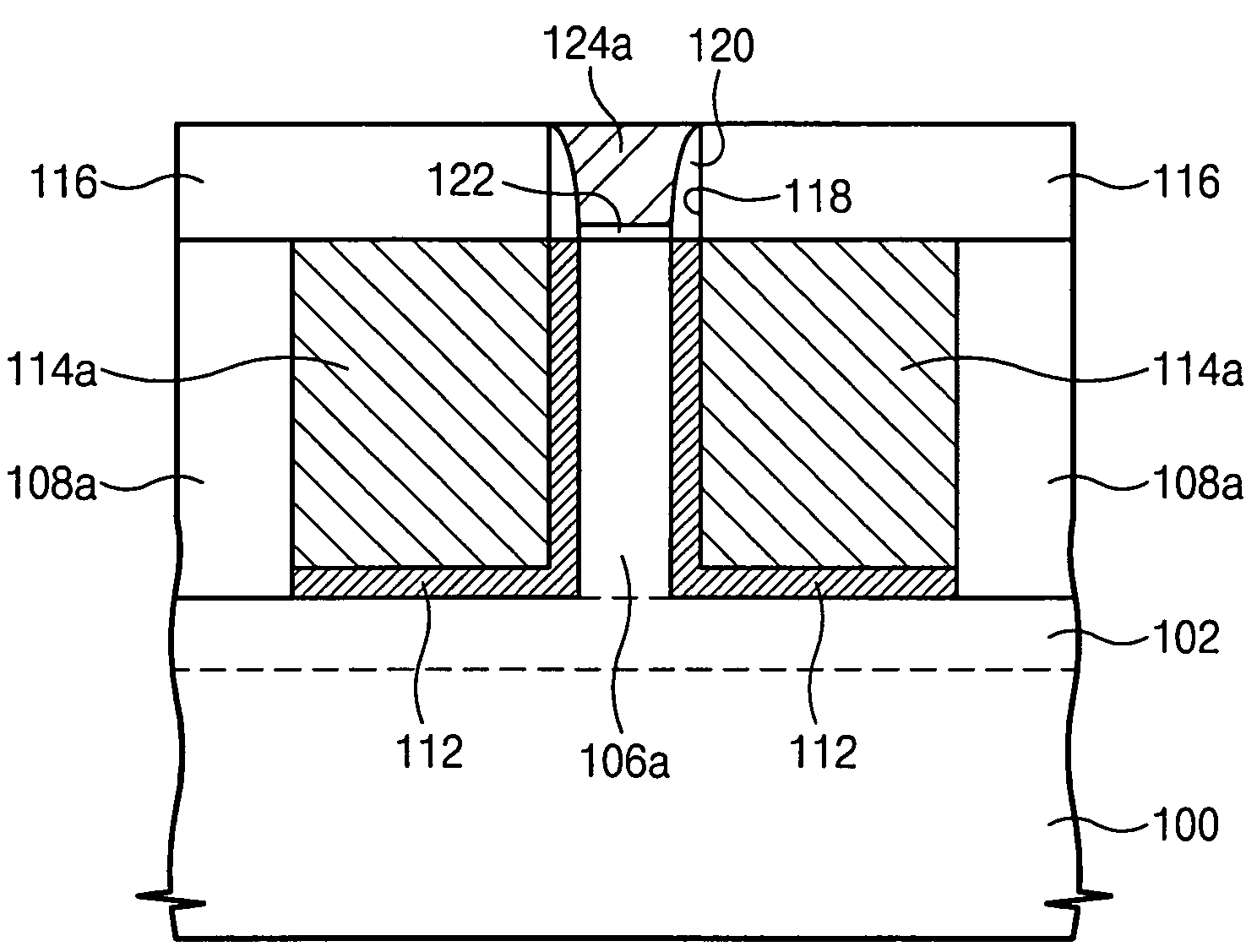

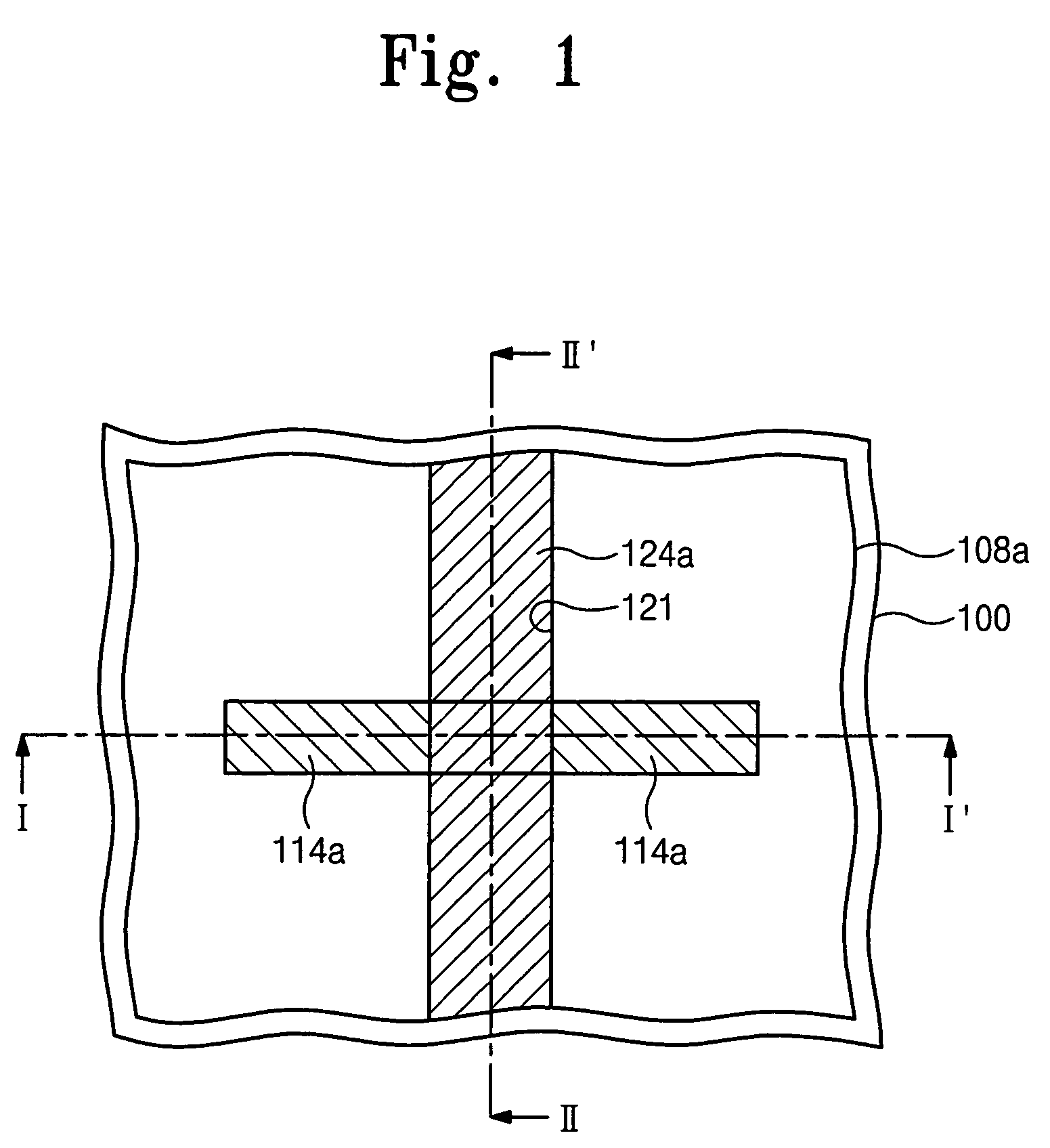

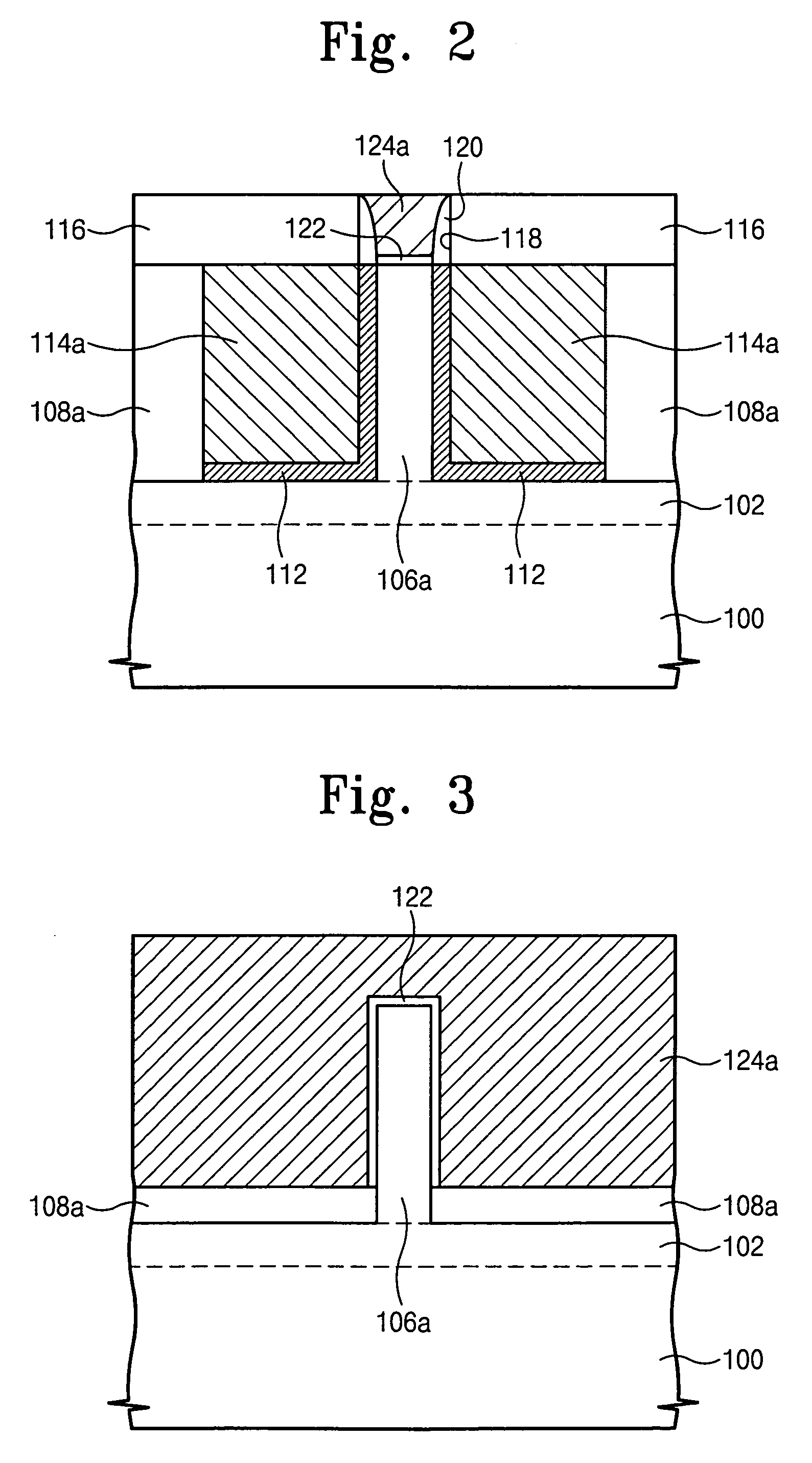

A MOS transistor includes a gate structure extending forrom a semiconductor substrate in a vertical direction is disclosed. The gate structure includes a gate electrode extending from the substrate in a vertical direction, and a gate insulation layer enclosing the gate electrode. A channel pattern encloses the gate insulation layer, and a first conductive pattern extends from a lower portion of the channel pattern in a first direction verticalperpendicular to the channel pattern and in parallel with the substrate. A second conductive pattern extends from an upper portion of the channel pattern in a second direction verticalperpendicular to the channel pattern and in parallel with the substrate. Accordingly, the channel length of the MOS transistor is determined by a distance between the first and second conductive patterns, and a channel width of the MOS transistor is determined by a diameter of the gate structure. Short channel and narrow width effects are sufficiently prevented in a MOS transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor devices having field effect transistors

A semiconductor device having a field effect transistor and a method of fabricating the same. In-situ doped epitaxial patterns are respectively formed at both sidewalls of a protruded channel pattern from a substrate by performing an in-situ doped epitaxial growth process. The in-situ doped epitaxial pattern has a conformal impurity concentration throughout. Accordingly, source / drain regions with a conformal impurity concentration are connected throughout a channel width of a channel region including both sidewalls of a protruded channel pattern. As a result, it is possible to maximize a driving current of the filed effect transistor, and an on-off characteristic can be highly stabilized.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of manufacturing a semiconductor device having a multi-channel type mos transistor

ActiveUS20080099849A1Reduce heat spreadLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialMetal silicide

In a method of manufacturing a semiconductor device, an active channel pattern is formed on a substrate. The active channel pattern includes preliminary gate patterns and single crystalline silicon patterns that are alternately stacked with each other. A source / drain layer is formed on a sidewall of the active channel pattern. Mask pattern structures including a gate trench are formed on the active channel pattern and the source / drain layer. The patterns are selectively etched to form tunnels. The gate trench is then filled with a gate electrode. The gate electrode surrounds the active channel pattern. The gate electrode is protruded from the active channel pattern. The mask pattern structures are then removed. Impurities are implanted into the source / drain regions to form source / drain regions. A silicidation process is carried out on the source / drain regions to form a metal silicide layer, thereby completing a semiconductor device having a MOS transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of forming a multi-bridge-channel MOSFET

ActiveUS20060024874A1Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

A multi-bridge-channel MOSFET (MBCFET) may be formed by forming a stacked structure on a substrate that includes channel layers and interchannel layers interposed between the channel layers. Trenches are formed by selectively etching the stacked structure. The trenches run across the stacked structure parallel to each other and separate a first stacked portion including channel patterns and interchannel patterns from second stacked portions including channel and interchannel layers remaining on both sides of the first stacked portion. First source and drain regions are grown using selective epitaxial growth. The first source and drain regions fill the trenches and connect to second source and drain regions defined by the second stacked portions. Marginal sections of the interchannel patterns of the first stacked portion are selectively exposed. Through tunnels are formed by selectively removing the interchannel patterns of the first stacked portion beginning with the exposed marginal sections. The through tunnels are surrounded by the first source and drain regions and the channel patterns. A gate is formed along with a gate dielectric layer, the gate filling the through tunnels and extending onto the first stacked portion.

Owner:SAMSUNG ELECTRONICS CO LTD

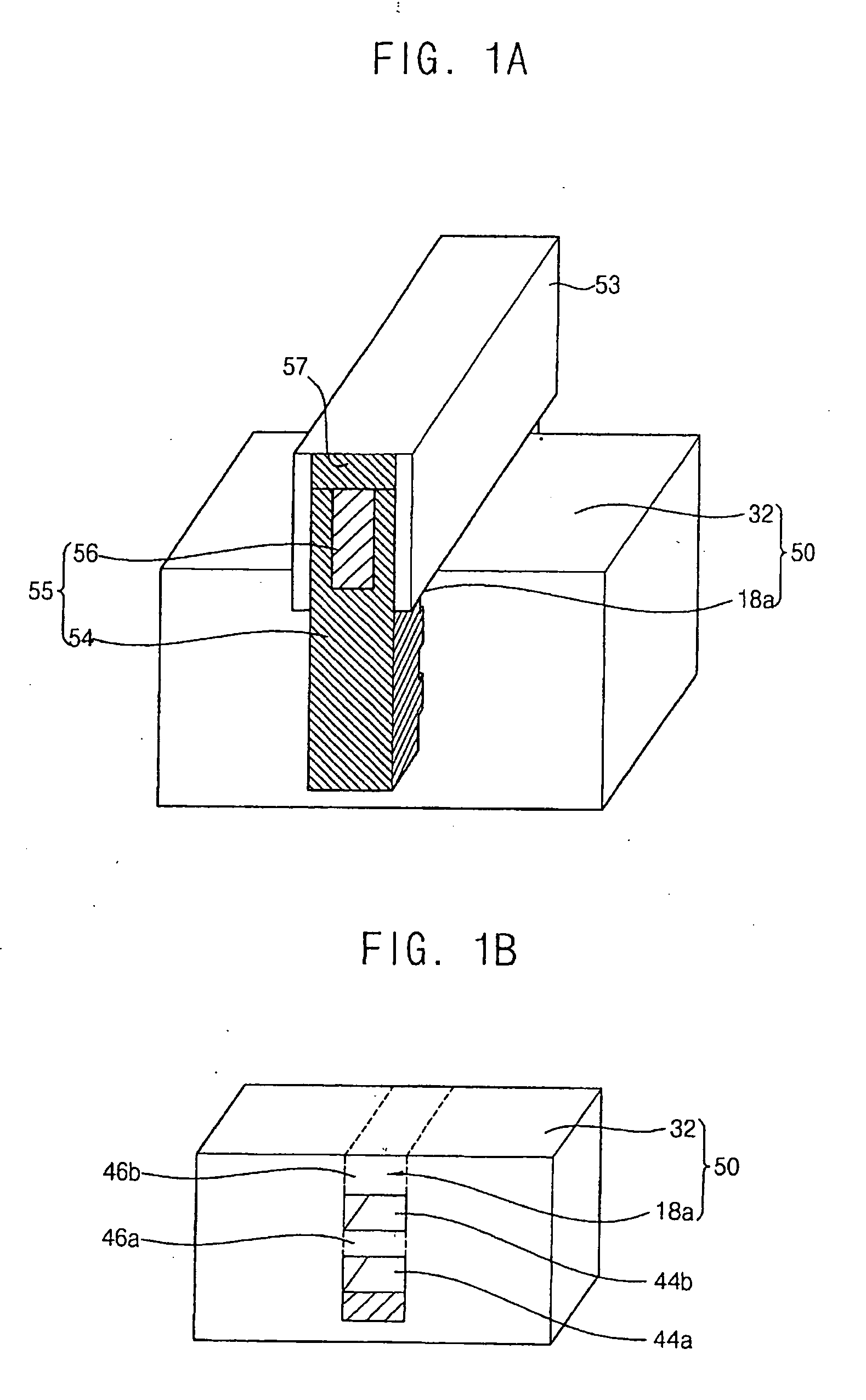

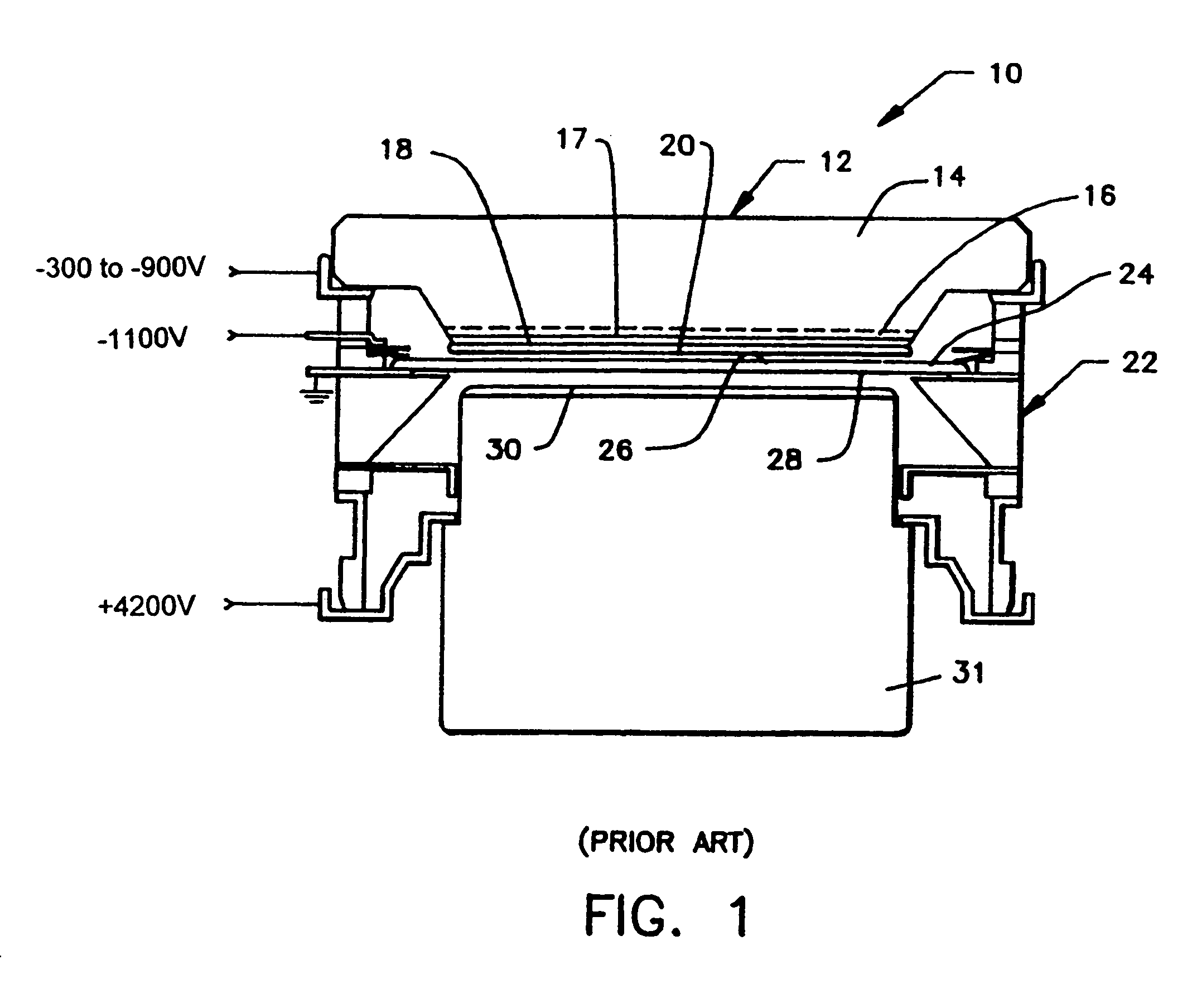

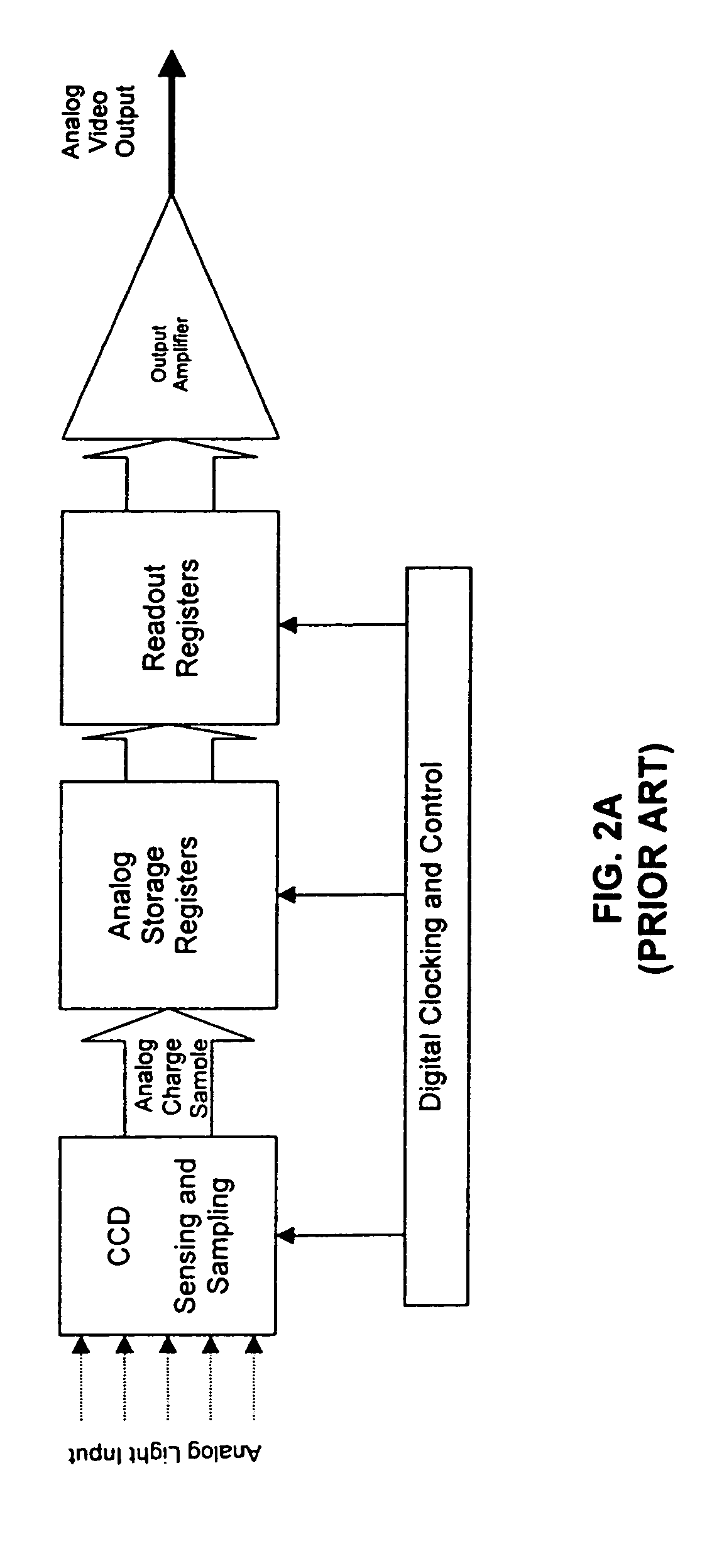

Intensified hybrid solid-state sensor

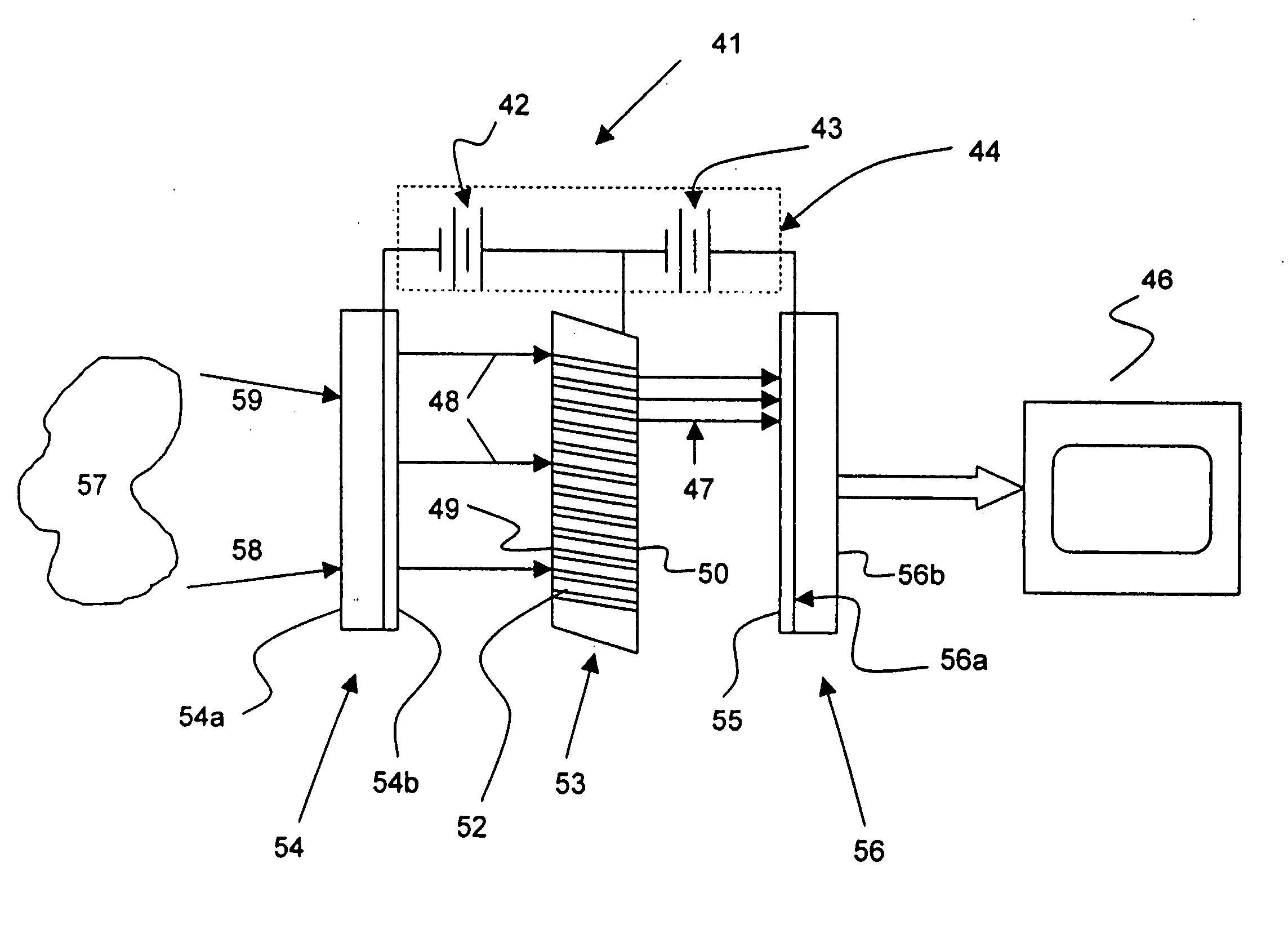

InactiveUS20050167575A1Television system detailsMaterial analysis by optical meansChannel patternImage signal

An intensified solid-state imaging sensor includes a photo cathode for converting light from an image into electrons, an electron multiplying device for receiving electrons from the photo cathode, and a solid-state image sensor including a plurality of pixels for receiving the electrons from the electron multiplying device through a plurality of channels of the electron multiplying device. The solid-state image sensor generates an intensified image signal from the electrons received from the electron multiplying device. The plurality of channels are arranged in a plurality of channel patterns, and the plurality of pixels are arranged in a plurality of pixel patterns. Each of the plurality of channel patterns is mapped to a respective one of the plurality of pixel patterns such that electron signals from each of the plurality of channel patterns is substantially received by the single respective one of the plurality of pixel patterns.

Owner:ELBIT SYSTEMS OF AMERICA LLC

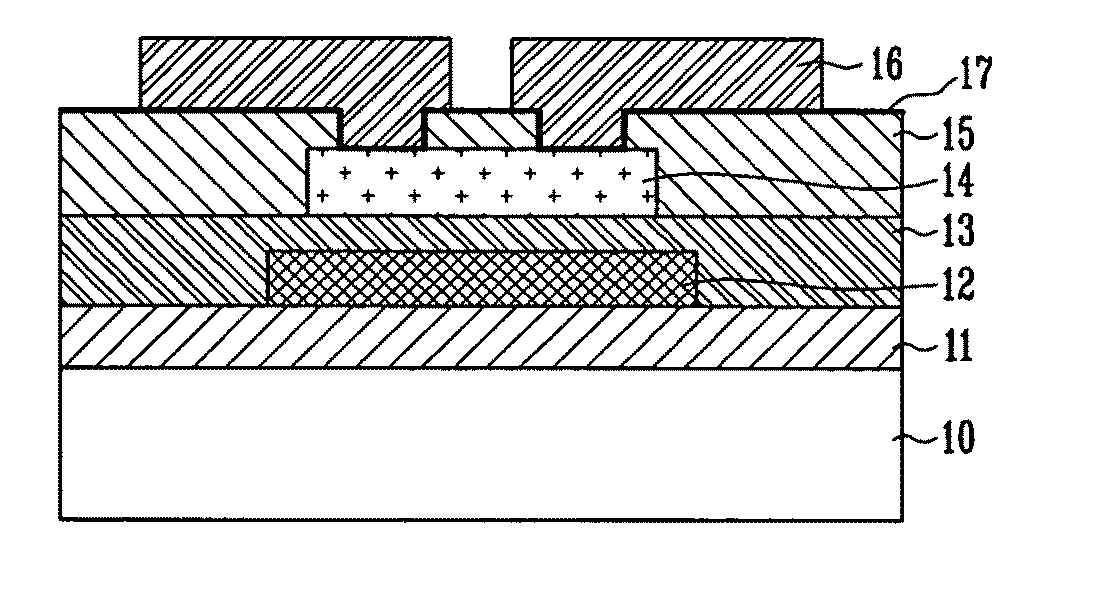

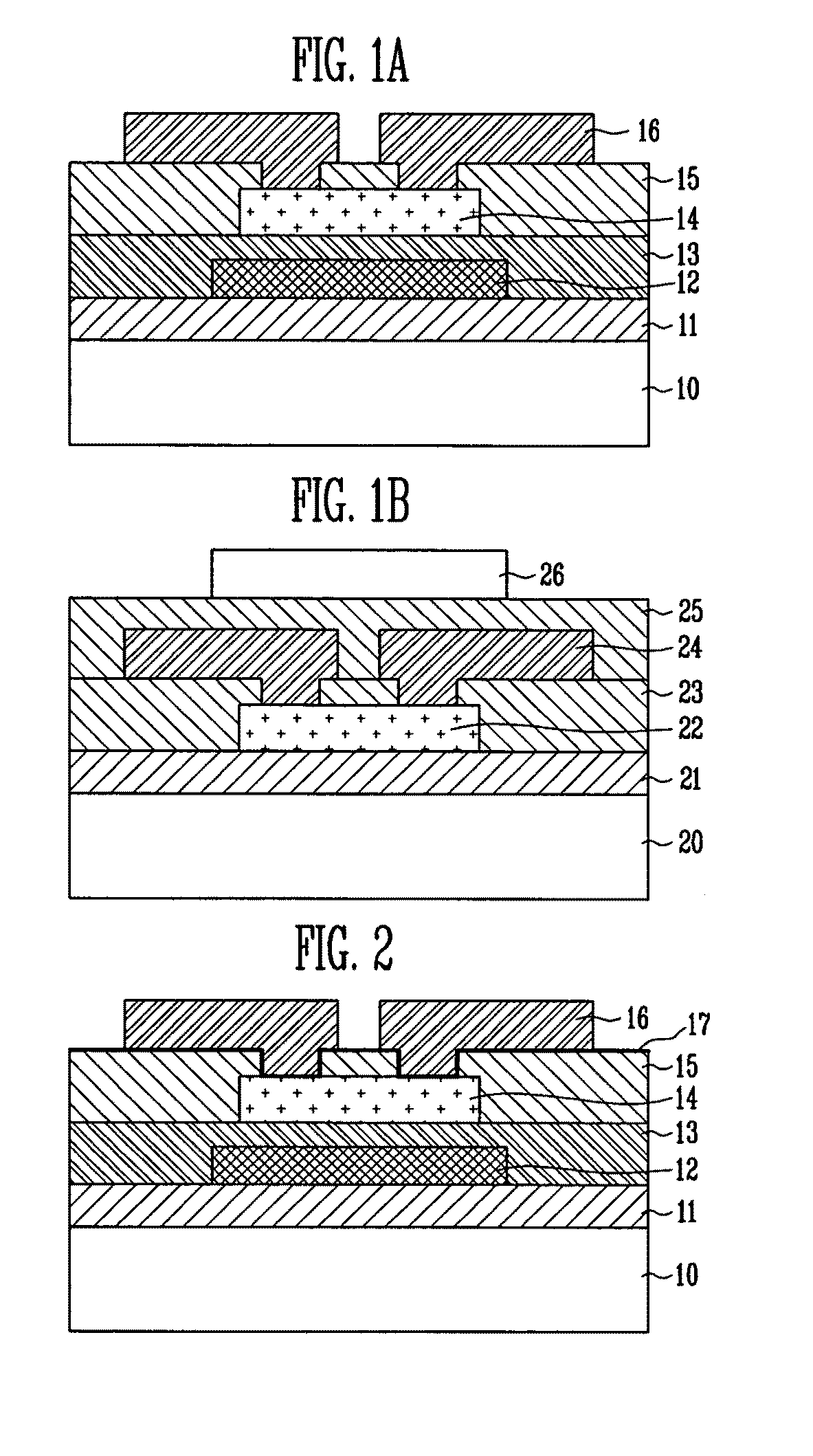

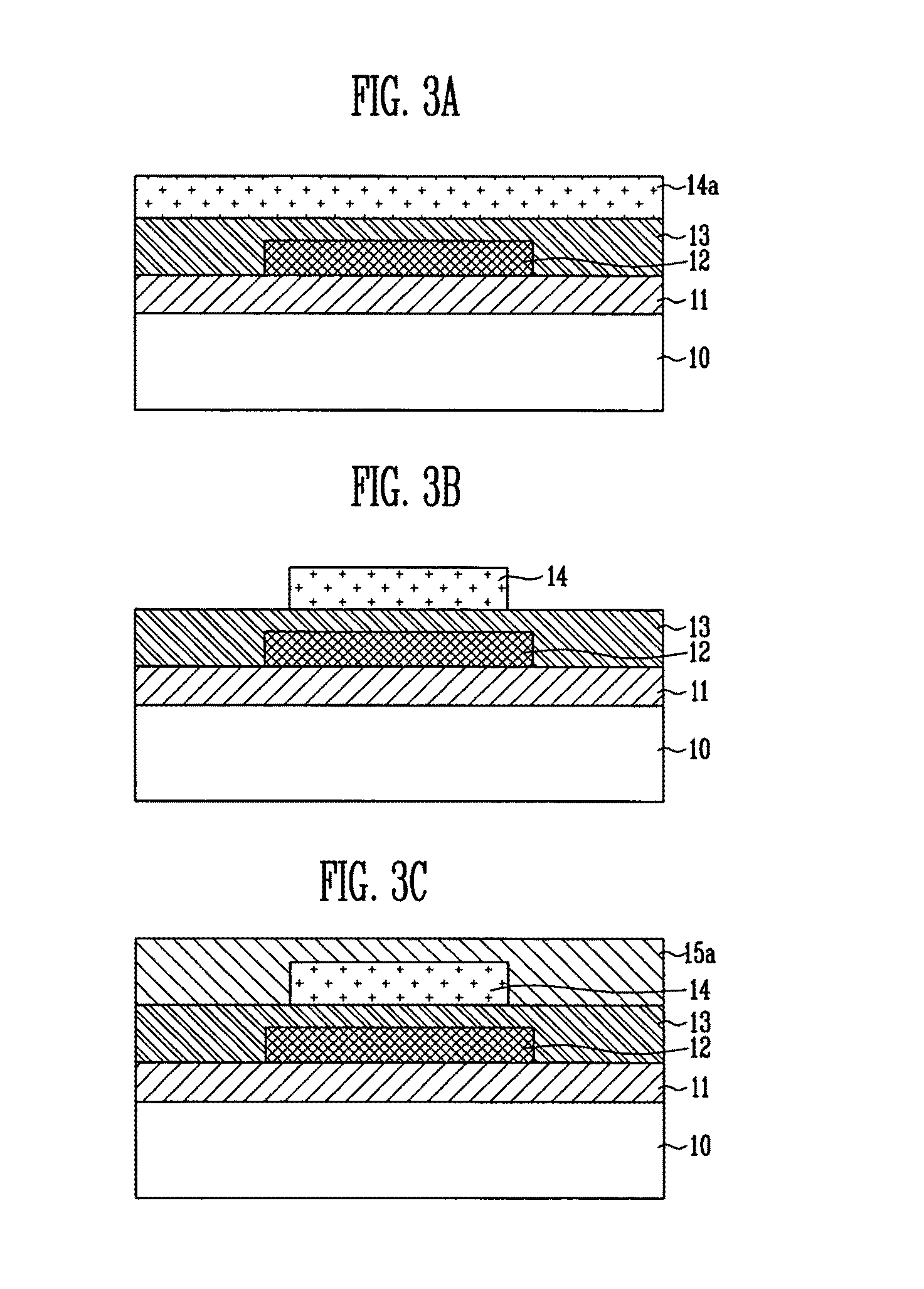

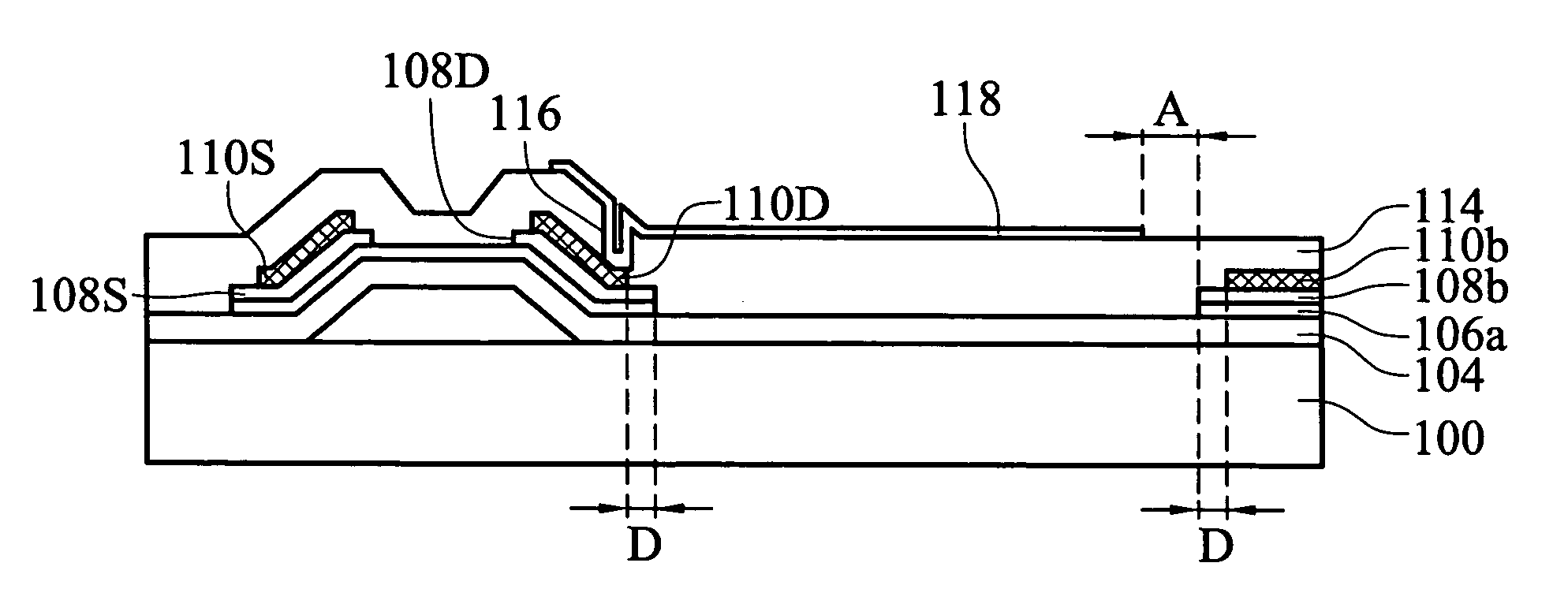

Thin film transistor and method of manufacturing the same

ActiveUS20090256147A1Without usingExcellent characteristicsTransistorSemiconductor/solid-state device manufacturingEngineeringChannel pattern

A thin film transistor, including a transparent channel pattern, a transparent gate insulating layer in contact with the channel pattern, a passivation film pattern disposed on the channel pattern, a source / drain coupled to the channel pattern through a via hole in the passivation film pattern, and a gate facing the channel pattern, the gate insulating layer interposed between the gate and the channel pattern, wherein the passivation film pattern includes at least one of polyimide, photoacryl, and spin on glass (SOG).

Owner:SAMSUNG DISPLAY CO LTD

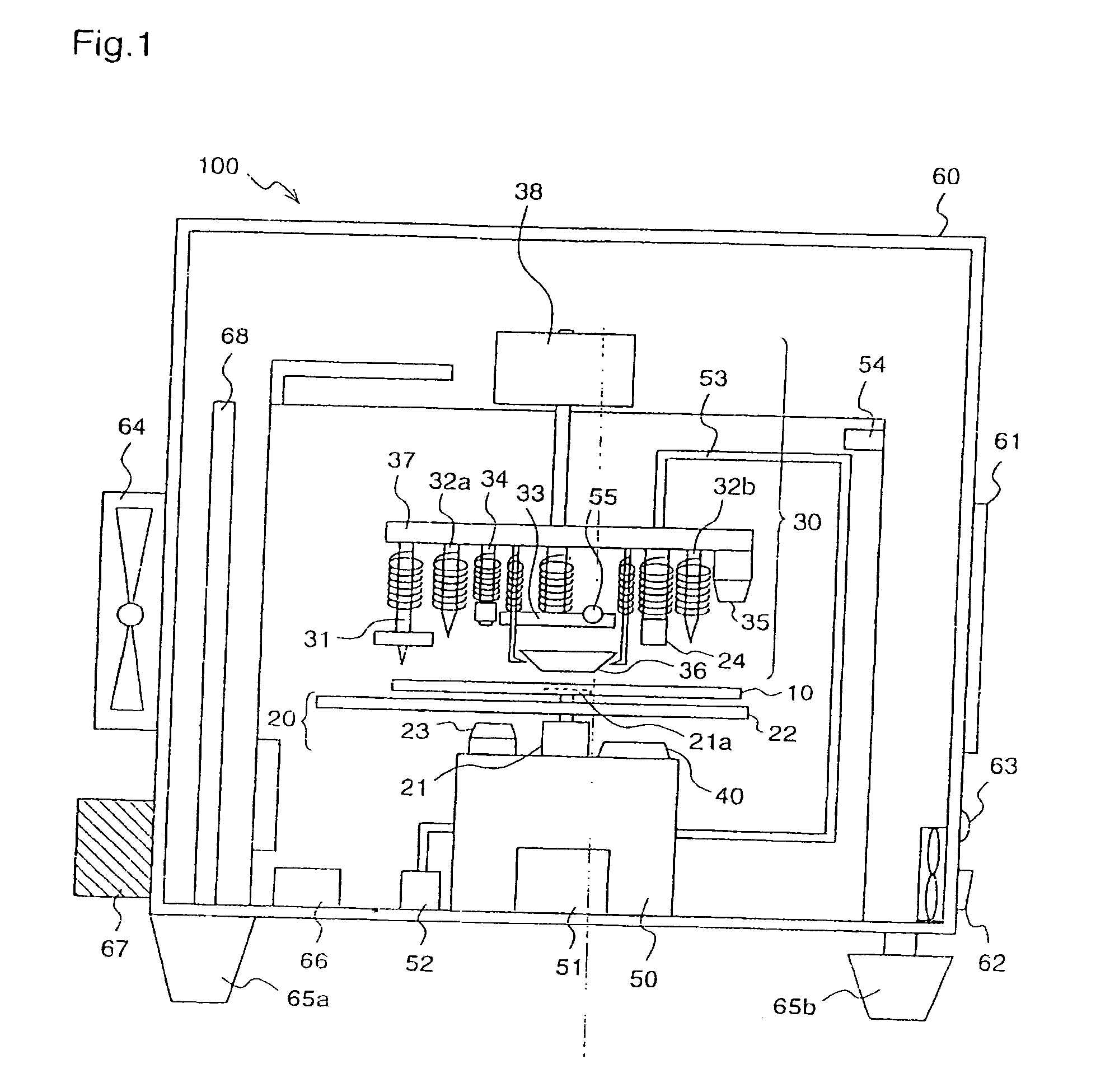

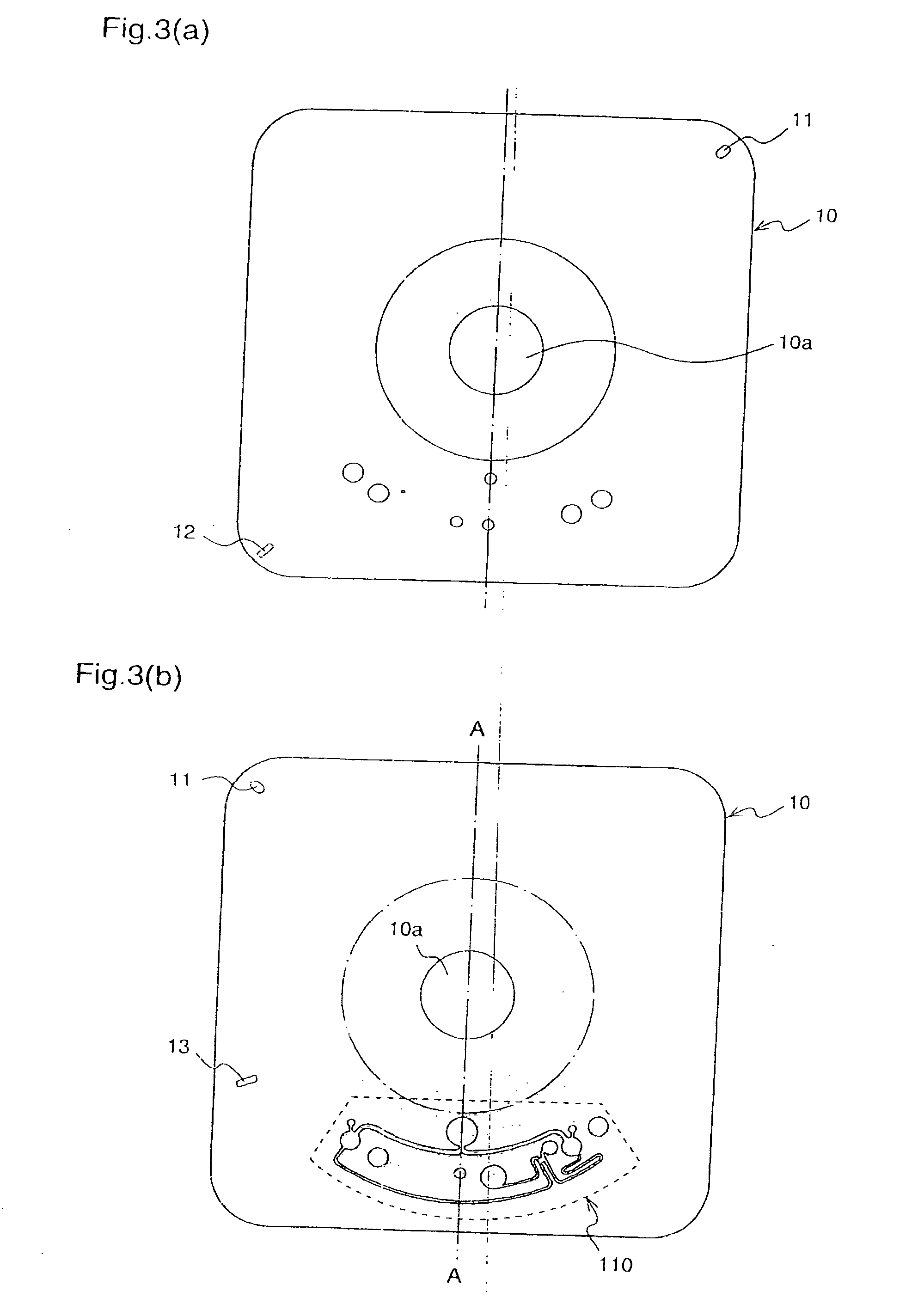

Microchip for sample, centrifugal dispension method of sample using the microchip and centrifugal dispenser

InactiveUS20060091085A1Lower the volumeUniform dispensingWater/sewage treatment by centrifugal separationHeating or cooling apparatusEngineeringChannel pattern

Owner:ISHIKAWA SEISAKUSHO +1

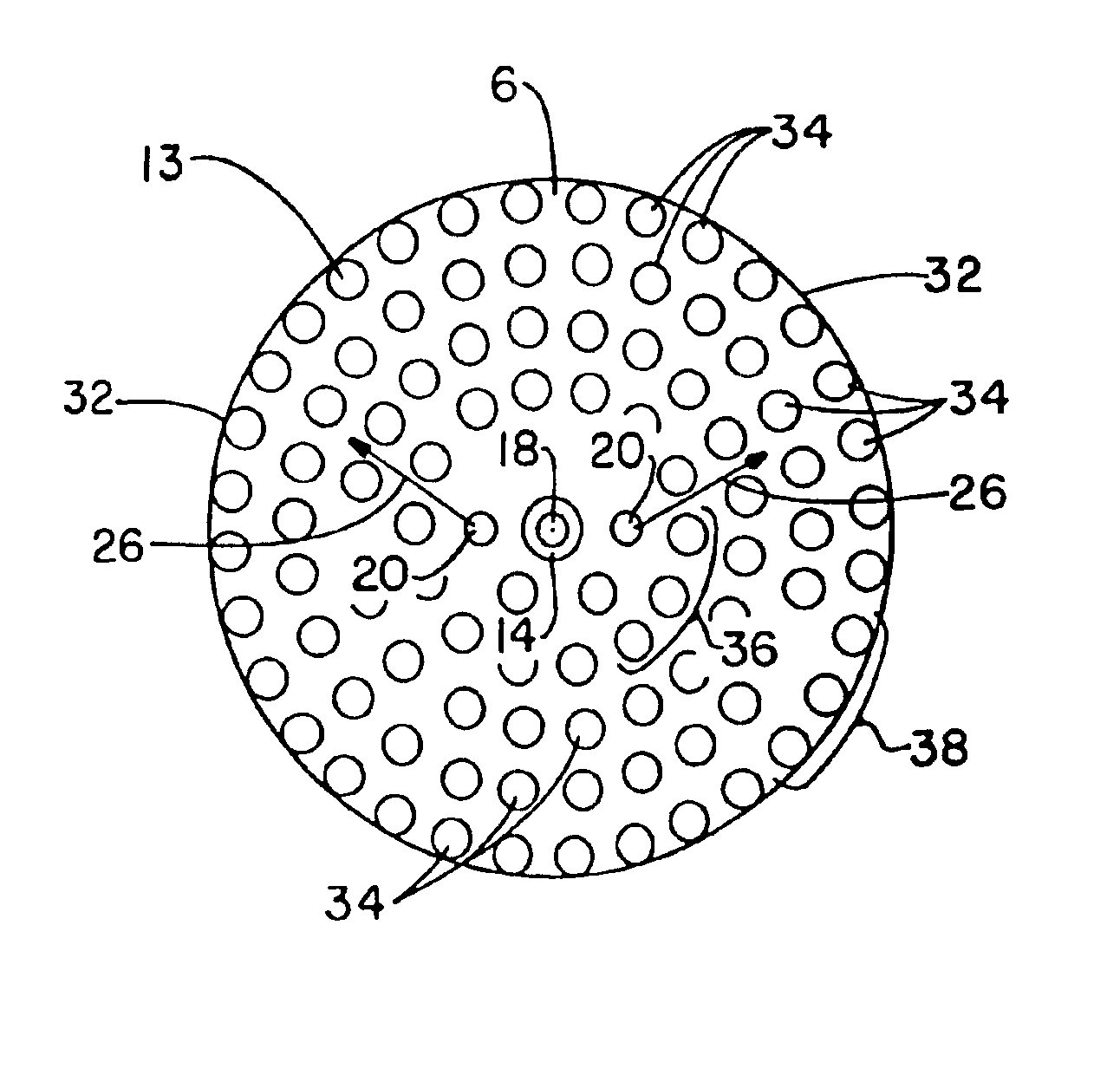

Electrochemical apparatus with reactant micro-channels

InactiveUS6878480B2Optimize allocationImproved volumetric power density and efficiencyFuel cells groupingFuel cell auxillariesFuel cellsEngineering

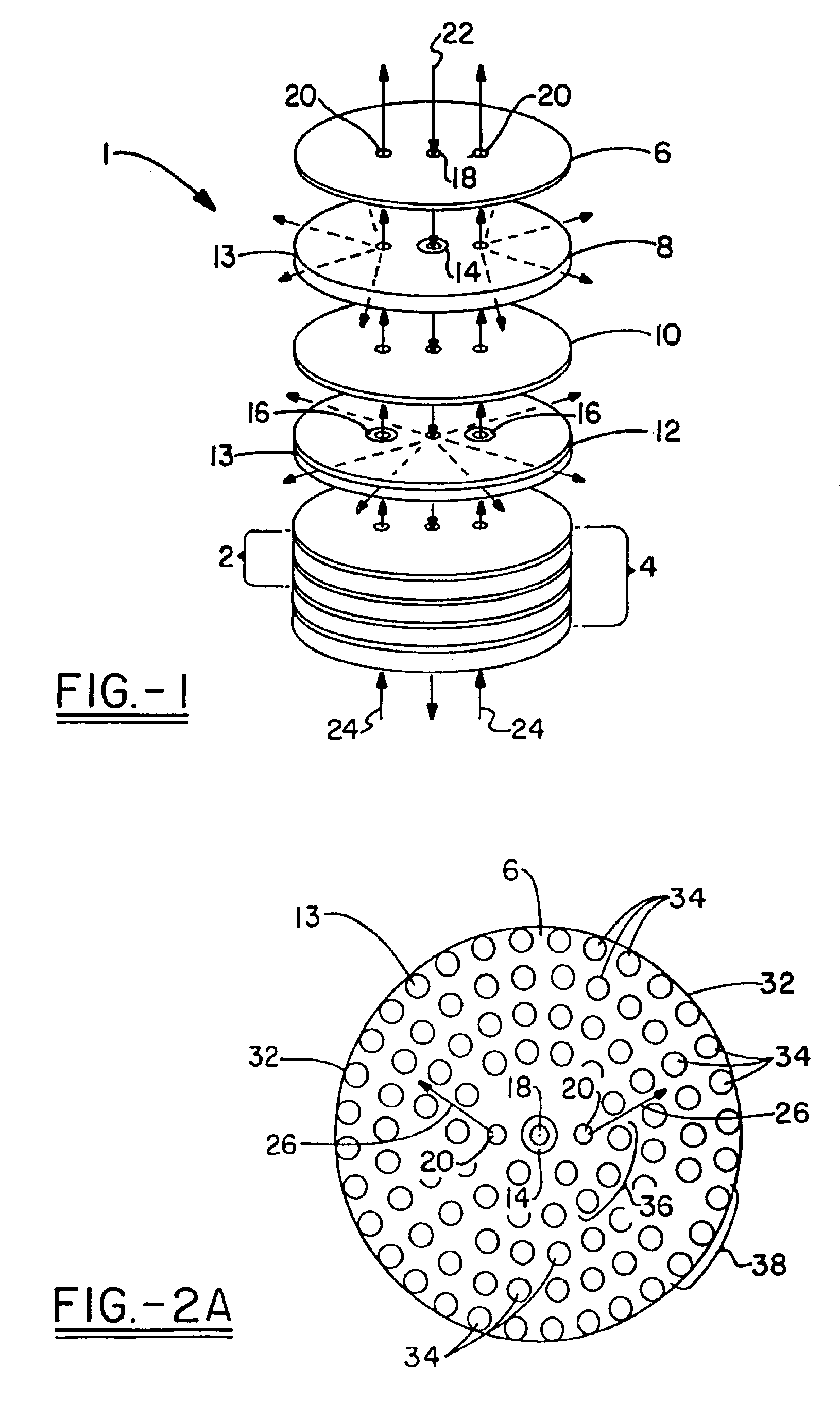

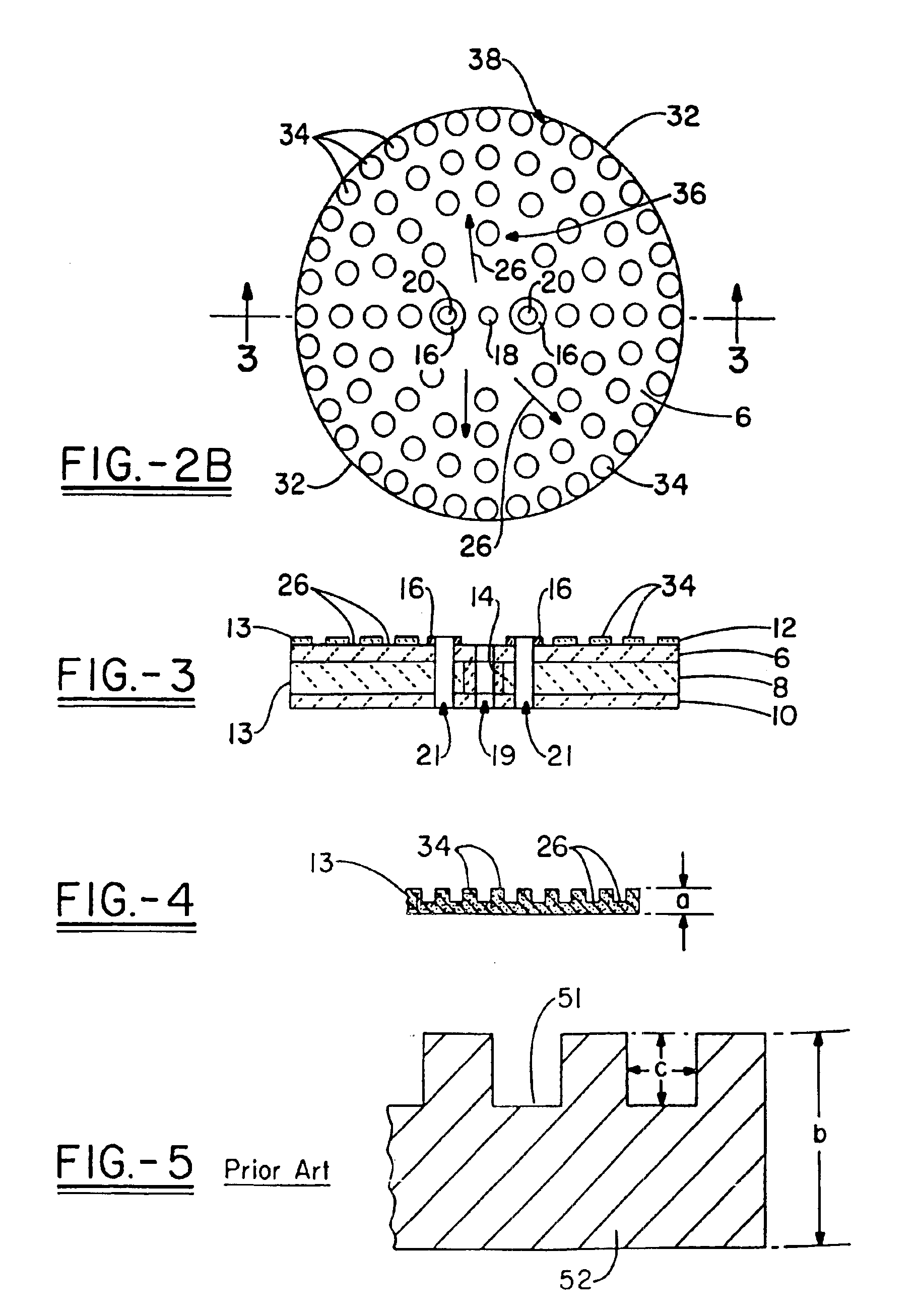

The present invention is directed generally to an electrochemical apparatus for oxidation or consumption of a fuel, and the generation of electricity, such as, a solid electrolyte fuel cell. The electrochemical apparatus (1) comprises at least one cell (2), wherein the cell (2) has a solid electrolyte (10) disposed between a unitary oxygen electrode (12) and a unitary fuel electrode (8), and at least one separator (6) contacting the surface of one of the electrodes (13) opposite of the electrolyte (10). At least one electrode (13) of the cell (2) defines a micro-channel pattern (26), wherein the micro-channel cross-section is preferably varied, such that reactant gas flowing through the micro channels achieves tailored local flow, pressure, and velocity distributions.

Owner:TECH MANAGEMENT

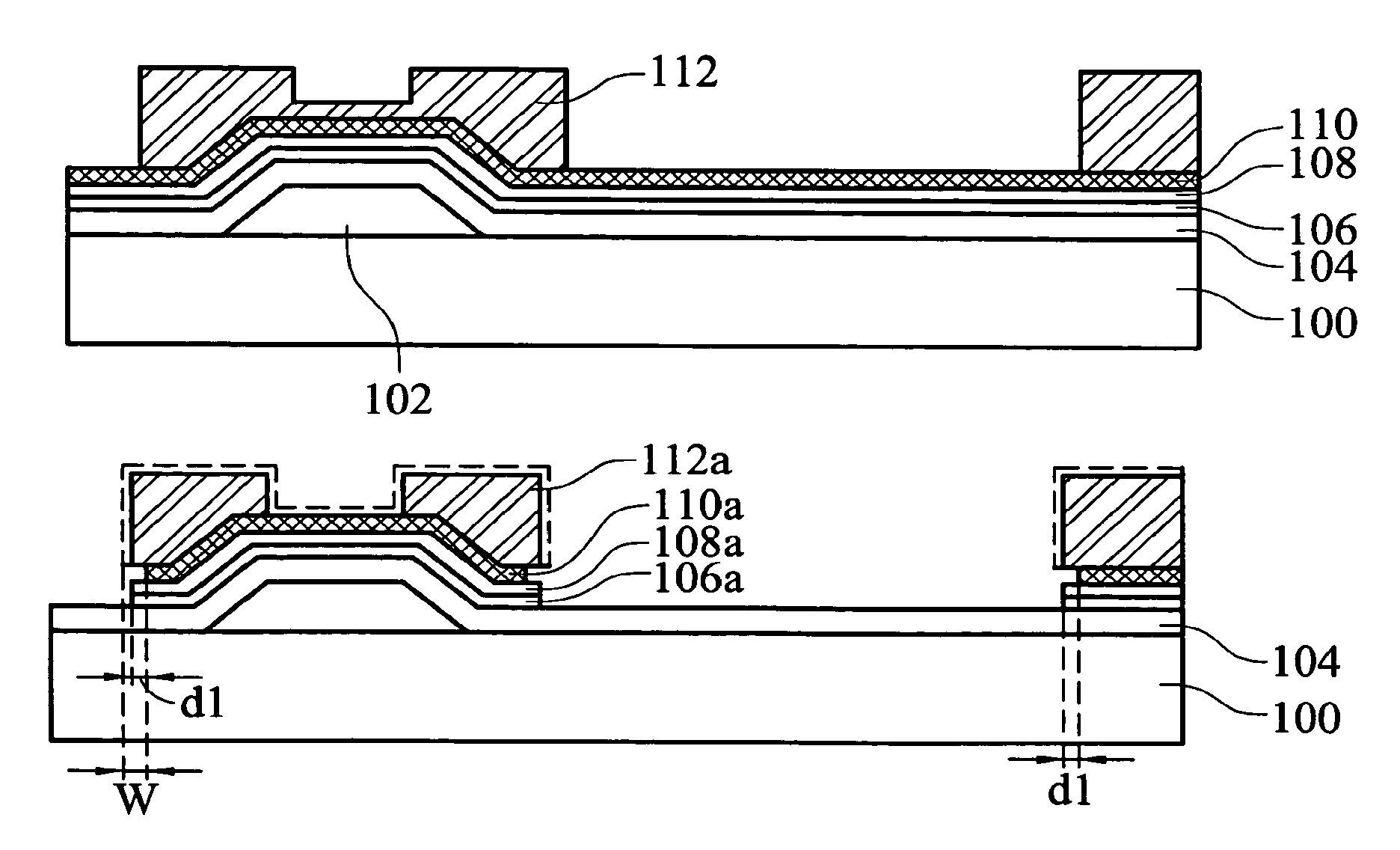

Method for forming a medium having data storage and communication capabilities

ActiveUS7051429B2Solid-state devicesSemiconductor/solid-state device manufacturingConductive materialsChannel pattern

A method for forming a medium having a substrate is formed have a patterned surface with a channel pattern and a transponder having a memory is provided in the channel pattern. A conductive material is deposited in the channel pattern with the conductive material operatively associated with the transponder.

Owner:EASTMAN KODAK CO

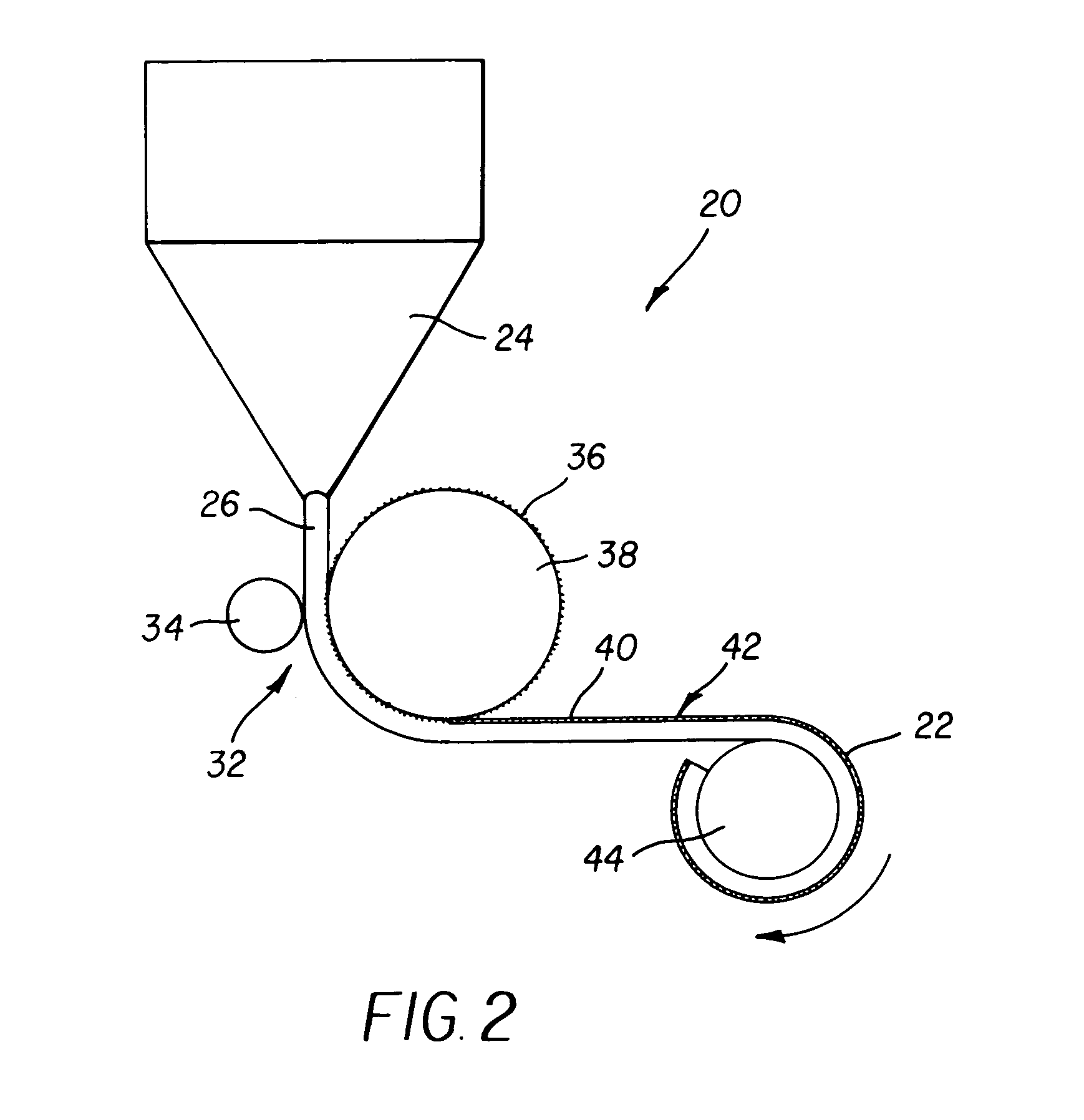

Disk-based fluid sample separation device

InactiveUS20120024083A1Simple processReduce manufacturing costWithdrawing sample devicesMaterial analysis by optical meansEngineeringChannel pattern

Owner:NAT TAIWAN UNIV

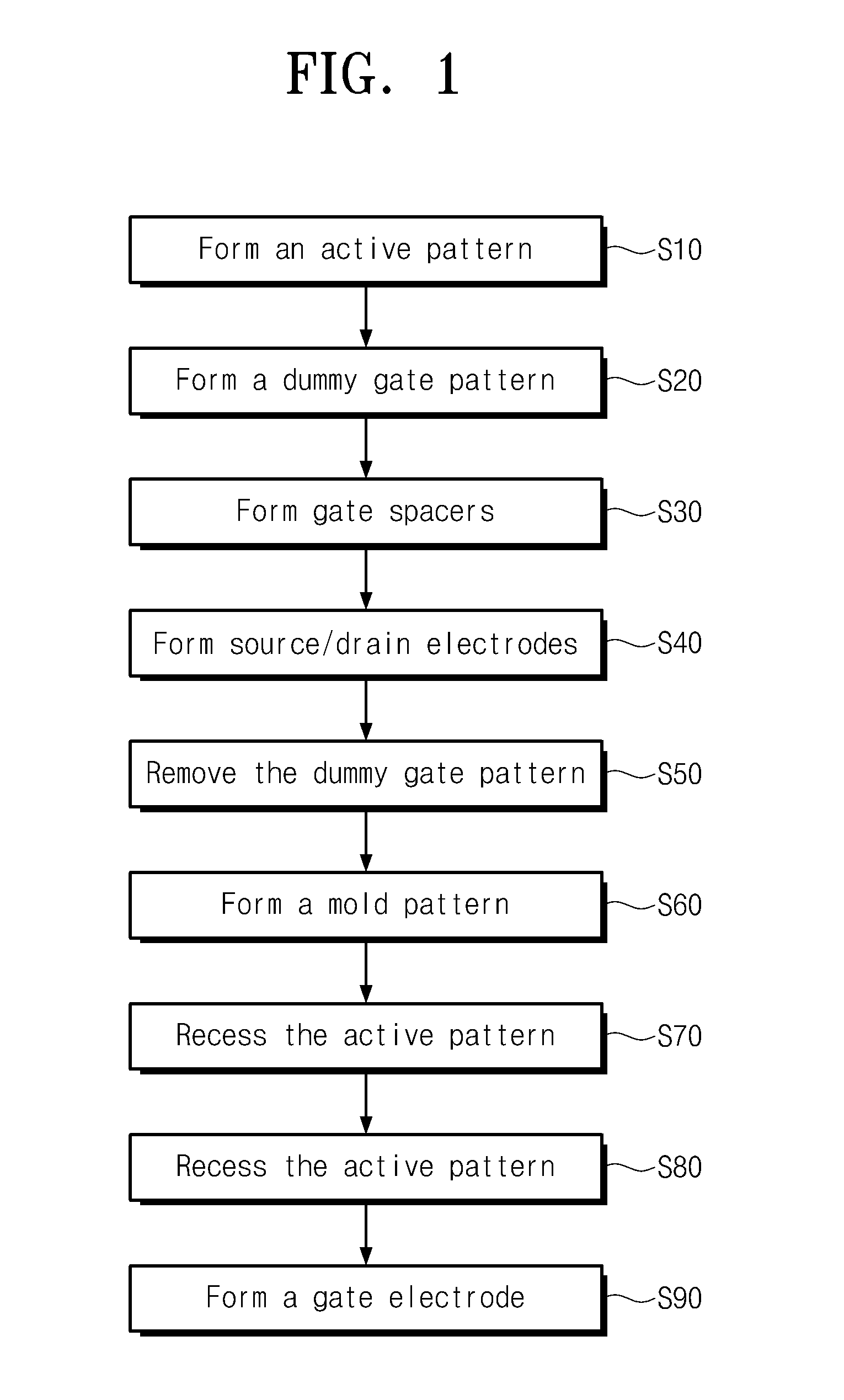

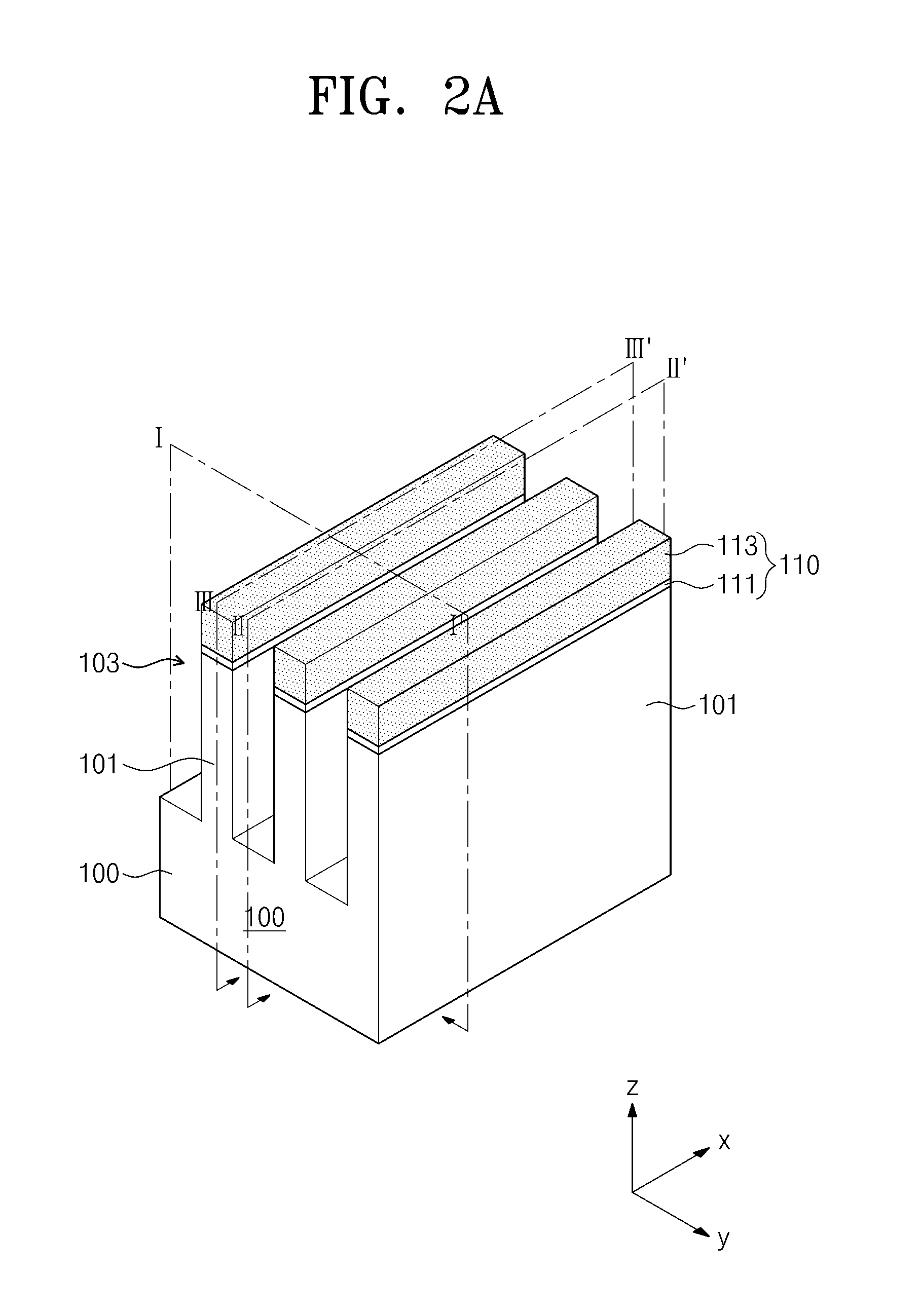

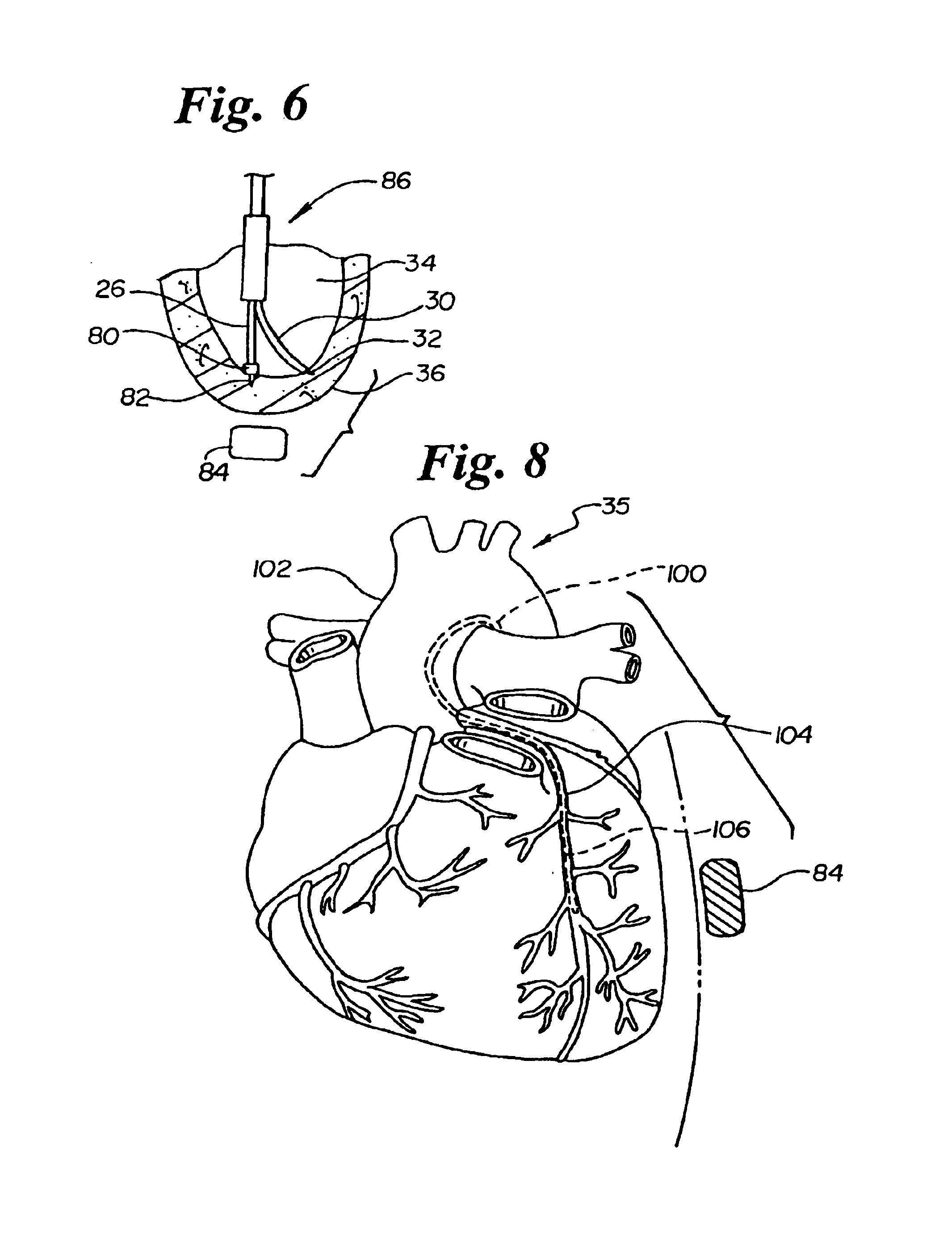

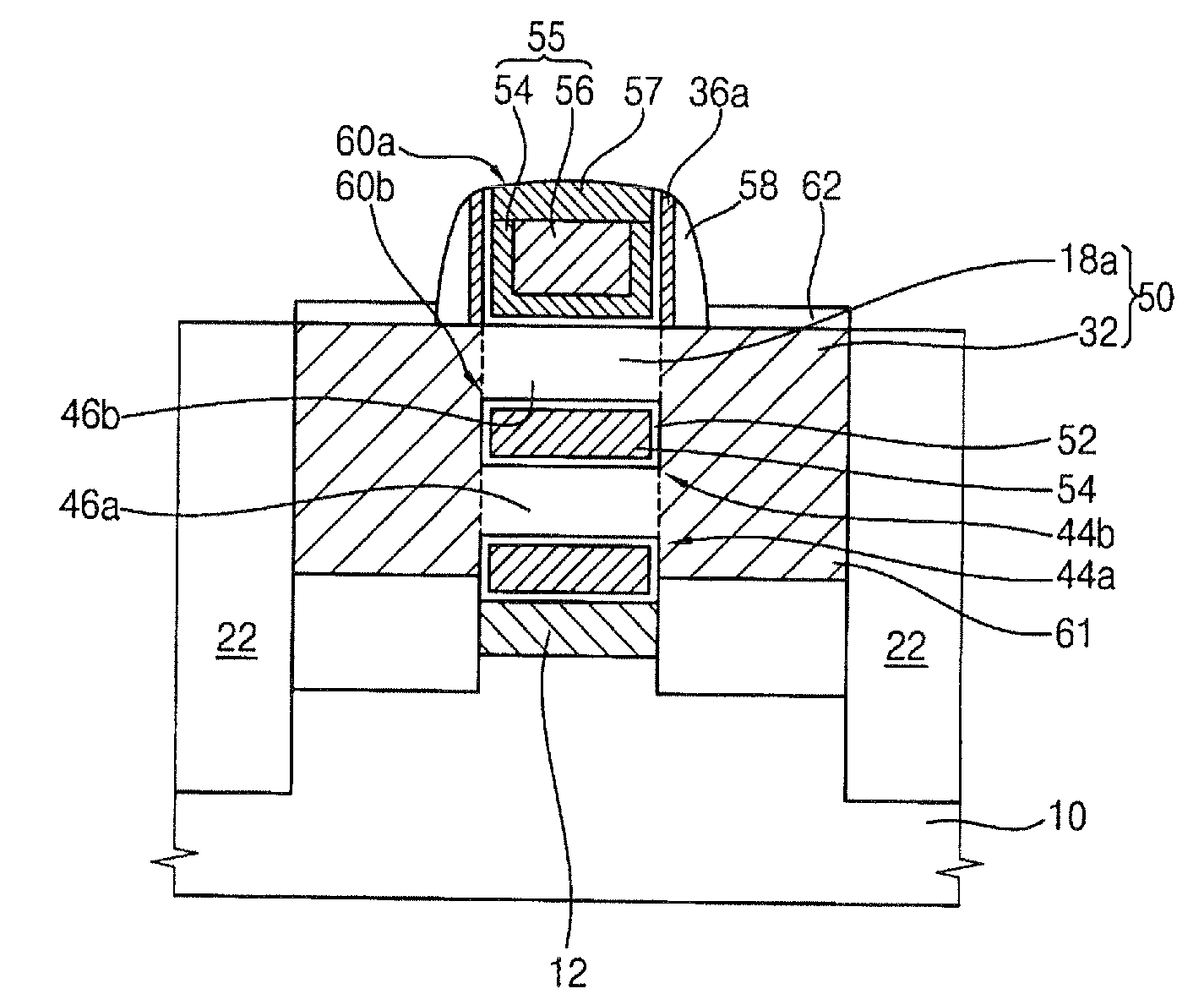

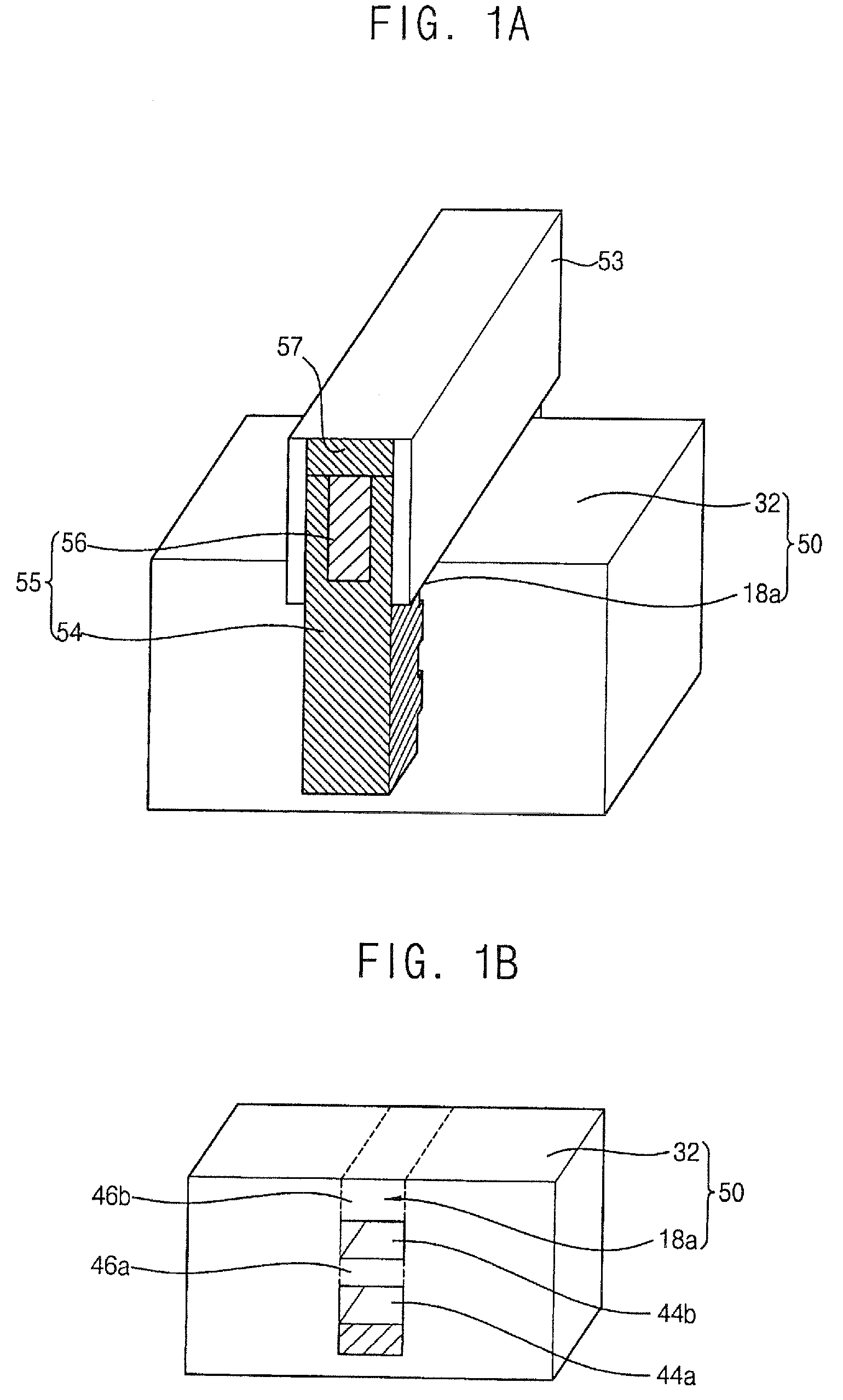

Semiconductor device and method of manufacturing the same

ActiveUS20150206956A1Excellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDevice material

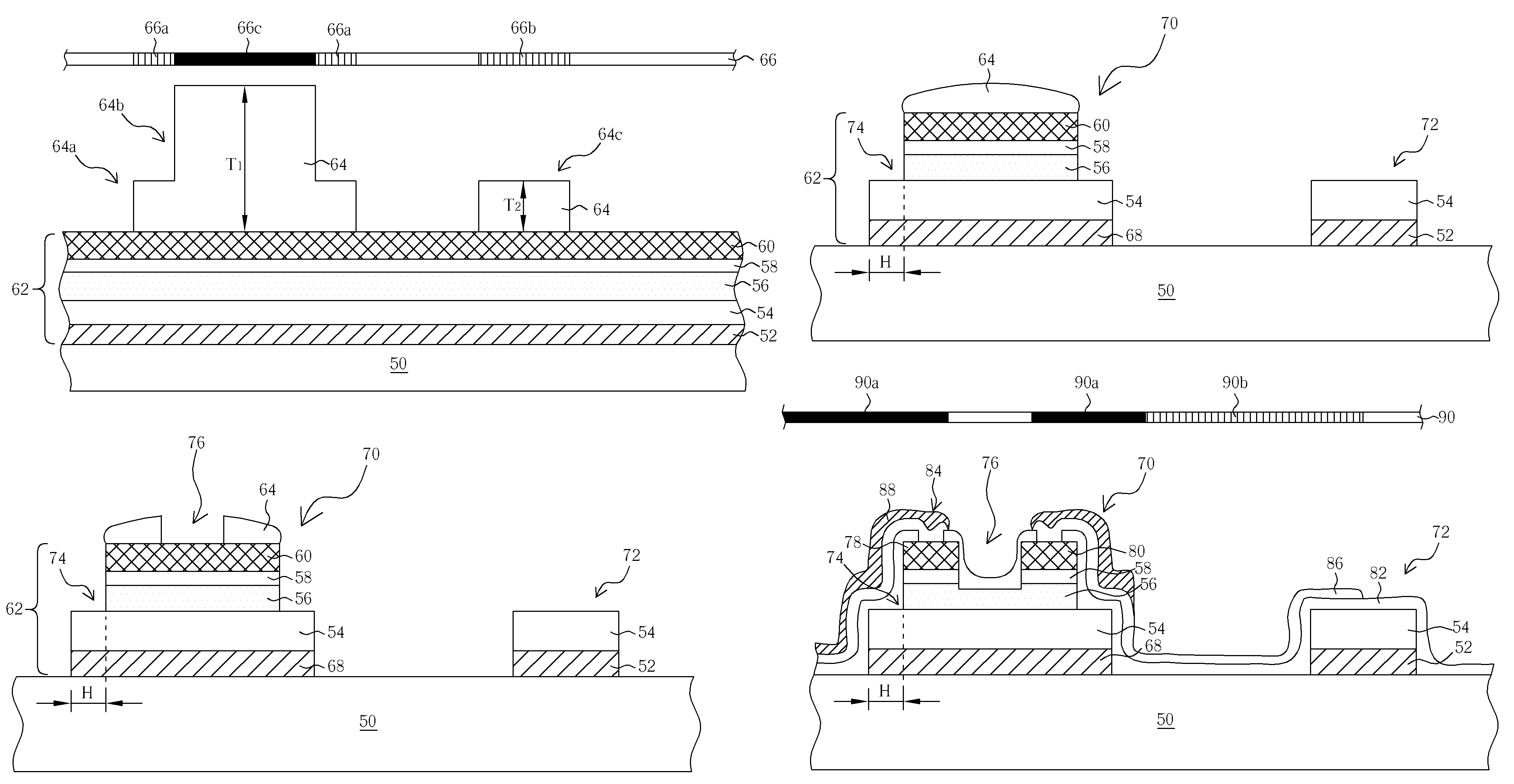

A method of manufacturing a semiconductor device includes forming an active pattern protruding from a semiconductor substrate, forming a dummy gate pattern crossing over the active pattern, forming gate spacers on opposite first and second sidewalls of the dummy gate pattern, removing the dummy gate pattern to form a gate region exposing an upper surface and sidewalls of the active pattern between the gate spacers, recessing the upper surface of the active pattern exposed by the gate region to form a channel recess region, forming a channel pattern in the channel recess region by a selective epitaxial growth (SEG) process, and sequentially forming a gate dielectric layer and a gate electrode covering an upper surface and sidewalls of the channel pattern in the gate region. The channel pattern has a lattice constant different from that of the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

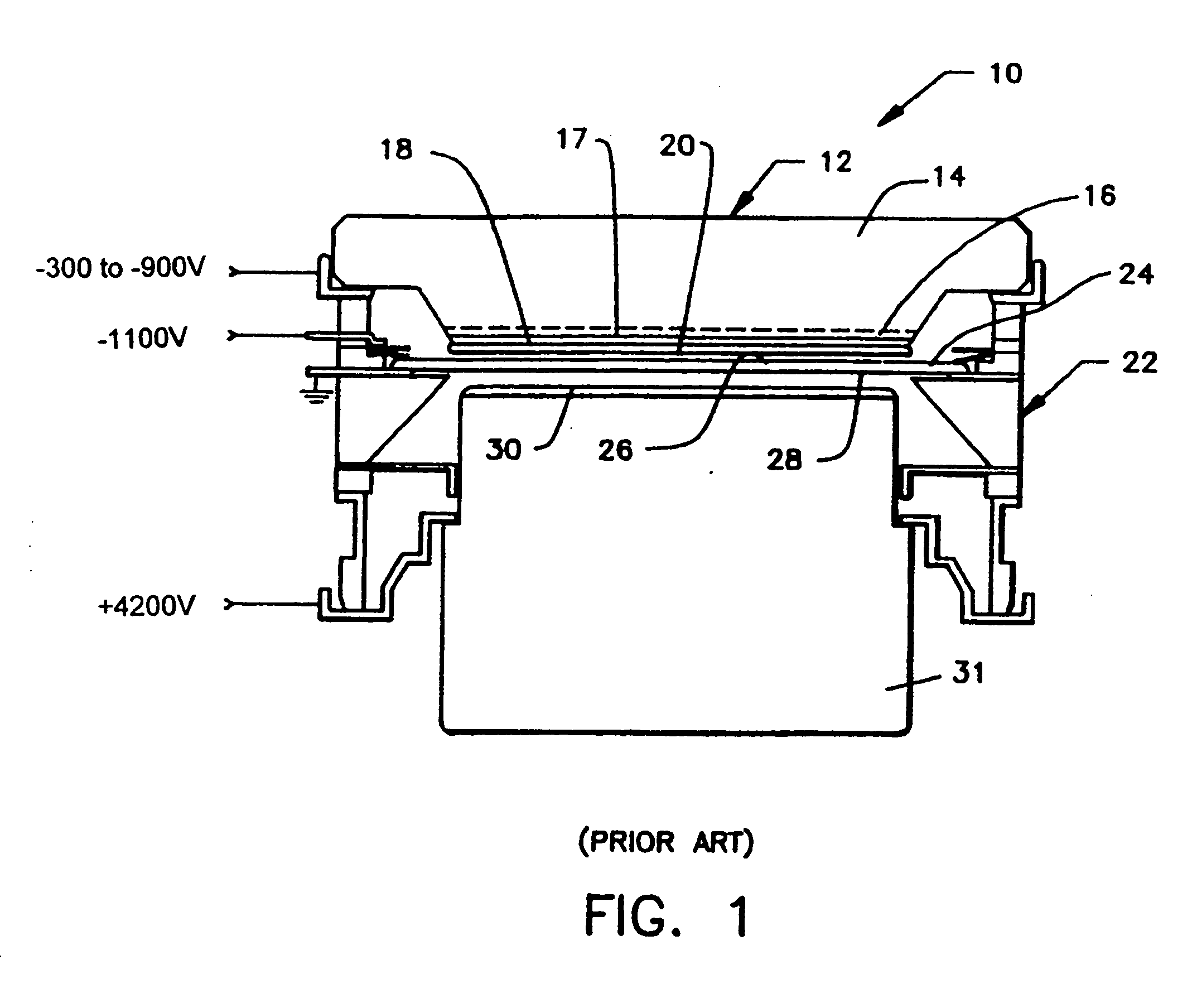

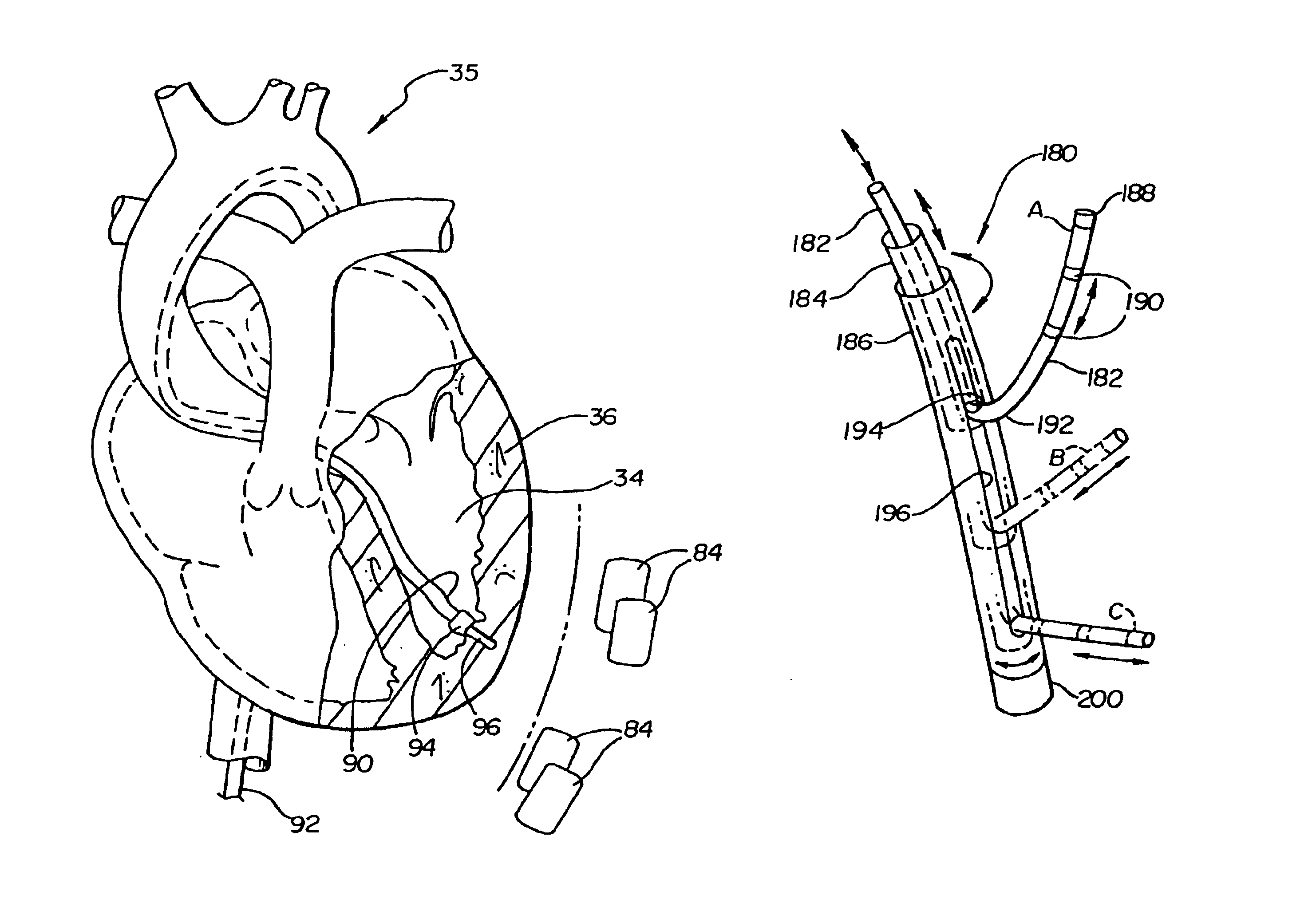

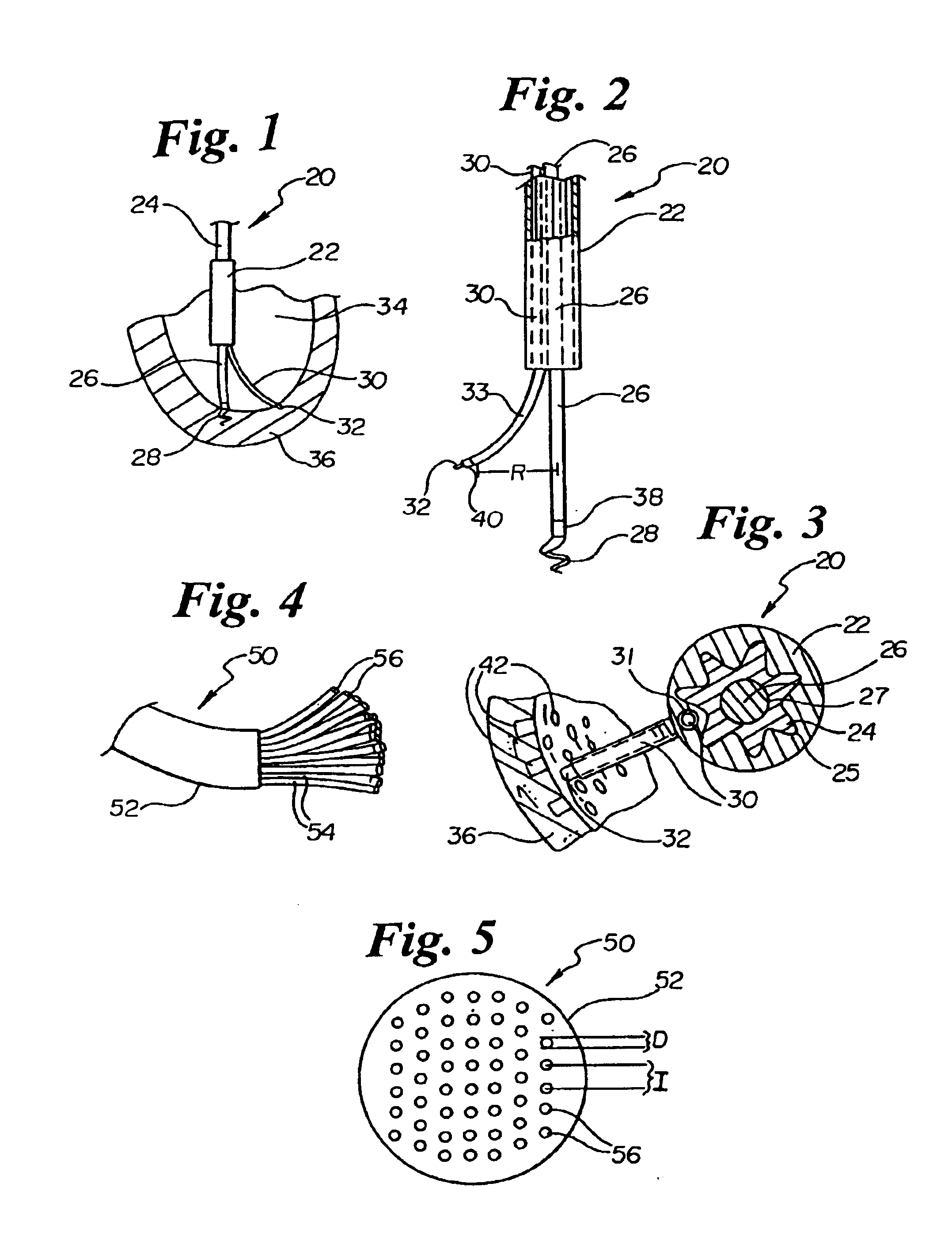

Percutaneous myocardial revascularization device and method

InactiveUS6951557B2Reduce in quantityReduce exerciseElectrotherapySurgical needlesCardiac muscleVideo fluoroscopy

Devices and methods for creating a series of percutaneous myocardial revascularization (PMR) channels in the heart. One method includes forming a pattern of channels in the myocardium leading from healthy tissue to hibernating tissue. Suitable channel patterns include lines and arrays. One method includes anchoring a radiopaque marker to a position in the ventricle wall, then using fluoroscopy repeatedly to guide positioning of a cutting tip in the formation of multiple channels. Another method uses radiopaque material injected into each channel formed, as a marker. Yet another method utilizes an anchorable, rotatable cutting probe for channel formation about an anchor member, where the cutting probe can vary in radial distance from the anchor. Still another method utilizes a multiple wire radio frequency burning probe, for formation of multiple channels simultaneously. Still another method utilizes liquid nitrogen to cause localized tissue death.

Owner:BOSTON SCI SCIMED INC

Semiconductor device having a multi-channel type MOS transistor

ActiveUS20100155827A1Reduce heat spreadLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialMetal silicide

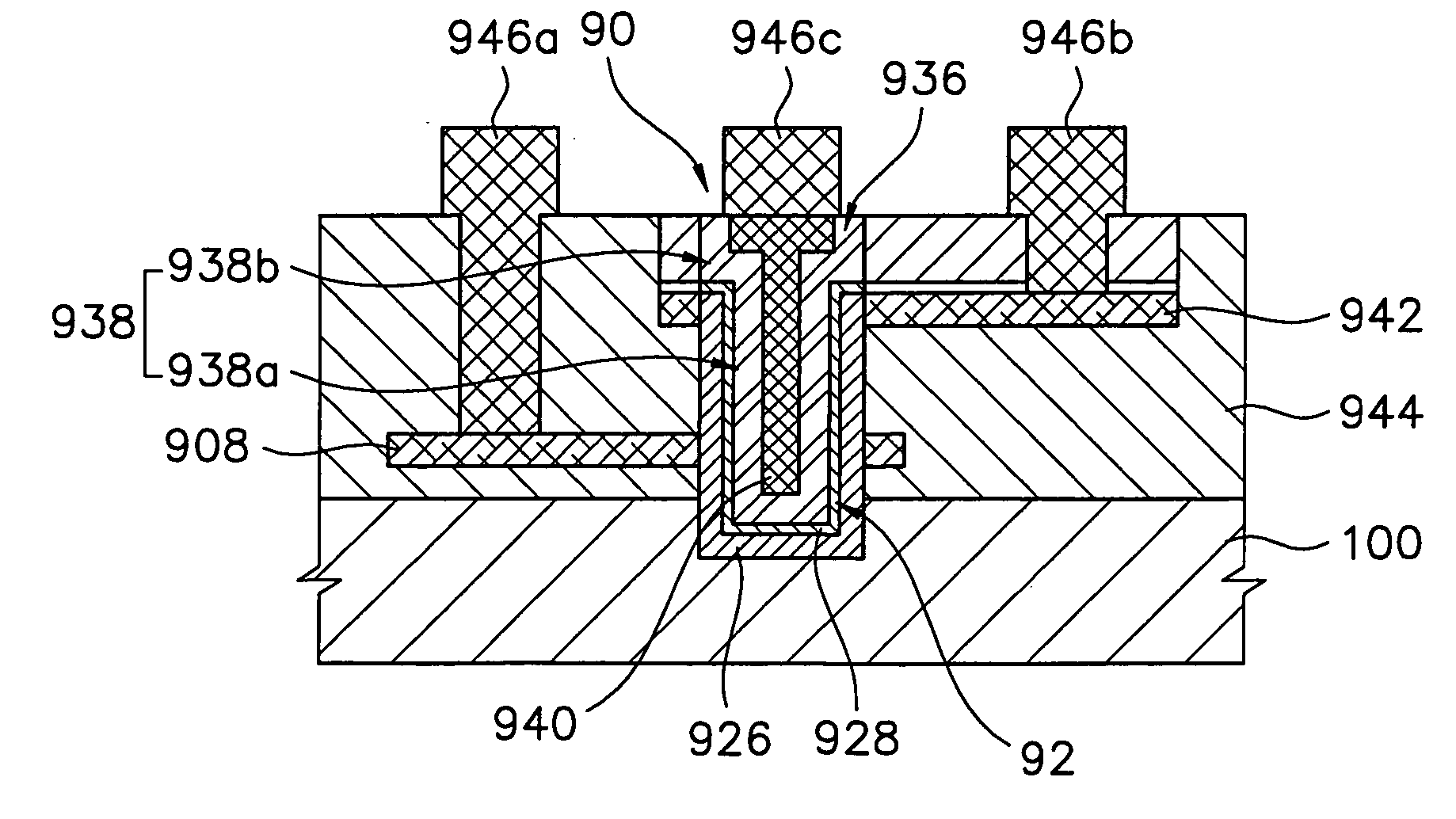

In a method of manufacturing a semiconductor device, an active channel pattern is formed on a substrate. The active channel pattern includes preliminary gate patterns and single crystalline silicon patterns that are alternately stacked with each other. A source / drain layer is formed on a sidewall of the active channel pattern. Mask pattern structures including a gate trench are formed on the active channel pattern and the source / drain layer. The patterns are selectively etched to form tunnels. The gate trench is then filled with a gate electrode. The gate electrode surrounds the active channel pattern. The gate electrode is protruded from the active channel pattern. The mask pattern structures are then removed. Impurities are implanted into the source / drain regions to form source / drain regions. A silicidation process is carried out on the source / drain regions to form a metal silicide layer, thereby completing a semiconductor device having a MOS transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

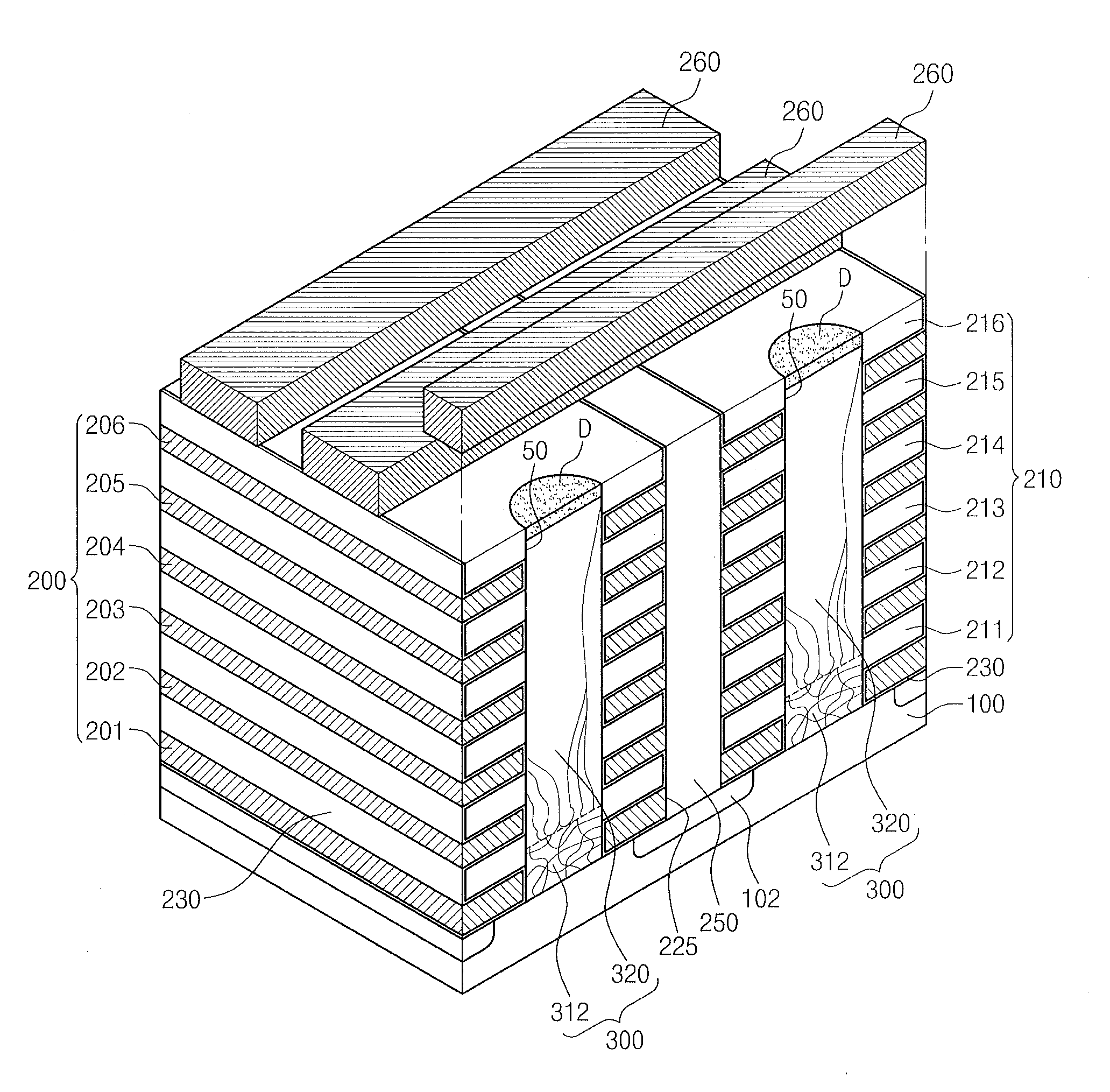

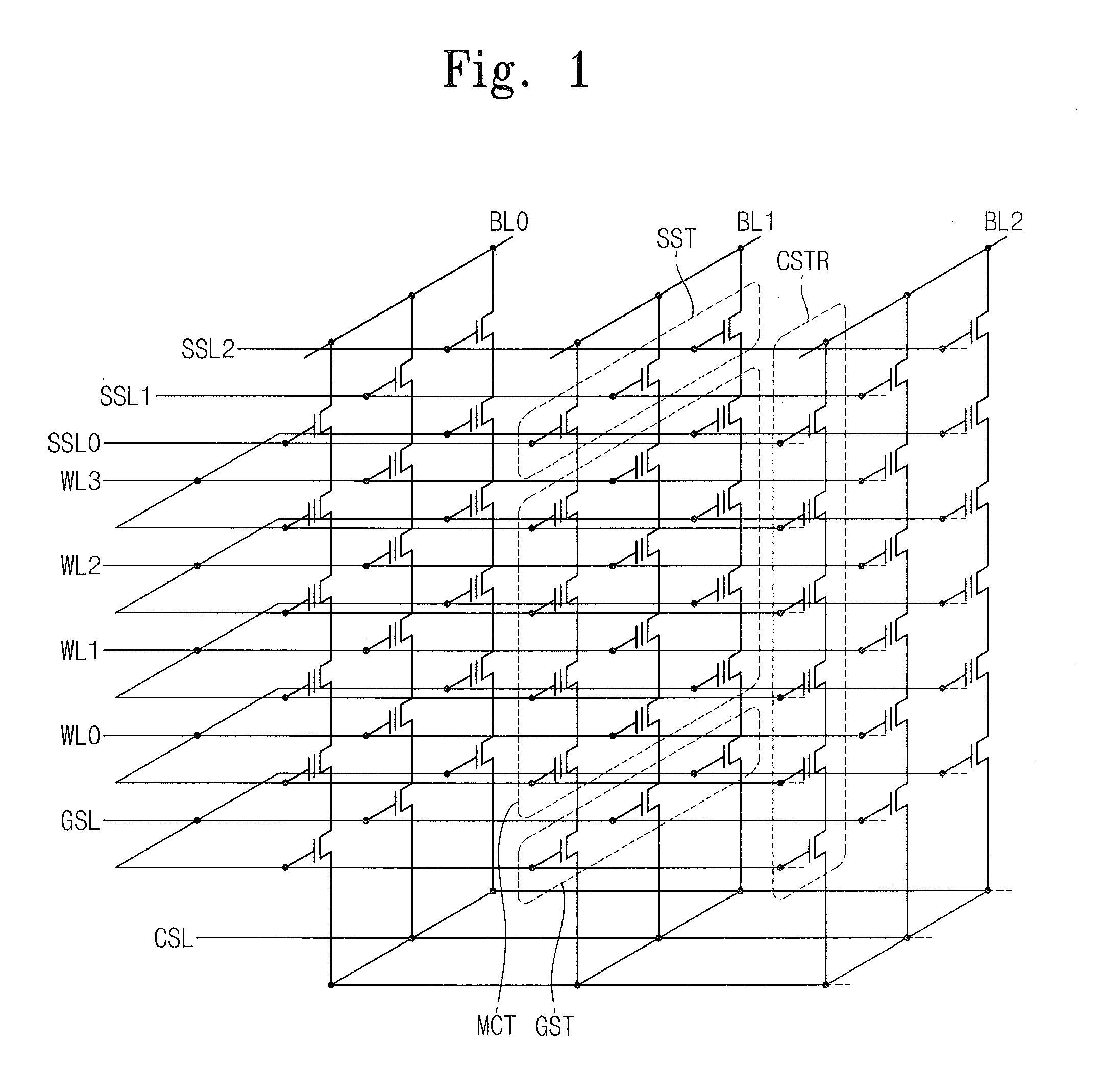

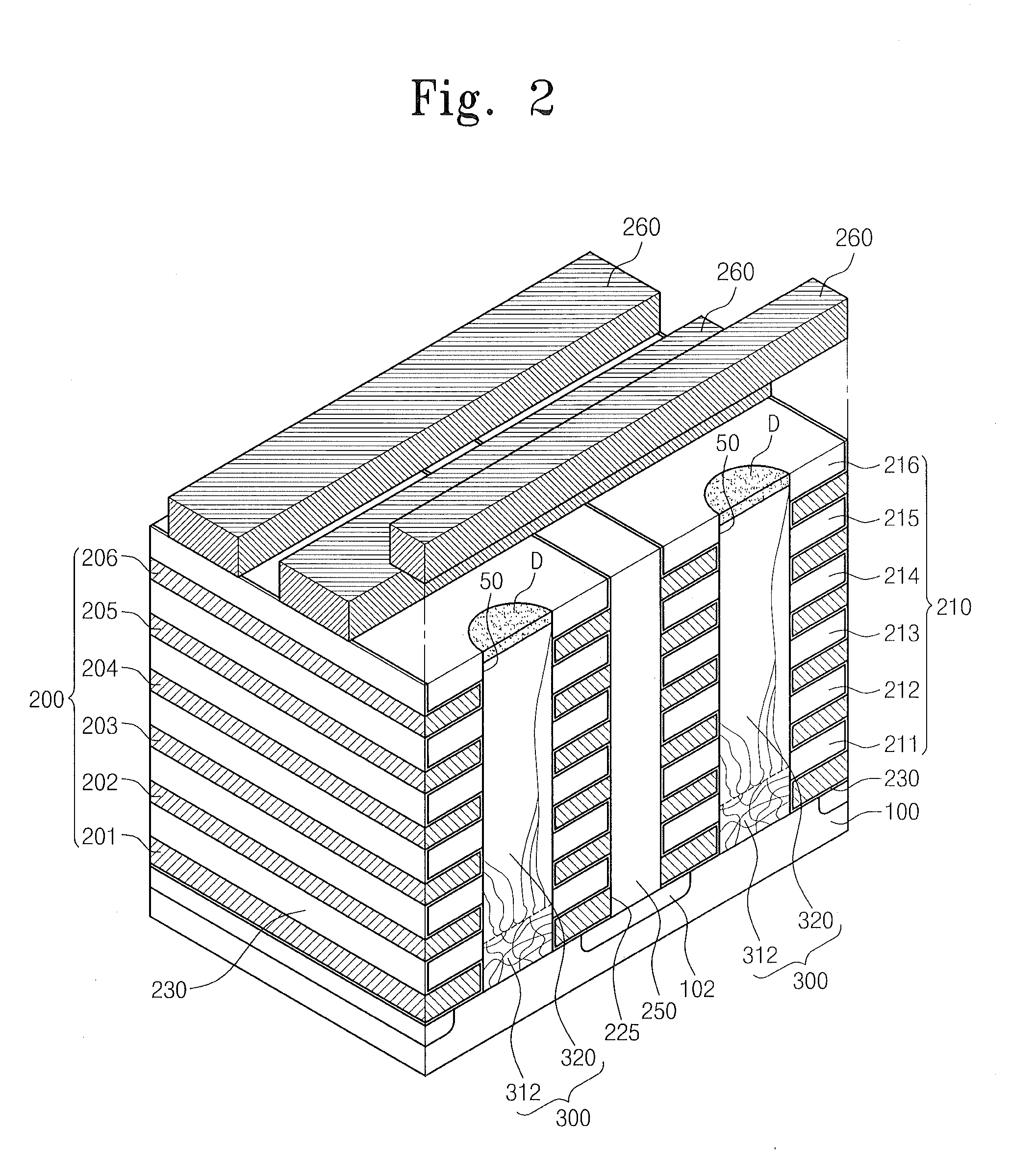

Multilayer semiconductor devices with channel patterns having a graded grain structure

ActiveUS20110186851A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

Memory devices include a stack of interleaved conductive patterns and insulating patterns disposed on a substrate. A semiconductor pattern passes through the stack of conductive patterns and insulating patterns to contact the substrate, the semiconductor pattern having a graded grain size distribution wherein a mean grain size in a first portion of the semiconductor pattern proximate the substrate is less than a mean grain size in a second portion of the semiconductor pattern further removed from the substrate. The graded grain size distribution may be achieved, for example, by partial laser annealing.

Owner:SAMSUNG ELECTRONICS CO LTD

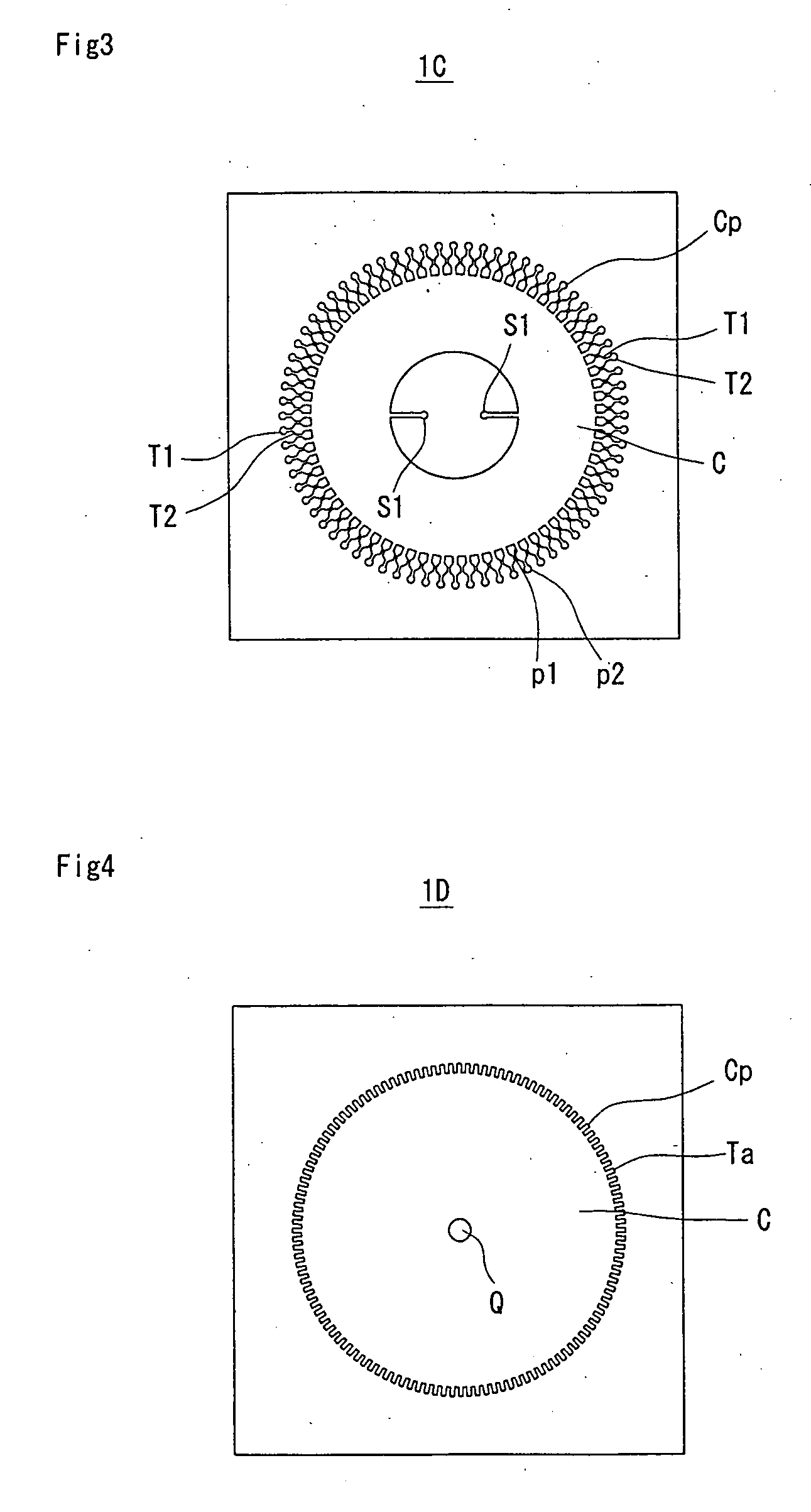

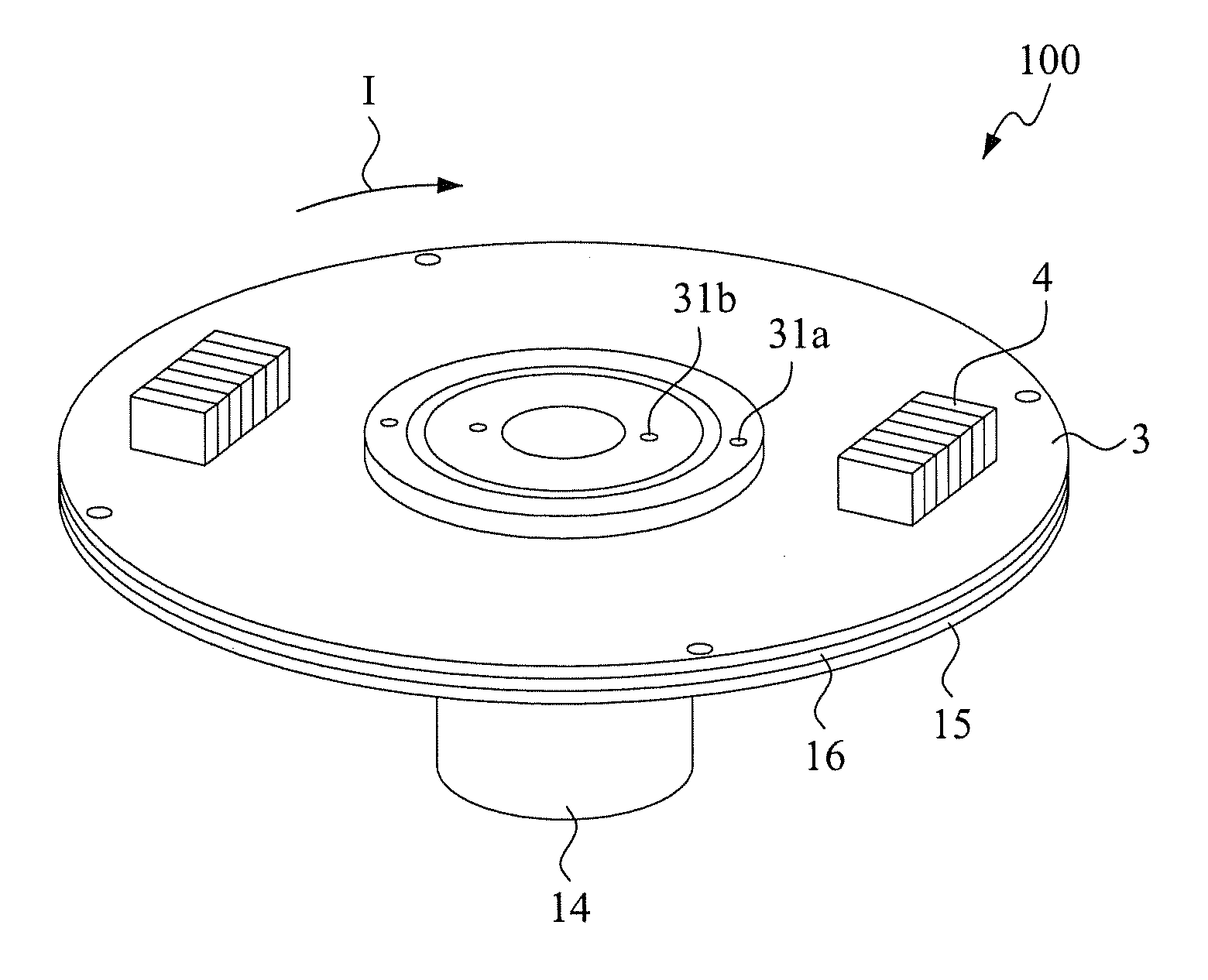

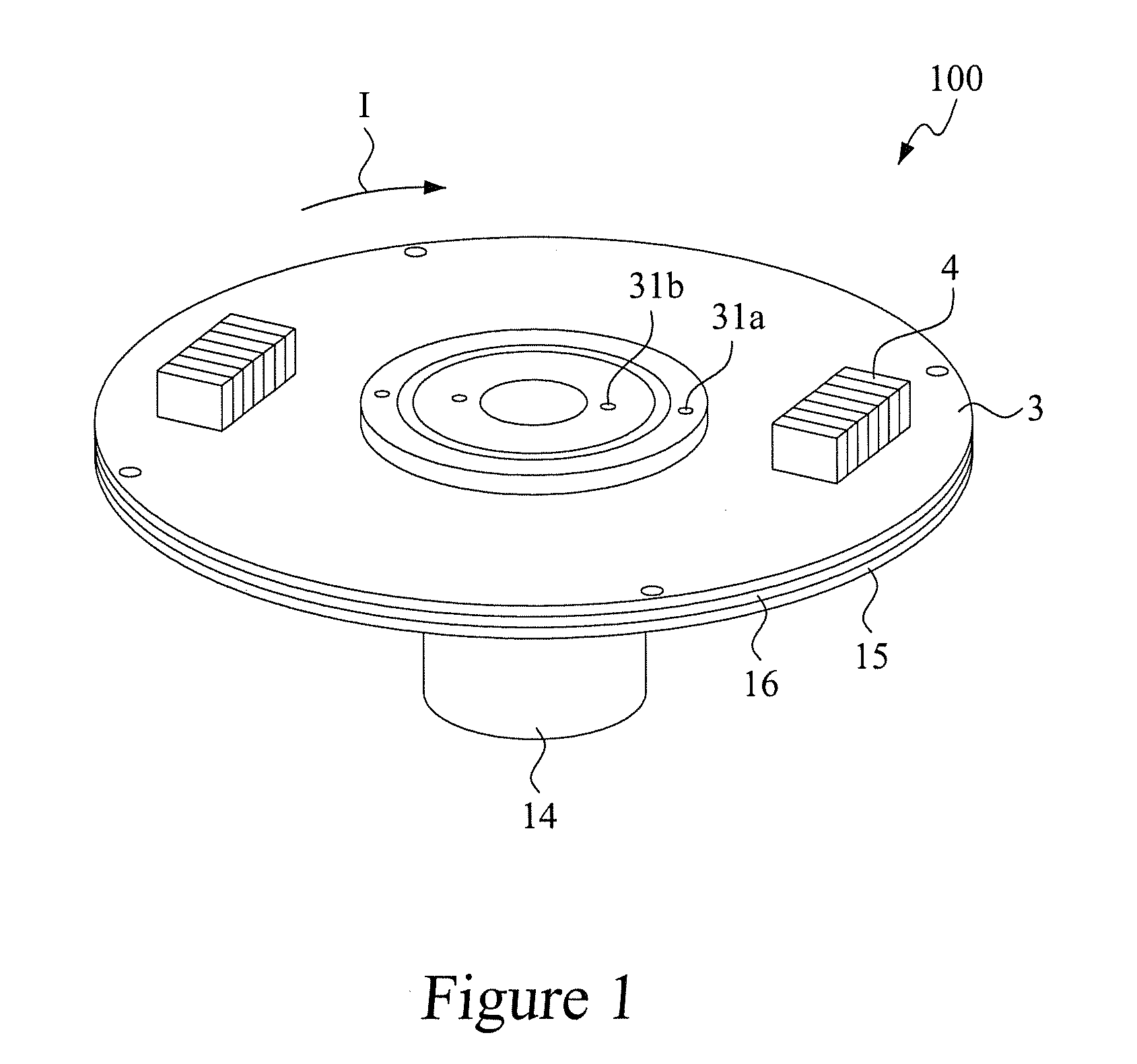

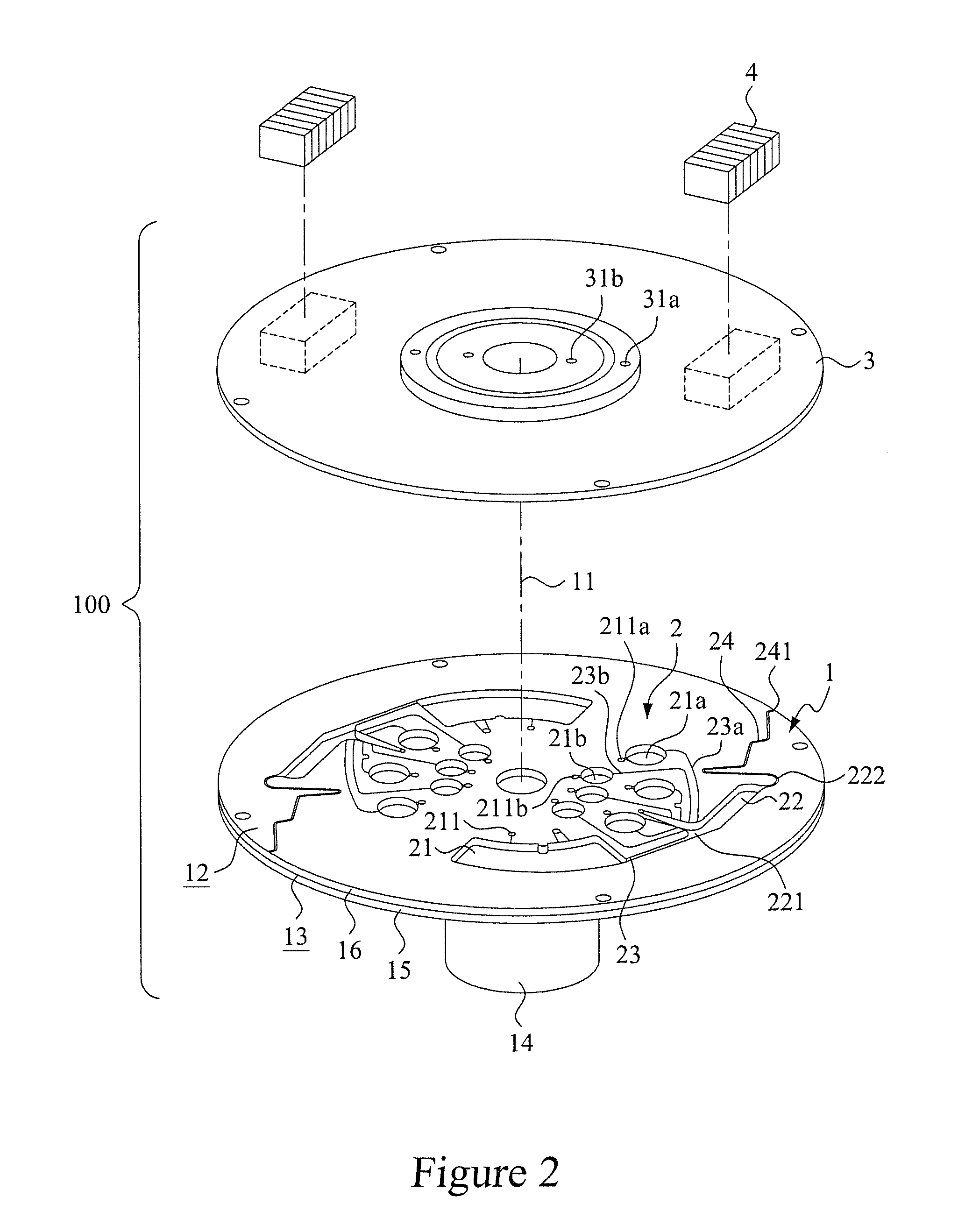

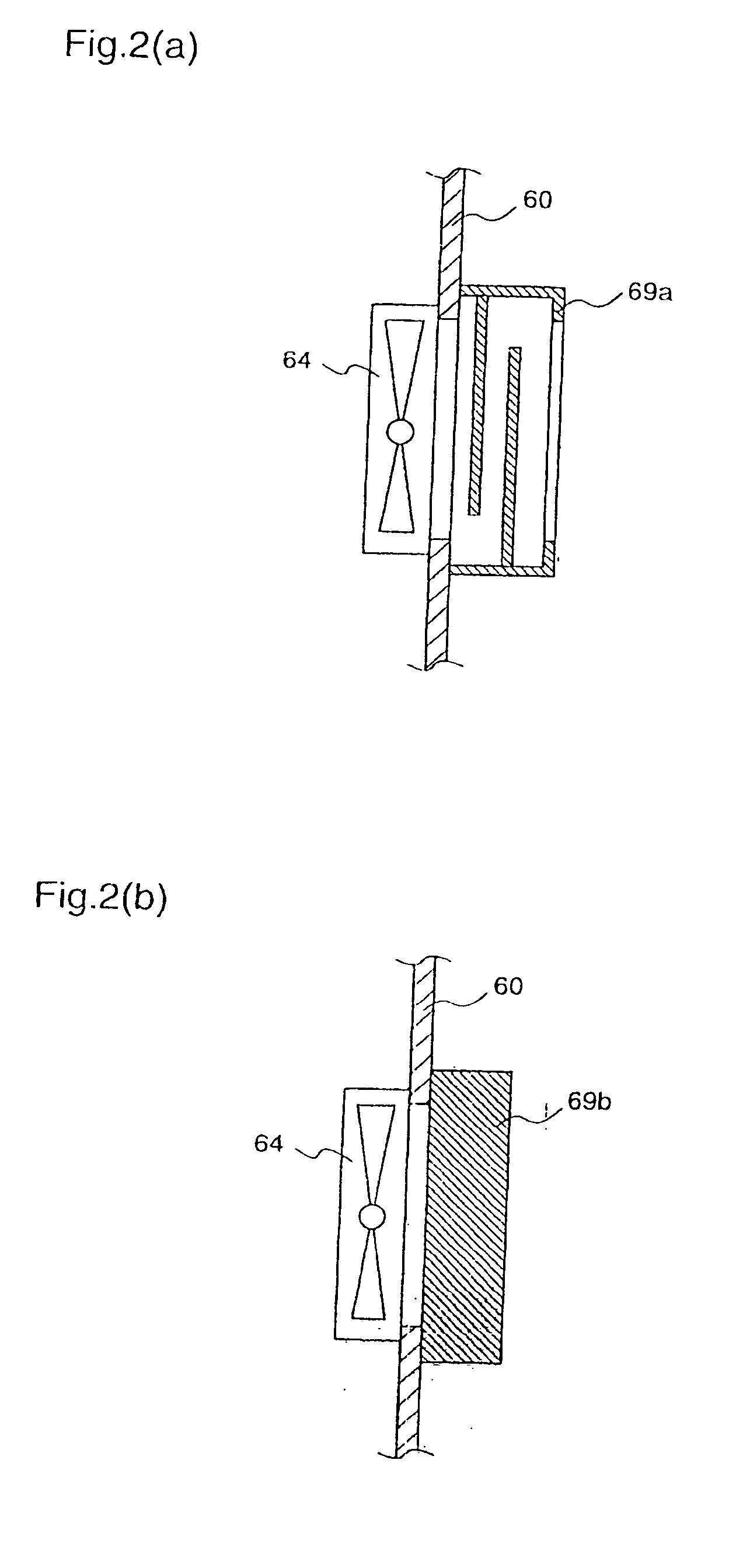

Biological sample discrimination device, biological sample discriminating method, and biological sample discriminating plate

InactiveUS20070148759A1The result is accurateShort timeBioreactor/fermenter combinationsBiological substance pretreatmentsEngineeringChannel pattern

There is provided a plate (10) on which a channel pattern (110) is formed, which channel pattern includes a first channel (116) into which a buffer agent is injected, and a second channel (117) having, in a portion thereof, a quantification part (117a) that has a portion common to the first channel and holds a predetermined amount of a biological sample, the biological sample being injected into the channel including the quantification part, and the plate (10) is rotated at a high speed by a filling unit (20) to fill the buffer agent in the first channel, and thereafter, the second channel is pressurized by a discrimination unit (30) to fill the biological sample in the second channel, and simultaneously, a predetermined amount of the biological sample is added into the buffer agent. Therefore, when performing discrimination of the biological sample, a discrimination result can be obtained accurately in a short time without the necessity of complicated preparation works.

Owner:PANASONIC CORP

Intensified hybrid solid-state sensor

InactiveUS7015452B2Television system detailsMultiplier circuit arrangementsChannel patternImage signal

Owner:ELBIT SYSTEMS OF AMERICA LLC

Method of manufacturing a semiconductor device having a multi-channel type MOS transistor

ActiveUS7696046B2Reduce heat spreadLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideEngineering

In a method of manufacturing a semiconductor device, an active channel pattern is formed on a substrate. The active channel pattern includes preliminary gate patterns and single crystalline silicon patterns that are alternately stacked with each other. A source / drain layer is formed on a sidewall of the active channel pattern. Mask pattern structures including a gate trench are formed on the active channel pattern and the source / drain layer. The patterns are selectively etched to form tunnels. The gate trench is then filled with a gate electrode. The gate electrode surrounds the active channel pattern. The gate electrode is protruded from the active channel pattern. The mask pattern structures are then removed. Impurities are implanted into the source / drain regions to form source / drain regions. A silicidation process is carried out on the source / drain regions to form a metal silicide layer, thereby completing a semiconductor device having a MOS transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

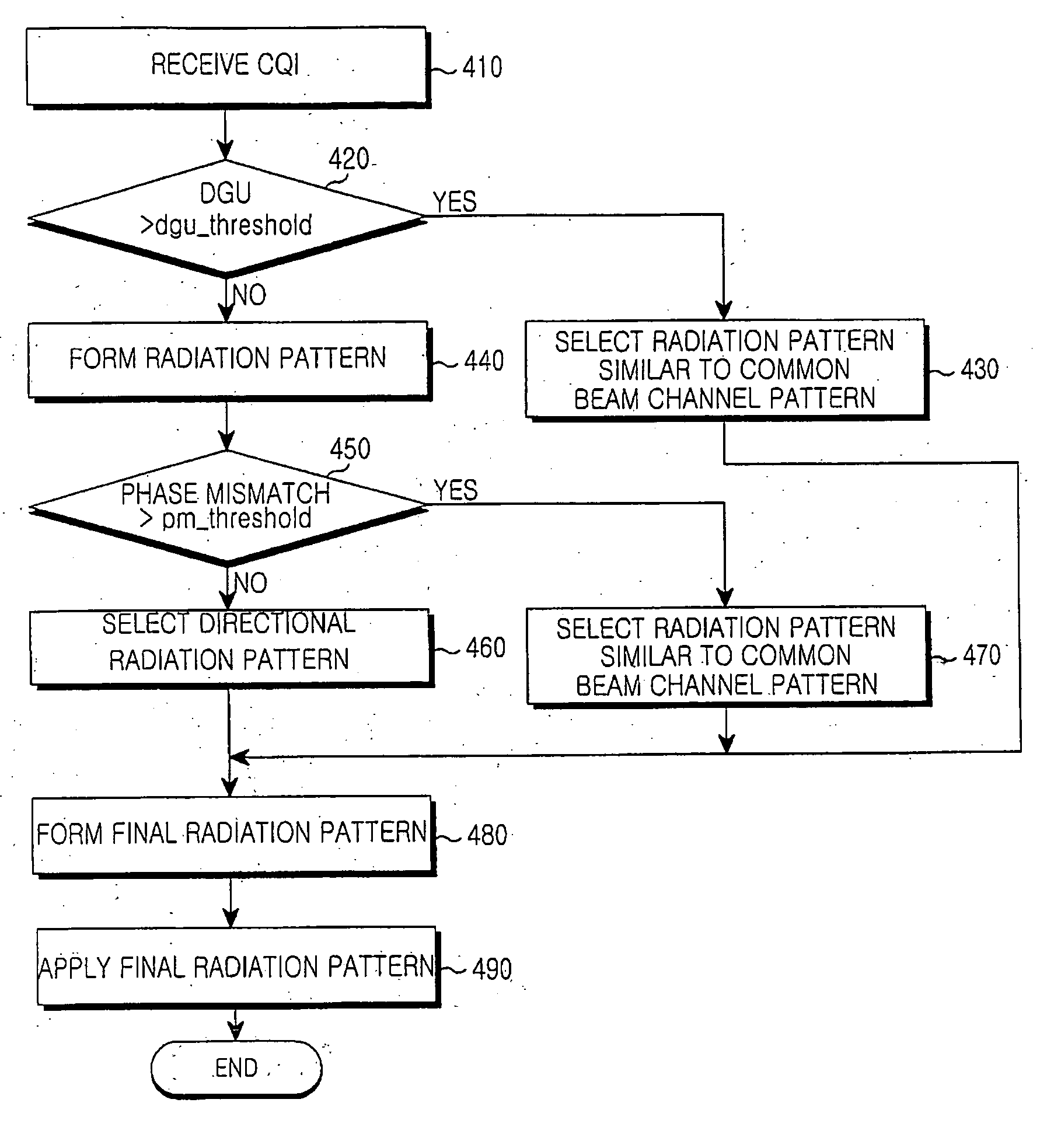

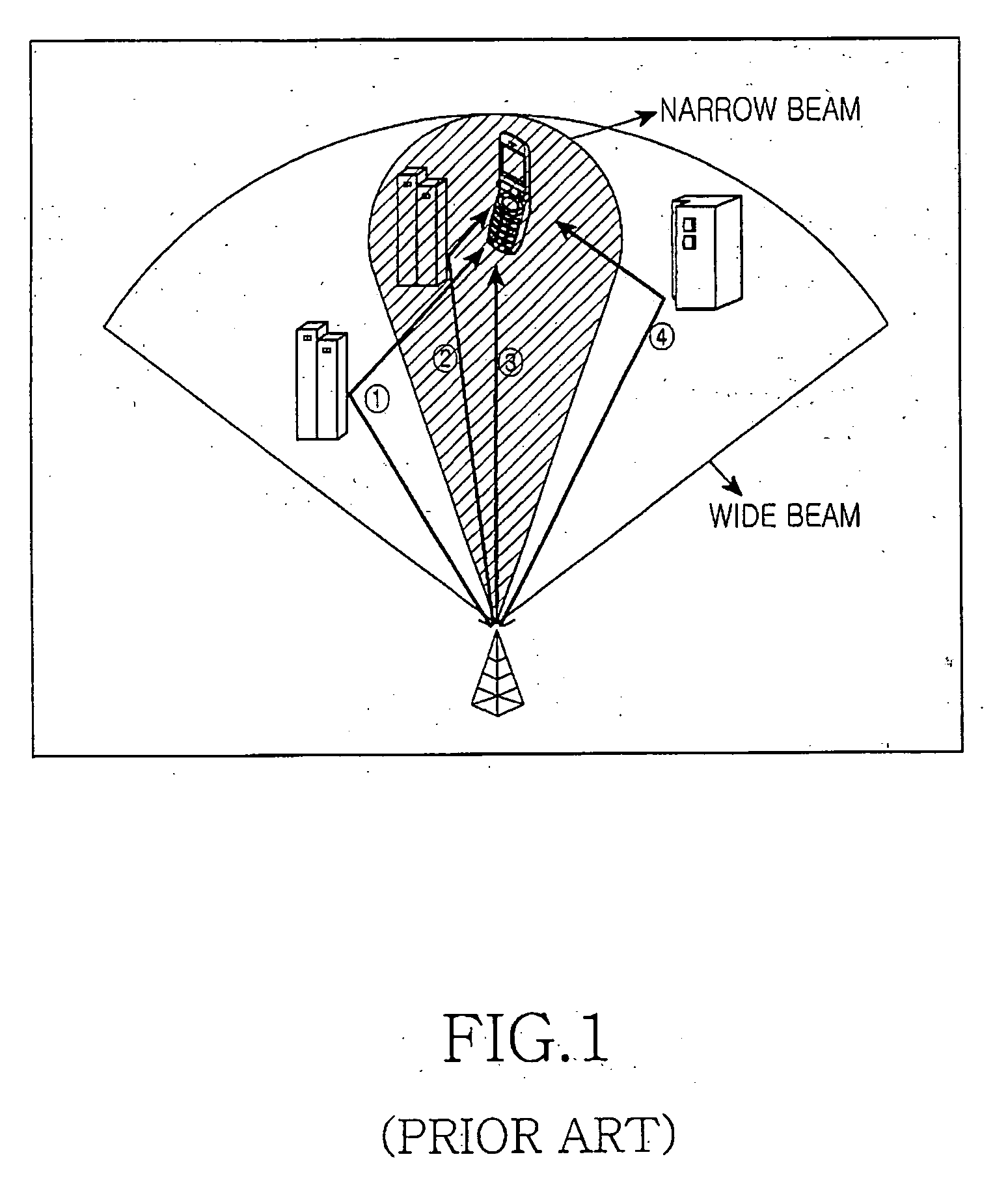

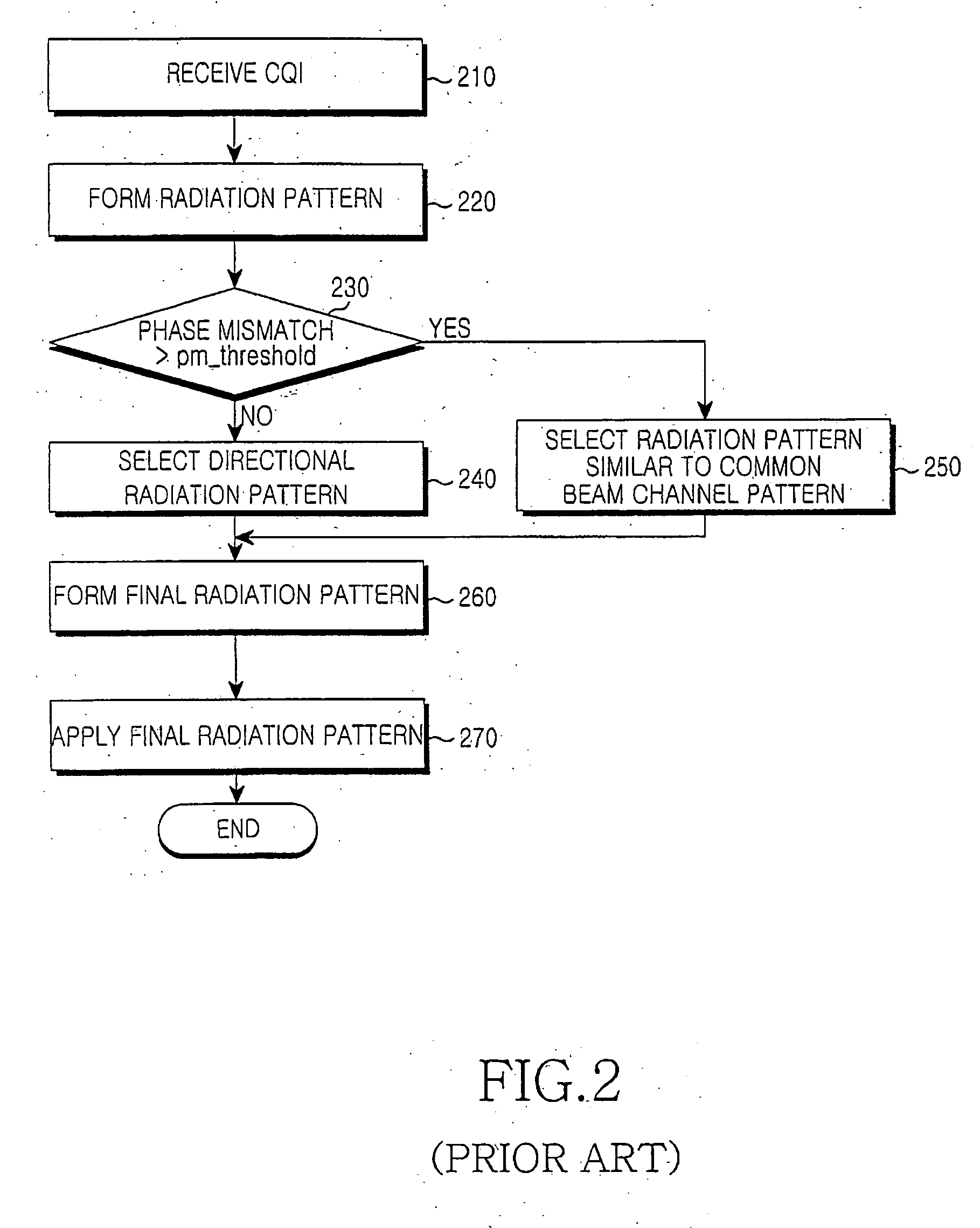

Apparatus and method for preventing call failure in an adaptive smart antenna system

InactiveUS20060245512A1Avoid failureIncrease transmit powerPower managementDiversity/multi-antenna systemsCommunications systemTransmitted power

A transmitter and transmission method for preventing a call failure using a system power value, caused by rapidly increasing transmit power against a large phase mismatch occurring before a phase mismatch correction cycle elapses in a smart-antenna communication system. In the transmitter and transmission method, if the system power value is higher than a power threshold, a radiation pattern similar to a common beam channel pattern is created.

Owner:SAMSUNG ELECTRONICS CO LTD

Zero layer alignment maker and preparation method

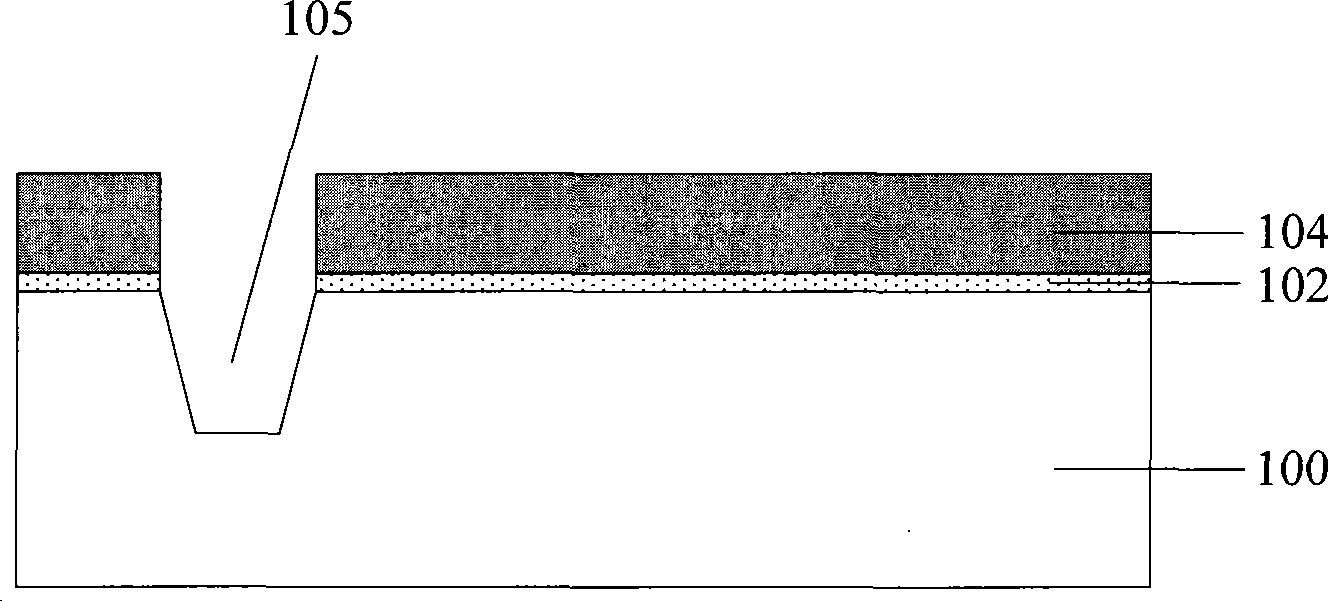

InactiveCN101446768AThe process steps are simpleHigh yieldPhotomechanical exposure apparatusMicrolithography exposure apparatusMedia layerPhotoresist

The invention provides a method for preparing zero layer alignment marker, comprising the steps as follows: a semiconductor underlayer which is sequentially provided with an oxidation cushion layer, a corrosion blocking layer and a photoresist is provided; a zero layer alignment marking pattern and a shallow channel pattern are defined on the photoresist layer; the photoresist layer is taken as a mask to etch the corrosion blocking layer, the oxidation cushion layer and the semiconductor underlayer and form the zero layer alignment marking channel and the shallow channel; after the photoresist layer is removed, the oxidation lining layer is formed on the internal wall of the zero layer alignment marking channel and the shallow channel; the zero layer alignment marking channel and the shallow channel are filled with insulated medium layer, thus forming the zero layer alignment marker and the shallow channel separation structure; subsequently, the corrosion blocking layer is removed. The invention also provides a zero layer alignment marker which simplifies the process steps.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Thin-film transistor and fabrication method thereof

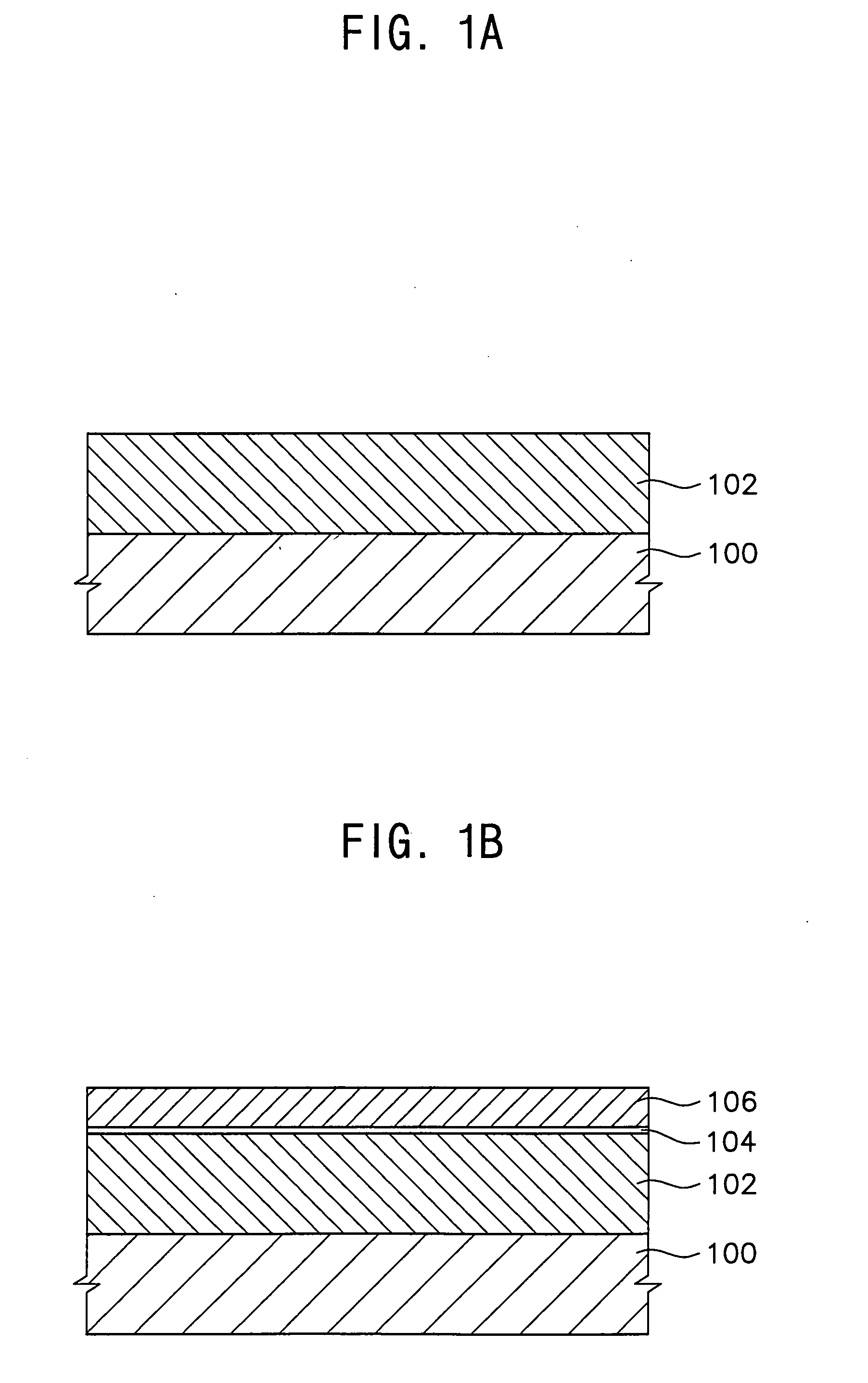

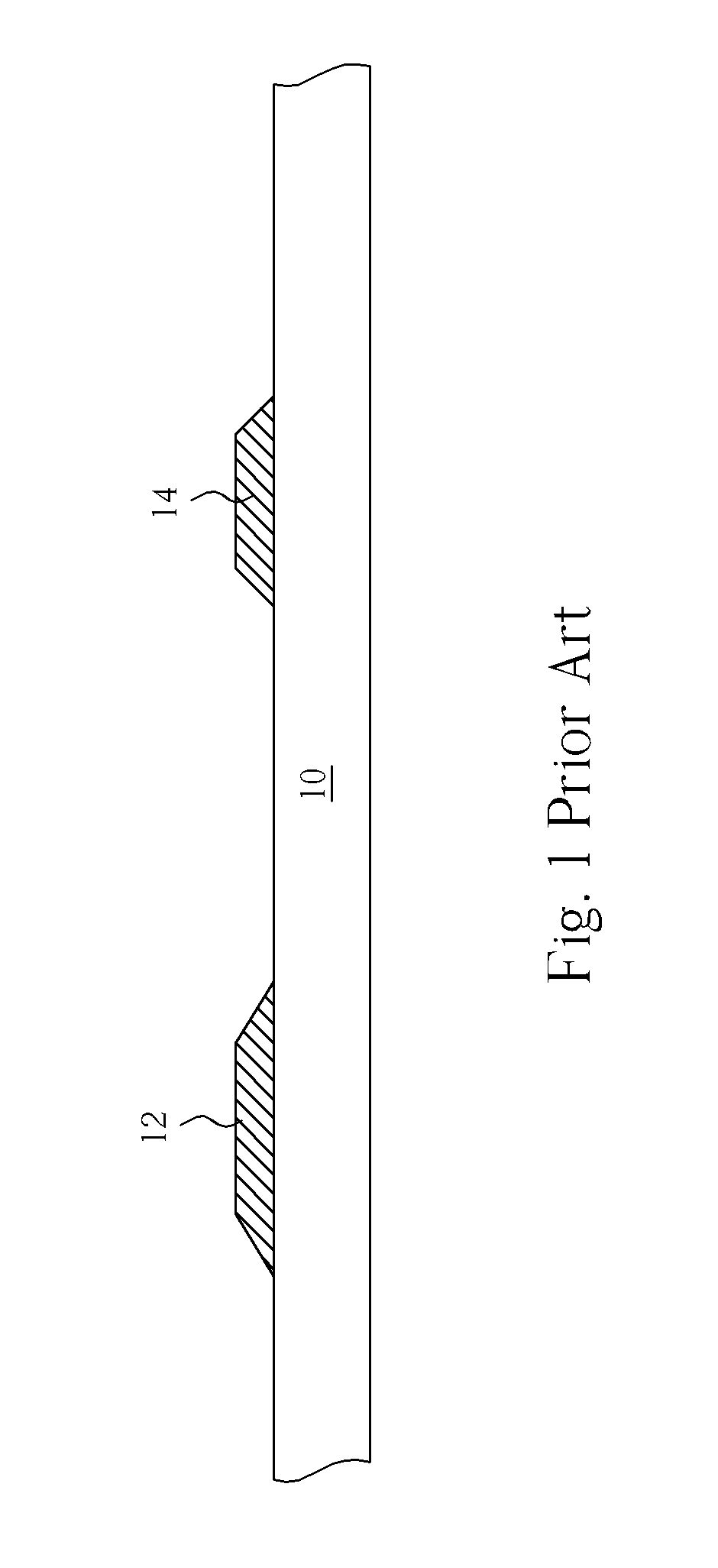

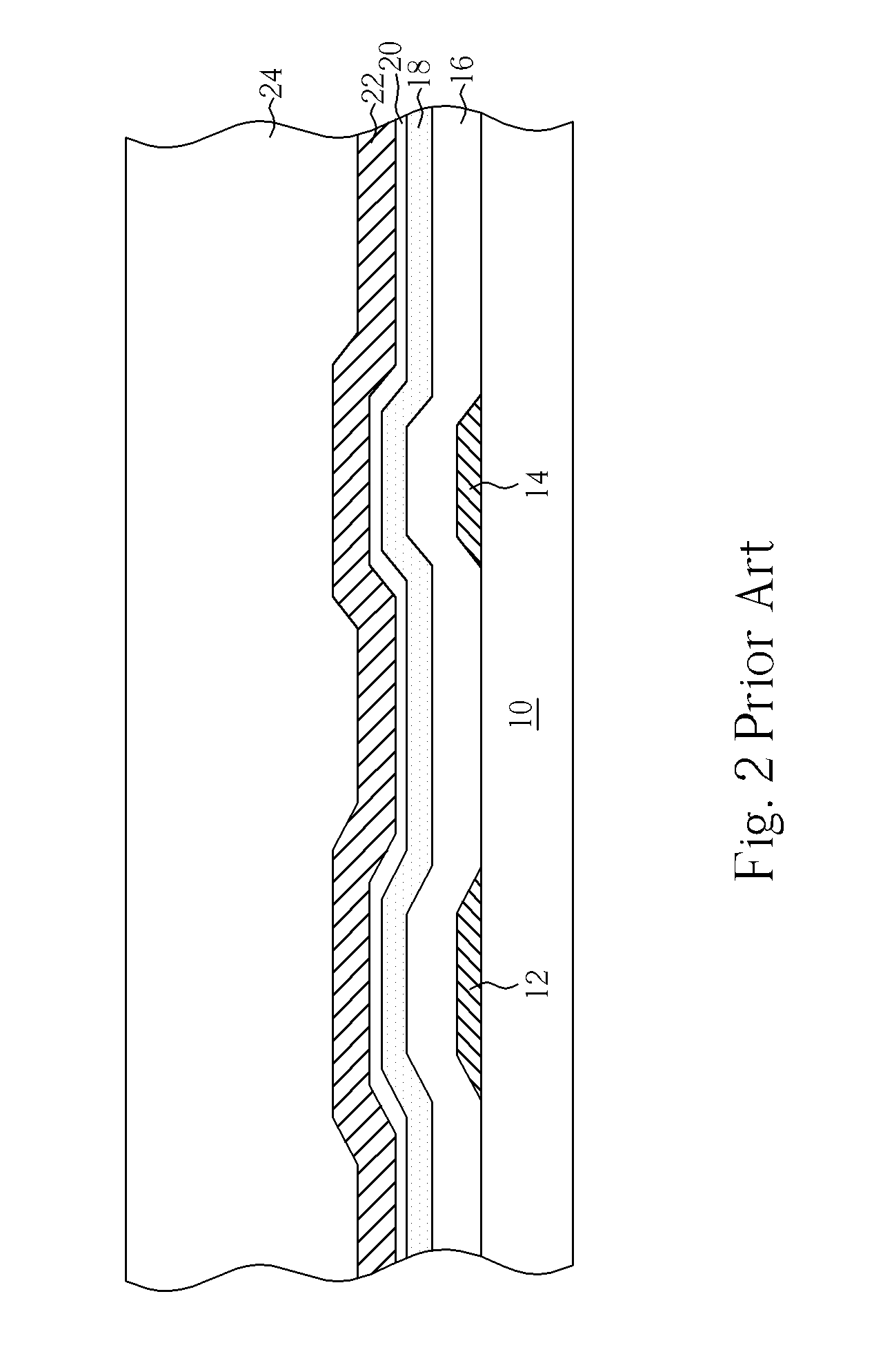

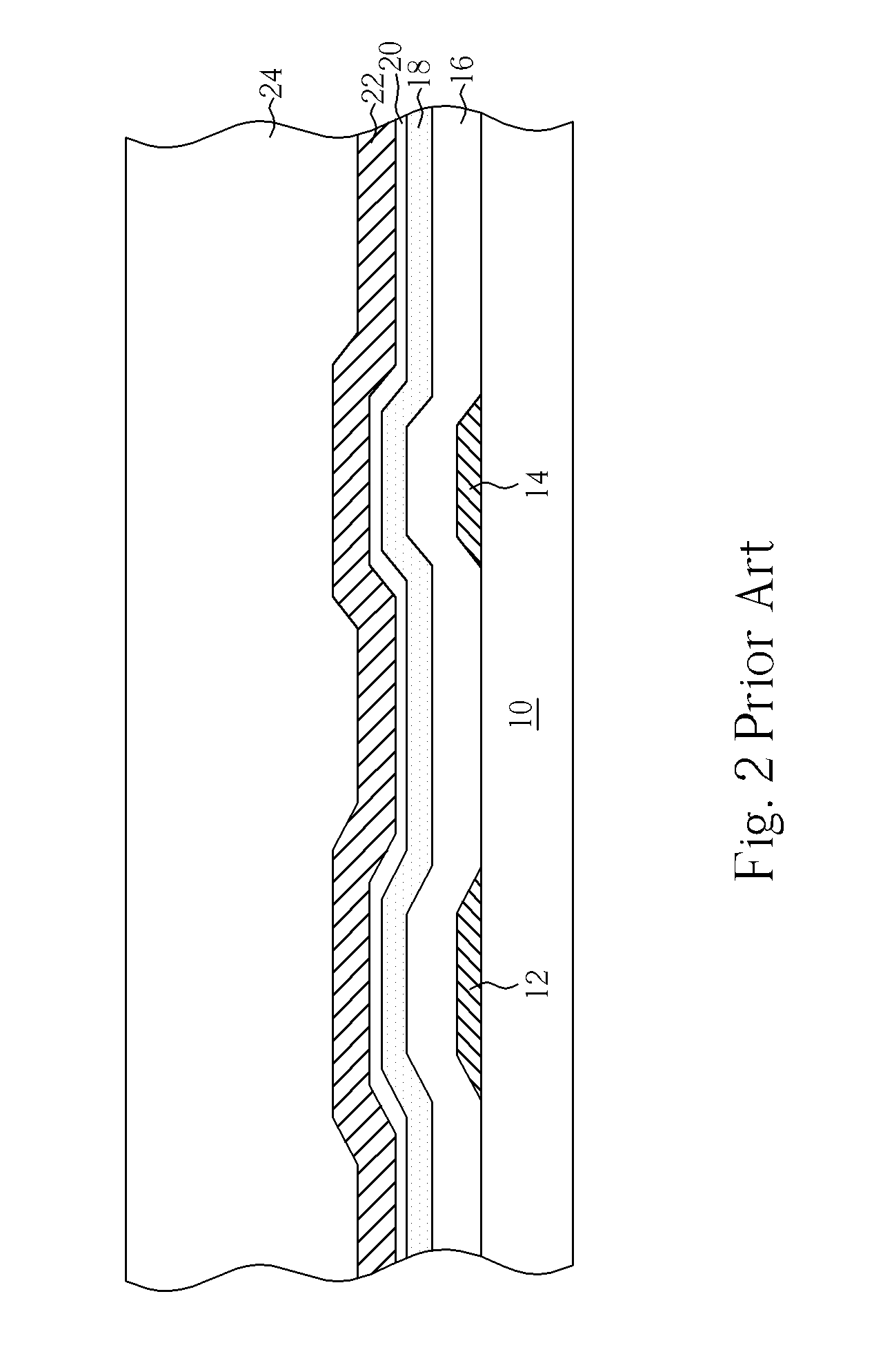

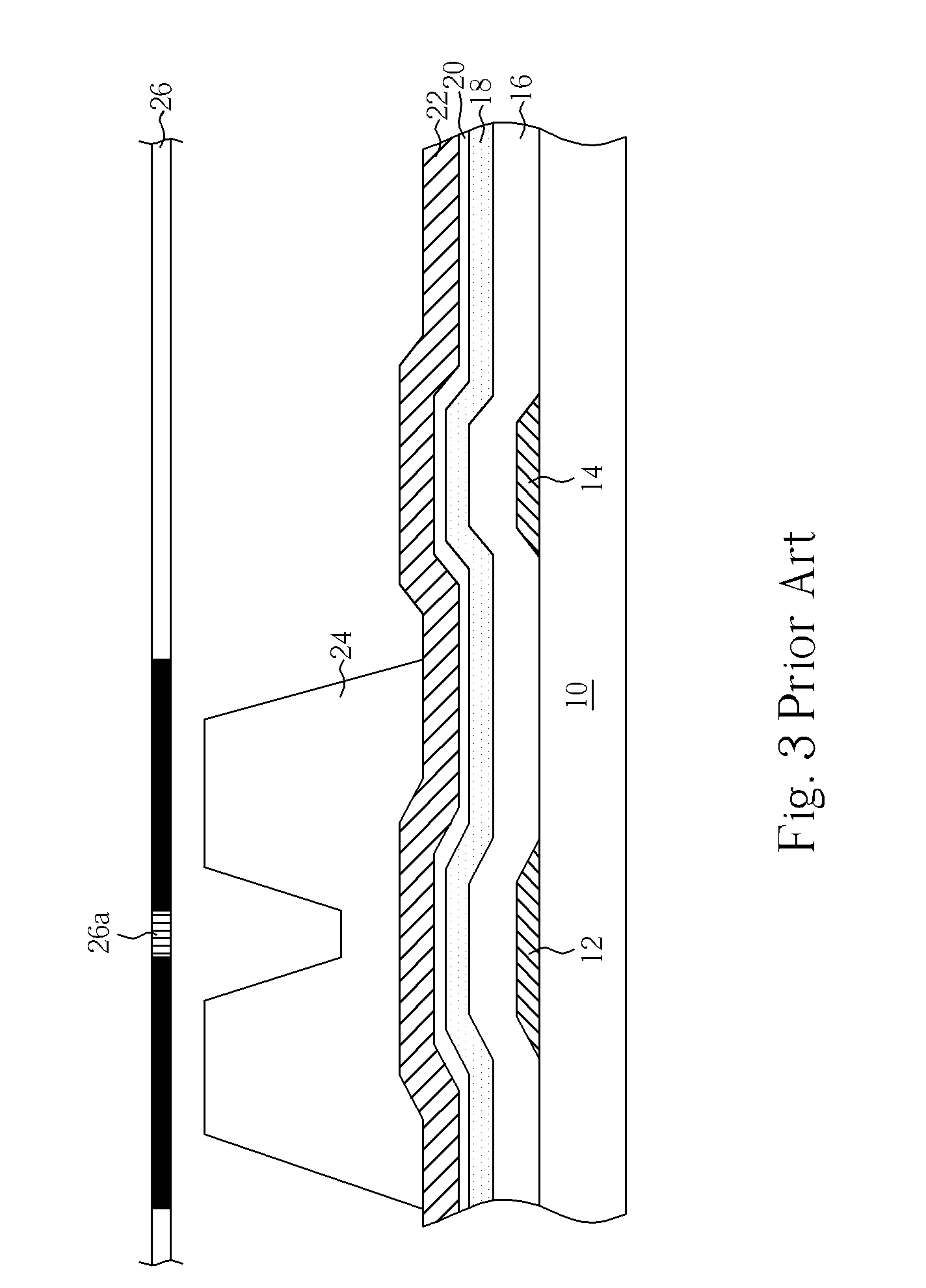

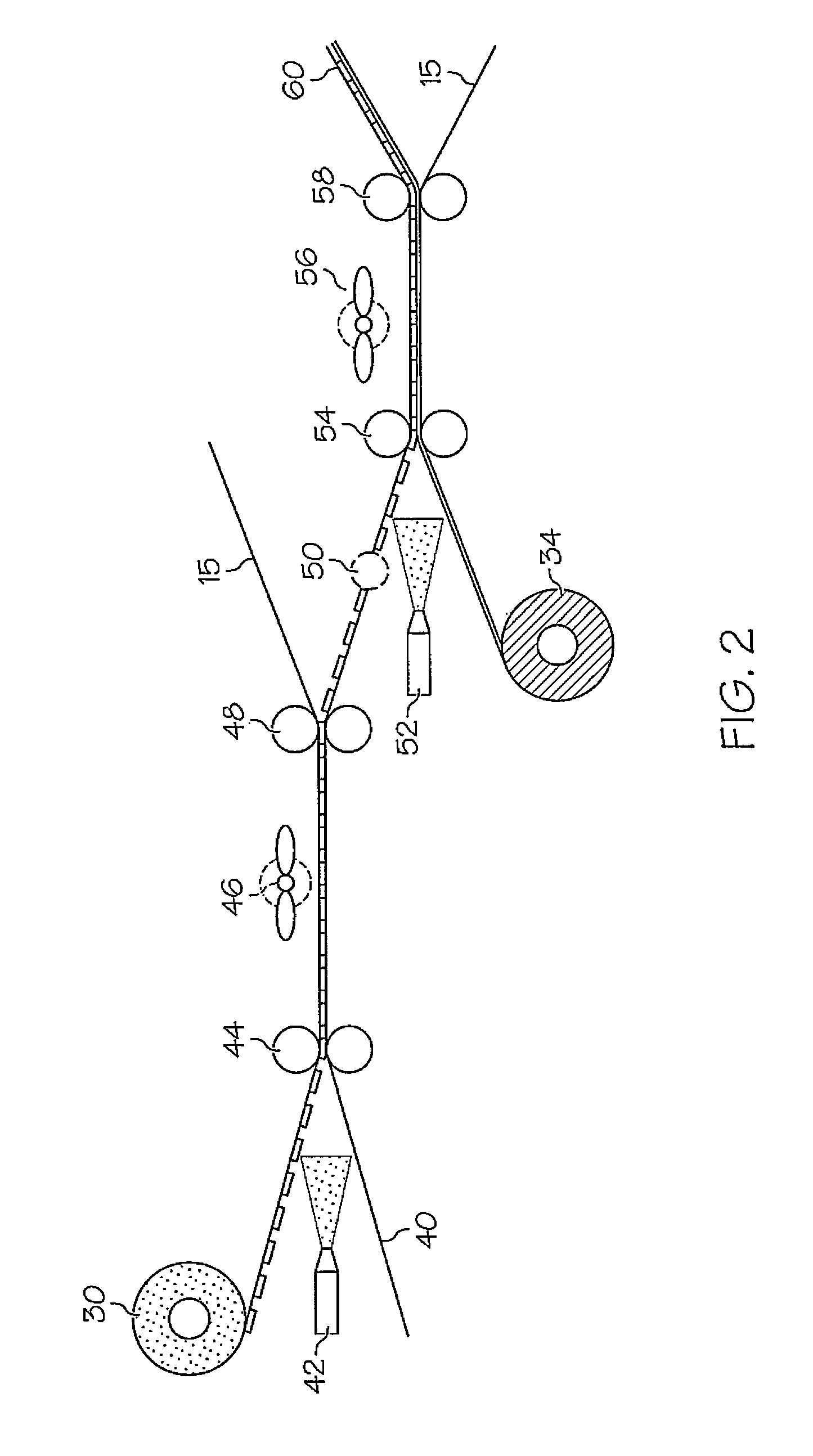

ActiveUS7413940B2Low costAvoid it happening againSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerChannel pattern

A fabrication method of a TFT includes successively forming four thin films containing a first conductive layer, an insulation layer, a semiconductor layer, and a second conductive layer on a substrate, performing a first PEP process to pattern the four thin films for forming a semiconductor island and a gate electrode with the semiconductor layer and the first conductive layer respectively. Then, a laser ablation process is performed to define a channel pattern in the four thin films and remove a portion of the second conductive layer so that unconnected source electrode and drain electrode are formed with the second conductive layer.

Owner:AU OPTRONICS CORP

Thin-film transistor and fabrication method thereof

ActiveUS20070269937A1Avoid it happening againQuality improvementSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerChannel pattern

A fabrication method of a TFT includes successively forming four thin films containing a first conductive layer, an insulation layer, a semiconductor layer, and a second conductive layer on a substrate, performing a first PEP process to pattern the four thin films for forming a semiconductor island and a gate electrode with the semiconductor layer and the first conductive layer respectively. Then, a laser ablation process is performed to define a channel pattern in the four thin films and remove a portion of the second conductive layer so that unconnected source electrode and drain electrode are formed with the second conductive layer.

Owner:AU OPTRONICS CORP

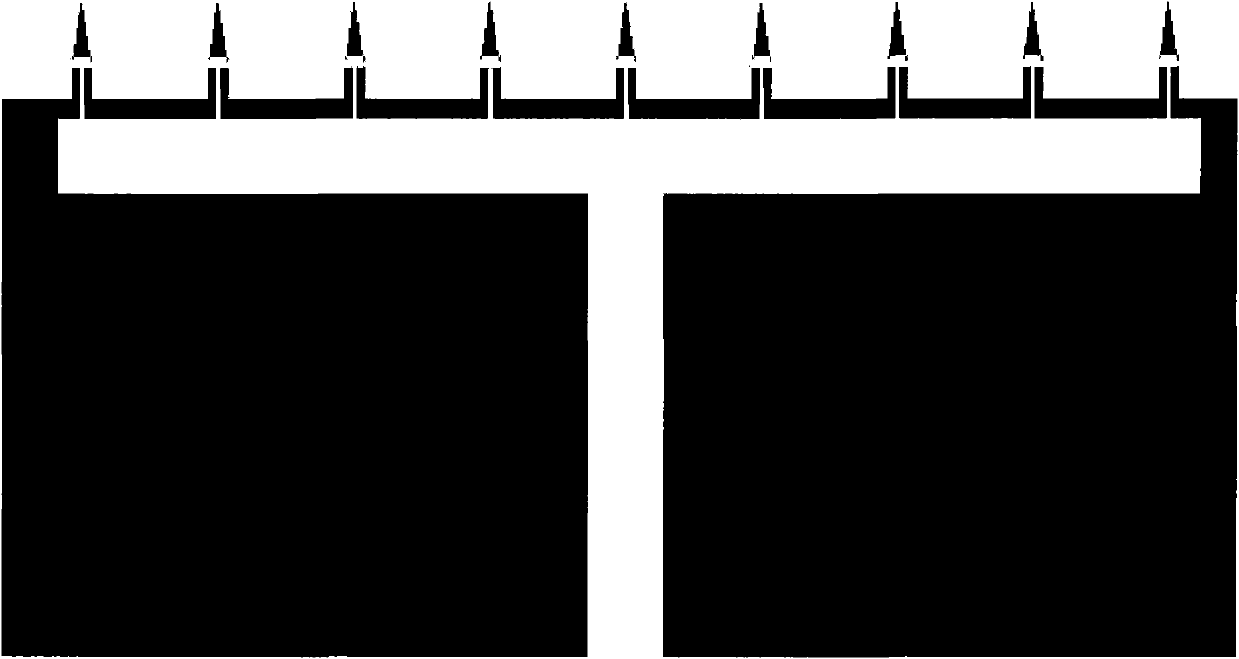

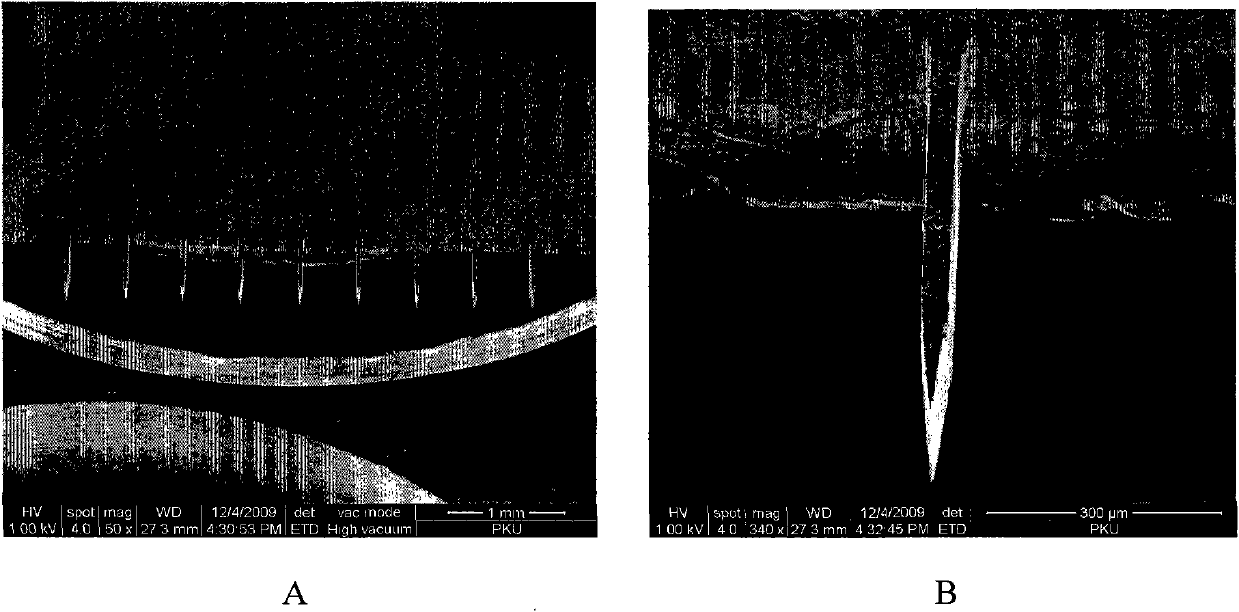

Method for preparing plane hollow microneedle for transdermal administration

InactiveCN101905856ATo achieve the purpose of sustained releasePrecise deliveryDecorative surface effectsMicroneedlesEnteral administrationChannel pattern

The invention discloses a method for preparing a plane hollow microneedle for transdermal administration, which comprises the following steps of: defining a microneedle flow channel pattern on one surface of a first metal substrate to form a trench, and defining a microneedle pattern on the other surface to form a cutting sign, wherein the central axis of the flow channel pattern is aligned with that of the microneedle pattern; bonding a second metal substrate with a trench surface of the first metal substrate; thinning a non-bonding surface of the second metal substrate, and allowing the cutting sign on the first metal substrate to align with and transfer to the non-bonding surface of the second metal substrate; and thinning a non-bonding surface of the first metal substrate, and cutting by aligning with the cutting sign on the second metal substrate to form the plane hollow microneedle. Based on the micromachining technology and by combining the conventional technology of machining and cutting at the same time, the method reduces the process difficulty, increases the using reliability of the microneedle, and is favorable for quantity production.

Owner:PEKING UNIV

Encapsulation method for plastic micro-flow control analysis chip

InactiveCN1557967AImprove fidelityNo deformationMicrobiological testing/measurementAdhesiveUltraviolet

The packing method for plastic chip for micro flow control includes copying the micro channel pattern via micro-copying process to plastic substrate, mixing dimethyl siloxane pre-polymer and curing agent in certain ratio, vacuum deairing, casting and curing to form polydimethyl siloxane set on the plastic substrate; painting ultraviolet cured adhesive around the substrate, adhering one layer of plastic sheet to constitute three-layer structure with raised packing strength; and irradiating with ultraviolet ray to complete the package of plastic chip. The present invention has simple technological process, less micro channel deformation, no jamming and very high packing strength.

Owner:SHANGHAI JIAO TONG UNIV

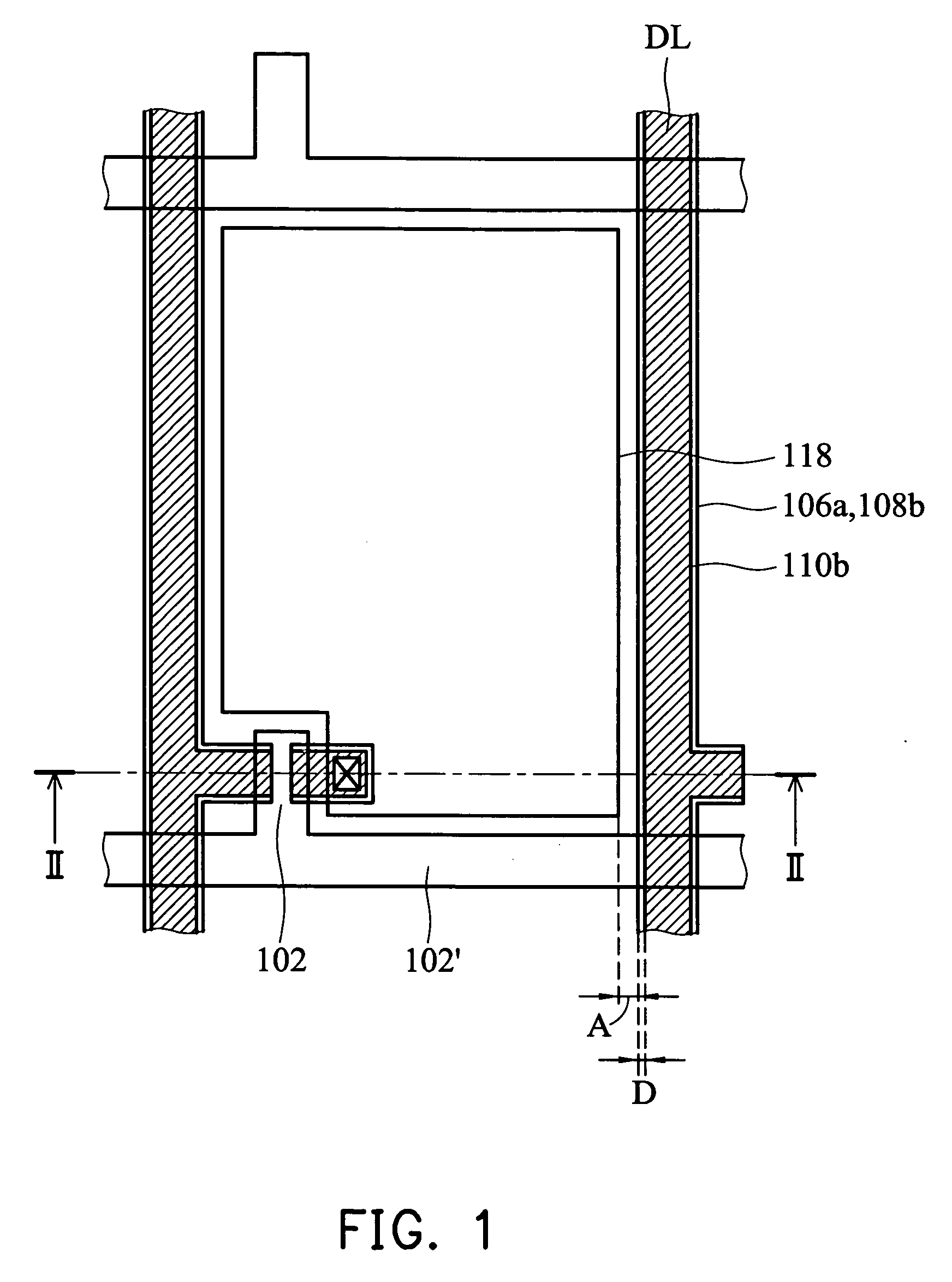

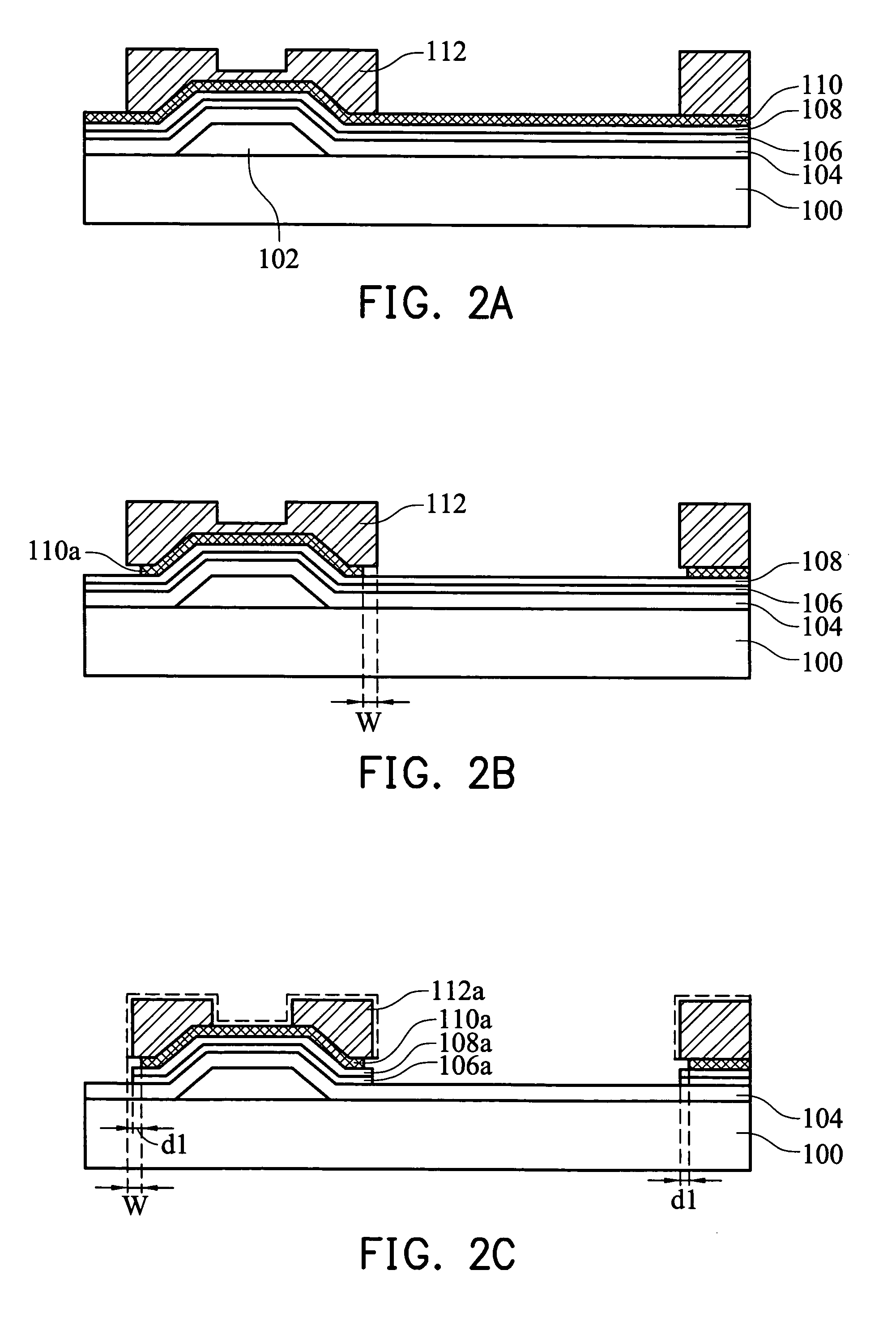

Flat panel display and fabrication method thereof

A flat panel display and fabrication method thereof. The present invention uses four etching processes to define a second conducting layer, a doped semiconductor layer and a semiconductor layer. The first etching process is a wet etching using a first resist layer to etch the second conducting layer. The second etching process is executed with an etchant comprising oxygen to etch the doped semiconductor layer and the semiconductor layer, and the first resist layer undergoes ashing during etching so as to become a second resist layer with a channel pattern. The third etching process is another wet etching, and the second conducting layer is etched again using the second resist layer as the etching mask. The fourth etching process is executed to dry etch the doped semiconductor layer using the second resist layer as the etching mask.

Owner:AU OPTRONICS CORP

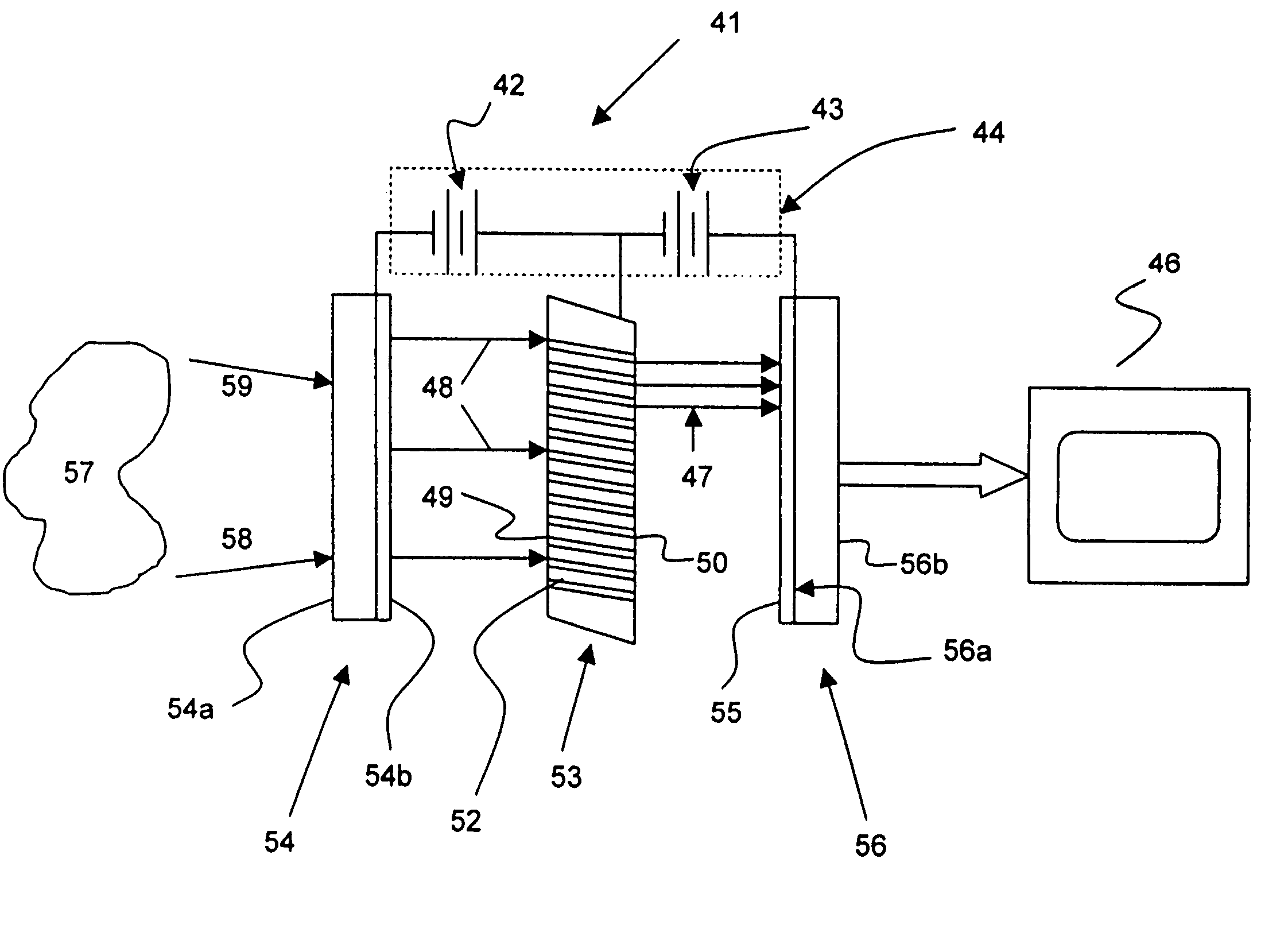

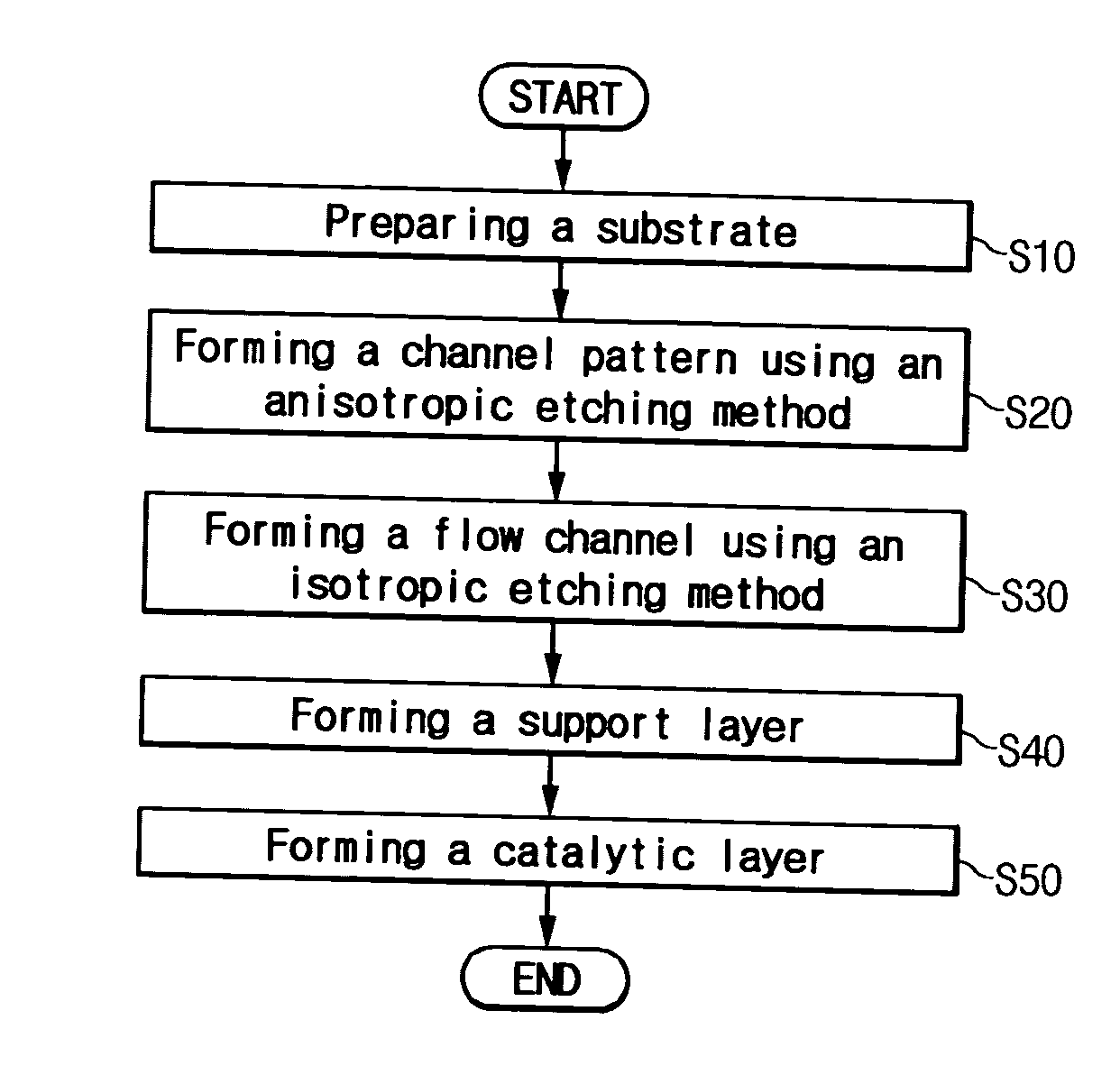

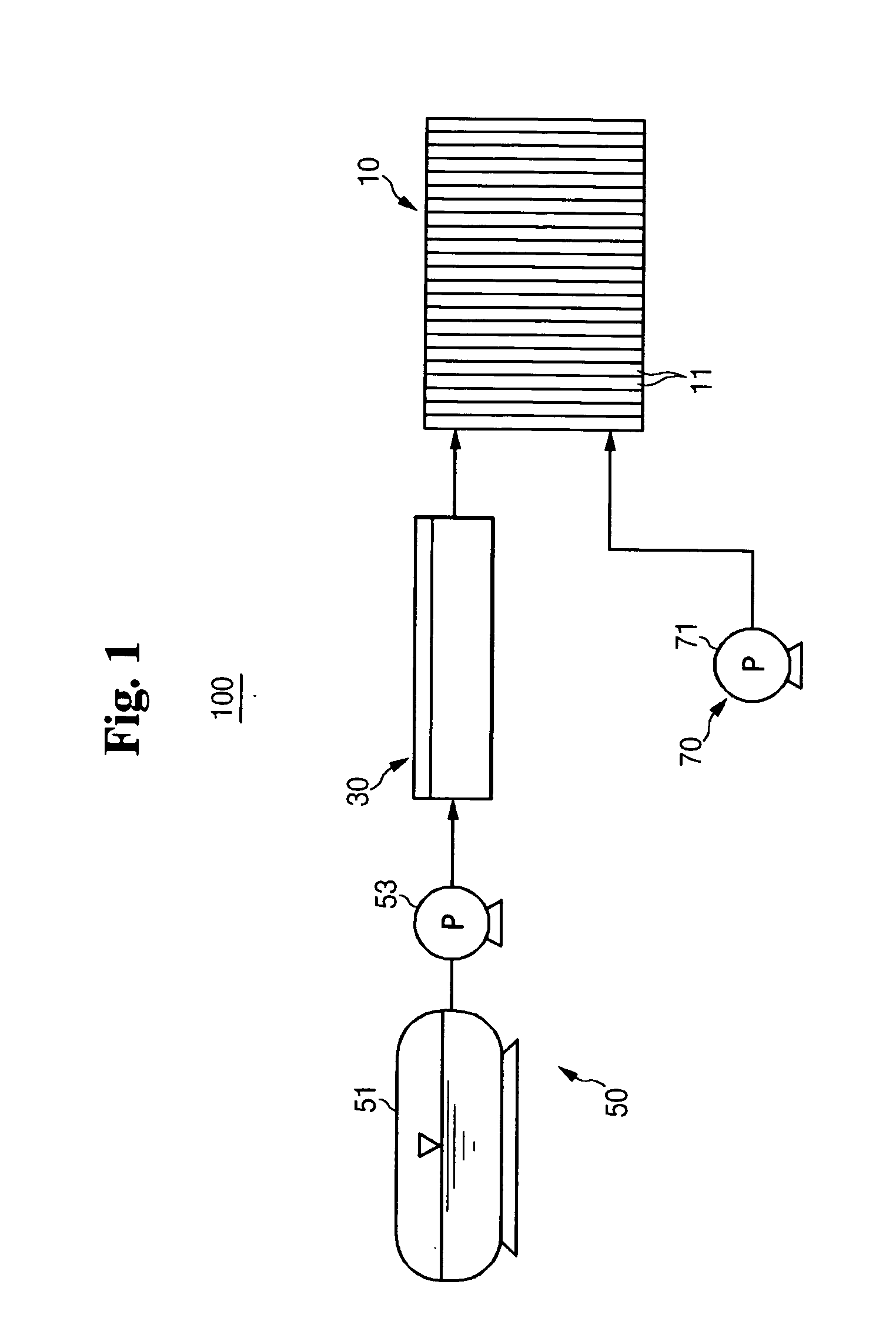

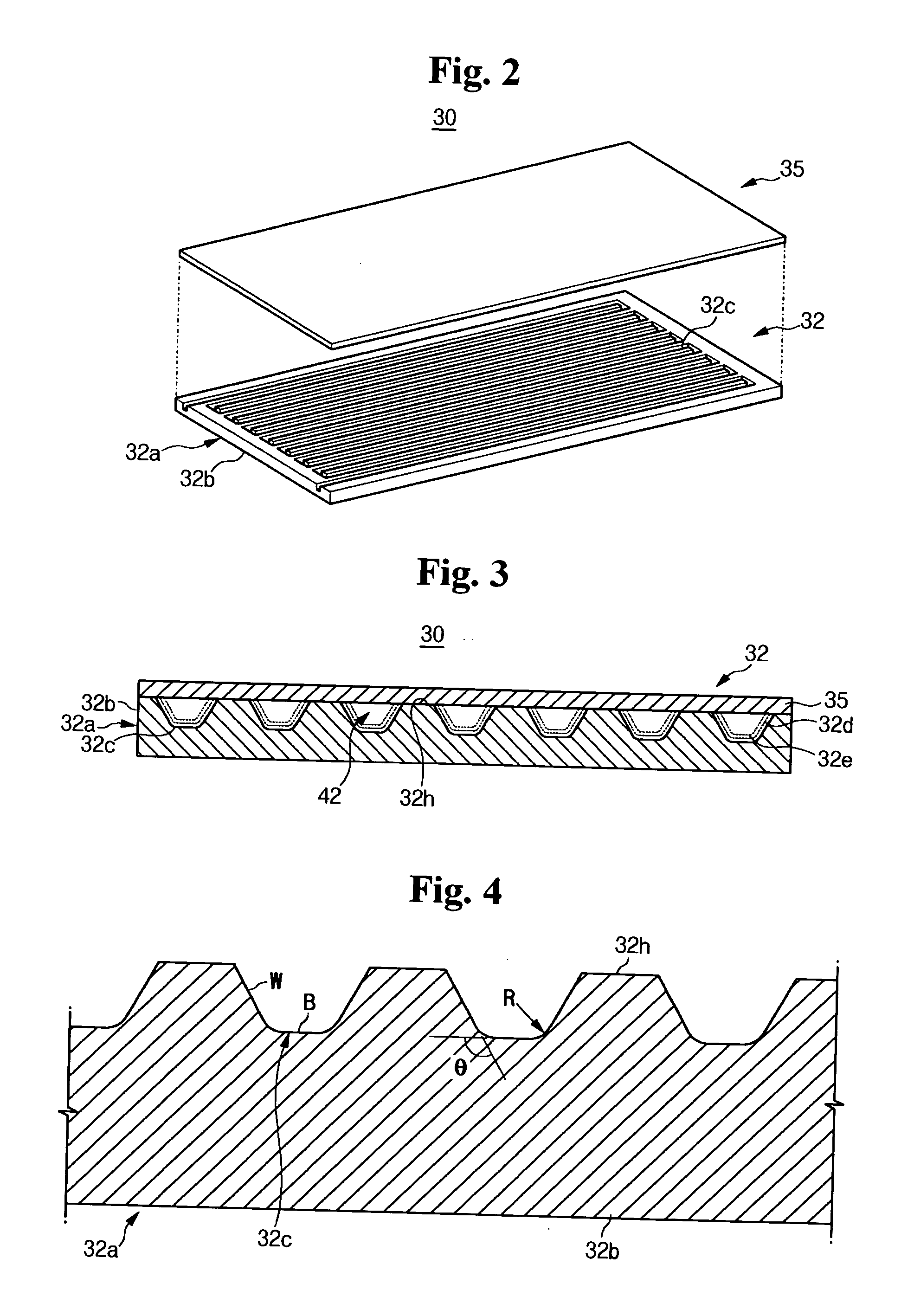

Reformer for fuel cell system and method of manufacturing reaction substrate used for the same

InactiveUS20050252081A1Reduce concentrationCombination devicesFinal product manufactureThermal energyFuel cells

There is provided a reformer for a fuel cell system, the reformer comprising: a reforming unit having a reaction substrate in which a catalyst layer is formed in a plurality of flow channels for allowing fuel to flow and for generating hydrogen through a reformation reaction of the fuel using thermal energy. When viewing a cross-section perpendicular to the flow direction of the flow channels, the reaction substrate defines each flow channel by a bottom portion and a pair of wall portions extending from the sides of the bottom portion, and a joint between the bottom portion and the wall portion is formed in a rounded shape. There is also provided a method of manufacturing a reaction substrate used for a reformer for a fuel cell system, the method comprising: (a) preparing a substrate; (b) anisotropically etching the upper surface of the substrate and forming a channel pattern of which a bottom portion and a wall portion are perpendicular to each other; (c) isotropically etching the channel pattern and forming a flow channel of which the joints between the bottom portion and the wall portions are rounded; (d) forming a support layer on the surface of the flow channel; and (e) forming a catalyst layer on the support layer.

Owner:SAMSUNG SDI CO LTD

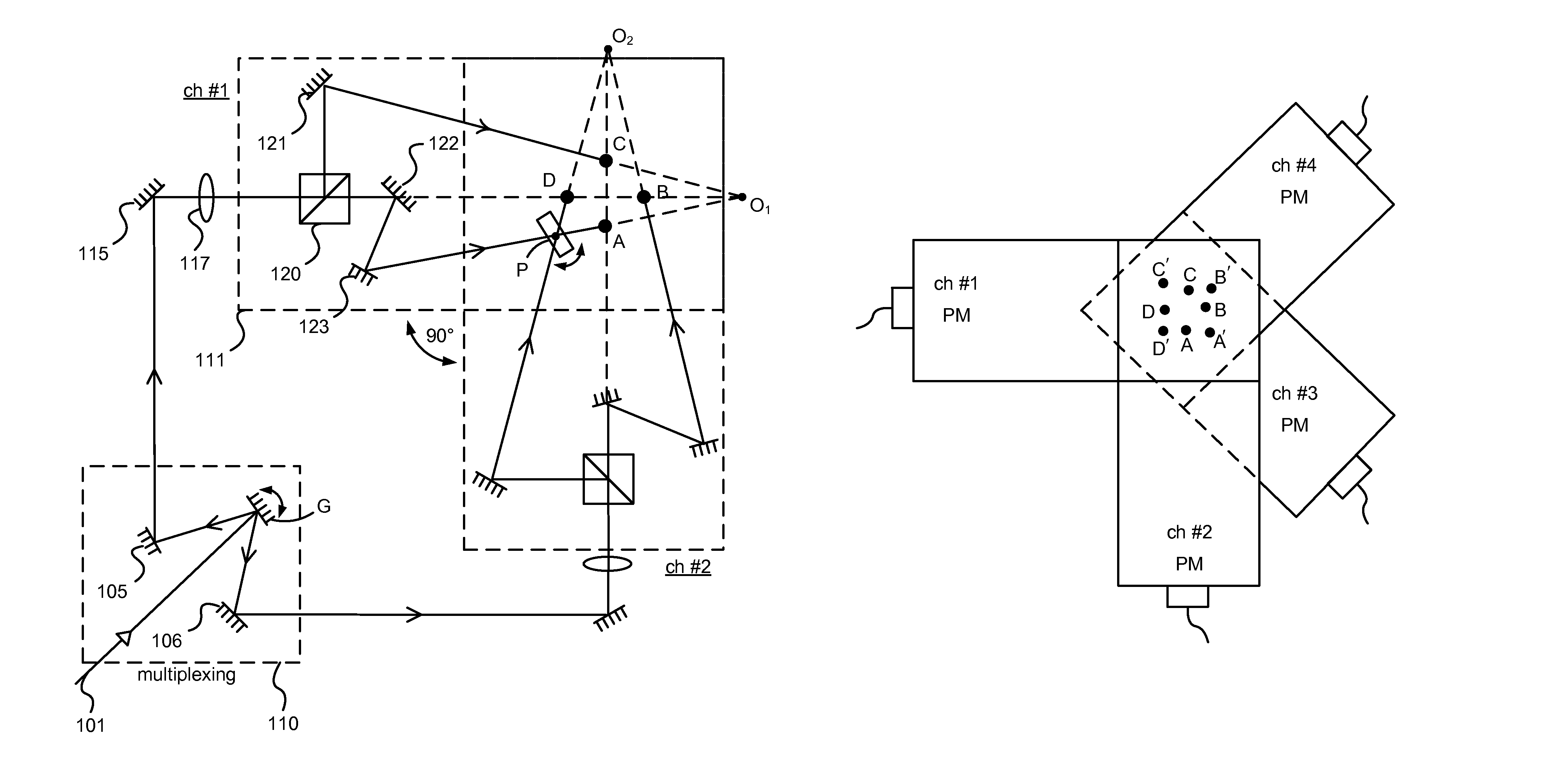

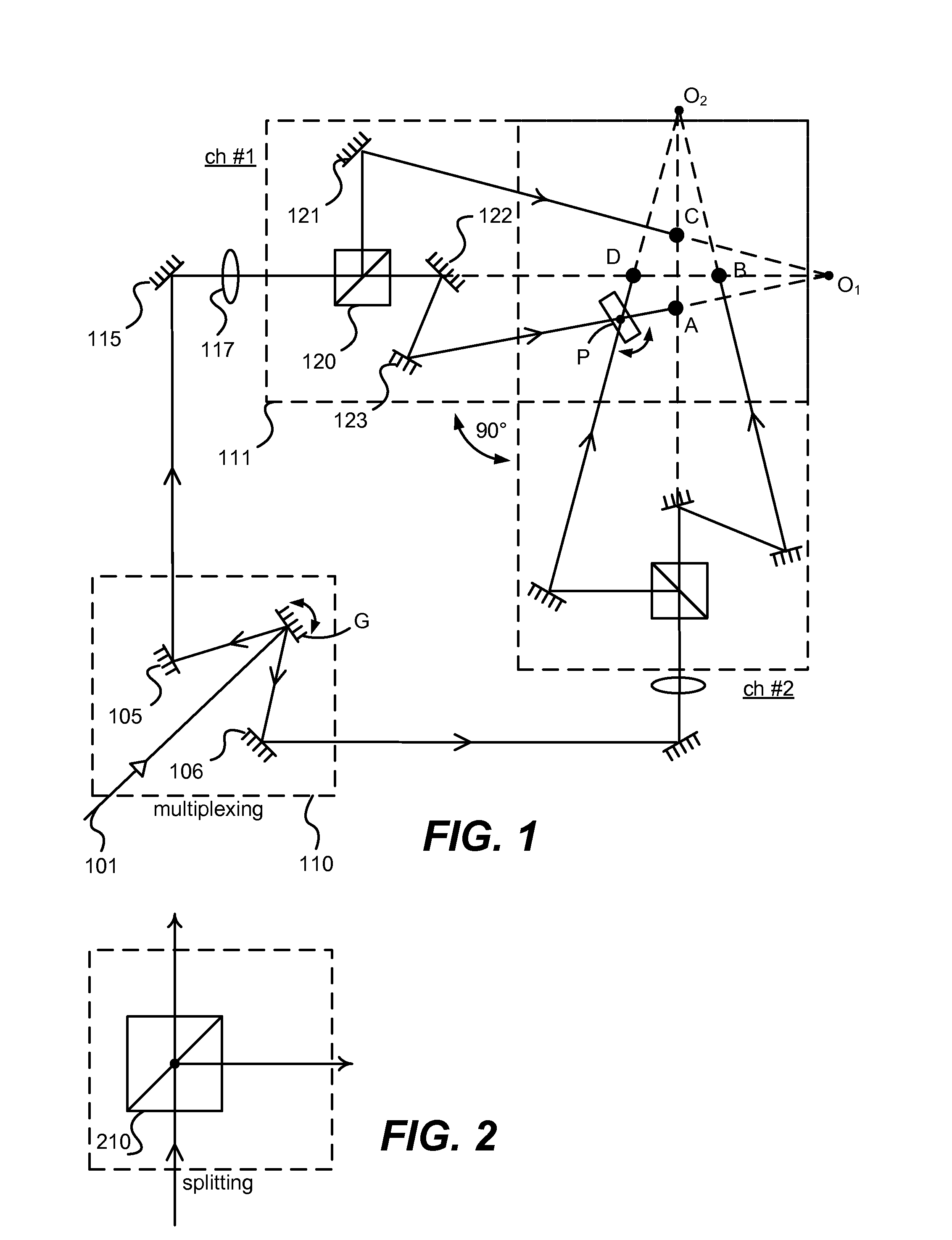

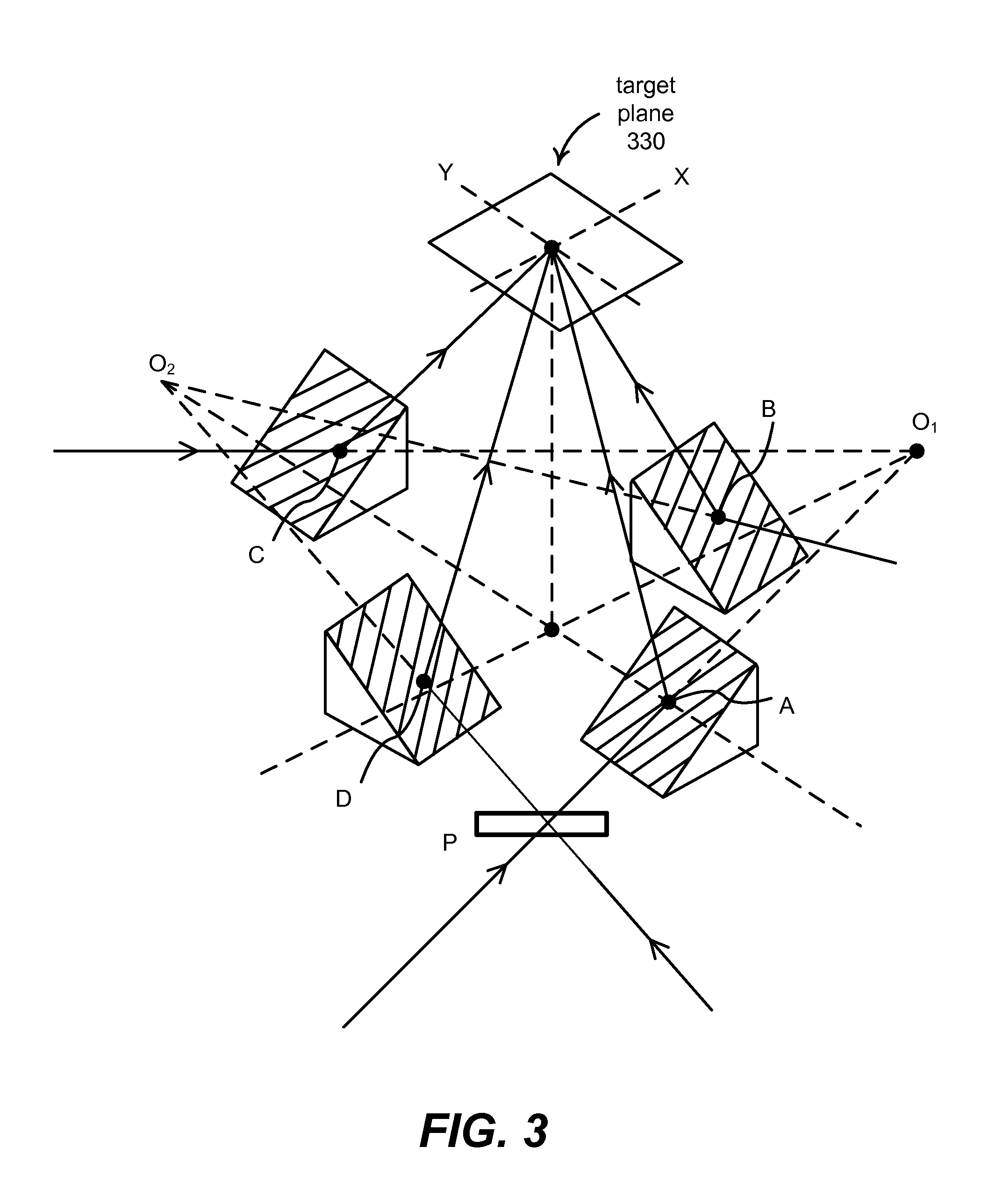

Modular pattern illumination and light beam multiplexing for selective excitation of microparticles

ActiveUS8817362B2Cosmonautic condition simulationsLaser using scattering effectsMultiplexingPhase shift module

A modular approach to a pattern illumination system for selective excitation of microparticles is used. A dual-channel pattern module having two single-channel pattern modules are oriented at a non-zero offset angle to each other. In this arrangement, a galvo-scanner based phase-shifting module is shared between the two channels. A set of tilt mirrors are used to direct the beams from the pattern modules onto the target plane. Additional layers of pattern modules can be added to accommodate any desirable number of additional channels. The additional layer(s) may be rotationally off-set from the other layer(s) by an angular amount to simplify the layout of optical components. A remote light source module may be connected to the pattern modules through optical fiber.

Owner:REBUS BIOSYSTEMS INC

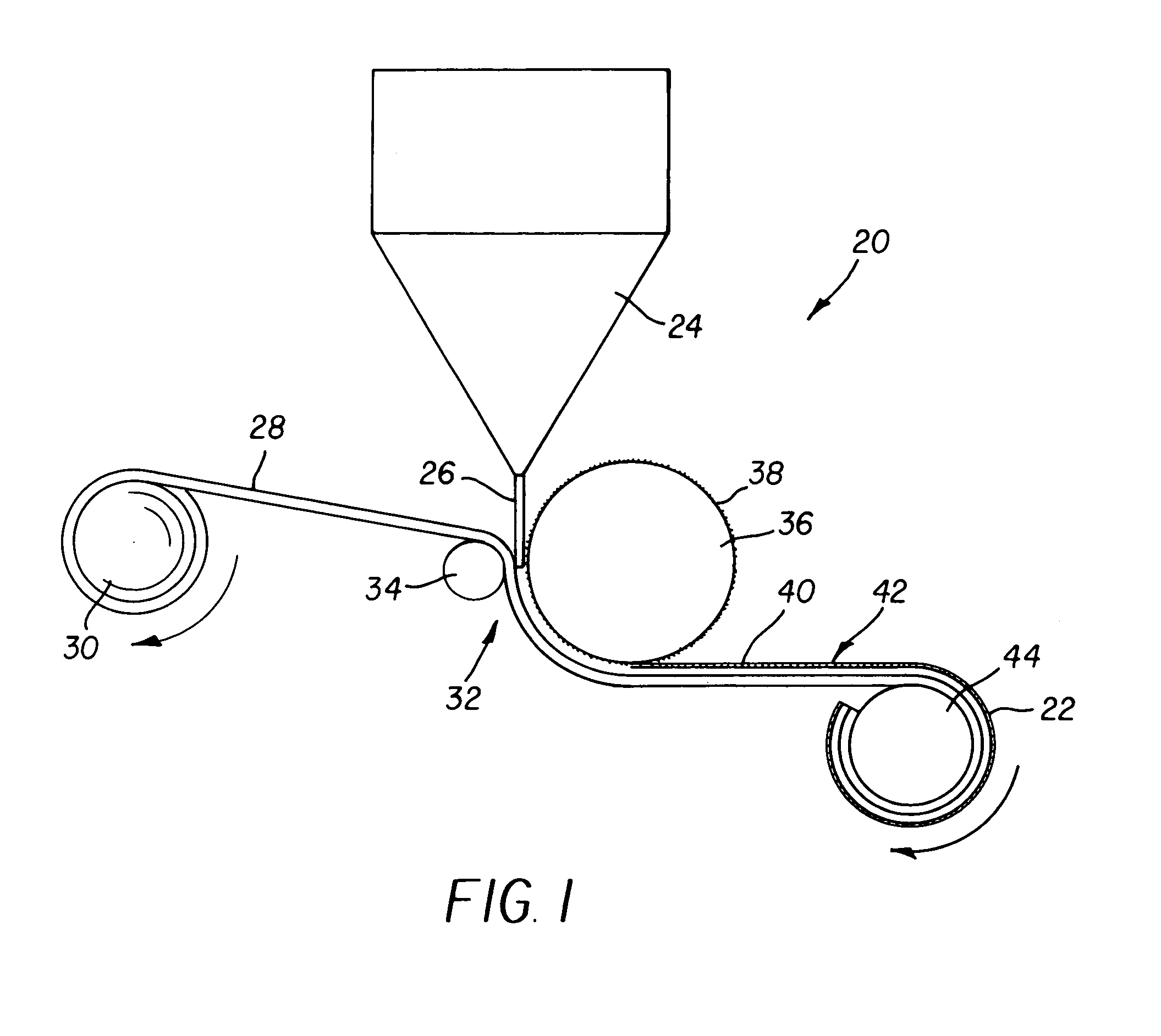

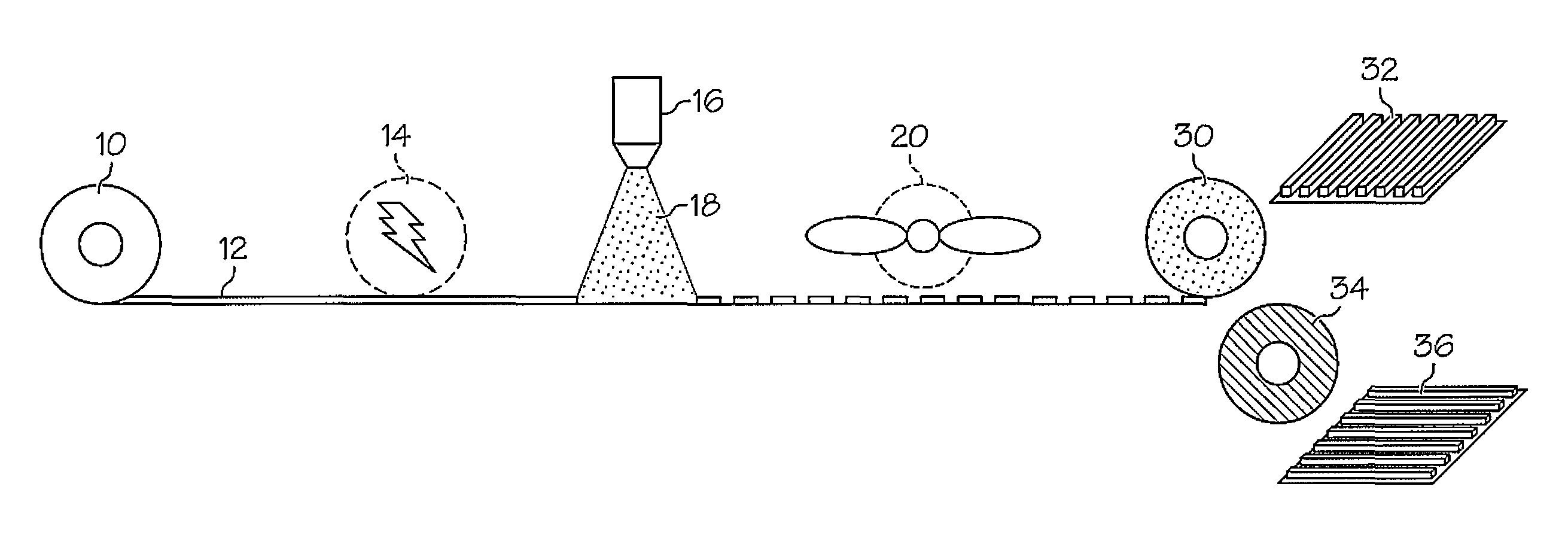

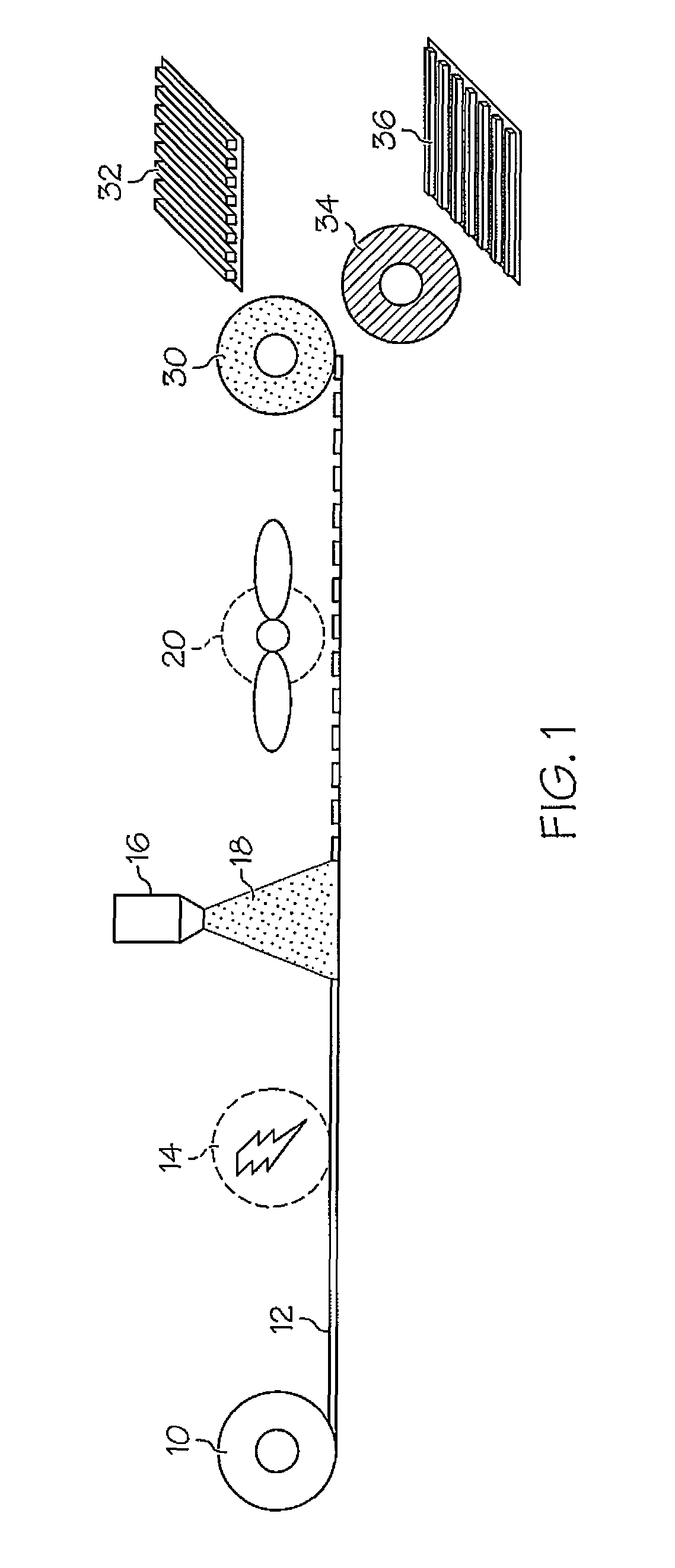

Method of forming layered-open-network polishing pads

The method forms a layered-open-network polishing pad useful for polishing at least one of magnetic, semiconductor and optical substrates. Exposing a first and second polymer sheet or film of a curable polymer to an energy source creates an exposure pattern in the first and second polymer sheet, the exposure pattern having elongated sections exposed to the energy source. Then removing polymer from the exposed first and second polymer sheets to forms elongated channels through the first and second polymer sheets in a channel pattern that corresponds to the exposure pattern. Attaching the first and second polymer sheets forms a polishing pad, the patterns of the first and second polymer sheets cross wherein the first polymer sheet supports the second polymer sheet and the elongated channels from the first and second polymer sheets connect and to form the layered-open-network polishing pad.

Owner:DOW GLOBAL TECH LLC

Flat panel display and fabrication method thereof

A flat panel display and fabrication method thereof. The present invention uses four etching processes to define a second conducting layer, a doped semiconductor layer and a semiconductor layer. The first etching process is a wet etching using a first resist layer to etch the second conducting layer. The second etching process is executed with an etchant comprising oxygen to etch the doped semiconductor layer and the semiconductor layer, and the first resist layer undergoes ashing during etching so as to become a second resist layer with a channel pattern. The third etching process is another wet etching, and the second conducting layer is etched again using the second resist layer as the etching mask. The fourth etching process is executed to dry etch the doped semiconductor layer using the second resist layer as the etching mask.

Owner:AU OPTRONICS CORP