Zero layer alignment maker and preparation method

A technology for zero-layer alignment marks and manufacturing methods, which is applied to the photoplate-making process of the pattern surface, the photoplate-making process exposure device, optics, etc., which can solve the cumbersome process steps, affect the process progress, and increase the exposure, development and etching steps and other issues to achieve the effect of simplifying the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

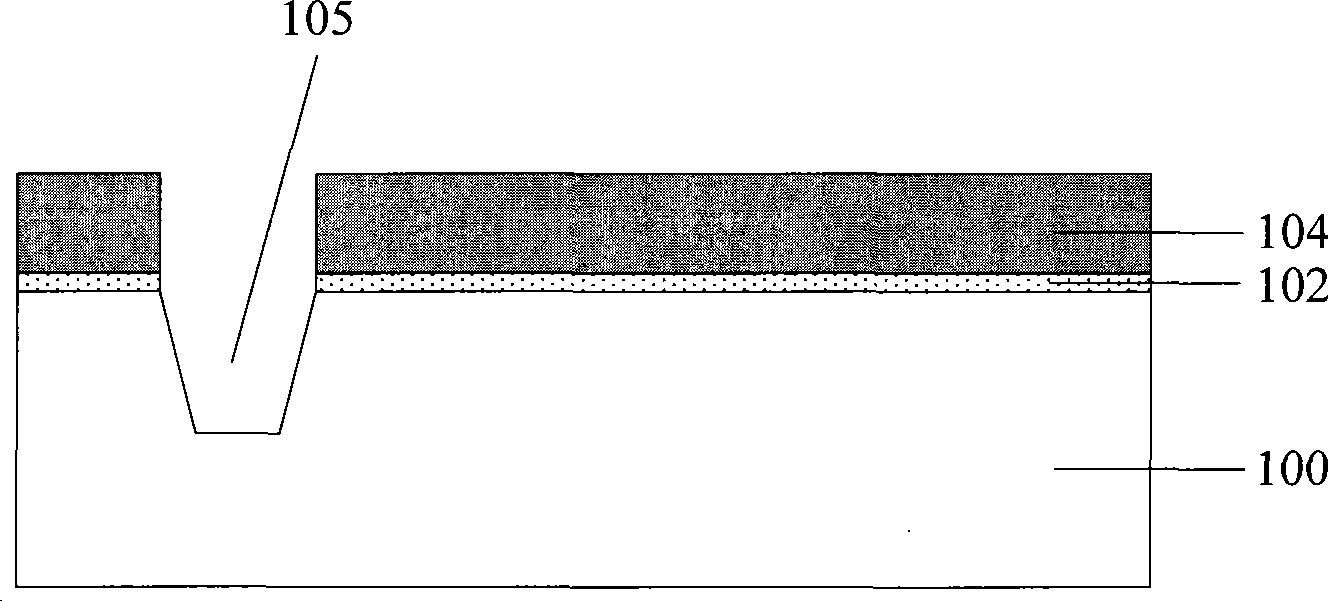

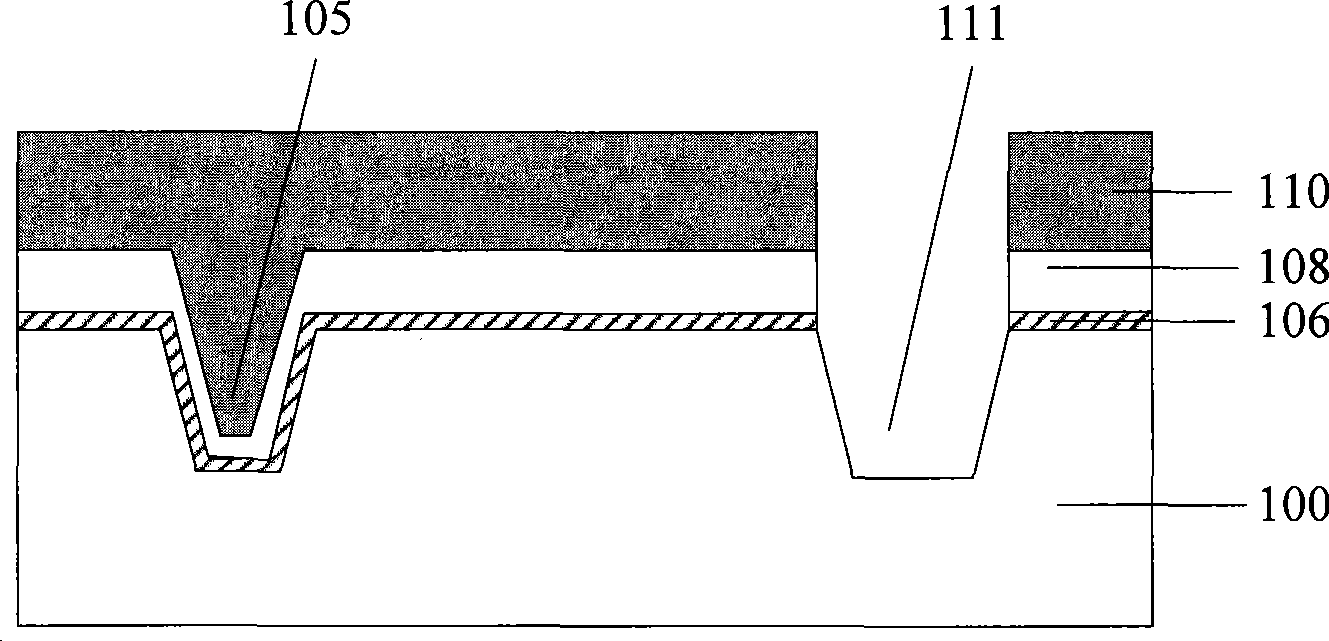

[0027] In the process of removing the corrosion barrier layer in the present invention, since there is no corrosion barrier layer on the side wall of the zero-layer alignment mark groove, the insulating dielectric layer in the zero-layer alignment mark groove can remain intact as a zero-layer alignment mark, so no The steps of exposure, development and etching need to be added to remove the insulating dielectric layer in the trench and the corrosion barrier layer under the insulating dielectric layer, so that the zero-layer alignment mark trench covering the pad oxide layer is used as the zero-layer alignment mark. The process steps are simplified.

[0028] Further, the zero-layer alignment mark and the shallow trench isolation structure are formed simultaneously, which simplifies the process steps and improves the yield.

[0029] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0030] Figur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More