Patents

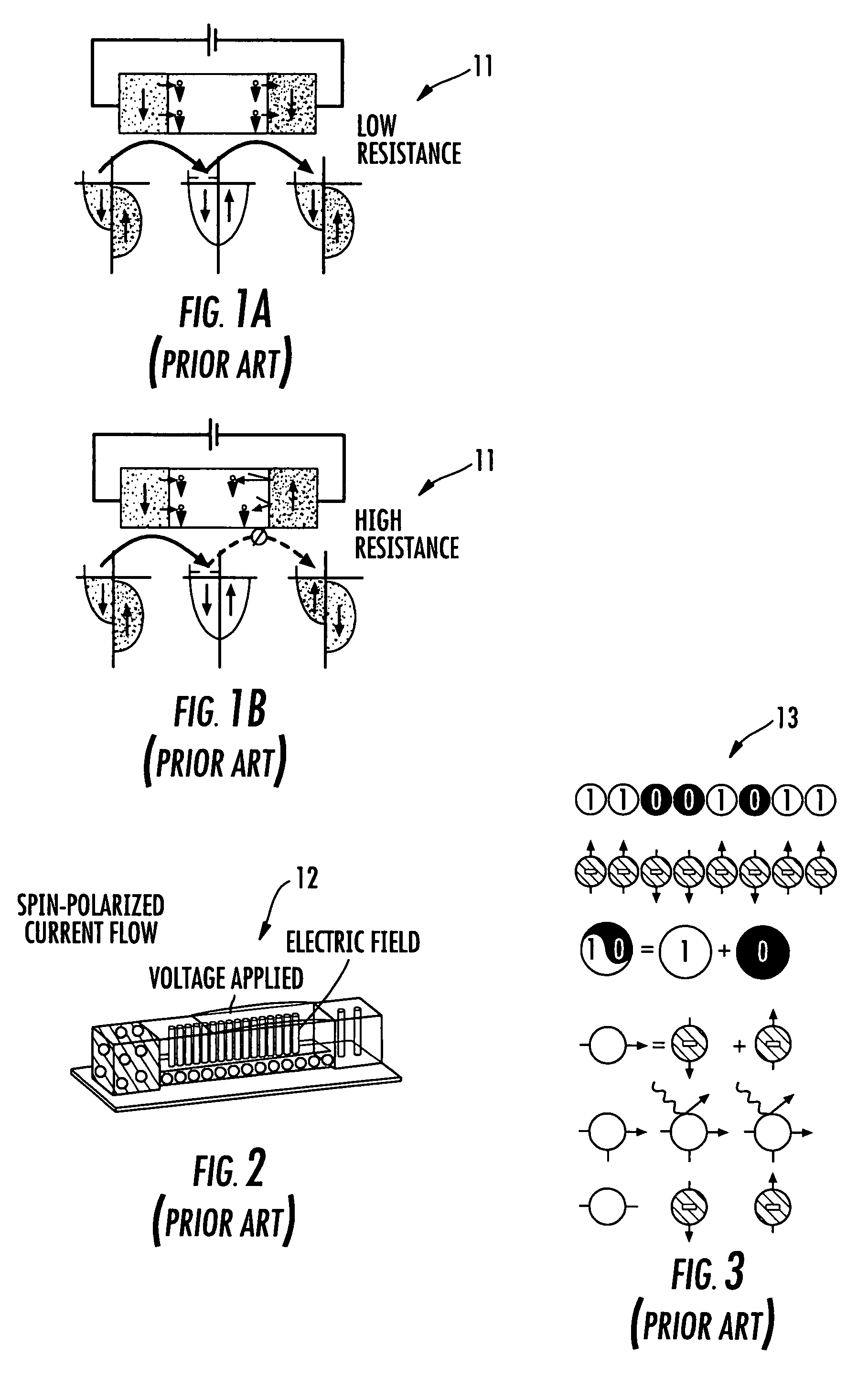

Literature

955results about How to "Increase the doping concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

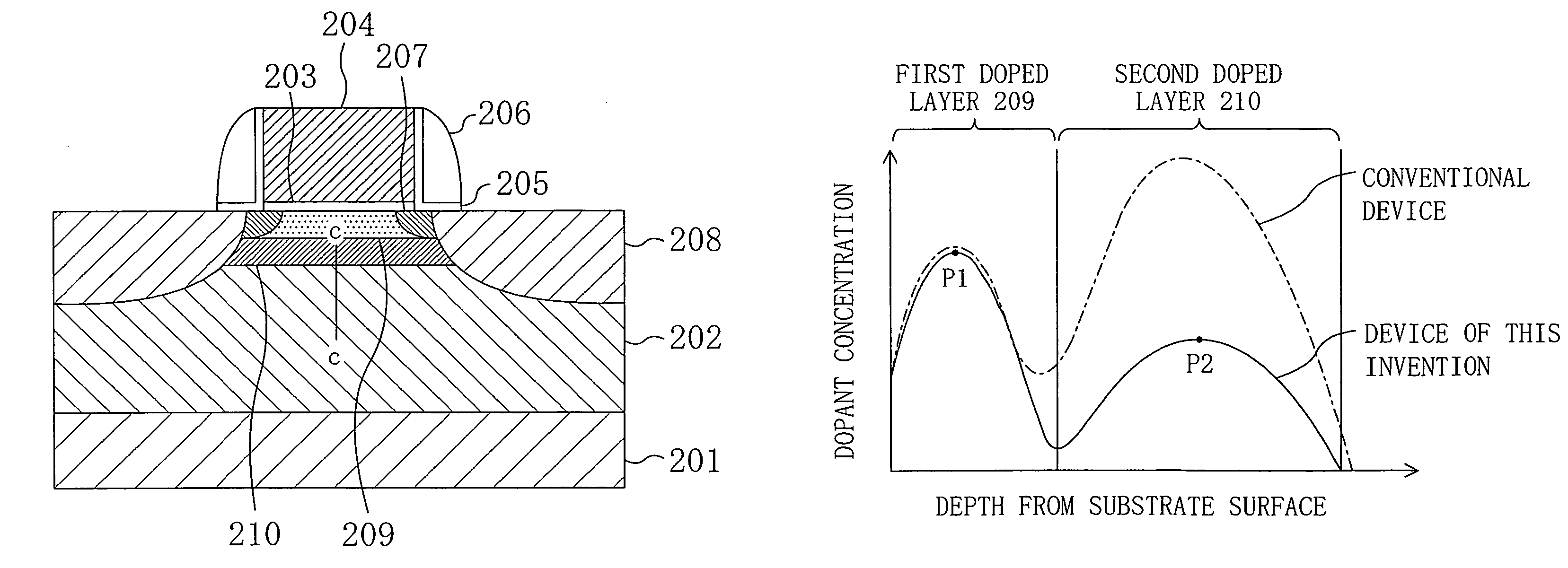

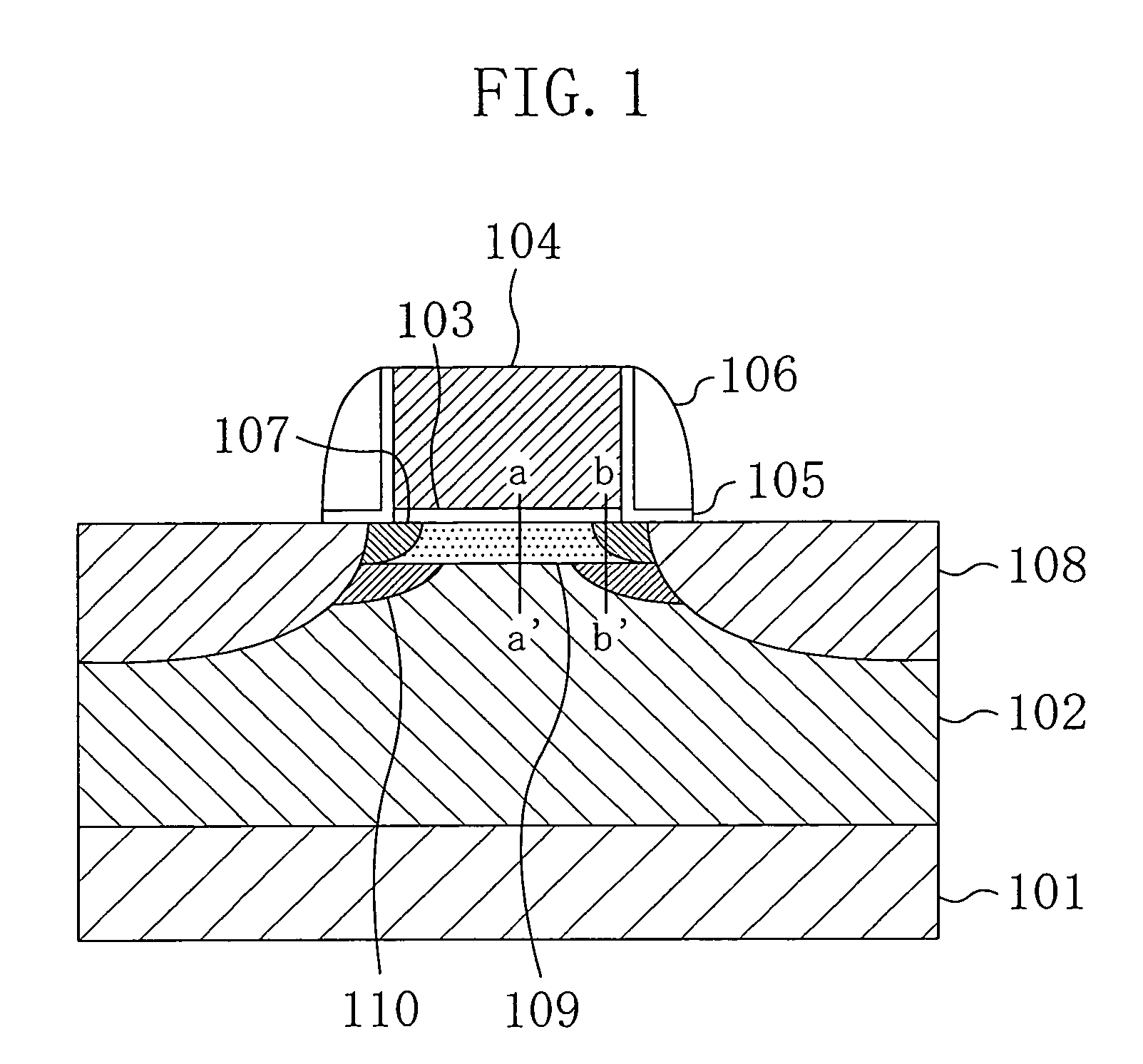

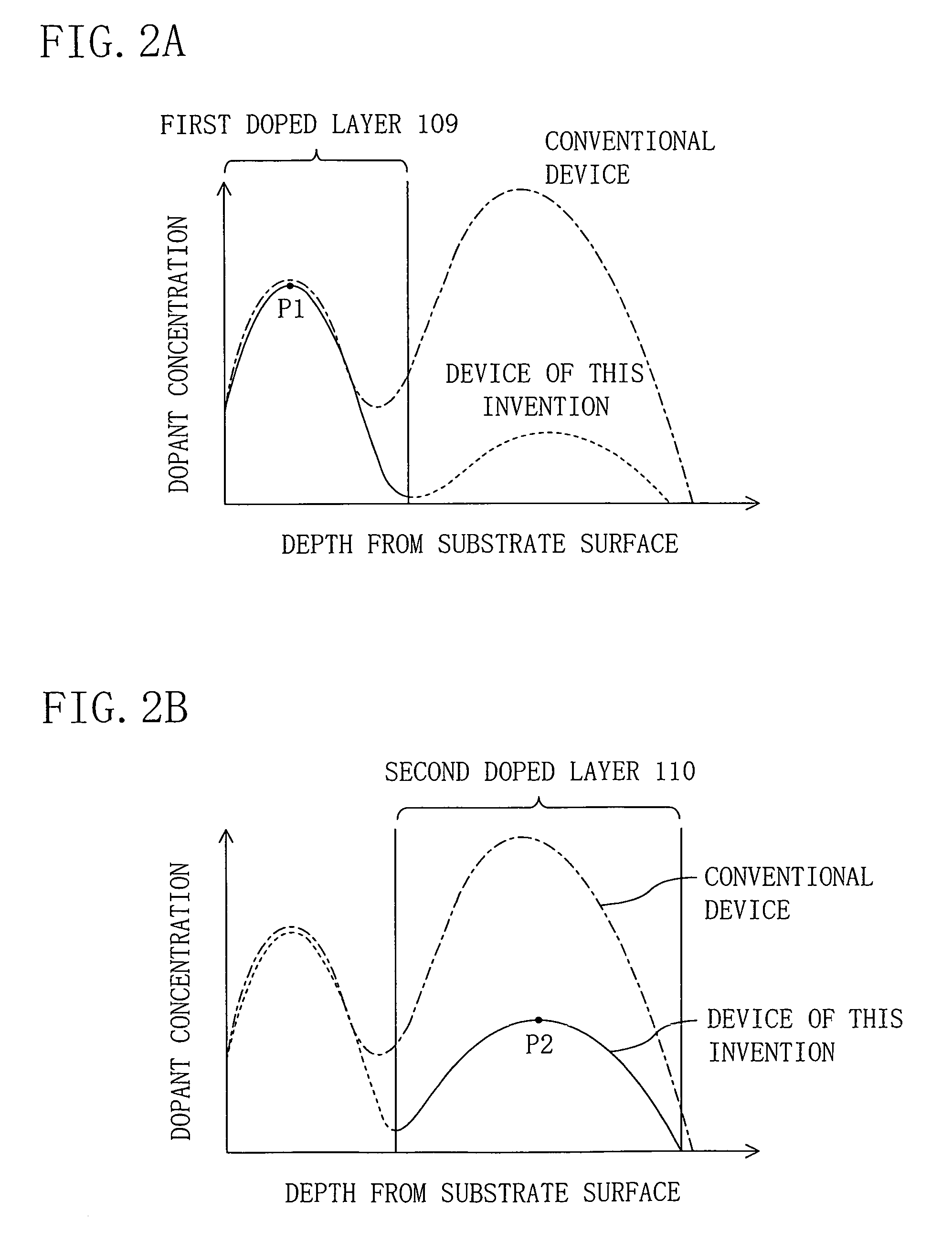

Semiconductor device and method for fabricating the same

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

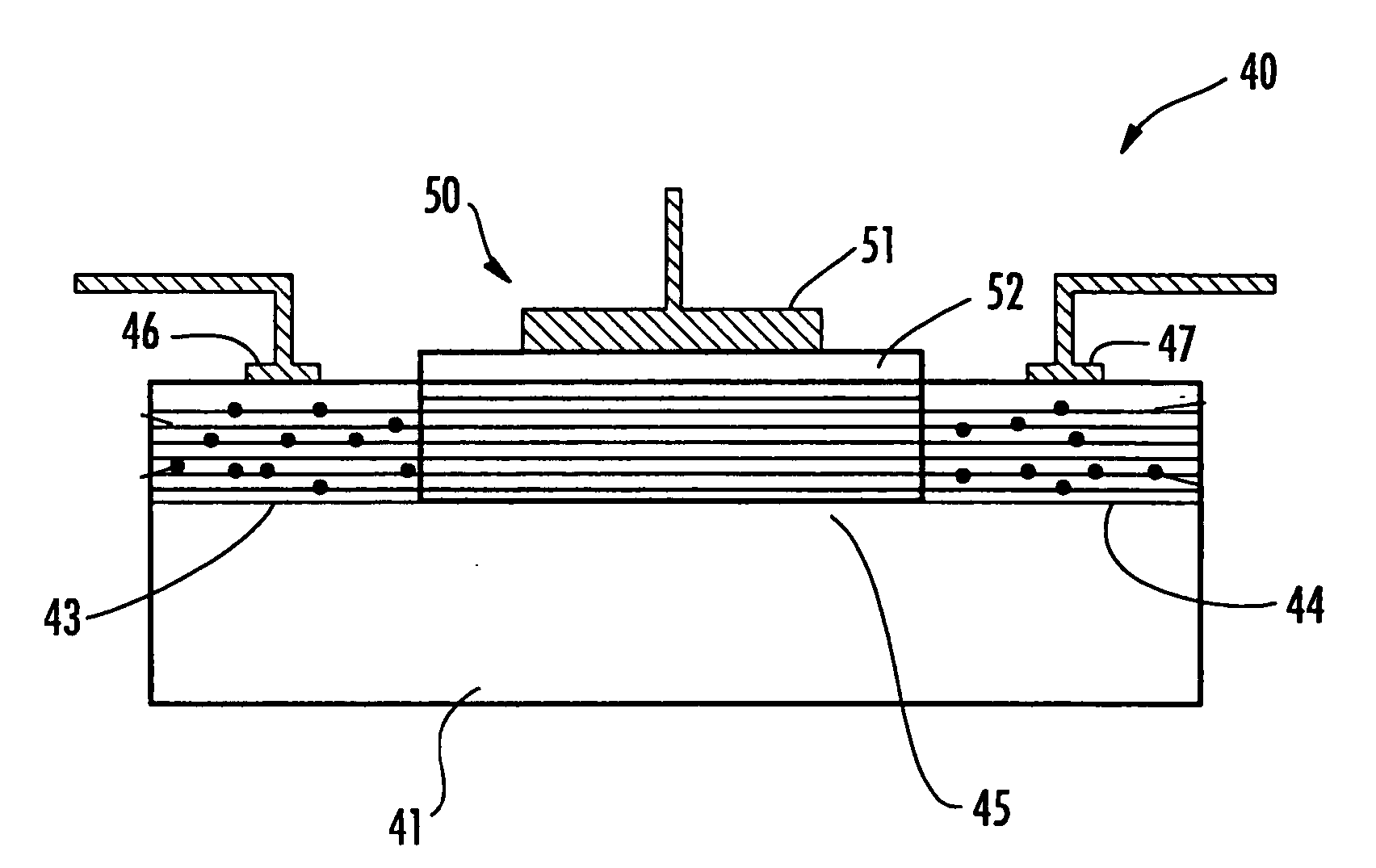

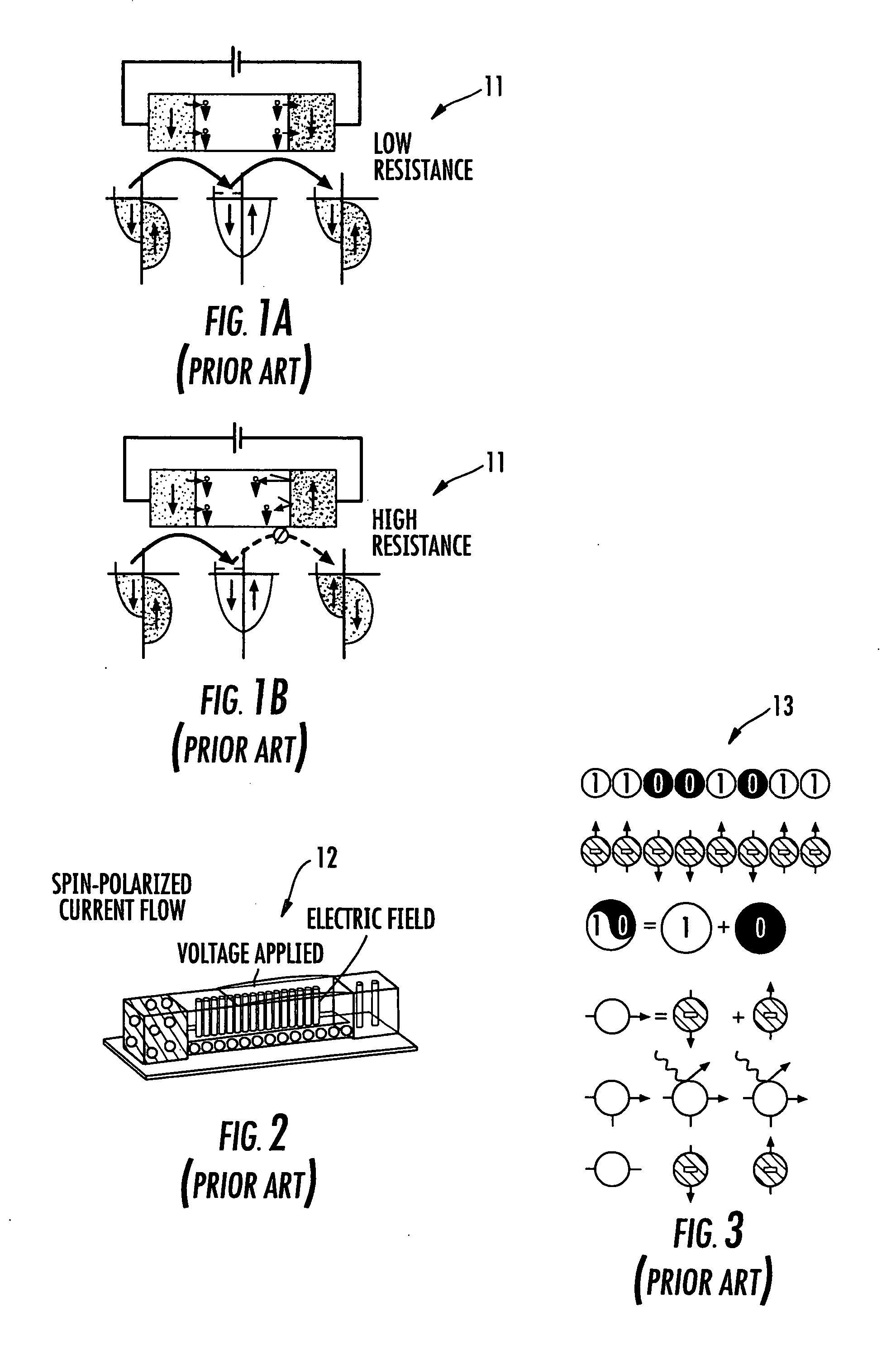

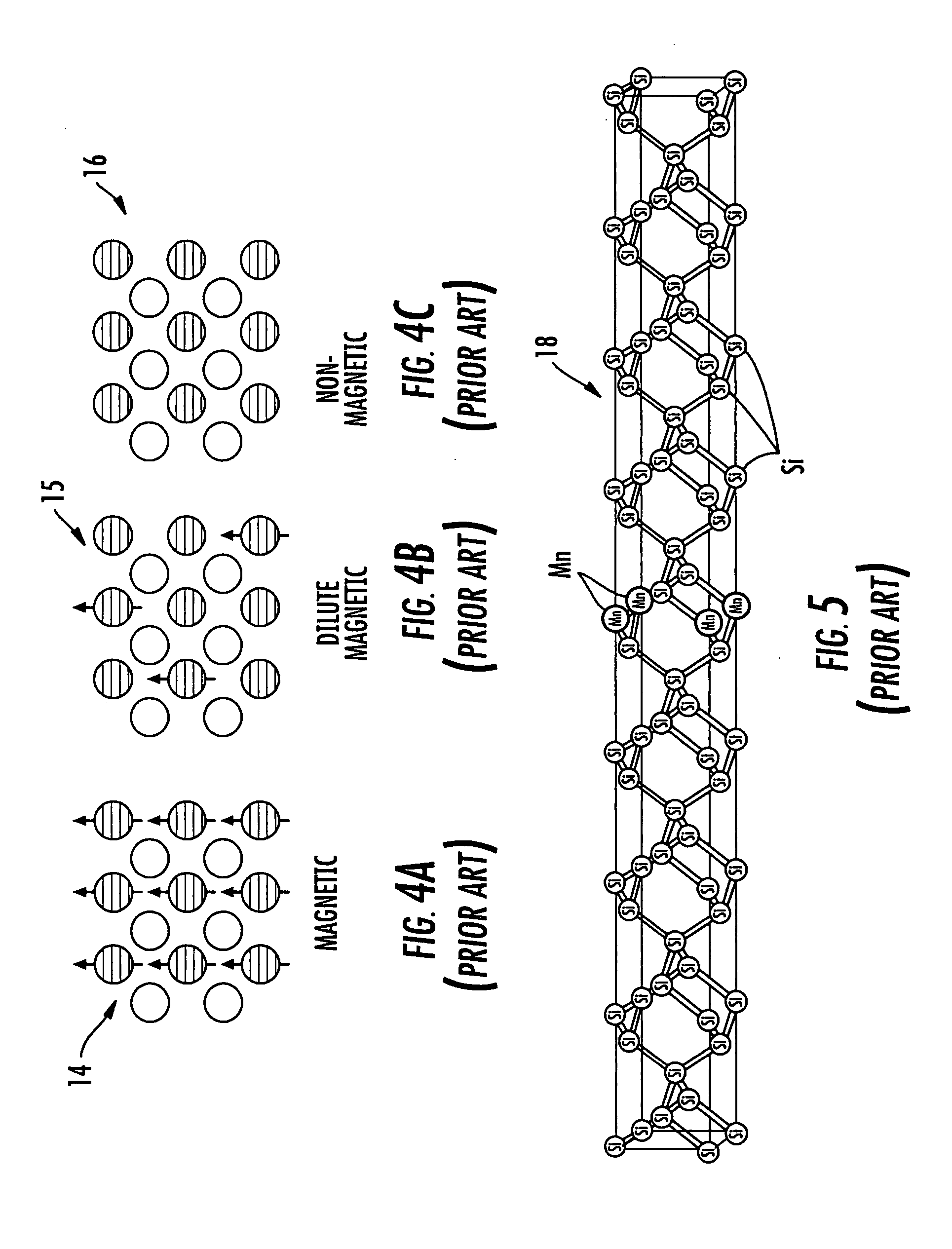

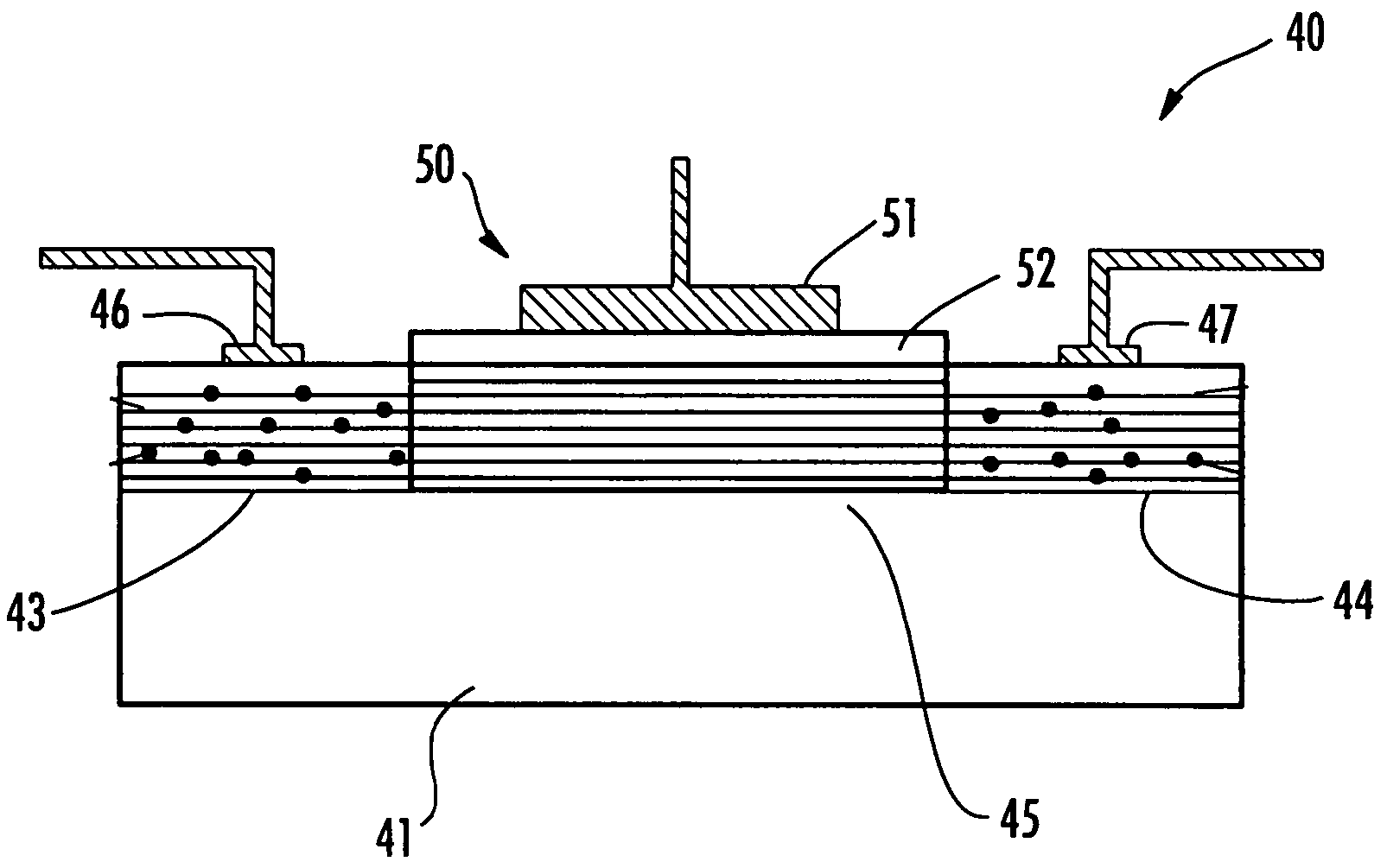

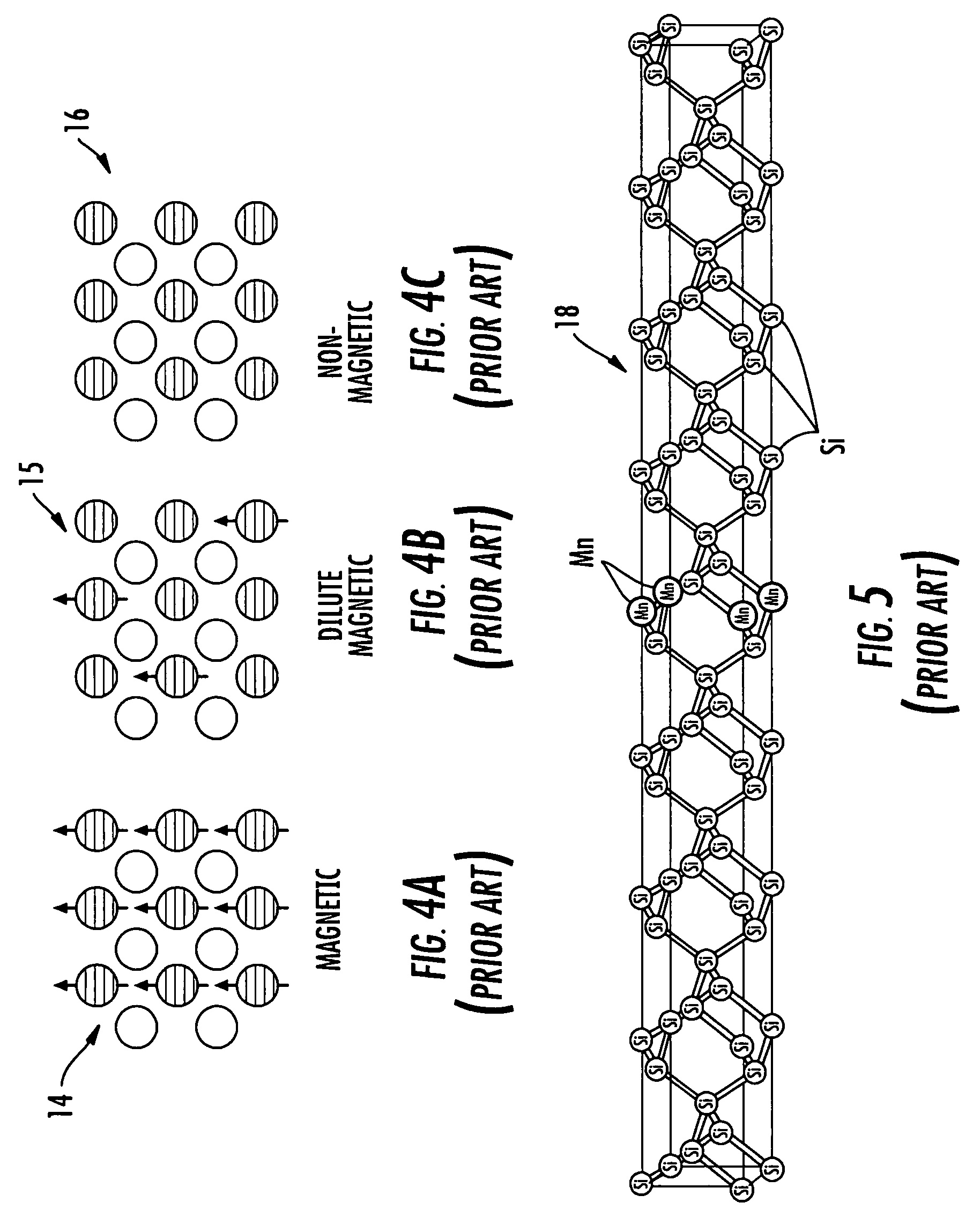

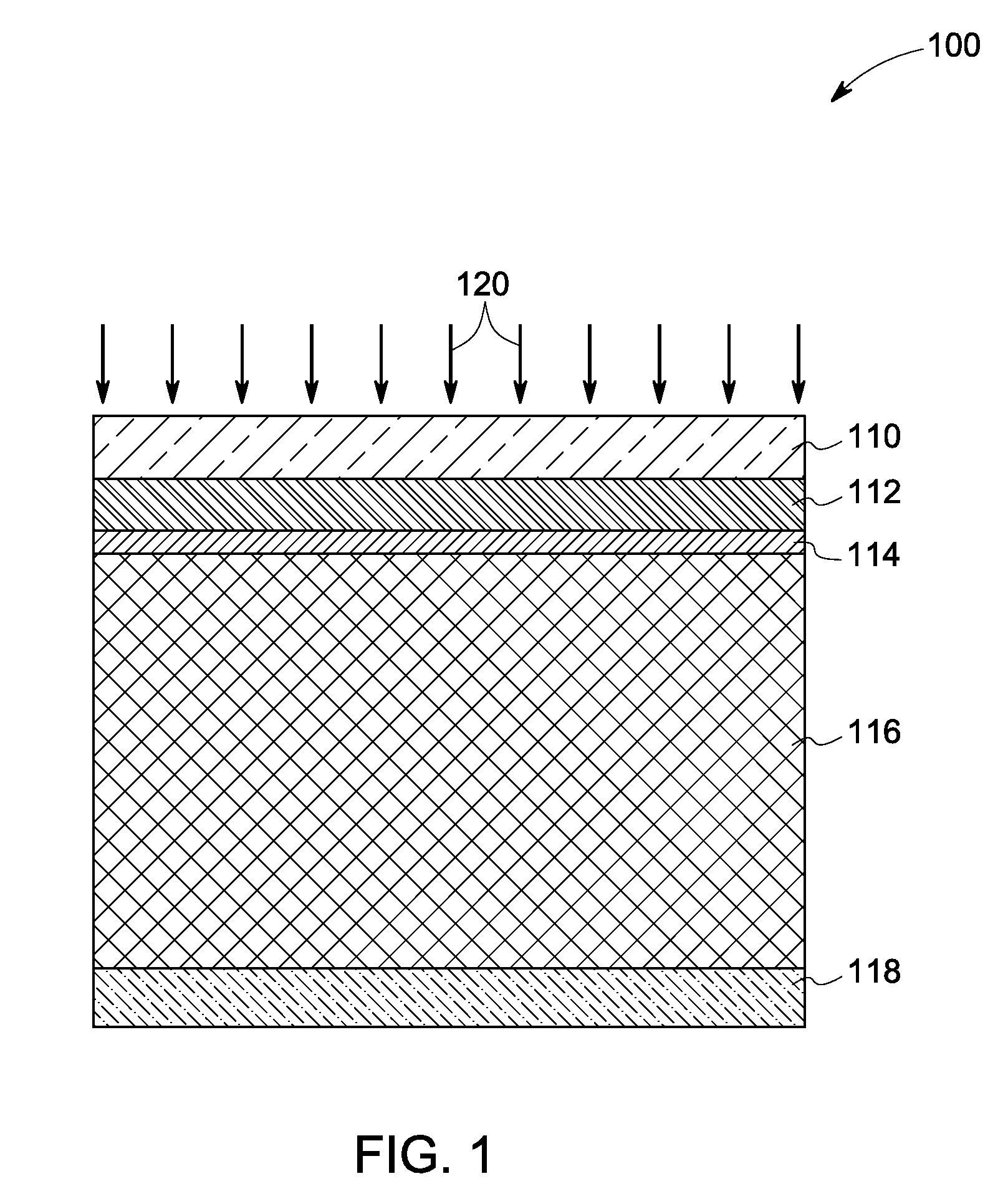

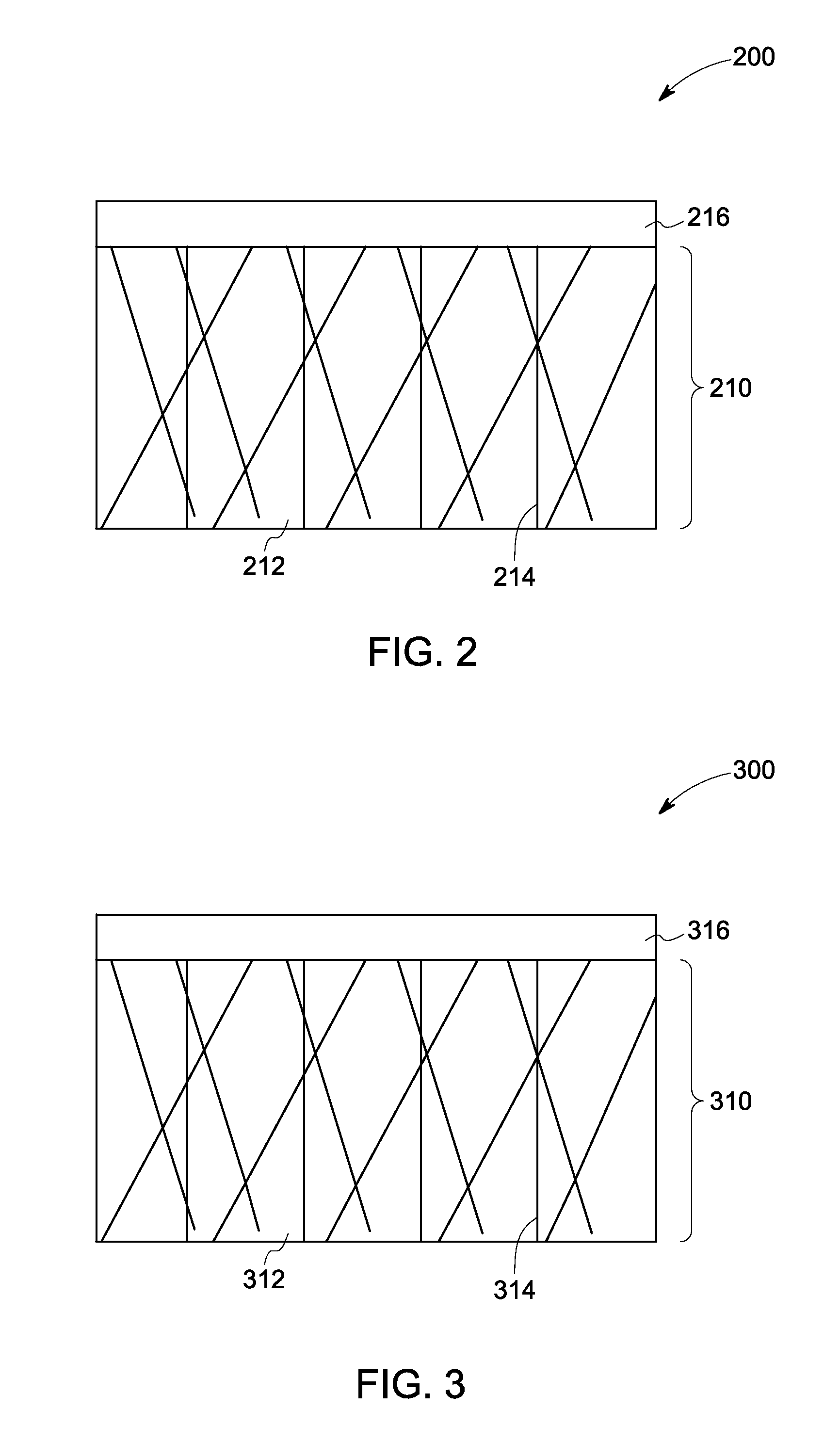

Spintronic devices with constrained spintronic dopant

InactiveUS20080012004A1Easy to manufactureGood spintronic characteristicNanomagnetismThin magnetic filmsDopantEngineering

A spintronic device may include at least one superlattice and at least one electrical contact coupled thereto, with the at least one superlattice including a plurality of groups of layers. Each group of layers may include a plurality of stacked base semiconductor monolayers defining a base semiconductor portion having a crystal lattice, at least one non-semiconductor monolayer constrained within the crystal lattice of adjacent base semiconductor portions, and a spintronic dopant. The spintronic dopant may be constrained within the crystal lattice of the base semiconductor portion by the at least one non-semiconductor monolayer. In some embodiments, the repeating structure of a superlattice may not be needed.

Owner:MEARS TECH

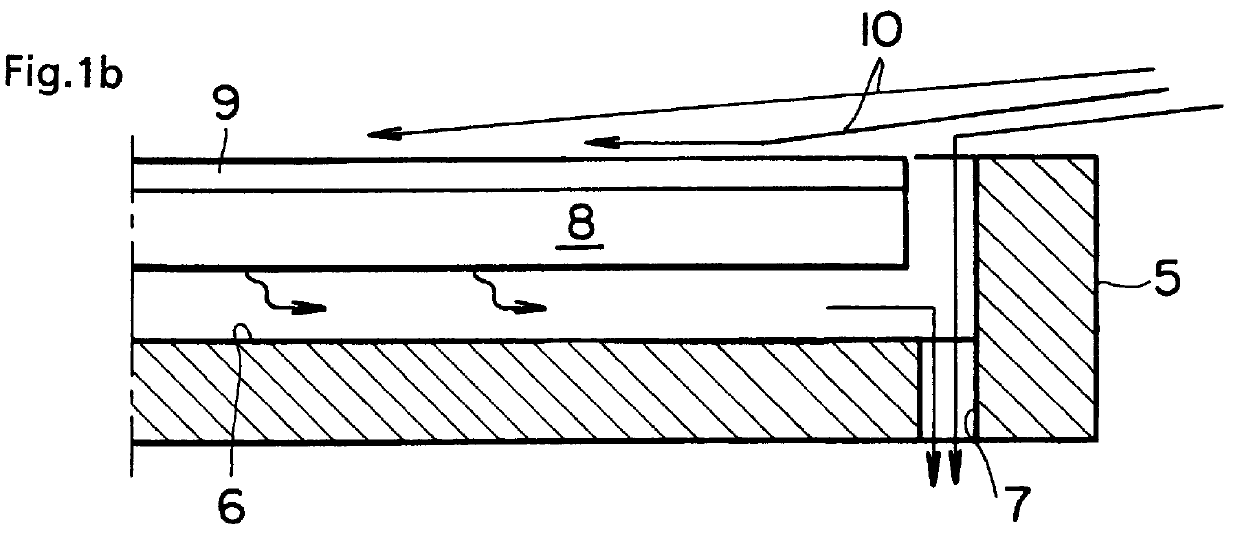

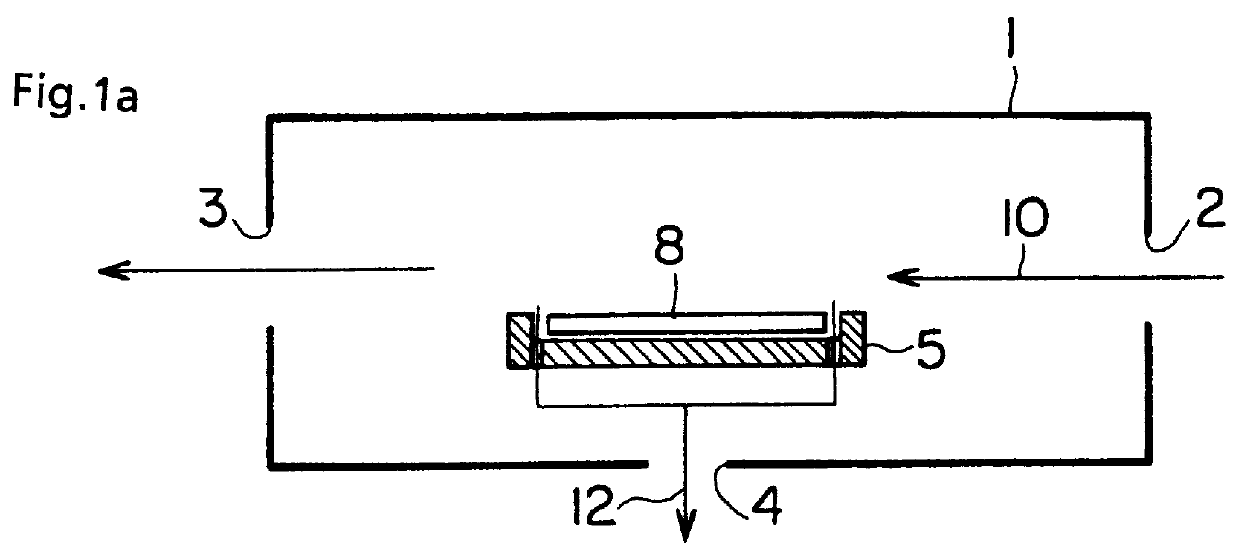

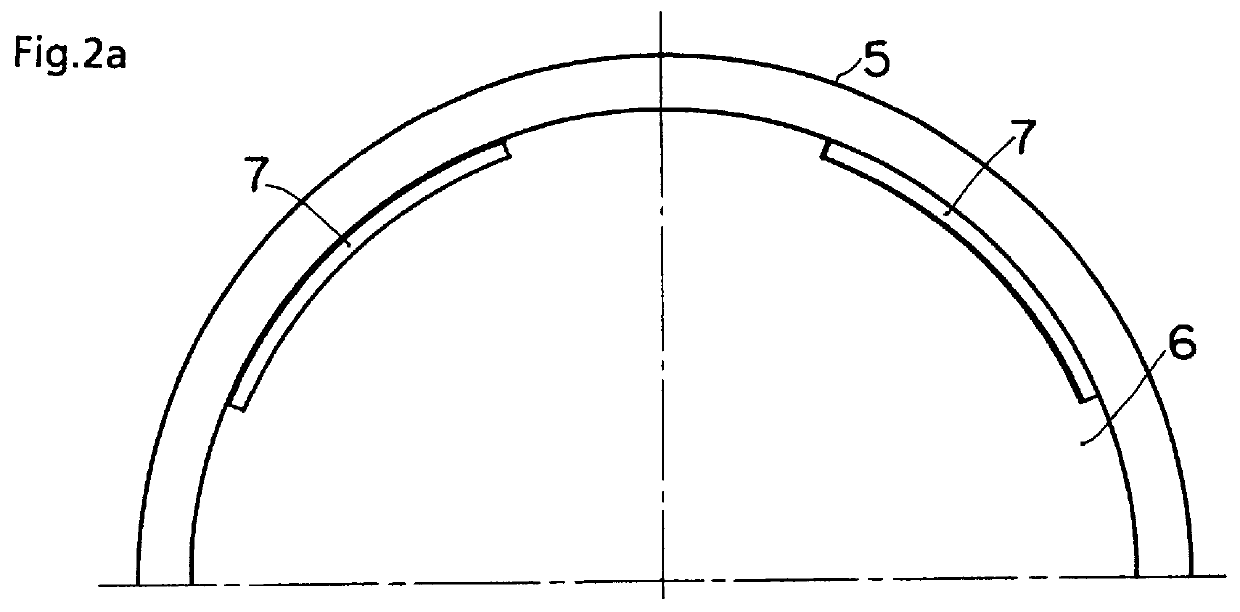

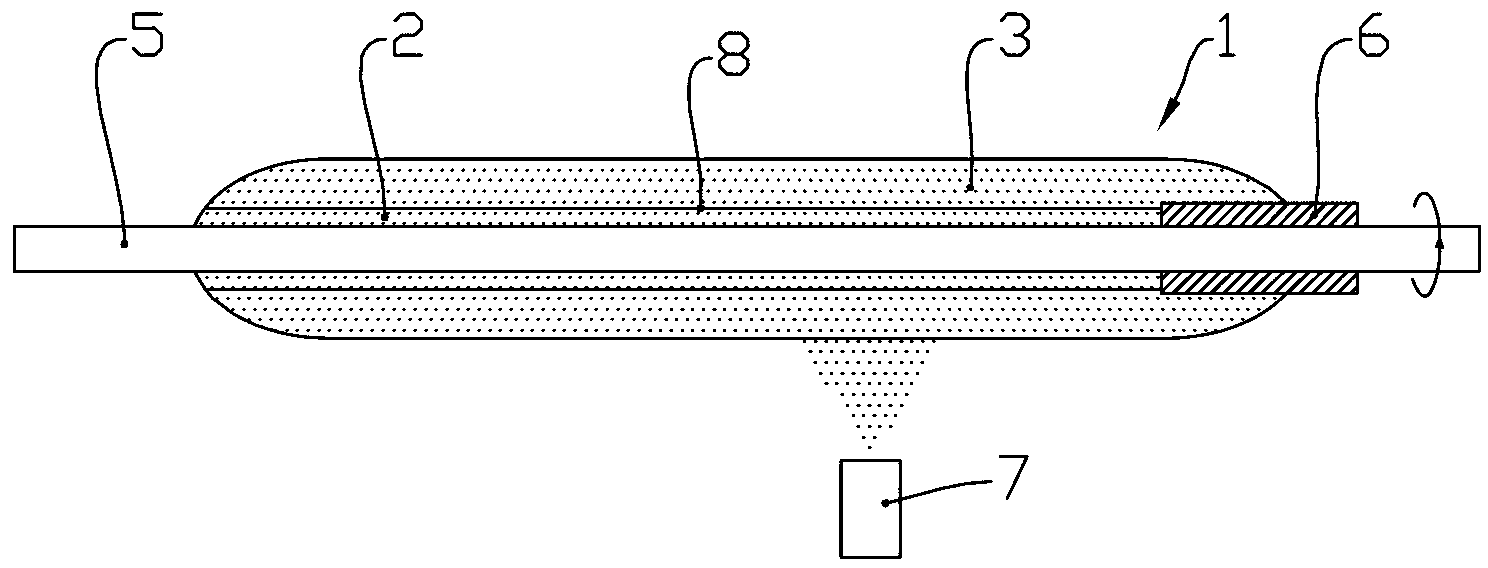

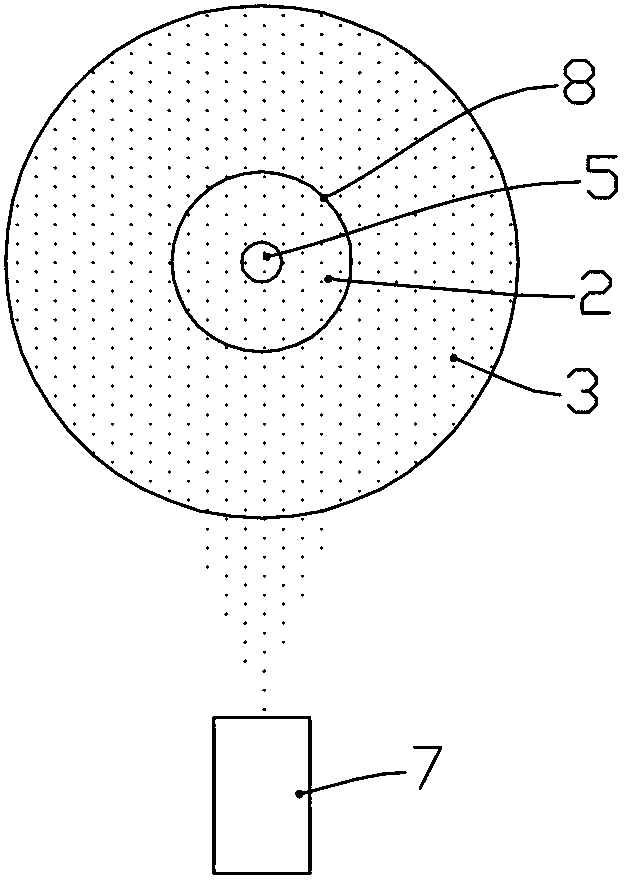

Susceptor for vapor-phase growth apparatus

InactiveUS6129047AUnwanted flowImprove efficiencyLiquid surface applicatorsSemiconductor/solid-state device manufacturingVapor phaseEngineering

It was an objective of the present invention to provide a susceptor which can prevent a increasing phenomenon of the dopant concentration of the epitaxial layer at the peripheral portion of the wafer. By providing a through-hole 7 passing through to a rear side at the outer peripheral side of the wafer inside the wafer pocket 6, a down flow of a reacting source gas from the upper surface of the susceptor 5 is formed, so that the unwanted flow of the dopant species being exhausted at the rear surface onto the wafer surface can be avoided. As a result, a raise in the dopant concentration at the outer peripheral portion of the epitaxial layer 9 can be controlled.

Owner:SUMITOMO MITSUBISHI SILICON CORP

Methods of making spintronic devices with constrained spintronic dopant

ActiveUS7625767B2Reduce the possibilityIncrease the doping concentrationNanomagnetismNanoinformaticsDopantEngineering

A method is for making a spintronic device and may include forming at least one superlattice and at least one electrical contact coupled thereto, with the at least one superlattice including a plurality of groups of layers. Each group of layers may include a plurality of stacked base semiconductor monolayers defining a base semiconductor portion having a crystal lattice, at least one non-semiconductor monolayer constrained within the crystal lattice of adjacent base semiconductor portions, and a spintronic dopant. The spintronic dopant may be constrained within the crystal lattice of the base semiconductor portion by the at least one non-semiconductor monolayer. In some embodiments, the repeating structure of a superlattice may not be needed.

Owner:ATOMERA INC

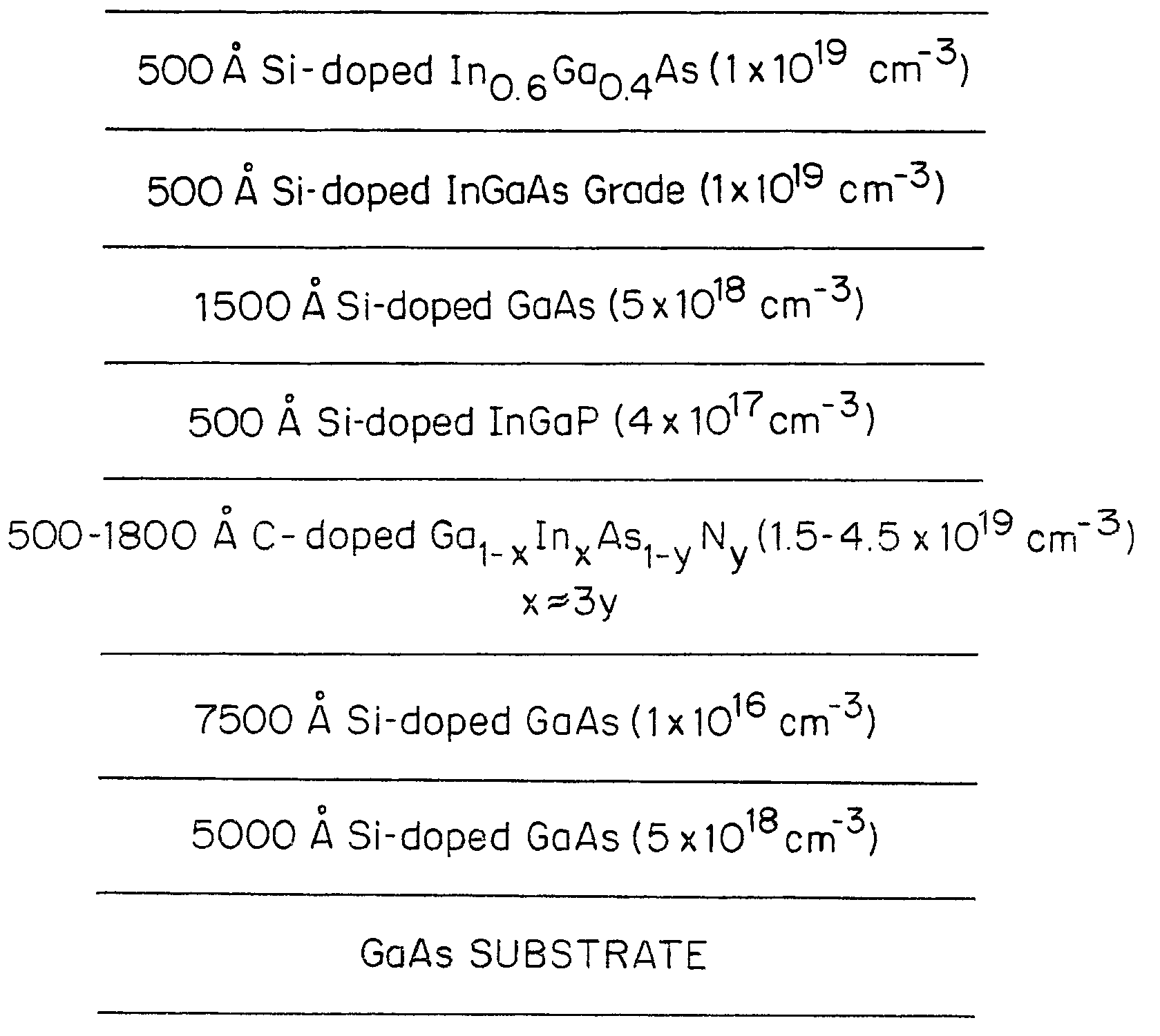

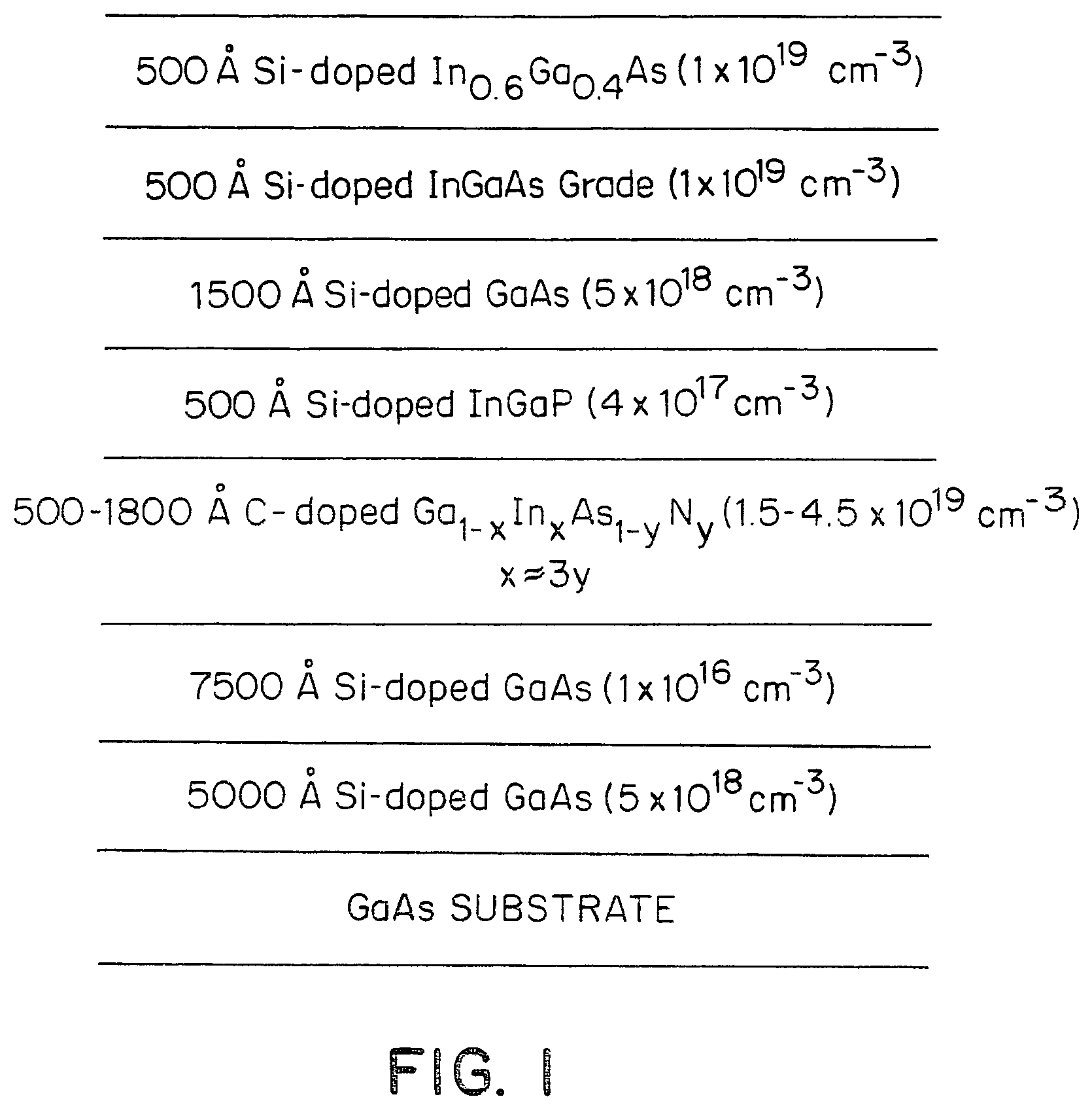

Bipolar transistor with lattice matched base layer

InactiveUS7186624B2Reduce gapLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionDopant

A semiconductor material which has a high carbon dopant concentration and is composed of gallium, indium, arsenic and nitrogen is disclosed. The material is useful in forming the base layer of gallium arsenide based heterojunction bipolar transistors because it can be lattice matched to gallium arsenide by controlling the concentration of indium and nitrogen. The disclosed semiconductor materials have a low sheet resistivity because of the high carbon dopant concentration obtained.

Owner:IQE KC

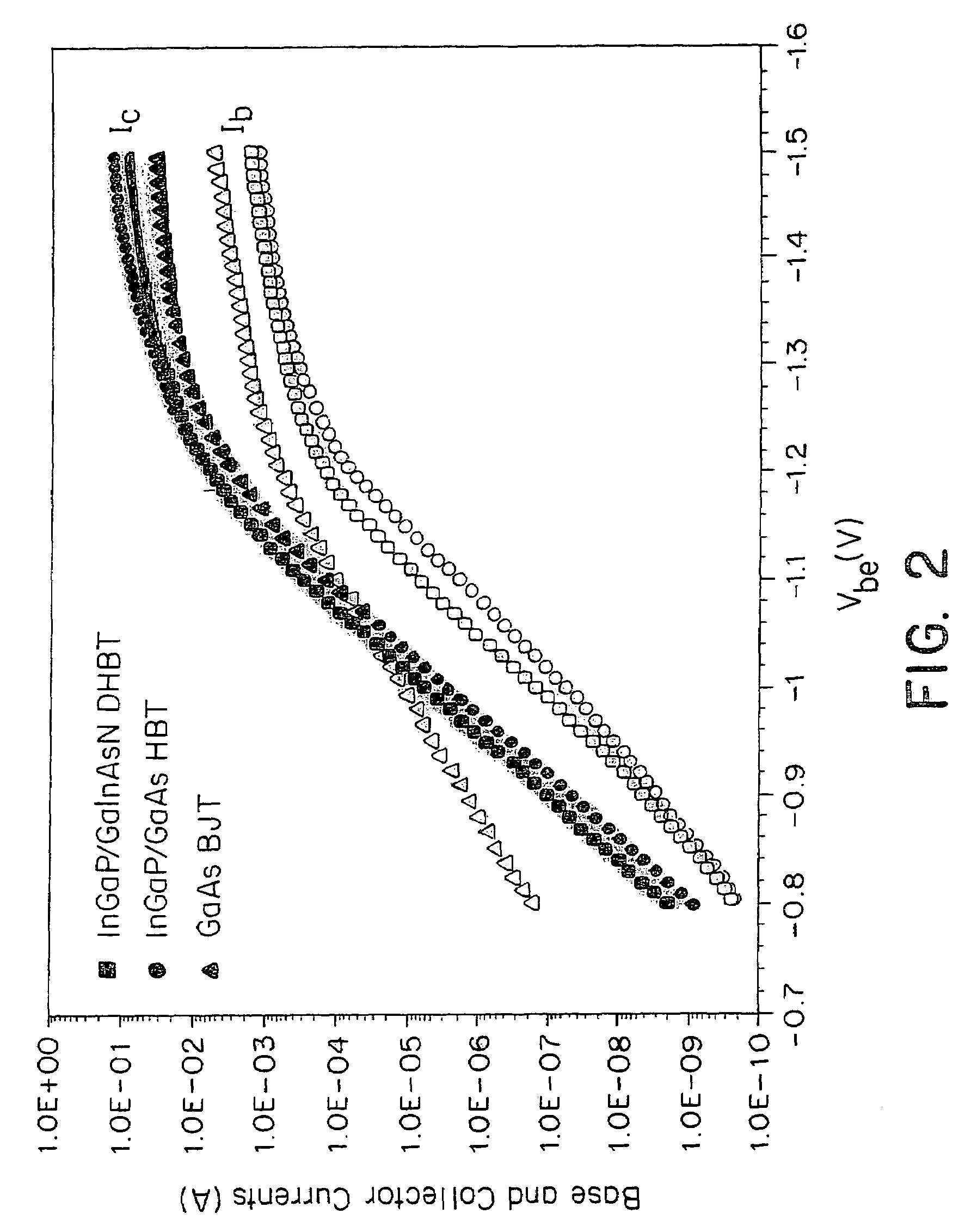

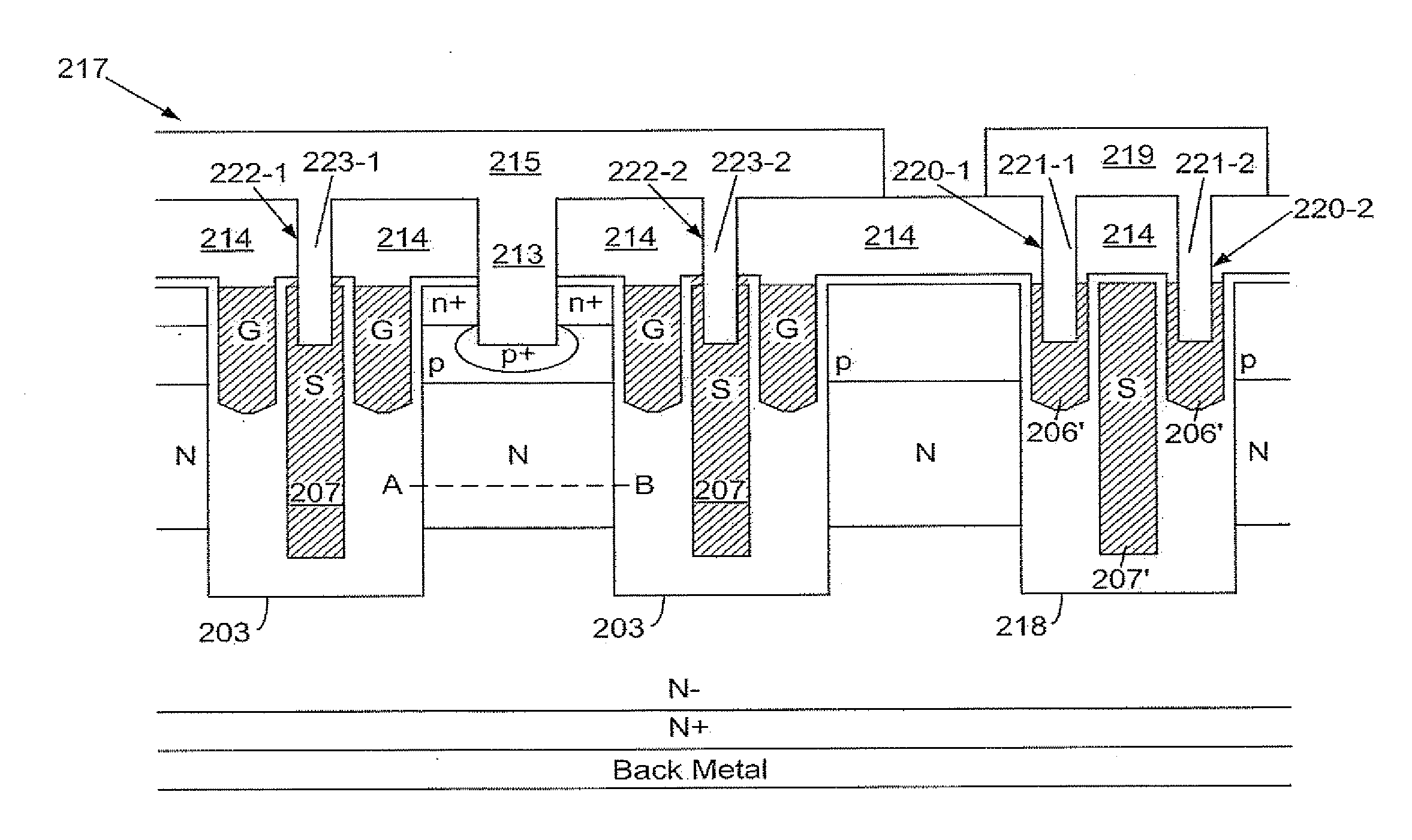

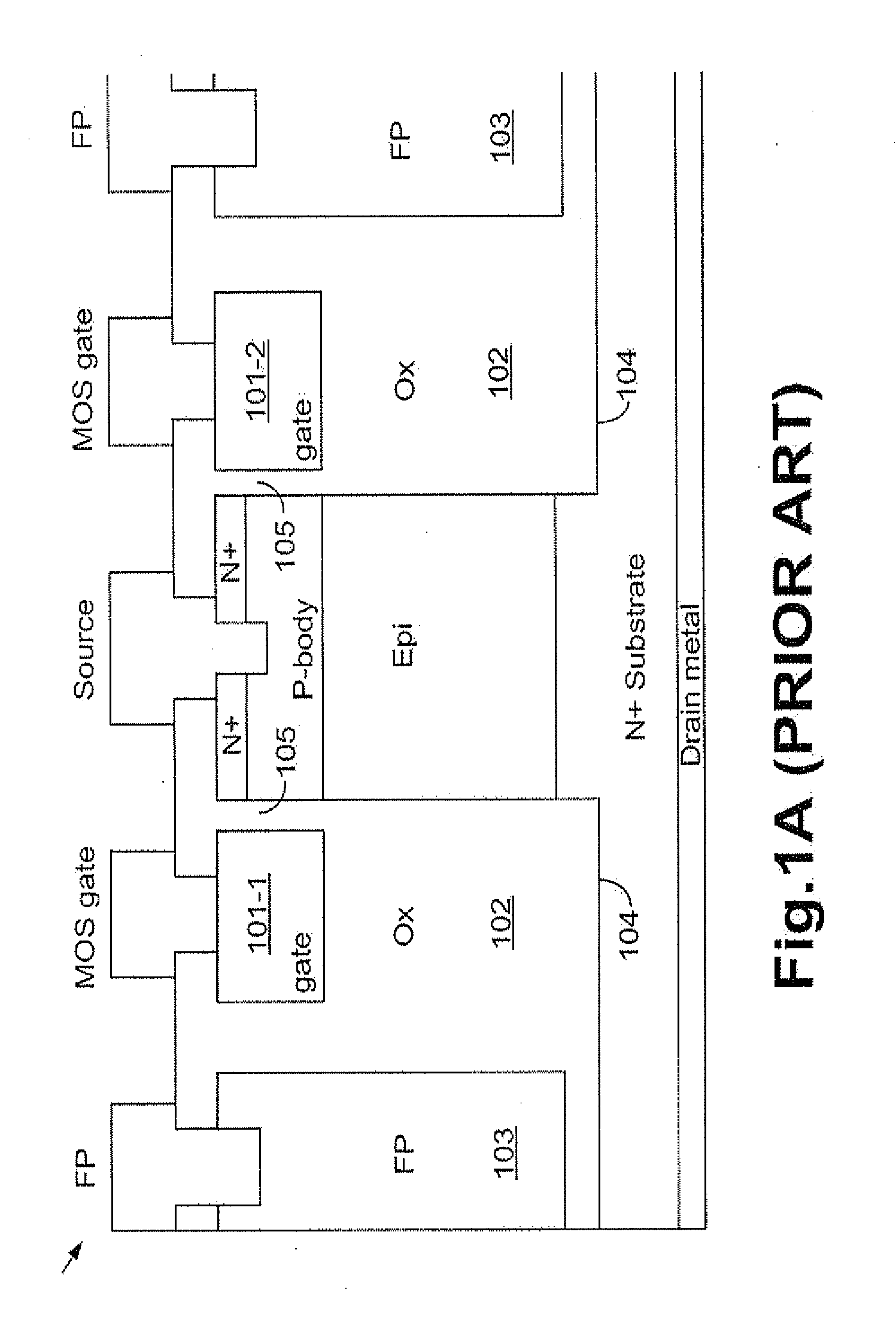

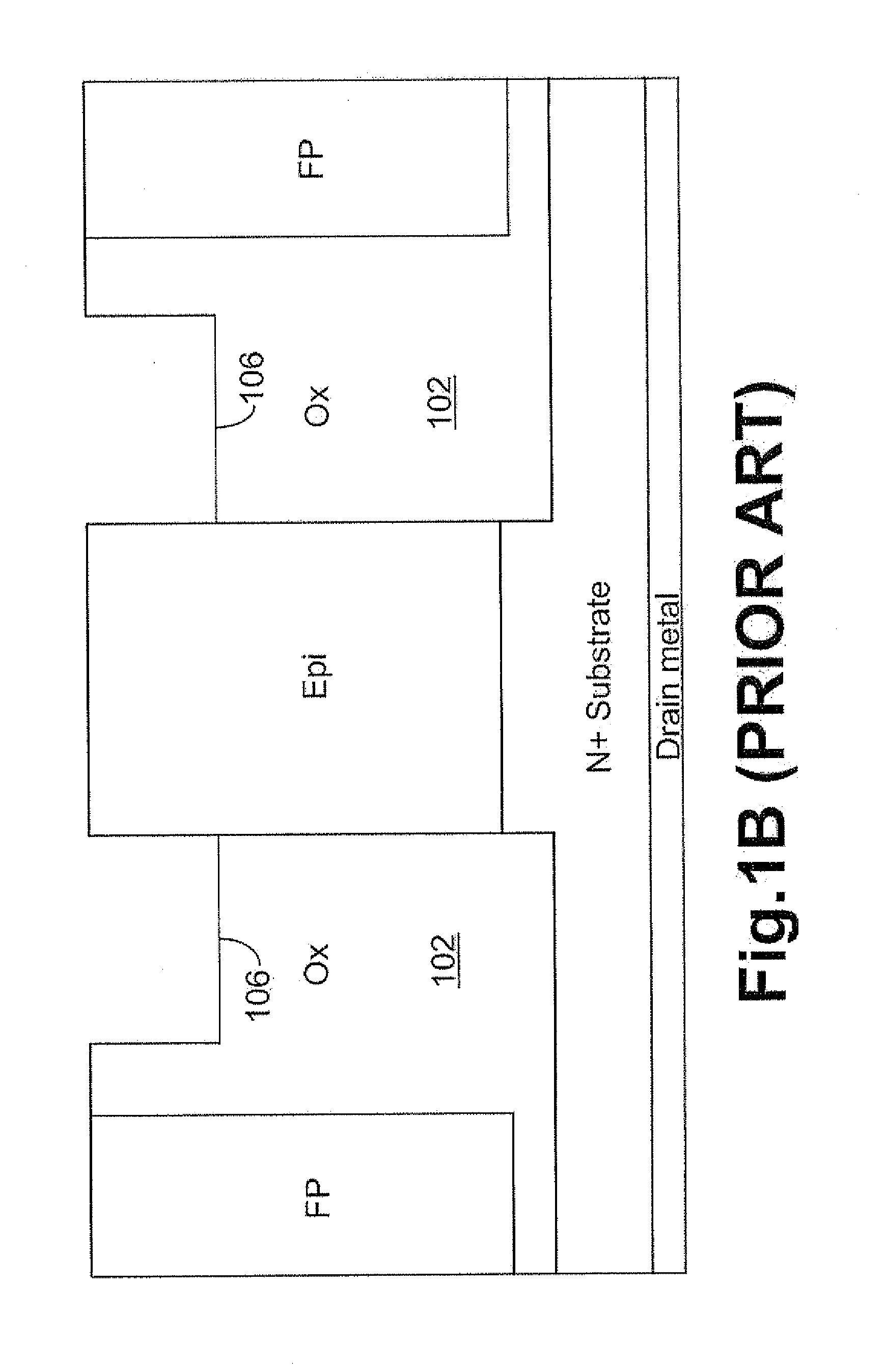

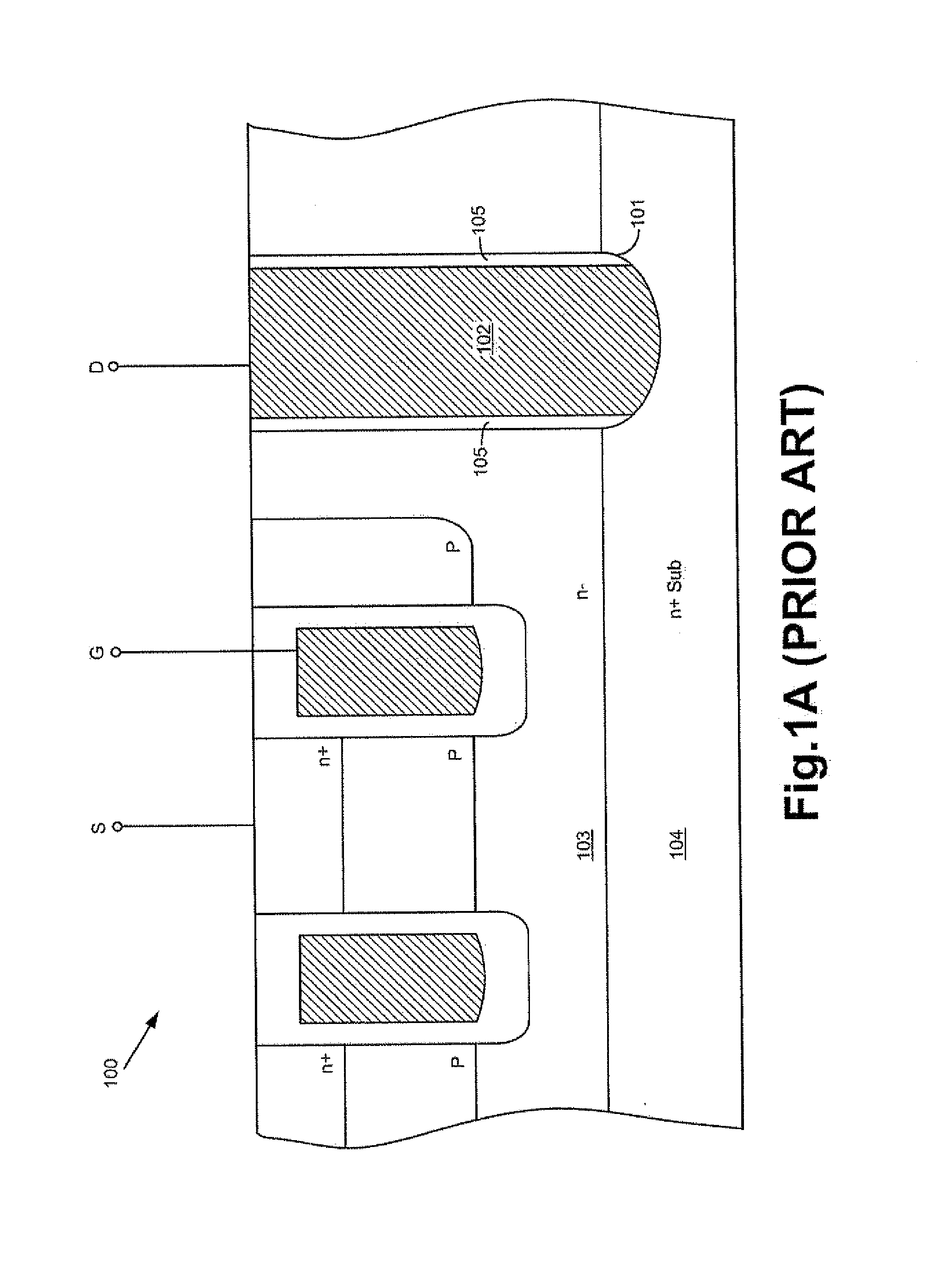

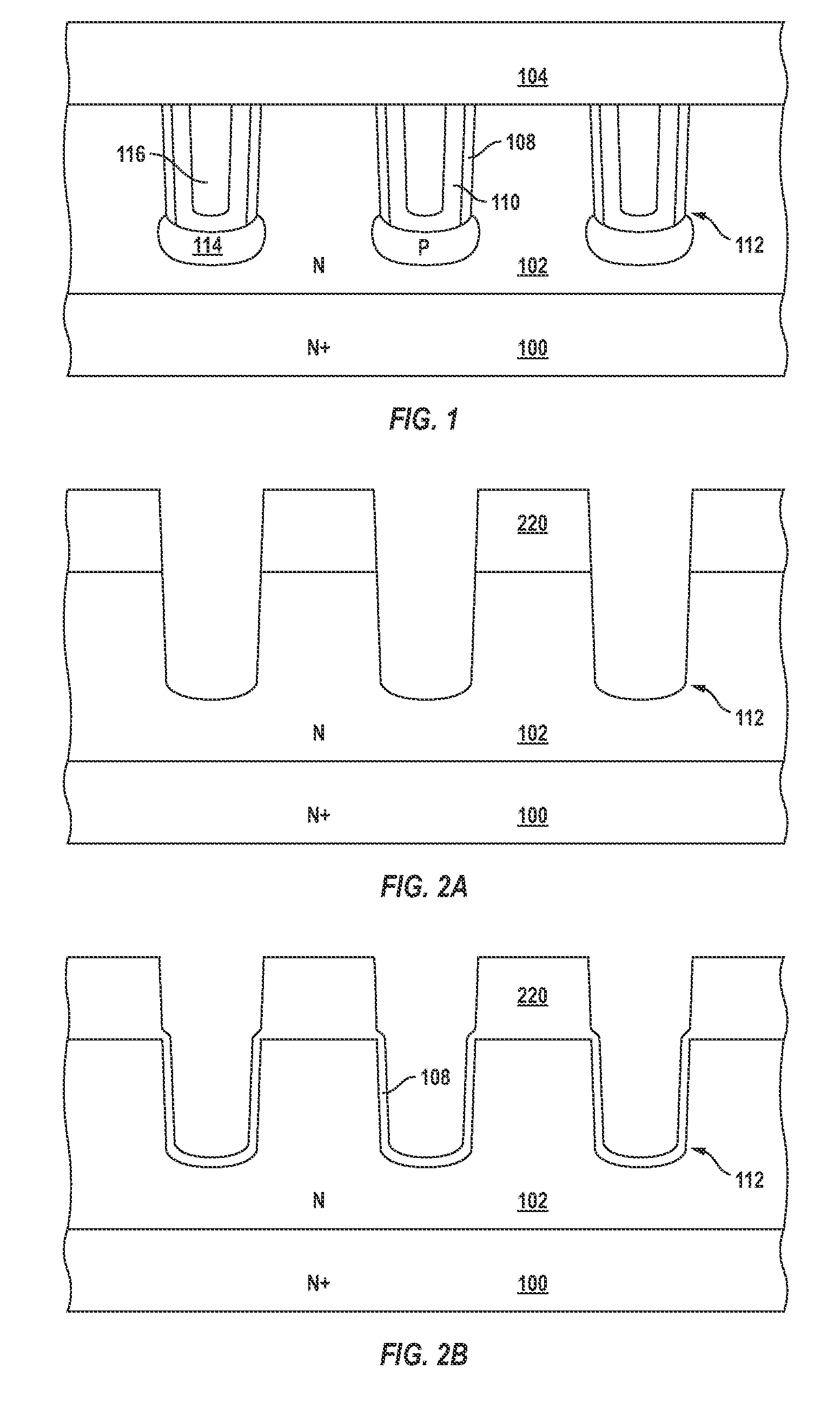

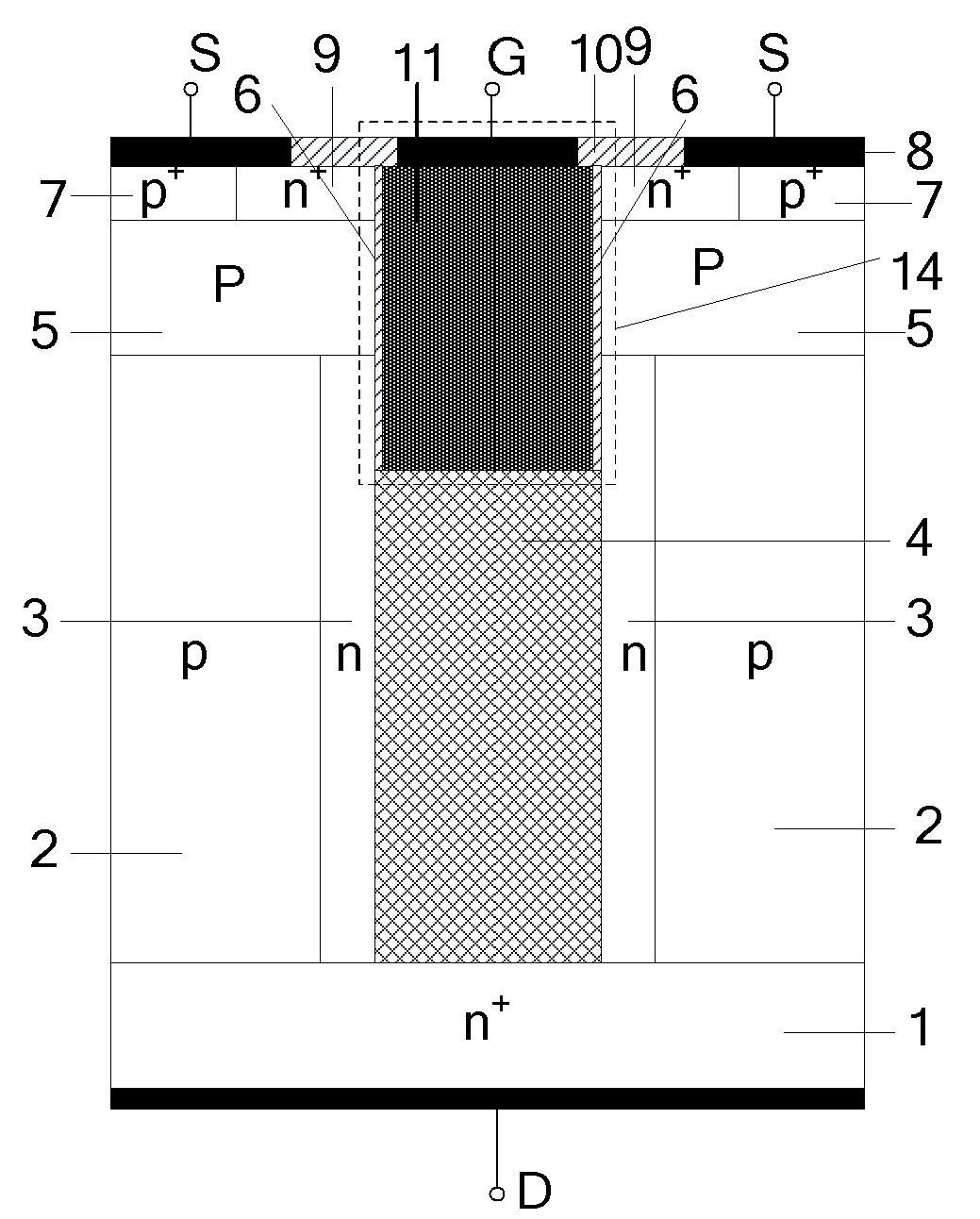

Trench mosfet with resurf stepped oxide and diffused drift region

ActiveUS20130168760A1Super cost-effectiveEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetEngineering

A trench MOSFET with split gates and diffused drift region for on-resistance reduction is disclosed. Each of the split gates is symmetrically disposed in the middle of the source electrode and adjacent trench sidewall of a deep trench. The inventive structure can save a mask for definition of the location of the split gate electrodes. Furthermore, the fabrication method can be implemented more reliably with lower cost.

Owner:FORCE MOS TECH CO LTD

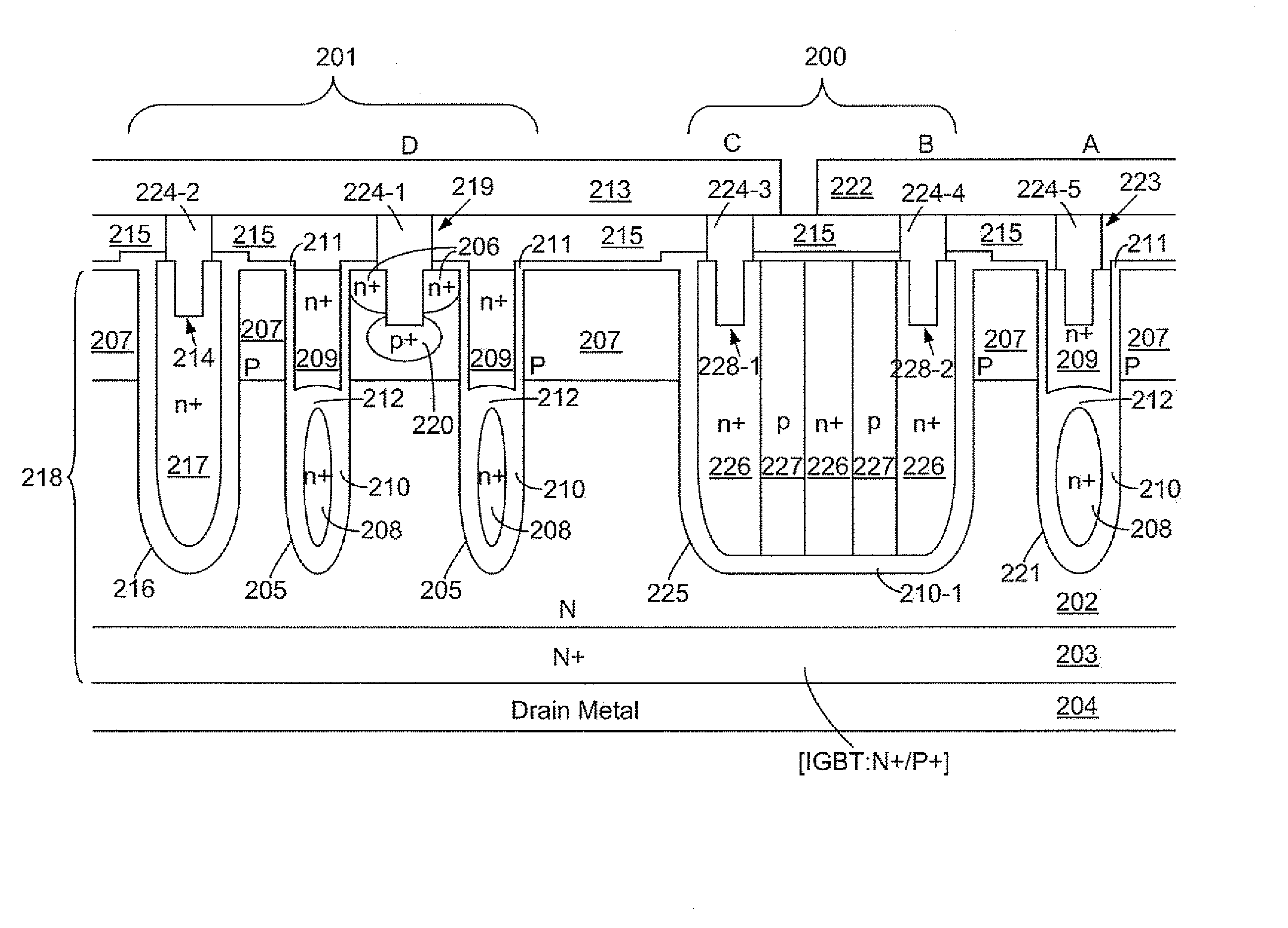

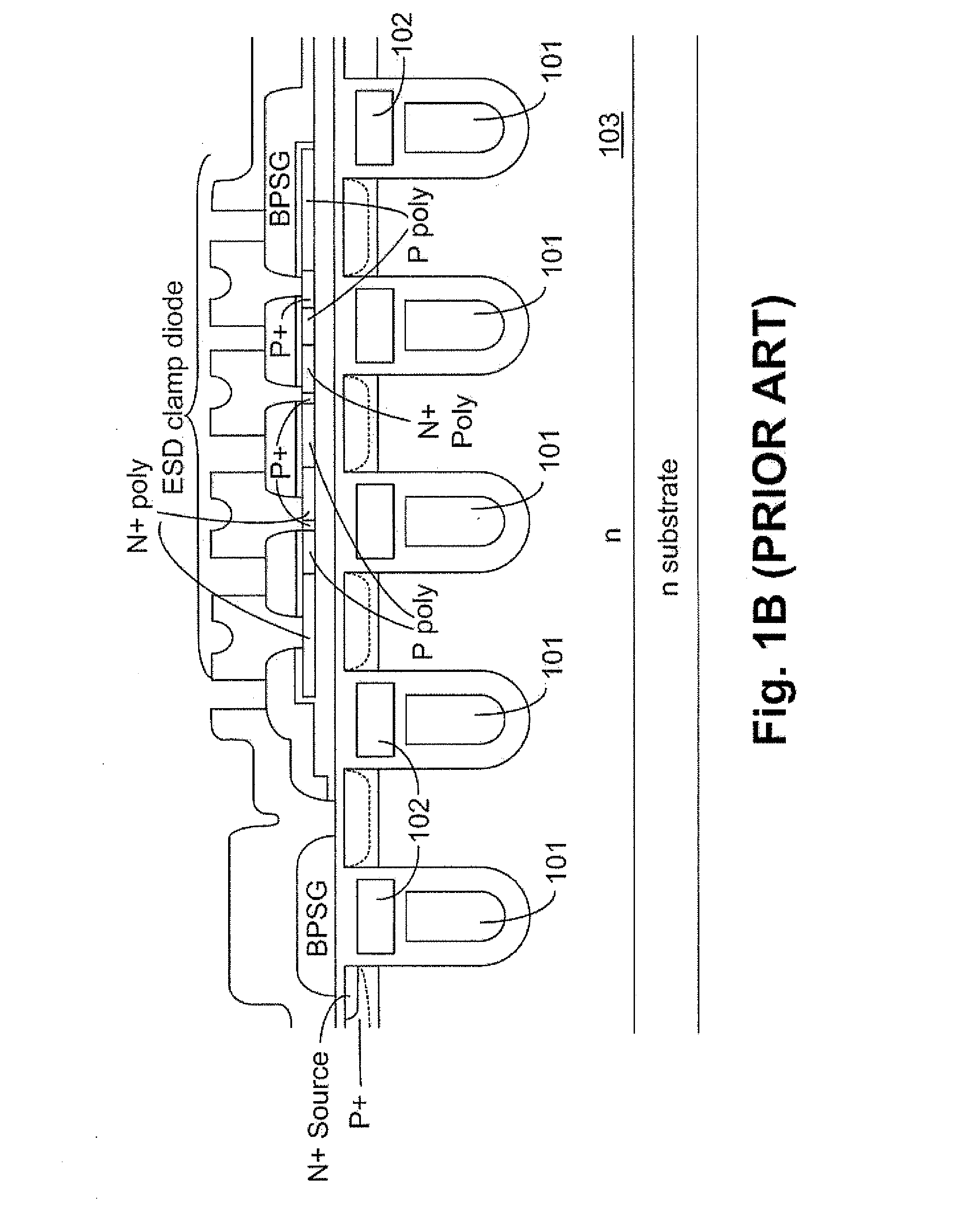

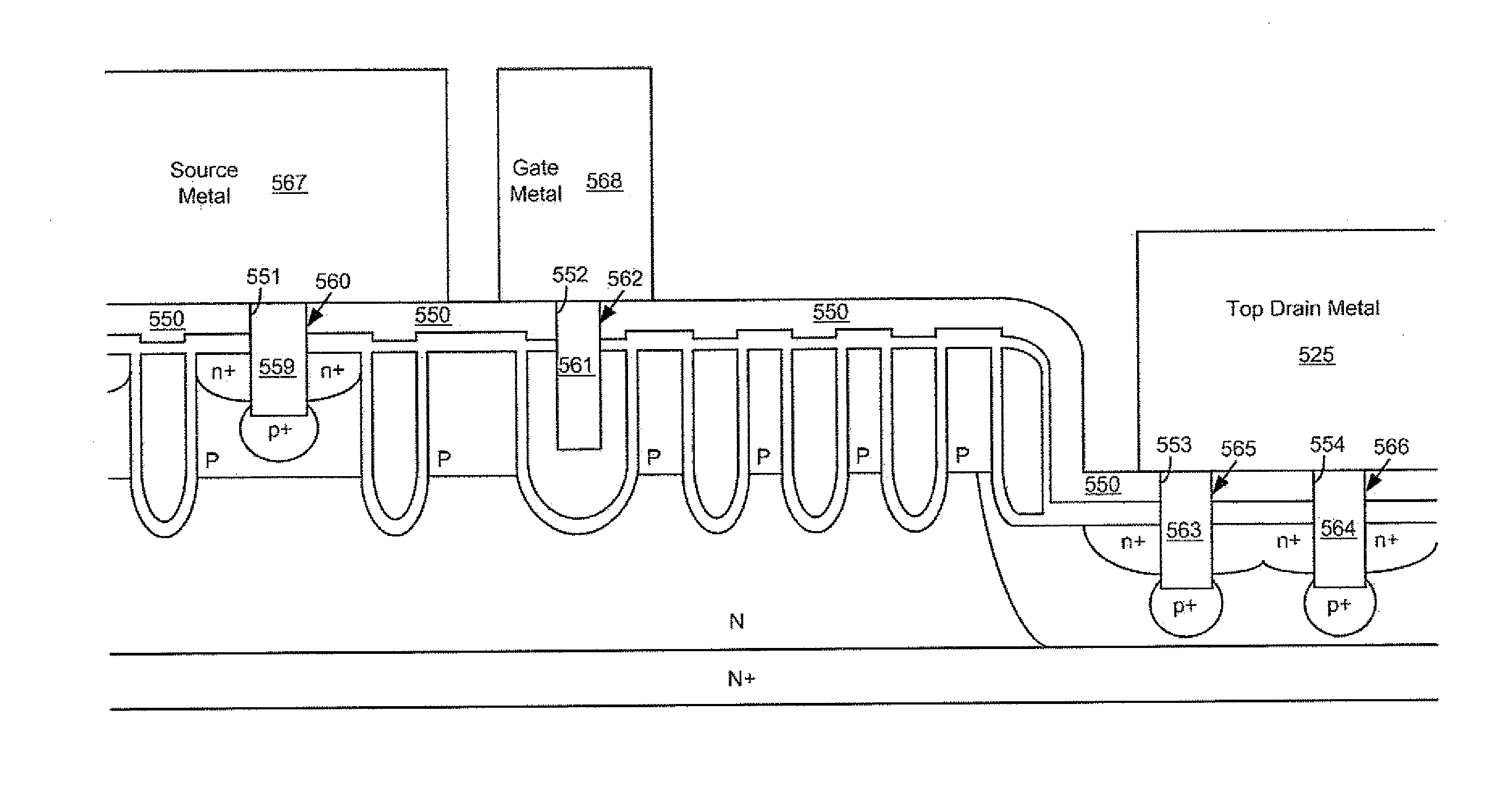

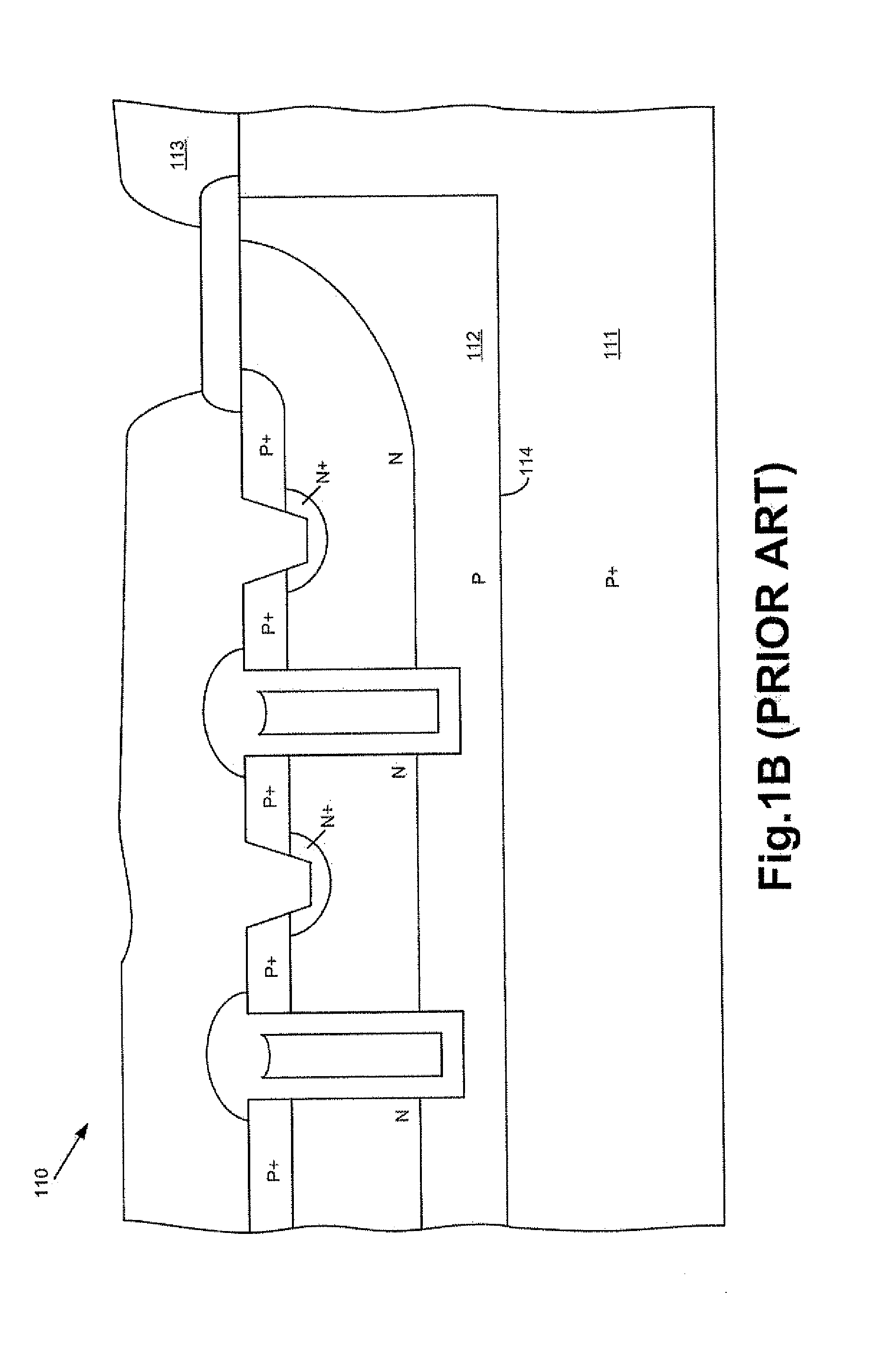

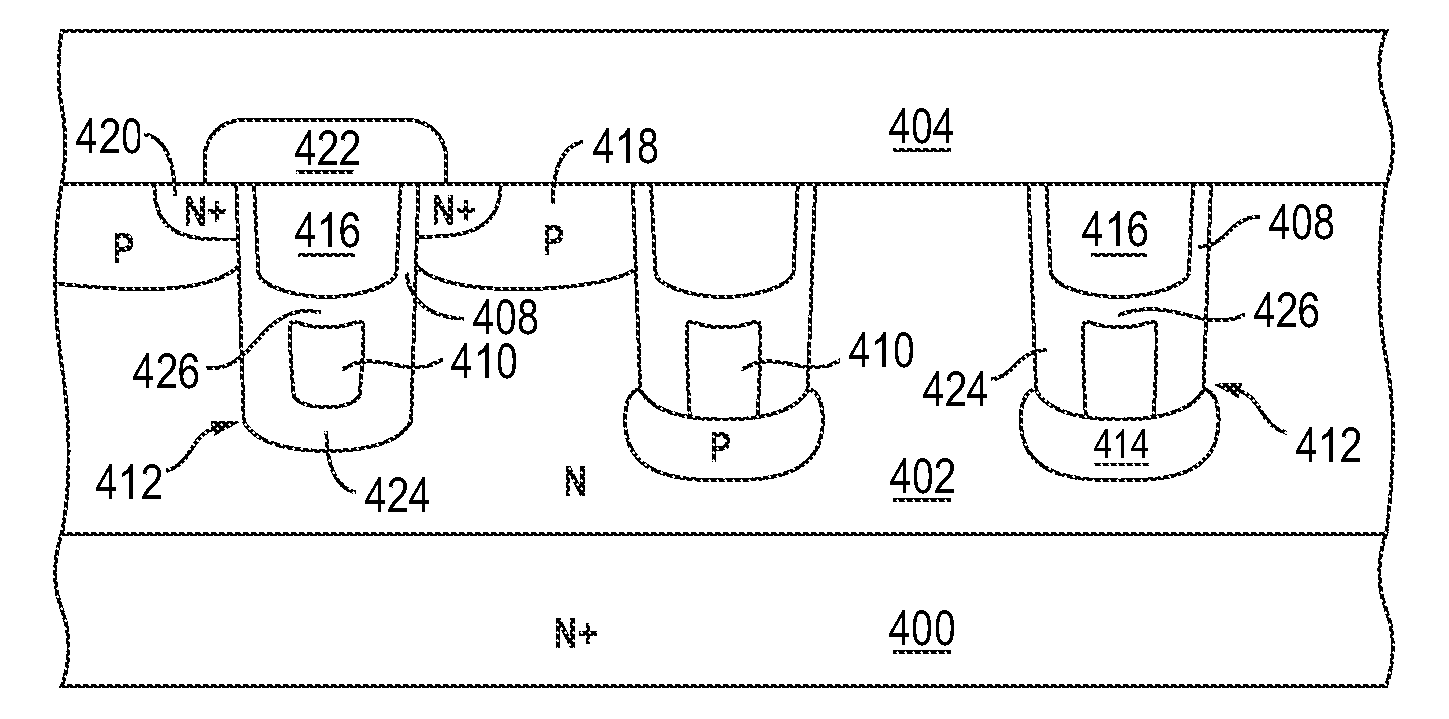

Semiconductor power devices integrated with a trenched clamp diode

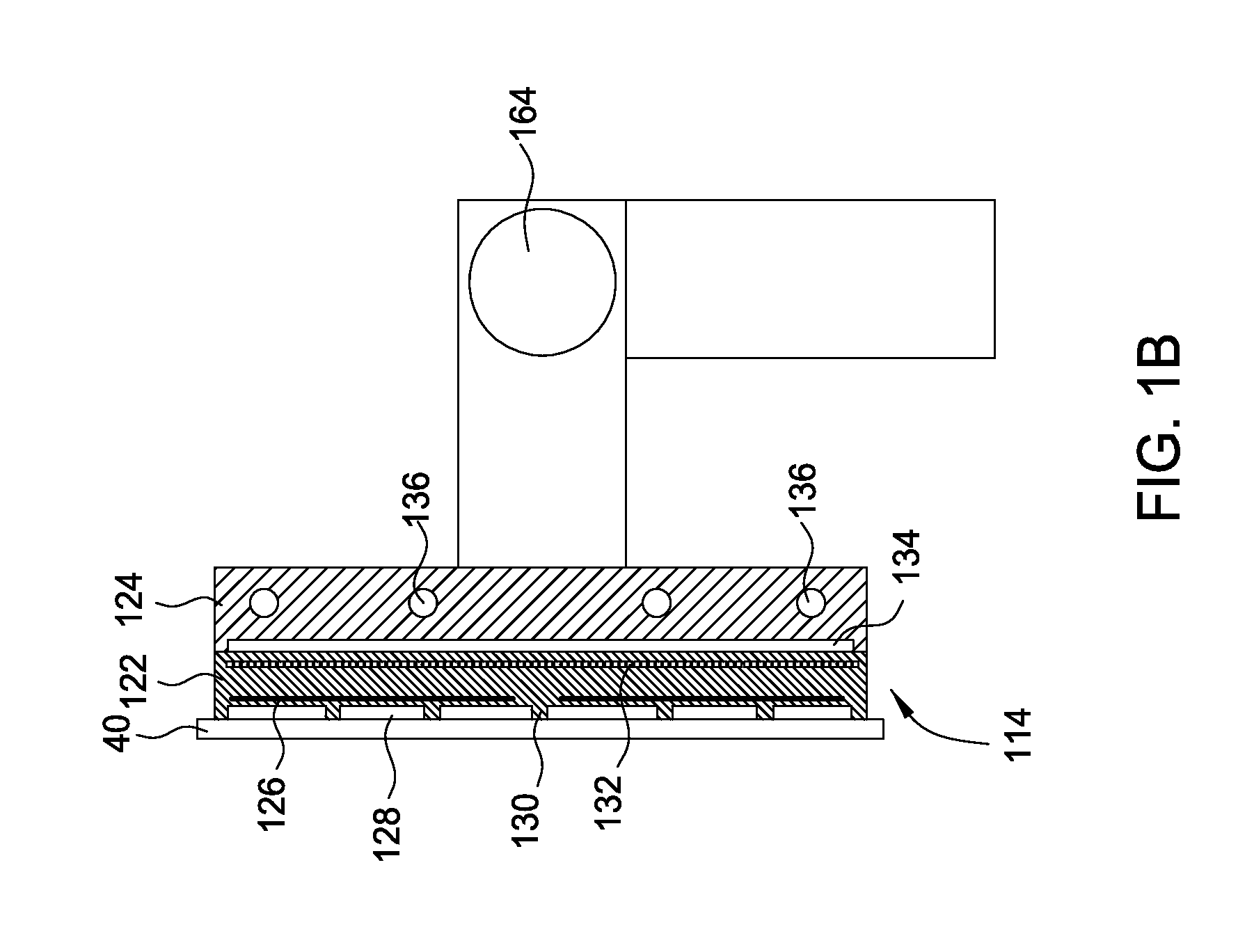

ActiveUS20130075810A1Cost reductionAdditional costSemiconductor/solid-state device detailsSolid-state devicesPolycrystalline siliconSemiconductor

A semiconductor power device having shielded gate structure integrated with a trenched clamp diode formed in a semiconductor silicon layer, wherein the shielded gate structure comprises a shielded electrode formed by a first poly-silicon layer and a gate electrode formed by a second poly-silicon layer. The trenched clamp diode is formed by the first poly-silicon layer. A shielded gate mask used to define the shielded gate is also used to define the trenched clamp diode. Therefore, one poly-silicon layer and a mask for the trenched clamp diode are saved.

Owner:FORCE MOS TECH CO LTD

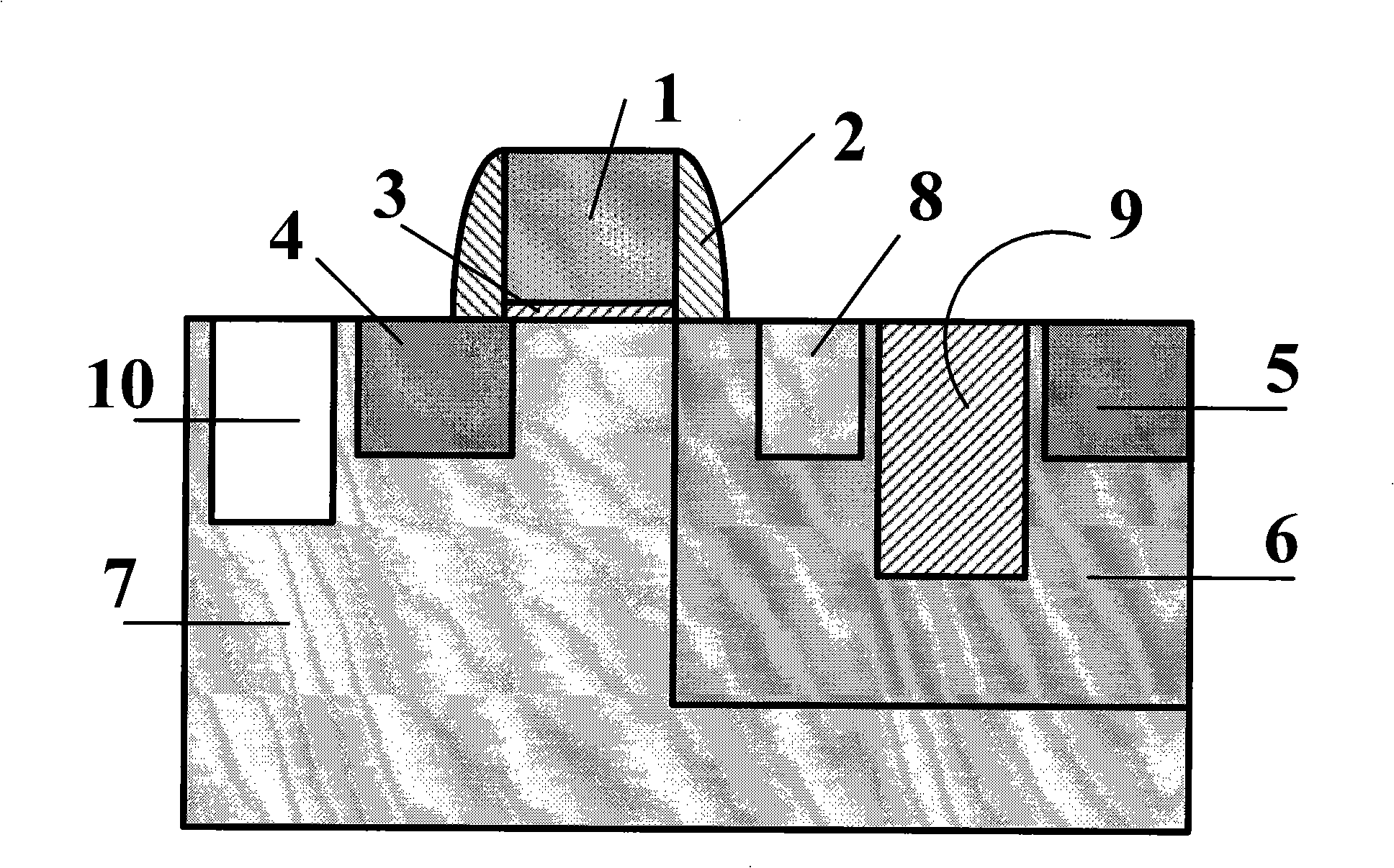

Semiconductor device

InactiveUS20070007537A1Increase the doping concentrationTransistorSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor package

A semiconductor device comprises: a first semiconductor layer of silicon carbide of a first conductivity type; a second semiconductor layer of silicon carbide of a second conductivity type selectively provided on the first semiconductor layer; a main electrode layer of silicon carbide of the first conductivity type selectively provided on the second semiconductor layer; a gate insulating film provided on the second semiconductor layer; a gate electrode formed on the gate insulating film; and a third semiconductor layer of the first conductivity type intervening a current path which is formed between the main electrode layer and the first semiconductor layer when an ON voltage is applied to the gate electrode. The third semiconductor layer is selectively provided on the first semiconductor layer and is adjacent to the second semiconductor layer. A doping density of the third semiconductor layer is higher than a doping density of the first semiconductor layer.

Owner:KK TOSHIBA

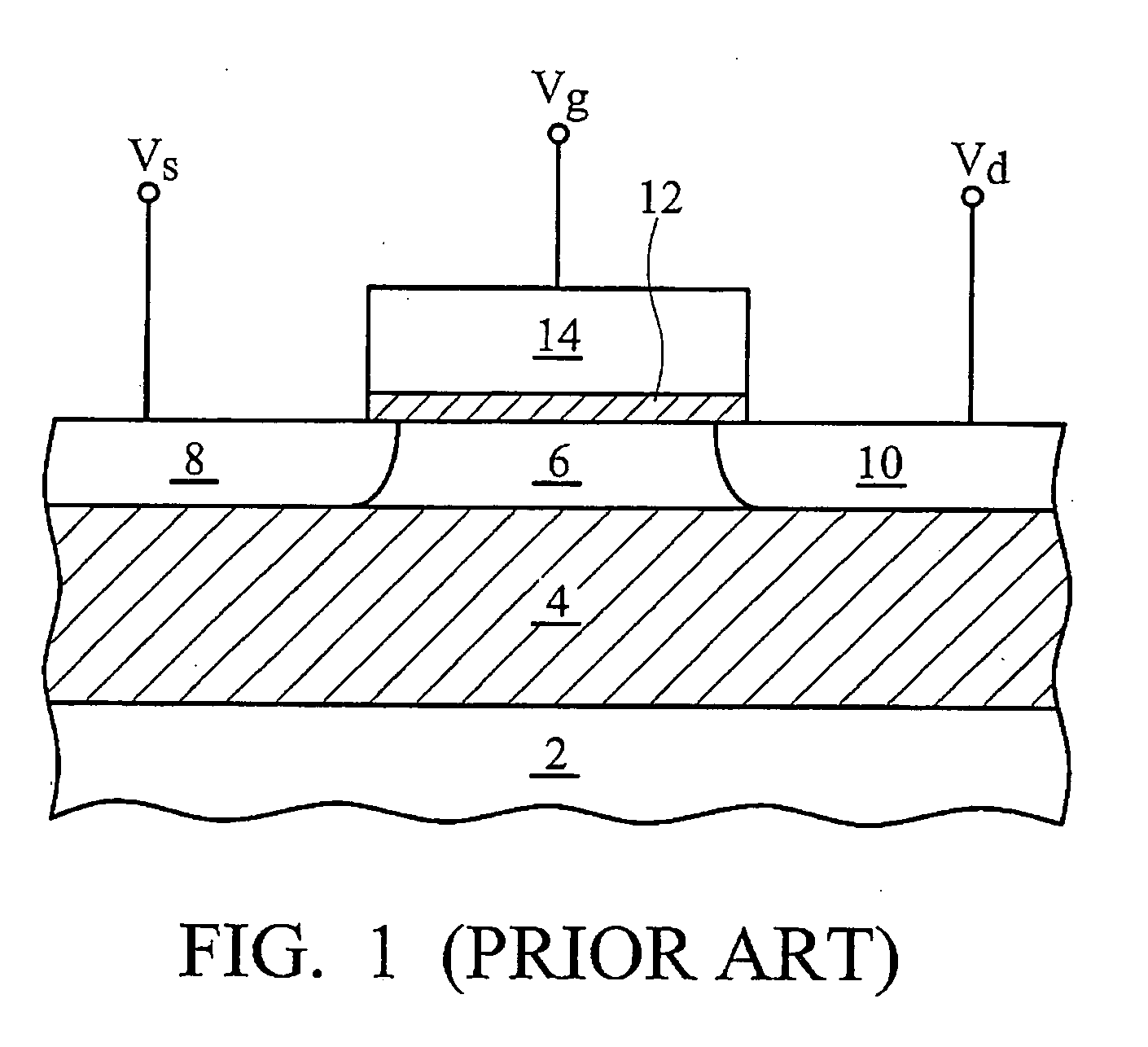

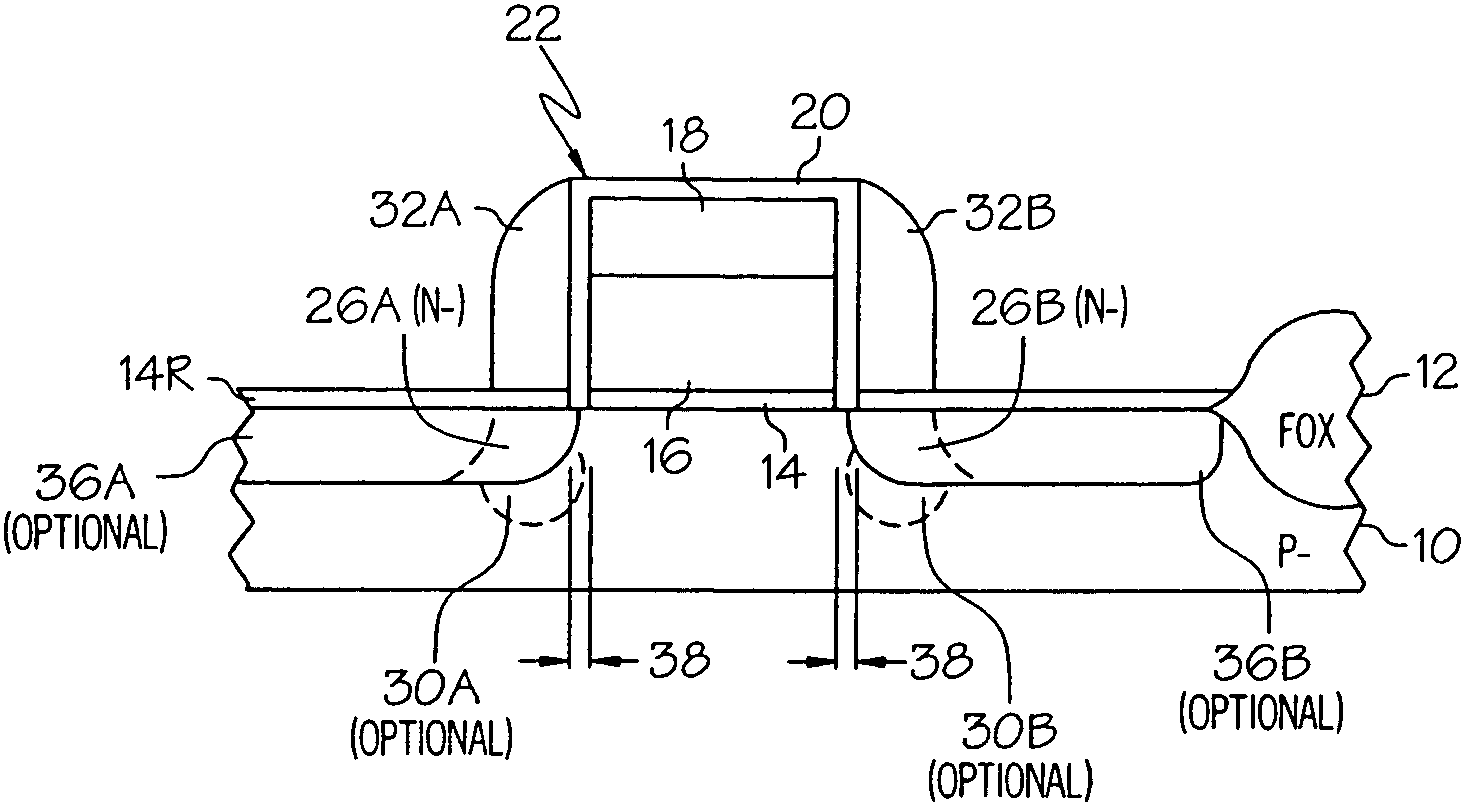

Capacitor-less 1T-DRAM cell with Schottky source and drain

InactiveUS20060125121A1Improve equipment reliabilityLower bandgapTransistorSolid-state devicesCapacitanceGate dielectric

A tunneling injection based Schottky source / drain memory cell comprising: a first semiconductor layer with a first conductivity type overlying an insulating layer, wherein the first semiconductor acts as a body region; a gate dielectric overlying the semiconductor layer; a gate electrode overlying the gate dielectric; a pair of spacers on sides of the gate electrodes; and a first Schottky barrier junction formed on a source region and a second Schottky barrier junction formed on a drain region on opposing sides of the body region. The source and the regions have an overlapping portion with the gate electrode and length of overlapping portion is preferably greater than about 5 Å. Interfacial layers are formed between the first and the second Schottky barrier regions.

Owner:TAIWAN SEMICON MFG CO LTD

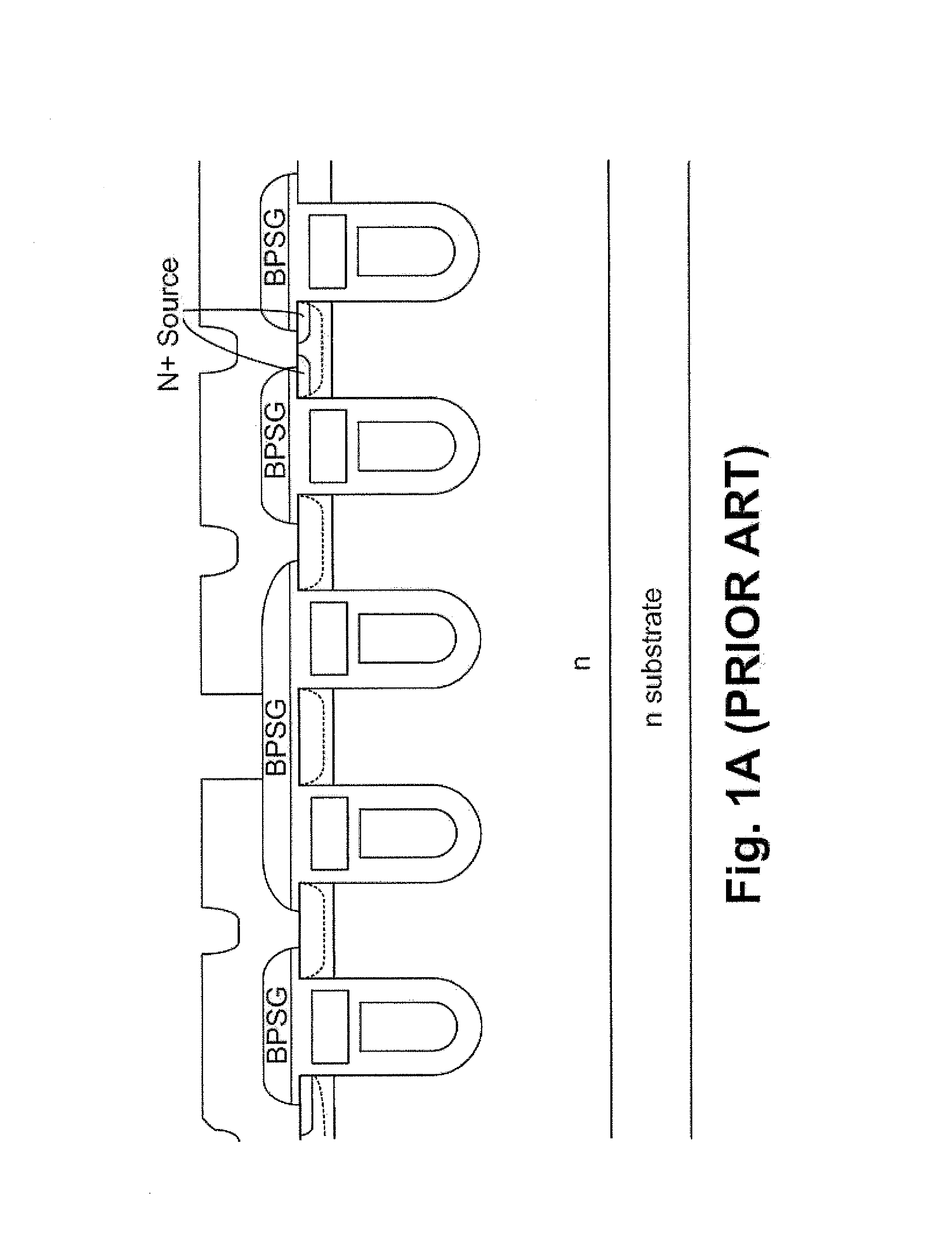

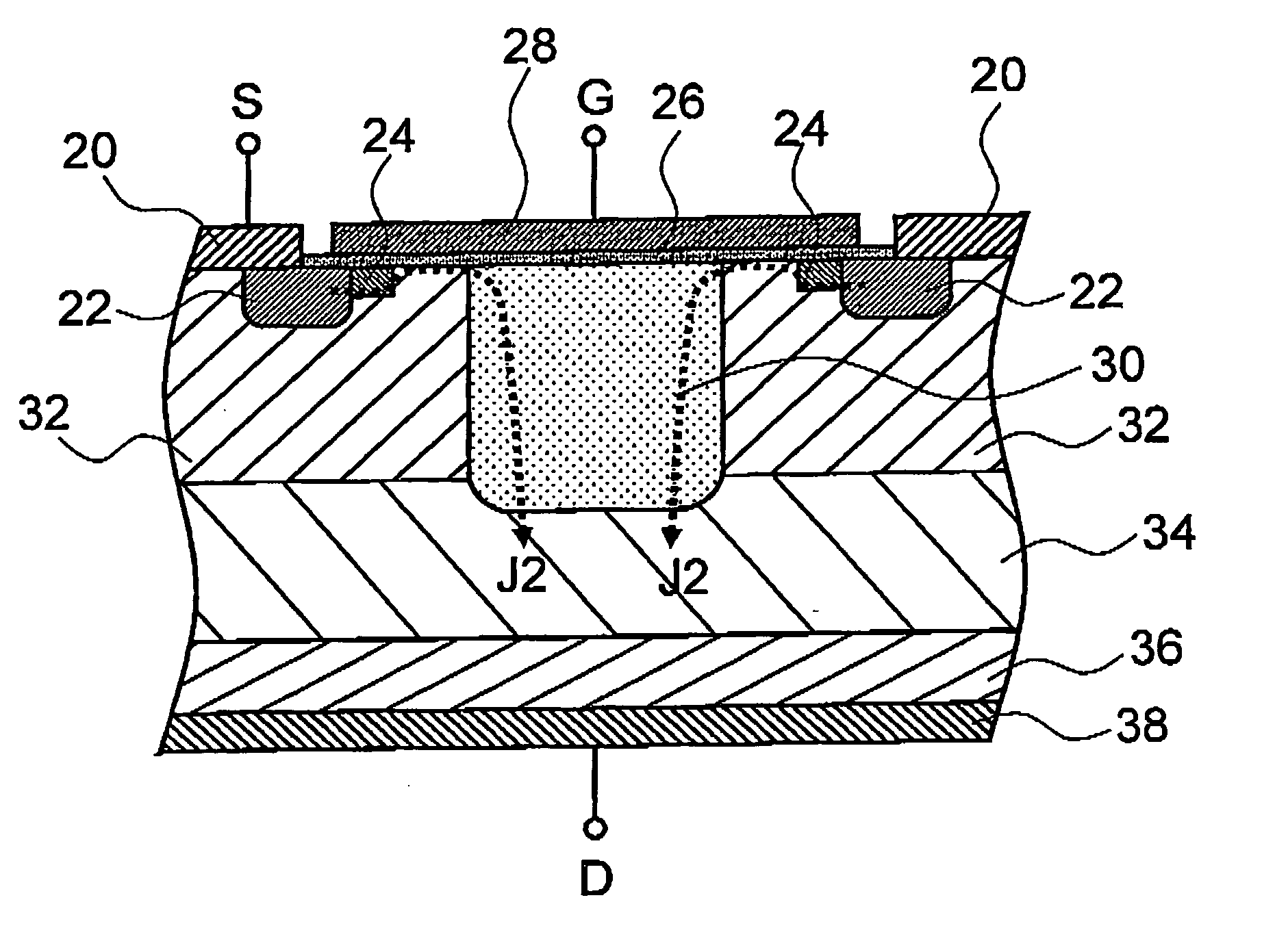

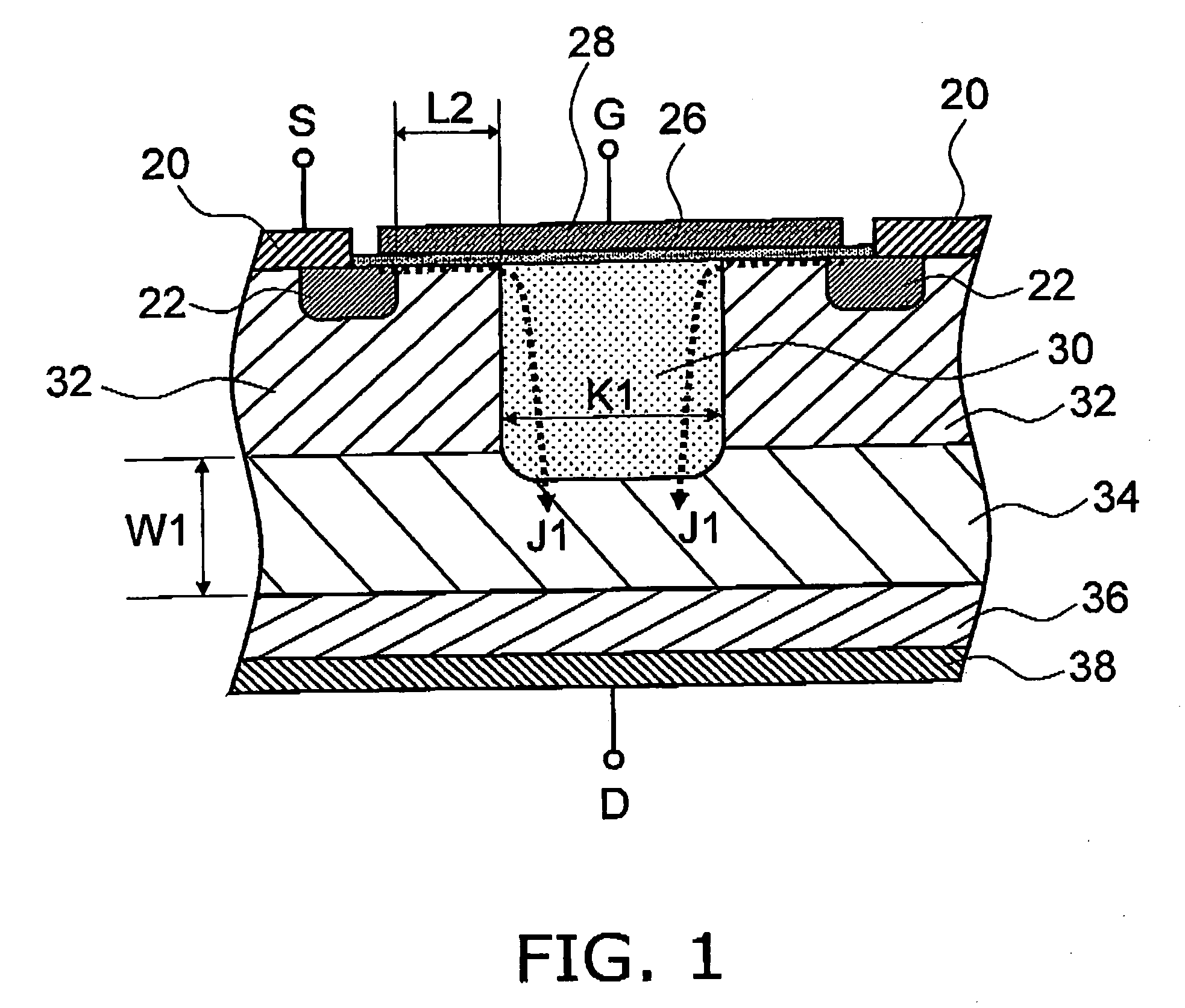

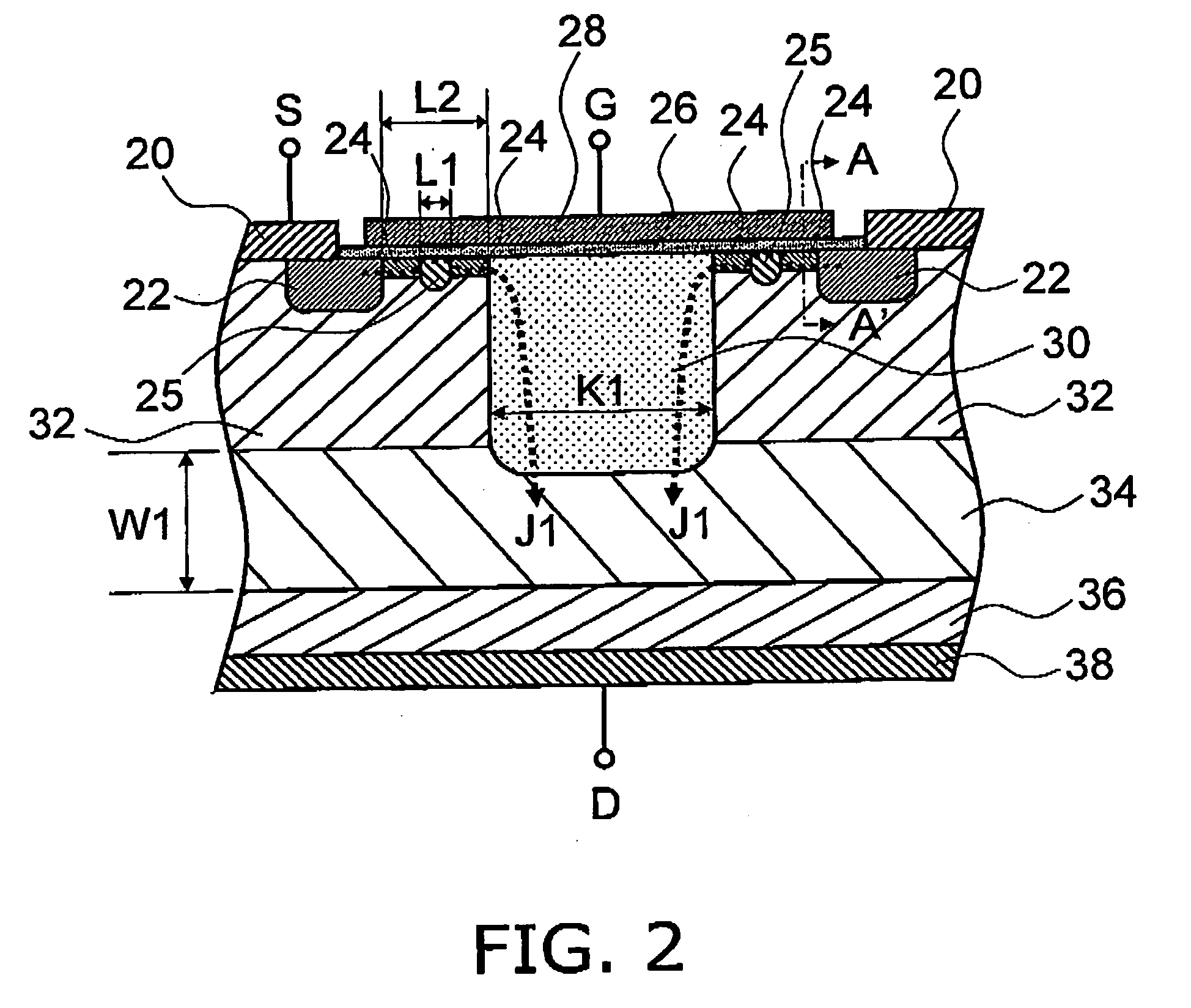

Trench mosfet having a top side drain

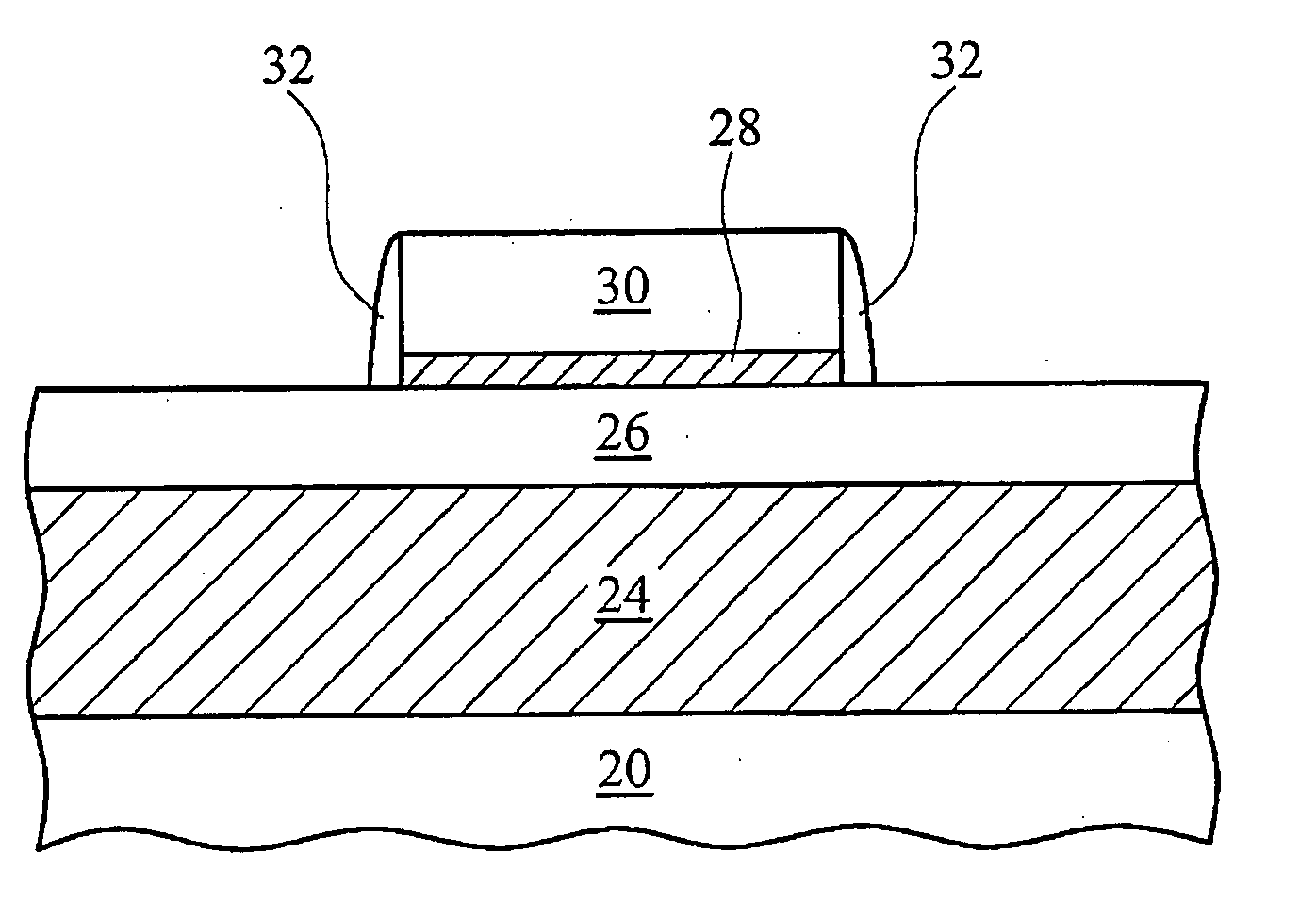

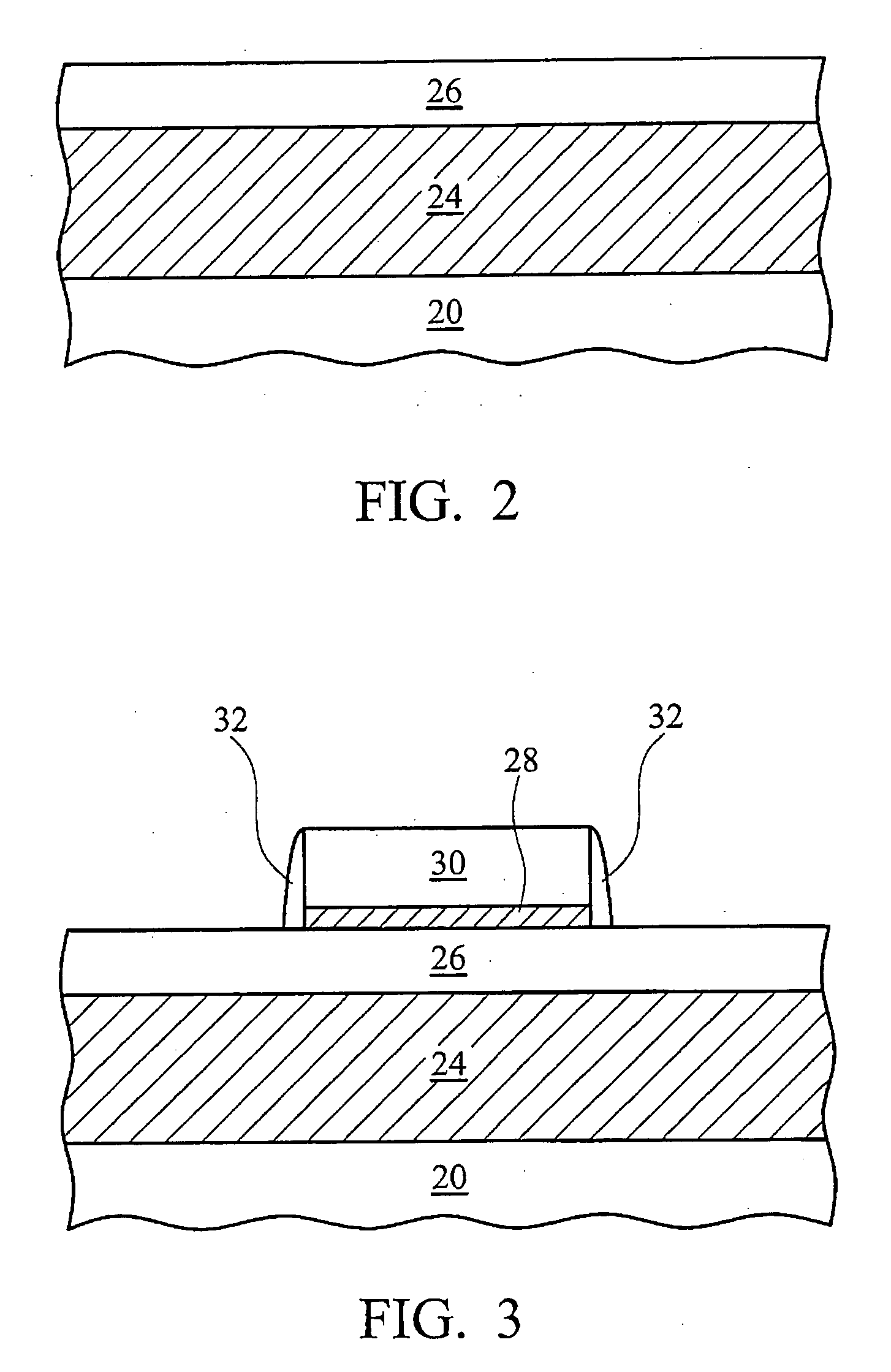

ActiveUS20130207172A1Increase the doping concentrationGreat junction depthTransistorSolid-state devicesTrench mosfetBody contact

This invention discloses a trench MOSFET comprising a top side drain region in a wide trench in a termination area besides a BV sustaining area, wherein said top side drain comprises a top drain metal connected to an epitaxial layer and a substrate through a plurality of trenched drain contacts, wherein the wide trench is formed simultaneously when a plurality of gate trenches are formed in an active area, and the trenched drain contacts are formed simultaneously when a trenched source-body contact is formed in the active area.

Owner:FORCE MOS TECH CO LTD

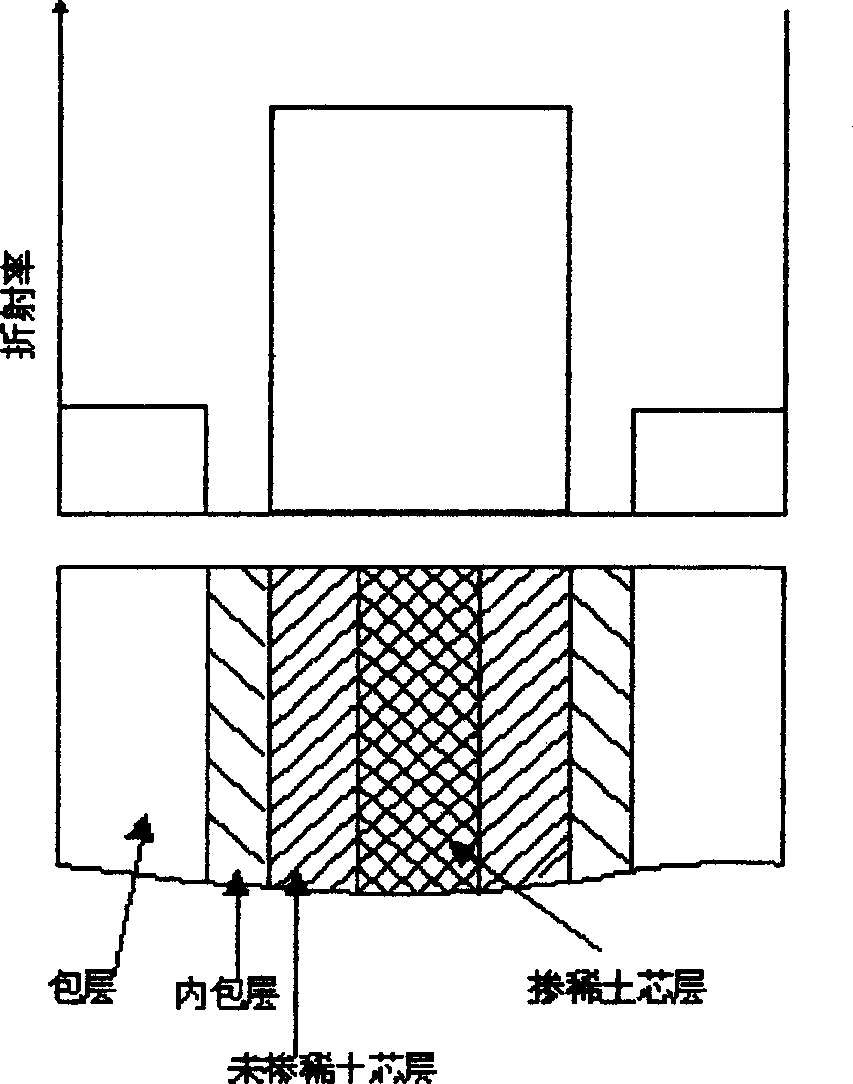

Optical fiber preform cladding fluorine doping method

ActiveCN103224325AReduce OH

<sup>-</sup>

contentSuitable for large-scale productionGlass making apparatusGlass fibre productsGlass transitionCore (optical fiber)

The present invention discloses an optical fiber preform cladding fluorine doping method, which comprises the following steps: depositing a core layer loose body on a target rod; heating the outer surface of the core layer loose body to form a dense layer, such that density of the dense layer is higher than density in the core layer loose body; depositing an inner cladding loose body outside the dense layer to form a core rod loose body comprising the core layer loose body and the inner cladding loose body; taking the target rod out to form a center hole in the center of the core rod loose body; placing the core rod loose body into a glass transition furnace, carrying out heating dewatering in a dewatering atmosphere, and introducing dewatering gas into the center hole during heating; heating the core rod loose body in a fluoride atmosphere, such that fluorine is selectively doped into the inner cladding loose body to form step refraction index distribution; and carrying out glass transition on the core rod loose body, such that the center hole is shrunk, the core layer loose body forms a core layer, and the inner cladding loose body forms an inner cladding so as to form a core rod. With the method, OH<-> content in the core layer can be effectively reduced, attenuation of optical fiber 1383 nm can be reduced, and fluorine distribution in a radial direction of the cladding is uniform.

Owner:ZHEJIANG FUTONG OPTICAL FIBER TECH +1

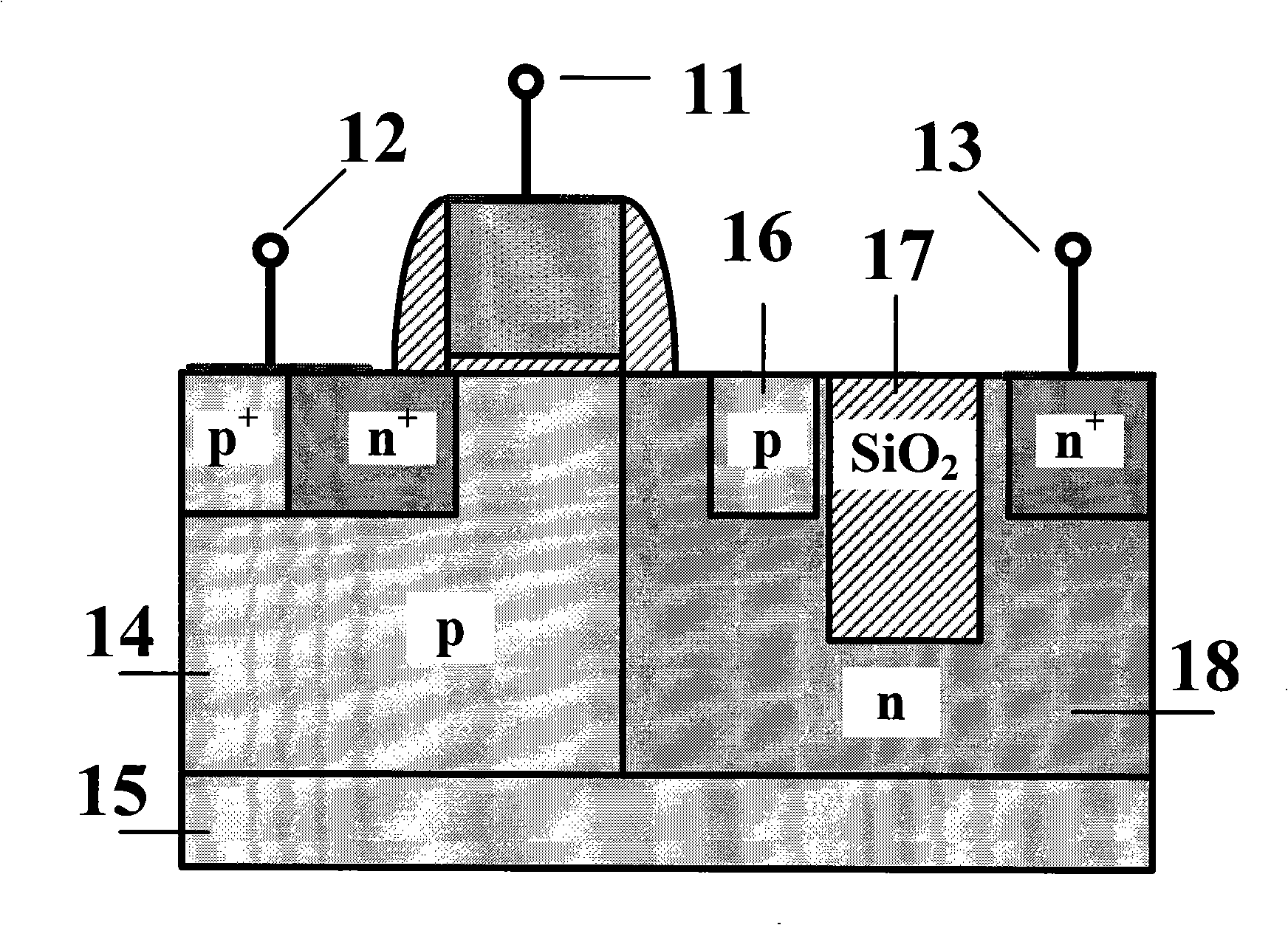

High pressure resistant lateral direction bilateral diffusion MOS transistor

InactiveCN101257047AImprove breakdown voltageIncrease the doping concentrationSemiconductor devicesEngineeringHigh pressure

The present invention discloses a transversal bilateral diffusion MOS transistor with high pressure resistant, which belongs to micro-electronics semi-conductor device field. The device includes a gate region, a source area, a drain region, a tagma, a gate medium and a drift region, the setting drift region is placed between the tagma and the drain region, and the doping type is opposite to the tagma, an insulating medium region and a doping region which is opposite to the doping type of the drift region are equipped in the drift region, and the doping concentration of the doping region is higher than that of the drift region, the doping region is adjacent to the tagma, however the insulating medium region is adjacent to the drain region. Because the insulating medium region and the doping region are inducted into the drift region at the same time, the effective depth of the drift region is reduced effectively to make the electric field more uniform and increase the equivalent length of the drift region, the resistant high Voltage characteristic of the transversal bilateral diffusion MOS transistor device of the present invention is good.

Owner:PEKING UNIV

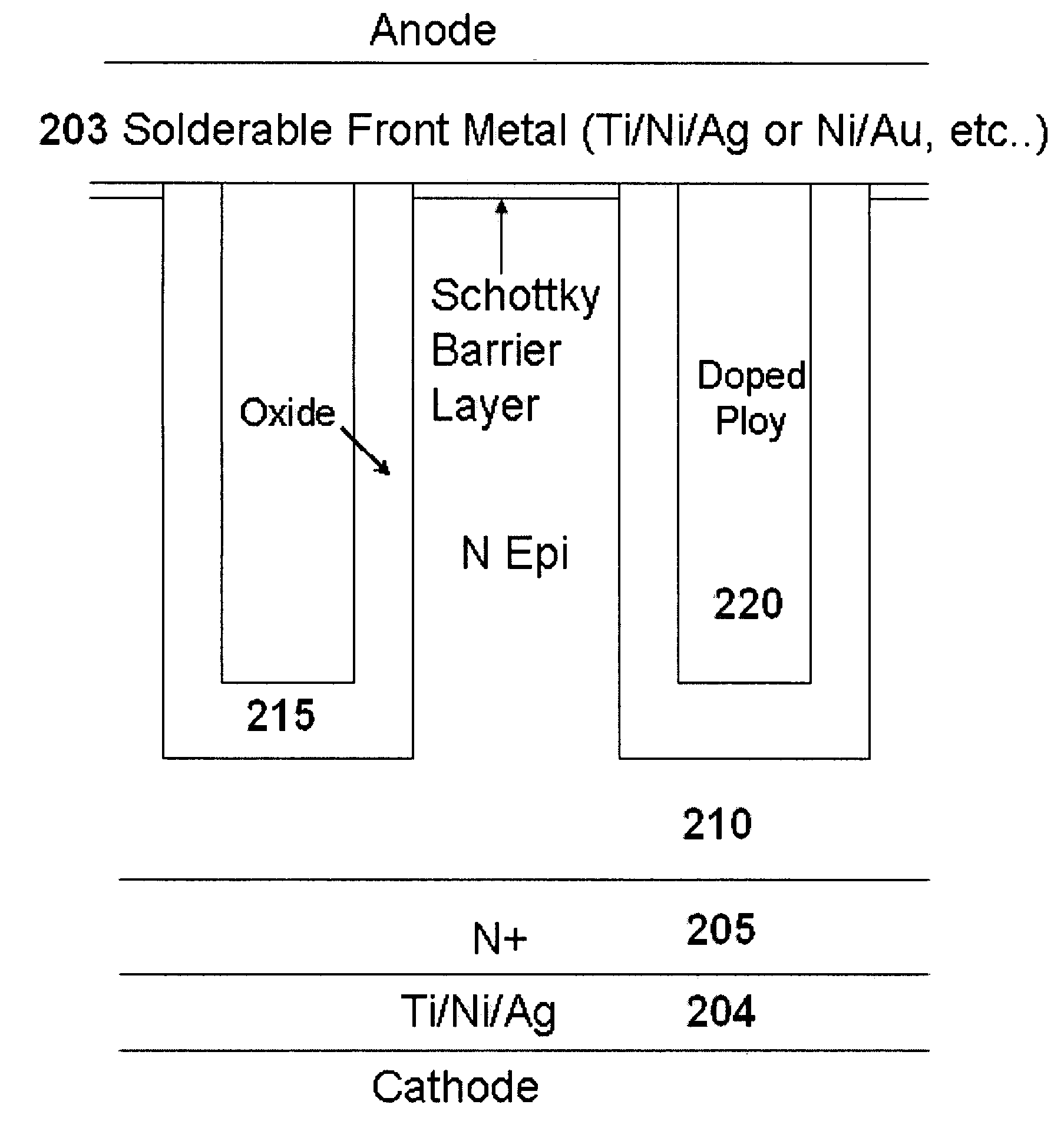

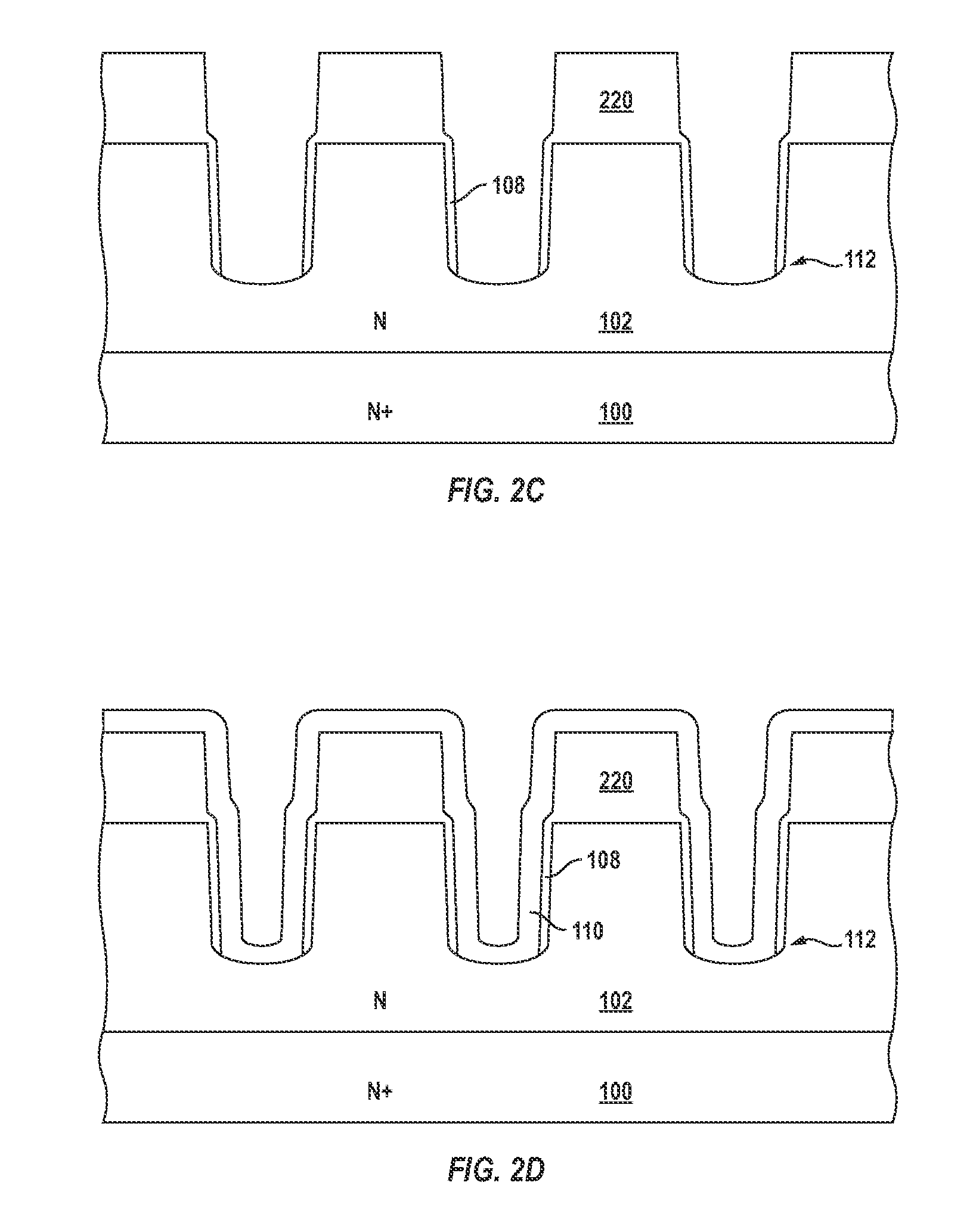

Trench schottky with multiple epi structure

InactiveUS20090309181A1Reduce doping concentrationIncrease the doping concentrationSemiconductor devicesDopantSchottky barrier

A trench Schottky barrier rectifier includes an cathode electrode at a face of a semiconductor substrate and an multiple epitaxial structure in drift region which in combination provide high blocking voltage capability with low reverse-biased leakage current and low forward voltage. The multiple structure of the drift region contains a concentration of first conductivity dopants therein which comprises two or three different uniform value from a Schottky rectifying junction formed between the anode electrode and the drift region. The thickness of the insulating region (e.g., SiO2) in the MOS-filled trenches is greater than 1000 Å to simultaneously inhibit field crowing and increase the breakdown voltage of the device. The multiple epi structure is preferably formed by epitaxial growth from the cathode region and doped in-situ.

Owner:FORCE MOS TECH CO LTD

Rectifier With PN Clamp Regions Under Trenches

A structure that includes a rectifier is formed as follows. A trench is formed in a semiconductor region of a first conductivity type. A dielectric layer is formed along opposing sidewalls of the trench but is discontinuous along the bottom of the trench. A doped liner is formed over the dielectric layer and along the bottom of the trench. The doped liner includes dopants of a second conductivity type and is in direct contact with the semiconductor region along the bottom of the trench. A portion of the dopants are diffused from the doped liner into the semiconductor region along the bottom of the trench to form a doped region. The doped region forms a PN junction with the surrounding semiconductor region.

Owner:SEMICON COMPONENTS IND LLC

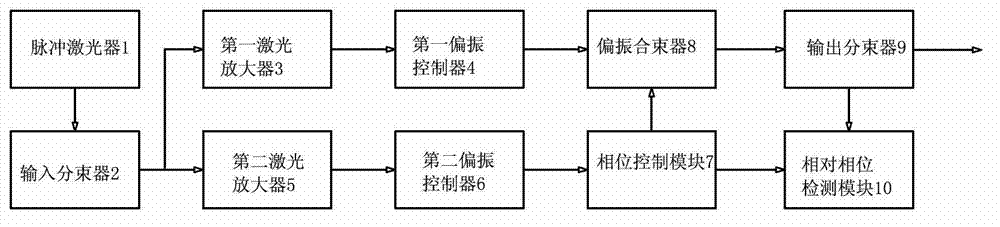

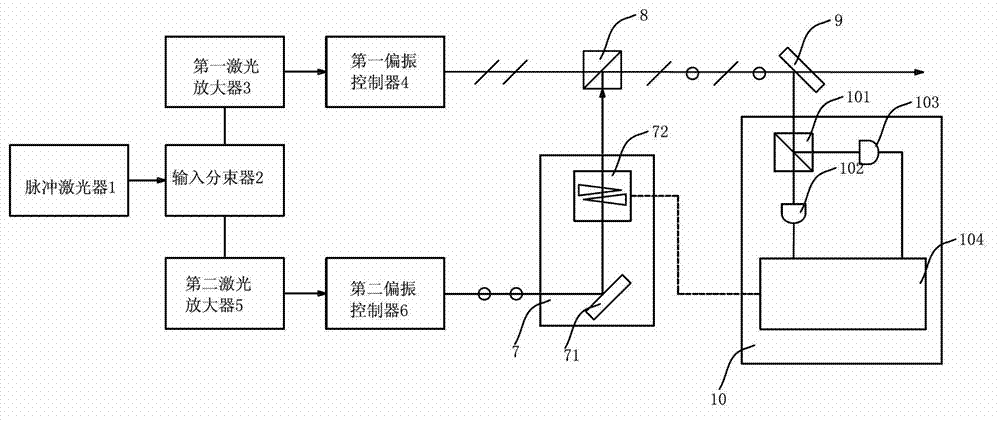

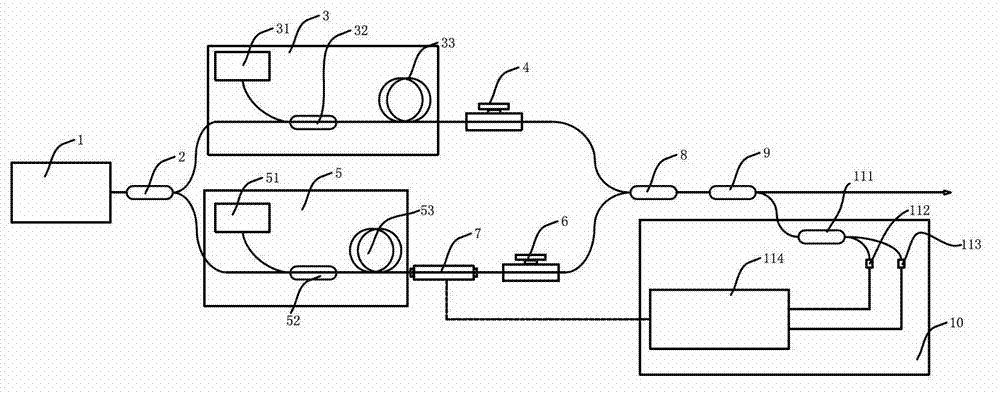

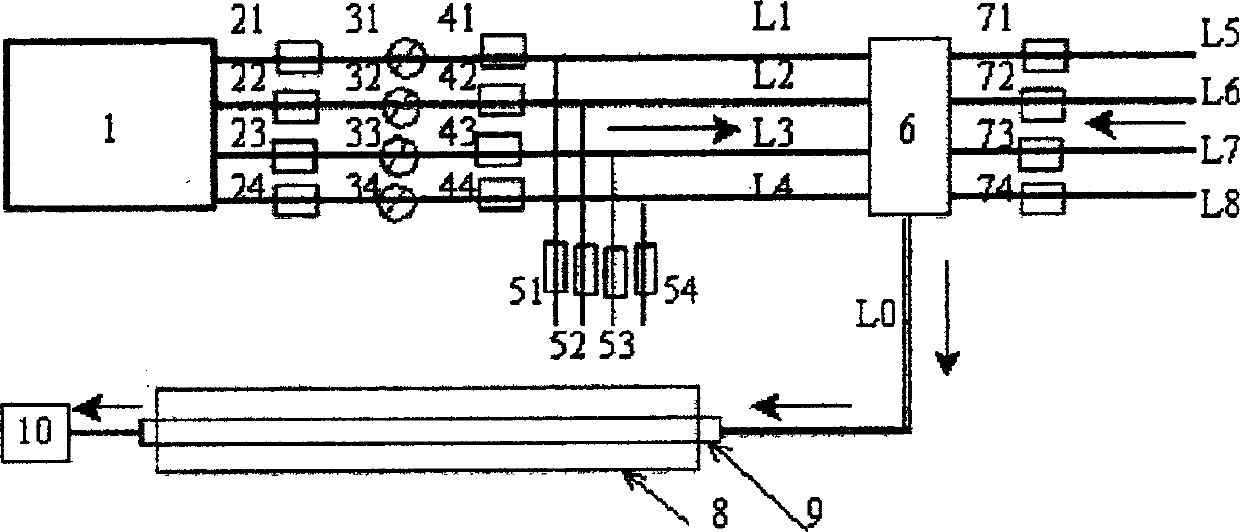

Polarization beam-combination device for pulsed laser

InactiveCN103033944AAchieve coaxial synthesisHigh synthesis efficiencyLaser detailsCoupling light guidesBeam splitterOptoelectronics

The invention discloses a polarization beam-combination device for a pulsed laser. The polarization beam-combination device comprises the pulsed laser, an input beam splitter, n laser amplifiers and n-1 polarization coherent beam-combination units. The pulsed laser outputs a beam of seed light. The input beam splitter divides the seed light into n sub-seed light beams. The n laser amplifiers respectively carry out power amplification to the n sub-seed light beams. The n-1 polarization coherent beam-combination units carry out pairwise polarization in-phase beam-combination for n-1 times to n laser beams output by the n laser amplifiers. N is a natural number which is bigger than or equal to two. An output end of the polarization beam-combination device is connected with an output beam splitter. A hard light output end of the output beam splitter is used as an output end of the polarization coherent beam-combination units. Light output from a low light output end of the output beam splitter shoots into a relative phase detection module of a drive phase control module, and the relative phase detection module enables phase positions of two laser beams to be consistent. Through adoption of a polarization detection method, the polarization beam-combination device detects the relative phase positions of the two laser beams, and is capable of achieving coaxial combination of a plurality of coherent light beams, high in combined efficiency and good in beam quality.

Owner:广东华快光子科技有限公司

Rare earth mixed transparent oxyfluoride glass ceramic and preparation process thereof

A transparent glass ceramics of RE-doped oxyfluoride is proportionally prepared from SiO2, Al2O3, EnF2, MF2 and ReF3, where M is 2-valence alkali-earth metal ion chosen from Mg, Ca, Sr, and Ba and Re is 3-valence RE ion chosen from La, Ce, Pr, Nd, Pm, Sm, Eu, Gd, Tb, Dy, Ho, Er, Tm, Yb and Lu, through high fusing and heat treating. It can be extensive used in laser, luminous and optical communication field.

Owner:ZHEJIANG UNIV

Method of manufacturing a multilayered doped conductor for a contact in an integrated circuit device

InactiveUS7195995B2Increase the doping concentrationLess susceptibleTransistorSemiconductor/solid-state device detailsDopantElectrical conductor

A method of manufacturing a memory device addressing reliability and refresh characteristics through the use of a multilayered doped conductor, and a method making is described. The multilayered doped conductor creates a high dopant concentration in the active area close to the channel region. The rich dopant layer created by the multilayered doped conductor is less susceptible to depletion from trapped charges in the oxide. This improves device reliability at burn-in and lowers junction leakage, thereby providing a longer period between refresh cycles.

Owner:MICRON TECH INC

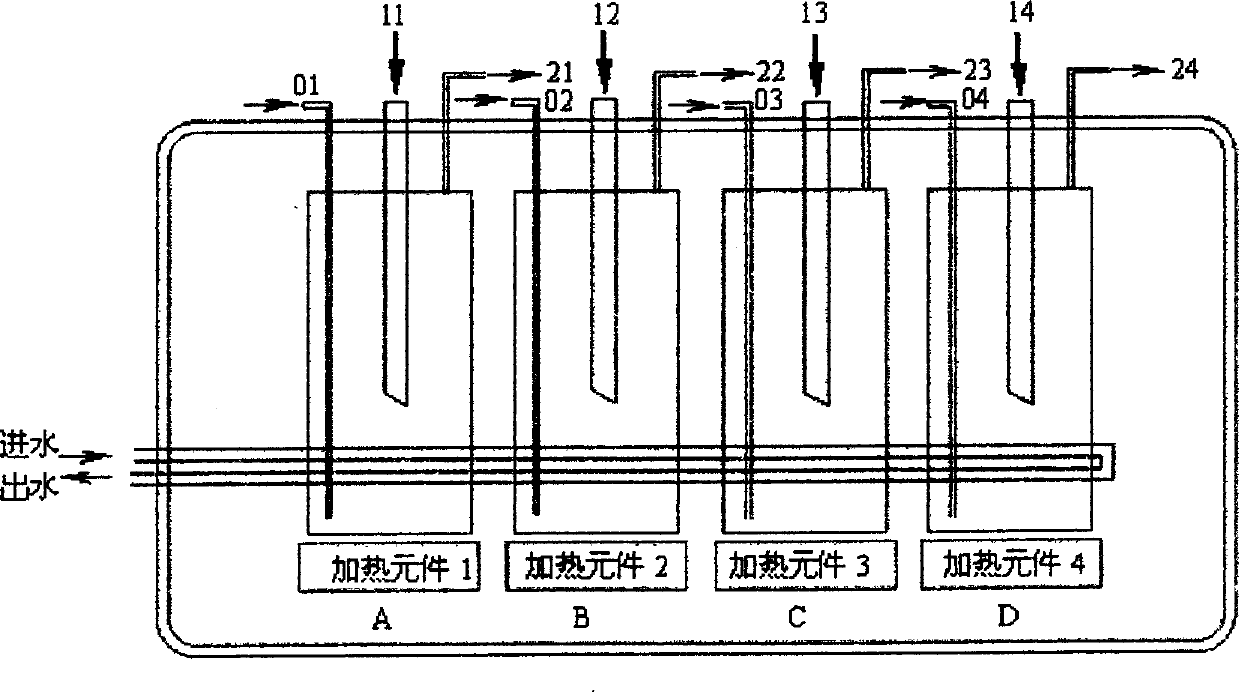

Method for manufacturing rare earth extended fibre-optical prefabricated bar

InactiveCN1490267APrecise control of doping amountImprove performanceGlass shaping apparatusGlass deposition burnersGas phaseRare earth

A process for preparing the prefabricated RE-doped optical-fibre rod features that the chemical gas-phase deposition of plasma is used to deposit the doped SiO2 layer on the inner surface of liner quartz tube and the evaporator is used to directly deliver the RE compound and other codoping agent into reaction tube for direct deposition without pollution.

Owner:FENGHUO COMM SCI & TECH CO LTD

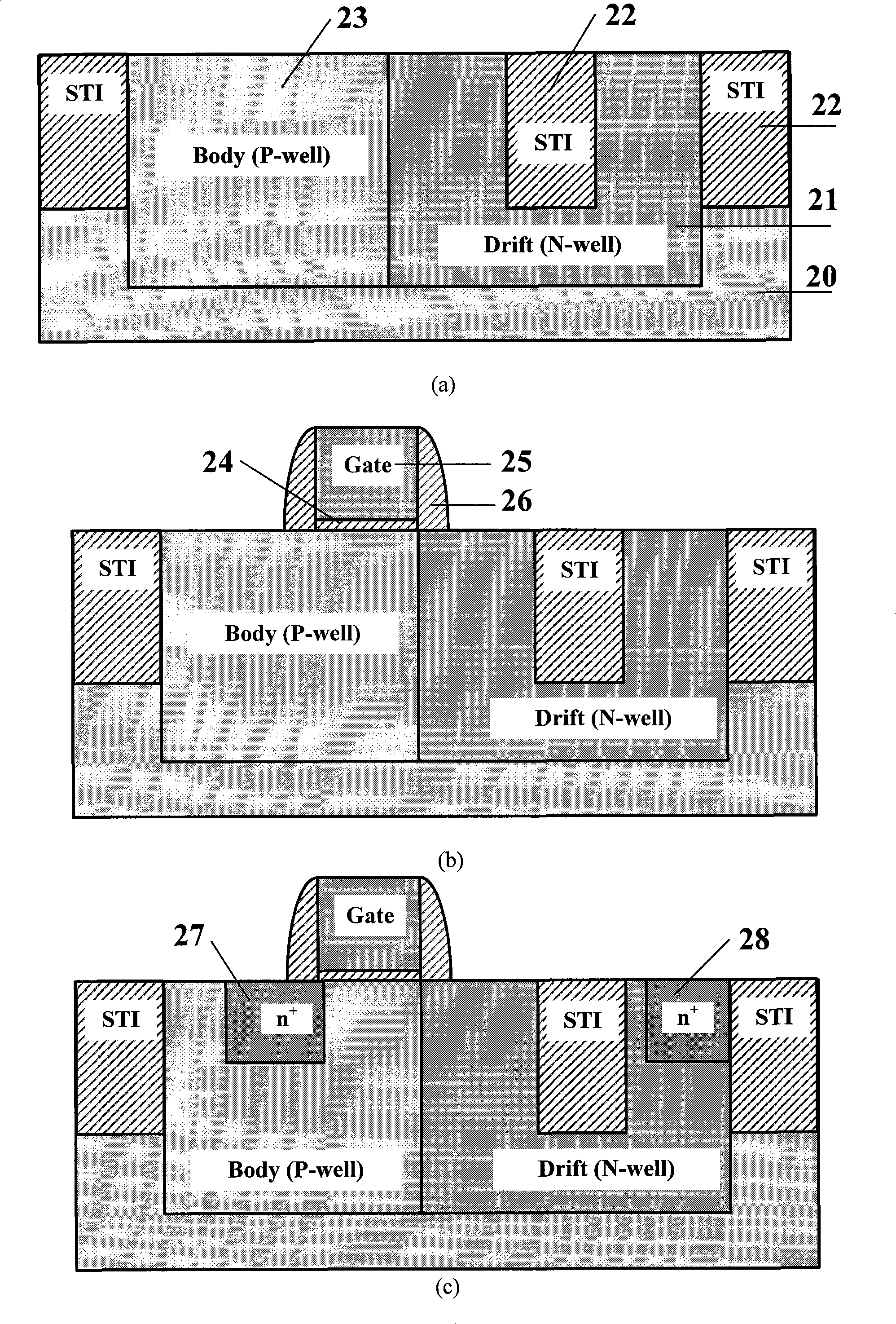

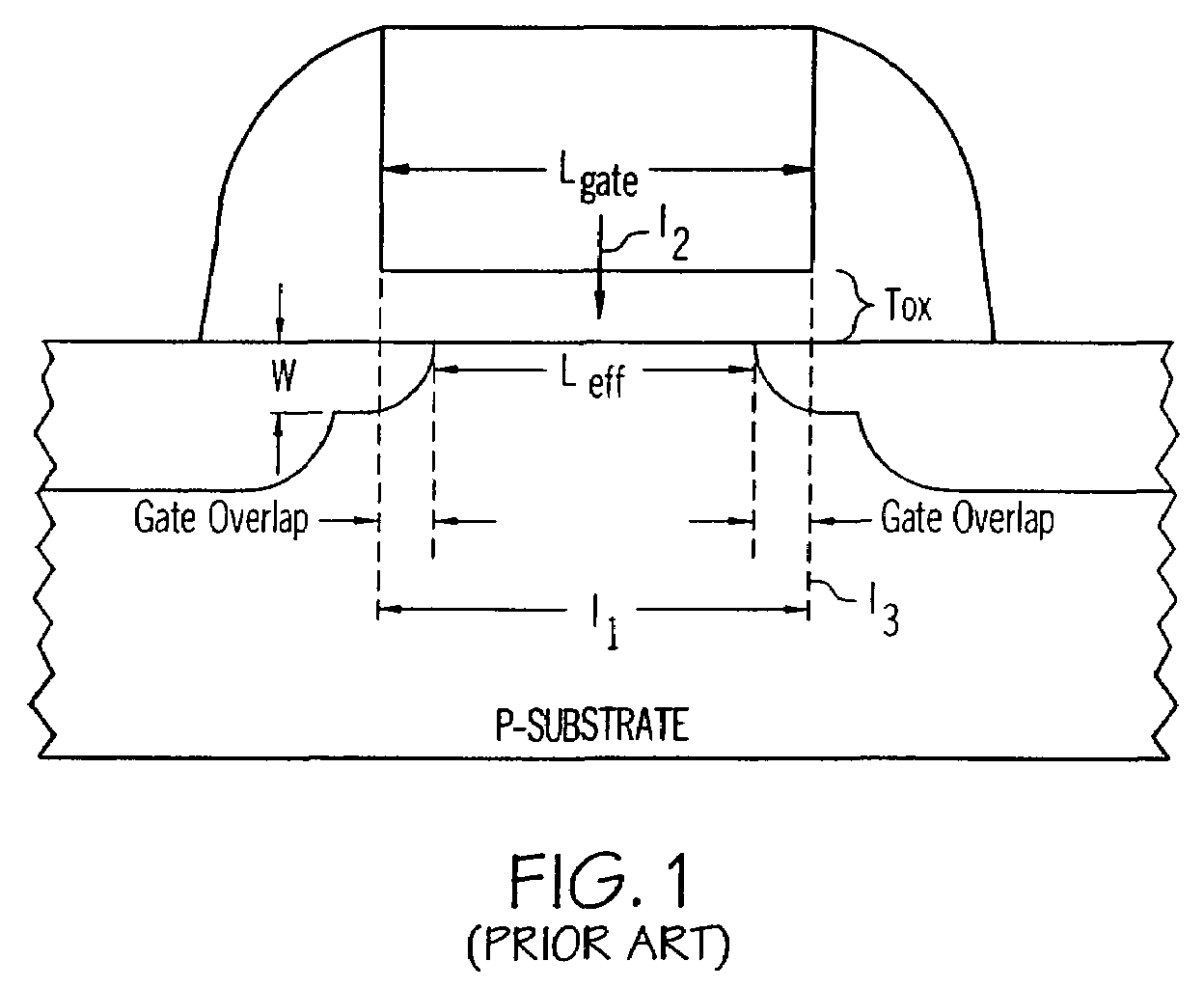

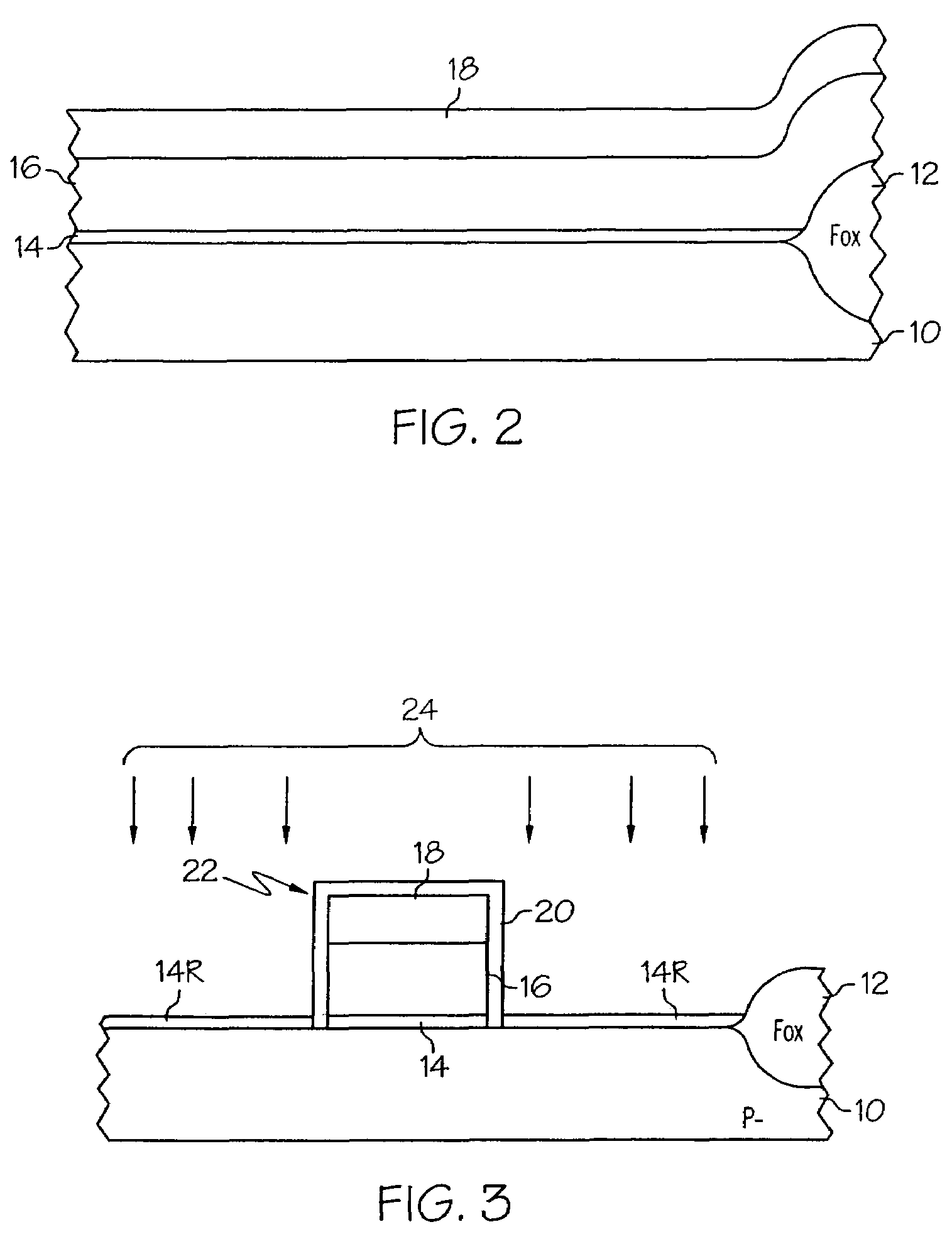

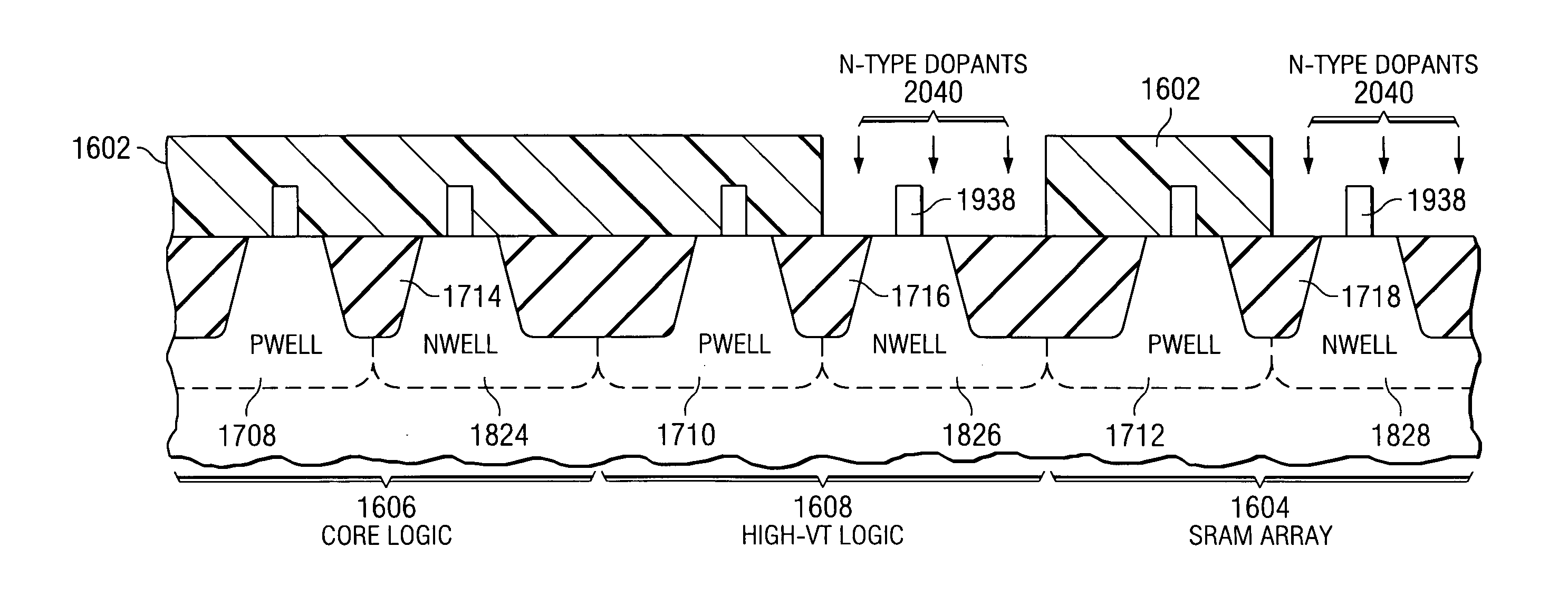

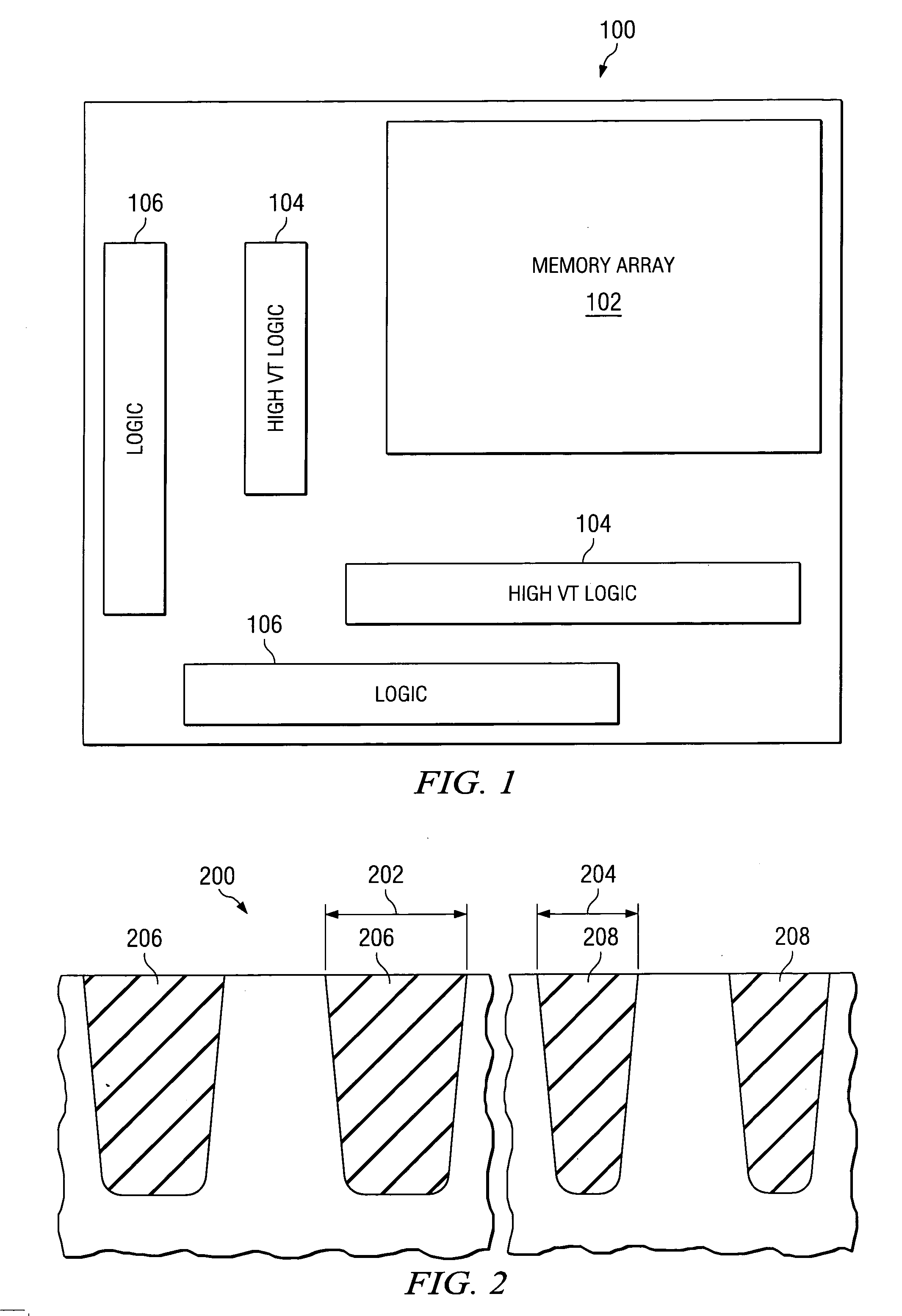

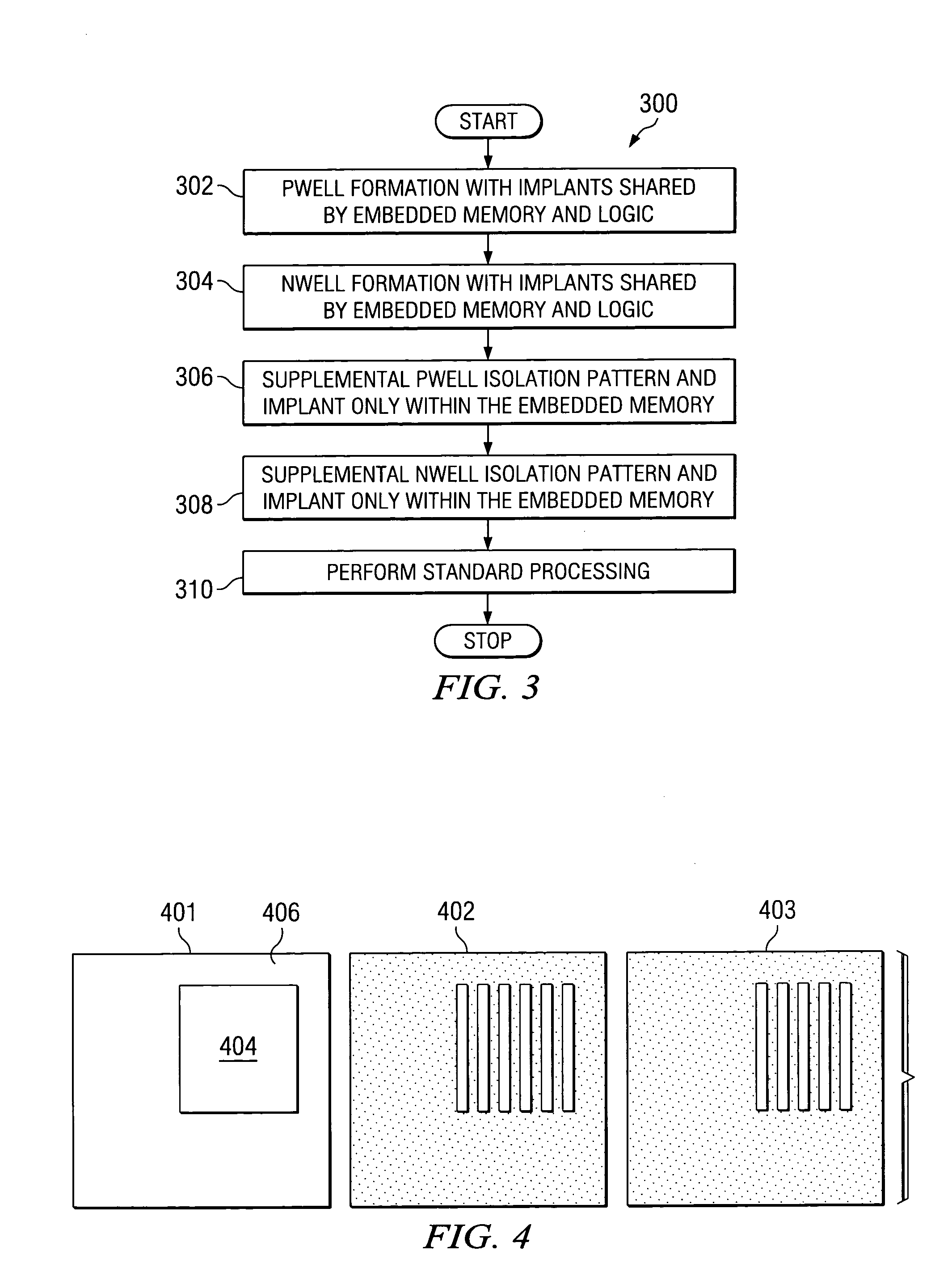

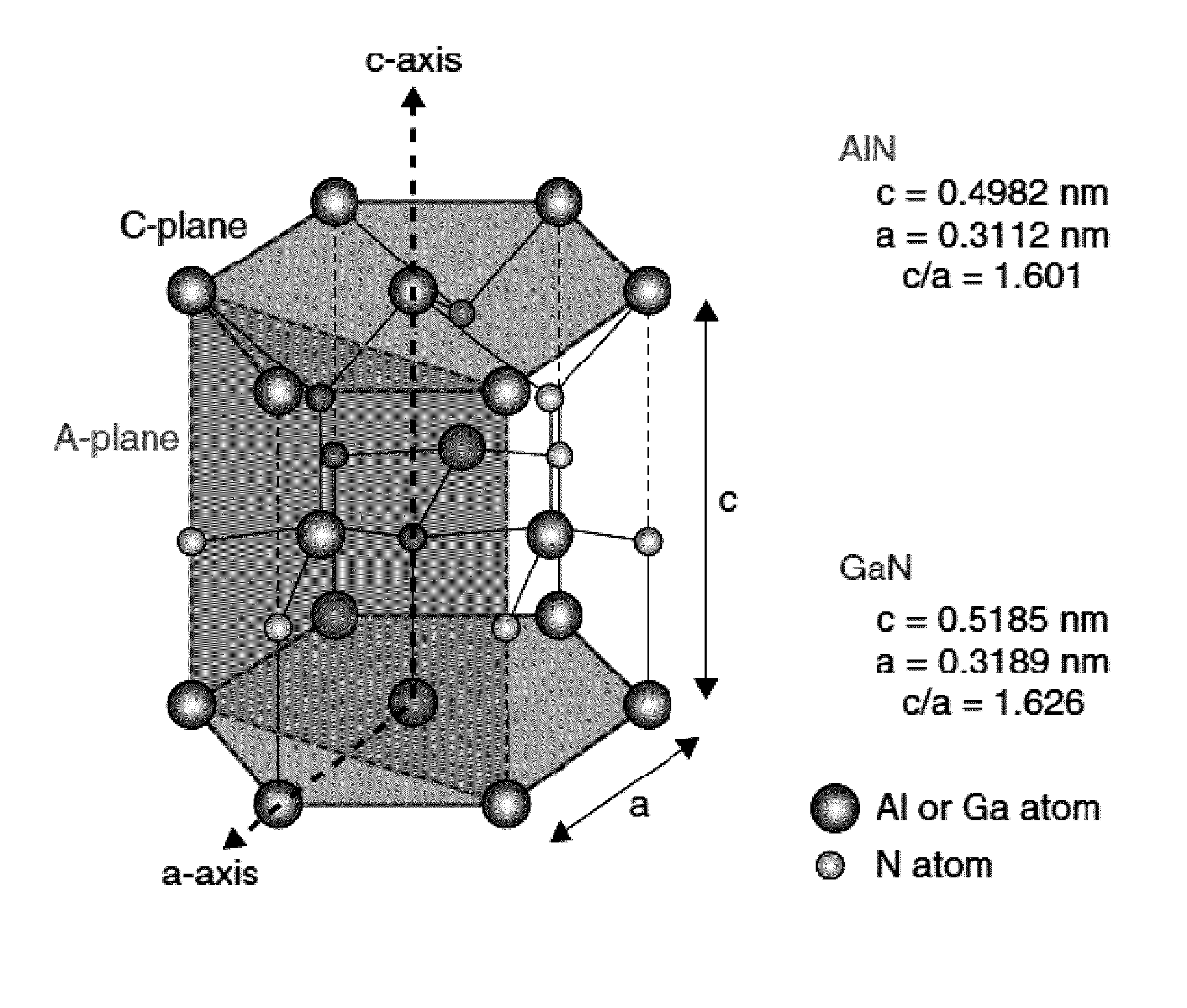

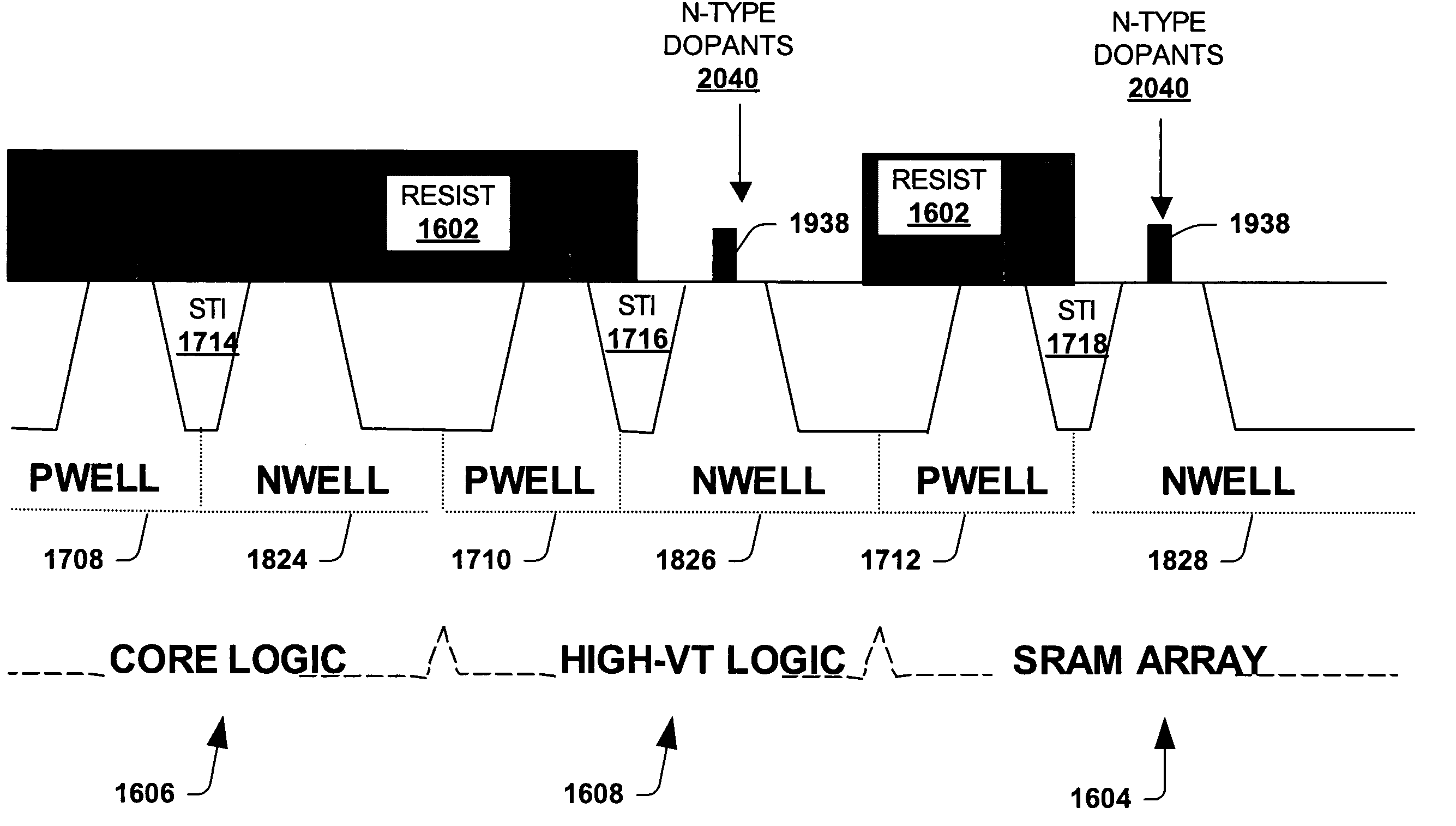

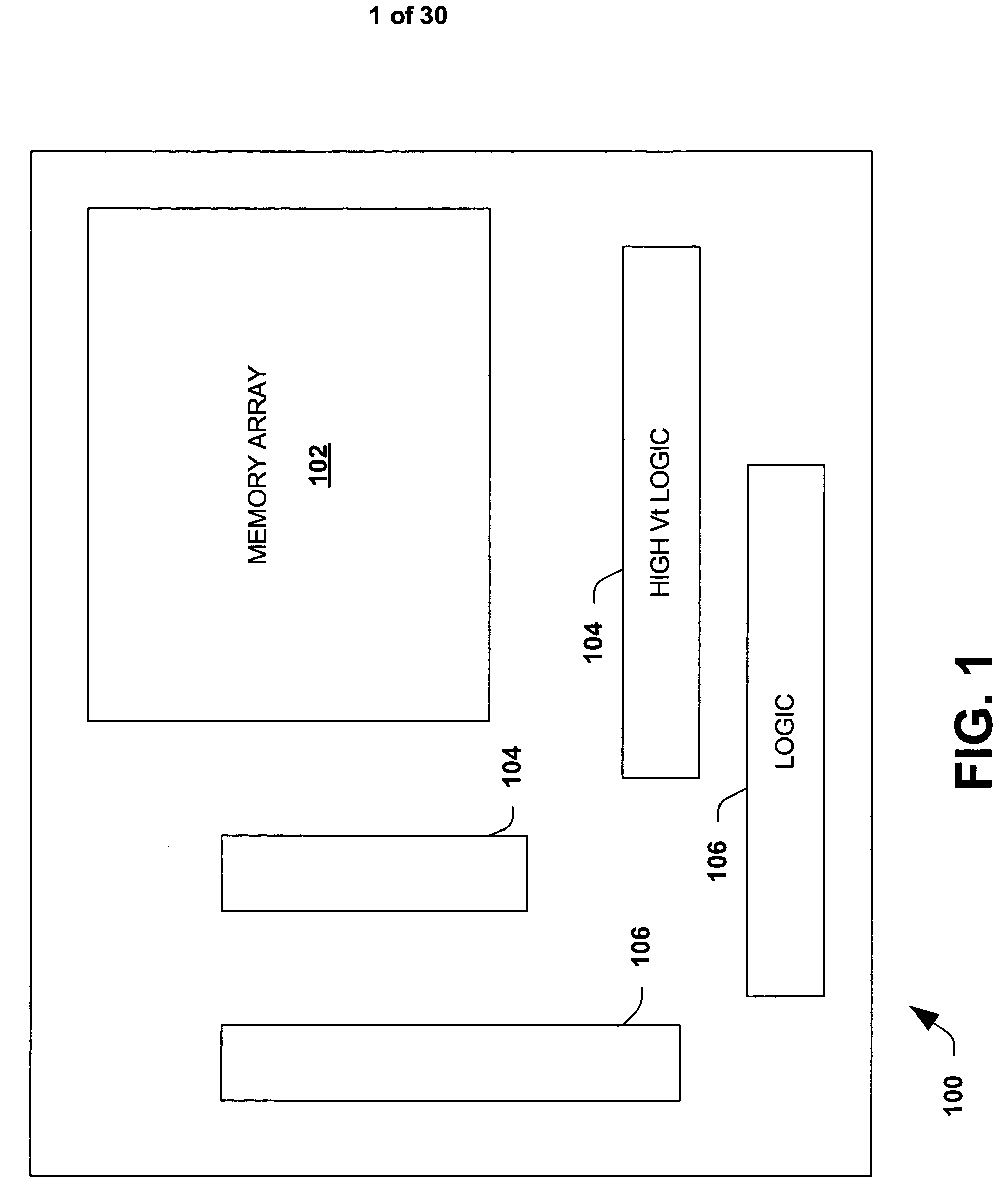

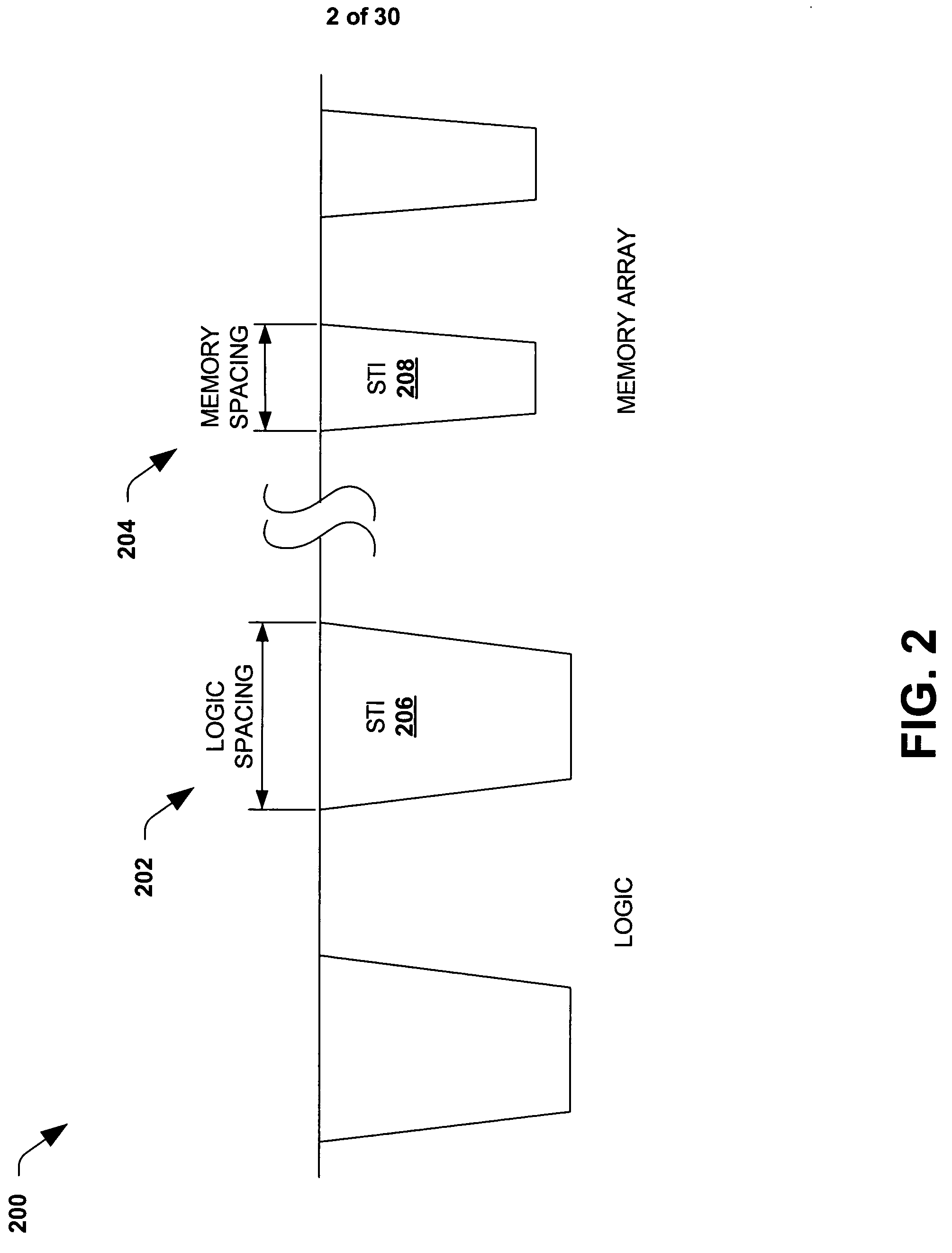

Application of different isolation schemes for logic and embedded memory

ActiveUS20050145949A1Easy to manufactureRun fastSolid-state devicesSemiconductor/solid-state device manufacturingDopantLogical part

The present invention facilitates semiconductor device fabrication by providing mechanisms for utilizing different isolation schemes within embedded memory and other logic portions of a device. The isolation mechanism of the embedded memory portion is improved relative to other portions of the device by increasing dopant concentrations or reducing the depth of the dopant profiles within well regions of the embedded memory array. As a result, smaller isolation spacing can be employed thereby permitting a more compact array. The isolation mechanism of the logic portion is relatively less than that of the embedded memory portion, which permits greater operational speed for the logic.

Owner:TEXAS INSTR INC

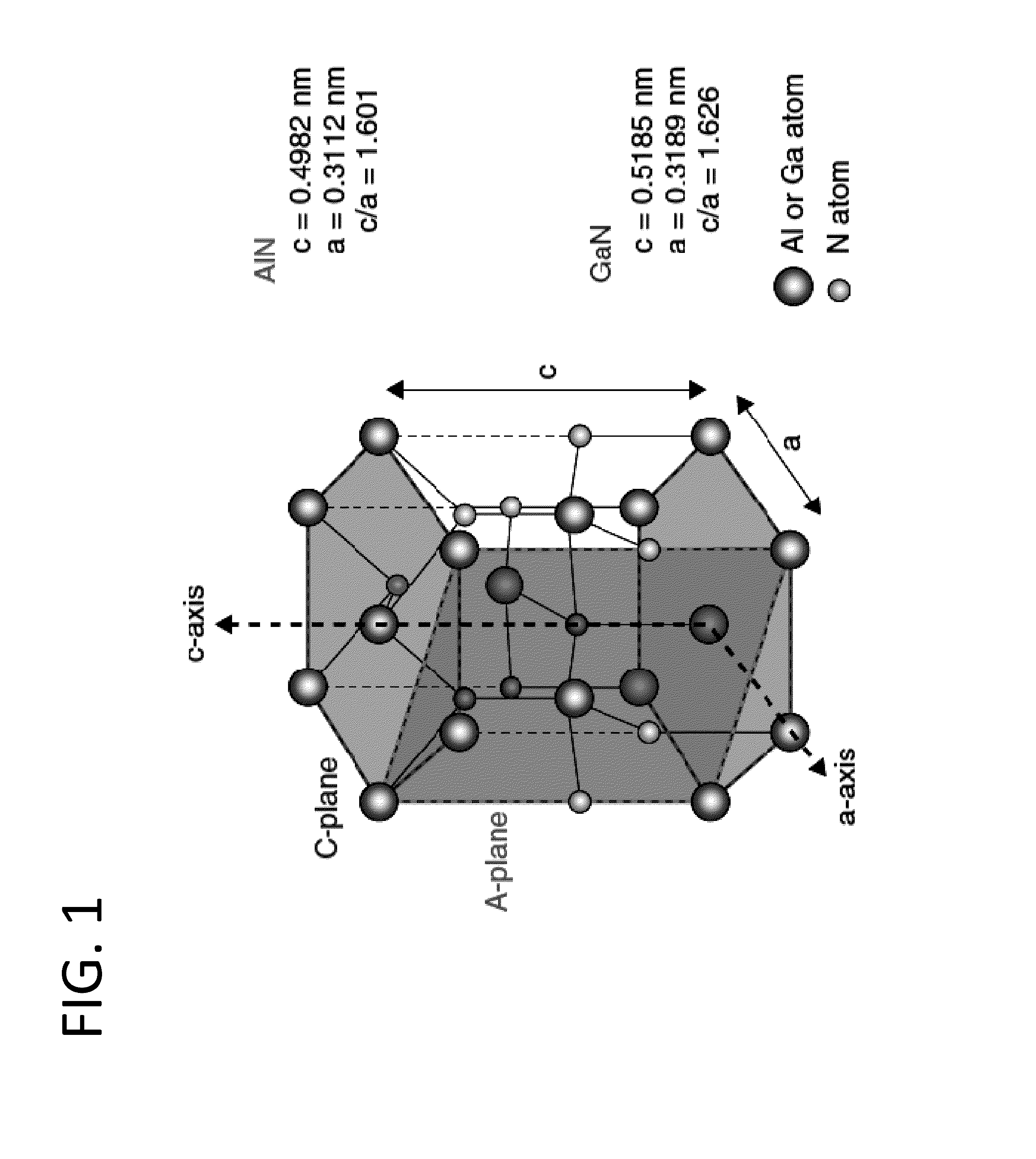

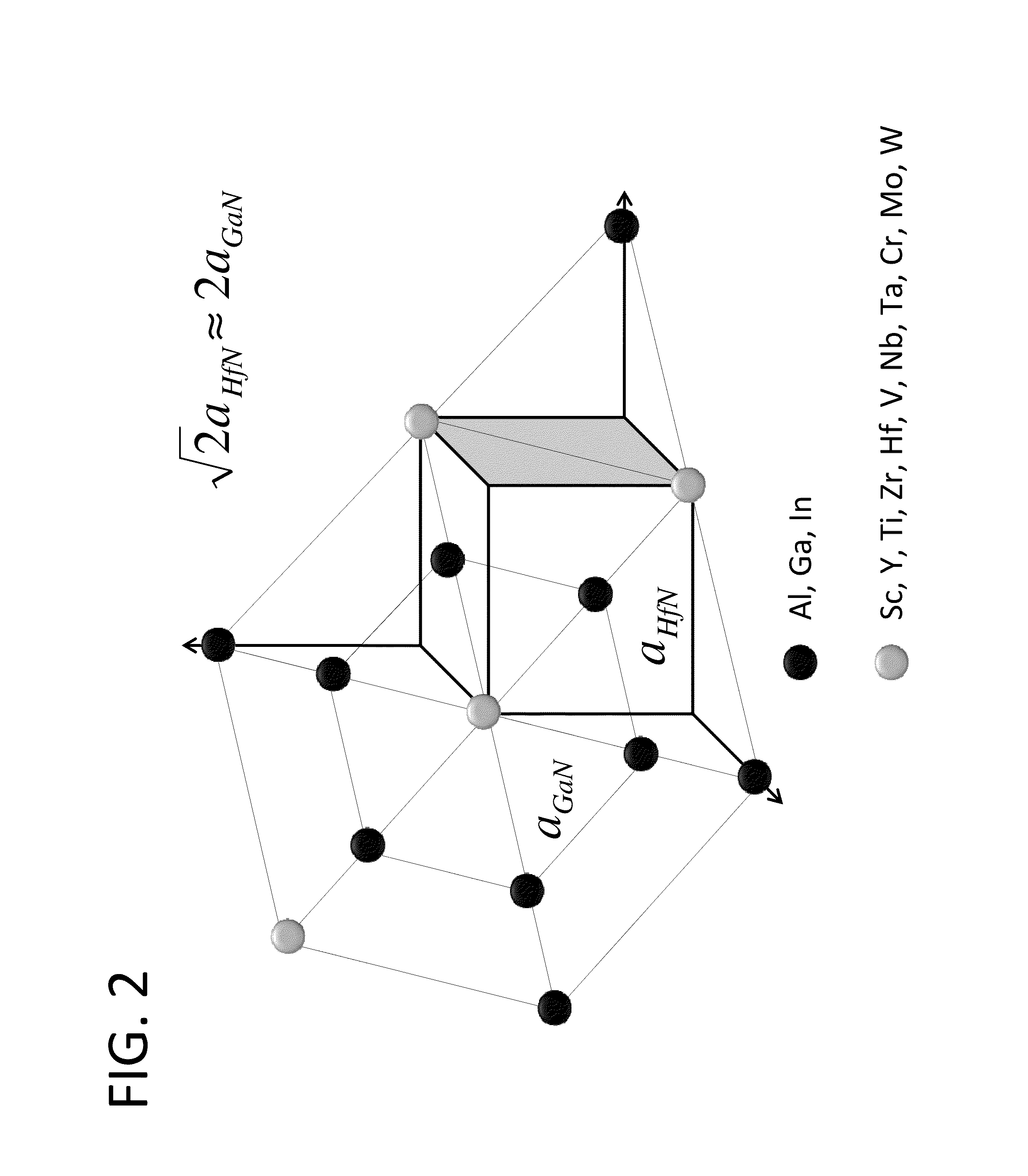

Light emitting device having group iii-nitride current spreading layer doped with transition metal or comprising transition metal nitride

InactiveUS20130048939A1Increase the doping concentrationReduce strainConductive materialSemiconductor/solid-state device manufacturingQuantum wellConductive materials

A light-emitting device, such as a light-emitting diode (LED), has a group III-nitride current spreading layer which is either doped with transition metal, or comprises alternating transition metal nitride layer and group III-nitride layer. Also provided is a light-emitting device, such as a light-emitting diode (LED), having a quantum well doped with transition metal. Also provided is a method of forming transition-metal containing AlInGaN electrical conductive material.

Owner:ZHEJIANG INVENLUX TECH

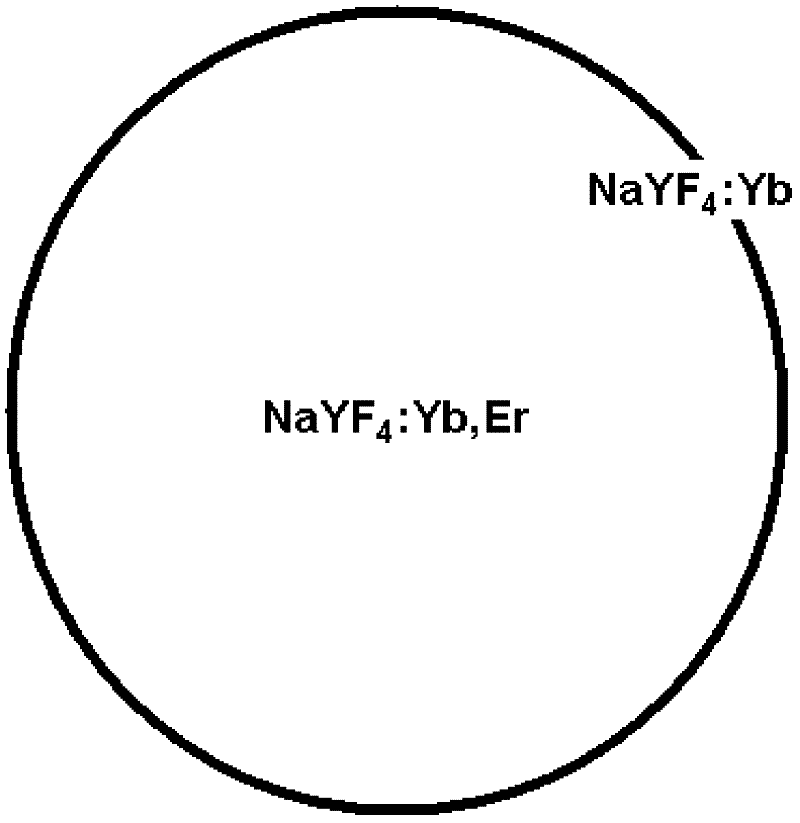

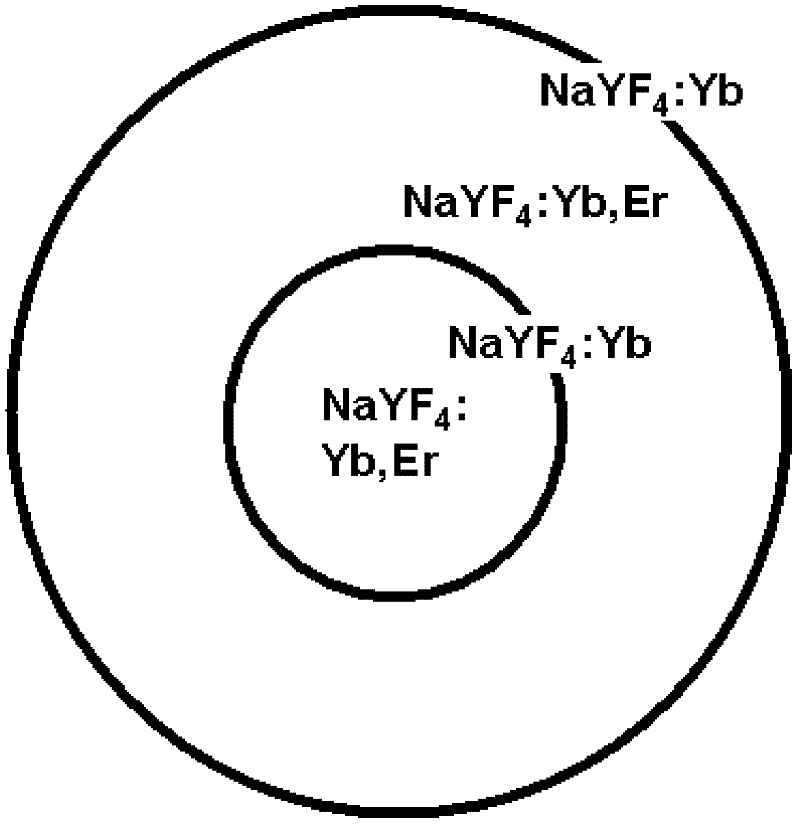

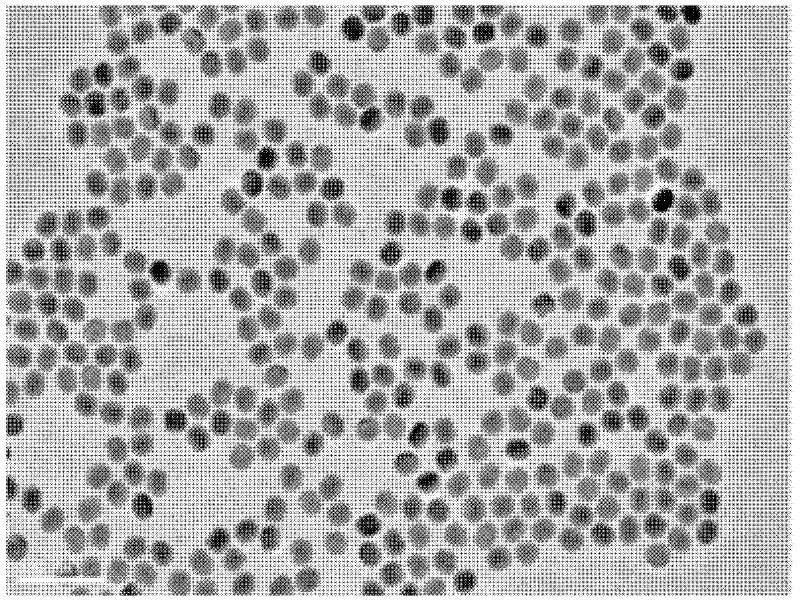

Rare earth up-conversion fluorescent material doped with luminescent center in different regions and preparation method thereof

The invention discloses a luminescent centre regionally doped rare earth upconversion luminescent material and a preparation method thereof, which relates to the technical field of structural design and preparation of luminescent materials. For solving the problems of small doping amount in the luminescent center and low luminescent efficiency of the rare earth upconversion luminescent material, the conventional materials of the same kind take NaYF4 as a matrix, are doped with rare earth sensitized ions and rare earth luminescent ions and has a core / shell structure and nanocrystalline micro structure, wherein a luminescent shell layer is coated outside the core / shell structure, and a sensitized layer is the outmost layer. The preparation method of the rare earth upconversion luminescent material comprises: after a trifluoroacetate thermal decomposition method is implemented, adding a luminescent shell layer precursor into solution of nanoparticle colloid with the luminescent core / shell structure, heating, and reacting to form the luminescent shell layer; cooling the product obtained by the previous step, adding a sensitized shell precursor layer, heating, reacting and obtaining a sensitized shell layer on the outside of the luminescent shell layer; and thus, obtaining the luminescent centre regionally doped rare earth upconversion luminescent material.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

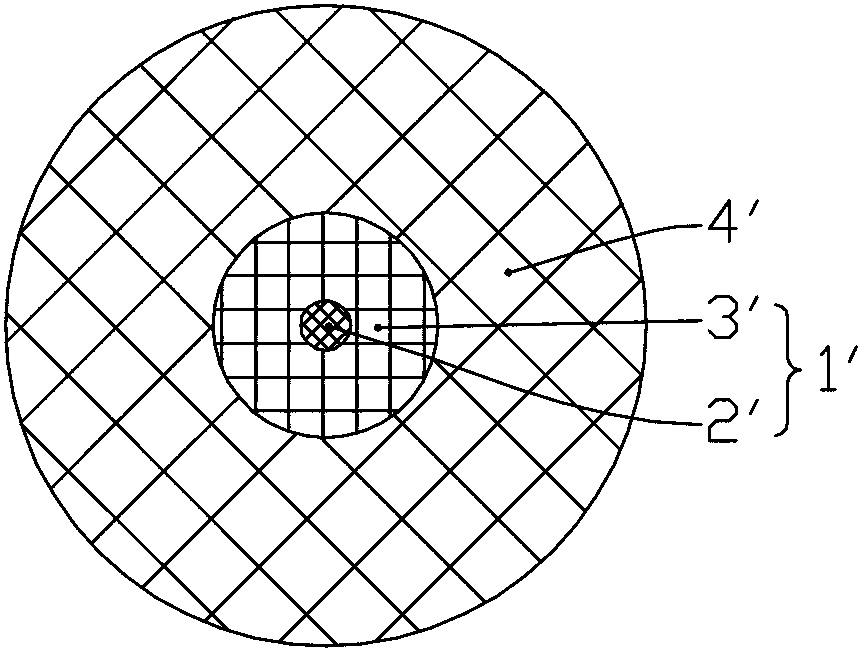

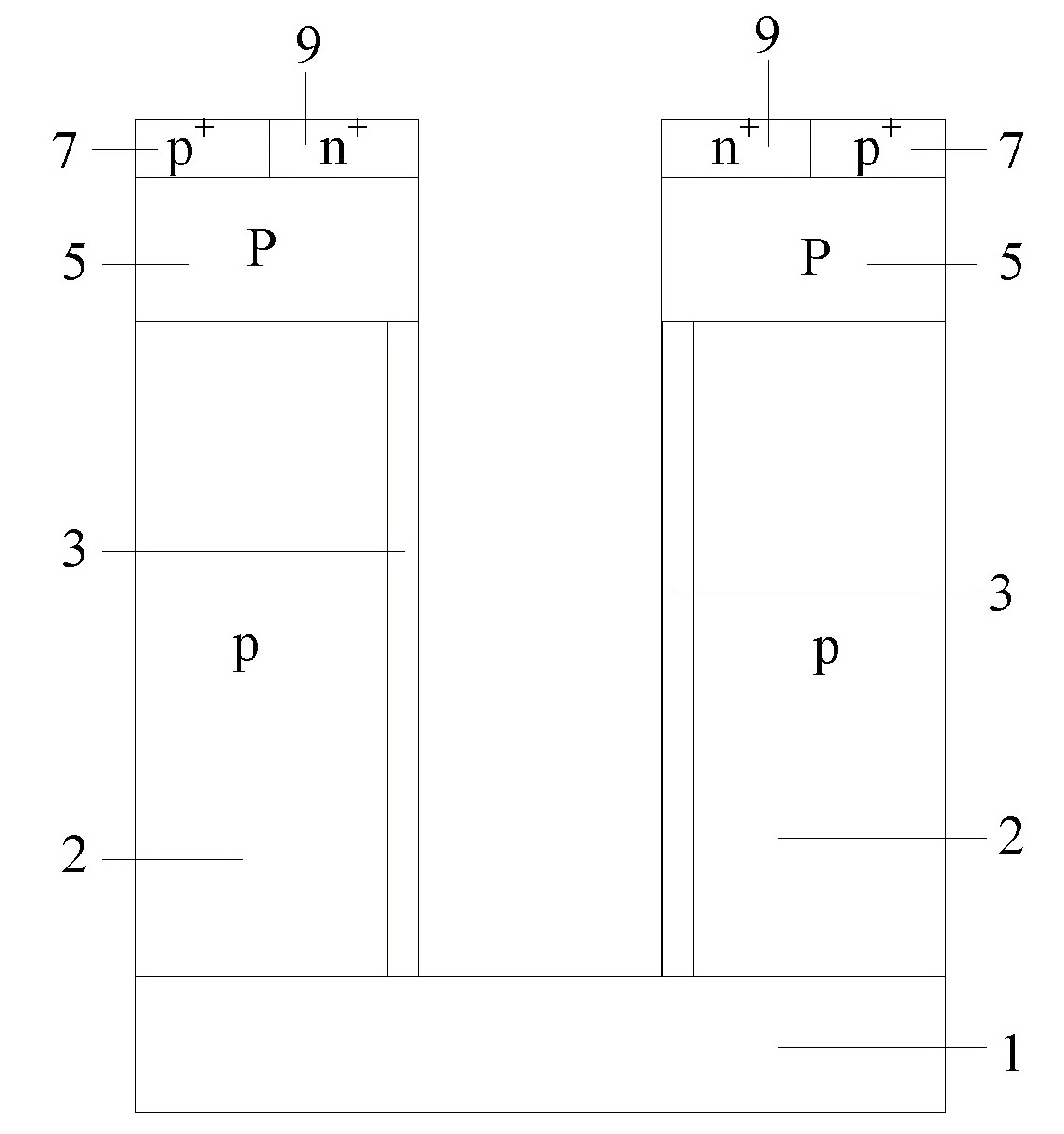

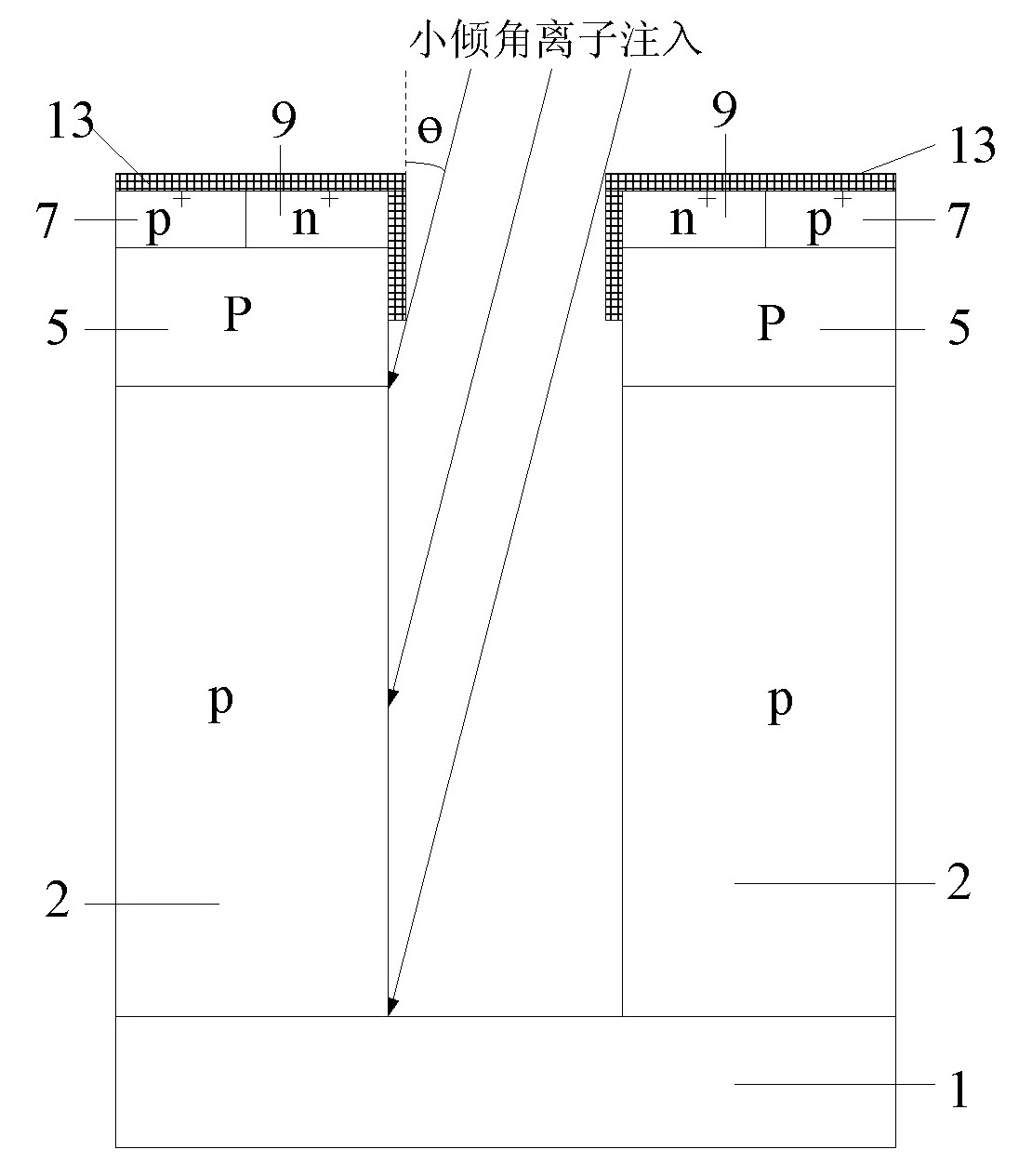

Trench type semiconductor power device

InactiveCN102110716AReduce areaLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationPower semiconductor device

The invention relates to a semiconductor device. The device comprises a semiconductor substrate, a semiconductor drift region on the semiconductor substrate, a high-K dielectric on the semiconductor substrate, an active region on the semiconductor drift region and a trench gate structure on the high-K dielectric, wherein the semiconductor drift region comprises a first conduction type semiconductor region and a second conduction type semiconductor region which form a super-junction structure; the high-K dielectric is adjacent to the second conduction type semiconductor region; the trench gate structure is adjacent to the active region; and the second conduction type semiconductor region is formed through ion implantation at a small inclination angle, so that the semiconductor device is narrow and has high concentration.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method for manufacturing insulated gate bipolar transistor (IGBT) device

ActiveCN102420133AEliminate temperature limitationsHigh activation rateSemiconductor/solid-state device manufacturingOhmic contactAlternating current

The invention discloses a method for manufacturing an insulated gate bipolar transistor (IGBT) device. The method sequentially comprises an ion injection step of forming a p type heavily doped collecting region on the back side of a silicon wafer, a partial or whole annealing step and a step of depositing surface metal on the front side of the silicon wafer; and after the p type heavily doped collecting region is formed on the back side of the silicon wafer, a layer of silicon dioxide is deposited on the back side of the p type heavily doped collecting region. The method has the advantages that the temperature limitation of the p type ion annealing on the back side of the silicon wafer is eliminated, and high activity rate is easy to obtain. Simultaneously, the p type impurity distribution in the p type heavily doped collecting region can be optimized. On one hand, the ohmic contact with back metal is easy to form, on the other hand, the emission efficiency of a precision navigation processor (PNP) is favorably controlled, and the alternating current characteristic of the IGBT device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Rare-earth element doped glass double-clad optic fibre and mfg. method thereof

InactiveCN1402028AGreat gain per unit lengthSimple preparation and drawing processOptical light guides

An RE doped optical fibre with dual glass clad layers, that is, coaxial internal and external clad layers. The fibre core is made of phosphate glass system. The internal clad layer is made of phosphate (or silicate) glass system. Its preparing process includes choosing the raw glass materials for fibre core and internal clad layer, melting, preparing prefabricated rod, and drawing. Its advantages are high concentration of doped RE ions, and gain, big excited emitting area, wide tunning range and low cost.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Application of different isolation schemes for logic and embedded memory

ActiveUS20050087810A1Easy to manufactureRun fastSolid-state devicesSemiconductor/solid-state device manufacturingDopantLogical part

The present invention facilitates semiconductor device fabrication by providing mechanisms for utilizing different isolation schemes within embedded memory and other logic portions of a device. The isolation mechanism of the embedded memory portion is improved relative to other portions of the device by increasing dopant concentrations or reducing the depth of the dopant profiles within well regions of the embedded memory array. As a result, smaller isolation spacing can be employed thereby permitting a more compact array. The isolation mechanism of the logic portion is relatively less than that of the embedded memory portion, which permits greater operational speed for the logic.

Owner:TEXAS INSTR INC

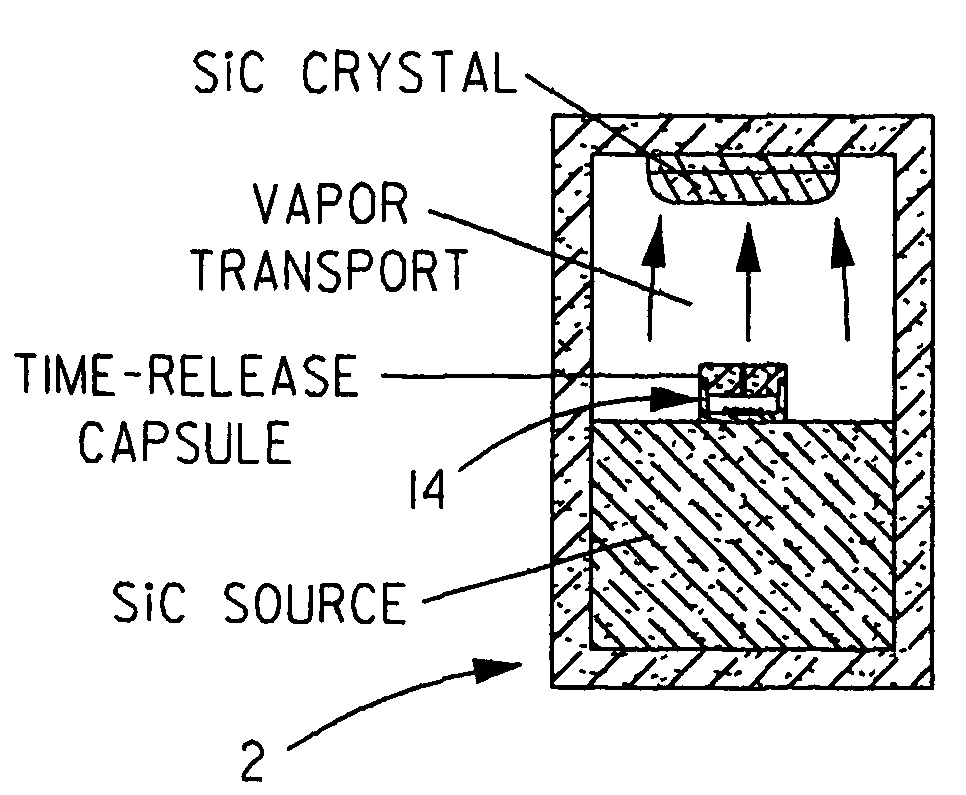

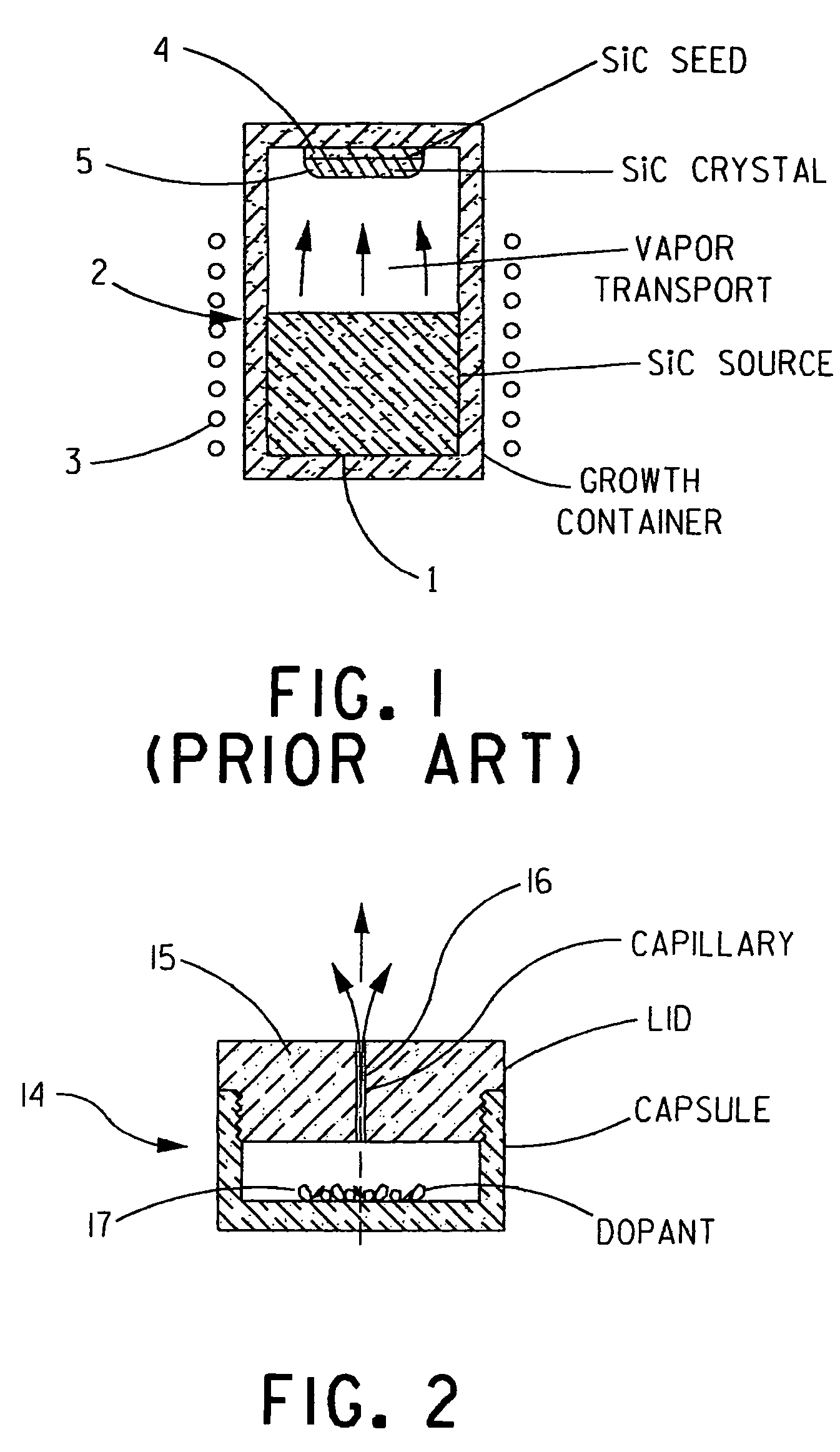

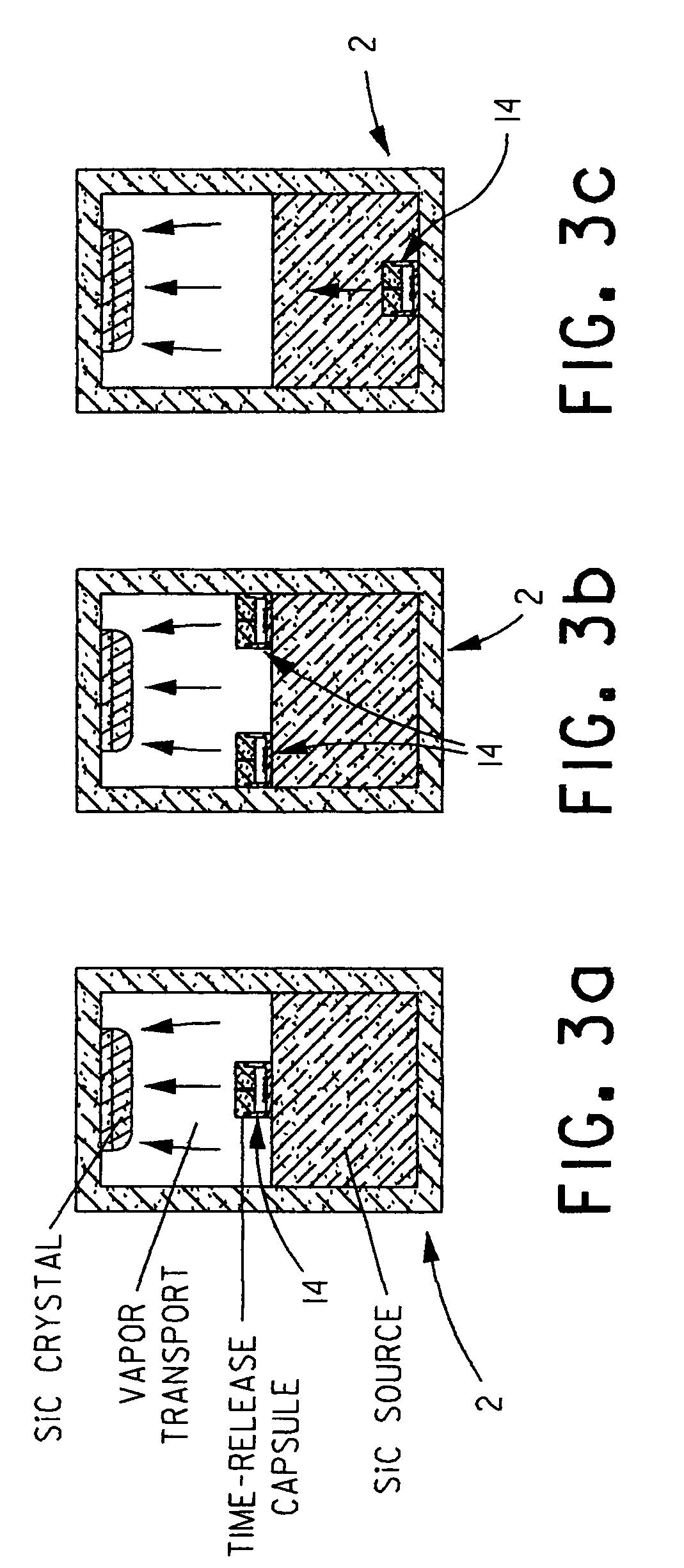

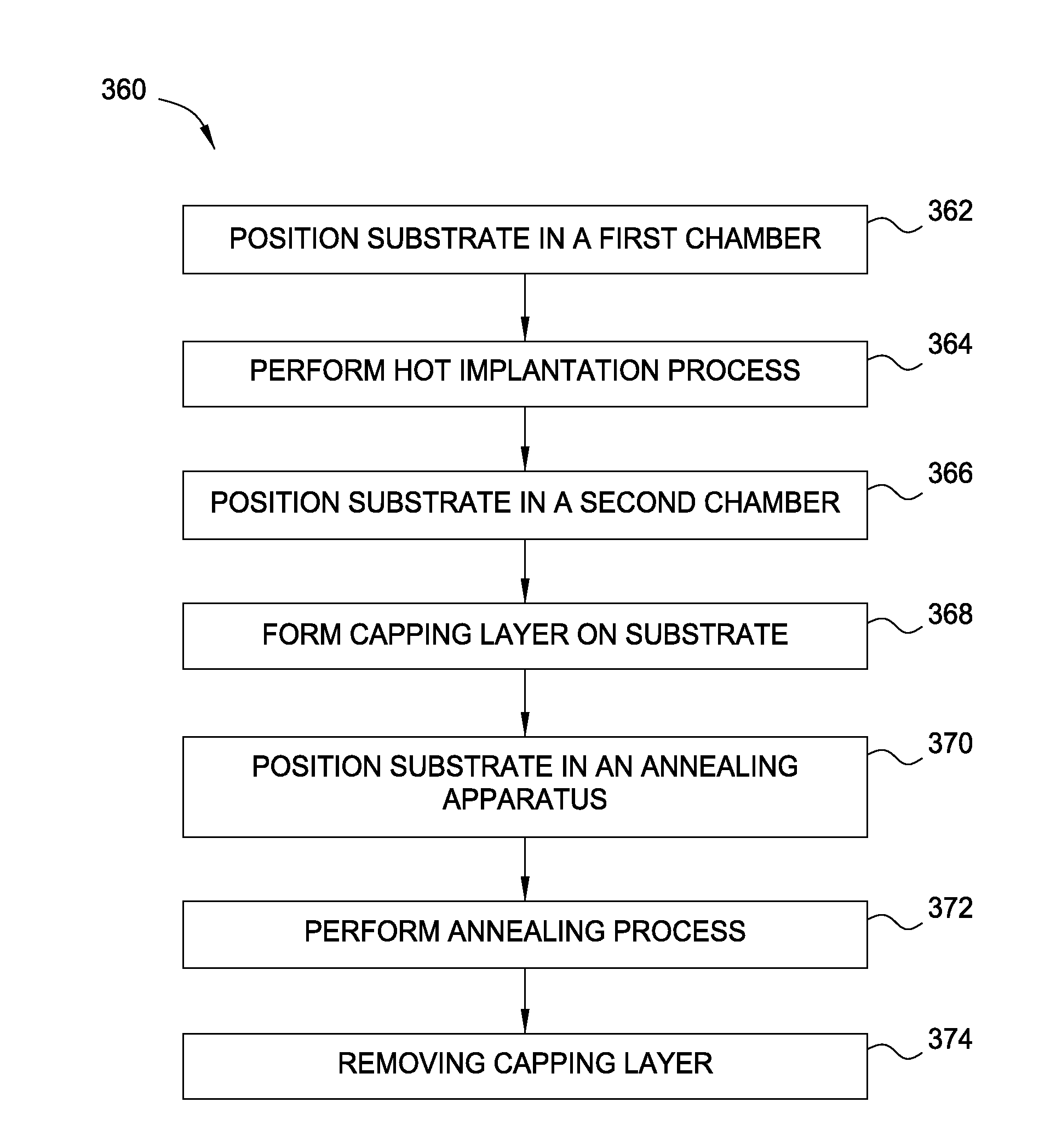

Method of and system for forming SiC crystals having spatially uniform doping impurities

ActiveUS7608524B2Increase the doping concentrationReduce doping concentrationPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantGas phase

In a physical vapor transport method and system, a growth chamber charged with source material and a seed crystal in spaced relation is provided. At least one capsule having at least one capillary extending between an interior thereof and an exterior thereof, wherein the interior of the capsule is charged with a dopant, is also provided. Each capsule is installed in the growth chamber. Through a growth reaction carried out in the growth chamber following installation of each capsule therein, a crystal is formed on the seed crystal using the source material, wherein the formed crystal is doped with the dopant.

Owner:II VI DELAWARE INC

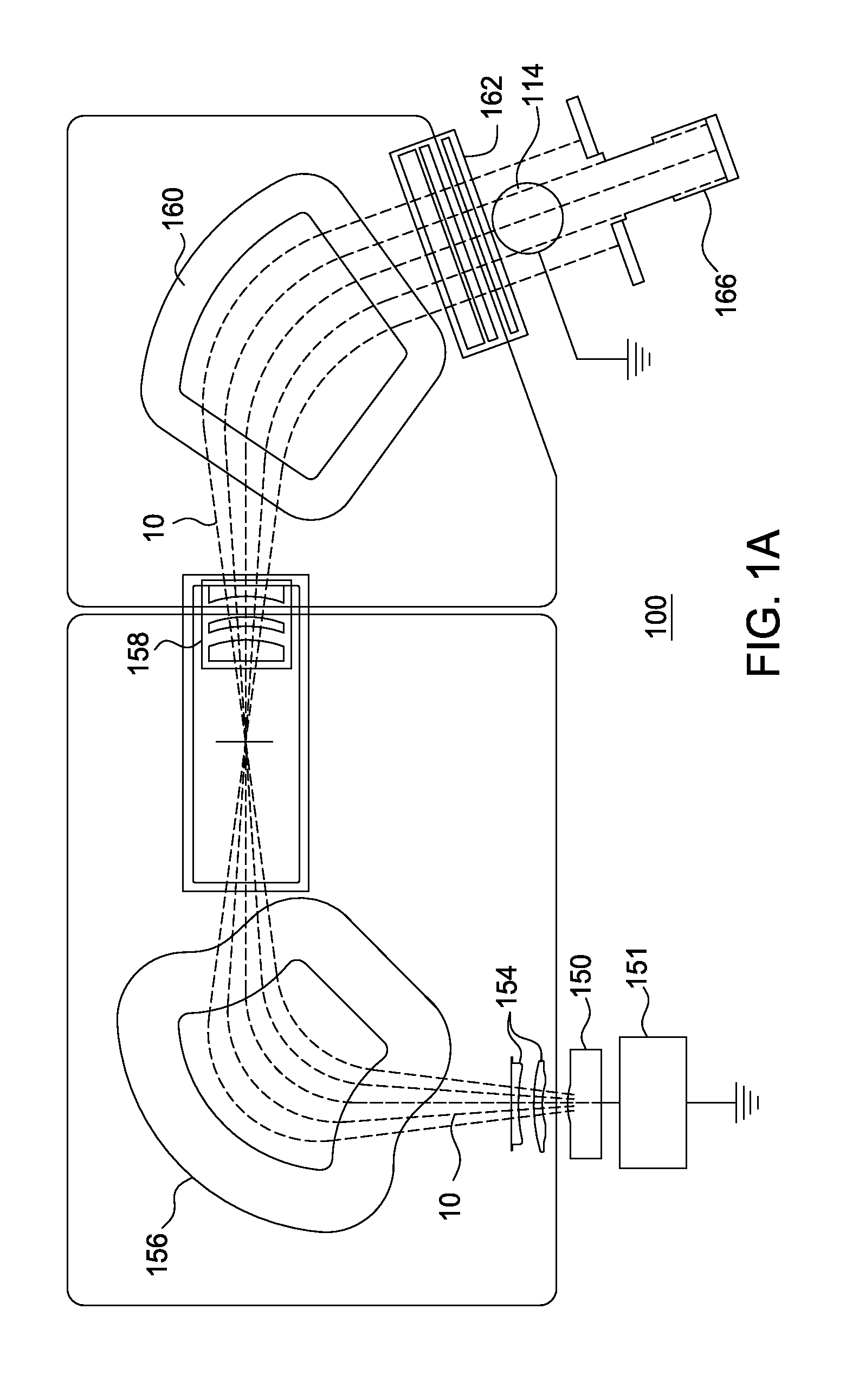

Enabling high activation of dopants in indium-aluminum-galium-nitride material system using hot implantation and nanosecond annealing

InactiveUS20150099350A1Reduce lattice damageReduce outgassingSemiconductor/solid-state device manufacturingDopantElectricity

Embodiments of the present disclosure generally relate to doping and annealing substrates. The substrates may be doped during a hot implantation process, and subsequently annealed using a nanosecond annealing process. The combination of hot implantation and nanosecond annealing reduces lattice damage of the substrates and facilitates a higher dopant concentration near the surface of the substrate to facilitate increased electrical contact with the substrate. An optional capping layer may be placed over the substrate to reduce outgassing of dopants or to control dopant implant depth.

Owner:APPLIED MATERIALS INC

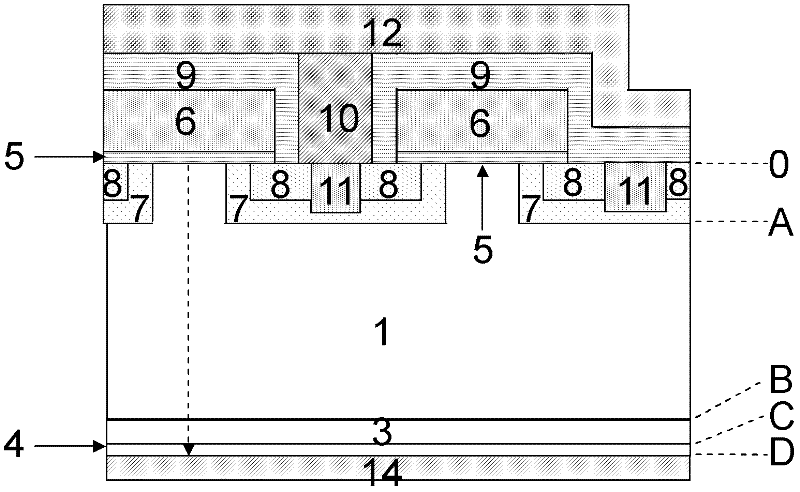

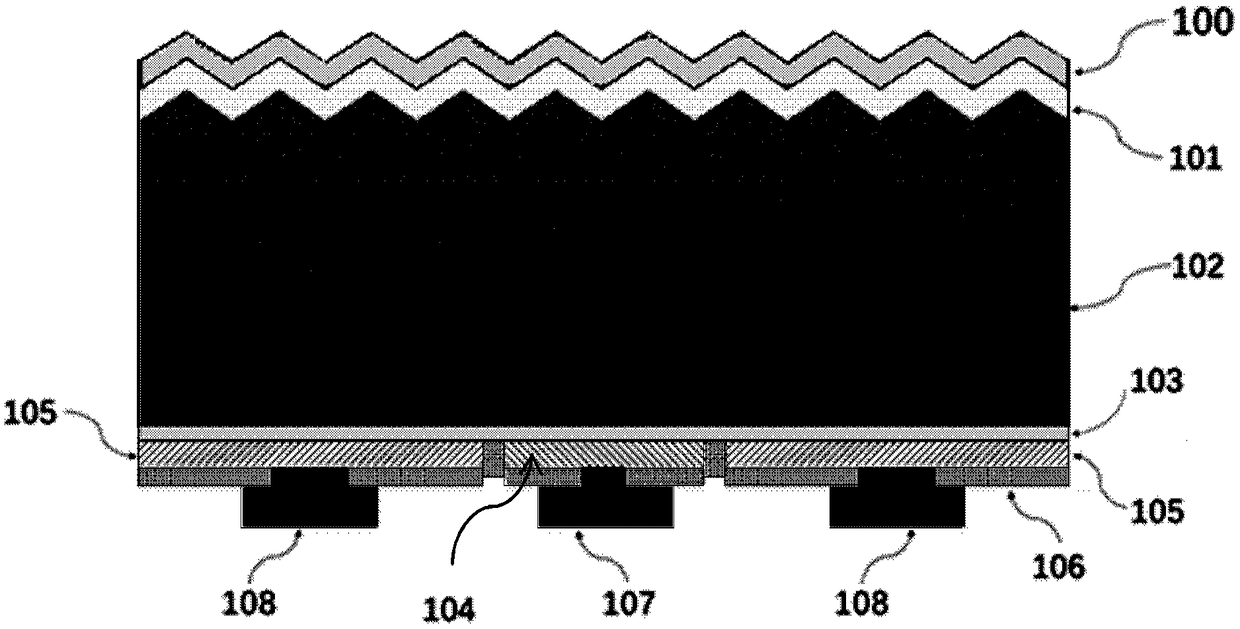

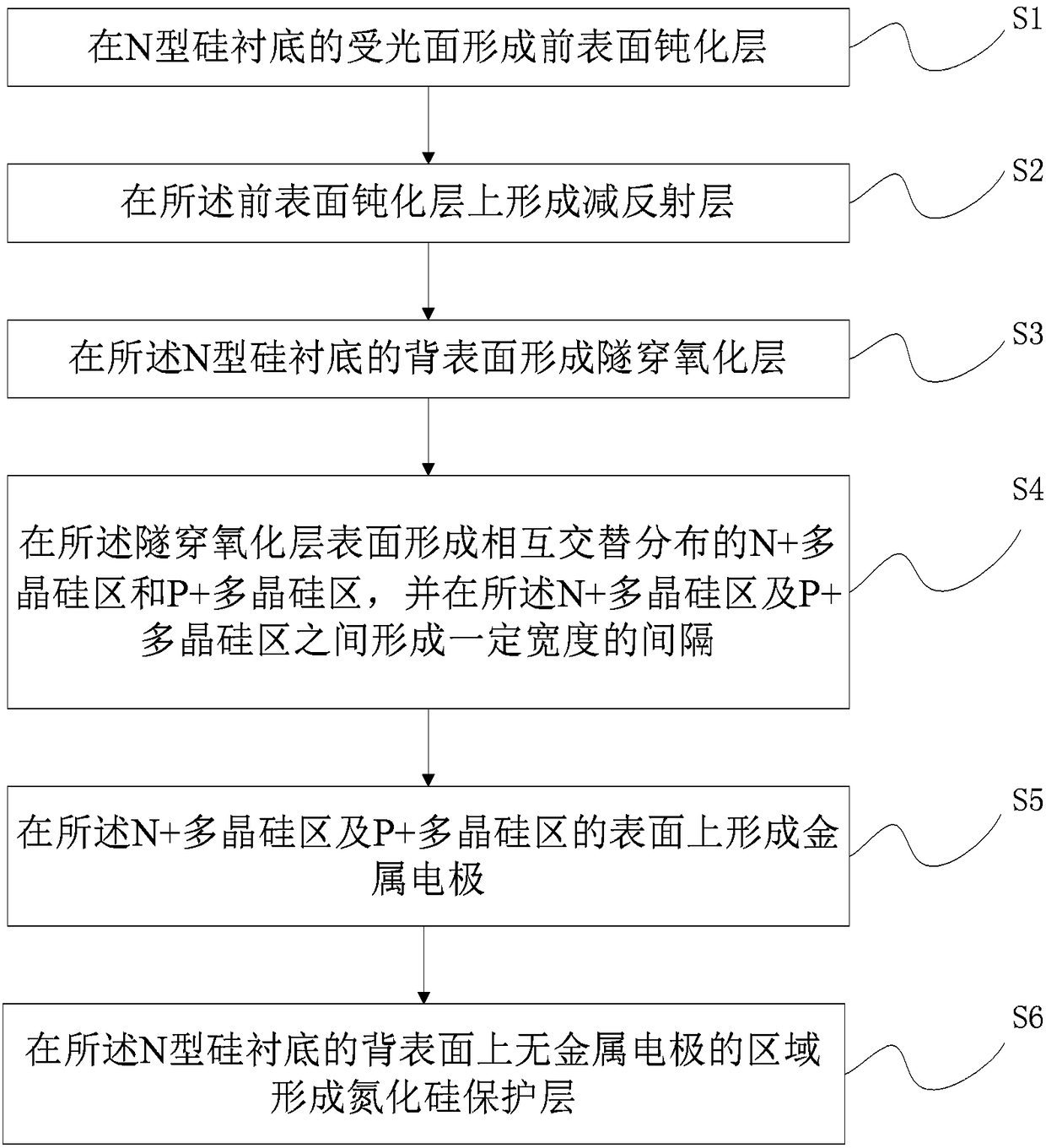

Crystalline silicon solar cell and preparation method thereof

InactiveCN108336154AReduce compound rateImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationCrystalline siliconN type silicon

The present invention provides a crystalline silicon solar cell and a preparation method thereof. The crystalline silicon solar cell comprises: an N-type silicon substrate; a tunneling oxide layer formed on the back surface of the N-type silicon substrate; and a polysilicon layer formed on the tunneling oxide layer, wherein the polysilicon layer comprises alternatively distributed N+ polysilicon areas and P+ polysilicon areas, and a space is arranged between each neighboring N+ polysilicon area and P+ polysilicon area. The tunneling oxide layer, the N+ polysilicon areas and the P+ polysiliconareas form a passivation contact structure on the back surface of the N-type silicon substrate. According to the crystalline silicon solar cell and the preparation method thereof, the recombination rate of the back surface of a battery is effectively reduced, and the open circuit voltage of the battery is improved. Compared with the conventional back knot and back contact solar cells, the doping process of the front surface is saved, the battery preparation process is simplified, the absorption loss of light is reduced, and thus the solar cell can facilitate the improvement of battery performance and the reduction of cost.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

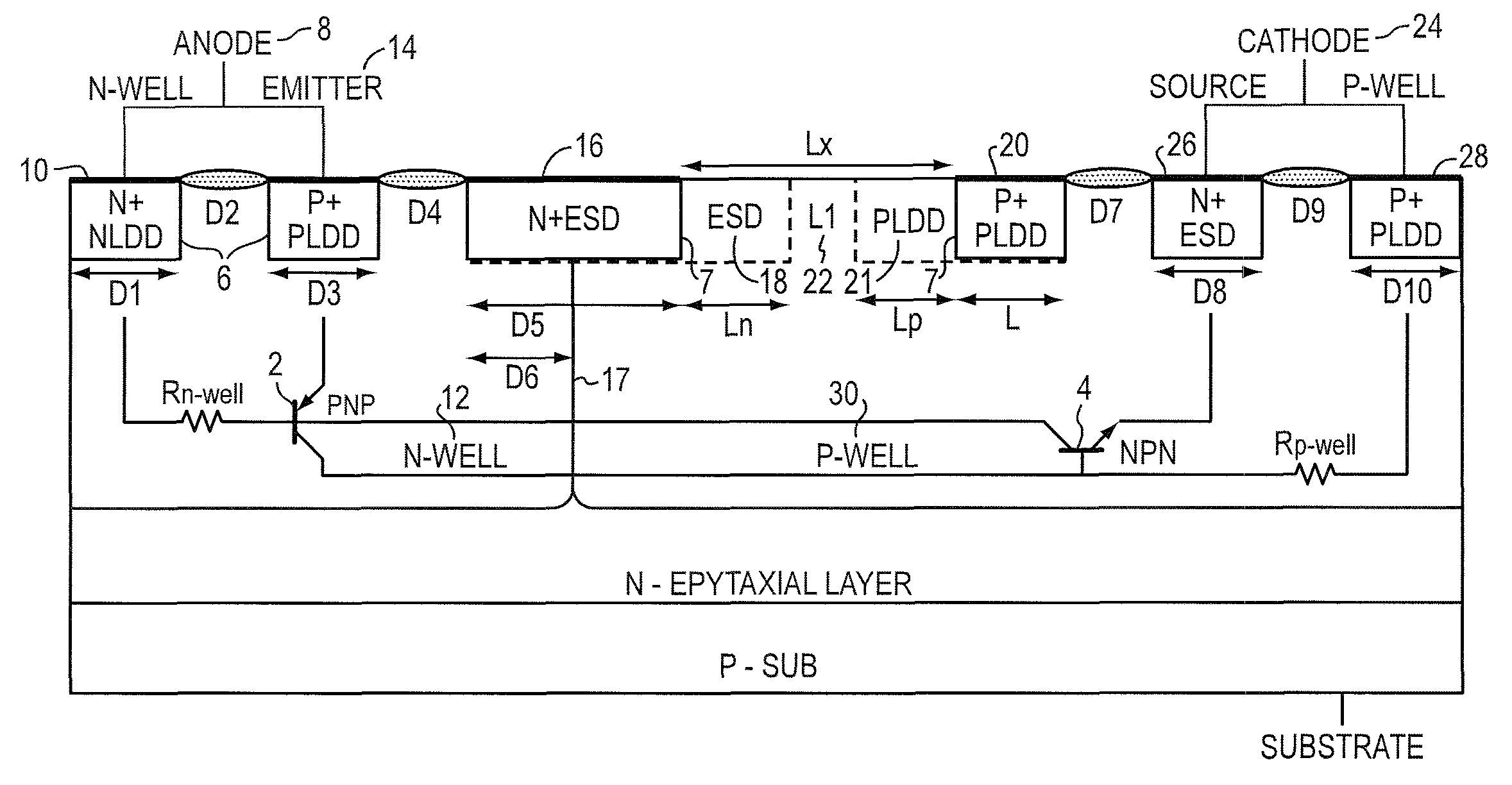

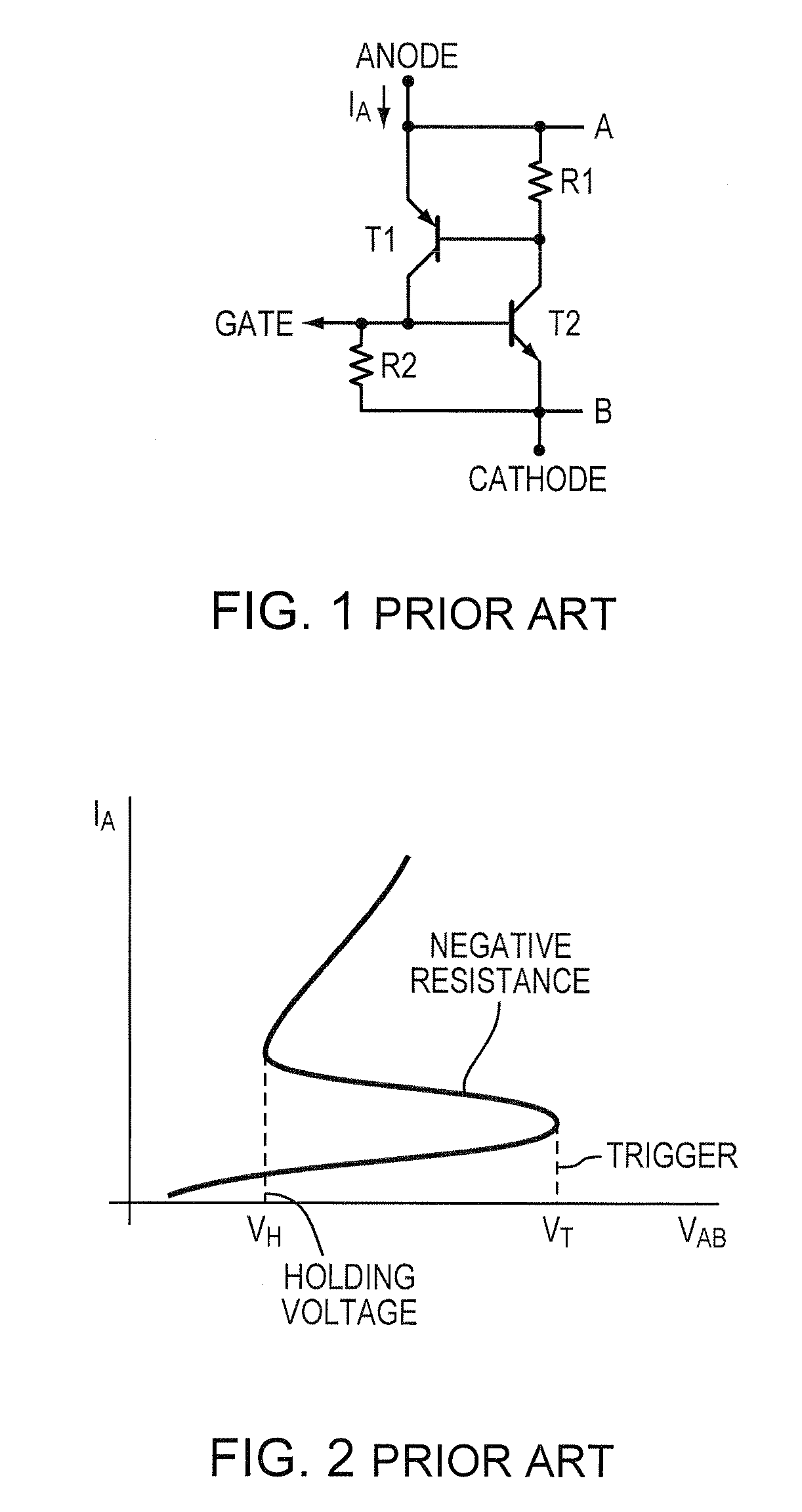

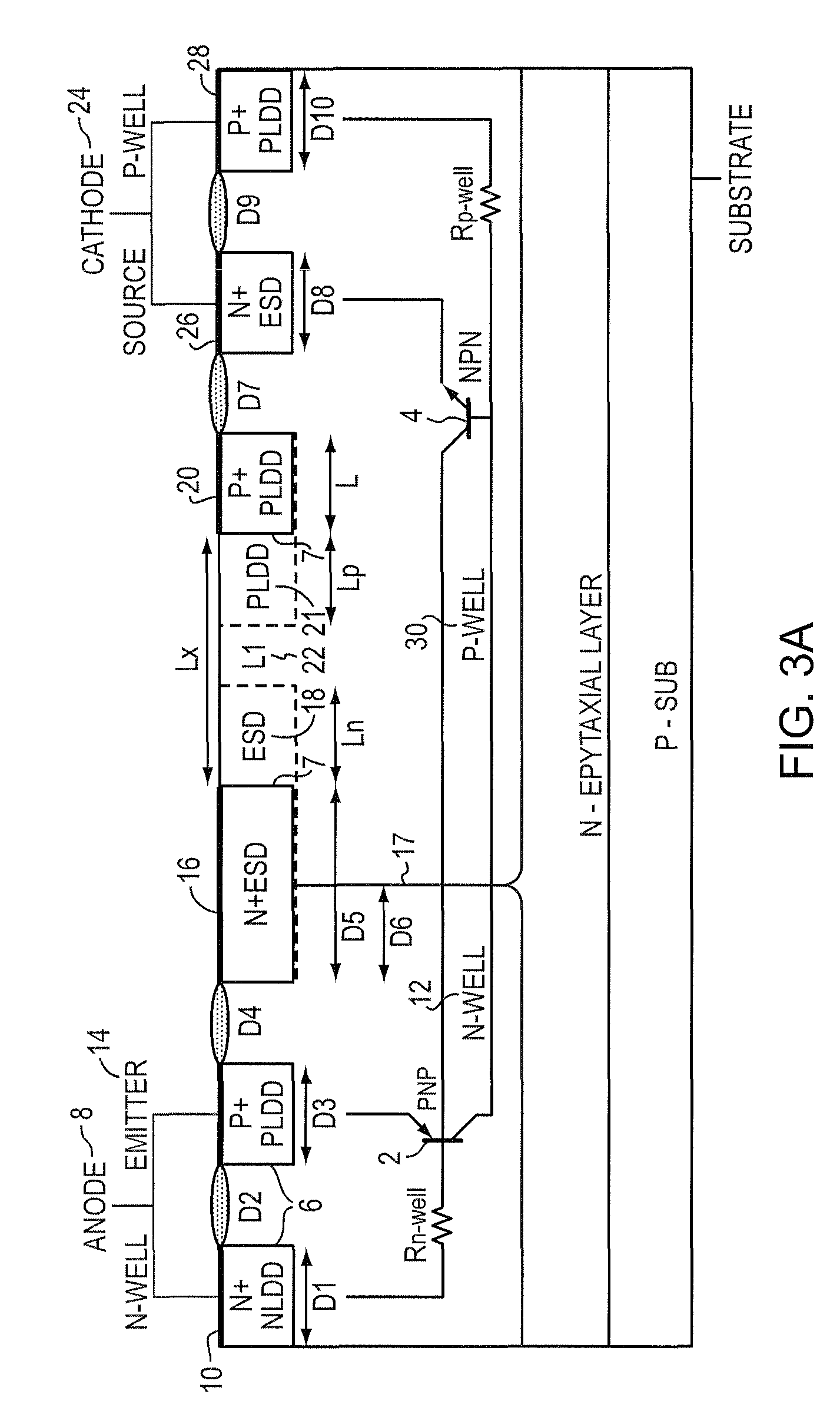

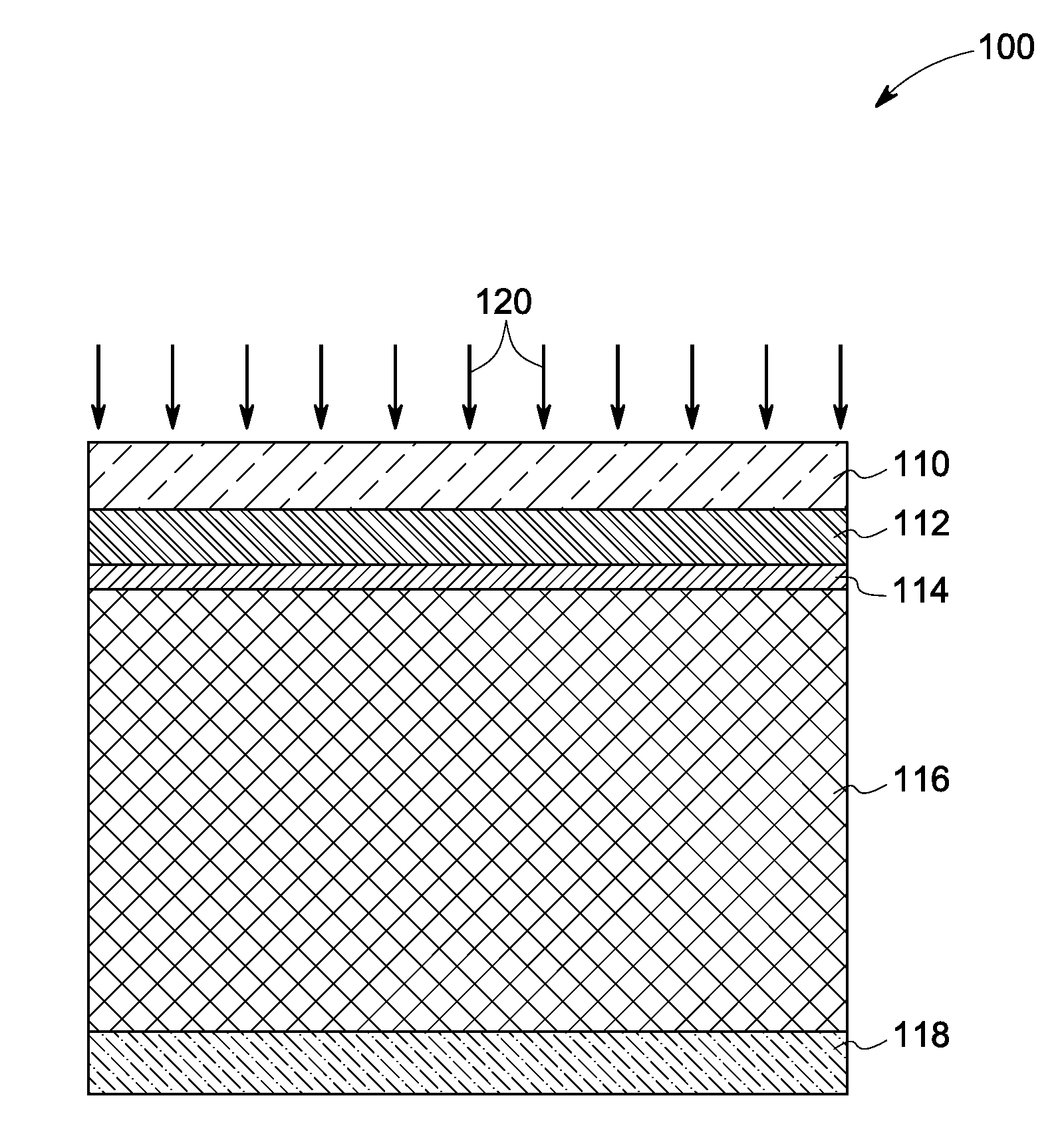

Un-assisted, low-trigger and high-holding voltage SCR

ActiveUS7719026B2Sacrificing ESD protection robustnessHigh n-type doping densityTransistorThyristorEngineeringExternal circuit

A protective SCR integrated circuit device is disclosed built on adjacent N and P wells and defining an anode and a cathode. In addition to the anode and cathode contact structures, the device has an n-type stack (N+ / ESD) structure bridging the N-Well and the P-Well, and a p-type stack (P+ / PLDD) structure in the P-Well. The separation of the n-type stack structure and the p-type stack structure provides a low triggering voltage without involving any external circuitry or terminal, that together with other physical dimensions and processing parameters also provide a relatively high holding voltage without sacrificing the ESD protection robustness. In an embodiment, the triggering voltage may be about 8V while exhibiting a holding voltage, that may be controlled by the lateral dimension of the n-type stack of about 5-7 V.

Owner:SEMICON COMPONENTS IND LLC

Layer for thin film photovoltaics and a solar cell made therefrom

InactiveUS20100243039A1Increase the doping concentrationSemiconductor/solid-state device manufacturingPhotovoltaic energy generationDopantSolar cell

A photovoltaic device is provided comprising a layer. The layer comprises a plurality of grains separated by grain boundaries wherein the grains are either p-type or n-type. The grain boundaries comprise an active dopant. The active dopant concentration in the grain boundaries is higher than the effective dopant concentration in the grains. The grains and grain boundaries may be of the same type or of the opposite type. Further, when the grain boundaries are n-type the bottom of the grain boundaries may be p-type. A method of making the layer is also disclosed.

Owner:FIRST SOLAR INC (US)