Patents

Literature

129results about How to "Prevent punch-through" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

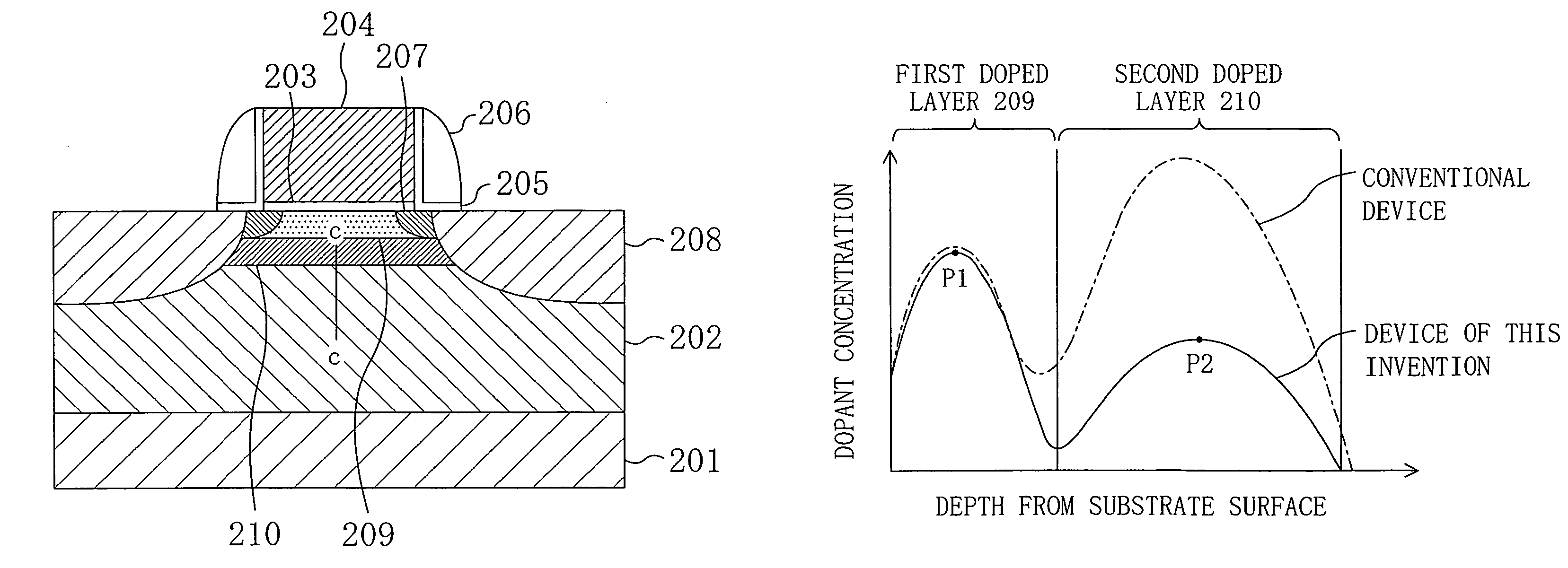

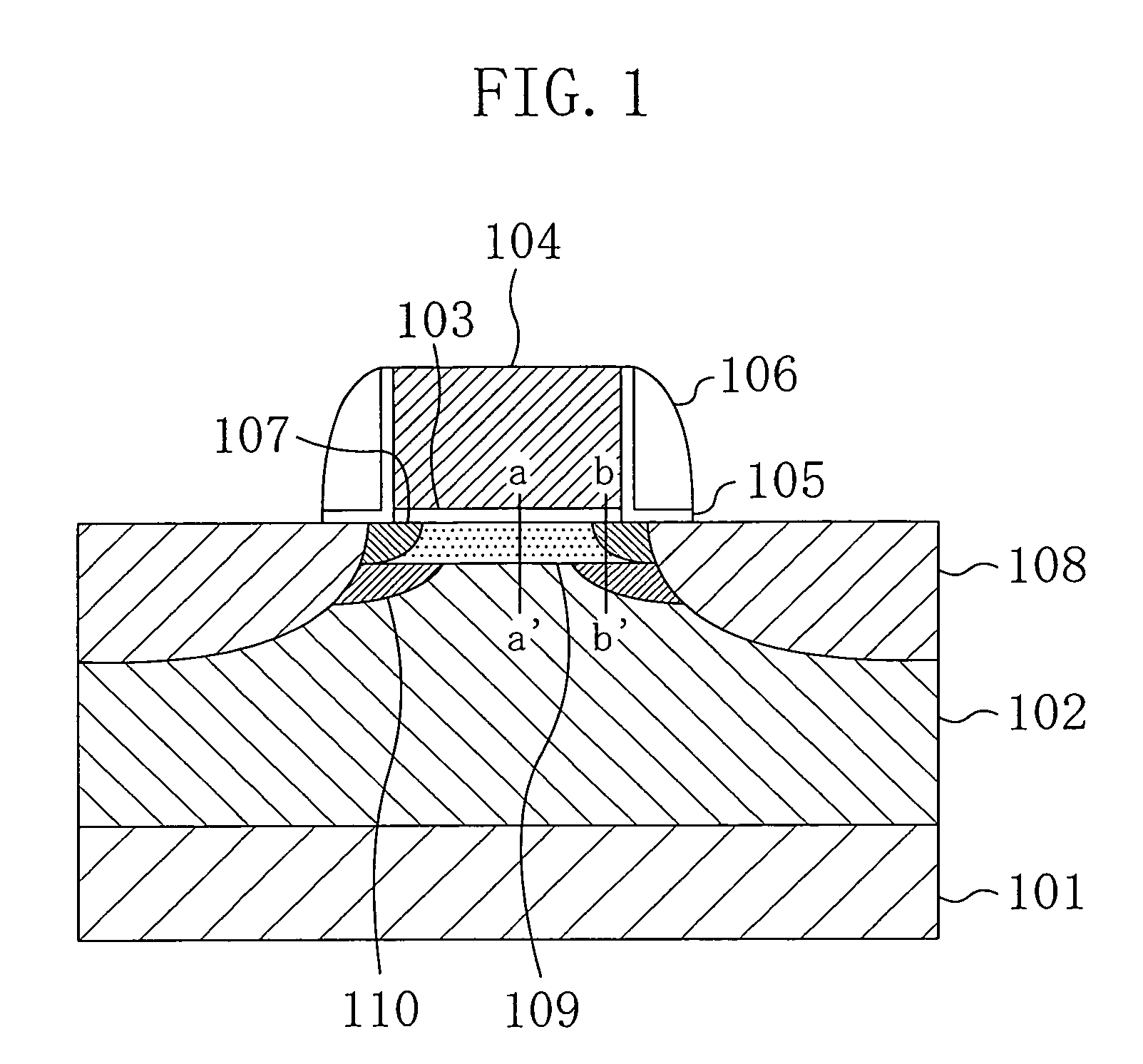

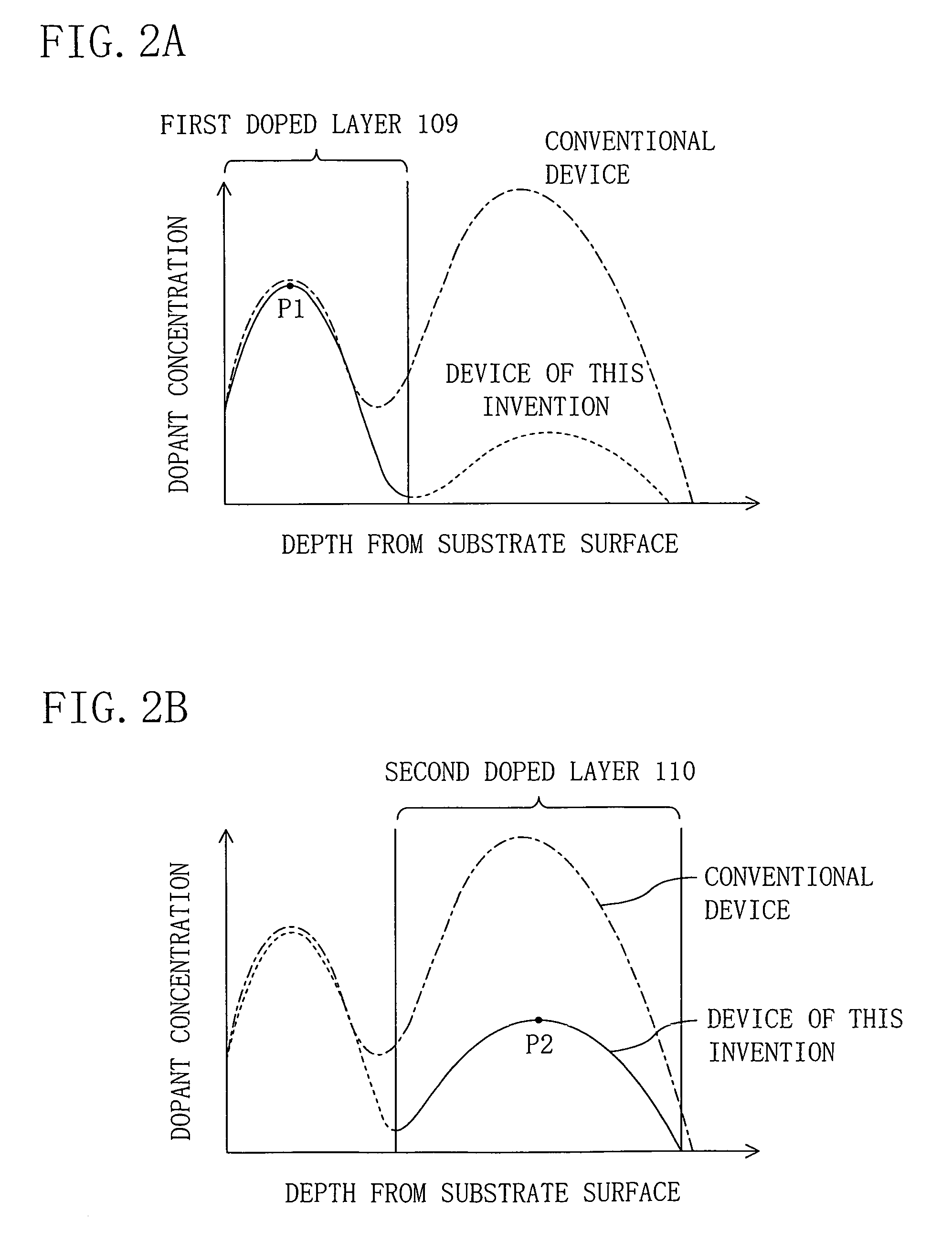

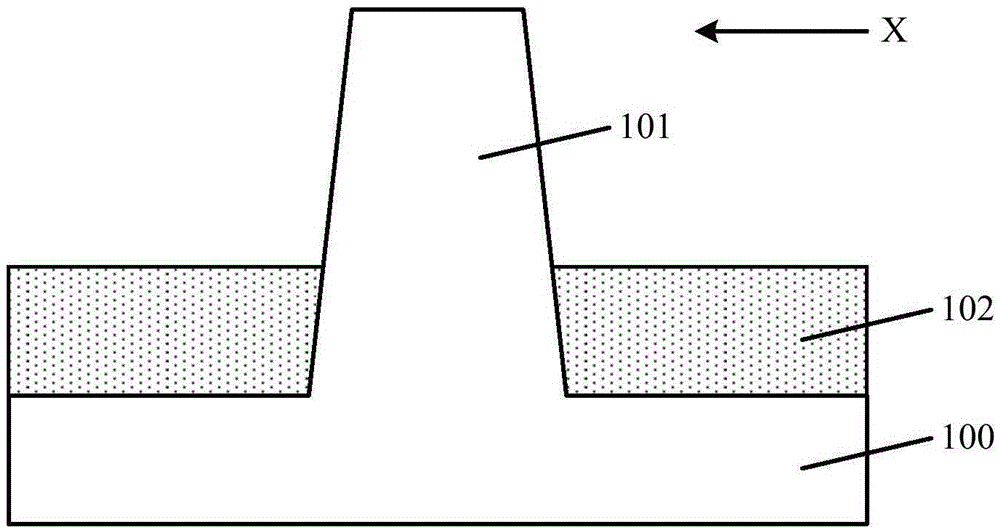

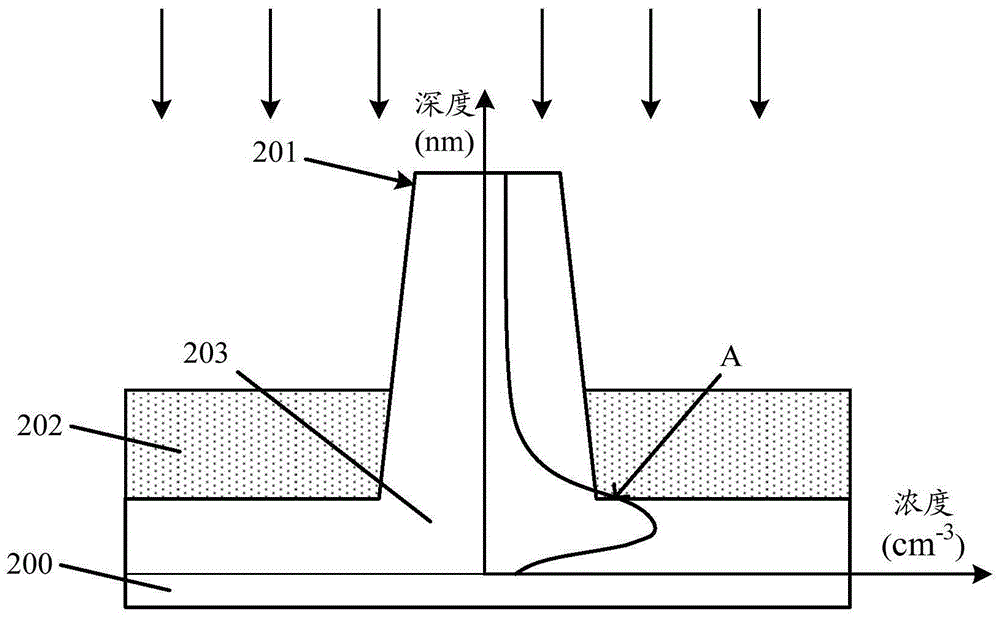

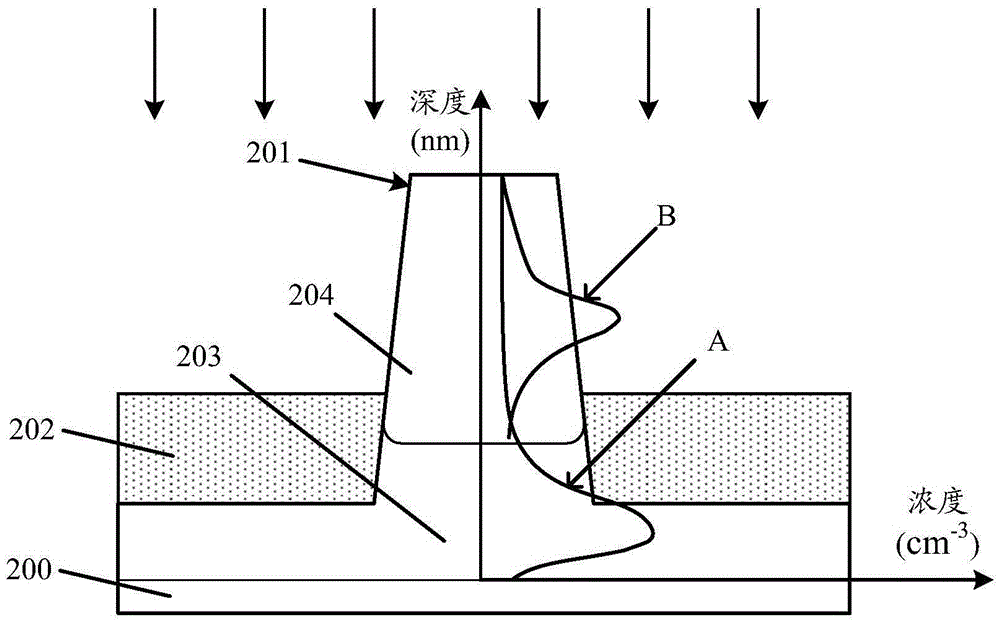

Semiconductor device and method for fabricating the same

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

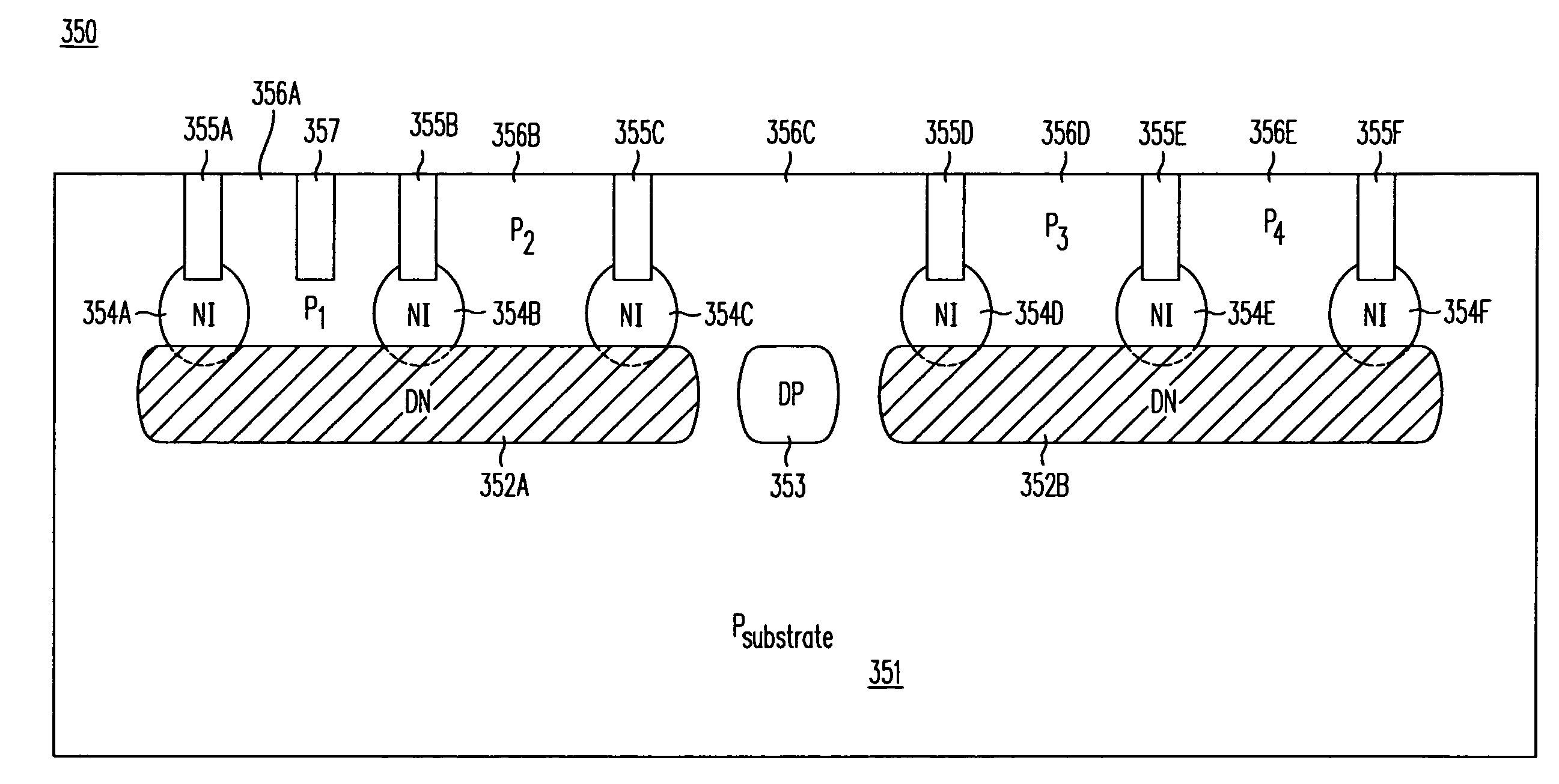

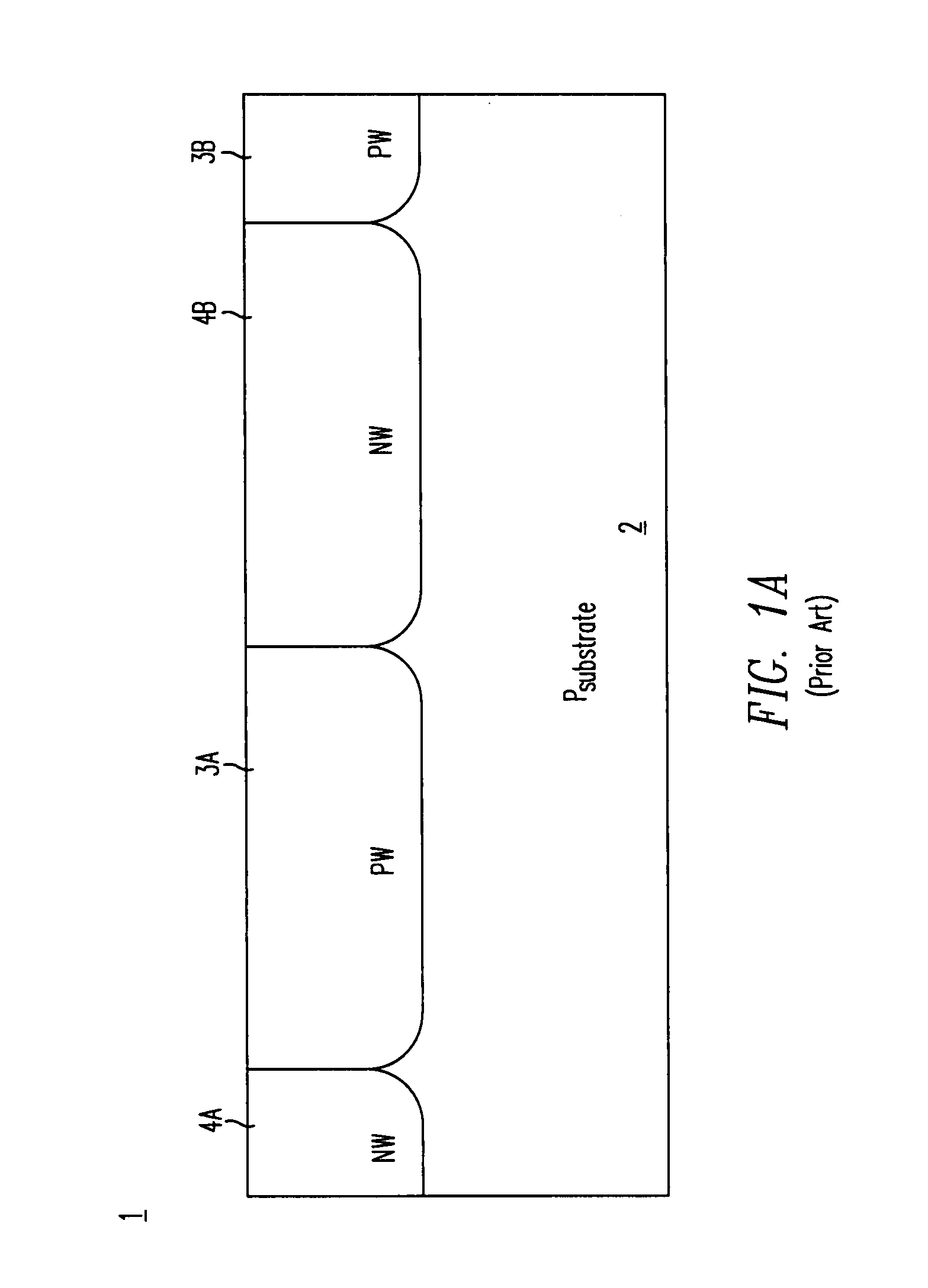

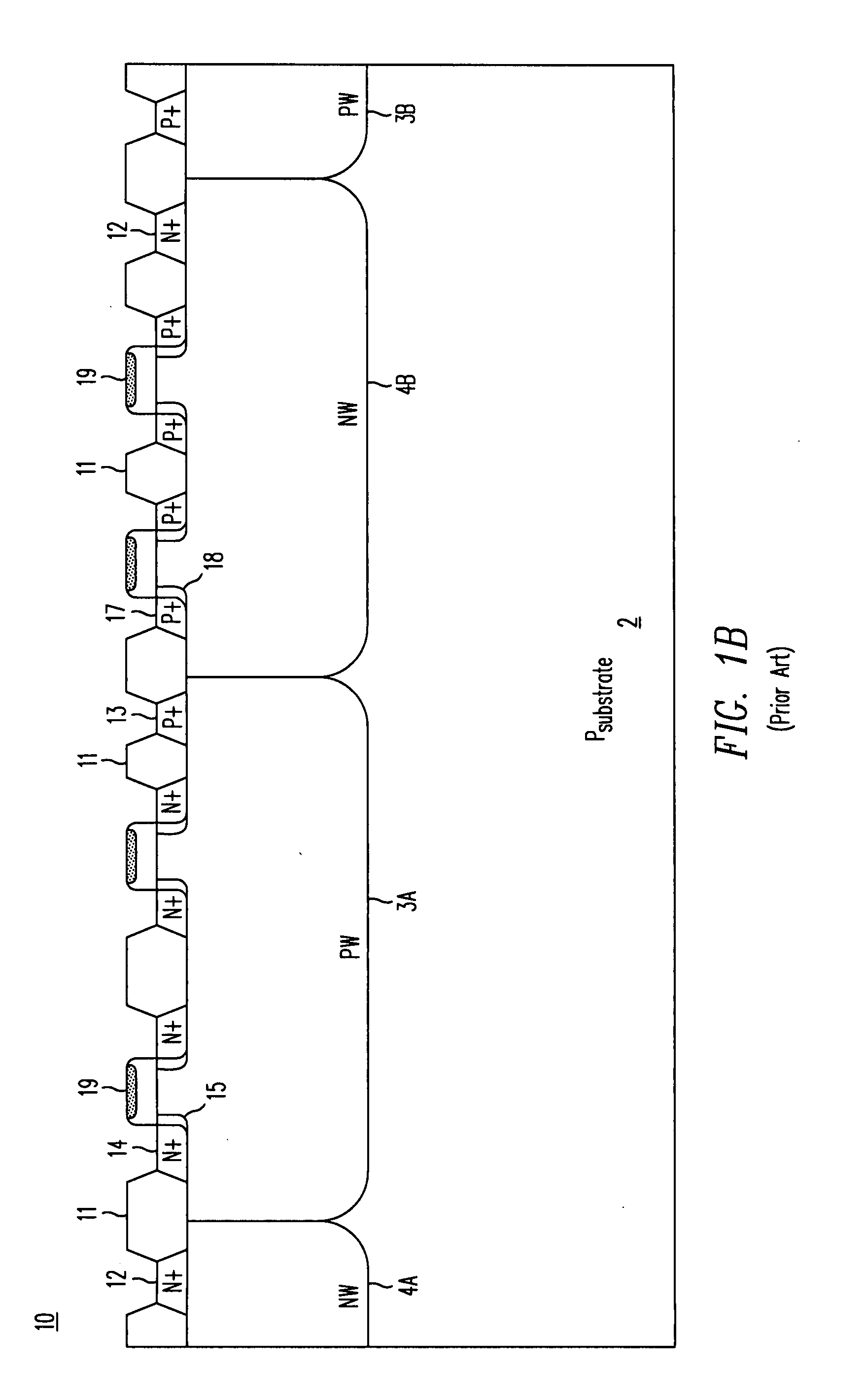

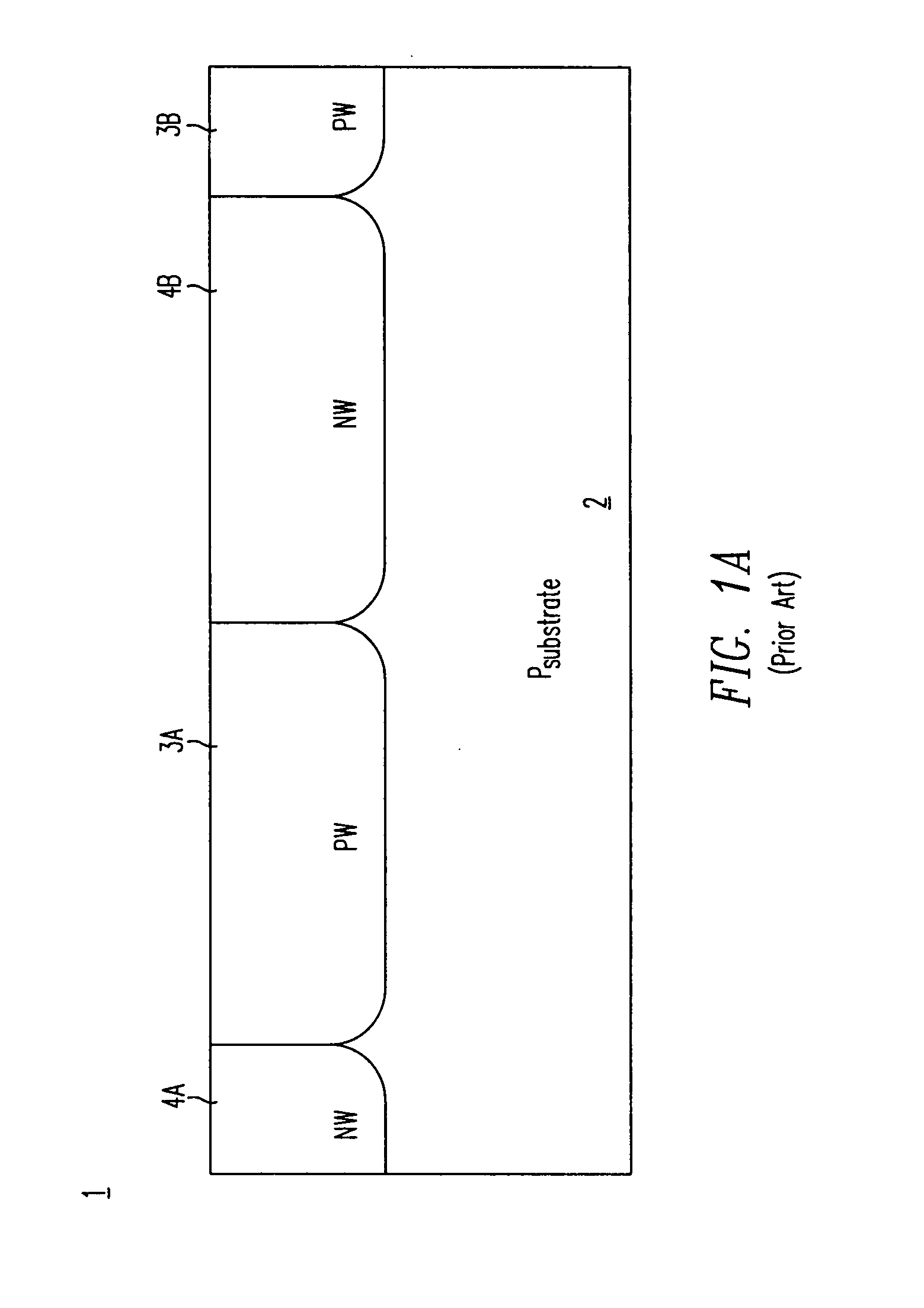

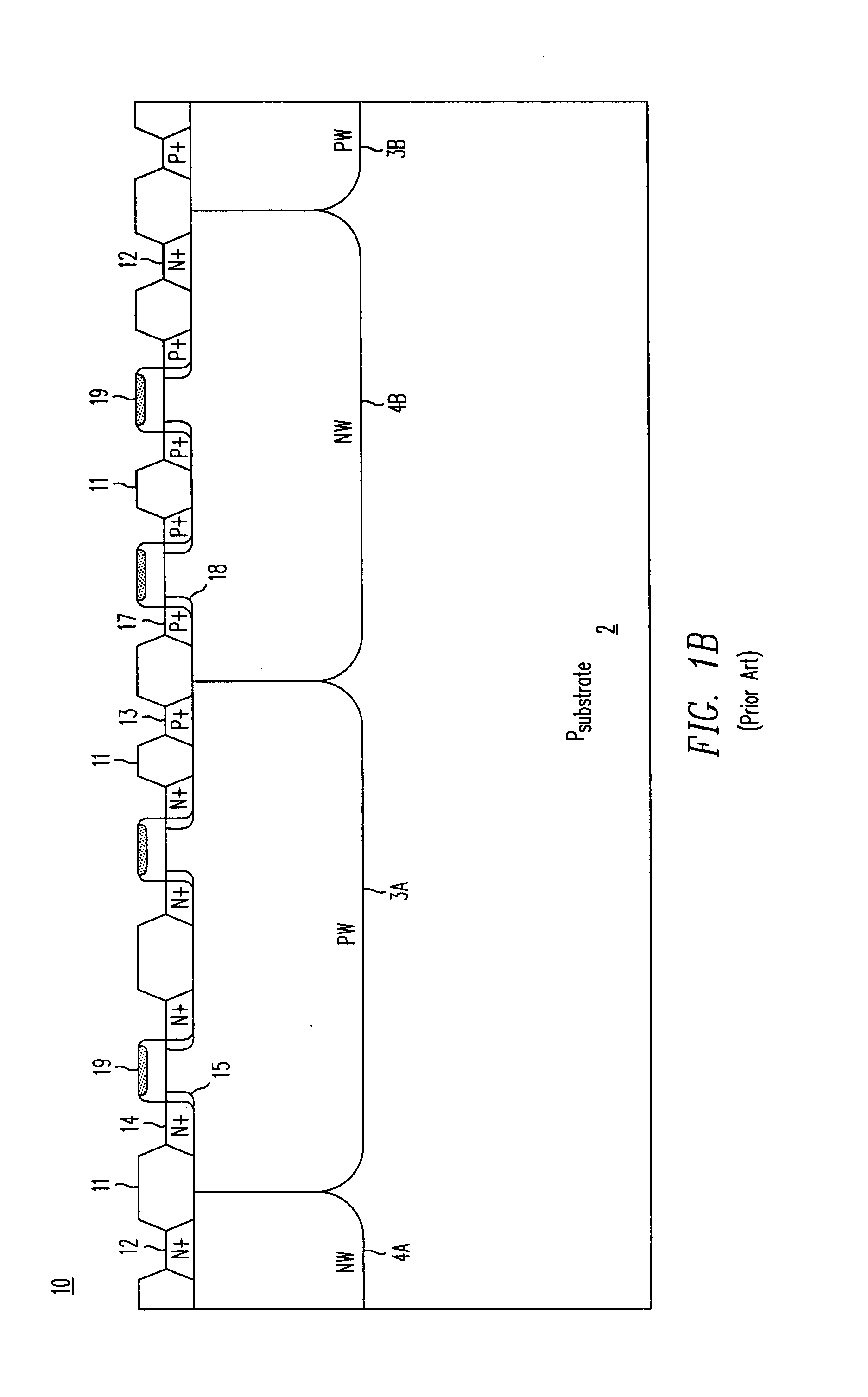

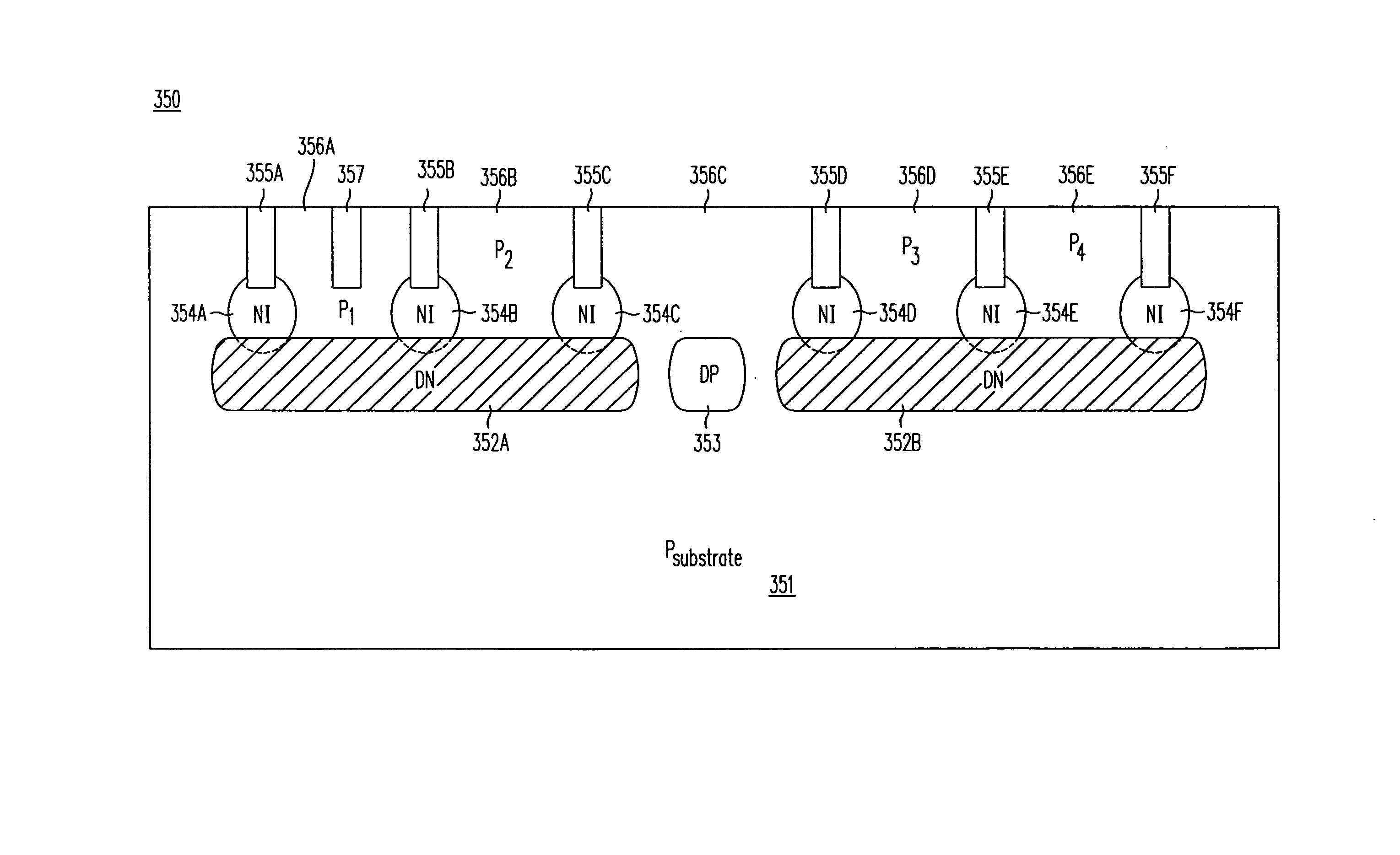

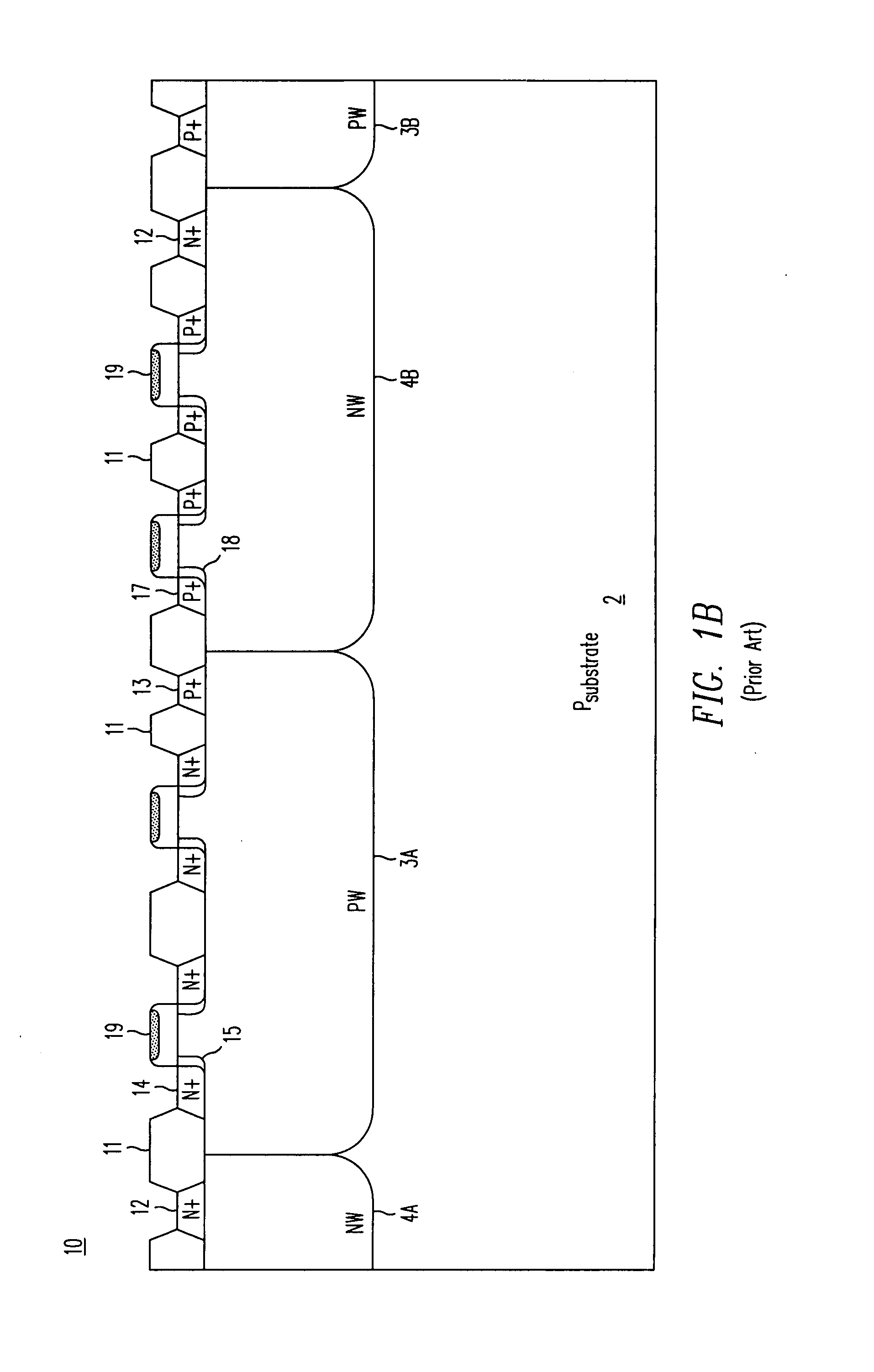

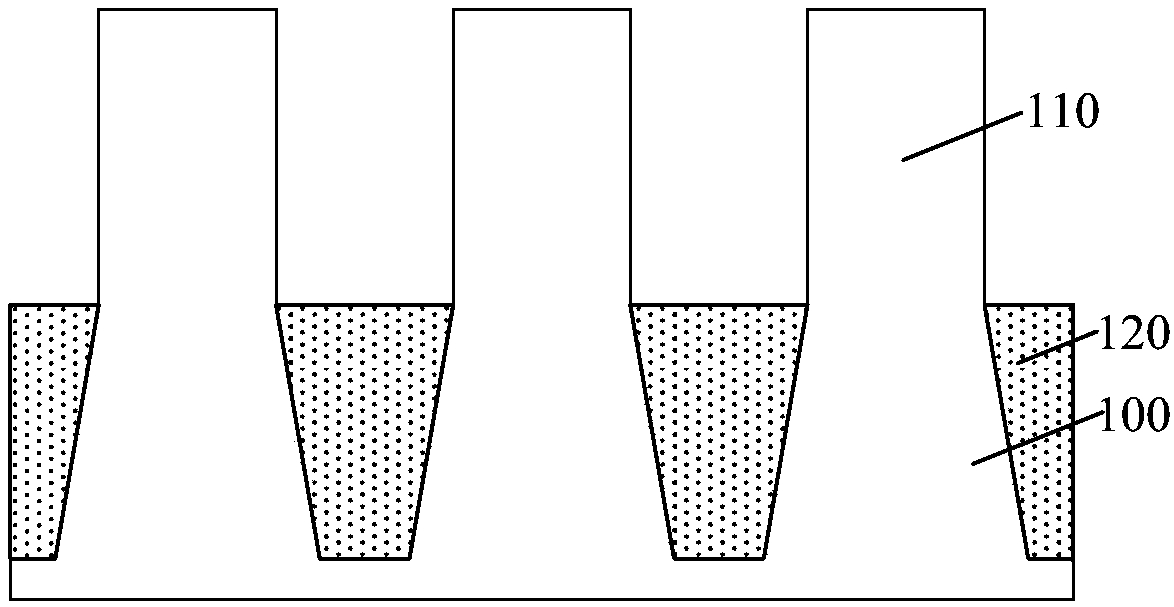

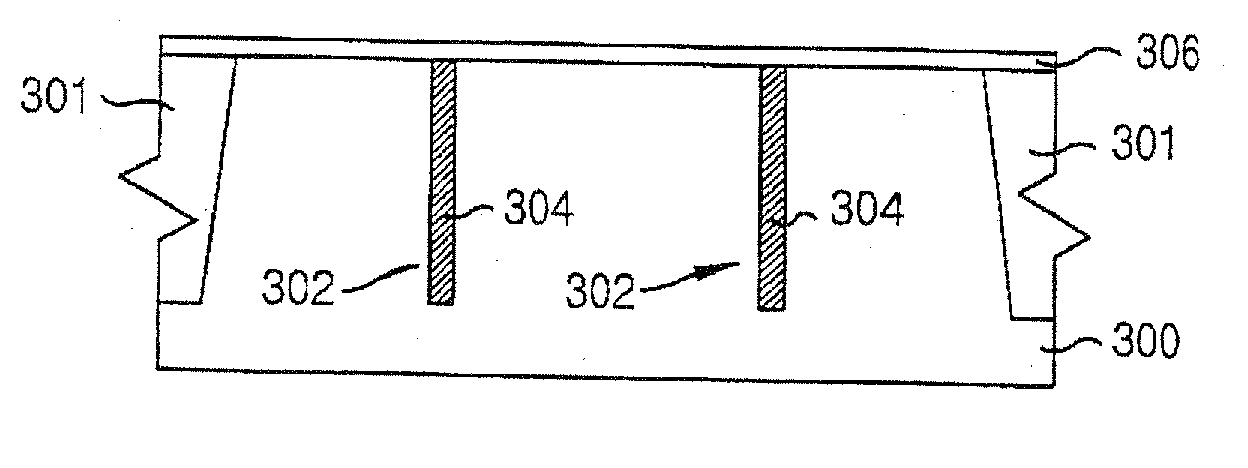

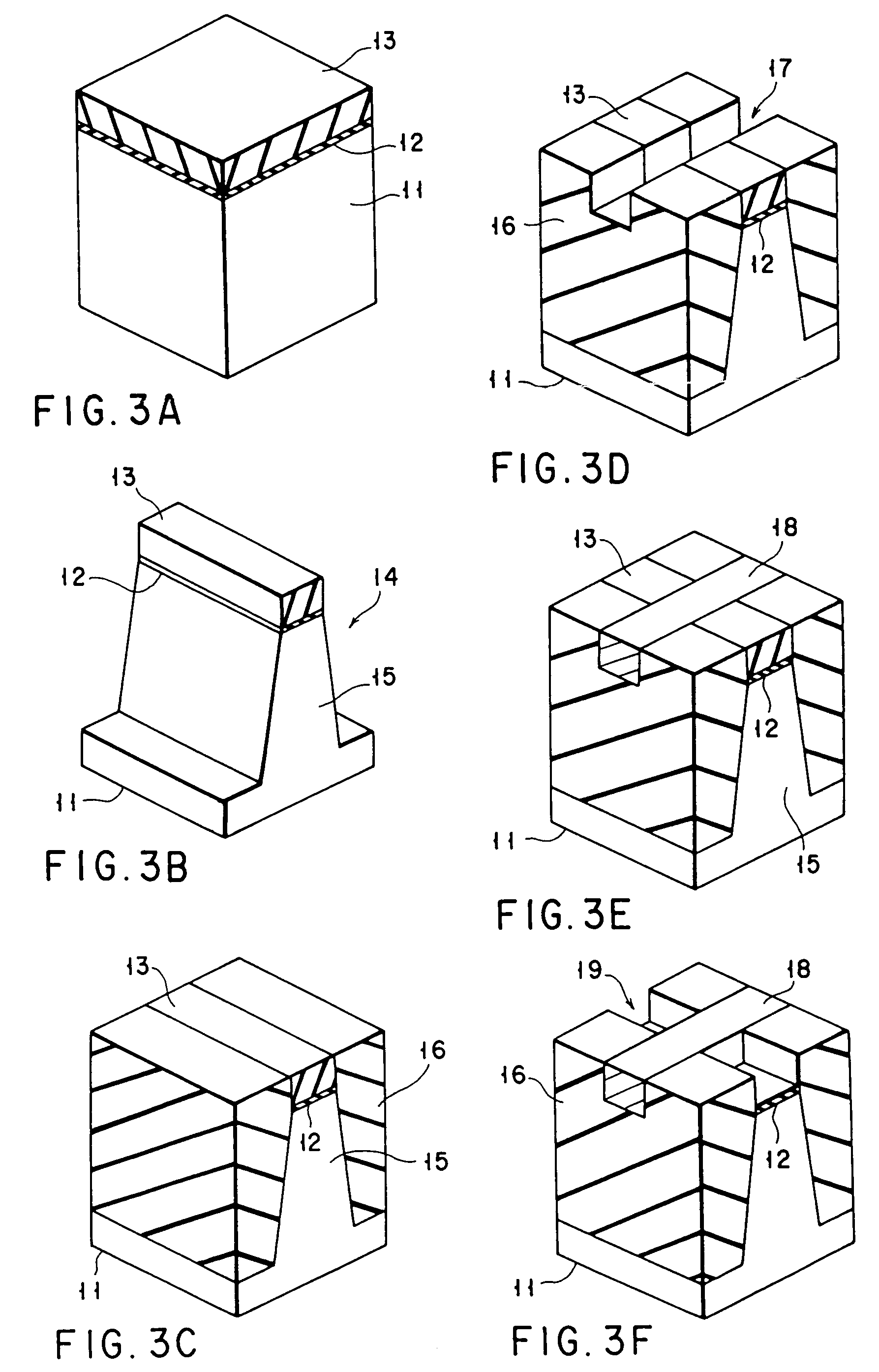

Isolation structures for integrated circuits and modular methods of forming the same

InactiveUS20070278612A1Prevent punch-throughHigh bulk densitySolid-state devicesSemiconductor/solid-state device manufacturingDopantCombined use

A variety of isolation structures for semiconductor substrates include a trench formed in the substrate that is filled with a dielectric material or filled with a conductive material and lined with a dielectric layer along the walls of the trench. The trench may be used in combination with doped sidewall isolation regions. Both the trench and the sidewall isolation regions may be annular and enclose an isolated pocket of the substrate. The isolation structures are formed by modular implant and etch processes that do not include significant thermal processing or diffusion of dopants so that the resulting structures are compact and may be tightly packed in the surface of the substrate.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

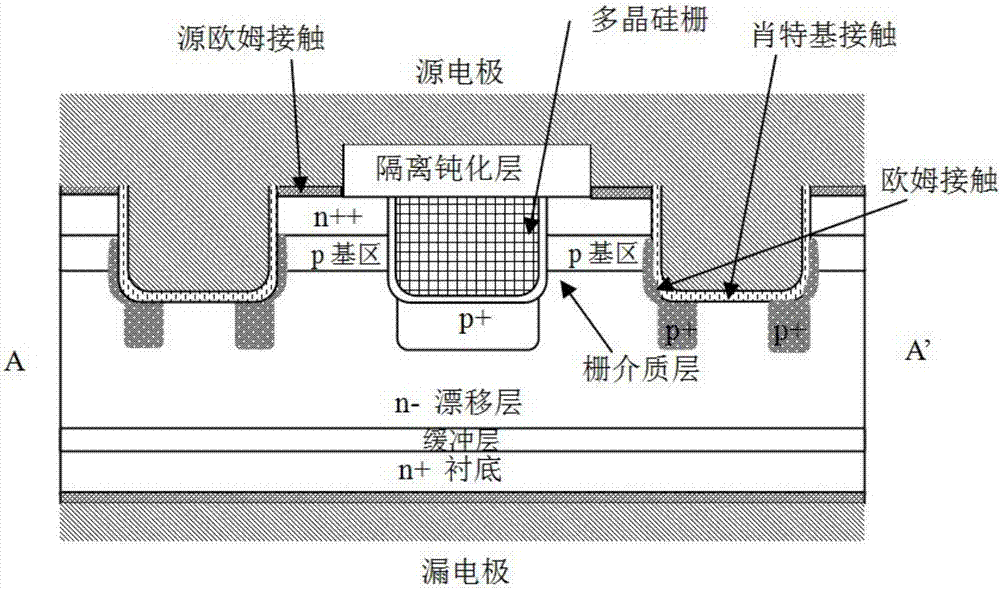

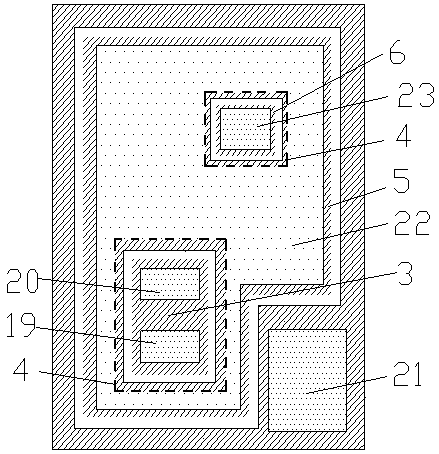

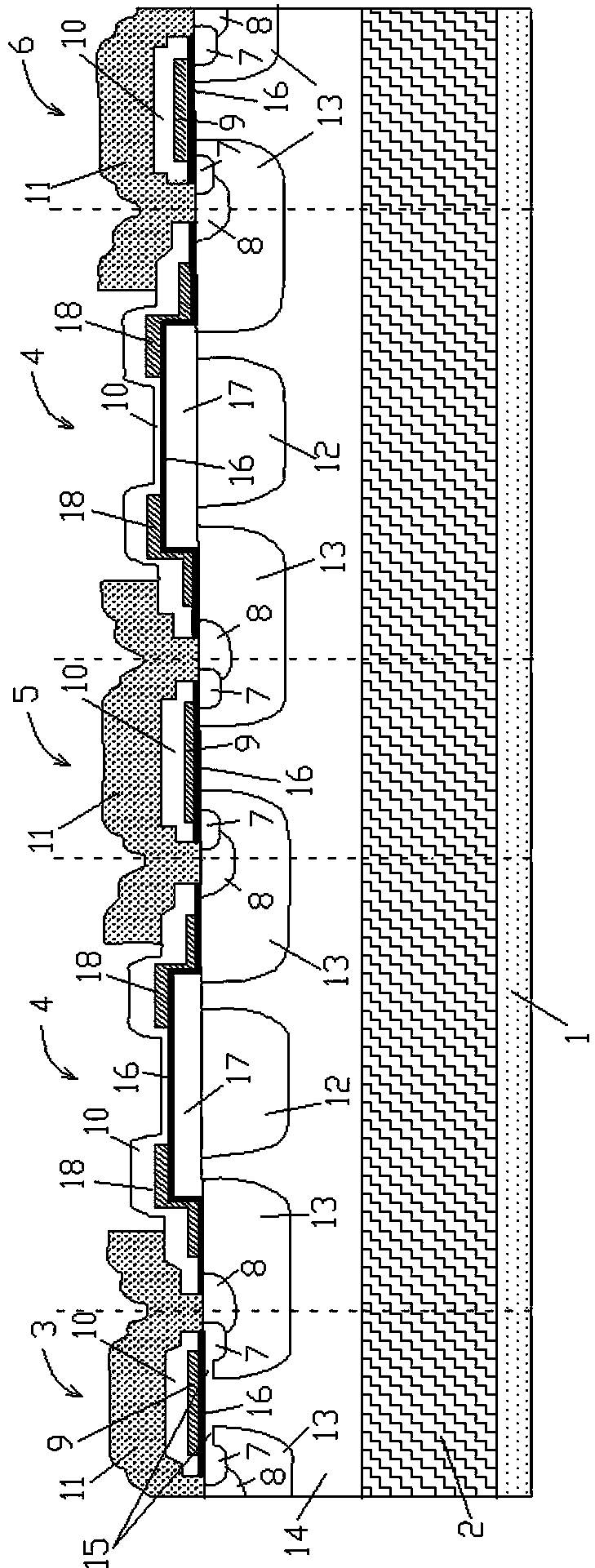

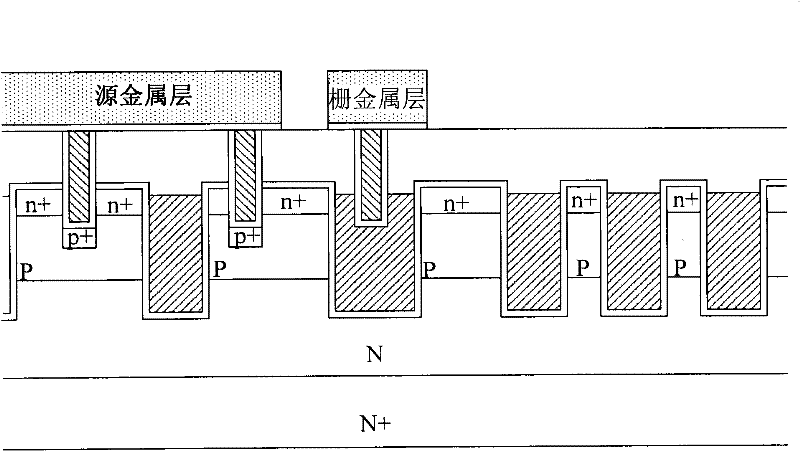

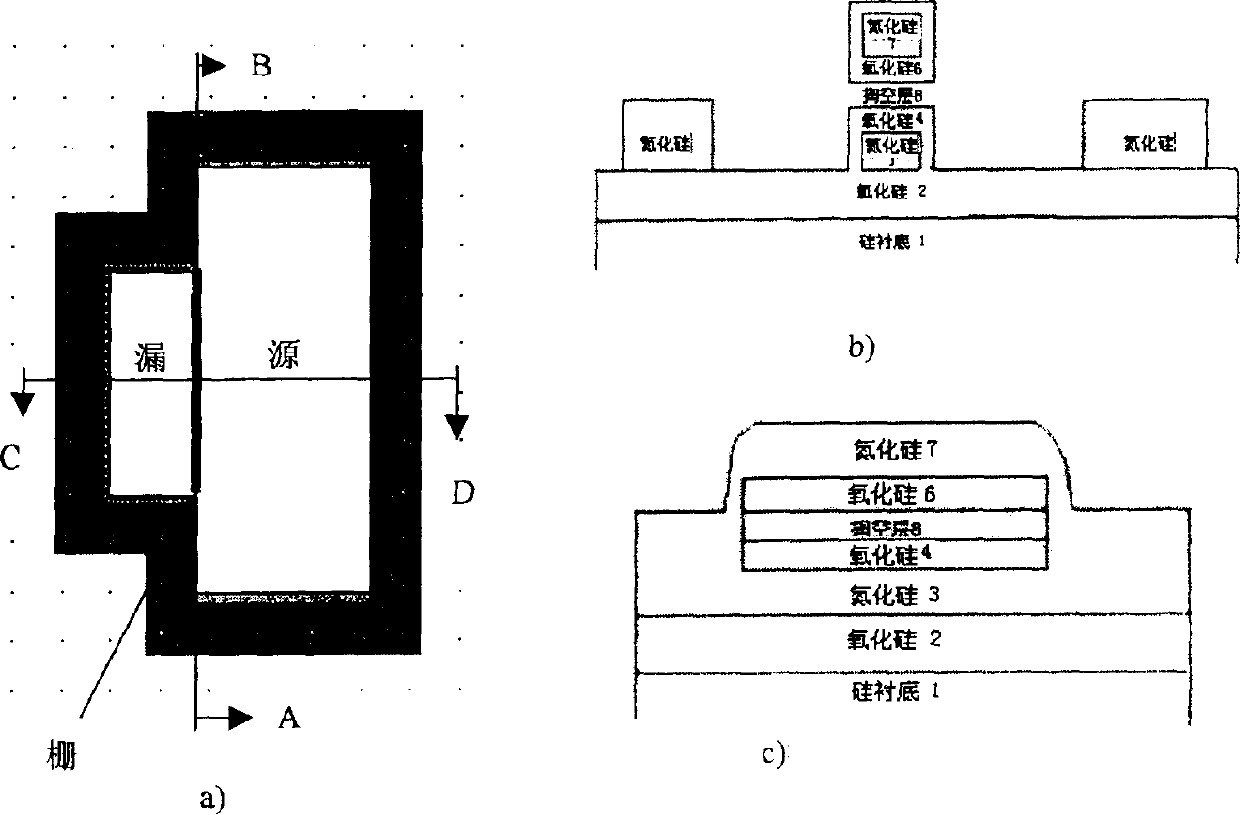

SiC dual-groove metal-oxide-semiconductor field-effect transistor (MOSFET) device integrated with Schottky diode and fabrication method of SiC dual-groove MOSFET device

ActiveCN106876485AImprove reliabilityAchieve shieldingSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETOhmic contact

The invention discloses a SiC dual-groove metal-oxide-semiconductor field-effect transistor (MOSFET) device integrated with a Schottky diode. Two grooves are formed in an original cell structure of an active region in the SiC dual-groove MOSFET device and are respectively a gate groove and a source groove, the gate groove is formed in the center of the original cell structure, the source groove is formed in the periphery of the gate groove, doping with a conductive type opposite to that of a drift region is performed in the peripheries of the bottoms of the gate groove and the source groove, Schottky contact is arranged at a central region of the bottom of the source groove, and the Schottky diode electrically communicating with a source is formed, ohmic contact is formed between the periphery of the bottom of the source groove and a doping region with the conductive type opposite to that of the drift region, and the depths of the two grooves are larger than that of a p base region. With the adoption of a source and gate dual-groove structure, the doping with the conductive type opposite to that of the drift region is performed on the peripheries of the bottoms of the gate groove and the bottom of the source groove, thus, the shielding of an MOS gate is achieved, and the gate reliability is improved; and meanwhile, an electric field of the base region can be shielded, and the base region is prevented from being penetrated; and moreover, an MPS Schottky diode having high surge capability is integrated.

Owner:BEIJING CENTURY GOLDRAY SEMICON CO LTD

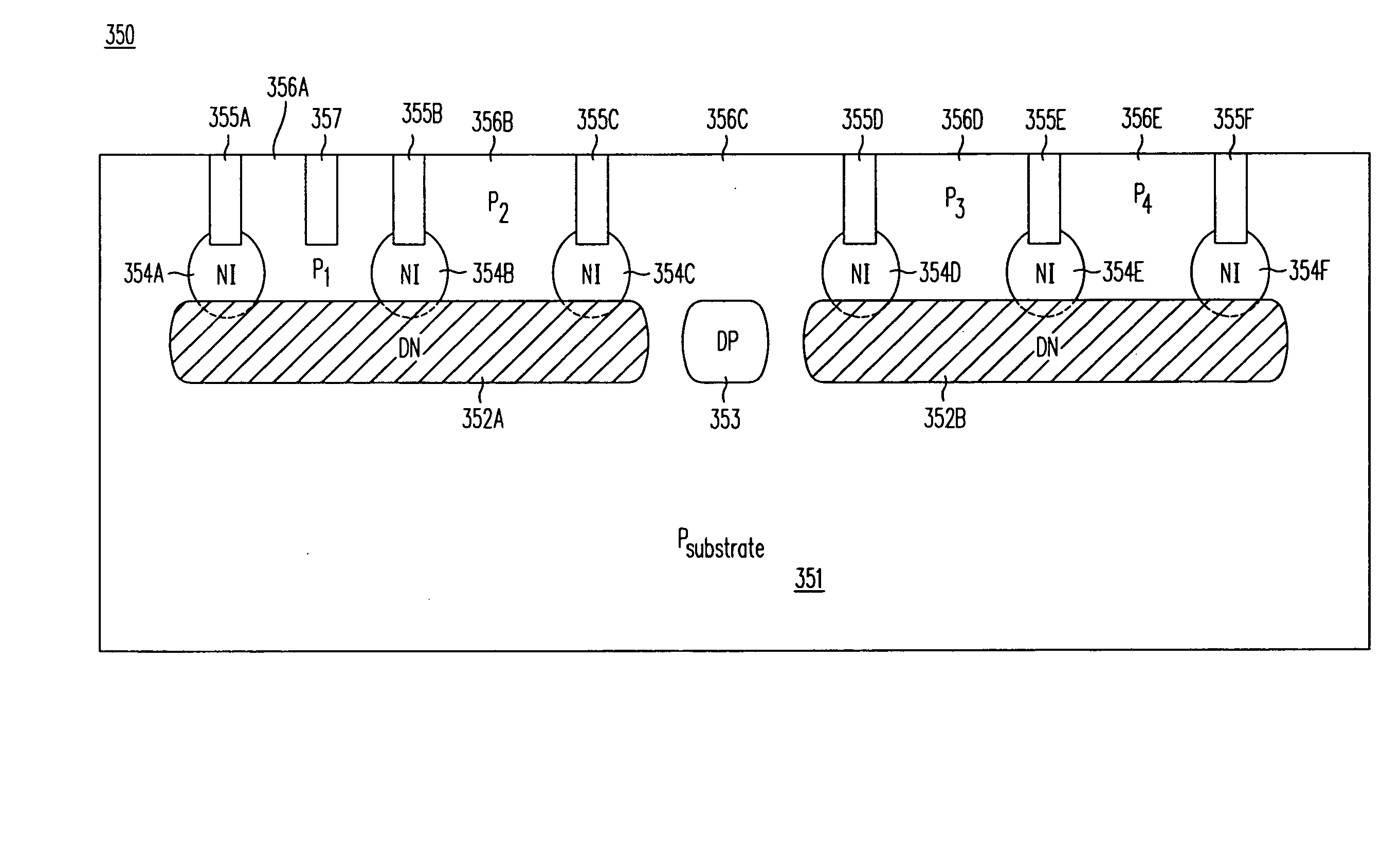

Isolation structures for integrated circuits and modular methods of forming the same

InactiveUS20080042232A1Prevent punch-throughHigh bulk densitySolid-state devicesSemiconductor/solid-state device manufacturingDopantCombined use

A variety of isolation structures for semiconductor substrates include a trench formed in the substrate that is filled with a dielectric material or filled with a conductive material and lined with a dielectric layer along the walls of the trench. The trench may be used in combination with doped sidewall isolation regions. Both the trench and the sidewall isolation regions may be annular and enclose an isolated pocket of the substrate. The isolation structures are formed by modular implant and etch processes that do not include significant thermal processing or diffusion of dopants so that the resulting structures are compact and may be tightly packed in the surface of the substrate.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

Isolation structures for integrated circuits and modular methods of forming the same

InactiveUS20080044978A1Prevent punch-throughHigh bulk densitySolid-state devicesSemiconductor/solid-state device manufacturingDopantEngineering

A variety of isolation structures for semiconductor substrates include a trench formed in the substrate that is filled with a dielectric material or filled with a conductive material and lined with a dielectric layer along the walls of the trench. The trench may be used in combination with doped sidewall isolation regions. Both the trench and the sidewall isolation regions may be annular and enclose an isolated pocket of the substrate. The isolation structures are formed by modular implant and etch processes that do not include significant thermal processing or diffusion of dopants so that the resulting structures are compact and may be tightly packed in the surface of the substrate.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED +1

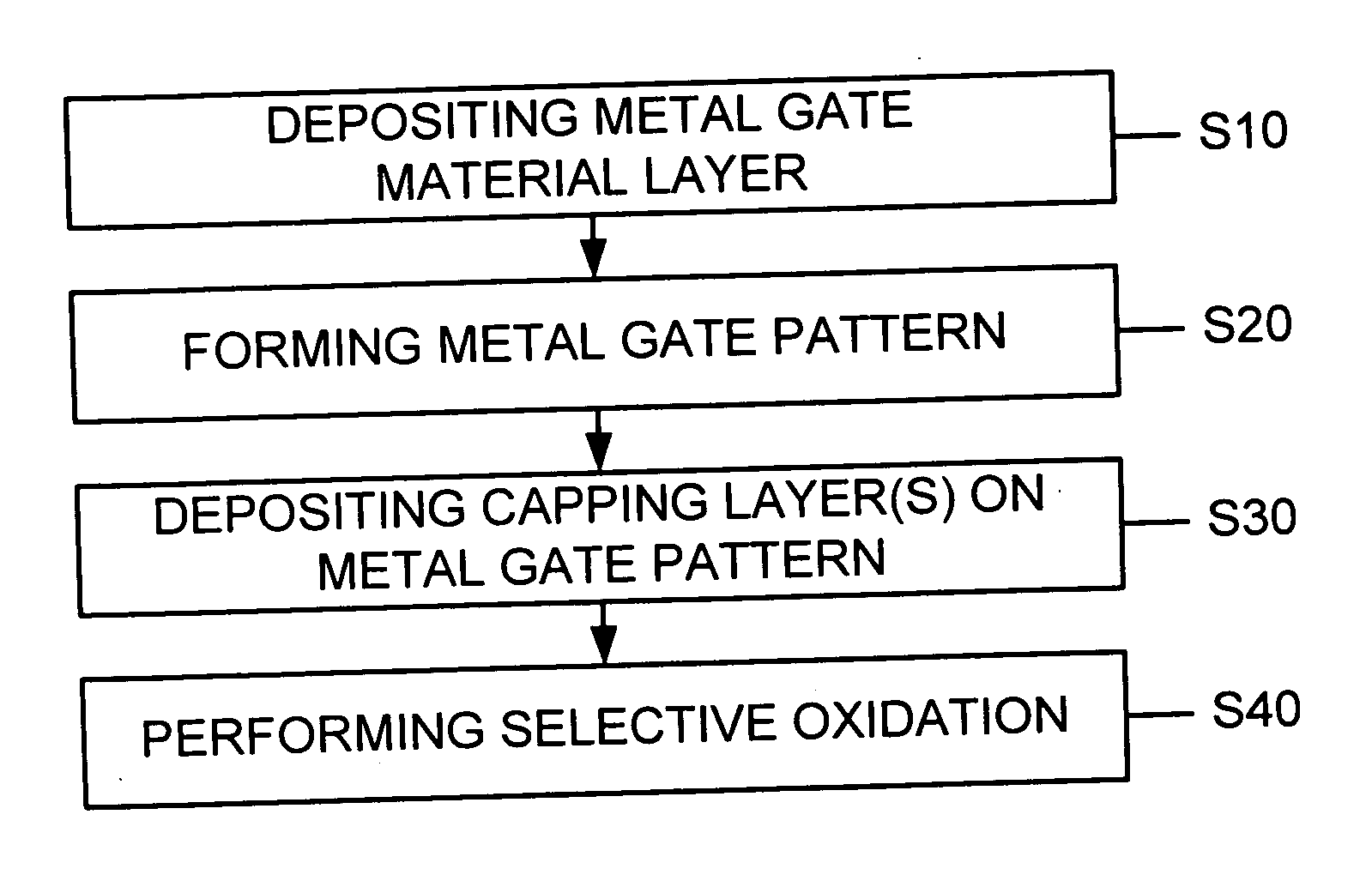

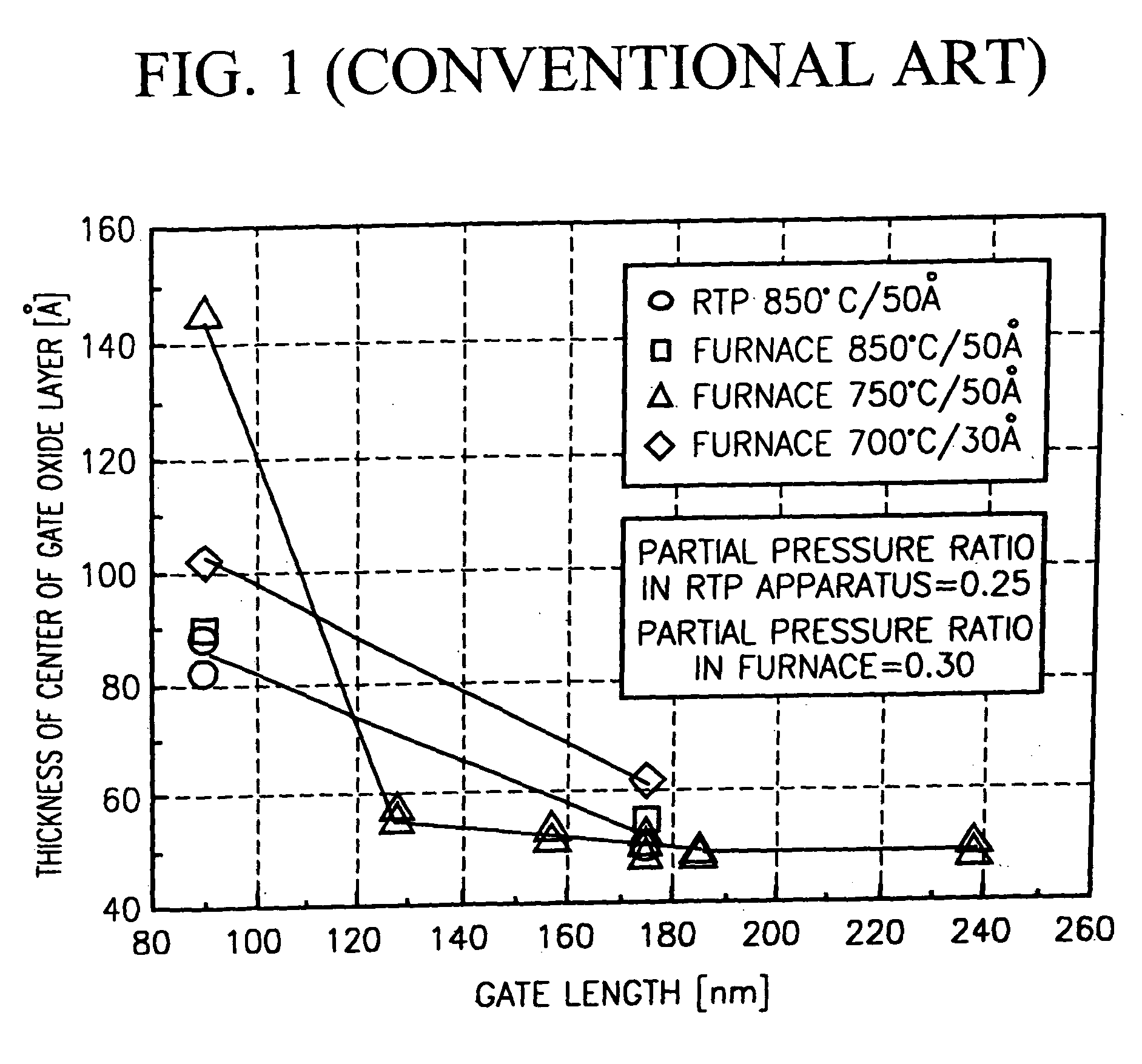

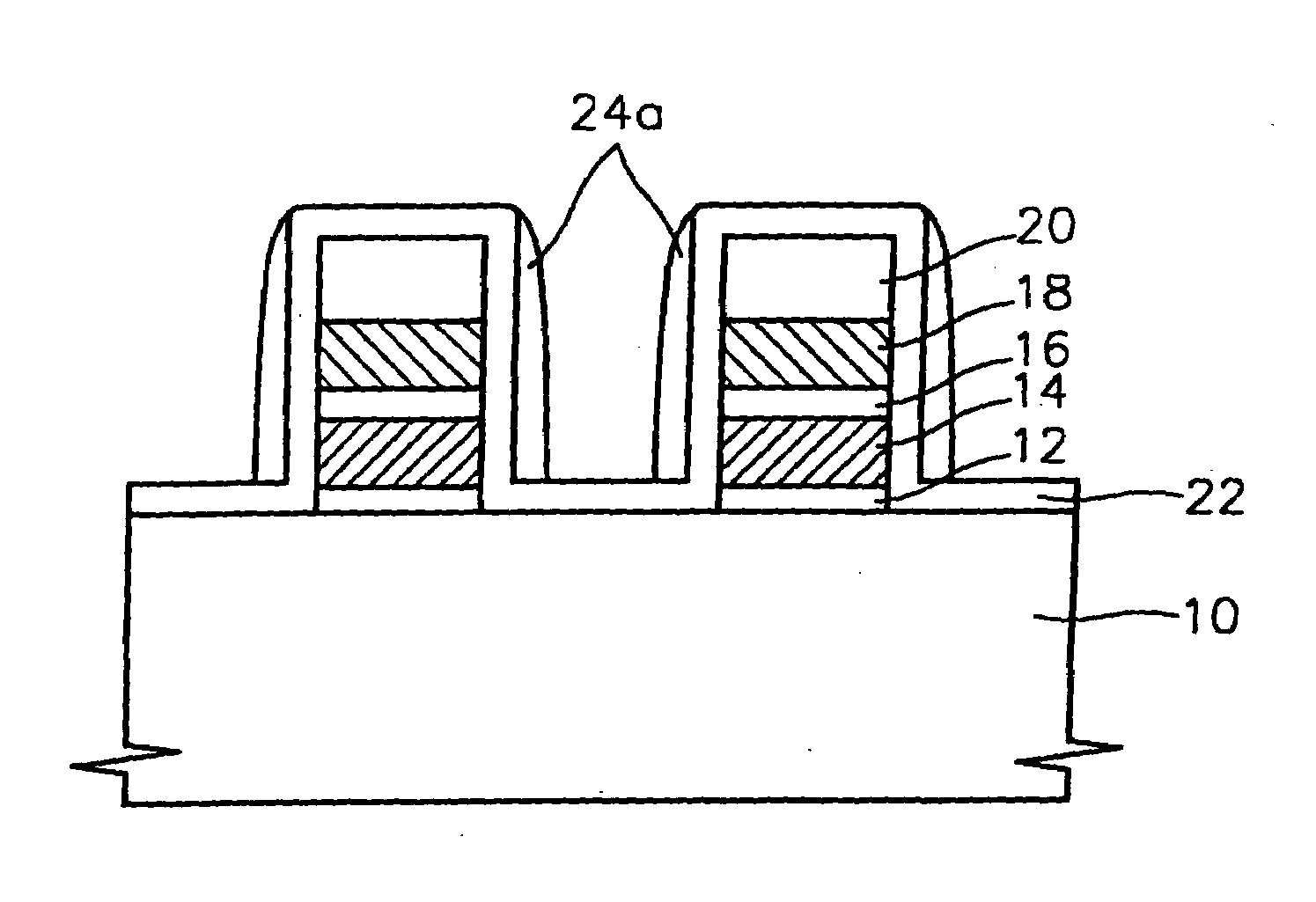

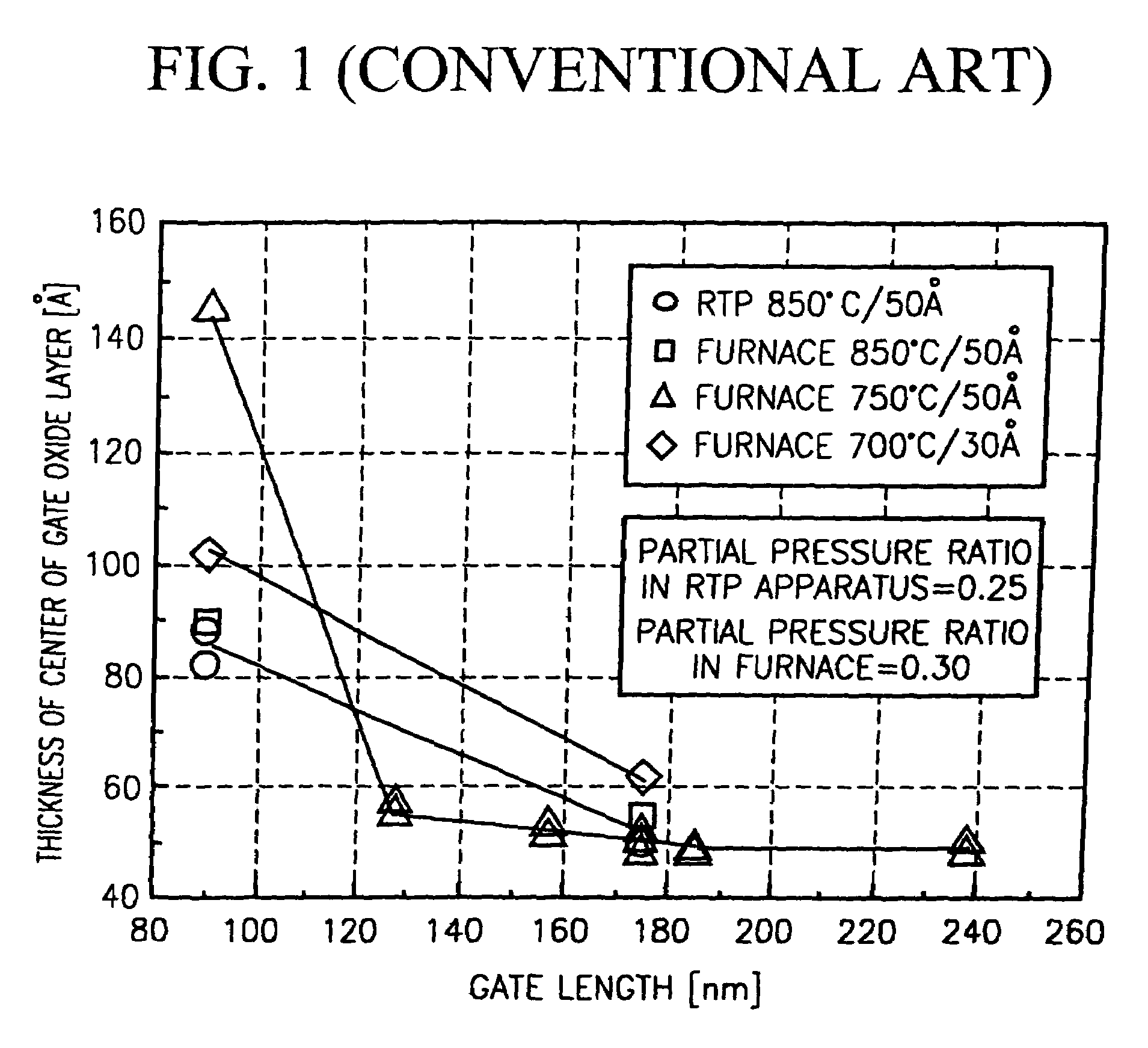

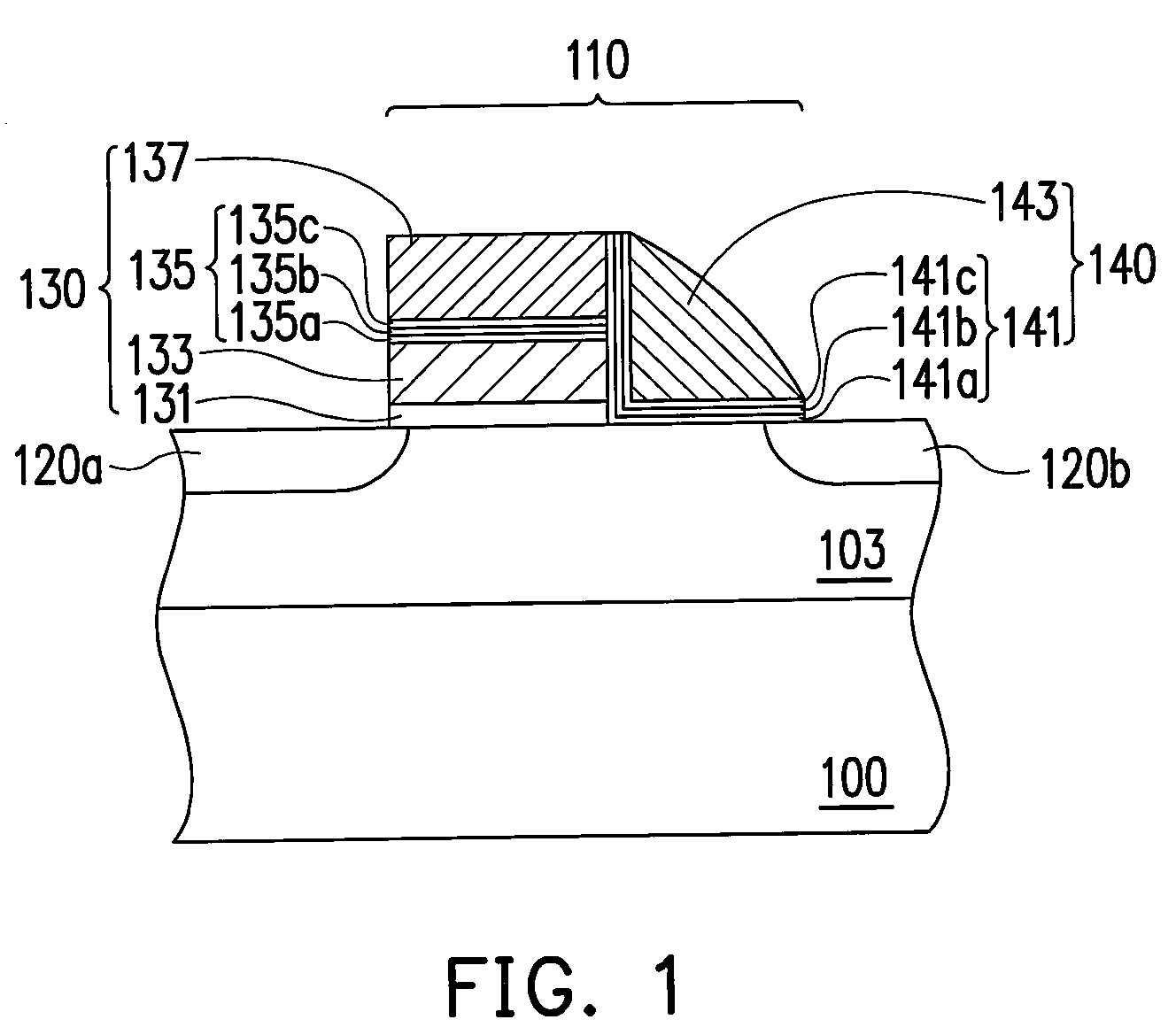

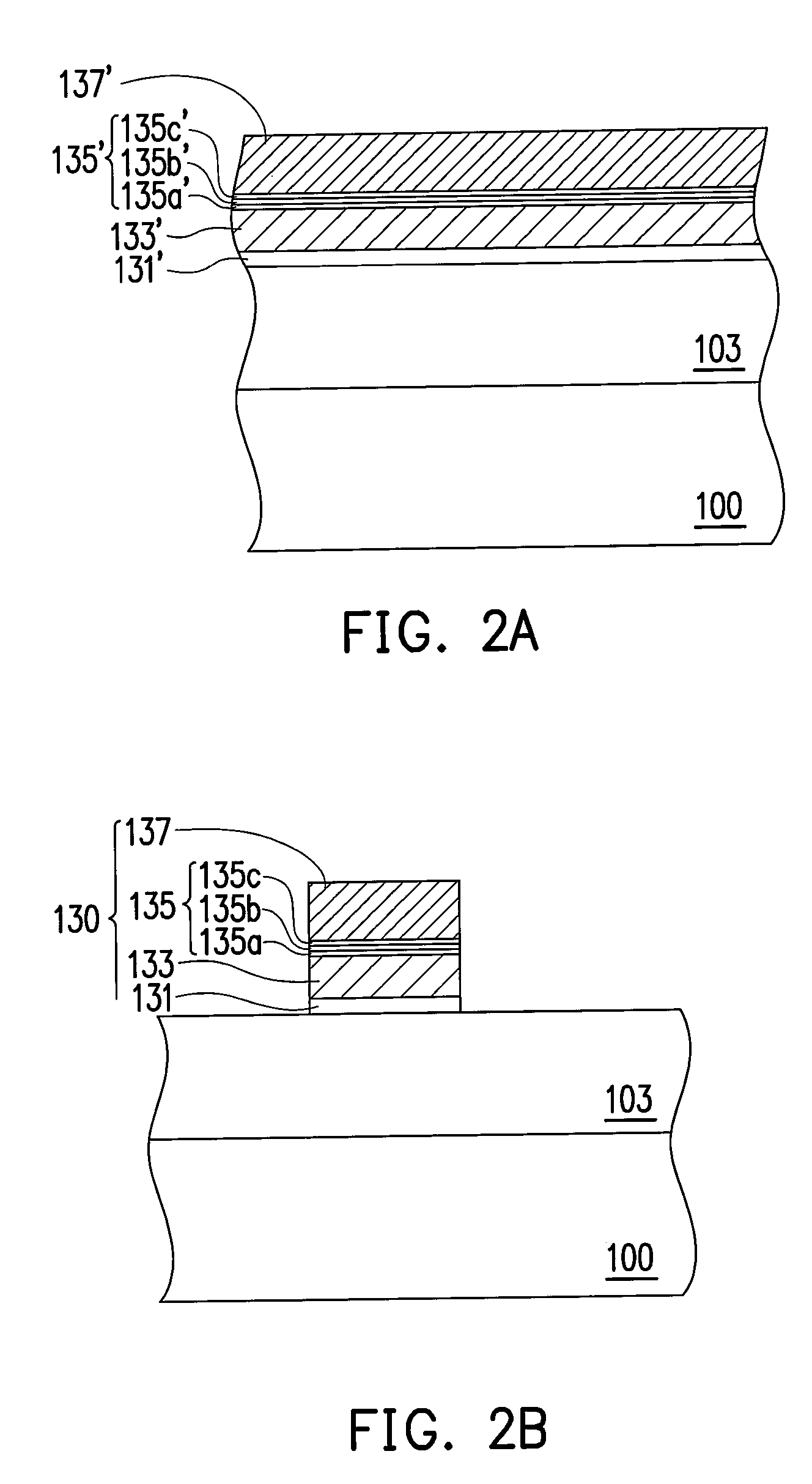

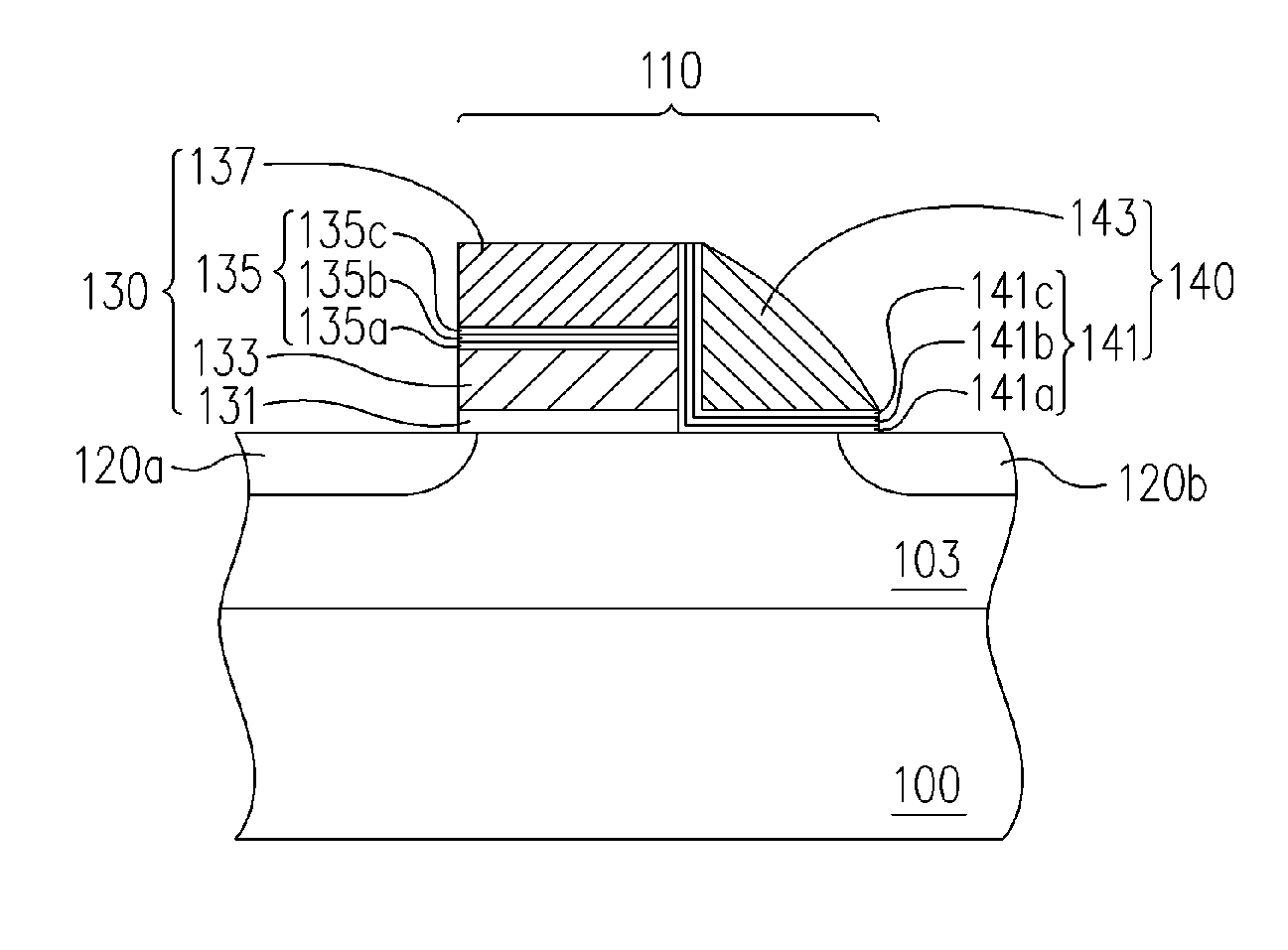

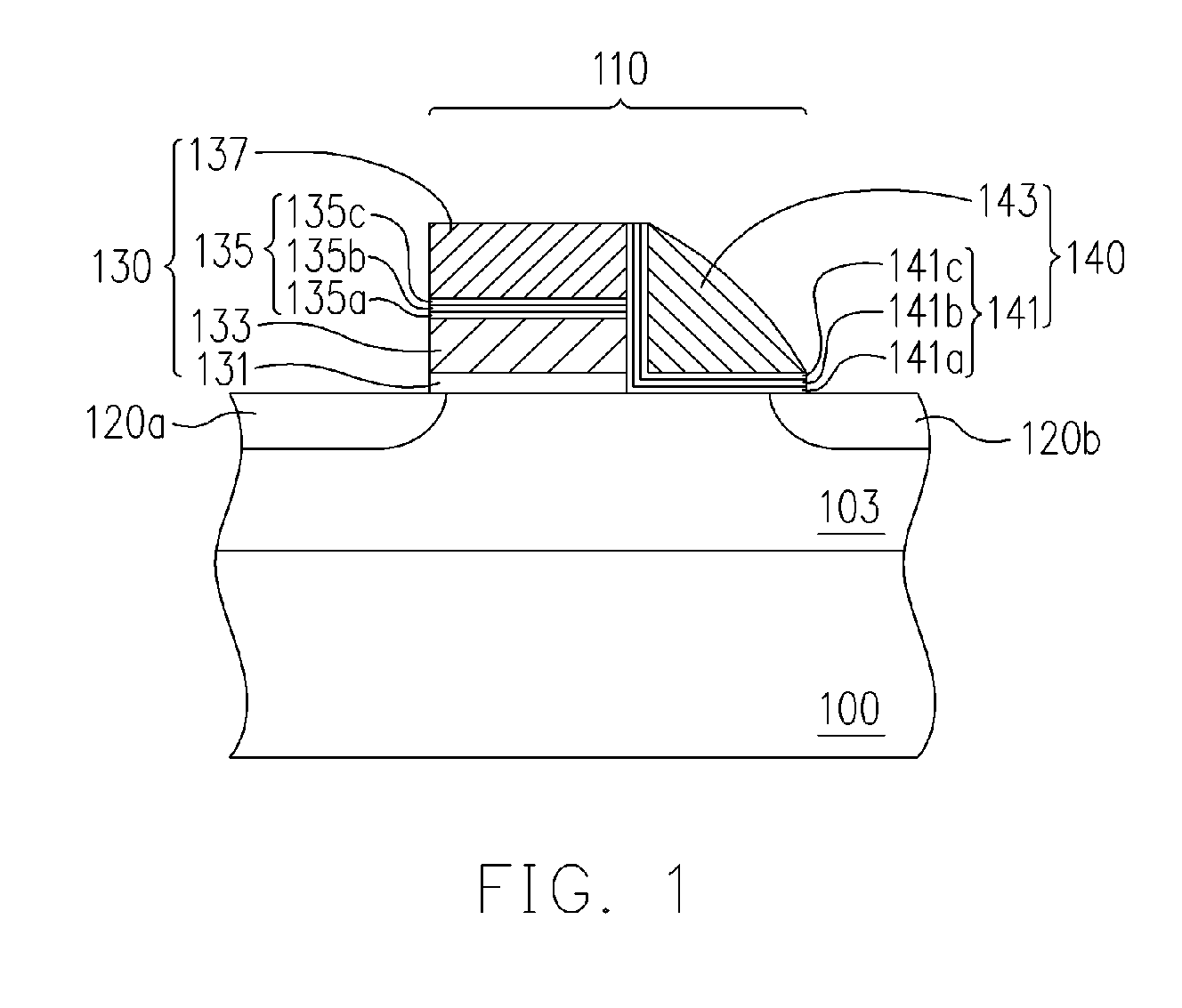

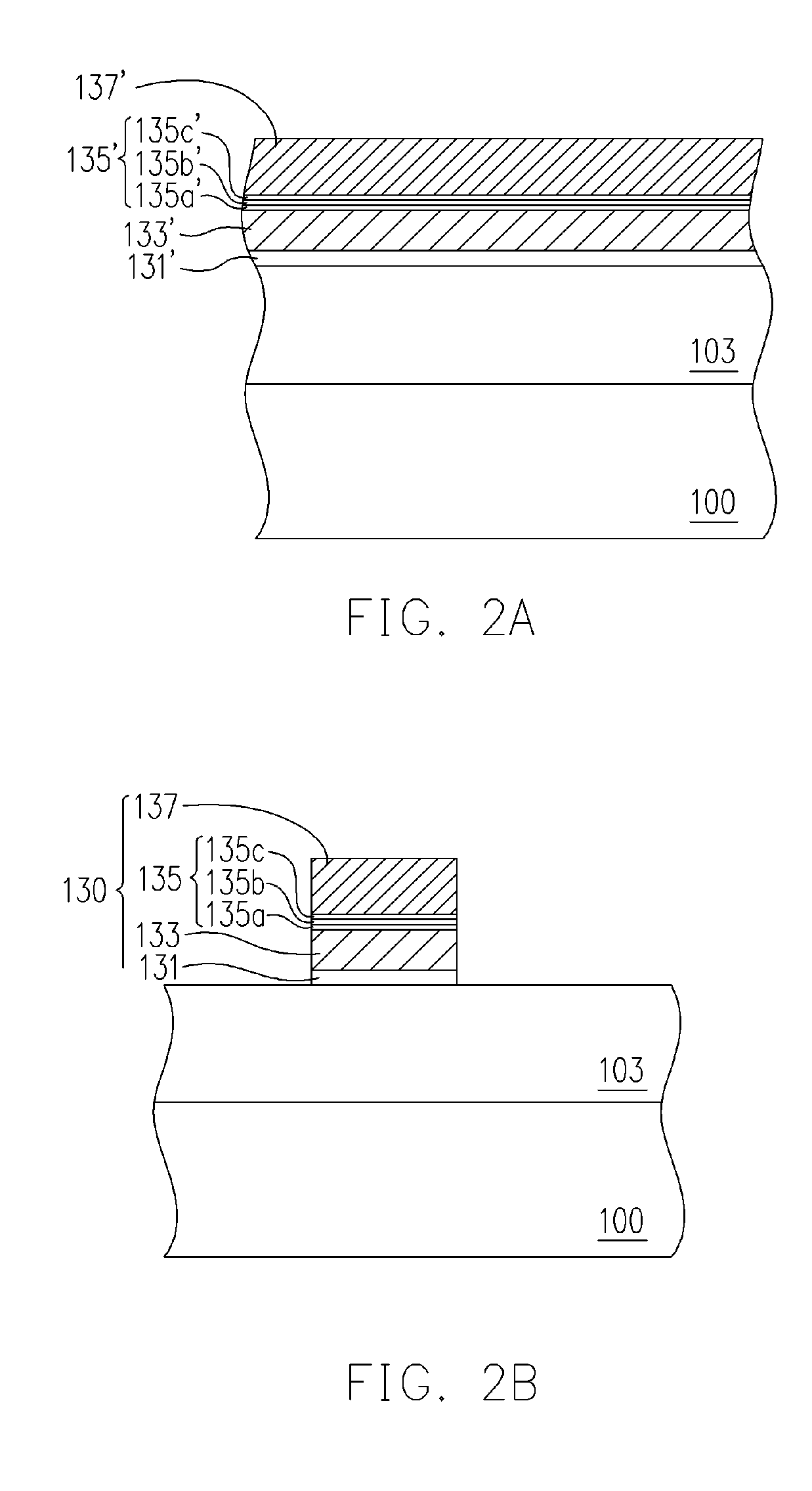

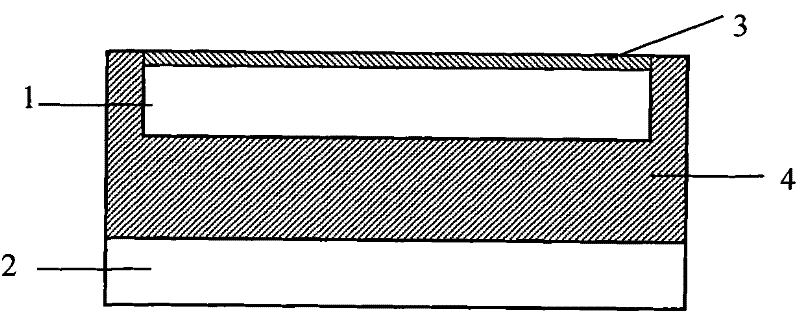

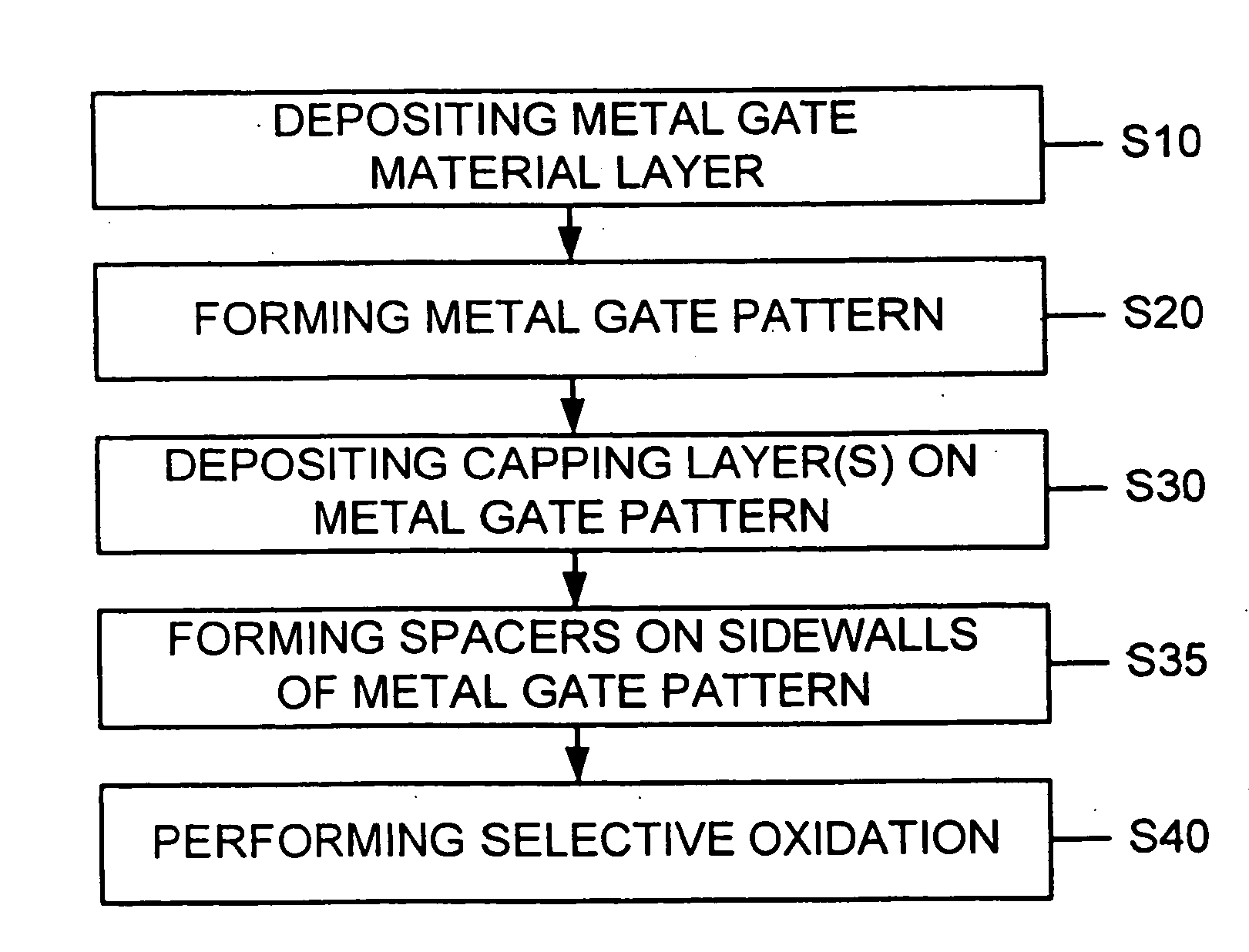

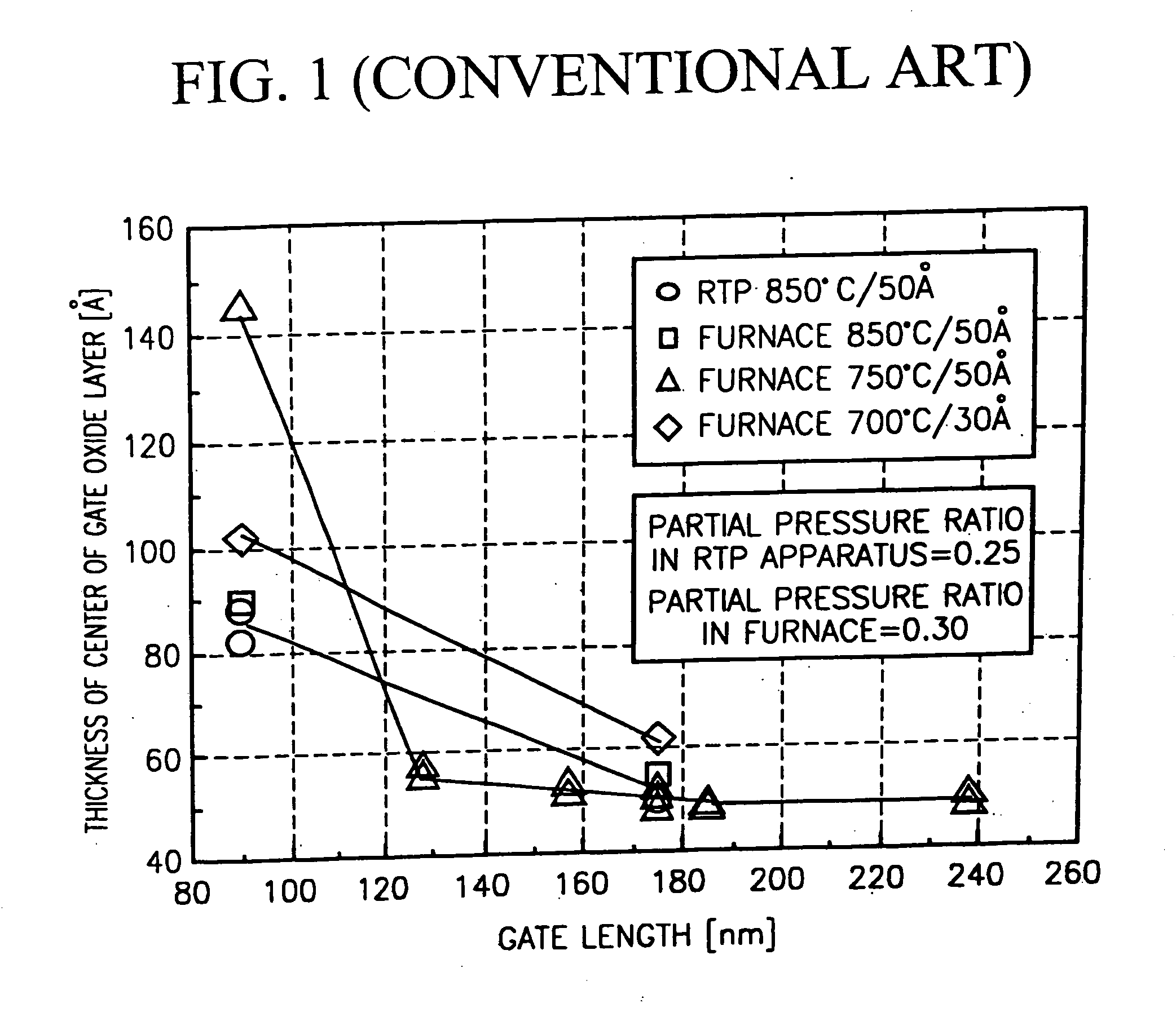

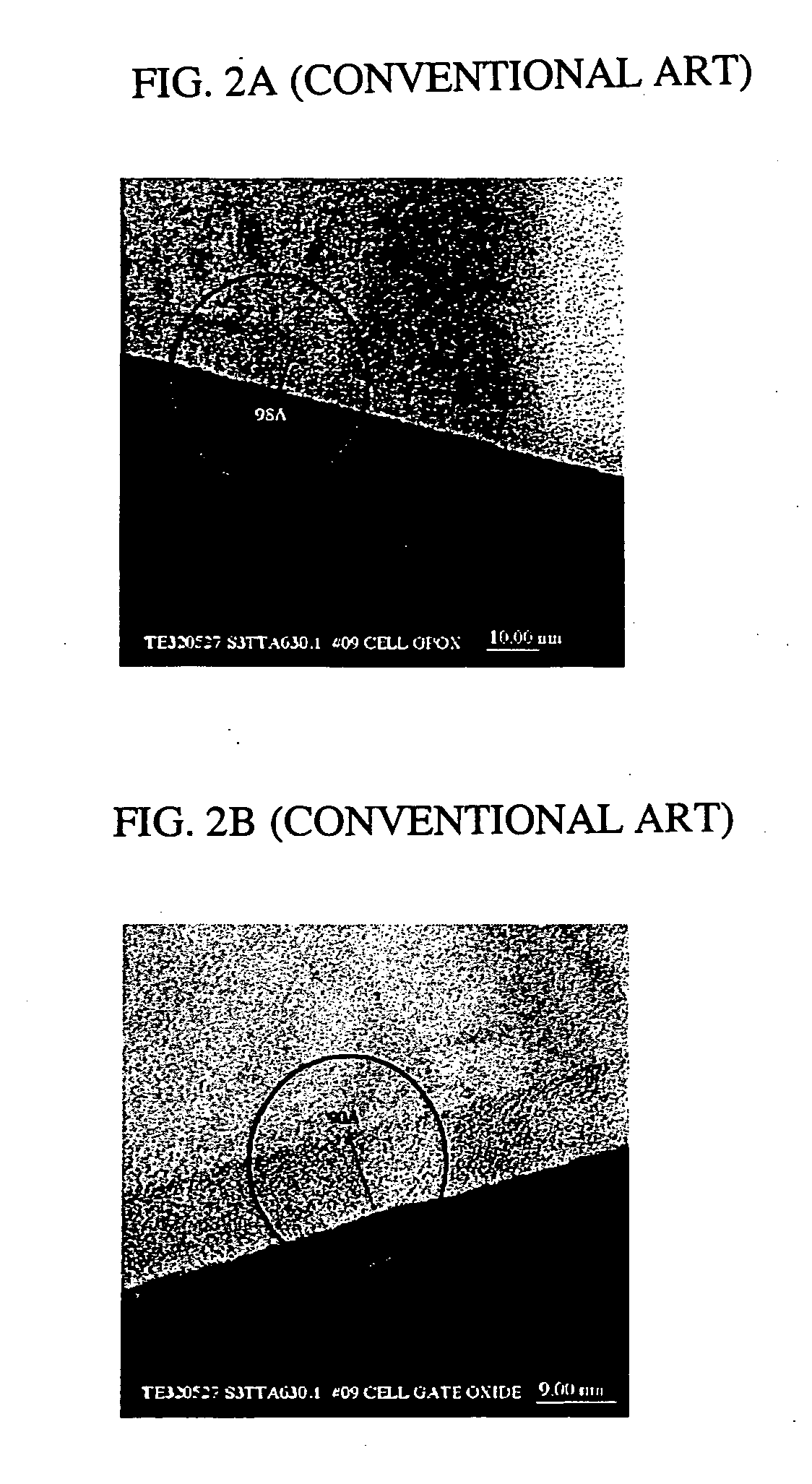

Methods of fabricating a semiconductor device having a metal gate pattern

InactiveUS20040132272A1Suppress DiffusePrevent punch-throughSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSilicon

A method of fabricating a semiconductor device having a metal gate pattern is provided in which capping layers are used to control the relative oxidation rates of portions of the metal gate pattern during a oxidation process. The capping layer may be a multilayer structure and may be etched to form insulating spacers on the sidewalls of the metal gate pattern. The capping layer(s) allow the use of a selective oxidation process, which may be a wet oxidation process utilizing partial pressures of both H2O and H2 in an H2-rich atmosphere, to oxidize portions of the substrate and metal gate pattern while suppressing the oxidation of metal layers that may be included in the metal gate pattern. This allows etch damage to the silicon substrate and edges of the metal gate pattern to be reduced while substantially maintaining the original thickness of the gate insulating layer and the conductivity of the metal layer(s).

Owner:SAMSUNG ELECTRONICS CO LTD

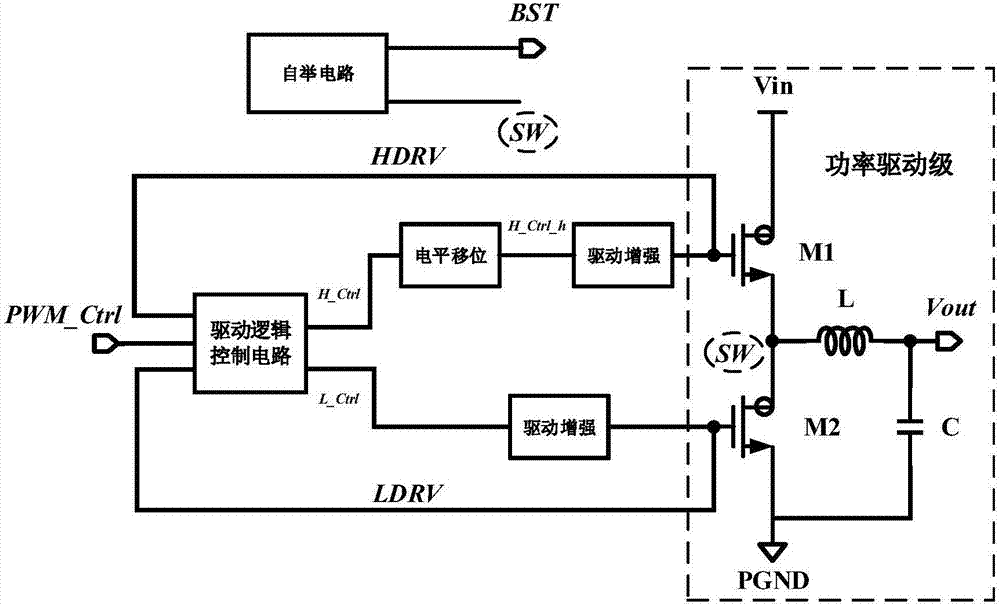

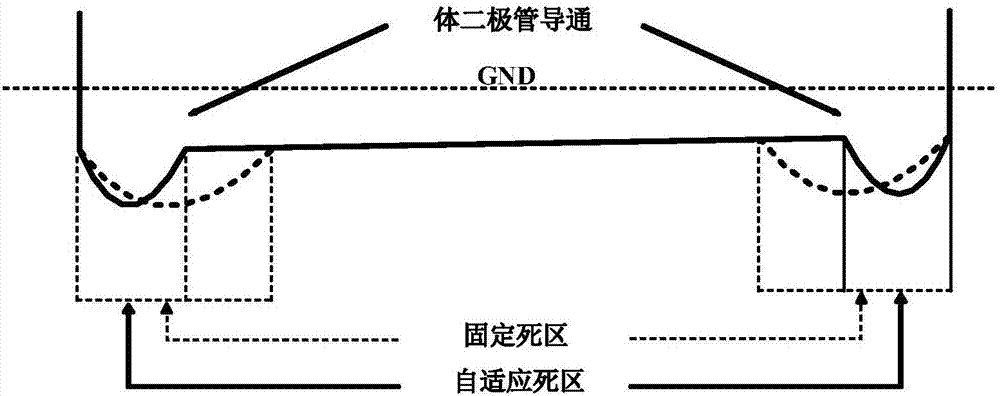

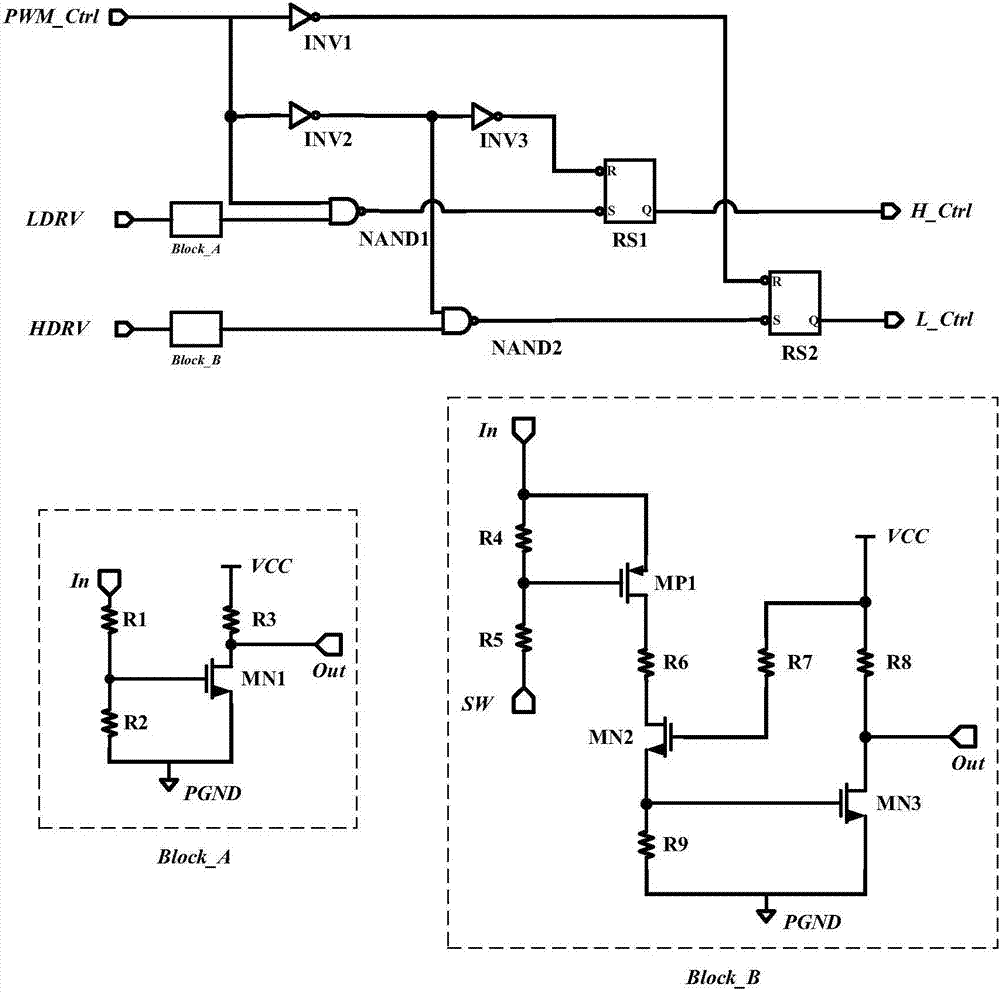

Gate driving circuit with self-adaptive dead time

InactiveCN107359787APrevent punch-throughSimple controlPower conversion systemsControl signalControl manner

The invention, which belongs to the technical field of electronic circuits, provides a gate driving circuit with self-adaptive dead time, wherein the gate driving circuit is suitable for a switch power supply circuit. With control by a drive logic control circuit, crossed condition of high-end and low-end driving units is realized, so that the self-adaptive dead time function is realized. A level shift circuit enables a control signal generated by the drive logic control circuit to be lifted to a power rail with high-end driving; and a bootstrap circuit generates the power rail with high-end driving by means of a charge pump. A first driving enhancement circuit and a second driving enhancement circuit enhance drive control signals to be gate drive signals with ampere levels. A power drive stage of the switch power supply circuit is connected to a gate drive signal generated by a gate drive circuit and an output voltage Vout is generated. According to the invention, the dead time is adjusted adaptively based on the dimension of the power tube to avoid penetration; and the control way is simple and self-adaptive dead time control is realized with low costs; and the universality is high.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

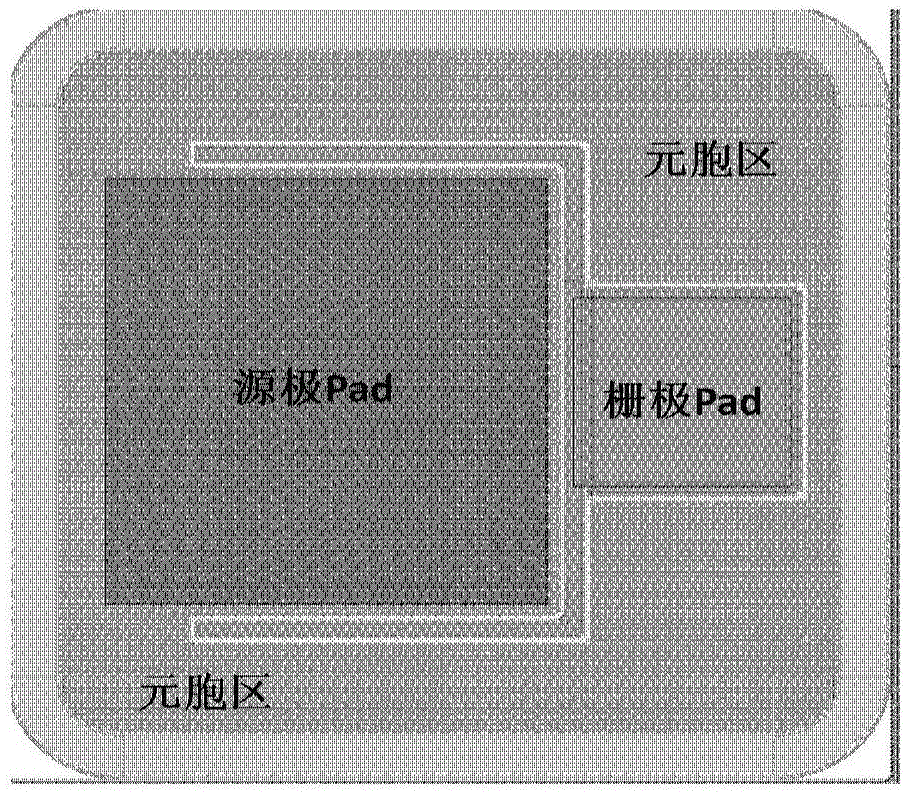

Enhanced type, depletion type and current induction integrated VDMOS power device

ActiveCN103872137APrevent punch-throughEasy to integrateSolid-state devicesSemiconductor devicesSystem integrationMiniaturization

The invention relates to an enhanced type, depletion type and current induction integrated VDMOS power device. The enhanced type, depletion type and current induction integrated VDMOS power device comprises an N-type substrate, and an N-type epitaxial layer is arranged on the N-type substrate. The enhanced type, depletion type and current induction integrated VDMOS power device is characterized in that an enhanced VDMOS, a depletion type VDMOS and a current induction VDMOS are arranged on the N-type epitaxial layer, and isolation structures are arranged between the enhanced VDMOS, the depletion type VDMOS and the current induction VDMOS; the enhanced type, depletion type and current induction integrated VDMOS power device integrates the three VDMOS devices, is flexible and diverse in application and combination, can be applied to circuits such as LED driving power supplies, power adapters and chargers and facilitate system integration and system miniaturization, and also has the advantages of being low in cost and simple in manufacture control; the isolation structures are adopted between the three VDMOS devices, and therefore punch-through between the devices can be effectively avoided. The enhanced type, depletion type and current induction integrated VDMOS power device has the advantages of being good in compatibility, high in reliability, low in manufacturing cost, easy in industrialization and the like.

Owner:XIAMEN YUANSHUN MICROELECTRONICS TECH +2

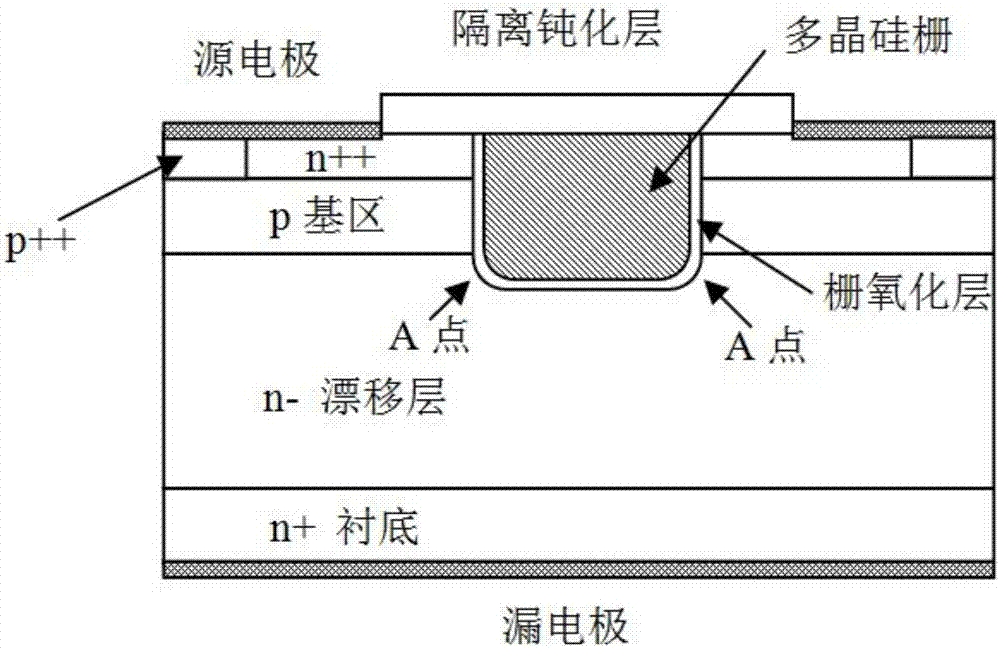

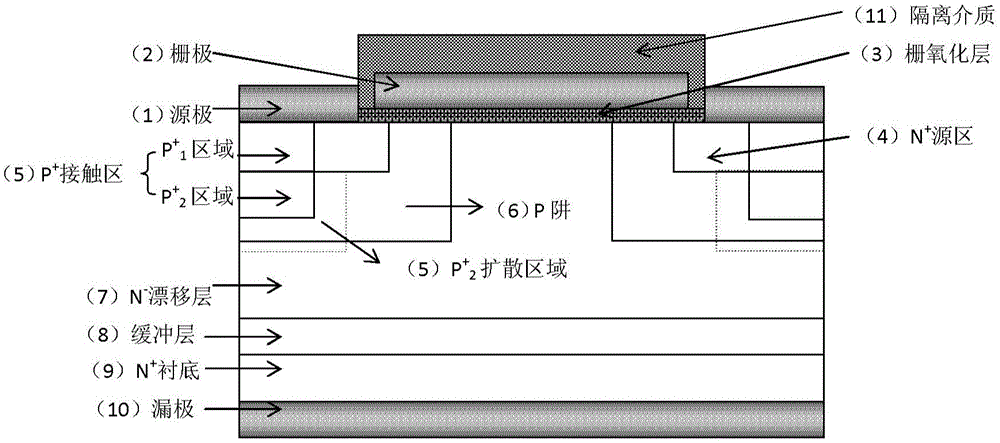

Silicon carbide metal-oxide-semiconductor field-effect-transistor (MOSFET) device and fabrication method thereof

ActiveCN105161539AAvoid avalanche breakdownGood source ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorPower MOSFET

The invention discloses a self-aligned silicon carbide metal-oxide-semiconductor field-effect-transistor (MOSFET) device with an optimized P<+> region and a fabrication method of the self-aligned silicon carbide MOSFET device. The self-aligned silicon carbide MOSFET device is formed by connecting a plurality of same cells in parallel, and the cells of the silicon carbide MOSFET device are uniformly arranged. Each cell of the silicon carbide MOSFET device comprises two sources, a grid, a grid oxide layer, two N<+> source regions, two P<+> contact regions, two P pits, an N<-> drift layer, a buffer layer, an N<+> substrate, a drain and an isolation dielectric layer. By optimizing the P<+> region, favorable source ohmic contact is formed, the on resistance is reduced, meanwhile, the source and the P pits are in short connection, parasitic negative-positive-negative (PNP) and a parasitic transistor effect of PiN are prevented, the conduction property and the breakdown property of the device can be compatible, and the device can be used in a high-voltage and high-frequency silicon carbide MOSFET device. A self-aligned fabrication method is adopted by the invention, the process is simplified, the channel size is accurately controlled, and a transverse or longitudinal power MOSFET can be fabricated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

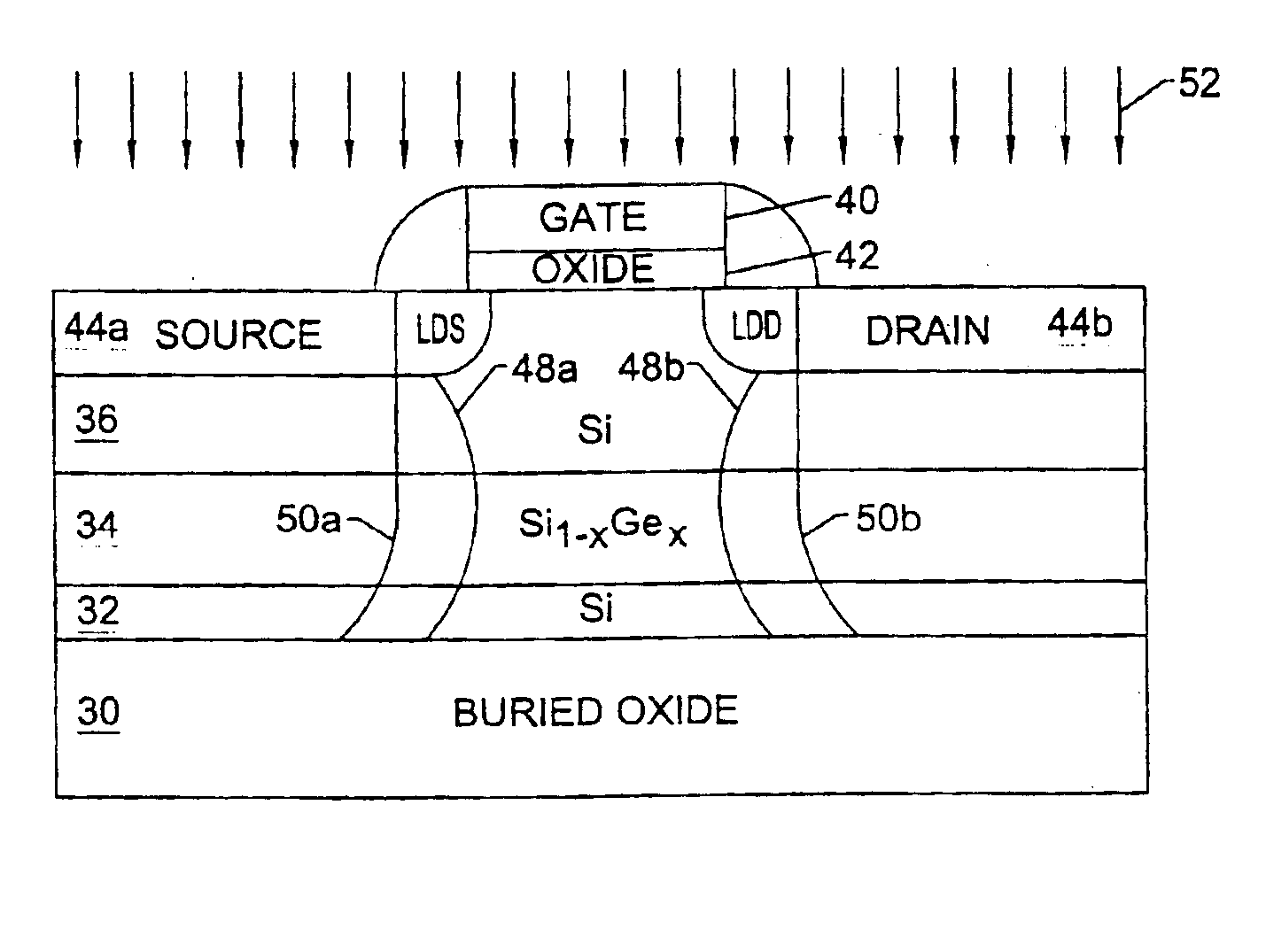

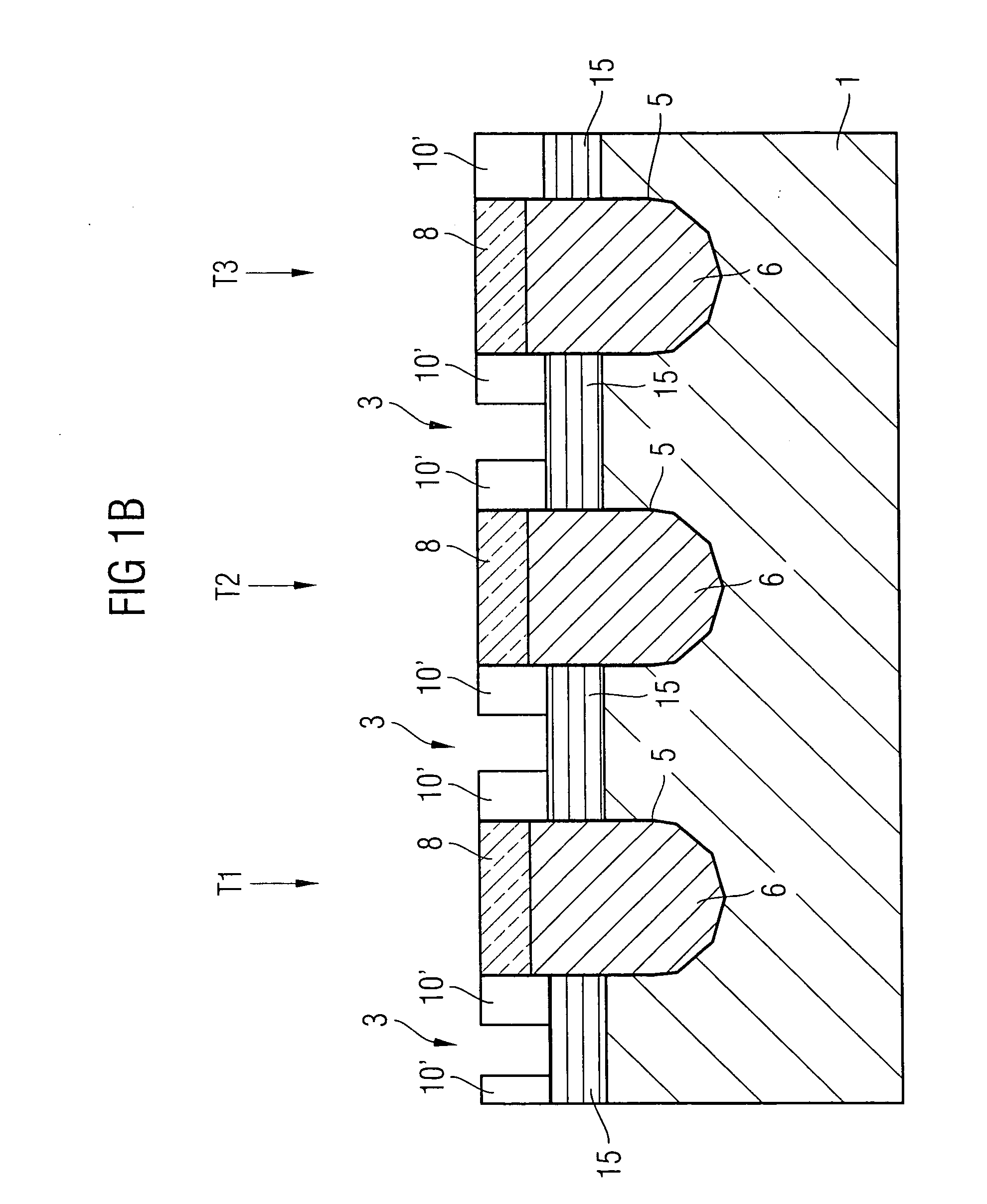

CMOS integrated circuit devices and substrates having buried silicon germanium layers therein and methods of forming same

CMOS integrated circuit devices include an electrically insulating layer and an unstrained silicon active layer on the electrically insulating layer. An insulated gate electrode is also provided on a surface of the unstrained silicon active layer. A Si1-xGex layer is also disposed between the electrically insulating layer and the unstrained silicon active layer. The Si1-xGex layer forms a first junction with the unstrained silicon active layer and has a graded concentration of Ge therein that decreases monotonically in a first direction extending from a peak level towards the surface of the unstrained silicon active layer. The peak Ge concentration level is greater than x=0.15 and the concentration of Ge in the Si1-xGex layer varies from the peak level to a level less than about x=0.1 at the first junction. The concentration of Ge at the first junction may be abrupt. More preferably, the concentration of Ge in the Si1-xGex layer varies from the peak level where 0.2<x<0.4 to a level where x=0 at the first junction. The Si1-xGex layer also has a retrograded arsenic doping profile therein relative to the surface. This retrograded profile may result in the Si1-xGex layer having a greater concentration of first conductivity type dopants therein relative to the concentration of first conductivity type dopants in a channel region within the unstrained silicon active layer. The total amount of dopants in the channel region and underlying Si1-xGex layer can also be carefully controlled to achieve a desired threshold voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

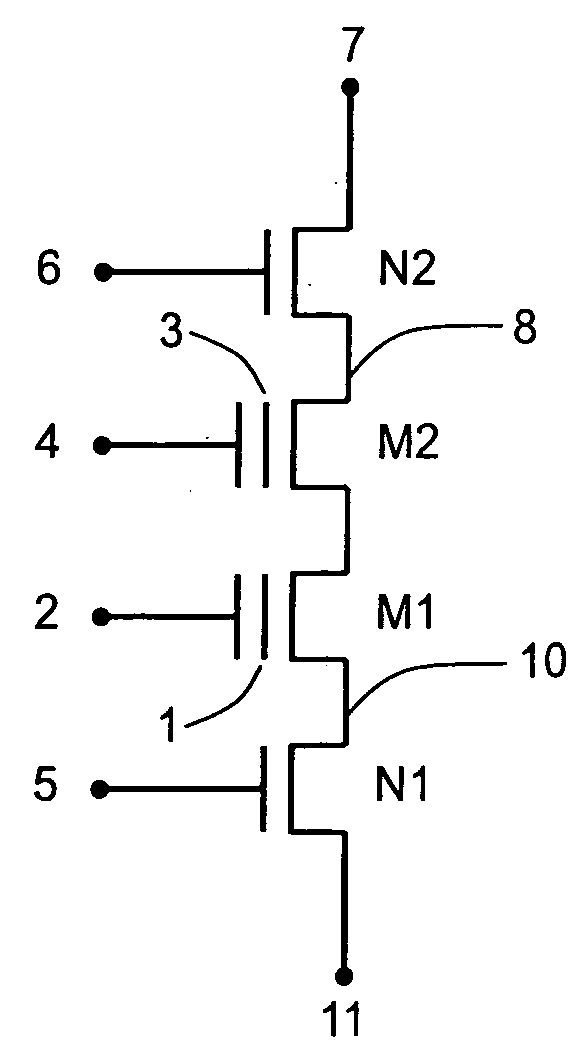

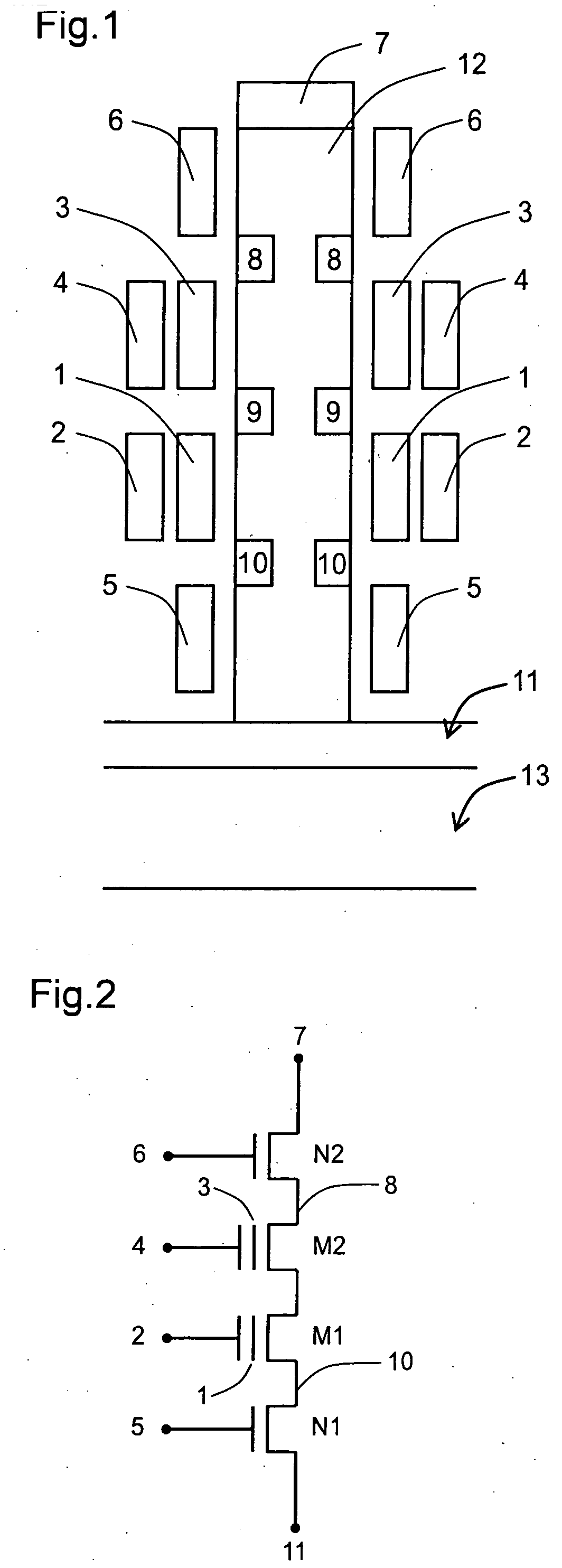

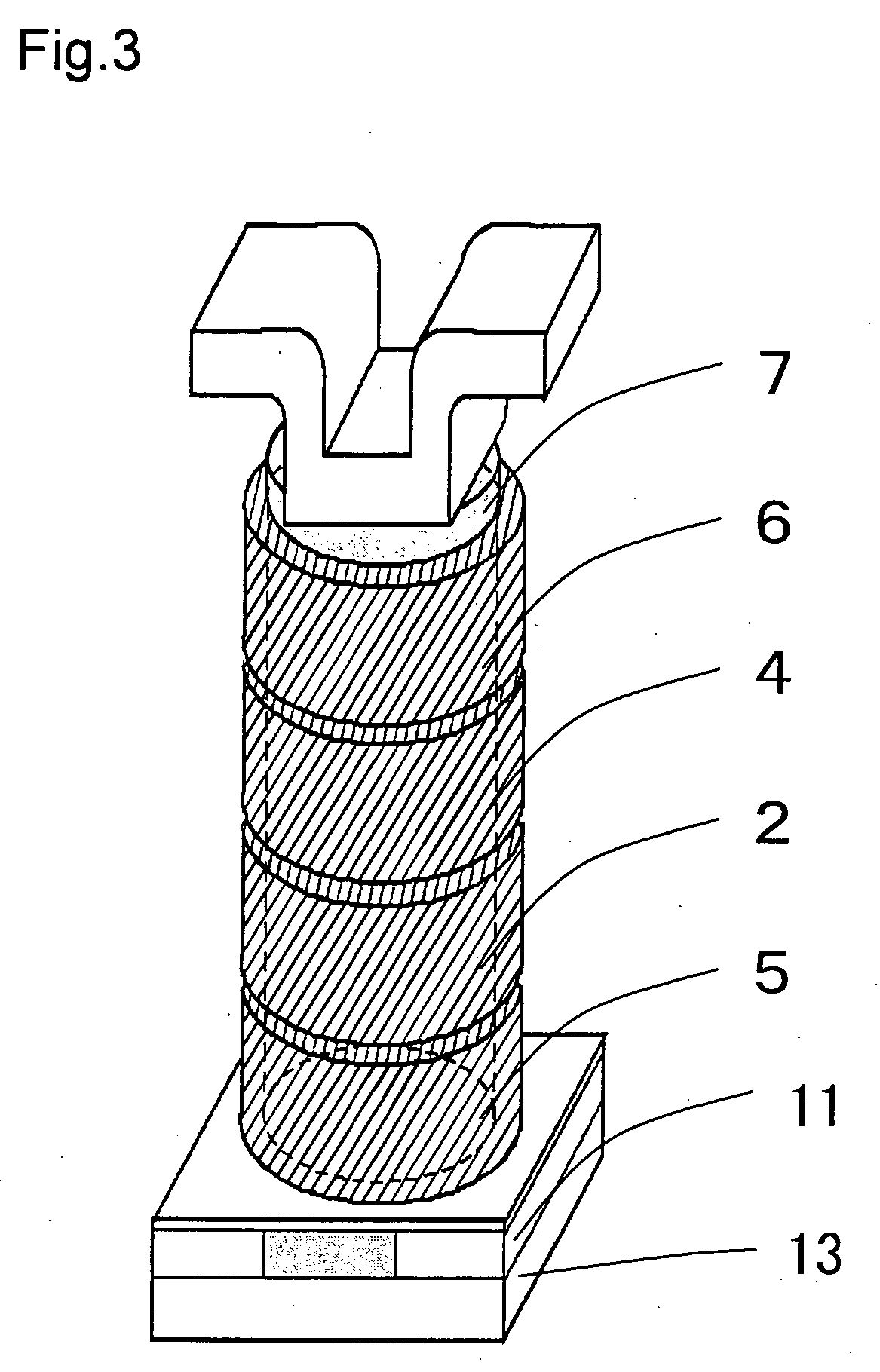

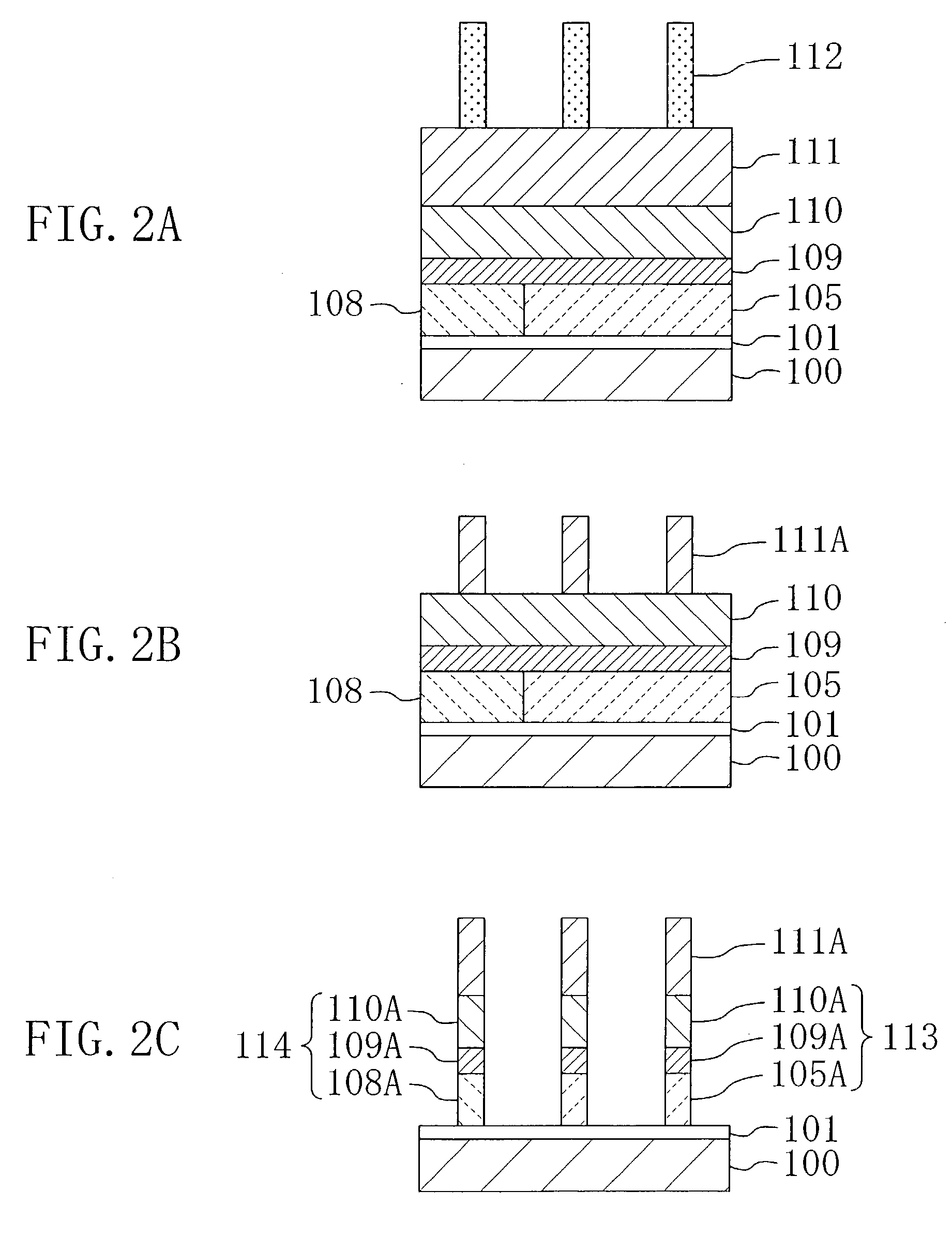

Memory cell unit, nonvolatile semiconductor device, and liquid crystal display device including the nonvolatile semiconductor device

InactiveUS20050051806A1Stable and reliablePrevent punch-throughTransistorStatic indicating devicesImpurity diffusionLiquid-crystal display

A memory cell unit including: a semiconductor substrate having a source diffusion layer provided in a surface thereof; a column-shaped semiconductor layer provided on the source diffusion layer and having a drain diffusion layer provided in an uppermost portion thereof; a memory cell arrangement which includes a plurality of memory cells arranged in series with the intervention of a first impurity diffusion layer; a first selection transistor connected to one end of the memory cell arrangement with the intervention of a second impurity diffusion layer and connected to the drain diffusion layer; and a second selection transistor connected to the other end of the memory cell arrangement with the intervention of a third impurity diffusion layer and connected to the source diffusion layer; wherein a distance between the third impurity diffusion layer and the source diffusion layer is greater than a distance between impurity diffusion layers disposed on opposite sides of each of the memory cells, whereby punch-through of the second selection transistor is prevented when a writing prevention voltage is applied between the source diffusion layer and the first impurity diffusion layer.

Owner:FUJO MASUOKA +1

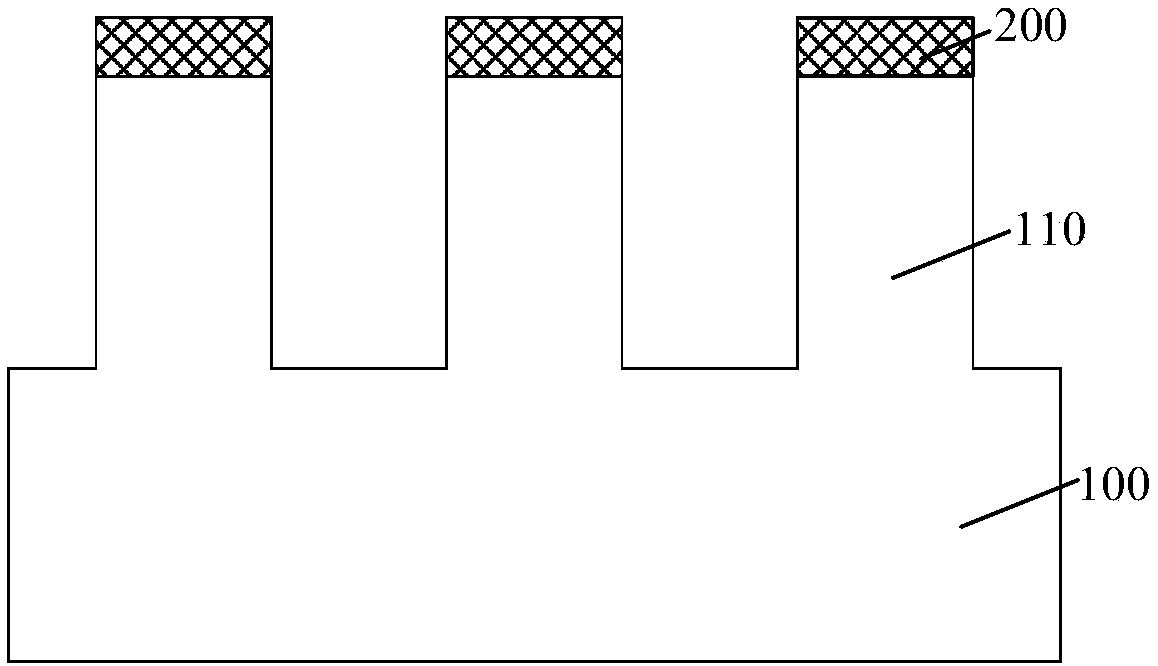

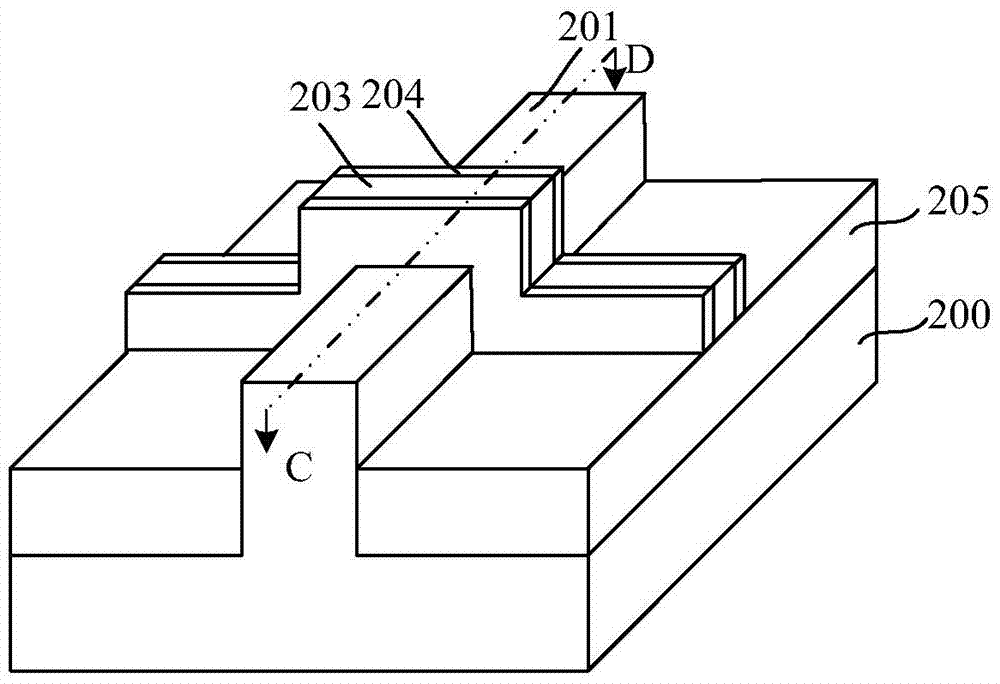

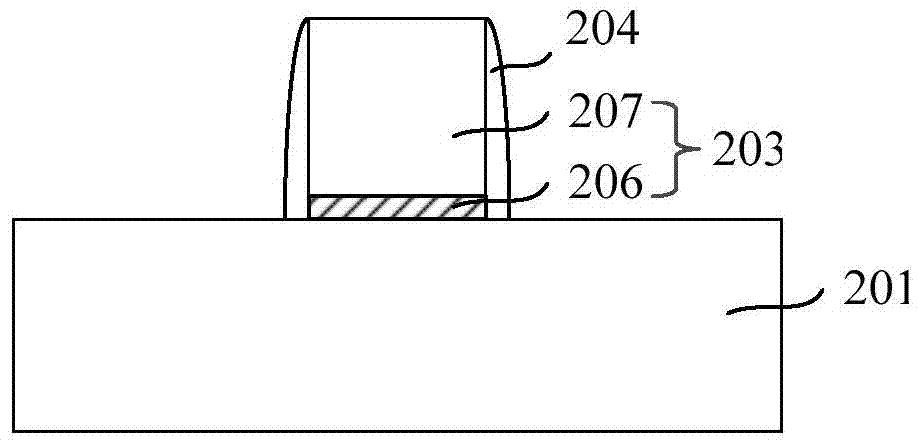

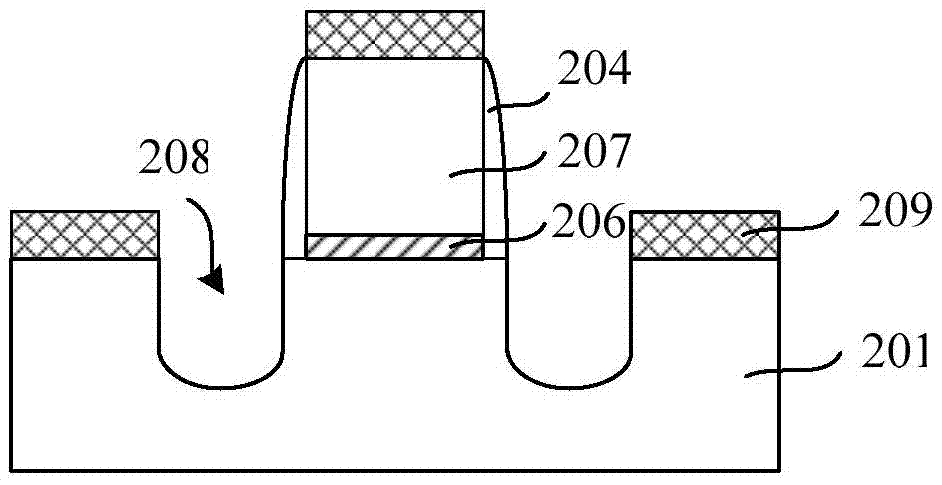

Semiconductor structure and manufacturing method thereof

InactiveCN107785261AInhibited DiffusionReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureEngineering

The invention discloses a semiconductor structure and a manufacturing method thereof. The method comprises steps: a base is provided, wherein the base comprises a substrate and fin parts protruding against the substrate; a gate structure which crosses over the fin parts and covers the top surfaces and the side wall surfaces of part of the fin parts is formed; the fin parts at two sides of the gatestructure are removed, and grooves with the substrate exposed are formed at two sides of the gate structure; the substrate at the bottom part of the groove is internally provided with an anti-diffusion doping area; and after the anti-diffusion doping area is formed, a stress layer is formed in the groove, and a source-drain doping area is formed in the stress layer. After the grooves with the substrate exposed are formed at two sides of the gate structure, the substrate at the bottom part of the groove is internally provided with the anti-diffusion doping area; later, after the stress layer is formed in the groove and the source-drain doping area is formed in the stress layer, the anti-diffusion doping area is located in the substrate at the bottom part of the source-drain doping area, the anti-diffusion doping area can suppress diffusion of doping ions of the source-drain doping area to a channel area, bottom through can be prevented from happening to the source-drain doping area, and channel leakage current can thus be reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Methods of fabricating a semiconductor device having a metal gate pattern

InactiveUS7109104B2Reduce layeringReduce oxidationSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

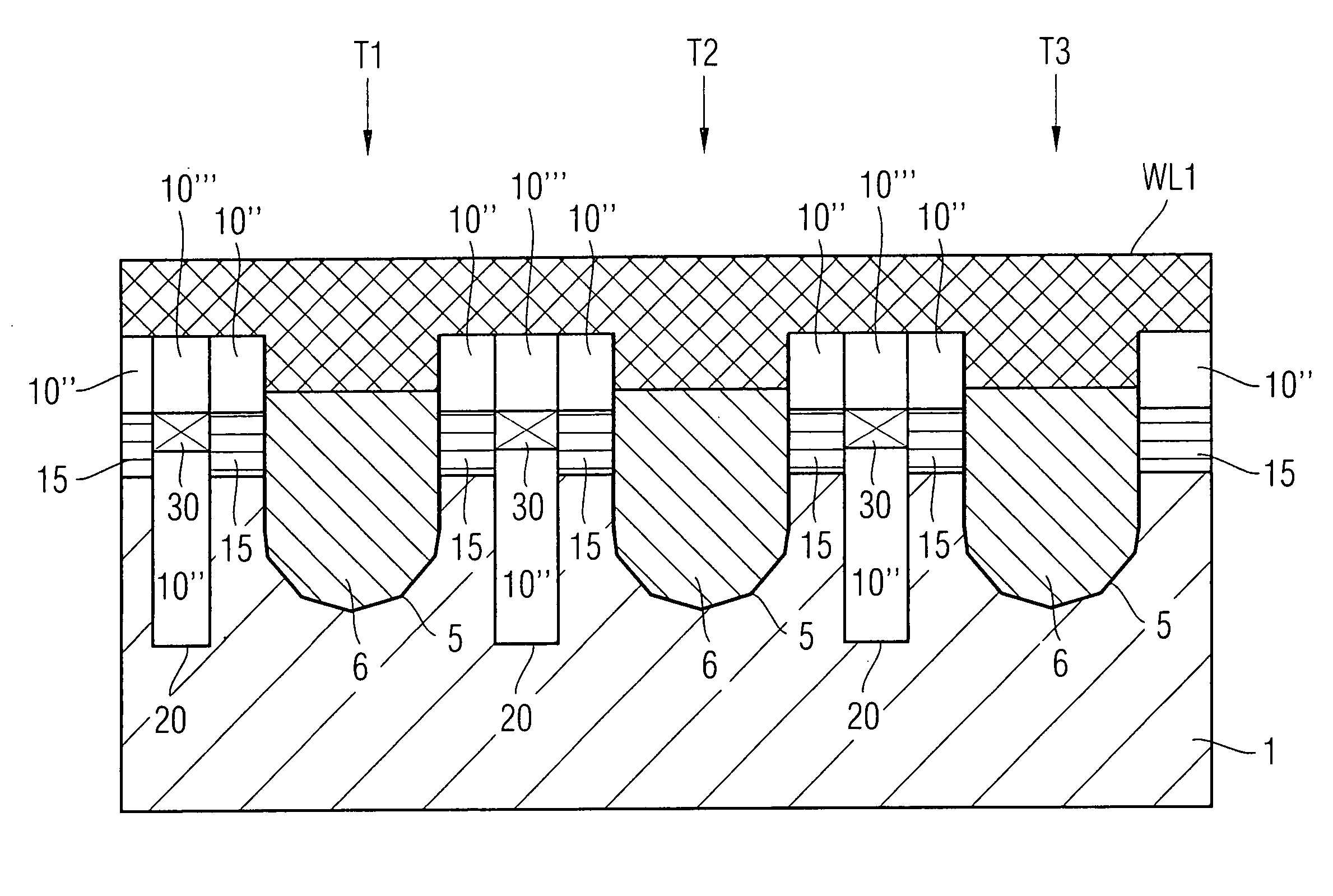

Transistor of a semiconductor device having a punchthrough protection layer and methods of forming the same

ActiveUS20050199930A1Prevent punch-throughTransistorSemiconductor/solid-state device detailsDevice materialEngineering

According to some embodiments of the invention, transistors of a semiconductor device have a punchthrough protection layer, and methods of forming the same are provided. A channel-portion hole extends downward from a main surface of a semiconductor substrate. A punchthrough protection layer and a channel-portion layer are sequentially formed at a lower portion of the channel-portion hole. A word line pattern fills an upper portion of the channel-portion hole, and is formed on the semiconductor substrate. The word line pattern is formed to have a word line and a word line capping layer pattern stacked thereon, and the channel-portion layer is a channel region. The punchthrough protection layer can reduce a leakage current of a capacitor of the transistor embodied in a DRAM.

Owner:SAMSUNG ELECTRONICS CO LTD

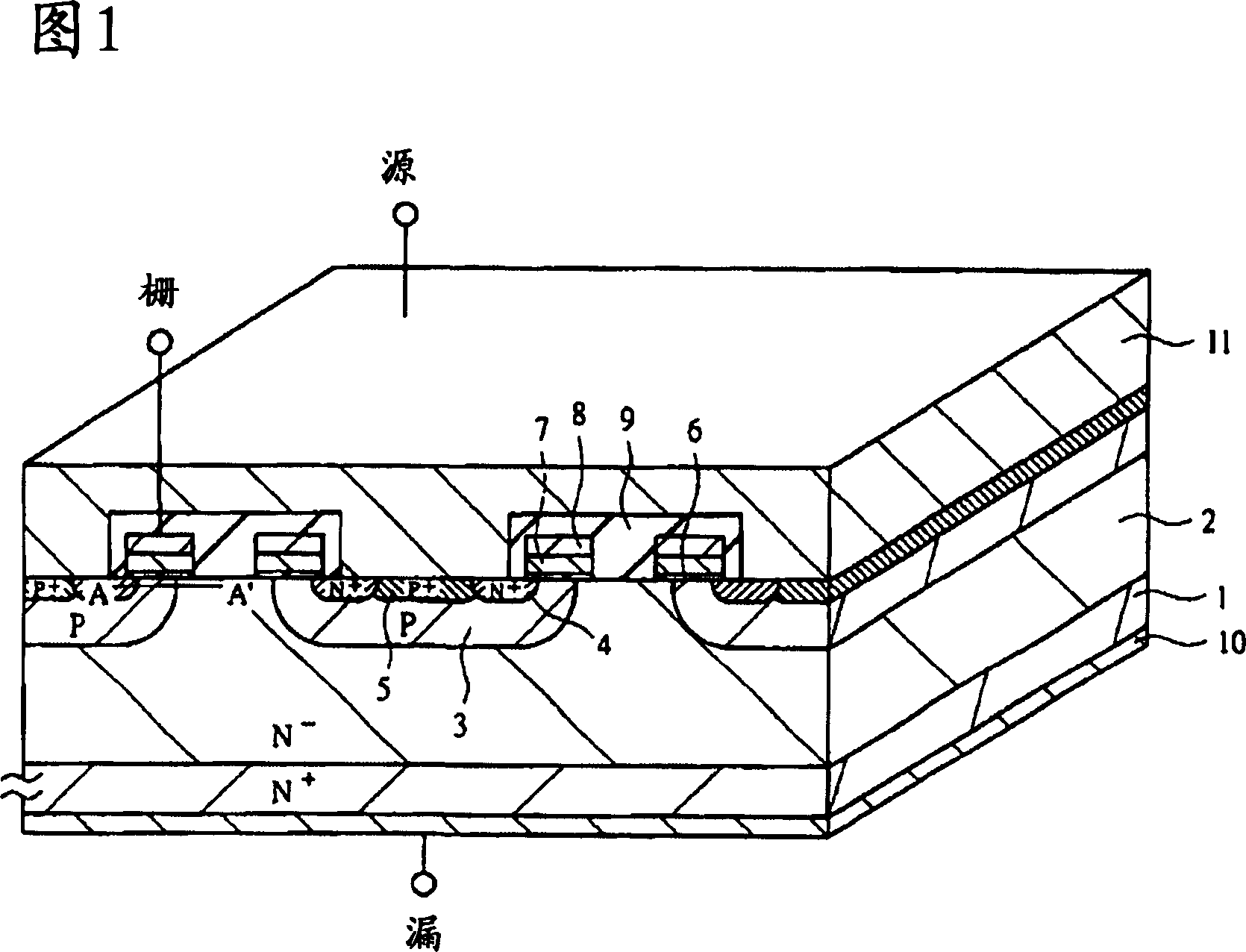

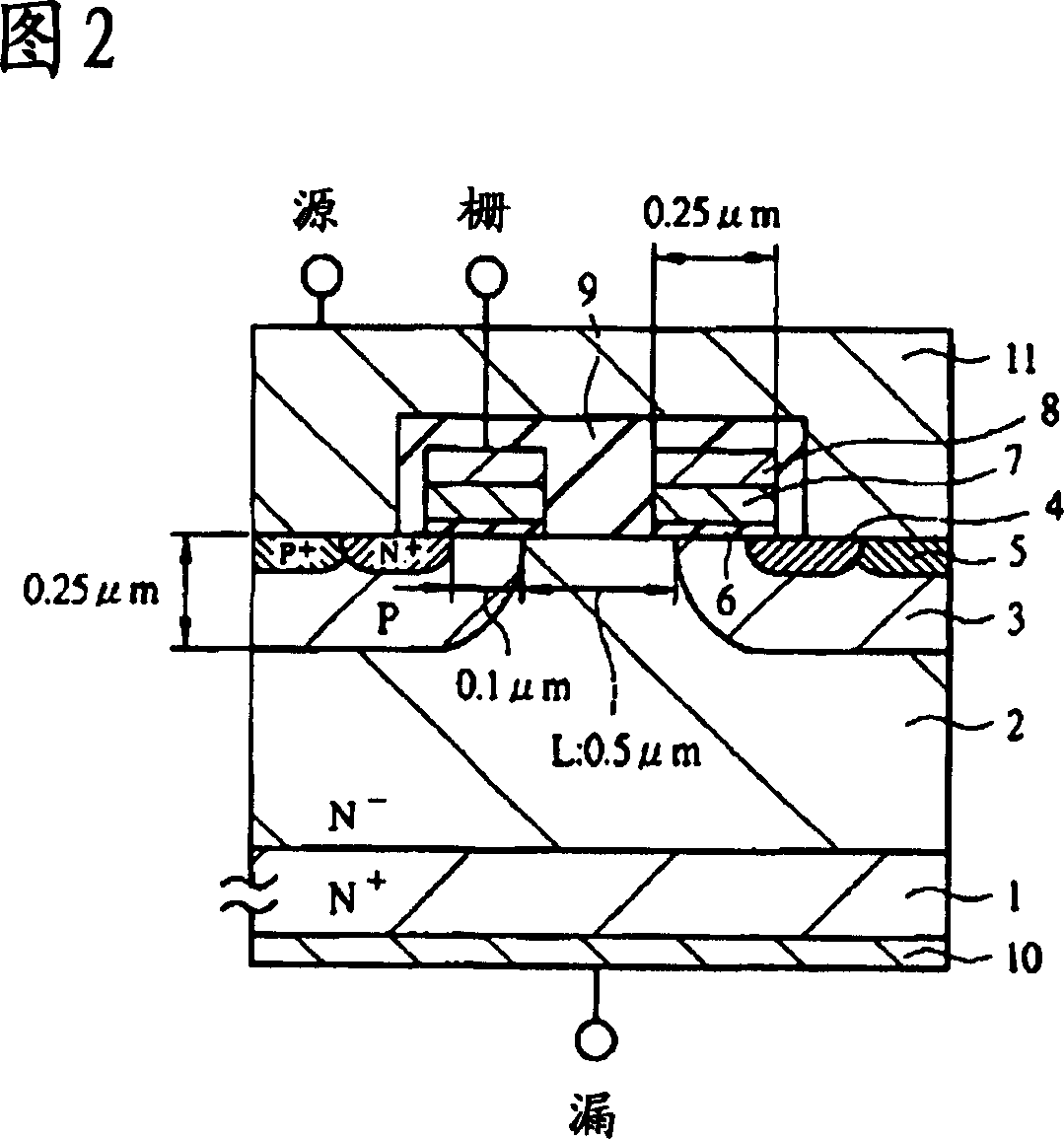

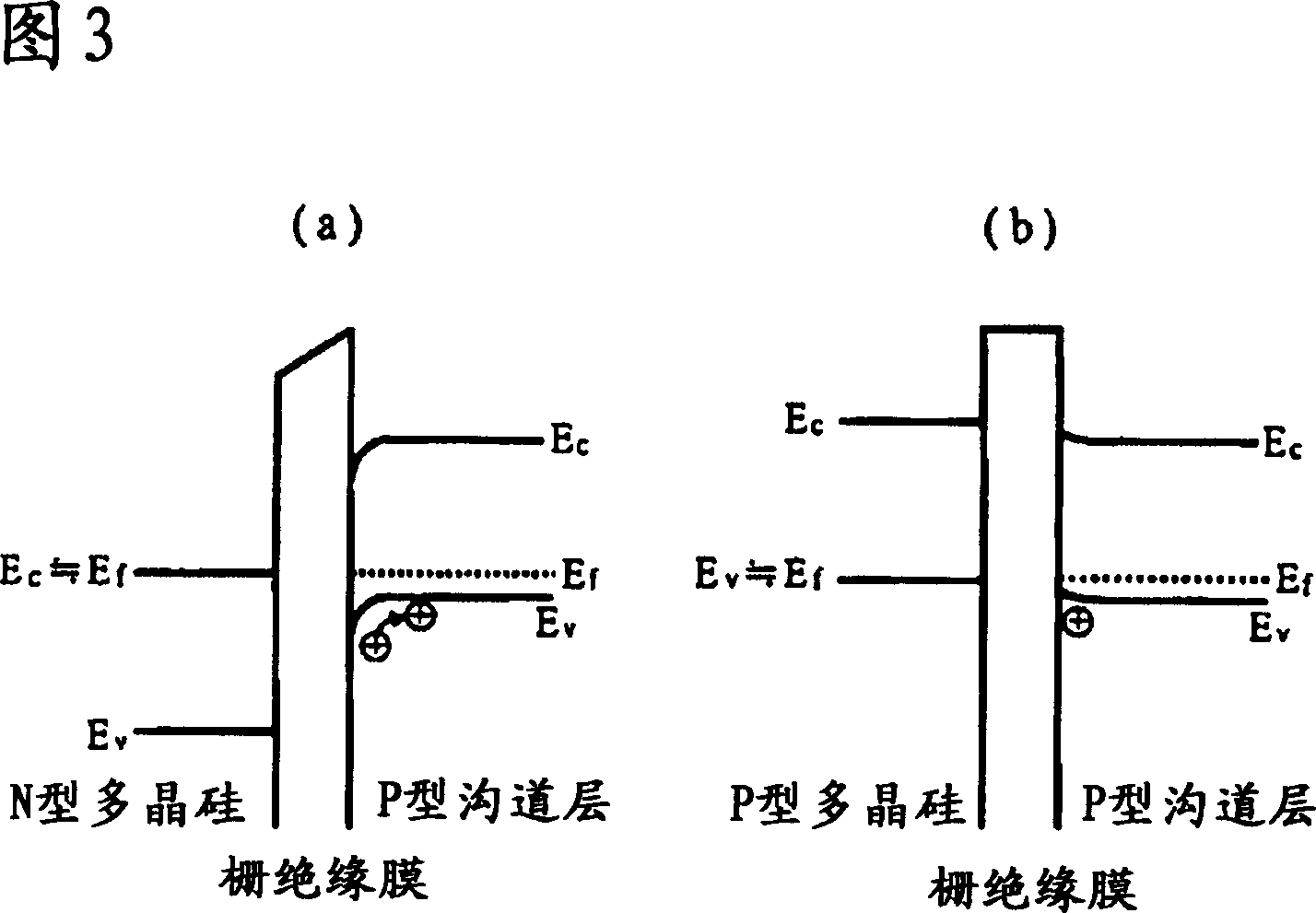

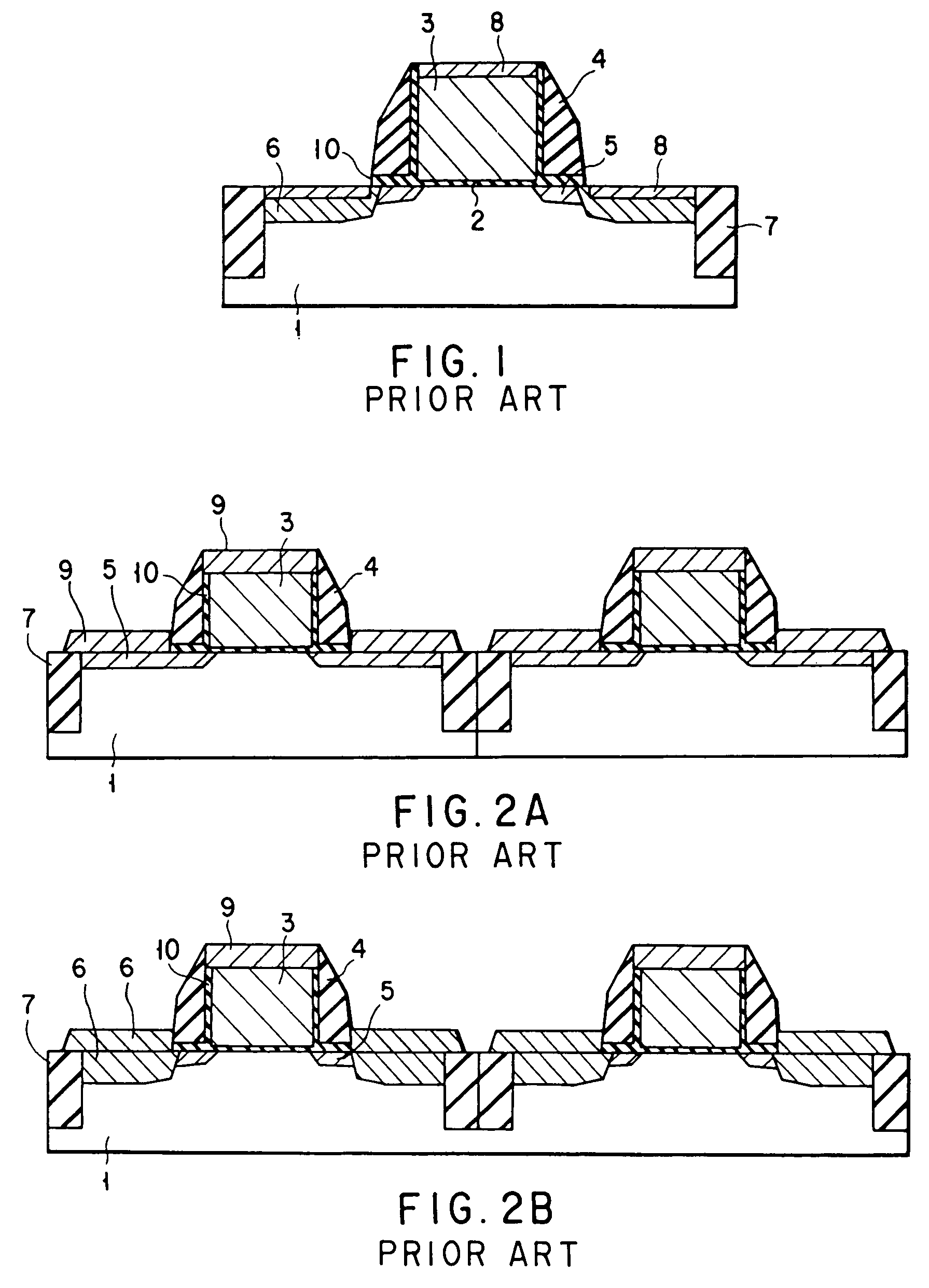

DMOSFET and planar type MOSFET

A technology capable of realizing a MOSFET with low ON-resistance and low feedback capacitance, in which the punch through of a channel layer can be prevented even when the shallow junction of the channel layer is formed in a planar type MOSFET is provided. A P type polysilicon 7 is used for a gate electrode in a planar type MOSFET, in particular, in an N channel DMOSFET.

Owner:RENESAS TECH CORP

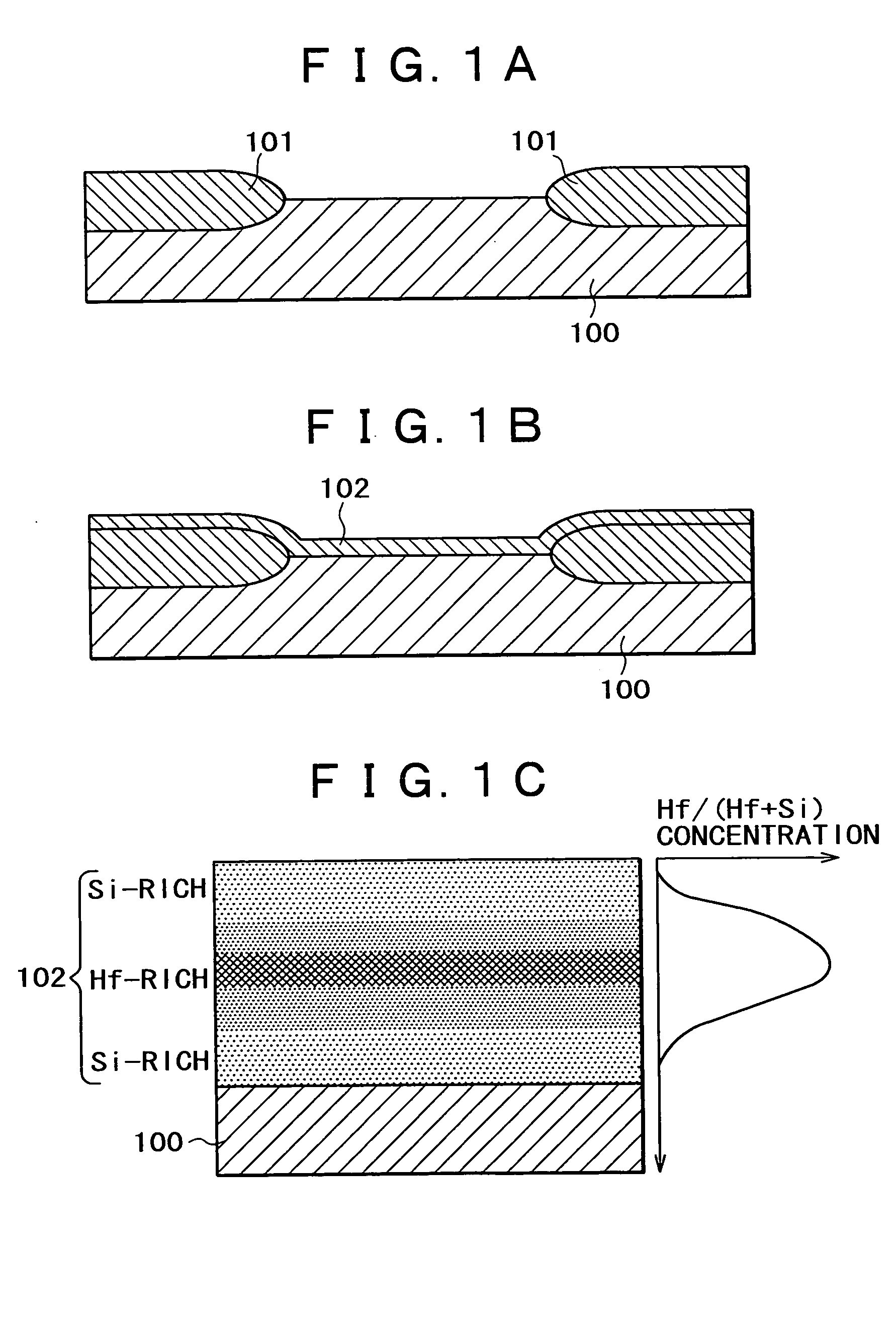

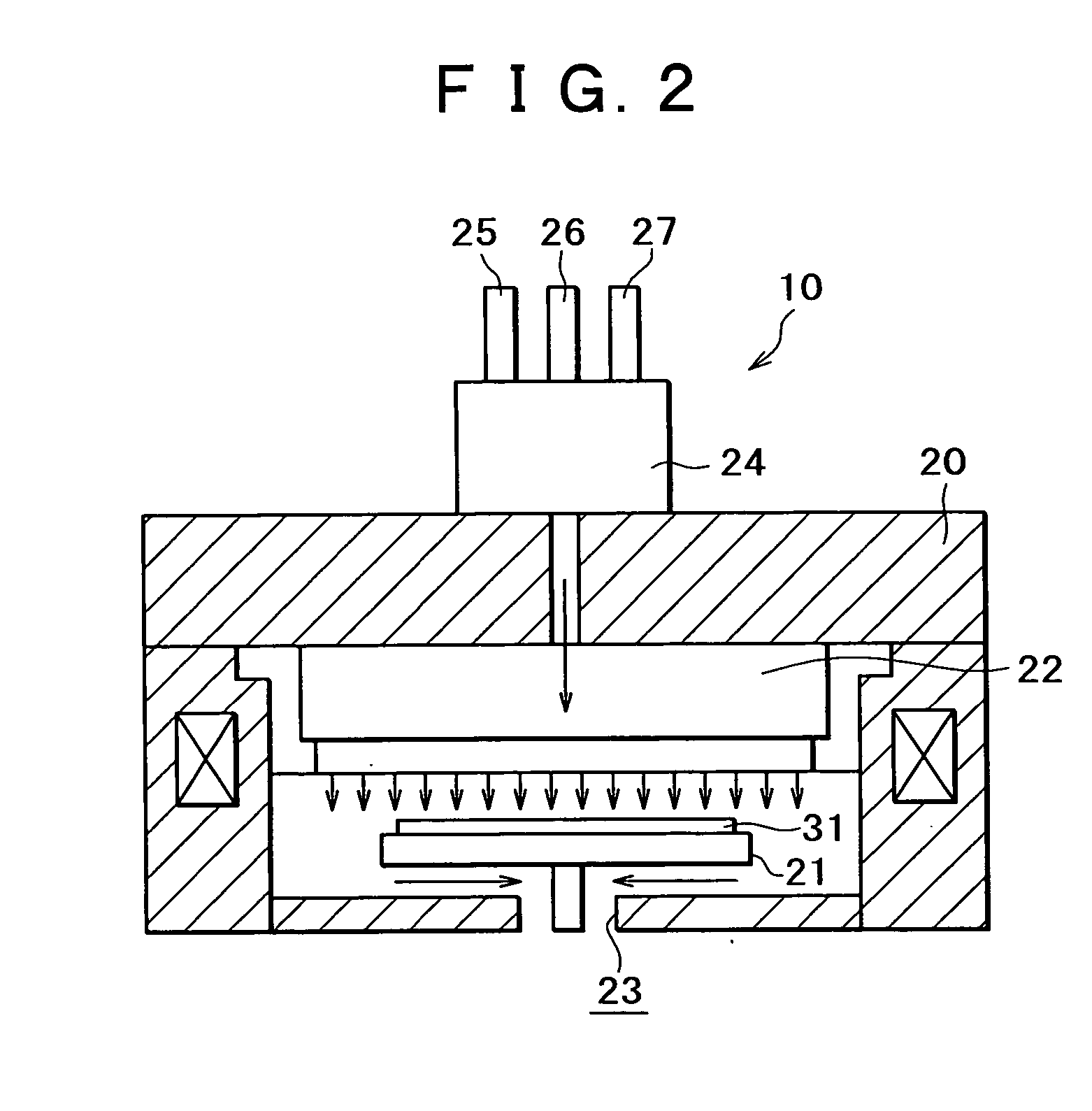

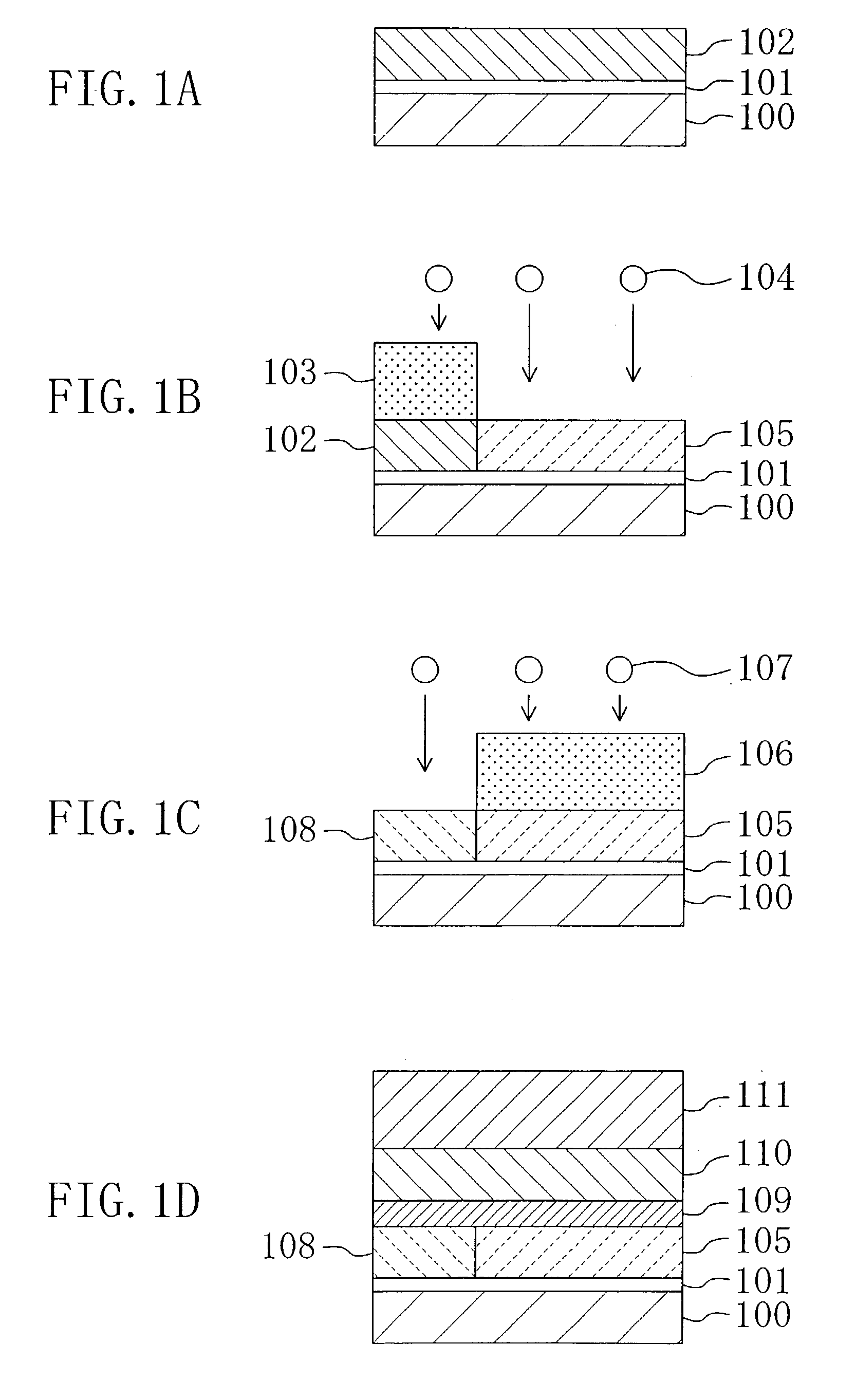

Method of producing insulator thin film, insulator thin film, method of manufacturing semiconductor device, and semiconductor device

ActiveUS20050116266A1Reduce concentrationLow mobilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialThin membrane

A method of producing an insulator thin film, for forming a thin film on a substrate by use of the atomic layer deposition process, includes a first step of forming a silicon atomic layer on the substrate and forming an oxygen atomic layer on the silicon atomic layer, and a second step of forming a metal atomic layer on the substrate and forming an oxygen atomic layer on the metal atomic layer, wherein the concentration of the metal atoms in the insulator thin film is controlled by controlling the number of times the first step and the second step are carried out.

Owner:SONY CORP

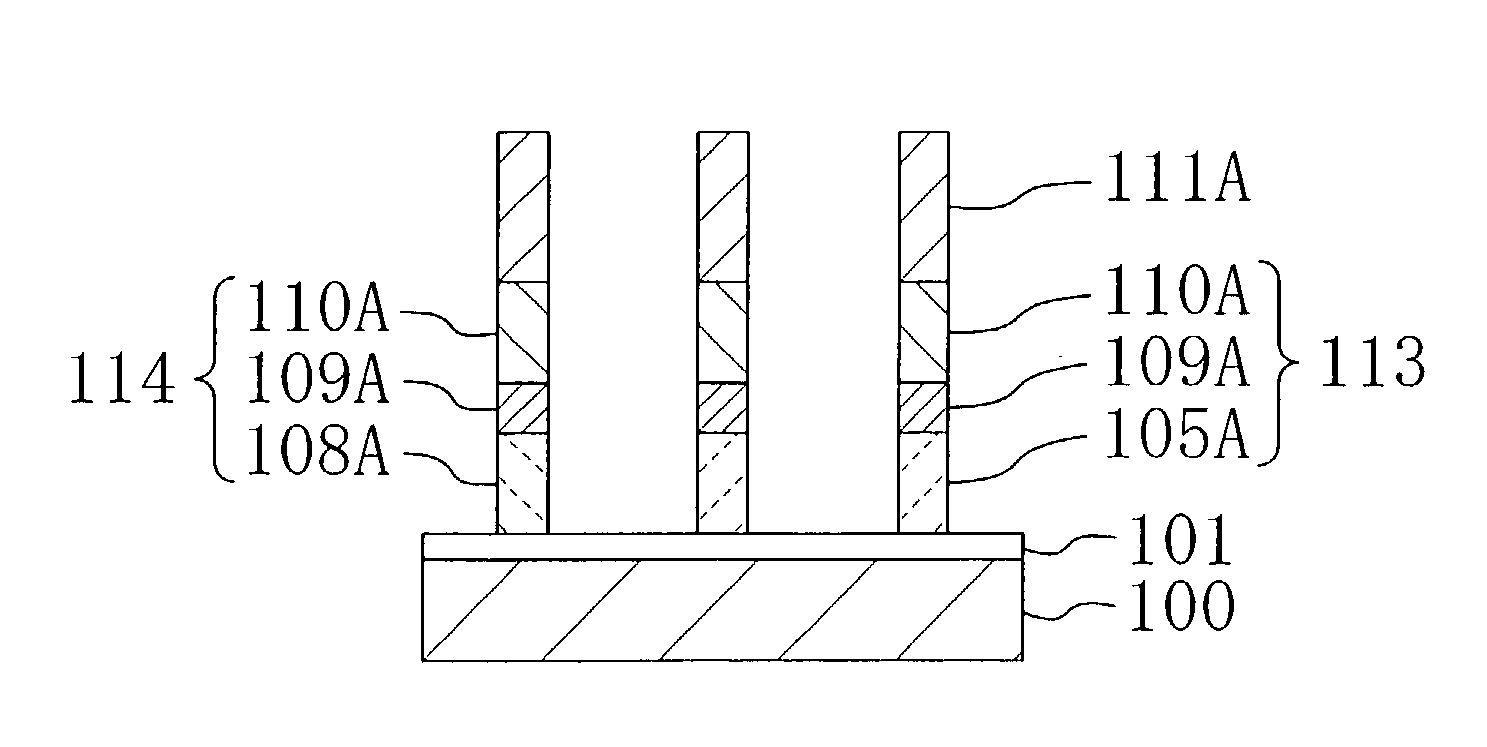

Method for fabricating semiconductor device

ActiveUS7166538B2Reduce number of grainPrevent punch-throughTransistorSemiconductor/solid-state device manufacturingSilicon oxideSemiconductor

After forming a gate insulating film on a semiconductor substrate, a silicon film is deposited on the gate insulating film, and a high-melting point metal film is deposited on the silicon film. After forming a hard mask made of a silicon oxide film or a silicon nitride film on the high-melting point metal film, the high-melting point metal film is dry etched by using the hard mask as a mask. After removing a residue or a natural oxide film present on the silicon film through dry etching, the silicon film is dry etched by using the hard mask as a mask. The residue or the natural oxide film is removed while suppressing excessive etching of the silicon film.

Owner:PANNOVA SEMIC

Semiconductor structure forming method

ActiveCN106449405AInhibited DiffusionSuppression of short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon ionSemiconductor structure

The invention provides a semiconductor structure forming method which comprises the following steps: providing a substrate with a well region, wherein a first type of ions are disposed in the well region; using a first anti-punch-through-injection process to inject the first type of ion into the well region wherein the depth of the first anti- punch-through injection process is less than the distance from the bottom of the well region to the top surface of the substrate, forming an anti-punch-through region in the well region; using a second anti- punch-through-injection process to inject carbon ions into the well region to form a carbon doped region in the well region wherein the doped concentration of the carbon ions is greater than that of the first type of ion in the anti-punch-through region and the carbon doped region surrounds the anti-punch-through region; and using a third anti-punch-through-injection process to inject nitrogen ions into the well region wherein the third anti-punch-through-injection depth is less than those of the first anti- punch-through -injection and the second anti-punch-through-injection, forming a nitrogen doped region between the anti- punch-through regions and the top part of the substrate. According to the semiconductor structure forming method, it is possible to improve the performances of a semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

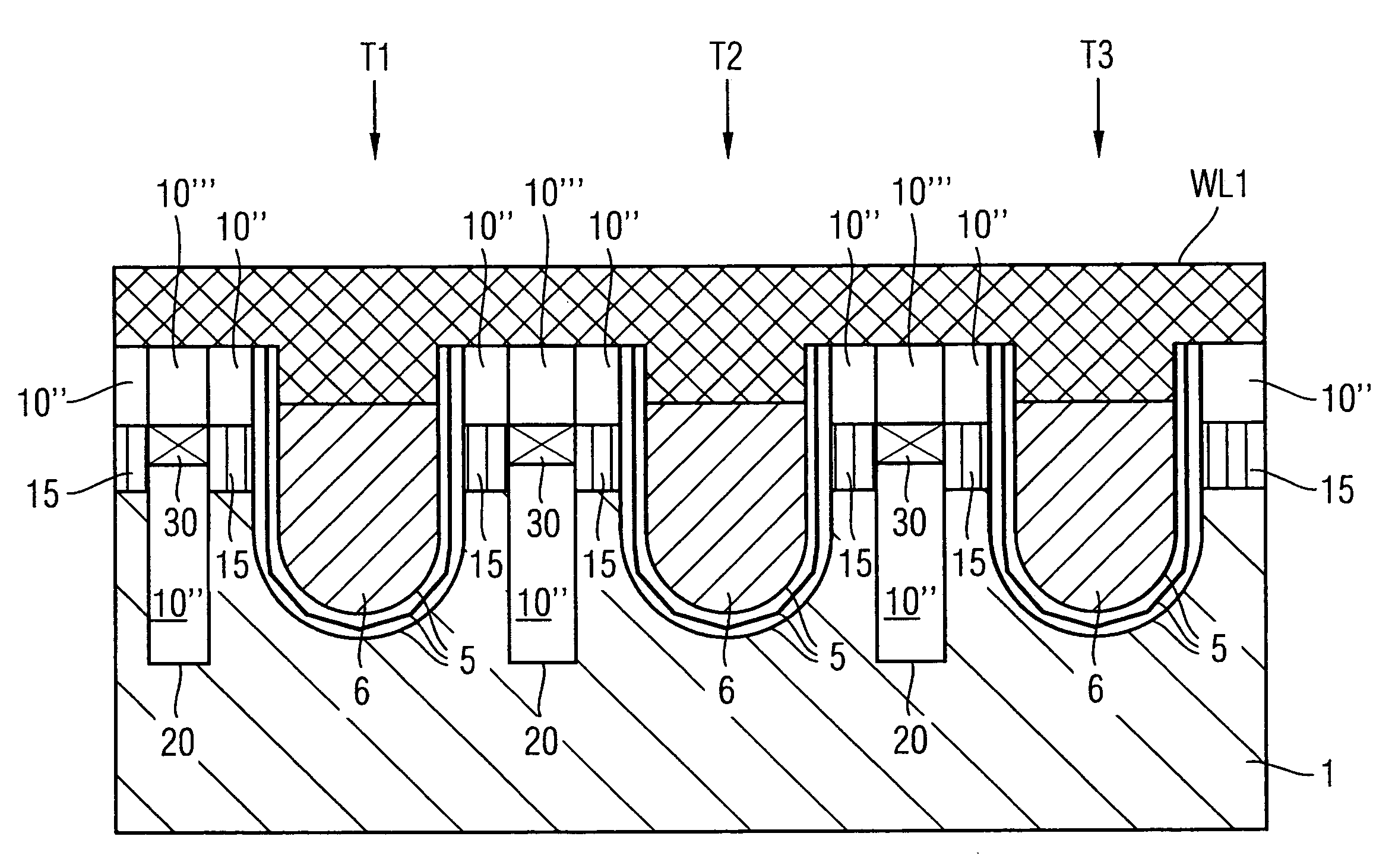

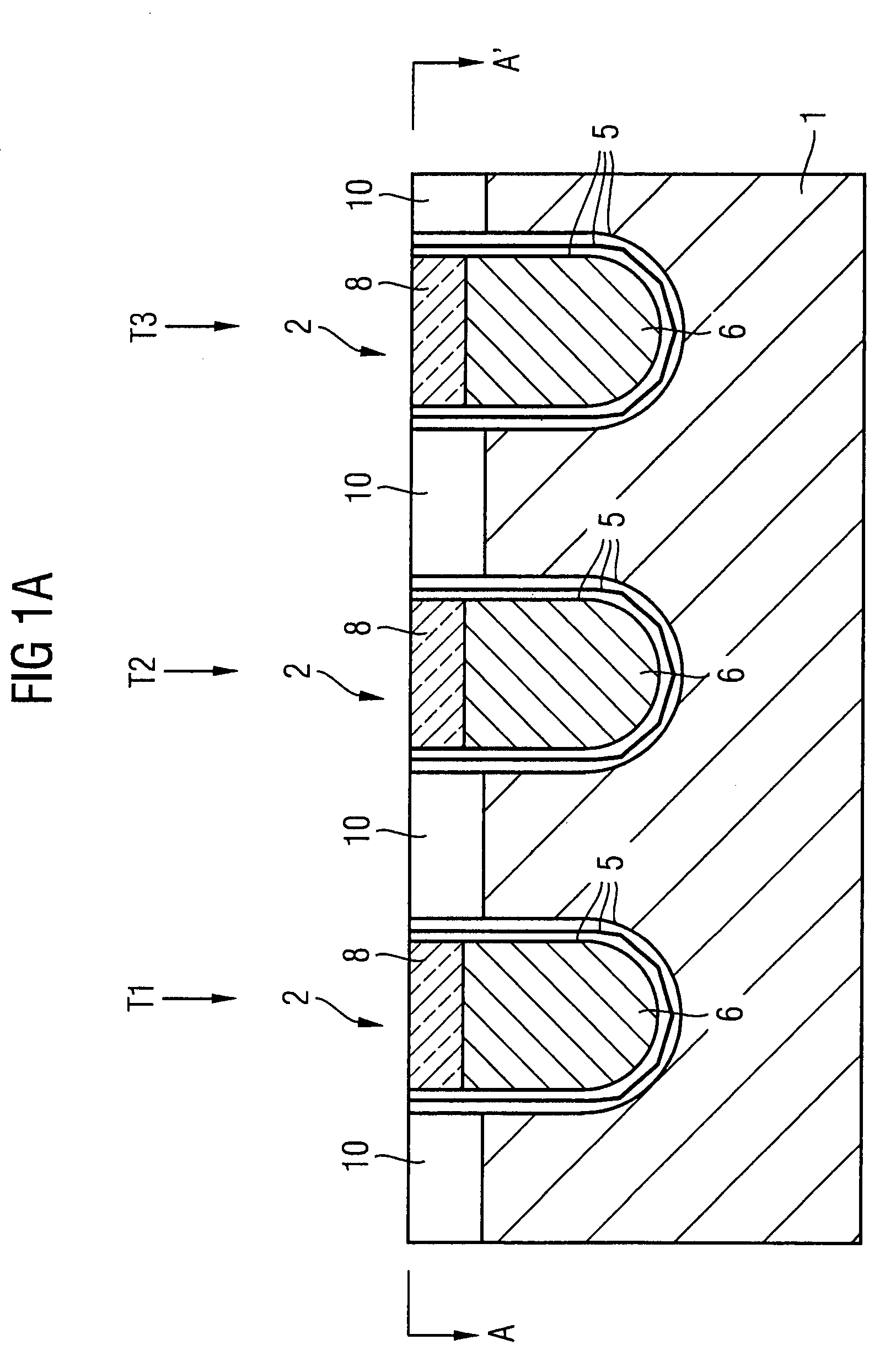

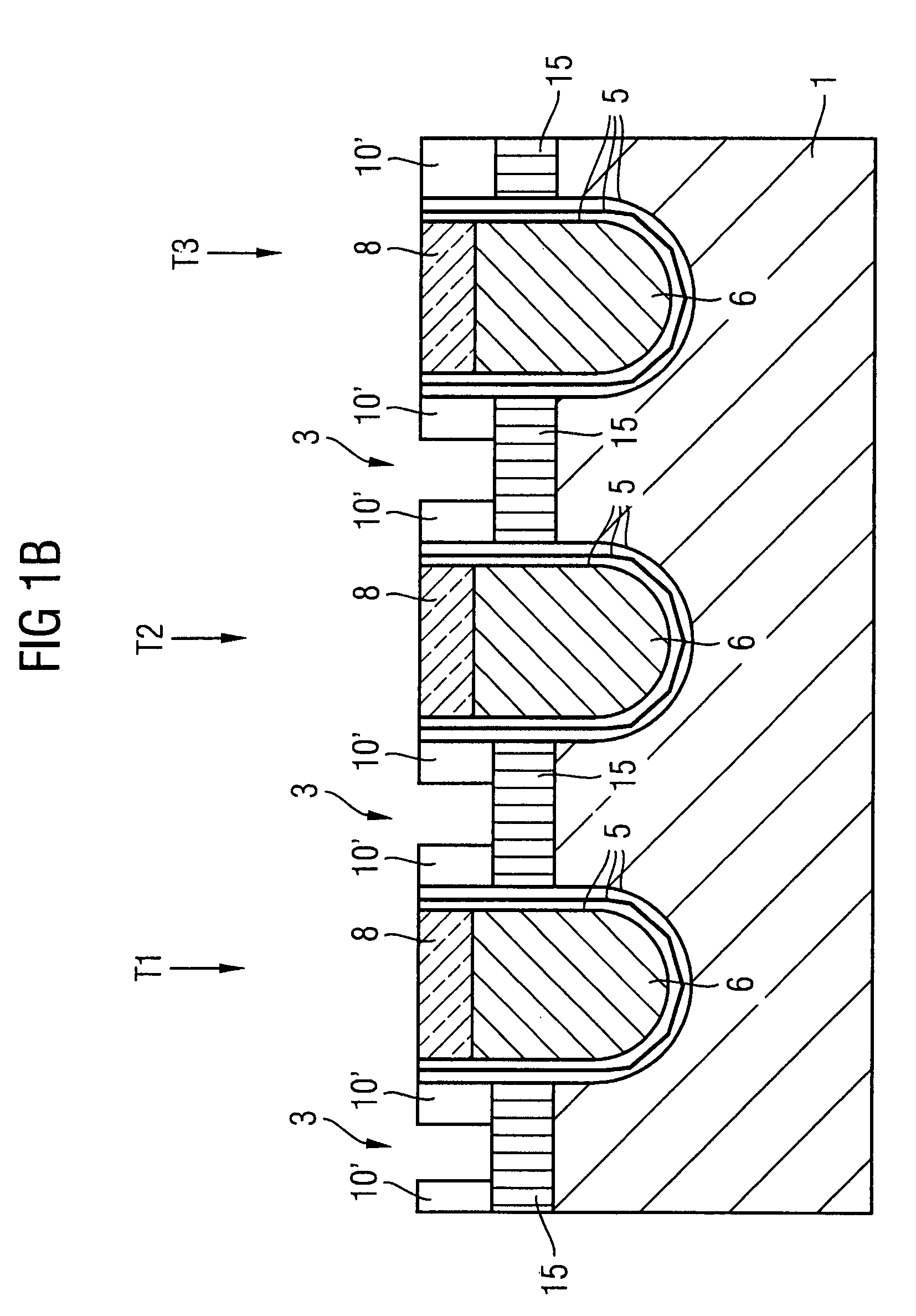

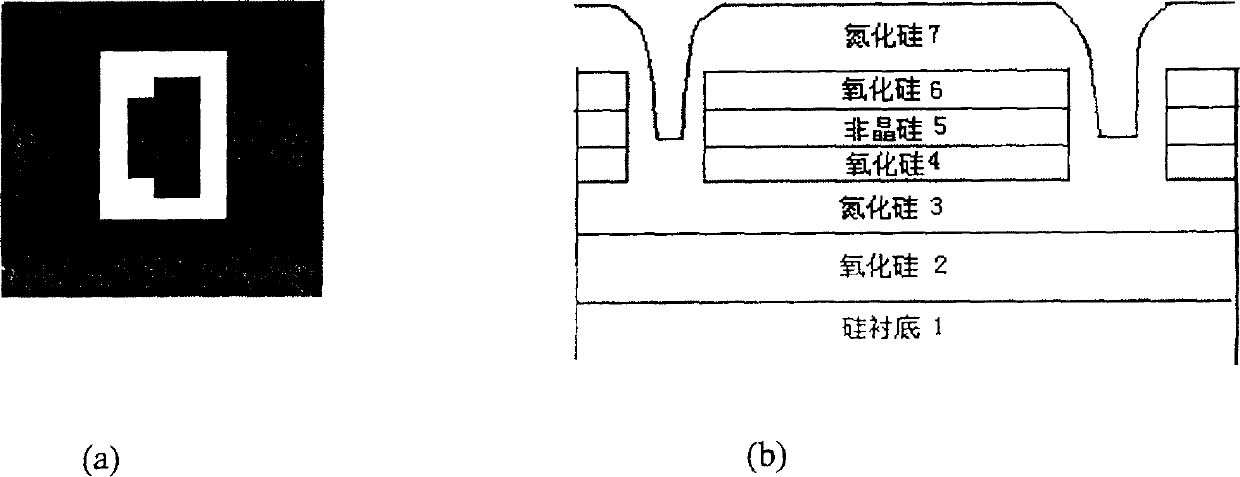

NROM semiconductor memory device and fabrication method

InactiveUS7344923B2Prevent punch-throughSolid-state devicesSemiconductor/solid-state device manufacturingDielectricMOSFET

An NROM semiconductor memory device and fabrication method are disclosed. According to one aspect, a method for fabricating an NROM semiconductor memory device can include providing a plurality of u-shaped MOSFETs, which are spaced apart from one another and have a multilayer dielectric. The dielectric suitable for charge trapping along rows in a first direction and alone columns in a second direction in trenches of a semiconductor substrate. Source / drain regions are provided between the u-shaped MOSFETs in interspaces between the rows which run parallel to the columns. Isolation trenches are provided in the source / drain regions between the u-shaped MOSFETs of adjacent columns as far as a particular depth in the semiconductor substrate. The isolation trenches are filled with an insulation material. Word lines are provided for connecting respective rows of u-shaped MOSFETs.

Owner:QIMONDA

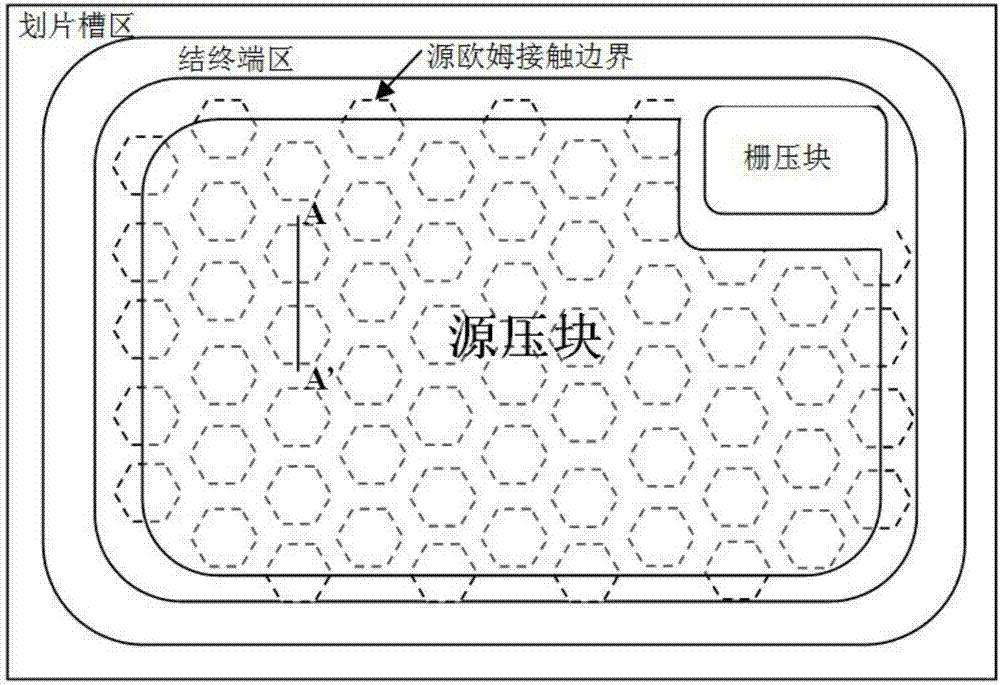

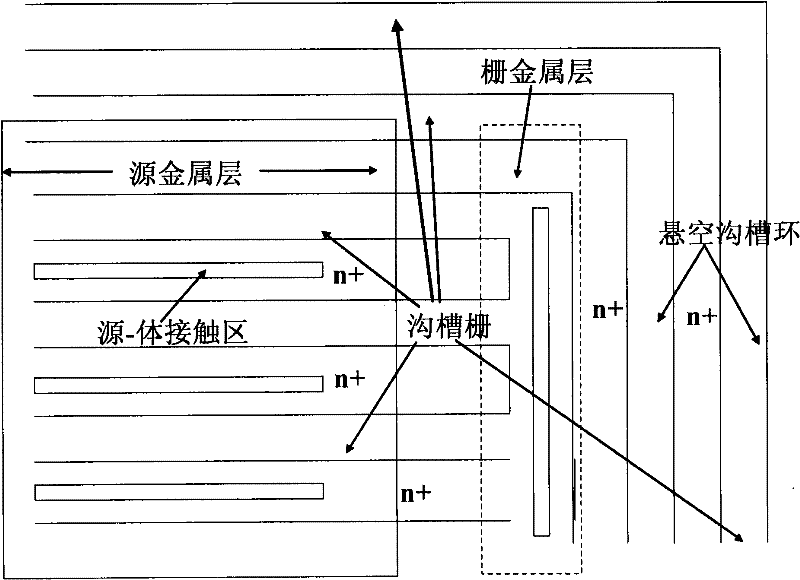

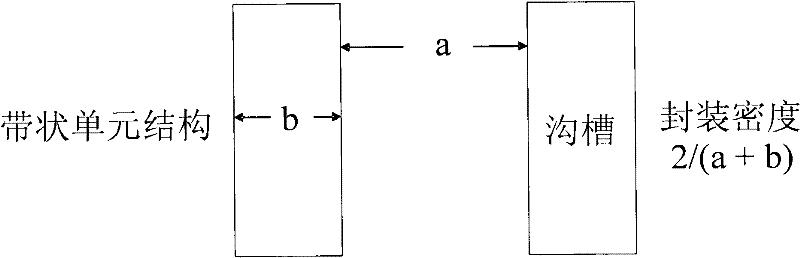

A kind of semiconductor power device and its manufacturing method

InactiveCN102263107AIncrease packing densityLow RdsTransistorSemiconductor/solid-state device manufacturingField-effect transistorSemiconductor

The invention discloses a trench metal oxide semiconductor field effect transistor device, which comprises a plurality of closed trench metal oxide semiconductor field effect transistor units surrounded by trench gates, forming a square or rectangular pattern in the active region. Closed cell structure. And in the terminal area of the device, multiple trench rings with floating voltage are included to improve the breakdown voltage of the device.

Owner:FORCE MOS TECH CO LTD

Fluted plane bigrid structure MOS device and its manufacturing method

InactiveCN1479355APrevent punch-throughSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon monoxideOptoelectronics

The part includes a substrate, a silicon monoxide layer. The silicon monoxide layer is deposited on the substrate, making entire part insulate from the substrate. Two grid electrodes are formed on silicon oxide layer. There is a groove between the two grid electrodes. The source electrode and drain electrode are formed on two sides of above grid electrode at plane higher than surface of the groove.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

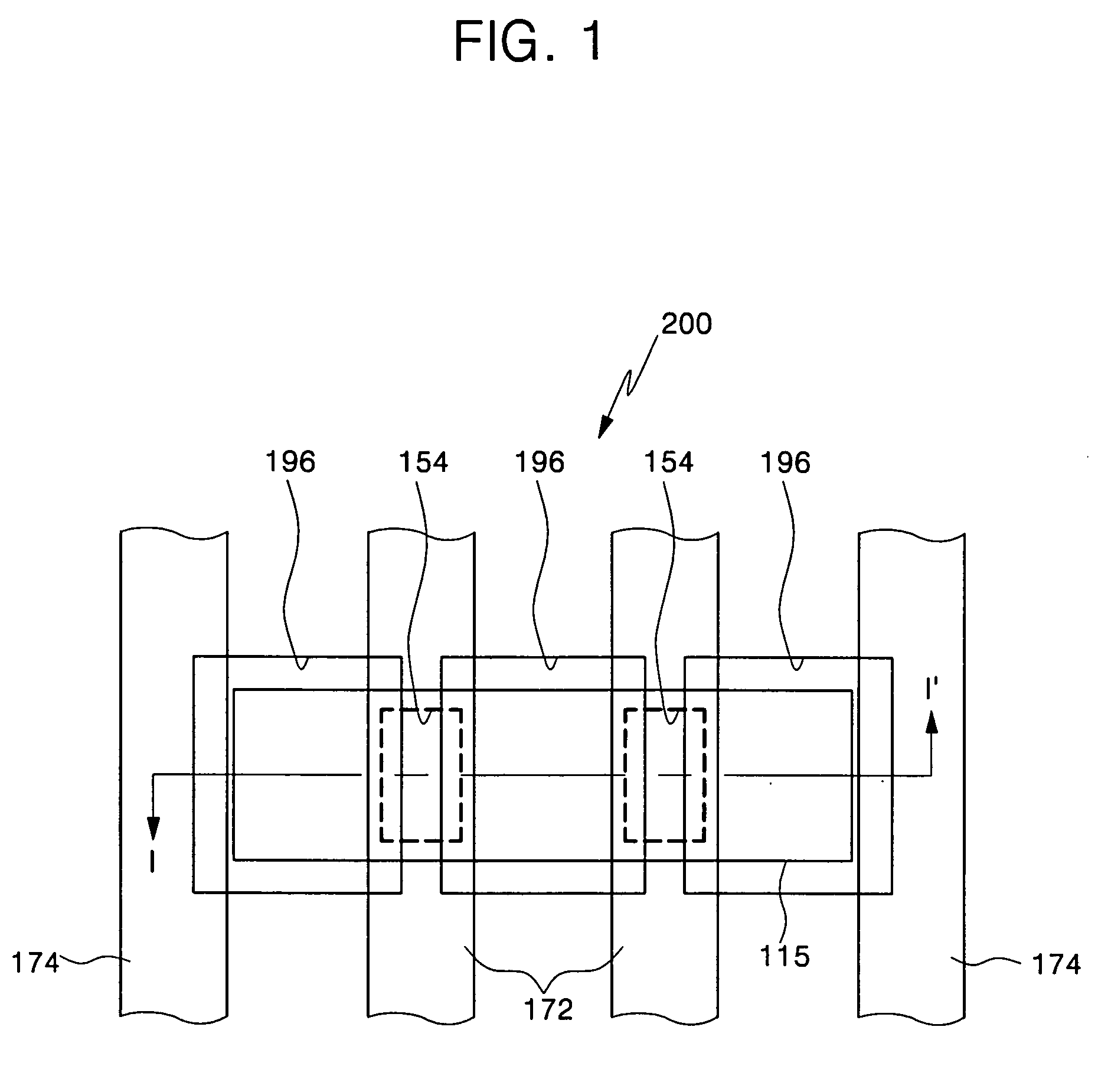

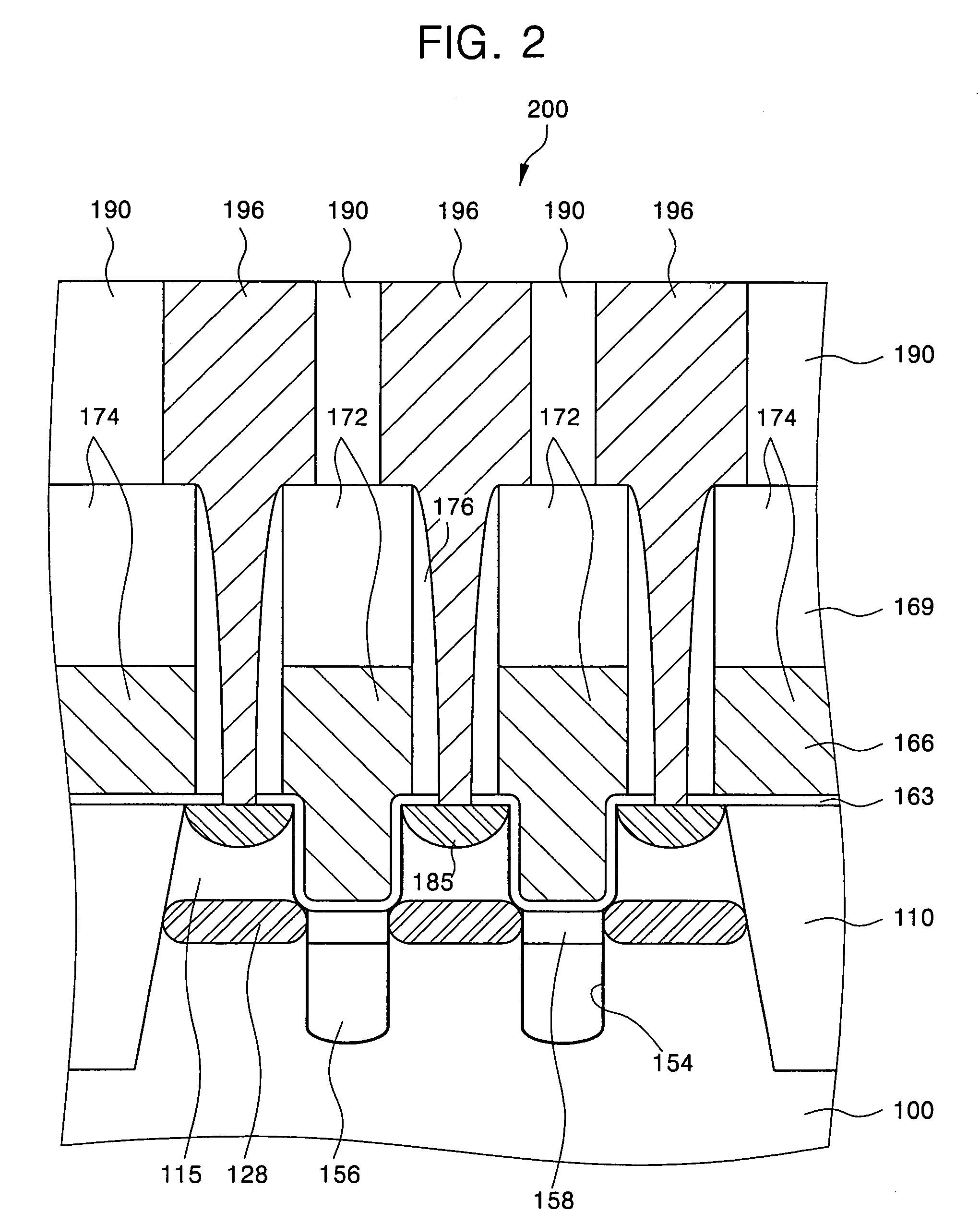

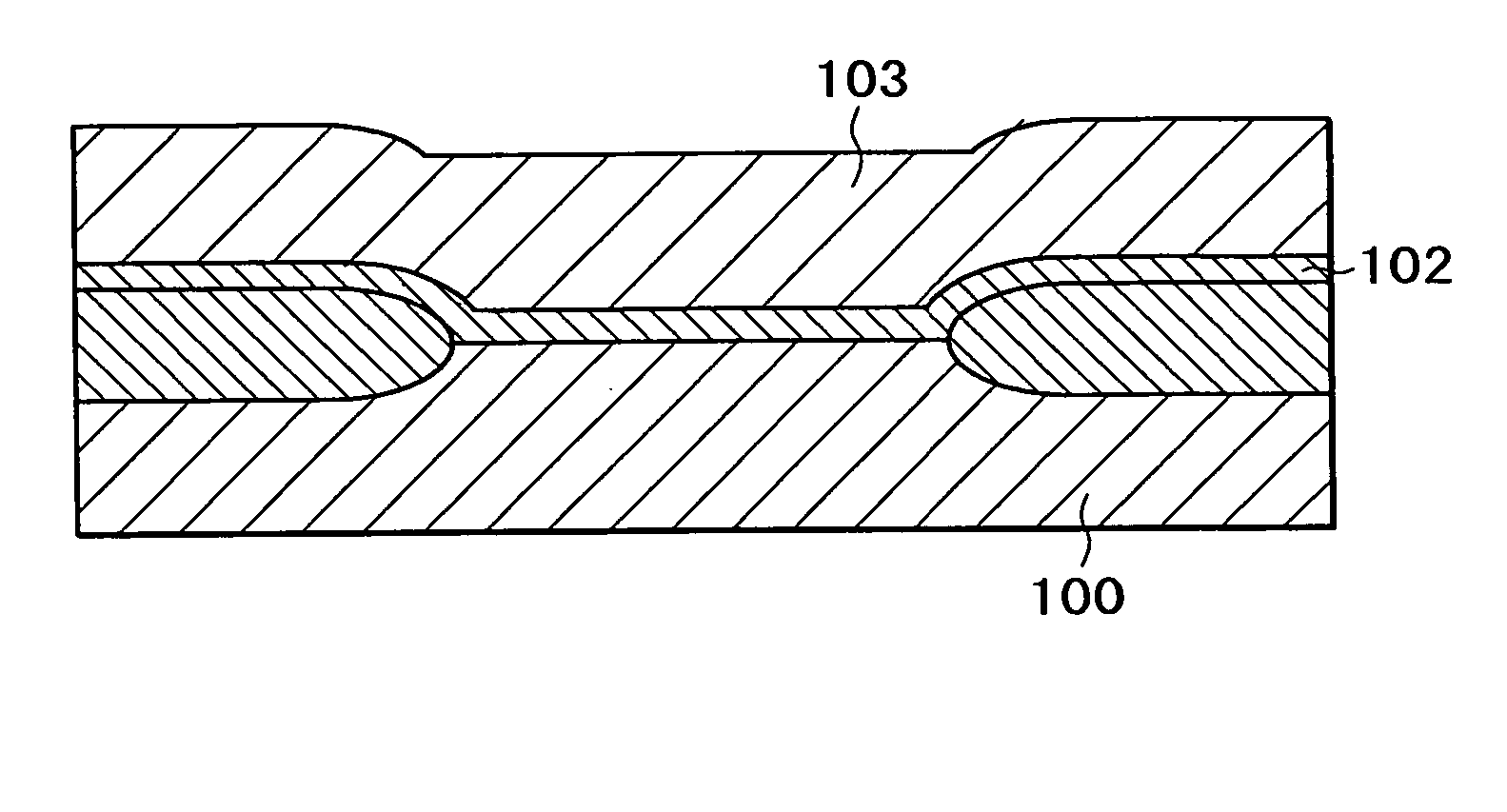

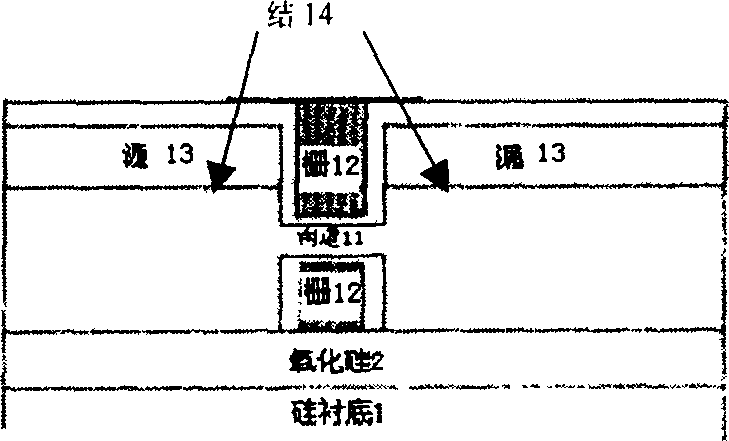

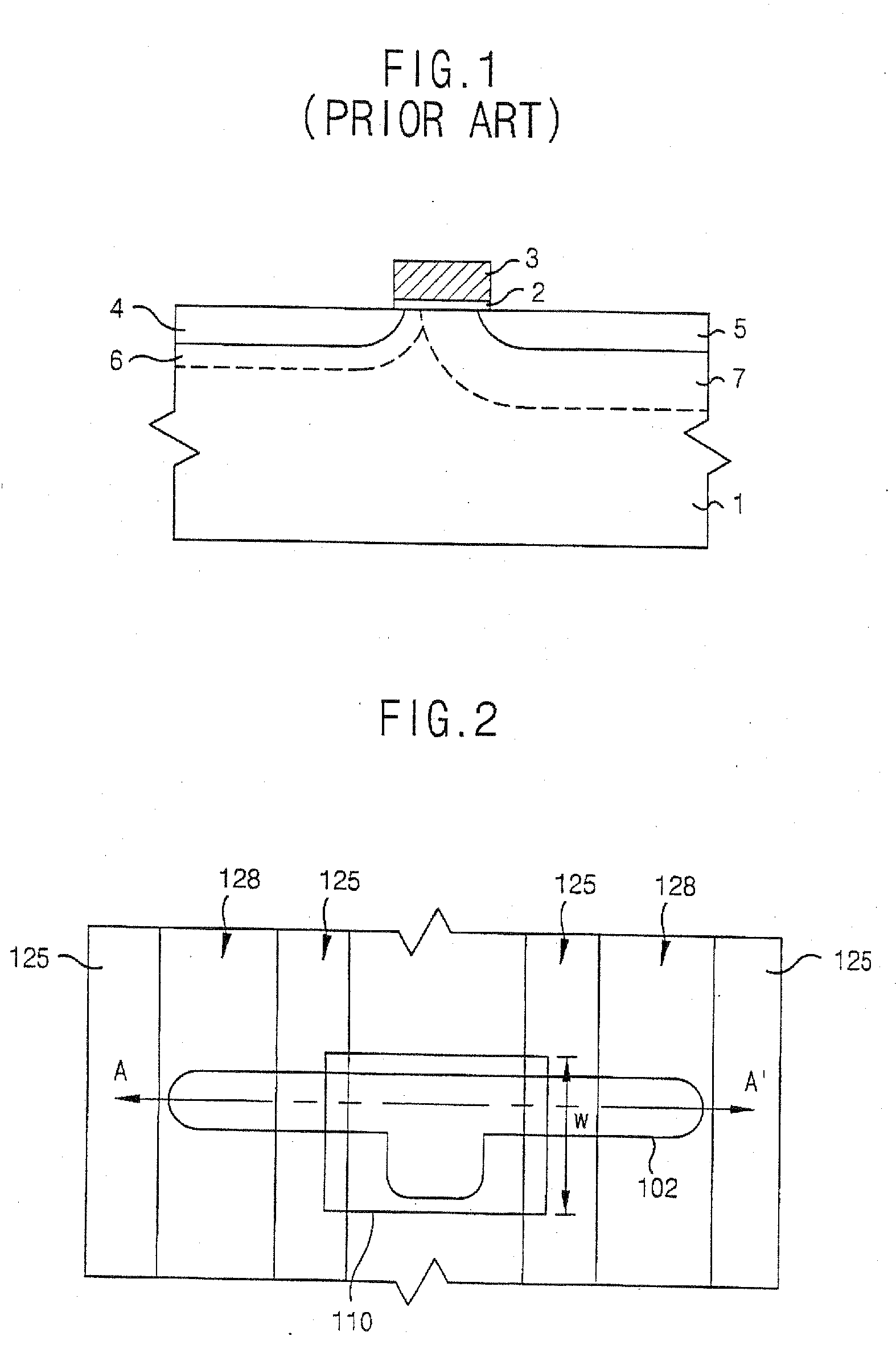

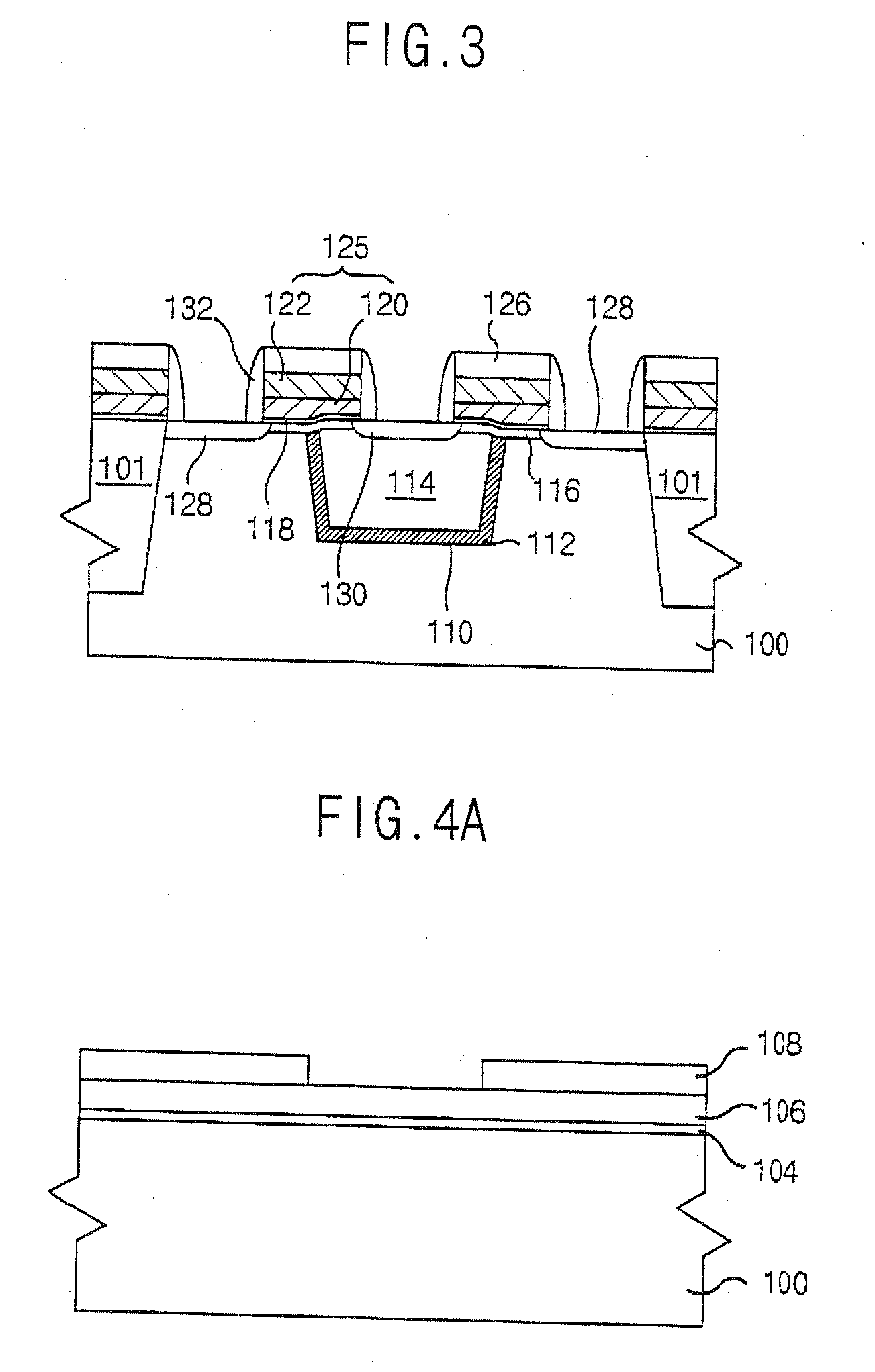

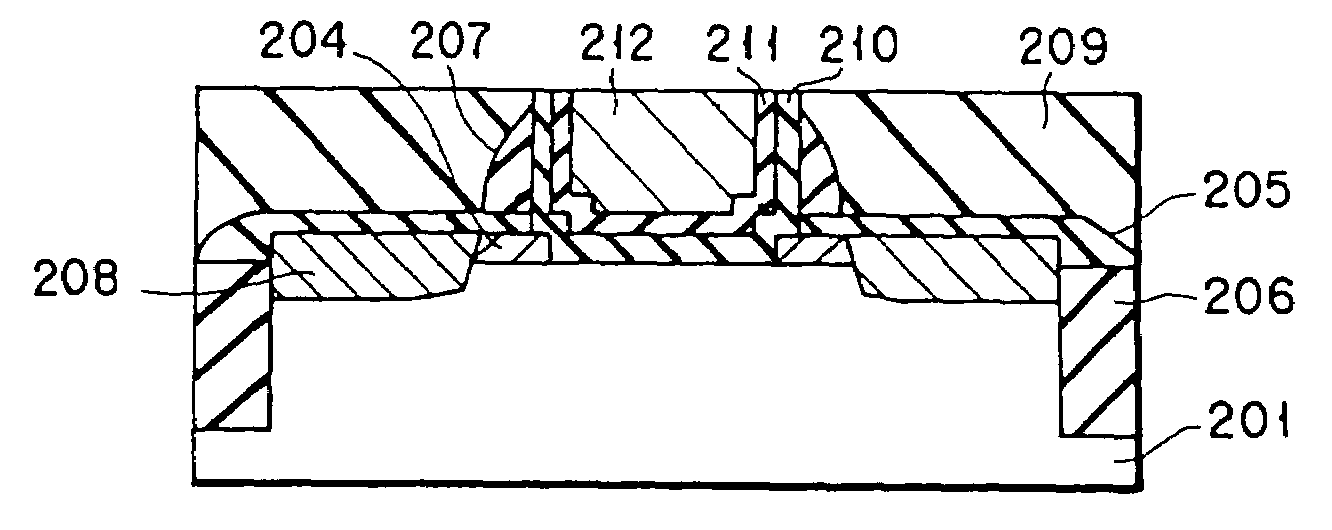

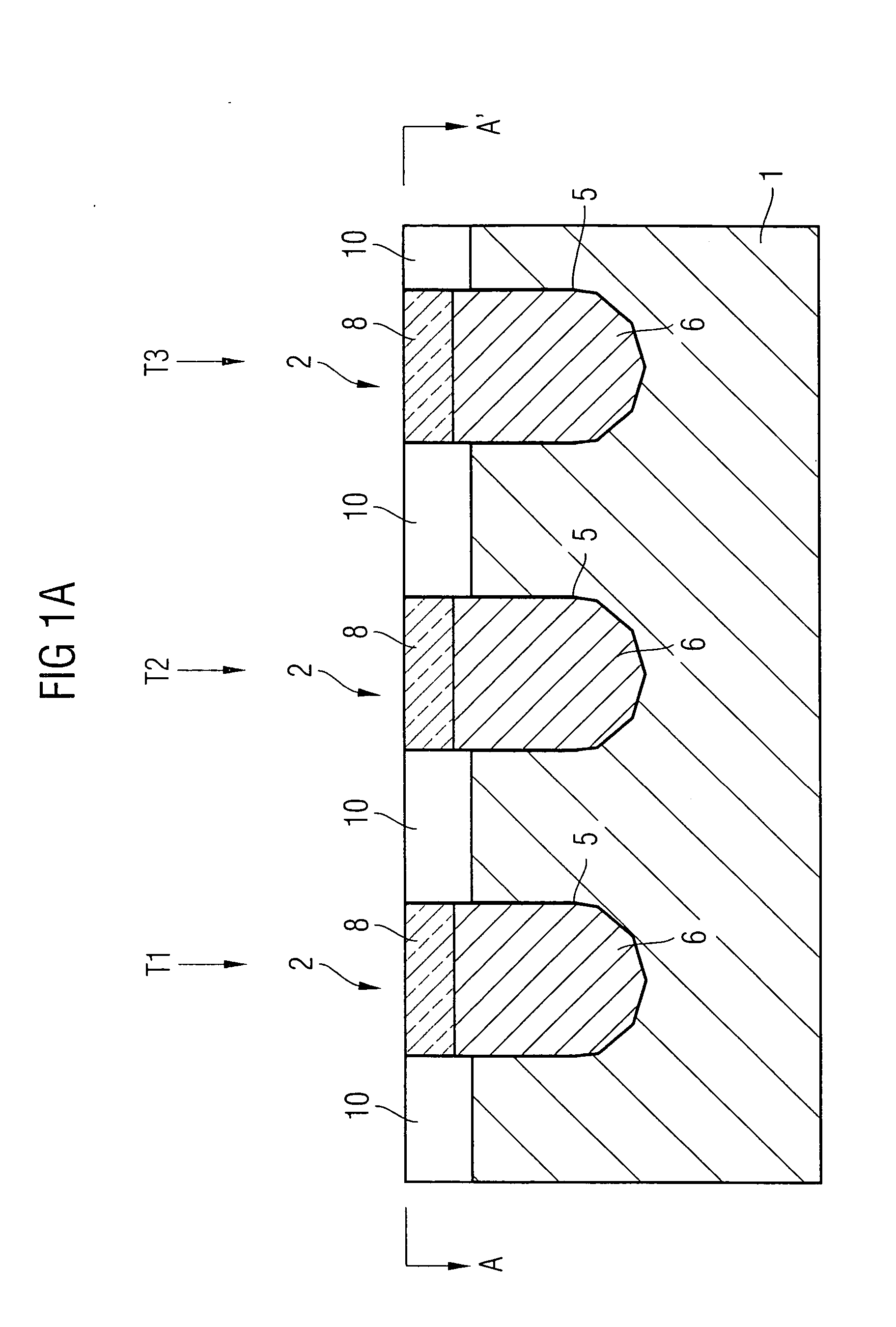

Semiconductor device and method of manufacturing the same

InactiveUS20070087500A1Improve operationPrevent punch-throughTransistorSolid-state devicesDevice materialSemiconductor

A semiconductor device and a method of manufacturing the same is disclosed. A trench is formed in an active region of a semiconductor substrate. A doped layer is formed on the inner walls of the trench. The trench is filled up with a first semiconductor layer. A gate insulating layer is formed on the first semiconductor layer and the substrate. Two gate electrodes are formed on the gate insulating layer such that the trench is located in between two gate electrodes. First and second impurity regions are formed in the substrate on both sides of each of the gate electrodes. Since the doped layer is locally formed in the trench area, the source and drain regions are completely separated from the heavily doped layer to weaken the electric field of PN junction, thereby improving refresh and preventing punchthrough between the source and drain.

Owner:SAMSUNG ELECTRONICS CO LTD

Manufacturing method of non-volatile memory

InactiveUS20080153232A1Simple processOperation efficiency is highSolid-state devicesSemiconductor/solid-state device manufacturingTrappingComputer science

A non-volatile memory including at least a substrate, a memory cell and source / drain regions is provided. The memory cell is disposed on the substrate and includes at least a first memory unit and a second memory unit. Wherein, the first memory unit, from the substrate up, includes a floating gate and a first control gate. The second memory unit is disposed on a sidewall of the first memory unit and includes a charge trapping layer and a second control gate. The two source / drain regions are disposed in the substrate at both sides of the memory cell.

Owner:POWERCHIP SEMICON CORP

Semiconductor device

InactiveUS7208797B2Small sizePrevent punch-throughTransistorSolid-state devicesSurface levelEngineering

There is provided a semiconductor device including a substrate, a device isolation insulating film formed on the substrate, a gate electrode formed on the substrate, a gate wiring layer formed in the device isolation insulating film and connected to the gate electrode, source and drain electrodes arranged on the substrate to face each other via the gate electrode, and an insulating film covering bottom and side surfaces of each of the gate electrode and the gate wiring layer, wherein the gate, source and drain electrodes and gate wiring layer have upper surface levels equal to or lower than that of the device isolation insulating film.

Owner:KK TOSHIBA

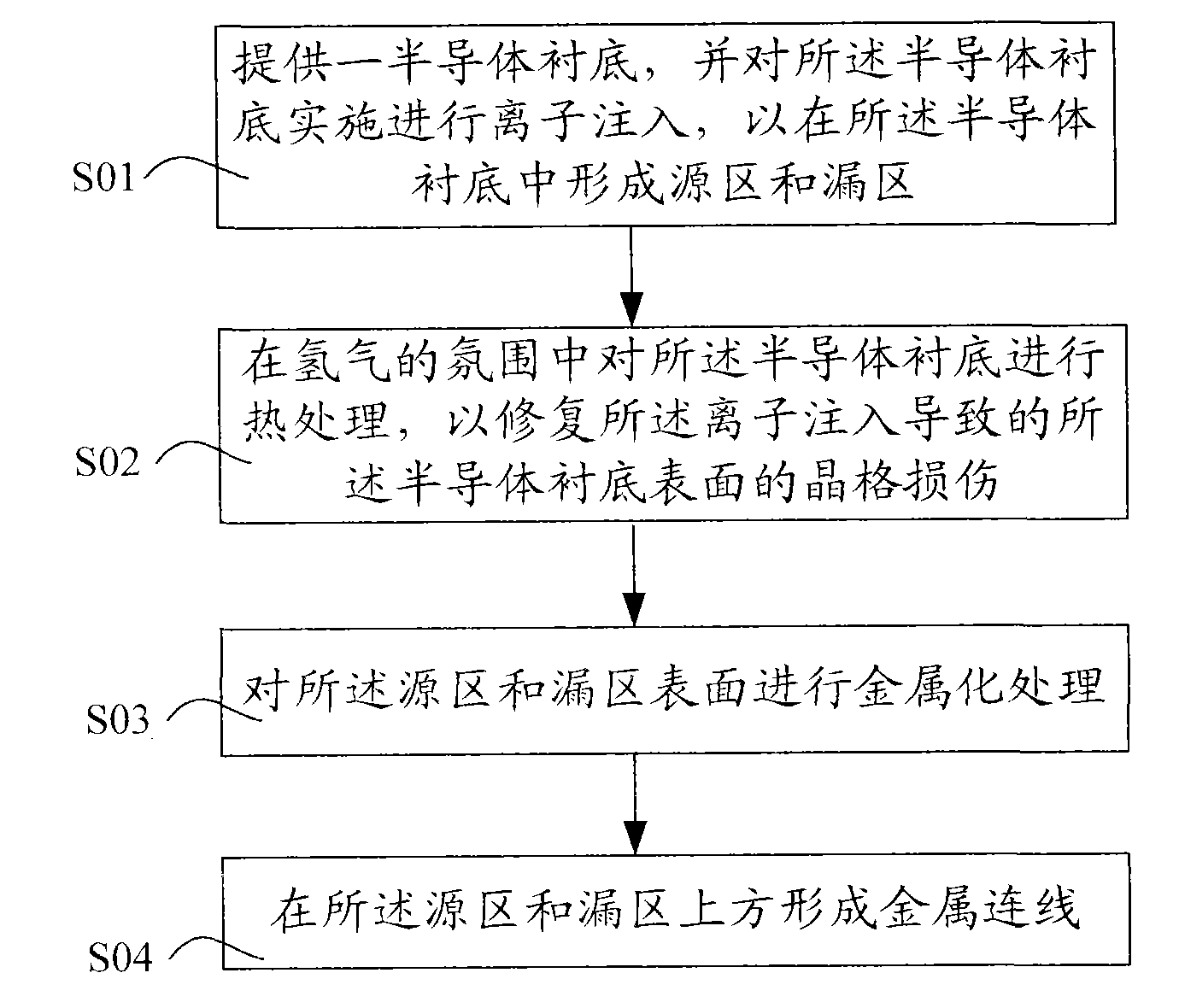

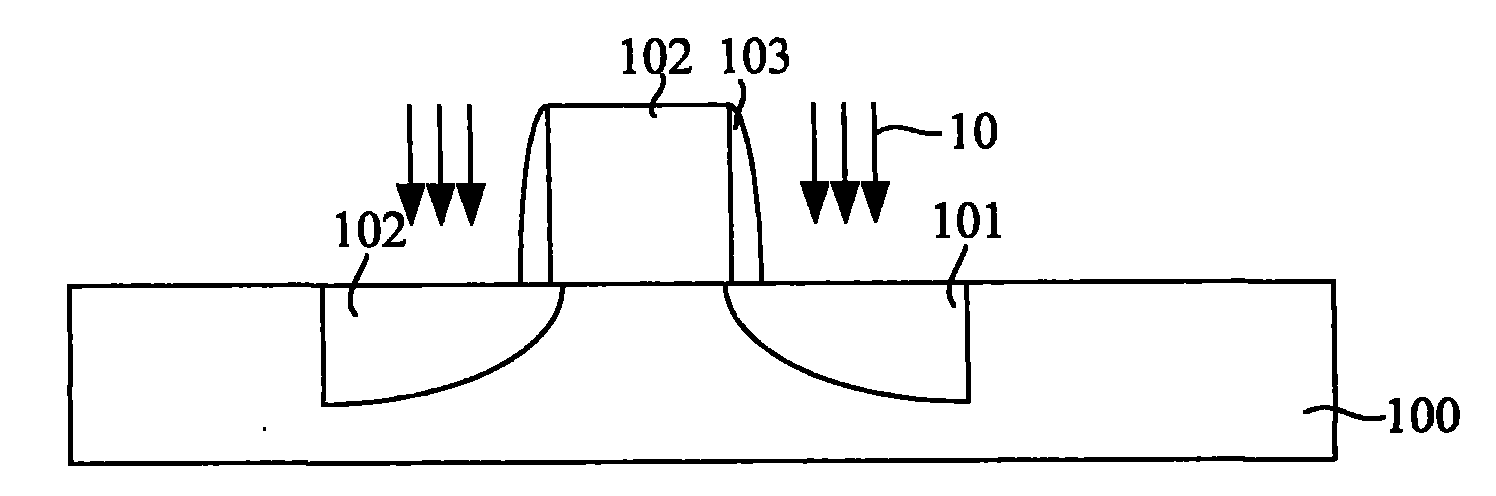

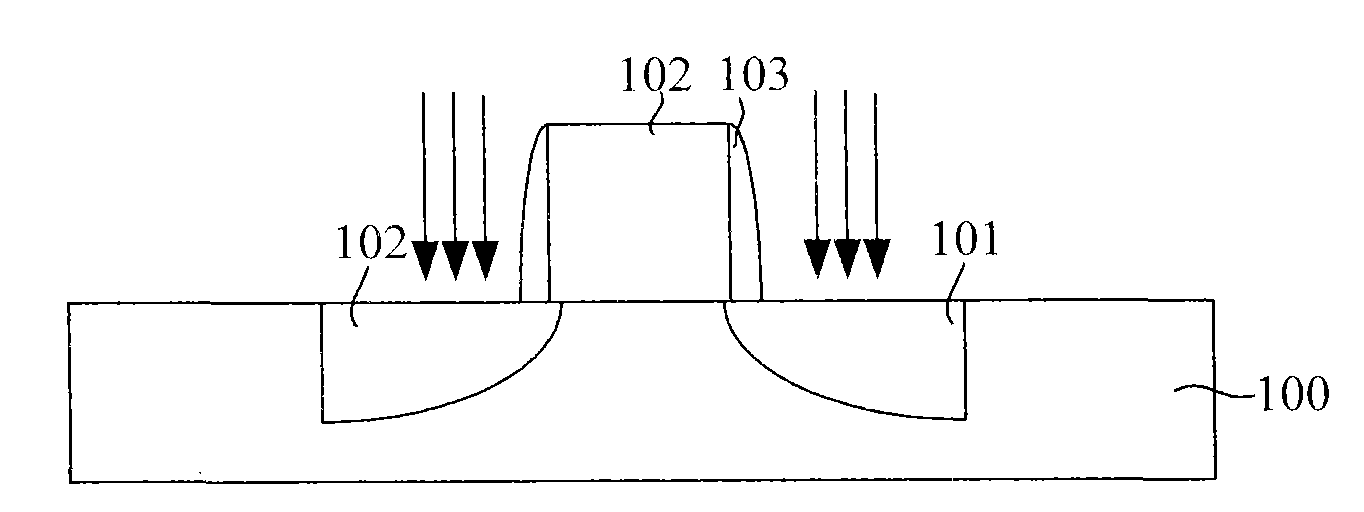

Method for repairing ion implantation damage

InactiveCN102655088AAvoid enteringPrevent punch-throughSemiconductor/solid-state device manufacturingElectrical conductorHydrogen atmosphere

The invention provides a method for repairing ion implantation damage, comprising the following steps of: providing a semiconductor substrate, and implementing ion implantation process on the semiconductor substrate; performing heat treatment process on the semiconductor substrate in a hydrogen atmosphere, so as to repair ion implantation damage; performing metallization treatment on the semiconductor substrate; and forming a metal connection wire above the semiconductor substrate. Via the method, the lattice damage on the surface of the semiconductor substrate caused by ion implantation can be repaired, thus effectively preventing the deposited metal from entering in the semiconductor substrate during the subsequent metallization treatment process, and then reducing a leakage current, and avoiding a problem of the penetration of a device.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Non-volatile memory, manufacturing method and operating method thereof

ActiveUS20060289925A1Improve efficiencyLow working voltageTransistorSolid-state devicesTrappingComputer science

A non-volatile memory including at least a substrate, a memory cell and source / drain regions is provided. The memory cell is disposed on the substrate and includes at least a first memory unit and a second memory unit. Wherein, the first memory unit, from the substrate up, includes a floating gate and a first control gate. The second memory unit is disposed on a sidewall of the first memory unit and includes a charge trapping layer and a second control gate. The two source / drain regions are disposed in the substrate at both sides of the memory cell.

Owner:POWERCHIP SEMICON MFG CORP

NROM semiconductor memory device and fabrication method

InactiveUS20060108646A1Prevent punch-throughSolid-state devicesSemiconductor/solid-state device manufacturingDielectricMOSFET

This invention relates to a method for producing an NROM semiconductor memory device and a corresponding NROM semiconductor memory device. The inventive production method comprises the following steps: a plurality of spaced-apart U-shaped MOSFETS are provided along rows in a first direction and along gaps in a second direction inside trenches of a semiconductor substrate, said U-shaped MOSFETS comprising a multilayer dielectric, especially an ONO dielectric, for trapping charges; source / drain areas are provided between the U-shaped MOSFETS in intermediate spaces located between the rows that extend parallel to the gaps; insulating trenches are provided in the source / drain areas between the U-shaped MOSFETS of adjacent gaps, down to a certain depth in the semiconductor substrate, said insulating trenches cutting up the source / drain areas into respective bit lines; the insulating trenches are filled with an insulating material; and word lines are provided for connecting respective rows of U-shaped MOSFETS.

Owner:QIMONDA

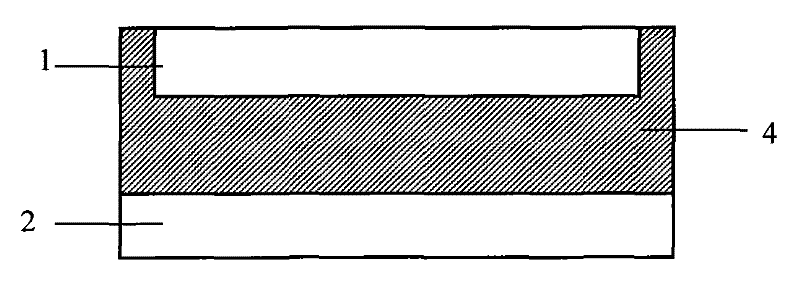

Manufacturing method of silicon MOS transistor on partially consumed insulating layer

InactiveCN101661889BImproving the ability to resist short channel effectEnhanced ability to resist short channel effectsSemiconductor/solid-state device manufacturingSilicon chipIon implantation

The invention discloses a manufacturing method of a PD SOI MOS transistor, which comprises the processes of defining an active area on an SOI silicon chip and doping after a gate electrode is formed, wherein the processes comprise the steps of: A. implanting angled ions by taking the gate electrode as a masking film, wherein the type of the implanted impurity is a first type of impurity with the same type as that of the impurity at the bottom inside the silicon film layer of the SOI silicon chip; B. implanting conventional ions by taking the gate electrode as the masking film, wherein the type of the implanted impurity is a second type of impurity with the type opposite to that of the first type of impurity; C. forming side wall layers at two sides of the gate electrode; D. implanting theangled ions by taking the gate electrode and the side wall layers as the masking film, wherein the type of the implanted impurity is the first type of impurity, and the ion implantation energy is setto be higher than that of the angled ions in step A; and E, implanting the conventional ions by taking the gate electrode and the side wall layers as the masking film, wherein the type of the implanted impurity is the second type of impurity. The method effectively inhibits the punch-through of DIBL effect and source leakage deep areas, thus greatly promoting the short channel effect resistant capability of the device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Methods of fabricating a semiconductor device having a metal gate pattern

InactiveUS20060270205A1Reduce layeringReduce oxidationSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

A method of fabricating a semiconductor device having a metal gate pattern is provided in which capping layers are used to control the relative oxidation rates of portions of the metal gate pattern during a oxidation process. The capping layer may be a multilayer structure and may be etched to form insulating spacers on the sidewalls of the metal gate pattern. The capping layer(s) allow the use of a selective oxidation process, which may be a wet oxidation process utilizing partial pressures of both H2O and H2 in an H2-rich atmosphere, to oxidize portions of the substrate and metal gate pattern while suppressing the oxidation of metal layers that may be included in the metal gate pattern. This allows etch damage to the silicon substrate and edges of the metal gate pattern to be reduced while substantially maintaining the original thickness of the gate insulating layer and the conductivity of the metal layer(s).

Owner:SAMSUNG ELECTRONICS CO LTD

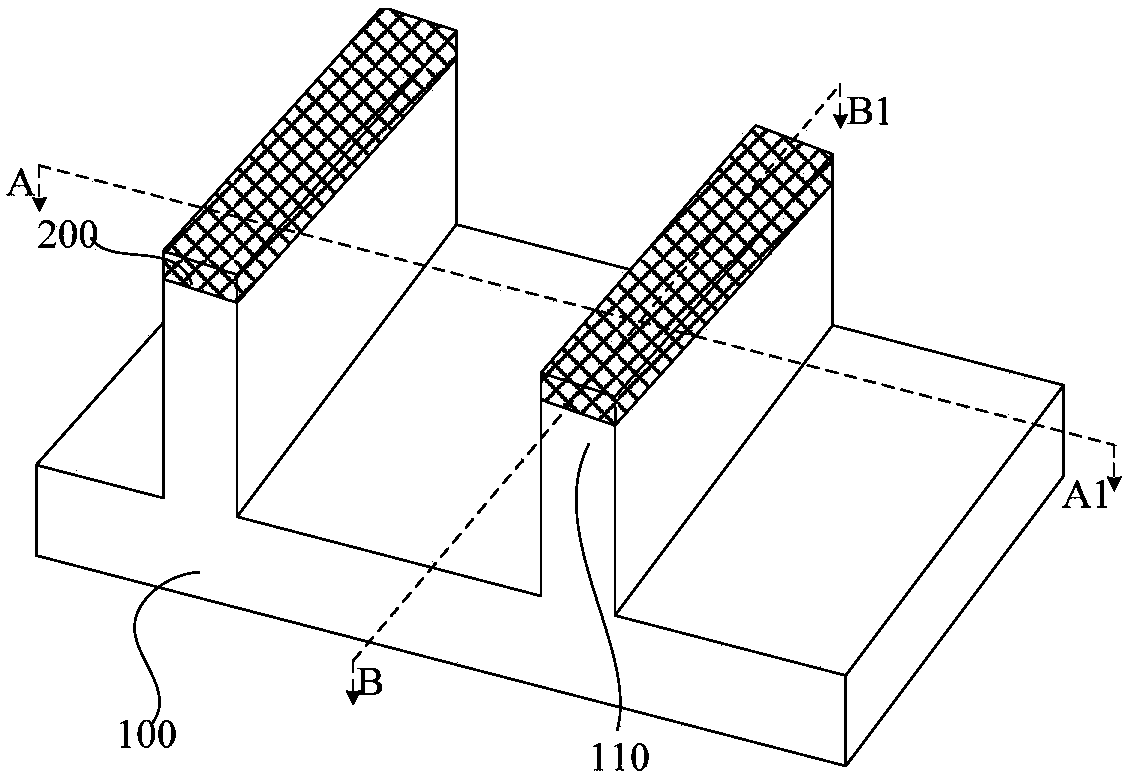

Formation method of fin-type field effect transistor

ActiveCN106856170ASpread evenlyEvenly distributedSemiconductor/solid-state device manufacturingSemiconductor devicesImpurity ionsEngineering

The invention provides a formation method of a fin-type field effect transistor. The method comprises: a semiconductor substrate is provided and a protruding fin part is formed on the semiconductor substrate; a gate structure stretching across and covering the side wall of the partial fin part and the top surface is formed; the fin part at the two sides of the gate structure is etched to form grooves; sacrificial layers doped with impurity ions are formed on the side walls and the bottom surface of the grooves; annealing is carried out on the sacrificial layers doped with impurity ions and thus the impurity ions in the sacrificial layers are diffused in the fin part in contact with the grooves to form a doping region; and then the sacrificial layers are removed. With the method, the impurity ions in the doping region can be distributed uniformly and the position of the doping region becomes accurate, so that an effect of preventing hot carrier injection or preventing punchthrough between source and drain regions can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1