Fluted plane bigrid structure MOS device and its manufacturing method

A technology of MOS device and double gate structure, which can be used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

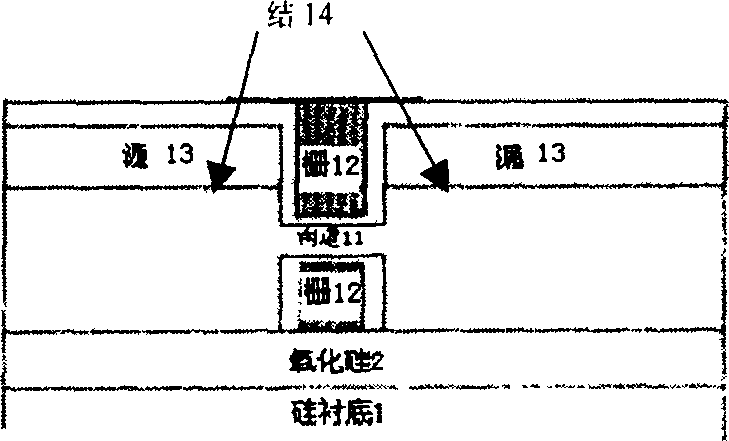

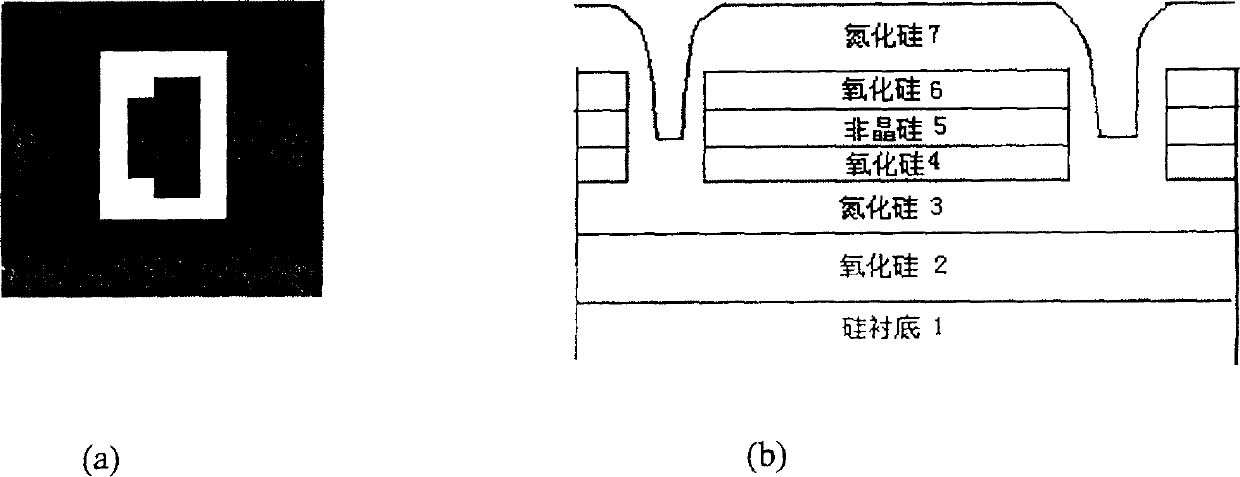

[0043] 1) To form the device structure as shown in Figure 1, first perform field oxidation on the single crystal silicon substrate 1 to form a buried oxide layer 2, and then deposit multiple layers of dielectrics, successively silicon nitride 3, silicon oxide 4, Amorphous silicon 5 and silicon oxide 6, as shown in Figure 2 (the first 9 steps in the process card).

[0044] 2) Lithograph the first layer (layout (a) in Figure 3, step 10 in the process card), etch off the top three layers to expose the silicon oxide layer 3 (steps 11-13 in the process card).

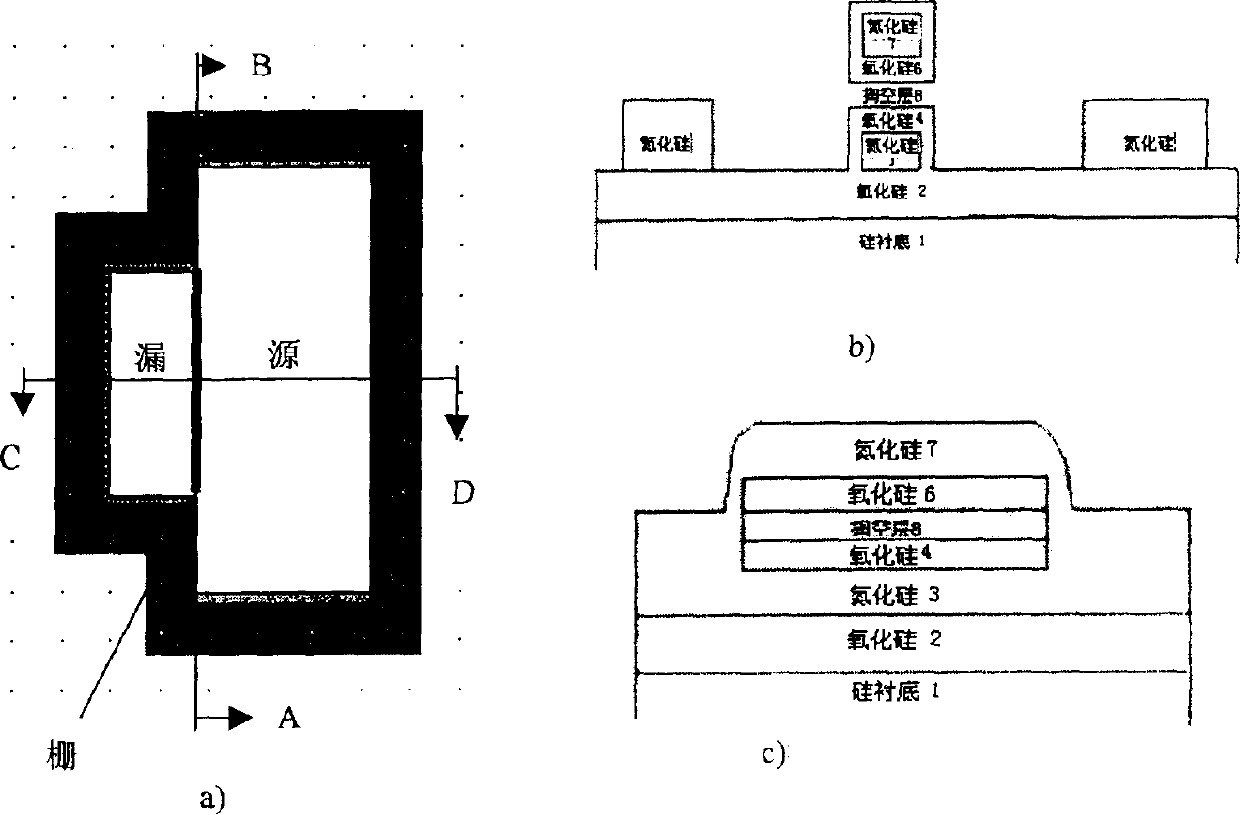

[0045] 3) As shown in Figure 3(b), deposit a layer of silicon nitride 7 to connect with the lower layer of silicon nitride 3 to ensure support for the hollowed out layer 8 (step 15 in the process card).

[0046] 4) Then perform the second photolithography (as shown in the layout (a) of Figure 4, step 22 in the process card), use electron beam exposure, and then etch (RIE) to etch dummy gate lines, from the top l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More