Manufacturing method of silicon MOS transistor on partially consumed insulating layer

A MOS transistor, silicon-on-insulator technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult integration of PDSOIMOS transistors, limited gate-to-channel control capability, and reduced threshold voltage, etc. Achieve the effect of enhancing the ability to resist short channel effects, suppressing the drain-induced barrier lowering effect, and reducing the impurity compensation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be described in further detail below with specific embodiments in conjunction with the accompanying drawings.

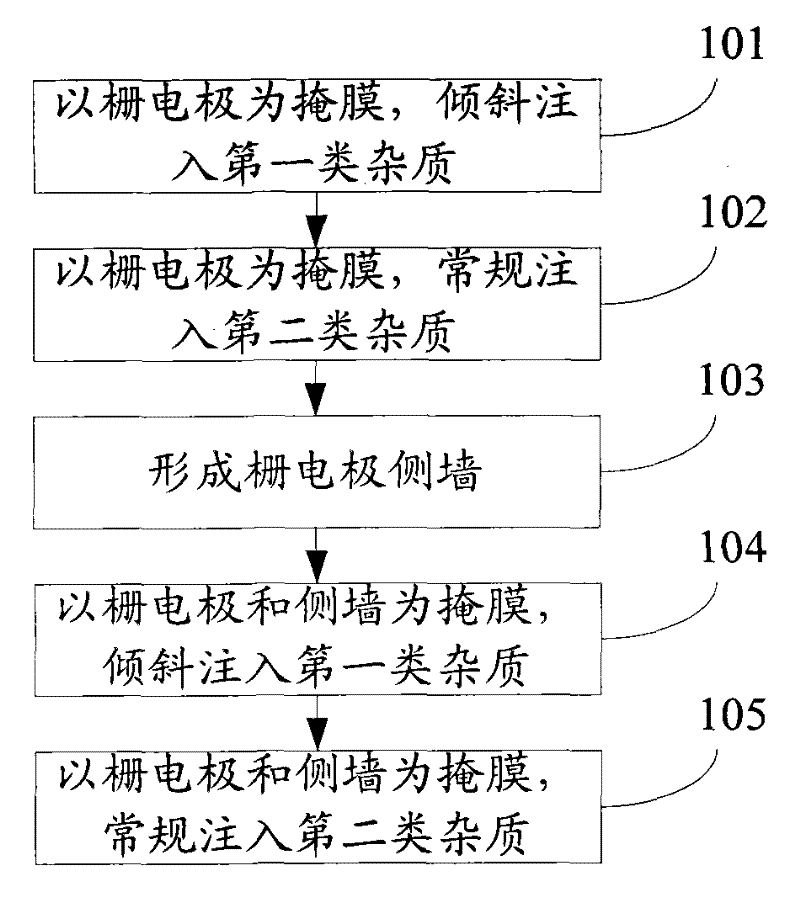

[0031] The present invention utilizes the structure of SOI silicon wafer, and through the design of the manufacturing process, when the body region of the PD SOI MOS transistor is doped, a heavily doped region is formed in the channel region, while no heavily doped region is formed in the source and drain regions. In order to maximize the channel effect of the control terminal, at the same time, it does not obviously bring various parasitic effects. In order to make the heavily doped region exhibit the above-mentioned distribution, the present invention adopts a two-time inclined ion implantation method combined with a reasonable combination of implantation energy and dose to implant a certain amount of impurities.

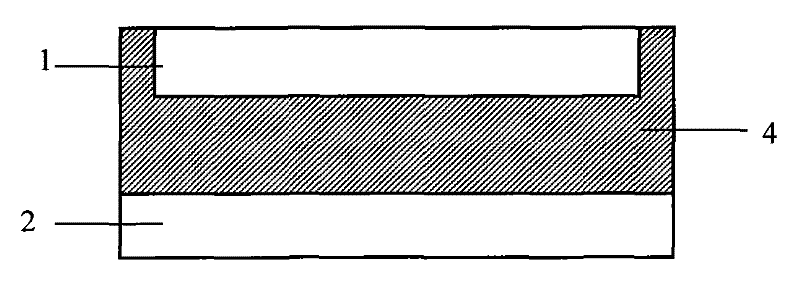

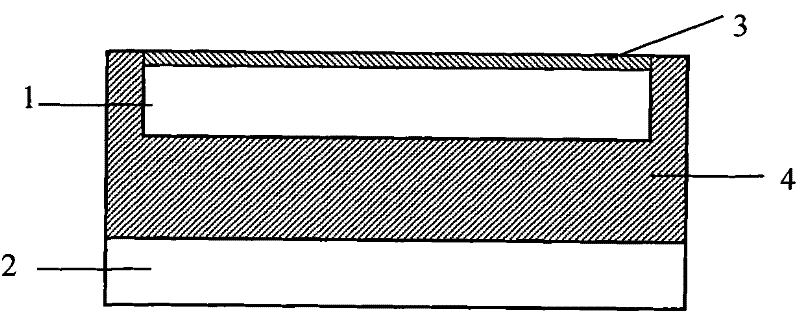

[0032] The structure of SOI wafer is as figure 1 As shown, it includes a bulk silicon substrate 2 , a buried oxide la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More