Patents

Literature

324 results about "Wafer stacking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

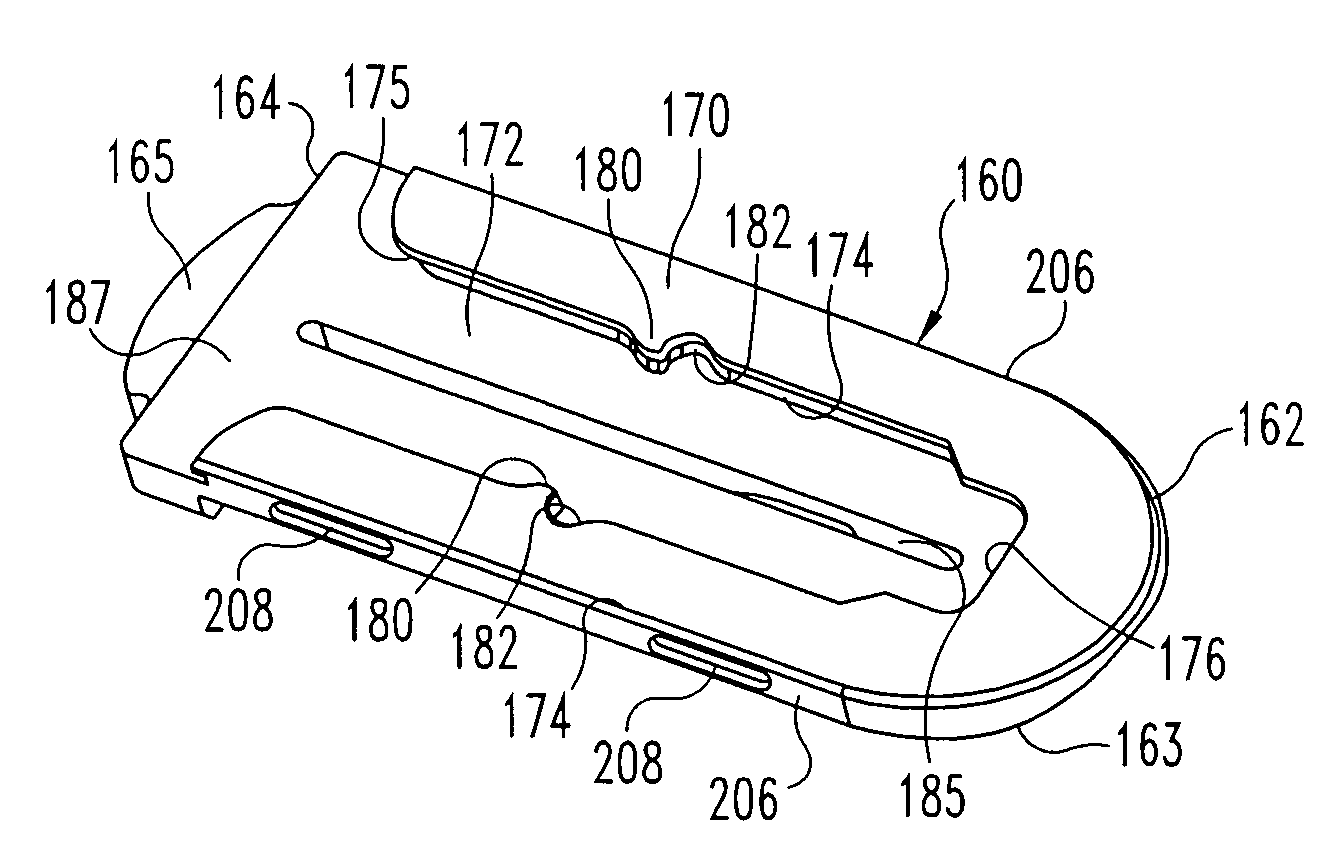

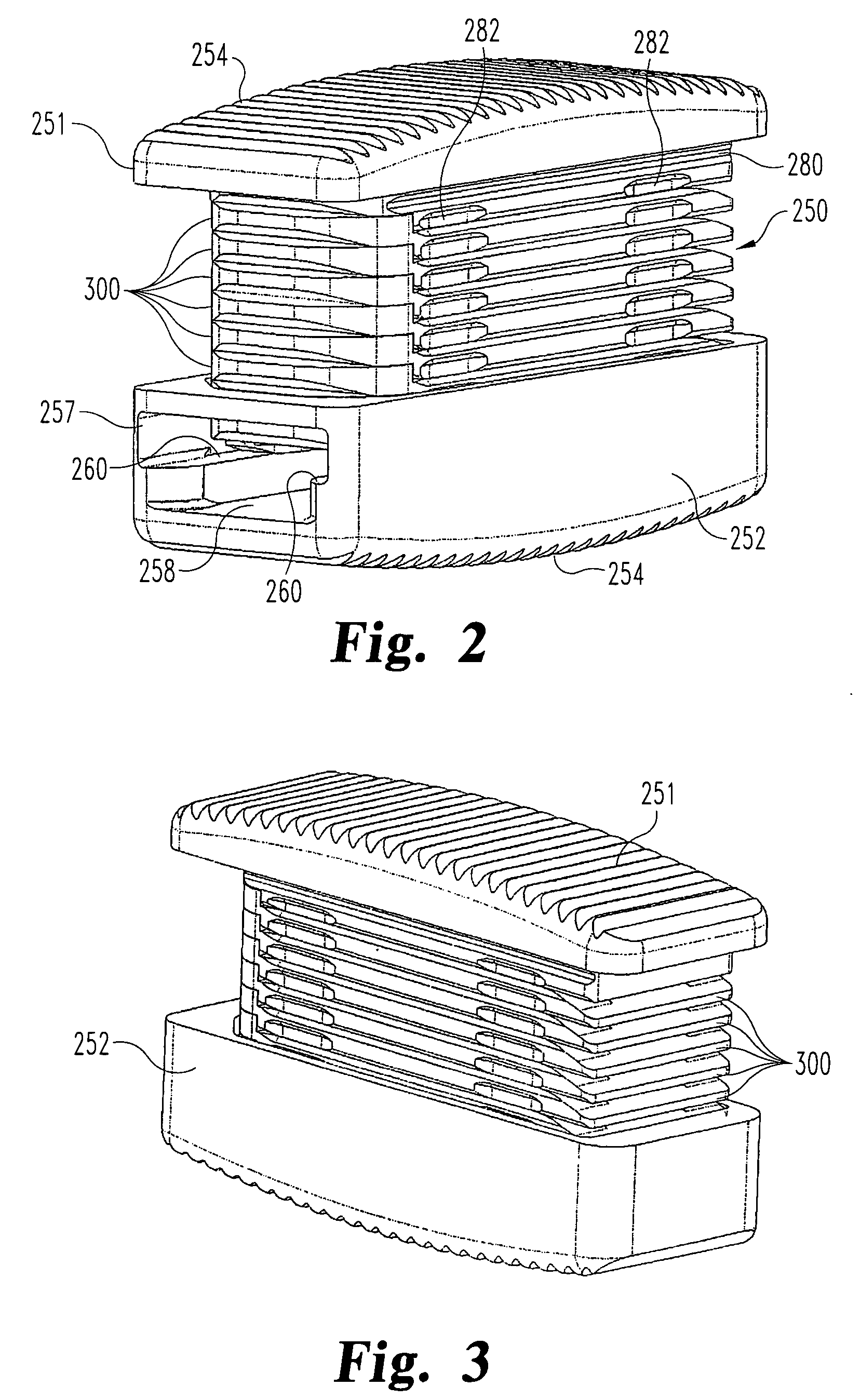

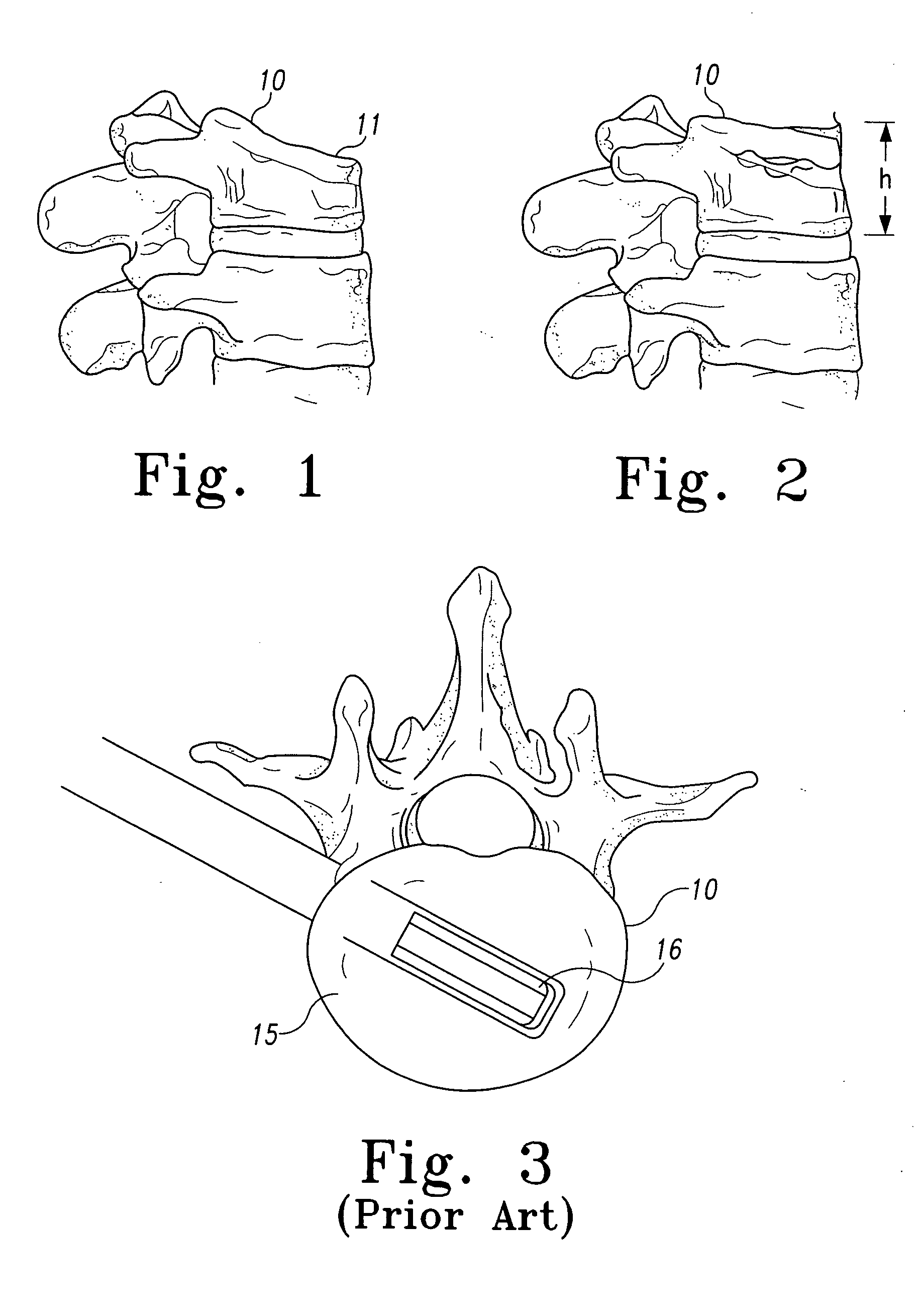

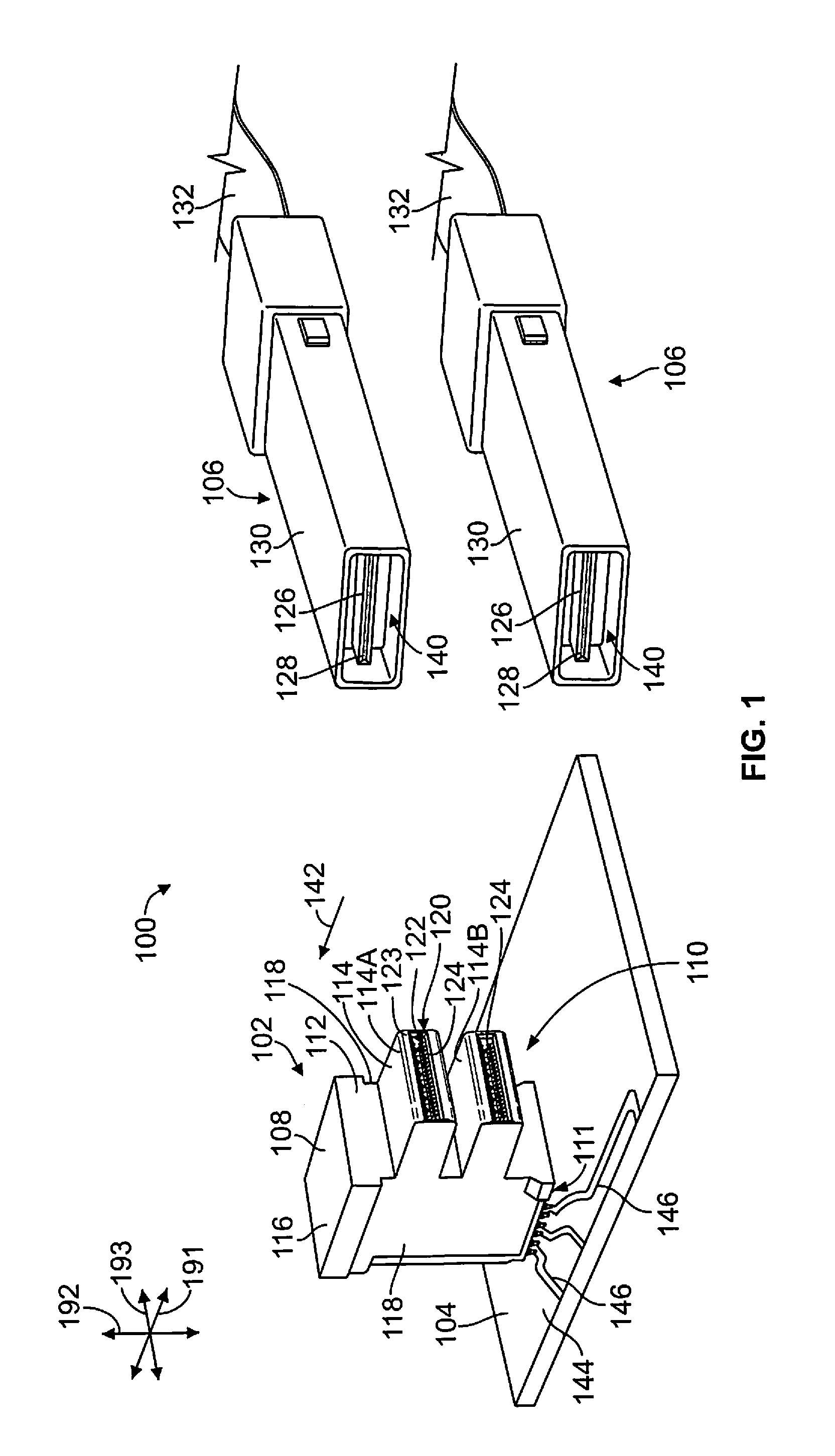

Expandable Interbody Fusion Device

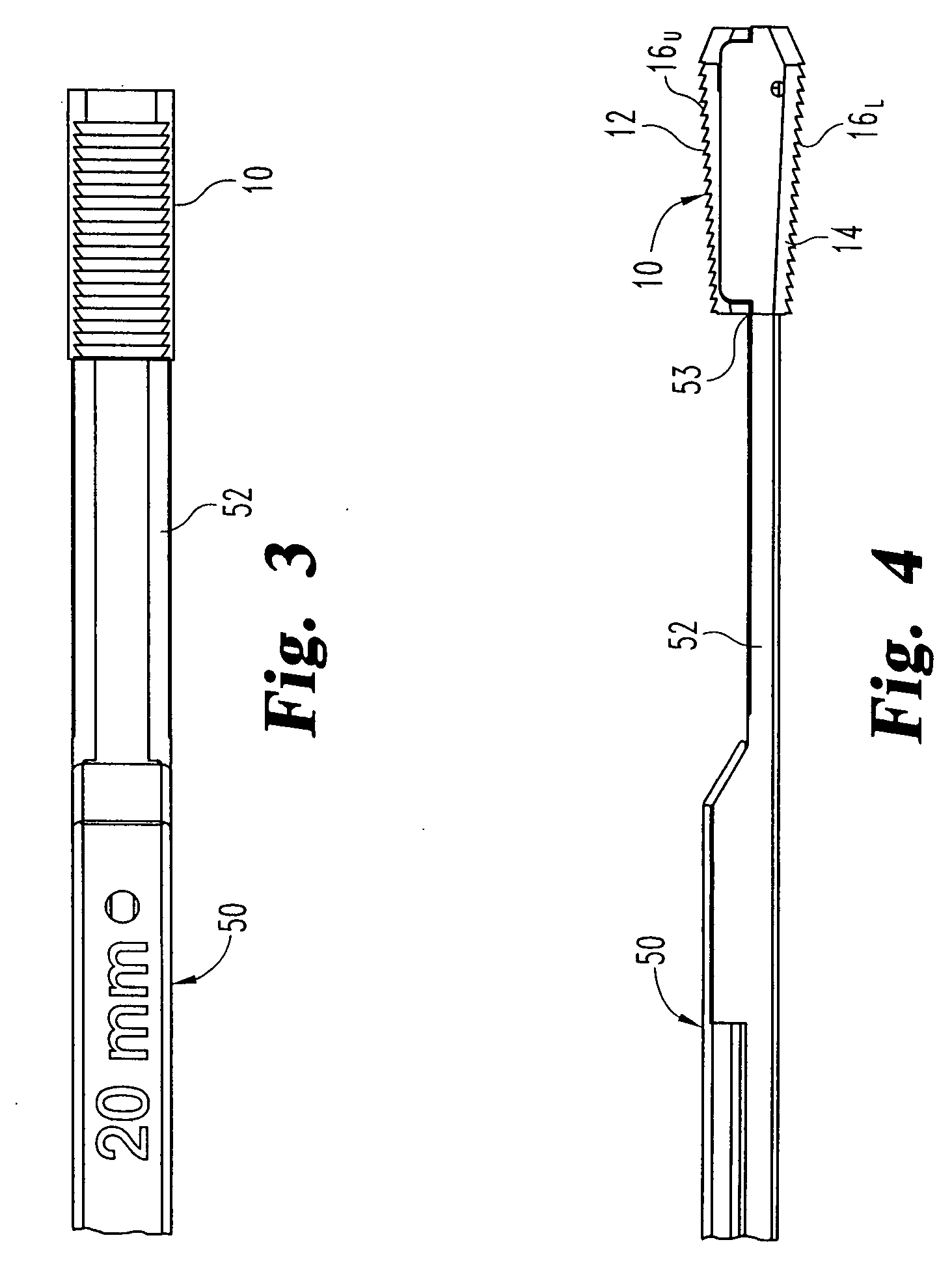

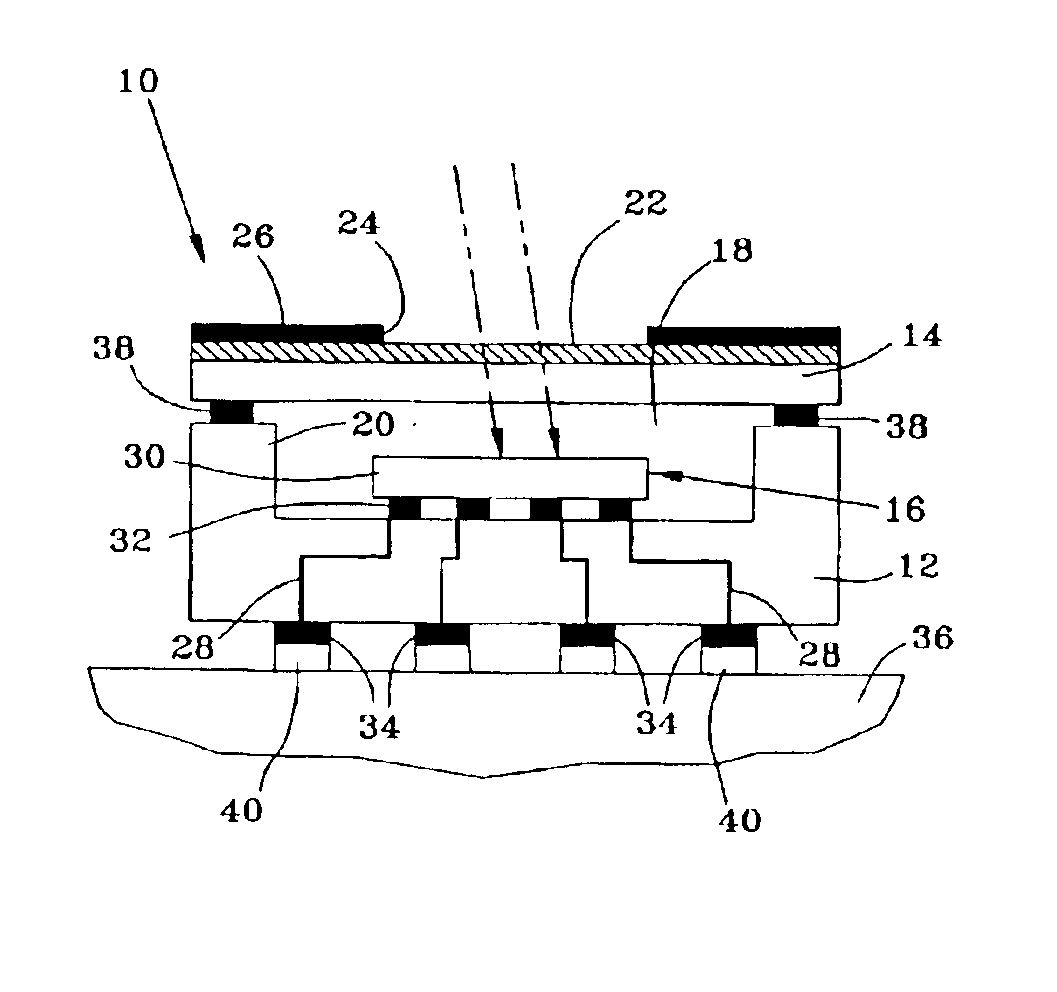

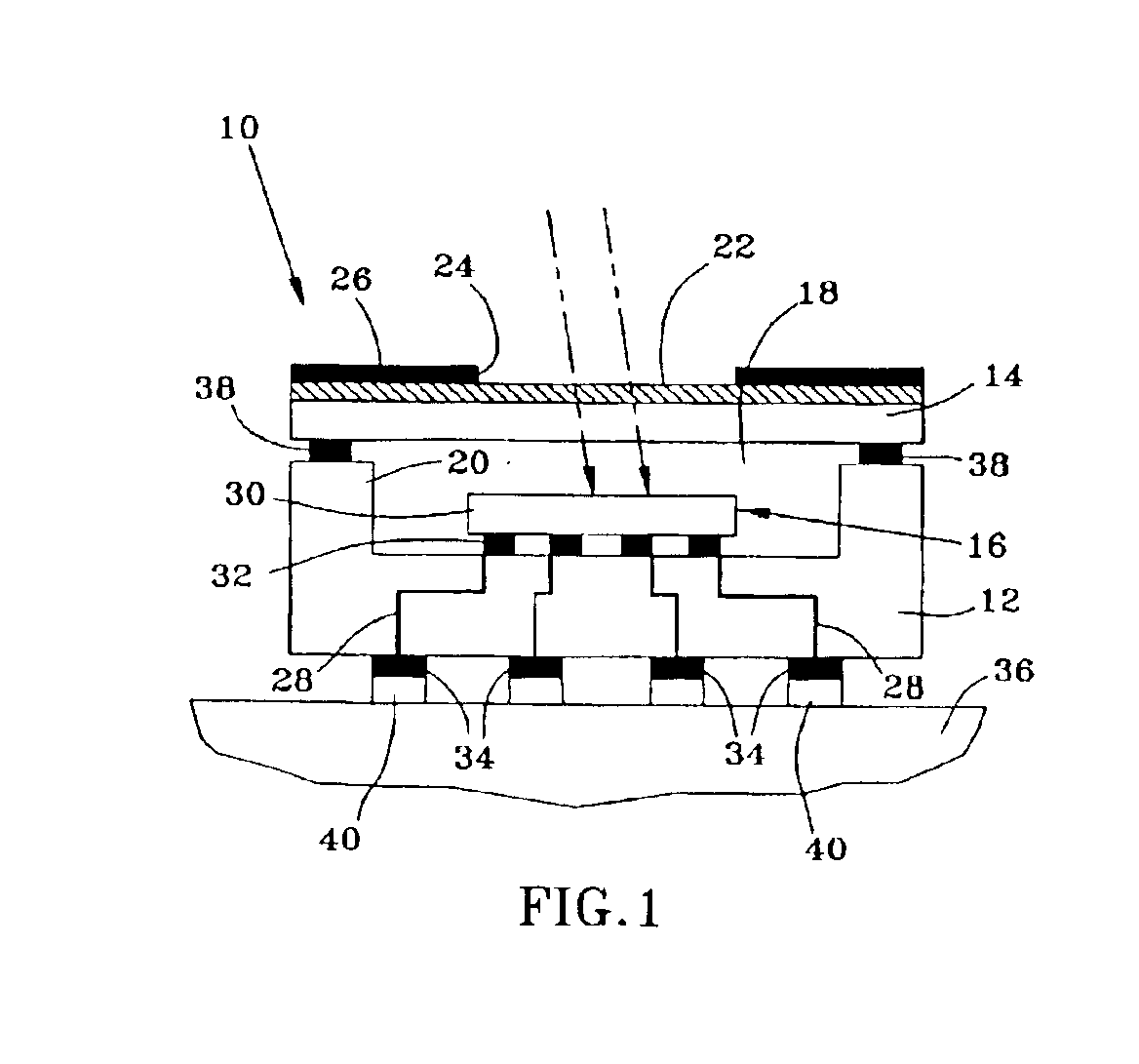

ActiveUS20080300598A1Prevent movementPrevent disengagement of the wafersJoint implantsSpinal implantsWafer stackingEngineering

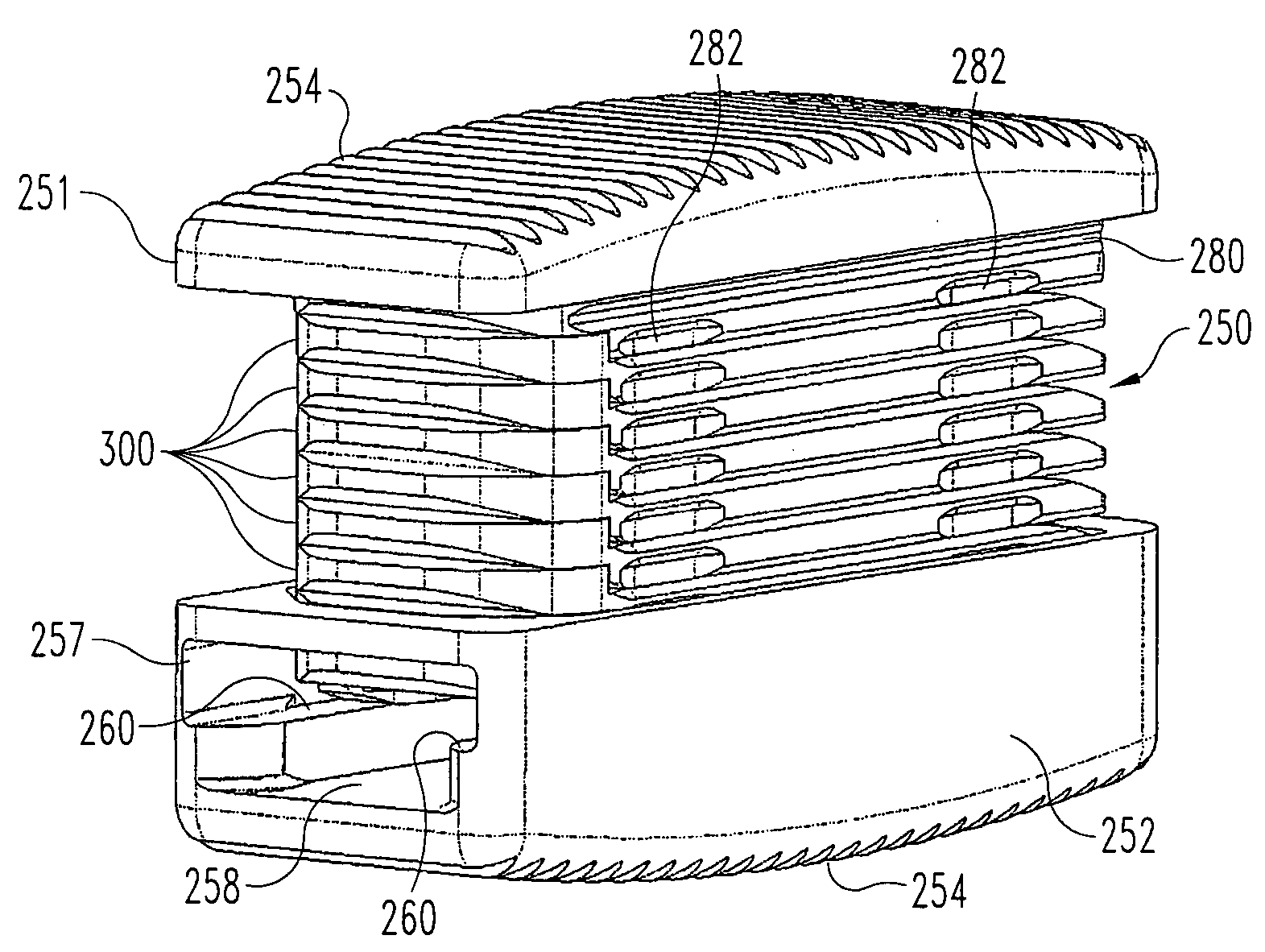

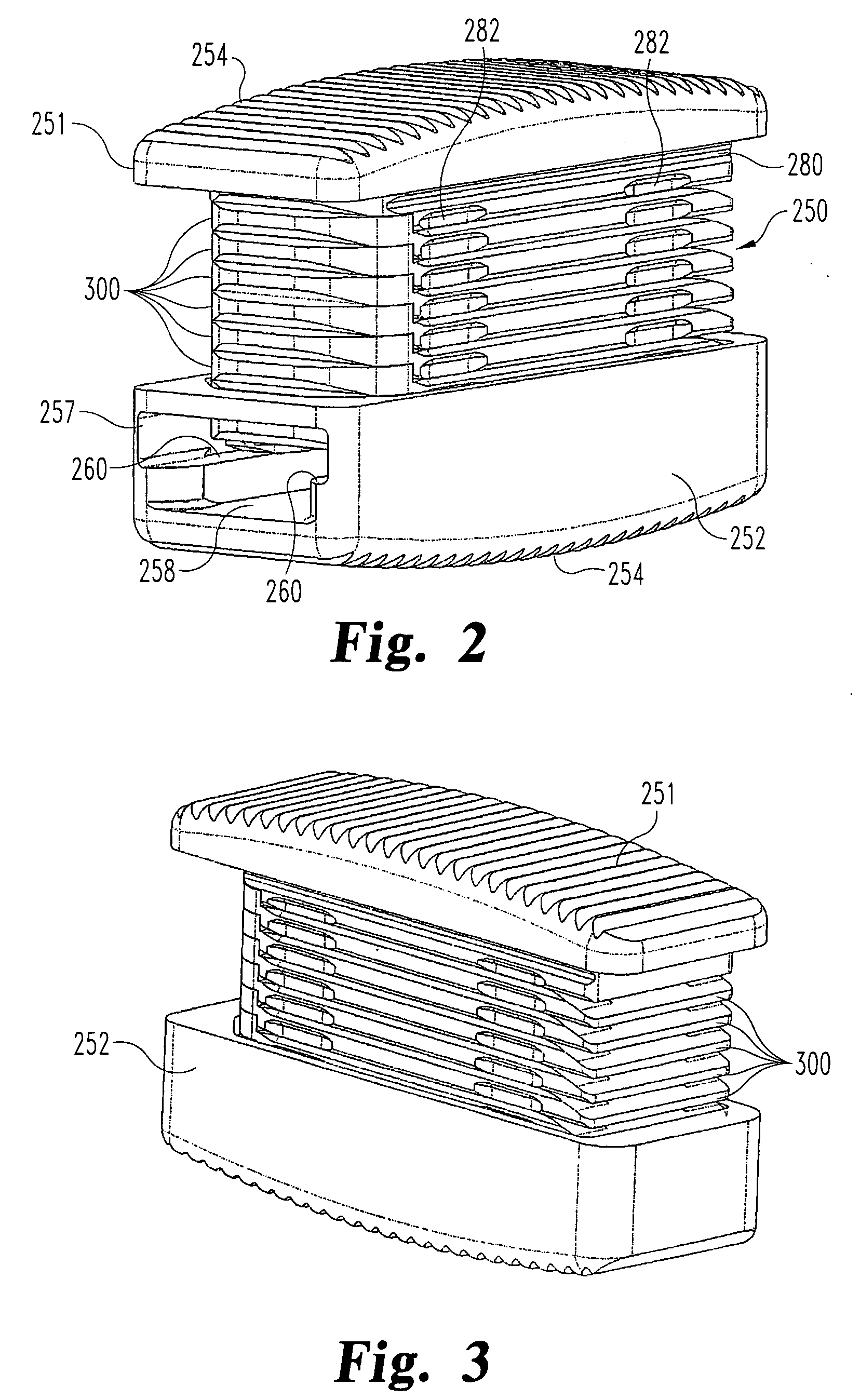

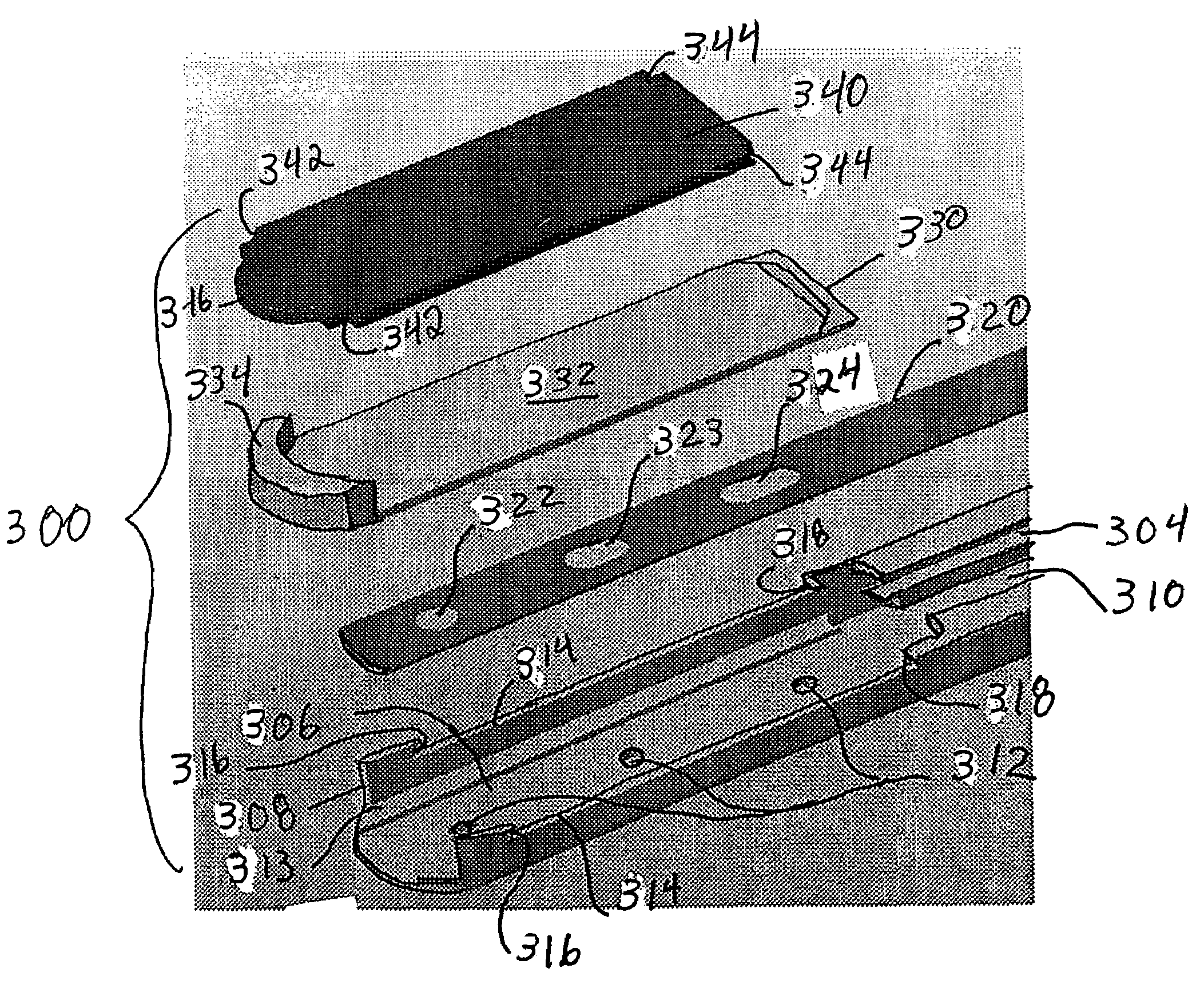

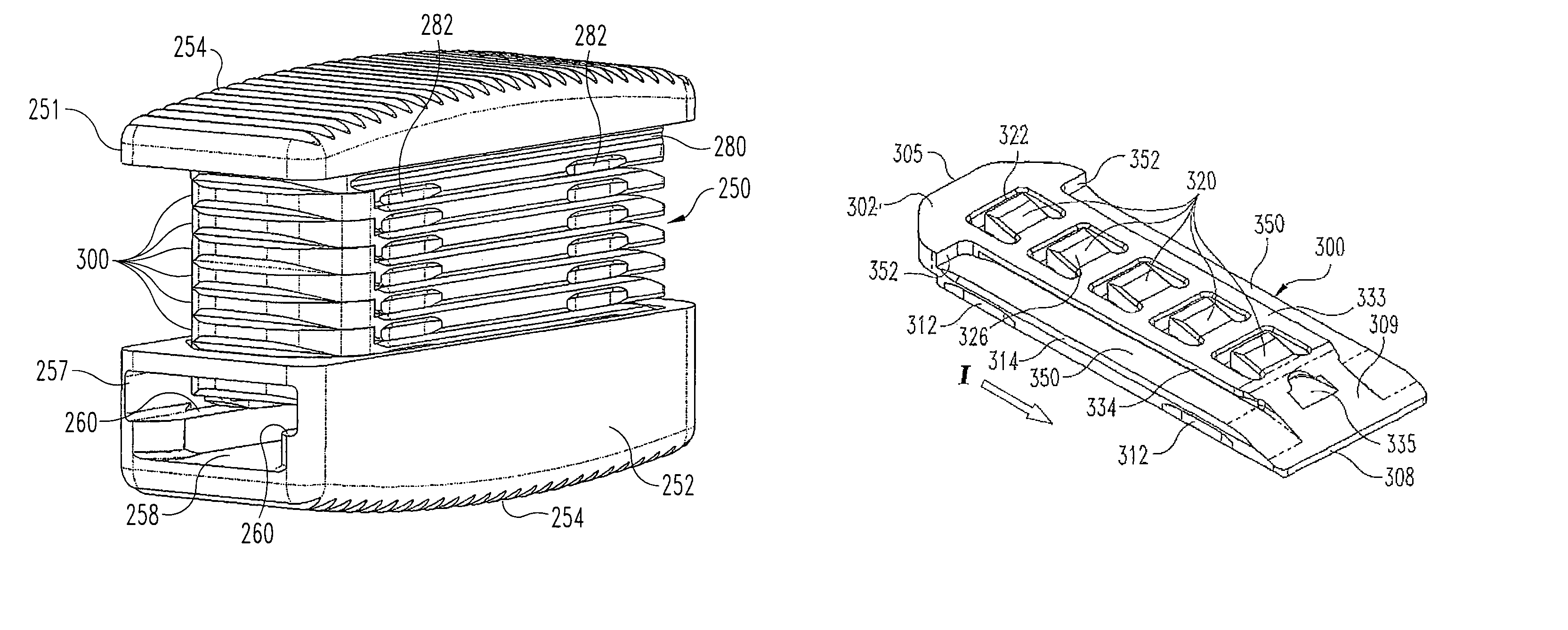

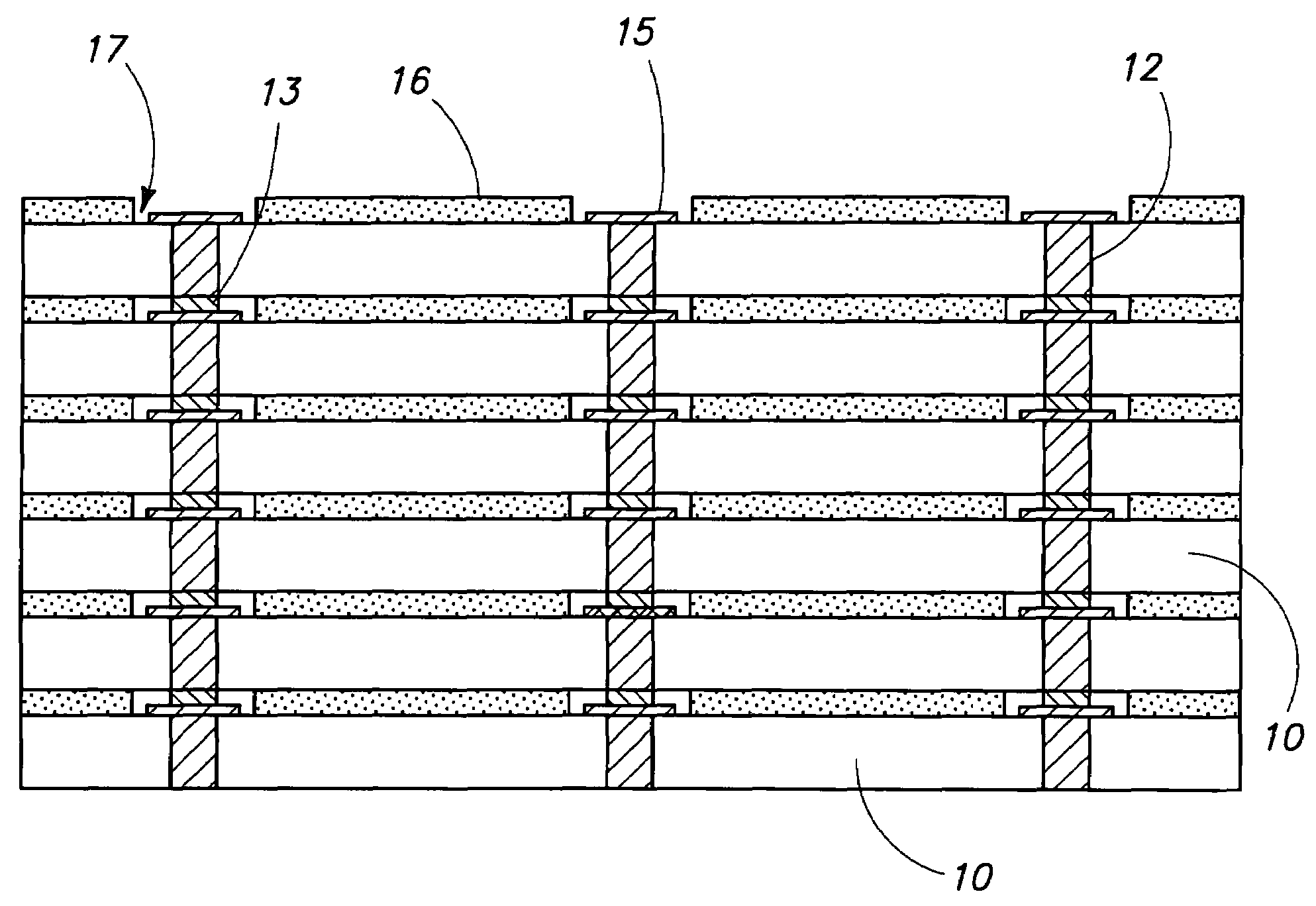

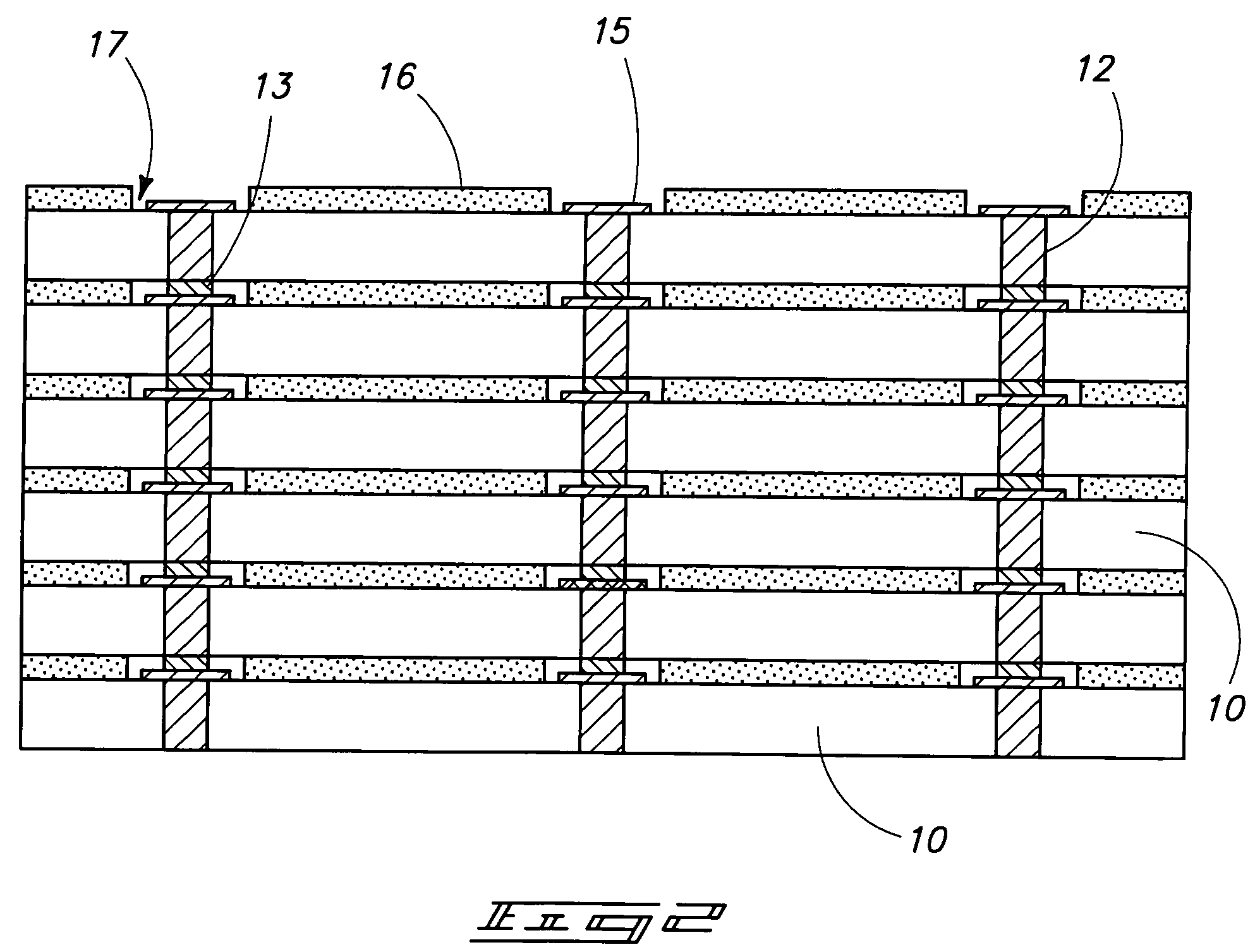

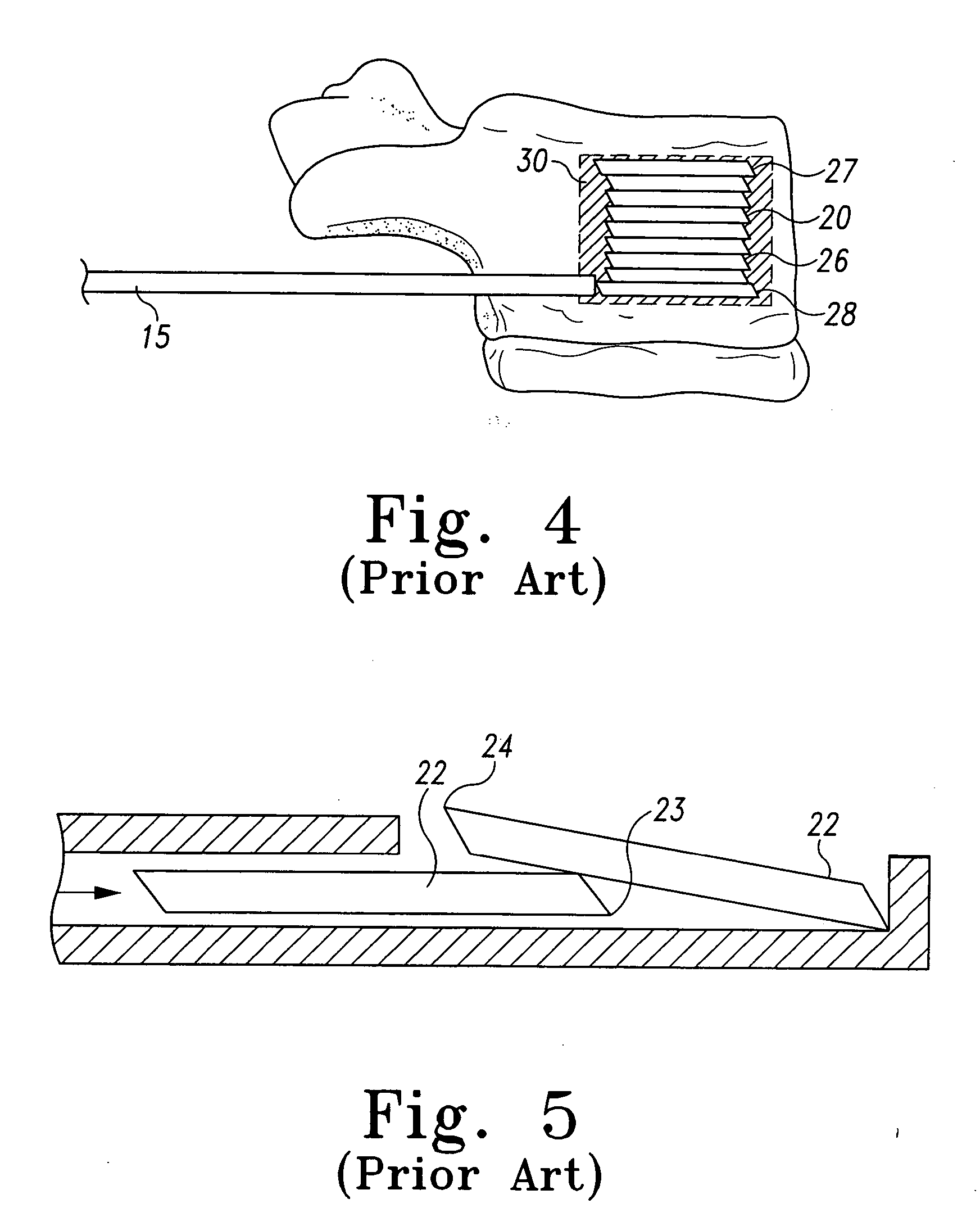

An expandable interbody fusion device includes superior and inferior endplates that are configured to receive a sequentially inserted stack of interlocking expansion members or wafers. The like-configured wafers include features on their top and bottom surfaces that interlock the wafers in multiple degrees of freedom so that the wafer stack is not disrupted when the fusion device is fully expanded. One of the interlocking features includes a plurality of prongs projecting from an upper surface of the wafers and into a recess defined in the lower surface of an adjacent previously inserted like-configured wafer. The prongs and recesses are configured to prevent retrograde movement of each new wafer in a direction opposite the direction of insertion. Other interlocking features prevent movement in the direction of insertion, transverse to the insertion direction and vertically within the stack.

Owner:SPINEWAVE

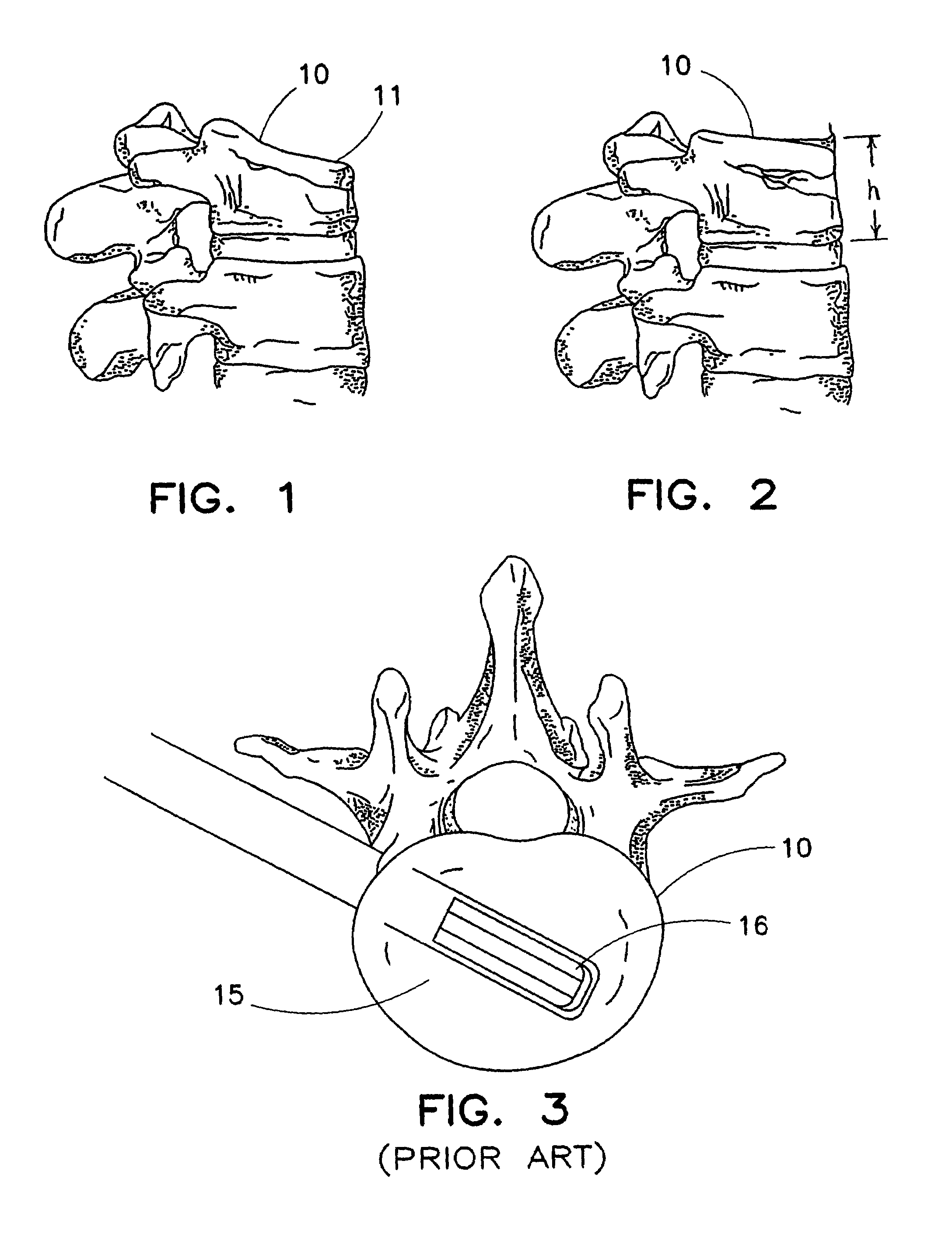

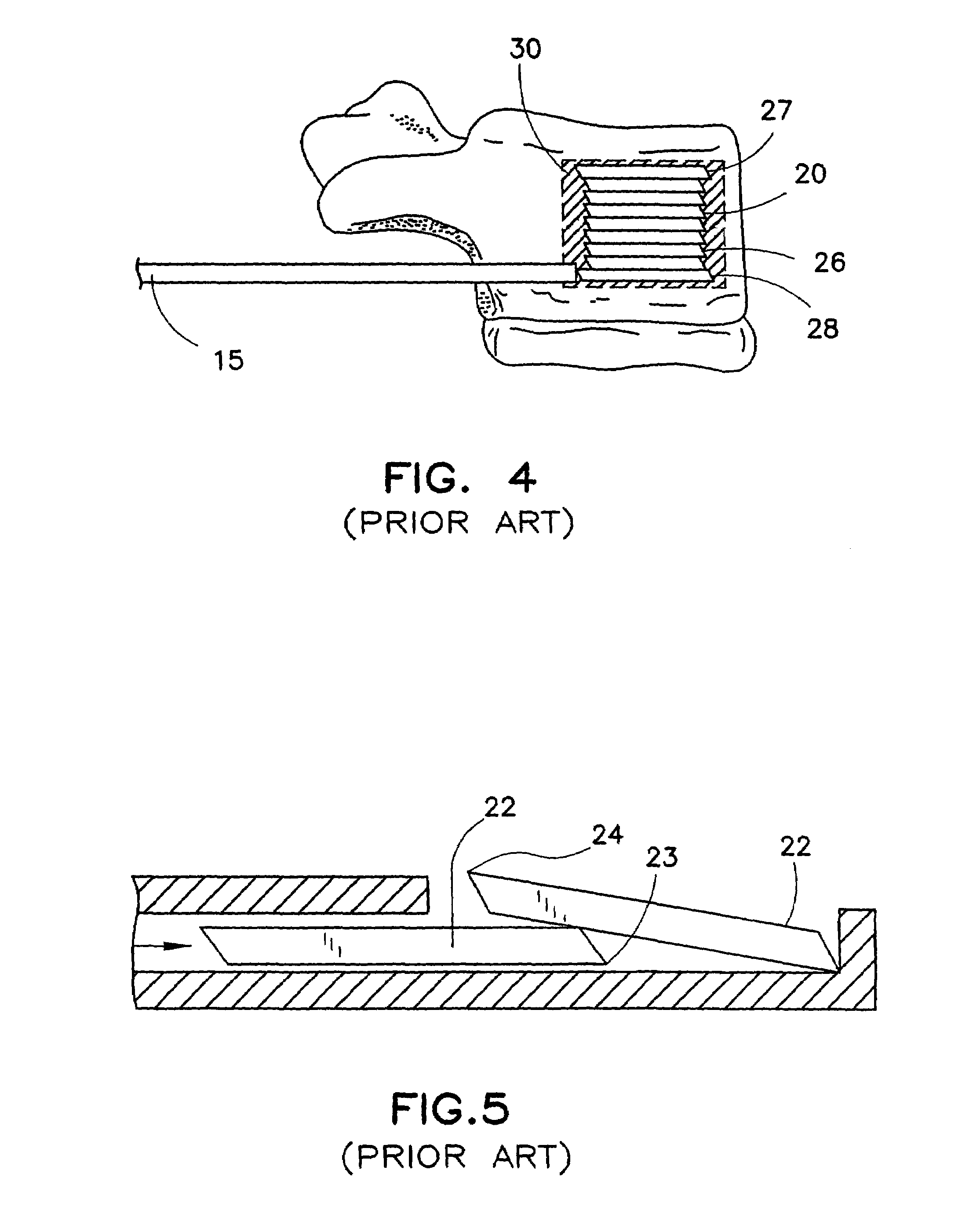

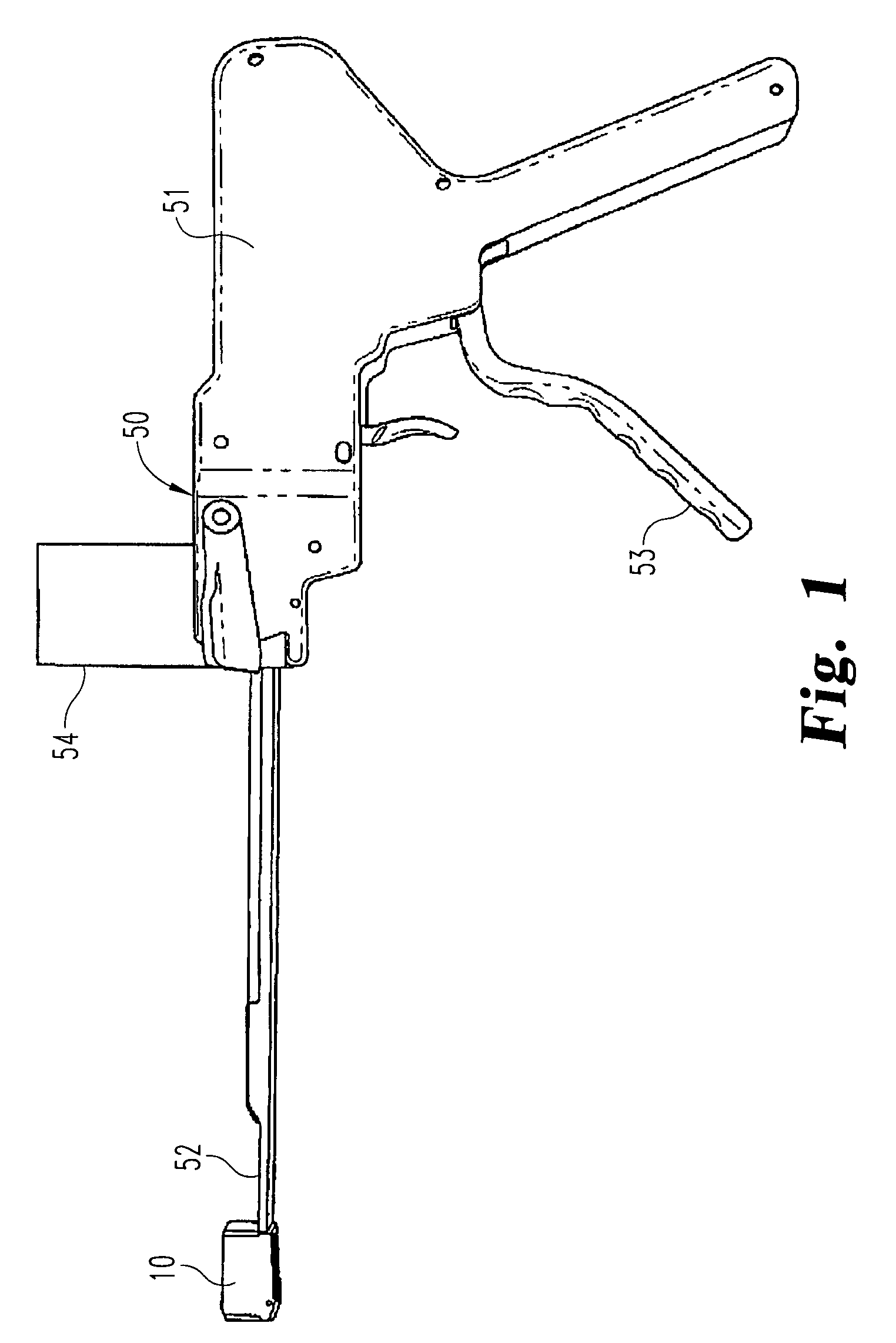

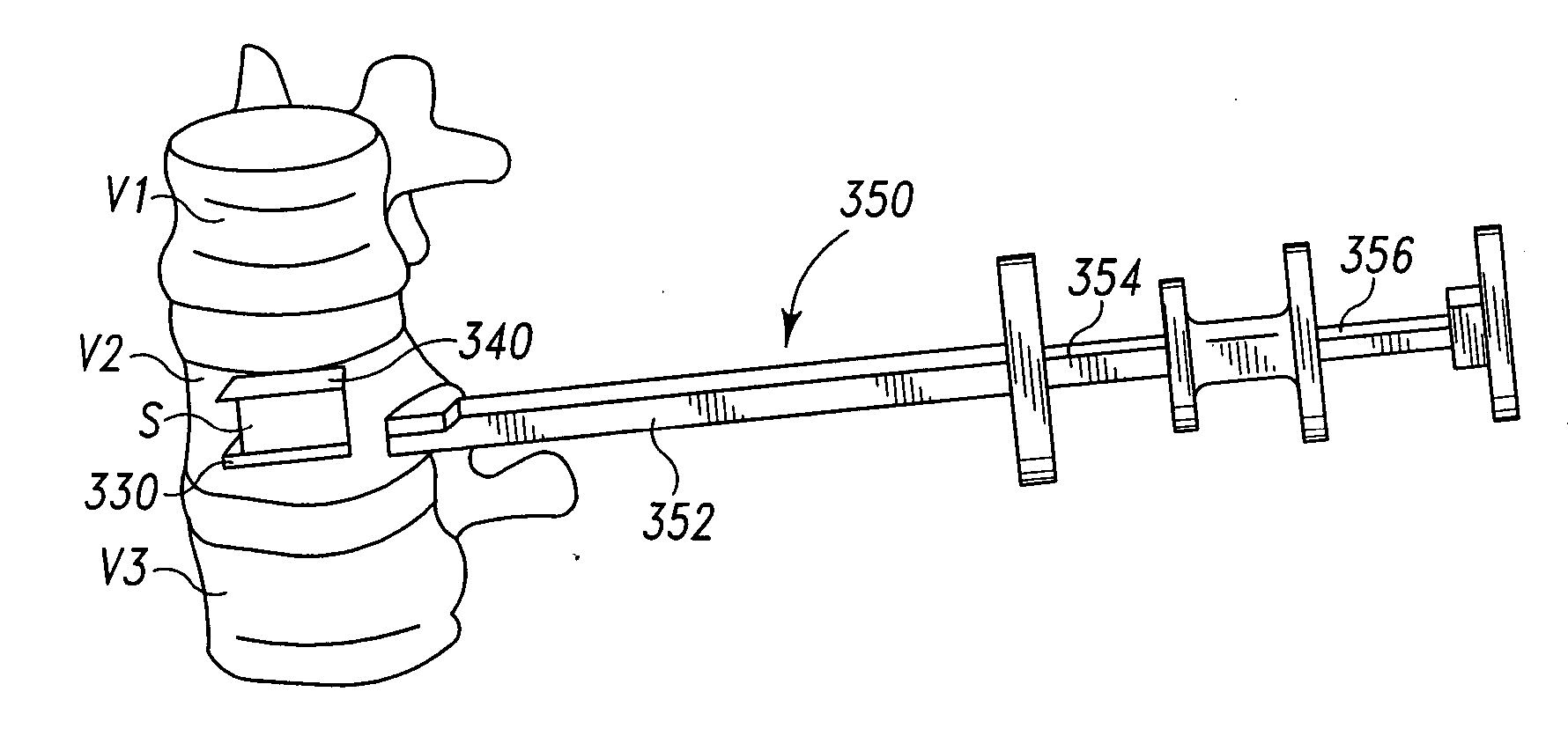

Tissue distraction device

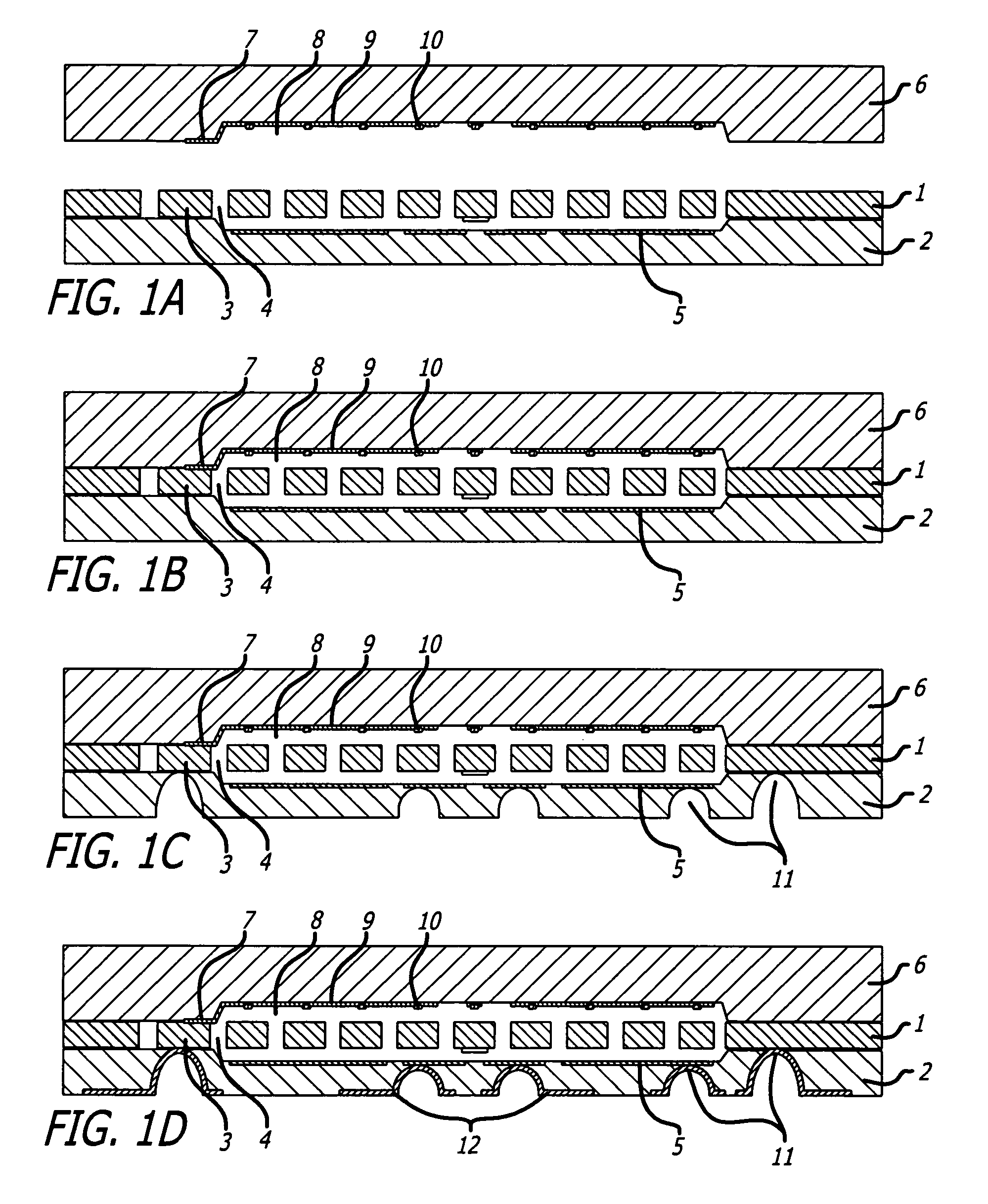

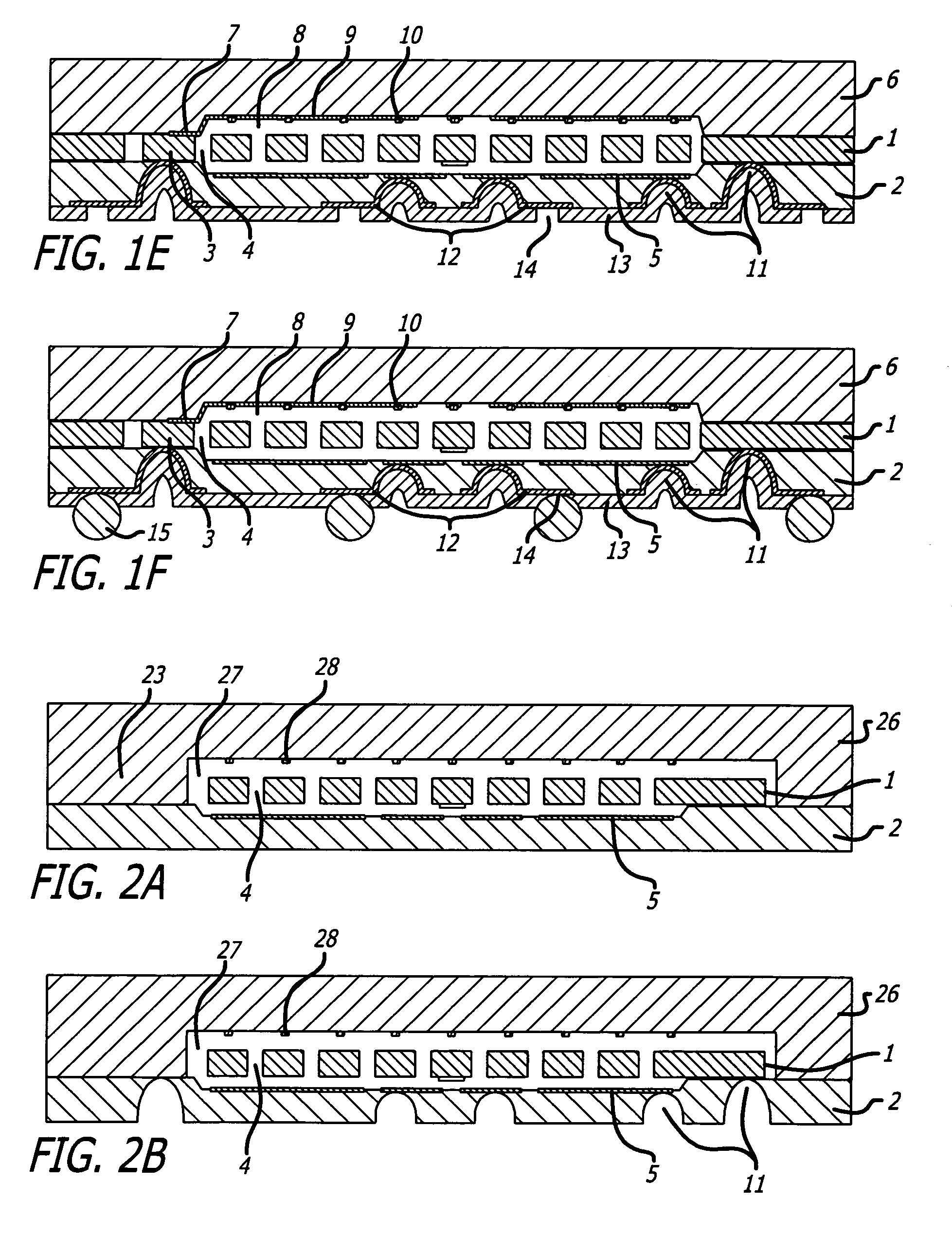

ActiveUS6997929B2Avoid relative motionInternal osteosythesisSpinal implantsDistractionWafer stacking

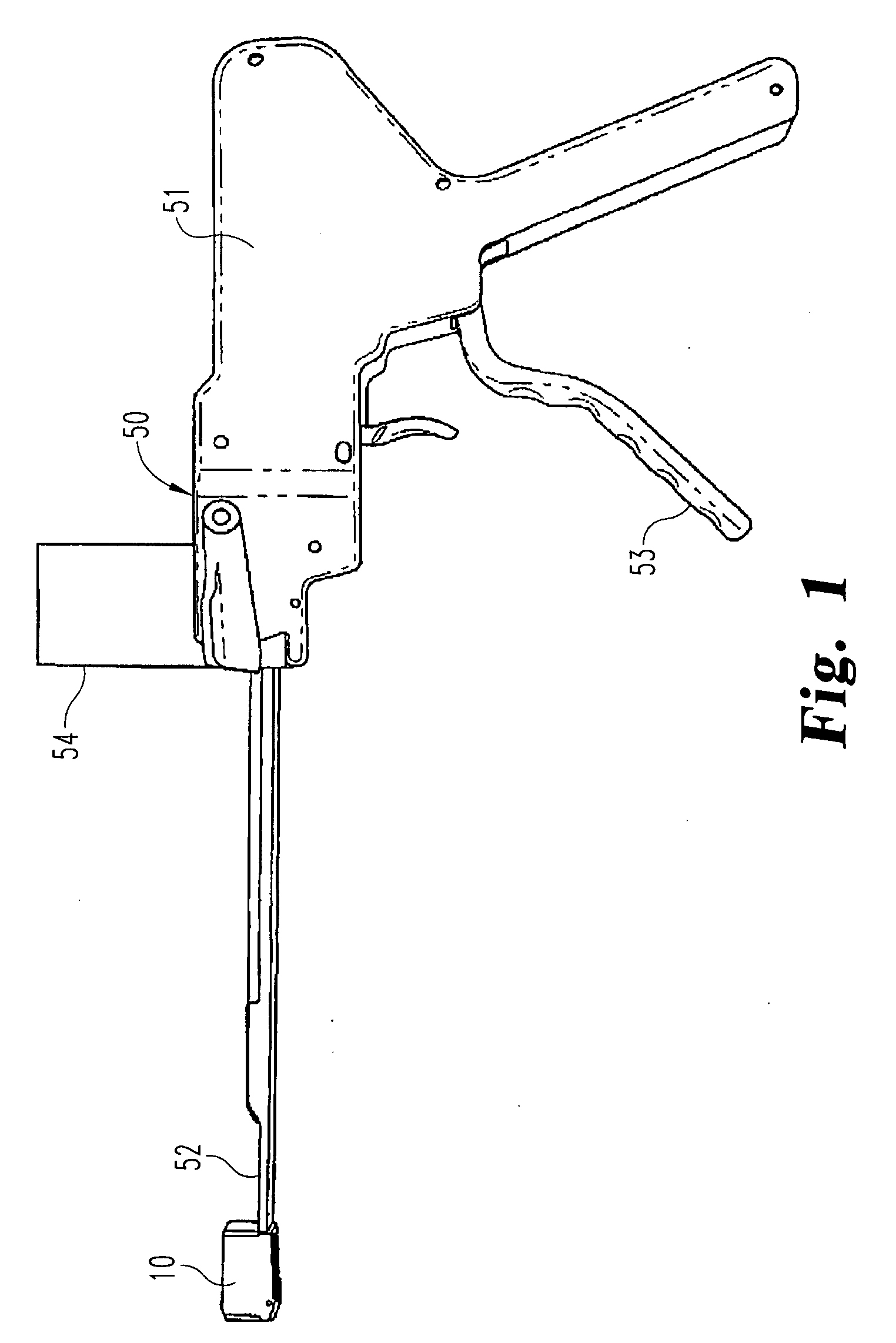

An apparatus and method for distracting, in a given direction, and supporting two tissue surfaces is provided. A plurality of wafers are consecutively inserted using a wafer insertion apparatus between the two tissue surfaces to create a column of wafers. A detachable wafer assembly is provided that includes a base wafer initially associated with a track assembly of a wafer insertion apparatus. The base wafer is dislodged from the track assembly so that the base wafer is left within the distraction site as the track assembly is removed. A top cap wafer is provided that is situated at the top of the wafer stack, in which the top cap wafer is larger than the remaining wafers to form a gap surrounding the stack to receive biologic material.

Owner:SPINEWAVE

Expandable interbody fusion device

An expandable interbody fusion device includes superior and inferior plates that are configured to receive a sequentially inserted stack of expansion members or wafers. The superior and inferior plates include features that at least initially interlock the two plates until the superior plate is dislodged by pressure from the growing wafer stack. The wafers include features on their top and bottom surfaces that interlock the wafers in multiple degrees of freedom so that the wafer stack is not disrupted when the fusion device is fully expanded. Each wafer also includes features that interlock with the inferior plate until the wafer id dislodged by sequential introduction of another wafer.

Owner:SPINEWAVE

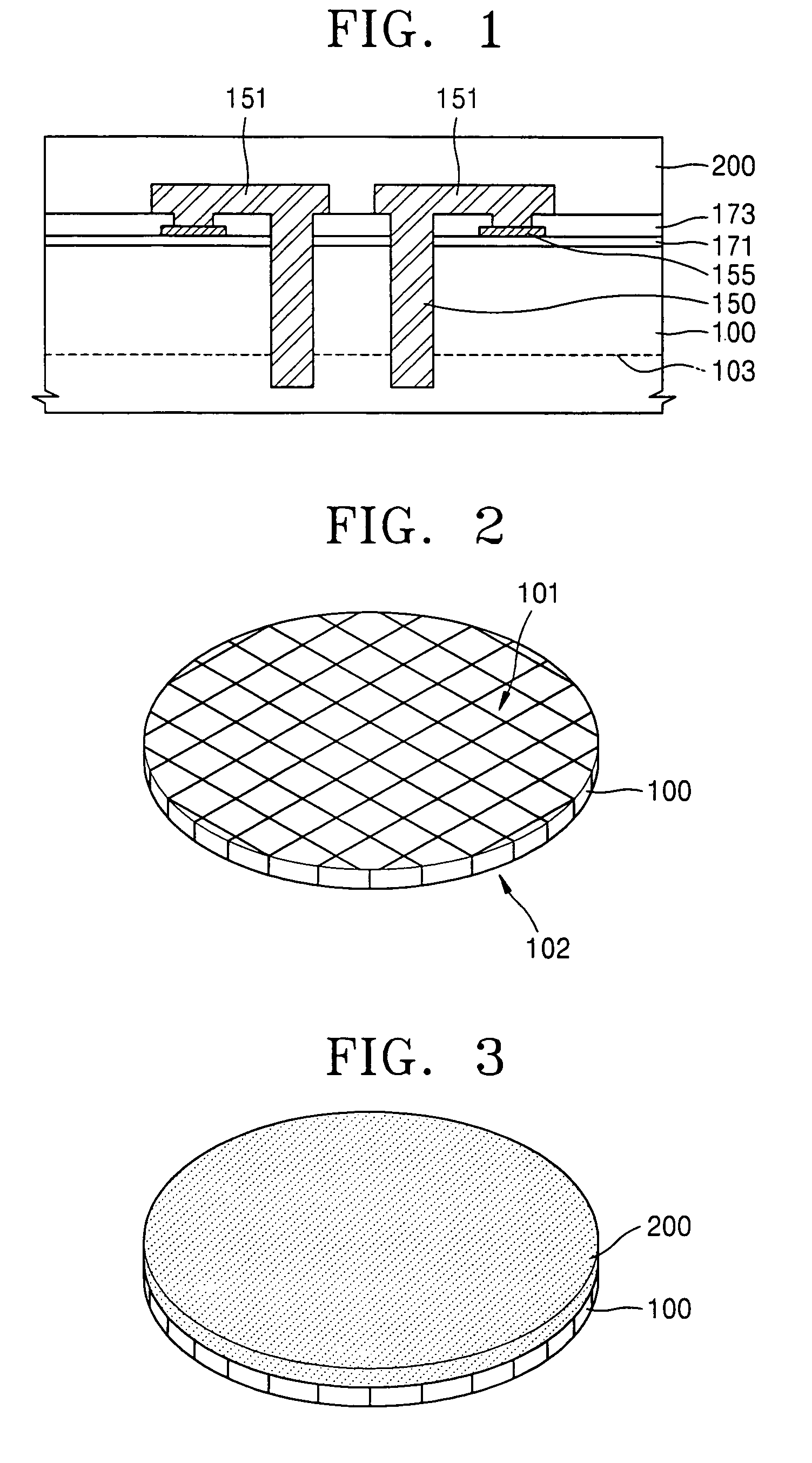

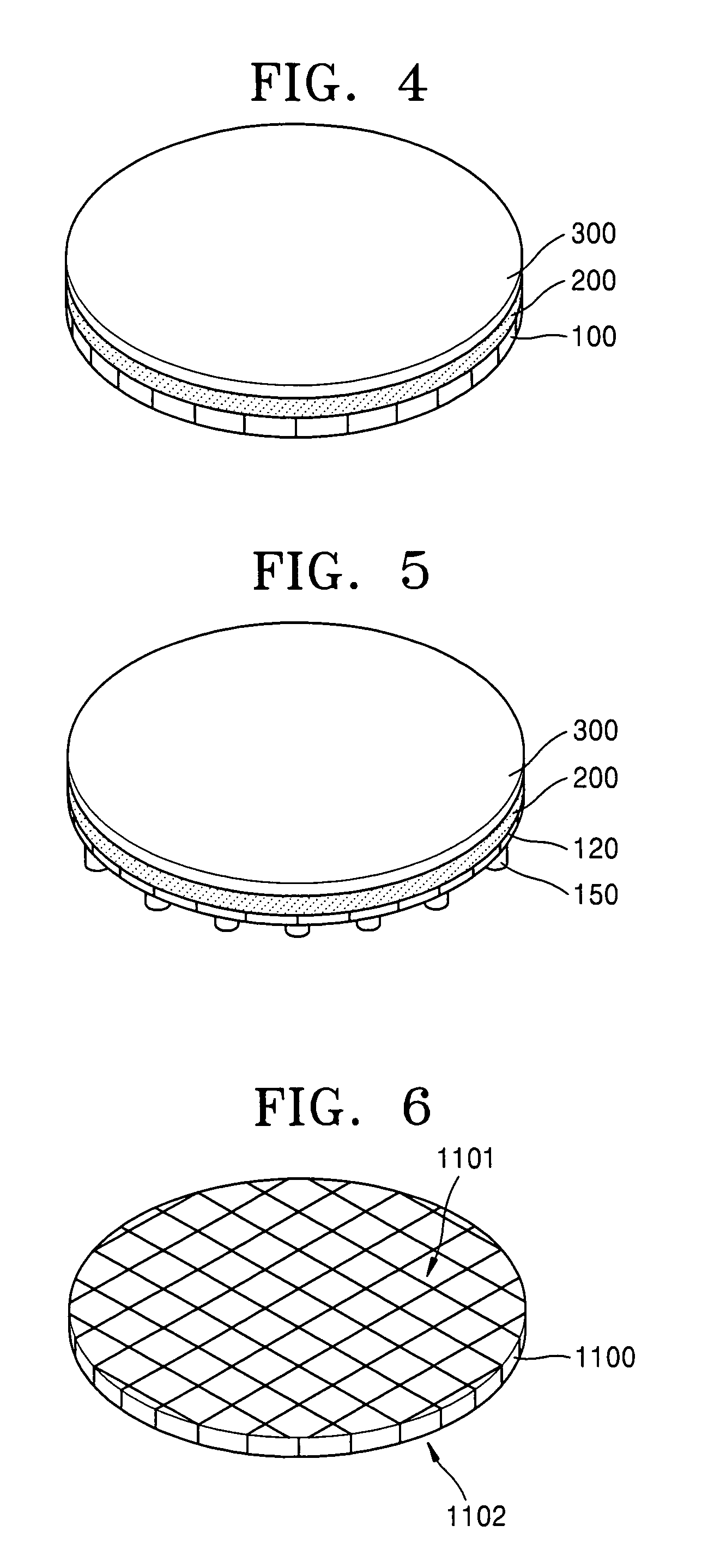

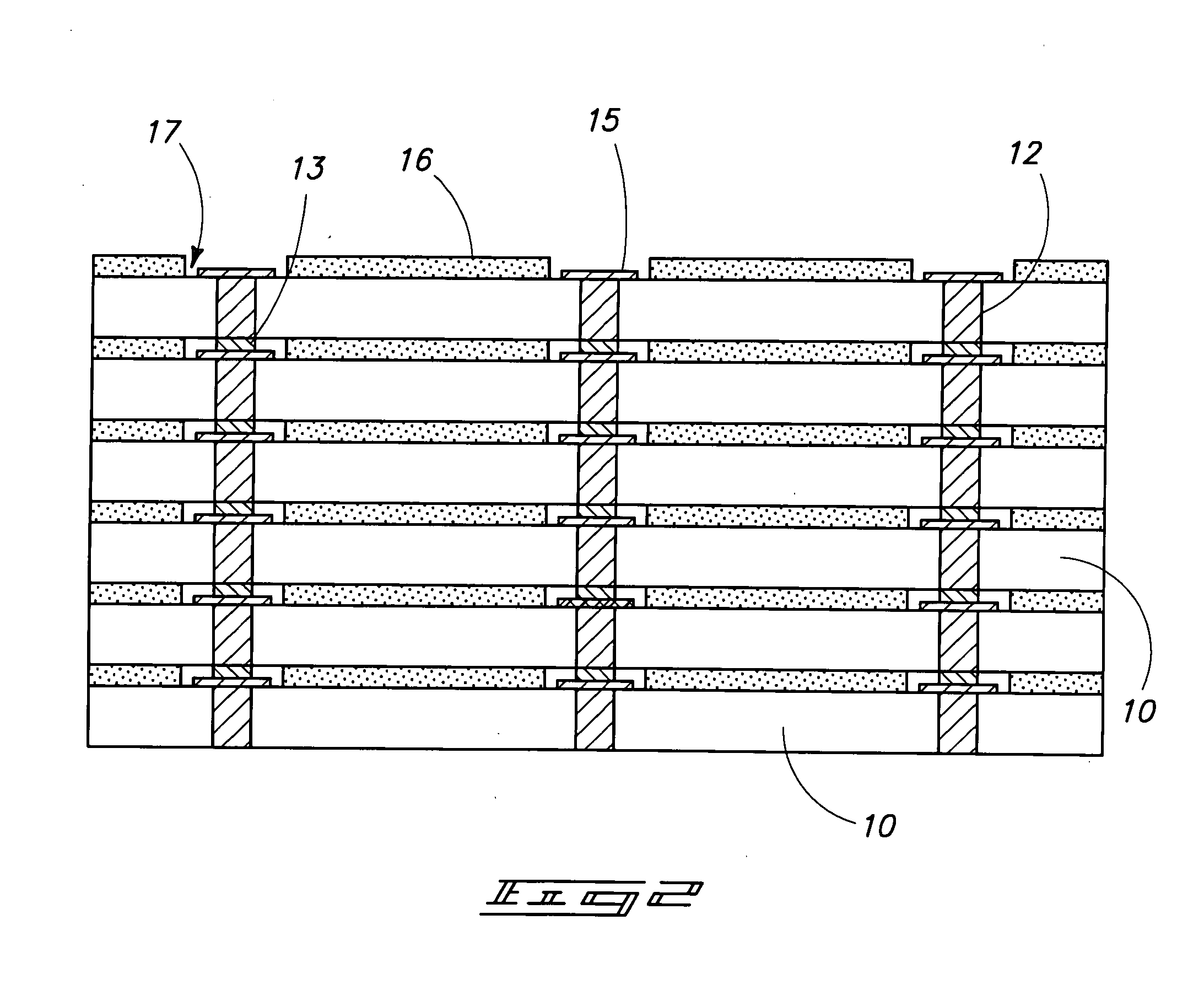

Method of forming a thin wafer stack for a wafer level package

InactiveUS7494845B2Reduce warpageTrend downSemiconductor/solid-state device detailsSolid-state devicesWaferingUltraviolet

A method of forming a stack of thin wafers provides a wafer level stack to greatly reduce process time compared to a method where individually separated chips are stacked after a wafer is sawed. A rigid planar wafer support member stabilizes and planarizes each wafer while it is thin or its thickness is reduced and during subsequent wafer processing. Thinned wafers are stacked and the external support members are removed by applying heat or ultraviolet (UV) light to an expandable adhesive layer between the support members and the thin wafers. The stacked wafers then can be further processed and packaged without thin-wafer warping, cracking or breaking. A wafer level package made in accordance with the invented method also is disclosed.

Owner:SAMSUNG ELECTRONICS CO LTD

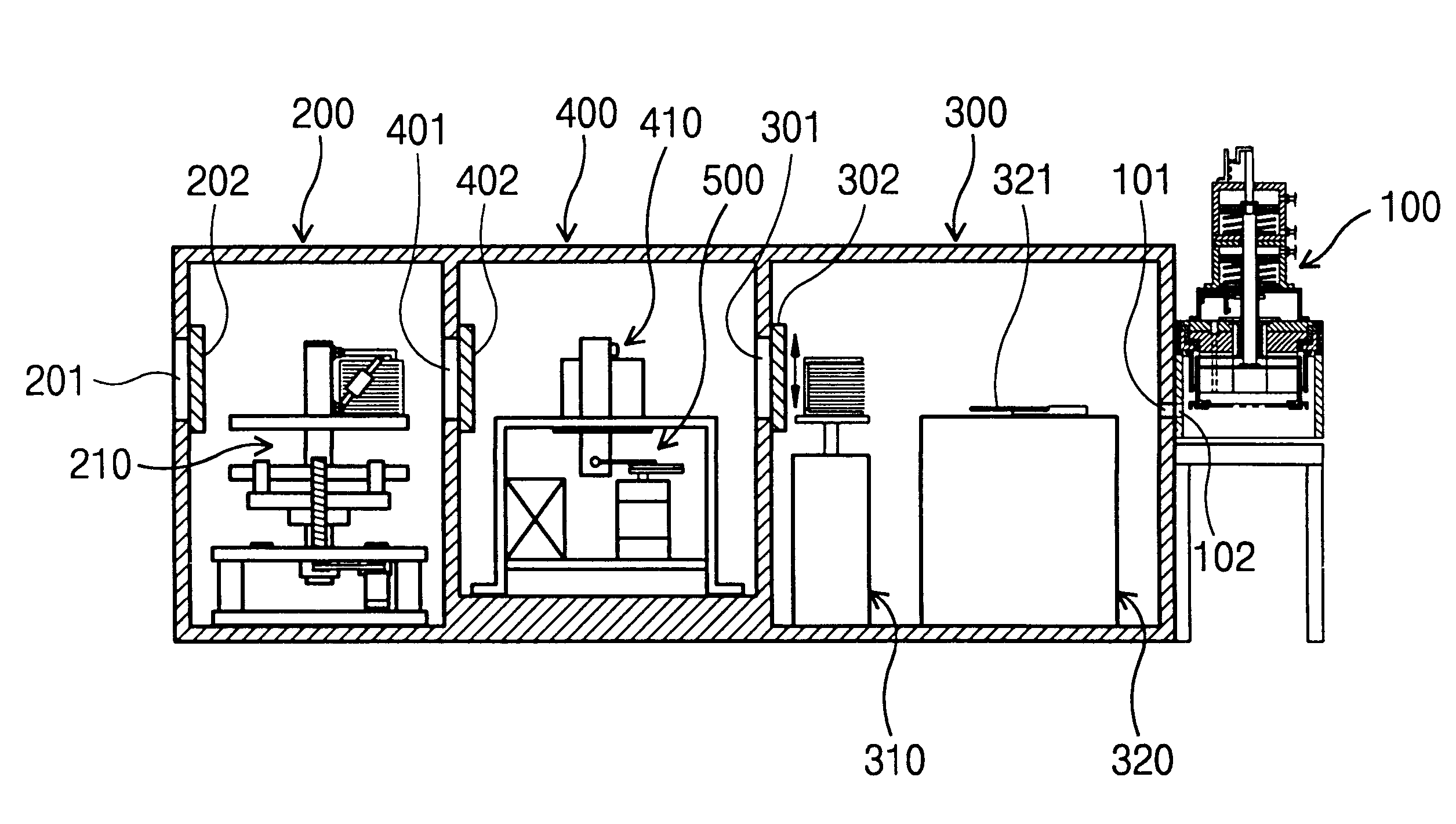

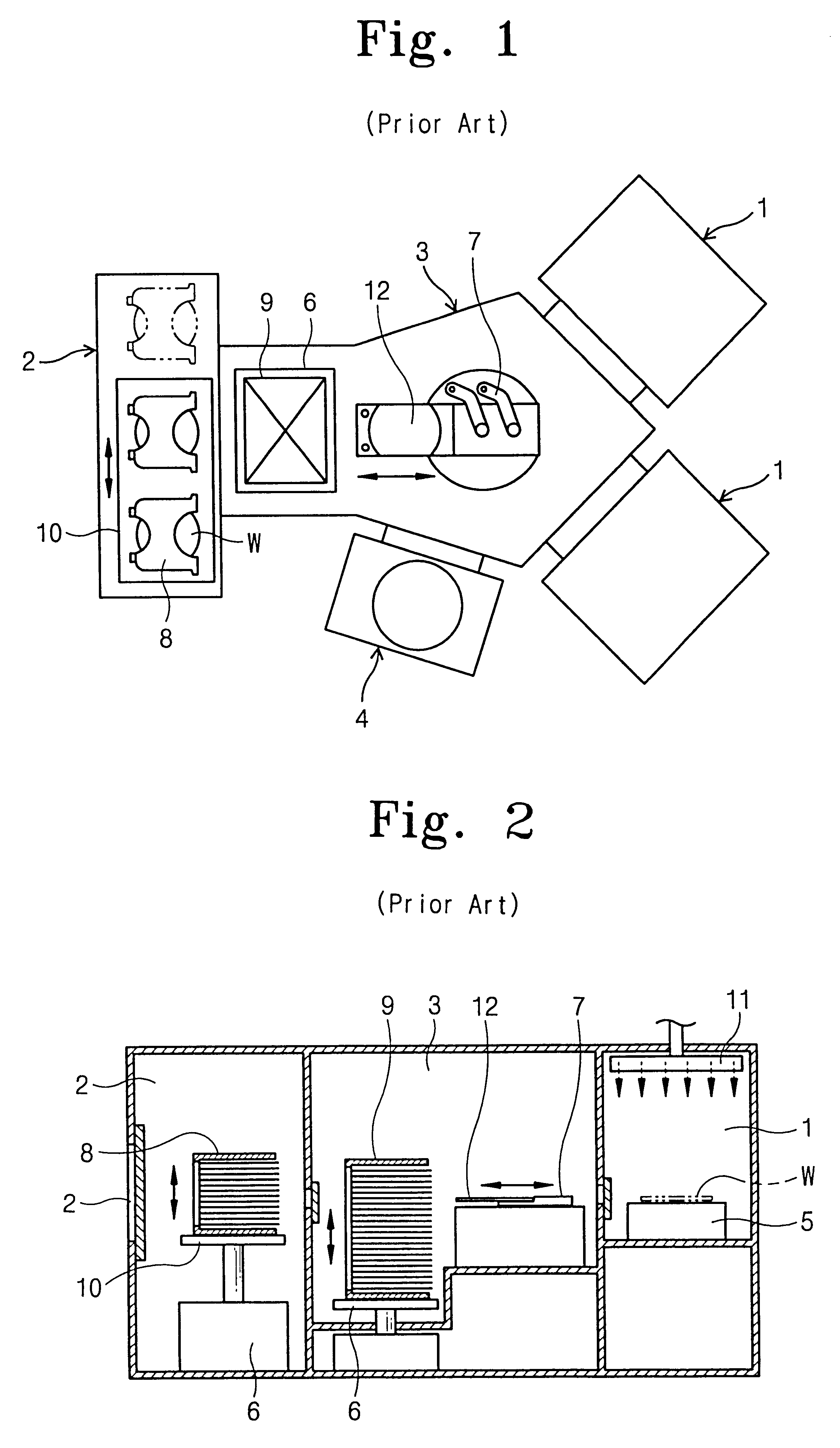

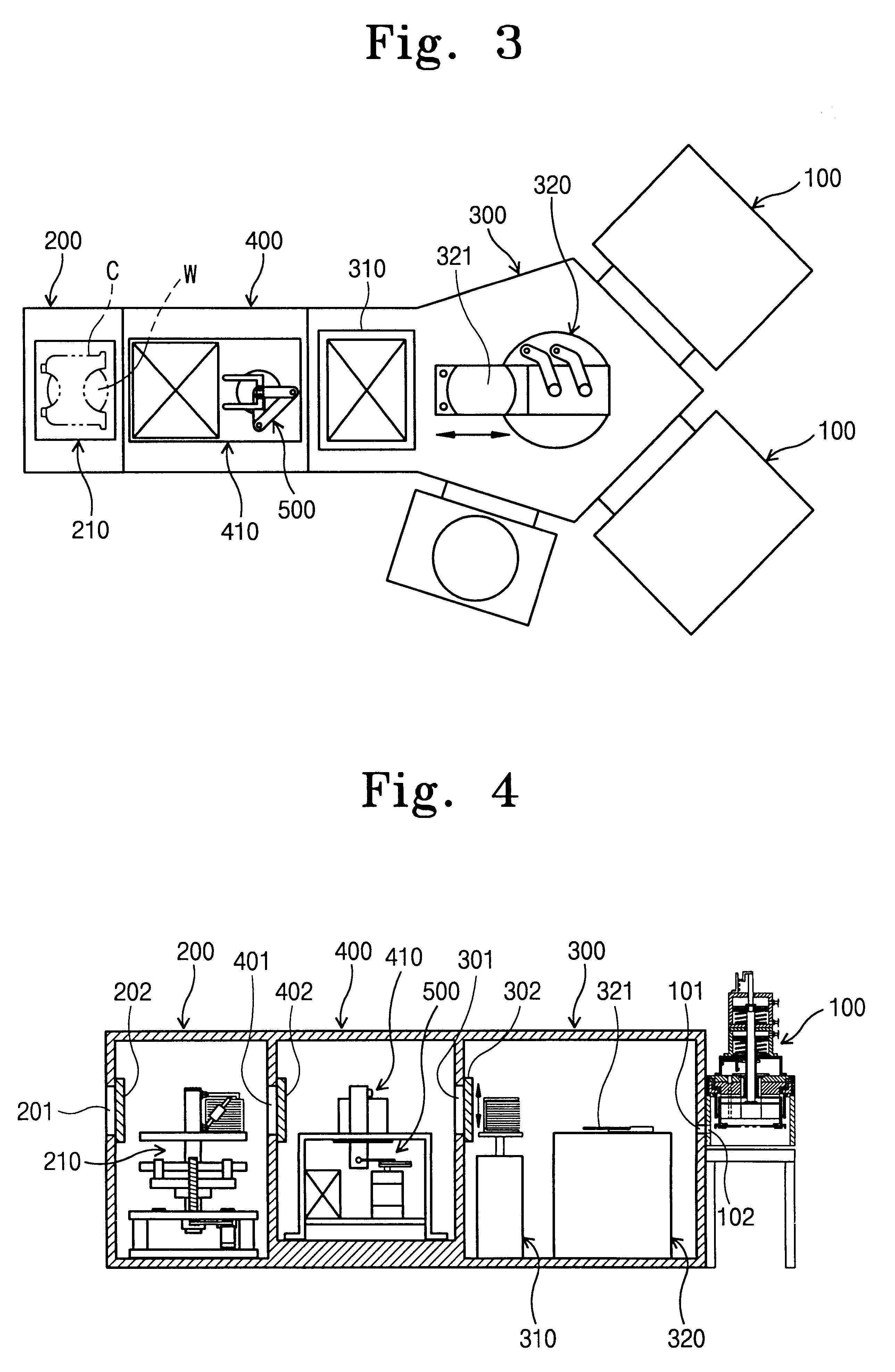

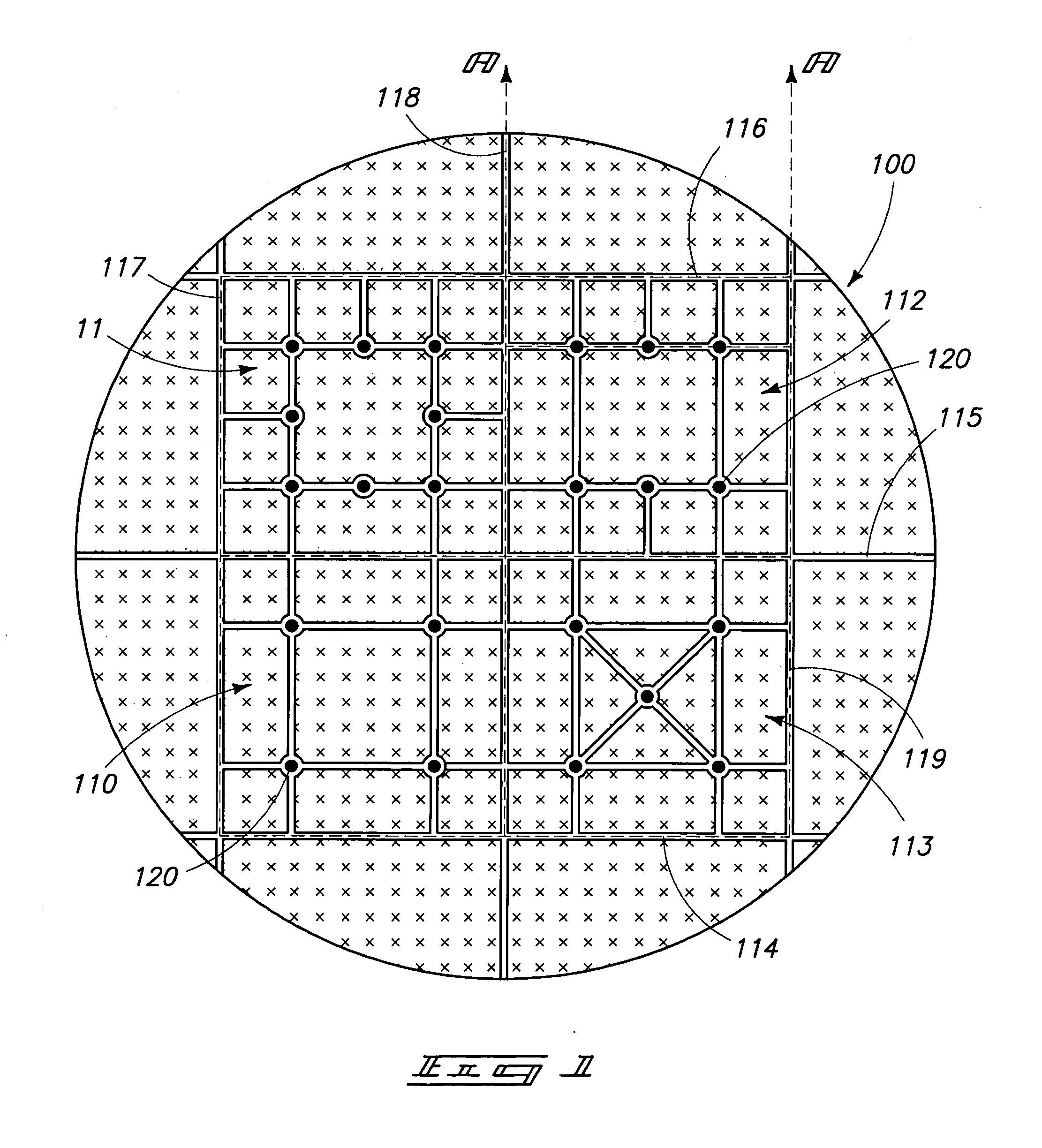

Etching apparatus for manufacturing semiconductor devices

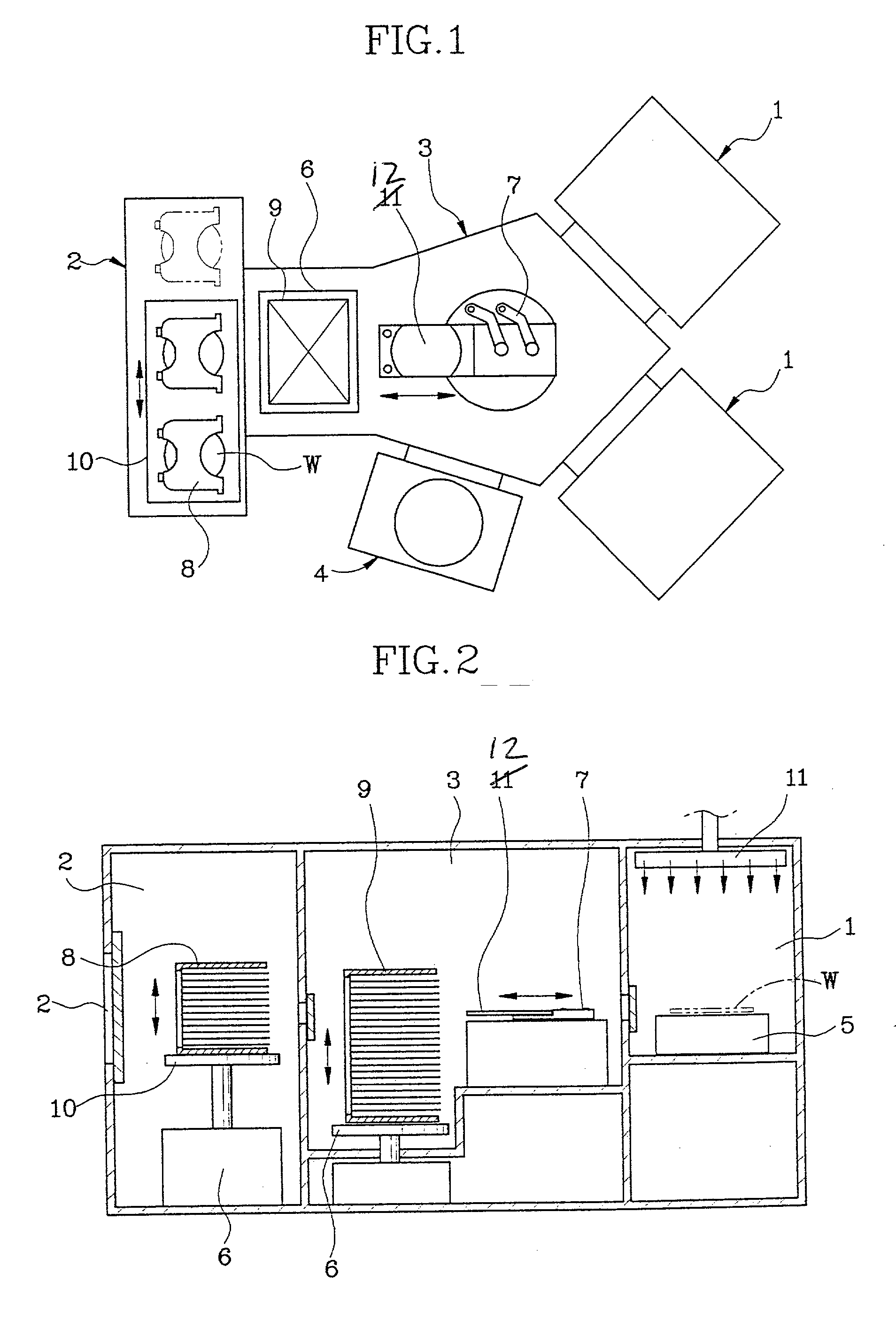

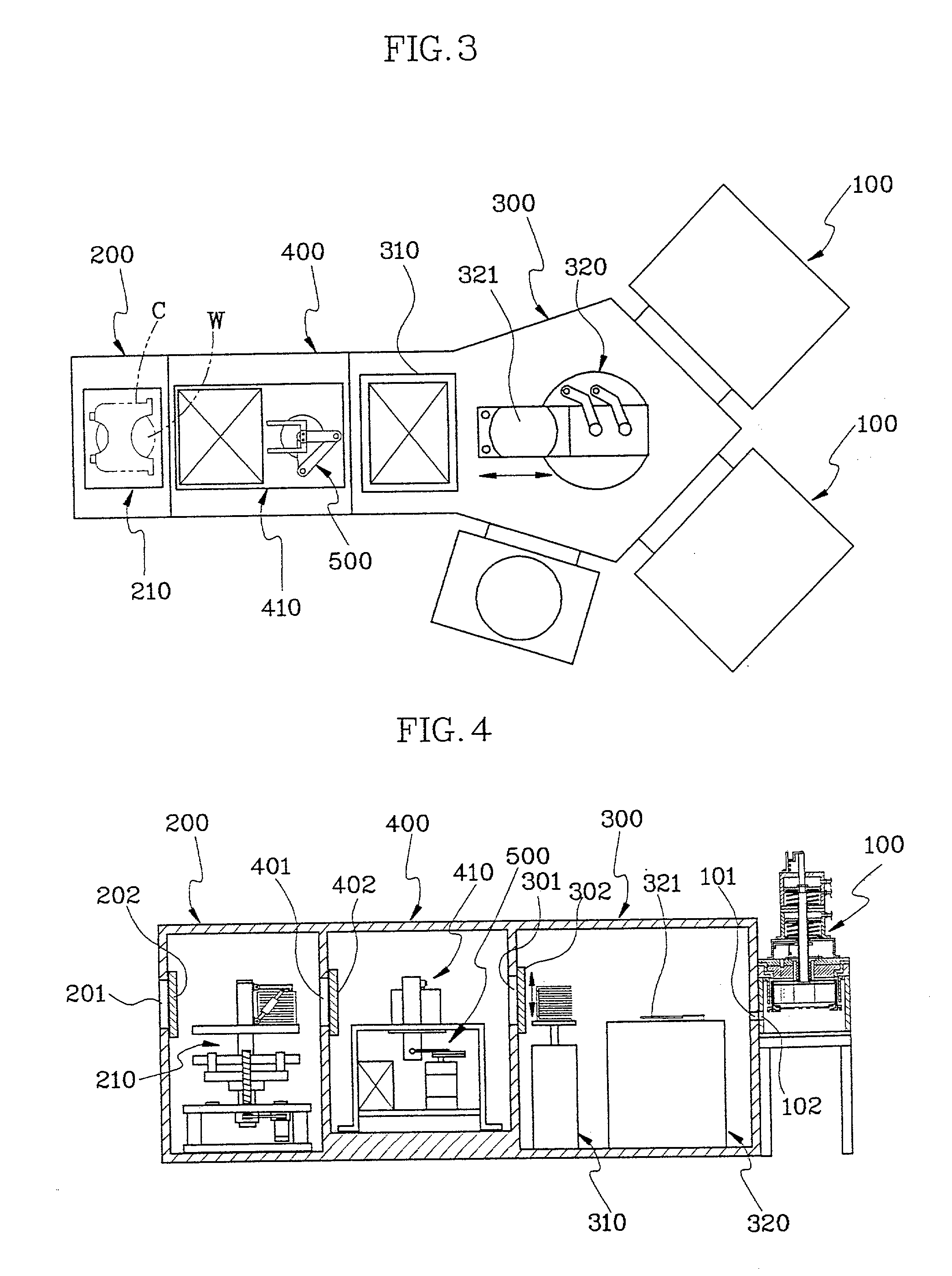

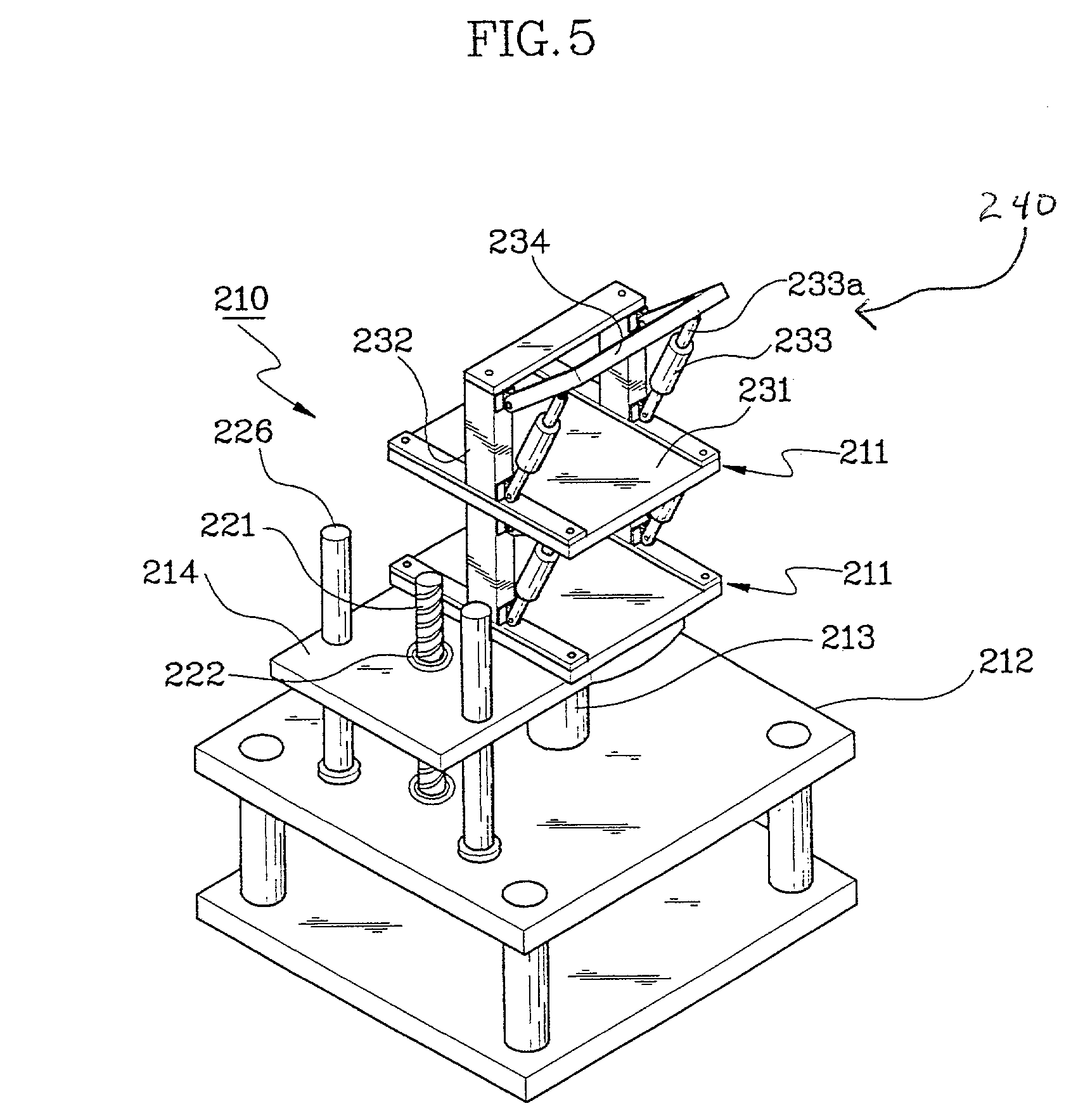

InactiveUS20010037856A1Operation efficiency can be improvedReduce processing timeSemiconductor/solid-state device manufacturingCharge manipulationMagnetic tapeWafer stacking

An etching apparatus for manufacturing semiconductor devices which reduces contamination of the processing surface of a wafer by transporting a plurality of wafers stacked in a cassette with their processing surfaces facing down from the cassette supply chamber to one or more process chambers where the etching operation is performed on each wafer, one at a time. The apparatus has a load lock chamber for transferring the wafers stacked in the cassette from the cassette supply chamber, which is maintained under atmospheric conditions, to the process chamber, which is maintained under a strong vacuum. The process chamber has a cathode to which a wafer is clamped by a wafer holder with its processing surface facing down; the process chamber may also have a removable lower cover for easy repair and cleaning. The apparatus may also have a wafer aligning chamber installed between the cassette supply chamber and the load lock chamber for simultaneously aligning all of the wafers n the cassette before they are transported to the load lock chamber. The wafer aligning chamber also has a cassette transport mechanism for transferring the cassette from a cassette supply table in the cassette supply chamber to an elevator installed in the load lock chamber.

Owner:SAMSUNG ELECTRONICS CO LTD

Expandable interbody fusion device

ActiveUS7967867B2Prevent disengagement of the wafersPrevent movementJoint implantsSpinal implantsWafer stackingEngineering

An expandable interbody fusion device includes superior and inferior endplates that are configured to receive a sequentially inserted stack of interlocking expansion members or wafers. The like-configured wafers include features on their top and bottom surfaces that interlock the wafers in multiple degrees of freedom so that the wafer stack is not disrupted when the fusion device is fully expanded. One of the interlocking features includes a plurality of prongs projecting from an upper surface of the wafers and into a recess defined in the lower surface of an adjacent previously inserted like-configured wafer. The prongs and recesses are configured to prevent retrograde movement of each new wafer in a direction opposite the direction of insertion. Other interlocking features prevent movement in the direction of insertion, transverse to the insertion direction and vertically within the stack.

Owner:SPINEWAVE

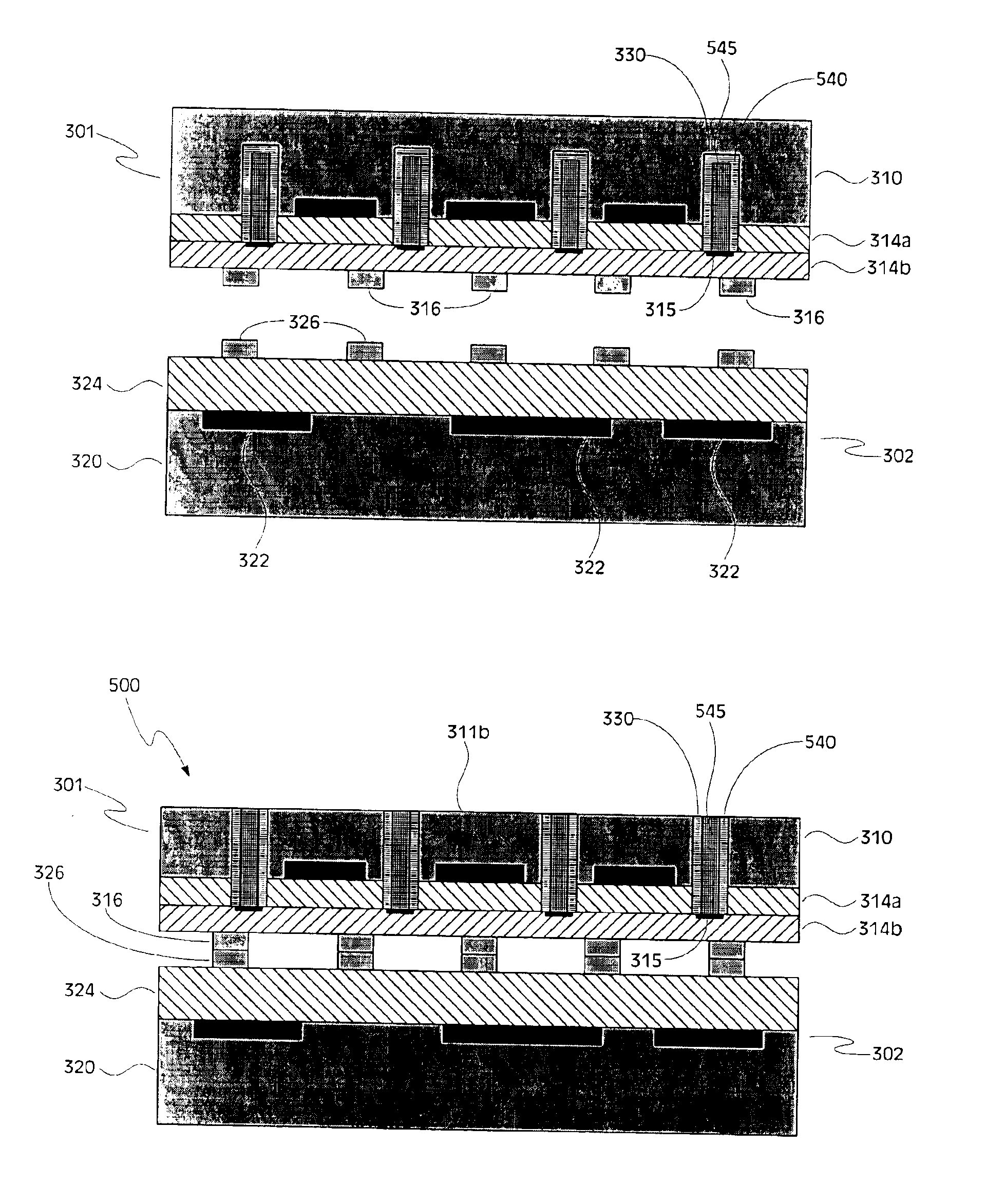

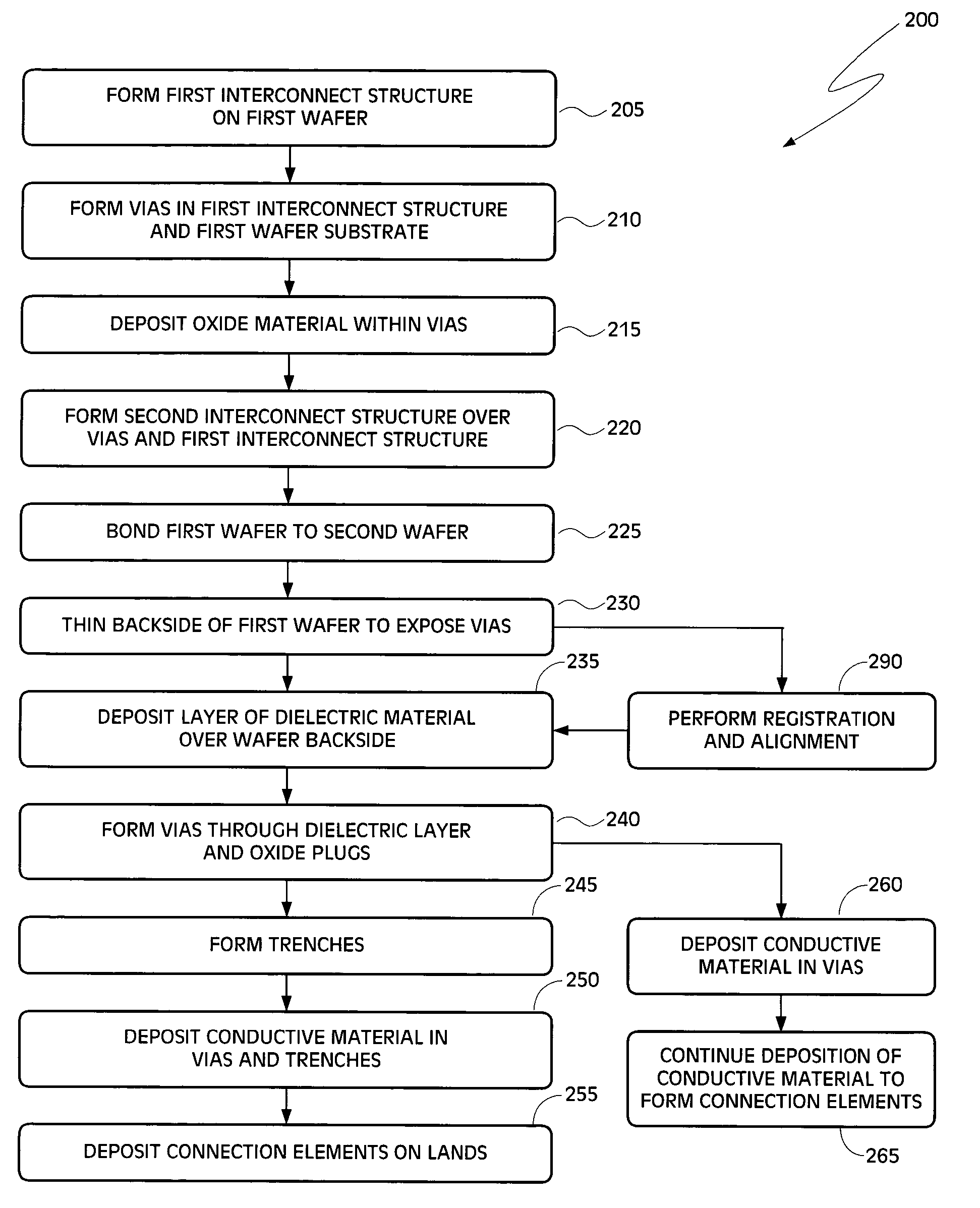

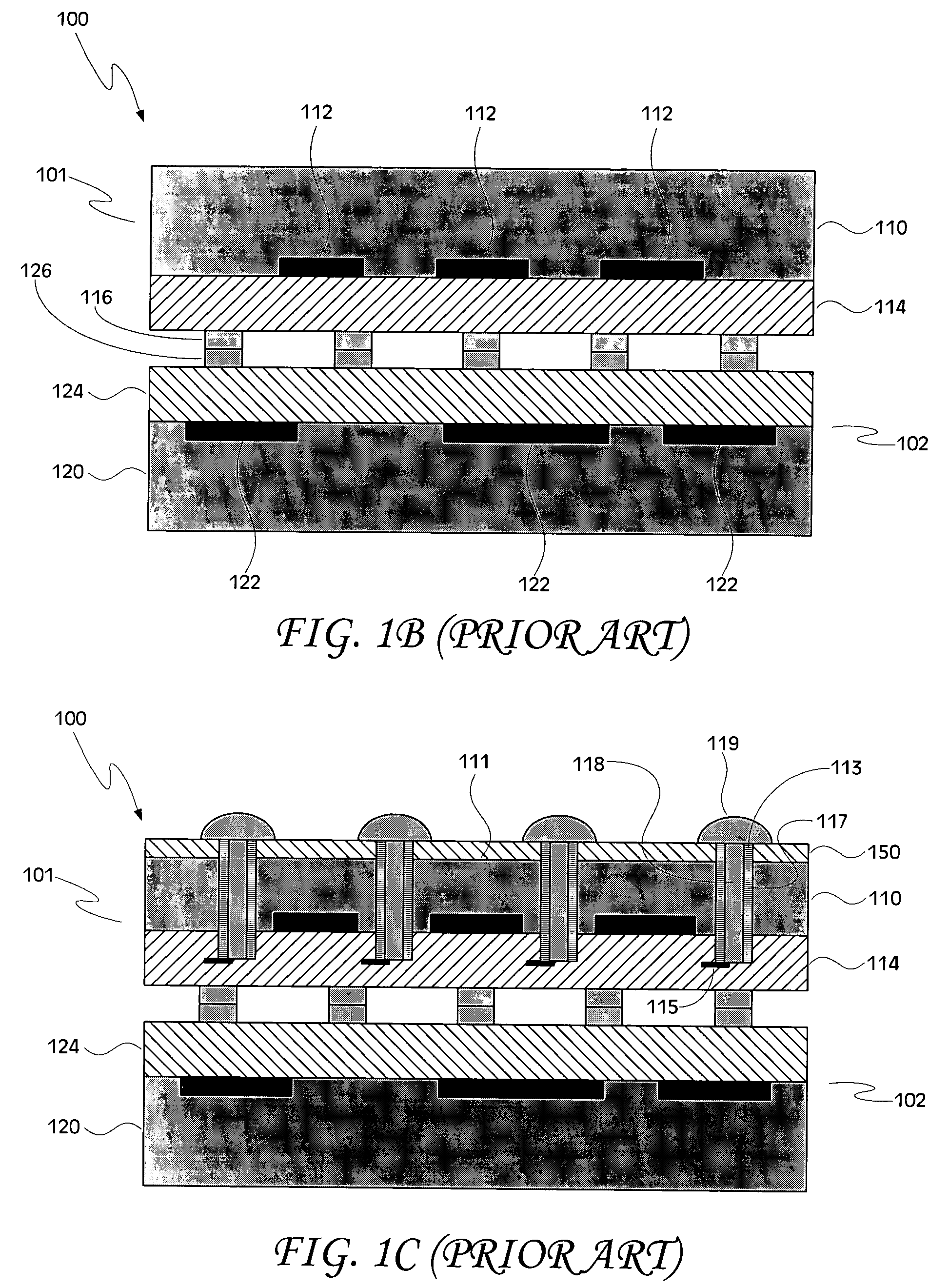

Methods of forming backside connections on a wafer stack

InactiveUS6897125B2Semiconductor/solid-state device detailsSolid-state devicesWafer stackingEngineering

Various methods of forming backside connections on a wafer stack are disclosed. To form the backside connections, vias are formed in a first wafer that is to be bonded with a second wafer. The vias used for the backside connections are formed on a side of the first wafer along with an interconnect structure, and the backside connections are formed on an opposing side of the first wafer using these vias.

Owner:TAHOE RES LTD

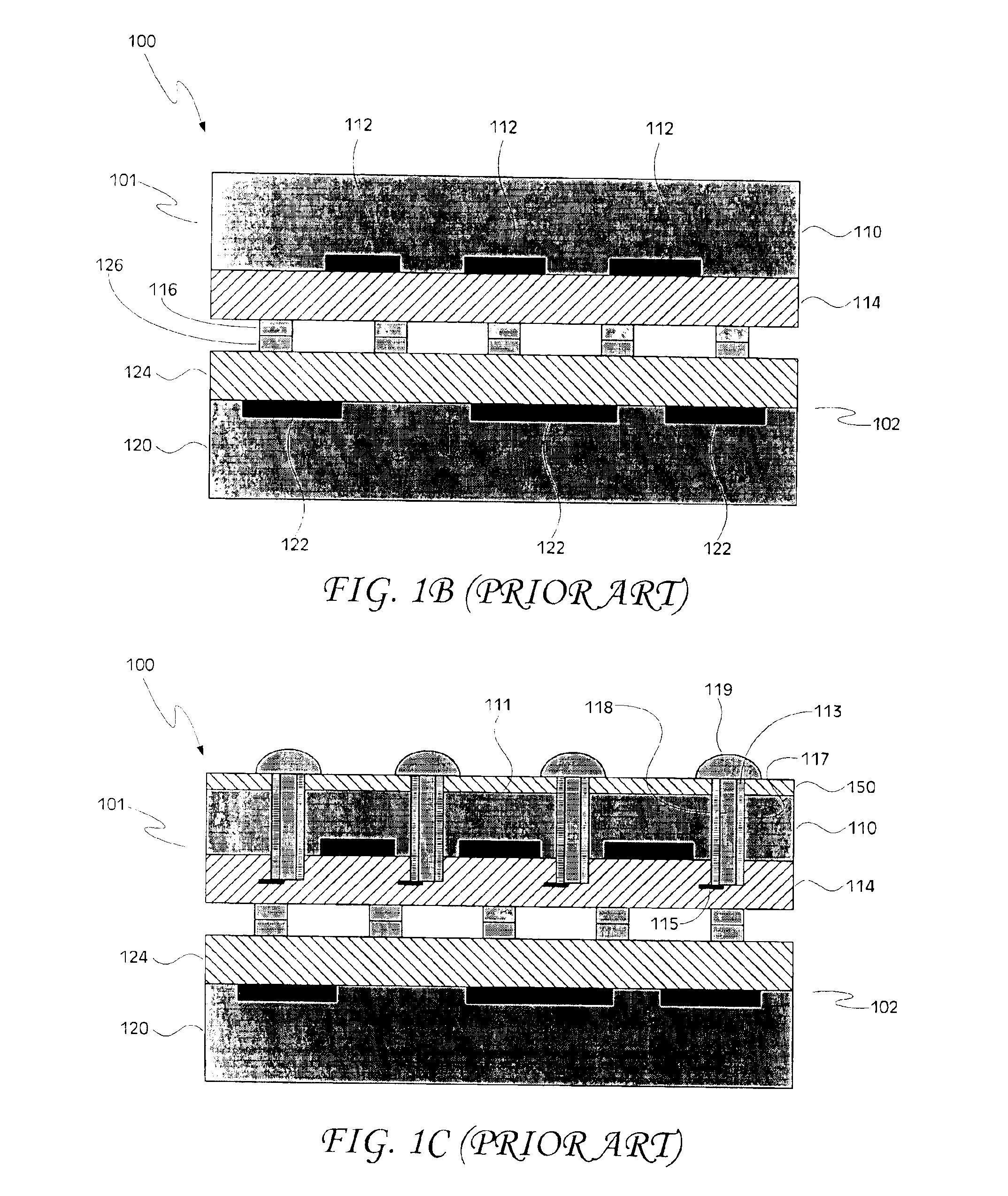

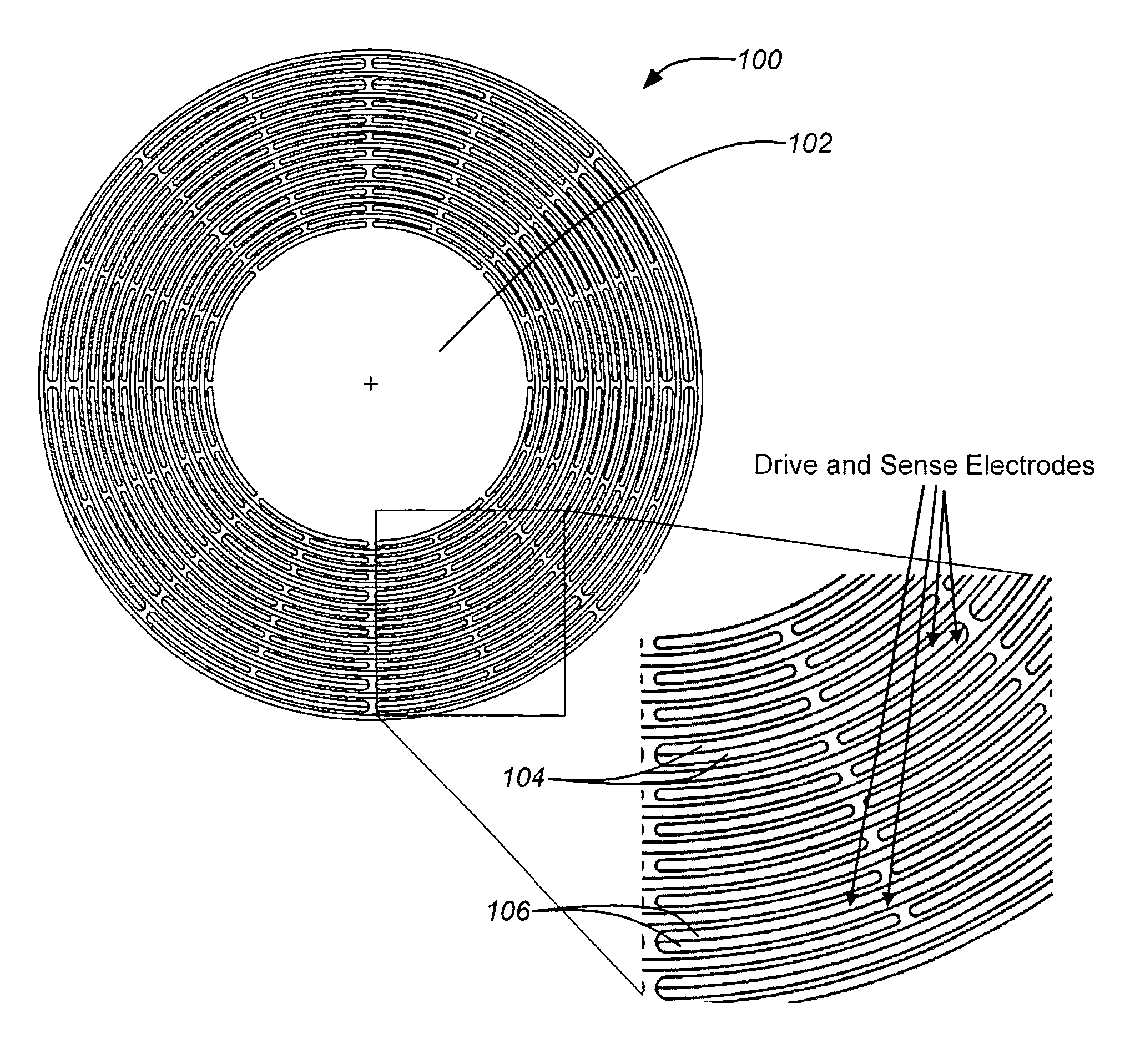

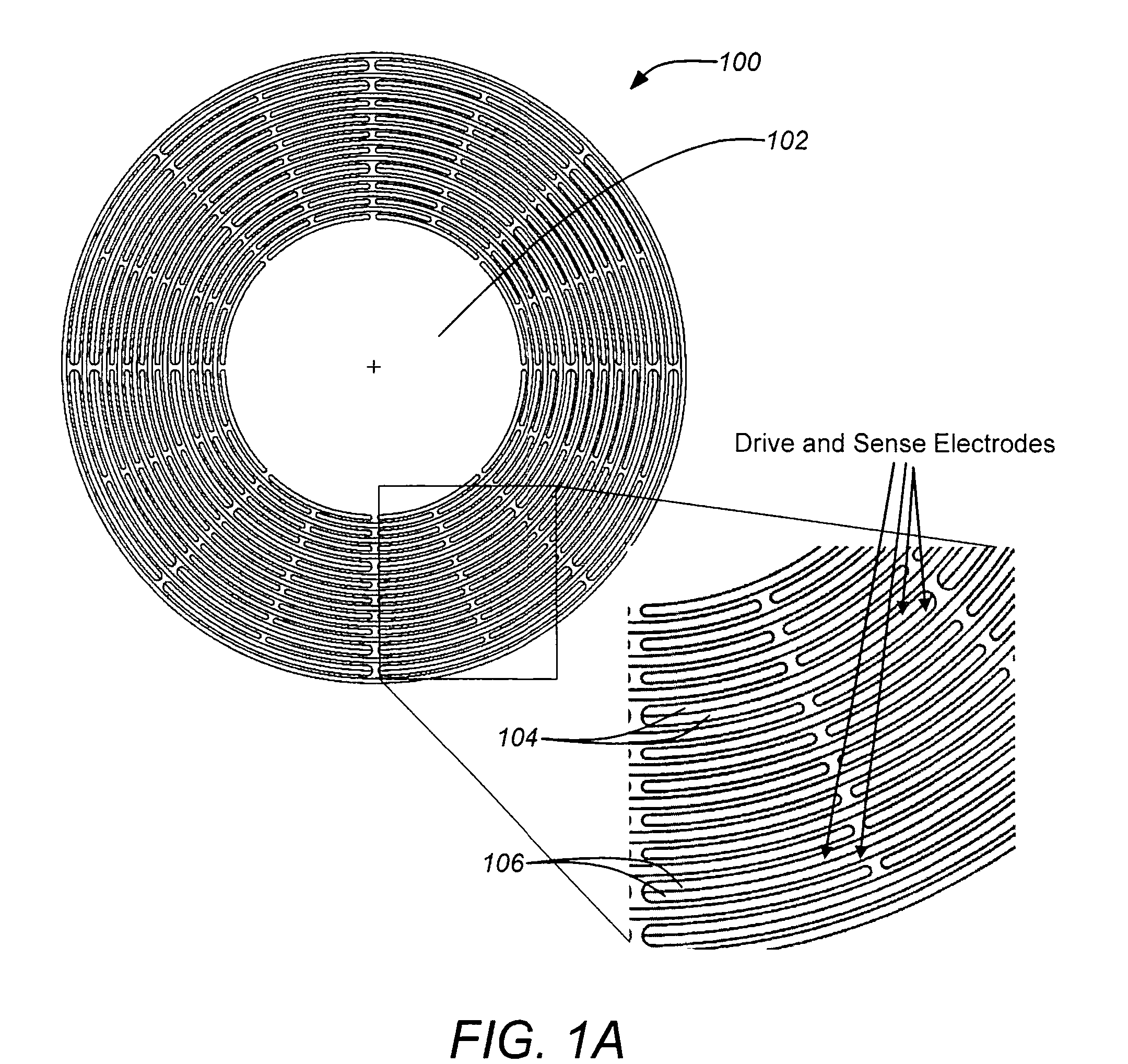

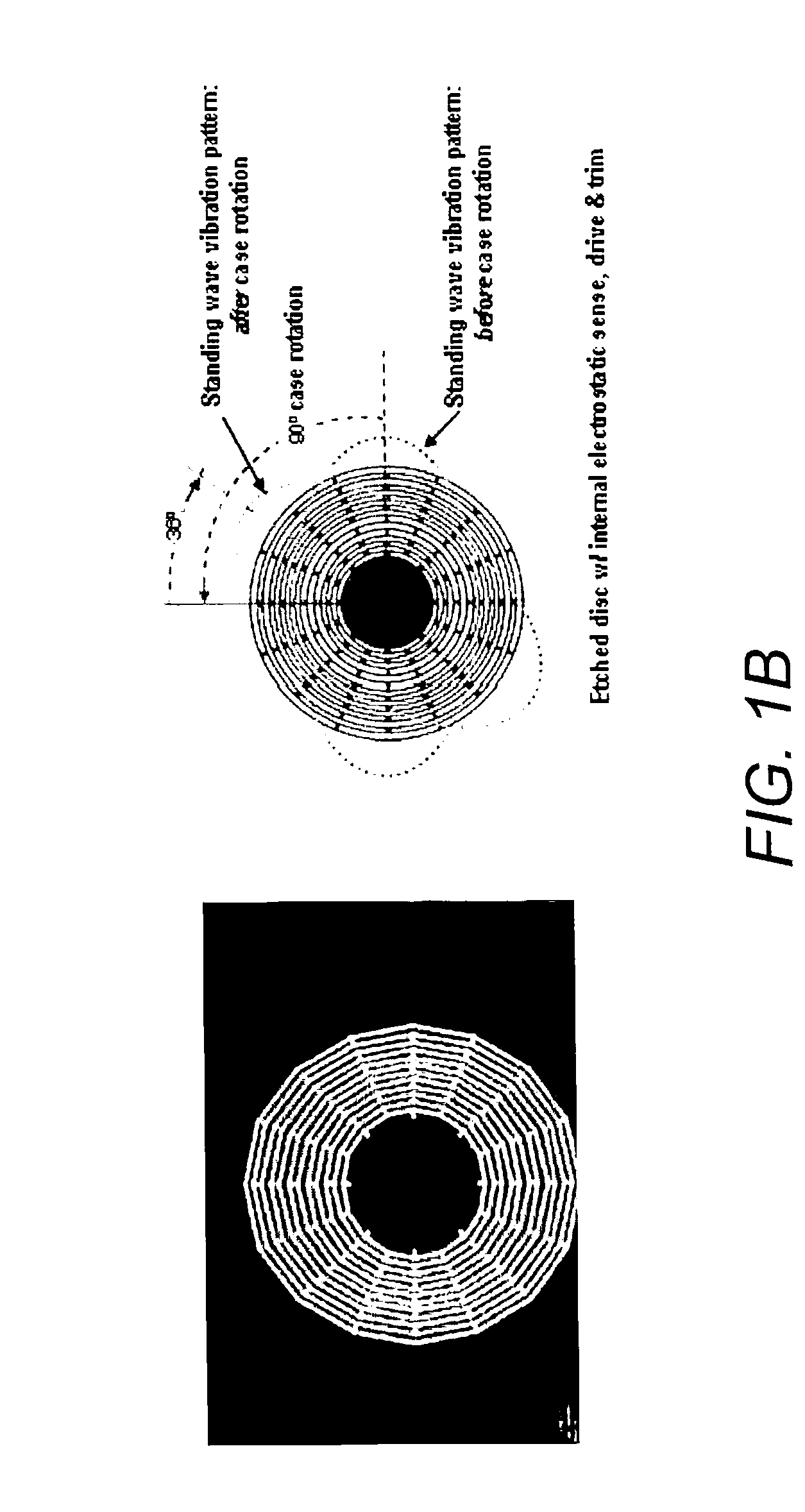

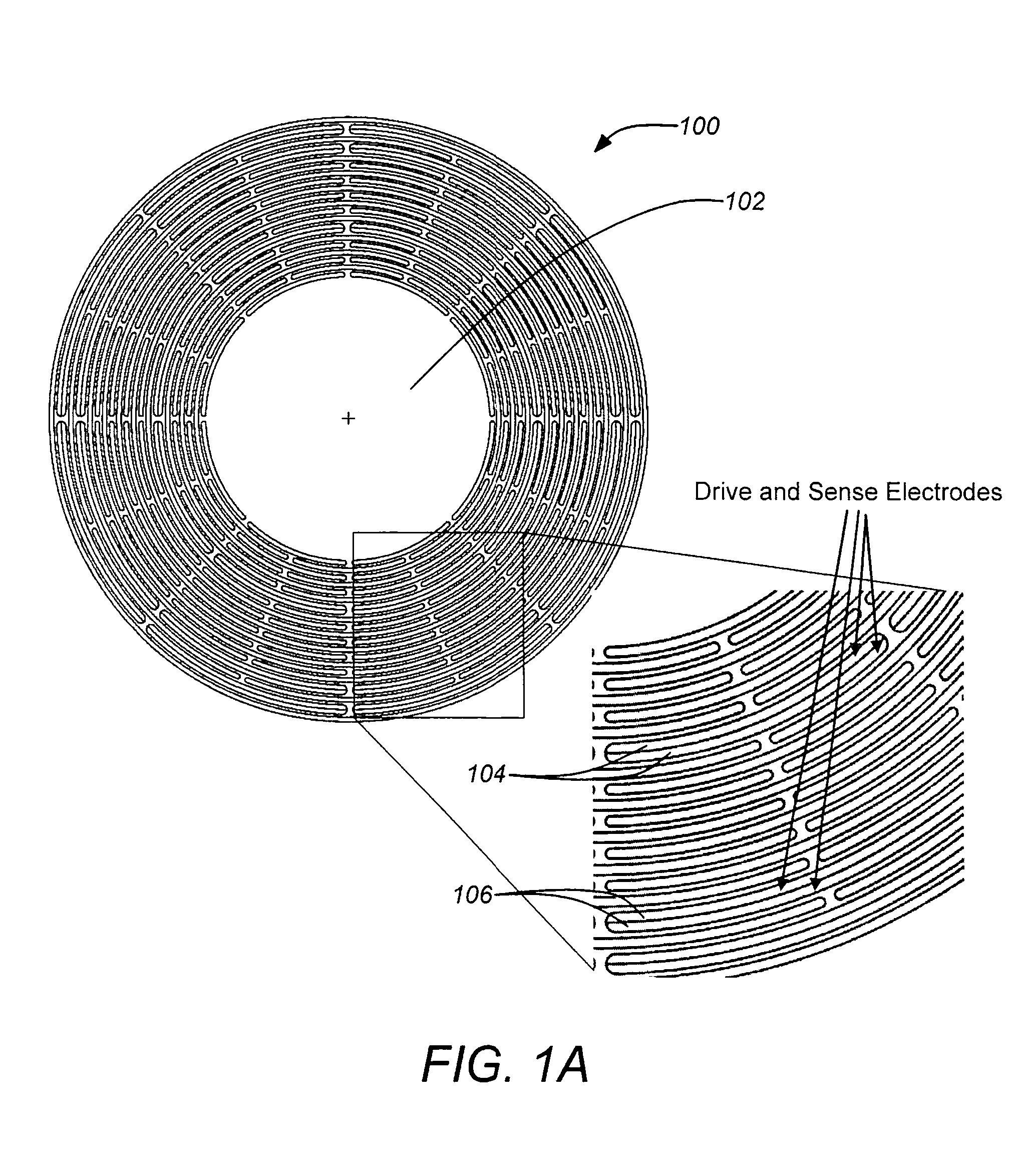

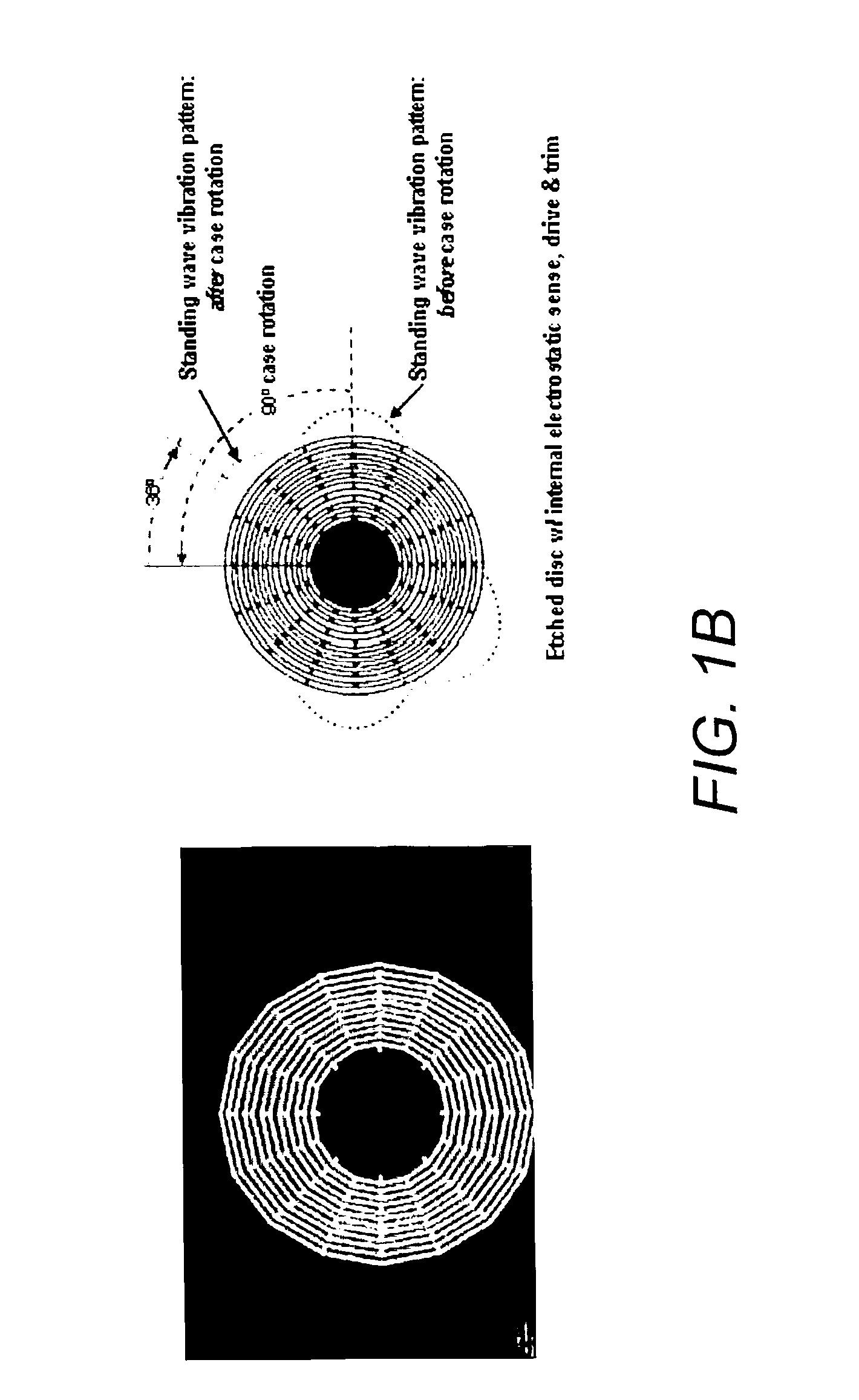

Disc resonator gyroscopes

ActiveUS20070017287A1Low anchor lossHigh QAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsCapacitanceCircular disc

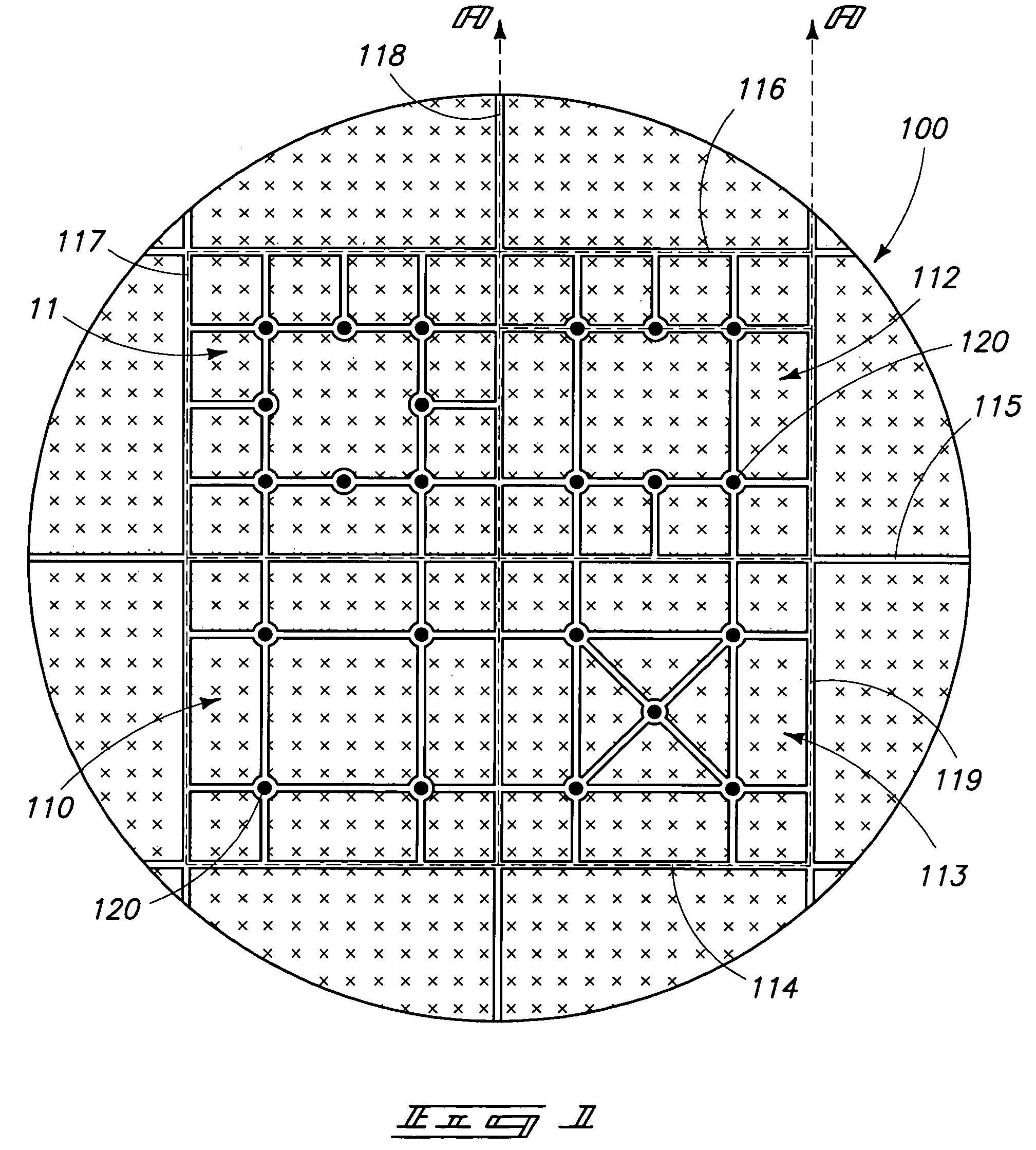

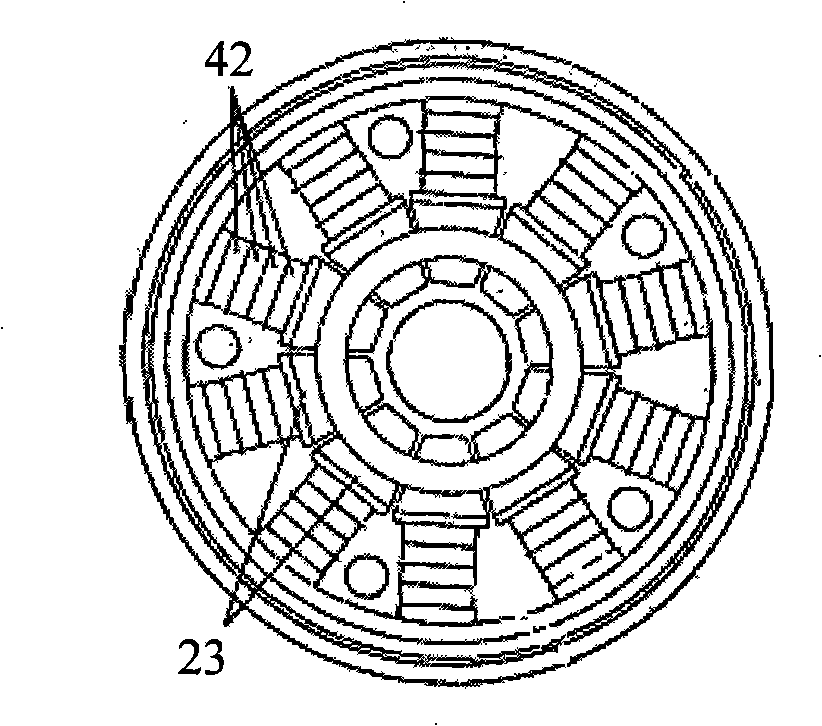

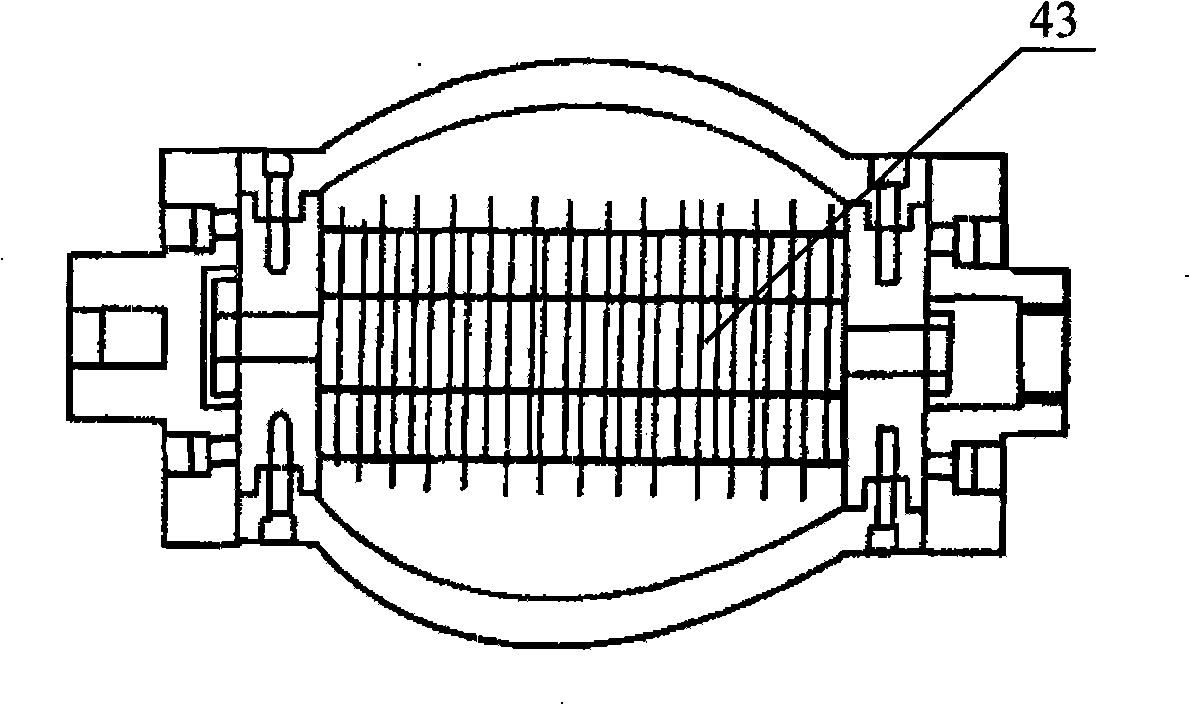

Embodiments of the present invention are directed to apparatuses and methods of making a micromachined resonator gyroscope, e.g. a disc resonator gyro (DRG), including one or more of the following novel features. Embodiments of the invention may comprise a triple-wafer stack gyroscope with an all fused quartz (or all silicon) construction for an electrical baseplate, resonator and vacuum cap. This can yield superior thermal stability over prior art designs. A typical resonator embodiment may include a centrally anchored disc with high aspect-ratio in-plane electrostatic drive and sense electrodes to create large capacitance. A silicon sacrificial layer may be employed for attaching a quartz resonator wafer to a quartz handle wafer for high aspect-ratio etching. In addition, embodiments of the invention may comprise a low thermal stress, wafer-level vacuum packaged gyroscope with on-chip getter. An ultra-thin conductive layer deposited on the quartz resonator may also be utilized for high Q.

Owner:THE BOEING CO

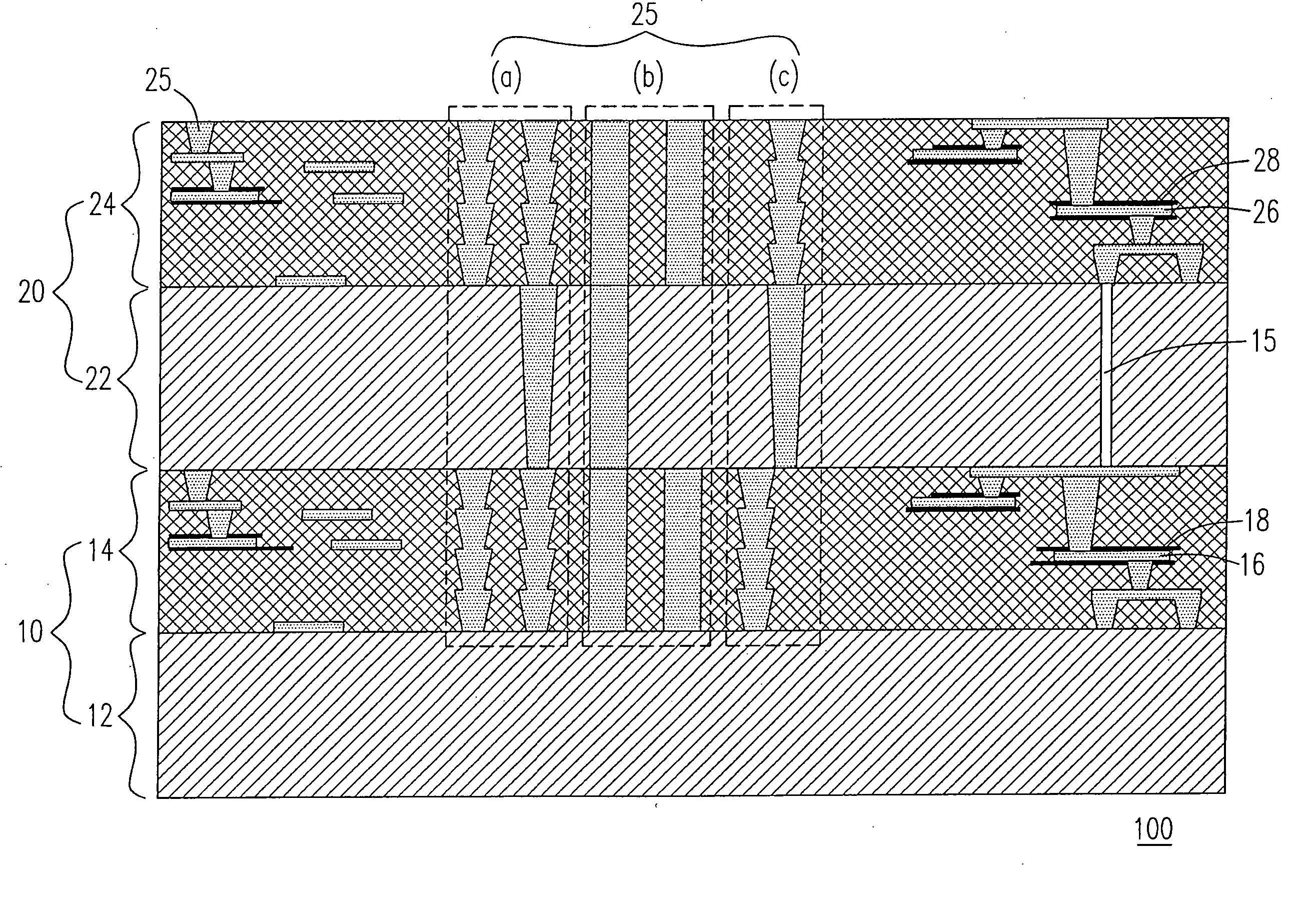

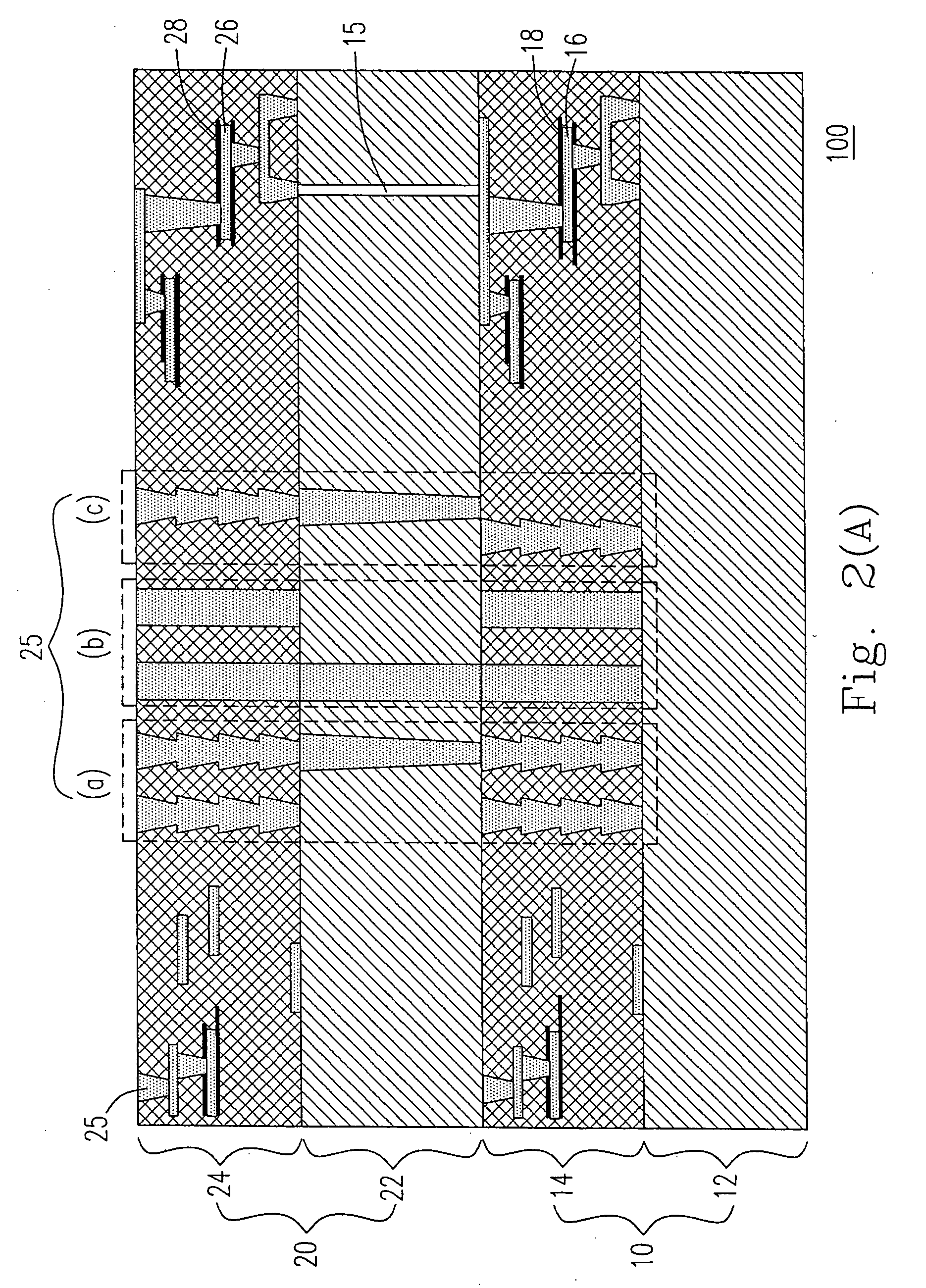

Bonding method for through-silicon-via based 3D wafer stacking

ActiveUS7683459B2Semiconductor/solid-state device detailsSolid-state devicesOutgassingWafer stacking

There is described a hybrid bonding method for through-silicon-via based wafer stacking. Patterned adhesive layers are provided to join together adjacent wafers in the stack, while solder bonding is used to electrically connect the vias. The adhesive layers are patterned to enable outgassing and to provide stress relief.

Owner:HONG KONG APPLIED SCI & TECH RES INST

Disc resonator gyroscopes

ActiveUS7581443B2Low anchor lossHigh QAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsCapacitanceGyroscope

Embodiments of the present invention are directed to apparatuses and methods of making a micromachined resonator gyroscope, e.g. a disc resonator gyro (DRG), including one or more of the following novel features. Embodiments of the invention may comprise a triple-wafer stack gyroscope with an all fused quartz (or all silicon) construction for an electrical baseplate, resonator and vacuum cap. This can yield superior thermal stability over prior art designs. A typical resonator embodiment may include a centrally anchored disc with high aspect-ratio in-plane electrostatic drive and sense electrodes to create large capacitance. A silicon sacrificial layer may be employed for attaching a quartz resonator wafer to a quartz handle wafer for high aspect-ratio etching. In addition, embodiments of the invention may comprise a low thermal stress, wafer-level vacuum packaged gyroscope with on-chip getter. An ultra-thin conductive layer deposited on the quartz resonator may also be utilized for high Q.

Owner:THE BOEING CO

Tissue distraction device

ActiveUS20060229629A1Avoid relative motionInternal osteosythesisJoint implantsDistractionWafer stacking

An apparatus and method for distracting, in a given direction, and supporting two tissue surfaces is provided. A plurality of wafers are consecutively inserted using a wafer insertion apparatus between the two tissue surfaces to create a column of wafers. A detachable wafer assembly is provided that includes a base wafer initially associated with a track assembly of a wafer insertion apparatus. The base wafer is dislodged from the track assembly so that the base wafer is left within the distraction site as the track assembly is removed. A top cap wafer is provided that is situated at the top of the wafer stack, in which the top cap wafer is larger than the remaining wafers to form a gap surrounding the stack to receive biologic material.

Owner:SPINEWAVE

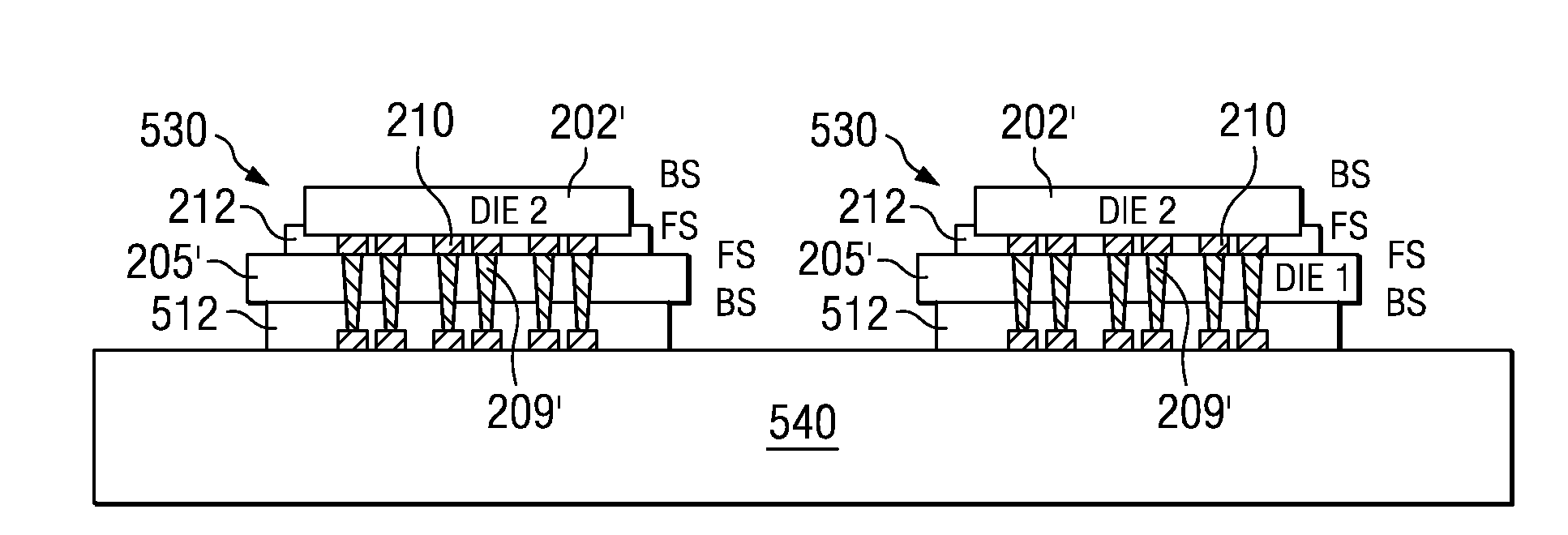

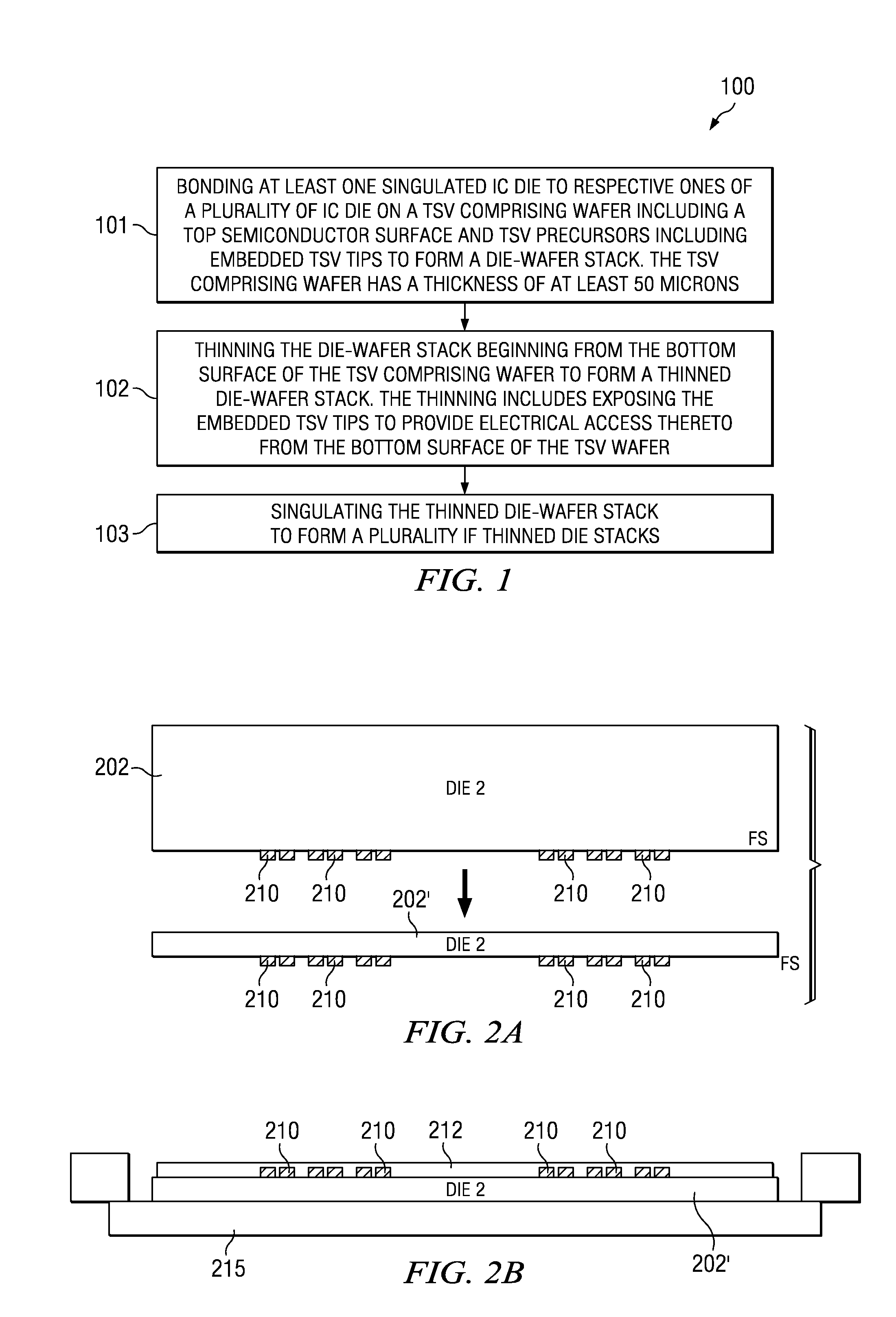

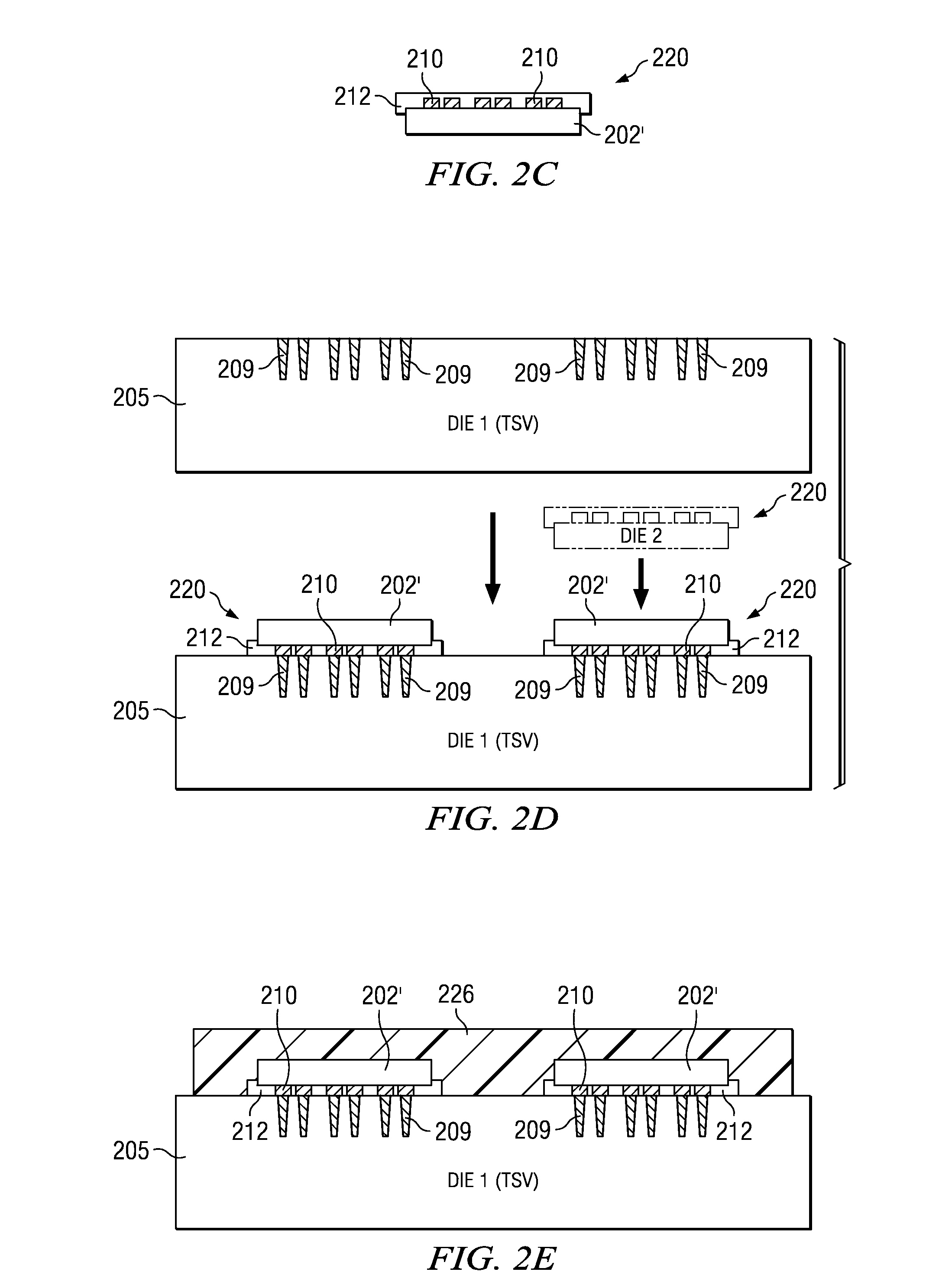

Bonding IC die to TSV wafers

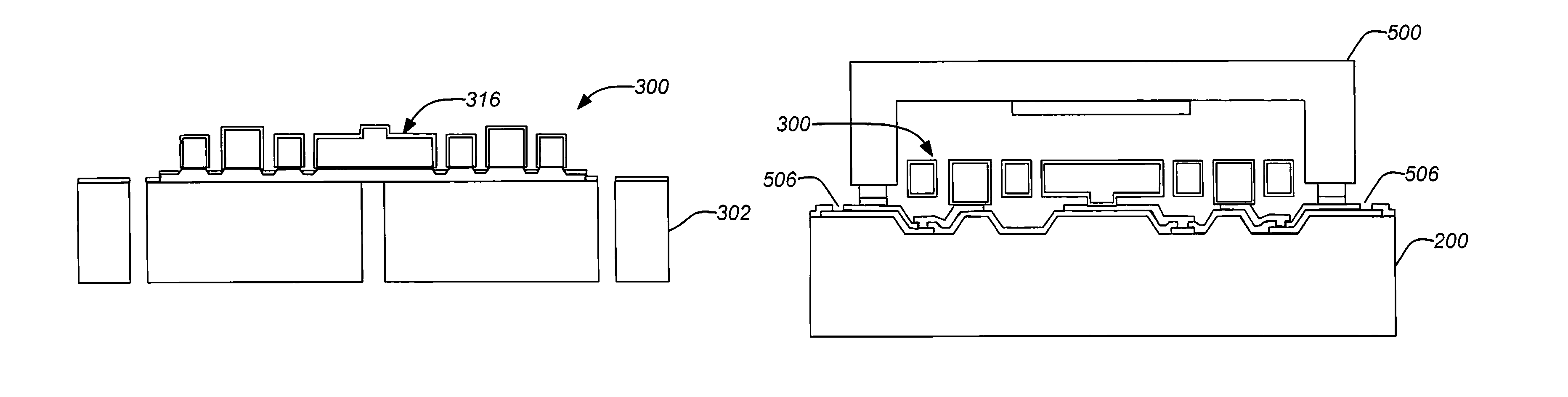

ActiveUS20100159643A1Reduces warpage/bowImprove flowSemiconductor/solid-state device detailsSolid-state devicesWafer stackingEngineering

A method for bonding IC die to TSV wafers includes bonding at least one singulated IC die to respective ones of a plurality of IC die on a TSV wafer that includes a top semiconductor surface and TSV precursors including embedded TSV tips to form a die-wafer stack. The die-wafer stack is thinned beginning from the bottom surface of the TSV wafer to form a thinned die-wafer stack. The thinning includes exposing the embedded TSV tips to provide electrical access thereto from the bottom surface of the TSV wafer. The thinned die-wafer stack can be singulated to form a plurality of thinned die stacks.

Owner:TEXAS INSTR INC

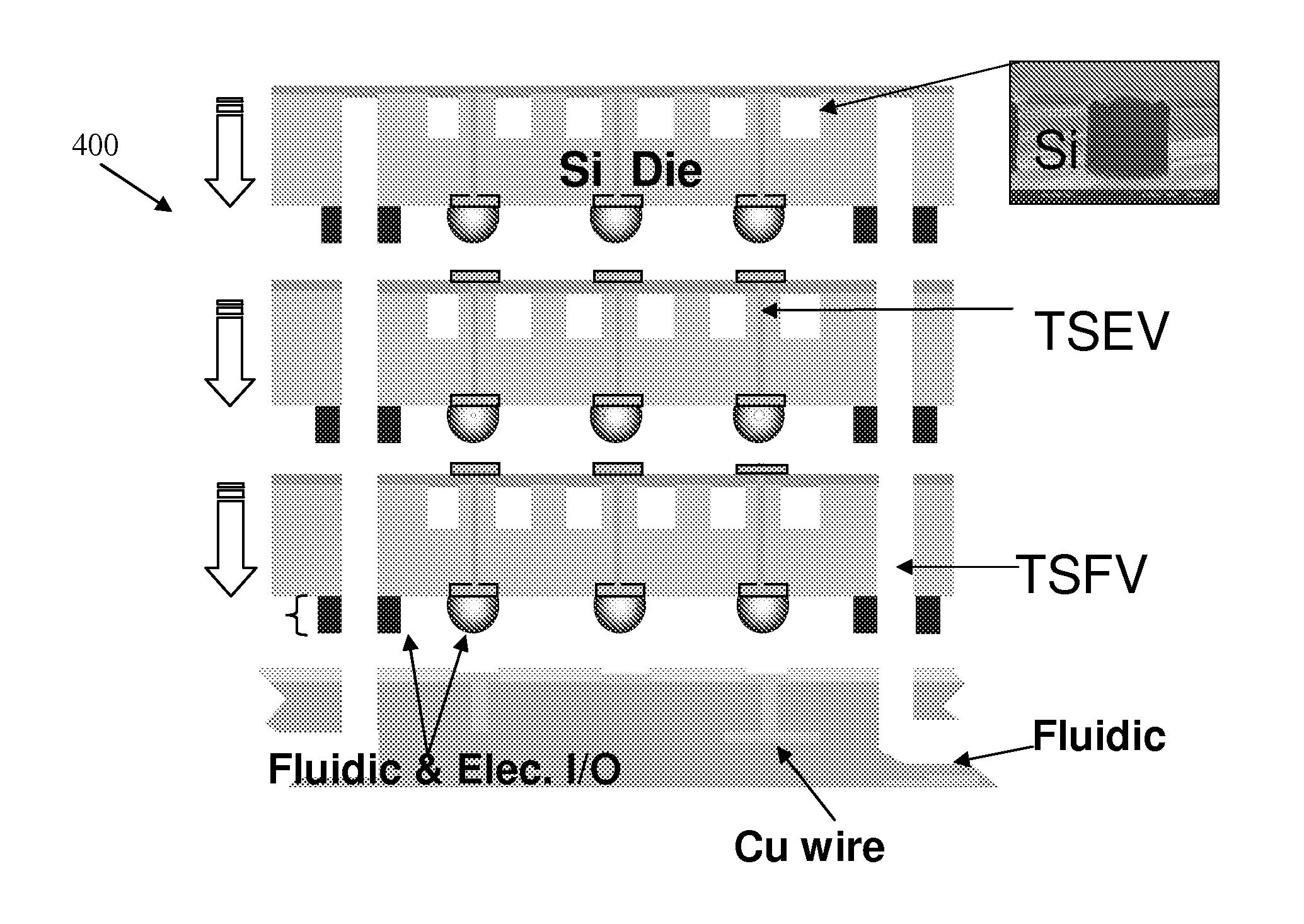

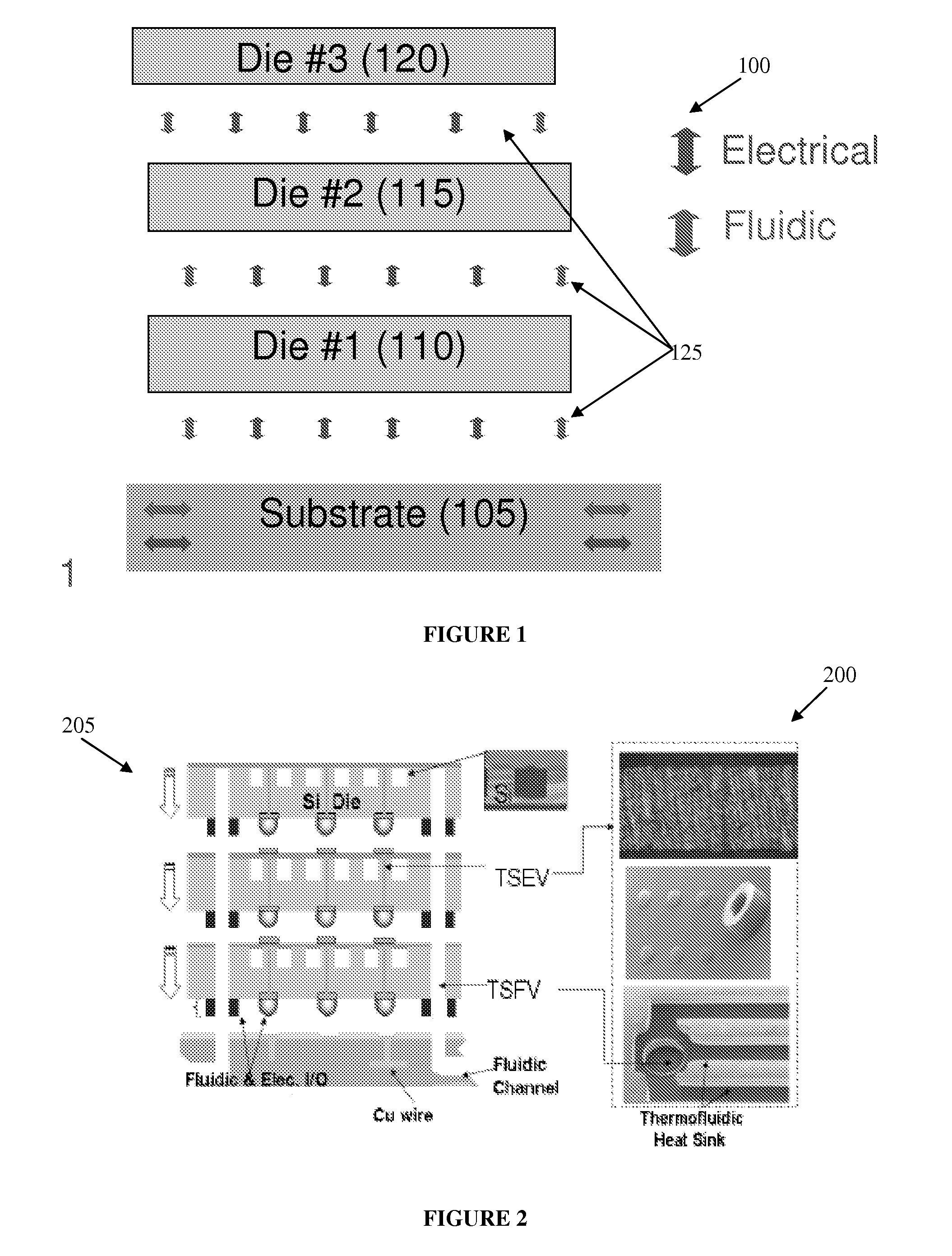

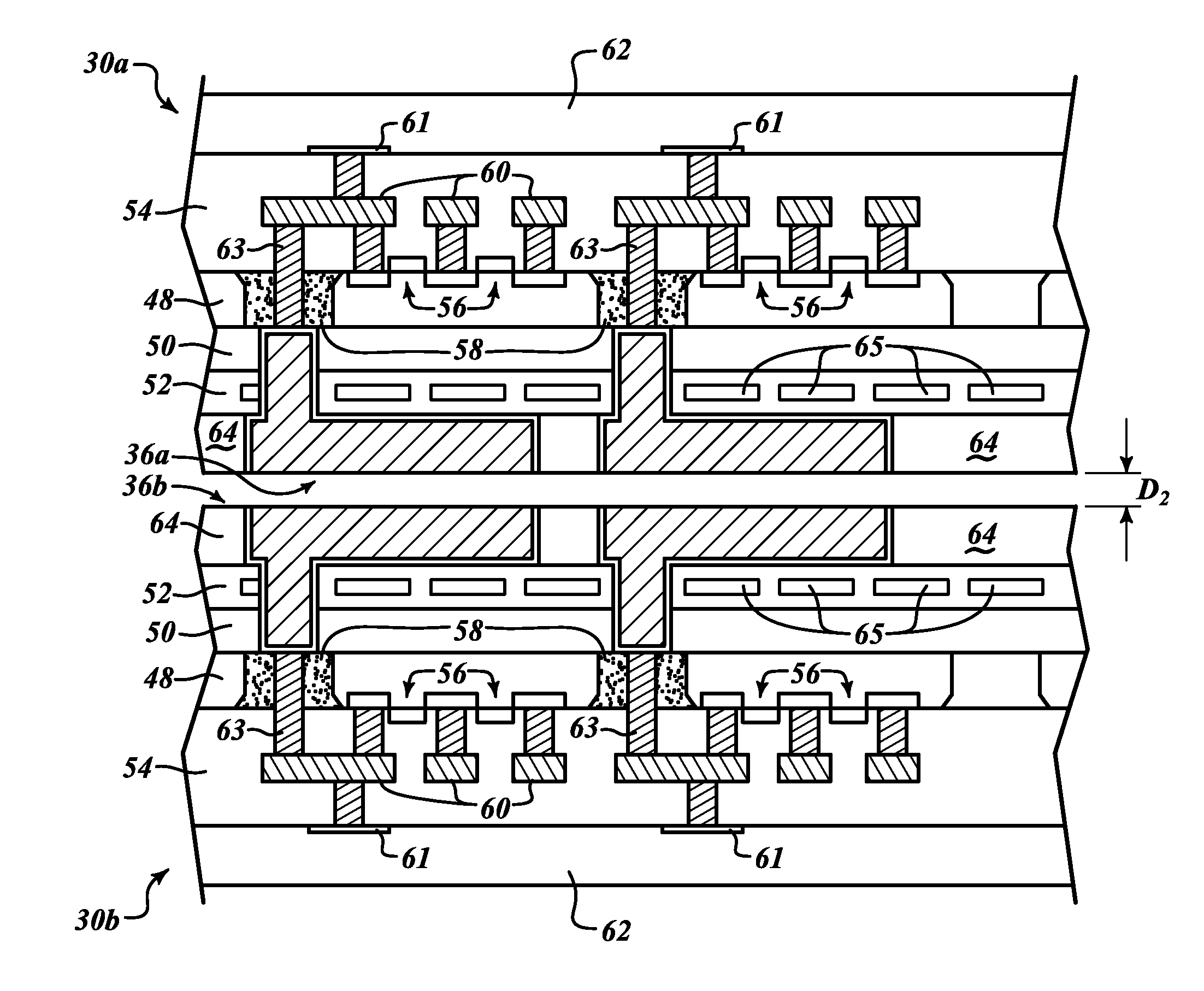

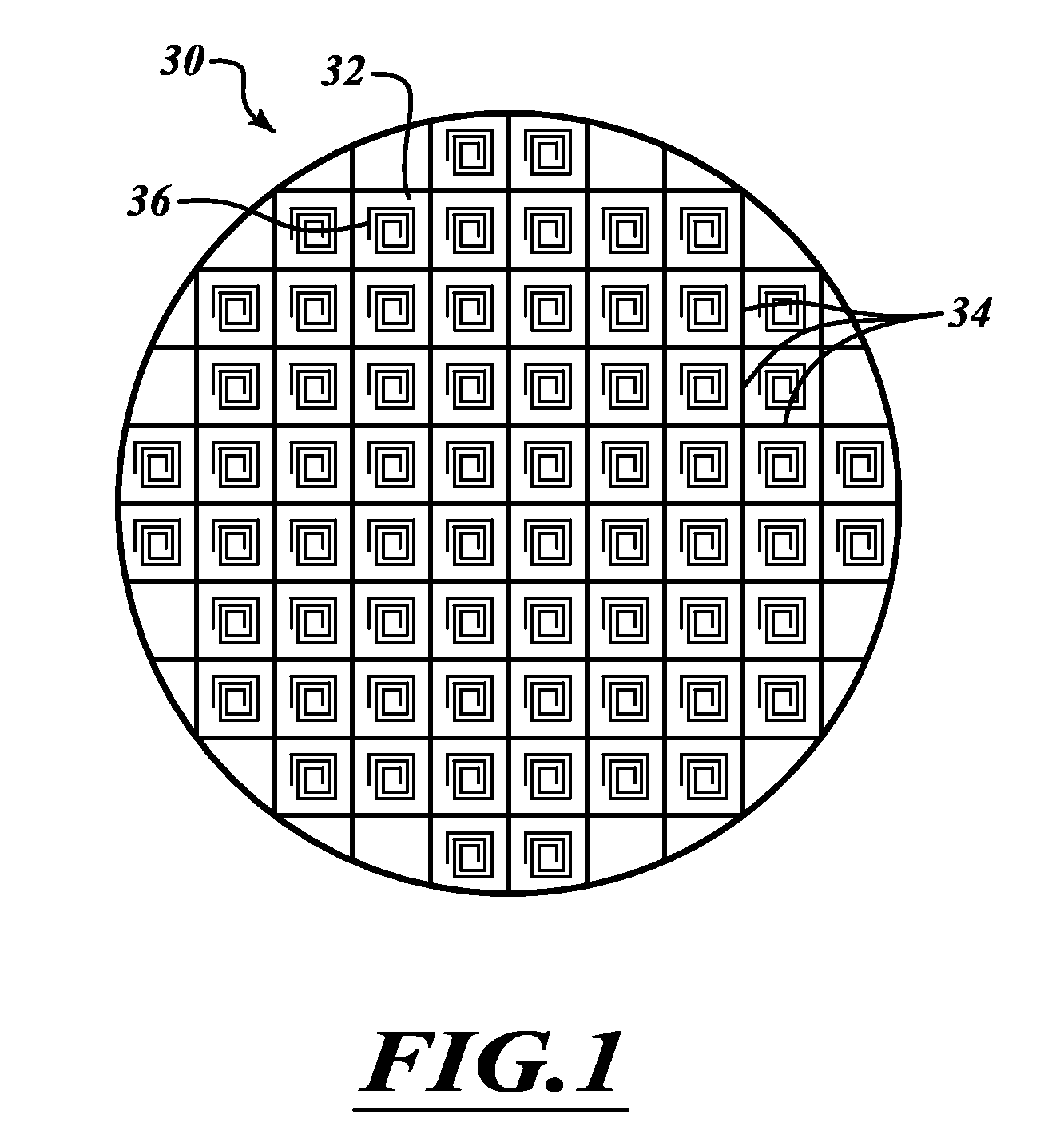

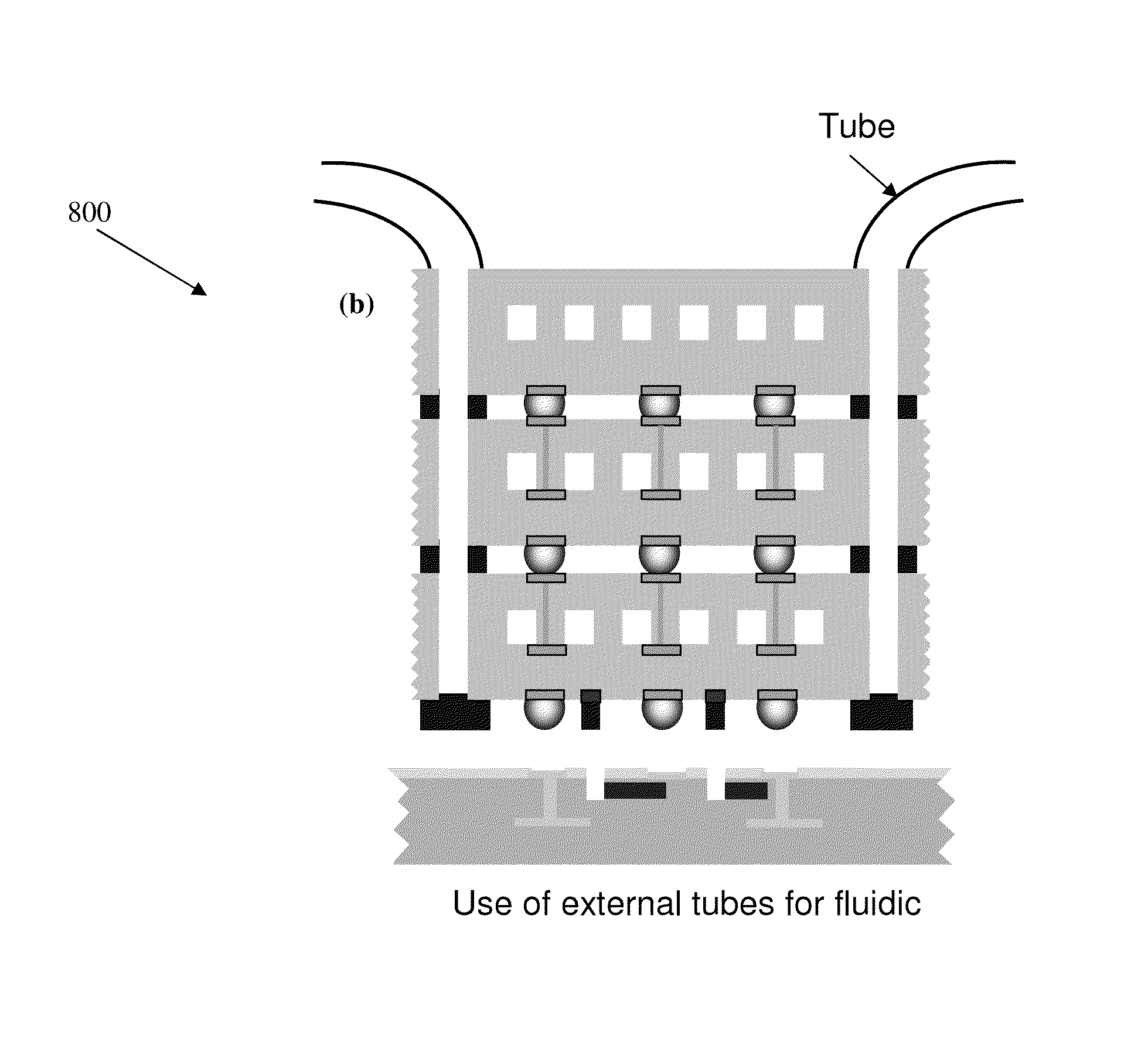

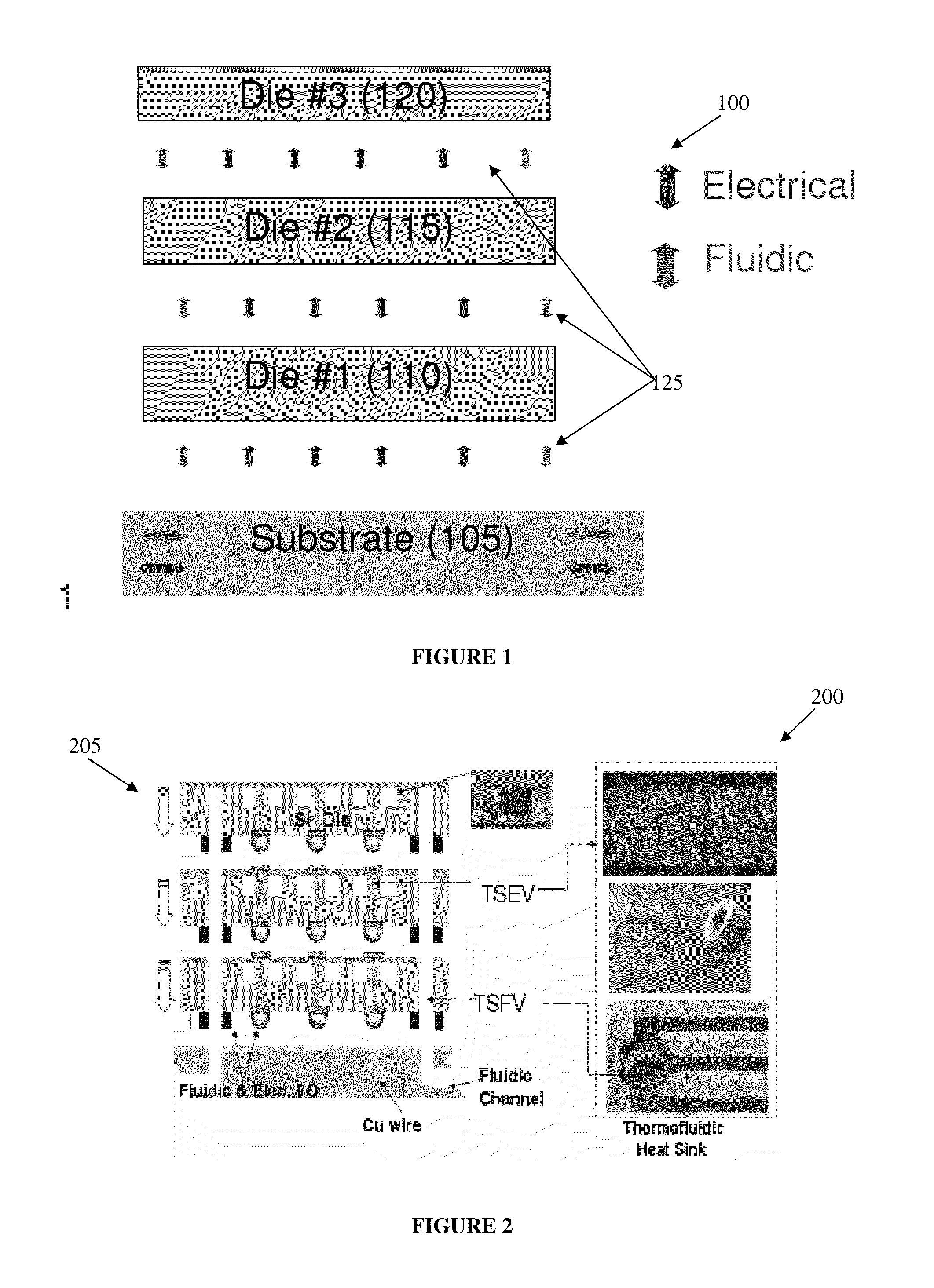

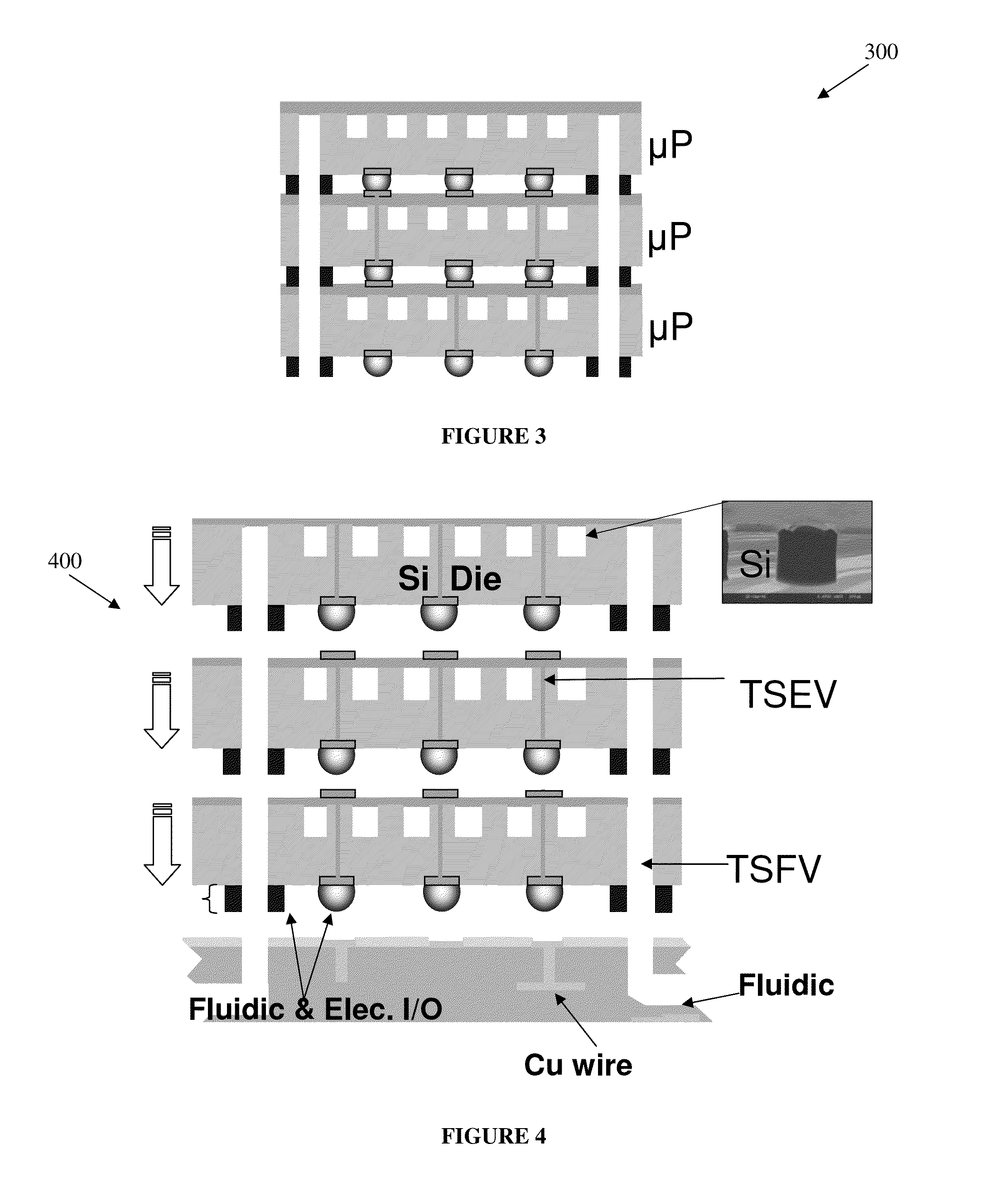

3-D ICs EQUIPPED WITH DOUBLE SIDED POWER, COOLANT, AND DATA FEATURES

ActiveUS20100187683A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorWafer stacking

Three dimensional integrated circuits with double sided power, coolant, and data features and methods of constructing same are provided. According to some embodiments, an integrated circuit package can generally comprise one or more semiconductor wafers and opposing end substrates. The semiconductor wafers can each have a top exterior surface and a bottom exterior surface. The plurality of semiconductor wafers can form a multi-dimensional wafer stack of die wafers such that adjacent wafers have facing surfaces. Each of the semiconductor wafers can comprise one or more channels formed through the wafers. A portion of the channels can extend generally between the top and bottom exterior surfaces of the semiconductor wafers. A portion of the channels can carry conductors for coupling the wafers and / or coolant for cooling the wafers. The opposing end substrates can be disposed proximate opposing ends of the multi-dimensional stack. The opposing end substrates can be configured to supply power, coolant, and data signals to opposing ends of the multi-dimensional wafer stack. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

Etching apparatus for manufacturing semiconductor devices

InactiveUS6340405B2Operation efficiency can be improvedReduce processing timeDecorative surface effectsSemiconductor/solid-state device manufacturingMagnetic tapeWafer stacking

An etching apparatus for manufacturing semiconductor devices which reduces contamination of the processing surface of a wafer by transporting a plurality of wafers stacked in a cassette with their processing surfaces facing down from the cassette supply chamber to one or more process chambers where the etching operation is performed on each wafer, one at a time. The apparatus has a load lock chamber for transferring the wafers stacked in the cassette from the cassette supply chamber, which is maintained under atmospheric conditions, to the process chamber, which is maintained under a strong vacuum. The process chamber has a cathode to which a wafer is clamped by a wafer holder with its processing surface facing down; the process chamber may also have a removable lower cover for easy repair and cleaning. The apparatus may also have a wafer aligning chamber installed between the cassette supply chamber and the load lock chamber for simultaneously aligning all of the wafers n the cassette before they are transported to the load lock chamber. The wafer aligning chamber also has a cassette transport mechanism for transferring the cassette from a cassette supply table in the cassette supply chamber to an elevator installed in the load lock chamber.

Owner:SAMSUNG ELECTRONICS CO LTD

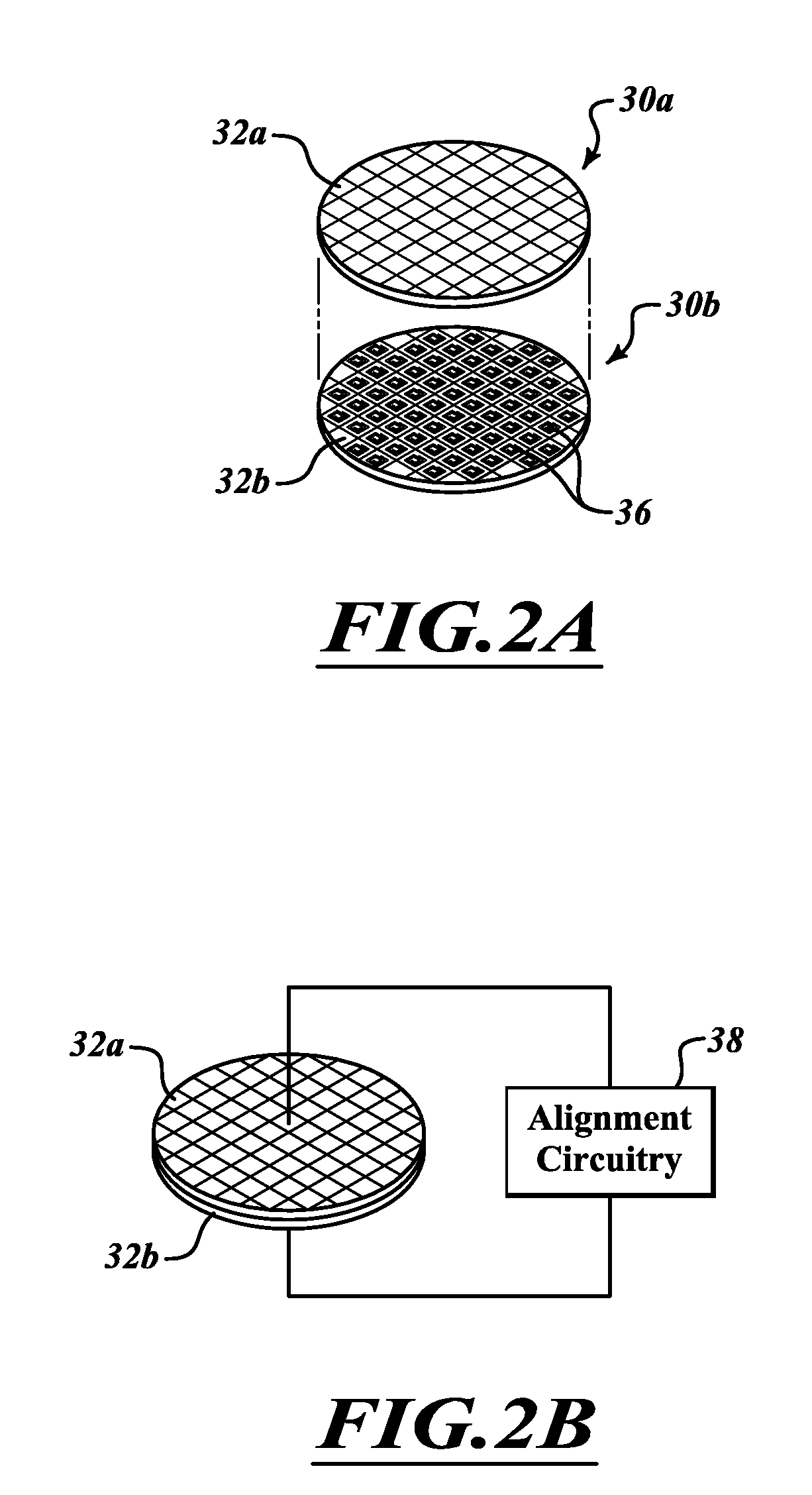

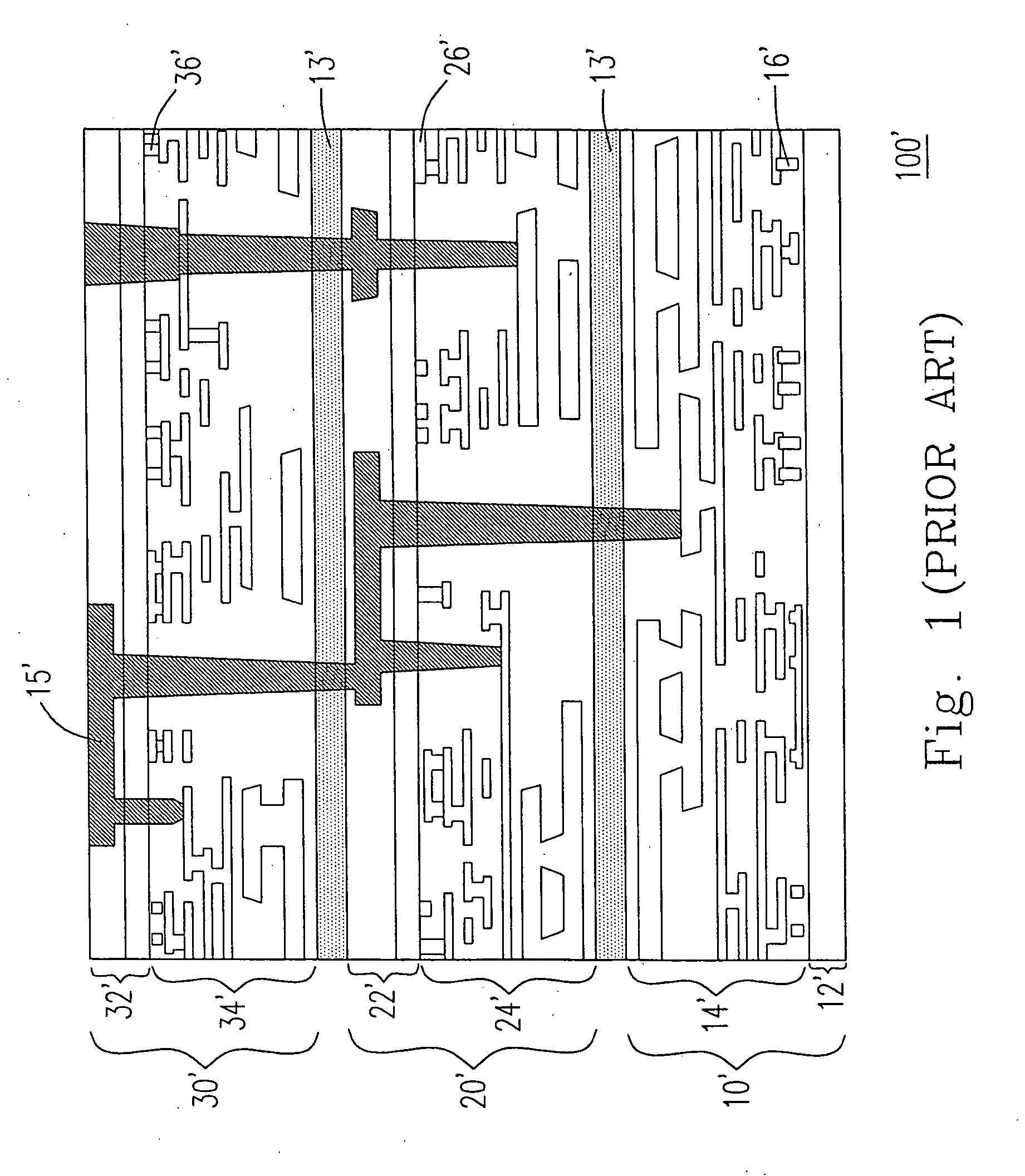

Using backside passive elements for multilevel 3D wafers alignment applications

ActiveUS20120187530A1High densityImprove performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsWafer stackingIntegrated circuit

Passive circuit elements are formed at surfaces of two integrated circuit wafers. The passive circuit elements are utilized to align the two integrated circuit wafers to form an integrated circuit wafer stack.

Owner:IBM CORP +1

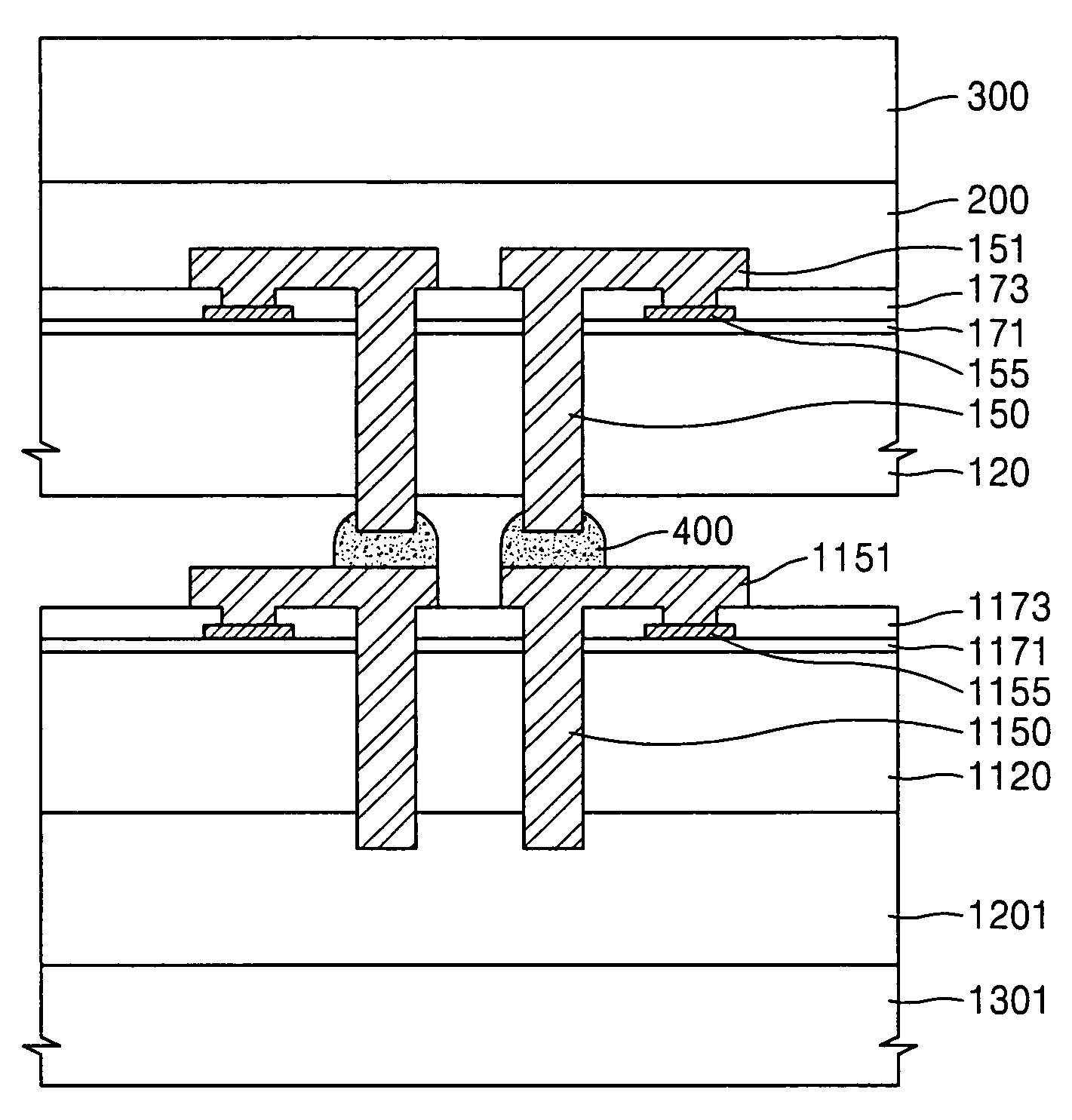

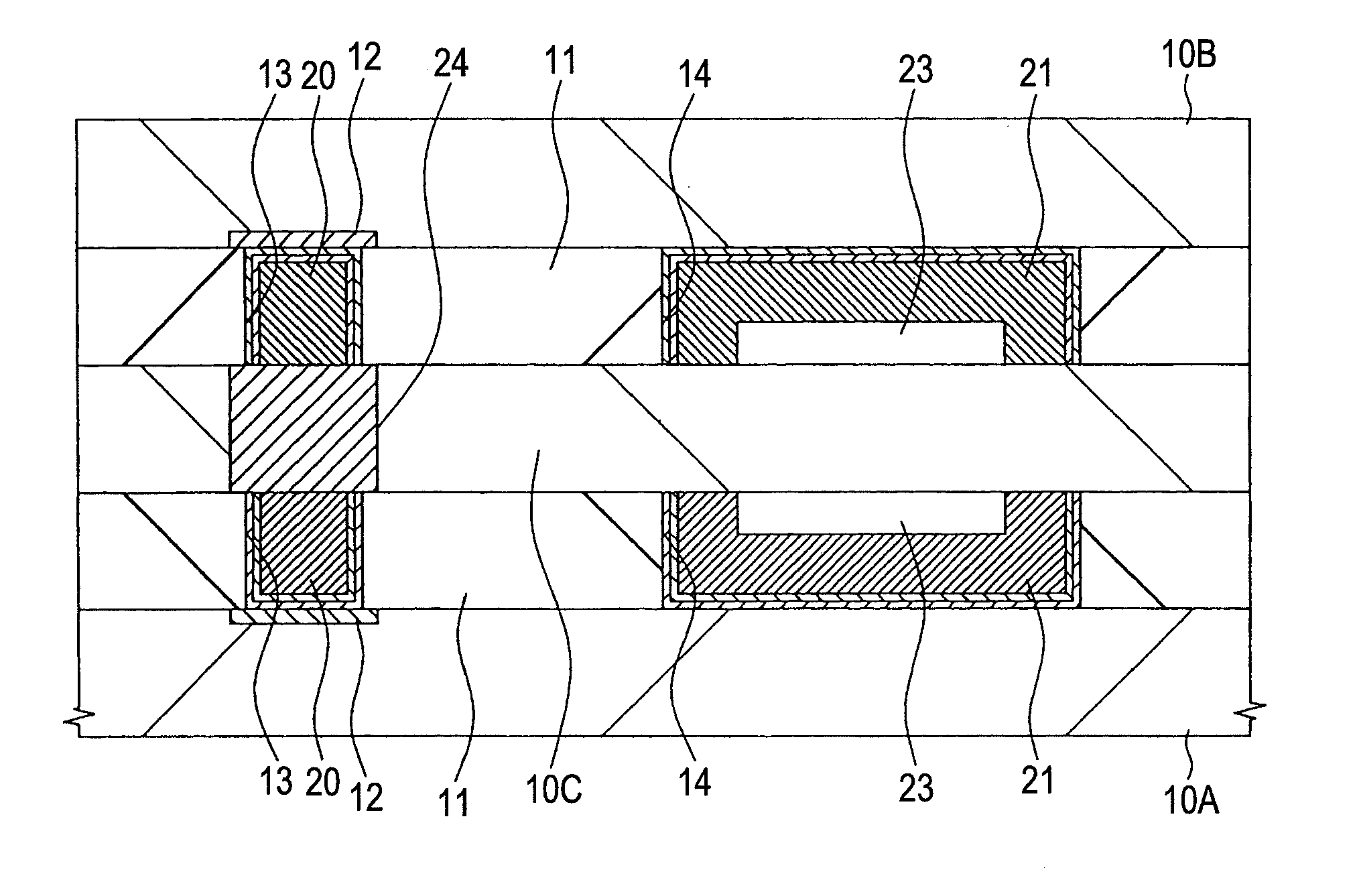

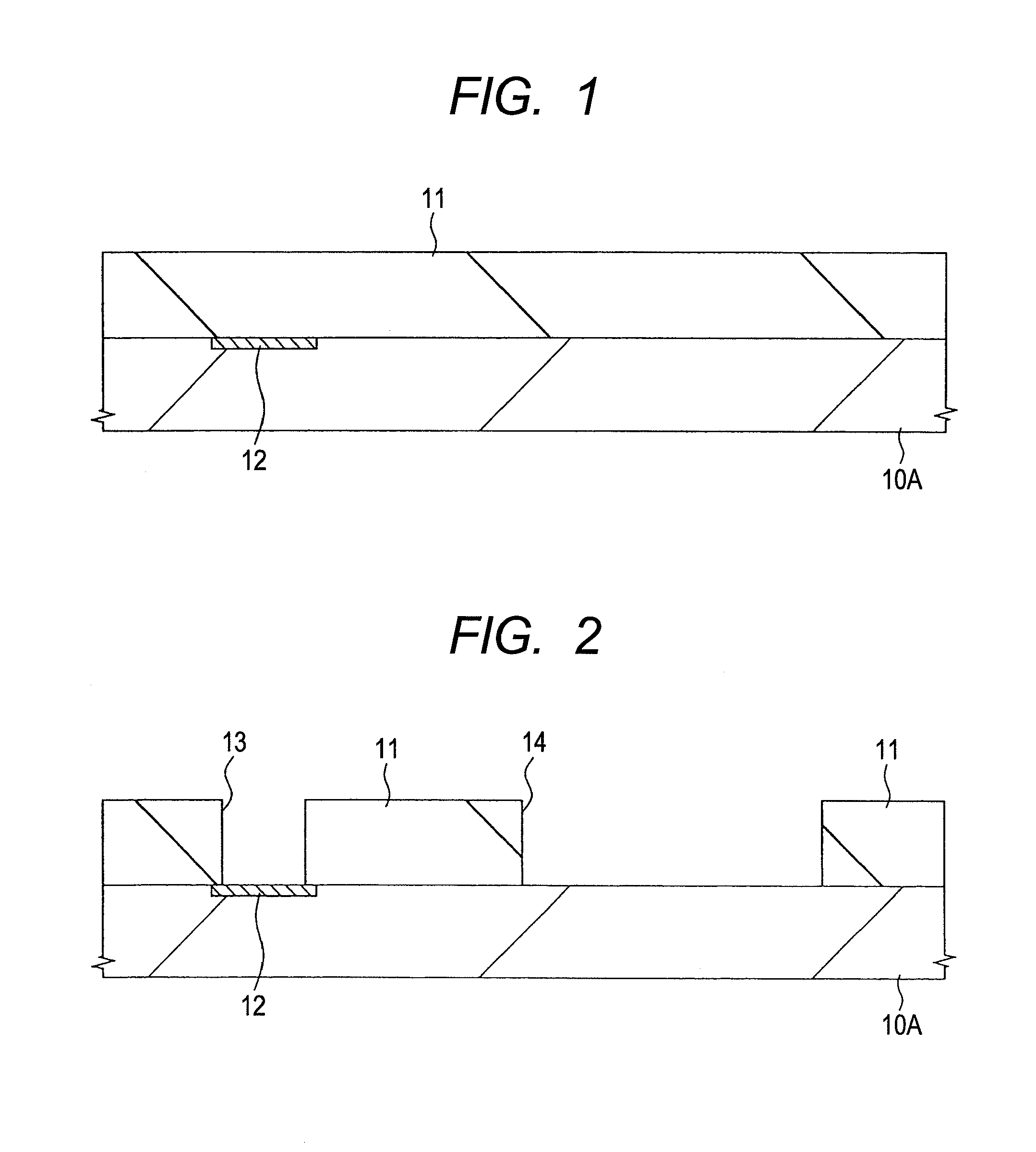

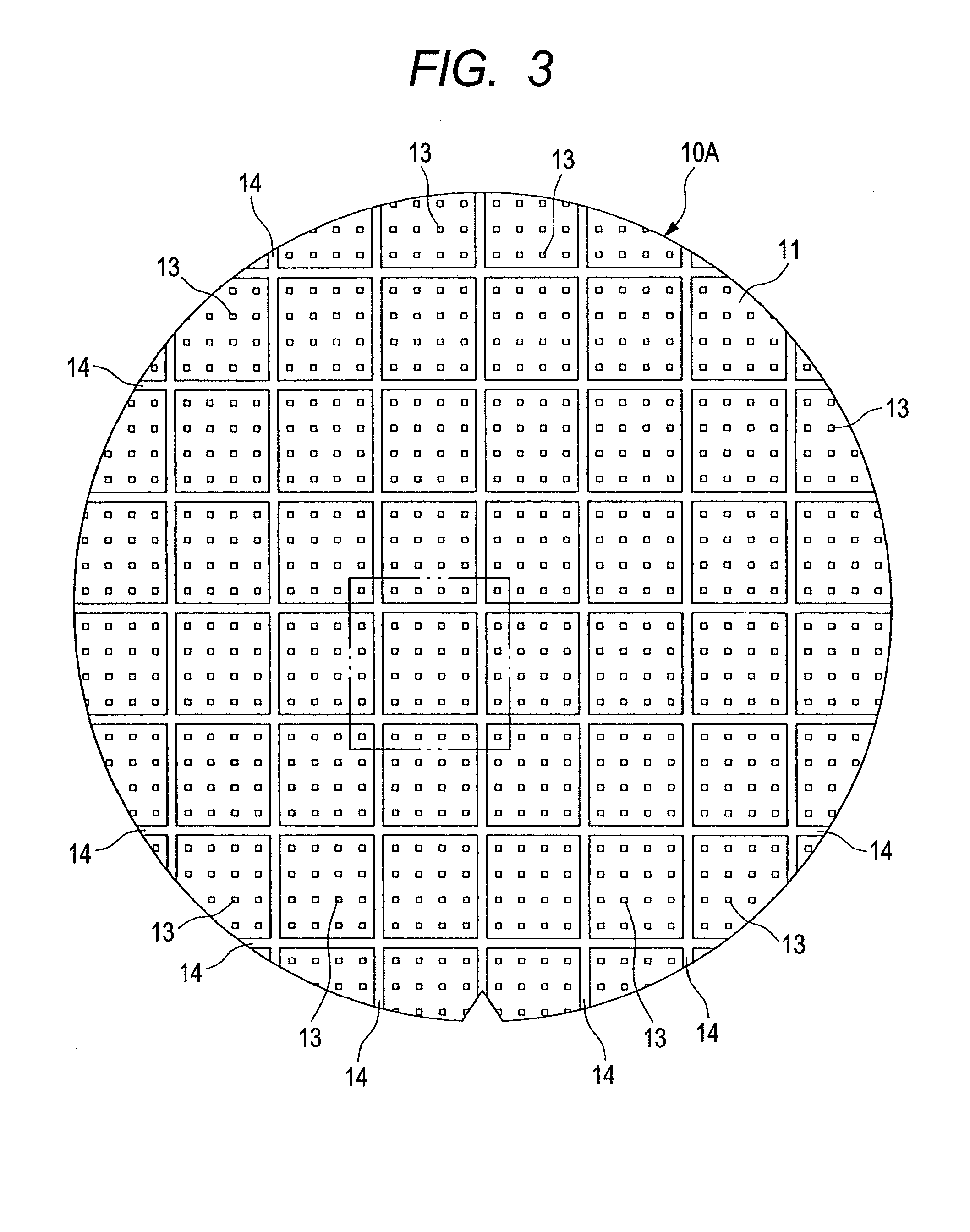

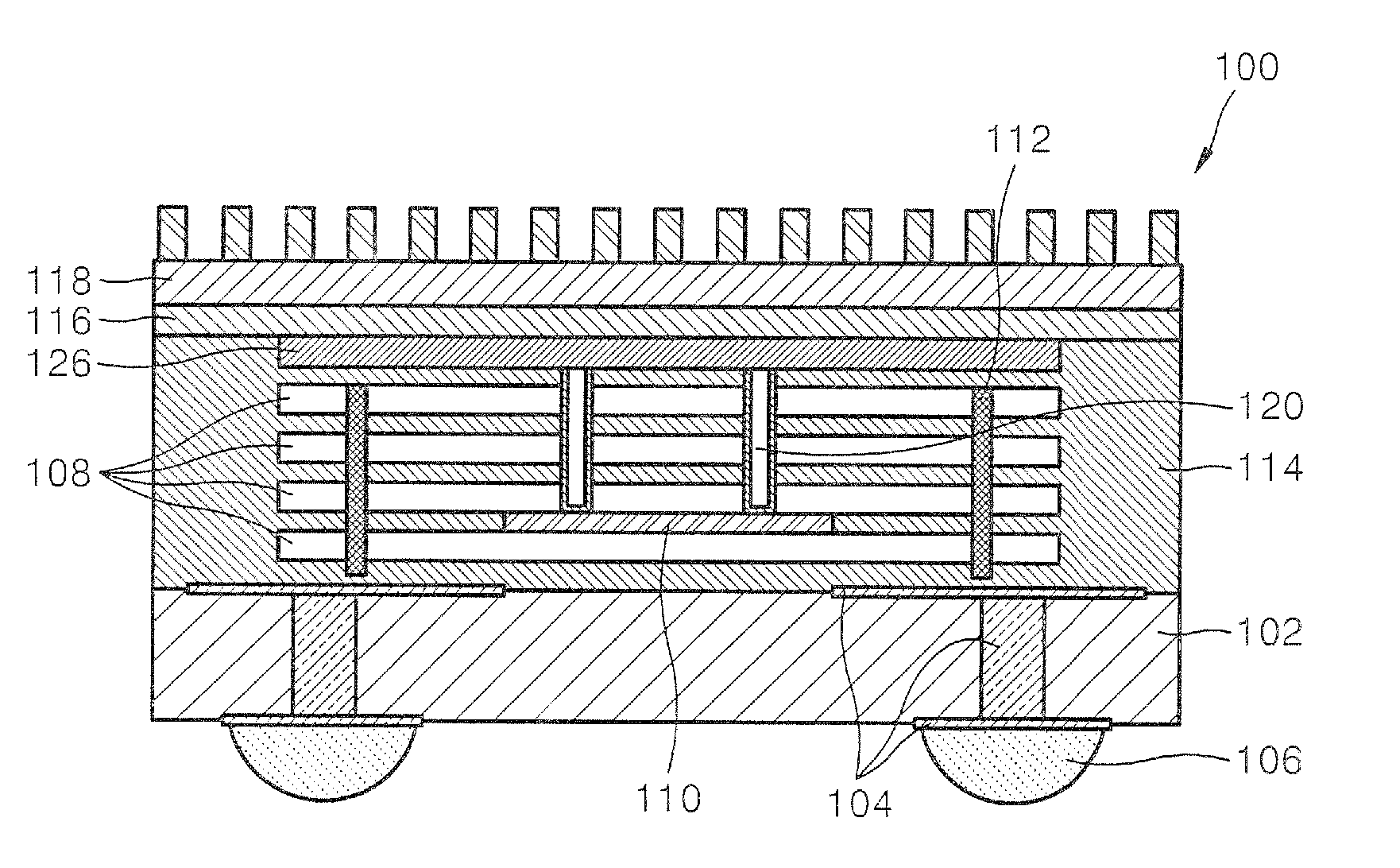

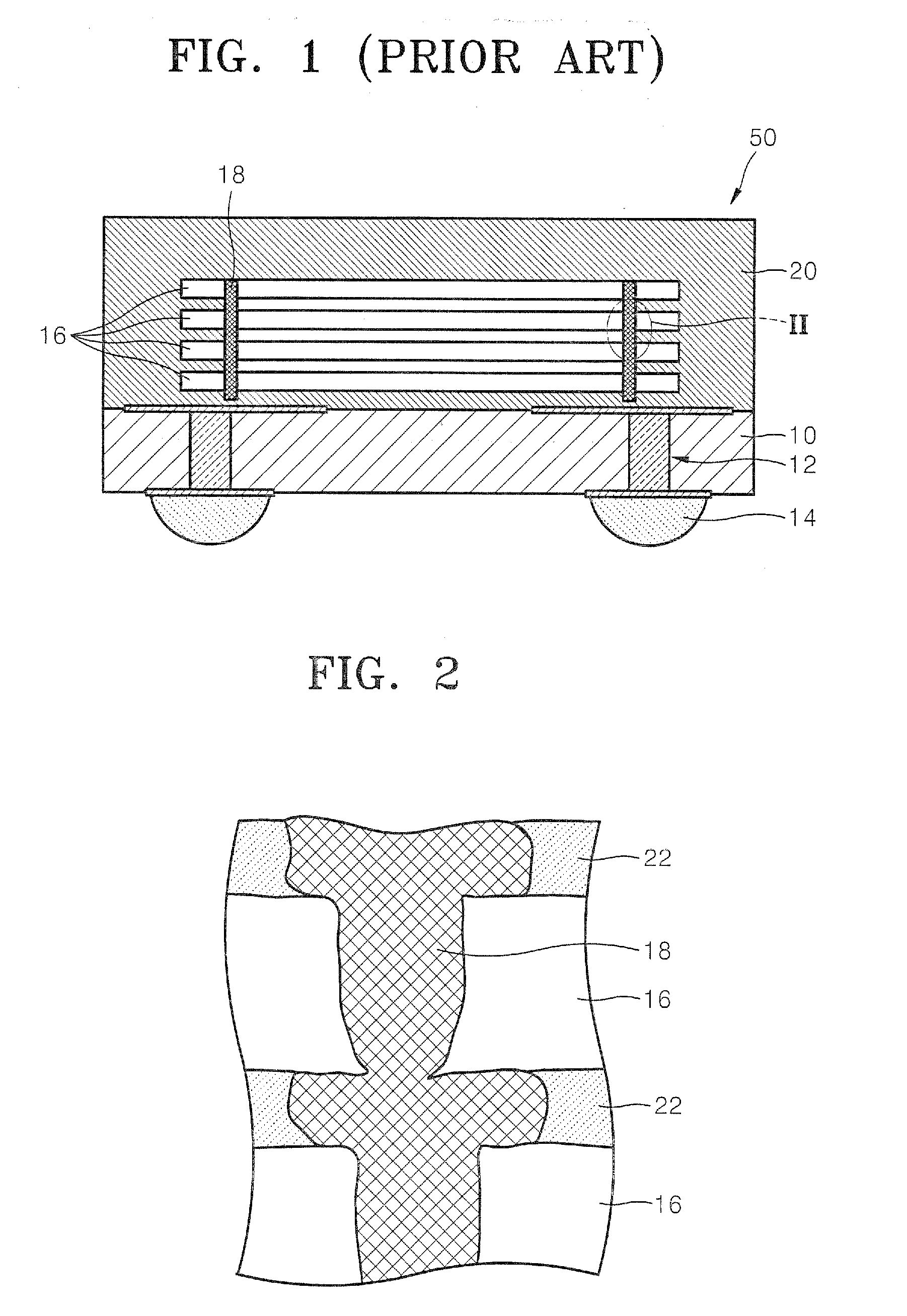

Semiconductor device and method for manufacturing the same

InactiveUS20120068355A1Reduce the likelihood of occurrenceReduce generationSemiconductor/solid-state device detailsSolid-state devicesWafer stackingSilicon

A semiconductor device including two silicon wafers stacked and bonded together with bumps of one wafer electrically coupled with those of the other wafer, in which generation of voids on the junction surface between the silicon wafers is suppressed. Due to a recess made in the surface of a buried conductive film, a cavity is formed in the junction surface between the silicon wafers. The ends of the cavity extend to the periphery of the junction surface between the silicon wafers. This allows the air trapped on the junction surface between the silicon wafers to get out through the cavity, thereby reducing the possibility of generation of voids on the junction surface.

Owner:HITACHI LTD

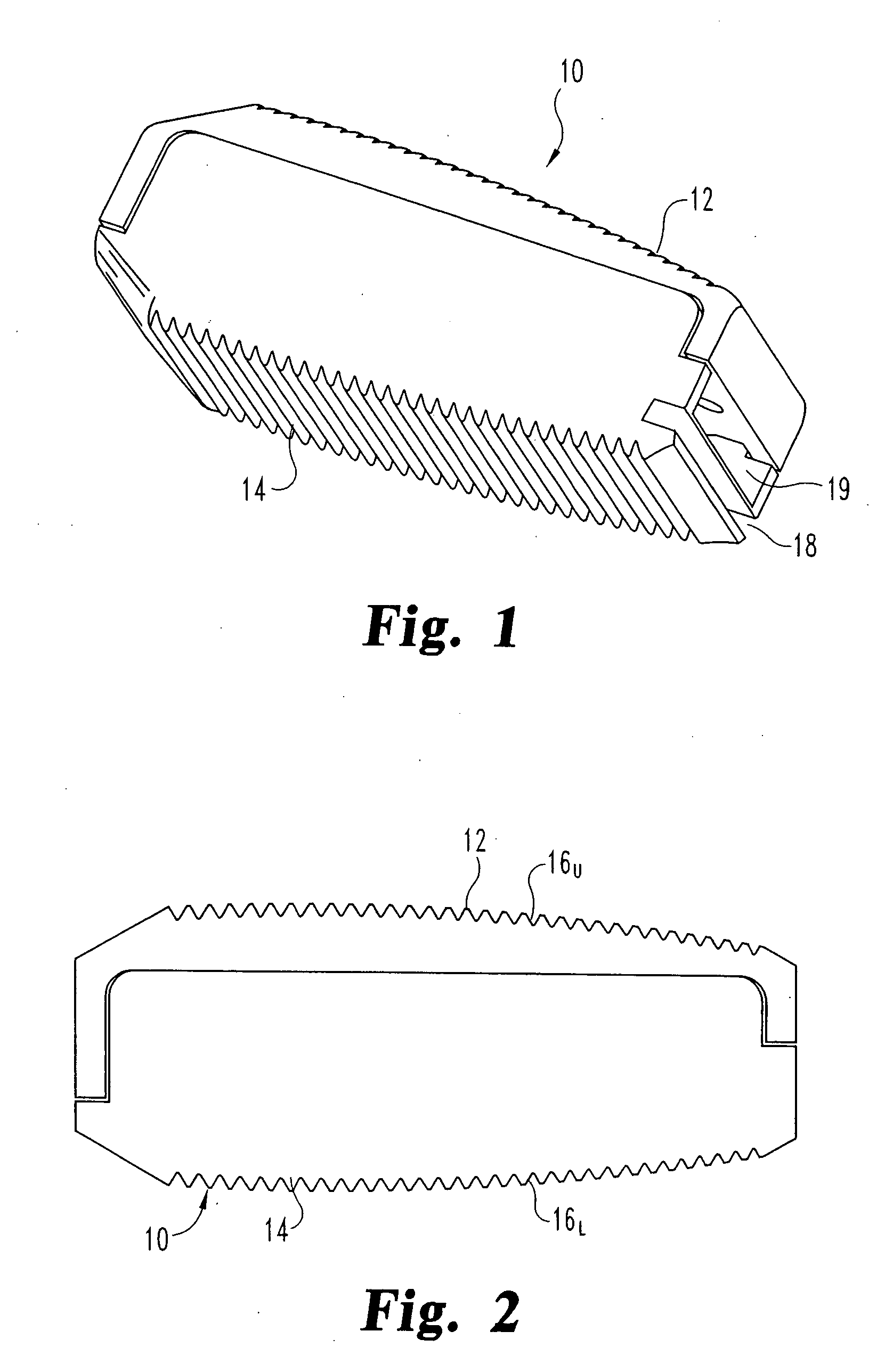

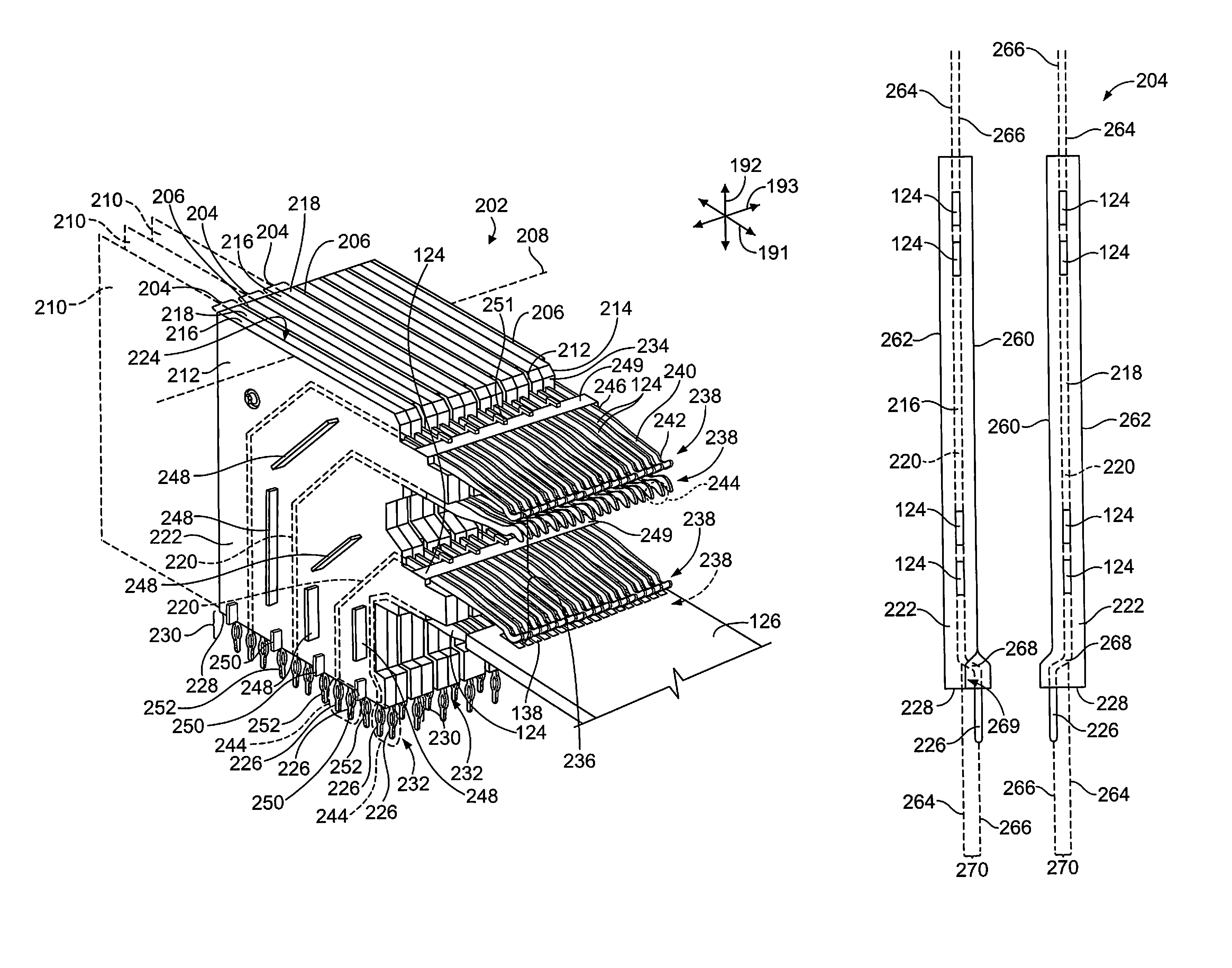

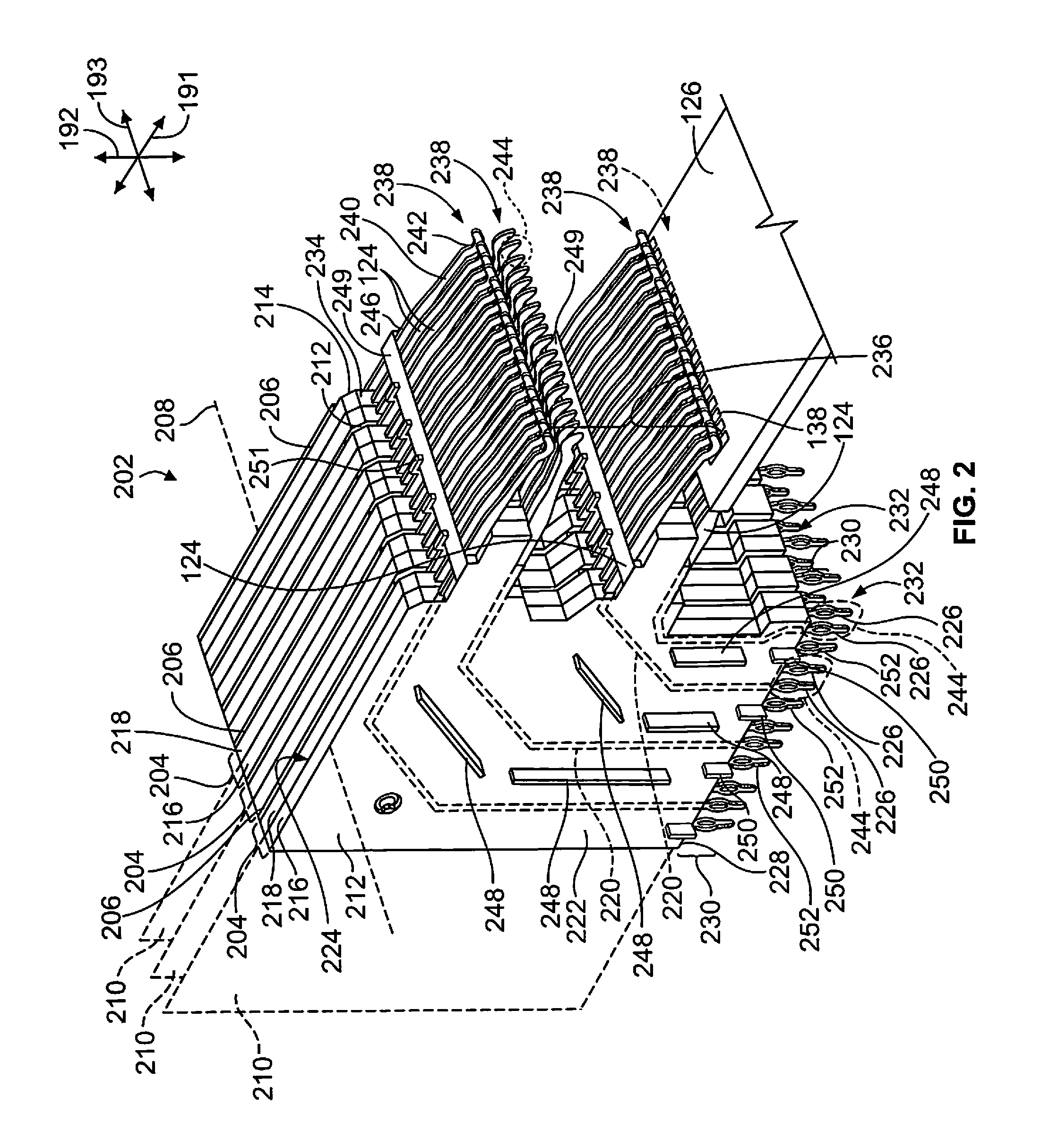

Electrical connector having contact modules

ActiveUS9413112B2Securing/insulating coupling contact membersFixed connectionsWafer stackingEngineering

An electrical connector includes a housing and a plurality of contact modules and ground plates held by the housing. Each contact module includes left and right signal wafers stacked next to each other along a stack axis. The signal wafers include electrical terminals held by a dielectric body. The electrical terminals have mounting contacts protruding from the dielectric body at a mounting face of the housing. The electrical terminals of at least one of the signal wafers in each contact module are jogged toward the other signal wafer such that the mounting contacts of each contact module align in a column. Each of the ground plates is disposed along an outer side of a corresponding contact module.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

Wafer level packaging process

ActiveUS7393758B2Improve performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHard metalWafer stacking

Owner:MAXIM INTEGRATED PROD INC

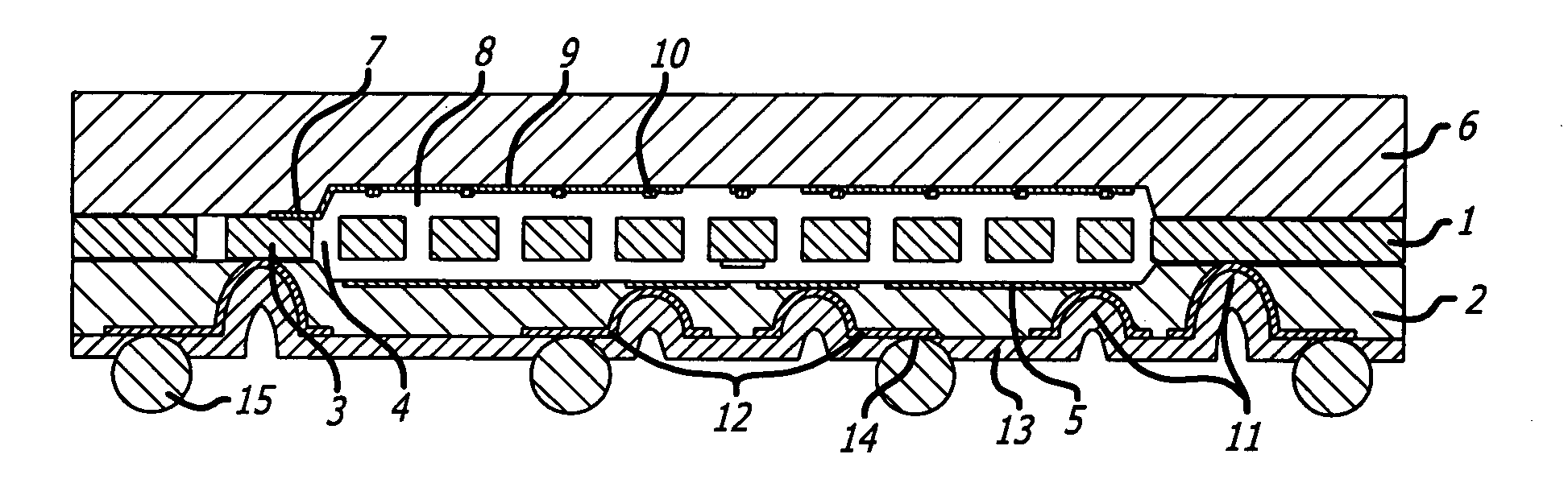

Surface-mount package for an optical sensing device and method of manufacture

InactiveUS6844606B2Shorten test timeReduces mounting costSemiconductor/solid-state device detailsSolid-state devicesSurface mountingWafer stacking

An optical sensor package capable of being surface mounted, and in a form that enables multiple packages to be fabricated simultaneously and then array tested in a wafer stack prior to singulation. The package comprises a chip carrier, a device chip electrically and mechanically connected to a first surface of the chip carrier with solder connections, and a capping chip secured to the chip carrier to hermetically enclose the device chip. The device chip has an optical sensing element on a surface thereof, while the capping chip has means for enabling radiation to pass therethrough to the device chip. The chip carrier includes conductive vias that are electrically connected to the solder connections of the device chip and extend through the chip carrier to bond pads on a second surface of the chip carrier, enabling the package to be surface mounted with solder connections to a suitable substrate.

Owner:XENOGENIC DEV LLC

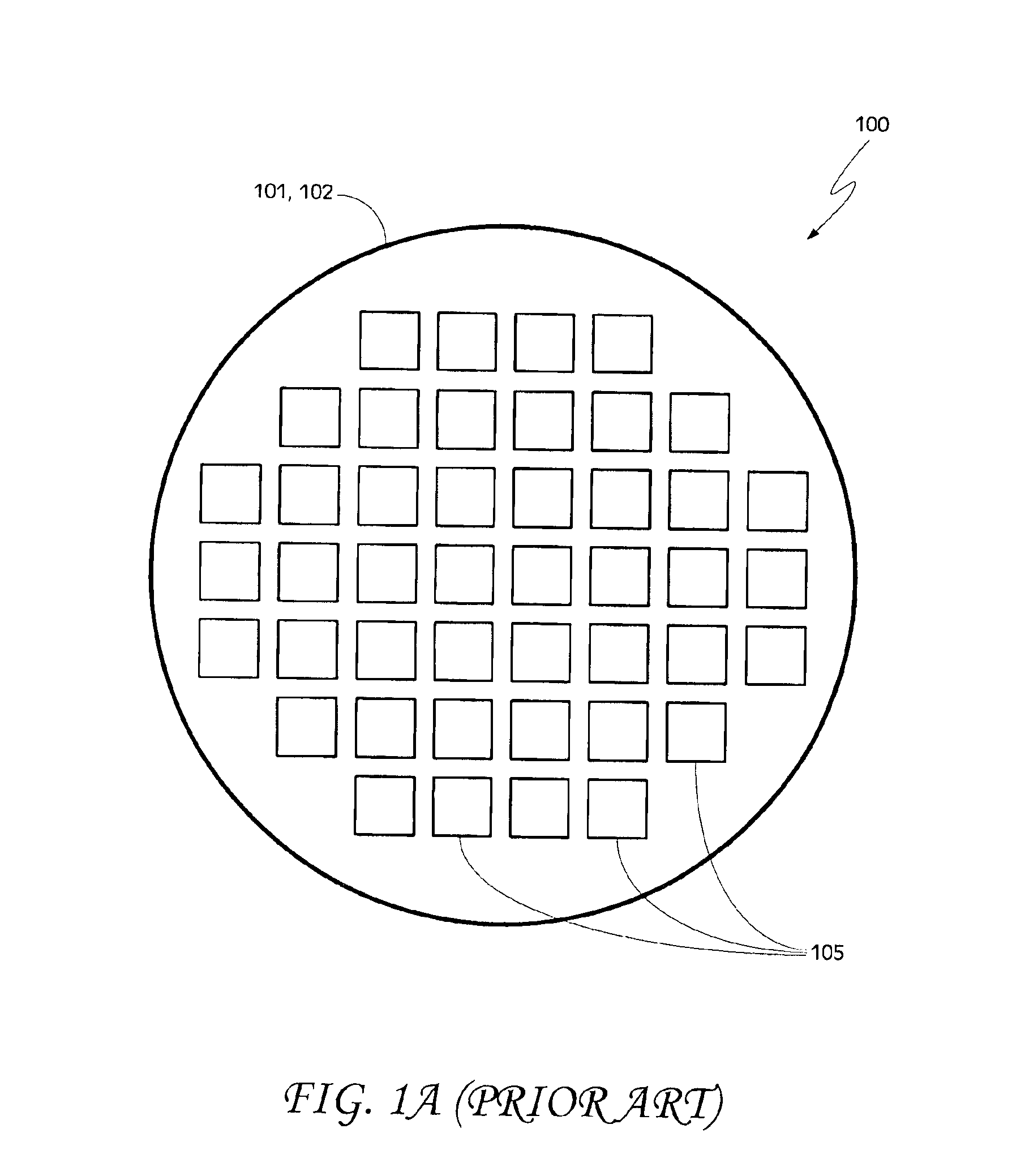

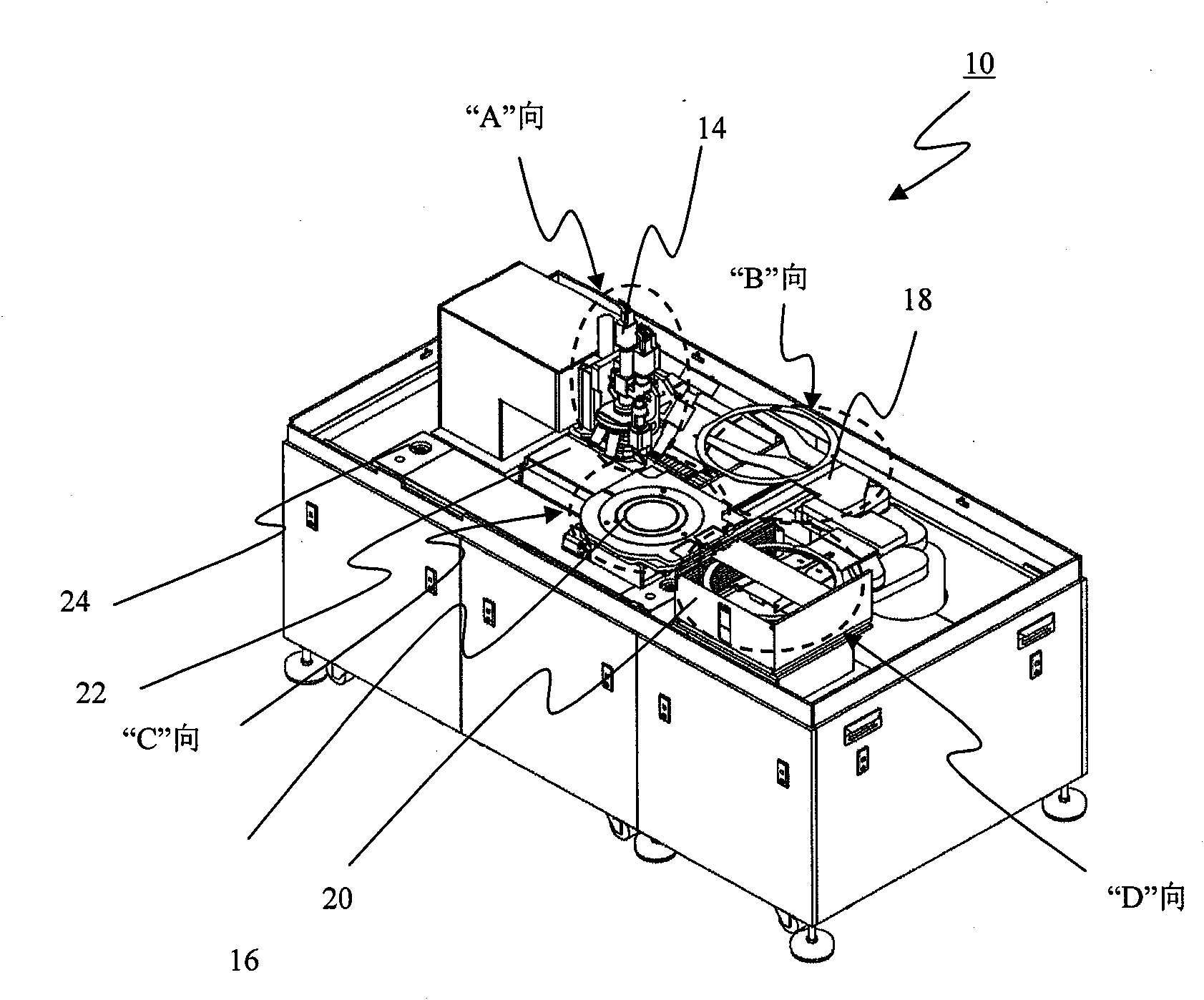

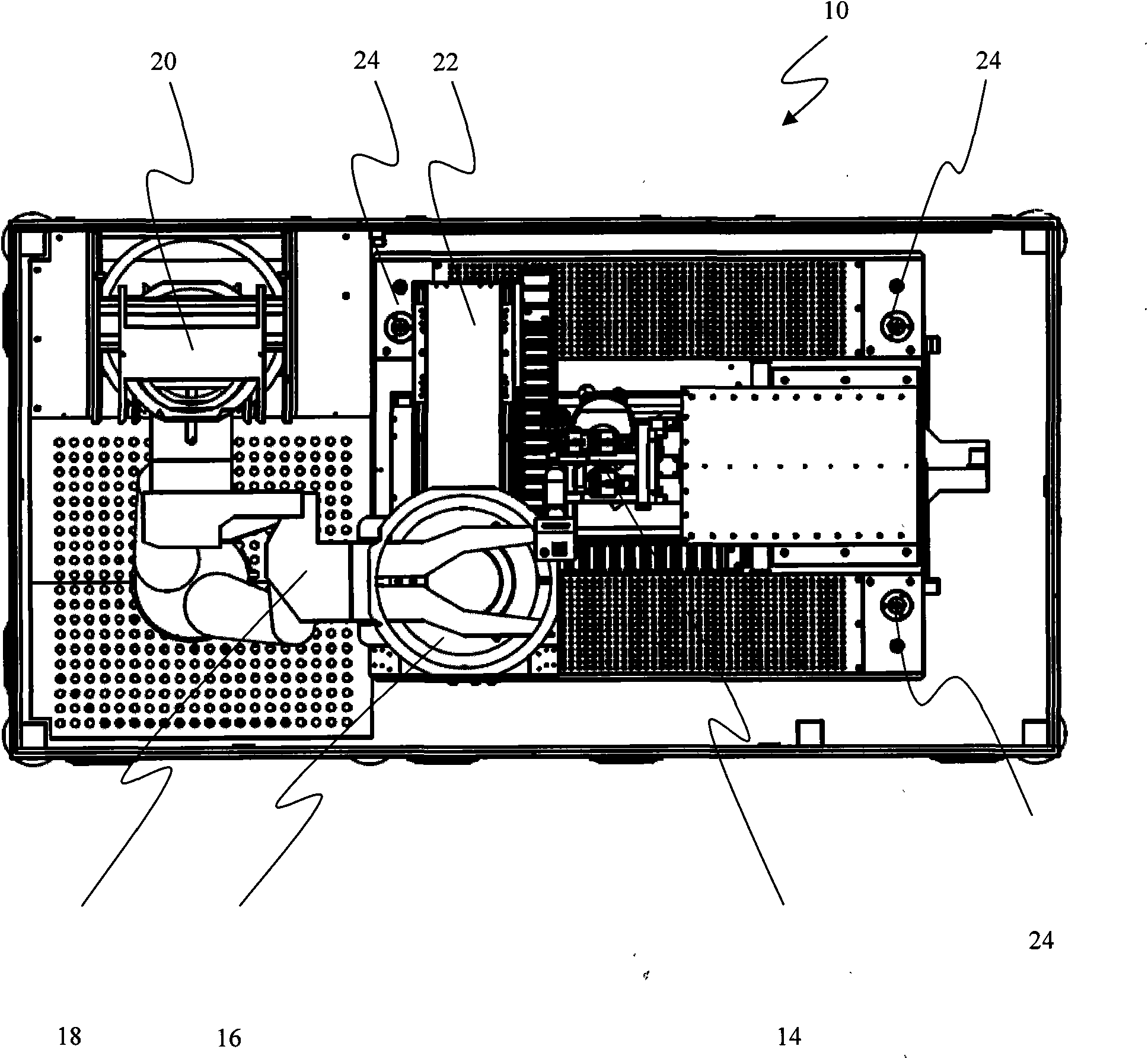

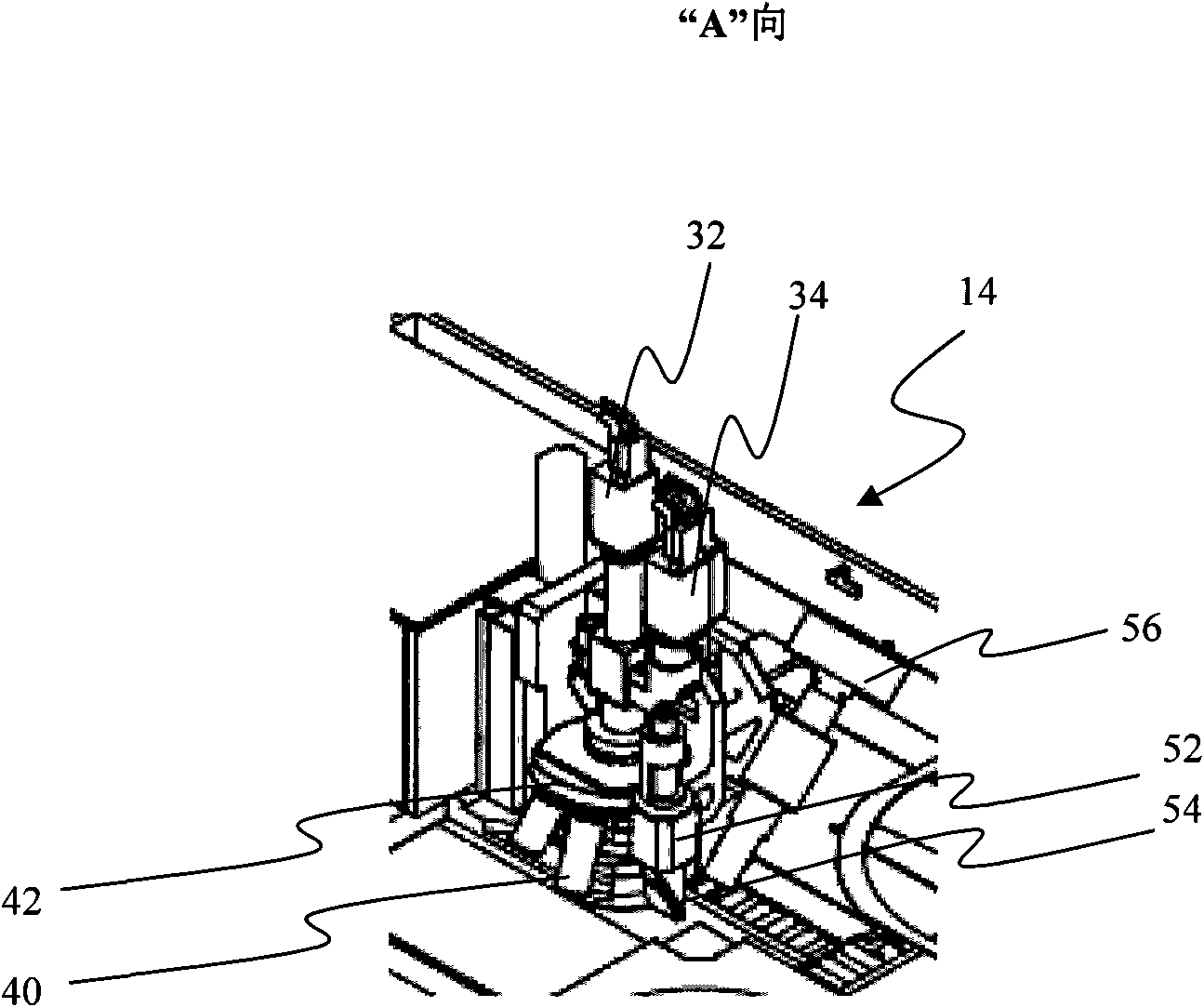

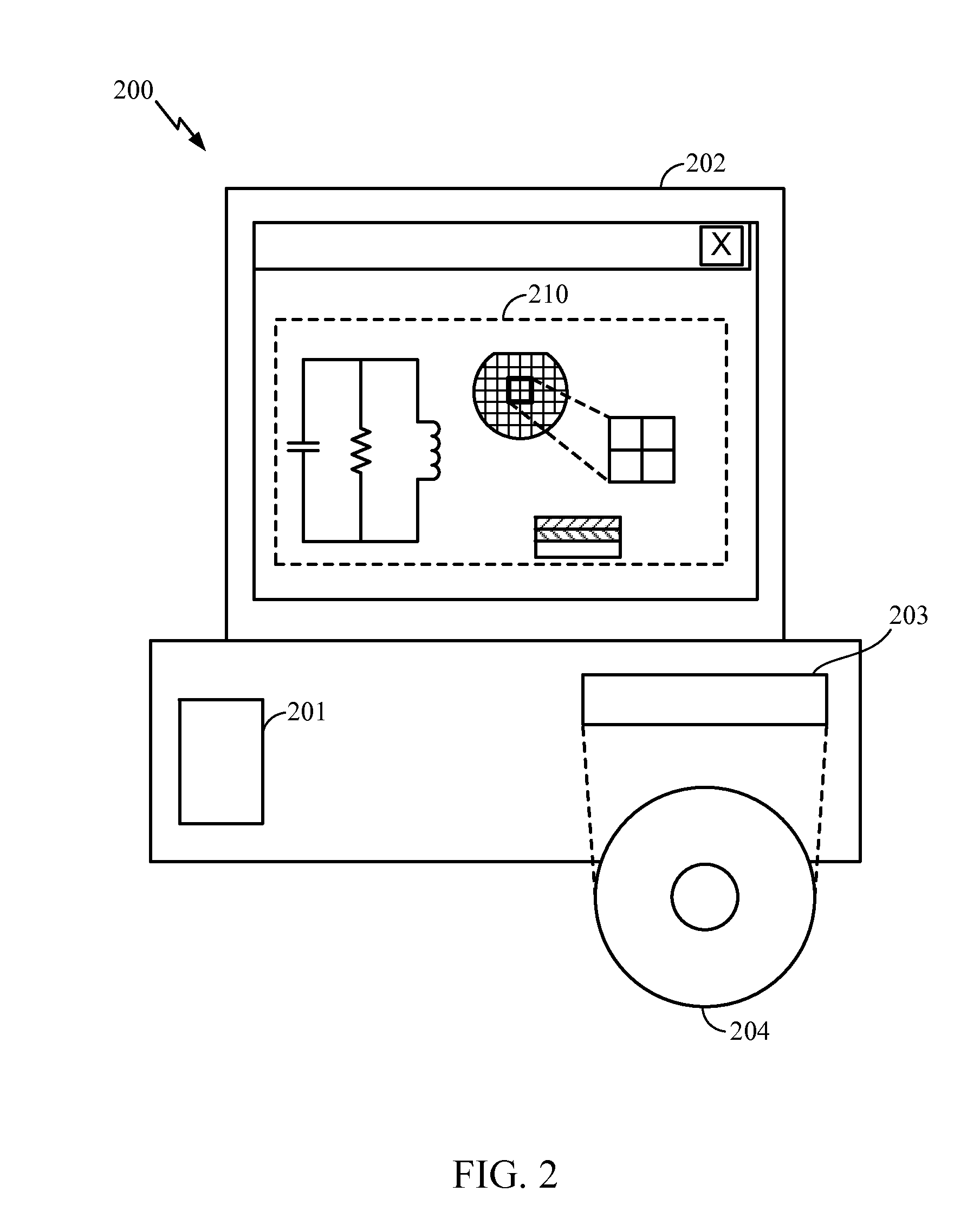

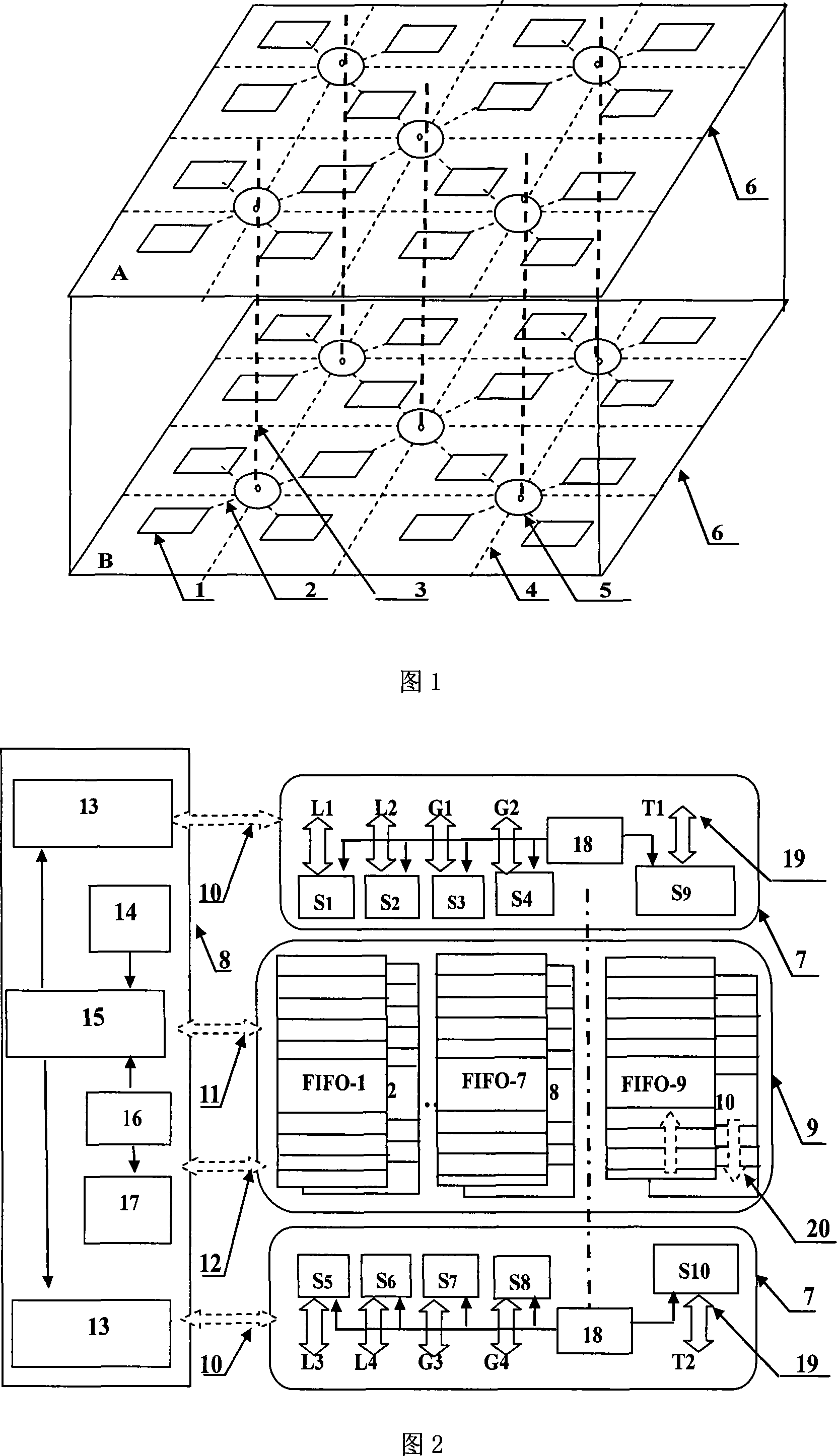

System and method for inspecting a wafer

The present invention provides a method and a system for inspecting a wafer. The system comprises an optical detection head, a wafer operation table, a wafer stack, a XY operation table and a vibration separator. The optical detection head comprises some lighters, an image collector, an objective lens and other optical componets. The system and the method can collect bright field image, dark field image, 3D image and redetection image. The collected image is converted to an image signal and is transmitted to a programmable controller for processing. The detection is performed in the wafer moving process. The collected image is compared with a reference picture for finding the defect on the wafer. The invention provides a process method used for generating an optimized reference image and an optimized process method for detecting the picture. The generation process of the reference picture is performed automatically.

Owner:SEMICON TECH & INSTR

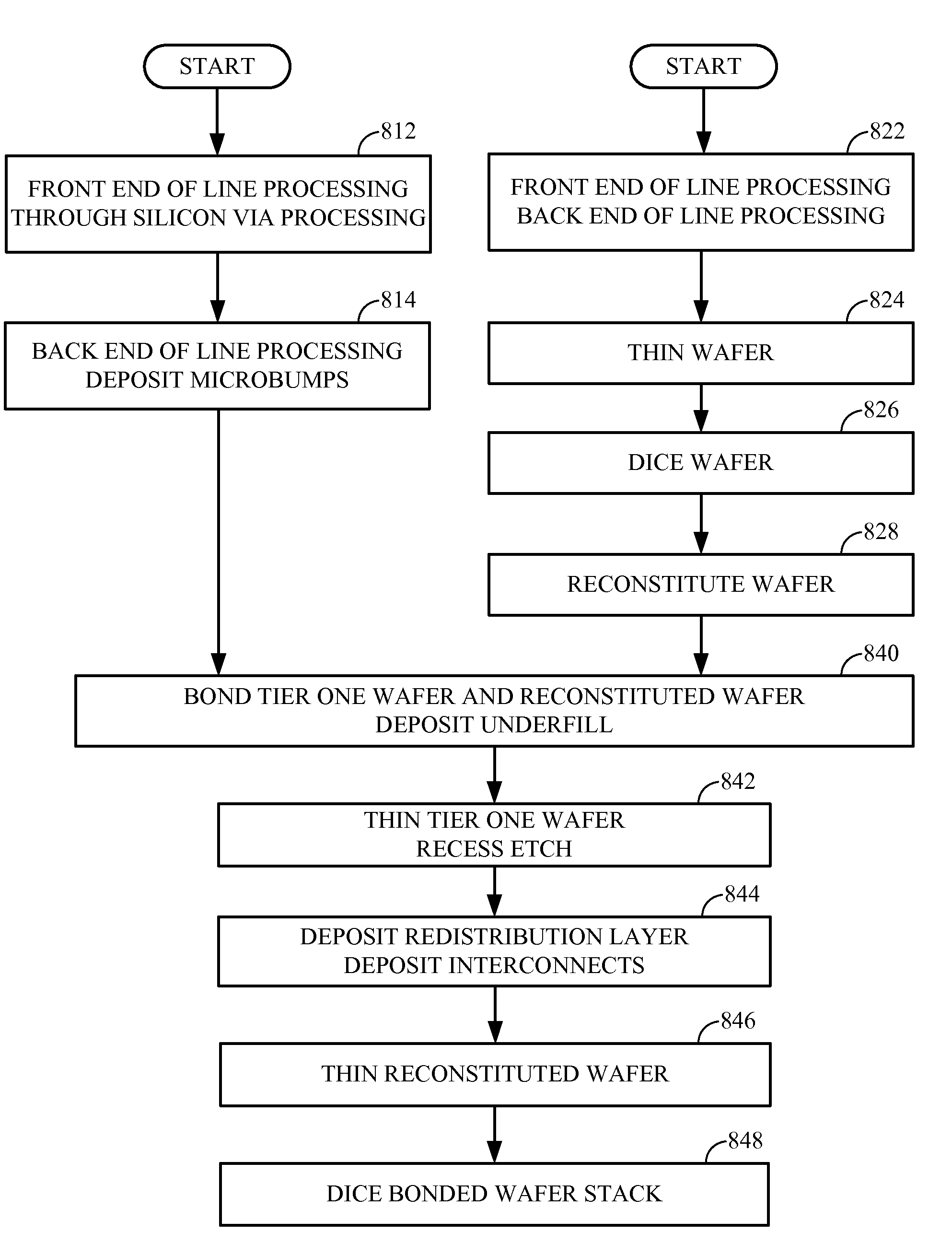

Semiconductor Wafer-To-Wafer Bonding For Dissimilar Semiconductor Dies And/Or Wafers

ActiveUS20110049694A1Semiconductor/solid-state device detailsSolid-state devicesWafer stackingWafer bonding

A semiconductor manufacturing process for wafer-to-wafer stacking of a reconstituted wafer with a second wafer creates a stacked (3D) IC. The reconstituted wafer includes dies, die interconnects and mold compound. When stacked, the die interconnects of the reconstituted wafer correspond to die interconnects on the second wafer. Wafer-to-wafer stacking improves throughput of the manufacturing process. The reconstituted wafer may include dies of different sizes than those in the second wafer. Also, the dies of the reconstituted wafer may be singulated from a wafer having a different size than the second wafer. Thus, this wafer-to-wafer manufacturing process may combine dies and / or wafers of dissimilar sizes.

Owner:QUALCOMM INC

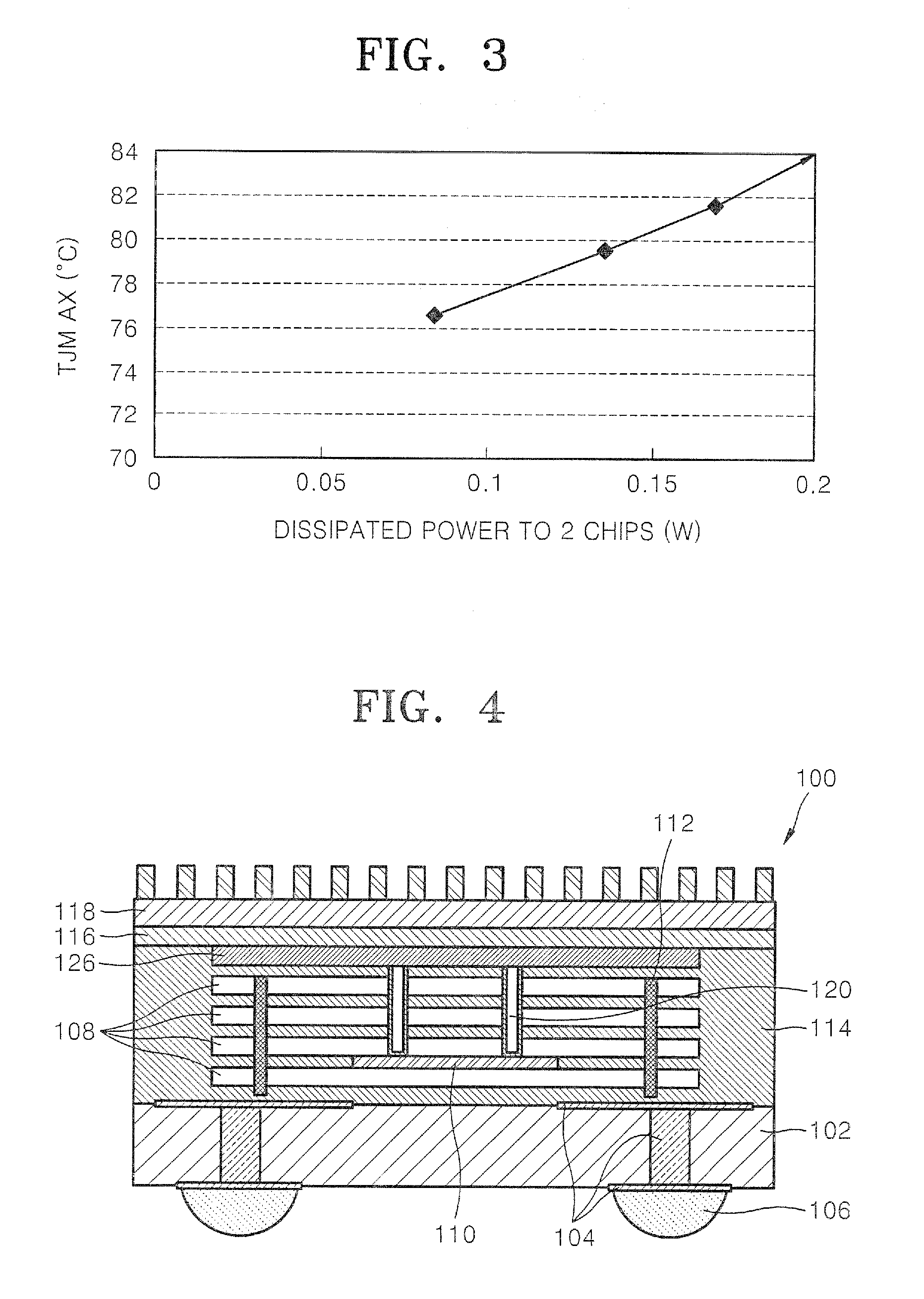

Wafer stacked package having vertical heat emission path and method of fabricating the same

ActiveUS20080099909A1Reduce heat buildupDissipate quicklySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A wafer stacked semiconductor package (WSP) having a vertical heat emission path and a method of fabricating the same are provided. The WSP comprises a substrate on which semiconductor chips are mounted; a plurality of semiconductor chips stacked vertically on the substrate; a cooling through-hole formed vertically in the plurality of semiconductor chips, and sealed; micro holes formed on the circumference of the cooling through-hole; and a coolant filling the inside of the cooling through-hole. Accordingly, the WSP reduces a temperature difference between the semiconductor chips and quickly dissipates the heat generated by the stacked semiconductor chips.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of forming backside connections on a wafer stack

ActiveUS20050059217A1Semiconductor/solid-state device detailsSolid-state devicesWafer stackingEngineering

Various methods of forming backside connections on a wafer stack are disclosed. To form the backside connections, vias are formed in a first wafer that is to be bonded with a second wafer. The vias used for the backside connections are formed on a side of the first wafer along with an interconnect structure, and the backside connections are formed on an opposing side of the first wafer using these vias.

Owner:TAHOE RES LTD

Wafer-to-wafer stack with supporting pedestal

ActiveUS20070090490A1Improve thermal conductivityAvoid damageTransistorSemiconductor/solid-state device detailsWafer stackingEngineering

A novel three dimensional wafer stack and the manufacturing method therefor are provided. The three dimensional wafer stack includes a first wafer having a first substrate and a first device layer having thereon at least one chip, a second wafer disposed above the first wafer and having a second substrate, and at least one pedestal arranged between and extending from the first substrate to the second substrate. The pedestal arranged in the device layer is used for preventing the low-k materials existing in the device layer from being damaged by the stresses.

Owner:IND TECH RES INST

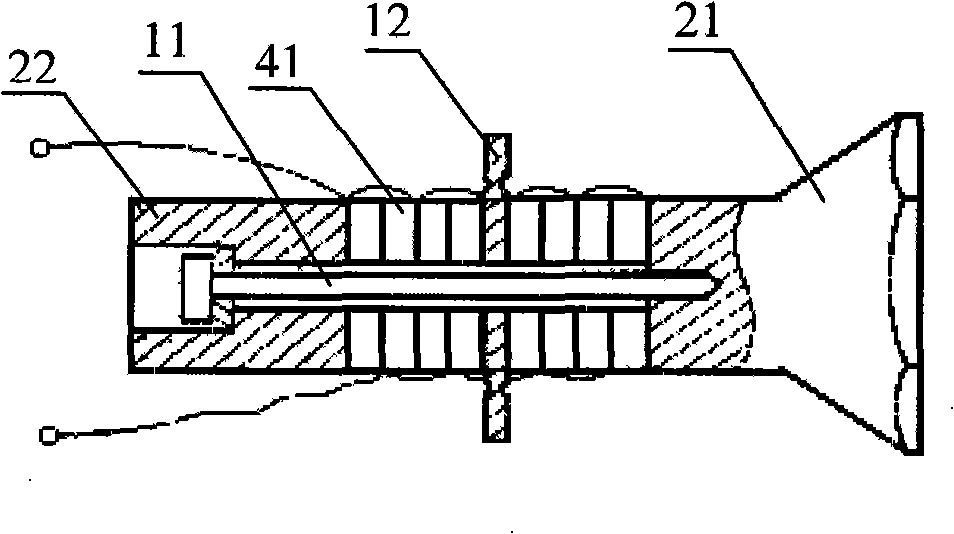

Cylindrical stack wafer underwater transducer

InactiveCN101321411AHigh sensitivityIncrease energy densityPiezoelectric/electrostrictive transducersTransducers for subaqueous useWaferingSound energy density

The invention provides an underwater acoustic transducer, comprising a piezoelectric ceramic wafer pack and metal cover plates on upper and lower ends thereof. The piezoelectric ceramic wafer pack is in a cylindrical shape and stacked by several circular piezoelectric ceramic wafers. Polarization direction of the piezoelectric ceramic wafers is along the thickness direction. 2 to 8 piezoelectric ceramic wafers form a group, and the wafer pack contains one or several groups of wafers, each is separated by a rubber chip. Metal sheets are clamped between adjacent wafers and between a wafer and a rubber chip. Contact conductors are welded on the metal sheets. The piezoelectric ceramic wafer pack and the upper and lower metal cover plates are further separated by the rubber chips. The cylindrical stacked wafer transducer of the invention is not only capable of maintaining characteristics of large transmitting sound energy density of traditional stacked wafer transducer and high sensitivity by reasonably designing diameter of piezoelectric stacked wafers, but capable of adjusting axial directivity open angle of the transducer by changing thickness of the piezoelectric wafer stack or adjusting the group number.

Owner:BEIJING INFORMATION SCI & TECH UNIV

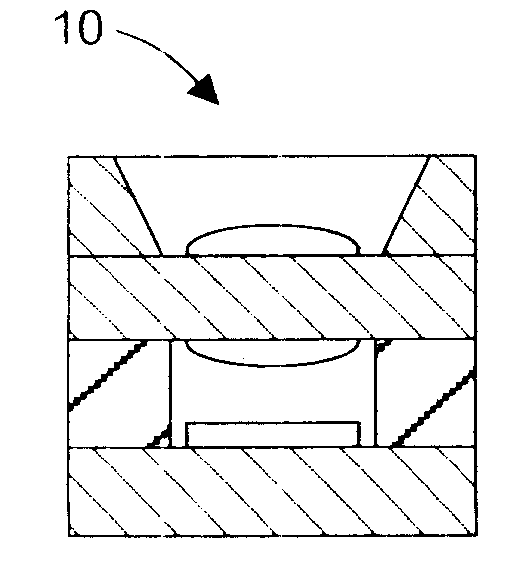

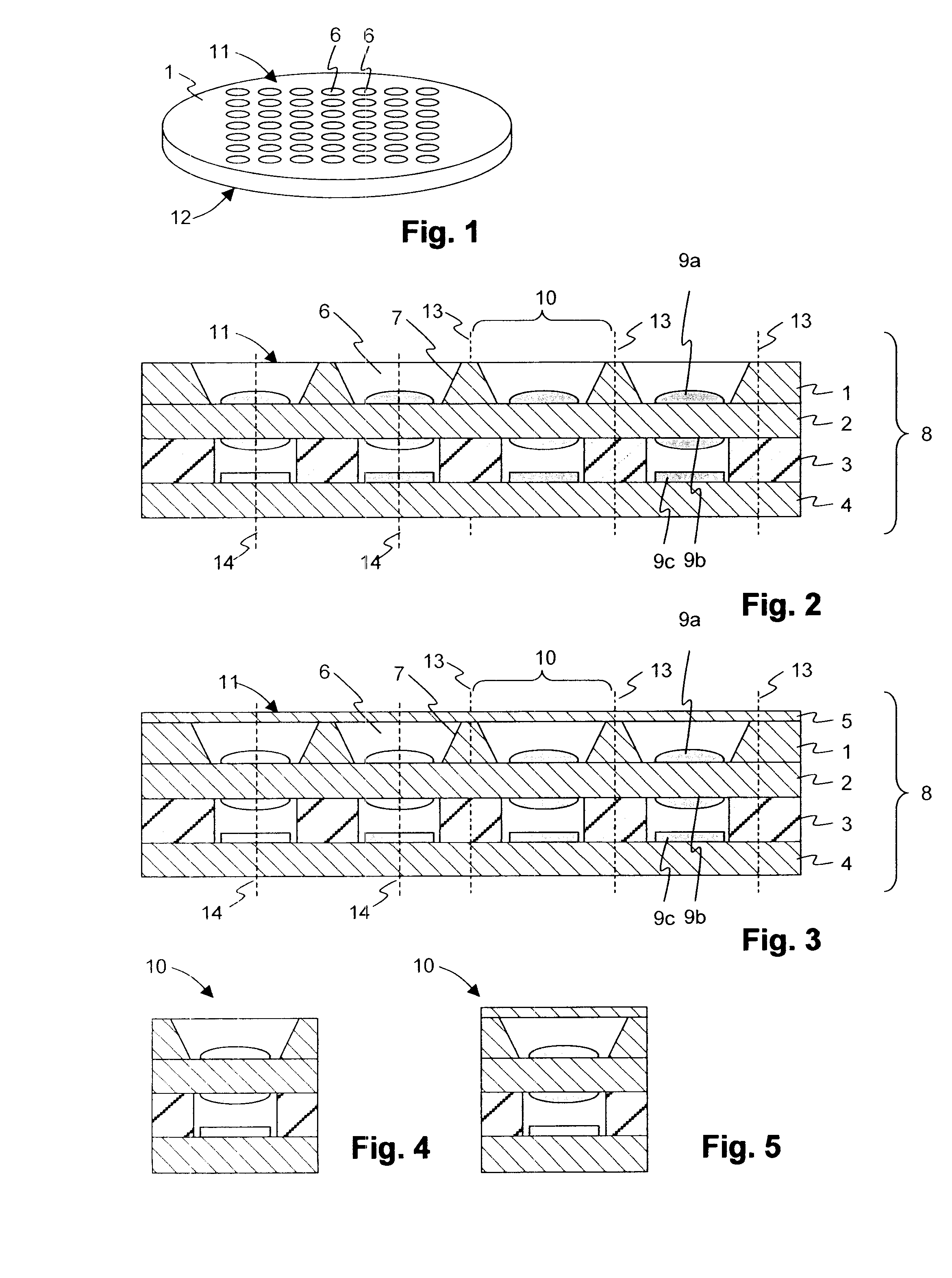

Wafer stack, integrated optical device and method for fabricating the same

In a method for fabricating an integrated optical device by creating a wafer stack by stacking at least a top wafer carrying as functional elements a plurality of lenses on at least one further wafer including further functional elements, and separating the wafer stack into a plurality of integrated optical devices, wherein corresponding functional elements of the top and further wafer are aligned with each other and define a plurality of main optical axes, a method for providing a sunshade plate as part of an integrated optical device (10), including the steps of: providing a sunshade plate having a plurality of through holes, the through holes being arranged to correspond to the arrangement of the functional elements on the top wafer; and stacking the sunshade plate on the top wafer, with the through holes being aligned with said main optical axes.

Owner:AMS SENSORS SINGAPORE PTE LTD

3-D ICs equipped with double sided power, coolant, and data features

ActiveUS8546930B2Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorWafer stacking

Three dimensional integrated circuits with double sided power, coolant, and data features and methods of constructing same are provided. According to some embodiments, an integrated circuit package can generally comprise one or more semiconductor wafers and opposing end substrates. The semiconductor wafers can each have a top exterior surface and a bottom exterior surface. The plurality of semiconductor wafers can form a multi-dimensional wafer stack of die wafers such that adjacent wafers have facing surfaces. Each of the semiconductor wafers can comprise one or more channels formed through the wafers. A portion of the channels can extend generally between the top and bottom exterior surfaces of the semiconductor wafers. A portion of the channels can carry conductors for coupling the wafers and / or coolant for cooling the wafers. The opposing end substrates can be disposed proximate opposing ends of the multi-dimensional stack. The opposing end substrates can be configured to supply power, coolant, and data signals to opposing ends of the multi-dimensional wafer stack. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

Bonding method for through-silicon-via based 3D wafer stacking

ActiveUS20090294916A1Semiconductor/solid-state device detailsSolid-state devicesOutgassingWafer stacking

There is described a hybrid bonding method for through-silicon-via based wafer stacking. Patterned adhesive layers are provided to join together adjacent wafers in the stack, while solder bondng is used to electrically connect the vias. The adhesive layers are patterned to enable outgassing and to provide stress relief.

Owner:HONG KONG APPLIED SCI & TECH RES INST

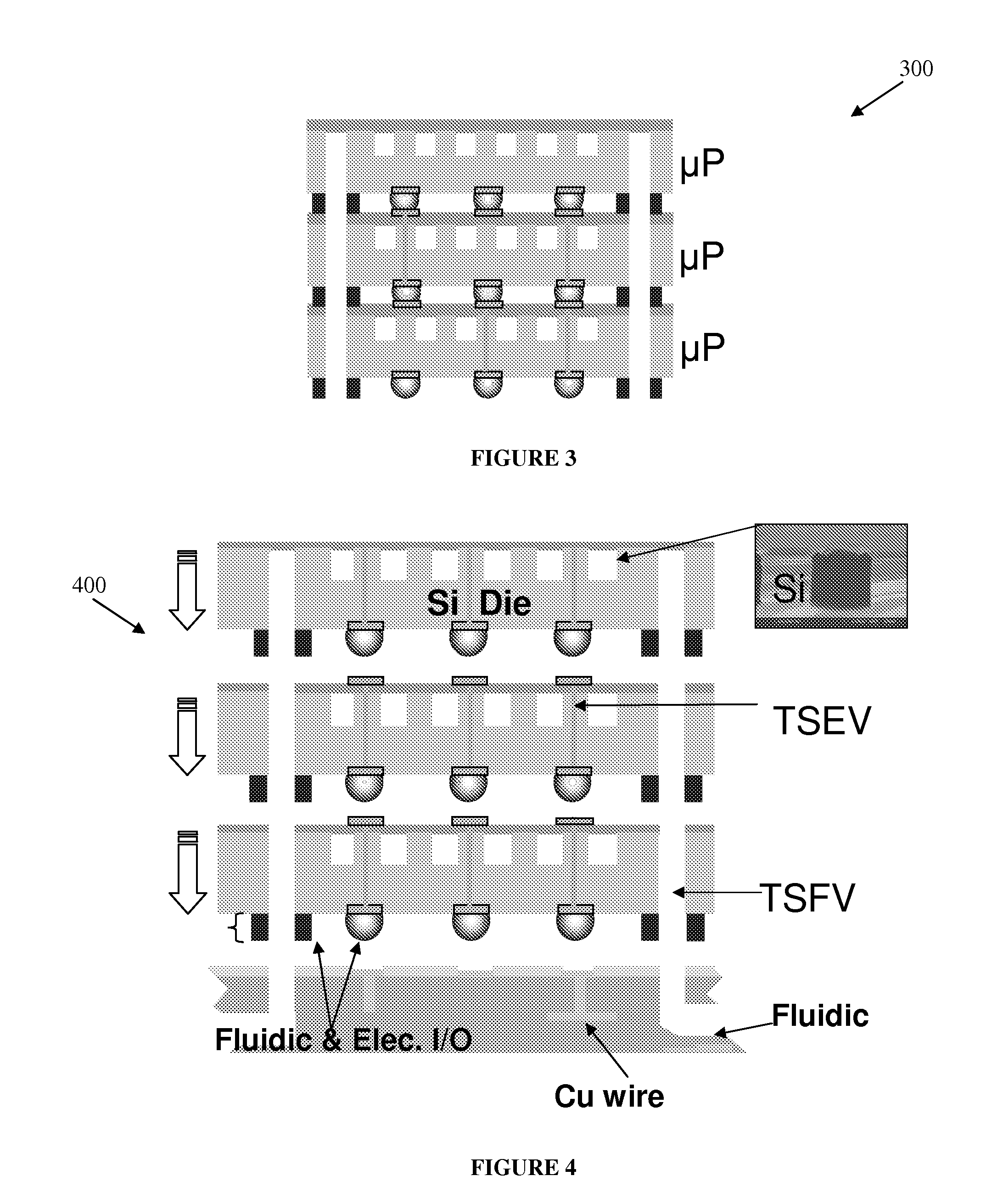

Three-dimensional multiprocessor system chip

InactiveCN101145147AReduce areaShorten the lengthSemiconductor/solid-state device detailsSolid-state devicesComputer architectureSignal delay

The present invention relates to a chip of a three-dimensional multiprocessor system and belongs to the technical field of an integrate circuit design and manufacture. The present invention comprises a plurality of processor cores, a plurality of three-dimensional network routers on the chip and a wafer chip of a semiconductor integrate circuit that integrates a plurality of processor cores with a plurality of three-dimensional network routers on the chip. The present invention relates to a manufacturing method for utilizing wafer piles to assemble a three-dimensional integrate circuit and a transmitting method of parallel network data. The present invention has the advantages that: first, the part, whole or three-dimensional data transmissions are respectively accomplished by different channels, and the transmission congestion of the network data on the chip is relieved. Second, the three-dimensional chip structure reduces the chip area of a complicated SLSI (super-large-scale integration) and improves the product yield in the course of production. Third, the length of an interconnection line is shortened, the delay time of signals is reduced, and the system performance is enhanced.

Owner:SHANDONG UNIV

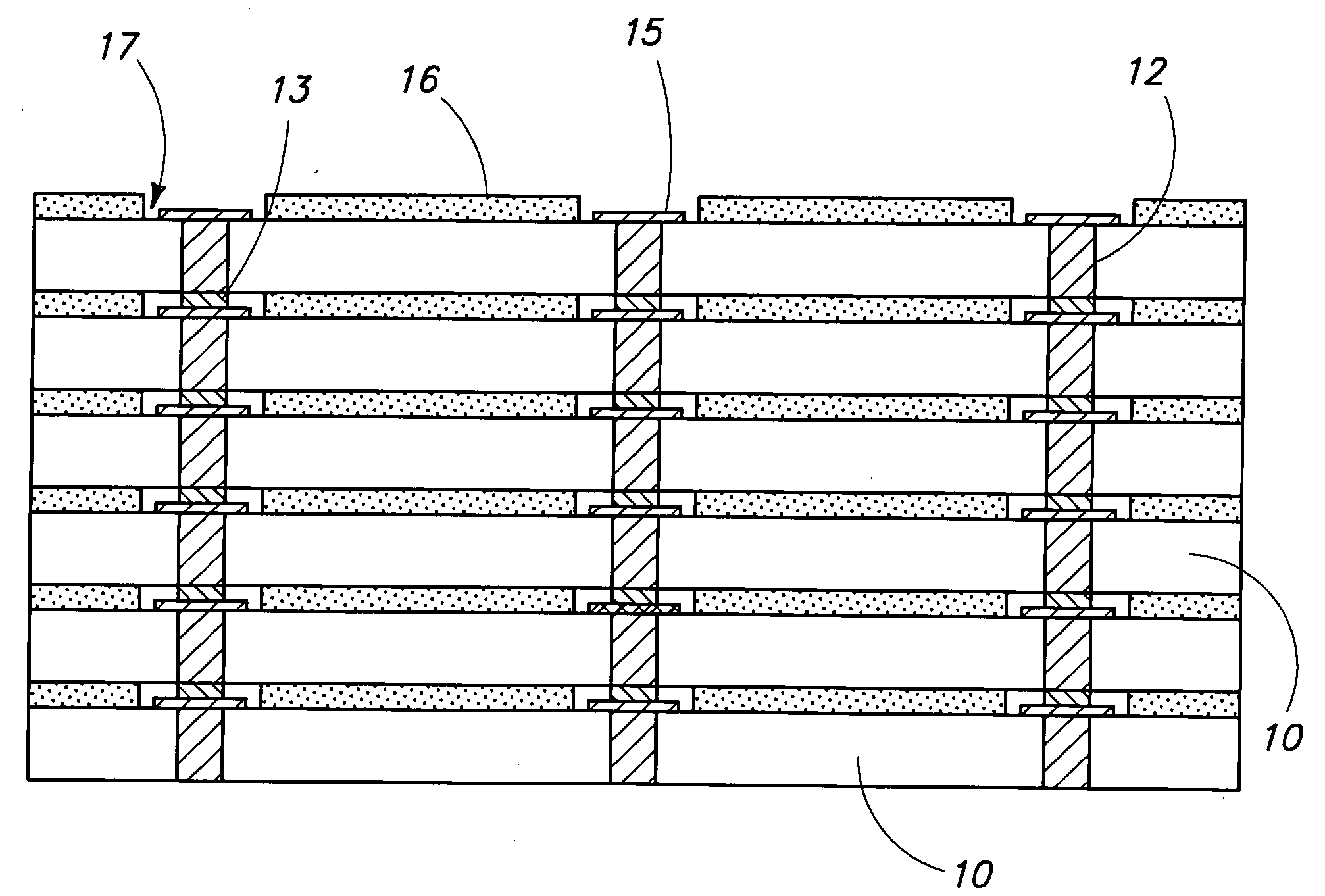

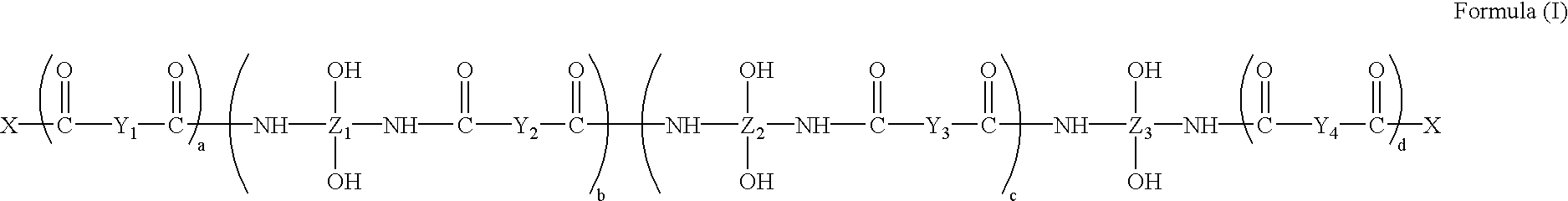

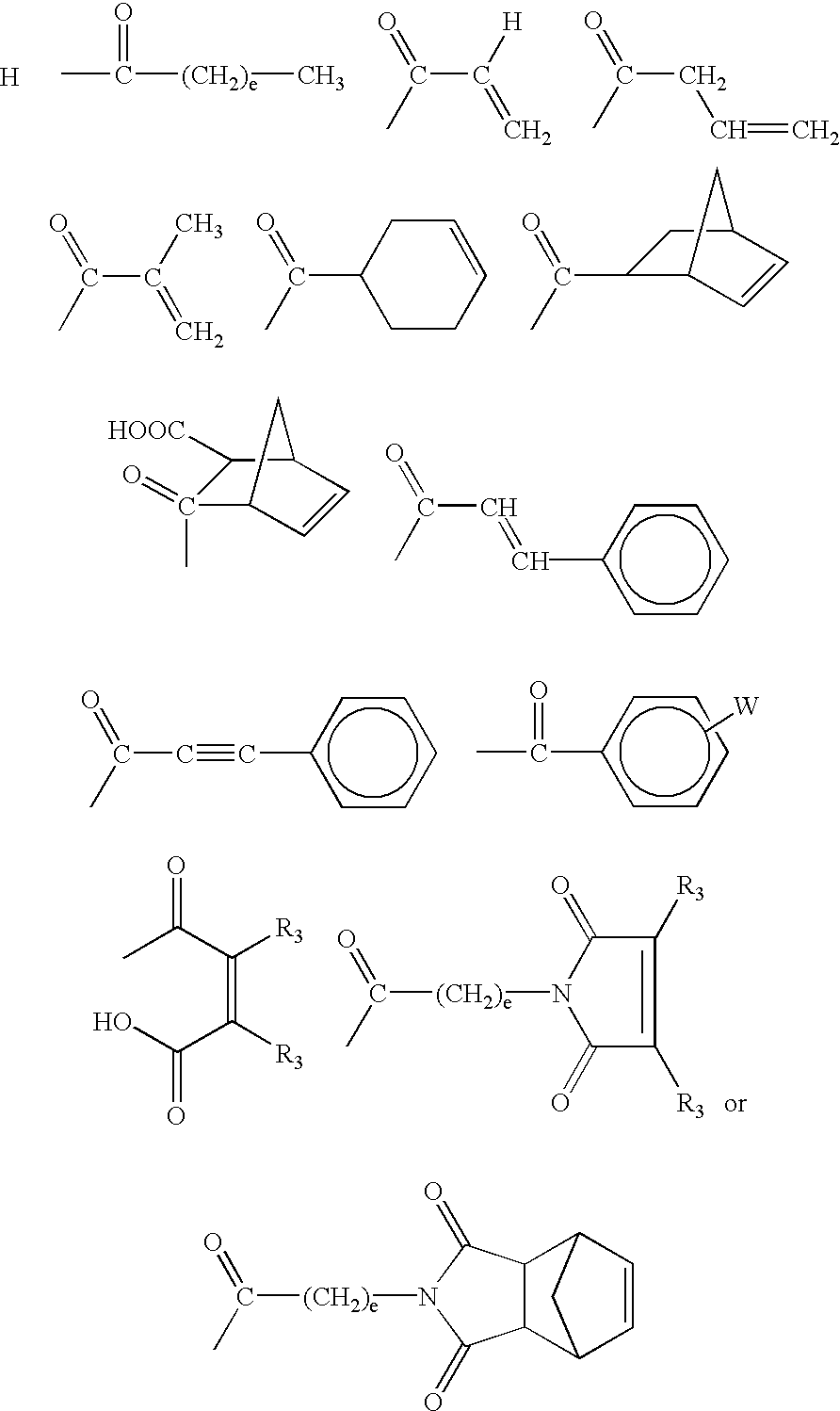

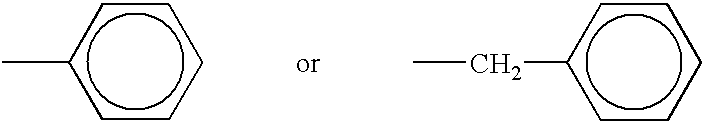

Adhesively bonded chip-and wafer stacks

InactiveUS20030150557A1Cost effective productionLow water absorptionSolid-state devicesCellulose adhesivesWafer stackingSemiconductor

The present invention describes the use of poly-o-hydroxy amides (PHAs) for adhesively bonding articles or materials, especially components used in the semiconductor industry, such as chips and wafers, a process for adhesively bonding materials, especially chips and / or wafers, chip and / or wafer stacks produced by the process, and adhesive compositions which comprise the poly-o-hydroxy amides of the formula (I).

Owner:POLARIS INNOVATIONS LTD