Patents

Literature

1078 results about "Chip carrier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

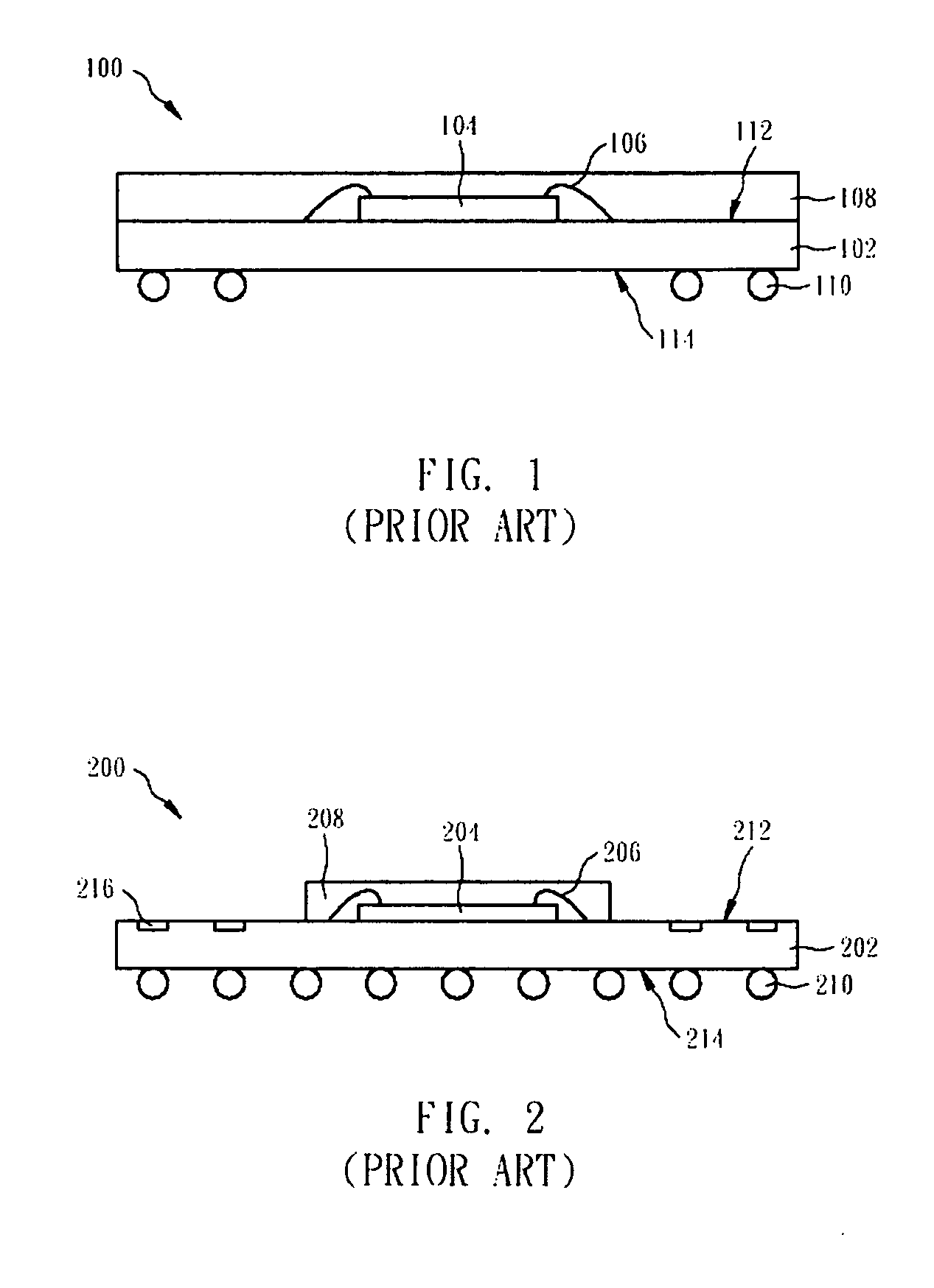

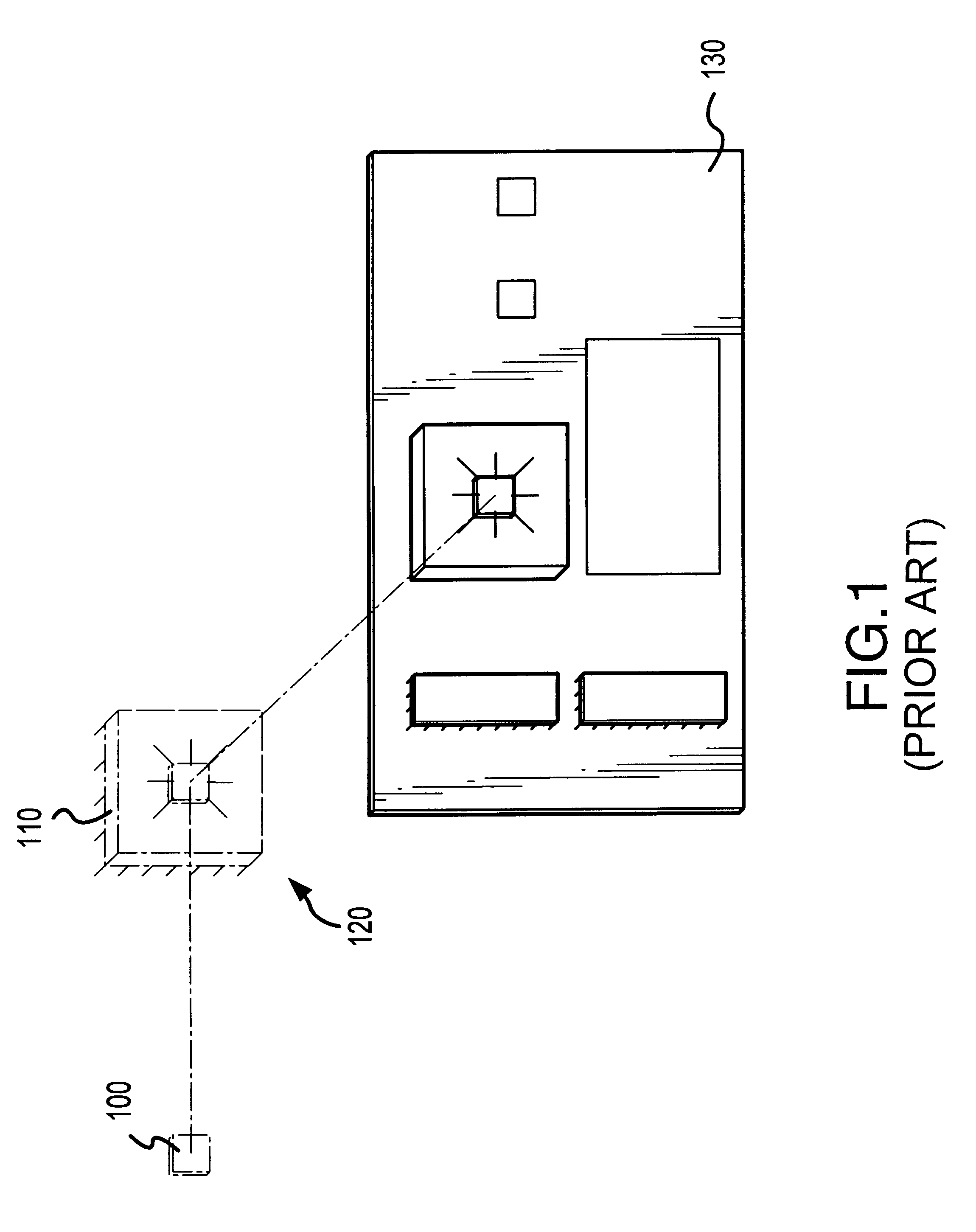

In electronics, a chip carrier is one of several kinds of surface-mount technology packages for integrated circuits (commonly called "chips"). Connections are made on all four edges of a square package; Compared to the internal cavity for mounting the integrated circuit, the package overall size is large.

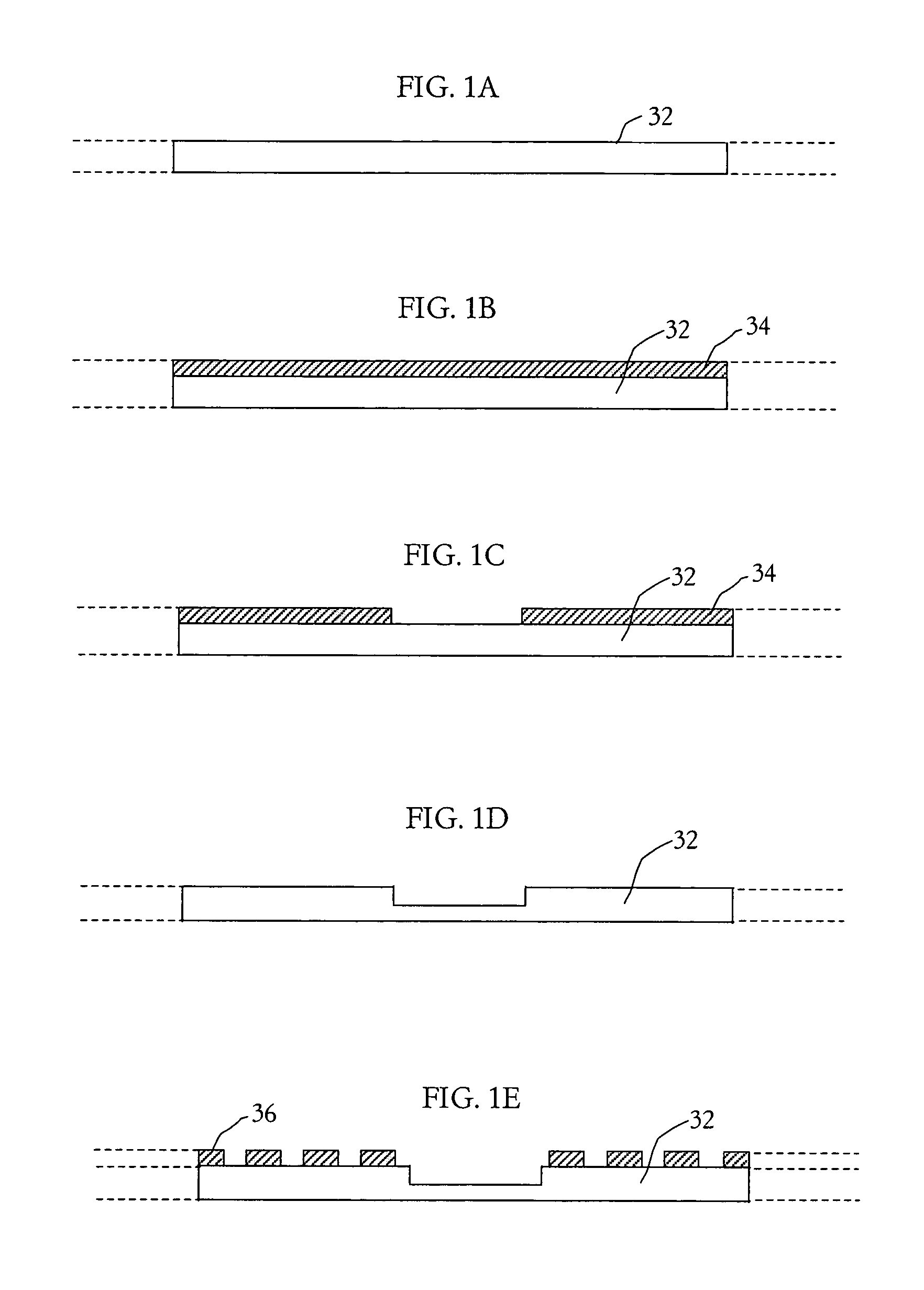

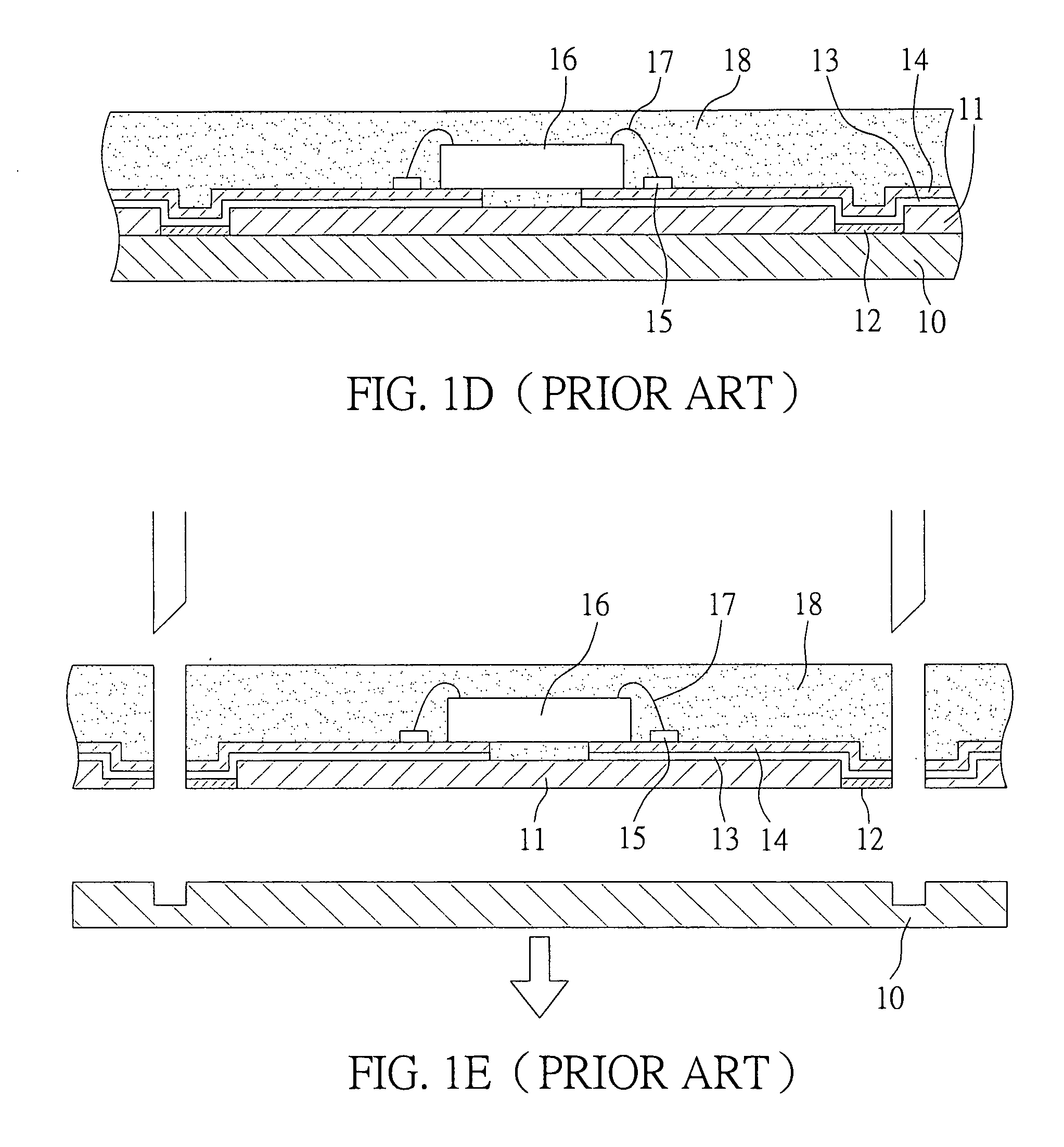

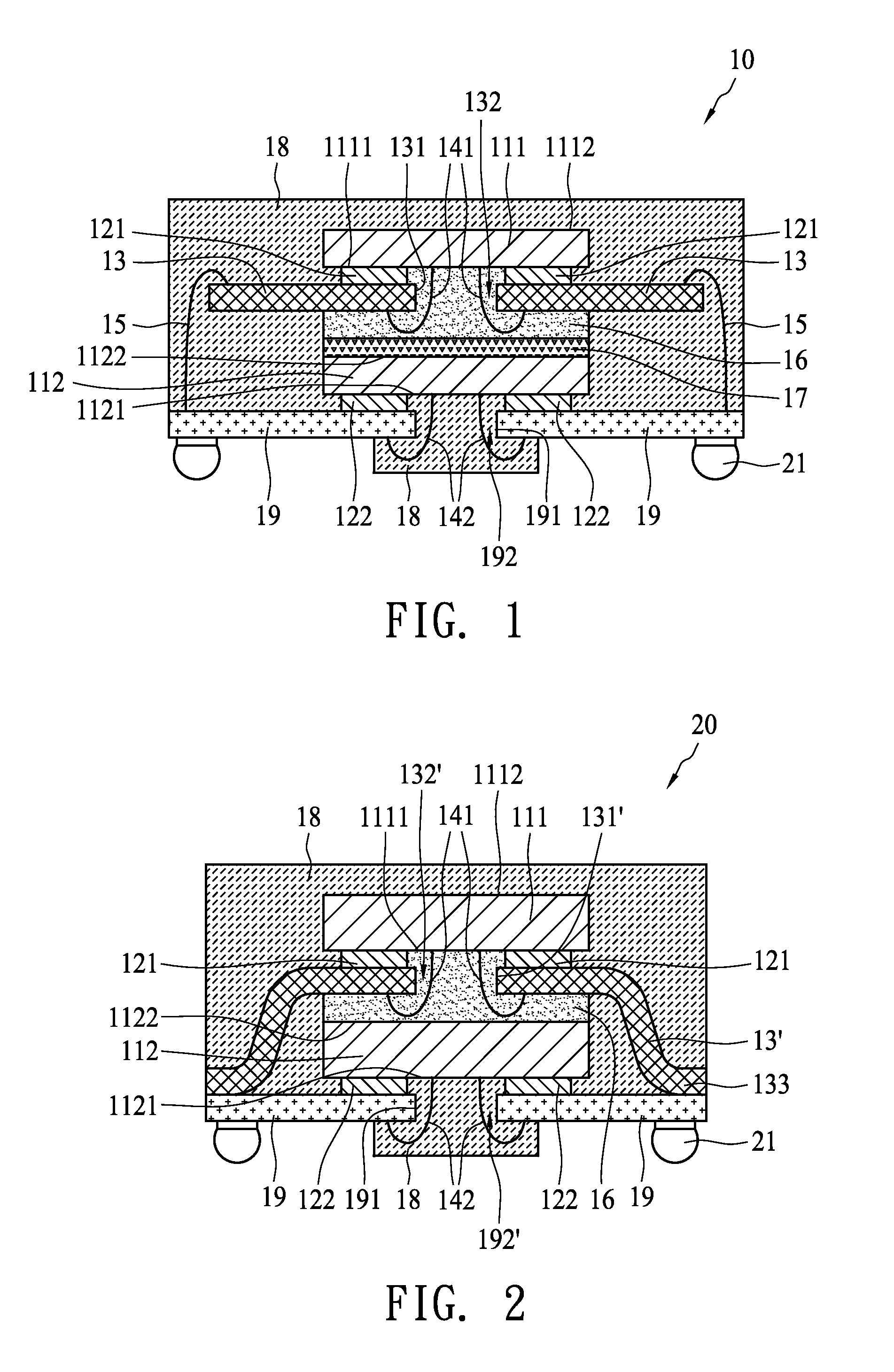

Wafer level package structure and fabrication methods

ActiveUS8759964B2Reduce harmSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

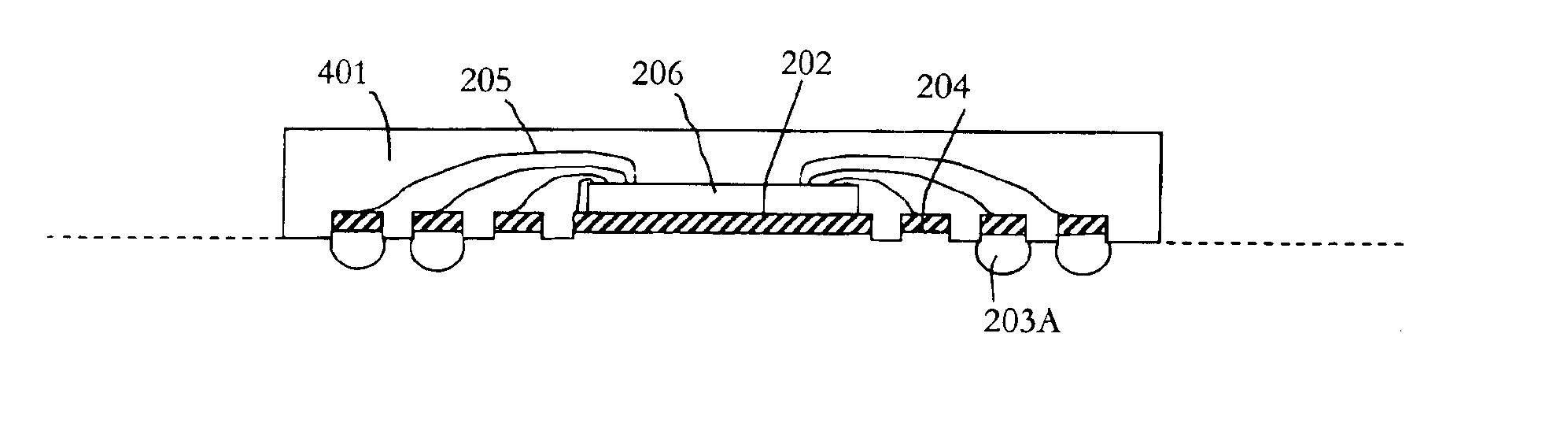

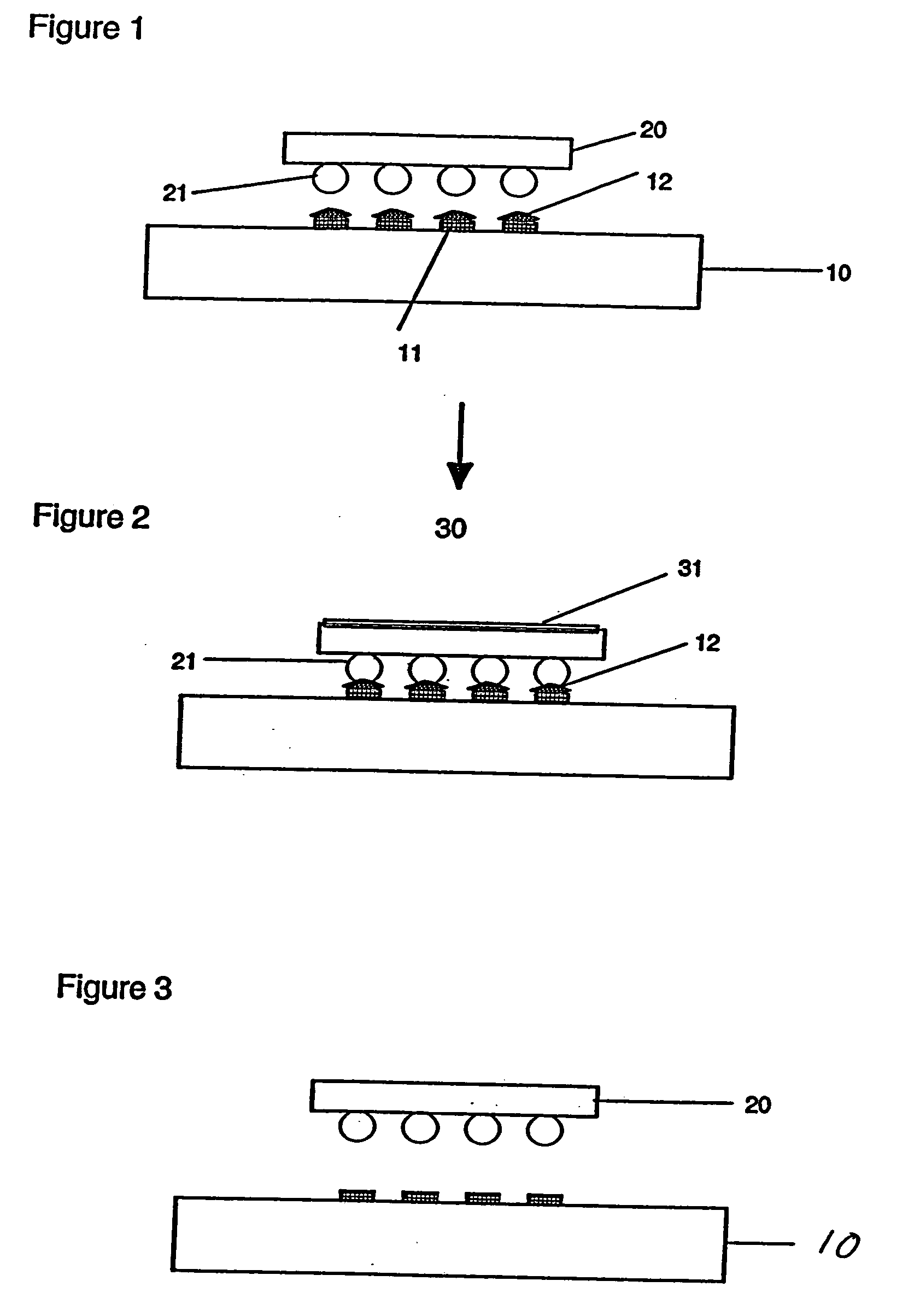

A method of forming a package structure with reduced damage to semiconductor dies is provided. The method includes providing a die comprising bond pads on a top surface of the die; forming bumps on the bond pads of the die, wherein the bumps have top surfaces higher than the top surface of the die; mounting the die on a chip carrier, wherein the bumps are attached to the chip carrier; molding the die onto the chip carrier with a molding compound; de-mounting the chip carrier from the die; and forming redistribution traces over, and electrically connected to, the bumps of the die.

Owner:TAIWAN SEMICON MFG CO LTD

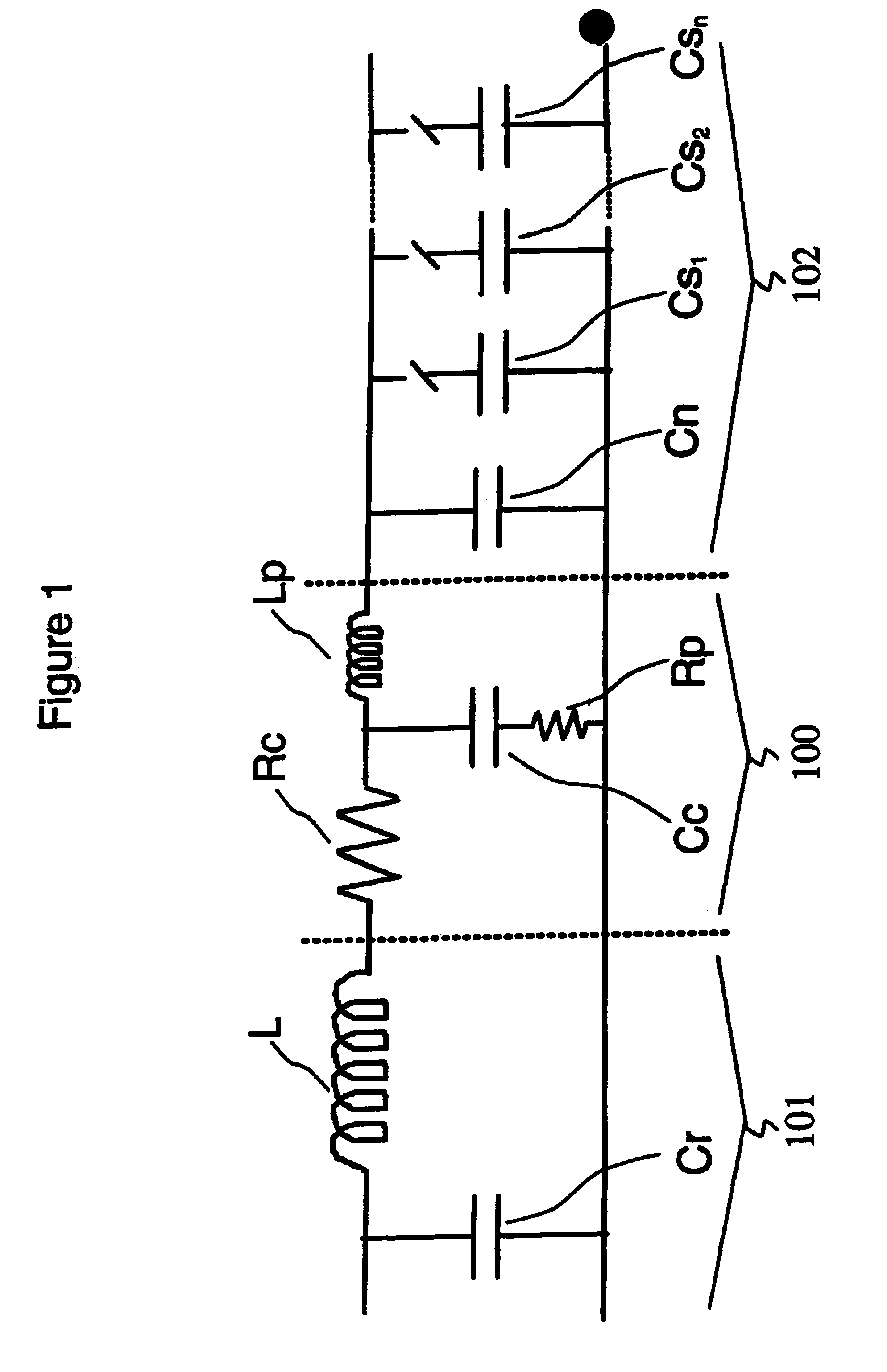

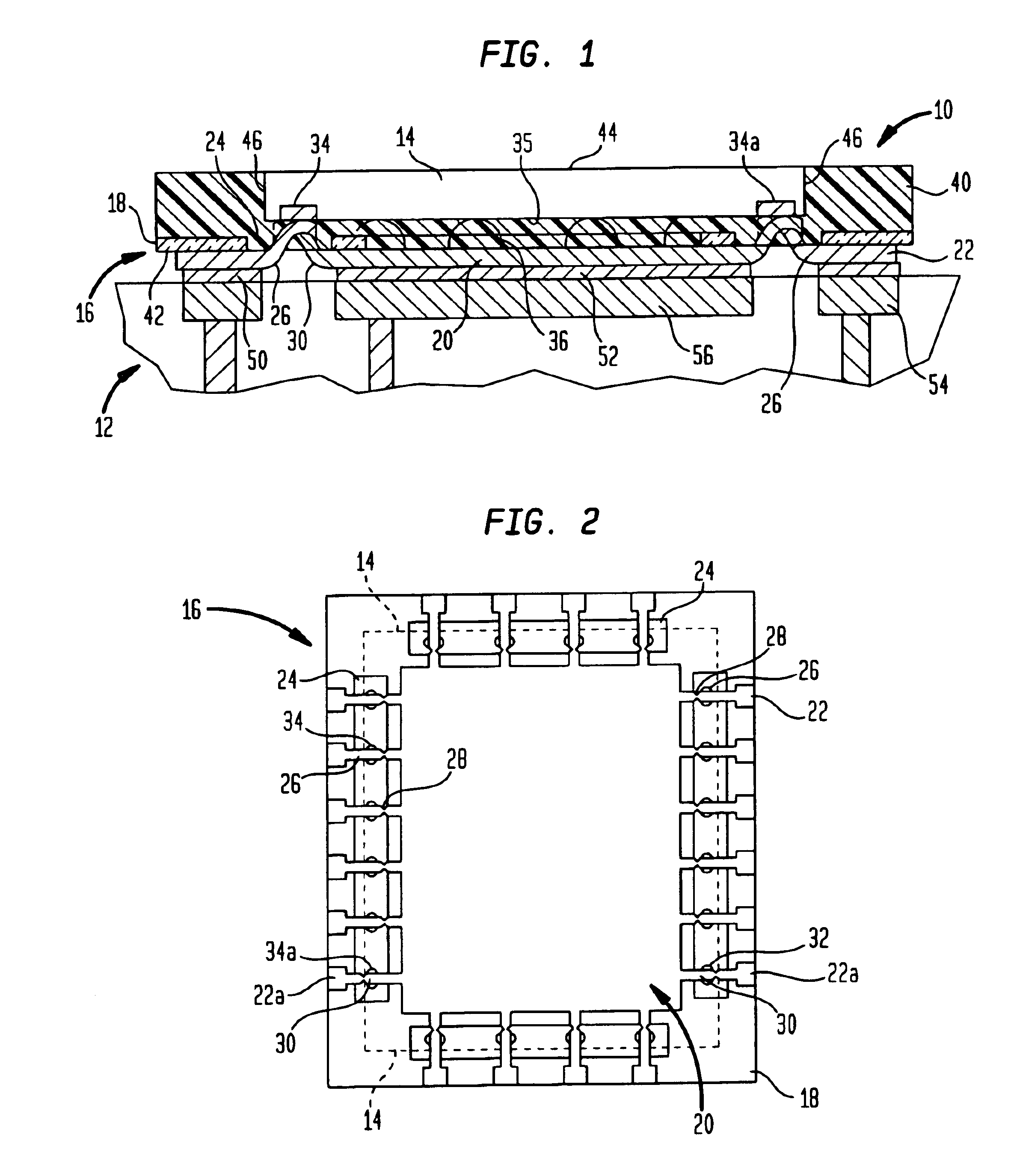

High density chip carrier with integrated passive devices

InactiveUS6962872B2Reduce inductanceEasy accessSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityEngineering

Owner:GLOBALFOUNDRIES U S INC

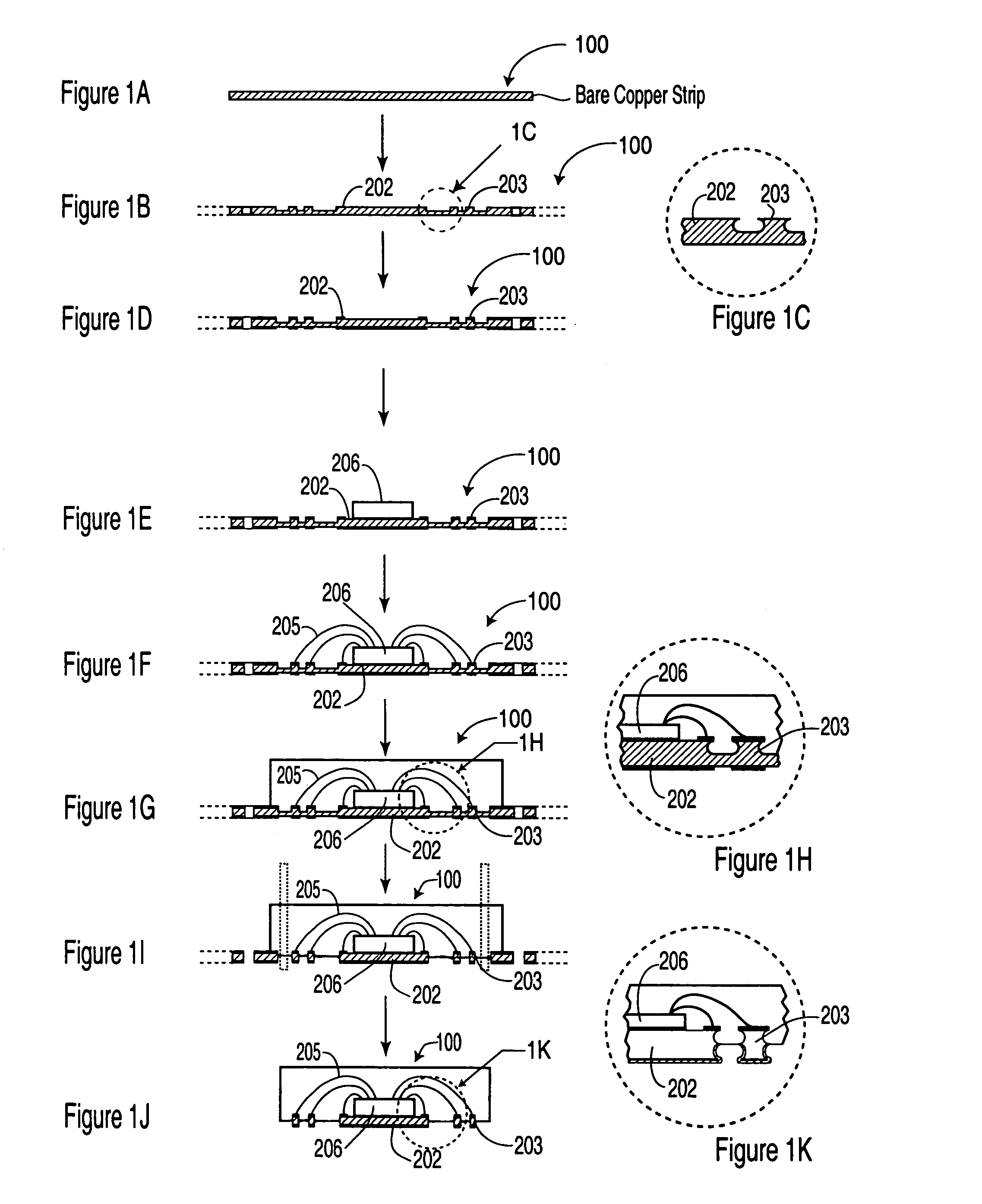

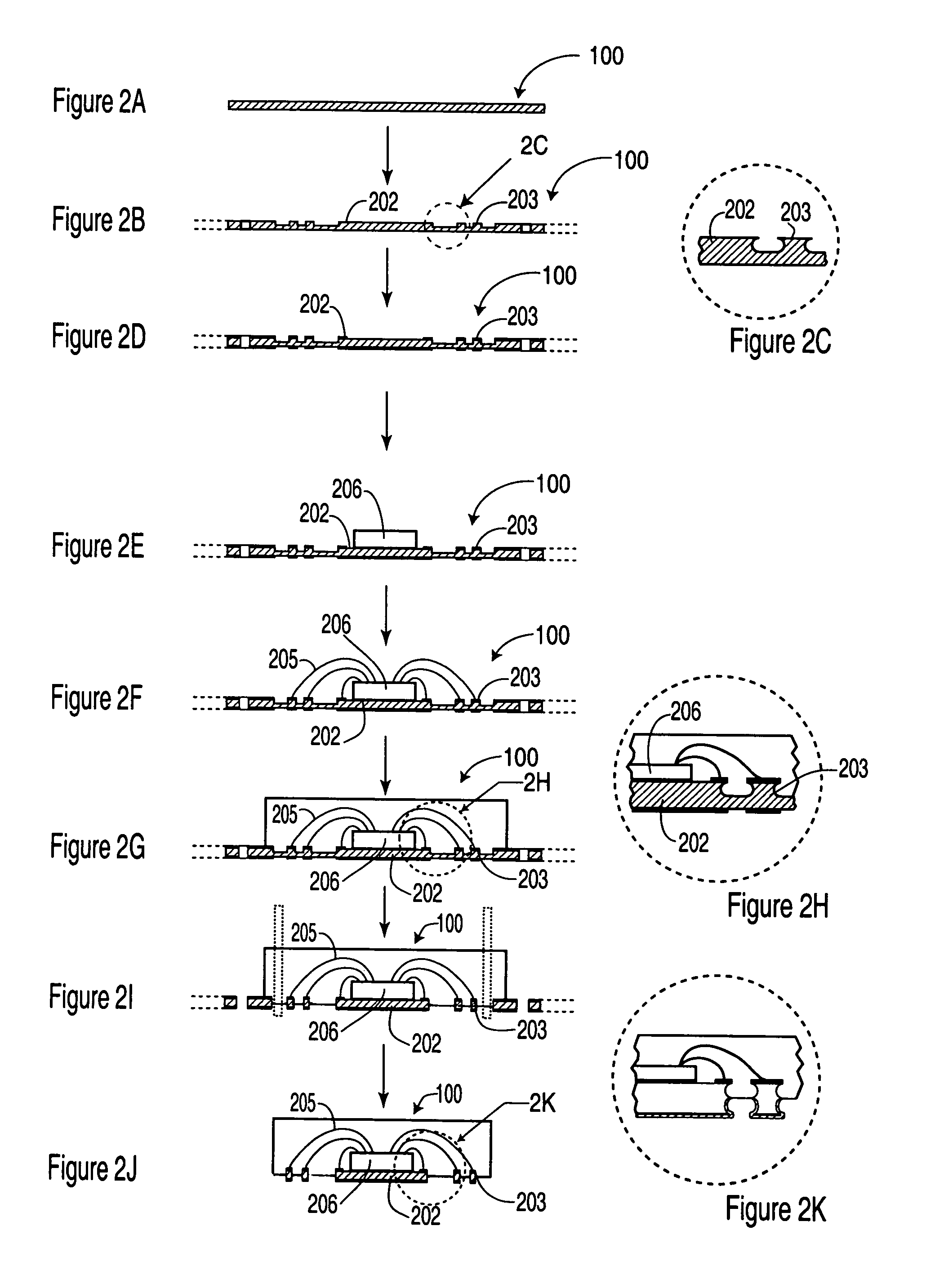

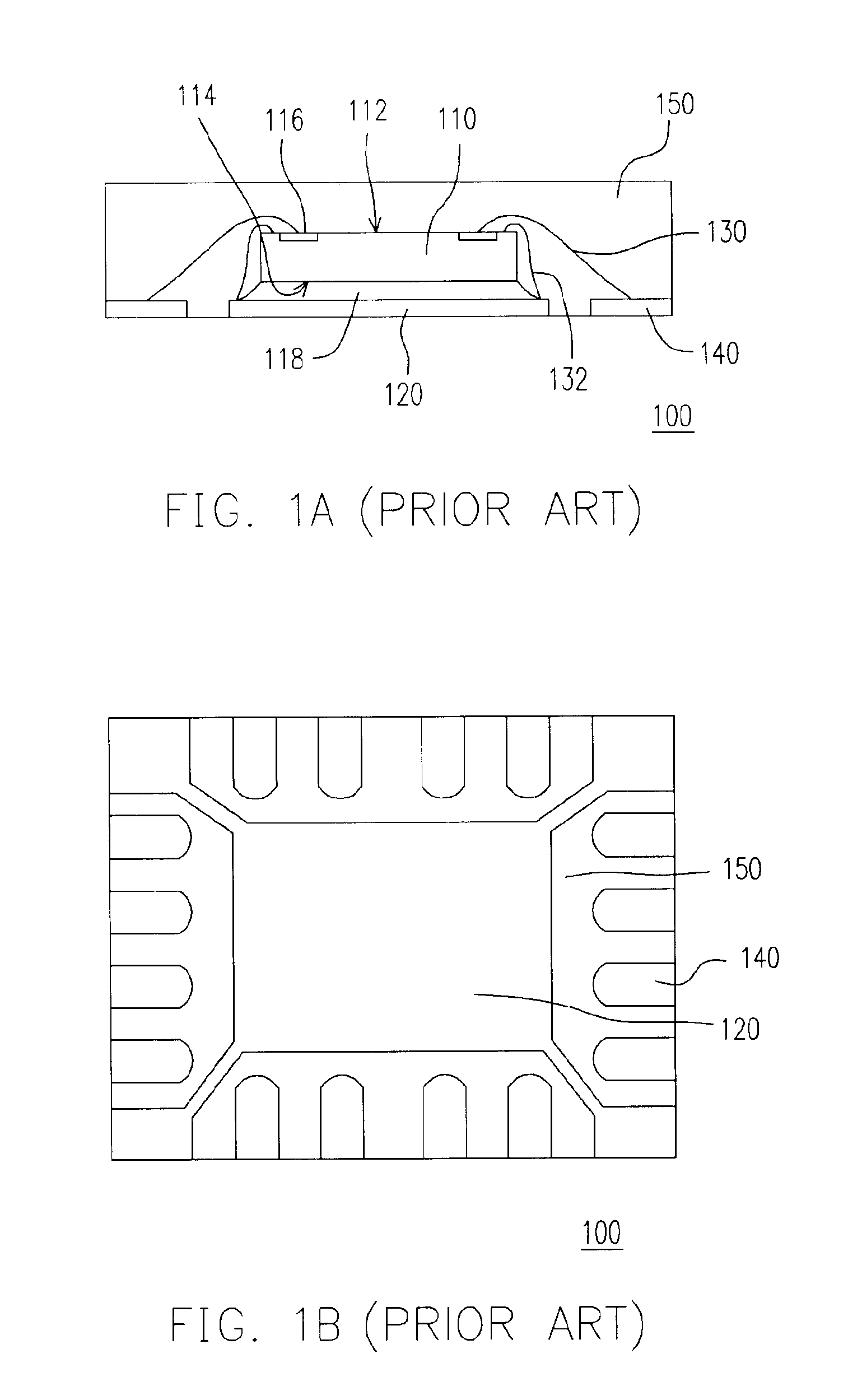

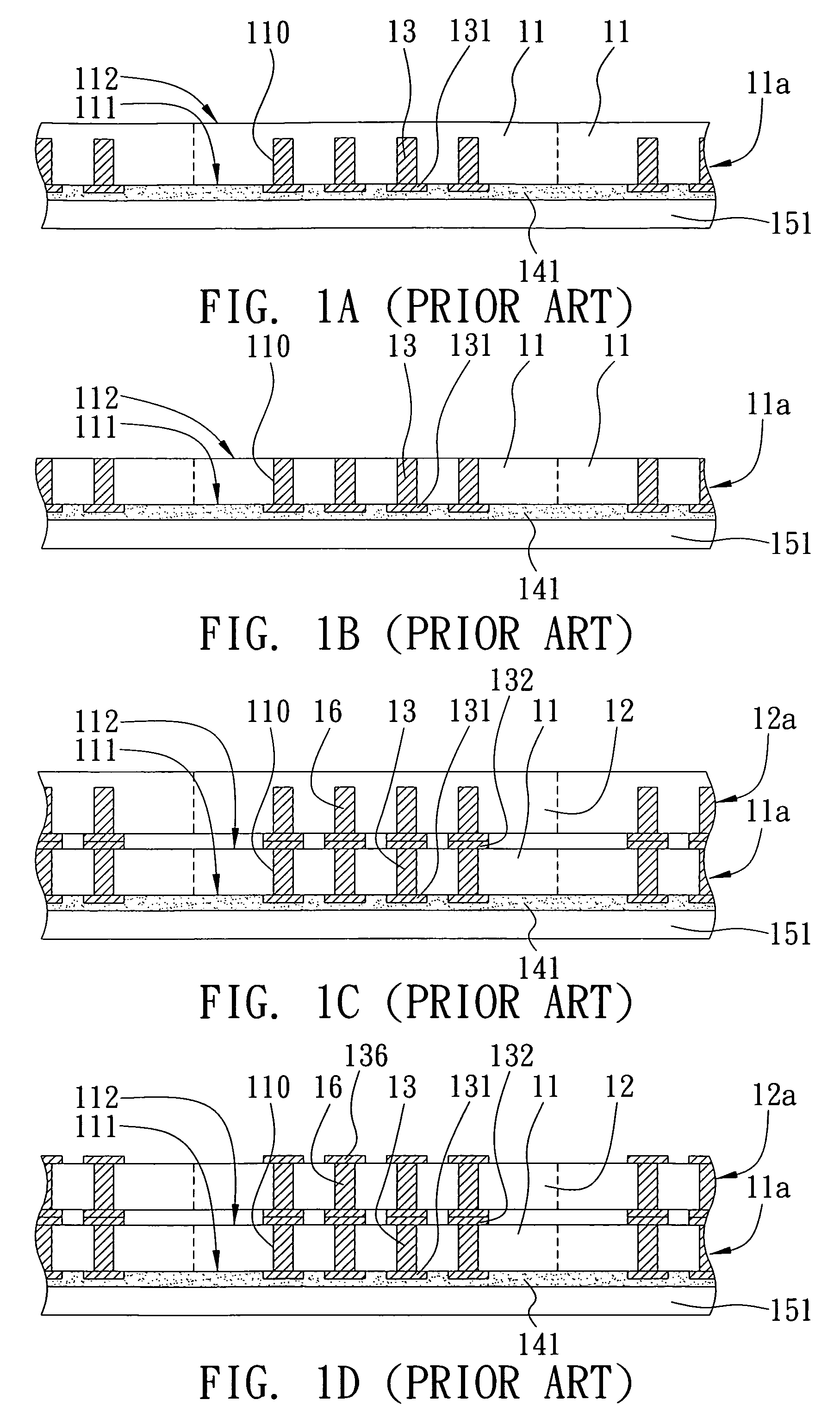

Leadless plastic chip carrier with standoff contacts and die attach pad

ActiveUS7049177B1Improve motherboard assemblyRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesEtchingContact pad

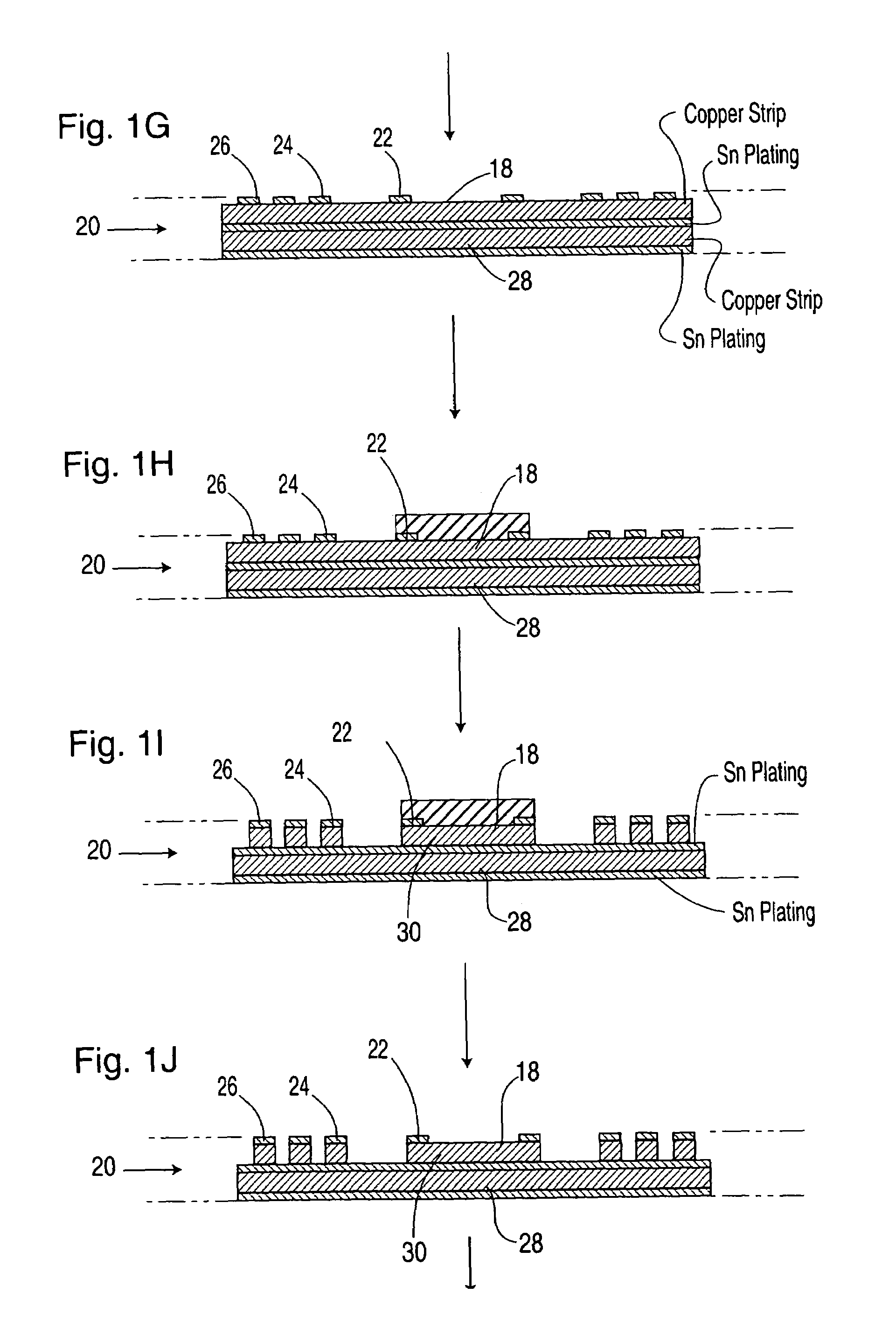

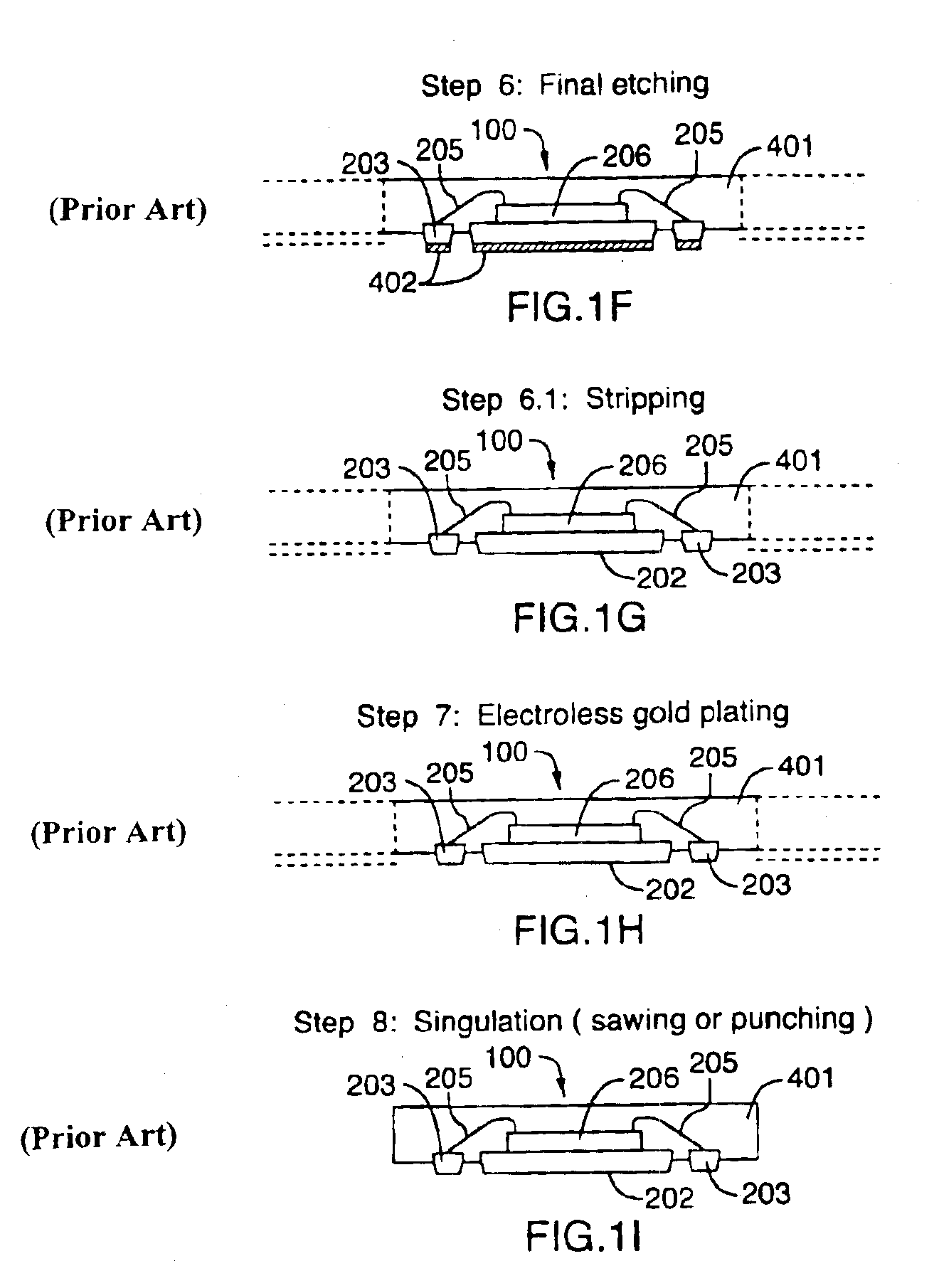

A process for fabricating a leadless plastic chip carrier includes selectively etching at least a first surface of a leadframe strip to partially define at least a plurality of contact pads and a die attach pad; selectively plating at least one layer of metal on a second surface of the leadframe strip, on an undersurface of at least the plurality of contact pads and the die attach pad; mounting a semiconductor die on the first surface, on the partially defined die attach pad; wire bonding the semiconductor die to ones of the contact pads; encapsulating the wire bonds and the semiconductor die in a molding material such that the molding material covers a first portion of the die attach pad and first portions of the contact pads; selectively etching a second surface of the leadframe strip to define a second portion of the contact pads and a second portion of the die attach pad by etching the second surface with the at least one layer of metal resisting etching; and singulating the leadless plastic chip carrier from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

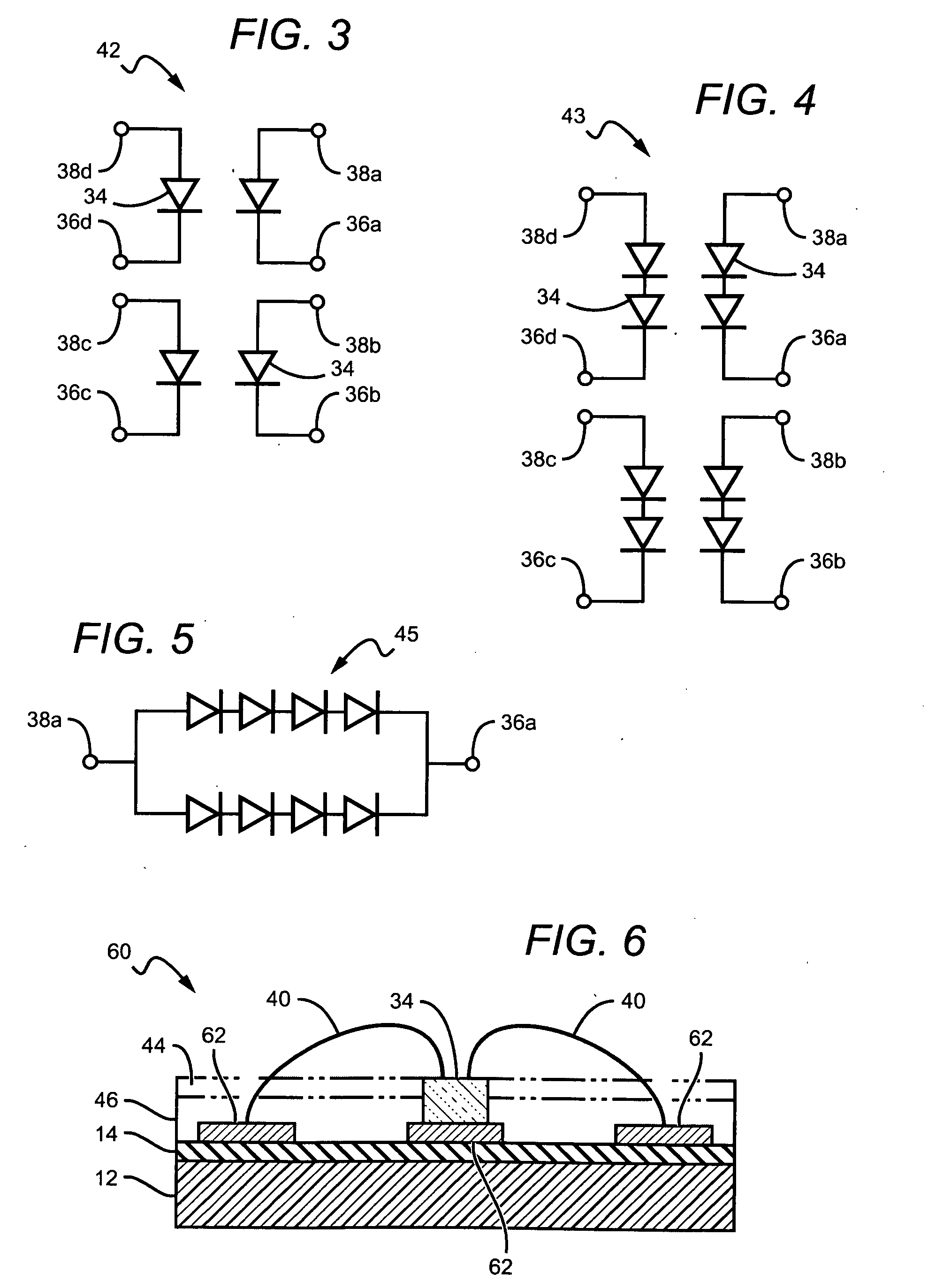

Low temperature co-fired ceramic (LTCC) tape compositions, light emitting diode (LED) modules, lighting devices and method of forming thereof

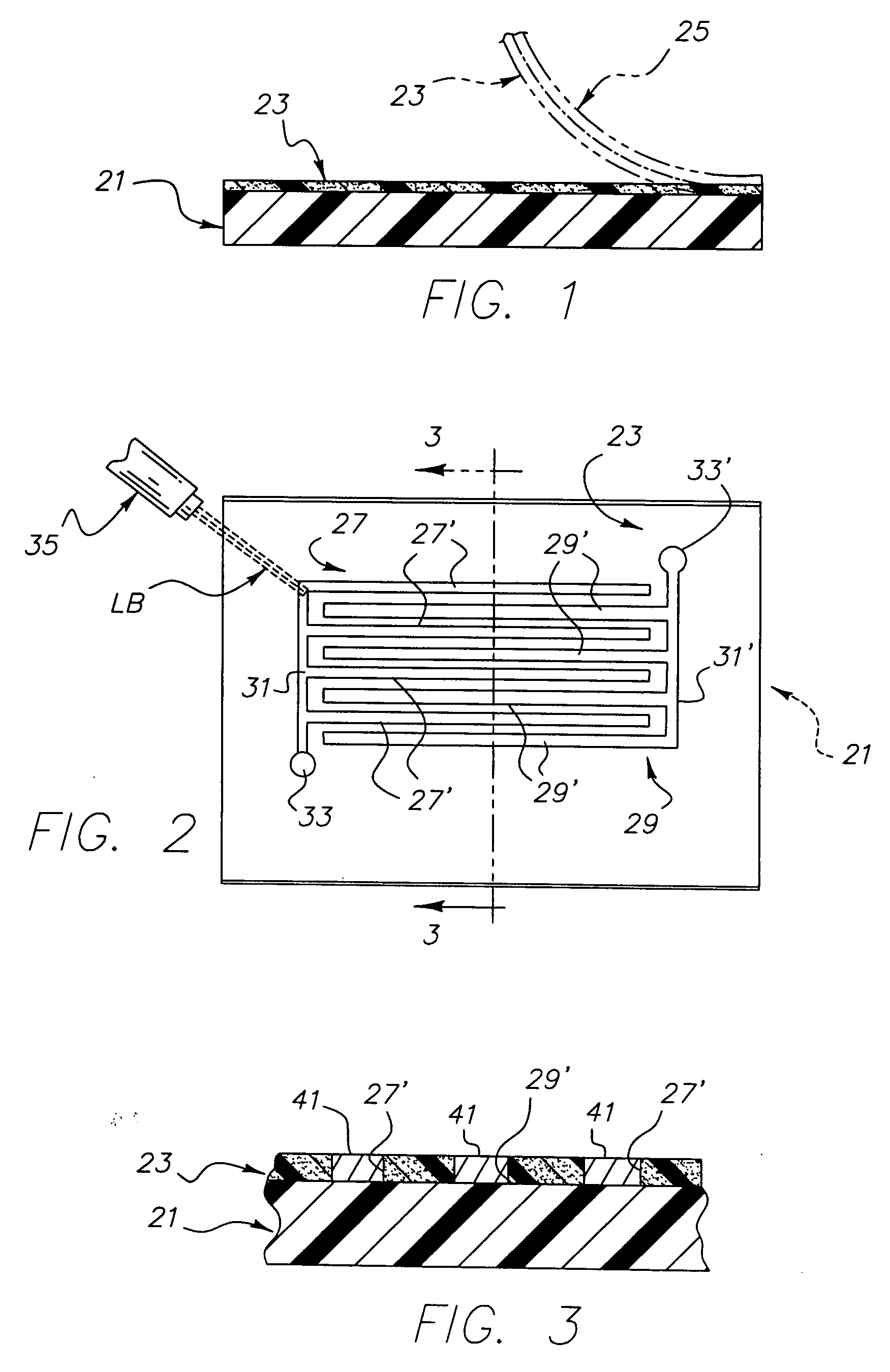

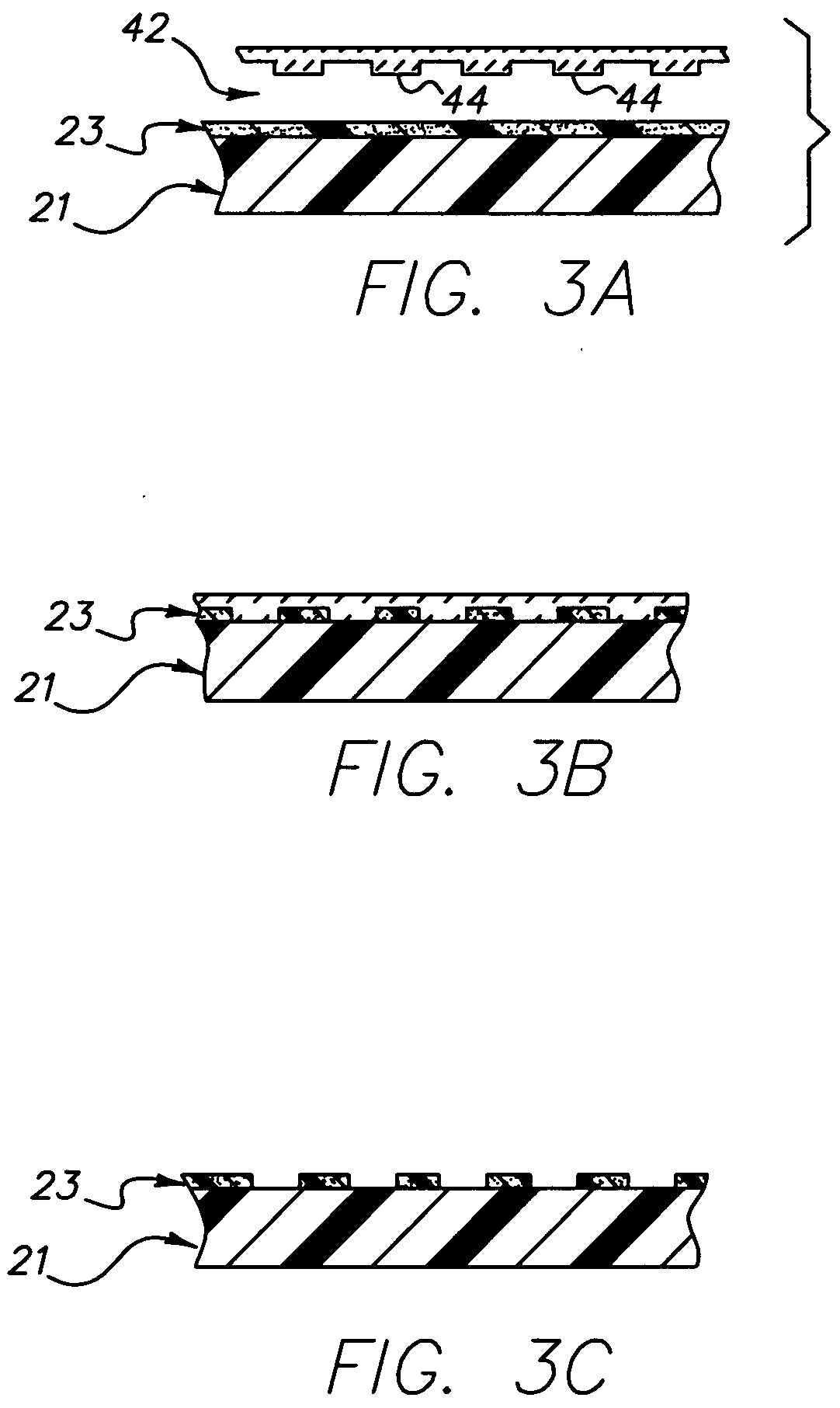

The present invention provides LTCC (low temperature co-fired ceramic) tape compositions and demonstrates the use of said LTCC tape(s) in the formation of Light-Emitting Diode (LED) chip carriers and modules for various lighting applications. The present invention also provides for the use of (LTCC) tape and LED modules in the formation of lighting devices including, but not limited to, LED devices, High Brightness (HB) LED backlights, display-related light sources, automotive lighting, decorative lighting, signage and advertisement lighting, and information display lighting.

Owner:EI DU PONT DE NEMOURS & CO

Process for fabricating a leadless plastic chip carrier

InactiveUS6946324B1Robust three dimensional structureReduce material costsSemiconductor/solid-state device detailsSolid-state devicesMetal stripsContact pad

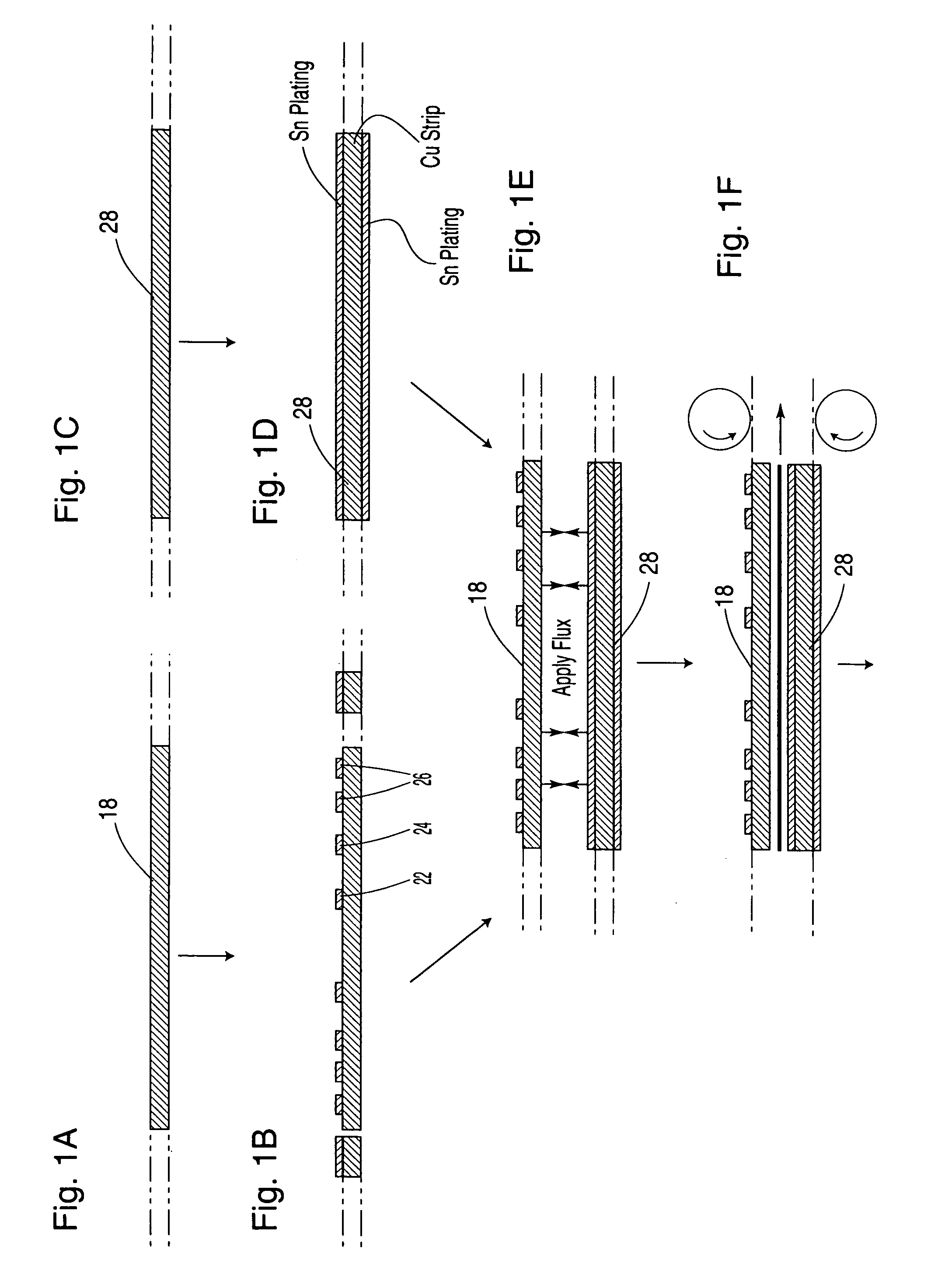

A process for fabricating a leadless plastic chip carrier includes laminating a first metal strip to a second metal strip to form a leadframe strip, selectively etching the first metal strip to define at least a row of contact pads, mounting a semiconductor die to either a die attach pad or the second metal strip and wire bonding the semiconductor die to ones of the contact pads, encapsulating a top surface of the leadframe strip in a molding material, removing the second metal strip, thereby exposing the die attach pad and the at least one row of contact pads, and singulating the leadless plastic chip carrier from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

Leadless plastic chip carrier with etch back pad singulation

InactiveUS6933594B2Improve interlockEasy alignmentSemiconductor/solid-state device detailsSolid-state devicesEtchingPunching

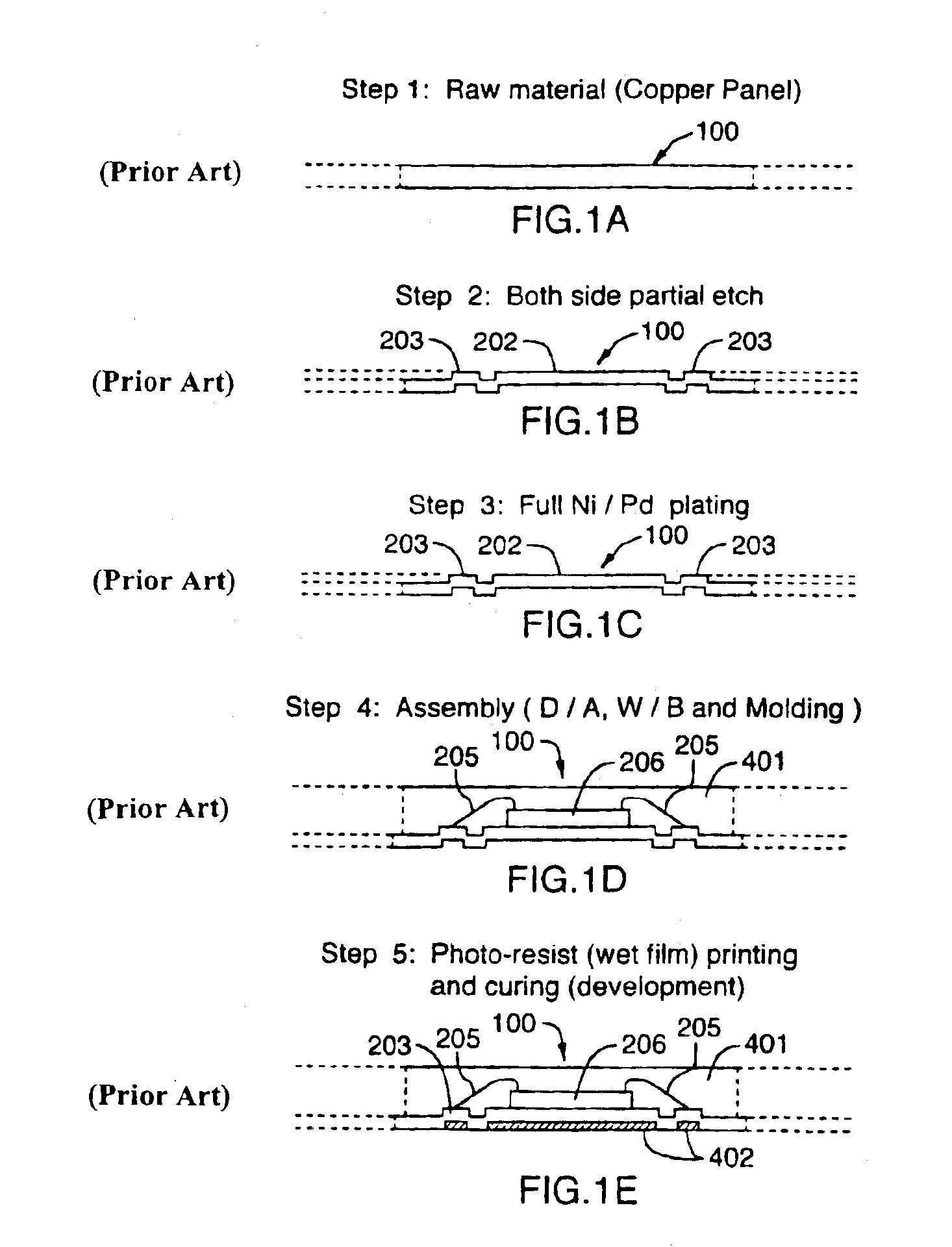

A leadless plastic chip carrier is constructed by half etching one or both sides of the package design onto a leadframe strip so as to create unique design features such as power and / or ground ring surrounding the die attach pad, interlocking rivet head construction for the contact pads, and an interlocking pattern for the die attach pad. After wire bonding and molding, a further etching is performed to isolate and expose contact pads. Singulation of individual chip packages from the leadframe strip is then performed by saw singulation or die punching.

Owner:UTAC HEADQUARTERS PTE LTD

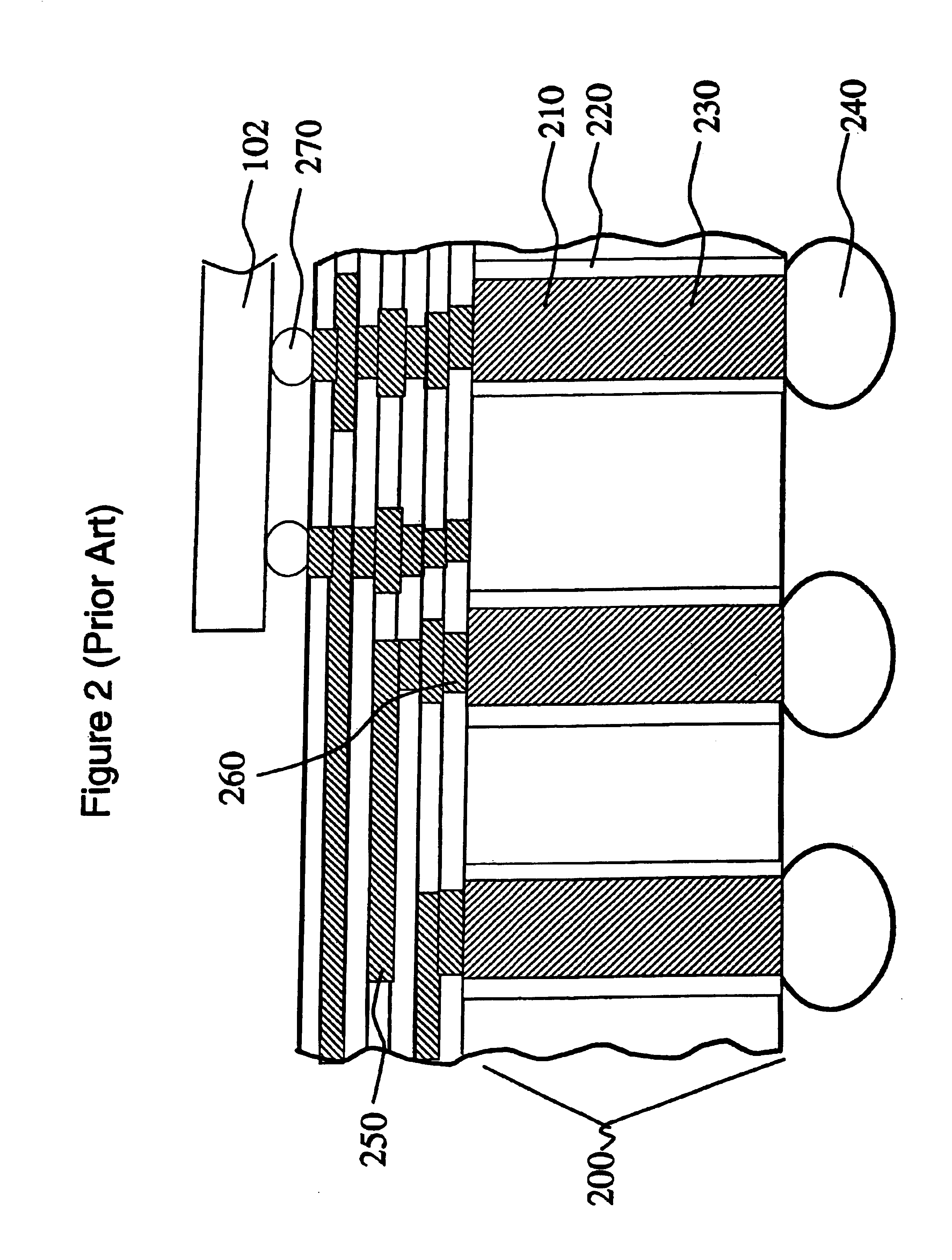

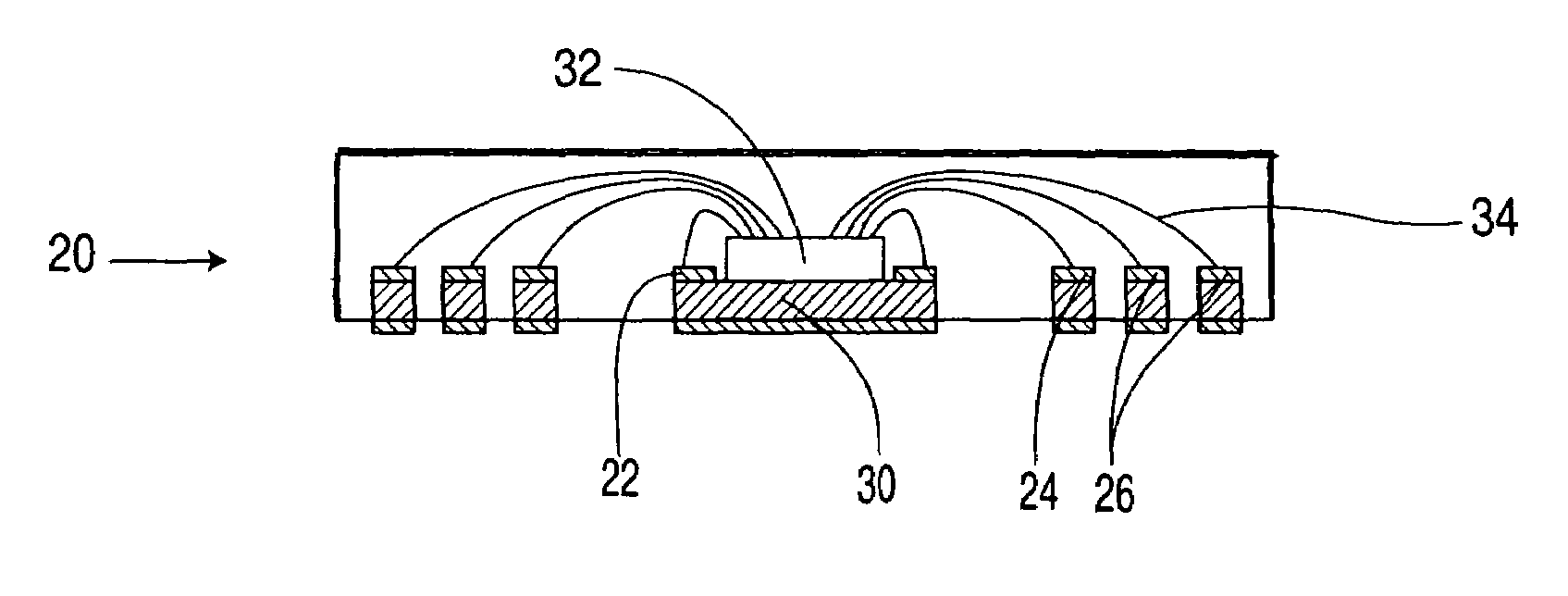

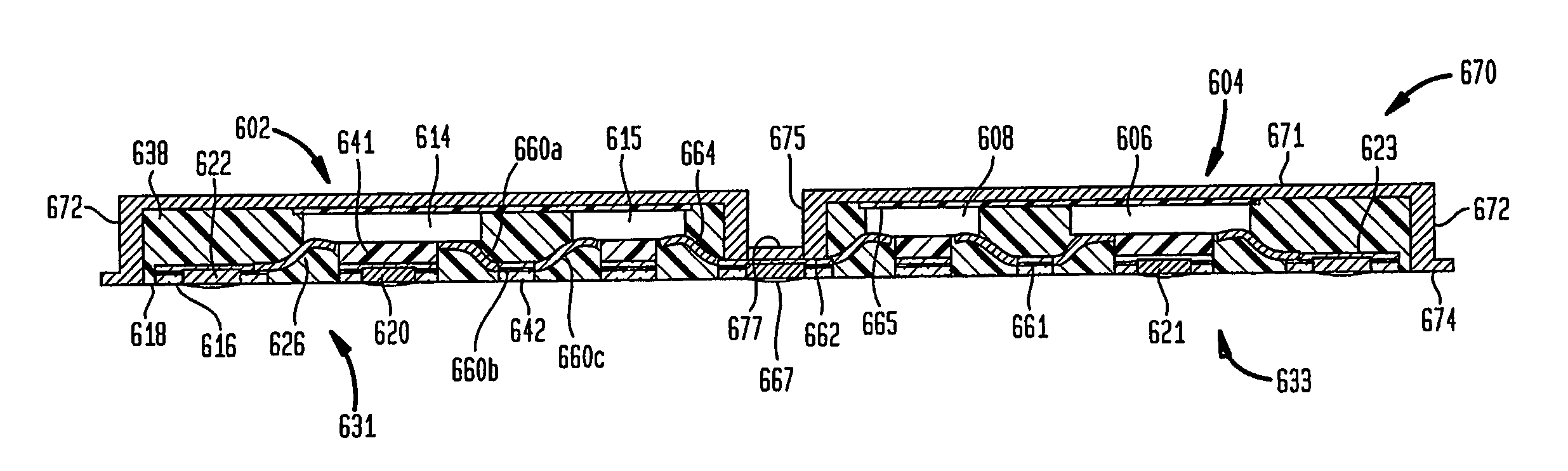

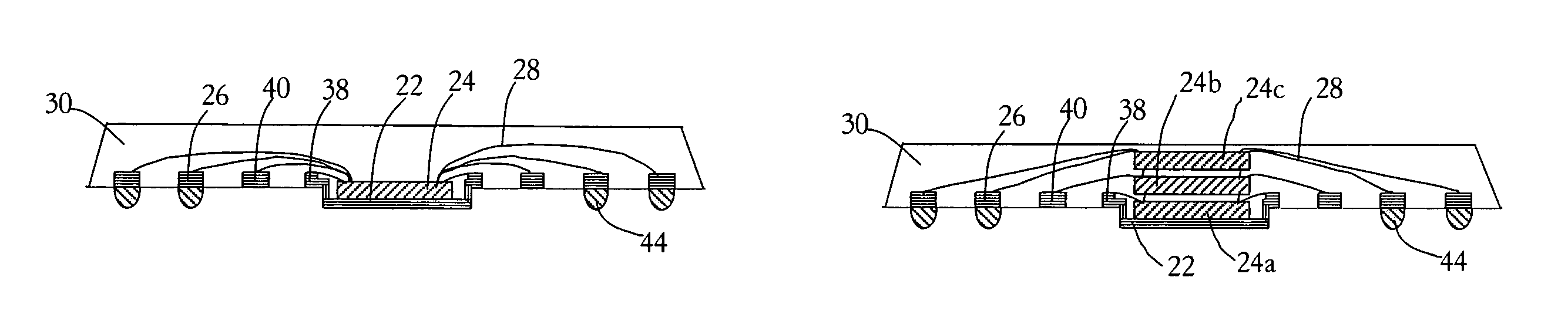

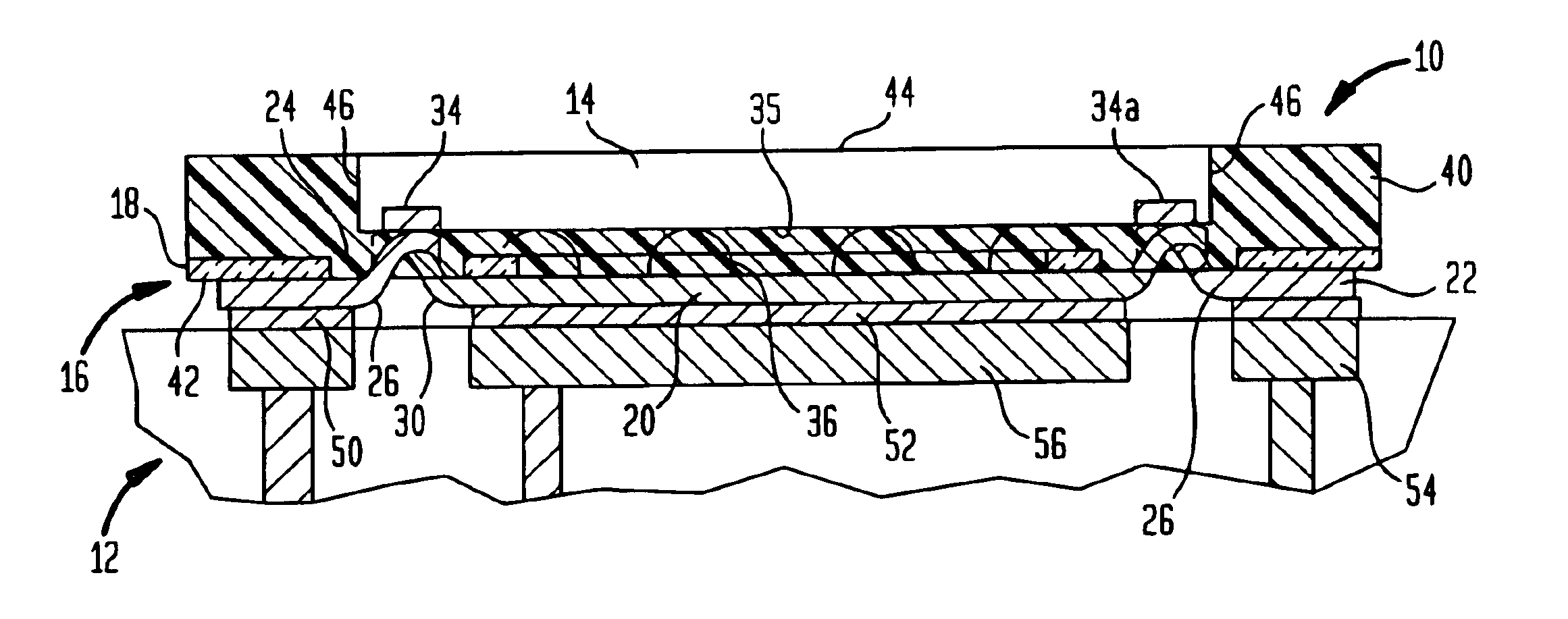

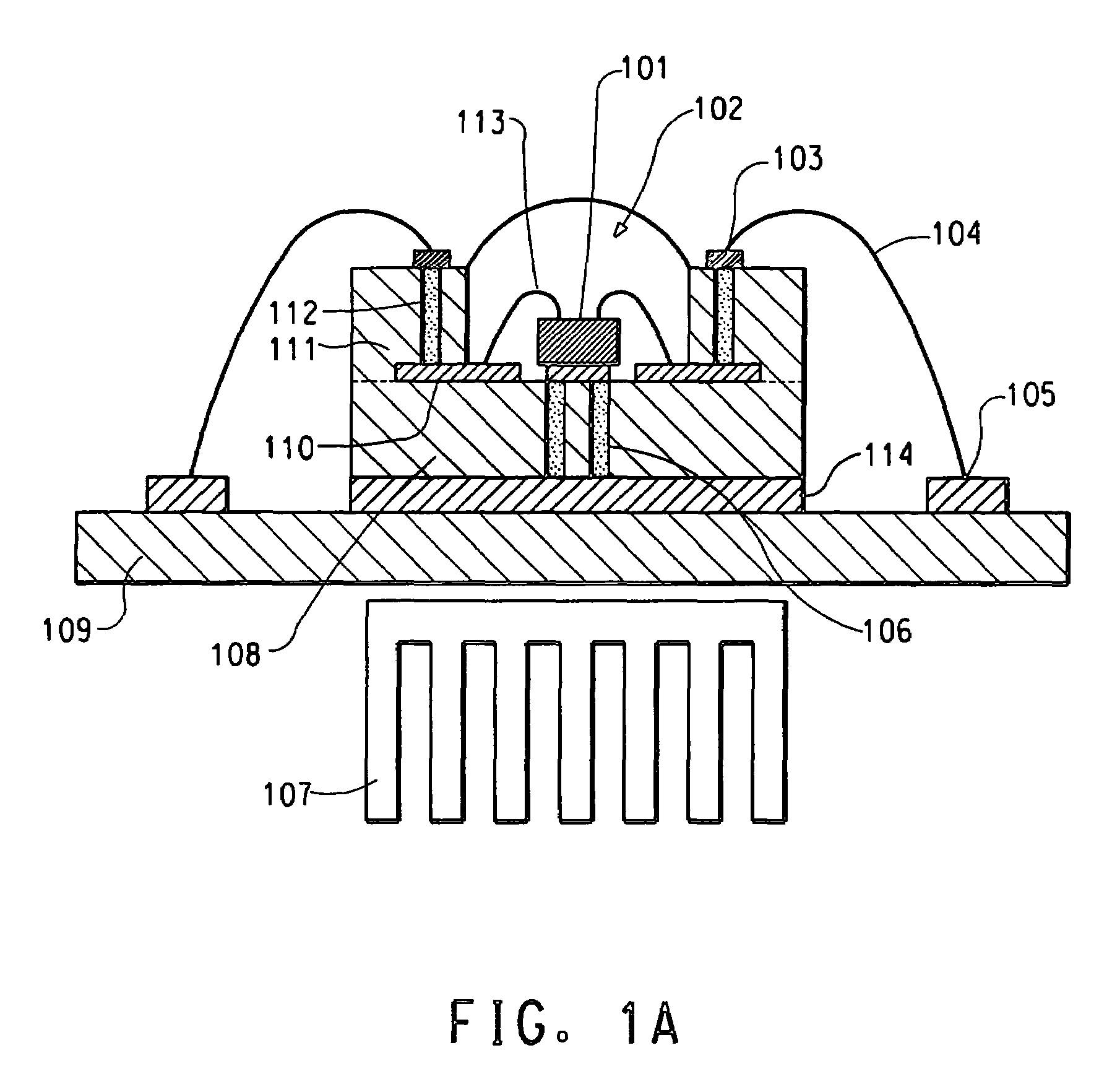

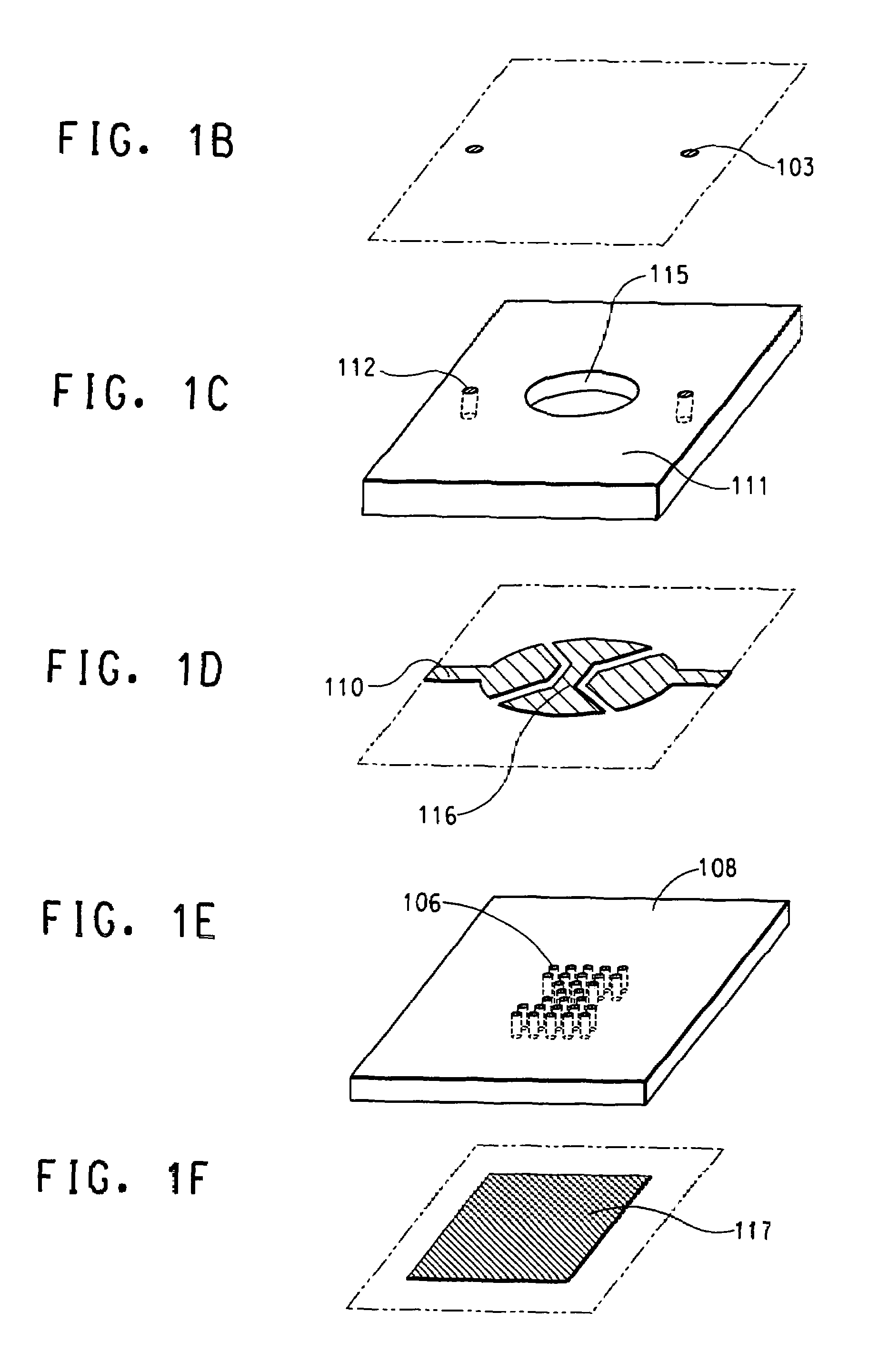

High-frequency chip packages

InactiveUS20050046001A1Improve heat transfer performanceEasy transferImpedence networksSemiconductor/solid-state device detailsElectrical conductorSemiconductor chip

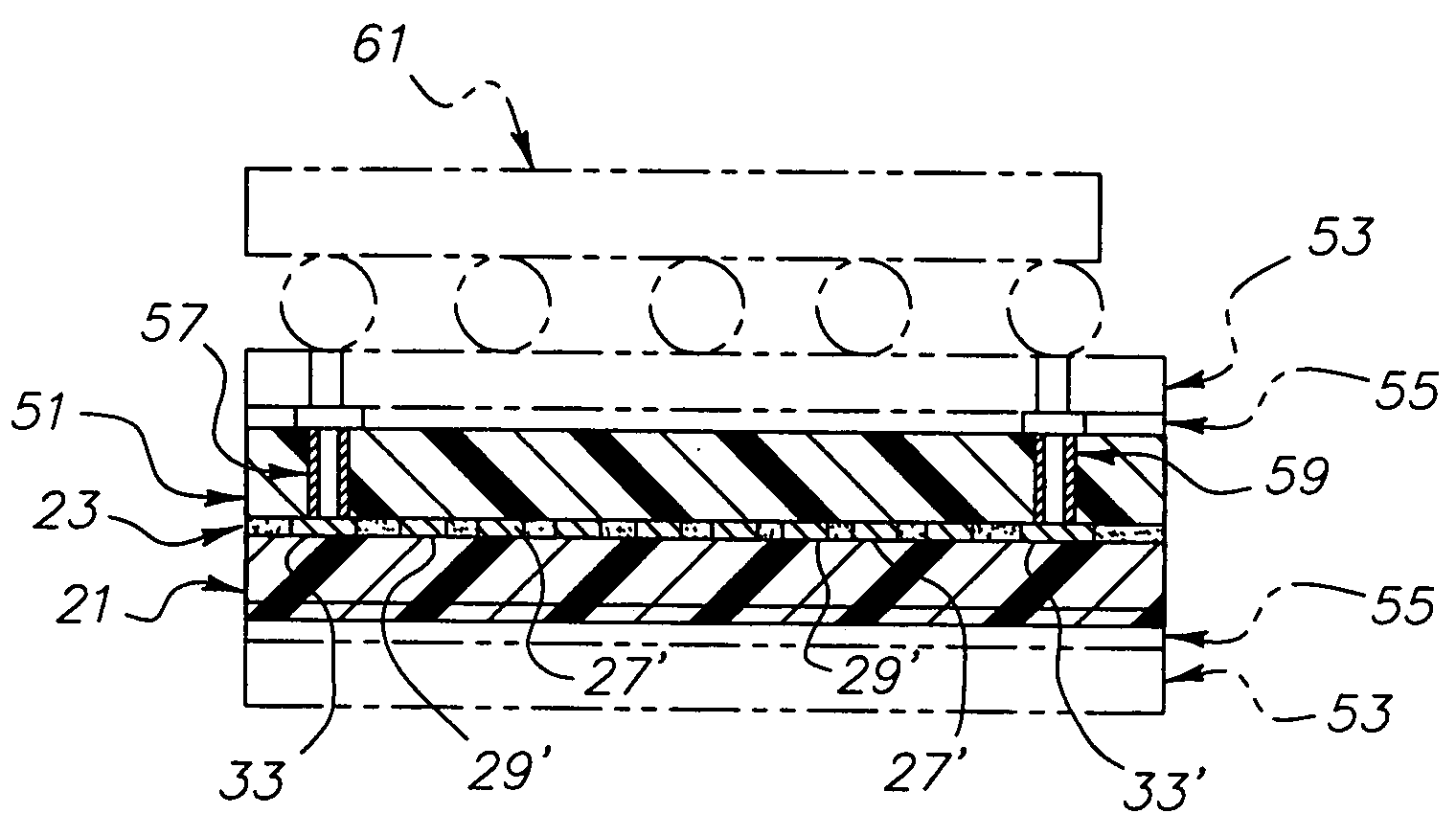

A packaged semiconductor chip includes features such as a chip carrier having a large thermal conductor which can be solder-bonded to a circuit board so as to provide enhanced thermal conductivity to the circuit board and electromagnetic shielding and a conductive enclosure which partially or completely surrounds the packaged chip to provide additional heat dissipation and shielding. The packaged unit may include both an active semiconductor chip and a passive element, desirably in the form of a chip, which includes resistors and capacitors. Inductors may be provided in whole or in part on the chip carrier. A module includes two circuits and an enclosure with a medial wall between the circuits to provide electromagnetic shielding between the circuits.

Owner:TESSERA INC

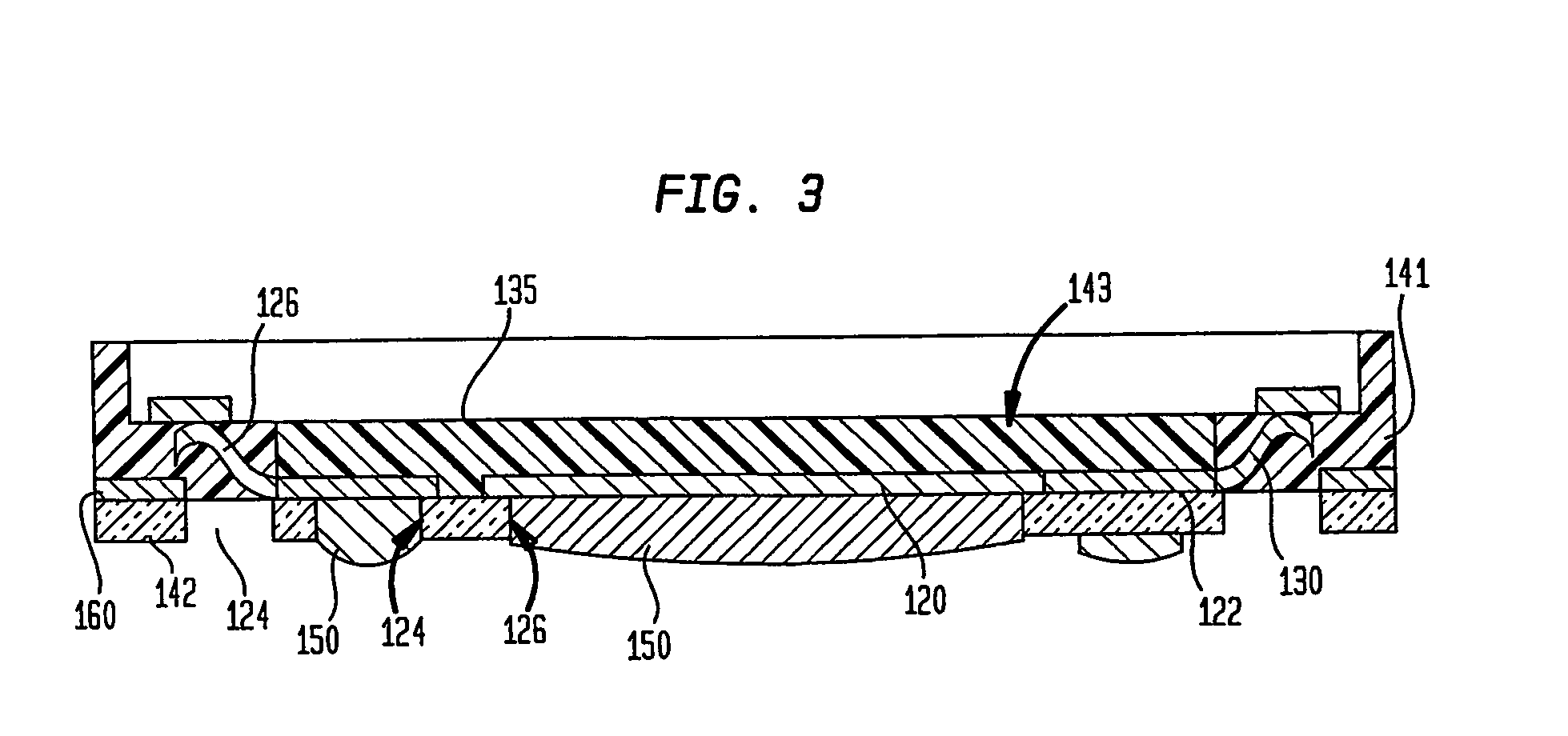

Thin leadless plastic chip carrier

ActiveUS7009286B1Thin package profileReduce electrical impedanceSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A leadless plastic chip carrier is fabricated by selectively etching a leadframe strip to reduce a thickness of the strip at a portion thereof. Selectively masking the surface of the leadframe strip using a mask, follows selectively etching, to provide exposed areas of the surface at the portion and contact pad areas on leadframe the strip. At least one layer of metal is deposited on the exposed areas to define a die attach pad on the portion of the leadframe strip with reduced thickness and to define contact pads on the surface of the strip. At least one semiconductor die is mounted to the die attach pad, followed by wire bonding the at least one semiconductor die to ones of the contact pads. The at least one semiconductor die, the wire bonds, and the contact pads are covered with an overmold material and the leadframe strip is etched to thereby remove the leadframe strip. The leadless plastic chip carrier is singulated from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

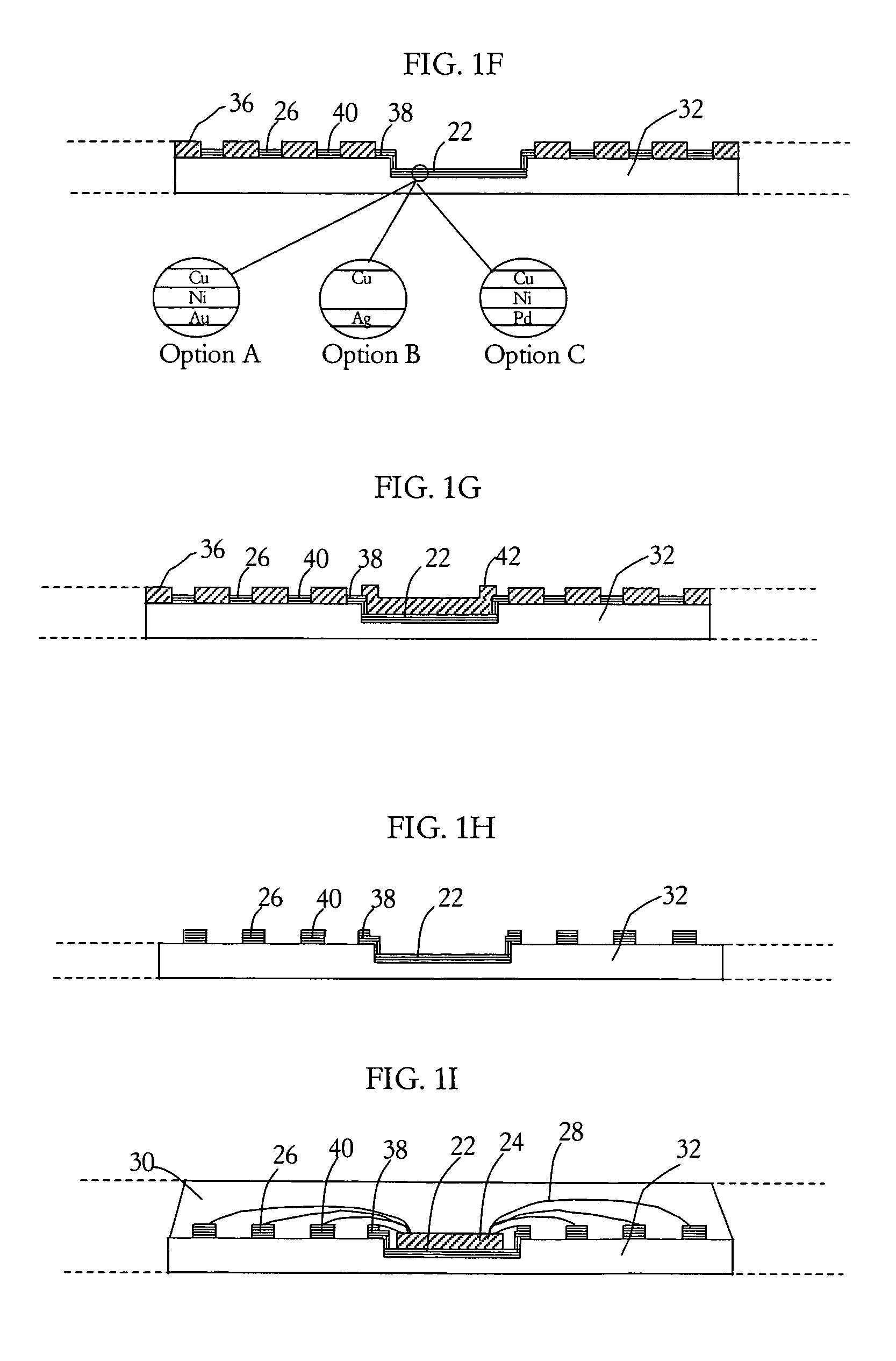

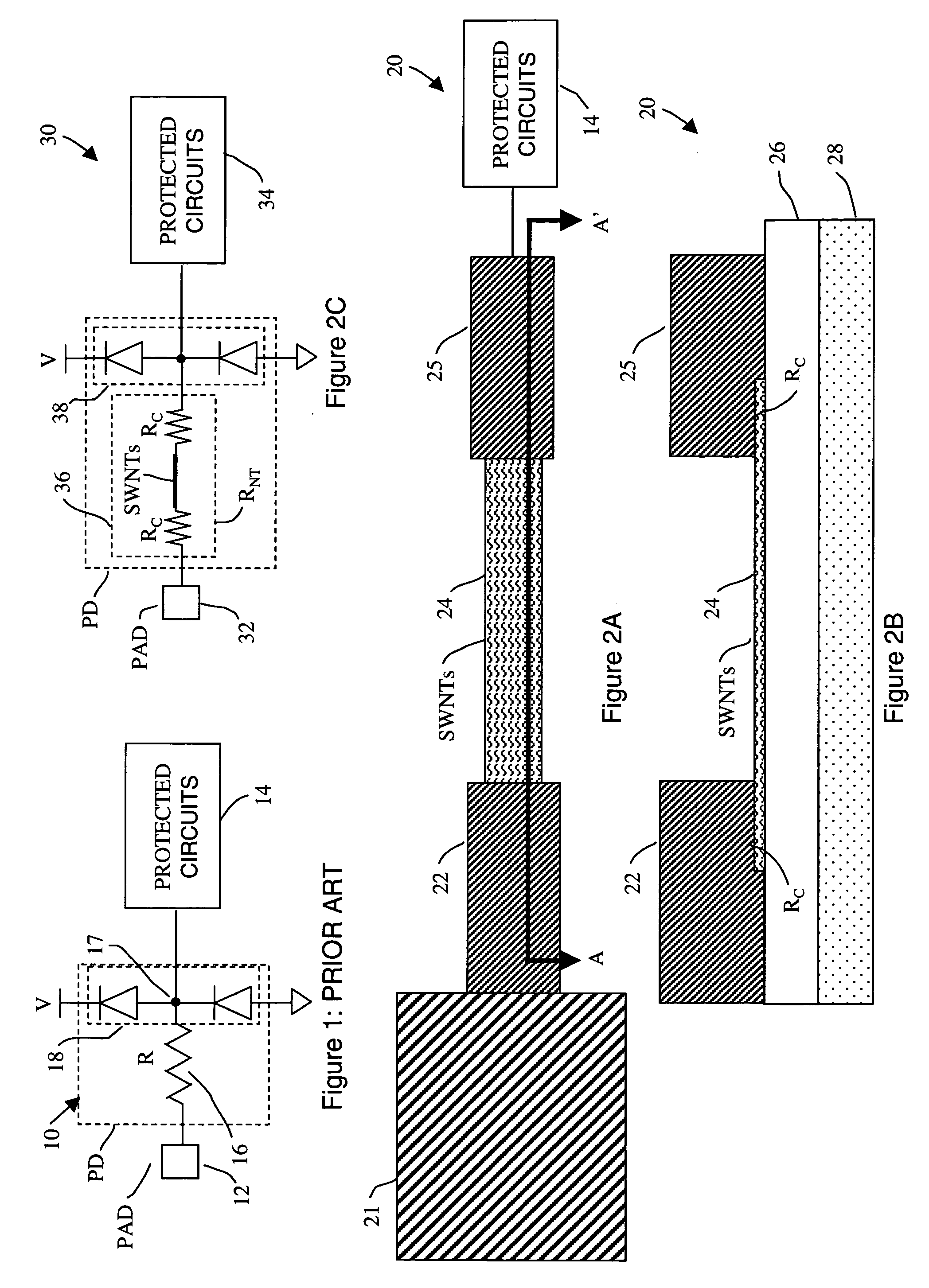

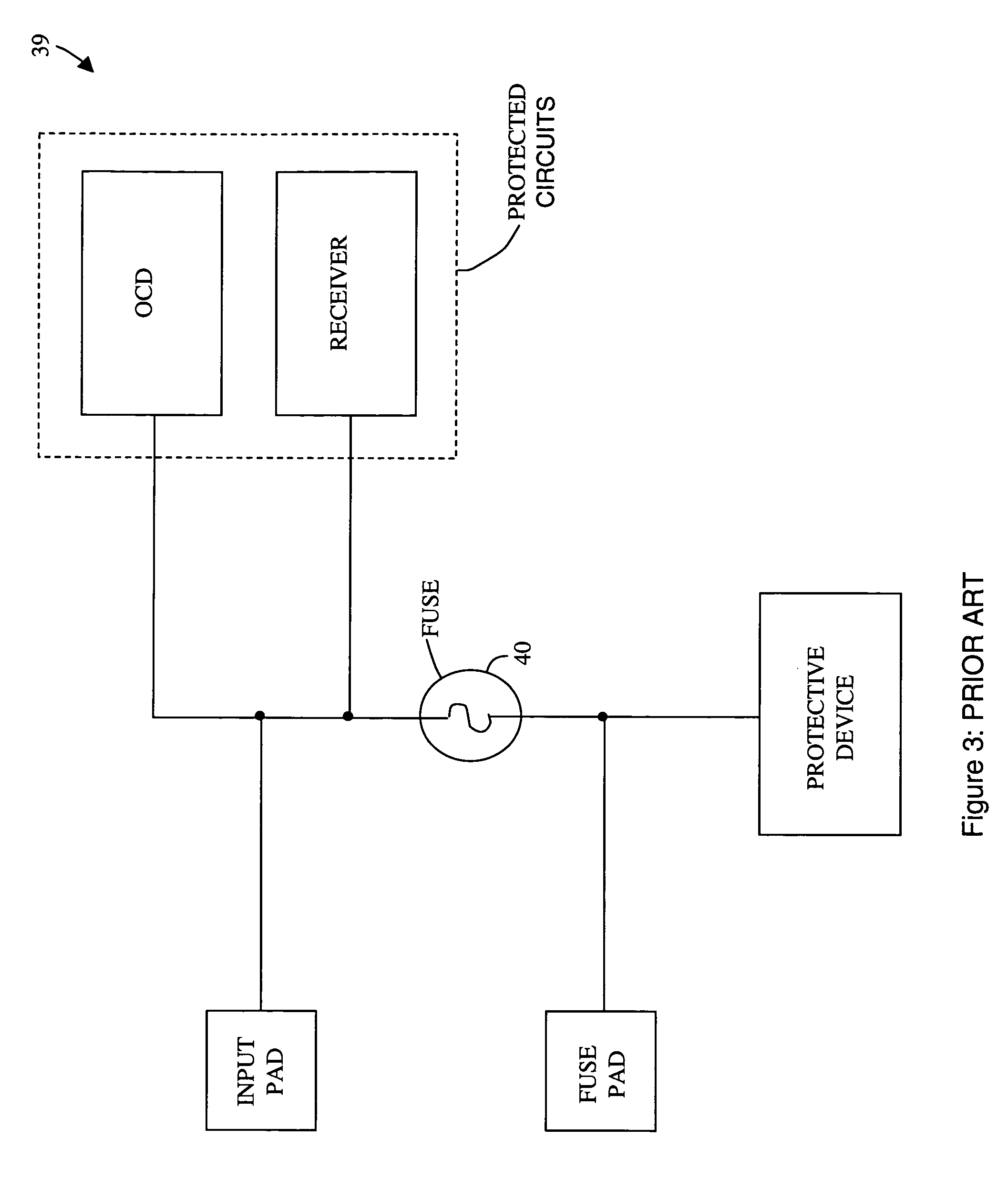

Nanotube ESD protective devices and corresponding nonvolatile and volatile nanotube switches

InactiveUS20060193093A1Nanoelectromechanical switchesSemiconductor/solid-state device detailsSignal onSemiconductor chip

Nanotube ESD protective devices and corresponding nonvolatile and volatile nanotube switches. An electrostatic discharge (ESD) protection circuit for protecting a protected circuit is coupled to an input pad. The ESD circuit includes a nanotube switch electrically having a control. The switch is coupled to the protected circuit and to a discharge path. The nanotube switch is controllable, in response to electrical stimulation of the control, between a de-activated state and an activated state. The activated state creates a current path so that a signal on the input pad flows to the discharge path to cause the signal at the input pad to remain within a predefined operable range for the protected circuit. The nanotube switch, the input pad, and the protected circuit may be on a semiconductor chip. The nanotube switch may be on a chip carrier. The deactivated and activated states may be volatile or non-volatile depending on the embodiment. The ESD circuit may be repeatedly programmed between the activated and deactivated states so as to repeatedly activate and deactivate ESD protection of the protected circuit. The nanotube switch provides protection based on the magnitude of the signal on the input pad.

Owner:NANTERO

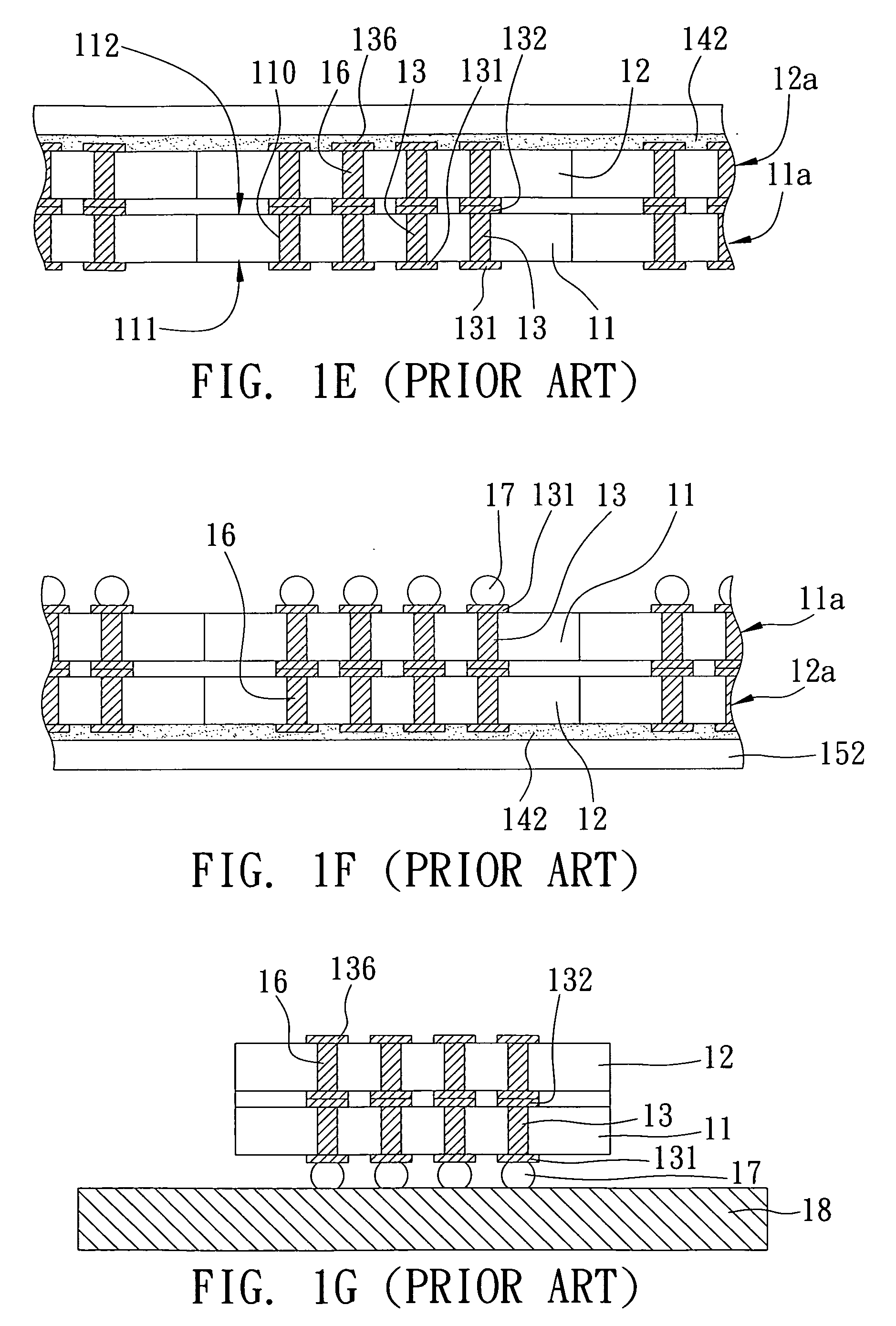

Semiconductor package and method for fabricating the same

InactiveUS20090102063A1Effective installationSmall sizeSemiconductor/solid-state device detailsSolid-state devicesManufacturing cost reductionResist

This invention provides a semiconductor package and a method for fabricating the same. The method includes: forming a first resist layer on a metal carrier; forming a plurality of openings penetrating the first resist layer; forming a conductive metal layer in the openings; removing the first resist layer; covering the metal carrier having the conductive metal layer with a dielectric layer; forming blind vias in the dielectric layer to expose a portion of the conductive metal layer; forming conductive circuit on the dielectric layer and conductive posts in the blind vias, such that the conductive circuit is electrically connected to the conductive metal layer via the conductive posts; electrically connecting at least one chip to the conductive circuit; forming an encapsulant for encapsulating the chip and the conductive circuit; and removing the metal carrier, thereby allowing a semiconductor package to be formed without a chip carrier. Given the conductive posts, both the conductive circuit and conductive metal layer are efficiently coupled to the dielectric layer to prevent delamination. Further, downsizing the blind vias facilitates the fabrication process and cuts the fabrication cost.

Owner:SILICONWARE PRECISION IND CO LTD

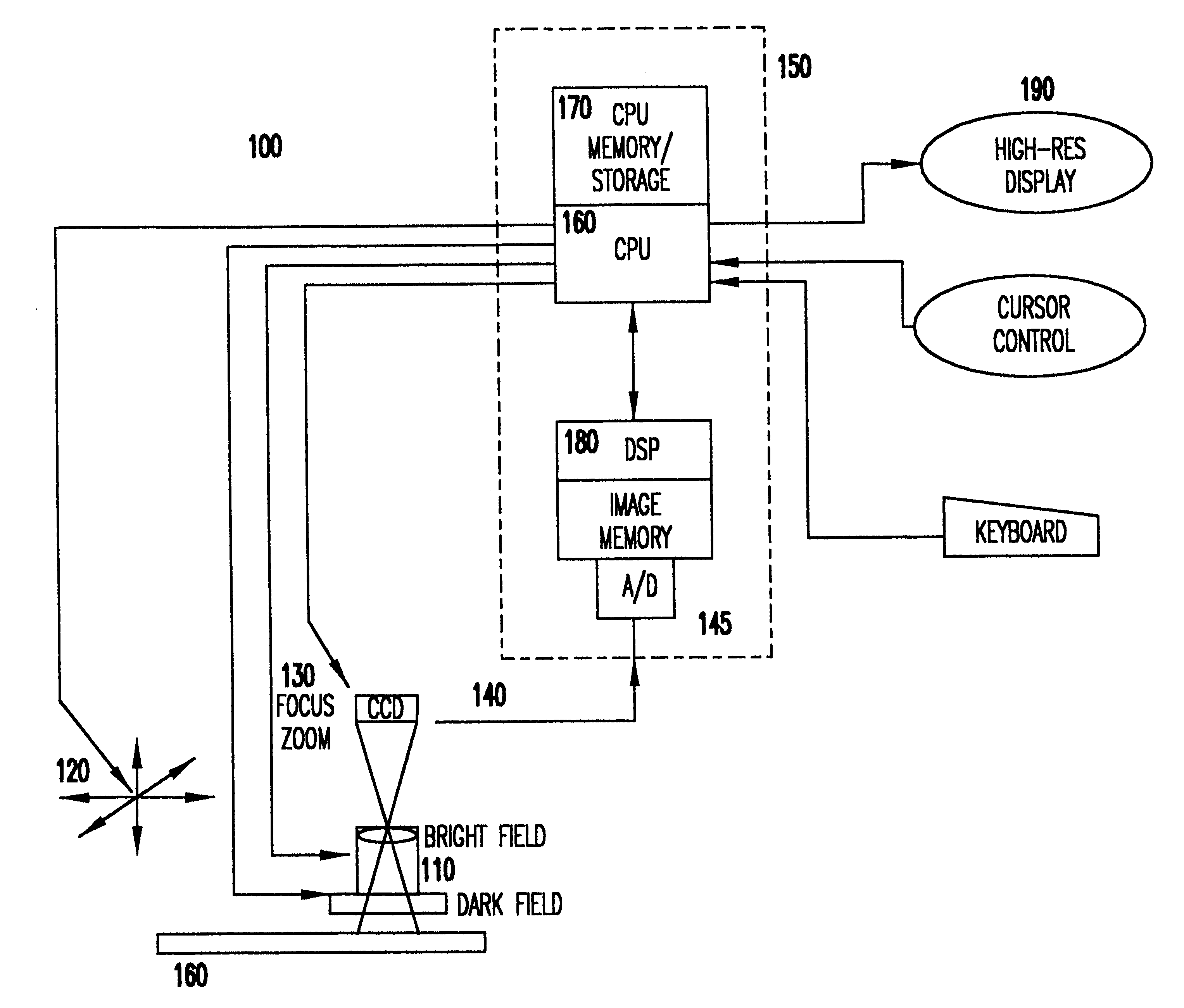

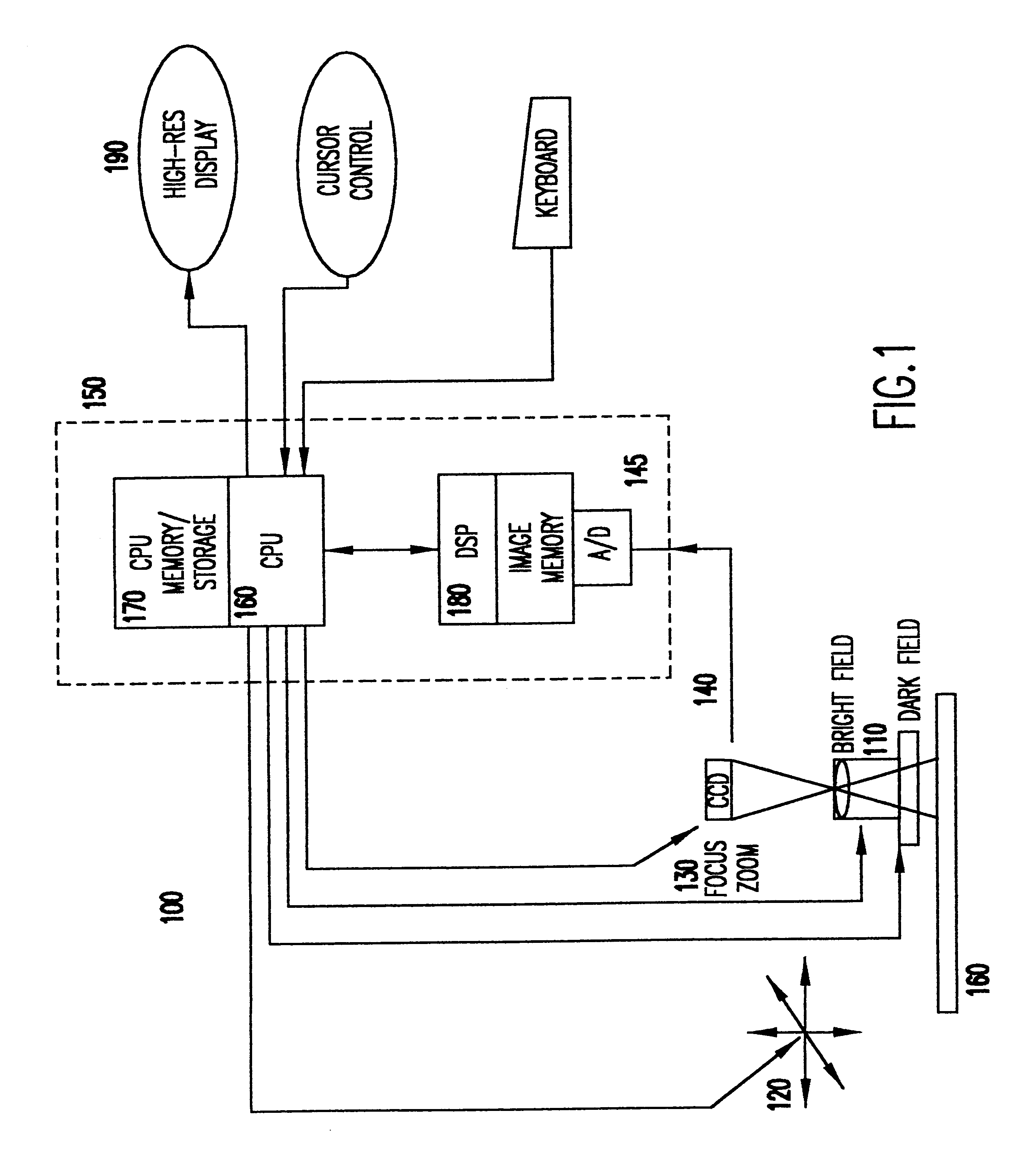

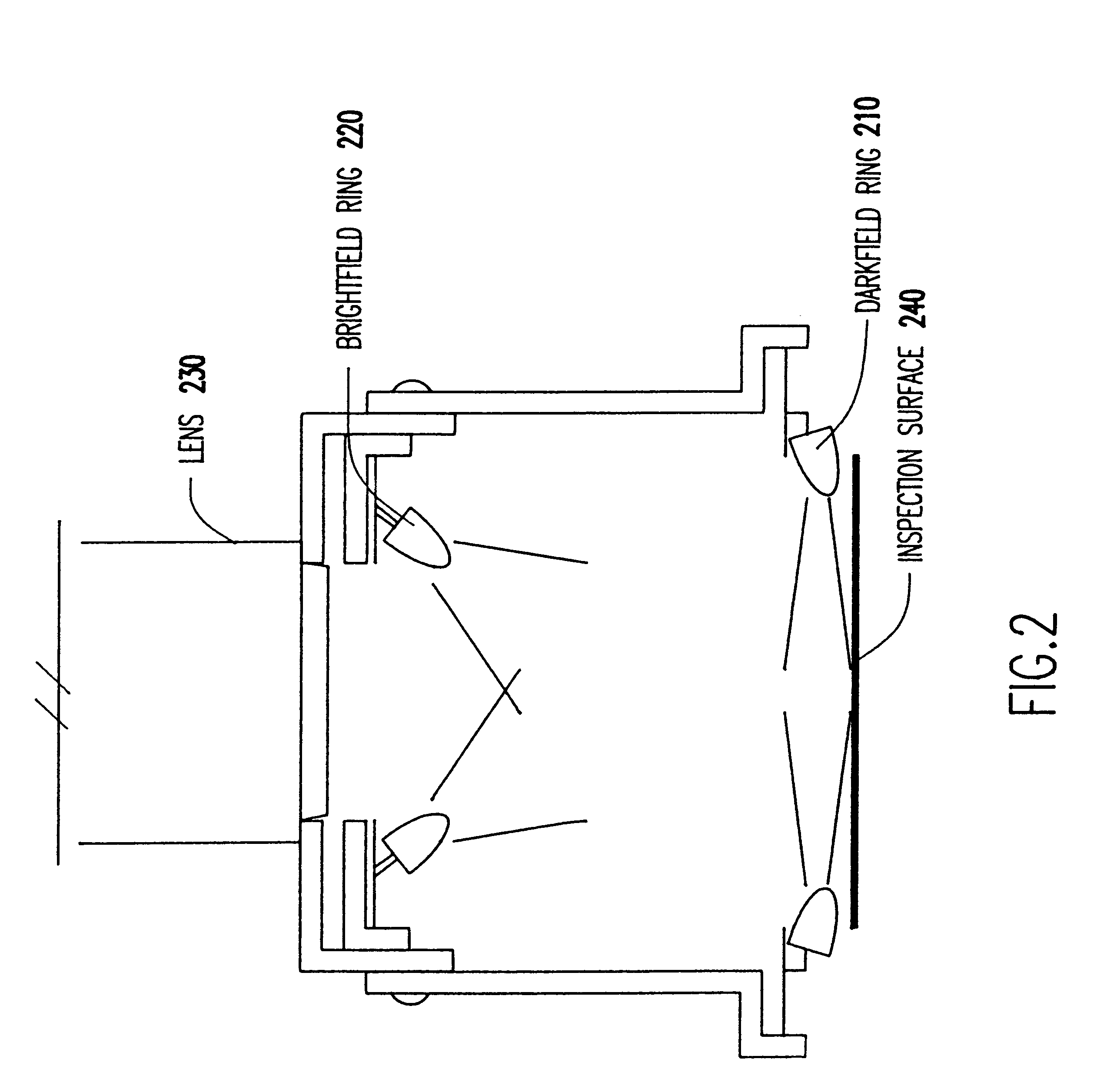

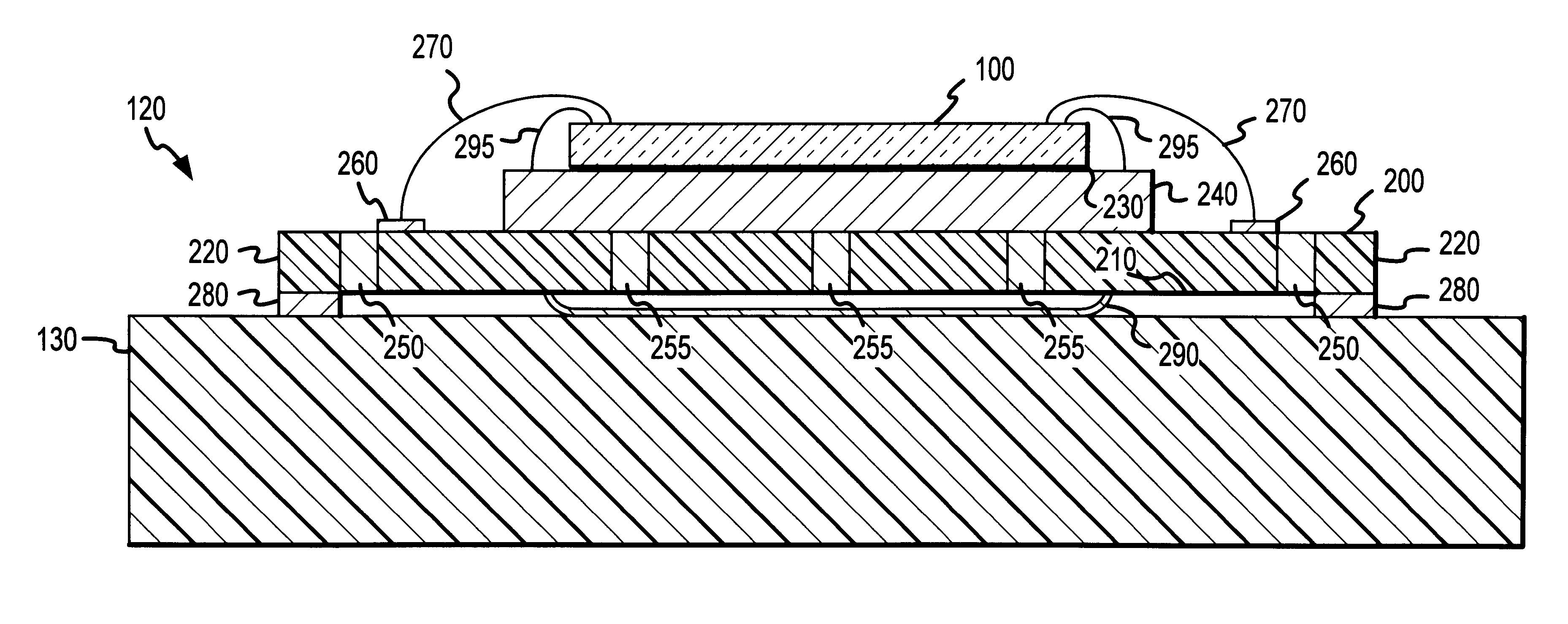

Automated inspection system for metallic surfaces

InactiveUS6198529B1Optically investigating flaws/contaminationUsing optical meansDigital signal processingVision processing

An automated inspection system particularly adapted for detection and discrimination of surface irregularities of specularly reflecting and other materials, such as are employed in laminate chip carriers and printed circuit boards, includes an area scan image sensor allowing illumination sources to surround an area of a surface being inspected. The illumination source preferably provides either or both bright field and dark field illumination of the surface; developing generally complementary images of surface irregularities. A self-registering rules-driven process for developing inspection masks reduces alignment operations and improves performance. Image enhancement and morphological operations to detect surface irregularities are performed by digital signal processing, preferably using a dedicated vision processor. Masks screen potential defects to critical mounting and bonding surfaces accurately without requiring alignment of data or reference images to acquired images. Since potential defects are copied from acquired images and stored, verification of defects may be performed without further access to the inspected part and without removal of the part to another specialized apparatus, simplifying processing and increasing throughput and operator efficiency.

Owner:GLOBALFOUNDRIES INC

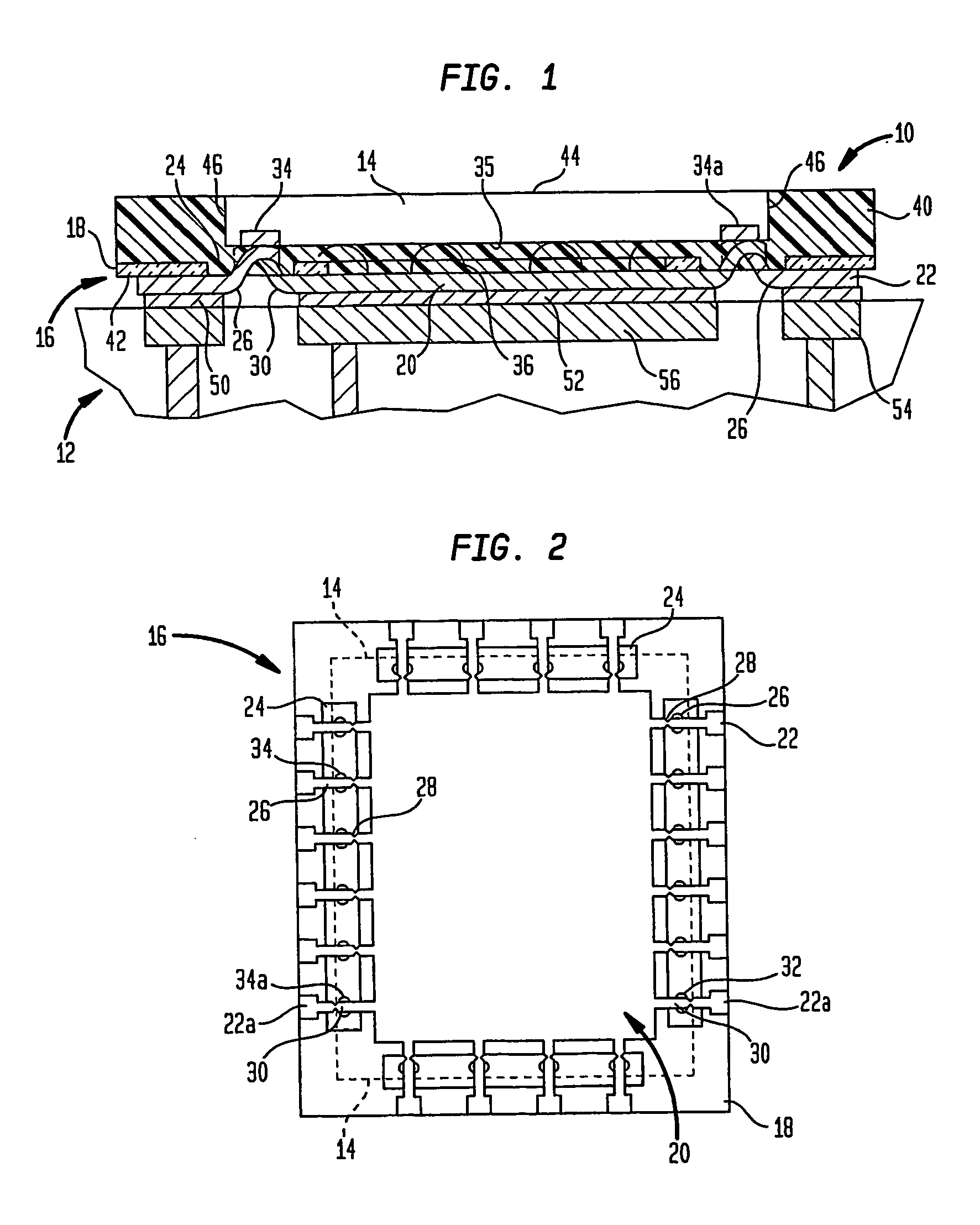

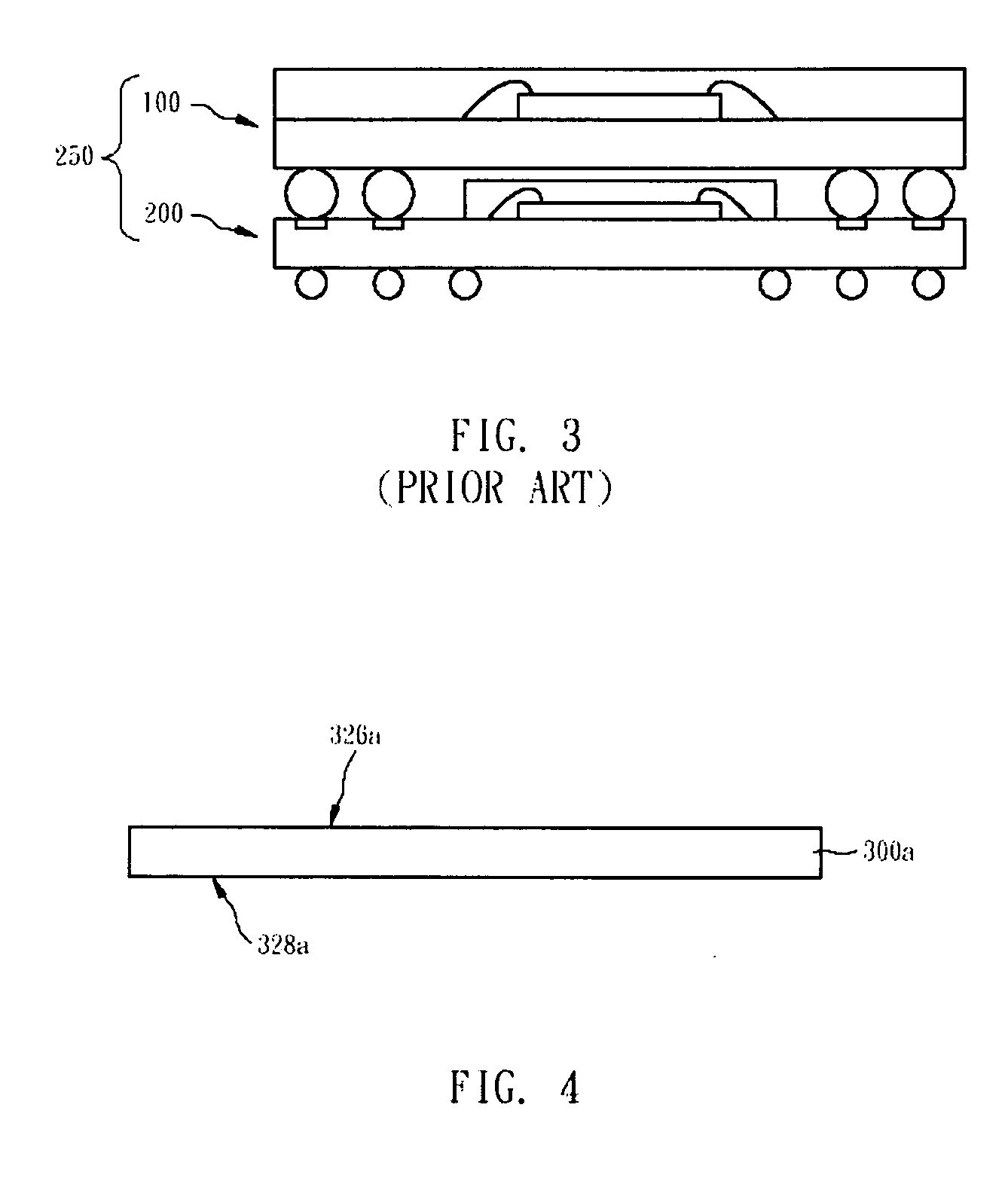

Quad flat no-lead chip carrier

ActiveUS6882057B2High I/O densityImprove chip qualitySemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

A quad flat no-lead chip carrier for a wire-bonded chip package is provided. The chip carrier comprises a conductive plate, a plurality of conductive columns and a plurality of dielectric walls. A chip is attached to the conductive plate. The conductive plate furthermore has a plurality of columnar through holes distributed around a chip-bonding region. The conductive columns are set up within the columnar through holes. The dielectric walls are set up between the sidewall of the conductive columns and the inner surface of the columnar through holes. The chip is electrically connected to the conductive columns via conductive wires. The bottom end of the conductive columns serves as input / output contacts for connecting with external contacts. The chip carrier is able to increase overall density of the input / output contacts and improve the electrical performance of the chip package.

Owner:VIA TECH INC

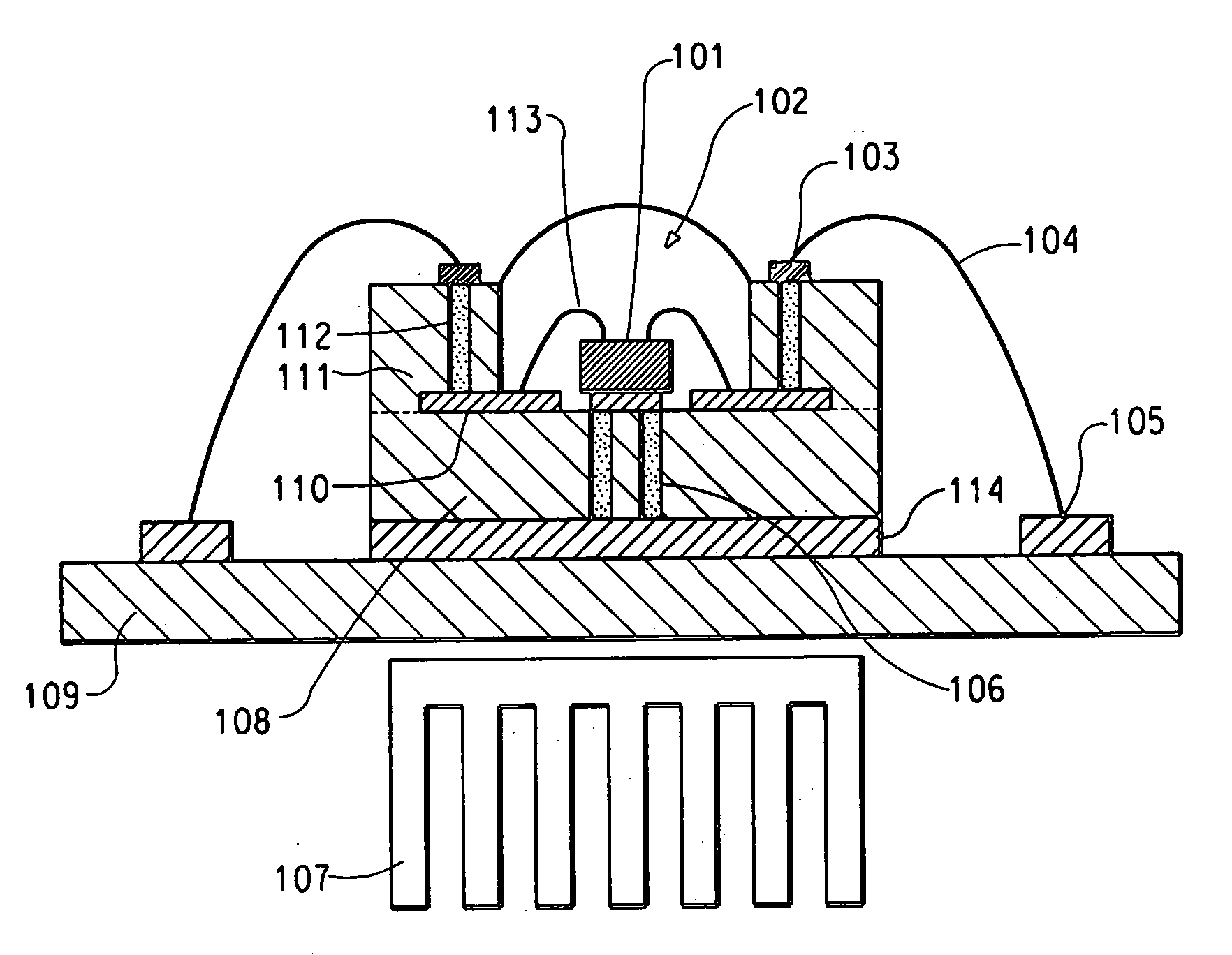

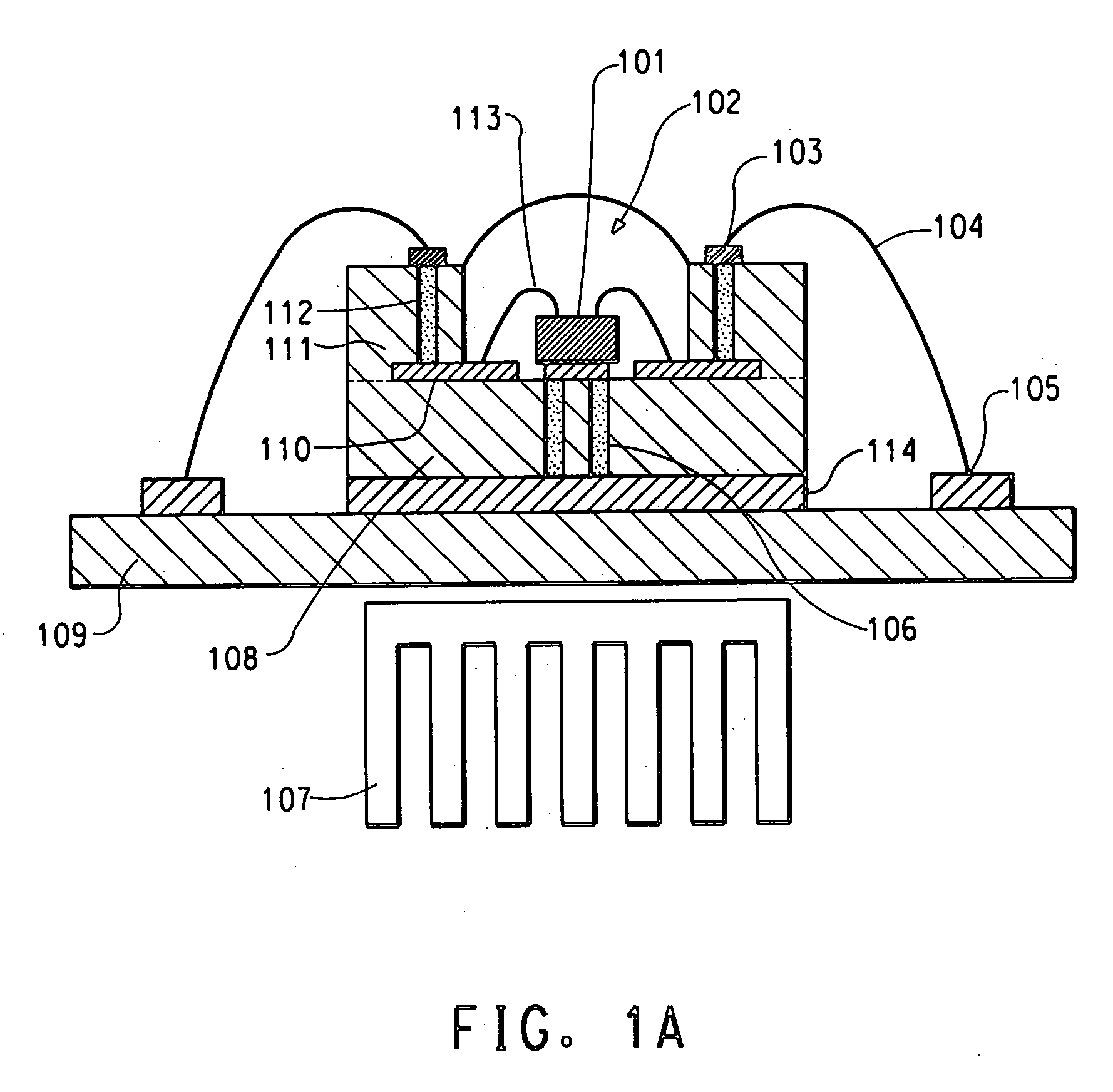

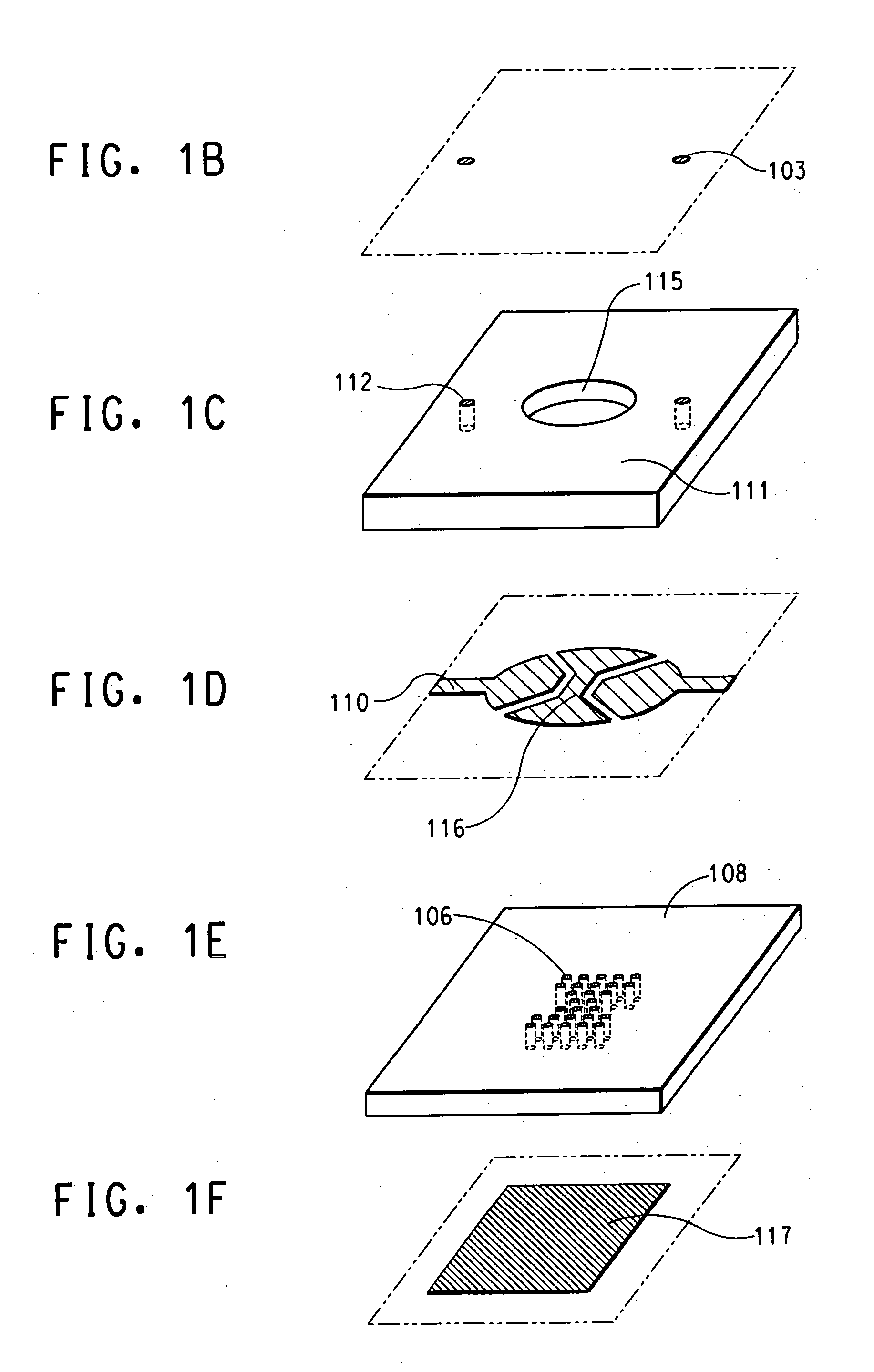

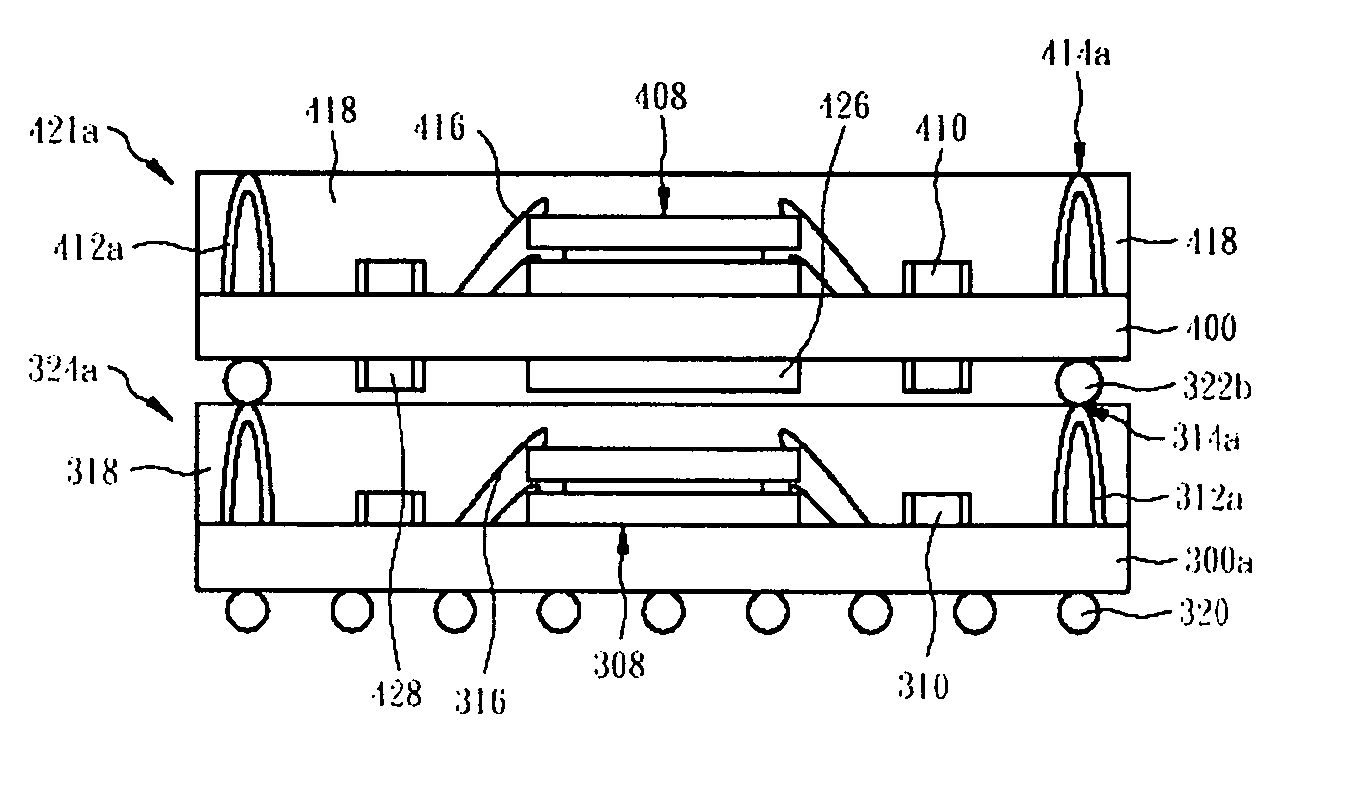

High-frequency chip packages

InactiveUS6856007B2Low costSave spaceImpedence networksSemiconductor/solid-state device detailsElectrical conductorSemiconductor chip

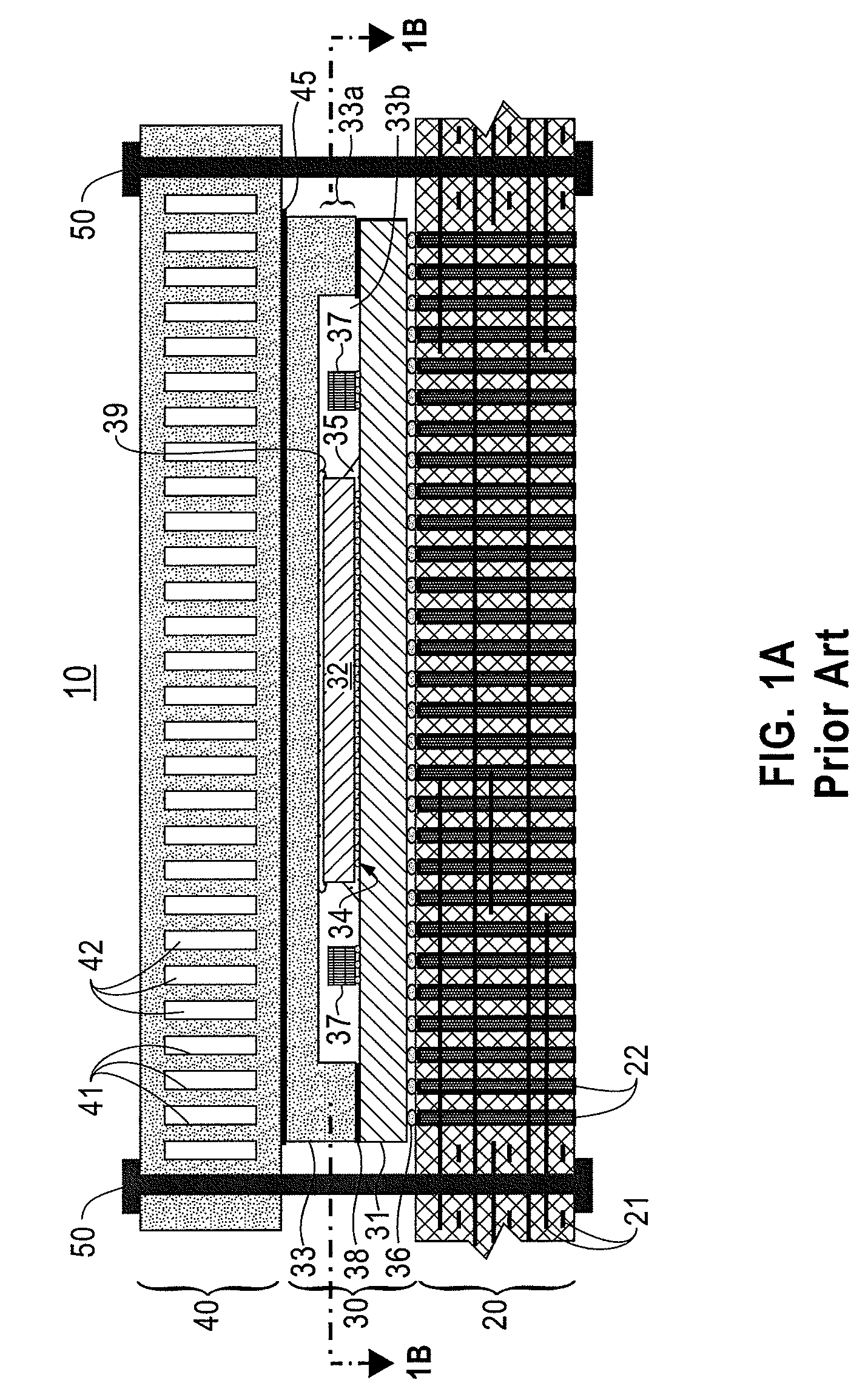

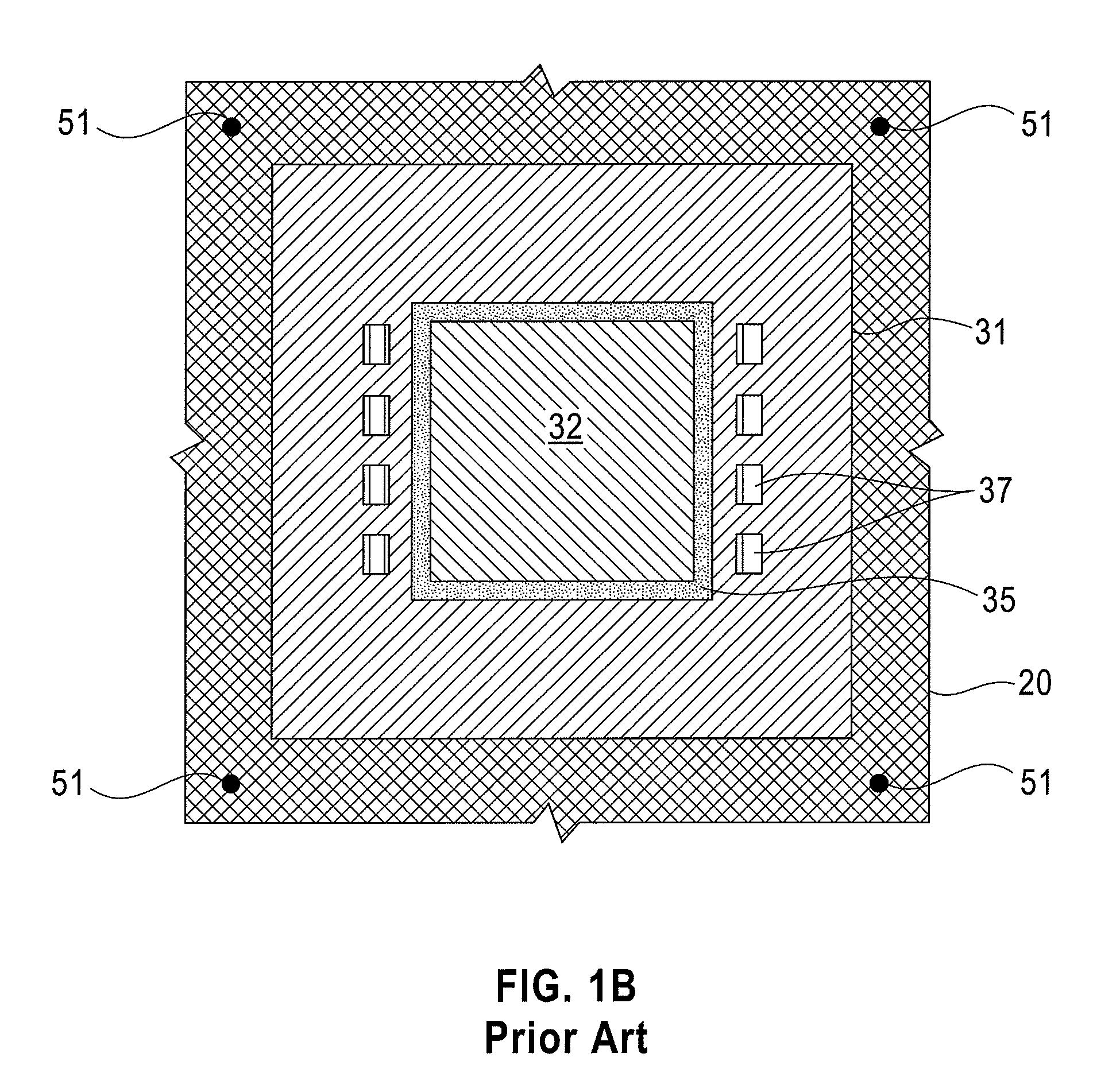

A packaged semiconductor chip includes features such as a chip carrier having a large thermal conductor which can be solder-bonded to a circuit board so as to provide enhanced thermal conductivity to the circuit board and electromagnetic shielding and a conductive enclosure which partially or completely surrounds the packaged chip to provide additional heat dissipation and shielding. The packaged unit may include both an active semiconductor chip and a passive element, desirably in the form of a chip, which includes resistors and capacitors. Inductors may be provided in whole or in part on the chip carrier. A module includes two circuits and an enclosure with a medial wall between the circuits to provide electromagnetic shielding between the circuits.

Owner:TESSERA INC

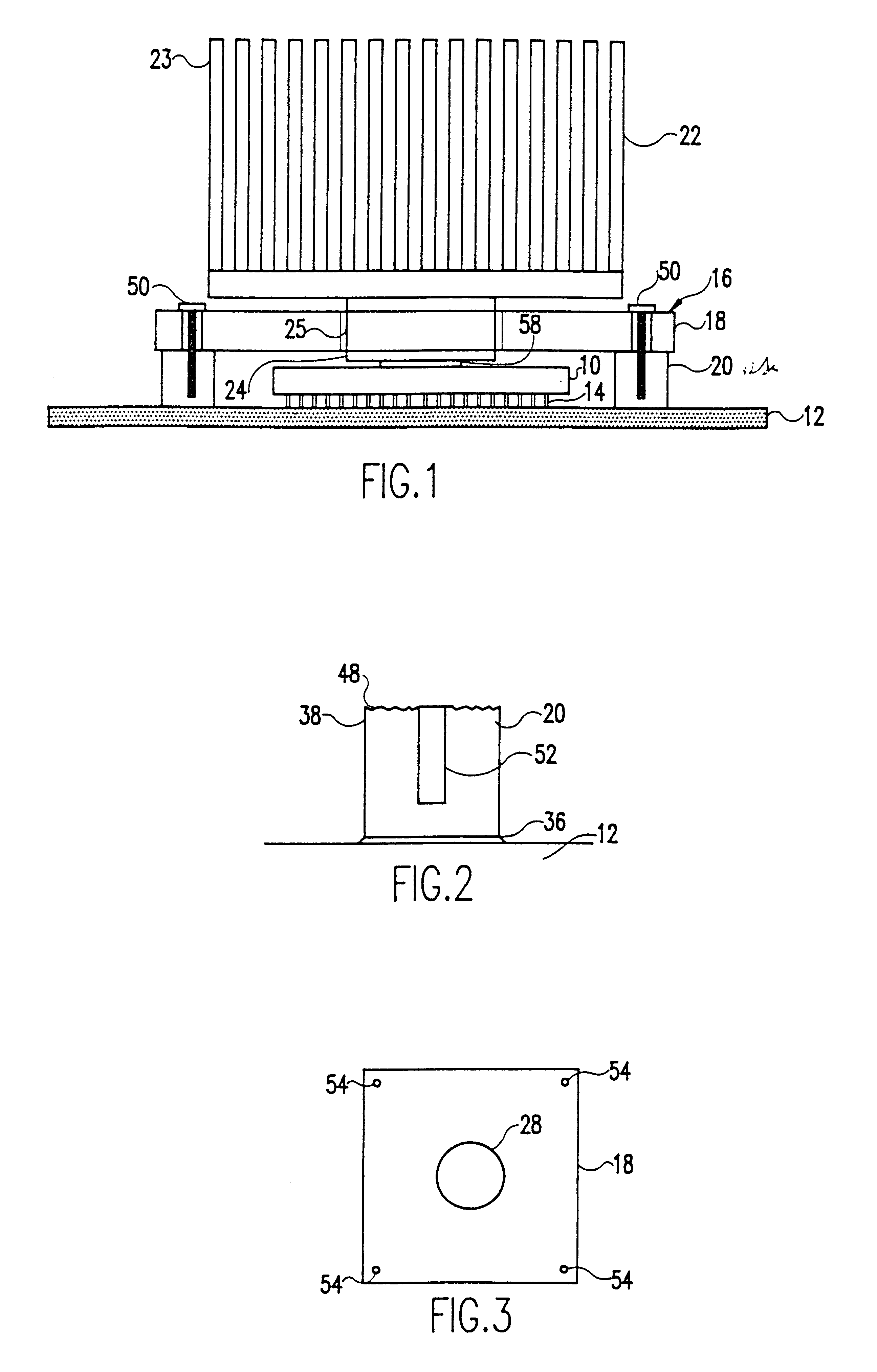

Zero force heat sink

InactiveUS6212070B1Semiconductor/solid-state device detailsSolid-state devicesSurface mountingSolder ball

A heat sink in a heat transfer relationship with a substrate such as an integrated chip, chip carrier, or other electronic package. The heat sink is connected to a frame which is connected to a printed circuit board or other suitable support on which the substrate is positioned. The heat sink, which extends through an aperture in the frame is coupled to a surface of the substrate. The heat sink is mechanically decoupled from the substrate. Large heat sinks may be thermally connected to surface mount substrates mounted using technologies such as ceramic ball or column grid arrays, plastic ball or column grid arrays, or solder balls or columns. The heat sink is attached coaxially through the aperture to the substrate. After assembly and lead / tin or other metallic surface mount interconnects are relaxed such that the substrate and is completely supported by the frame and the heat sink imparts zero or nearly zero downward force. Because the heat sink moves freely within the aperture during assembly, the heat sink package is useful for a variety of different substrates. Preferably, the frame is a plate and a plurality of studs. The plate material are selected to match the thermal expansion of the underlying support, and the stud material matched the thermal expansion of the substrate. Thus, the frame construction allows matching expansion and contraction of the assembly to the underlying substrate and support.

Owner:IBM CORP

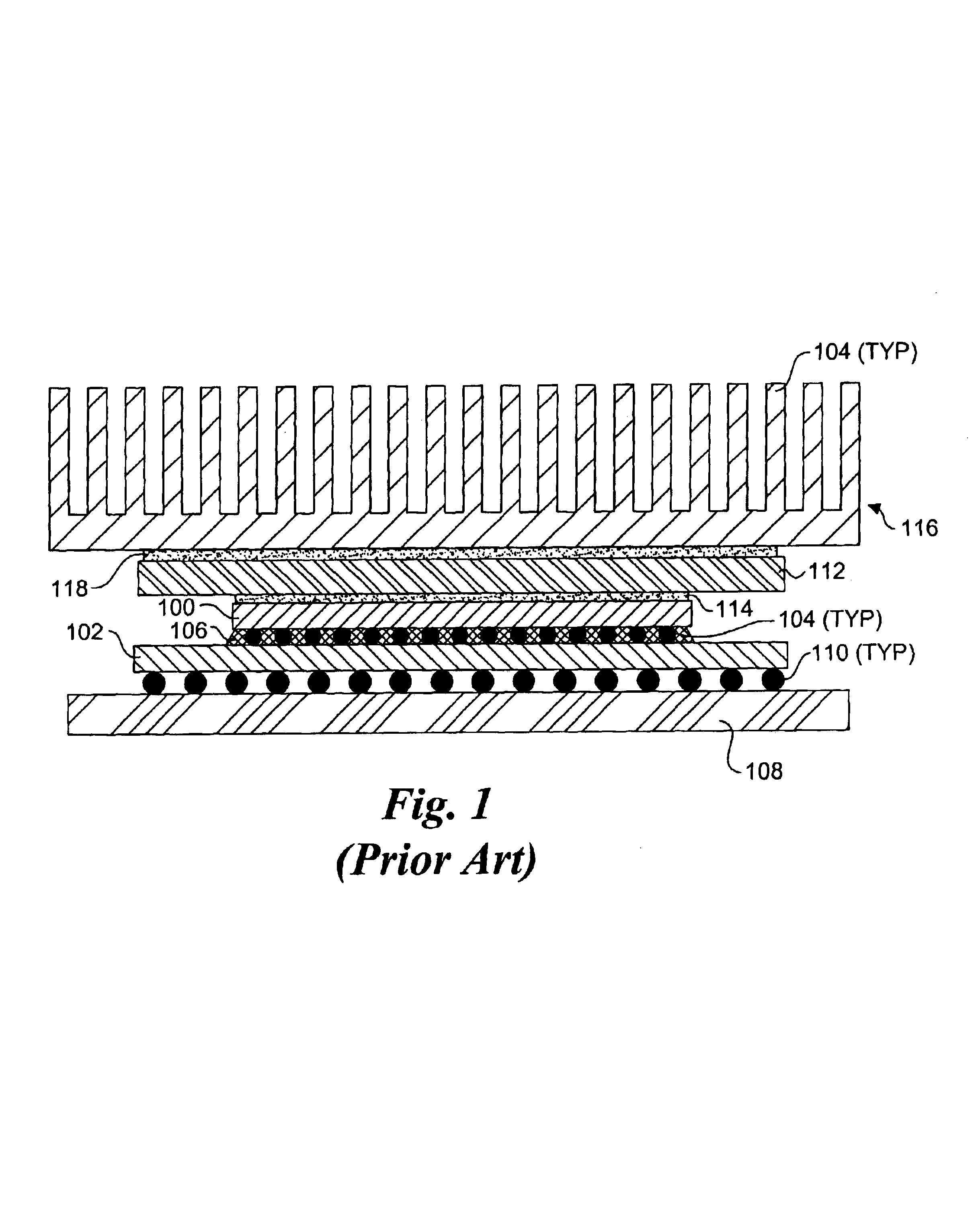

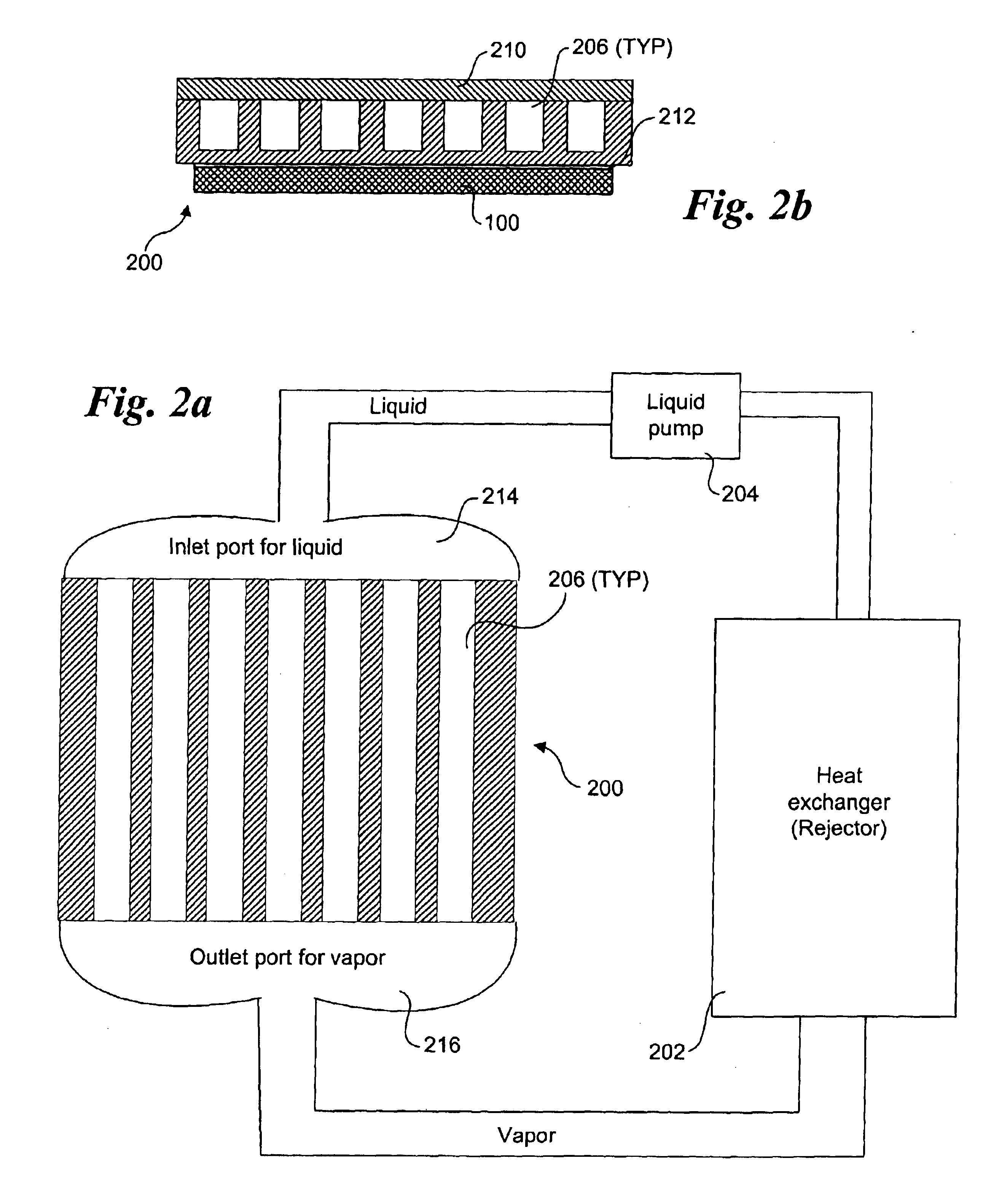

Two-phase cooling utilizing microchannel heat exchangers and channeled heat sink

InactiveUS6903929B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

Integrated circuit (IC) packages employing two-phase microchannel heat exchangers for cooling the packages' IC dies and cooling systems employing the same are disclosed. The heat exchangers include thermal masses having a plurality of microchannels formed therein. In one set of configurations, the IC die is thermally coupled to a pair of microchannel heat exchangers disposed on opposite sides of the die. Top-side microchannel heat exchangers include a thermal mass having a plurality of open microchannels having wall bases that are hermetically sealed with the top surface of the die, thus forming a plurality of closed microchannels. Alternatively, a separate microchannel heat exchanger is thermally coupled to an IC die and operatively coupled to the IC die via coupling to a substrate on which the IC die is mounted. Bottom-side heat exchangers include substrates and chip carriers having microchannels formed therethrough that are thermally coupled to the IC die. The cooling systems employ a plurality of microchannel heat exchangers to cool selected electronic components.

Owner:TAHOE RES LTD

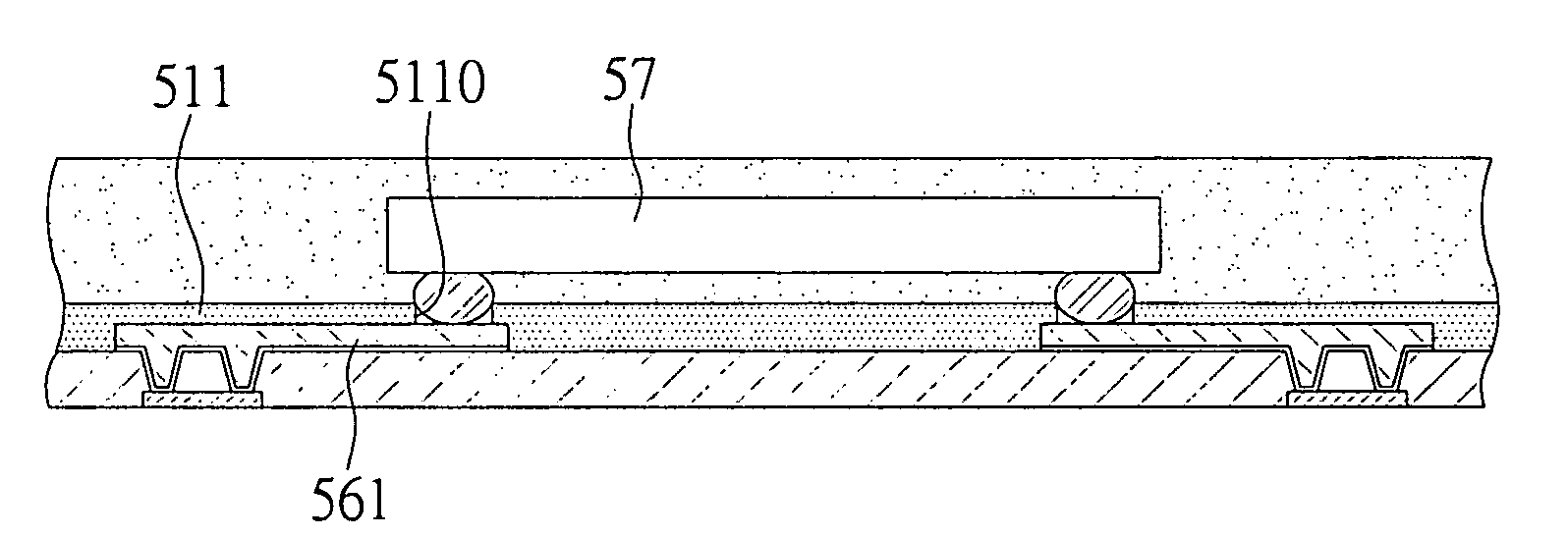

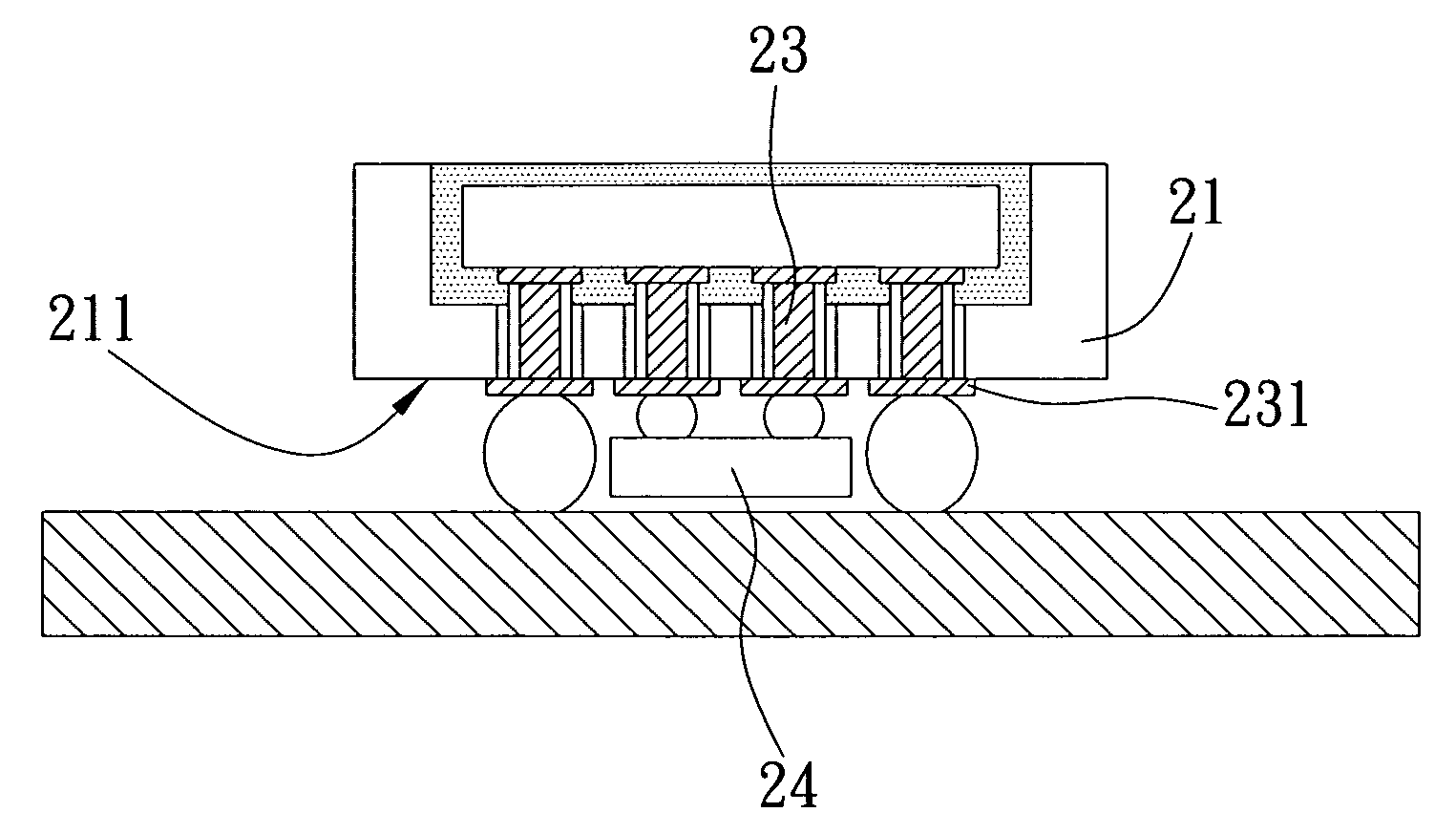

Method for manufacturing stacked package structure

InactiveUS20070254406A1Reduce areaIncrease productionSolid-state devicesSemiconductor/solid-state device manufacturingElectrical connectionEngineering

Owner:ADVANCED SEMICON ENG INC

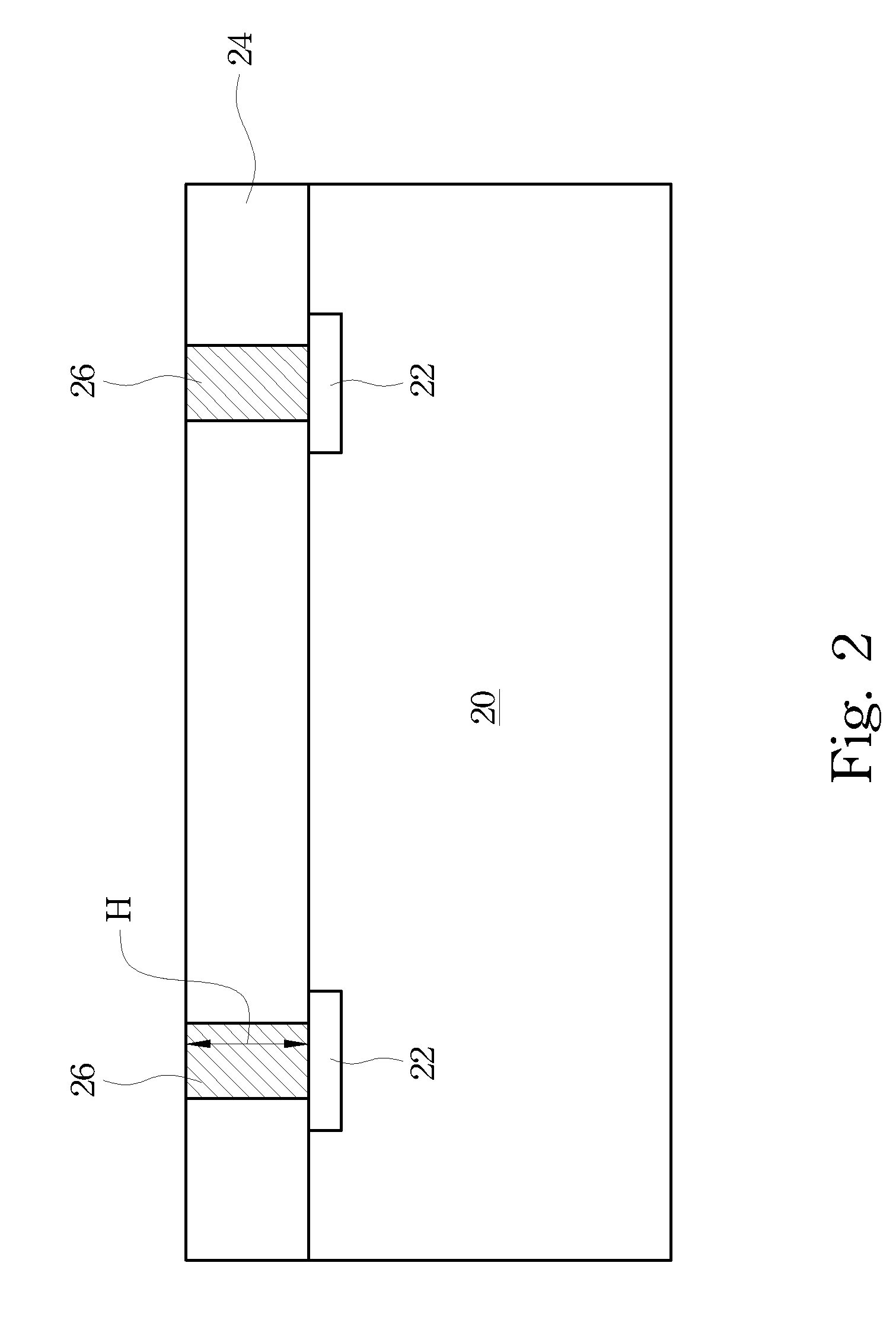

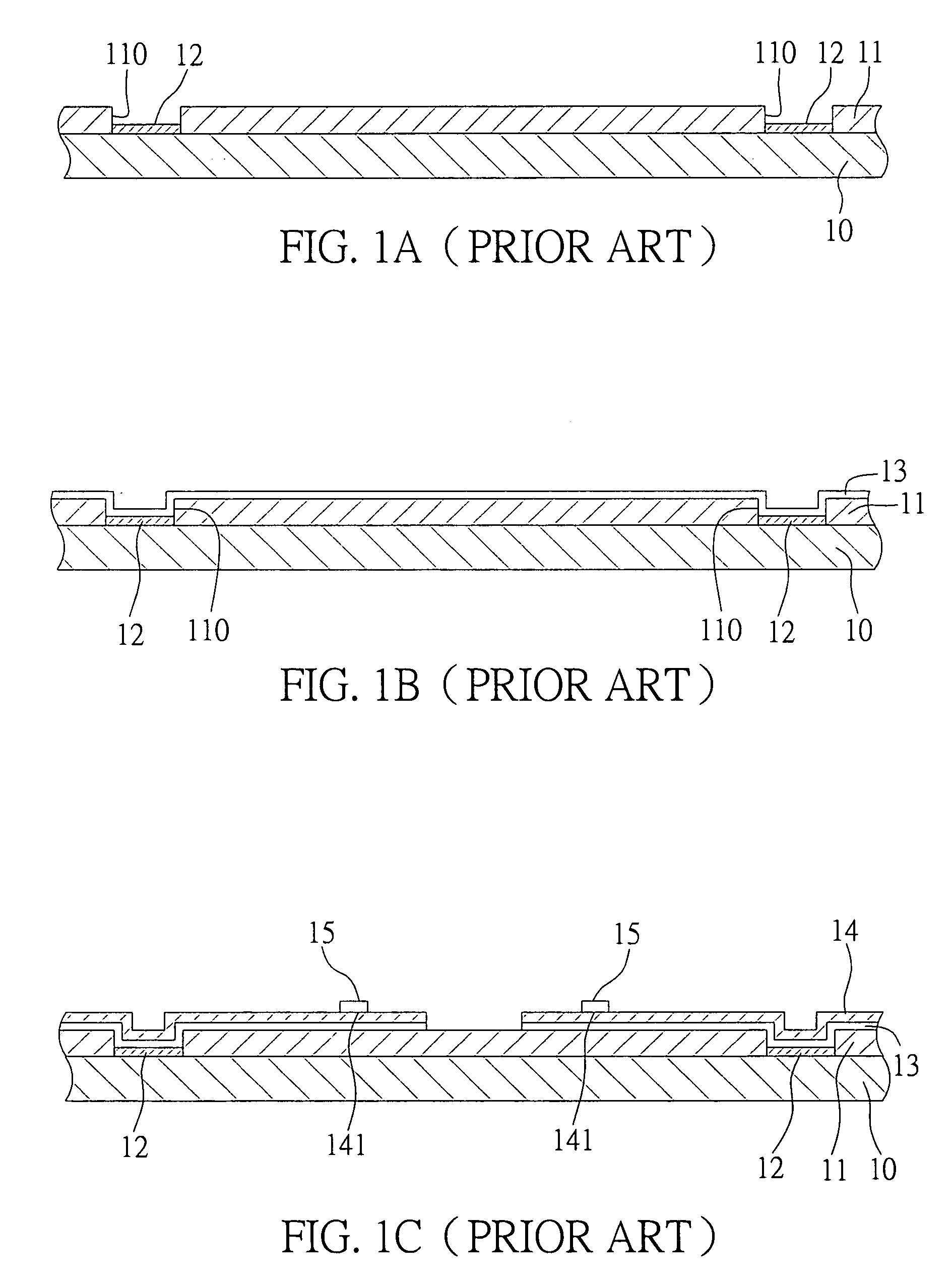

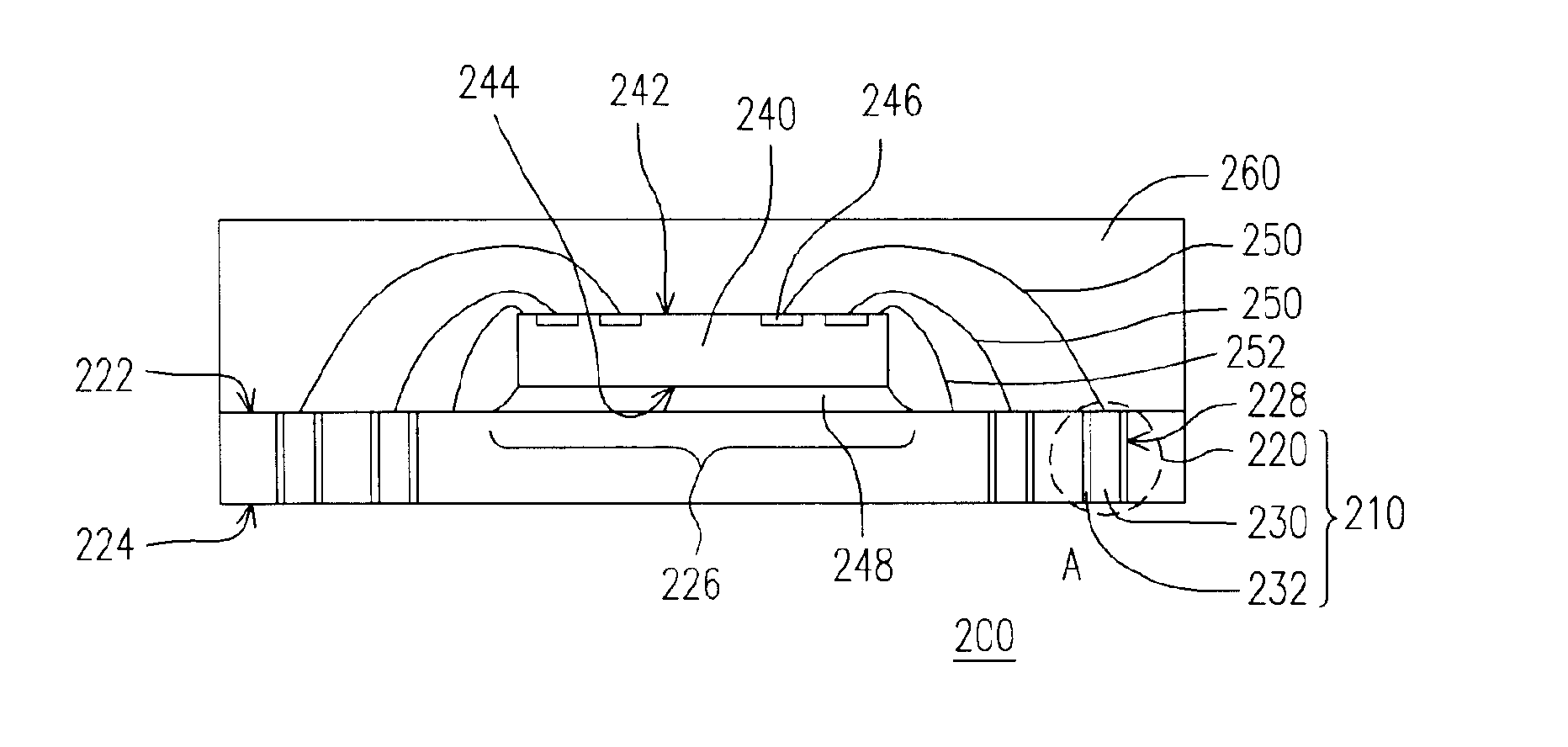

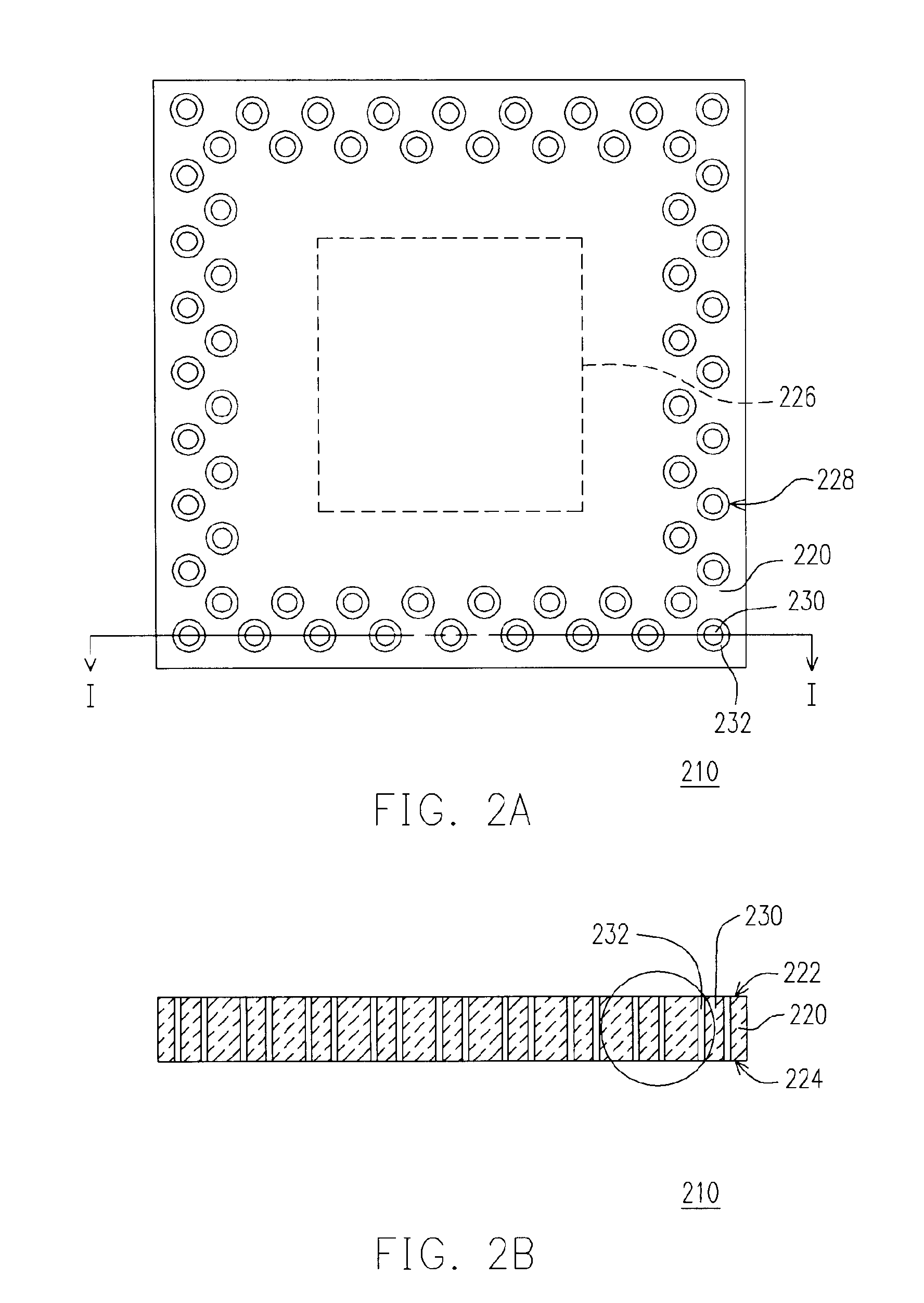

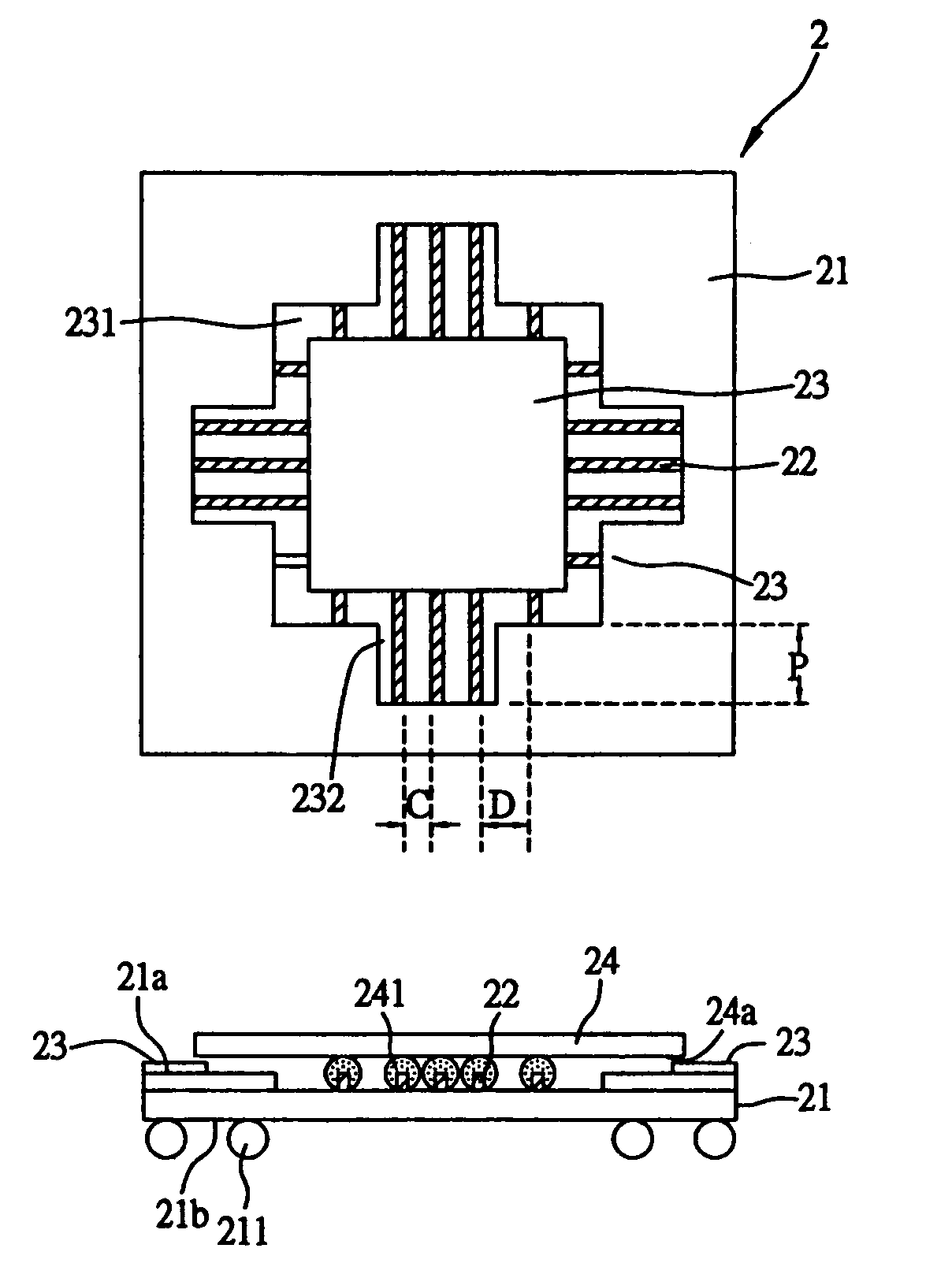

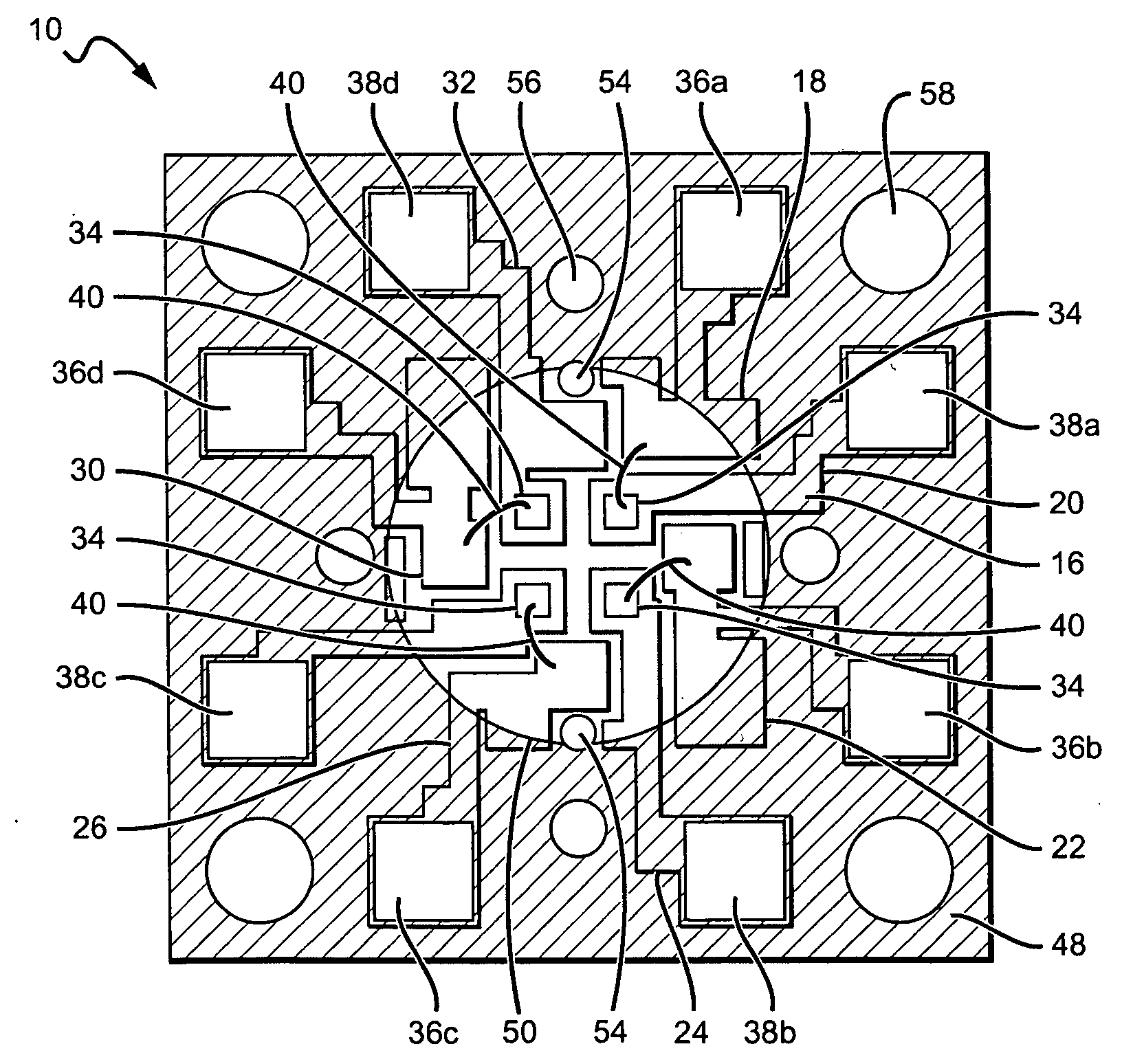

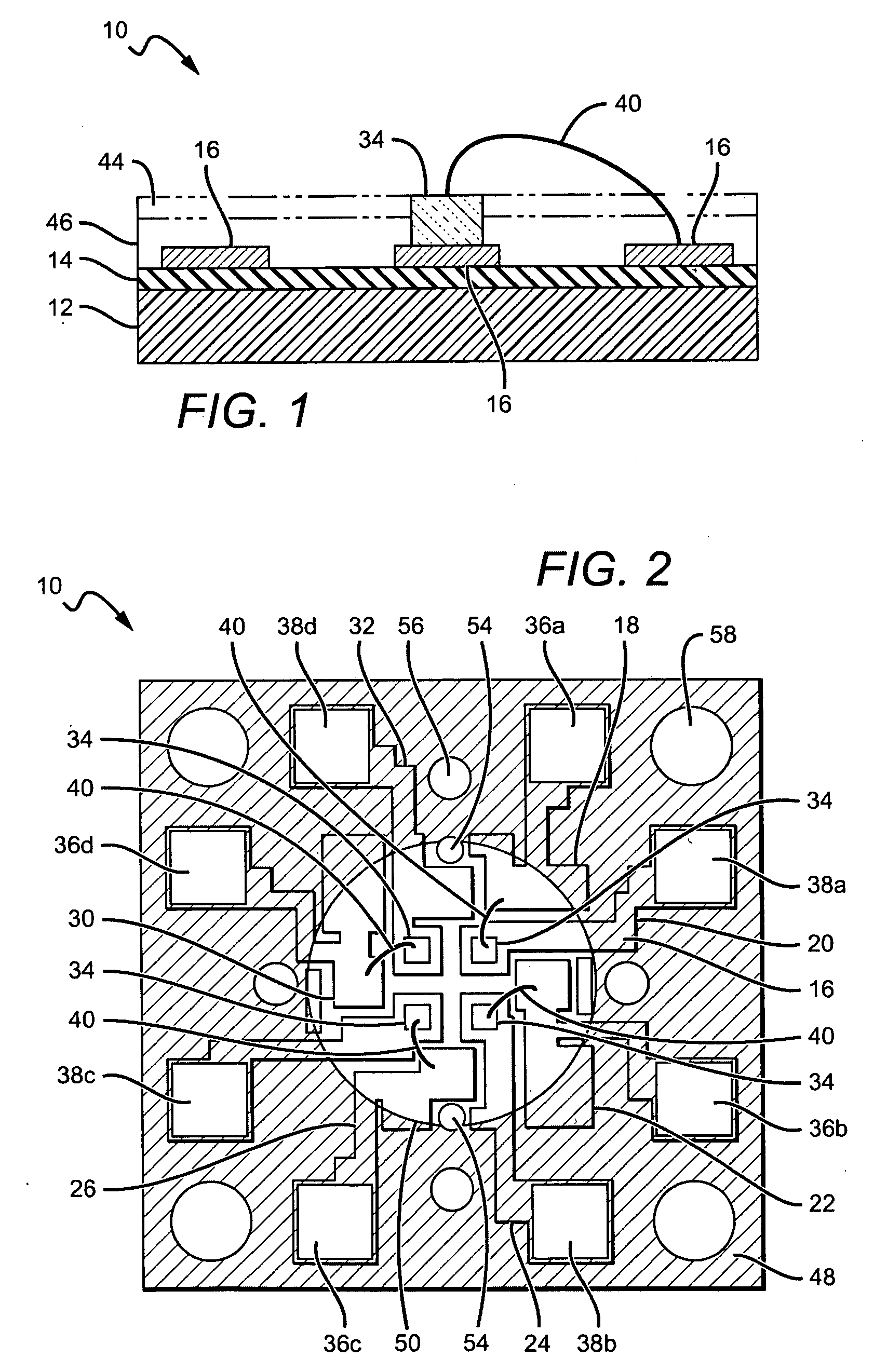

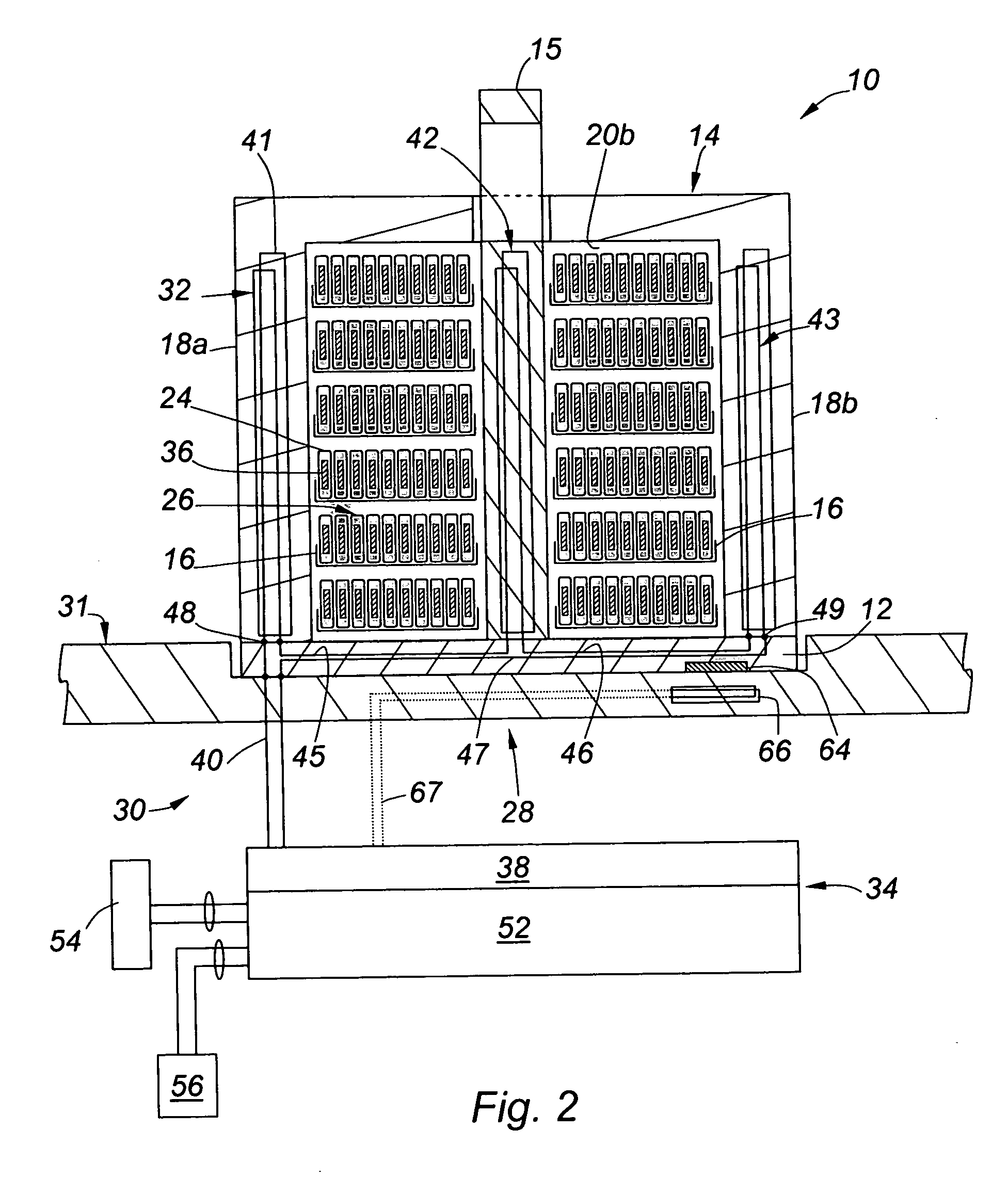

Chip carrier for semiconductor chip

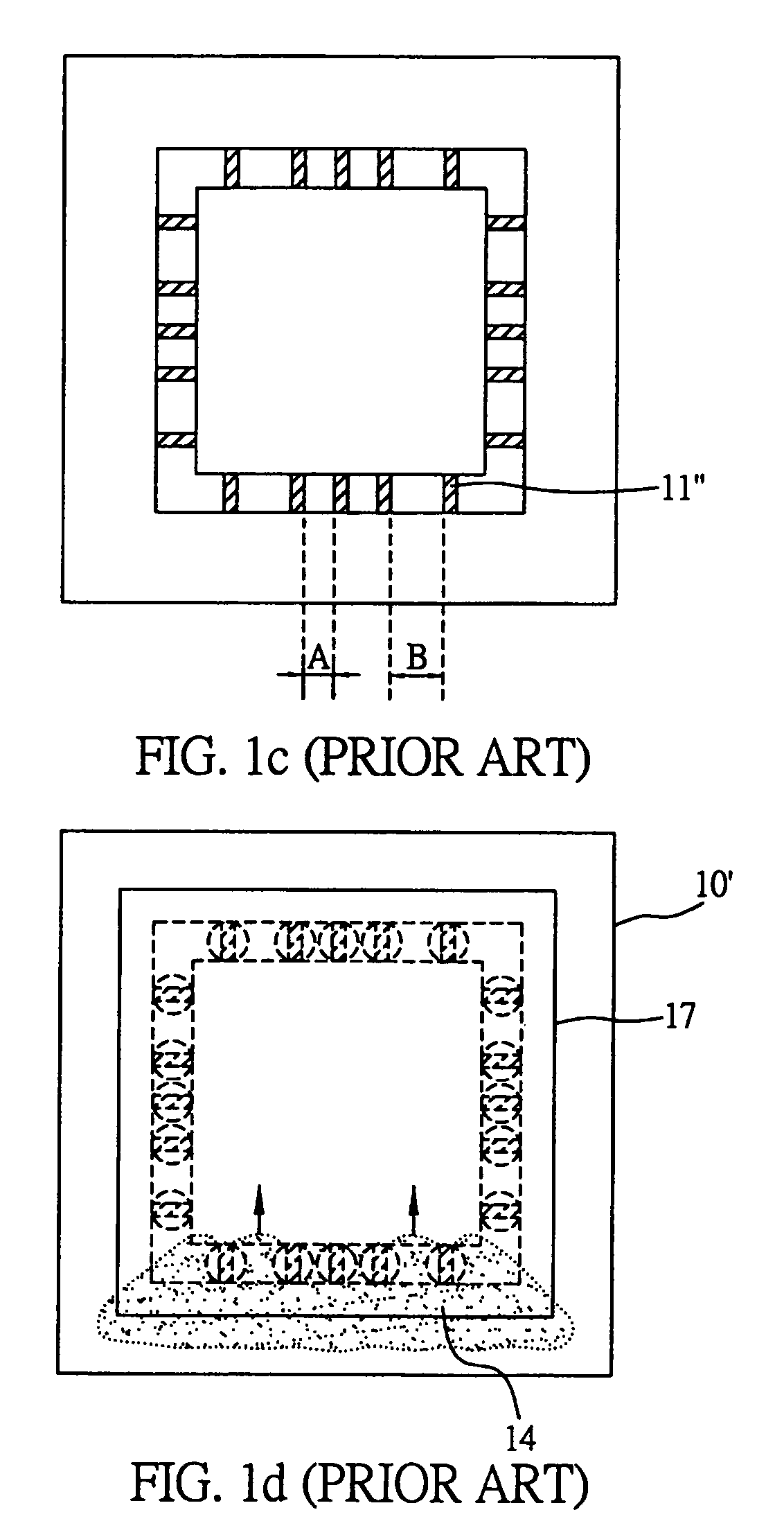

ActiveUS7102239B2Reduce formationInhibition effectSemiconductor/solid-state device detailsSolid-state devicesSolder maskSemiconductor chip

A chip carrier for a semiconductor chip is provided. A plurality of solder pads for bump soldering are formed on a chip mounting surface of the chip carrier, to allow a flip chip to be mounted and electrically connected to the chip carrier. A solder mask layer is formed on the chip carrier, wherein a plurality of openings are provided in the solder mask layer to expose the solder pads, and an outwardly opening extended portion is formed respectively from the openings corresponding to the solder pads having a relatively narrower pitch therebetween, so as to prevent formation of voids during an underfill process for filing a gap between the flip chip and the chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Castellation wafer level packaging of integrated circuit chips

InactiveUS6855572B2Characteristic is reliableEasy to produceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSealant

Systems and methods for packaging integrated circuit chips in castellation wafer level packaging are provided. The active circuit areas of the chips are coupled to castellation blocks and, depending on the embodiment, input / output pads. The castellation blocks and input / output pads are encapsulated and held in place by an encapsulant. When the devices are being fabricated, the castellation blocks and input / output pads are sawed through. If necessary, the wafer portion on which the devices are fabricated may be thinned. The packages may be used as a leadless chip carrier package or may be stacked on top of one another. When stacked, the respective contacts of the packages are preferably coupled. Data may be written to, and received from, packaged chips when a chip is activated. Chips may be activated by applying the appropriate signal or signals to the appropriate contact or contacts.

Owner:MICRON TECH INC

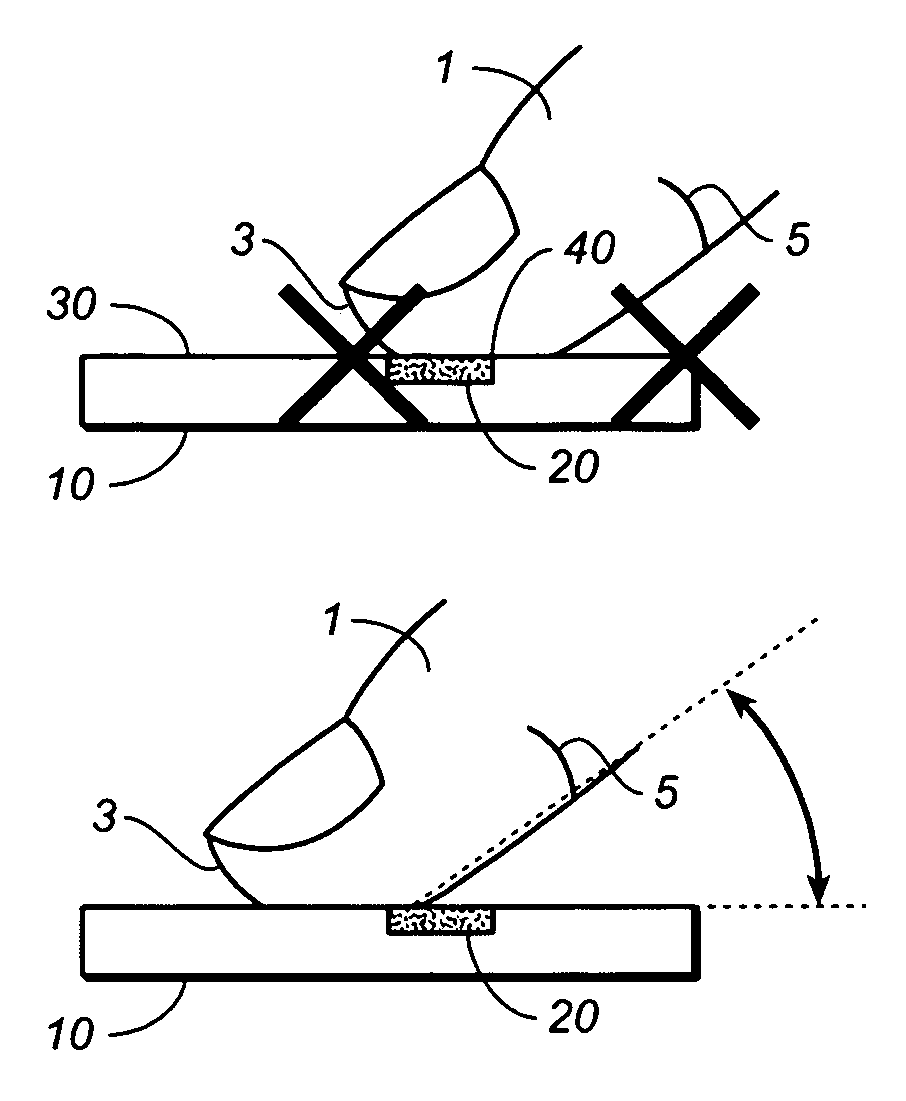

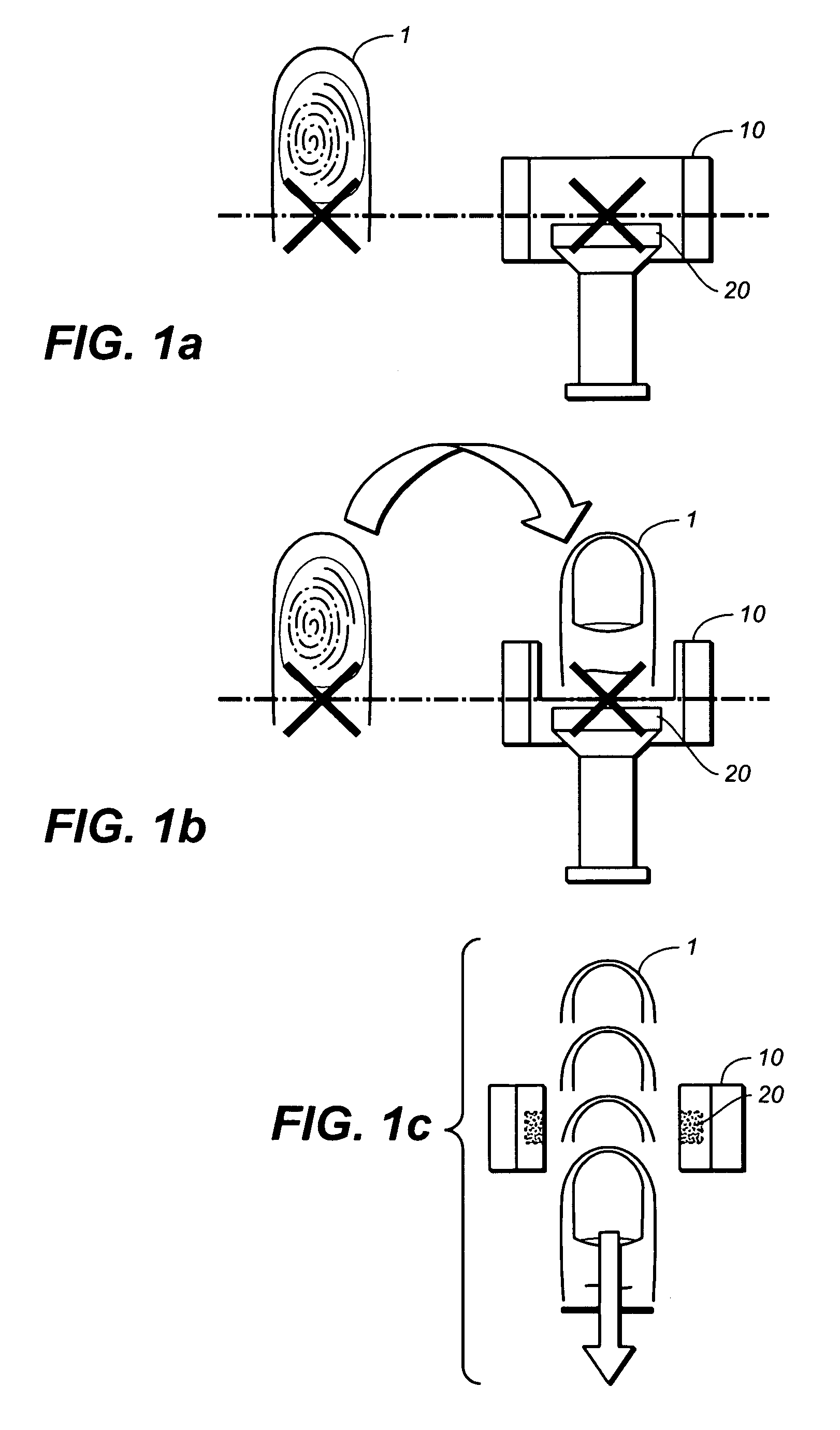

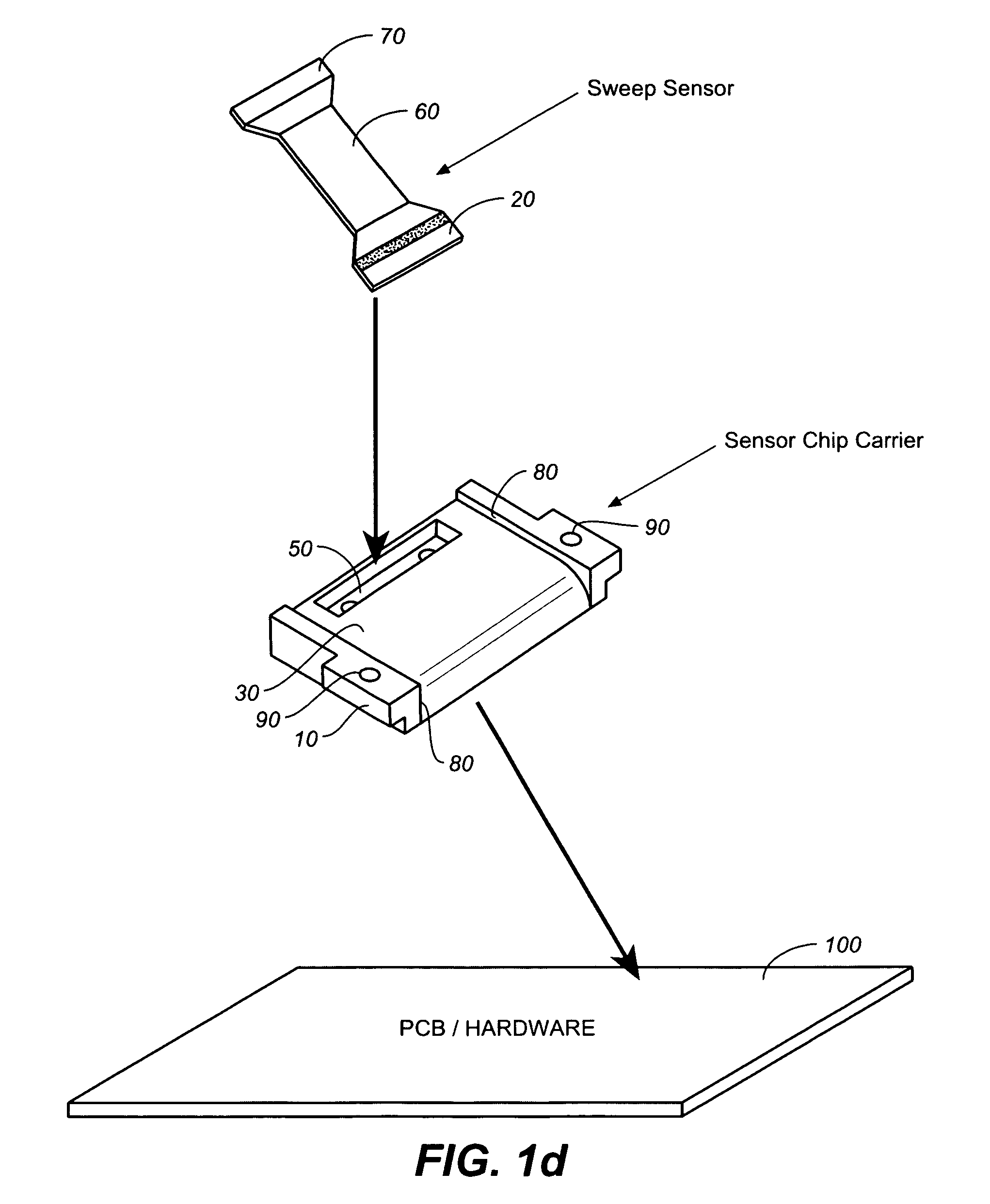

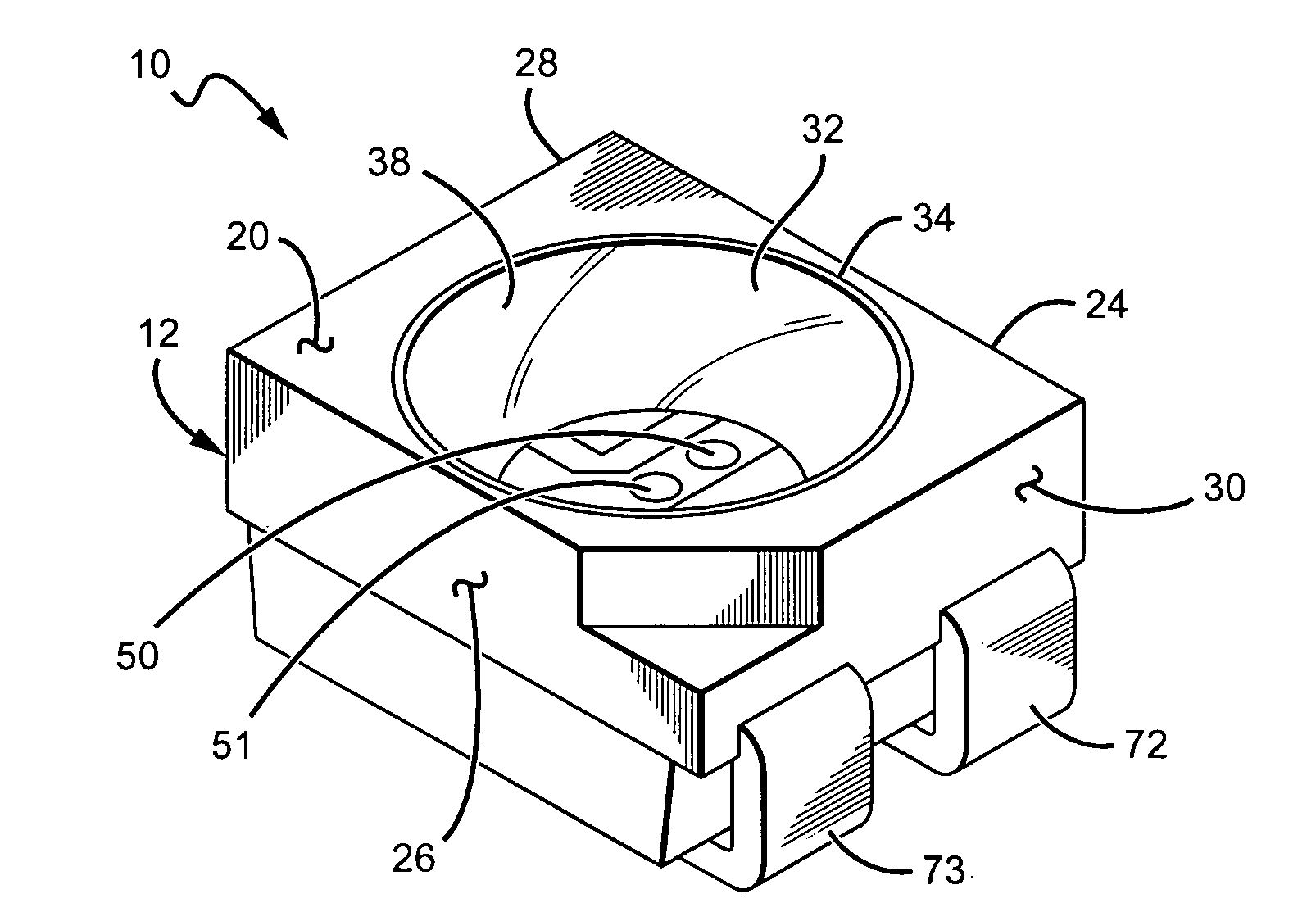

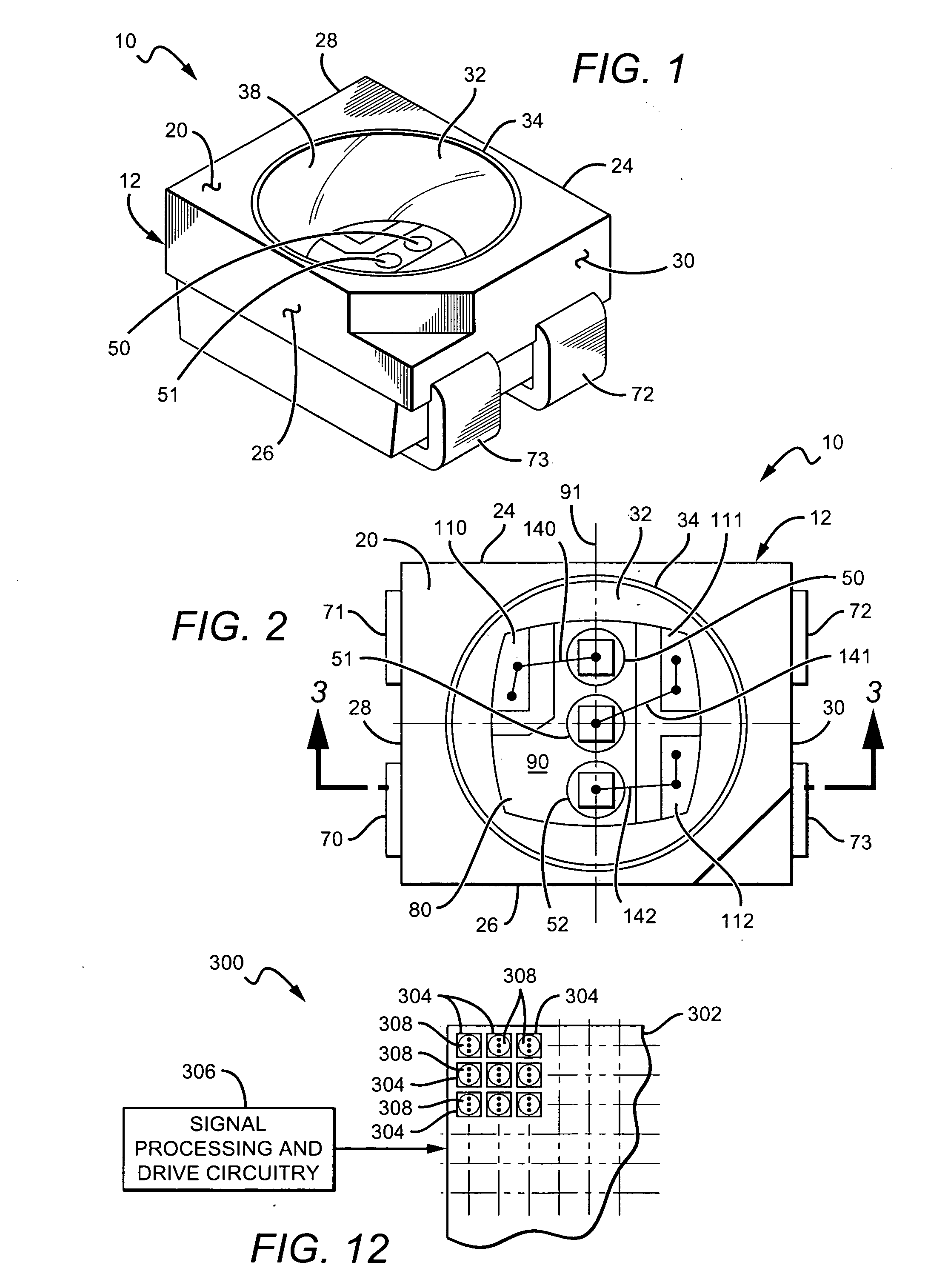

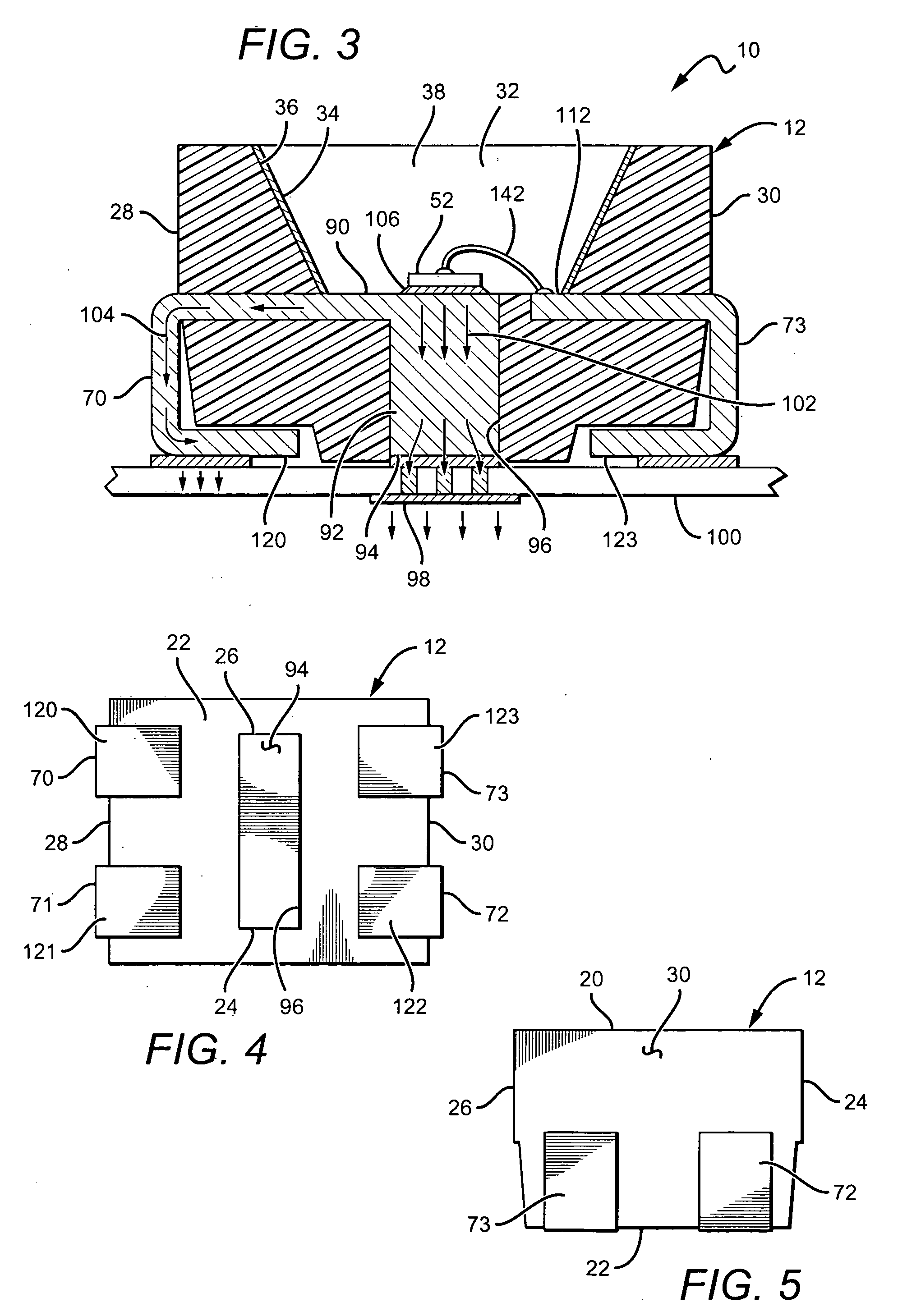

Chip carrier for fingerprint sensor

ActiveUS7146029B2Assisted movementEasy alignmentCharacter and pattern recognitionLong axisEngineering

A carrier for a sweep-type fingerprint sensor and a method of operation are disclosed. The carrier has a recess for receiving and mounting the fingerprint sensor and one or more tactile elements for assisting the user in positioning a finger, and in correctly moving the finger across the sensor being read. In one embodiment the tactile element consists of an oval ridge, or a portion thereof, defining a major axis which is lies in the sweep direction. The tip of the finger is initially positioned in the arcuate portion of the oval ridge and is moved across the sensor, generally along the axis of the oval. The side walls of the ridge assist the user in correctly moving the finger across the sensor.

Owner:FUJITSU SEMICON LTD

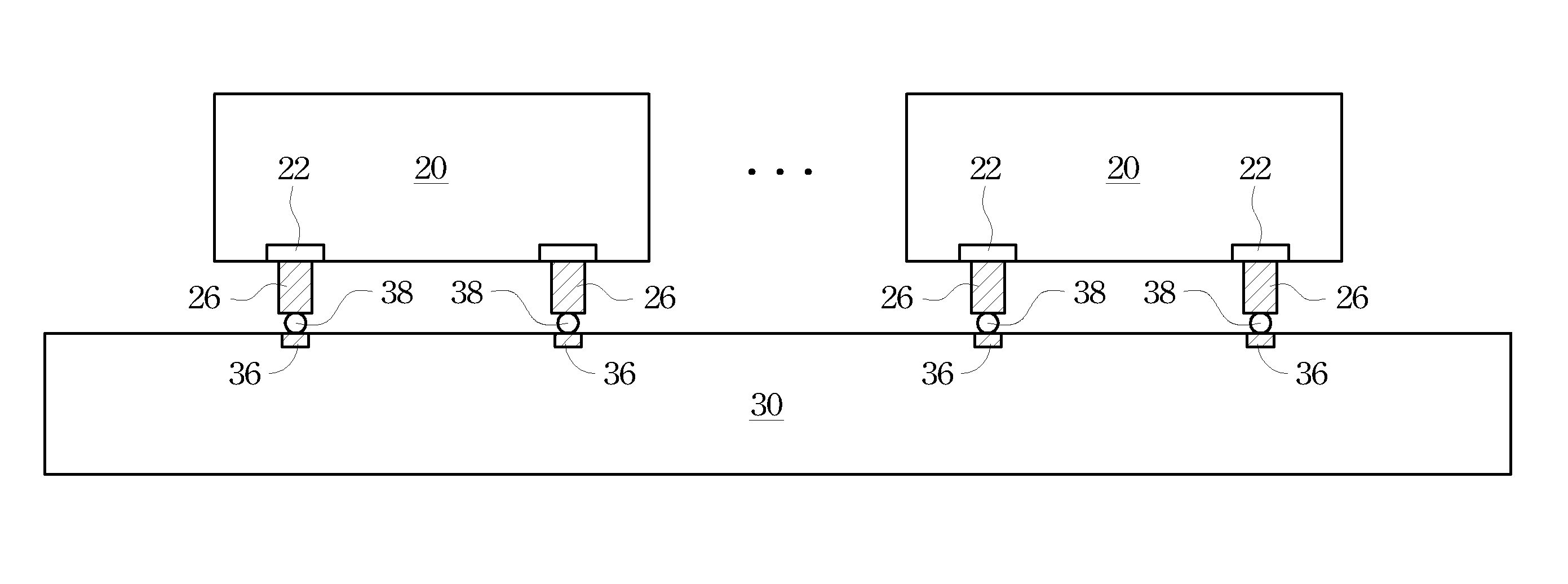

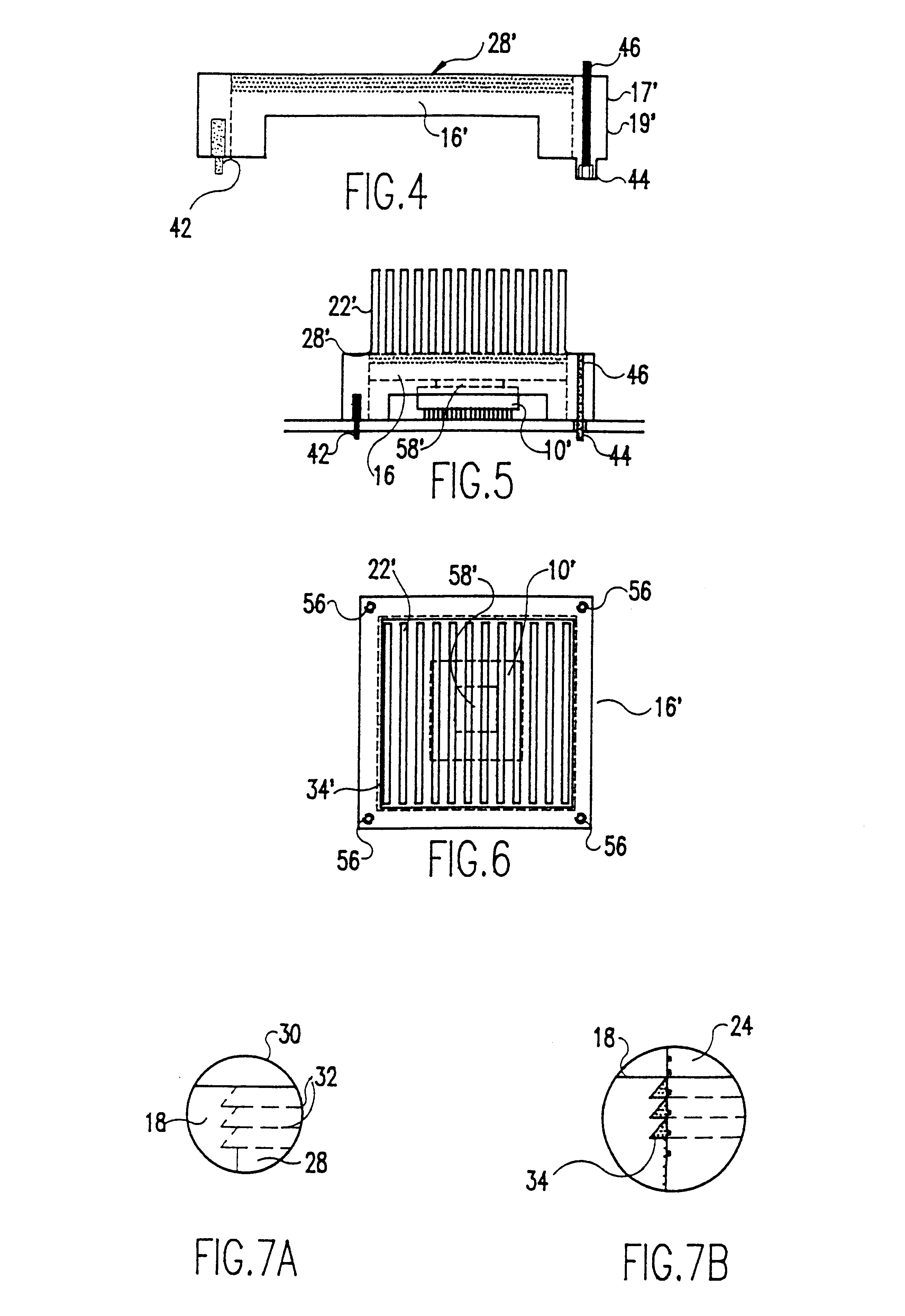

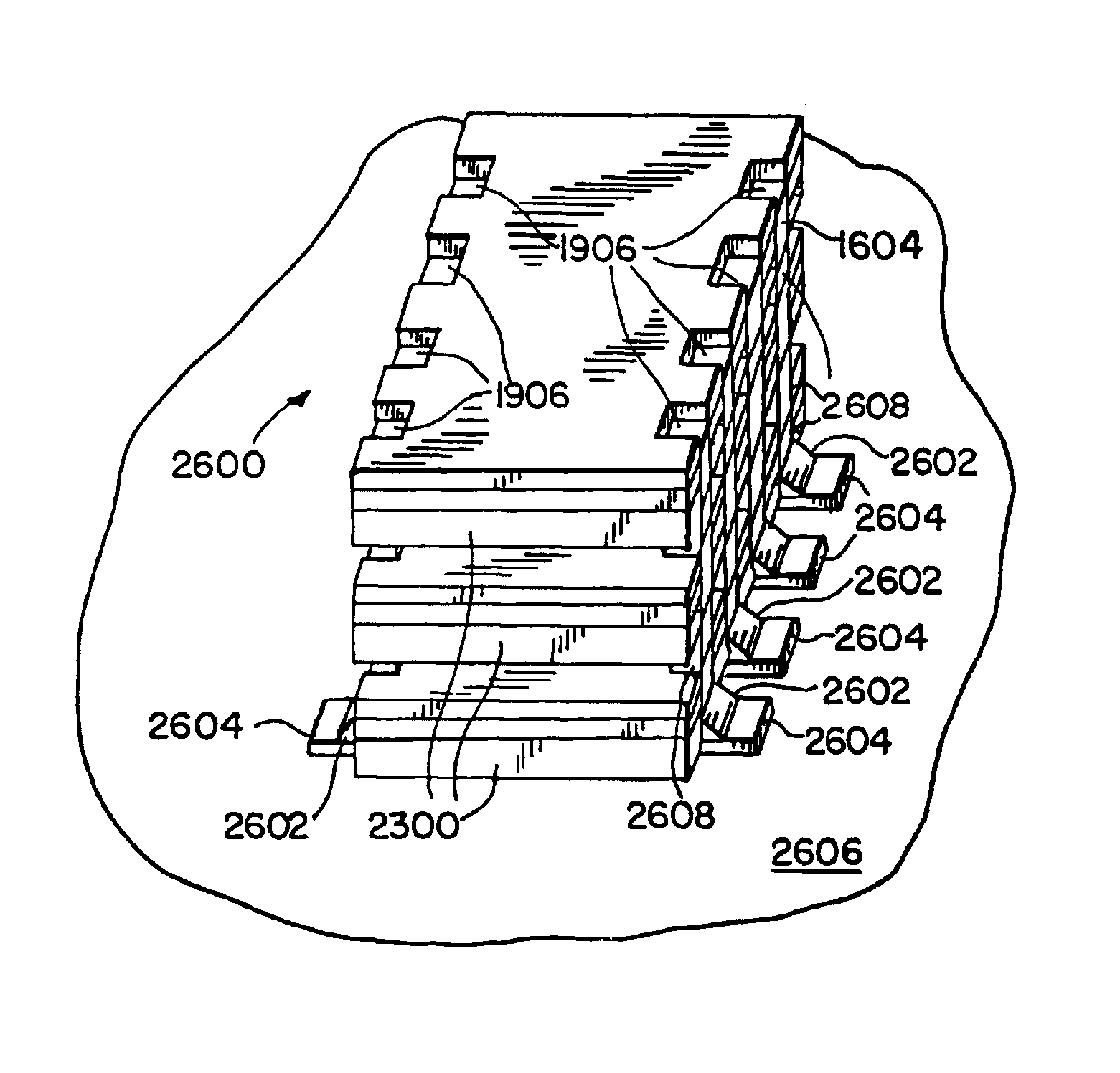

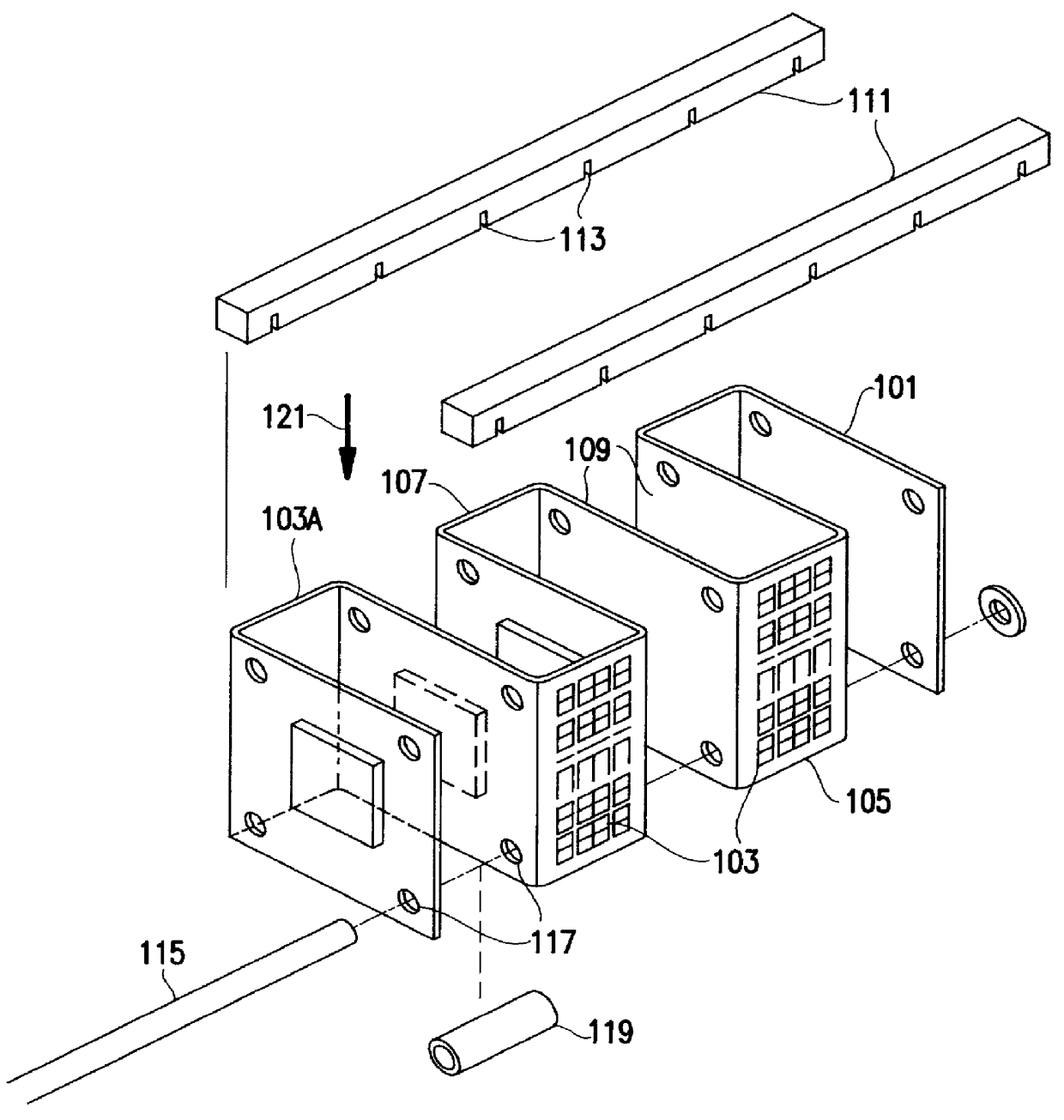

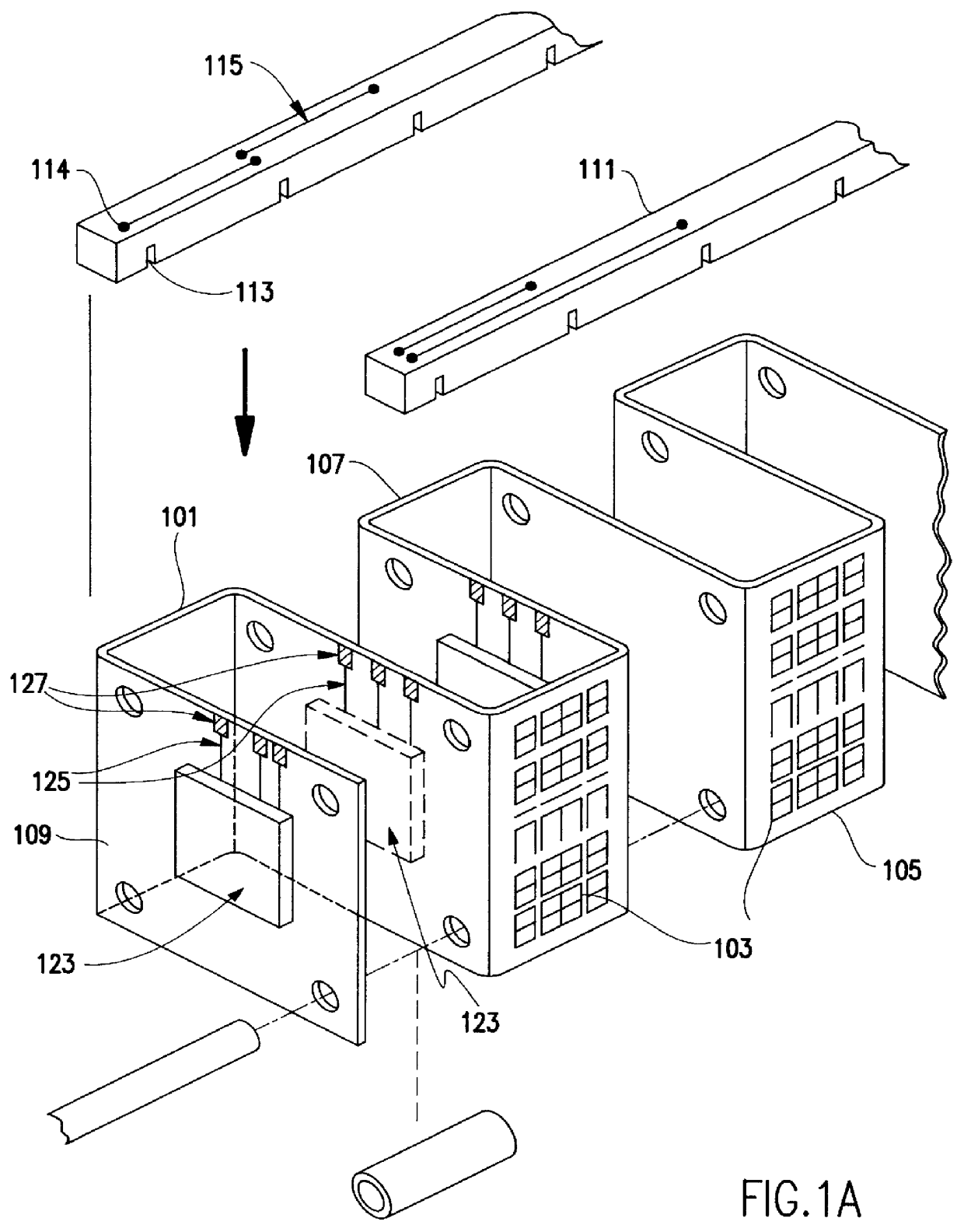

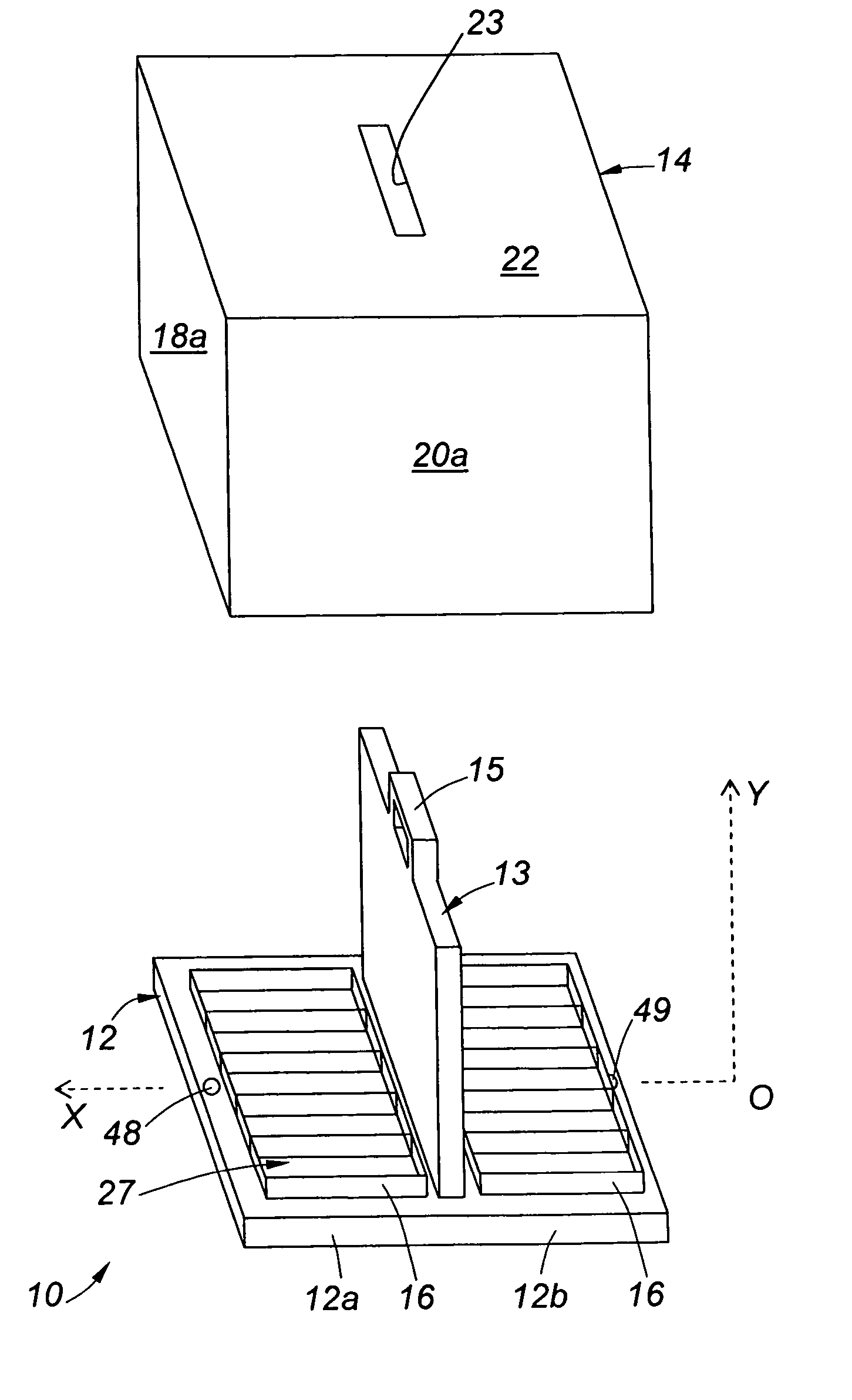

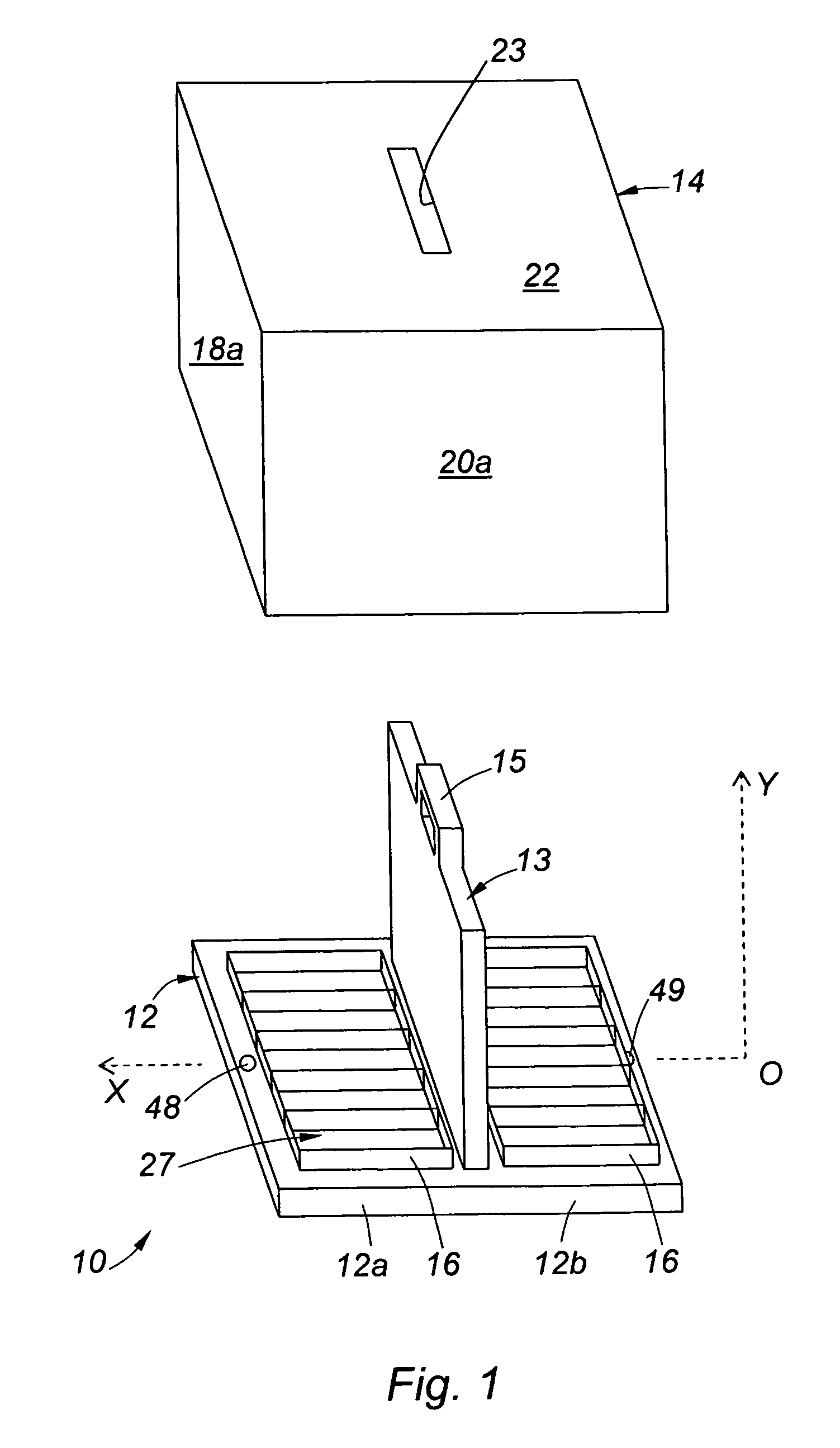

Free standing, three dimensional, multi-chip, carrier package with air flow baffle

InactiveUS6061245ARun fastElectrically conductive connectionsSemiconductor/solid-state device detailsEngineeringChip carrier

An efficient cooling mechanism for a multi-chip carrier can be provided while conserving board surface area. Flexible circuitized material is used to form multi-chip carriers with air baffle capability. The flex is folded or curved into the desired shape and held in position with a support structure. Bonding sites for chips are located on regions through the carrier. Shapes which provide air baffle capabilities include coils, spring-like coils and serpentines.

Owner:IBM CORP

Multi-chip light emitting diode modules

ActiveUS20100117099A1Increased luminous flux outputImprove cooling effectLight absorption dielectricsSemiconductor/solid-state device detailsLuminous fluxReflective layer

A multi-chip lighting module is disclosed for maximizing luminous flux output and thermal management. In one embodiment, a multi-chip module device comprises a substantially thermally dissipative substrate with a dark insulating layer deposited on a surface of the substrate. A plurality of light emitting devices is also provided. An electrically conductive layer is applied to a surface of the substrate, with the conductive layer comprising a plurality of chip carrier parts each having a surface for carrying at least one of the light emitting devices. Each light emitting device has a first and a second electrical terminal. A reflective layer is also provided that at least partially covers the conductive layer.

Owner:CREELED INC

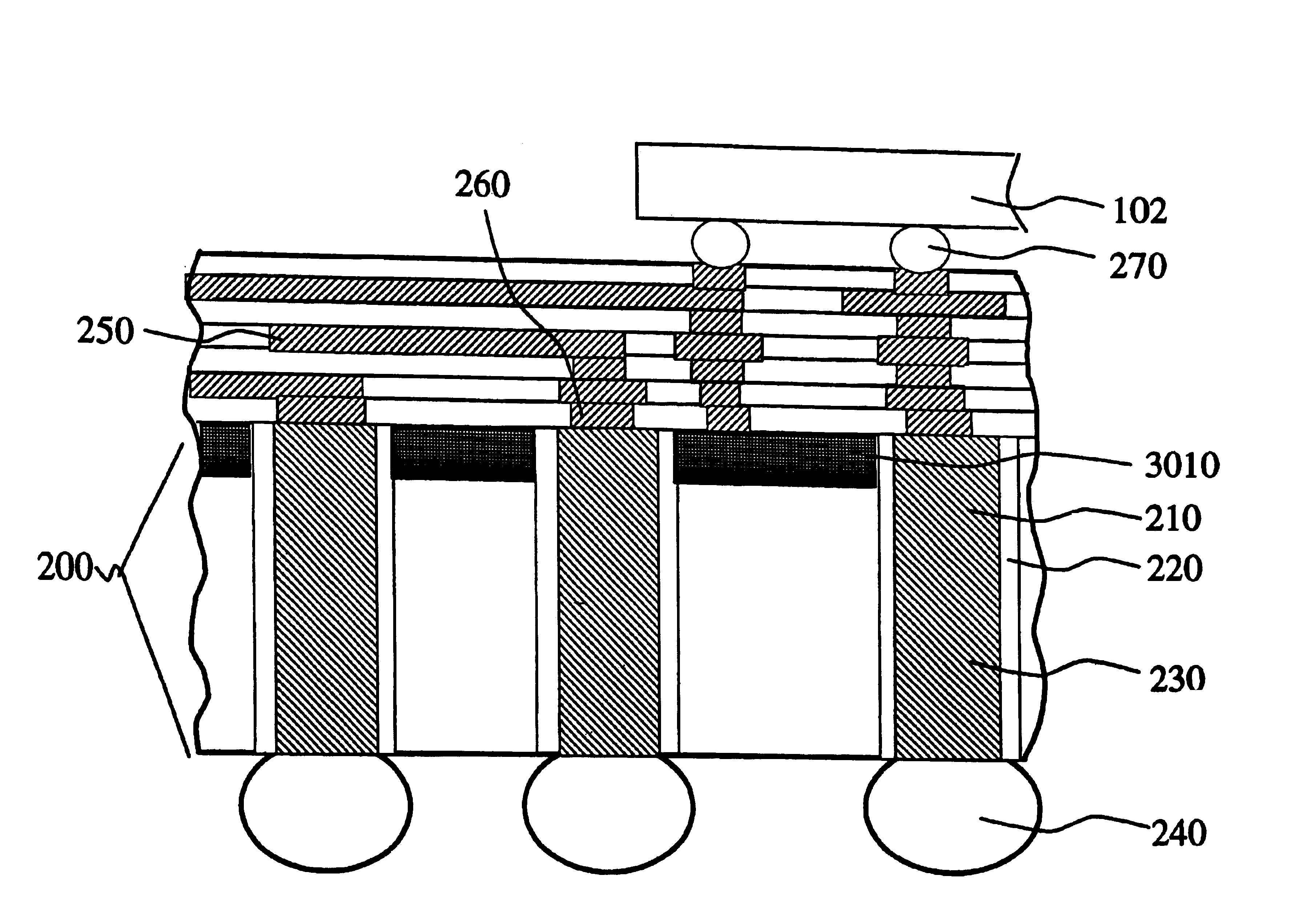

Multi-chip stack structure having through silicon via and method for fabrication the same

InactiveUS20090032928A1Simplify the manufacturing processReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesChip stackingContamination

The invention discloses a multi-chip stack structure having through silicon via and a method for fabricating the same. The method includes: providing a wafer having a plurality of first chips; forming a plurality of holes on a first surface of each of the first chips and forming metal posts and solder pads corresponding to the holes so as to form a through silicon via (TSV) structure; forming at least one groove on a second surface of each of the first chips to expose the metal posts of the TSV structure so as to allow at least one second chip to be stacked on the first chip, received in the groove and electrically connected to the metal posts exposed from the groove; filling the groove with an insulating material for encapsulating the second chip; mounting conductive elements on the solder pads of the first surface of each of the first chips and singulating the wafer; and mounting and electrically connecting the stacked first and second chips to a chip carrier via the conductive elements. The wafer, which is not totally thinned but includes a plurality of first chips, severs a carrying purpose during the fabrication process and thereby solves problems, namely a complicated process, high cost, and adhesive layer contamination, facing the prior art that entails repeated use of a carrier board and an adhesive layer for vertically stacking a plurality of chips and mounting the stacked chips on a chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Low temperature co-fired ceramic (LTCC) tape compositions, light emitting diode (LED) modules, lighting devices and method of forming thereof

InactiveUS7550319B2Extended service lifeSemiconductor/solid-state device detailsCeramicsEffect lightDisplay device

The present invention provides LTCC (low temperature co-fired ceramic) tape compositions and demonstrates the use of said LTCC tape(s) in the formation of Light-Emitting Diode (LED) chip carriers and modules for various lighting applications. The present invention also provides for the use of (LTCC) tape and LED modules in the formation of lighting devices including, but not limited to, LED devices, High Brightness (HB) LED backlights, display-related light sources, automotive lighting, decorative lighting, signage and advertisement lighting, and information display lighting.

Owner:EI DU PONT DE NEMOURS & CO

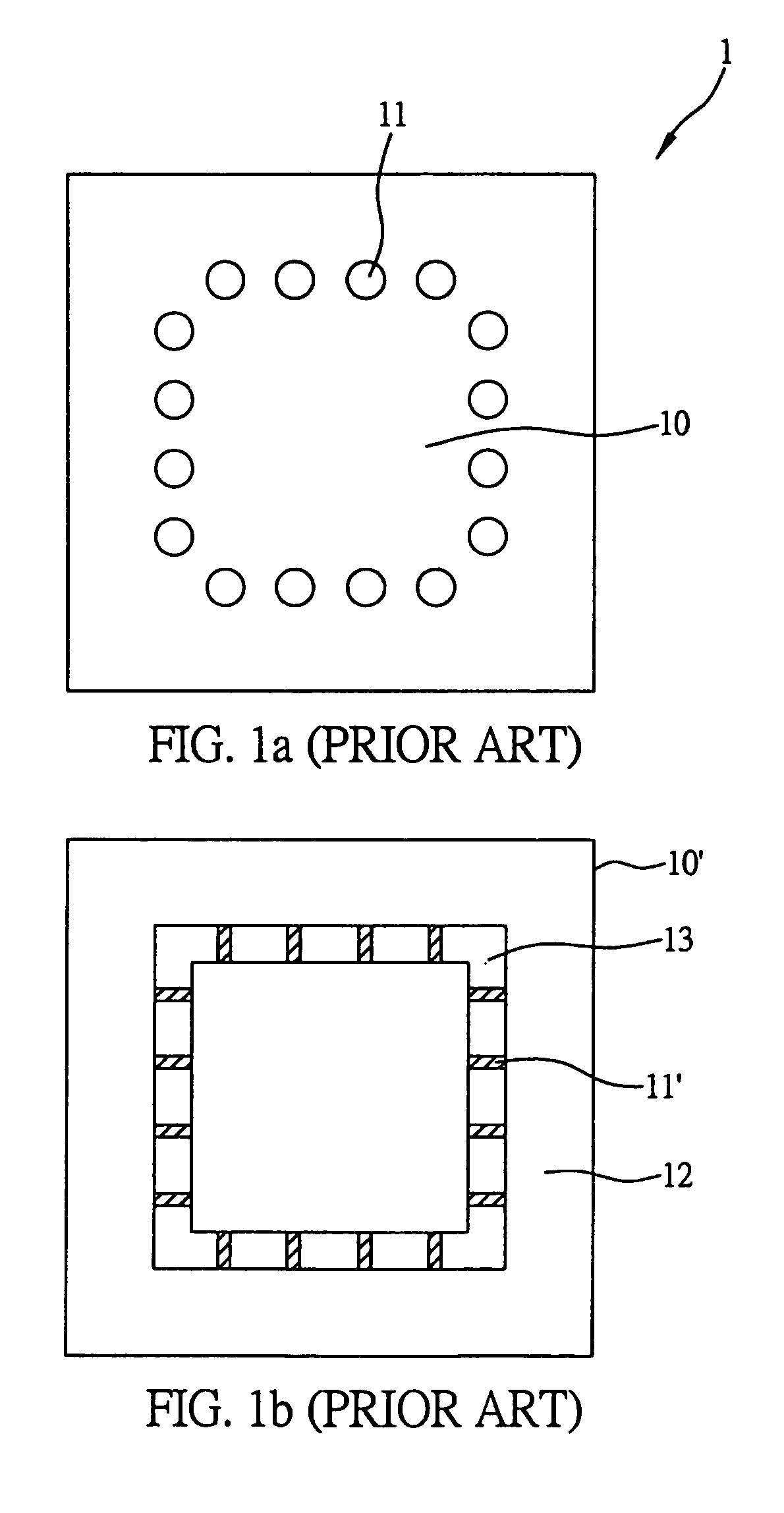

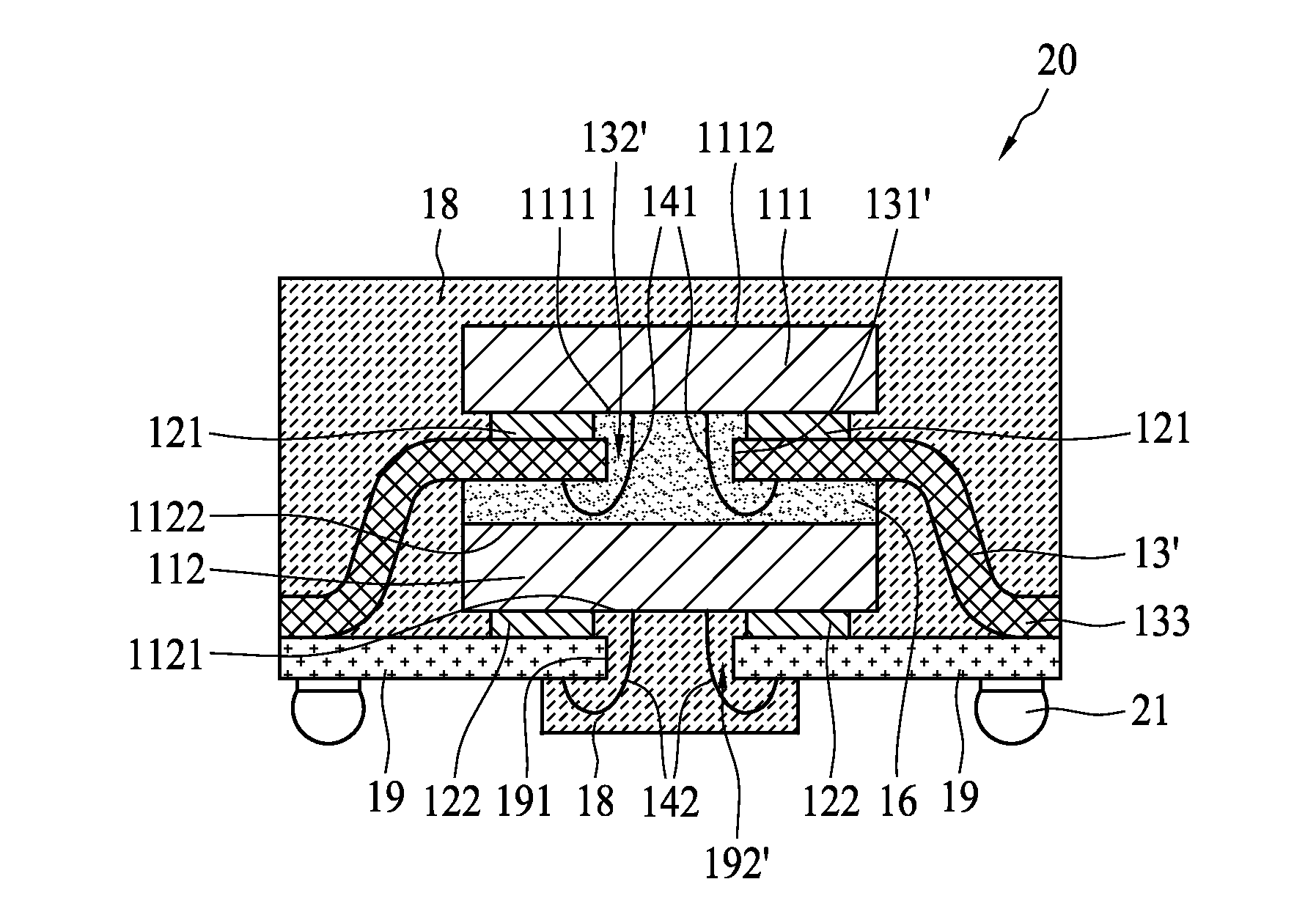

Stacked multichip package

InactiveUS20100244278A1High yieldSemiconductor/solid-state device detailsSolid-state devicesChip carrierActive surface

A stacked multichip package comprises a first chip having a first active surface and a first rear surface, a first chip carrier having a first opening and being configured to carrier the first active surface, a plurality of first conductive leads passing through the first opening and being configured to electrically connect the first active surface and the first chip carrier, a second chip having a second active surface and a second rear surface, an adhesive layer configured to enclose the first conductive leads and to electrically couple the first chip carrier to the second rear surface, a second chip carrier having a second opening and being electrically connected to the second active surface, and a plurality of conductive leads passing through the second opening and being configured to electrically connect the second active surface and the second chip carrier.

Owner:CHIPMOS TECH INC

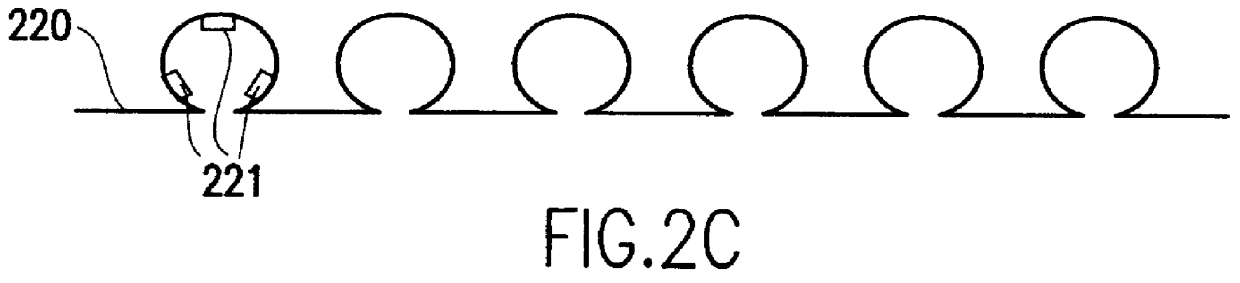

LED surface-mount device and LED display incorporating such device

InactiveUS20090072251A1High color fidelitySolid-state devicesSemiconductor devicesLED displaySurface mounting

In one embodiment, a surface-mount device comprises a casing having opposed, first and second main surfaces, side surfaces, and end surfaces. A lead frame partially encased by the casing comprises (1) an electrically conductive LED chip carrier part having a surface carrying a linear array of three LEDs adapted to be energized to produce in combination a substantially full range of colors, each LED having a first electrical terminal and a second electrical terminal, the first terminal of each of the three LEDs being electrically and thermally coupled to the chip carrying surface of the chip carrier part; and (2) three electrically conductive connection parts separate from the chip carrier part, each of the three connection parts having a connection pad, the second terminal of each of the three LEDs being electrically coupled to the connection pad of a corresponding one of the three connection parts with a single wire bond. The linear array of LEDs extends in a first direction, and each of the chip carrier part and three connection parts has a lead. The leads are disposed in parallel relationship with each other and extend through the end surfaces of the casing in a second direction, the second direction being orthogonal to the first direction. An array of the surface-mount devices may be used in an LED display such as an indoor LED screen.

Owner:CREE HUIZHOU SOLID STATE LIGHTING

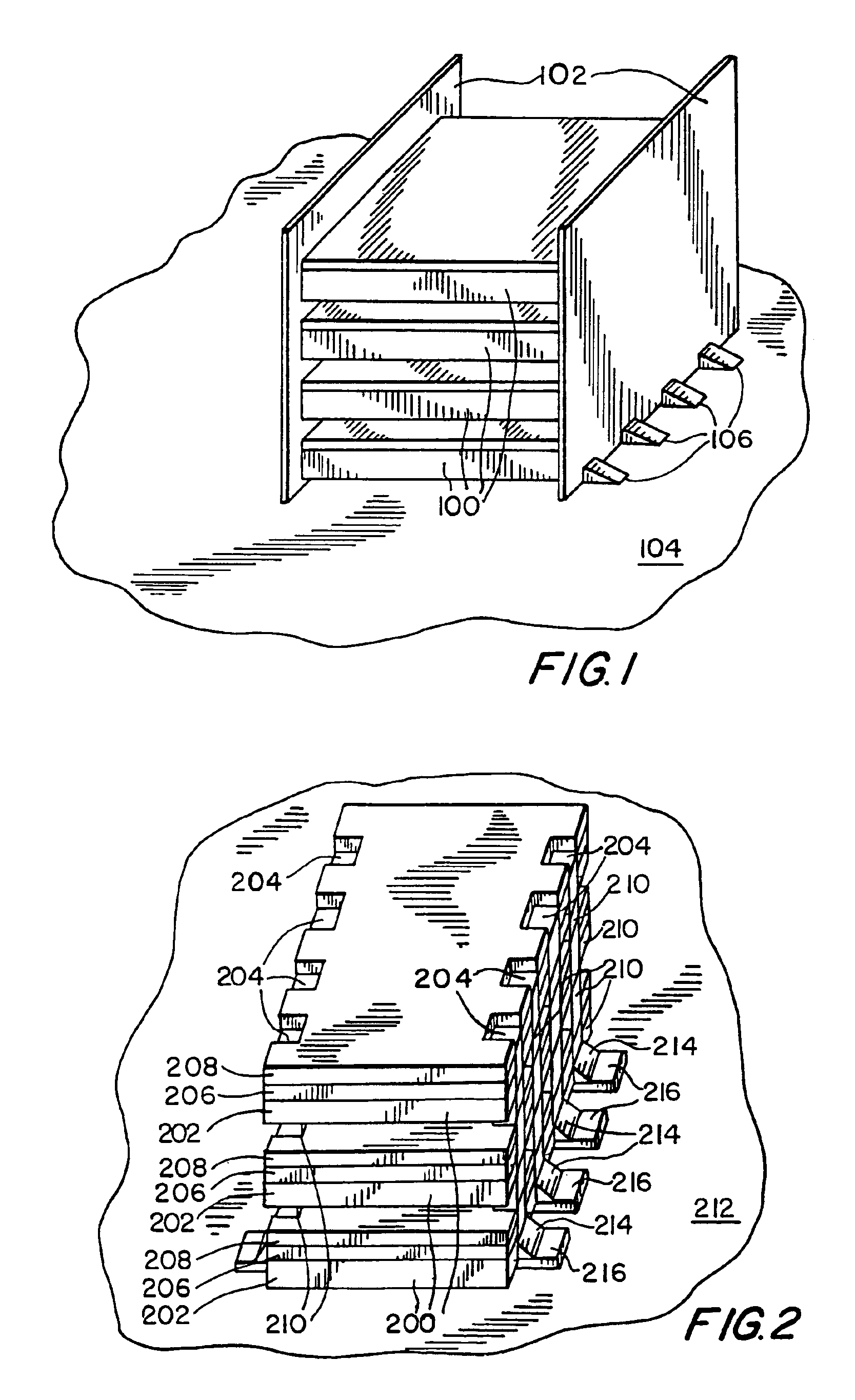

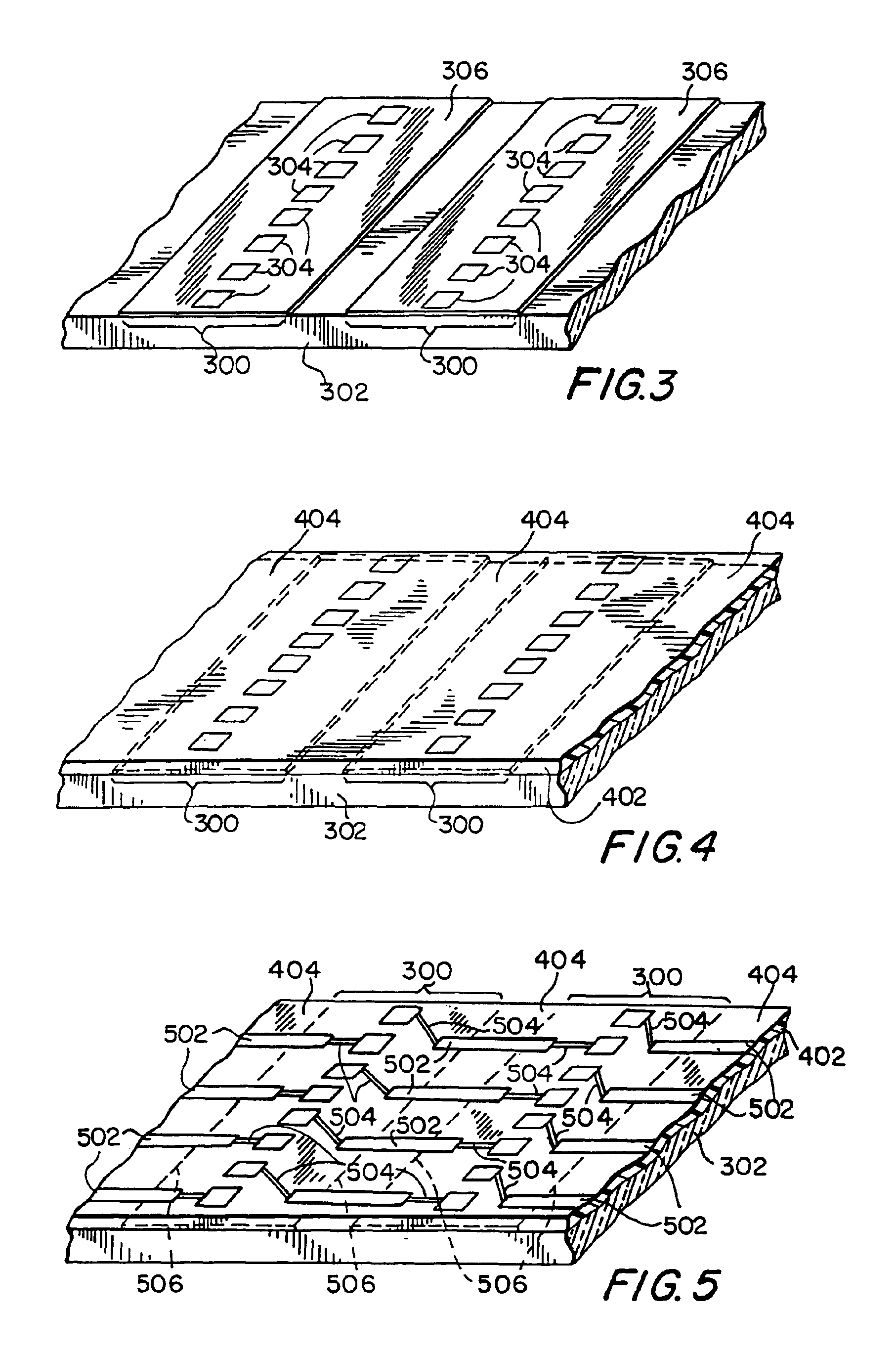

Method of making a circuitized substrate having at least one capacitor therein

InactiveUS20080248596A1Enhance circuitized substrate artEnhance the circuitized substrate artThin/thick film capacitorPrinted circuit aspectsCapacitanceConductive materials

A method of making a circuitized substrate which includes at least one and possibly several capacitors as part thereof. In one embodiment, the substrate is produced by forming a layer of capacitive dielectric material on a dielectric layer and thereafter forming channels with the capacitive material, e.g., using a laser. The channels are then filled with conductive material, e.g., copper, using selected deposition techniques, e.g., sputtering, electro-less plating and electroplating. A second dielectric layer is then formed atop the capacitor and a capacitor “core” results. This “core” may then be combined with other dielectric and conductive layers to form a larger, multilayered PCB or chip carrier. In an alternative approach, the capacitive dielectric material may be photo-imageable, with the channels being formed using conventional exposure and development processing known in the art. In still another embodiment, at least two spaced-apart conductors may be formed within a metal layer deposited on a dielectric layer, these conductors defining a channel there-between. The capacitive dielectric material may then be deposited (e.g., using lamination) within the channels.

Owner:ENDICOTT INTERCONNECT TECH

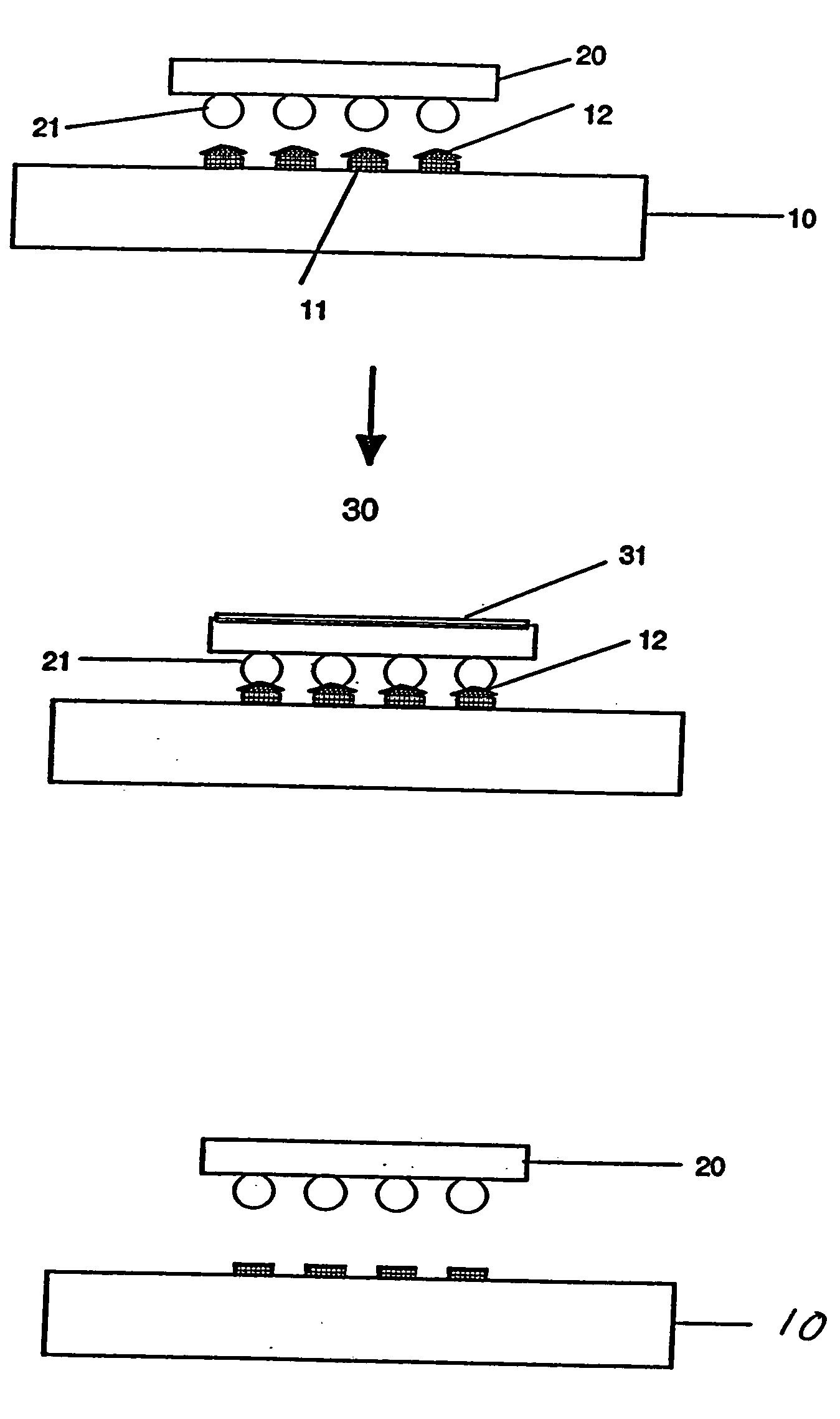

Temporary chip attach method using reworkable conductive adhesive interconnections

InactiveUS20060014309A1Keep the pressureSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsEngineeringInterconnection

A method for temporary chip attach to determine known good die using a reworkable conductive adhesive interconnection between the chip carrier and die. The die is easily separated from the chip carrier after test, without the use of potentially damaging shear forces, by subjecting the TCA assembly to a rework solution.

Owner:IBM CORP

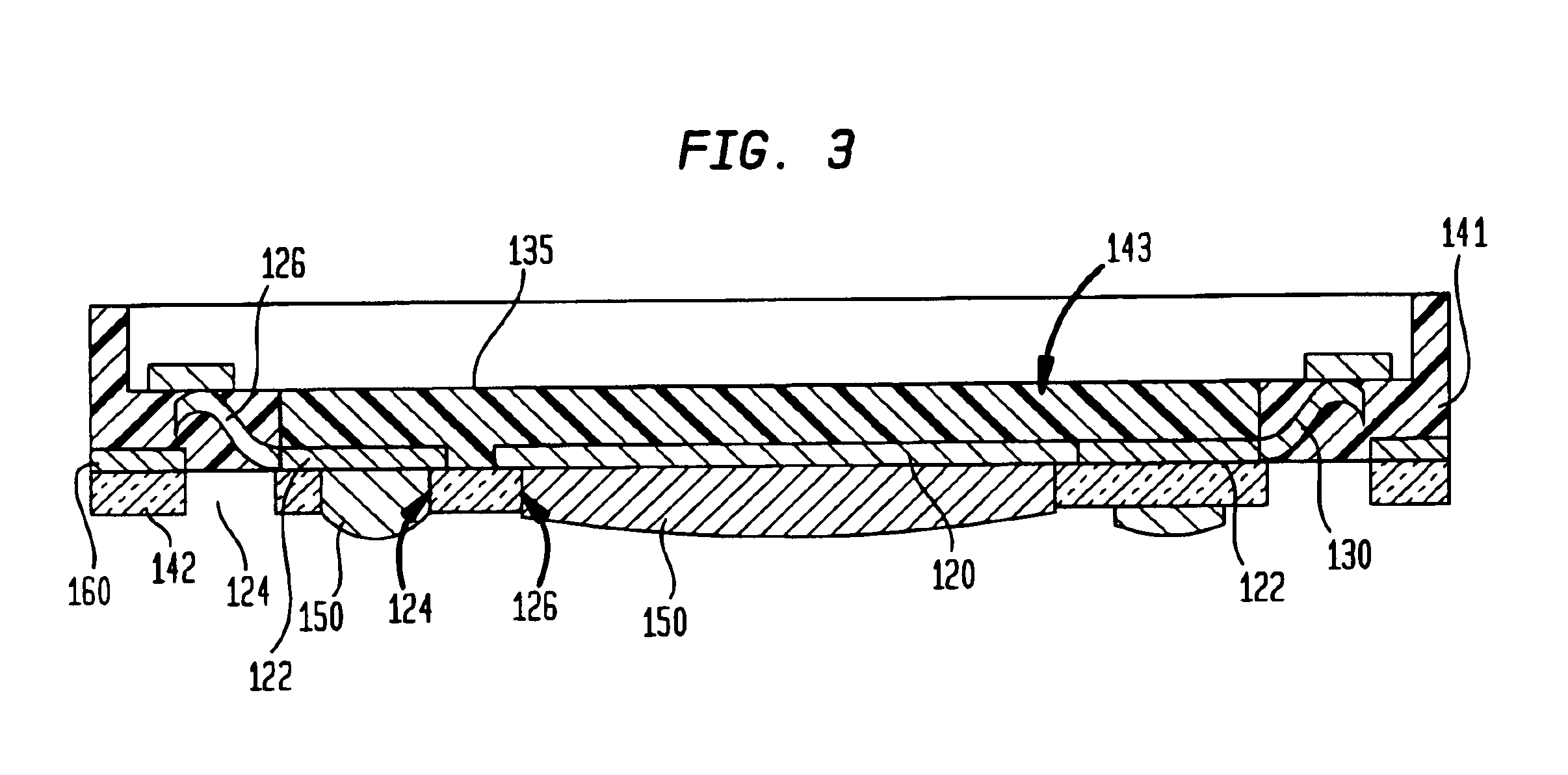

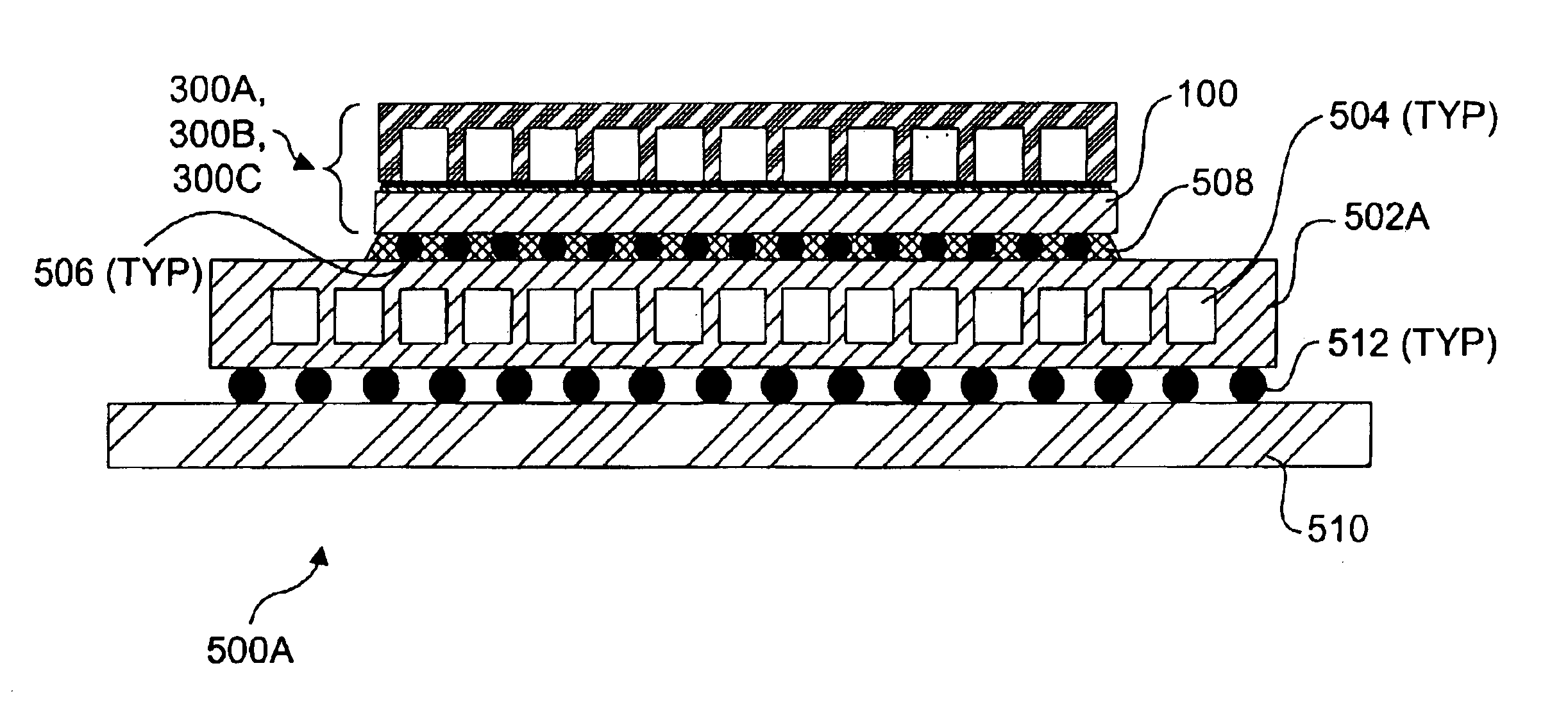

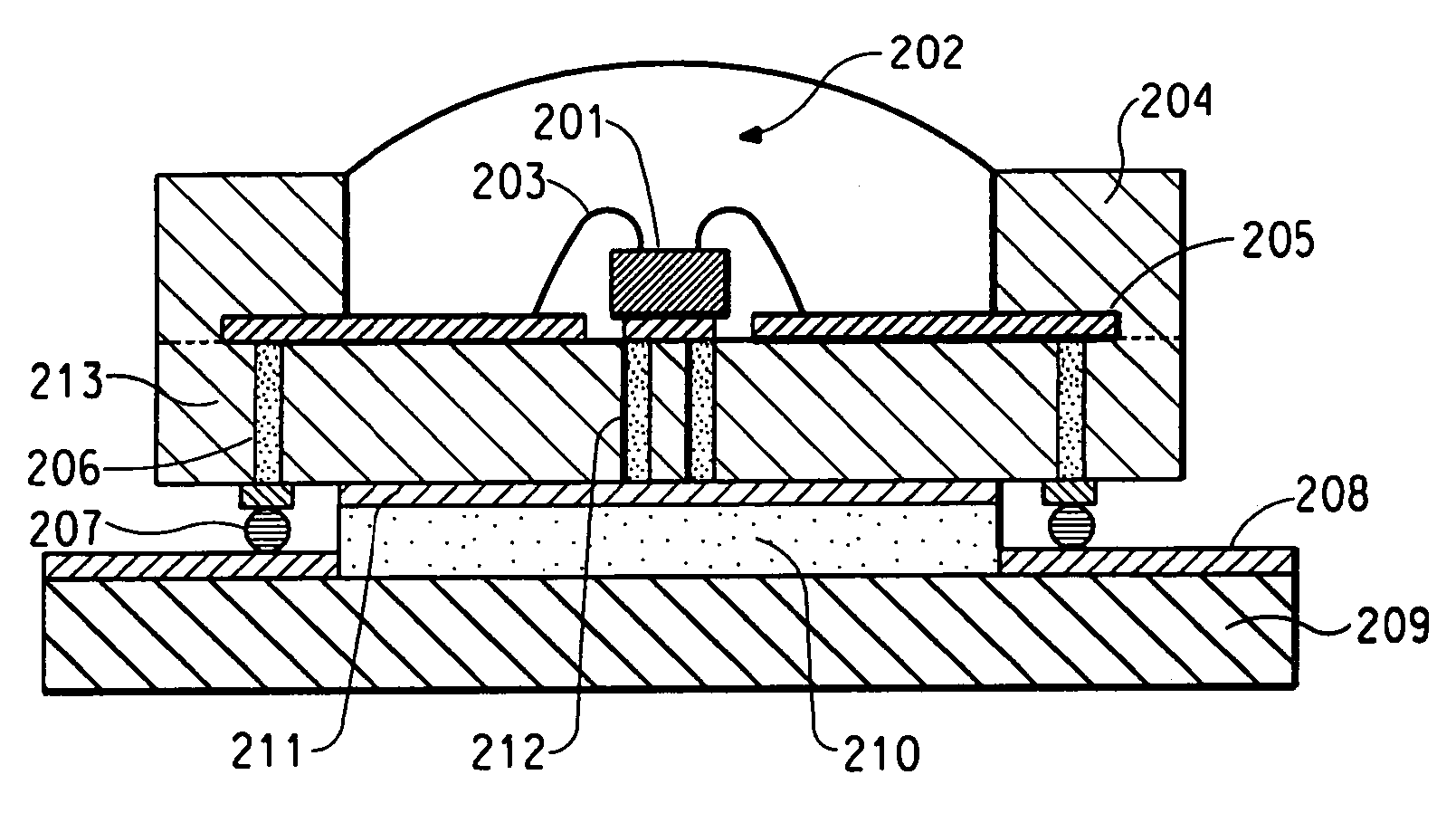

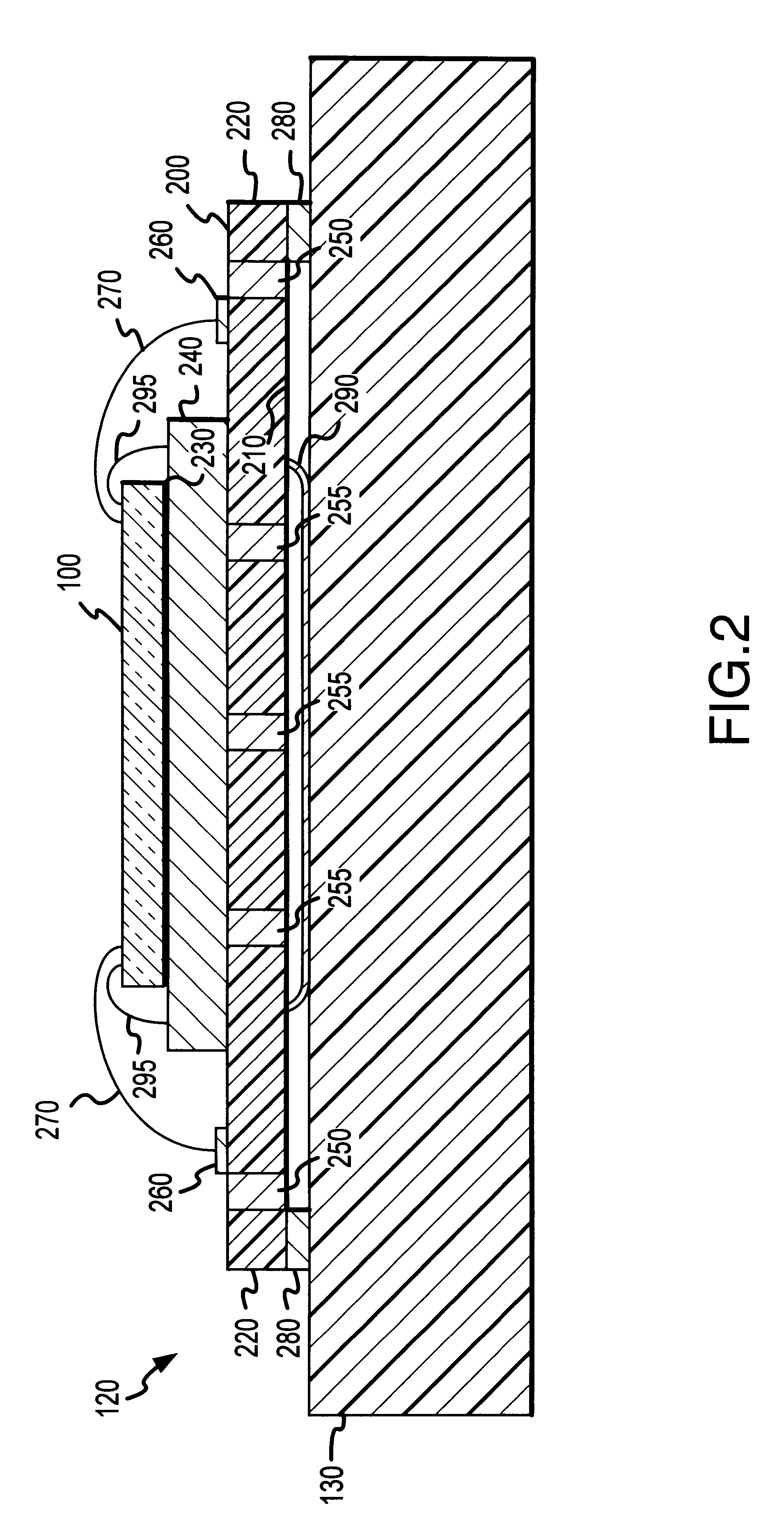

Semiconductor Package Structures Having Liquid Coolers Integrated with First Level Chip Package Modules

InactiveUS20090283902A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageChip carrier

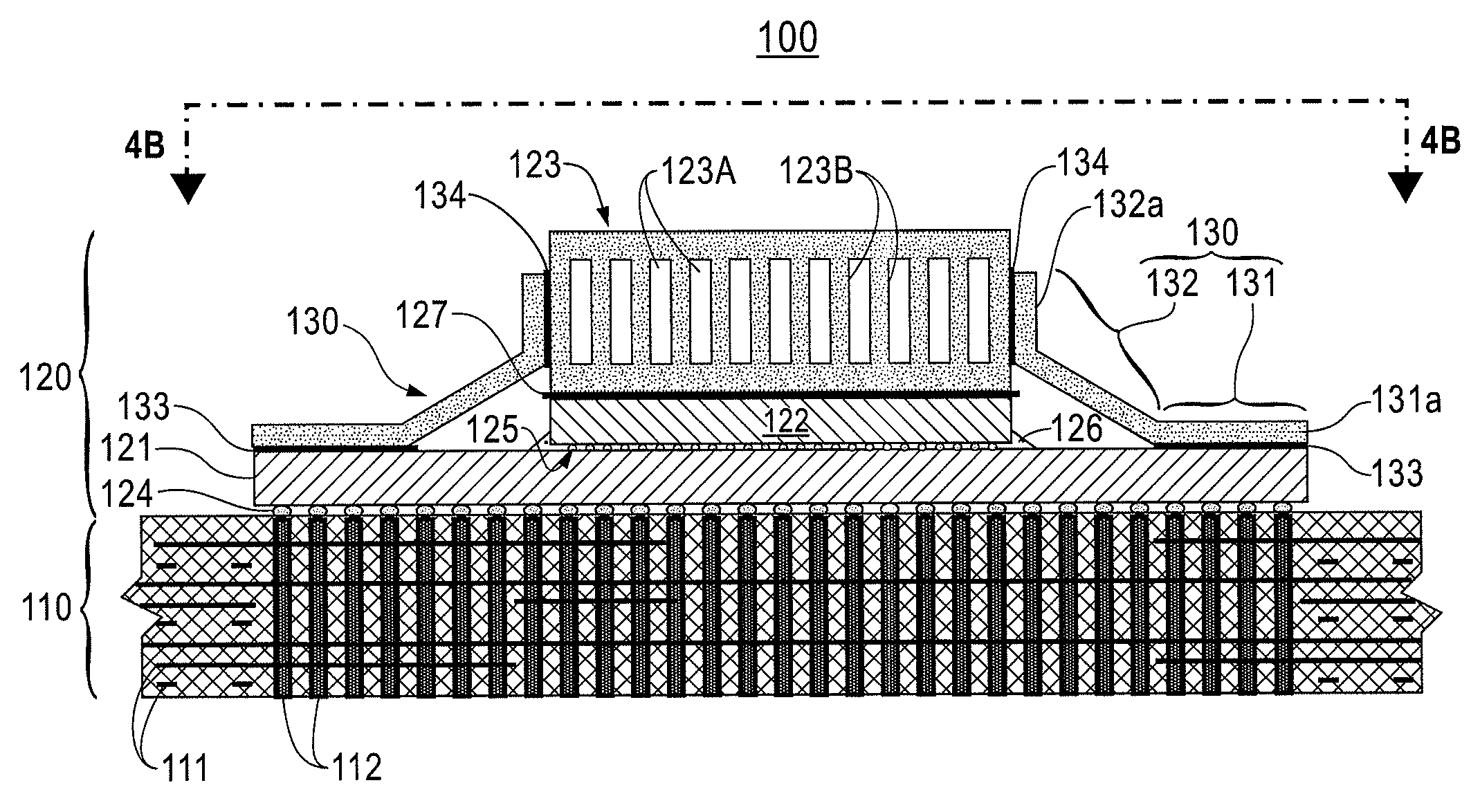

Semiconductor package structures are provided which are designed to have liquid coolers integrally packaged with first level chip modules. In particular, apparatus for integrally packaging a liquid cooler device within a first level chip package structure include structures in which a liquid cooler device is thermally coupled directly to the back side of an integrated circuit chip flip-chip mounted on flexible chip carrier substrate. The liquid cooler device is mechanically coupled to the package substrate through a metallic stiffener structure that is bonded to the flexible package substrate to provide mechanical rigidity to the flexible package substrate.

Owner:GLOBALFOUNDRIES INC

Equipment for transporting chips and chip carrier structure therefor

InactiveUS20070026949A1Improve reliabilityEasy loading and unloadingCoin countersApparatus for meter-controlled dispensingDocking stationRadio frequency

The equipment for transporting chips carrying coded information includes a movable structure carrying chips with an electronic circuit arranged in columns in stacked racks and a docking station for the carrier structure in the place of storage of the chips, for example the vault of the casino, or at their place of use, for example a gaming table. The carrier structure includes a plane base divided by a partition with a handle for carrying two stacks of racks of chips and a lid. The docking station integrates part of an RFID contactless radio-frequency reading station for reading the coded information carried by the chips of at least one column to determine or verify the content of at least one batch of chips present in the carrier structure, in particular to draw up or to check an inventory thereof. The read station includes a read unit with a digital section and an analog section provided with a wide-loop antenna with three loops respectively integrated into the walls of the lid and the median partition fixed to the plane base.

Owner:GAMING PARTNERS INTERNATIONAL CORPORATION

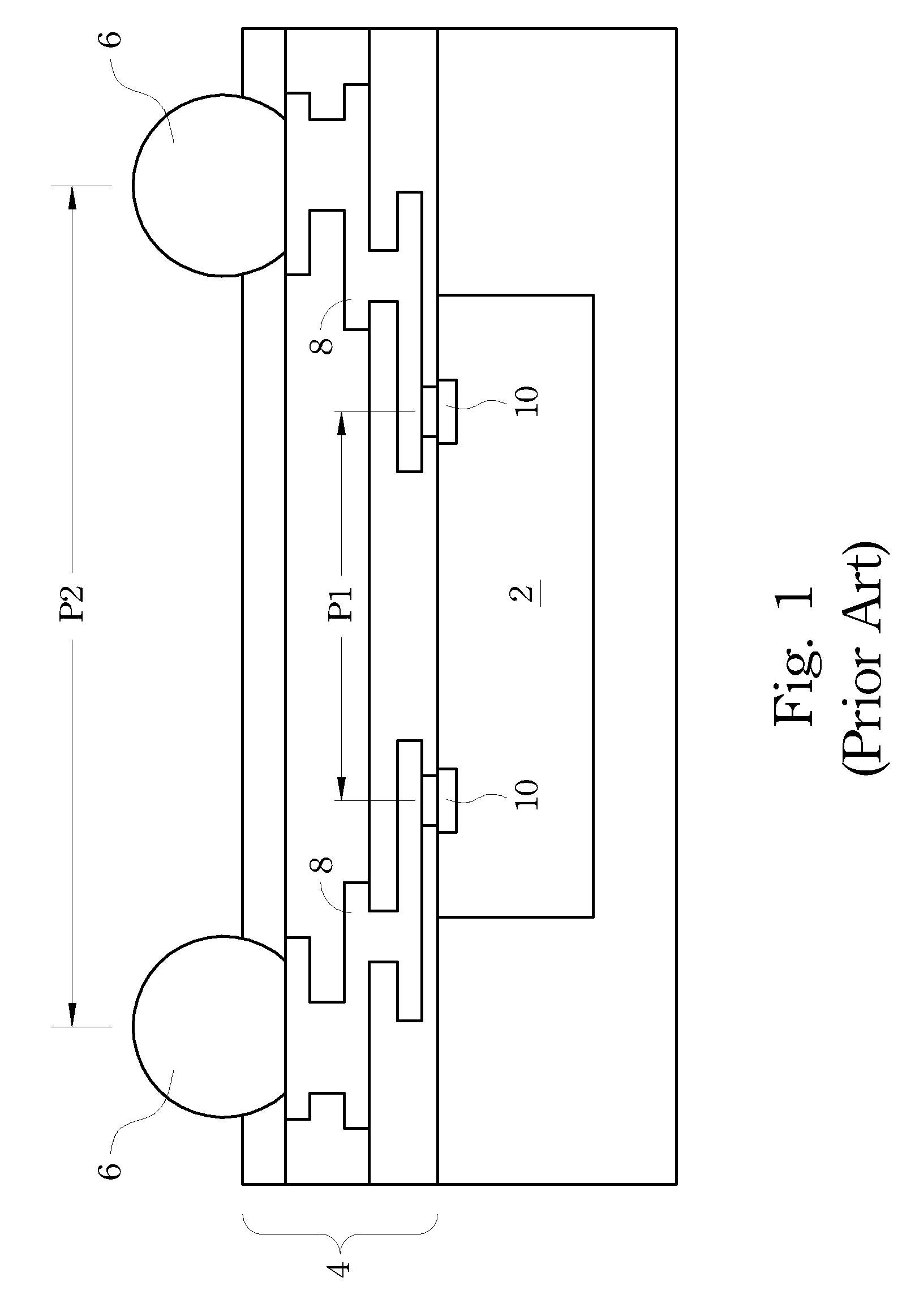

Leadless chip carrier design and structure

InactiveUS6191477B1Semiconductor/solid-state device detailsSolid-state devicesChip carrierSemiconductor

A semiconductor device is provided in the form of a chip carrier (e.g., chip / IC scale carrier for RF applications) that includes an integrated circuit chip attached to a die attach pad. The device has an interconnect substrate having an upper surface and a lower surface, with a plurality of vias passing through the thickness of the interconnect substrate from the upper surface to the lower surface. The die attach pad is located on the upper surface of the interconnect substrate, and a heat spreader is located on the lower surface of the interconnect substrate. A first group of vias is positioned to intersect both the die attach pad and the heat spreader. A second group of vias is positioned away from the die attach pad and the heat spreader. The upper surface has a plurality of bond pads that are abutting the second group of vias and the lower surface has a plurality of lands that are also abutting the second group of vias.

Owner:SKYWORKS SOLUTIONS INC