SiC dual-groove metal-oxide-semiconductor field-effect transistor (MOSFET) device integrated with Schottky diode and fabrication method of SiC dual-groove MOSFET device

A Schottky diode and double-groove technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as poor reliability of gate dielectrics, concentrated electric field, and easy breakdown of gate dielectrics. Increase reliability and prevent punch-through

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will now be described more fully with reference to the accompanying drawings, in which exemplary embodiments of the invention are shown. This invention may, however, be embodied in many different forms and should not be construed as limited to the exemplary embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

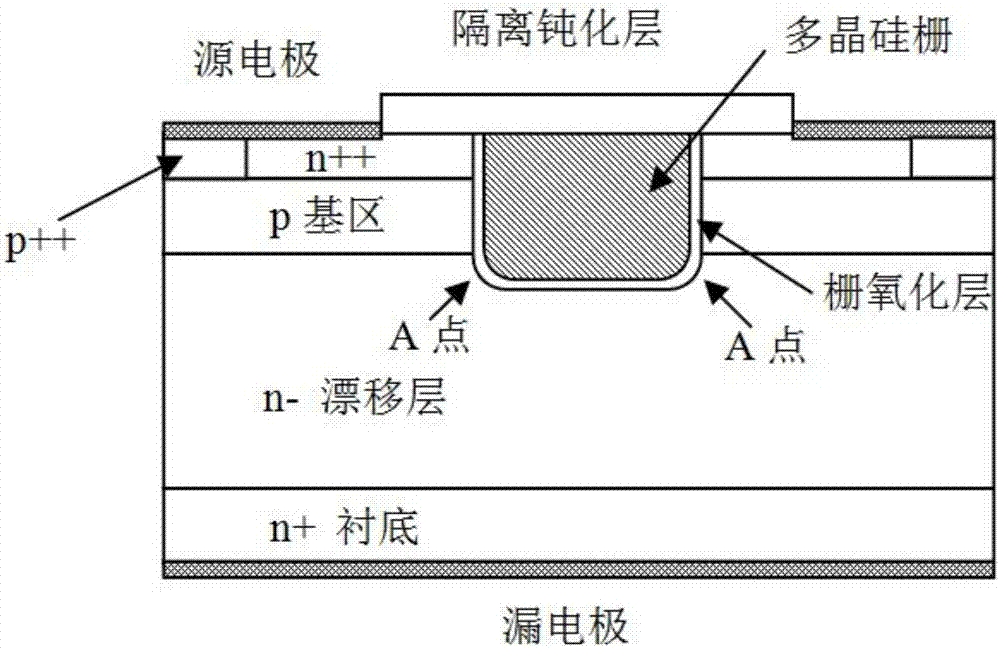

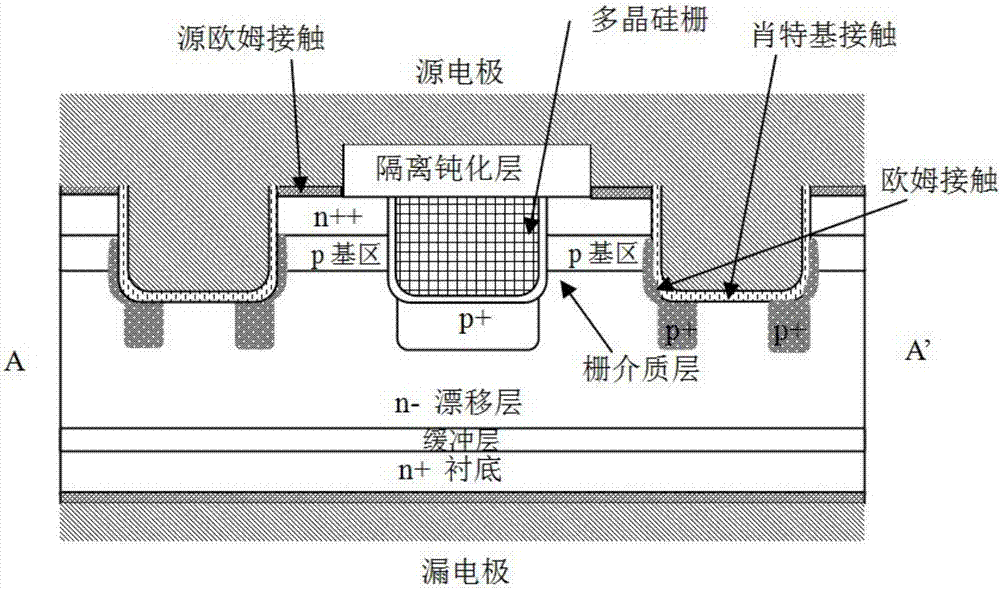

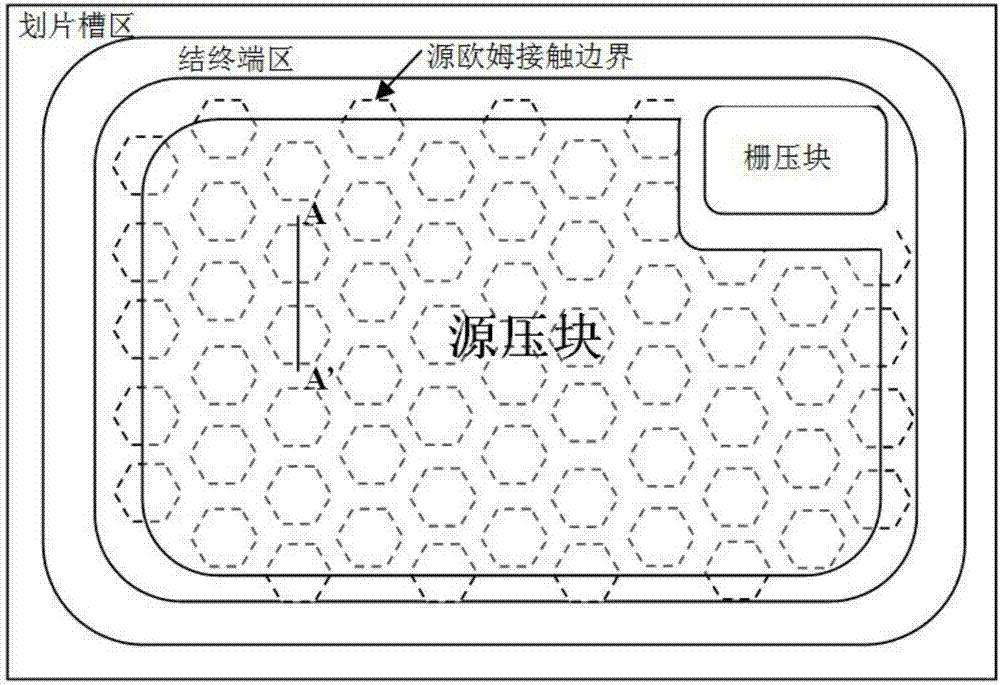

[0046] like figure 2 As shown, the present invention provides a SiC double-groove MOSFET device with an integrated Schottky diode. The original cell structure of the active region of the SiC double-groove MOSFET device is sequentially drain and n+ substrate from bottom to top , buffer layer, n-drift layer, p base region and n++ layer; two grooves are arranged in the original cell structure, which are respectively arranged in the gate groove in the center of the original cell structure and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More