Manufacturing method of non-volatile memory

a manufacturing method and non-volatile memory technology, applied in the field of semiconductor devices, can solve the problems of adverse impact on the electrical performance of the memory, uneven distribution of electrons injected in the silicon nitride layer, and data misjudgment, so as to reduce the operation voltage of the memory, inject and pull electrons more quickly, and improve the efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

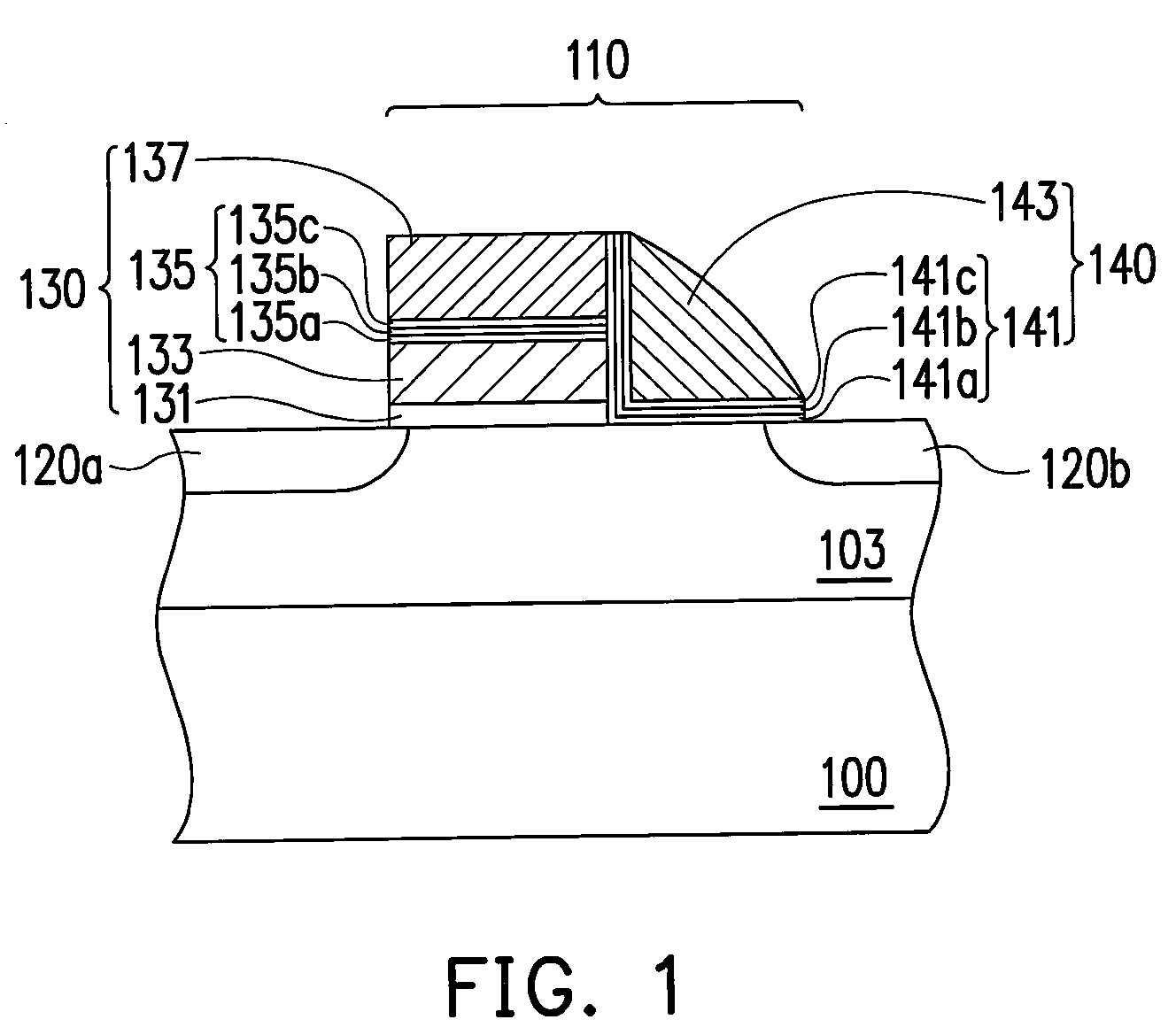

[0044]FIG. 1 is a schematic structural cross-sectional view of a non-volatile memory in an embodiment of the present invention.

[0045]Referring to FIG. 1, the non-volatile memory includes at least a substrate 100, memory cells 110 and source / drain regions 120a and 120b. The memory cell 110 is disposed on the substrate 100 and includes at least a memory unit 130 and another memory unit 140. Wherein, the memory unit 130, from the substrate 100 up, includes at least a tunneling dielectric layer 131, a floating gate 133, an inter-gate dielectric layer 135 and a control gate 137. The memory unit 140 is disposed on a sidewall of the memory unit 130. The memory unit 140 includes, for example, a control gate 143 and a charge trapping structure 141. The control gate 143 is disposed on a sidewall of the memory unit 130 and the charge trapping structure 141 is disposed between the control gate 143 and the memory unit 130, and between the control gate 143 and the substrate 100. The source / drain ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More