DMOSFET and planar type MOSFET

A planar and N-type technology, applied in diodes, semiconductor devices, electrical components, etc., can solve the problems of reducing on-resistance, channel layer punch-through, and withstand voltage drop, achieving reduced loss, low feedback capacitance, low Effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. In addition, in all the drawings for explaining the embodiment, as a matter of principle, the same reference numerals are given to the same members, and overlapping description thereof will be omitted.

[0047] (Embodiment 1)

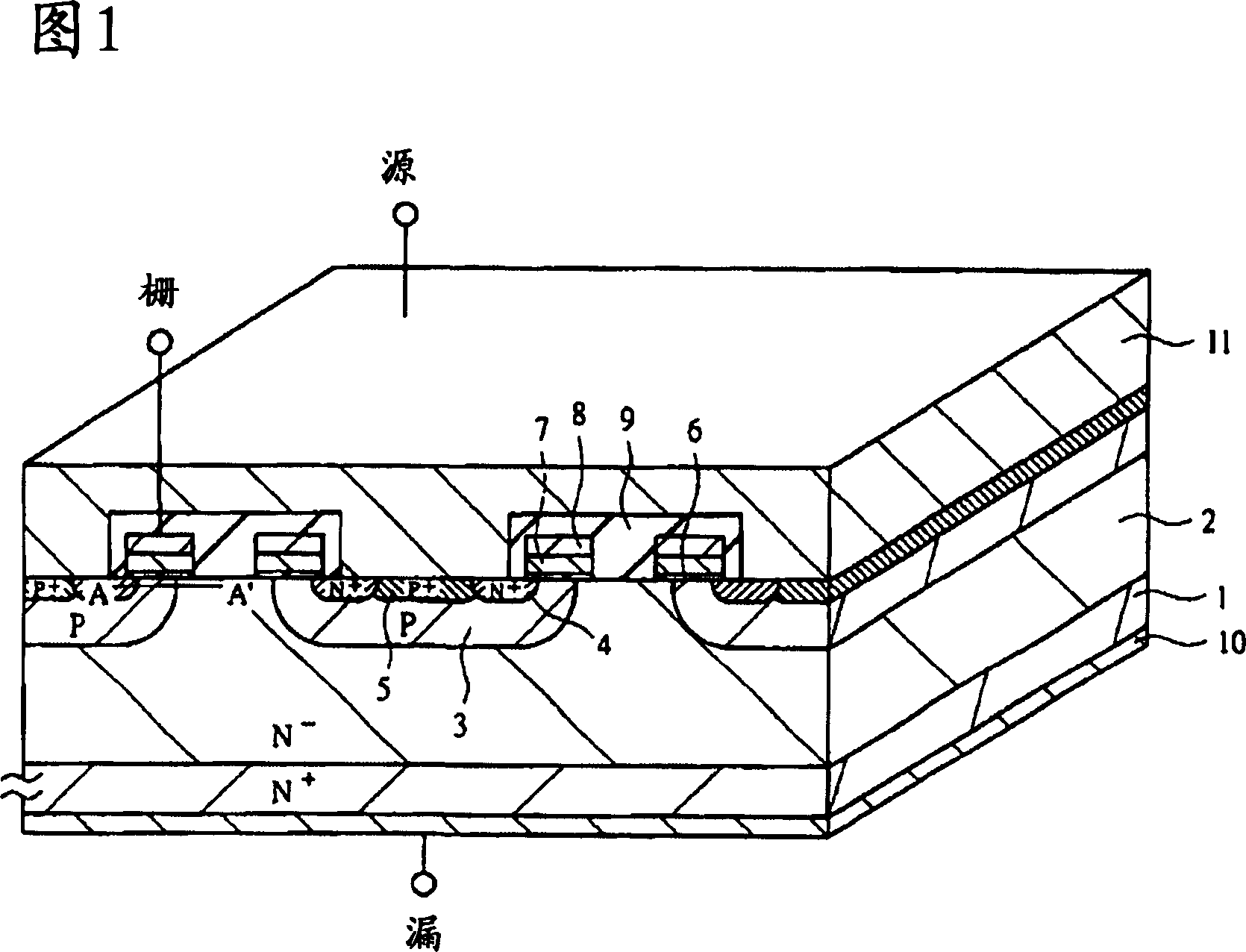

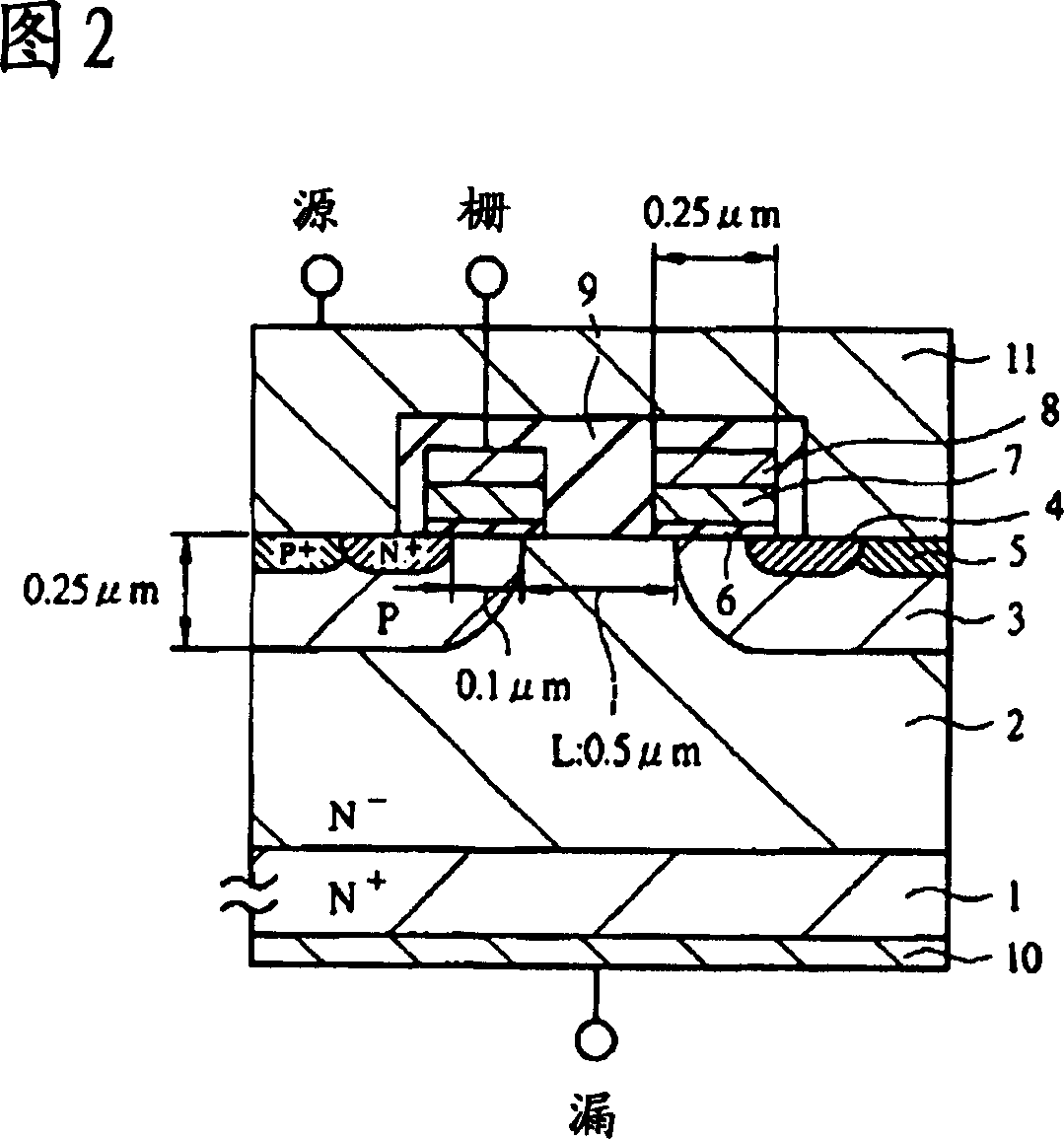

[0048] Embodiment 1 of the present invention will be described using FIGS. 1 to 8 . Fig. 1 shows a cross-sectional structure of a planar MOSFET according to Embodiment 1 of the present invention. Fig. 2 shows an example of dimensions of the planar MOSFET according to Embodiment 1 of the present invention.

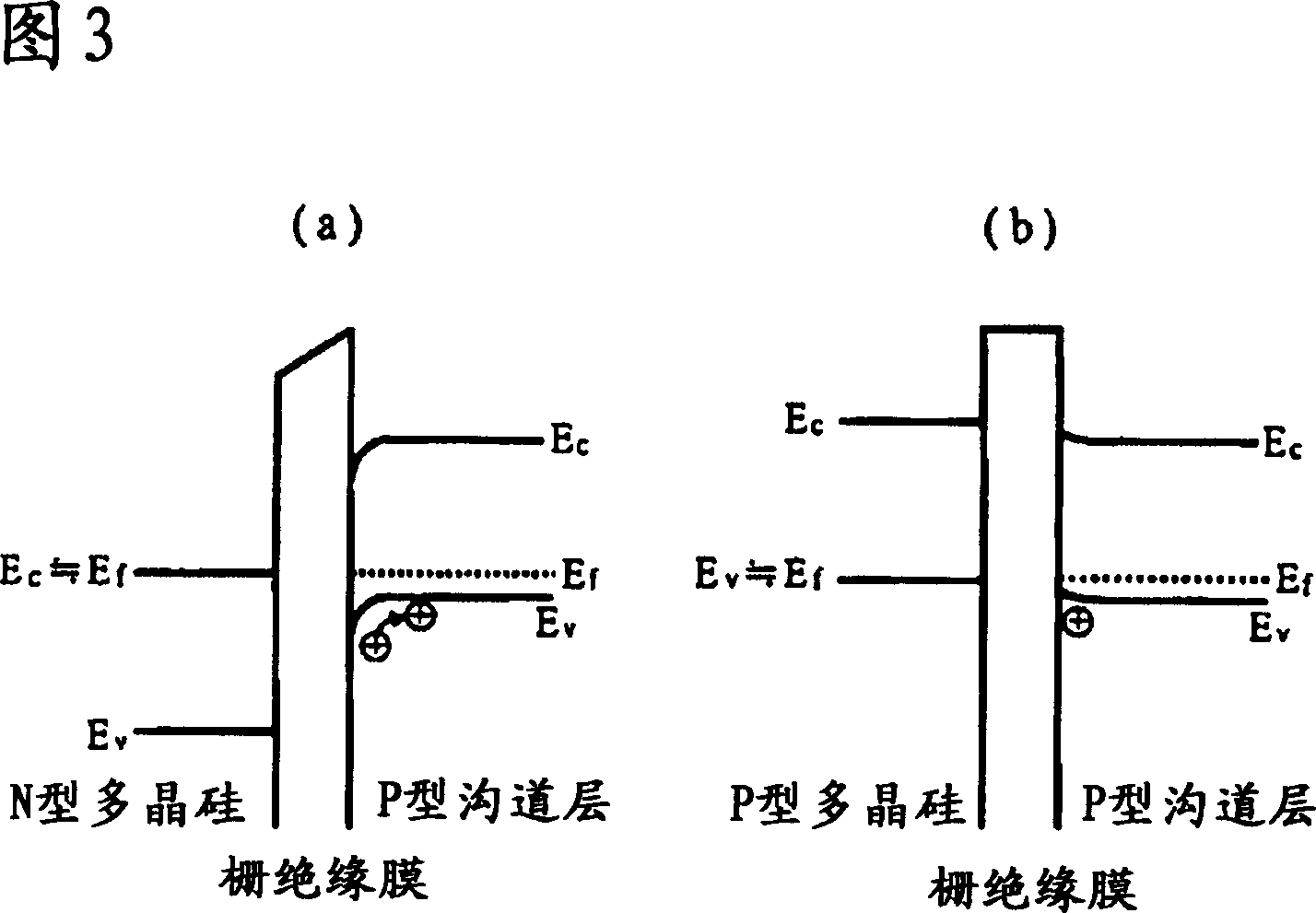

[0049]The planar MOSFET of the present embodiment 1, as shown in FIG. 1, is a planar N-channel DMOSFET (double-diffused MOSFET). + N on substrate 1 - epitaxial layer 2, in which the N - P-type channel layer 3, N + The source region 4 and the body contact region 5 form the P-type polysilicon 7 of the gate electrode through the gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More