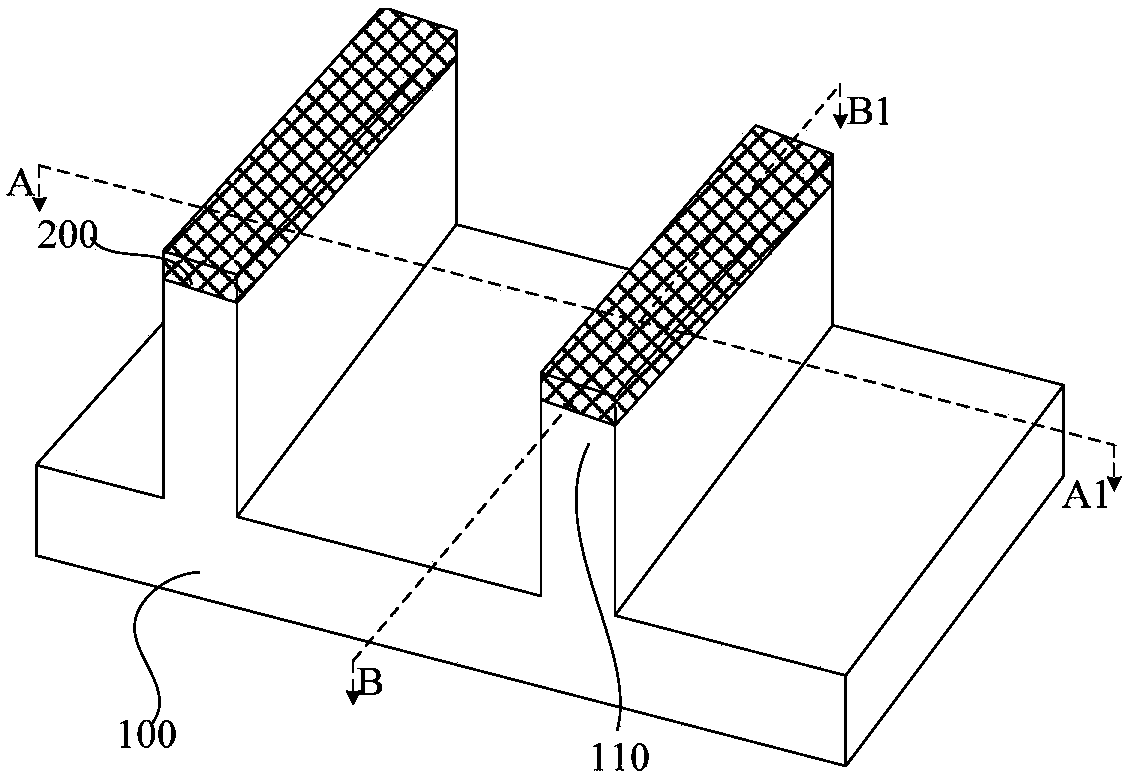

Semiconductor structure and manufacturing method thereof

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems that the electrical properties of semiconductor structures need to be improved, and achieve the effect of reducing channel leakage current and improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

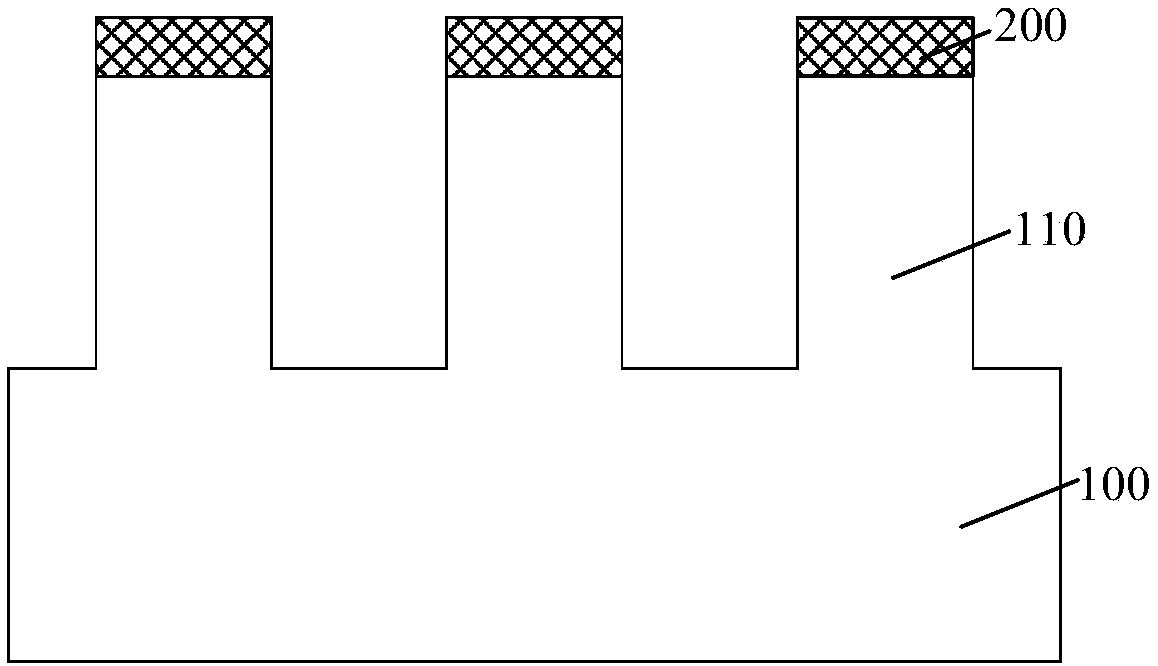

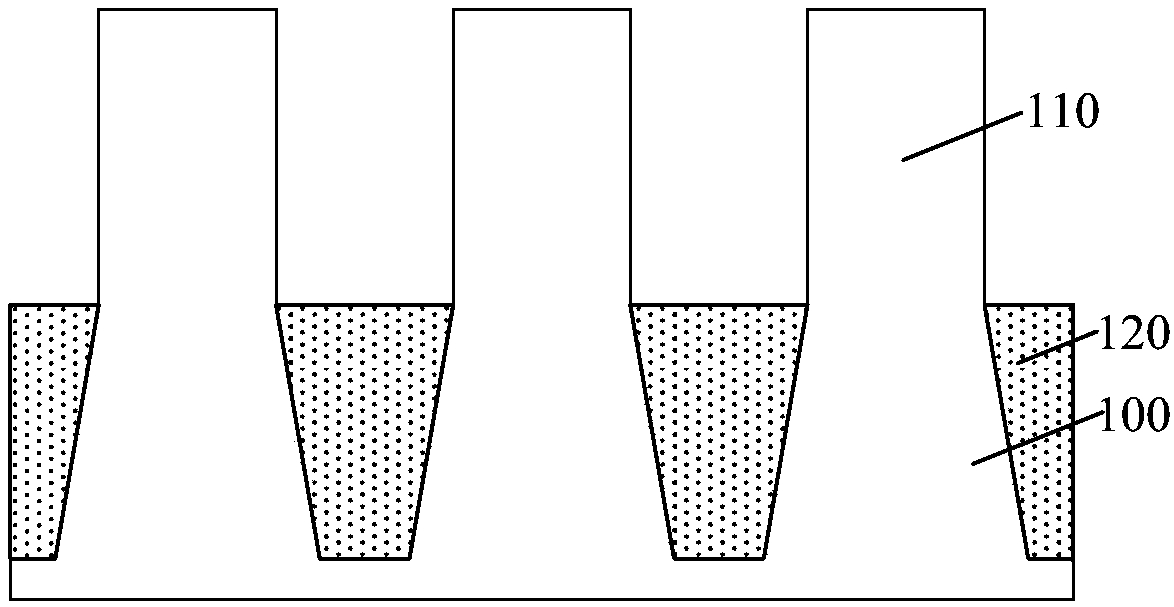

Embodiment Construction

[0035] It is known from the background technology that the electrical performance of the semiconductor structure needs to be improved. The reasons are:

[0036] In order to improve the short-channel effects (SCE: short-channel effects) and reduce the increase of the channel leakage current of the transistor, generally the method of reducing the injection energy of the light doping (LDD) process is adopted; or, the pre-amorphization doping is adopted Pre-amorphization Implantation (PAI) process to achieve the purpose of ultra shallow junction (Ultra Shallow Junction, USJ), thereby reducing the channel leakage current of the semiconductor structure and reducing the short channel effect.

[0037] However, after the introduction of the FinFET structure, due to the three-dimensional structure limitation, it is difficult to do the doping process on the bottom of the fin portion, so that the bottom punch through of the source and drain doped regions is likely to occur, and it is difficult...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More