Semiconductor structure forming method

A semiconductor and anti-penetration technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor performance and serious short channel, and achieve short channel effect suppression, stable electrical performance, and device performance. stable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] As mentioned in the background art, as the size of semiconductor devices shrinks and the degree of integration increases, the feature size of FinFETs also shrinks accordingly, which makes the short channel of FinFETs increasingly serious and poor in performance.

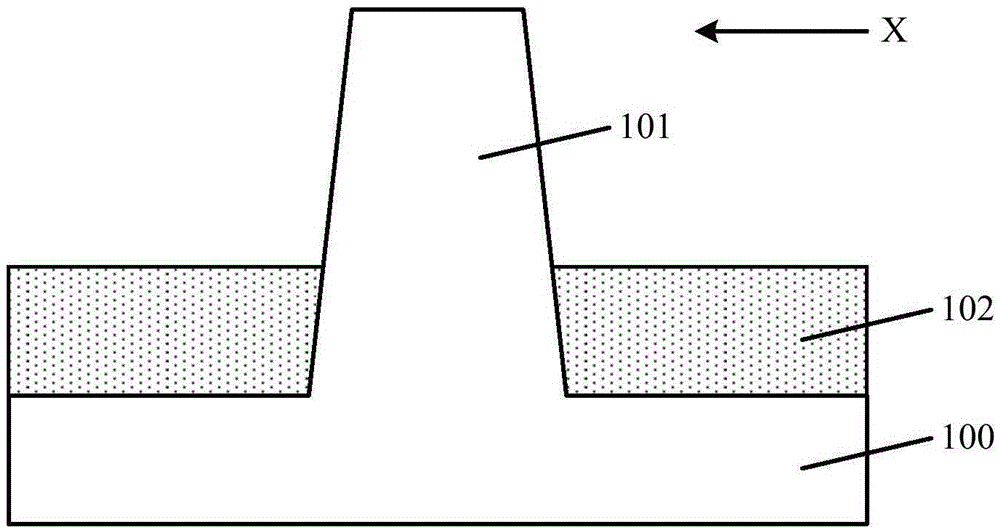

[0033] Please refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of a fin for forming a fin field effect transistor according to an embodiment of the present invention, including: a substrate 100, a fin 101 located on the surface of the substrate 100, and an isolation layer 102 located on the surface of the fin 101. The isolation layer 102 covers part of the sidewall surface of the fin portion 101 , and the surface of the isolation layer 102 is lower than the top surface of the fin portion 101 .

[0034] Wherein, the base 100 and the fin 101 have well regions inside. When the FinFET is a PMOS transistor, the well is doped with N-type ions; when the FinFET is an NMOS transistor, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More