Patents

Literature

283 results about "Hot-carrier injection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

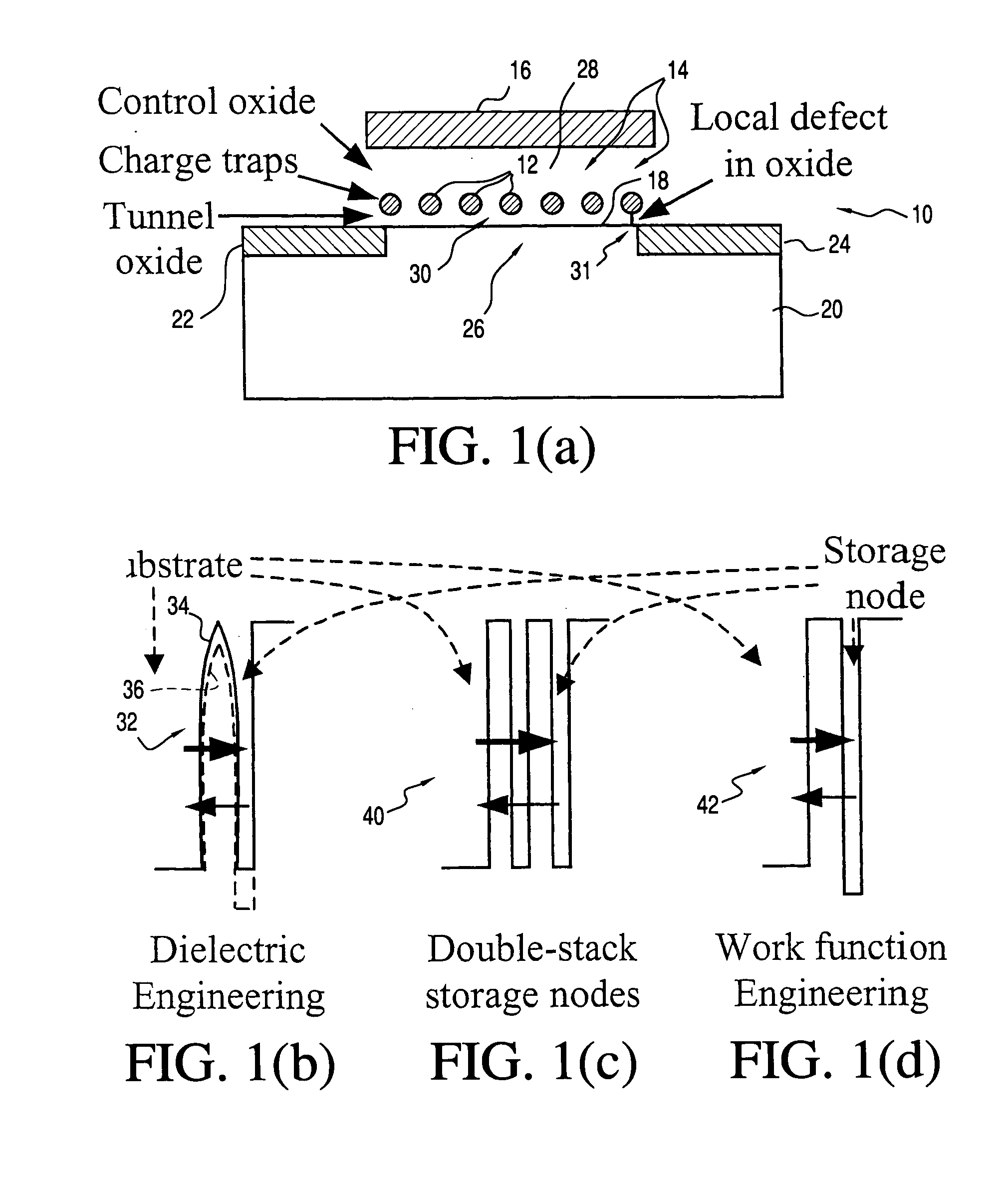

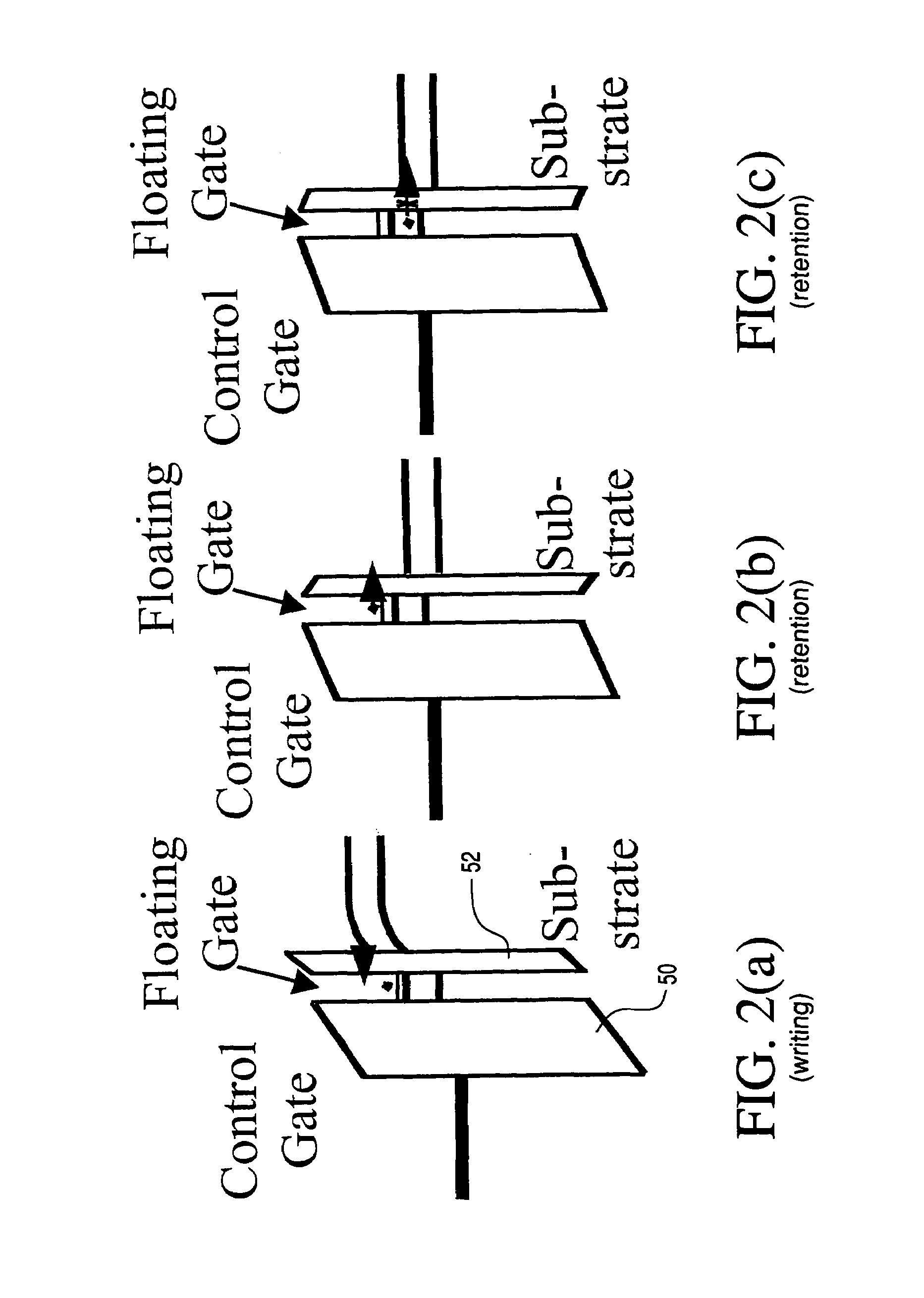

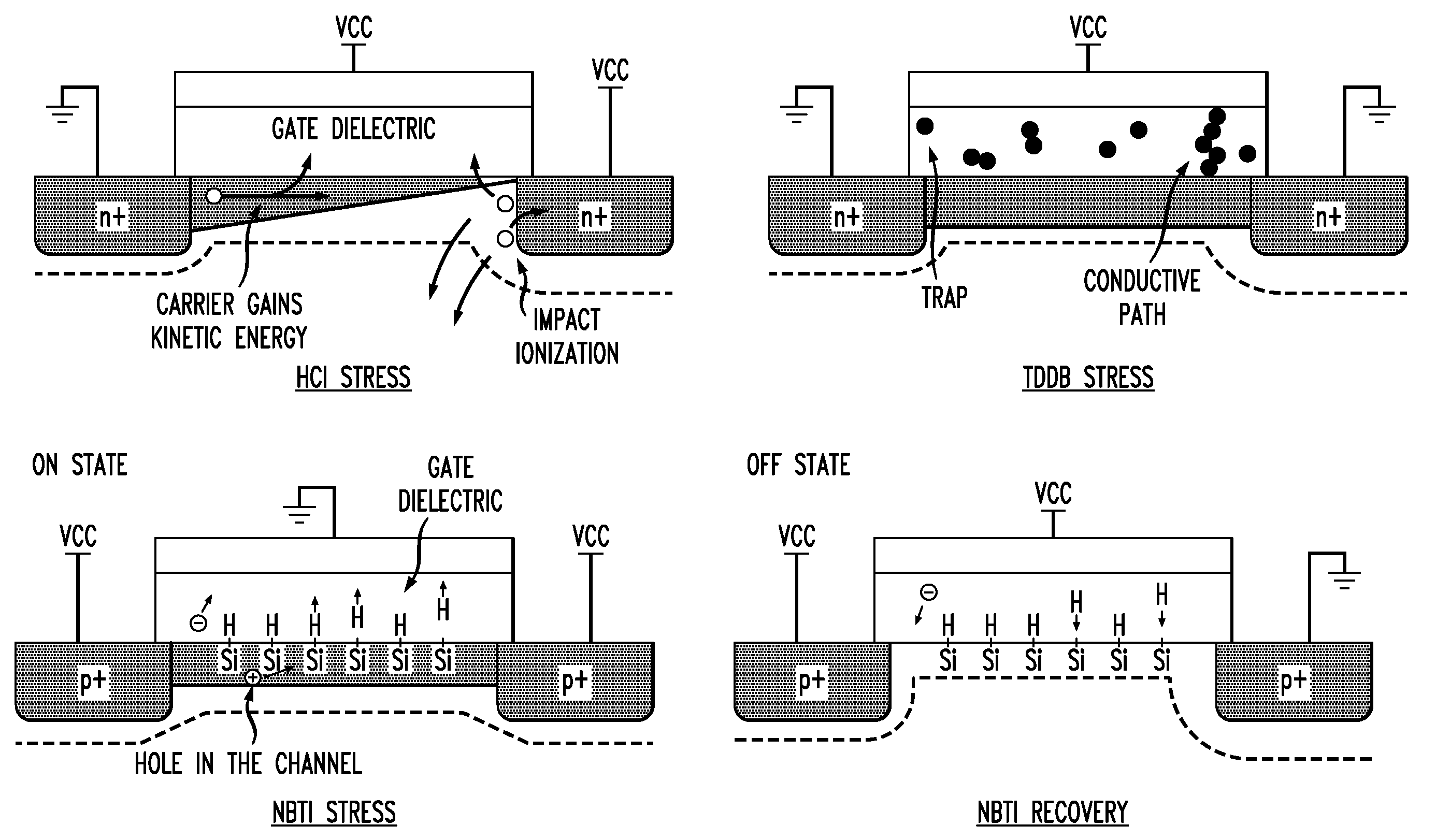

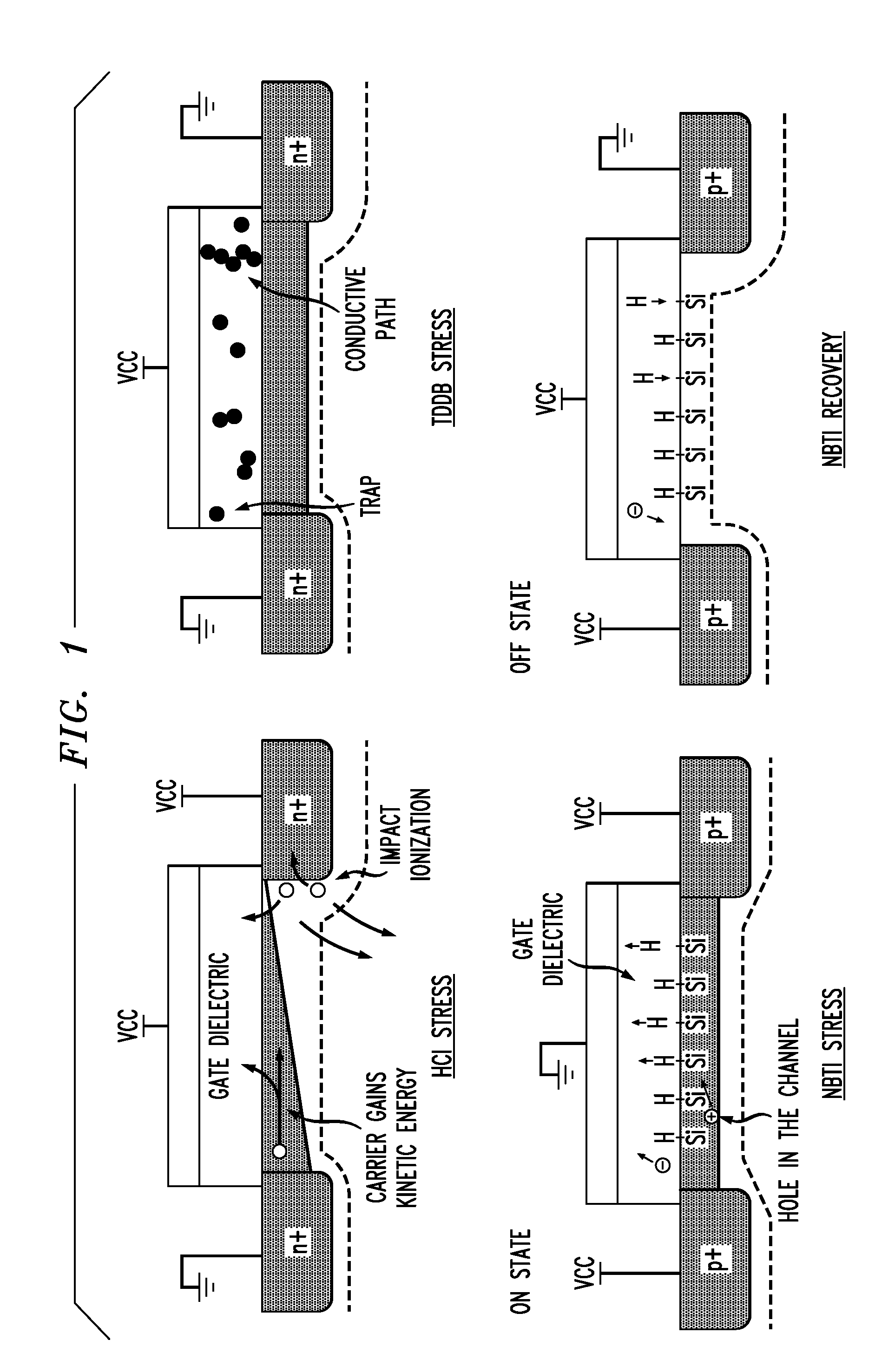

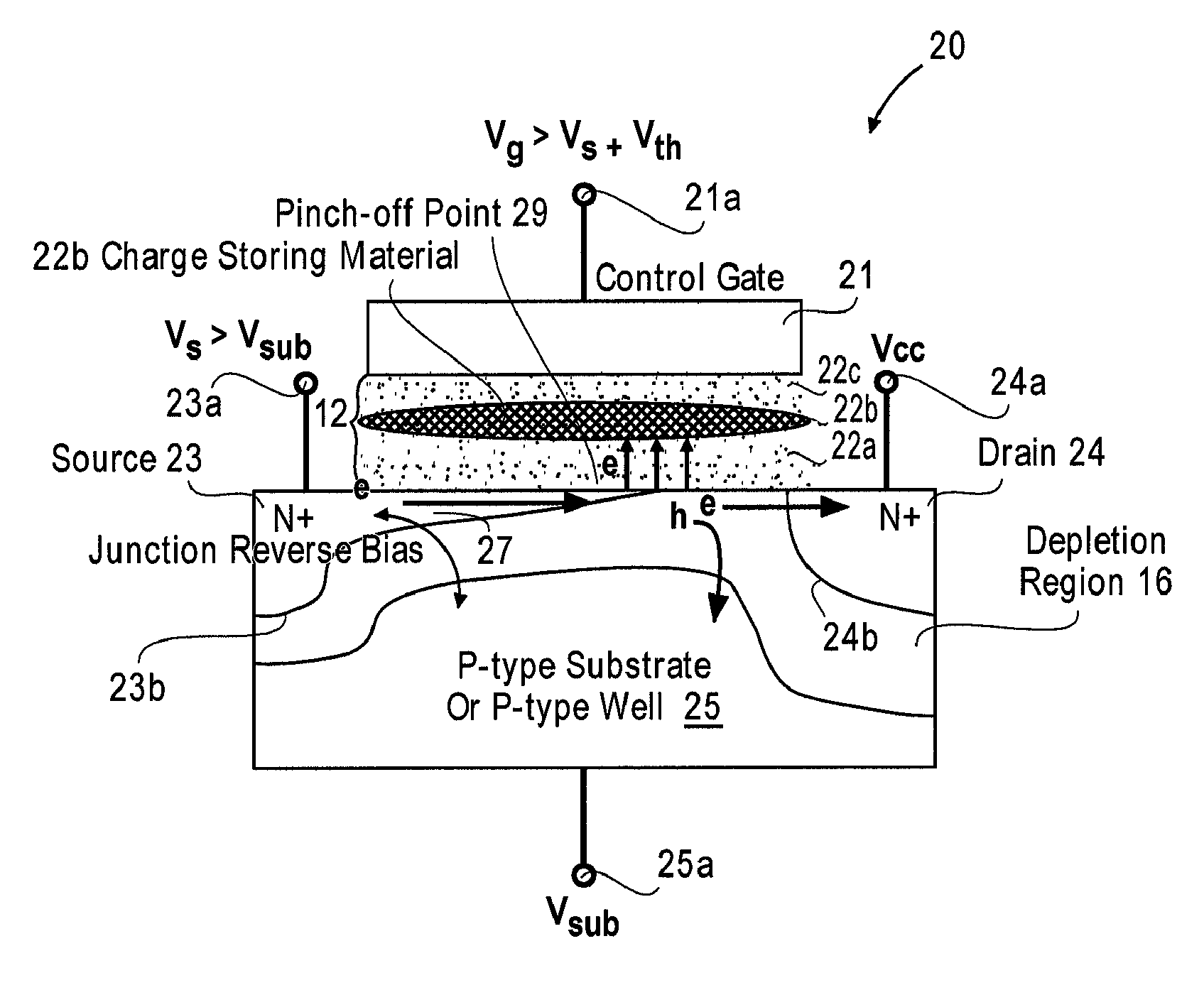

Hot carrier injection (HCI) is a phenomenon in solid-state electronic devices where an electron or a “hole” gains sufficient kinetic energy to overcome a potential barrier necessary to break an interface state. The term "hot" refers to the effective temperature used to model carrier density, not to the overall temperature of the device. Since the charge carriers can become trapped in the gate dielectric of a MOS transistor, the switching characteristics of the transistor can be permanently changed. Hot-carrier injection is one of the mechanisms that adversely affects the reliability of semiconductors of solid-state devices.

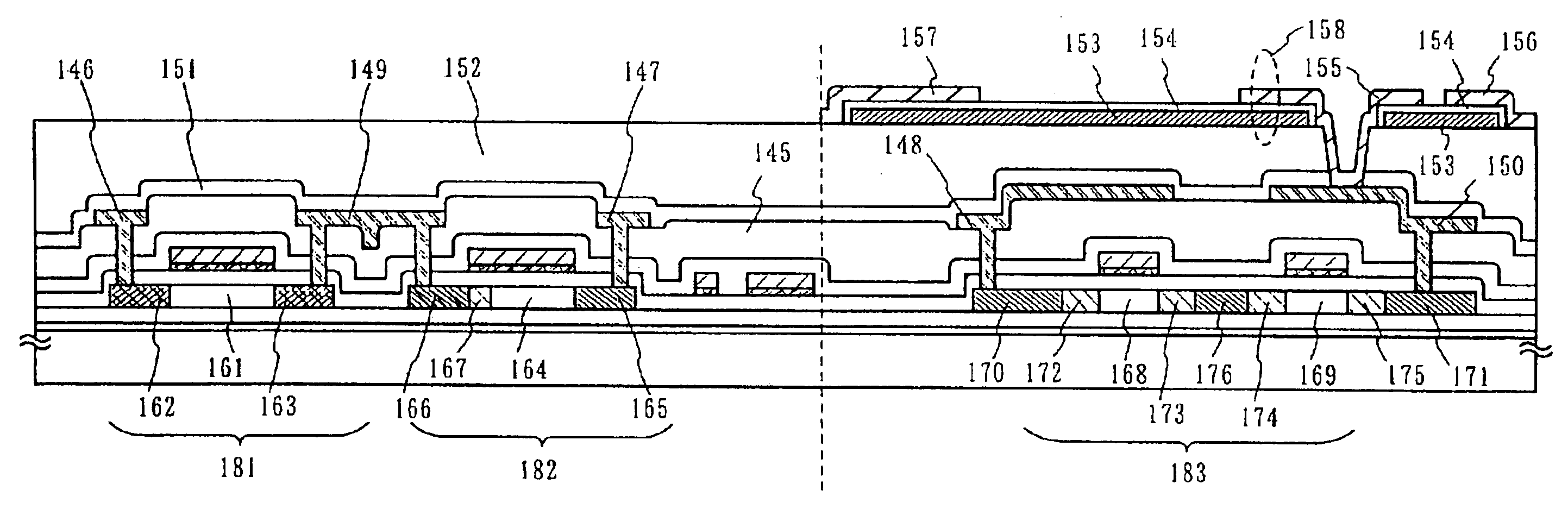

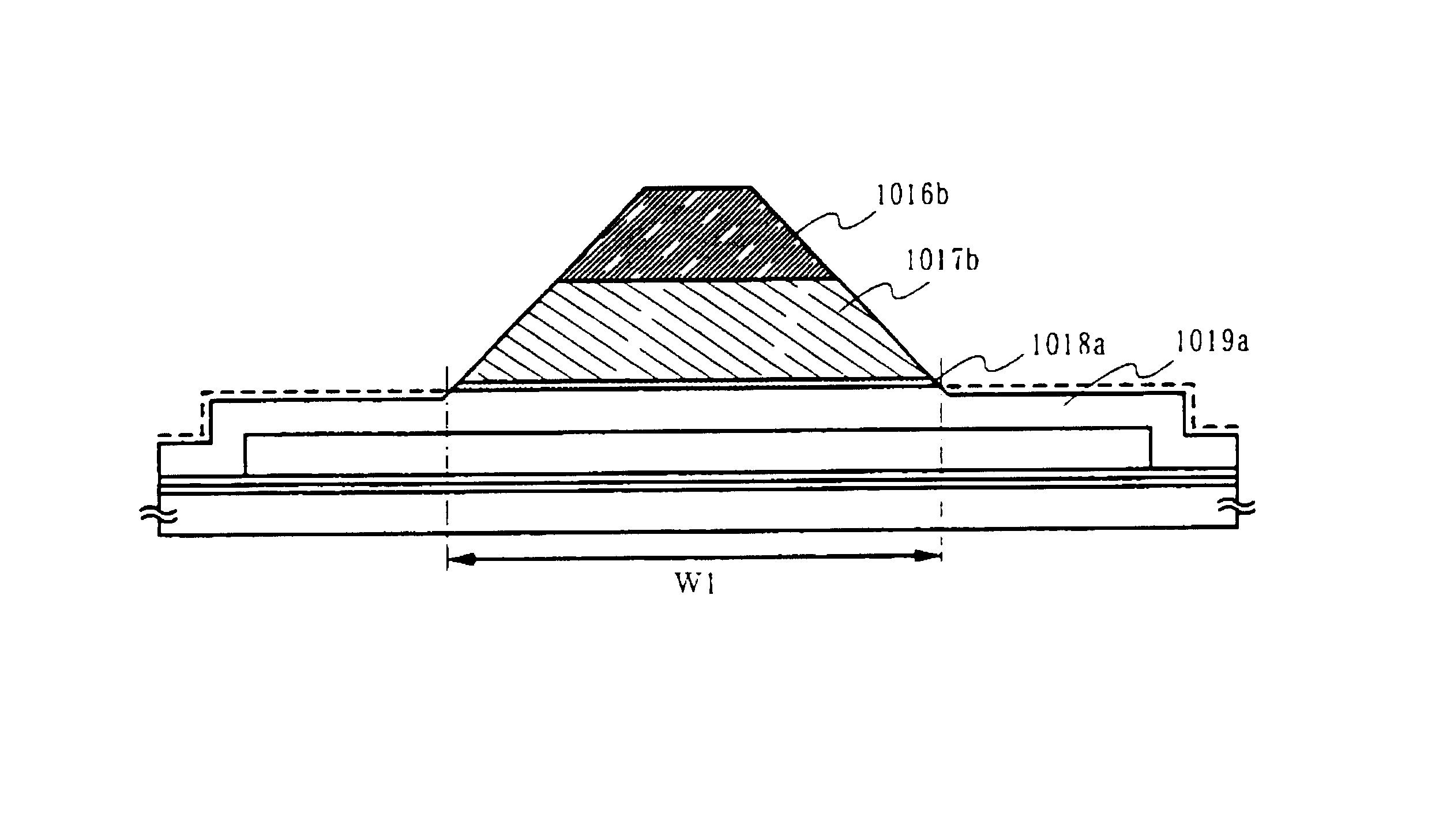

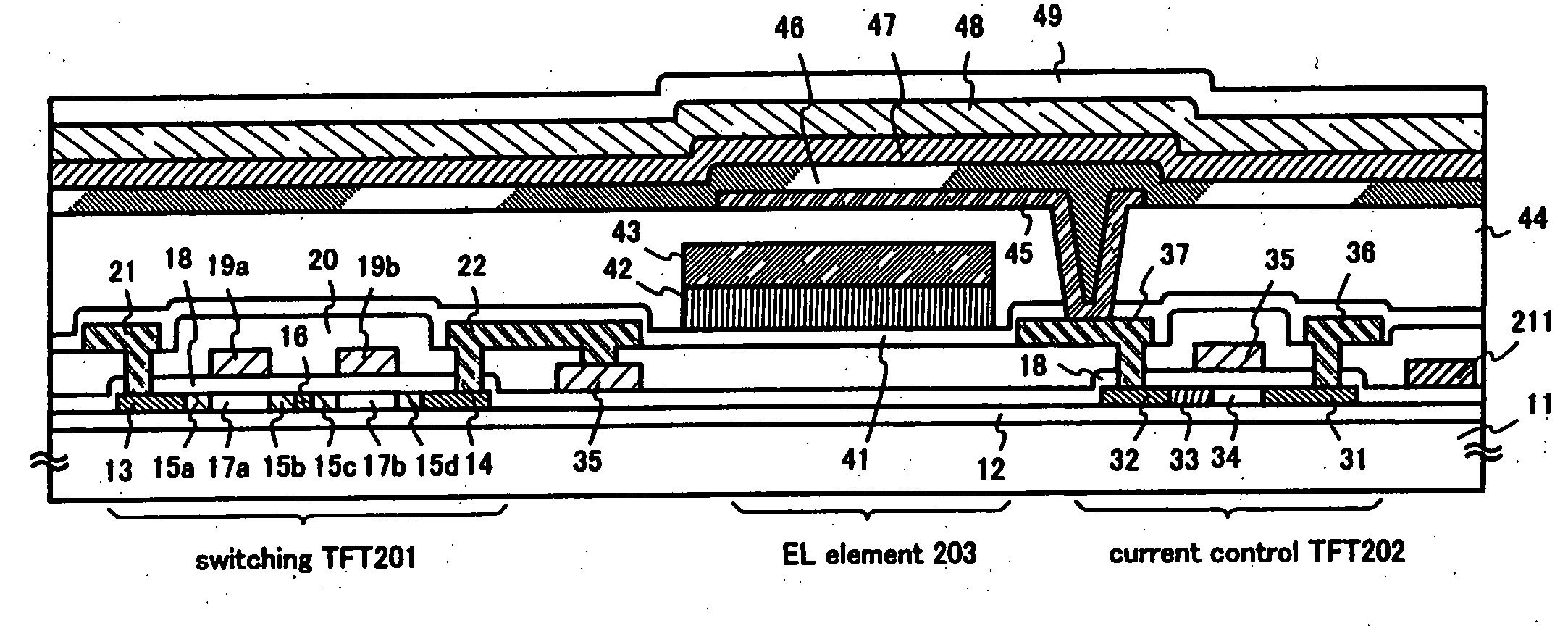

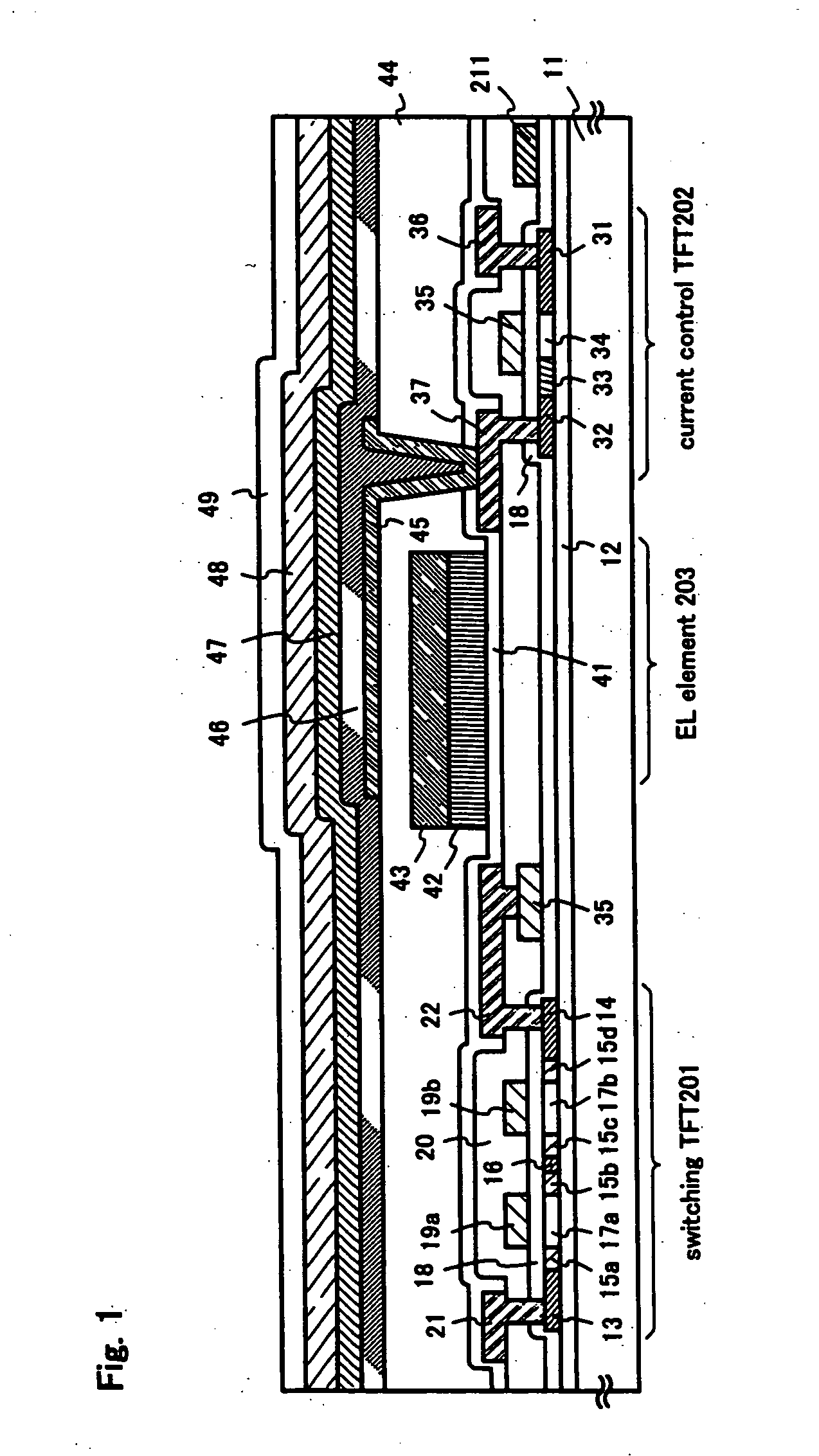

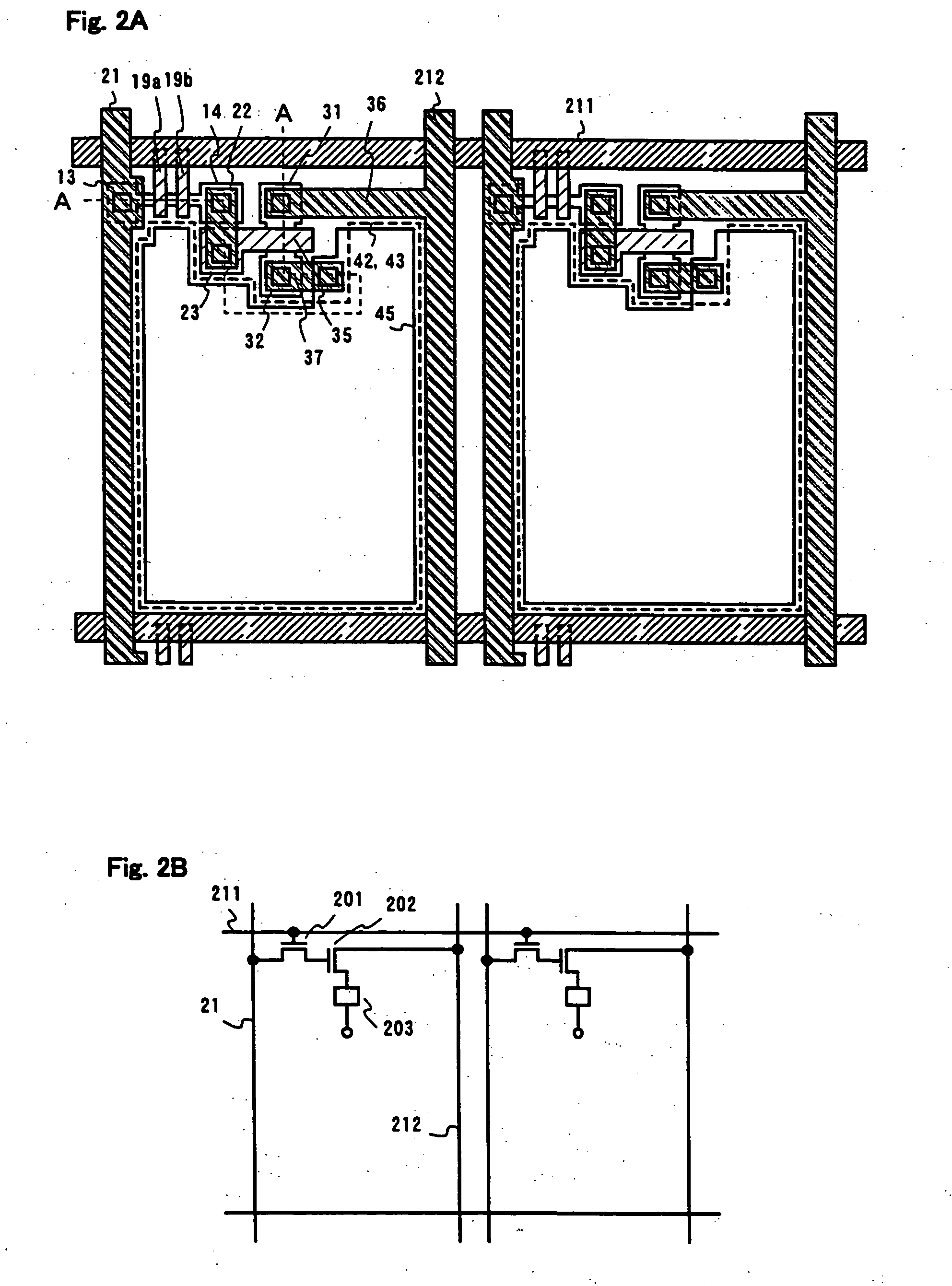

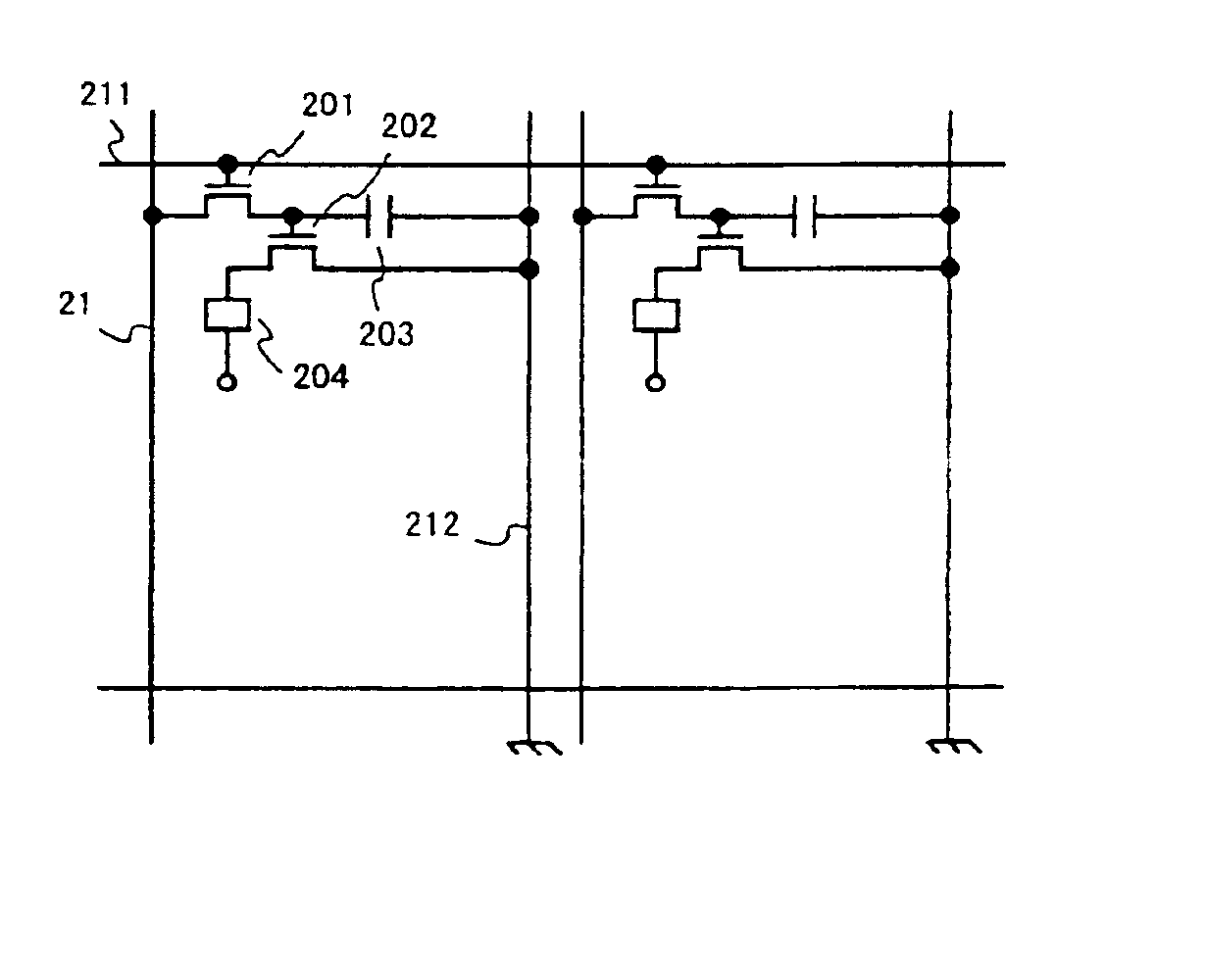

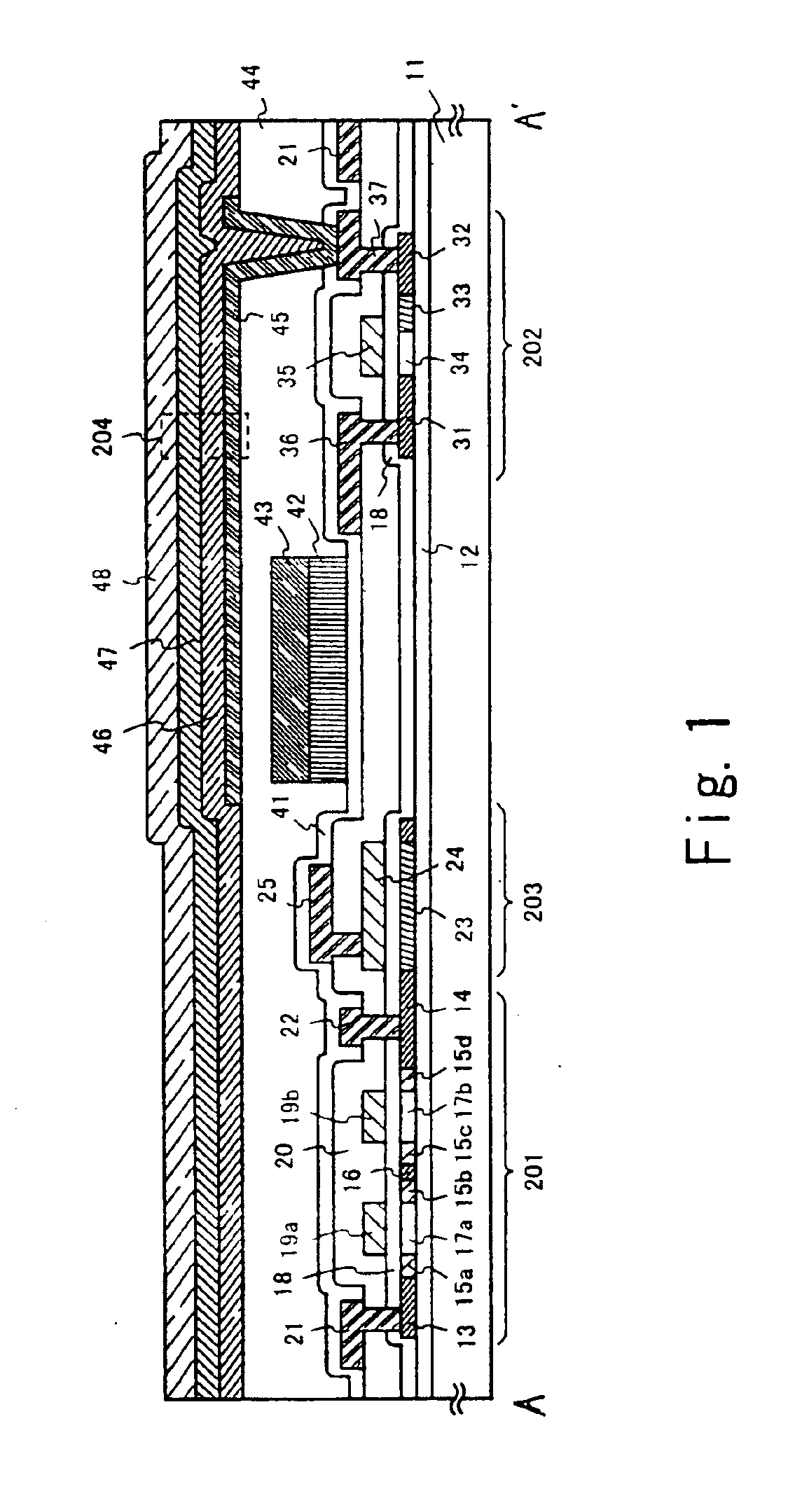

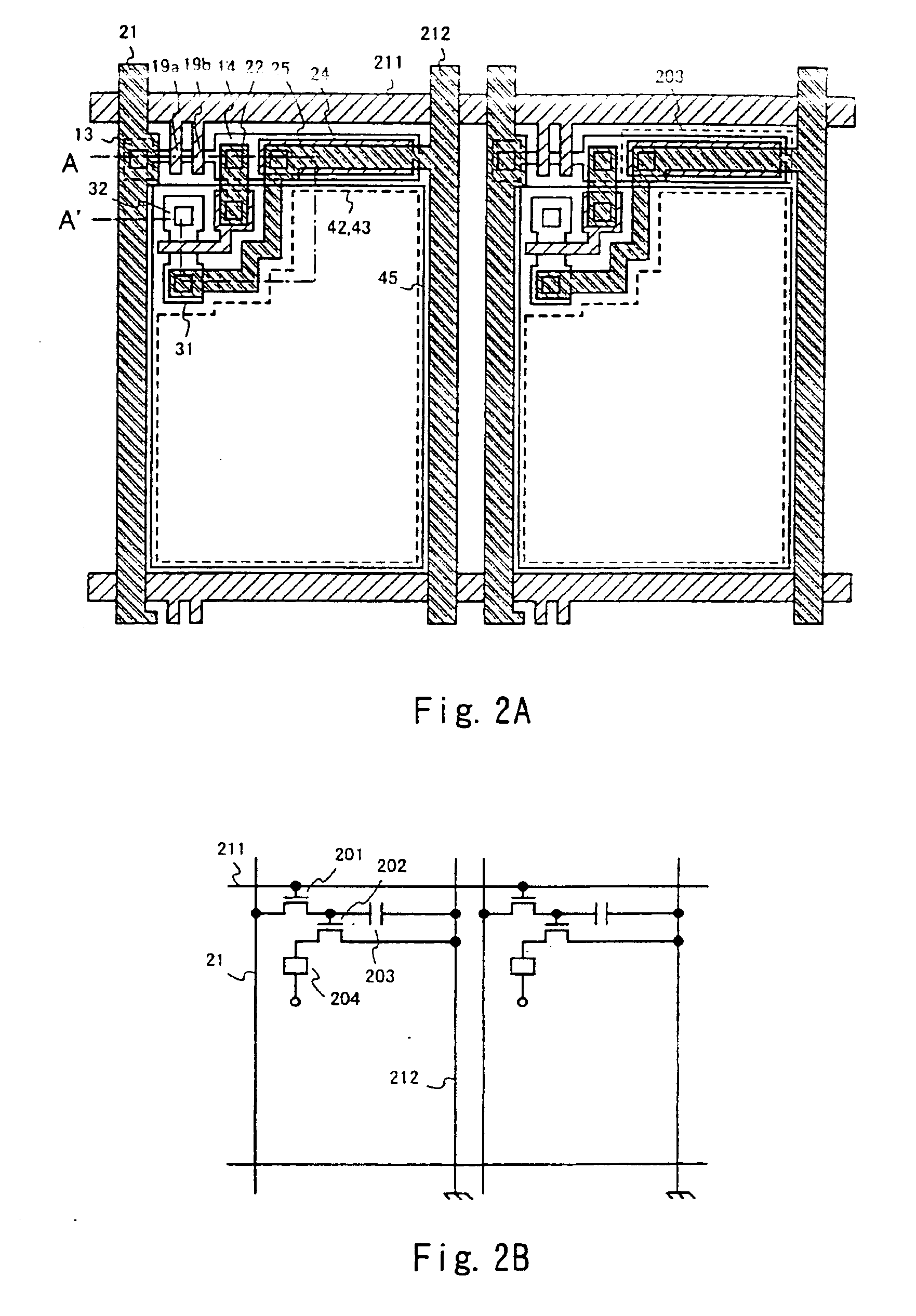

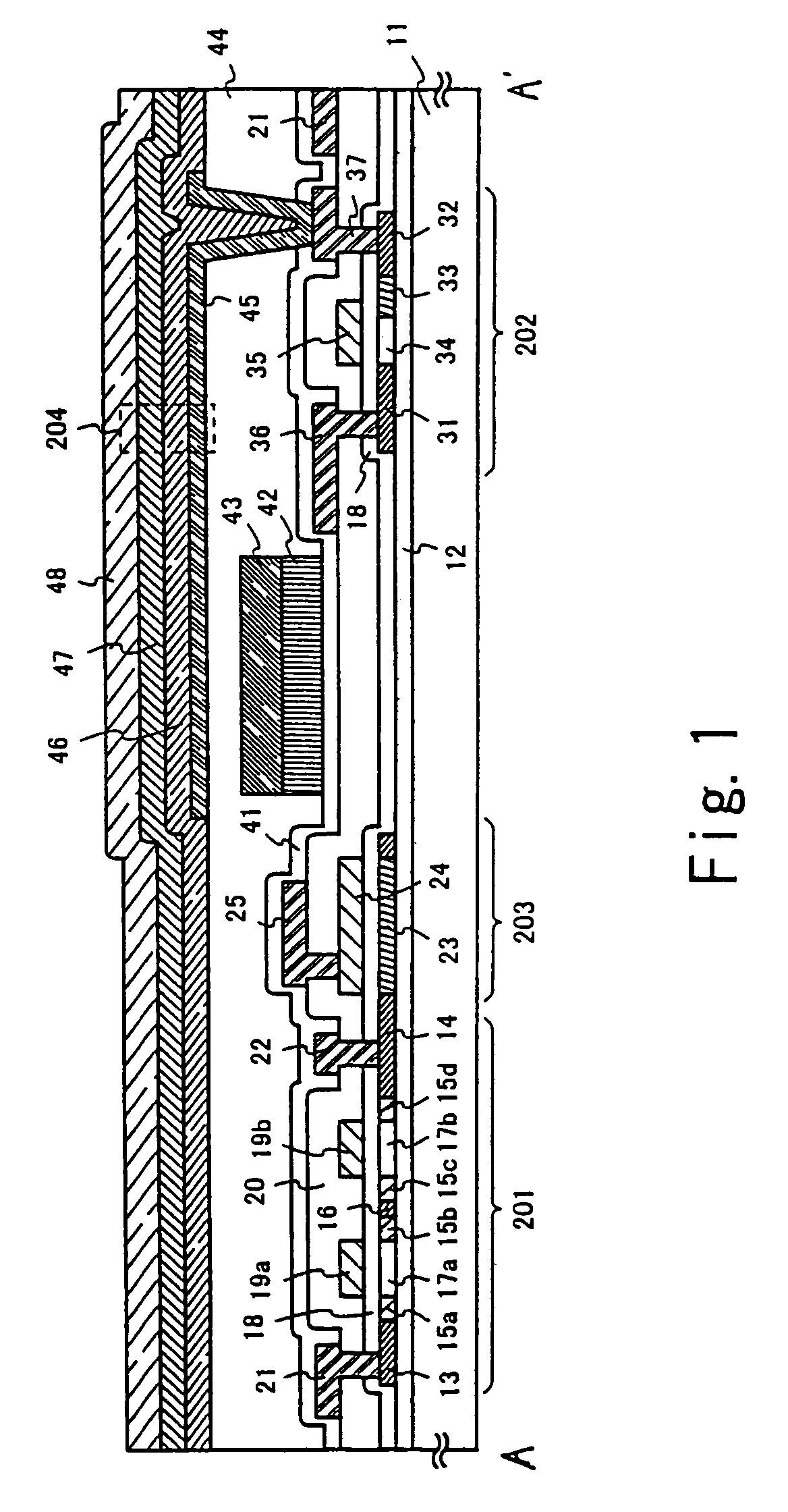

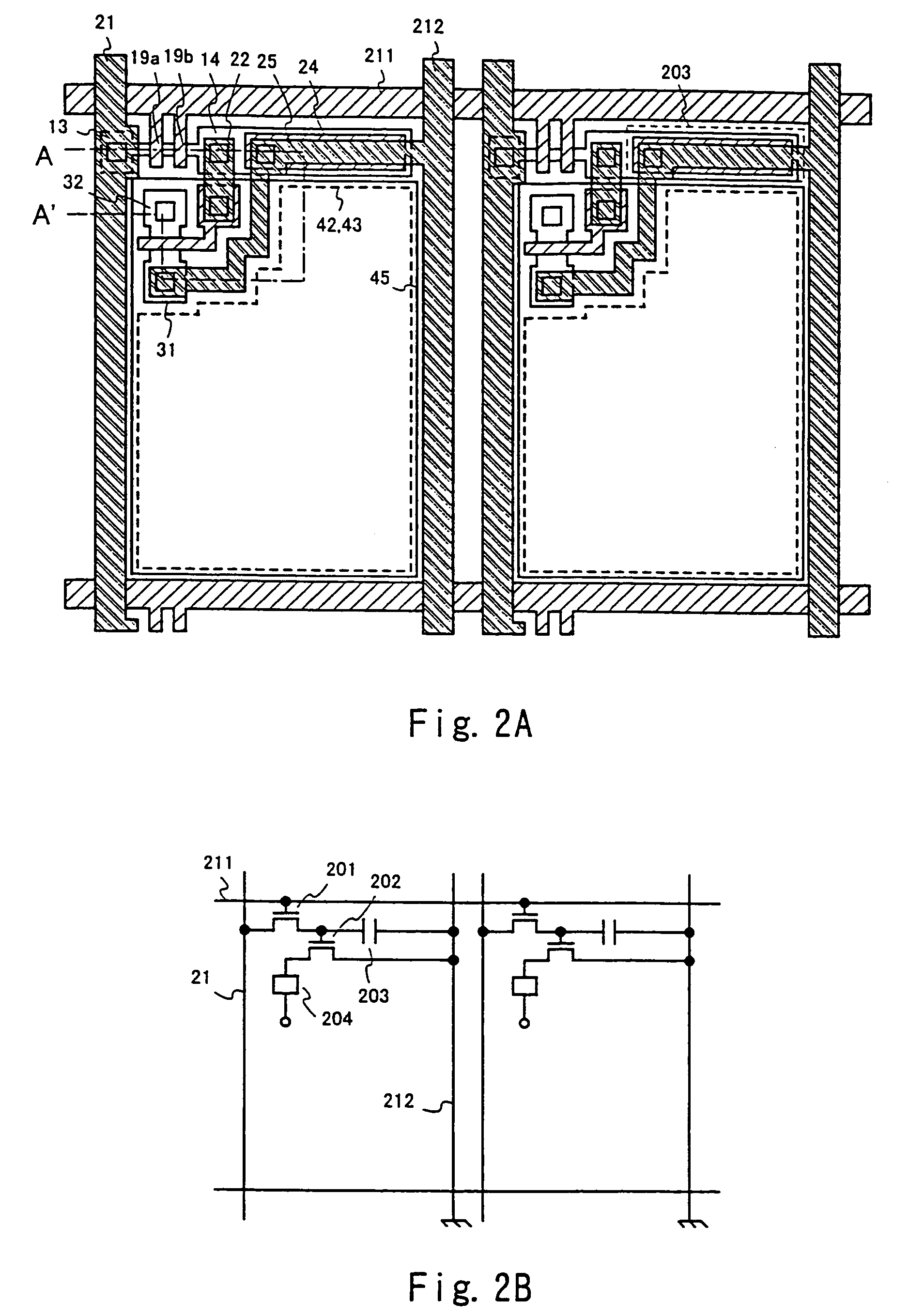

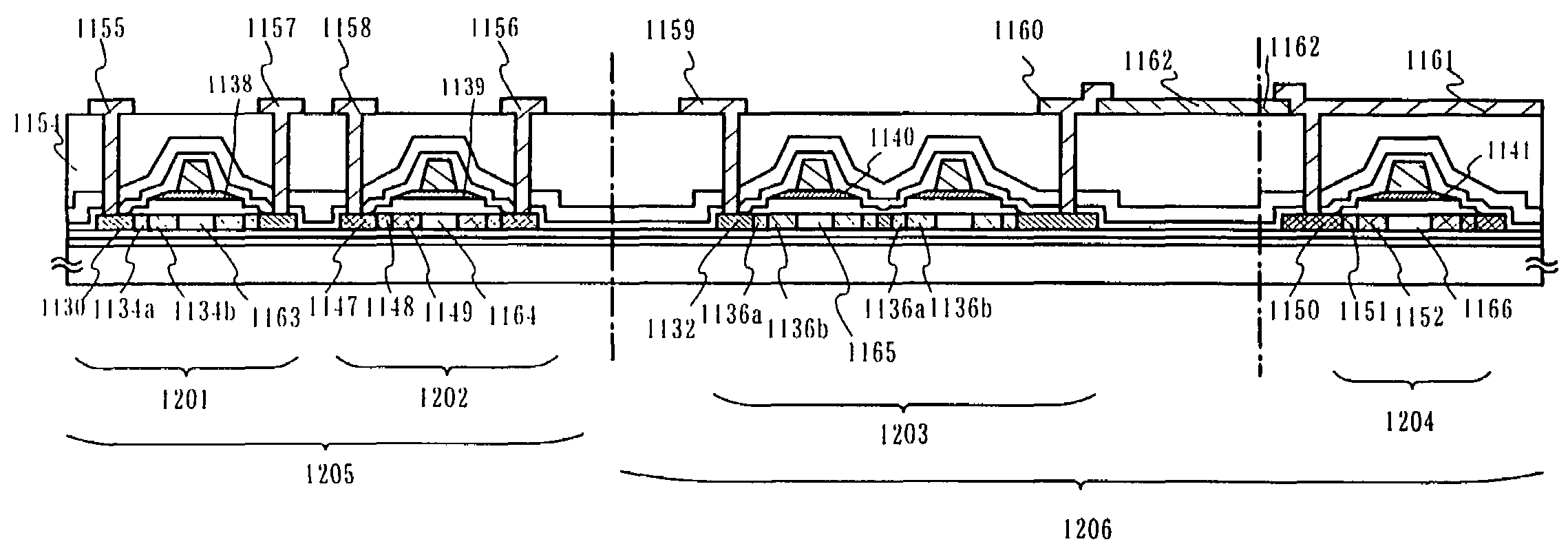

Electro-optical device and electronic device

InactiveUS20040065902A1Simple structureTransistorElectroluminescent light sourcesDisplay deviceEngineering

An object of the present invention is to provide an EL display device having a high operation performance and reliability. The switching TFT 201 formed within a pixel has a multi-gate structure, which is a structure which imposes an importance on reduction of OFF current value. Further, the current control TFT 202 has a channel width wider than that of the switching TFT to make a structure appropriate for flowing electric current. Morever, the LDD region 33 of the current control TFT 202 is formed so as to overlap a portion of the gate electrode 35 to make a structure which imposes importance on prevention of hot carrier injection and reduction of OFF current value.

Owner:SEMICON ENERGY LAB CO LTD

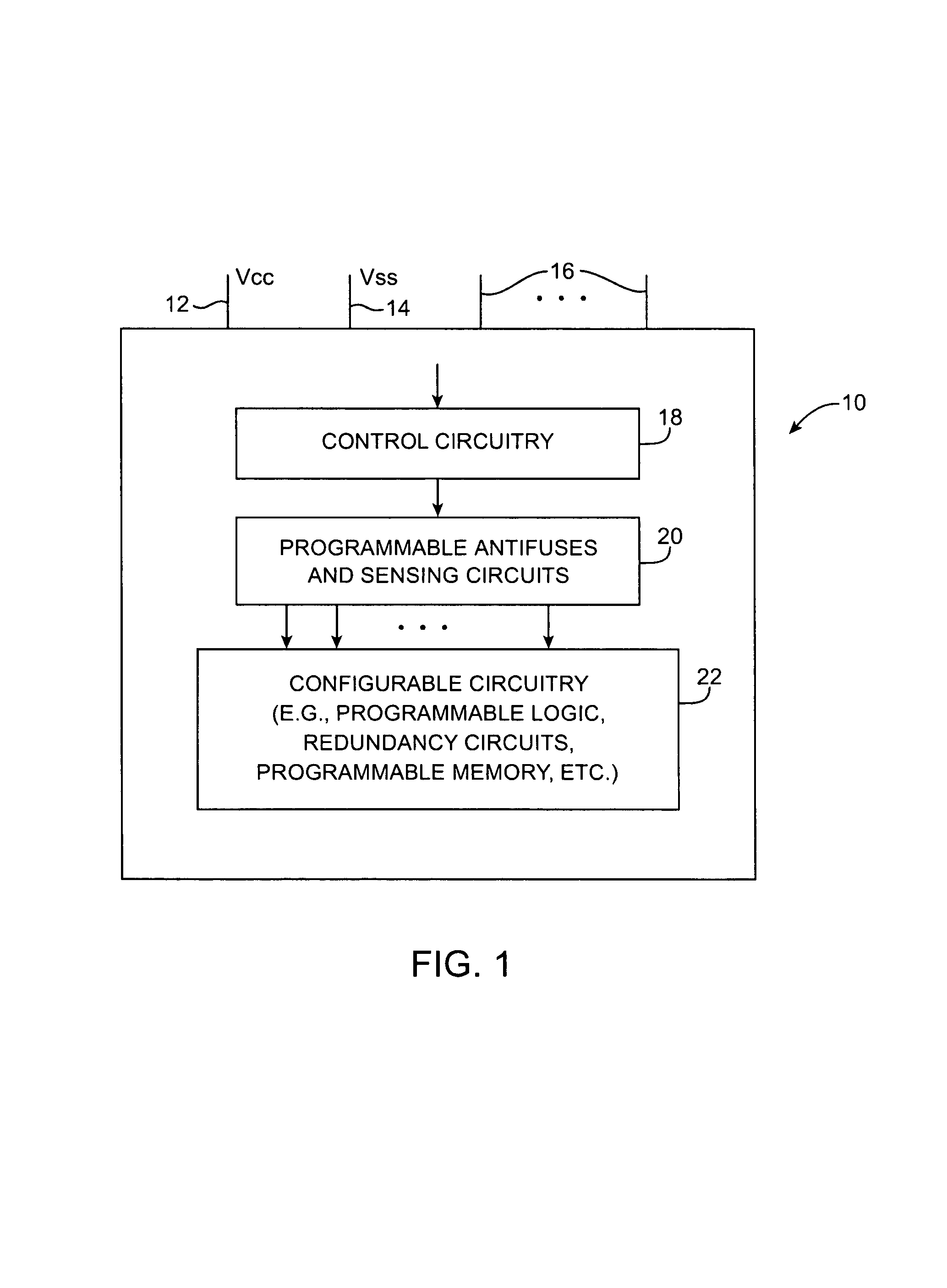

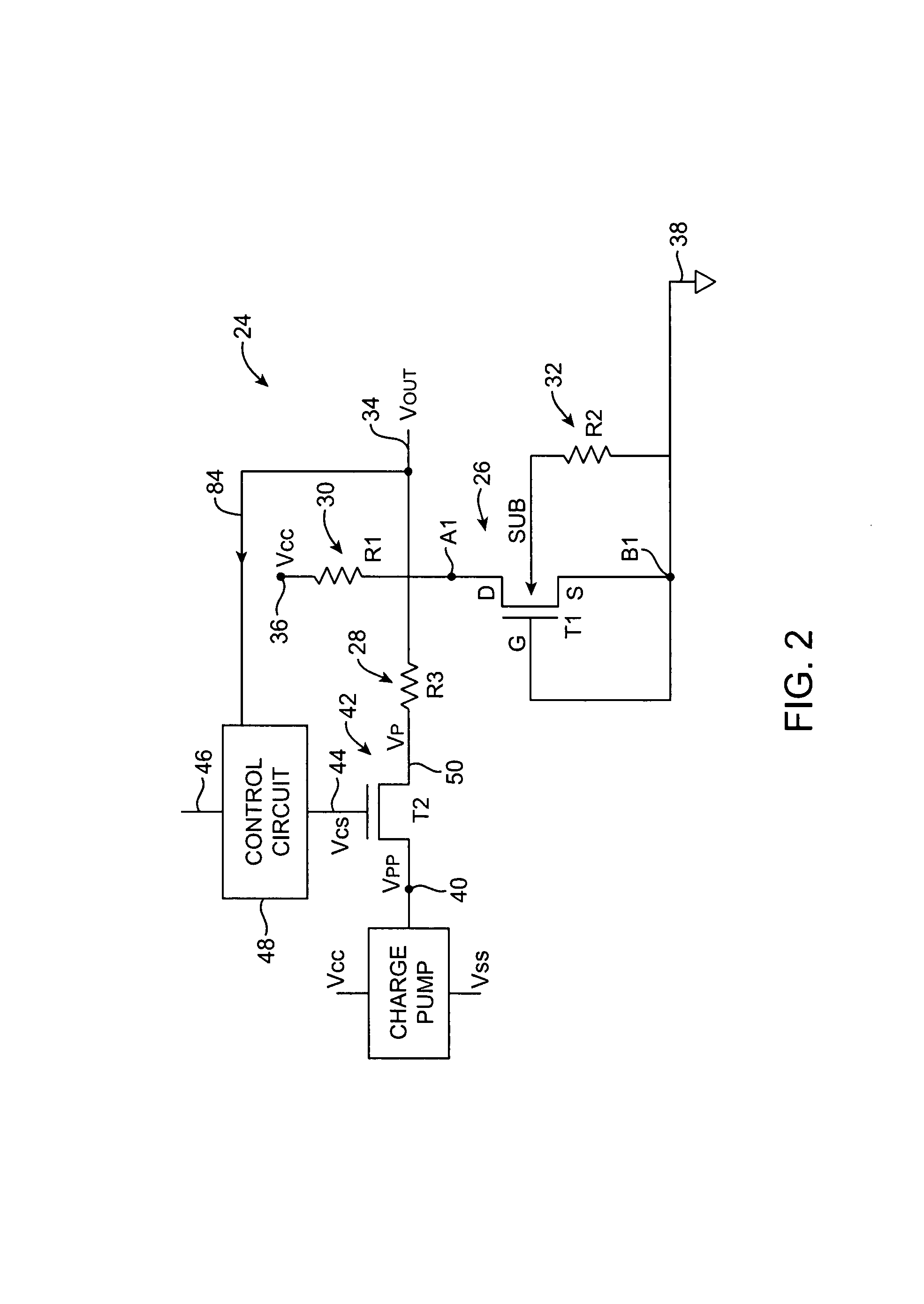

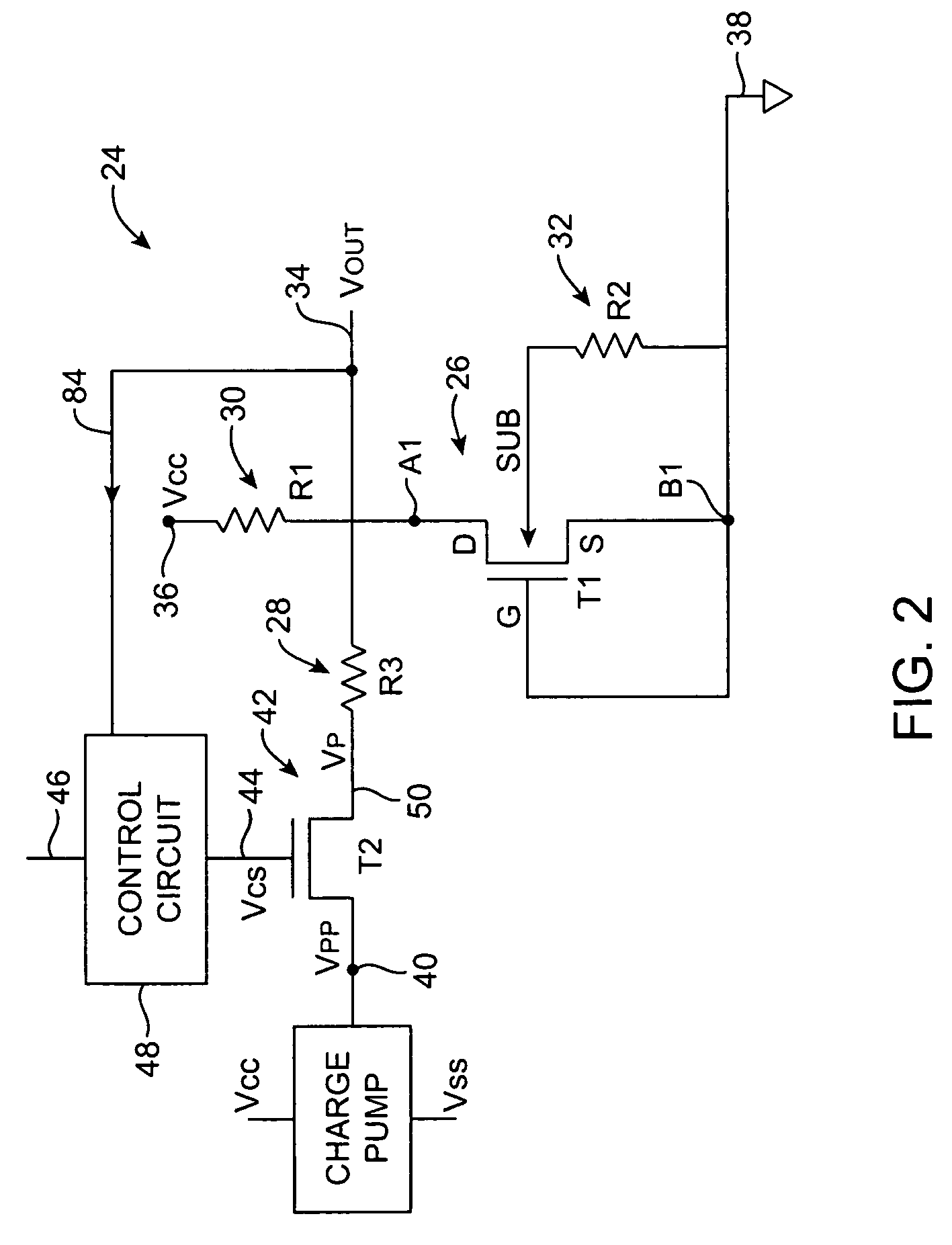

Electrically-programmable transistor antifuses

InactiveUS7157782B1Minimize powerMinimize timeTransistorSemiconductor/solid-state device detailsHigh resistanceEngineering

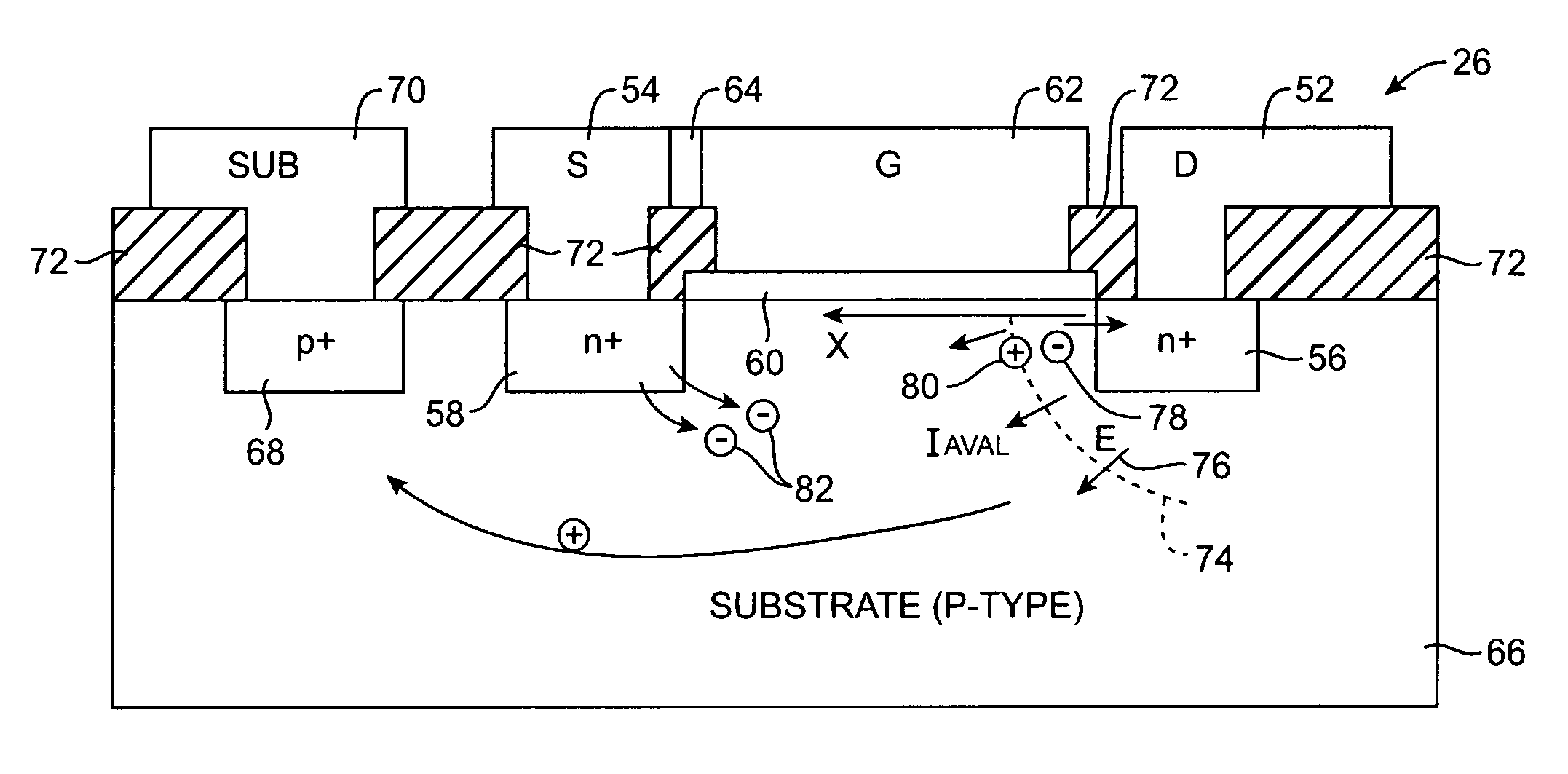

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) transistor serves as an electrically-programmable antifuse. The antifuse transistor has source, drain, gate, and substrate terminals. The gate has an associated gate oxide. In its unprogrammed state, the gate oxide is intact and the antifuse has a relatively high resistance. During programming, the gate oxide breaks down, so in its programmed state the antifuse transistor has a relatively low resistance. The antifuse transistor can be programmed by injecting hot carriers into the substrate of the device in the vicinity of the drain. Because there are more hot carriers at the drain than at the substrate, the gate oxide is stressed asymmetrically, which enhances programming efficiency. Feedback can be used to assist in turning the antifuse transistor on to inject the hot carriers.

Owner:ALTERA CORP

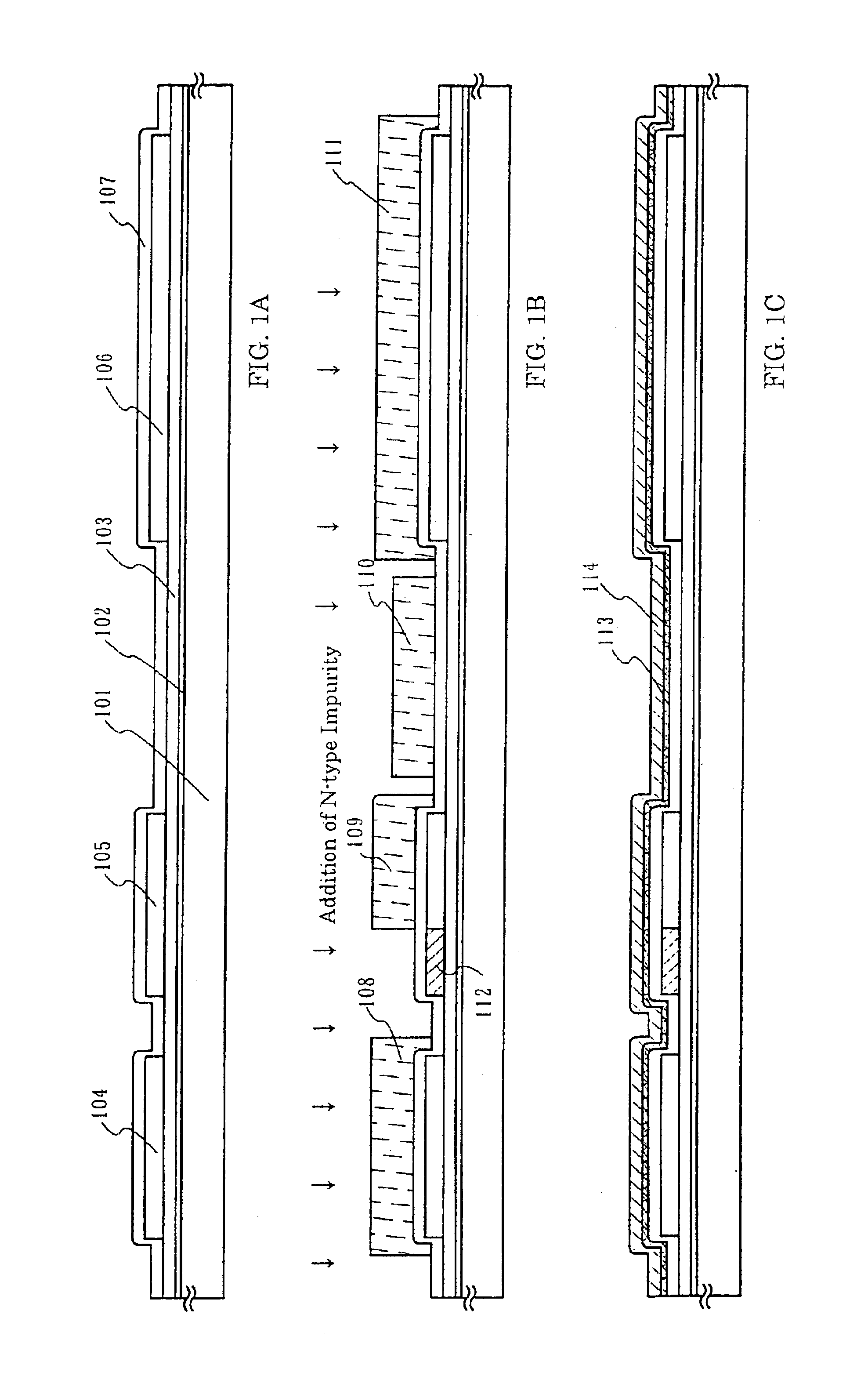

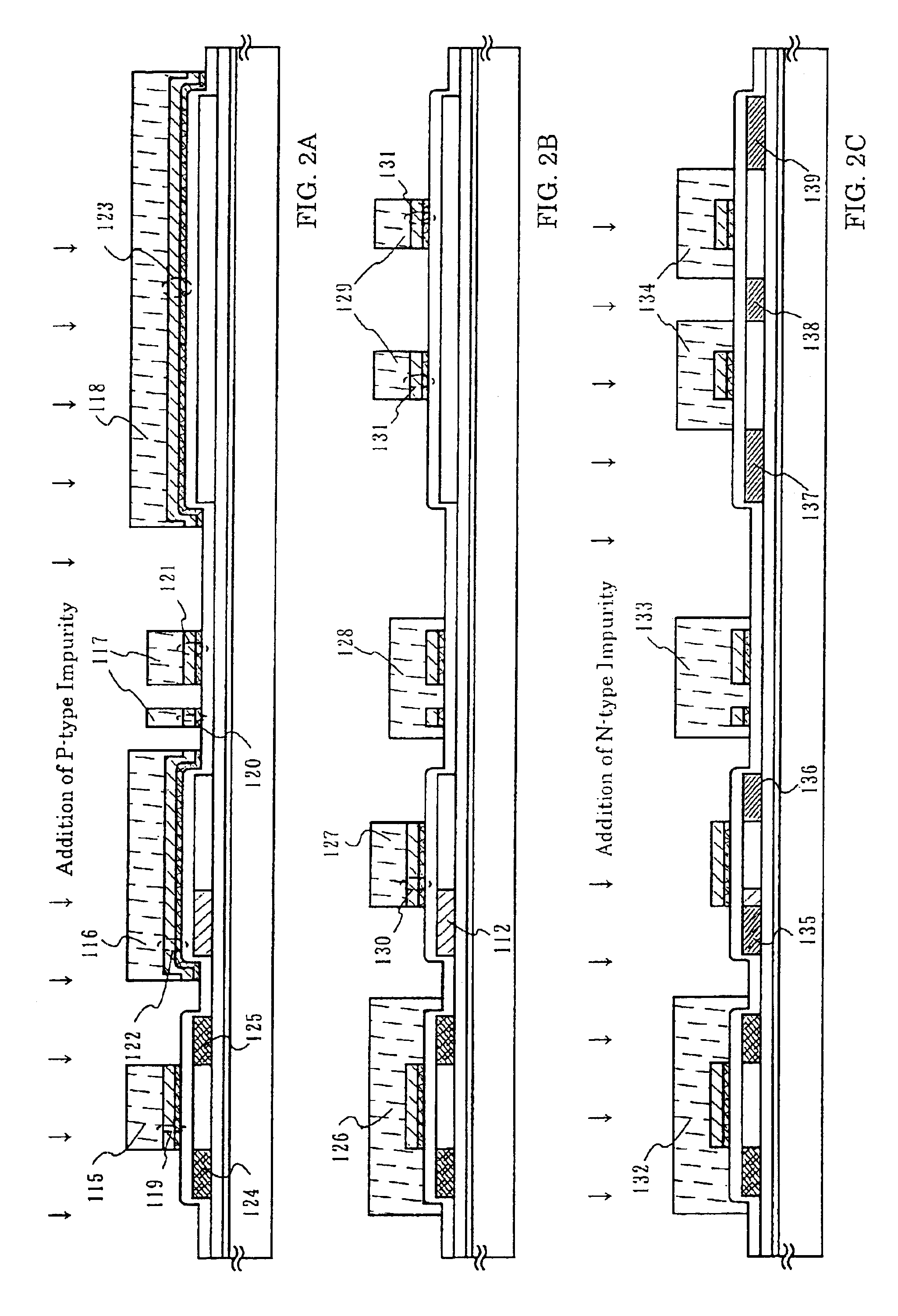

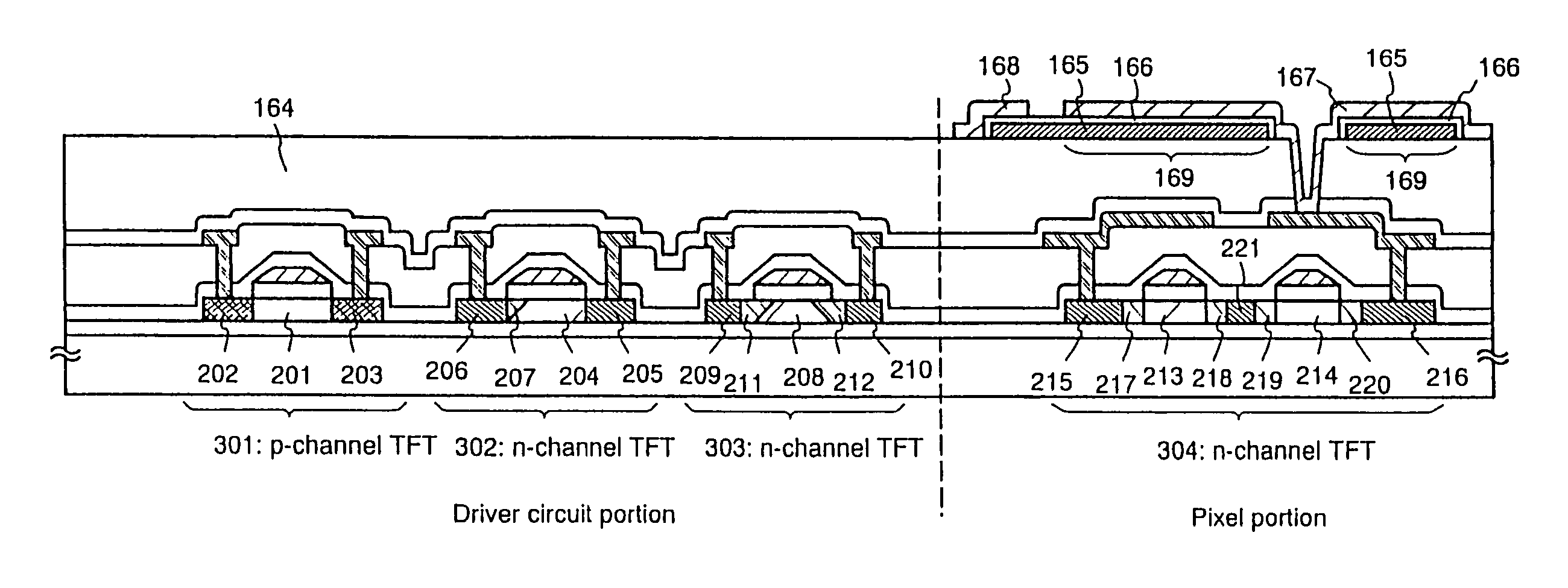

Semiconductor device and fabrication method thereof

InactiveUS6967129B2Improve performanceImprove reliabilityTransistorElectroluminescent light sourcesHigh concentrationEngineering

This invention provides a semiconductor device having high operation performance and high reliability. An LDD region 707 overlapping with a gate wiring is arranged in an n-channel TFT 802 forming a driving circuit, and a TFT structure highly resistant to hot carrier injection is achieved. LDD regions 717, 718, 719 and 720 not overlapping with a gate wiring are arranged in an n-channel TFT 804 forming a pixel unit. As a result, a TFT structure having a small OFF current value is achieved. In this instance, an element belonging to the Group 15 of the Periodic Table exists in a higher concentration in the LDD region 707 than in the LDD regions 717, 718, 719 and 720.

Owner:SEMICON ENERGY LAB CO LTD

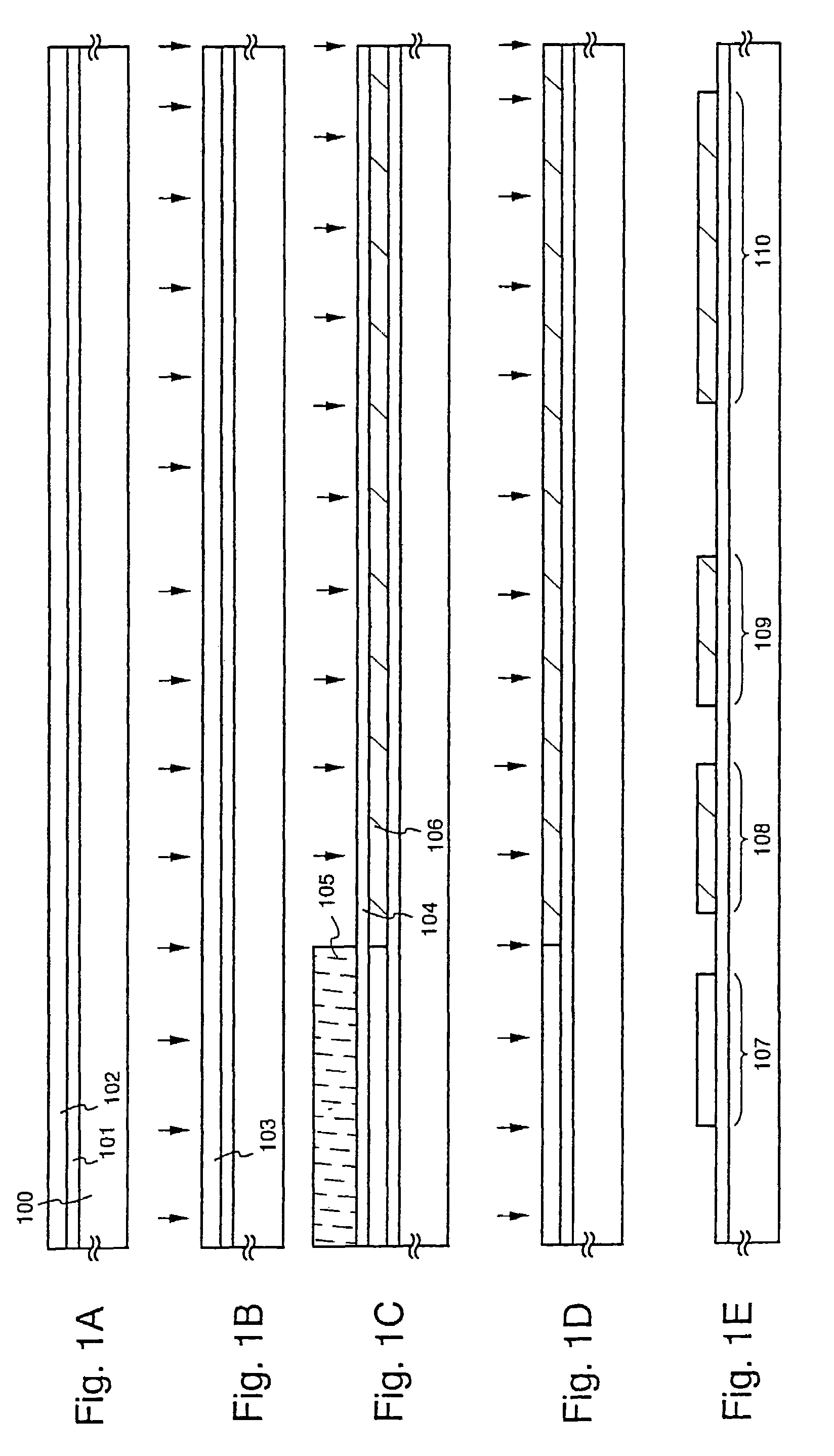

Electro-optical device and manufacturing method thereof

Owner:SEMICON ENERGY LAB CO LTD

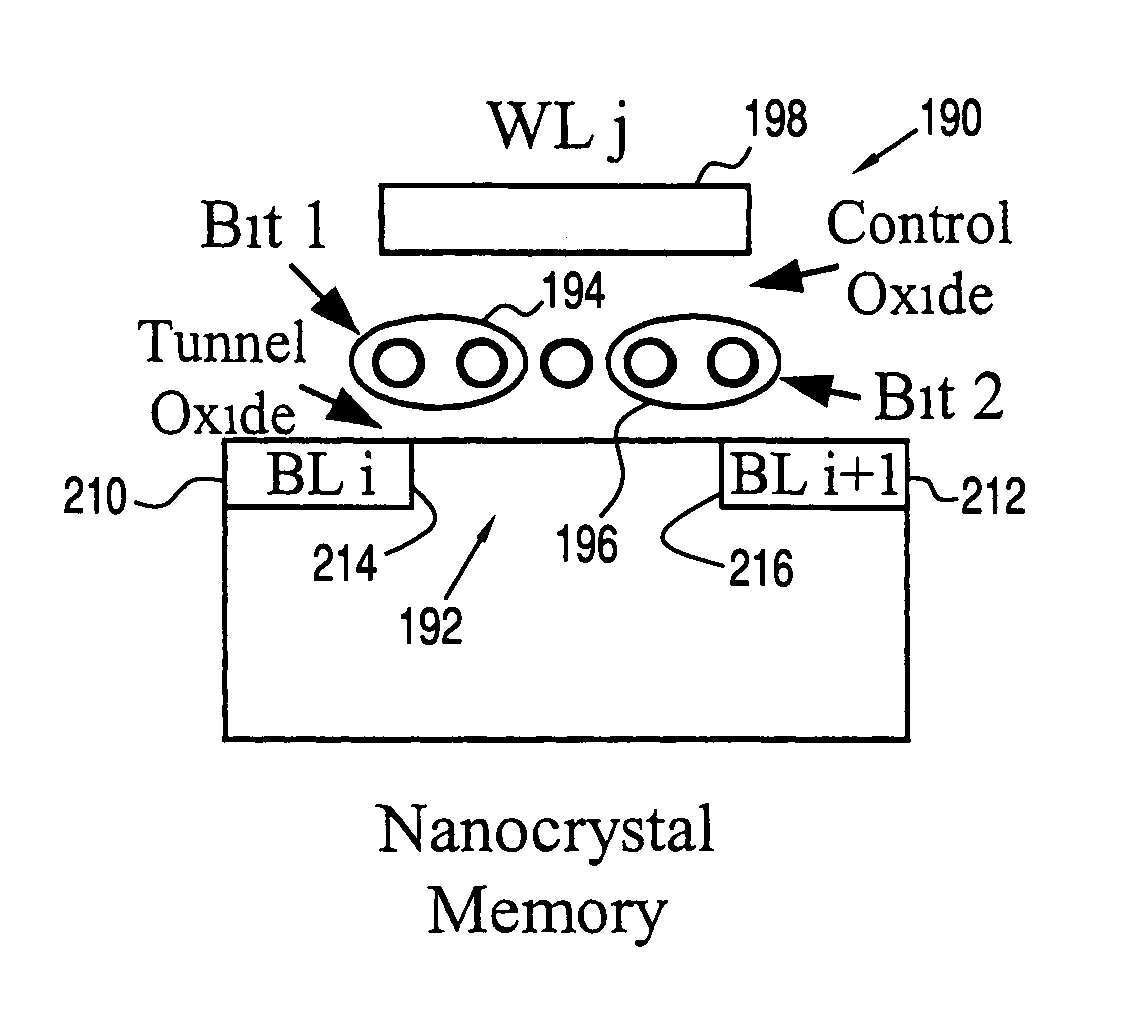

Multibit metal nanocrystal memories and fabrication

ActiveUS7259984B2Improve performanceImprove charge retentionNanoinformaticsRead-only memoriesRetention timeSemiconductor nanocrystals

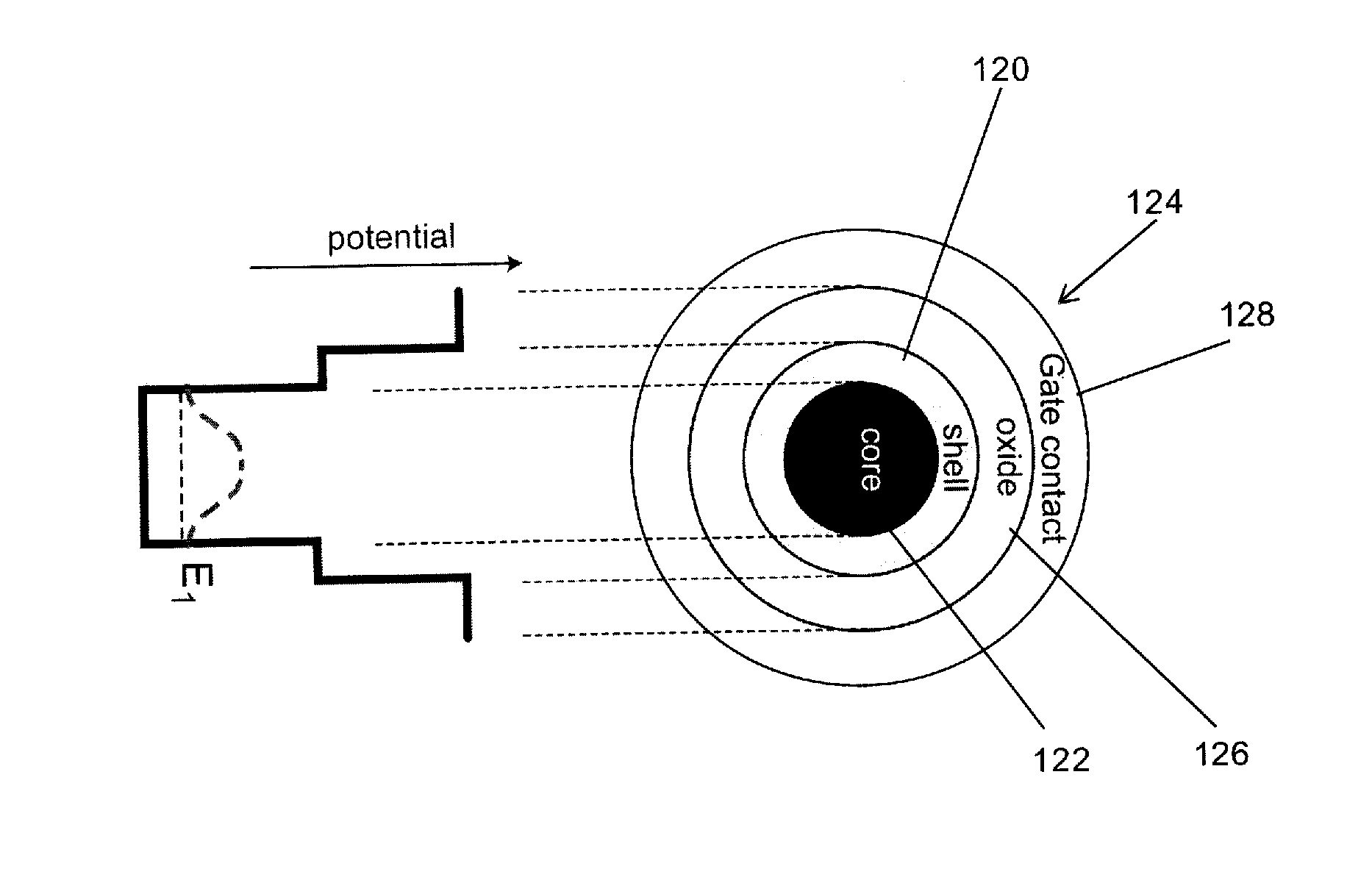

Metal nanocrystal memories are fabricated to include higher density states, stronger coupling with the channel, and better size scalability, than has been available with semiconductor nanocrystal devices. A self-assembled nanocrystal formation process by rapid thermal annealing of ultra thin metal film deposited on top of gate oxide is integrated with NMOSFET to fabricate such devices. Devices with Au, Ag, and Pt nanocrystals working in the F-N tunneling regime, with hot-carrier injection as the programming mechanism, demonstrate retention times up to 106s, and provide 2-bit-per-cell storage capability.

Owner:CORNELL RES FOUNDATION INC

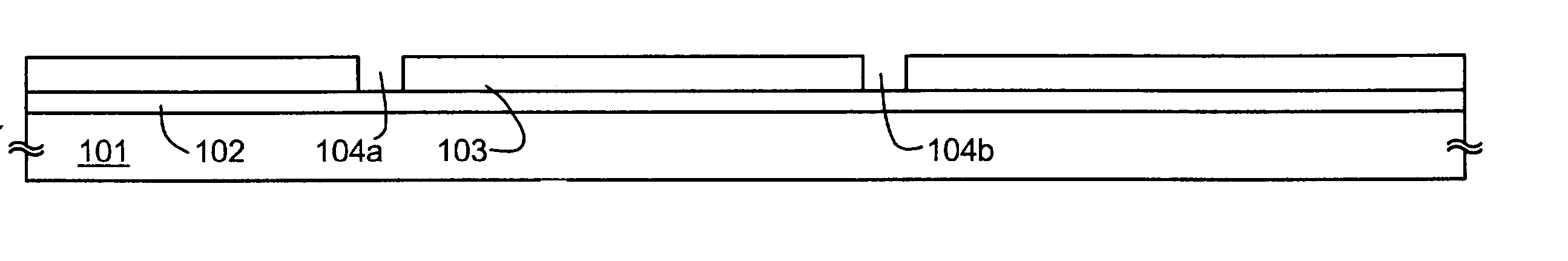

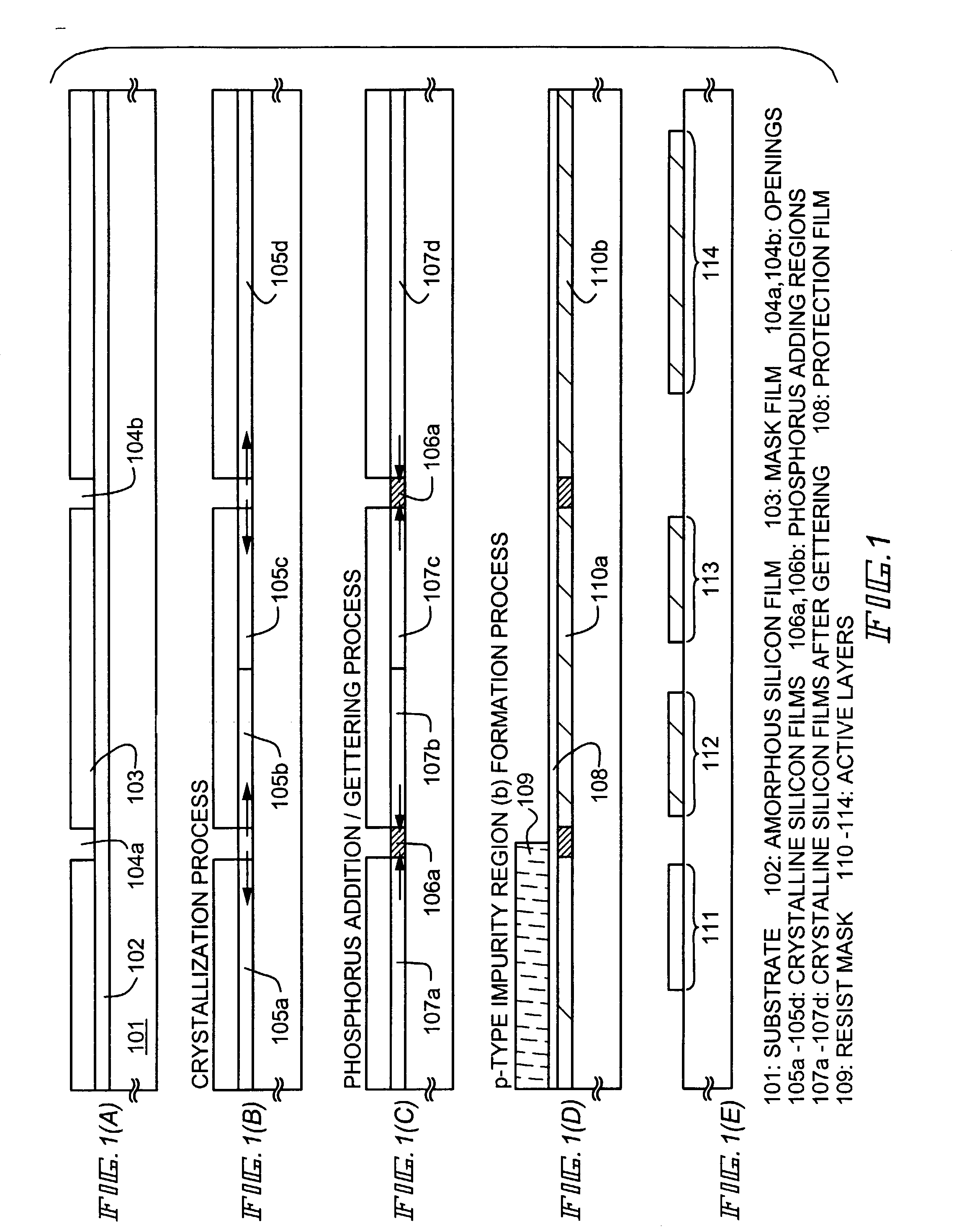

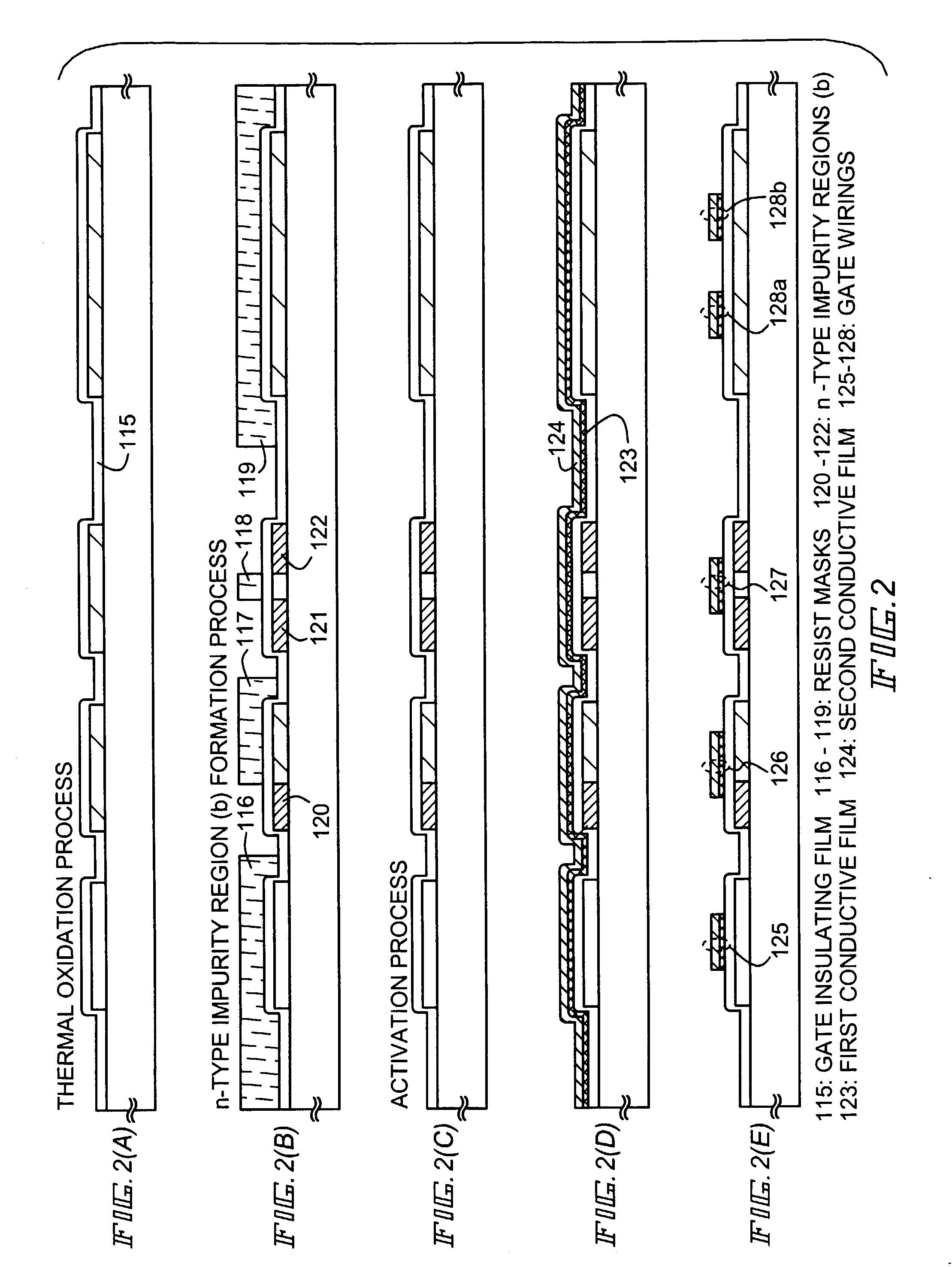

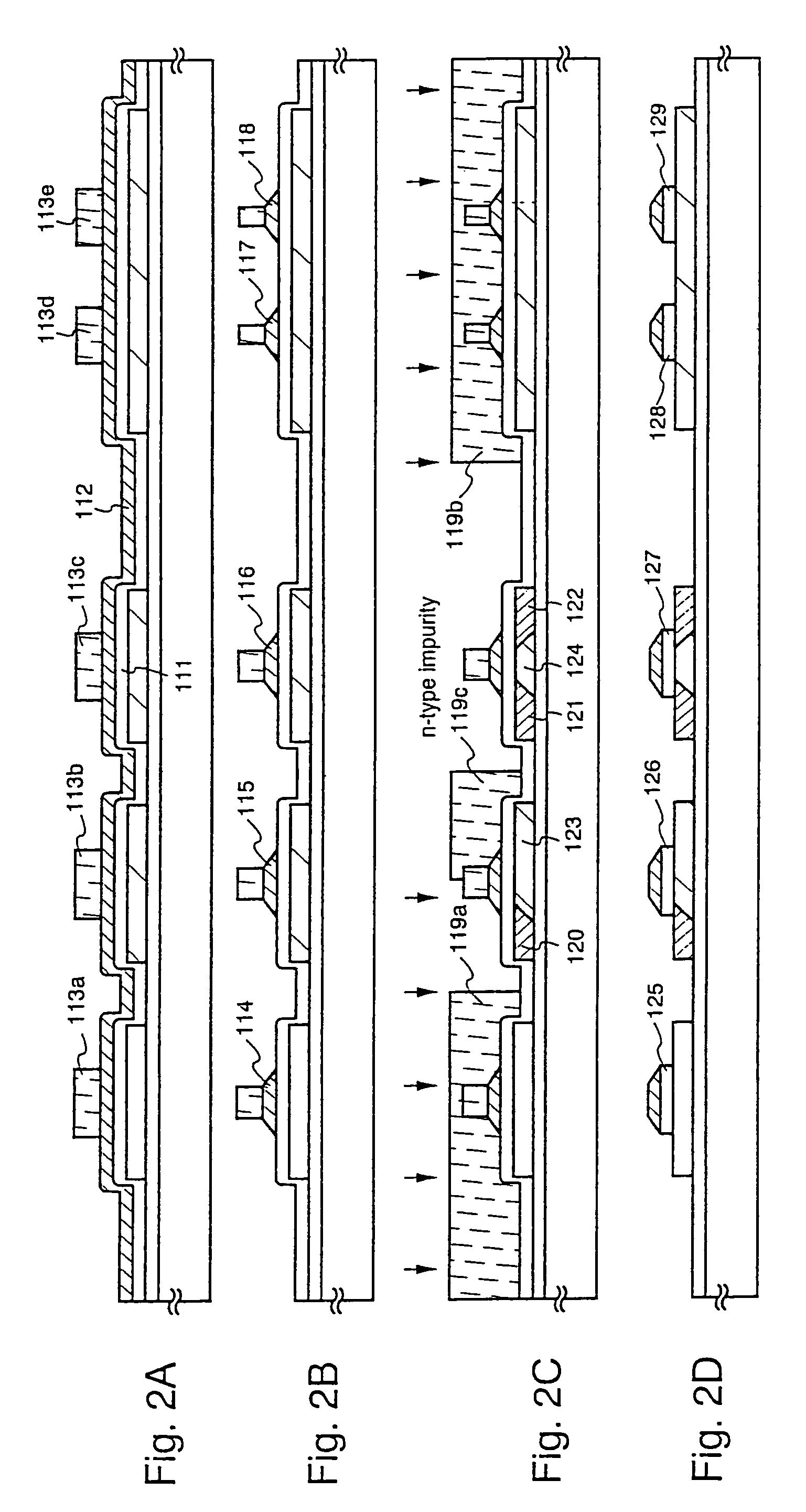

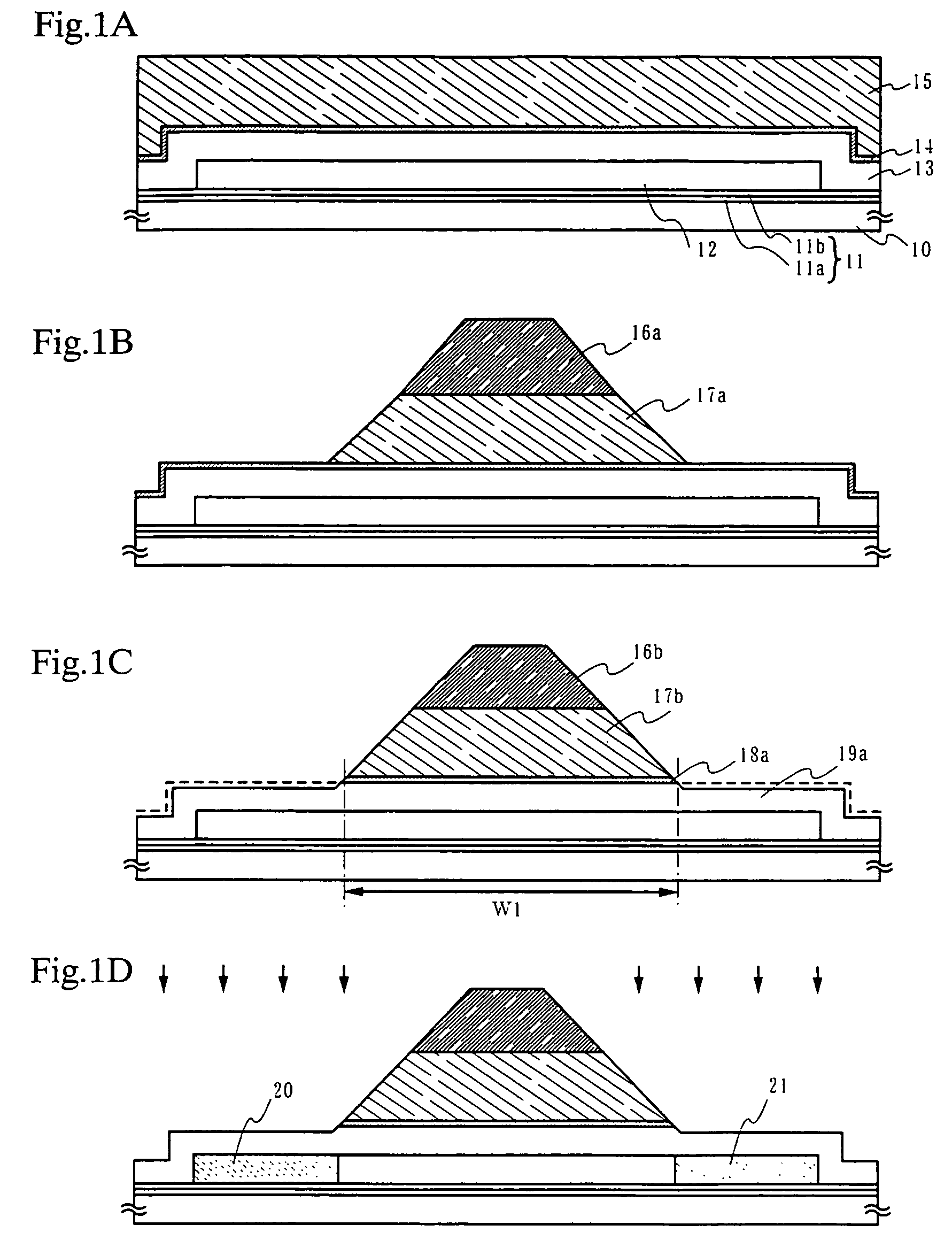

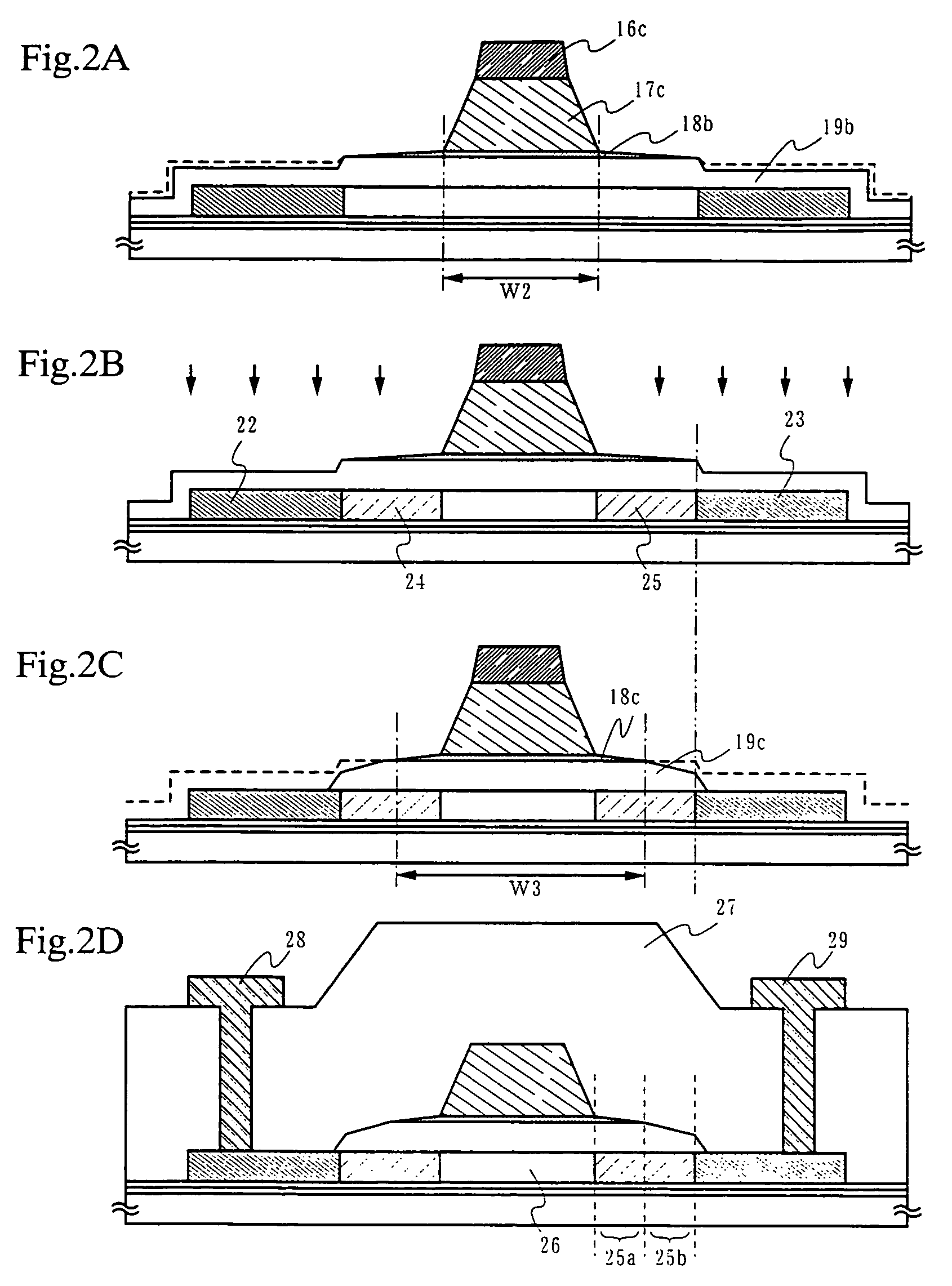

Semiconductor device and manufacturing method thereof

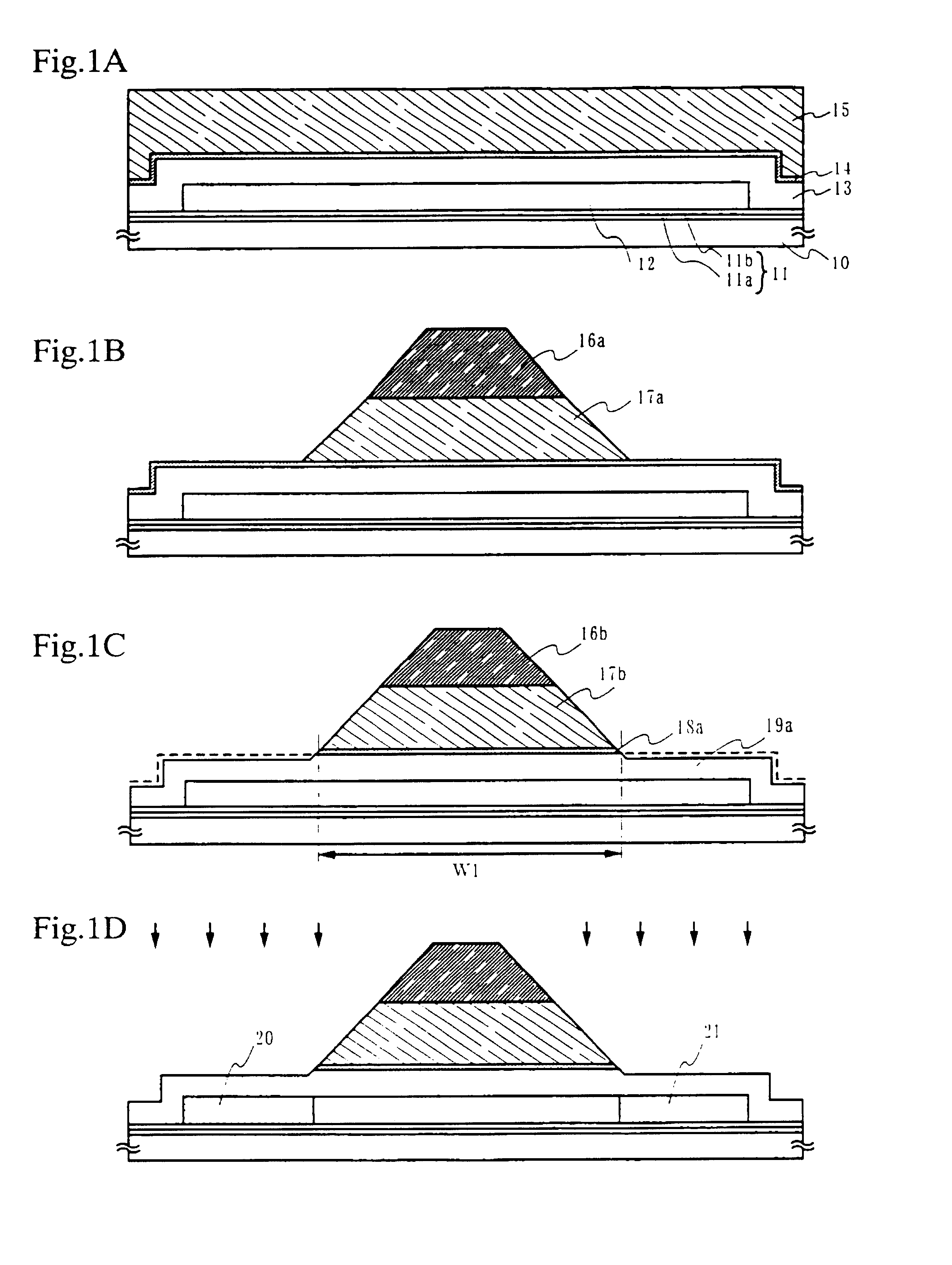

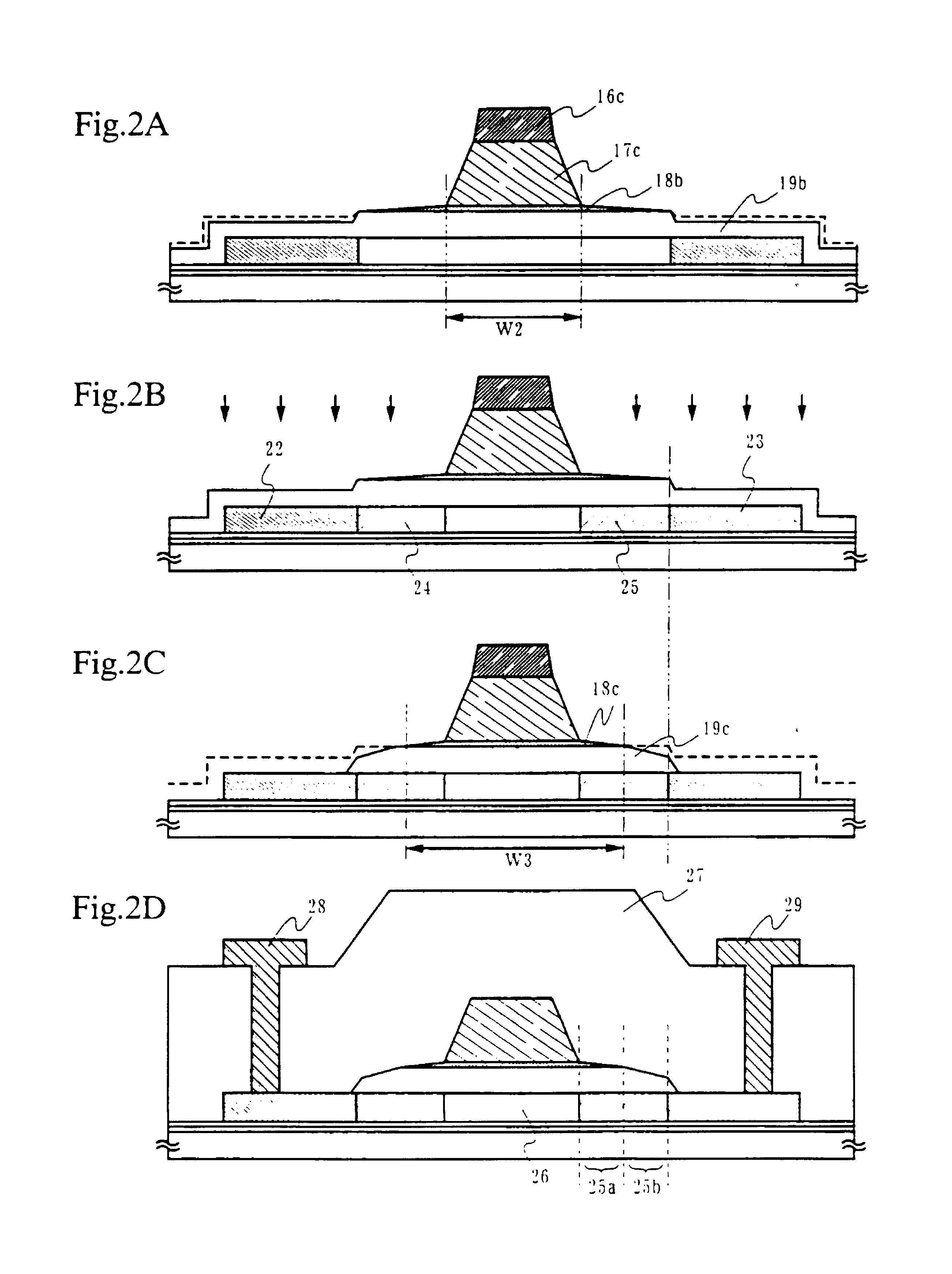

InactiveUS7151015B2Improvement of operation characteristicImprove reliabilityTransistorSolid-state devicesImpuritySemiconductor

There has been a problem that the manufacturing process is complicated and the number of processes is increased when a TFT with an LDD structure or a TFT with a GOLD structure is formed. In a method of manufacturing a semiconductor device, after low concentration impurity regions (24, 25) are formed in a second doping process, a width of the low concentration impurity region which is overlapped with the third electrode (18c) and a width of the low concentration impurity region which is not overlapped with the third electrode can be freely controlled by a fourth etching process. Thus, in a region overlapped with the third electrode, a relaxation of electric field concentration is achieved and then a hot carrier injection can be prevented. And, in the region which is not overlapped with the third electrode, the off-current value can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

Electro-optical device and electronic device

InactiveUS20050161672A1Guaranteed uptimeImprove reliabilityTransistorElectroluminescent light sourcesDisplay deviceEngineering

An object of the present invention is to provide an EL display device having a high operation performance and reliability. The switching TFT 201 formed within a pixel has a multi-gate structure, which is a structure which imposes an importance on reduction of OFF current value. Further, the current control TFT 202 has a channel width wider than that of the switching TFT to make a structure appropriate for flowing electric current. Morever, the LDD region 33 of the current control TFT 202 is formed so as to overlap a portion of the gate electrode 35 to make a structure which imposes importance on prevention of hot carrier injection and reduction of OFF current value.

Owner:SEMICON ENERGY LAB CO LTD

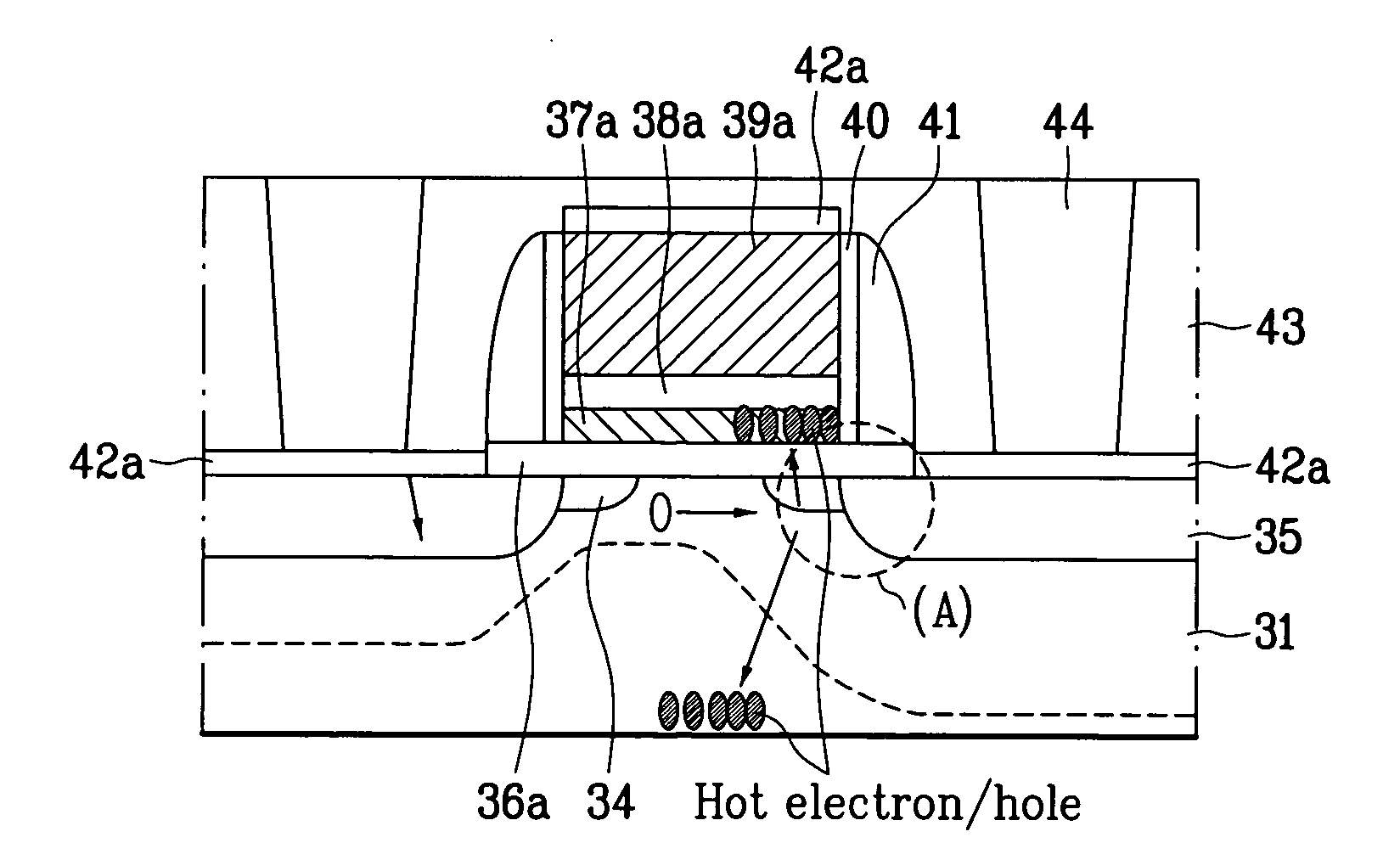

Semiconductor device and manufacturing method thereof

InactiveUS7015141B2Guaranteed uptimeImprove reliabilityTransistorSolid-state devicesEngineeringImpurity

A semiconductor device having high operating performance and reliability, and a manufacturing method thereof are provided.An LDD region 207 provided in an n-channel TFT 302 forming a driving circuit enhances the tolerance for hot carrier injection. LDD regions 217–220 provided in an n-channel TFT (pixel TFT) 304 forming a pixel portion greatly contribute to the decrease in the OFF current value. Here, the LDD region of the n-channel TFT of the driving circuit is formed such that the concentration of the n-type impurity element becomes higher as the distance from an adjoining drain region decreases.

Owner:SEMICON ENERGY LAB CO LTD

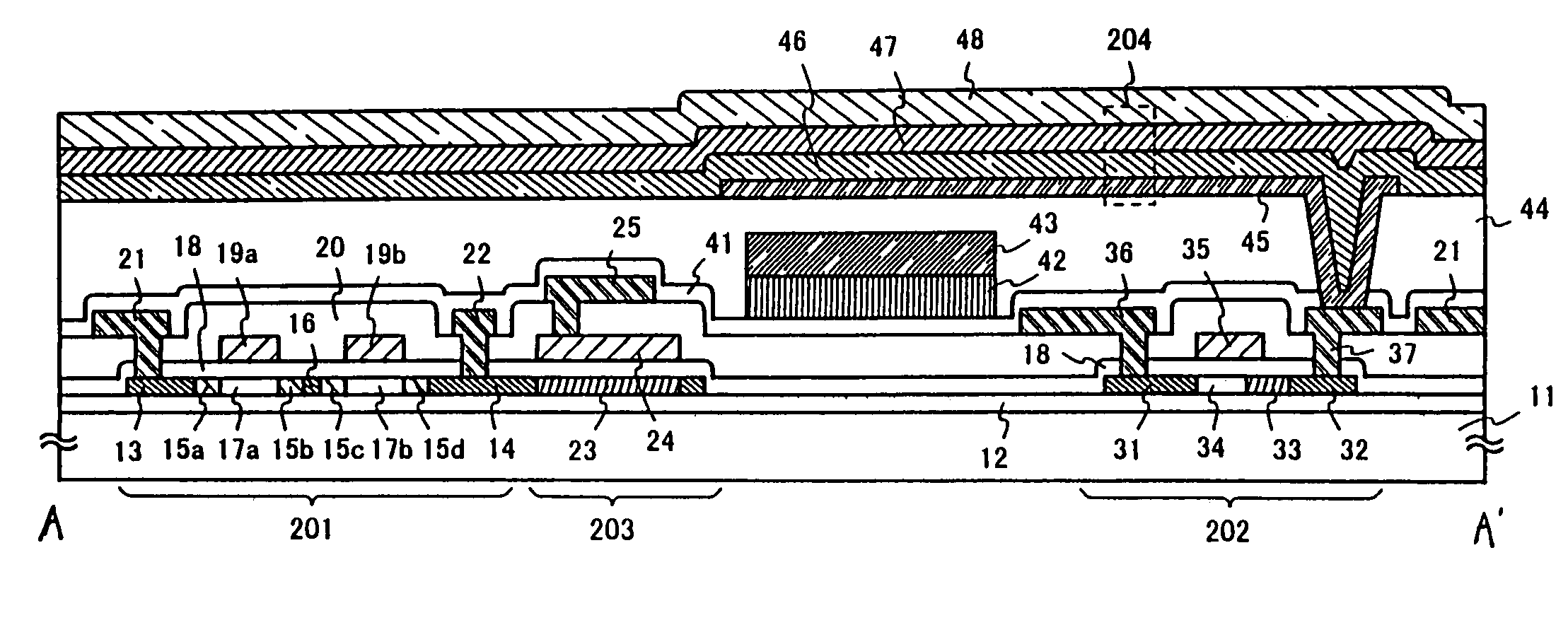

Electronic device and electronic apparatus

InactiveUS6879309B2Guaranteed uptimeImprove reliabilityTransistorStatic indicating devicesHot-carrier injectionElectronic equipment

An EL display having high operating performance and reliability is provided. LDD regions 15a through 15d of a switching TFT 201 formed in a pixel are formed such that they do not overlap gate electrodes 19a and 19b to provide a structure which is primarily intended for the reduction of an off-current. An LDD region 22 of a current control TFT 202 is formed such that it partially overlaps a gate electrode 35 to provide a structure which is primarily intended for the prevention of hot carrier injection and the reduction of an off-current. Appropriate TFT structures are thus provided depending on required functions to improve operational performance and reliability.

Owner:SEMICON ENERGY LAB CO LTD

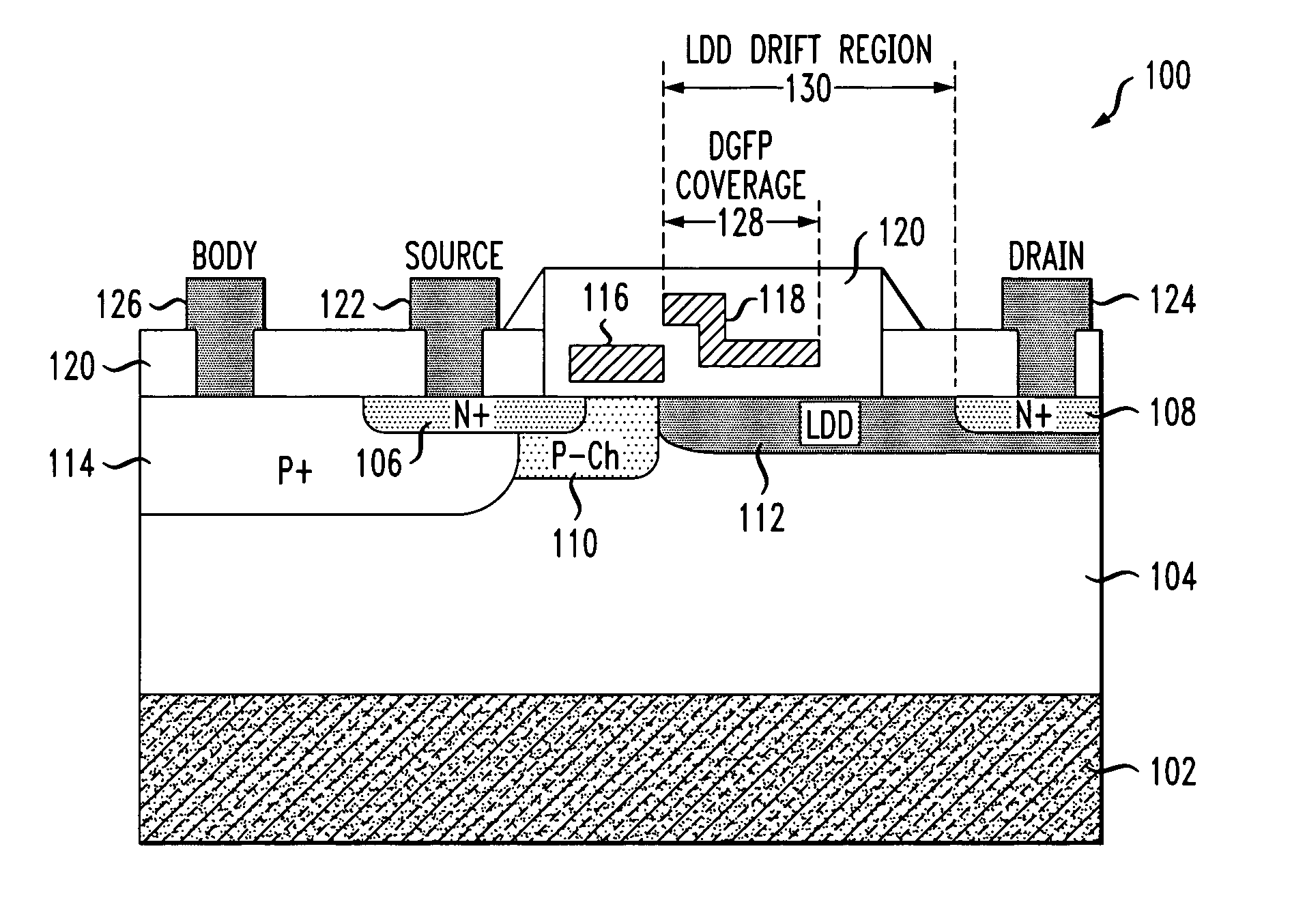

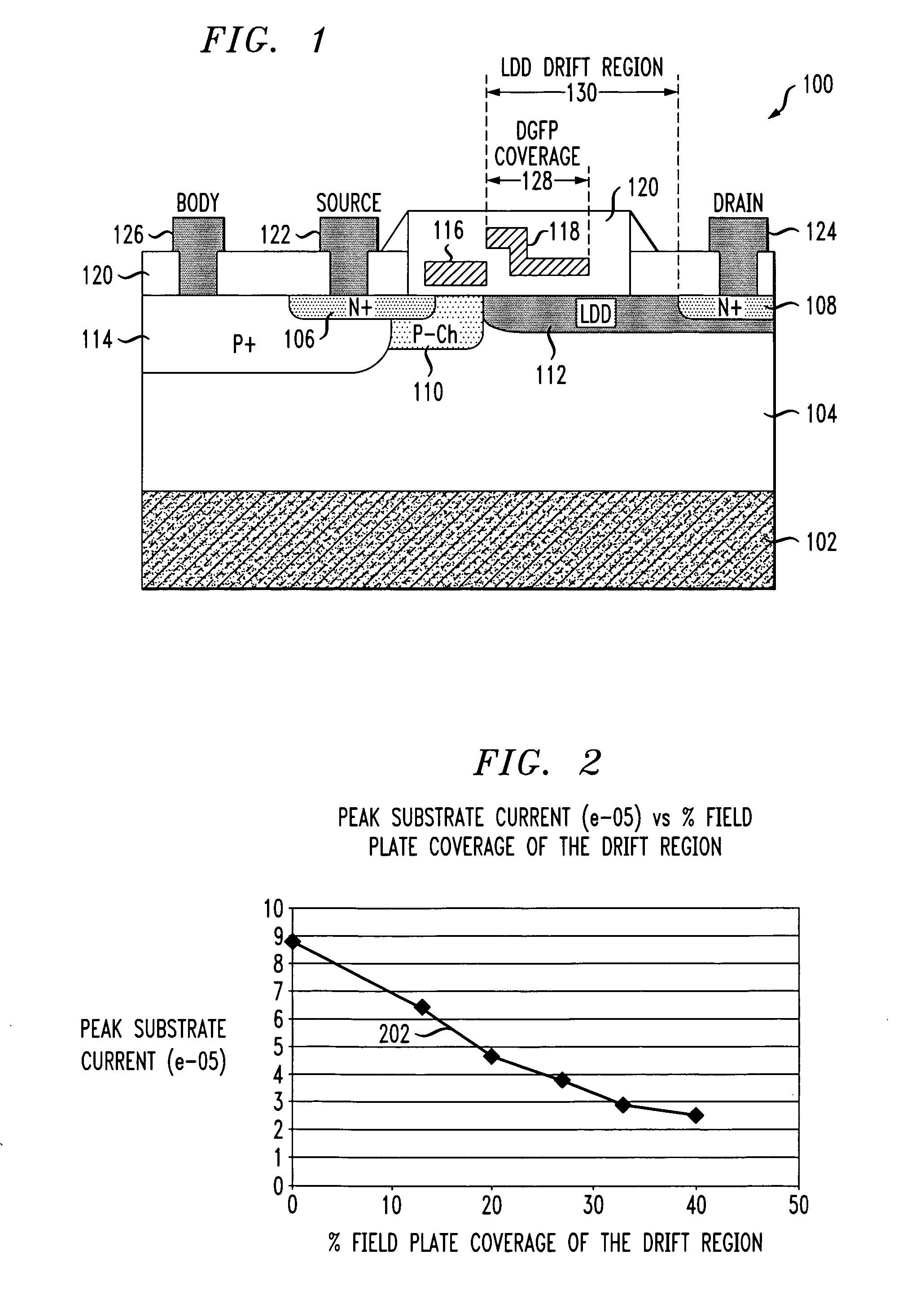

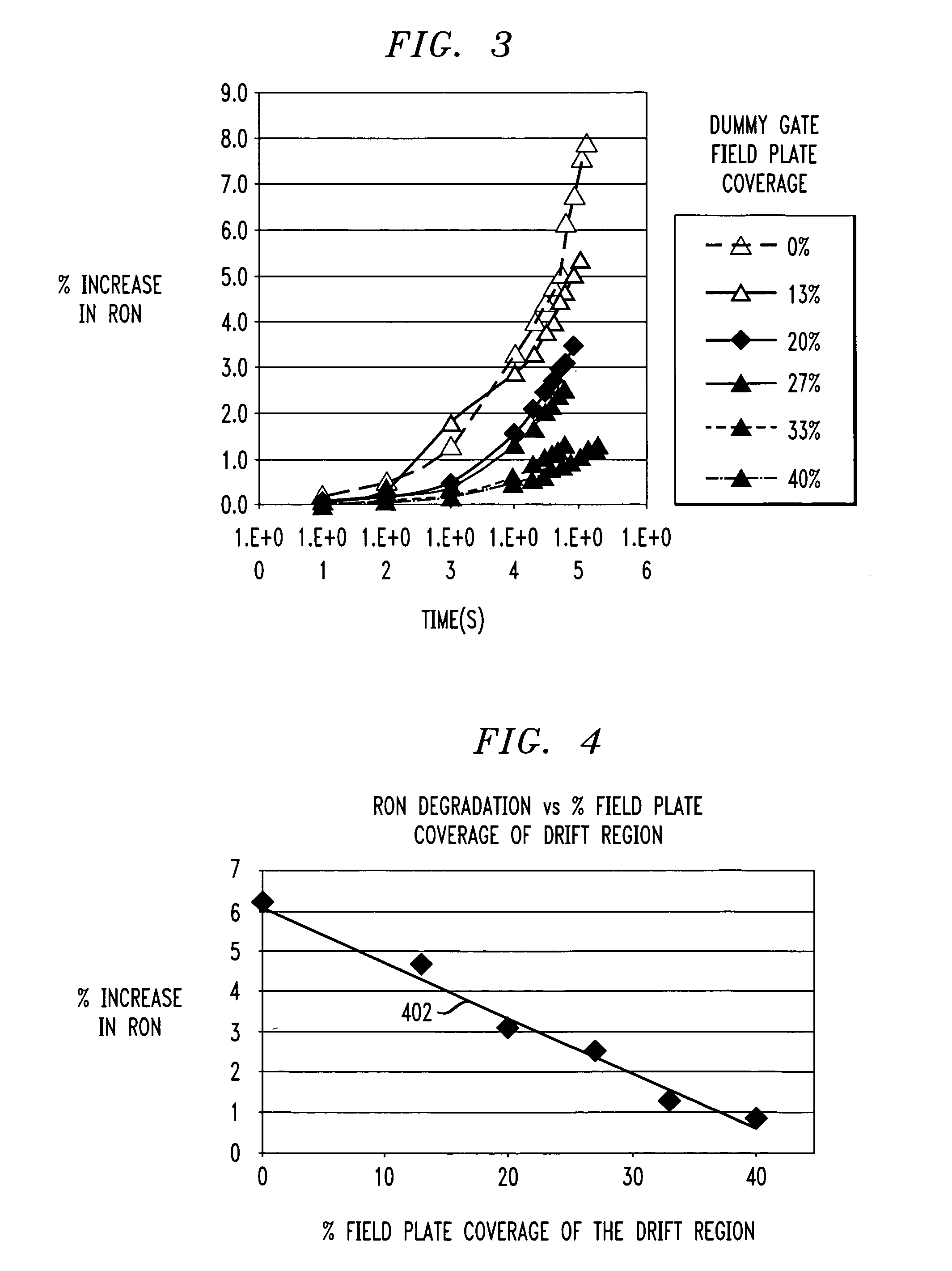

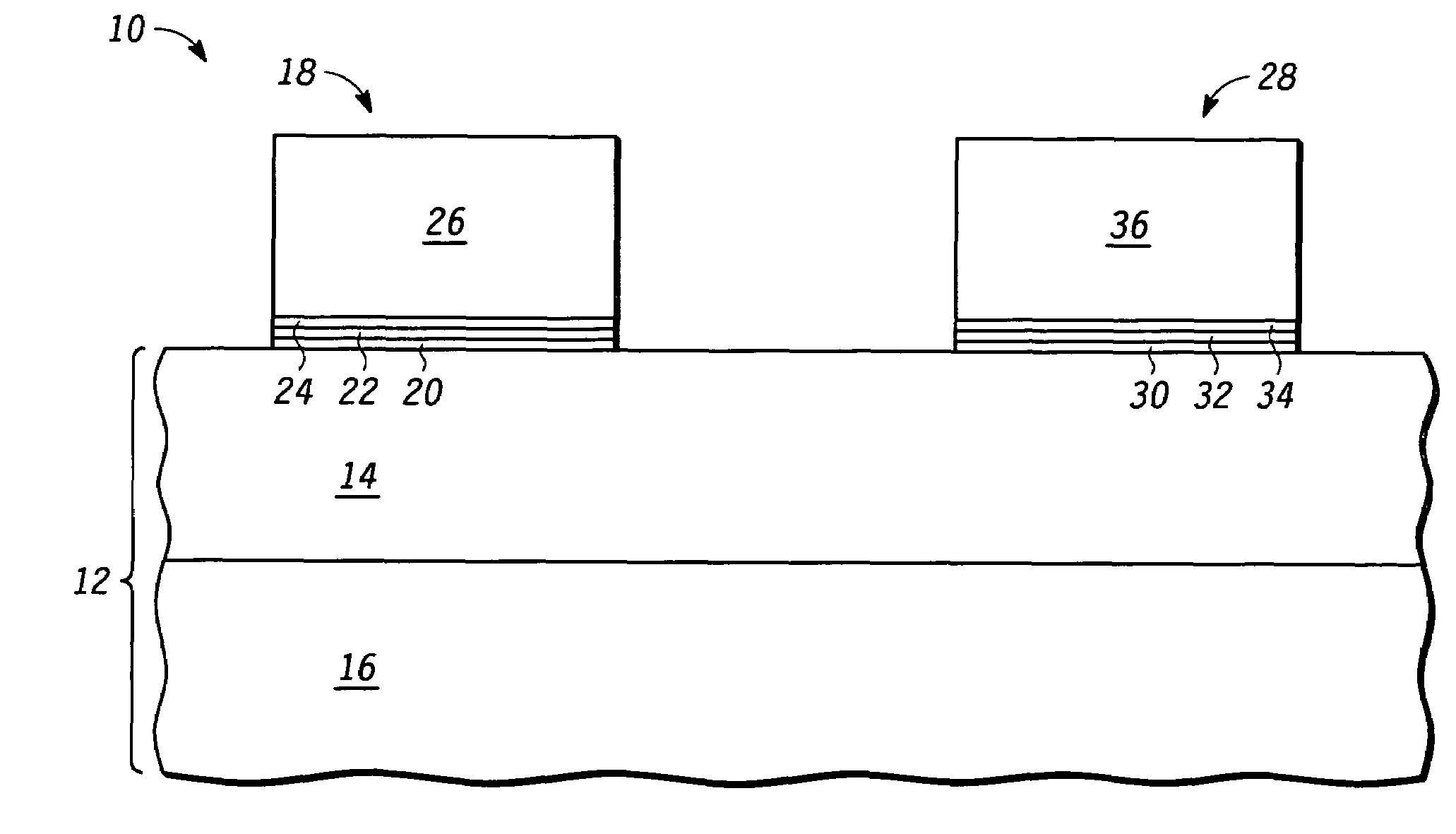

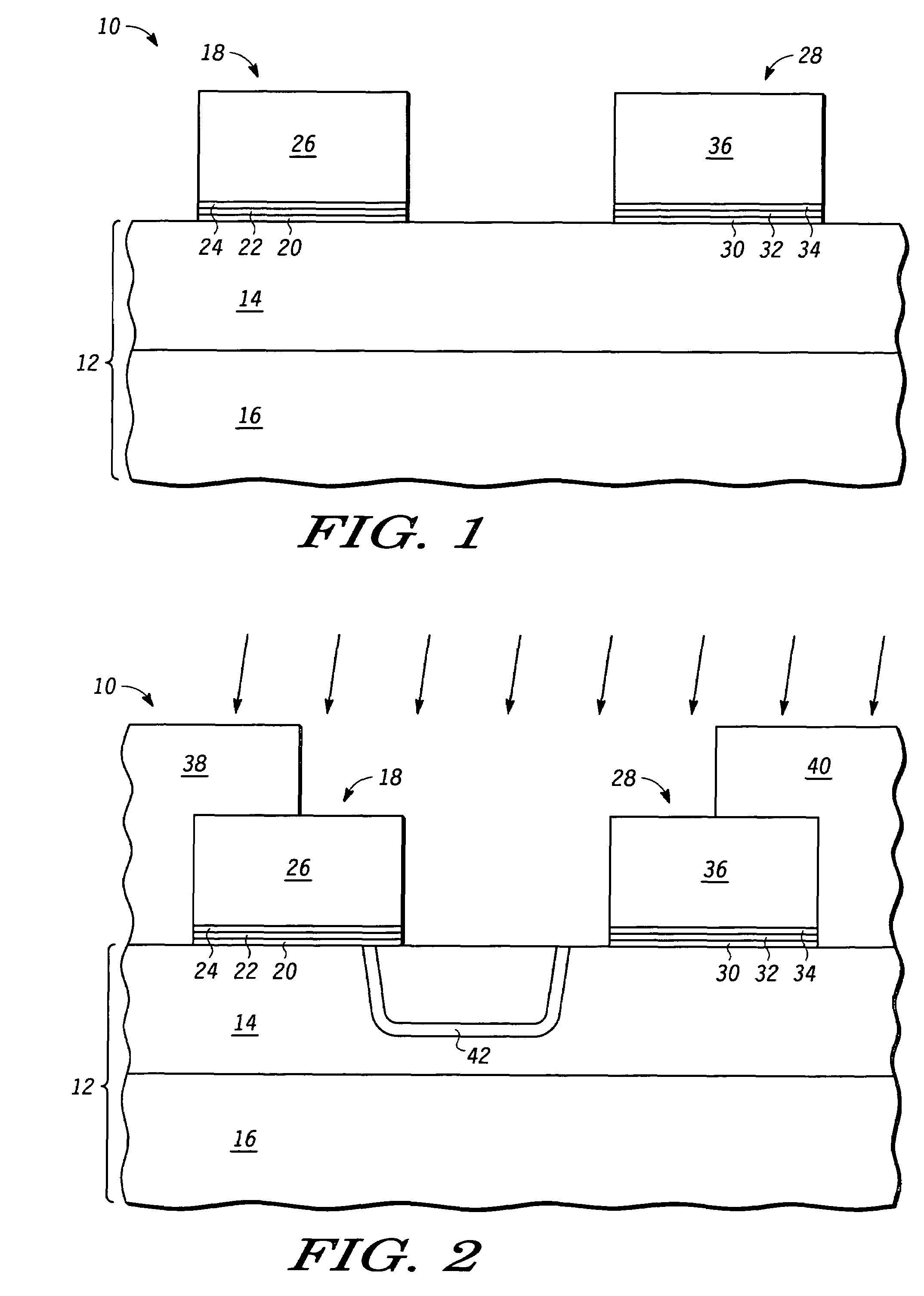

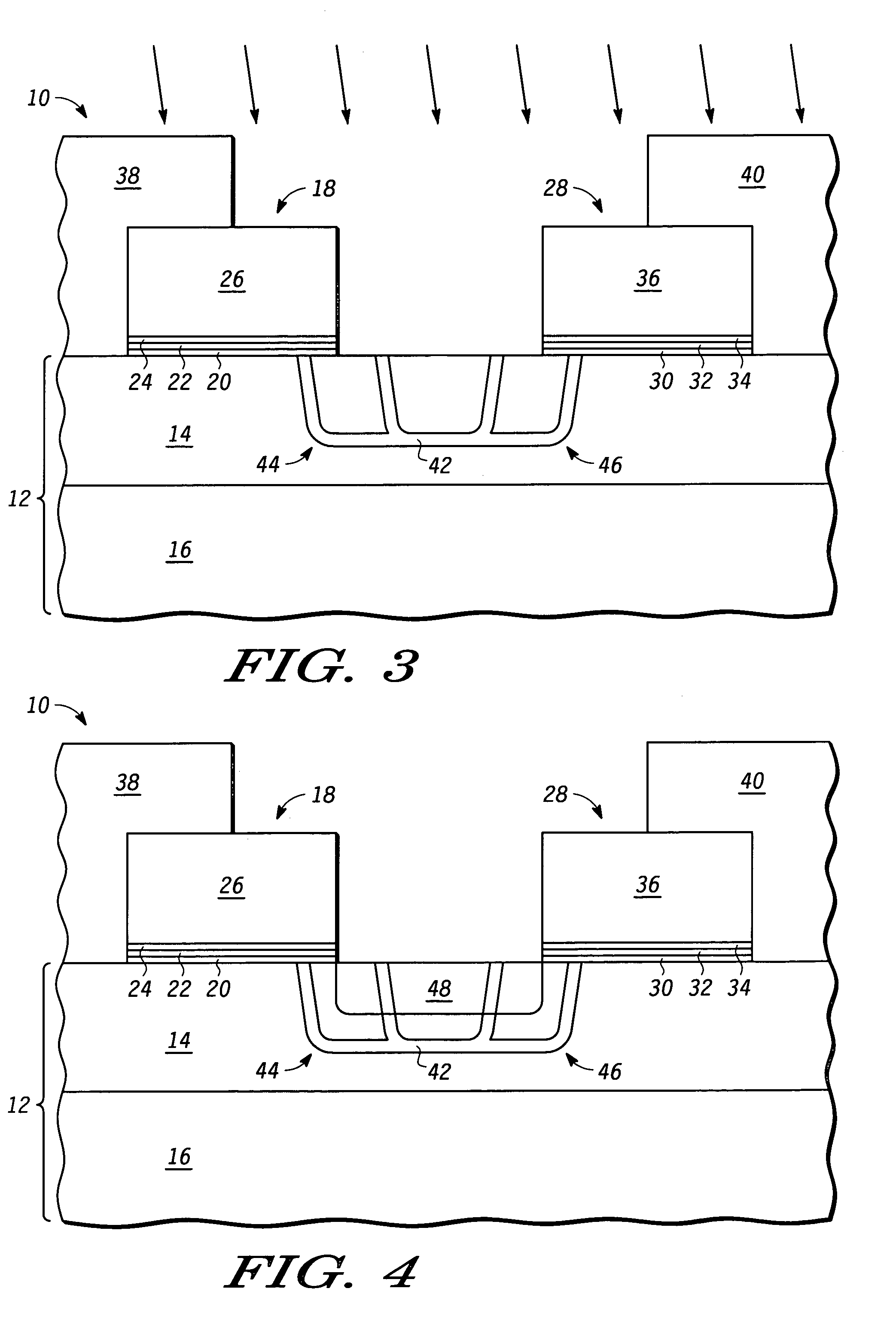

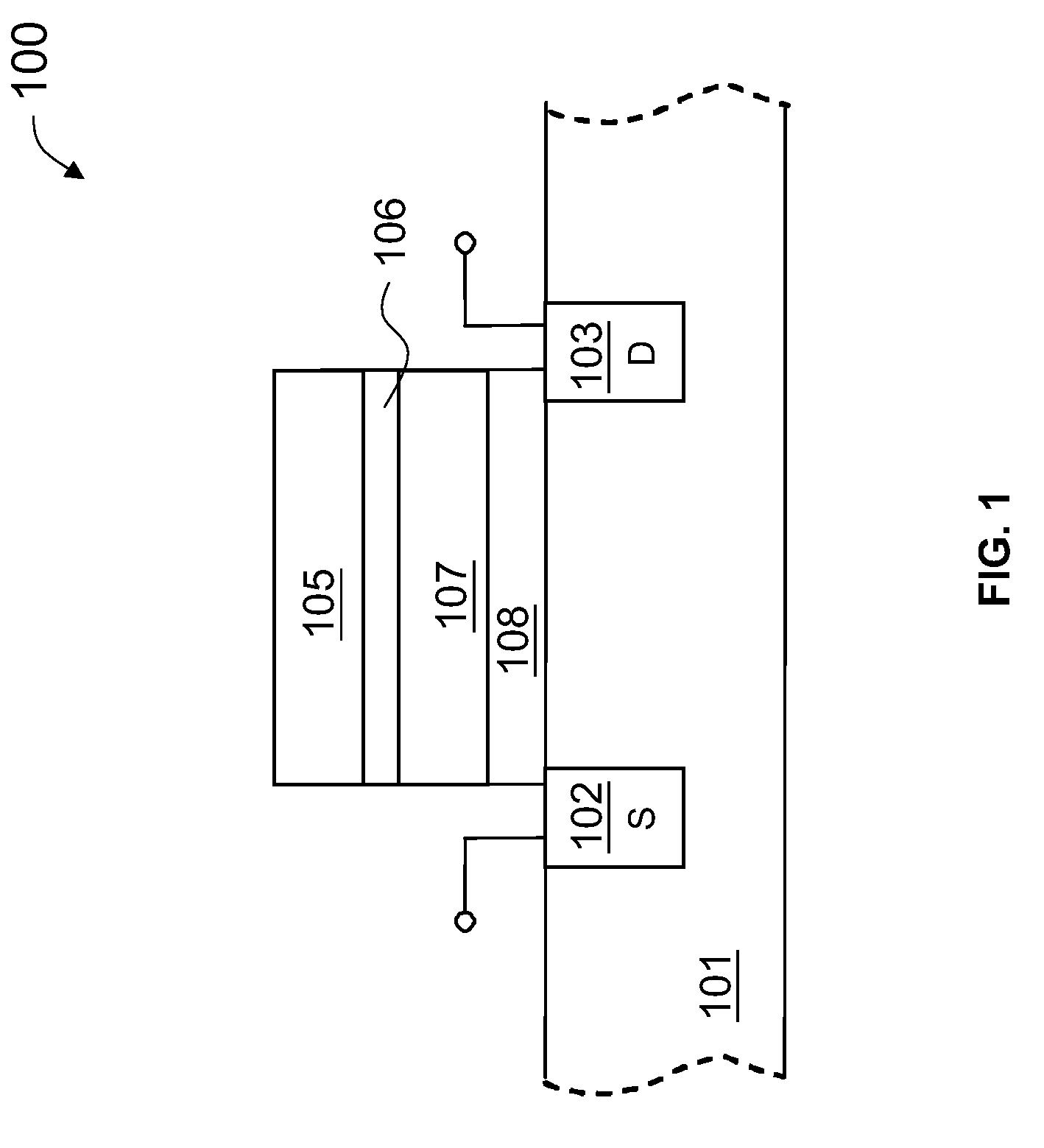

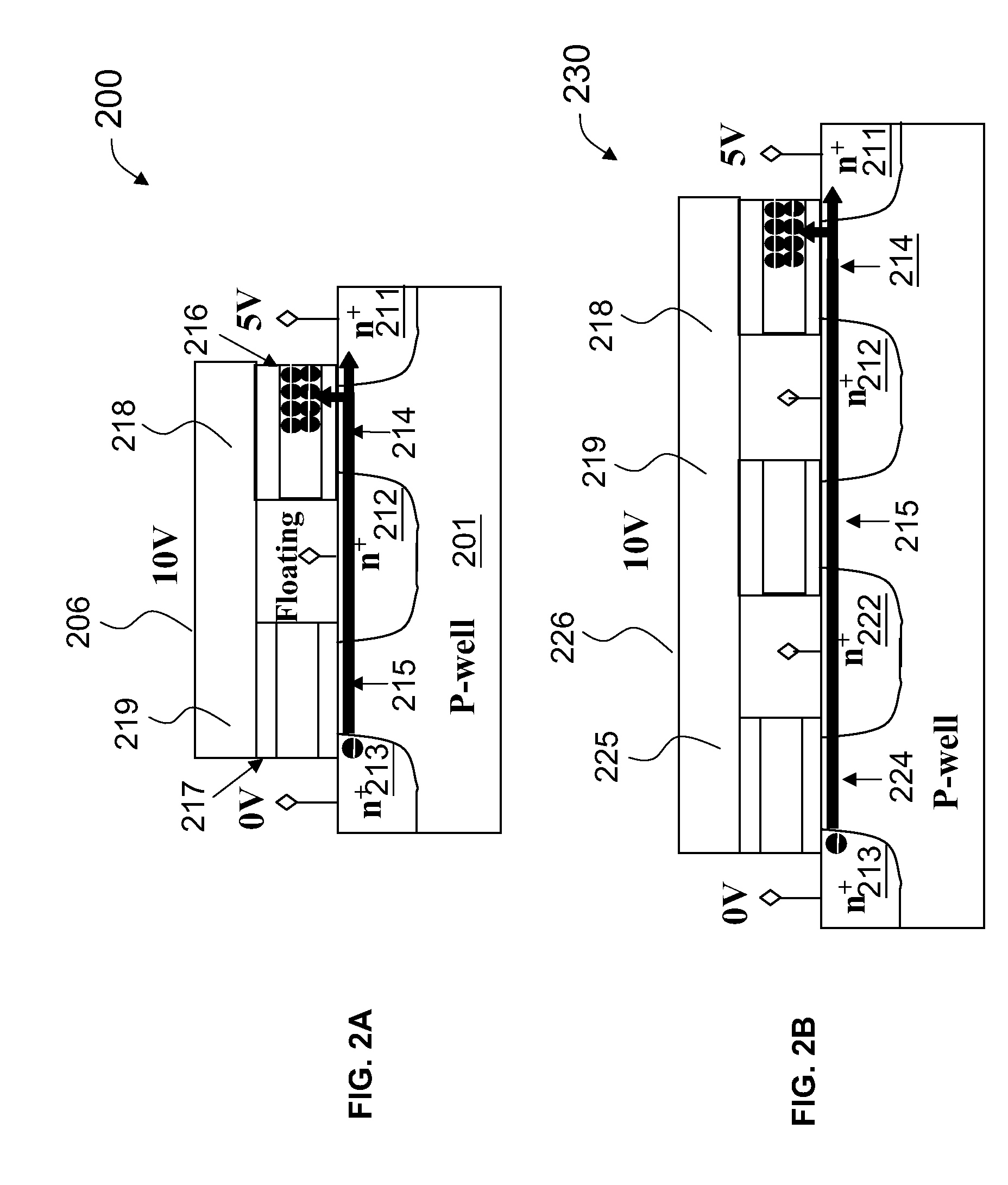

Control of hot carrier injection in a metal-oxide semiconductor device

ActiveUS20050156234A1Reduce HCI degradationLow costSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsSemiconductor

An MOS device is formed including a semiconductor layer of a first conductivity type, and first and second source / drain regions of a second conductivity type formed in the semiconductor layer proximate an upper surface of the semiconductor layer, the first and second source / drain regions being spaced apart relative to one another. A drift region is formed in the semiconductor layer proximate the upper surface of the semiconductor layer and at least partially between the first and second source / drain regions. An insulating layer is formed on at least a portion of the upper surface of the semiconductor layer and above at least a portion of the drift region. A gate is formed on the insulating layer and at least partially between the first and second source / drain regions. The MOS device further includes a shielding structure formed on the insulating layer above at least a portion of the drift region. The shielding structure is configured such that an amount of hot carrier injection degradation in the MOS device is controlled as a function of an amount of coverage of the shielding structure over an upper surface of the drift region.

Owner:BELL SEMICON LLC

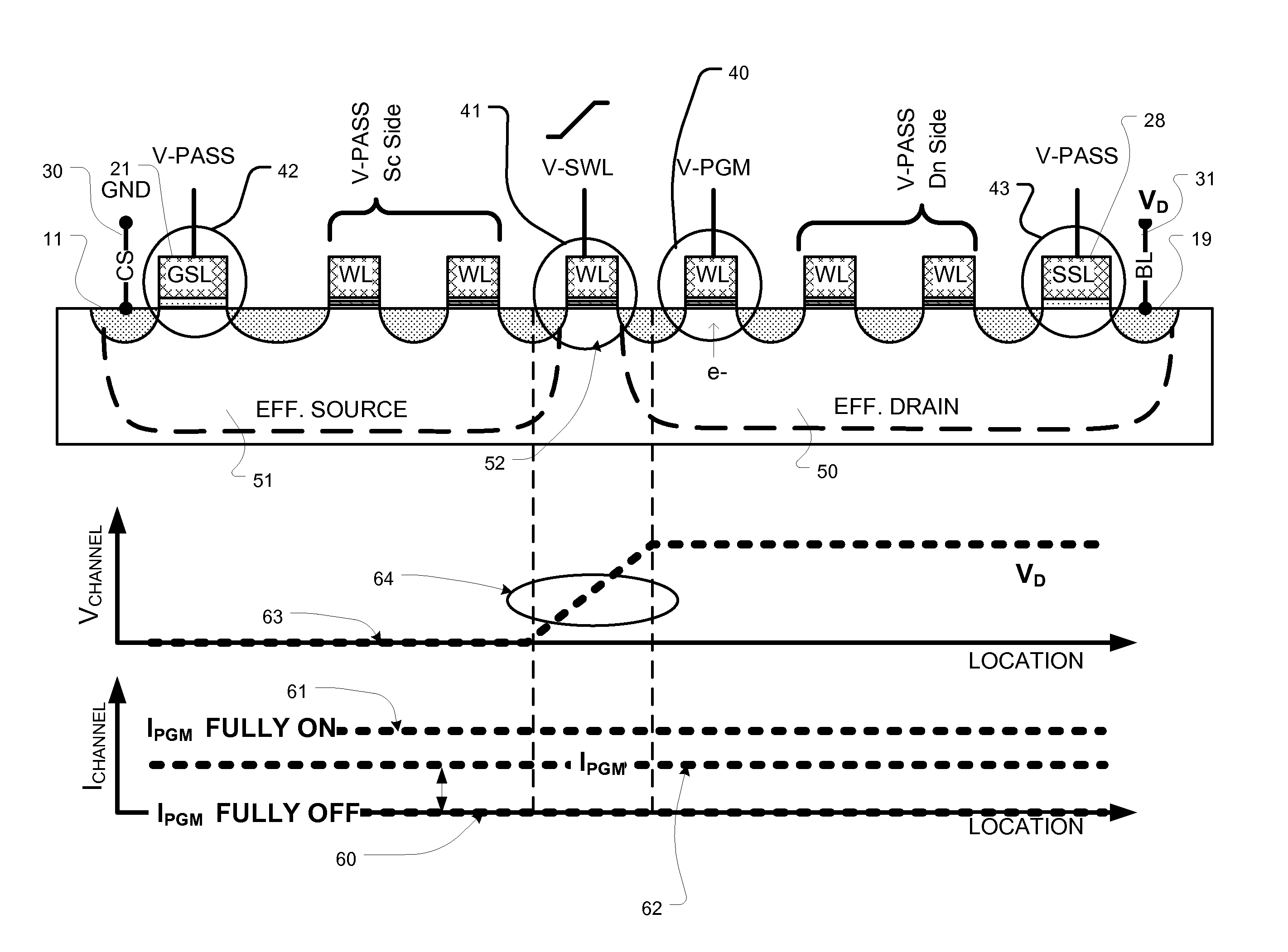

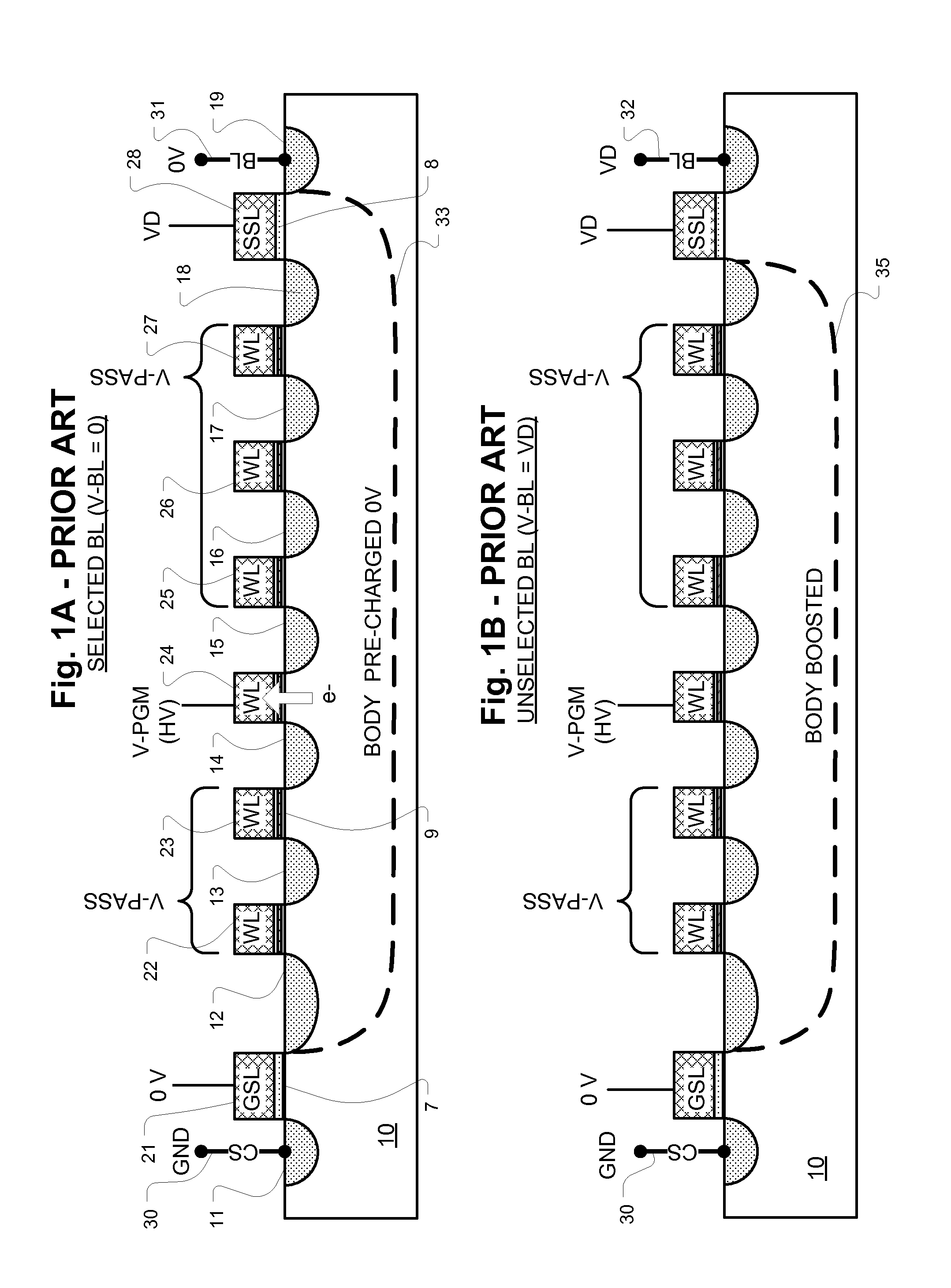

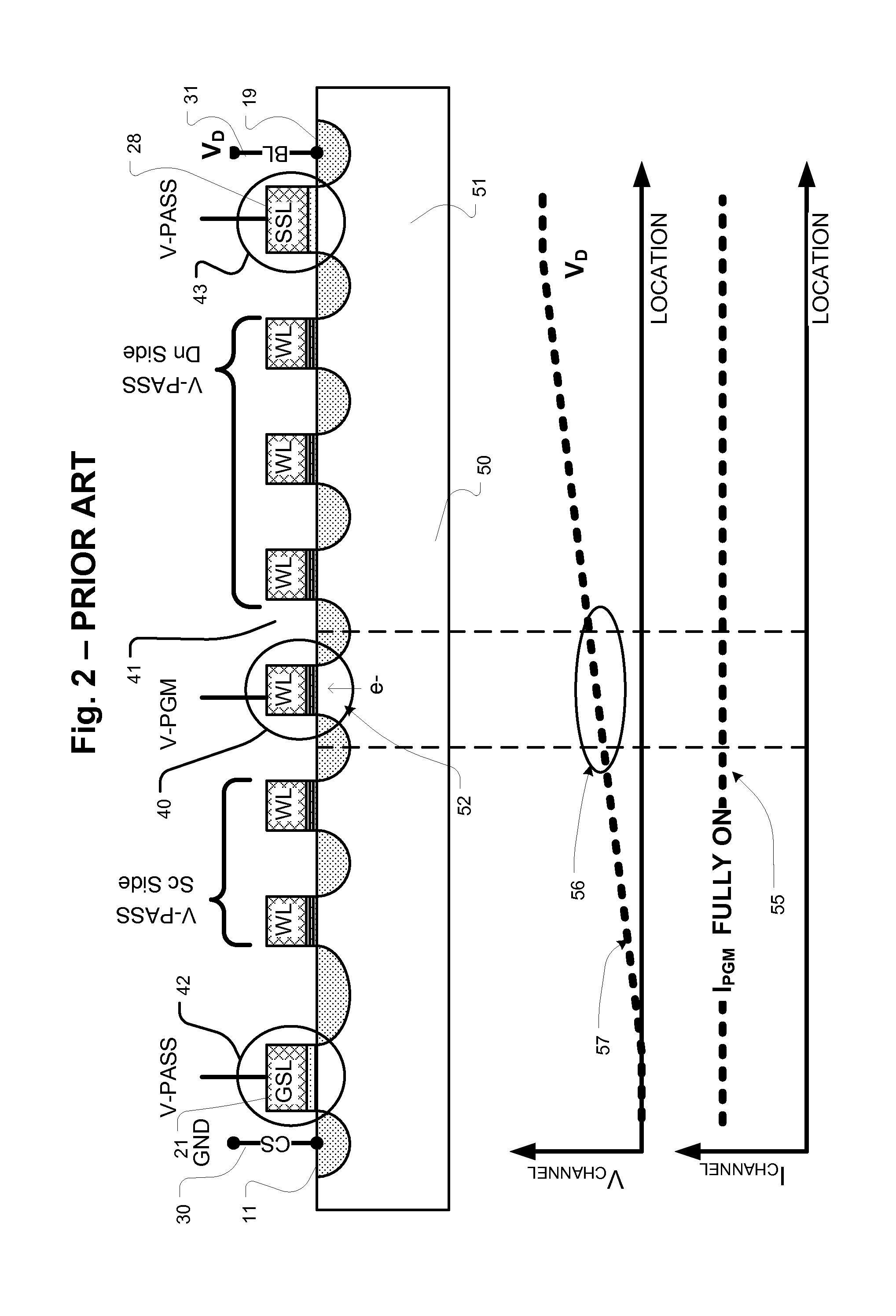

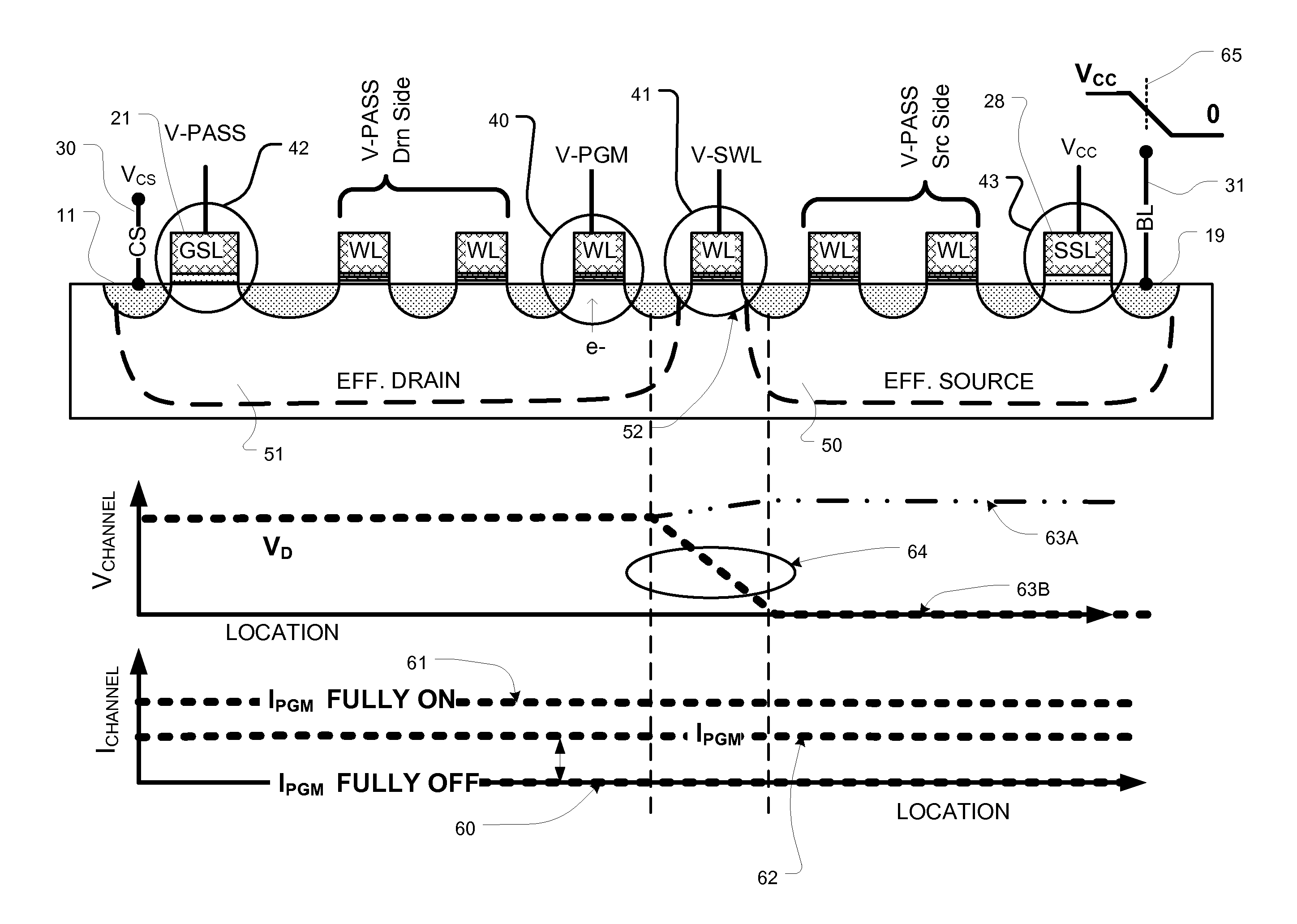

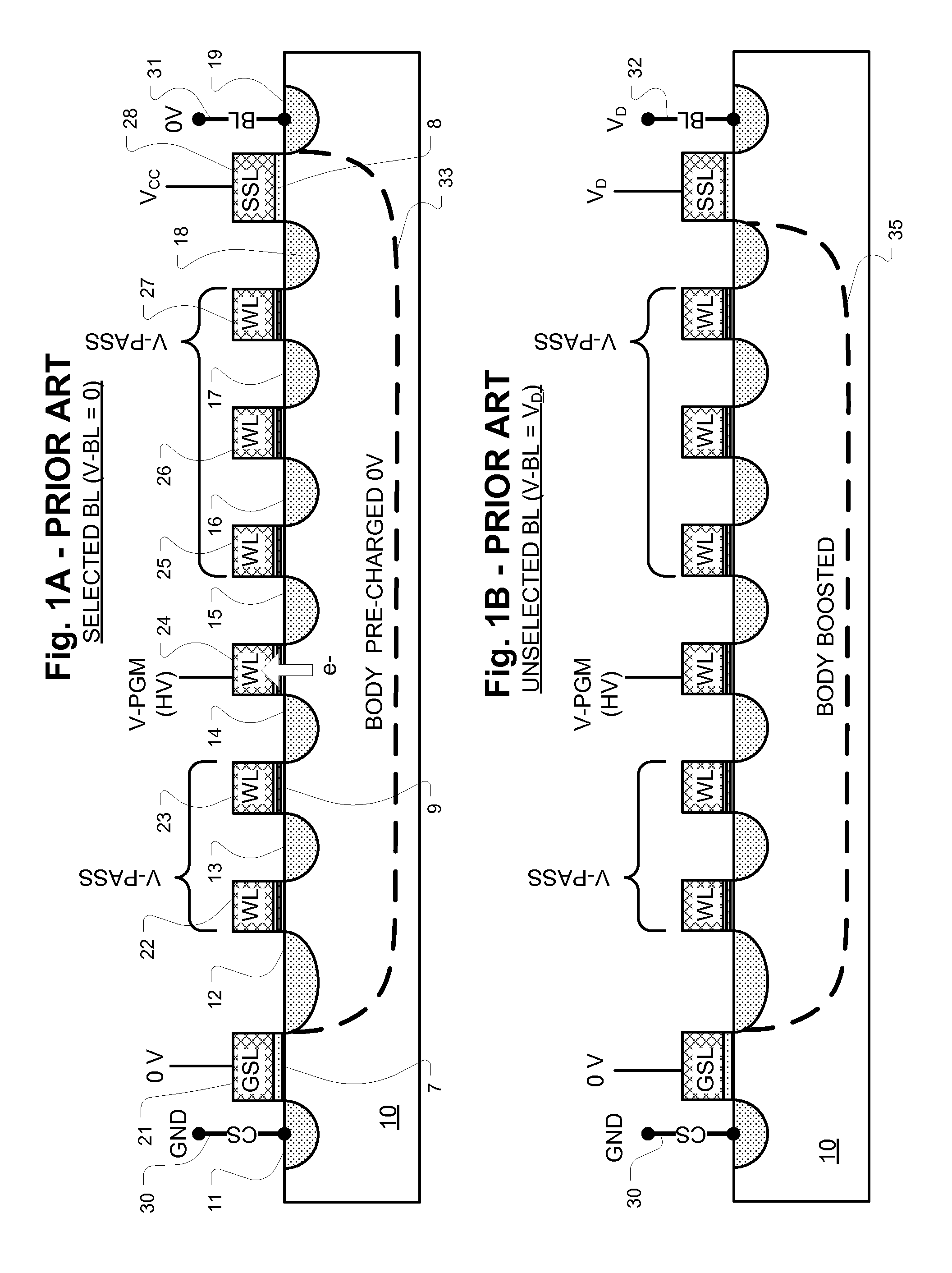

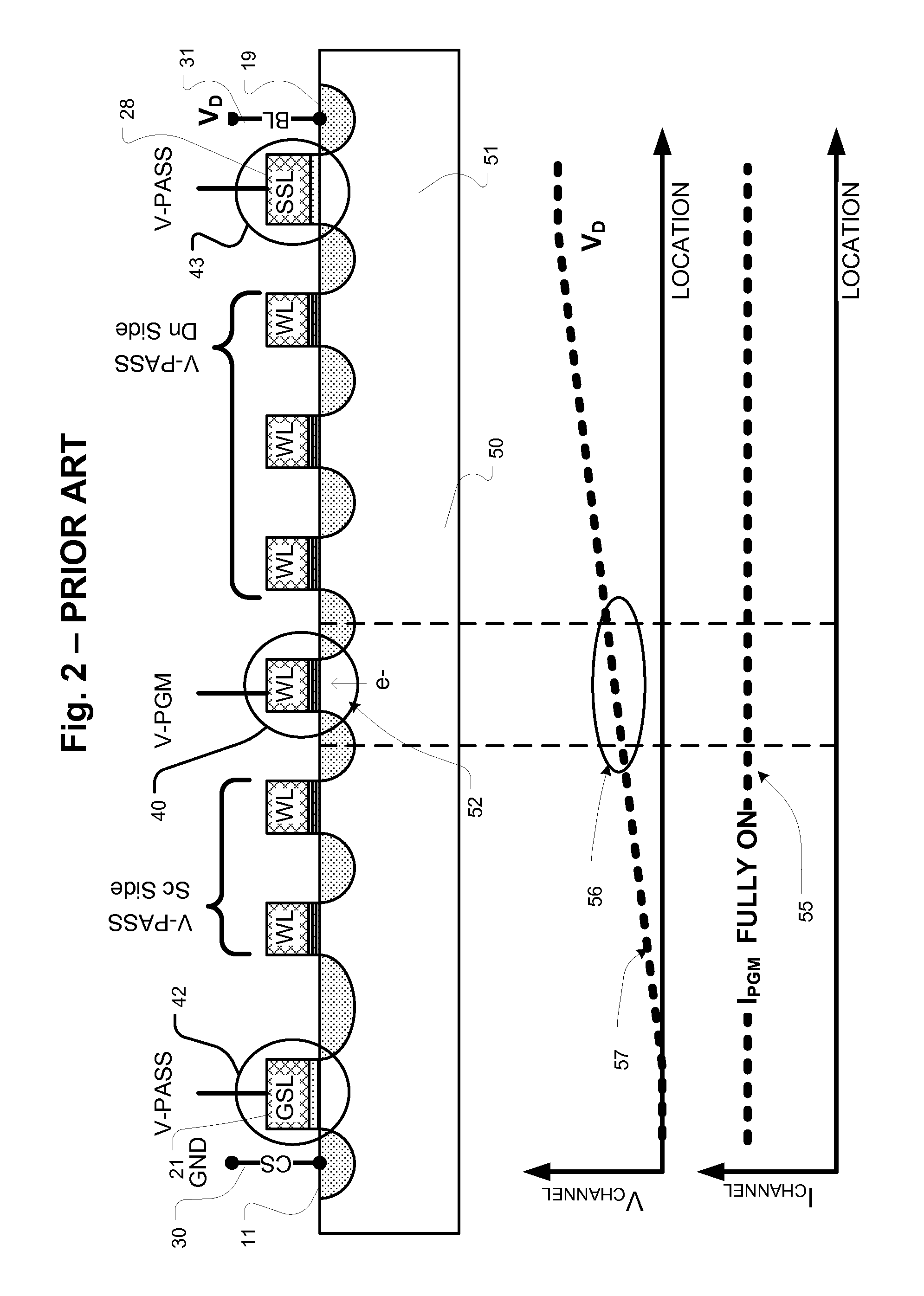

Low voltage programming in NAND flash

A memory device includes a plurality of memory cells arranged in series in the semiconductor body, such as a NAND string, having a plurality of word lines. A selected memory cell is programmed by hot carrier injection. The program operation is based on metering a flow of carriers between a first semiconductor body region on a first side of the selected cell in the NAND string and a second semiconductor body region on a second side of the selected cell. A program potential higher than a hot carrier injection barrier level is applied to the selected cell, and then the drain to source voltage across the selected cell and the flow of carriers in the selected cell reach a level sufficient to support hot carrier injection, which is controlled by a switch cell adjacent the selected cell.

Owner:MACRONIX INT CO LTD

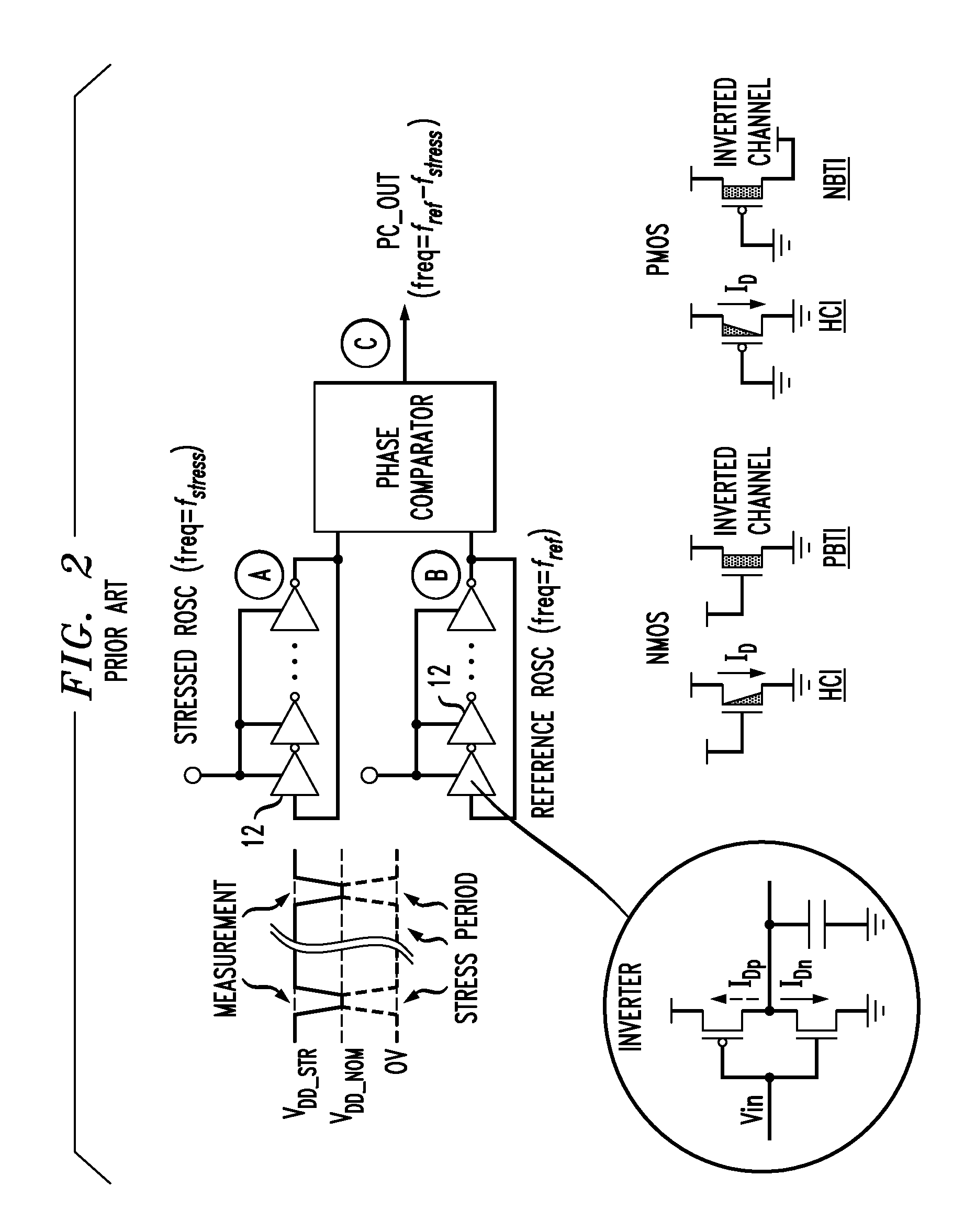

Apparatus and method for measuring degradation of CMOS VLSI elements

ActiveUS20130015876A1Minimization requirementsEliminate the effects ofSemiconductor operation lifetime testingDielectricAND gate

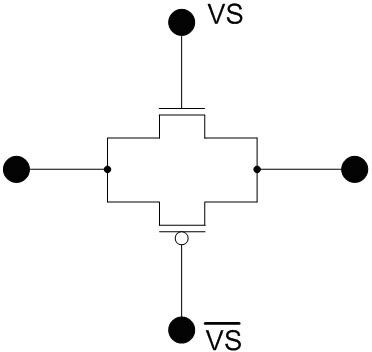

The reliability of an integrated circuit is inferred from the operational characteristics of sample metal oxide semiconductor (MOS) devices switchably coupled to drain / source bias and gate input voltages that are nominal, versus voltage and current conditions that elevate stress and cause temporary or permanent degradation, e.g., hot carrier injection (HCI), bias temperature instability (BTI, NBTI, PBTI), time dependent dielectric breakdown (TDDB). The MOS devices under test (preferably both PMOS and NMOS devices tested concurrently or in turn) are configured as current sources in the supply of power to a ring oscillator having cascaded inverter stages, thereby varying the oscillator frequency as a measure of the effects of stress on the devices under test, but without elevating the stress applied to the inverter stages.

Owner:TAIWAN SEMICON MFG CO LTD

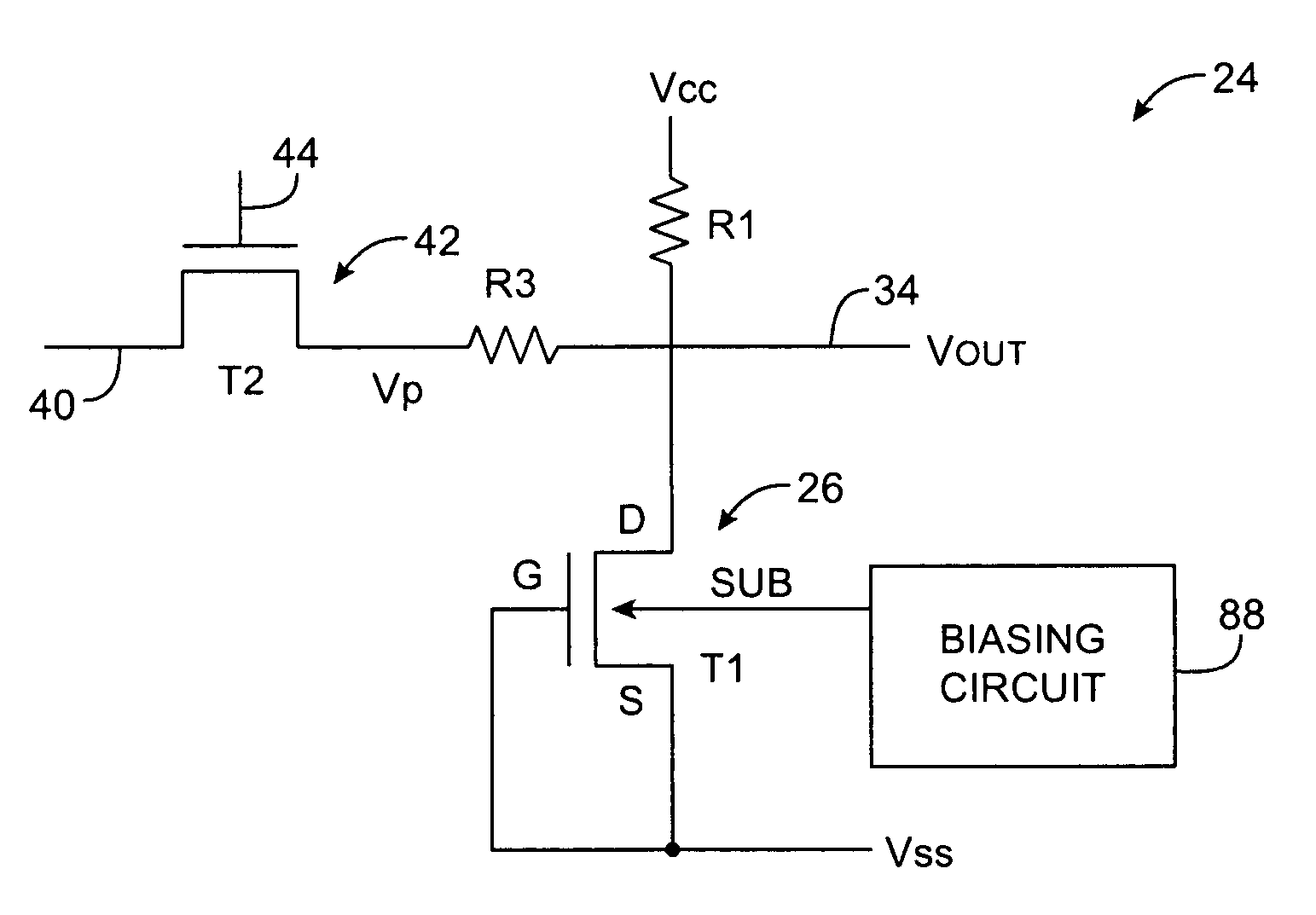

Electrically-programmable transistor antifuses

InactiveUS7772591B1Minimize powerMinimize timeTransistorSemiconductor/solid-state device detailsHigh resistanceEngineering

Integrated circuit antifuse circuitry is provided. A metal-oxide-semiconductor (MOS) transistor serves as an electrically-programmable antifuse. The antifuse transistor has source, drain, gate, and substrate terminals. The gate has an associated gate oxide. In its unprogrammed state, the gate oxide is intact and the antifuse has a relatively high resistance. During programming, the gate oxide breaks down, so in its programmed state the antifuse transistor has a relatively low resistance. The antifuse transistor can be programmed by injecting hot carriers into the substrate of the device in the vicinity of the drain. Because there are more hot carriers at the drain than at the substrate, the gate oxide is stressed asymmetrically, which enhances programming efficiency. Feedback can be used to assist in turning the antifuse transistor on to inject the hot carriers.

Owner:ALTERA CORP

Electronic device and electronic apparatus

InactiveUS7274349B2Improve performanceImprove reliabilityTransistorStatic indicating devicesHot-carrier injectionElectronic equipment

Owner:SEMICON ENERGY LAB CO LTD

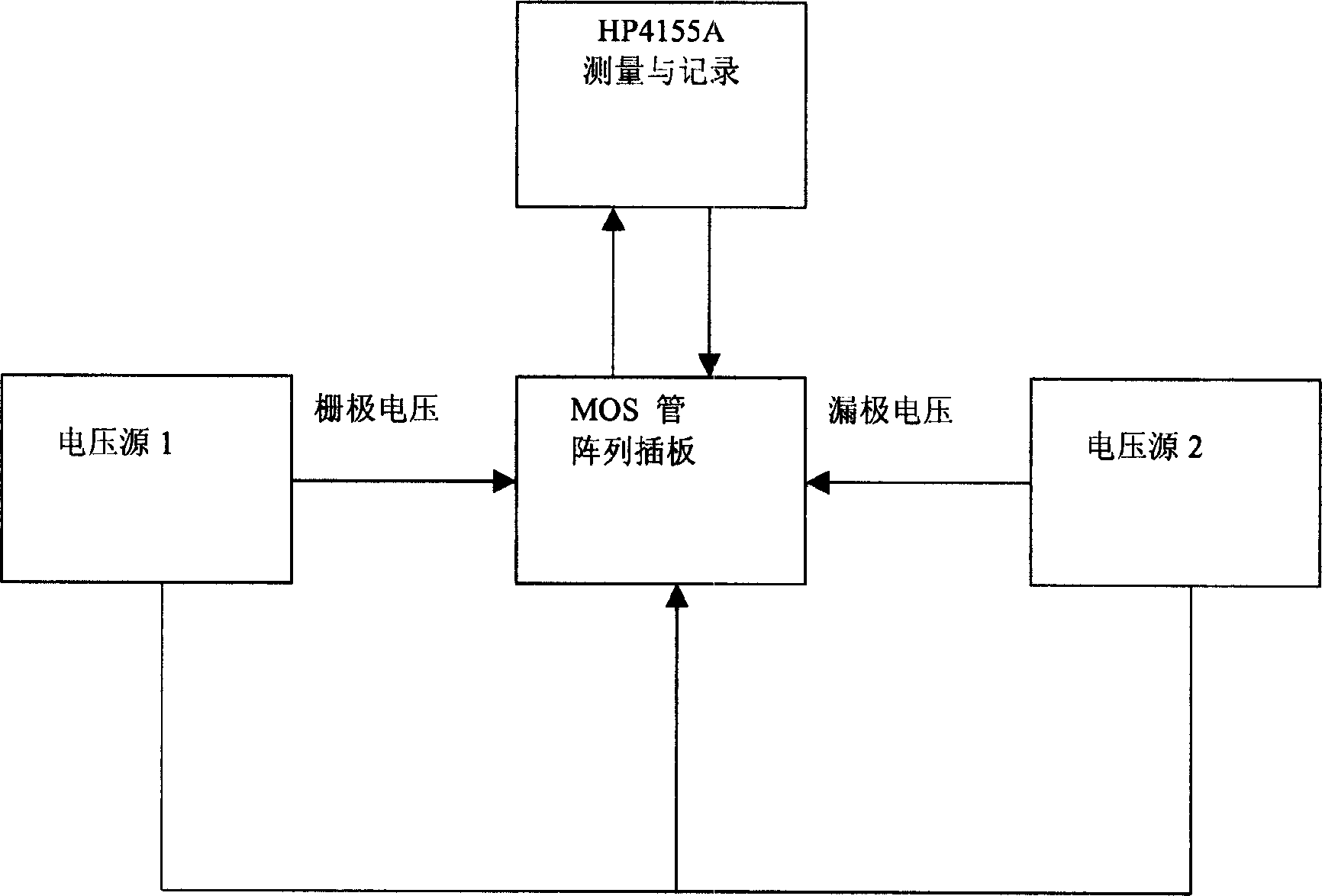

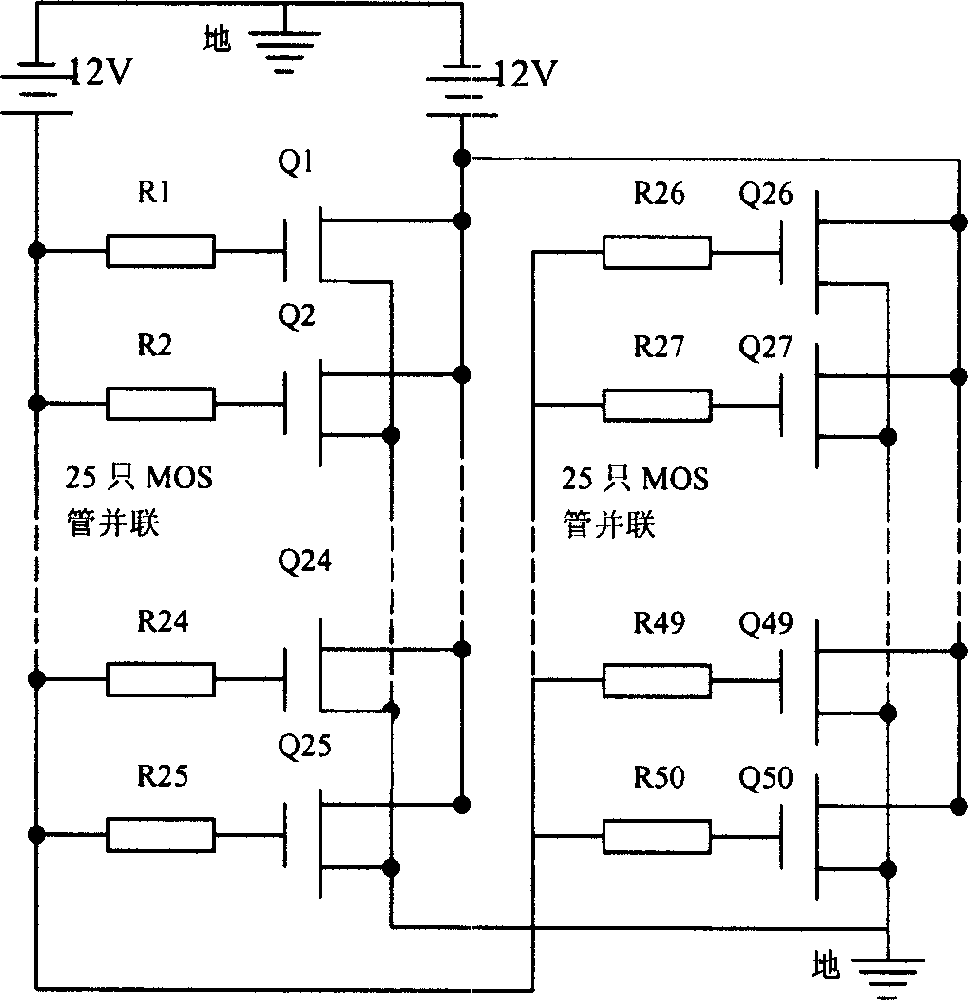

MOS device hot carrier injection effect measuring method

InactiveCN1588104ALow costNot lostSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingFast measurementHeat carrier

The invention is a measuring method for MOS device heat carrier injecting effect. At first, the stress voltage value of drain and grid electrode of the device needed to be measured are determined according to the standard measuring device, and records the initial data through the data recording program; then the device needed to be measured is placed into the socket of the circuit board, at the same time, supplies voltage to the drain and grid electrode; shuts off the stress voltage at time point after 10, 20. and 50 seconds, the MOS is pulled out form the circuit board, and the degeneration quantity of designated parameter measured by the device are recorded; after the first time of data recording, all the MOS tubes are inserted into the original socket of the circuit board, then carries on correspondent voltage stress to the next time point, then stops the stress, then pulls out the MOS tubes form the circuit board, records the measured degeneration data, repeats the above mentioned steps until the degeneration quantity accords to the demands.

Owner:信息产业部电子第五研究所

Semiconductor device and manufacturing method thereof

InactiveUS7161177B2Excellent characteristicsImprove reliabilityTransistorSolid-state devicesSemiconductorImpurity

Owner:SEMICON ENERGY LAB CO LTD

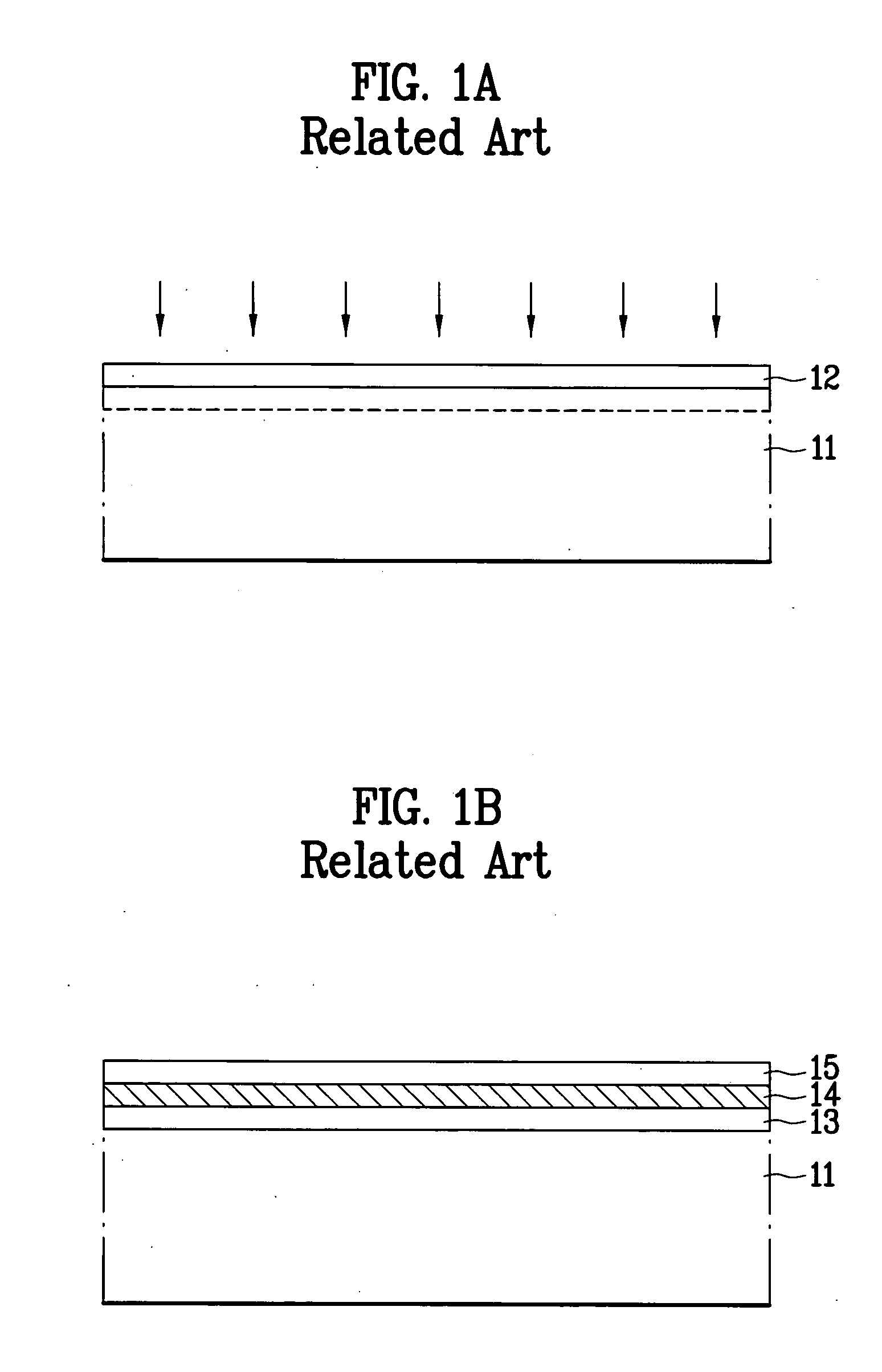

Method for fabricating flash memory device

ActiveUS20050245037A1Improves hot carrier injection efficiencyImprove carrier injection efficiencySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A method for fabricating a flash memory device is disclosed that improves hot carrier injection efficiency by forming a gate after forming source and drain implants using a sacrificial insulating layer pattern, which includes forming a sacrificial insulating pattern layer over a flash memory channel region of a semiconductor substrate; forming source and drain regions in the semiconductor substrate by ion implantation using the sacrificial insulating pattern layer as a mask; removing portions of the sacrificial insulating pattern layer; sequentially forming an ONO-type dielectric layer and a gate material layer; selectively etching the gate material layer and at least part of the gate dielectric layer to form a gate; and forming gate sidewall spacers at sides of the gate.

Owner:MARVELL ASIA PTE LTD +1

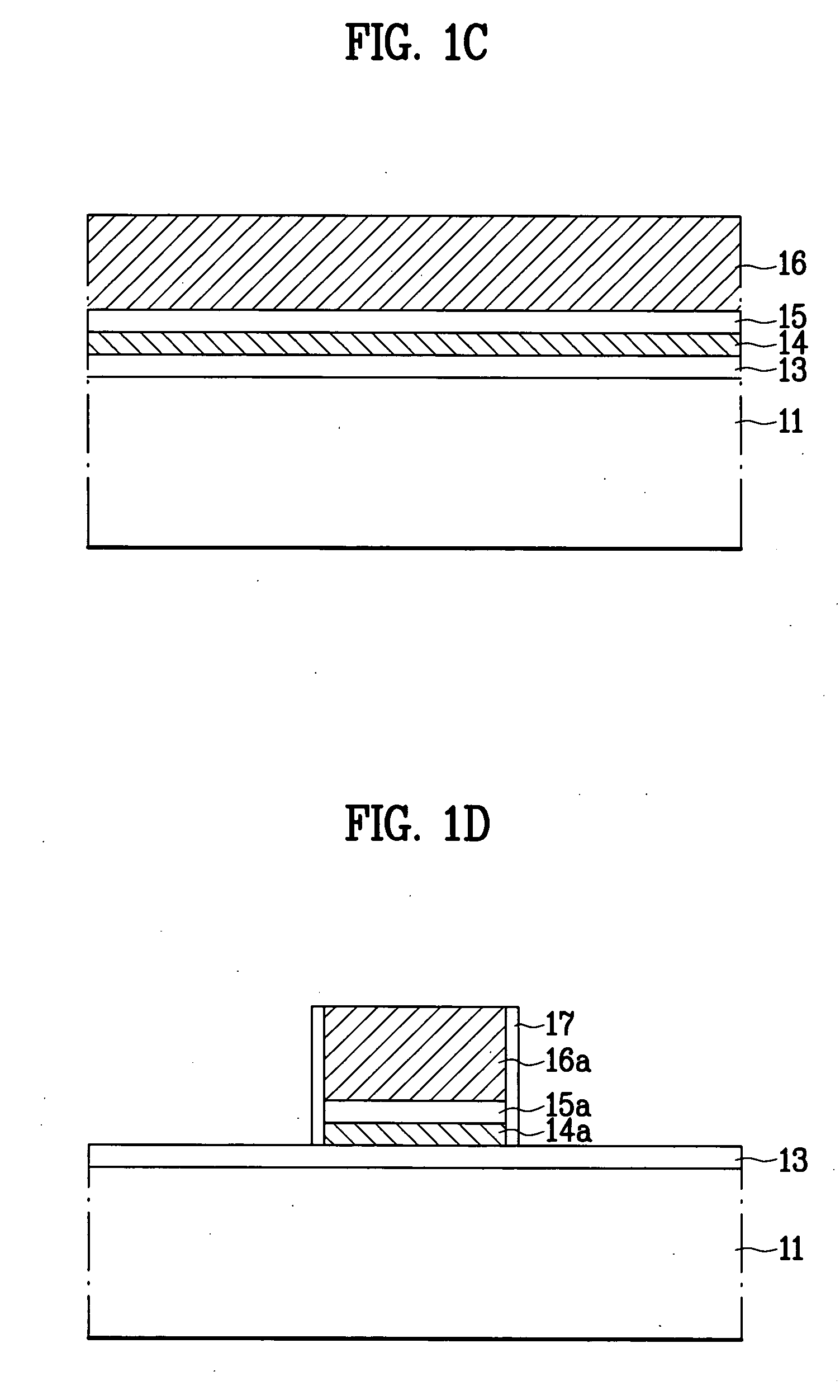

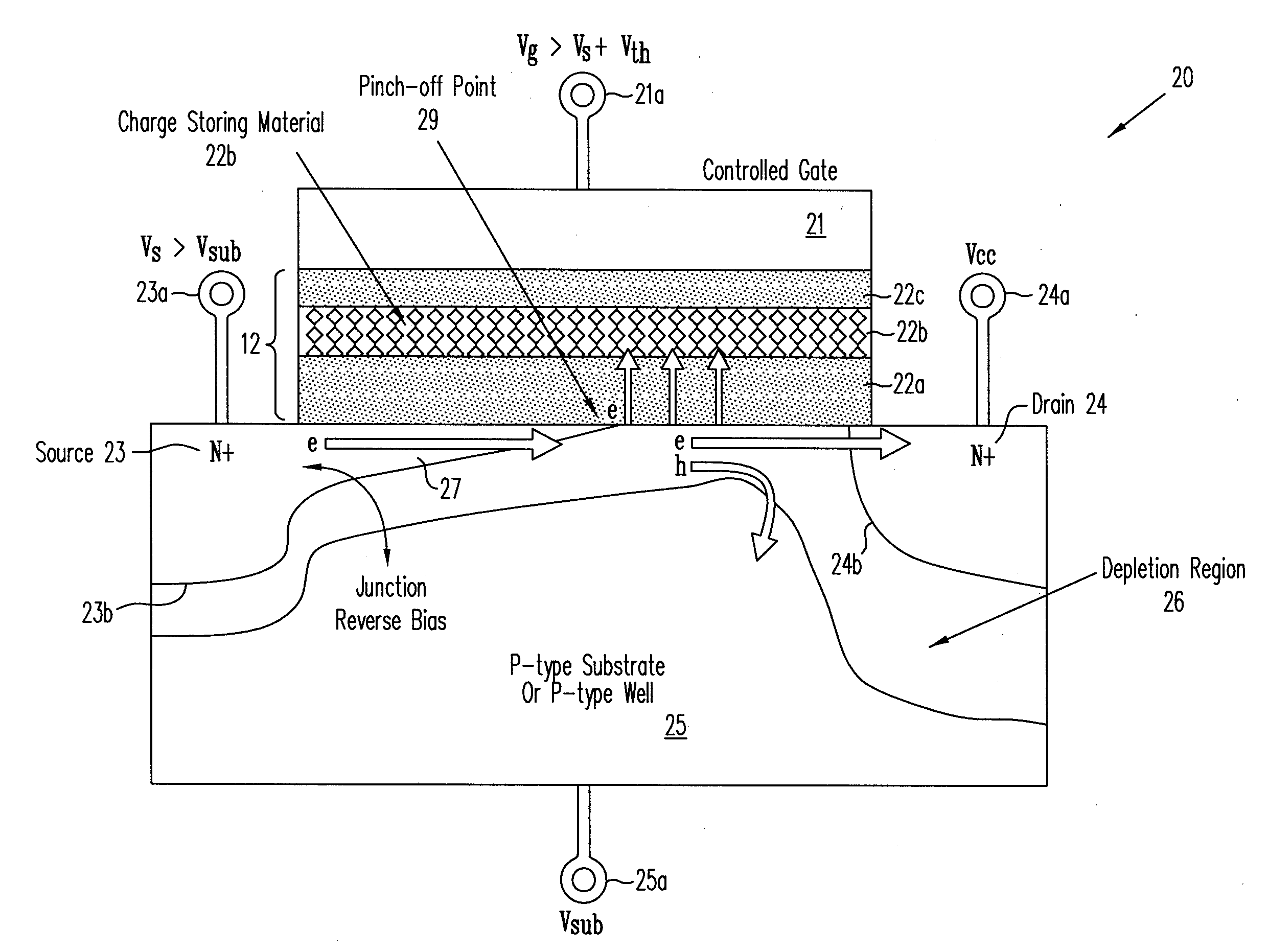

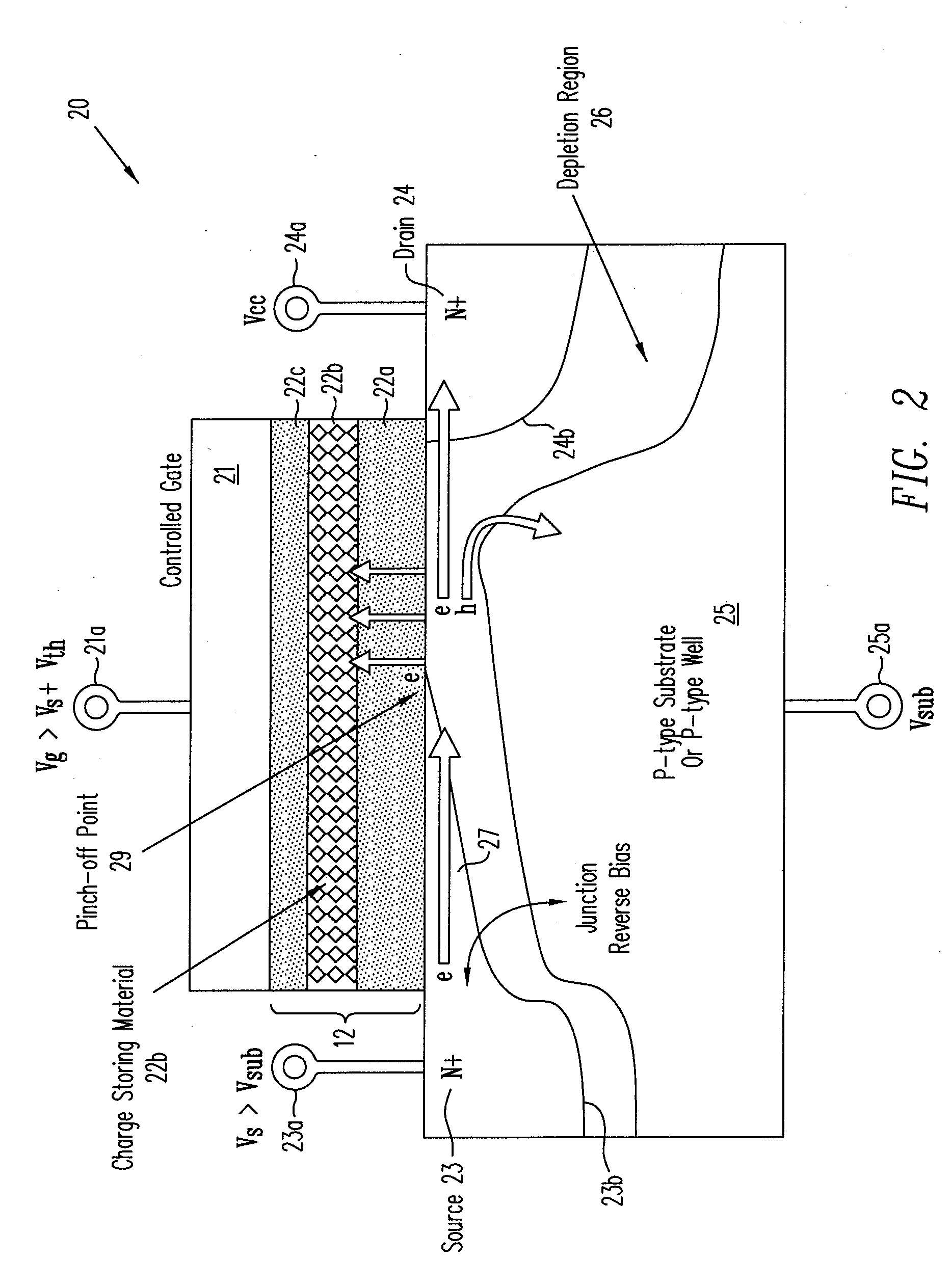

Methods and structures for highly efficient hot carrier injection programming for non-volatile memories

ActiveUS20090021984A1Improve programming efficiencyHigh injection rateRead-only memoriesDigital storageMOSFETVoltage amplitude

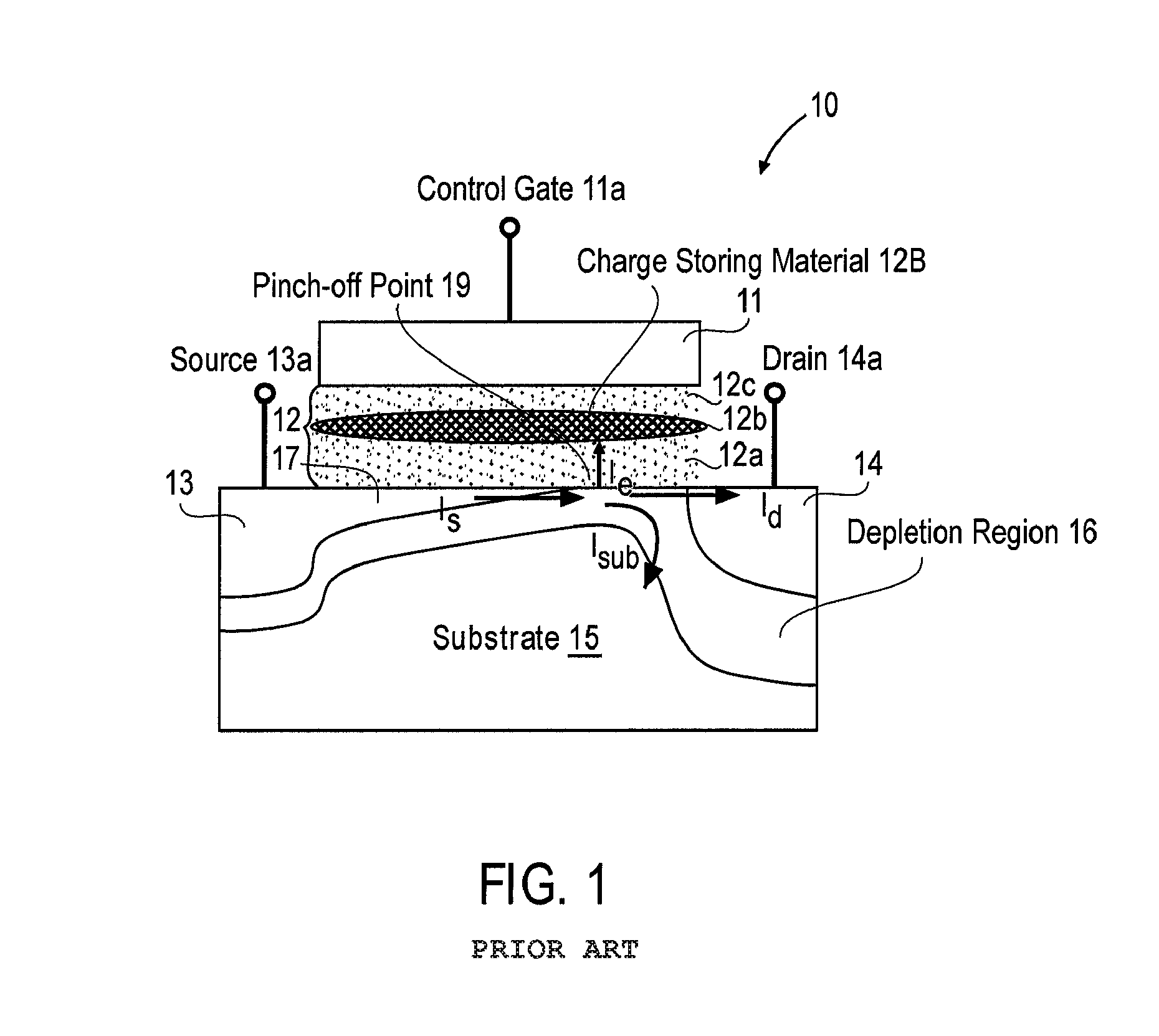

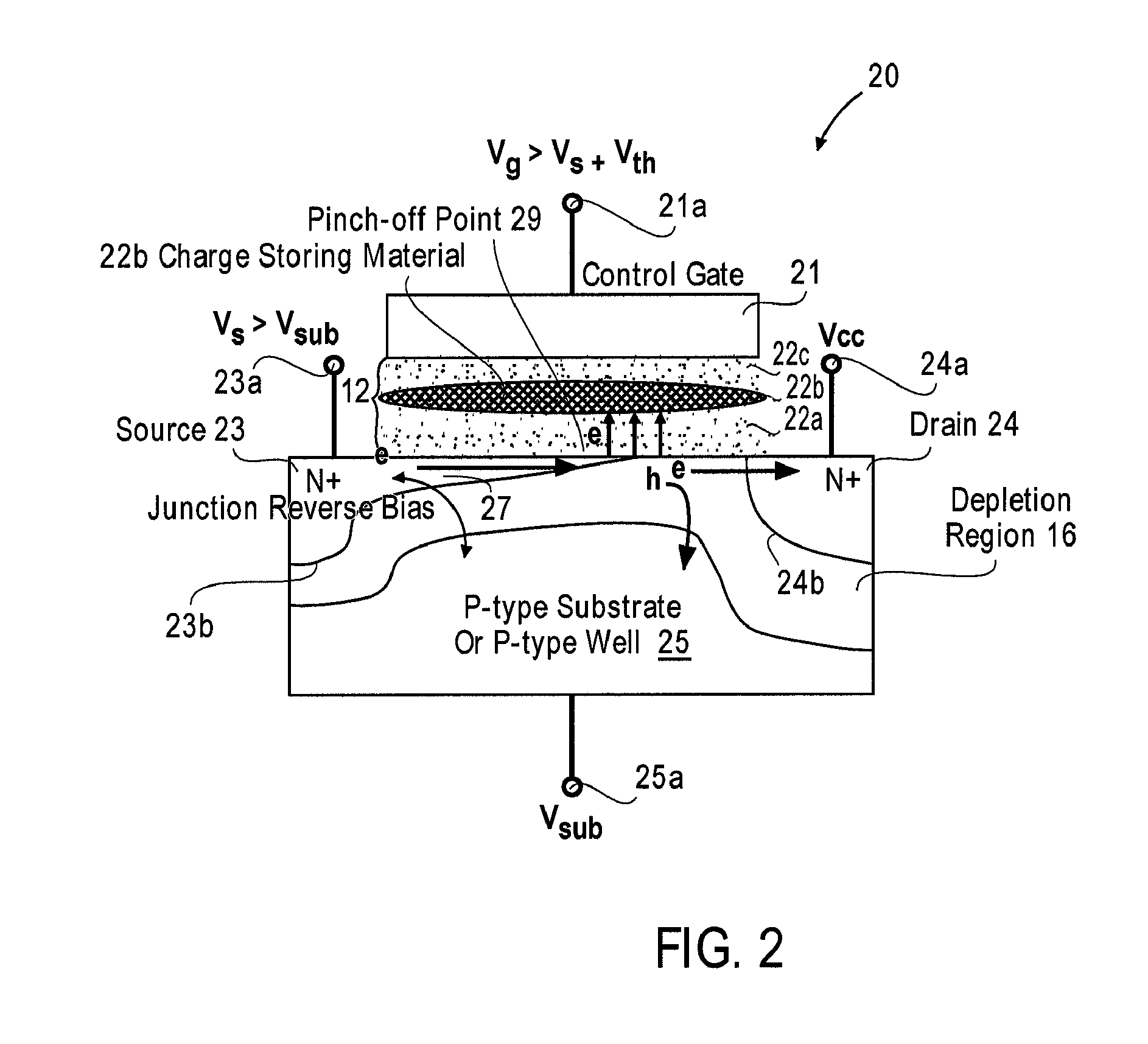

A metal oxide semiconductor field effect transistor (MOSFET) in a non-volatile memory cell has a source, a drain and a channel region between the source and the drain, all formed in a substrate of opposite conductivity type to the conductivity type of the source and drain. The MOSFET is programmed by connecting the drain electrode to the supply source of the main voltage, Vcc, provided to said non-volatile memory cell and supplying selected voltages to the source and substrate so as to invert a portion of the channel region extending from the source toward the drain. The inverted portion of the channel region ends at a pinch-off point before reaching the drain. By controlling the reverse bias across the PN junction between the source and the substrate, the pinch-off point of the inversion region is pulled back toward the source thereby to increase the programming efficiency of the MOSFET.Methods and structures for highly efficient Hot Carrier Injection (HCI) programming for Non-Volatile Memories (NVM) apply the main positive supply voltage Vcc to, the drain electrode of the NVM cell from the chip main voltage supply in contrast to the conventional method using a higher voltage than Vcc. The source electrode and substrate are reverse biased with a differential voltage relative to the drain, while a voltage pulse is applied to the control gate of the NVM cell to turn on the NVM cell for programming. To optimize the programming condition, the source voltage and the substrate voltage are then adjusted to achieve the maximum threshold voltage shifts under the same applied gate voltage pulse condition (i.e. using a gate pulse with the same voltage amplitude and duration regardless of the source voltage and the substrate voltage). The substrate voltage to the drain voltage can not exceed the avalanche multiplication junction breakdown for a small programming current during the bias voltage adjustment.

Owner:PEGASUS SEMICON SHANGHAI CO LTD

Methods for programming a floating body nonvolatile memory

A technique to speed up the programming of a non-volatile memory device that has a floating body actively removes holes from the floating body that have accumulated after performing hot carrier injection (HCI). The steps of HCI and active hole removal can be alternated until the programming is complete. The active hole removal is faster than passively allowing holes to be removed, which can take milliseconds. The active hole removal can be achieved by reducing the drain voltage to a negative voltage and reducing the gate voltage as well. This results in directly withdrawing the holes from the floating body to the drain. Alternatively, reducing the drain voltage while maintaining current flow stops impact ionization while sub channel current collects the holes. Further alternatively, applying a negative gate voltage causes electrons generated by band to band tunneling and impact ionization near the drain to recombine with holes.

Owner:NXP USA INC

Low voltage programming in NAND flash with two stage source side bias

ActiveUS20130088920A1Low working voltageResolve low GCR issueRead-only memoriesDigital storageLow voltageCharge carrier

A memory device includes a plurality of memory cells arranged in series in the semiconductor body, such as a NAND string, having a plurality of word lines. A selected memory cell is programmed by hot carrier injection. The program operation is based on metering a flow of carriers between a first semiconductor body region on a first side of the selected cell in the NAND string and a second semiconductor body region on a second side of the selected cell. A program potential higher than a hot carrier injection barrier level is applied to the selected cell, and then the drain to source voltage across the selected cell and the flow of carriers in the selected cell reach a level sufficient to support hot carrier injection, which is controlled by a combination of a switch cell adjacent the selected cell and modulation of a source side voltage applied to the NAND string.

Owner:MACRONIX INT CO LTD

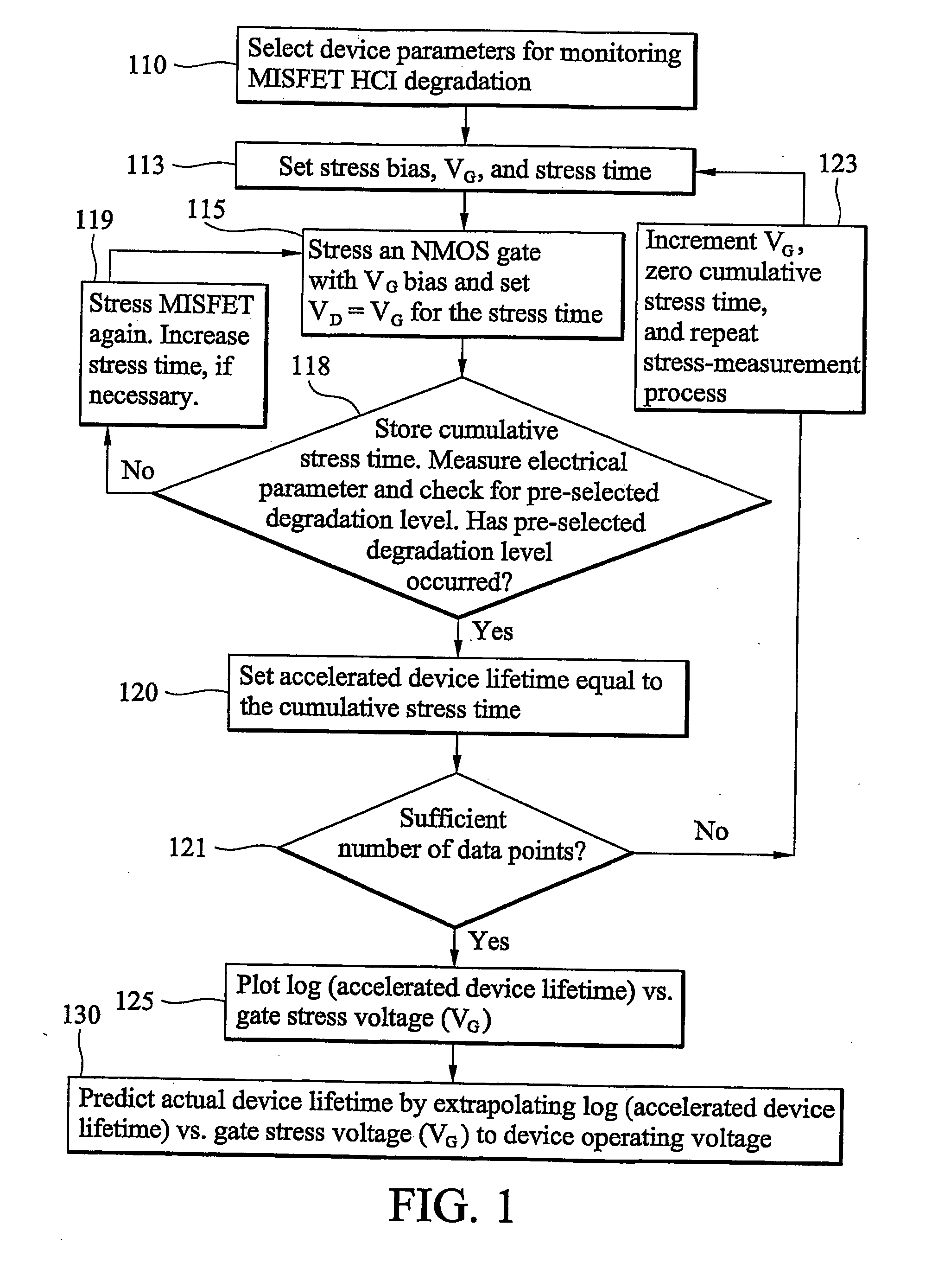

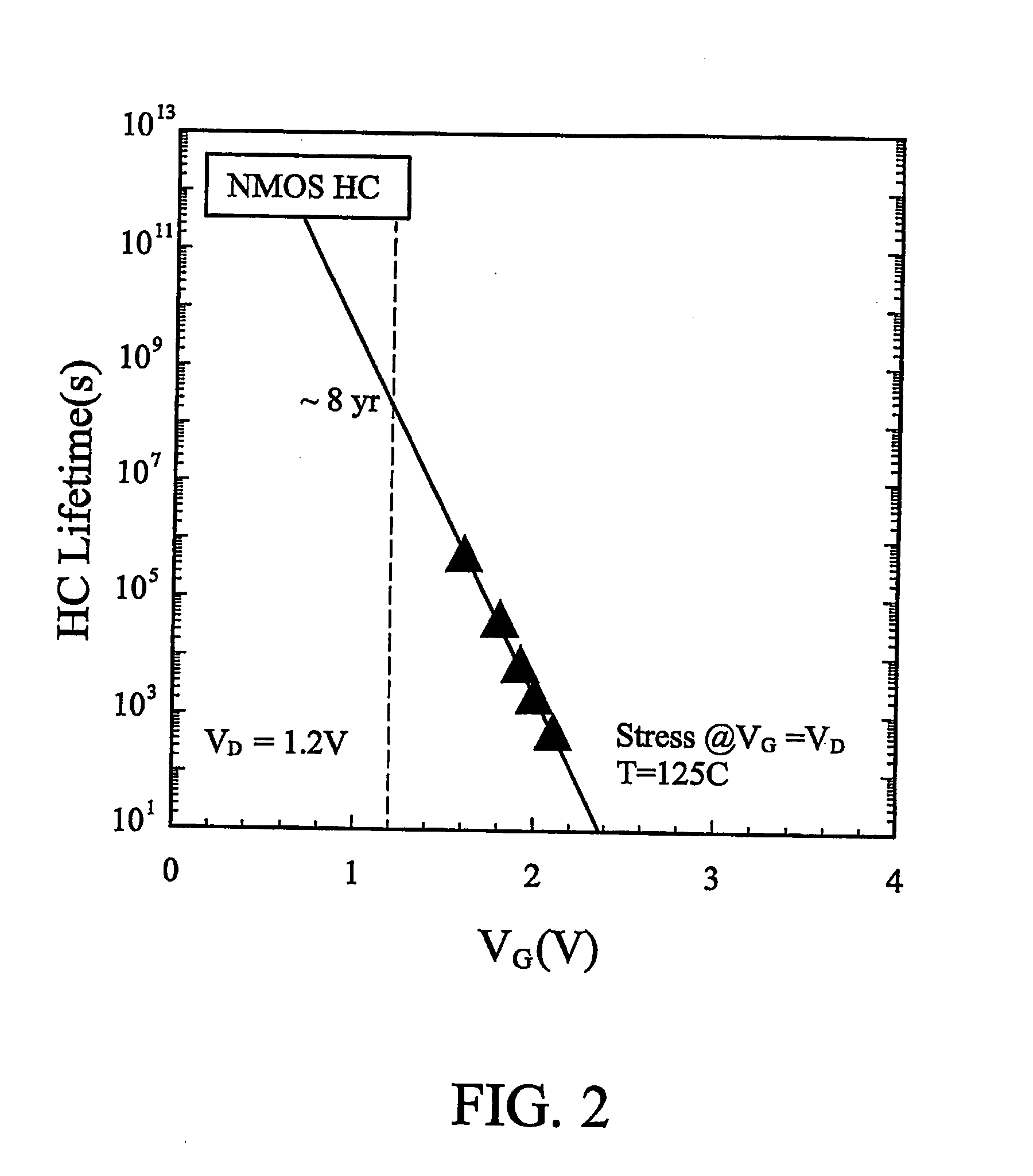

Method of predicting high-k semiconductor device lifetime

InactiveUS20060158210A1Semiconductor/solid-state device manufacturingSemiconductor operation lifetime testingDielectricElectricity

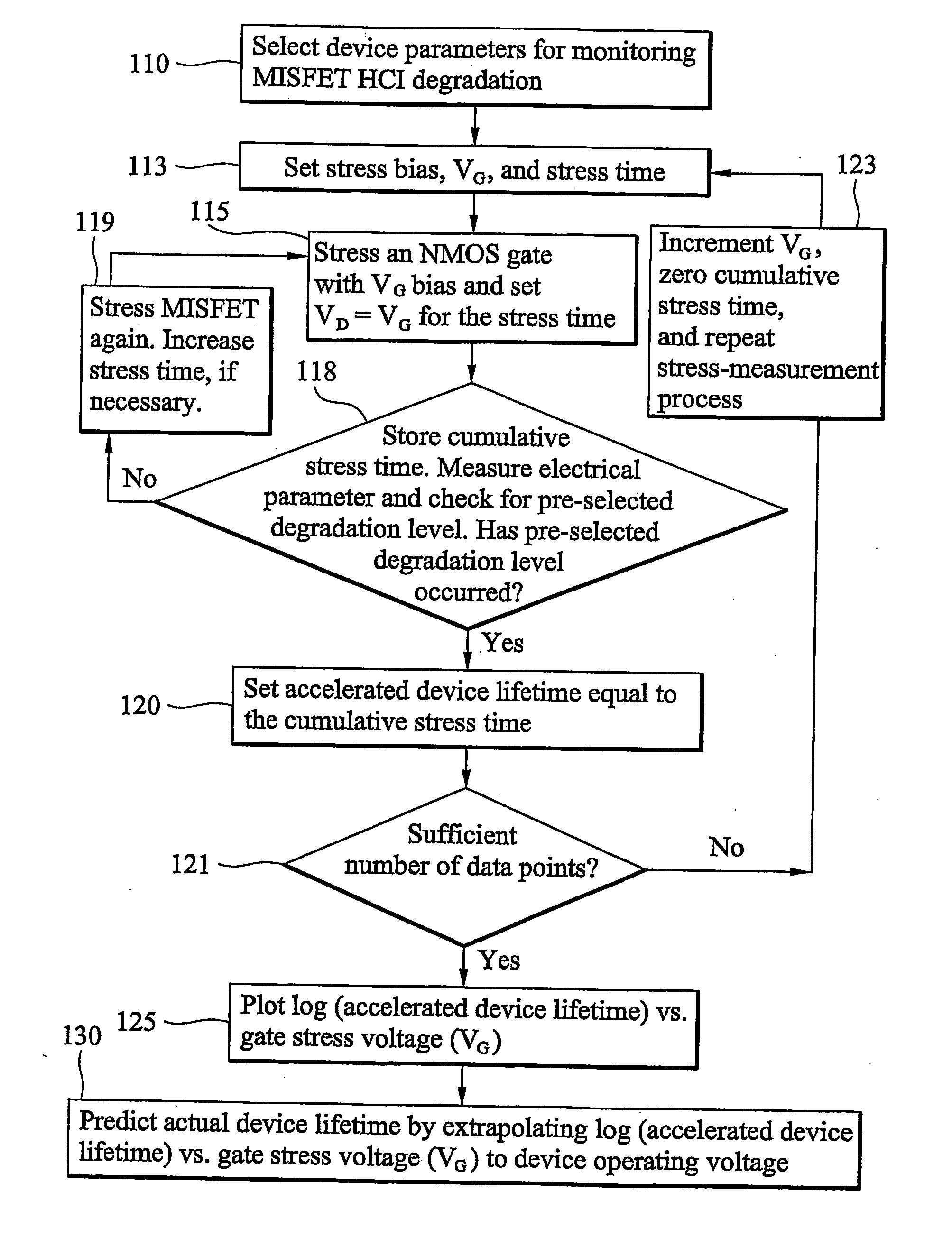

A preferred embodiment of the invention provides a method for testing a MISFET to determine the effect of hot carrier injection (HCI) on integrated circuit lifetime. The method comprises applying a positive stress voltage to a gate having a high-k dielectric, while simultaneously holding a drain voltage equal to the stress voltage. Using a stress voltage that is greater than a normal operating voltage accelerates the degradation and failure of the integrated circuit. Embodiments include monitoring electrical parameters such as threshold voltage, transconductance, linear drain current, or saturation drain current. A pre-selected shift in a monitored electrical parameter indicates device failure. Embodiments include analyzing the data by plotting the logarithm of an accelerated device lifetime versus the gate stress voltage. The device lifetime under operating conditions is predicted by extrapolating the plot for a given device operating voltage.

Owner:TAIWAN SEMICON MFG CO LTD

Operation methods for memory cell and array for reducing punch through leakage

ActiveUS20090116286A1Reduces punch through leakageWide rangeSolid-state devicesRead-only memoriesEngineeringStorage material

A method for programming a first memory cell in a memory array. In a specific embodiment, each memory cell has a drain, a source, a channel, and a control gate overlying a charge storage material and the channel. The source of the first memory cell is coupled to the drain of a second memory cell. A voltage is applied to the drain of the first memory cell, and the source of the second memory cell is grounded. The method includes floating the drain of the second memory cell and the source of the first memory cell and turning on the channels of the first and second memory cells, effectively forming an extended channel region. Hot carriers are injected to the charge storage material of the first cell to program the first memory cell. The extended channel lowers electrical fields and reduces punch through leakage in unselected memory cells.

Owner:MACRONIX INT CO LTD

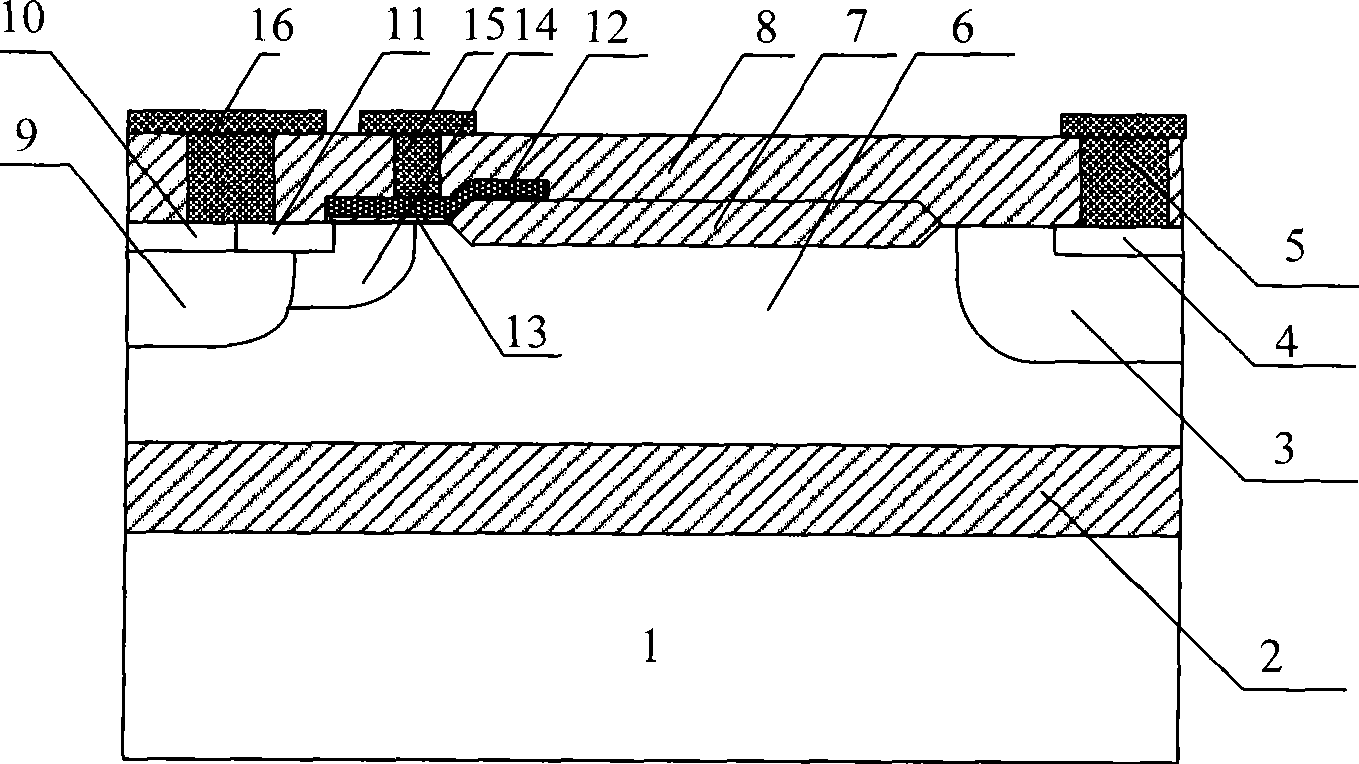

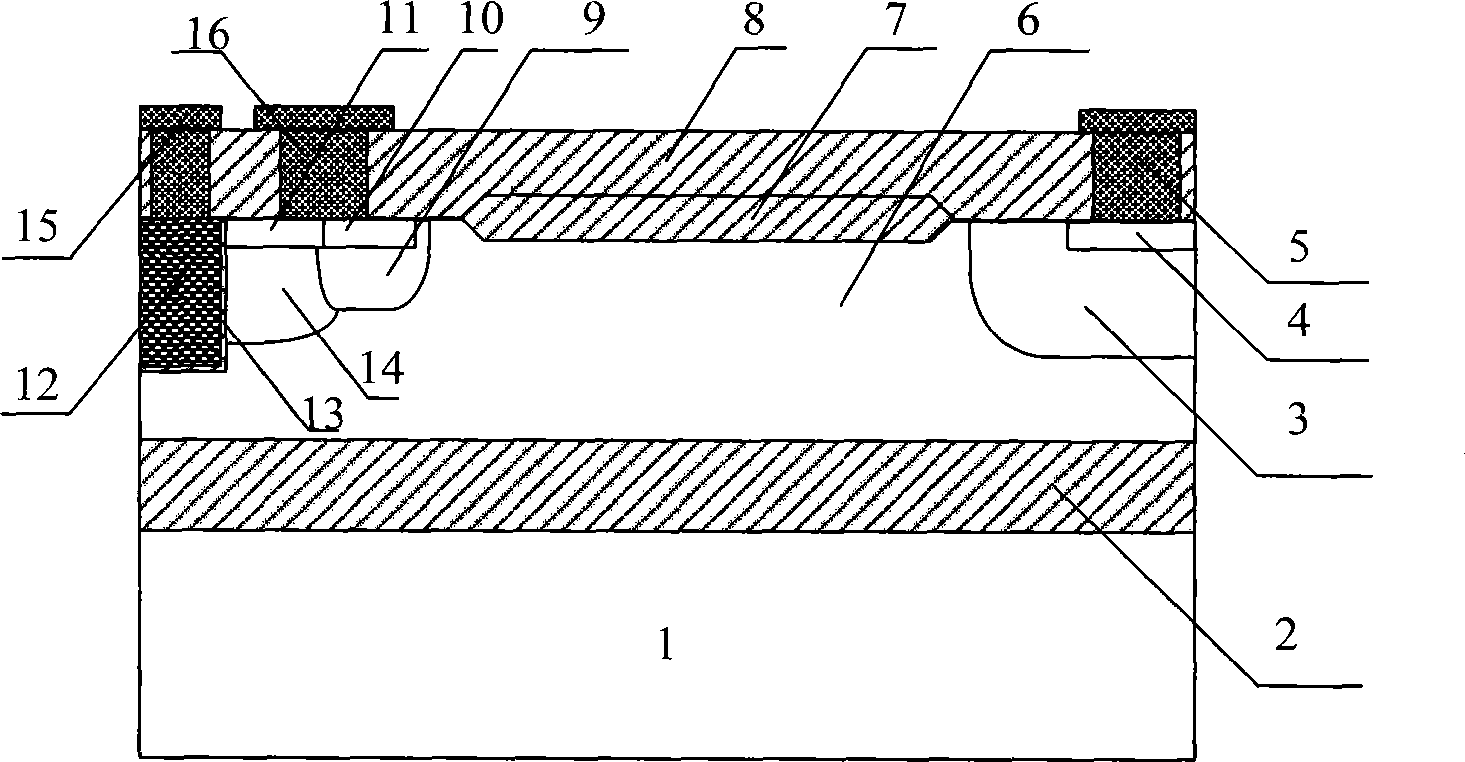

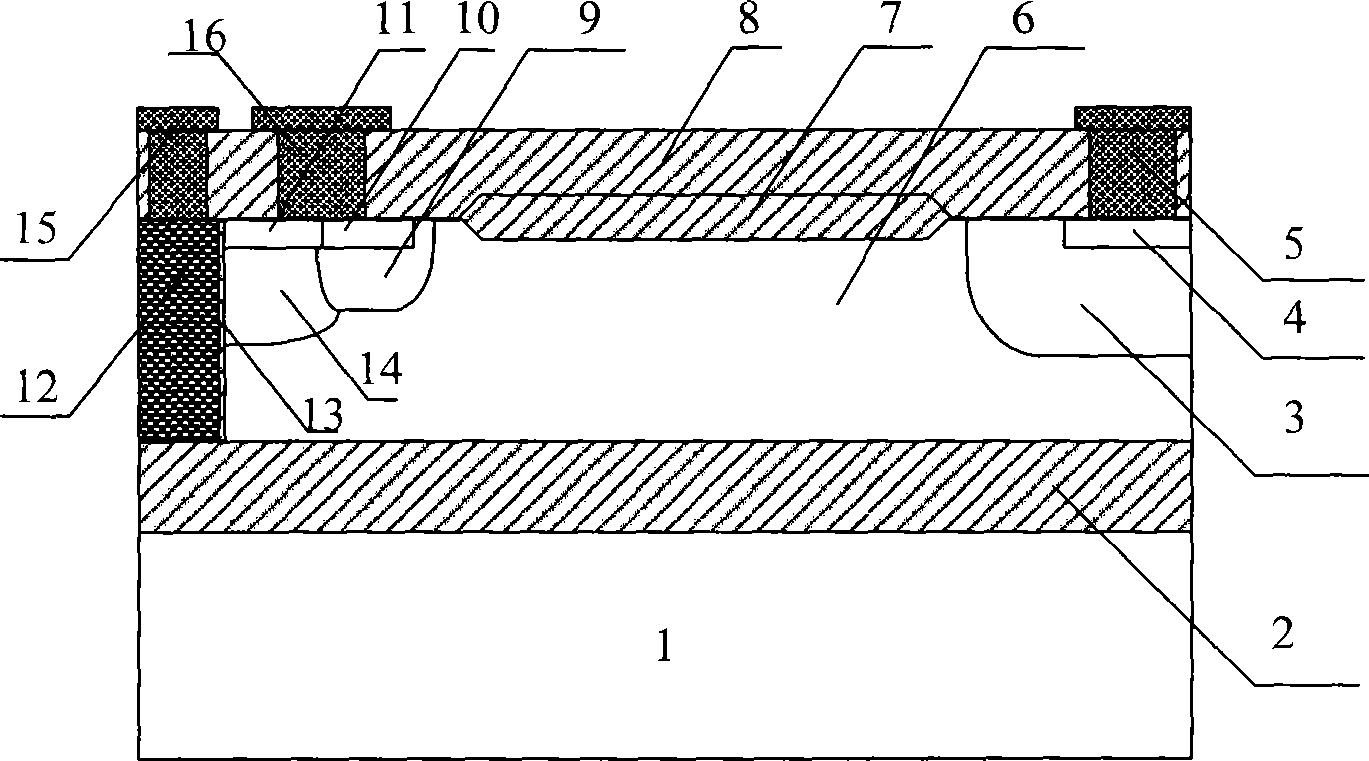

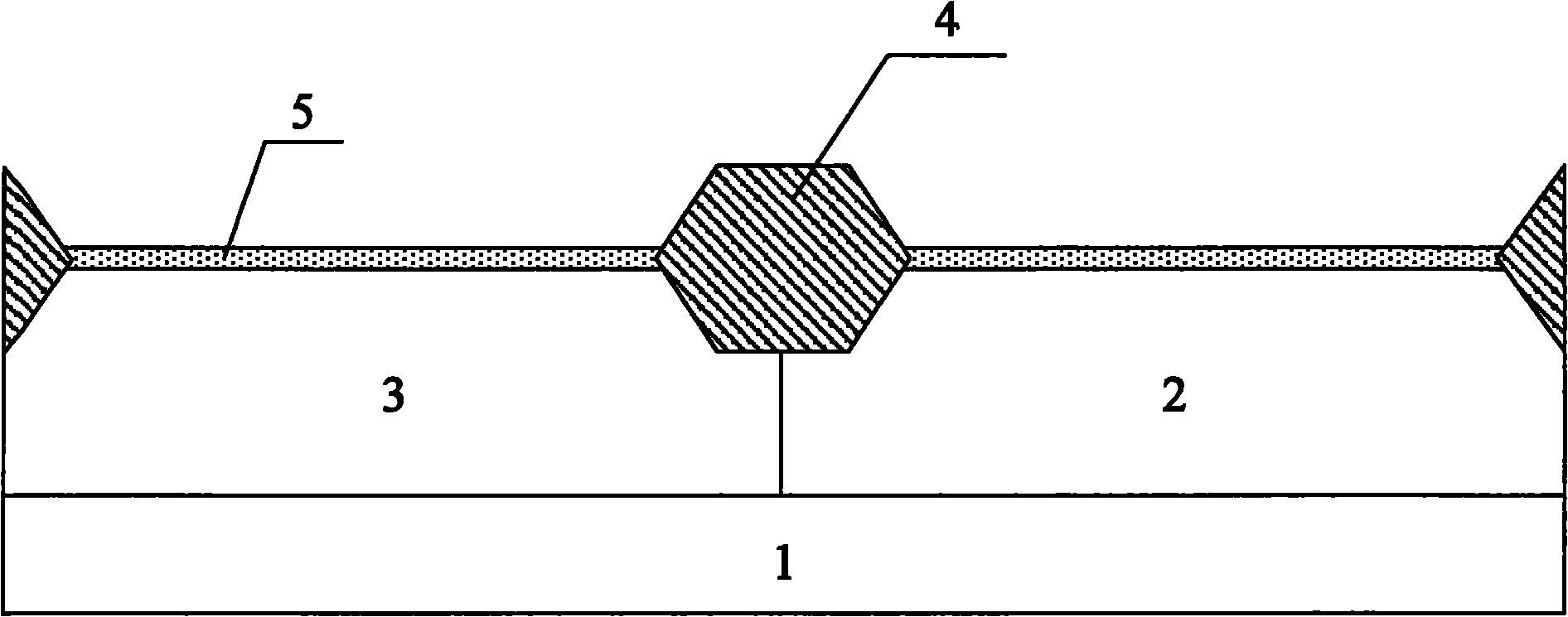

Trench gate SOI LIGBT device

InactiveCN101419981AReduce base currentPrevent openingSemiconductor devicesTrench gateDielectric layer

The invention discloses a groove-gate SOI LIGBT device, and relates to semiconductor power device technologies. The groove-gate SOI LIGBT device comprises a substrate, a buried oxide layer, an N-type buffer layer, an anode P<+> region, an anode metal, an N-type drift region, a field oxide layer, a front metal dielectric layer, a P<+> region, an N<+> region, a polysilicon groove gate, an LIGBT device gate oxide layer, a P-type channel region, a polysilicon groove-gate metal and a cathode metal, the cathode metal is connected with the P<+> region and the N<+> region, and the P<+> region 10 is arranged between the N<+>region 11 and the anode P<+> region 4. The groove-gate SOI LIGBT device reduces the electric field intensity around the gate oxide layer, prevents a hot carrier from being implanted into the gate oxide, and improves the reliability of the device.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method and structures for highly efficient hot carrier injection programming for non-volatile memories

ActiveUS7733700B2High rateReduce voltage dropRead-only memoriesDigital storageMOSFETVoltage amplitude

A method programs a memory cell by controlling a reverse bias voltage across the PN junction between a source electrode of a MOSFET in the memory cell and the substrate, and pulling back the pinch-off point of the inversion region toward the source electrode, thereby increasing the programming efficiency of the memory cell. The method applies the main positive supply voltage Vcc to, the drain electrode of the memory cell from the chip main voltage supply, rather than the conventional method of using a higher voltage than Vcc. To optimize the programming condition, the source voltage and the substrate voltage are adjusted to achieve the maximum threshold voltage shifts under the same applied gate voltage pulse condition (i.e. using the gate pulse with the same voltage amplitude and duration regardless of the source voltage and the substrate voltage). The substrate voltage to the drain voltage can not exceed the avalanche multiplication junction breakdown for a small programming current during the bias voltage adjustment.

Owner:PEGASUS SEMICON SHANGHAI CO LTD

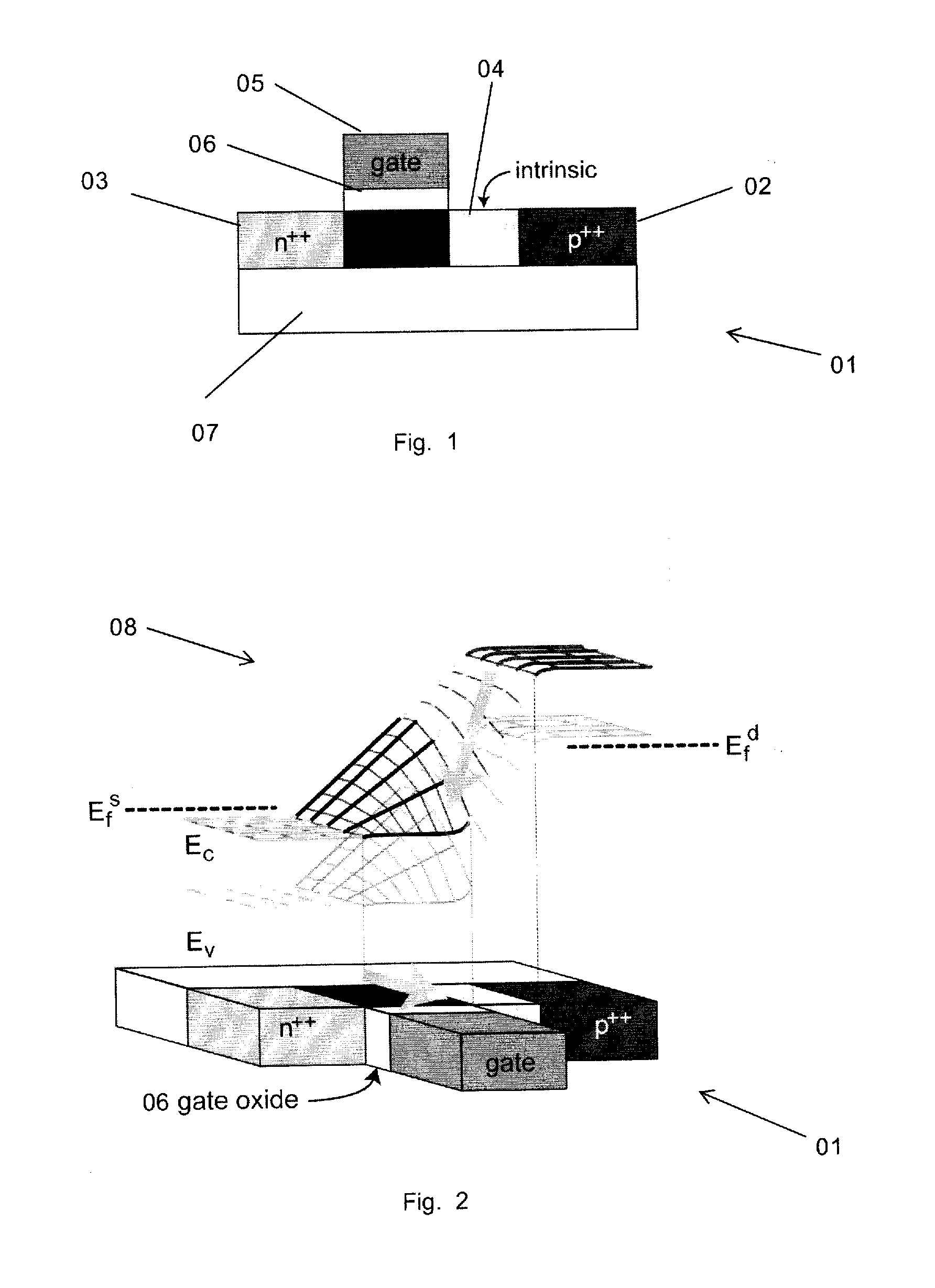

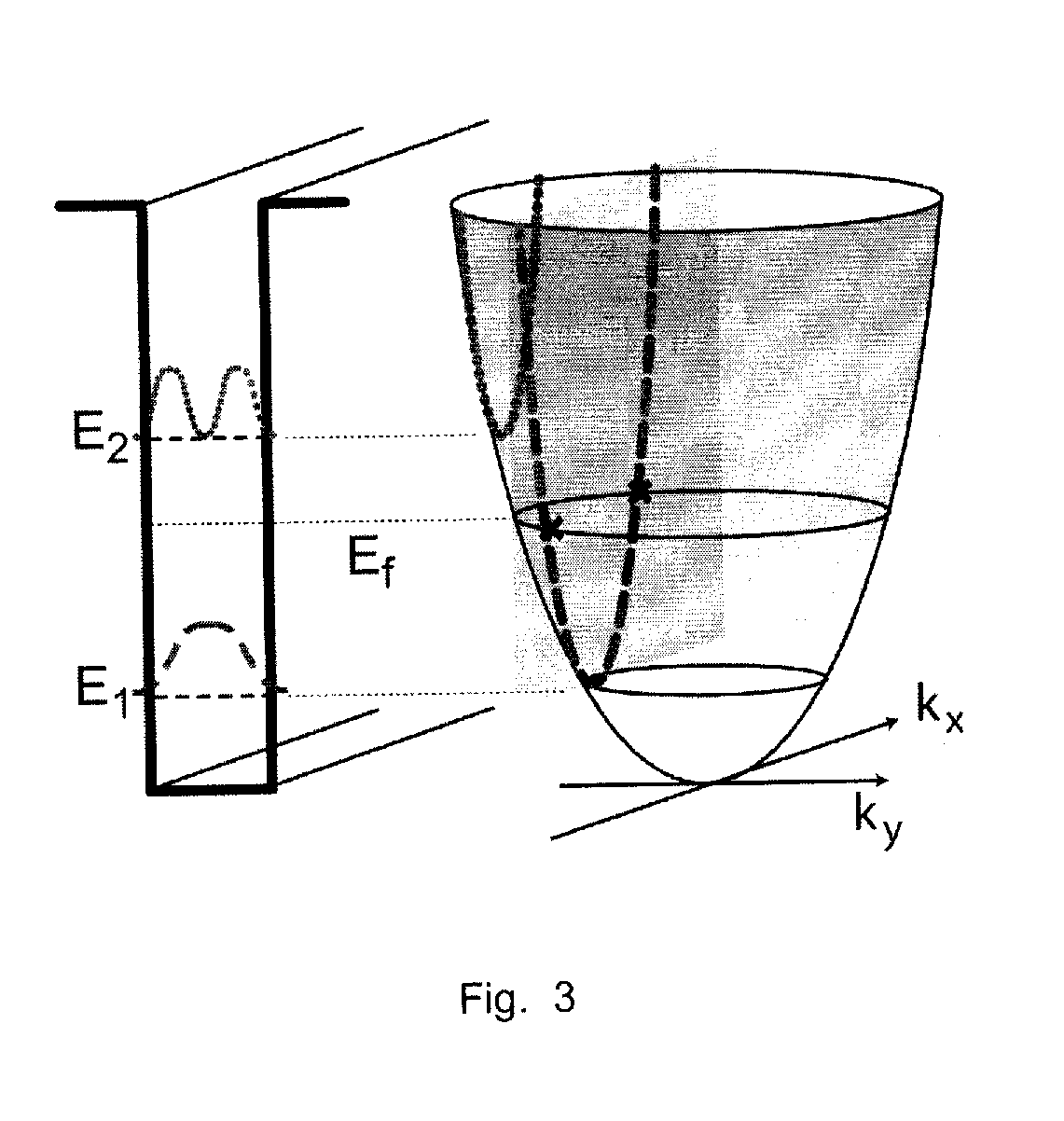

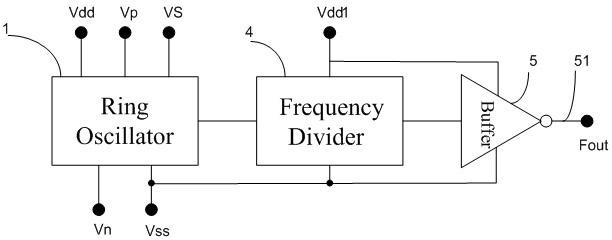

Impact ionization field-effect transistor

An Impact Ionization Field-Effect Transistor (I-MOS) device in which device degradation caused by hot carrier injection into a gate oxide is prevented. The device includes source, drain, and gate contacts, and a channel between the source and the drain. The channel has a dimension normal to the direction of a charge carrier transport in the channel such that the energy separation of the first two sub-bands equals or exceeds the effective energy band gap of the channel material.

Owner:GLOBALFOUNDRIES US INC

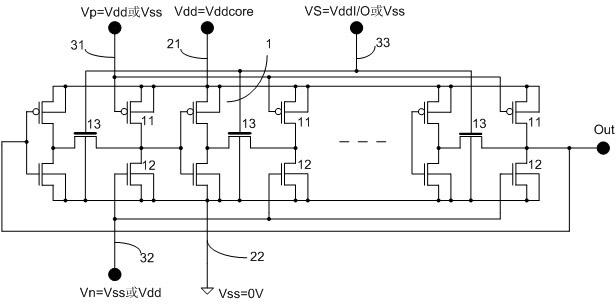

Circuit and method for testing reliability of integrated circuit

ActiveCN102590735AMeasuring and differentiating degradationElectrical testingCircuit reliabilityHemt circuits

The invention belongs to the technical field of integrated circuit test, and in particular relates to a circuit and a method for testing reliability of an integrated circuit. According to the core circuit of the testing circuit, auxiliary p-type metal oxide semiconductor field effect transistors (pMOSFETs) and n-type metal oxide semiconductor field effect transistors (nMOSFETs) are connected between every two stages of inverters of a ring oscillator (RO) and between a high level Vdd and low potential Vss, and a switch transistor is plugged in an input and output connecting line. By controlling the grid voltages of the auxiliary transistors and the switch transistor, normal oscillation of the RO can be realized in the core circuit, dynamic stress is applied to complementary metal oxide semiconductor field effect transistors (CMOSFETs) of the RO, and negative bias temperature instability (NBTI), positive bias temperature instability (PBTI) and hot carrier injection (HCI) stresses are respectively applied to the pMOSFETs or the nMOSFETs of the RO. The testing circuit has the functions of: degradation measurement of the pMOSFETs in the RO under the NBTI stress, degradation measurement of the nMOSFETs under the PBTI stress, degradation measurement of the pMOSFETs under the HCI stress, degradation measurement of the nMOSFETs under the HCI stress, and comparison with degradation measurement of the CMOSFETs under the dynamic stress.

Owner:FUDAN UNIV

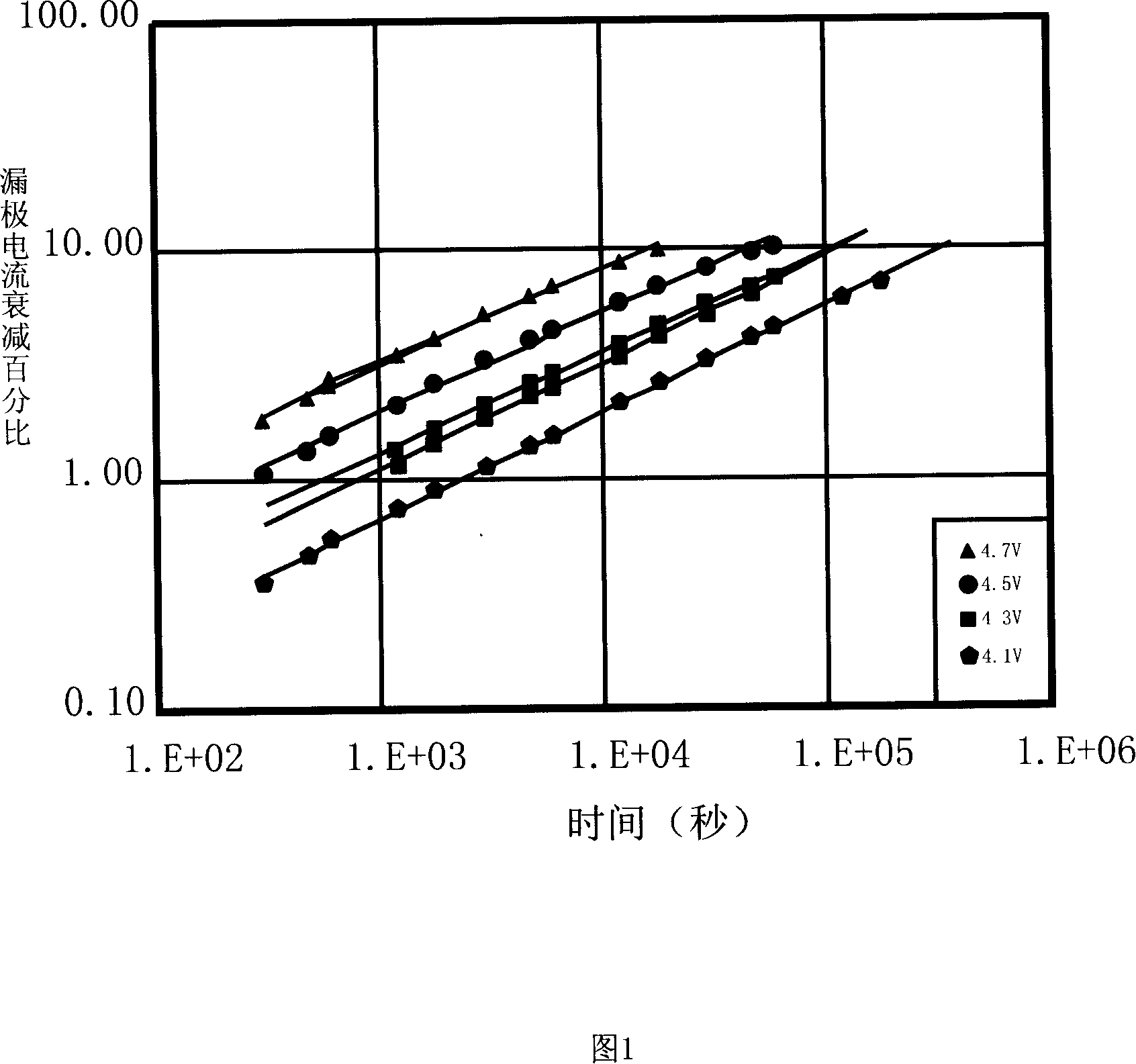

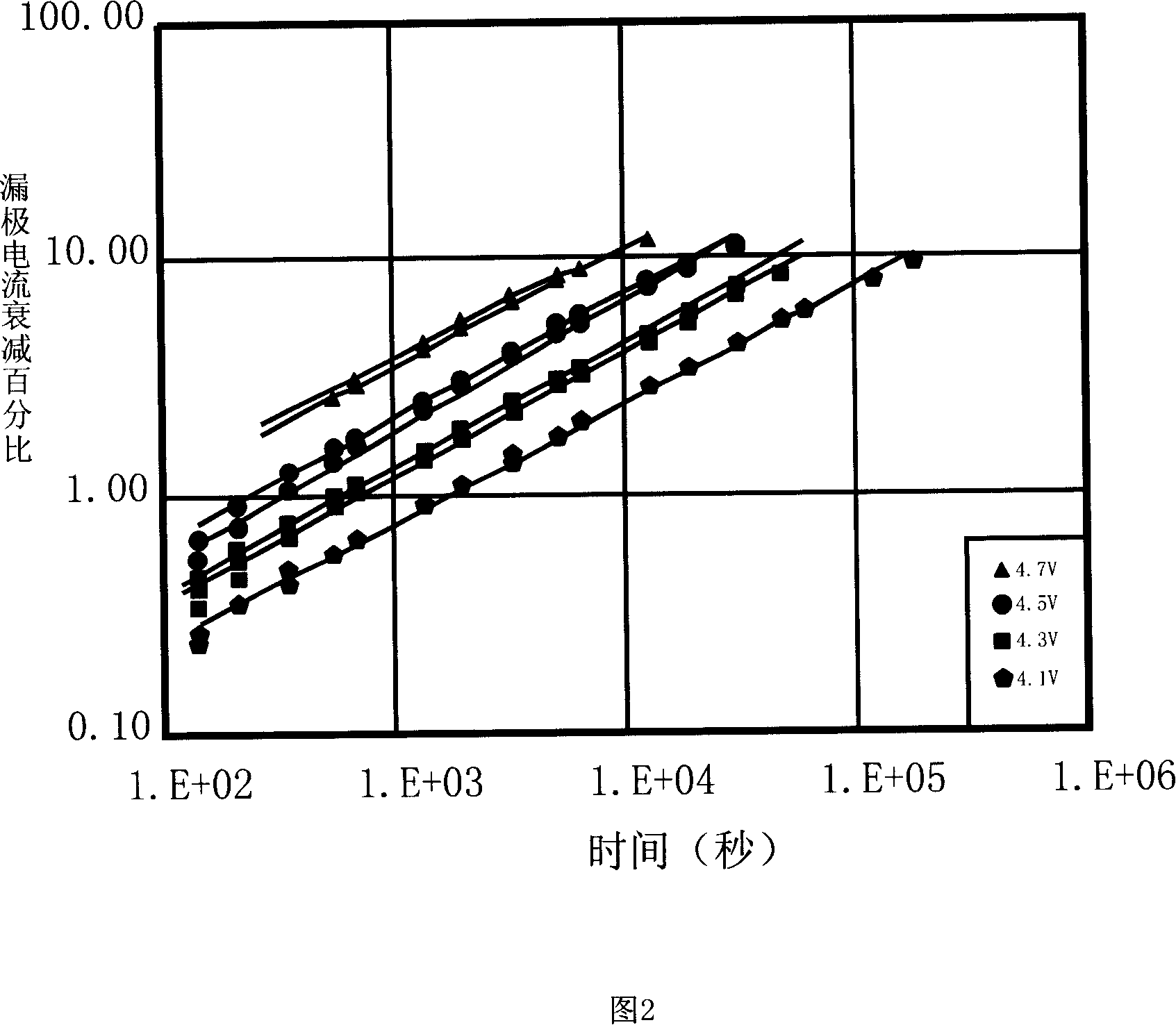

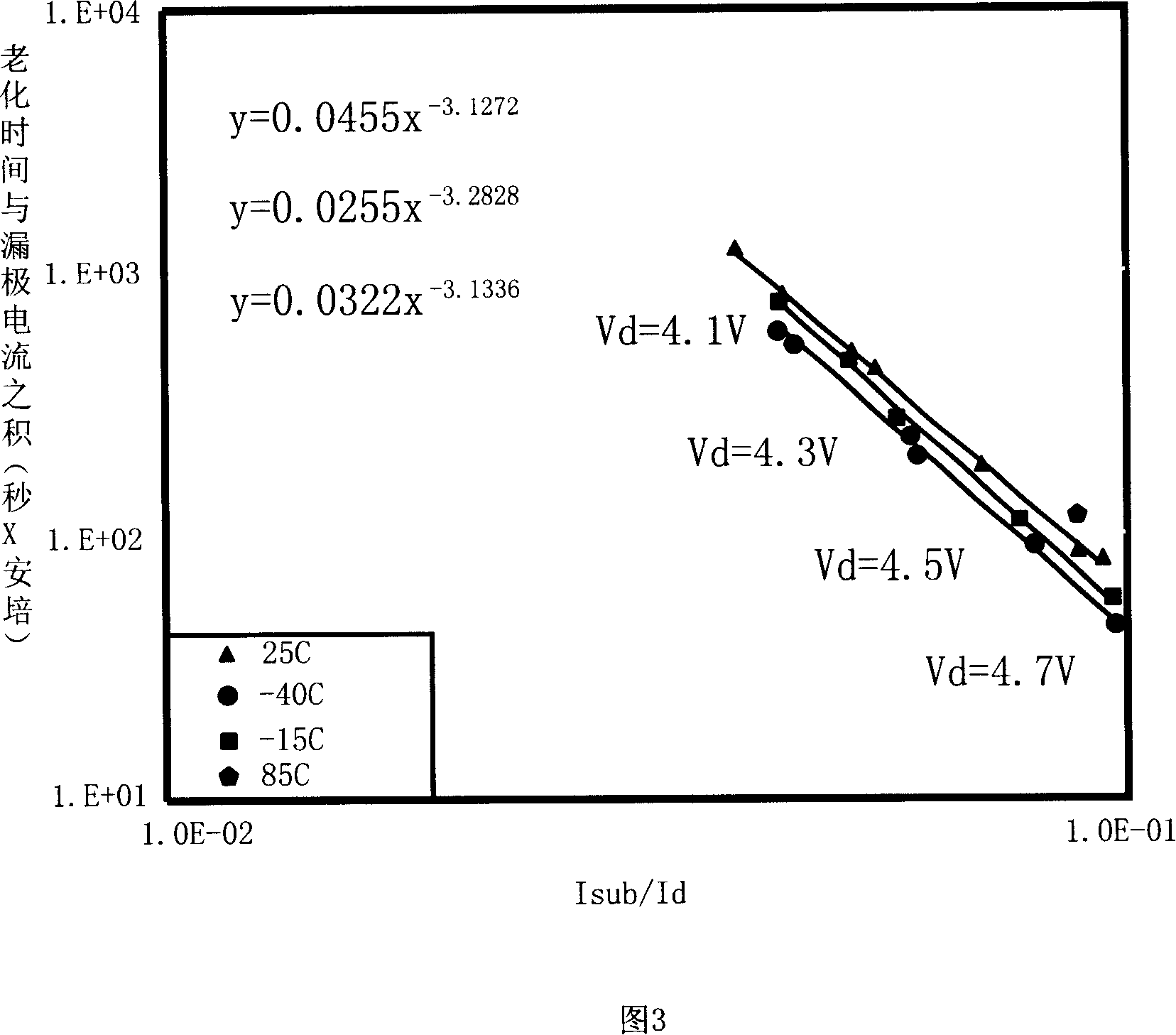

Method of accelerating hot carrier injection investigating

InactiveCN101089642AEasy accessFast measurement timeSemiconductor/solid-state device testing/measurementIndividual semiconductor device testingElectrical currentHot-carrier injection

A method for speeding up test of hot carrier injection includes separately measuring curve of drain electrode current and substrate current to time under different temperature and different bias voltage, setting failure condition and naming time realizing said failure condition to be failure time (FT), plotting out product of FT and drain electrode saturated current (DESC) and quotient of substrate current and DESC to obtain their relation, plotting out FT and temperature to obtain their relation and making low temperature failure test to derive out FT at the other temperature according to said relation of FT and temperature.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

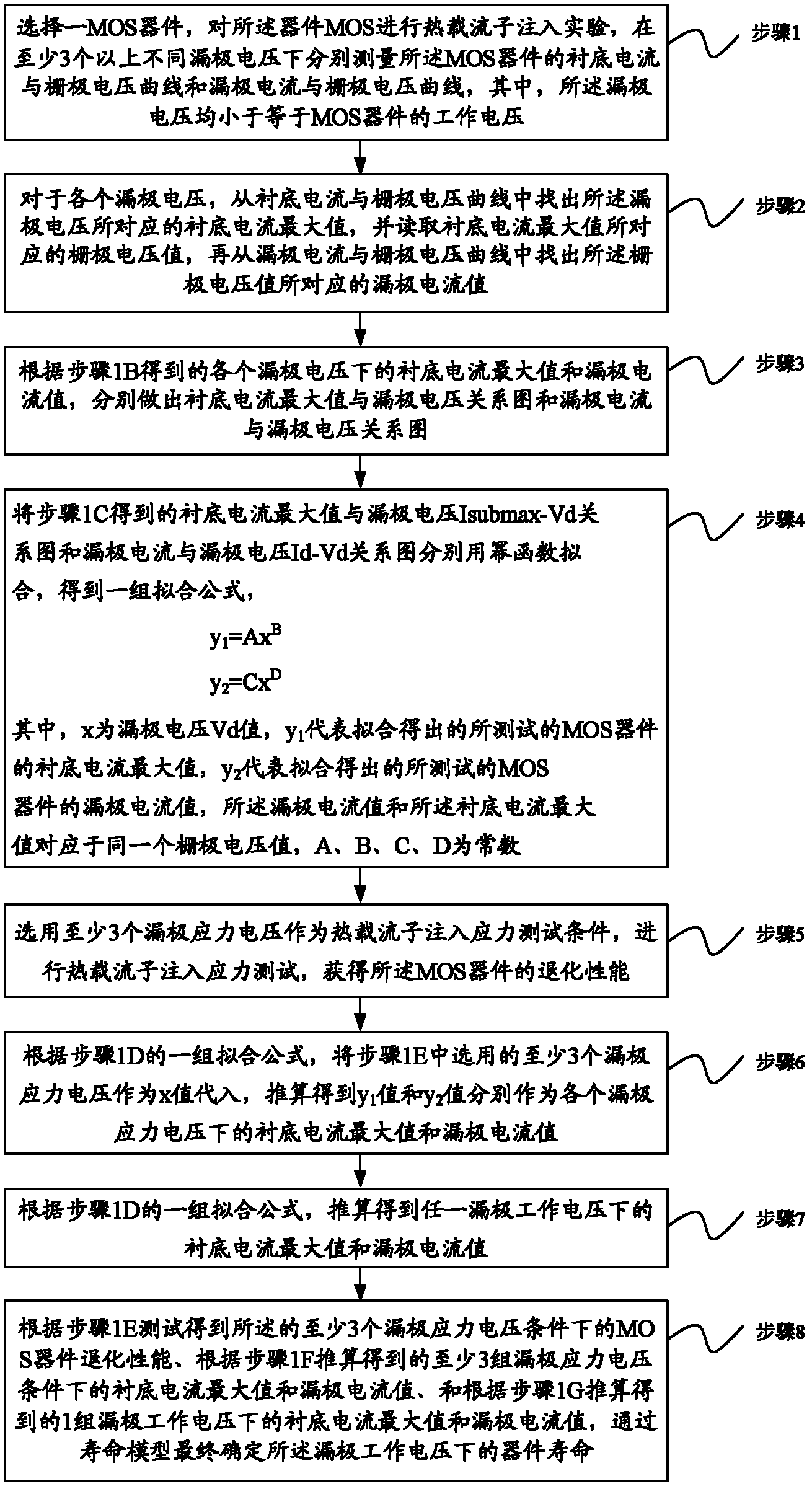

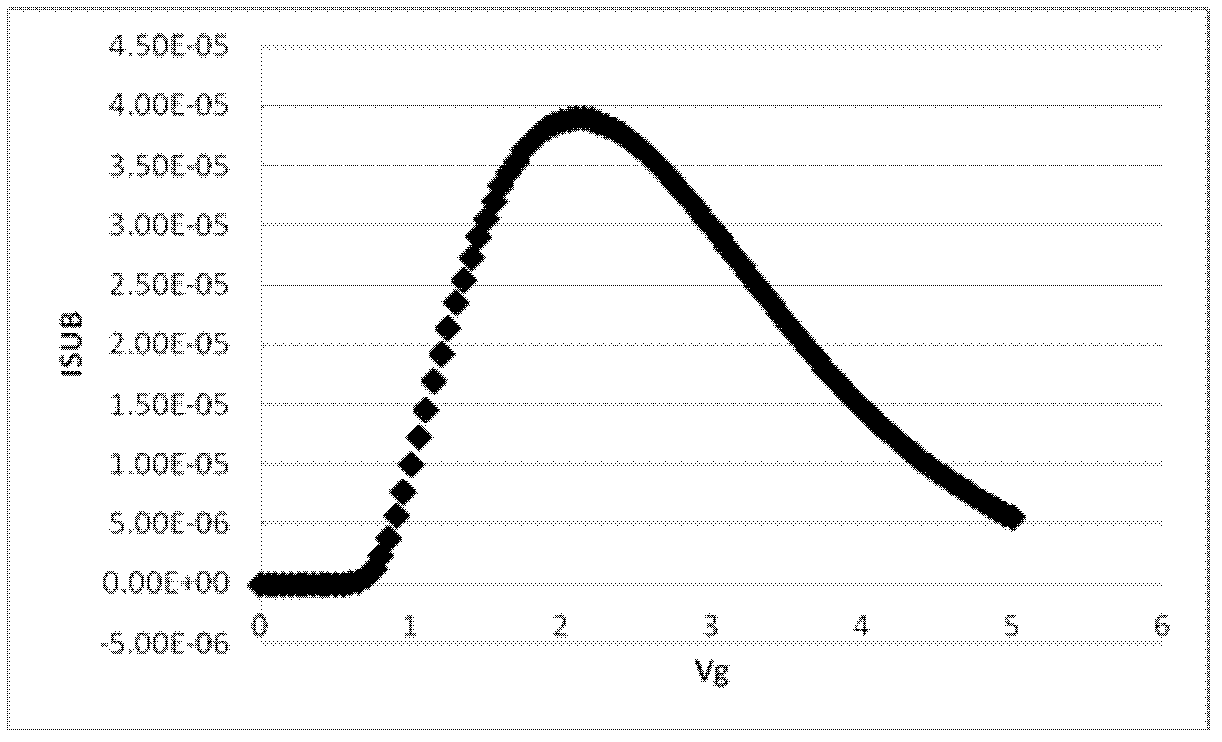

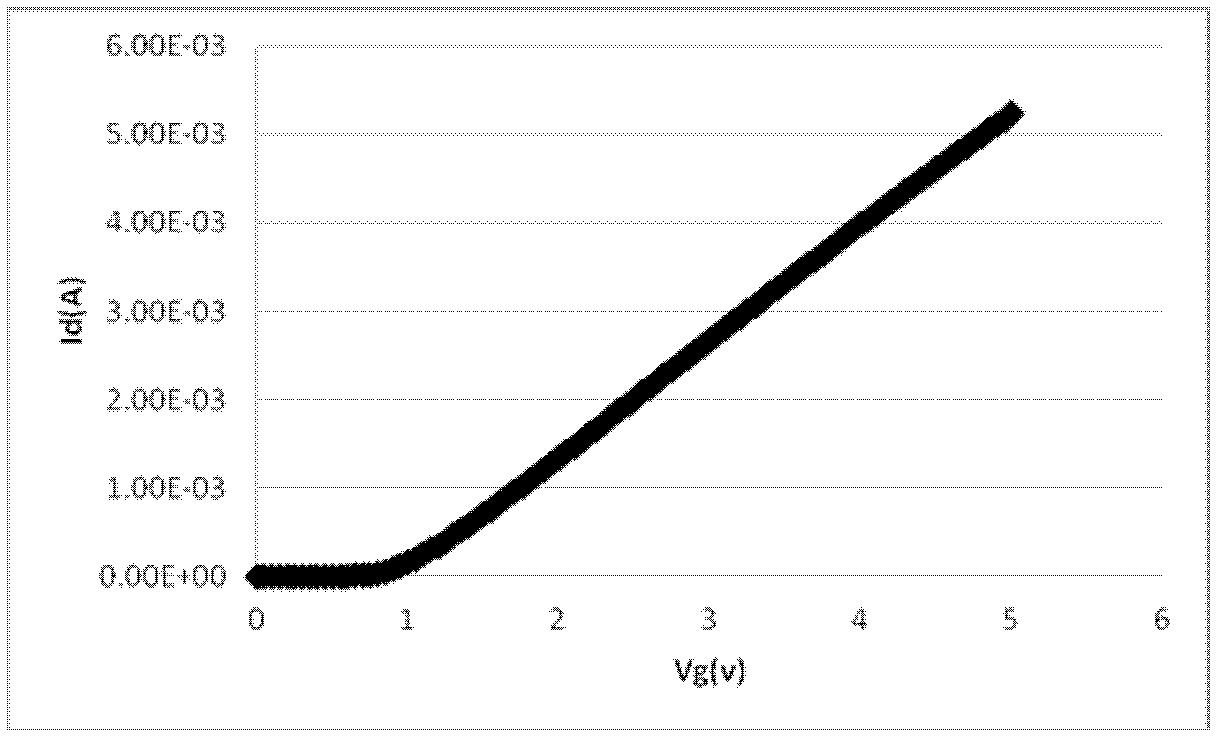

Method for determining service life of hot carrier injection device

ActiveCN102495345AReduce evaluation costsIncrease flexibilityIndividual semiconductor device testingEngineeringOxide semiconductor

The invention provides a method for determining the service life of a hot carrier injection (HCI) device. The method comprises the following steps of: measuring Isub-Vg curves and Id-Vg curves of a device under three different Vds; finding out an Isubmax value, a Vg value under the Isubmax value and an Id value under the Vg value respectively for each group of the Isub-Vg curve and the Id-Vg curve; drawing an Isubmax-Vd relational graph and an Id-Vd relational graph by using the values obtained in the former step; fitting the Isubmax-Vd relational graph and the Id-Vd relational graph respectively by using a power function to obtain a fitting formula; and deducting a group of Isubmax values and Id values under a Vd working voltage condition according to the fitting formula, deducting three groups of Isubmax values and Id values under an HCI stress test condition according to the fitting formula, deducting the device degeneration performance obtained by the HCI stress test, and deducting the final service life of the device through a service life model. According to the method, the HCI service life of a metal oxide semiconductor (MOS) device is estimated by using a small number of samples, and the service life of the device under any working voltage can be obtained, so that the estimation cost is reduced, and the estimation flexibility is improved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

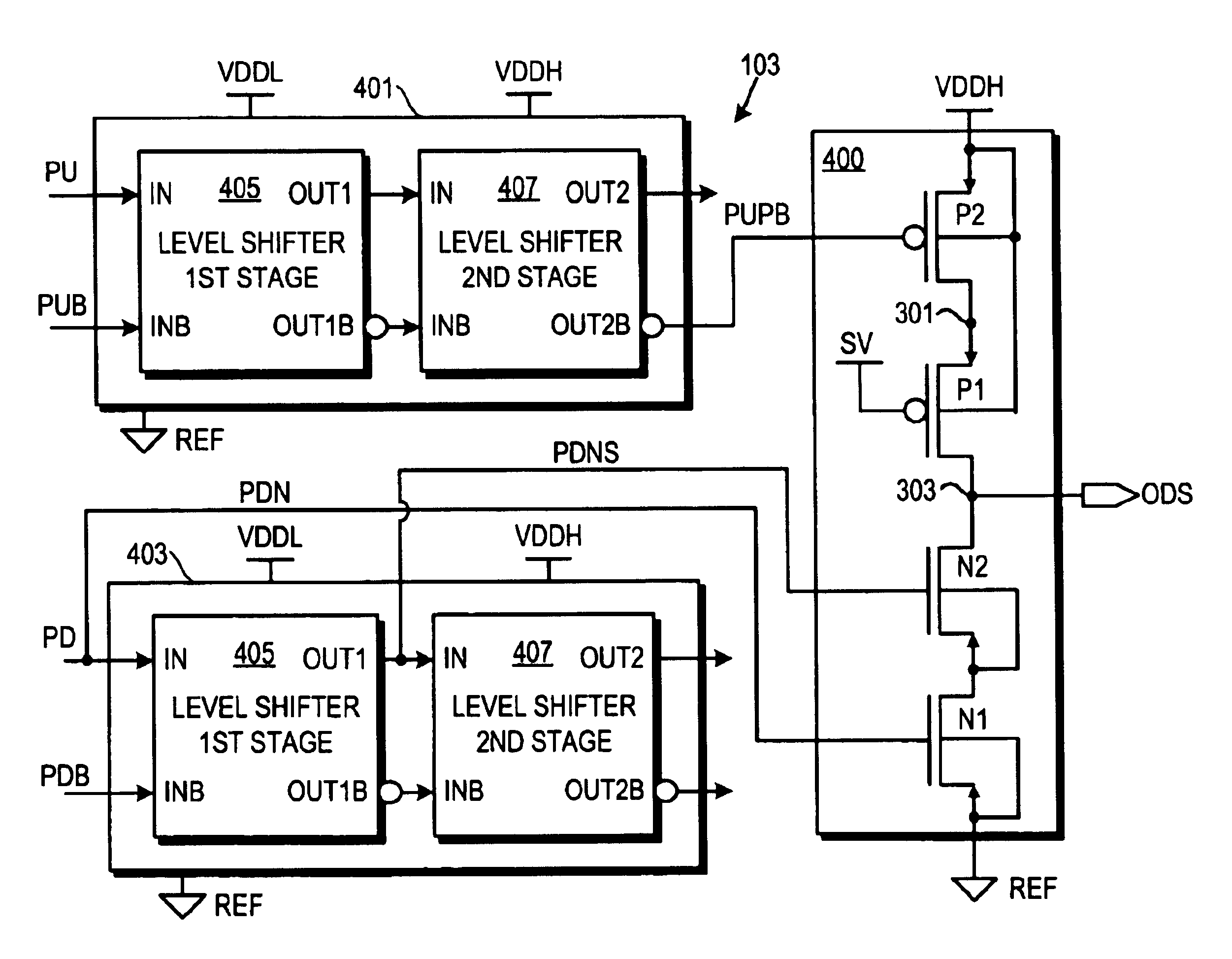

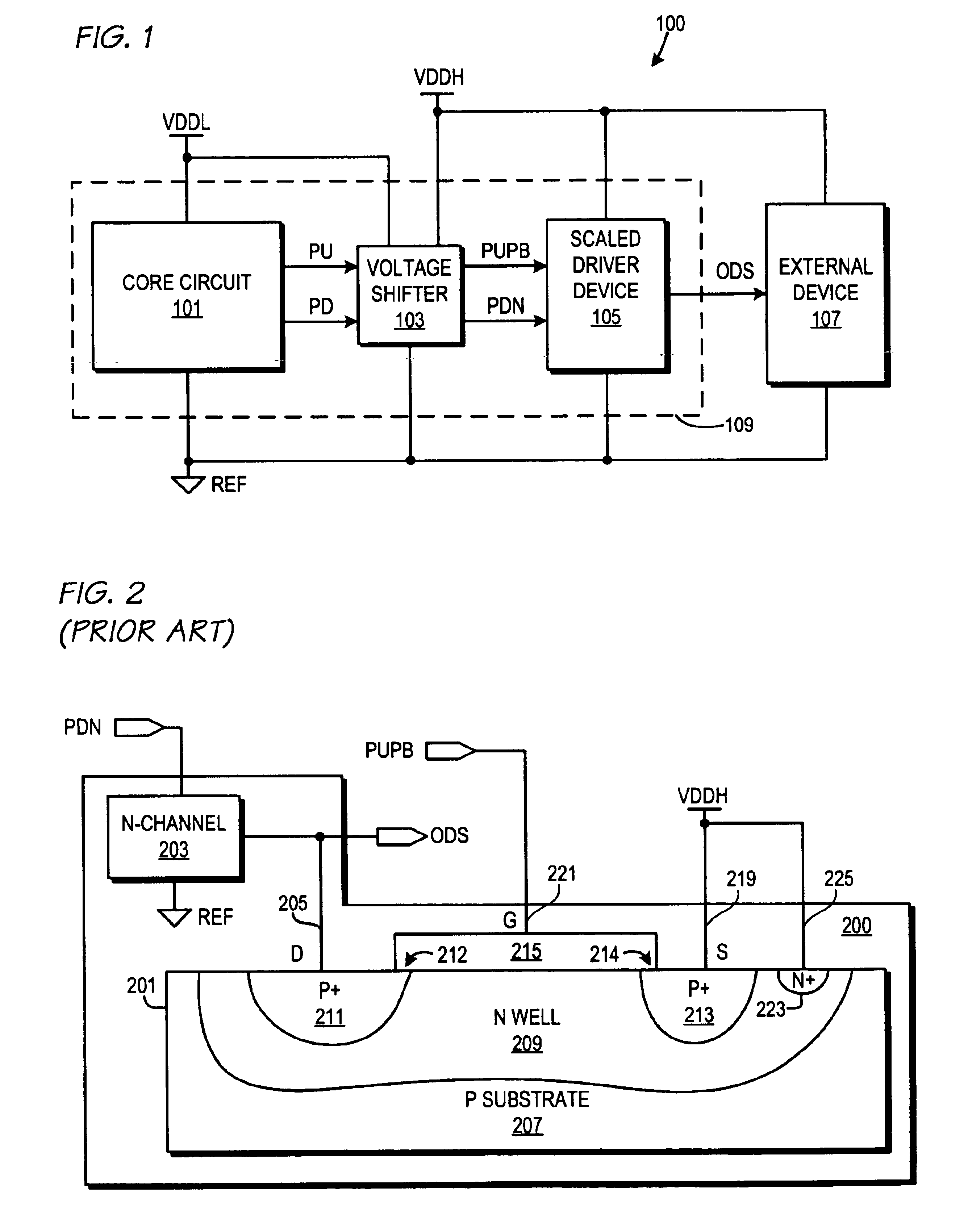

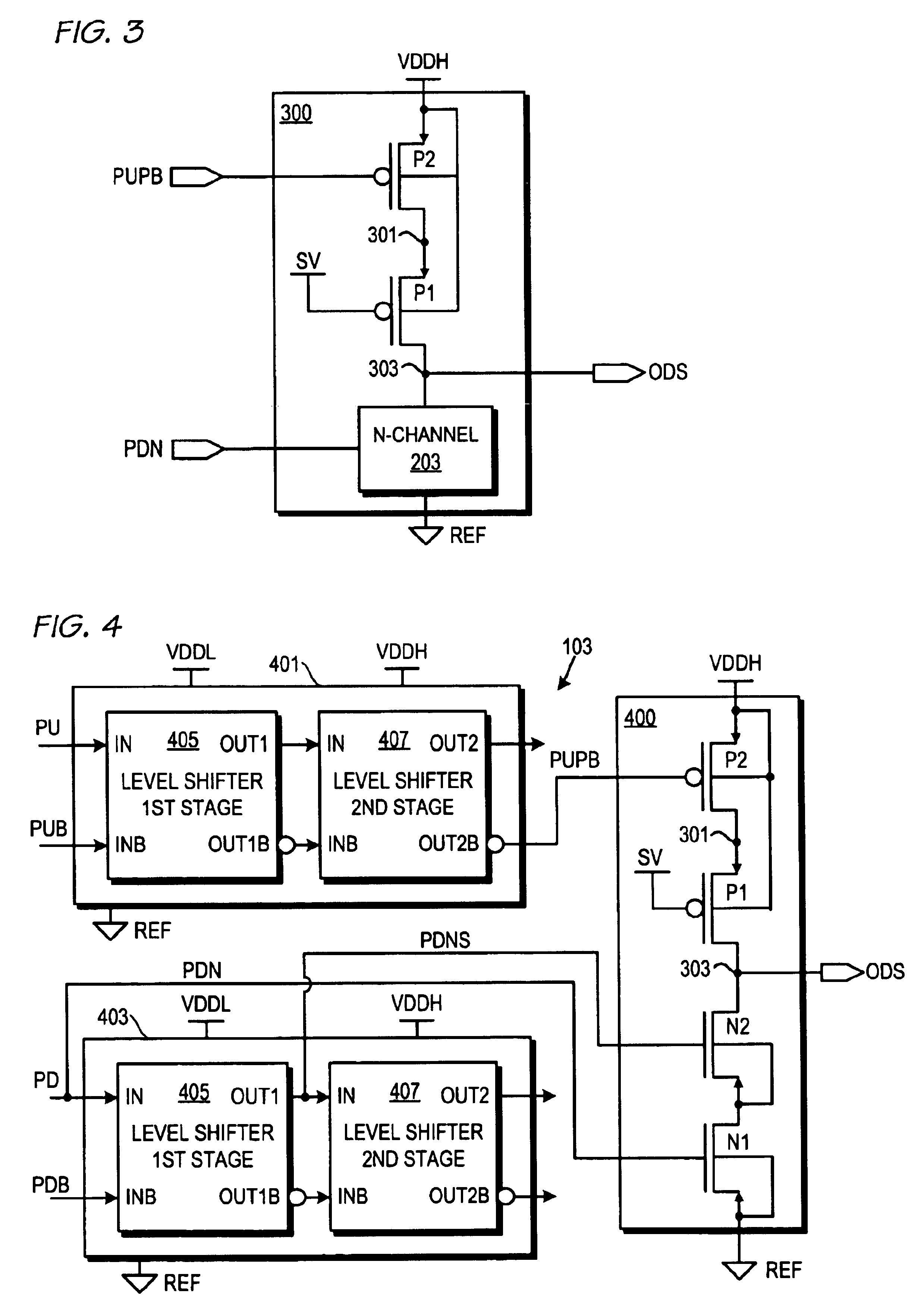

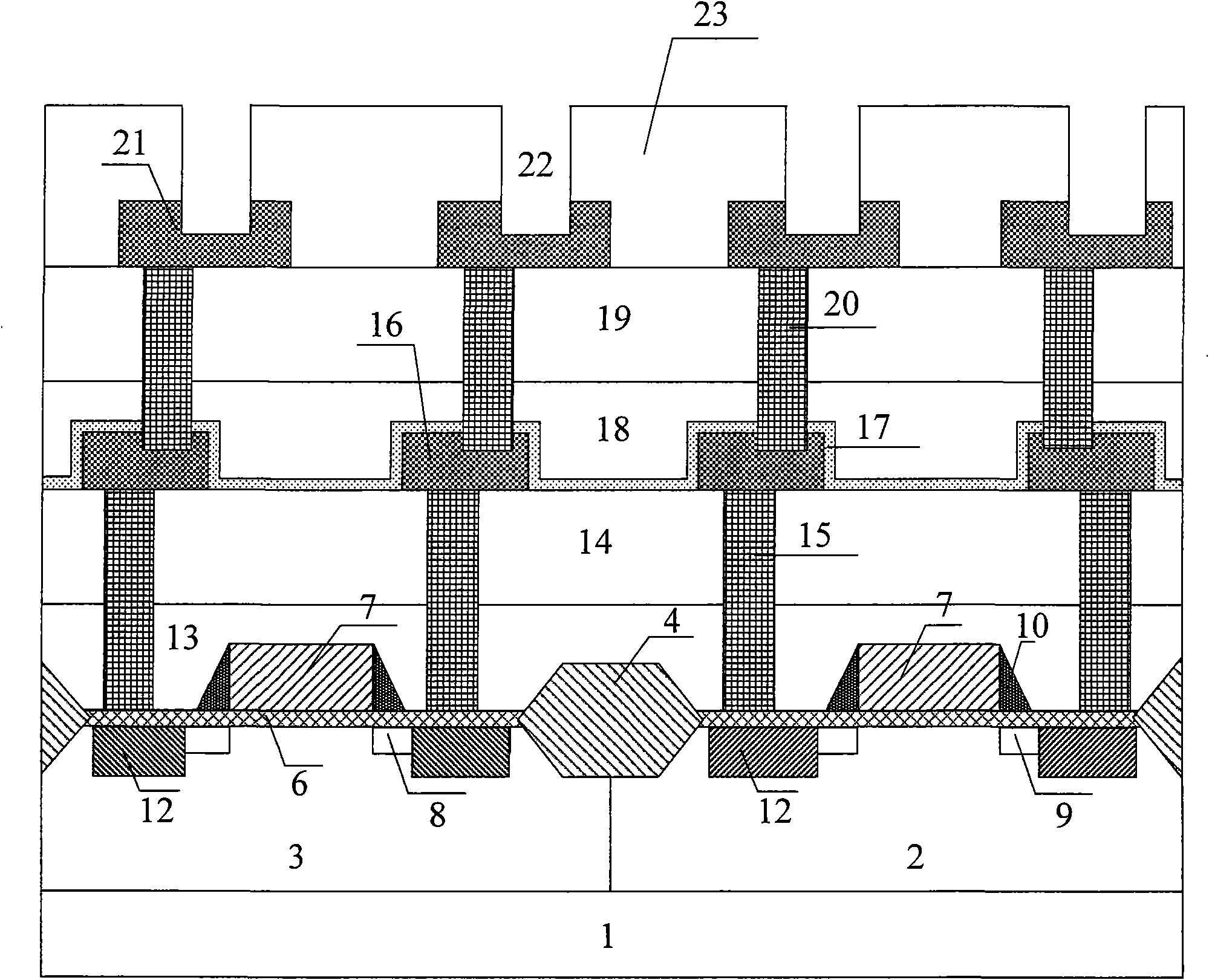

Thin gate oxide output drive

An output driver circuit including first and second cascoded scaled P-channel devices coupled to first and second cascoded scaled N-channel devices. The P-channel devices are coupled together at a first node and between an output and a first source voltage having an elevated voltage level. The N-channel devices are coupled between the output and a reference source voltage. The first scaled P-channel device has a gate that receives a pull-up signal and the second scaled P-channel device has a gate coupled to a static voltage. The second P-channel device and the static voltage are configured to protect the first P-channel device from gate oxide breakdown when the first device is turned off. The first N-channel device has a gate receiving a voltage-limited pull-down signal and the second N-channel device has a gate receiving a lower voltage pull-down signal. The cascoded N-channel devices divide load and prevent hot carrier injection effects.

Owner:IP FIRST

Metal oxide semiconductor (MOS) field effect transistor (FET) structure and preparation method thereof

ActiveCN102054839AWide distributionReduce electric field strengthTransistorSemiconductor/solid-state device detailsMOSFETMetal interconnect

The invention provides a metal oxide semiconductor (MOS) field effect transistor (FET) structure and a preparation method thereof. The MOSFET structure is used for improving reliability of hot carrier injection. In an MOS component structure and a preparation process thereof, lightly doped leak injection with a wide angle and a middle dose is adopted to reduce the probability of the hot carrier injection; a first metal layer is etched to form a metal interconnect metallic line, and then silicon-enriched silicon dioxide is used to replace traditional common silicon dioxide, so that the redundant dangling bonds of the Si in the layer are used for combining Si with other atoms (such as H), thus Si in a channel is combined with other atoms (such as N) to form firmer bonds so as to resist impact of carriers, maximally improve transconductance service life of the MOS component, improve the reliability of the hot carrier injection, and ensure current driving capacity of the MOS component; and meanwhile, in the preparation method of the MOSFET structure provided by the invention, conventional processes are utilized, thus having good process latitude and enhancing product yield to a certain extent.

Owner:CSMC TECH FAB2 CO LTD