Patents

Literature

57 results about "Device degradation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The degradation device is designed to deliver separated solid material to the degradation device, in particular to the reactor device, for renewed degradation as substrate. well as methods for the fabrication of implantable degradable devices of the present invention which contain one or more degradable biopolymer fibers.

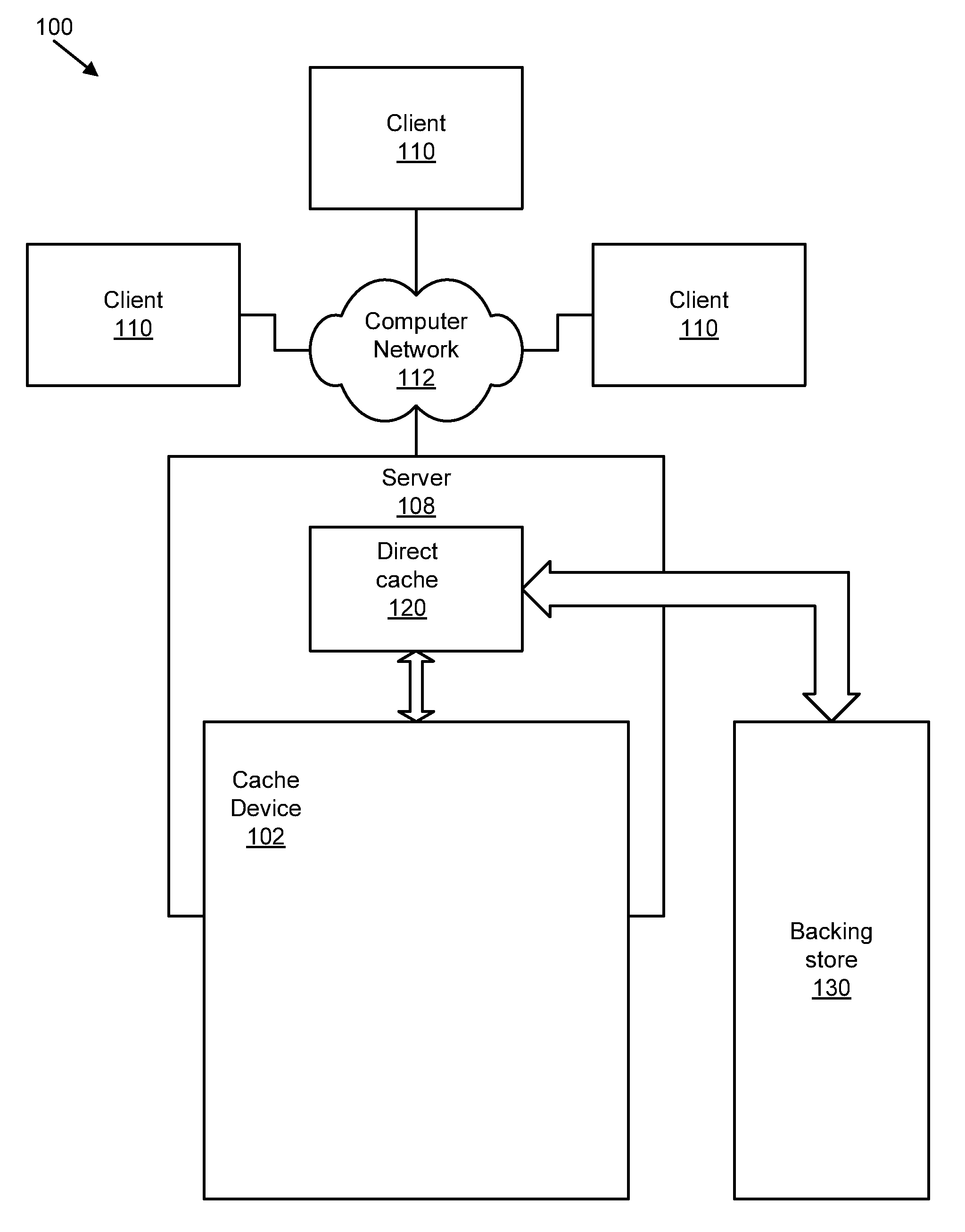

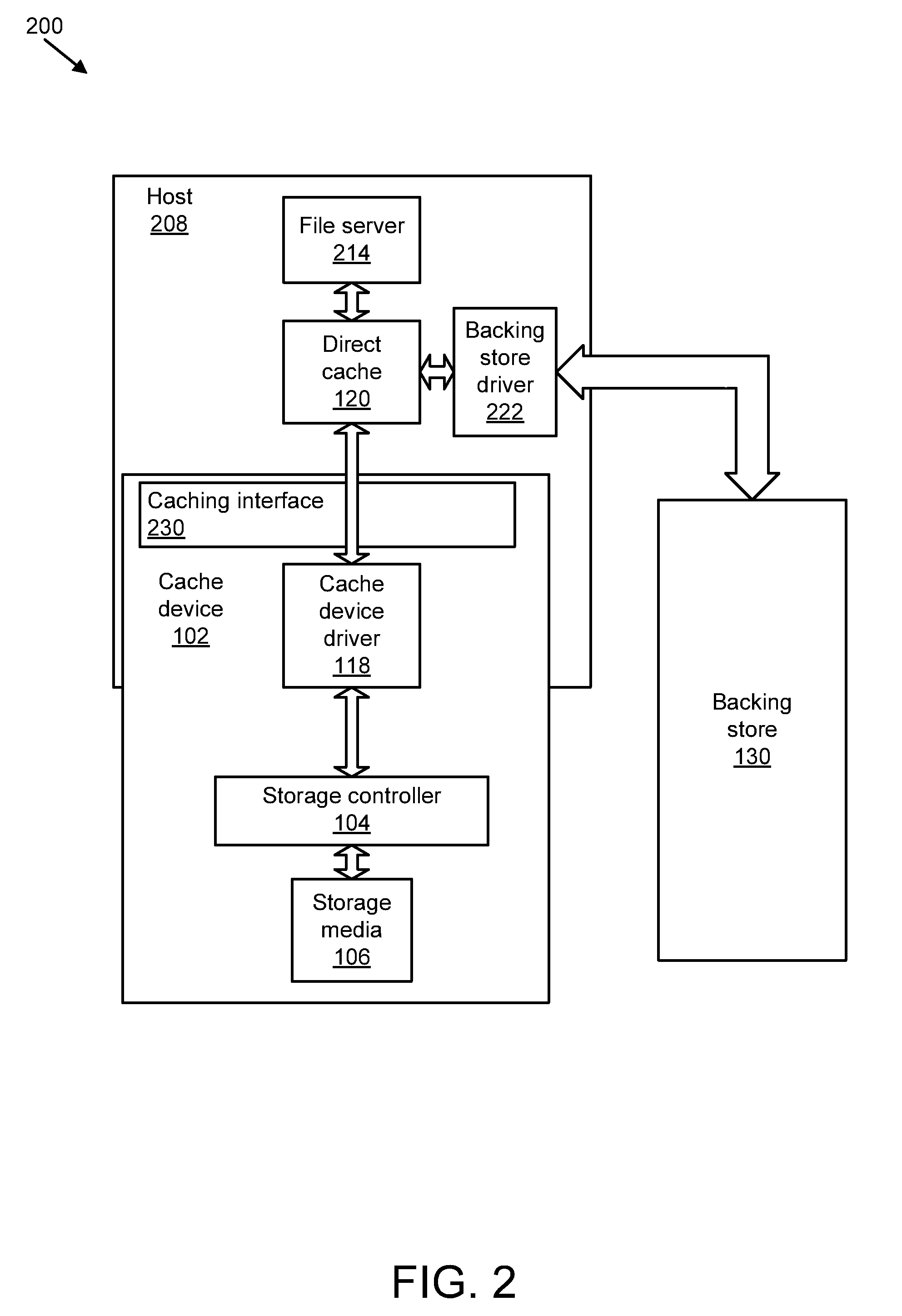

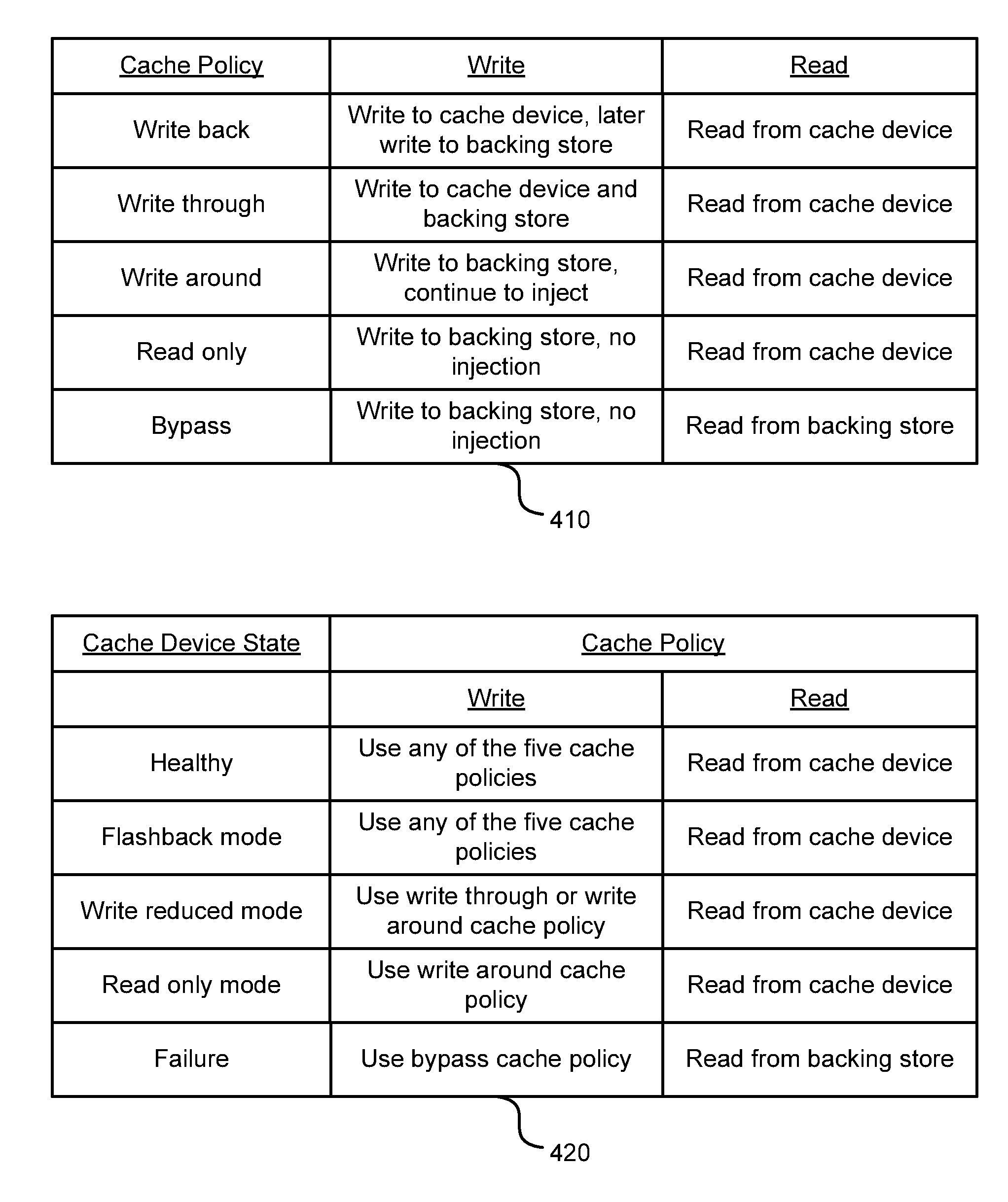

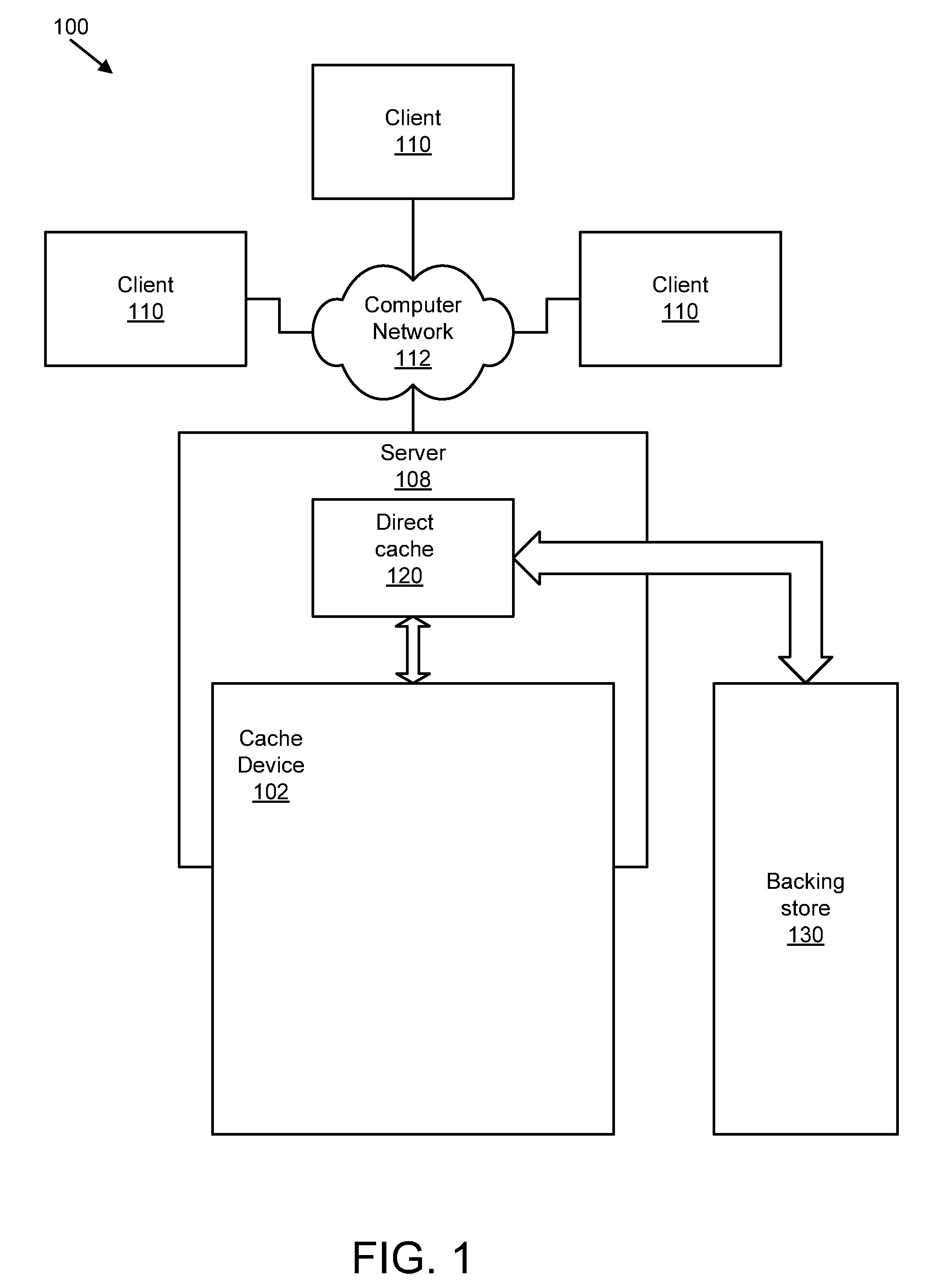

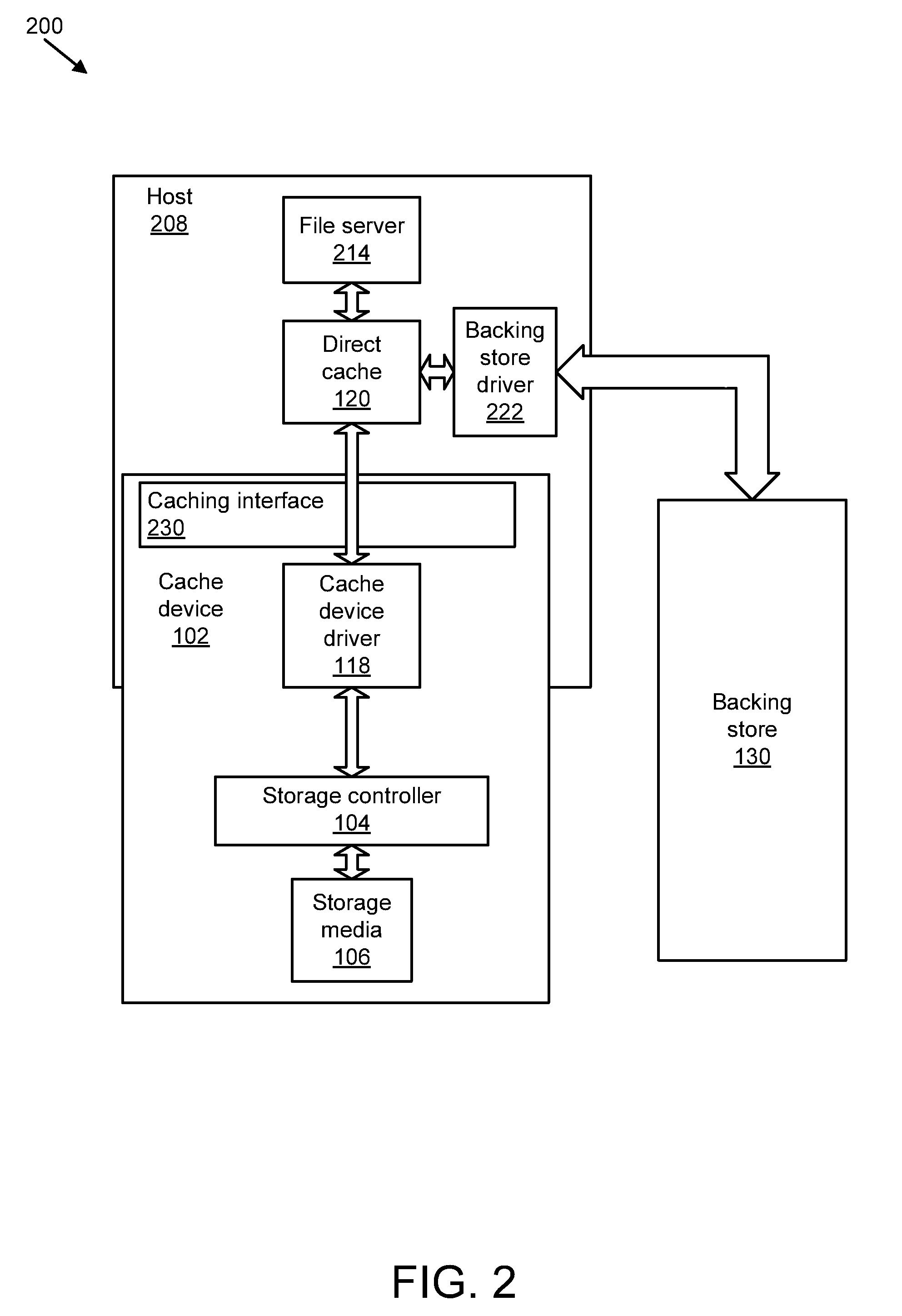

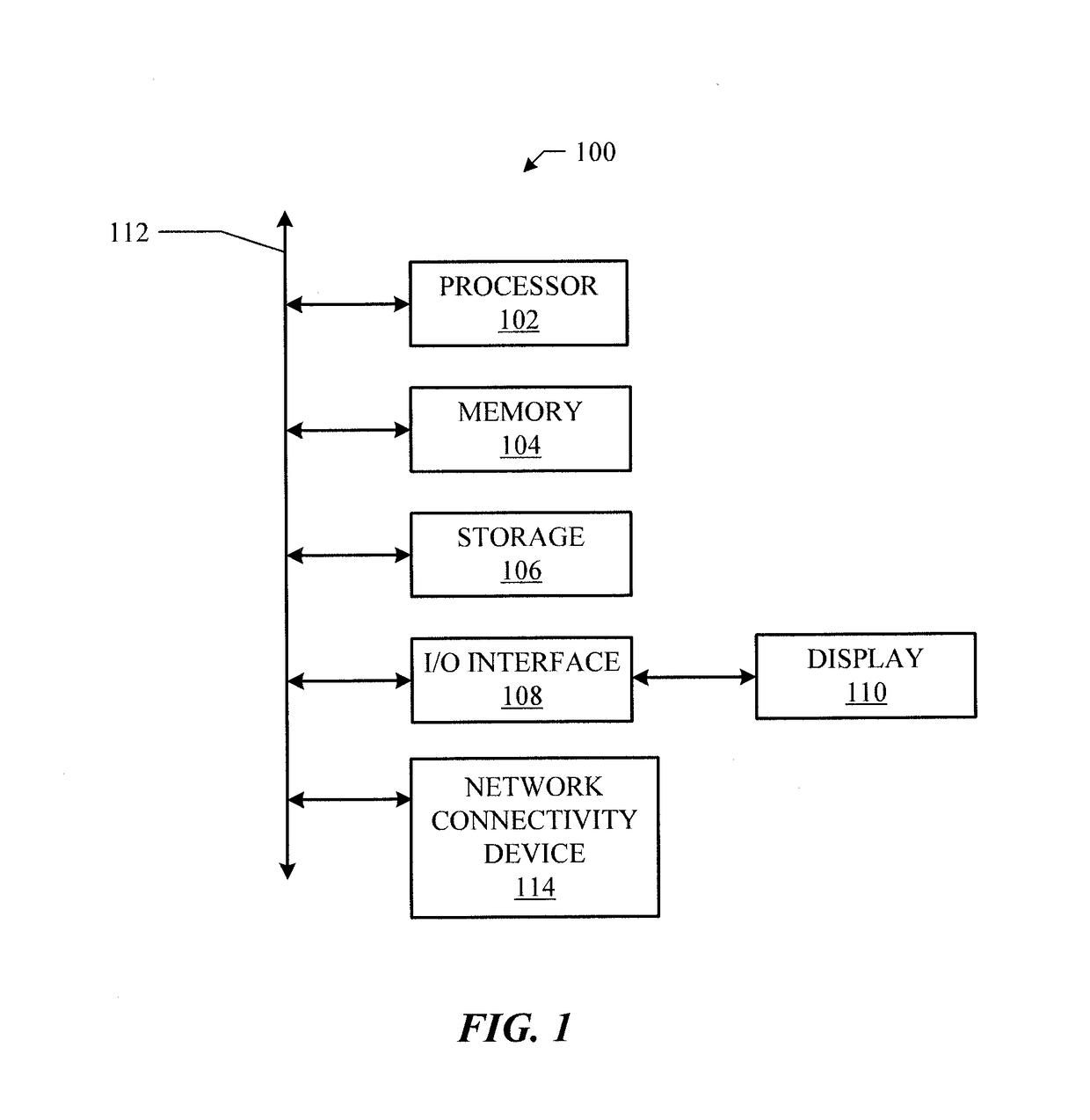

Apparatus, system, and method for graceful cache device degradation

ActiveUS20110047437A1Reduce riskLoss of dataMemory architecture accessing/allocationProgram synchronisationRisk levelClient-side

An apparatus, system, and method are disclosed for graceful cache device degradation. The method may include determining the risk of data loss on the cache device, which may increase (as with Flash memory) with use and age. If the risk of data loss on the cache devices exceeds a threshold risk level, a modified cache policy may be implemented for the cache device to reduce the risk of data loss below the threshold level. This process may iterate until the cache device cannot guarantee performance sufficient to merit continued use of the cache device, and the cache device is logically removed from the system. The changes in cache policy and in the risk of data loss may be hidden from clients that make use of the cache device. The cache policies may transition, for example, in the following order: write back; write through; write around; read only; and bypass.

Owner:SANDISK TECH LLC

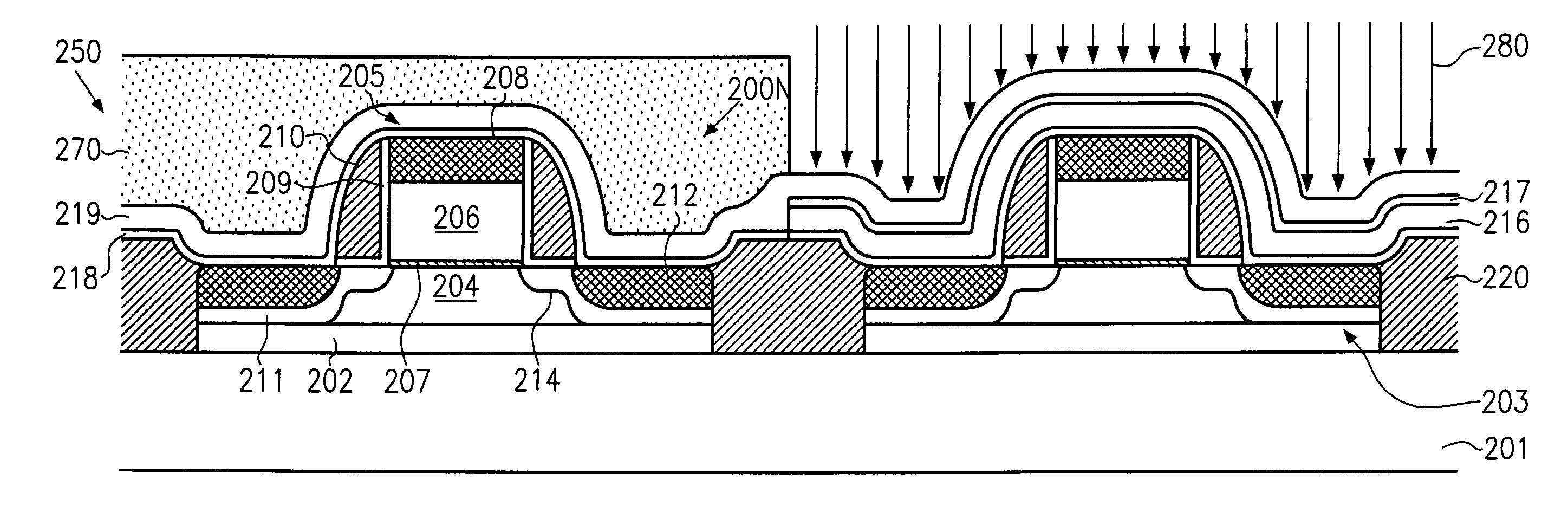

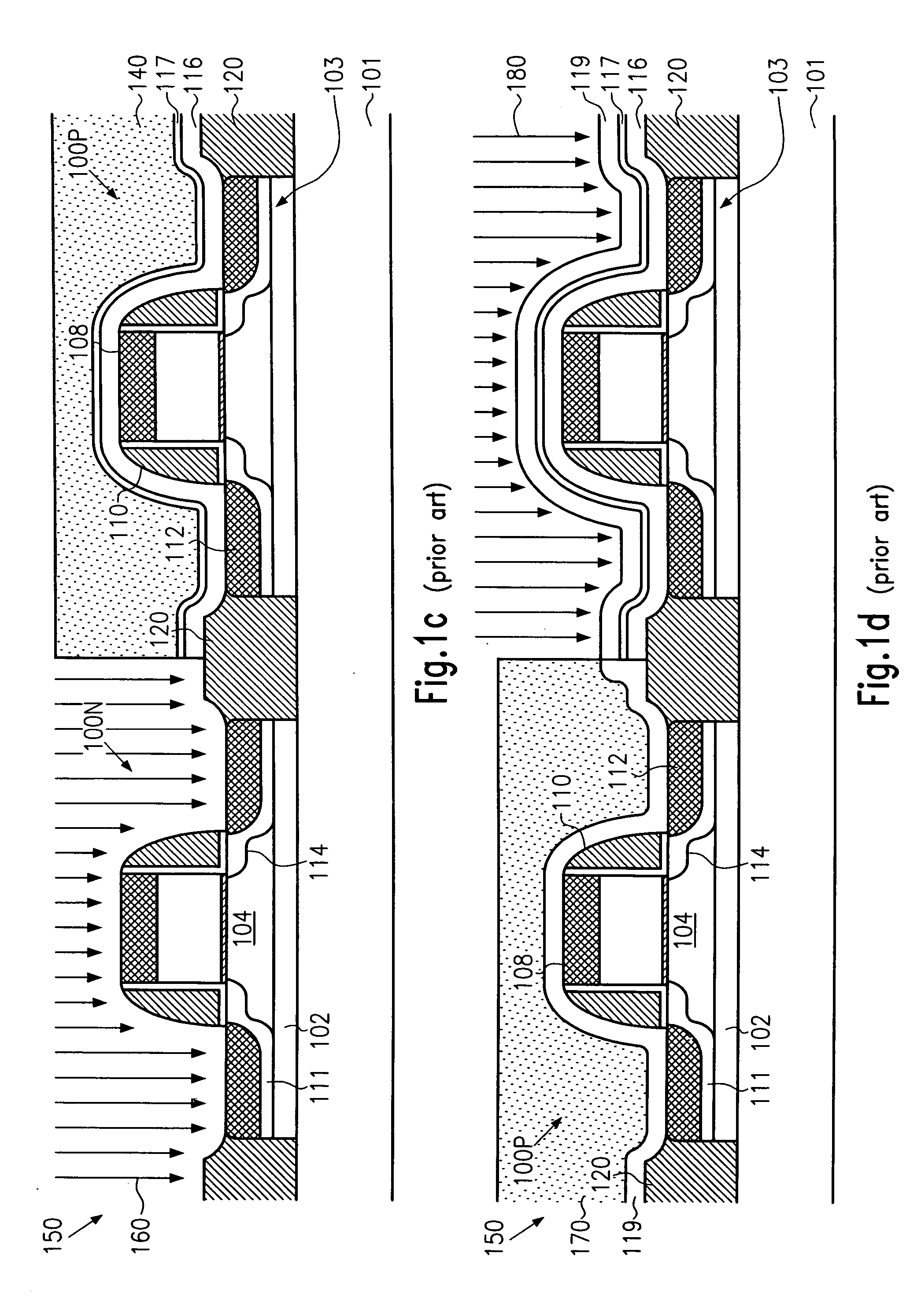

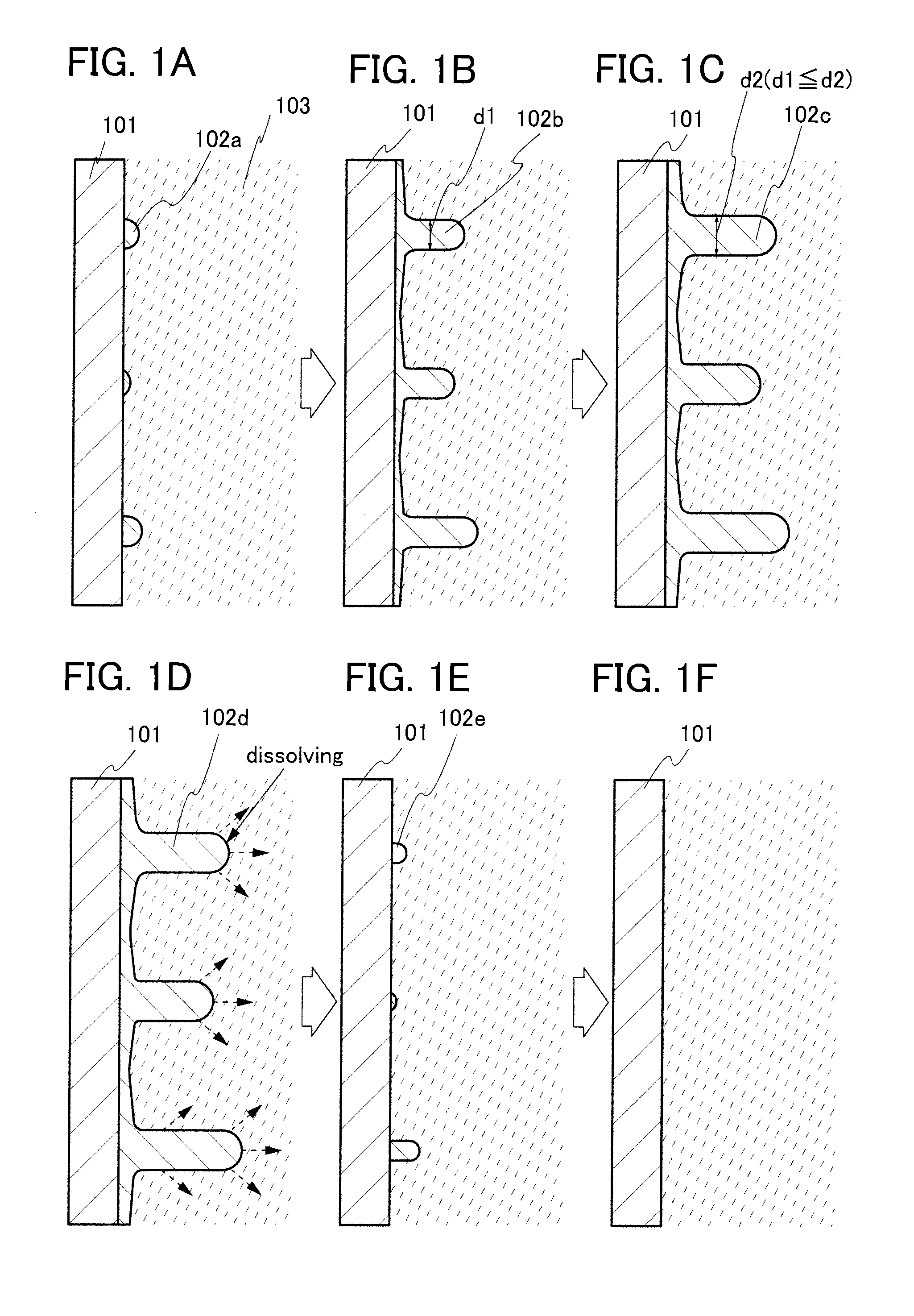

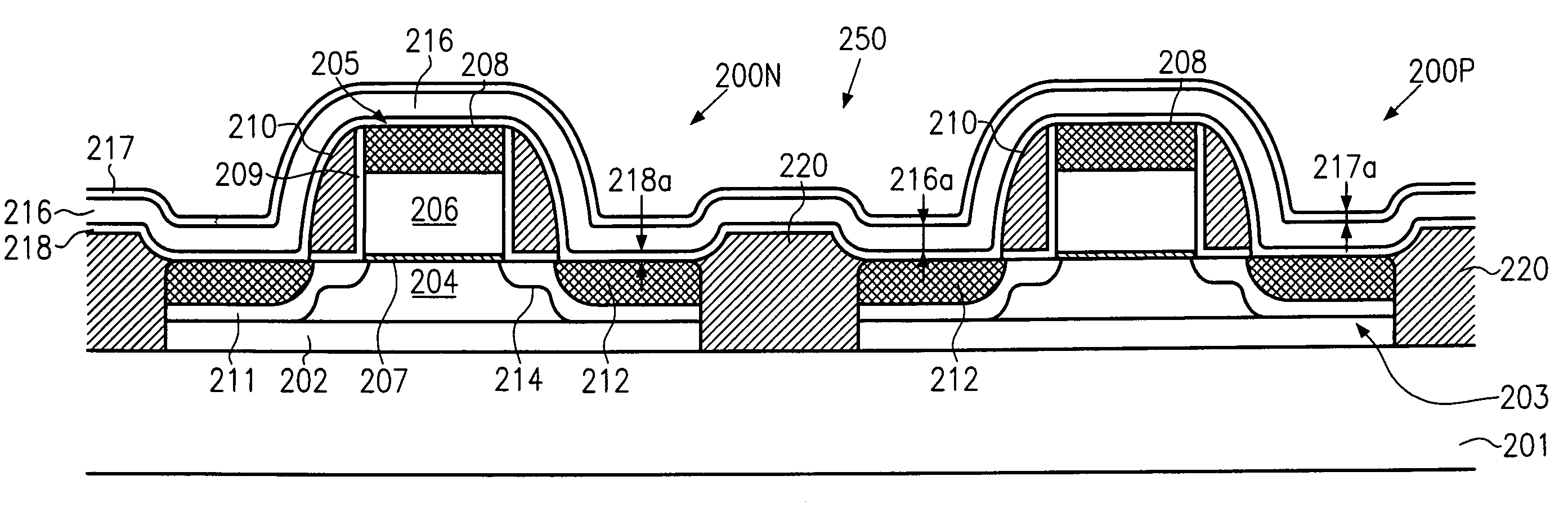

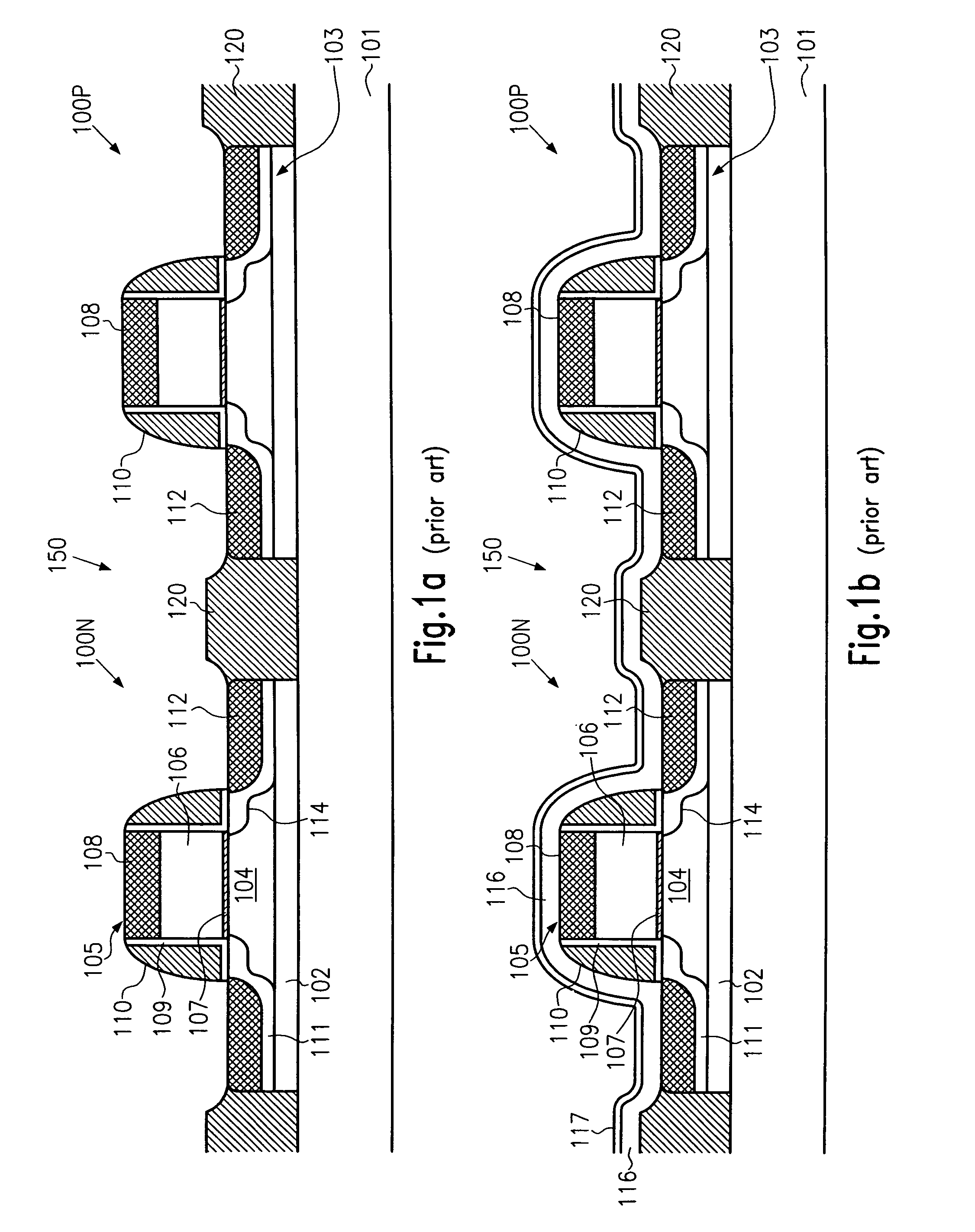

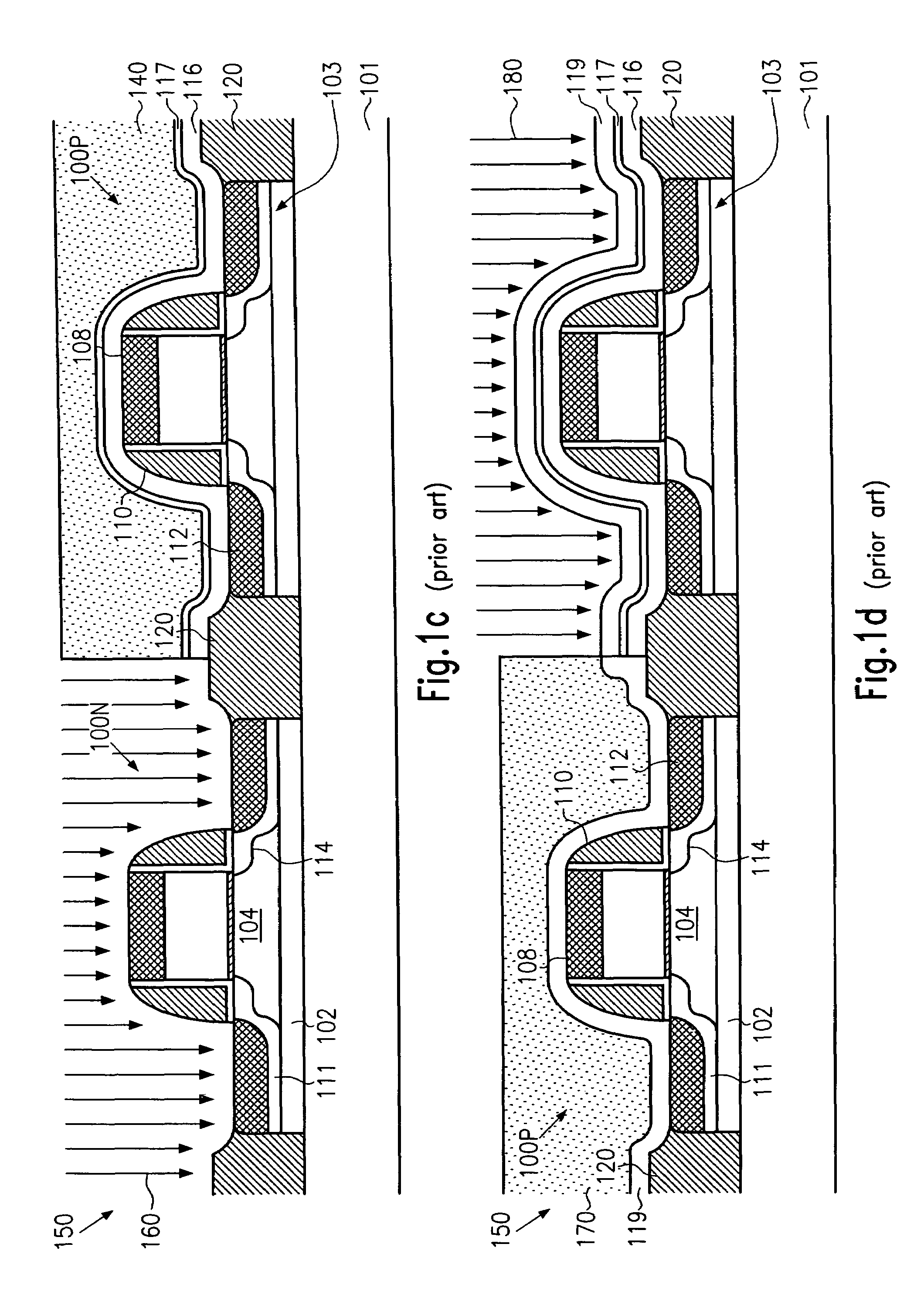

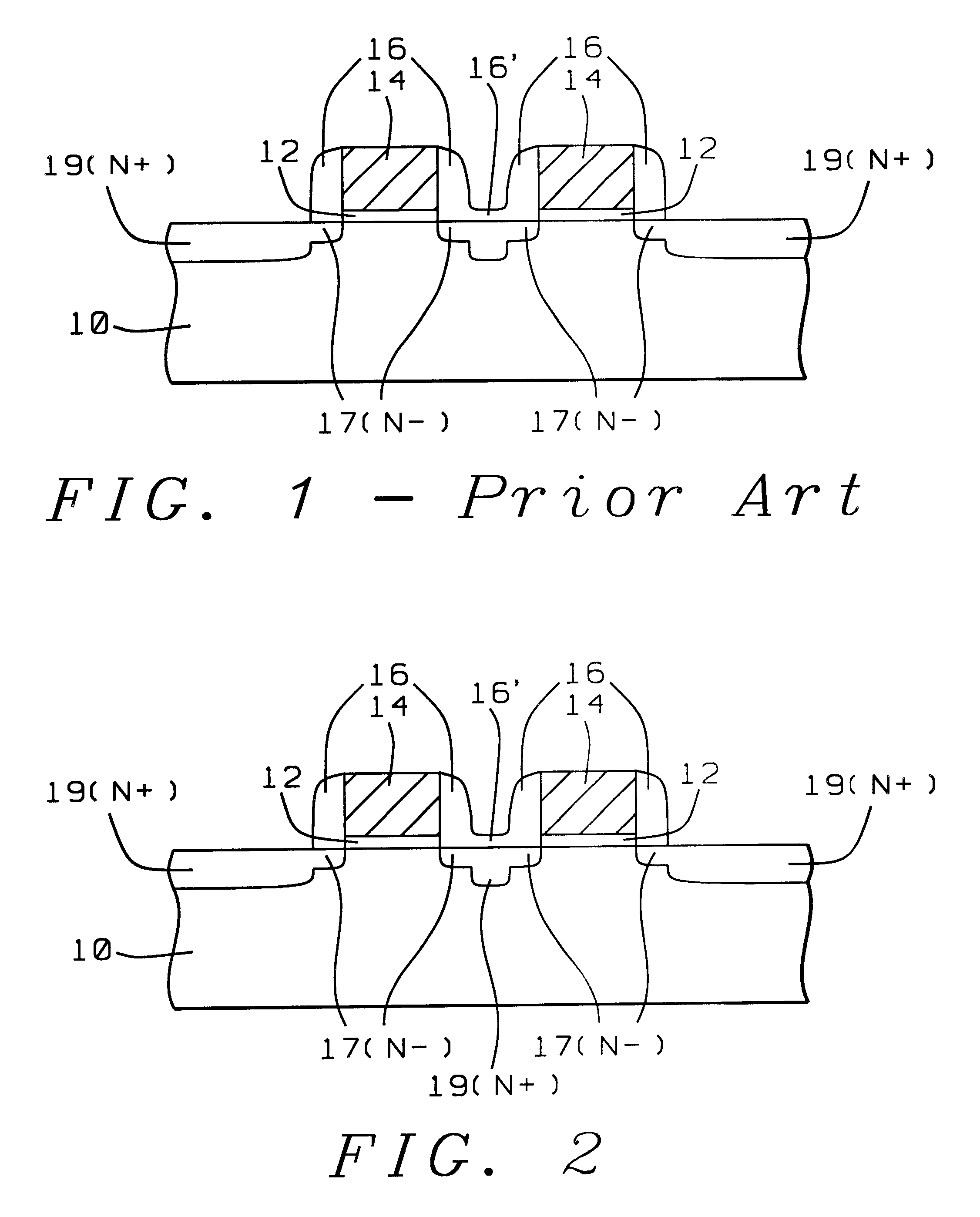

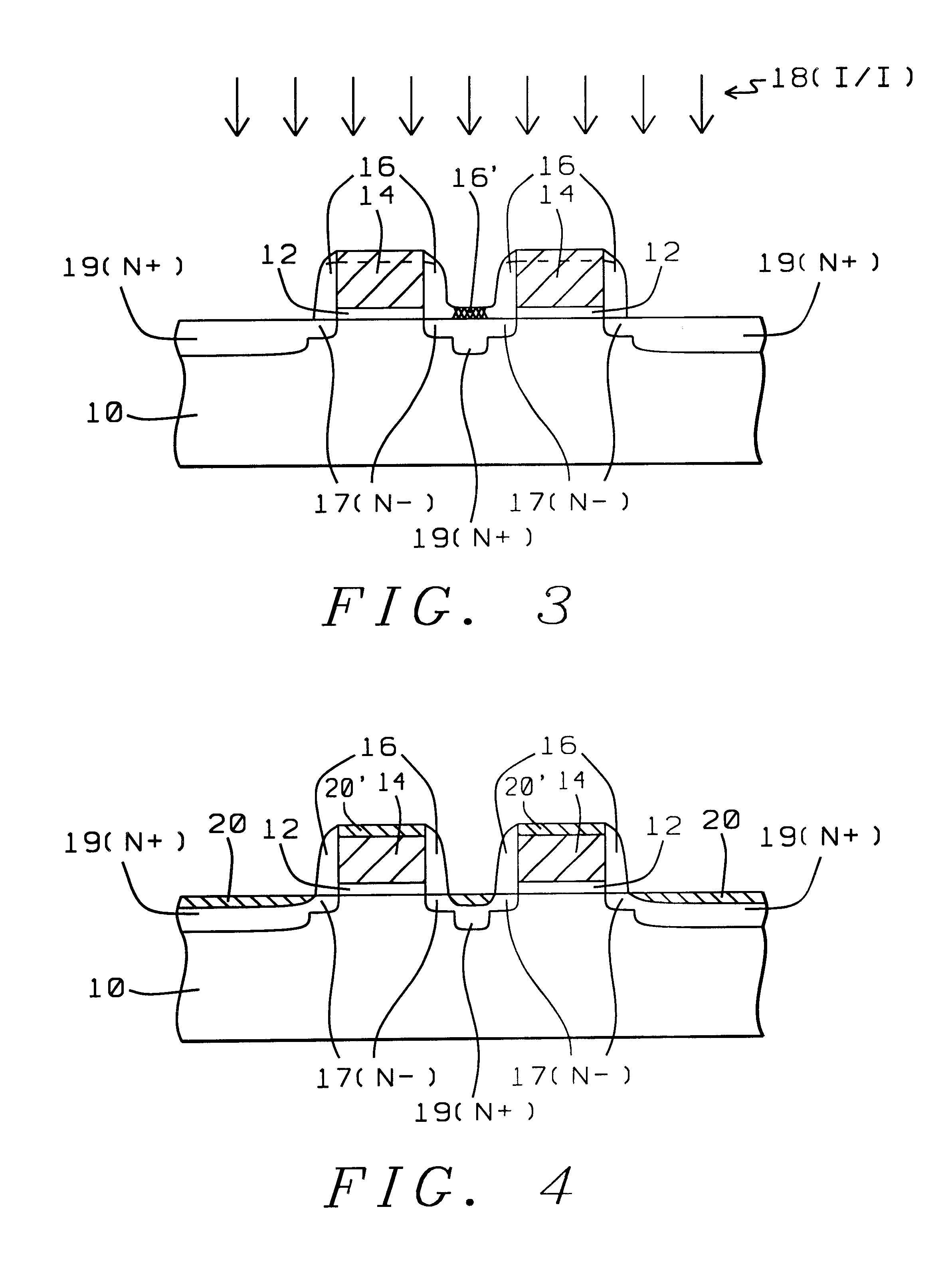

Technique for creating different mechanical strain in different channel regions by forming an etch stop layer stack having differently modified intrinsic stress

ActiveUS20060091471A1Avoiding and at least significantly reducing damageSemiconductor/solid-state device detailsSolid-state devicesMetal silicideEngineering

A technique is provided that allows the formation of contact etch stop layers having different intrinsic stress for different transistors, while substantially avoiding any device degradation owing to the partial removal of the contact etch stop layer. Hereby, an additional thin etch stop layer is provided prior to the formation of the contact etch stop layers, thereby substantially maintaining the integrity of metal silicide regions, when a portion of an initially deposited contact etch stop layer is removed.

Owner:INNOVATIVE FOUNDRY TECH LLC

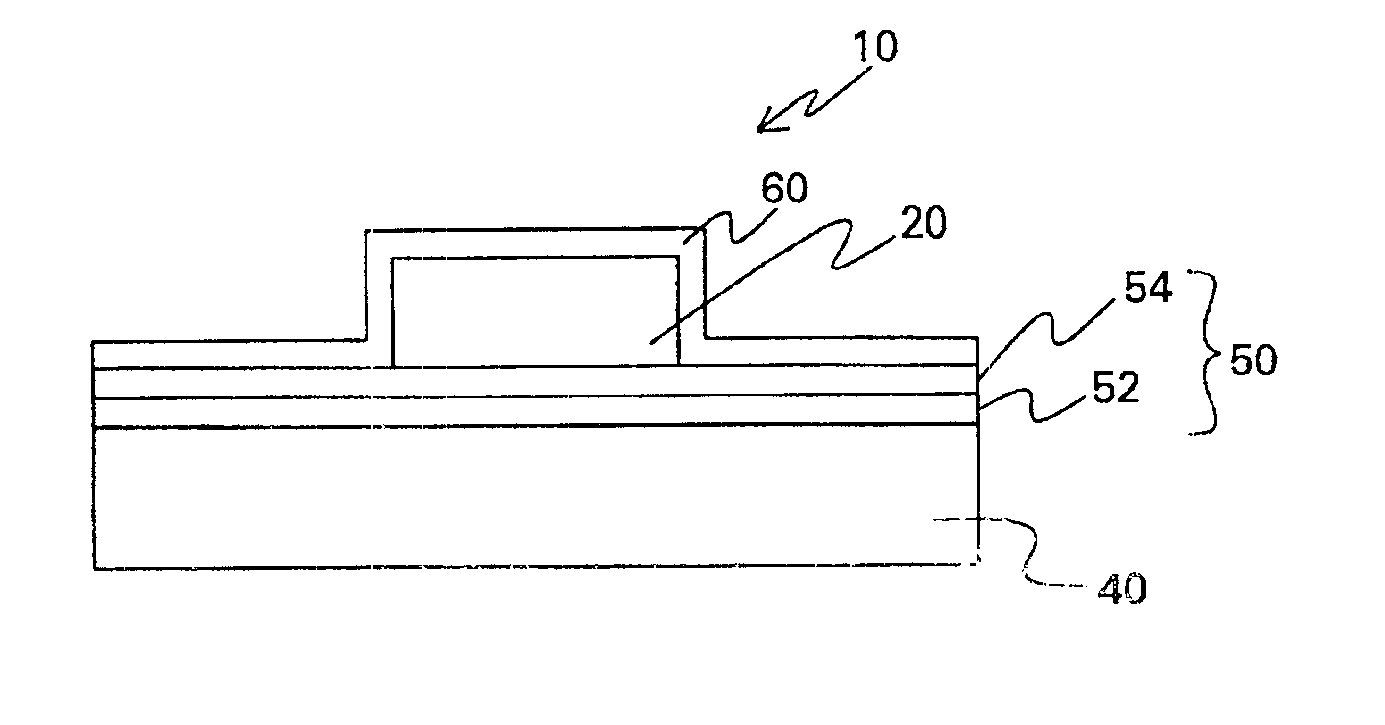

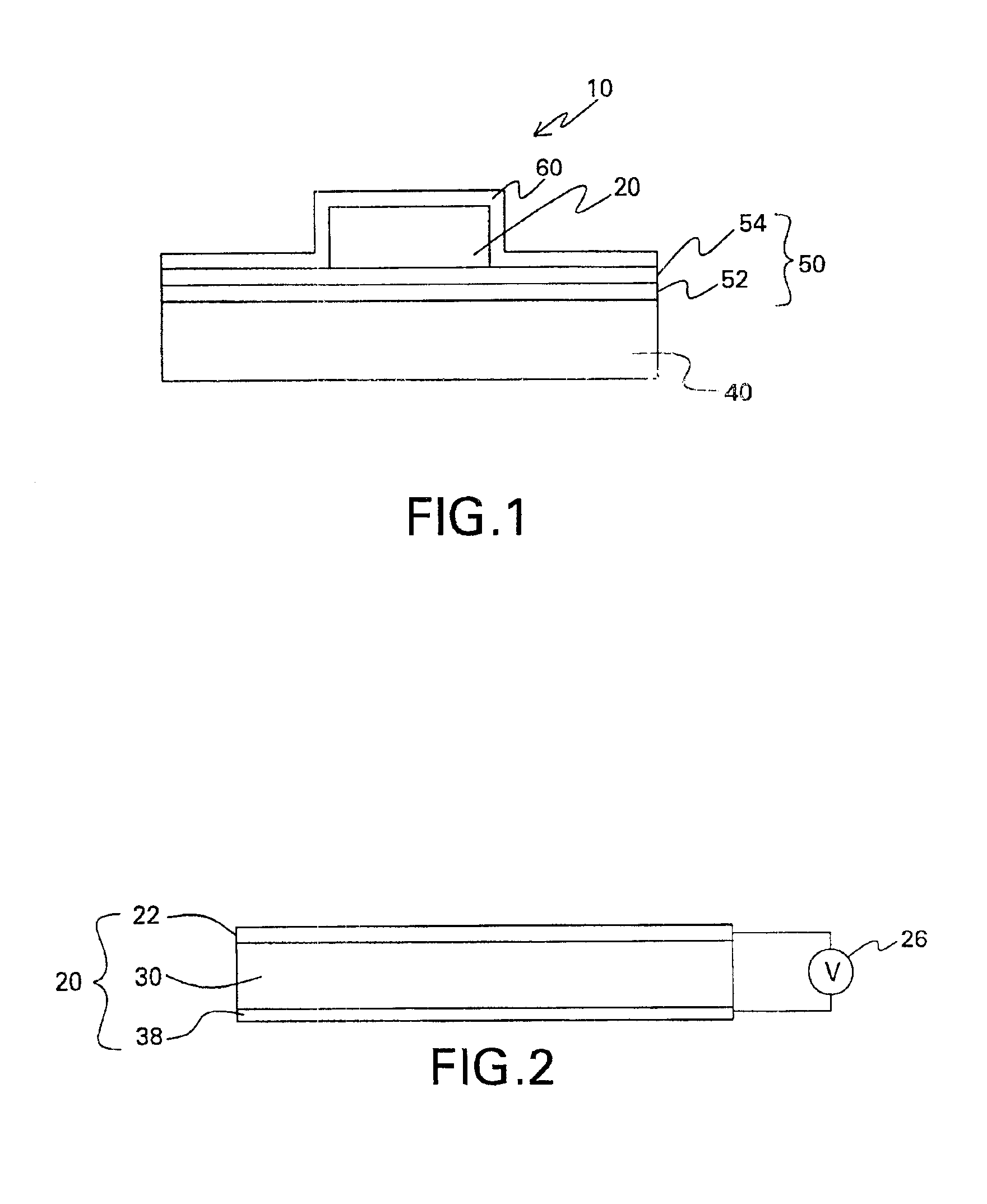

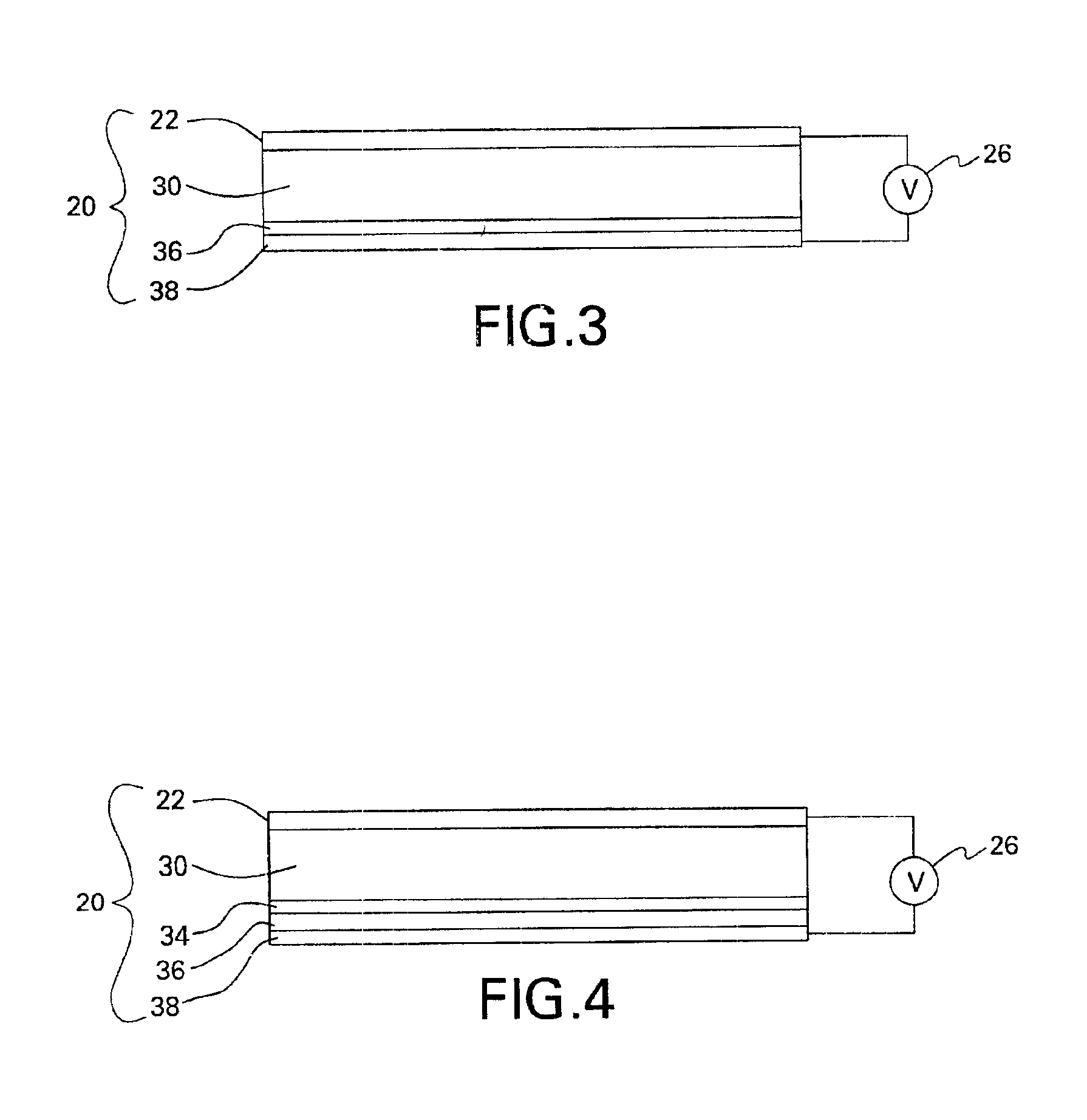

Mechanically flexible organic electroluminescent device with directional light emission

InactiveUS6891330B2Improve external quantum efficiencyDischarge tube luminescnet screensElectroluminescent light sourcesQuantum efficiencyOrganic electroluminescence

A mechanically flexible and environmentally stable organic electroluminescent (“EL”) device with directional light emission comprises an organic EL member disposed on a flexible substrate, a surface of which is coated with a multilayer barrier coating which includes at least one sublayer of a substantially transparent organic polymer and at least one sublayer of a substantially transparent inorganic material. The device includes a reflective metal layer disposed on the organic EL member opposite to the substrate. The reflective metal layer provides an increased external quantum efficiency of the device. The reflective metal layer and the multilayer barrier coating form a seal around the organic EL member to reduce the degradation of the device due to environmental elements.

Owner:BOE TECH GRP CO LTD

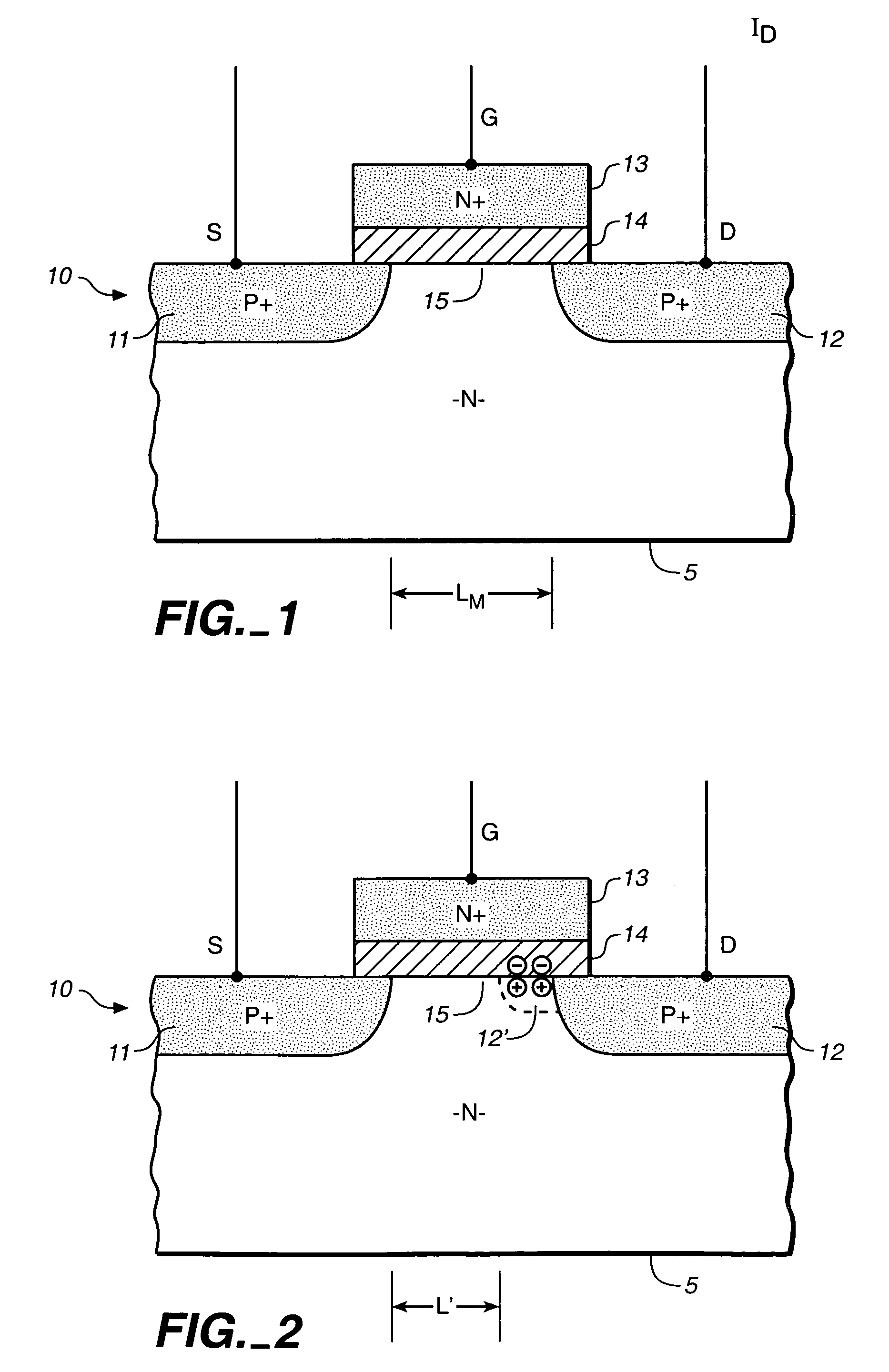

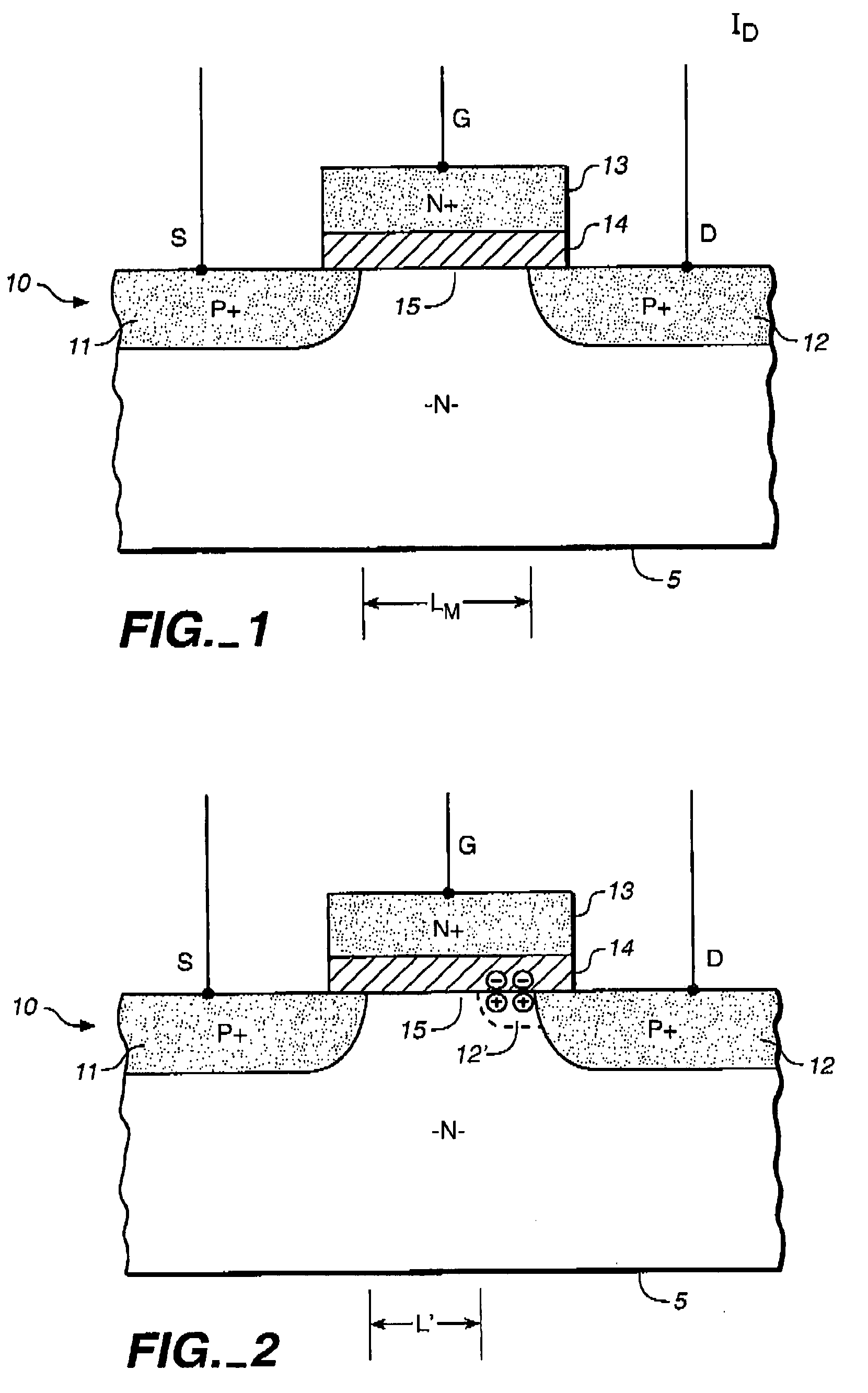

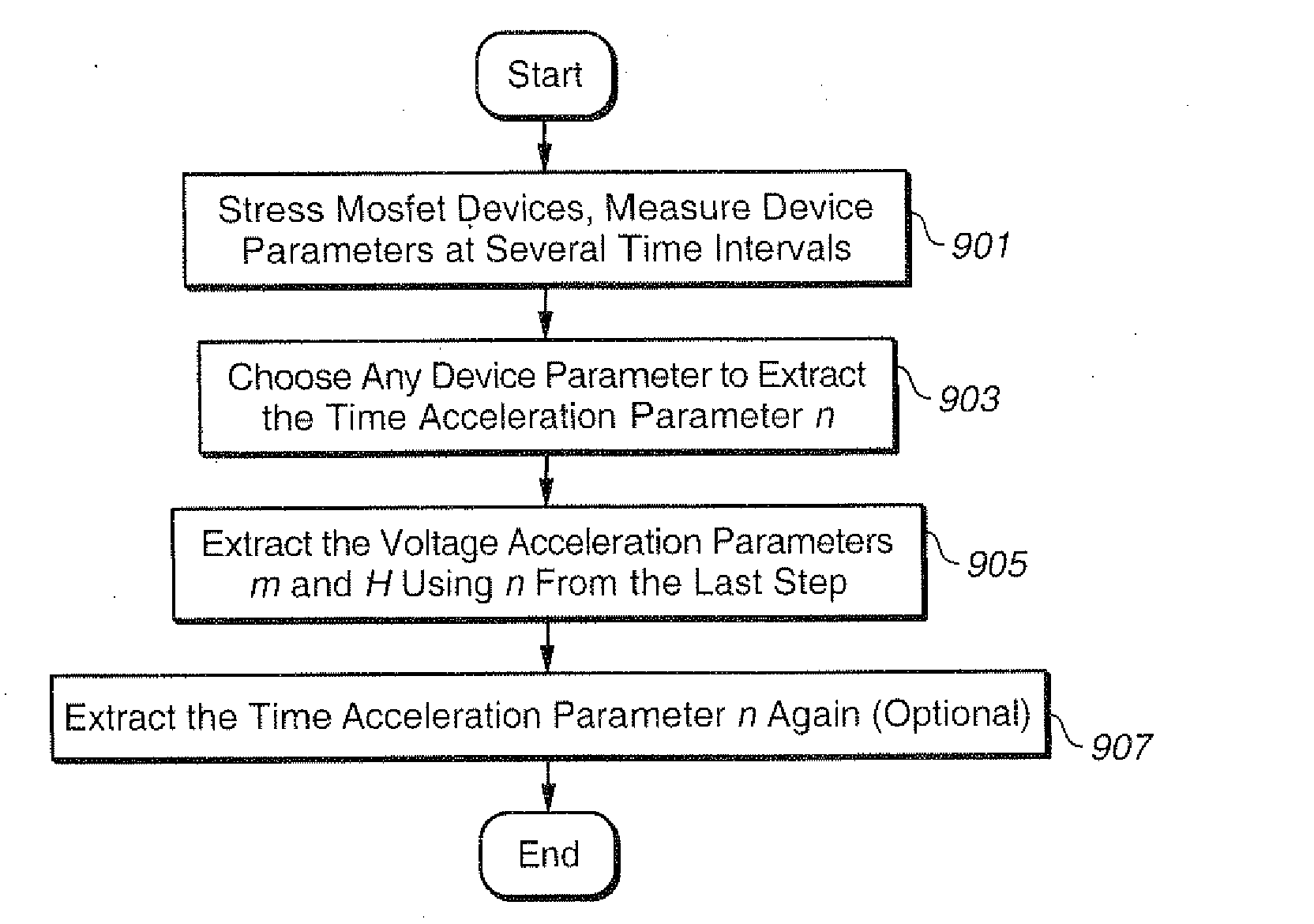

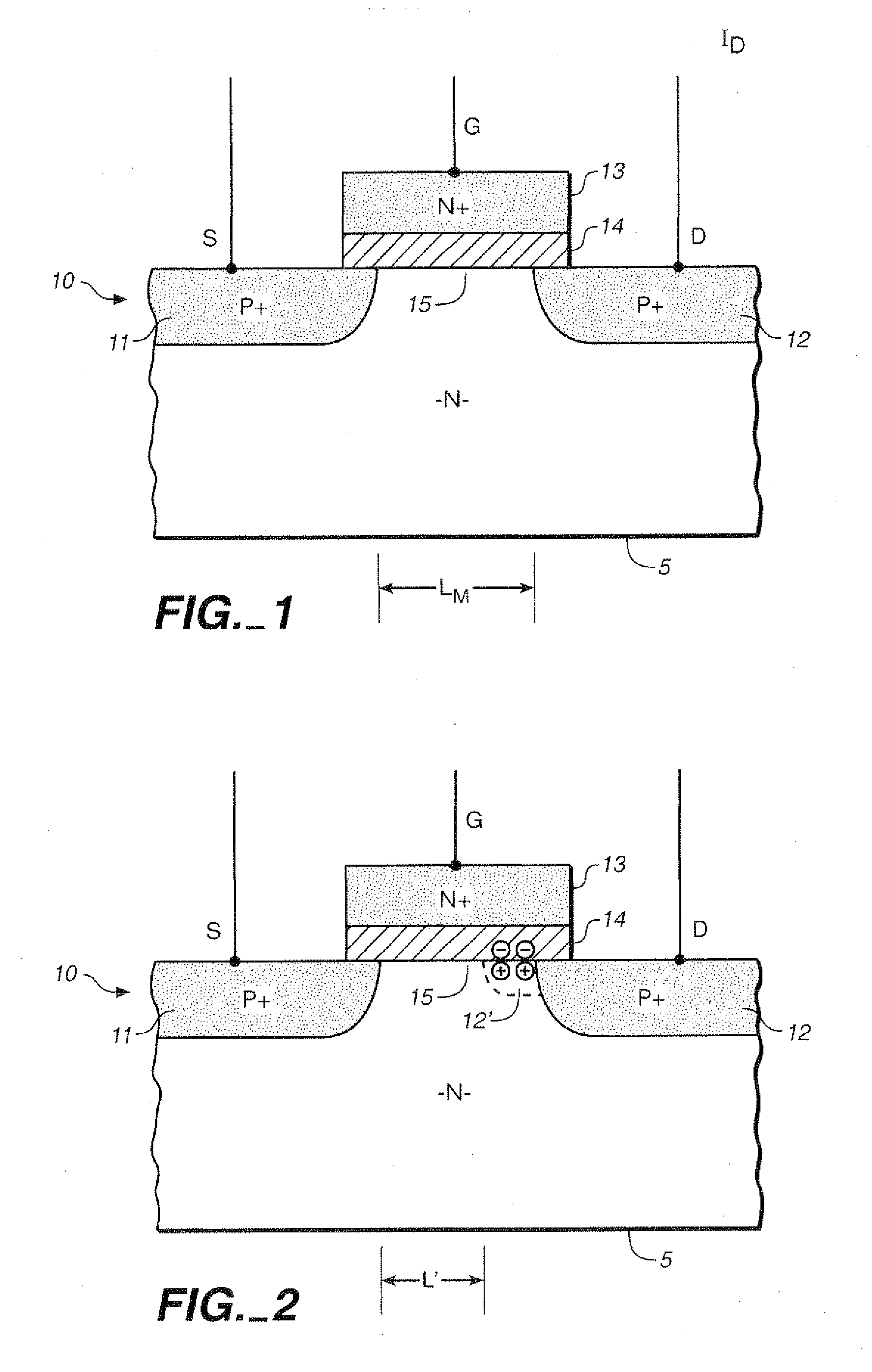

Hot-carrier device degradation modeling and extraction methodologies

ActiveUS7567891B1Improve accuracySimple methodLogic circuits characterised by logic functionResistance/reactance/impedenceModel parametersEngineering

The present invention is directed to a number of improvements in methods for hot-carrier device degradation modeling and extraction. Several improvements are presented for the improvement of building device degradation models, including allowing the user to select a device parameter used to build the device degradation model independent of the device parameter selected. The user can also select the functional relation between stress time and degradation level. To further improve accuracy, multiple acceleration parameters can be used to account for different regions of the degradation process. Analytical functions may be used to represent aged device model parameters, either directly or by fitting measured device parameters versus device age values, allowing devices with different age values to share the same device model. The concept of binning is extended to include device degradation. In addition to a binning based on device width and length, age is added. In an exemplary embodiment, only devices with minimum channel length have degraded models constructed. The present invention also allows the degradation of one device parameter to be determined based on an age value derived from another parameter. In yet another aspect, a degraded device is modeled as a fresh device with a voltage source connected to a terminal.

Owner:CADENCE DESIGN SYST INC

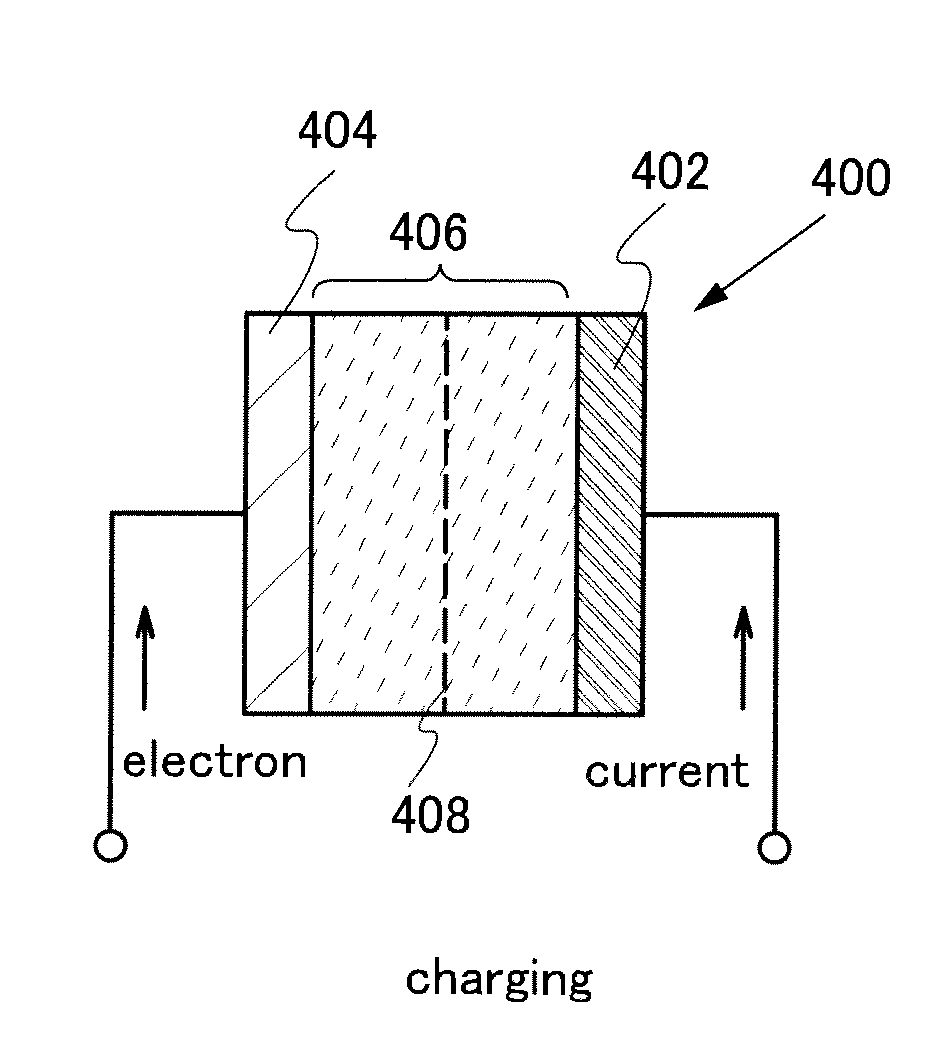

Electronic device

ActiveUS20140197802A1Prevent degradationMaximize and maintain chargeSecondary cells charging/dischargingElectric powerElectricityLithium

Degradation of a battery is prevented or the degree of the degradation is reduced, and charge and discharge performance of the battery is maximized and maintained for a long time. A reaction product, which is formed on an electrode surface and causes various malfunctions and degradation of a battery such as a lithium-ion secondary battery, is dissolved by application of electrical stimulus, specifically, by applying a signal to supply a current reverse to a current with which the reaction product is formed (reverse pulse current).

Owner:SEMICON ENERGY LAB CO LTD

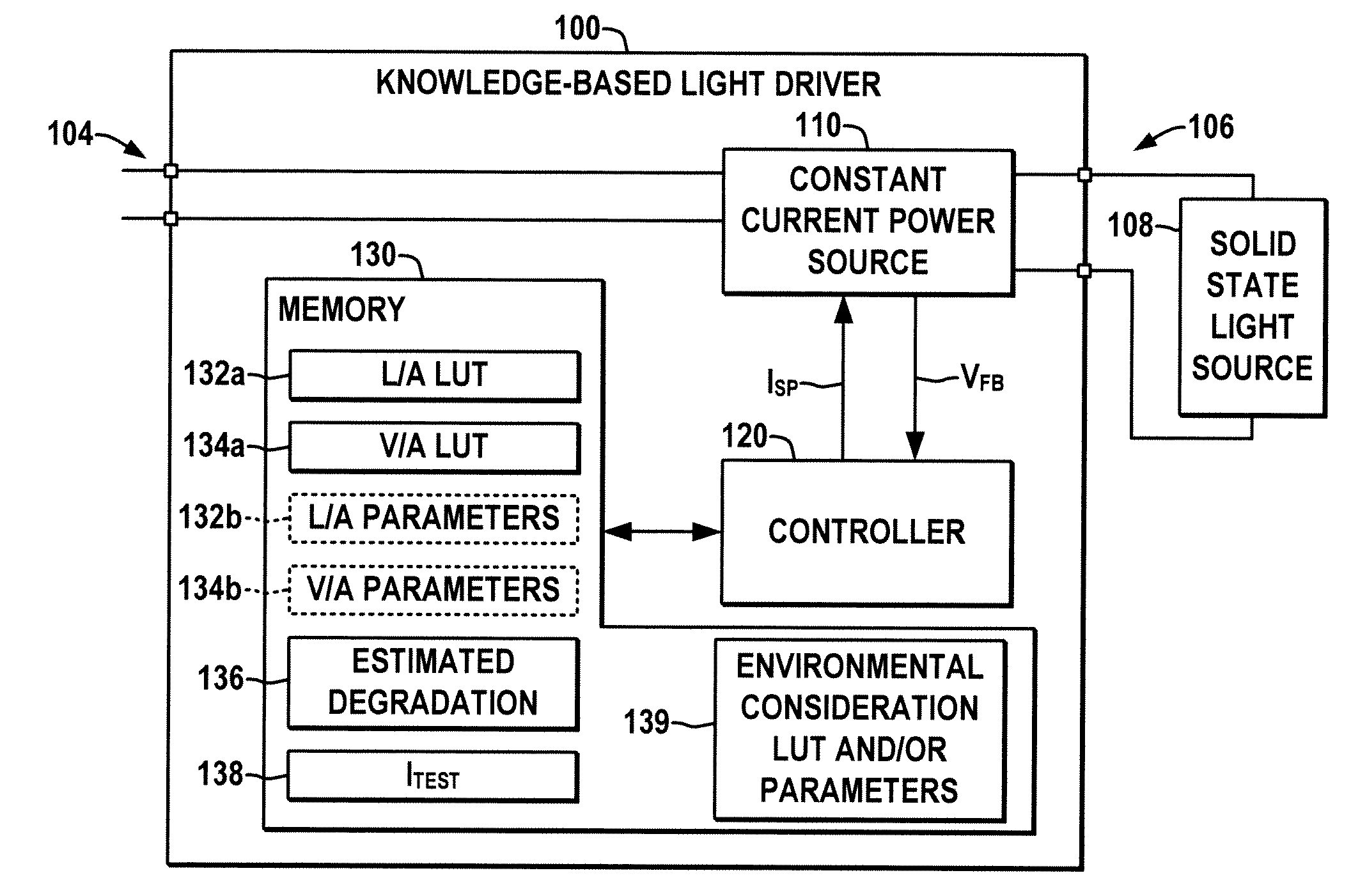

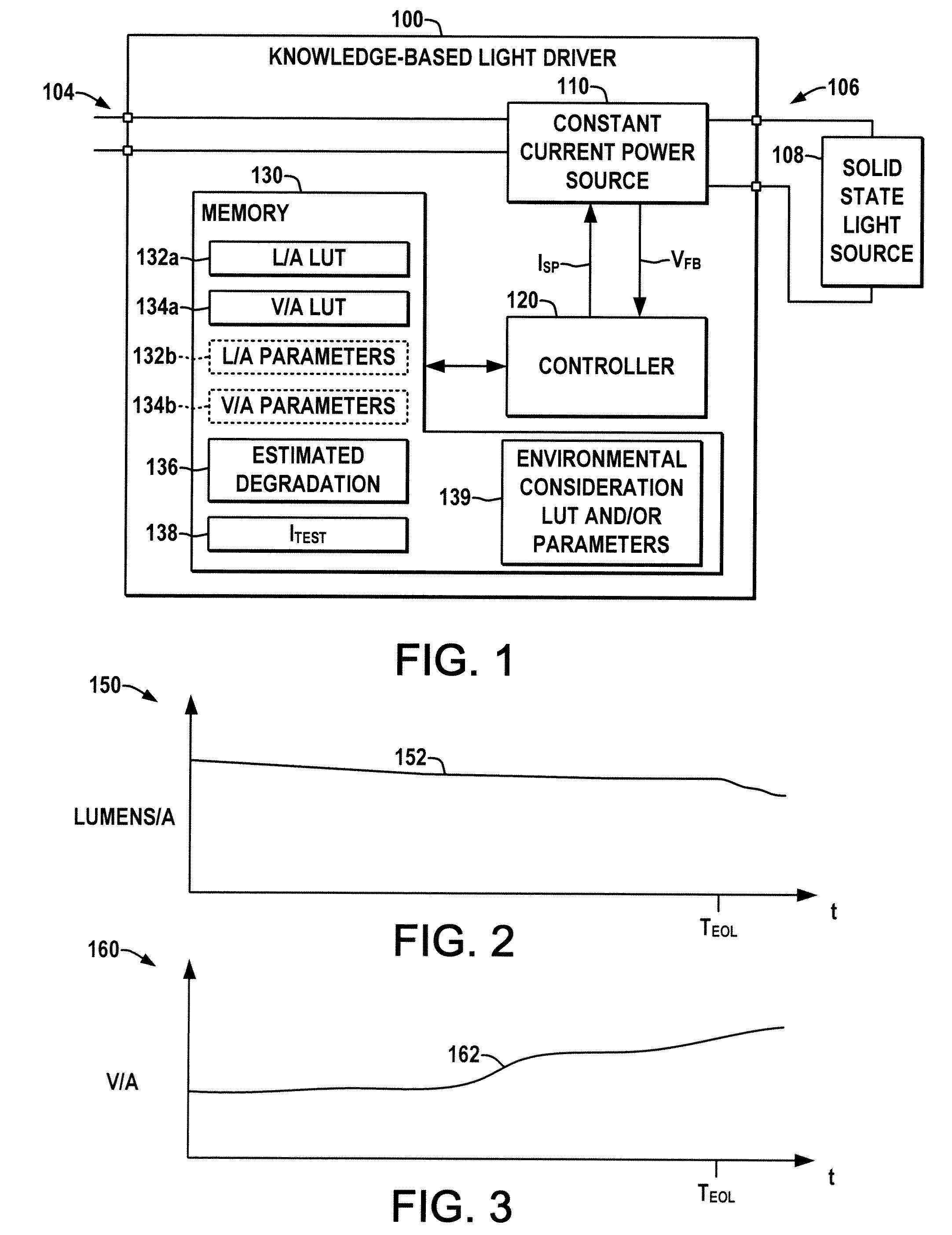

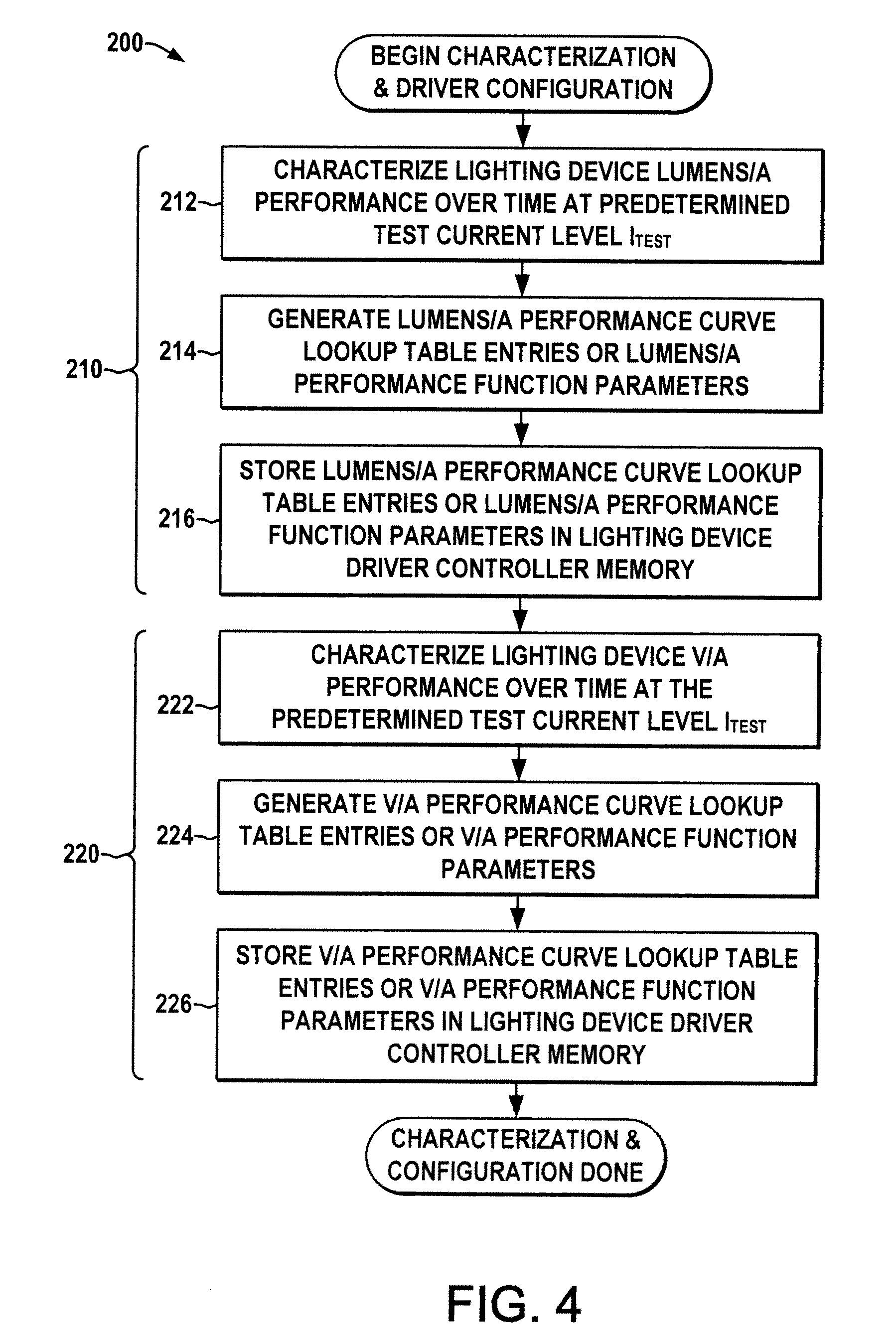

Knowledge-based driver apparatus for high lumen maintenance and end-of-life adaptation

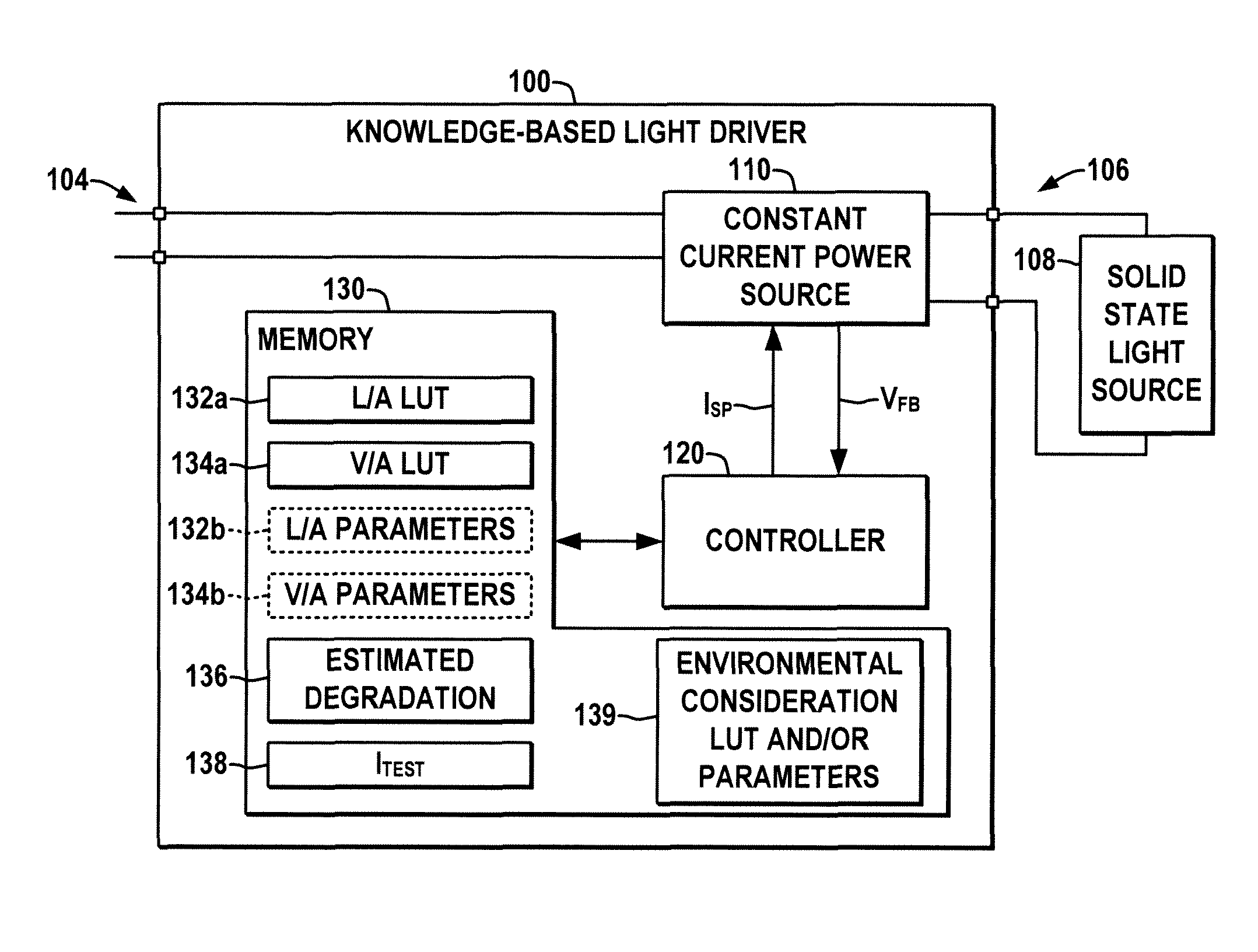

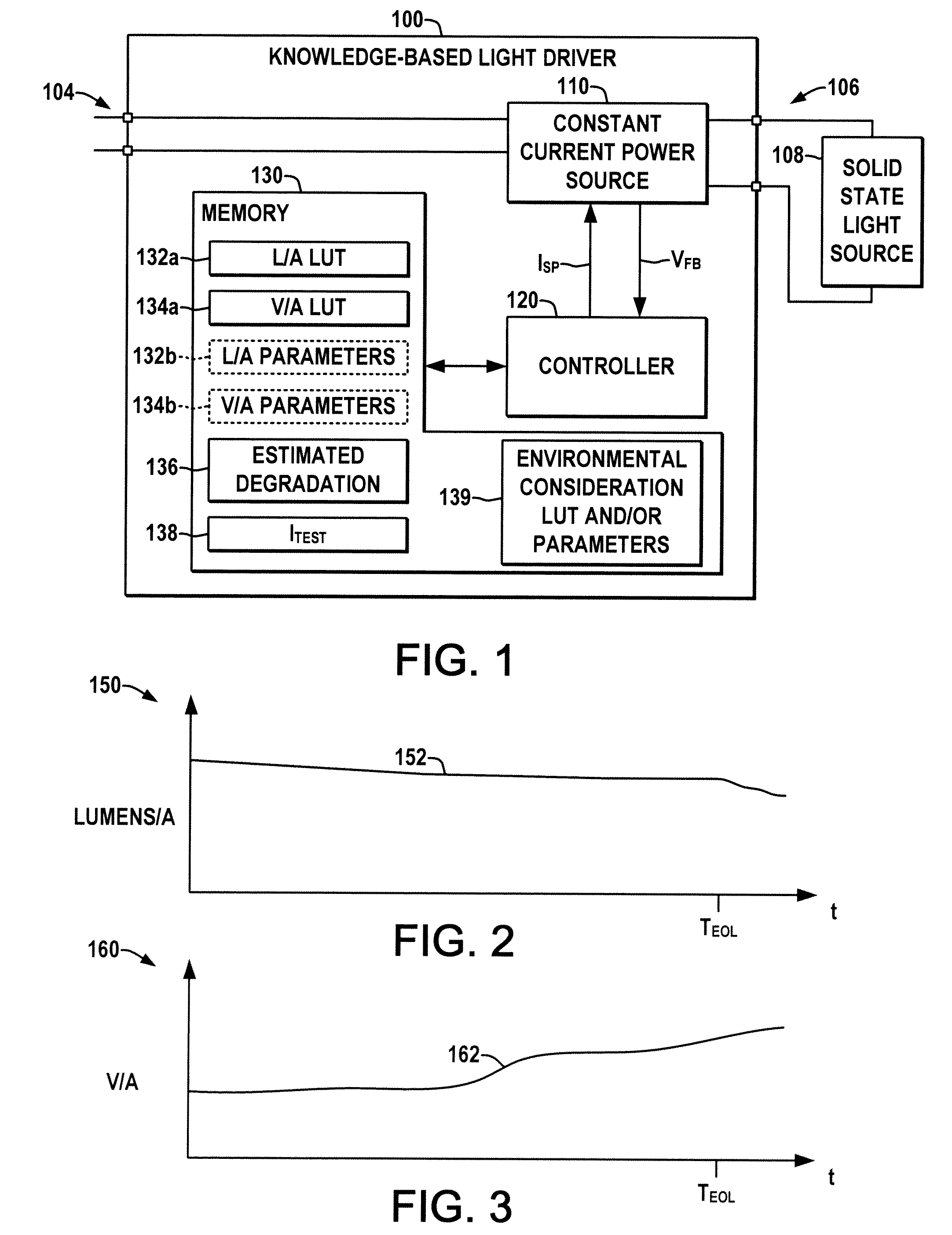

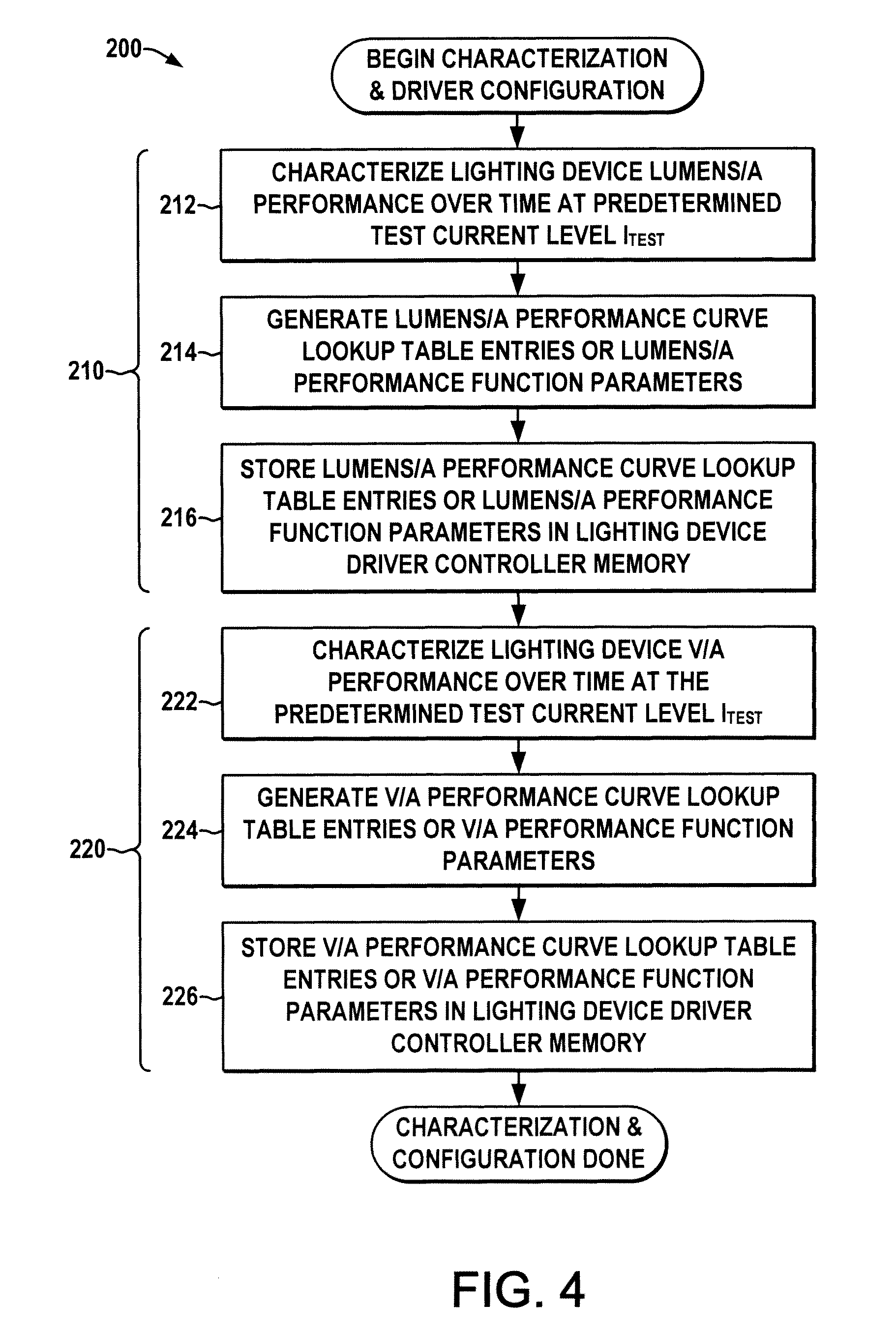

ActiveUS20110089855A1Facilitate constant lumen operationAccuracyElectrical apparatusStatic indicating devicesDriving currentLumen maintenance

A knowledge-based driver is provided for powering a solid-state light source with a constant current, including a memory that stores lumens per amp and volts per amp performance characterizations of the light source over time, and a controller that operates in a test mode to estimate the light source degradation based on voltage feedback obtained at a predetermined test current value, and to adjust the drive current in normal operating mode according to the estimated device degradation to implement constant lumens control without external optical feedback components.

Owner:GE LIGHTING SOLUTIONS LLC

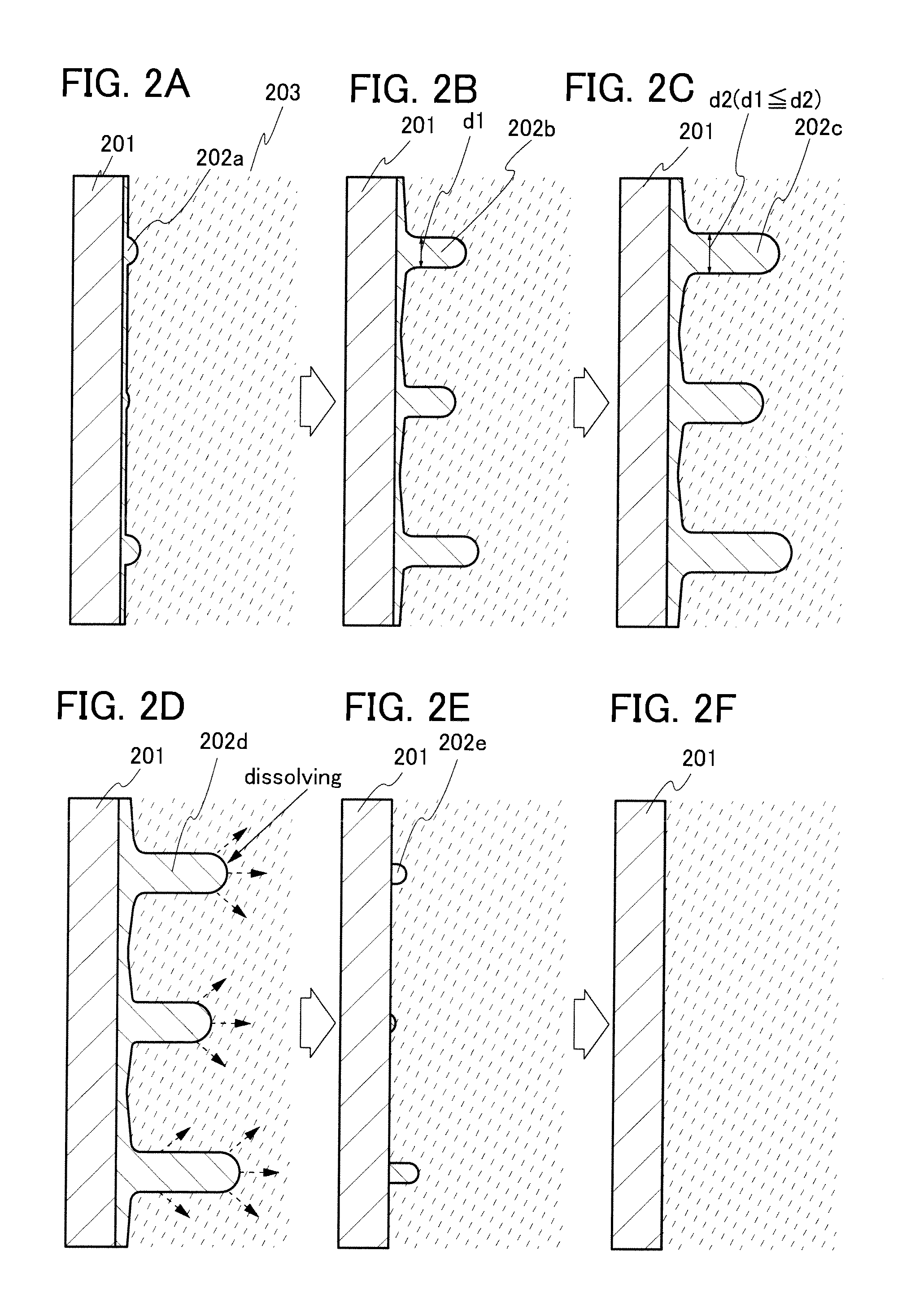

Technique for creating different mechanical strain in different channel regions by forming an etch stop layer stack having differently modified intrinsic stress

ActiveUS7396718B2Avoiding and at least significantly reducing damageSemiconductor/solid-state device detailsSolid-state devicesSalicideMetal silicide

A technique is provided that allows the formation of contact etch stop layers having different intrinsic stress for different transistors, while substantially avoiding any device degradation owing to the partial removal of the contact etch stop layer. Hereby, an additional thin etch stop layer is provided prior to the formation of the contact etch stop layers, thereby substantially maintaining the integrity of metal silicide regions, when a portion of an initially deposited contact etch stop layer is removed.

Owner:INNOVATIVE FOUNDRY TECH LLC

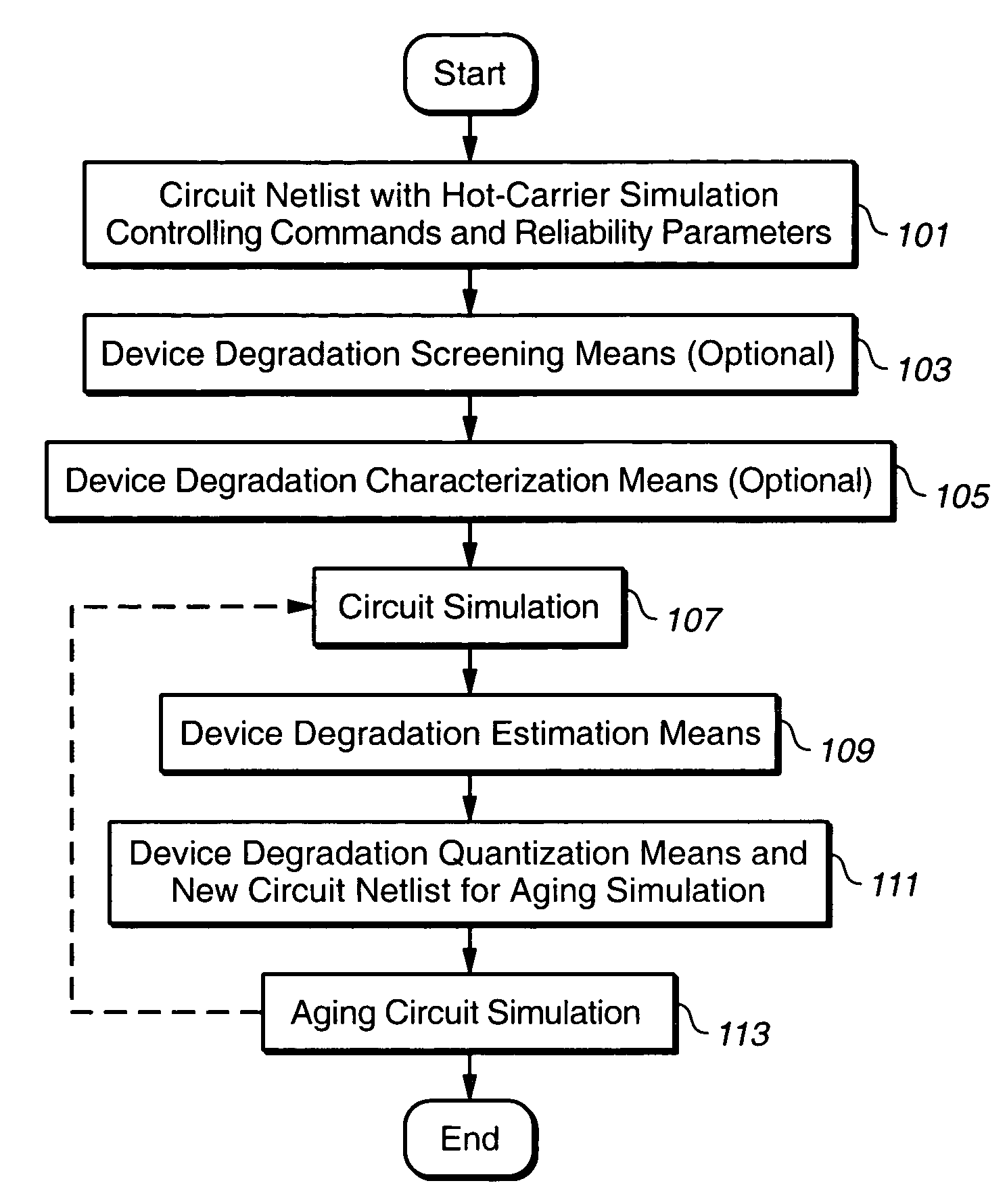

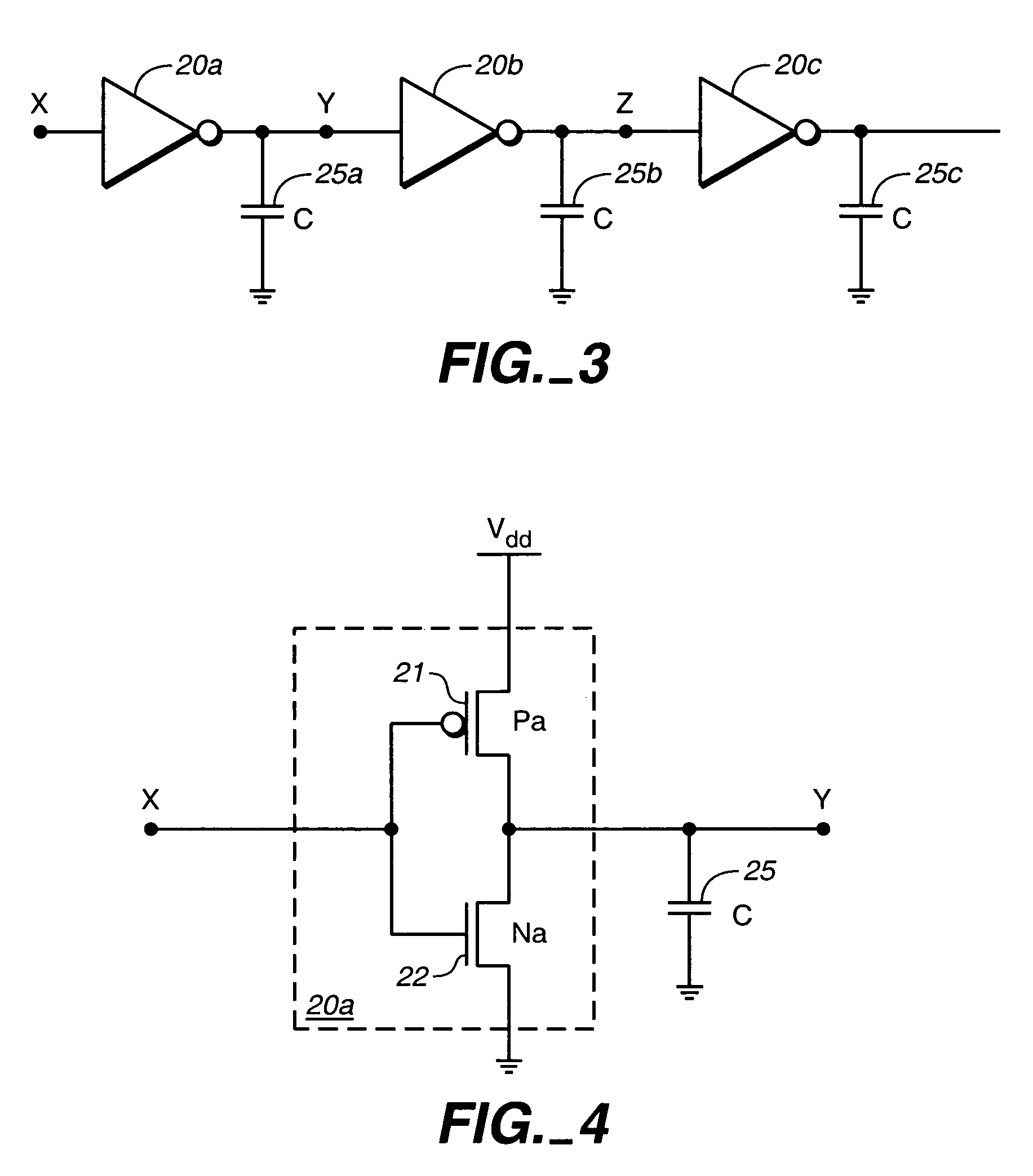

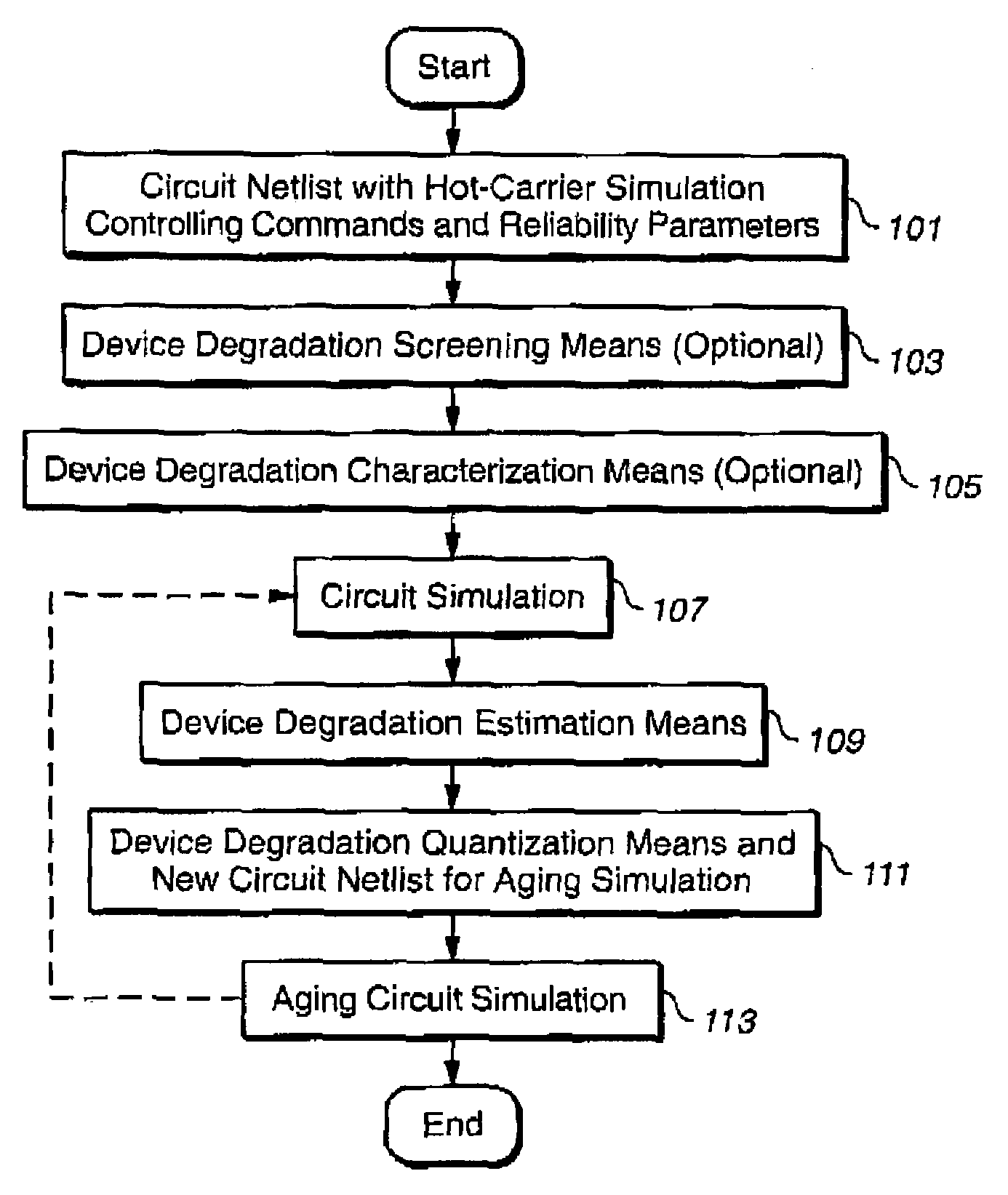

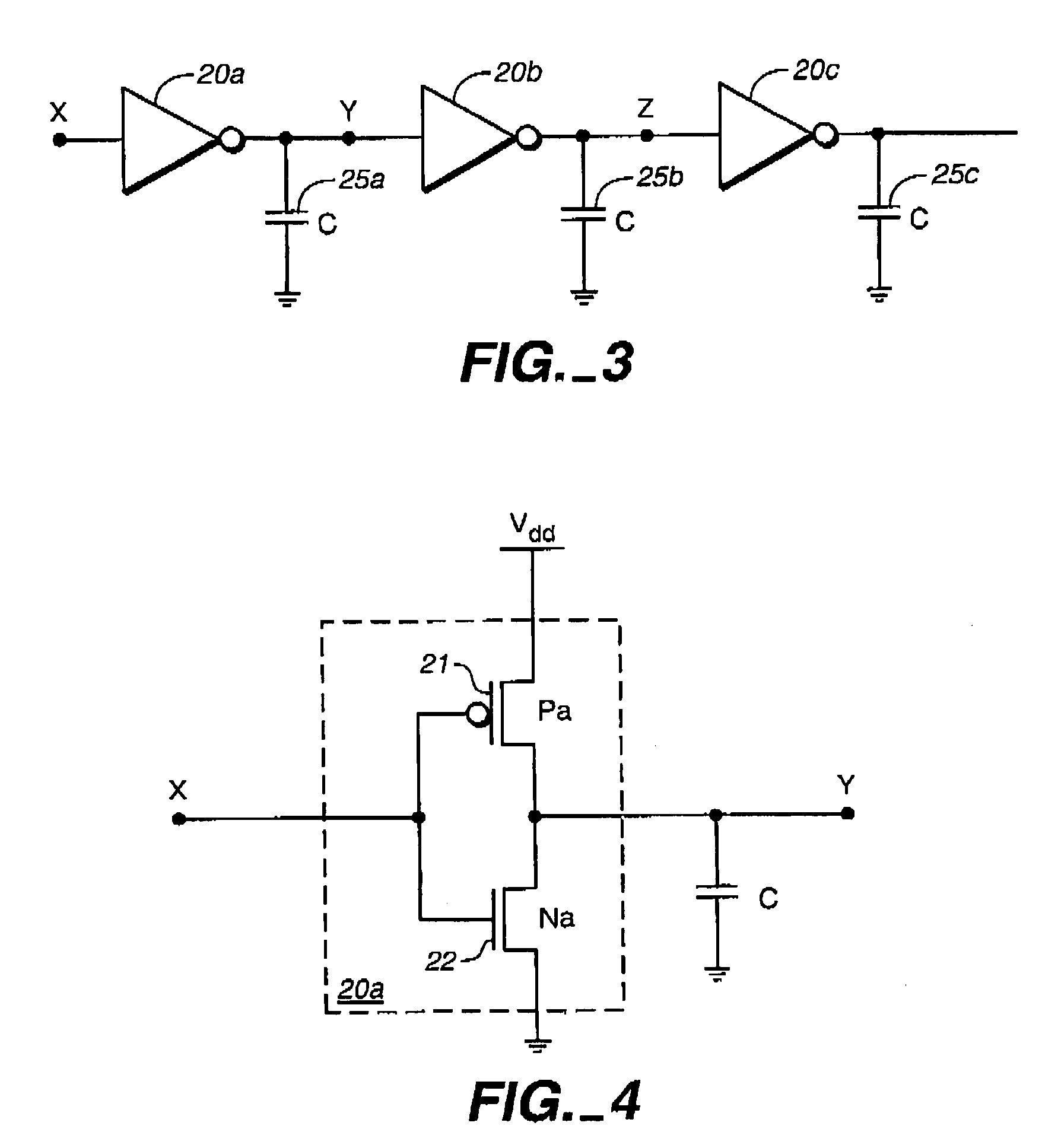

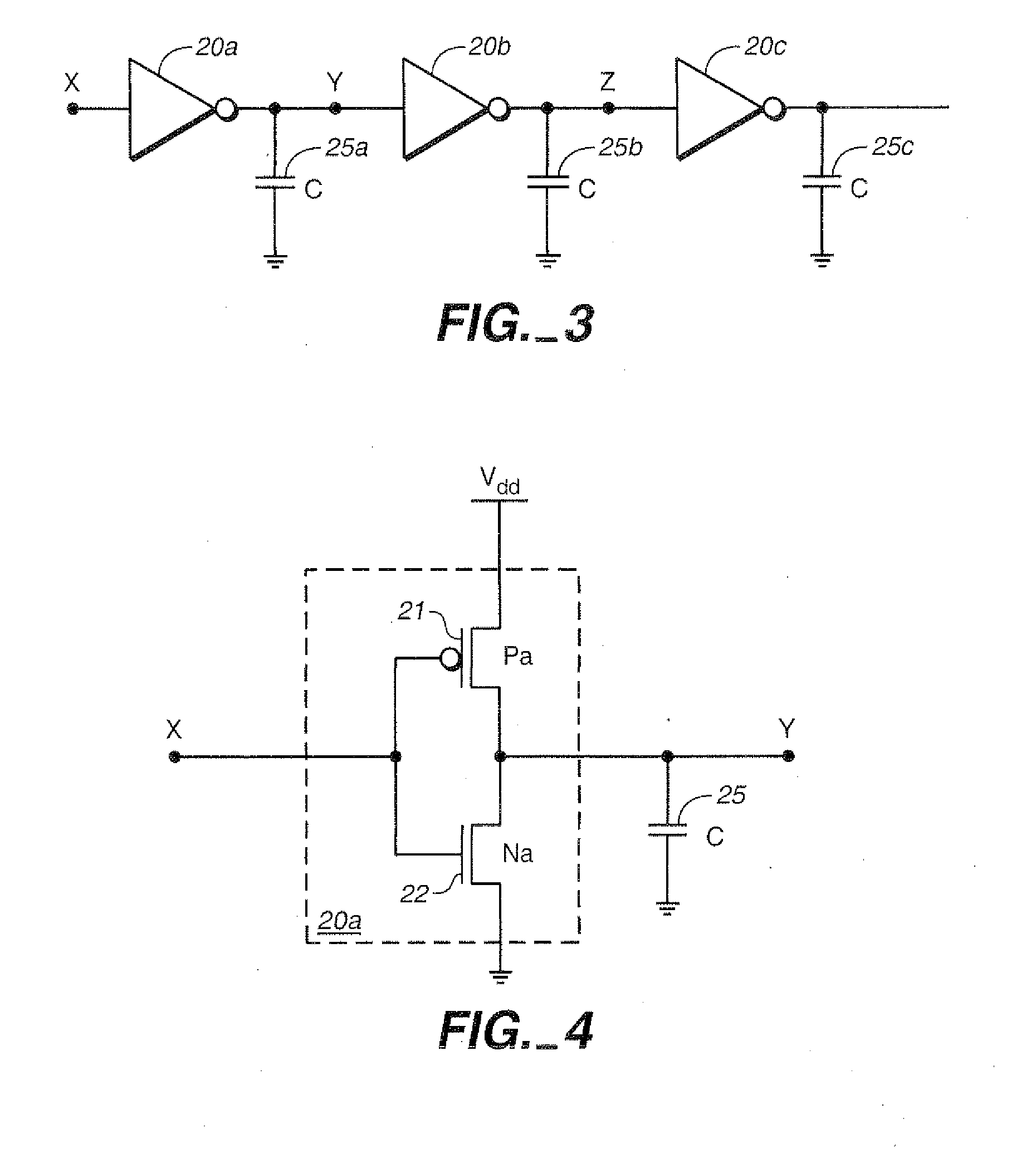

Hot carrier circuit reliability simulation

InactiveUS7292968B2Shorten the timeSimple methodAnalogue computers for electric apparatusComputer aided designElectricityDevice type

The present invention is directed to a number of improvements in methods for reliability simulations in aged circuits whose operation has been degraded through hot-carrier or other effects. A plurality of different circuit stress times can be simulated within a single run. Different aging criteria may be used for different circuit blocks, circuit block types, devices, device models and device types. The user may specify the degradation of selected circuit blocks, circuit block types, devices, device models and device types independently of the simulation. Device degradation can be characterized in tables. Continuous degradation levels can be quantized. Techniques are also described for representing the aged device in the netlist as the fresh device augmented with a plurality of independent current sources connected between its terminals to mimic the effects of aging in the device. The use of device model cards with age parameters is also described. To further improve the circuit reliability simulation, a gradual or multi-step aging is used instead of the standard one step aging process. Many of these features can be embedded within the circuit simulator. A user data interface is also presented to implement these techniques and further allow users to enter their device models not presented in the simulator. For example, a proprietary model of, say, the substrate current in an NMOS could used be with a SPICE simulator employing a different model to simulate the aging of the circuit.

Owner:CADENCE DESIGN SYST INC

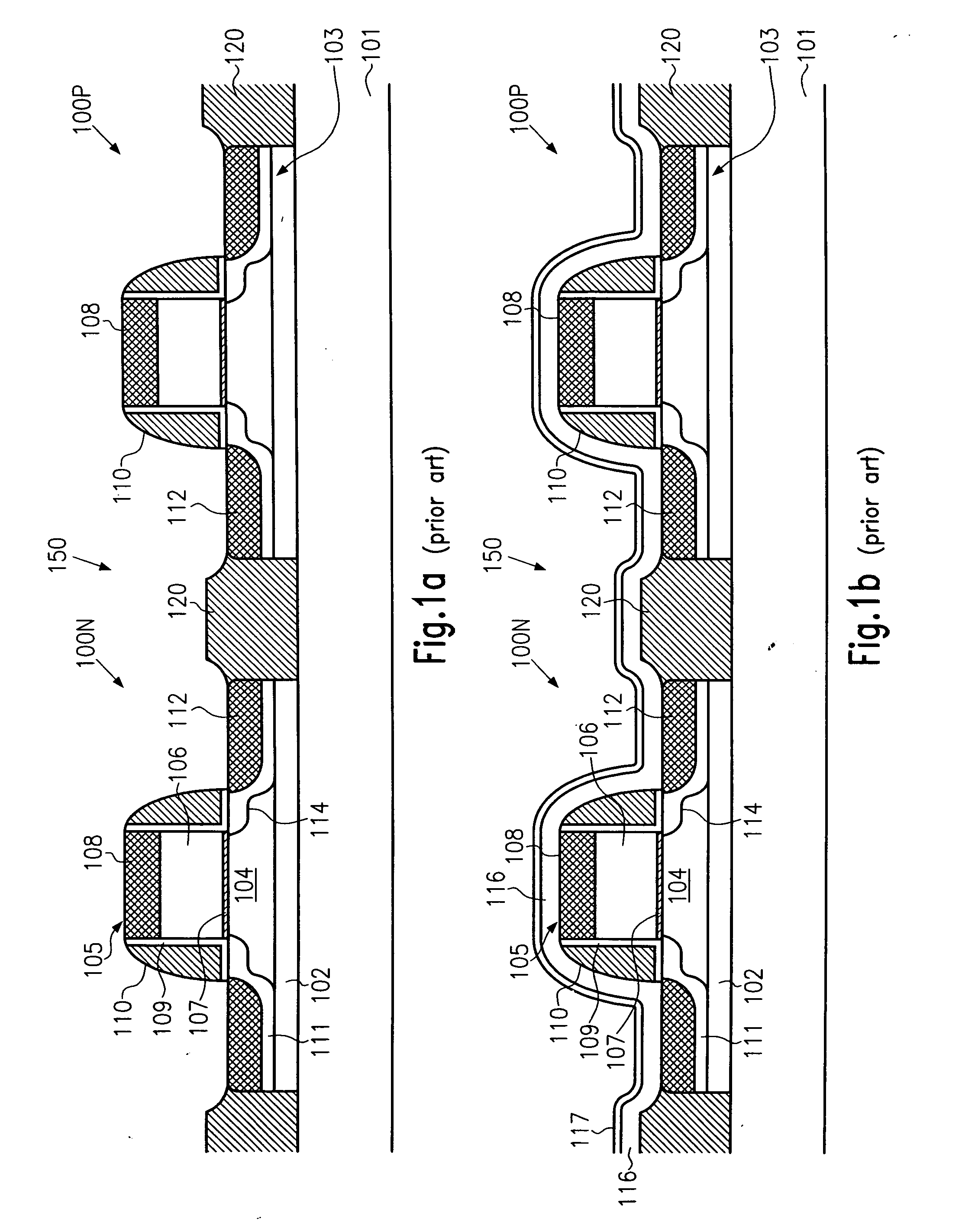

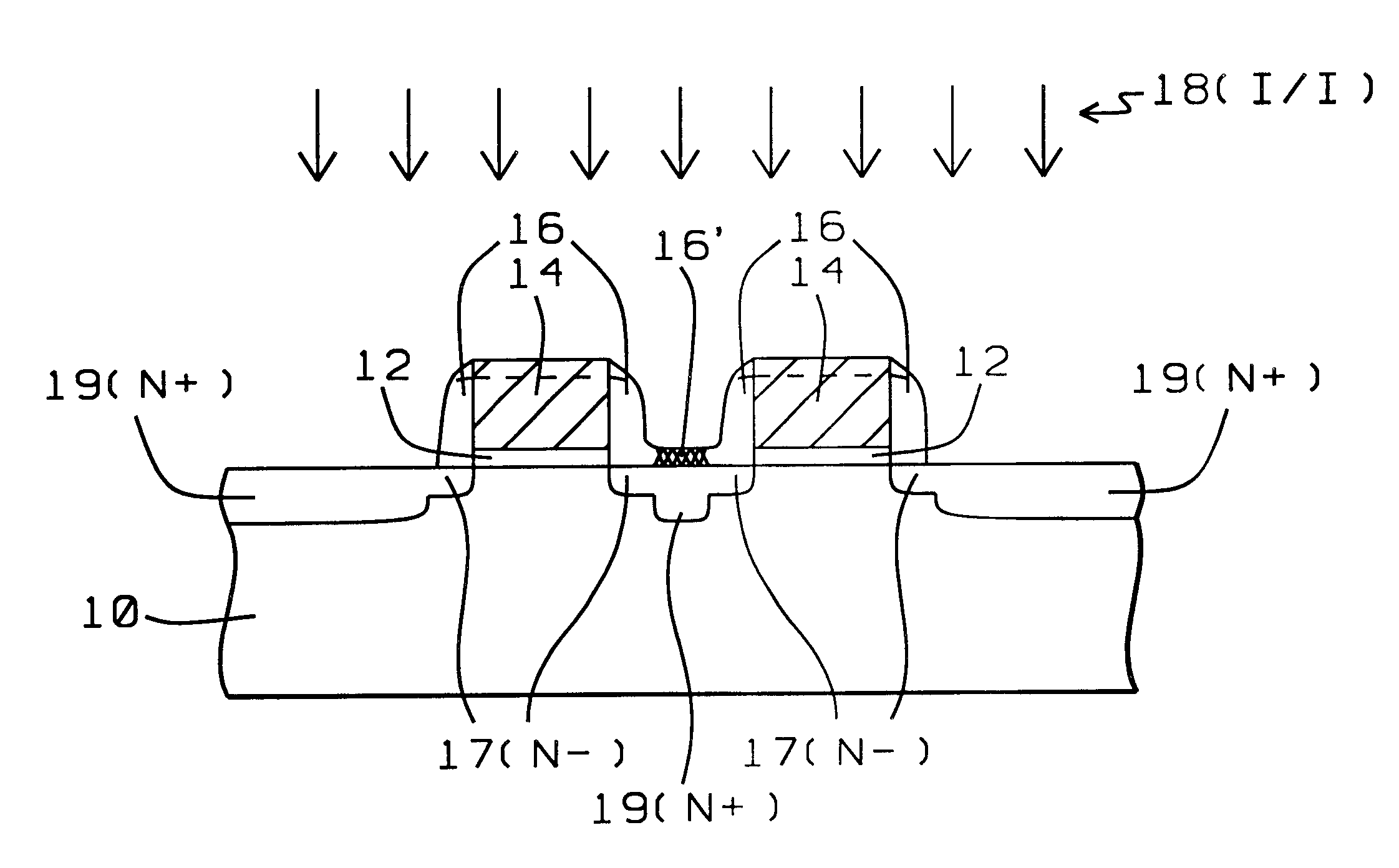

Method for making low-resistance silicide contacts between closely spaced electrically conducting lines for field effect transistors

InactiveUS6451701B1Semiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideField-effect transistor

A method for making reliable low-resistance contacts between closely spaced FET gate electrodes having high-aspect-ratio spacings. Polysilicon gate electrodes are formed. A conformal insulating layer is deposited and anisotropically etched back to form sidewall spacers on the gate electrodes. During conventional etch-back, the etch rate of the insulating layer between the closely spaced gate electrodes is slower resulting in a residual oxide that prevents the formation of reliable low-resistance contacts. This residual oxide requires an overetch in a hydrofluoric acid solution prior to forming silicide contacts. The wet overetch results in device degradation. A nitrogen or germanium implant is used to amorphize the oxide and to increase the wet etch rate of the residual oxide. Using this amorphization the wet etch that is commonly used as a pre-clean prior to forming silicide contacts can be used to remove the residual silicon oxide without overetching. The implant also results in a smoother interface between the silicide and the silicon substrate, which results in lower sheet resistance.

Owner:TAIWAN SEMICON MFG CO LTD

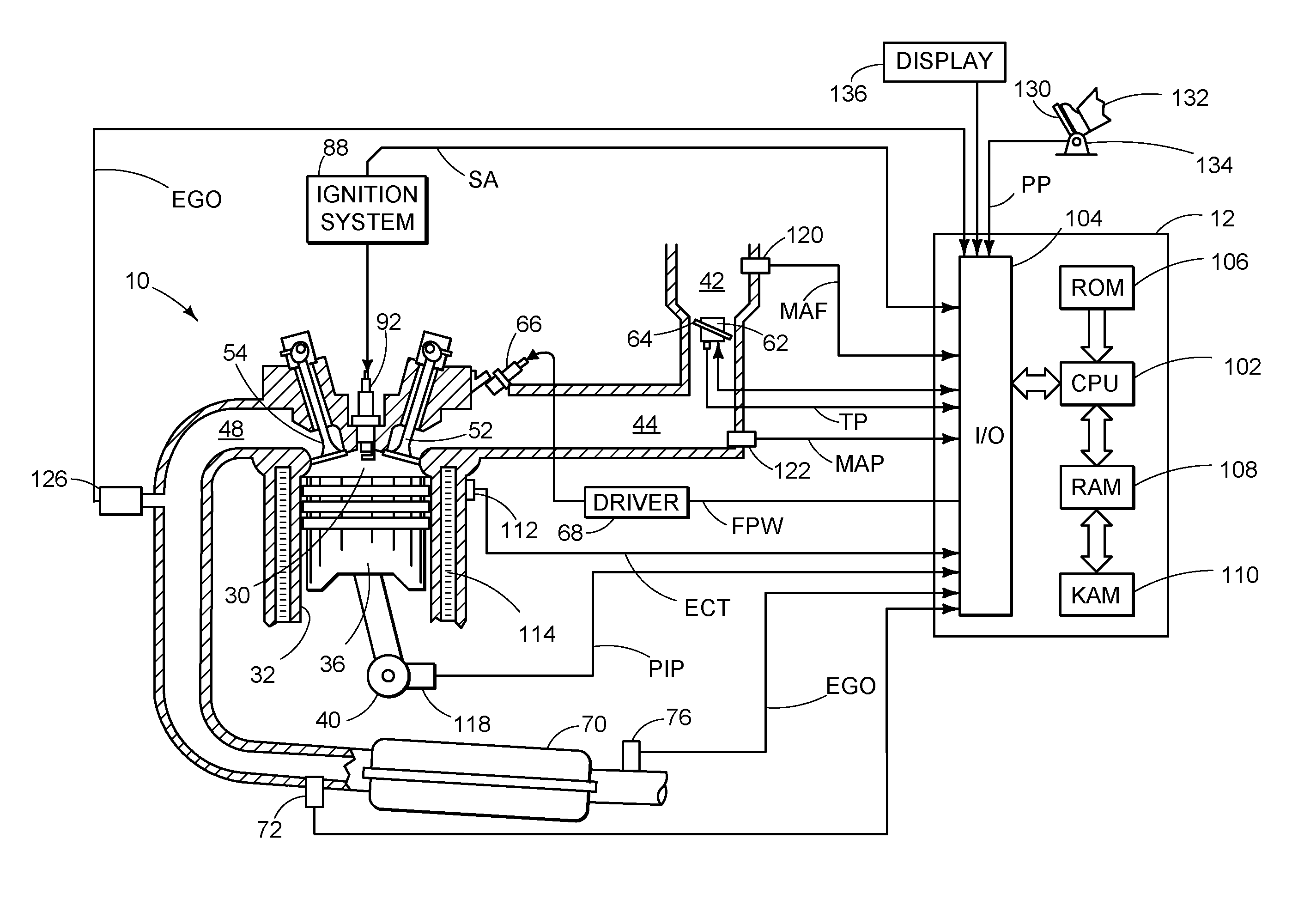

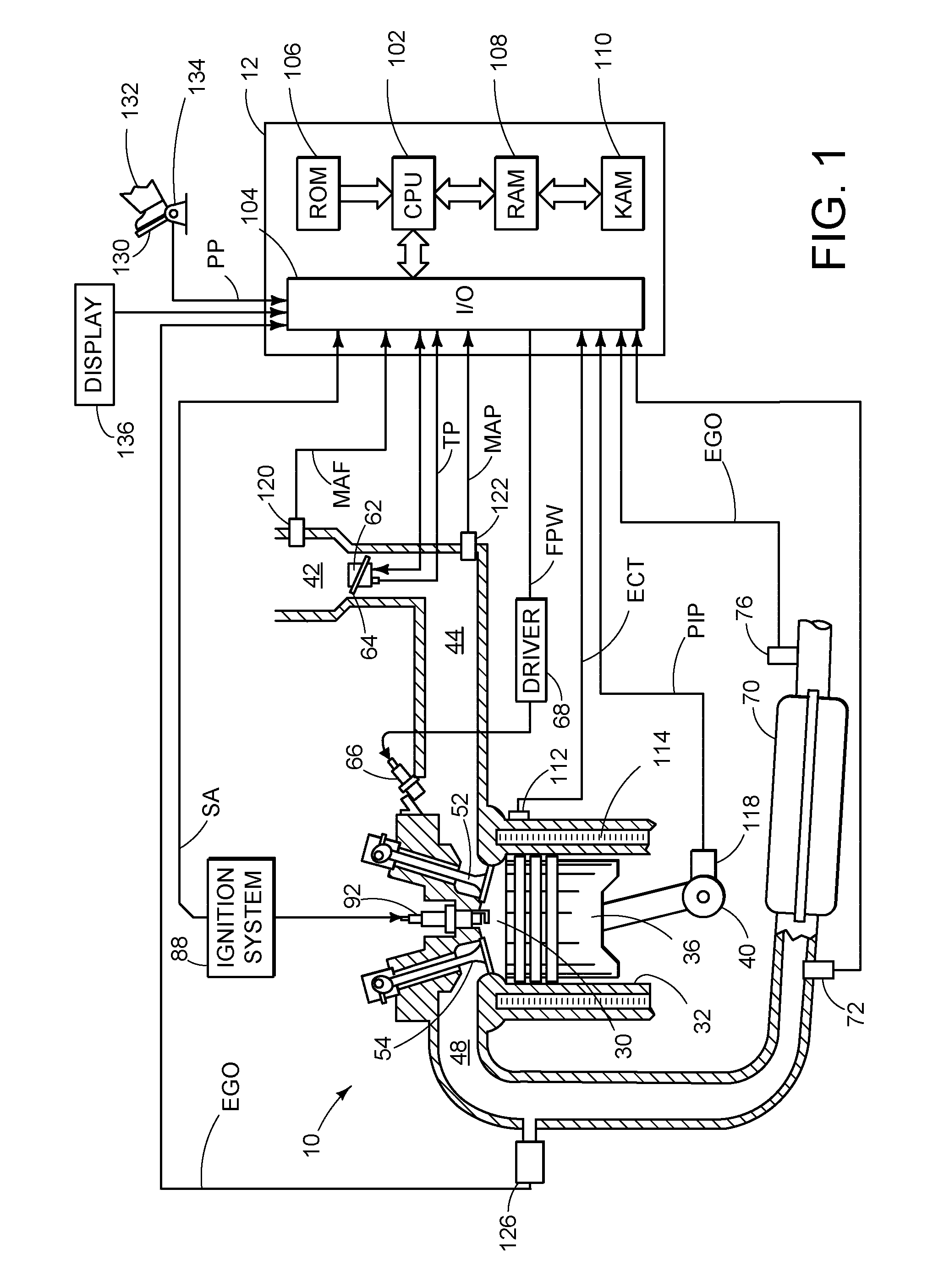

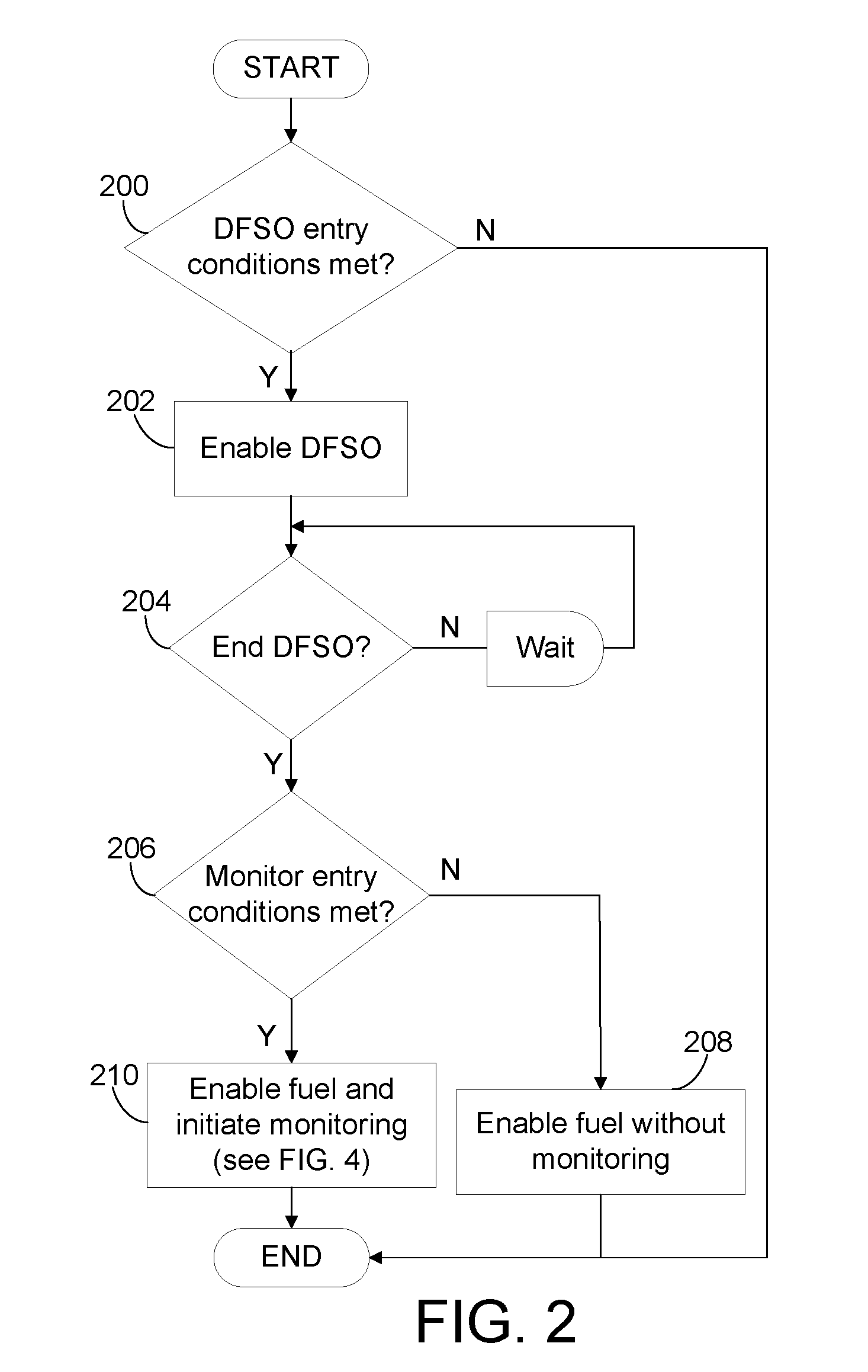

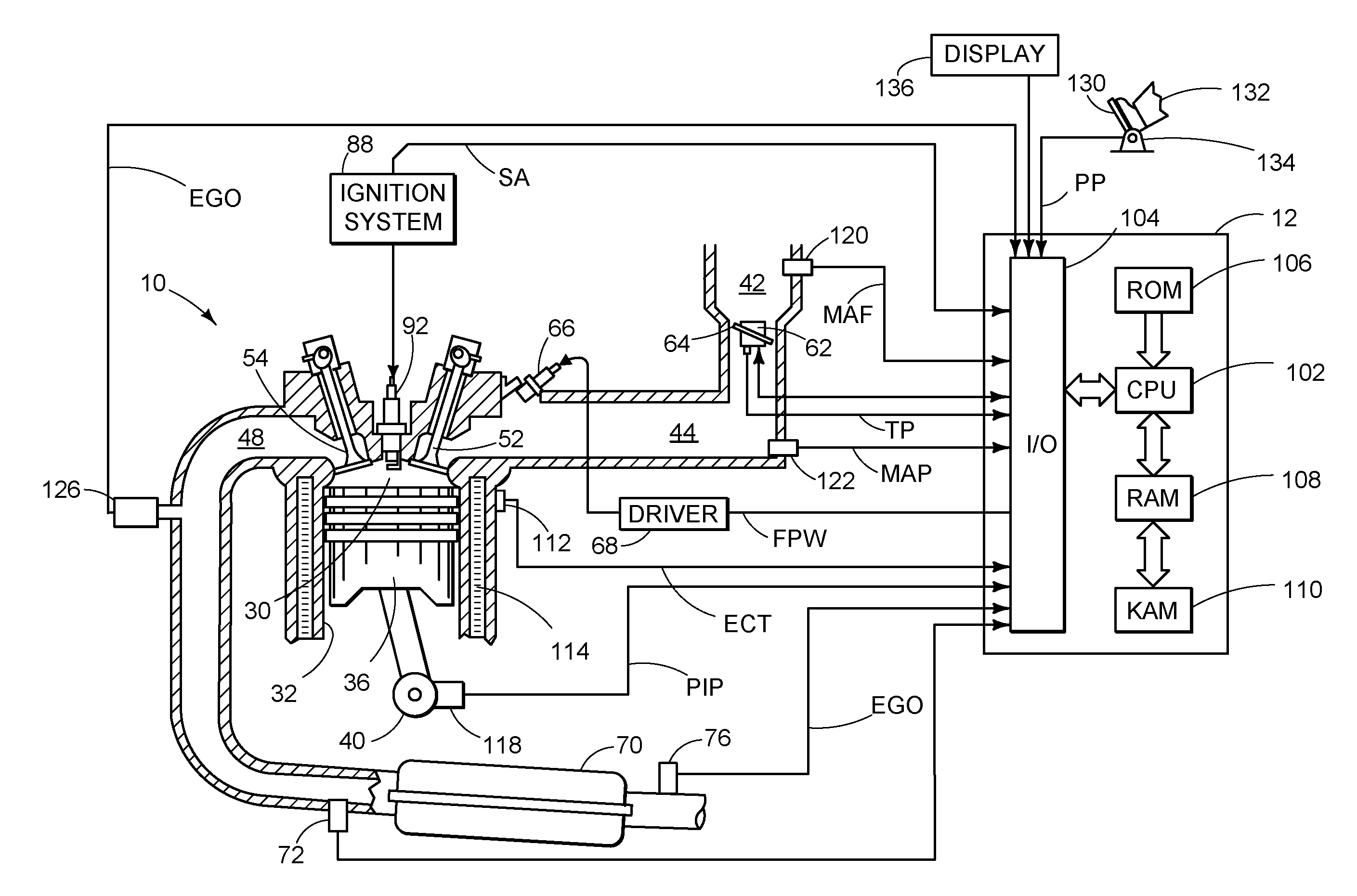

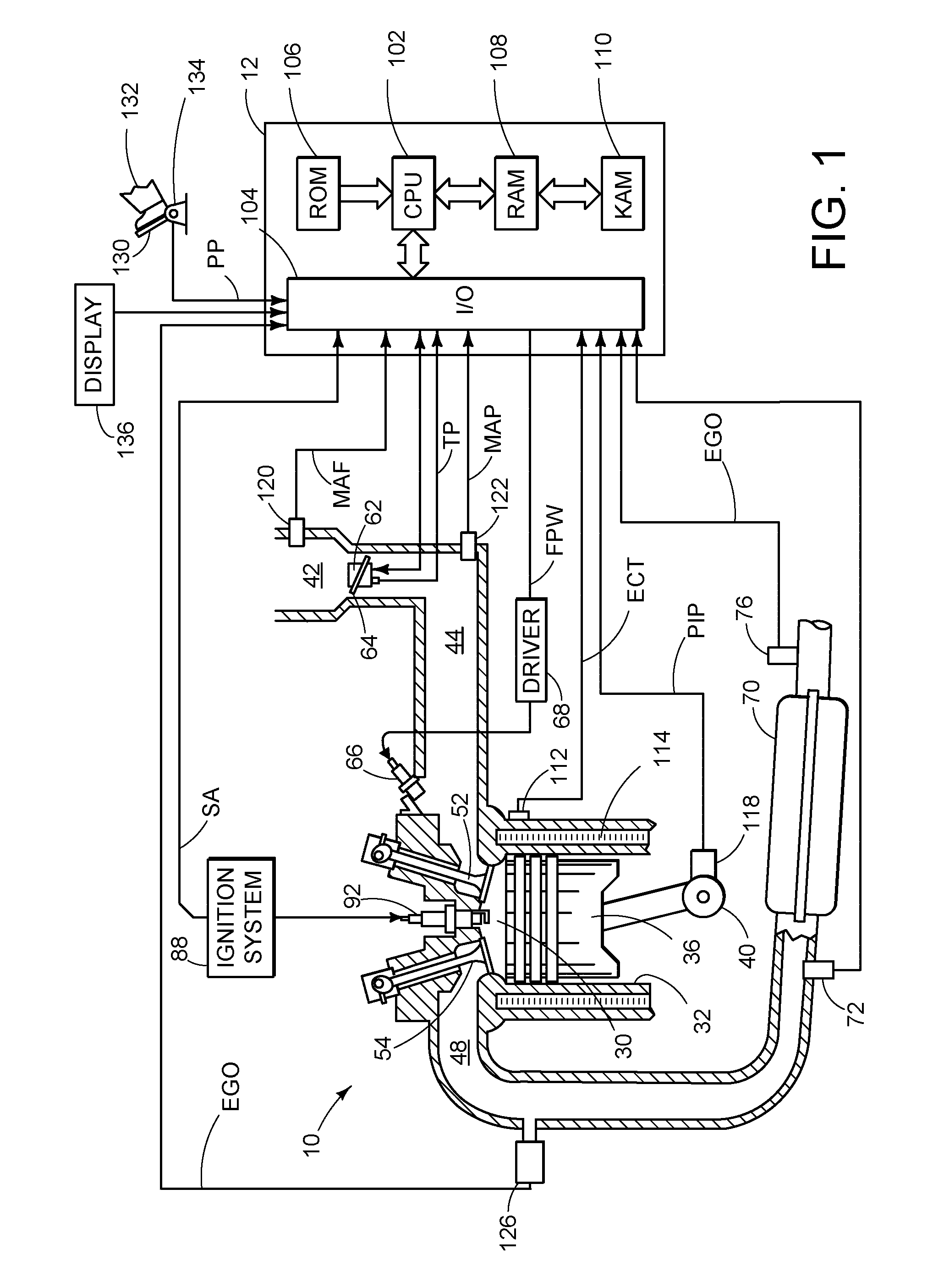

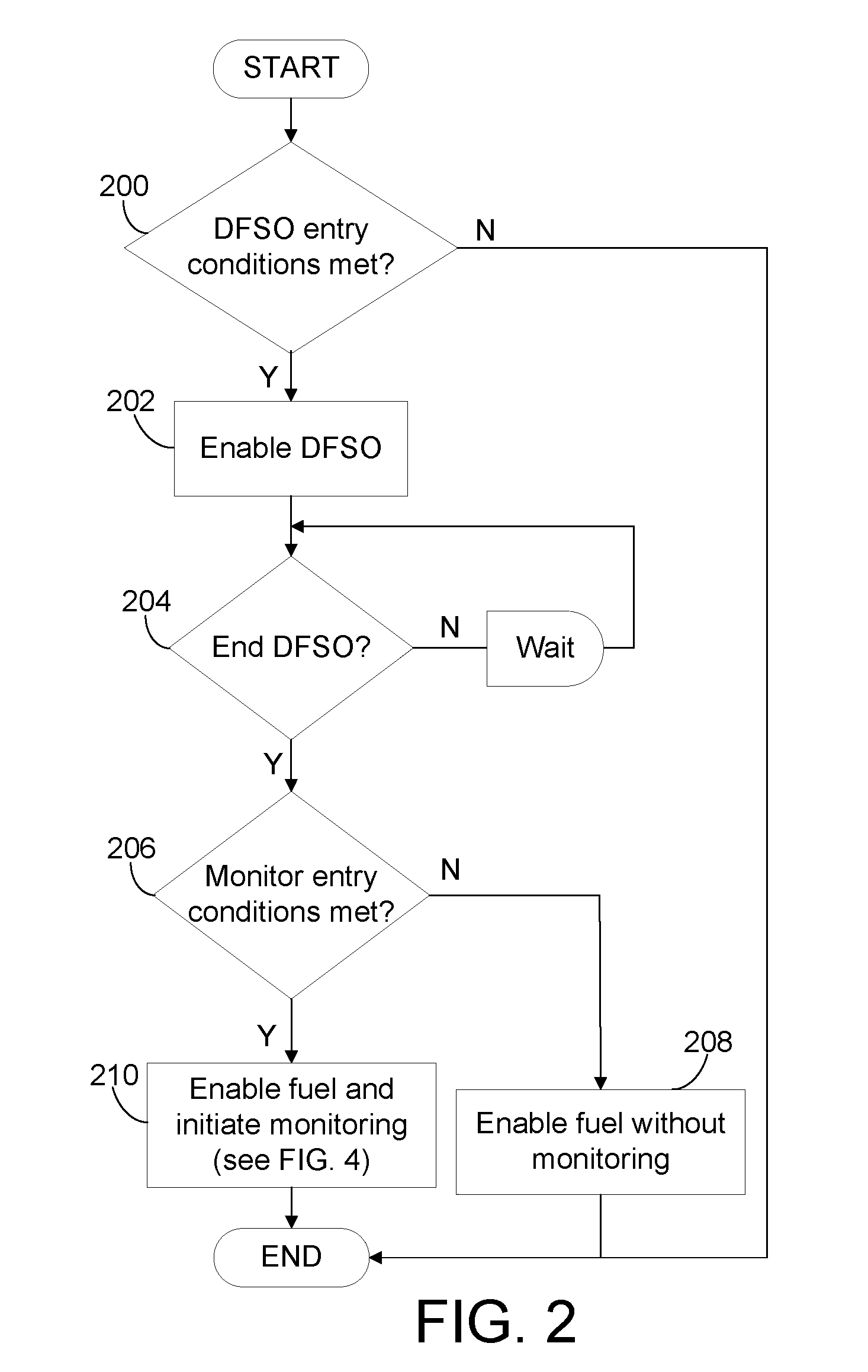

Integrated fuel catalyst monitor

ActiveUS20110083425A1Reduce capacityLow efficiencyElectrical controlInternal combustion piston enginesProcess engineeringOxygen

A method is provided for monitoring an emission device coupled to an engine. In one example approach, the method comprises: following a deceleration fuel shut-off duration, indicating degradation of the emission device based on an amount of rich products required to cause a sensor to become richer than a threshold. The amount of rich products required may be correlated to an amount of oxygen stored in the emission device. The indication of emission device degradation may be further based on air mass and temperature during delivery of the required rich products.

Owner:FORD GLOBAL TECH LLC

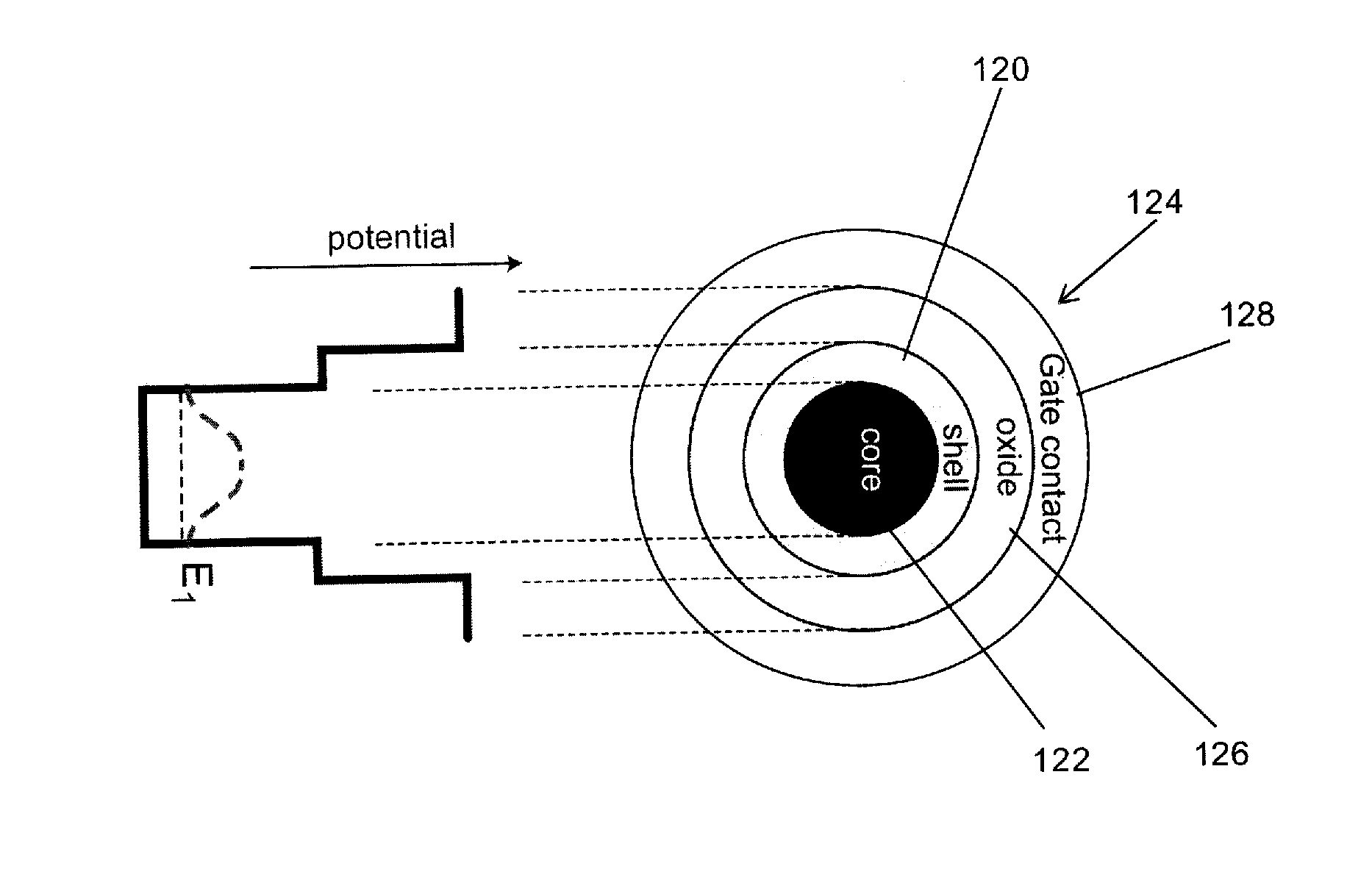

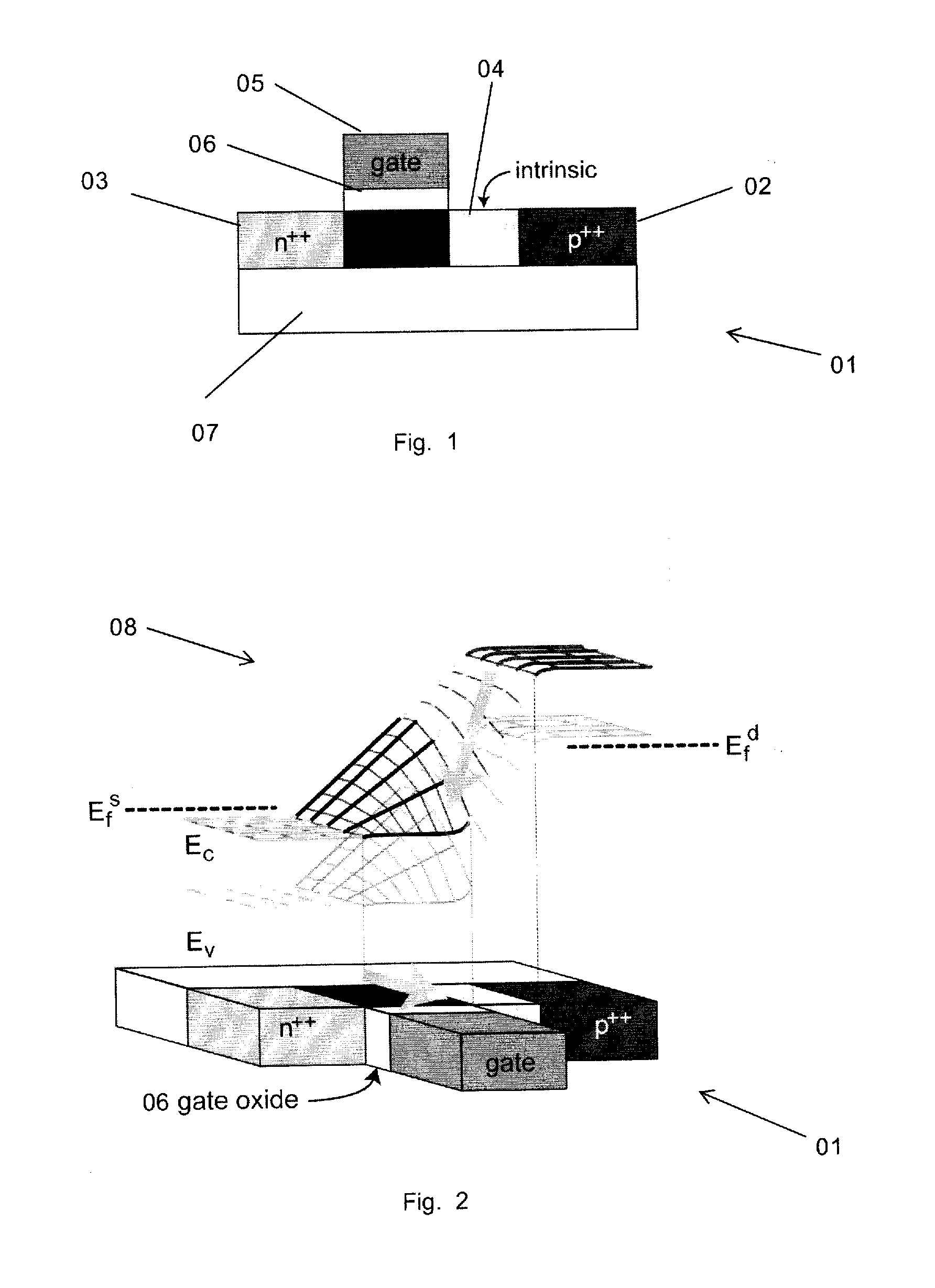

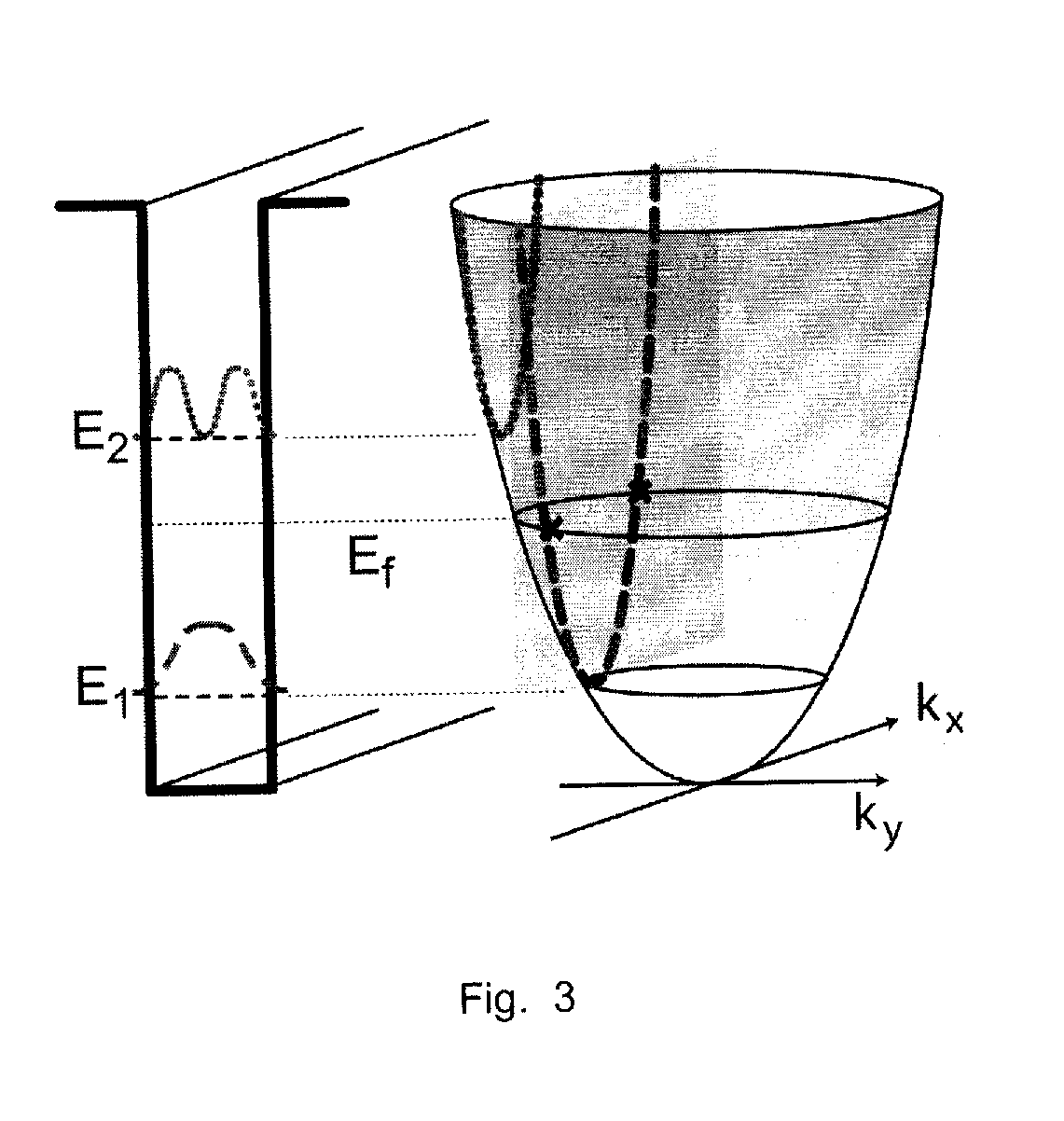

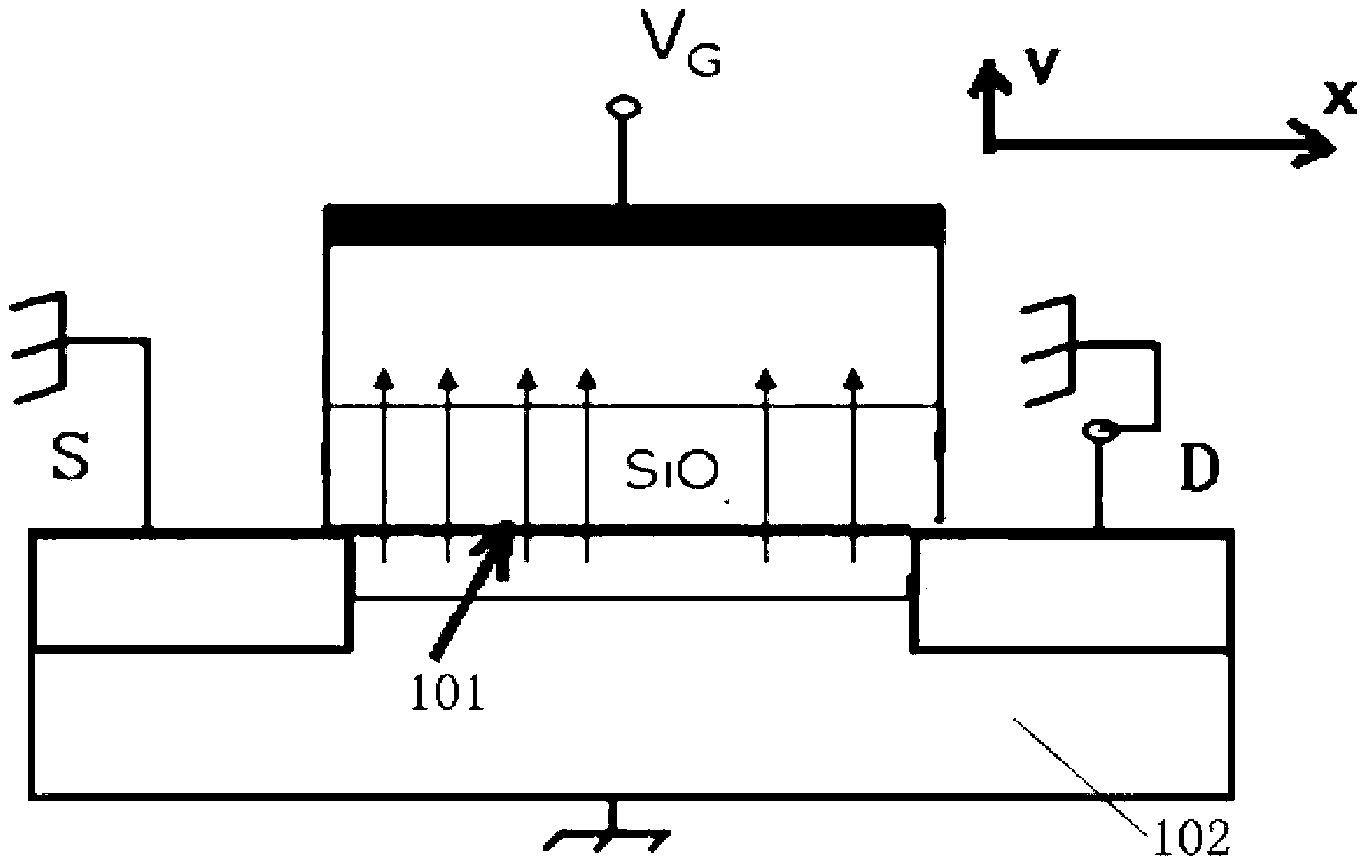

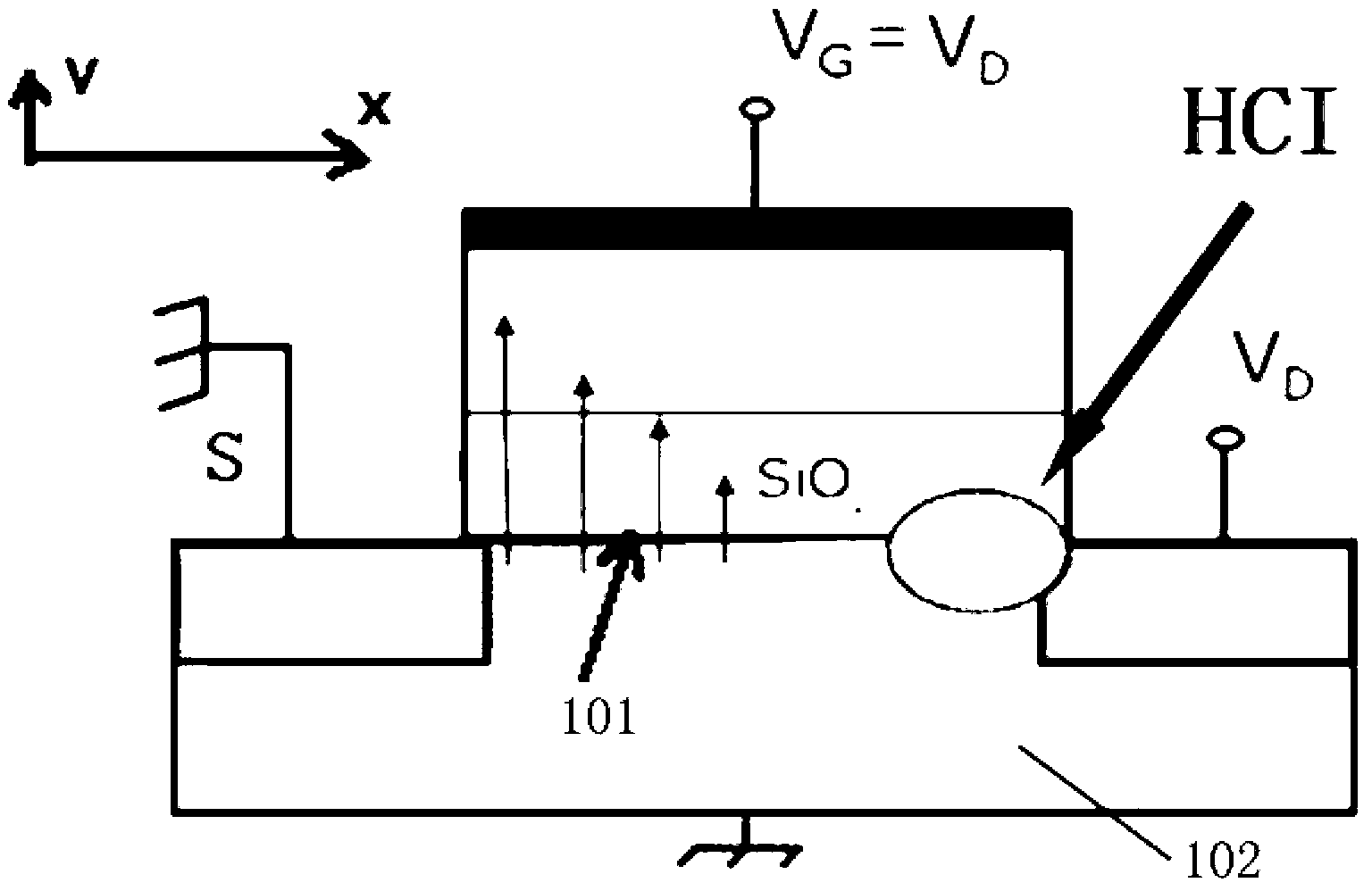

Impact ionization field-effect transistor

An Impact Ionization Field-Effect Transistor (I-MOS) device in which device degradation caused by hot carrier injection into a gate oxide is prevented. The device includes source, drain, and gate contacts, and a channel between the source and the drain. The channel has a dimension normal to the direction of a charge carrier transport in the channel such that the energy separation of the first two sub-bands equals or exceeds the effective energy band gap of the channel material.

Owner:GLOBALFOUNDRIES US INC

Hot-Carrier Device Degradation Modeling and Extraction Methodologies

InactiveUS20090299716A1Improve accuracySimple methodAnalogue computers for electric apparatusComputer aided designEngineeringModel parameters

Owner:LIU ZHIHONG +5

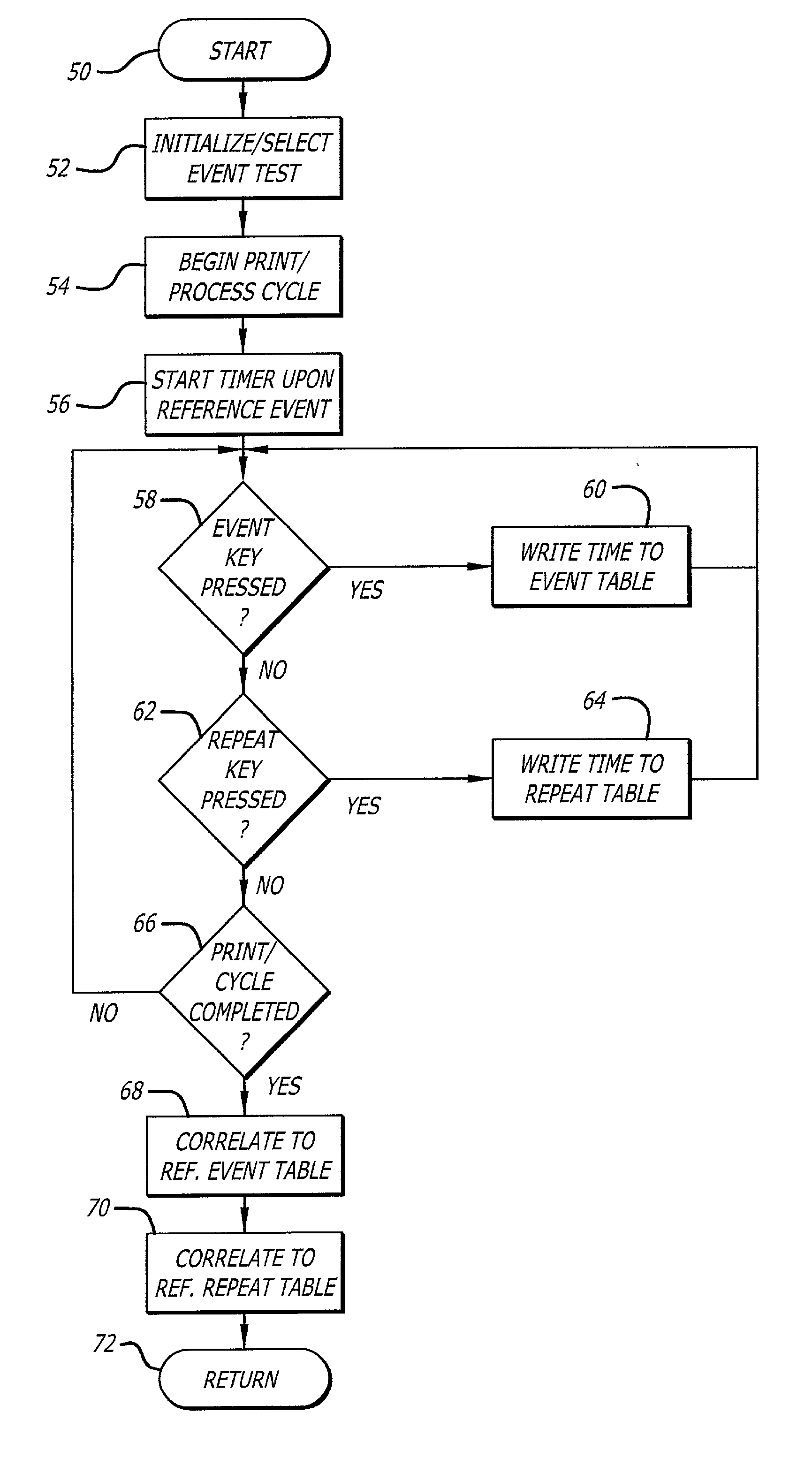

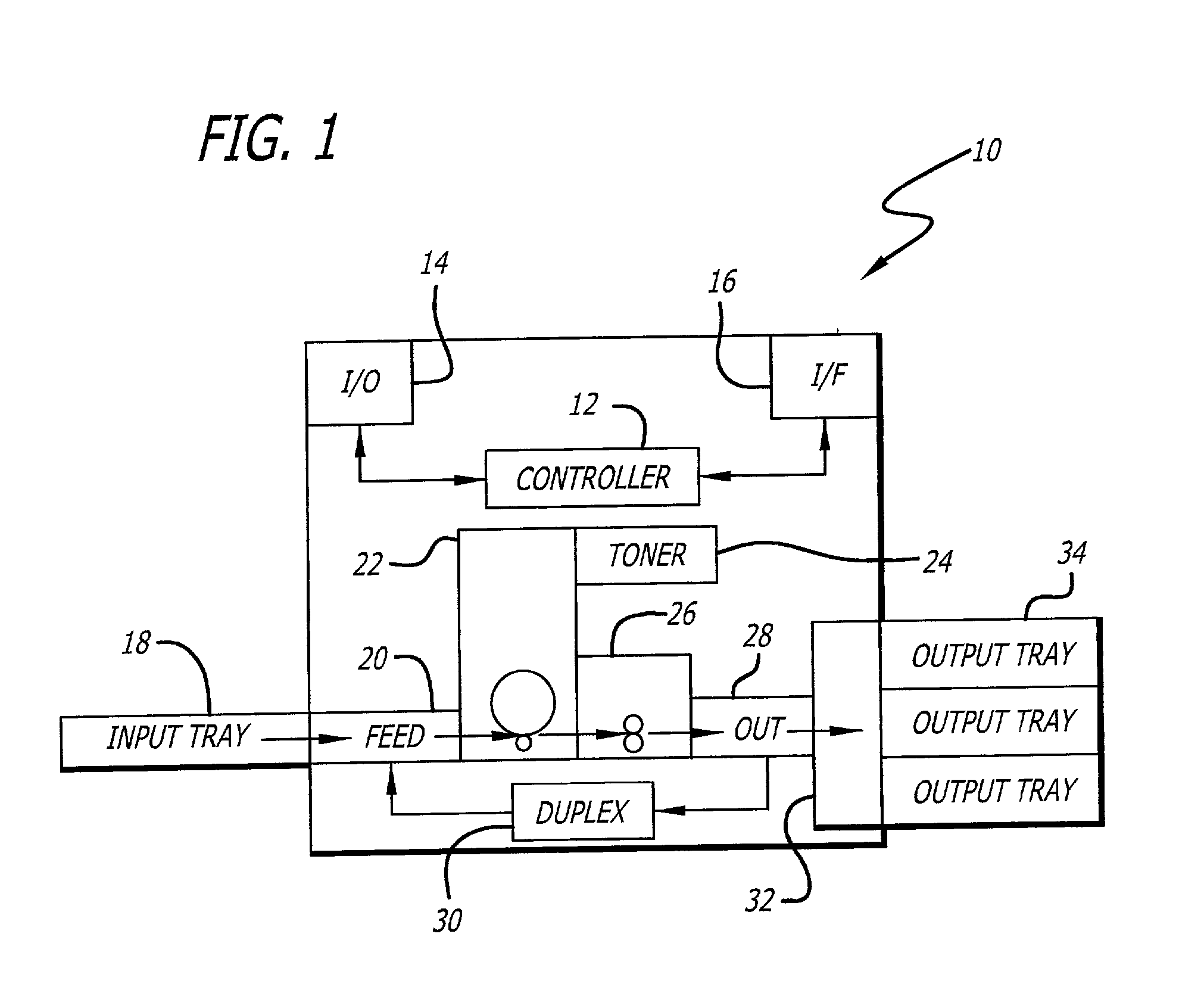

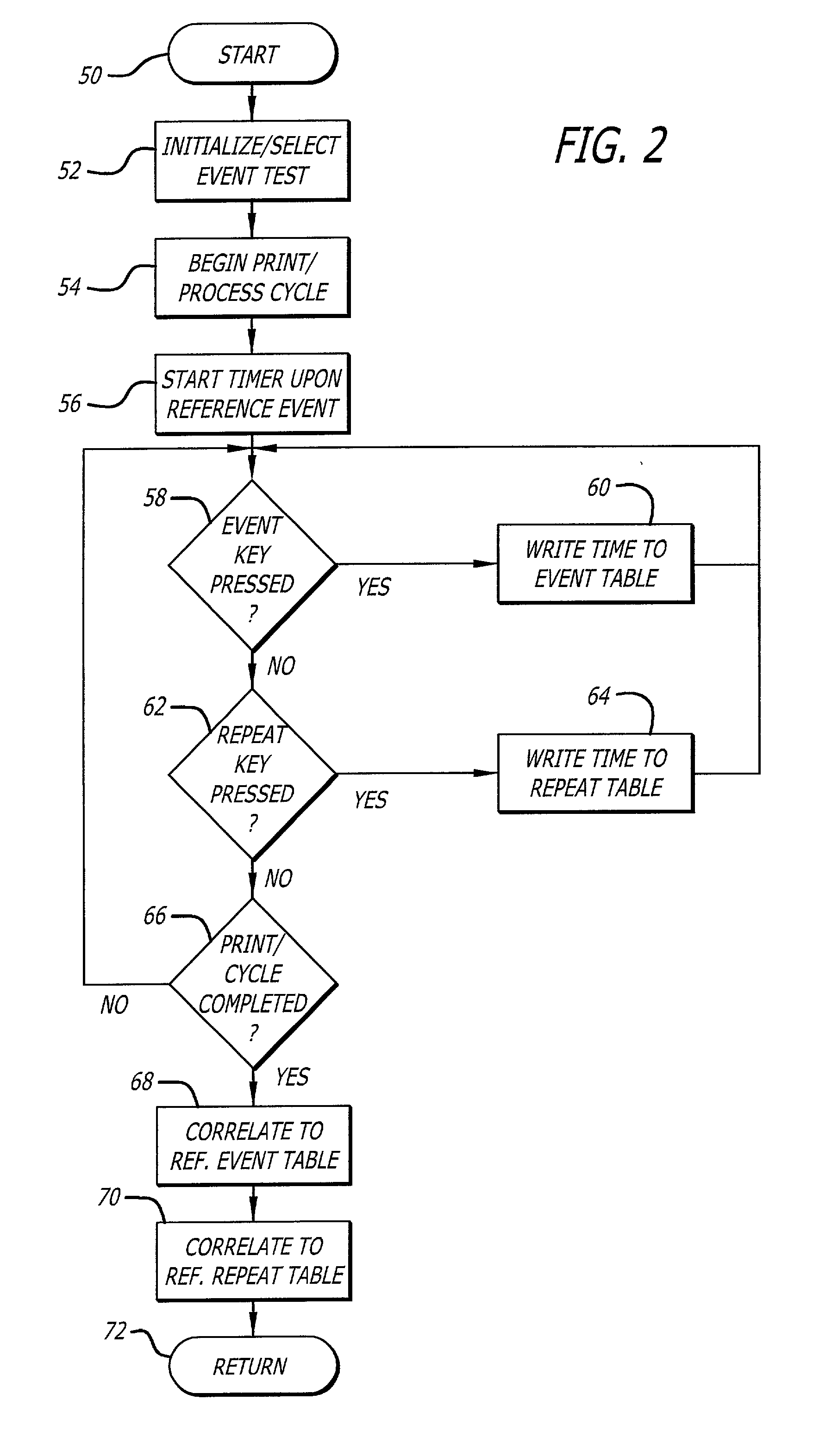

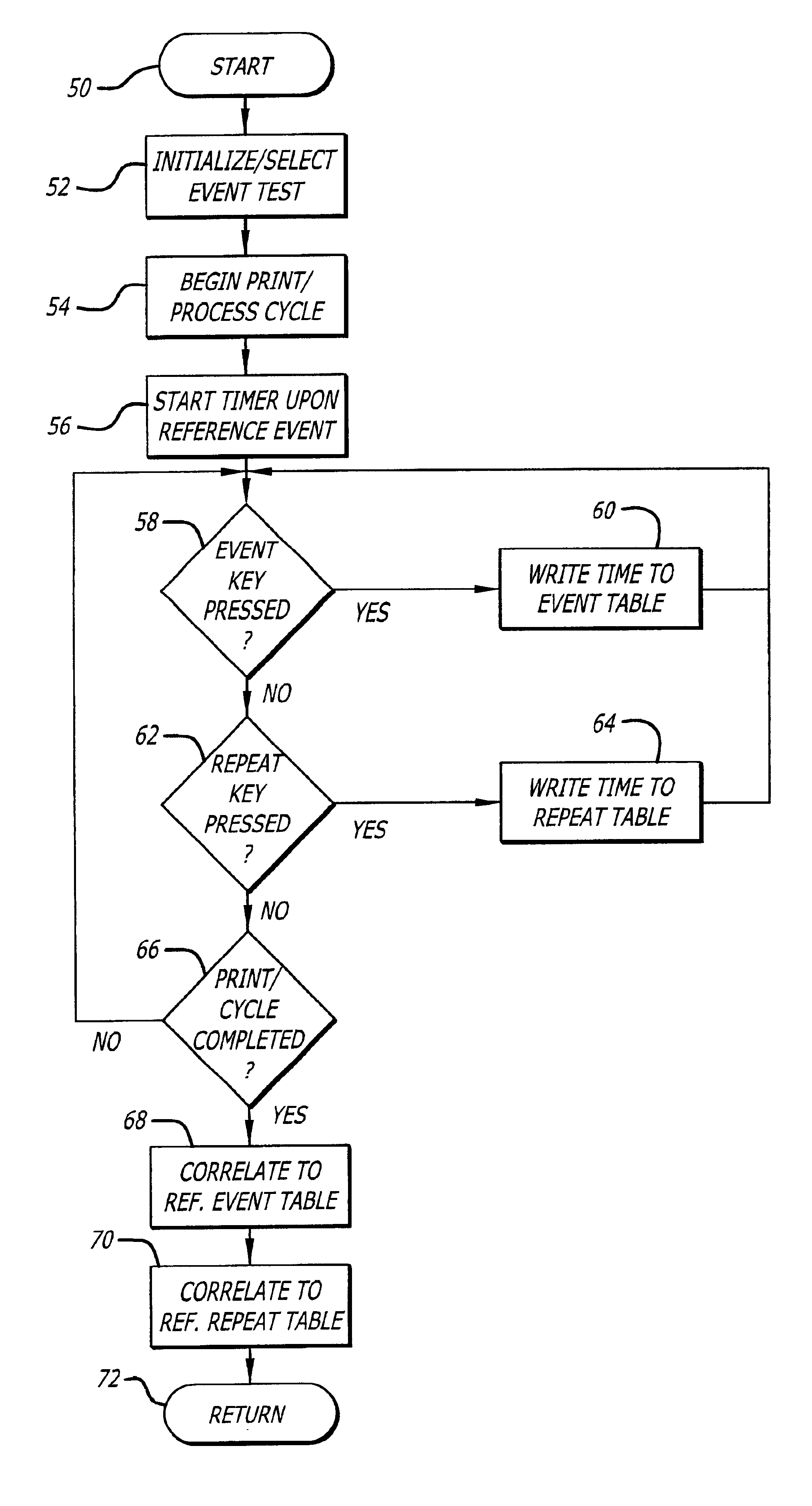

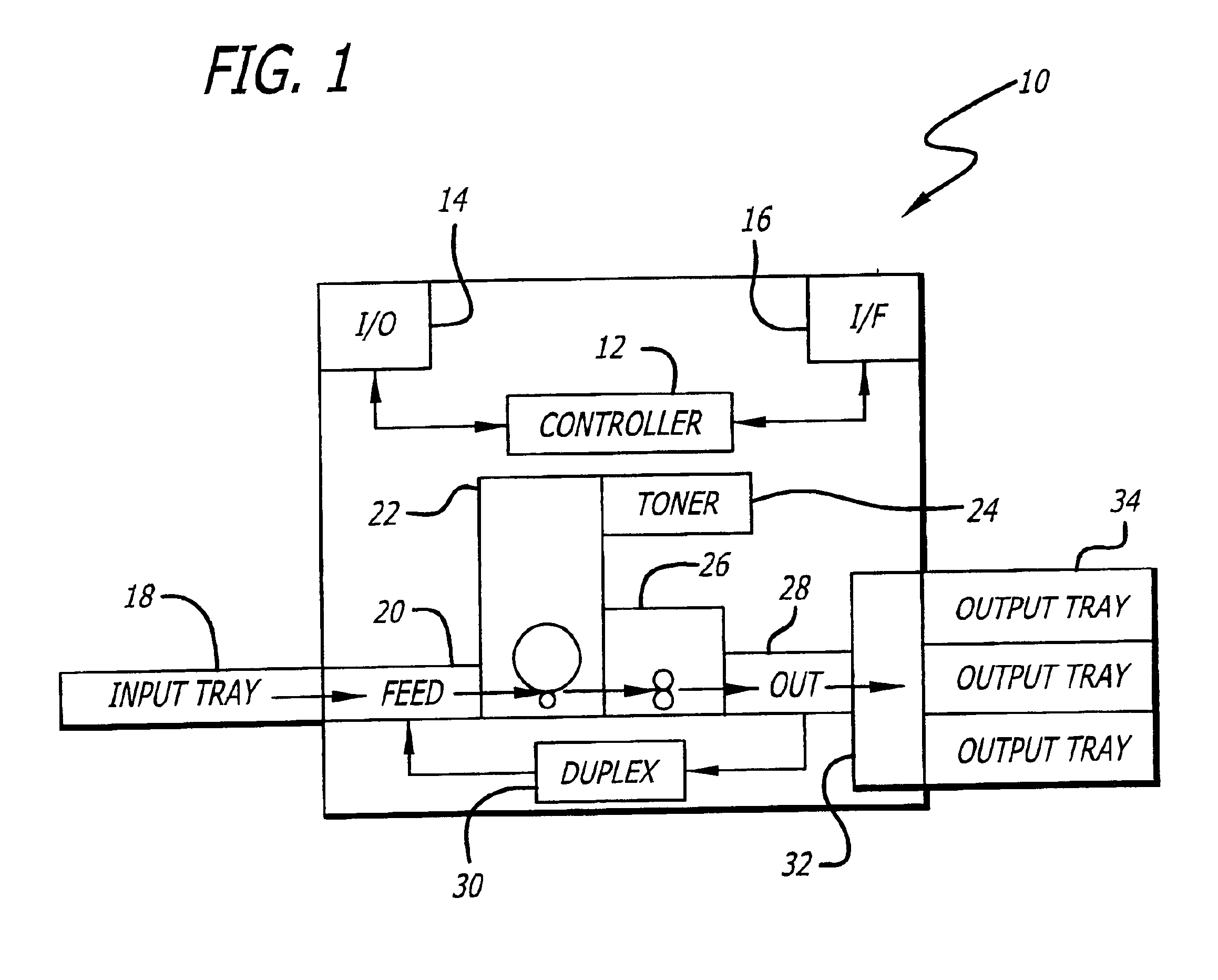

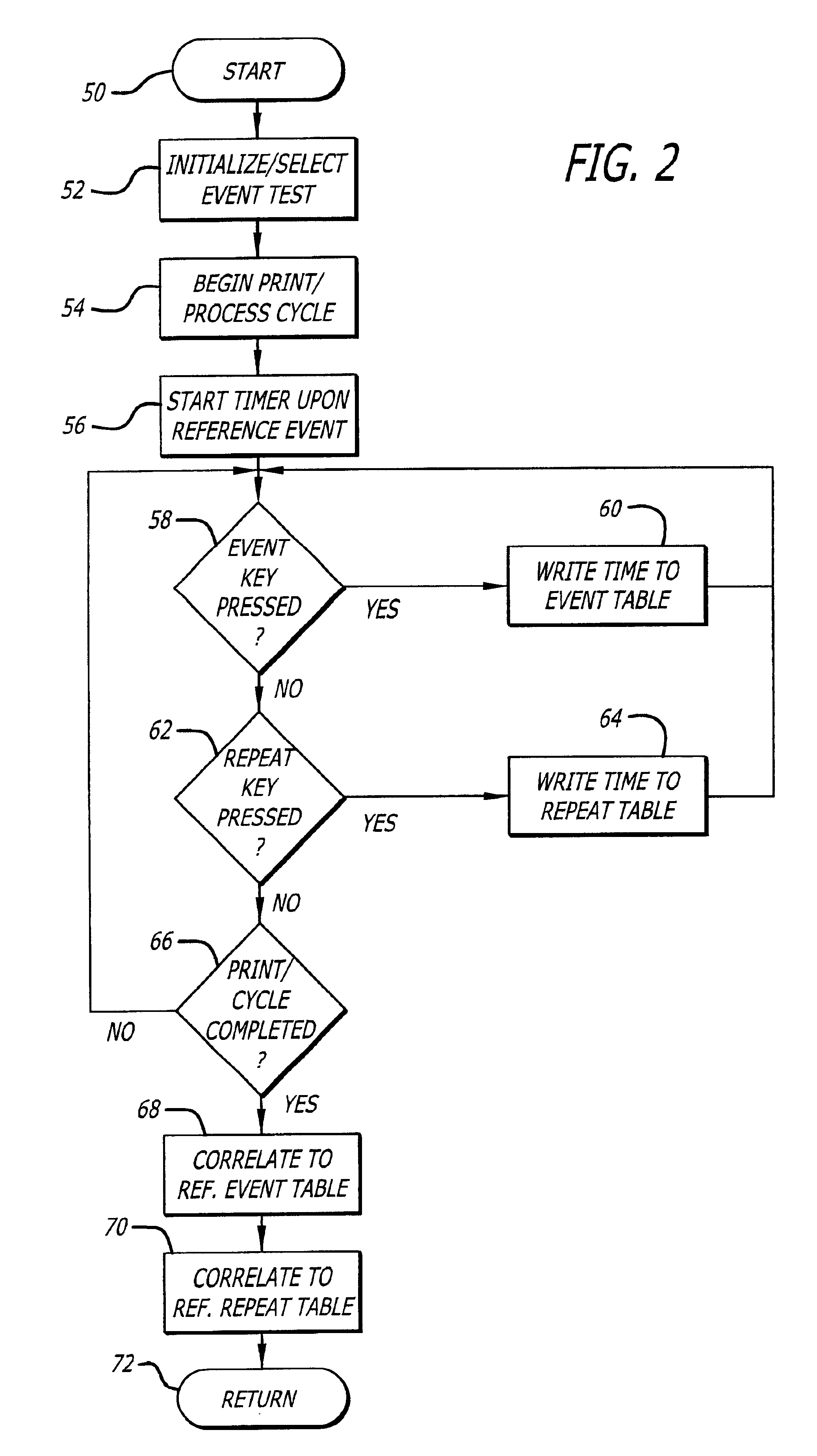

Systems and methods for device degradation determination and resolution by event occurence recordation and timing analysis

A method and apparatus for determining the cause of degradation in a product or device. A reference time is established and recorded, then a process or function of the device or product is enabled. As anomalous events occur, a user actuates an actuator that causes the recordation of an event time with respect to the reference time. Events may be repetitive or non-repetitive. At completion of the function, the recorded times are compared to a table of known product or device cycle function times, and a correlation is made to determine the most likely cycle function related to the events recorded. This information can then be correlated to parts previously known to operate at such times thereby providing a diagnostic tool useful in maintenance or repair of the device or product.

Owner:HEWLETT PACKARD DEV CO LP

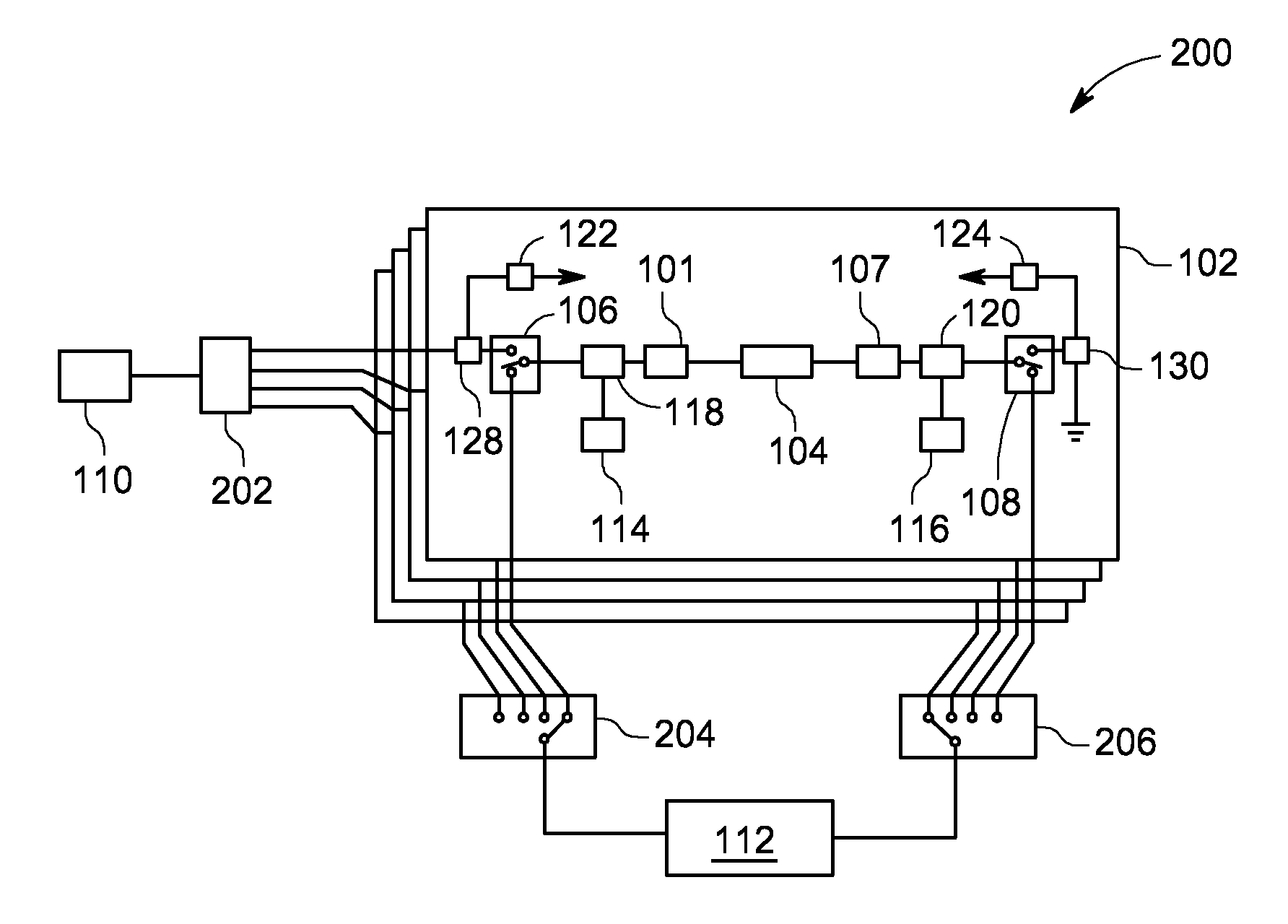

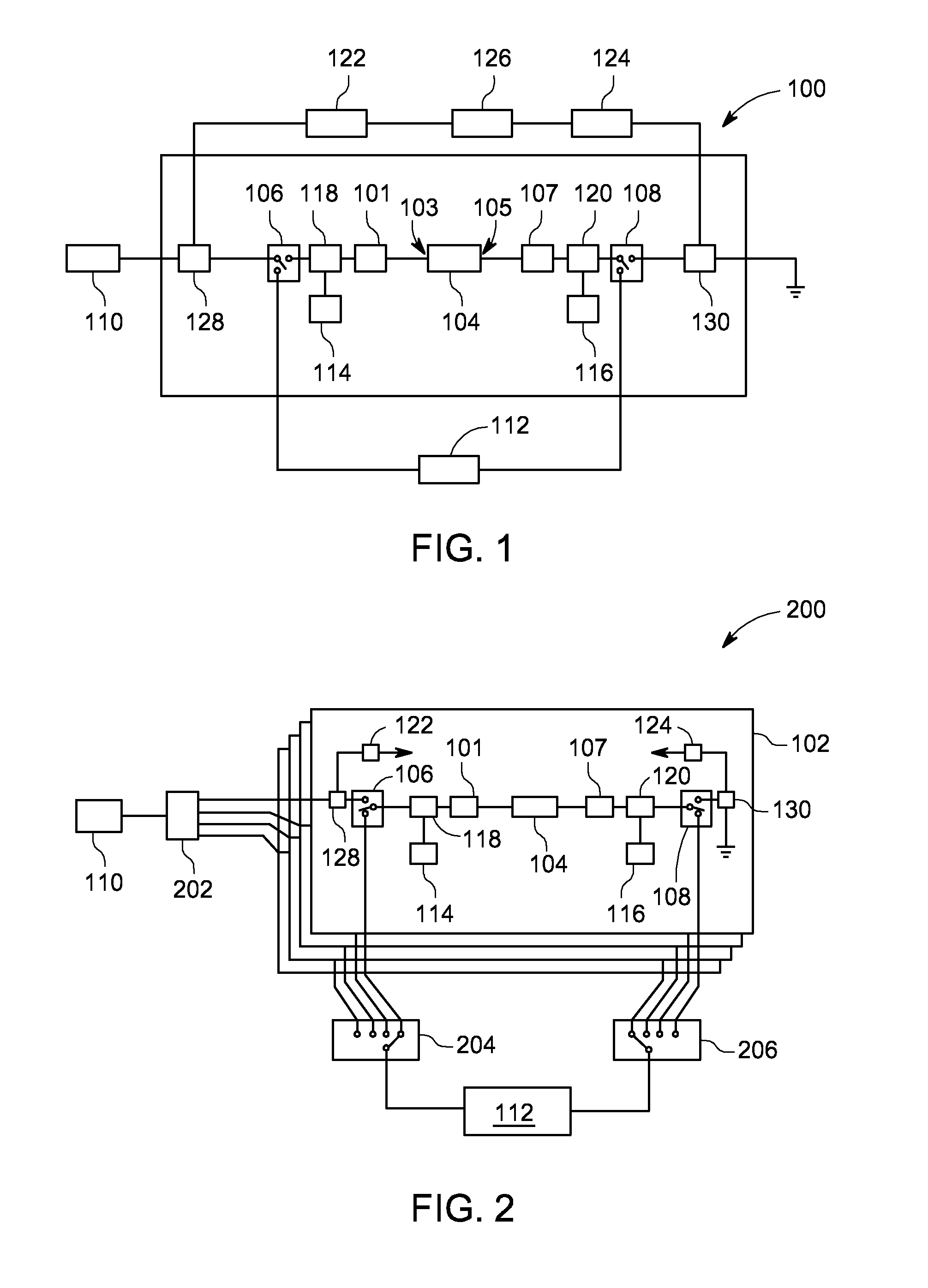

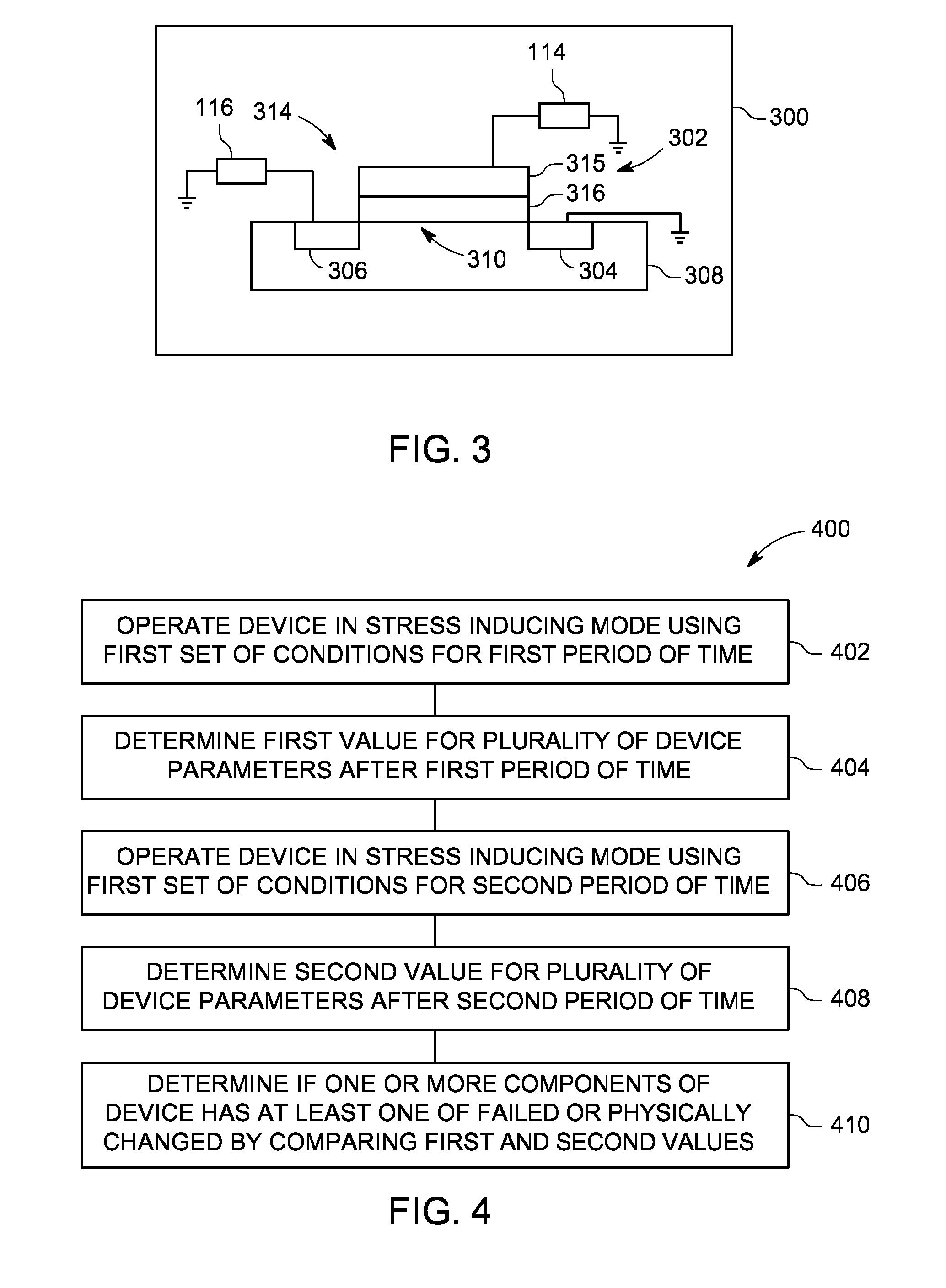

Method and apparatus for accelerating device degradation and diagnosing the physical changes of the device during the degradation process

Embodiments of the present invention comprise methods and apparatus for testing devices. In some embodiments, a method for testing a device includes operating the device in a stress inducing mode using a first set of conditions for a first period of time; determining a first value for a plurality of device parameters after the first period of time; operating the device in the stress inducing mode using the first set of conditions for a second period of time; determining a second value for the plurality of device parameters after the second period of time; and determining if one or more components of the device has at least one of failed or physically changed by comparing the first and second values for the plurality of device parameters.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

Apparatus, system, and method for graceful cache device degradation

ActiveUS8443134B2Reduce riskEasy accessMemory architecture accessing/allocationProgram synchronisationRisk levelData loss

Apparatuses, systems, and methods are disclosed for implementing a cache policy. A method may include determining a risk of data loss on a cache device. The cache device may comprise a non-volatile storage device configured to perform cache functions for a backing store. The cache device may implement a cache policy. A method may include determining that a risk of data loss on the cache devices exceeds a threshold risk level. A method may include implementing a modified cache policy for the cache device in response to the risk of data loss exceeding the threshold risk level. The modified cache policy may reduce the risk of data loss below the threshold level.

Owner:SANDISK TECH LLC

Systems and methods for device degradation determination and resolution by event occurrence recordation and timing analysis

A method and apparatus for determining the cause of degradation in a product or device. A reference time is established and recorded, then a process or function of the device or product is enabled. As anomalous events occur, a user actuates an actuator that causes the recordation of an event time with respect to the reference time. Events may be repetitive or non-repetitive. At completion of the function, the recorded times are compared to a table of known product or device cycle function times, and a correlation is made to determine the most likely cycle function related to the events recorded. This information can then be correlated to parts previously known to operate at such times thereby providing a diagnostic tool useful in maintenance or repair of the device or product.

Owner:HEWLETT PACKARD DEV CO LP

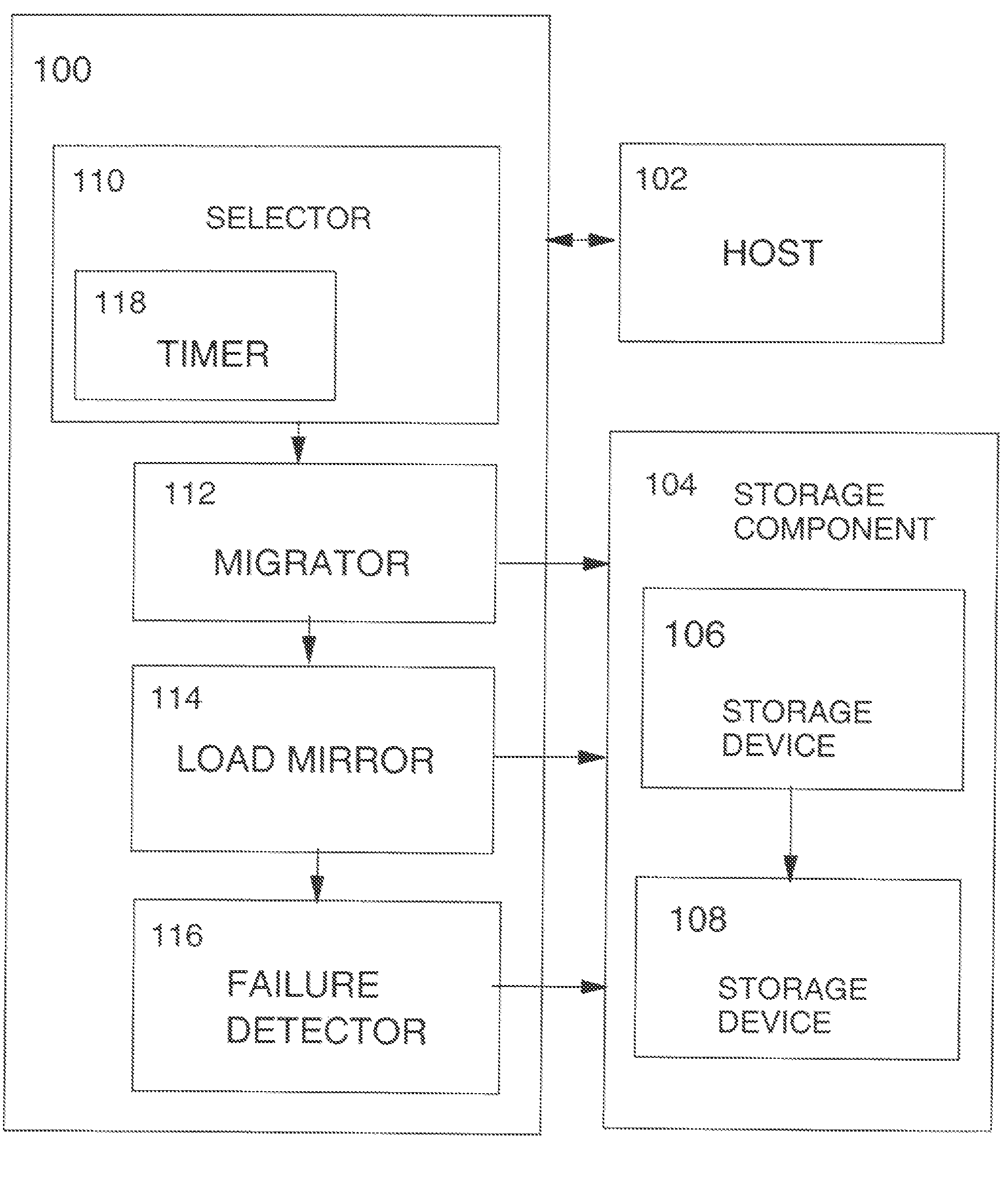

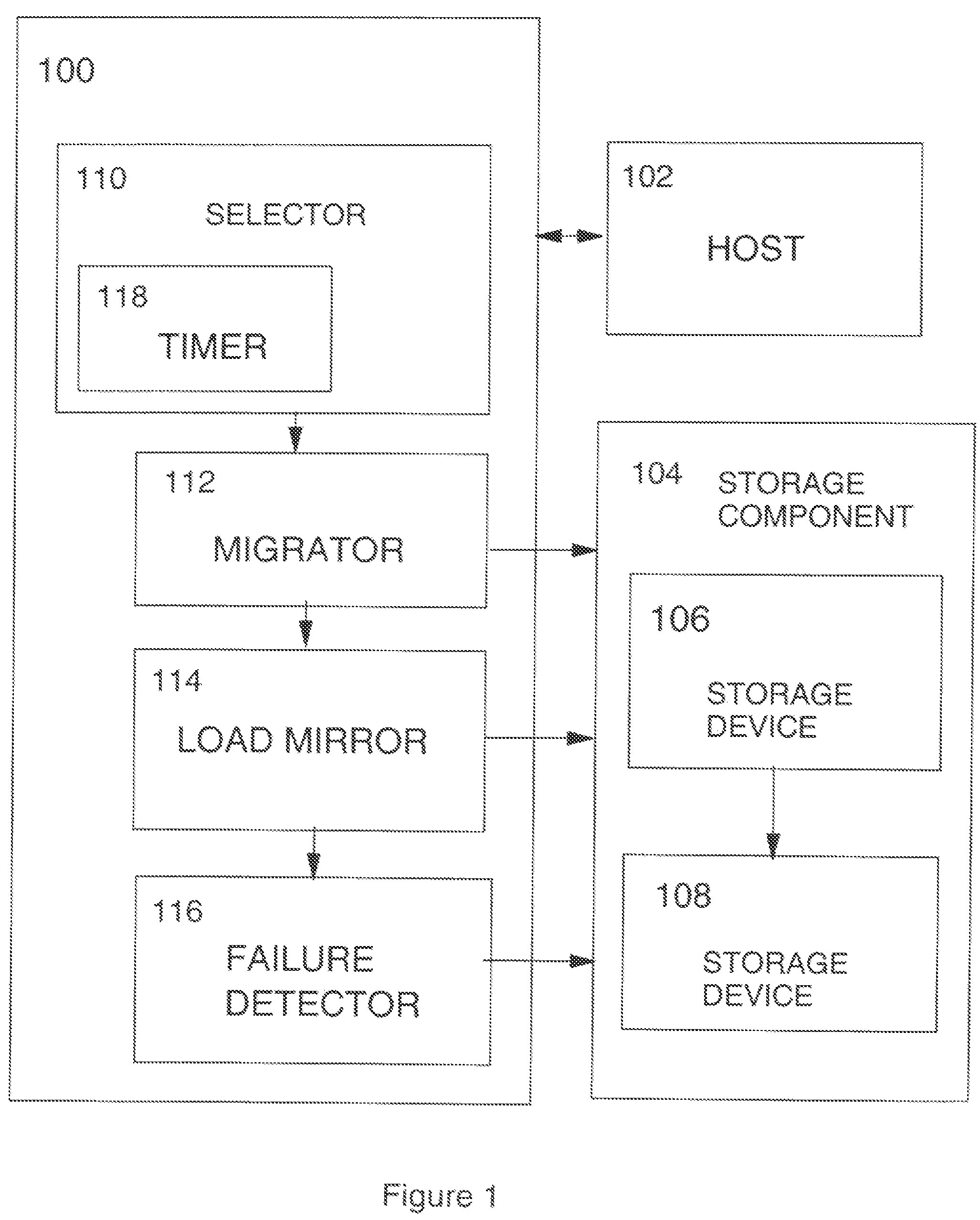

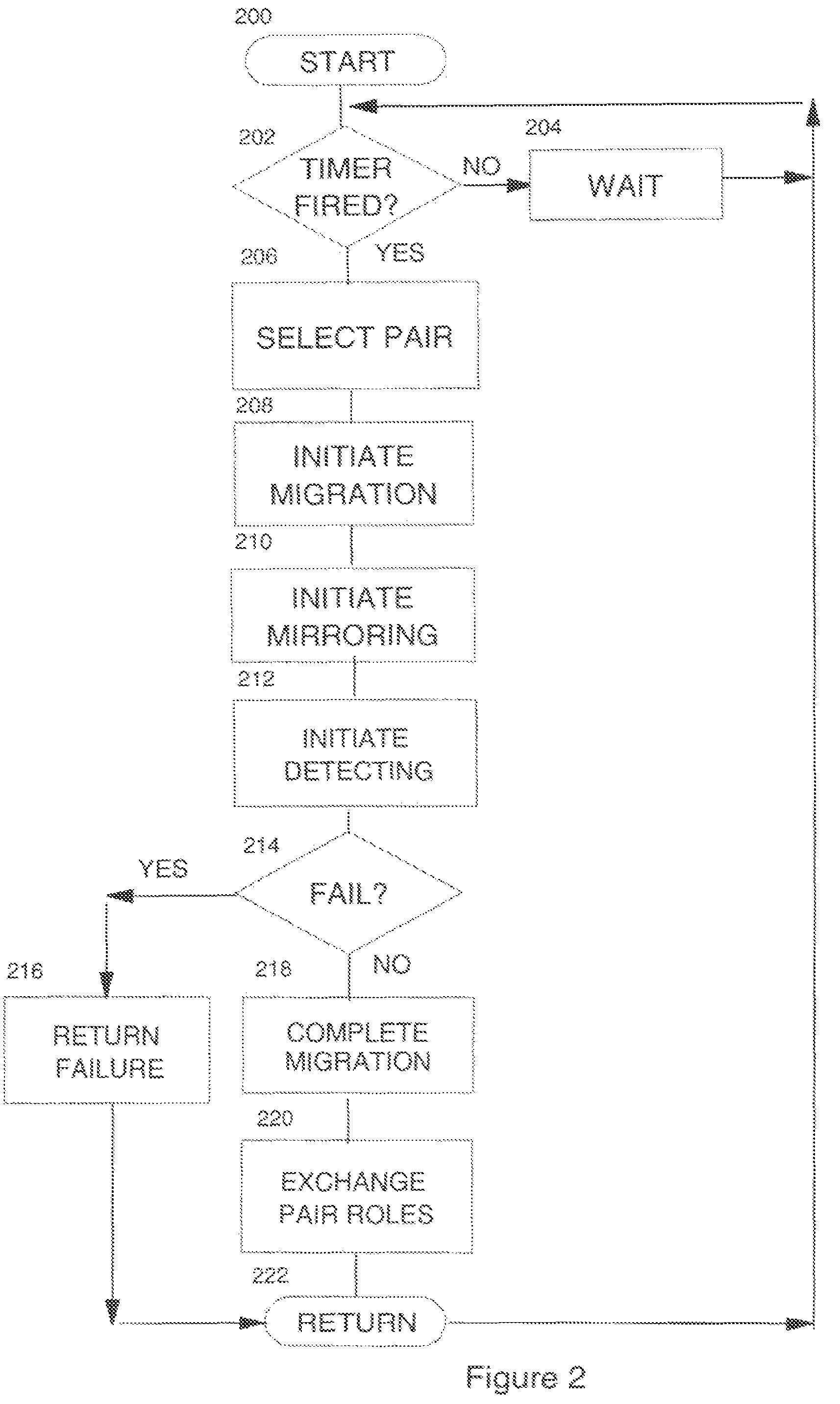

Early detection of storage device degradation

An apparatus operable with a host and a data storage component for detecting a storage device susceptible to failure under I / O workload is provided. The apparatus includes a selector component for selecting a pair of storage devices in the data storage component. A data migration control component is provided for initiating migration of data from a first to a second storage device of the pair of storage devices. An I / O workload mirroring component is provided for mirroring an I / O workload from a first of the pair of storage devices to a second of the pair of storage devices. A storage device failure detecting component for detecting failure of one of the pair of storage devices is also included. The selector component further comprises a timer component for periodically initiating the selecting.

Owner:INT BUSINESS MASCH CORP

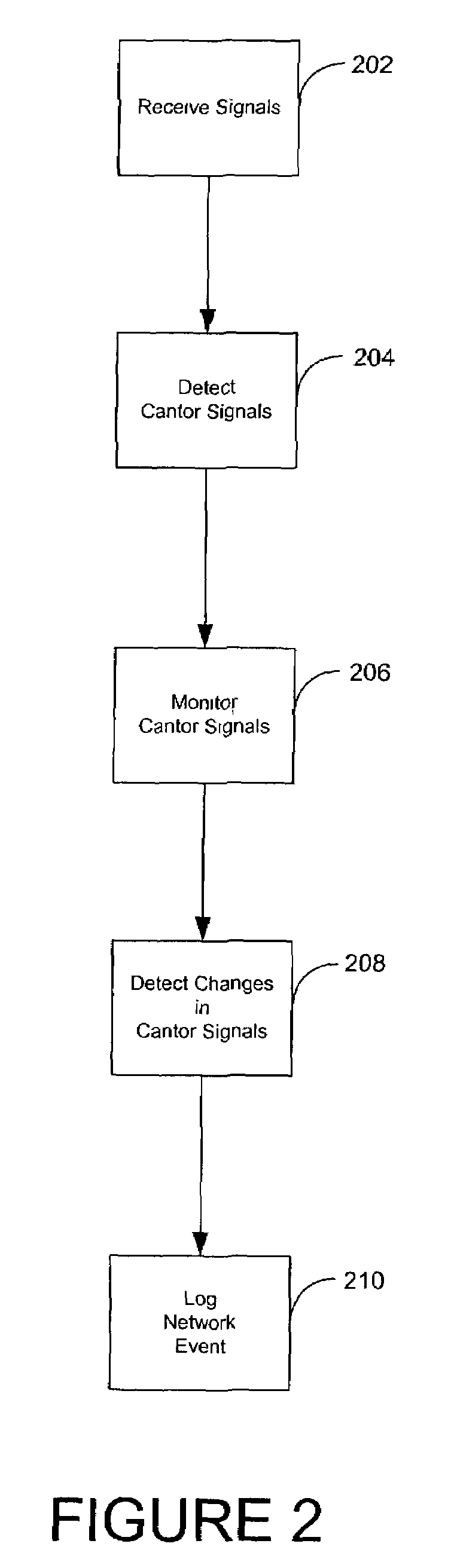

Network system health monitoring using cantor set signals

InactiveUS7283480B1Error preventionFrequency-division multiplex detailsState of healthNetworked system

Non-invasive systems and methods monitor network system health by monitoring signals inherently on the network. These signals are deciphered and characterized using Cantor set theory such that a signature of the network is determined. Variations in the characteristics of the reflected signals indicate a network event, such as changes in network topology often due to device degradation, system failure, or physical intrusion. The source of the reflected signals can be characterized and the location on the network identified.

Owner:LOCKHEED MARTIN CORP

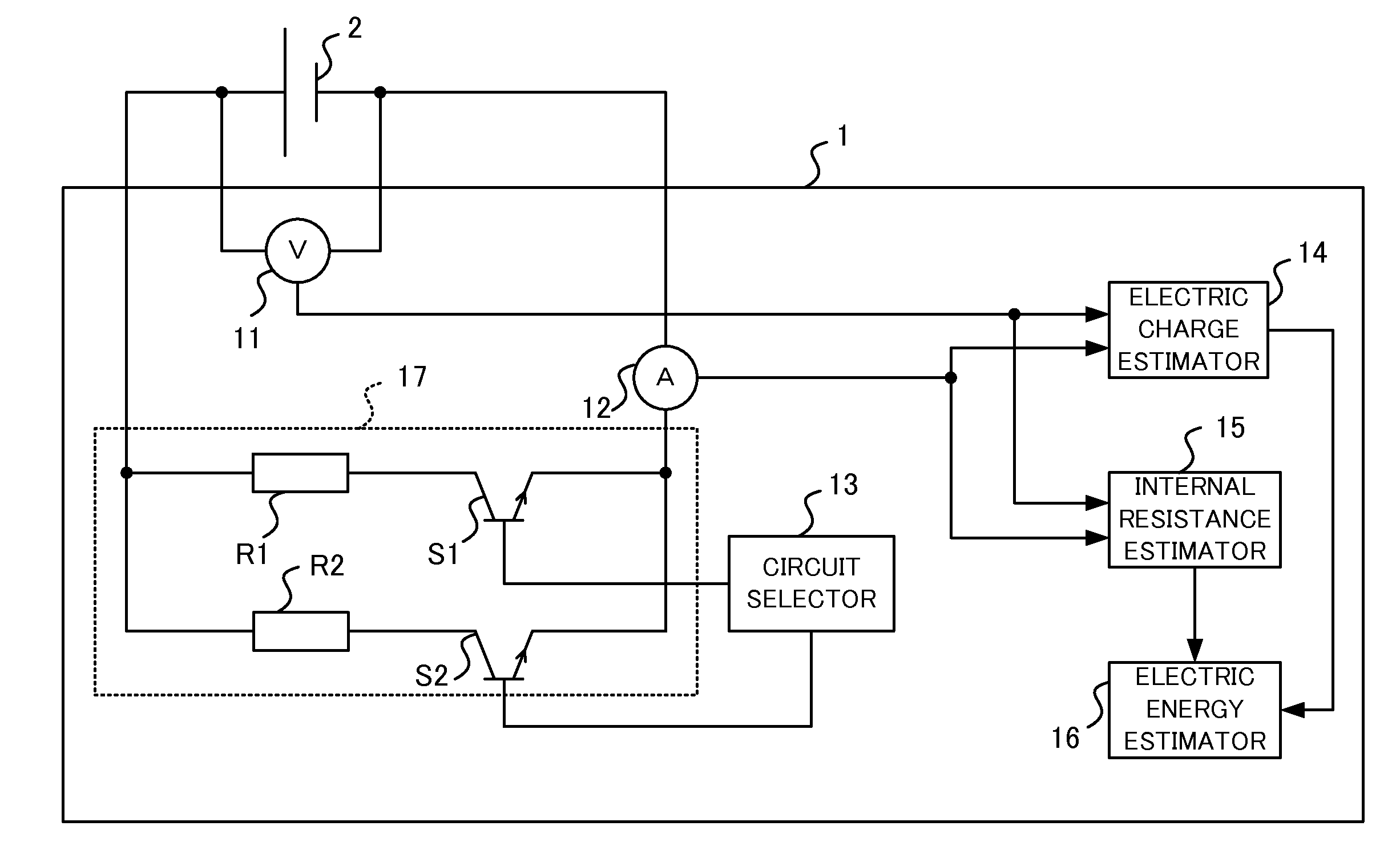

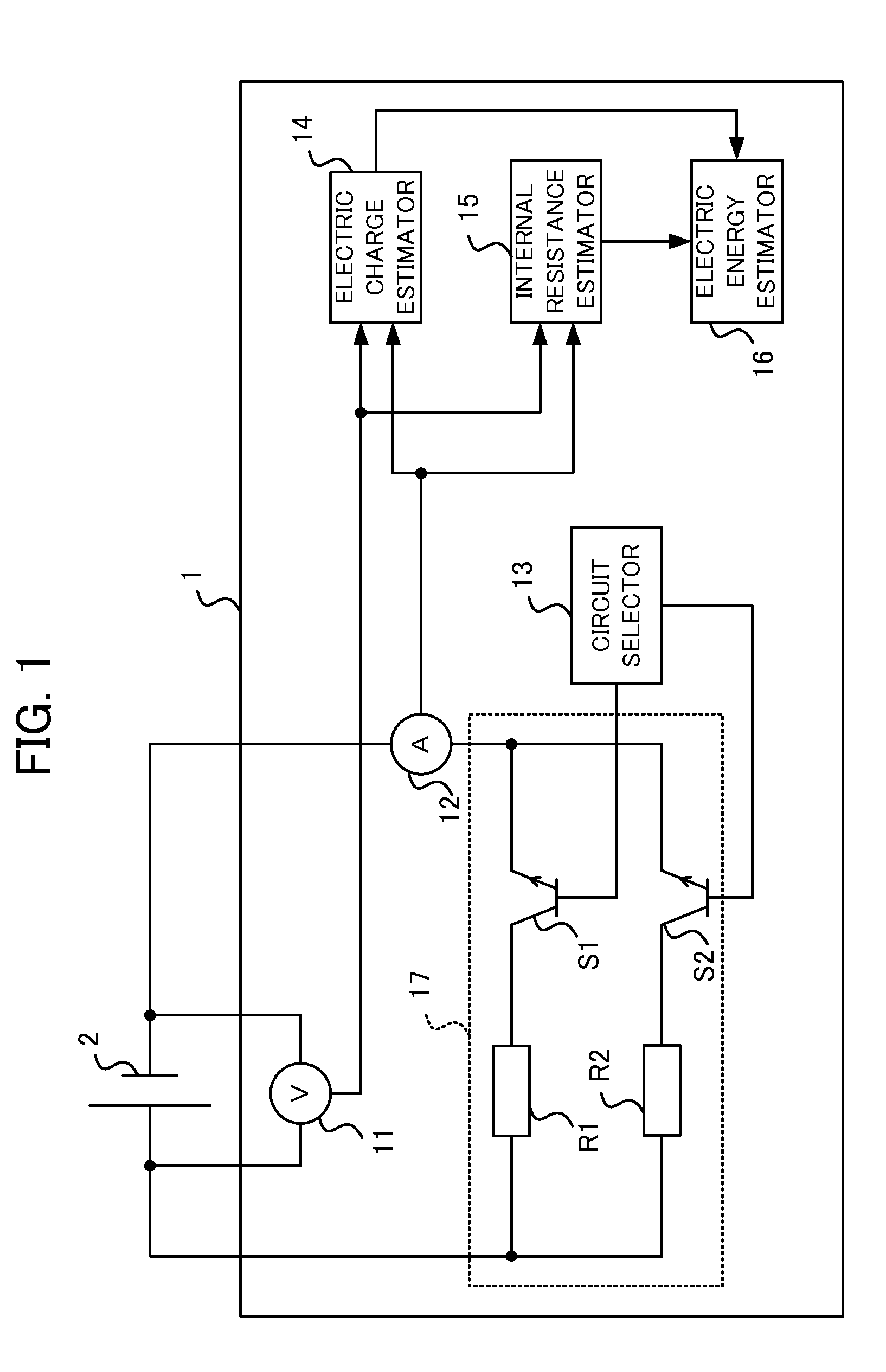

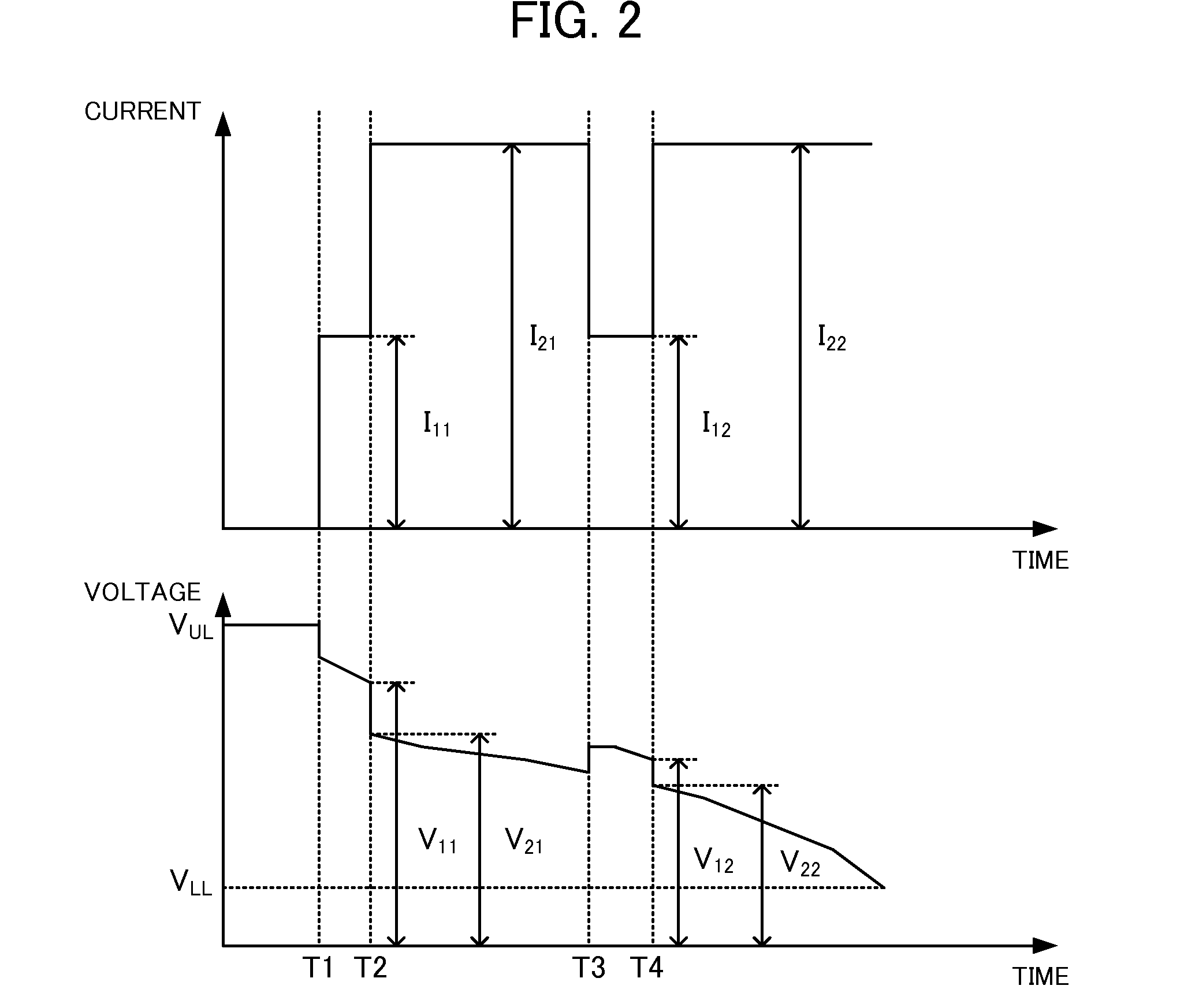

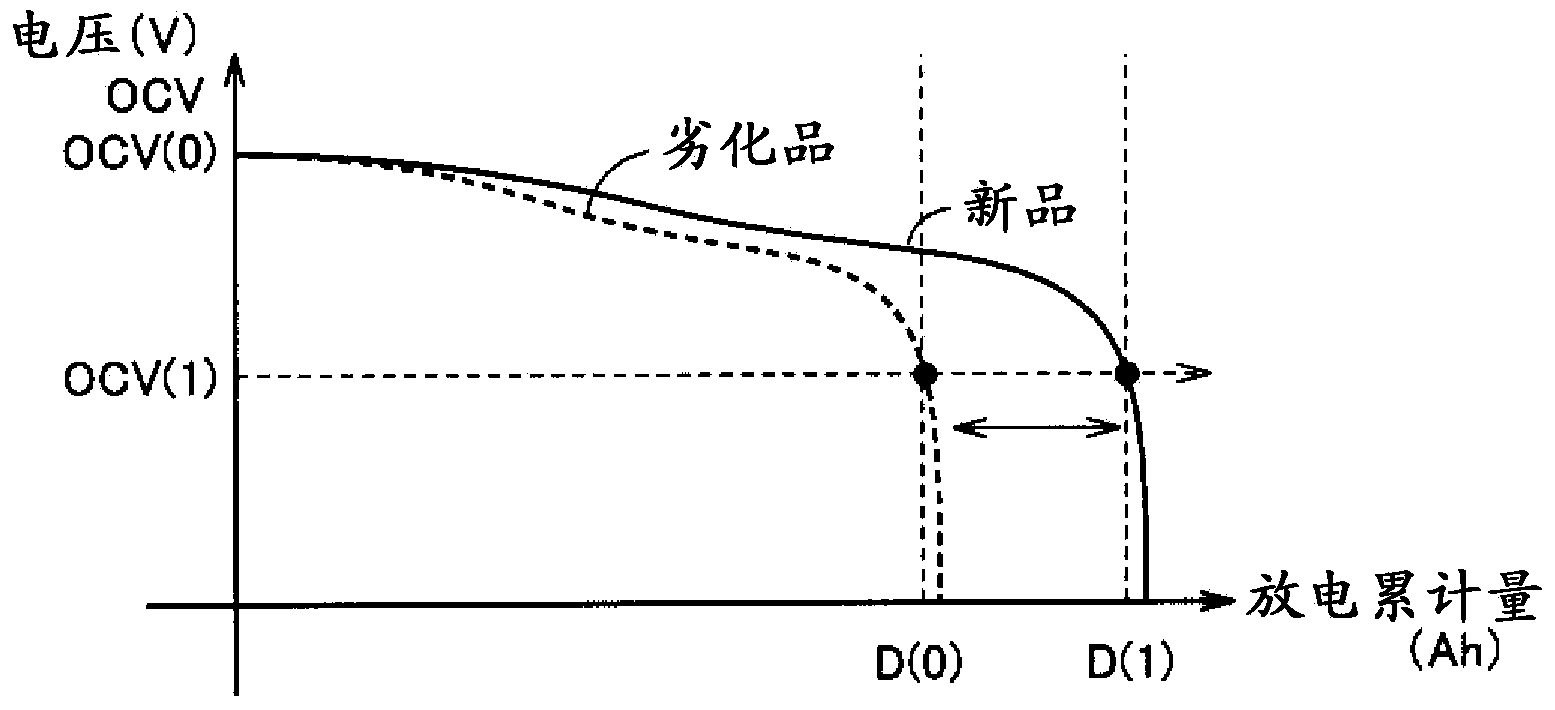

Apparatus and method for estimating power storage device degradation

ActiveUS20150369870A1Improve accuracyMaterial analysis by electric/magnetic meansElectrical testingLower limitElectrical resistance and conductance

Switches change the resistance value of a charge / discharge circuit in a period from starting a discharging at an upper limit voltage until the voltage reaches a lower limit voltage. An electric charge estimator computes electric charge by time-integrating current from a start of the discharging to an arbitrarily determined time, and computes a relationship between electric charge and voltage of a power storage device. An internal resistance estimator computes internal resistance based on voltages and currents of the storage device at times when resistance values are different. An electric energy estimator computes a relationship between electric charge and open voltage based on electric charge, voltage, current and internal resistance of the storage device. During charging or discharging of the storage device, the electric energy estimator estimates the electric energy of the power storage device based on the electric charge, the open voltage, the internal resistance, and the charge / discharge current.

Owner:MITSUBISHI ELECTRIC CORP

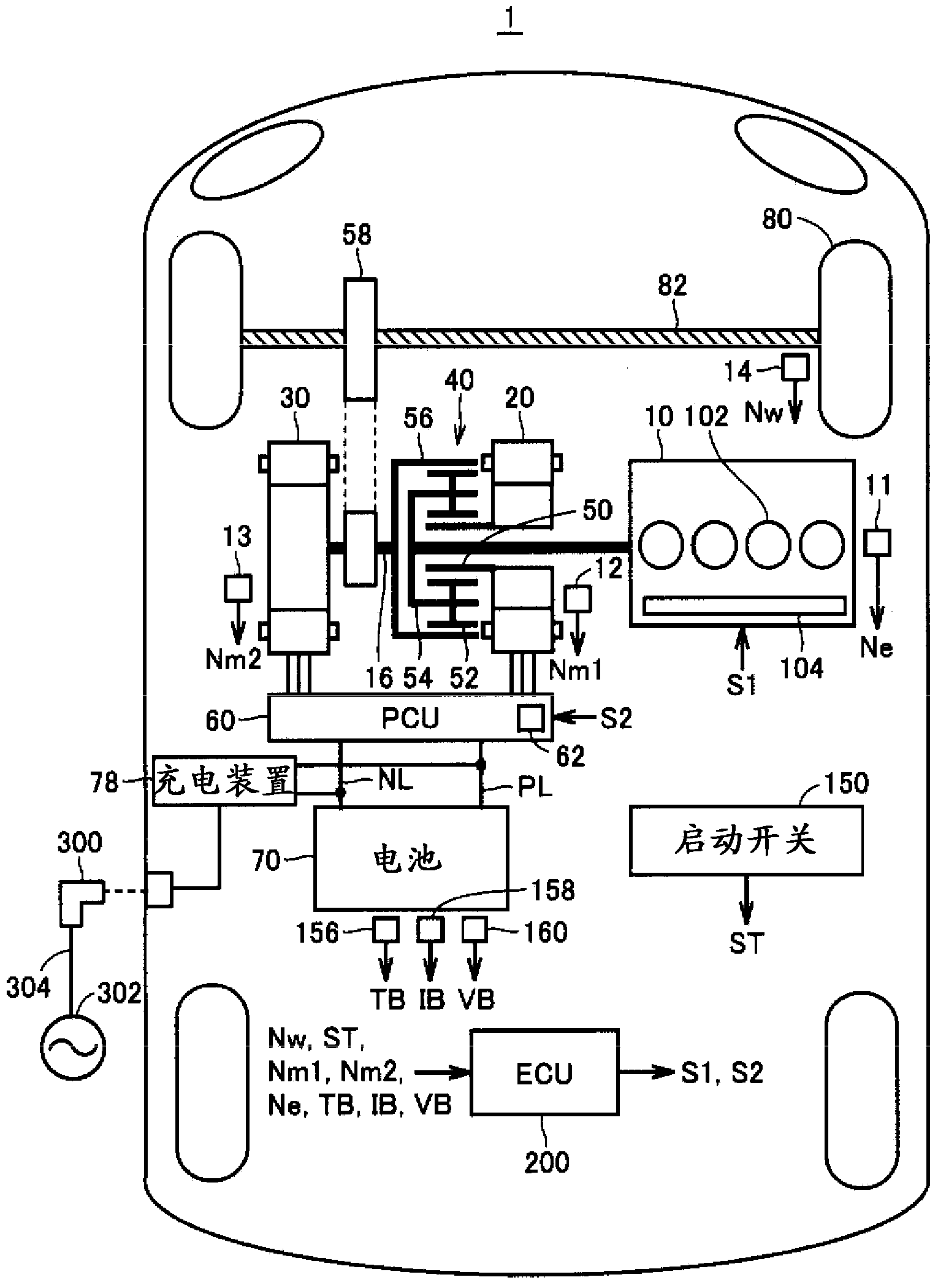

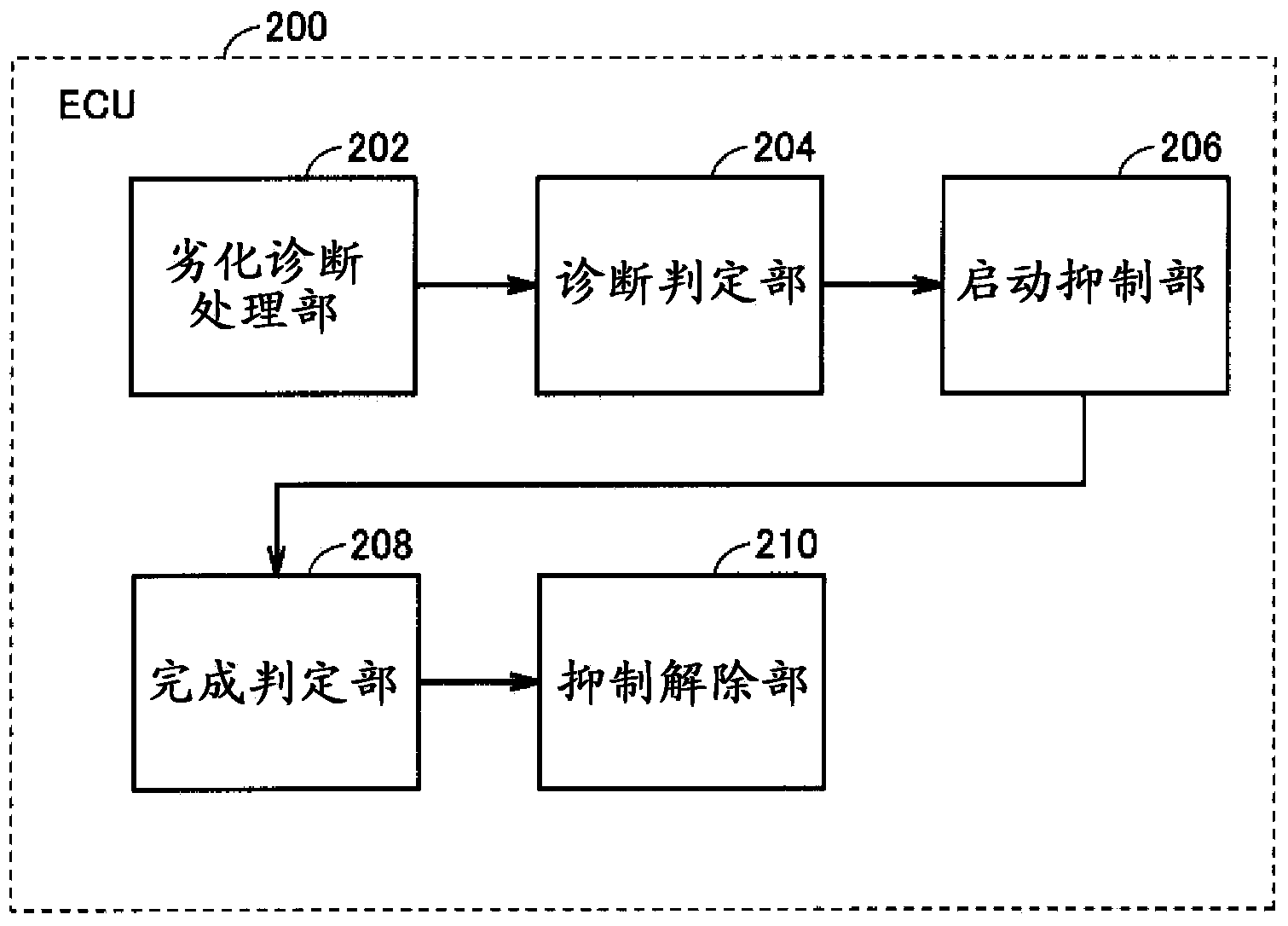

Vehicle and method for diagnosing battery device degradation

ActiveCN103415428ASuppresses voltage fluctuationsAccurate diagnosisHybrid vehiclesPropulsion using engine-driven generatorsEngineeringDiagnostic methods

Owner:TOYOTA JIDOSHA KK

Integrated fuel catalyst monitor

ActiveUS8756915B2Reduce capacityLow efficiencyElectrical controlInternal combustion piston enginesProcess engineeringOxygen

Owner:FORD GLOBAL TECH LLC

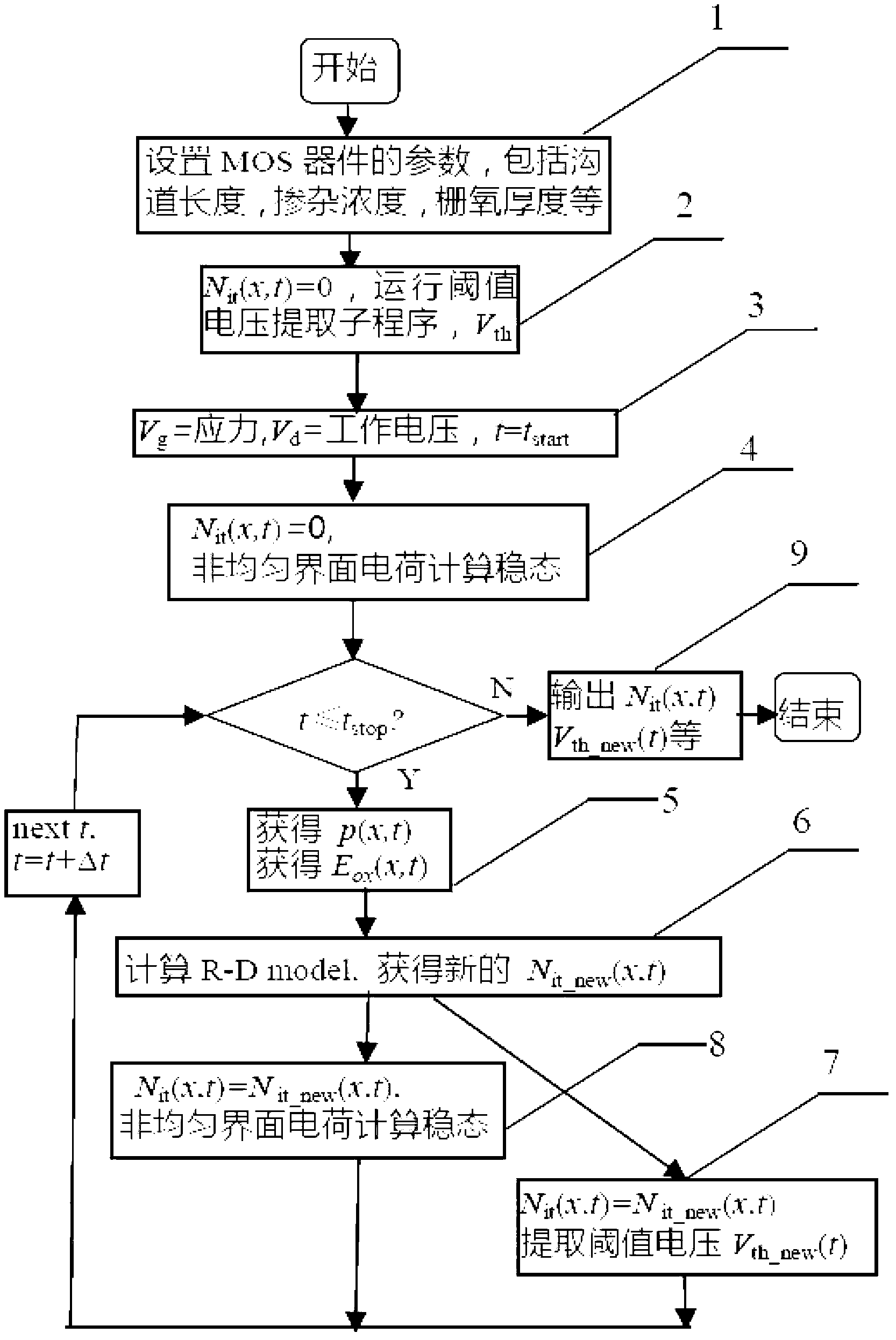

Numerical simulation method and system of MOS device inhomogeneous interface degeneration electric charges

The invention is applicable to the technical field of MOS devices, and provides a numerical simulation method and system of MOS device inhomogeneous interface degradation electric charges. The ground floor of software is modified, a functional model for calculating the number of the inhomogeneous interface electric charges Nit (x,t) is added, and therefore numerical simulation of influences of the inhomogeneous interface electric charges on device performance can be achieved. An interface electric charge degradation model interface is further added for achieving the numerical simulation method, and therefore the numerical simulation on the inhomogeneous interface electric charges caused by various effects can be achieved. A device parameter extraction interface is further added for achieving the numerical simulation method, and device parameters comprising threshold voltage, output characteristics, transconductance, electrons, hole concentration distribution, potential distribution, electric field distribution and the like can be extracted. According to a degradation model of an NBTI, unique change rules of the pure polarization NBTI effect under HCI stress can be disclosed, the relationship between device degradation and the service life is deeply understood, the process design is guided, and the development of reliability studying of integrated circuits can be further promoted.

Owner:SHENZHEN UNIV

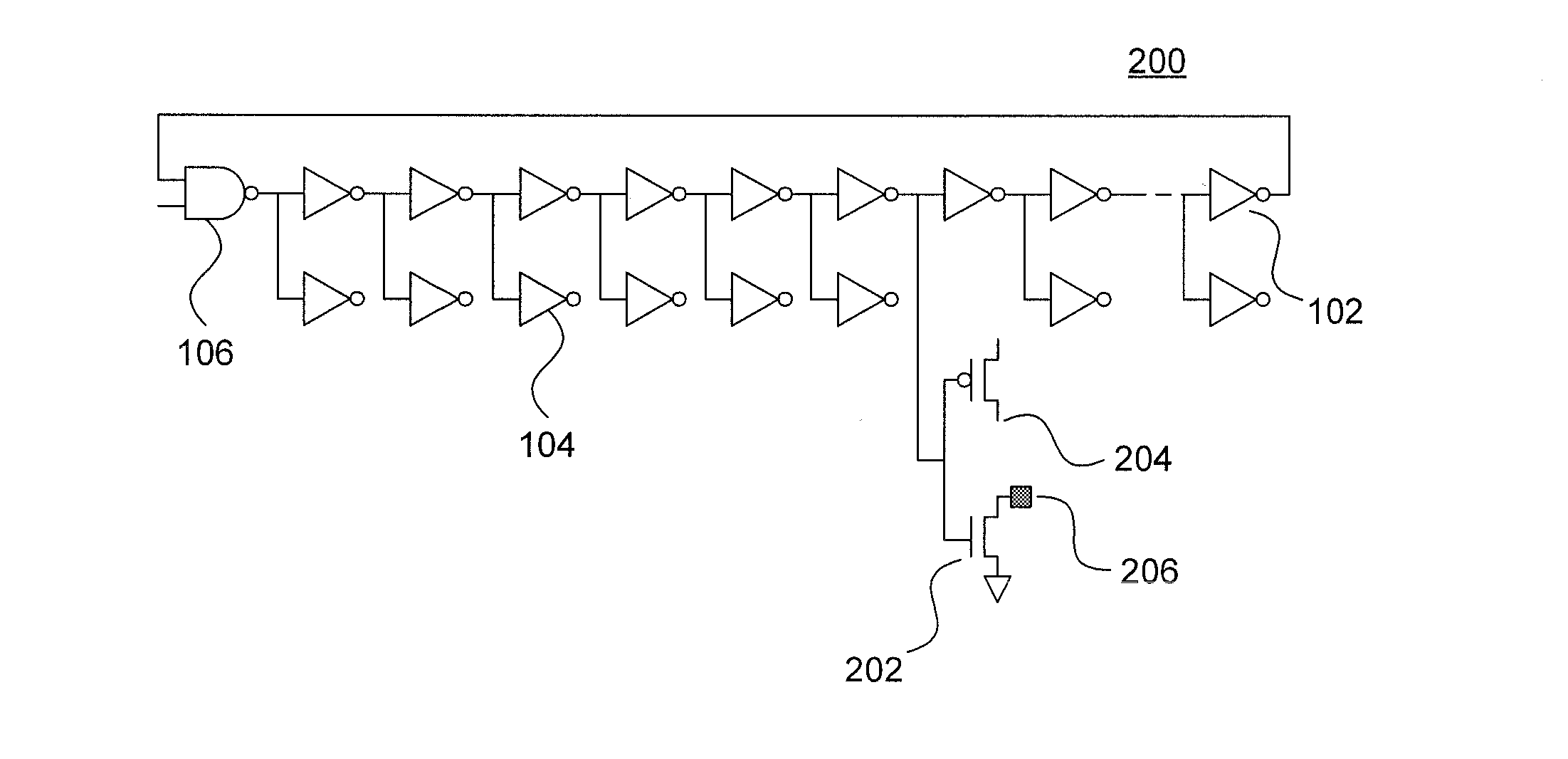

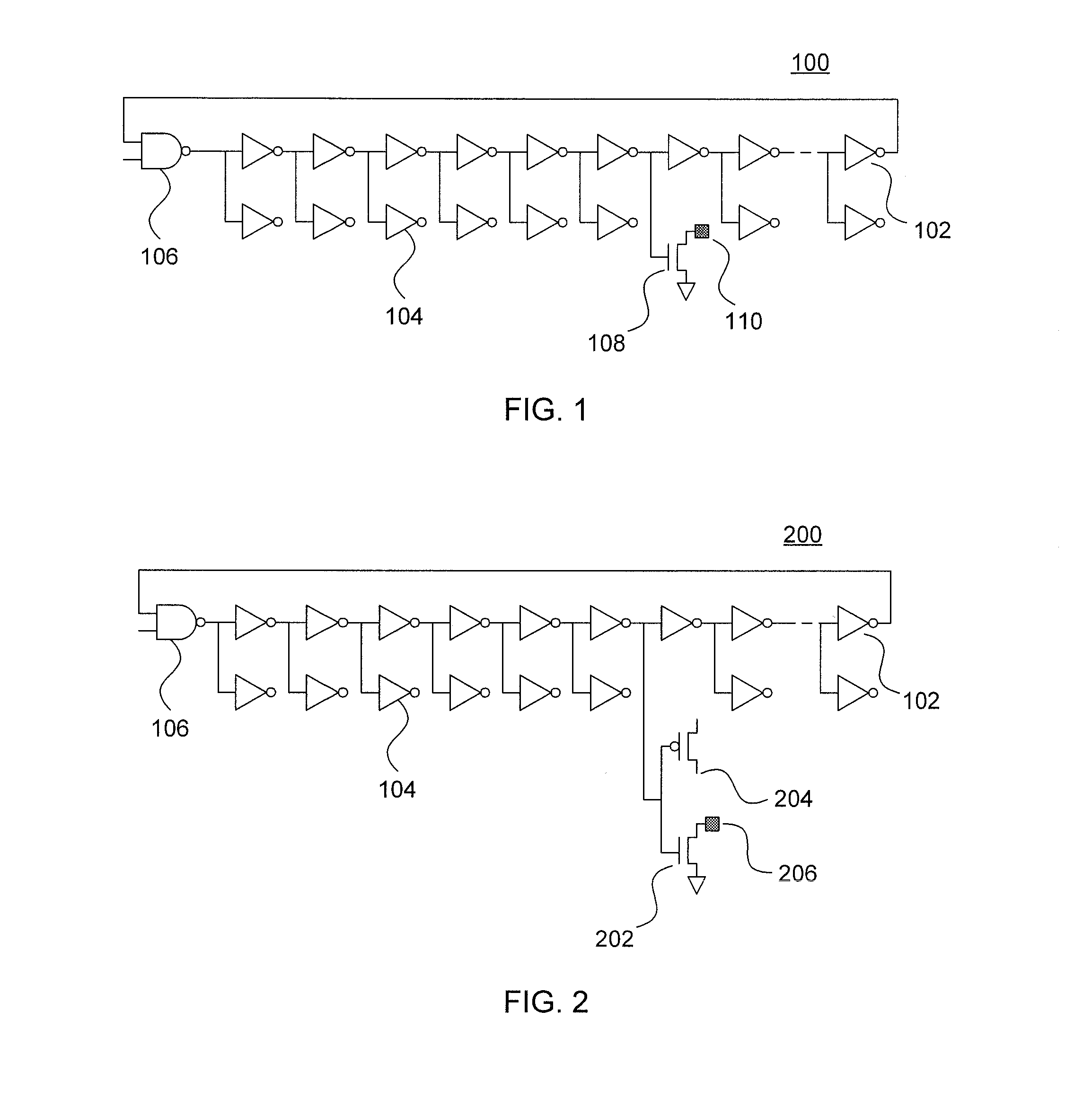

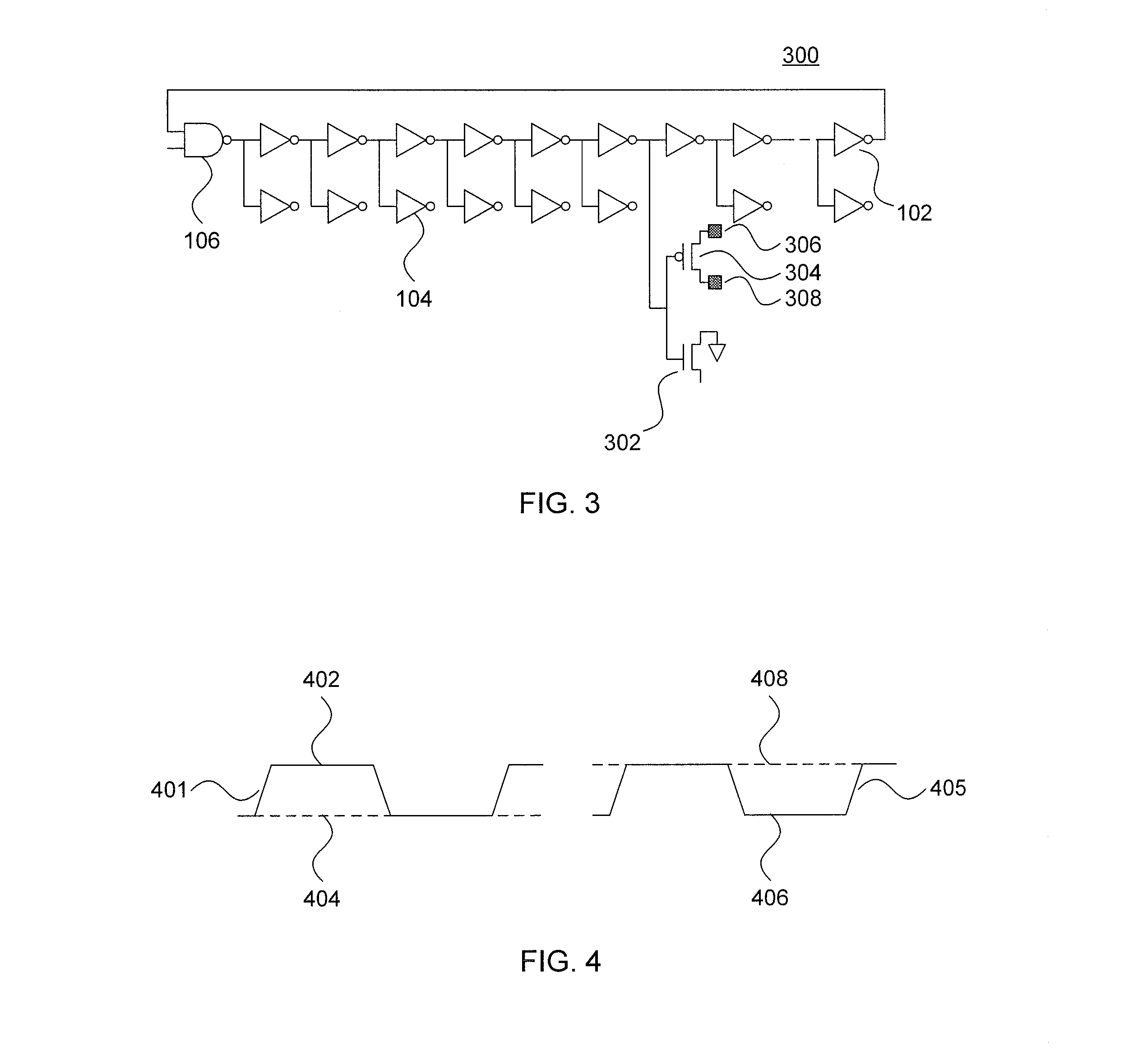

Measuring individual device degradation in CMOS circuits

Methods and systems for measuring degradation includes measuring an initial electrical characteristic of a test device in a ring oscillator that includes multiple oscillator stages, each having a delay stage and one or more fan-out devices, and a test stage having a delay stage and the test device. The ring oscillator is operated for a period of time. The electrical characteristic of the test device is measured after operating the ring oscillator. A level of degradation in the test device is determined using a processor based on the measurements of the electrical characteristic of the test device.

Owner:IBM CORP

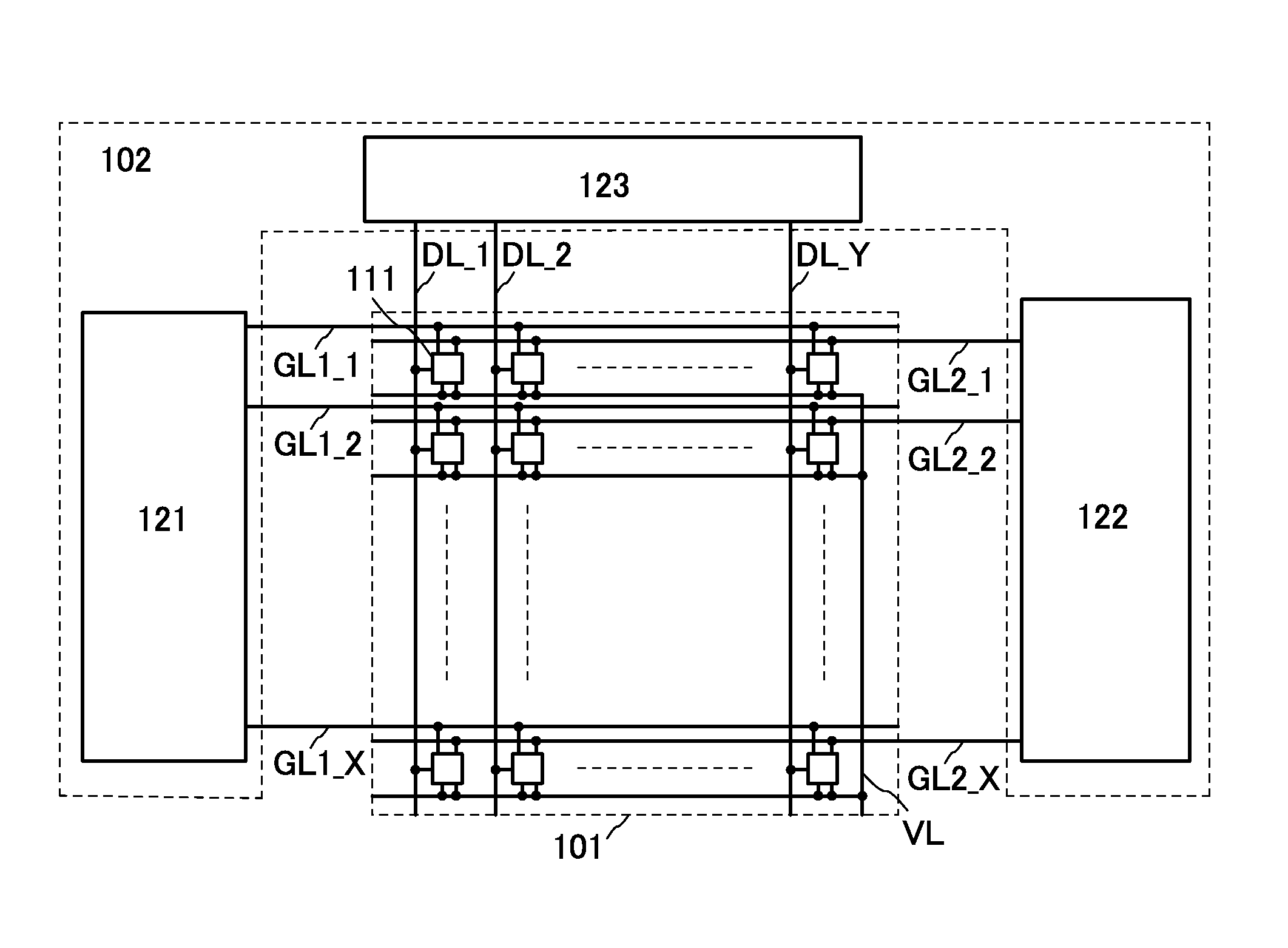

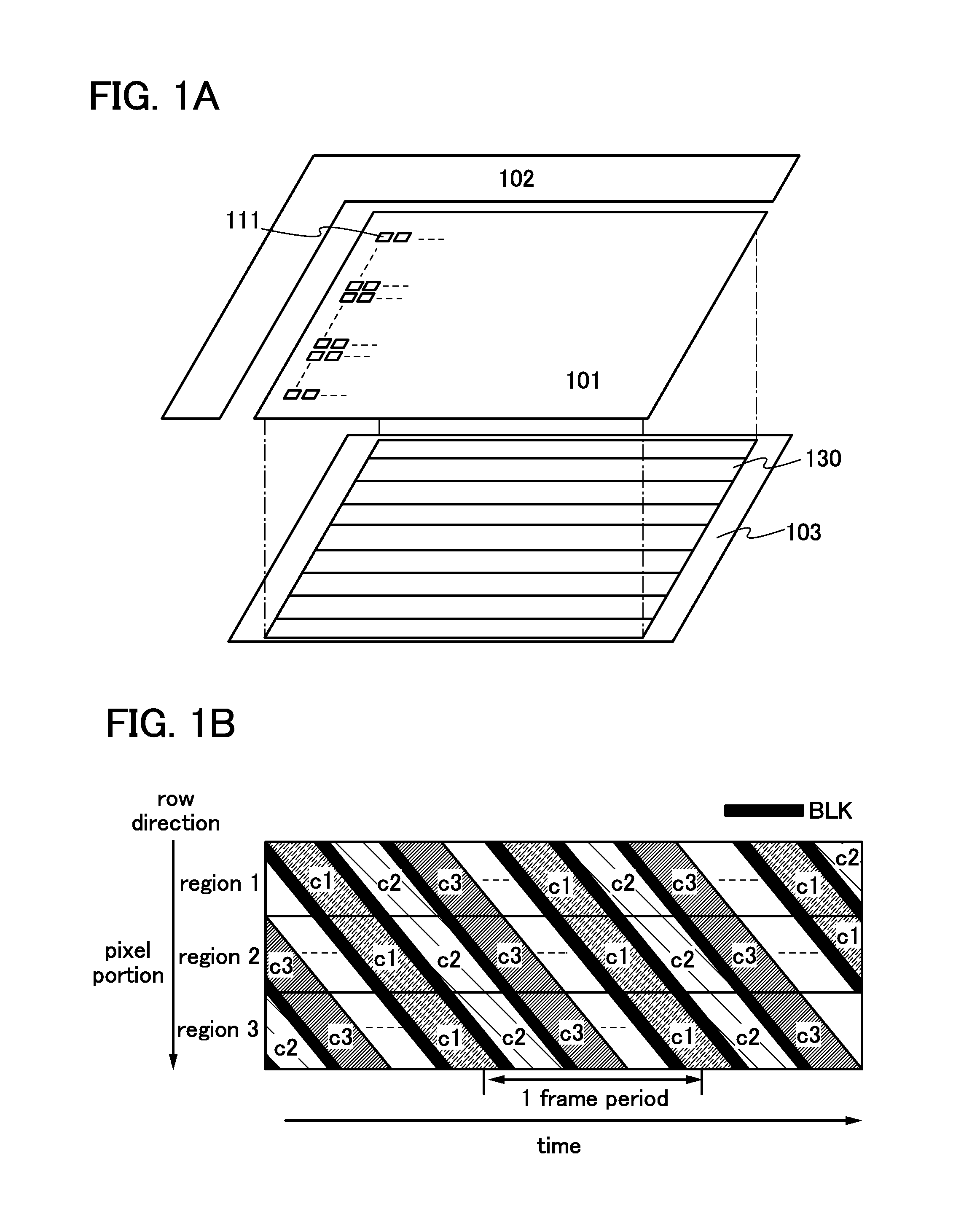

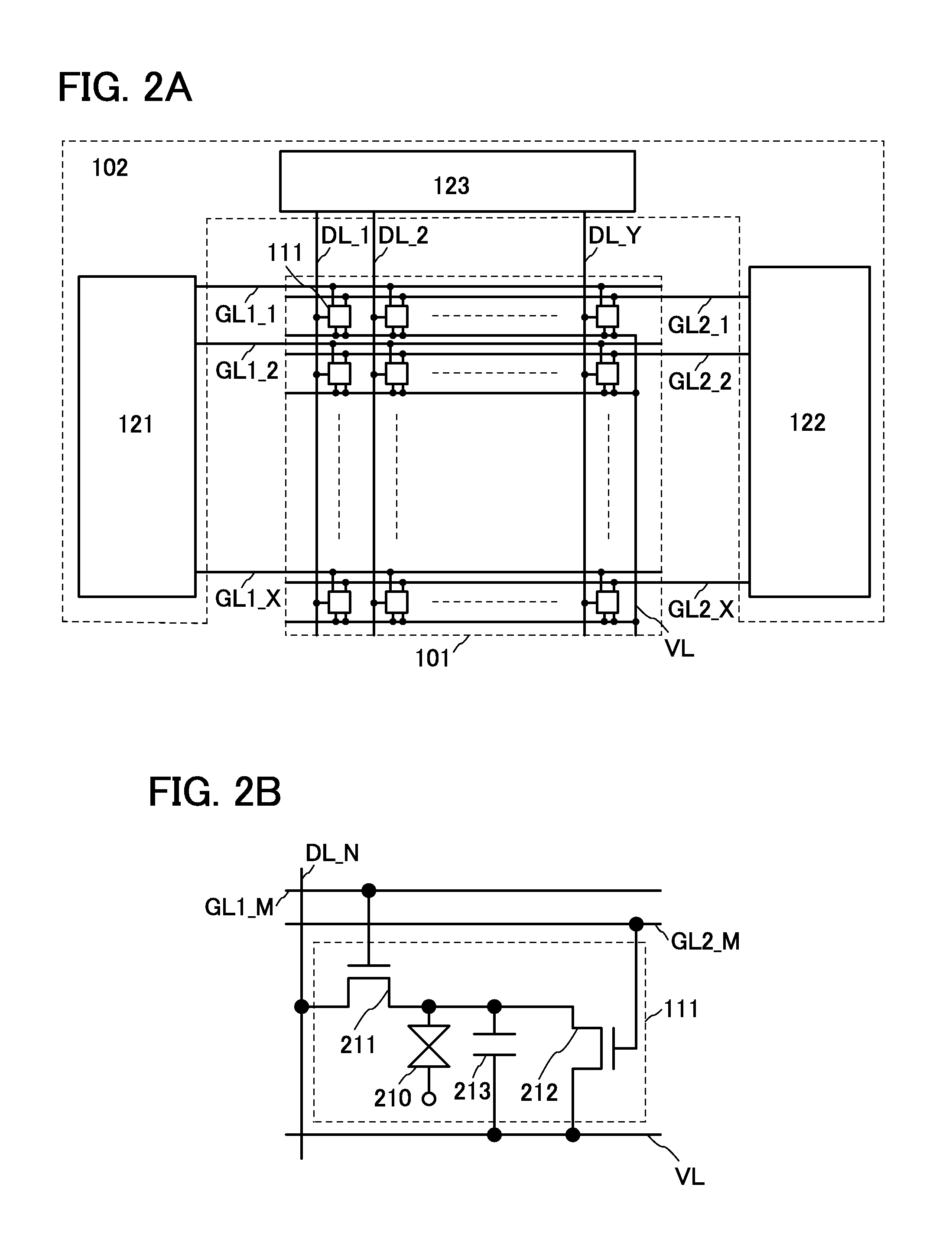

Method for driving display device, display device, and electronic device

InactiveUS20130235093A1Reduce image qualityGood colorCathode-ray tube indicatorsInput/output processes for data processingImaging qualityComputer graphics (images)

Degradation in image quality of a display image is prevented. A pixel portion which includes a plurality of pixel circuits in row and column directions is divided into a plurality of regions in the row direction. In each of the plurality of regions, operation in which data is written to the pixel circuits on a row basis and the pixel circuits to which the data is written are irradiated with light corresponding to the written data is performed a plurality of times in one frame period in such a manner that at least three single-color image data for displaying the three primary colors are written in one frame period; and black image data is written to the pixel circuits every time before any of the plurality of single-color image data is written to the pixel circuits in each of the plurality of regions.

Owner:SEMICON ENERGY LAB CO LTD

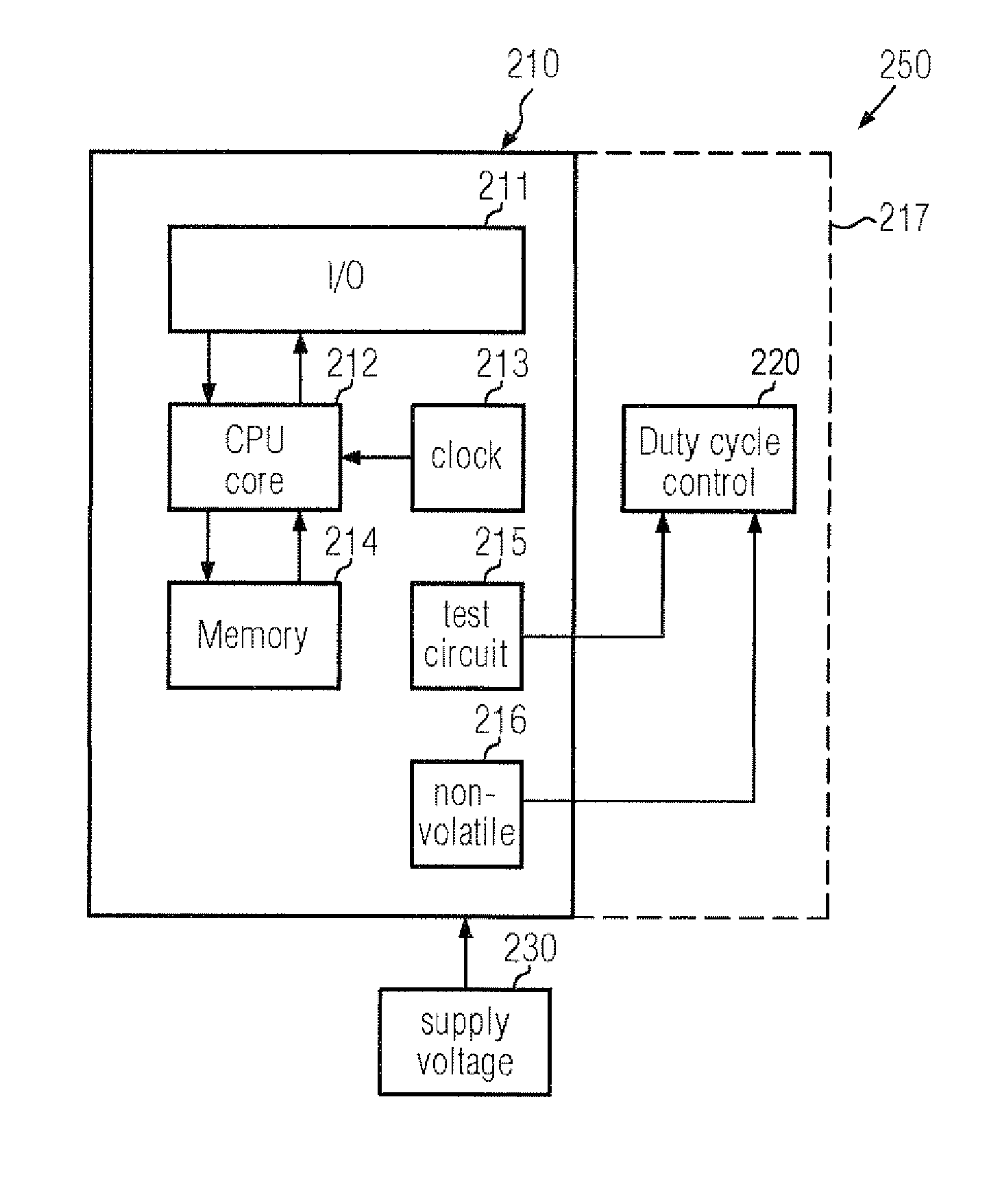

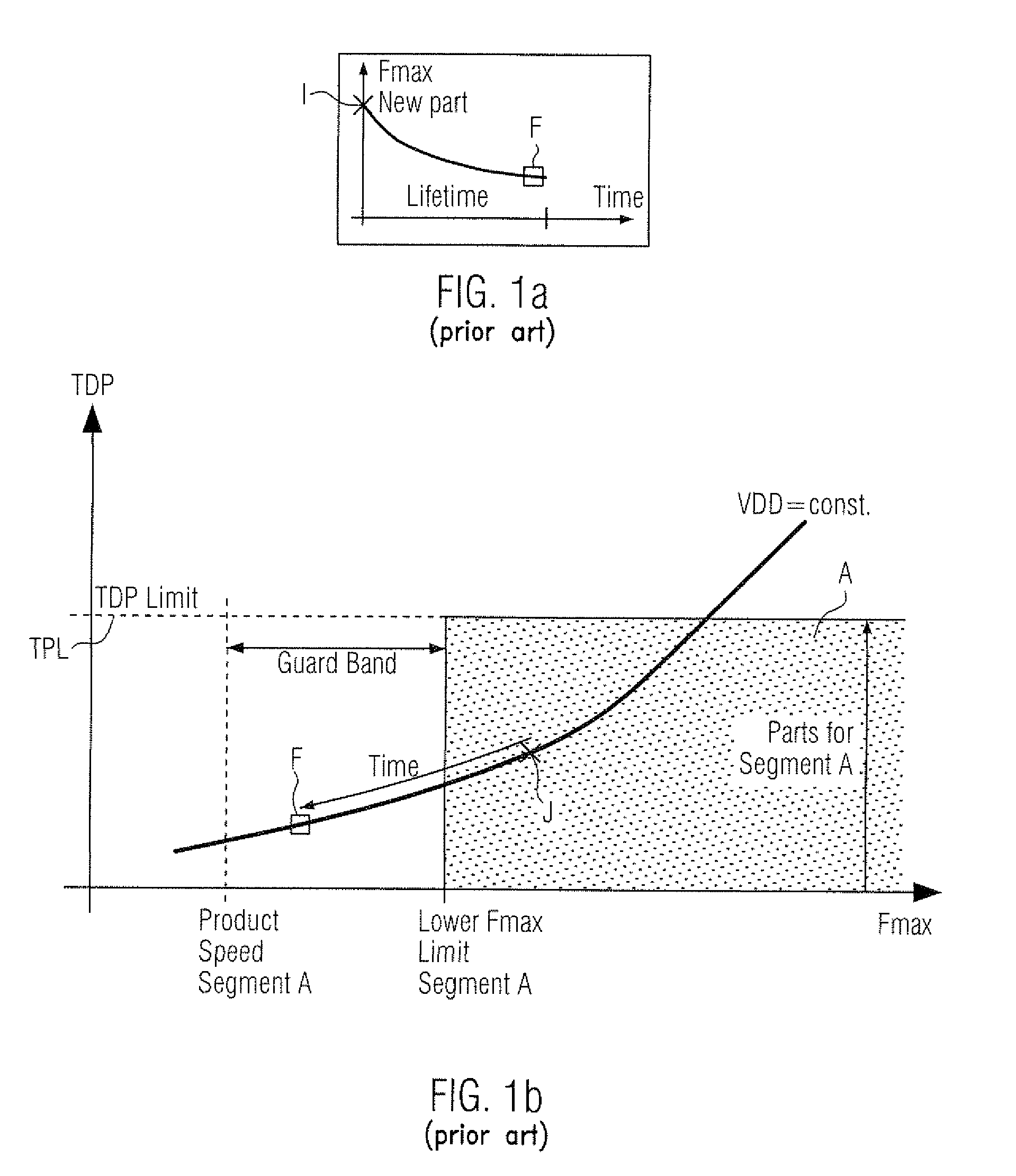

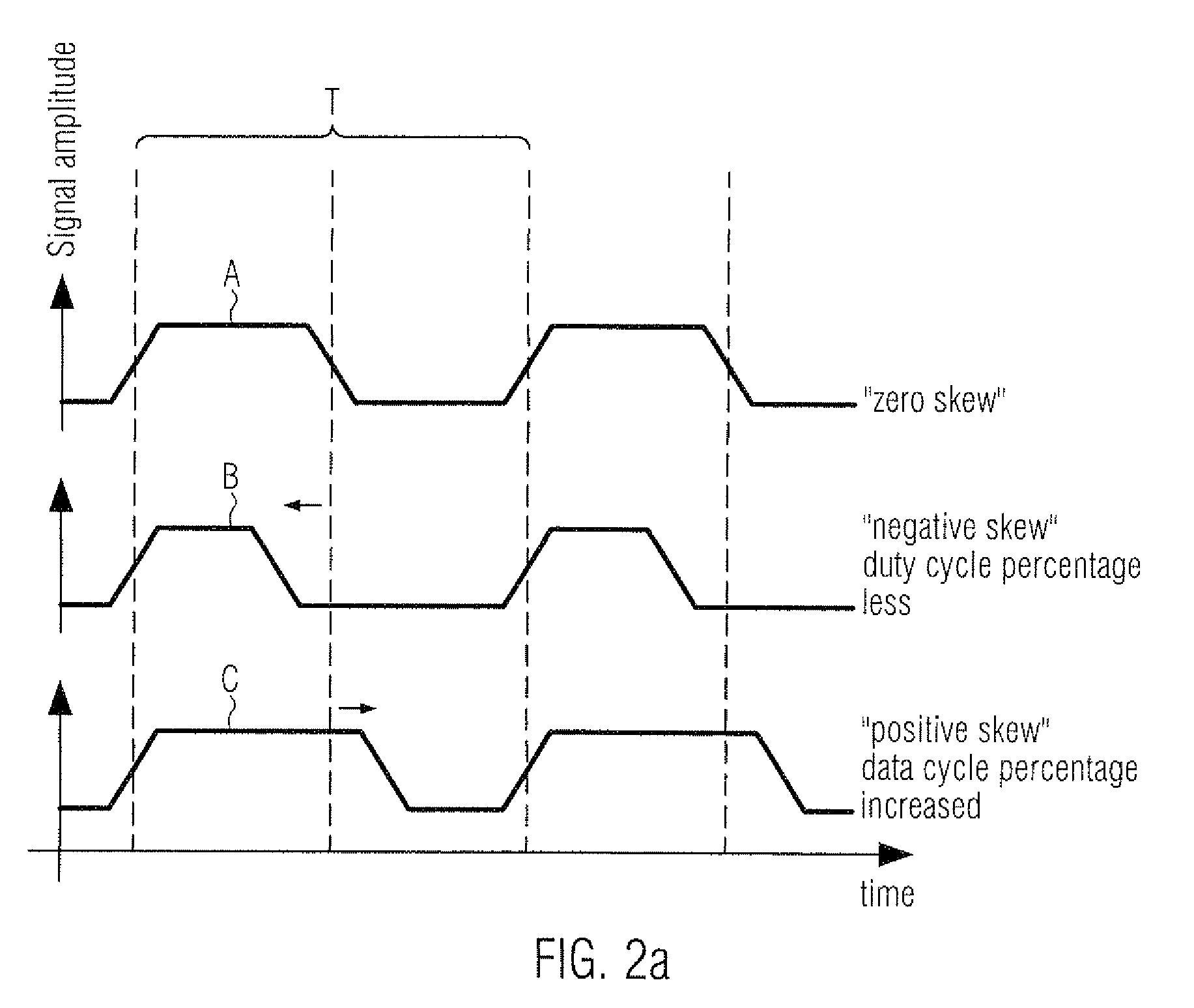

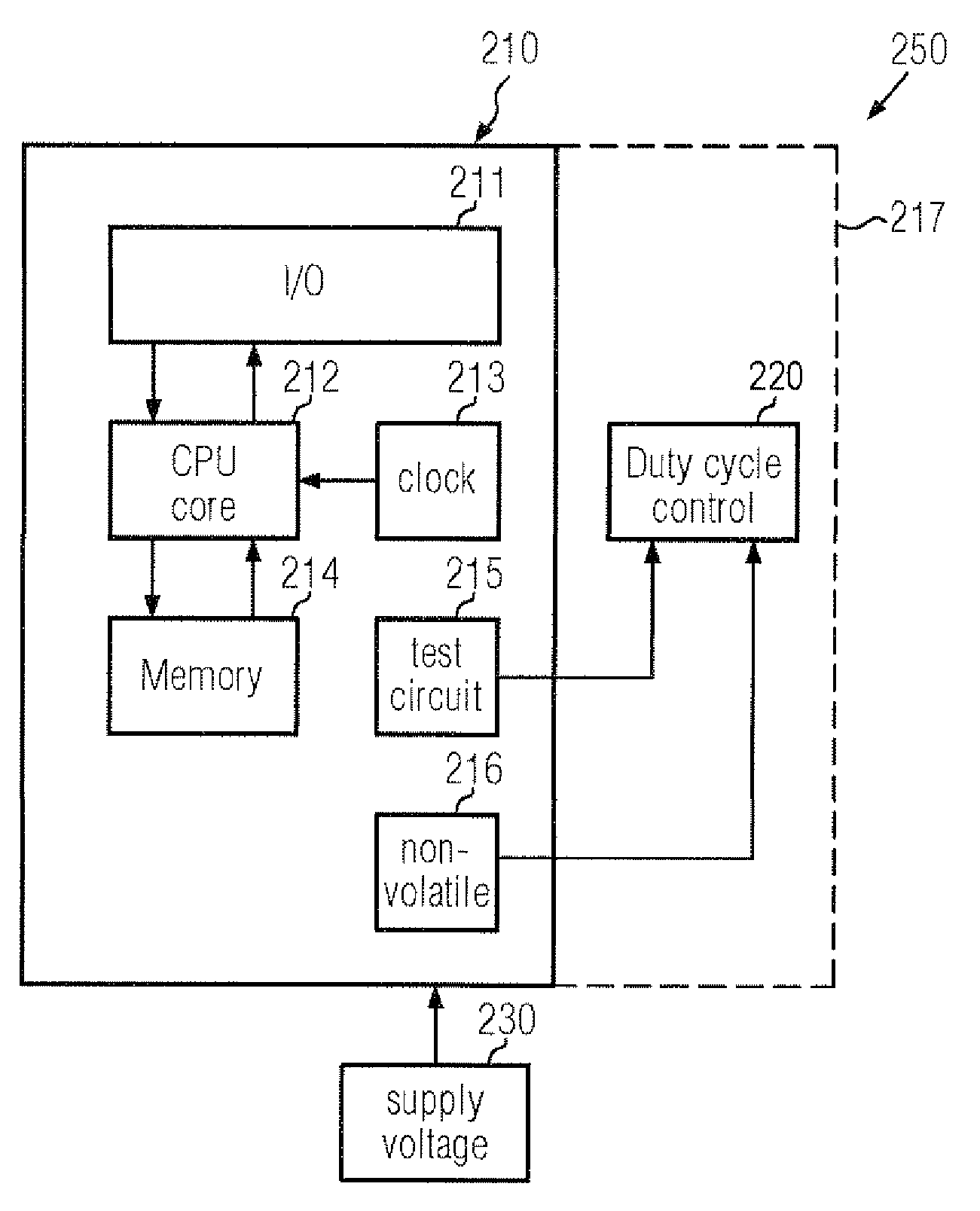

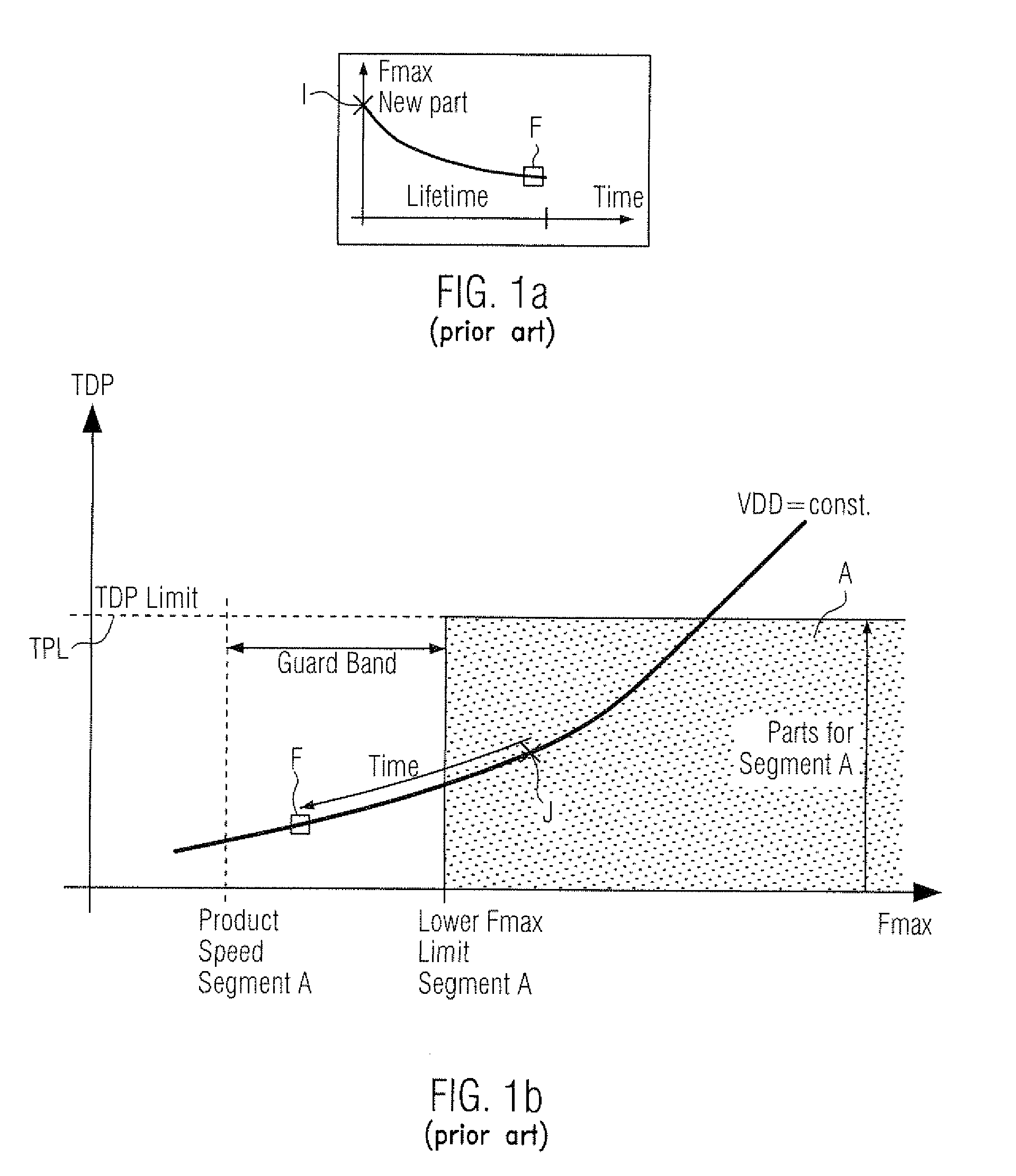

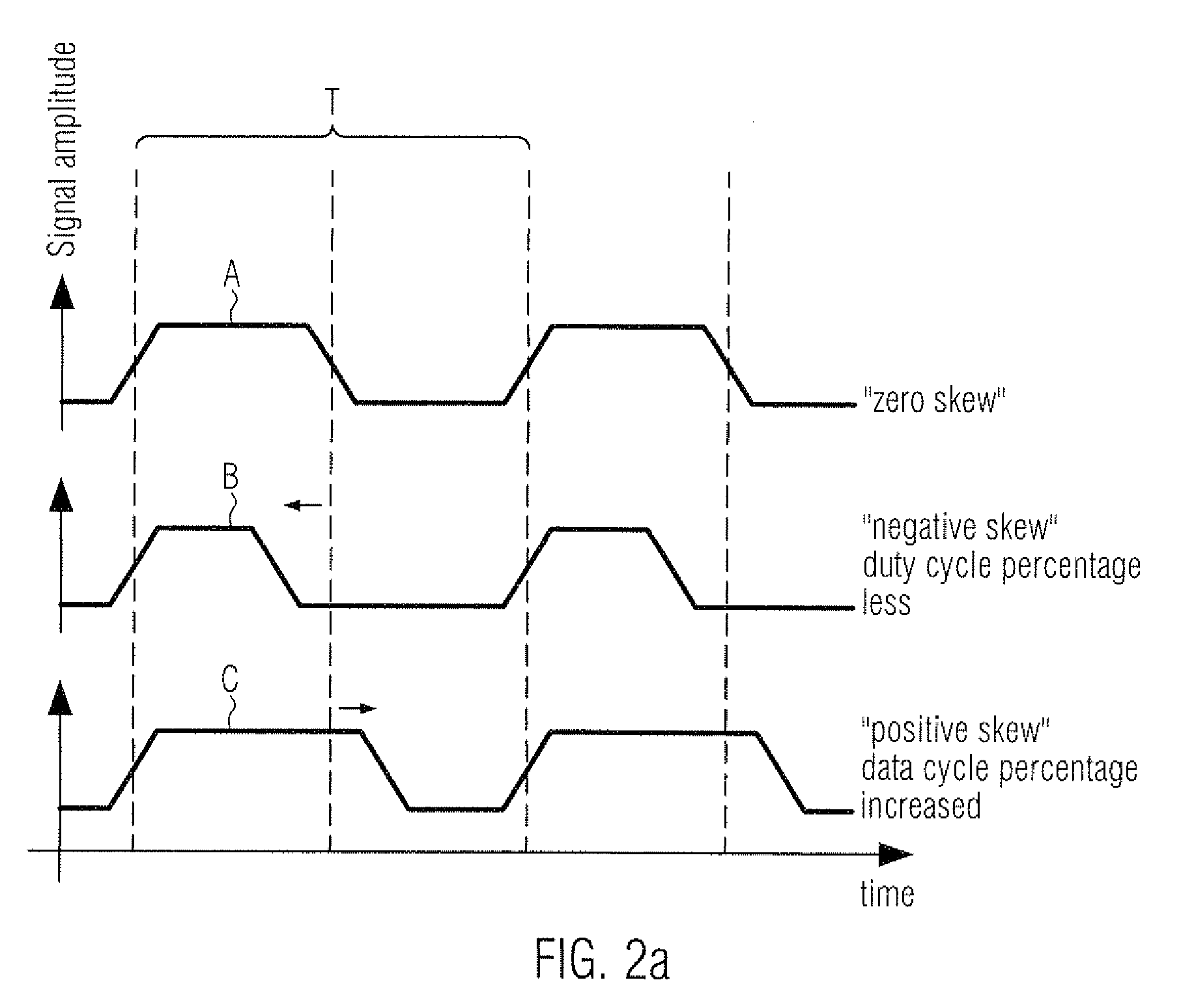

Compensation of degradation of performance of semiconductor devices by clock duty cycle adaptation

ActiveUS8018260B2Lower performance requirementsEffective control mechanismDigital circuit testingReliability/availability analysisEngineeringSelf adaptive

The device degradation of integrated circuits may be compensated for by appropriately adapting the duty cycle of the clock signal. For this purpose, a correlation between the duty cycle and the overall performance characteristics of the integrated circuit may be established and may be used during the normal field operation of the device in order to modify the duty cycle. Hence, an efficient control strategy may be implemented since the duty cycle may be efficiently controlled, while at the same time a change of clock signal frequency and / or an increase of supply voltage may not be required.

Owner:ADVANCED MICRO DEVICES INC

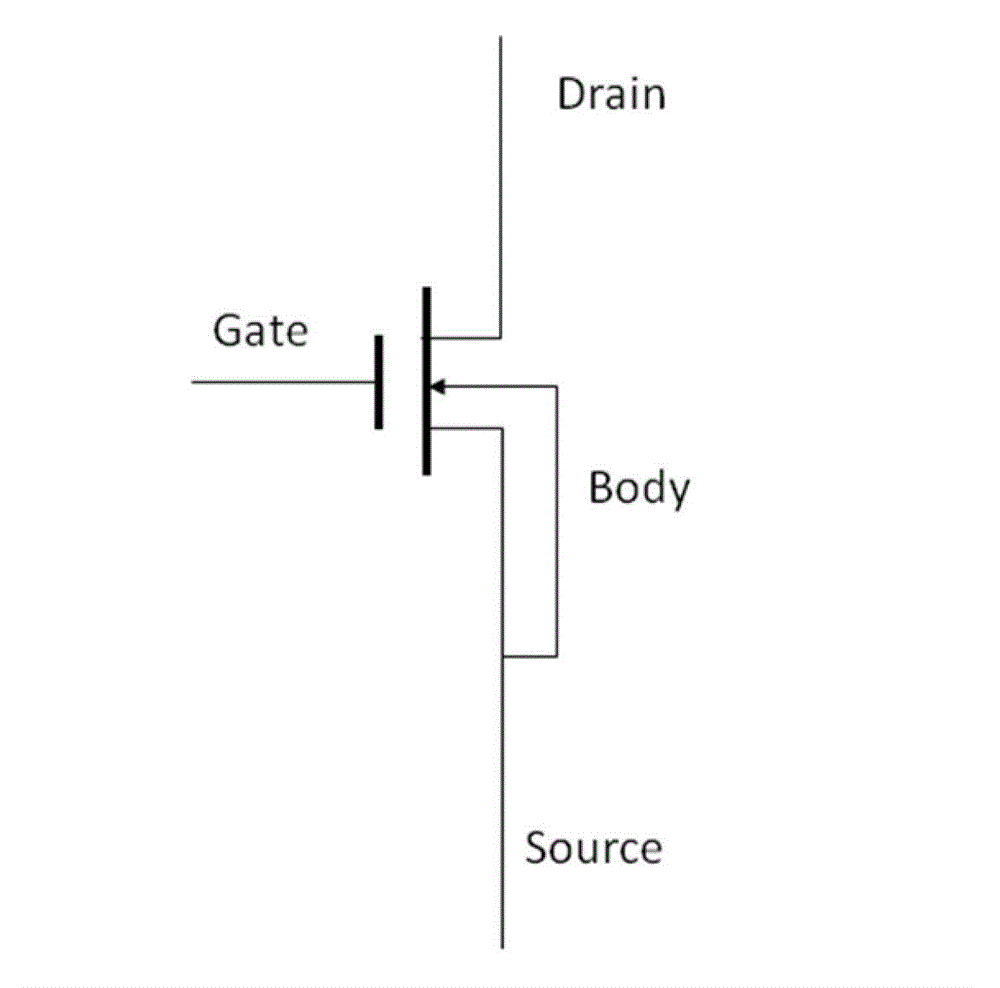

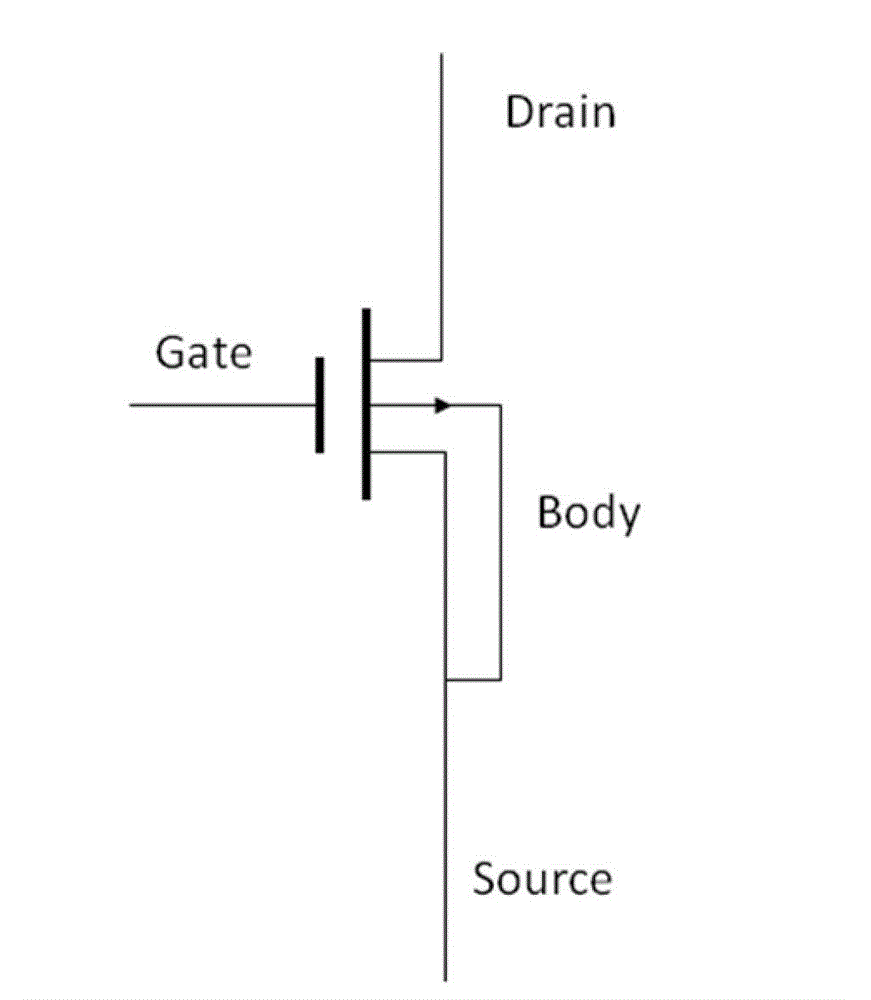

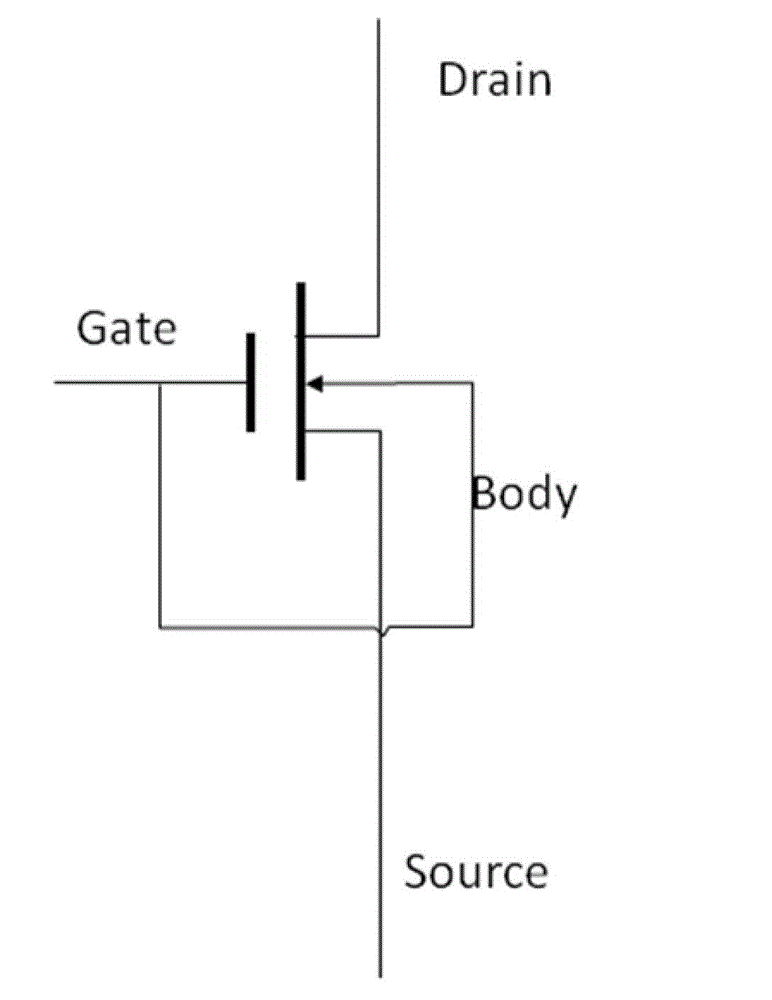

Semiconductor device for expanding safety operation area

InactiveCN103151373AReduce the carrier barrier heightReduce electric field strengthSemiconductor devicesElectrical resistance and conductanceField-effect transistor

The invention provides a semiconductor device for expanding a safety operation area, comprising a field effect transistor and a potential correlation circuit, wherein the field effect transistor is provided with a grid electrode and a body electrode; and the body electrode of the field effect transistor is connected with the grid electrode through the potential correlation circuit so that the potential of the body electrode is correlated with the potential of the grid electrode. According to the semiconductor device disclosed by the invention, the problem of device degradation caused by an HCI (Human Computer Interaction) effect can be avoided; and the safety operation area of the field effect transistor is further expanded and an opening resistance is reduced.

Owner:胡勇海

Compensation of degradation of performance of semiconductor devices by clock duty cycle adaptation

ActiveUS20100134167A1Lower performance requirementsEffective control mechanismDigital circuit testingReliability/availability analysisSelf adaptiveSemiconductor

The device degradation of integrated circuits may be compensated for by appropriately adapting the duty cycle of the clock signal. For this purpose, a correlation between the duty cycle and the overall performance characteristics of the integrated circuit may be established and may be used during the normal field operation of the device in order to modify the duty cycle. Hence, an efficient control strategy may be implemented since the duty cycle may be efficiently controlled, while at the same time a change of clock signal frequency and / or an increase of supply voltage may not be required.

Owner:ADVANCED MICRO DEVICES INC

Knowledge-based driver apparatus for high lumen maintenance and end-of-life adaptation

ActiveUS8072163B2Easy to operateAccuracyElectrical apparatusStatic indicating devicesDriving currentOperation mode

A knowledge-based driver is provided for powering a solid-state light source with a constant current, including a memory that stores lumens per amp and volts per amp performance characterizations of the light source over time, and a controller that operates in a test mode to estimate the light source degradation based on voltage feedback obtained at a predetermined test current value, and to adjust the drive current in normal operating mode according to the estimated device degradation to implement constant lumens control without external optical feedback components.

Owner:GE LIGHTING SOLUTIONS LLC

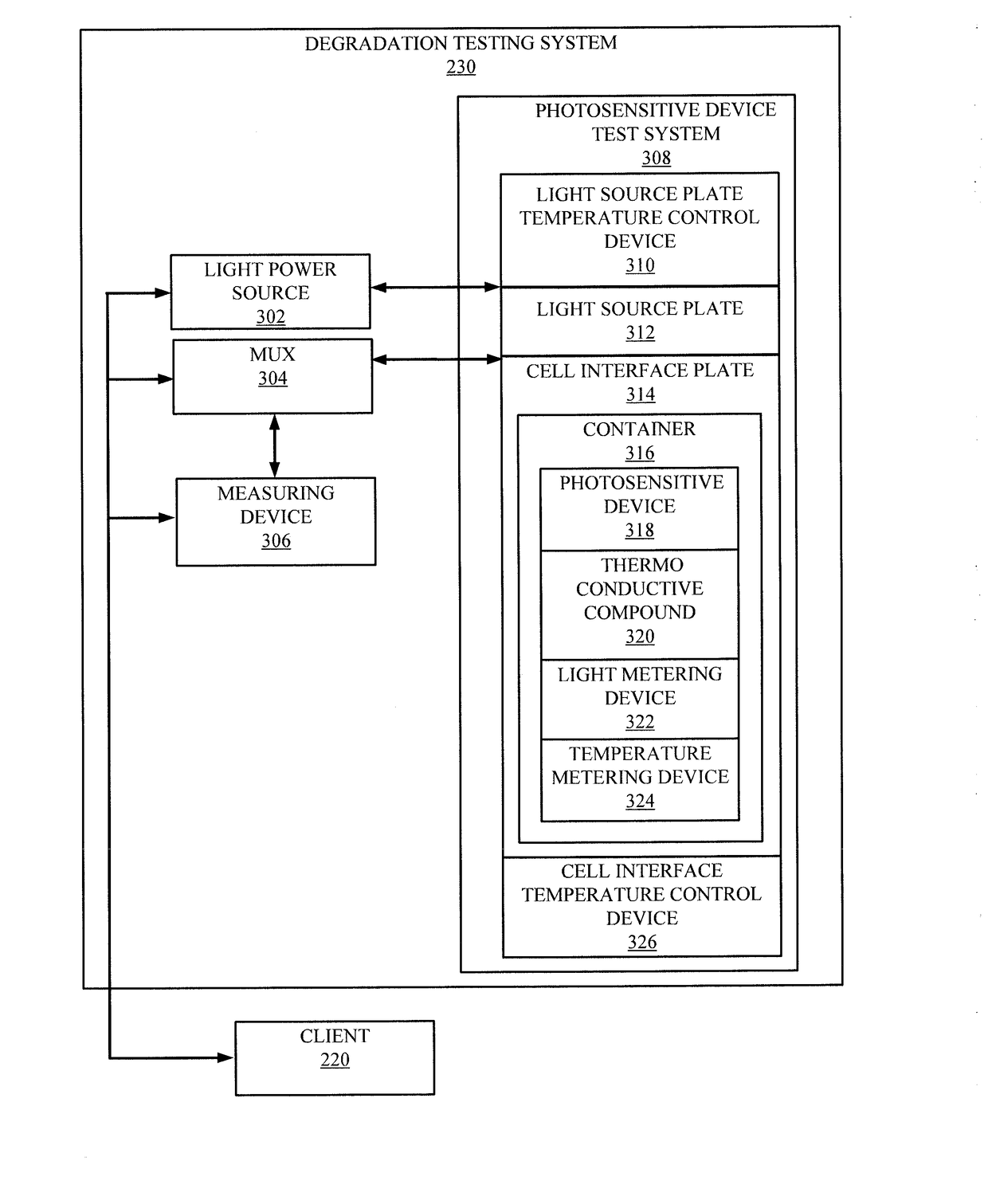

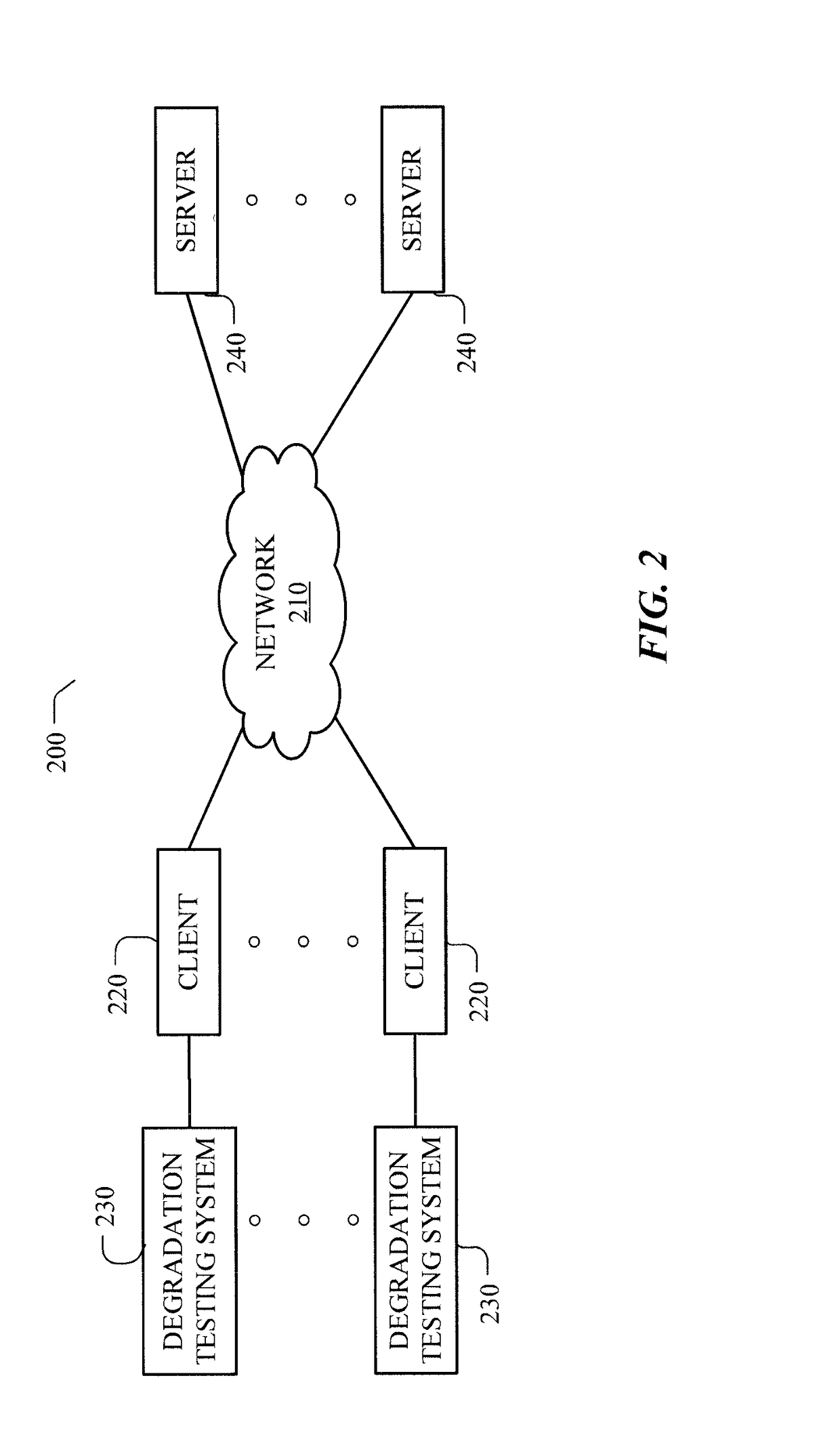

System and method for testing photosensitive device degradation

The performance of photosensitive devices over time may be tested by configuring a photosensitive device test system that includes a light source plate that exposes photosensitive devices within a container to a specified light intensity. The light intensity may be adjusted by a programmable power source according to one or more thresholds. A test may last for a set duration with performance measurements being taken at predetermined intervals throughout the duration. Feedback from the photosensitive device test system may be recorded to determine whether to increase light intensity, to stop testing, to continue testing, and whether one or more environmental conditions should be altered. Measurements may be sent to a client for analysis and display to a user.

Owner:CUBICPV INC

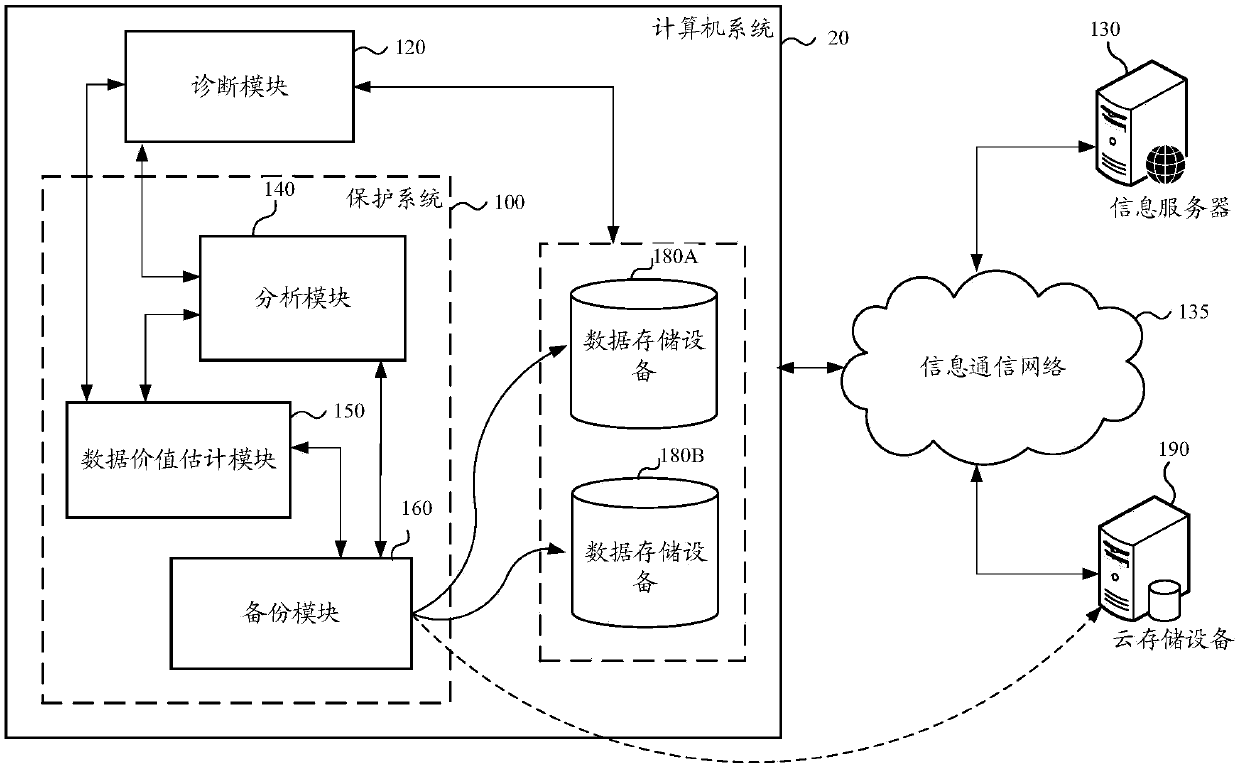

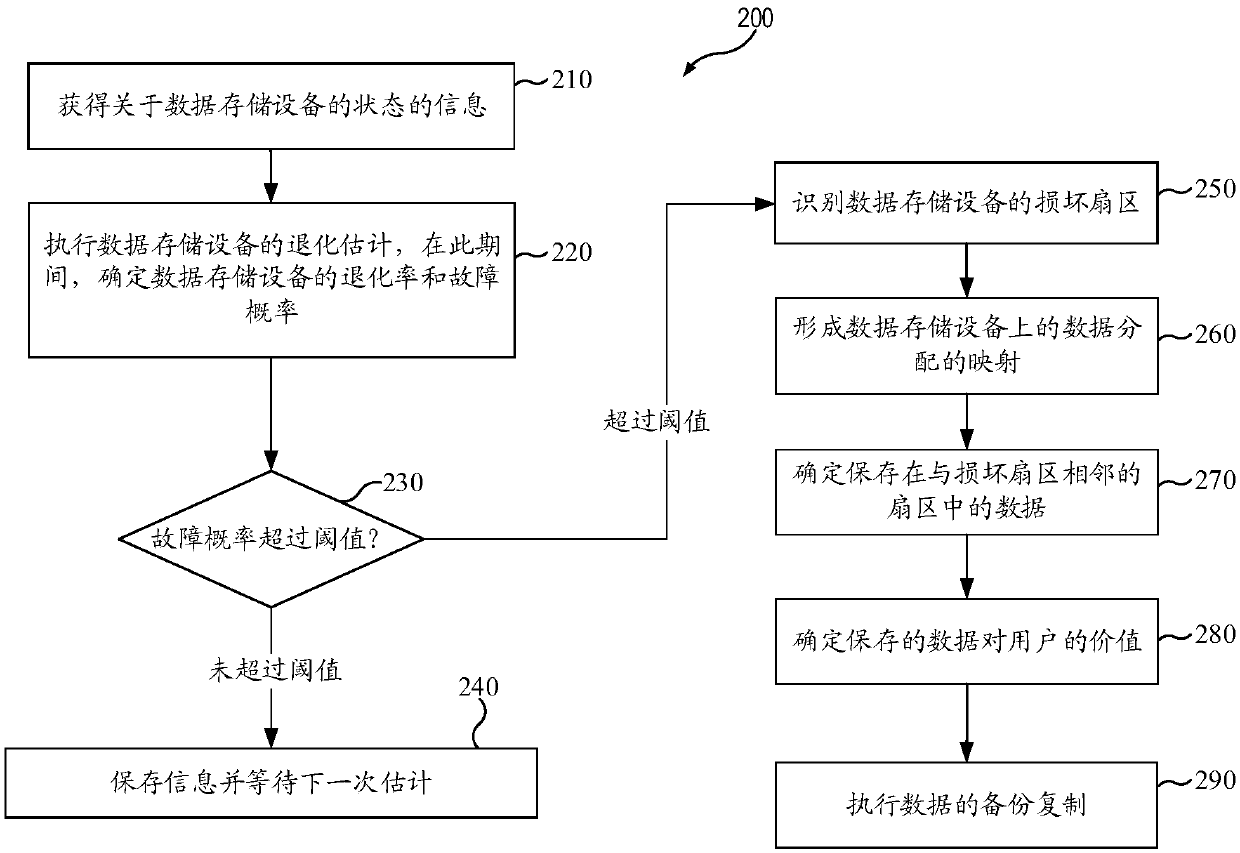

Systems and methods of estimating and managing storage device degradation

Systems and methods of estimating and managing storage device degradation are disclosed. Degradation of the data storage device is estimated during which a degradation rate and a probability of failure of the data storage device are determined. When the probability is greater than a given threshold, a corrupted sector of the data storage device is identified by scanning a surface of the data storage device. Based on the analysis of at least metadata of the data, a value level (i.e., the value of the protected data to the user) is determined for at least the data in the sector near the corrupted sector to determine that the data may be lost, and a copy is established based on the value level of the data and the degradation rate of the data storage device.

Owner:AO KASPERSKY LAB