Metal oxide semiconductor (MOS) field effect transistor (FET) structure and preparation method thereof

A technology of field effect transistors and semiconductors, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as enlargement, difficulty in meeting requirements, and difficulty in achieving high-reliability hot-carrier injection, etc., to achieve Effects of reducing electric field strength, increasing process cost, and improving hot carrier injection (HCI) resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

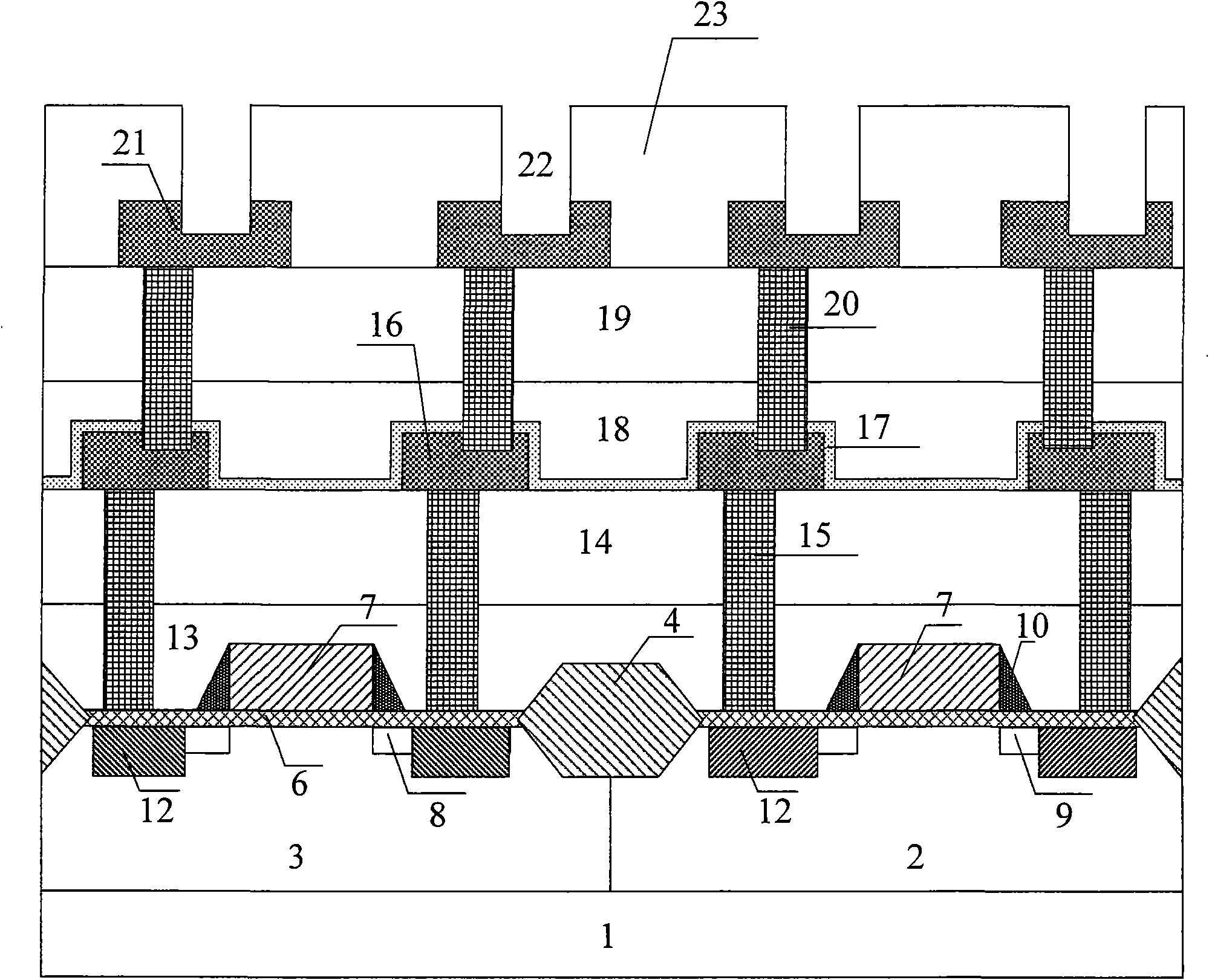

[0040] figure 1 It is a schematic diagram of a specific embodiment of the structure of a MOS field effect transistor provided by the present invention.

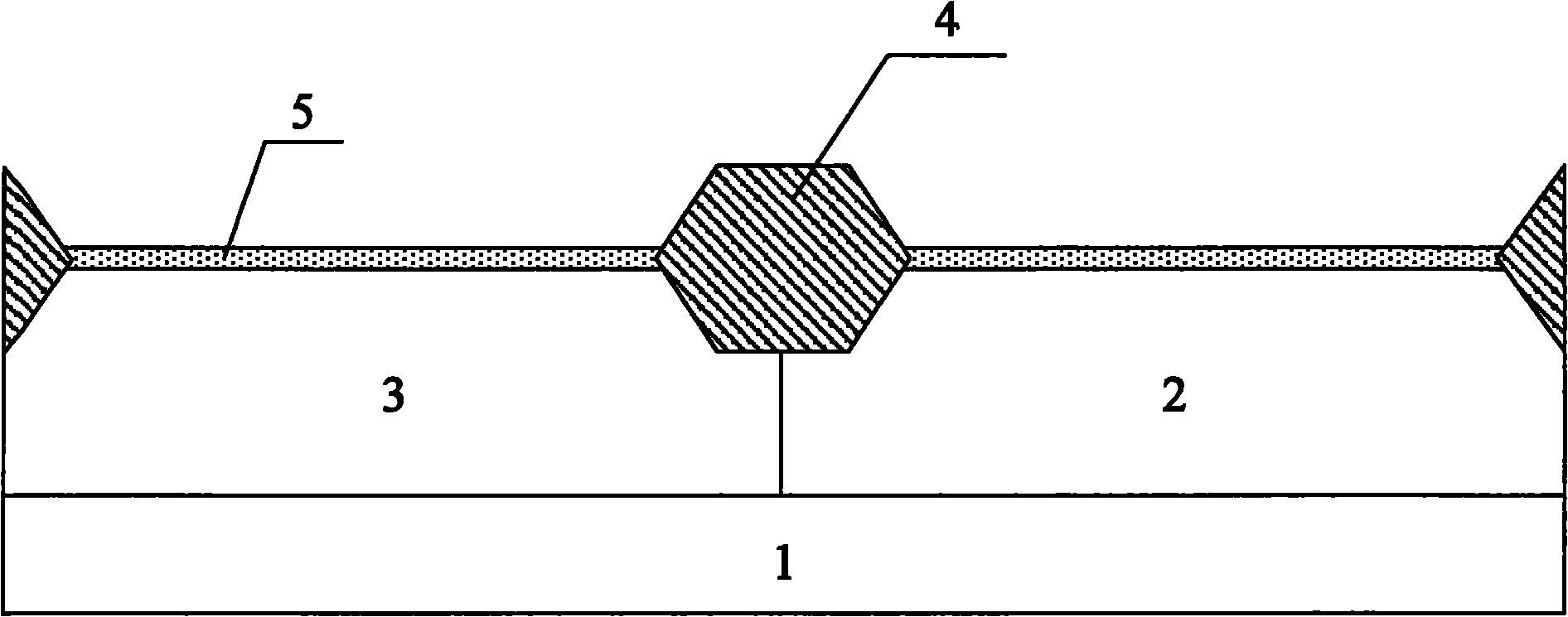

[0041] Such as figure 1 As shown, on the oriented P-type silicon substrate 1, there are N well region 2 and P well region 3, and there is a layer of gate oxide 6 on the upper surface of N well region 2 and P well region 3. , a polysilicon gate 7 is deposited on the gate oxide 6, and a layer of spacer (Spacer) 10 is deposited on the sidewall of the polysilicon gate 7, which is used to define the diffusion region of the lightly doped drain (LDD) structure, thereby avoiding short channels effect, the side wall (Spacer) 10 is orthoethyl silicate (TEOS). In addition, there is a field oxidation region 4 on the surf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More