Circuit and method for testing reliability of integrated circuit

A technology of integrated circuits and test circuits, applied in the field of integrated circuit reliability test circuits and testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

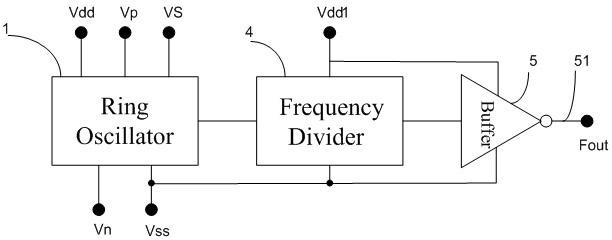

[0026] The circuit and method of the invention are used for testing the reliability of integrated circuits, especially for NBTI degradation testing of pMOSFETs in integrated circuits, PBTI degradation testing of nMOSFETs, and HCI degradation testing of pMOSFETs and nMOSFETs. The whole circuit as figure 1 As shown, there are a total of 7 external electrical contact pads (Pad), which are the high power supply terminal Vdd of the core circuit, the high power supply terminal Vdd1 of the frequency divider and buffer, and the common low power supply terminal of the core circuit, frequency divider and buffer Vss, three control terminals VS, Vp and Vn, the output terminal Fout of the circuit.

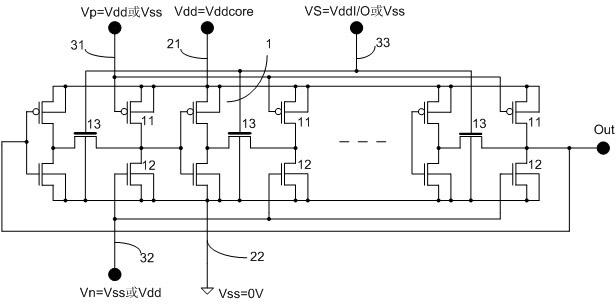

[0027] figure 2 It is the core circuit composed of ring oscillator RO, switch S and auxiliary nMOSFETs and pMOSFETs. The core circuit includes a ring oscillator RO (1). Between each two-stage inverter of RO, a group of auxiliary pMOSFETs (11) and nMOSFETs (12) are connected, and the sources...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More