Patents

Literature

278 results about "Positive bias" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Positive Bias. Positive bias refers to the human tendency to overestimate the possibility of positive (good) things happening in life or in research. In publication, it is the preference for publishing research that has a positive (eventful) outcome, than an uneventful or negative outcome.

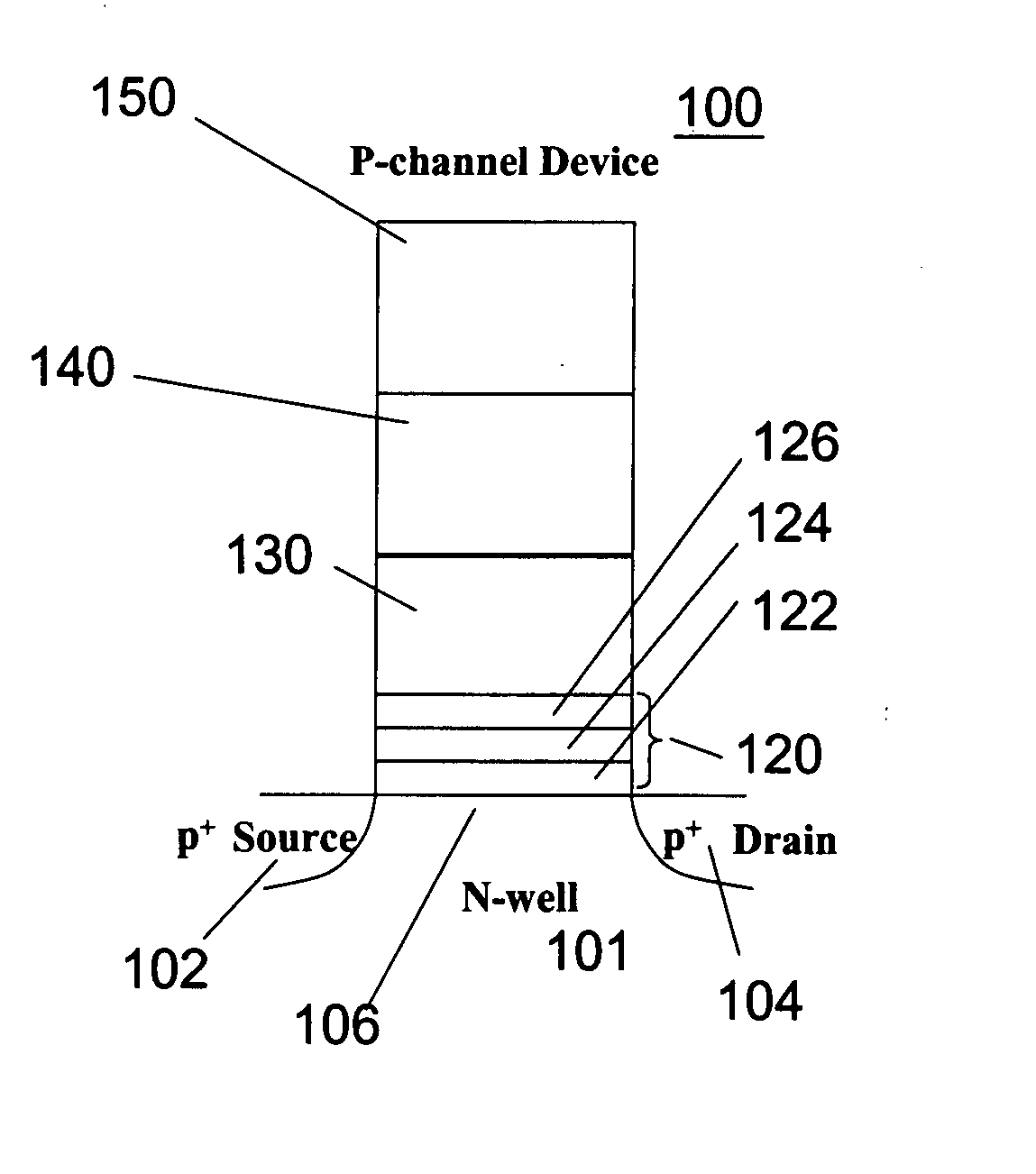

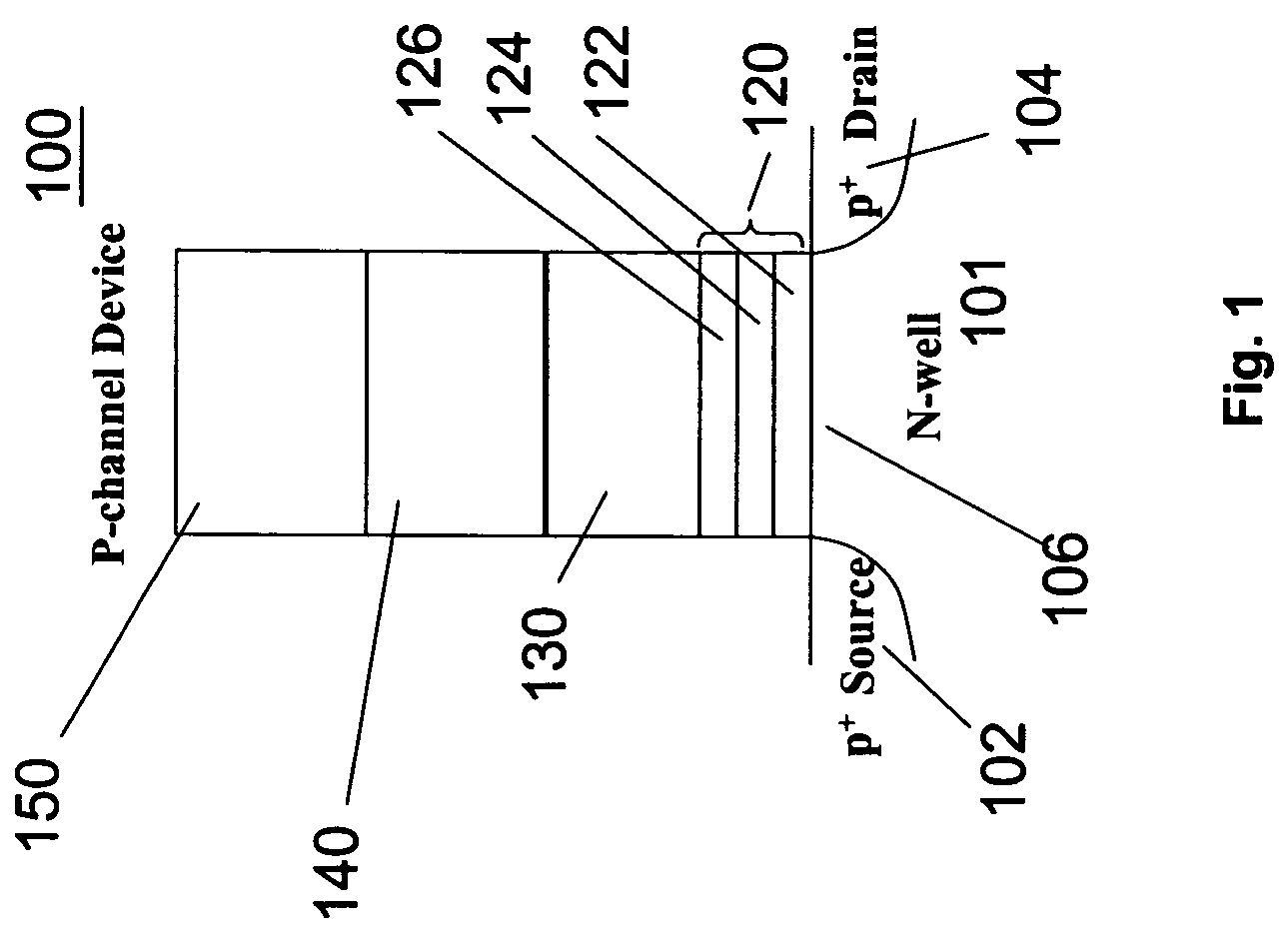

Methods of operating p-channel non-volatile memory devices

ActiveUS20060281260A1Disturbing effectNegative biasSolid-state devicesRead-only memoriesBit lineEngineering

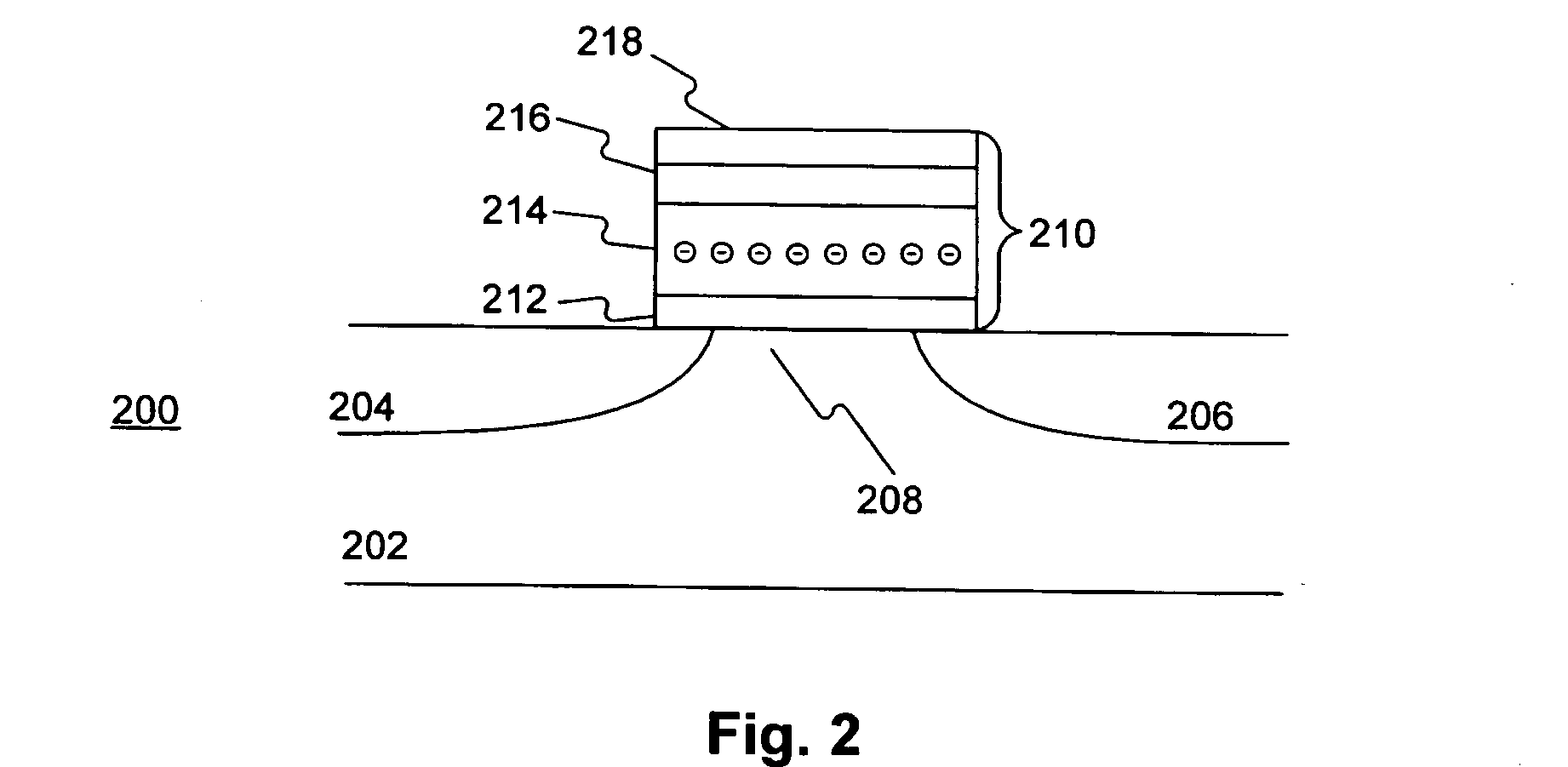

Methods of operating non-volatile memory devices are described. The memory devices comprise memory cells having an n-type semiconductor substrate and p-type source and drain regions disposed below a surface of the substrate and separated by a channel region. A tunneling dielectric layer is disposed above the channel region. A charge storage layer is disposed above the tunneling dielectric layer. An upper insulating layer is disposed above the charge storage layer, and a gate is disposed above the upper insulating multi-layer structure. A positive bias is applied to a word lines of the memory device in a selected memory cell and a negative bias is applied to a bit line in the selected cell.

Owner:MACRONIX INT CO LTD

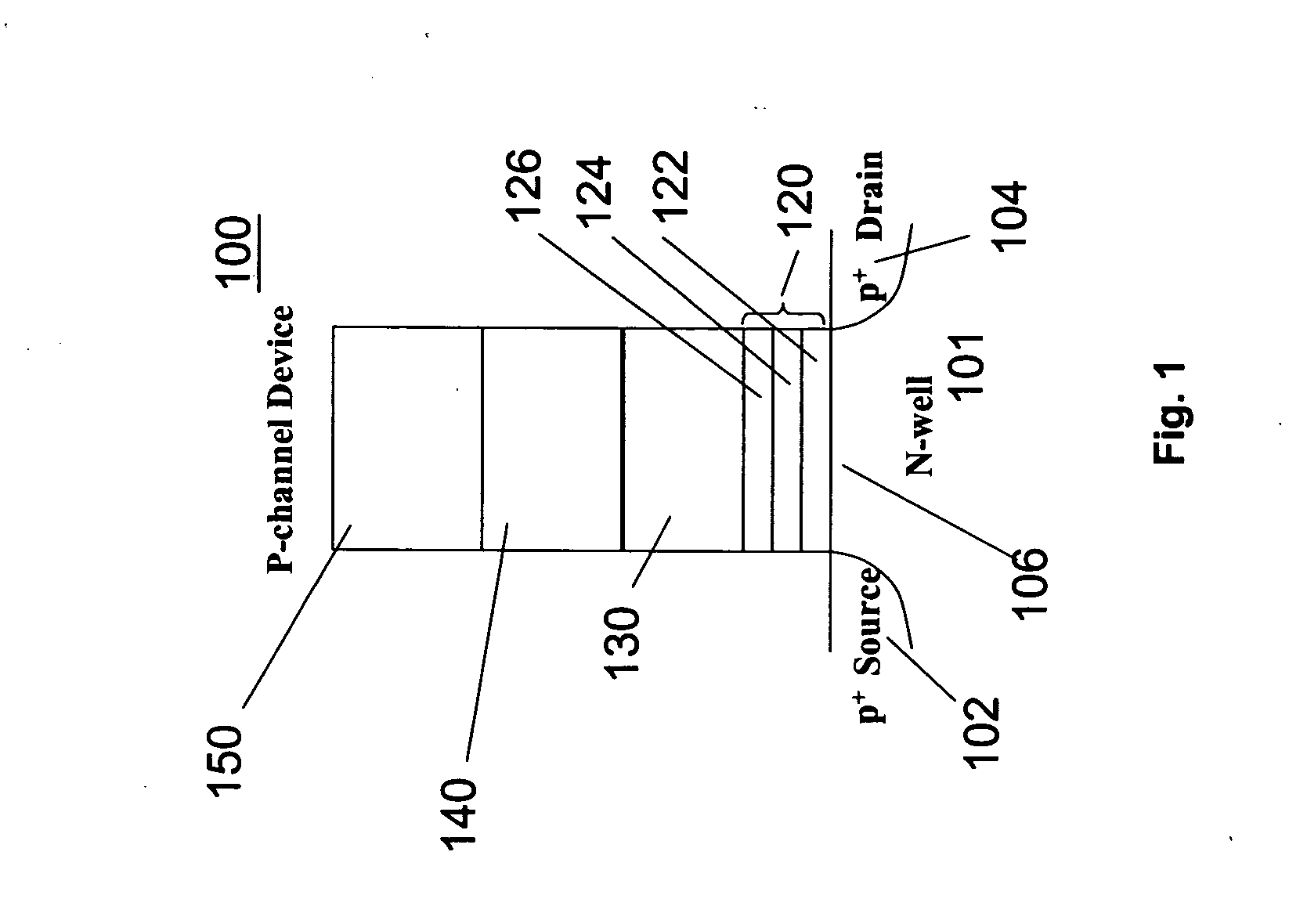

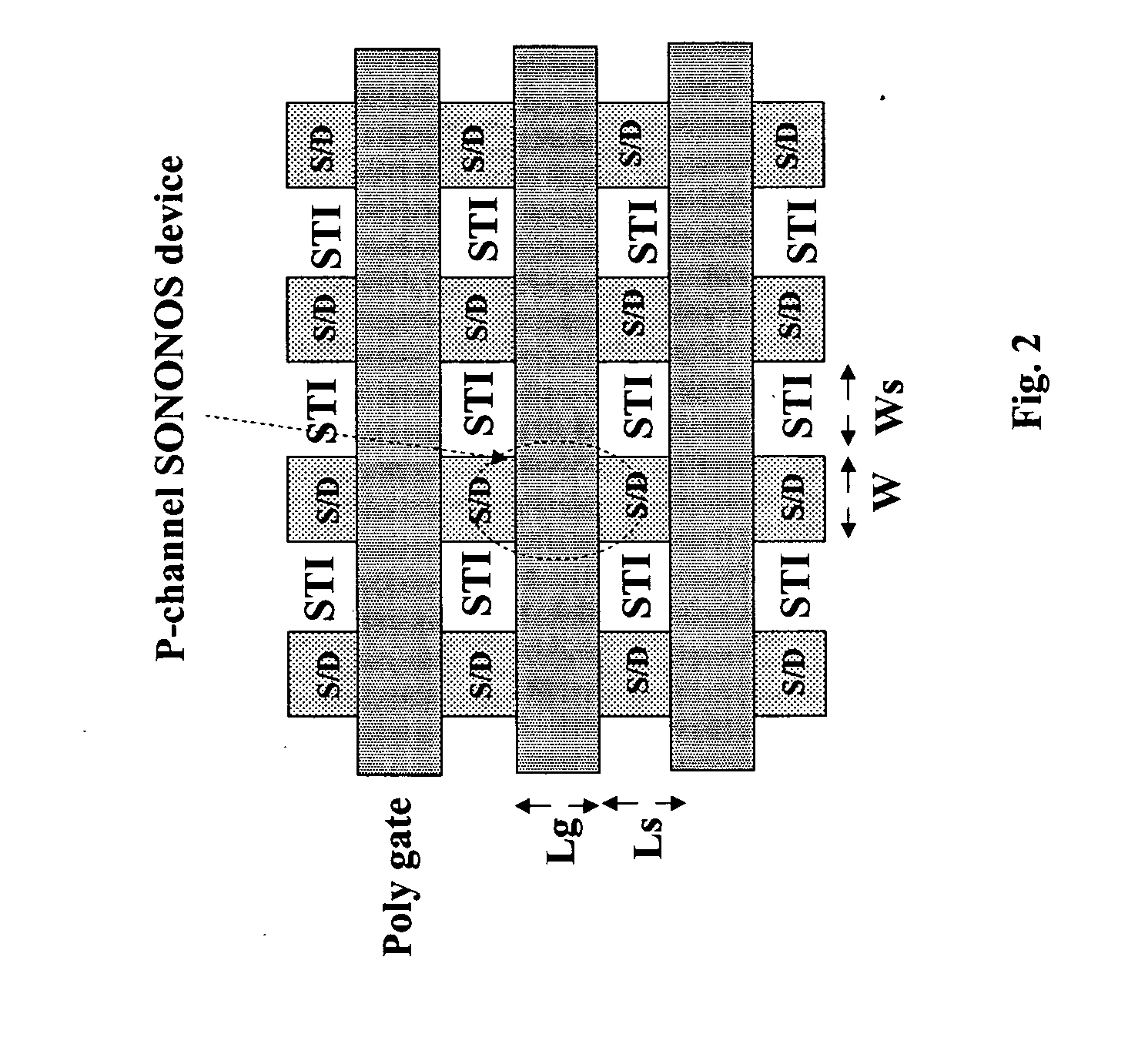

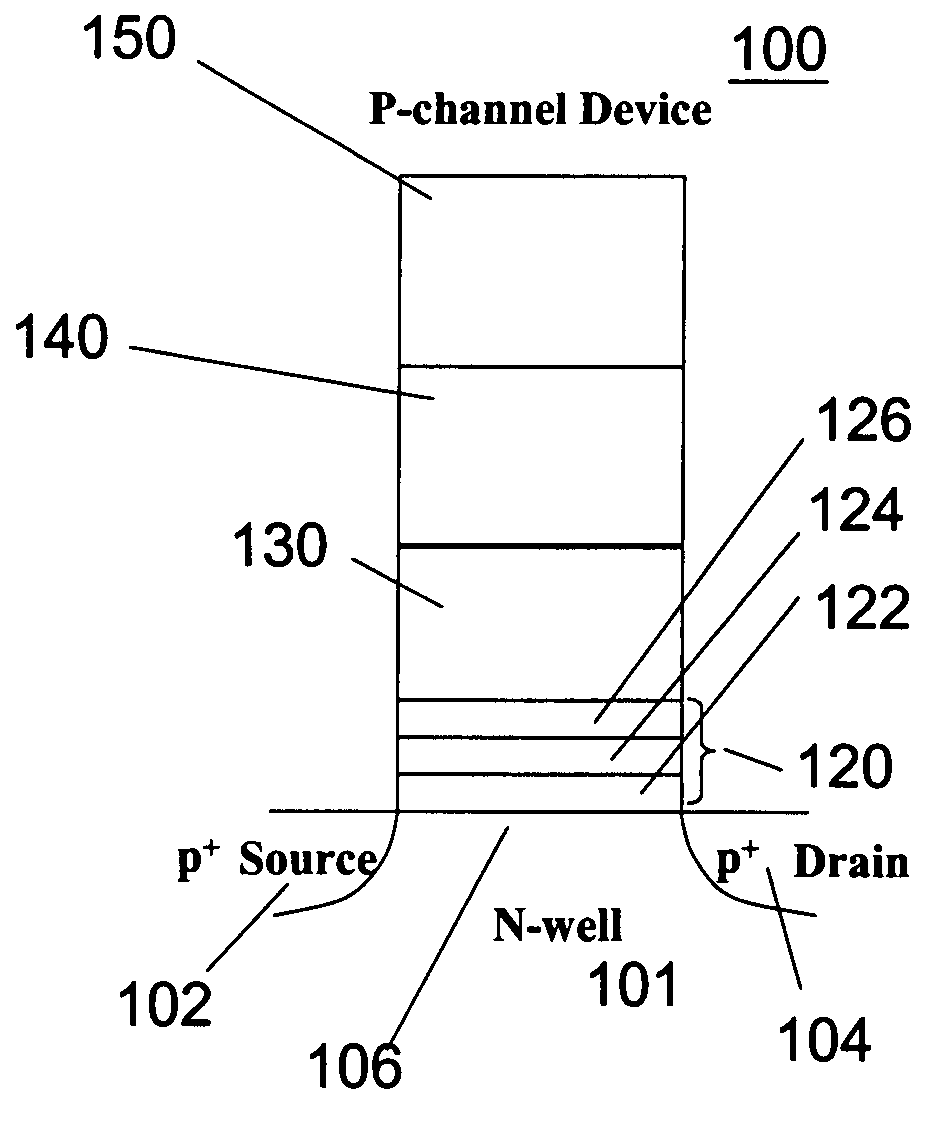

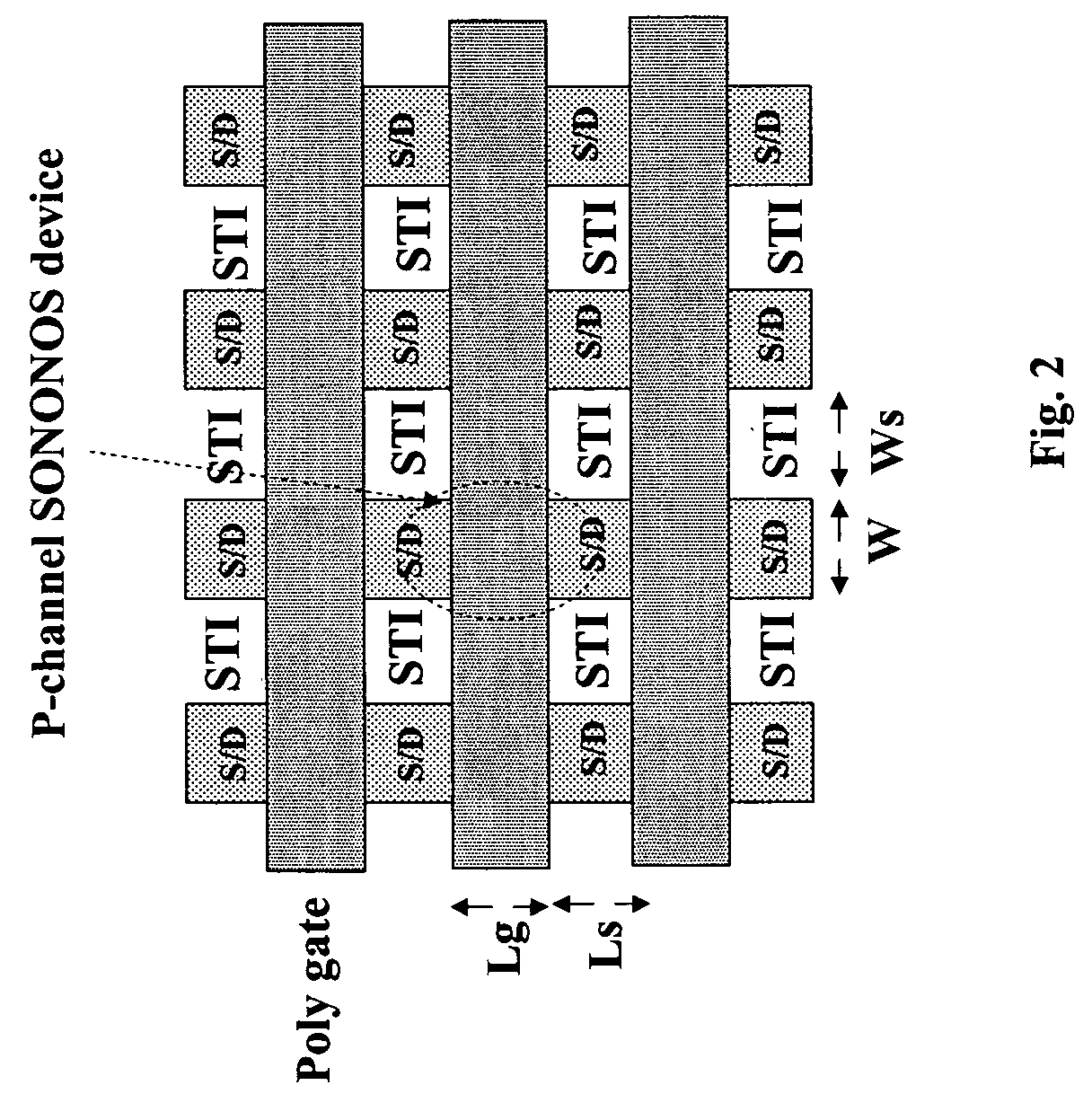

Program/erase method for p-channel charge trapping memory device

ActiveUS20050270849A1Improve efficiencyIncrease speedTransistorSolid-state devicesBit lineComputer science

A method of operating a memory device is disclosed, wherein the memory device includes an n-type substrate and a plurality of memory cells formed thereon, each memory cell corresponding to a word line, a first bit line, and second bit line, and including a first bit portion and a second bit portion each for storing one bit of information. The method includes resetting a selected memory cell by applying a first negative bias to the word line of the selected memory cell and applying a ground bias to the first and second bit lines, and programming the first bit portion of the selected memory cell by applying a first positive bias to the word line of the selected memory cell, applying a second negative bias to the first bit line of the selected memory cell, and applying a ground bias to the second bit line of the selected memory cell.

Owner:MACRONIX INT CO LTD

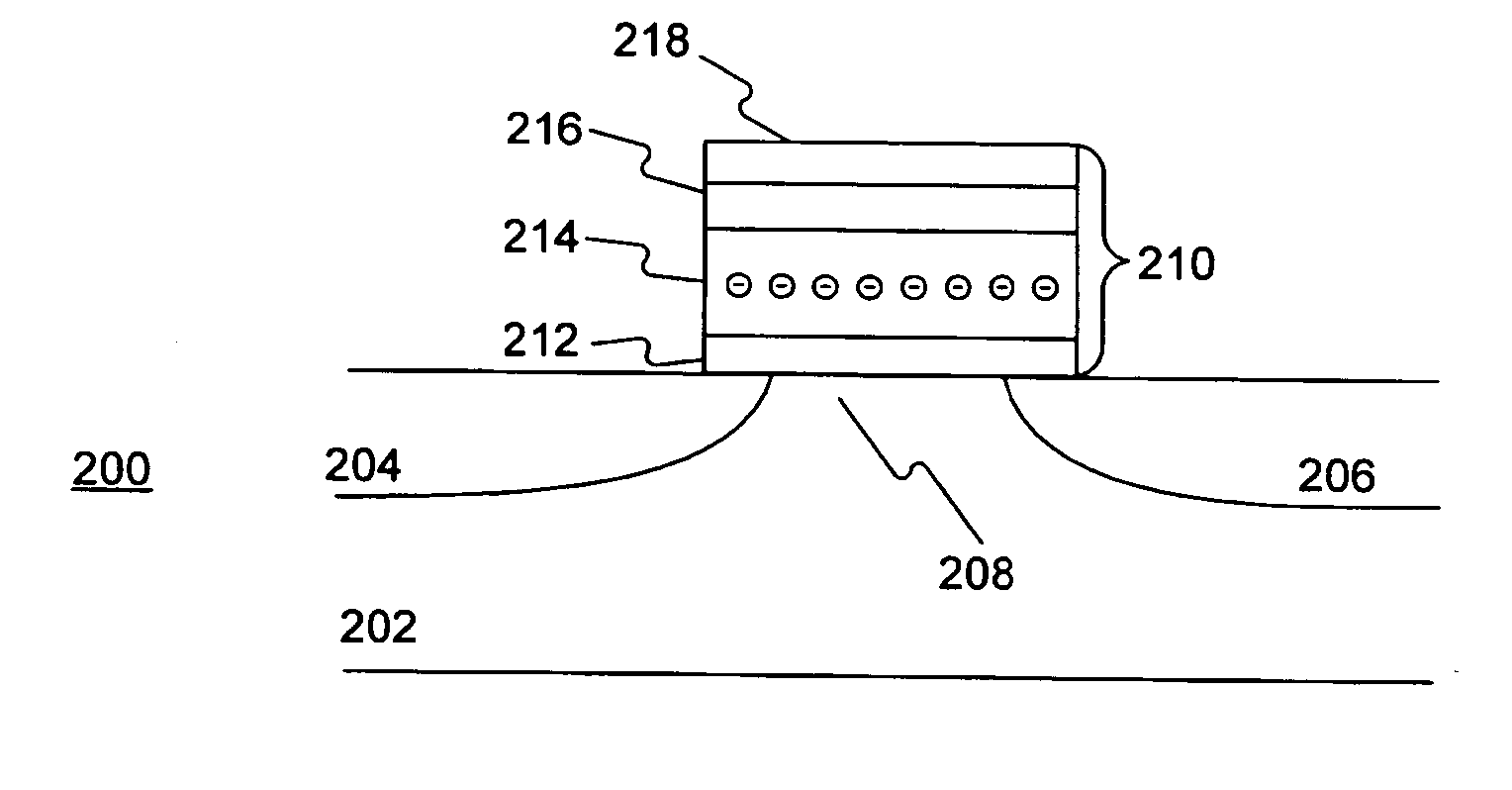

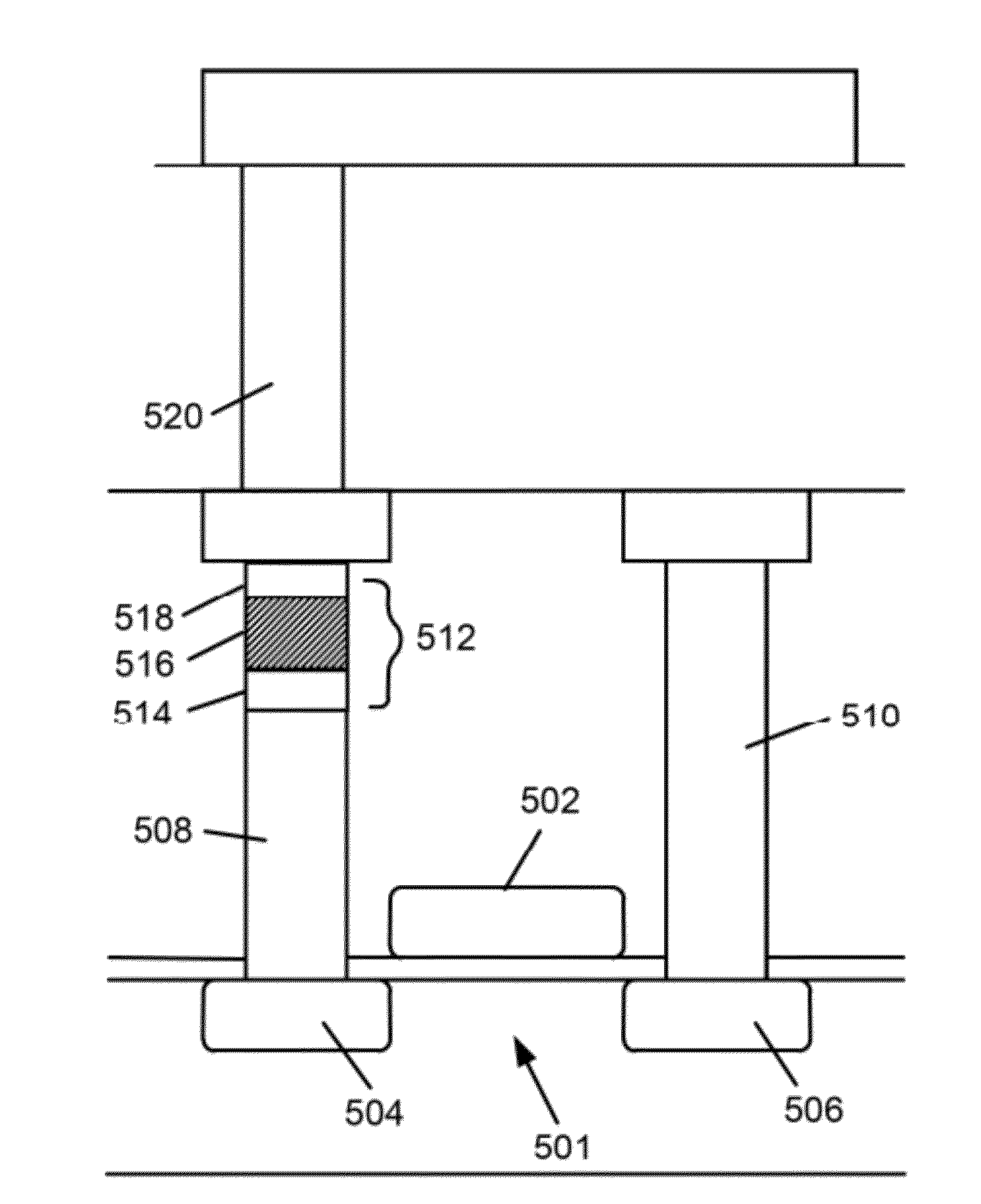

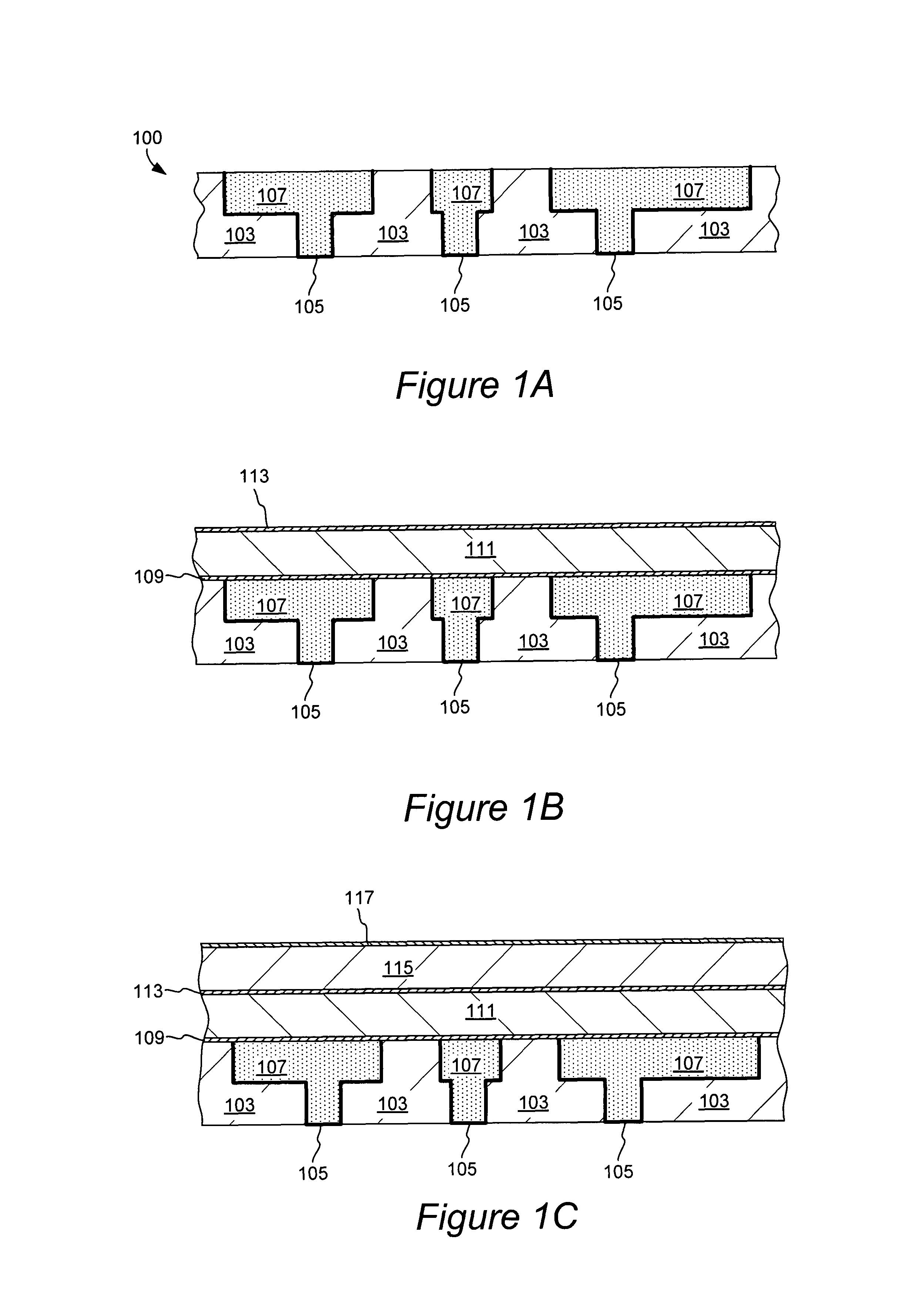

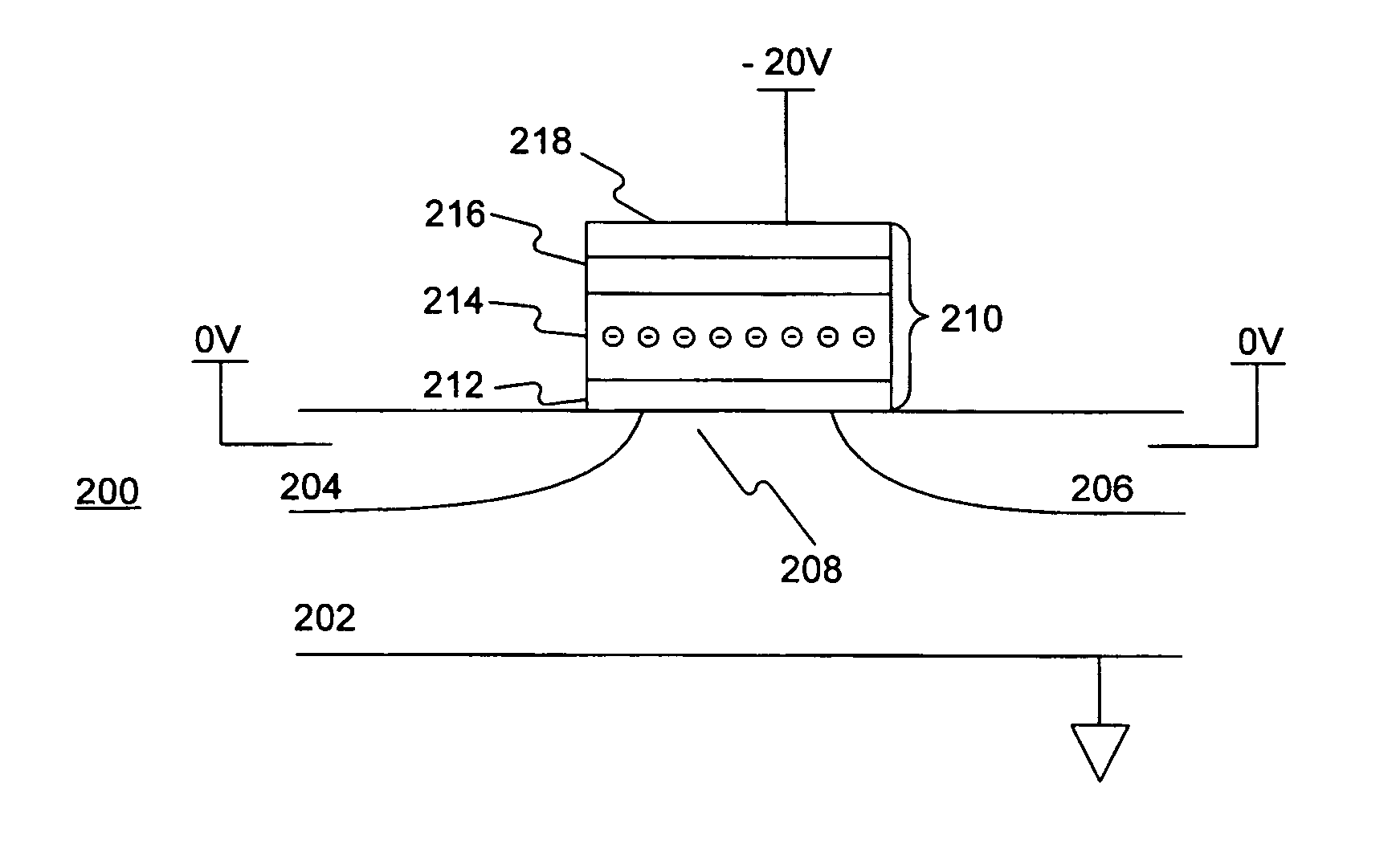

Integration of an amorphous silicon resistive switching device

InactiveUS20120074507A1Data stabilityImprove good performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricElectrical conductor

An integrated circuit device. The integrated circuit device includes a semiconductor substrate having a surface region. A gate dielectric layer overlies the surface region of the substrate. The device includes a MOS device having a p+ active region. The p+ active region forms a first electrode for a resistive switching device. The resistive switching device includes an amorphous silicon switching material overlying the p+ active region and a metal electrode overlies the first metal conductor structure. The metal electrode includes a metal material, upon application of a positive bias to the metal electrode, forms a metal region in the amorphous silicon switching material. The MOS device provides for a select transistor for the integrated circuit device.

Owner:CROSSBAR INC

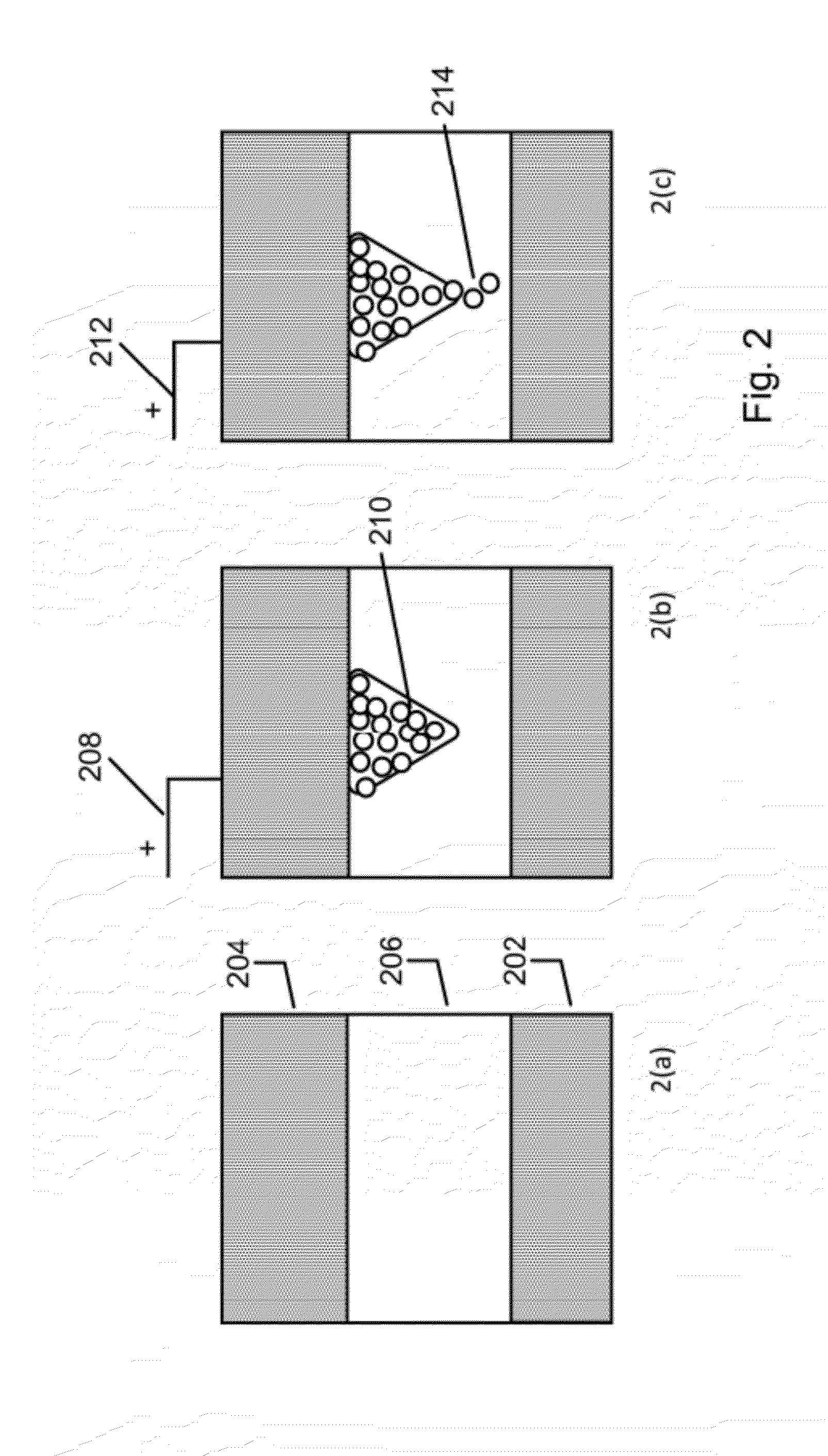

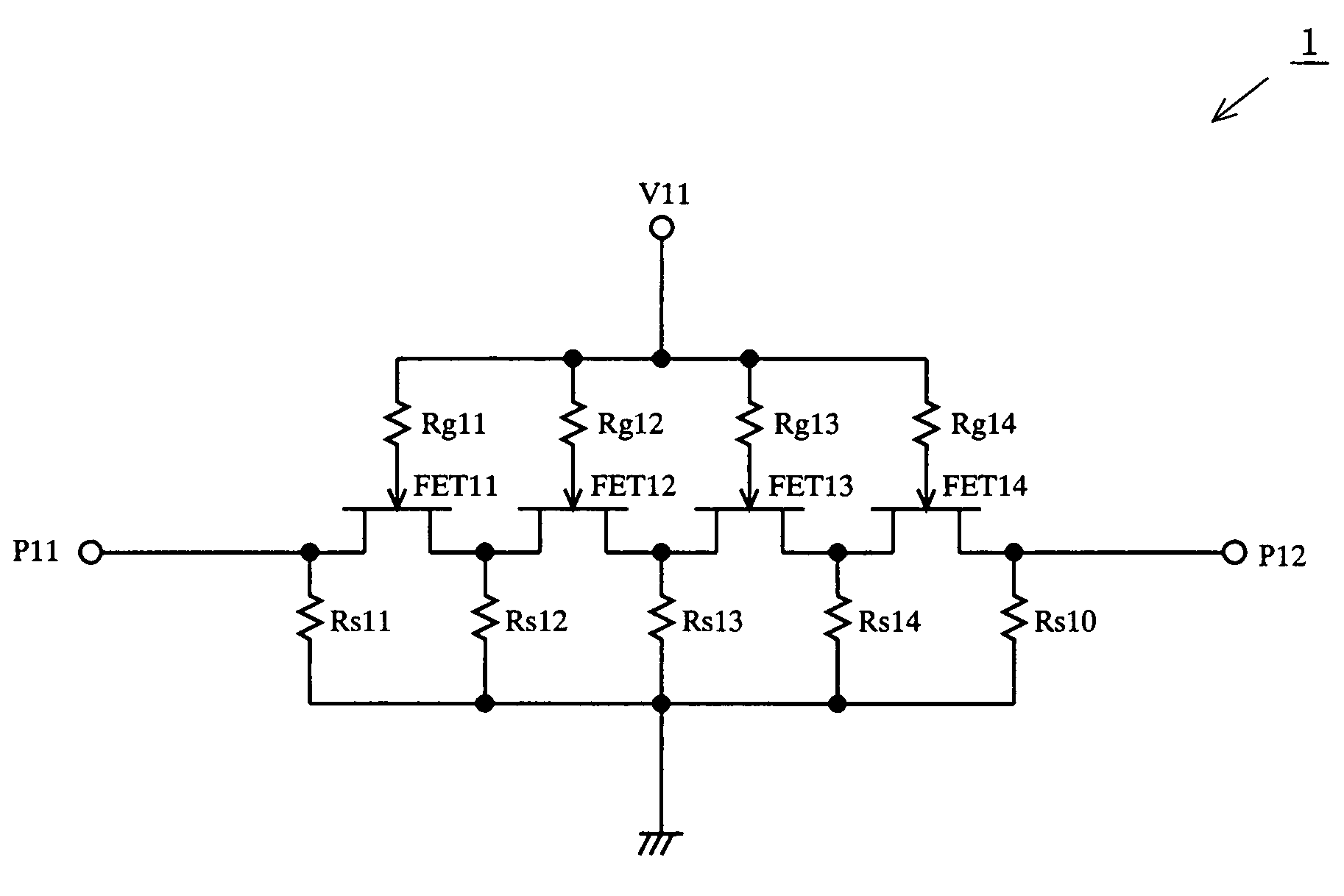

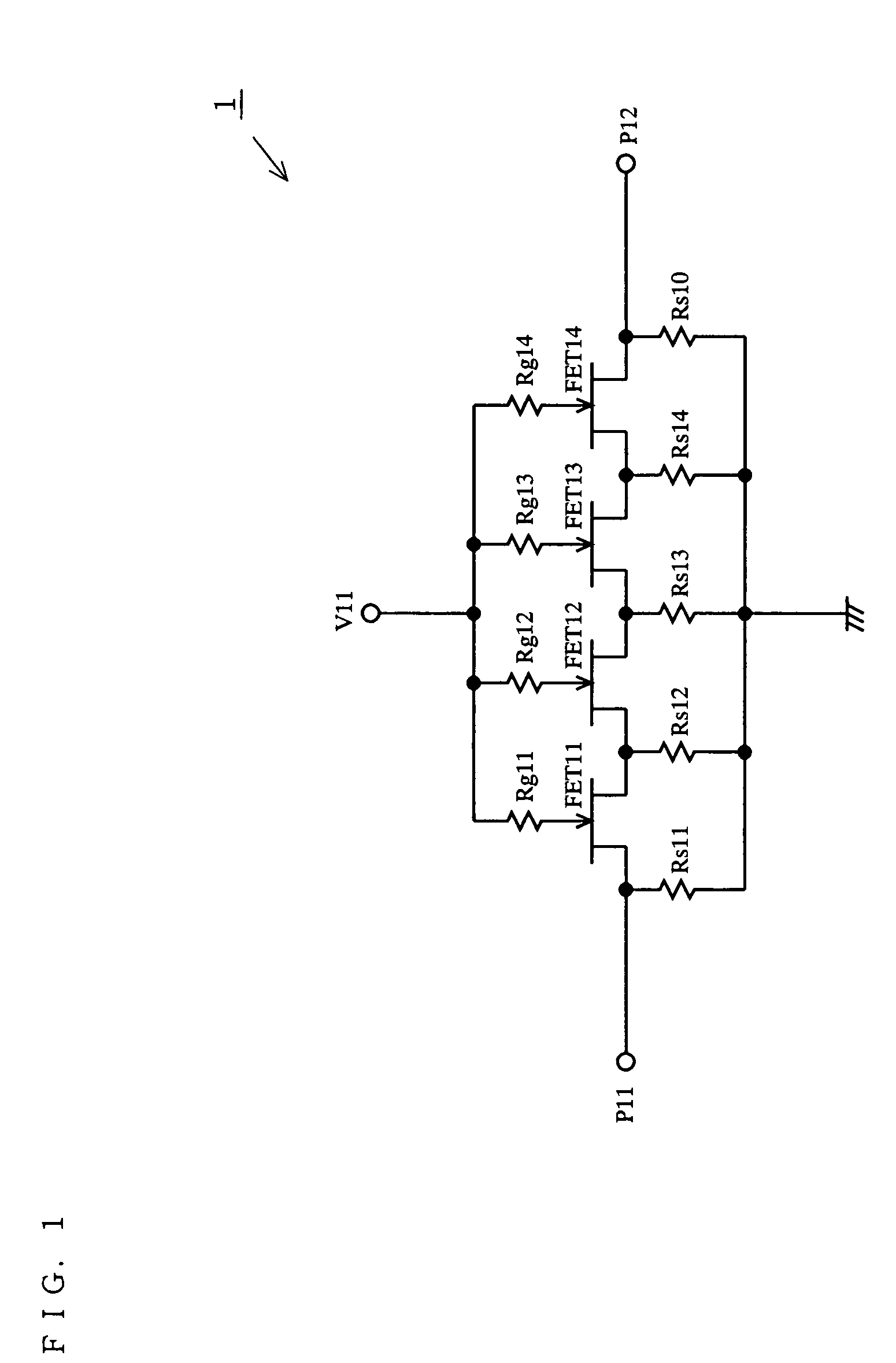

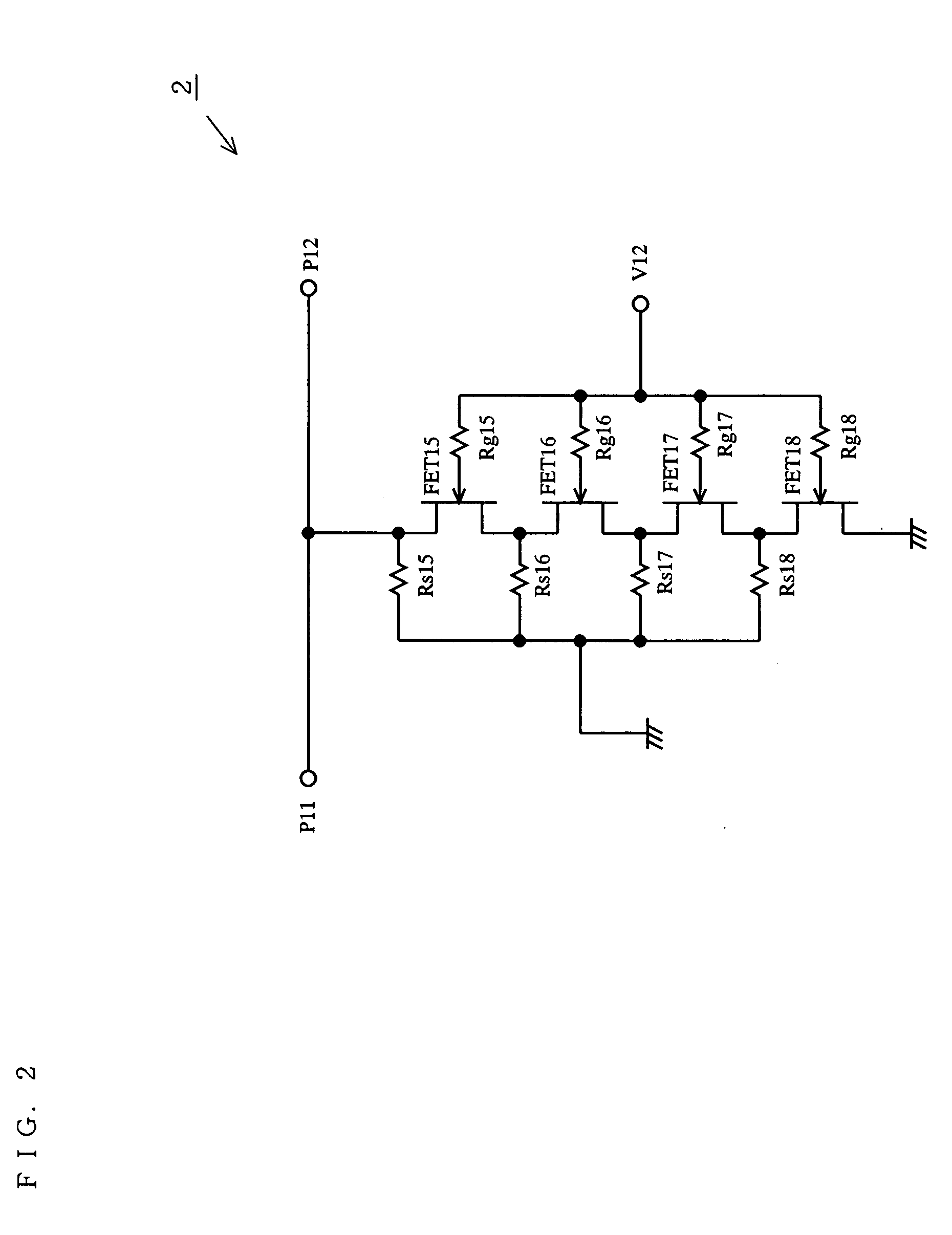

Radio frequency switching circuit, radio frequency switching device, and transmitter module device

InactiveUS20070290744A1Desirable radio frequency characteristicDesirable endurancePower amplifiersSolid-state devicesHigh pressureWide band

The present invention provides an inexpensive radio frequency switching circuit having desirable radio frequency characteristics over a wide band and desirable endurance against the inflow of a high voltage signal such as an electrostatic surge. Either a negative bias voltage or a positive bias voltage being greater than or equal to 0V and less than or equal to a Schottky forward voltage is used for the control terminals V11 and V12 for controlling FETs 11 to 18 and FETs 21 to 28 so as to turn ON / OFF the path extending from the first input / output terminal P11 to the second input / output terminal P12 and the path extending from the first input / output terminal P11 to the third input / output terminal P13. Thus, it is possible to eliminate the need for DC cut capacitors.

Owner:PANASONIC CORP

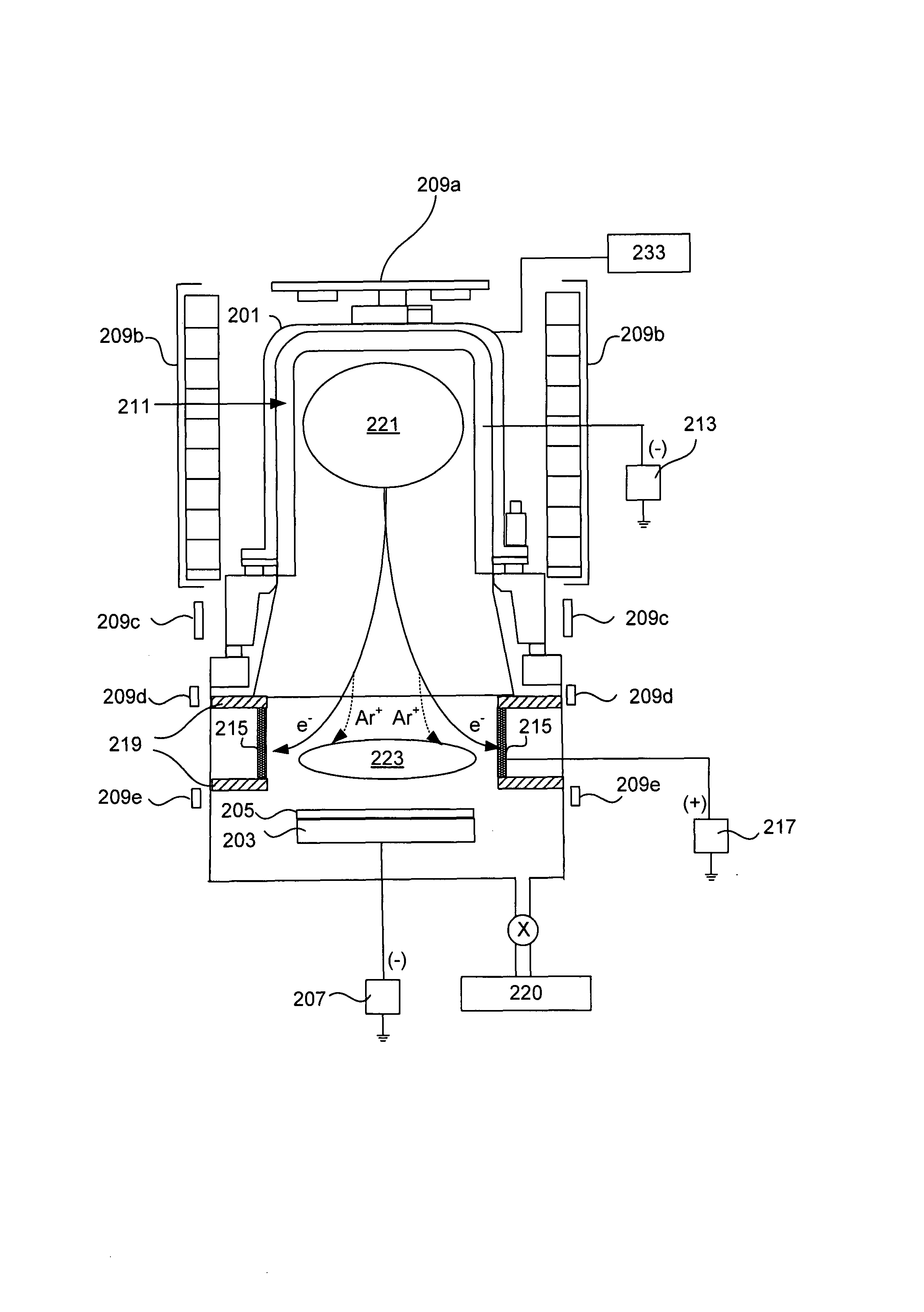

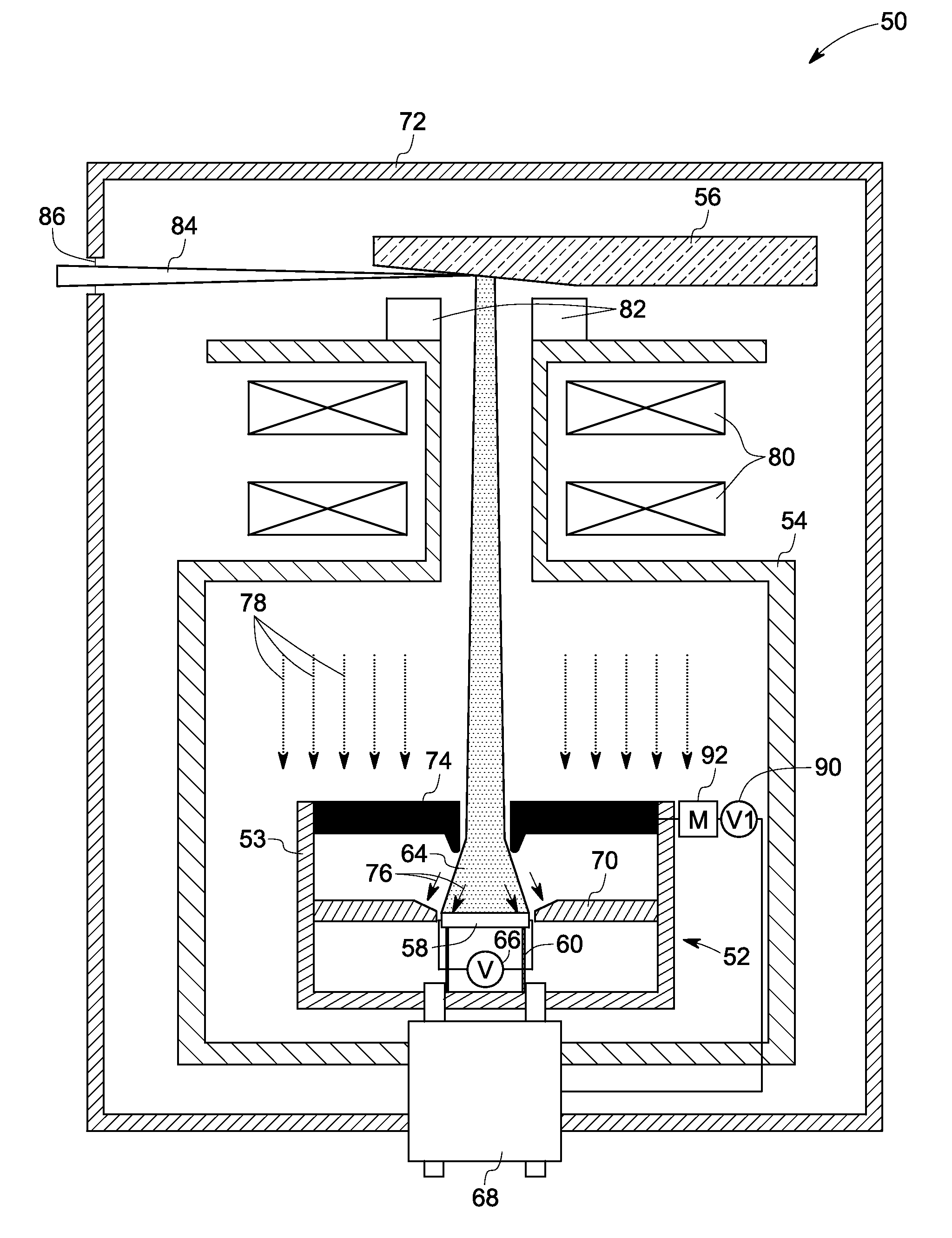

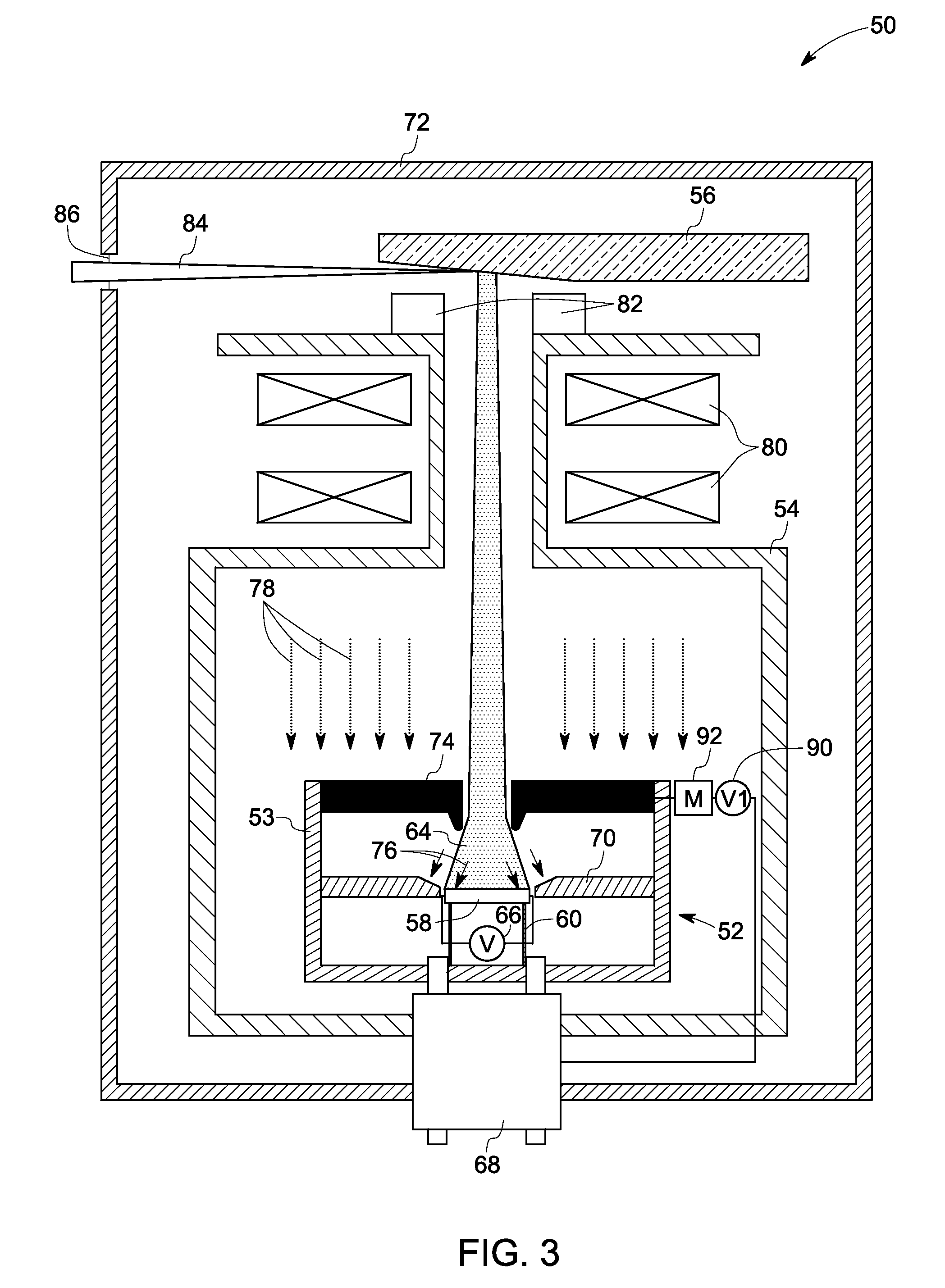

Method and apparatus for increasing local plasma density in magnetically confined plasma

ActiveUS7922880B1Easily damagedLow reliabilityCellsElectric discharge tubesPlasma densityHigh density

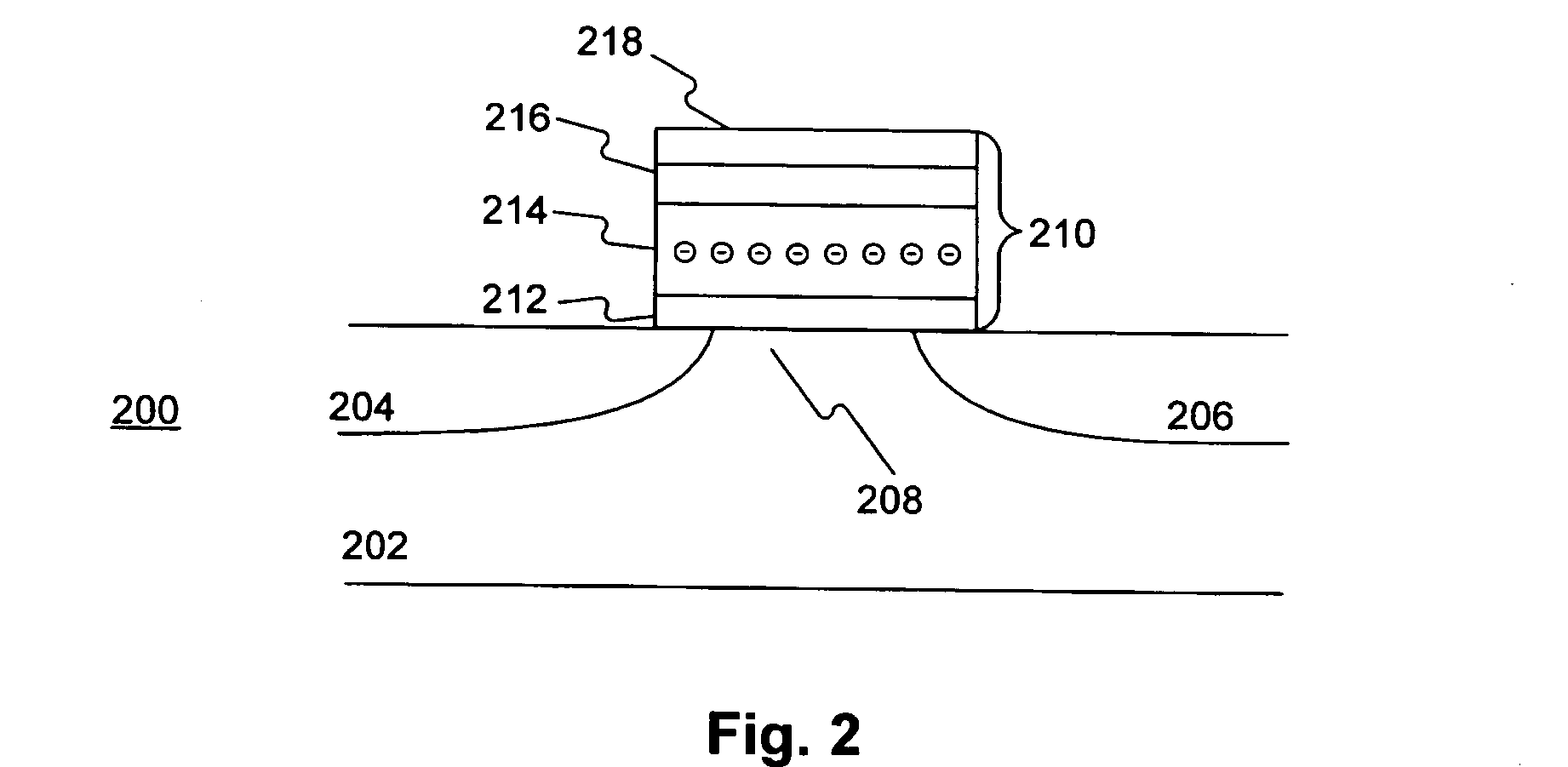

Local plasma density, e.g., the plasma density in the vicinity of the substrate, is increased by providing an ion extractor configured to transfer ions and electrons from a first region of magnetically confined plasma (typically a region of higher density plasma) to a second region of plasma (typically a region of lower density plasma). The second region of plasma is preferably also magnetically shaped or confined and resides between the first region of plasma and the substrate. A positively biased conductive member positioned proximate the second region of plasma serves as an ion extractor. A positive bias of about 50-300 V is applied to the ion extractor causing electrons and subsequently ions to be transferred from the first region of plasma to the vicinity of the substrate, thereby forming higher density plasma. Provided methods and apparatus are used for deposition and resputtering.

Owner:NOVELLUS SYSTEMS

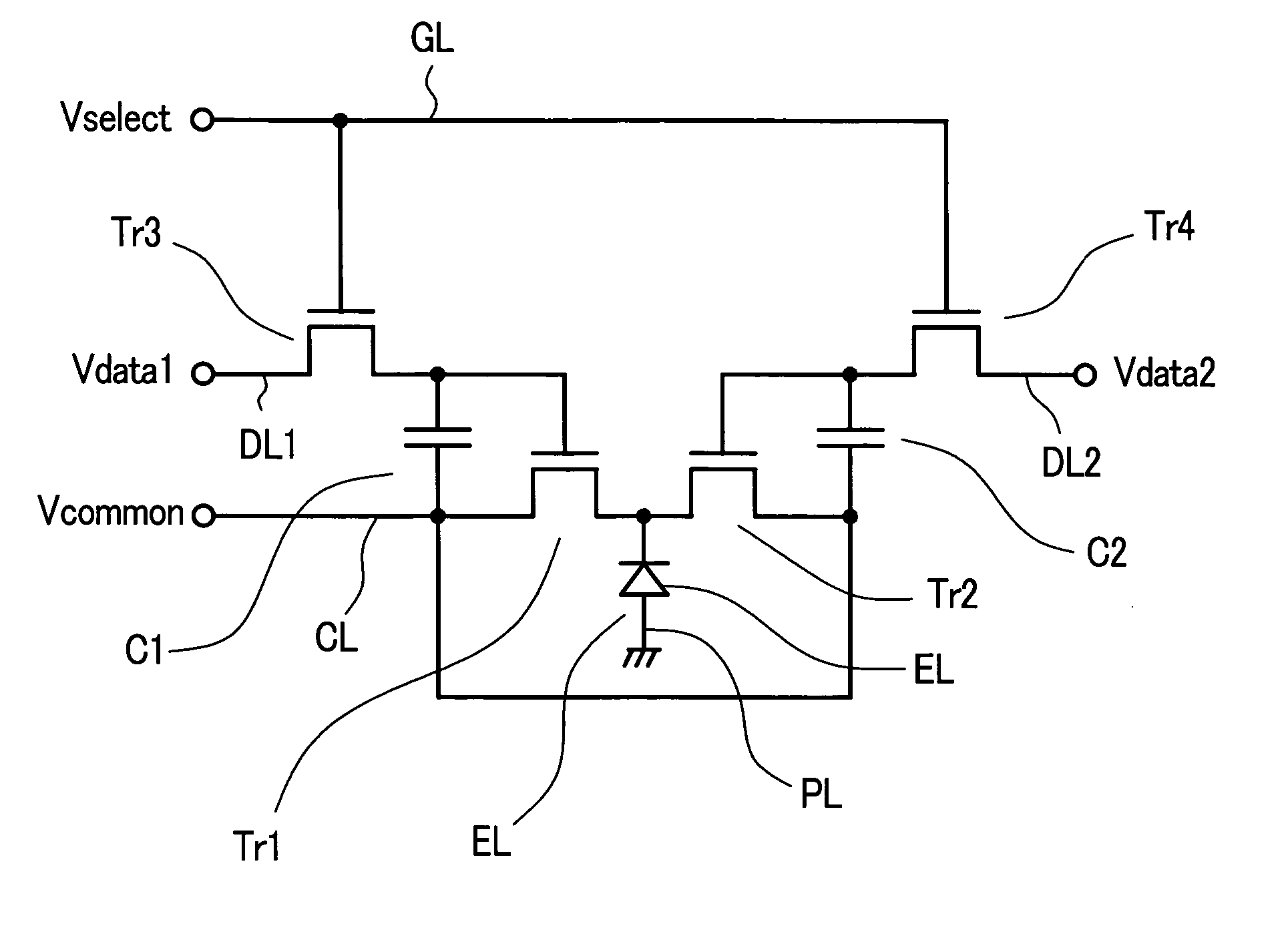

Display device and driving method thereof

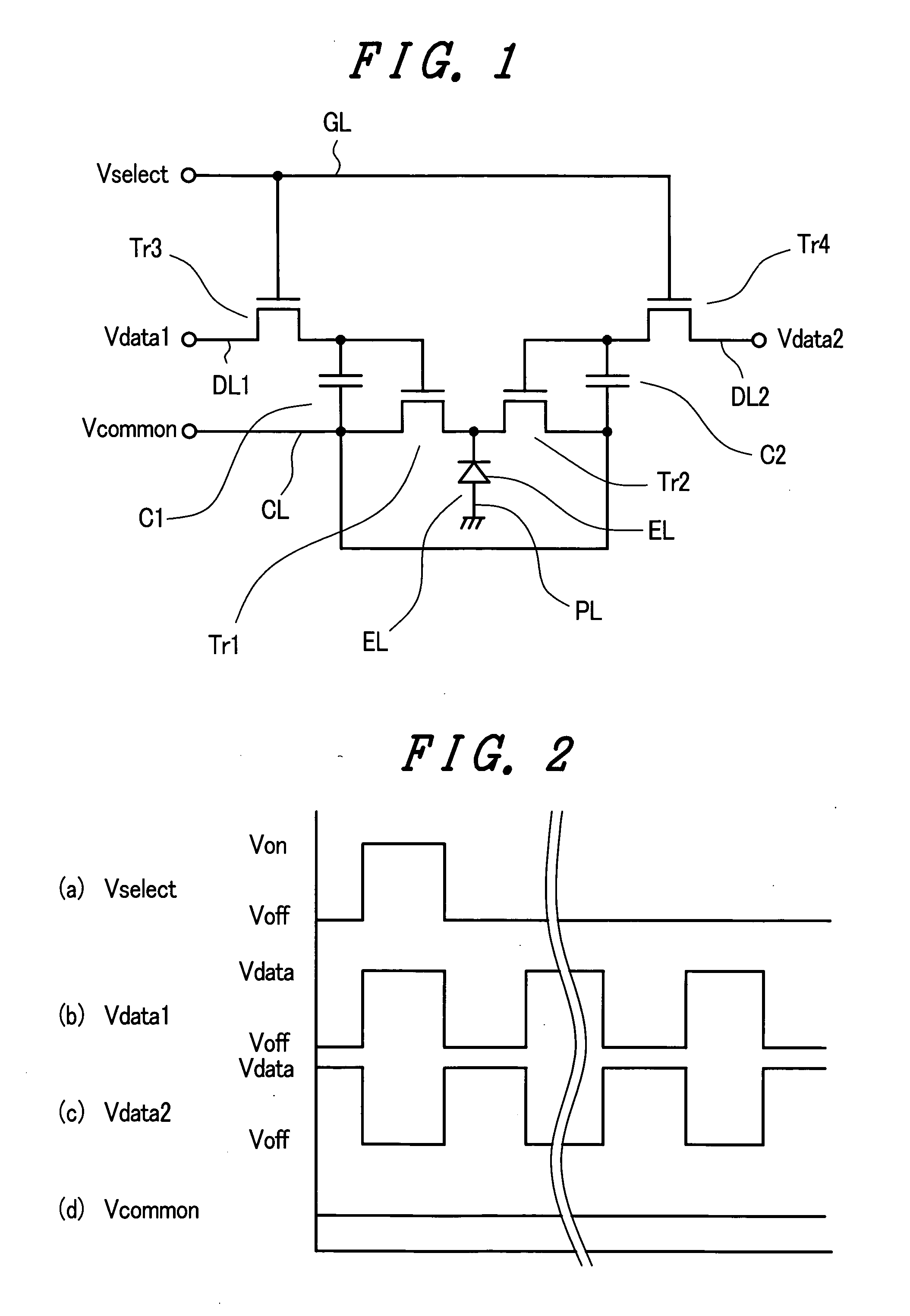

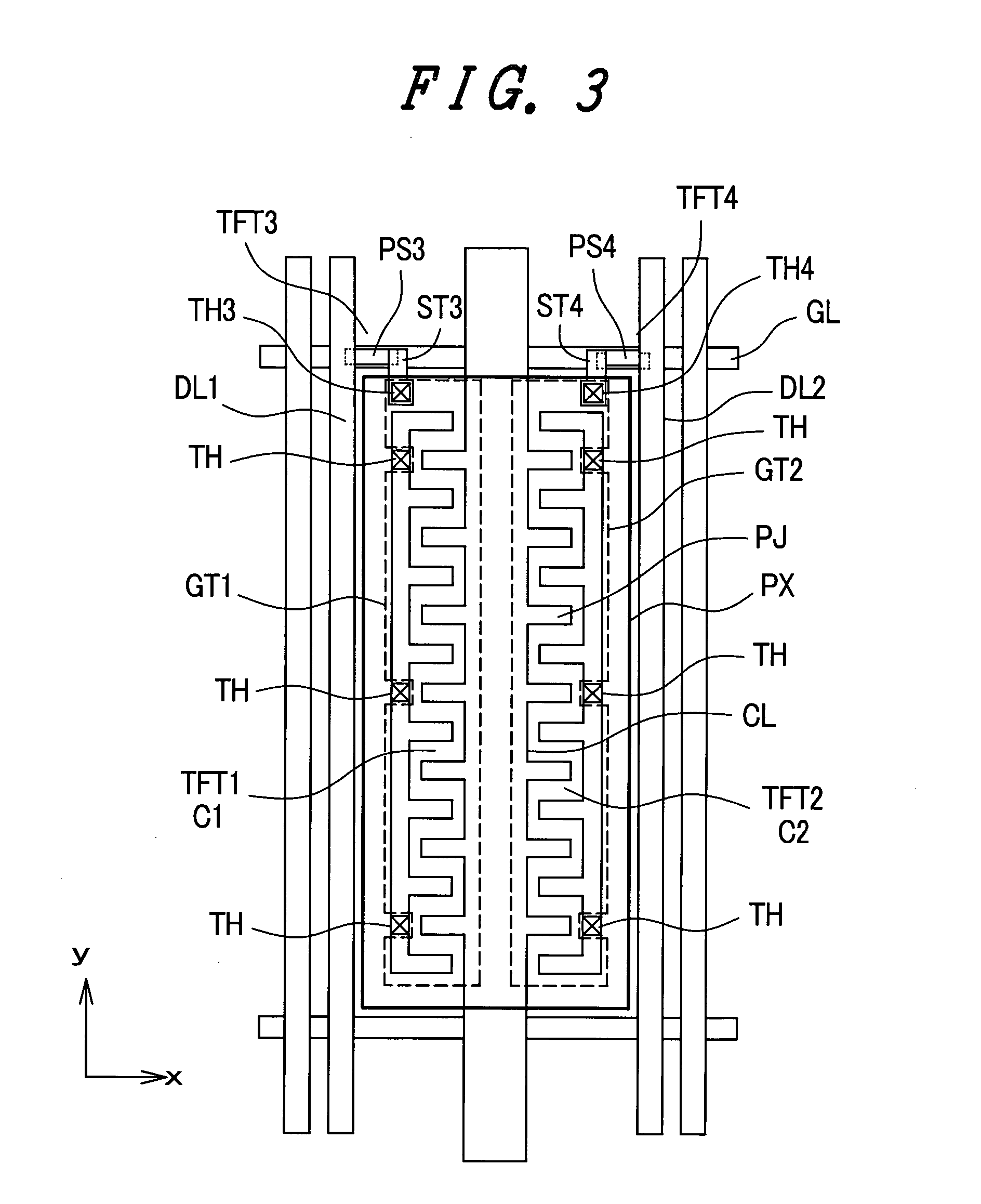

ActiveUS20060125741A1Improve mobilitySufficient quantityElectrical apparatusElectroluminescent light sourcesDisplay deviceData signal

The present invention enhances a display quality of a display device as a task. As means for solving such a task, the present invention provides a display device including a light emitting element and a switching element in a pixel, wherein the switching element is provided for supplying a power source to the light emitting element and is constituted of a first switching element and a second switching element. The first switching element and the second switching element are configured to be operated, in response to inputting of data signals into the inside of the pixel, one switching element assumes a positive bias state and another switching element assumes a reverse bias state, and the bias states are alternately changed over between the first switching element and the second switching element in response to time-sequential inputting of the data signals, and the supply of the power source to the light emitting element is performed by way of either one of the first switching element and the second switching element.

Owner:SAMSUNG DISPLAY CO LTD

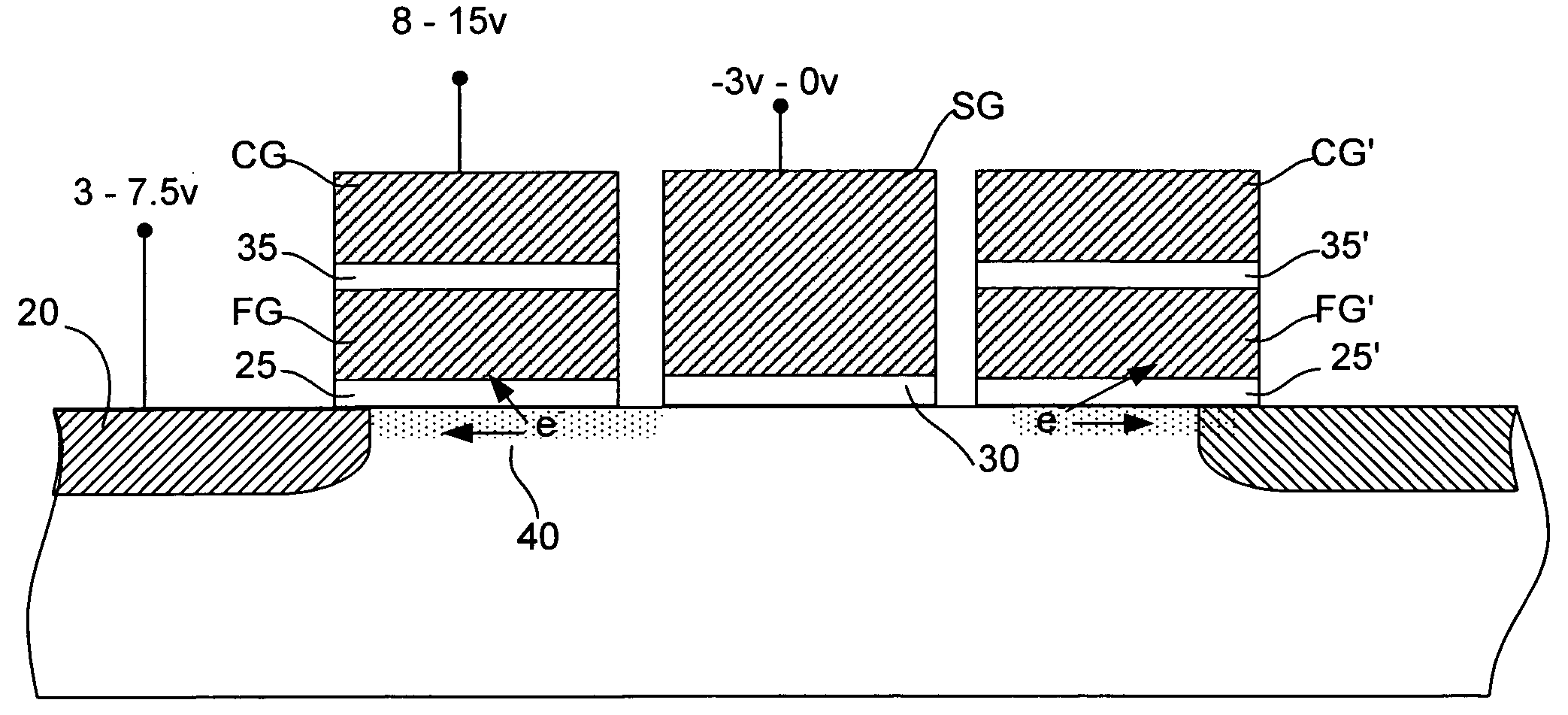

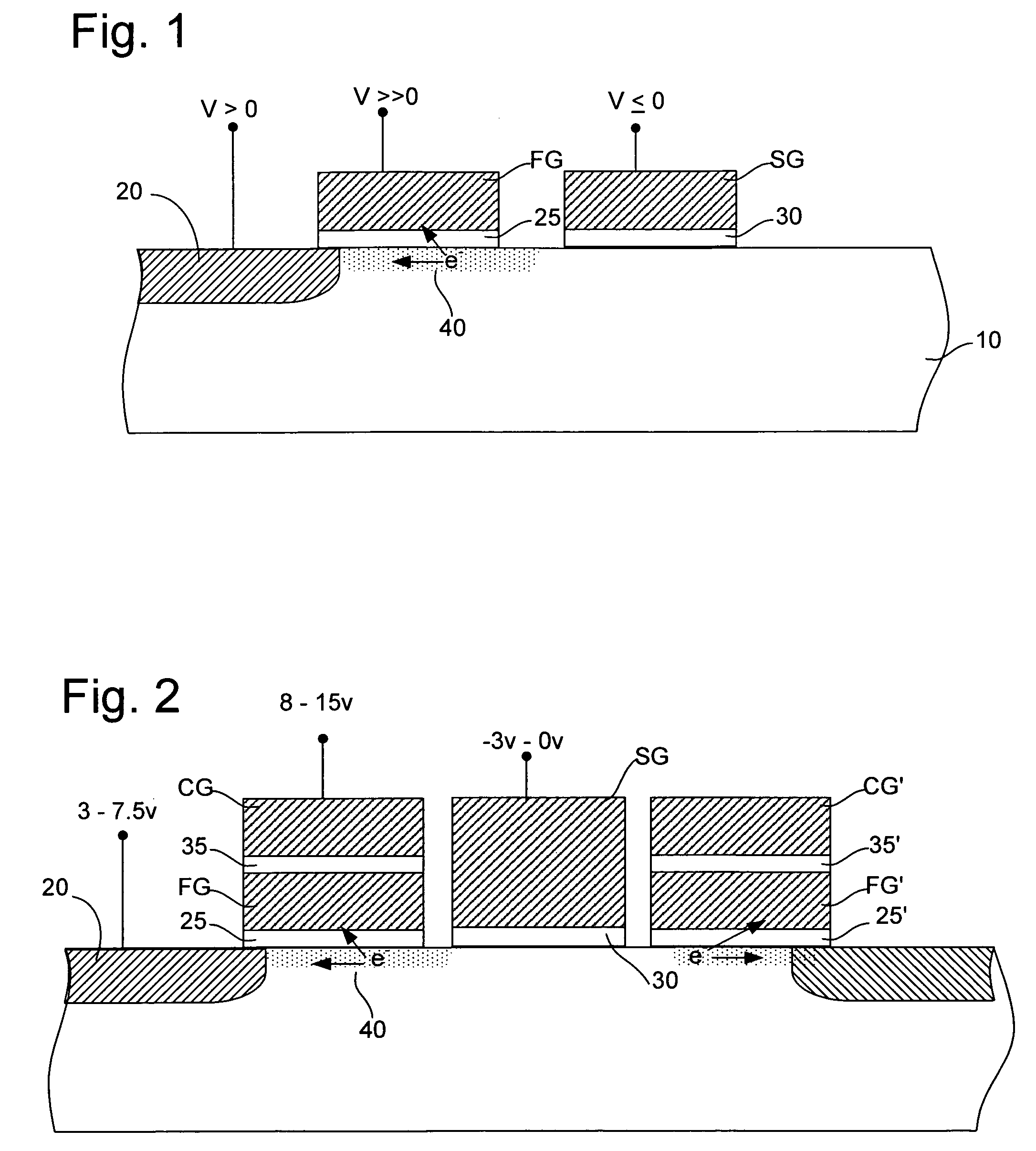

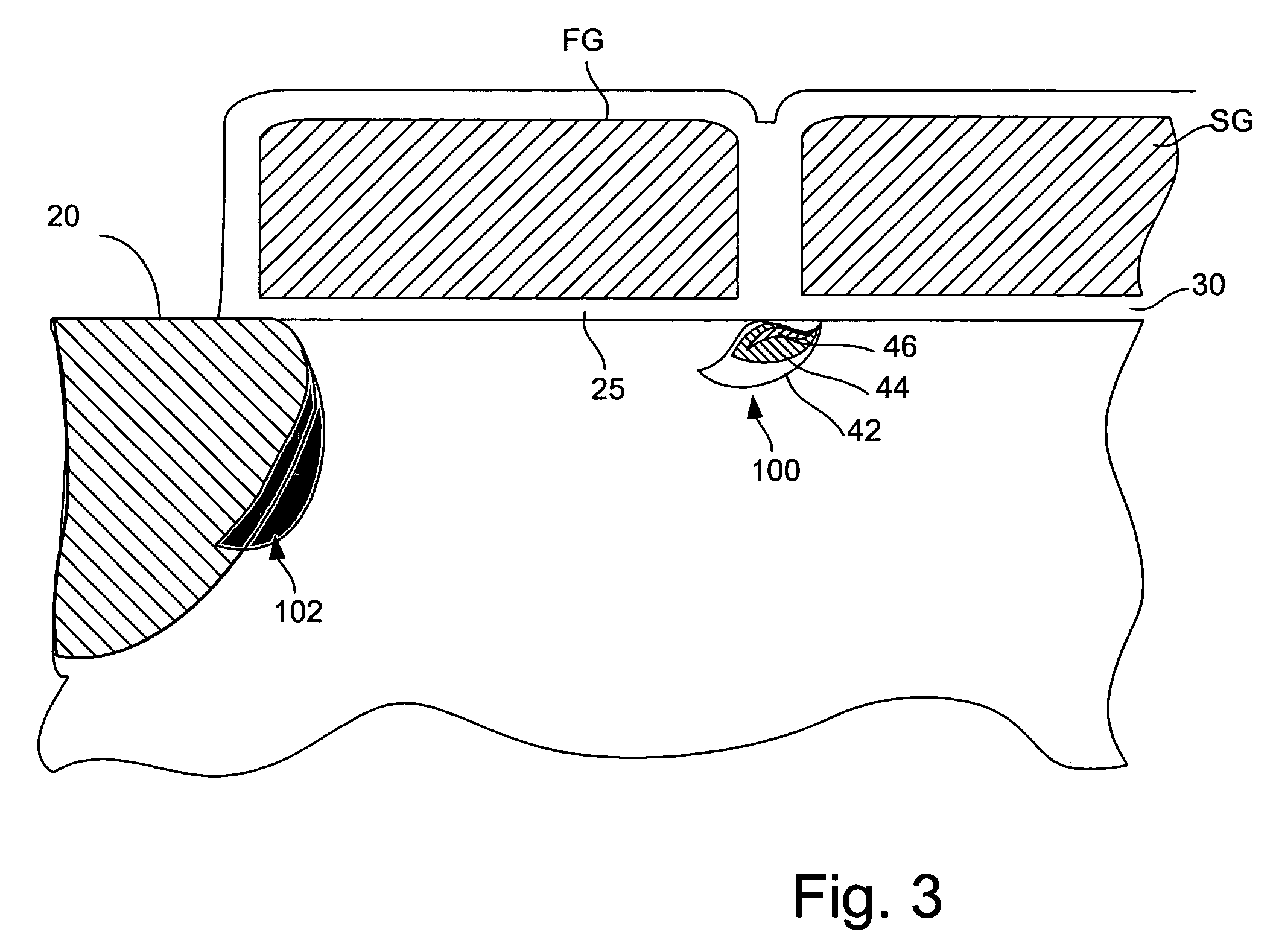

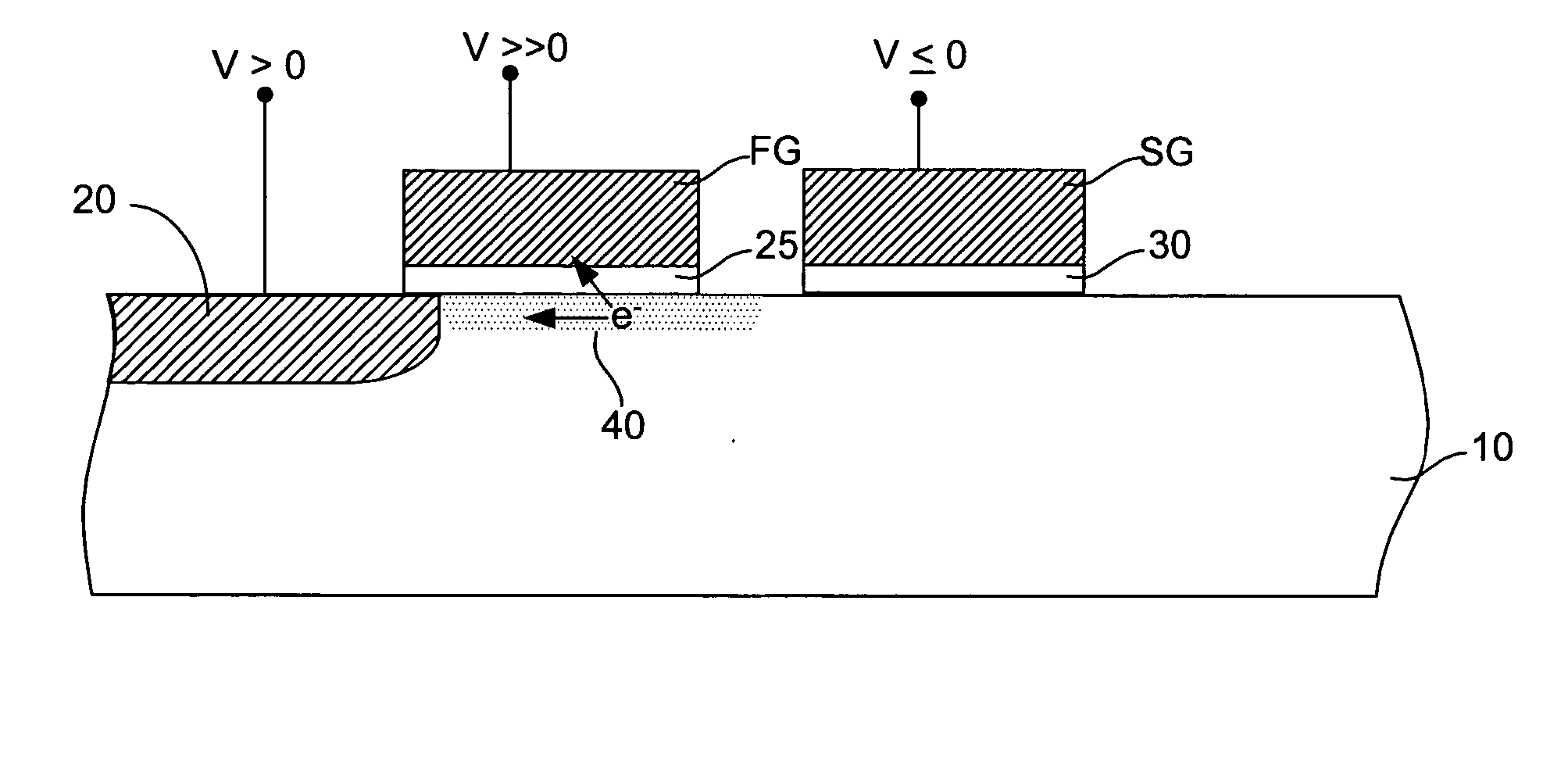

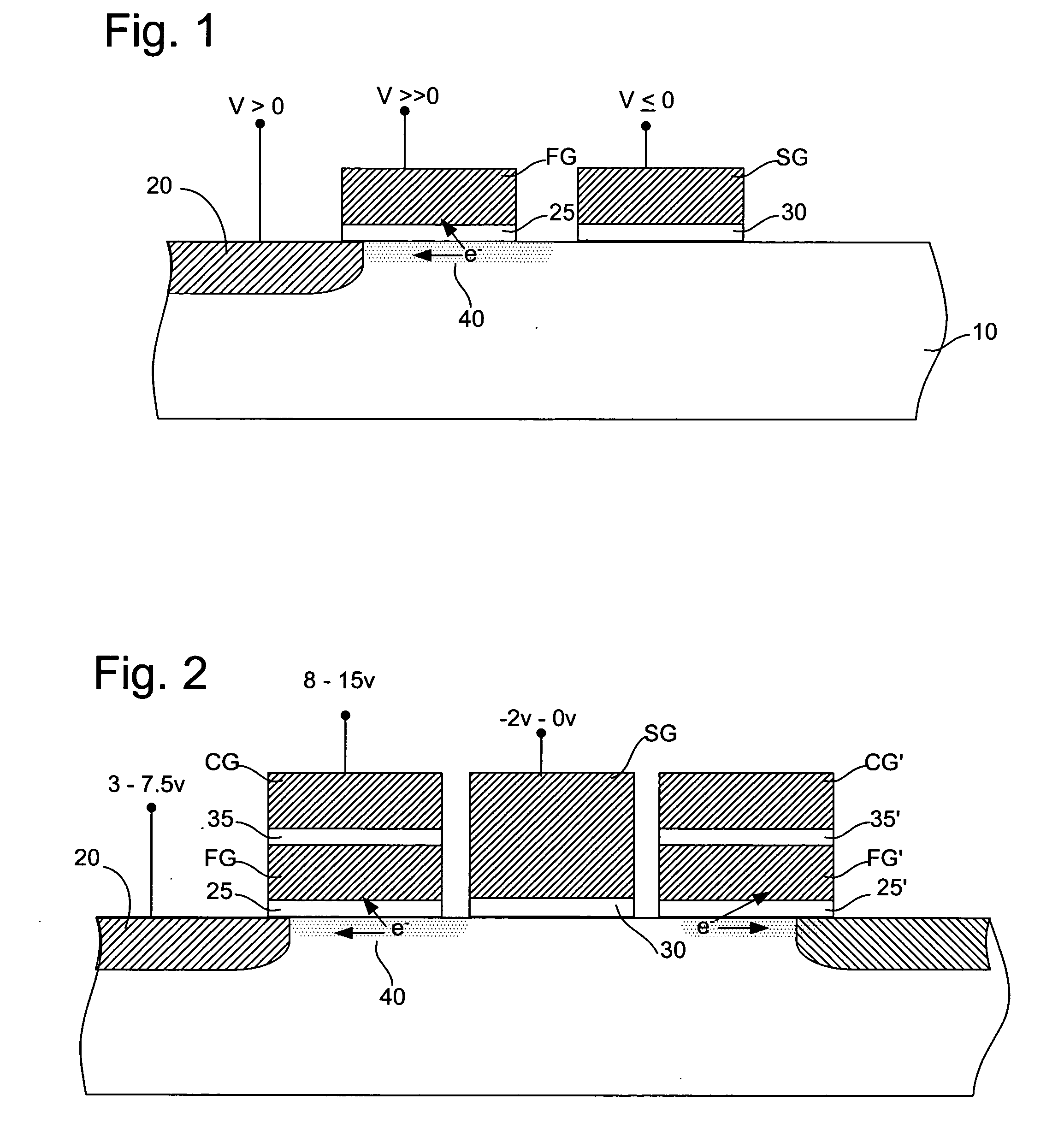

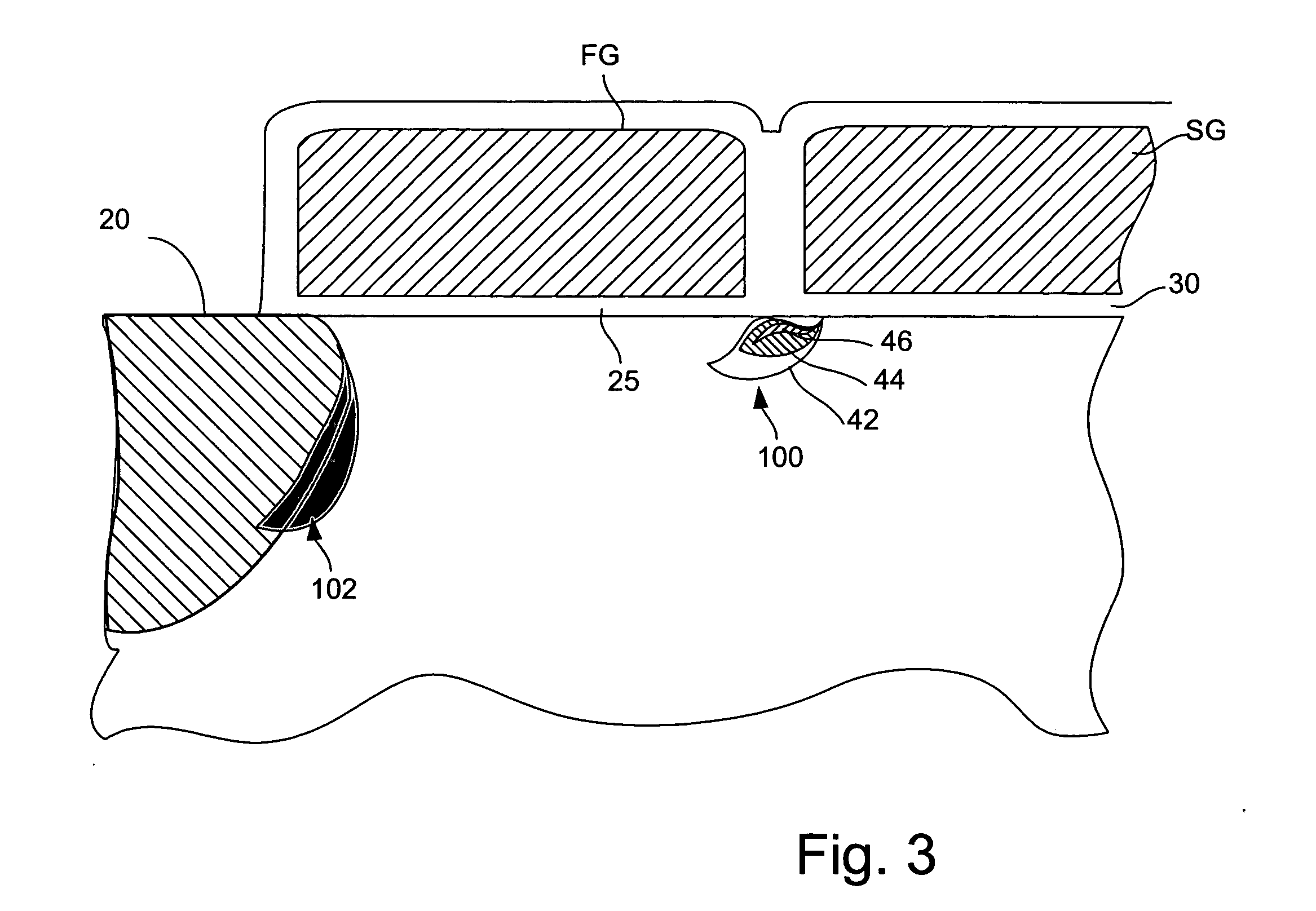

Flash memory programming using gate induced junction leakage current

A method for programming a storage element and a storage element programmed using gate induced junction leakage current are provided. The element may include at least a floating gate on a substrate, an active region in the substrate, and a second gate adjacent to the floating gate. The method may include the steps of: creating an inversion region in the substrate below the floating gate by biasing the first gate; and creating a critical electric field adjacent to the second gate. Creating a critical electric field may comprise applying a first positive bias to the active region; and applying a bias less than the first positive bias to the second gate. The element further includes a first bias greater than zero volts applied to the active region and a second bias greater than the first bias applied to the floating gate and a third bias less than or equal to zero applied to the second gate. The first and third bias are selected to create leakage current in the substrate between the floating gate and the select gate.

Owner:SANDISK TECH LLC

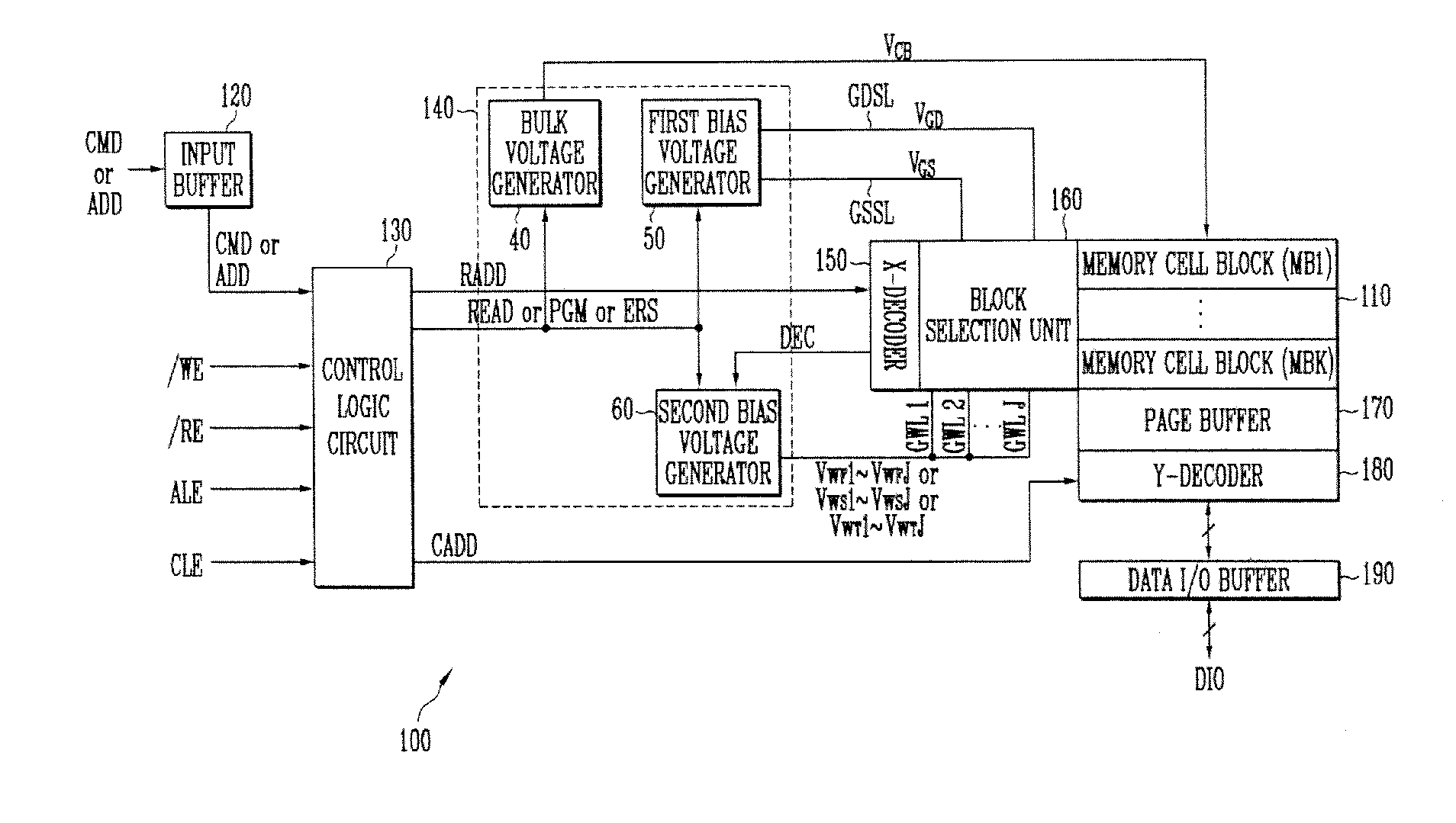

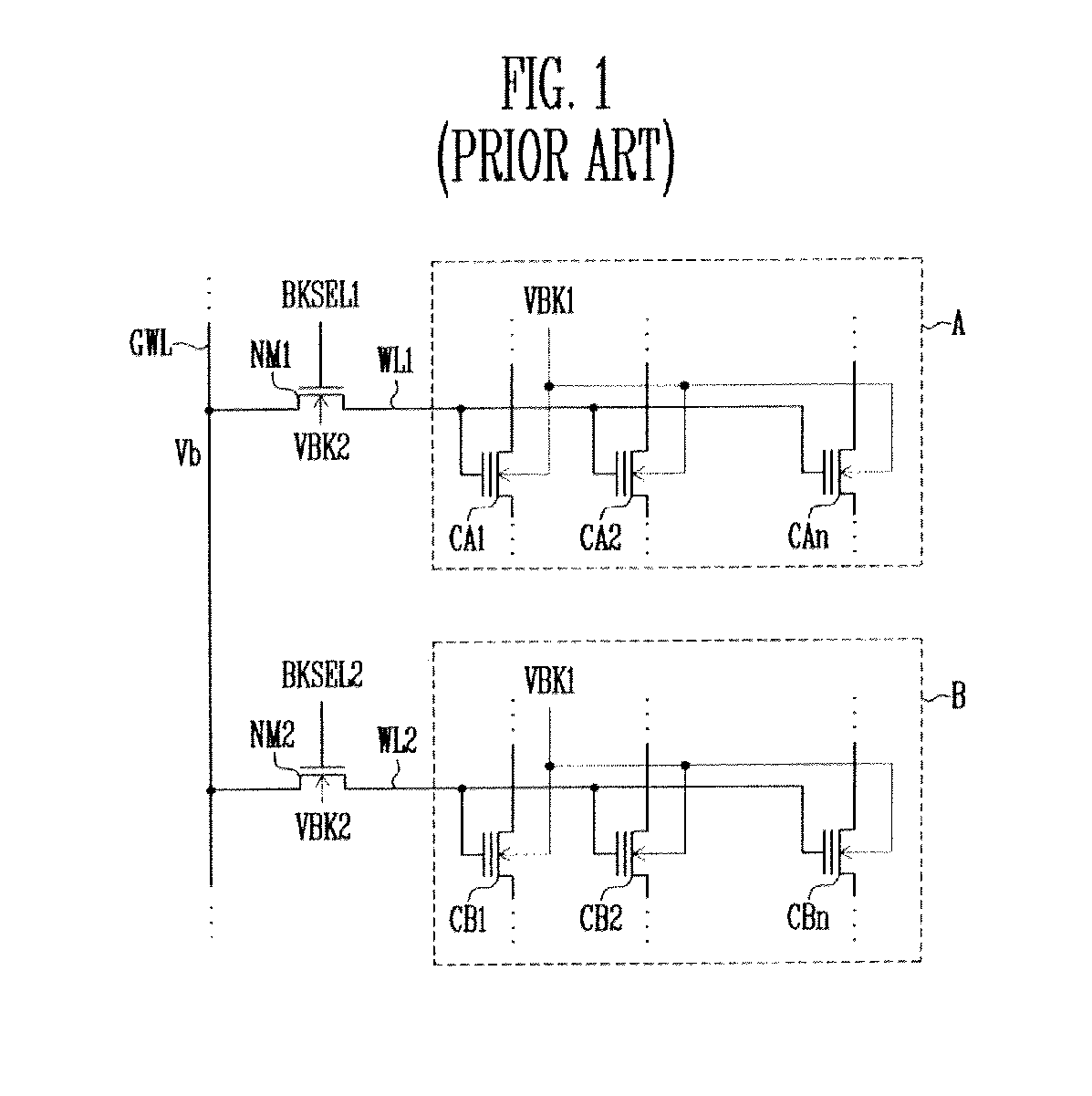

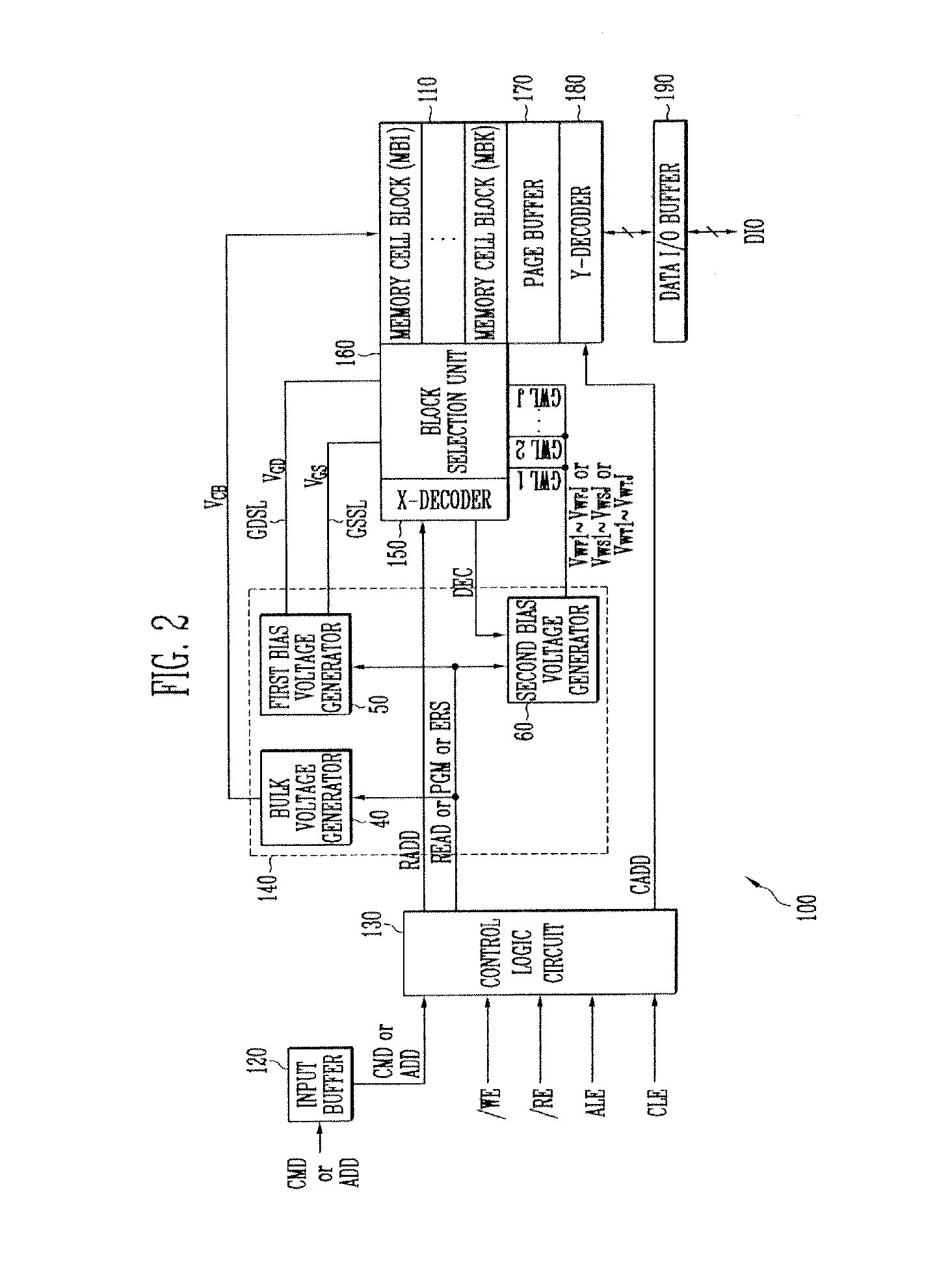

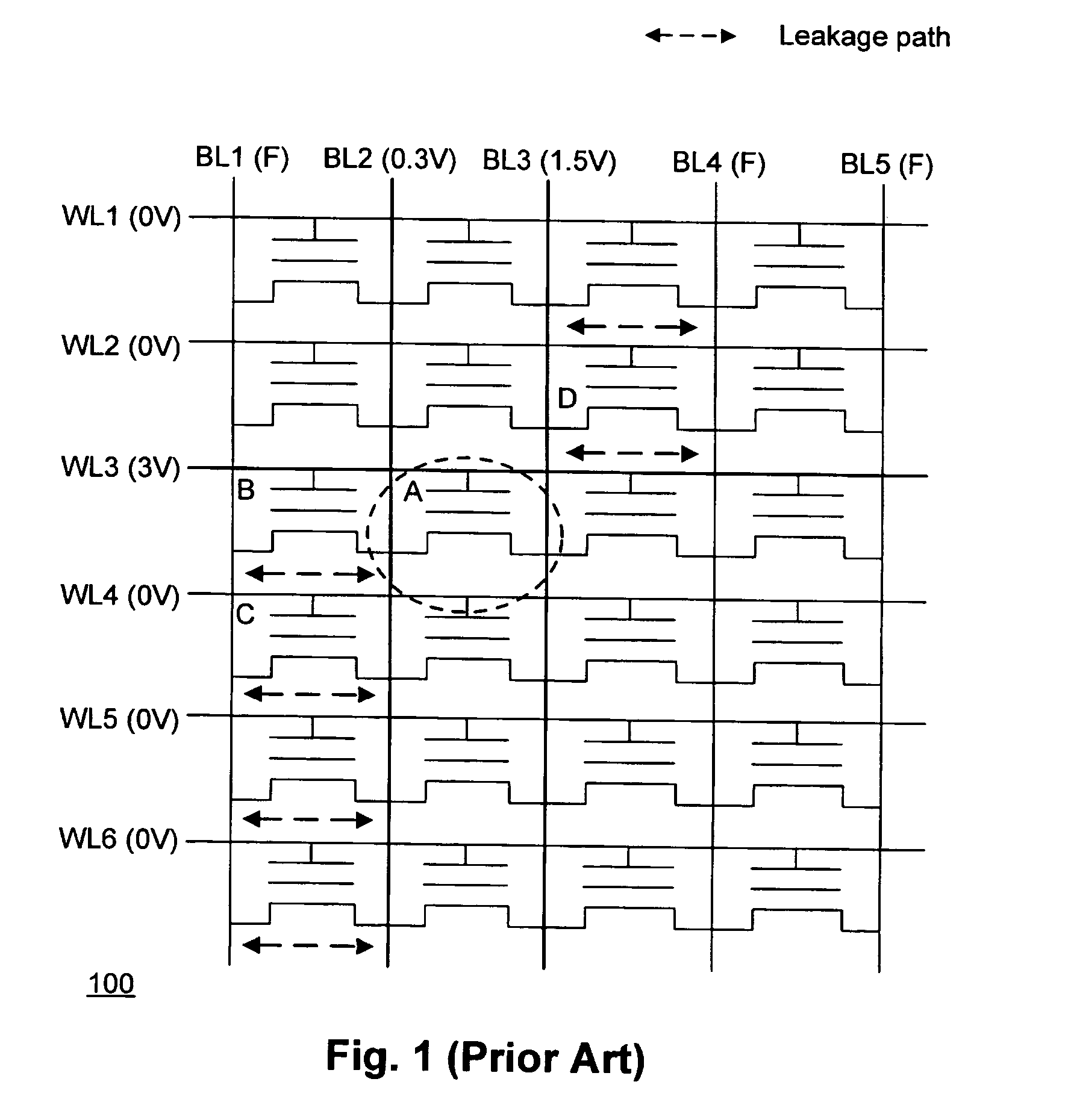

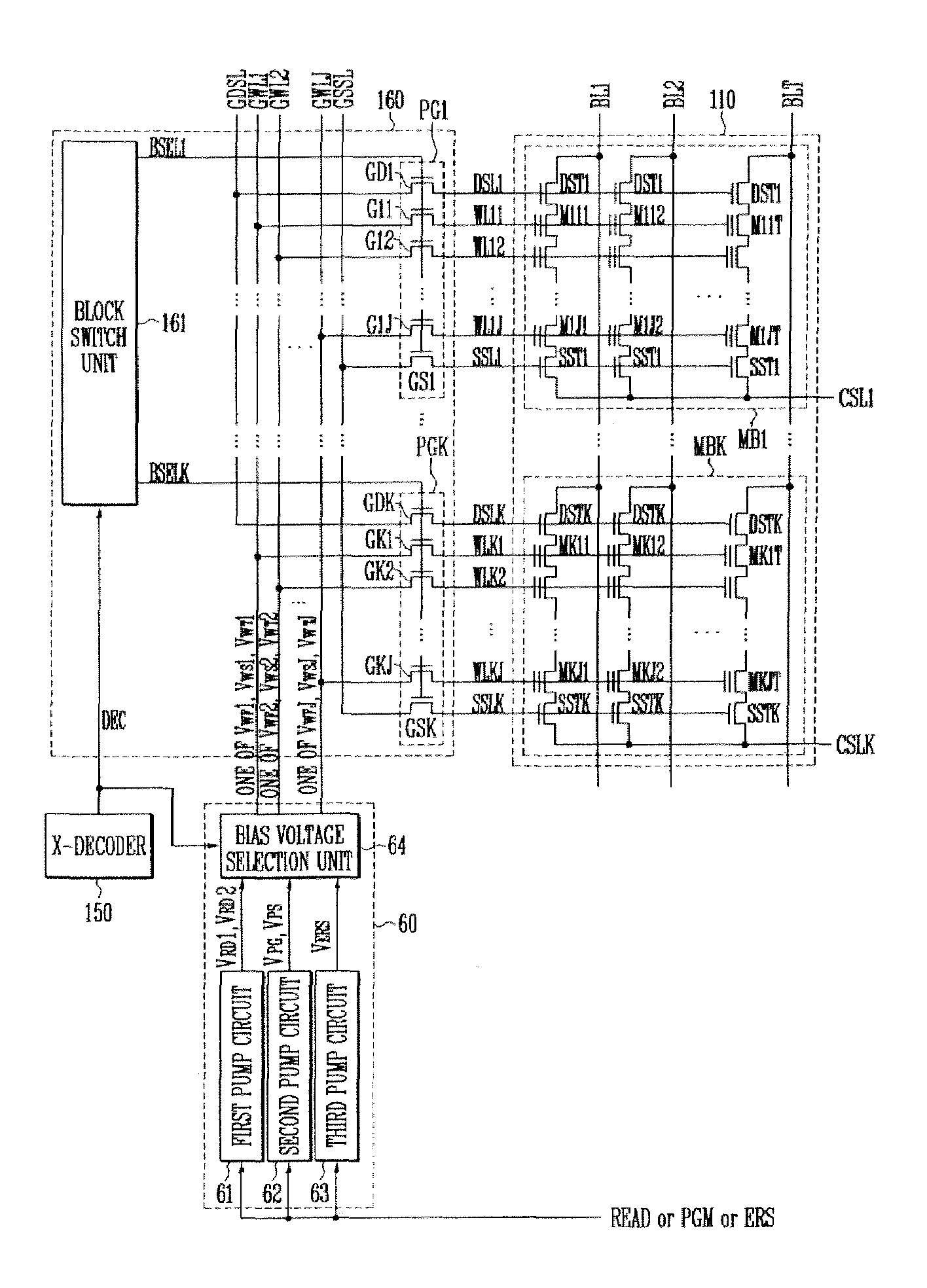

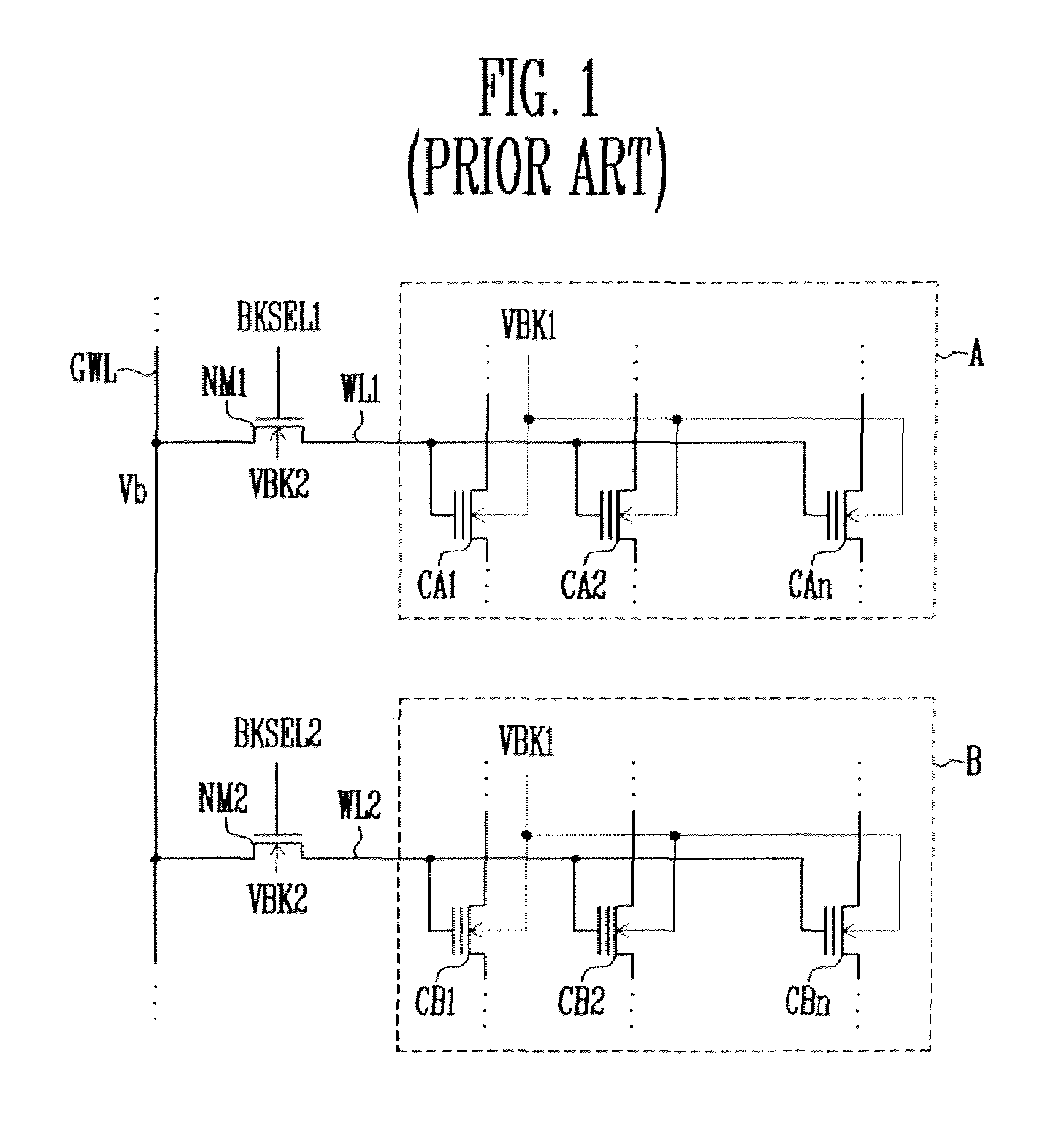

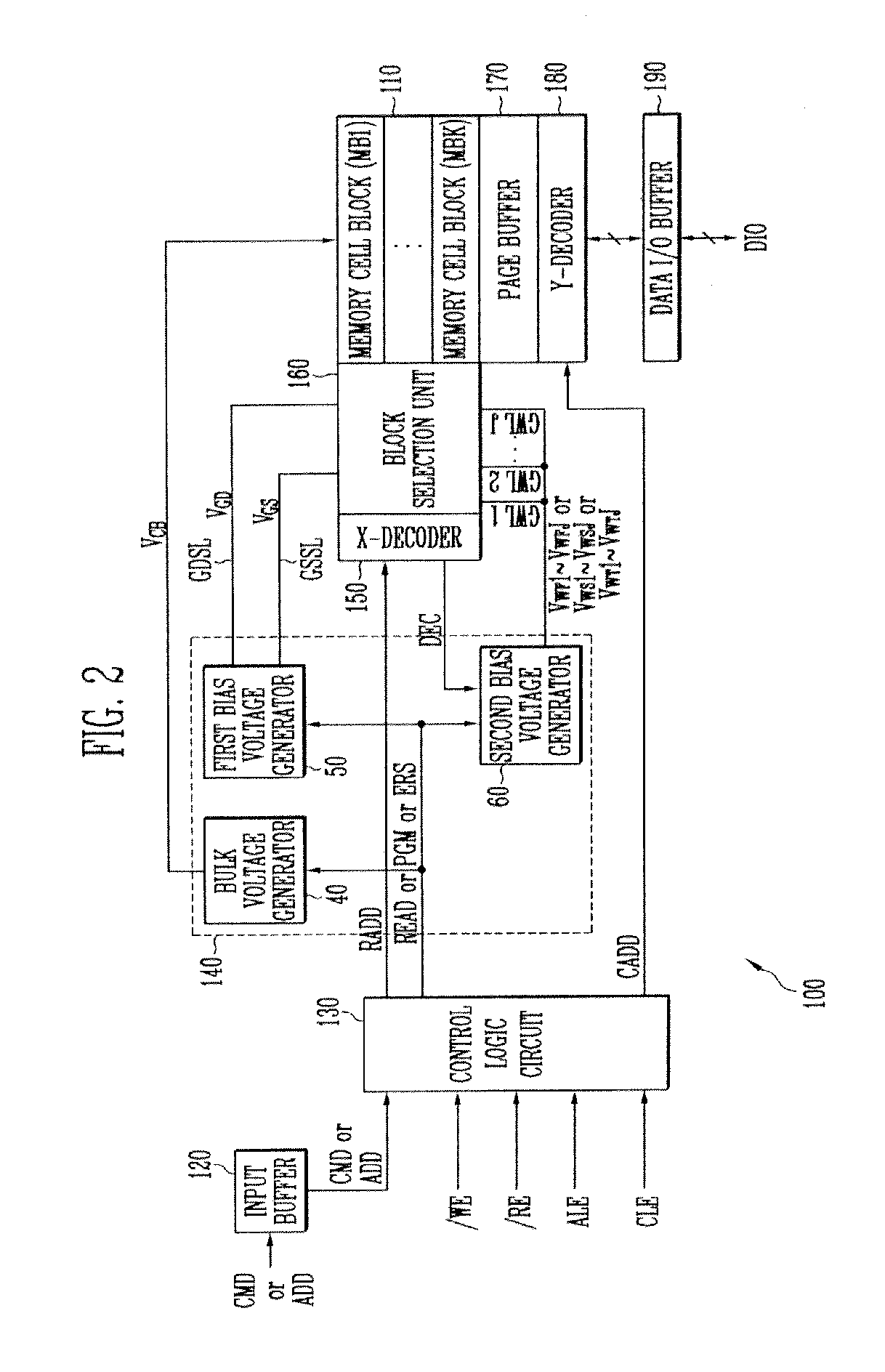

Flash Memory Device with Improved Erase Function and Method for Controlling Erase Operation of the Same

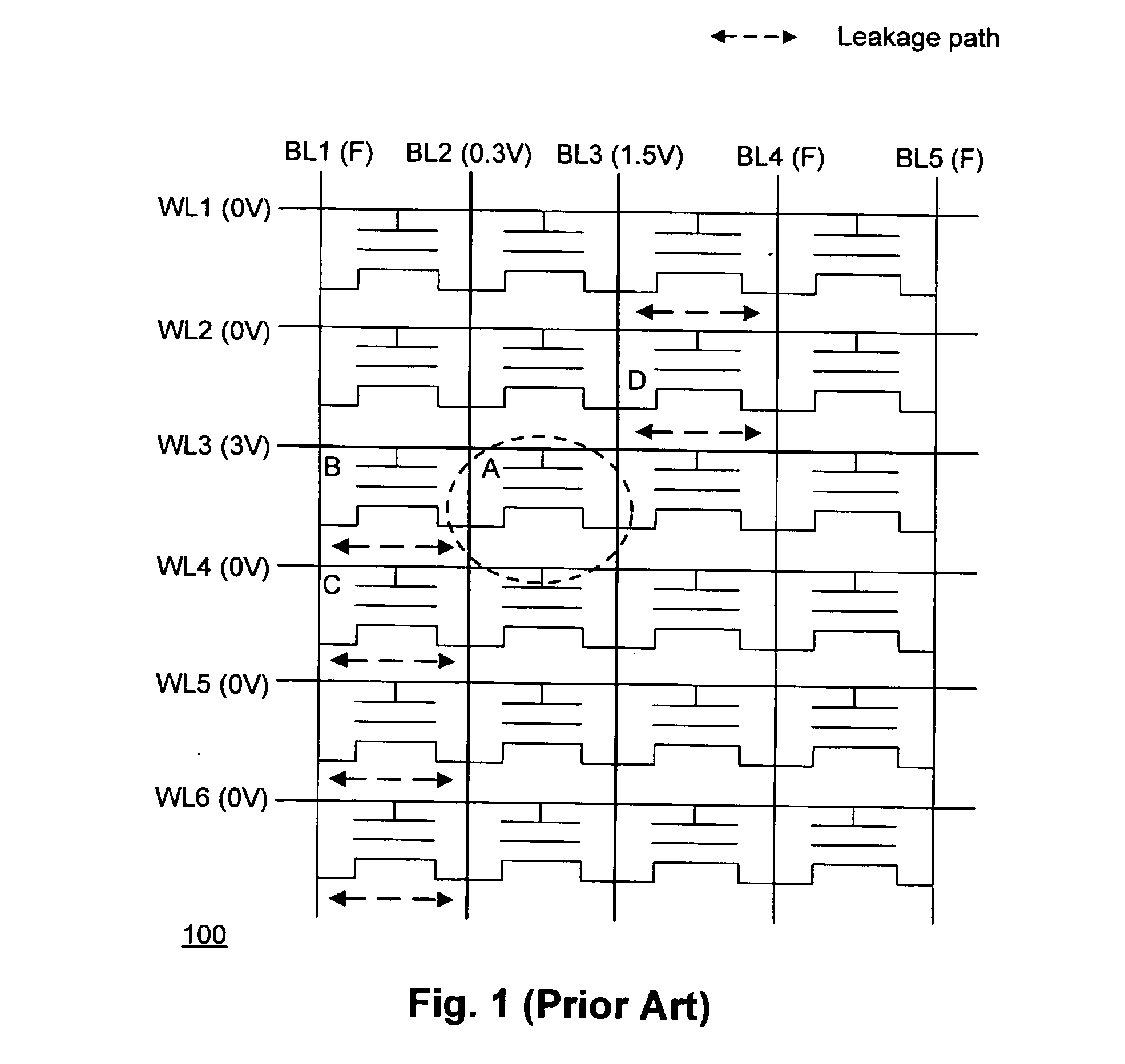

The present patent relates to flash memory devices with improved erase function, and method of controlling an erase operation of the same. According to the present patent, the flash memory device includes memory cell blocks, each having a plurality of memory cells sharing local word lines and bit lines, an X-decoder which decodes a row address signal and outputs the decoded signal, a block selection unit, which selects some of the memory cell blocks in response to the decoded signal, and connects local word lines of the selected memory cell blocks to corresponding global word lines, respectively, and a high voltage generator, which generates word line bias voltages in response to one of a read command, a program command and an erase command, and supplies the generated word line bias voltages to the global word lines in response to the decoded signal, respectively, wherein the word line bias voltages, which are generated by the high voltage generator in response to the erase command, have a positive value, respectively. Accordingly, a positive bias voltage is applied to a global word line in an erase operation. It is thus possible to prevent a shallow erase phenomenon of non-selected memory cell blocks due to the leakage current of pass gates.

Owner:SK HYNIX INC

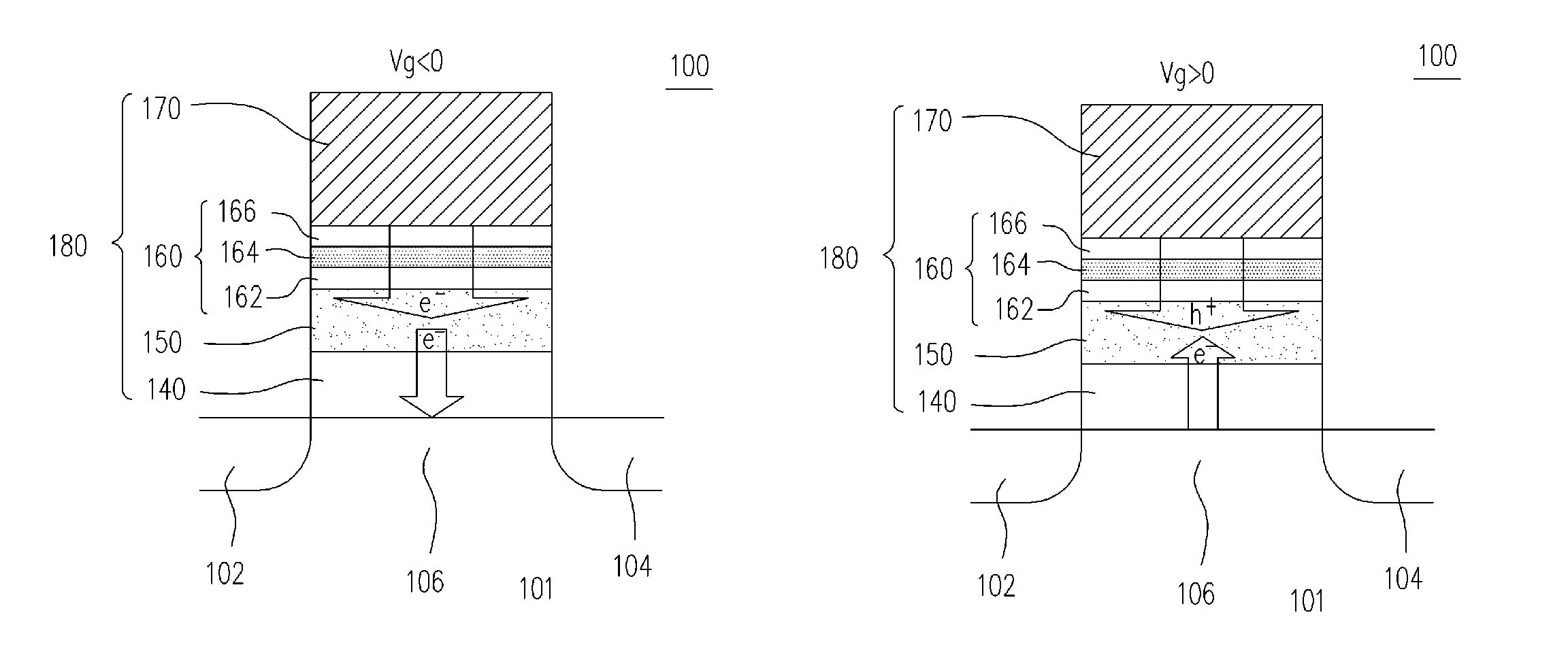

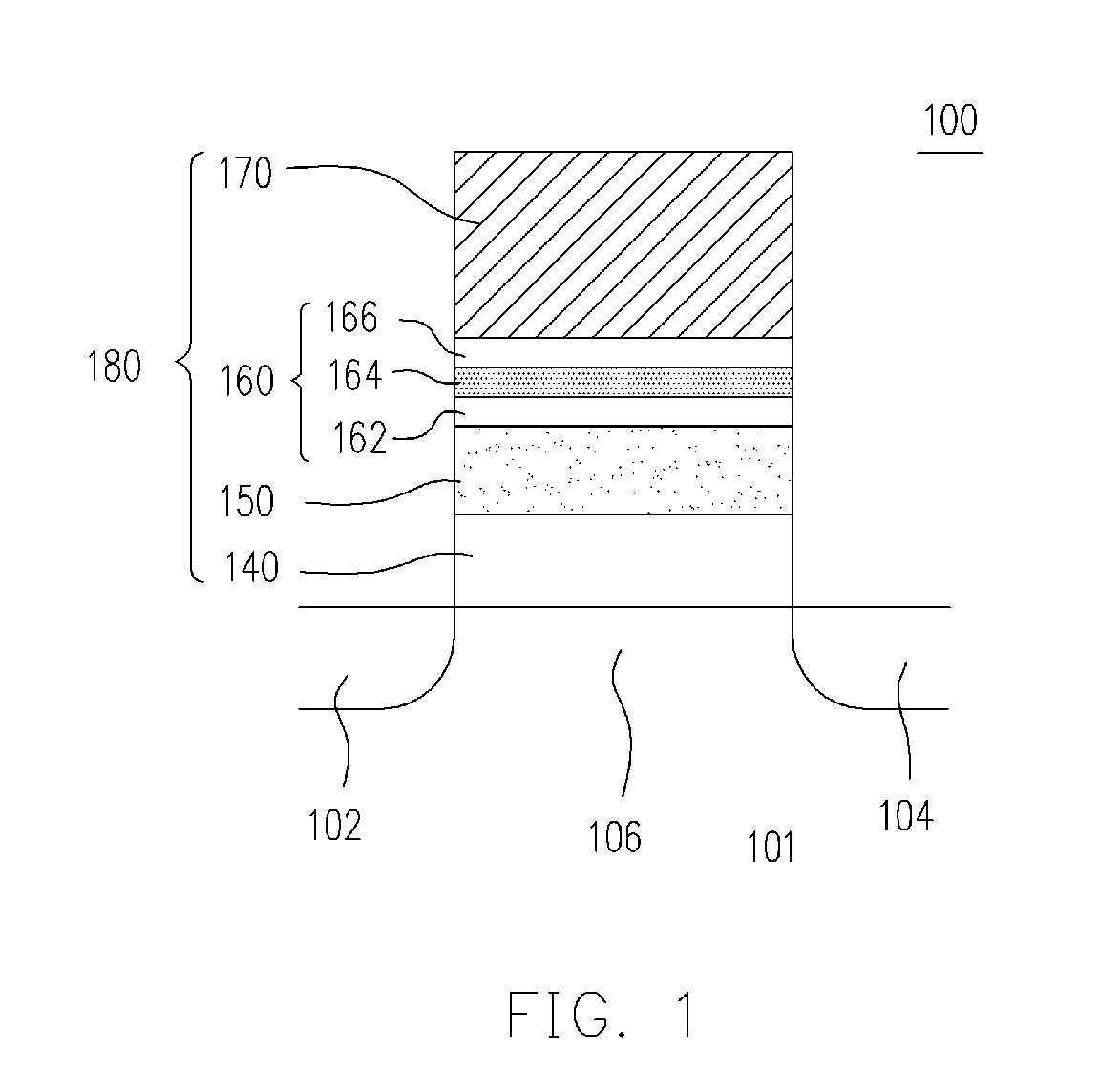

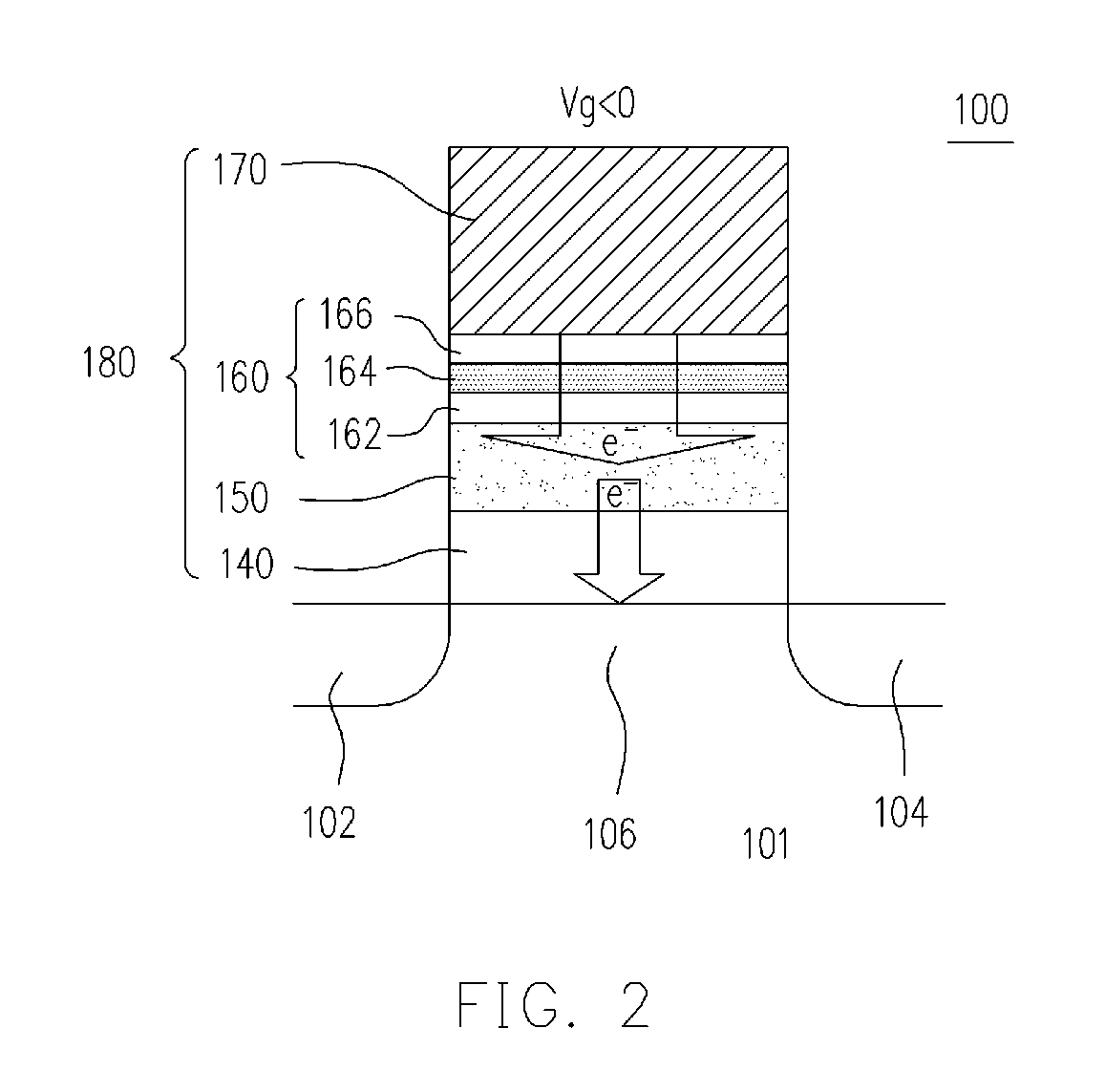

Operating method of non-volatile memory device

An operating method of non-volatile memory device is provided. The device includes memory cells having a semiconductor substrate, a stack layer, and source and drain regions disposed below a surface of the substrate and separated by a channel region. The stack layer includes an insulating layer disposed on the channel region, a charge storage layer disposed on the insulating layer, a multi-layer tunneling dielectric structure on the charge storage layer, and a gate disposed on the multi-layer tunneling dielectric structure. A negative bias is supplied to the gate to inject electrons into the charge storage layer through the multi-layer tunneling dielectric structure by −FN tunneling so that the threshold voltage of the device is increased. A positive bias is supplied to the gate to inject holes into the charge storage layer through the multi-layer tunneling dielectric structure by +FN tunneling so that the threshold voltage of the device is decreased.

Owner:MACRONIX INT CO LTD

Methods of operating p-channel non-volatile memory devices

ActiveUS7636257B2Negative biasDisturbing effectSolid-state devicesRead-only memoriesBit lineElectricity

Owner:MACRONIX INT CO LTD

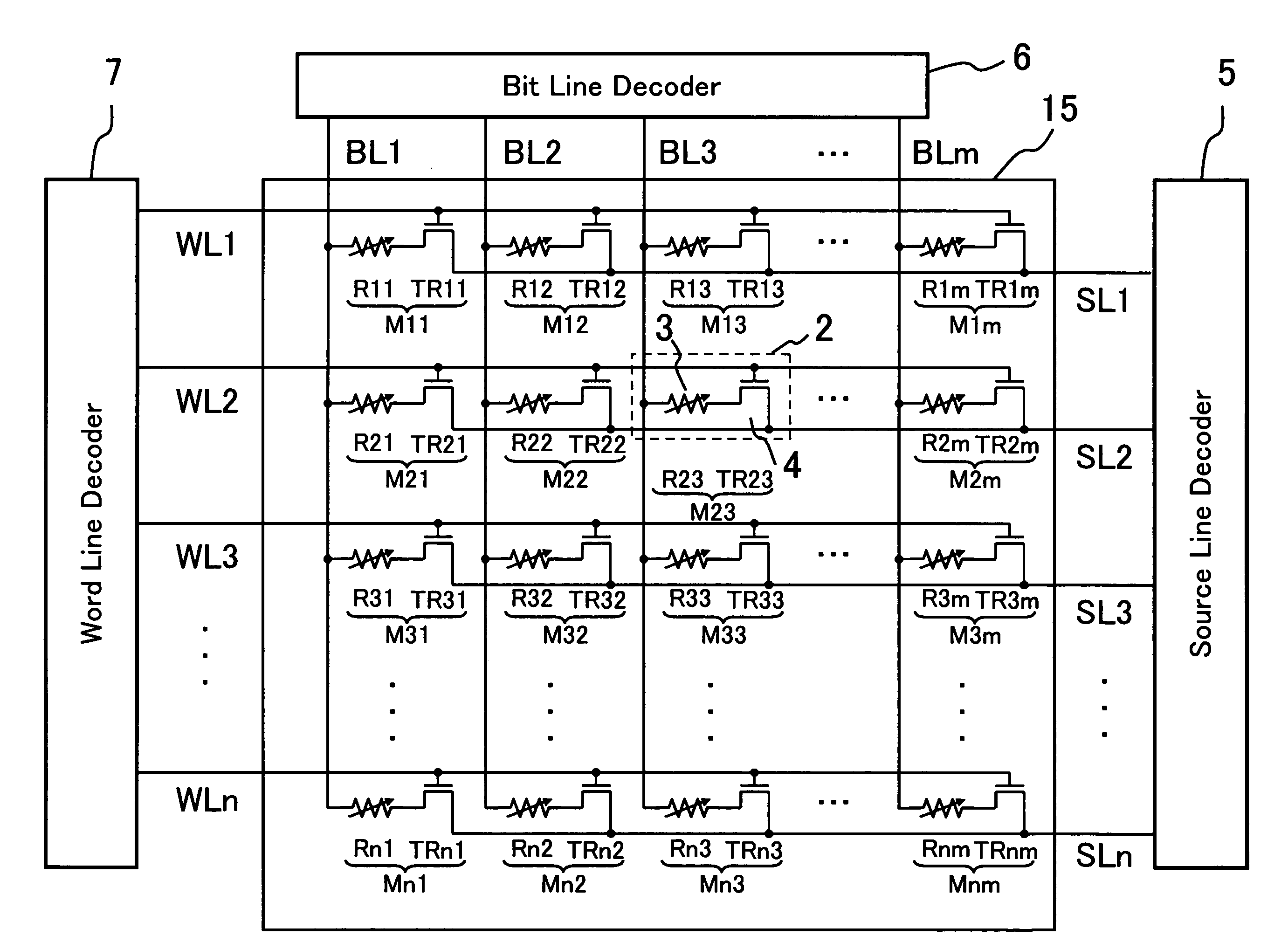

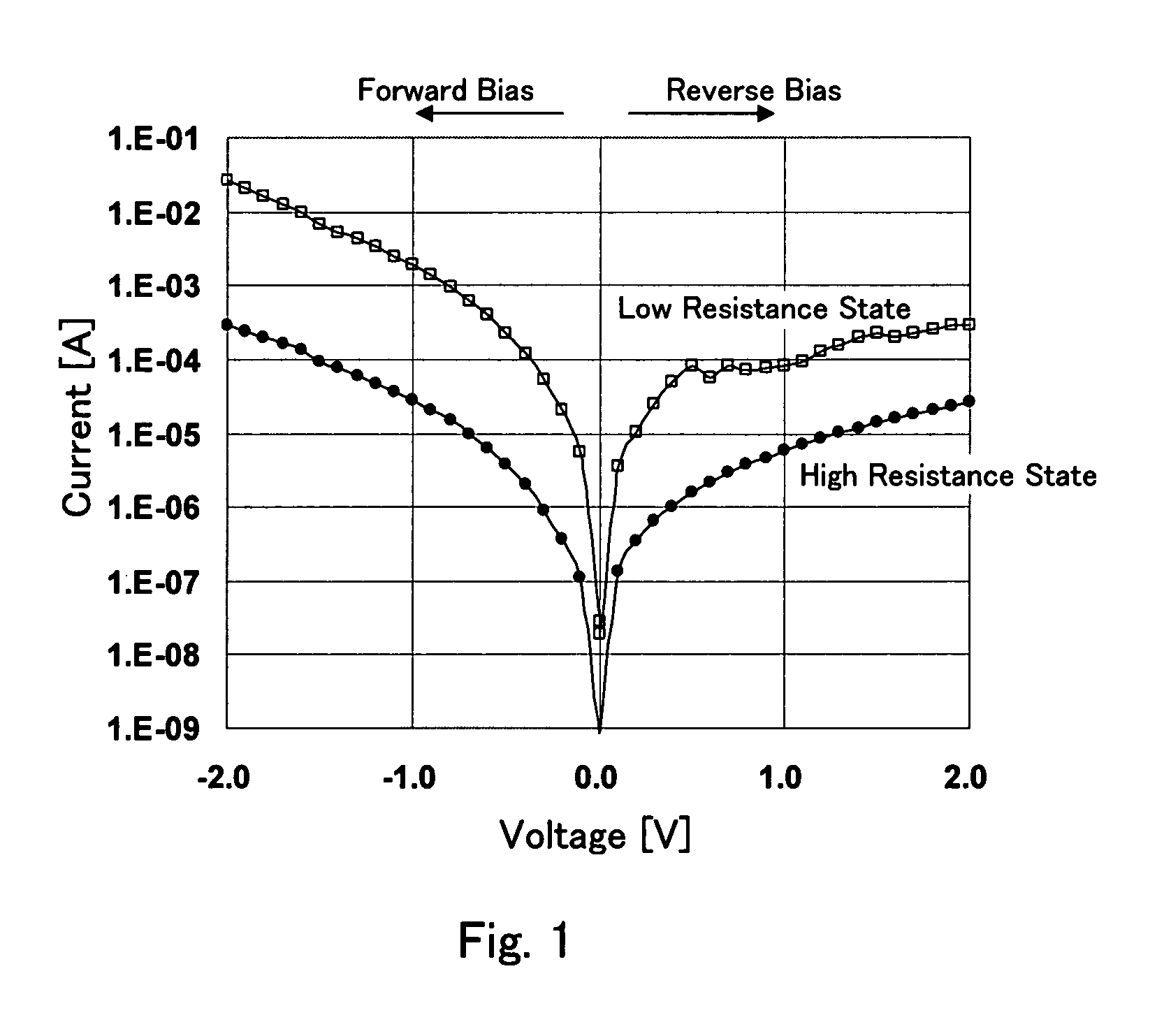

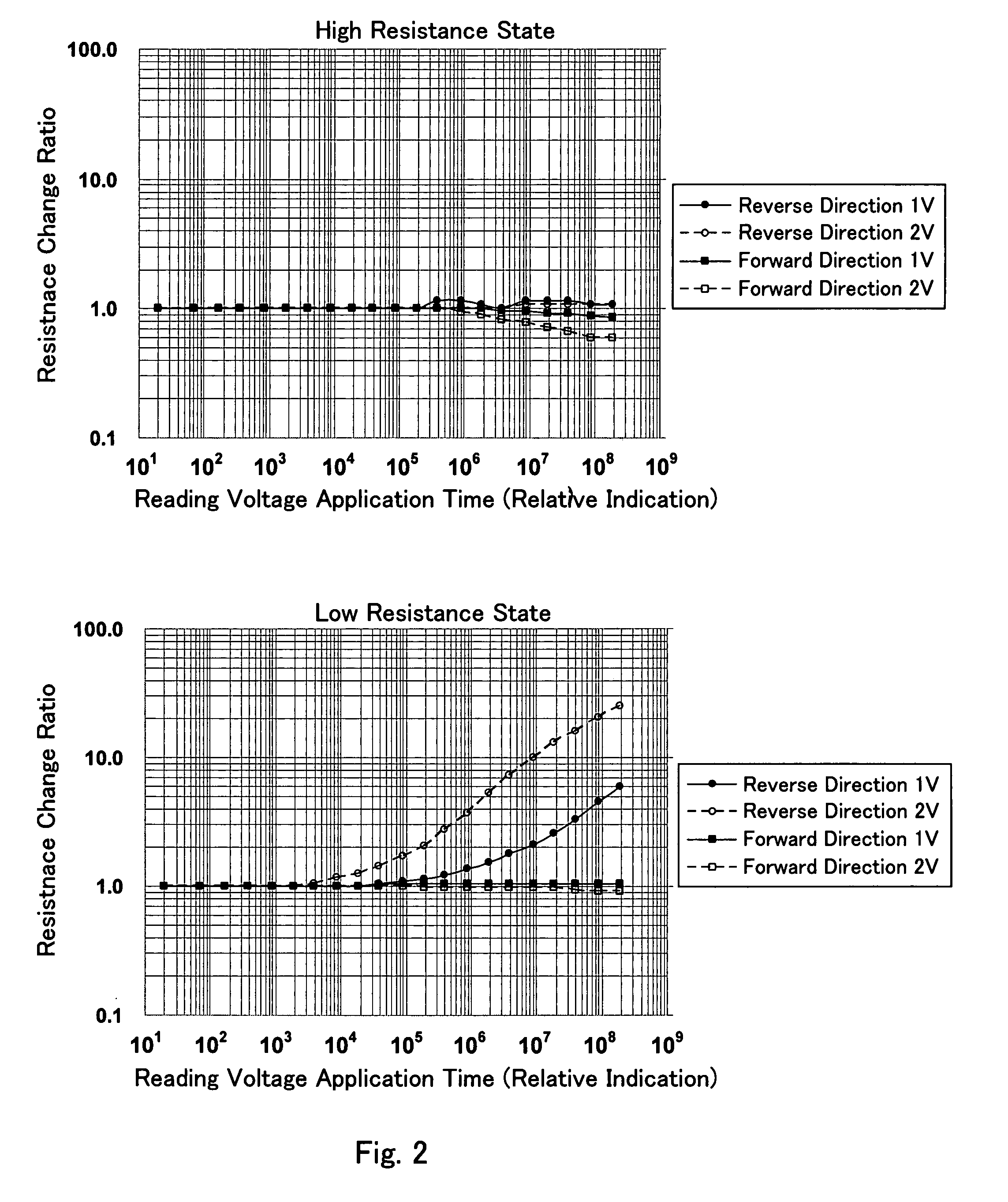

Nonvolatile semiconductor memory device

InactiveUS20080025072A1Keep reading marginAvoid changeRead-only memoriesDigital storageHemt circuitsEngineering

A nonvolatile semiconductor memory device comprises a memory cell including a variable resistance element changing its electric resistance by voltage application and having current-voltage characteristics in which a positive bias current flowing when a positive voltage is applied from one electrode as a reference electrode to the other electrode through an incorporated rectifier junction is larger than a negative bias current, a memory cell selection circuit for selecting the memory cell from the memory cell array, a voltage supply circuit for supplying a voltage to the memory cell so that a predetermined positive voltage corresponding to the reading operation is applied to the other electrode of the variable resistance element, in the reading operation, and a readout circuit for detecting the amount of the positive bias current and reading the information stored in the selected memory cell, in order to suppress the reading disturbance of the memory cell.

Owner:SHARP KK +1

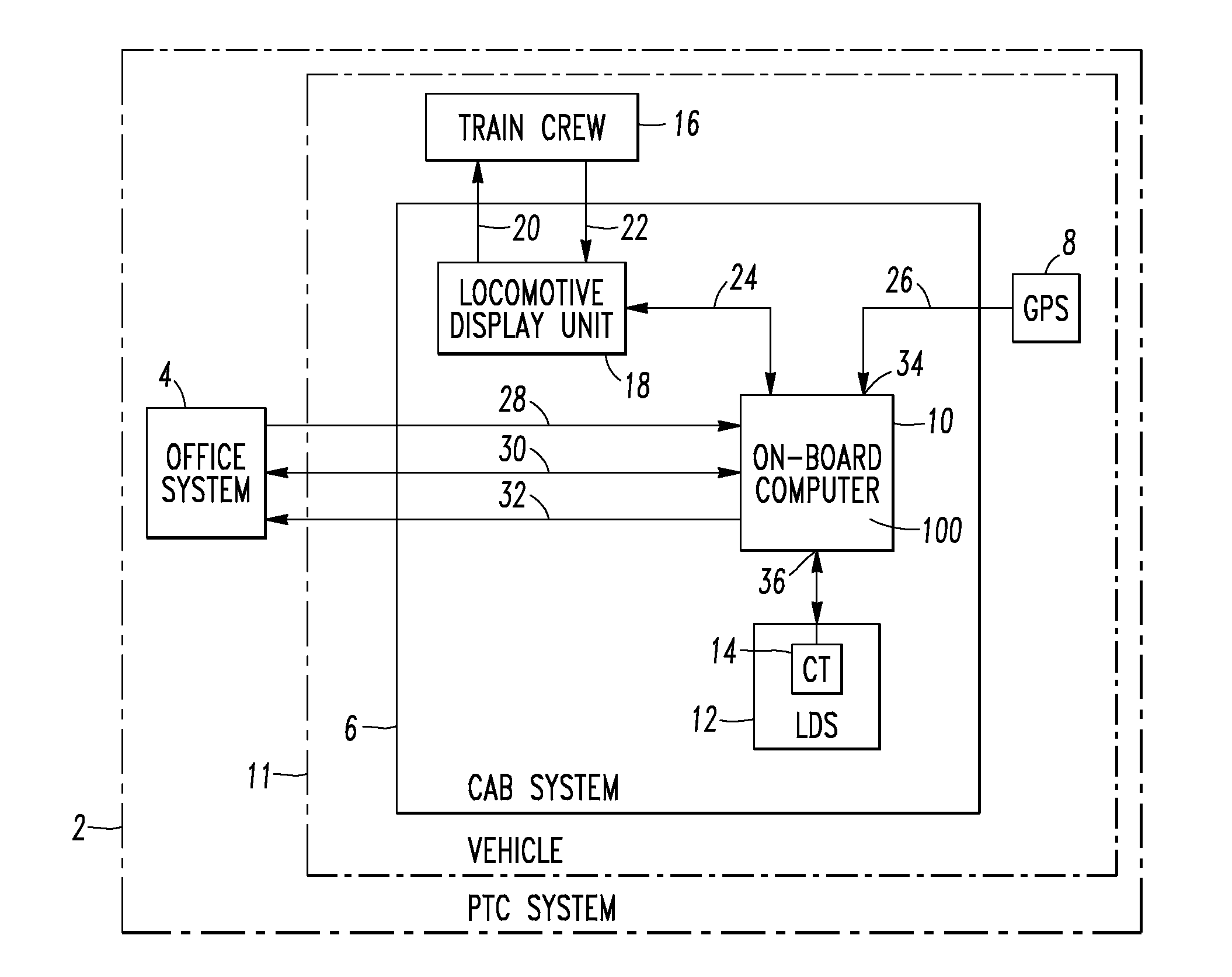

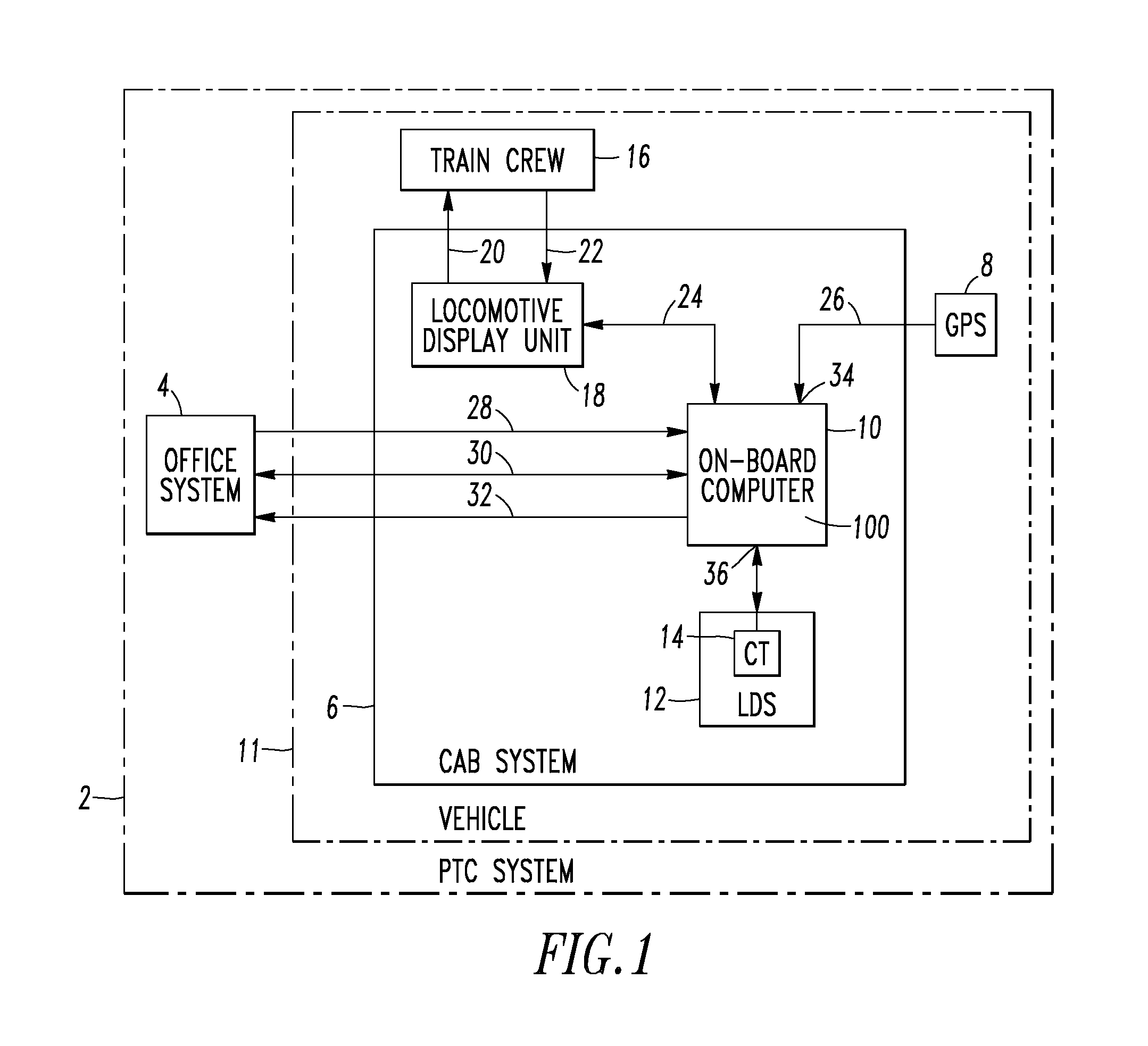

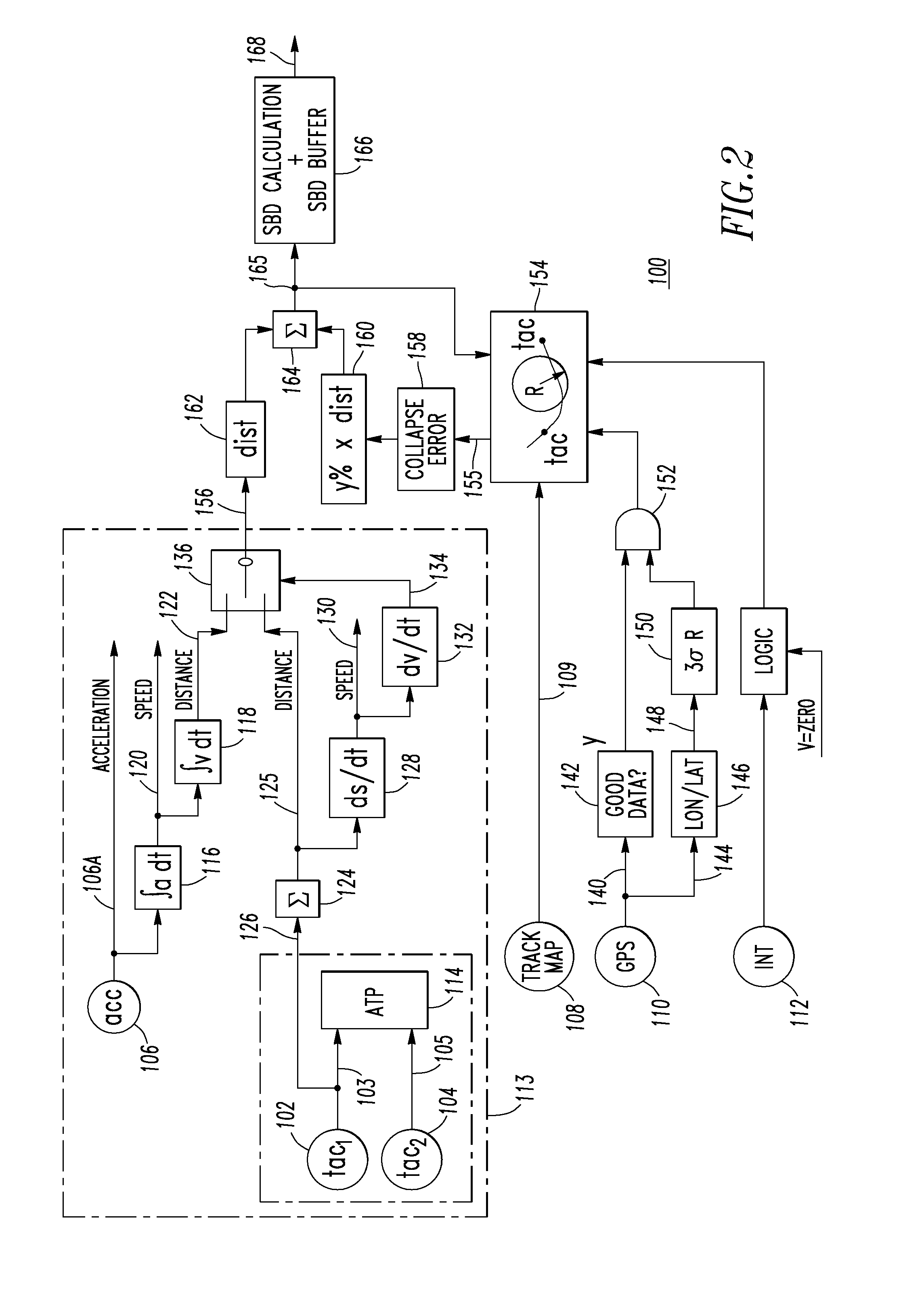

Vital system for determining location and location uncertainty of a railroad vehicle with respect to a predetermined track map using a global positioning system and other diverse sensors

ActiveUS7966126B2Road vehicles traffic controlRailway signalling and safetyEngineeringGlobal positioning system receiver

A system includes a global positioning system receiver to determine position of a railroad vehicle, a predetermined track map of possible coordinates of the vehicle, motion sensors providing a positive bias error to determine change in location of the vehicle, an acceleration sensor to determine acceleration of the vehicle, and a processor to vitally determine the location and the location uncertainty of the vehicle on the track map. The processor verifies one motion sensor with another motion sensor, determines a slip or slide condition of the vehicle from one of the motion sensors, determines speed and position of the vehicle from the acceleration sensor during the slip or slide condition, verifies the position of the vehicle from the global positioning system receiver based upon the track map, and corrects the positive bias error of the motion sensors using the position of the vehicle from the global positioning system receiver.

Owner:ANSALDO STS USA INC

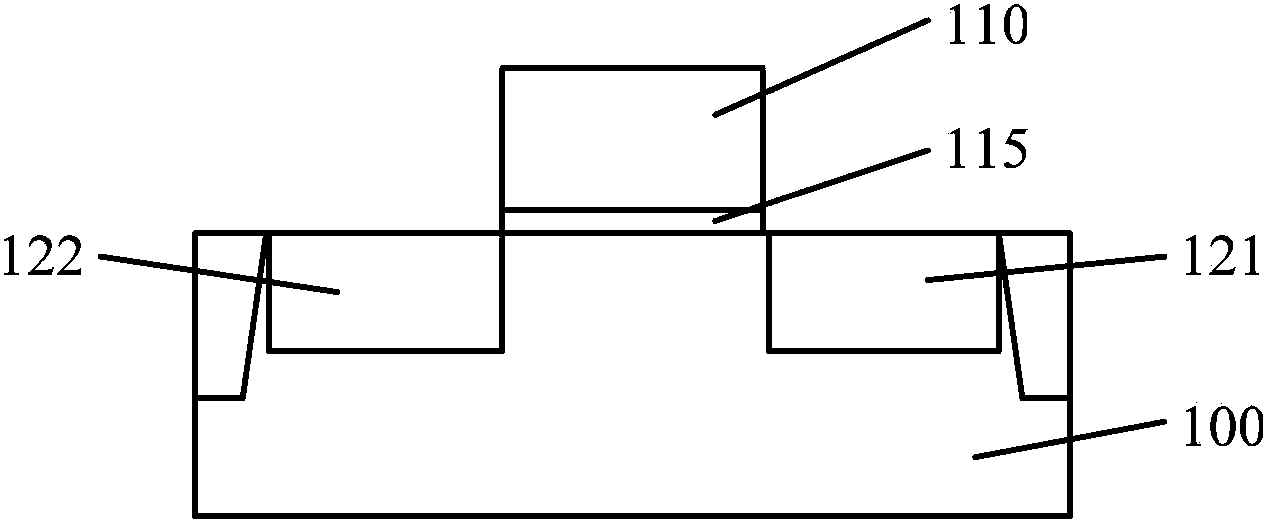

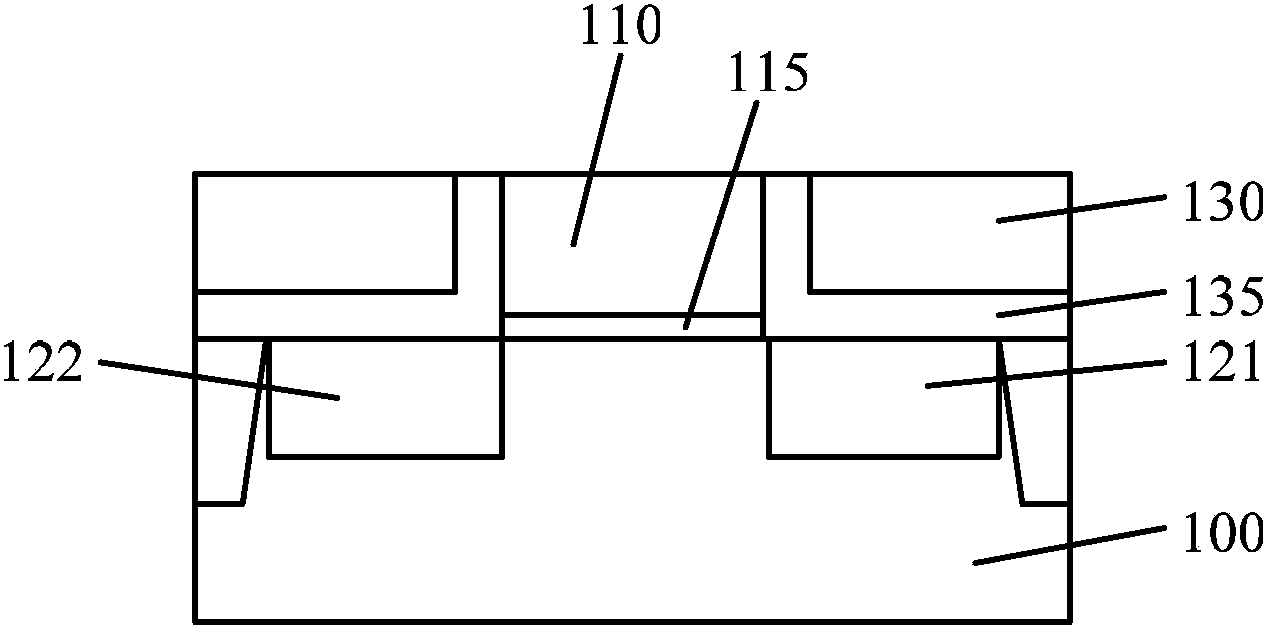

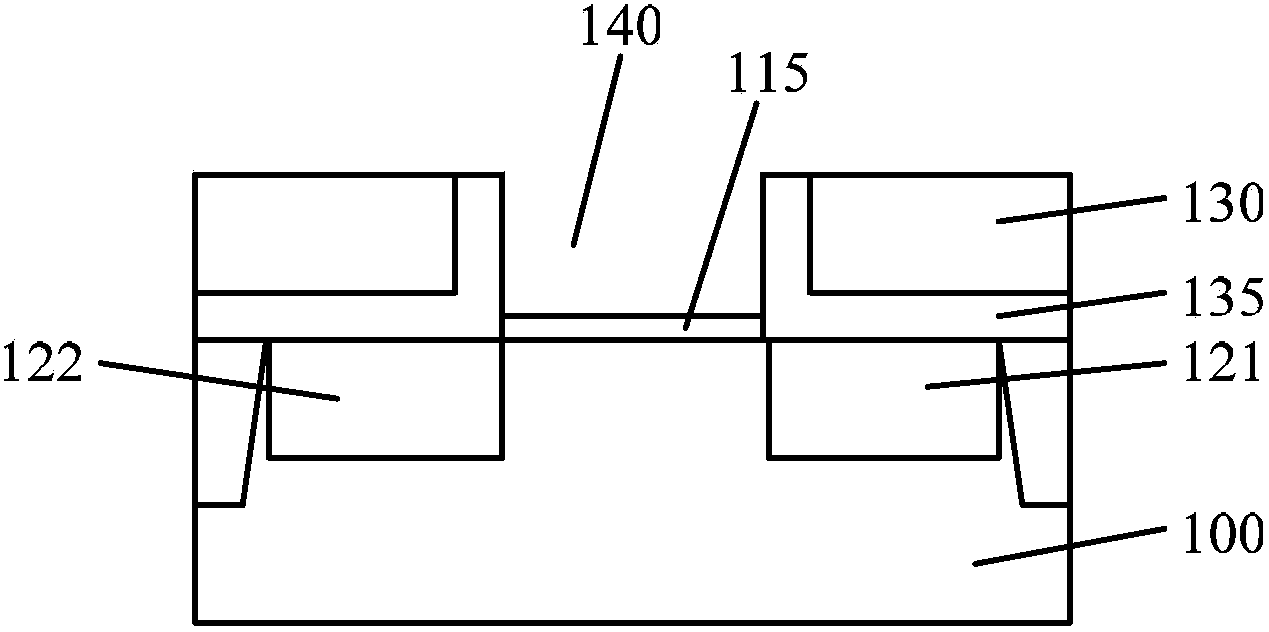

Forming method of metal gate, forming method of MOS transistor and forming method of CMOS structure

ActiveCN103681276AStrong oxidation abilityReduced negative bias temperature instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesBond energyOxygen vacancy

Owner:SEMICON MFG INT (SHANGHAI) CORP

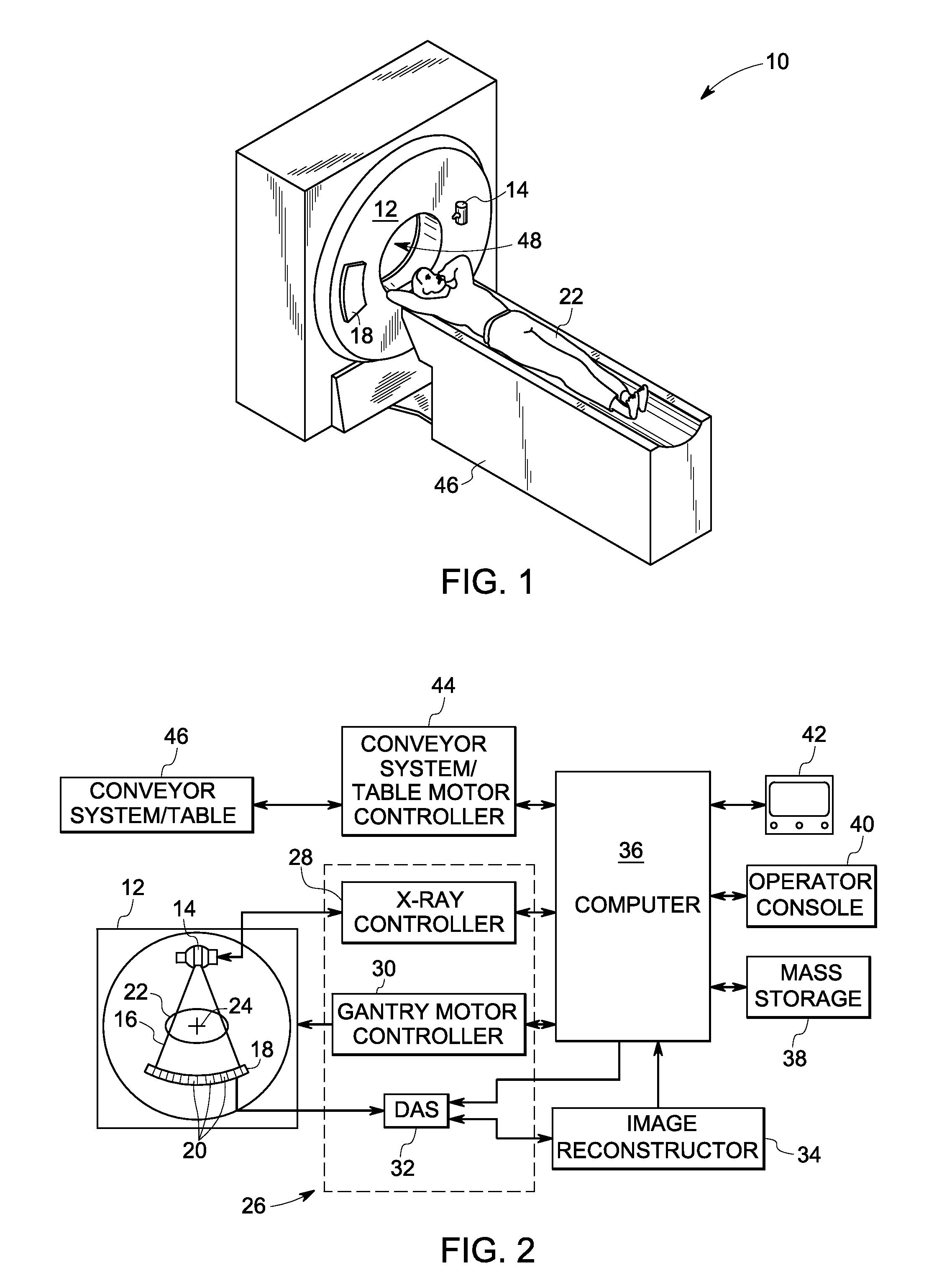

X-ray tube for microsecond x-ray intensity switching

ActiveUS20110142193A1Material analysis using wave/particle radiationRadiation/particle handlingX-rayElectron bunches

An injector for an X-ray tube is presented. The injector includes an emitter to emit an electron beam, at least one focusing electrode disposed around the emitter, wherein the at least one focusing electrode focuses the electron beam and at least one extraction electrode maintained at a positive bias voltage with respect to the emitter, wherein the at least one extraction electrode controls an intensity of the electron beam.

Owner:GENERAL ELECTRIC CO

Program/erase method for P-channel charge trapping memory device

ActiveUS7133316B2Improve efficiencyIncrease speedTransistorSolid-state devicesBit lineComputer science

A method of operating a memory device is disclosed, wherein the memory device includes an n-type substrate and a plurality of memory cells formed thereon, each memory cell corresponding to a word line, a first bit line, and second bit line, and including a first bit portion and a second bit portion each for storing one bit of information. The method includes resetting a selected memory cell by applying a first negative bias to the word line of the selected memory cell and applying a ground bias to the first and second bit lines, and programming the first bit portion of the selected memory cell by applying a first positive bias to the word line of the selected memory cell, applying a second negative bias to the first bit line of the selected memory cell, and applying a ground bias to the second bit line of the selected memory cell.

Owner:MACRONIX INT CO LTD

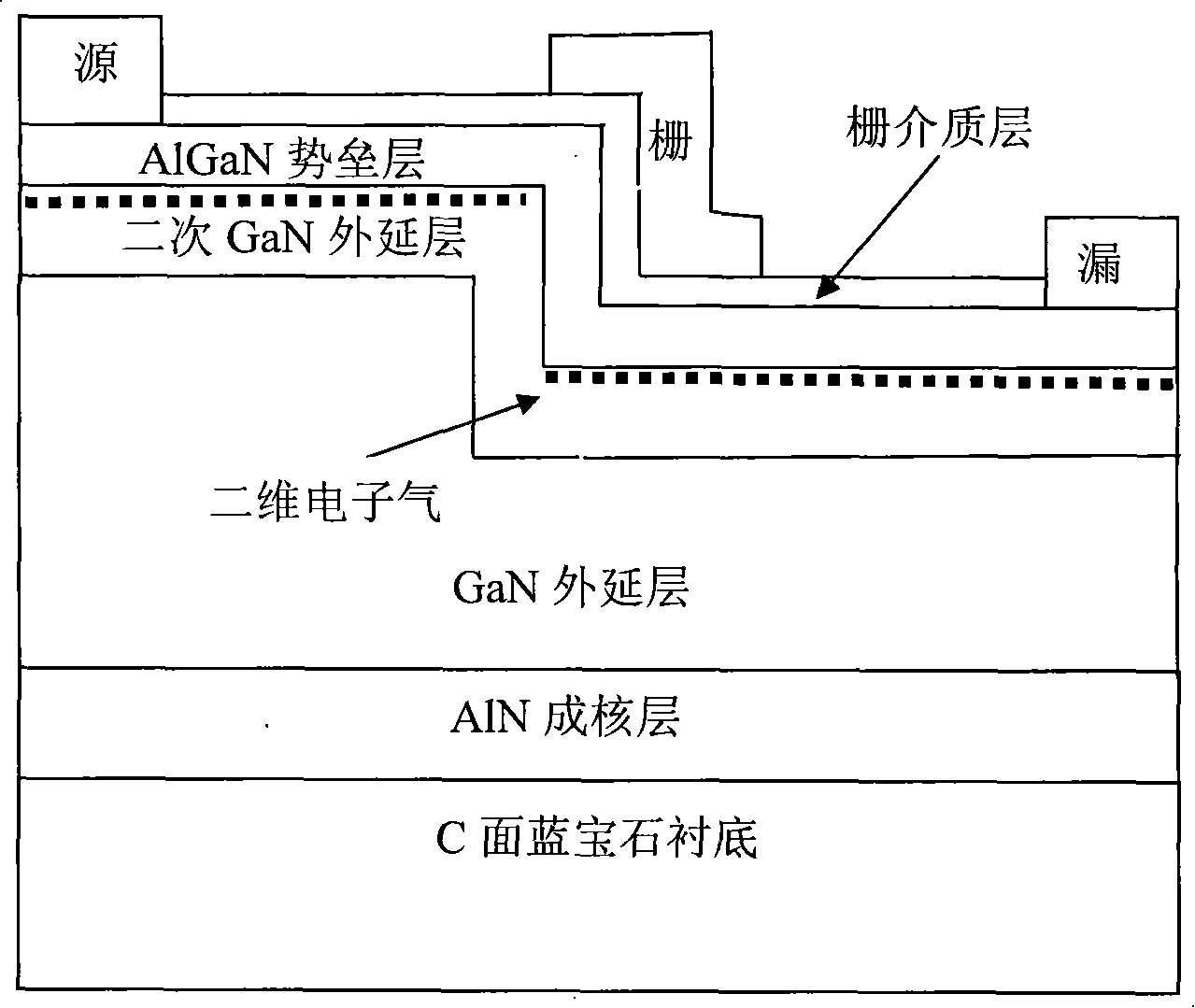

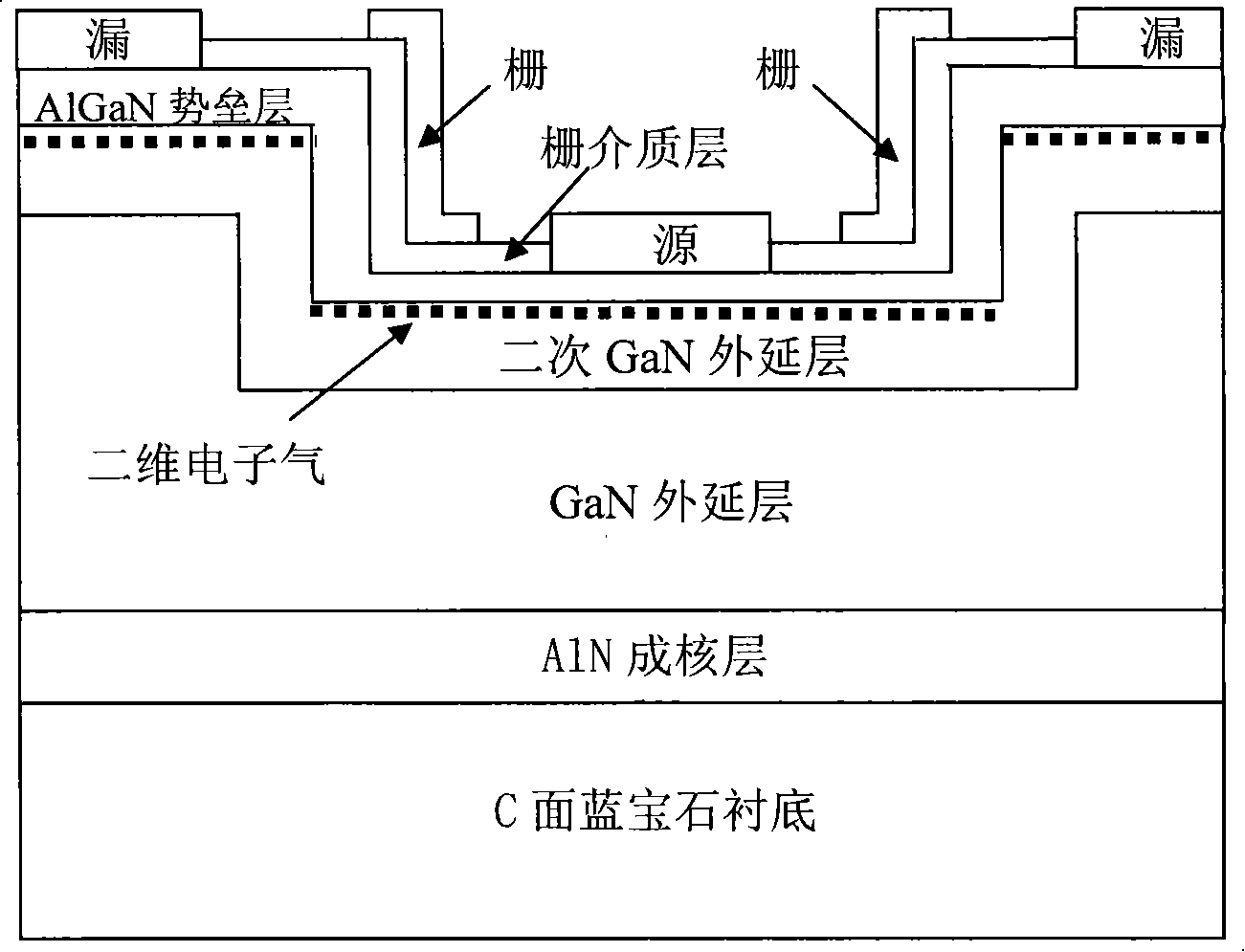

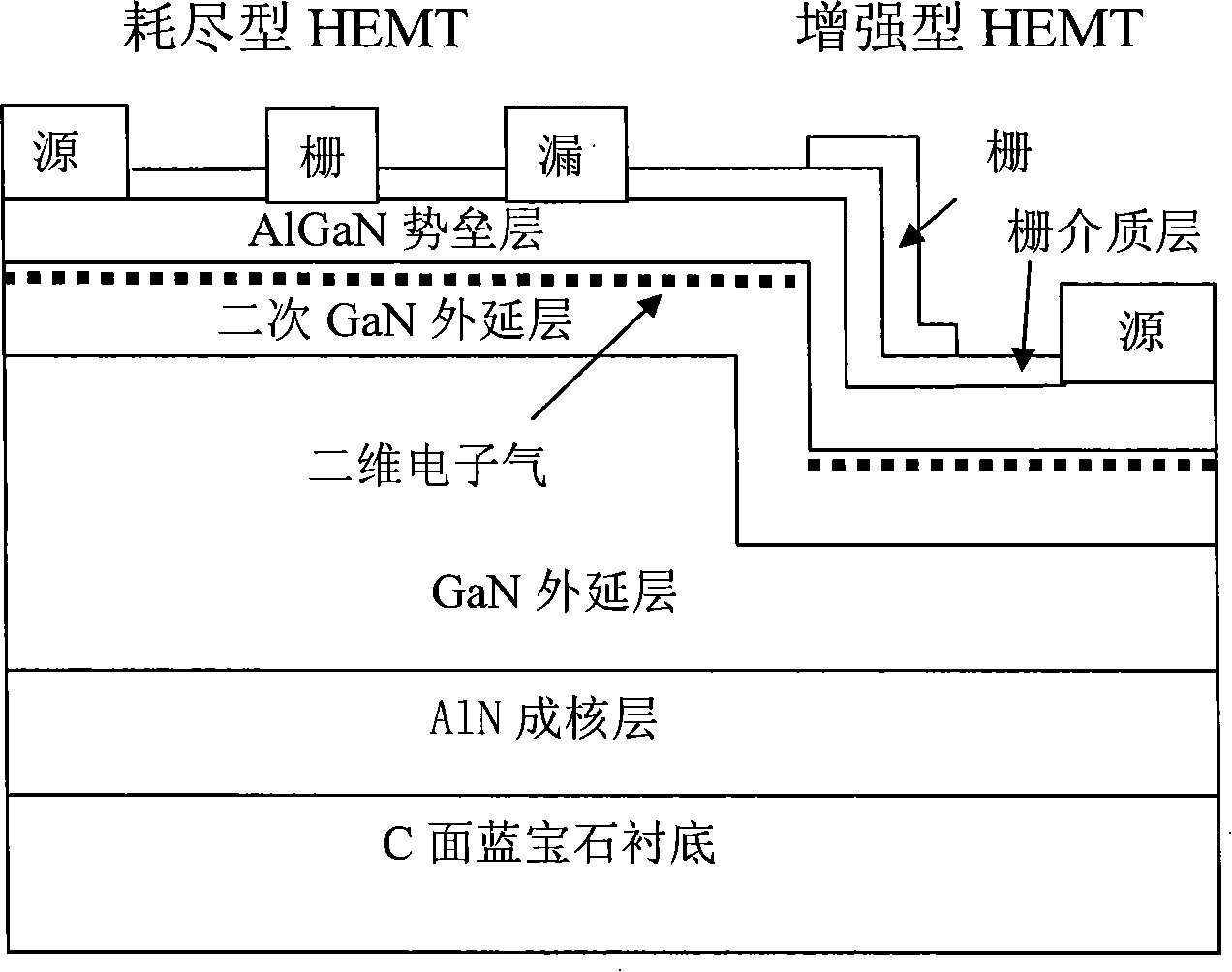

Realizing method of novel enhancement type AlGaN/GaN HEMT device

InactiveCN101252088AHigh depletion rateRaise the threshold voltageSemiconductor/solid-state device manufacturingHeterojunctionElectron

The invention discloses a realization method for a novel enhancement type AlGaN / GaN HEMT device, relating to the microelectronic technical field. The realization method has low cost, simple technique, good repeatability, high reliability and small damage on materials. The enhancement type HEMT device with high threshold voltage and nano-sized effective channel length can be obtained. The invention adopts the method of etching a table top after growth of an AlN nucleating layer and a GaN epitaxial layer and before growth of a secondary GaN epitaxial layer and an AlGaN layer to make heterojunction materials on the side face of the table top grow along the nonpolarized direction, thereby the air density of two-dimensional electrons in the heterojunction materials on the side face of the table top is greatly reduced. A grid electrode of the device is produced on the side face of the table top; under the condition of no additional voltage on the grid electrode, a conductive channel can not be switched on or weakly switched on; under the condition of certain additional positive bias on the grid electrode, the conductive channel is switched on. The invention can be used in a high-temperature high-frequency high-power situation, a high-power switch and a digital circuit.

Owner:XIDIAN UNIV

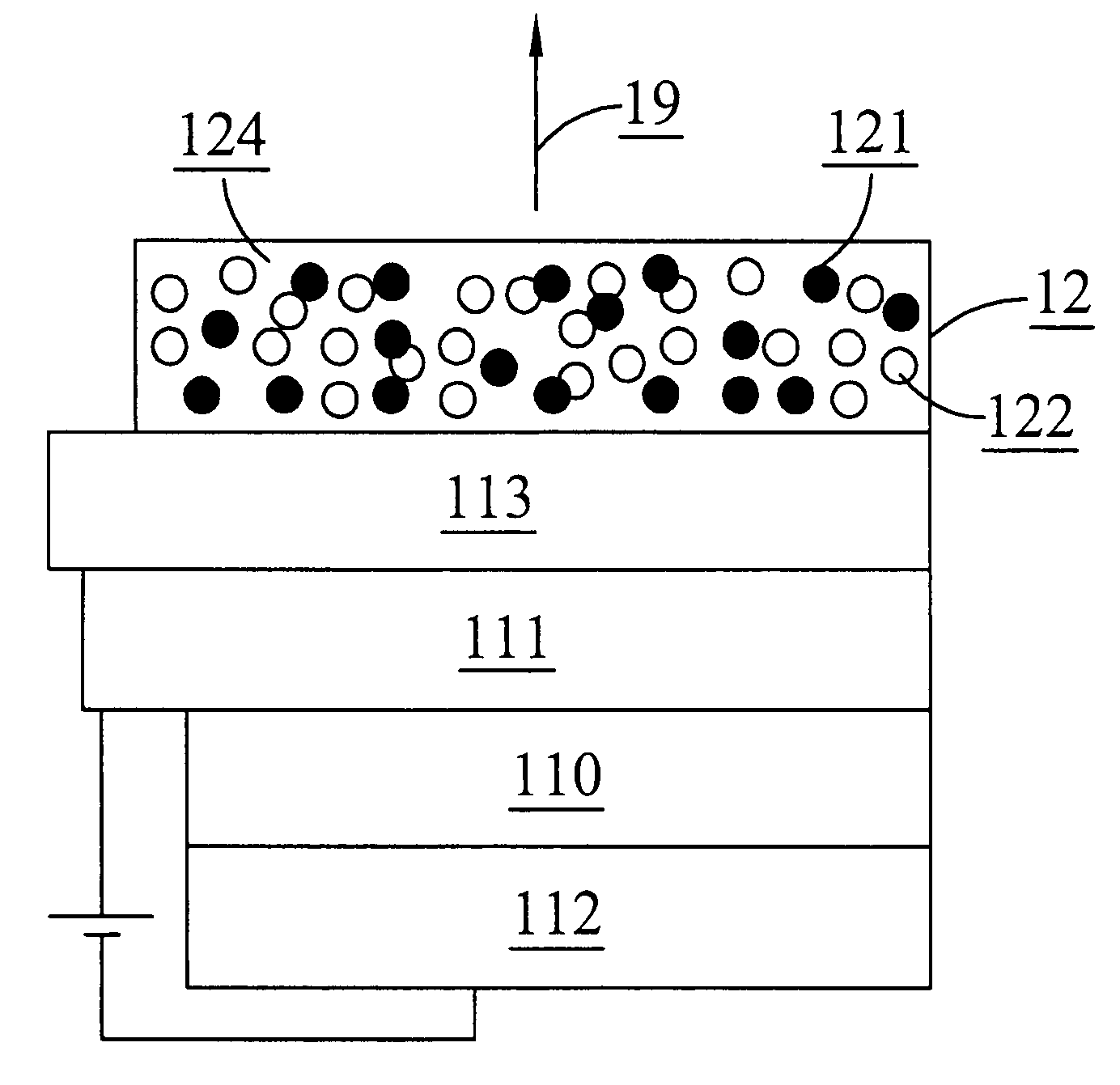

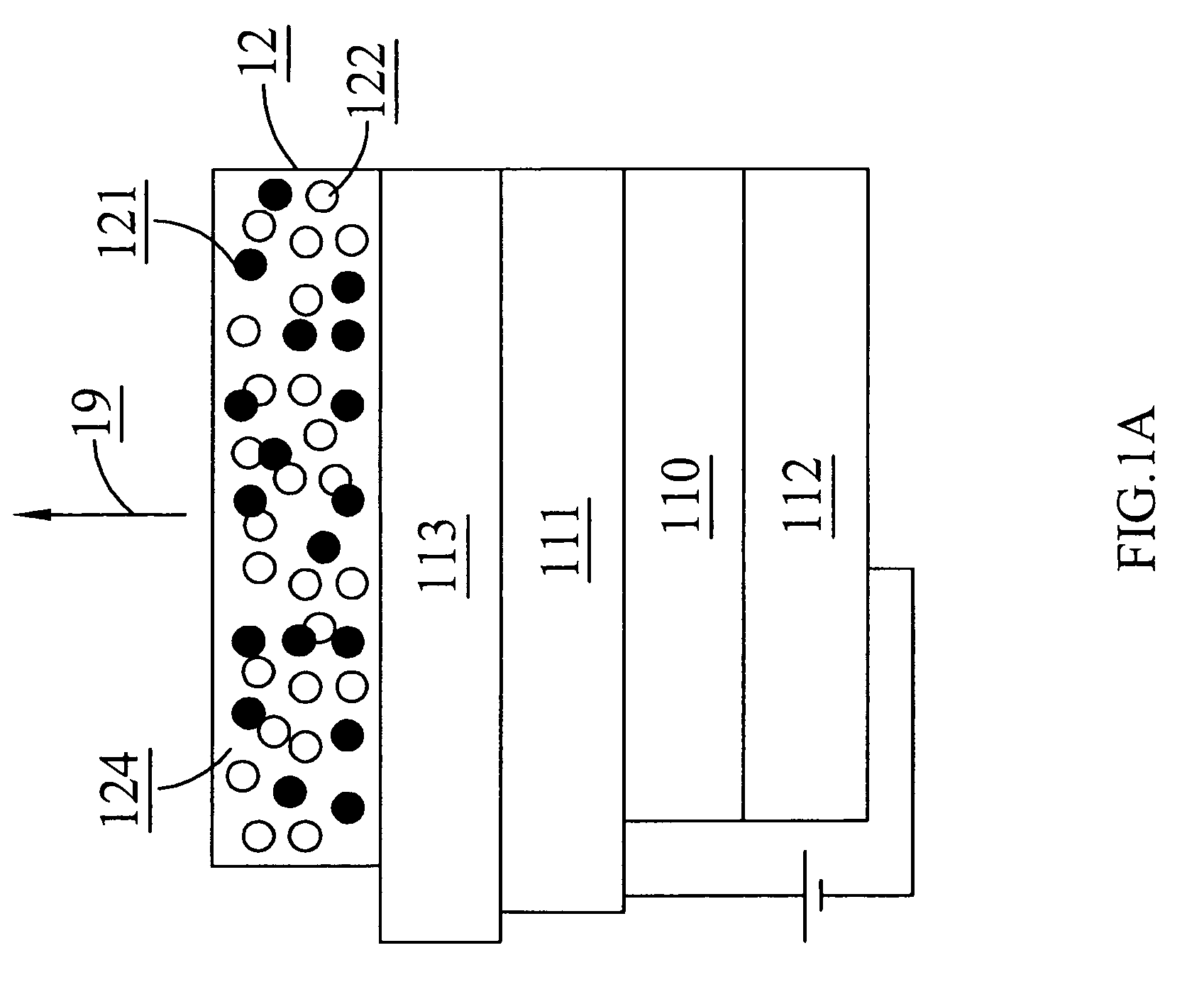

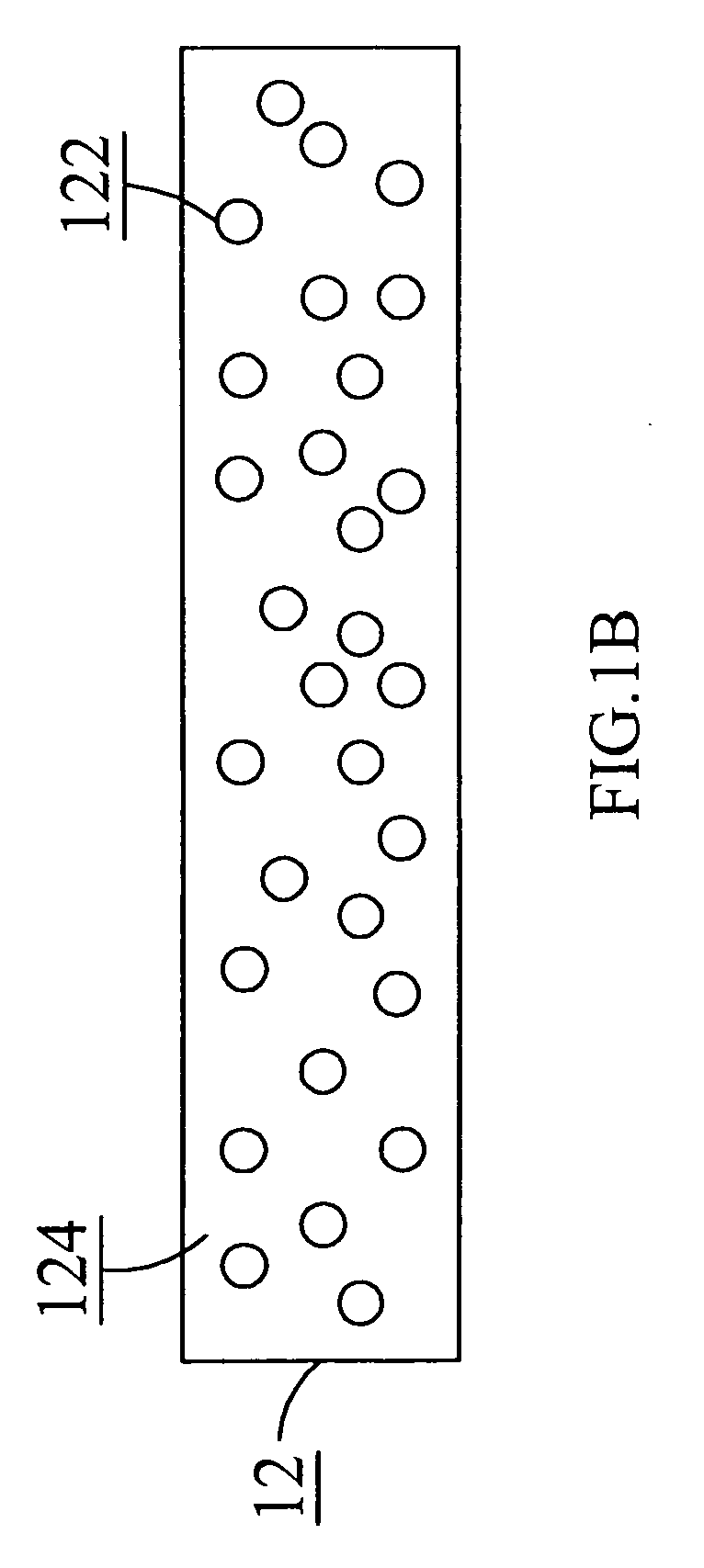

Organic semiconductor infrared distance sensing apparatus and organic infrared emitting apparatus thereof

An organic semiconductor infrared distance sensing apparatus and an organic infrared emitting apparatus thereof are disclosed. The organic semiconductor infrared distance sensing apparatus comprises an organic infrared emitting apparatus and an organic infrared receiving apparatus. The organic infrared emitting apparatus has a positive electrode layer and a negative electrode layer to form an electric field, and organic light emitting molecules are sandwiched between the two layers and correspond to the positive electrode layer and the negative electrode layer. Under a positive bias, a plurality of electrons and holes are respectively injected from electrodes and recombine with each other to emit photons. An infrared organic conversion layer absorbs and transfers the energy to infrared emitting molecules to emit infrared light. The organic infrared receiving apparatus receives the infrared light reflected by an obstacle to generate photocurrent which varies with distance, thereby sensing the distance between the obstacle and the apparatus.

Owner:NAT CHIAO TUNG UNIV

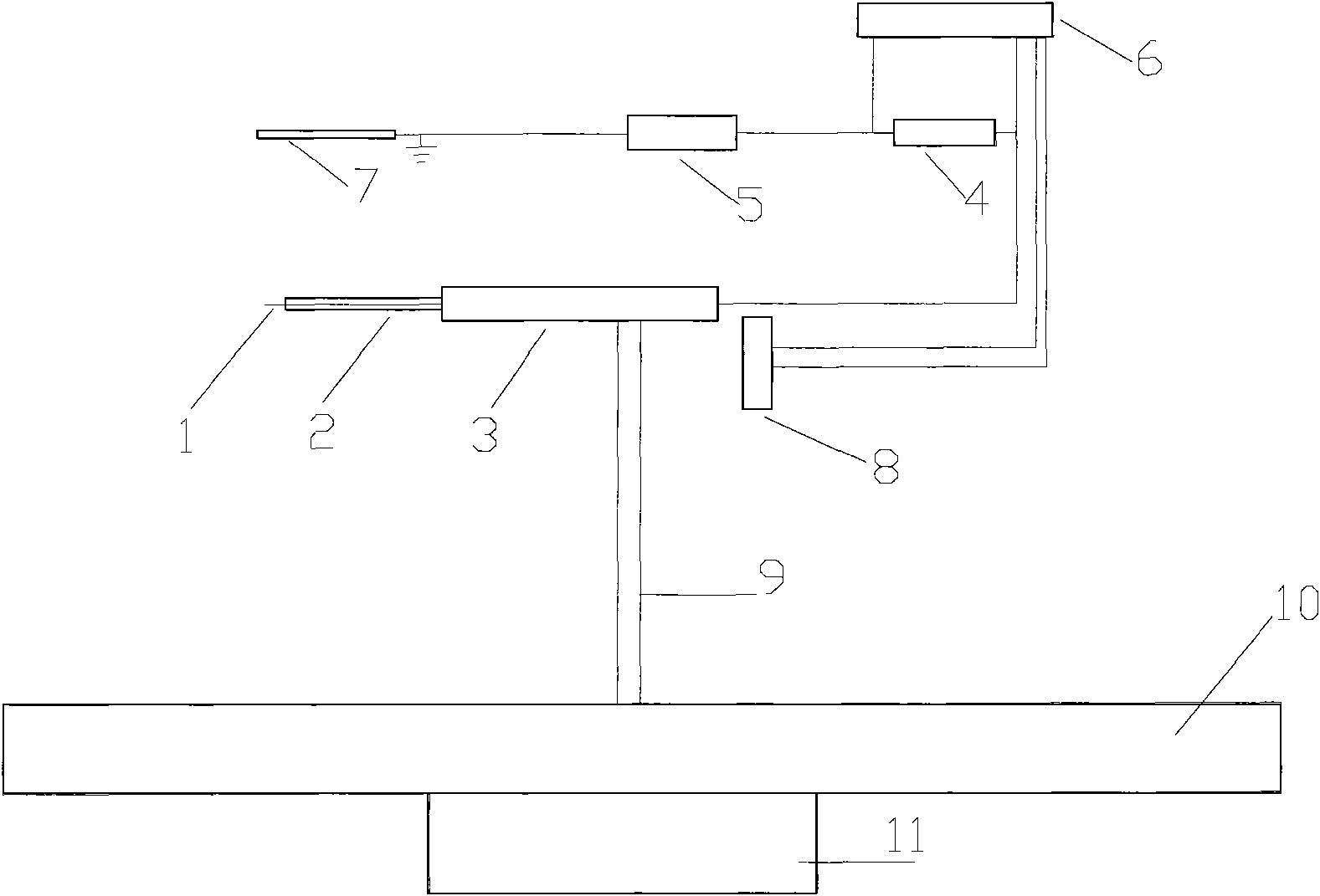

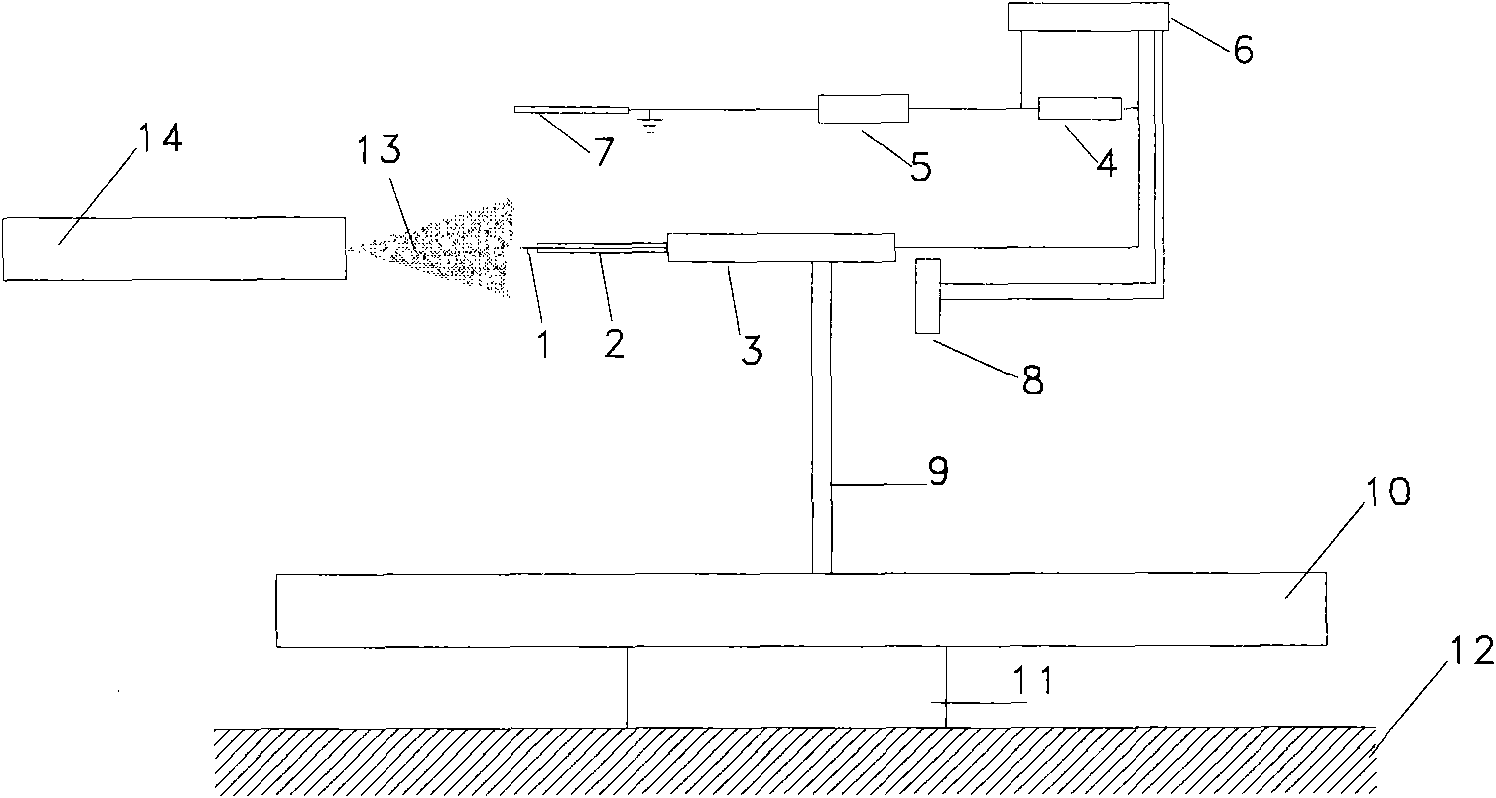

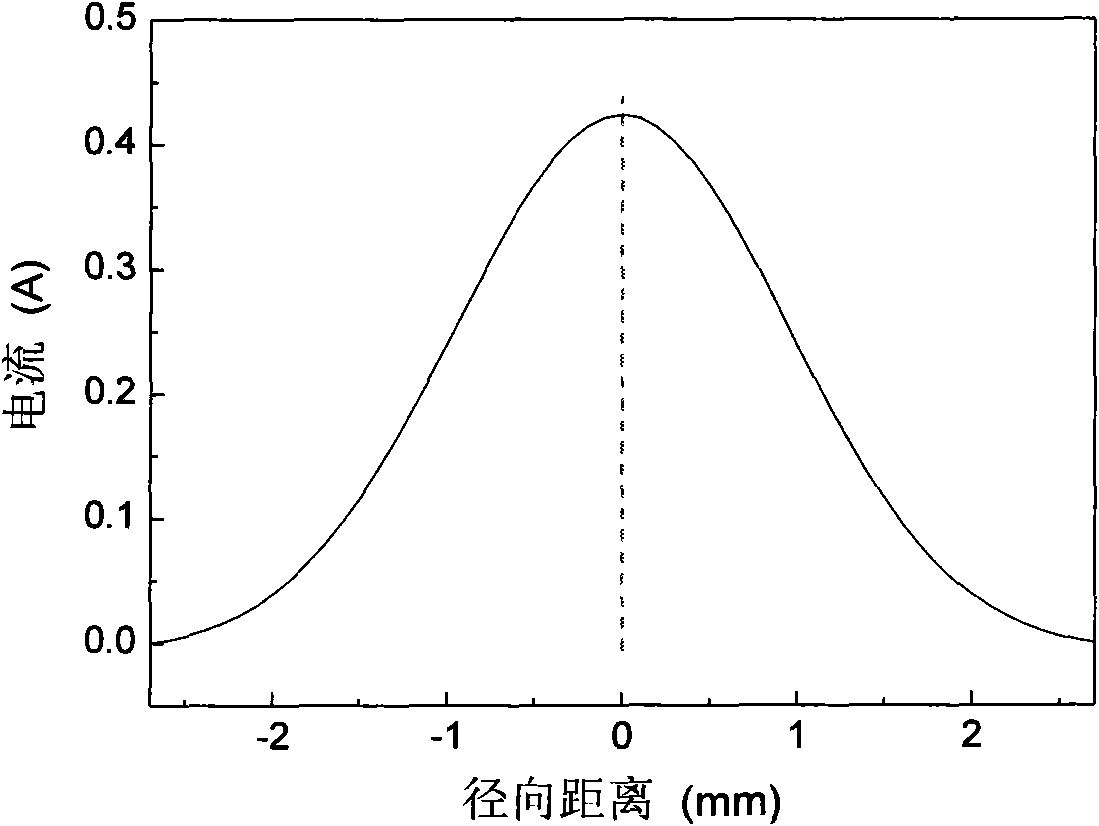

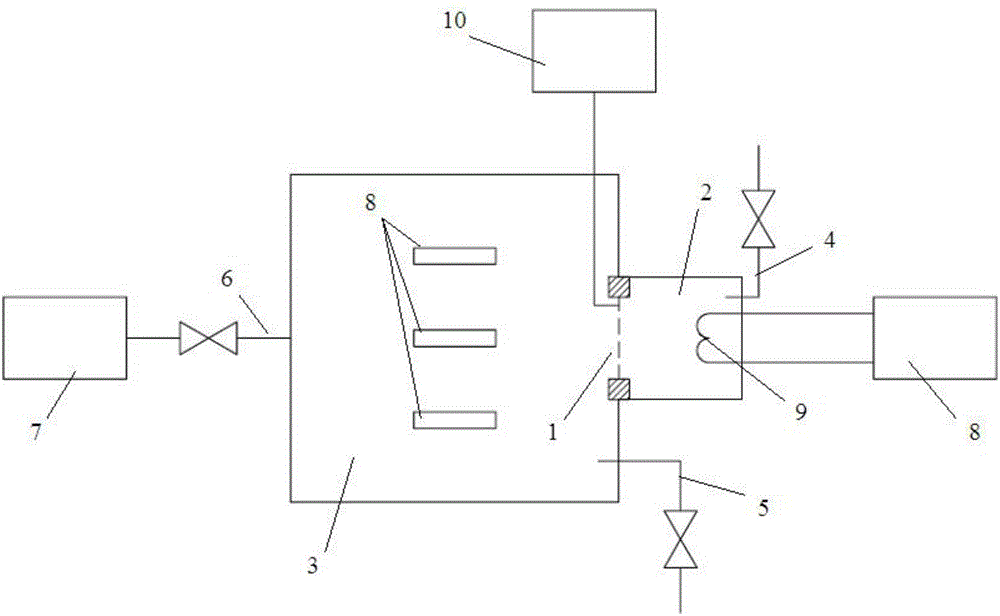

Measuring device and method of thrust vector of detection space plasma thruster

InactiveCN101614606ANovel measuring methodEasy to operateUsing electrical meansApparatus for force/torque/work measurementElectrical resistance and conductanceMeasurement device

The invention relates to a measuring device and a method of the thrust vector of a detection space plasma thruster. The measuring device of the thrust vector mainly comprises an electrostatic probe, an electrostatic probe regulating mechanism, a locating piece and a data acquisition and processing system. The method comprises the following steps: first fixing the electrostatic probe on a movable platform, simultaneously regulating the position of the electrostatic probe, installing the locating piece on the position which the probe can contact when the axis of the probe coincides with that of the plasma thruster, collecting the electrons jetted on the local position by the thruster in real time by the electrostatic probe on which positive bias voltage is applied when the movable platform moves at a constant speed along the direction vertical to the axis of the thruster, thus collecting the voltage signals at both ends of sample resistance in real time by the data acquisition and processing system when current flows through a probe circuit, and educing deflection of the actual thrust vector from the design objective by comparing the differences between the time corresponding to the vertex of the voltage signals at both ends of the sample resistance and the sudden change time of the voltage signals at both ends of the locating piece according to the moving speed of a translation stage and the distance from the electrostatic probe to the exit of the thruster.

Owner:INST OF MECHANICS - CHINESE ACAD OF SCI

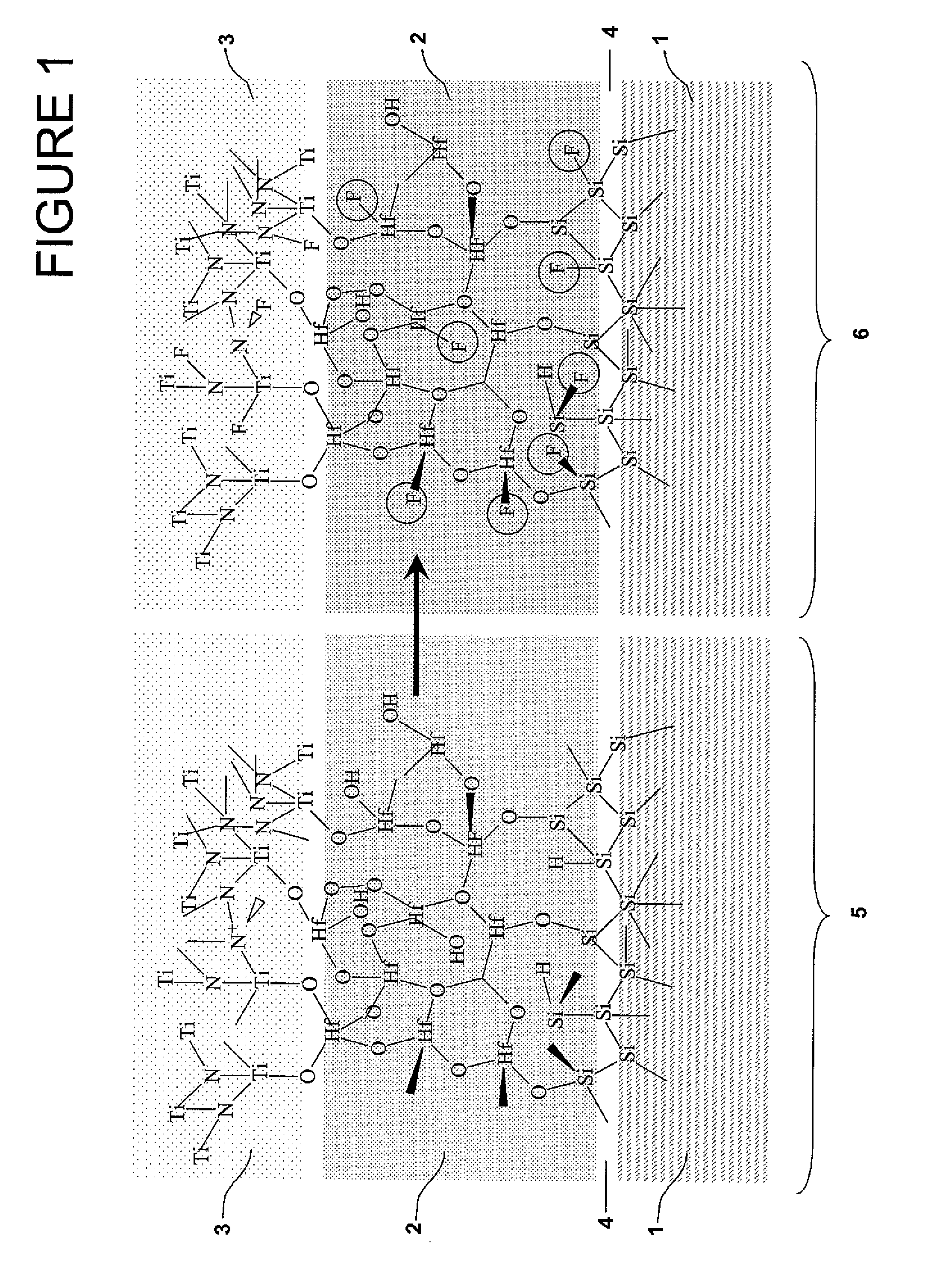

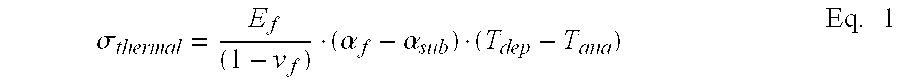

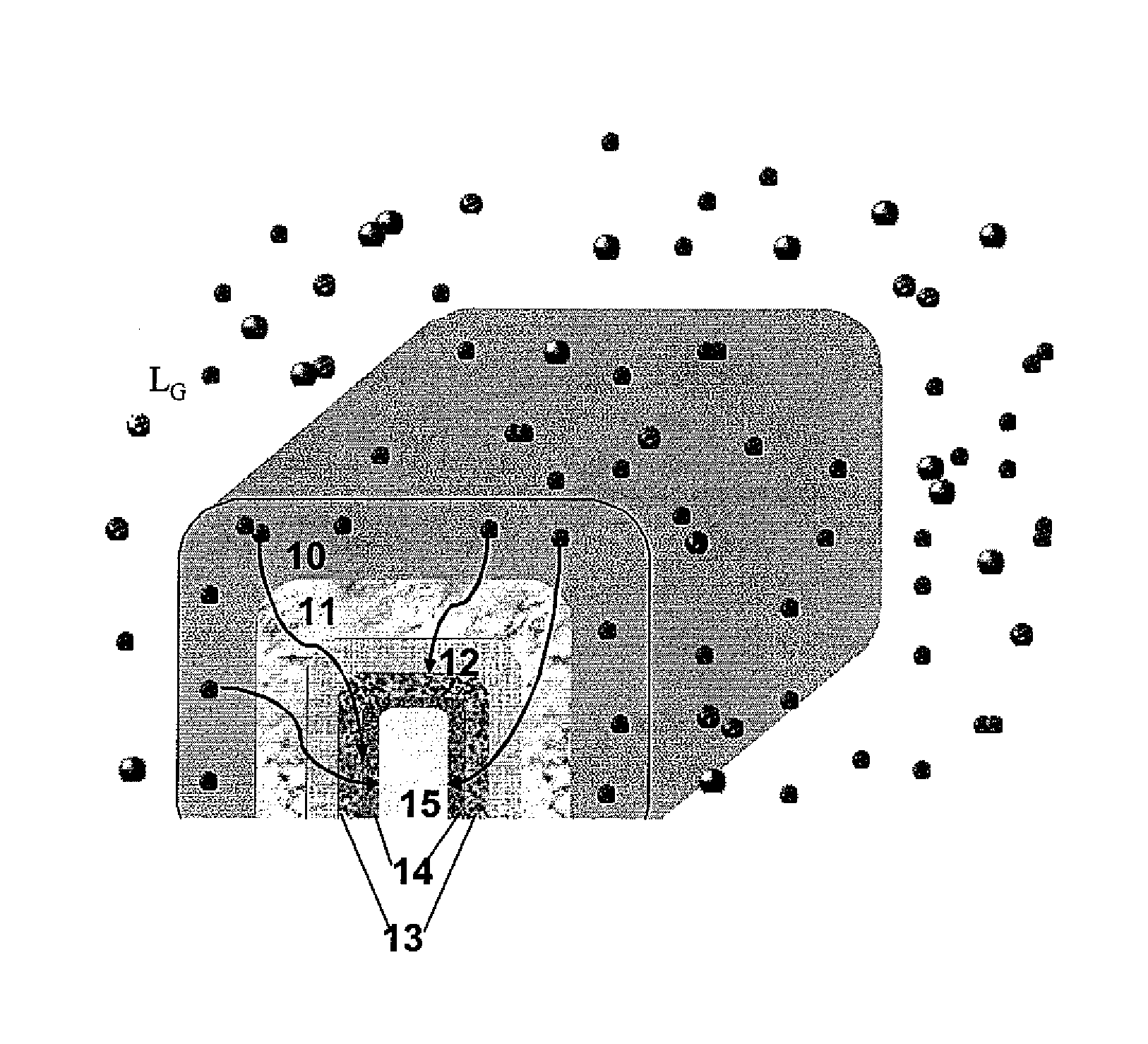

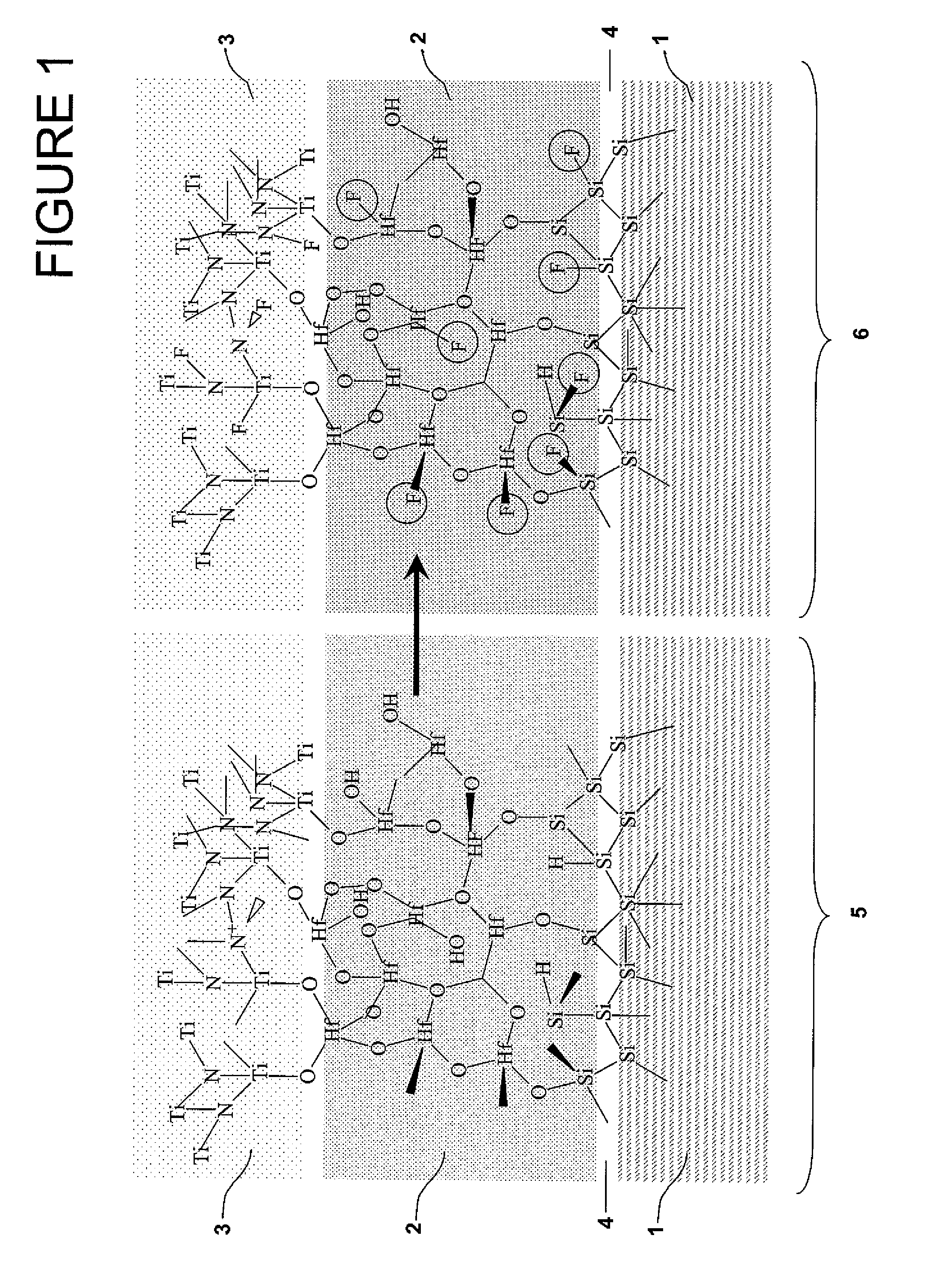

Use of f-based gate etch to passivate the high-k/metal gate stack for deep submicron transistor technologies

ActiveUS20080164539A1Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDriving current

A new, effective and cost-efficient method of introducing Fluorine into Hf-based dielectric gate stacks of planar or multi-gate devices (MuGFET), resulting in a significant improvement in both Negative and Positive Bias Temperature Instabilities (NBTI and PBTI) is provided. The new method uses an SF6 based metal gate etch chemistry for the introduction of Fluorine, which after a thermal budget within the standard process flow, results in excellent F passivation of the interfaces. A key advantage of the method is that it uses the metal gate etch for F introduction, requiring no extra implantations or treatments. In addition to the significant BTI improvement with the novel method, a better Vth control and increased drive current on MuGFET devices is achieved.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

Flash memory programming using gate induced junction leakage current

ActiveUS20050099849A1Increase electron-hole pair generationIncreasing pair generationRead-only memoriesDigital storageJunction leakageElectric field

A method for programming a storage element and a storage element programmed using gate induced junction leakage current are provided. The element may include at least a floating gate on a substrate, an active region in the substrate, and a second gate adjacent to the floating gate. The method may include the steps of: creating an inversion region in the substrate below the floating gate by biasing the first gate; and creating a critical electric field adjacent to the second gate. Creating a critical electric field may comprise applying a first positive bias to the active region; and applying a bias less than the first positive bias to the second gate. The element further includes a first bias greater than zero volts applied to the active region and a second bias greater than the first bias applied to the floating gate and a third bias less than or equal to zero applied to the second gate. The first and third bias are selected to create leakage current in the substrate between the floating gate and the select gate.

Owner:SANDISK TECH LLC

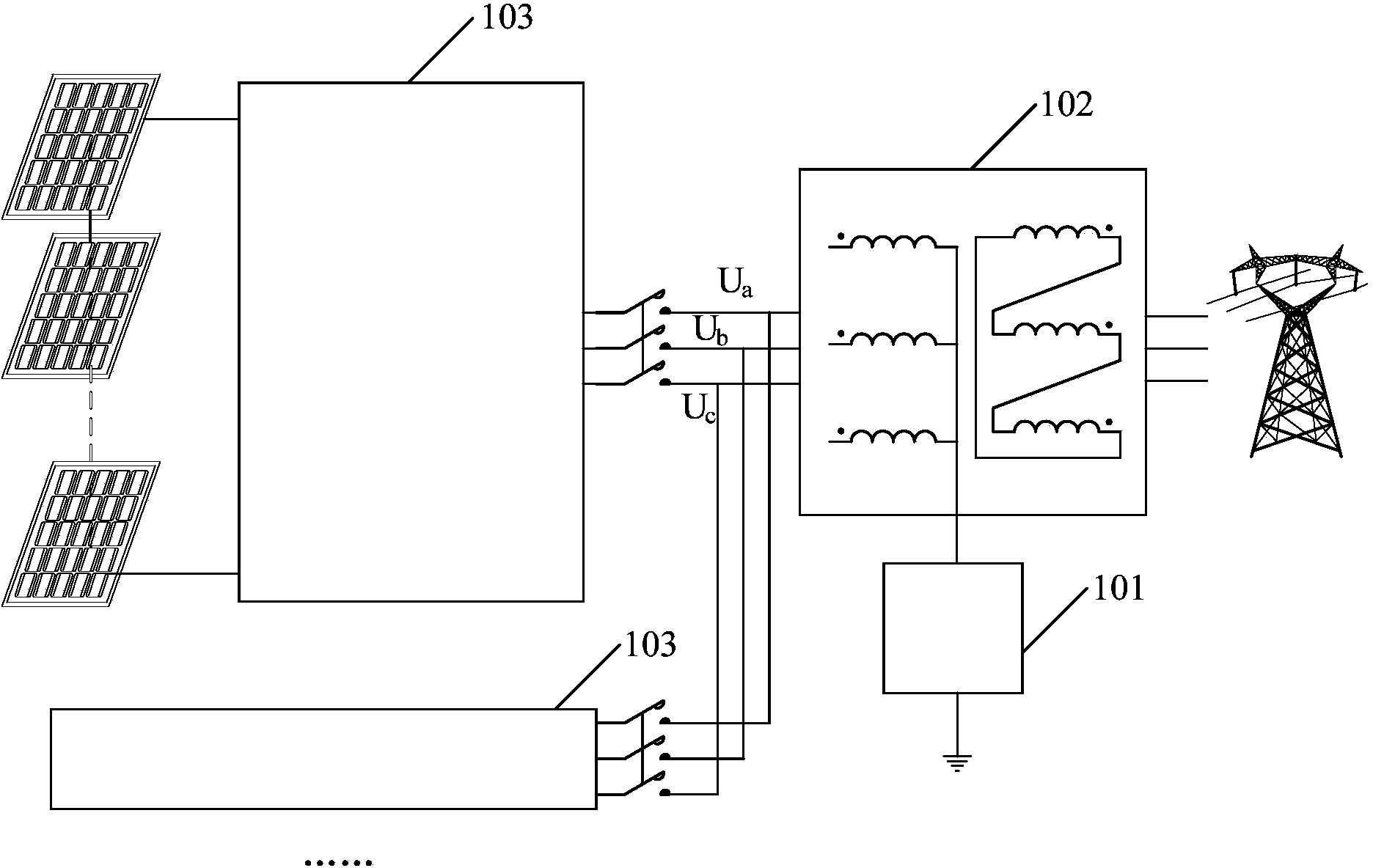

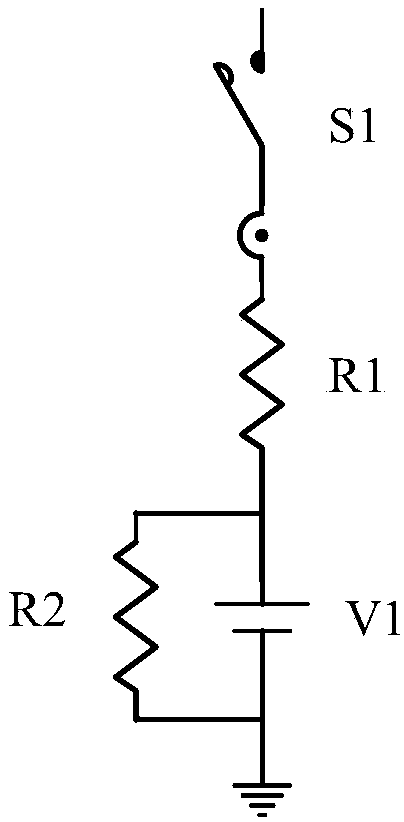

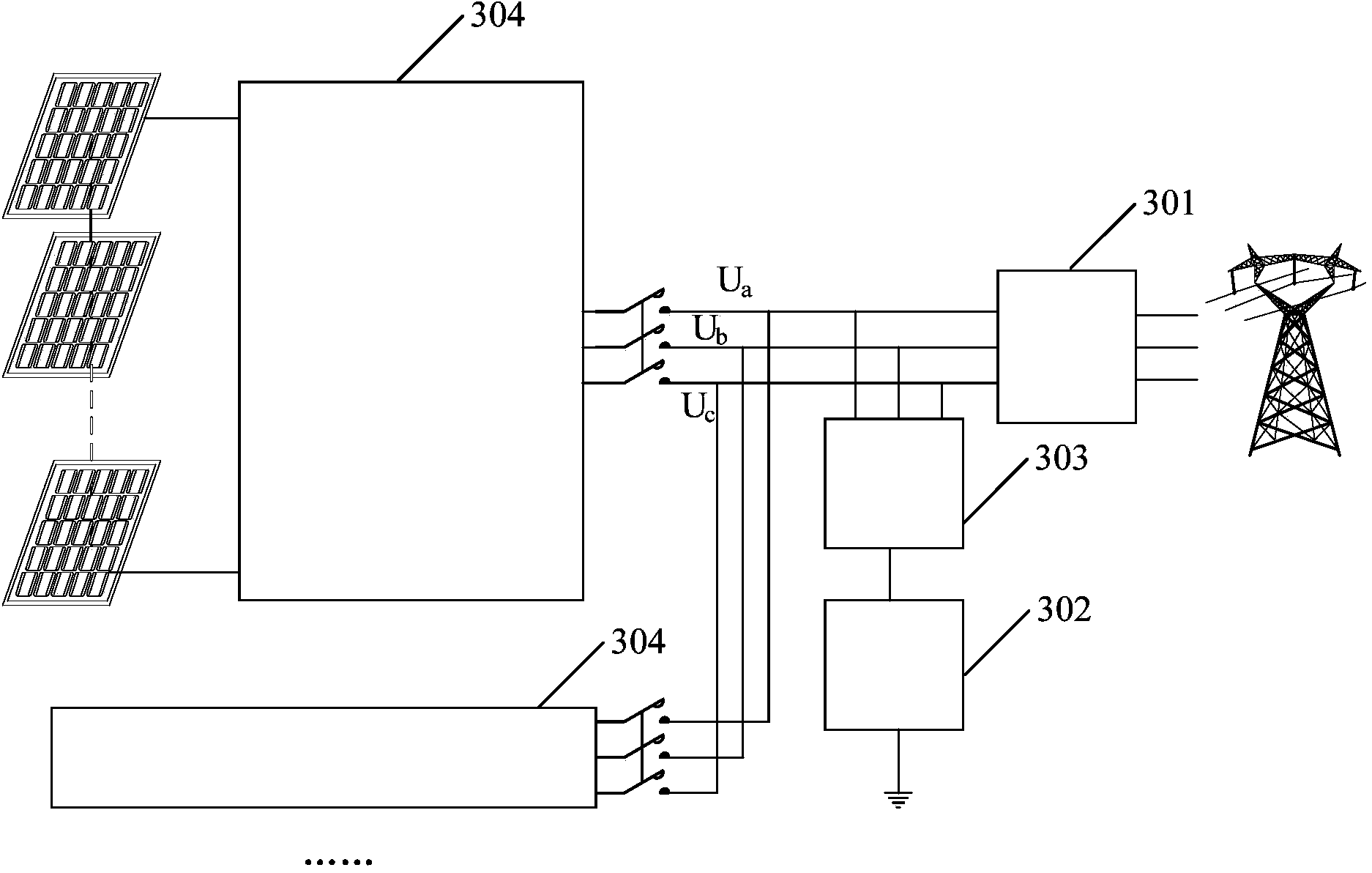

Device for restraining PID effect of photovoltaic panel

ActiveCN103973217AInhibition of PID effectIncreased voltage to groundPhotovoltaicsPhotovoltaic energy generationPower inverterPhotovoltaic power station

The invention discloses a device for restraining the PID effect of a photovoltaic panel. According to the device, the voltage to ground of a neutral point on the alternating-current boosting side of a photovoltaic power station is boosted through a voltage boosting circuit so that the voltage to ground of the preceding photovoltaic panel of an inverter can be boosted, the photovoltaic panel has positive bias relative to the ground, and the PID effect of the photovoltaic panel can be restrained. According to the device, not all the inverters or photovoltaic panels need to be processed, and the device has the advantages that the device is easy to implement and low in cost, detection of insulation resistance is not influenced, and the device is particularly suitable for the application that serial-type photovoltaic inverters are used for building a photovoltaic power station.

Owner:SINENG ELECTRIC CO LTD

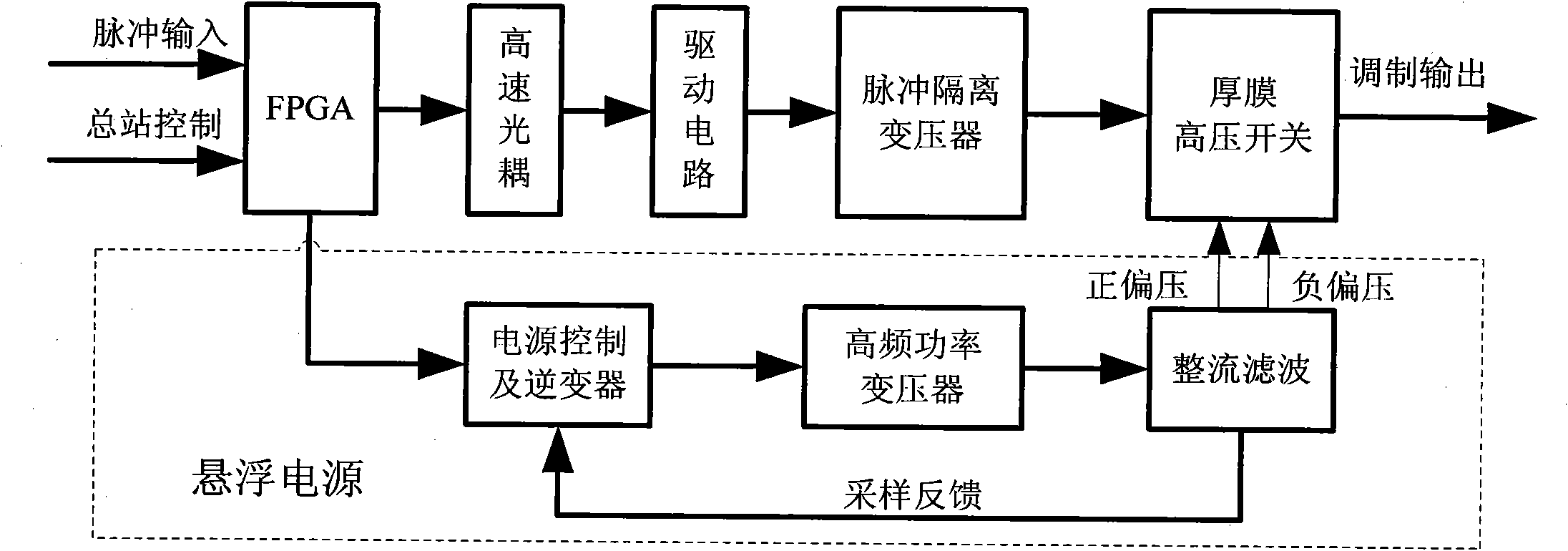

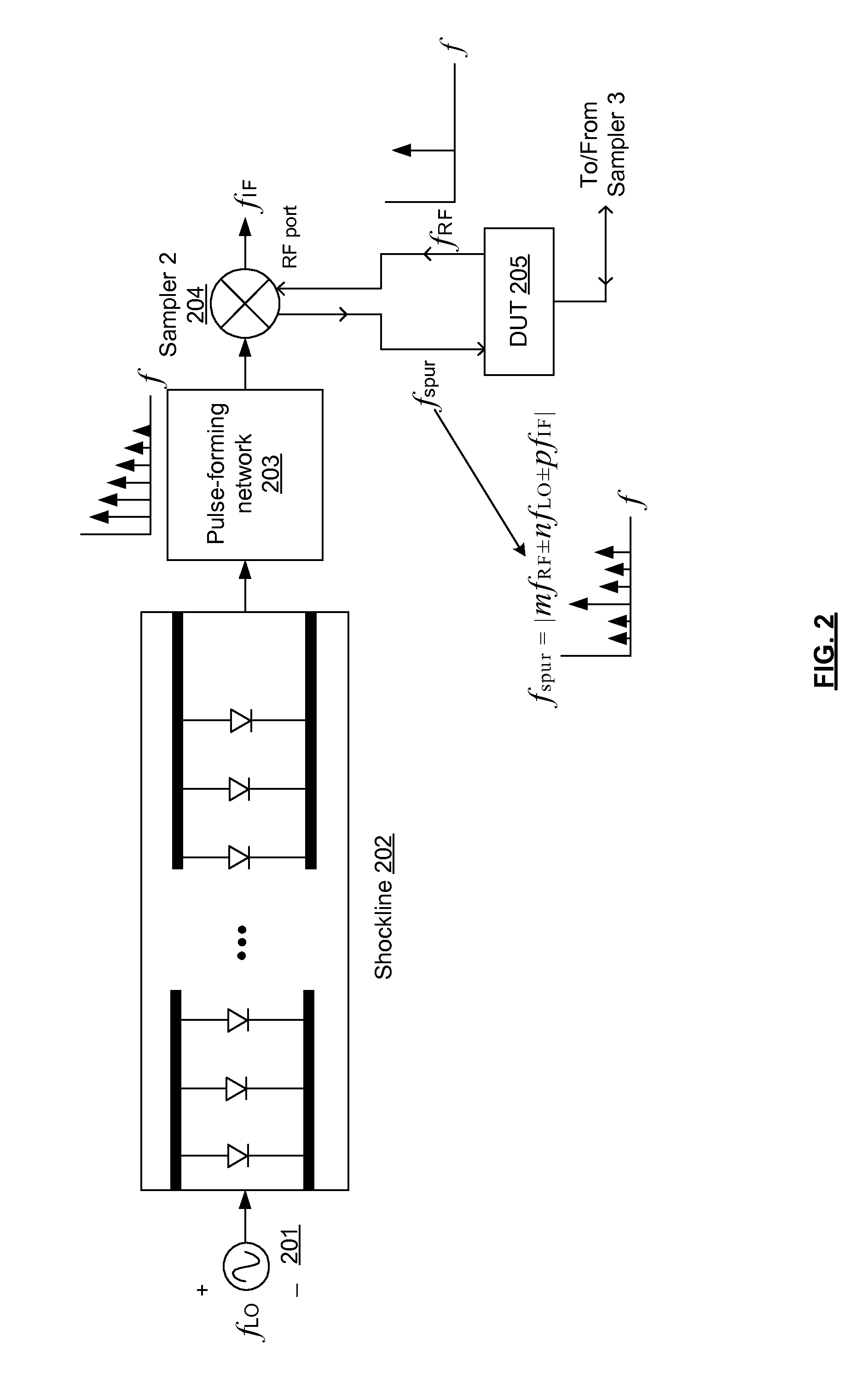

General thick film type floating plate modulator

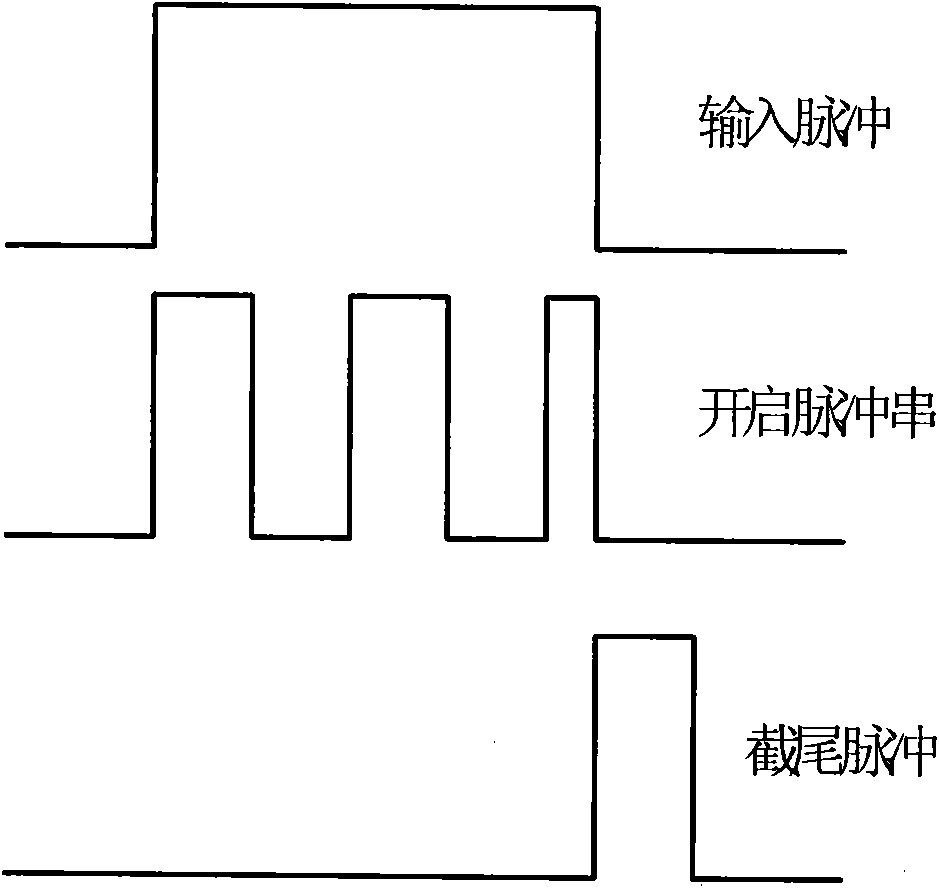

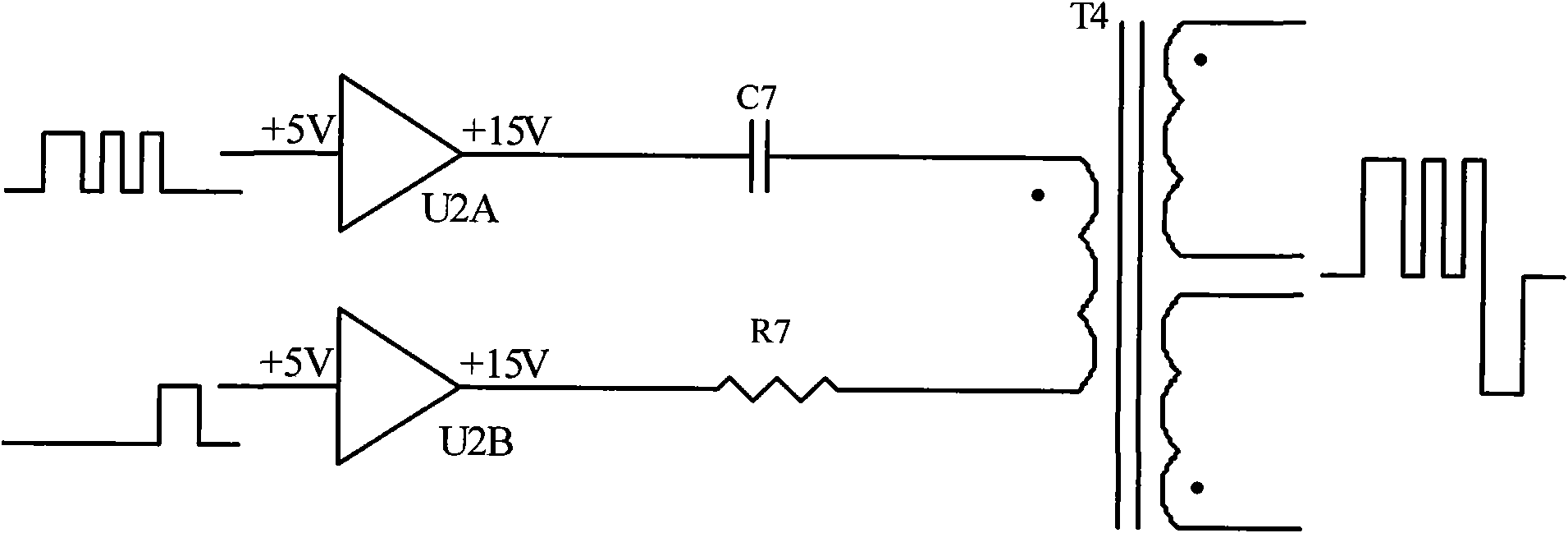

InactiveCN101895278AAvoiding the problem of limited range-time productSimple structurePulse shapingPulse amplitude modulationSoftware languageEngineering

The invention relates to a general thick film type floating plate modulator, which comprises a control component FPGA, a high-speed logic optocoupler, a driving circuit, an impulse isolation transformer, a thick film high-pressure switching circuit and a suspension power supply, wherein the FPGA uses VHDL language to modulate ultra-wide impulse into opening impulse train and truncation impulse; an isolation strip wave duct amplifier of the high-speed logic optocoupler is used for striking a light to protect the FPGA; the driving circuit adopts a high-speed driver to amplify the opening impulse train and the truncation impulse; the impulse isolation transformer comprises a primary electrode and a dual-secondary electrode; the thick film high-pressure switching circuit is composed of an opening tube and a truncation tube auxiliary circuit; the opening impulse train and the truncation impulse are transmitted to the thick film high-pressure switching circuit through the impulse isolation transformer; and the on / off of the opening tube and the truncation tube are switched to realize compatibility of the ultra-wide impulse and a narrow impulse. The invention adopts software language to realize opening / parameters adjustment of the truncation impulse and uses reference level of a low-pressure high-efficiency inverter to adjust positive bias so as to realize generality and interchangeability.

Owner:中国兵器工业第二〇六研究所

Method of coating a cutting tool

InactiveUS20050145479A1Reduce residual stressImproved thickness distributionVacuum evaporation coatingSputtering coatingTarget surfaceSputtering

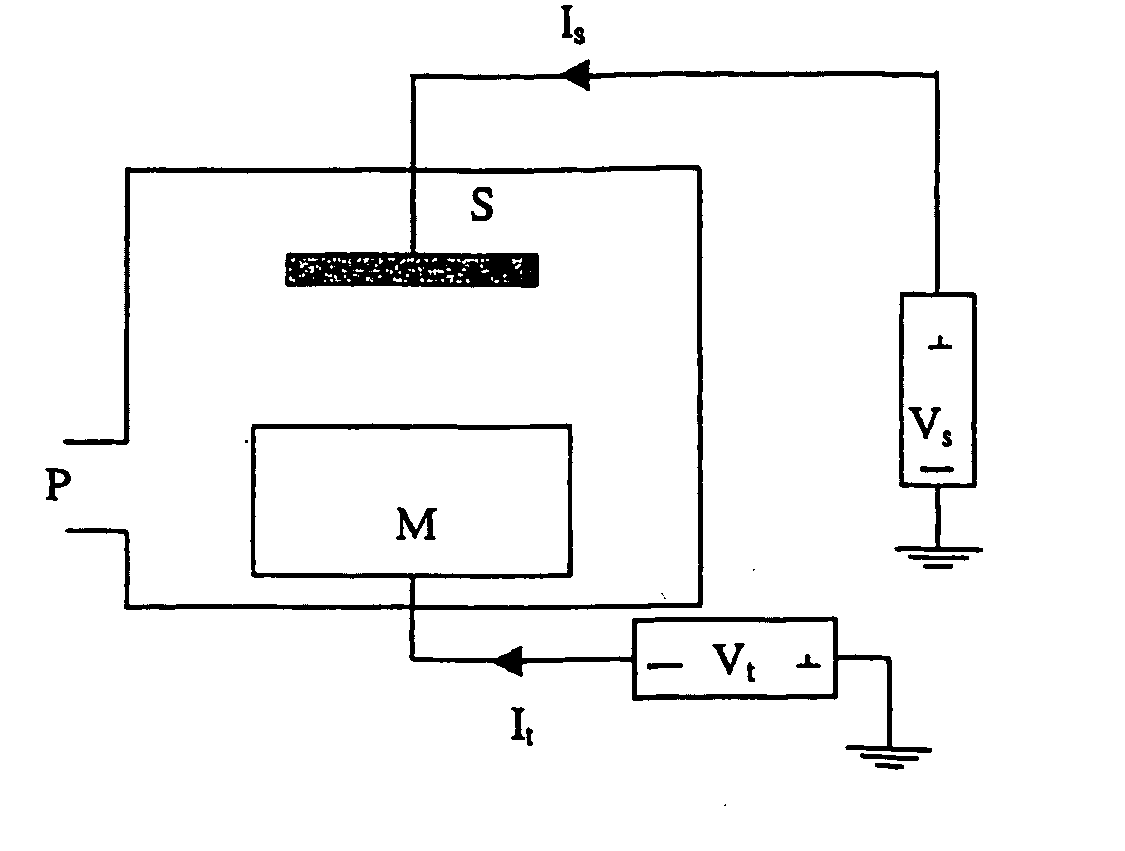

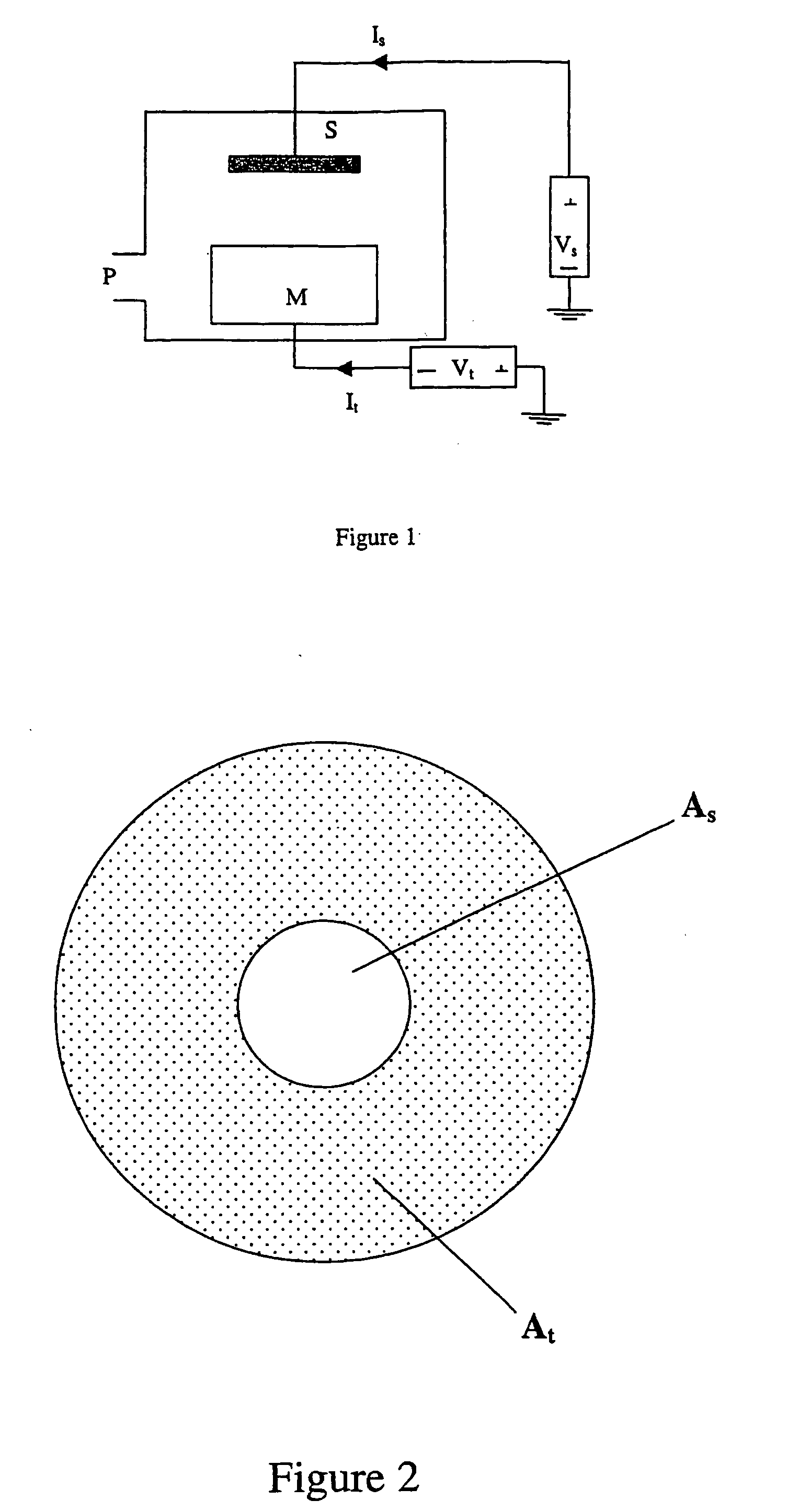

A method of depositing a nitride-based wear resistant layer on a cutting tool for machining by chip removal using reactive magnetron sputtering has a deposition rate, td, higher than 2 nm / s, a positive bias voltage, Vs, (with respect to ground potential) between +1 V and +60 V applied to the substrate, a substrate current density, Is / As, larger than 10 mA / cm2, a target surface area, At, larger than 0.7 times the substrate surface area, As, and a distance between the target surface and the substrate surface, dt, less than (At)0.5.

Owner:SECO TOOLS AB

Use of F-based gate etch to passivate the high-k/metal gate stack for deep submicron transistor technologies

ActiveUS8319295B2Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDriving current

A new, effective and cost-efficient method of introducing Fluorine into Hf-based dielectric gate stacks of planar or multi-gate devices (MuGFET), resulting in a significant improvement in both Negative and Positive Bias Temperature Instabilities (NBTI and PBTI) is provided. The new method uses an SF6 based metal gate etch chemistry for the introduction of Fluorine, which after a thermal budget within the standard process flow, results in excellent F passivation of the interfaces. A key advantage of the method is that it uses the metal gate etch for F introduction, requiring no extra implantations or treatments. In addition to the significant BTI improvement with the novel method, a better Vth control and increased drive current on MuGFET devices is achieved.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

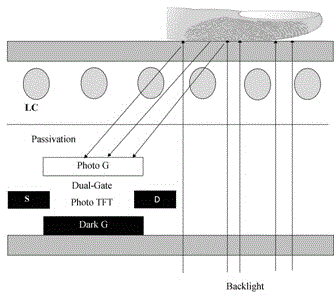

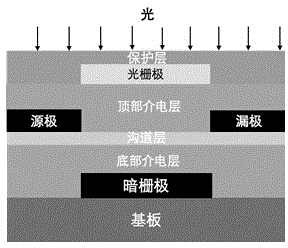

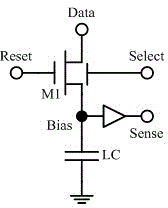

Touch display screen drive and fingerprint image acquisition method

ActiveCN104573648AImprove signal-to-noise ratioHigh resolutionPrint image acquisitionInput/output processes for data processingGratingSignal-to-noise ratio (imaging)

The invention relates to a touch display screen drive and fingerprint image acquisition method. A display unit is driven through a bigrid photoelectric thin film transistor and fingerprint images are acquired. The display unit driving process specifically includes the following procedures that the zero voltage or the positive bias voltage is applied to an optical grid of the bigrid photoelectric thin film transistor, the positive voltage is applied to a dark grid, at the moment, display signals are sent to the display unit through the drain and the source of the bigrid photoelectric thin film transistor, and the display unit is driven through the display signals. The display unit fingerprint image acquisition process includes the following procedures that the negative bias voltage is applied to the optical grid, made of a transparent conductive material, of the bigrid photoelectric thin film transistor, the positive bias voltage is applied to the dark grid, and fingerprint images acquired by the bigrid photoelectric thin film transistor can be output through the source. Due to the fact that the method does not depend on a separation device, the method has the advantages that production cost is low, power consumption is low, and the signal to noise ratio and the resolution ratio of the acquired fingerprint images are high.

Owner:SYSU CMU SHUNDE INT JOINT RES INST

Flash memory device with improved erase function and method for controlling erase operation of the same

The present patent relates to flash memory devices with improved erase function, and method of controlling an erase operation of the same. According to the present patent, the flash memory device includes memory cell blocks, each having a plurality of memory cells sharing local word lines and bit lines, an X-decoder which decodes a row address signal and outputs the decoded signal, a block selection unit, which selects some of the memory cell blocks in response to the decoded signal, and connects local word lines of the selected memory cell blocks to corresponding global word lines, respectively, and a high voltage generator, which generates word line bias voltages in response to one of a read command, a program command and an erase command, and supplies the generated word line bias voltages to the global word lines in response to the decoded signal, respectively, wherein the word line bias voltages, which are generated by the high voltage generator in response to the erase command, have a positive value, respectively. Accordingly, a positive bias voltage is applied to a global word line in an erase operation. It is thus possible to prevent a shallow erase phenomenon of non-selected memory cell blocks due to the leakage current of pass gates.

Owner:SK HYNIX INC

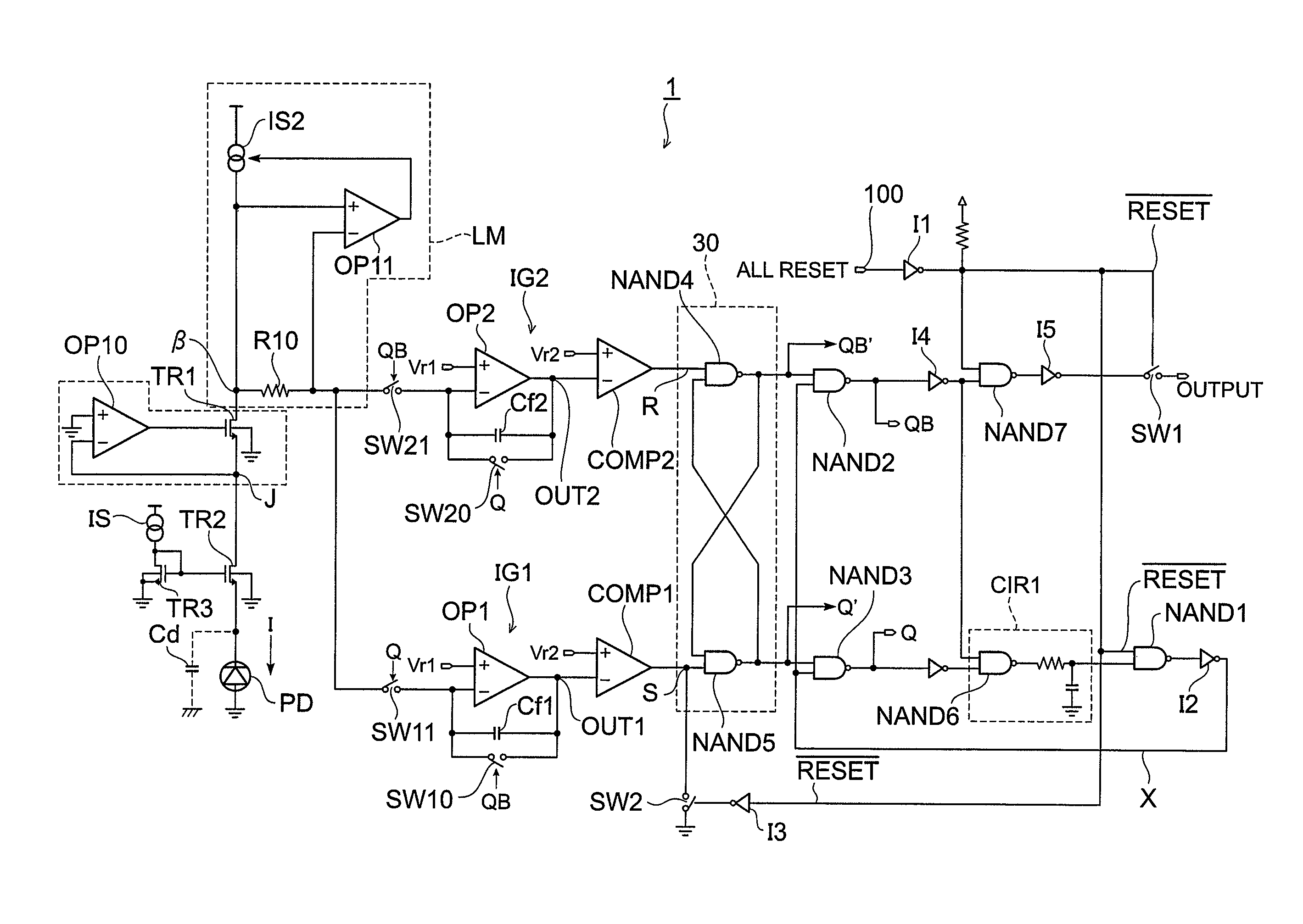

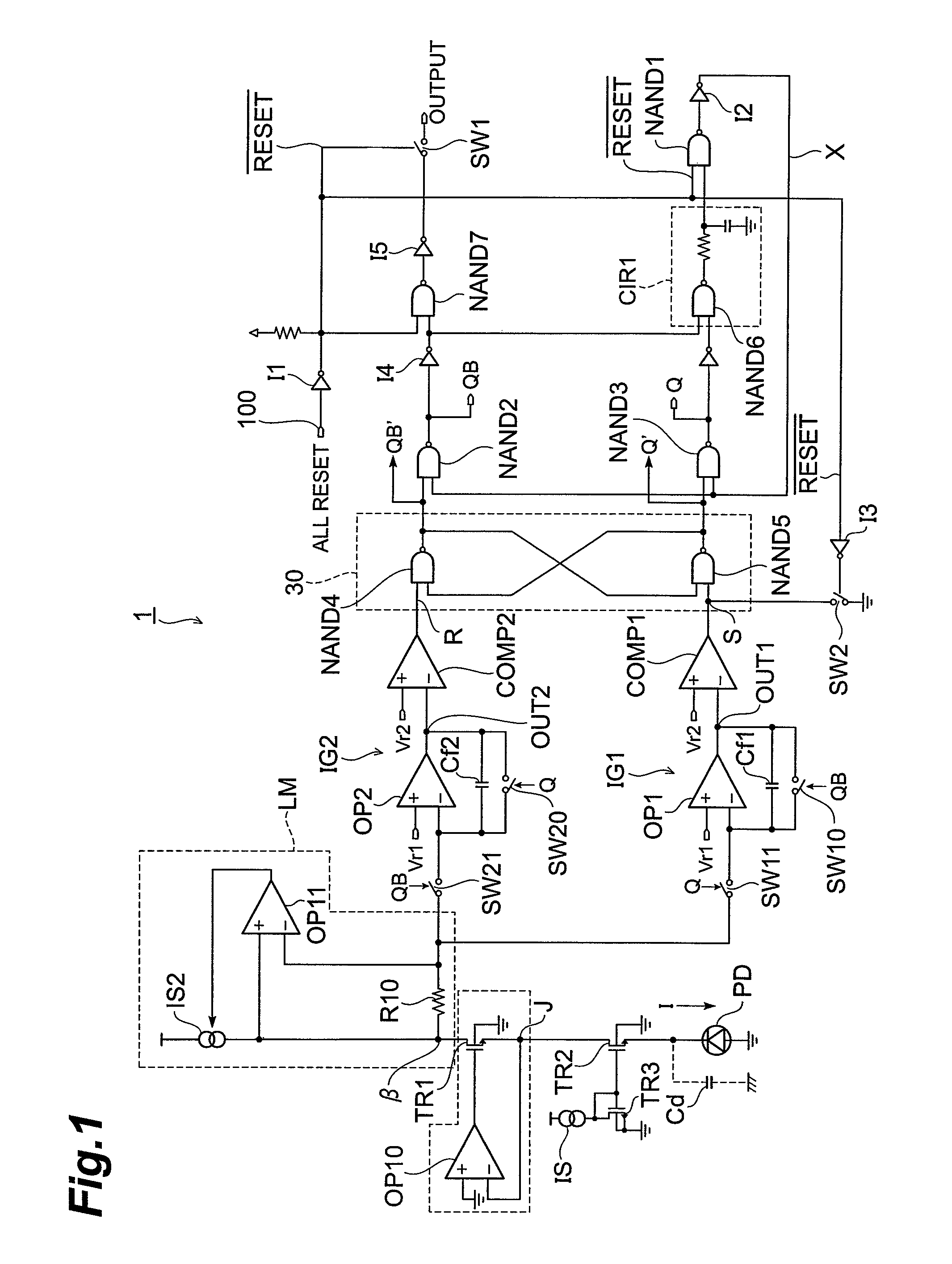

Photodetection circuit

ActiveUS8143564B2Oscillation suppressionMinimize the effect of parasitic capacitanceMultiplier circuit arrangementsMaterial analysis by optical meansElectrical resistance and conductancePhotodiode

Owner:HAMAMATSU PHOTONICS KK

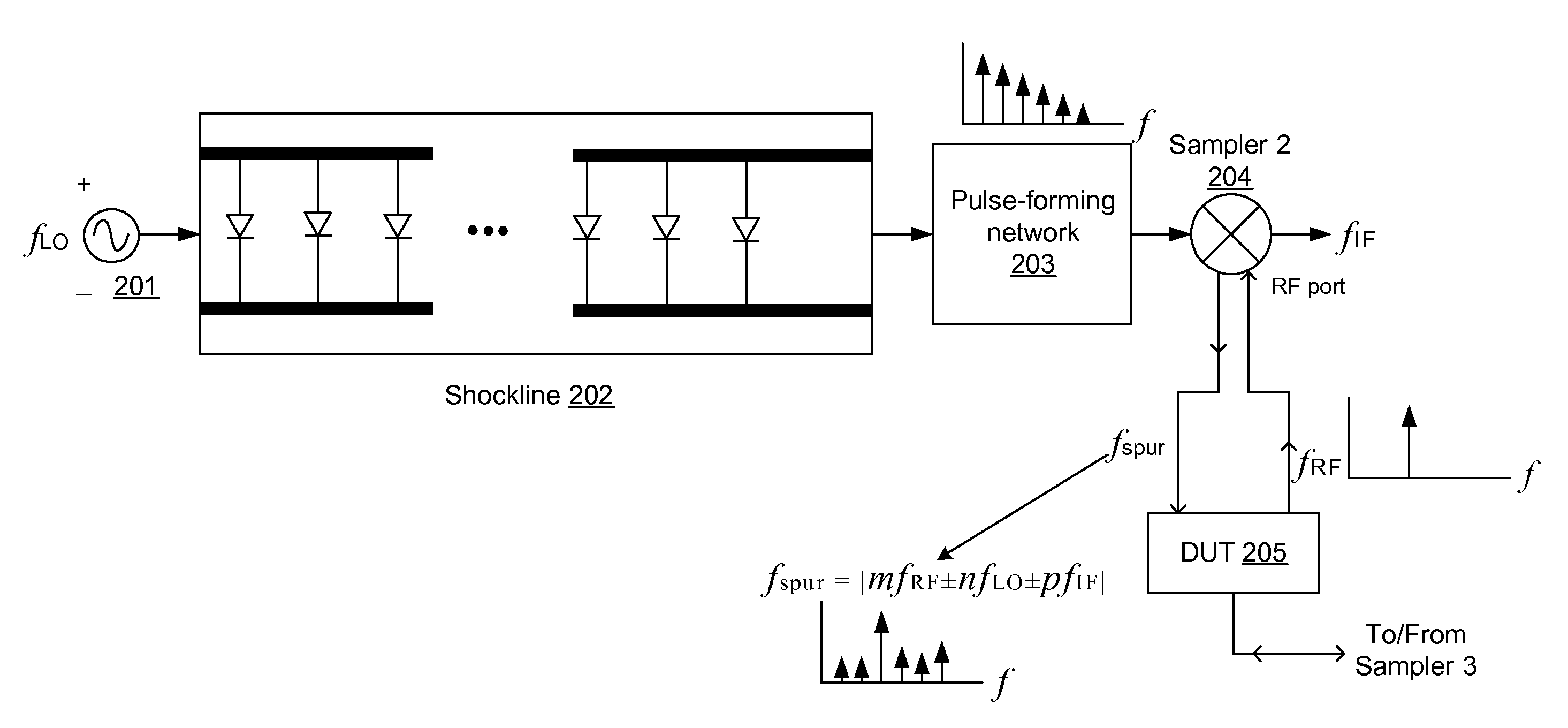

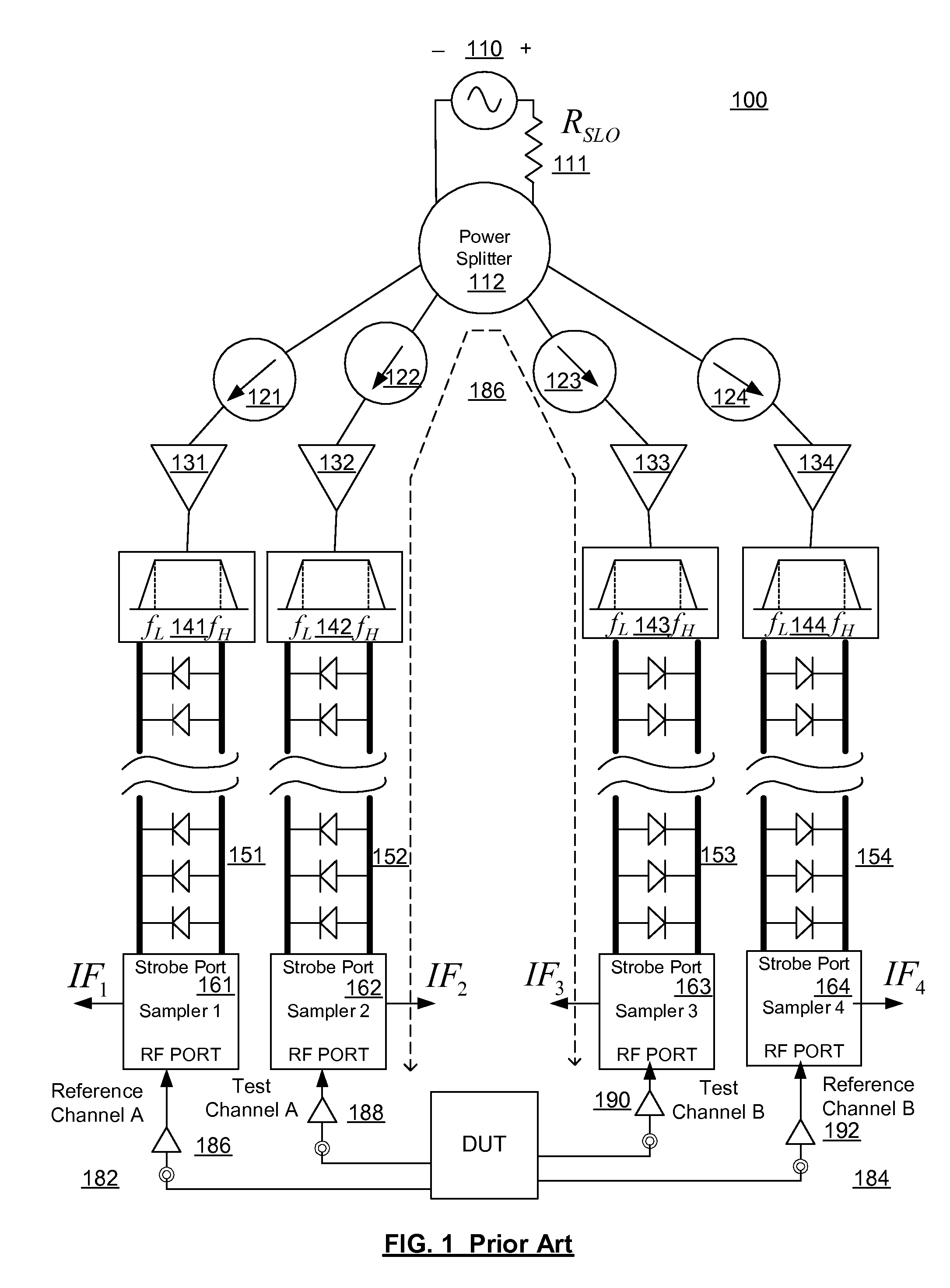

Apparatus for enhancing the dynamic range of shockline-based sampling receivers

ActiveUS8718586B2Improve dynamic rangeReduced isolationResistance/reactance/impedenceRadio transmissionHarmonicOperation mode

Shockline-based samplers of a vector-network analyzer (VNA) have enhanced dynamic range by using a dynamic bias network applied to the non-linear transmission lines (NLTLs) or shocklines. The bias voltage applied to the NLTL provides direct control over the falling-edge shockline compression, and thus the insertion loss and overall RF bandwidth of the sampler. Alternating between a forward bias voltage to turn off a shockline sampler when it is not needed and thereby reducing spurious generation and improving isolation can be alternatively applied with a reverse bias voltage to turn on the shockline sampler in a normal operation mode. By measuring the shockline output and providing feedback in the reverse-bias mode, the bias voltage can be dynamically adjusted to significantly increase the performance of the NLTL based sampler. In the presence of a strong positive bias voltage, the incoming LO and its harmonics experience large ohmic losses thus preventing gating pulses from forming in the shockline. The ohmic losses enable strong isolation between the LO sampling channels and will increase spectral purity at the VNA test ports.

Owner:ANRITSU CO

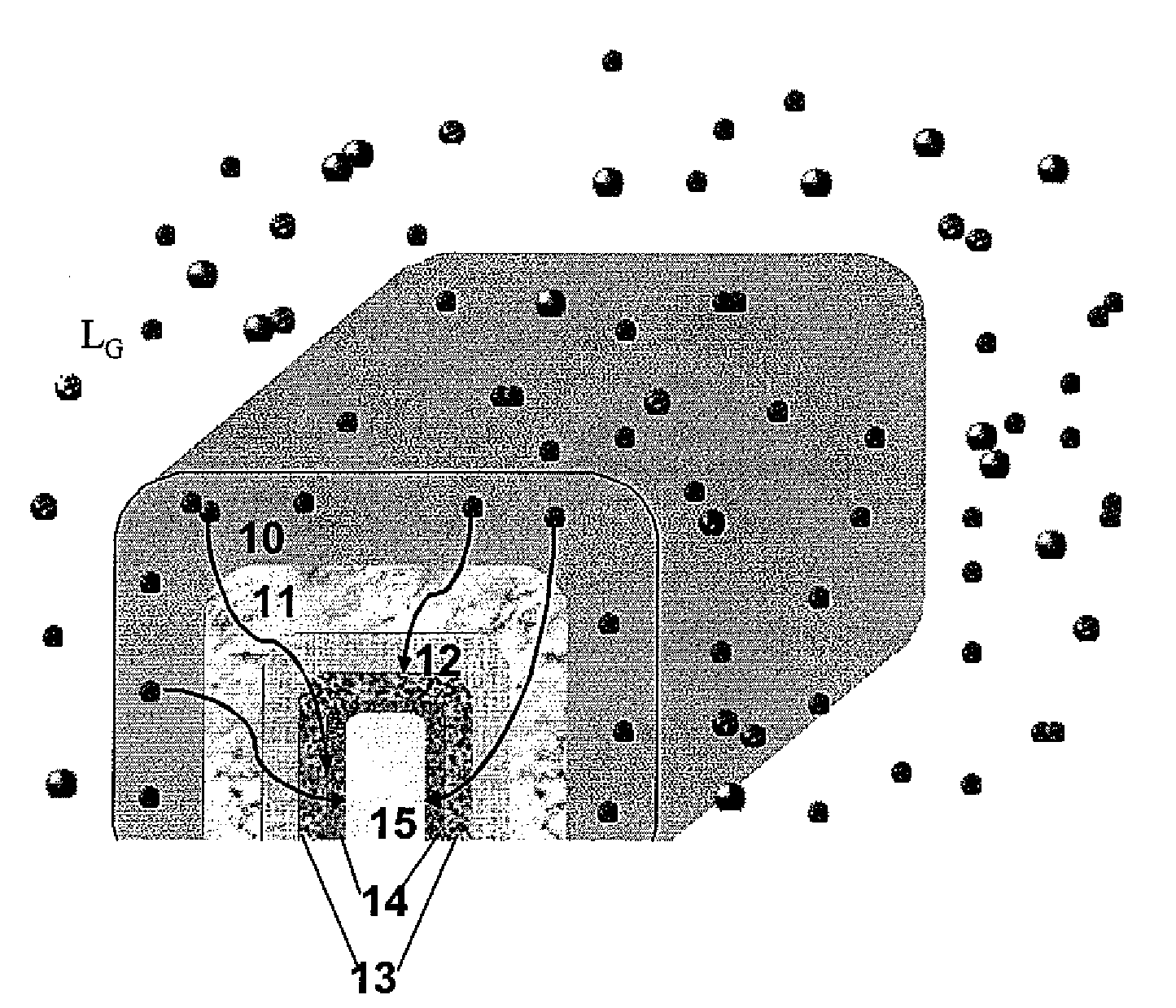

Device and method for forming surface coating with adoption of grid control and plasma-initiated gas-phase polymerization

ActiveCN105949836AShort duration of actionSimple structureElectric discharge tubesVacuum evaporation coatingGas phasePolymer coatings

The invention discloses a device and a method for forming a surface coating with adoption of grid control and plasma-initiated gas-phase polymerization, and belongs to the technical field of plasma. The device and the method are used for preparing the polymer coating on the surface of a substrate. The method is characterized in that a vacuum chamber is divided into a discharging cavity and a processing chamber by a metal grid mesh; the metal grid mesh is insulated from the vacuum chamber; carrier gas and monomer steam are fed into the discharging cavity and the processing chamber through different pipes respectively; a to-be-processed substrate is put into the processing chamber; continuous discharging plasma is generated in the discharging cavity, pulse positive bias is applied to the metal grid mesh, and the plasma is released to enter the processing cavity to initiate monomer polymerization. The method has advantages that the power supply structure is stable, the price is low, debugging is easy, the plasma is stable, the acting time of the plasma can be shortened to the microsecond level, and the like.

Owner:JIANGSU FAVORED NANOTECHNOLOGY CO LTD

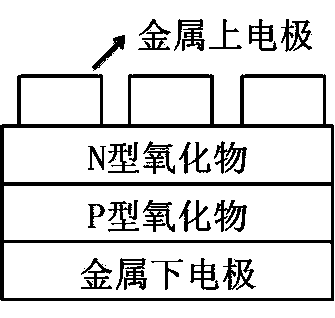

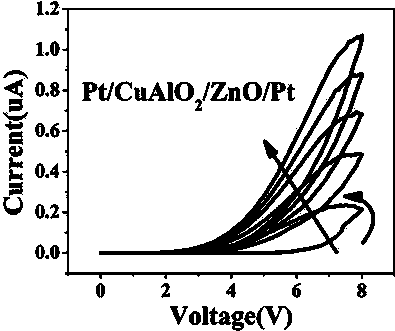

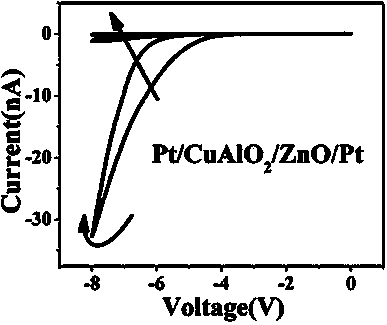

Memristor based on pn heterostructure and manufacturing method thereof

ActiveCN104051545AIncrease flexibilityWeak selectivitySemiconductor/solid-state device manufacturingDiodeElectrical resistance and conductanceOxygen ions

The invention belongs to the technical field of information storage, and particularly relates to a memristor based on a pn heterostructure and a manufacturing method of the memristor. The memristor comprises an upper electrode and a lower electrode, and the pn heterostructure composed of p-type oxide (such as CuAlO2 and NiO) and n-type oxide (such as ZnO and TiO2) is inserted between the upper electrode and the lower electrode. Positive bias voltages are continuously applied to the lower electrode, and oxygen ions in a depletion layer can be gradually migrated to one side of a p-type region from an n-type region. The vacancy concentration of positive ions on one side of the p-type region and the vacancy concentration of oxygen on one side of the n-type region are increased at the same time, the width of the depletion layer of a pn joint is gradually reduced, and therefore device resistance is gradually lowered, and the resistance memory behavior is achieved. The characteristic that the physical property of the pn joint is easy to modulate is utilized, and flexibility of regulating and controlling the resistance memory performance is increased. Selectivity on materials is poor, the performance of the resistance memory behavior is stable, the half-quantitative study on a resistance memory device is facilitated, and the basis is laid for device deign and further development.

Owner:NORTHEAST NORMAL UNIVERSITY