Patents

Literature

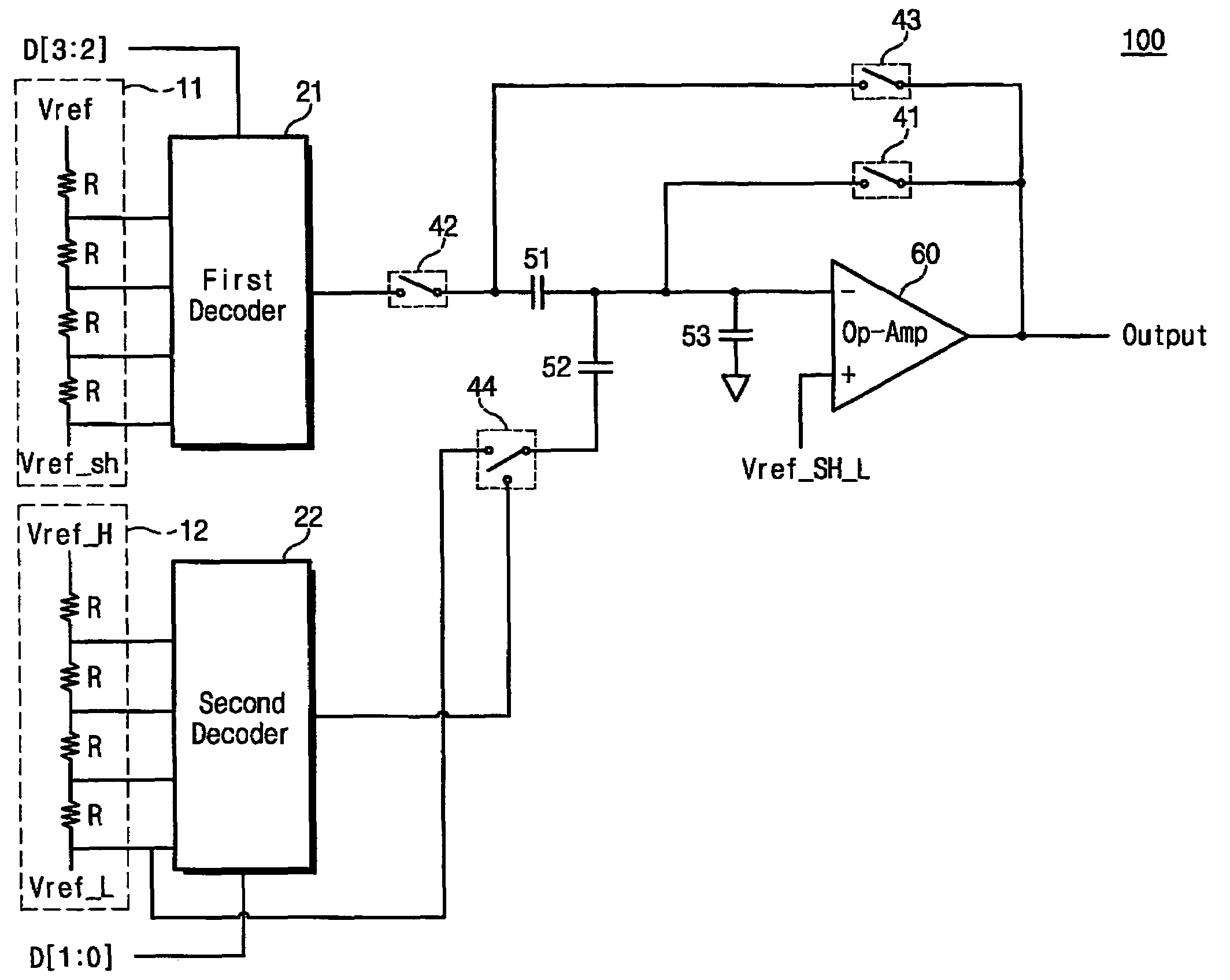

106results about How to "Minimize the effect of parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Shielded through-via

InactiveUS7589390B2Minimize the effect of parasitic capacitanceImprove isolationSemiconductor/solid-state device detailsPrinted circuit aspectsParasitic capacitanceEngineering

Owner:TELEDYNE SCI & IMAGING

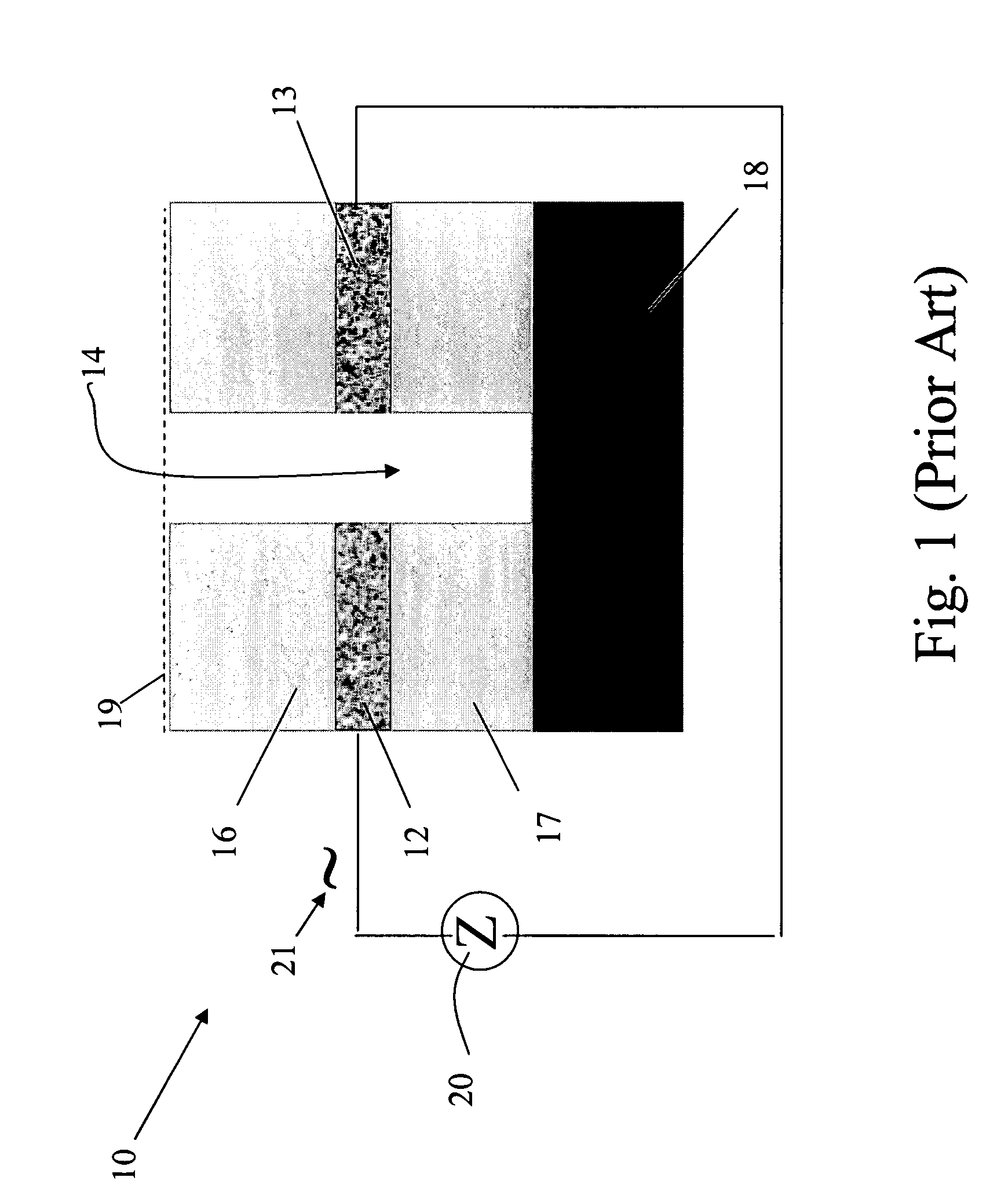

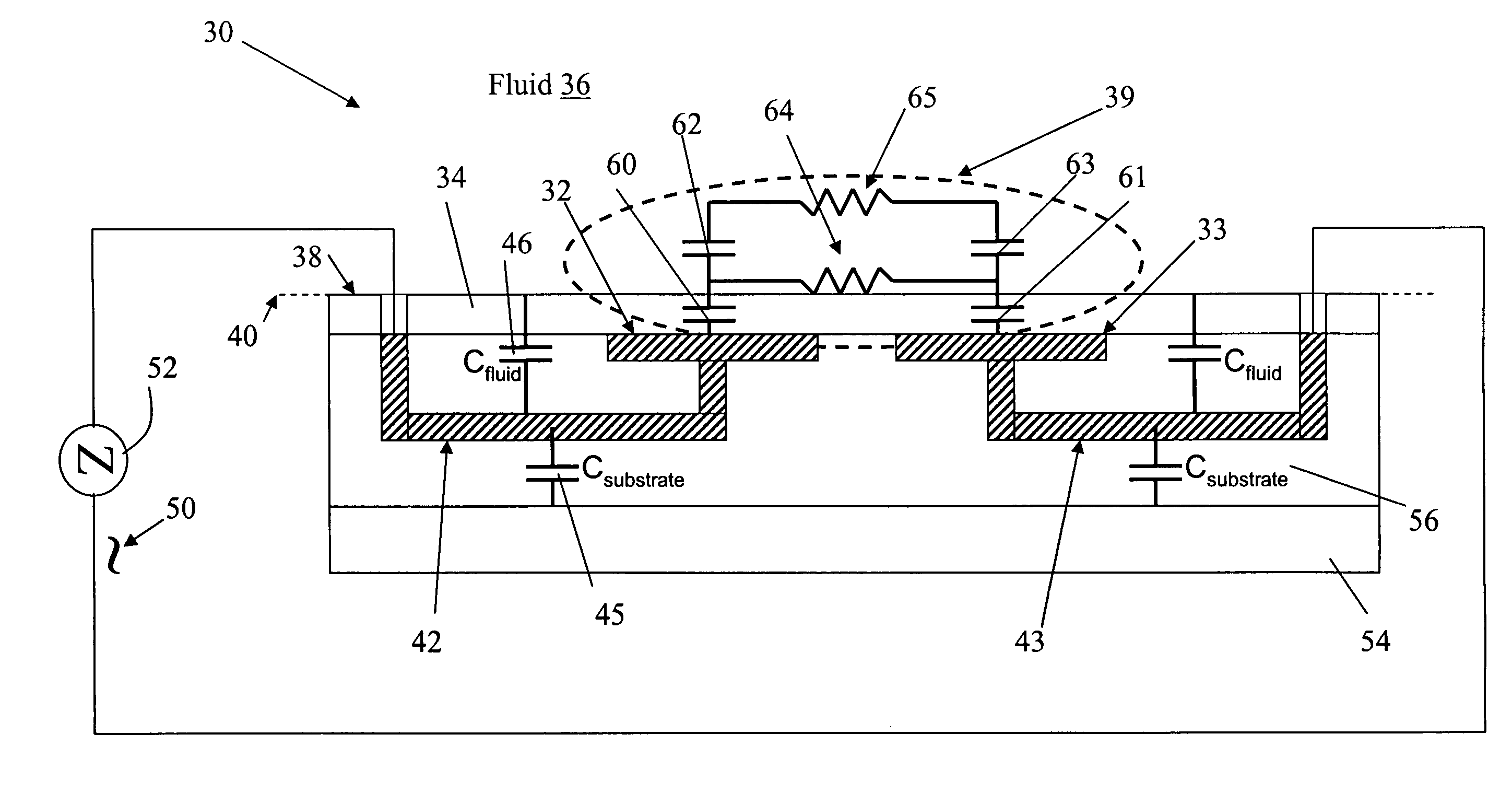

Micro sensor for electrochemically monitoring residue in micro channels

InactiveUS7332902B1Reduce effectExtend measurement bandwidthElectrolysis componentsVolume/mass flow measurementMicroelectronicsAspect ratio

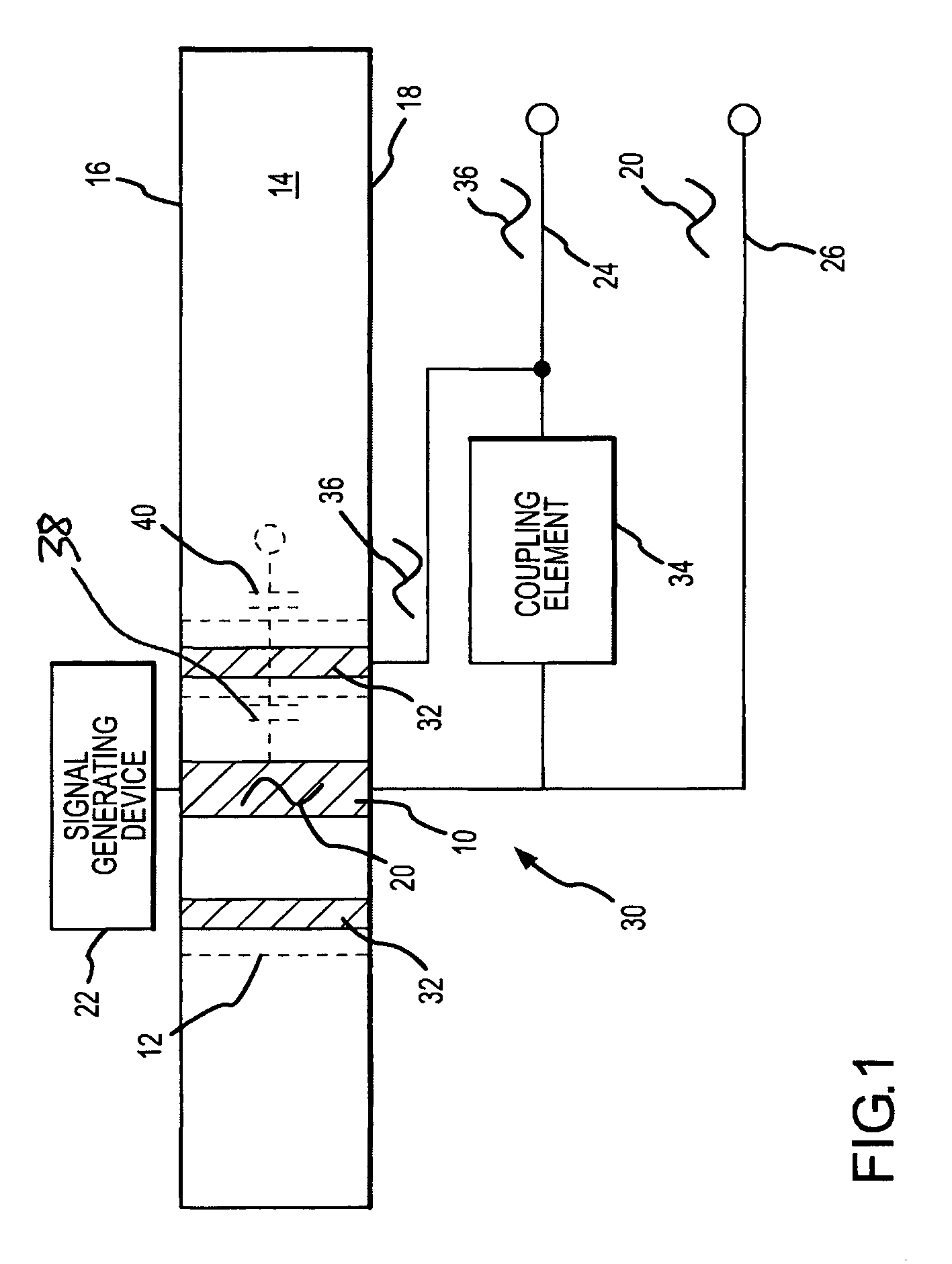

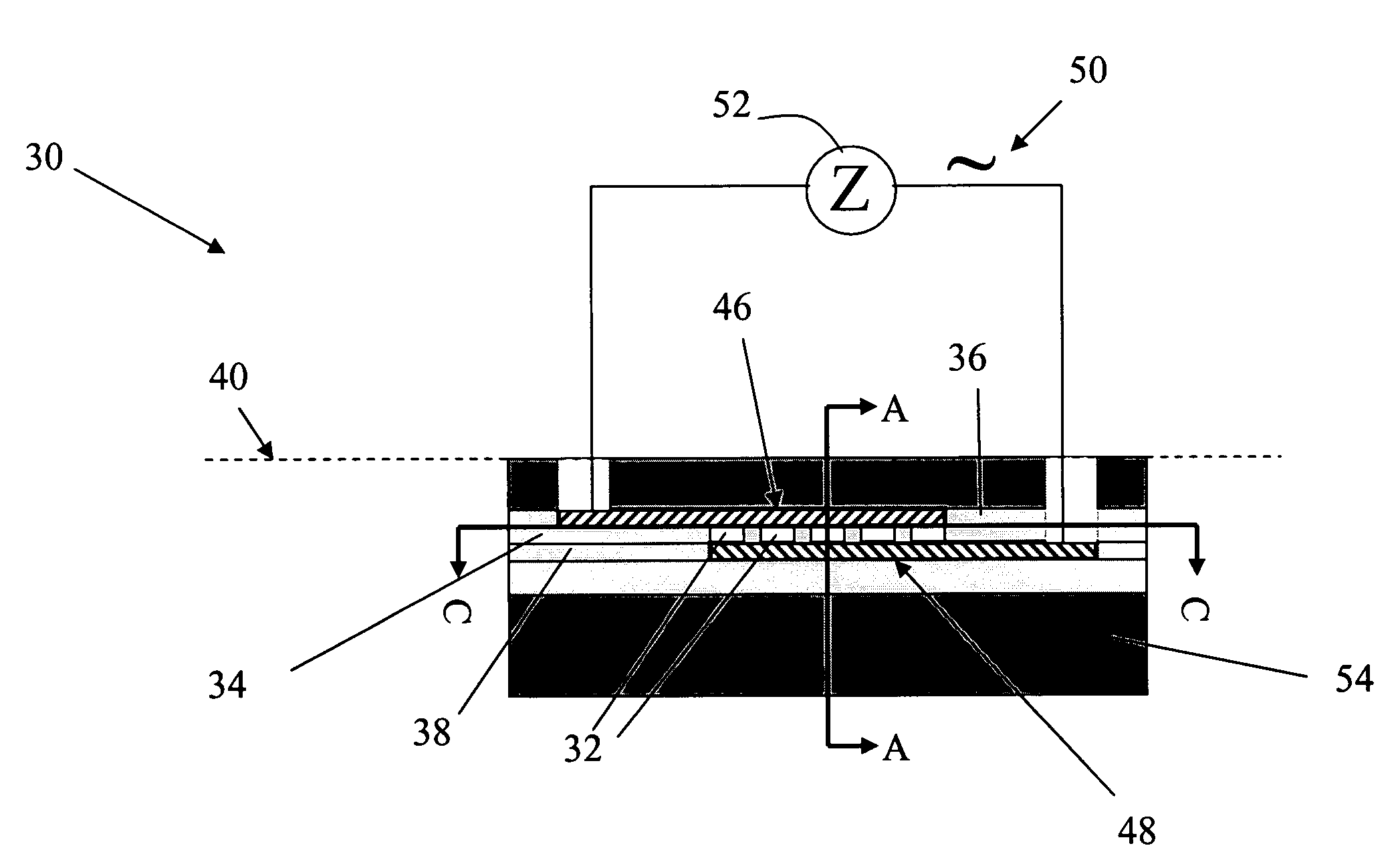

The present invention provides a micro sensor for monitoring the cleaning and drying processes for very high aspect ratio micro channels in dielectric films oriented parallel to the fluid-solid interface during the manufacture of ICs, MEMS and other micro-devices. The micro sensor can be used to monitor “vertical” micro features common in microelectronics fabrication or “horizontal” micro features found in MEMS or microfluidic fabrication. By forming the micro channels parallel to the interface, the channels can be made with much higher and well controlled aspect ratios. In addition, multiple sensors can sense the impedance at various points along the micro features. The addition of a guard reduces the effects of any parasitic capacitance, which extends the measurement bandwidth of the sensor.

Owner:ENVIRONMENTAL METROLOGY CORP

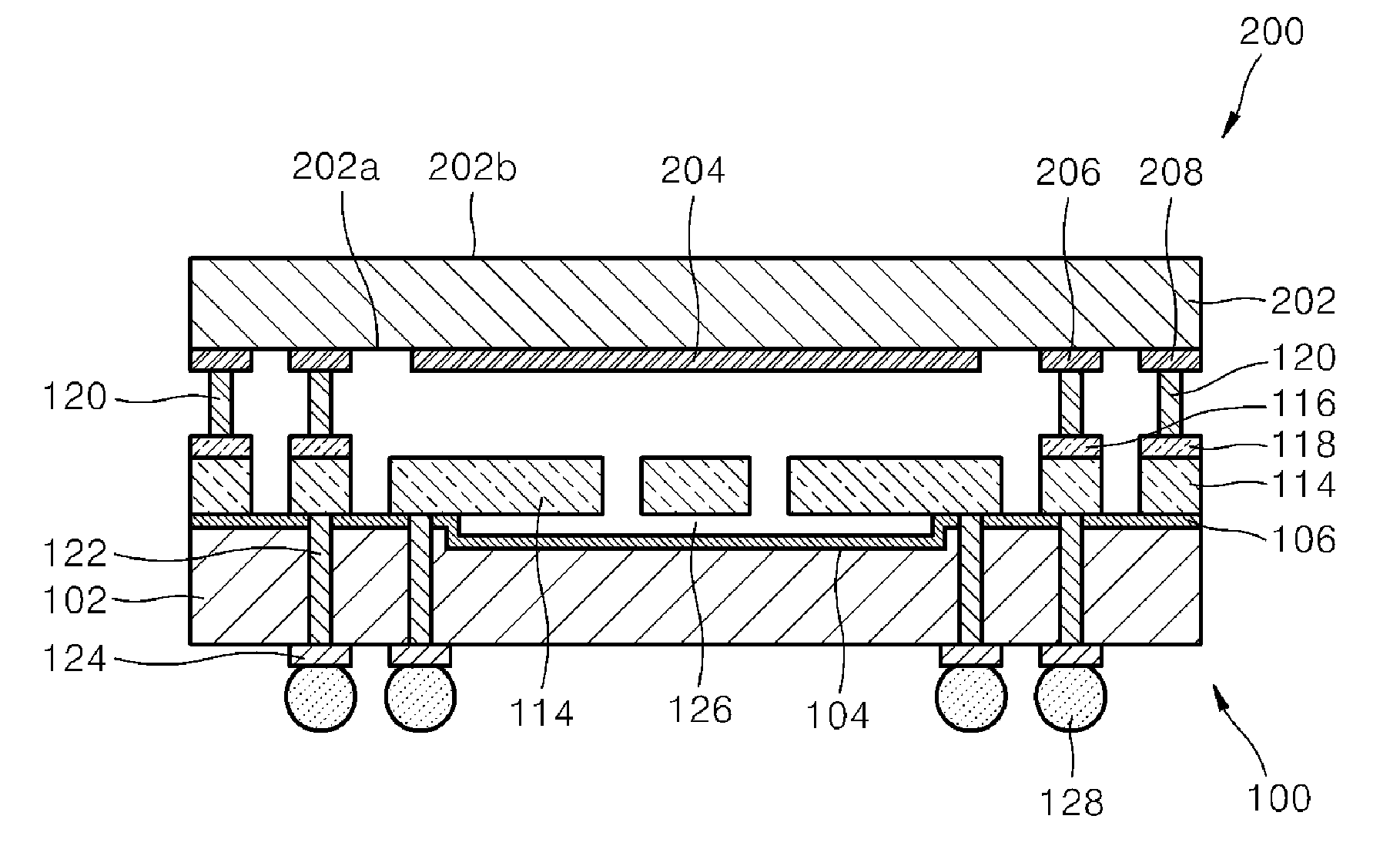

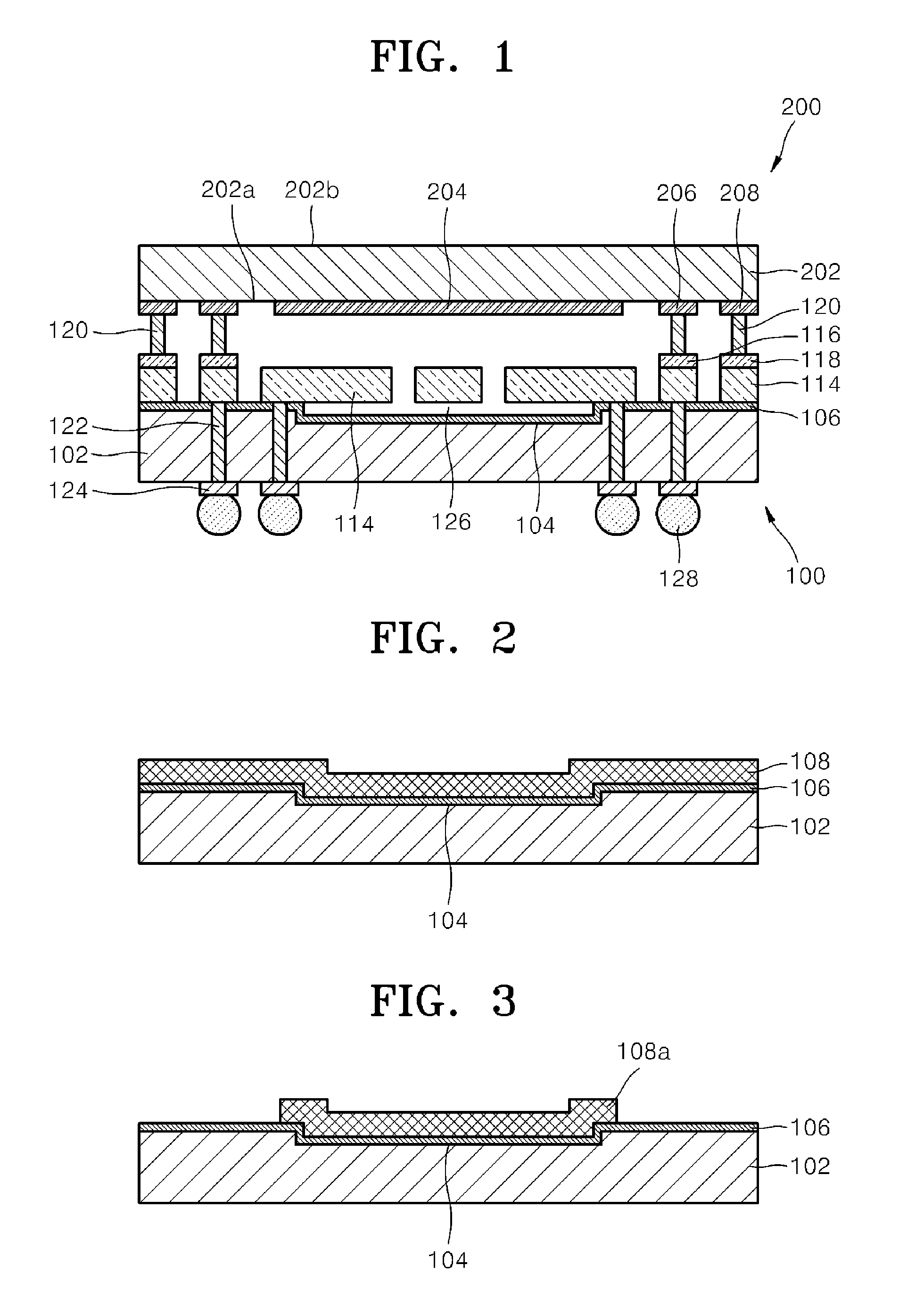

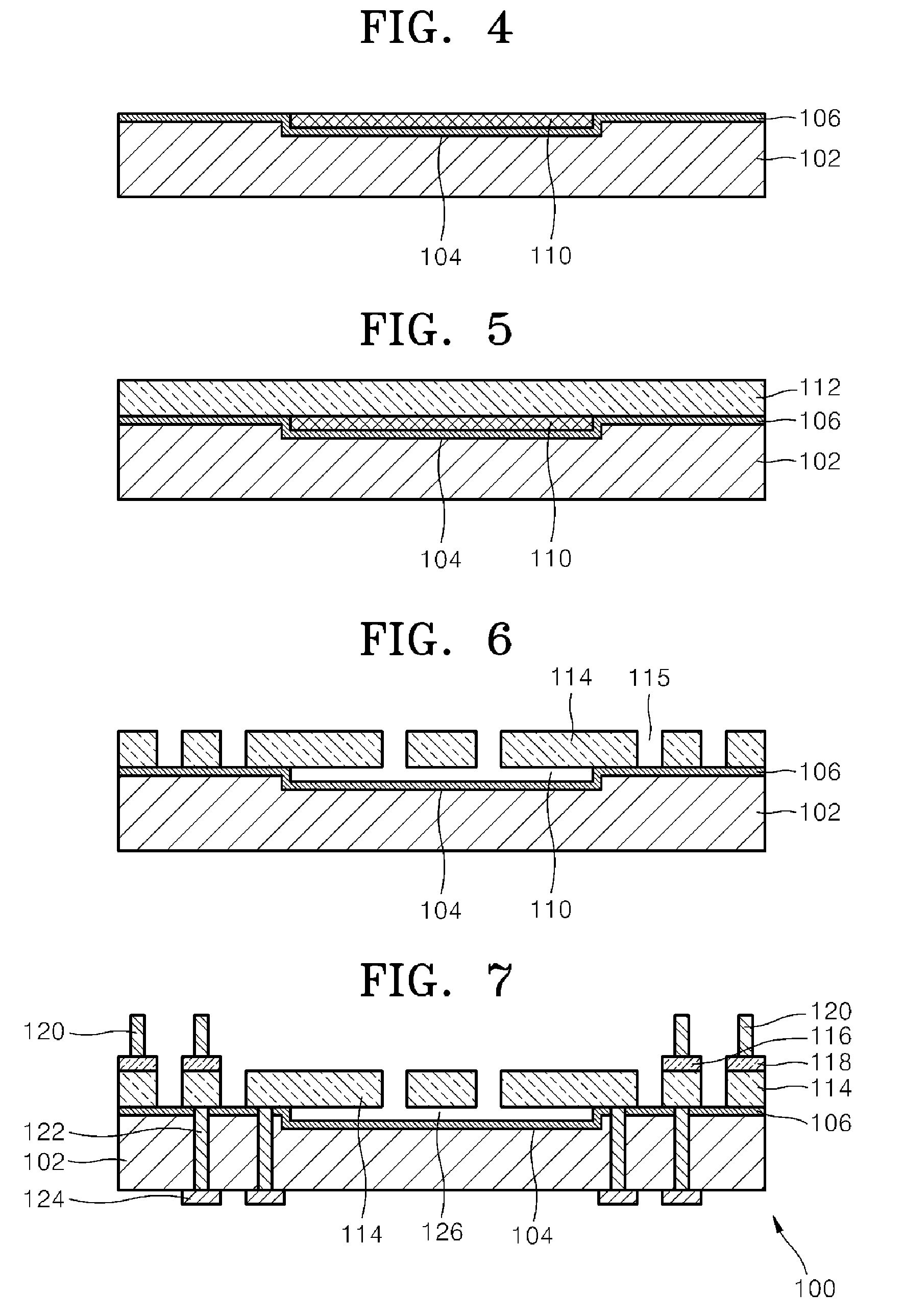

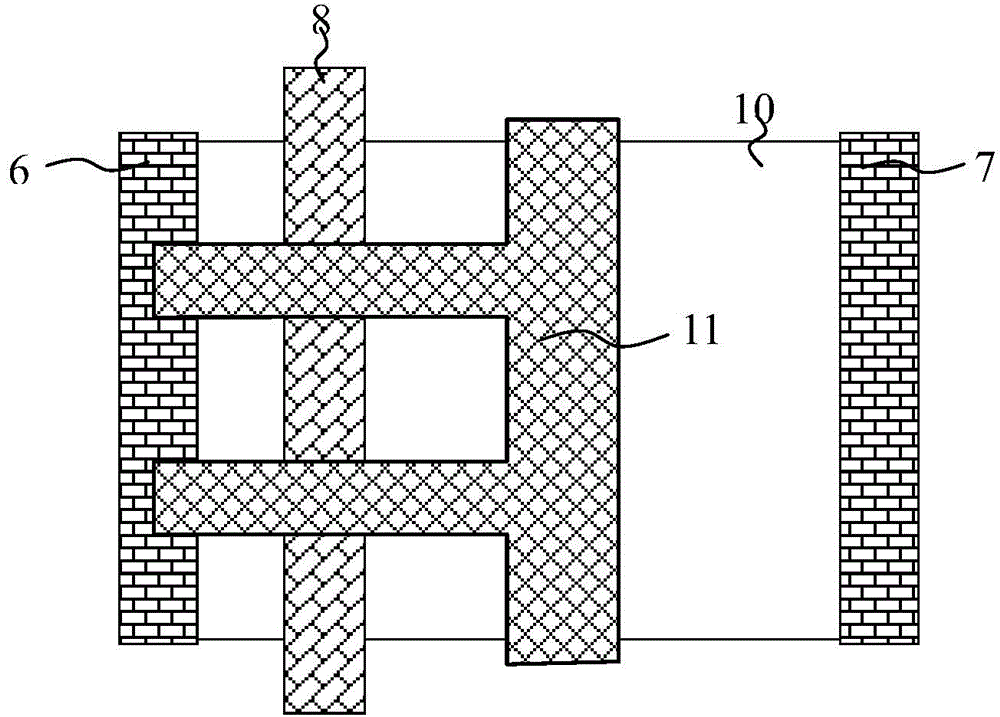

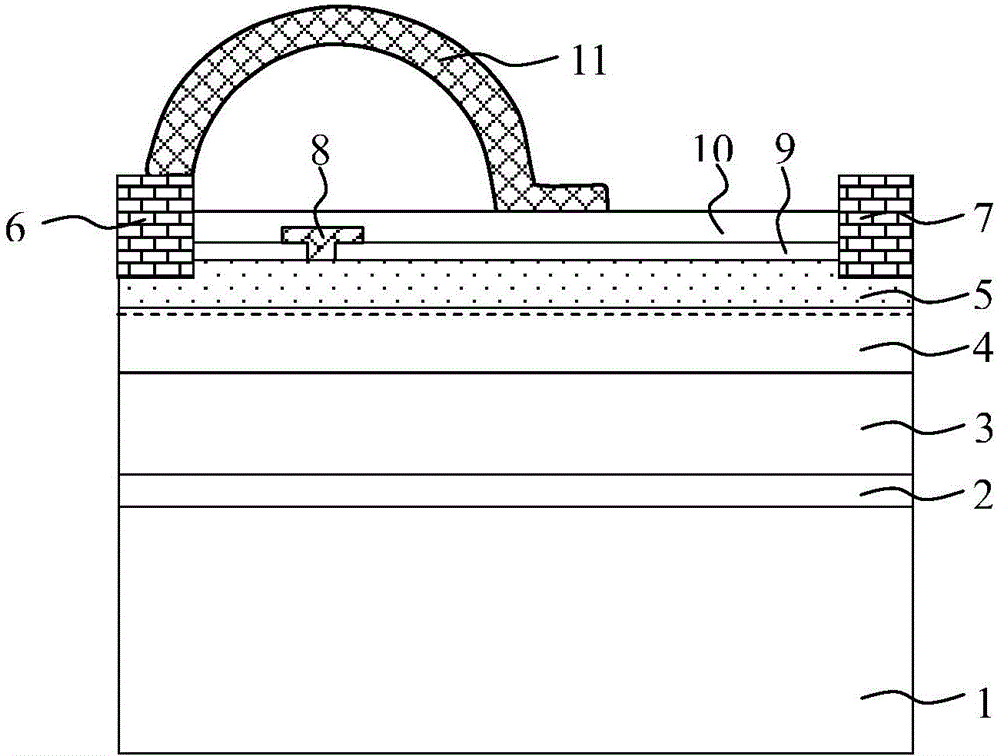

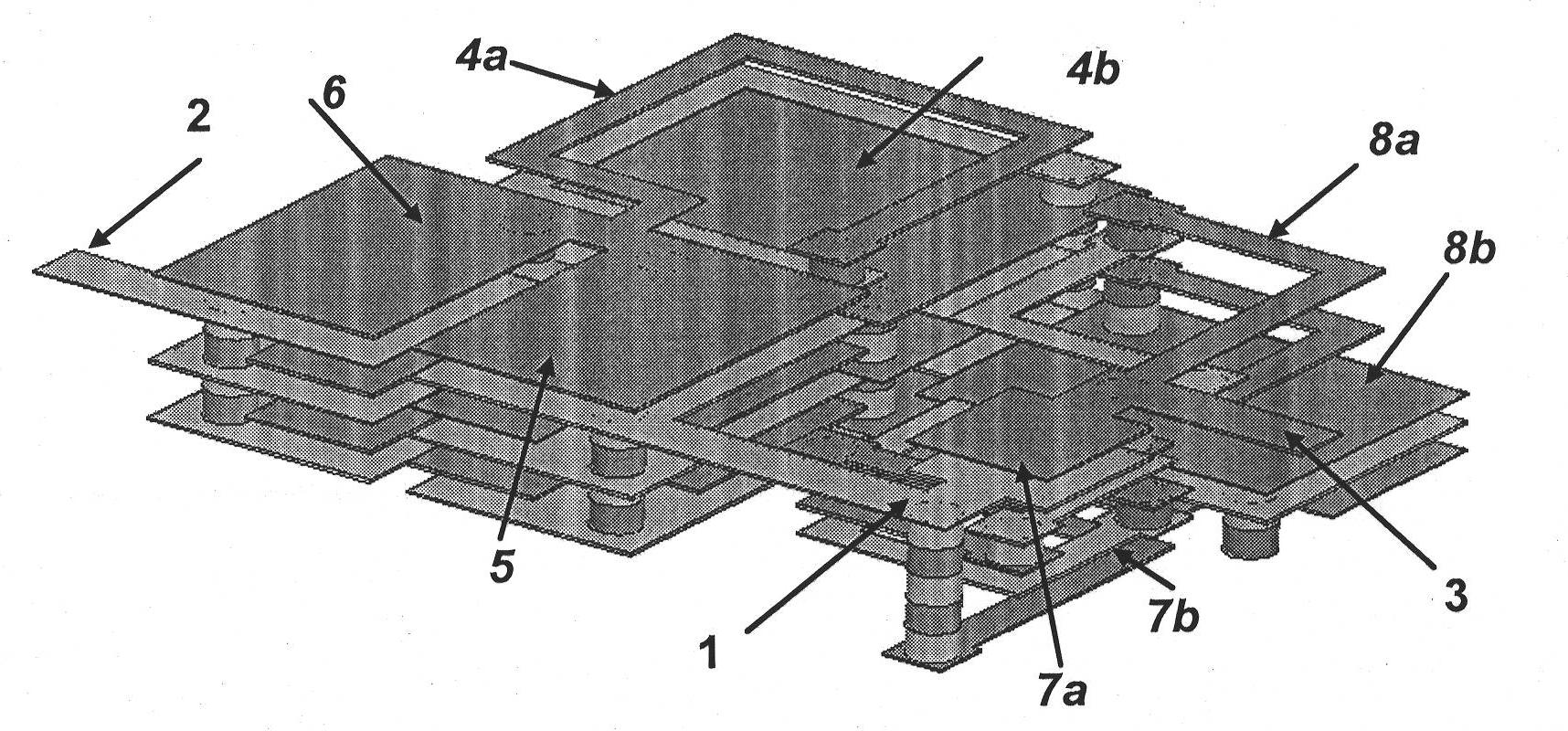

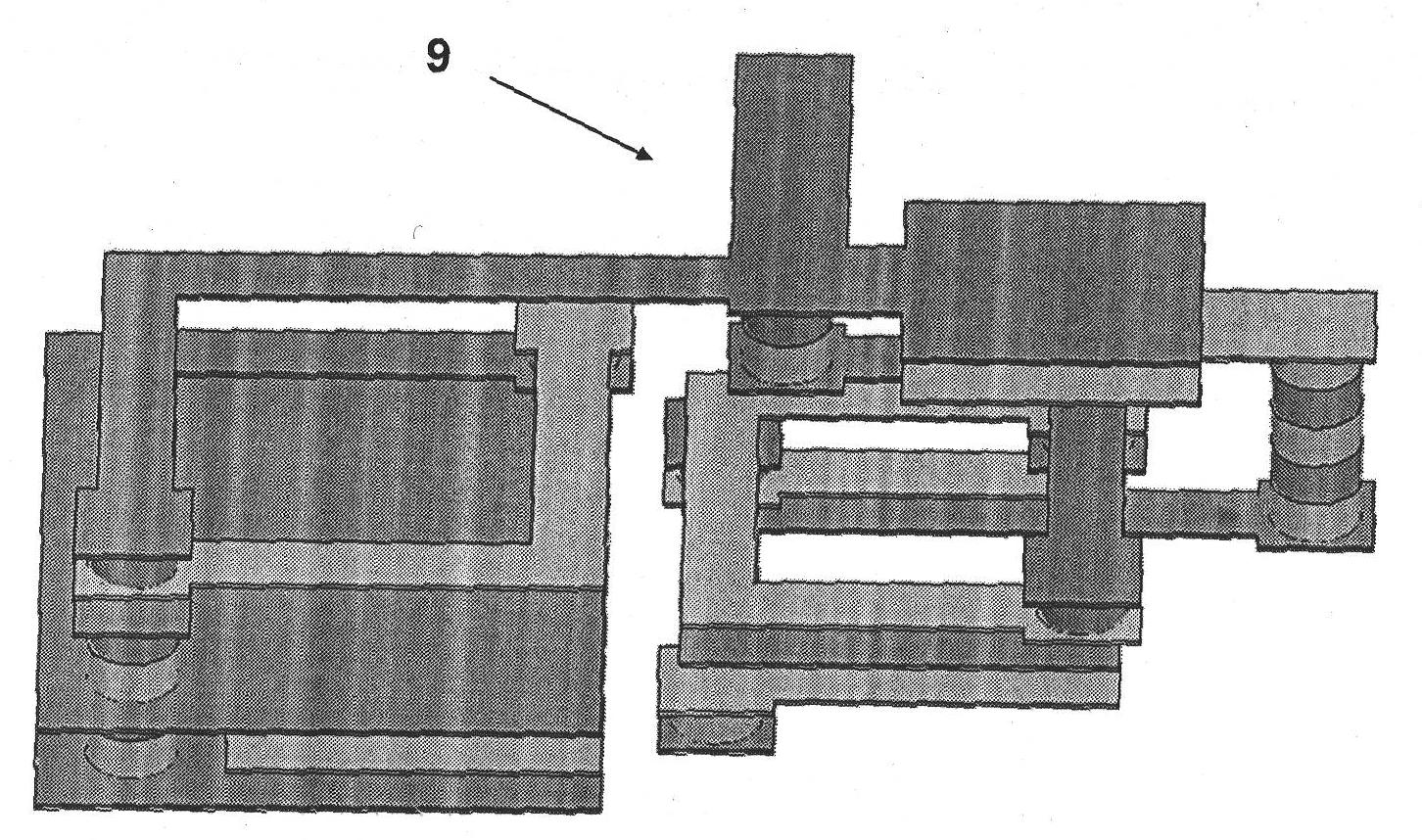

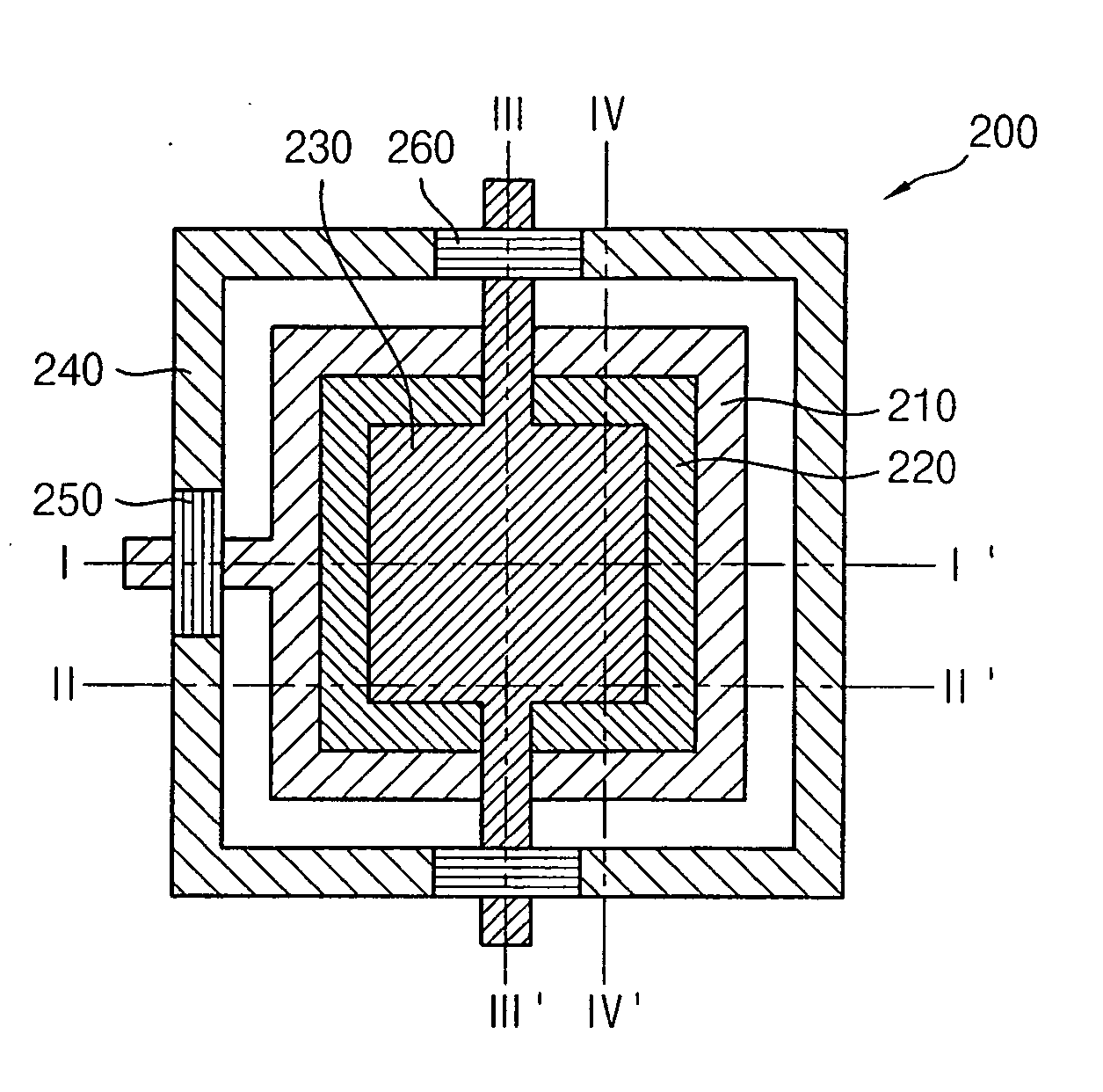

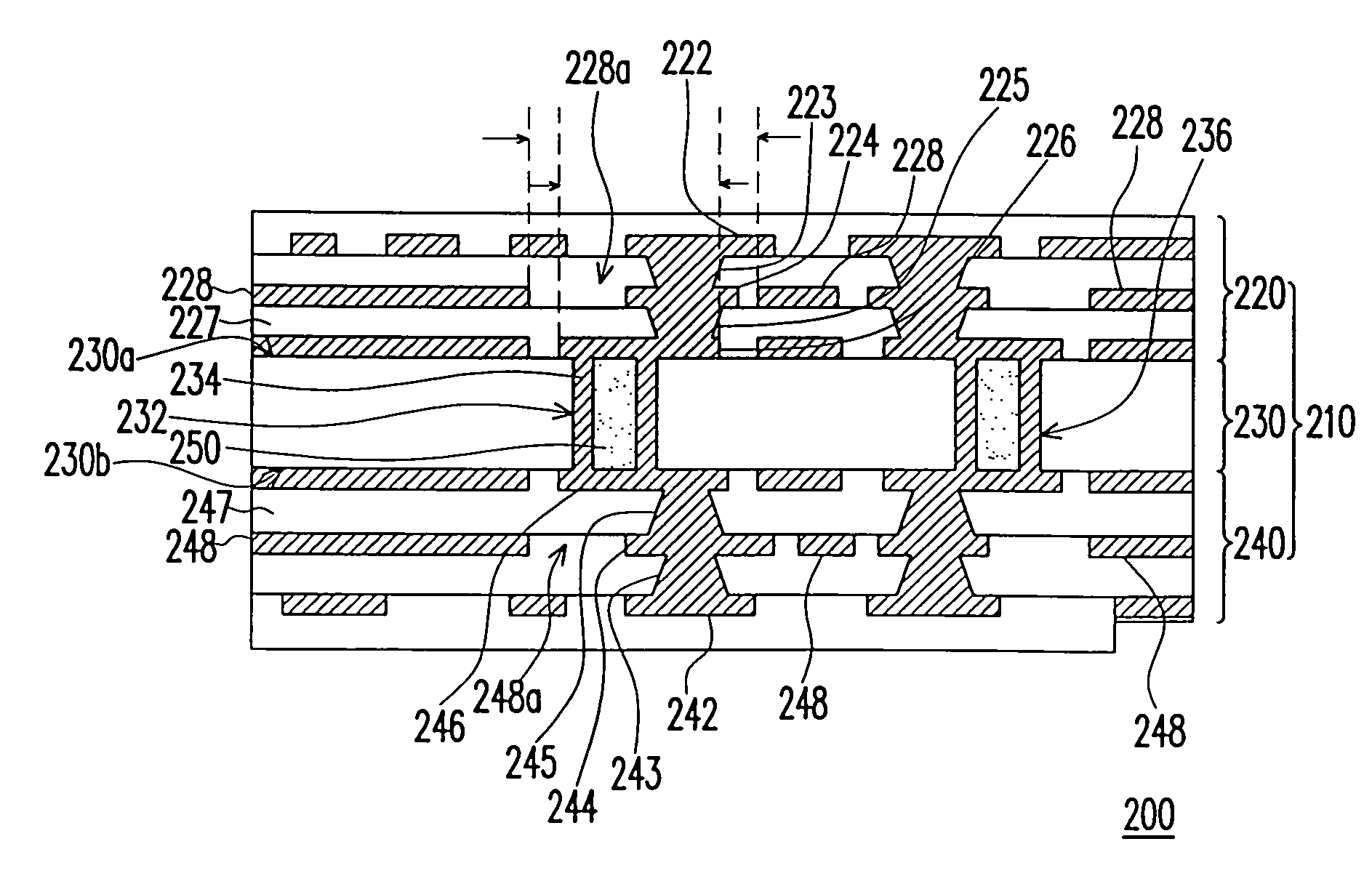

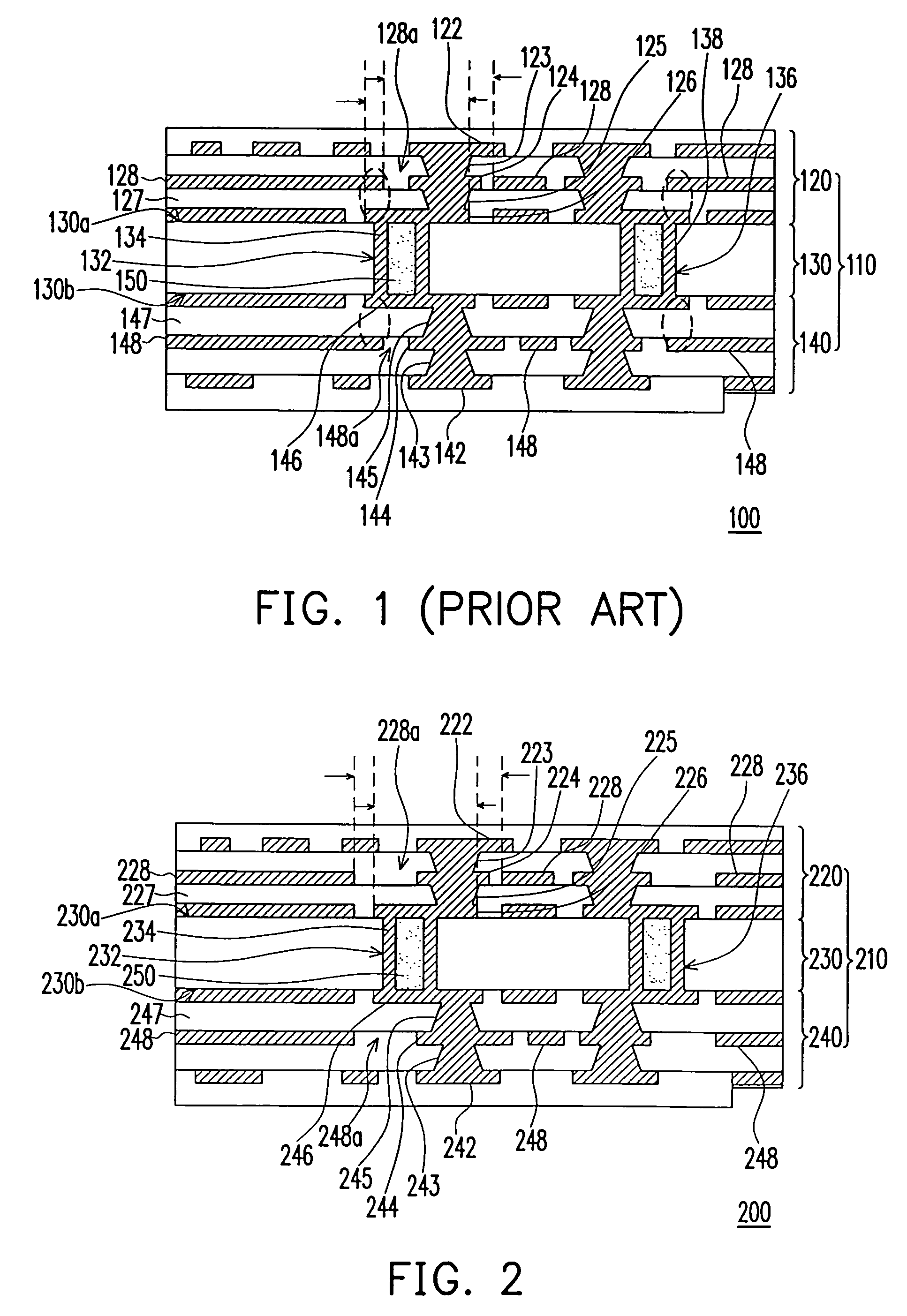

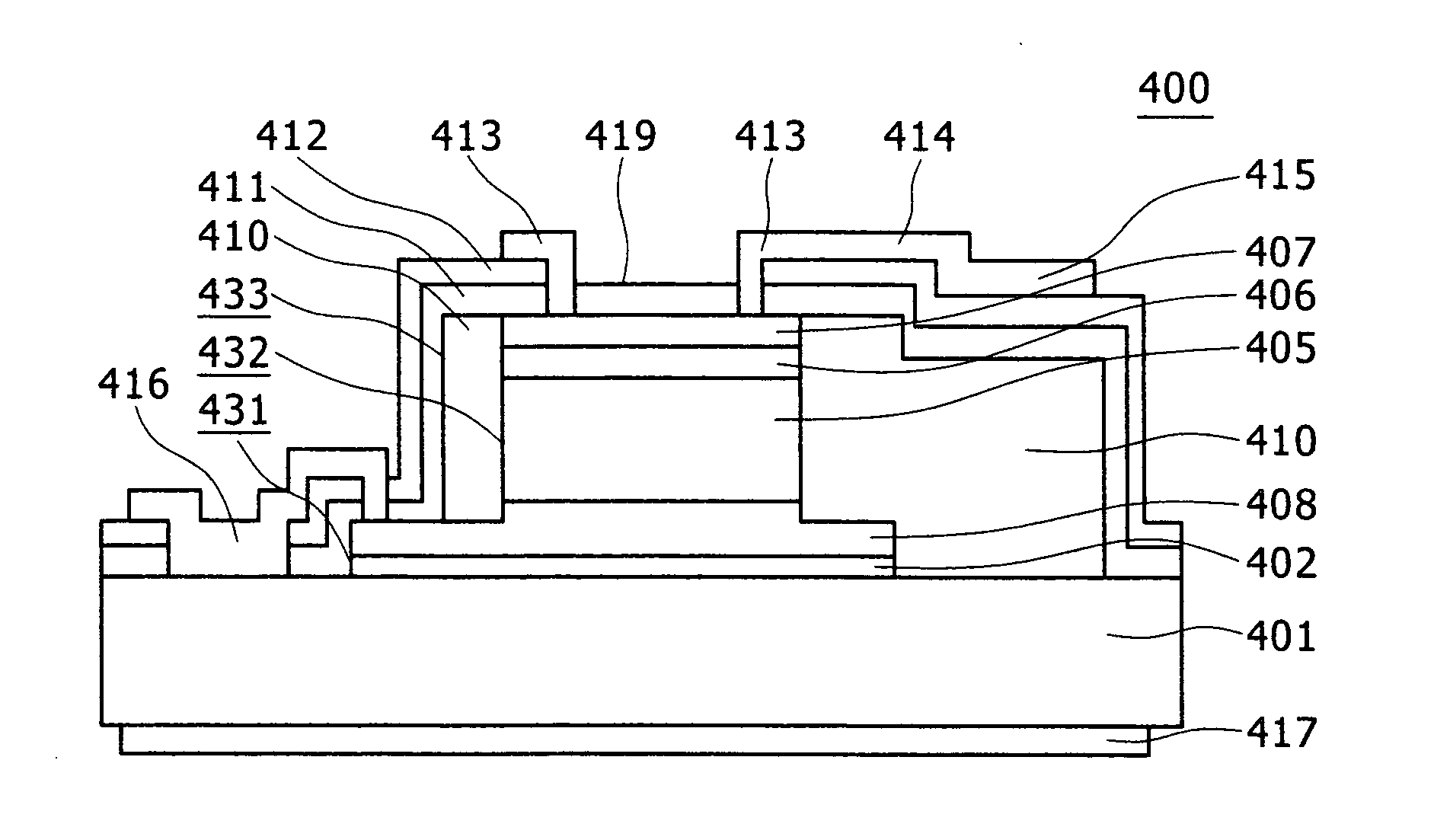

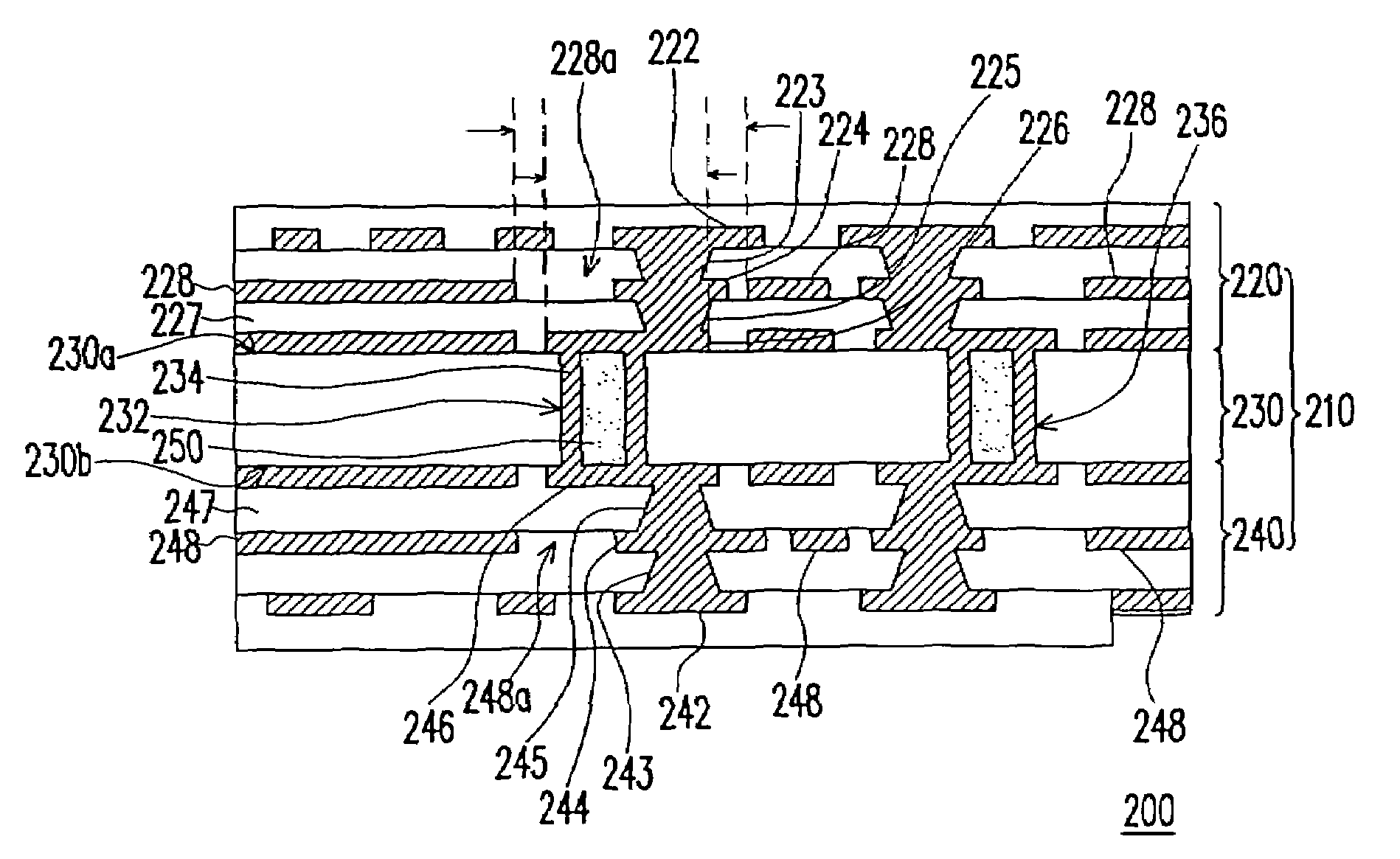

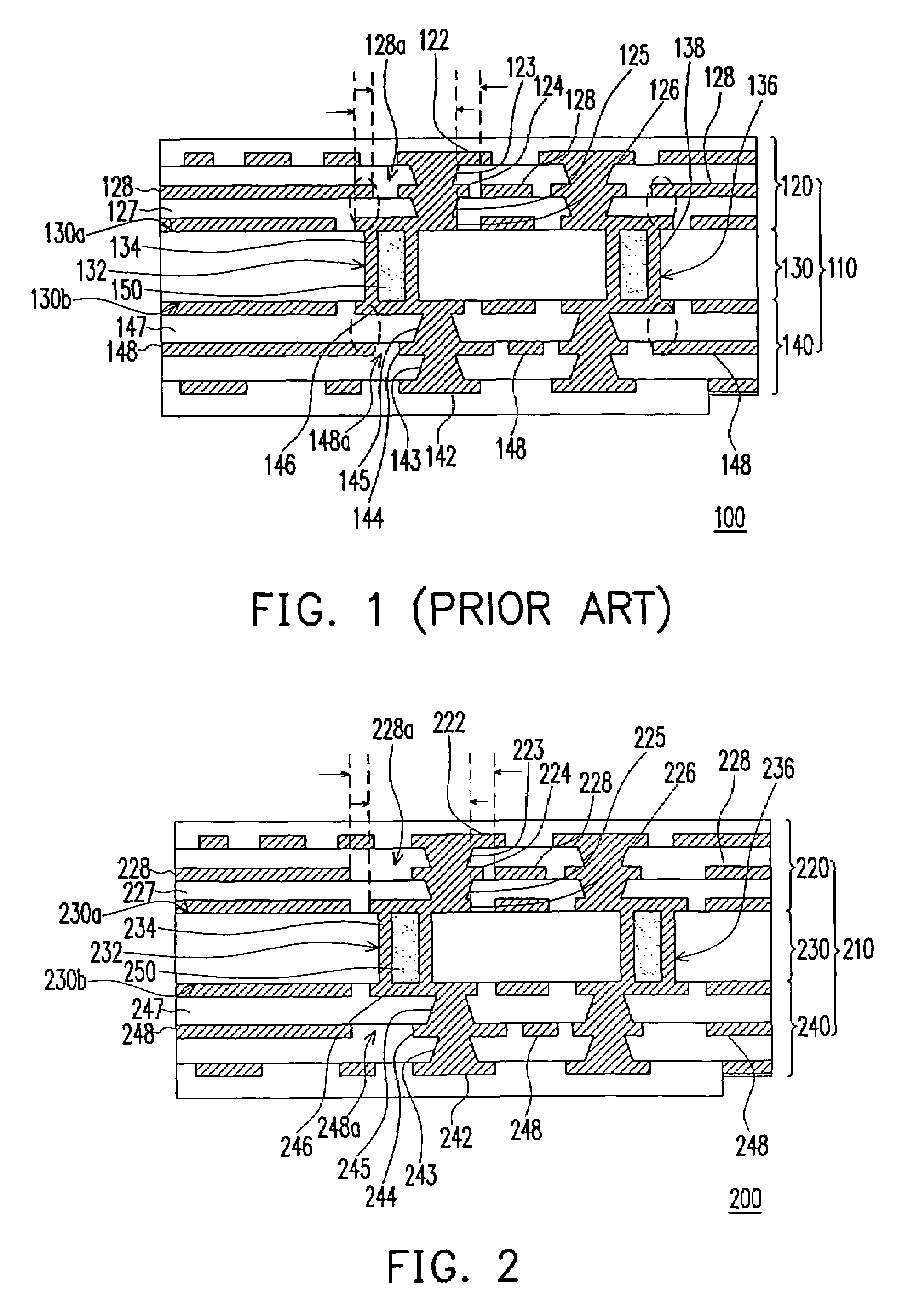

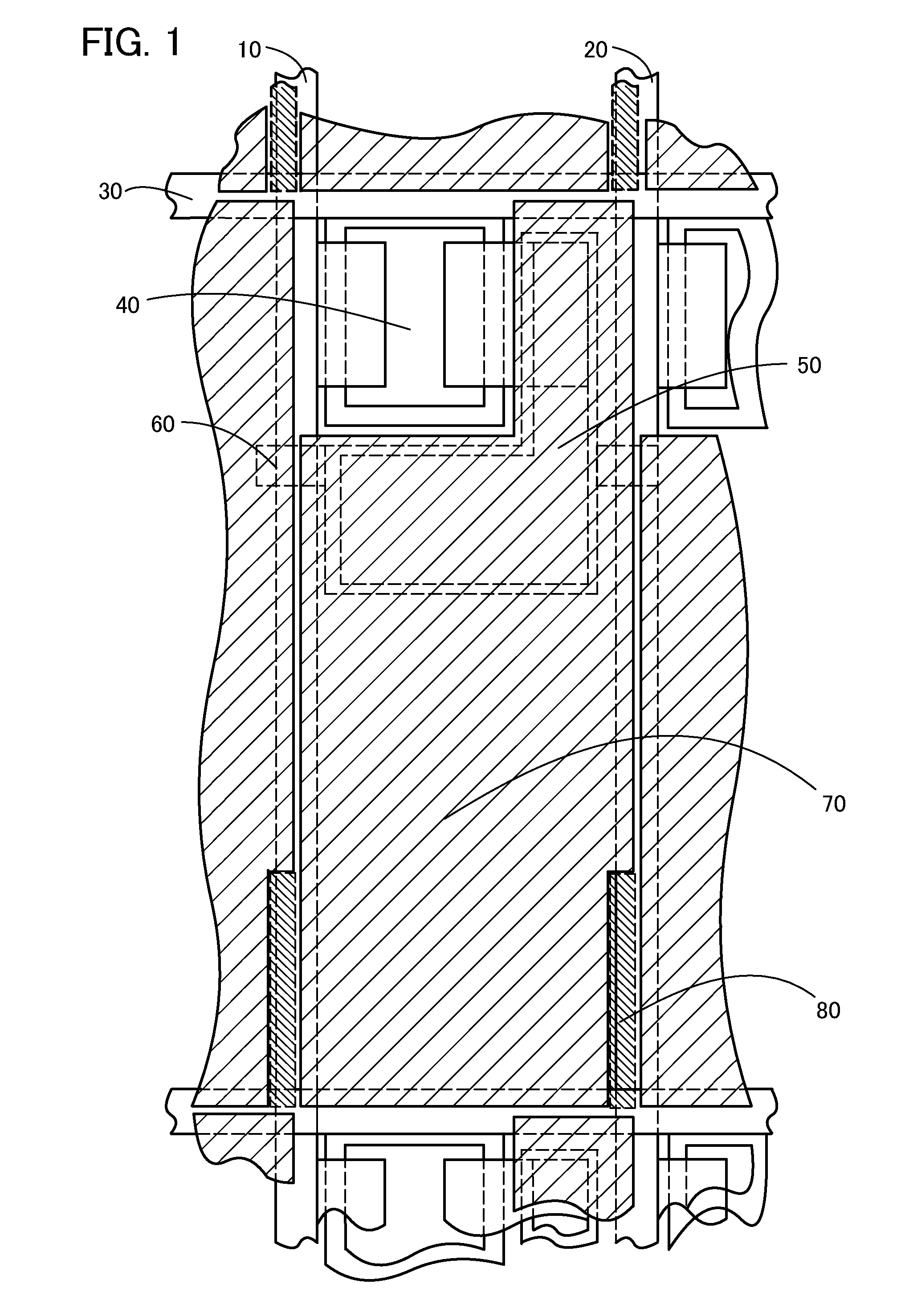

MEMS package and packaging method thereof

InactiveUS20100096713A1Increase productionMinimize the effect of parasitic capacitanceAcceleration measurement using interia forcesTransducer detailsElectrical and Electronics engineeringMechanical system

Provided are a Micro Electro-Mechanical System (MEMS) package and a method of packaging the MEMS package. The MEMS package includes: a MEMS device including MEMS structures formed on a substrate, first pad electrodes driving the MEMS structures, first sealing parts formed at an edge of the substrate, and connectors formed on the first pad electrodes and the first sealing parts; and a MEMS driving electronic device including second pad electrodes and second sealing parts respectively corresponding to the first pad electrodes and the first sealing parts to be sealed with and bonded to the MEMS device through the connectors to form an air gap having a predetermined width.

Owner:ELECTRONICS & TELECOMM RES INST

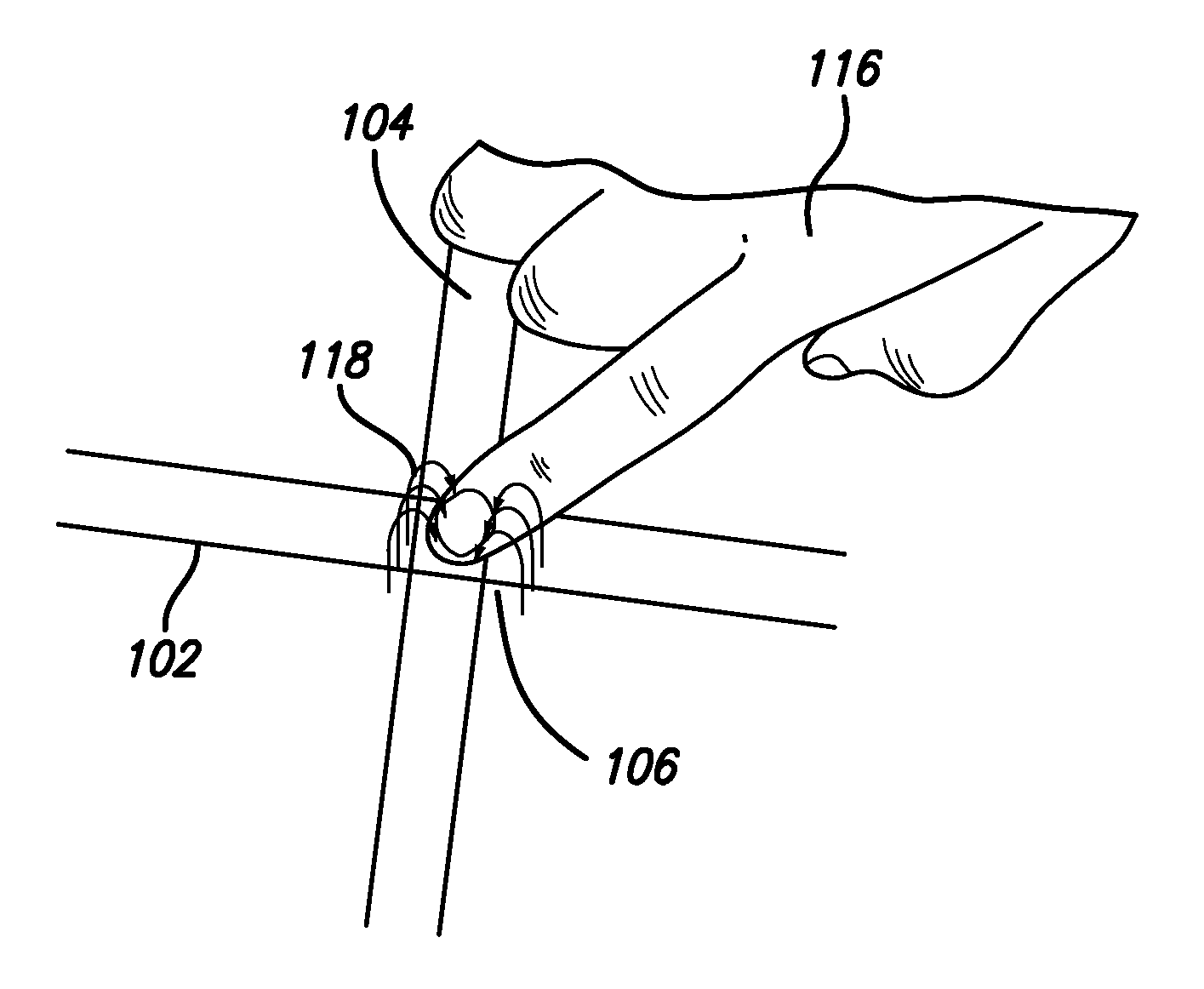

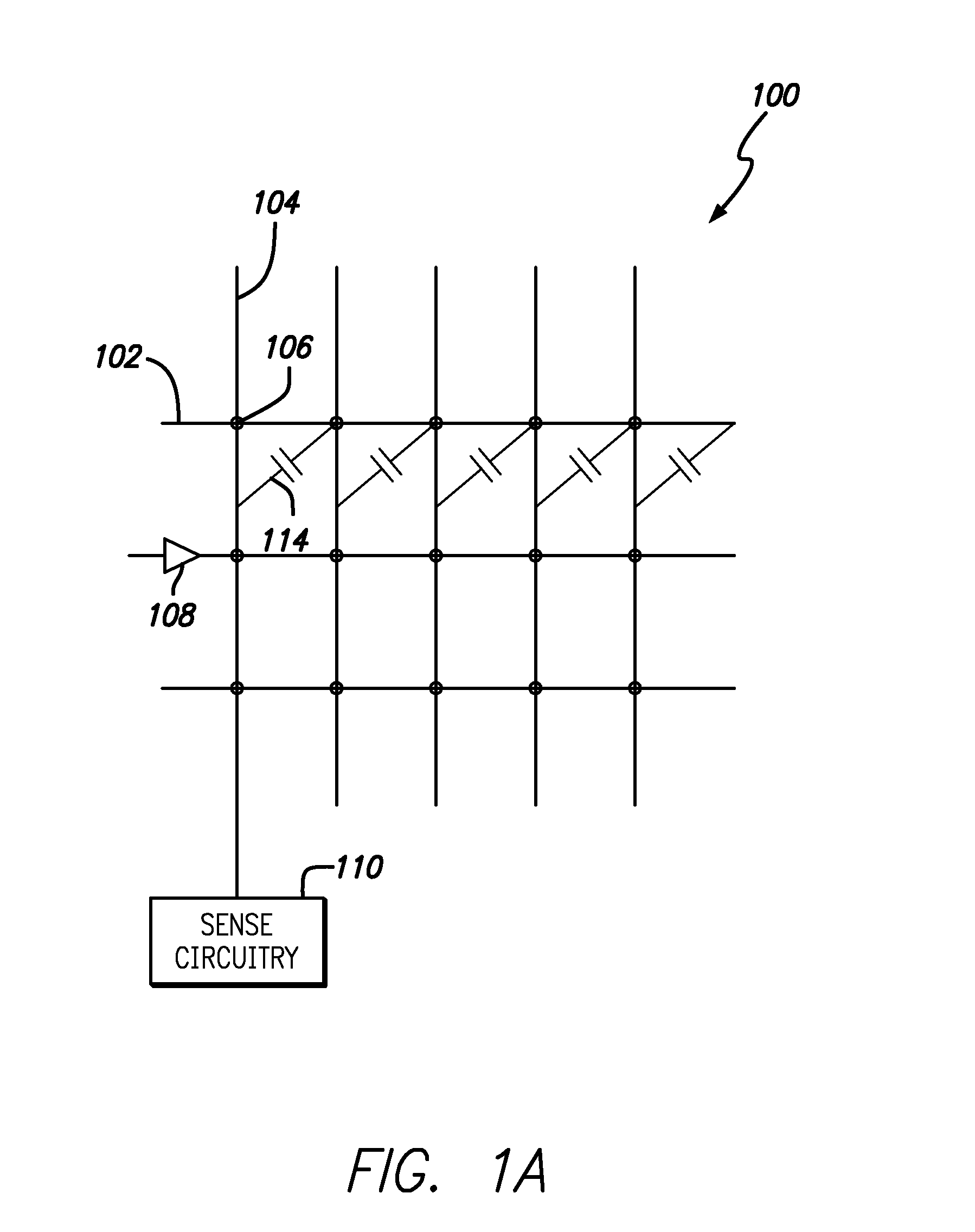

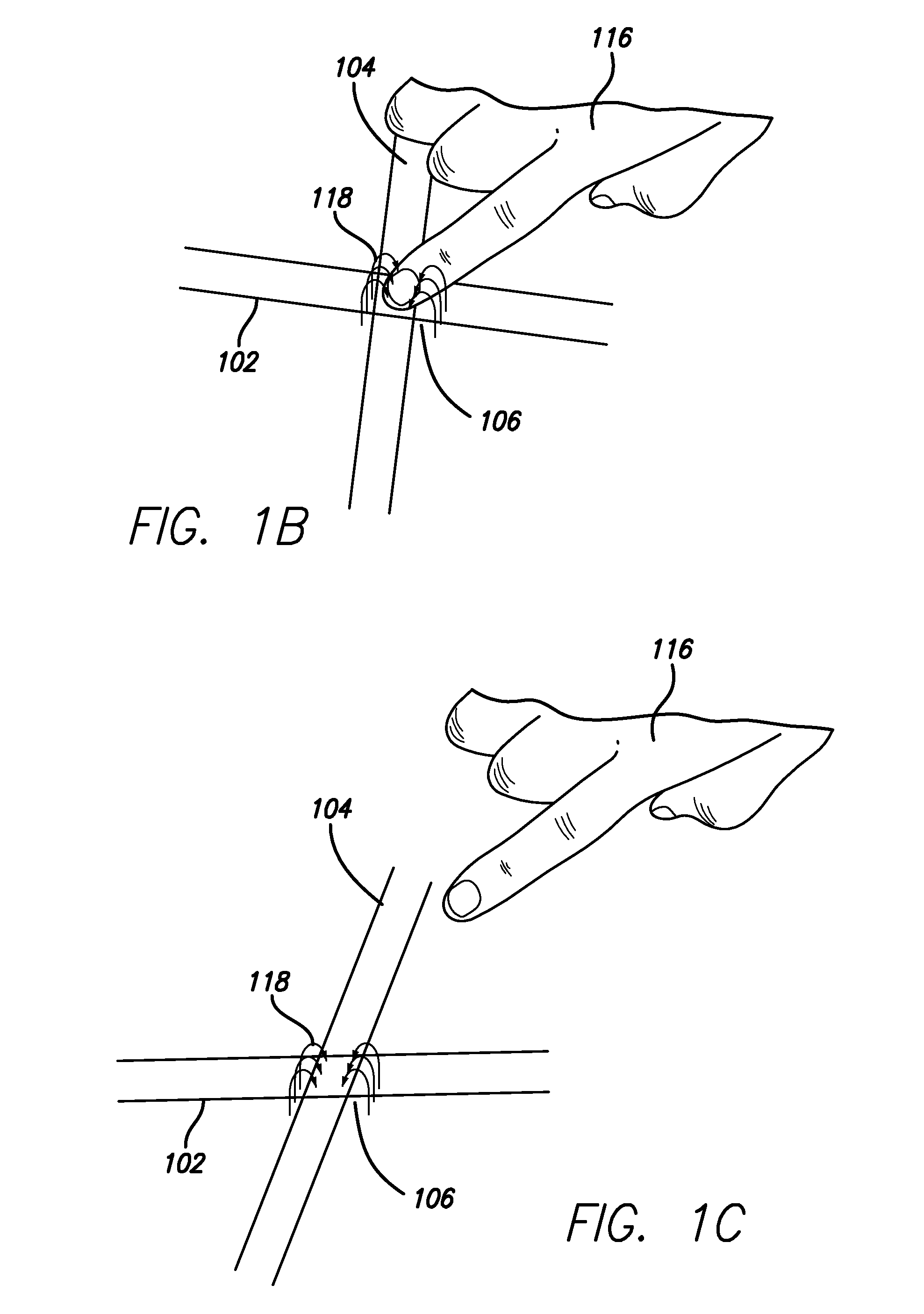

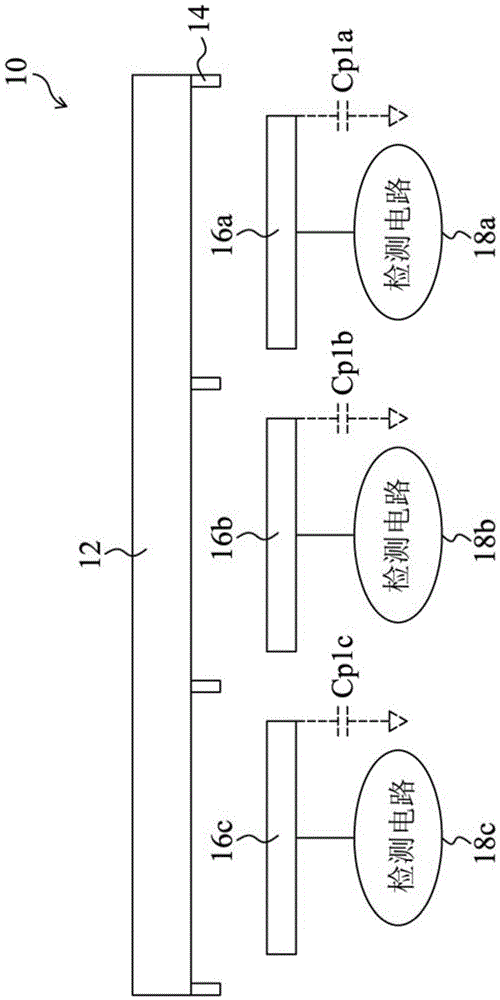

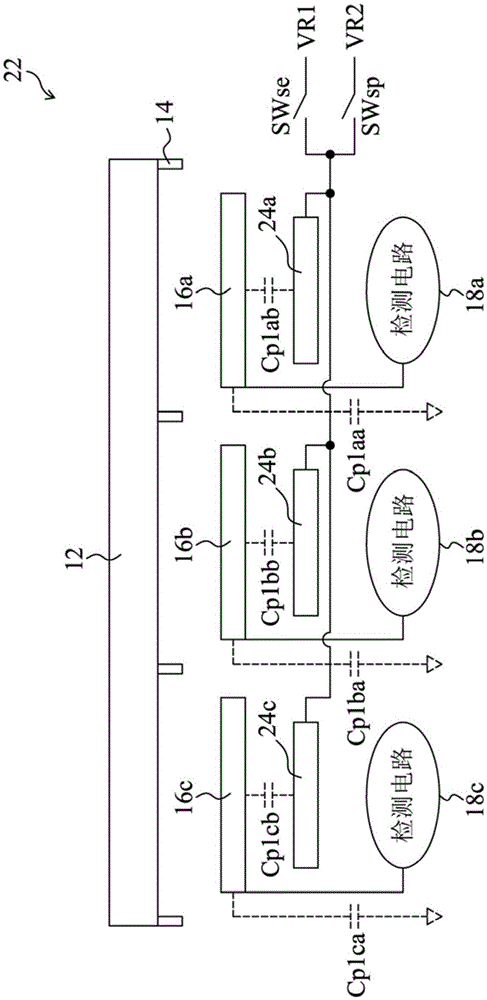

Self capacitance implementation method

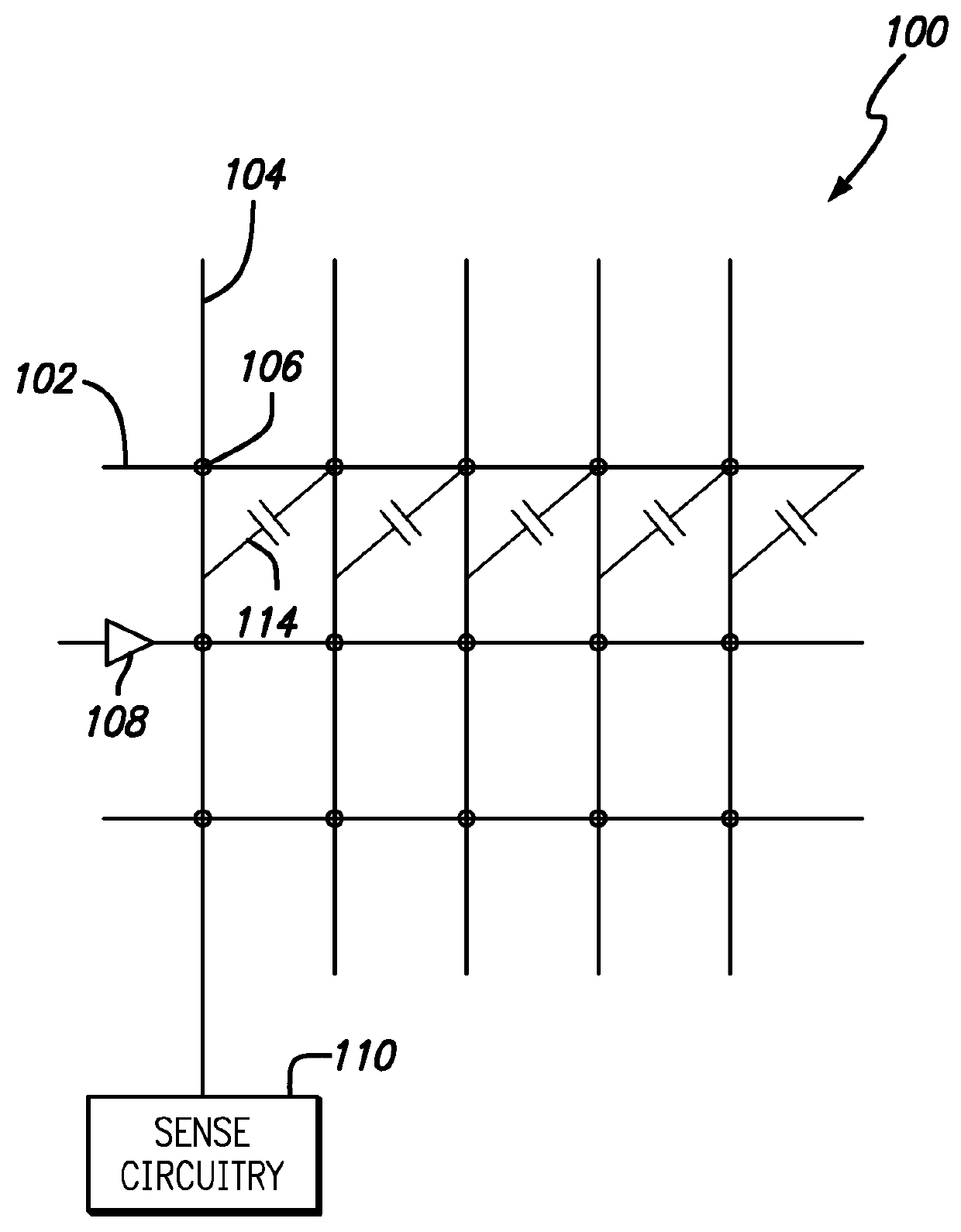

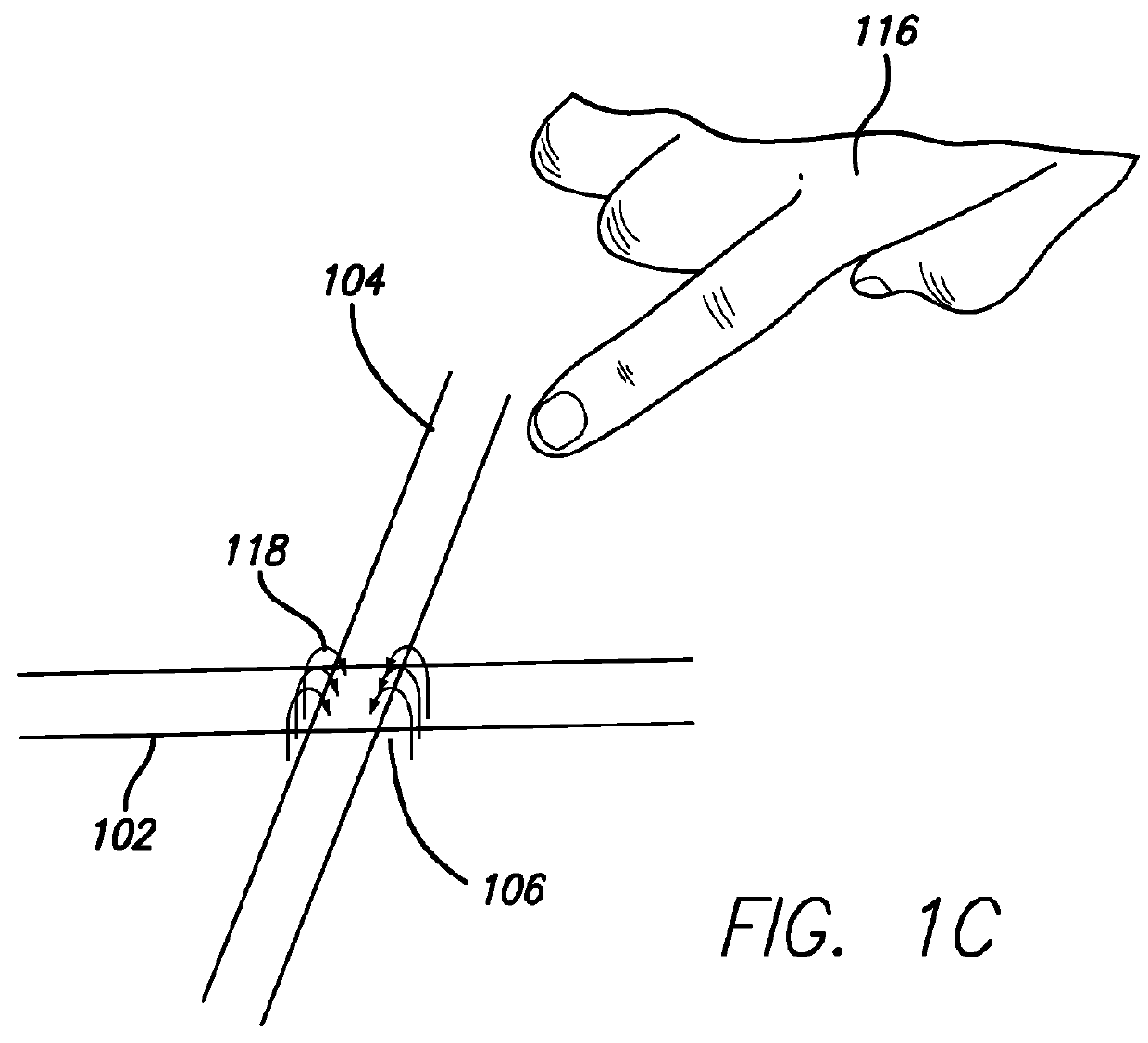

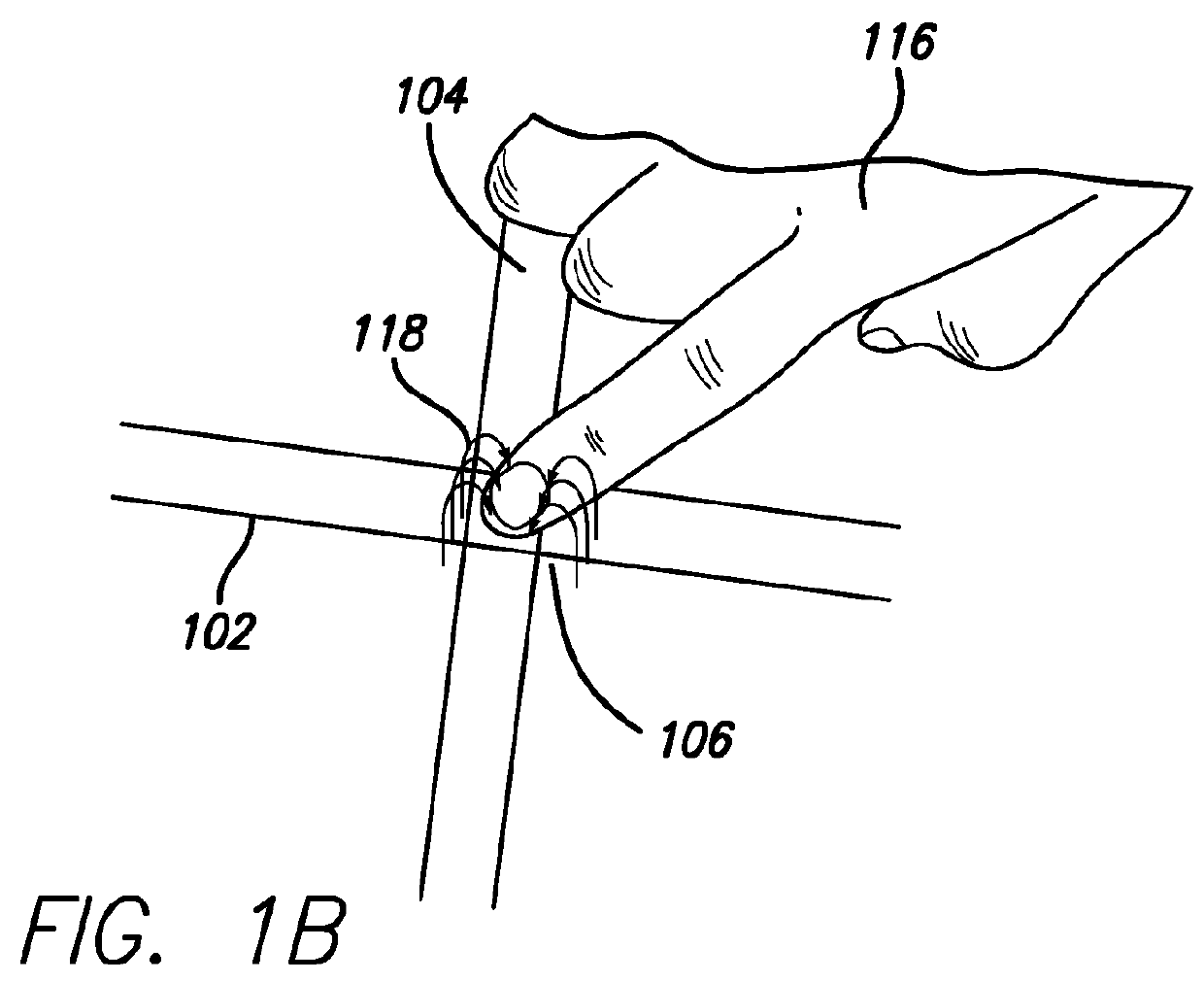

ActiveUS20140085246A1Reduce impactReliable detectionInput/output processes for data processingParasitic capacitanceComputer science

A circuit for detecting a touch or proximity event on a touch input device is provided. The circuit is able to mitigate the effects that parasitic capacitance has on a self-capacitance touch sensor panel by injecting a signal into the sensing circuitry. The signal is adjusted until it calibrates the circuitry for the effects that parasitic capacitance imparts on the detection of touch or proximity events on a touch sensor panel.

Owner:APPLE INC

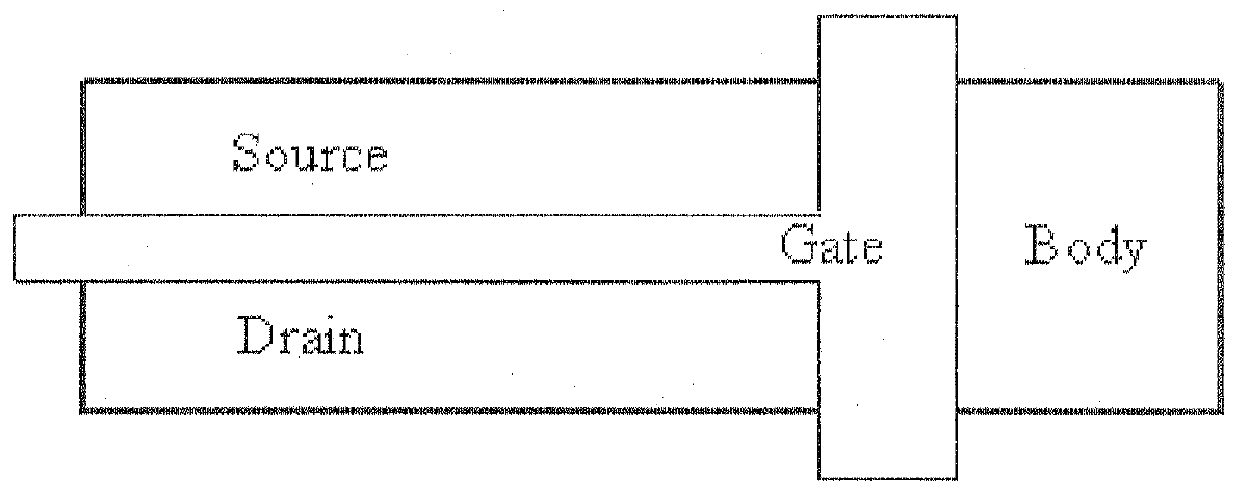

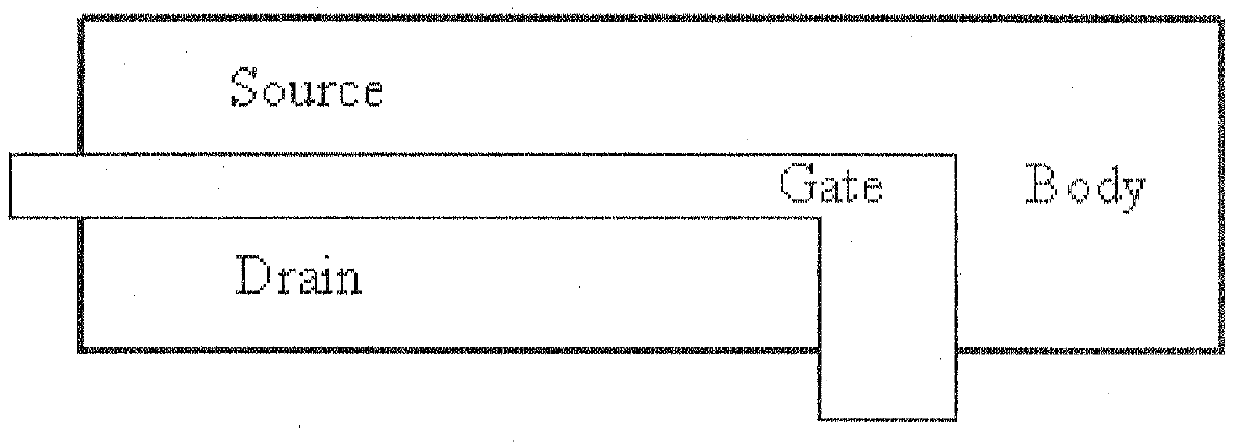

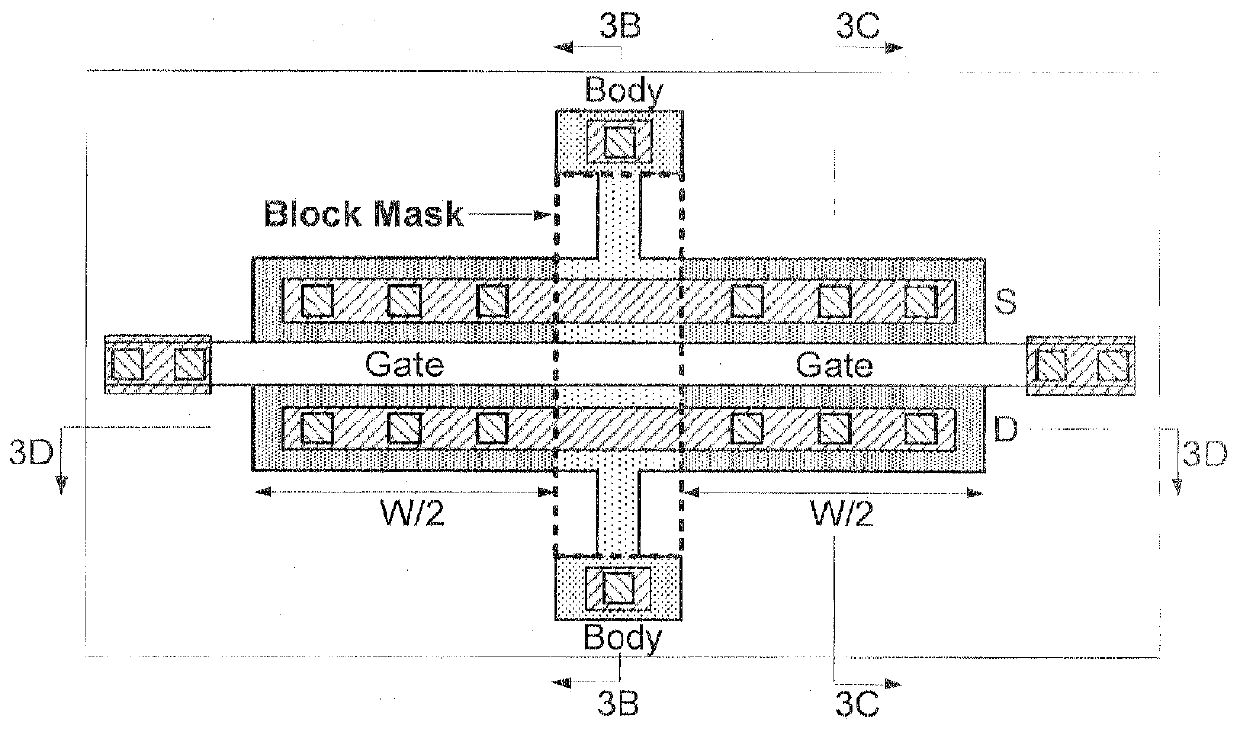

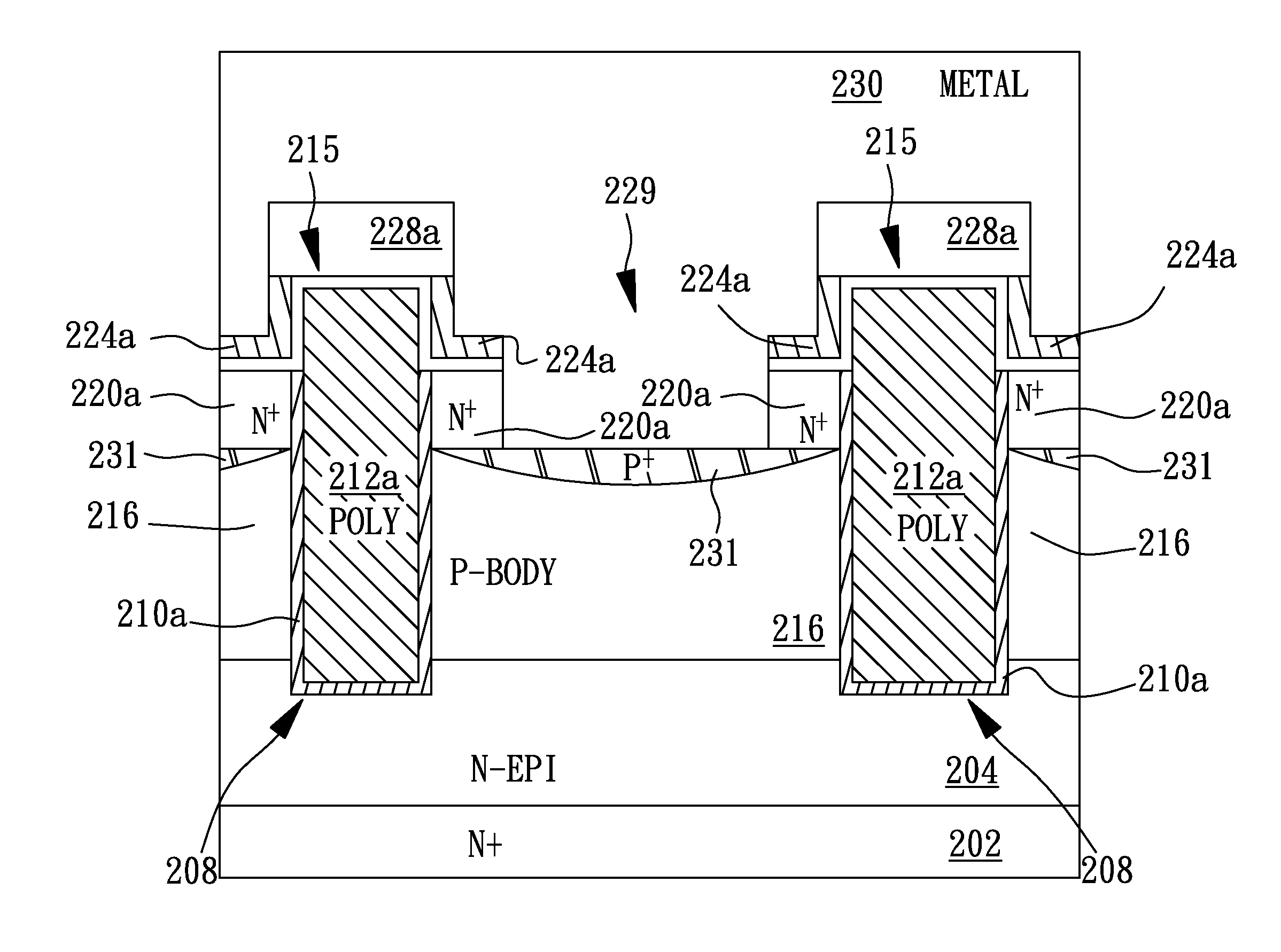

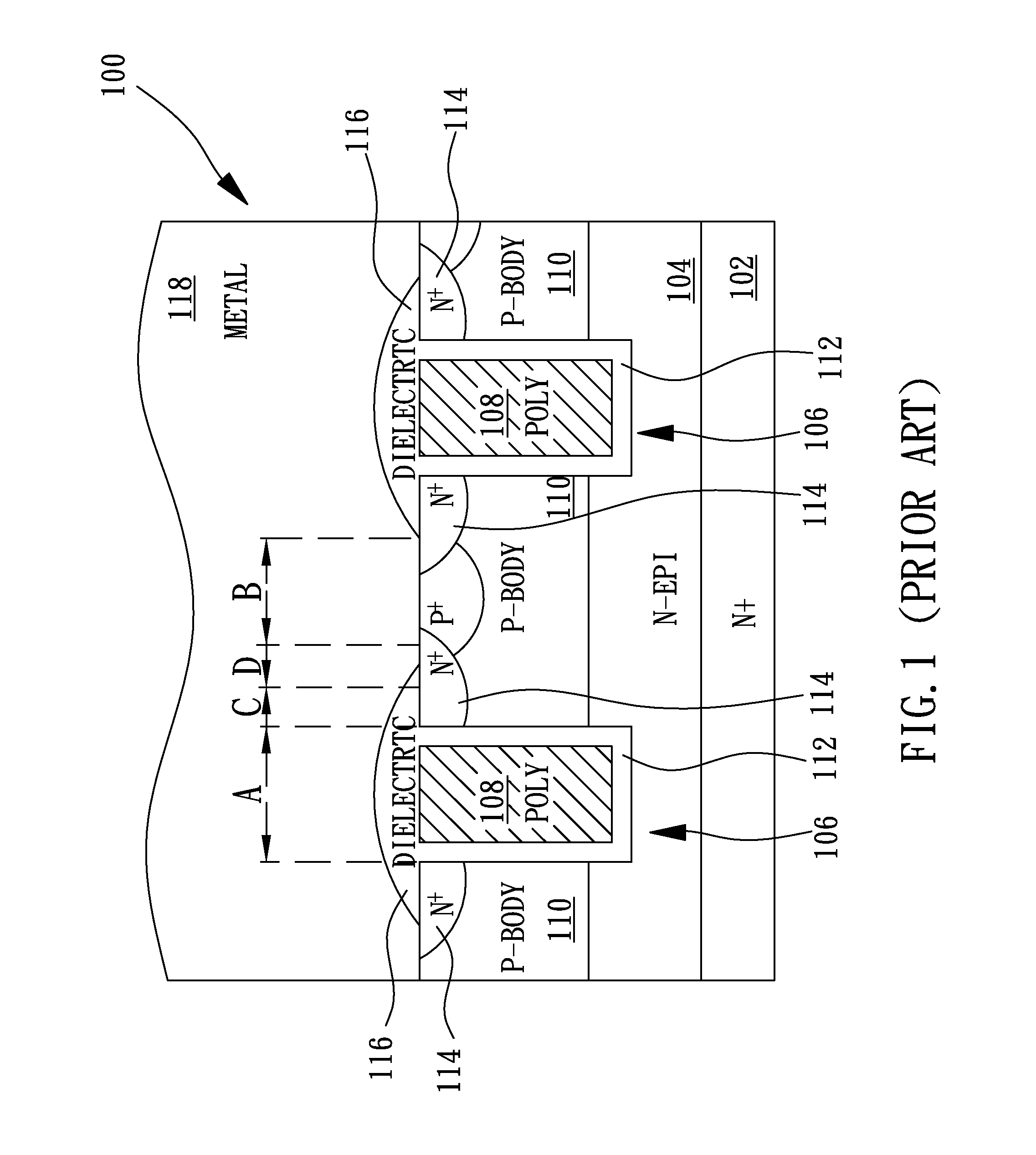

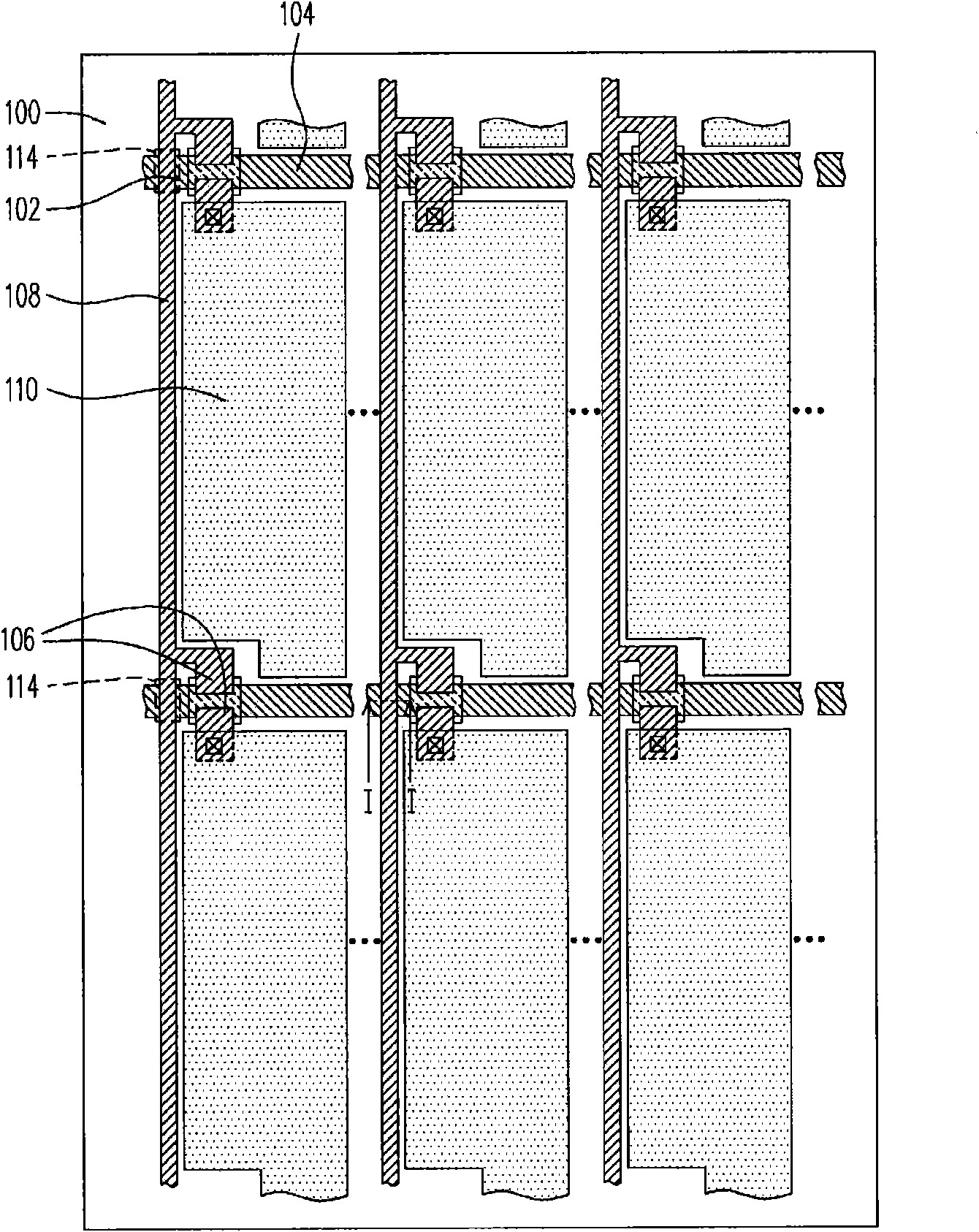

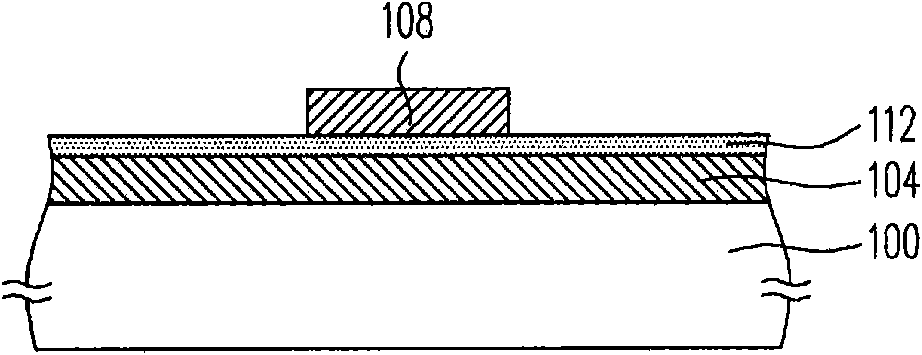

Body contact structure for a semiconductor device

InactiveUS20120205744A1Reduce parasitic capacitanceReduced Routing ComplexitySemiconductor/solid-state device manufacturingSemiconductor devicesSalicidePower semiconductor device

Embodiments of the invention provide SOI body-contacted transistors that can be used for high frequency analog and digital circuits. In accordance with certain embodiments of the invention, the SOI transistor gate can have an “I” shape, similar to the shape of the gate of a floating body SOI transistor. However, a body region is provided that extends perpendicular to the width direction of the gate and is contacted at an end of the extended body region. To form such a body contact structure, a source / drain implant block mask and silicide block mask are used during the formation of the source / drain regions. The source / drain implant block mask and silicide block mask can be formed on the same region, but the silicide block mask can allow for the body contact portion at the end of the extended body region to be silicided during the siliciding of the source / drain regions.

Owner:O KENNETH K +1

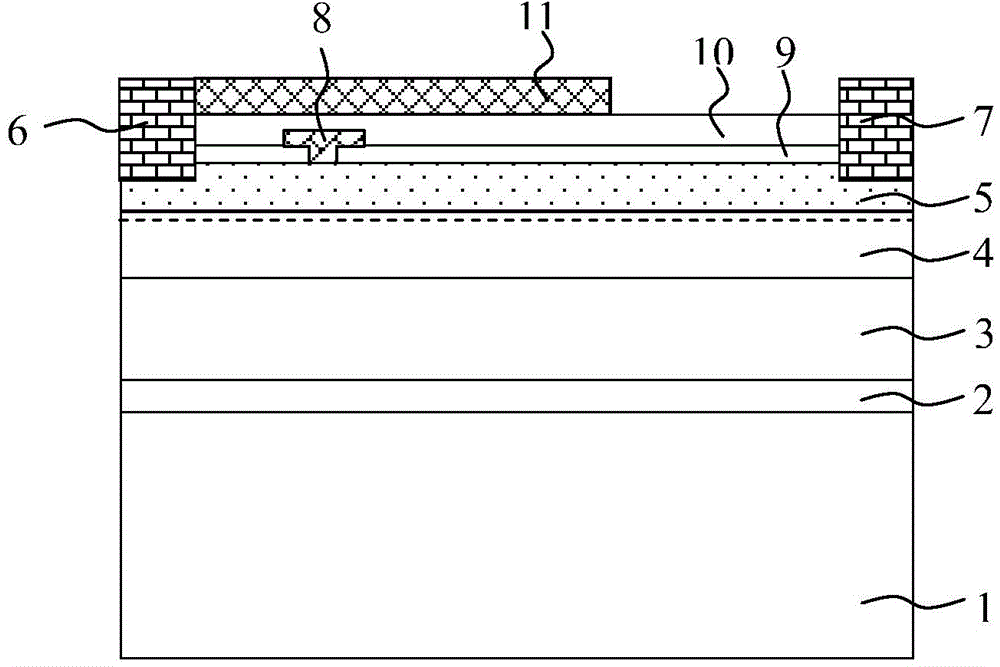

Semiconductor device and manufacturing method thereof

ActiveCN104157691AImprove reliabilityMinimize the effect of parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectric field modulationCapacitance

The invention discloses a semiconductor device and a manufacturing method thereof. The semiconductor device comprises a substrate, a semiconductor layer located on the substrate, a source and a drain located on the semiconductor layer, a gate located between the source and the drain, a source field plate located on the semiconductor layer and connected with the source, wherein the source field plate passes across the gate, the gate / source region and part of the gate / drain region, and air isolation is carried out; one end of the source field plate is connected with the source; two or more than two metal field plates are connected in parallel to form connection between the source field plate and the source; and the other end of the source field plate is located on the semiconductor layer, close to the gate, between the gate and the drain. A role of electric field modulation of the source field plate can be fully played, parasitic gate / source capacitance and parasitic conduction resistance can be fully reduced, and reliability of the device is improved.

Owner:GPOWER SEMICON

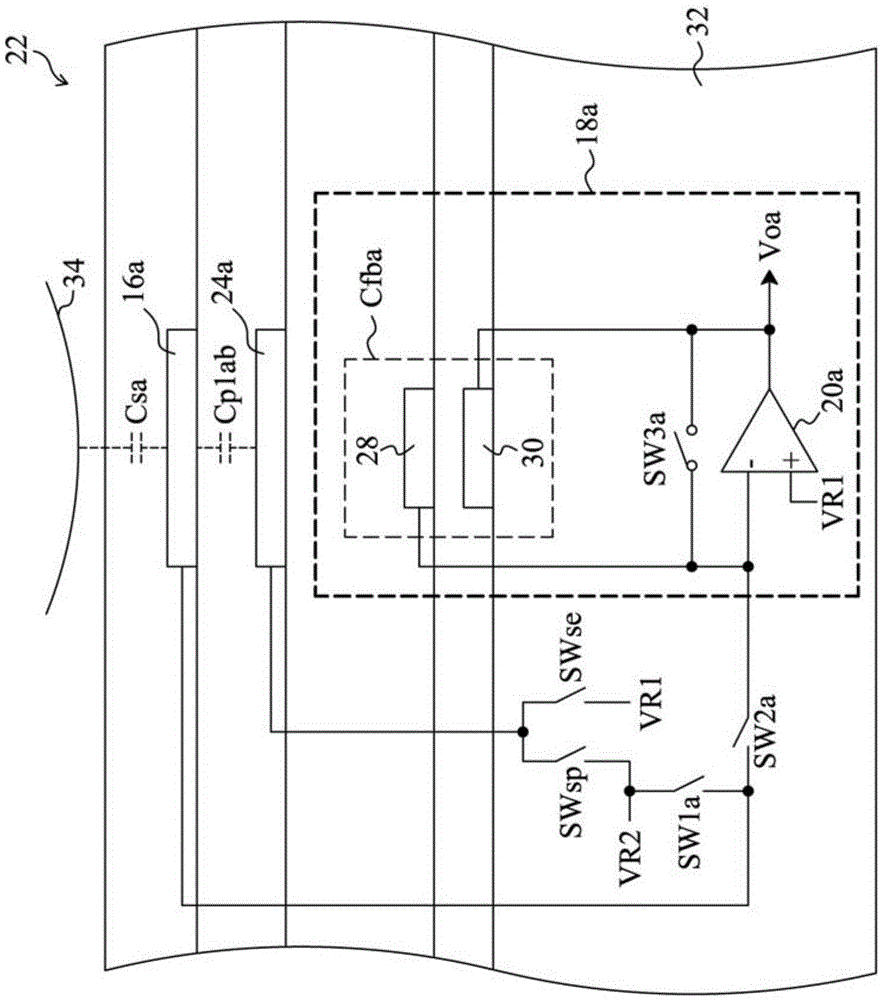

Fingerprint Sensing Device And Fingerprint Sensing Method Thereof

InactiveCN105740756AAvoid interferenceReduce parasitic capacitancePrint image acquisitionCapacitanceEngineering

Owner:ELAN MICROELECTRONICS CORPORATION

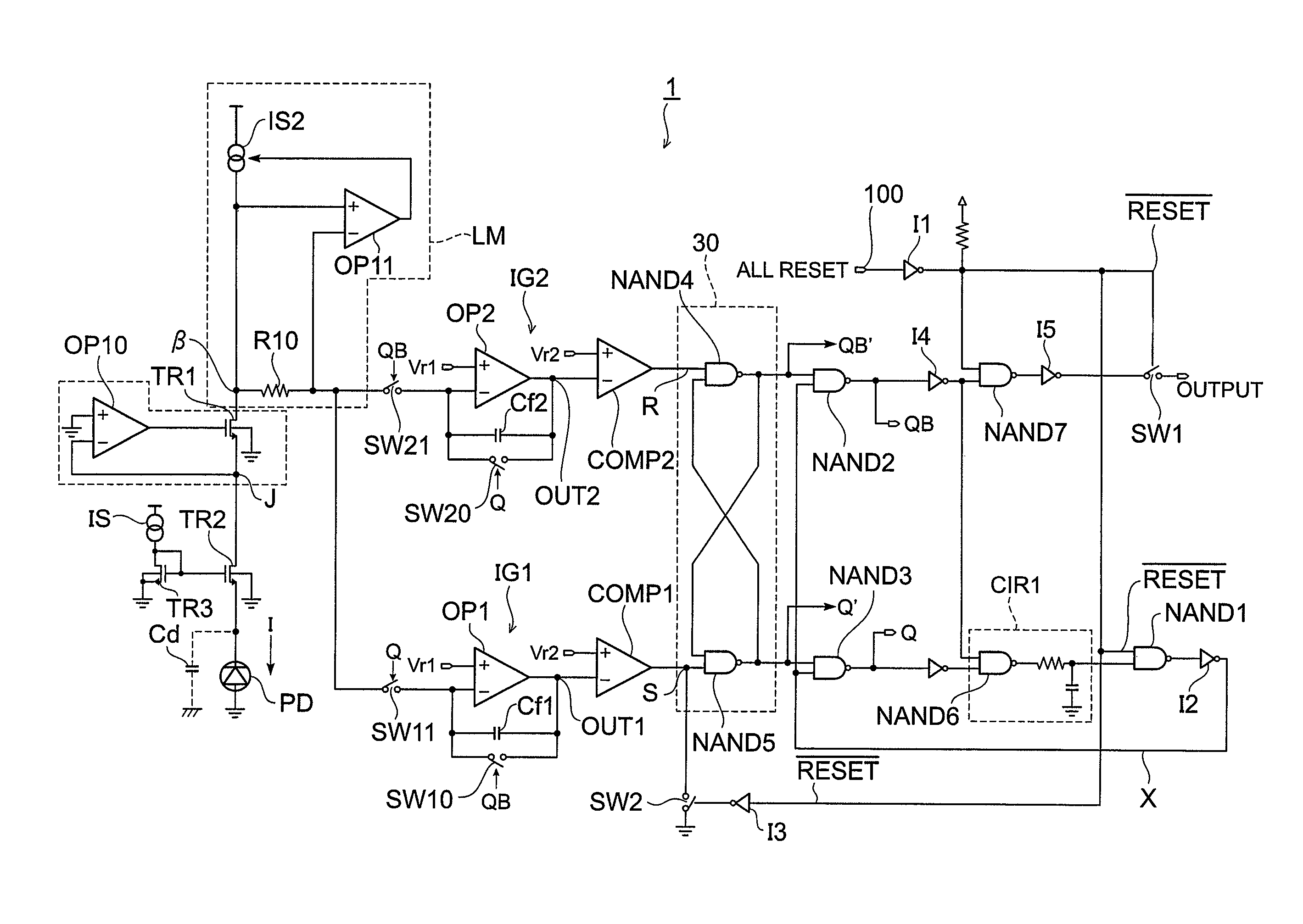

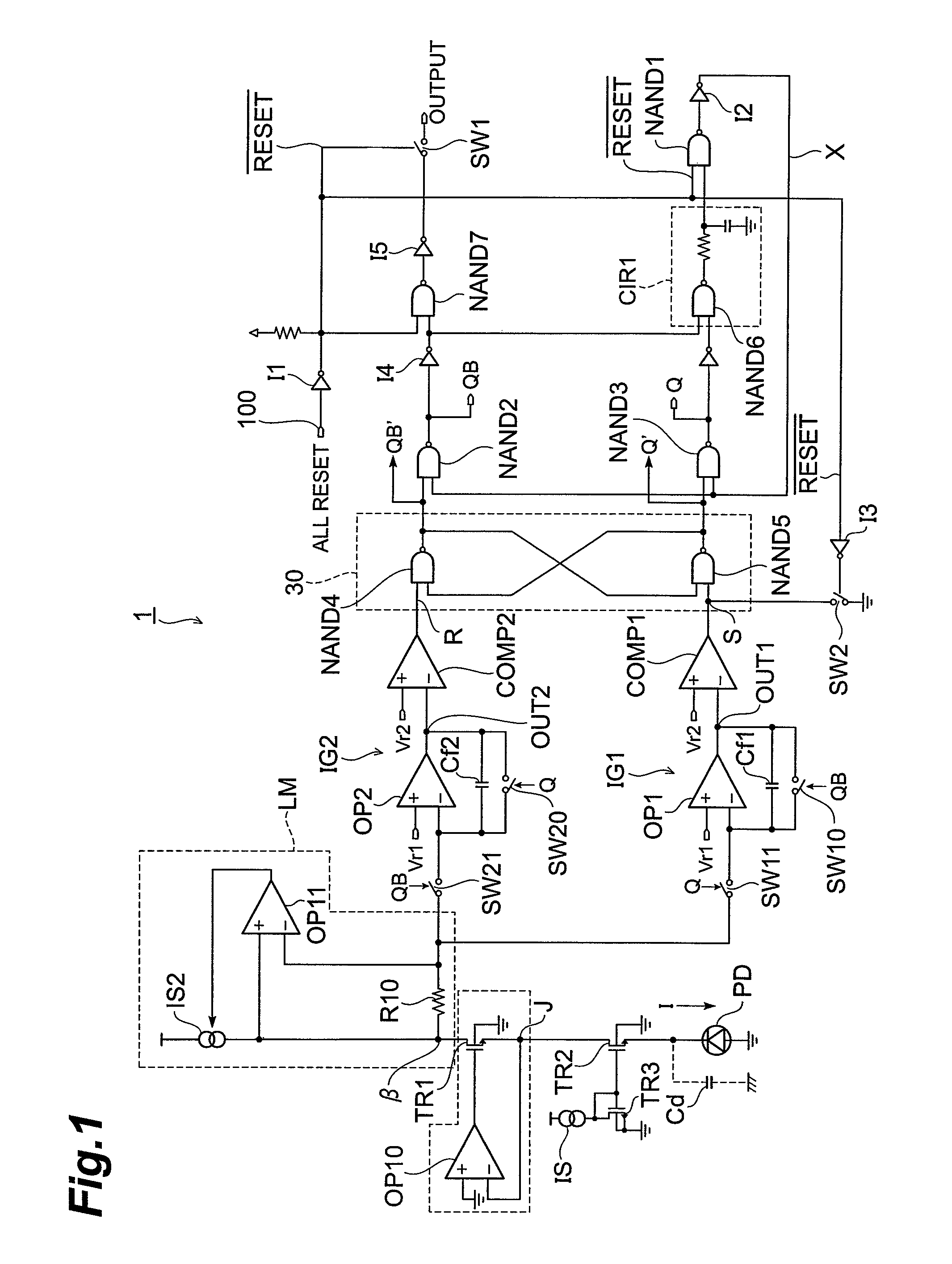

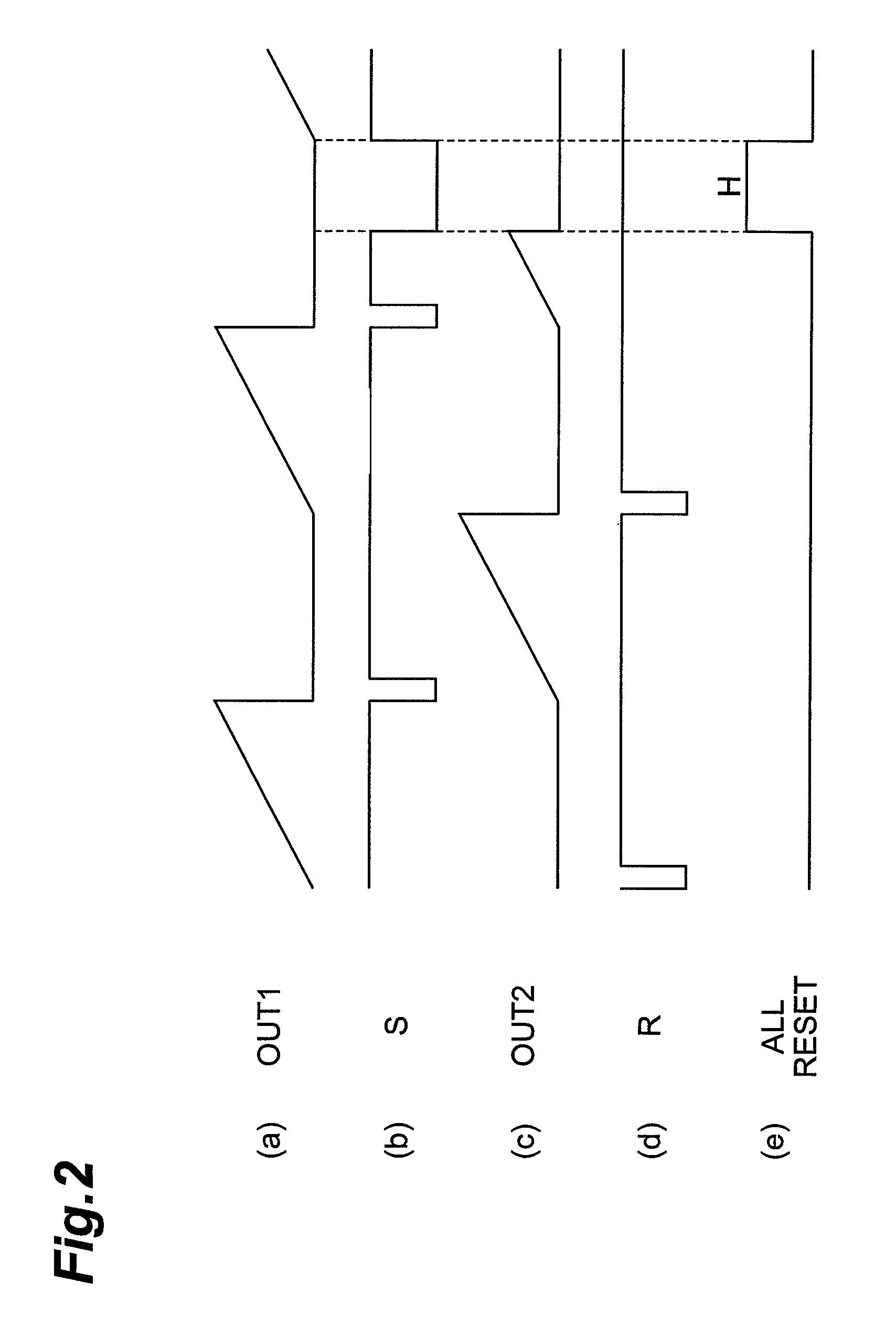

Photodetection circuit

ActiveUS8143564B2Oscillation suppressionMinimize the effect of parasitic capacitanceMultiplier circuit arrangementsMaterial analysis by optical meansElectrical resistance and conductancePhotodiode

Owner:HAMAMATSU PHOTONICS KK

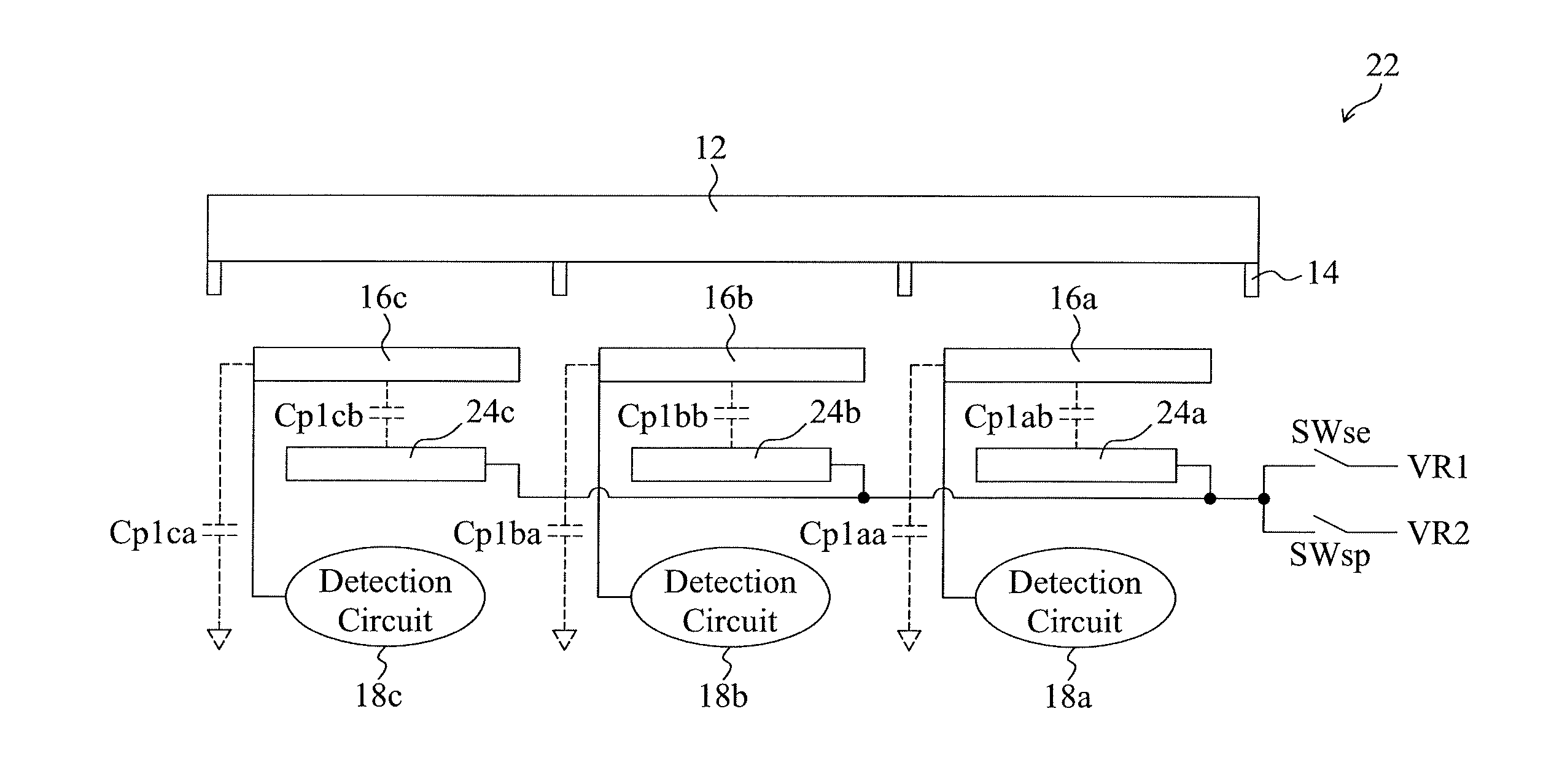

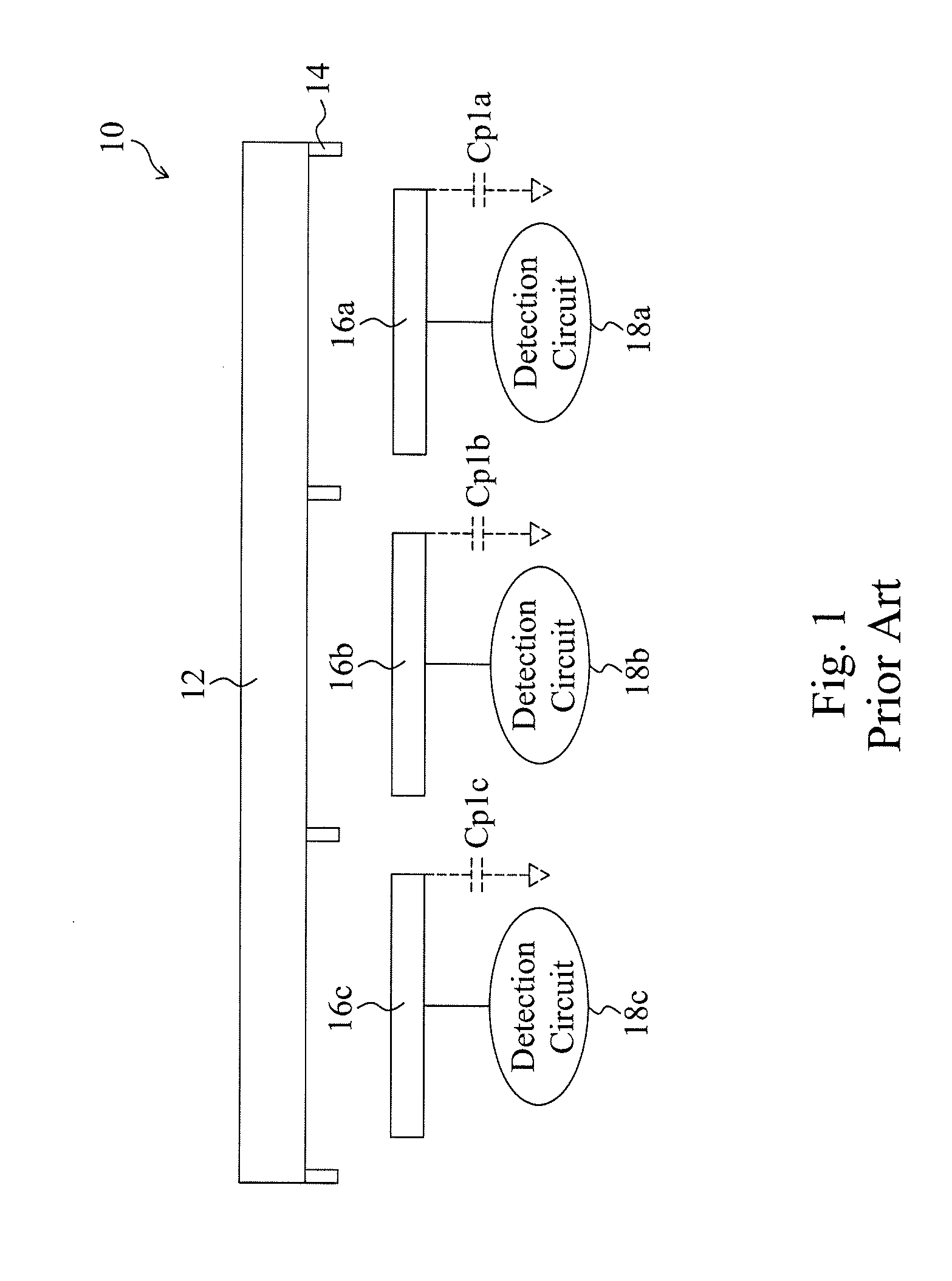

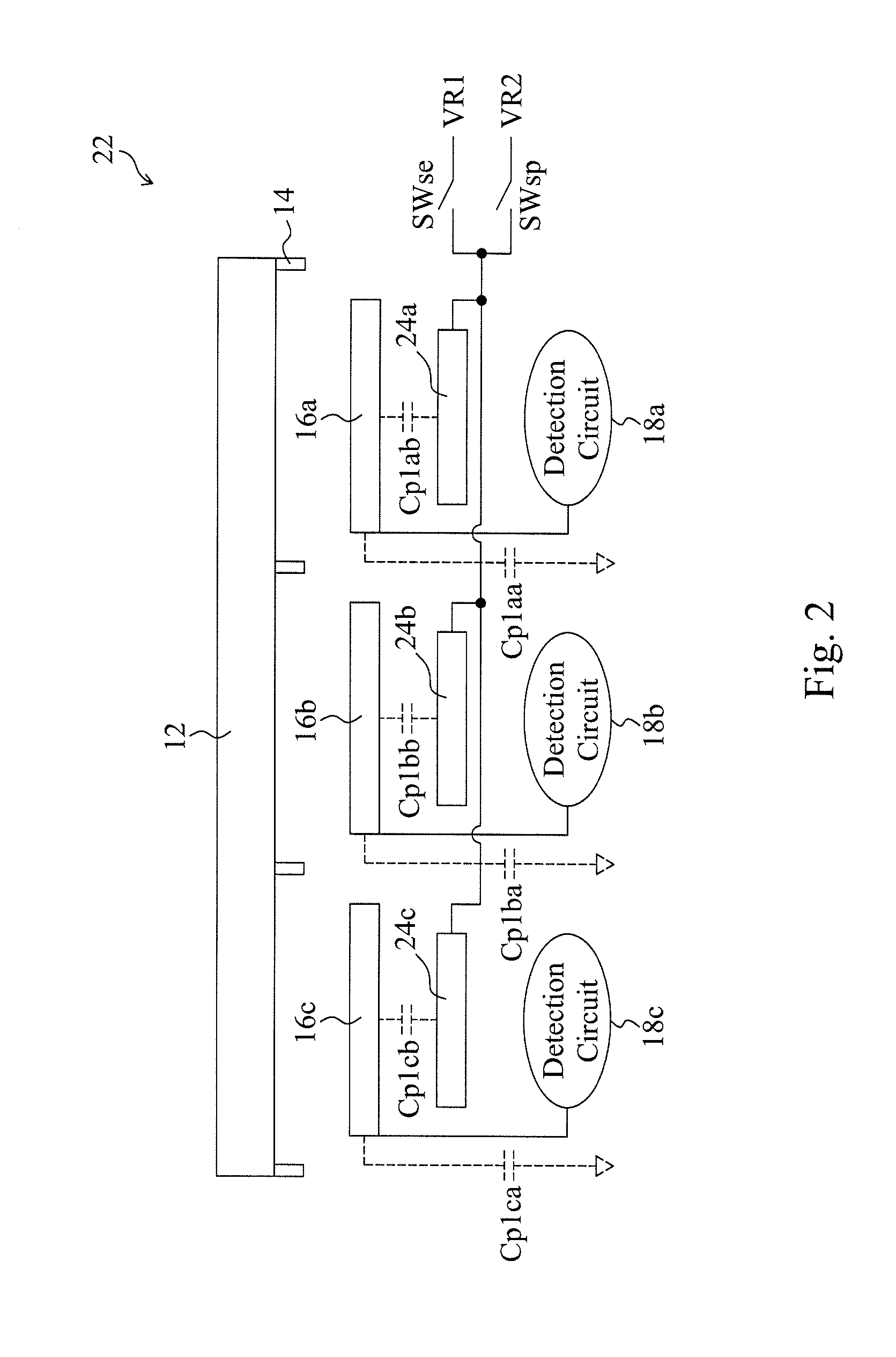

Fingerprint sensing device and fingerprint sensing method thereof

InactiveUS20160188949A1Reduce parasitic capacitorLarge signal dynamic rangePrint image acquisitionFingerprintElectrical conductor

A fingerprint sensing device comprises a shielding plate configured between an electrode plate and a detection circuit for reducing a parasitic capacitor between the electrode plate and a conductor thereunder. Consequently, a larger signal dynamic range can be achieved and the electrode plate can be prevented from operation noise interference of the detection circuit. The shielding plate and the electrode plate have the same potential. Accordingly, a parasitic capacitor effect between the shielding plate and the electrode plate can be eliminated. Thus, the fingerprint sensing device of the present invention has a better noise resistibility.

Owner:ELAN MICROELECTRONICS CORPORATION

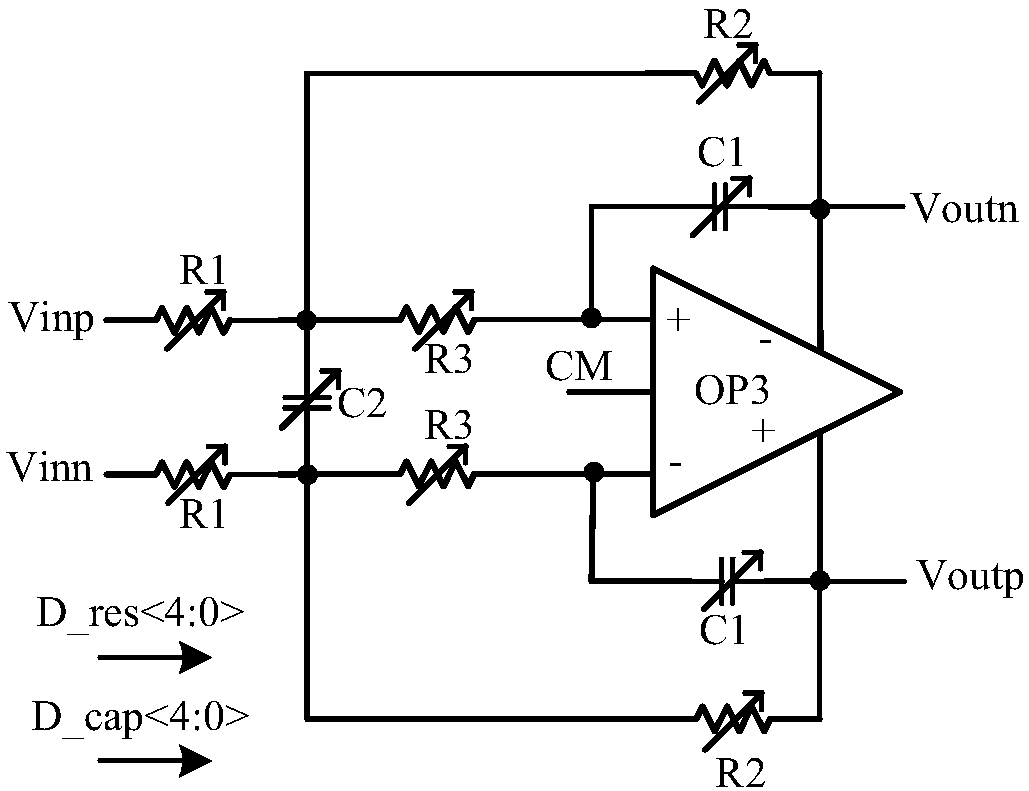

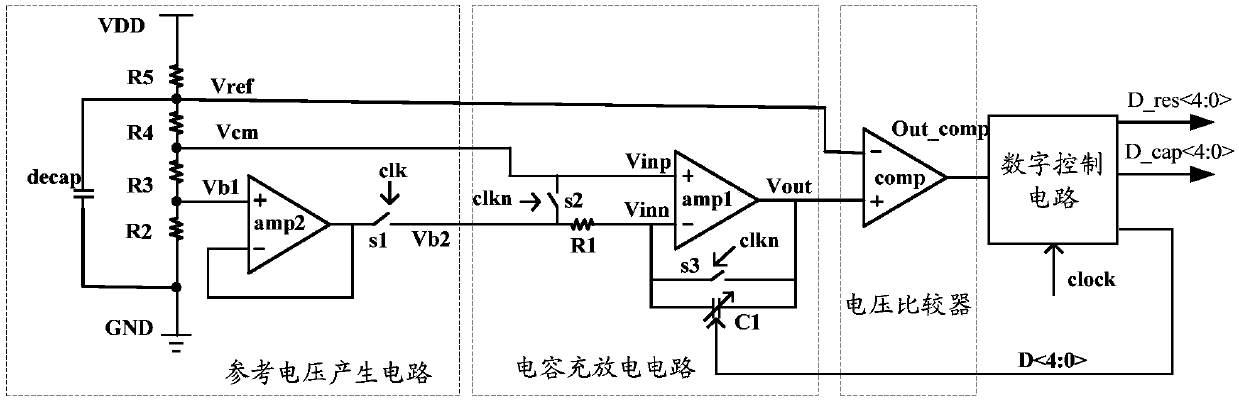

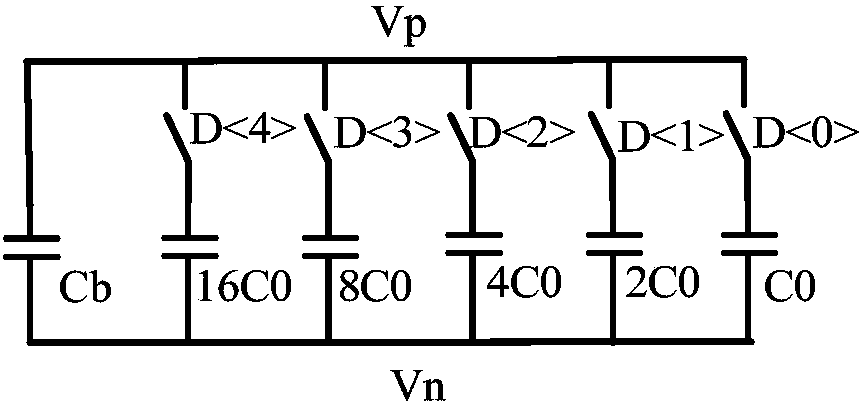

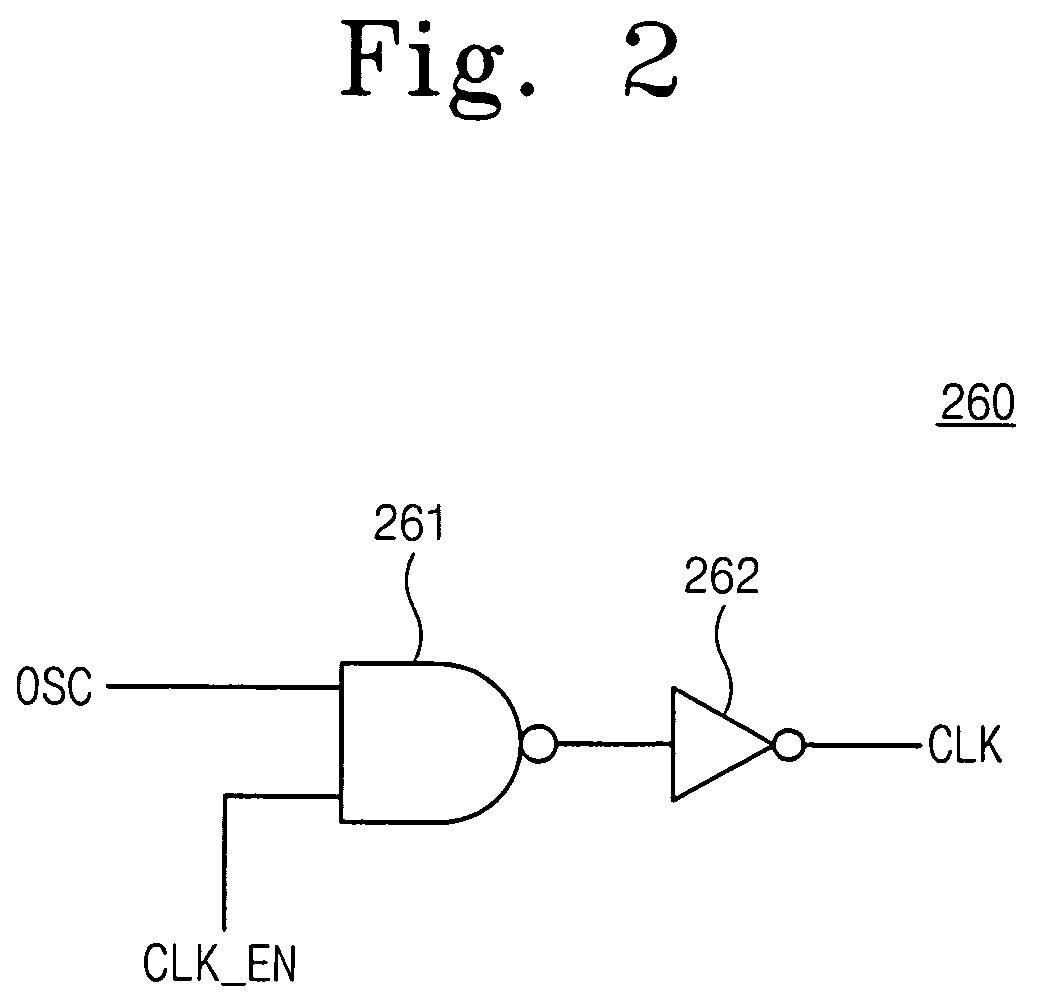

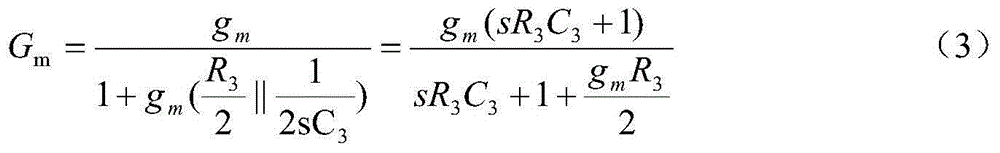

Calibrating circuit and calibrating method

ActiveCN108023571AReduce complexityReduce demandFrequency selective two-port networksCapacitanceControl signal

The embodiment of the invention discloses a calibrating circuit. The calibrating circuit comprises a reference voltage generation circuit, a capacitor charging and discharging circuit, a voltage comparer and a digital control circuit, wherein the capacitor charging and discharging circuit and the voltage comparer are connected with the reference voltage generation circuit; the capacitor charging and discharging circuit is connected with the voltage comparer; the digital control circuit is connected with the voltage comparer; the digital control circuit is connected with the capacitor chargingand discharging circuit; the reference voltage generation circuit is used for generating a first reference voltage, a second reference voltage and a third reference voltage, and buffering the first reference voltage to obtain a first voltage; the capacitor charging and discharging circuit is used for generating a second voltage according to the first voltage, the second reference voltage and a received first clock signal; the voltage comparer is used for comparing the second voltage with the third reference voltage to obtain a voltage comparison output signal; and the digital control circuit is used for generating a first digital control signal, a second digital control signal and a third digital control signal according to the voltage comparison output signal. The embodiment of the invention further discloses a calibrating method.

Owner:SANECHIPS TECH CO LTD

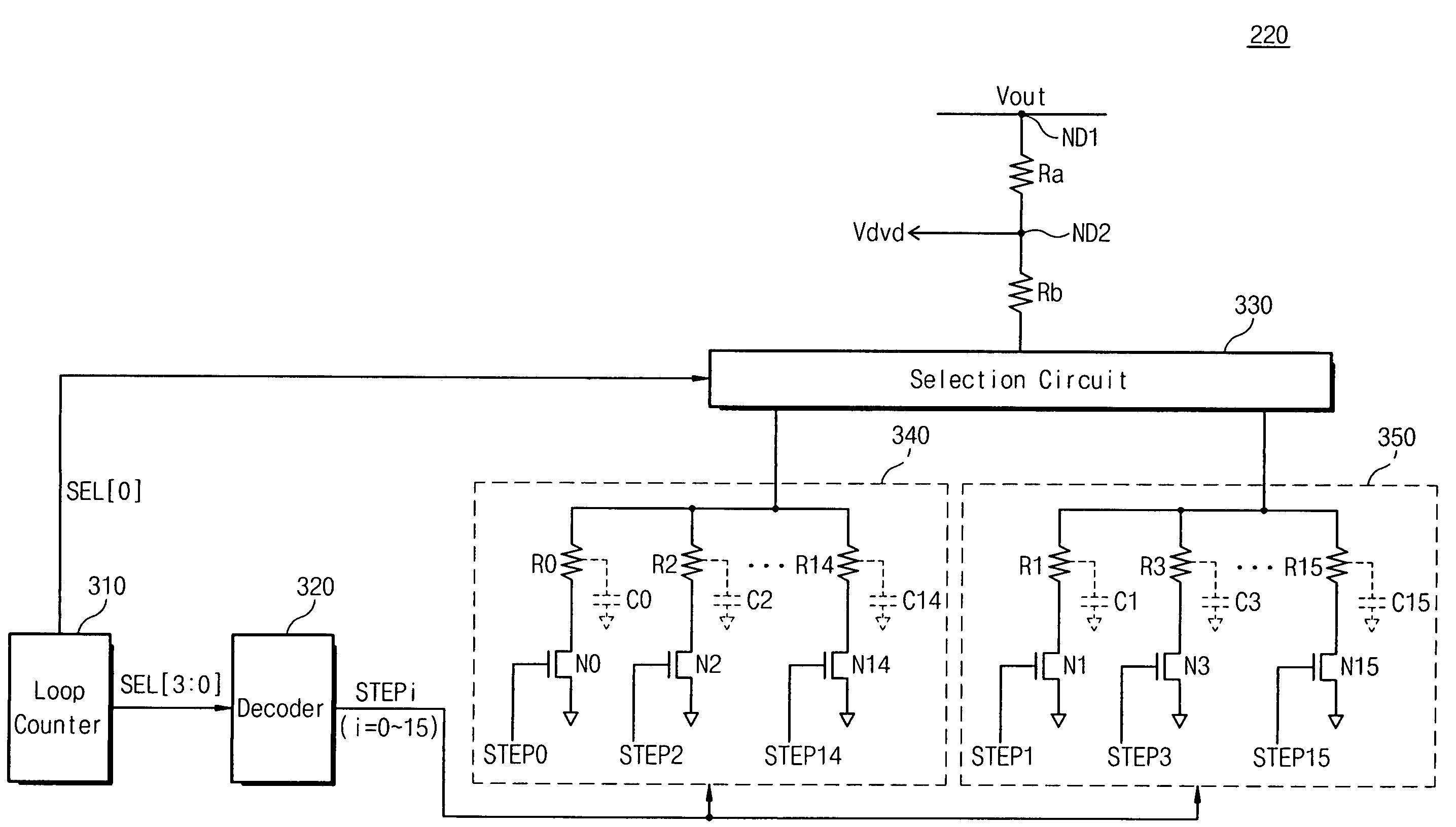

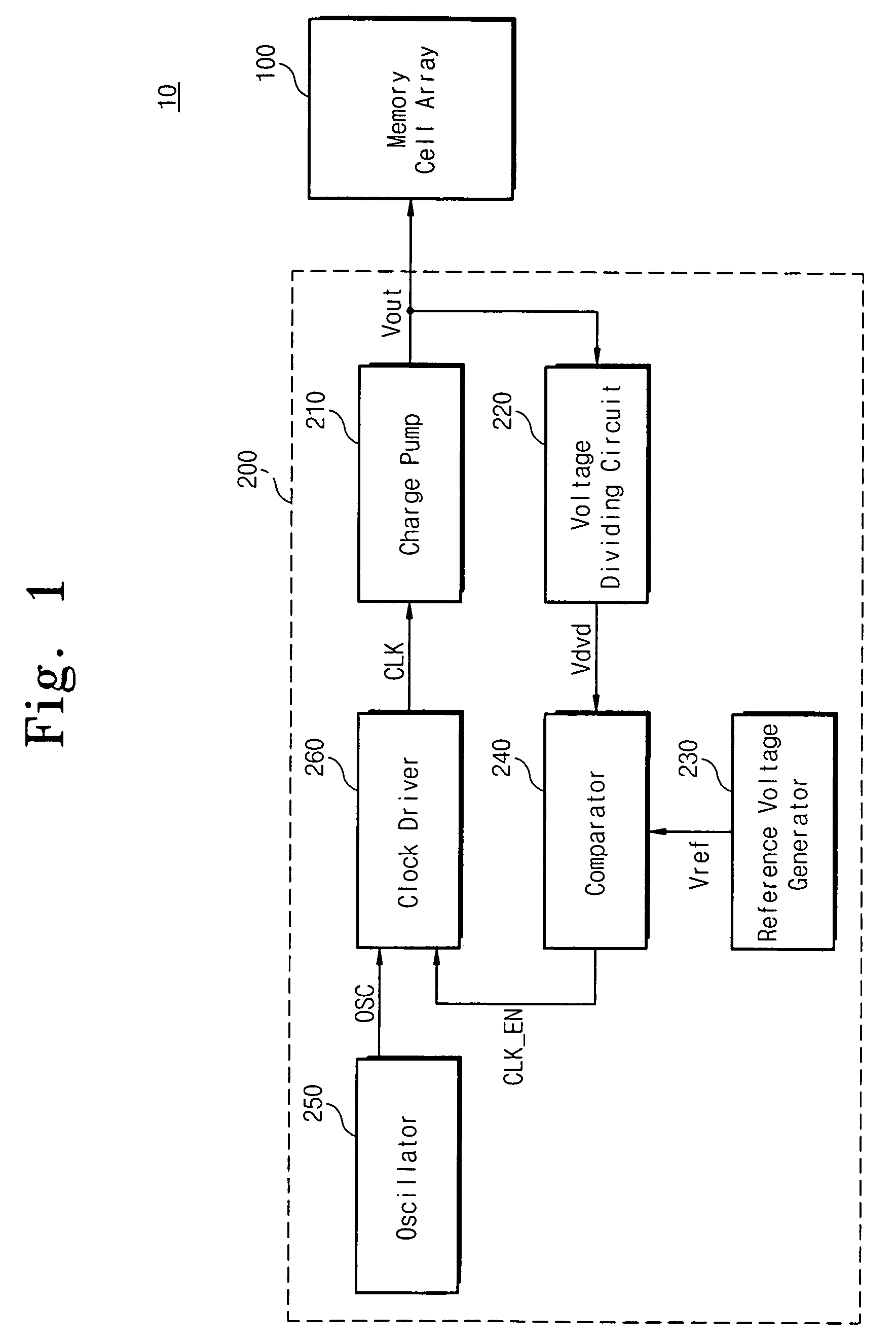

Wordline voltage generating circuit including a voltage dividing circuit for reducing effects of parasitic capacitance

ActiveUS7272047B2Minimize the effect of parasitic capacitanceRead-only memoriesDigital storageControl signalDividing circuits

Disclosed is a voltage dividing circuit reducing effects of a parasitic capacitance and a wordline voltage generating circuit including that. The voltage dividing circuit according to an aspect of the present invention includes a first resistor, a plurality of second resistors, and a selection means. The first resistor is connected between an output voltage node and a dividing voltage node. The plurality of second resistors are connectable between the dividing voltage node and a ground. The second resistors are sequentially selected in response to a step control signal and connected to ground. In order to reduce the sum of a parasitic capacitance existing in the second resistors, the resistors are arranged in groups, and the selection means connects only that group that contains a selected resistor to the dividing voltage node.

Owner:SAMSUNG ELECTRONICS CO LTD

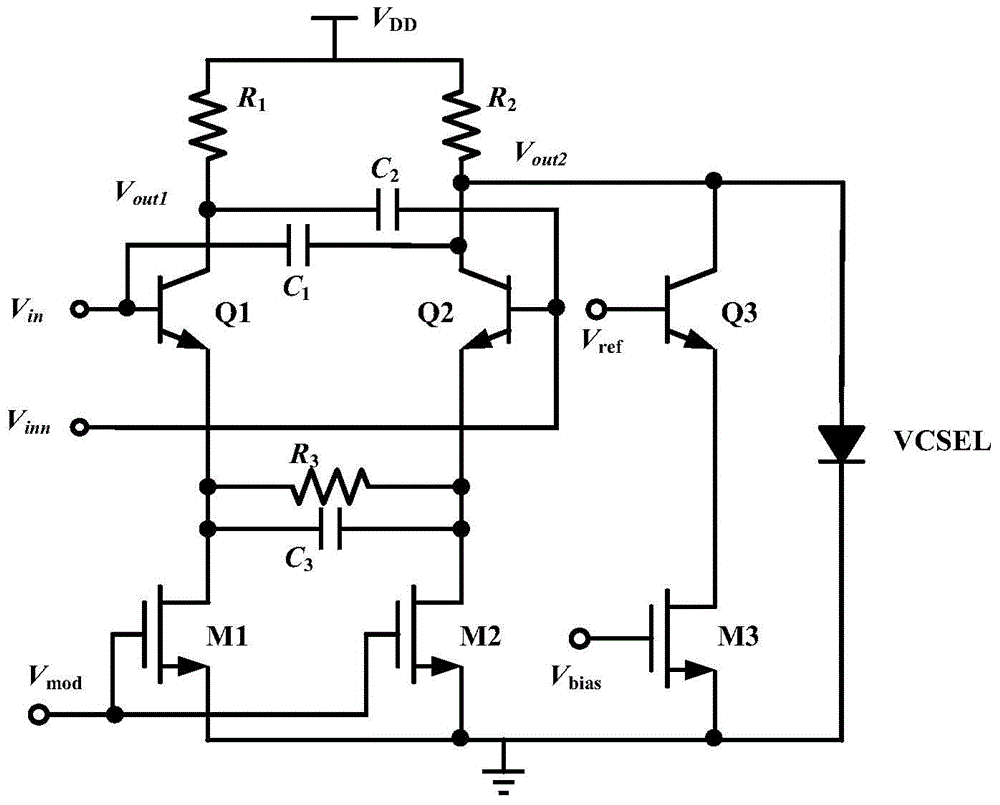

Ultra high speed laser driver circuit with bandwidth compensation and driver chip

ActiveCN104617483AMinimize the effect of parasitic capacitanceHigh bandwidthLaser detailsSemiconductor lasersEngineeringFeedback circuits

The invention discloses an ultra high speed laser driver circuit with bandwidth compensation and a diver chip; the feedback circuit composed of two cross coupling capacitors and the capacitor and the resistor connected in a parallel mode is used for executing the laser driver bandwidth compensation. For two cross coupling capacitors, the stray capacitance between the base and the collector can be eliminated; for the feedback mode of one capacitor and one resistor, one zero point is generated for compensating the pole for realizing the bandwidth compensation; and the modulating current directly flows to the laser diode through the load resistor, so that the laser diode can obtain larger modulating current. The laser driver circuit and the driver chip having pre-emphasis function are simple in structure, high in bandwidth, large in modulating current and low in power consumption; the chip adopts the resistor and capacitor for expanding the bandwidth, the occupied area is small and the chip cost is reduced; the work speed is 40Gb / s through the 0.13 mum BiCMOS process certification and the output modulating current is greater than 10 mA.

Owner:SOUTHEAST UNIV

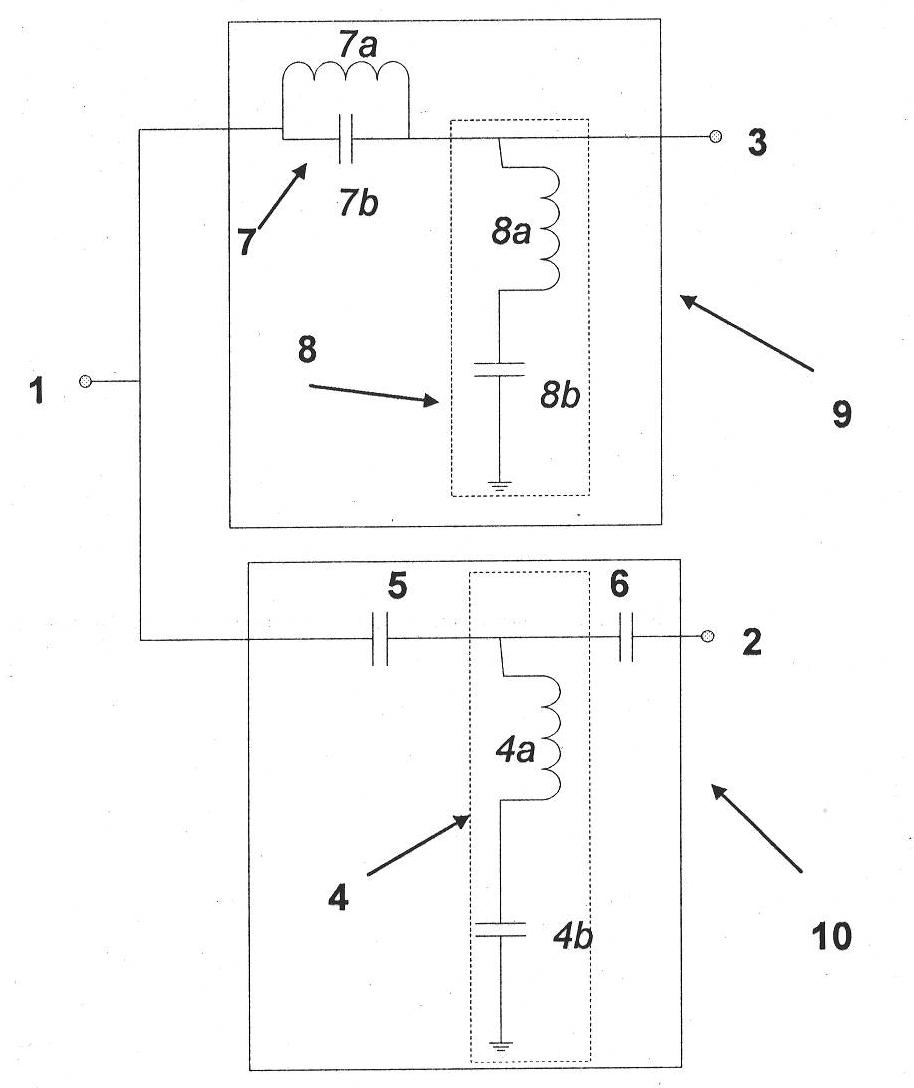

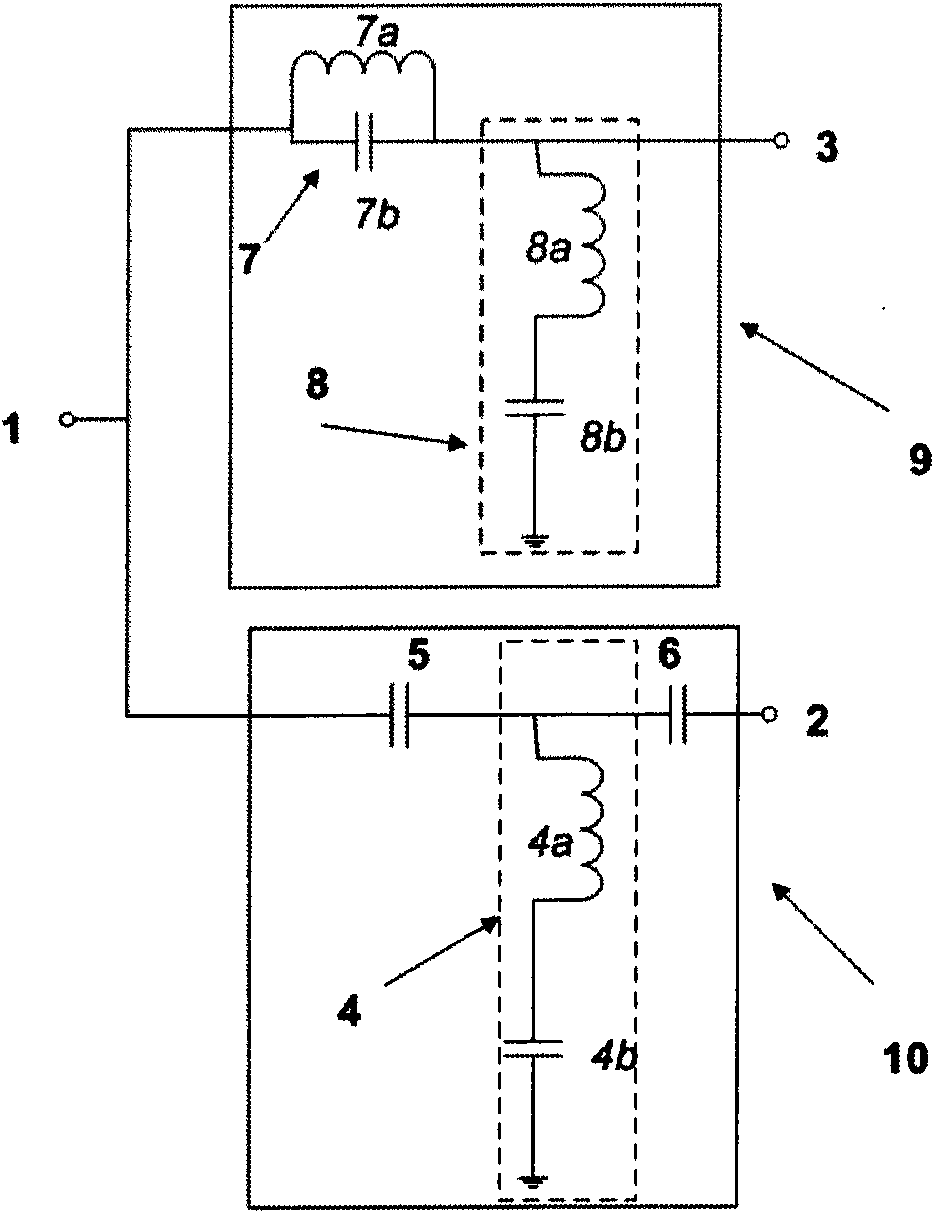

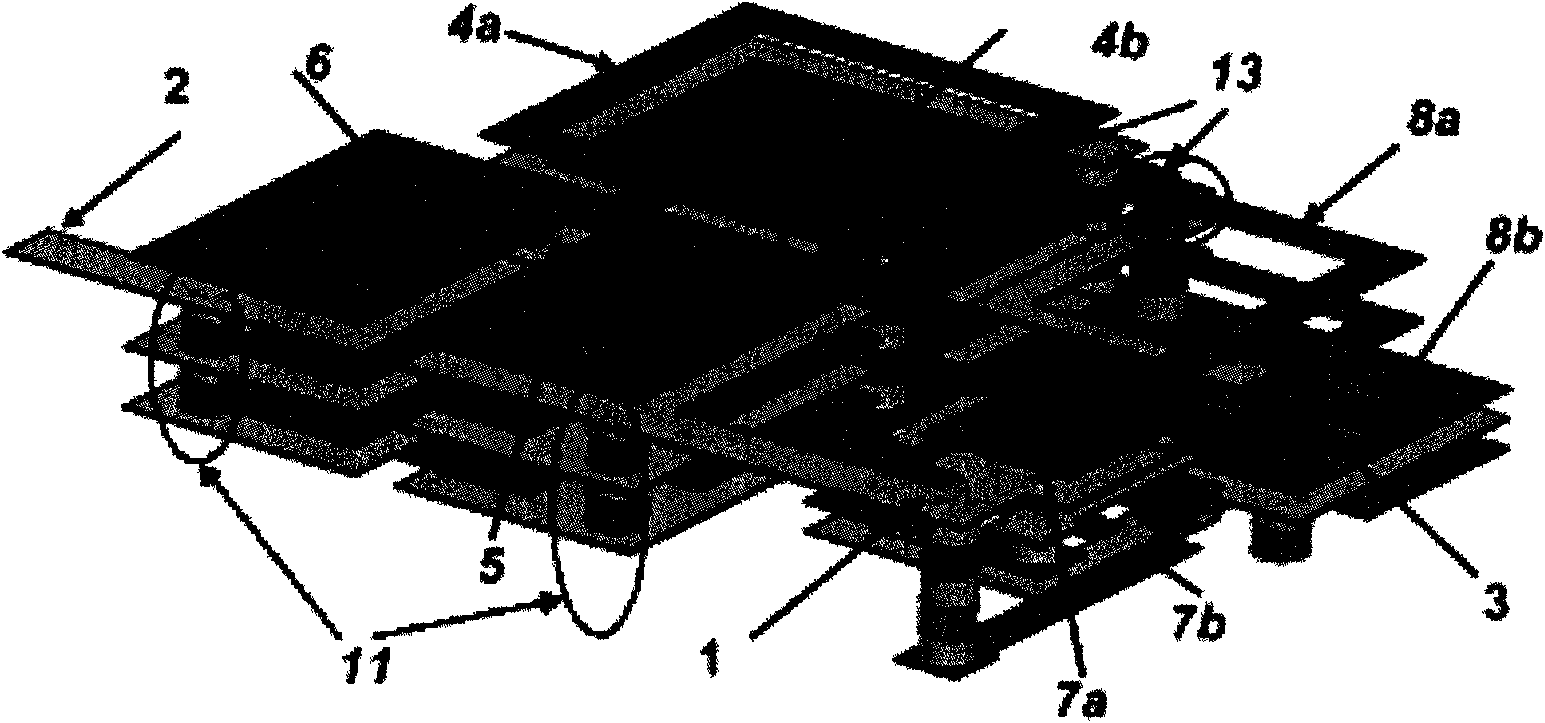

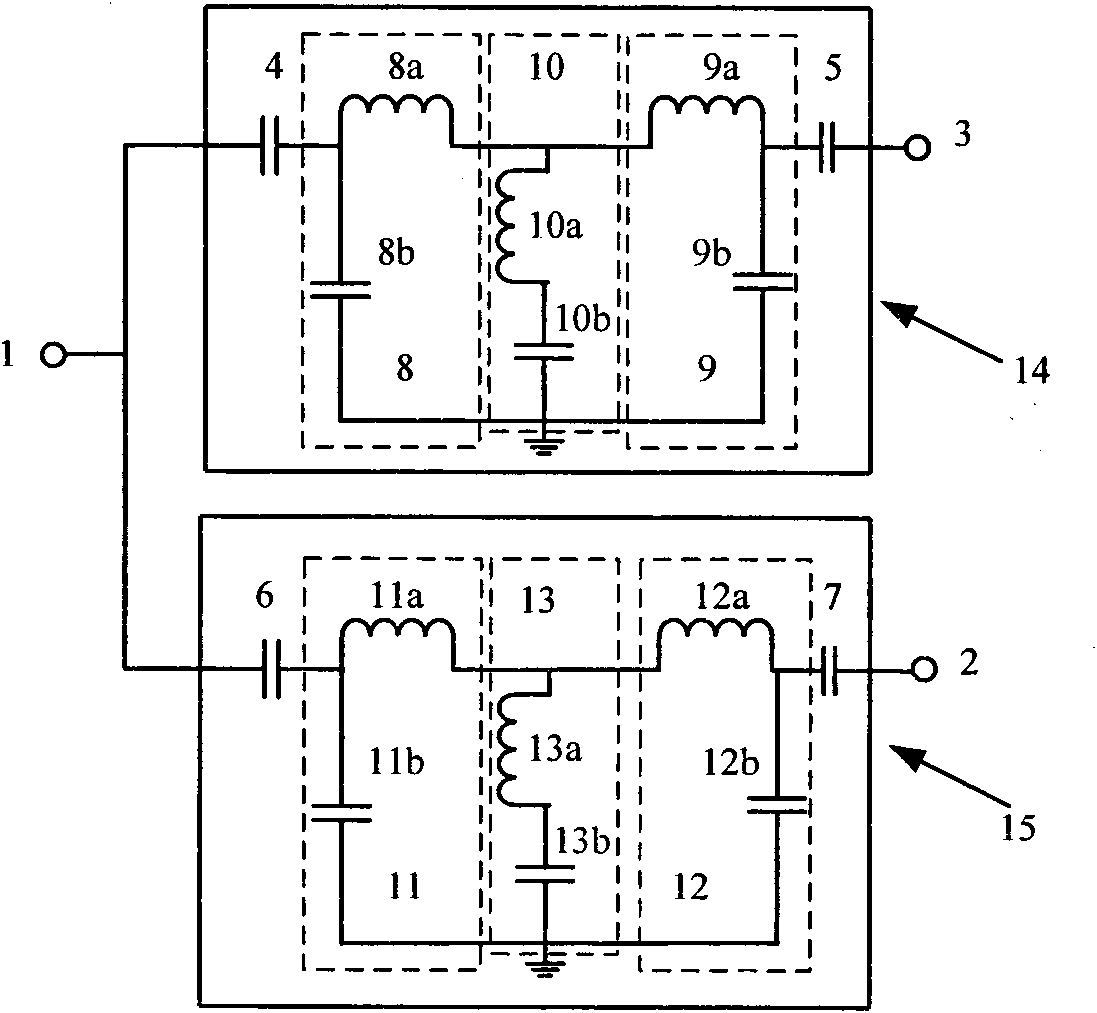

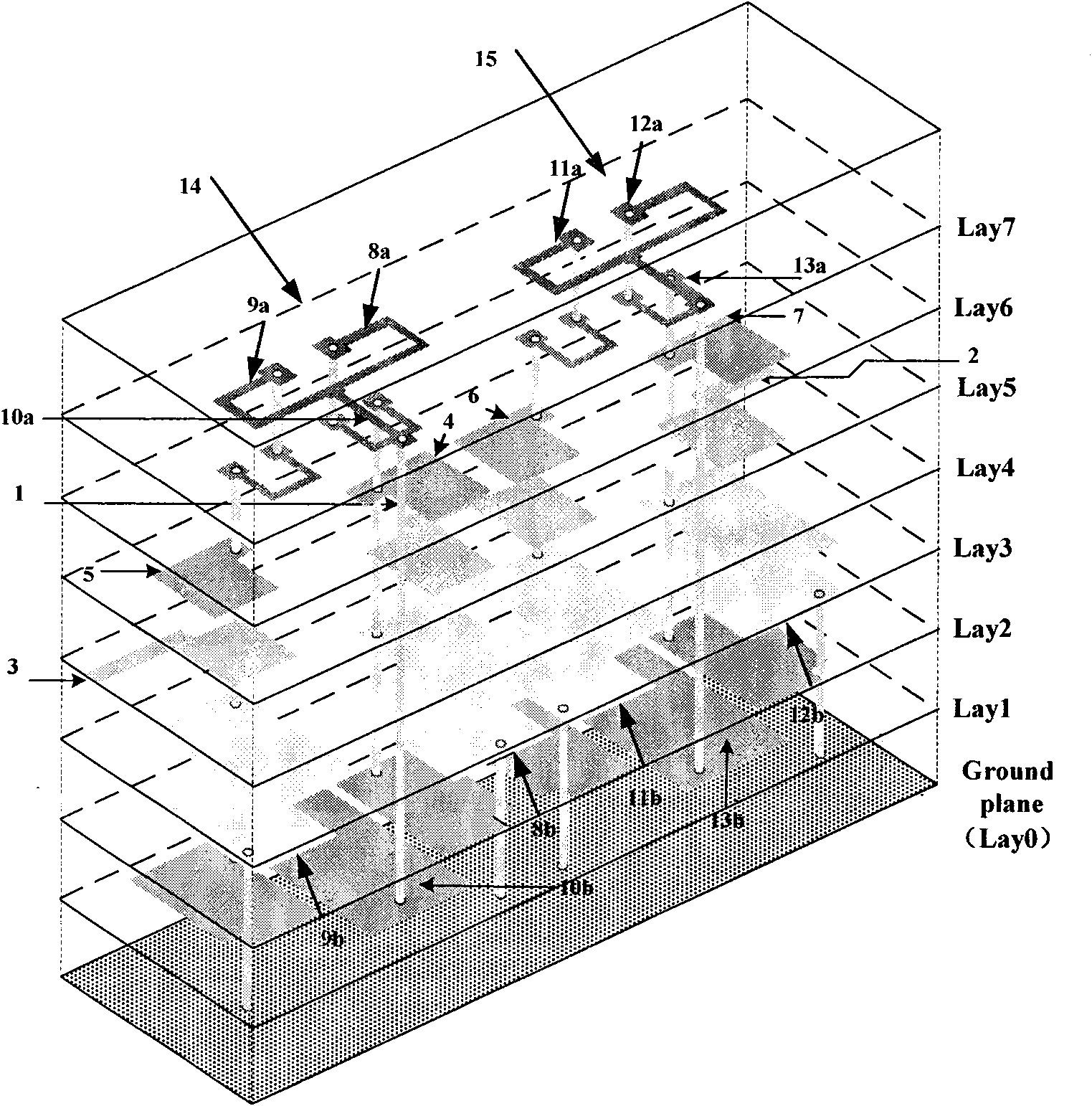

Low temperature cofired ceramic (LTCC)-process-based duplexer with novel structure

InactiveCN102255609AMinimize the effect of parasitic capacitanceIncrease the areaMultiple-port networksCapacitanceResonator

The invention discloses a duplexer, which is applied to global system for mobile communication (GSM) / data communication system (DCS) frequency bands and realized by a low temperature cofired ceramic (LTCC) technology. The duplexer comprises a high-pass filter connected with a common port and a low-pass filter connected with the common port. A low temperature series resonator which attenuates low frequency component is connected in parallel between the common port and the high-pass filter, two capacitors with equal capacitance are connected in series between the common port and the high-pass filter, and the high-pass filter forms a maximal transmission coefficient point in a high frequency pass band; and a series resonator which attenuates high frequency components is connected in parallel between the common port and the low-pass filter, and a parallel resonator which attenuates higher frequency components is connected in series between the common port and the low-pass filter.

Owner:SHANGHAI JIAOTAI INFORMATION TECH

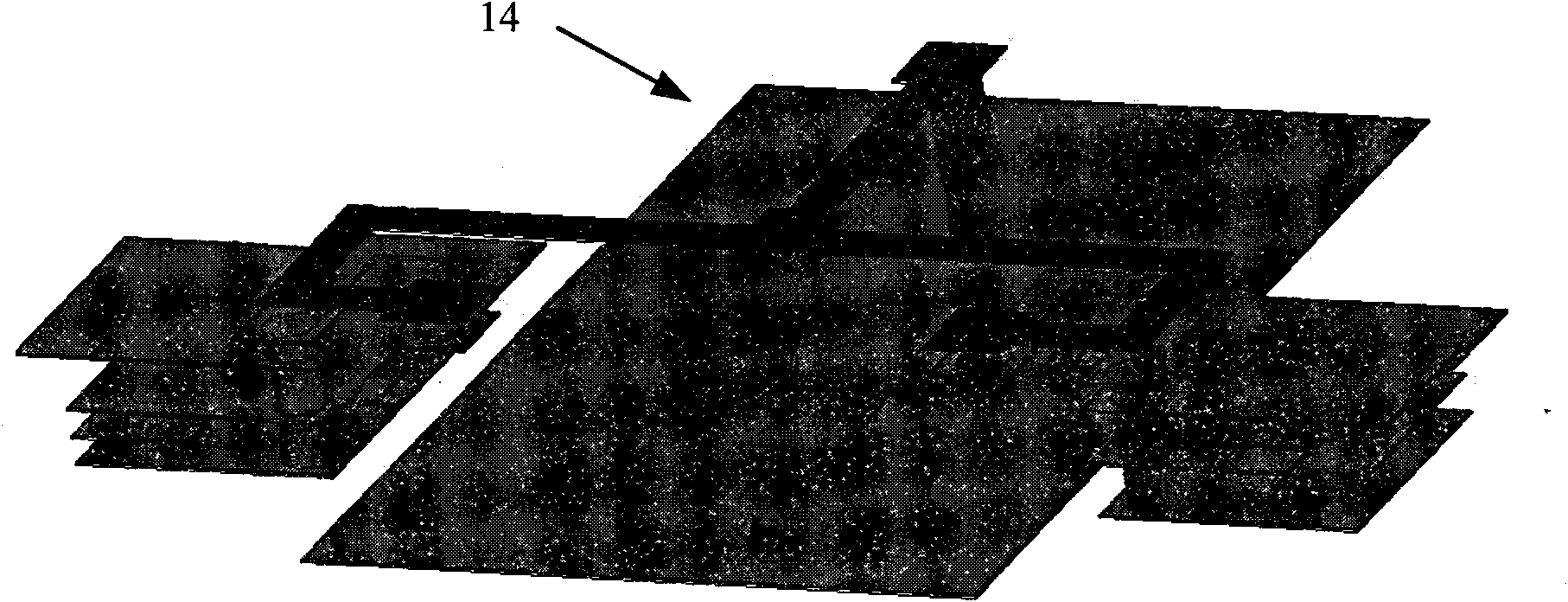

Micro low-temperature co-fired ceramic duplexer used for GSM/DCS

InactiveCN101662266AImprove transmission performanceImprove performanceMultiple-port networksCo-fired ceramicGSM

The invention relates to a micro low-temperature co-fired ceramic duplexer used for a GSM / DCS, belonging to the technical field of wireless communication elements and comprising a high-pass filteringpart and a low-pass filtering part, wherein the input end of the high-pass filtering part and the input end of the low-pass filtering part are connected in parallel as public antenna ports; the outputend of the high-pass filtering part is taken as a high-frequency output port, and the output end of the low-pass filtering part is taken as a low-frequency output port. The invention enables that theduplexer can be flexibly allocated in three-dimensional space by adopting a multilayer micro low-temperature co-fired ceramic technology, thereby leading the structure to be more compact and achieving the miniaturization aim. The allocation of the micro low-temperature co-fired ceramic duplexer can reduce the parasitic capacitance effect to large extent in the circuit operation and ensures that the parasitic capacitance part is added in an allocated capacitor, and the quantity value of the capacitor of the parasitic capacitance part is still equal to the originally-designed quantity value.

Owner:SHANGHAI JIAO TONG UNIV

Self capacitance implementation method

ActiveUS9377907B2Reduce impactReliable detectionInput/output processes for data processingParasitic capacitanceComputer science

A circuit for detecting a touch or proximity event on a touch input device is provided. The circuit is able to mitigate the effects that parasitic capacitance has on a self-capacitance touch sensor panel by injecting a signal into the sensing circuitry. The signal is adjusted until it calibrates the circuitry for the effects that parasitic capacitance imparts on the detection of touch or proximity events on a touch sensor panel.

Owner:APPLE INC

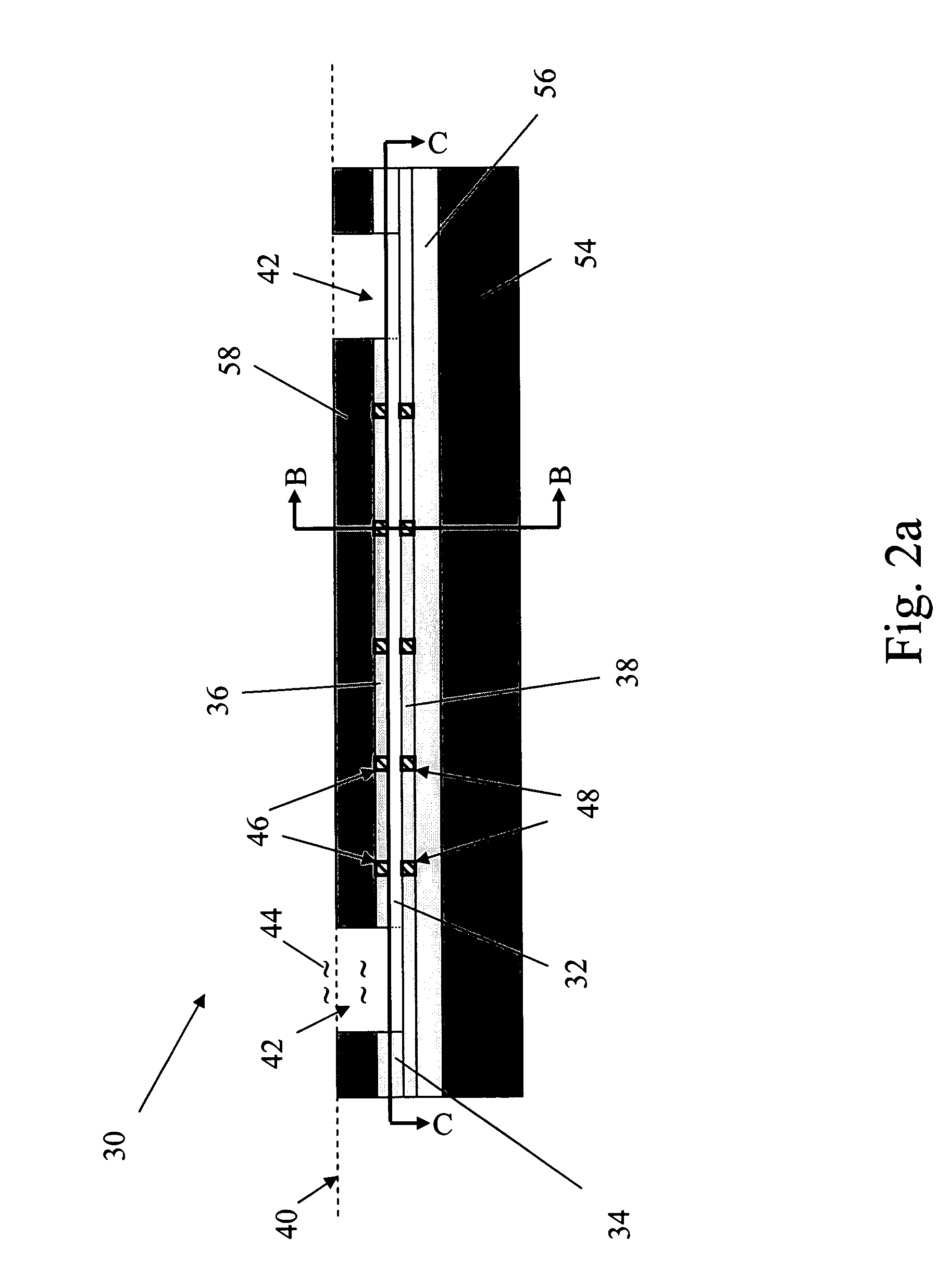

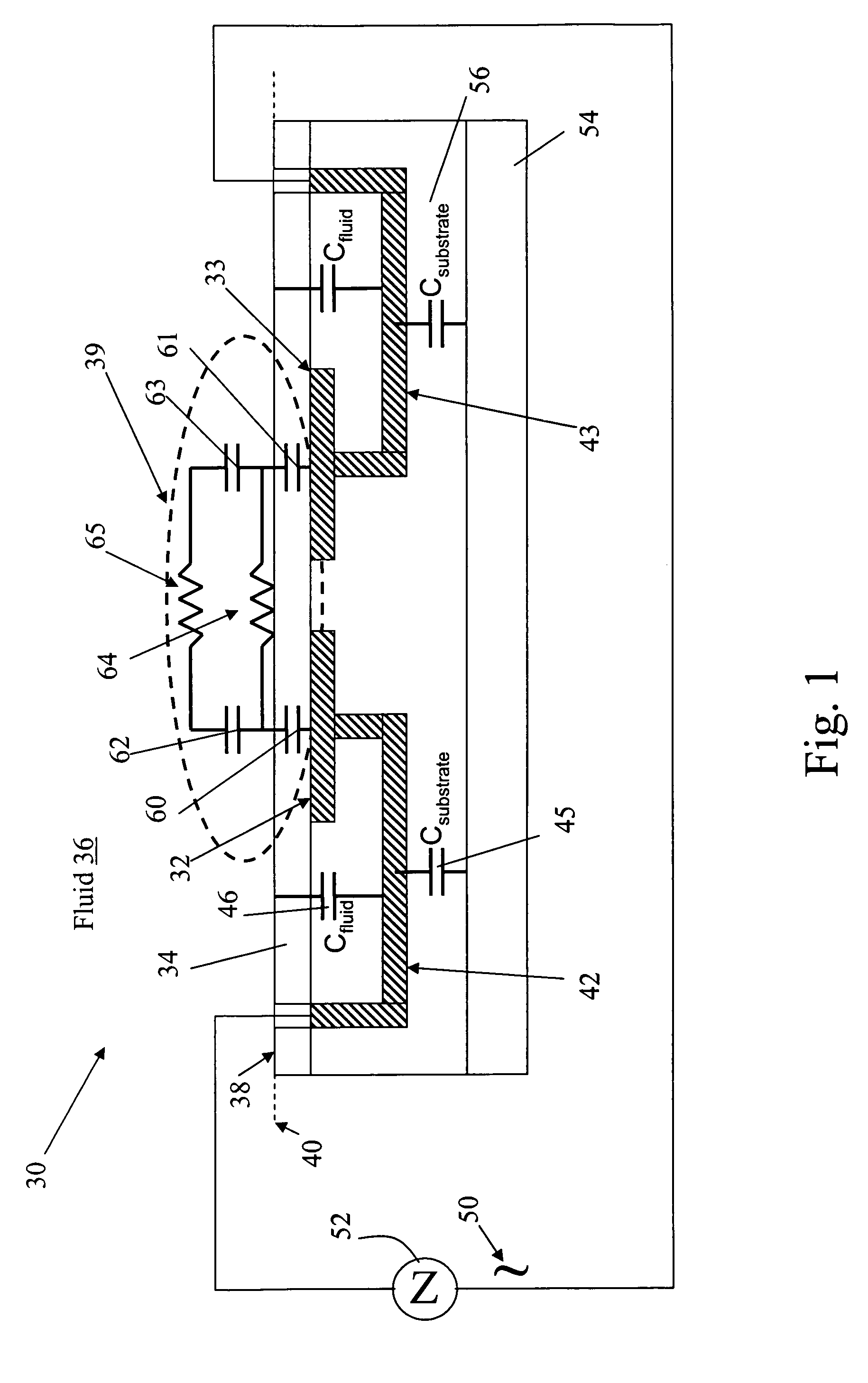

Surface micro sensor and method

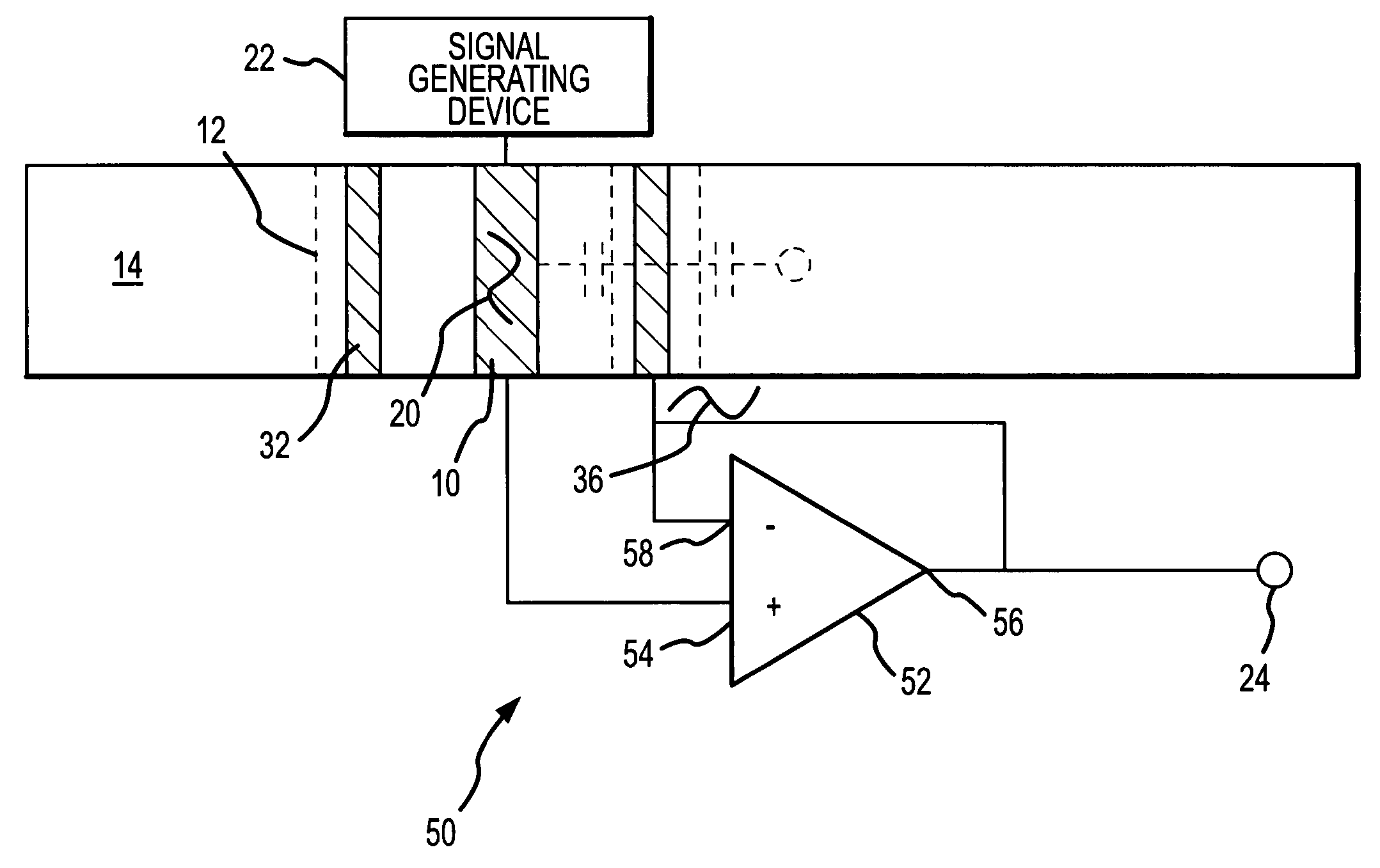

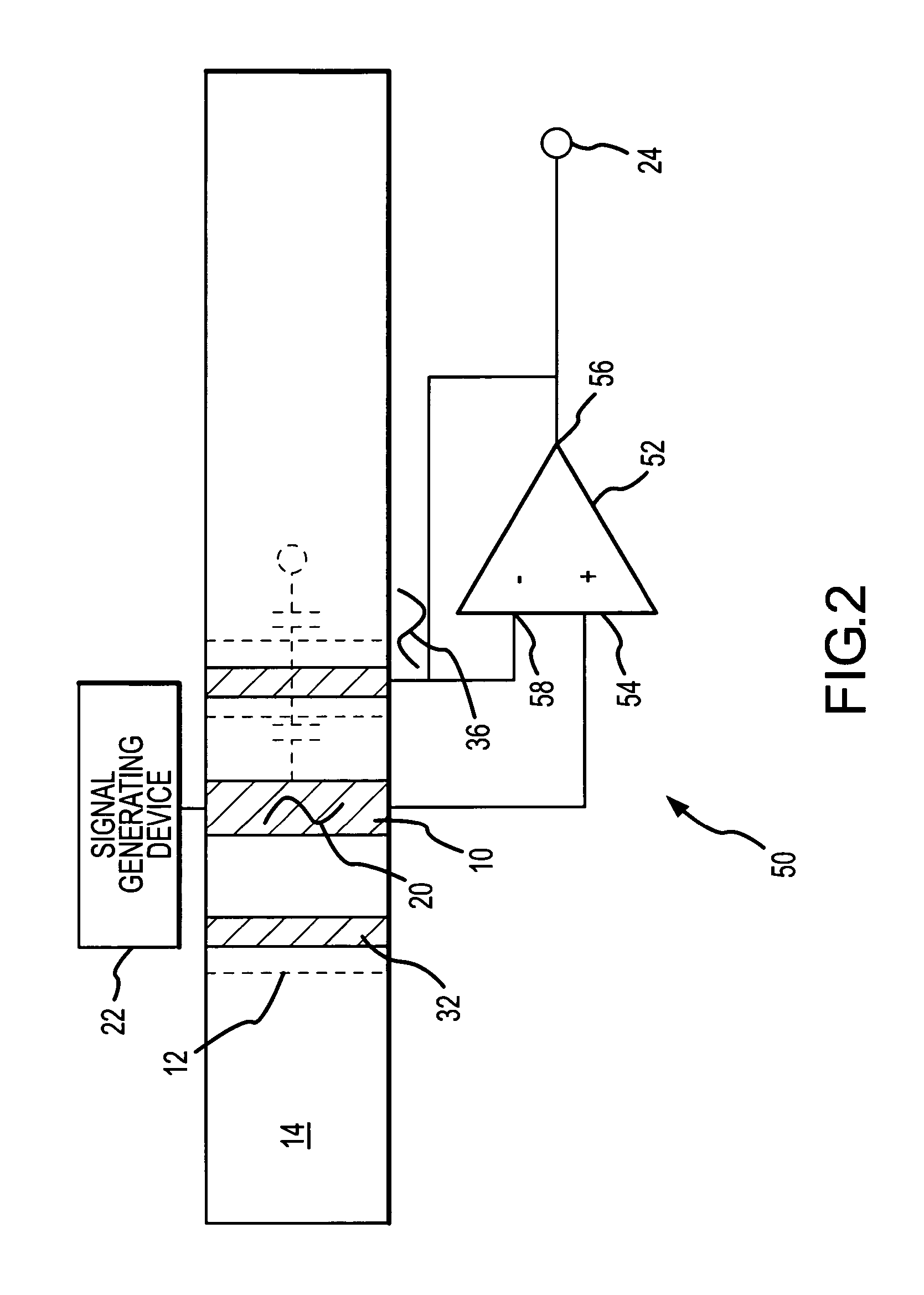

InactiveUS7489141B1Reduce effectExtend measurement bandwidthResistance/reactance/impedenceMaterial analysis by electric/magnetic meansMicroelectronicsElectricity

The present invention provides a micro sensor for monitoring the cleaning and drying processes of surfaces of dielectric films, micro features in porous dielectric films and biologic or other cells common in microelectronics fabrication, MEMS fabrication or microbiology test system fabrication. By embedding electrodes in the surface of a supporting dielectric, the sensor can probe the surface and pores of a covering dielectric or a cell on the covering dielectric. The addition of a guard reduces the effects of any parasitic capacitance, which extends the measurement bandwidth of the sensor and allows it to be manufactured at the scale of a single cell, a feature that is particularly important for applications in microbiology.

Owner:ENVIRONMENTAL METROLOGY CORP

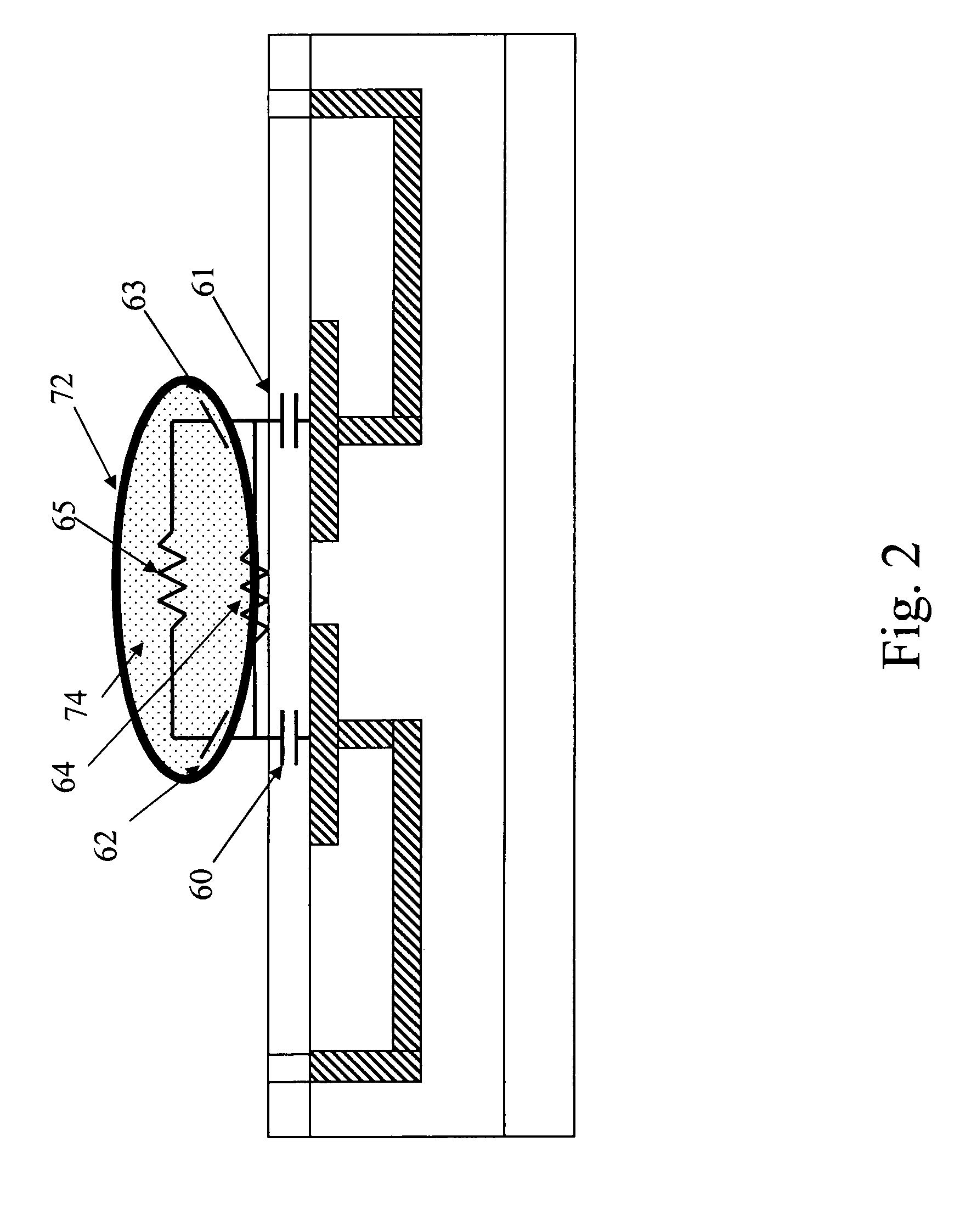

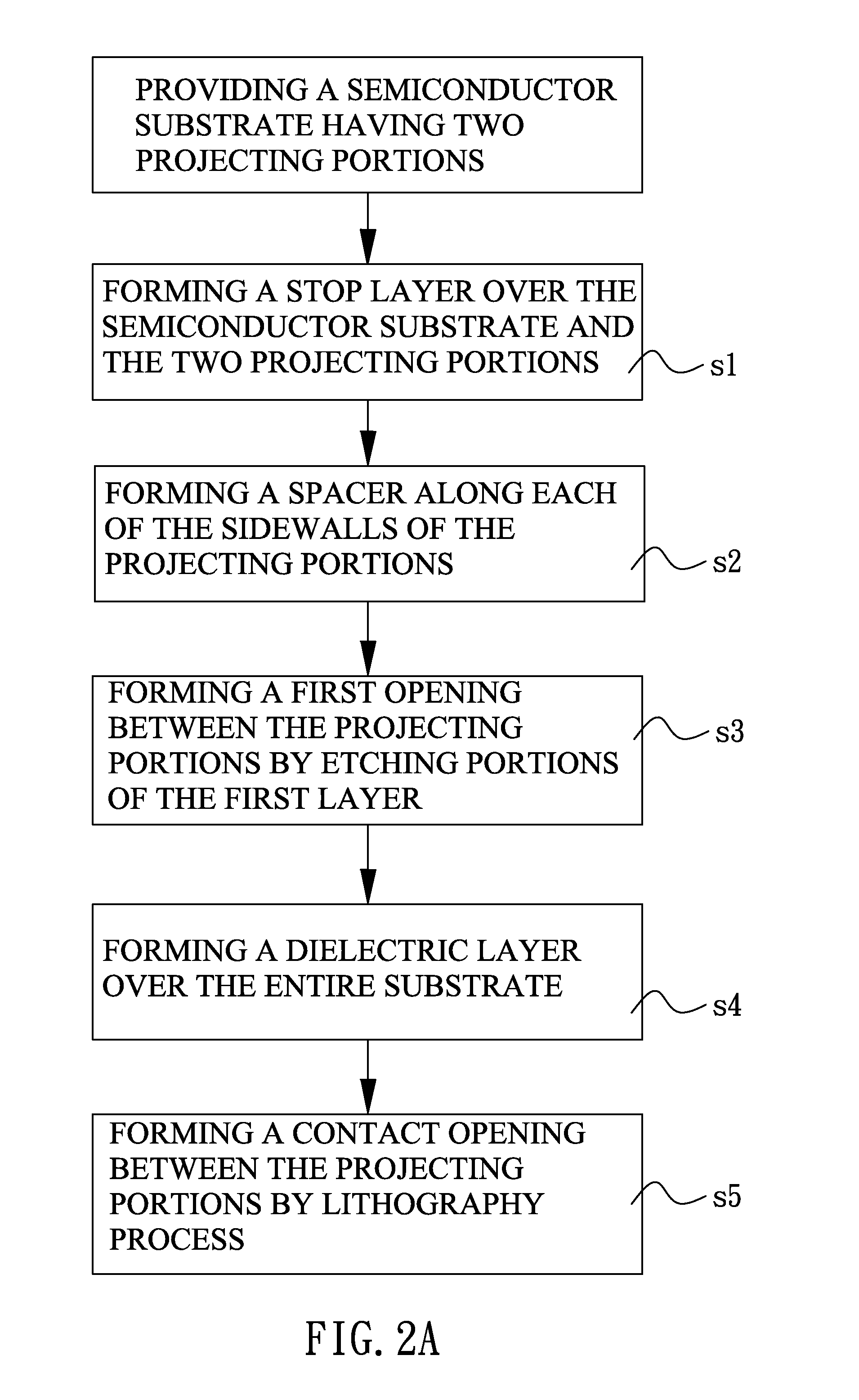

Method of forming a self-aligned contact opening in MOSFET

ActiveUS20130049104A1Increase contactReduce the cell pitch without increasing the process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETLithography process

A method of forming a contact opening in a semiconductor substrate is presented. A plurality of trench gates each having a projecting portion are formed in a semiconductor substrate, and a stop layer is deposited over the semiconductor substrate extending over the projecting portions, wherein each portion of the stop layer along each of the sidewalls of the projecting portions is covered by a spacer. By removing the portions of the stop layer not covered by the spacers by utilizing a relatively higher etching selectivity of the stop layer to the spacers, the openings between adjacent projecting portions with an L-type shape on each sidewall can be formed, and a lithography process can be performed to form self-aligned contact openings thereafter.

Owner:SINOPOWER SEMICON

Novel LTCC (Low Temperature Co-Fired Ceramic) duplexer used for RFID (Radio Frequency Identification Devices) 2.4G

InactiveCN102340289AFlexible configurationReduce the purpose of miniaturizationMultiple-port networksTransmission zerosEngineering

The invention discloses a duplexer which is applied to RFID 2.4G uplink and downlink frequency bands and is realized by the LTCC technology. The duplexer comprises an uplink band pass filter and a downlink band pass filter, wherein the uplink band pass filter is connected with a community port and is designed by a lumped element; the downlink frequency band filter is connected with the community port and is designed by a lumped element; the uplink band pass filter filters a high-frequency part higher than the upper cutoff frequency of the uplink band pass filter; a serial resonator is introduced into the uplink band pass filter to generate the transmission zero of the RFID 2.4G downlink band pass so as to improve the suppression performance of the downlink frequency band; the downlink band pass filter filters a lower-frequency part lower than the cutoff frequency of the downlink band pass filter; and the serial resonator is introduced into the downlink band pass filter to generate the transmission zero of the RFID 2.4G uplink band pass so as to improve the suppression performance of the uplink frequency band, thereby ensuring that signals in the uplink frequency band and the downlink frequency band do not mutually affect, improving performance, and simplifying the design.

Owner:SHANGHAI JIAOTAI INFORMATION TECH

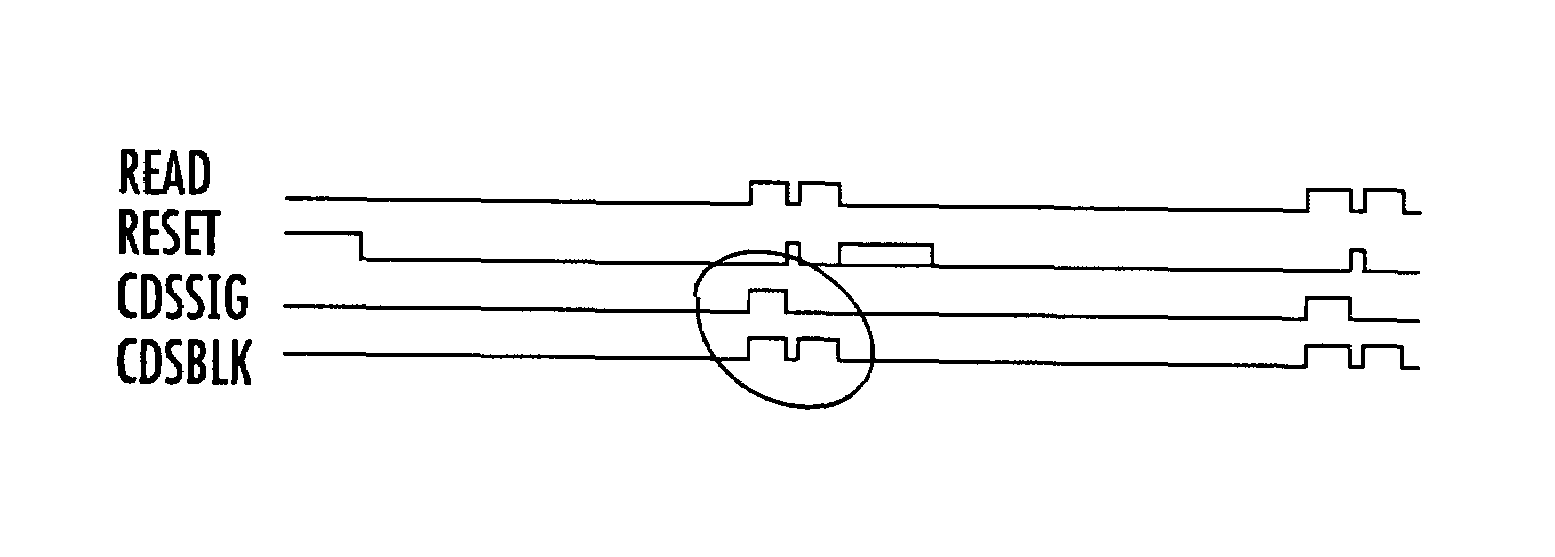

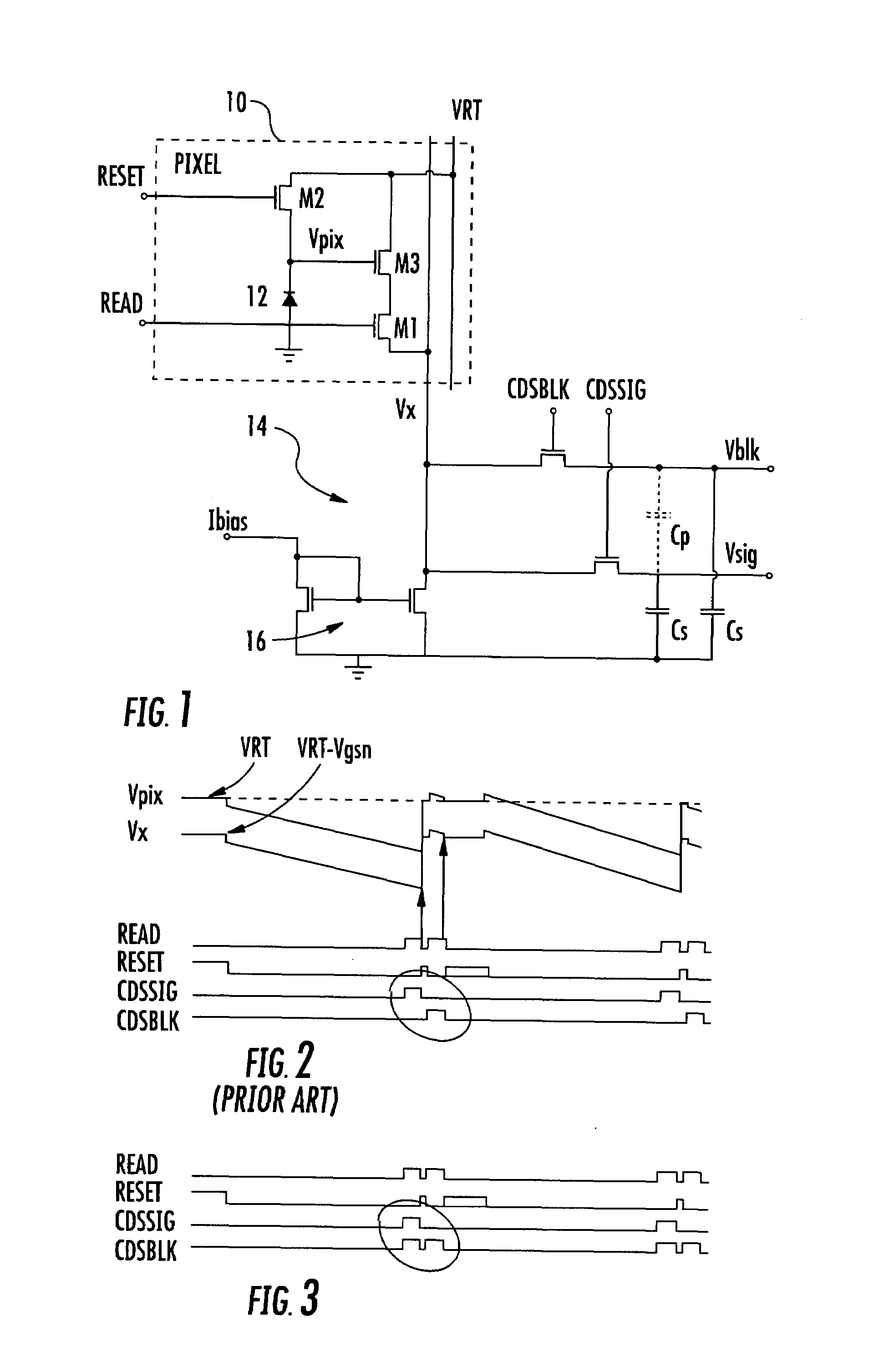

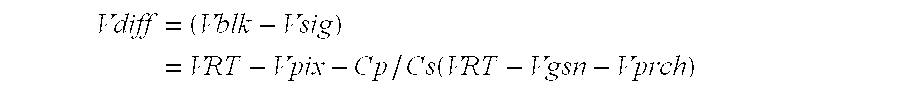

Active-pixel image sensors

ActiveUS7253837B2FPN can be reducedMinimize the effect of parasitic capacitanceTelevision system detailsTelevision system scanning detailsParasitic capacitancePre-charge

An image sensor has an array of pixels read by column circuits to provide reset and read samples on a pair of sample capacitors. To alleviate the effects of parasitic capacitance in the region of the sample capacitors, a modified timing arrangement is used. Both sample switches are operated simultaneously to pre-charge both sample capacitors with a pixel signal value. One sample switch is operated after reset to apply a reset value to one of the pre-charged sample capacitors.

Owner:STMICROELECTRONICS SRL

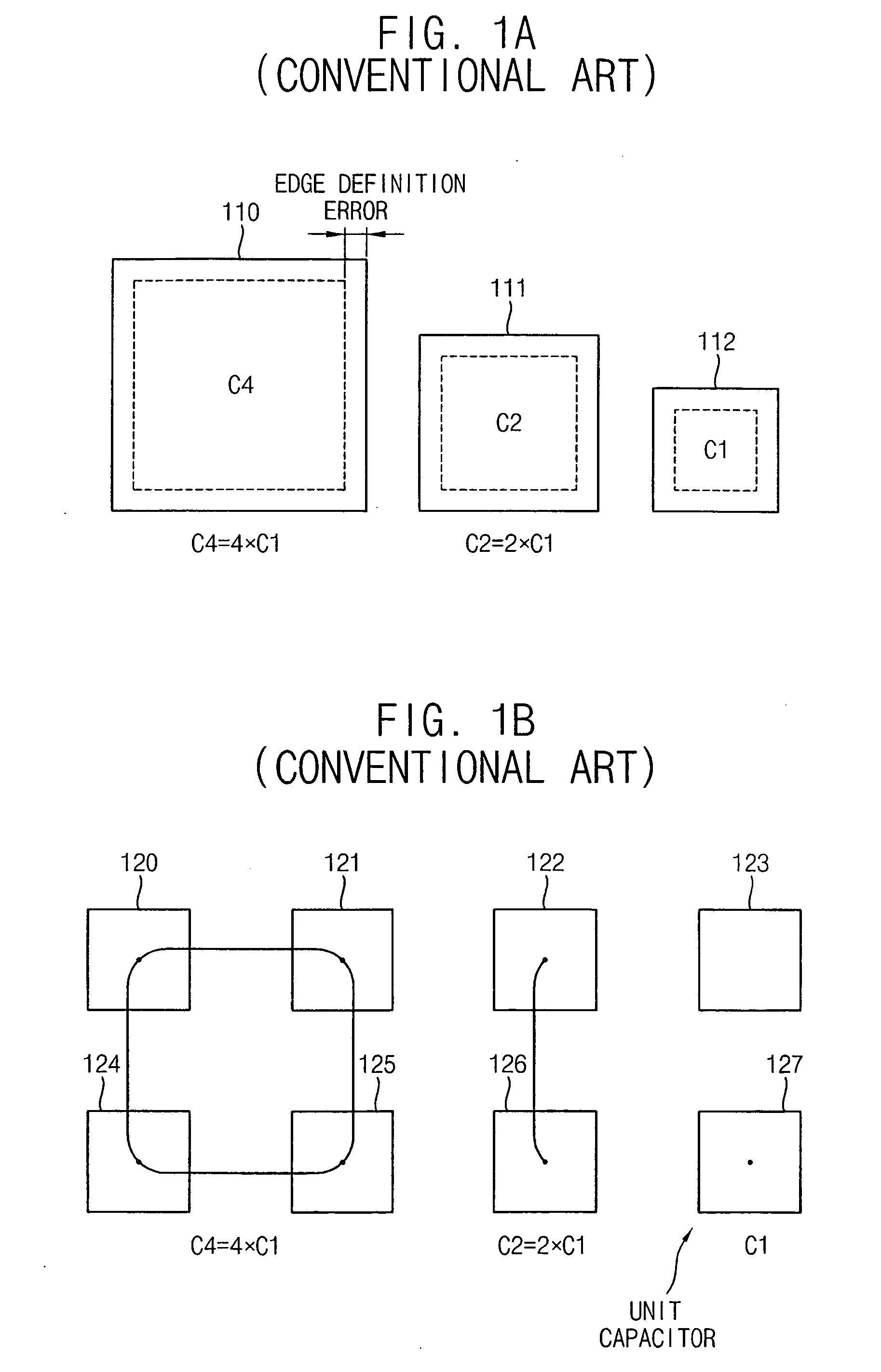

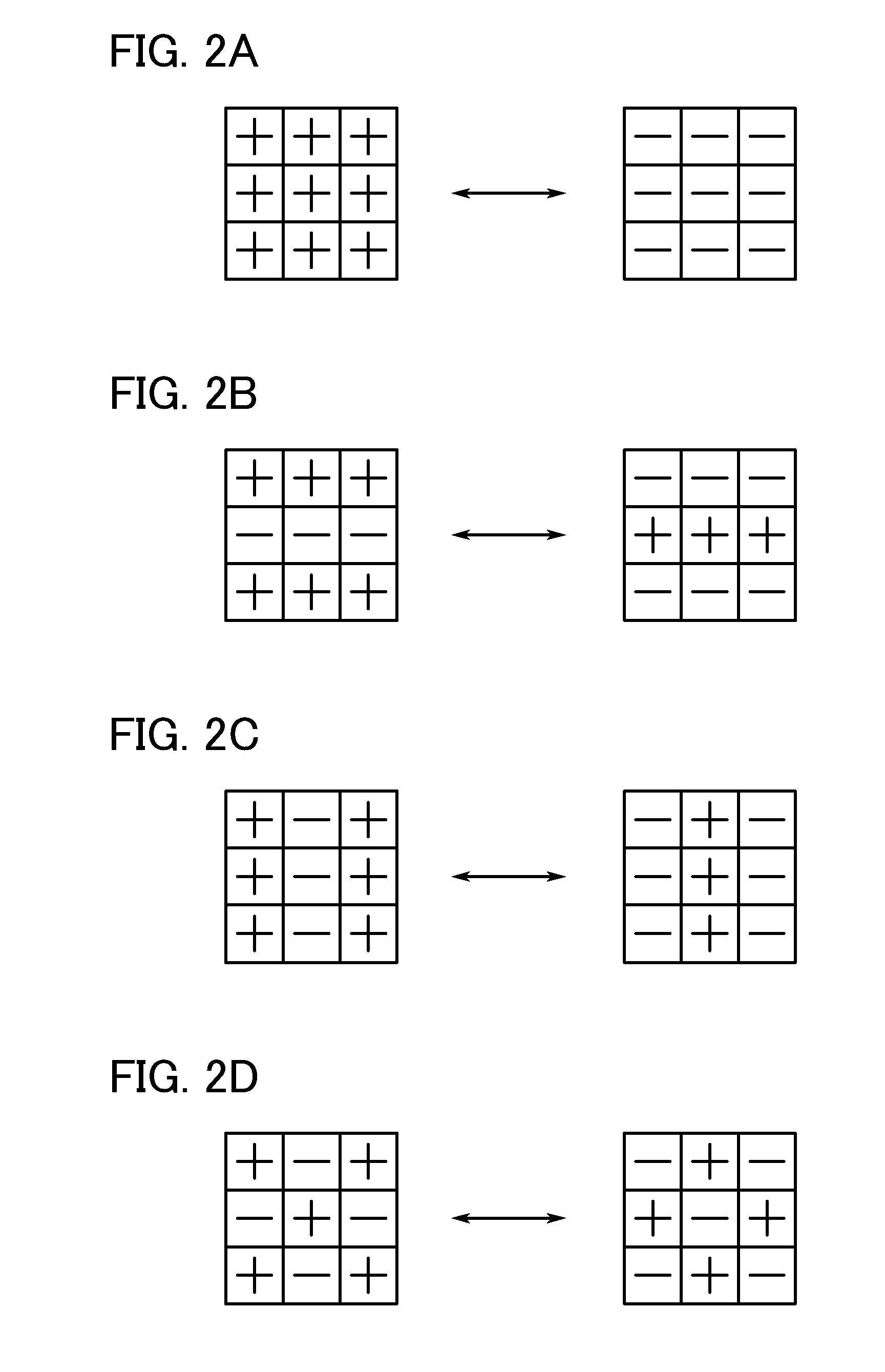

Capacitor and capacitor array

ActiveUS20070138587A1Minimize the effect of parasitic capacitanceReduce impactSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitanceEngineering

In a capacitor and a capacitor array configured for reducing an effect of parasitic capacitance, the capacitor array can have a matrix configuration that includes a plurality of unit capacitors. The unit capacitors include a lower electrode and an upper electrode that constitute a plate capacitor, as well as shielding structures which enclose the capacitor. The unit capacitors are connected by an upper electrode connecting line with a first direction to constitute a plurality of capacitor columns, wherein the unit capacitors are also arranged in rows, in a second direction perpendicular to the first direction, and wherein lower electrode lead lines are disposed between the capacitor columns, the lower electrode lead lines being connected to the respective lower electrodes of each of the unit capacitors.

Owner:SAMSUNG ELECTRONICS CO LTD +1

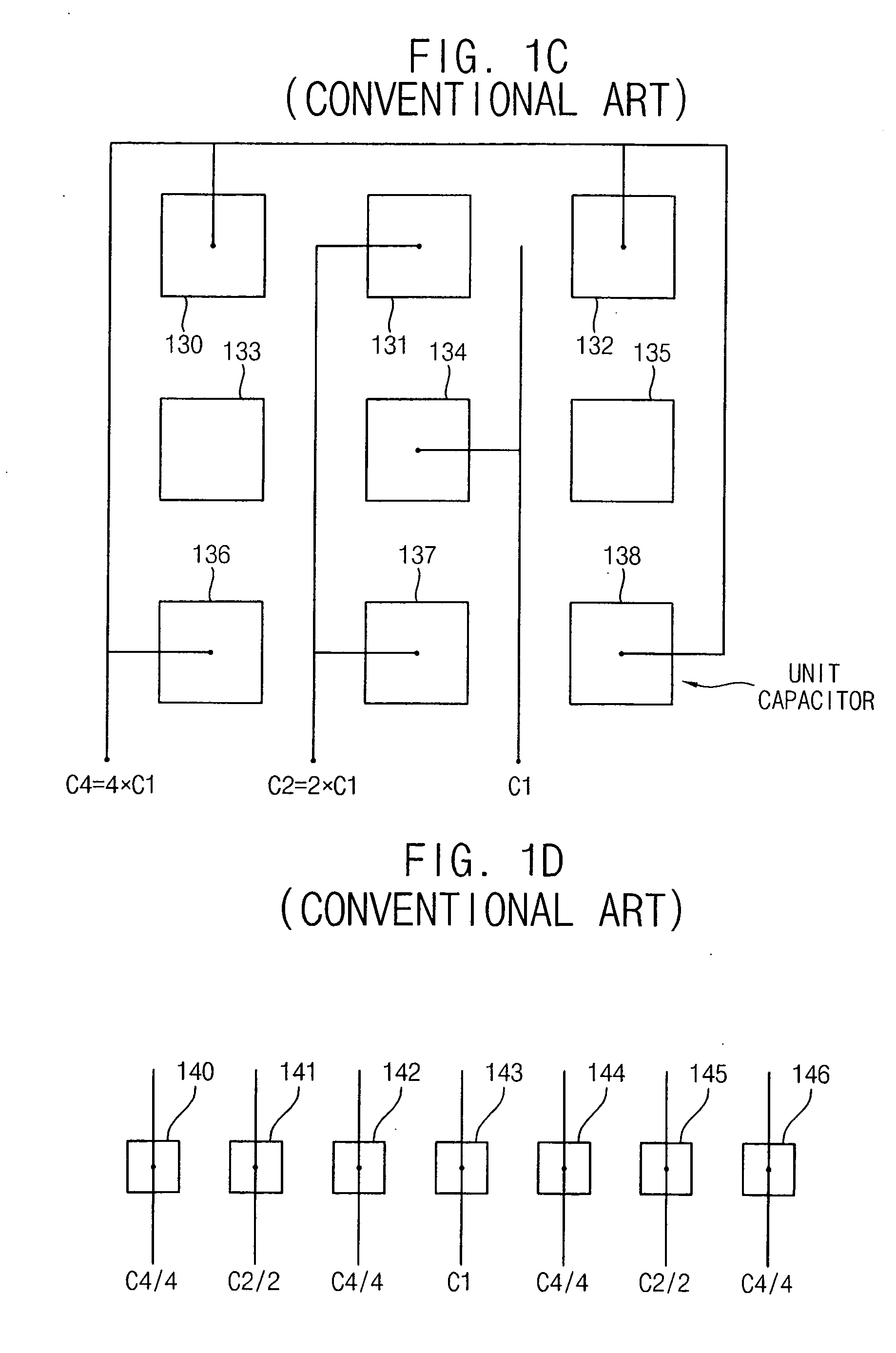

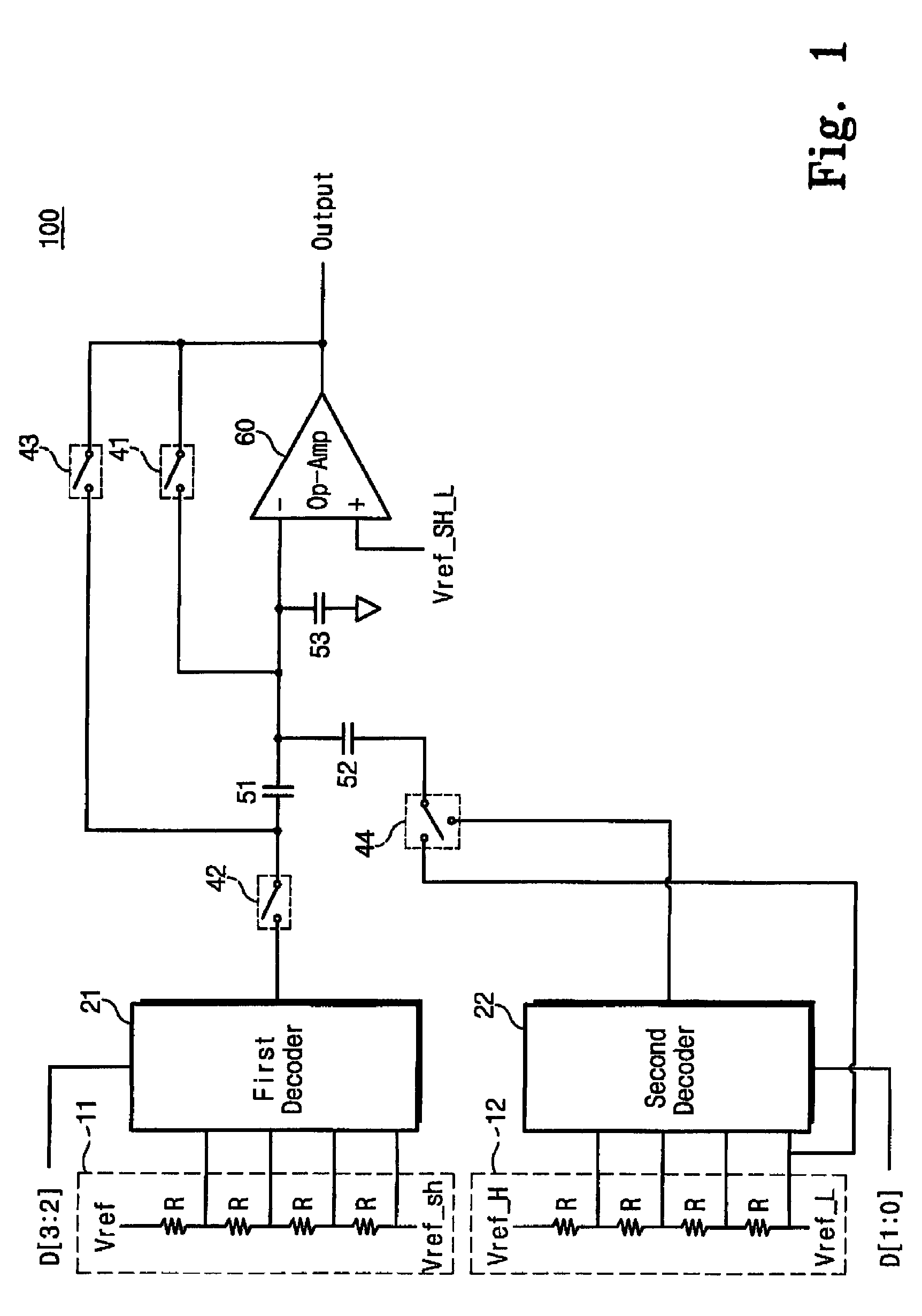

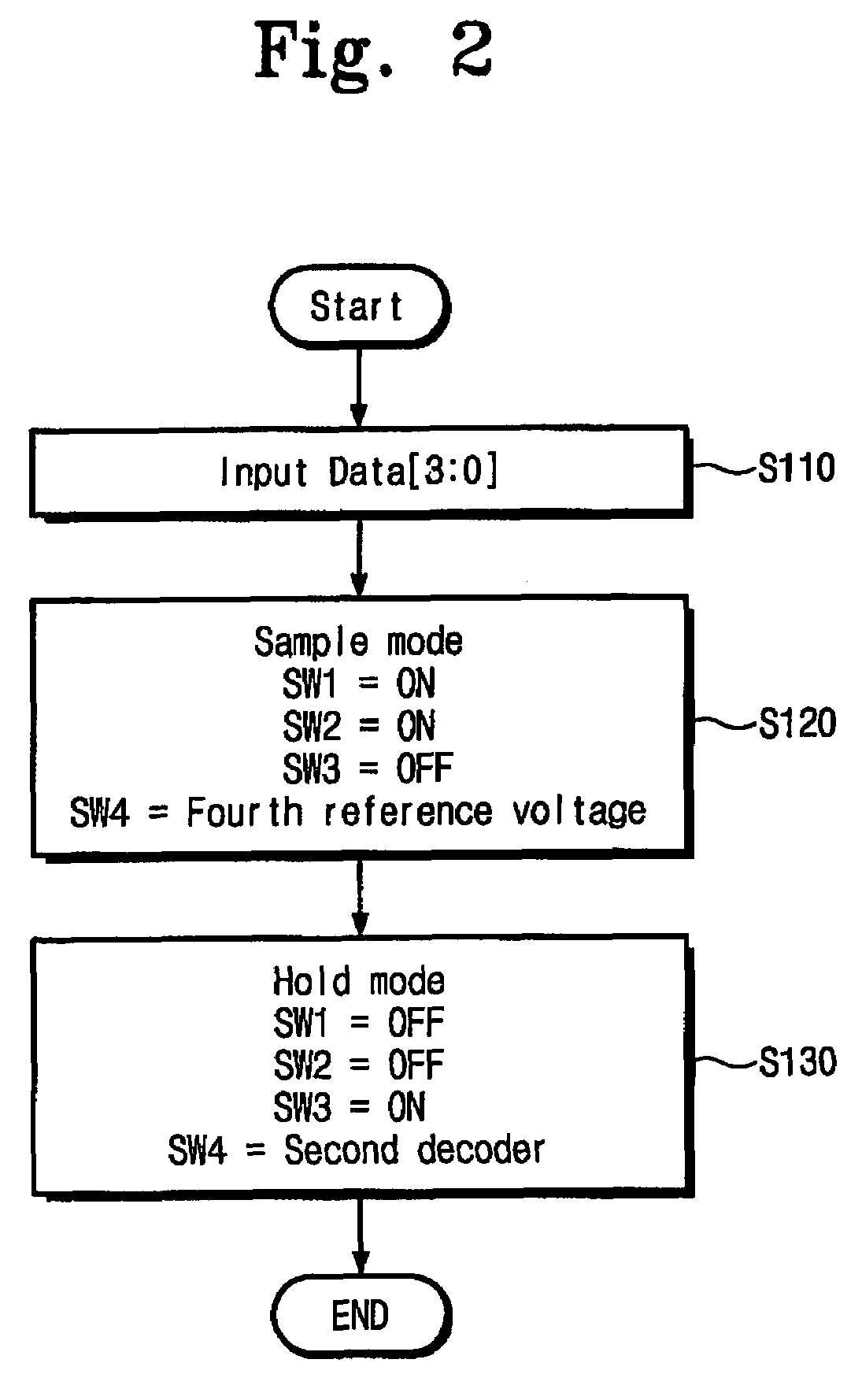

Digital to analog converter and source driver

InactiveUS7453386B2Reduce outputMinimize the effect of parasitic capacitanceElectric signal transmission systemsStatic indicating devicesDigital dataSample Mode

A digital to analog converter (DAC) converting digital data into a corresponding analog voltage is disclosed. The digital data includes upper bit data and lower bit data and the DAC includes; a first resistor circuit dividing first and second reference voltages to output a plurality of first division voltages, a first decoder selecting one of the first division voltages in response to the upper bit data, a second resistor circuit dividing third and fourth reference voltages to output a plurality of second division voltages, a second decoder selecting one of the second division voltages in response to the lower bit data, and a sample and hold circuit including a first capacitor and a second capacitor, and outputting the analog voltage in response to an output voltage from the first decoder and an output voltage from the second decoder, wherein the sample and hold circuit samples the output voltage of the first decoder during a sample mode, and adds the output voltages of the first and second decoders through the first and second capacitors to output a combined voltage during a hold mode.

Owner:SAMSUNG ELECTRONICS CO LTD

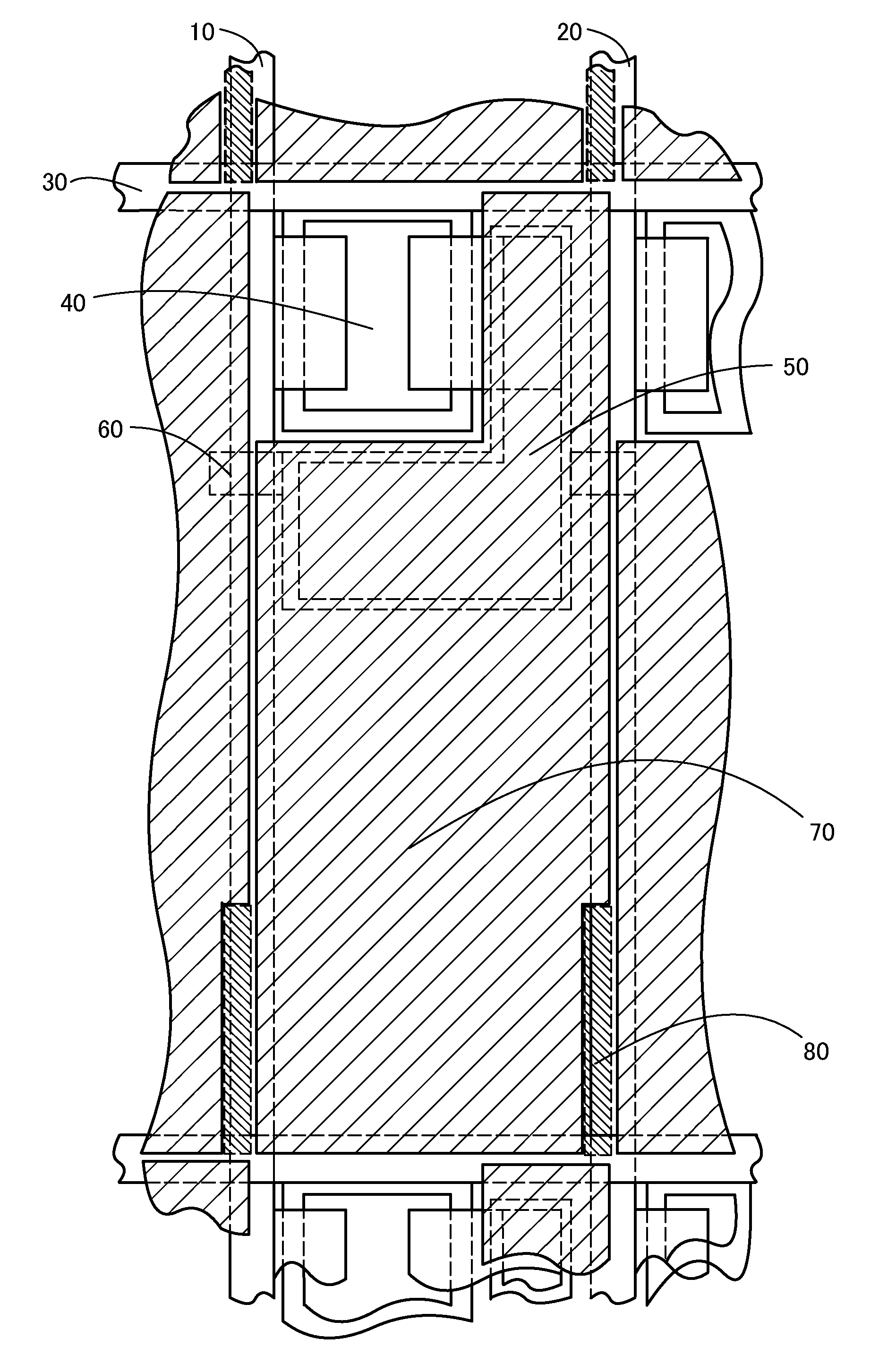

Signal transmission structure and circuit substrate thereof

ActiveUS20060065434A1Improve signal transmission qualityMinimize the effect of parasitic capacitanceSemiconductor/solid-state device detailsCross-talk/noise/interference reductionEngineeringDielectric layer

A signal transmission structure suitable for a multi-layer circuit substrate comprising a core layer and at least a dielectric layer is provided. The signal transmission structure according to the present invention comprises a first via landing pad and a reference plane. The first via landing pad is disposed on a first surface of the core layer, and covering one end of the through hole of the core layer. The dielectric layer covers the first via landing pad and the first surface of the core layer. And the first reference plane is disposed above the dielectric layer, having a first opening disposed above one end of the through hole. Wherein, the area where the first reference plane is projected on the first surface of the core layer does not overlap with the area where the first via landing pad is projected on the first surface of the core layer.

Owner:VIA TECH INC

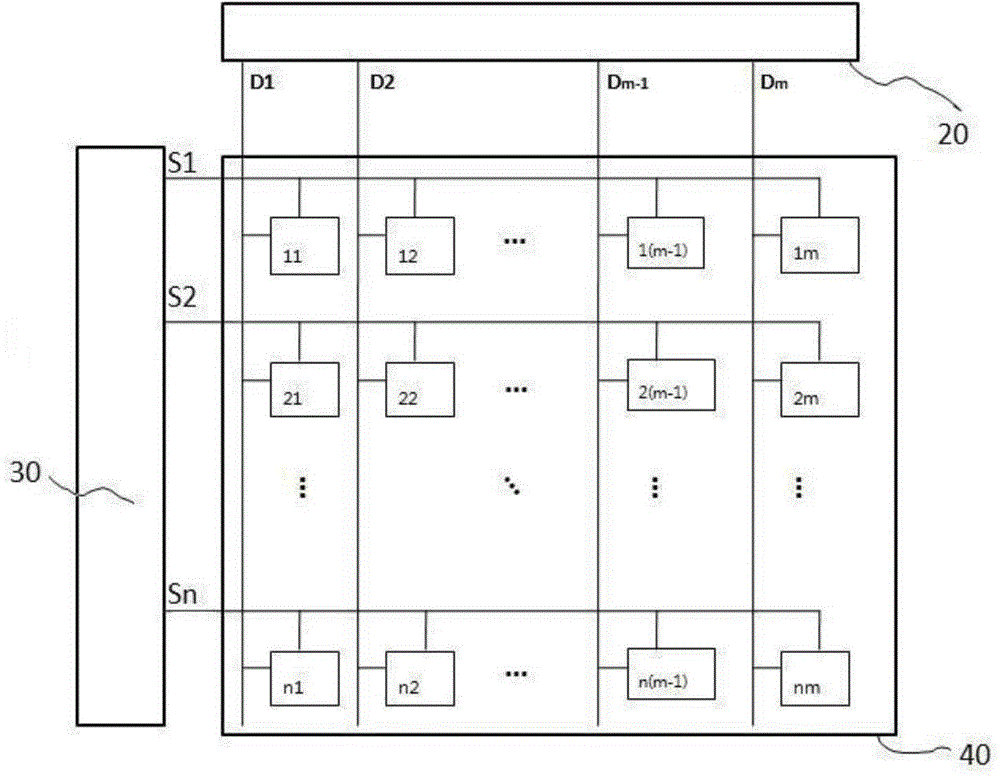

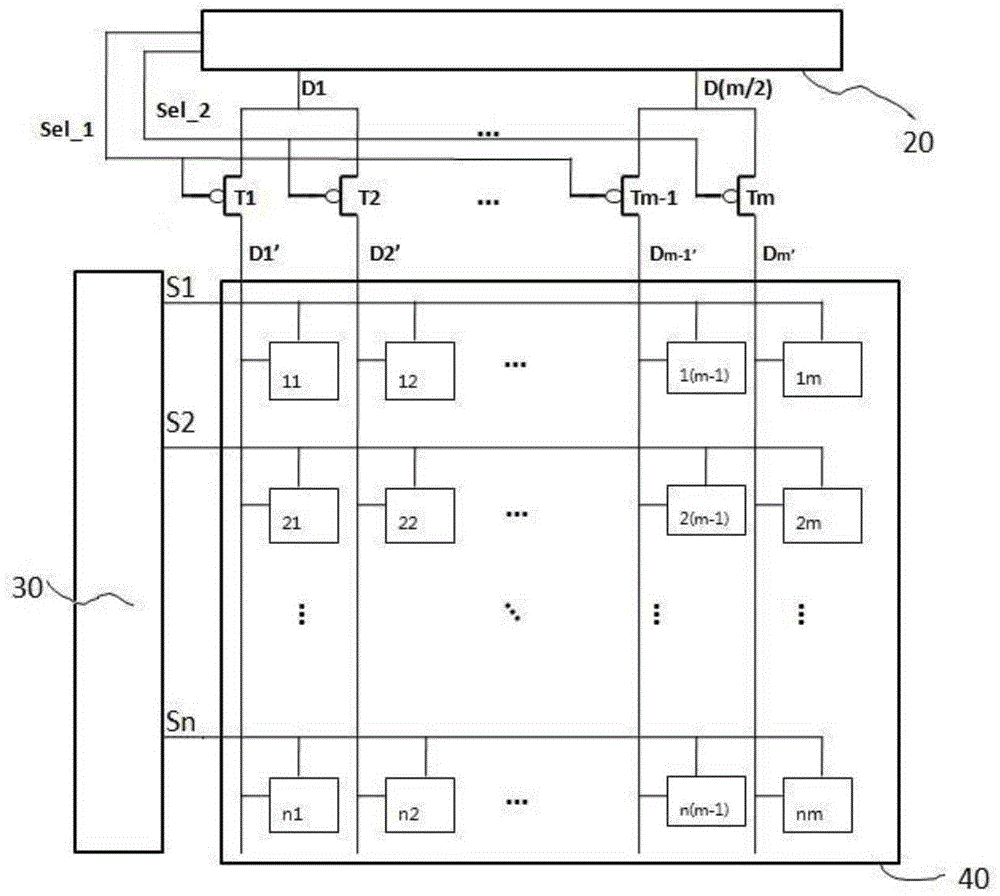

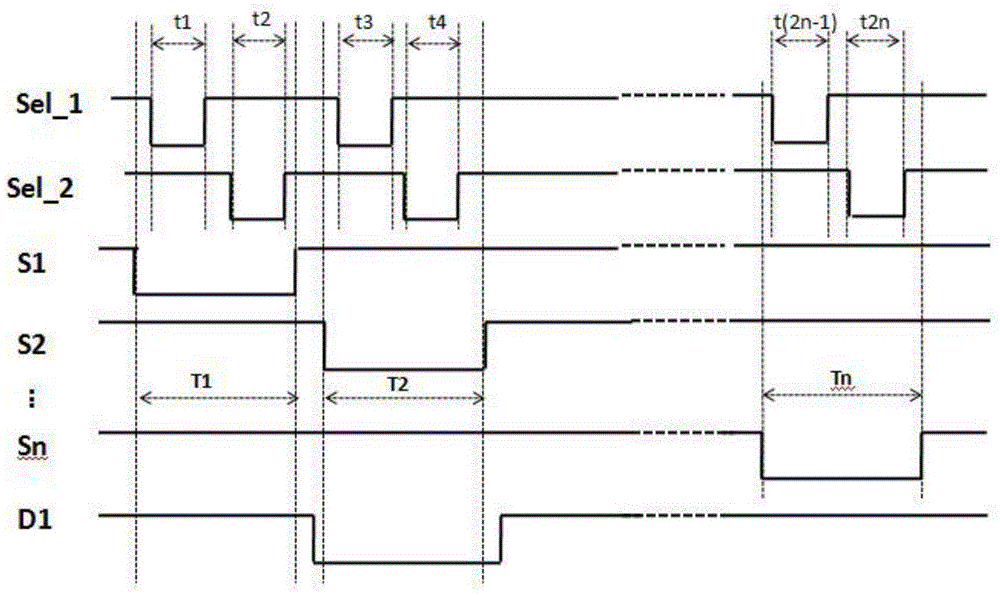

Data driving circuit, driving method thereof, and organic light-emitting display device

ActiveCN105810143AMinimize the effect of parasitic capacitanceImprove responsivenessStatic indicating devicesCapacitanceParasitic capacitor

The invention provides a data driving circuit with a data signal multiplexing structure. The data driving circuit also comprises a power line for connecting a power and a second transistor connected to a power supply line. The source electrode of the second transistor is electrically connected to the power supply line. The gate of the second transistor is electrically connected to a control line in a same line. The drain electrode of the second transistor is electrically connected to different signal lines, and the connection points are between the first transistor and a display area. Through connecting a compensation power supply in the signal line, a pixel unit is initialized so as to reduce the influence of a parasitic capacitor in the pixel unit, and thus the response characteristics and display characteristics of an organic light-emitting display device with the application of the data driving circuit is effectively improved.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT +1

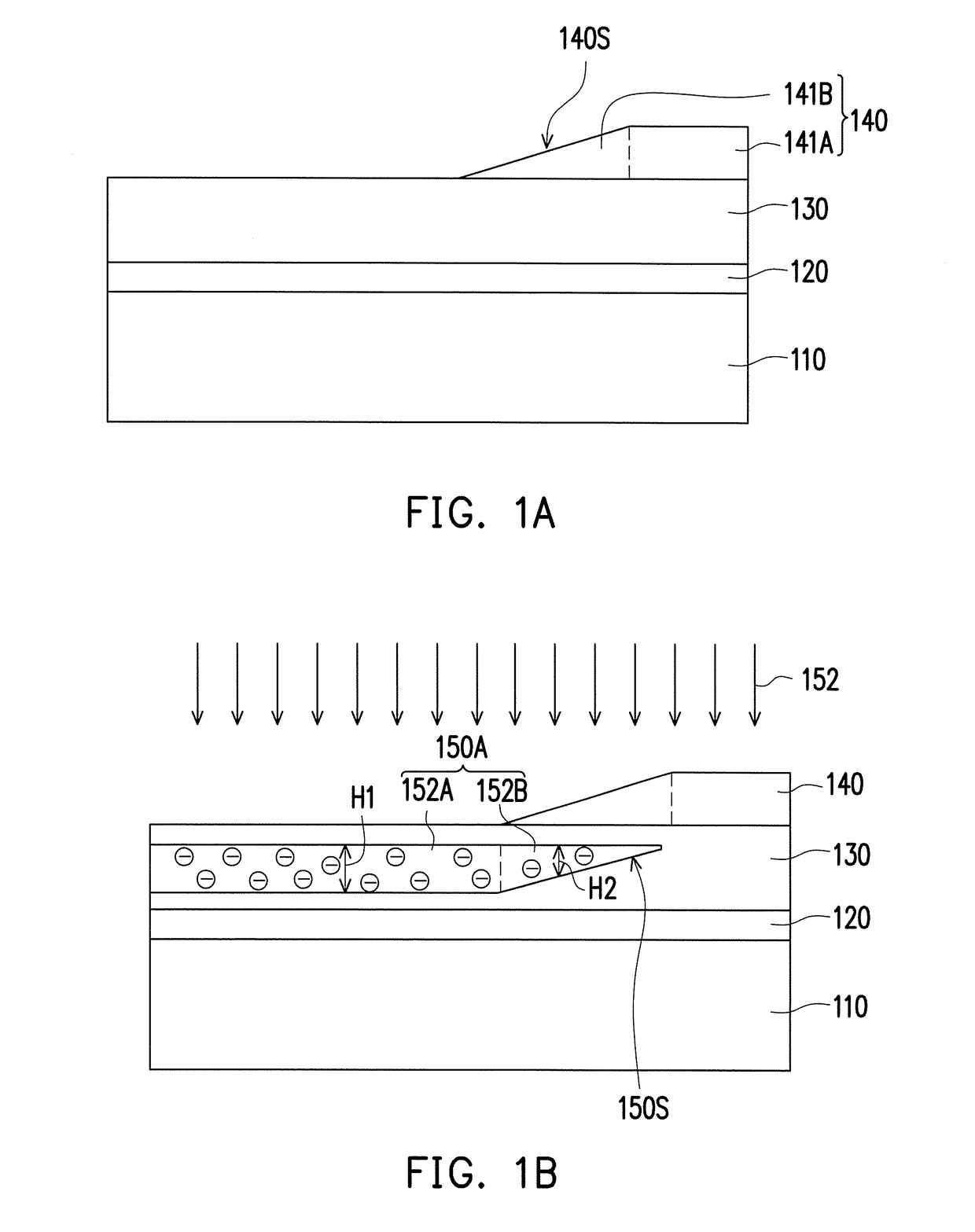

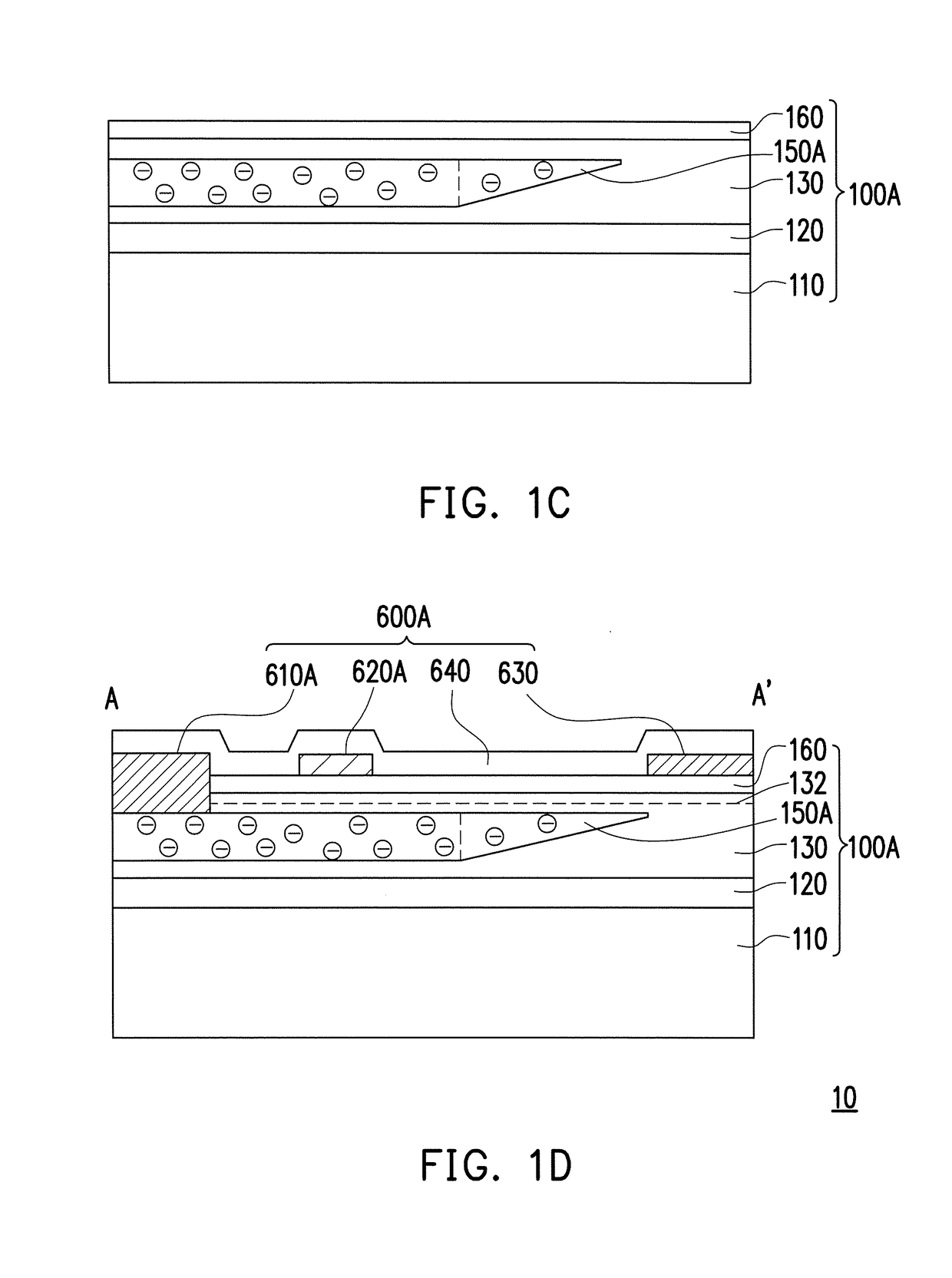

Semiconductor substrate and semiconductor device

ActiveUS20180175186A1Effective dispersionReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorElectron

A semiconductor substrate and a semiconductor device are disclosed. The semiconductor substrate includes a base layer, a buffer layer disposed on the base layer, a channel layer disposed on the buffer layer, a barrier layer disposed on the channel layer, and a buried field plate region embedded in the channel layer. In an embodiment, the channel layer includes a two-dimensional electron gas (2DEG), and the buried field plate region is located below the two-dimensional electron gas.

Owner:NUVOTON

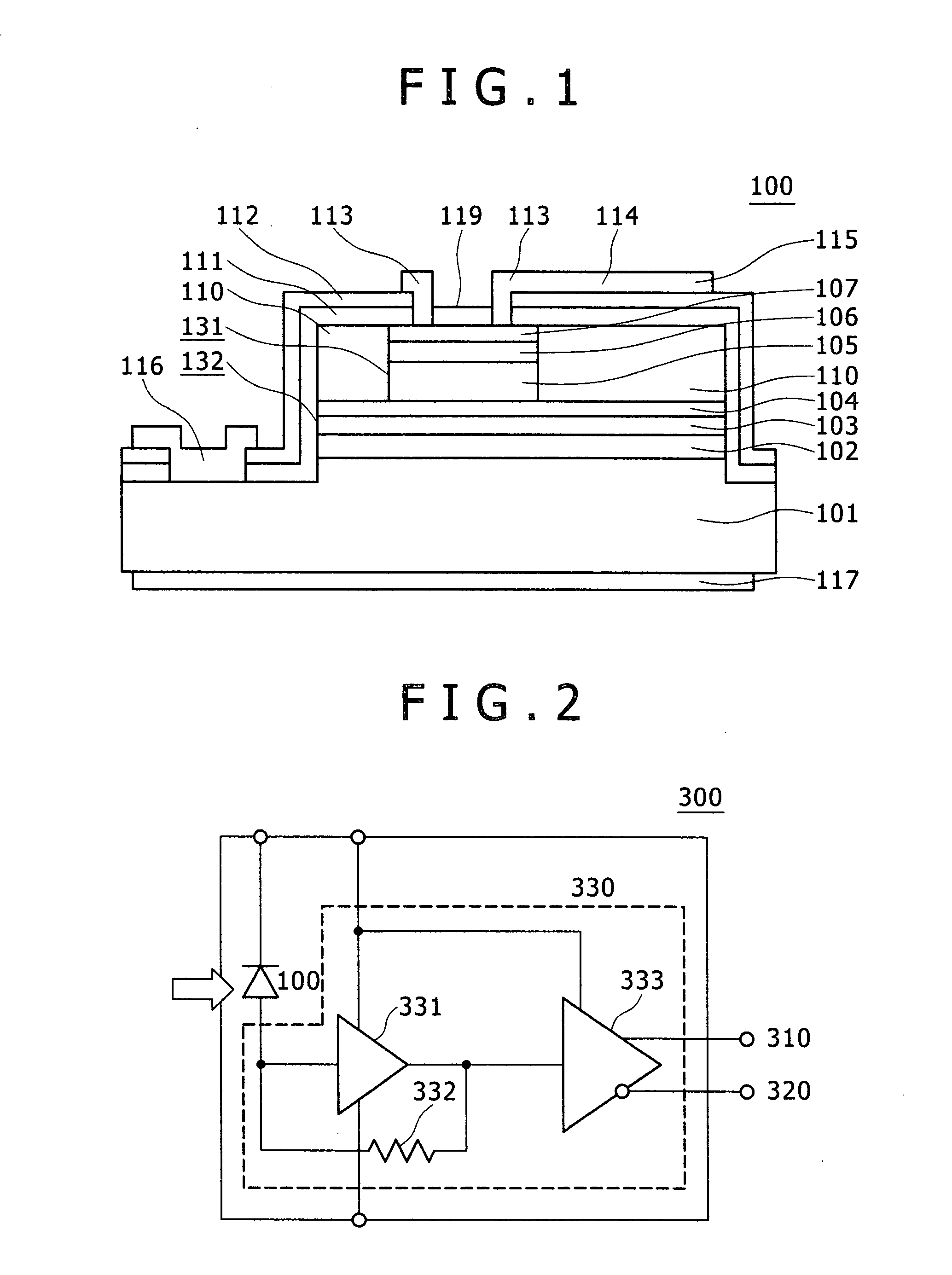

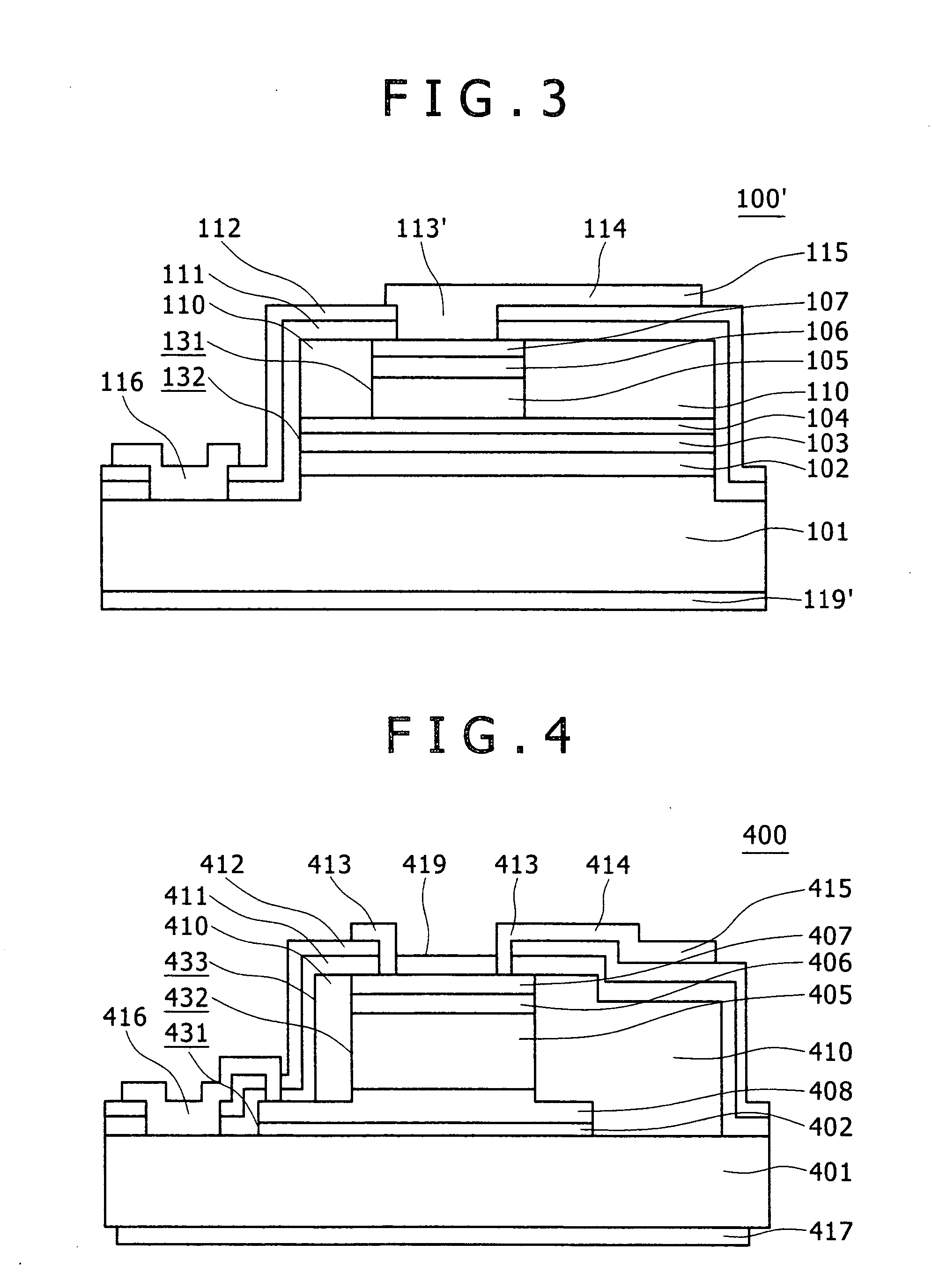

Optical device and optical module

InactiveUS20070249109A1Increase resistanceReduce capacitanceLaser detailsSemiconductor/solid-state device manufacturingElectrical resistance and conductanceHigh resistance

A high resistance re-grown layer is disposed around an optical device having a mesa structure. Thus, a mesa portion having a plane direction that appears in etching of a circular main structure is coated with the re-grown layer. Because of this coating, it is possible to reduce the capacitance in this portion as well as to avoid the risk of disconnection with respect to all the wiring directions. The thickness of the re-grown layer can be set to be equal to the thickness of the main structural part. Particularly, when a conductive substrate is used, a substantial reduction effect of parasitic capacitance can be expected from a combination with plural dielectric films.

Owner:OPNEXT JAPAN INC

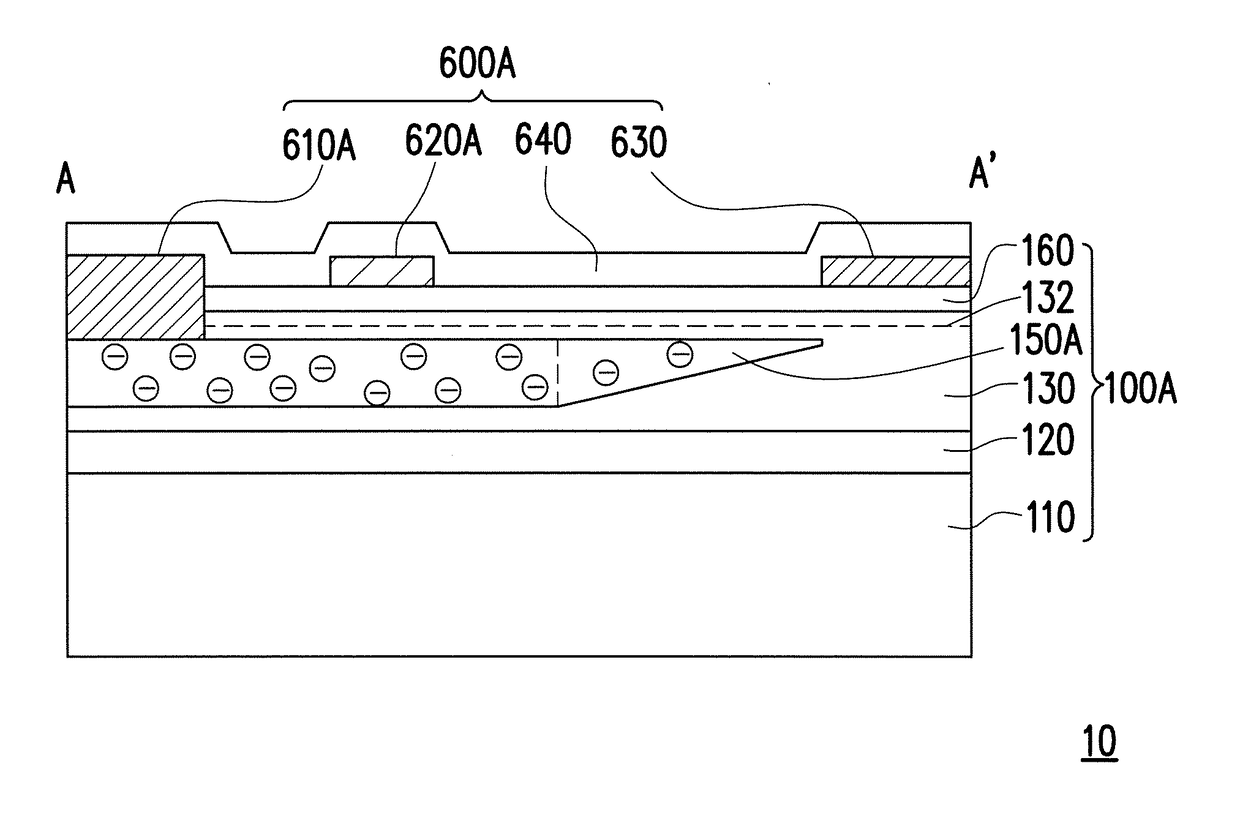

Liquid crystal display, active element array substrate and method for manufacturing active element array substrate

ActiveCN101593731AImprove performanceMinimize the effect of parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesLiquid-crystal displayEngineering

The invention discloses a liquid crystal display, an active element array substrate and a method for manufacturing the active element array substrate. The method for manufacturing the active element array substrate comprises the following steps: forming a first patterned conductive layer on an insulating substrate provided with a plurality of scanning lines; forming an insulating layer covering the first patterned conductive layer on the insulating substrate; forming a patterned semiconductor on the insulating layer; forming a patterned insulating layer on the insulating layer; forming a second patterned insulating layer provided with a plurality of data lines and a plurality of source electrodes and drain electrodes on the insulating layer, which are connected with the data lines, wherein the data lines and the scanning liners intersect above the patterned insulating, and the source electrodes, the drain electrodes, the patterned semiconductor insulating layer, the insulating layer and the scanning lines form a plurality of active elements. In the invention, the resistance-capacitance delay is improved on the active elements.

Owner:INNOLUX CORP

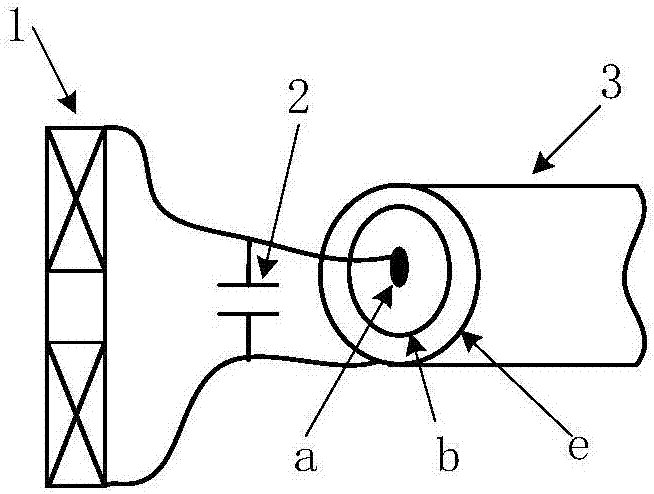

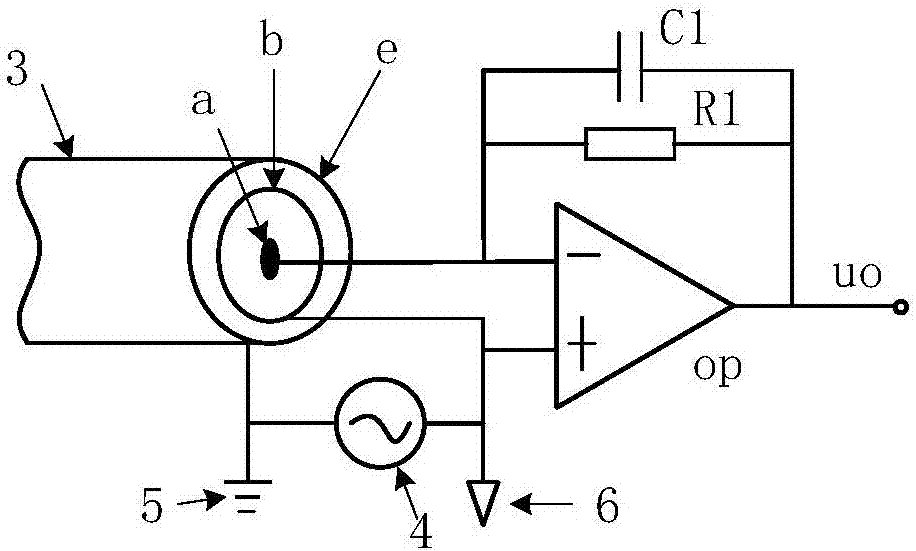

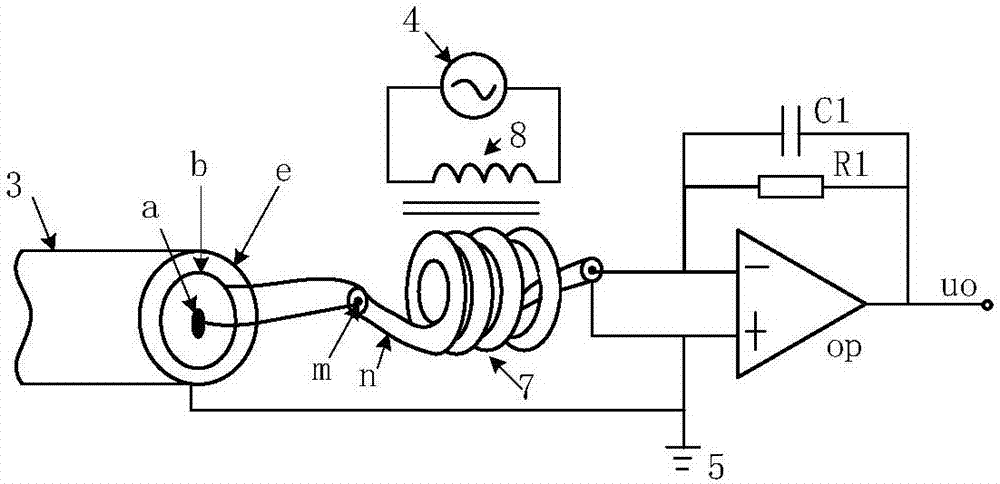

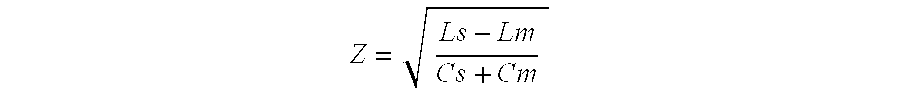

High-speed current vortex sensor

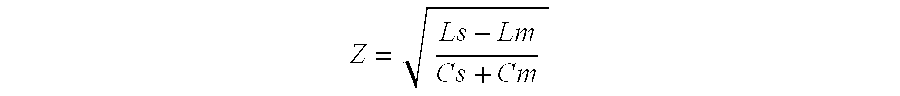

InactiveCN107121153AEliminate the effects of parasitic capacitanceImprove stabilityConverting sensor output electrically/magneticallyPhysicsLc resonant circuit

The invention provides a high-speed current vortex sensor and relates to the field of distance measurement and sensors, wherein the frequency response of the sensor can be improved, and the influence of the parasitic capacitance of a transmission cable can be eliminated. In this way, the measurement precision and the measurement stability of the sensor are improved, and the measurement distance is increased. According to the technical scheme of the invention, the high-speed current vortex sensor comprises a detection coil, a high-stability capacitor and three coaxial cables. The high-frequency alternating current in the coil generates an alternating magnetic field, and also generates a closed induced eddy current in a to-be-measured metal conductor. The induced eddy current acts on the detection coil in turn, so that the characteristic impedance of a resonant LC circuit formed by the detection coil and the high-stability capacitor changes. The change of the characteristic impedance is transmitted to a far end through the three coaxial cables. Therefore, the changed characteristic impedance can be measured at the far end. The high-speed current vortex sensor is mainly applied to distance measurement occasions.

Owner:TIANJIN UNIV

Signal transmission structure and circuit substrate thereof

ActiveUS7291916B2Improve signal transmission qualityMinimize the effect of parasitic capacitanceCross-talk/noise/interference reductionPrinted electric component incorporationEngineeringDielectric layer

A signal transmission structure suitable for a multi-layer circuit substrate comprising a core layer and at least a dielectric layer is provided. The signal transmission structure according to the present invention comprises a first via landing pad and a reference plane. The first via landing pad is disposed on a first surface of the core layer, and covering one end of the through hole of the core layer. The dielectric layer covers the first via landing pad and the first surface of the core layer. And the first reference plane is disposed above the dielectric layer, having a first opening disposed above one end of the through hole. Wherein, the area where the first reference plane is projected on the first surface of the core layer does not overlap with the area where the first via landing pad is projected on the first surface of the core layer.

Owner:VIA TECH INC

Display device

ActiveUS20110156994A1Reduce voltage fluctuationReduce effectStatic indicating devicesSemiconductor/solid-state device manufacturingOxide semiconductorEngineering

To provide a display device which can realize multi-gray scale display by reducing voltage fluctuation of a pixel, a display device includes a plurality of source signal lines, a plurality of gate signal lines which is provided so as to intersect with the source signal lines, and a pixel electrode to which a signal voltage of the source signal line is applied through a transistor including an oxide semiconductor, which is provided near an intersection portion of the source signal line and the gate signal line; in which in the pixel electrode which is provided between a pair of the adjacent source signal lines, edge portions thereof overlap with edge portions of the source signal lines and an overlapped area with one of the source signal lines is substantially equal to an overlapped area with the other source signal line.

Owner:SEMICON ENERGY LAB CO LTD

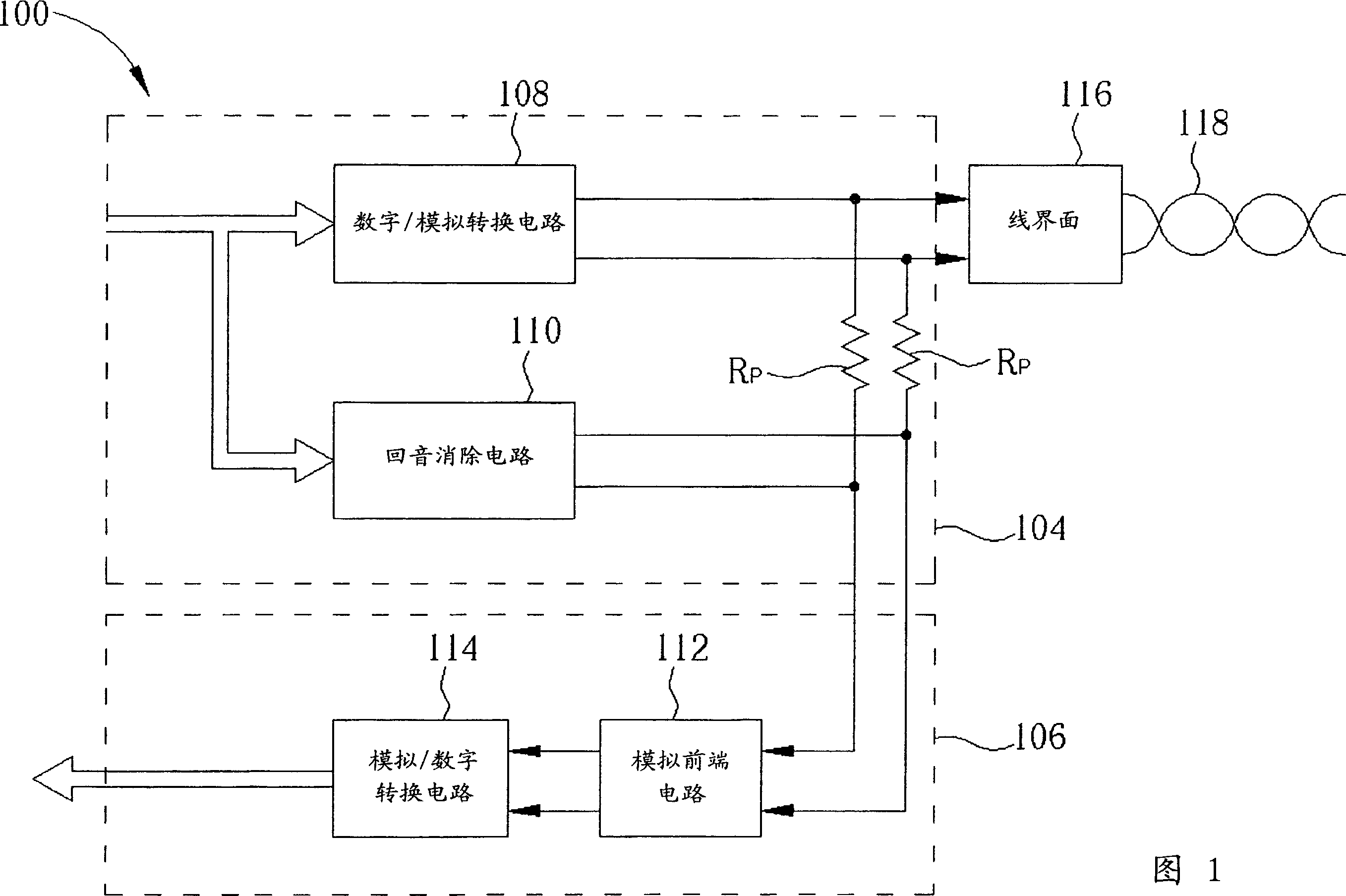

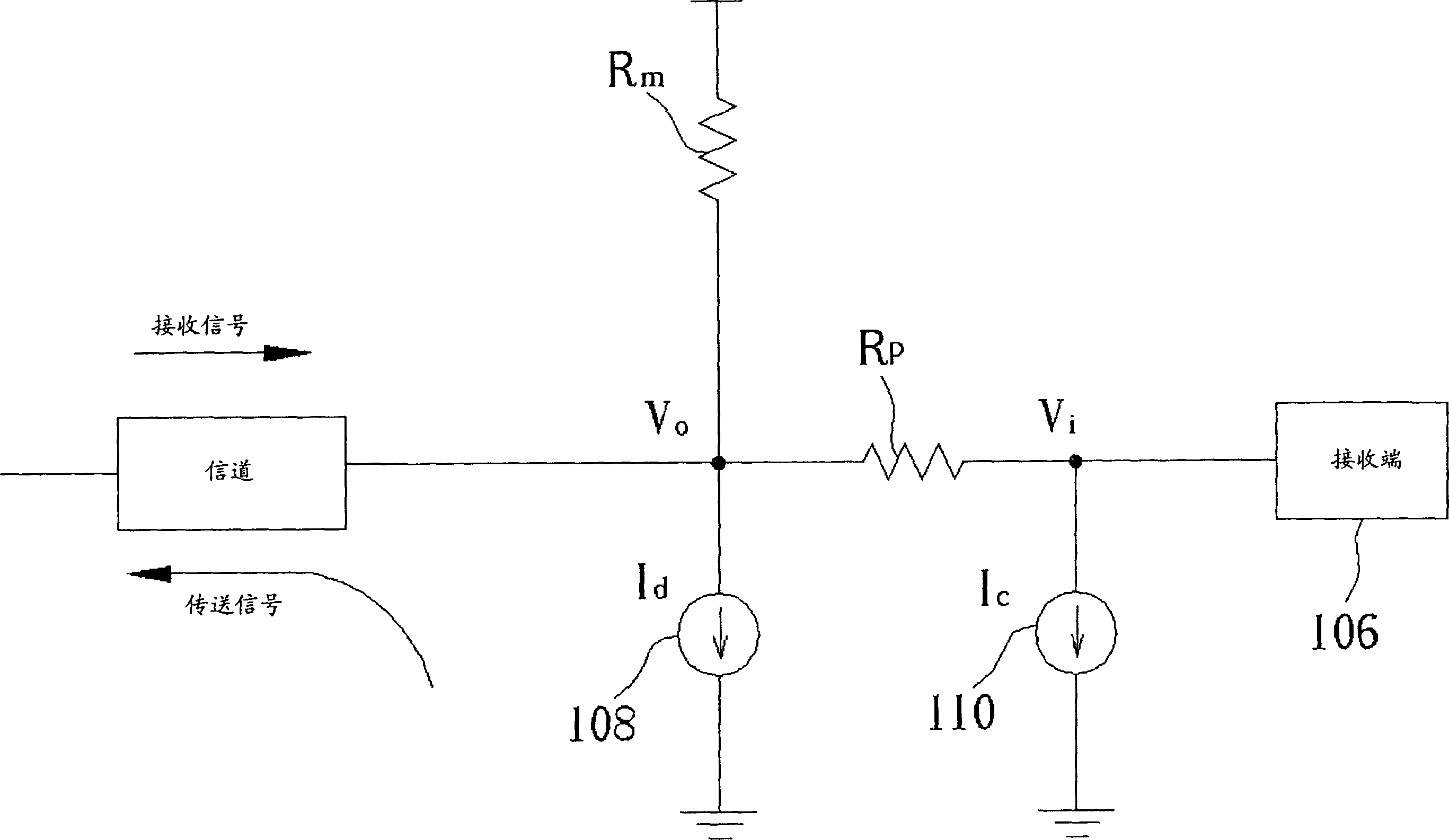

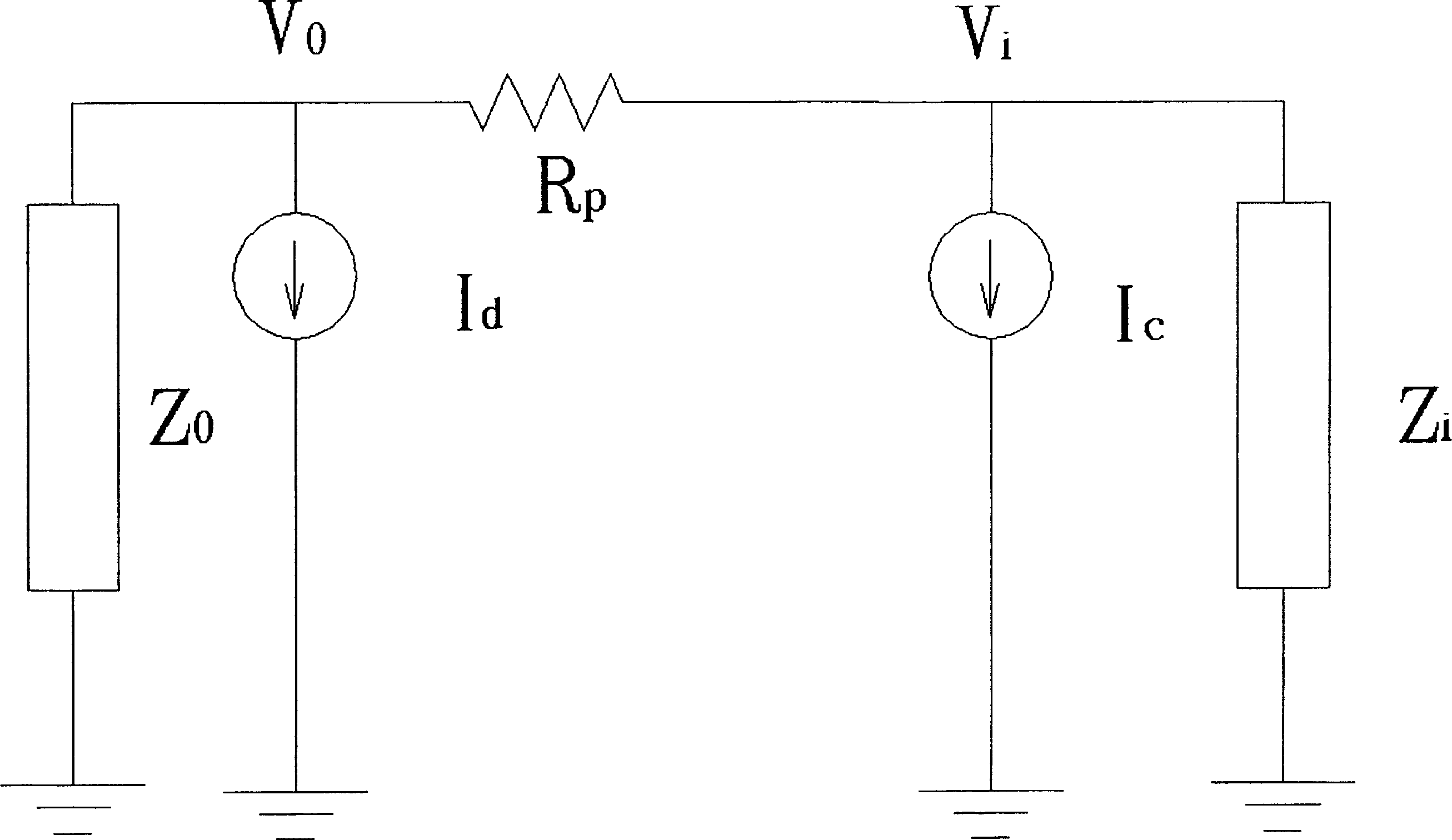

Adjustable echo eliminating apparatus for all duplex communication systems

ActiveCN1655468AMinimize the effect of parasitic capacitanceEcho Interference MinimizationLine-transmissionCommunications systemEngineering

This invention relates to full duplex communication system echo cancellation device, wherein the system comprises one sending end to send one near end signal and one receiving end to receive one remote signal. The echo cancellation device comprises the following parts: one wave filter to output one filter signal according to the near end signal; one echo cancellation circuit coupled on the filter to output one echo cancellation signal according to the filter signals; at least one echo cancellation resistance coupled to the sending end, receiving end and the echo cancellation circuit, wherein the circuit comprises one lifting current source to lift the direct current level.

Owner:REALTEK SEMICON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com