Forming method of metal gate, forming method of MOS transistor and forming method of CMOS structure

一种金属栅极、金属层的技术,应用在半导体器件、半导体/固态器件制造、电气元件等方向,能够解决高K栅介质层与硅衬底界面缺陷等问题,达到正偏压温度不稳定性降低、负偏压温度不稳定性降低的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

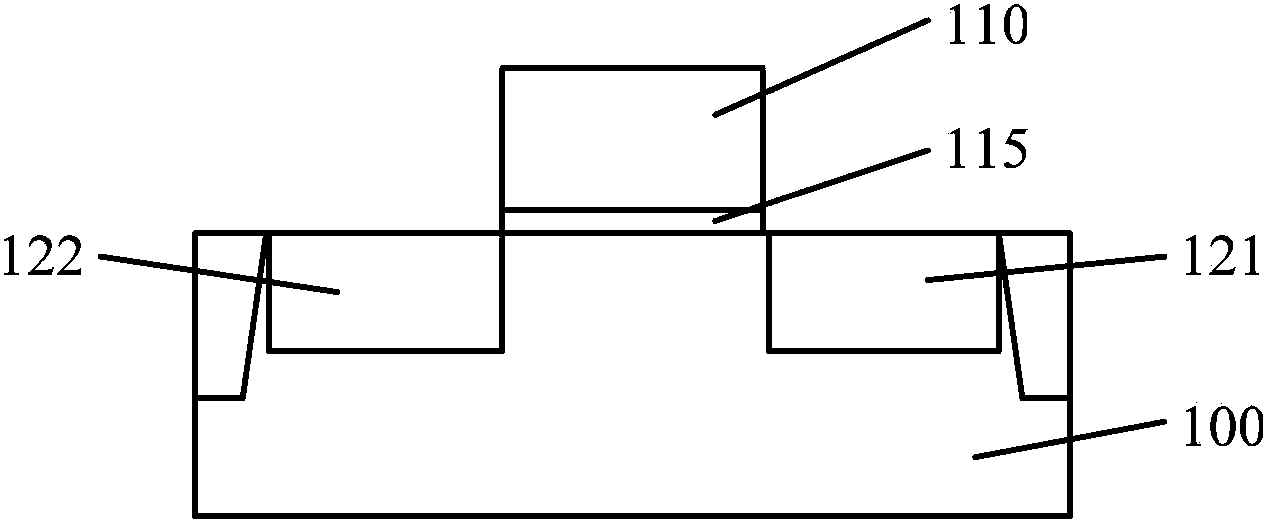

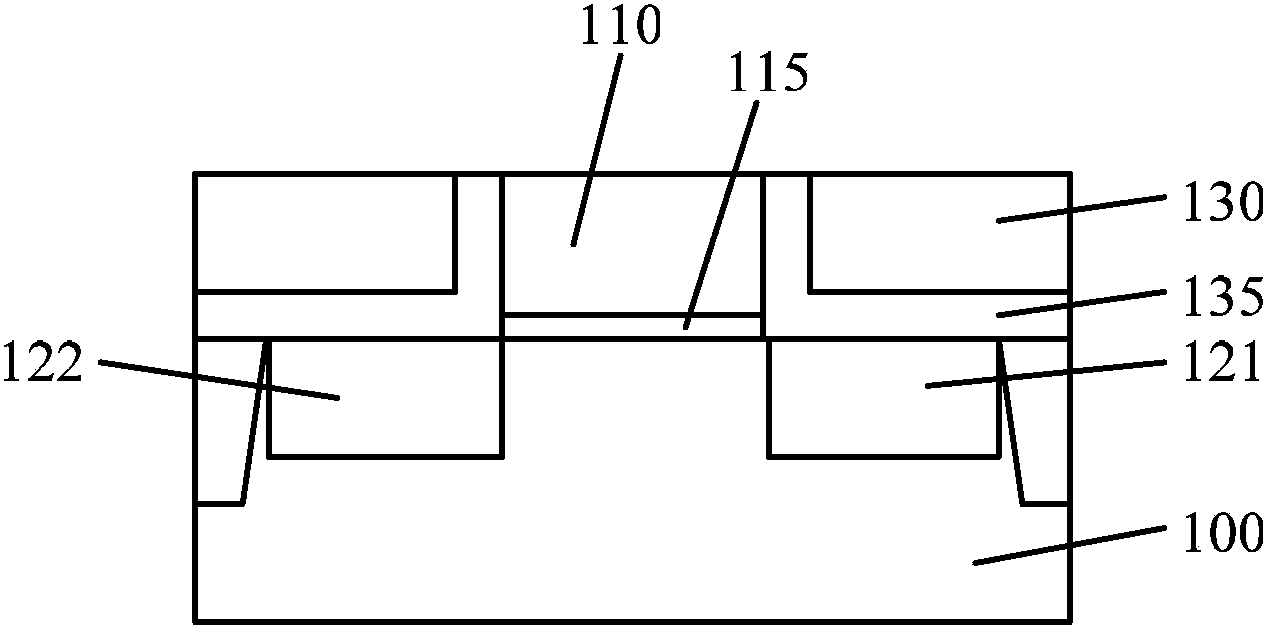

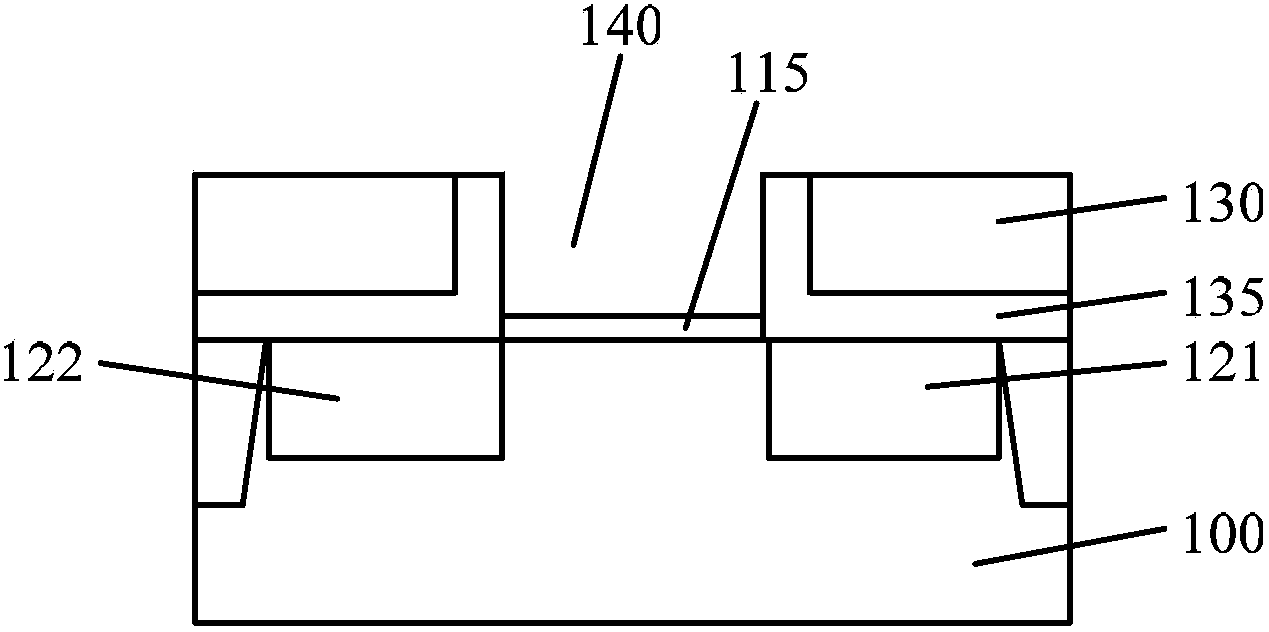

[0027] Please refer to Figure 1 to Figure 8 , is a schematic flowchart of the formation process of the MOS transistor with a metal gate according to the first embodiment of the present invention.

[0028] Please refer to figure 1 , providing a semiconductor substrate 100, forming a second silicon oxide layer 115 on the surface of the semiconductor substrate 100, forming a polysilicon dummy gate 110 on the surface of the second silicon oxide layer 115, and semiconductors on both sides of the polysilicon dummy gate 110 A source 121 and a drain 122 are formed in the substrate 100 .

[0029] The semiconductor substrate 100 is a silicon substrate, a germanium substrate, a silicon nitride substrate or a silicon-on-insulator substrate or the like. Those skilled in the art can select the type of the semiconductor substrate 100 according to the semiconductor devices formed on the semiconductor substrate 100 , so the type of the semiconductor substrate should not limit the protection...

no. 2 example

[0060] Please refer to Figure 9 to Figure 16 , is a schematic flowchart of the formation process of the CMOS structure with a metal gate according to the second embodiment of the present invention.

[0061] Please refer to Figure 9 , provide a semiconductor substrate 200, the semiconductor substrate 200 has a first region 201 and a second region 202, a second silicon oxide layer 215 is formed on the surface of the semiconductor substrate 200, and the first region 201 on the first region 201 A first polysilicon dummy gate 211 is formed on the surface of the silicon dioxide layer 215, a second polysilicon dummy gate 212 is formed on the surface of the second silicon oxide layer 215 on the second region 202, and a second polysilicon dummy gate 212 is formed on the surface of the first polysilicon A first source 221 and a first drain 222 are formed in the semiconductor substrate 200 on both sides of the dummy gate 211, and a second source 223 and a second drain 222 are formed i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More