Trench gate SOI LIGBT device

A trench gate and device technology, applied in the field of semiconductor power devices, can solve problems such as prone to latch-up effect, LIGBT loses gate control ability, device failure, etc., and achieves the effects of preventing injection, avoiding opening, and reducing electric field strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

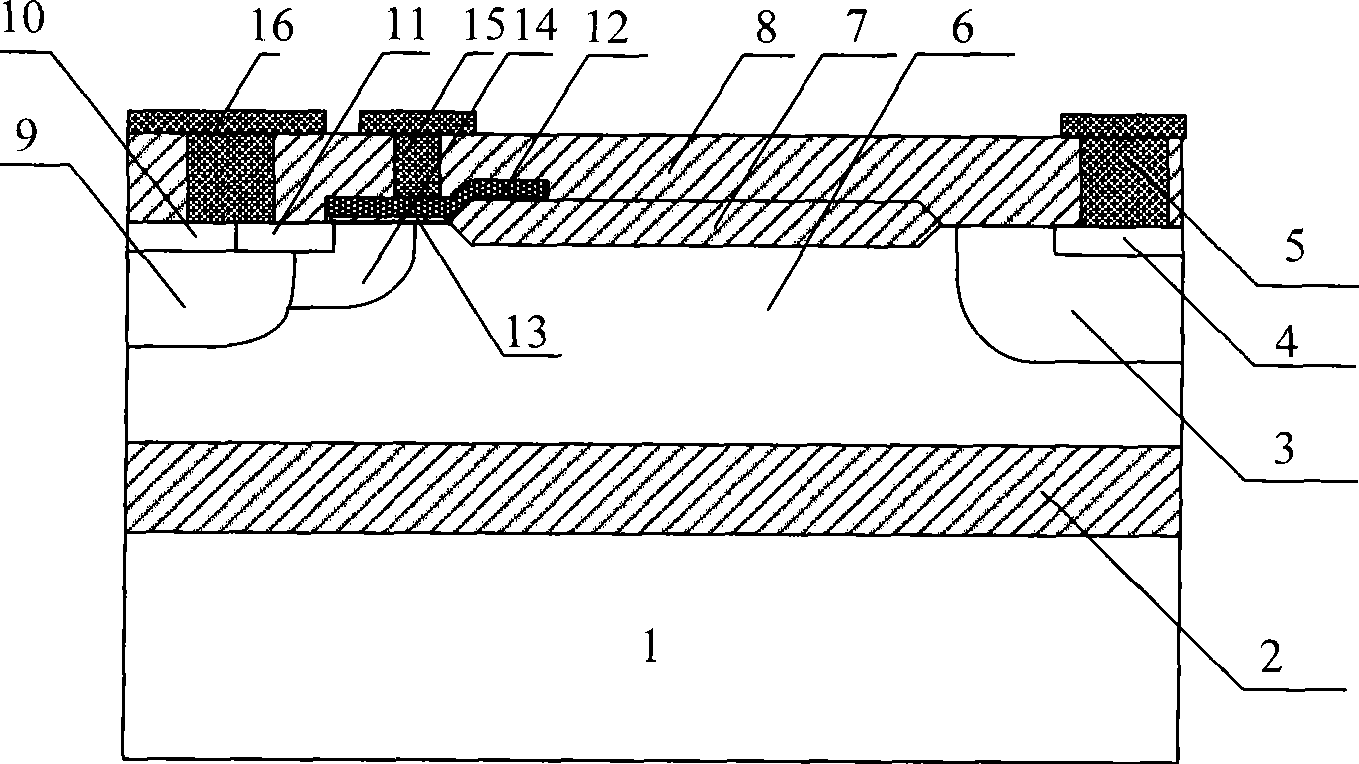

Embodiment 1

[0019] see figure 2 . Among them, the anode P + Region 4 is connected to anode metal 5, the concentration of P-type region 9 is higher than that of P-type channel region 14, and P + District 10 and N + Region 11 is in contact with cathode metal 16 . N + The region 11 is connected to the polysilicon trench gate 12 through the gate oxide layer of the LIGBT device, and the polysilicon trench gate 12 is connected to the polysilicon trench gate metal 15 .

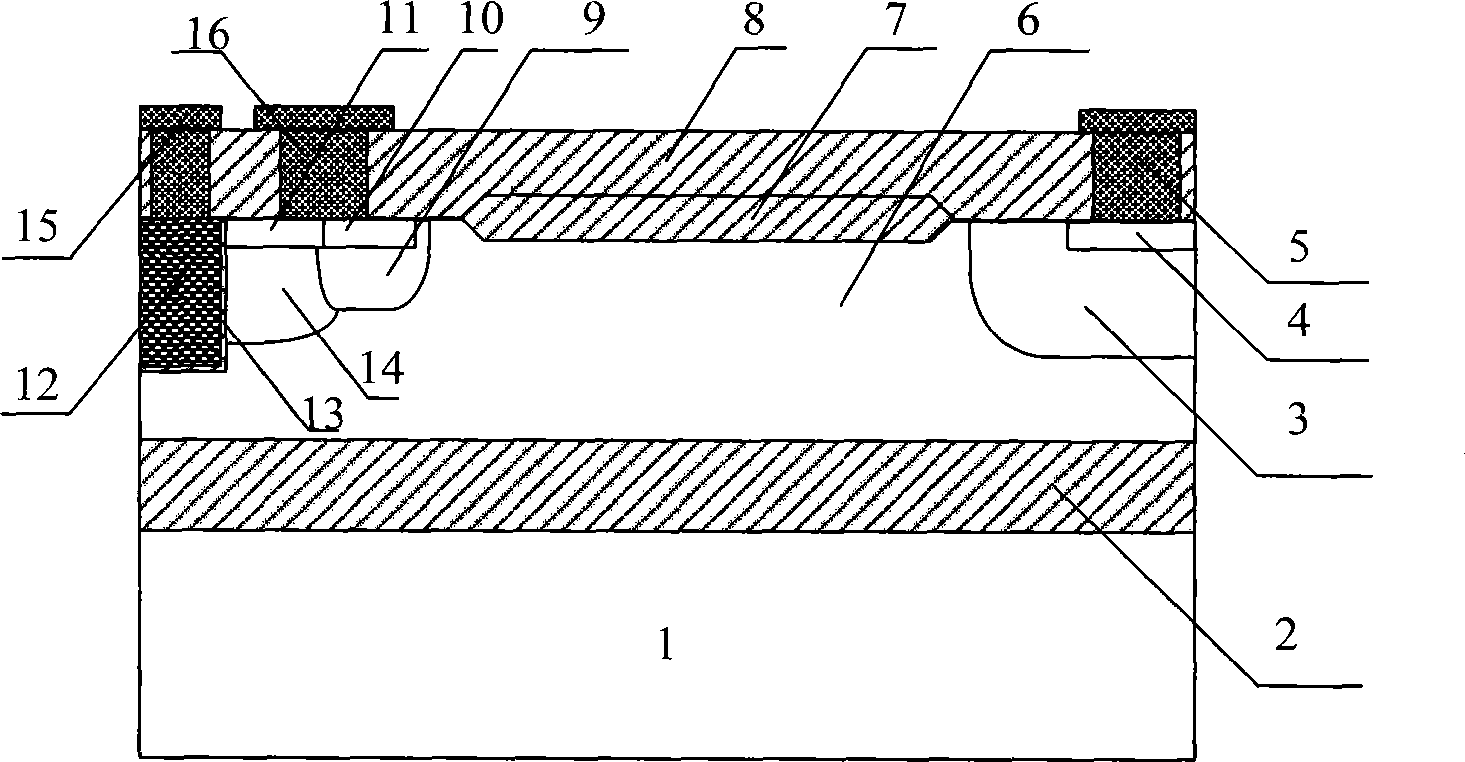

Embodiment 2

[0021] see image 3 . The difference between this embodiment and Embodiment 1 is that the polysilicon trench gate 12 of this embodiment is in contact with the buried oxide layer 2, and by means of the JFET effect, the depletion of the N-type drift region 6 under the P-type channel region 14 is enhanced to further reduce the The electric field strength near the gate oxide layer 13 is increased.

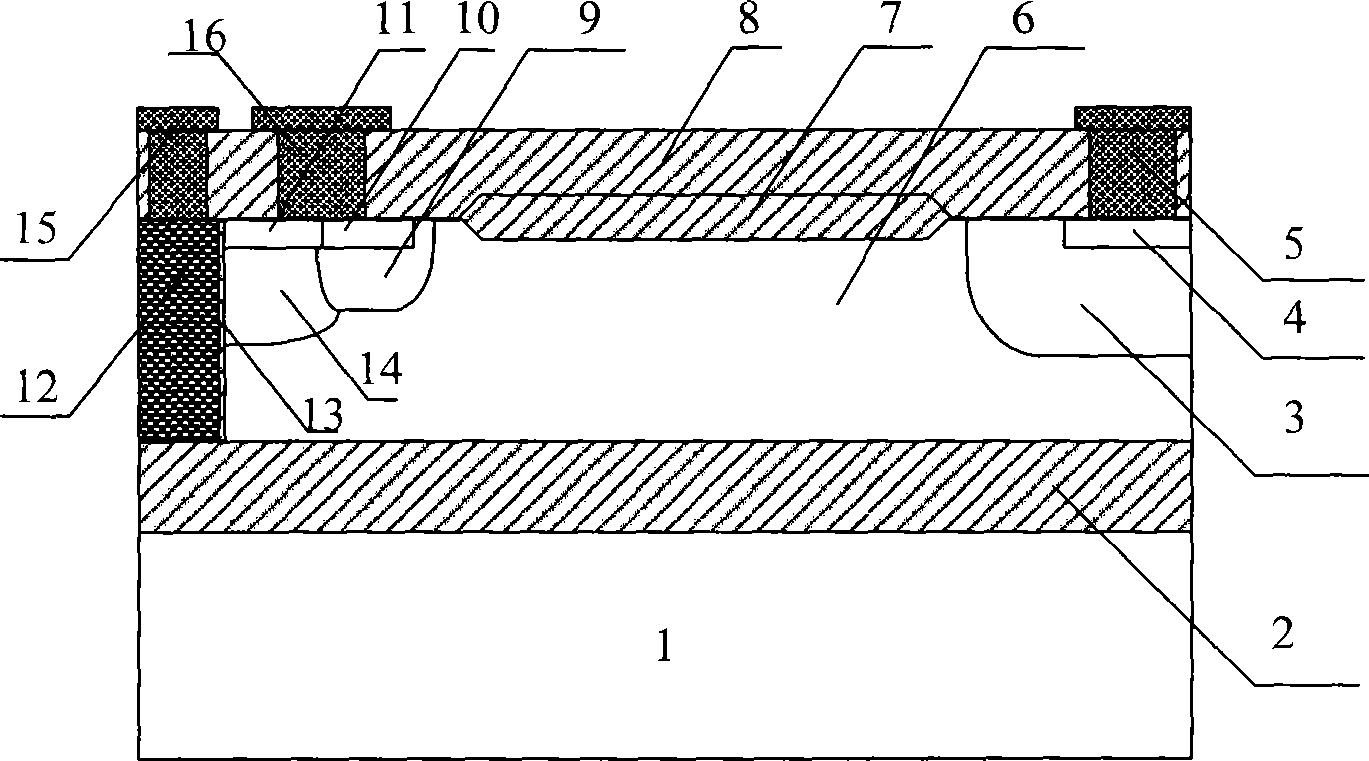

Embodiment 3

[0023] see Figure 4 . In this embodiment, the P-type region 9 is formed simultaneously with the P-type channel region 14, thereby saving the number of mask plates and reducing process complexity.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More